Verification method of FPGA universal configurable UART protocol based on UVM

A verification method and protocol technology, applied in the field of FPGA logic verification, can solve problems such as low verification efficiency and achieve the effect of improving verification efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

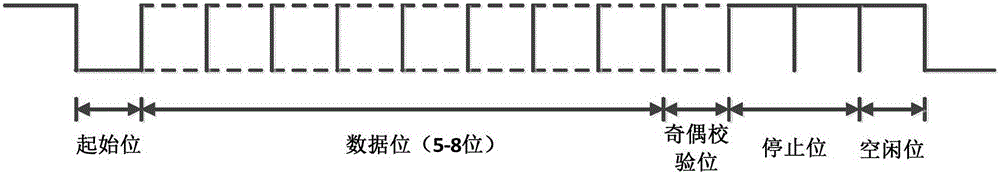

Method used

Image

Examples

Embodiment Construction

[0026] In order to have a further understanding and understanding of the structural features of the present invention and the achieved effects, the preferred embodiments and accompanying drawings are used for a detailed description, as follows:

[0027] like figure 2 Shown, a kind of verification method of FPGA general configurable UART agreement based on UVM, comprises the following steps:

[0028] Step 1. Build the UVM verification platform

[0029] The UVM verification platform is built with SystemVerilog and UVM class library; the UVM verification platform includes a UART verification environment, a scoreboard and a UART configuration module; the first agent and the second agent are encapsulated in the UART verification environment; the second agent is encapsulated in the first agent A monitor, an incentive generator, and a driver; the second monitor is encapsulated in the second agent;

[0030] Step 2. Define the UART_config class to form a URAT configuration module

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More