Random verification method and device for verifying processor chip after manufacturing

A post-processor, random verification technology, applied in software testing/debugging and other directions, can solve the problem that random verification methods cannot be directly applied to chip verification, and achieve the effect of satisfying coverage and improving verification efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] In order to make the object, technical solution and advantages of the present invention clearer, the random verification method and device for manufacturing post-processor chip verification of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention rather than limit the present invention.

[0041] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

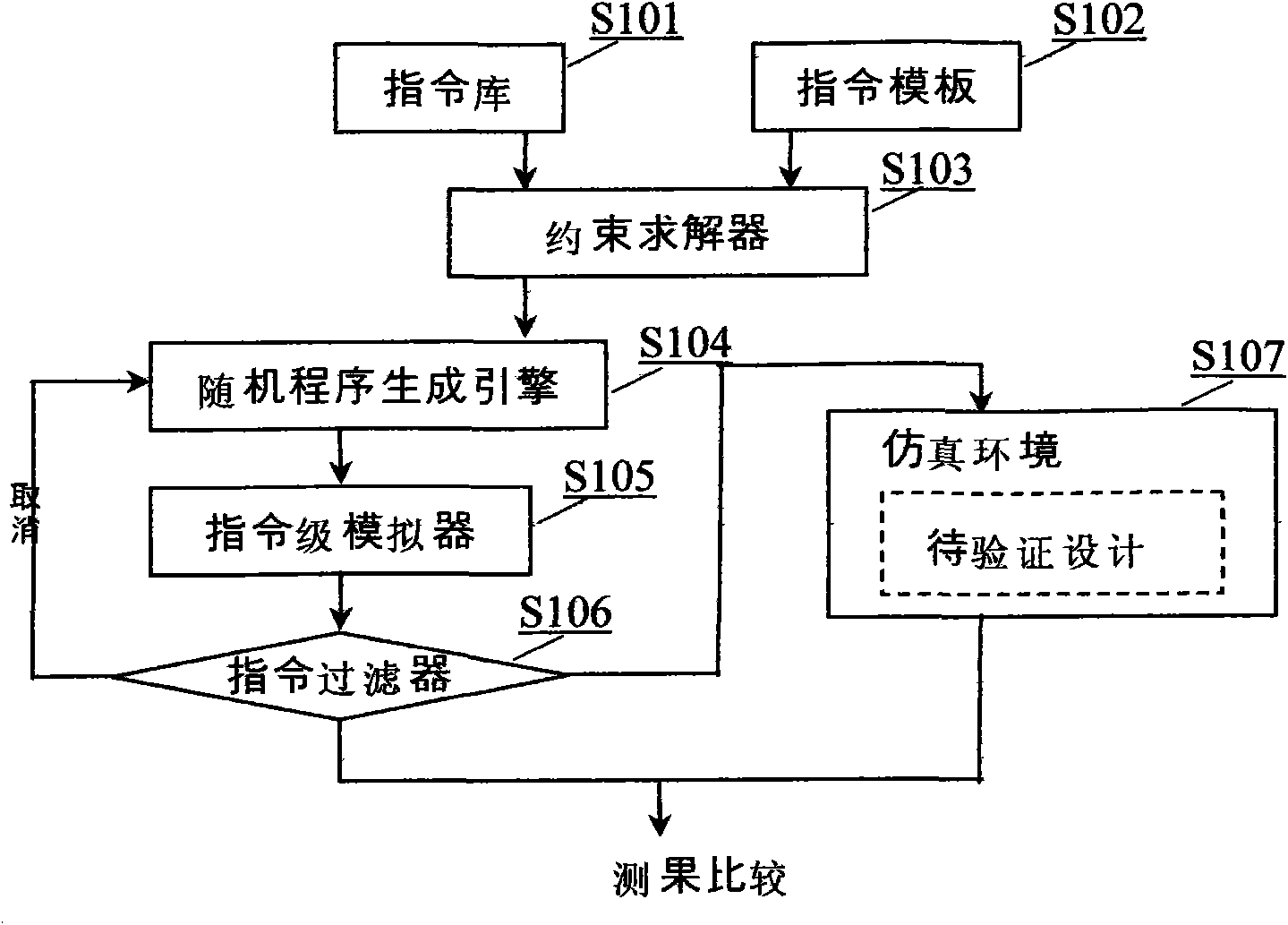

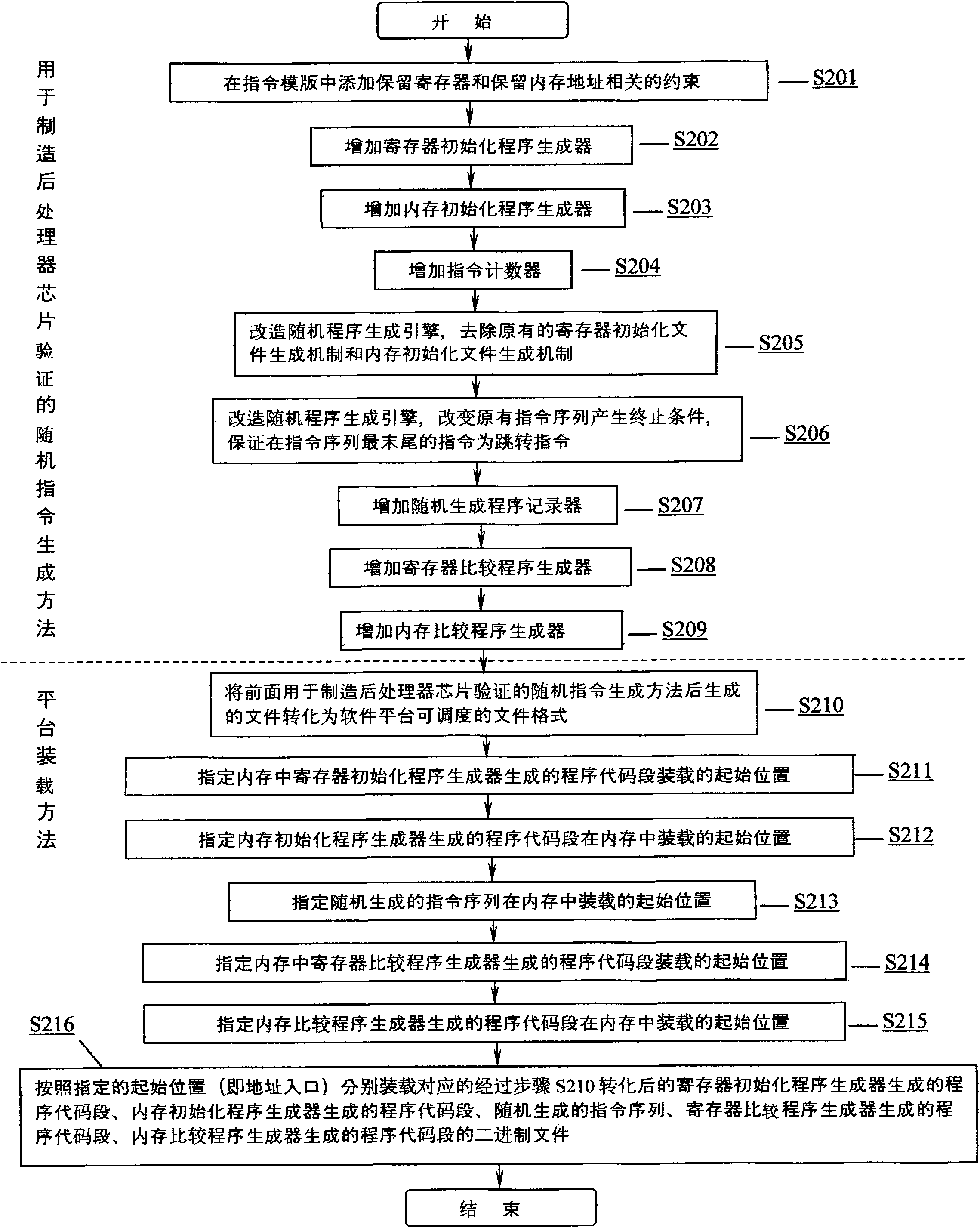

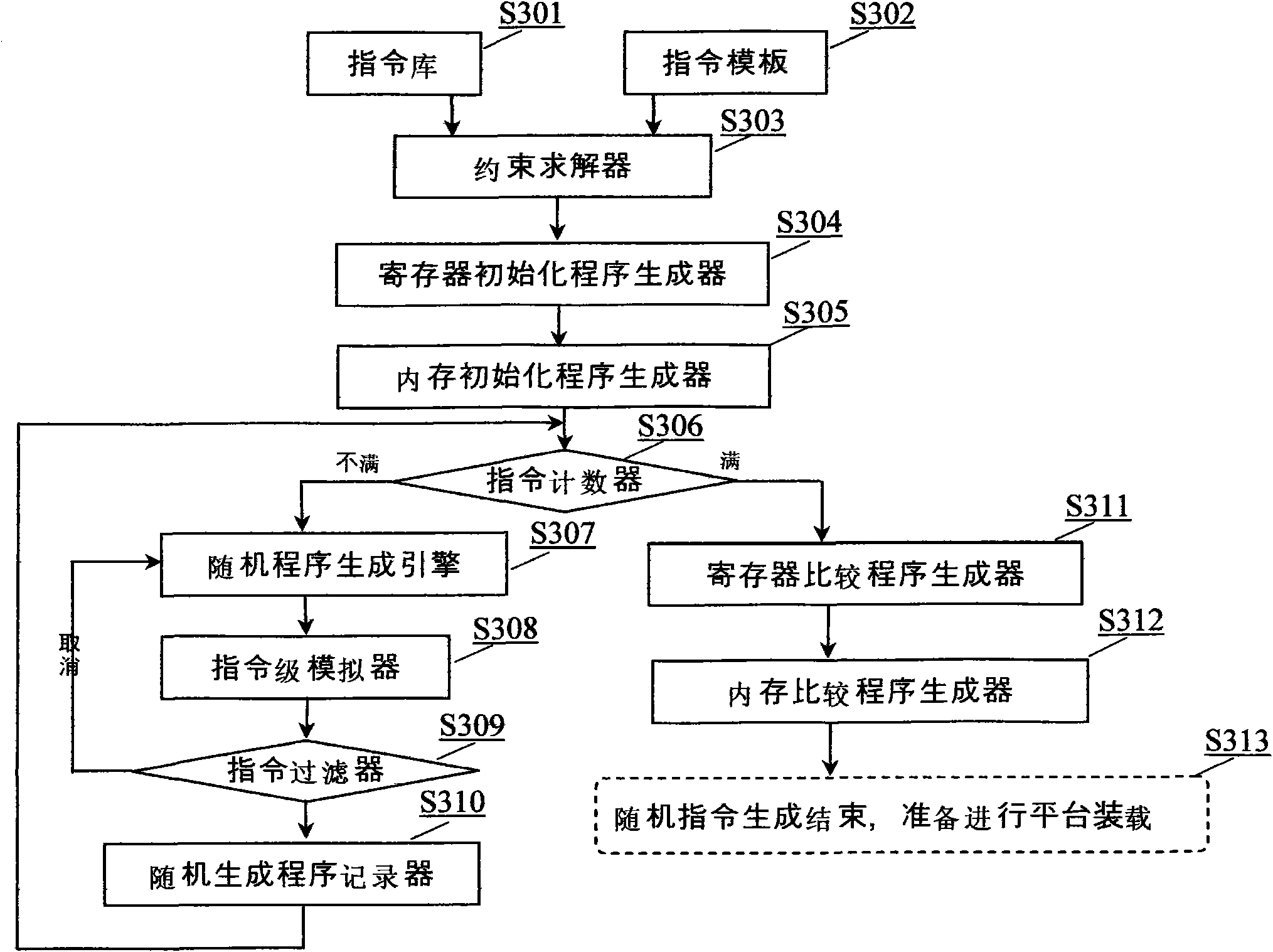

[0042] According to a specific embodiment of the present invention, a random verification method for verification of post-manufacturing processor chips is provided. The method includes two parts: a random command generation method and a platform loading method for post-manufacturing chip verification.

[0043] A method for generating random instructions for...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More