Patents

Literature

41 results about "SystemVerilog" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

SystemVerilog, standardized as IEEE 1800, is a hardware description and hardware verification language used to model, design, simulate, test and implement electronic systems. SystemVerilog is based on Verilog and some extensions, and since 2008 Verilog is now part of the same IEEE standard. It is commonly used in the semiconductor and electronic design industry as an evolution of Verilog.

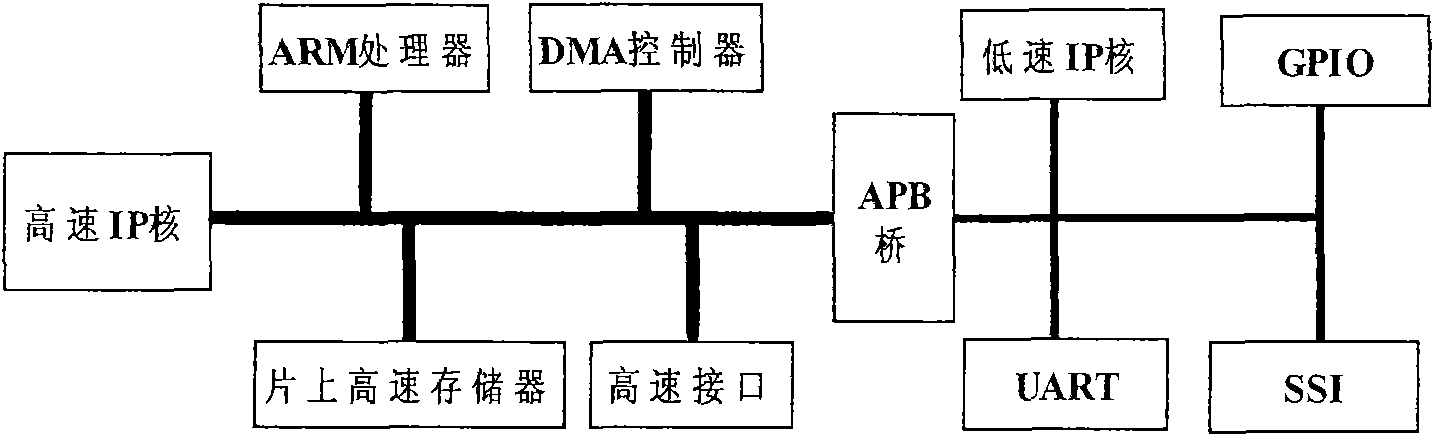

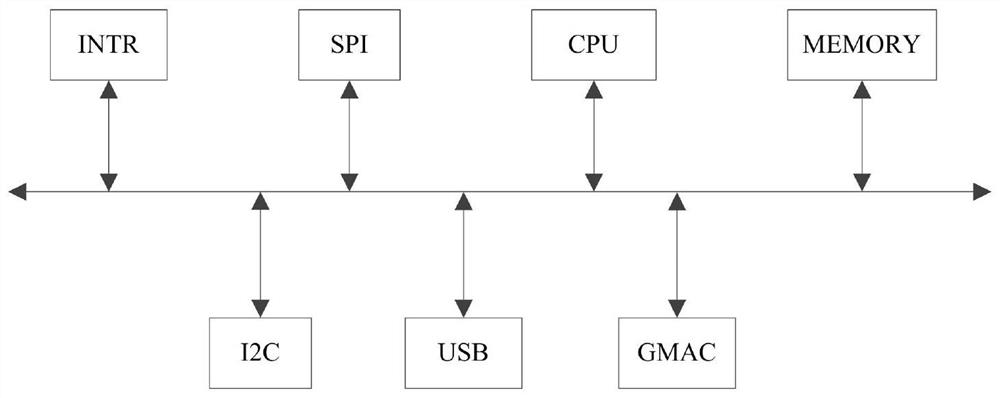

Universal method and platform for verifying compatibility between intellectual property (IP) core and advanced microcontroller bus architecture (AMBA) bus interface

InactiveCN102117238AImprove verification efficiencyImprove accuracyFunctional testingValidation methodsIntellectual property

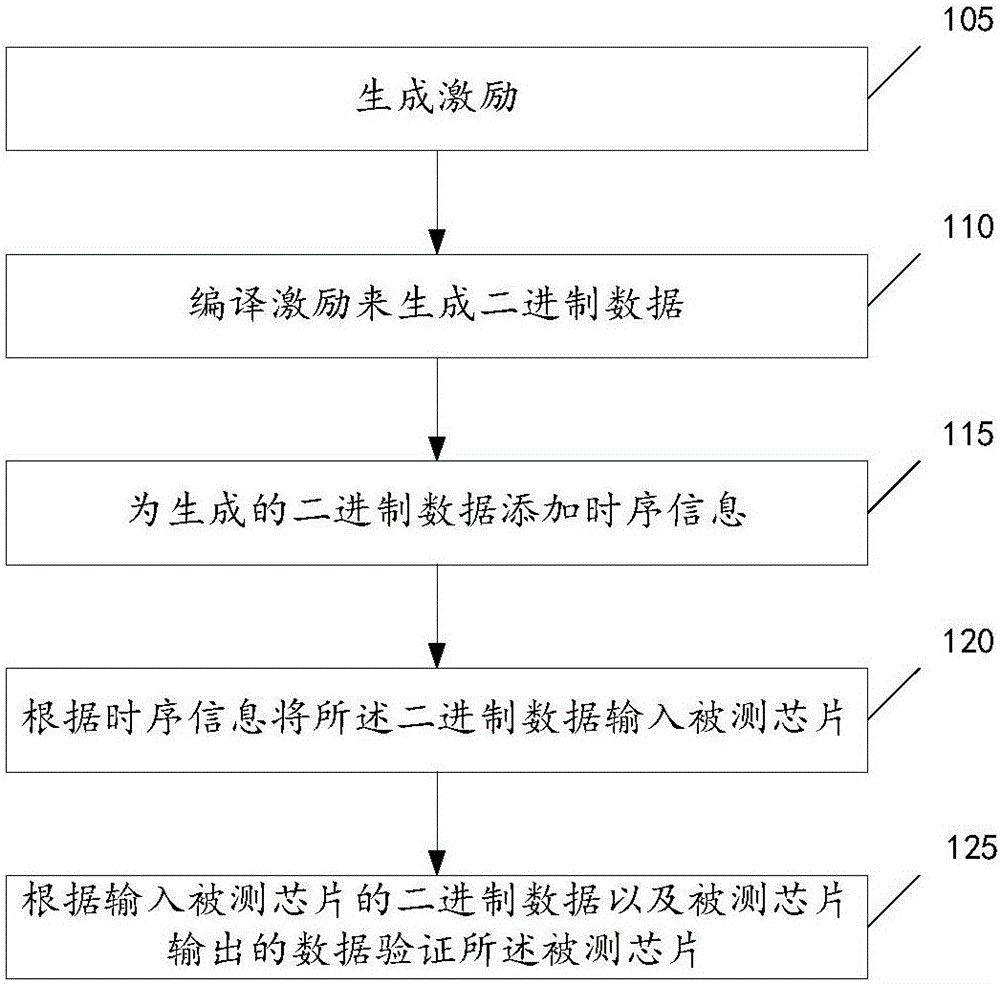

The invention provides a universal platform of verifying compatibility between an intellectual property (IP) core and an advanced microcontroller bus architecture (AMBA) bus interface, which comprises a functional simulation tool, an AMBA bus infrastructure, a third-party verification IP core, a controller, a driver, a stimulus, a checker, an advanced peripheral bus (APB) bridge, an advanced high-performance bus (AHB) master interface, an AHB slave interface and an APB slave interface, wherein all the modules are connected to form an integrated coordinating verification environment by adopting a verification component and hierarchical packaging and interconnections ways provided by a SystemVerilog language and advanced verification methodology (AVM). The platform can verify the compatibility of different types of IP core interfaces, and the development time and cost of the verification platform and a verification method are reduced. The invention also provides the universal method for verifying the compatibility between the IP core and the AMBA bus interface. In the method, excitation is produced more normatively, scientifically and accurately, unnecessary iteration is reduced and the verification time is shortened.

Owner:SHANGHAI SILICON INTPROP EXCHANGE

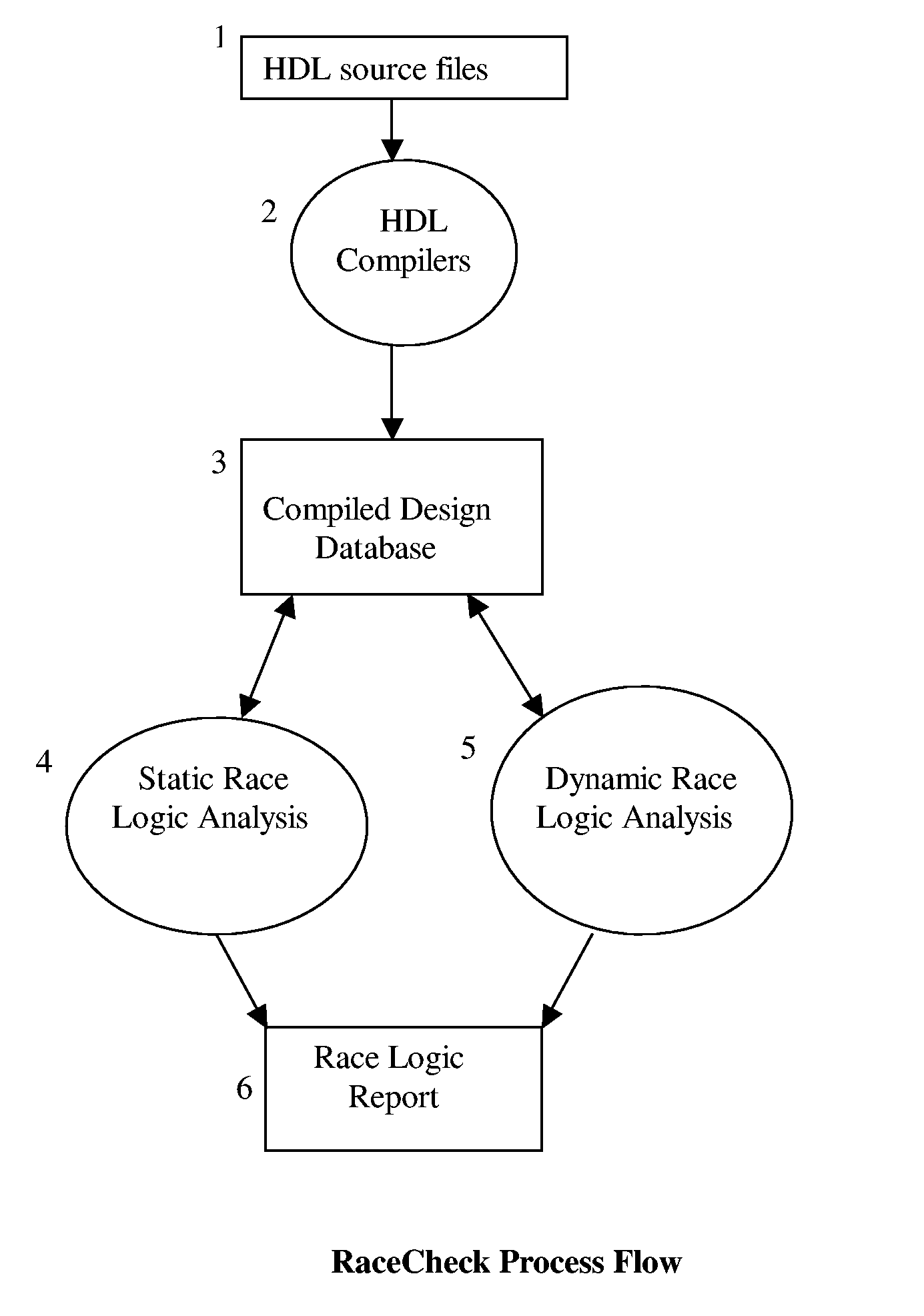

RaceCheck: A Race Logic Ana,yzer Program for Digital Integrated Circuits

ActiveUS20060075367A1Reduce effortShorten the timeElectrical testingDesign optimisation/simulationTime informationSystemC

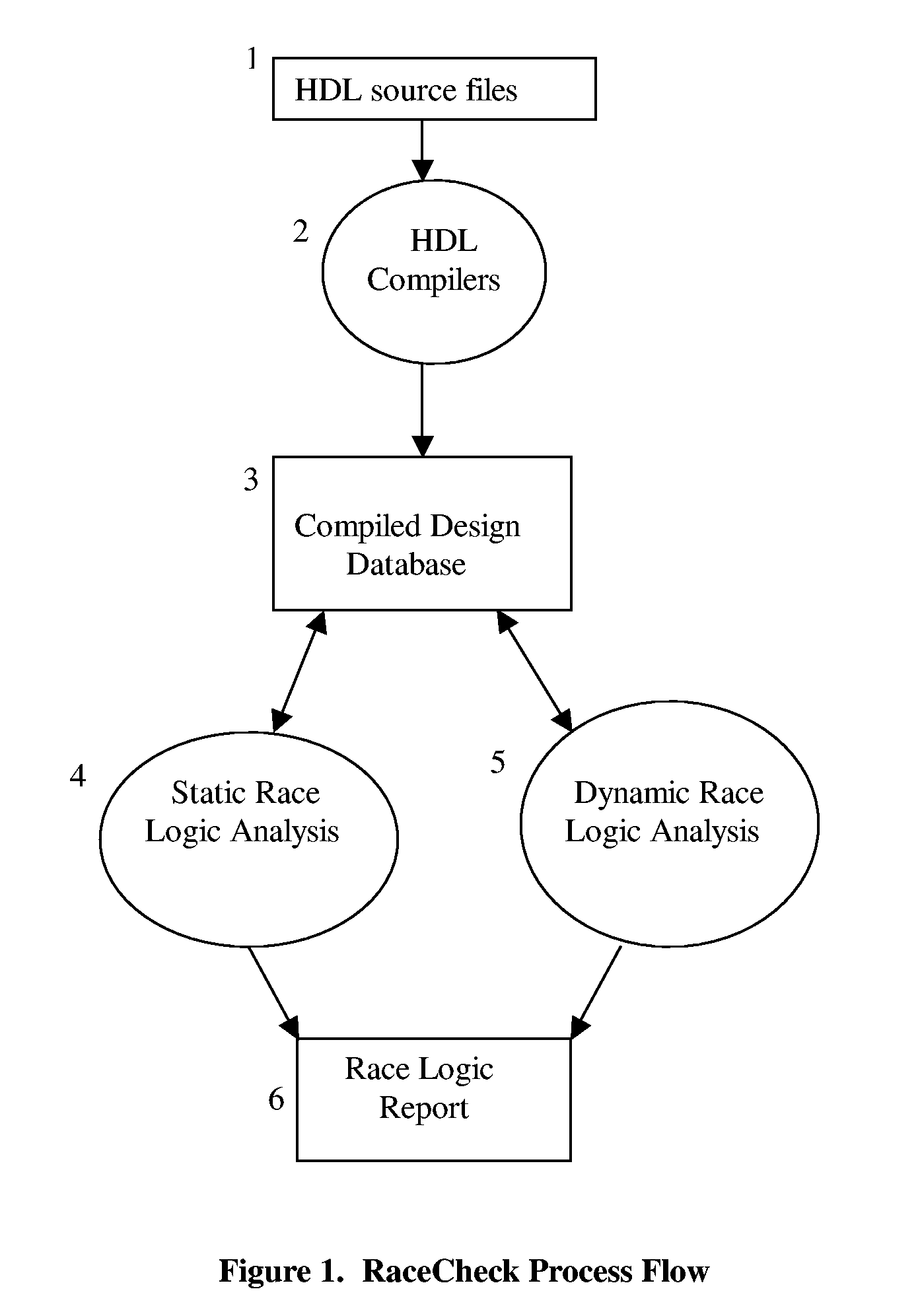

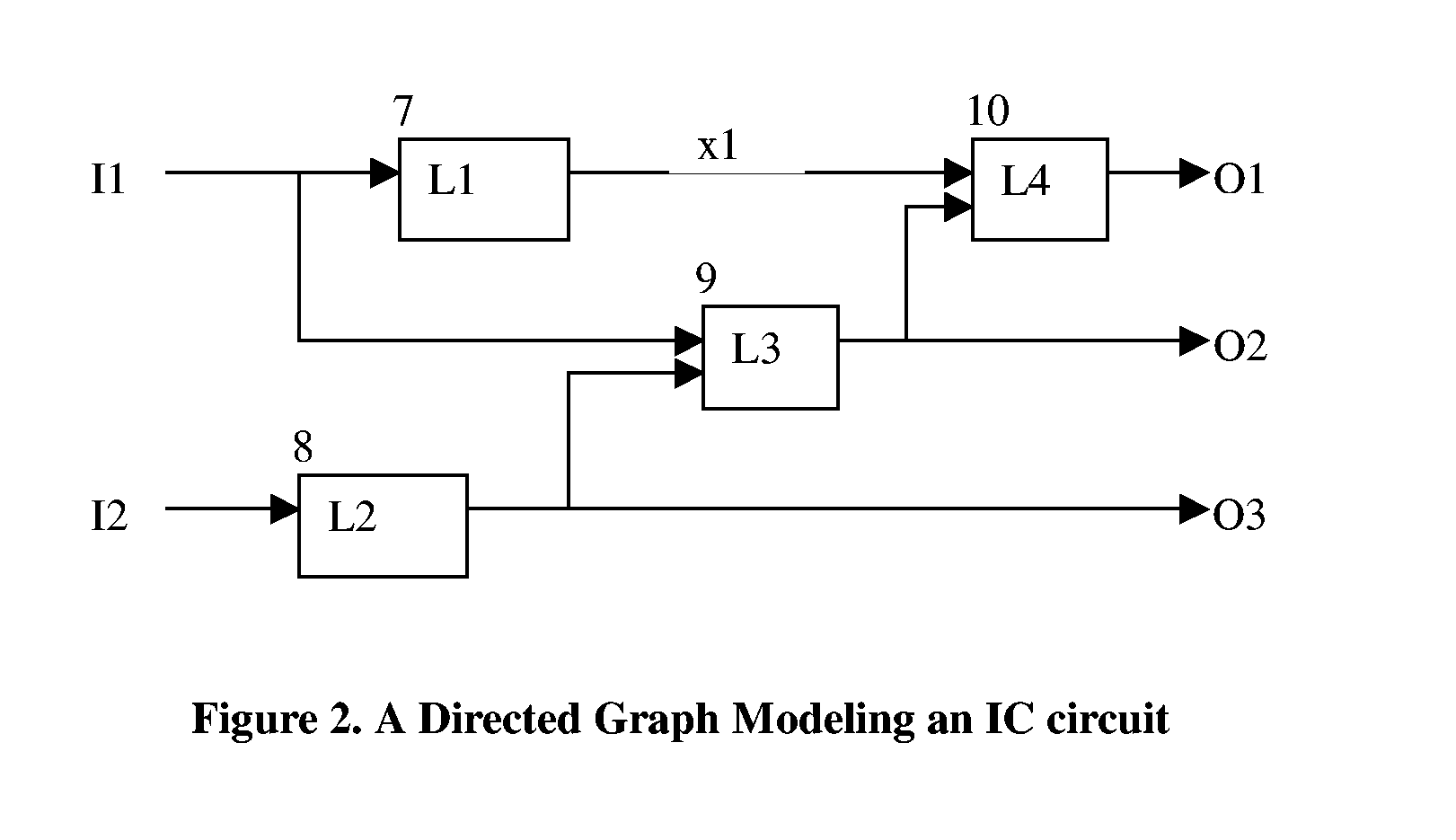

This invention describes a race logic audit program, RaceCheck, which is unique from the prior arts. Specifically, RaceCheck can perform both static and dynamic race logic analysis, and it works with a plurality of hardware description languages (HDL), which include but not limited to: VHDL, Verilog, SystemVerilog, and SystemC. Furthermore, RaceCheck makes use of both structural and timing information of IC designs, as well as binary-decision diagram (BDD) and automatic test pattern generation (ATPG) techniques to derive accurate race logic analysis results with few false violations. Finally, RaceCheck can detect concurrent invocation races of the $random system function, concurrent invocation races of user-defined tasks and functions, zero-delay combination loops, and RaceCheck's dynamic analysis engine uses a HDL simulation kernel to perform timing-accurate race logic analysis. All these aforementioned features are unique for the invention and have not been reported in any prior arts.

Owner:DYNETIX DESIGN SOLUTIONS

Communication interface method of processor reference model under multiple simulation and verification platforms

InactiveCN102567122AImprove efficiencyQuality improvementInterprogram communicationPerformance functionReference model

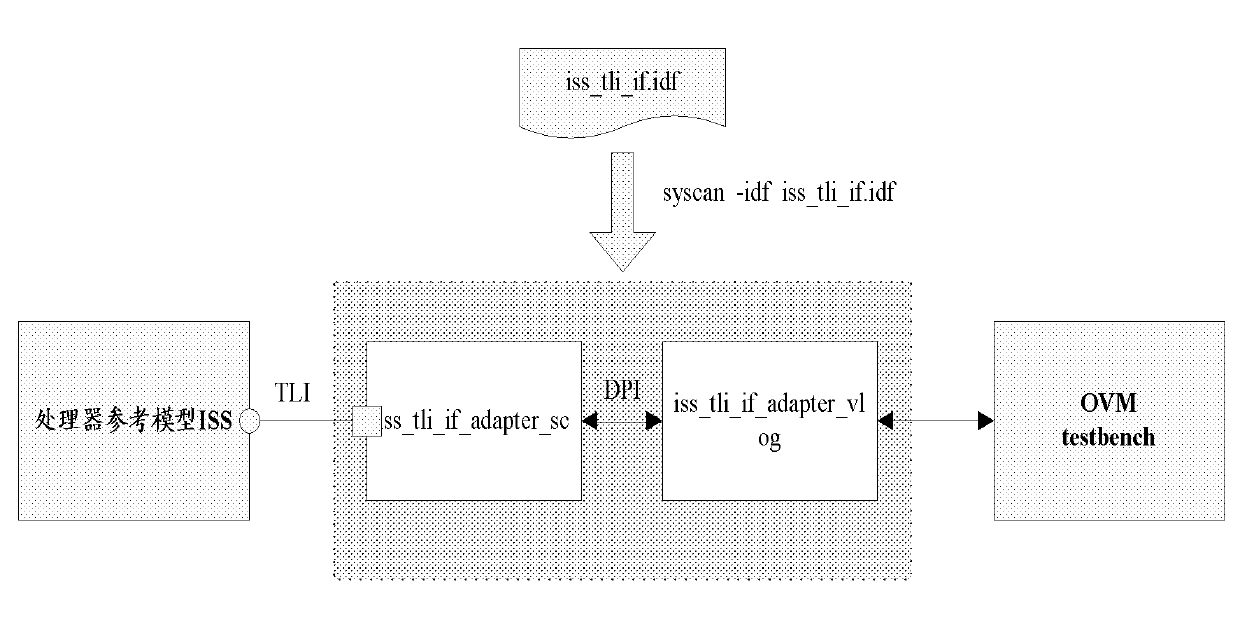

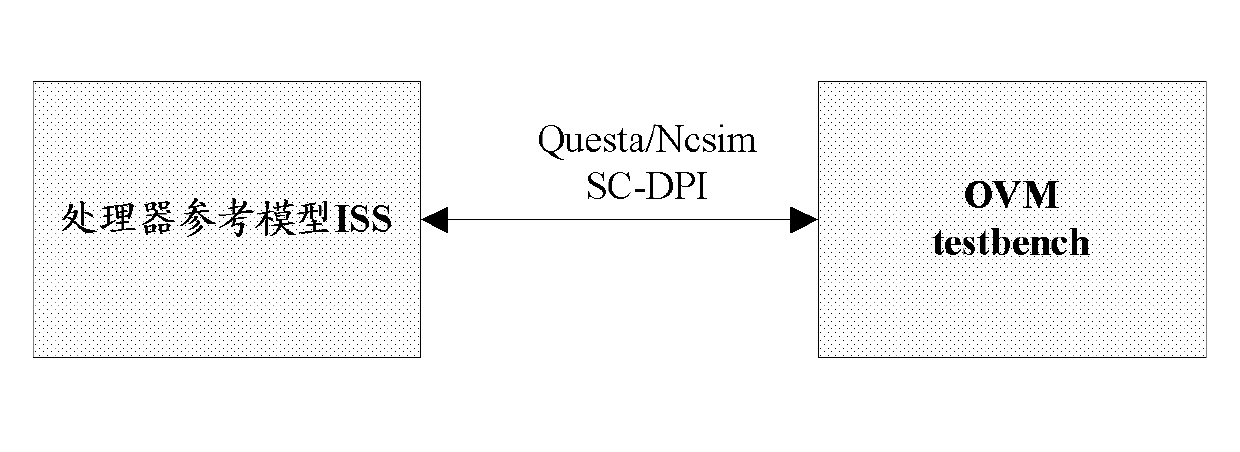

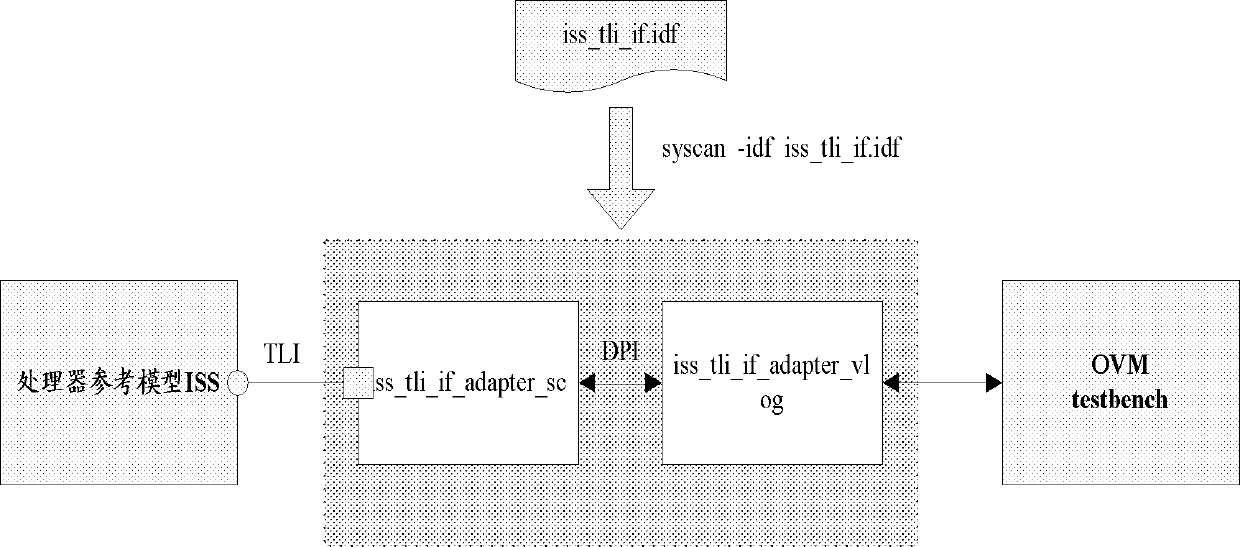

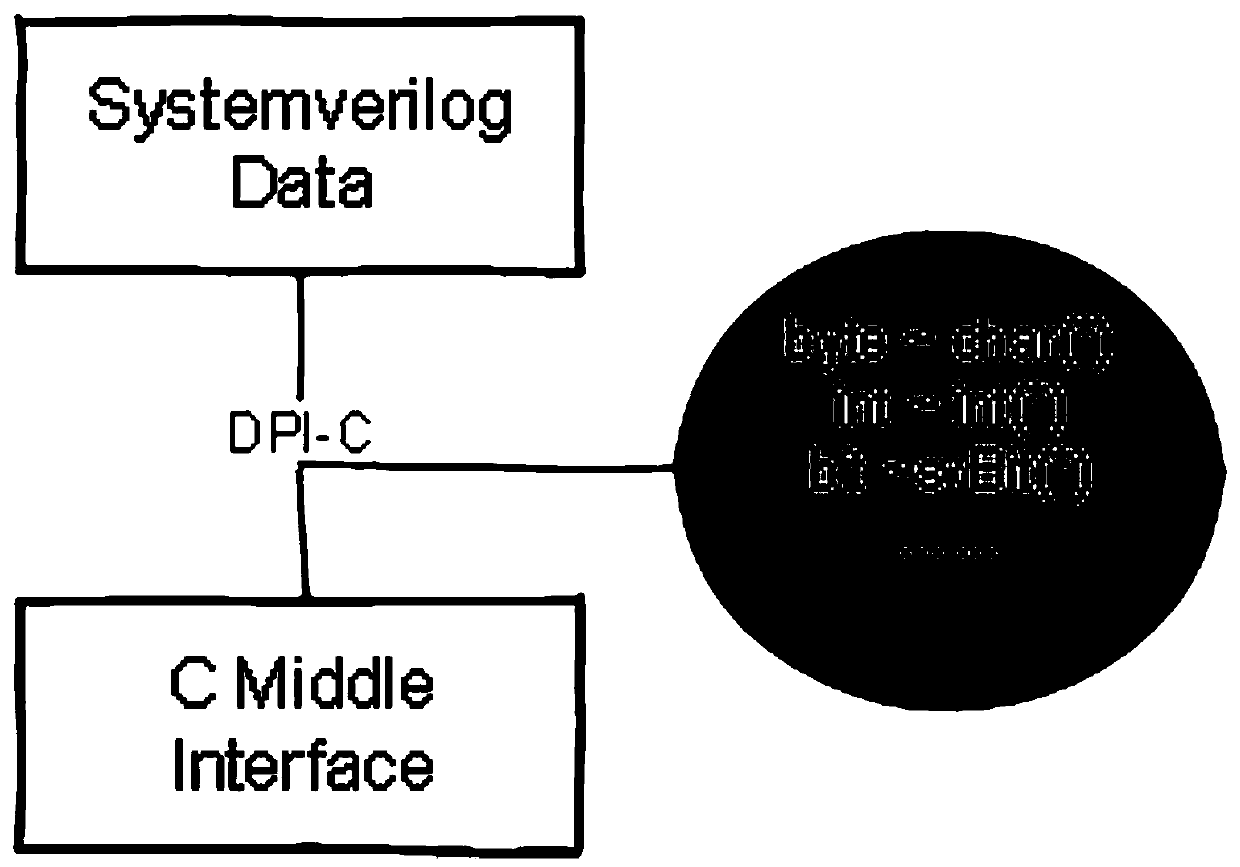

The invention relates to a communication interface method of a processor reference model under multiple simulation and verification platforms, wherein the communication interface method is used for realizing a blockable communication interface between the processor reference model and the verification platforms. The communication interface method comprises the steps of: under a VCS (Verilog Compiler Simulator) simulation and verification platform, defining a transaction-level communication interface according to an interface requirement of the processor reference model, fulfilling the function of a defined interface function to realize the interaction with the processor reference model, compiling an interface definition file and generating a corresponding SystemC / SystemVerilog adapter by using a VCS tool command, and exporting an interface performance function of a subsequent adapter to SystemVerilog by using a DPI (Direct Programming Interface); and under a Questa / Ncsim simulation platform, constructing a SystemC module, defining a member function, exporting a macro interface function embedded in a simulation tool to verilog, and importing the interface function by using an import sentence in the verilog.

Owner:北京国睿中数科技股份有限公司

Python language based Rapidio switcher logic simulation verification platform and method

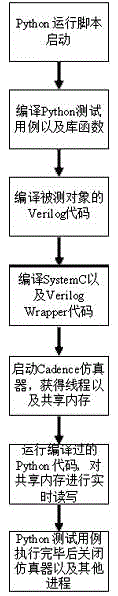

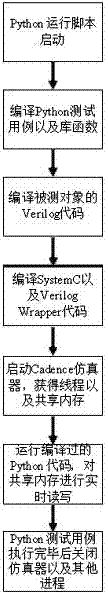

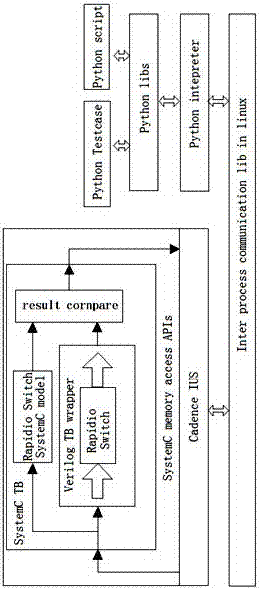

ActiveCN104965750AImprove writing efficiencyImprove reusabilitySoftware simulation/interpretation/emulationSystemCPython language

The present invention discloses a Python language based Rapidio switcher logic simulation verification platform and method. The verification platform comprises: a SystemC interface function for interpreting Python semantics, a DPI interface function used by SystemC to call SystemVerilog, and a test case and a running script realized by Python. According to the present invention, an interpreter between the Python language and the SystemC language is added, so that the Python language can directly control stimulus input of a logic simulator and compare responsive output and the test case programmed by using Python can be used directly in logic simulation and applied on a Rapidio switcher. By using the above environment, the programming efficiency and reusability of the test case can be greatly improved.

Owner:SHANDONG LANGCHAO YUNTOU INFORMATION TECH CO LTD

Verification method and platform based on SystemVerilog language

InactiveCN105975726AEasy to transplantEasy maintenanceCAD circuit designSpecial data processing applicationsData validationComputer architecture

Owner:SICHUAN DOUQI TECH

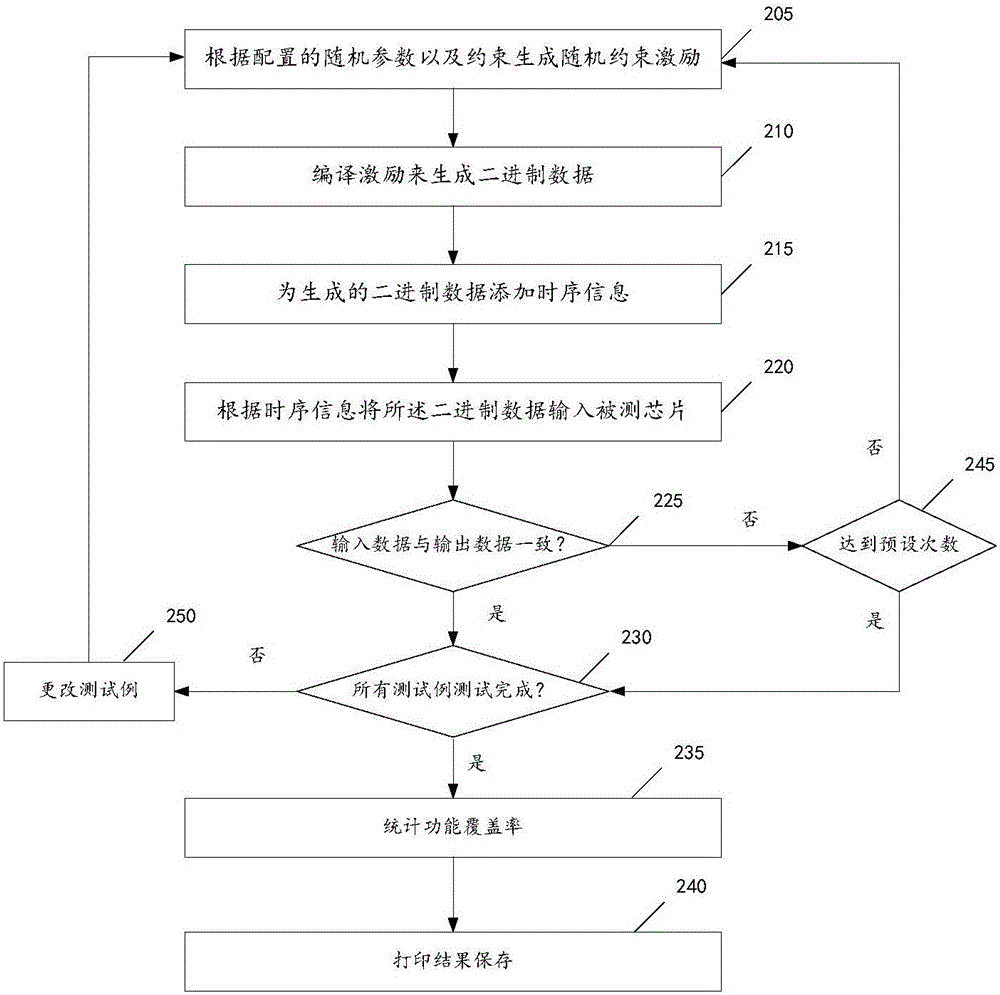

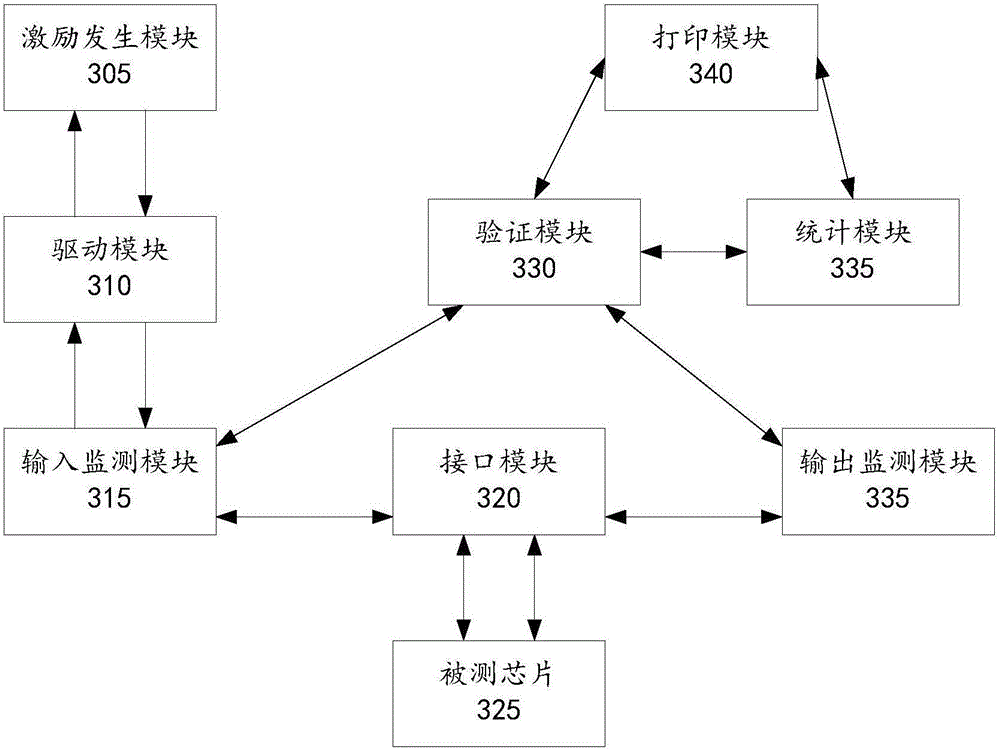

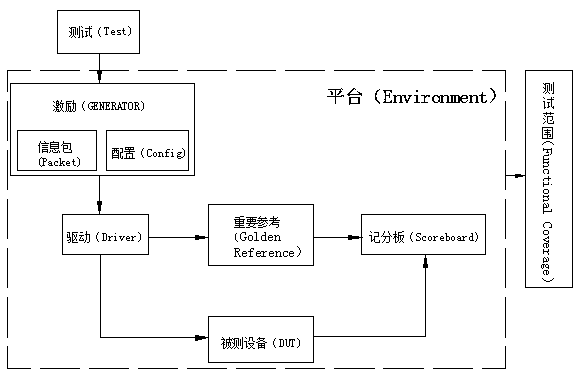

SystemVerilog based random verification platform and method

InactiveCN104392066ACorrectness of judgmentEasy to controlSpecial data processing applicationsComputer architectureDevice under test

The invention discloses a SystemVerilog based random verification platform and method, and relates to the field of chip design. The SystemVerilog based random verification platform comprises a Test module, a Generator module, a Driver module, a DUT (device under test) module, a Golden Reference module, a Scoreboard module, a Coverage module, an Environment module and the like, wherein the Test module instantiates environment to start testing; the Generator module generates all test excitation; the Driver module receives the test excitation and drives the DUT module and the Golden Reference module, the Scoreboard module judges the function correctness of the DUT module, and the Coverage module accounts the coverage of the test. By means of the random verification method, interfaces among chips are controlled and monitored, the universality of verification environment is improved, and the verification efficiency is substantially improved.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

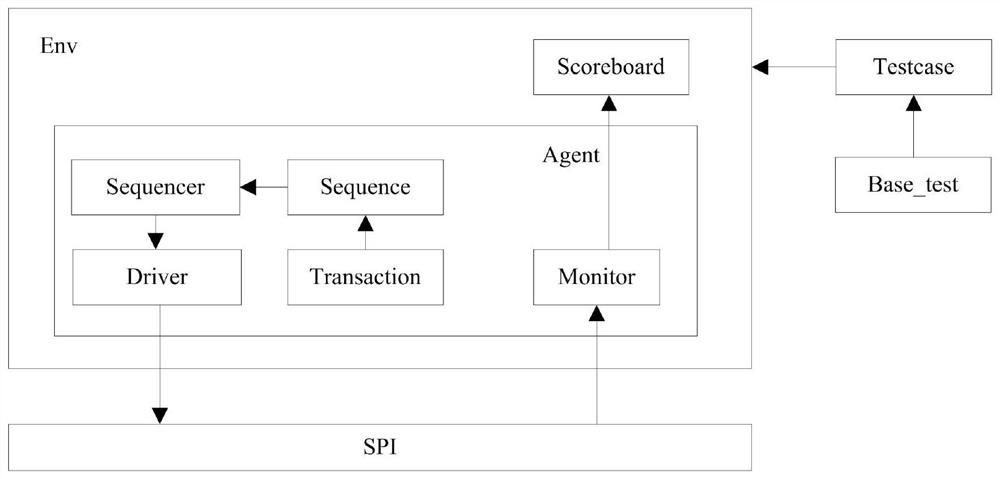

SPI verification platform based on UVM

InactiveCN112463497AFast convergenceConvenience in constructing test casesFaulty hardware testing methodsVerificationTest scene

The invention discloses an SPI verification platform based on a UVM, and belongs to the field of IP verification in integrated circuit design. According to the method for building the module-level reusable verification environment, the connection mode of all components in the verification environment is explained, the definition format of the transaction-level SPI data is given, test cases can beconveniently built in the built verification environment, and convergence of the coverage rate is accelerated. According to the method, the latest UVM verification methodology and the SystemVerilog language are adopted to build a verification environment; the proposed UVM verification environment is concise and expandable, high in portability and easy to reuse; various test scenes can be flexiblyconstructed, constrained random excitation is added, and coverage rate convergence is accelerated.

Owner:58TH RES INST OF CETC

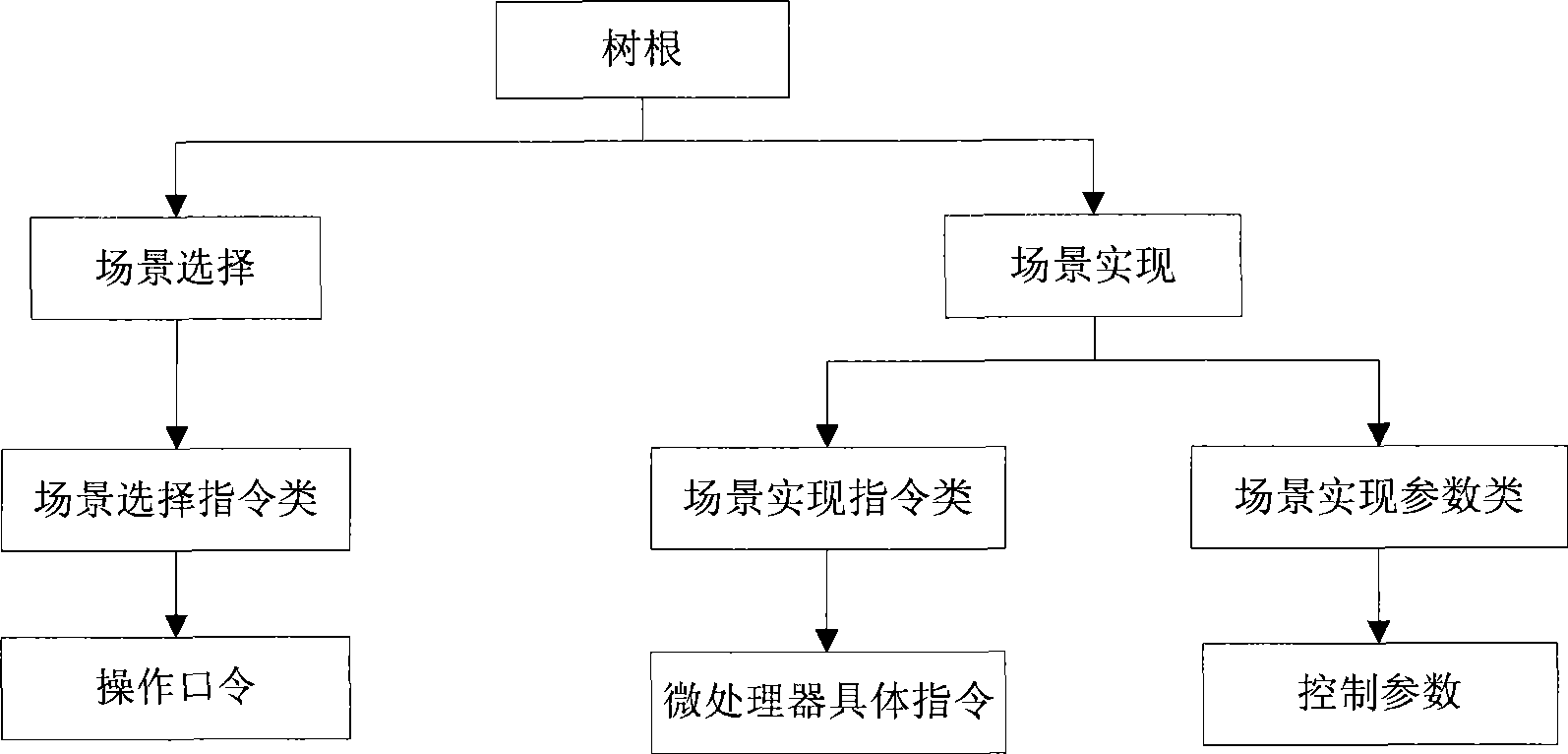

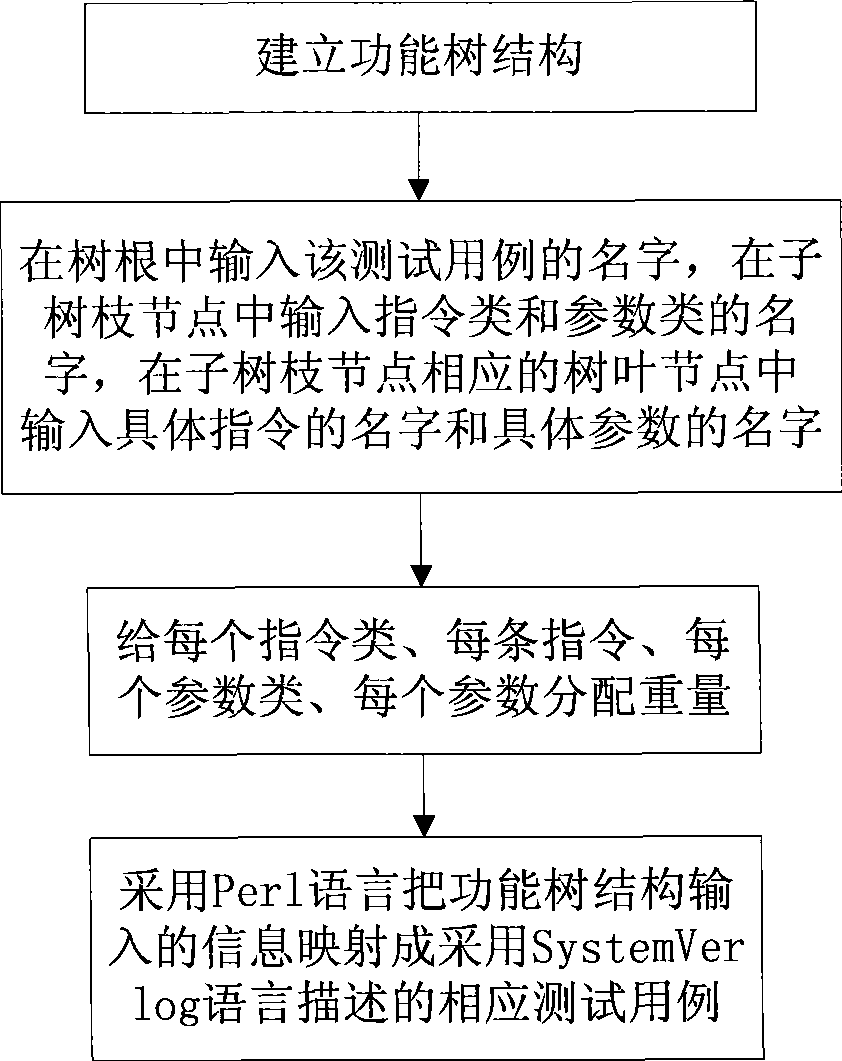

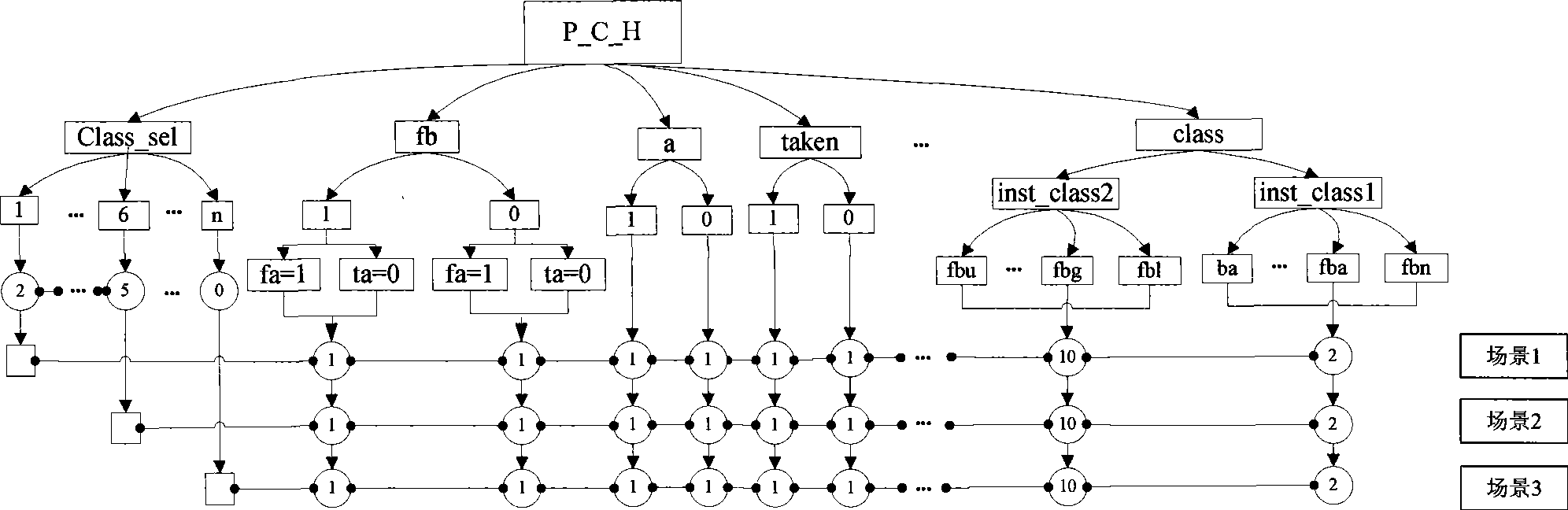

Function tree structure of micro-processor function validation test case and its automatic generation method

InactiveCN101499105AClear structureClear relationshipSpecial data processing applicationsTheoretical computer scienceReusability

The invention provides a function tree structure of a microprocessor function validate testing example and an automatic generating method. A method using the function tree structure describes a testing example, the function tree structure has clear structure layer, relationship between various indication and parameter is clear for processing description using programming language; the function tree structure is mapped to a testing example described by SystemVerilog language using Perl language automatically, only needing inputting corresponding indication according with the function tree structure can generate the testing example automatically, according, time for covering the function tree structure into the testing example is reduced and a validity efficiency is increased, and a product without defect come into a market can be realized in a short time; in addition, the method can increase or decrease indication or parameter according with various product based on existing function tree structure that can be suitable for generating the testing example of various product automatically, according, increase reusability of the testing example.

Owner:BEIJING MXTRONICS CORP +1

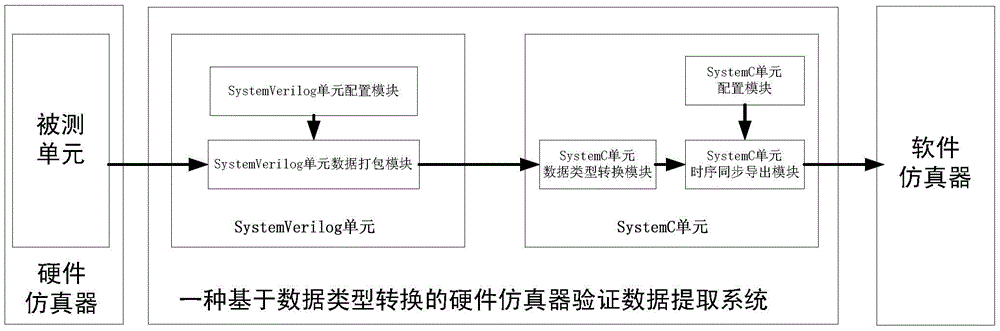

Data type conversion-based hardware simulator validation data extraction system

ActiveCN105653409ASimple structureEasy to implementFaulty hardware testing methodsSystemCData ingestion

The invention provides a data type conversion-based hardware simulator validation data extraction system. The system comprises a SystemVerilog unit and a SystemC unit, wherein the SystemVerilog is used for receiving input data sent from an external hardware simulator, checking the input data, packing the data into a data package and then sending the data package to the SystemC unit; and the SystemC unit is used for 6 data types defined in SystemVerilog into 6 data types defined in SystemVerilog according to a one-to-one corresponding manner, sending the data package to a software simulator according to the simulation precision of the software simulator, extracting the running result of a tested unit running on the hardware simulator with relatively high efficiency, and comparing the running result with a structure preset in the software simulator on a workstation so as to realize the determination of the running result of the tested unit. The method has the advantages of being flexible in data package, high in simulation speed and flexible in software simulator interface.

Owner:BEIJING MXTRONICS CORP +1

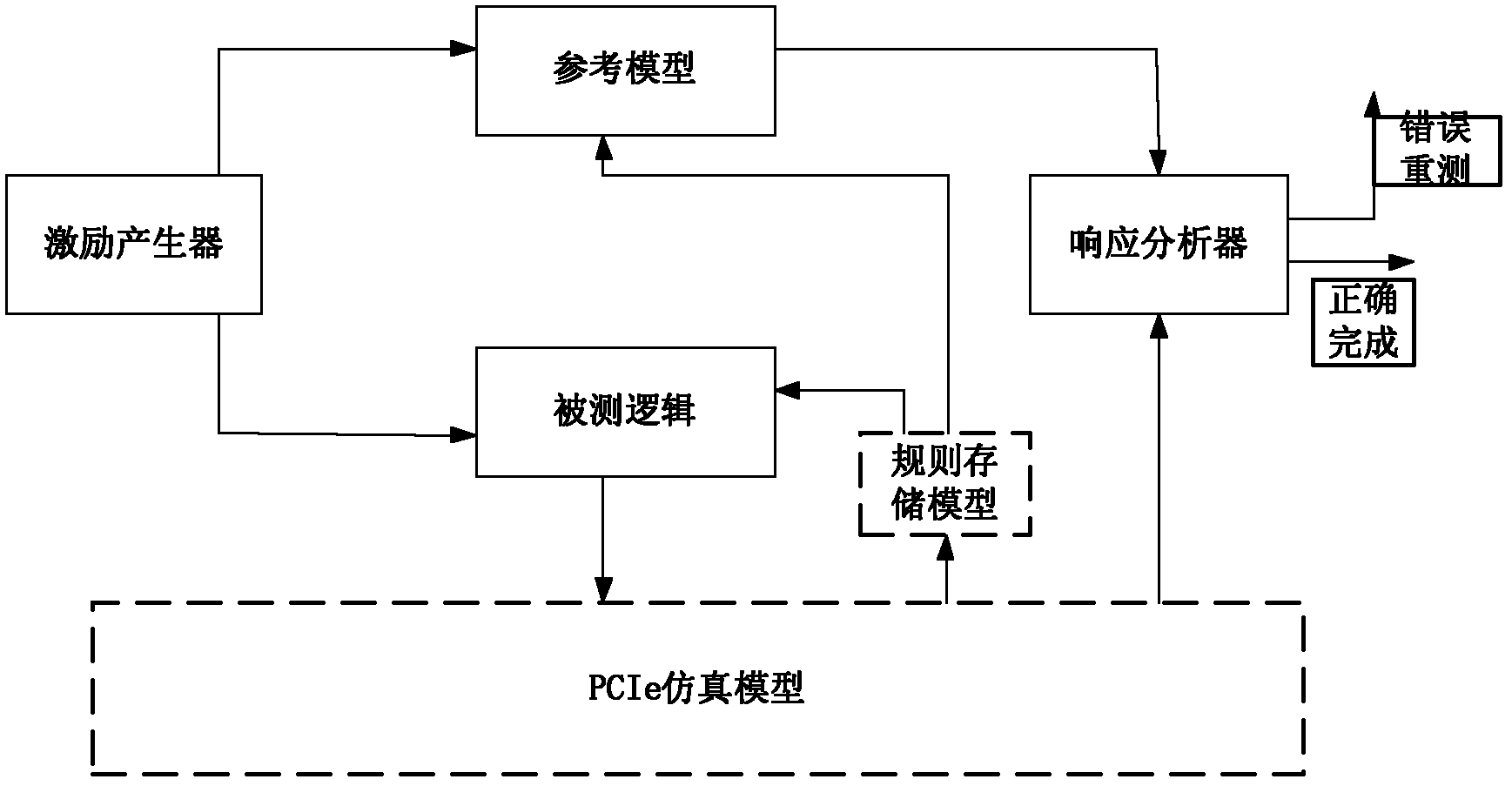

System and method for testing single-packet regular matching logic

ActiveCN102495778AImprove programming efficiencyImprove verification efficiencyLogical operation testingProgramming languageProgram Efficiency

The invention provides a method for testing single-packet regular matching logic. A peripheral component interface express (PCIe) simulation model simulates the characteristic of a PCIe bus and receives a host command which comprises a write command and a read command. Compared with the prior art, the method has the advantages that: 1) the efficiency of a program which is compiled by using a SystemVerilog language is quite high, a complicated function can be realized by using smaller code line number, and validation efficiency is improved; and 2) a constraint-based random simulation validation method using the SystemVerilog language is a high-efficiency function validation method, the validation efficiency of the function can be greatly improved, and the functional defect of a product which is sold in the market is avoided.

Owner:DAWNING INFORMATION IND BEIJING +1

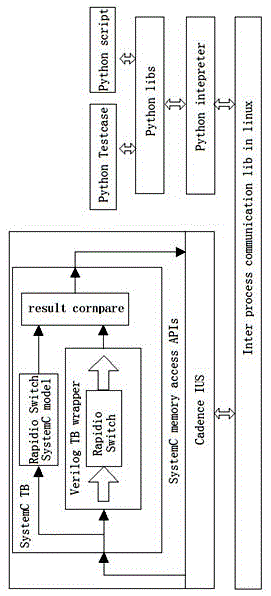

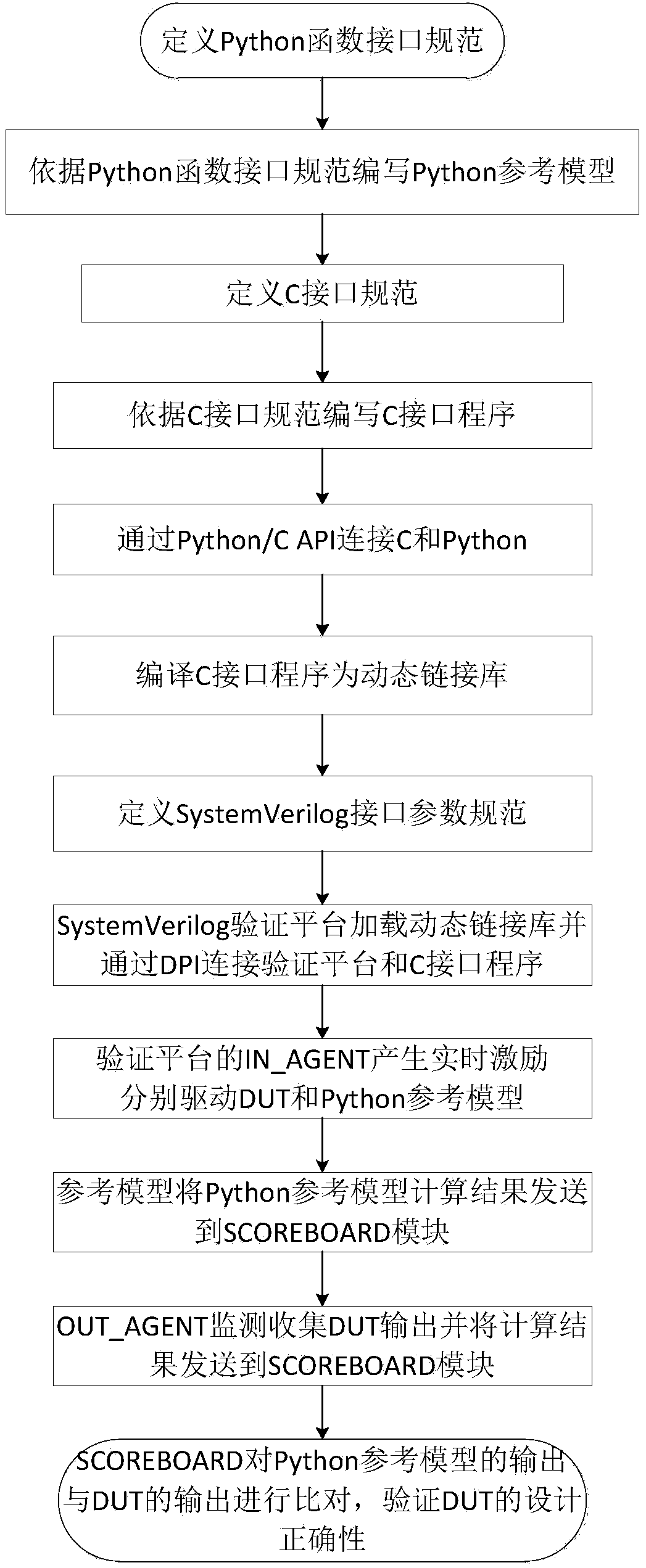

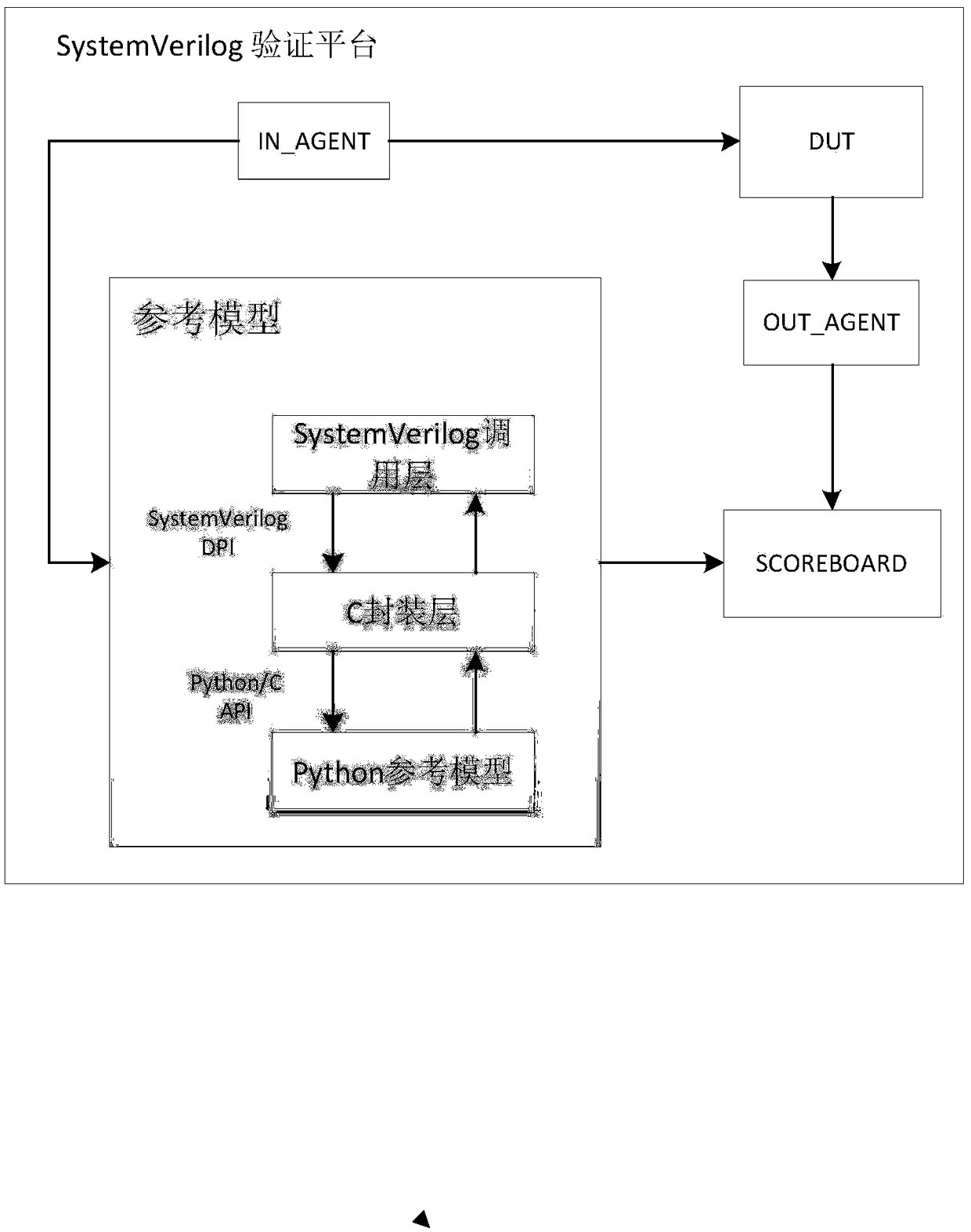

Method for improving automatic verification platform efficiency through building reference model by using Python

ActiveCN108829382AExcellent development efficiencyImprove verification efficiencySoftware designModel driven codePython languageReference model

The invention discloses a method for improving automatic verification platform efficiency through building a reference model by using Python. A C program is used as a middle layer, so that the C program can call a Python reference model via a C / Python API, and can call a C interface program of the middle layer via a SystemVerilog DPI, and thus the purpose that the SystemVerilog verification platform calls the Python is achieved. According to the method provided by the invention, the reference model can be compiled by using the Python language, and the Python reference model can be dynamicallycalled in real time in the verification platform. The method of developing the program by using the Python language has many advantages, particularly has extremely high efficiency during complex algorithms such as long integer operation; according to the method, the problem of interaction between the SystemVerilog language and the Python language is solved, so that the Python program can server asthe reference model in the verification platform, the verification efficiency and quality are greatly enhanced, and the verification cost is reduced.

Owner:BEIJING CEC HUADA ELECTRONIC DESIGN CO LTD

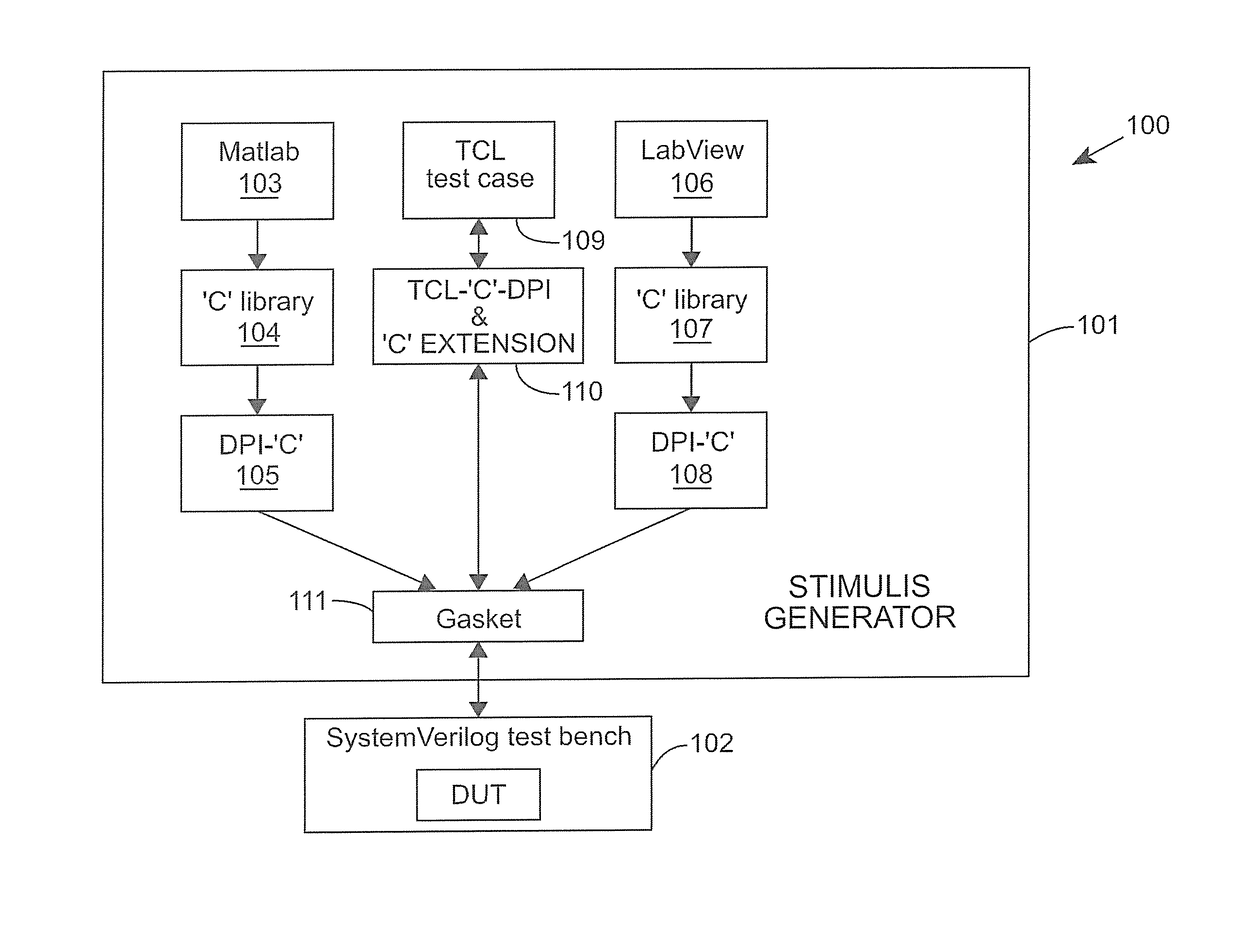

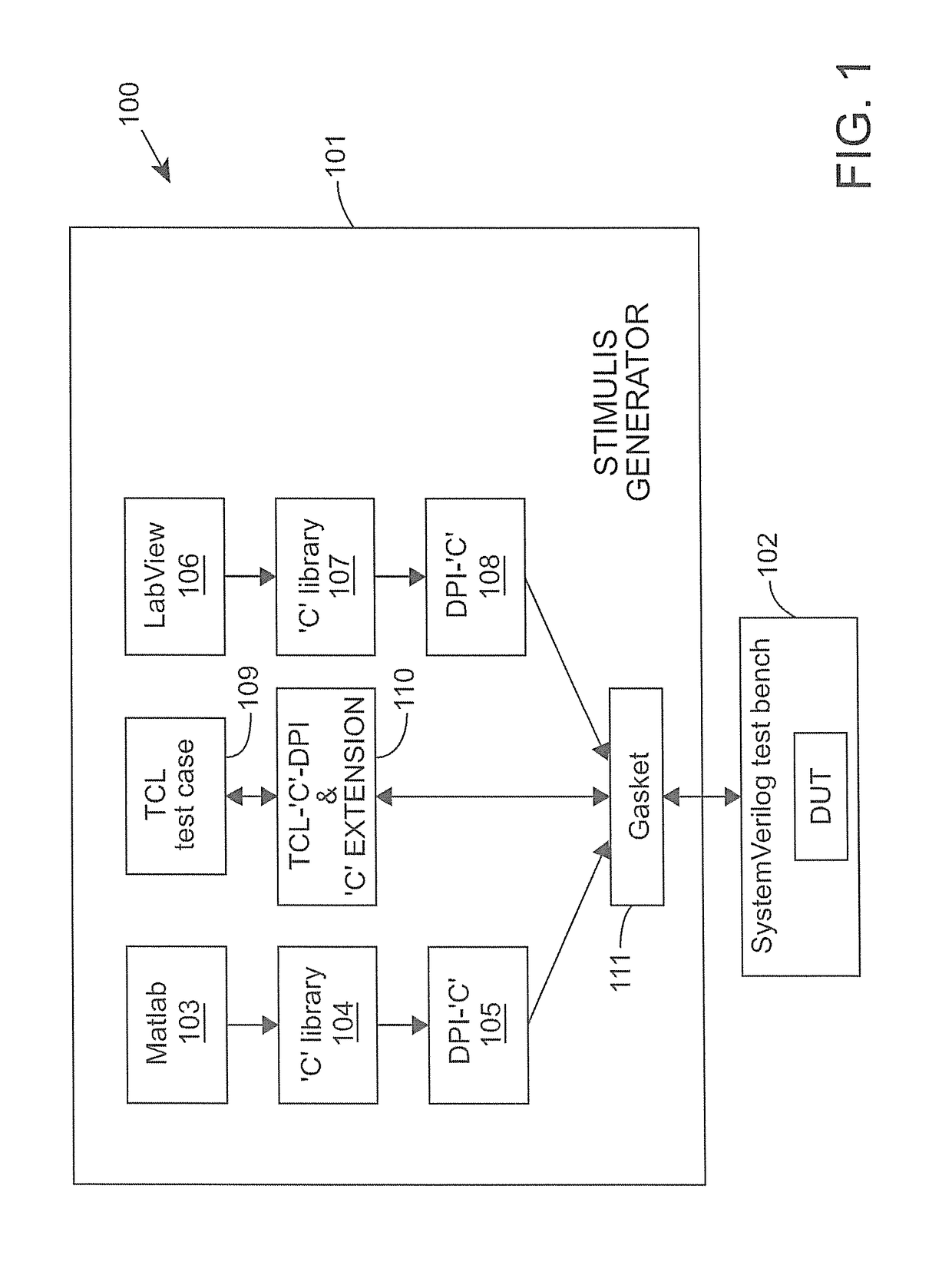

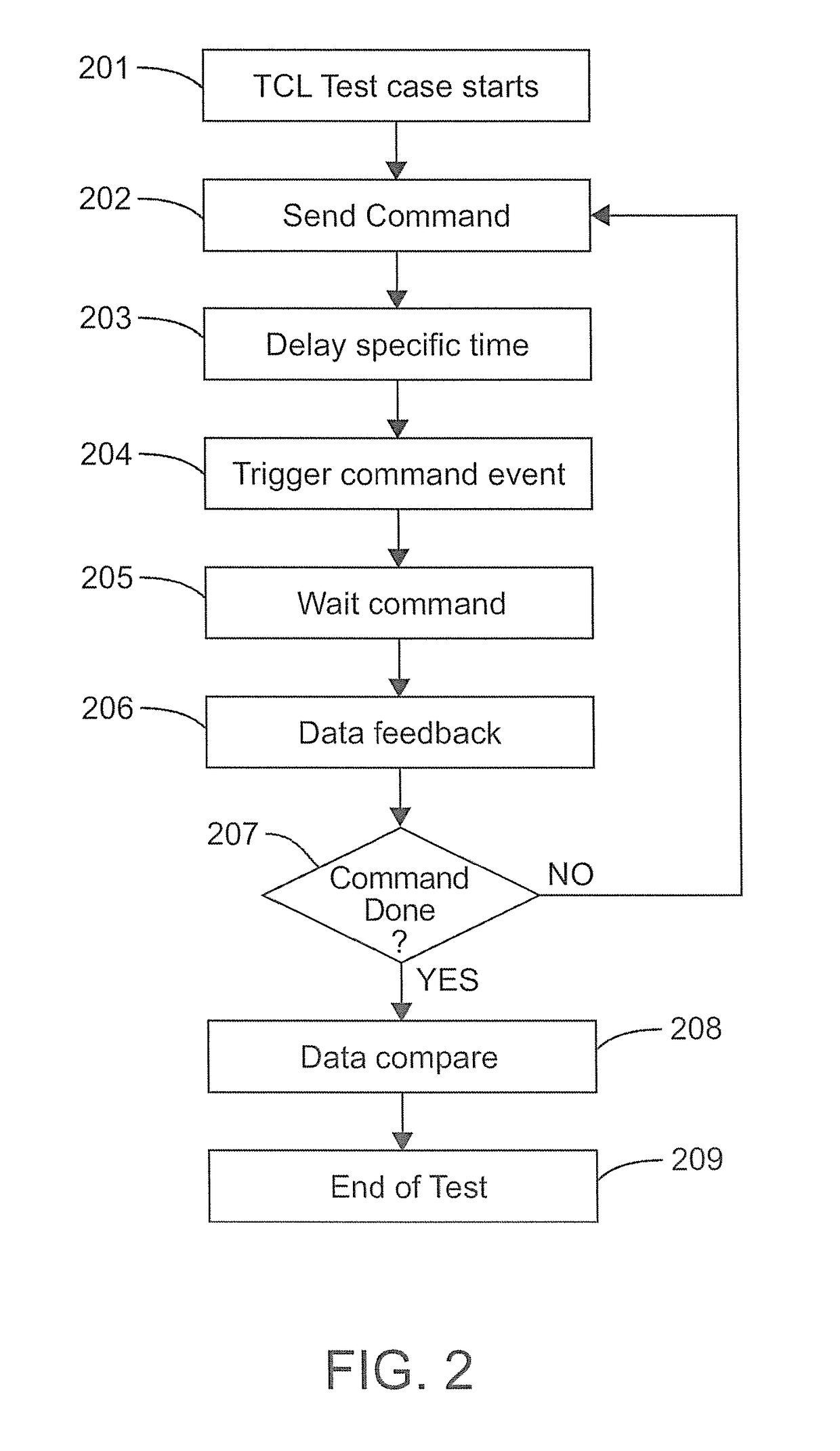

Method and apparatus for system design verification

ActiveUS9690888B2CAD circuit designSpecial data processing applicationsScripting languageSystems design

Owner:NXP USA INC

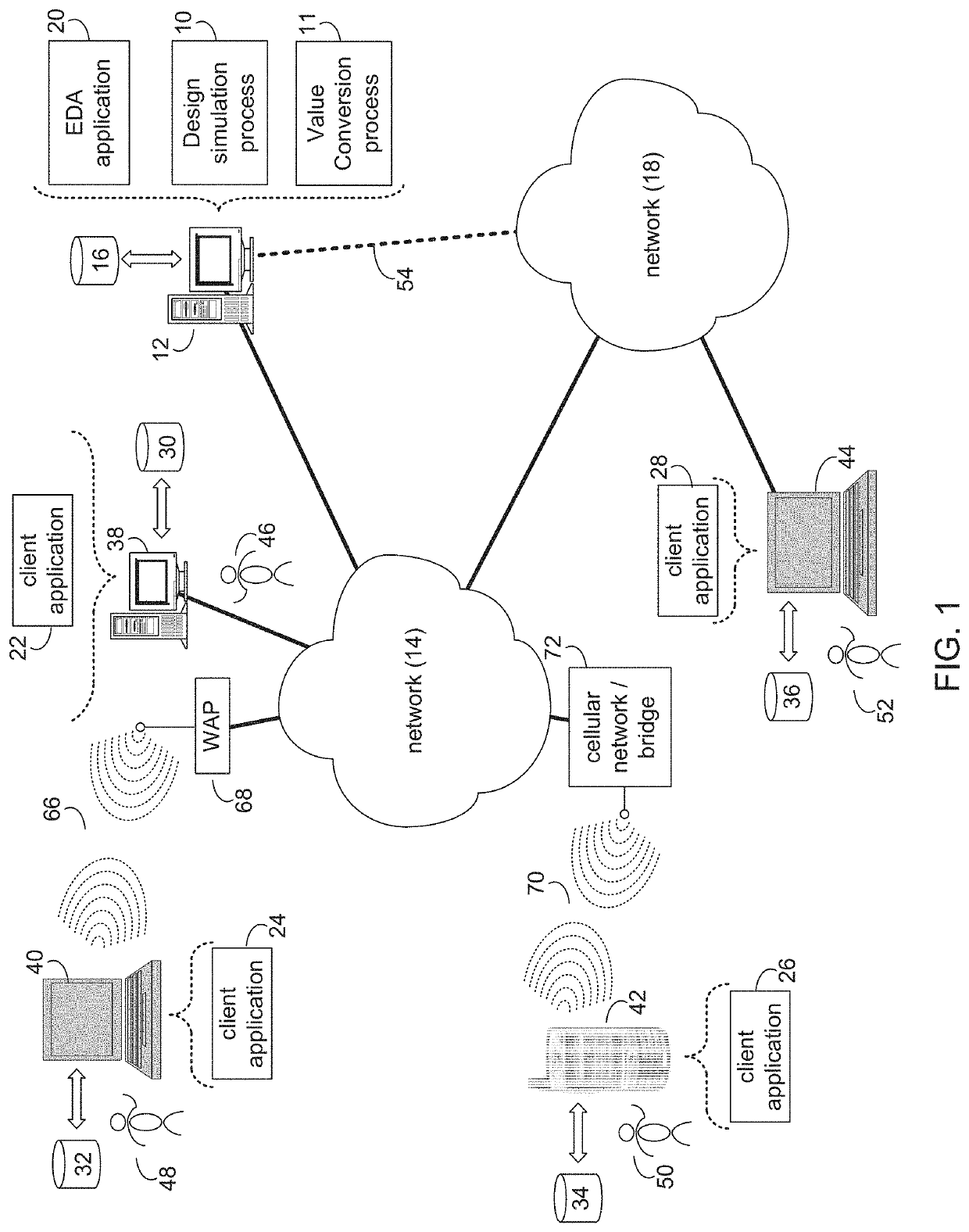

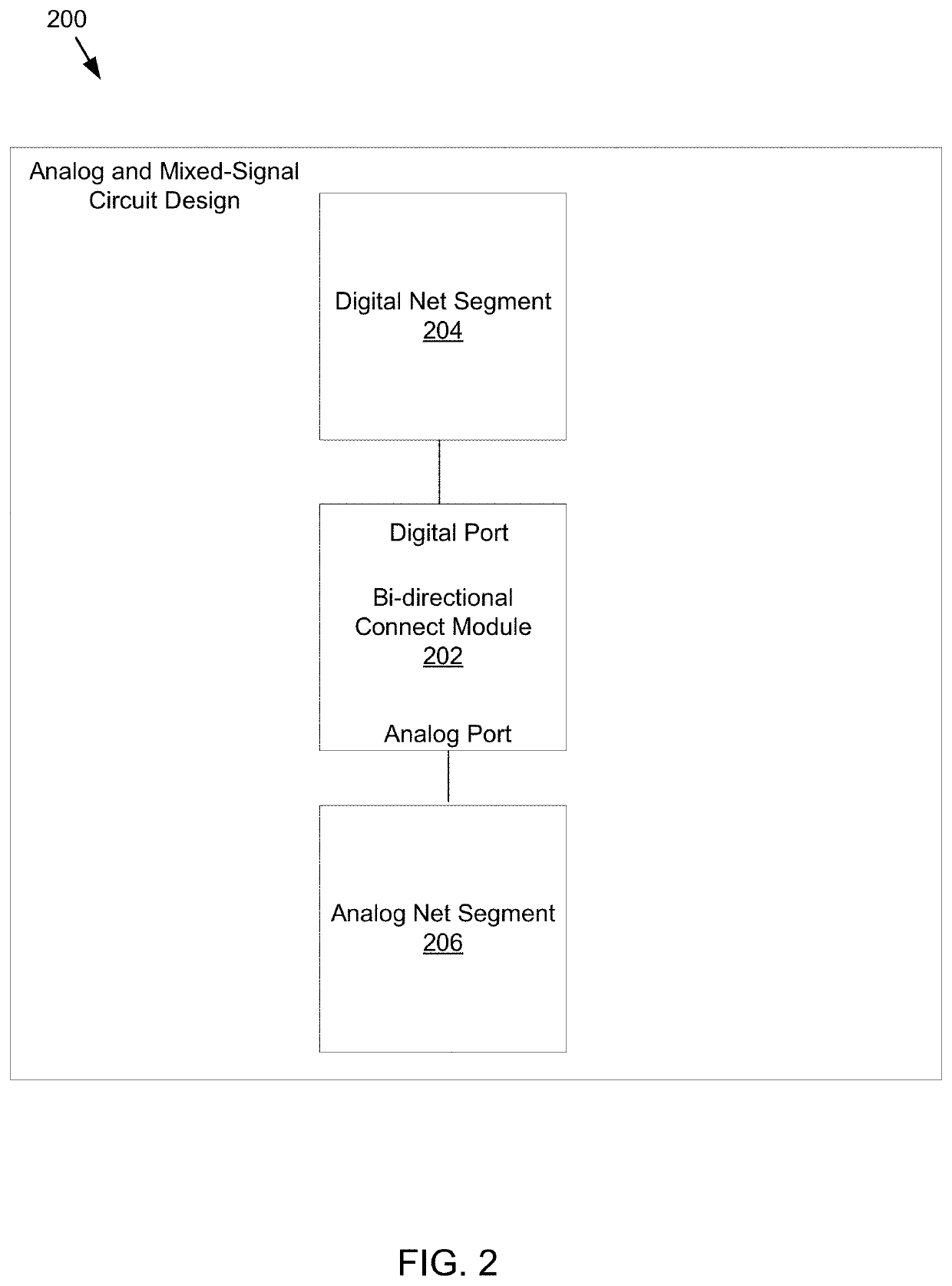

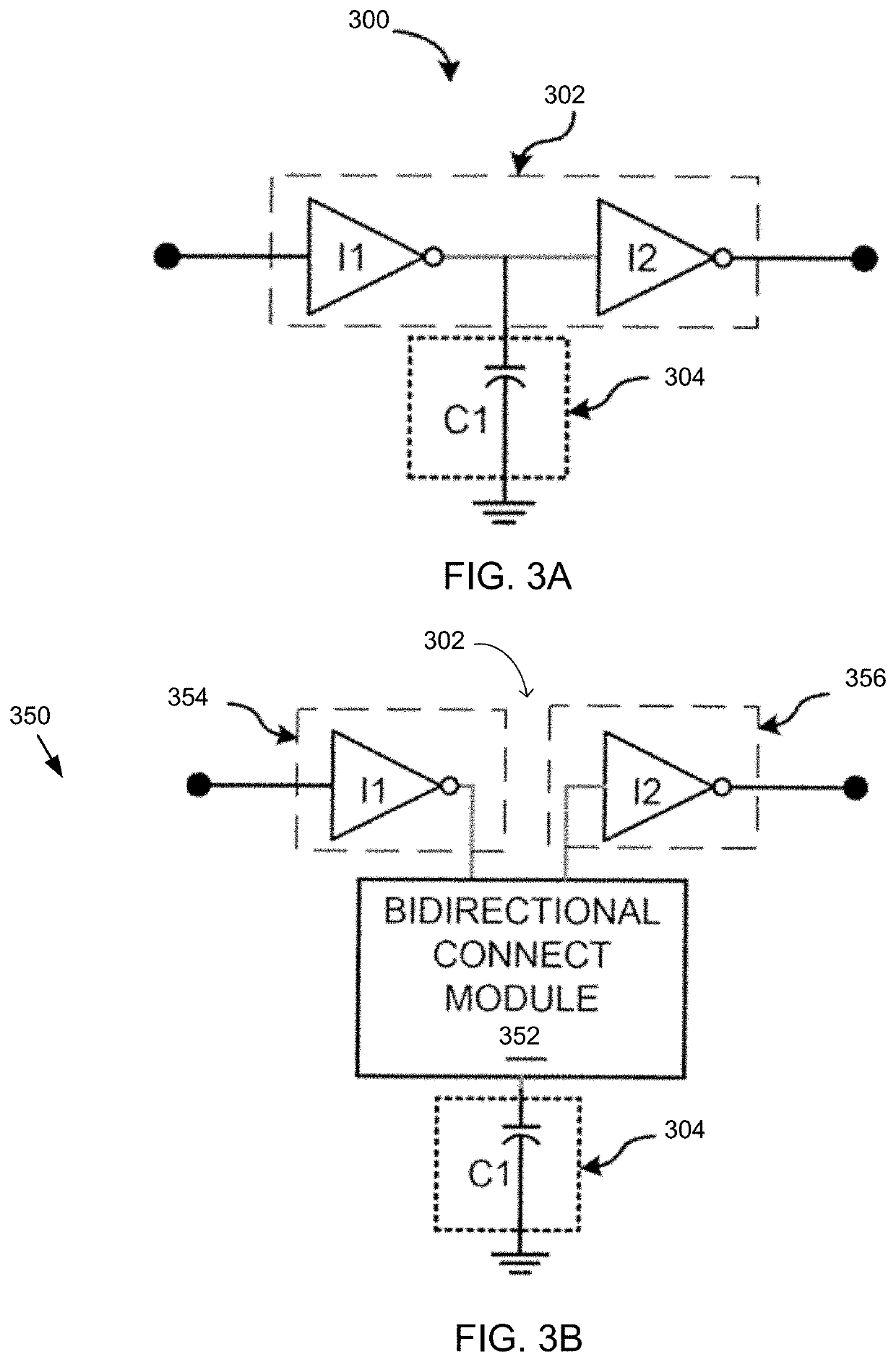

System, method, and computer program product for connecting power supplies in a mixed signal design

The present disclosure relates to a computer-implemented method for converting between a SystemVerilog user-defined net (“UDN”) and an IEEE supply net is provided. The method may include providing a value conversion table (“VCT”) definition associated with an electronic circuit design. The method may also include mapping, using at least one processor during a simulation, between a SystemVerilog UDN field and a IEEE supply net field. The method may further include converting at least one value between the SystemVerilog UDN field and the IEEE supply net field based upon, at least in part, the VCT definition.

Owner:CADENCE DESIGN SYST INC

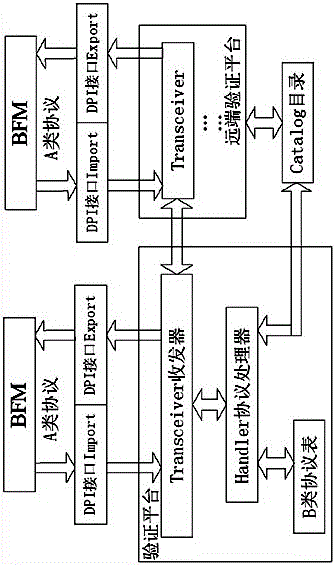

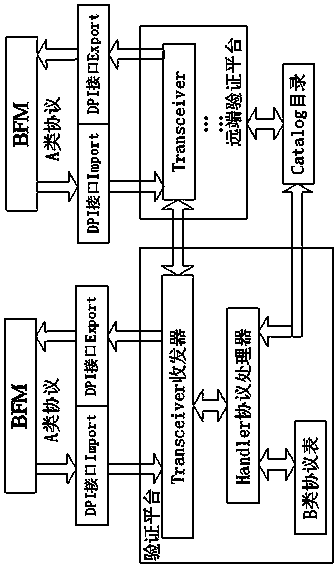

BFM (Bus Function Model)-based method for SystemVerilog to build protocol verification platform

ActiveCN105930299AEasy to handleImprove throughputDigital computer detailsElectric digital data processingArray data structureTransceiver

The invention discloses a BFM (Bus Function Model)-based method for SystemVerilog to build a protocol verification platform. The method comprises the following implementation process: building a Transceiver which is in charge of transceiving and disassembling / assembling an A-class protocol message; building a Catalog structure which is in charge of recording consistency information; realizing a protocol table model which is in charge of realizing protocol conversion; and building a Handler which is in charge of processing the protocol. The method simplifies a protocol processing process, adopts a one-by-one way, does not relate to a resource dispatching problem, improves protocol conversion communication among multiple clumps, and fully utilizes the verification characteristics of sv, the handling capacity of the protocol message is enlarged by a queue and a dynamic associative array, the Catalog structure is visible on the whole platform, and communication between the Transceiver and the BFM adopts a simple DPI interface.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

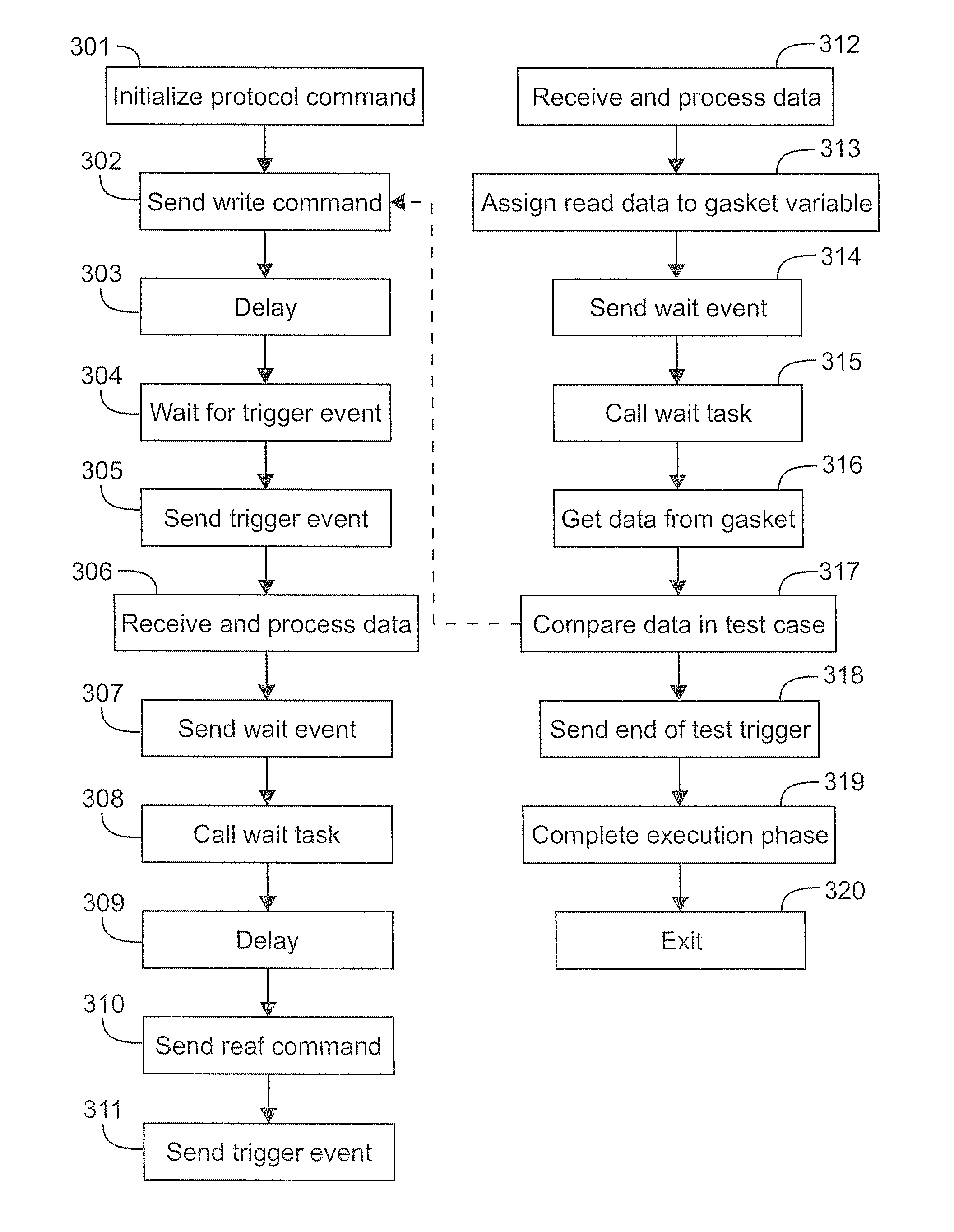

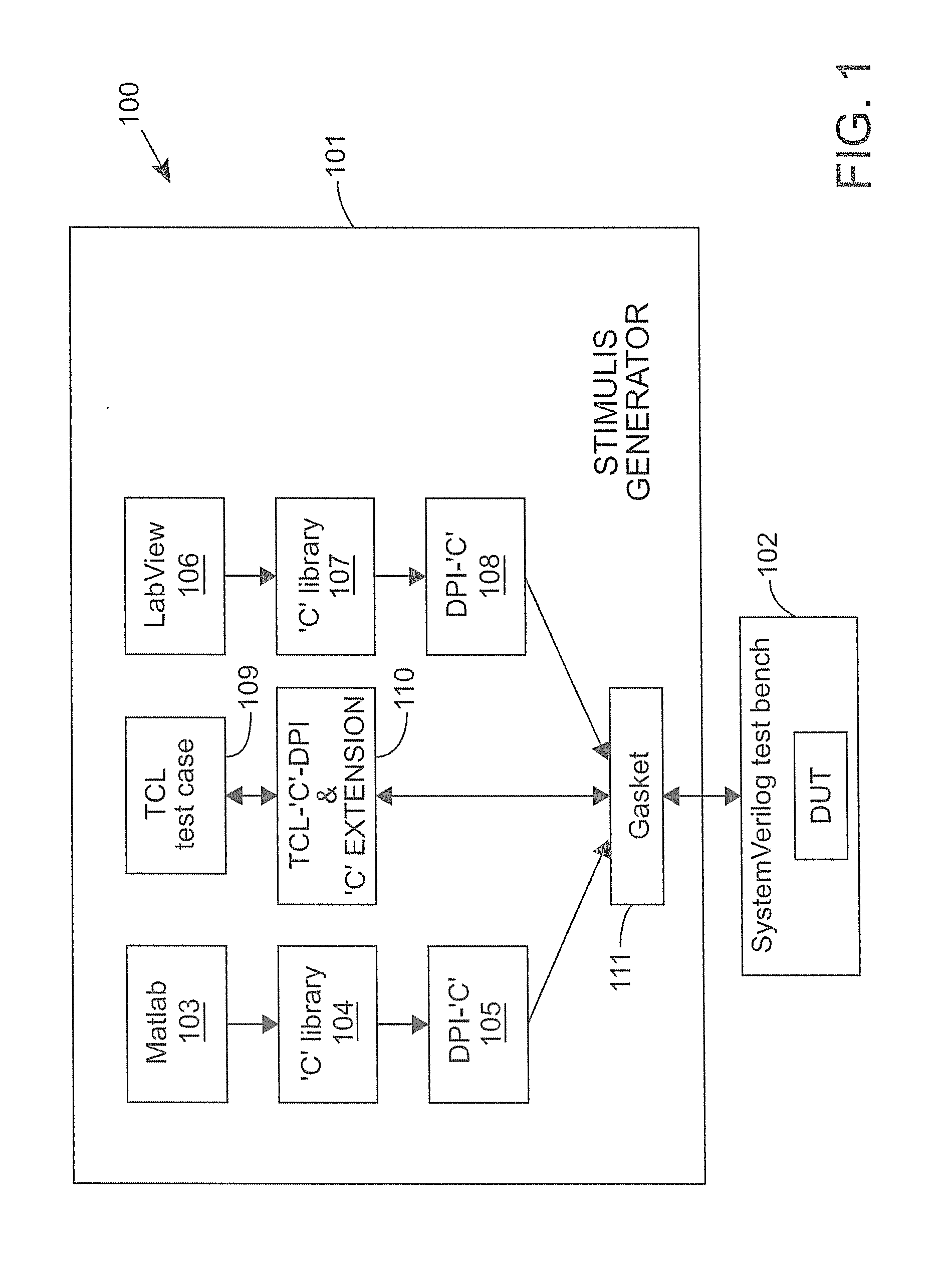

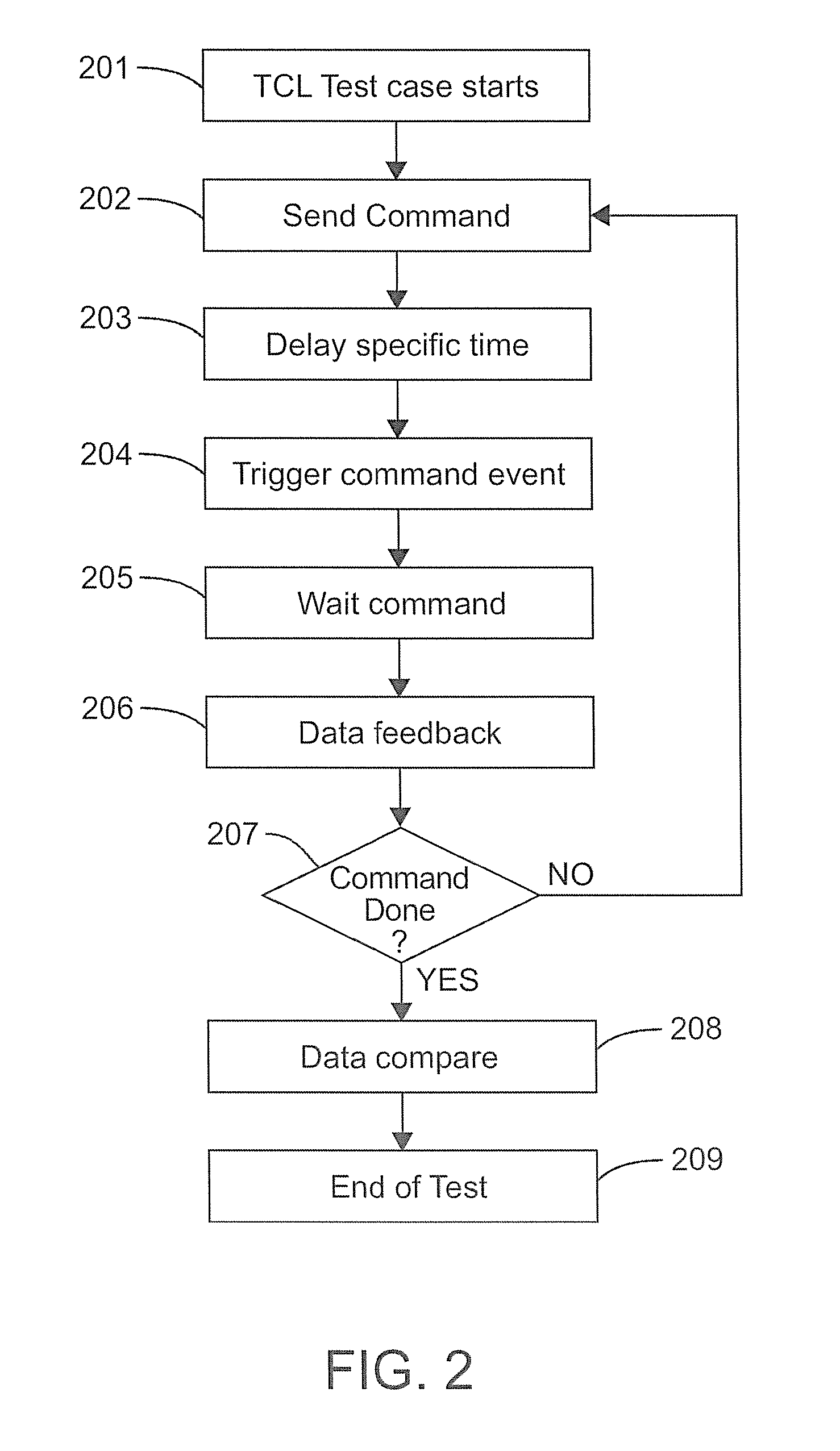

Method and apparatus for system design verification

ActiveUS20160306913A1CAD circuit designSpecial data processing applicationsScripting languageSystems design

An apparatus for system design verification has a test case module for compiling a test case in a scripting language (such as TCL) and a testbench including the design under test and operating with a Hardware Descriptor Language (such as SystemVerilog). A stimulus generated by the test case module is applied to the testbench through an interface gasket based on ‘C’.

Owner:NXP USA INC

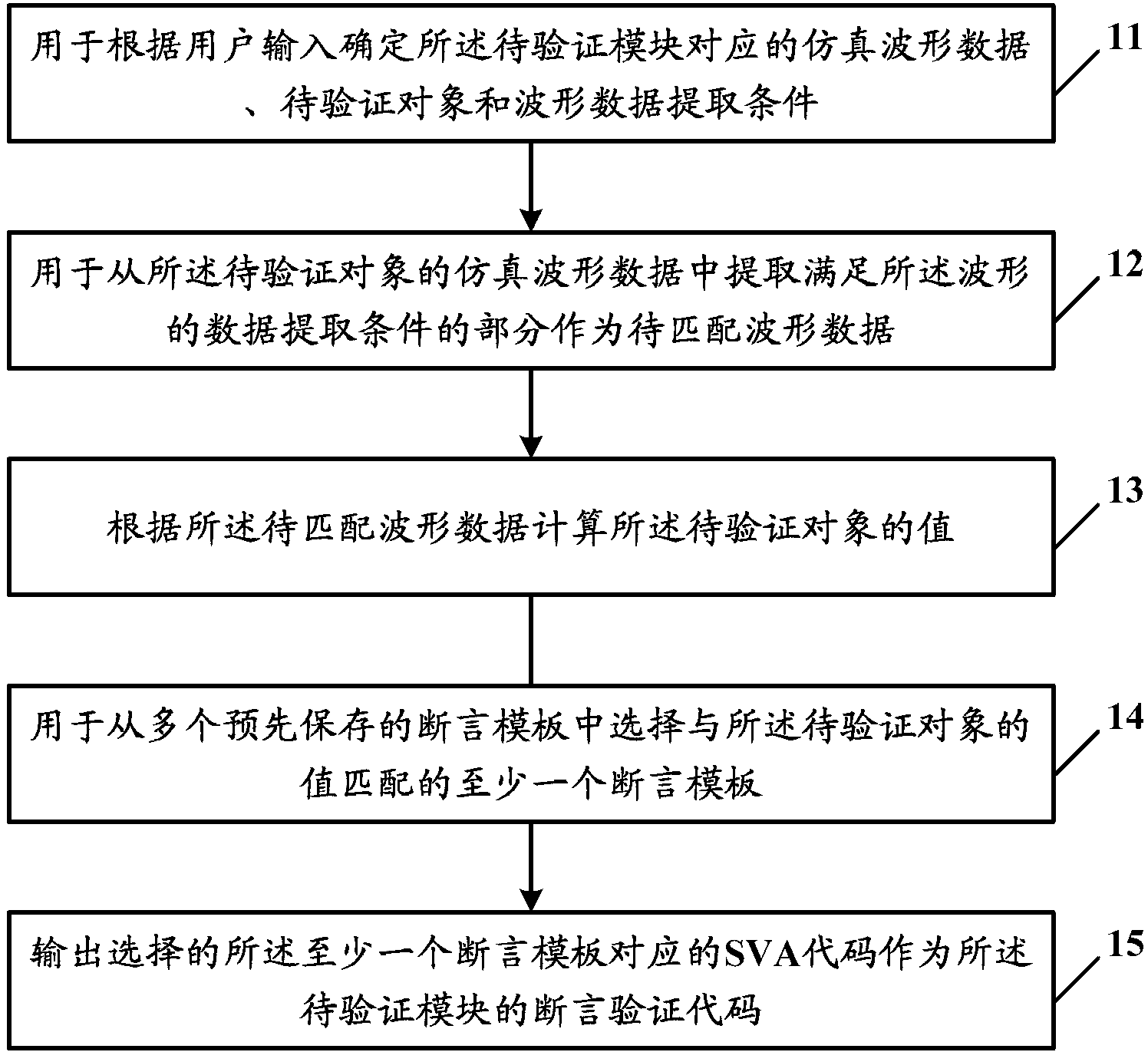

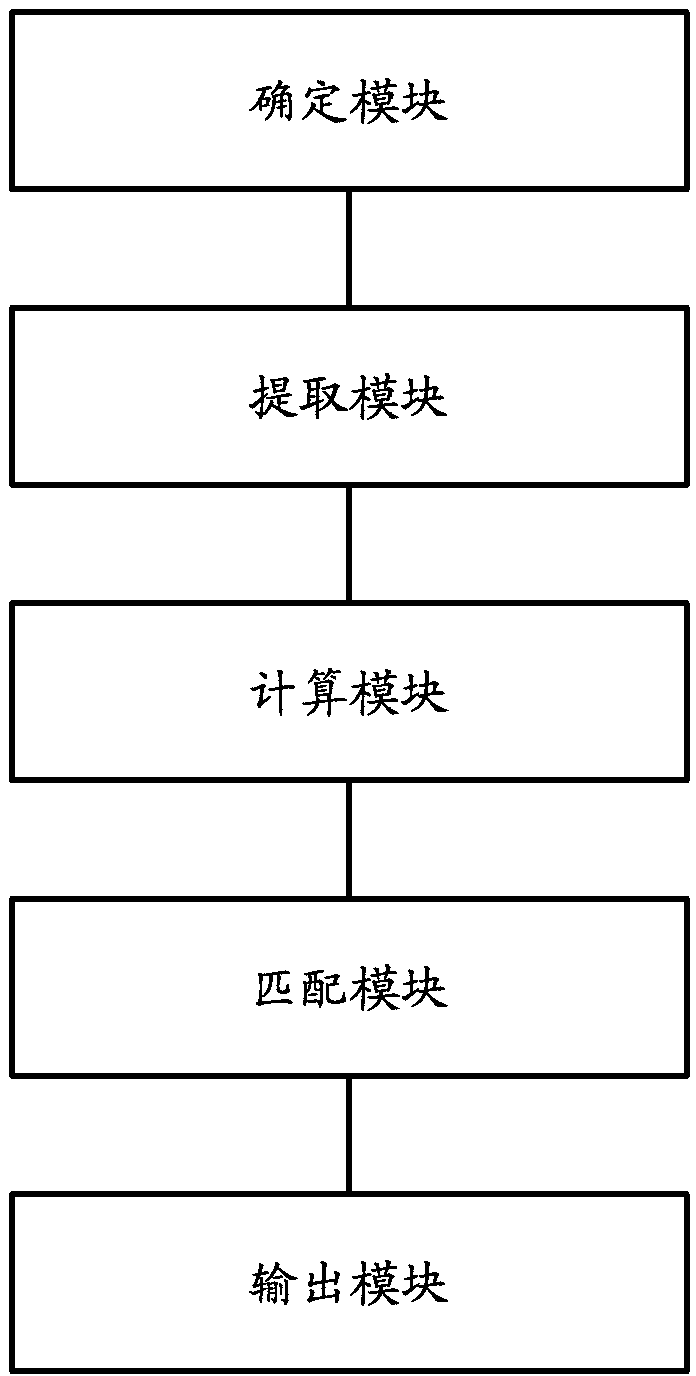

Method and device for automatically generating assertion

ActiveCN103019745AReduce difficulty of useGuarantee the progress of the projectSpecific program execution arrangementsProgramming languageUser input

The invention discloses a method and device for automatically generating an assertion. The method is used for generating an assertion verification code for a to-be-verified module, and comprises the steps as follows: determining simulation waveform data, a to-be-verified object and a waveform data extraction condition corresponding to the to-be-verified module according to user input; extracting a part of the simulation waveform data meeting the waveform extraction condition from the simulation waveform data of the to-be-verified object as to-be-matched waveform data; calculating the value of the to-be-verified object according to the to-be-matched waveform data; selecting at least one assertion template matched with the value of the to-be-verified object from a plurality of pre-stored assertion modules; and outputting an SVA (SystemVerilog Assertion) code corresponding to the selected assertion module as the assertion verification code of the to-be-verified module. According to the method, the using difficulty of the assertion code in the project development process is lowered and the project progress is guaranteed.

Owner:青岛中星微电子有限公司

Rapidio switcher logic simulation verification platform and method based on python language

ActiveCN104965750BImprove writing efficiencyImprove reusabilitySoftware simulation/interpretation/emulationPython languageSystemC

The present invention discloses a Python language based Rapidio switcher logic simulation verification platform and method. The verification platform comprises: a SystemC interface function for interpreting Python semantics, a DPI interface function used by SystemC to call SystemVerilog, and a test case and a running script realized by Python. According to the present invention, an interpreter between the Python language and the SystemC language is added, so that the Python language can directly control stimulus input of a logic simulator and compare responsive output and the test case programmed by using Python can be used directly in logic simulation and applied on a Rapidio switcher. By using the above environment, the programming efficiency and reusability of the test case can be greatly improved.

Owner:SHANDONG LANGCHAO YUNTOU INFORMATION TECH CO LTD

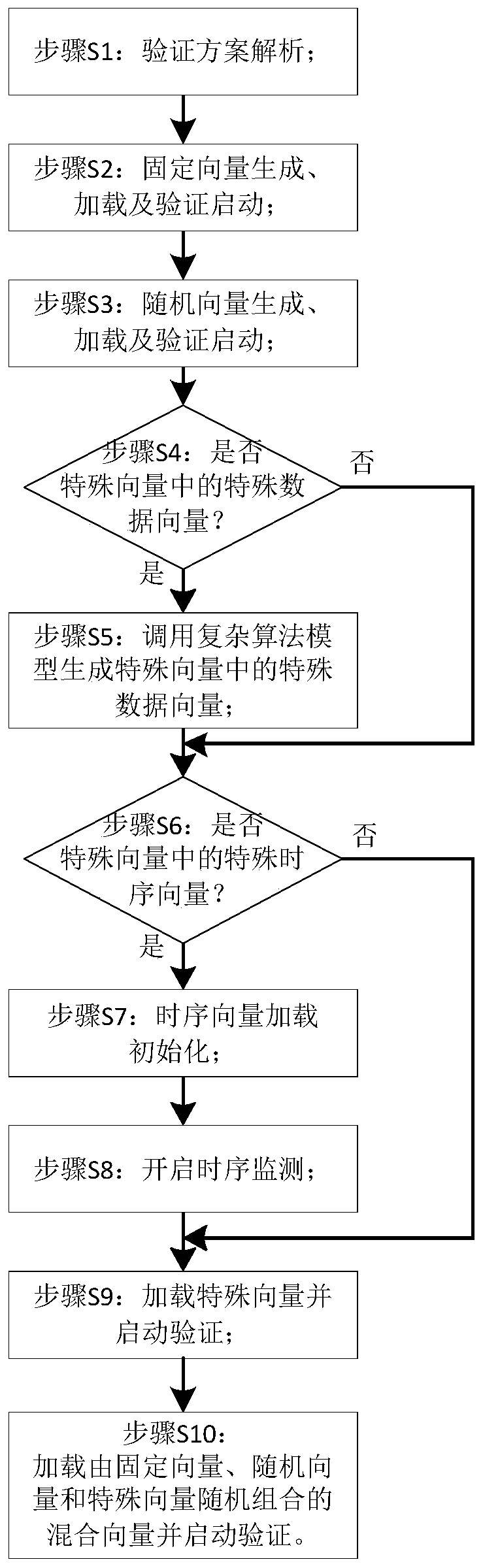

Test excitation generator of complex algorithm and control method thereof

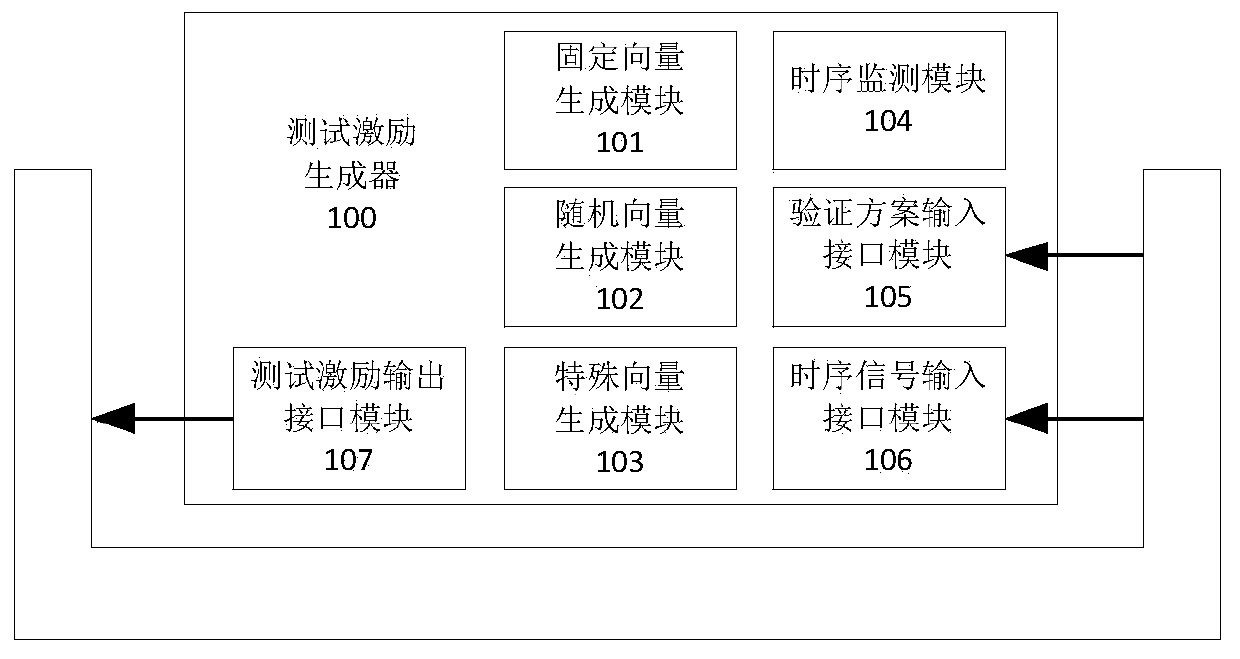

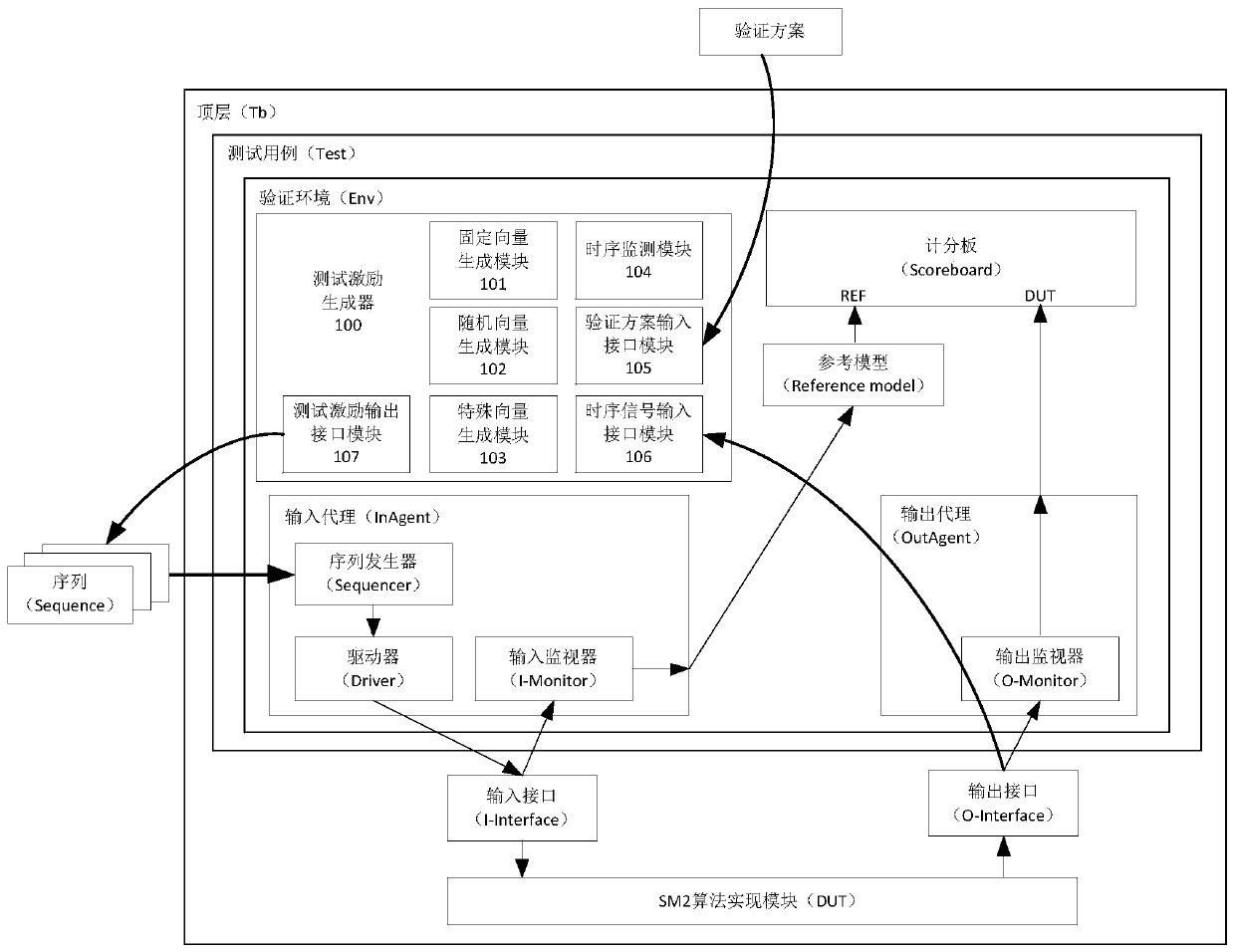

PendingCN110688821ADesign optimisation/simulationSpecial data processing applicationsAlgorithmControl signal

The invention relates to a test excitation generator of a complex algorithm and a control method of the test excitation generator. The test excitation generator comprises a fixed vector generation module, a random vector generation module, a special vector generation module, a time sequence monitoring module, a verification scheme input interface module, a time sequence signal input interface module and a test excitation output interface module. The fixed vector generation module generates excitation such as register reset read-write attributes, and the random vector generation module generates constrained randomized excitation; the special vector generation module generates special excitation which cannot be generated by adopting a SystemVerilog randomization command; the test excitationgenerator obtains a control signal through the verification scheme input interface module, controls different vector generation modules to generate corresponding test excitation, and outputs the testexcitation through the test excitation output interface module; the test excitation generator acquires a control signal through the time sequence signal input interface module, and controls the loading and verification starting of the output test excitation; the time sequence monitoring module monitors state information of the complex algorithm verification system through the time sequence signalinput interface module. The method is suitable for test excitation generation of a complex algorithm realized by pure hardware or software and hardware collaboration, and the quality and efficiency ofcomplex algorithm verification can be effectively improved.

Owner:BEIJING CEC HUADA ELECTRONIC DESIGN CO LTD

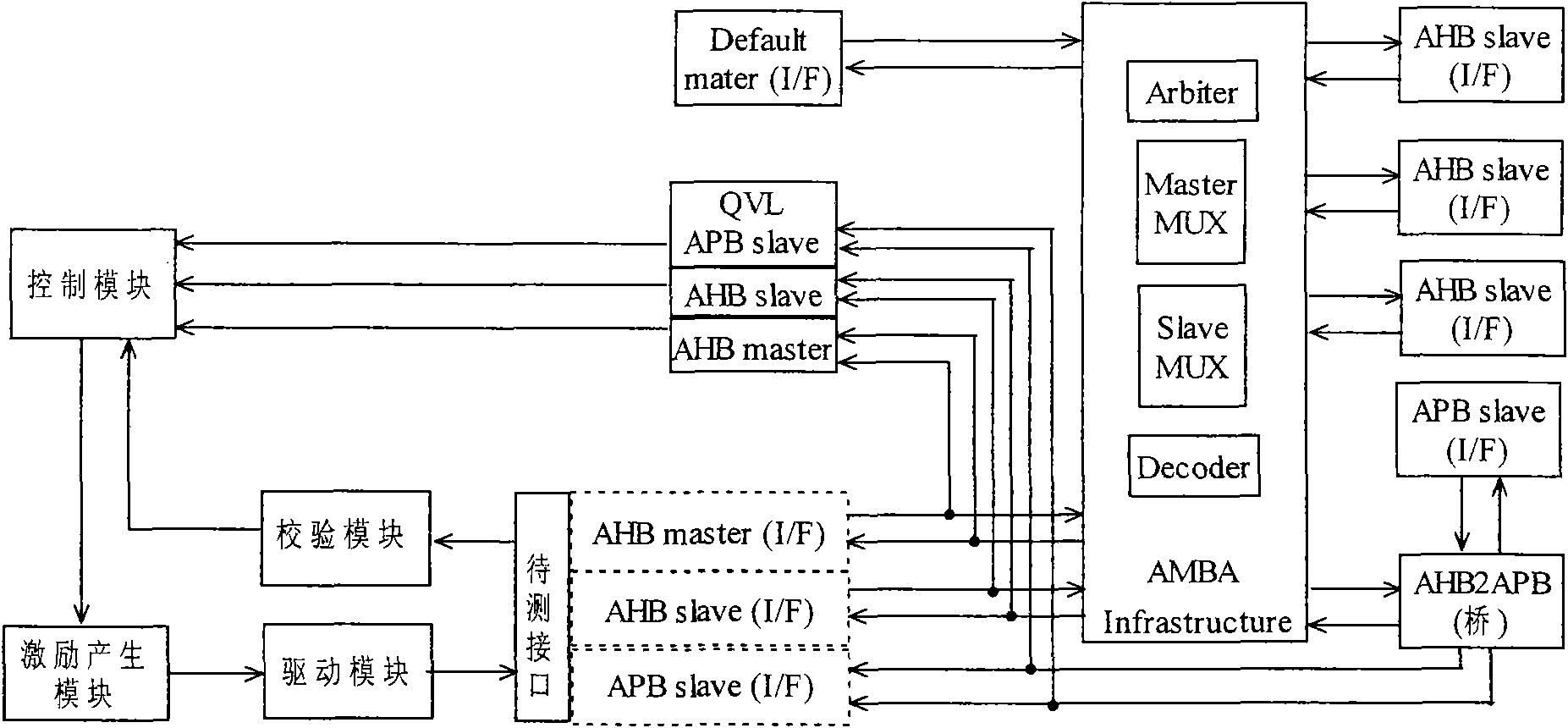

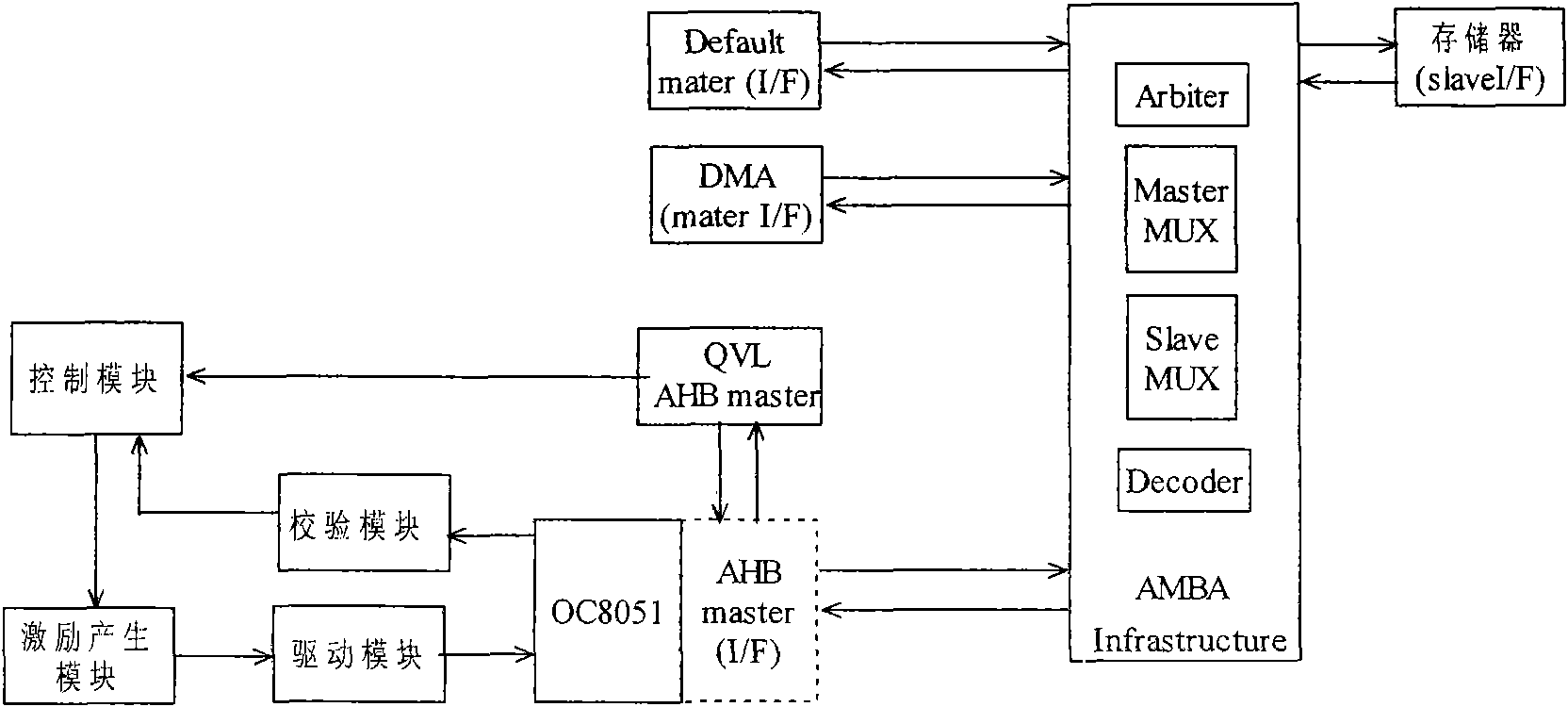

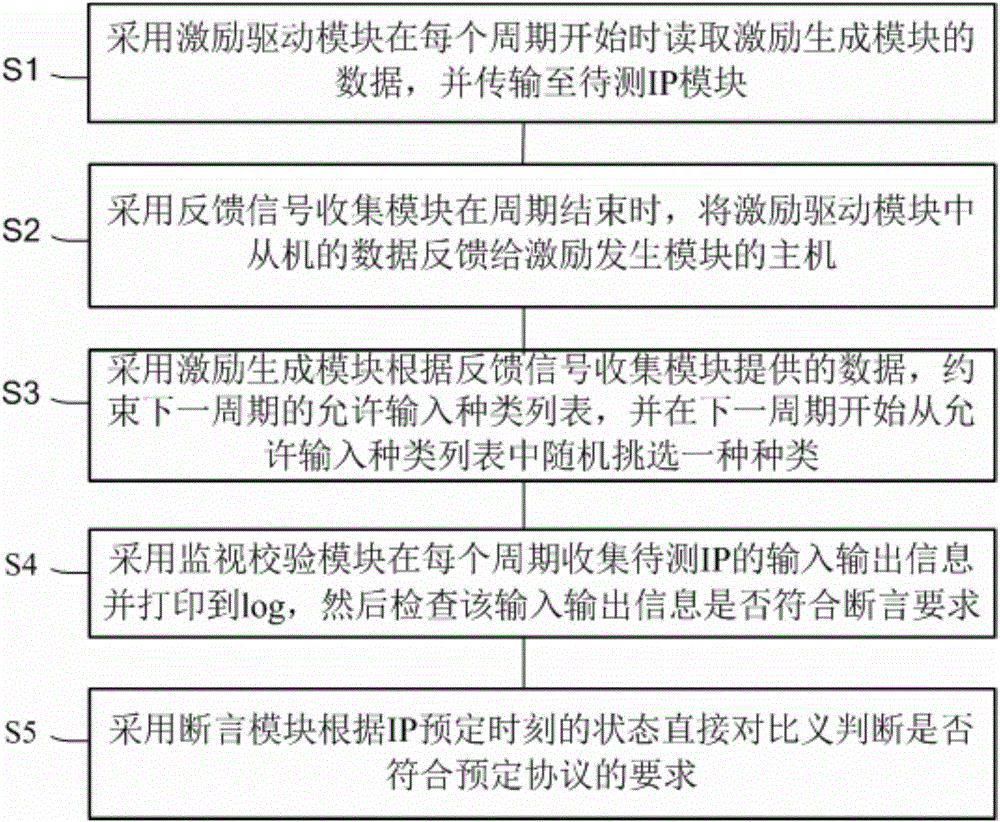

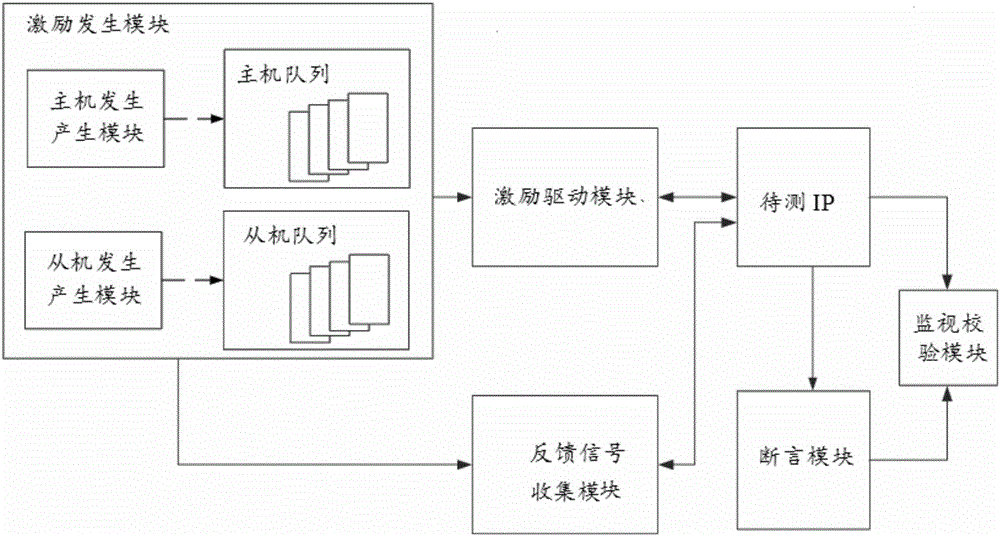

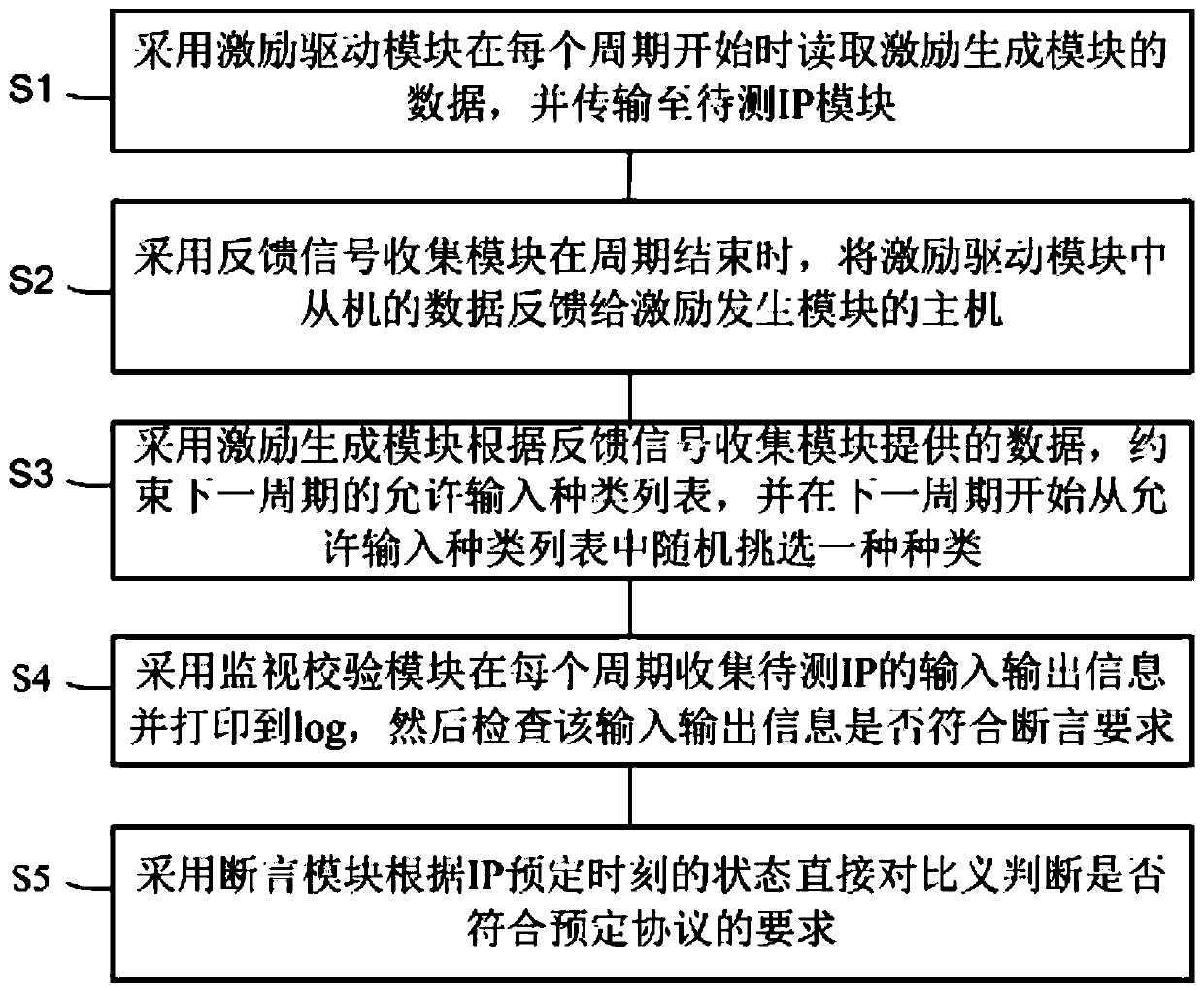

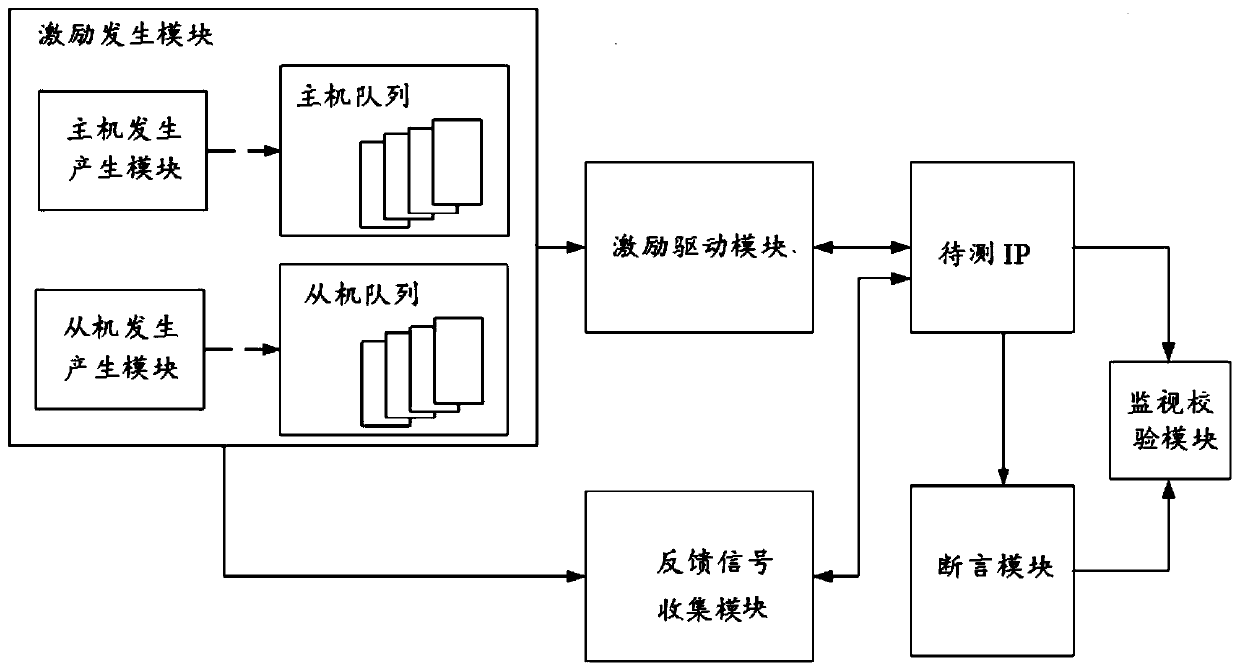

AHB core random verification method based on systemverilog

ActiveCN106502900AConvenient for subsequent debuggingHigh speedSoftware testing/debuggingComputer moduleReal-time computing

The invention provides an AHB core random verification method based on systemverilog. The method comprises the following steps: reading data of an excitation generating module at the beginning of each period by use of an excitation driving module, and transmitting the data to a to-be-tested IP module; feeding back the data of a slave in the excitation driving module to a host of the excitation generating module at the end of the period by use of a feedback signal collecting module; restraining an allowable input kind list of a next period according to the data provided by the feedback signal collecting module by use of the excitation generating module, and randomly selecting one kind from the allowable input kind list at the beginning of the next period; collecting input-output information of the to-be-tested IP at each period by use of a monitoring check module, printing the input-output information to log, and then checking whether the input-output information meets an assertion requirement; directly comparing whether the judgment meets the requirement of a predetermined protocol according to the state of the IP at a predetermined moment by use of an assertion module.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

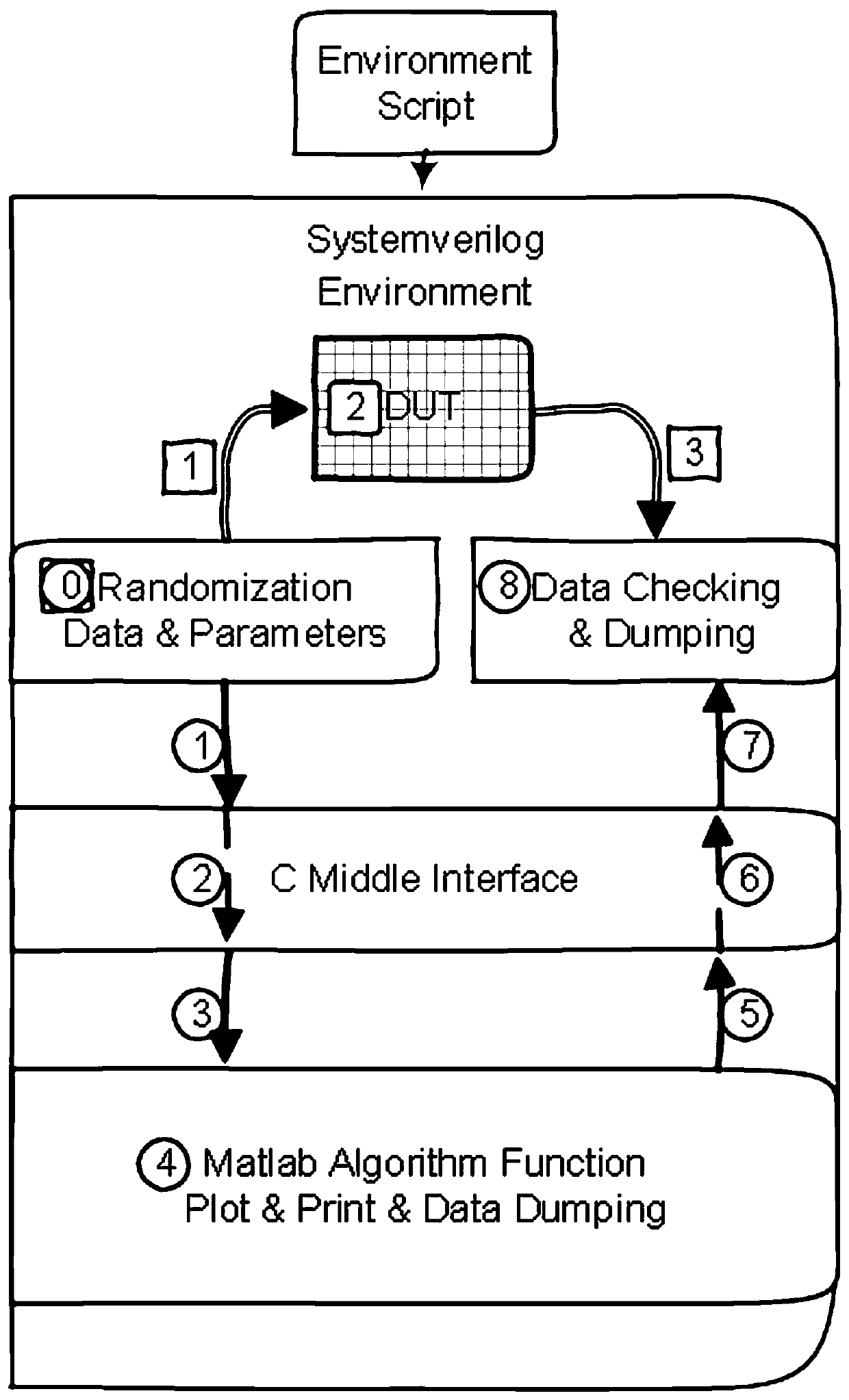

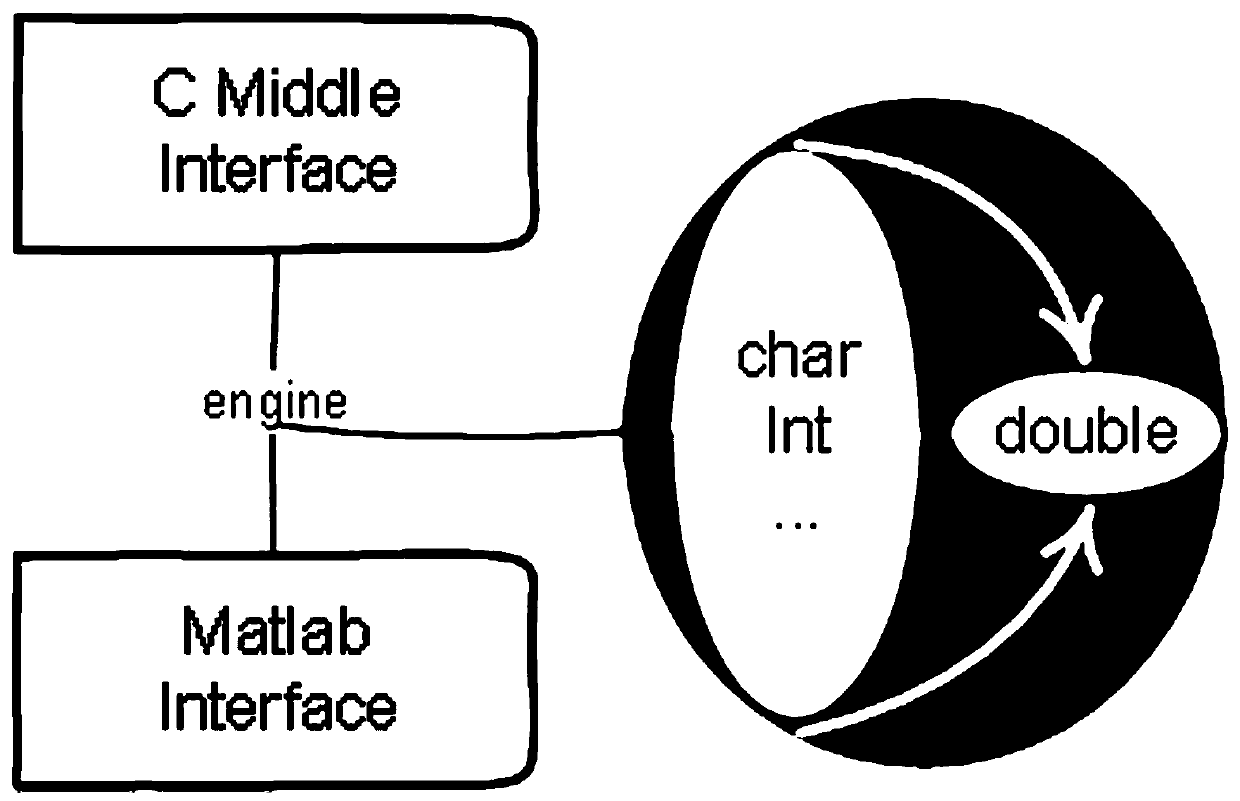

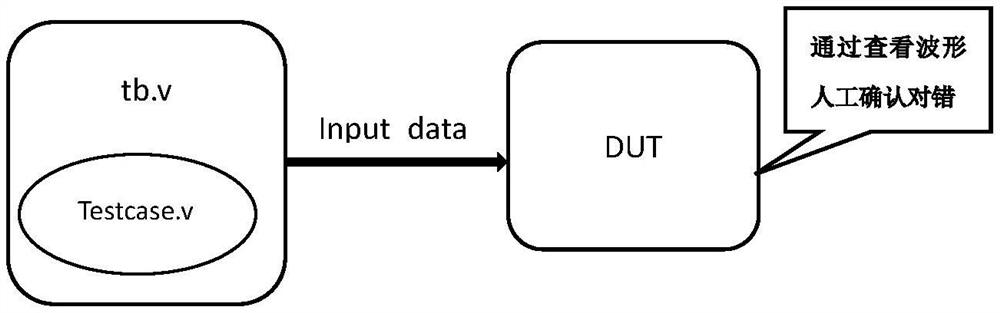

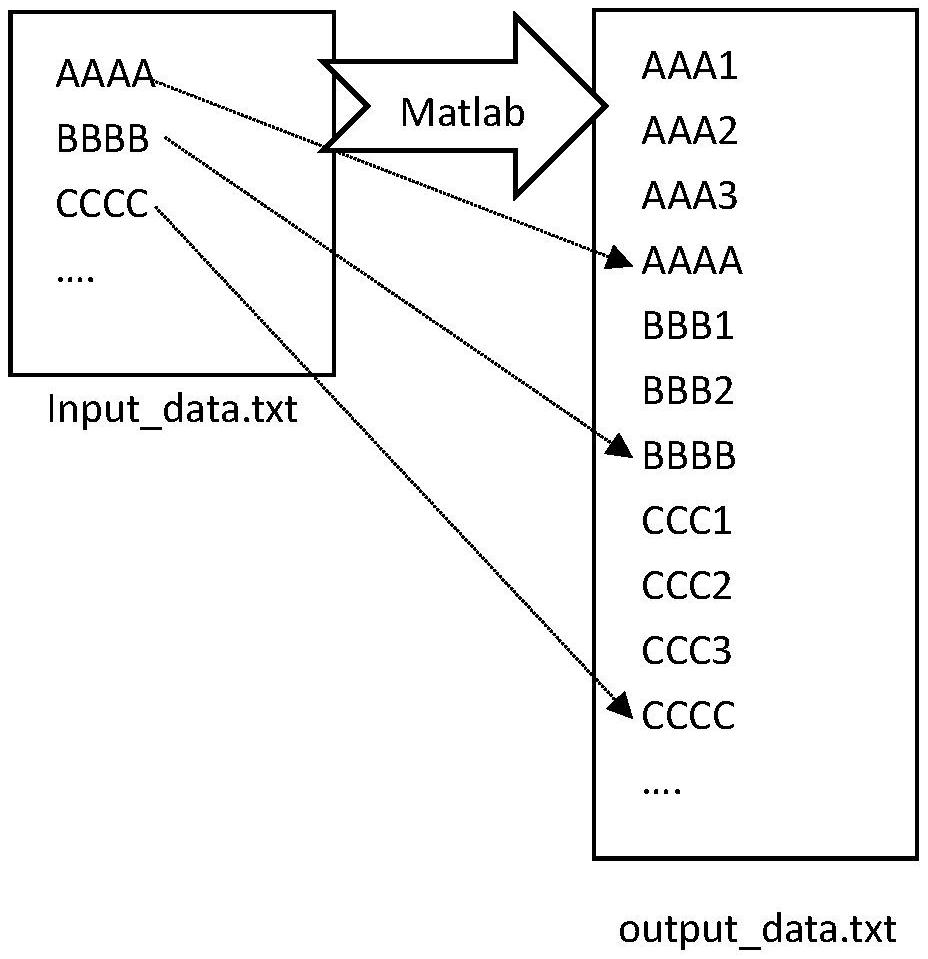

Extensible full-random full-automatic verification method based on Systemverilog and Matlab algorithms

ActiveCN110674616ADoes not consume simulation timeIncrease coverageComputer aided designSpecial data processing applicationsConcurrent computationTheoretical computer science

The invention discloses an extensible full-random full-automatic verification method based on Systemverilog and Matlab algorithms. The whole verification method is divided into two branches, and the two branches operate in parallel, and mutual interaction depends on global variable control, wherein the environment control part generates all required configuration parameters and original to-be-tested data according to given or immediately generated random seeds and all set constraints, and the first branch is a model path, and the second branch is a real data path. Through parallel calculationof the two paths, a correct result can be obtained no matter which path is calculated by a simulation tool firstly, and all simulation time is consumed in a real data path, and a model path only occupies some simulation CPU calculation time, so that the simulation speed is greatly increased.

Owner:BEIJING ZHILIANAN TECH

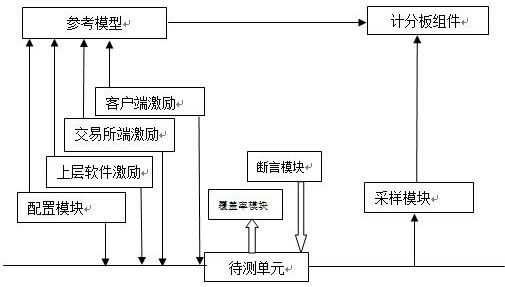

Verification platform and method applied to security futures counter

PendingCN112486835AFully randomizedAchieve the desired outputFinanceSoftware testing/debuggingReference modelingTest efficiency

The invention provides a verification platform and method applied to a securities futures counter. A to-be-tested unit is connected with a coverage rate module, an assertion module is connected with the to-be-tested unit; a configuration module, an upper software excitation module, an excitation module and a client excitation module are respectively connected with the to-be-tested unit and a reference model, and the reference module is in comparison connection with a scoreboard. and the to-be-tested unit is connected with the scoreboard comparison module through the sampling module. The verification platform constructed by using the verification methodology of the UVM is randomized more fully, verification management is performed in combination with scripts and coverage rate analysis reports, convergence can be achieved in a short time, the test efficiency and reliability are greatly improved, a complete reference model is provided on a verification architecture, the expected output ofthe verification platform is achieved by using a systemverilog language, the expected output is compared with the sampled RTL service output and table entry update, the output of a specific module orthe assertion error of a time sequence is directly positioned by giving a fault, and positioning and modifying are easy to achieve.

Owner:南京艾科朗克信息科技有限公司

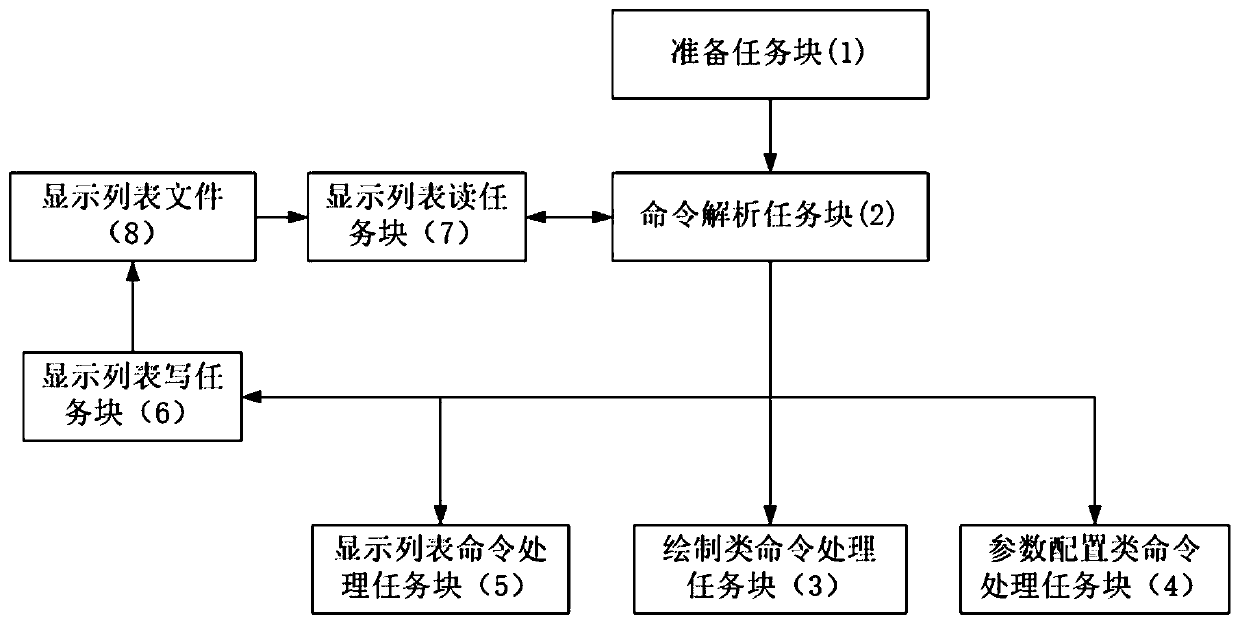

Graphic command pre-decoding model based on SystemVerilog, in particular to graphic command pre-decoding model based on SystemVerilog

ActiveCN111028133AEasy to buildConvenient verification workProcessor architectures/configurationEnergy efficient computingGraphicsDisplay list

The invention belongs to the field of computer graphics, and in particular to a graphic command pre-decoding model based on a SystemVerilog dynamic array and a task. The model comprises a preparationtask block, a command analysis task block, a drawing type command processing task block, a parameter configuration type command processing task block, a display list command processing task block, a display list writing task block and a display list reading task block. In the working process of the model, operation data and output results are dynamic arrays of SystemVerilog, read and write tasks of a preparation task and a display list further achieve interaction with files, and data comparison and check in the verification process are facilitated. The processing process does not contain a time sequence, processing tasks of various commands store results into corresponding dynamic arrays, the process is clear, maintenance is convenient, and the simulation speed is greatly increased.

Owner:XIAN AVIATION COMPUTING TECH RES INST OF AVIATION IND CORP OF CHINA

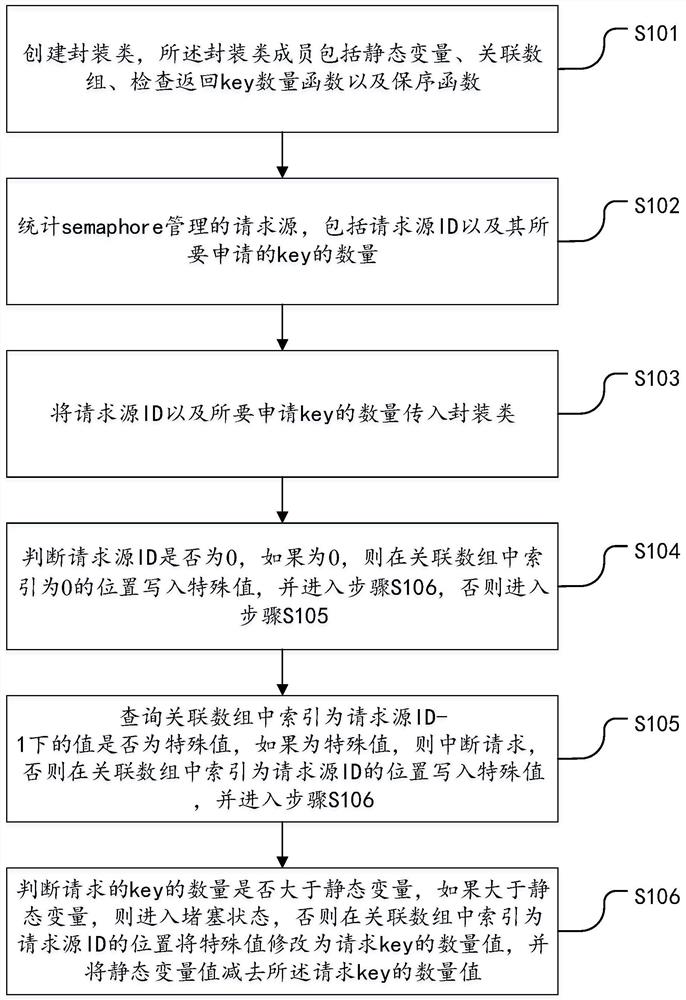

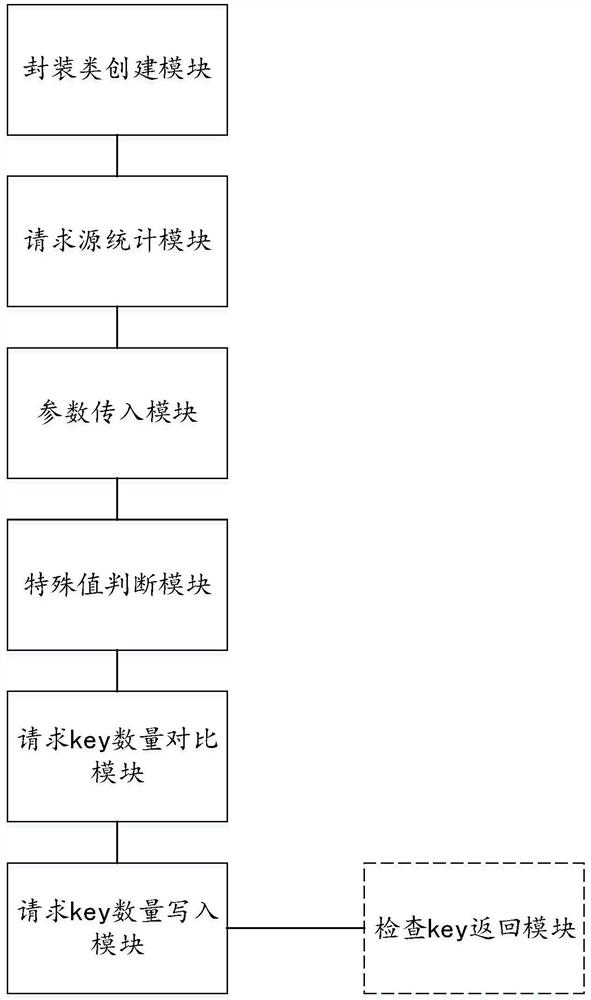

A control method and system for realizing semaphore order preservation in systemverilog

ActiveCN108089848BGuaranteed processing orderSoftware designCreation/generation of source codeSequence controlAssociative array

The invention provides a control method and system for realizing semaphore order preservation in systemverilog, which determines whether the current request source is waiting according to the value of a static variable, and determines whether the current request source is interrupted according to whether the value in the associative array is a special value. Implement order-preserving control of semaphore. The present invention constructs encapsulation classes, sets static variables, associative arrays, checks the function of returning key quantity and order preservation function, when requesting to apply for a key, according to the record value in the associative array, it is determined whether the previous request is blocked, so as to decide the present invention. Whether the second request is interrupted, so as to ensure the processing order of the request, solve the hidden defects of semaphore in the existing systemverilog and the situation that may cause the request to be out of order, make full use of the life cycle of static variables and the built-in associative array can be added at any time Or delete the characteristics of the element, supervise and effectively control the key return of the semaphore and the request for the key.

Owner:INSPUR SUZHOU INTELLIGENT TECH CO LTD

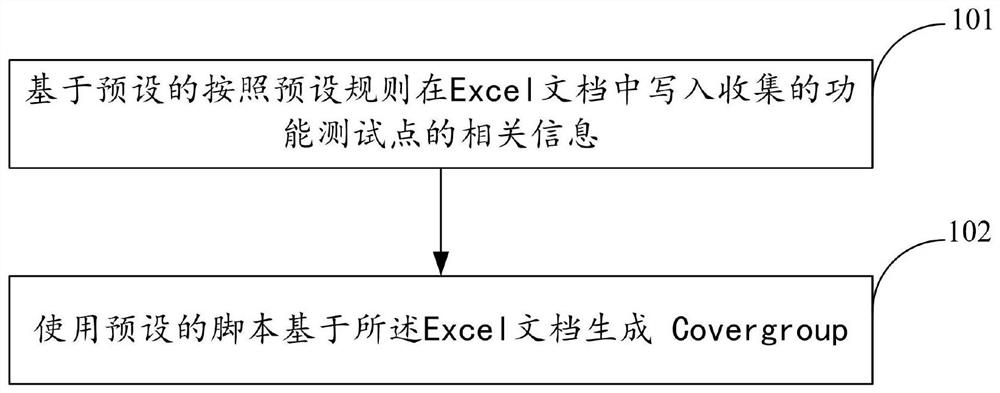

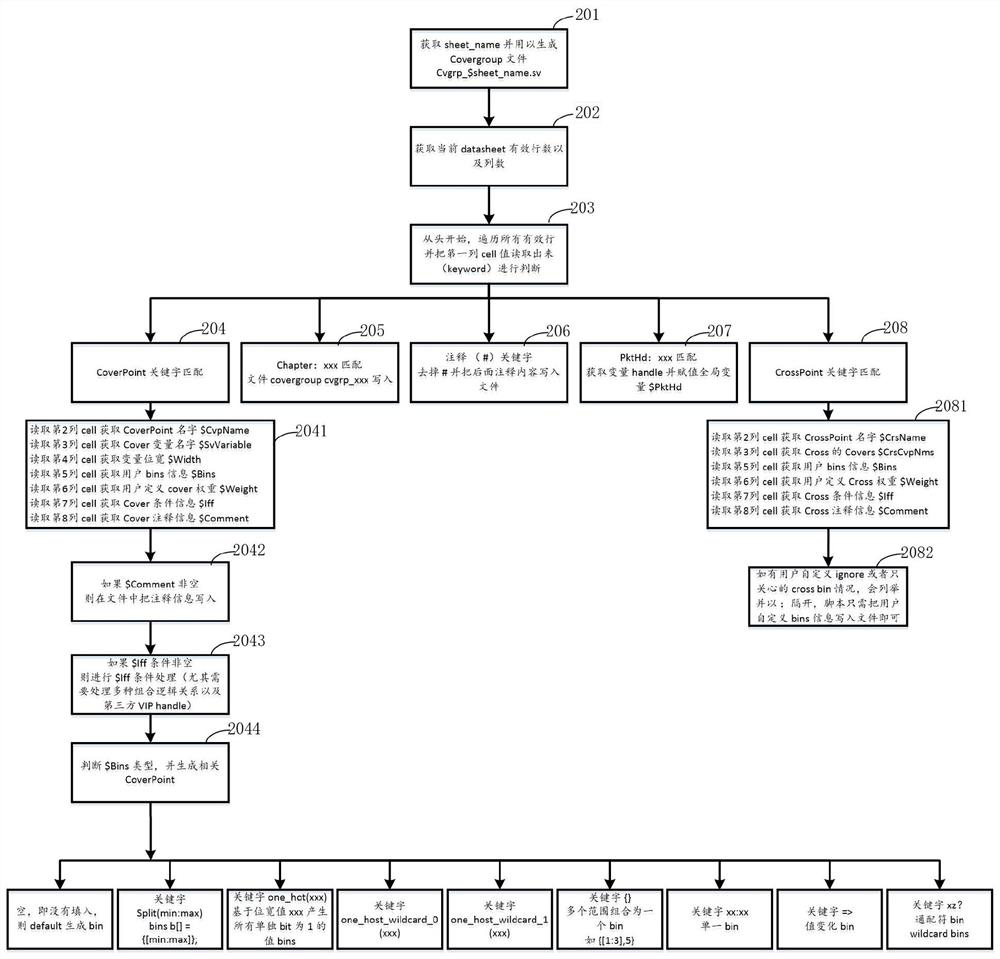

SystemVerilog coverage set generation method and device

ActiveCN113158607AImprove efficiencyAvoid workloadComputer aided designSpecial data processing applicationsFunctional testingRelevant information

The invention relates to a SystemVerilog coverage set generation method and device. The method comprises the following steps: writing related information of collected function test points into an Excel document according to a preset rule based on a preset rule; and generating a coverage set based on the Excel document by using a preset script. By the adoption of the technical scheme, a verification worker only needs to quantify the function points in the Excel file through a more friendly input interface, and then the Perl automatically generates the coverage set based on the file so as to improve efficiency. And the problems of large workload and low efficiency of manual writing of the coverage set are avoided.

Owner:四川微巨芯科技有限公司

A method of building a protocol verification platform based on BFM systemverilog

ActiveCN105930299BEasy to handleImprove throughputDigital computer detailsElectric digital data processingProtocol processingTransceiver

The invention discloses a method for building a protocol verification platform based on BFM-based SystemVerilog. The implementation process of the method is as follows: build a Transceiver to be responsible for sending and receiving, dismantling / grouping Class A protocol messages; build a Catalog directory structure and be responsible for recording consistency information ; Realize the protocol table model, responsible for implementing protocol conversion; build Handler, responsible for protocol processing. The method of the present invention simplifies the protocol processing process, adopts the one-by-one mode, no longer involves resource scheduling issues, improves protocol conversion communication between multiple clumps, and fully utilizes the verification characteristics of sv, queues, and dynamic associative arrays The throughput of the protocol message is increased, the catalog structure is visible on the whole platform, and the communication between the Transceiver and the BFM adopts a simpler DPI interface.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

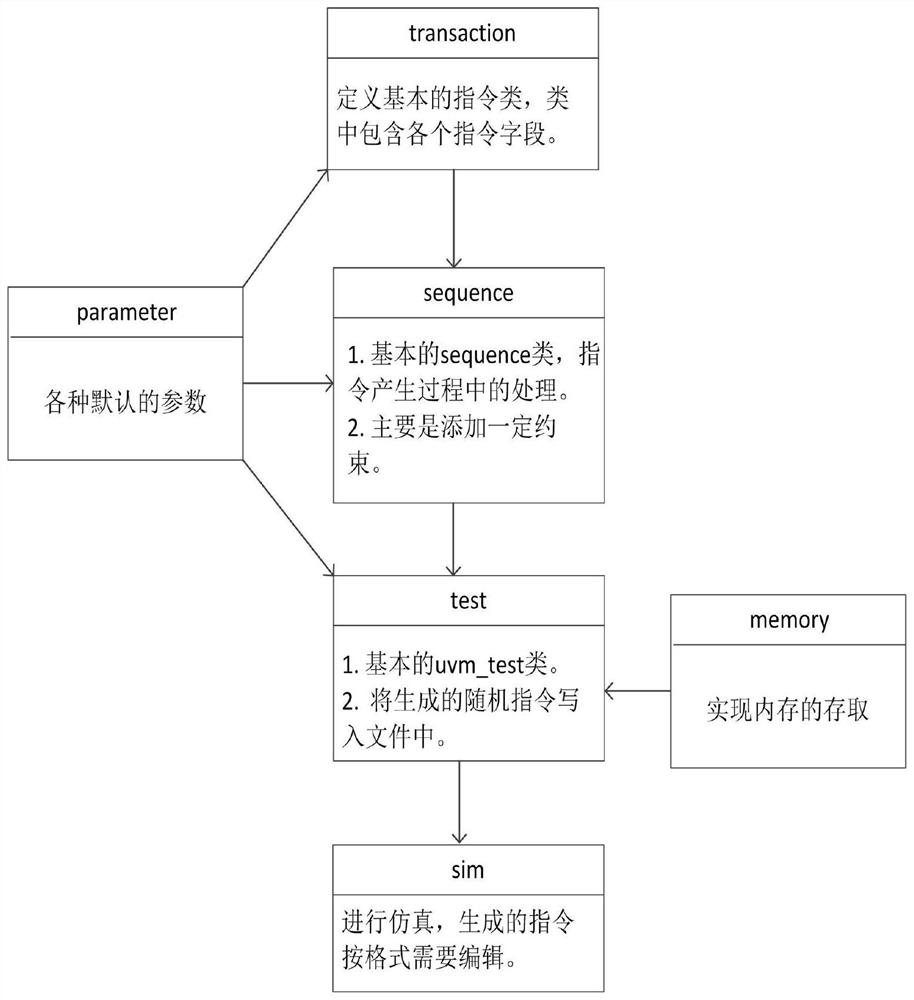

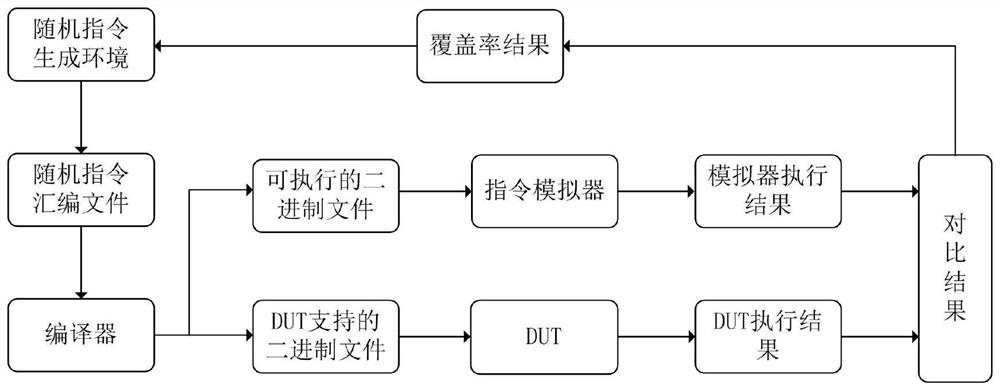

Random instruction generation environment based on novel processor architecture

PendingCN114428642AImprove performanceQuick buildConditional code generationGeneration processMemory cell

The invention relates to the technical field of integrated circuit processor design verification, in particular to a random instruction generation environment based on a novel processor architecture, which utilizes a UVM and SystemVerilog verification technology and mainly comprises a transaction module for coding all instructions of the novel processor architecture, a random instruction generation module for generating a random instruction, a random instruction generation module for generating a random instruction, a random instruction generation module for generating a random instruction, and a random instruction generation module for generating a random instruction, in an instruction generation process, a constraint sequence module, a test module, a memory module, a module, a parameter module and a sim simulation module are added, wherein the test module is used for defining an execution sequence; the memory module is used for realizing read-write of a memory unit; the module is used for realizing automatic comparison; the random instruction generation environment based on the novel processor architecture is high in modularity, good in reusability, high in instruction generation speed, wide in applied function scene, high in reliability and capable of meeting the requirement for verification of modern large-scale processor instruction sets.

Owner:中电科申泰信息科技有限公司

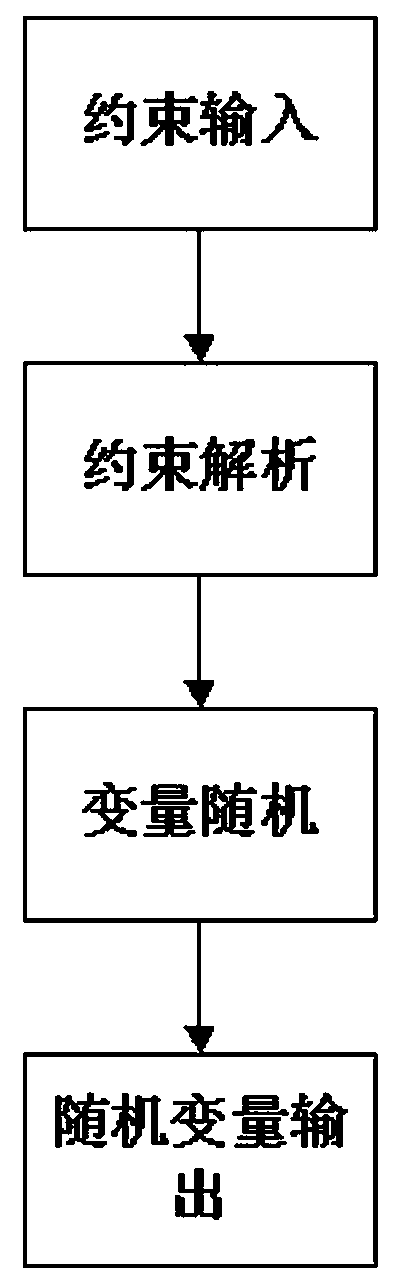

Universal variable constraint signal randomizing method

PendingCN110990210ASimple and convenient random operationImprove work efficiencyError detection/correctionAlgorithmControl signal

The invention discloses a universal variable constraint signal randomizing method. According to the method, a four-value variable in a SystemVerilog language is used for representing a constraint relation between signals, the constraint relation is transmitted into a program block through a program interface, the program block analyzes the constraint, and a random variable value meeting the constraint relation is randomly obtained according to the constraint. When control signals with different constraint relations are randomized, the randomization operation of the signals can be simply and conveniently finished under the condition of not increasing codes. The method is simple and convenient to implement, random signals with different constraints are randomized by using one program block,corresponding constraint program codes do not need to be written for different constraint relationships, a code quantity is reduced, and working efficiency is improved.

Owner:SHANDONG SINOCHIP SEMICON

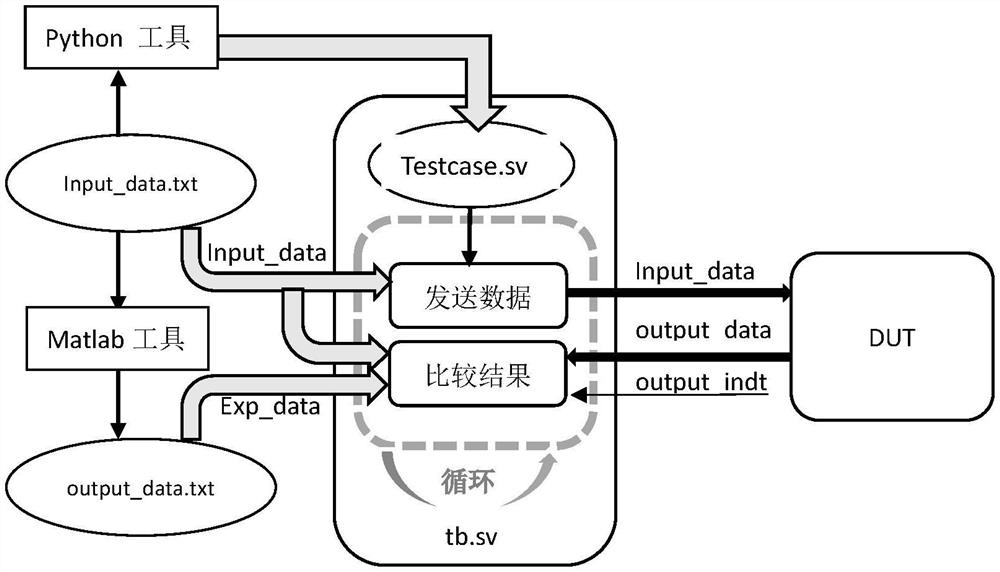

Efficient digital circuit algorithm verification device

The invention provides an efficient digital circuit algorithm verification device in order to improve complexity and low efficiency in algorithm verification of a digital circuit. The verification platform is combined with a systemverilog verification language, an algorithm tool Matlab and an automatic running script Python, so that the algorithm verification becomes intelligent and efficient.

Owner:上海明矽微电子有限公司

A random verification method of ahb kernel based on systemverilog

ActiveCN106502900BConvenient for subsequent debuggingHigh speedSoftware testing/debuggingComputer scienceHost machine

The invention provides an AHB core random verification method based on systemverilog. The method comprises the following steps: reading data of an excitation generating module at the beginning of each period by use of an excitation driving module, and transmitting the data to a to-be-tested IP module; feeding back the data of a slave in the excitation driving module to a host of the excitation generating module at the end of the period by use of a feedback signal collecting module; restraining an allowable input kind list of a next period according to the data provided by the feedback signal collecting module by use of the excitation generating module, and randomly selecting one kind from the allowable input kind list at the beginning of the next period; collecting input-output information of the to-be-tested IP at each period by use of a monitoring check module, printing the input-output information to log, and then checking whether the input-output information meets an assertion requirement; directly comparing whether the judgment meets the requirement of a predetermined protocol according to the state of the IP at a predetermined moment by use of an assertion module.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

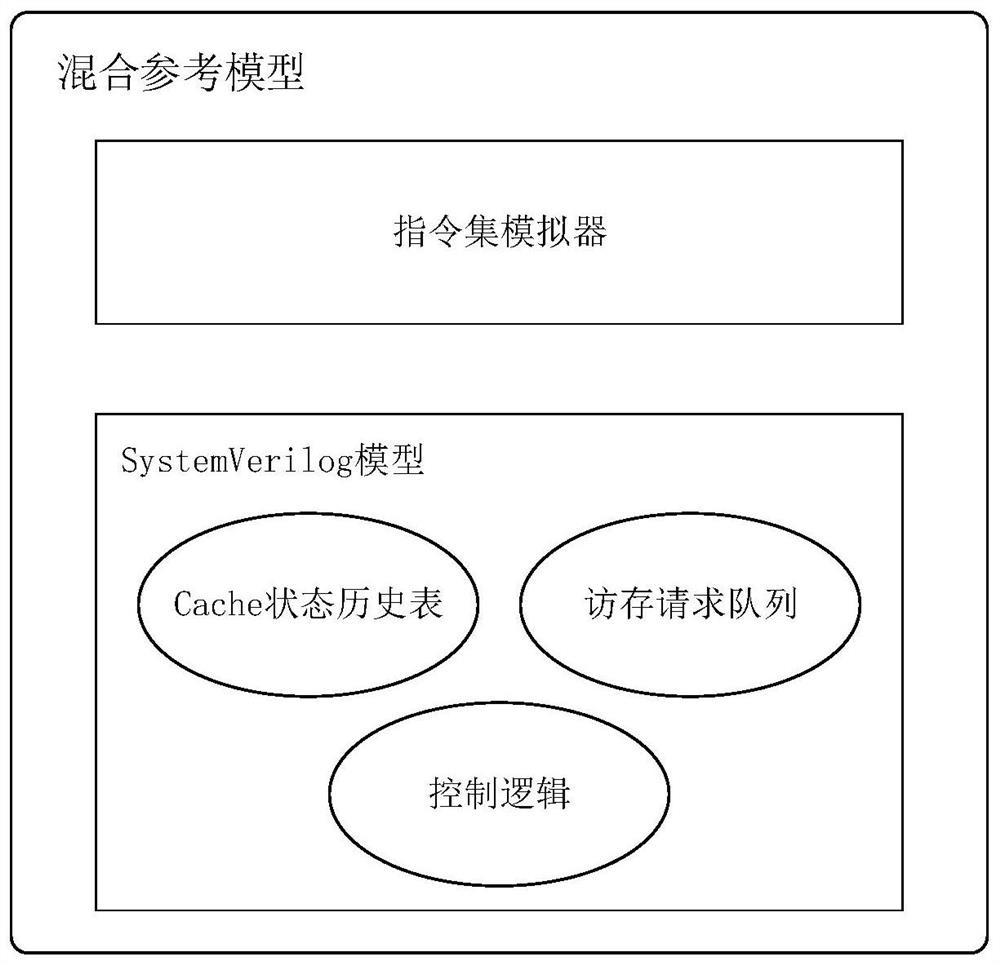

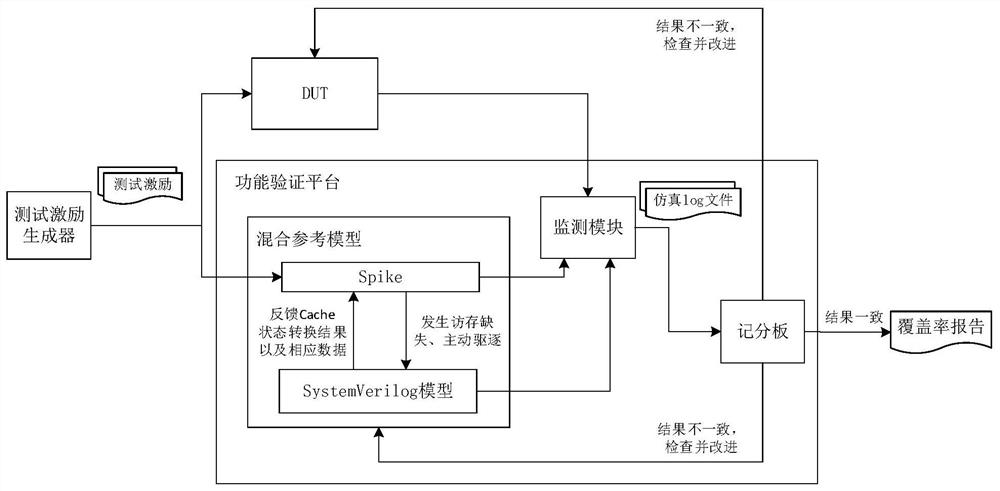

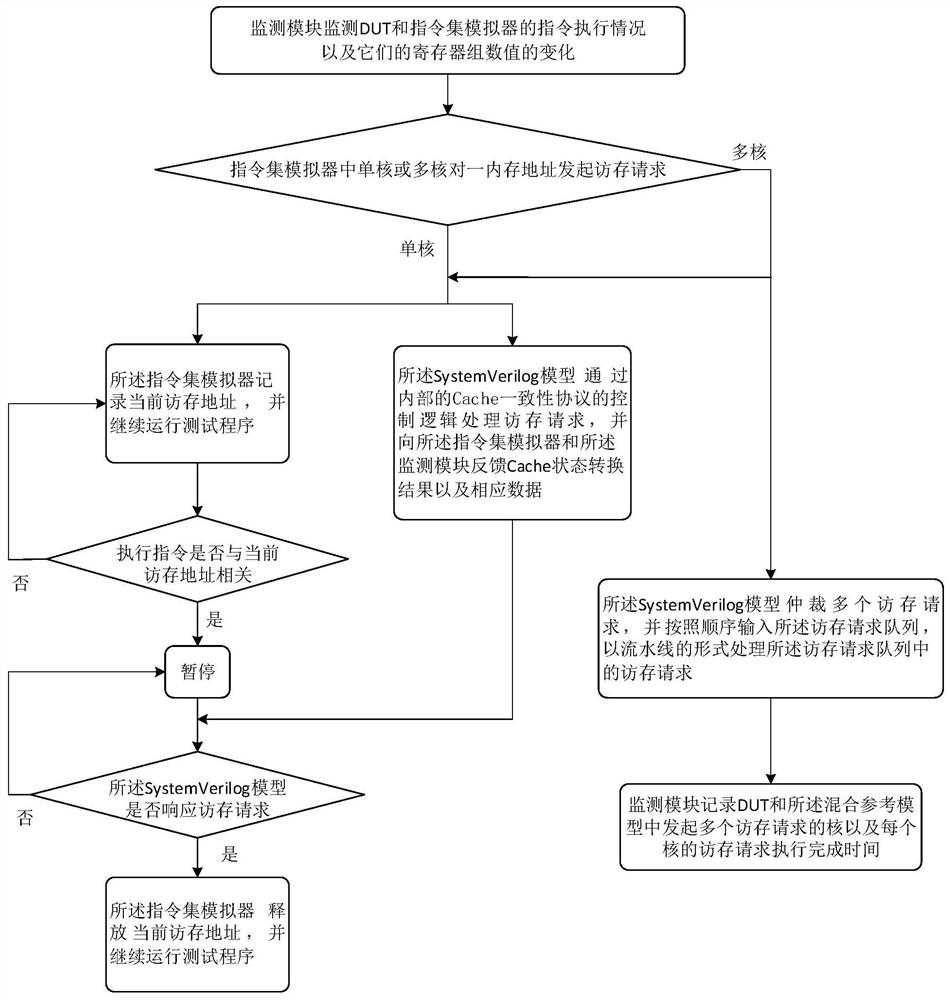

Multi-core processor function verification platform and method based on hybrid reference model

PendingCN113076709AReduce design time overheadSimple designCAD circuit designSpecial data processing applicationsReference modelingCache consistency

The invention discloses a multi-core processor function verification platform and method based on a hybrid reference model, and belongs to the technical field of integrated circuits. A hybrid reference model in the platform is composed of an instruction set simulator and a SystemVerilog model. The instruction set simulator is a function precision-level model and is used for verifying whether each instruction in the multi-core processor is correctly executed or not; the SystemVerilog model is a function and time sequence precision level hybrid model and is used for verifying whether the memory access instruction executed by the multi-core processor and the Cache consistency operation process are correct or not. According to different instruction set architectures, verification personnel can directly adopt existing instruction set simulators such as Spike and ARMulator, and the design time cost of a reference model can be effectively shortened. According to the invention, the instruction set simulator and the SystemVerilog model can run at the same time, so that the simulation speed of the verification platform is effectively improved.

Owner:JIANGNAN UNIV