Multi-core processor function verification platform and method based on hybrid reference model

A multi-core processor and reference model technology, which is applied in electrical digital data processing, special data processing applications, instruments, etc., can solve the problems of increased difficulty in reference model design and a large amount of time spent by verification personnel.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

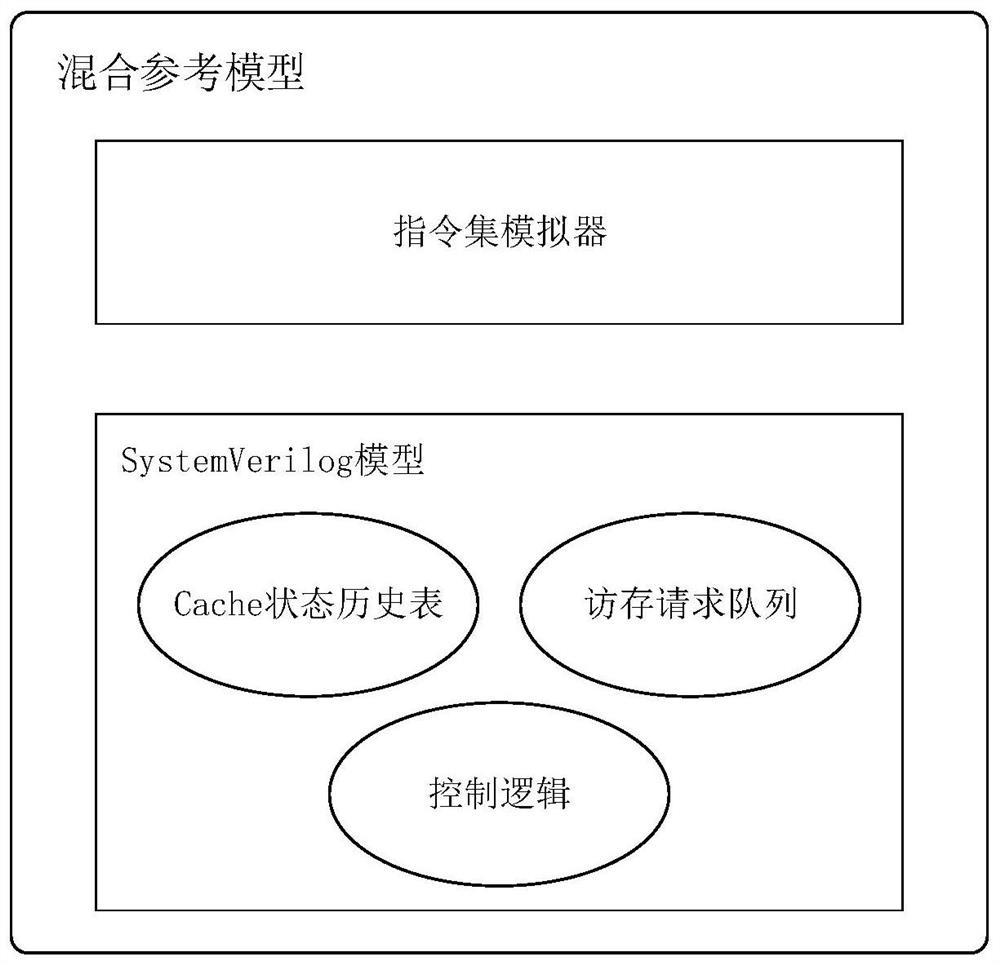

[0034] This embodiment provides a mixed reference model of a multi-core processor function verification platform based on a mixed reference model, see figure 1 The hybrid reference model is composed of an instruction set simulator and a Systemverilog model; the instruction set simulator is a functional precision level model for verifying whether each instruction in the multi-core processor is correctly executed correctly; SystemverIlog model is functional and timing accurate level The mixing model is used to verify that the interview instruction executed by the multi-core processor and whether the Cache consistency operation process is correct. The SystemVerilog model includes control logic, a cache status history table, and an intermittent request queue for a Cache consistency protocol.

[0035] It is to be described, and the verifier can effectively shorten the design time overhead of the reference model directly with an existing instruction simulator, such as Spike, Armulator, ...

Embodiment 2

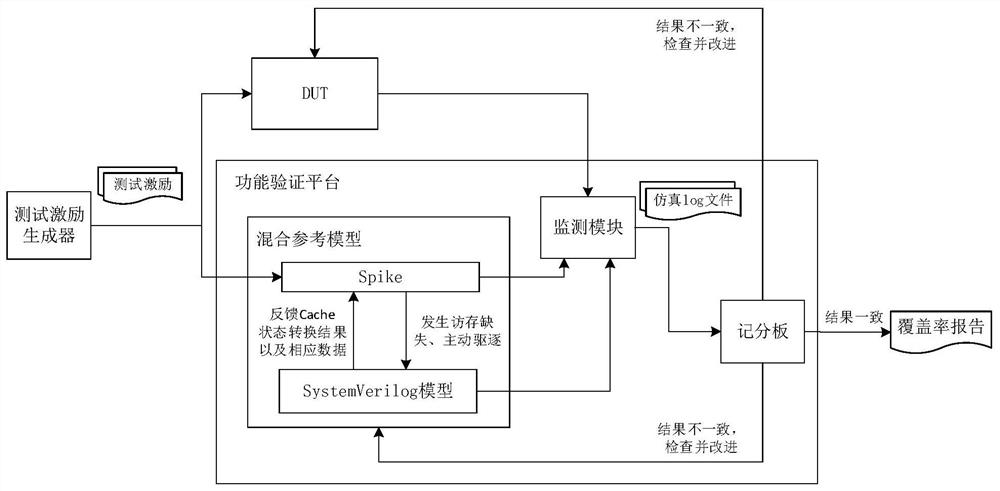

[0037]This embodiment provides a multi-core processor function authentication method based on a mixed reference model, and the multi-core processor system to be tested is a RISC-V multicore processor system as an example, the multi-core processor function based on a mixed reference model. The verification platform includes a multi-core processor system (DUT), a test excitation generator, a hybrid reference model, and the SYSTEMVERILOG language-based monitoring module and a scoreboard; where the multi-core processor system is RISC. -V multicore processor system.

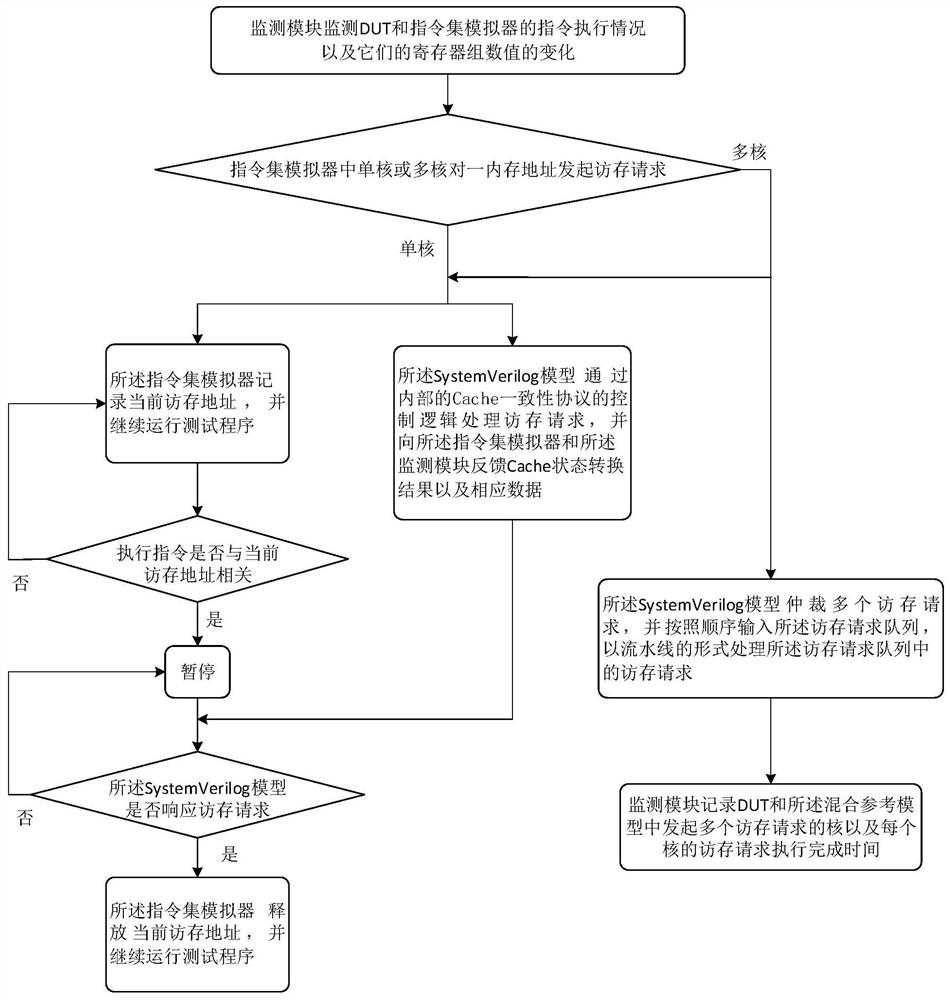

[0038] Such as figure 2 As shown, the monitoring module monitors the status conversion and timing relationship generated in the Cache consistency operation process generated in the Cache consistency operation process of the DUT and the SYSTEMVERILOG model for each execution of the NUT and the SYSTEMVERILOG model. And control the synergy of the instruction set simulator and the SystemverIlog model.

[0039] The verificatio...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More