Wiring optimization method and device of superconducting integrated circuit, storage medium and terminal

An integrated circuit and wiring technology, applied in the field of superconducting integrated circuit layout, can solve the problems of being unable to apply high-scale superconducting integrated circuits, taking a long time, and affecting the design iteration cycle of superconducting integrated circuits, so as to reduce design time overhead and be compatible Good performance and reduced design cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0055] In order to solve the technical problems existing in the prior art, an embodiment of the present invention provides a wiring optimization method for a superconducting integrated circuit.

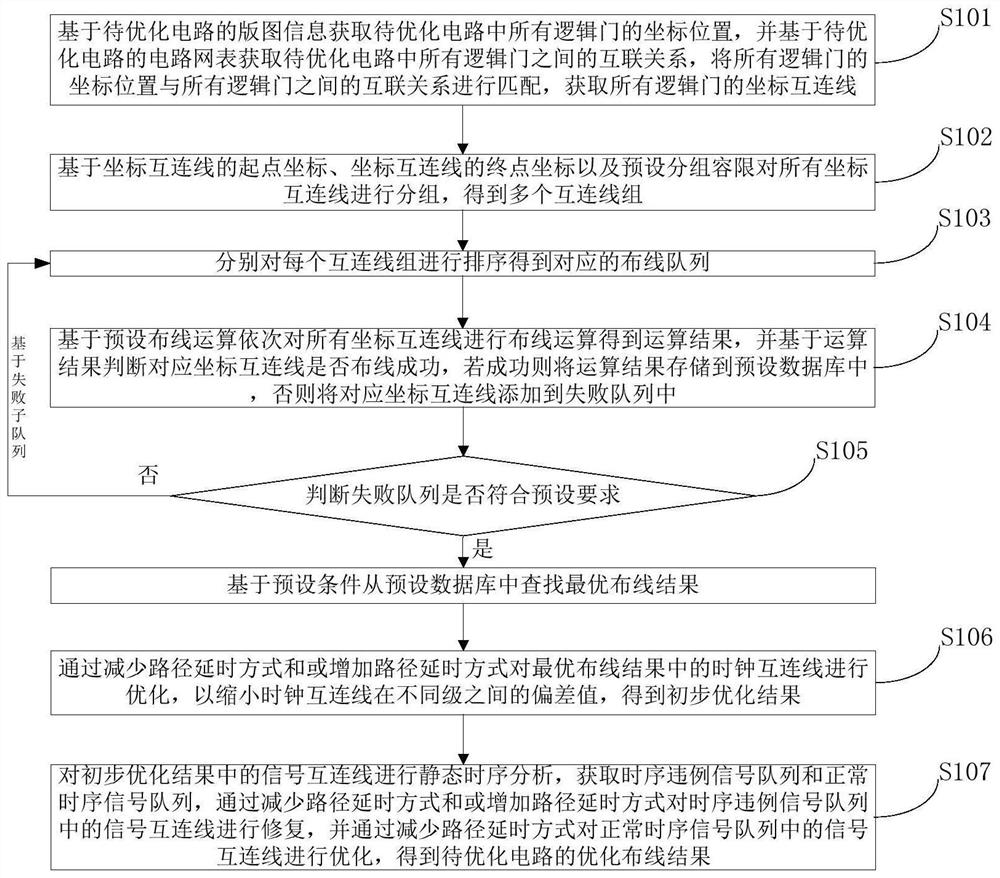

[0056] figure 1 A schematic flow chart showing a wiring optimization method for a superconducting integrated circuit according to an embodiment of the present invention; refer to figure 1 As shown, the wiring optimization method for a superconducting integrated circuit in the embodiment of the present invention includes the following steps.

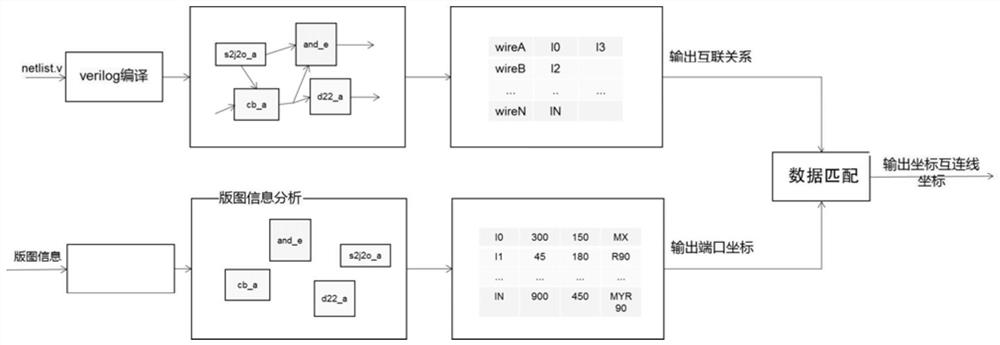

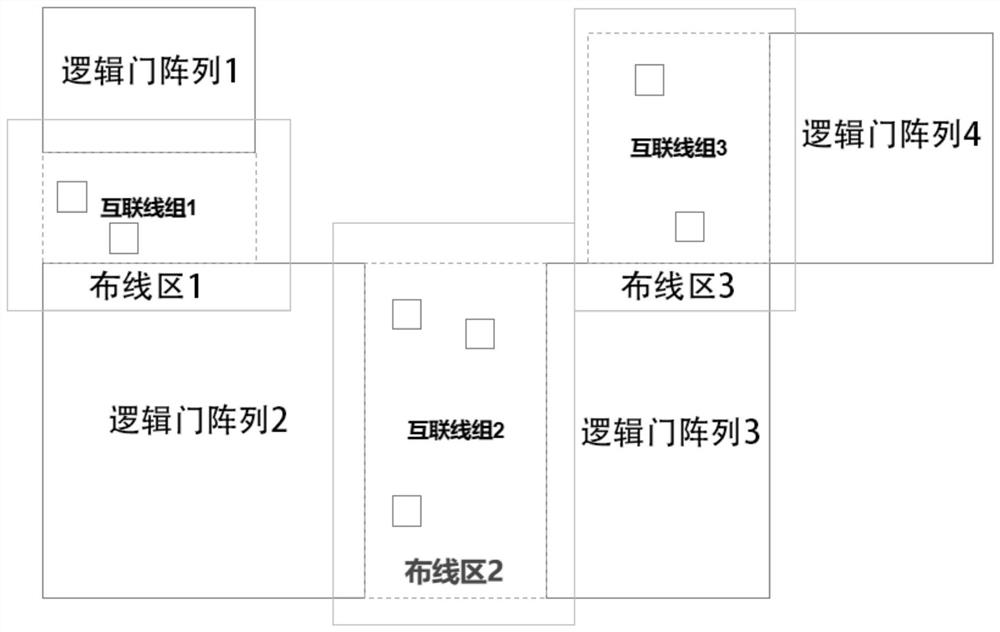

[0057] In step S101, the coordinate positions of all logic gates in the circuit to be optimized are obtained based on the layout information of the circuit to be optimized, and the interconnection relationship between all logic gates in the circuit to be optimized is obtained based on the circuit netlist of the circuit to be optimized. The coordinate position is matched with the interconnection relationship between all logic gates, and the coord...

Embodiment 2

[0088] In order to solve the above-mentioned technical problems existing in the prior art, an embodiment of the present invention also provides a wiring optimization device for a superconducting integrated circuit.

[0089] Figure 12 It shows a schematic structural diagram of a wiring optimization device for a superconducting integrated circuit in Embodiment 2 of the present invention; refer to Figure 12 As shown, the wiring optimization device for a superconducting integrated circuit according to the embodiment of the present invention includes a coordinate interconnection acquisition module, a wiring operation module, an optimal wiring result acquisition module, a clock optimization module, and a wiring optimization module.

[0090] The coordinate interconnection acquisition module is used to obtain the coordinate positions of all logic gates in the circuit to be optimized based on the layout information of the circuit to be optimized, and obtain the interconnection relati...

Embodiment 3

[0097] In order to solve the above-mentioned technical problems existing in the prior art, the embodiment of the present invention also provides a storage medium, which stores a computer program, and when the computer program is executed by a processor, the wiring optimization of the superconducting integrated circuit of the first embodiment can be realized all steps in the method.

[0098] The specific steps of the method for optimizing the wiring of a superconducting integrated circuit and the beneficial effects obtained by using the readable storage medium provided by the embodiment of the present invention are the same as those of the first embodiment, and will not be repeated here.

[0099] It should be noted that the storage medium includes various media capable of storing program codes such as ROM, RAM, magnetic disk or optical disk.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More