Patents

Literature

63 results about "Superconducting integrated circuits" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

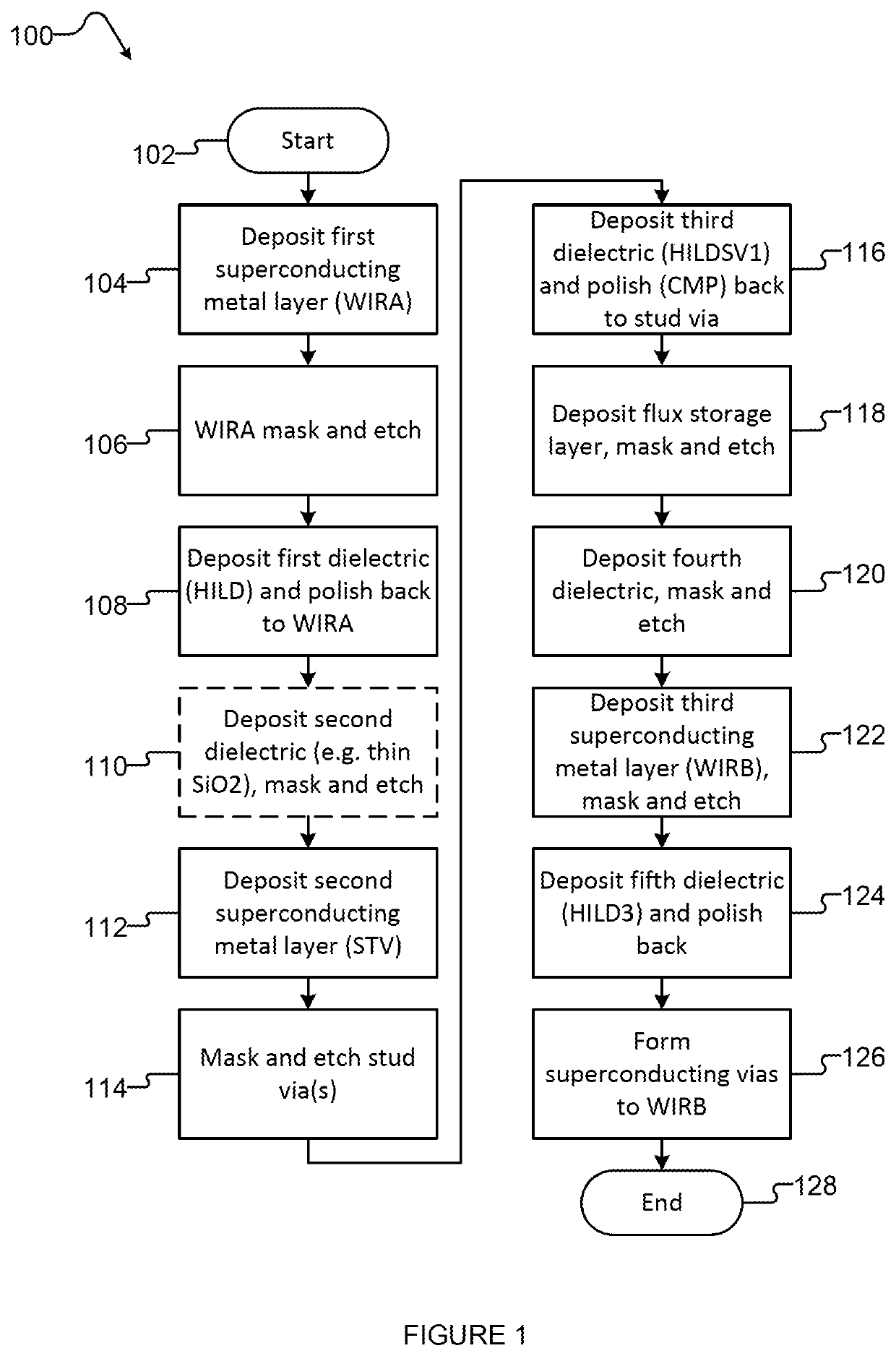

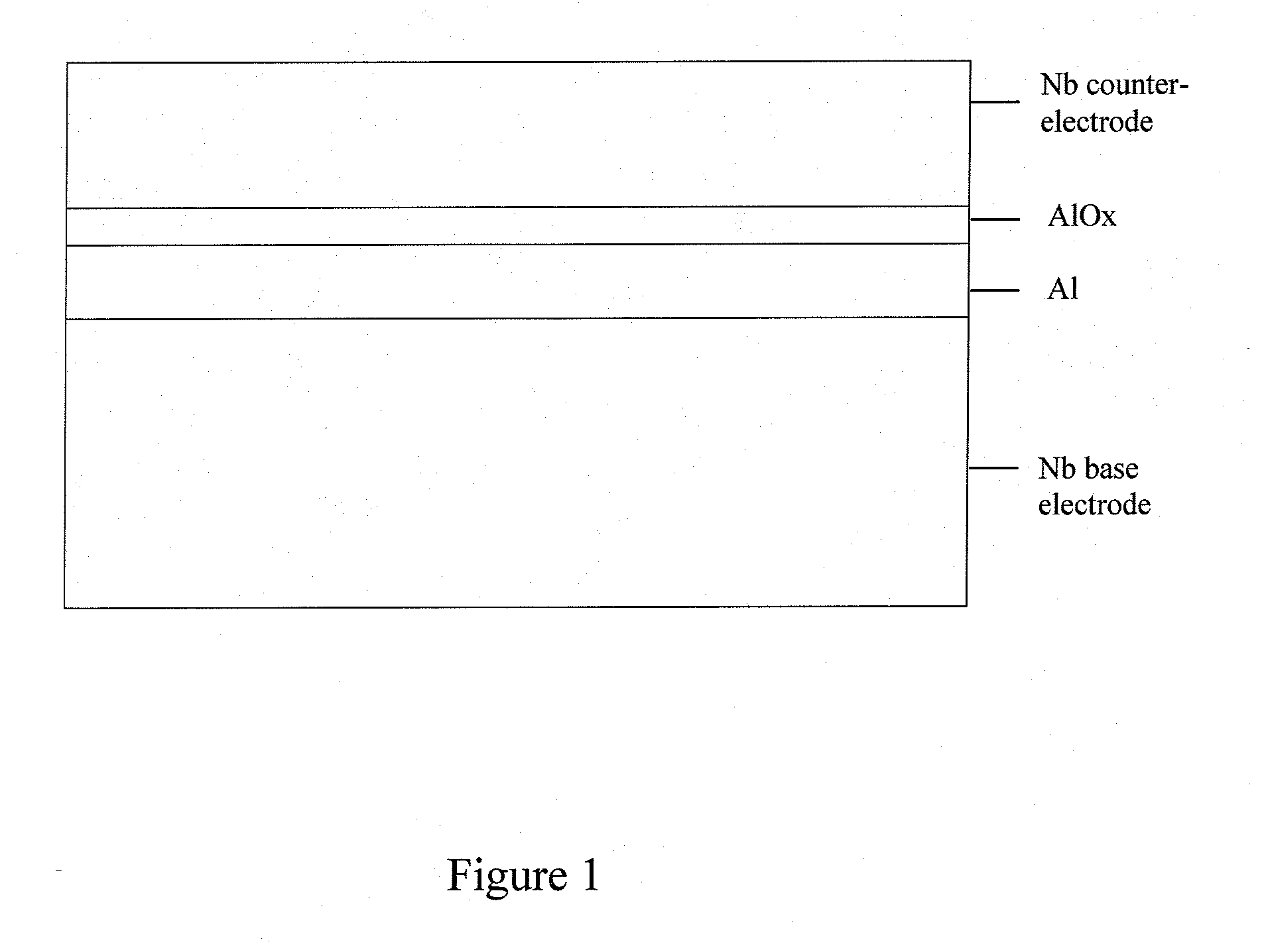

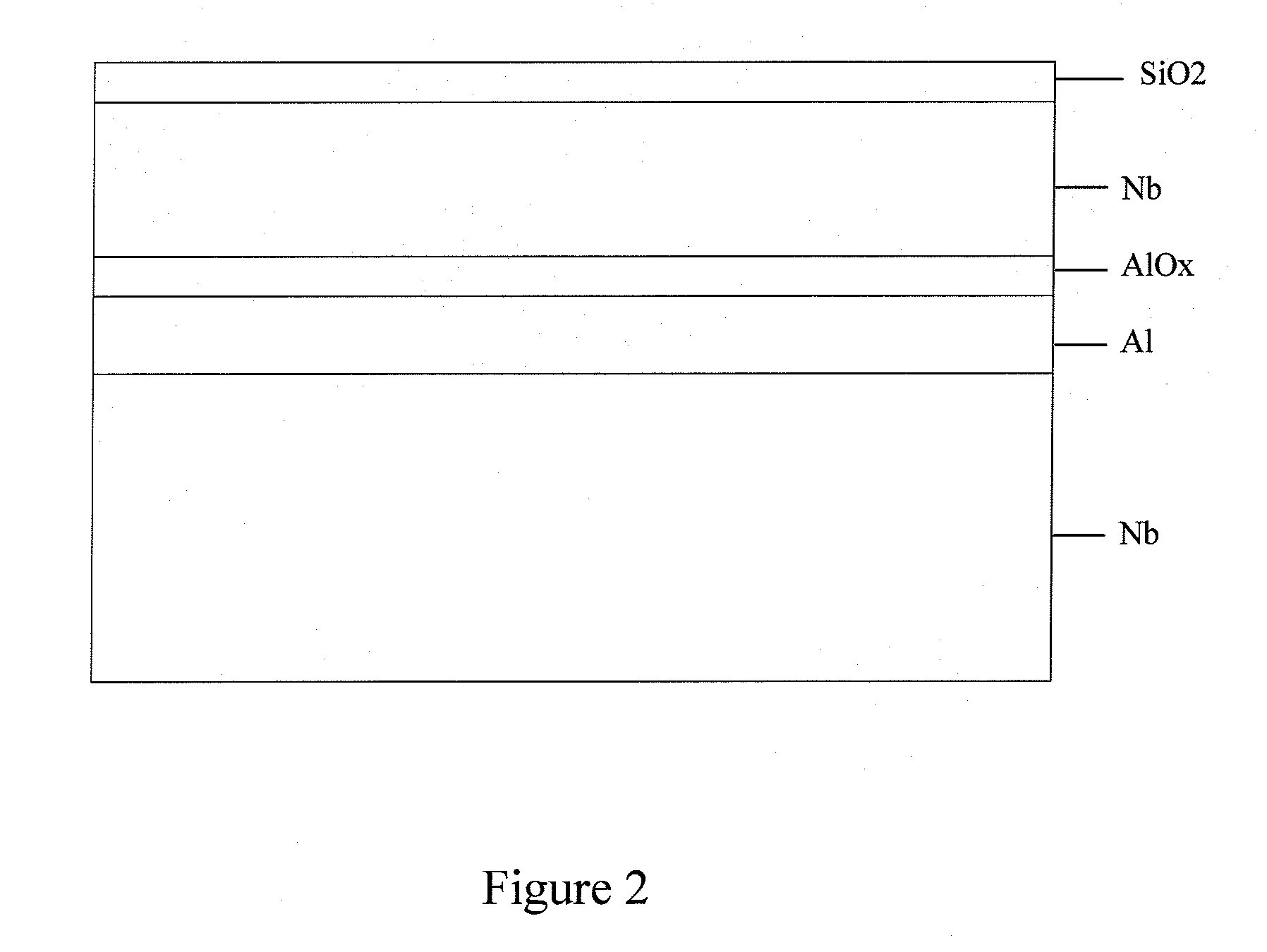

Systems and methods for fabrication of superconducting integrated circuits

ActiveUS20150119252A1Avoid overall overheatingQuantum computersLiquid surface applicatorsDielectricNiobium

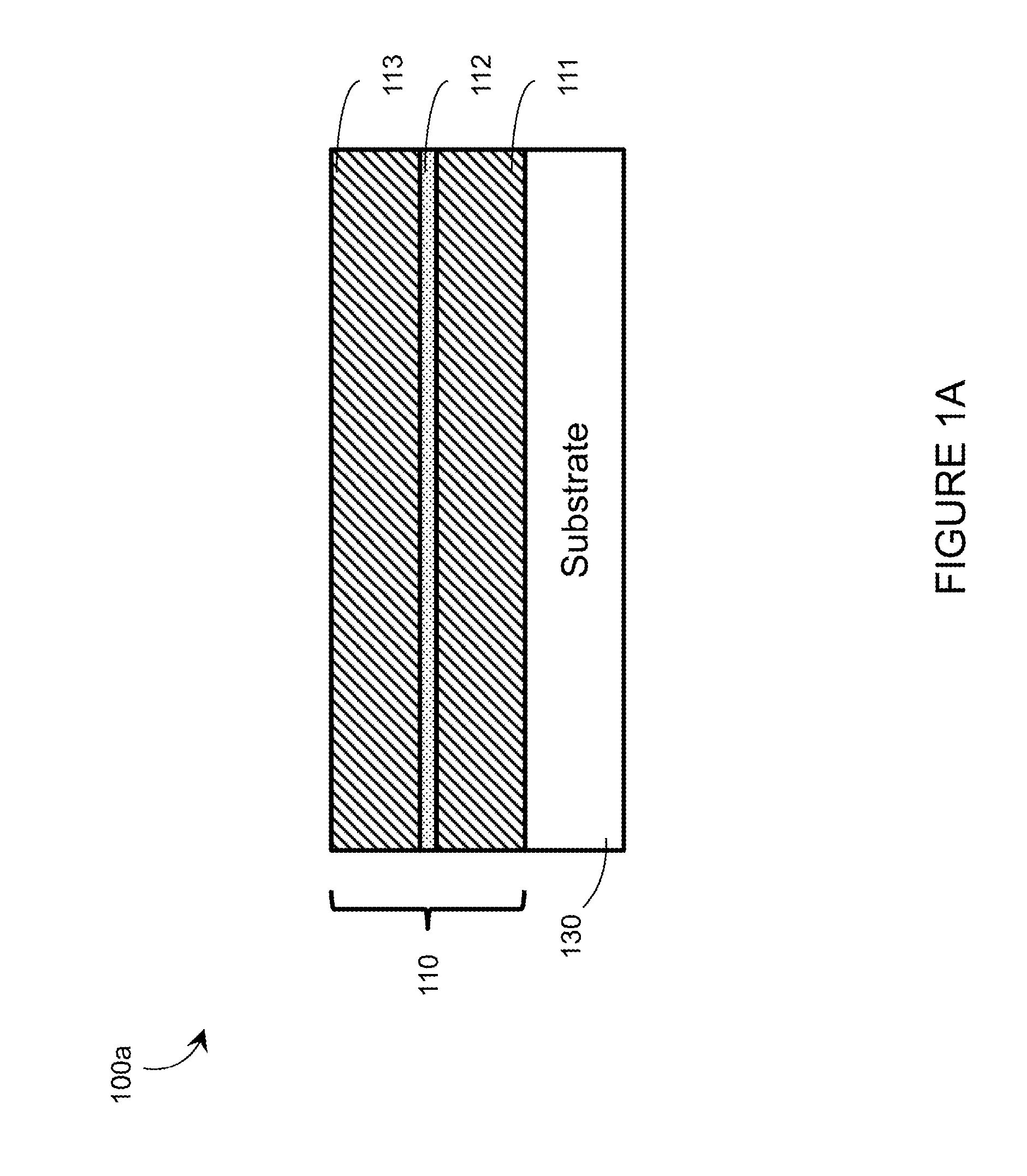

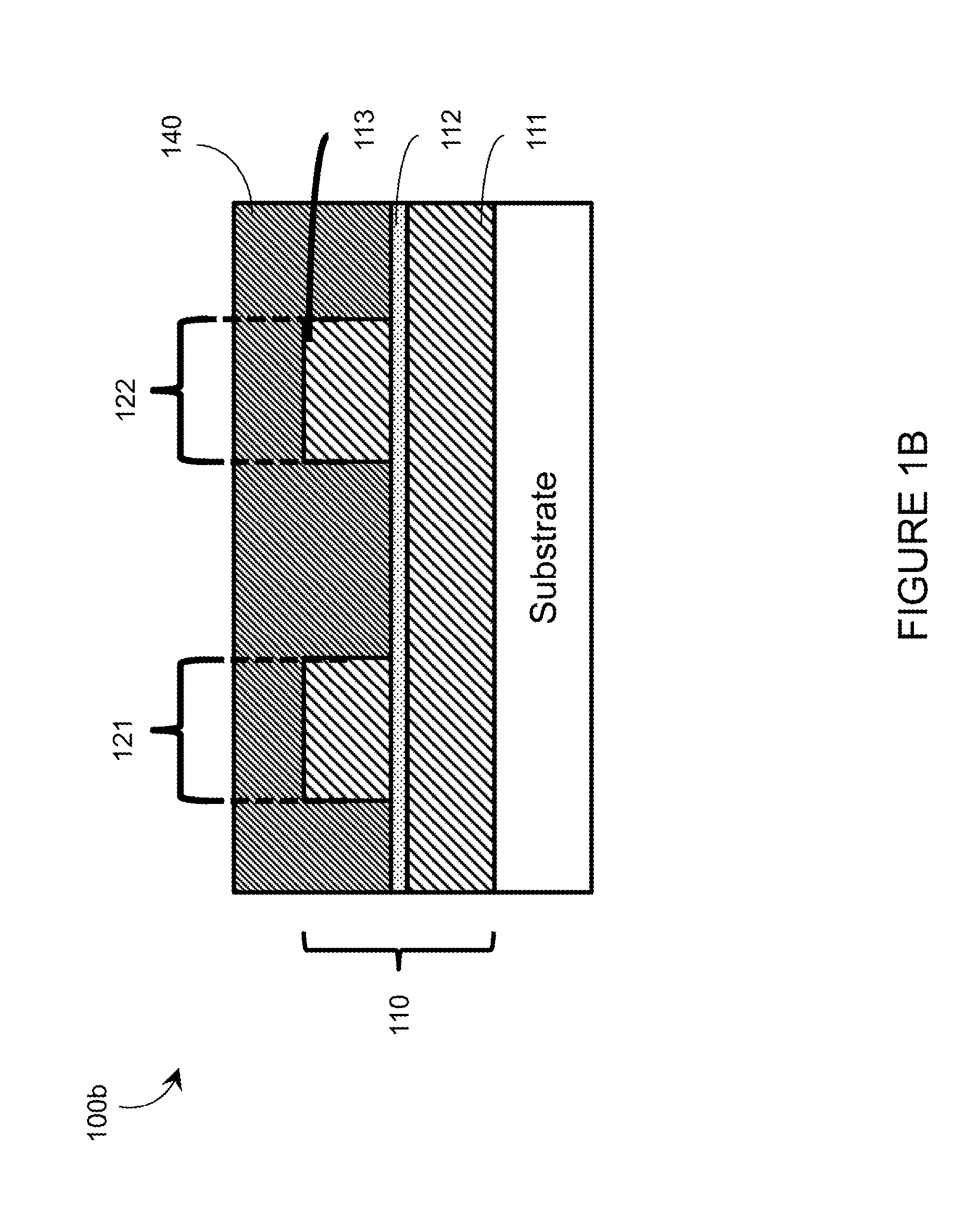

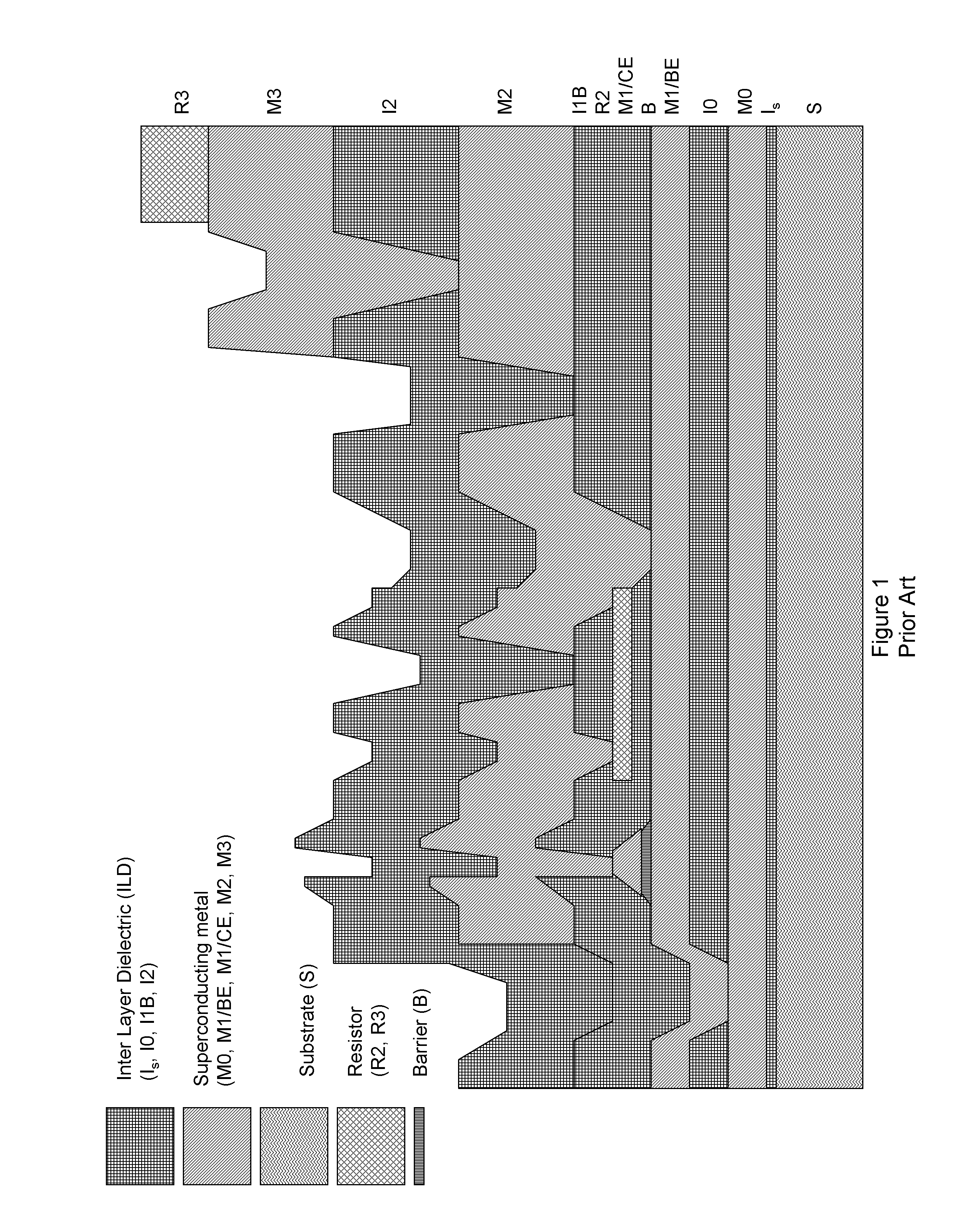

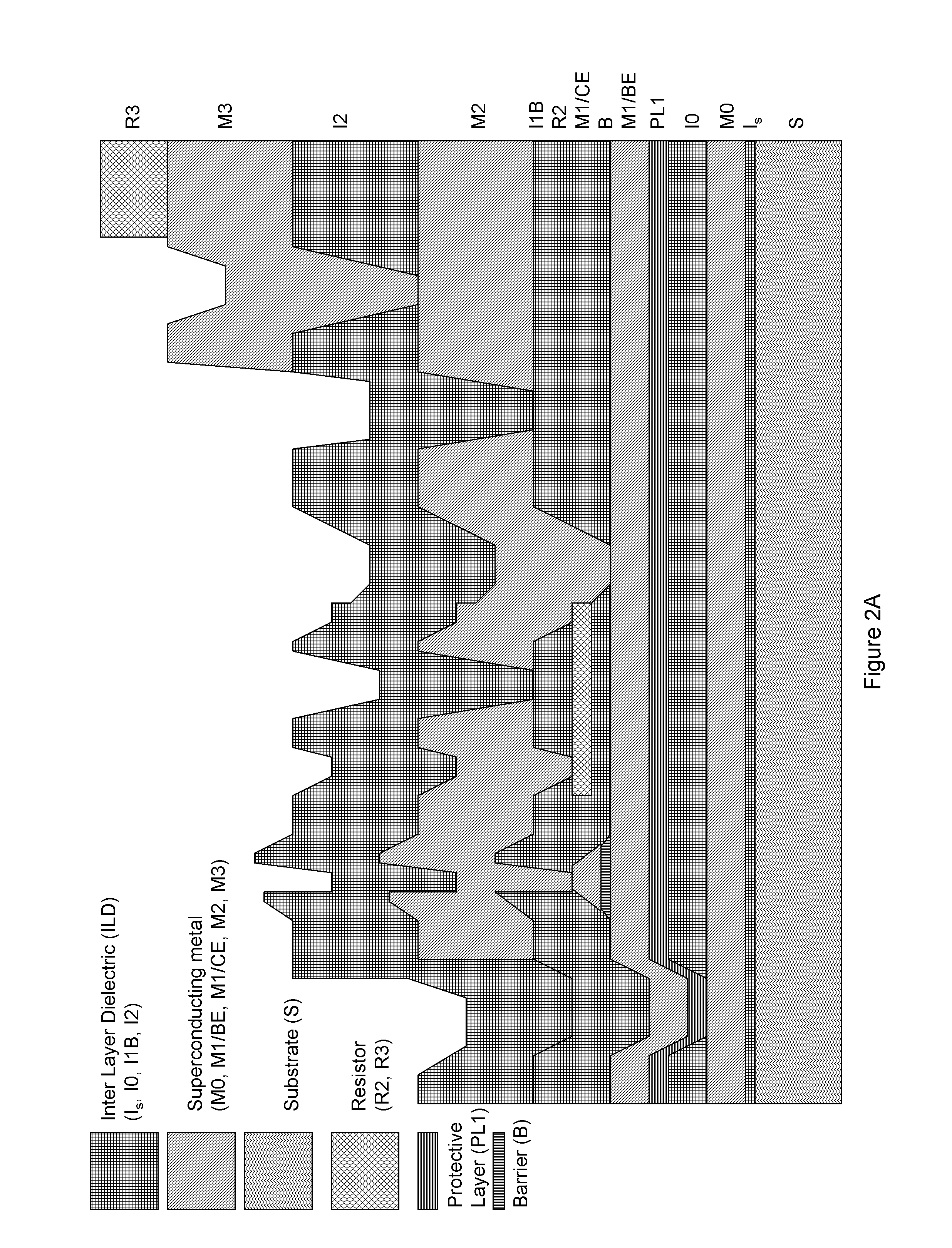

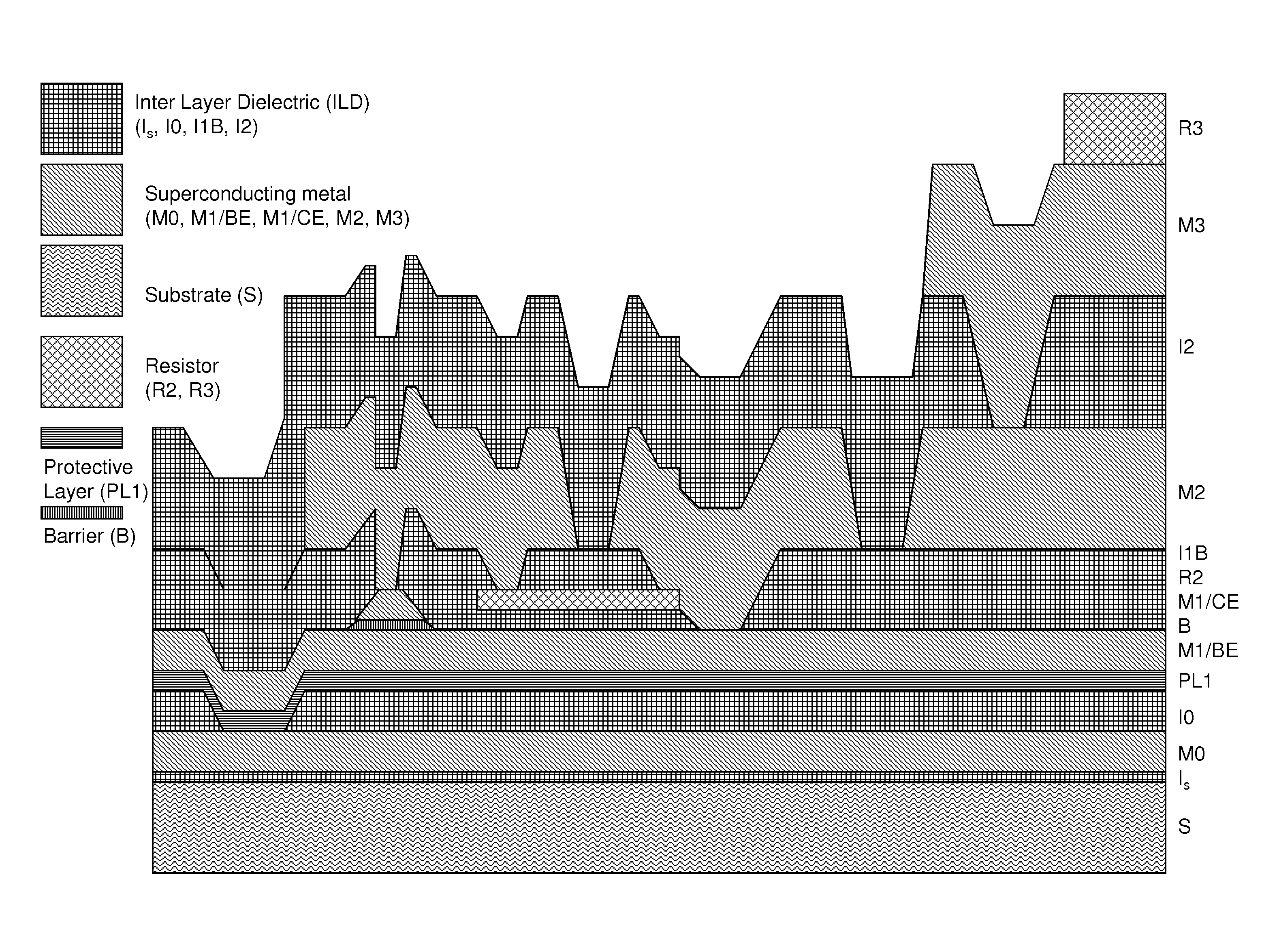

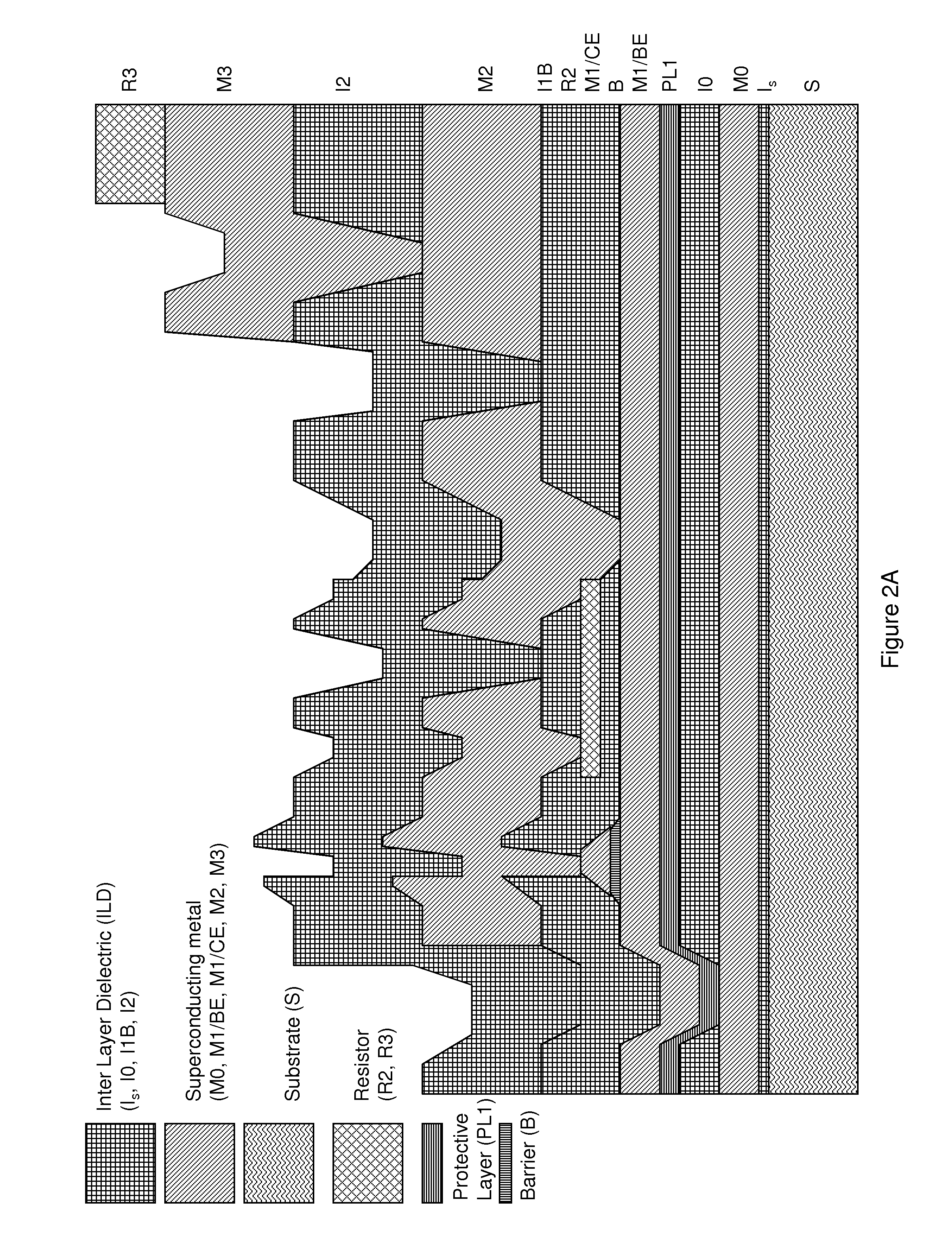

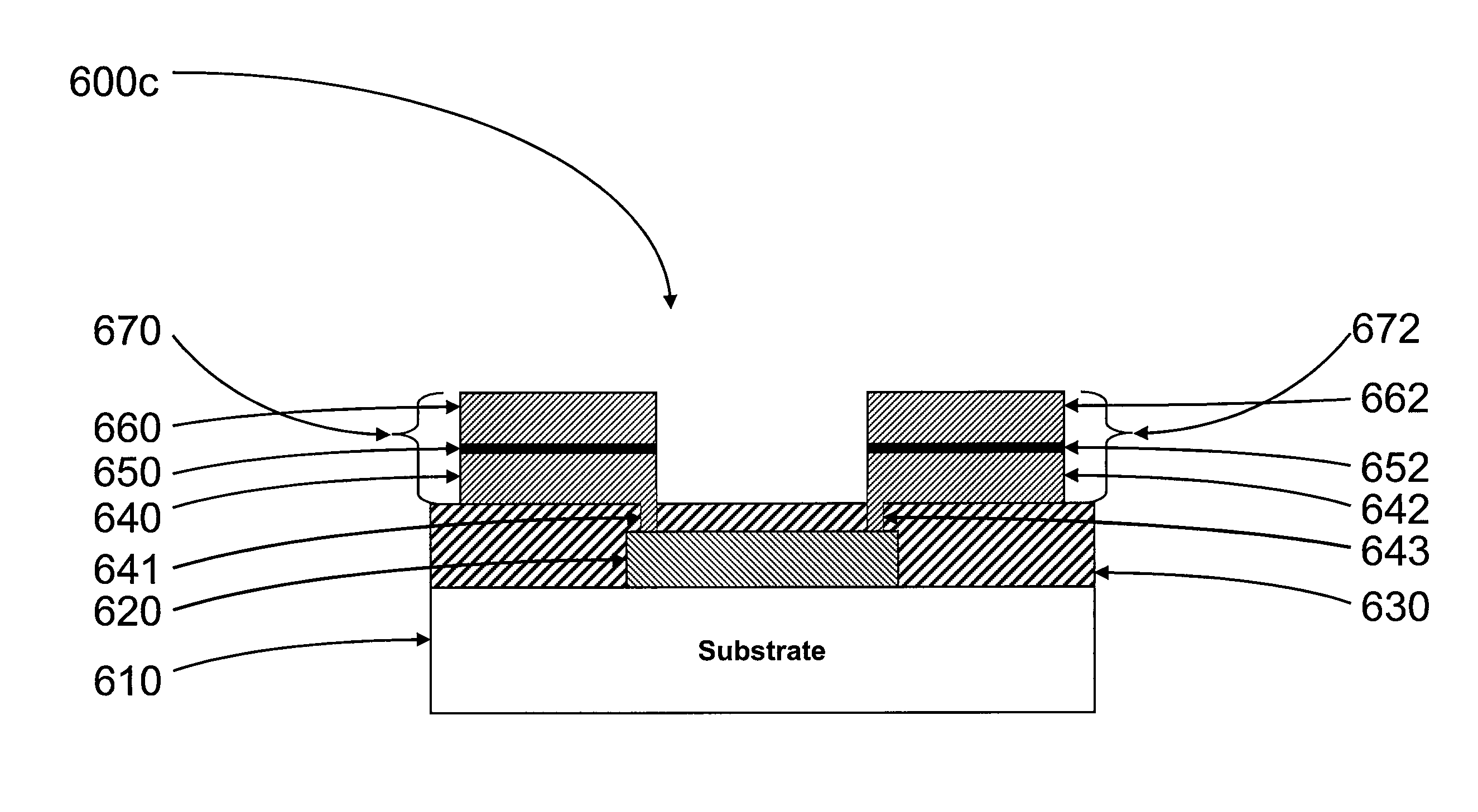

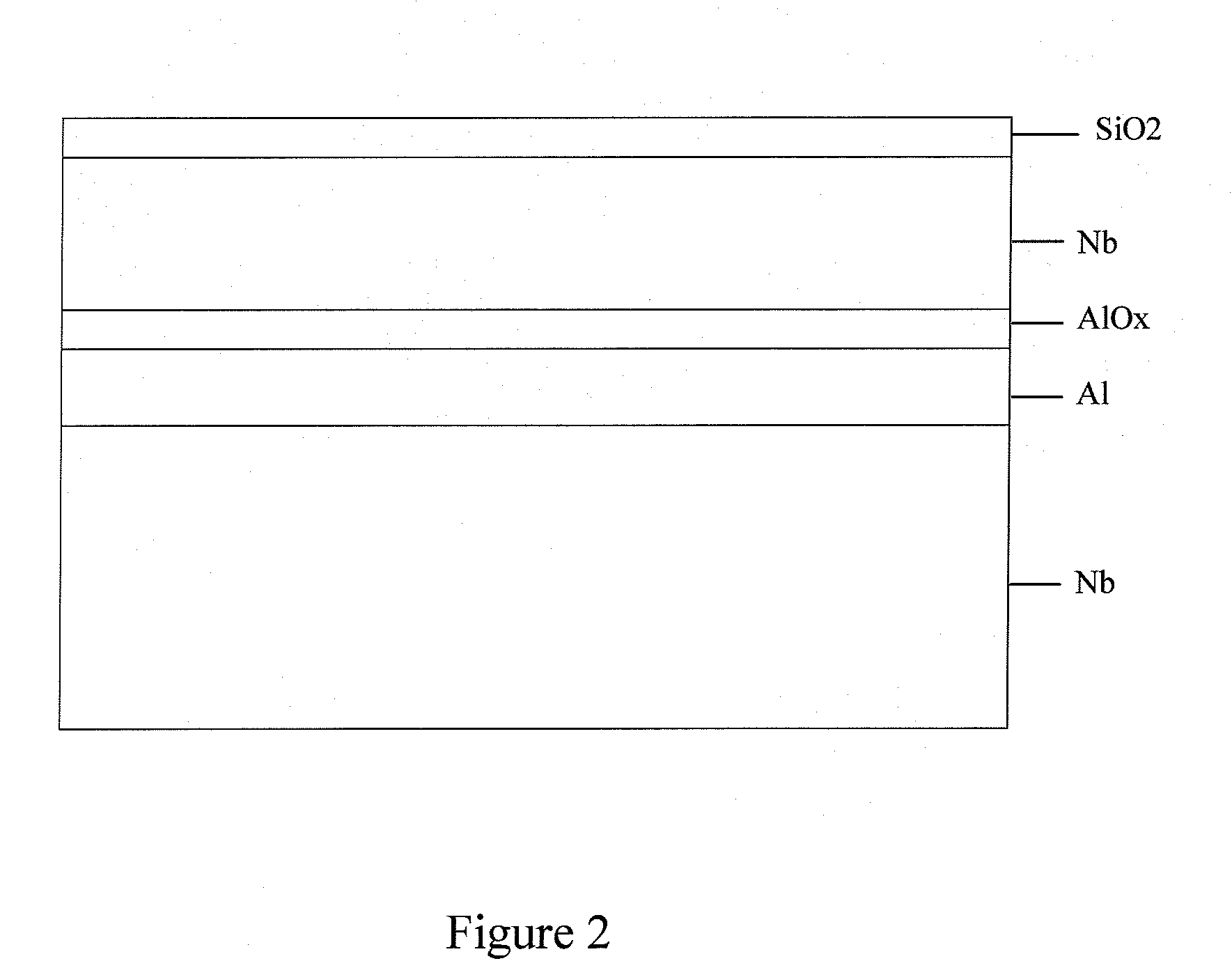

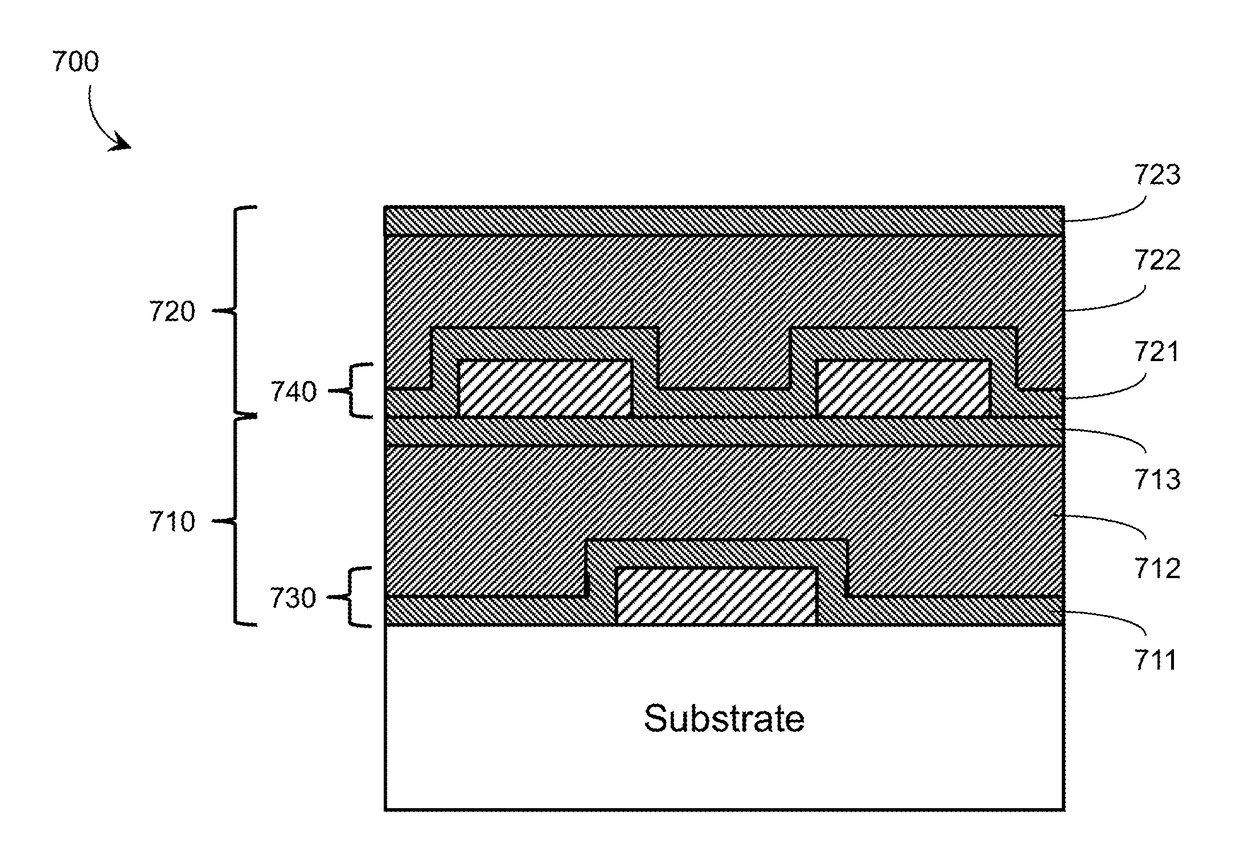

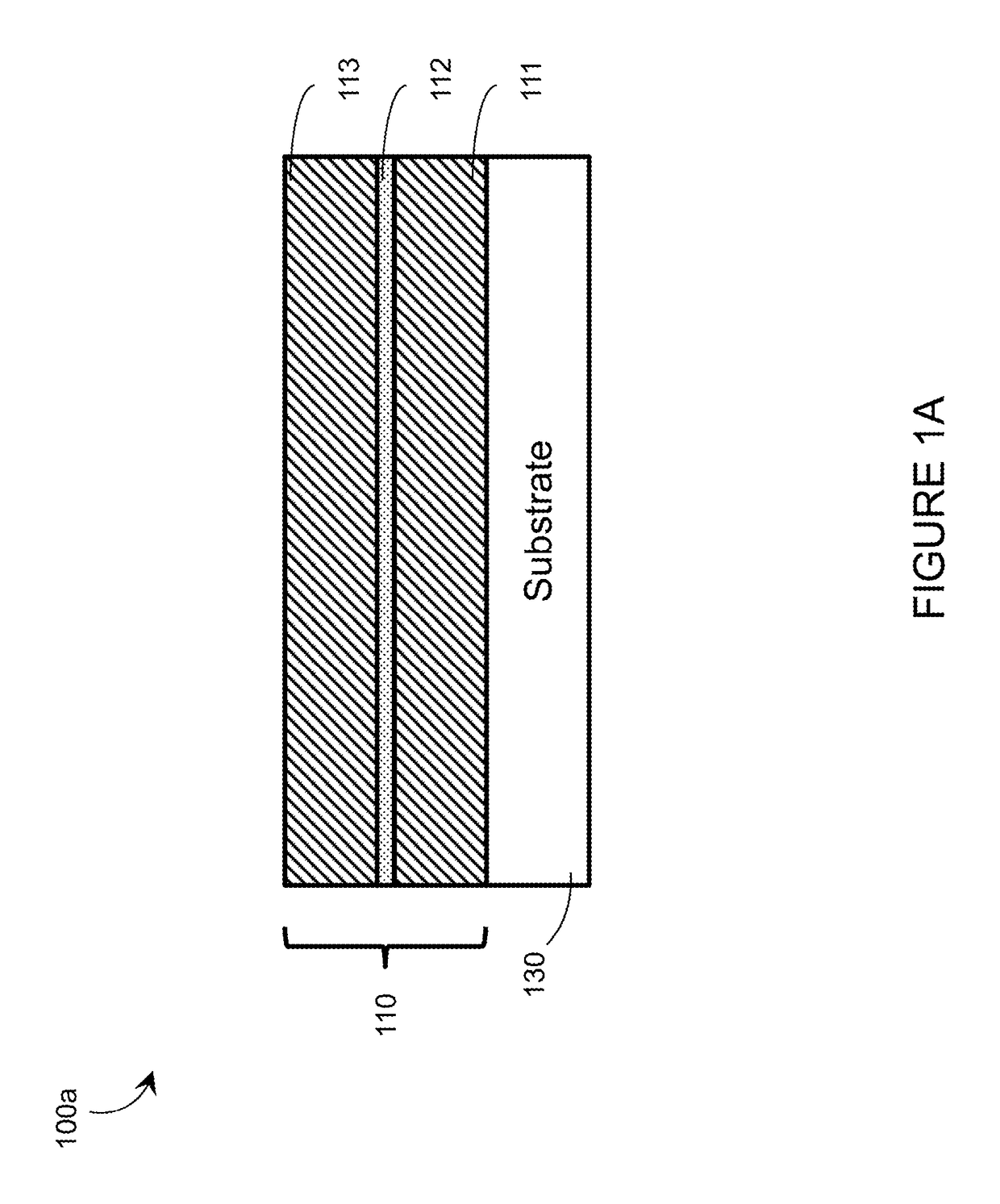

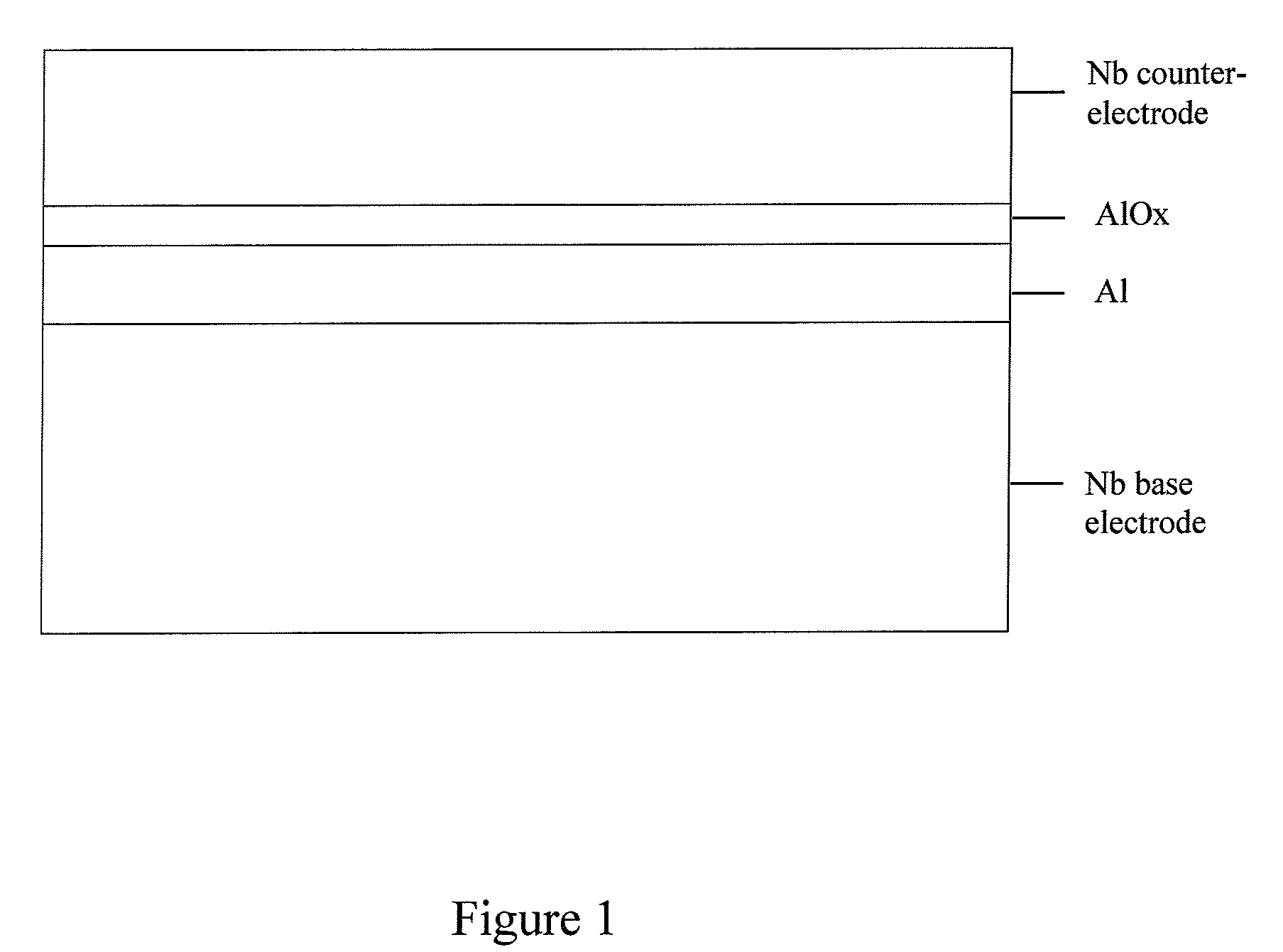

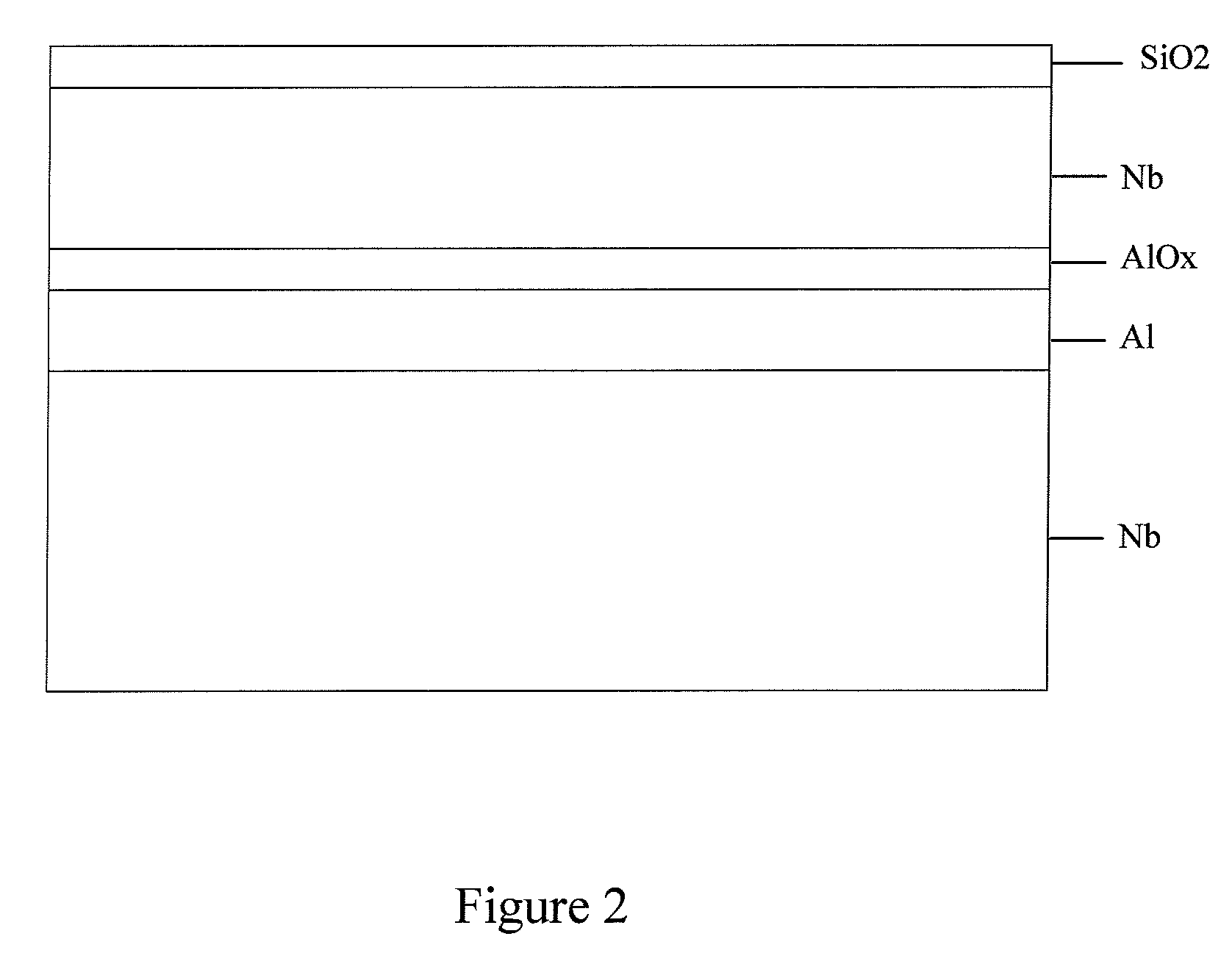

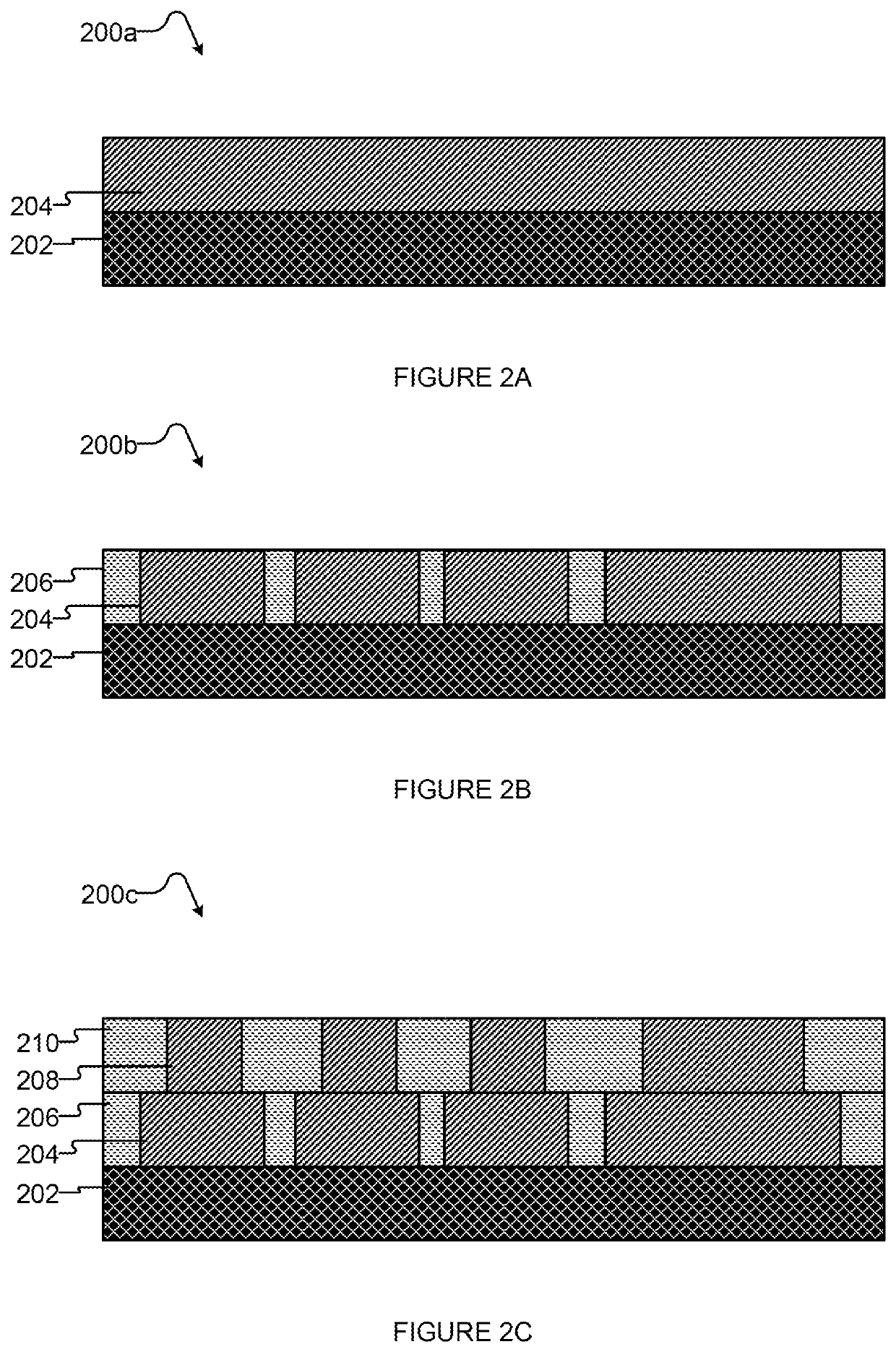

Various techniques and apparatus permit fabrication of superconductive circuits. A niobium / aluminum oxide / niobium trilayer may be formed and individual Josephson Junctions (JJs) formed. A protective cap may protect a JJ during fabrication. A hybrid dielectric may be formed. A superconductive integrated circuit may be formed using a subtractive patterning and / or additive patterning. A superconducting metal layer may be deposited by electroplating and / or polished by chemical-mechanical planarization. The thickness of an inner layer dielectric may be controlled by a deposition process. A substrate may include a base of silicon and top layer including aluminum oxide. Depositing of superconducting metal layer may be stopped or paused to allow cooling before completion. Multiple layers may be aligned by patterning an alignment marker in a superconducting metal layer.

Owner:D WAVE SYSTEMS INC

System and method for providing multi-conductive layer metallic interconnects for superconducting integrated circuits

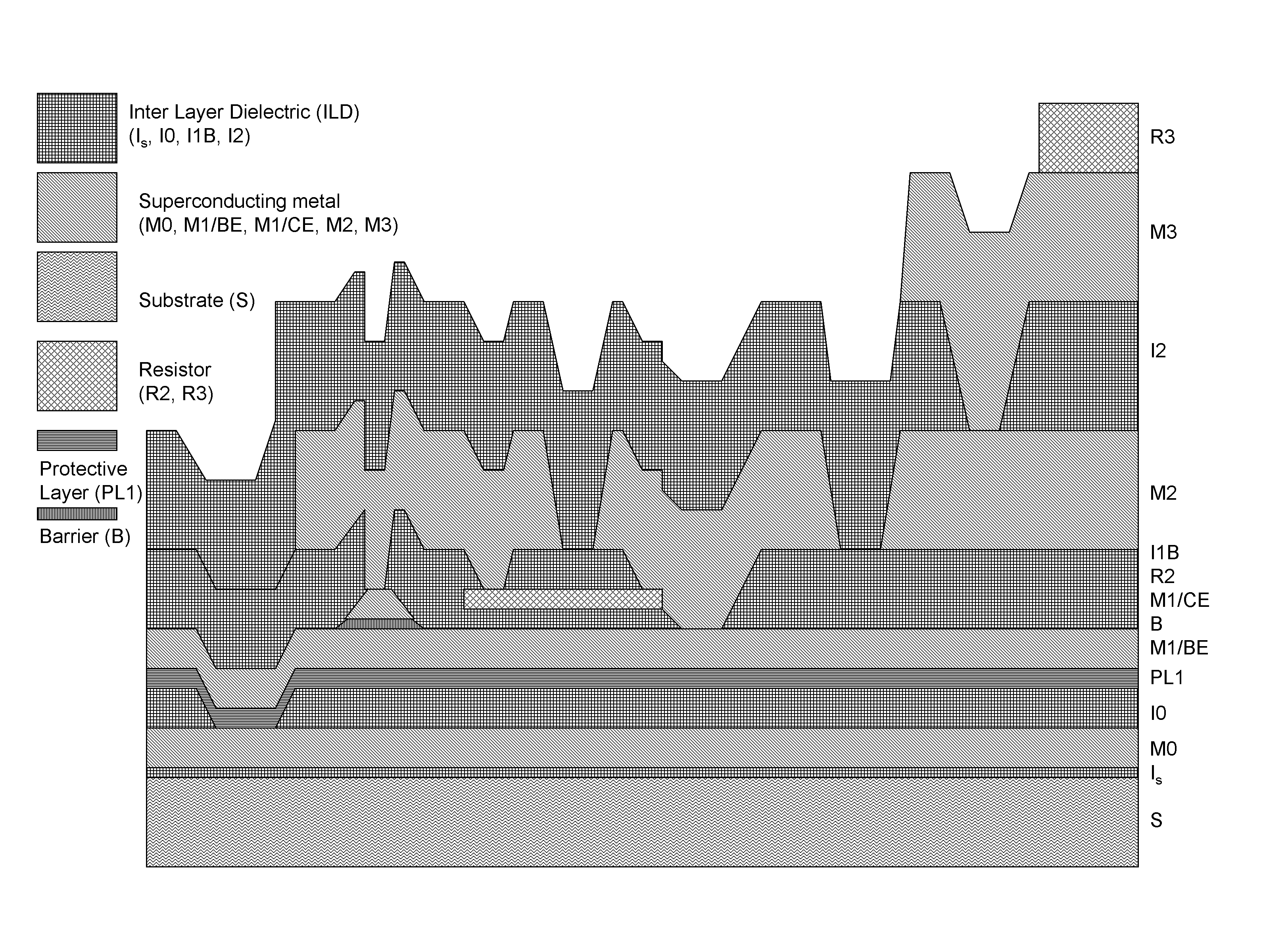

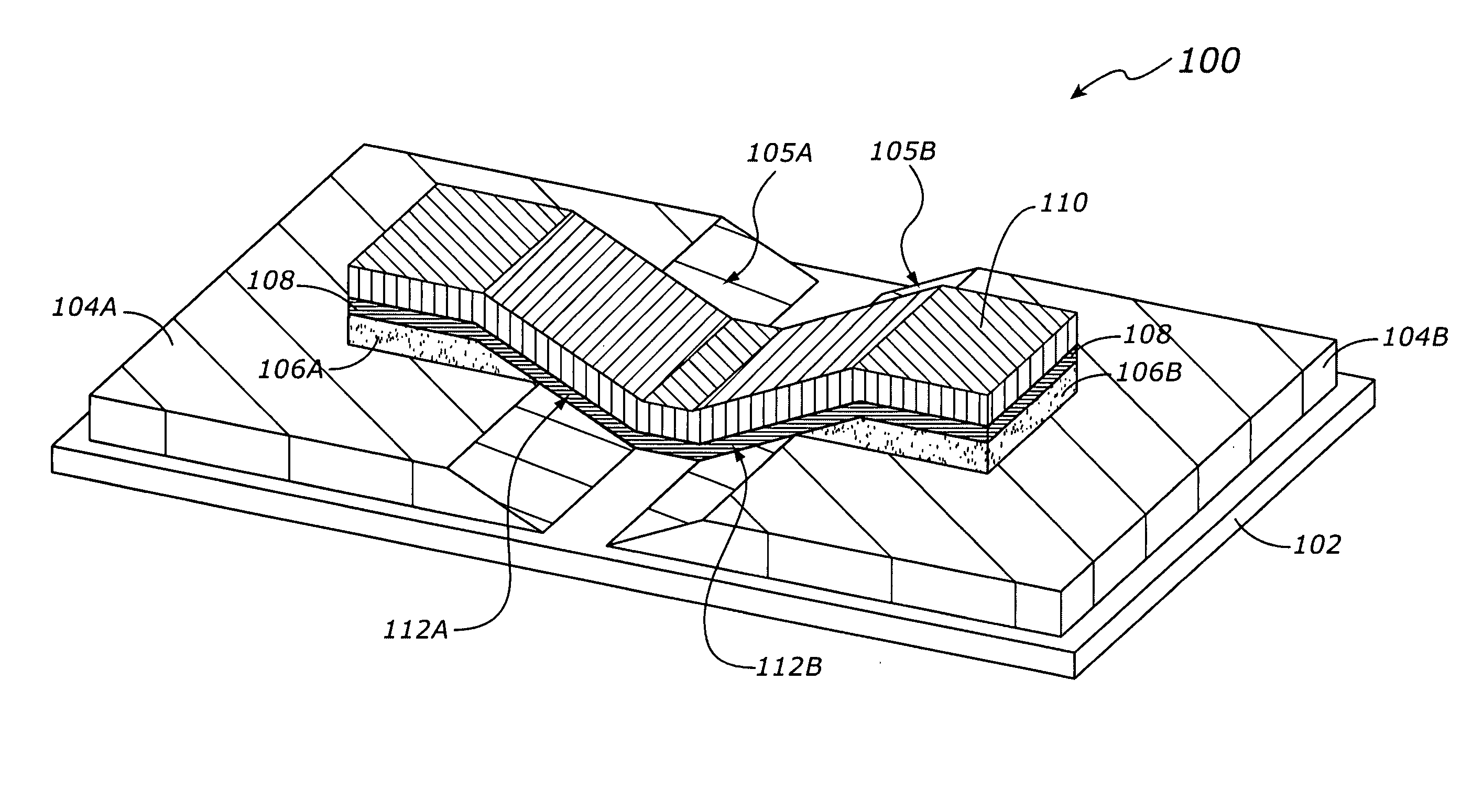

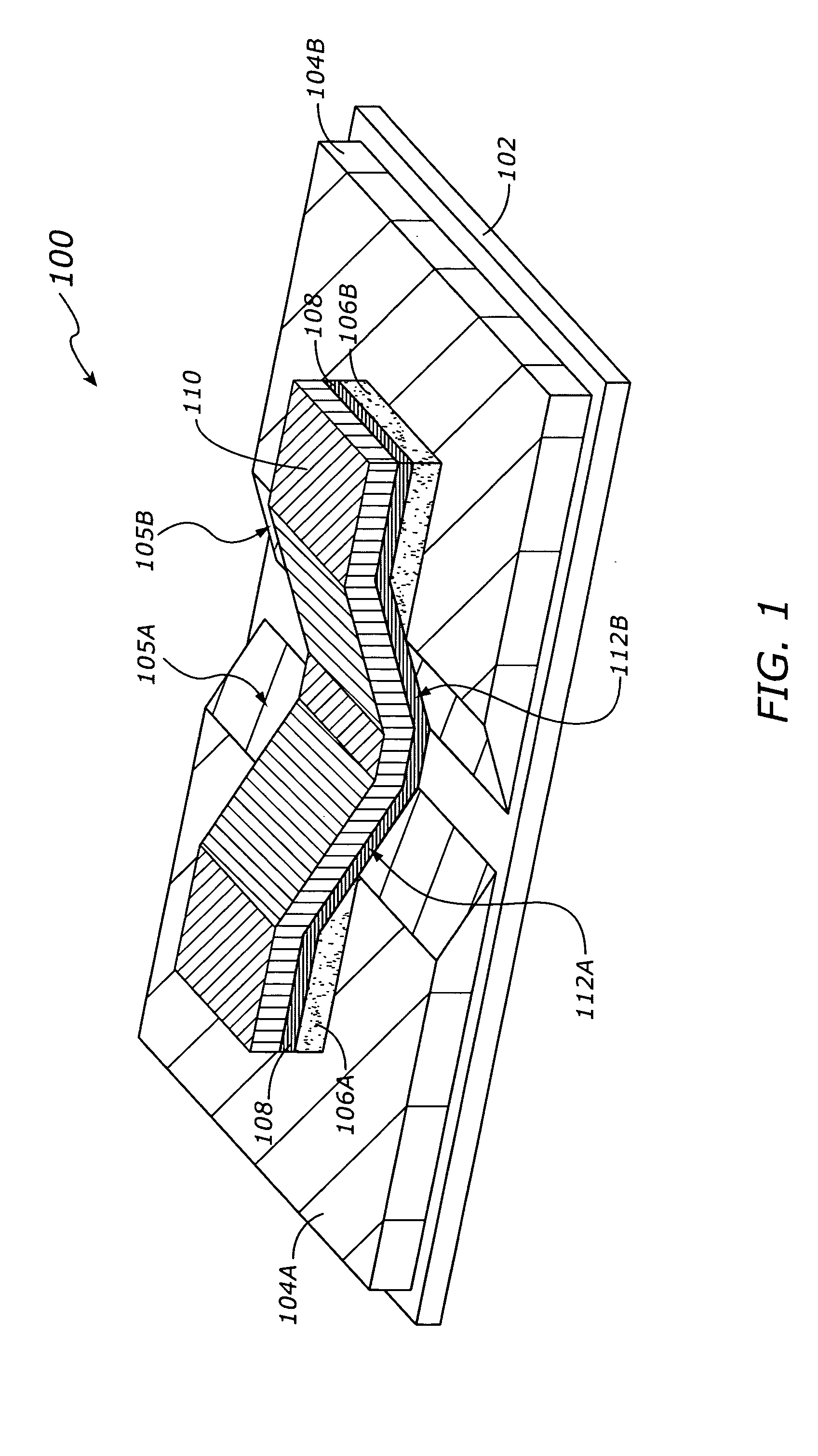

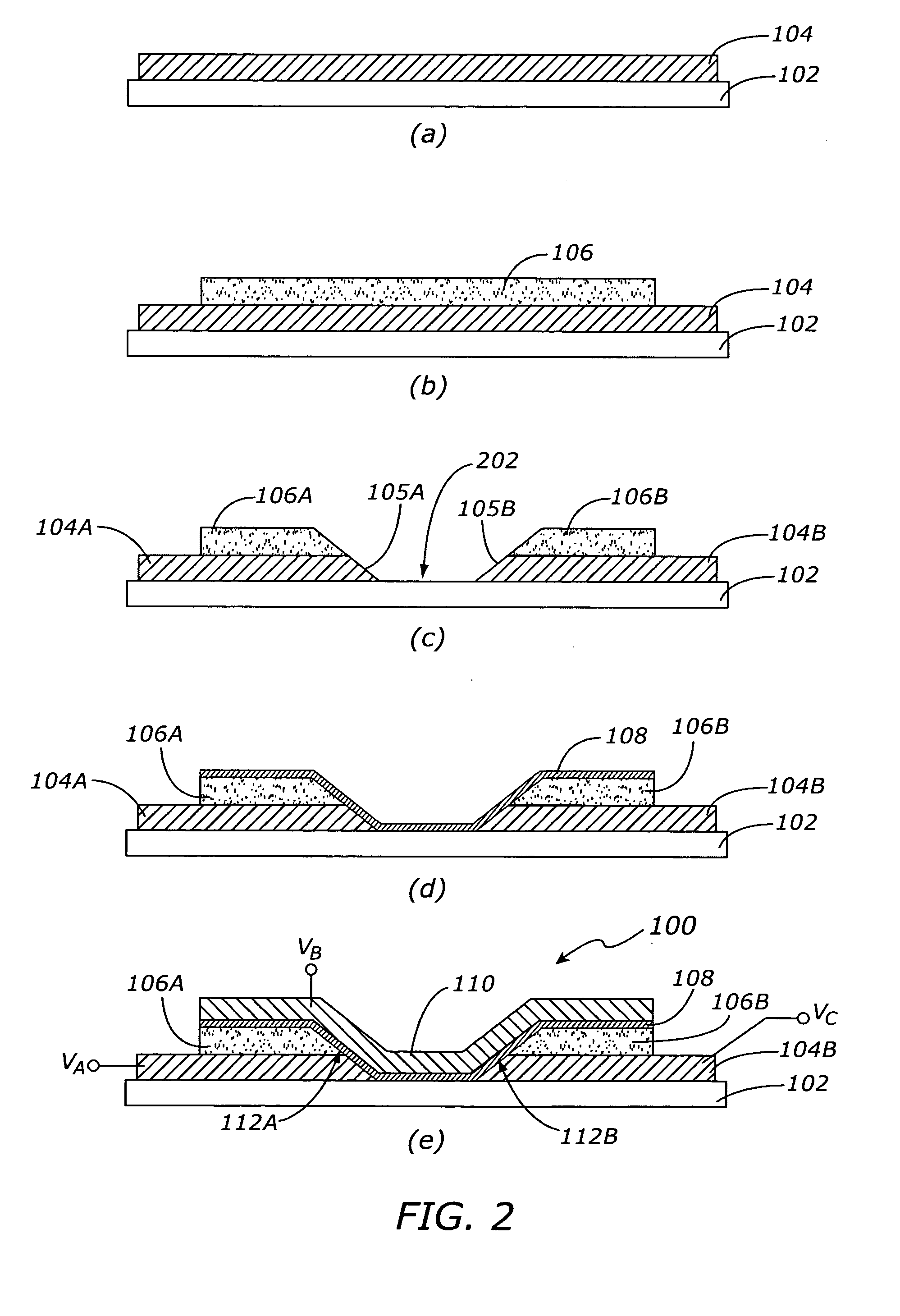

ActiveUS8437818B1Reduce and prevent diffusion of impurityReduce non-uniformitySuperconductors/hyperconductorsSemiconductor/solid-state device detailsImpurity diffusionRapid single flux quantum

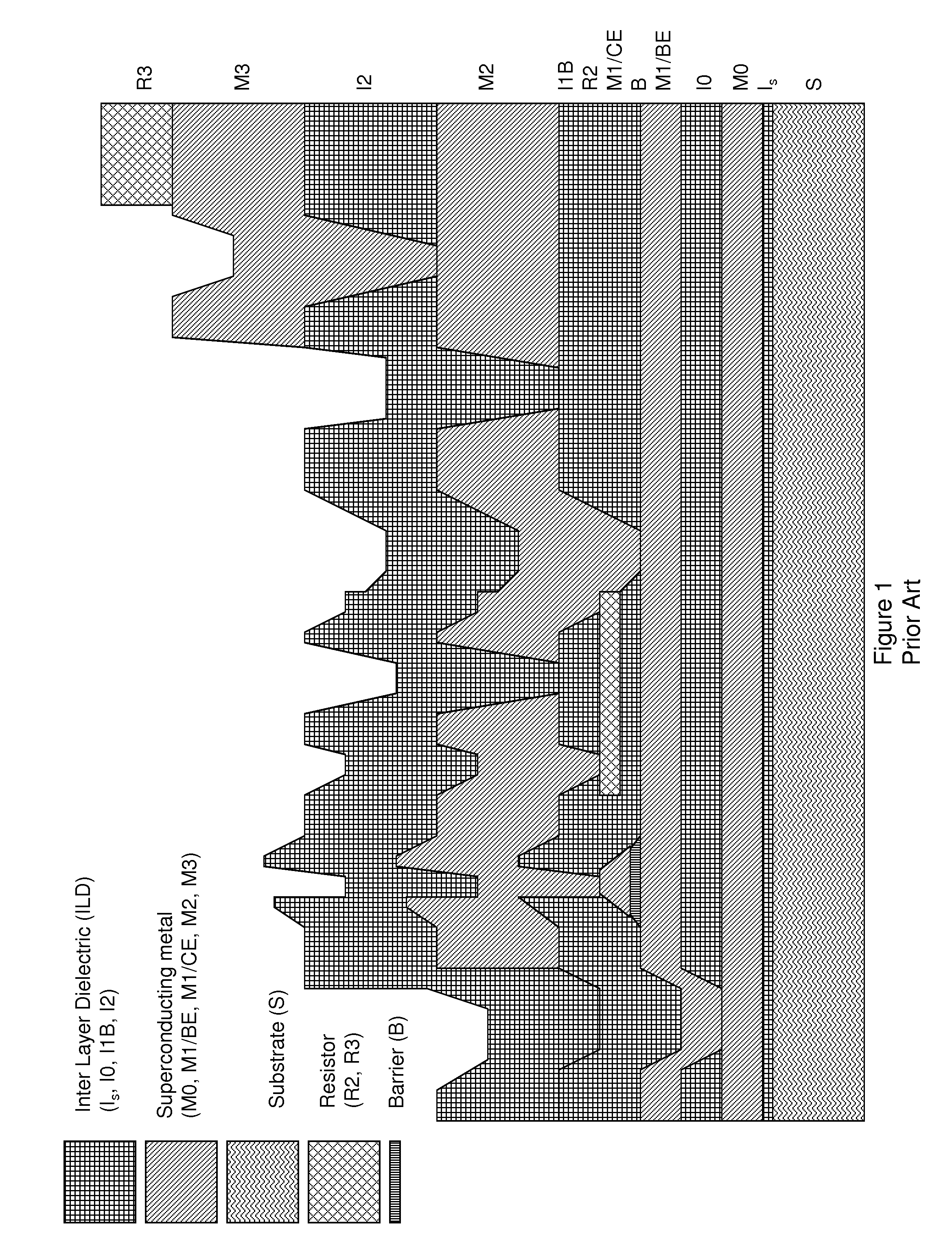

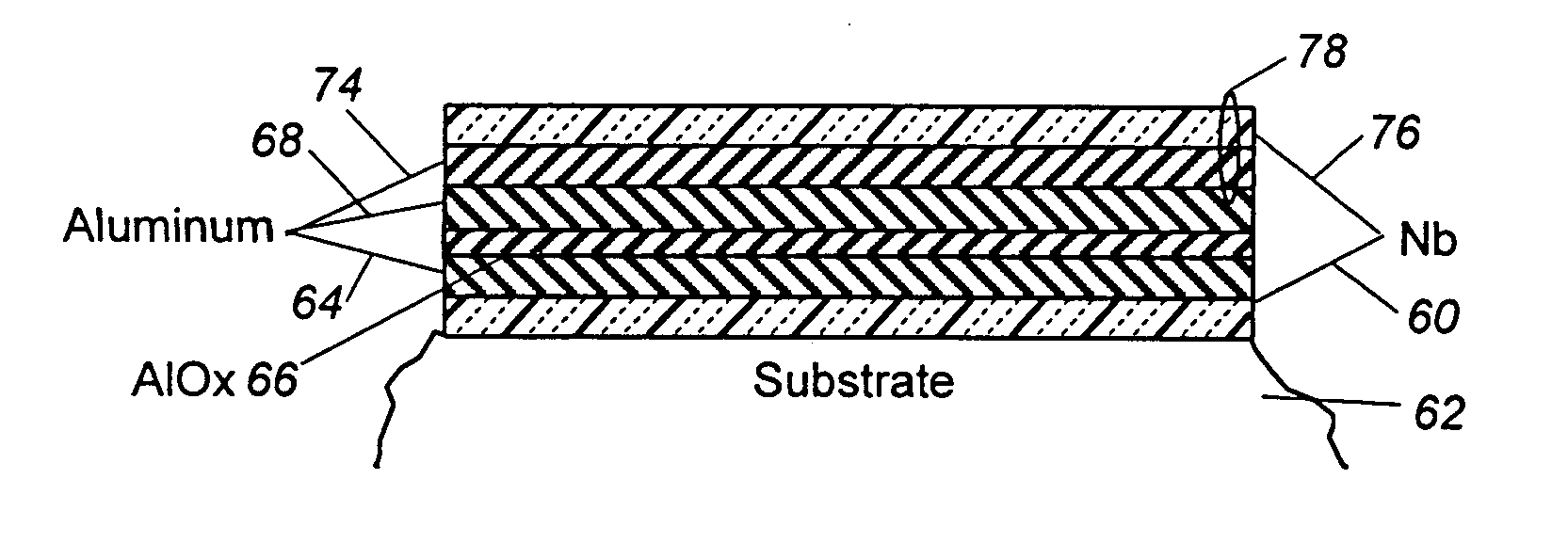

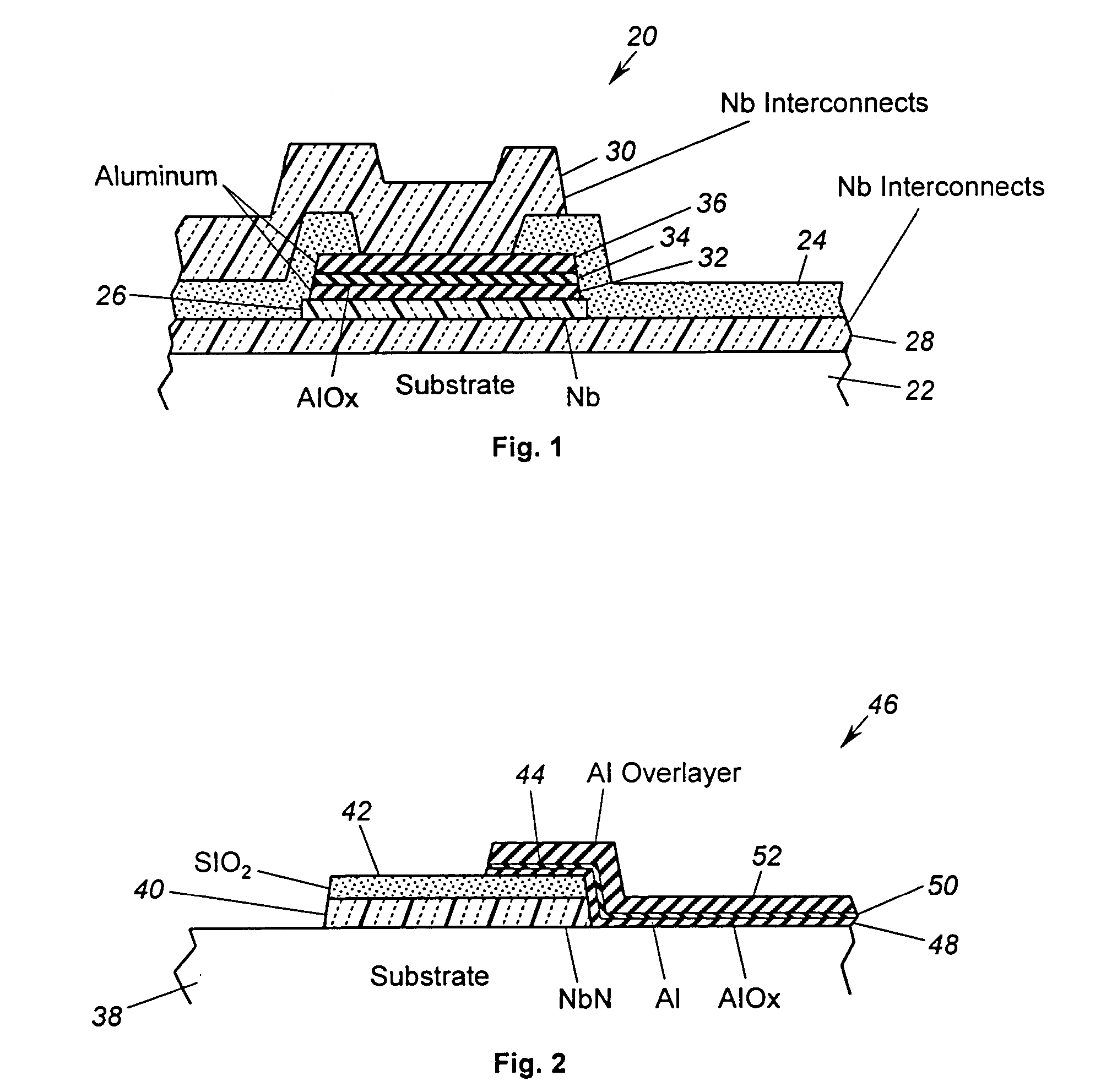

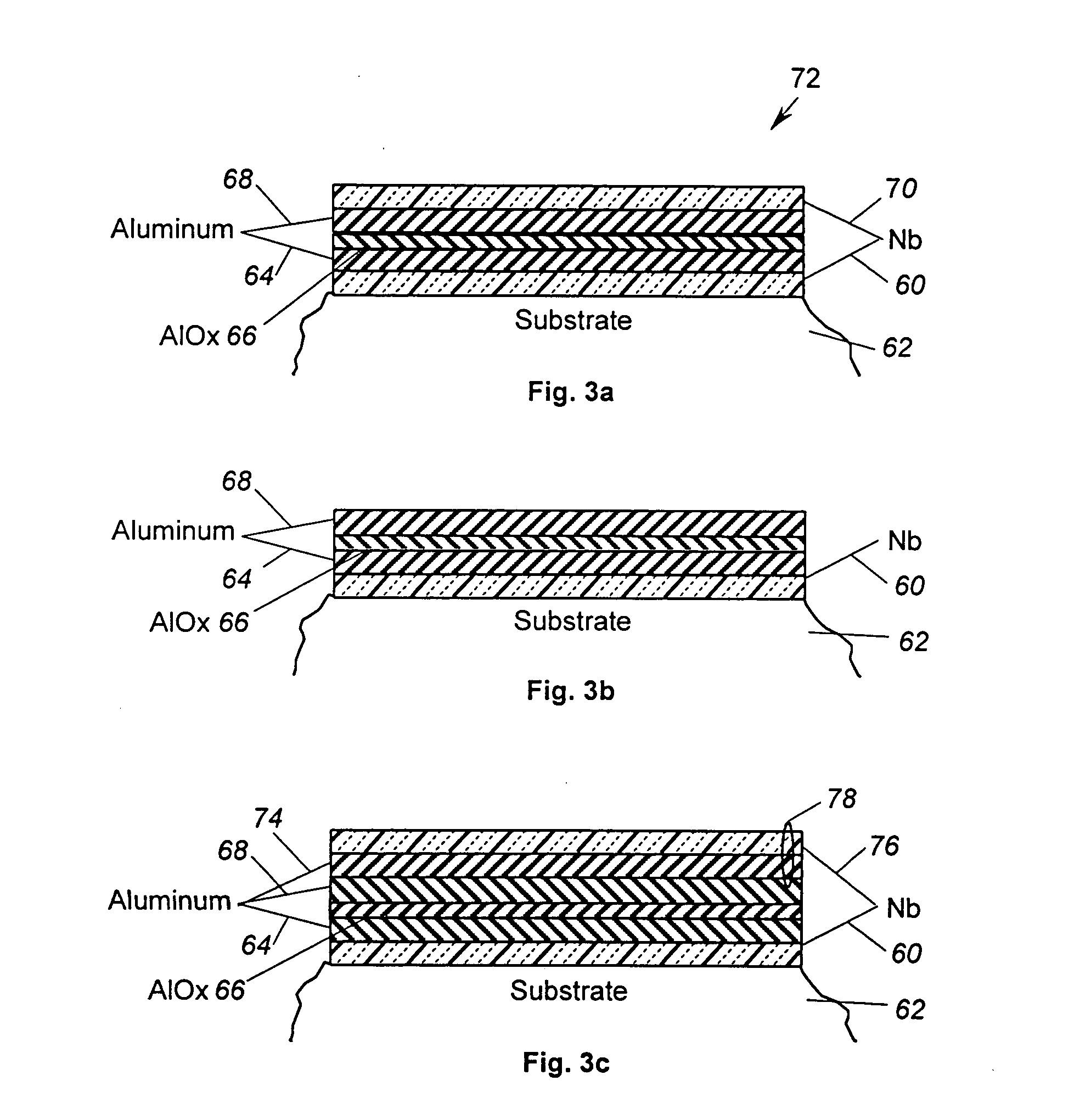

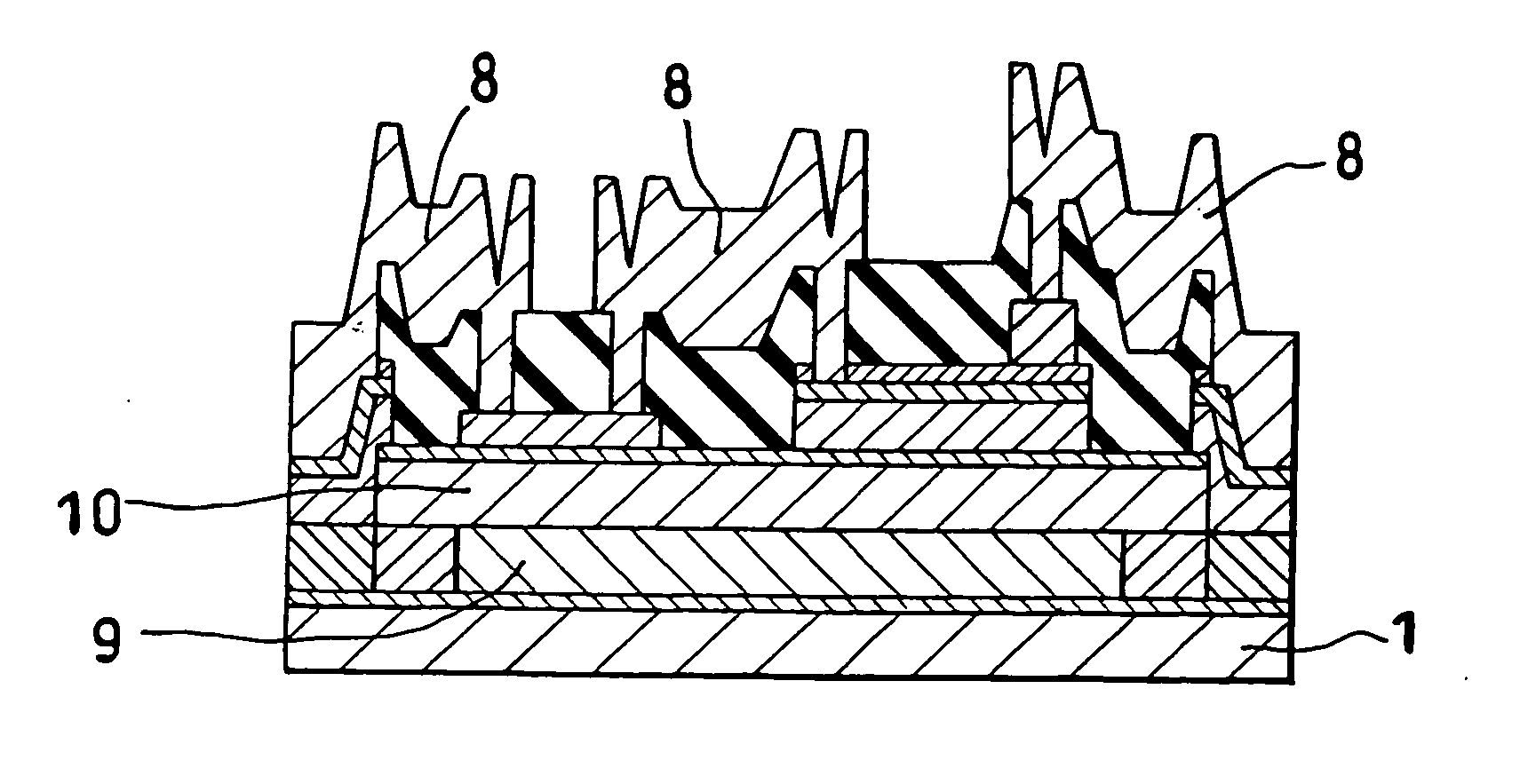

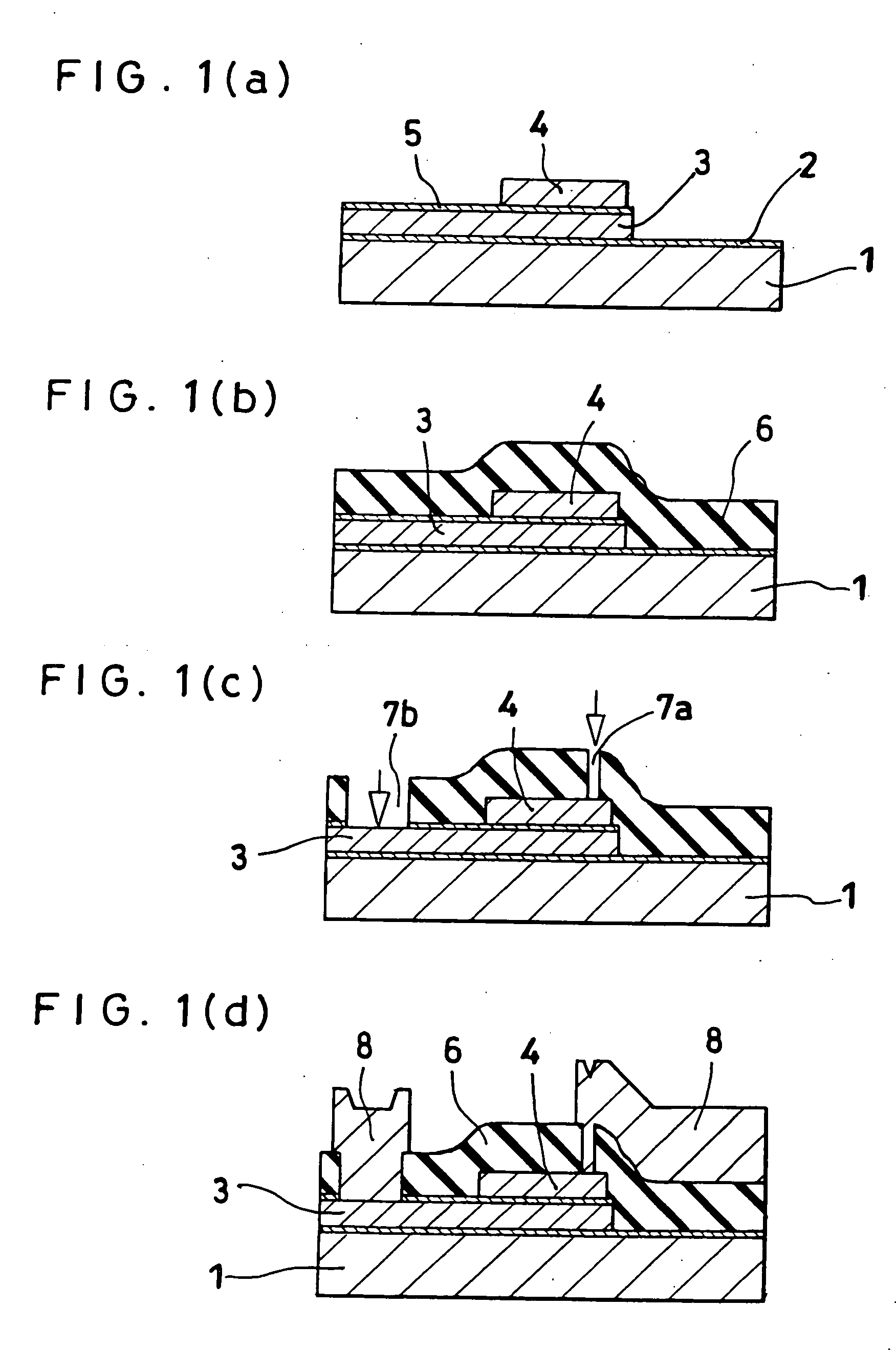

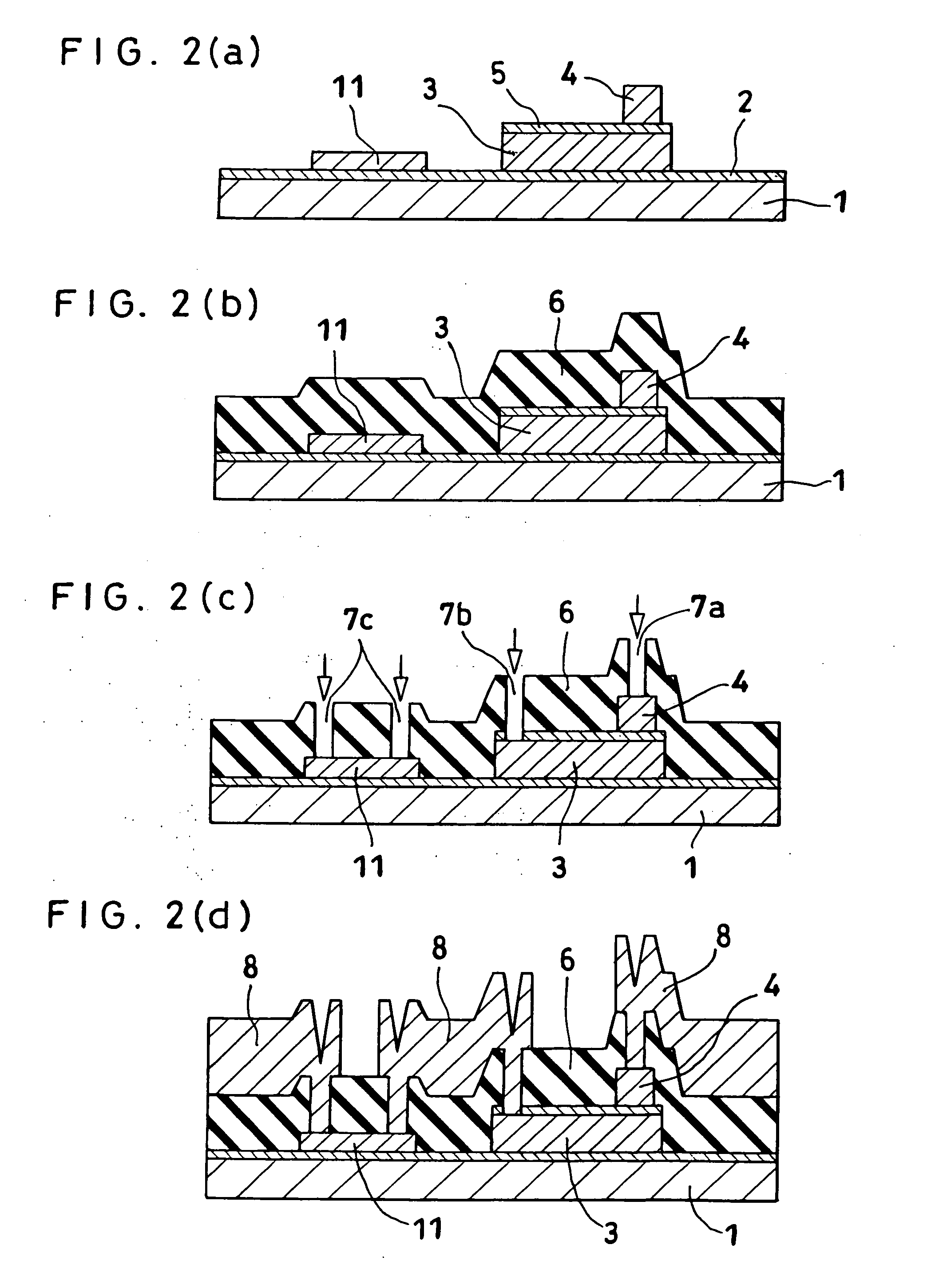

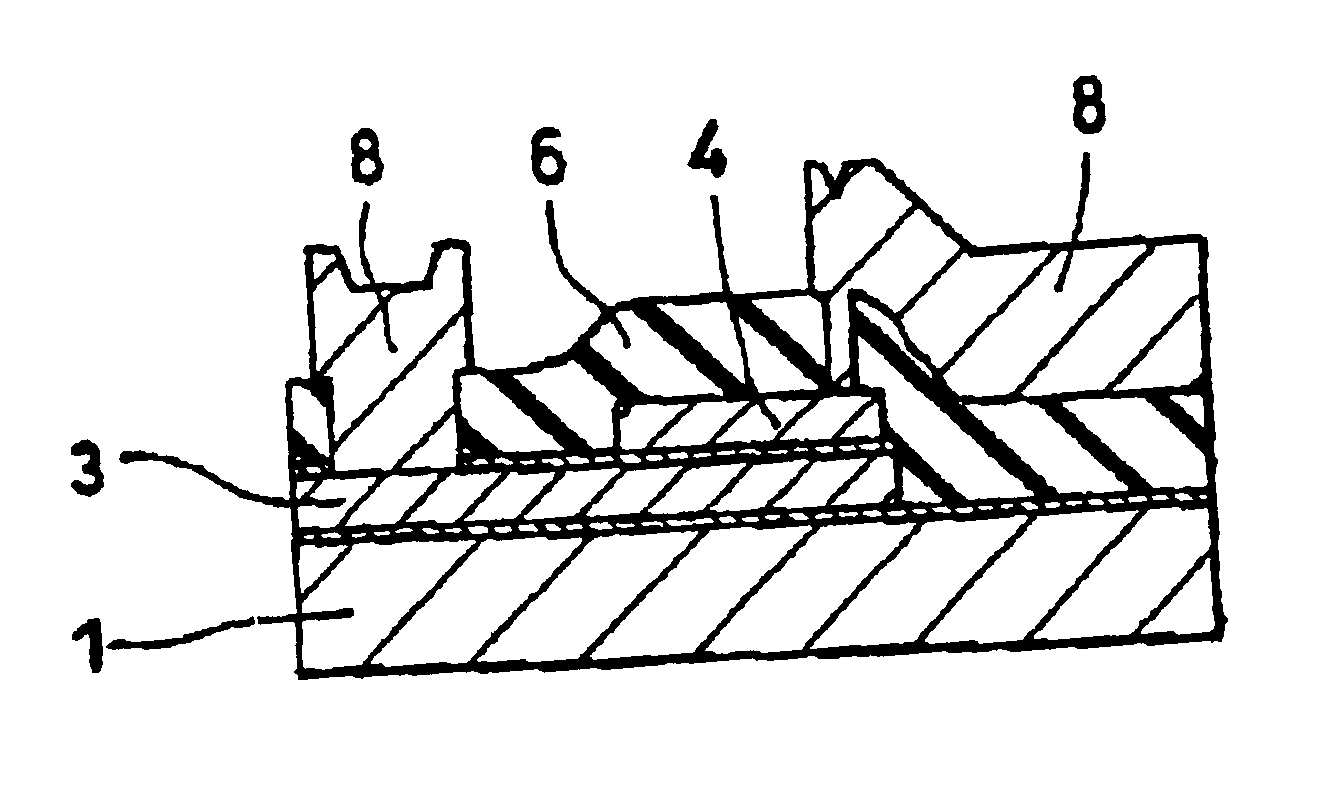

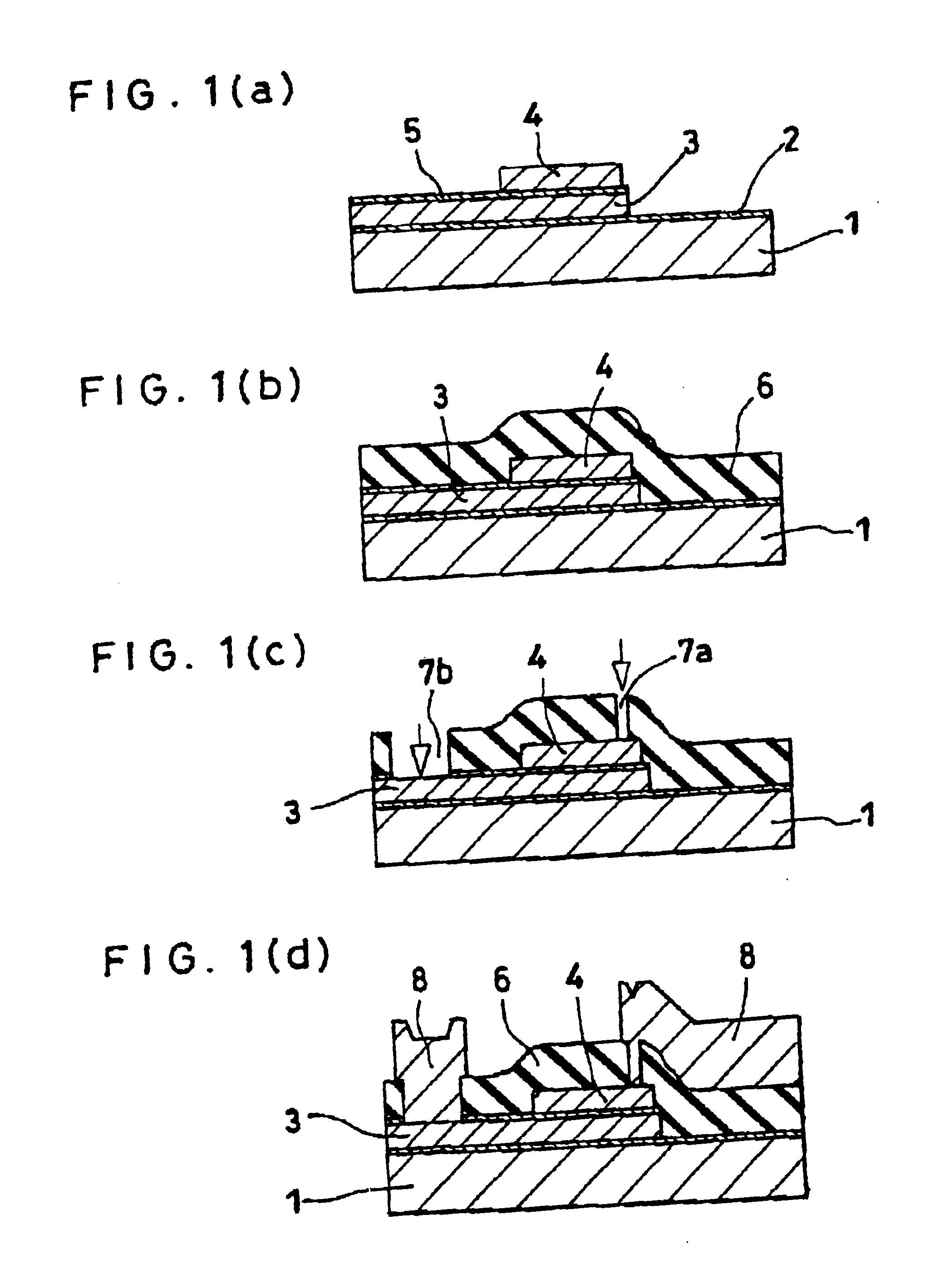

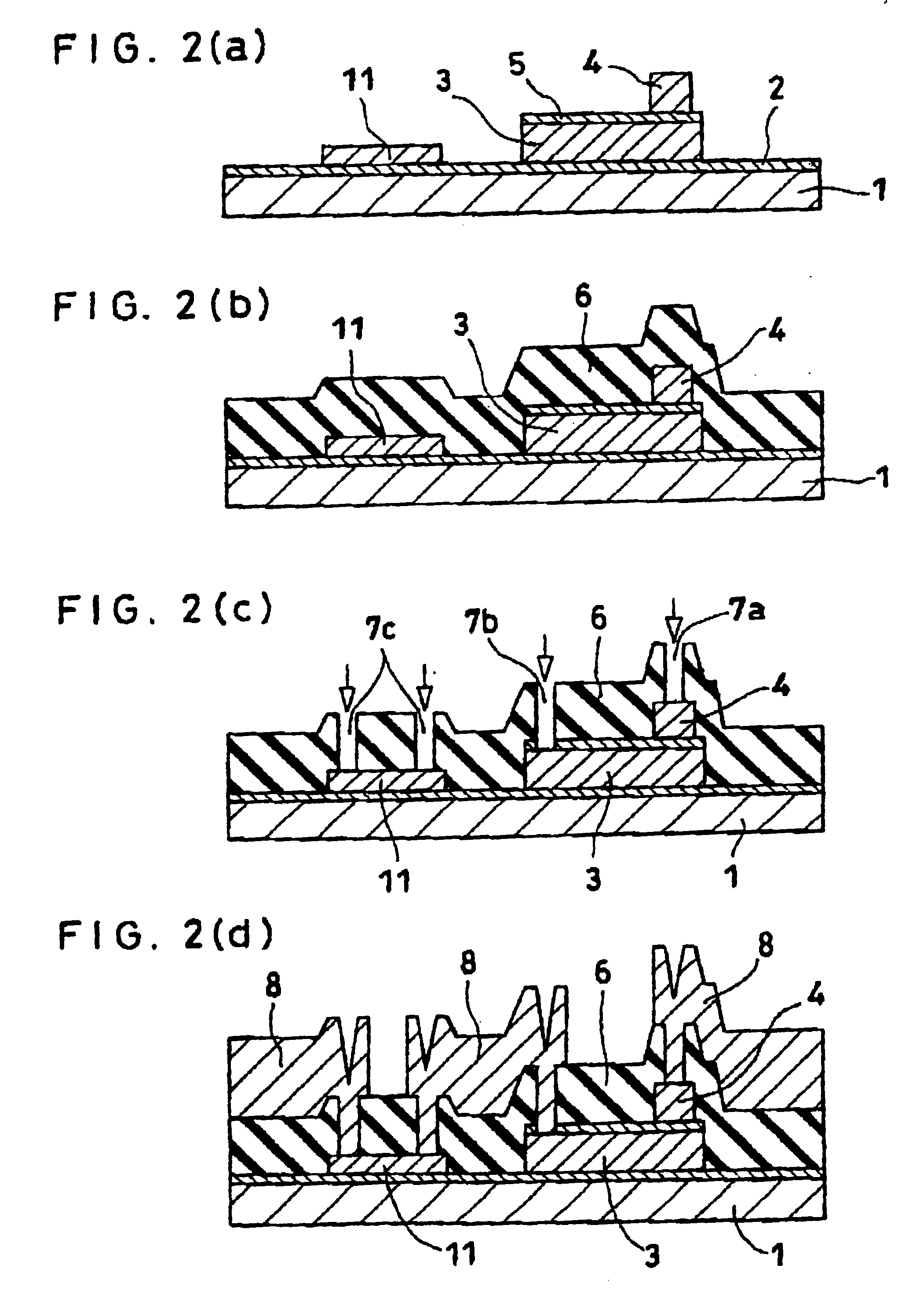

Superconducting integrated circuits require several wiring layers to distribute bias and signals across the circuit, which must cross each other both with and without contacts. All wiring lines and contacts must be fully superconducting, and in the prior art each wiring layer comprises a single metallic thin film. An alternative wiring layer is disclosed that comprises sequential layers of two or more different metals. Such a multi-metallic wiring layer may offer improved resistance to impurity diffusion, better surface passivation, and / or reduction of stress, beyond that which is attainable with a single-metallic wiring layer. The resulting process leads to improved margin and yield in an integrated circuit comprising a plurality of Josephson junctions. Several preferred embodiments are disclosed, for both planarized and non-planarized processes. These preferred and other methods may be applied to digital circuits based on Rapid Single Flux Quantum logic, and to quantum computing using Josephson junction qubits.

Owner:SEEQC INC

Low-power biasing networks for superconducting integrated circuits

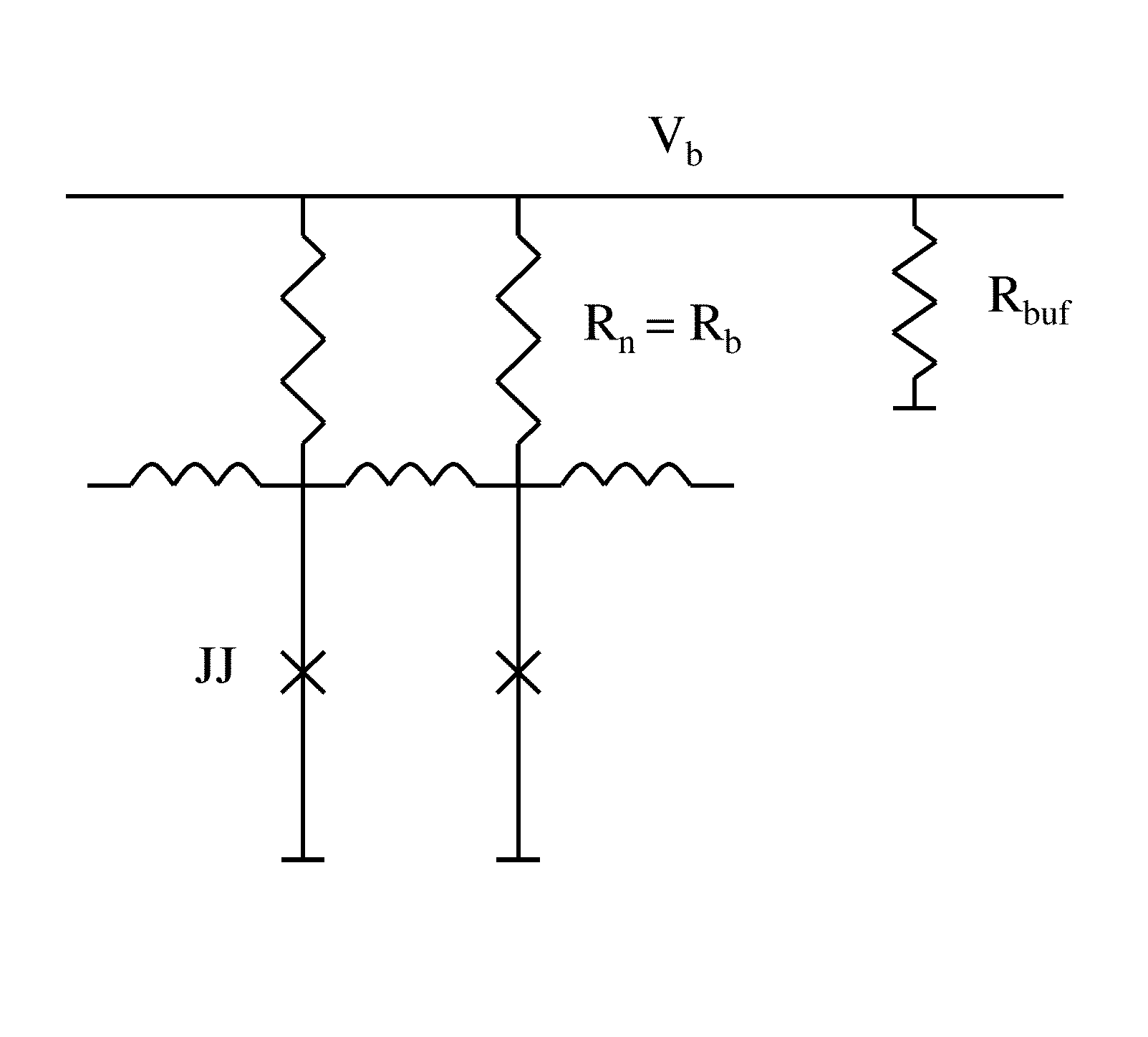

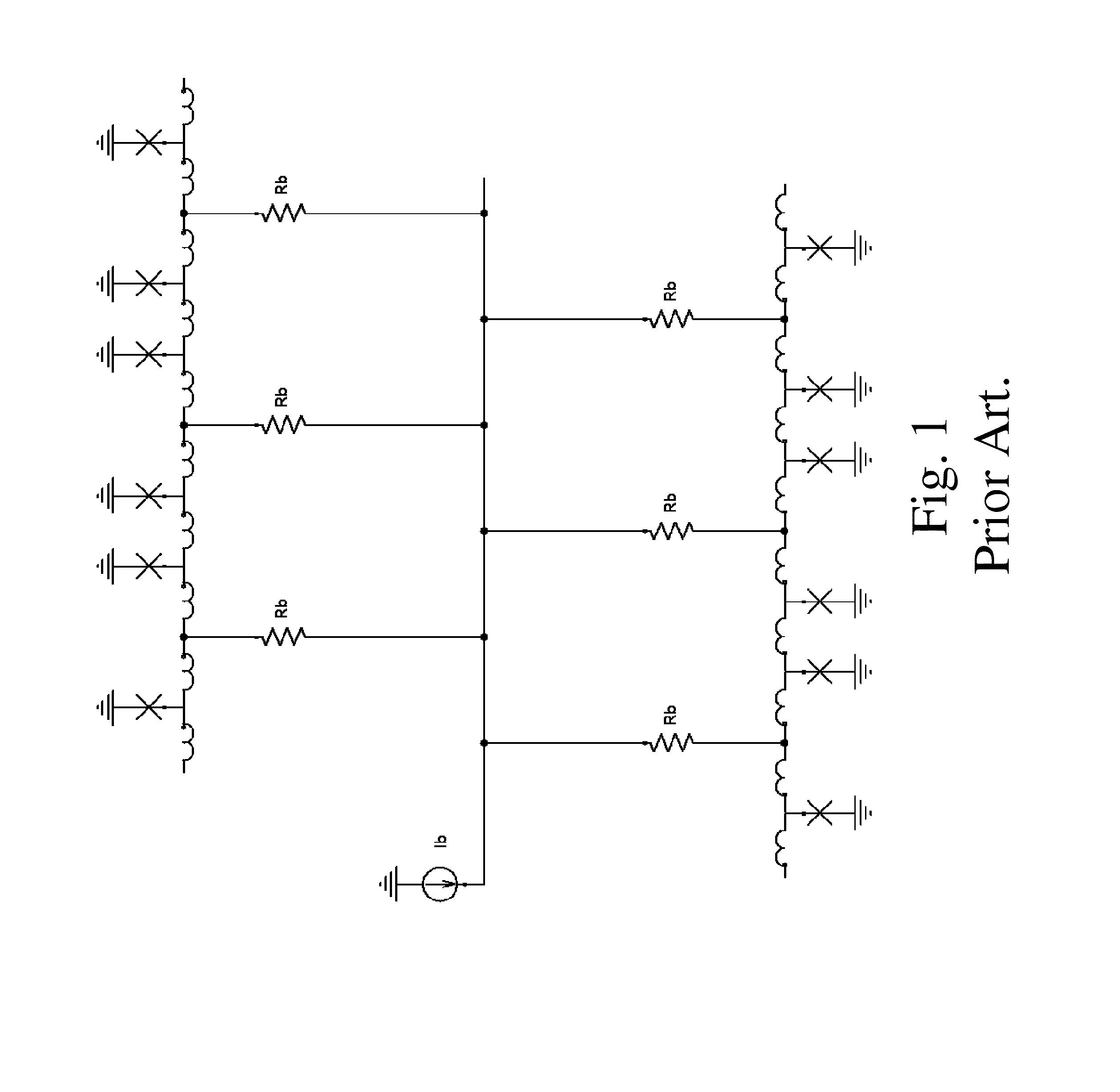

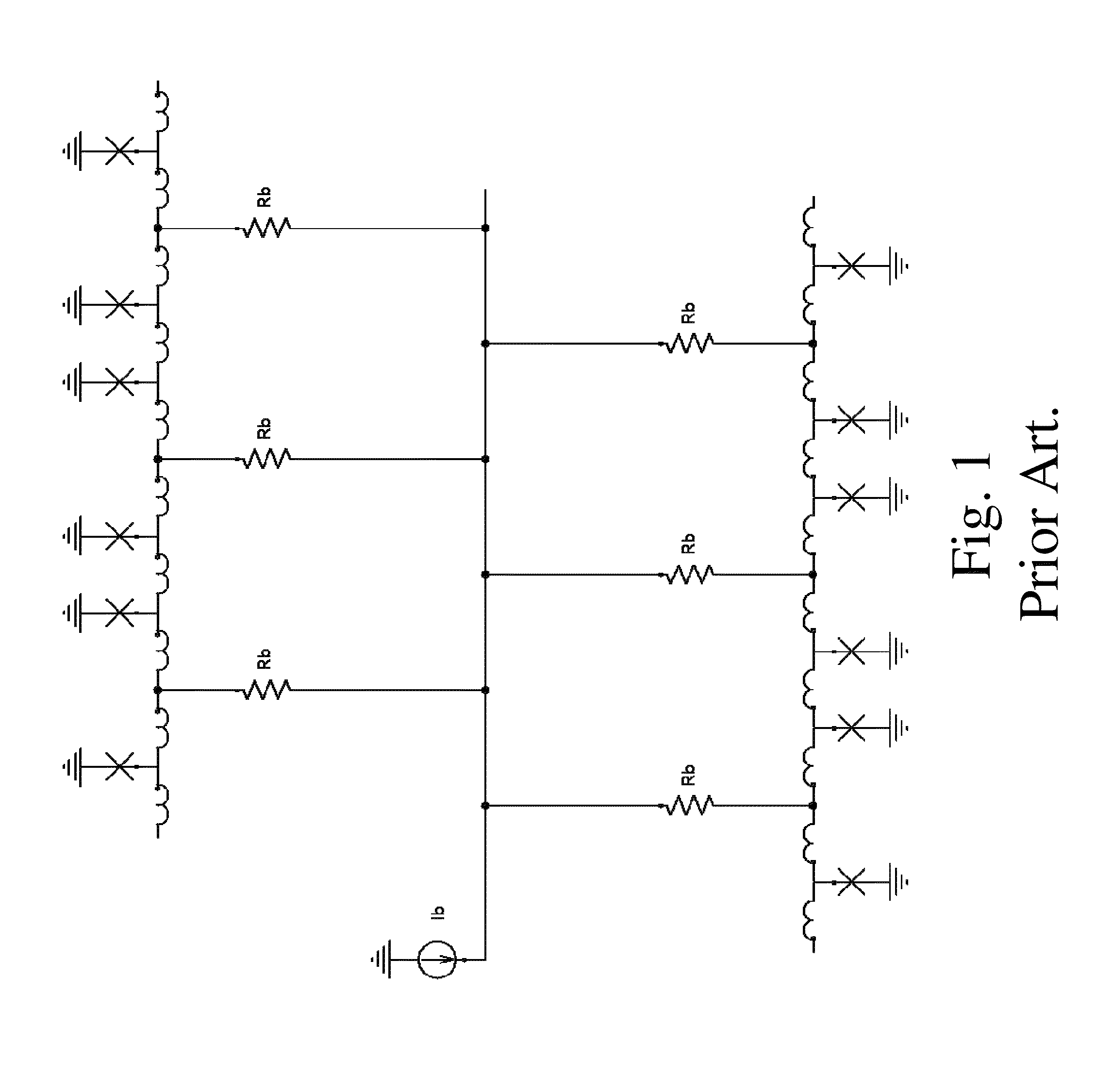

ActiveUS8571614B1Maintain stabilityHigh dynamic impedanceSemiconductor/solid-state device detailsSolid-state devicesEngineeringSuperconducting integrated circuits

A superconducting integrated circuit, comprising a plurality of superconducting circuit elements, each having a variation in operating voltage over time; a common power line; and a plurality of bias circuits, each connected to the common power line, and to a respective superconducting circuit element, wherein each respective bias circuit is superconducting during at least one time portion of the operation of a respective superconducting circuit element, and is configured to supply the variation in operating voltage over time to the respective superconducting circuit element.

Owner:SEEQC INC

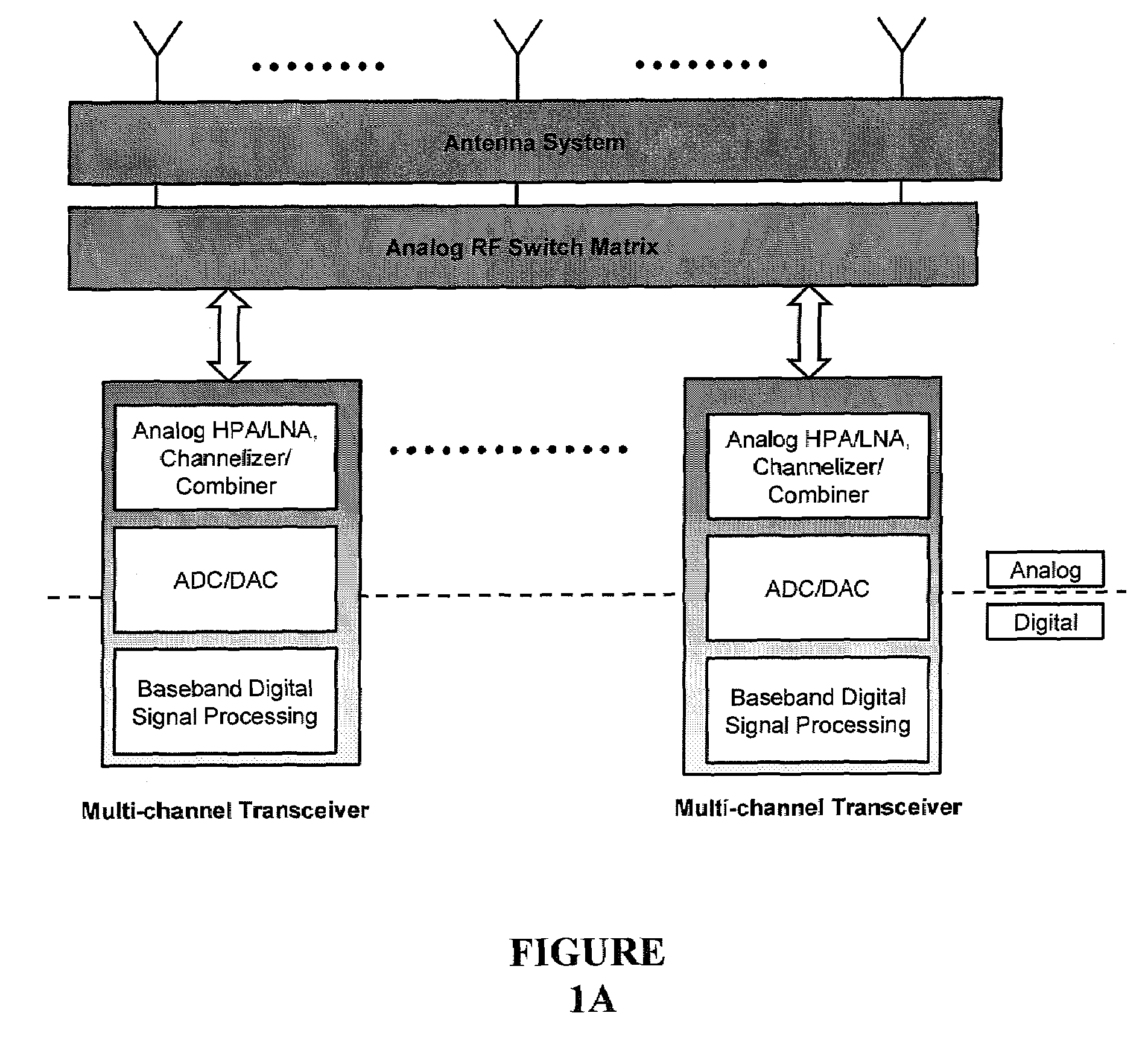

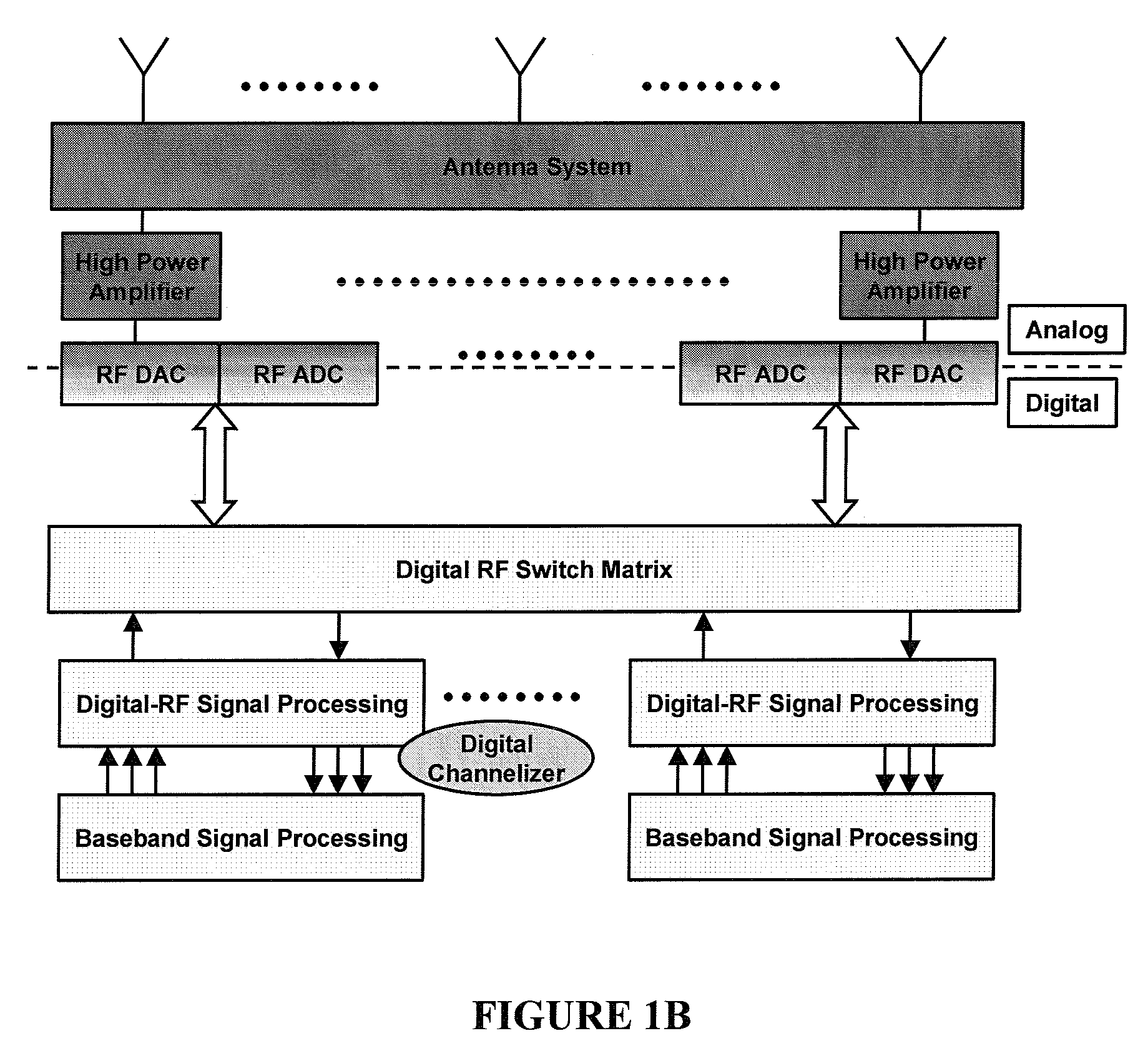

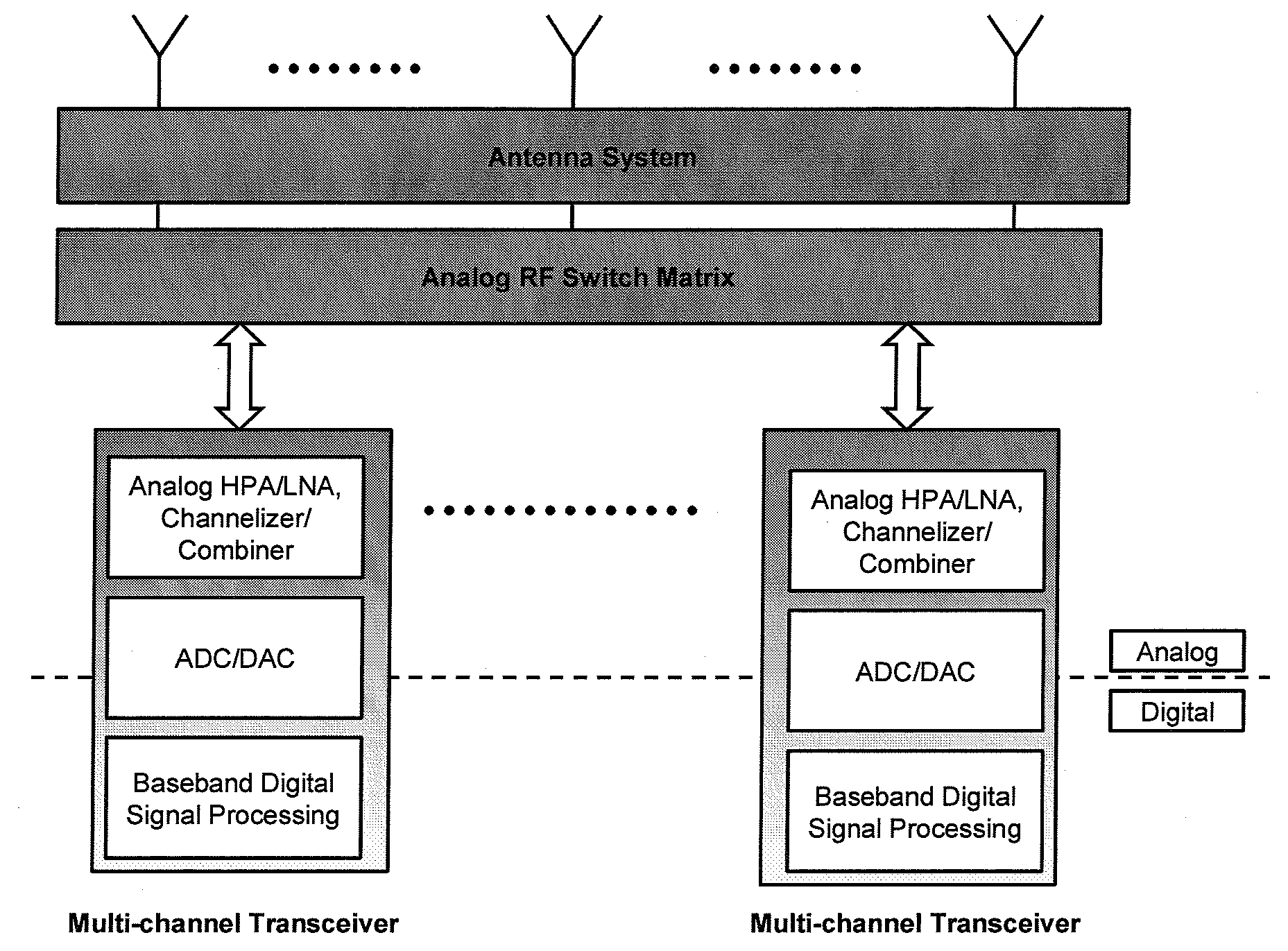

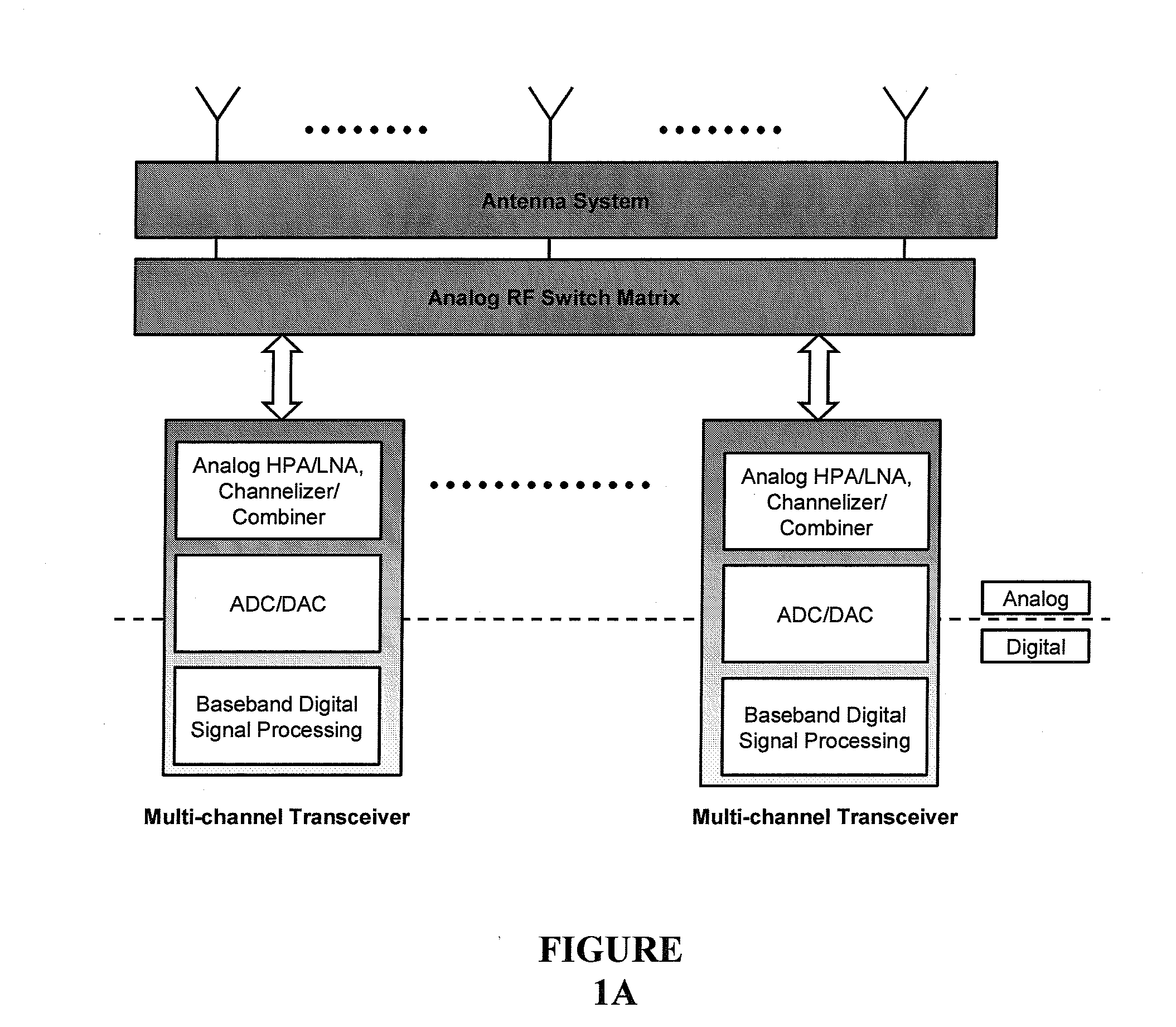

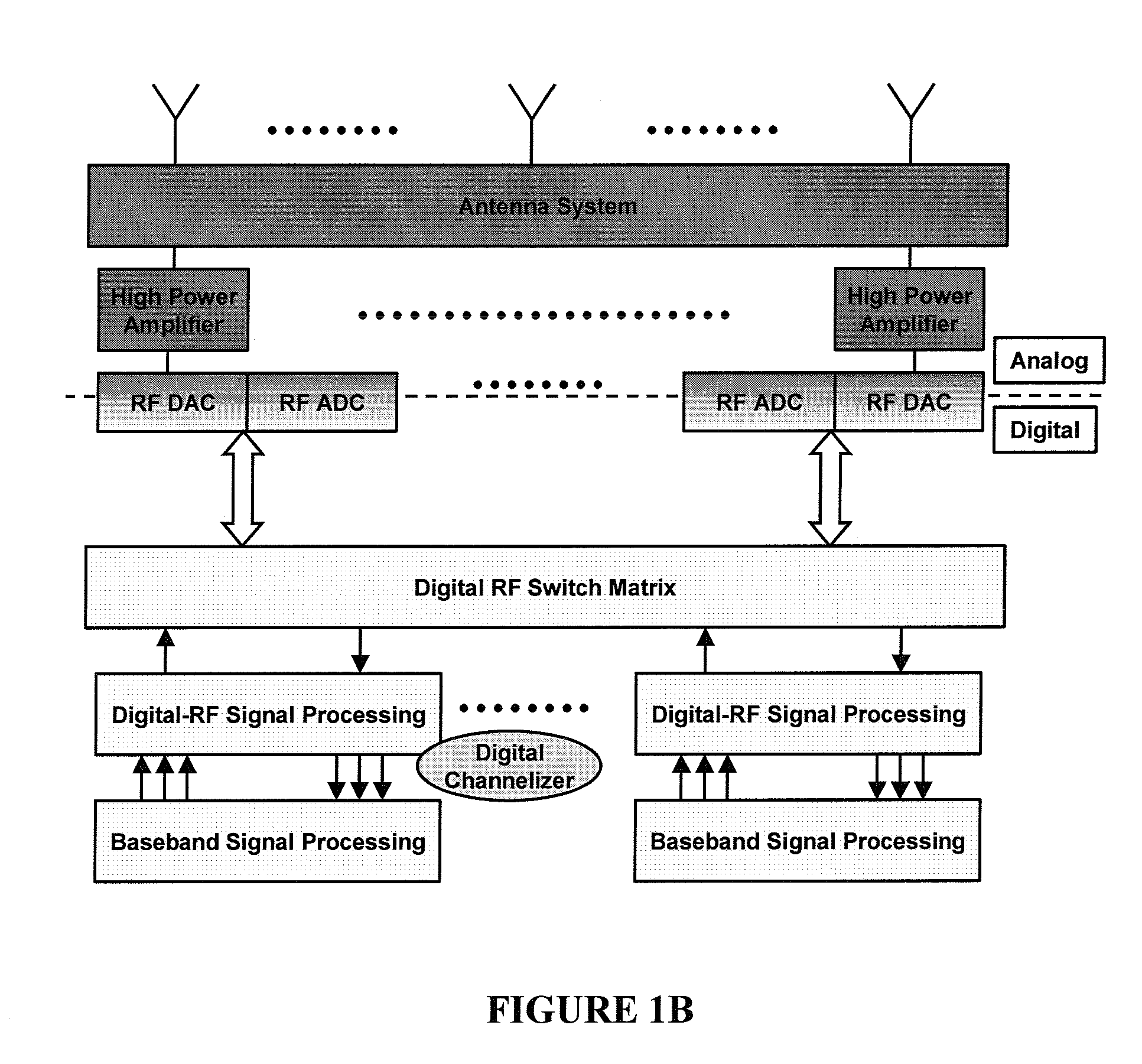

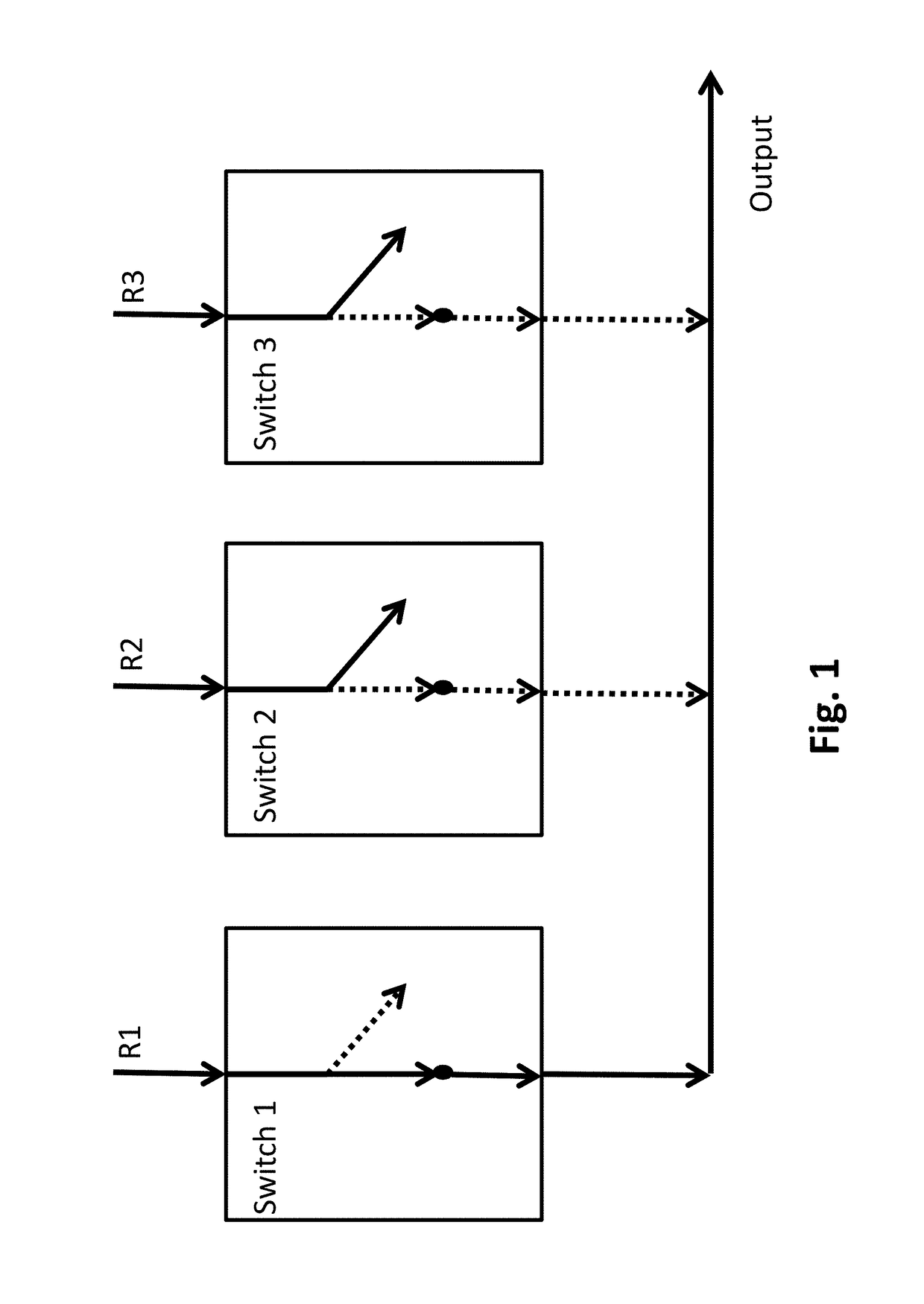

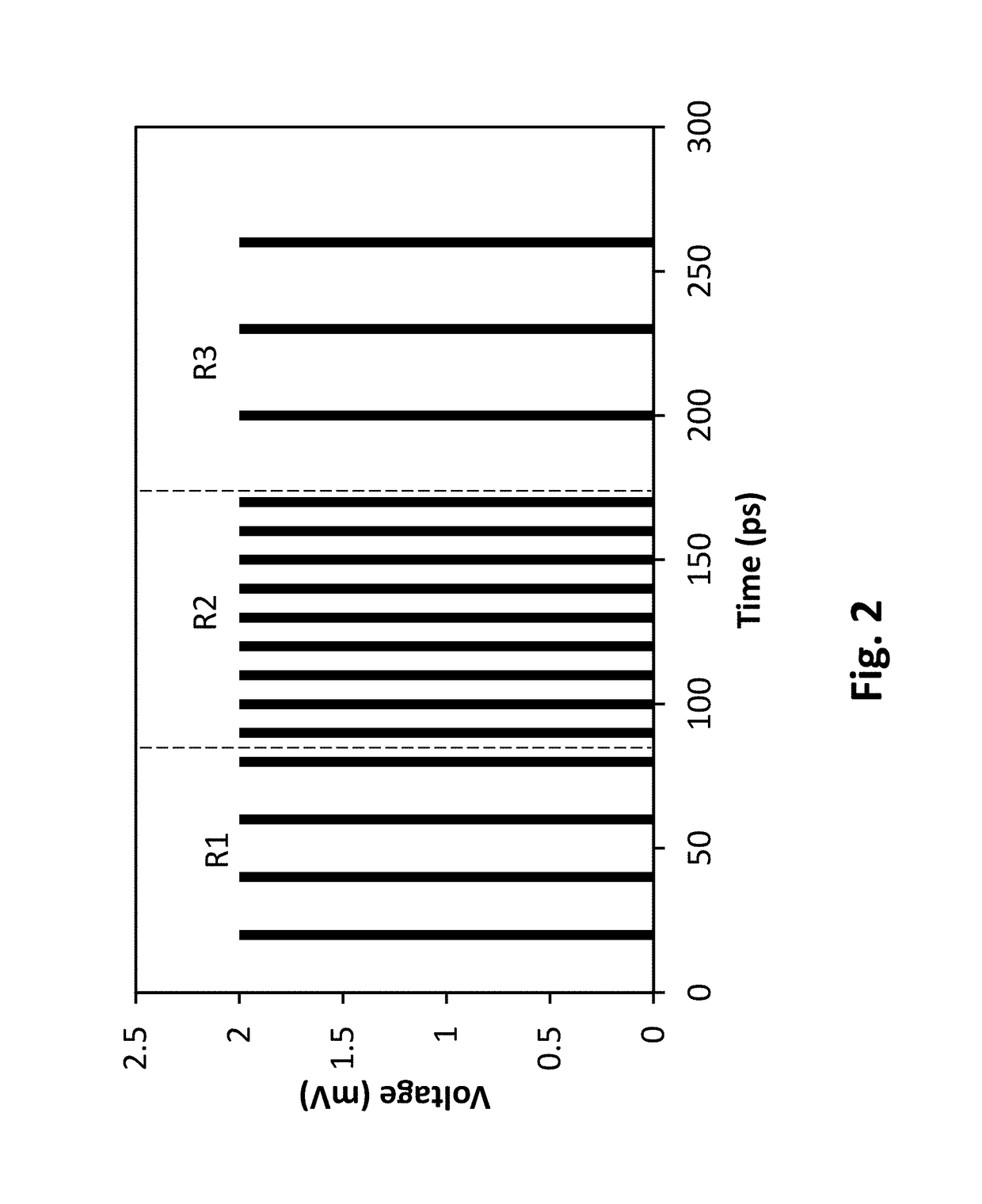

Digital routing switch matrix for digitized radio-frequency signals

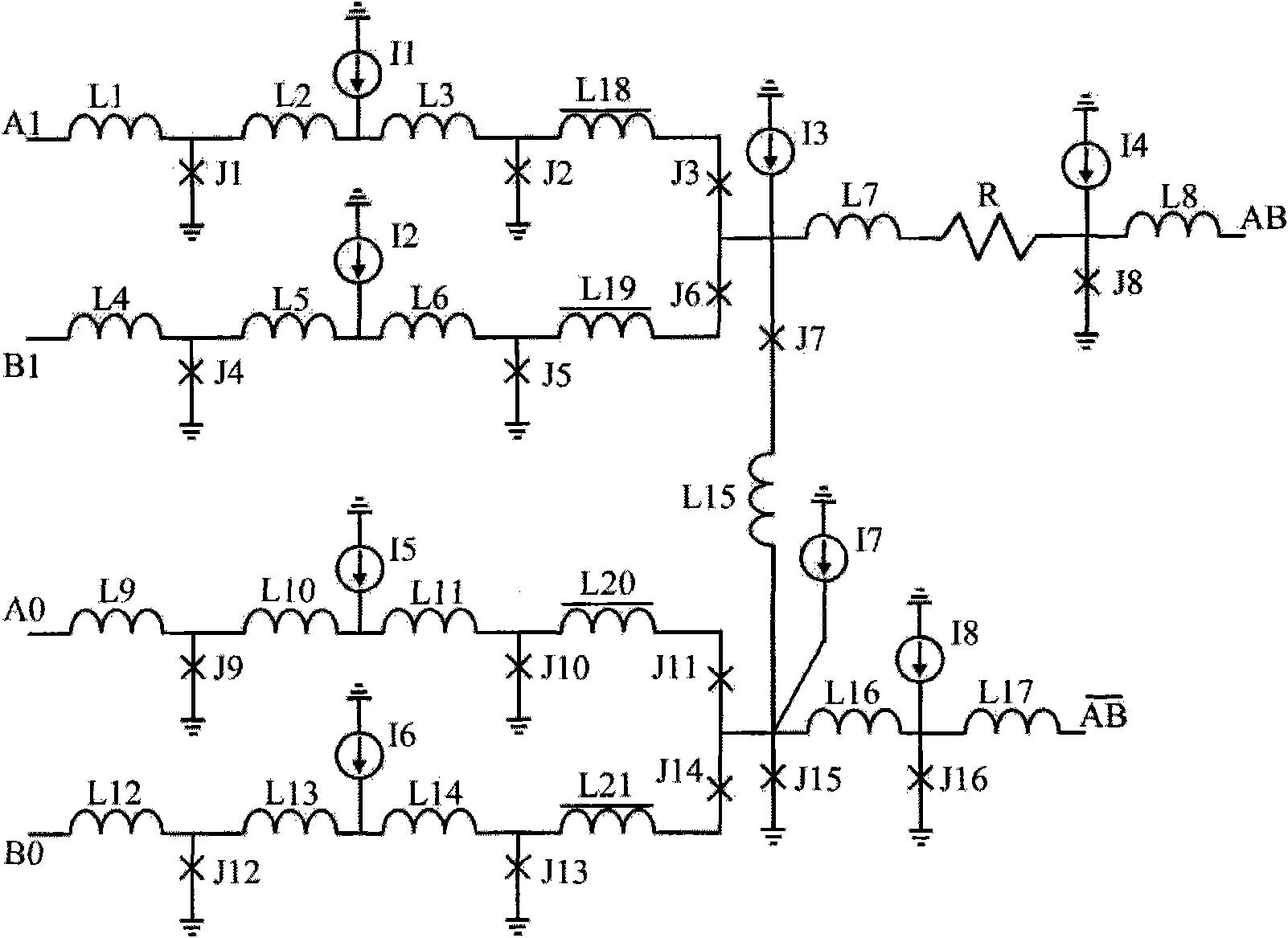

InactiveUS7362125B2Efficient executionPrecise processingElectronic switchingSubstation equipmentMulti bandTransceiver

Routing and distribution of radio-frequency (RF) signals is commonly achieved in the analog domain. However, improved performance and simplified circuit architectures may be obtained by first digitizing the RF signal, and then carrying out all routing in the digital domain. A new generation of scalable digital switches has been developed, which routes both the data and clock signals together, this being necessary to maintain the integrity of the digitized RF signal. Given the extremely high switching speeds necessary for these applications (tens of GHz), this is implemented using Rapid-Single-Flux-Quantum (RSFQ) logic with superconducting integrated circuits. Such a digital switch matrix may be applied to either the receiver or transmitter components of an advanced multi-band, multi-channel digital transceiver system, and is compatible with routing of signals with different clock frequencies simultaneously within the same switch matrix.

Owner:HYPRES

System and method for providing multi-conductive layer metallic interconnects for superconducting integrated circuits

ActiveUS8301214B1Reduce and prevent diffusion of impurityReduce non-uniformitySuperconductors/hyperconductorsSemiconductor/solid-state device detailsImpurity diffusionRapid single flux quantum

Superconducting integrated circuits require several wiring layers to distribute bias and signals across the circuit, which must cross each other both with and without contacts. All wiring lines and contacts must be fully superconducting, and in the prior art each wiring layer comprises a single metallic thin film. An alternative wiring layer is disclosed that comprises sequential layers of two or more different metals. Such a multi-metallic wiring layer may offer improved resistance to impurity diffusion, better surface passivation, and / or reduction of stress, beyond that which is attainable with a single-metallic wiring layer. The resulting process leads to improved margin and yield in an integrated circuit comprising a plurality of Josephson junctions. Several preferred embodiments are disclosed, for both planarized and non-planarized processes. These preferred and other methods may be applied to digital circuits based on Rapid Single Flux Quantum logic, and to quantum computing using Josephson junction qubits.

Owner:SEEQC INC

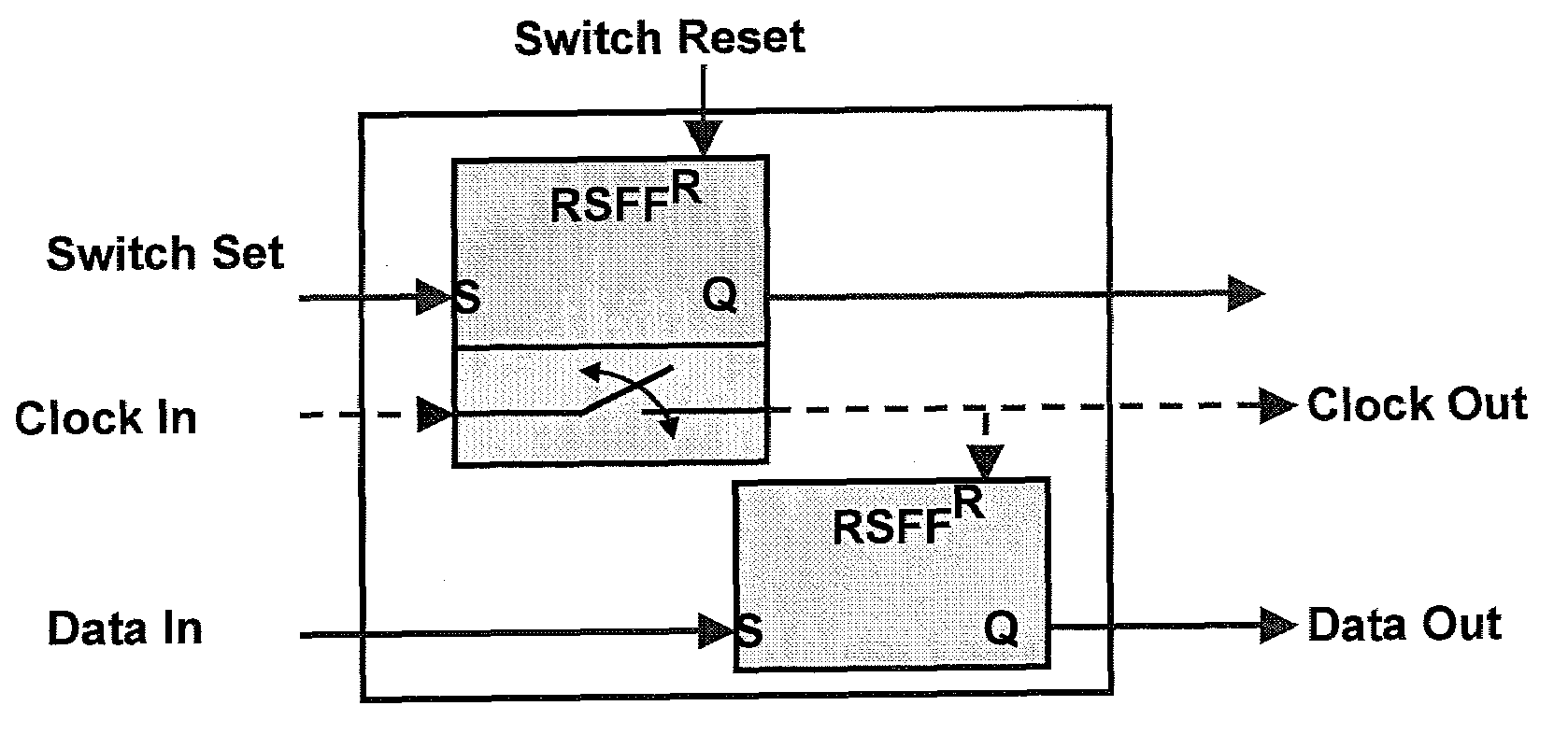

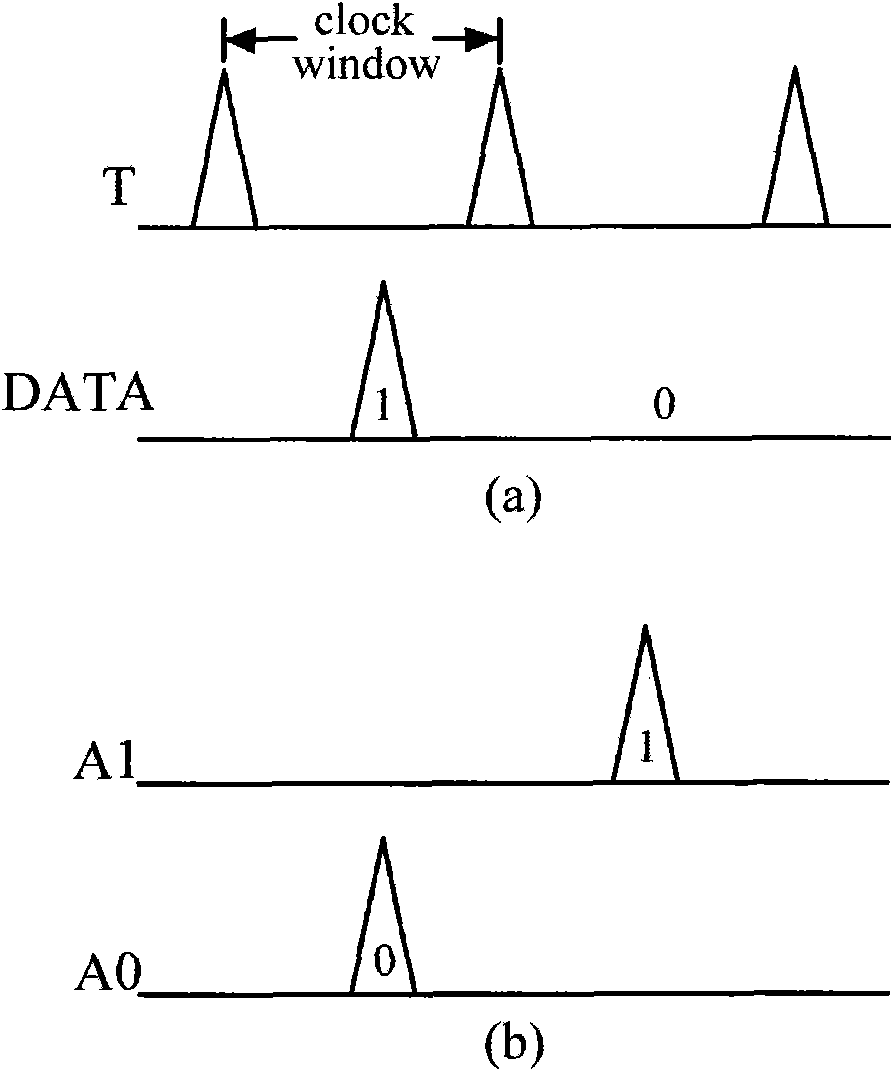

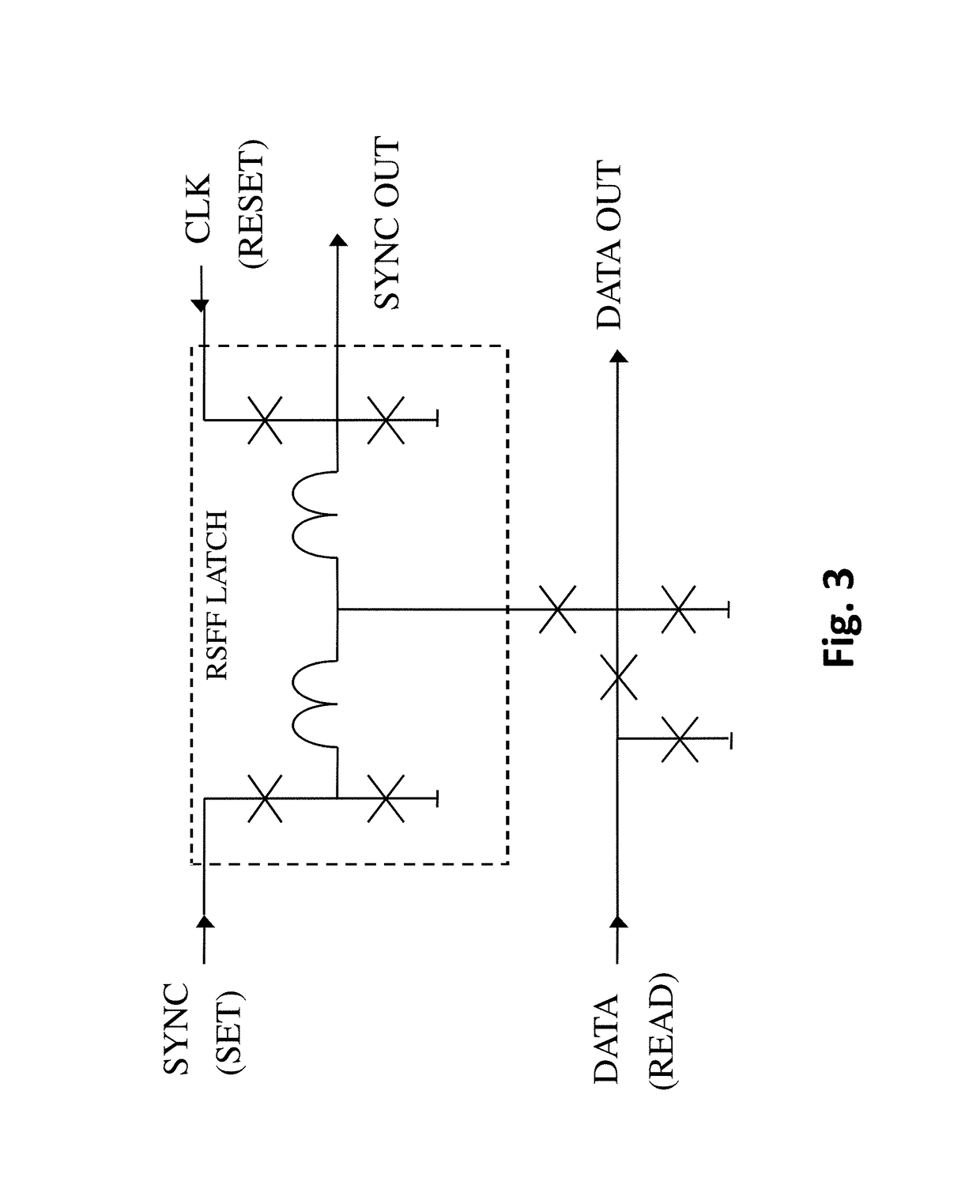

Superconducting digital first-in first-out buffer using physical back pressure mechanism

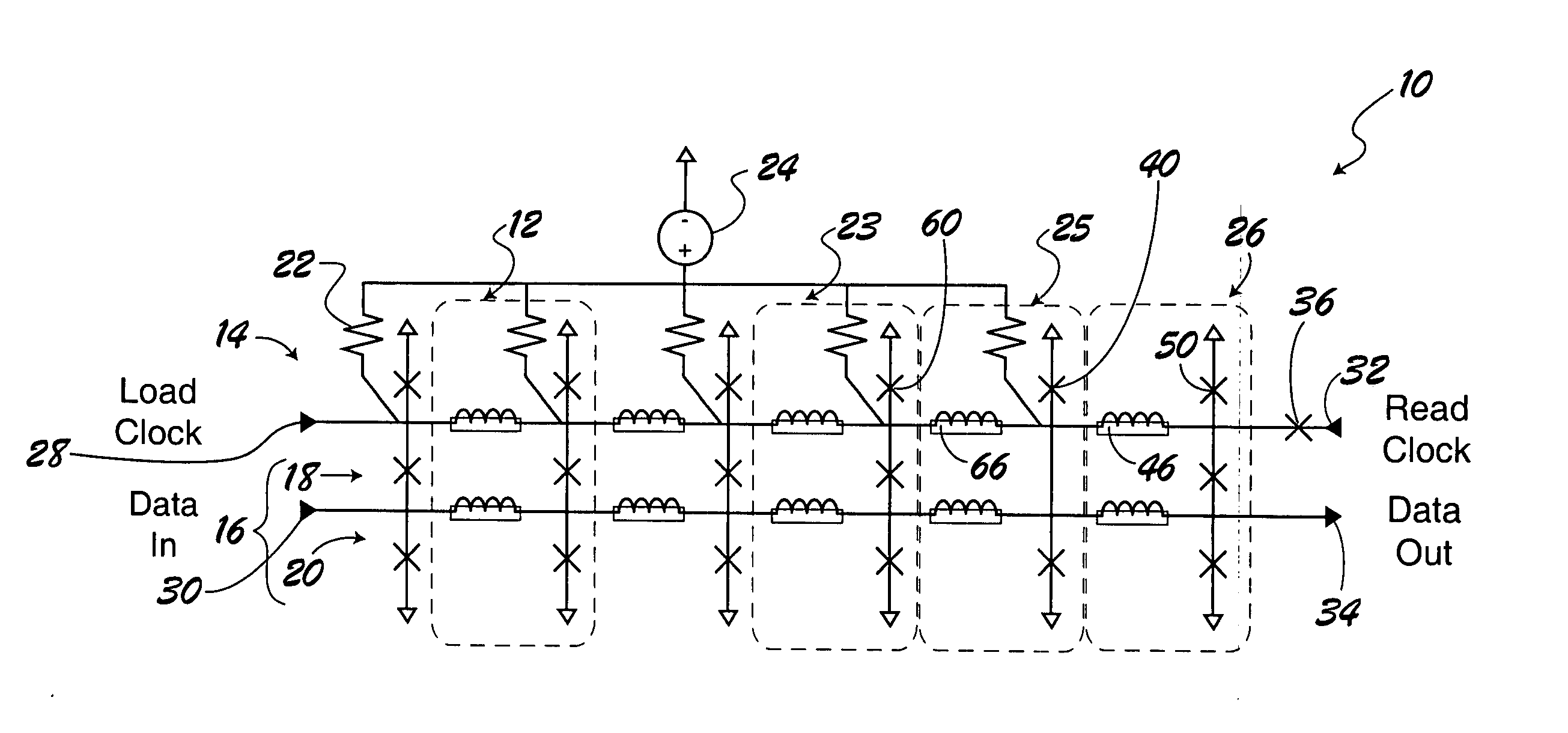

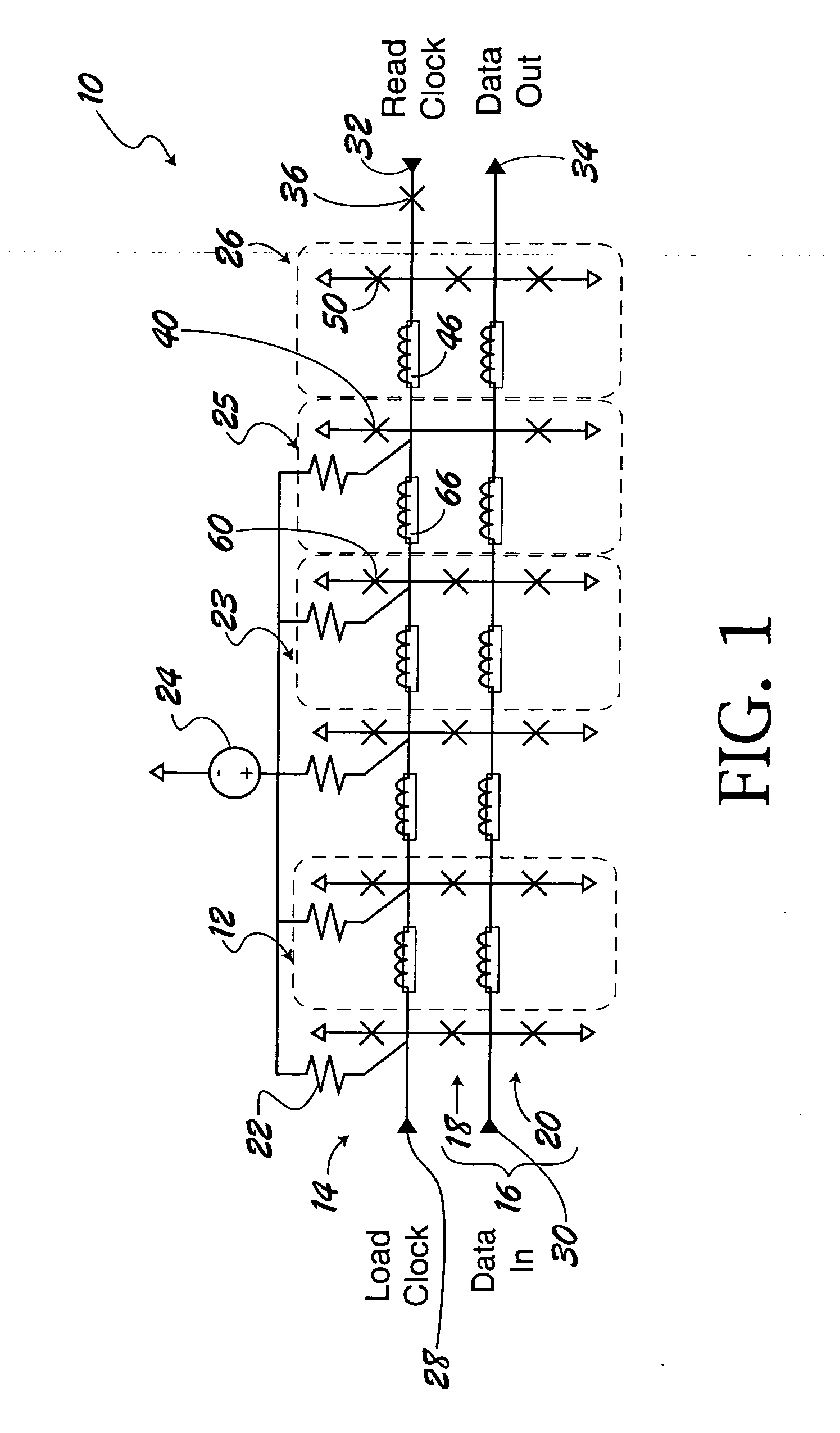

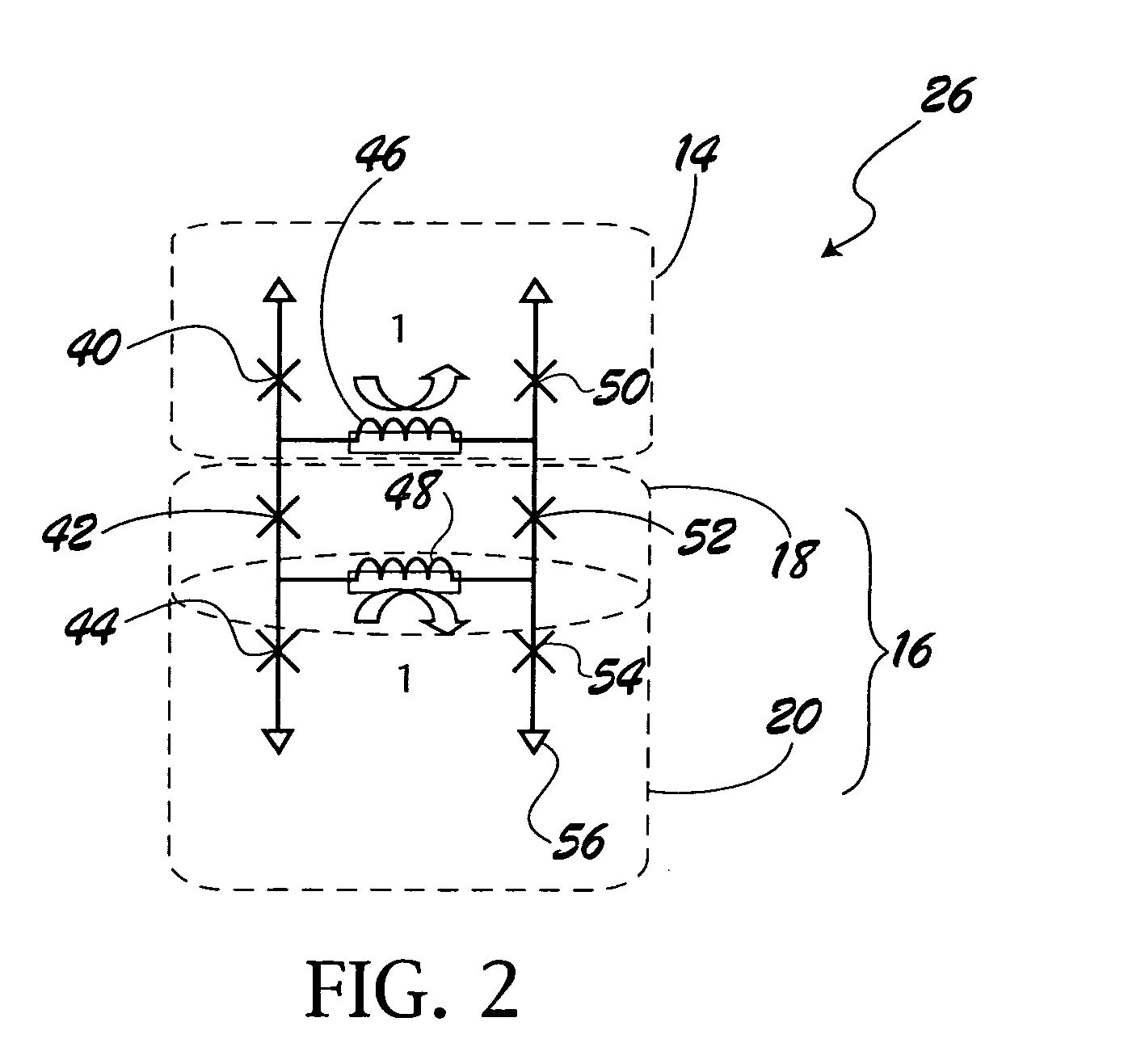

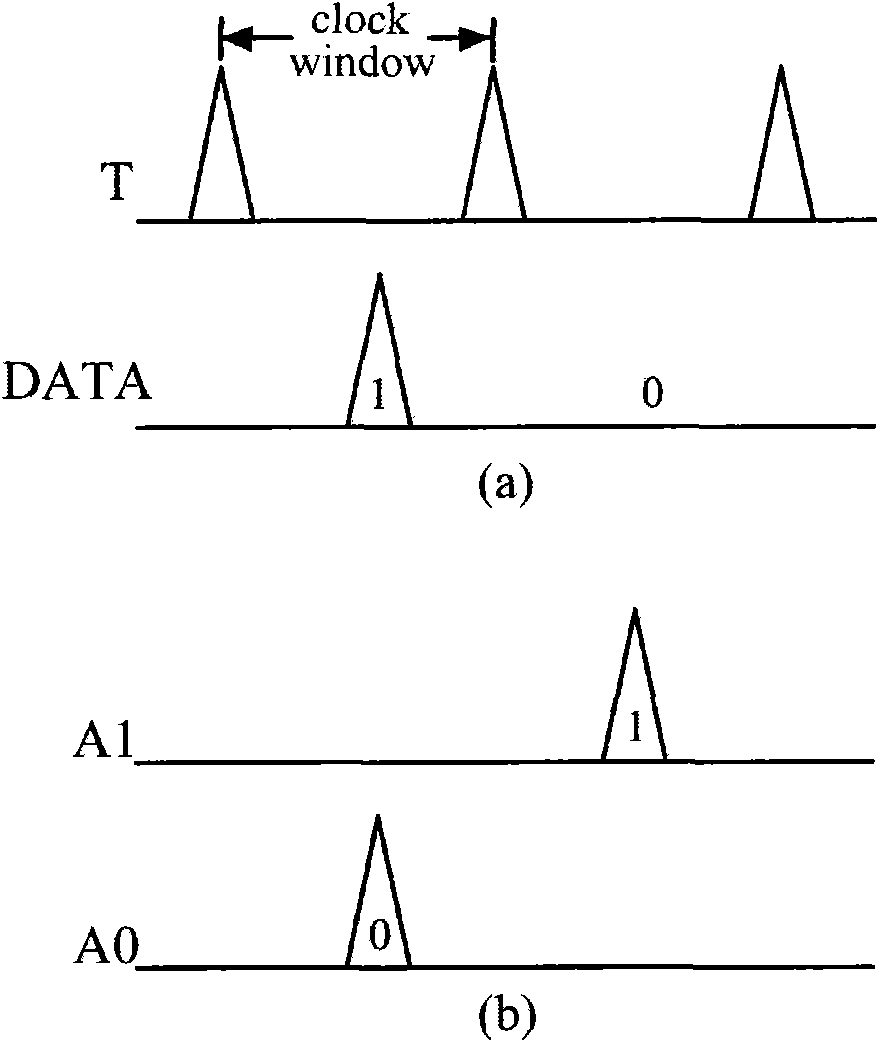

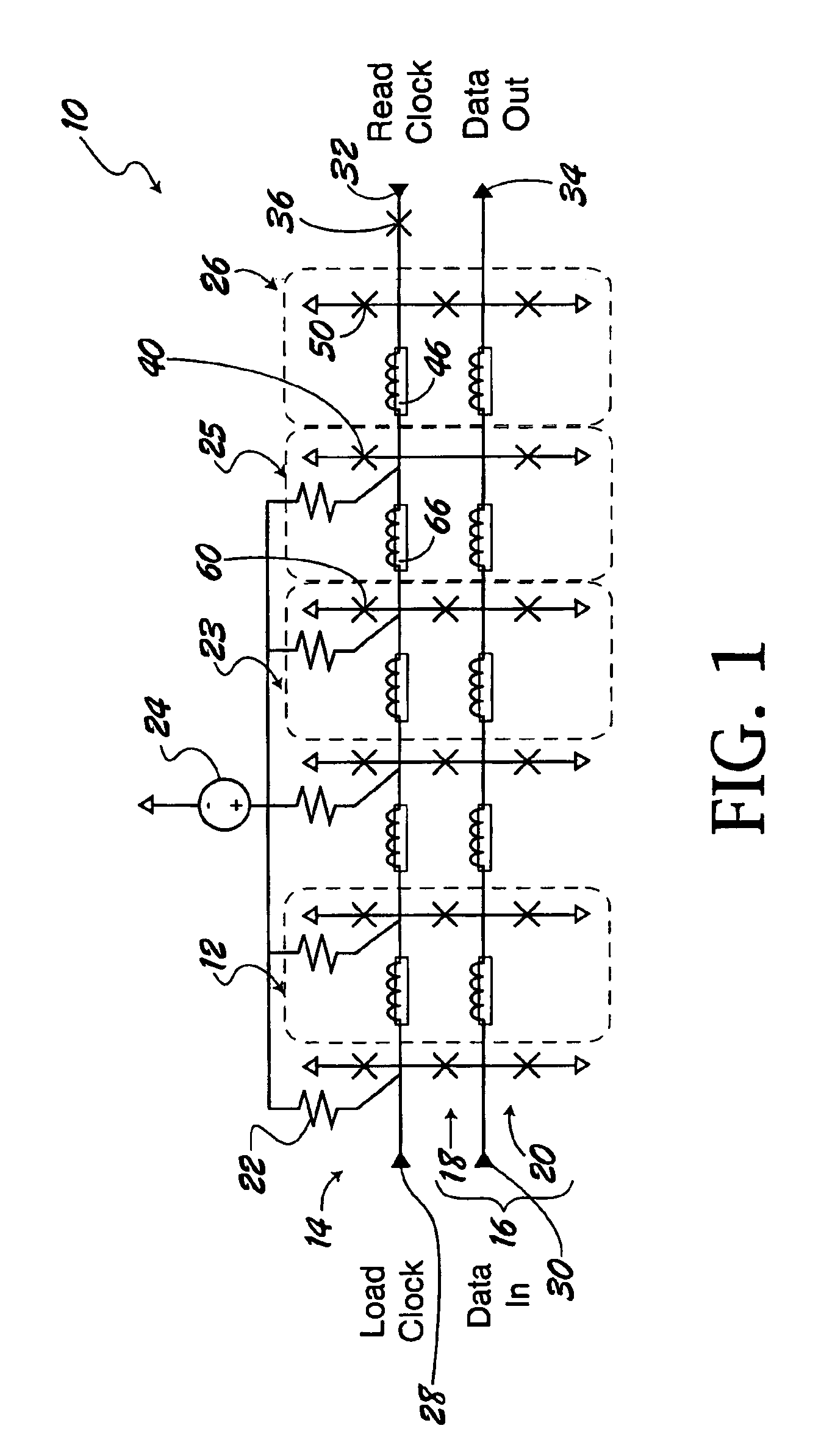

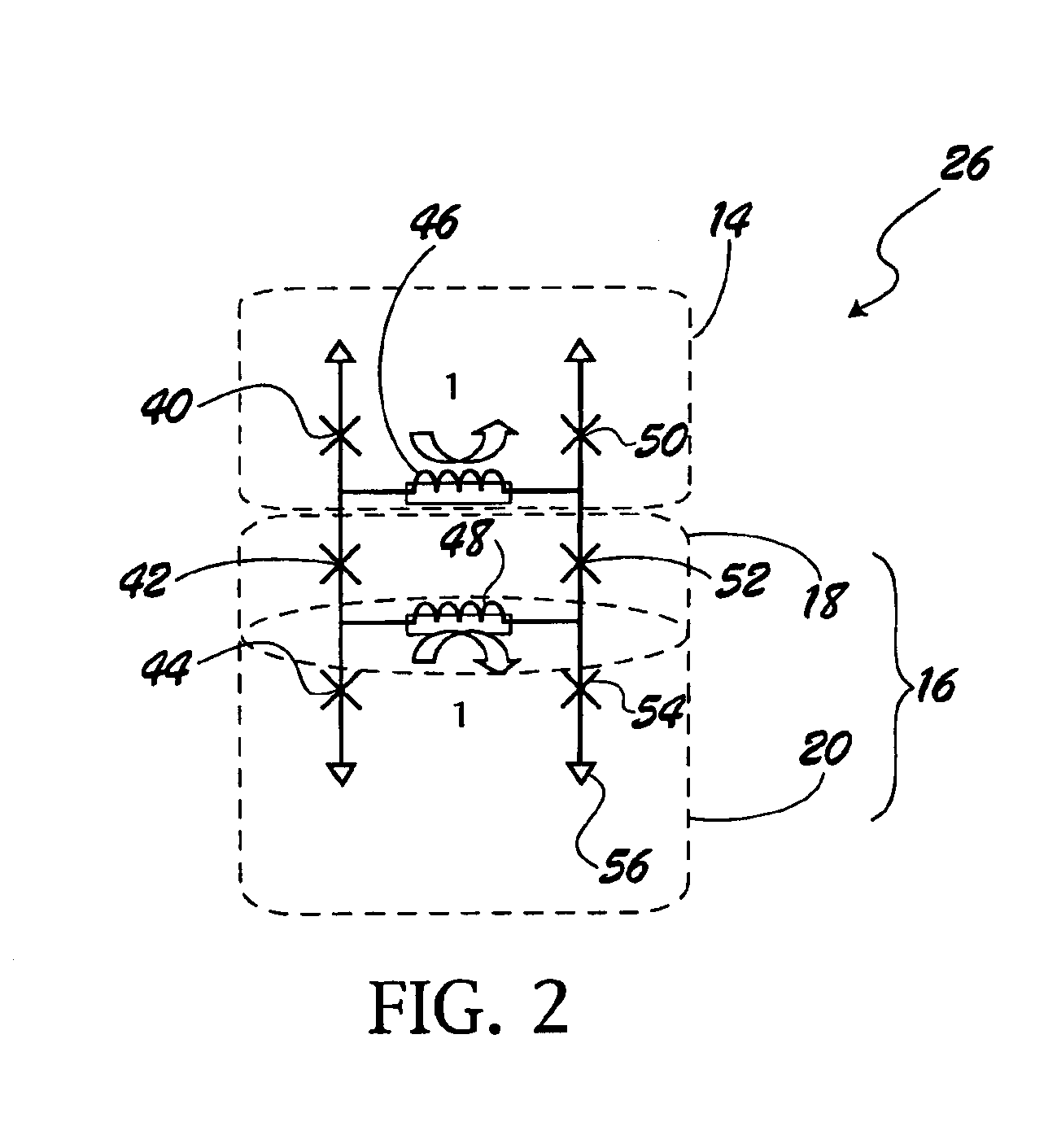

InactiveUS20050023518A1Digital storageDissimilar materials junction devicesData signalComputer science

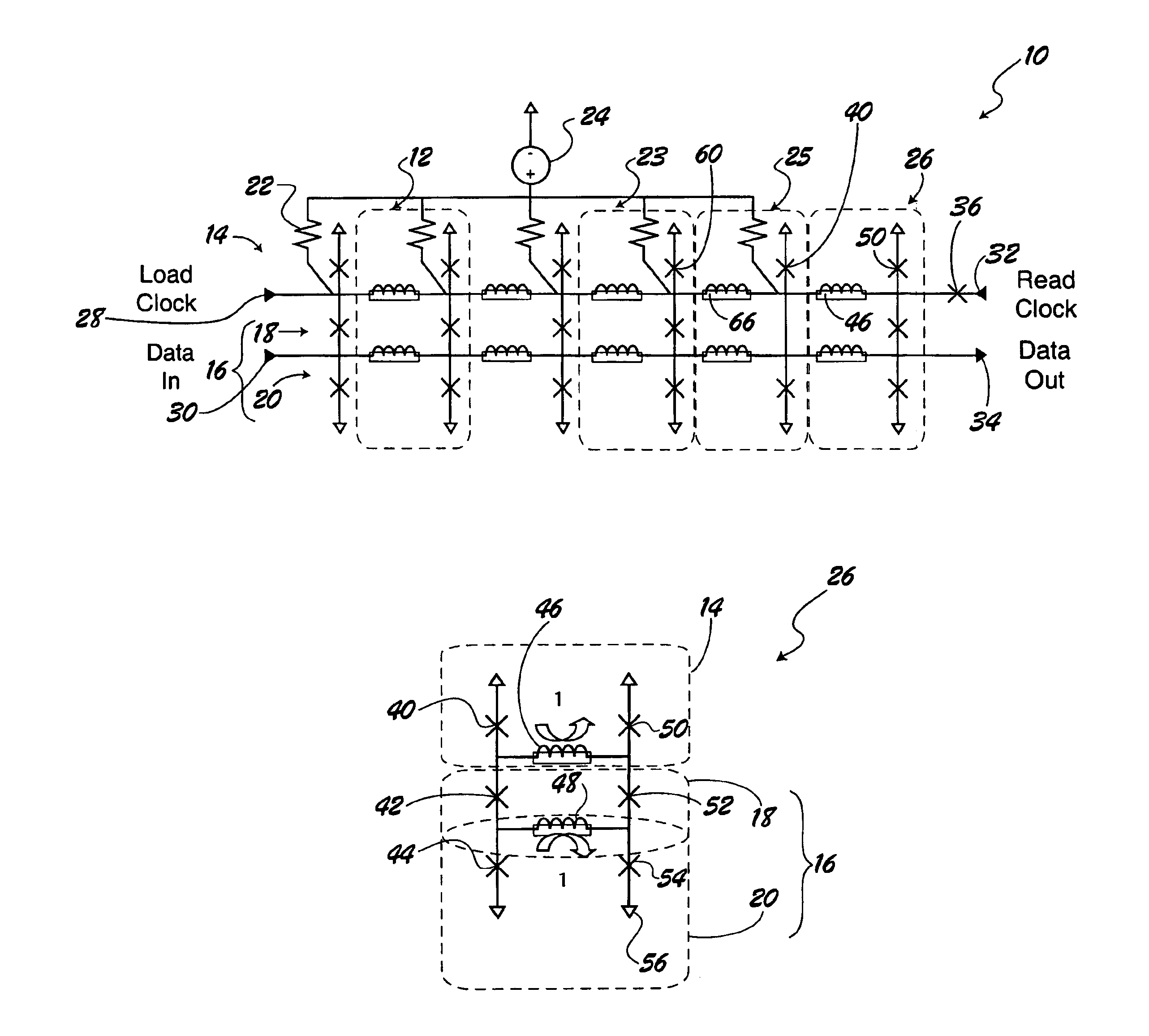

A digital first-in first-out (FIFO) buffer (10) for use with Single Flux Quantum (SFQ) superconductive integrated circuits. The digital FIFO buffer (10) includes a clock-storage circuit (14) for receiving and storing load and read clock signals (100, 104) and a data-storage circuit (16) connected to the clock-storage circuit (14) for receiving and storing data signal pulses (102) in the order which the data signal pulses (102) are received relative to the load clock signal (100). The data-storage circuit (16) outputs the SFQ pulse signal independent of the load clock signal (100). The previously stored clock and data signal pulses (100, 102) provide physical back pressure to their subsequent signal pulses.

Owner:NORTHROP GRUMAN CORP

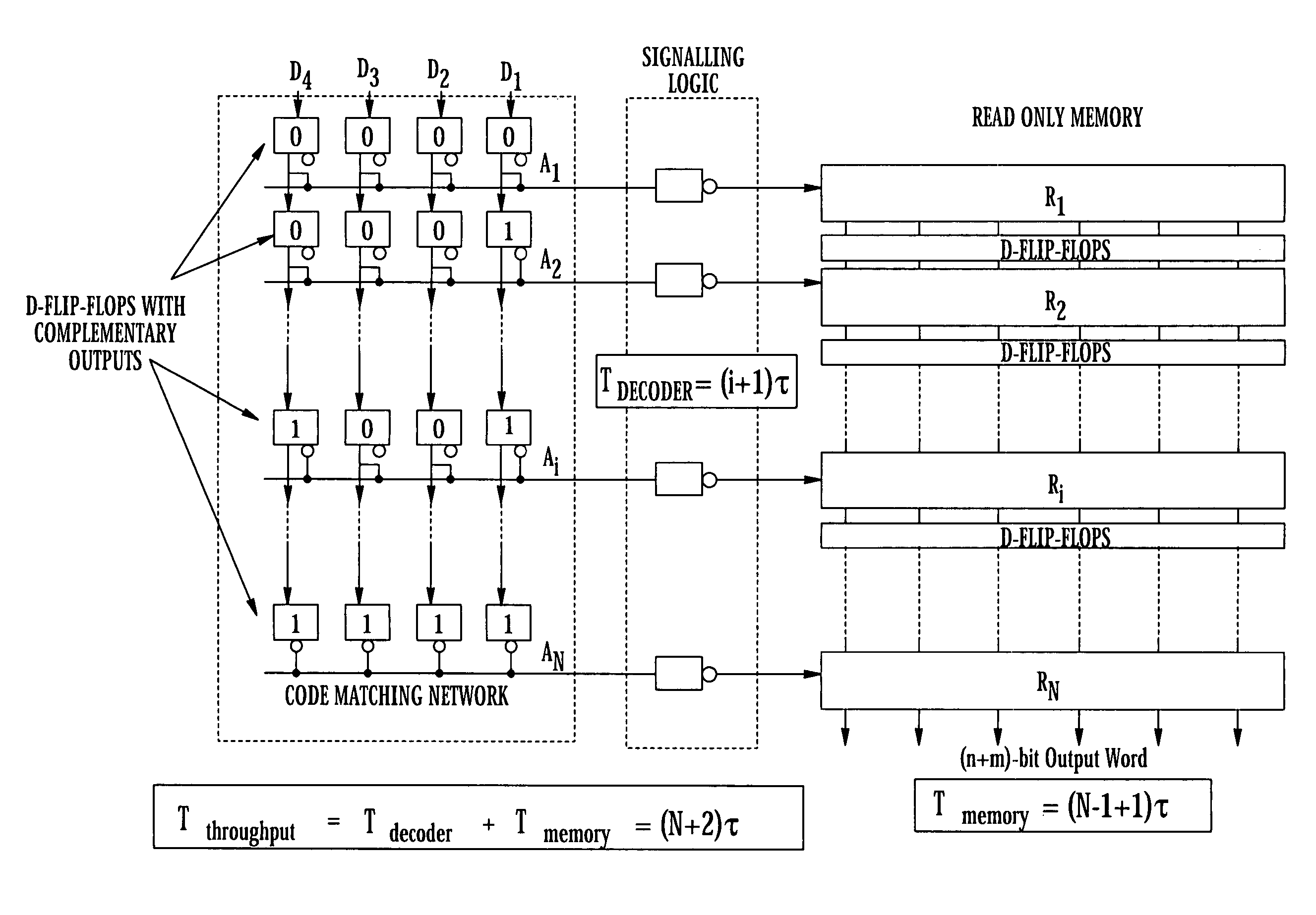

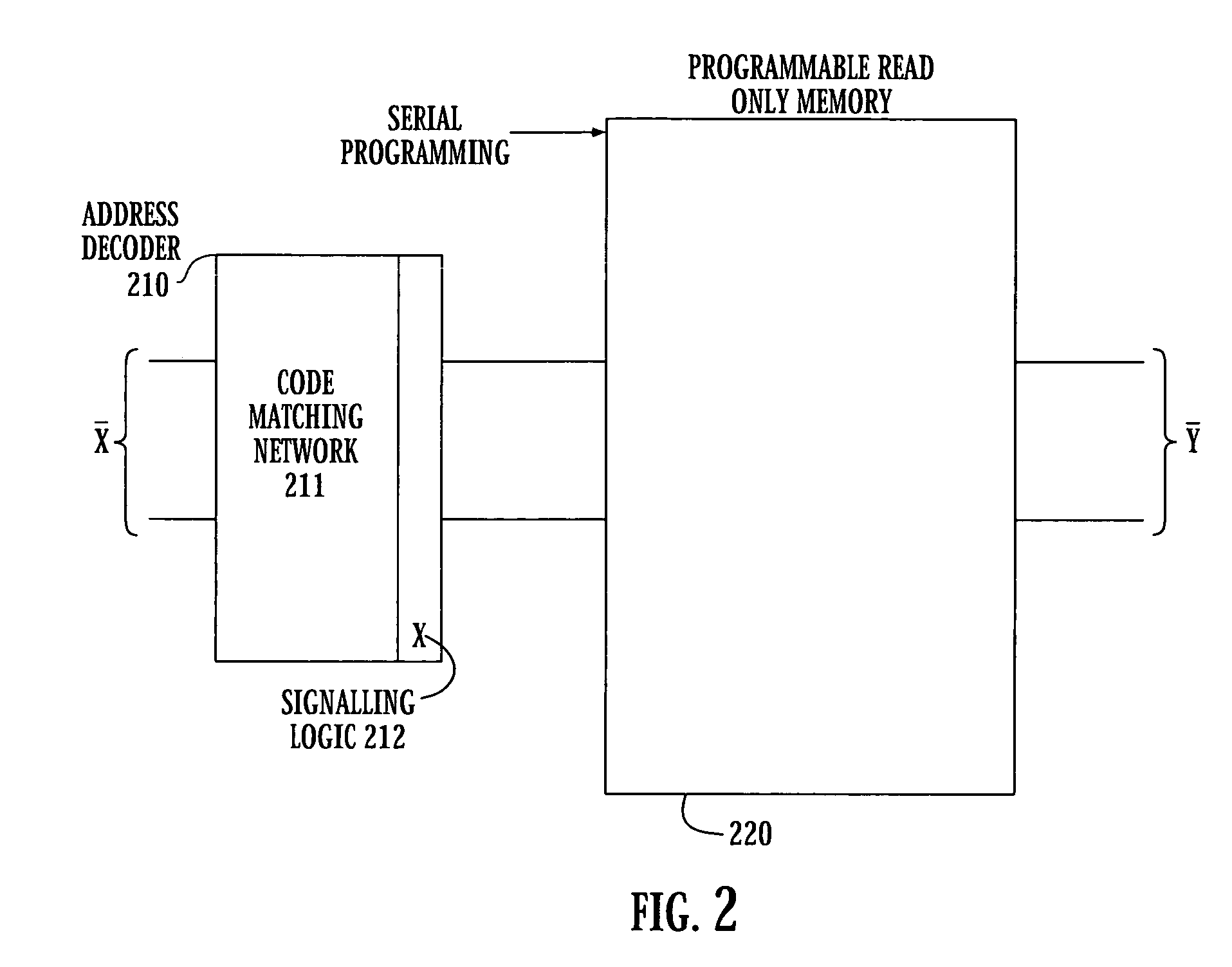

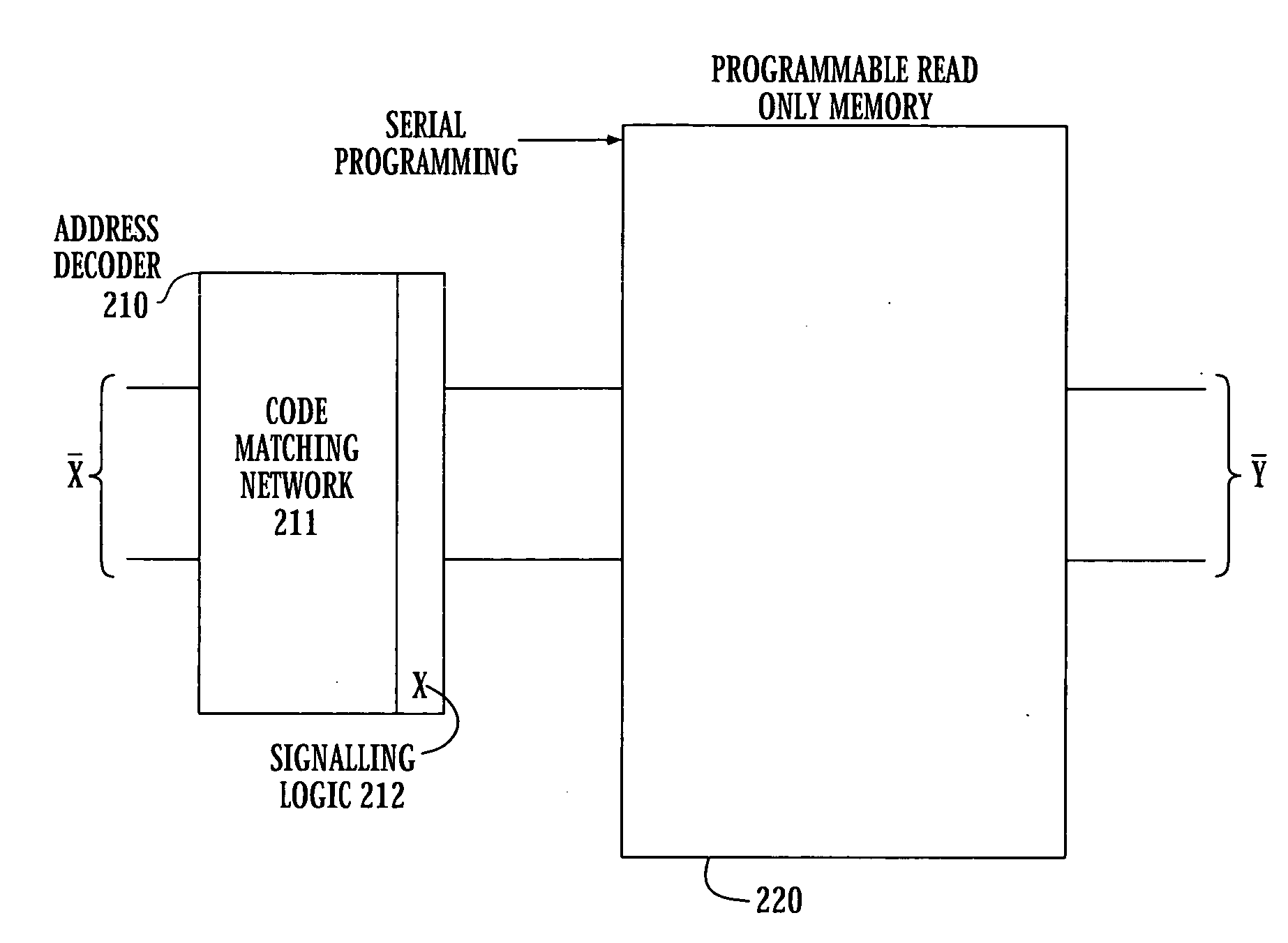

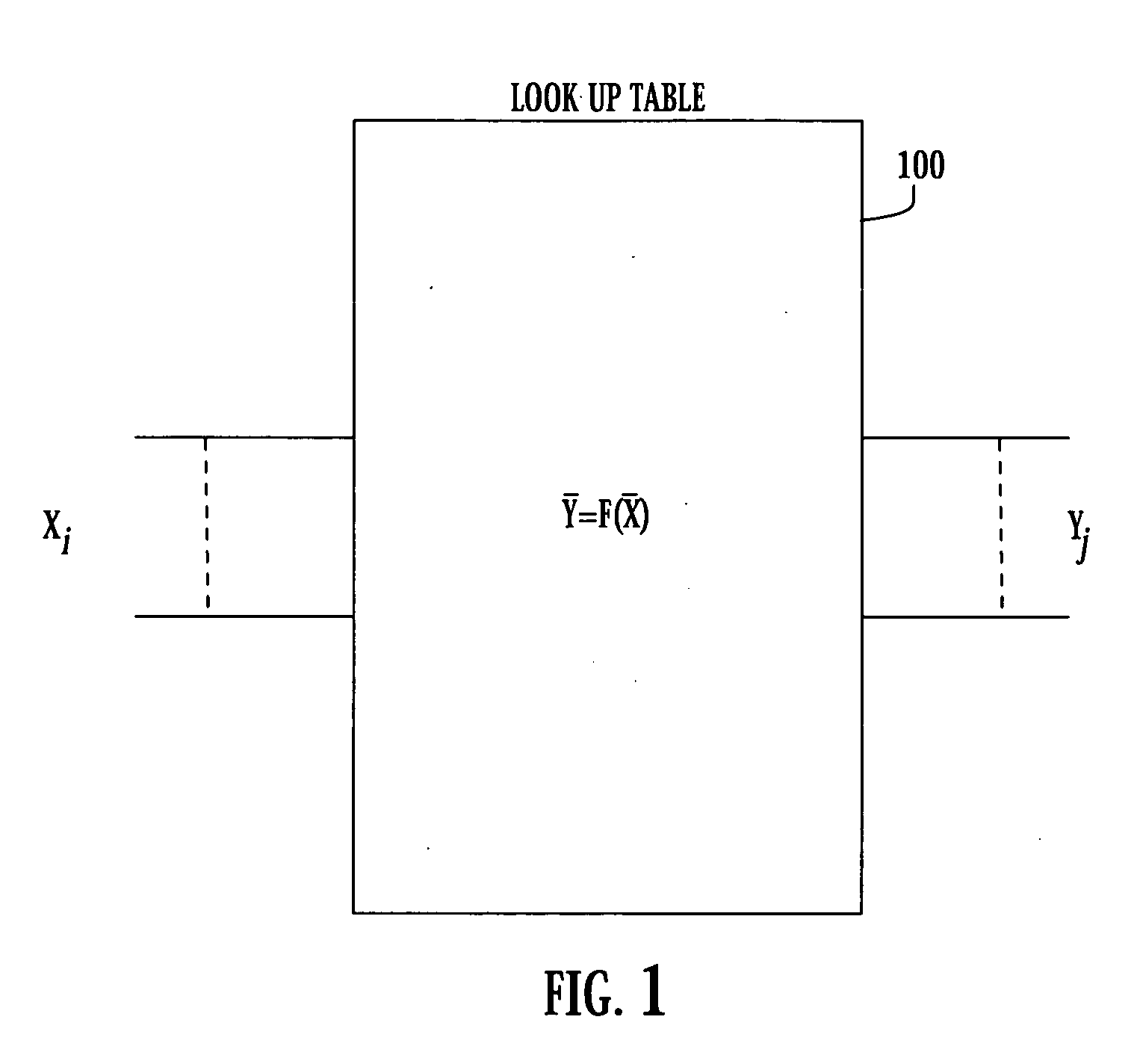

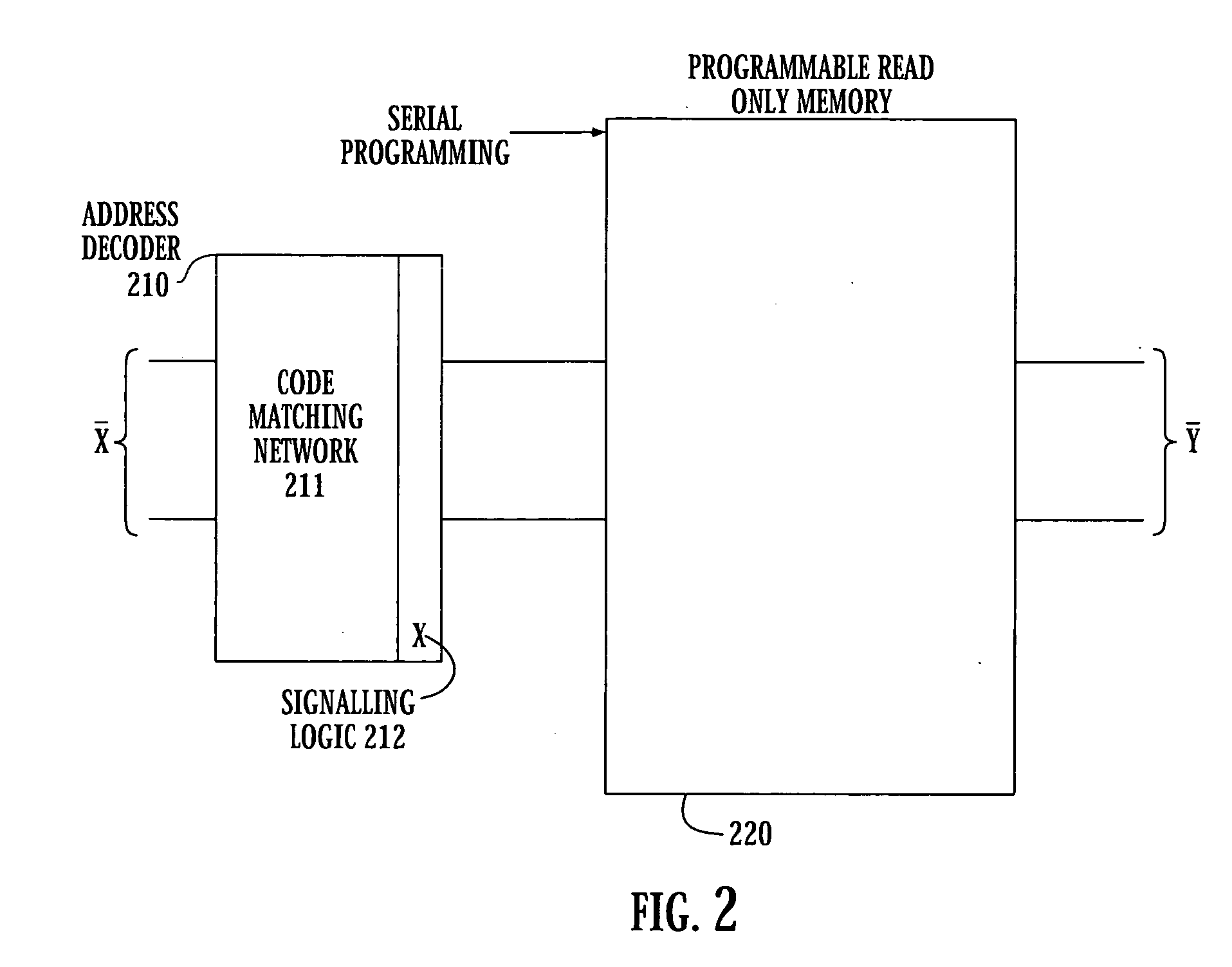

Superconducting circuit for high-speed lookup table

ActiveUS7443719B2Superconductors/hyperconductorsRead-only memoriesProgrammable read-only memoryReprogramming

A high-speed lookup table is designed using Rapid Single Flux Quantum (RSFQ) logic elements and fabricated using superconducting integrated circuits. The lookup table is composed of an address decoder and a programmable read-only memory array (PROM). The memory array has rapid parallel pipelined readout and slower serial reprogramming of memory contents. The memory cells are constructed using standard non-destructive reset-set flip-flops (RSN cells) and data flip-flops (DFF cells). An n-bit address decoder is implemented in the same technology and closely integrated with the memory array to achieve high-speed operation as a lookup table. The circuit architecture is scalable to large two-dimensional data arrays.

Owner:SEEQC INC

Systems and methods for fabrication of superconducting integrated circuits

Various techniques and apparatus permit fabrication of superconductive circuits and structures, for instance Josephson junctions, which may, for example be useful in quantum computers. For instance, a low magnetic flux noise trilayer structure may be fabricated having a dielectric structure or layer interposed between two elements or layers capable of superconducting. A superconducting via may directly overlie a Josephson junction. A structure, for instance a Josephson junction, may be carried on a planarized dielectric layer. A fin may be employed to remove heat from the structure. A via capable of superconducting may have a width that is less than about 1 micrometer. The structure may be coupled to a resistor, for example by vias and / or a strap contact connector.

Owner:D WAVE SYSTEMS INC

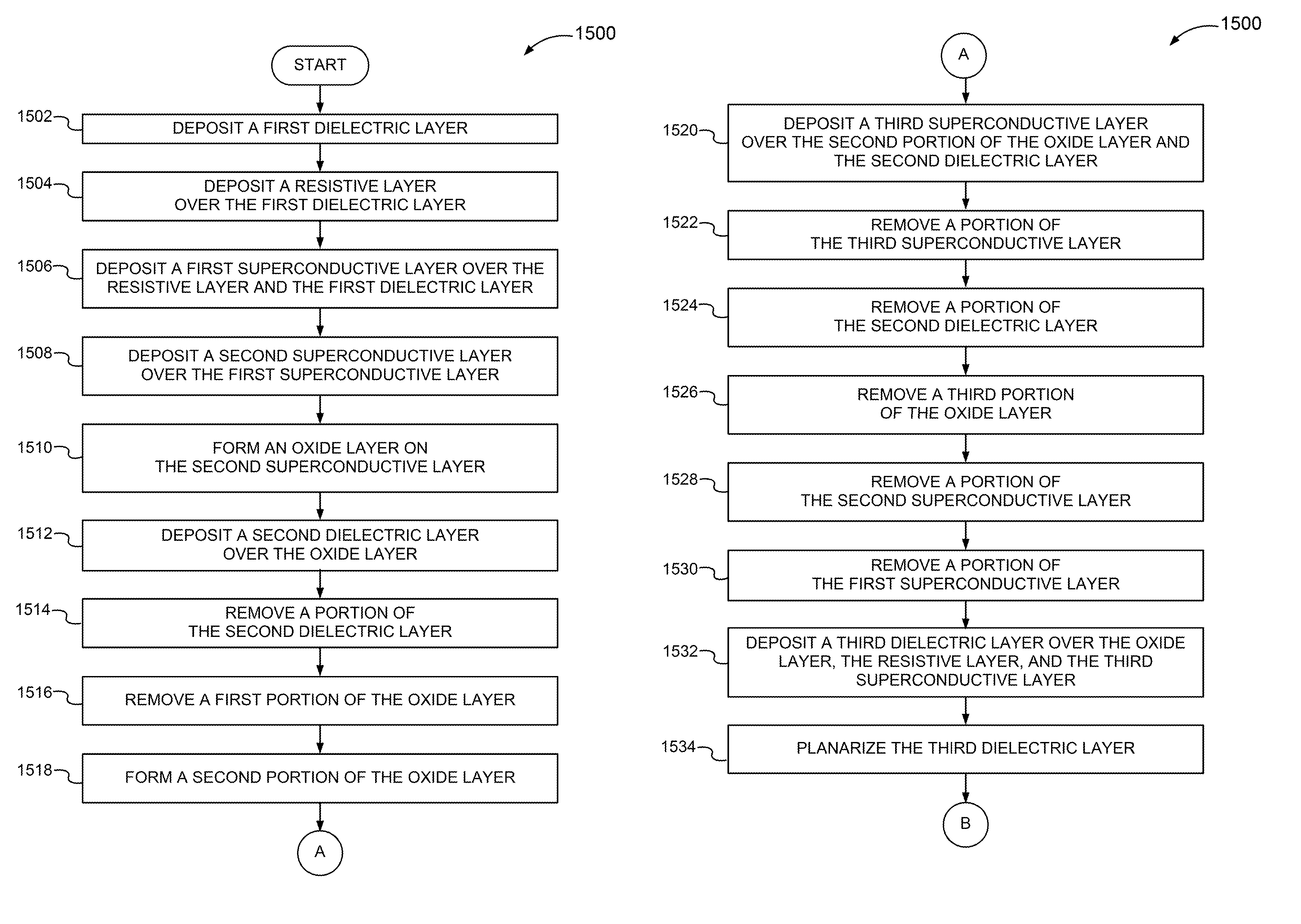

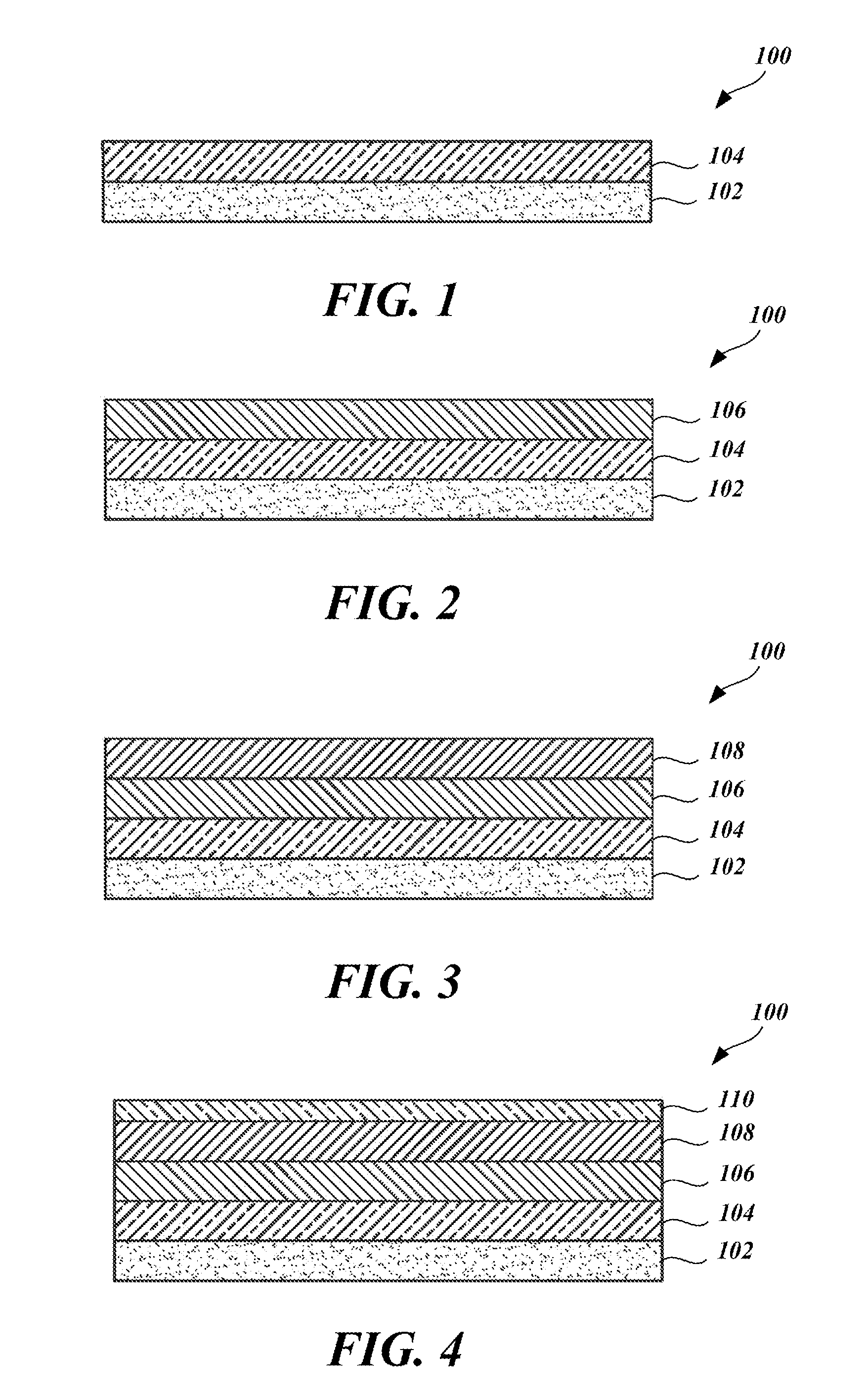

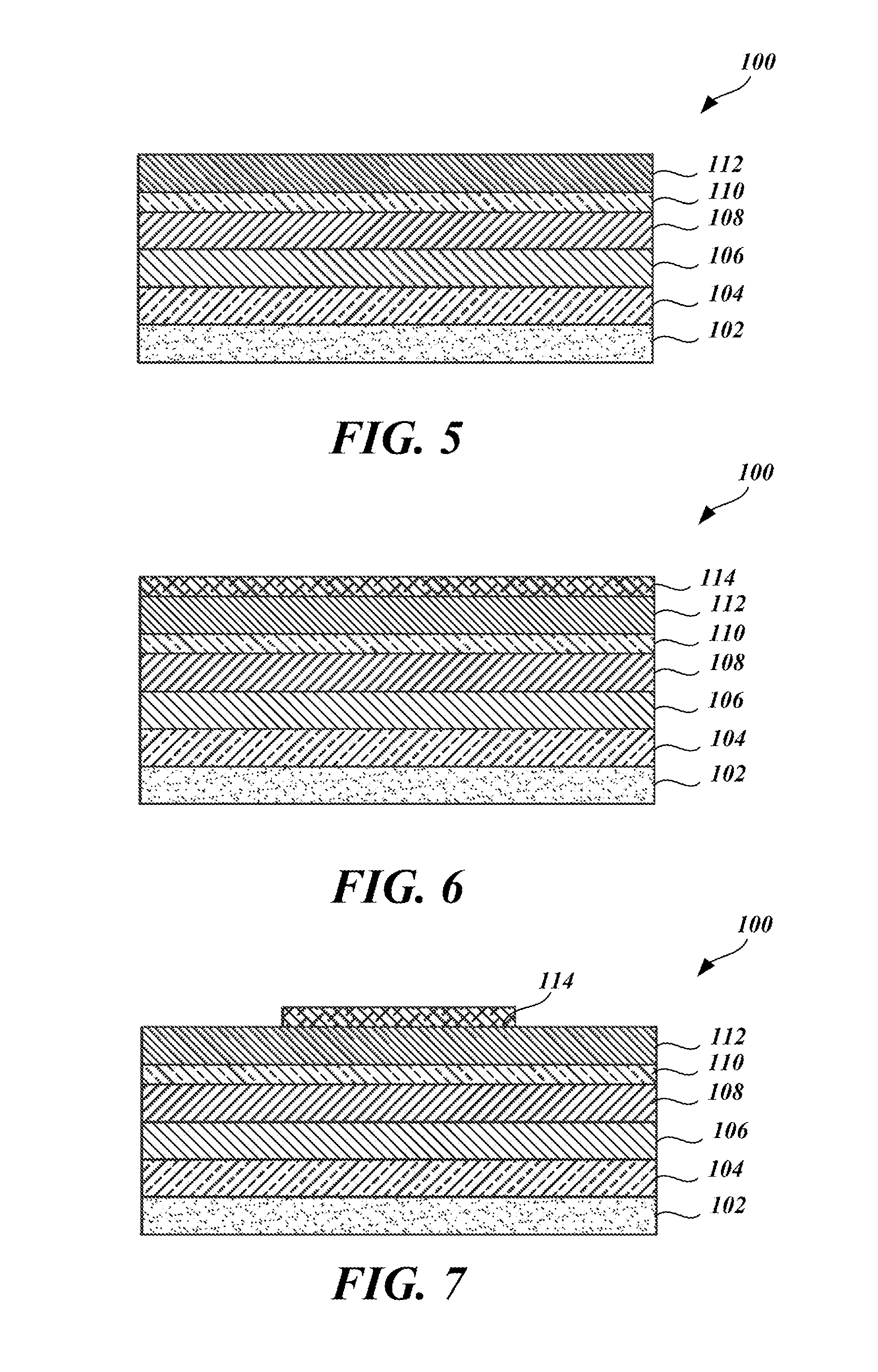

Systems and methods for fabrication of superconducting circuits

In one aspect, fabricating a superconductive integrated circuit with a Josephson junction includes applying oxygen or nitrogen to at least part of a structure formed from an outer superconductive layer to passivate an artifact, if any, left from removing the portion of the outer superconductive layer. In another aspect, a first superconductive layer is deposited, a second superconductive layer is deposited on the first superconductive layer, an oxide layer is formed on the first superconductive layer, a dielectric layer is deposited on the oxide layer, a portion of the dielectric layer is removed, a first portion of the oxide layer is removed, a second oxide portion is formed in place of the first portion of the oxide layer, and a third superconductive layer is deposited on the dielectric layer and the second oxide portion.

Owner:D WAVE SYSTEMS INC

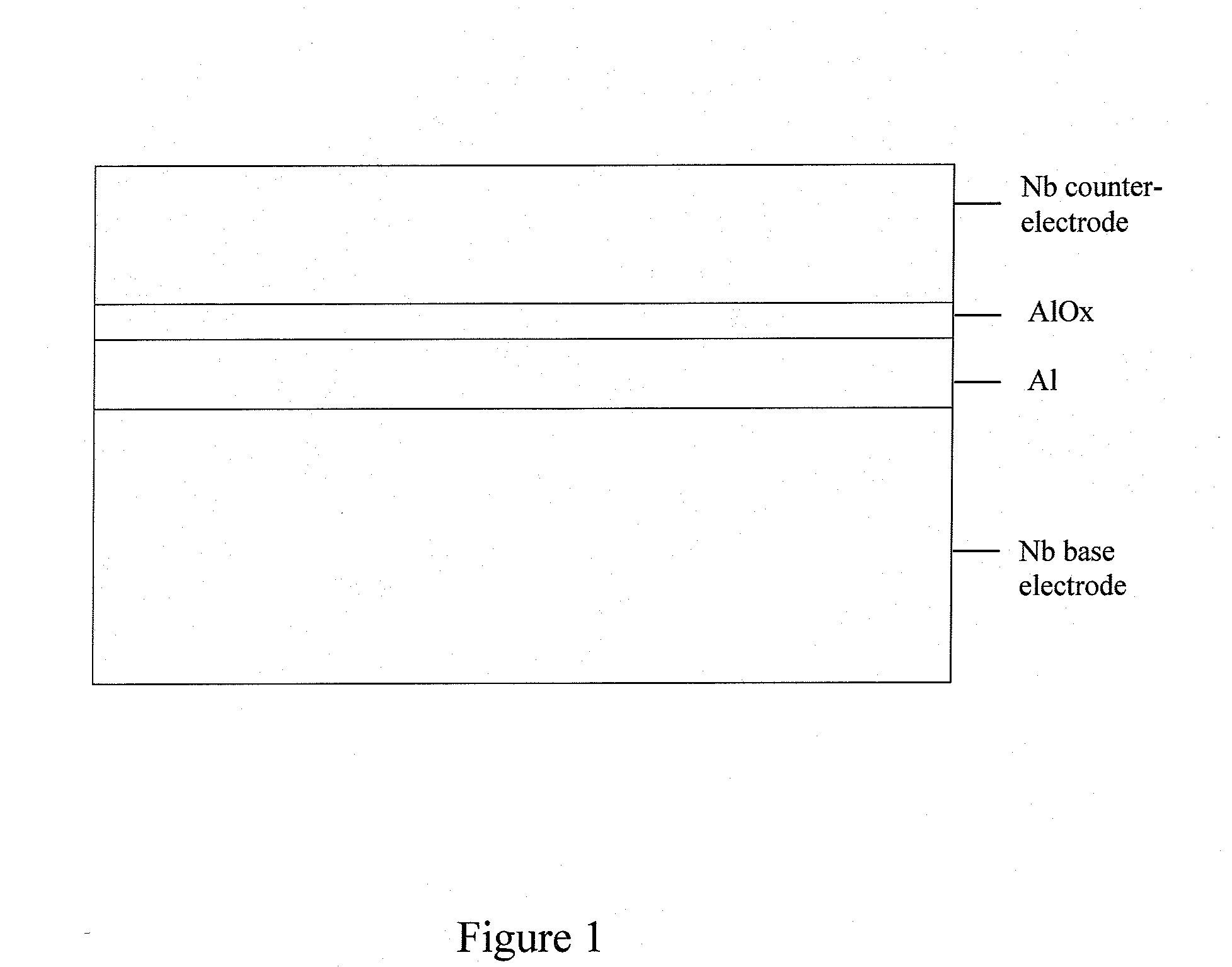

A1/A1Ox/A1 resistor process for integrated circuits

InactiveUS20050062131A1Solid-state devicesResistor manufactureSuperconducting integrated circuitsIntegrated circuit

A structure and a method for forming a vertical resistor on a superconducting integrated circuit. The resistance structure is formed from a Al / AlOx / Al material system. In particular, the resistance structure includes a layer of aluminum, in-situ oxidation of the aluminum surface and further deposition of aluminum. The resistance of the Al / AlOx / Al structure primarily comes from the aluminum oxide layer rather than the aluminum. As such, any aluminum removed during the interconnect pre-cleaning process will have a negligible impact on the overall resistance of the structure.

Owner:NORTHROP GRUMAN CORP

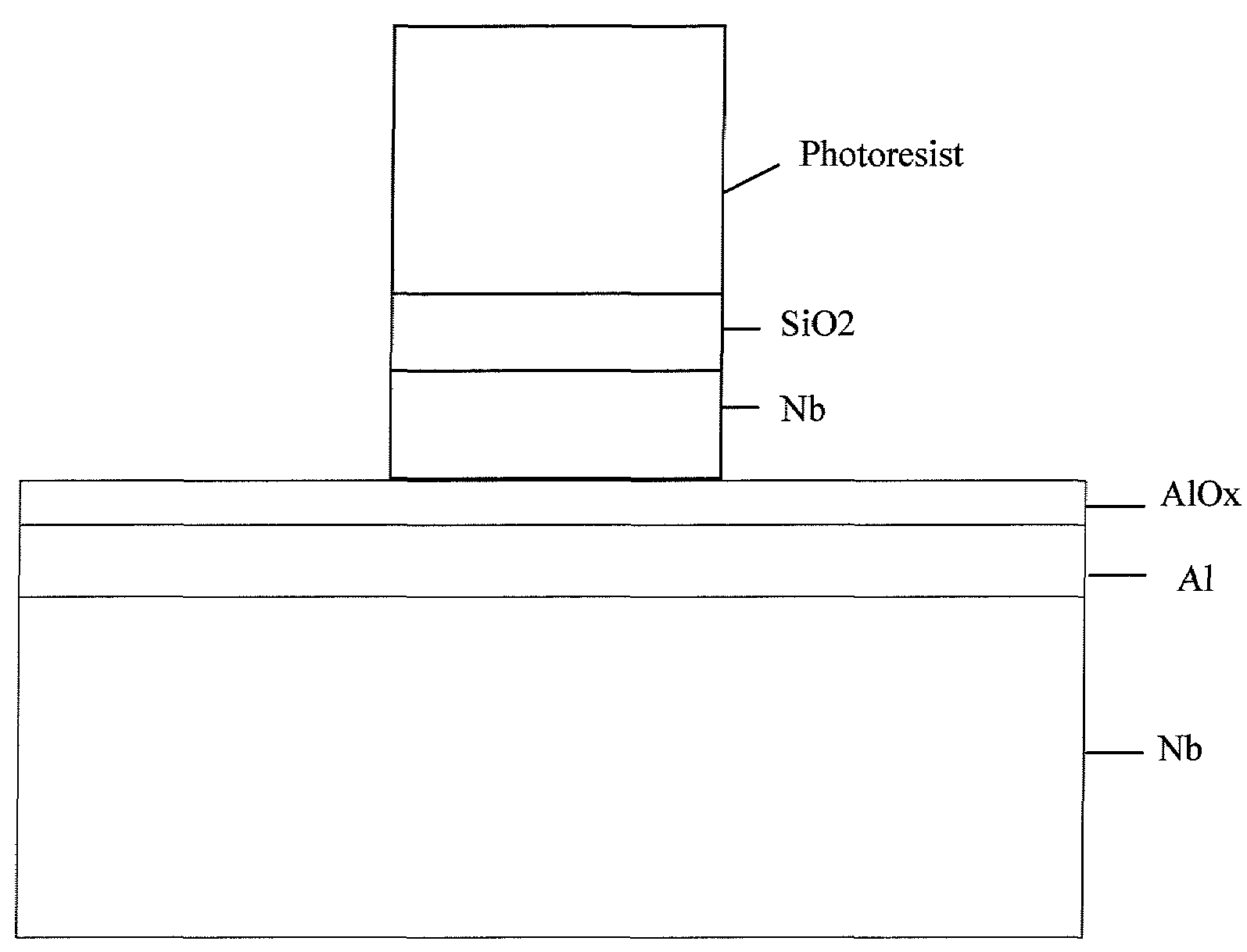

Double-Masking Technique for Increasing Fabrication Yield in Superconducting Electronics

ActiveUS20080070325A1Improve reliabilityHigh yieldSemiconductor/solid-state device manufacturingSuperconductor devicesResistNiobium

Owner:SEEQC INC

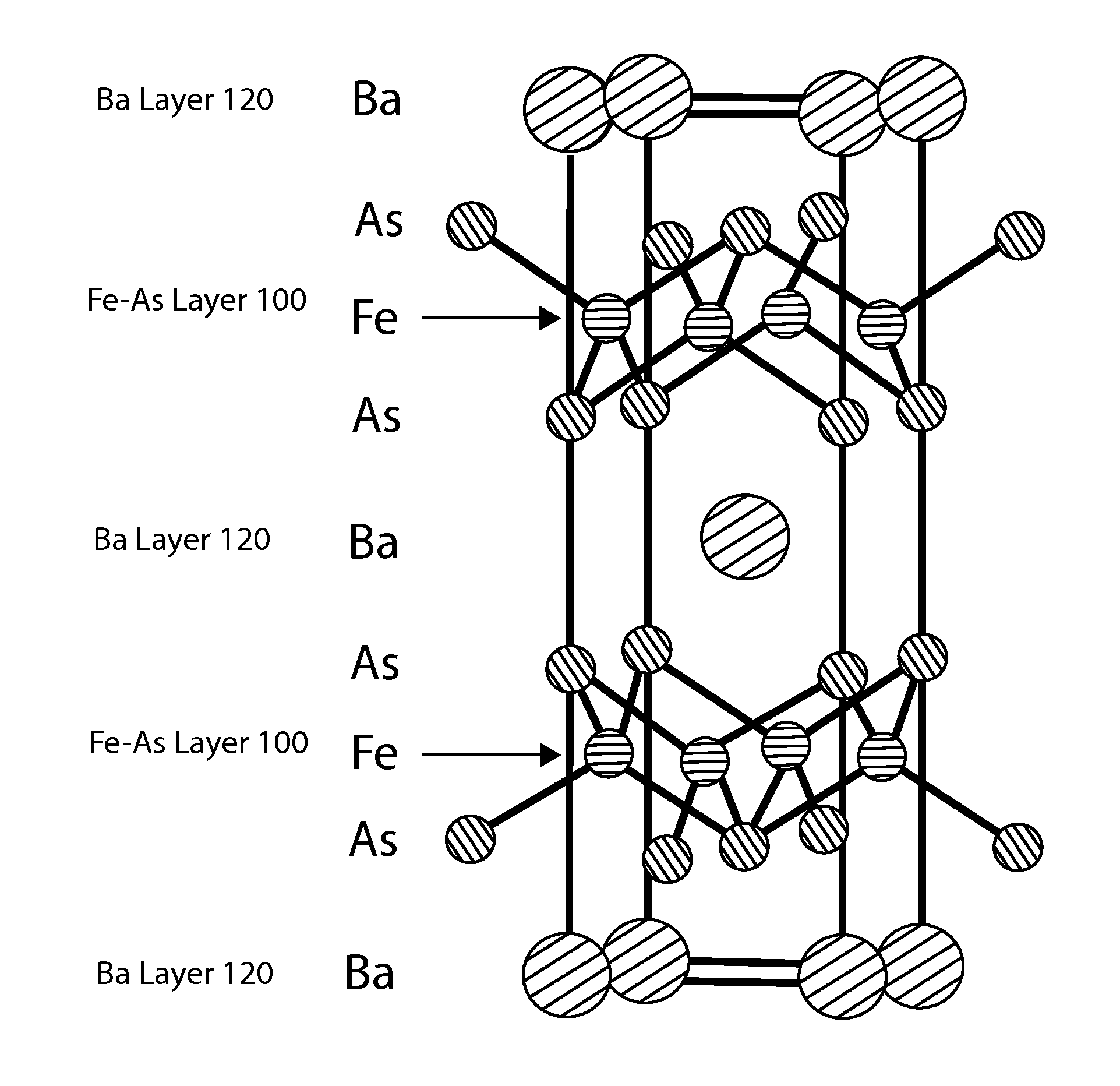

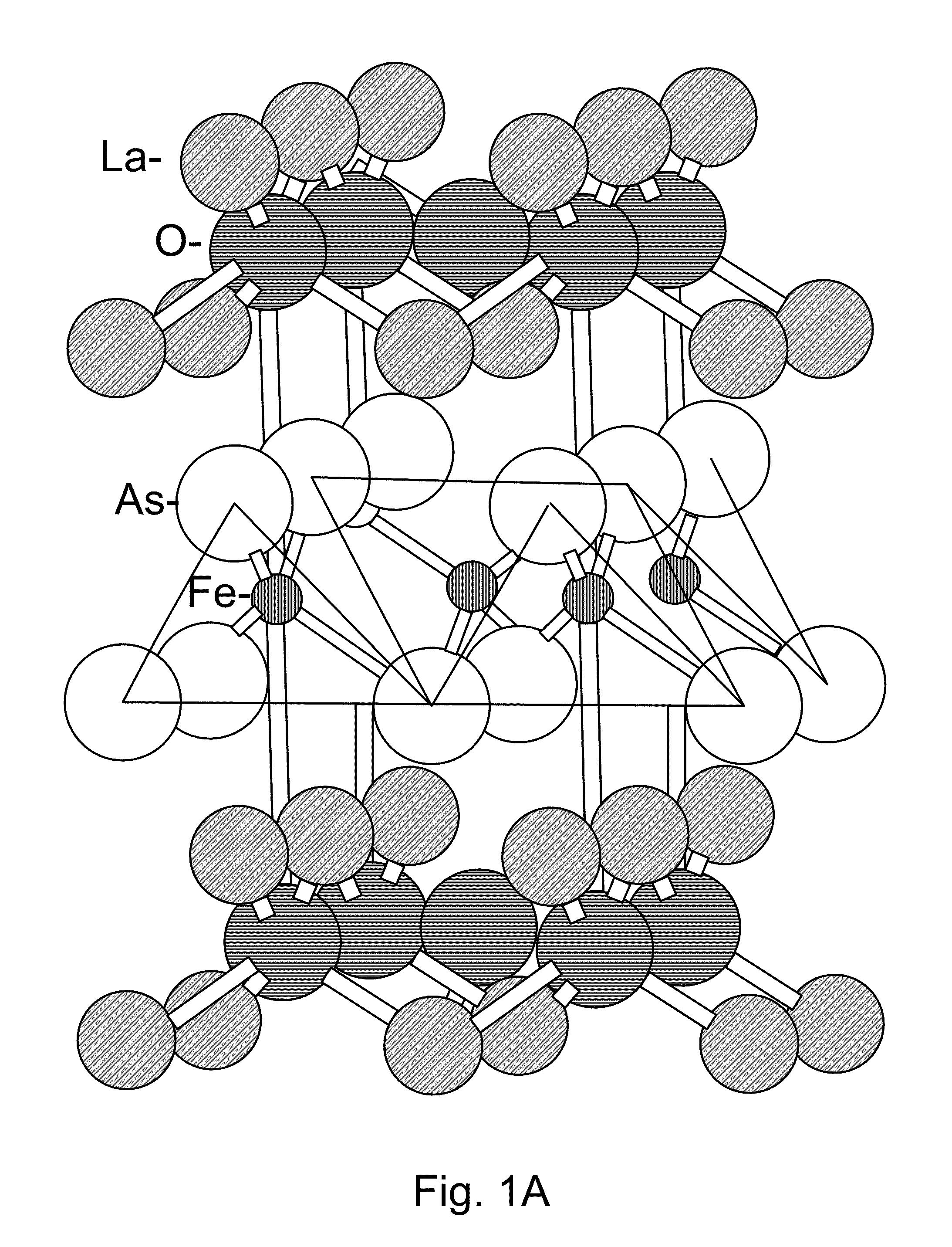

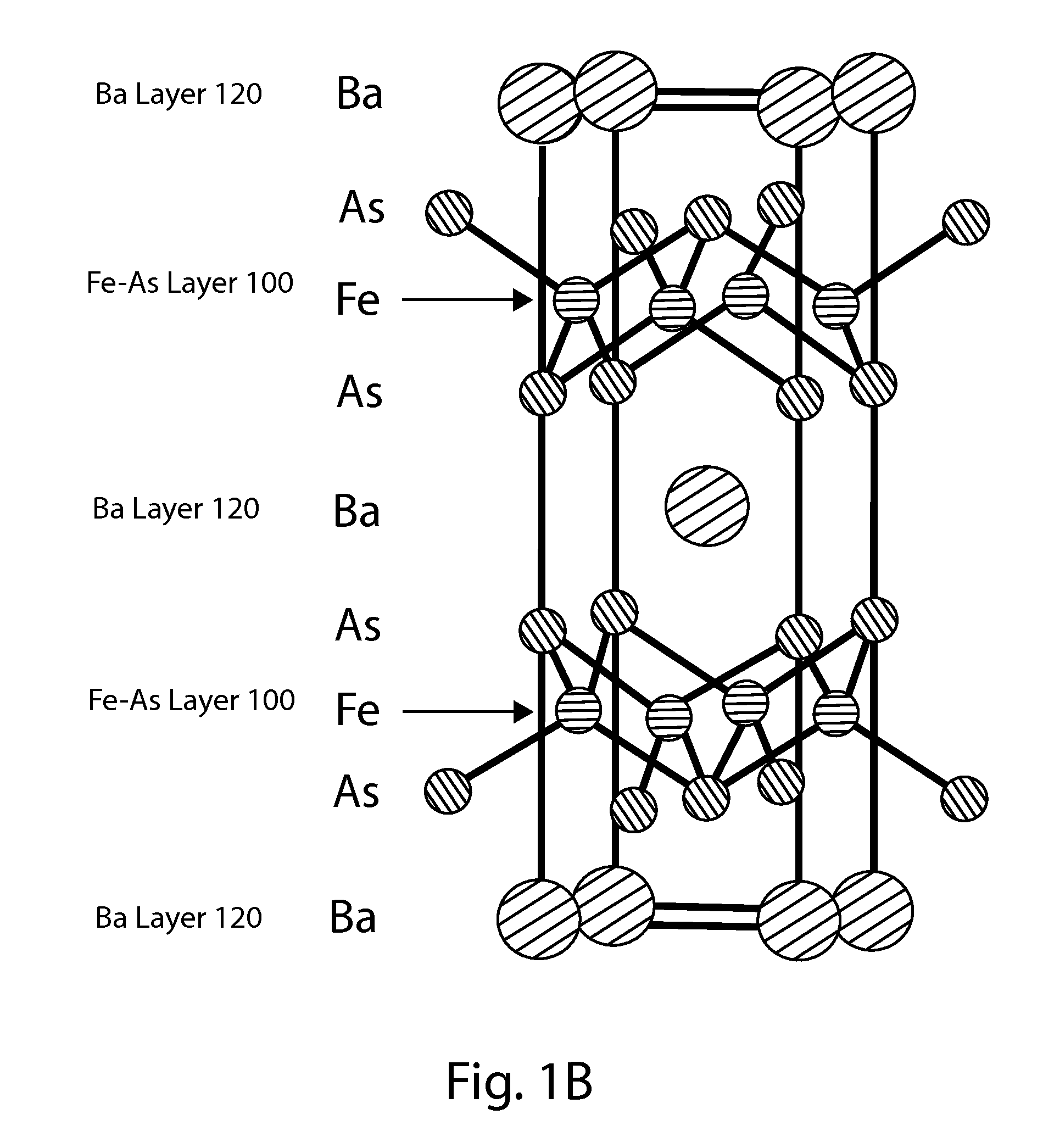

Superconducting integrated circuit technology using iron-arsenic compounds

A new family of superconducting materials with critical temperature up to 55 K have recently been discovered, comprising a crystal structure with atomic layers of iron and arsenic alternating with atomic layers of rare-earth oxide or alkaline earth. The present invention identifies structures for integrated circuit elements (including Josephson junctions) in these and related materials. These superconducting circuit elements will operate at a higher temperature than low-temperature superconductors such as niobium, and may be easier to manufacture than prior-art high-temperature superconductors based on copper-oxides.

Owner:HYPRES

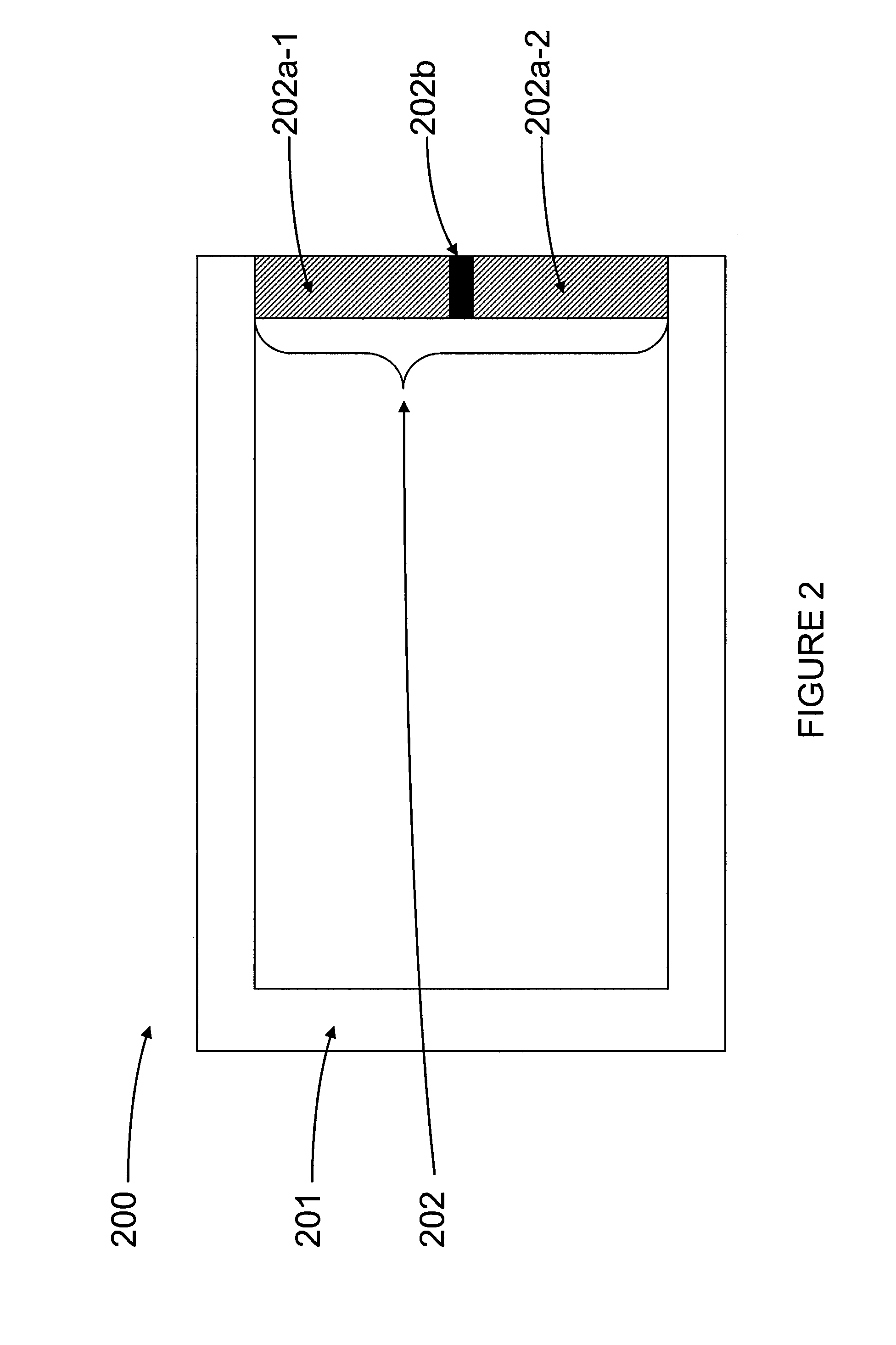

System and method for superconducting multi-chip module

ActiveUS20200119251A1Shorten the timeReduce leakageSemiconductor/solid-state device detailsSolid-state devicesIndium bumpEngineering physics

A method for bonding two superconducting integrated circuits (“chips”), such that the bonds electrically interconnect the chips. A plurality of indium-coated metallic posts may be deposited on each chip. The indium bumps are aligned and compressed with moderate pressure at a temperature at which the indium is deformable but not molten, forming fully superconducting connections between the two chips when the indium is cooled down to the superconducting state. An anti-diffusion layer may be applied below the indium bumps to block reaction with underlying layers. The method is scalable to a large number of small contacts on the wafer scale, and may be used to manufacture a multi-chip module comprising a plurality of chips on a common carrier. Superconducting classical and quantum computers and superconducting sensor arrays may be packaged.

Owner:SEEQC INC

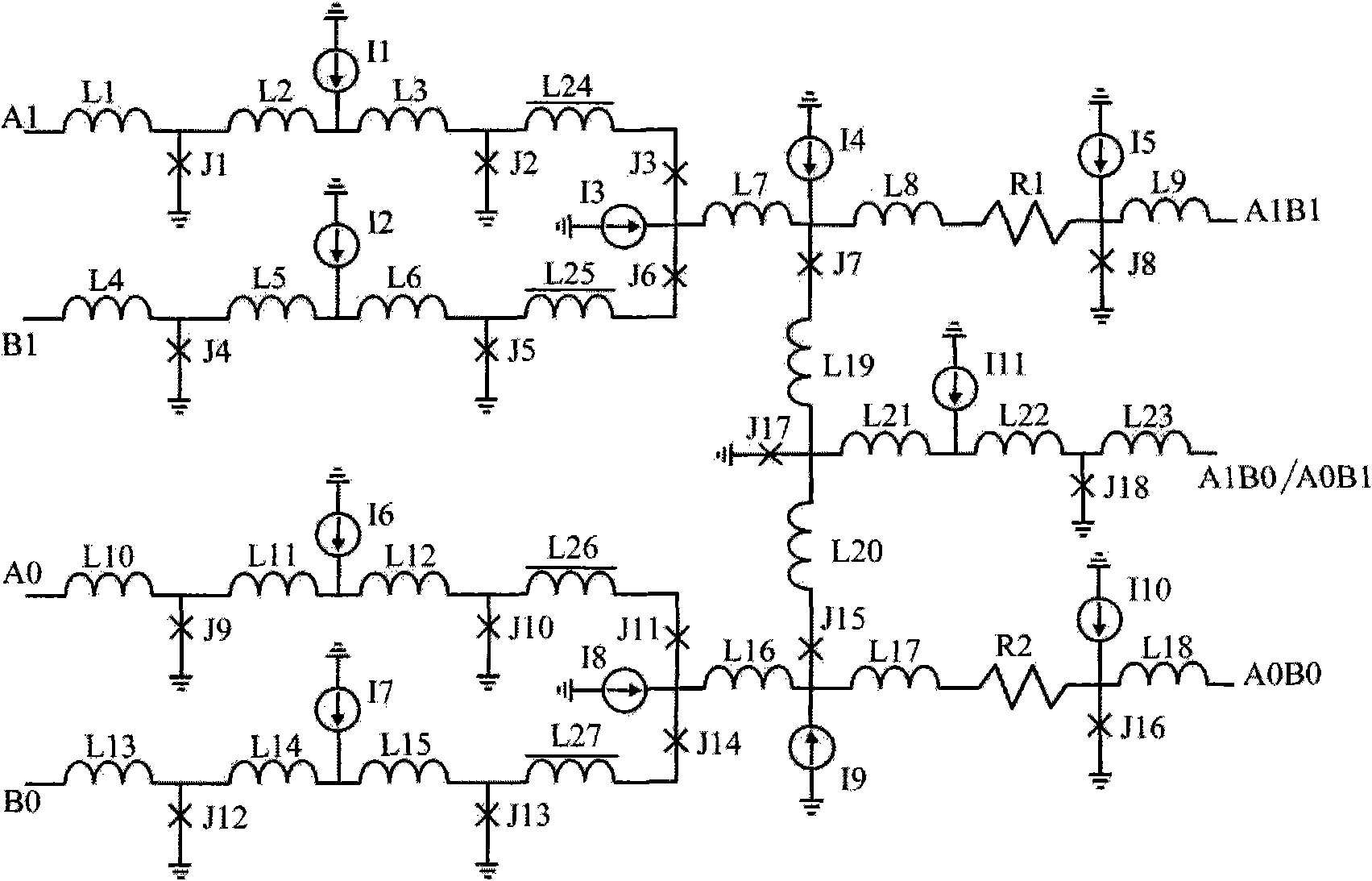

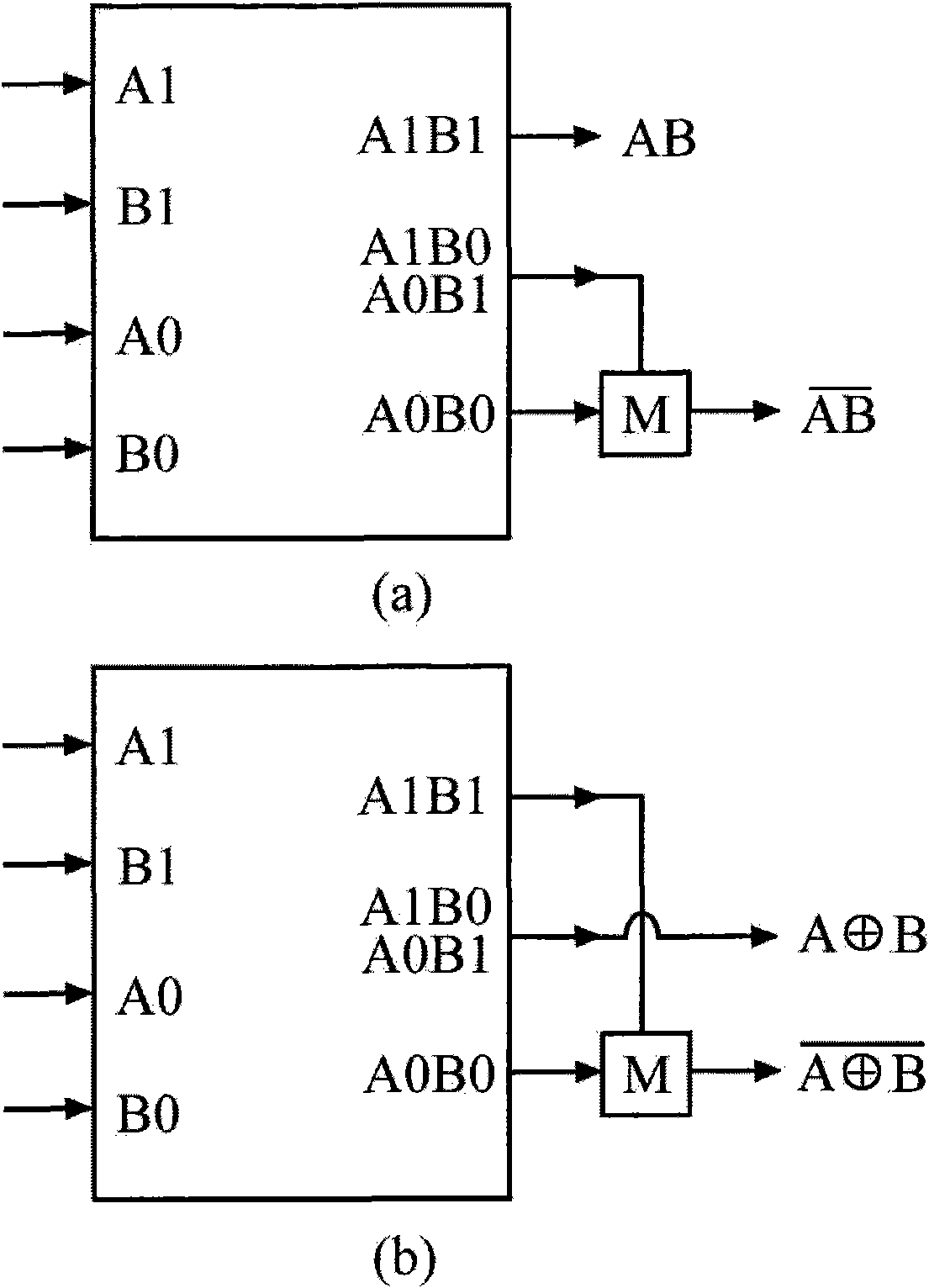

Resistive superconductive asynchronous bilinear logic universal gate circuit

InactiveCN101626233ALess number of Josephson knotsReduce time delayLogic circuits characterised by logic functionInductorLogic gate

The invention relates to a resistive superconductive asynchronous bilinear logic universal gate circuit. A logic gate structure of the prior superconductive asynchronous bilinear circuit has the defects of great amount of used Josephson junctions and difficult wiring. The resistive superconductive asynchronous bilinear logic universal gate circuit comprises four Josephson quantum interference devices and two choking resistors, and each Josephson quantum interference device comprises four Josephson junctions and three connecting inductors, wherein two adjacent Josephson quantum interference devices share two Josephson junctions. The logic gate structure proposed by the invention utilizes resistors to consume a loop current remained in the gate circuit after the logic gate is triggered so as to greatly reduce the number of the needed Josephson junctions. The invention is favorably compatible to the wiring convenience. Compared with the prior art, circuittopology in a sequential structure is easier to apply to a large-scale superconductive integrated circuit.

Owner:HANGZHOU DIANZI UNIV

Systems and methods for fabrication of superconducting integrated circuits

Various techniques and apparatus permit fabrication of superconductive circuits. A niobium / aluminum oxide / niobium trilayer may be formed and individual Josephson Junctions (JJs) formed. A protective cap may protect a JJ during fabrication. A hybrid dielectric may be formed. A superconductive integrated circuit may be formed using a subtractive patterning and / or additive patterning. A superconducting metal layer may be deposited by electroplating and / or polished by chemical-mechanical planarization. The thickness of an inner layer dielectric may be controlled by a deposition process. A substrate may include a base of silicon and top layer including aluminum oxide. Depositing of superconducting metal layer may be stopped or paused to allow cooling before completion. Multiple layers may be aligned by patterning an alignment marker in a superconducting metal layer.

Owner:D WAVE SYSTEMS INC

Superconducting integrated circuit and methods of forming same

InactiveUS20050092981A1Solid-state devicesDissimilar materials junction devicesCopperSuperconducting integrated circuits

An integrated circuit formed on a substrate suitably includes a number of superconducting junctions. Each superconducting junction includes a first superconducting material disposed upon the substrate, an insulating material formed on the first superconducting material, and a second superconducting material formed on the insulating material to create a Josephson junction. The second superconducting material is a different material from the first superconducting material to aid in manufacturability. Any number of electrically conductive interconnects are also provided to interlink the superconducting junctions to thereby form the integrated circuit. Examples of superconducting materials that may be used for the various layers include YBaCu3O7-y (YBCO) and Bi2Sr2CaCu2Oy (Bi2212). Various circuits and techniques relating to superconducting devices are also described.

Owner:THE BOEING CO

Resistive superconductive asynchronous bilinear logic AND gate circuit

InactiveCN101626234AReduce in quantityReduce time delayLogic circuits characterised by logic functionInductorLogic gate

The invention relates to a resistive superconductive asynchronous bilinear logic AND gate circuit. A logic gate structure of the prior superconductive asynchronous bilinear circuit has the defects of great amount of used Josephson junctions and difficult wiring. The resistive superconductive asynchronous bilinear logic AND gate circuit comprises four Josephson quantum interference devices and a choking resistor, the first Josephson quantum interference device or the second Josephson quantum interference device comprises four Josephson junctions and two connecting inductors; and the third Josephson quantum interference device or the fourth Josephson quantum interference device comprises three Josephson junctions and a connecting inductor. The logic AND gate circuit proposed by the invention utilizes resistors to consume a loop current remained in the gate circuit after the logic gate is triggered so as to greatly reduce the number of the needed Josephson junctions. The invention is favorably compatible to the wiring convenience. Compared with the prior art, circuittopology in a sequential structure is easier to apply to a large-scale superconductive integrated circuit.

Owner:HANGZHOU DIANZI UNIV

Digital Routing Switch Matrix for Digitized Radio-Frequency Signals

InactiveUS20070293160A1Efficient executionPrecise processingElectronic switchingSubstation equipmentMulti bandTransceiver

Routing and distribution of radio-frequency (RF) signals is commonly achieved in the analog domain. However, improved performance and simplified circuit architectures may be obtained by first digitizing the RF signal, and then carrying out all routing in the digital domain. A new generation of scalable digital switches has been developed, which routes both the data and clock signals together, this being necessary to maintain the integrity of the digitized RF signal. Given the extremely high switching speeds necessary for these applications (tens of GHz), this is implemented using Rapid-Single-Flux-Quantum (RSFQ) logic with superconducting integrated circuits. Such a digital switch matrix may be applied to either the receiver or transmitter components of an advanced multi-band, multi-channel digital transceiver system, and is compatible with routing of signals with different clock frequencies simultaneously within the same switch matrix.

Owner:HYPRES

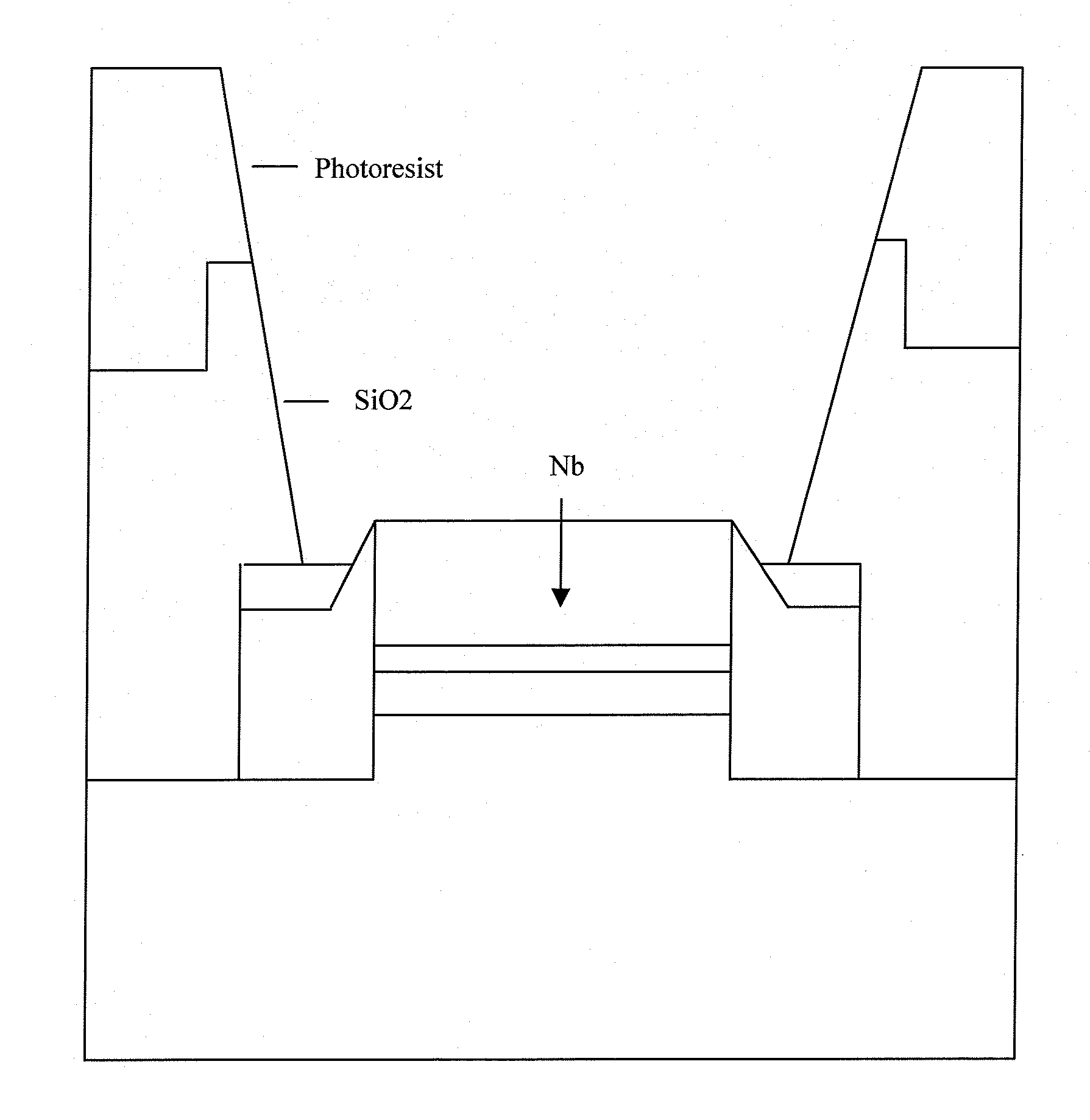

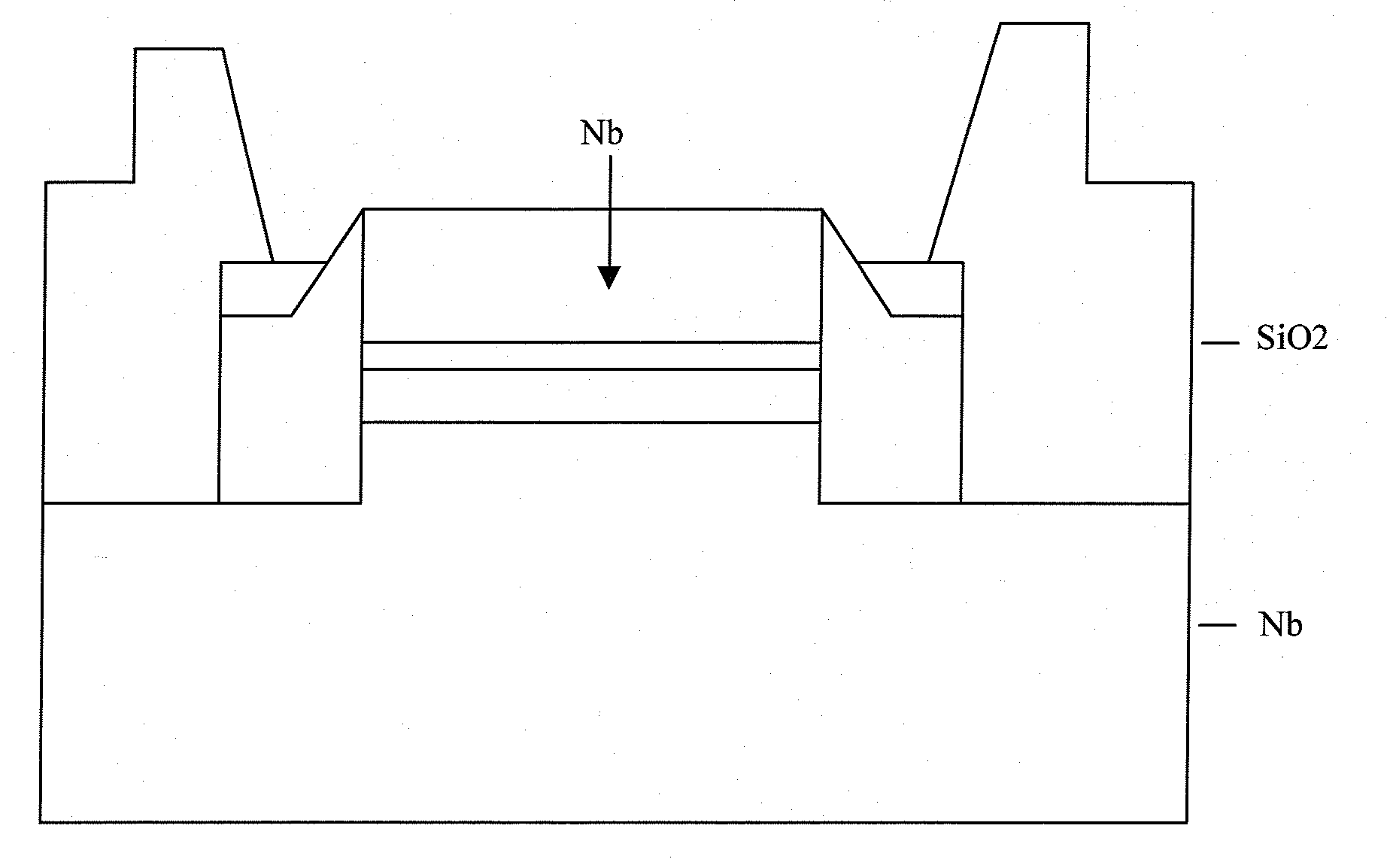

Double-masking technique for increasing fabrication yield in superconducting electronics

ActiveUS7615385B2Improve reliabilityHigh yieldSemiconductor/solid-state device manufacturingSuperconductor devicesResistNiobium

A new technique is presented for improving the microfabrication yield of Josephson junctions in superconducting integrated circuits. This is based on the use of a double-layer lithographic mask for partial anodization of the side-walls and base electrode of the junctions. The top layer of the mask is a resist material, and the bottom layer is a dielectric material chosen so as to a) maximize adhesion between the resist and the underlying superconducting layer, b) be etch-compatible with the underlying superconducting layer, and c) be insoluble in the resist and anodization processing chemistries. In a preferred embodiment of the invention, the superconductor is niobium, the material on top of this is silicon dioxide, and the top layer is conventional photoresist or electron-beam resist. The use of this combination results in a substantial increase in the fabrication yield of high-density superconducting integrated circuits due to increase in junction uniformity and reduction in defect density. An additional improvement over the prior art involves the replacement of a wet-etch step with a dry etch more compatible with microlithography.

Owner:SEEQC INC

Superconducting circuit for high-speed lookup table

ActiveUS20070194958A1Rapid parallel pipelined readoutSlow serial reprogramming of memory contentSuperconductors/hyperconductorsRead-only memoriesProgrammable read-only memoryRapid single flux quantum

A high-speed lookup table is designed using Rapid Single Flux Quantum (RSFQ) logic elements and fabricated using superconducting integrated circuits. The lookup table is composed of an address decoder and a programmable read-only memory array (PROM). The memory array has rapid parallel pipelined readout and slower serial reprogramming of memory contents. The memory cells are constructed using standard non-destructive reset-set flip-flops (RSN cells) and data flip-flops (DFF cells). An n-bit address decoder is implemented in the same technology and closely integrated with the memory array to achieve high-speed operation as a lookup table. The circuit architecture is scalable to large two-dimensional data arrays.

Owner:SEEQC INC

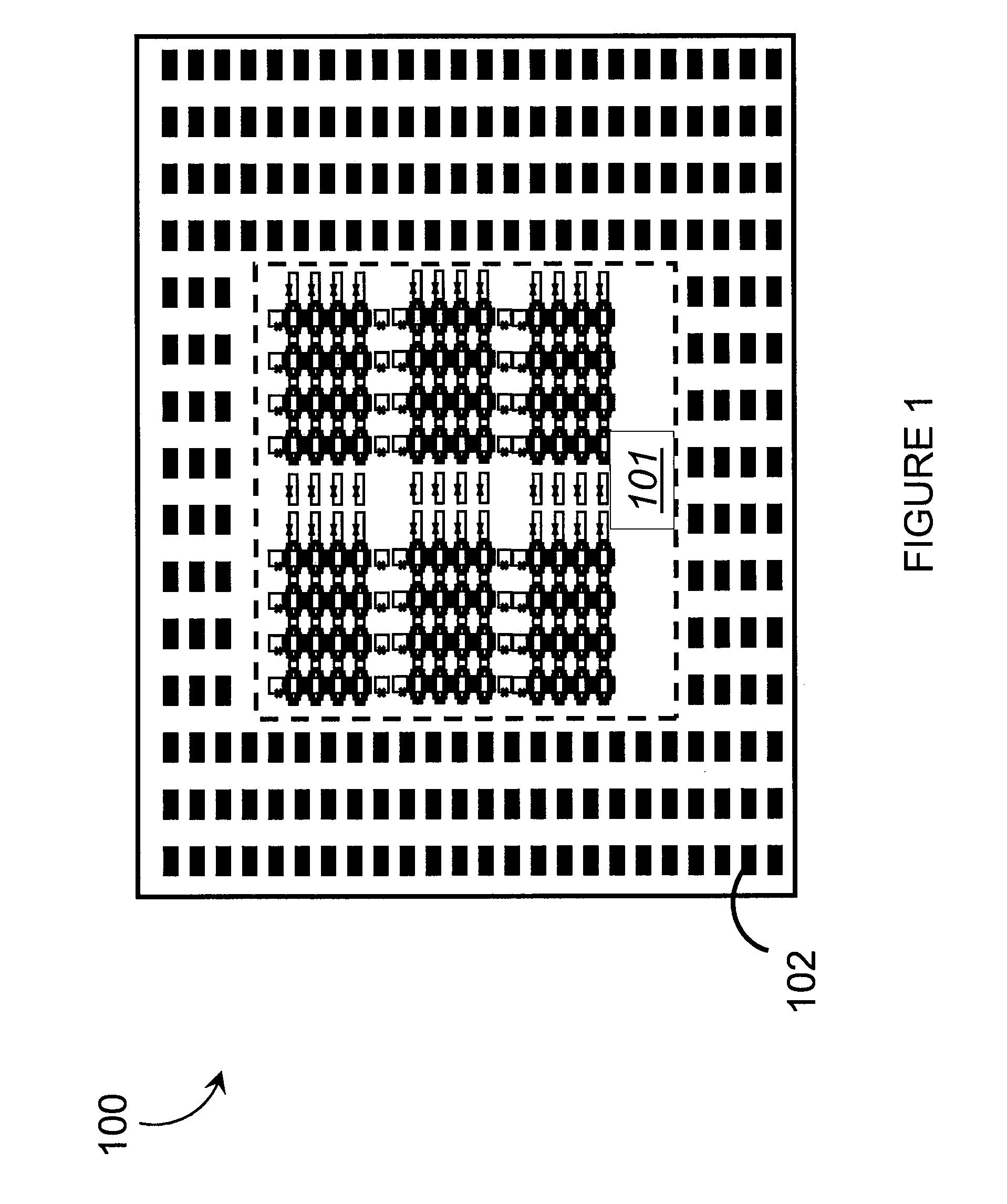

Systems and methods for fabrication of superconducting integrated circuits

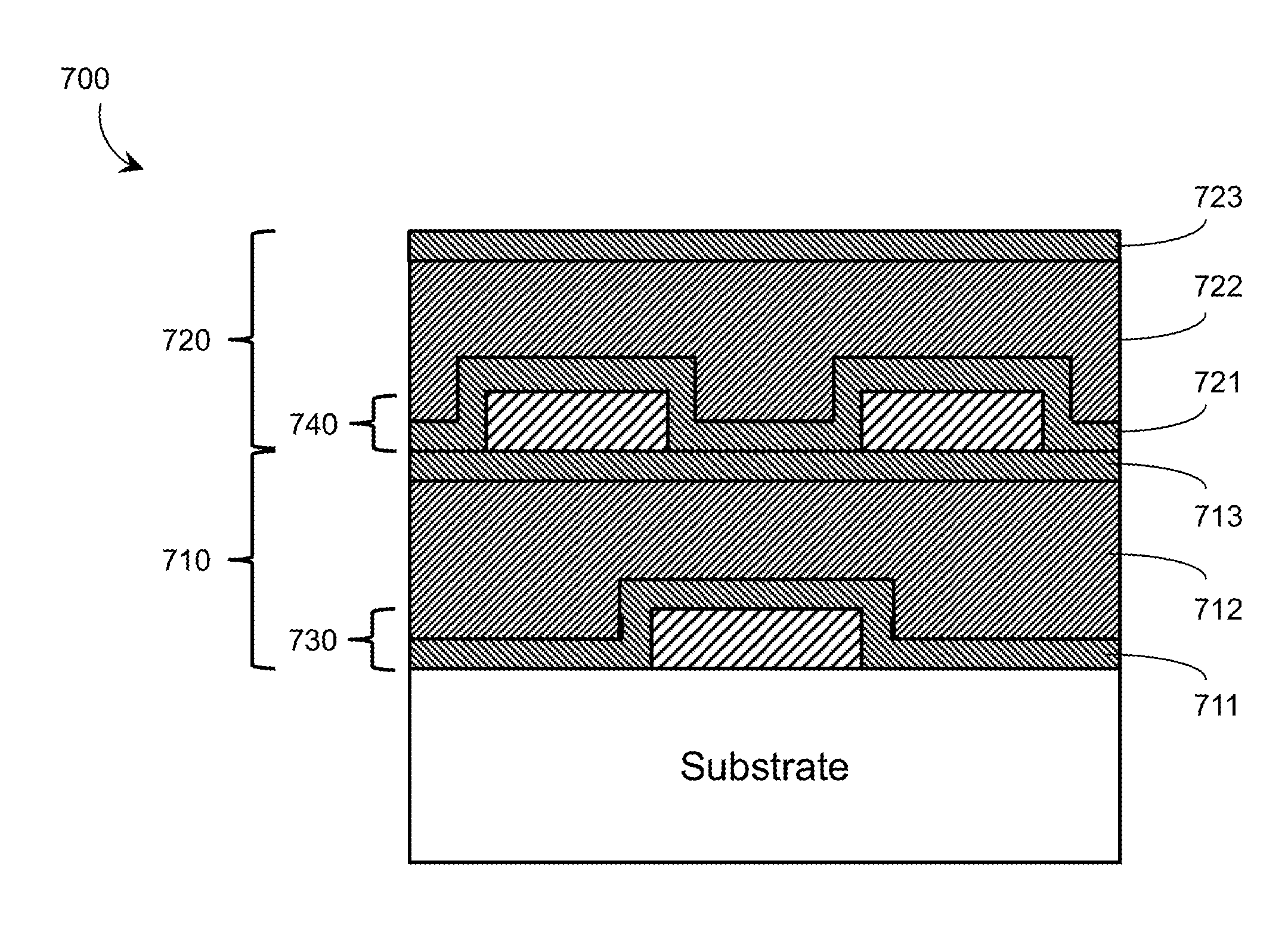

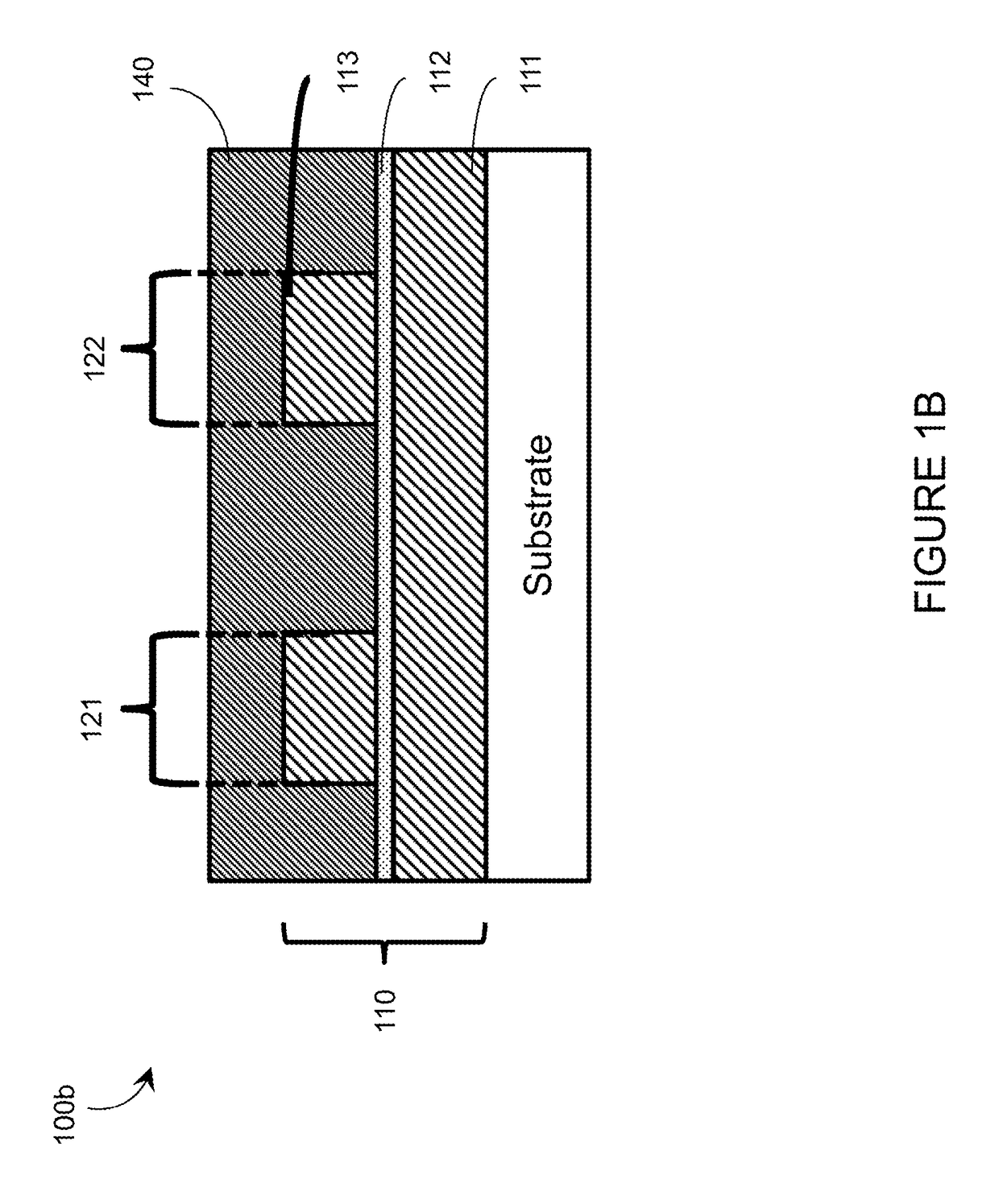

ActiveUS20200144476A1Significant proportionSemiconductor/solid-state device detailsSolid-state devicesIntegrated circuit manufacturingHemt circuits

Various techniques and apparatus permit fabrication of superconductive circuits. A superconducting integrated circuit comprising a superconducting stud via, a kinetic inductor, and a capacitor may be formed. Forming a superconducting stud via in a superconducting integrated circuit may include masking with a hard mask and masking with a soft mask. Forming a superconducting stud via in a superconducting integrated circuit may include depositing a dielectric etch stop layer. Interlayer misalignment in the fabrication of a superconducting integrated circuit may be measured by an electrical vernier. Interlayer misalignment in the fabrication of a superconducting integrated circuit may be measured by a chain of electrical verniers and a Wheatstone bridge. A superconducting integrated circuit with three or more metal layers may include an enclosed, matched, on-chip transmission line. A metal wiring layer in a superconducting integrated circuit may be encapsulated.

Owner:D WAVE SYSTEMS INC

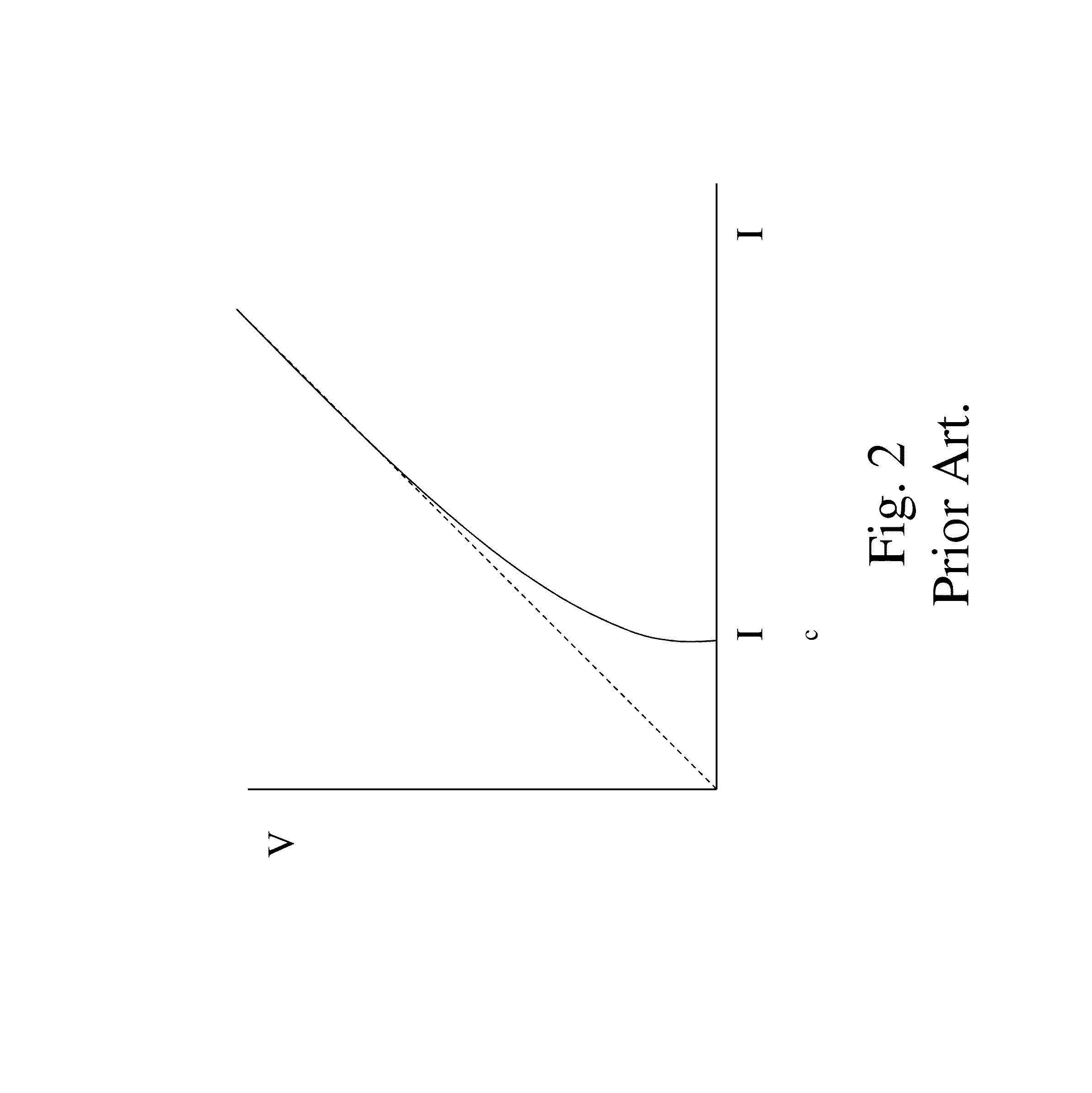

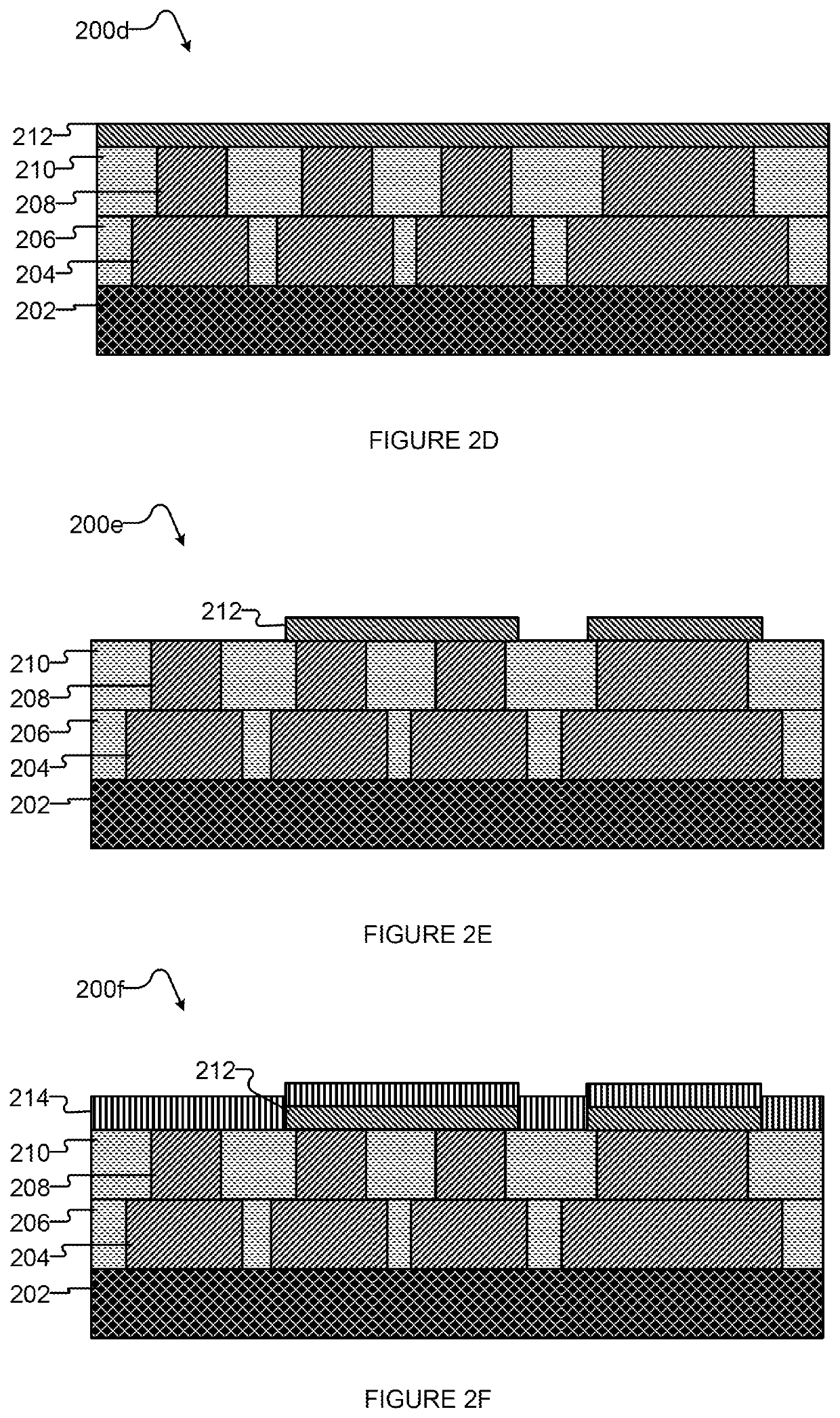

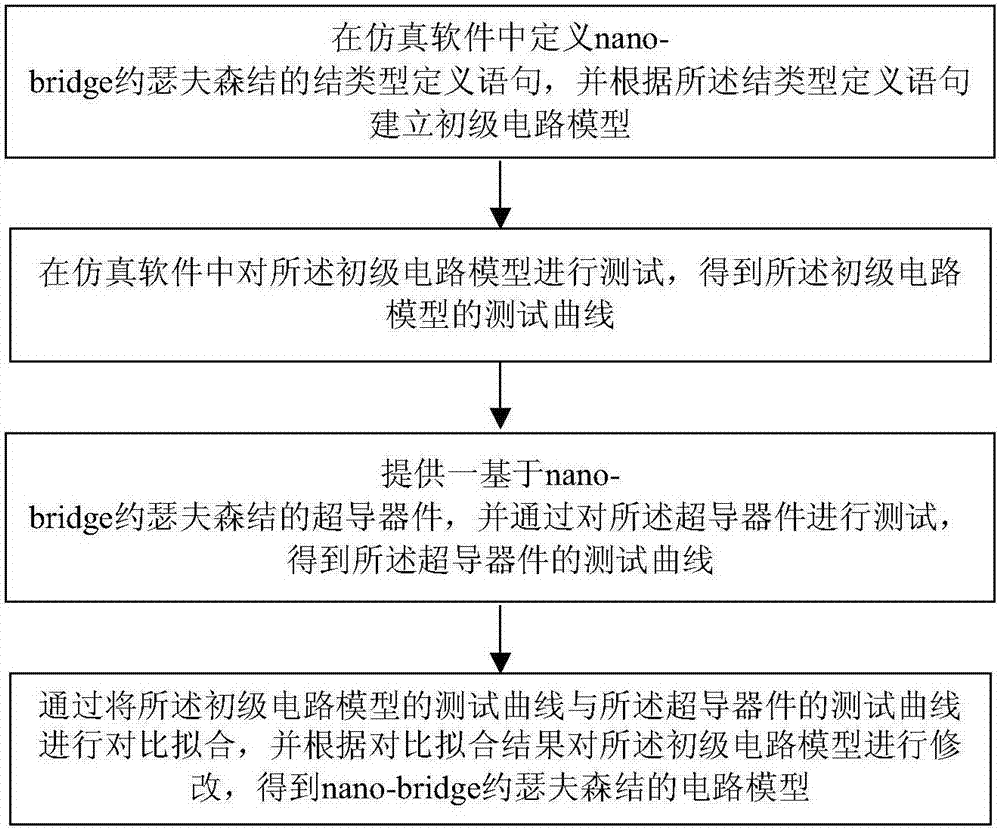

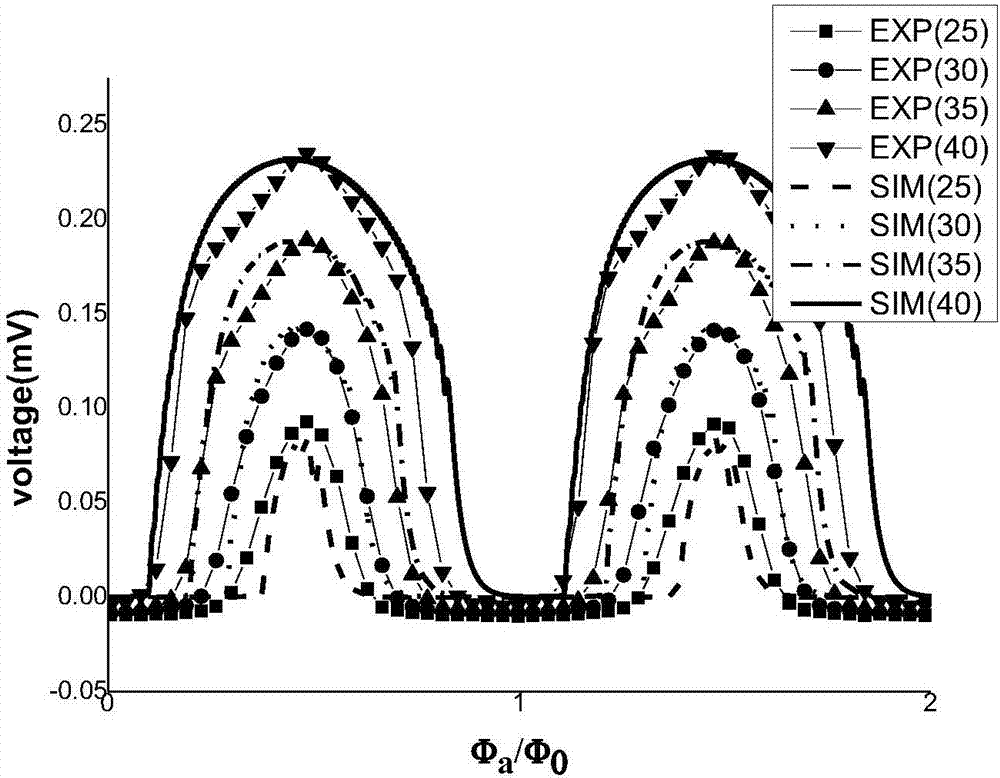

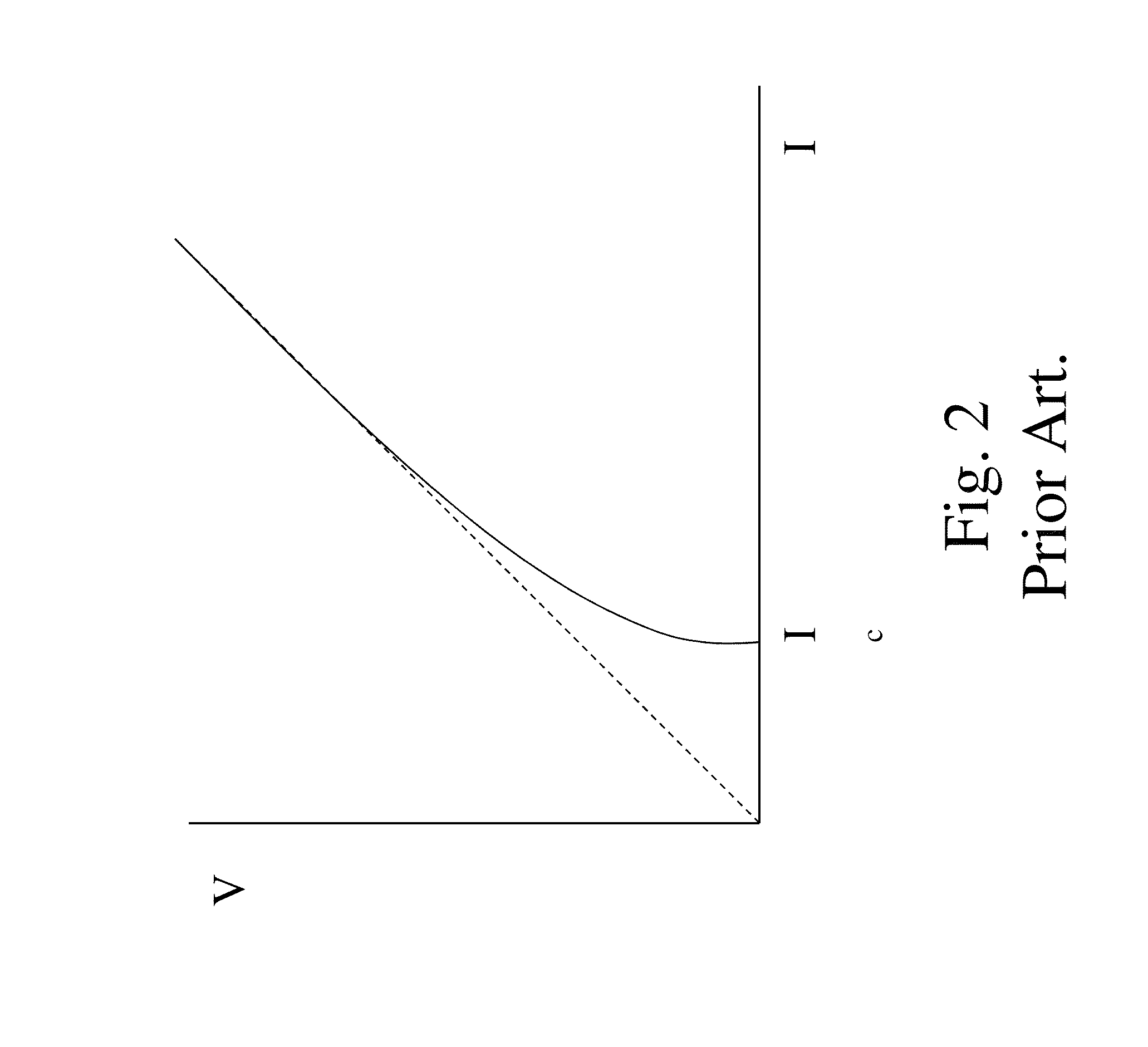

Structure and establishment method of Josephson junction circuit model and structure and establishment method of superconducting integrated circuit

InactiveCN107704649AHighly integratedAddress Design GapsSpecial data processing applicationsIntegrated circuit layoutCircuit models

The invention provides a structure and an establishment method of a Josephson junction circuit model and a structure and an establishment method of a superconducting integrated circuit. The establishment method of the circuit model includes: defining a junction type definition statement of a nano-bridge Josephson junction in simulation software, and establishing a primary circuit model according to the junction type definition statement; testing the primary circuit model to obtain corresponding testing curves; providing a superconducting device based on the nano-bridge Josephson junction, andobtaining corresponding testing curves through testing the same; and then obtaining the circuit model through comparing and fitting the obtained testing curves and modifying the primary circuit modelaccording to comparison and fitting results. Through the structures and the establishment methods of the invention, problems that the nano-bridge Josephson junction circuit model does not exist in existing simulation software, and the nano-bridge Josephson junction cannot be used to realize design of the superconducting integrated circuit are solved.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

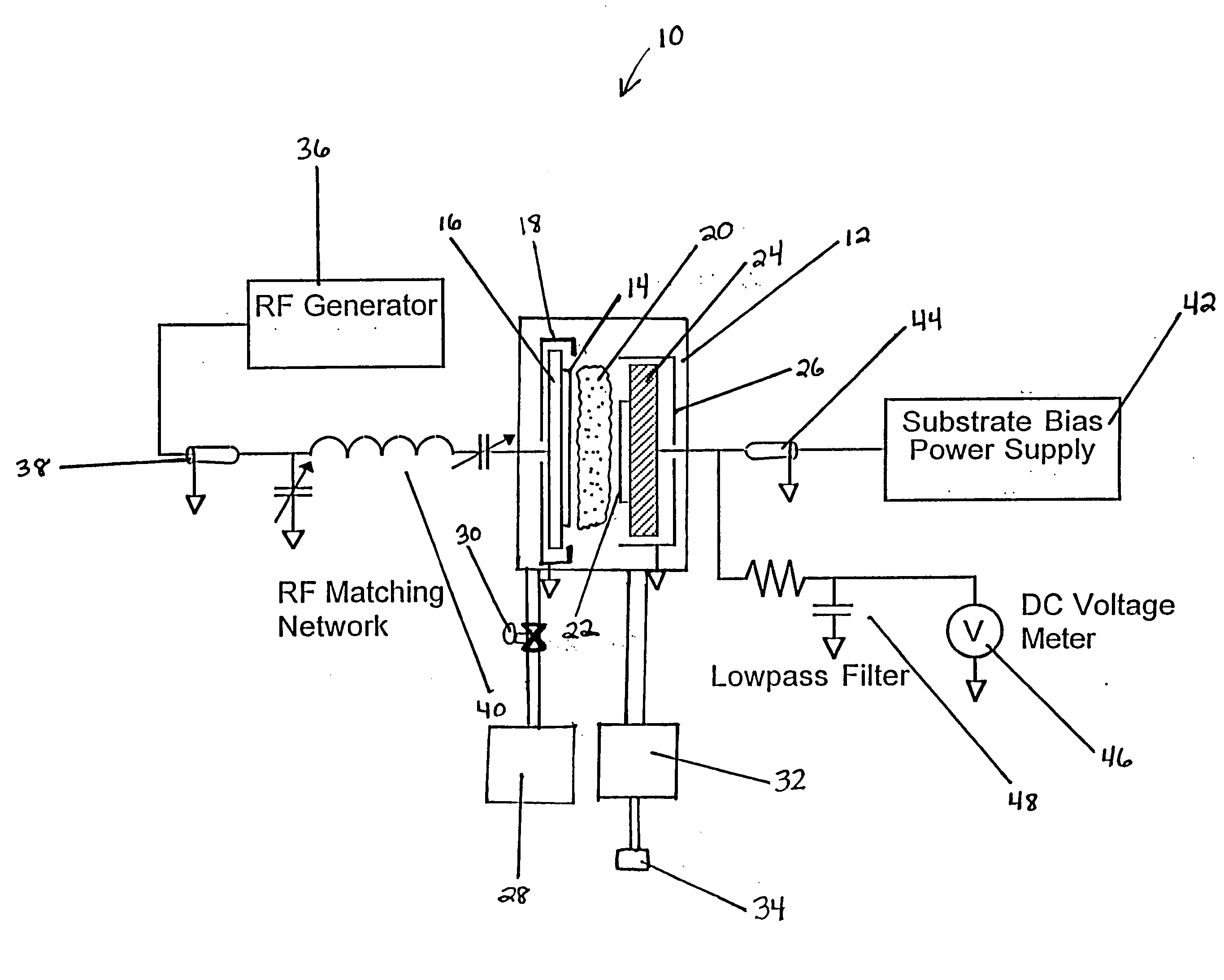

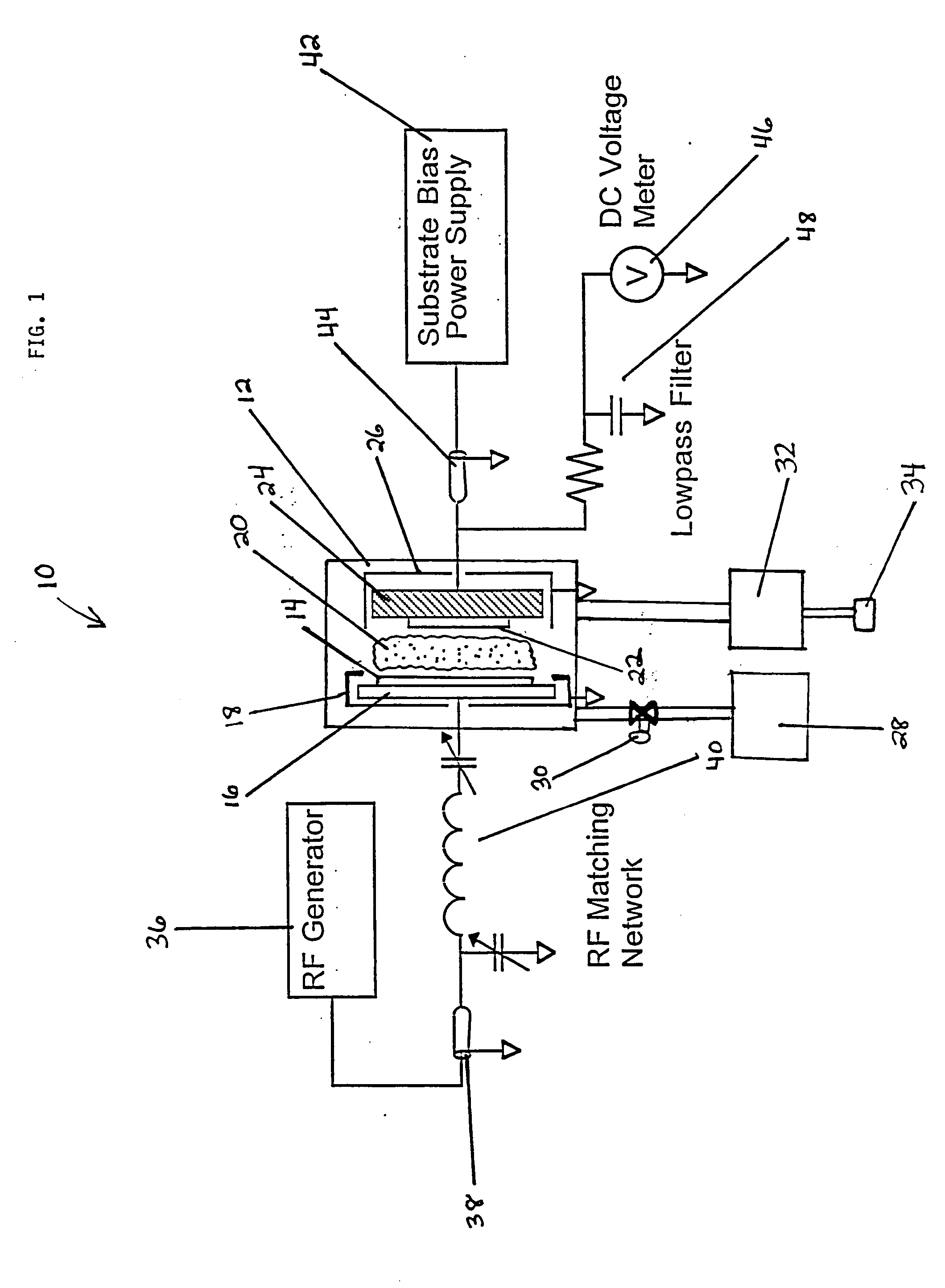

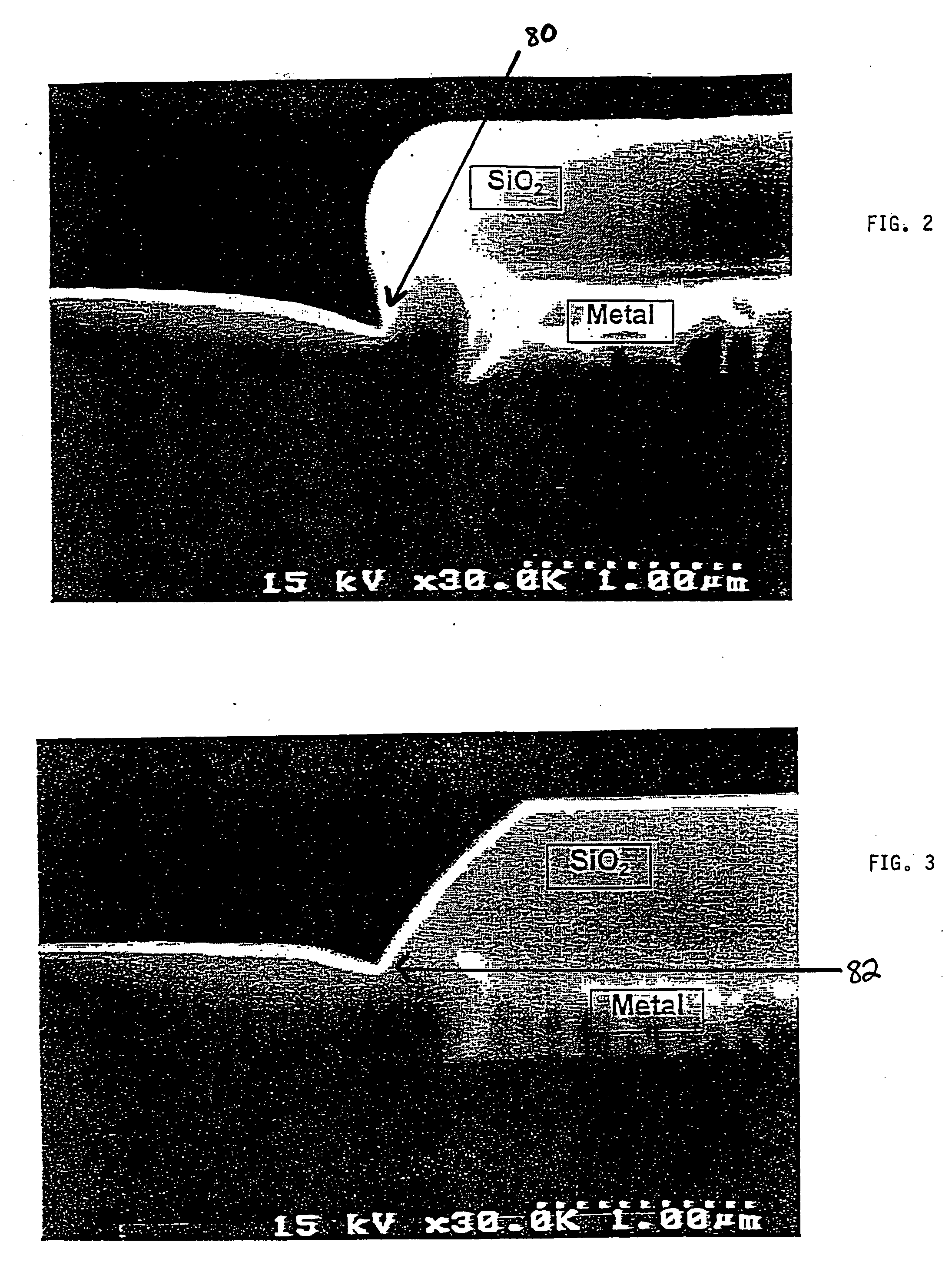

Method for producing substantially planar films

InactiveUS20050267000A1Sufficient energySuperconductors/hyperconductorsSemiconductor/solid-state device detailsSurface roughnessOptoelectronics

This present invention is directed to a method for producing very smooth, substantially planar films for use in the manufacture of high performance superconductive integrated circuits (ICs) and in the fabrication of tunnel junctions. The method of the present invention applies a low frequency AC bias voltage to a substrate and uses a sputtered target material, such as silicon dioxide, to effectively produce very smooth and substantially planar films, and in particular, oxide films and metal films. The method produces films, such as oxide films, on a bare or uncoated substrate, the films having a surface roughness of less than about 0.1 nanometer. The method also produces films on a conductive or coated substrate, the films having a surface roughness of less than about 1.0 nanometer.

Owner:KERBER GEORGE L

Superconducting integrated circuit and method for fabrication thereof

InactiveUS20050191763A1Reduce in quantityImprove reliabilitySuperconductors/hyperconductorsSemiconductor/solid-state device detailsEngineeringSuperconducting integrated circuits

A superconducting integrated circuit includes a substrate, a multilayer structure formed on the substrate and composed of a lower superconducting electrode, a tunnel barrier and an upper superconducting electrode sequentially joined together upward in the order mentioned, and an insulating layer perforated to form via holes to get electrical contacts with the lower and upper electrodes. The insulating layer is formed of a high-resolution, photosensitive, solvent-soluble, organic insulating material. The superconducting integrated circuit is produced by a method that includes the steps of depositing the multiplayer on the substrate, applying the insulating material to the front surface of the substrate inclusive of the multiplayer, forming the via holes in the insulating material by the lithographic technique at the prospective positions to get electrical contacts with the upper and lower electrodes, and laying wirings for connecting the upper and lower electrodes through the via holes.

Owner:NAT INST OF ADVANCED IND SCI & TECH +1

Low-power biasing networks for superconducting integrated circuits

ActiveUS9240773B1Reduce and eliminate DC power dissipationReduce power consumptionSuperconductors/hyperconductorsSolid-state devicesEngineeringSuperconducting integrated circuits

A superconducting integrated circuit, comprising a plurality of superconducting circuit elements, each having a variation in operating voltage over time; a common power line; and a plurality of bias circuits, each connected to the common power line, and to a respective superconducting circuit element, wherein each respective bias circuit is superconducting during at least one time portion of the operation of a respective superconducting circuit element, and is configured to supply the variation in operating voltage over time to the respective superconducting circuit element.

Owner:SEEQC INC

System and method for array diagnostics in superconducting integrated circuit

ActiveUS10222416B1Digital circuit testingCounting chain pulse countersMultiplexerIntegrated circuit layout

A superconducting circuit is disclosed for fast digital readout of on-chip diagnostics in an array of devices in an integrated circuit. The digital readout comprises a digital RSFQ multiplexer to select the readout channel. This permits a large number of devices to be tested with a minimum of input and output lines. The devices may comprise digital devices (such as elementary RSFQ cells), or analog devices (such as inductors, resistors, or Josephson junctions) with a SQUID quantizer to generate a digital signal. The diagnostic array and the digital multiplexer are preferably configured to operate as part of the same integrated circuit at cryogenic temperatures.

Owner:HYPRES

Superconducting integrated circuit and method for fabrication thereof

InactiveUS6911665B2Reduce in quantityImprove reliabilitySuperconductors/hyperconductorsSemiconductor/solid-state device detailsEngineeringElectrode Contact

A superconducting integrated circuit includes a substrate, a multilayer structure formed on the substrate and composed of a lower superconducting electrode, a tunnel barrier and an upper superconducting electrode sequentially joined together upward in the order mentioned, and an insulating layer perforated to form via holes to get electrical contacts with the lower and upper electrodes. The insulating layer is formed of a high-resolution, photosensitive, solvent-soluble, organic insulating material. The superconducting integrated circuit is produced by a method that includes the steps of depositing the multiplayer on the substrate, applying the insulating material to the front surface of the substrate inclusive of the multiplayer, forming the via holes in the insulating material by the lithographic technique at the prospective positions to get electrical contacts with the upper and lower electrodes, and laying wirings for connecting the upper and lower electrodes through the via holes.

Owner:NAT INST OF ADVANCED IND SCI & TECH +1

Superconducting digital first-in first-out buffer using physical back pressure mechanism

A digital first-in first-out (FIFO) buffer (10) for use with Single Flux Quantum (SFQ) superconductive integrated circuits. The digital FIFO buffer (10) includes a clock-storage circuit (14) for receiving and storing load and read clock signals (100, 104) and a data-storage circuit (16) connected to the clock-storage circuit (14) for receiving and storing data signal pulses (102) in the order which the data signal pulses (102) are received relative to the load clock signal (100). The data-storage circuit (16) outputs the SFQ pulse signal independent of the load clock signal (100). The previously stored clock and data signal pulses (100, 102) provide physical back pressure to their subsequent signal pulses.

Owner:NORTHROP GRUMAN CORP

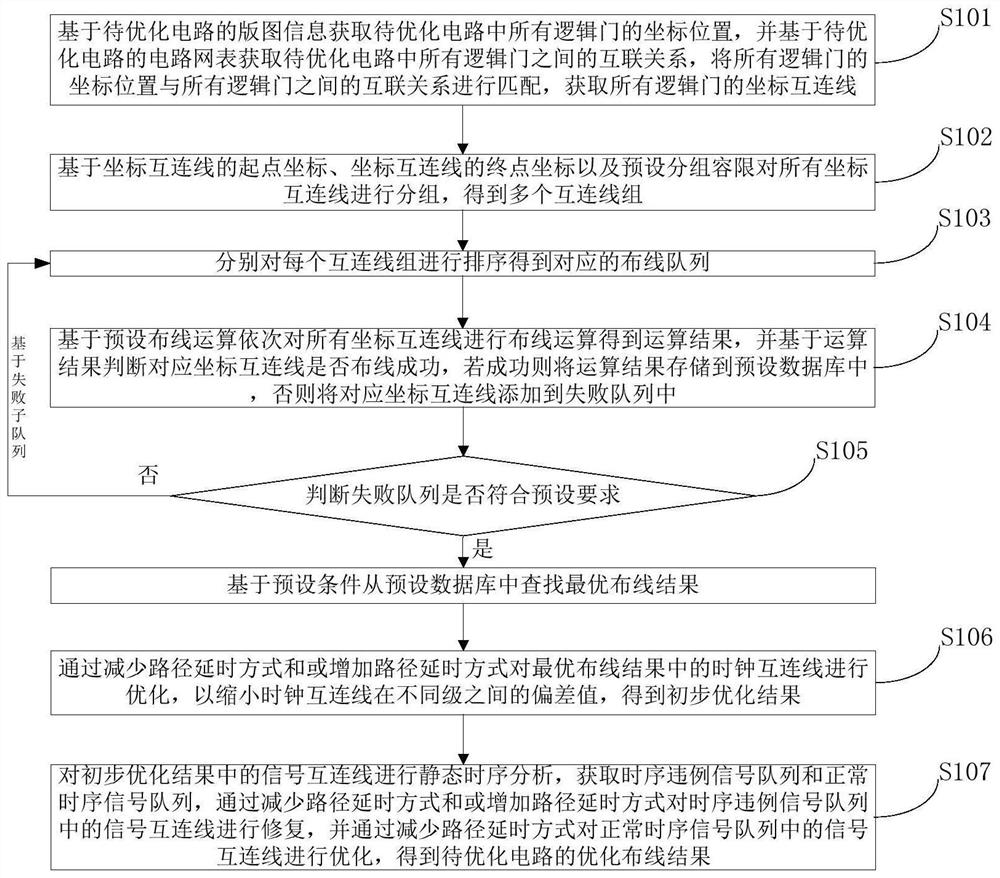

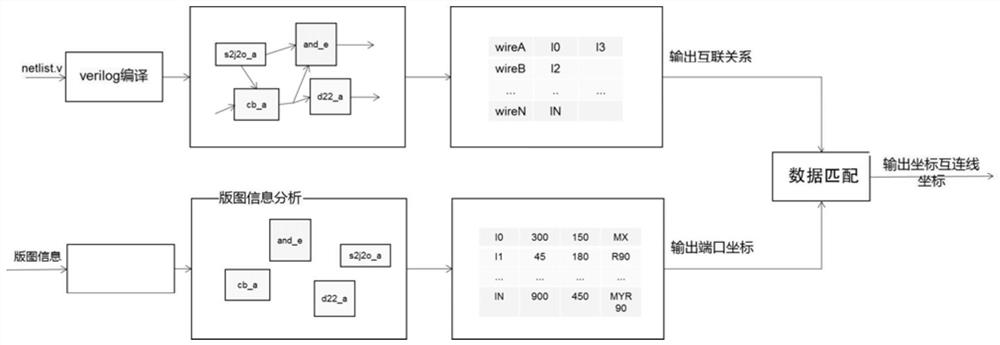

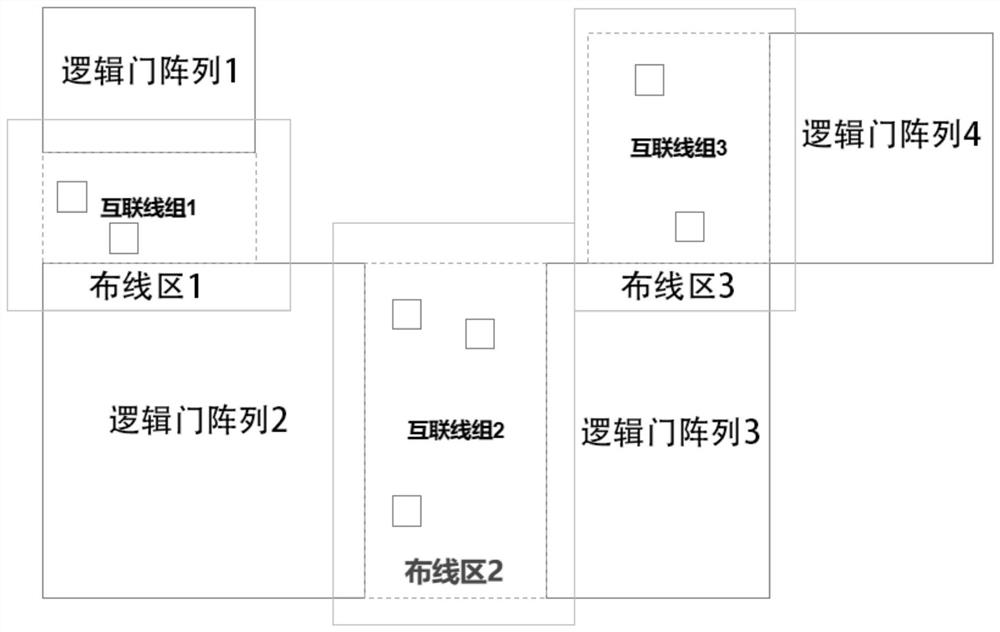

Wiring optimization method and device of superconducting integrated circuit, storage medium and terminal

ActiveCN113779924AImplement autorouting problemsImprove compatibilityComputer aided designSpecial data processing applicationsPathPingHemt circuits

The invention discloses a wiring optimization method and device for a superconducting integrated circuit, a storage medium and a terminal. The method comprises the steps: obtaining logic gate coordinate interconnection lines based on the layout information of a to-be-optimized circuit and a circuit netlist, carrying out the wiring operation of all coordinate interconnection lines, and storing the operation result of successful wiring in a preset database, adding the coordinate interconnection line corresponding to the wiring failure into a failure queue; obtaining an optimal wiring result based on the failure queue; and optimizing the clock interconnection line and the signal interconnection line in the optimal wiring result based on a path delay reducing mode and / or a path delay increasing mode to obtain an optimized wiring result of the to-be-optimized circuit. According to the method, the automatic wiring problem after the superconducting integrated circuit is arranged is solved, the design cost is reduced, and the design time overhead caused by manual wiring is reduced.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Double-masking technique for increasing fabrication yield in superconducting electronics

InactiveUS20090315021A1Improve reliabilityHigh yieldSolid-state devicesSemiconductor/solid-state device manufacturingResistNiobium

An improved microfabrication technique for Josephson junctions in superconducting integrated circuits, based on the use of a double-layer lithographic mask for partial anodization of the side-walls and base electrode of the junctions. The top layer of the mask is a resist material, and the bottom layer is a dielectric material chosen so to maximize adhesion between the resist and the underlying superconducting layer, be etch-compatible with the underlying superconducting layer, and be insoluble in the resist and anodization processing chemistries. The superconductor is preferably niobium, under a silicon dioxide layer, with a conventional photoresist or electron-beam resist as the top layer. This combination results in a substantial increase in the fabrication yield of high-density superconducting integrated circuits, increase in junction uniformity and reduction in defect density. A dry etch more compatible with microlithography may be employed.

Owner:HYPRES