Patents

Literature

379results about How to "Improve simulation speed" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

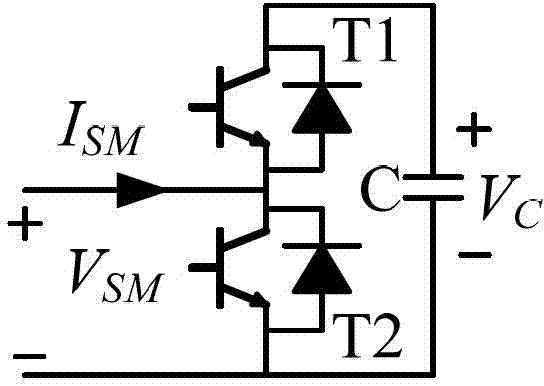

Modular multilevel converter (MMC) topology converter efficient electromagnetism transient state simulation method

ActiveCN103116665AReduce interface callsImprove Simulation EfficiencySpecial data processing applicationsTransient stateComputer Aided Design

The invention discloses a modular multilevel converter (MMC) topology converter efficient electromagnetism transient state simulation method. The method comprises the following steps: (1) building a thevenin equivalent circuit of a submodule and acquiring the hevenin equivalent circuit of a series subnodule, (2) opening power system computer aided design (PSCAD) and operating Fortran script editing user-defined module, (3) replacing at least one submodule by using the user-defined module, (4) using status bit to show insulated gate bipolar transistor (IGBT) status in the user-defined module of the PSCAD, (5) and figuring submodule capacitor voltage and submodule current by using a difference equation. The method reduces the number of nodes of a MMC topology converter model, and is quick in simulation speed and high in efficiency.

Owner:GLOBAL ENERGY INTERCONNECTION RES INST CO LTD +3

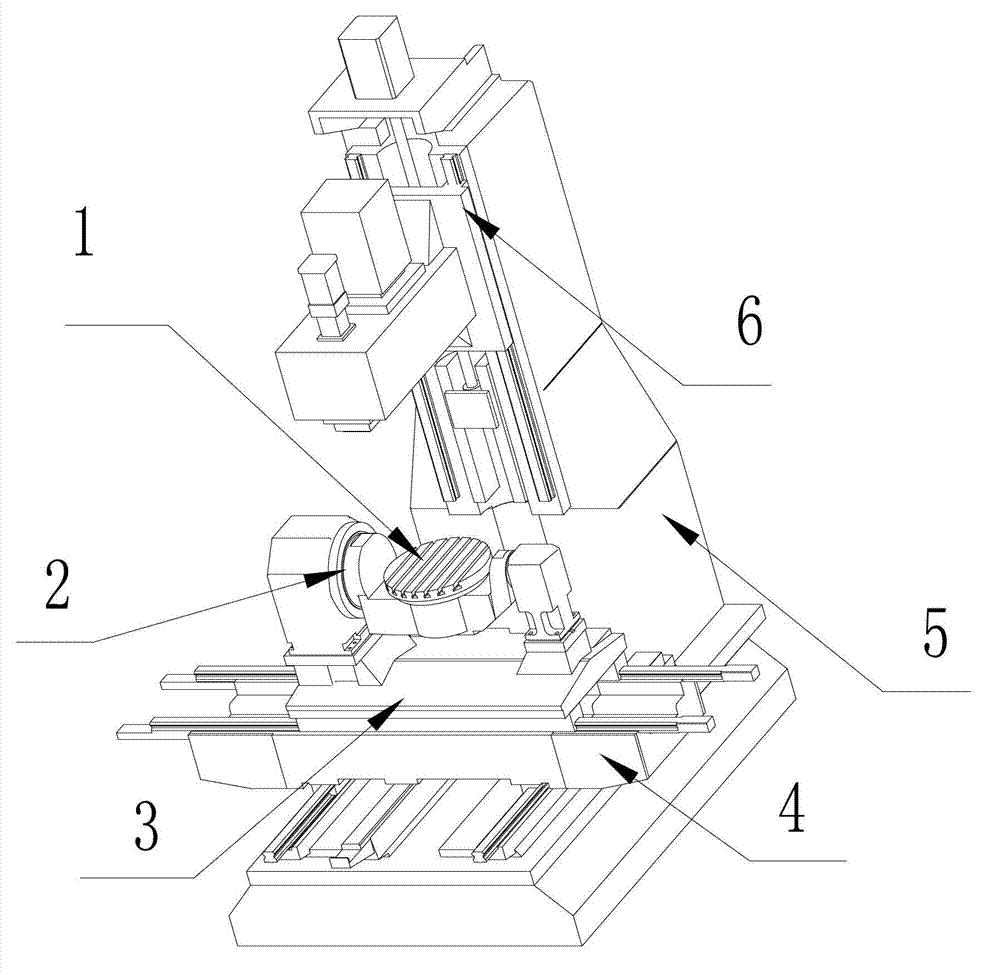

Double-turntable five-axis numerical control machine tool virtual assembling and numerical control machining simulation method

InactiveCN102866638AImprove Simulation EfficiencyImprove manufacturing precisionSimulator controlNumerical controlDimensional modeling

The invention discloses a double-turntable five-axis numerical control machine tool virtual assembling and numerical control machining simulation method and provides a simulation method capable of improving simulation efficiency under the premise of guaranteeing simulation correctness. The method includes: modeling; conducting three-dimensional modeling of blanks and clamps required in all moving components, a machine tool body and numerical control machining; connecting all moving components and the machine tool body to conduct virtual assembling according to a moving relation by using a Pro / E three-dimensional platform; operating a virtual simulating machine tool; outputting models of all components in a standard template library (STL) form on the basis of the same coordinate system; establishing a double-turntable five-axis numerical control machine tool virtual model; establishing a model tree in VERICUT, and the sequence of model components includes two branches: machine tool body Base - Y axis - X axis - A axis - C axis - clamp - blank and machine tool body Base - Z axis - main axis - tool; the STL assembly model output by Pro / E is led into corresponding components in VERICUT directly, namely the double-turntable five-axis numerical control machine tool virtual model is established; and numerical control machining simulation is operated.

Owner:TIANJIN UNIV OF COMMERCE

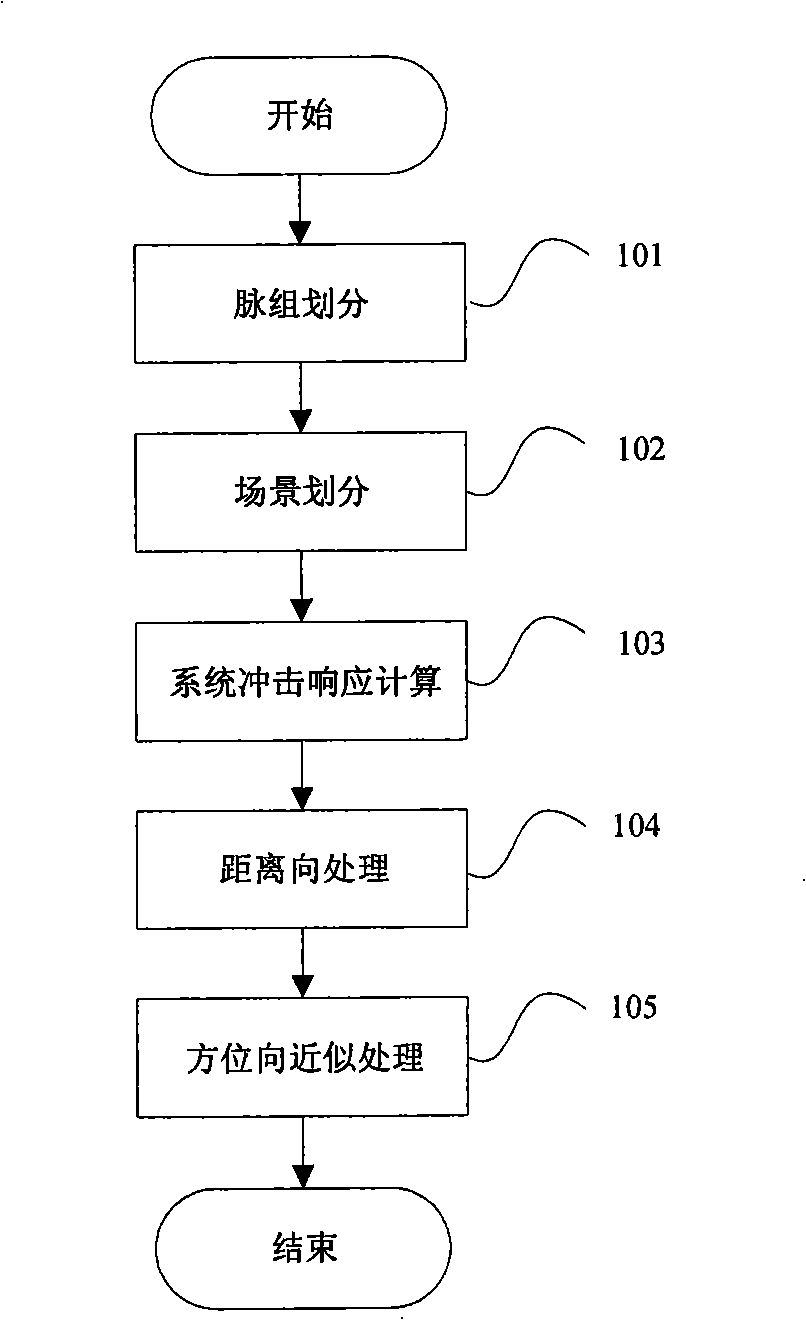

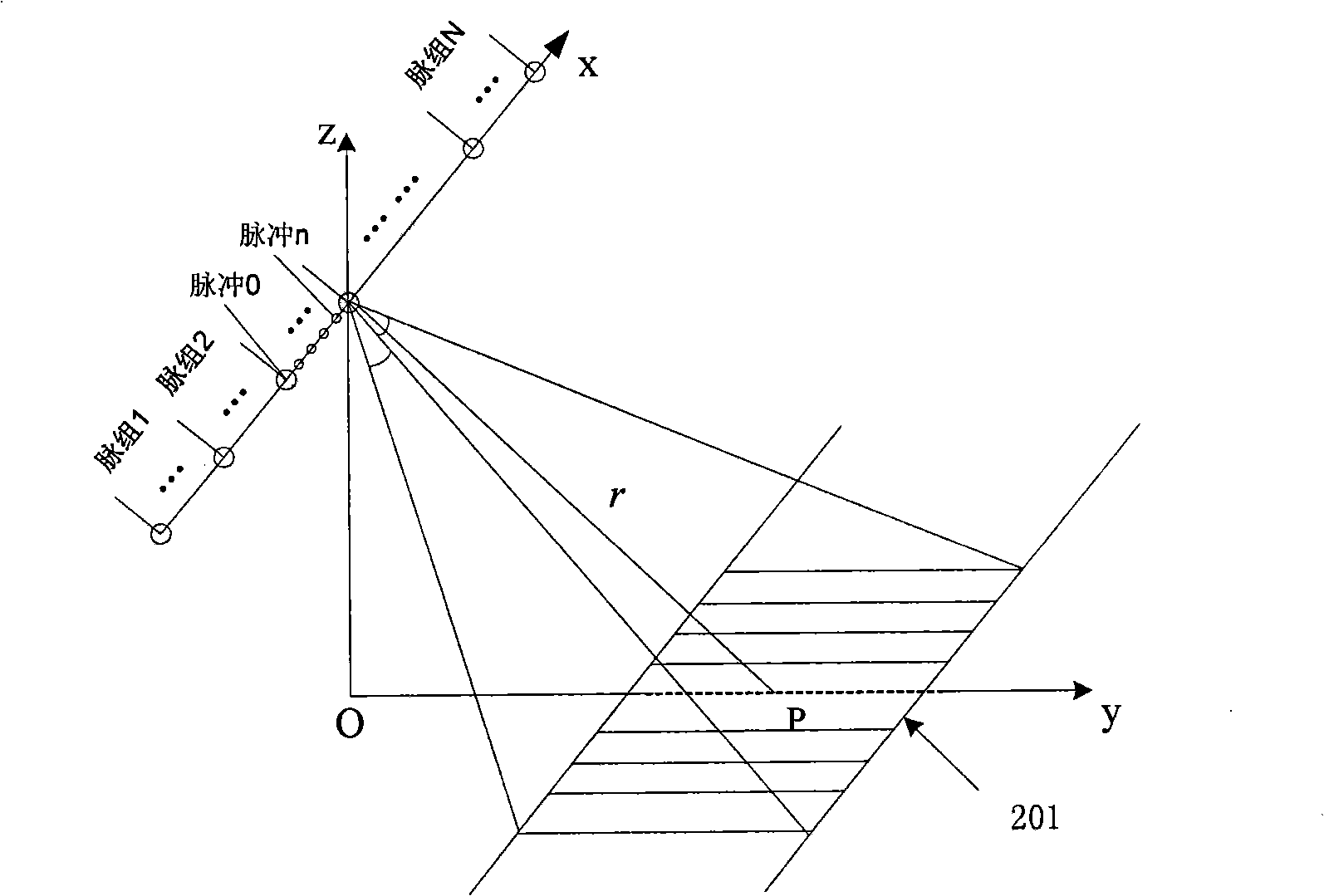

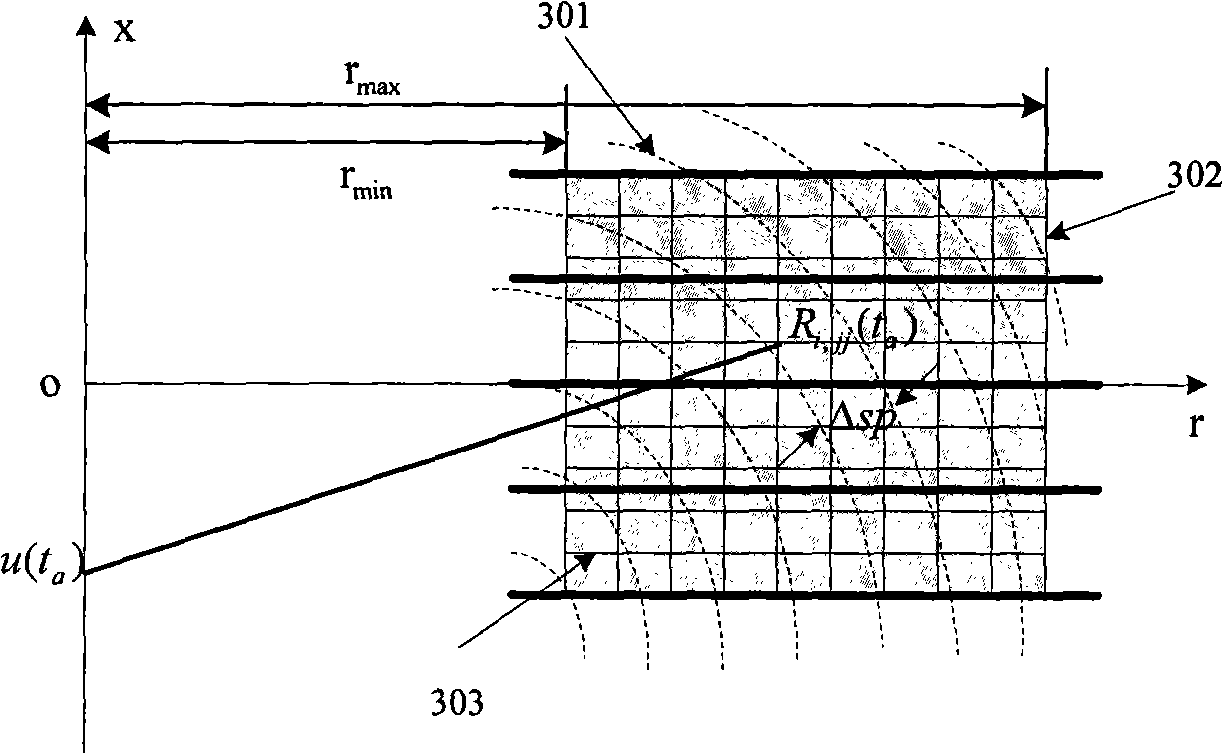

SAR echo rapid simulation method based on sub-aperture and equivalent scatterer

InactiveCN101526614ASmall amount of calculationImprove simulation speedRadio wave reradiation/reflectionRadarAzimuth direction

The invention relates to a synthetic aperture radar echo rapid simulation method based on sub-aperture and equivalent scatterer, comprising the following steps: 1) pulses corresponding to all track points are divided into a plurality of pulse groups with equal length along the radar flying direction; 2) a scene is divided into a plurality of small rectangular scenes with the same size, and equidistance rings are divided according to the distance between a radar platform and the target scene; 3) in every equidistance annular region of the small rectangular scene, the backscattering coefficient of the equivalent scatterer is calculated, and a pulse response function of the system is obtained; 4) the range direction processing is carried out, and an echo signal of the central pulse of the pulse groups is obtained by the convolution of an emission signal and the pulse response function; 5) azimuth direction processing is carried out, and echo signals of any other pulses in the pulse groups are calculated by the echo signal of the central impulse in the impulse groups. The method of the invention has the advantages of rapid speed and high precision of the frequency domain processing method, introduces the expansion approximate processing of the azimuth direction and effectively improves the simulation velocity.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

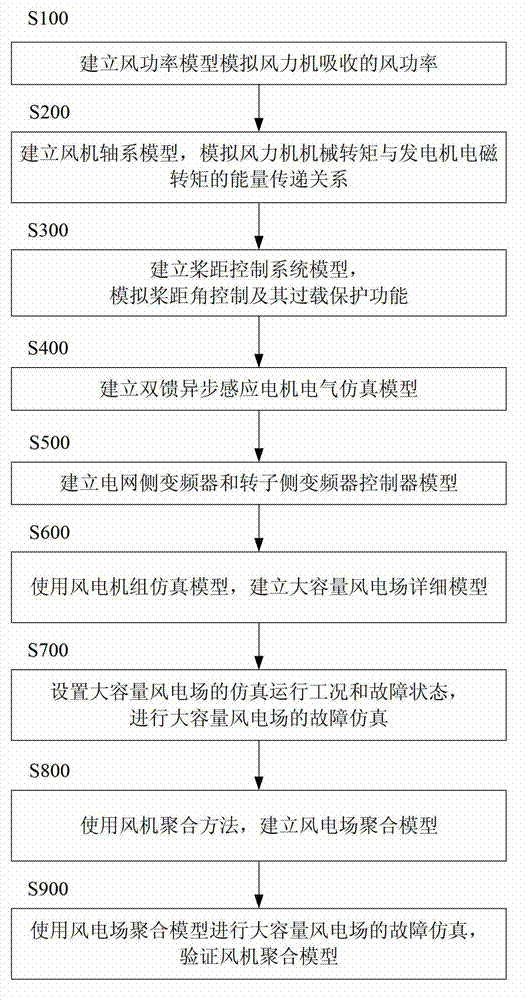

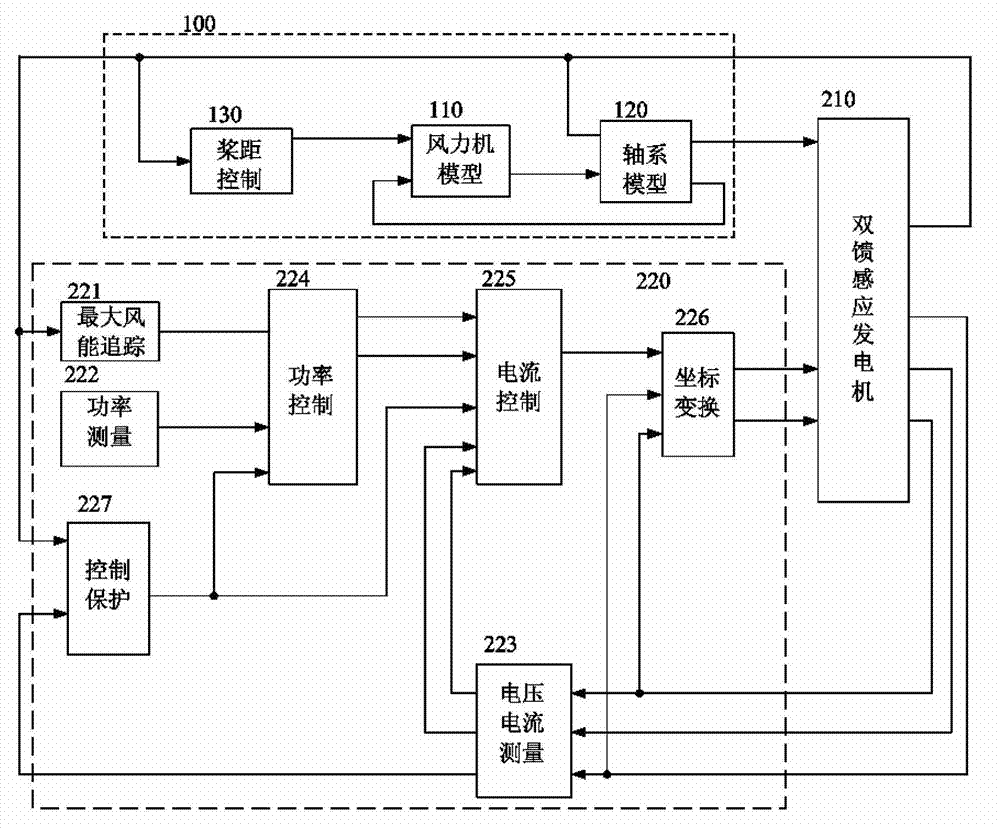

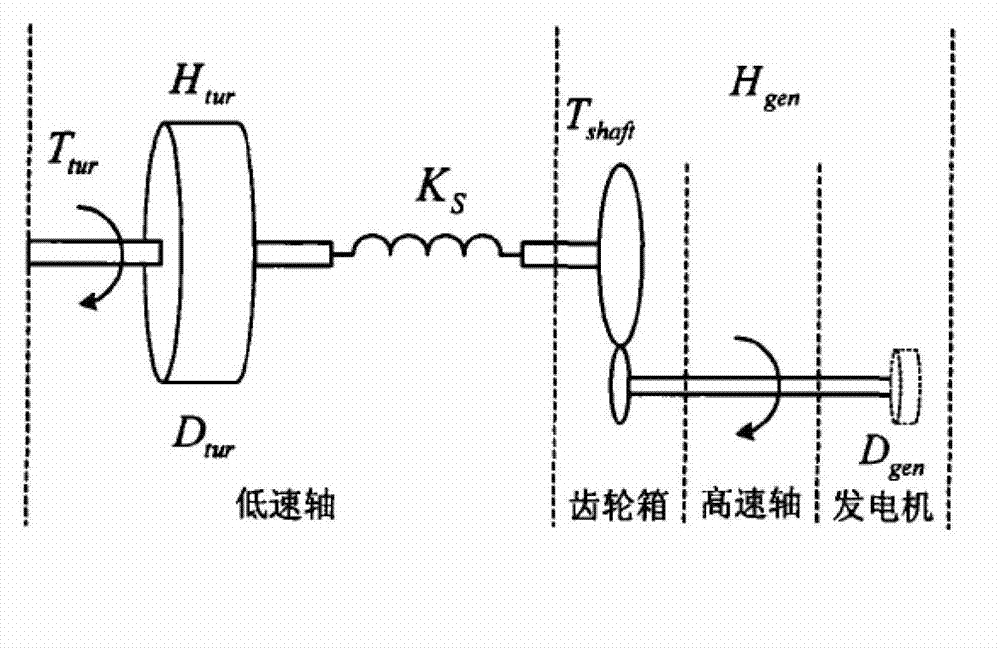

Aggregation model building and simulating method for high-capacity wind power plant fan

InactiveCN103034763AImprove simulation speedApplicable stability analysisSpecial data processing applicationsRenewable energy source integrationFrequency changerConstant frequency

The invention provides an aggregation model building and simulating method for a high-capacity wind power plant fan, and relates to a wind turbine system, and particular to a method for the modeling analysis of a doubly-fed induction generator system using computer programs. The method comprises the following steps of: building a wind power model to simulate wind power absorbed by a wind machine; building a fan shaft system model; building a propeller pitch control system model; building a doubly-fed asynchronous induction motor electric simulation model; building a power grid-side frequency converter and rotor-side frequency converter controller model; building a high-capacity wind power plant detailed model and a wind power plant aggregation model; and setting the simulation run working condition and the failure state of a wind turbine generator system, so that the fault simulation can be carried out, and the fan aggregation model can be verified. According to the method, the detailed model and the high-capacity wind power plant fan aggregation model, which accord with the physical property of a doubly-fed variable-speed constant-frequency wind turbine generator, can be built, so that the simulation precision can completely meet the requirement, and the simulation speed can be greatly improved; and therefore, the method is suitable for the stability analysis after the wind power accesses into a large-scale power grid.

Owner:SHANGHAI MUNICIPAL ELECTRIC POWER CO +2

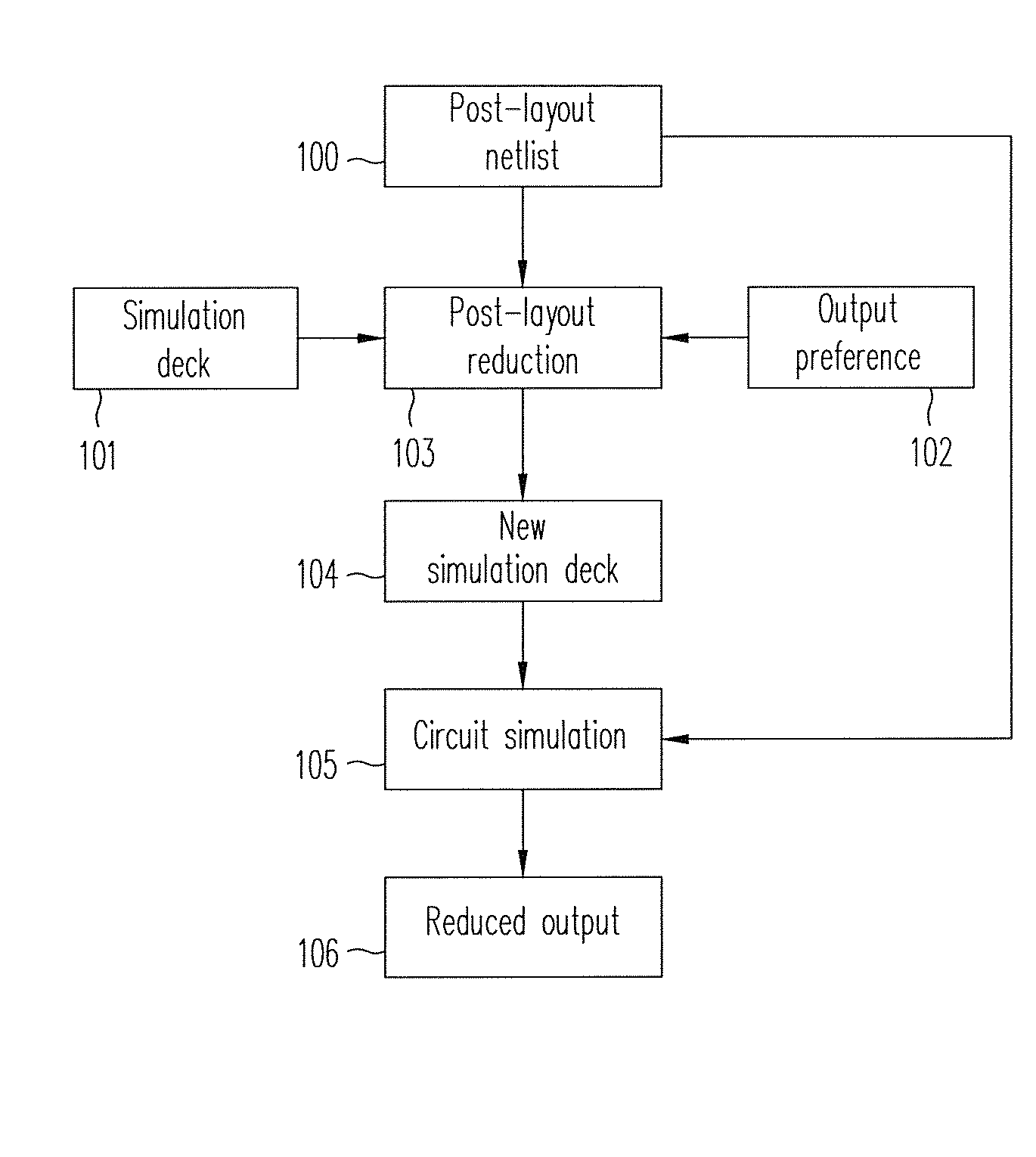

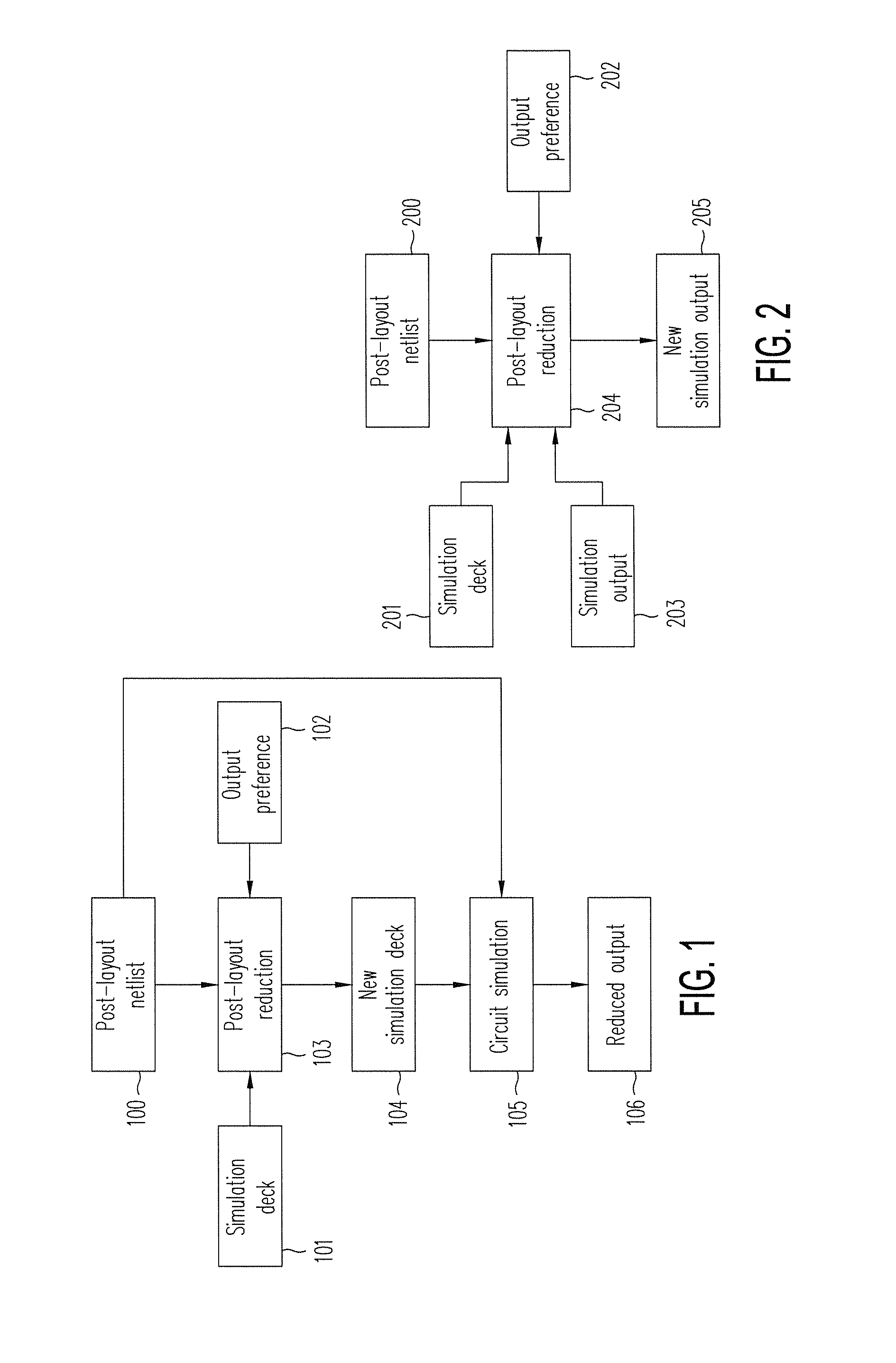

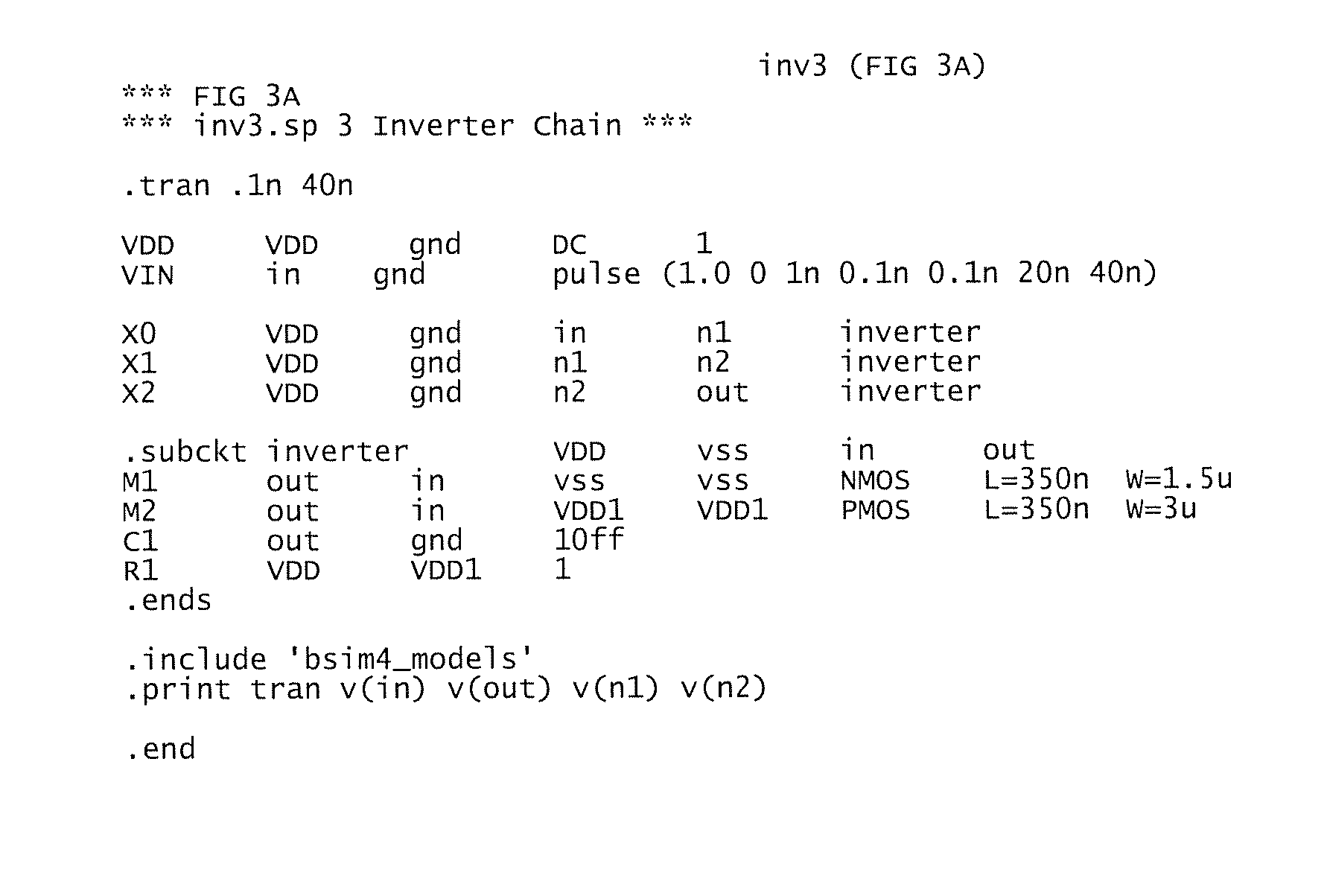

Methods for reducing post layout circuit simulation results

InactiveUS20150269297A1Reduce file sizeImproving circuit simulation speedCAD circuit designSoftware simulation/interpretation/emulationProduction ratePost processor

A method for reducing the size of post-layout circuit simulation output waveform database without a loss of essential information and accuracy. The reduced waveform database requires significantly less storage than the typical waveform database for post-layout simulation, thereby improving the time required for a waveform tool to access, and for a user to navigate, the post-layout simulation results. The method therefore greatly improves designer productivity during circuit verification and debugging phases. The method can be carried out in a preprocessor to a circuit simulator, in a post-processor to a circuit simulator, or may be directly built into a circuit simulator. The method is applicable to any post-layout netlists with schematic node names or circuit element names.

Owner:ANALOG DESIGN AUTOMATION

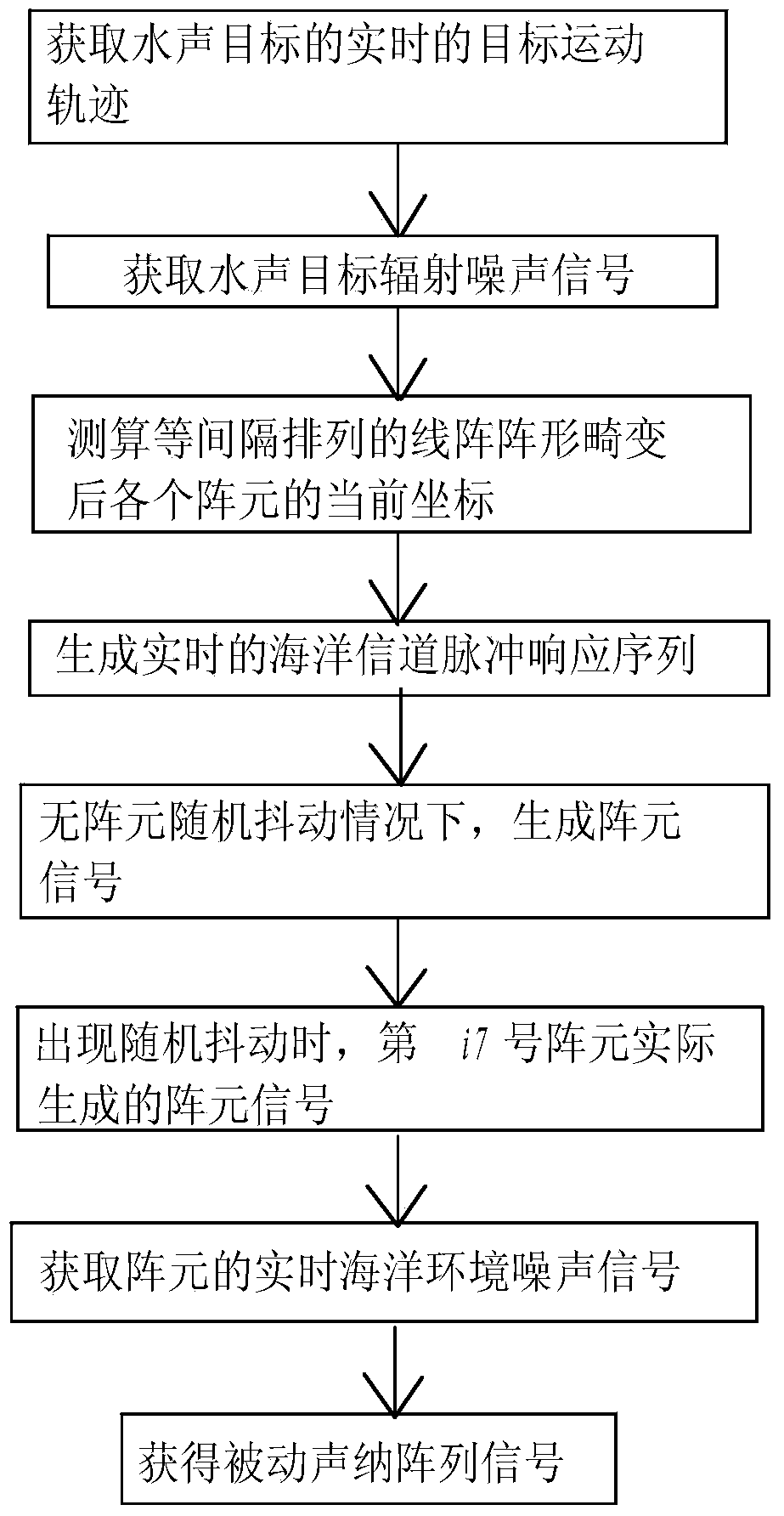

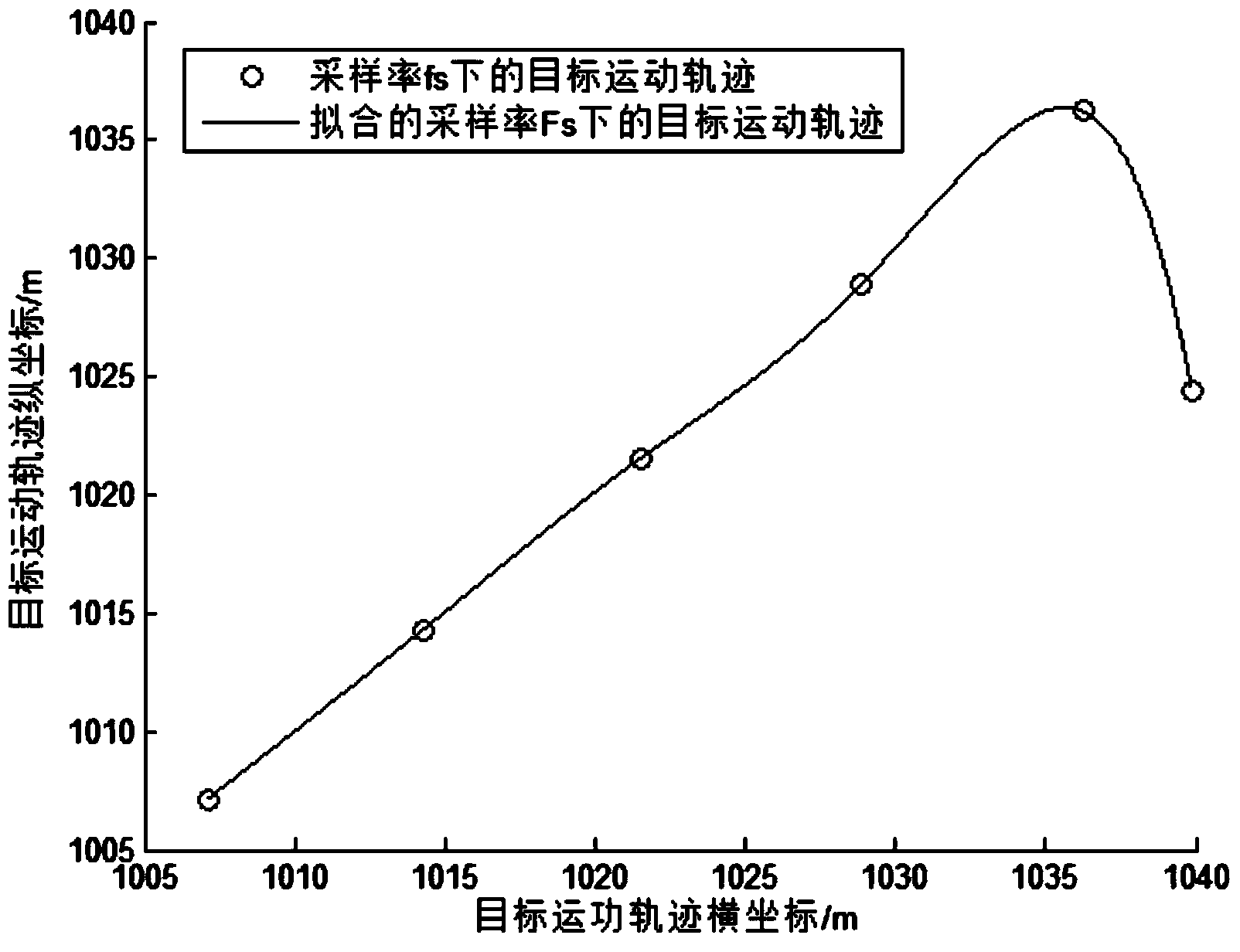

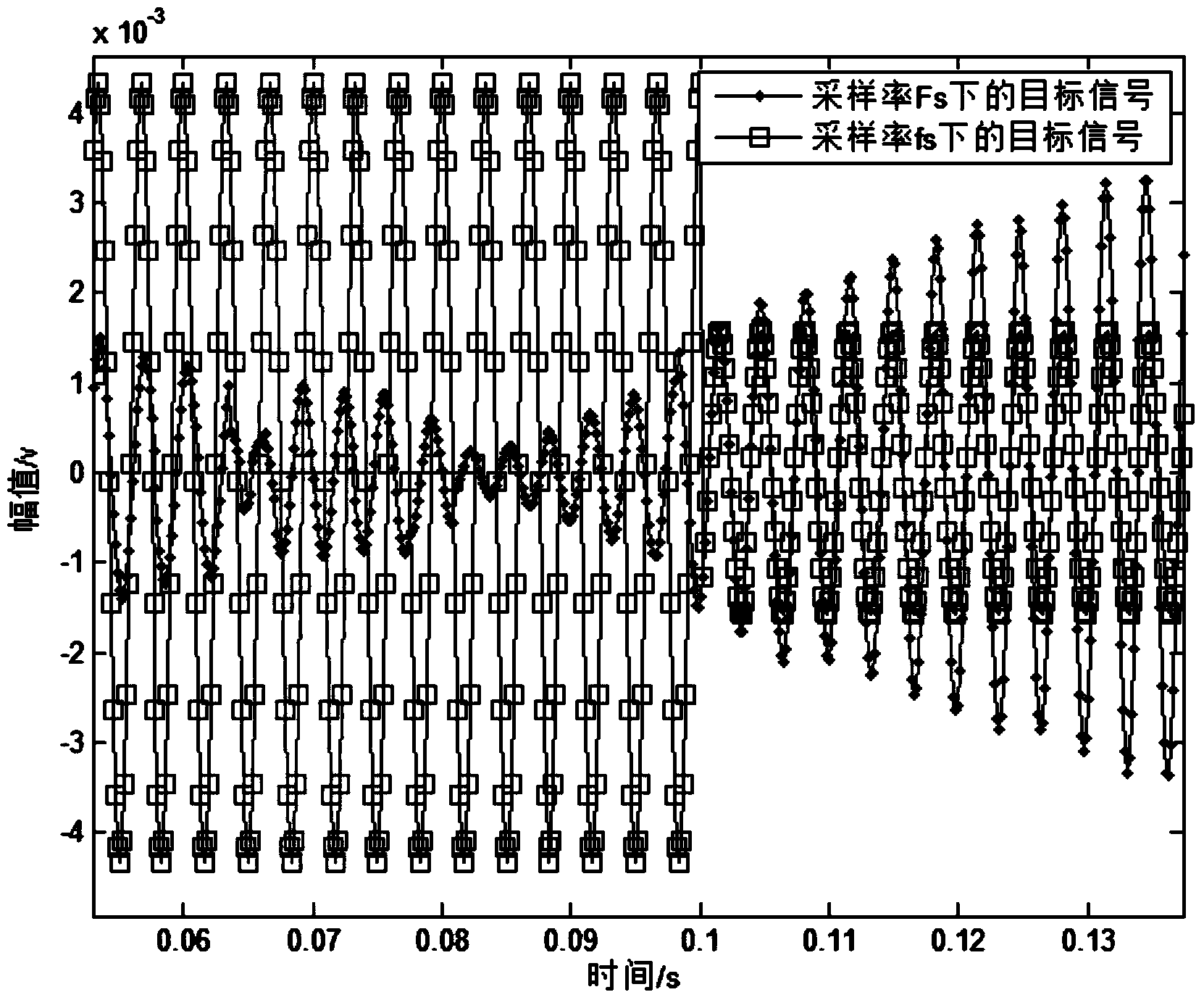

Simulation method for open type array signal

ActiveCN103926579AIncrease opennessSmooth motion trackAcoustic wave reradiationArray elementLinear arrays

The invention discloses a simulation method for an open type array signal. The method includes the following steps of firstly, obtaining the real-time target movement path of an underwater sound target; secondly, obtaining an underwater sound target radiation noise signal; thirdly, calculating coordinates of all array elements of linear arrays arrayed at equal intervals after array form distortion; fourthly, generating a real-time ocean channel pulse response sequence; fifthly, generating array element signals under the condition that no array element random shaking exists; sixthly, obtaining an array element signal, practically generated, of the i7th array element when random shaking occurs; seventhly, obtaining real-time ocean environment noise signals of the array elements; eighthly, obtaining a passive sonar array signal. By means of the simulation method, openness of an array signal simulation system can be achieved.

Owner:SOUTHEAST UNIV

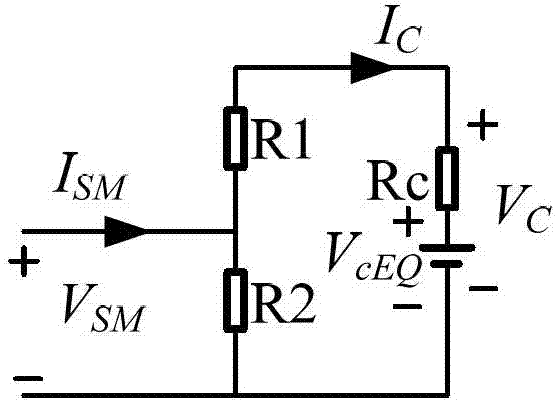

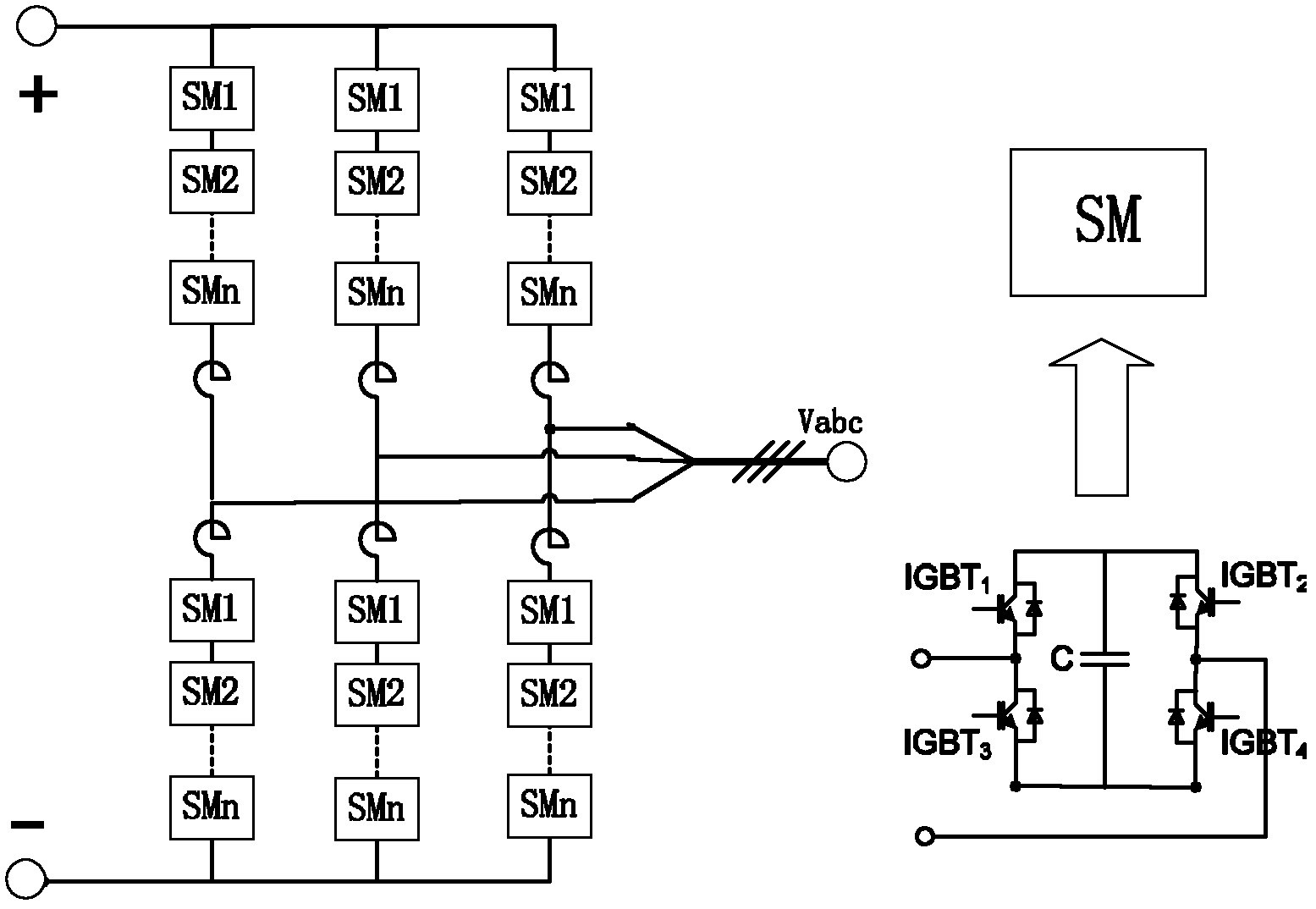

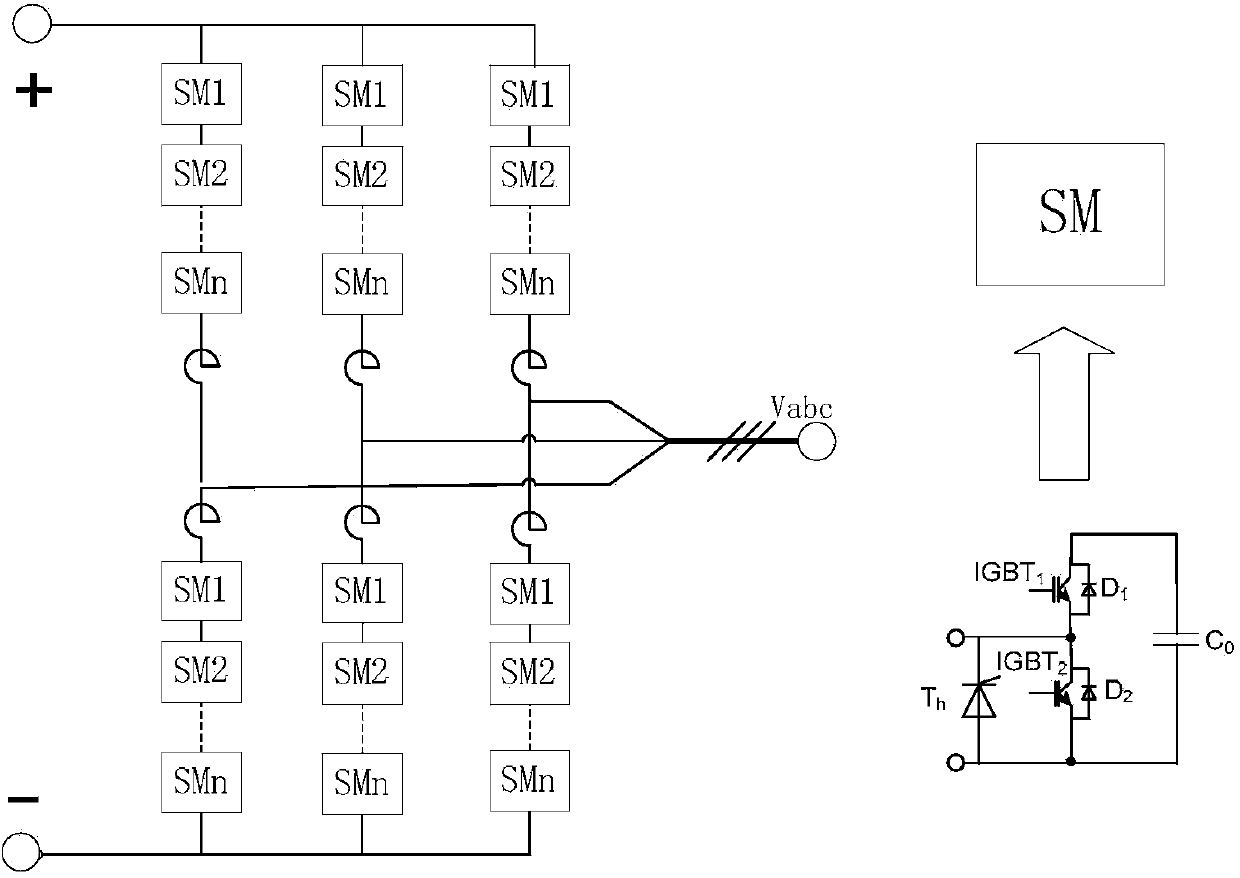

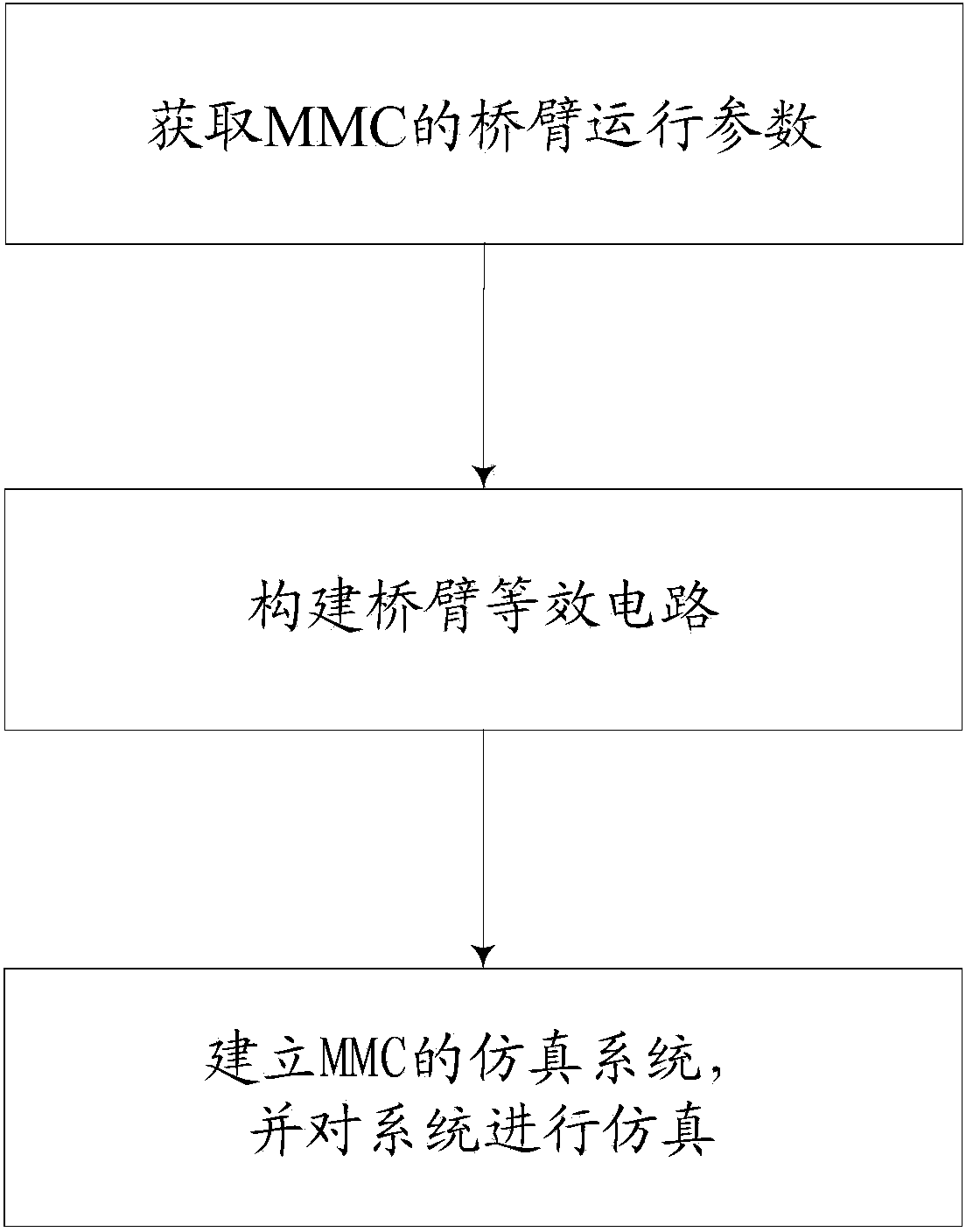

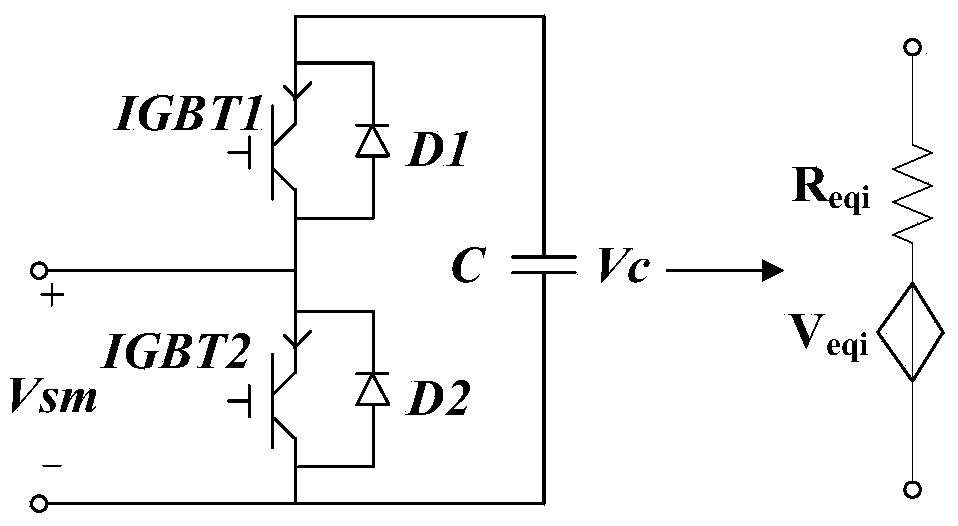

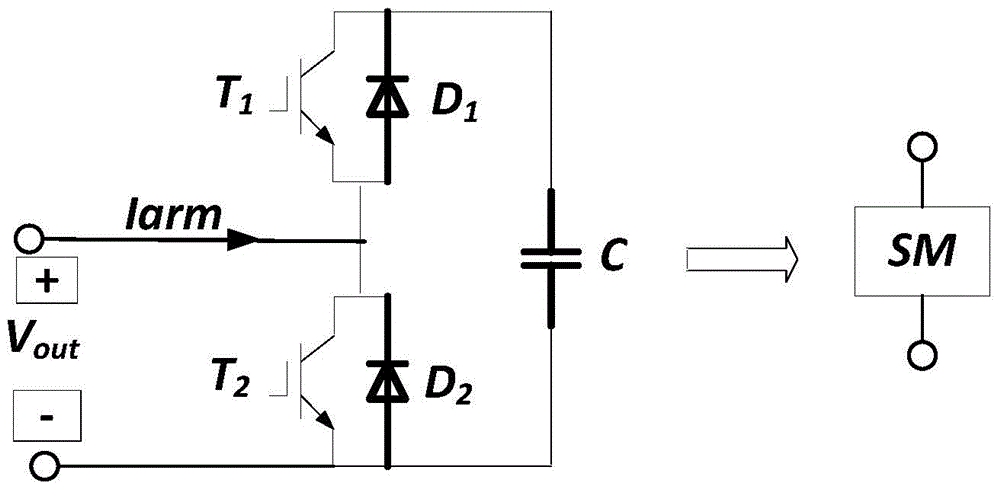

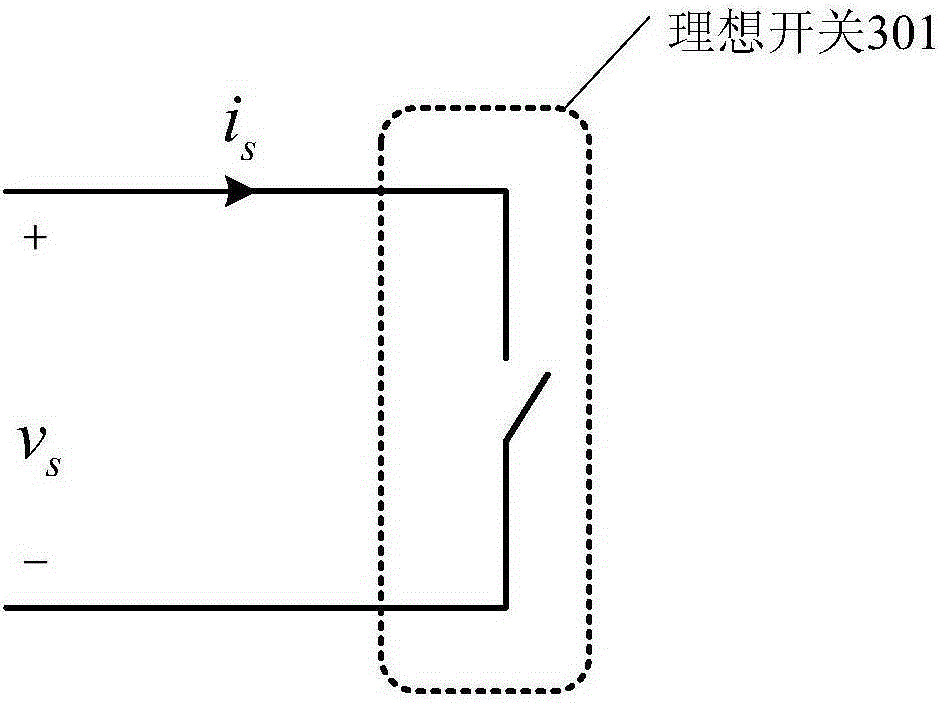

Simulation method of MMC (modular multilevel converter) and application thereof

ActiveCN102663174AImprove simulation speedReduce the number of nodesSpecial data processing applicationsElectrical resistance and conductanceVoltage source

The invention discloses a simulation method of an MMC (modular multilevel converter). The simulation method comprises the following steps: (1) obtaining operation parameters of an SM (Submodule); (2) construction an equivalent circuit of SM; (3) establishing an artificial circuit of SM; and (4) establishing a simulation system of MMC and simulating the system. According to the simulation method provided by the invention, by the utilization of numerical calculation and electromagnetic simulation internal mechanism, the SM in the MMC can be equivalent to a simple branch formed by a controlled voltage source and an adjustable resistor effectively, and the number of nodes of the system and the corresponding simulation calculation can be greatly reduced, so that on the premise that the simulation precision is ensured, the simulation speed of the MMC is greatly promoted, and the method is applied for MMC design.

Owner:ZHEJIANG UNIV

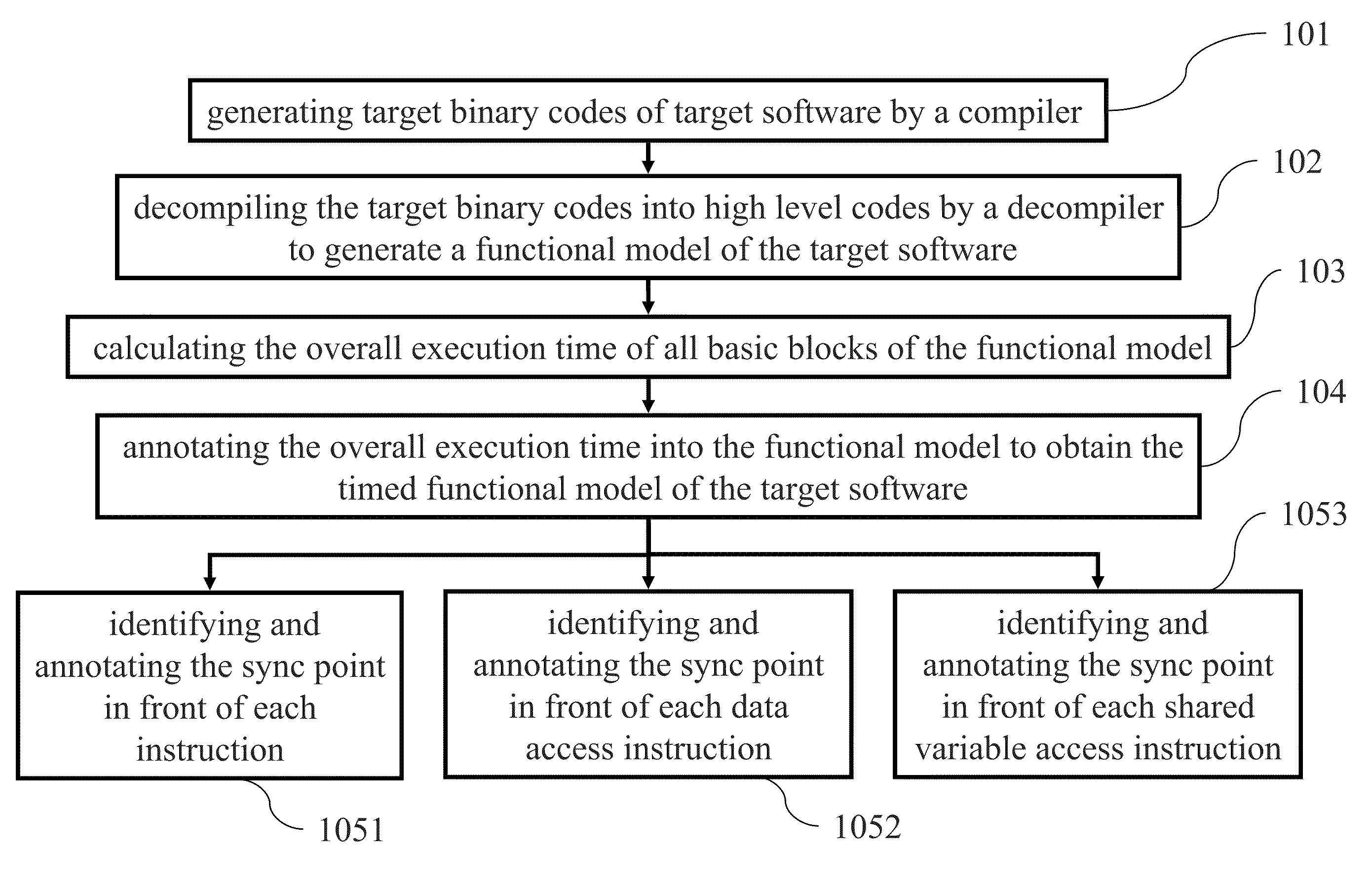

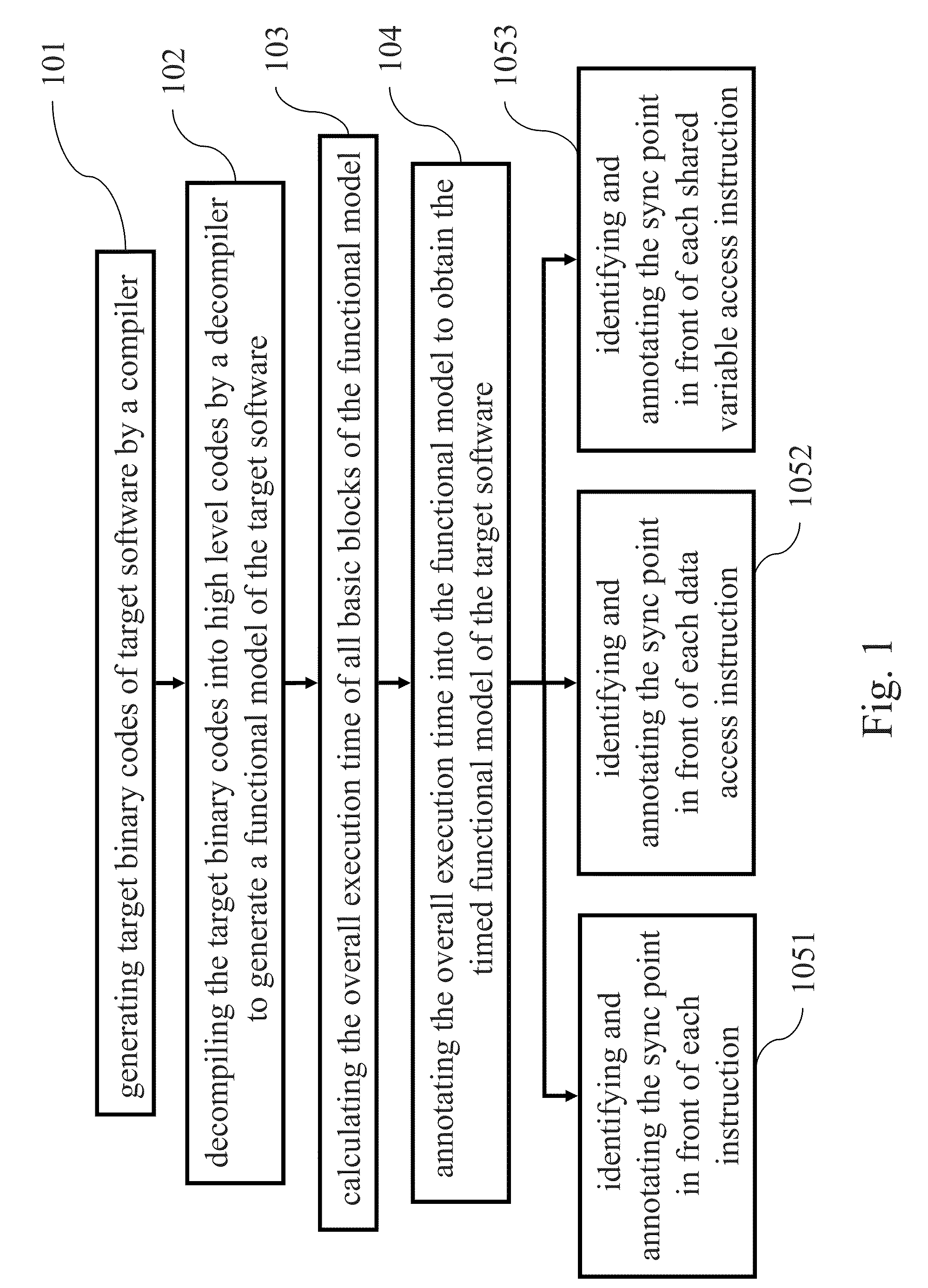

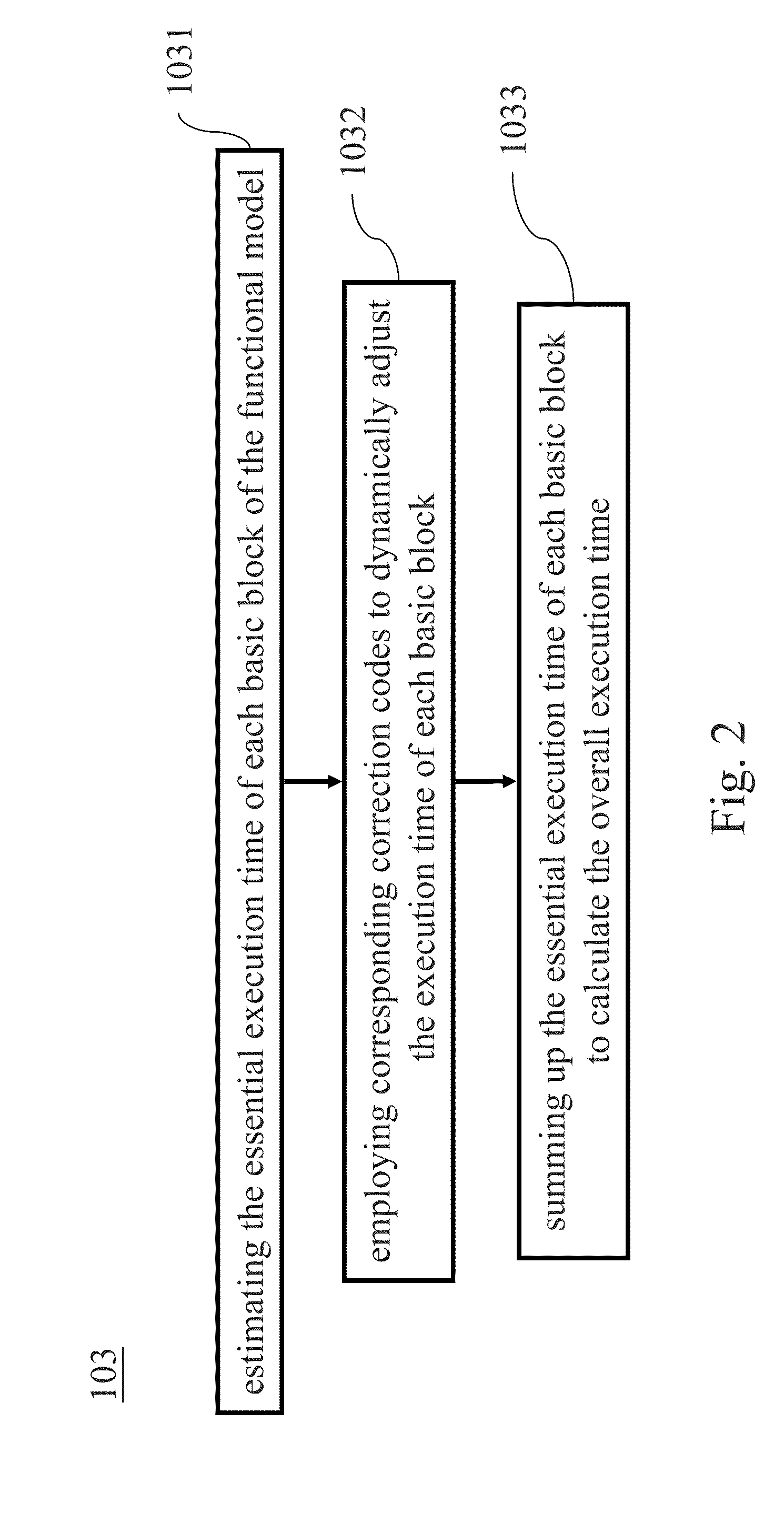

Method, System and Computer Readable Medium for Generating Software Transaction-Level Modeling (TLM) Model

InactiveUS20110197174A1Improve simulation speedMaintain accuracyDecompilation/disassemblySpecific program execution arrangementsBasic blockDecompiler

The present invention discloses a system for generating a software TLM model, comprising a processing unit; a compiler coupled to the processing unit to generate target binary codes of a target software; a decompiler coupled to the processing unit to decompile the target binary codes into high level codes, for example C or C++ codes, to generate a functional model of the target software, wherein the functional model includes a plurality of basic blocks; an execution time calculating module coupled to the processing unit to calculate overall execution time of the plurality of the basic blocks of the functional model; a sync point identifying module coupled to the processing unit to identify sync points of the software transaction-level modeling model; and a time annotating module coupled to the processing unit to annotate the overall execution time of the basic blocks and the sync points into the functional model to obtain the software transaction-level modeling model.

Owner:NATIONAL TSING HUA UNIVERSITY

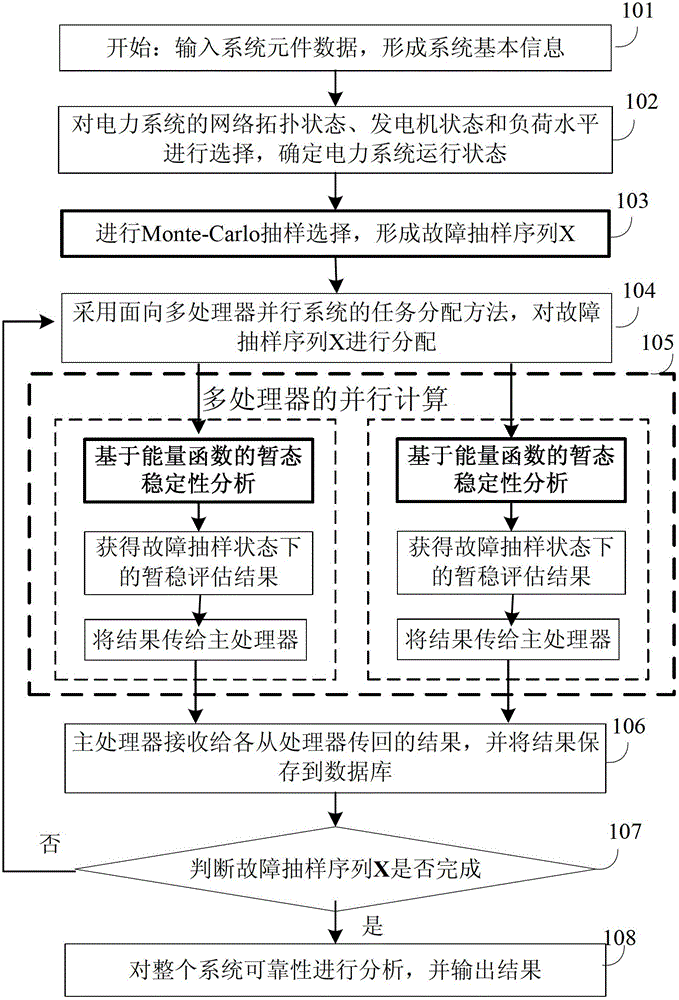

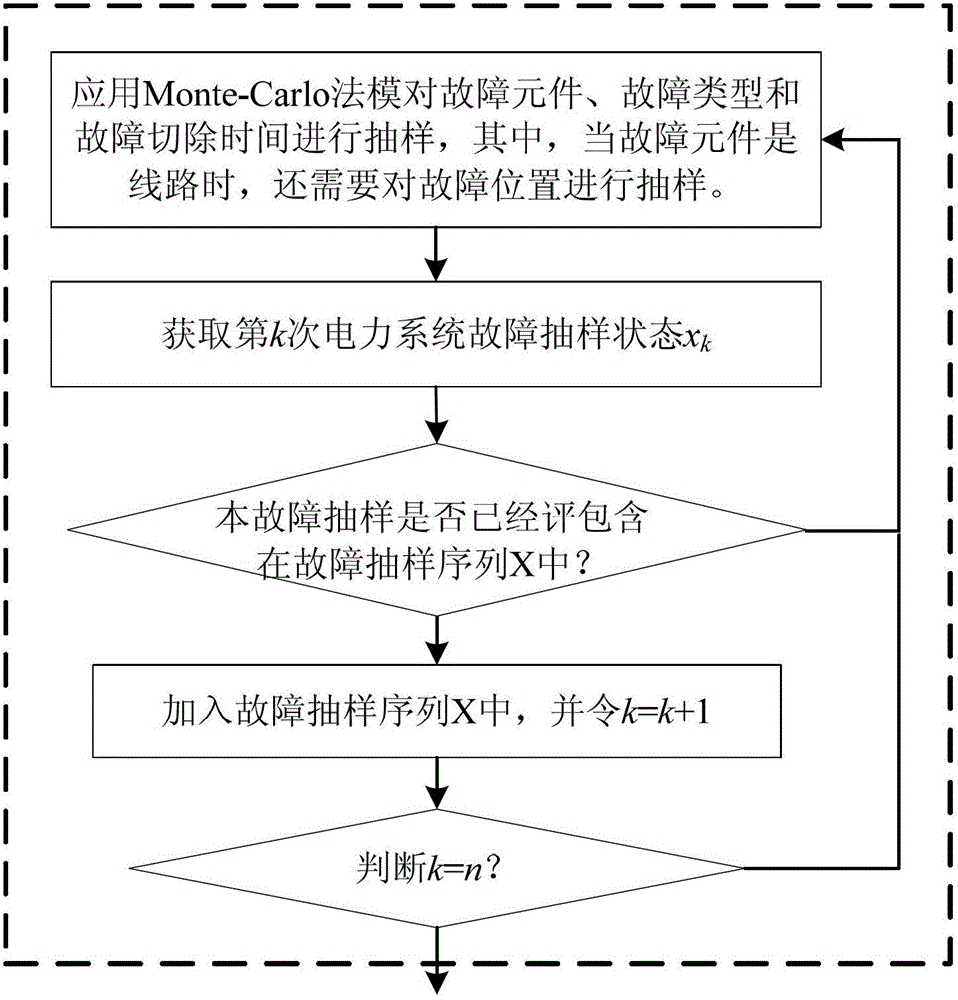

Method for improving transient stability analysis efficiency of electric power system

ActiveCN102723712AFast evaluationStable levelAc network circuit arrangementsTransient stateDistribution method

The invention discloses a method for improving a transient stability analysis efficiency of an electric power system and relates to the field of the electric power system. The method comprises the following steps of: initializing element parameters of the electric power system and inputting data of the electric power system; selecting a network topology state, a generator state and a load level of the electric power system, and determining an operation state of the electric power system; carrying out Monte Carlo sampling selection on the operation state of the electric power system to form a fault sampling sequence; utilizing a task distribution method facing to a multiprocessor parallel system and distributing the fault sampling sequence; carrying out transient stability analysis on a fault sample based on an energy function method by each processor; receiving a result returned by a processor by a main processor and storing the result into a database; and when the fault sampling sequence X is finished, calculating the possibility index of the transient stability of the electric power system and outputting the result. The method disclosed by the invention meets the requirements of instantaneity of information of the electric power system and improves the analysis efficiency and the safety of the electric power system.

Owner:TIANJIN UNIV

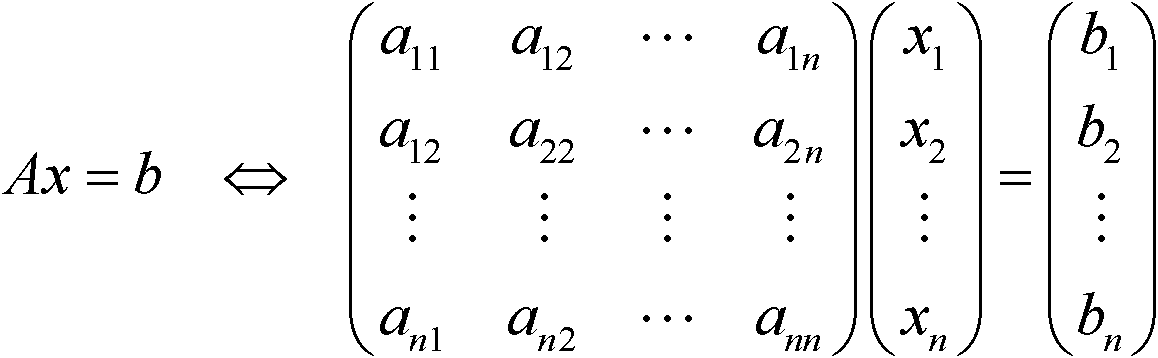

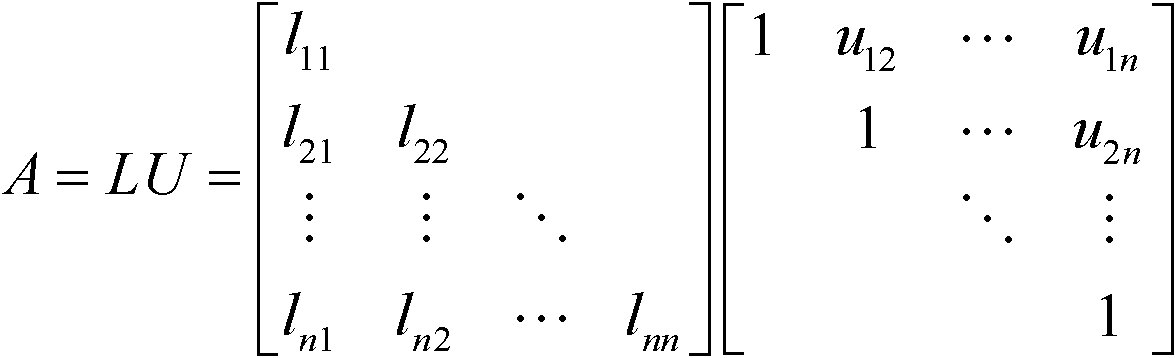

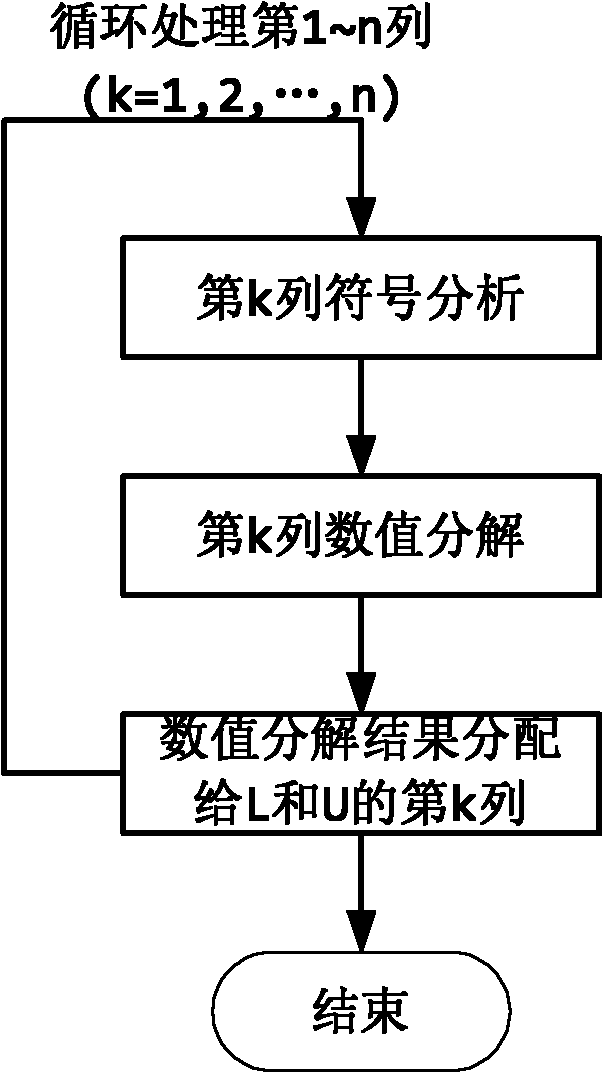

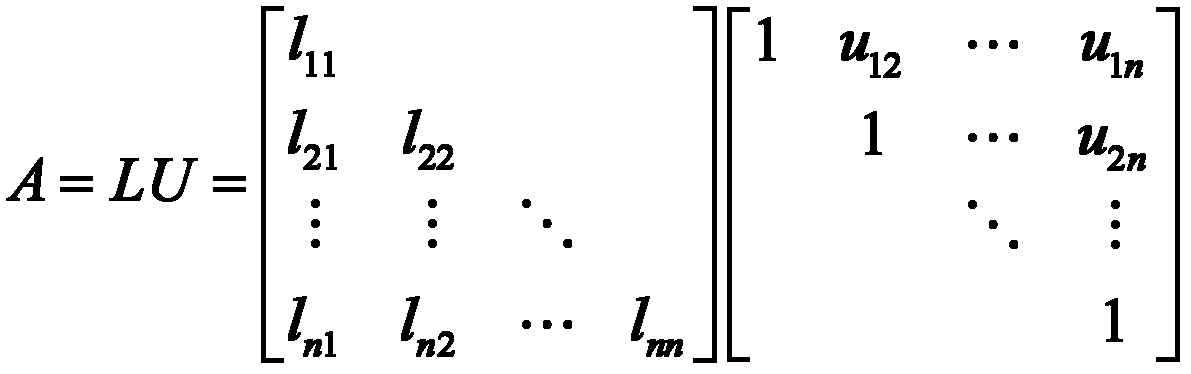

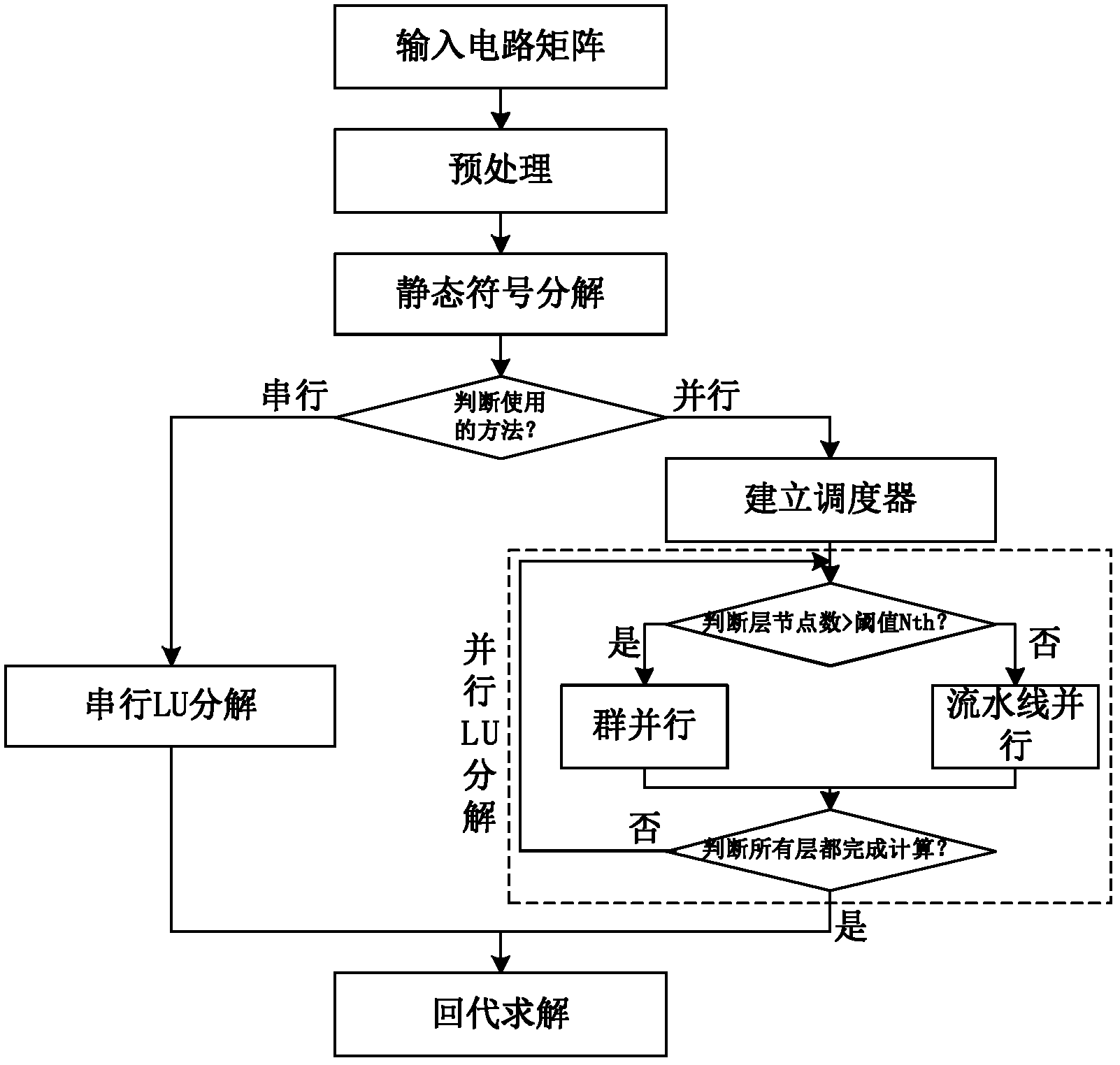

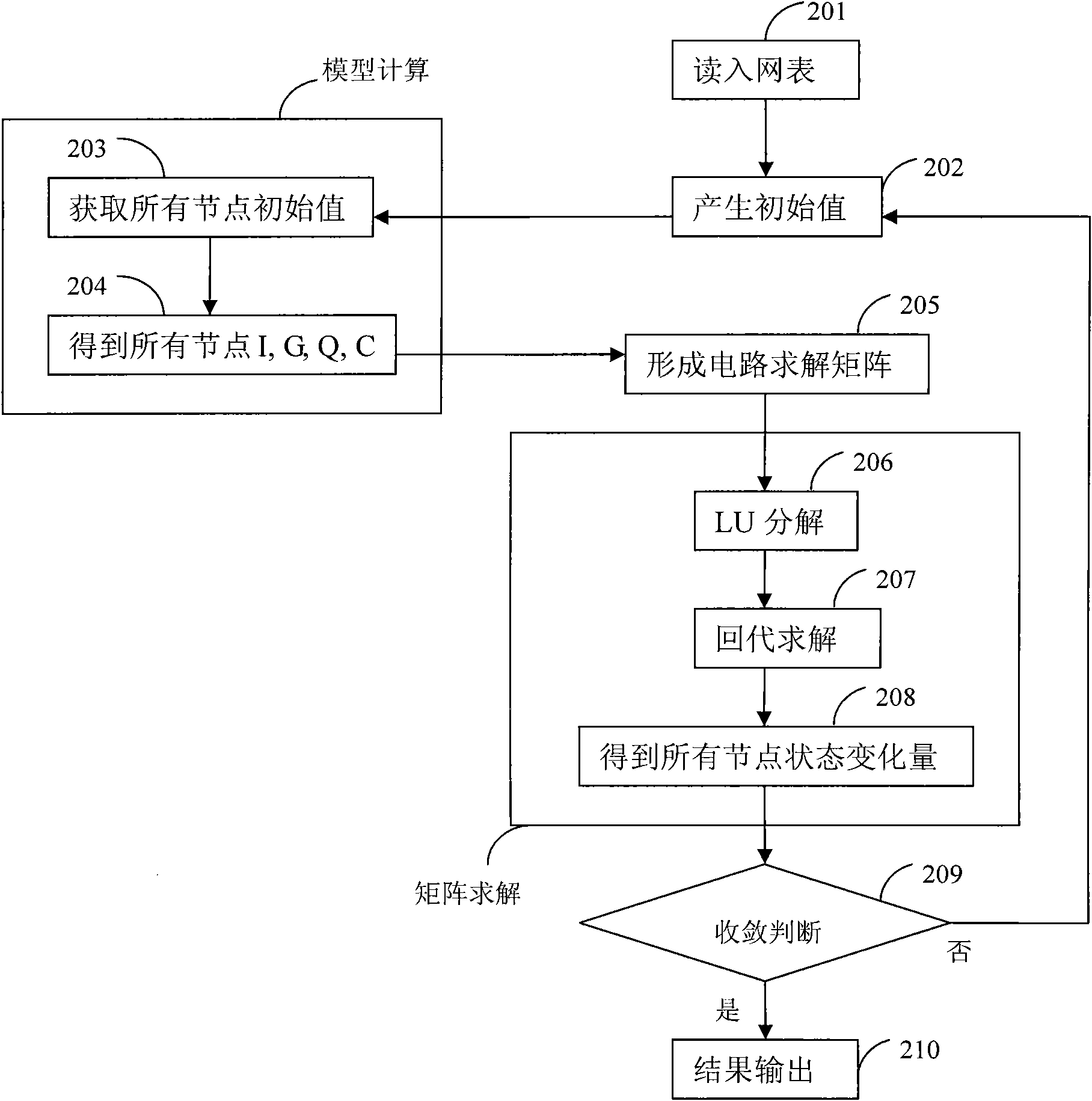

Deleted graph-based parallel decomposition method for circuit sparse matrix in circuit simulation

ActiveCN102156777AImprove simulation speedGuaranteed a high degree of parallelismSpecial data processing applicationsAlgorithmDecomposition

The invention provides a deleted graph-based parallel decomposition method for a circuit sparse matrix in circuit simulation, belonging to the field of electronic design automation (EDA). The method is characterized in that a deleted graph is extracted from a symbolic analysis result of a circuit matrix for representing data independence in a lower-upper (LU) decomposition process; and two different parallel methods, namely a group parallel method and stream-line parallel method, are used according to different structures of the deleted graph, so that the calculation time of LU decomposition is reduced, and the speed of circuit simulation is accelerated. Test results on a series of test circuit matrixes indicate that the LU decomposition speed according to the invention is 1.66-7.72 times faster than that of LU decomposition software KLU when the count of parallel threads is 1-8.

Owner:TSINGHUA UNIV

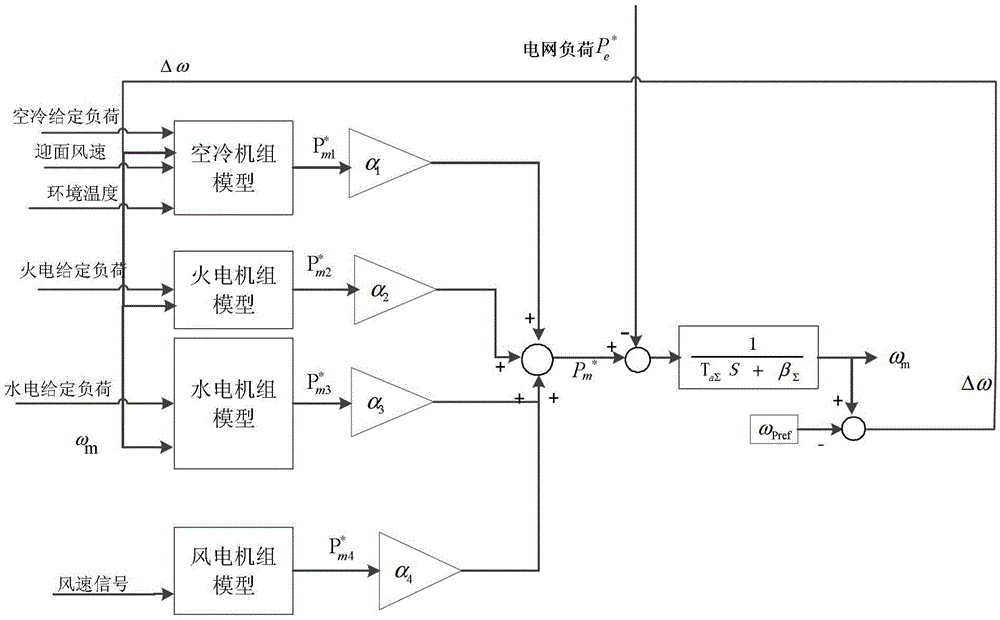

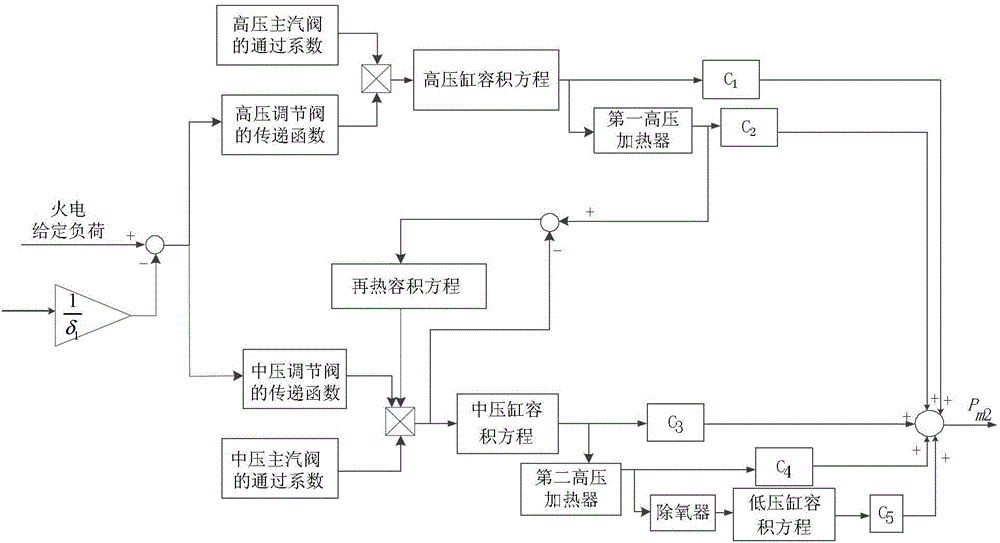

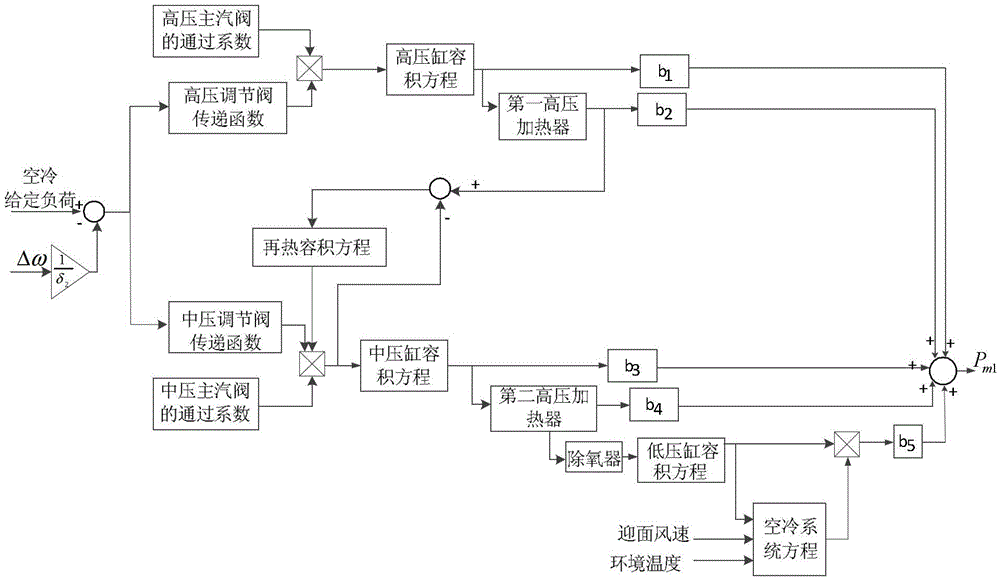

Mechanism-based mathematic model establishing method suitable for frequency modulation analysis of multi-machine power system

InactiveCN103336911ASafe and stable operationImprove simulation speedSpecial data processing applicationsMathematical modelEngineering

The invention relates to a mechanism-based mathematic model establishing method suitable for frequency modulation analysis of a multi-machine power system, which relates to a mathematic model suitable for the frequency modulation analysis of the multi-machine power system. For solving the problems that the frequency modulation computation speed is low and the influence of the randomness of meteorological parameters on frequency modulation is not considered when a regional power system model is applied to the frequency modulation analysis, the method comprises the following steps that a regional power system model including a wind power generation unit, a hydro-power generation unit, a thermal power generation unit and an air cooling unit is established, the air cooling unit model inputs environmental temperature, face velocity, preset load and frequency offset, the thermal power generation unit model inputs the preset load and the frequency offset, the hydro-power generation unit model inputs the preset load and the frequency offset, the wind power generation unit model inputs wind speed signals, all active power output by all unit models is respectively multiplied by each power share coefficient and then is superposed so that the per-unit value of unit electric energy production is obtained, the offset of system frequency is obtained by utilizing a rotor equation, and the offset is taken as the frequency offset during next frequency modulation. Therefore the mechanism-based mathematic model establishing method disclosed by the invention is applied to the frequency modulation analysis of the multi-machine power system.

Owner:HARBIN INST OF TECH

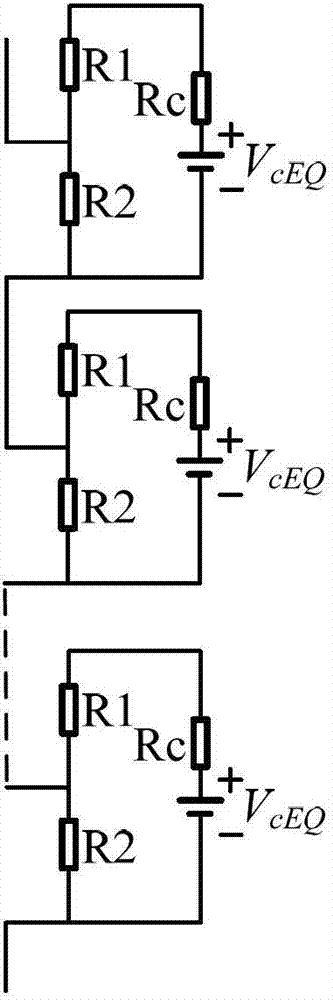

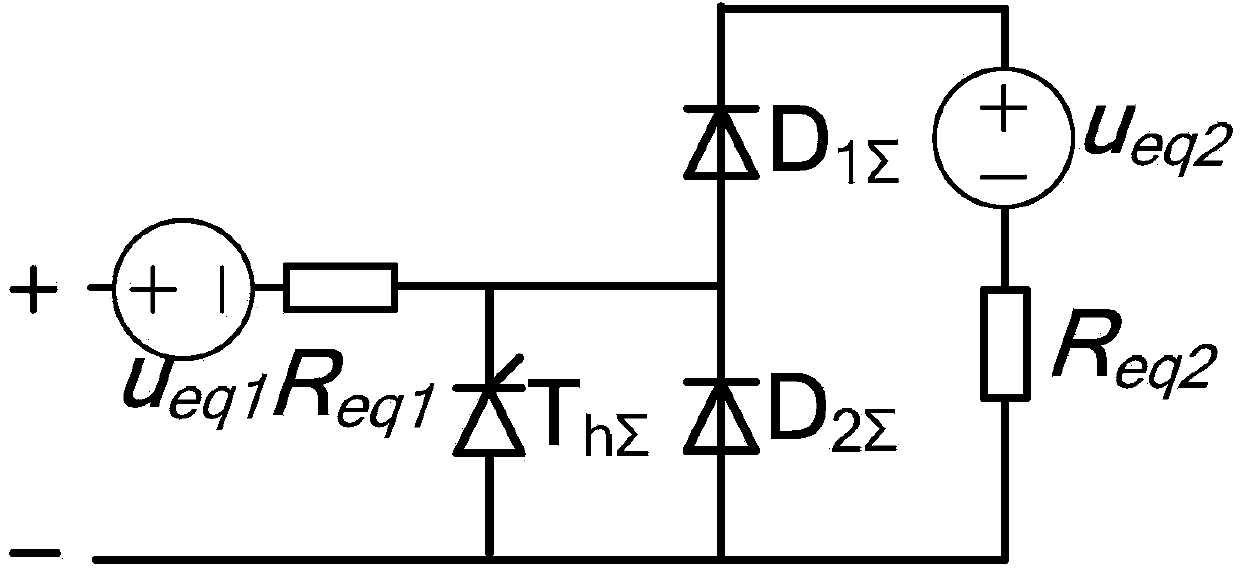

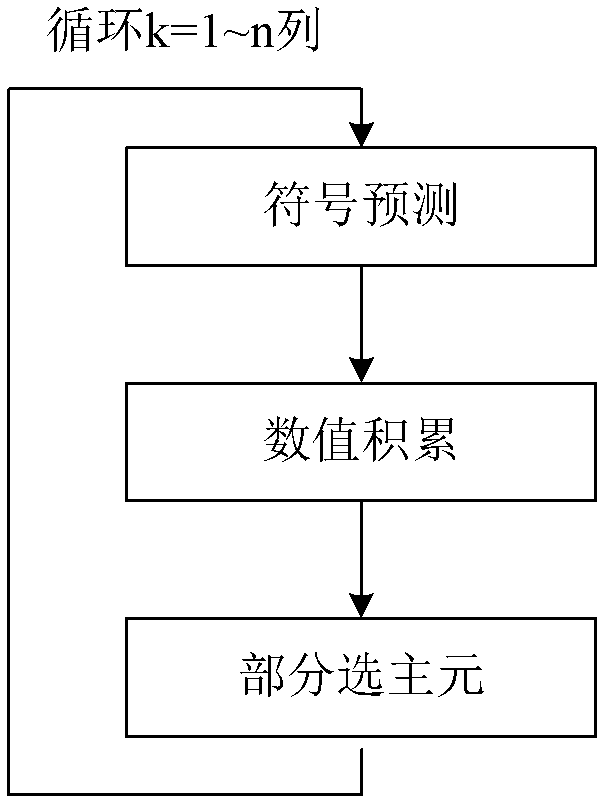

MMC (Modular Multilevel Converter) bridge arm equivalent simulation method

ActiveCN103746583AImprove simulation speedReduce the number of nodesAc-dc conversionSwitching signalOperand

The invention discloses an MMC (Modular Multilevel Converter) bridge arm equivalent simulation method which is mainly used for solving the defect of a simulation technique during the shutting of an MMC. The method comprises the following steps of 1, obtaining bridge arm operating parameters of the MMC, wherein the bridge arm operating parameters comprise bridge arm current and switch signals S1-S3 of each submodule in a bridge arm; 2, constructing a bridge arm equivalent circuit according to the bridge arm operating parameters, wherein the bridge arm equivalent circuit comprises two equivalent voltage sources, two equivalent resistors, two equivalent diodes and an equivalent thyristor; 3, building an MMC simulation system according to the bridge arm equivalent circuit, and performing simulation on the system. According to the MMC bridge arm equivalent simulation method, the complicated bridge arm circuit in the MMC is effectively equivalent to a simple circuit, the node amount and the corresponding simulation operand of the system are greatly reduced, the simulation speed of the MMC is greatly promoted, and very high simulation precision is realized during the normal operation and the shutting of the MMC.

Owner:ZHEJIANG UNIV +1

Adaptive parallel LU decomposition method aiming at circuit simulation

ActiveCN102426619AImprove simulation speedReduce decomposition timeSpecial data processing applicationsQR decompositionDecomposition

The invention discloses an adaptive parallel LU decomposition method aiming at circuit simulation and belongs to the field of EDA (electronic design automation). The method is characterized in that LU decomposition is carried out on a circuit matrix by automatically selecting a serial or parallel method based on the characteristics of the circuit matrix, so that each circuit matrix can carry out LU decomposition under the optical performance. In the parallel method, data dependency is extracted from the structure of each circuit matrix, and parallel dispatching is carried out on the tasks in the LU decomposition process based on the data dependency, so as to accelerating the circuit simulation. Test results on the circuit matrixes show that the method provided by the invention can accurately determine the serial or parallel method suitable for each circuit matrix, and for the matrixes suitable for the parallel method, the decomposition speed of the method is 2.11-8.38 times that of LUdecomposition software KLU in geometric average when the number of parallel threads is 1-8.

Owner:TSINGHUA UNIV

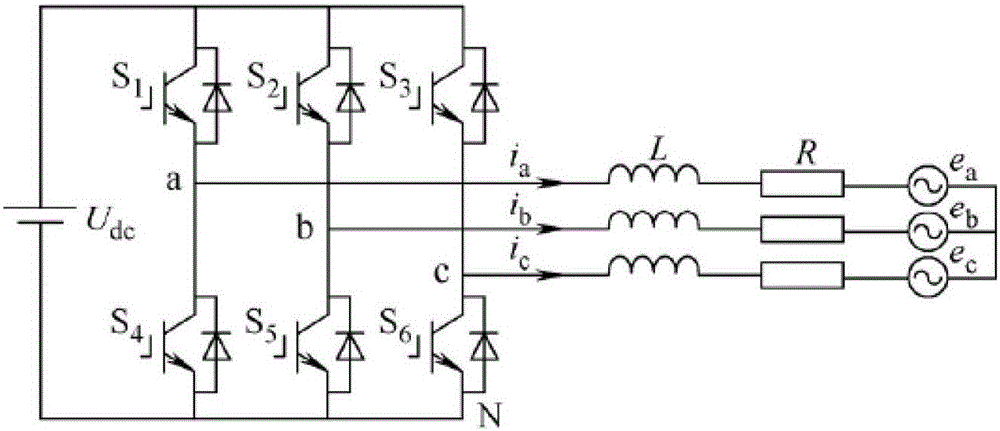

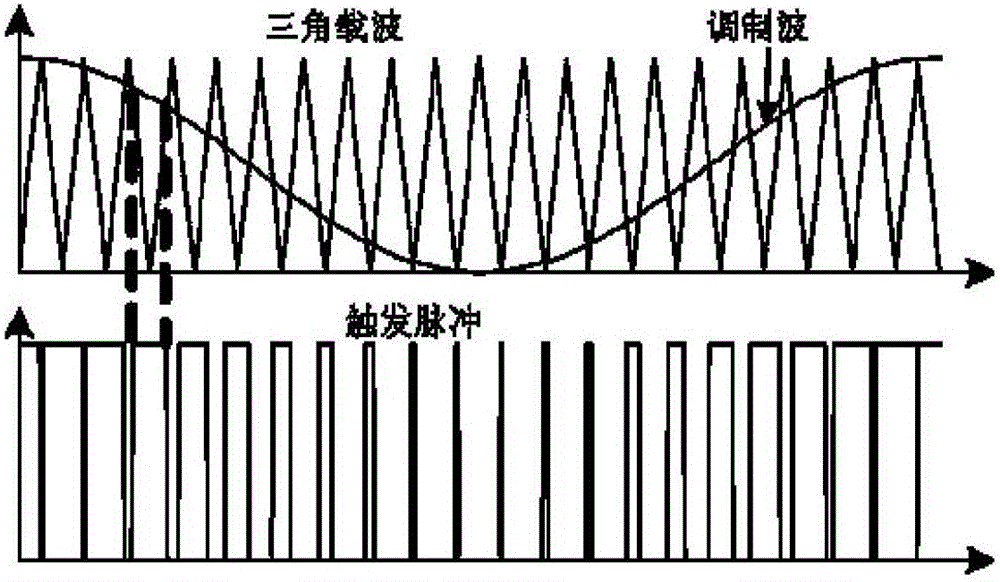

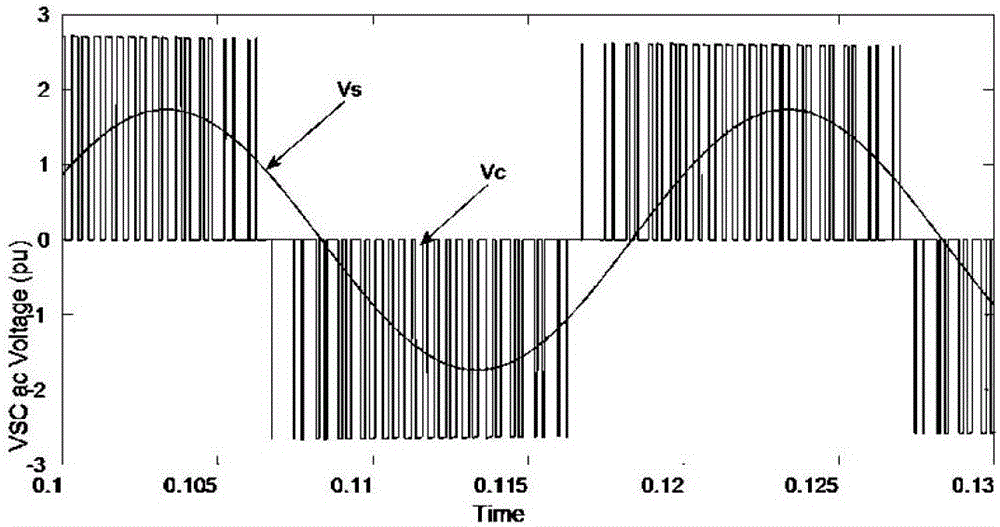

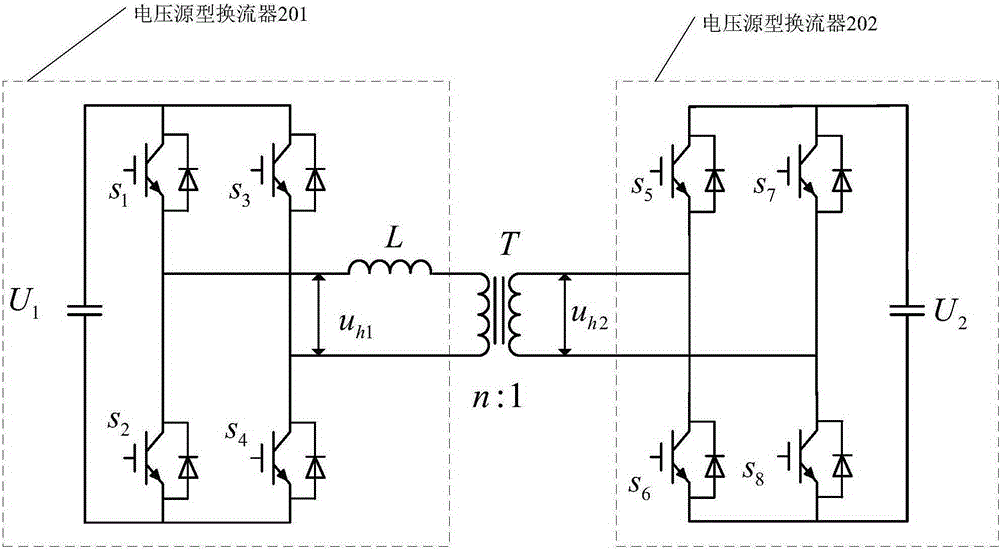

Average value modeling and control method applicable to VSC-MTDC(Voltage Sourced Converters Multi-terminal Direct Current) system

InactiveCN106208124AConsistent dynamic responseSmall amount of calculationElectric power transfer ac networkMathematical modelSimulation

The invention provides an average value modeling and control method applicable to a VSC-MTDC (Voltage Sourced Converters Multi-terminal Direct Current) system. The method comprises the following steps of 1, building a mathematical model of a VSC based on d and q rotational coordinates, and calculating active power and reactive power of an AC side of a converter by combining a VSC-MTDC power transmission system; 2, building a VSC-MTDC controller by taking the active power and the reactive power of the AC side of the converter as reference values to achieve cooperative control of a plurality of converter stations; and 3, simplifying a control process of the VSC-MTDC, and building a VSC-MTDC average value model. The average value model can be applied to a multi-terminal direct current power transmission system, the simulation speed is greatly increased, the simulation efficiency is improved, and the mathematical calculation amount is reduced.

Owner:SHANGHAI JIAO TONG UNIV

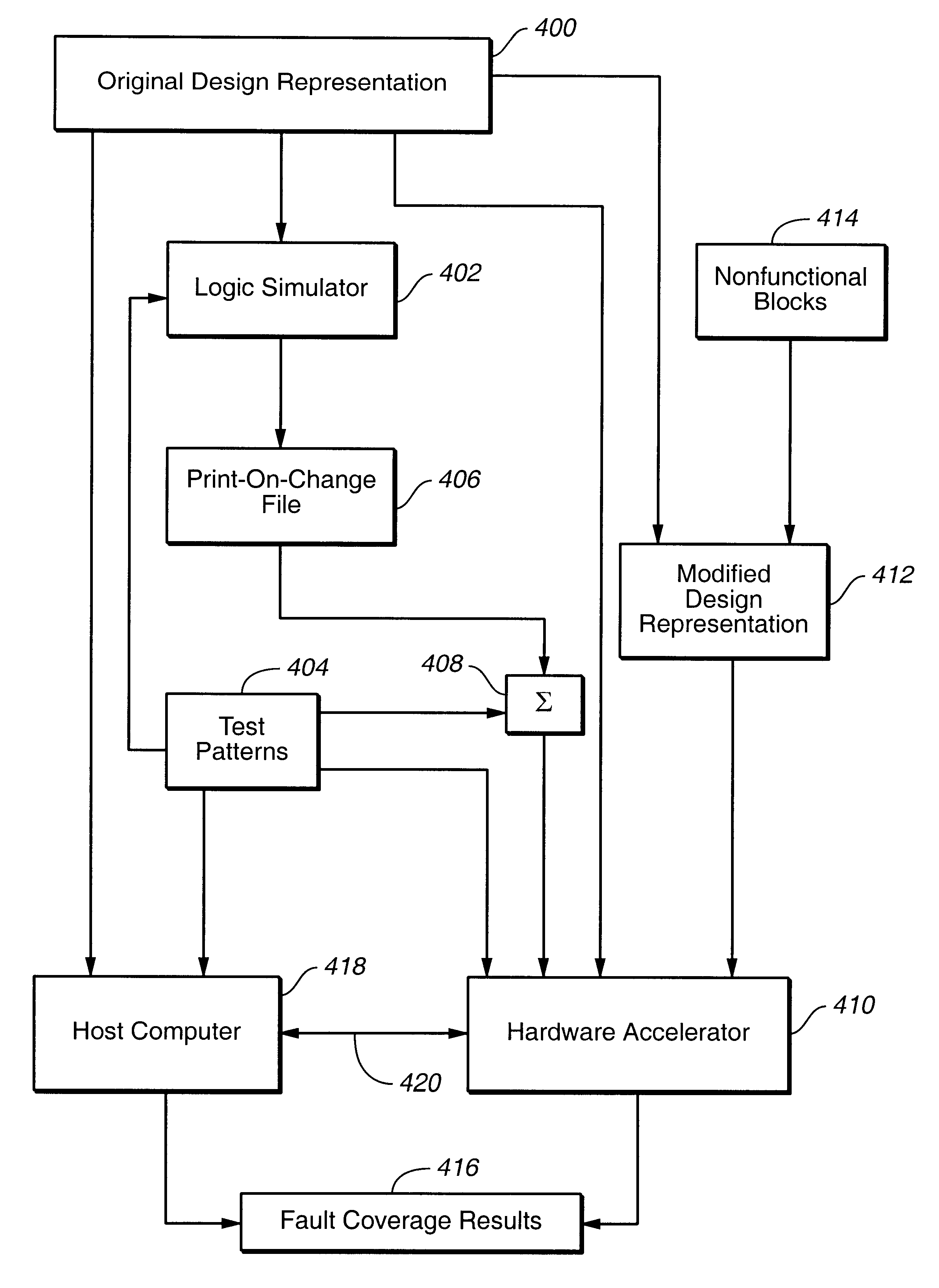

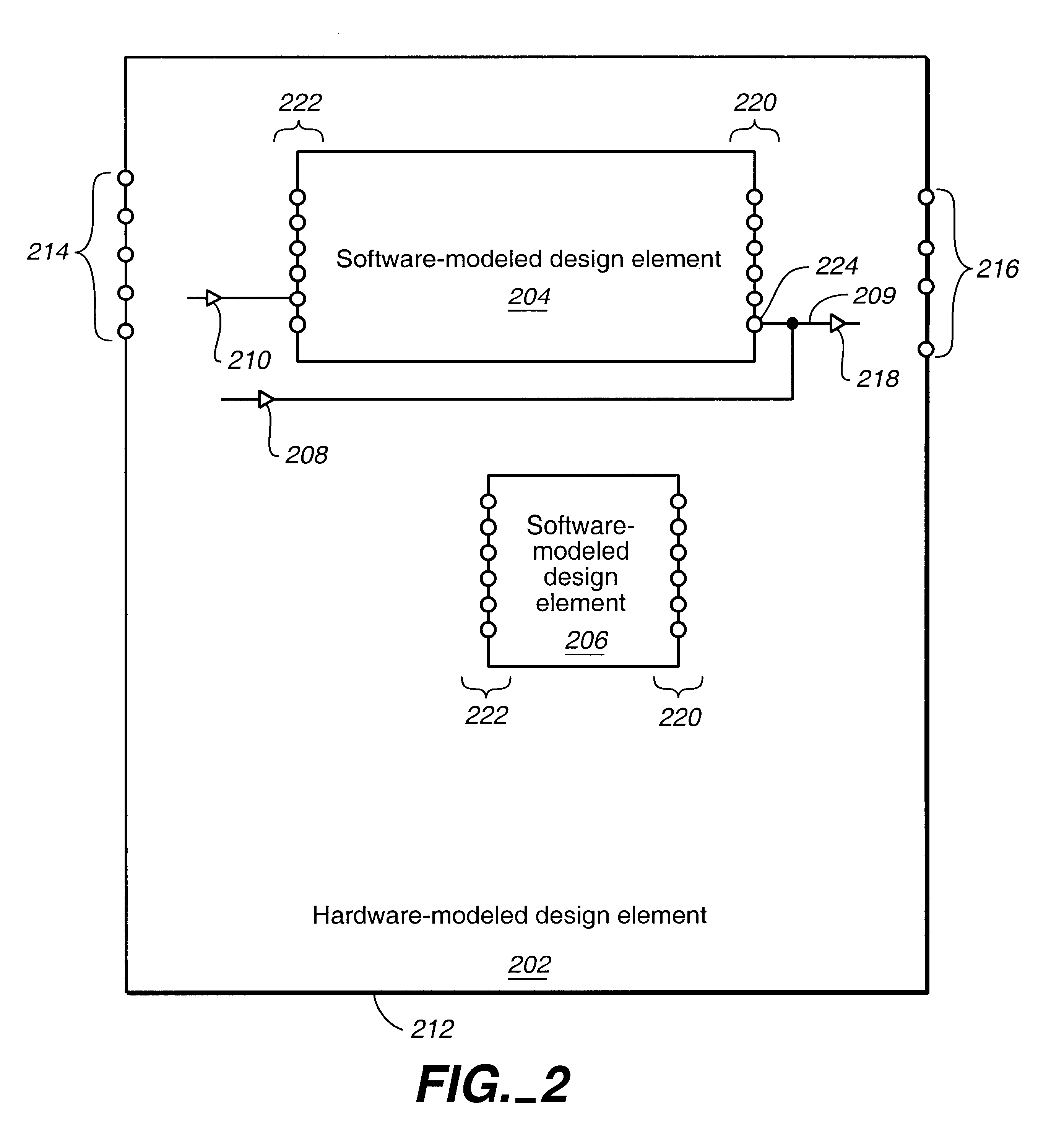

Modified design representation for fast fault simulation of an integrated circuit

InactiveUS6370492B1Improve simulation speedAnalogue computers for electric apparatusFunctional testingFault coverageEngineering

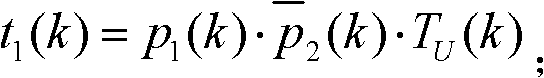

A system and method perform a two-pass fault simulation on an original design representation including a software-modeled design element and a hardware-modeled design element. Logic simulation generates input stimulus for a port on the boundary of the software-modeled design element and the hardware-modeled design element, where such ports are output ports of the software-modeled design element and input ports of the hardware-modeled design element. The input stimulus is merged with test patterns for the original design representation. A modified design representation is generated by replacing the software-modeled design element with a nonfunctional block. Most or all possible faults in the hardware-modeled design representation are seeded. The modified design representation is fault simulated in a first pass using the merged input stimulus and test patterns. Any unseeded faults from the first pass and other possible faults in the software-modeled design representation are then seeded and the original design representation is fault simulated in a second pass. The fault coverage results of the two passes are aggregated to generate an overall fault coverage for the original design representation.

Owner:BELL SEMICON LLC

Method and device for simulating power electronic system

InactiveCN102096747AAccurate and efficient calculationImprove simulation speedSpecial data processing applicationsElectronic systemsLow speed

The invention provides a method and a device for simulating a power electronic system in order to solve the problem of low speed of power electronic system simulation in the prior art. The method comprises the following steps of: calculating variation of a topological structure caused by starting and stopping operation of a simulation system by using a Petri Net matrix model; updating a state equation of a continuous sub system of the simulation system according to information of the variation of the topological structure; and calculating the state equation of the continuous sub system to determine a value of a state variable of the simulation system. By using the technical scheme, the power electronic system simulation can be carried out efficiently.

Owner:长沙高新开发区德研电气技术有限公司

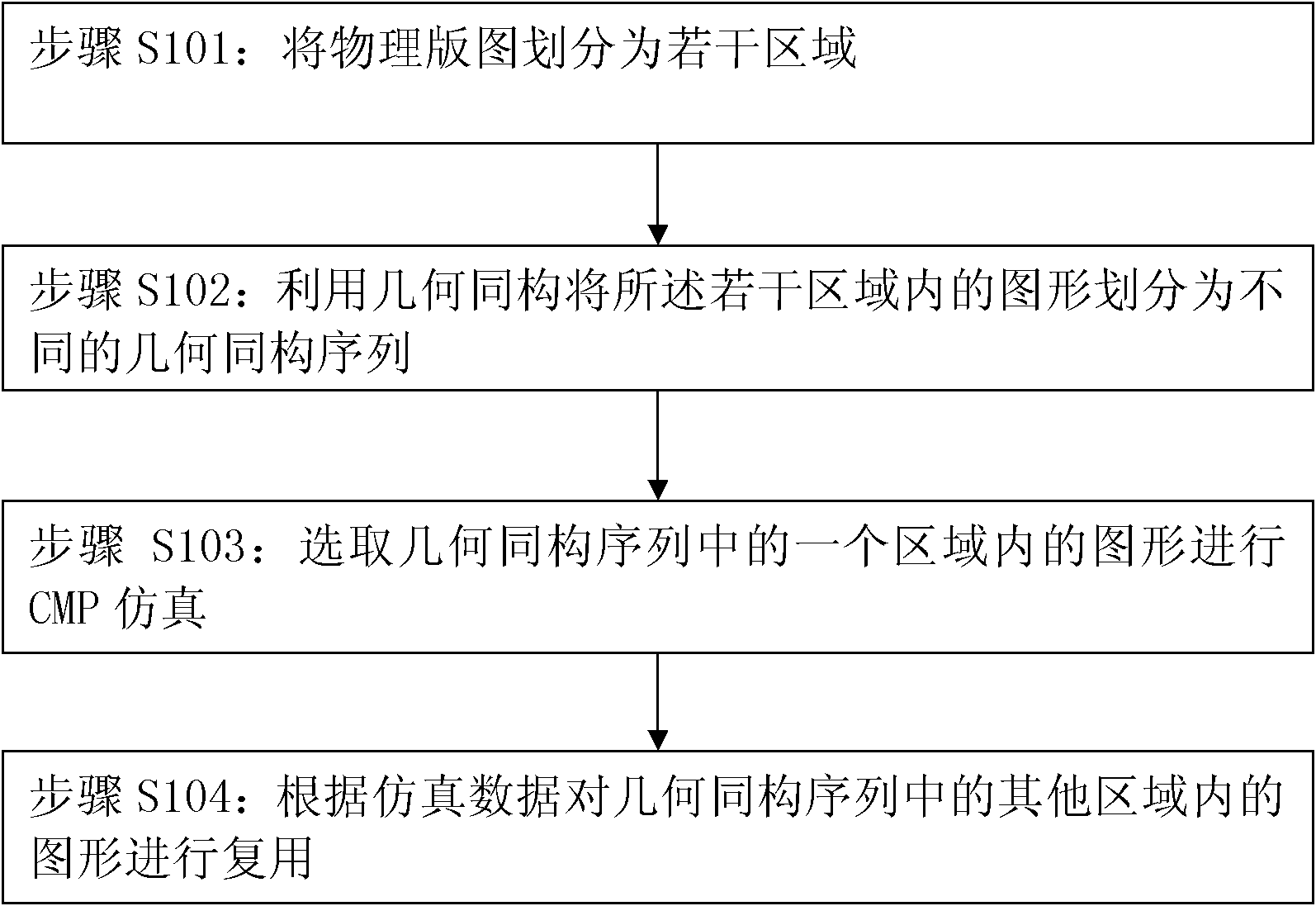

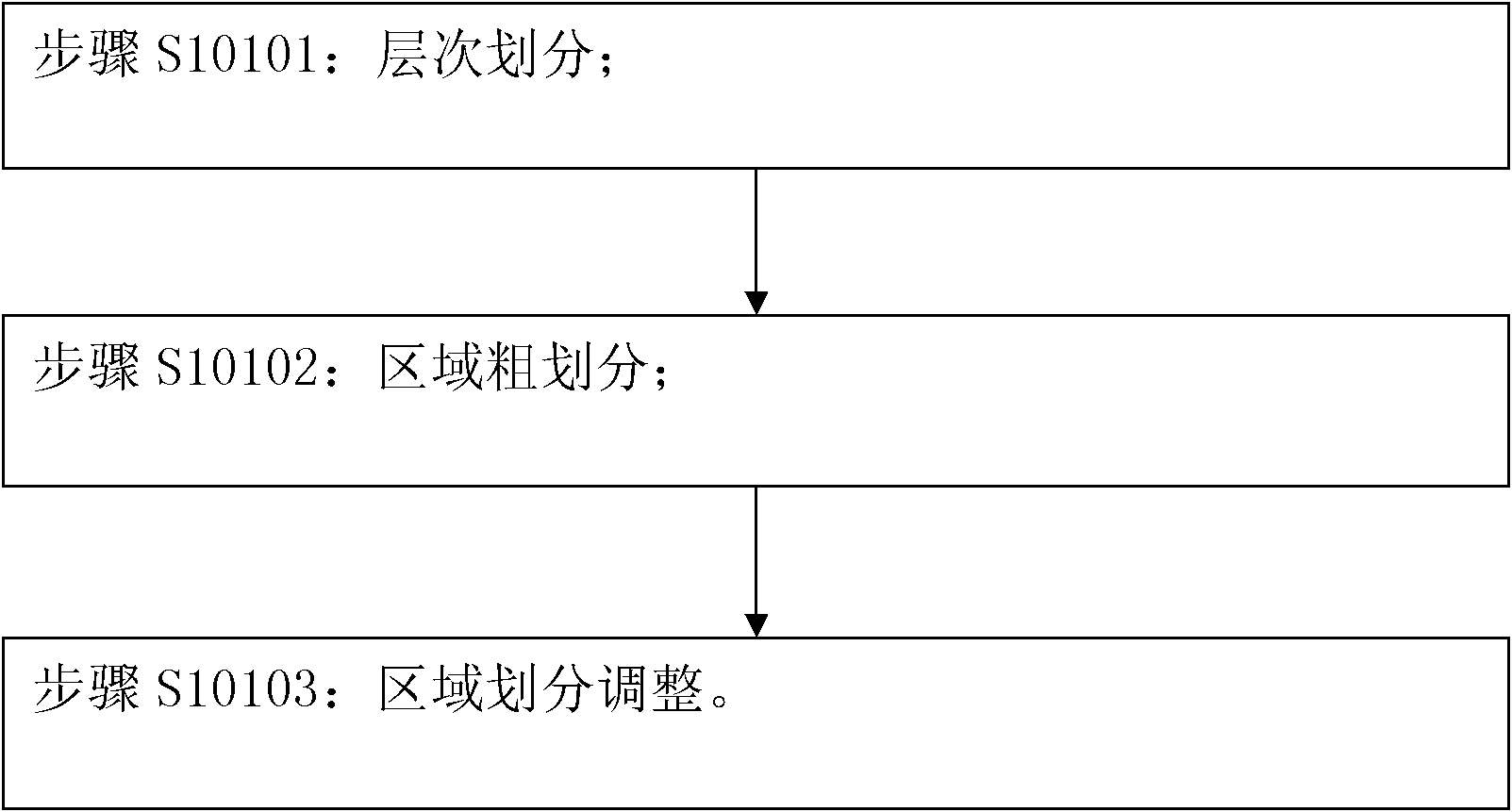

Method and device for accelerating emulation of CMP (Chemical Mechanical Polishing)

ActiveCN102508981AImprove simulation speedReduced CMP simulation timeSpecial data processing applicationsGraphicsMultiplexing

The invention discloses a method and a device for accelerating the emulation of a CMP (Chemical Mechanical Polishing). The method for accelerating the emulation of the CMP comprises the following steps of: firstly, dividing a physical layout into a plurality of areas; secondly, dividing graphs in the areas into different geometry isomorphic sequences by using a geometry isomorphism; thirdly, selecting the graph in one area of the geometry isomorphic sequence for carrying out CMP emulation; fourthly, multiplexing the graphs in other areas in the geometry isomorphic sequences according to emulation data. According to the method and the device disclosed by the invention, through the division of the physical layout, the geometry isomorphism of the graphs in the areas, the CMP emulation in the areas and the multiplexing of CMP emulation data in the areas, the emulation speed of the CMP of a whole chip is increased and the emulation time of the CMP of the whole chip is shortened; and a CMP emulation task is merged in a graph isomorphic way; and on the basis of the graph isomorphism, primary calculation for the same CMP emulation task of the physical layout is carried out and the emulation result of the CMP is multiplexed, and thereby the emulation speed of the CMP of the whole chip is increased by reducing the quantity of the CMP emulation tasks.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

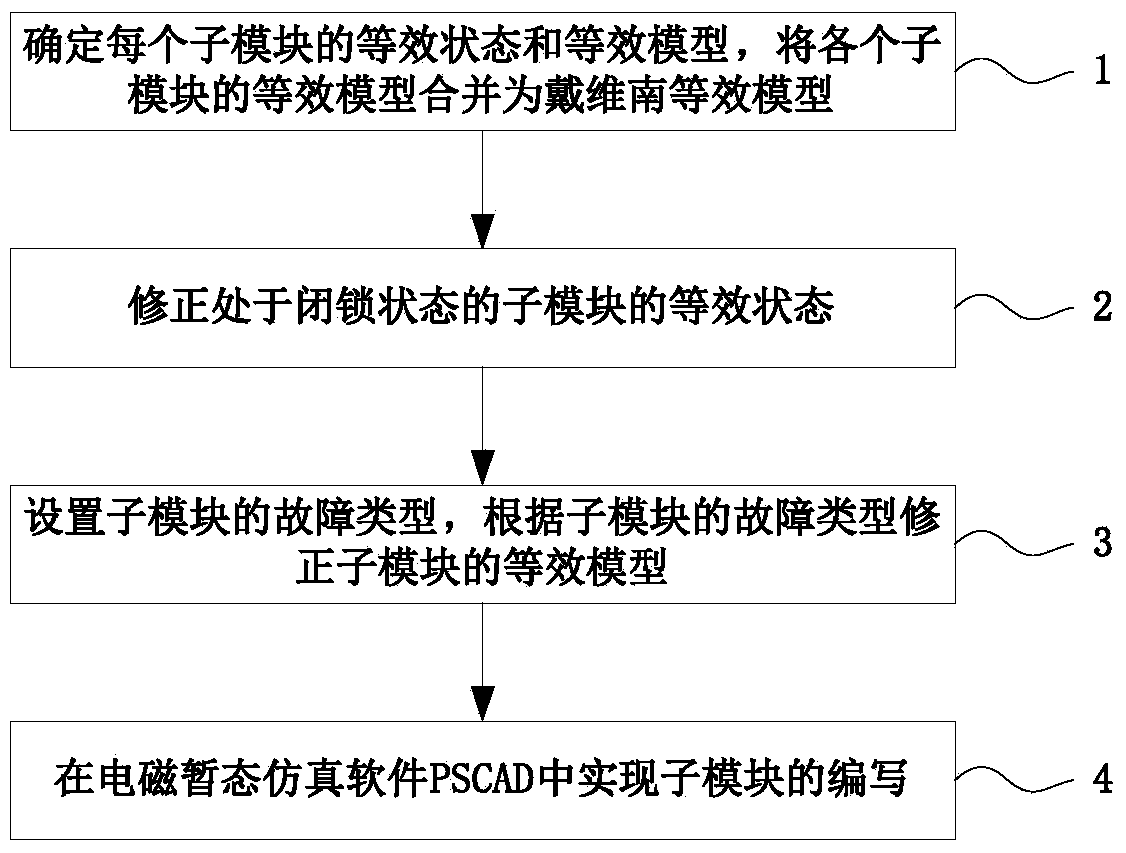

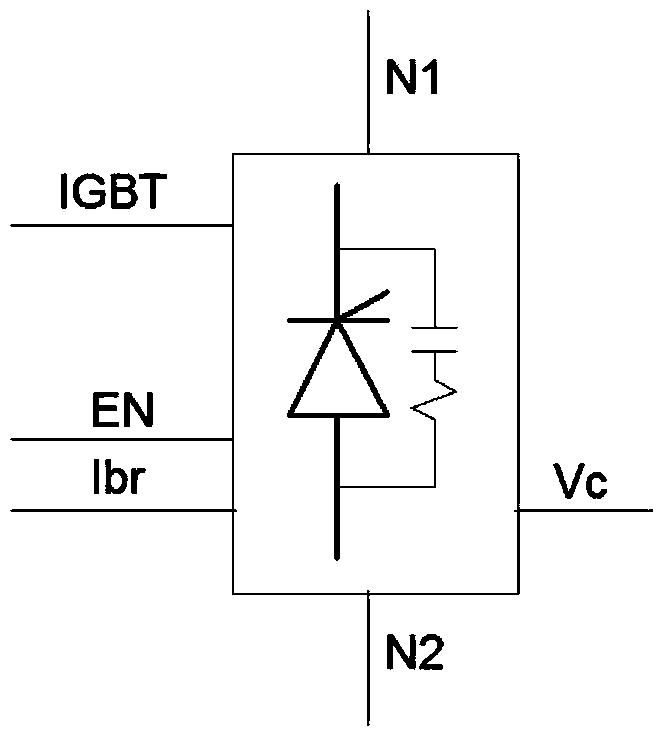

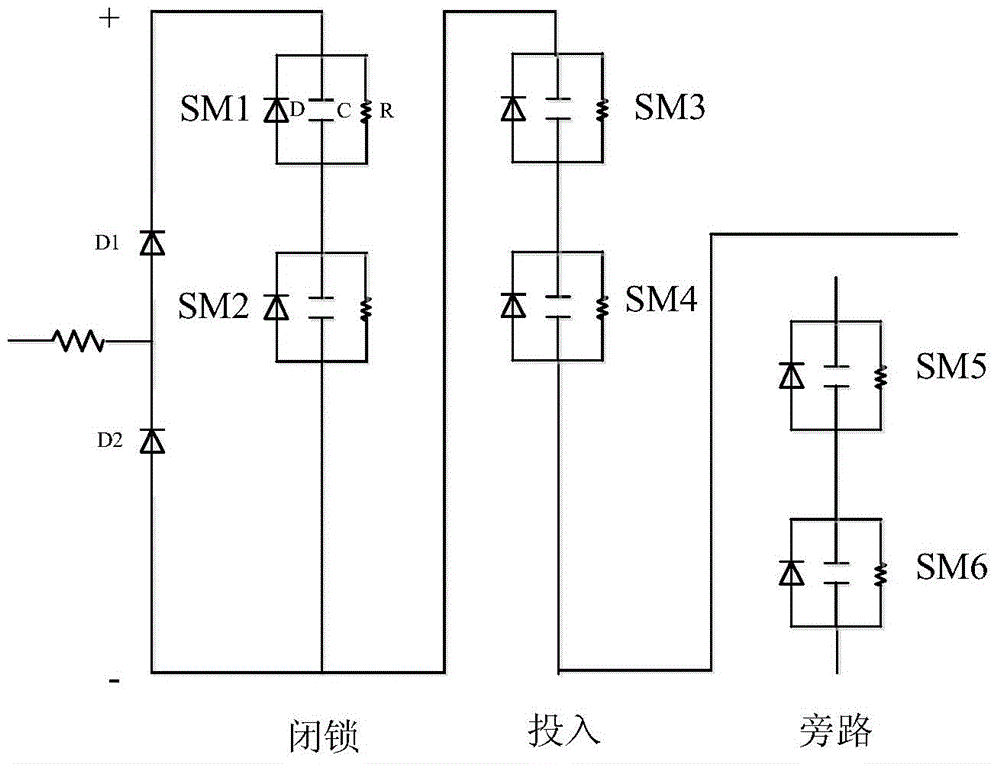

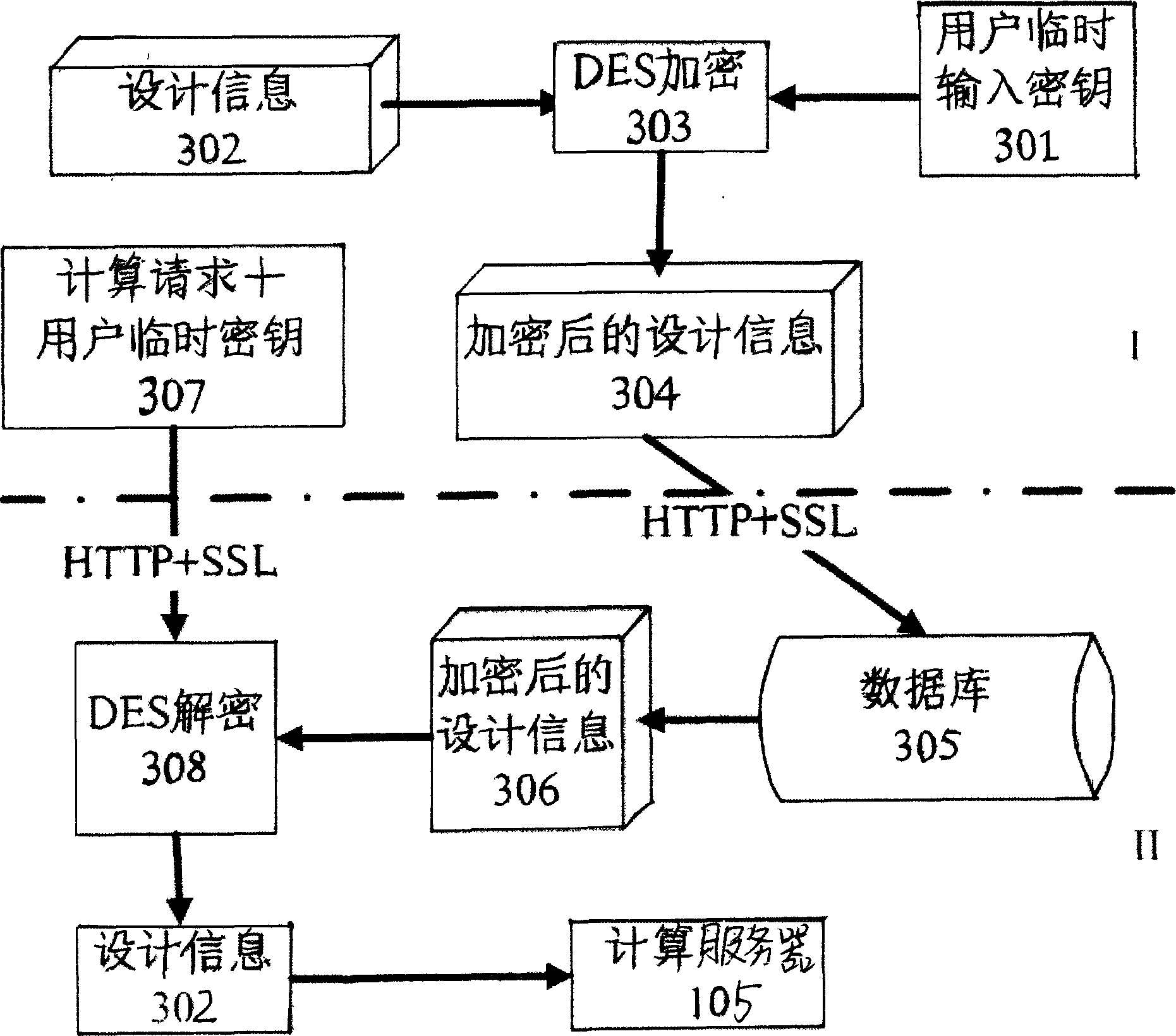

Designing method of MMC multi-sub-module user-defined integrated component

ActiveCN104199997AOvercoming the defect of too much workloadSolve the problem of locking state equivalenceSoftware simulation/interpretation/emulationSpecial data processing applicationsElectric power systemSimulation

The invention discloses a designing method of an MMC multi-sub-module user-defined integrated component in the technical field of electric power system operation and control. The method comprises the steps that the equivalent state and the equivalent model of each sub-module are determined, and the equivalent models of the sub-modules are combined into a Thevenin equivalent model; the equivalent state of a sub-module in a locking state is corrected; the fault types of the sub-modules are set, and the equivalent models of the sub-modules are corrected according to the fault types of the sub-modules; and compiling of the sub-modules is achieved in electromagnetic transient simulation software PSCAD is achieved. The shortcomings that according to an existing sub-module equivalent model, workload is large when a large-scale MMC system is established are overcome, equivalence of the sub-module locking states is achieved, and the problem that an existing equivalent model cannot set a failure is solved.

Owner:NORTH CHINA ELECTRIC POWER UNIV (BAODING)

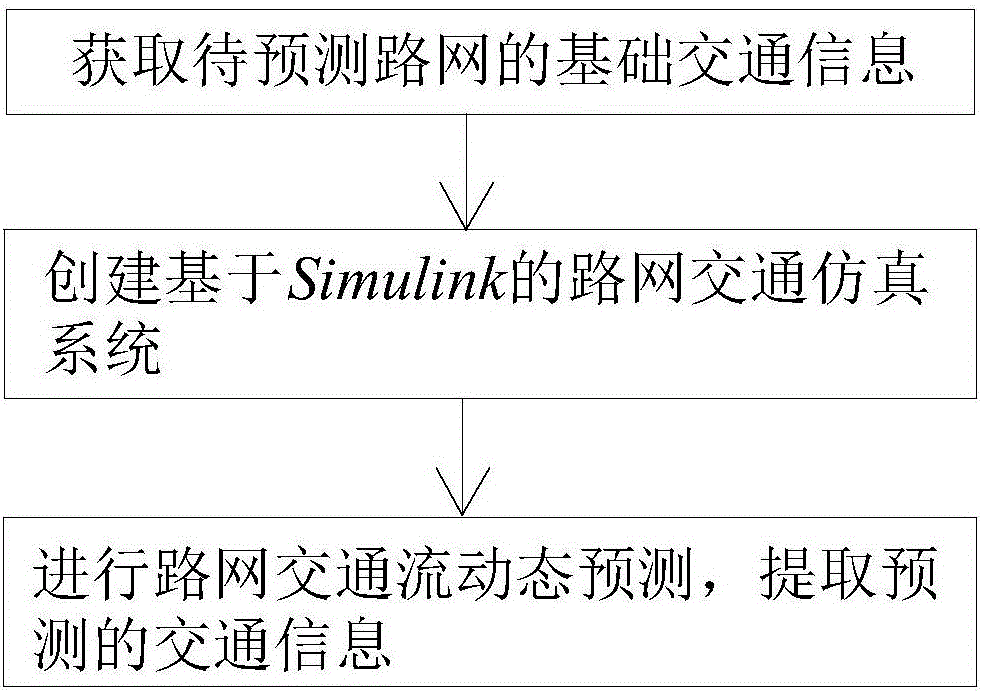

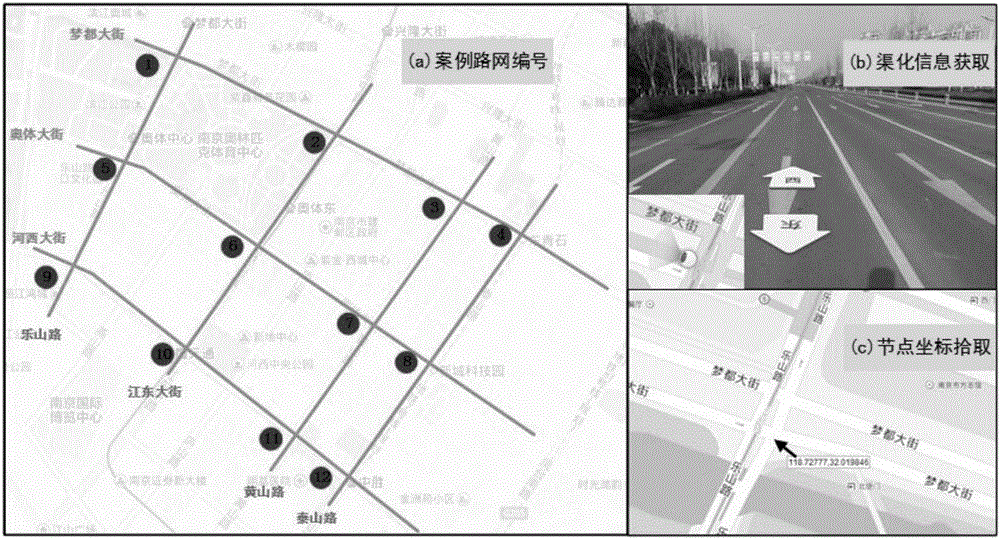

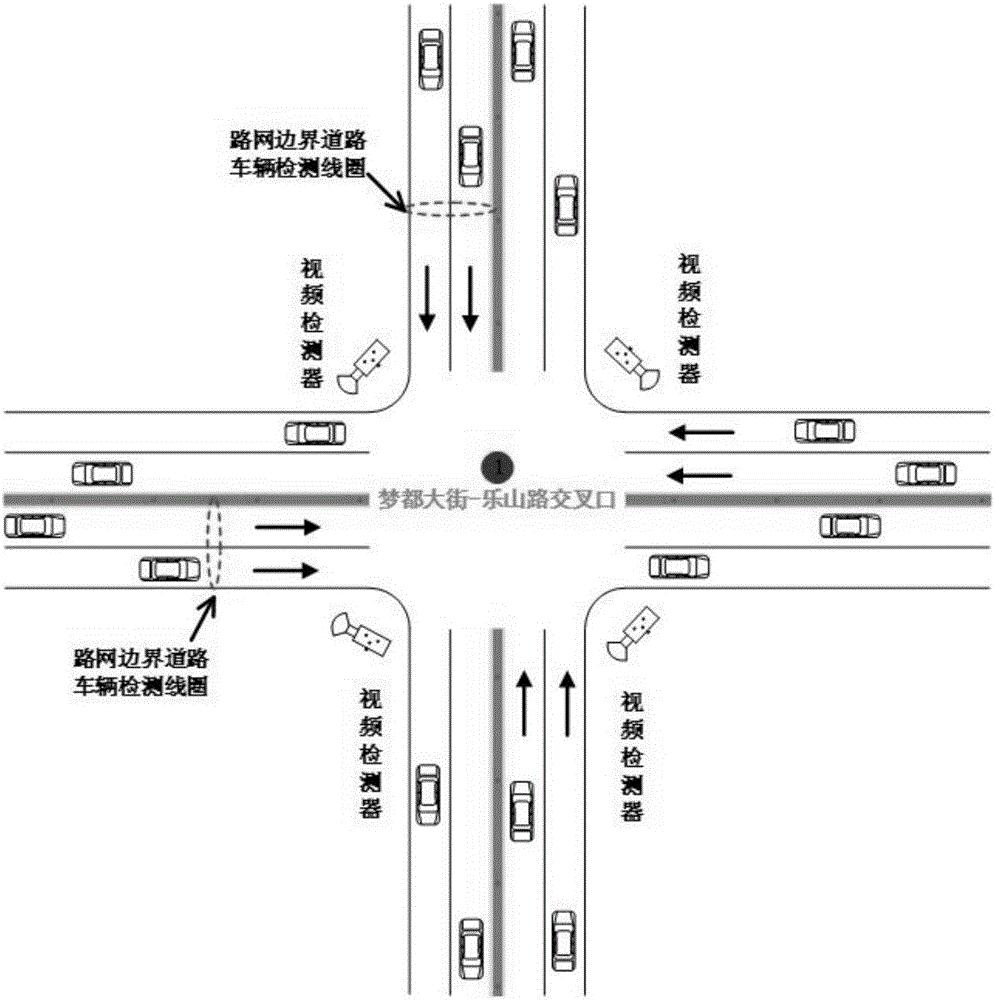

Road network dynamic traffic flow prediction method based on Simulink simulation

ActiveCN106846818ARealize dynamic simulation predictionPrediction accuracy advantageDetection of traffic movementDesign optimisation/simulationSimulationRoad networks

The invention discloses a road network dynamic traffic flow prediction method based on Simulink simulation. The method comprises the following steps that 10, basic traffic information of a to-be-predicted road network is acquired, wherein the basic traffic information comprises road network topological structure information and road network traffic operation information; 20, a road network traffic simulation system based on Simulink is created according to the acquired basic traffic information of the to-be-predicted road network; 30, dynamic road network traffic flow prediction is conducted according to the created road network traffic simulation system, and predicted traffic information is extracted. According to the prediction method, the dynamic traffic flow information operating on a large-scale city road network can be precisely predicted in real time.

Owner:河南省城乡规划设计研究总院股份有限公司

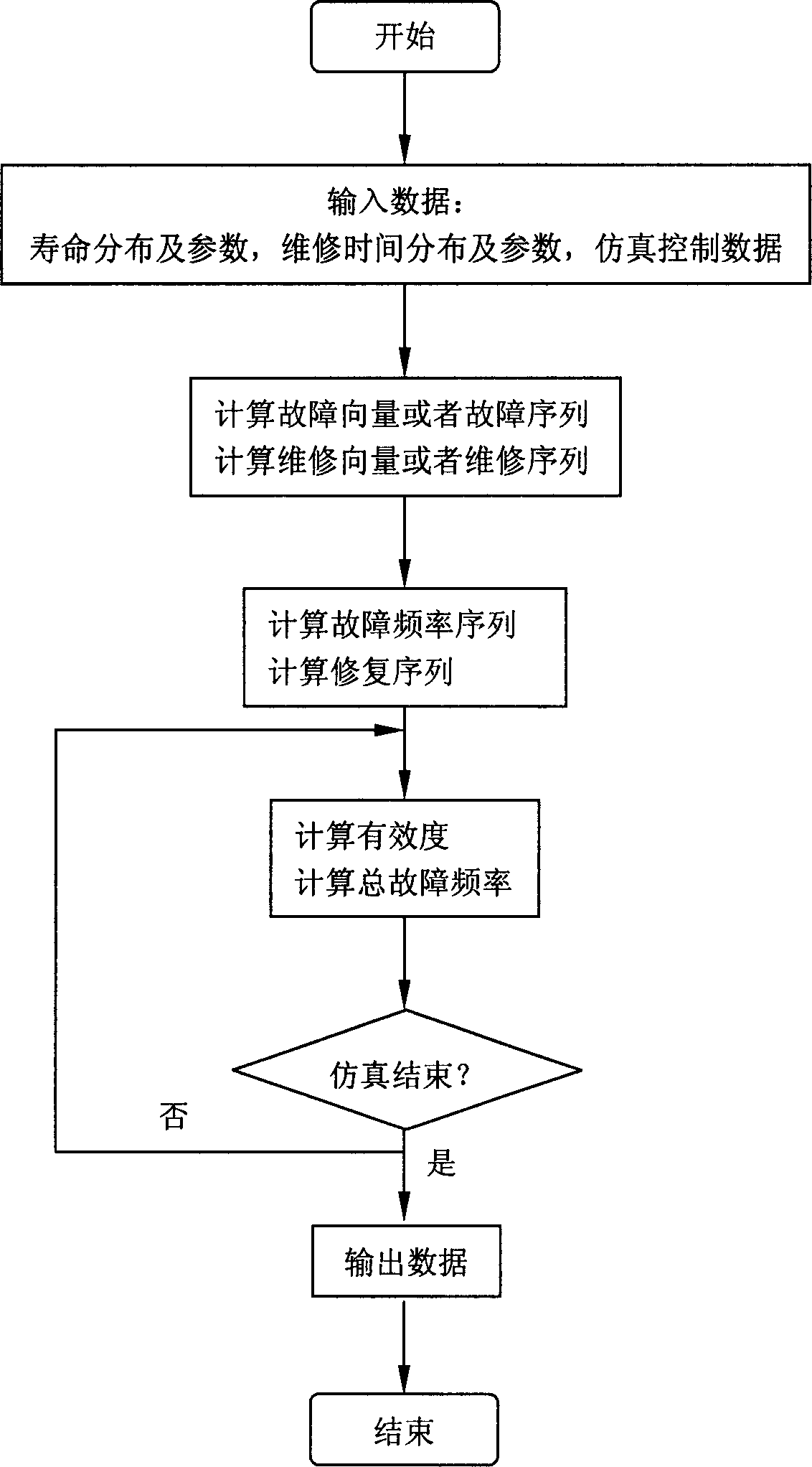

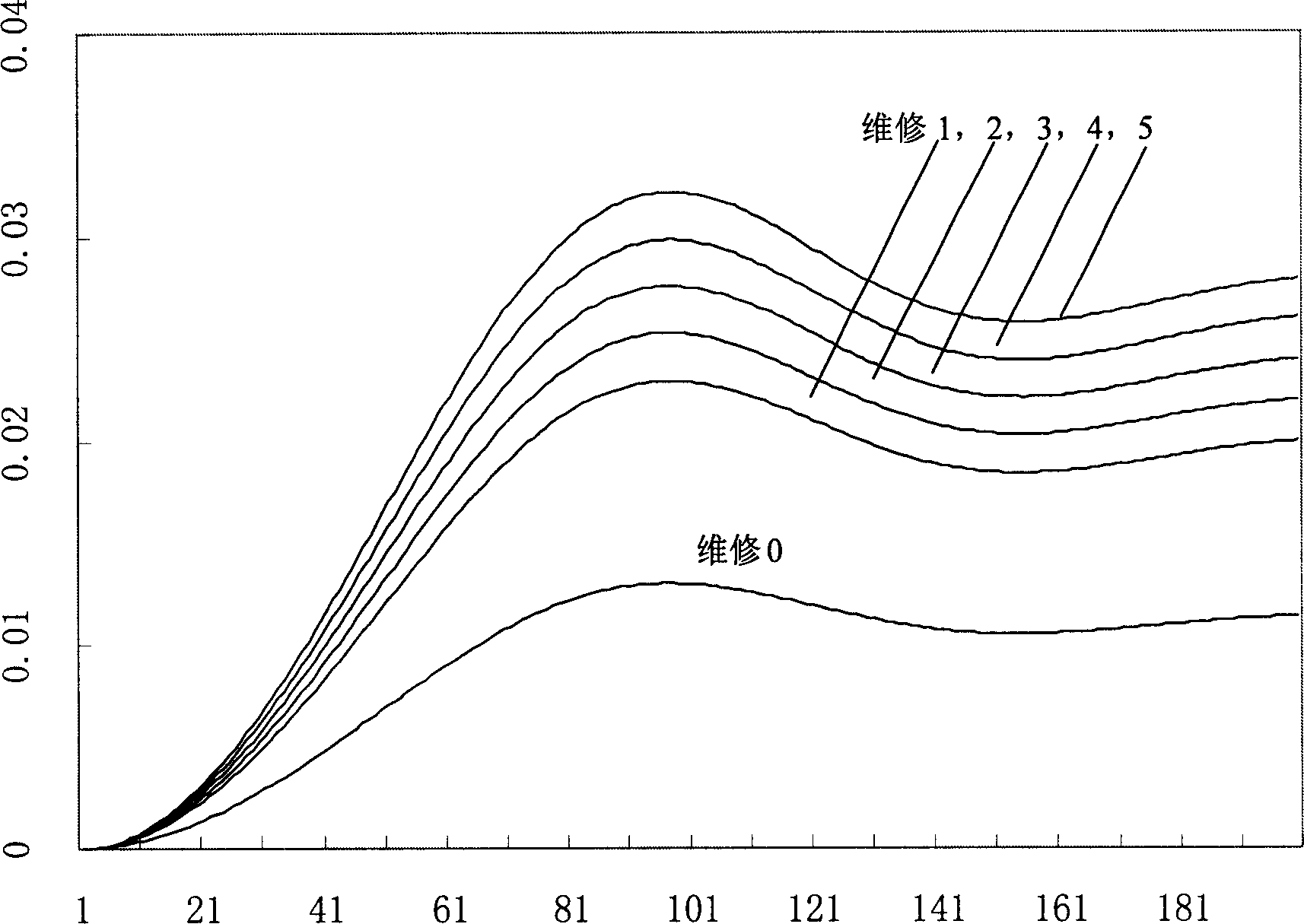

Simulation technology based on after repair and repair time product effectiveness

InactiveCN1858753ASmall amount of calculationImprove simulation speedSpecial data processing applicationsProduct systemRepair time

This invention discloses an emulation technology based on post maintenance and the validity of products in maintenance including: a, structuring a maintenance vector or a sequence, b, structuring a fault frequency sequence, c, structuring a repairing sequence, d, computing the elements of the fault frequency sequence and reparing sequence, e, computing the validity of products and total fault frequency, which makes up some shortcomings of the Markov and Monte-Carlo method and is used in researching the influence of maintenance mode and time to product reliabilities.

Owner:YANSHAN UNIV

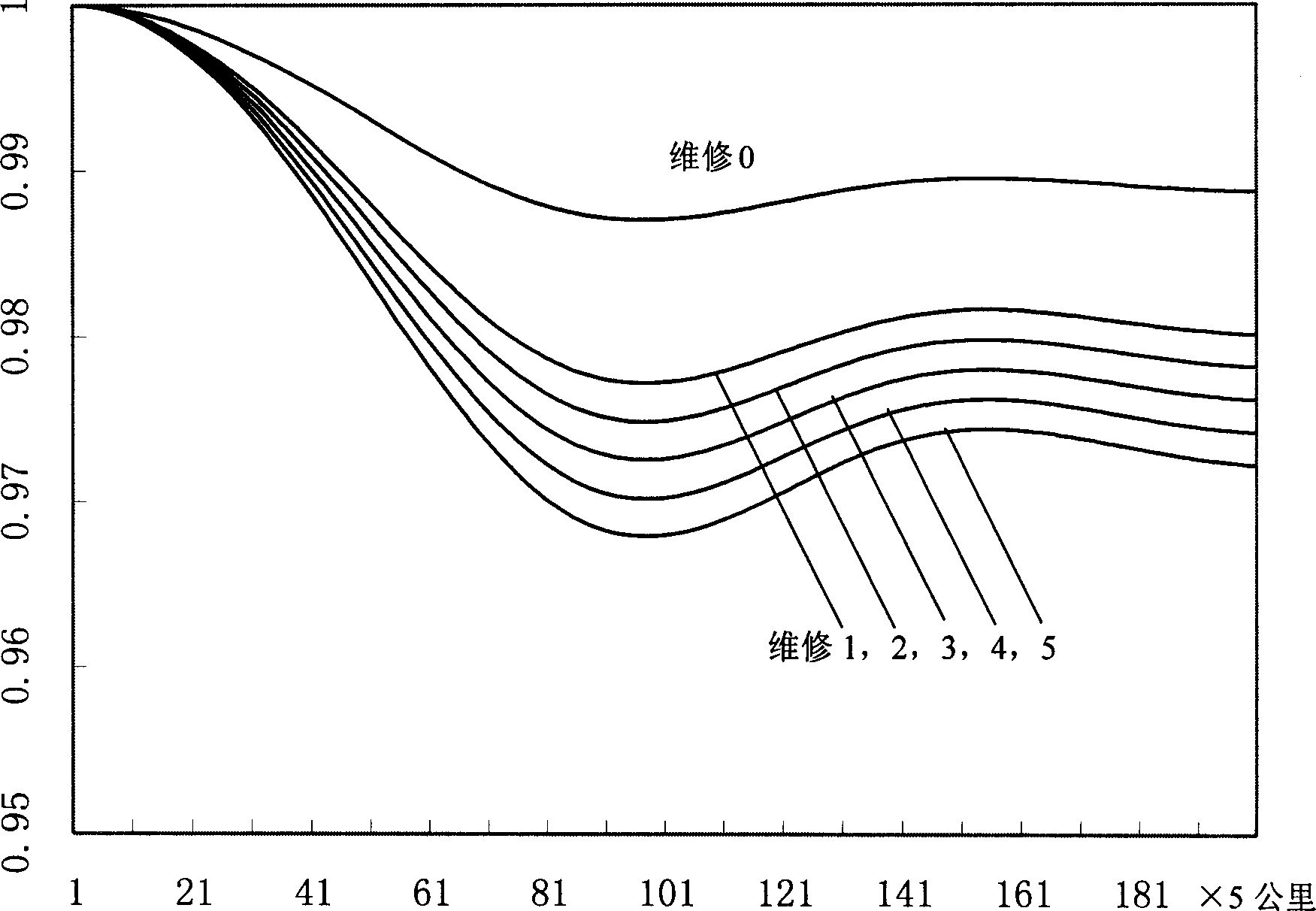

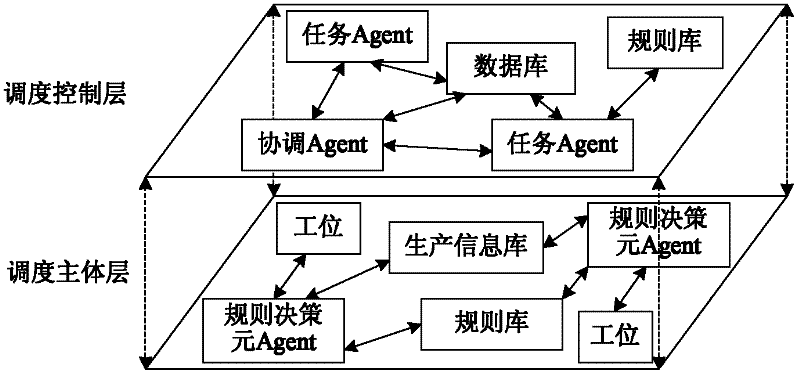

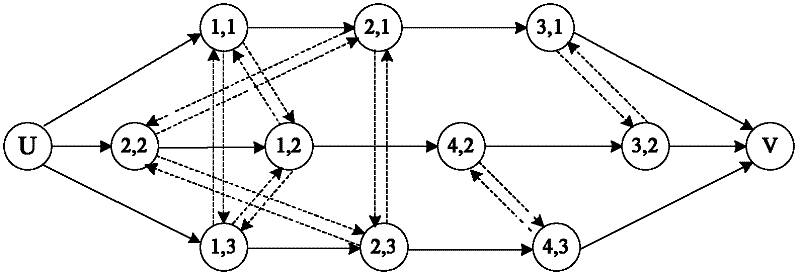

Method for carrying out dispatching control on multi-variety multi-process manufacturing enterprise workshop on basis of ACA (Automatic Circuit Analyzer) model

The invention relates to a method for carrying out dispatching control on a multi-variety multi-process manufacturing enterprise workshop on the basis of an AC (Automatic Circuit Analyzer) model, which comprises the following steps of: 1, setting a target function of the multi-variety multi-process manufacturing enterprise workshop, and when task information of a task Agent is sent to a decision Agent by a coordination Agent, representing the task information with a directed graph G by the decision Agent and using a dispatching rule which is obtained by the decision Agent through a random algorithm as an initial solution of a tabu search algorithm; 2, by a rule decision element Agent, firstly, calculating a target value F, then searching other dispatching methods from the dispatching field by the tabu search algorithm, and using a solution with the minimum target value as the adopted rule; and 3, carrying out state changing on each cell (i.e. a station) in a cell space according to the dispatching rule awarded by the rule decision element. According to the invention, a complex dispatching system can be described, the practical production is well reflected, the computational efficiency of a model is also considered, and the problem of dispatching the dynamic and complex multi-variety multi-process manufacturing enterprise workshop is rapidly and accurately solved.

Owner:ZHEJIANG UNIV OF TECH

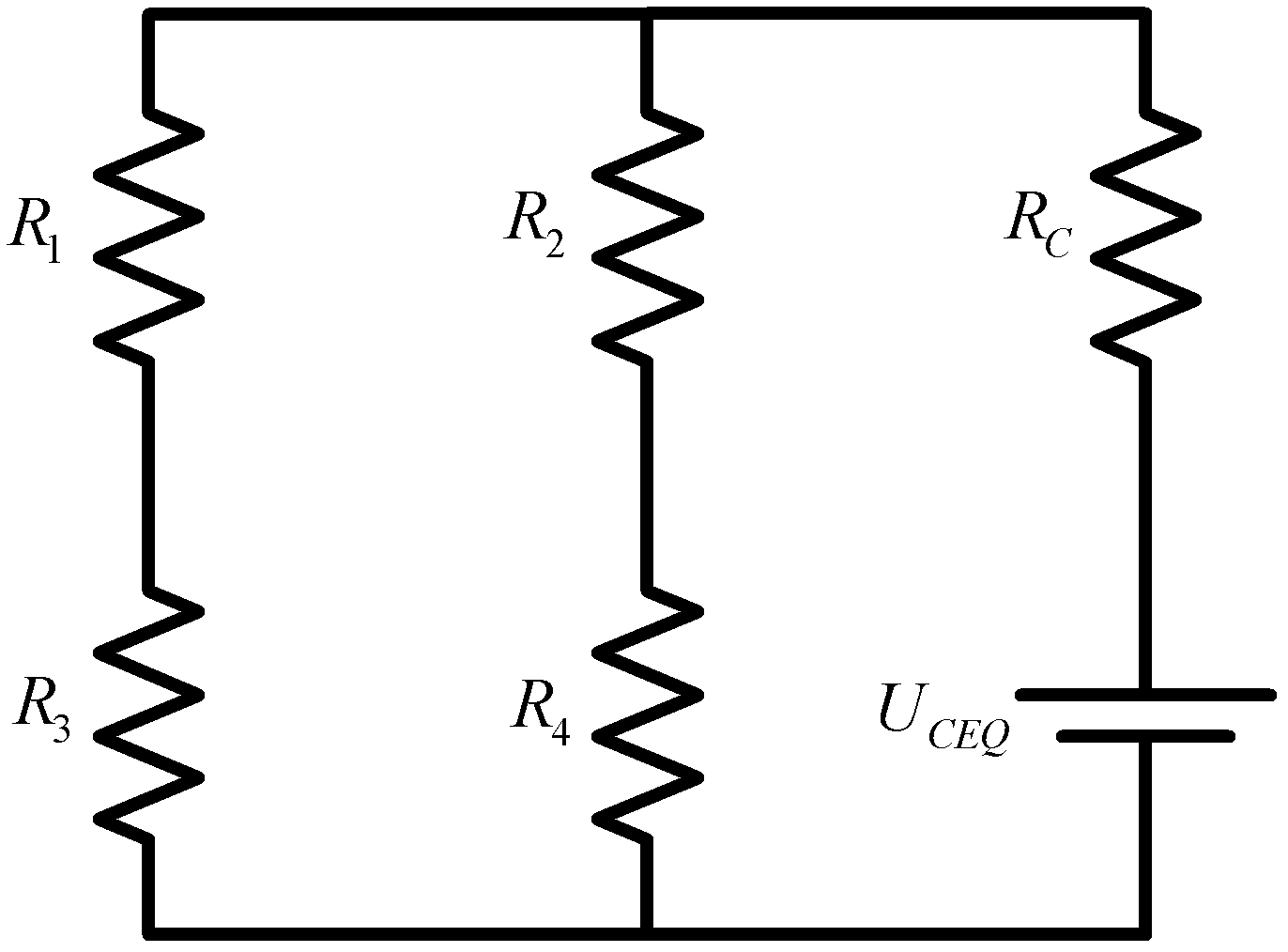

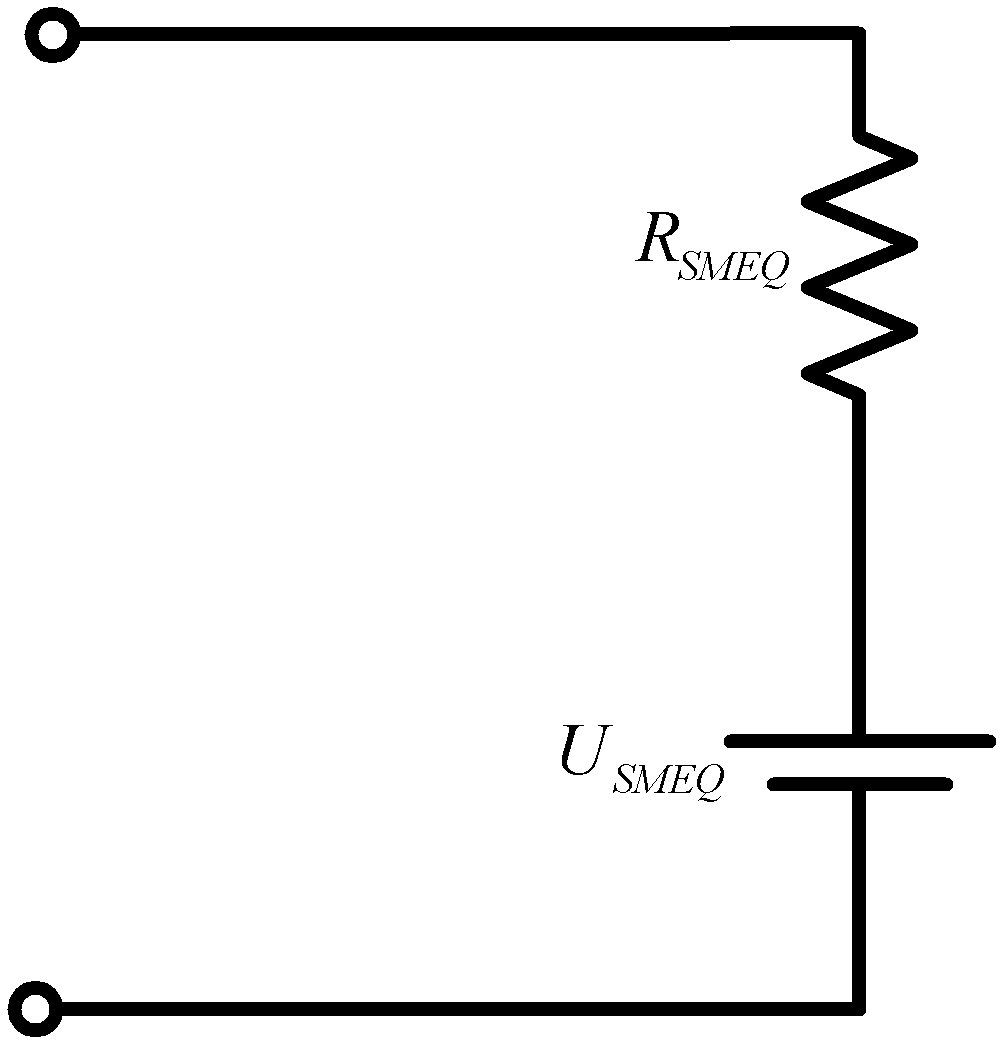

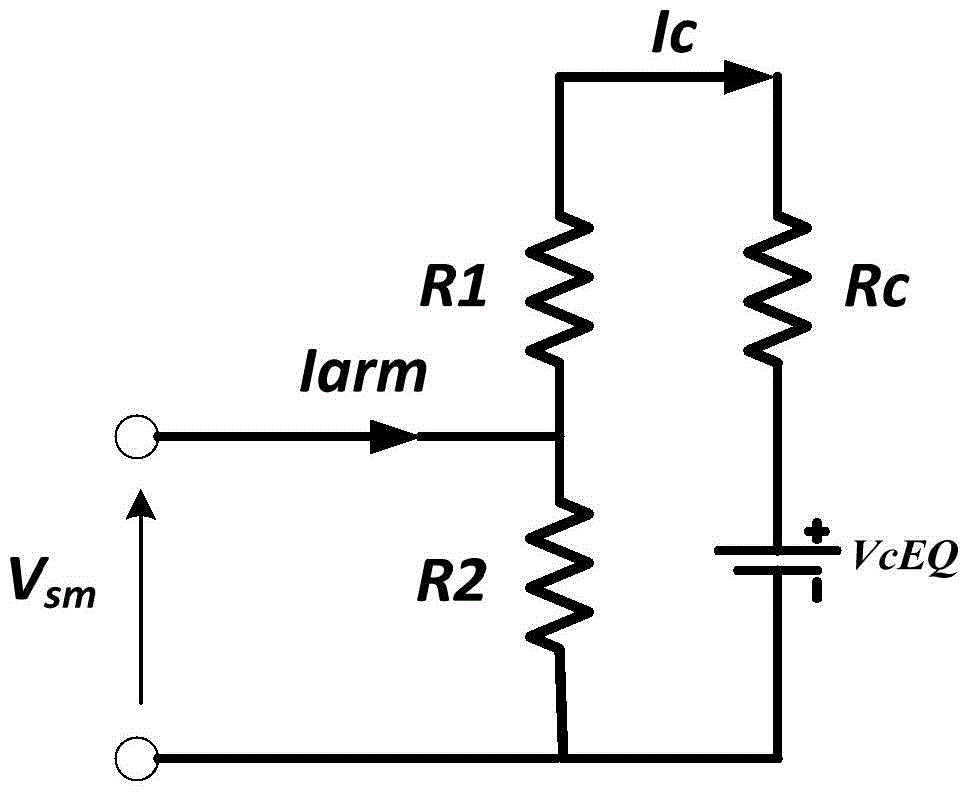

MMC (modular multilevel converter) equivalent modeling method with module latching function

ActiveCN103605850AReduce complexityImprove simulation speedSpecial data processing applicationsElectrical resistance and conductanceModel method

The invention relates to modeling methods of MMC (modular multilevel converter) submodules, in particular to an MMC equivalent modeling method with a module latching function. The method is characterized in that an IGBT (insulated gate bipolar transistor) series branch of a submodule is enabled to be equivalent to a resistor series branch, and a capacitor branch is enabled to be equivalent to a resistor and power source series branch. The method includes the following steps: 1, determining equivalent voltage Vsm and equivalent resistance RsmEQ of a module equivalent circuit; 2, determining equivalent circuit parameters. By the method, electromagnetic transient simulation can be performed on a modularized multilevel converter accurately and quickly, and the submodule latching function is provided, so that simulation efficiency is greatly improved and time for simulation is reduced.

Owner:STATE GRID CORP OF CHINA +2

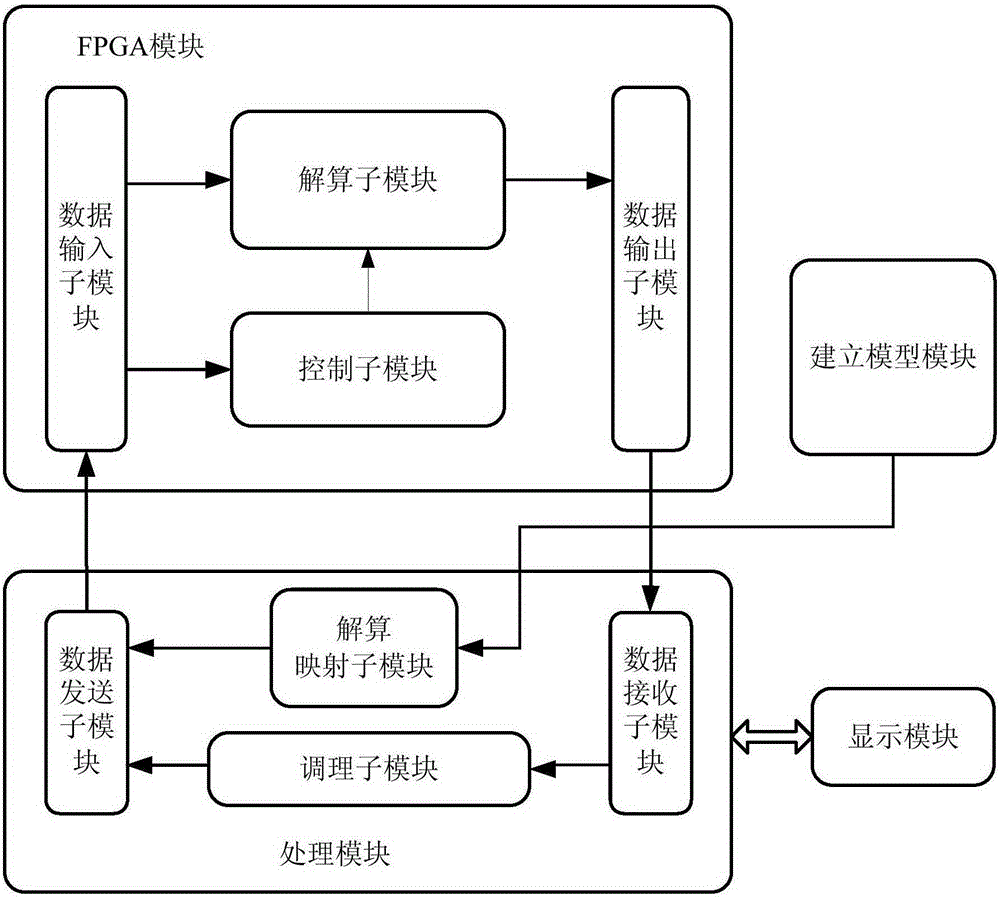

FPGA-based simulation system and method

ActiveCN105302956AShorten the development cycleImprove simulation speedSpecial data processing applicationsComputer scienceSimulation system

The invention relates to the technical field of simulation, and discloses an FPGA-based simulation system and method. The FPGA-based simulation system comprises a model establishing module, a processing module and an FPGA module, wherein the model establishing module is connected with the FPGA module through the processing module; the model establishing module is used for establishing a circuit topology model of a device to be simulated by utilizing a graphical programming method; the processing module is used for mapping the circuit topology model established by the model establishing module to the FPGA module, controlling the FPGA module to calculate according to the circuit topology model and carrying out analog simulation on the device to be simulated; and the FPGA module is furthermore used for compiling the circuit topology model when firstly receiving the circuit topology model of the device to be simulated. In such way, the simulation speed of the device to be simulated can be improved.

Owner:SHANGHAI KELIANG INFORMATION ENG

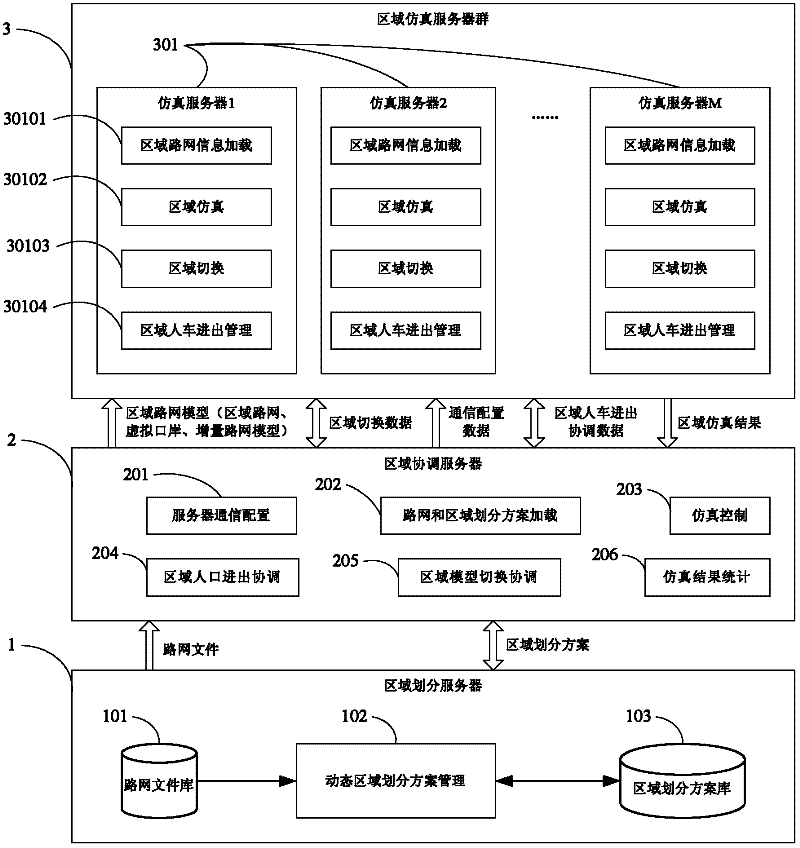

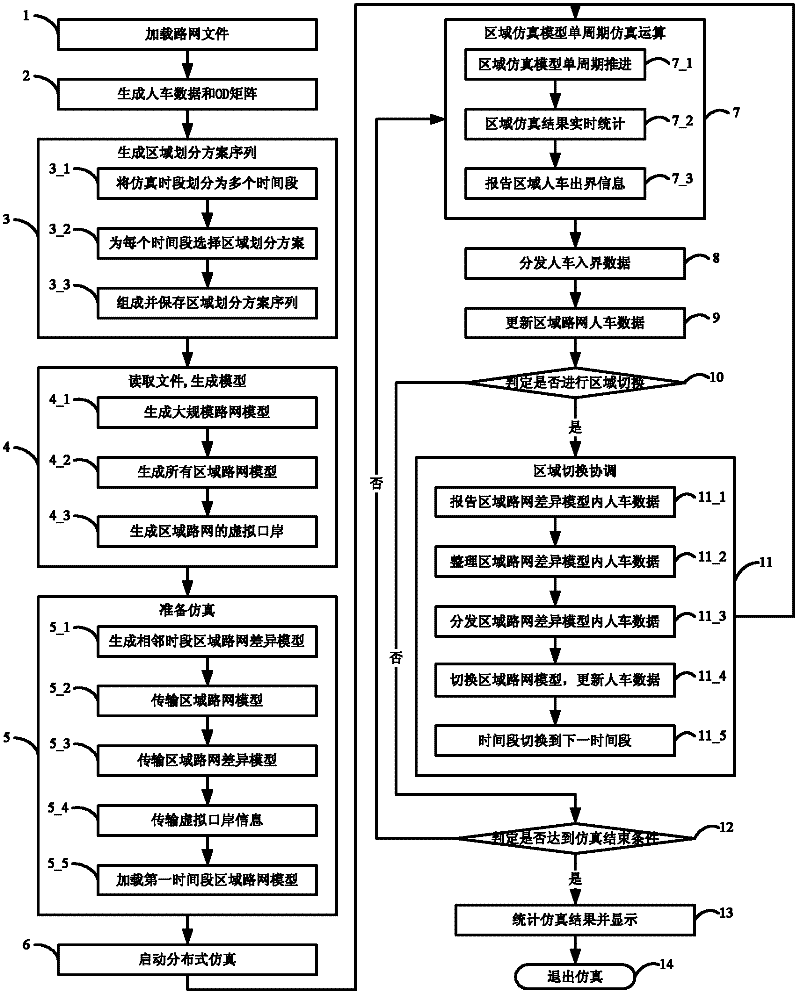

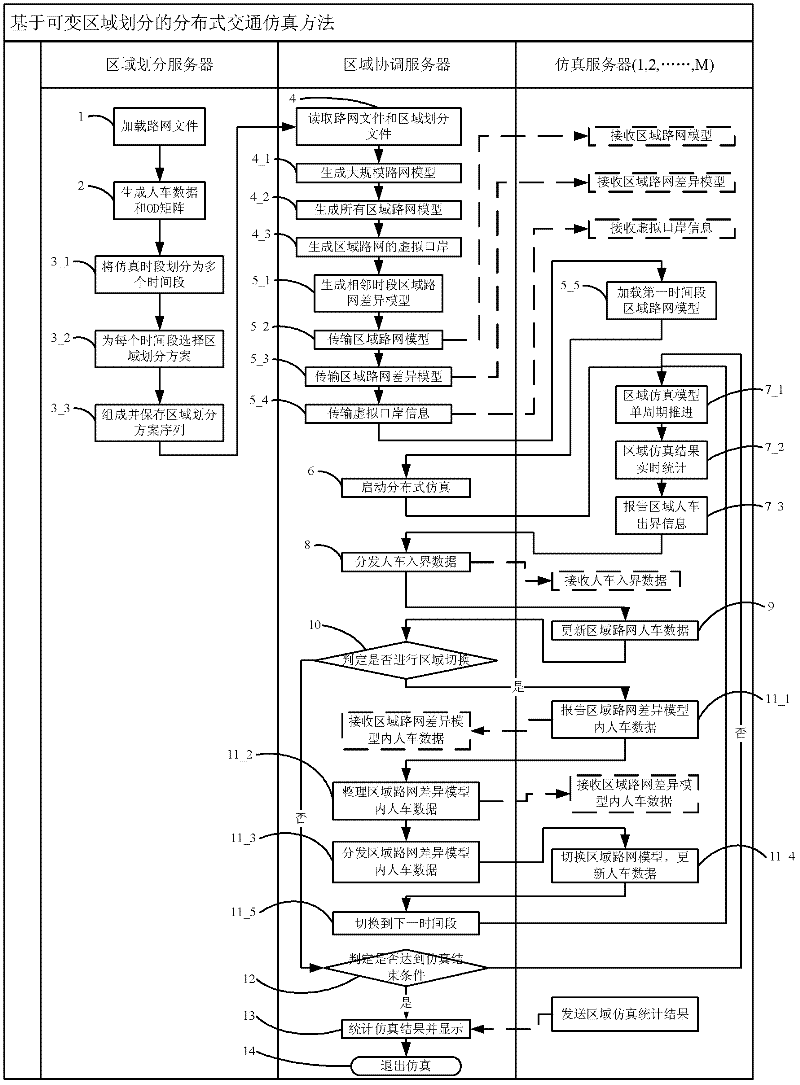

Distributed traffic simulation system and simulation method based on variable region division

ActiveCN102542106AAvoid load imbalance issuesSpeed Up Distributed Simulation RunsRoad vehicles traffic controlSpecial data processing applicationsLine segmentDistribution rule

The invention discloses a distributed traffic simulation system and a simulation method based on variable region division. According to the invention, a long time segment is divided into a plurality of continuous short time segments; change of distribution of people and vehicle on road network in the short time segments is much smaller than that in the total time segment; and in each short time segment, a region division scheme is adopted according to the distribution rule of people and vehicles, and the change of the number of people and vehicle in the time segments in the region is decreased, therefore, the purpose of balancing the load of each simulation server is achieved.

Owner:INST OF AUTOMATION CHINESE ACAD OF SCI

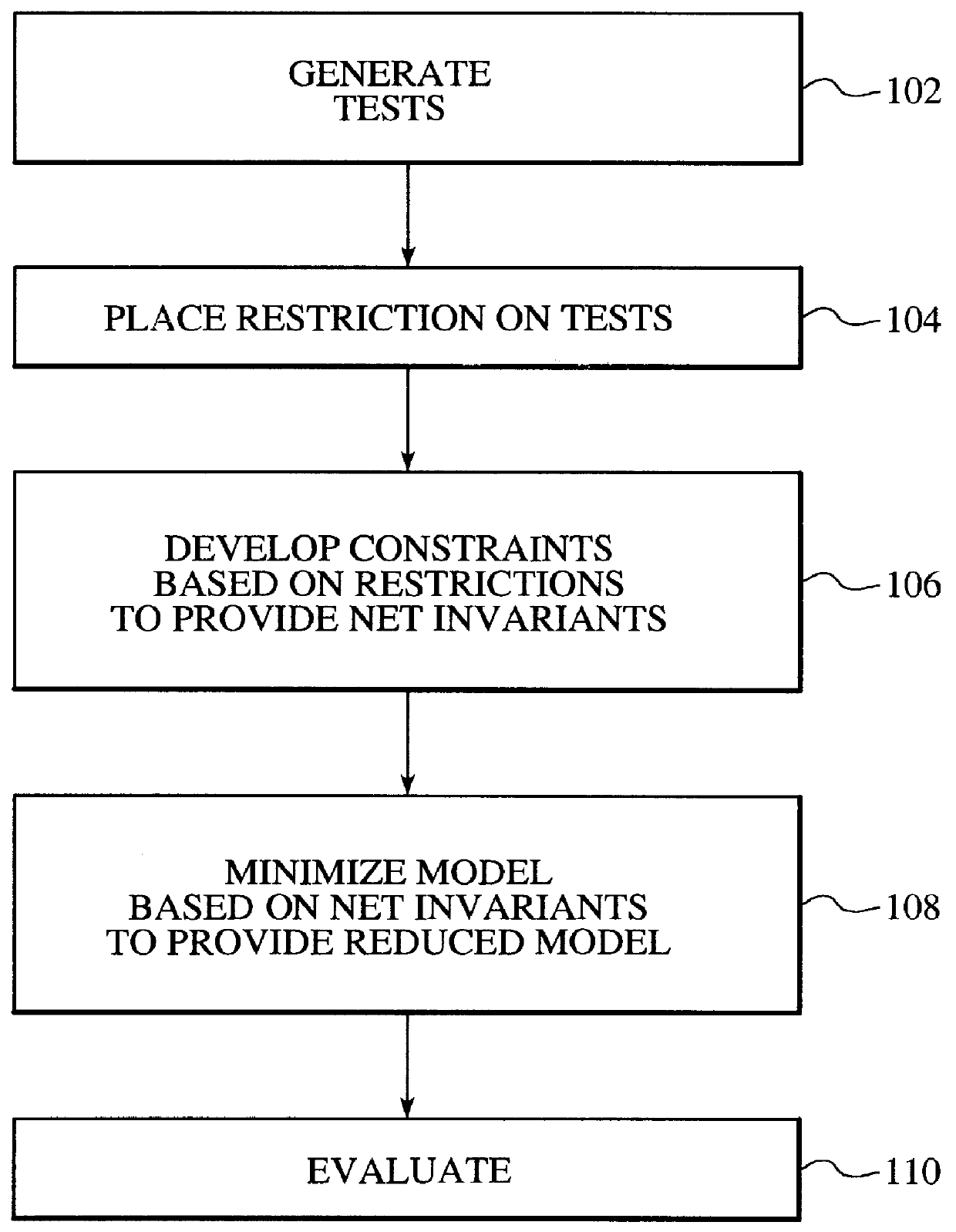

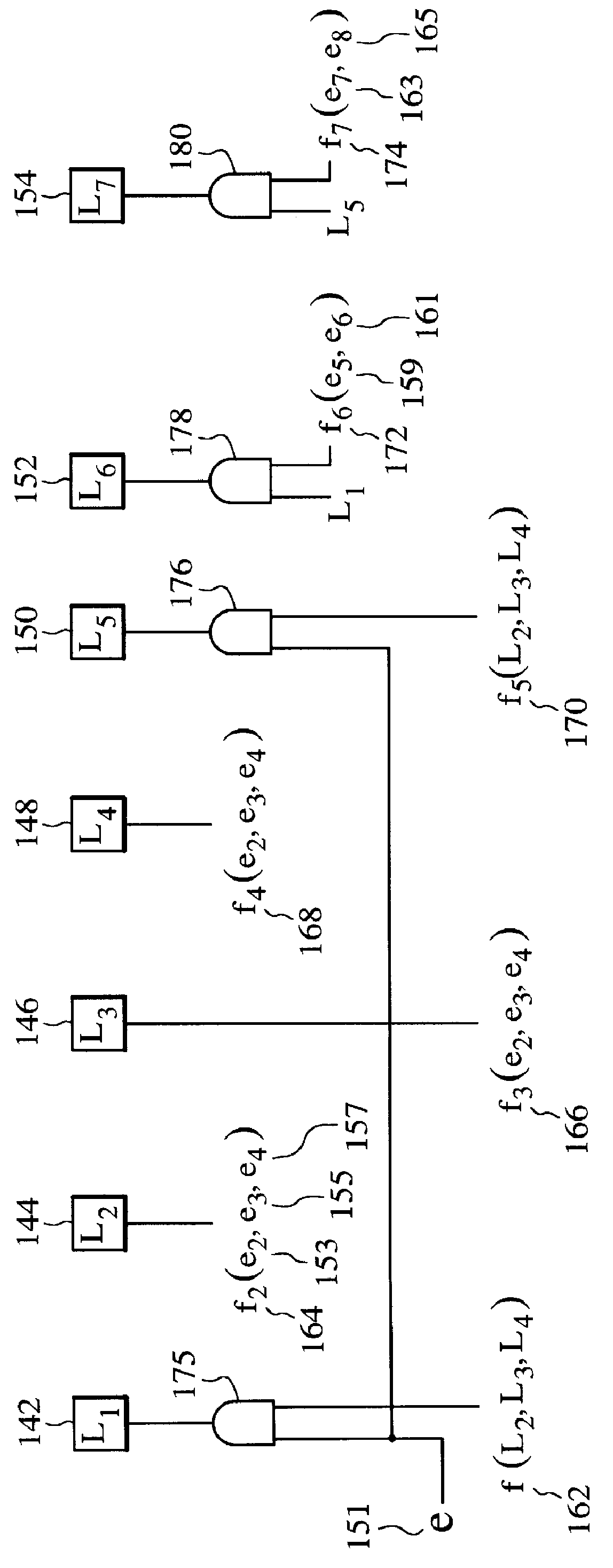

System and method for model size reduction of an integrated circuit utilizing net invariants

InactiveUS6049662AReduce the amount requiredImprove simulation speedDigital circuit testingAnalogue computers for electric apparatusReduced modelMinimization algorithm

The present invention provides a system and method for verifying an integrated circuit model. The model includes a plurality of net variables. The system and method comprises generating a plurality of tests for simulating the integrated circuit, precalculating a reduced model based upon the generated tests, and evaluating the reduced model. In a preferred embodiment, the present invention includes restricting the test that are generated. Then net invariants for the integrated circuit are generated by translating the restricted plurality of tests to a smaller set of possible values for the net variables. Thereafter, a minimization algorithm or procedure is utilized to minimize the logic used in the particular system based upon the latch constraints. This system produces a reduced model which reduces the amount of the integrated circuit that must be simulated thereby increasing the simulation speed thereof. Accordingly, the present invention integrates an event-driven simulation and a cycle simulation in such a manner that the saving can be proportional to the size of the reduction of the model. In many environments this reduction is significant because it allows for a significant reduction in space which has a clear bearing on the verification process.

Owner:IBM CORP

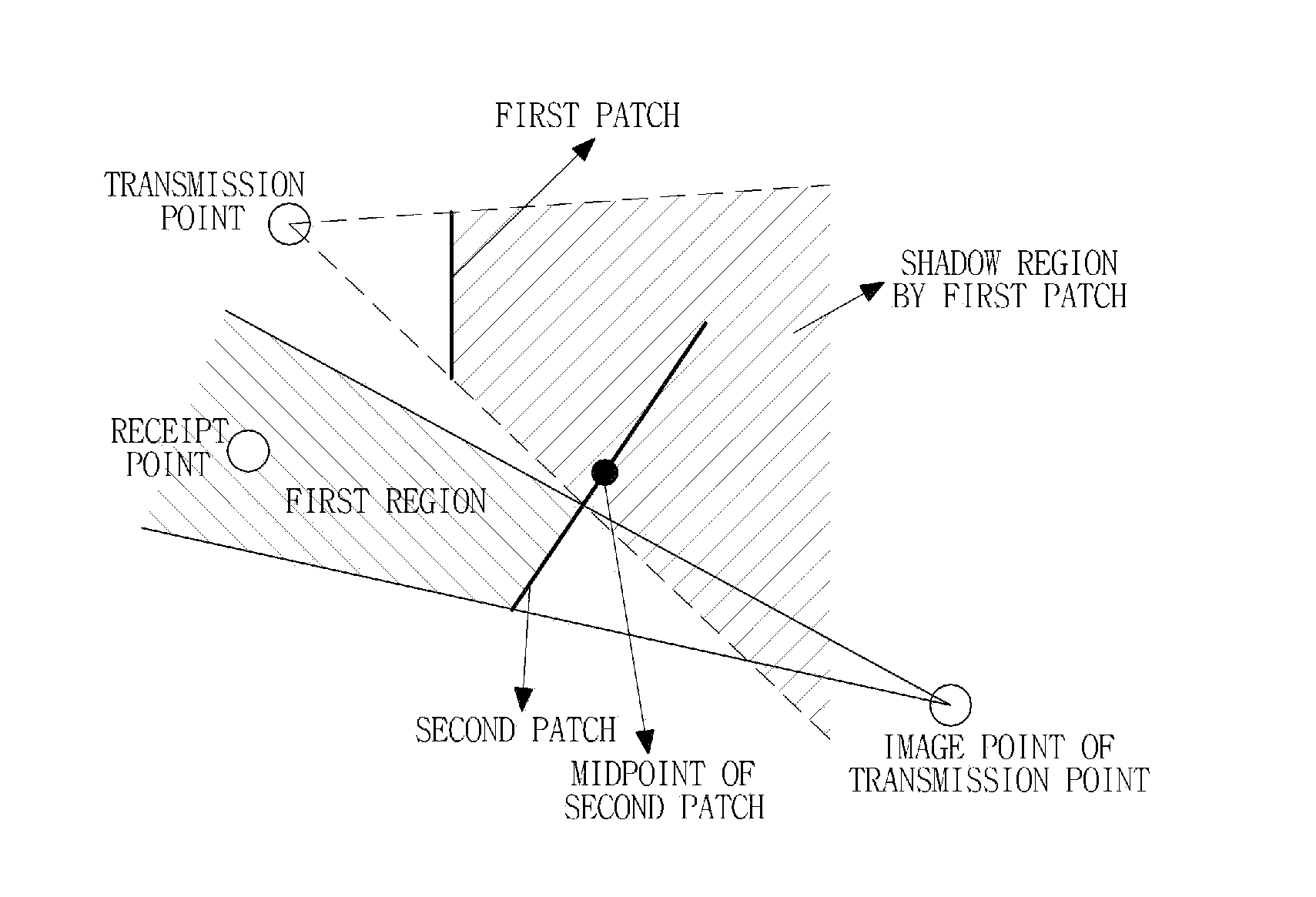

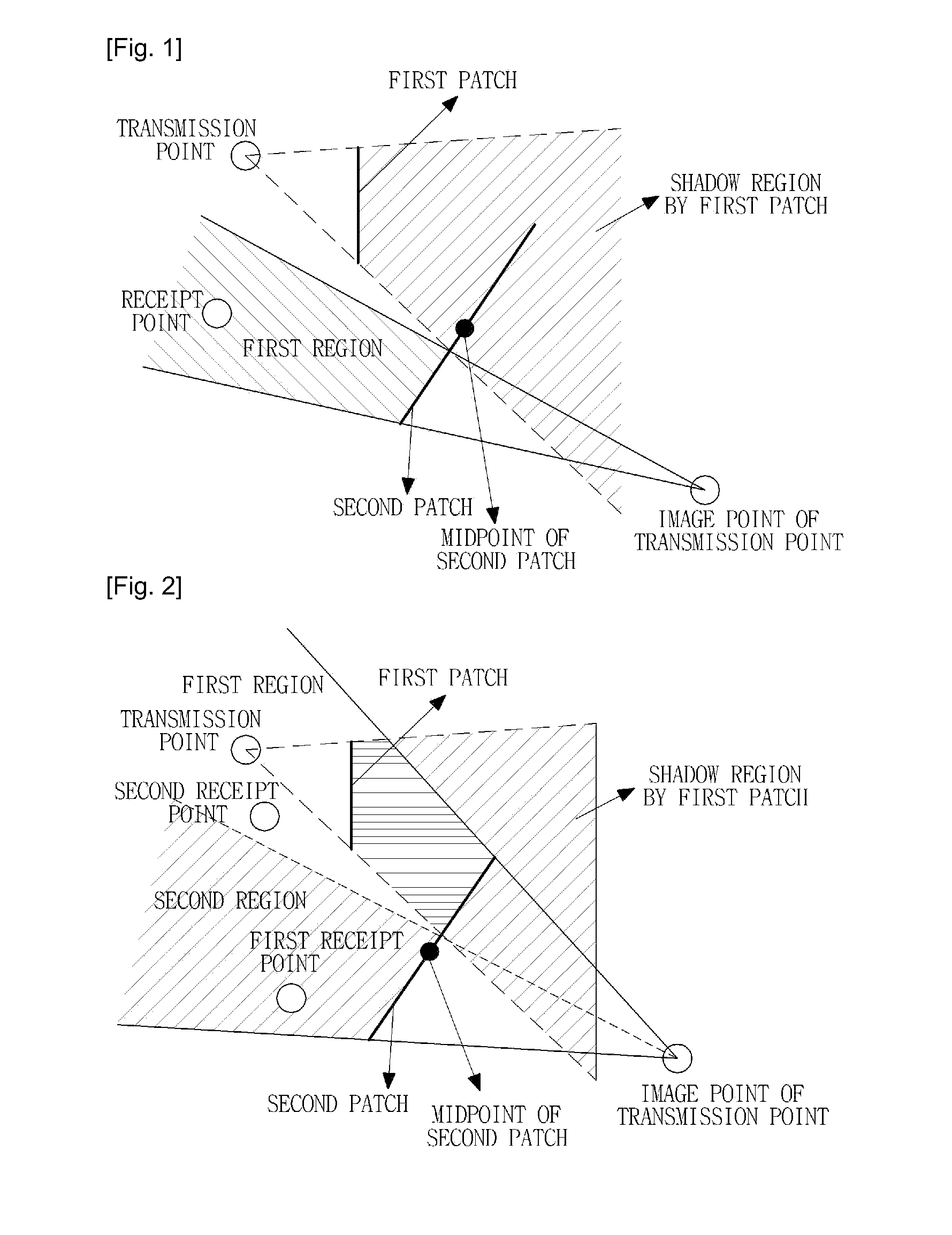

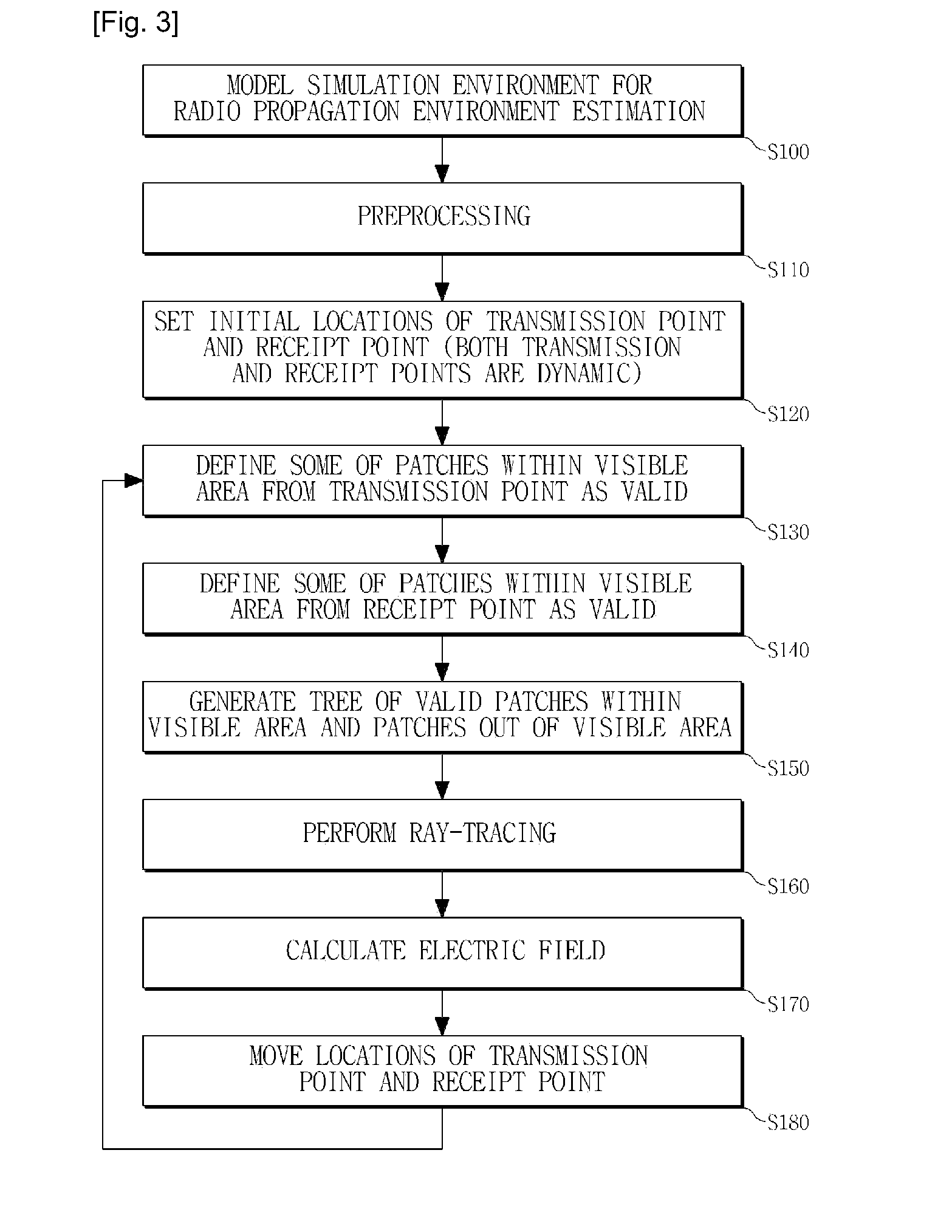

Method of three dimensional ray tracing in the dynamic radio wave propagation environment

InactiveUS20110153294A1Improve simulation speedImprove accuracyTransmission monitoringElectromagnetic transmissionRadio equipmentEngineering

Disclosed is a three dimensional ray tracing method in a dynamic radio wave propagation environment. The method of tracing three dimensional ray in a dynamic radio wave propagation environment, by which cross tests are performed on a plurality of radio wave blocking obstacle surfaces according to a ray tube tracing scheme based on an image method in a simulation area, in which the plurality of radio wave blocking obstacle surfaces are modeled, to detect a radio path between a first point and a second point, the method comprising: defining at least a part of the radio wave blocking obstacle surfaces as valid radio wave blocking obstacle surfaces, the radio wave blocking obstacle surfaces being within a visible region from the first point of which location varies dynamically; and tracing a ray between the first point and the second point by taking into consideration only the defined valid radio wave blocking obstacle surfaces to be simulated. Accordingly, even when both locations of a transmission point and a receipt point vary, a three dimensional ray tracing for radio wave propagation prediction is possible and simulation efficiency can be maintained.

Owner:ELECTRONICS & TELECOMM RES INST

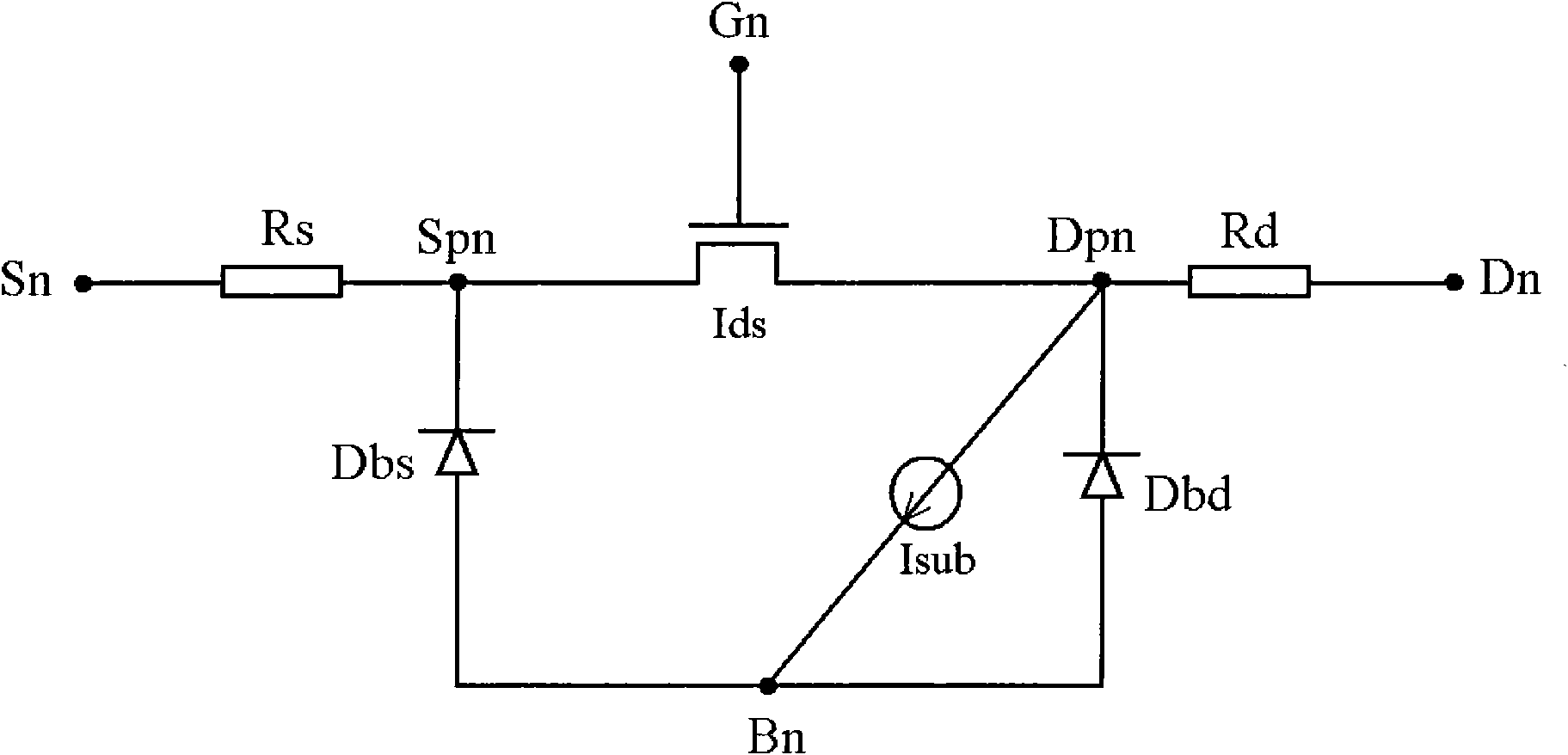

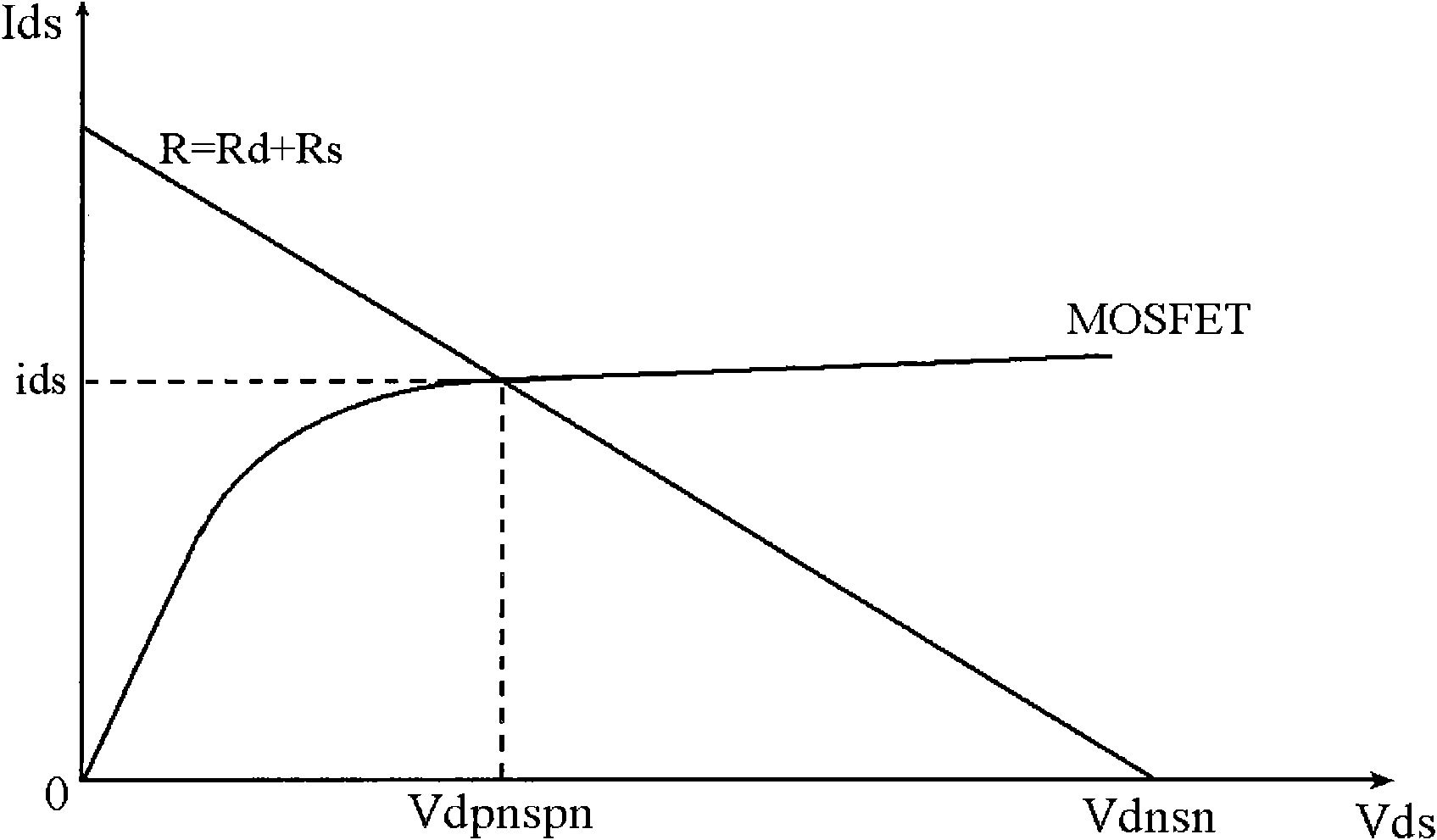

Method for eliminating internal nodes of metal-oxide-semiconductor field effect transistor (MOSFET) used in rapid circuit simulation

InactiveCN101901288AGuaranteed accuracyImprove simulation speedSpecial data processing applicationsMOSFETElectrical resistance and conductance

The invention provides a method for eliminating internal nodes of a metal-oxide-semiconductor field effect transistor (MOSFET) used in rapid circuit simulation. The method comprises the following steps of: making a 4-node MOSFET model which does not comprise any internal node equivalent to a 6-node MOSFET model which comprises internal nodes in a circuit simulation process; solving the voltages of two internal nodes of the MOSFET by an analytic method; calculating the change of an internal node voltage along with an external node voltage; and finally obtaining a transient conductance relation among external nodes of all apparatuses used in matrix calculation. The method has the advantages of ensuring circuit simulation accuracy by considering the effect of MOSFET parasitic resistance on an electrical property, eliminating the internal nodes of the MOSFET, reducing a circuit solving matrix, reducing matrix solving time and increasing circuit simulation speed.

Owner:北京华大九天科技股份有限公司

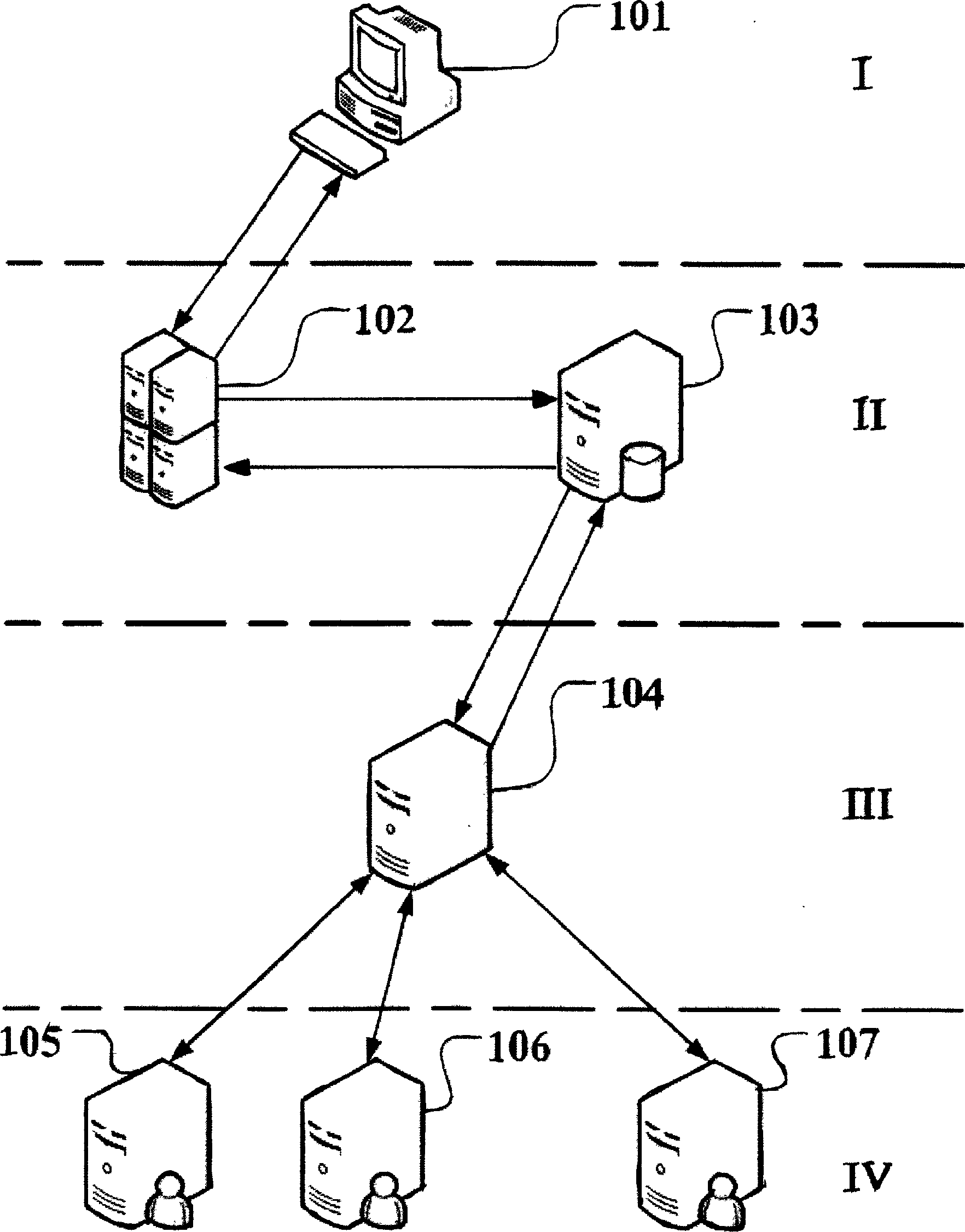

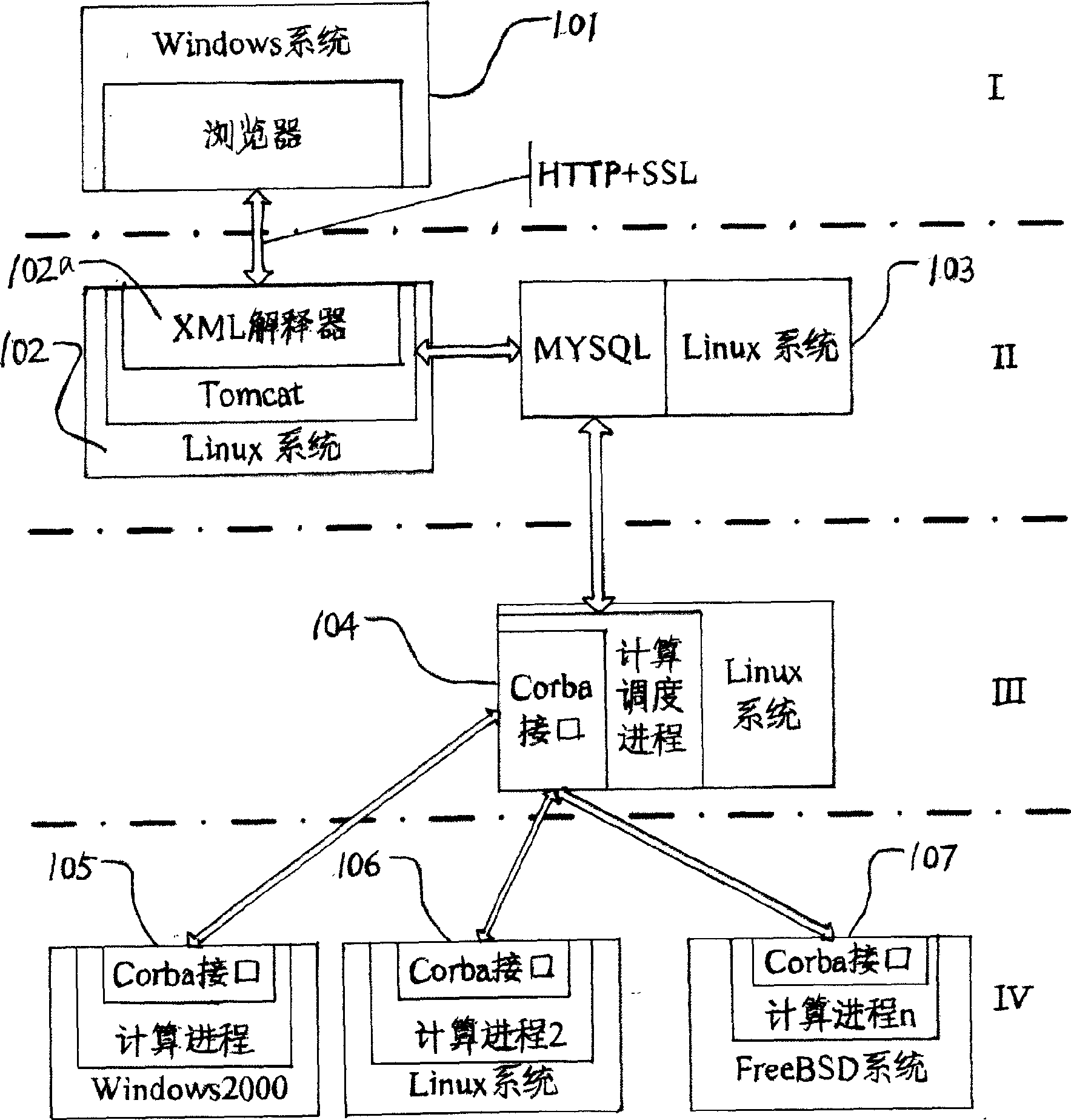

Structure of network simulation service

ActiveCN1783056ANovel network design service modelSolve interface problemsSoftware simulation/interpretation/emulationSpecial data processing applicationsApplication serverCoupling

The network simulation service structure includes: the first layer of client layer including client terminals; the second layer of expert knowledge layer including application server and database server and for customizing design process for professional product design with fused expertí»s design experiences and realizing coupling of background simulation tools; the third layer of calculation dispatching layer including dispatching server; and the fourth layer of calculation layer includes N computing servers for completing the computing task of the computing queue. The present invention provides one novel kinds of simulation system structure to provide the users with novel network design service.

Owner:杭州麦科斯韦网络科技有限公司

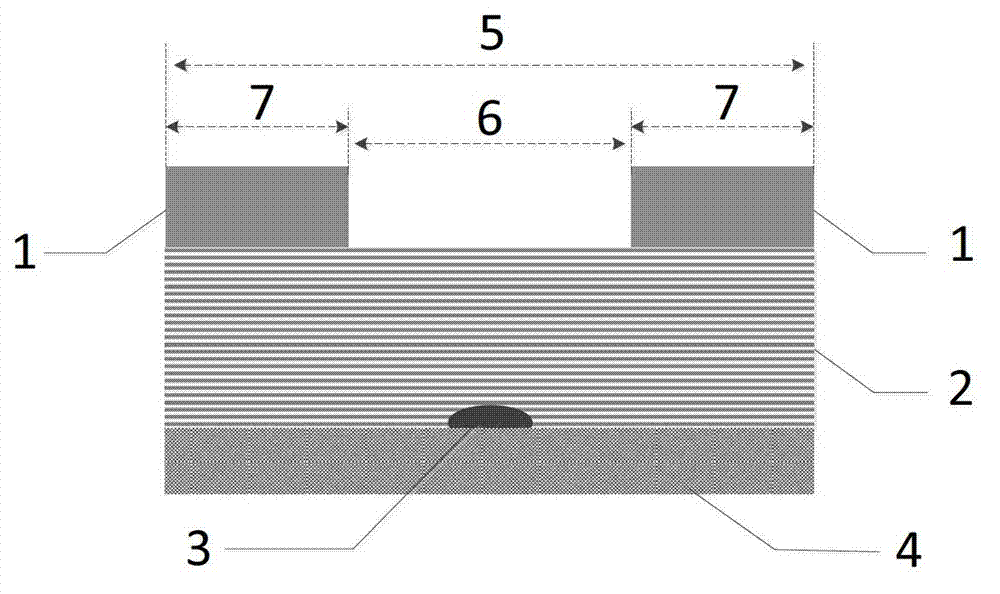

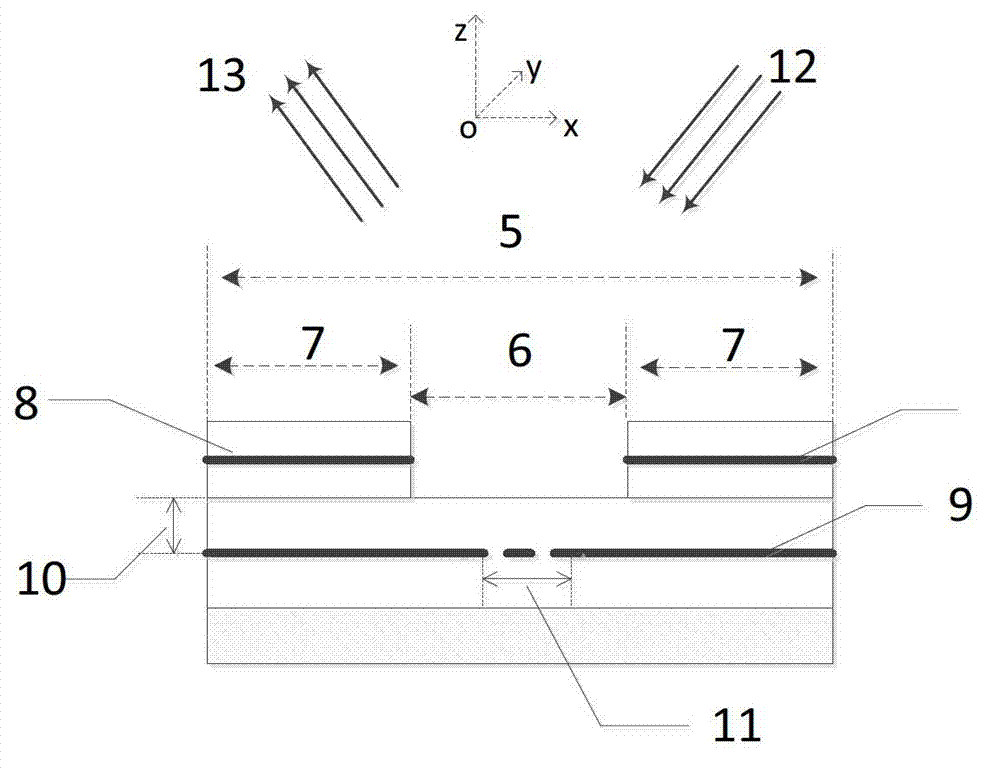

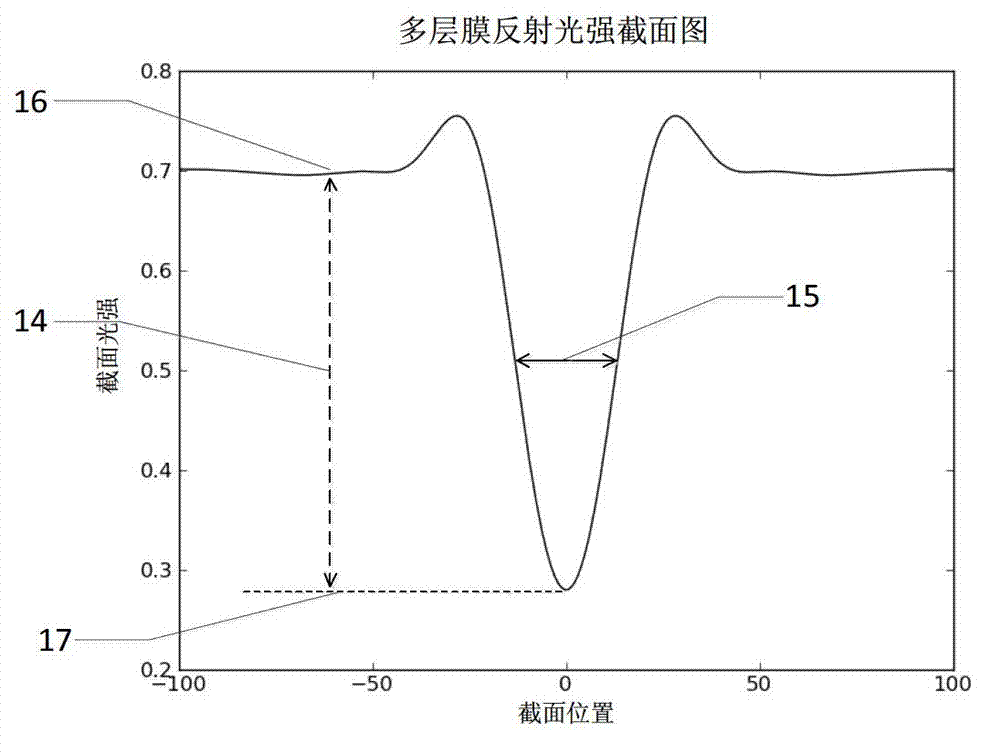

Fast simulation method for extreme ultraviolet photoetching thick mask defects

ActiveCN103197503AImprove simulation speedRapid Implementation of Simulation StudiesPhotomechanical exposure apparatusMicrolithography exposure apparatusMultilayer membranePlane mirror

The invention discloses a fast simulation method for extreme ultraviolet photoetching thick mask defects. The method is implemented through that a defect multilayer membrane is equivalent to a defect-free plane mirror and a defect panel mirror; firstly, the diffraction spectrum of a mask absorption layer is obtained through thin-mask approximation, and the mask absorption layer subjected to phase compensation is reflected through the defect multilayer membrane; then, an operation of phase compensation is performed again; and finally, through thin-mask approximation and phase compensation, the mask diffraction spectrum of extreme ultraviolet photoetching defects is obtained. According to the invention, the influence of defects on mask imaging can be effectively simulated, and the simulation speed of extreme ultraviolet photoetching thick mask defects can be improved.

Owner:SHANGHAI INST OF OPTICS & FINE MECHANICS CHINESE ACAD OF SCI

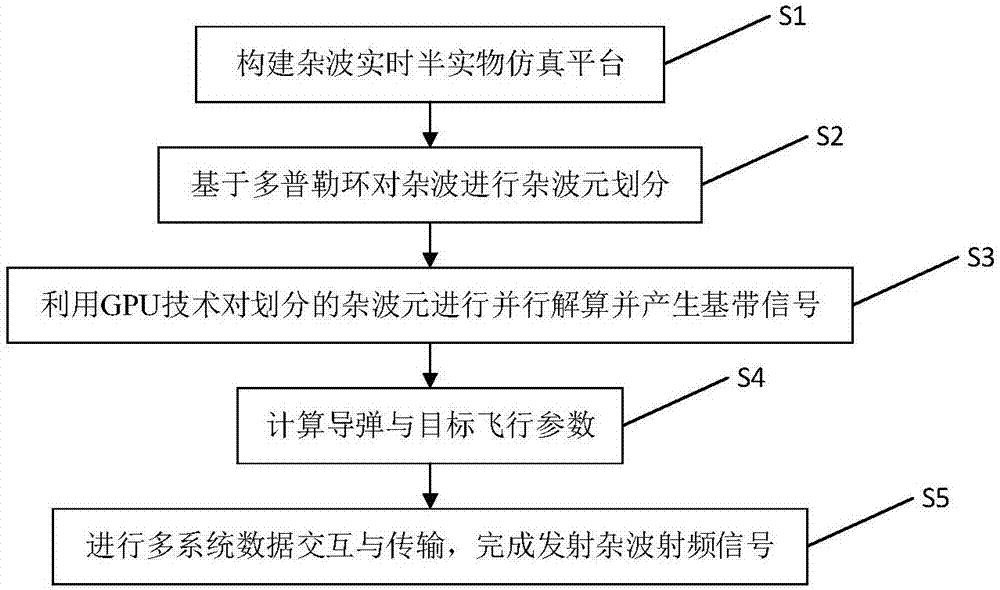

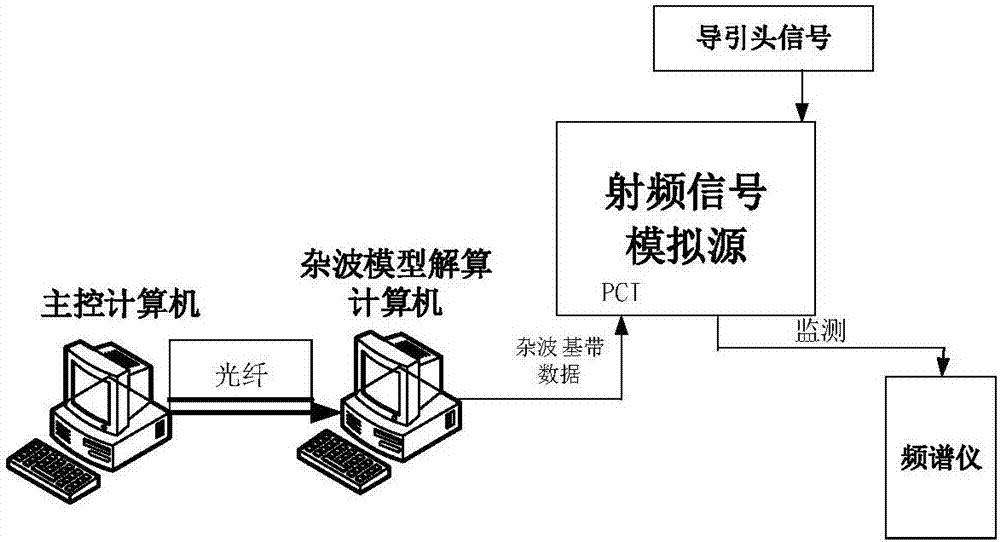

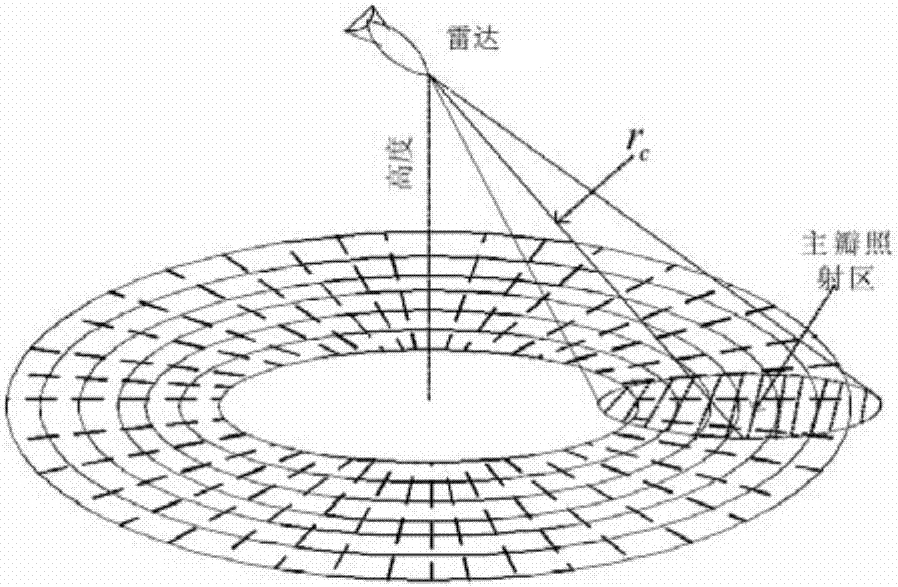

GPU-based RF semi-physical clutter simulation method

InactiveCN107229038ASimulation guaranteeImprove simulation speedWave based measurement systemsSustainable transportationOperational systemSimulation

The invention discloses a GPU-based RF semi-physical clutter simulation method, which comprises the steps of: constructing a clutter real-time semi-physical simulation platform; subjecting clutter to clutter element division based on a Doppler ring; performing parallel calculation on the divided clutter elements and generating a baseband signal by utilizing a GPU technology; calculating missile and target flight parameters; and conducting multi-system data interchange and transmission, and completing the transmission of a clutter RF signal. The GPU-based RF semi-physical clutter simulation method realizes model parallel calculation on ground division of iso-Doppler rings and equidistance rings in a clutter model through establishing the clutter real-time semi-physical simulation platform and utilizing thread blocks and thread programming in the CUDA, realizes parallel acceleration of the clutter model by utilizing the GPU technology, realizes the data interchange and transmission between the GPU and an RTX real-time operating system, accelerates the simulation speed, and ensures the realistic performance of a homing head electromagnetic environment.

Owner:BEIJING SIMULATION CENT