Patents

Literature

135results about How to "Fast evaluation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Performance Evaluation System

InactiveUS20120124559A1Fast executionFast evaluationMultiple digital computer combinationsElectrical appliancesClient-sideSelf adaptive

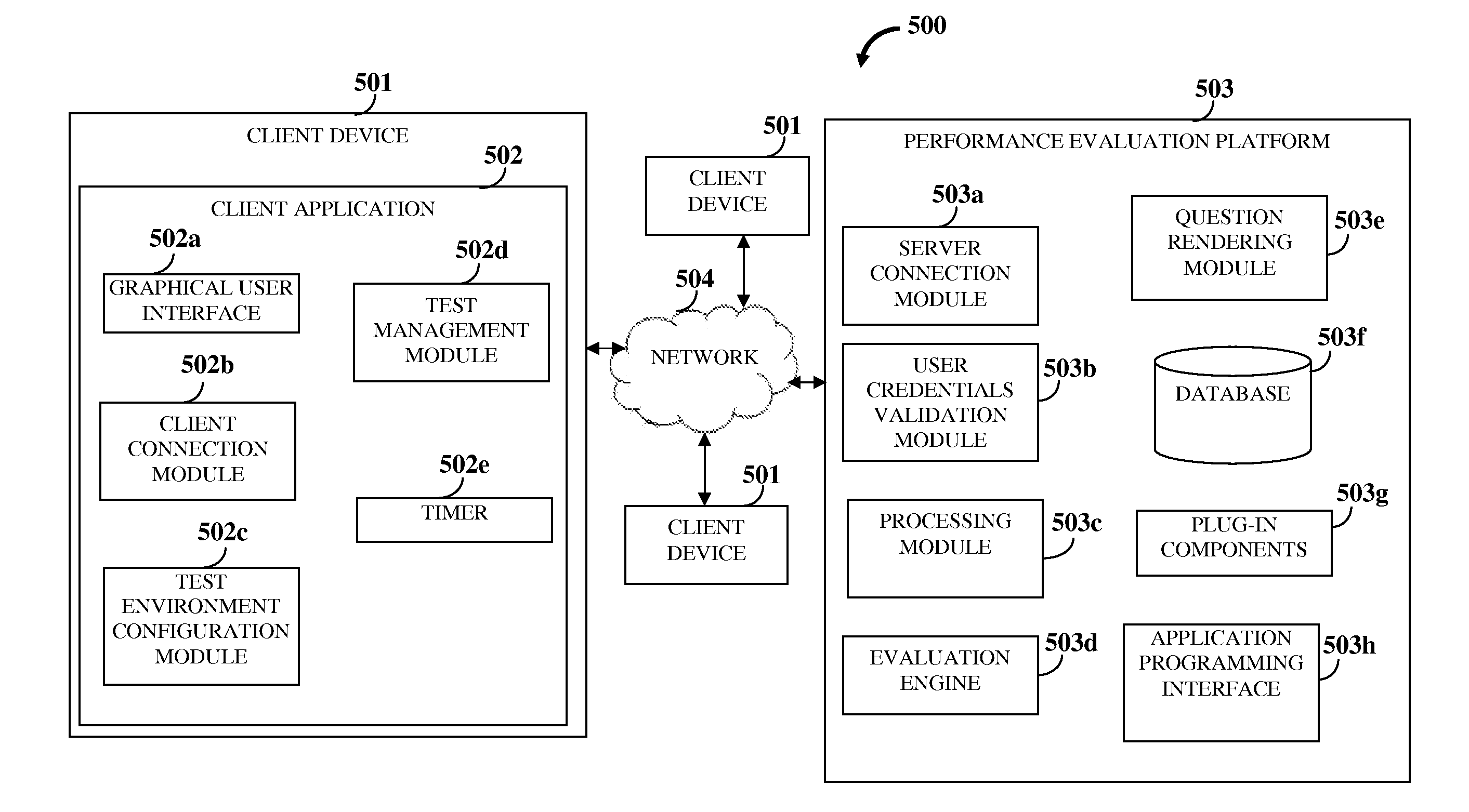

A computer implemented method and system for concurrently evaluating performance of multiple users in one or more tests provides a performance evaluation platform that is accessible to a client application on each of multiple client devices via a network. The client application manages interaction of the users with the performance evaluation platform via the network. The client application, in communication with the performance evaluation platform, configures an adaptive test environment at each of the client devices of the users based on one or more tests selected by the users. The client application on each of the client devices loads the selected tests from the performance evaluation platform and transmits solution responses to the selected tests acquired from the users to the performance evaluation platform. The performance evaluation platform configures processing elements for concurrently processing the solution responses and concurrently evaluates the performance of the users in the selected tests.

Owner:KONDUR SHANKAR NARAYANA

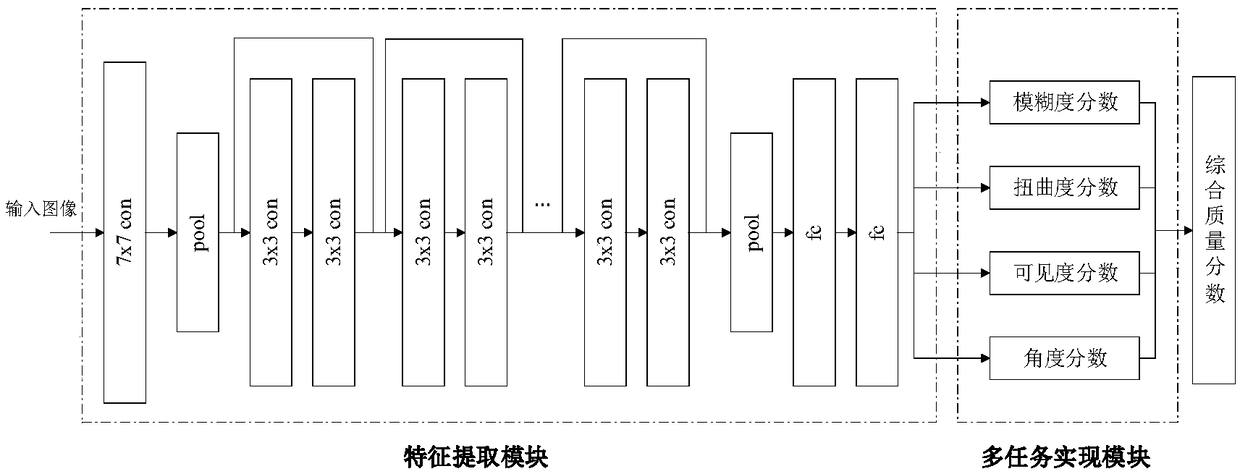

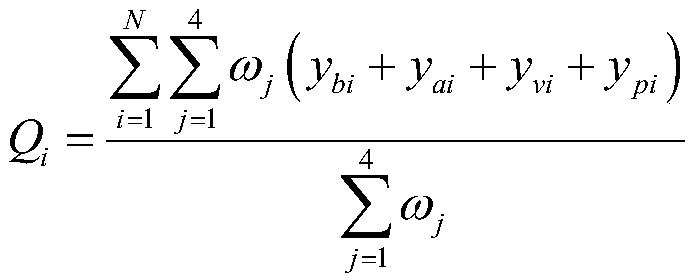

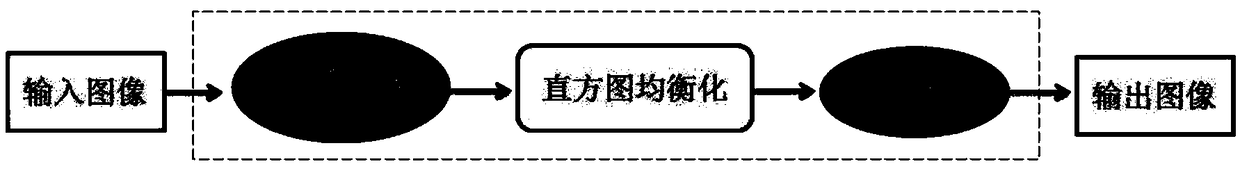

Face image quality evaluation method based on multidirectional evaluation standard and system thereof

InactiveCN108960087AImprove performanceFast evaluationCharacter and pattern recognitionNeural architecturesImaging qualityQuality assessment

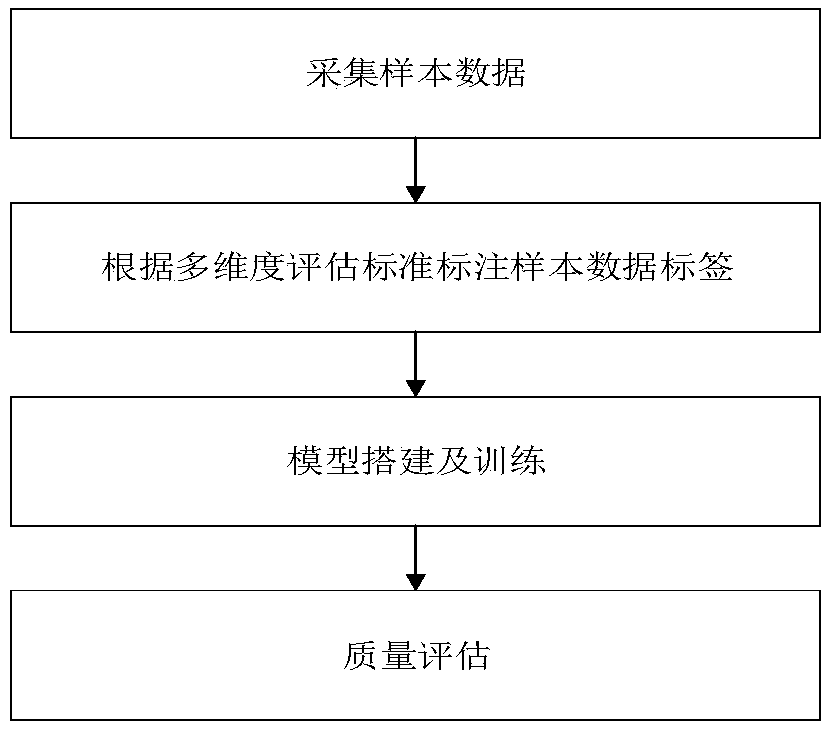

The invention provides a face image quality evaluation method based on a multidirectional evaluation standard and a system thereof. The method comprises the steps of acquiring a face image as trainingdata; classifying the training data according to degrading characteristics with different dimensions; performing preliminary evaluation and marking on each kind of images in the classified training data; establishing a branch task which corresponds with each kind of dimension characteristics according to the classification result of the degrading characteristics with different dimensions; establishing a quality evaluation model, performing training, performing multi-branch task predicating on an input to-be-evaluated face image according to the quality evaluation model after training, therebyfinishing face image quality evaluation. According to the method and the system, the image characteristics are extracted by means of a deep neural network, and furthermore comprehensive quality evaluation to multiple image quality affecting factors is finished. An obtained image comprehensive quality score is relatively same with the subjective evaluation of human eyes, and furthermore a relatively high evaluation speed is realized. After the low-quality image is filtered, face identification performance can be effectively improved.

Owner:CHONGQING INST OF GREEN & INTELLIGENT TECH CHINESE ACADEMY OF SCI

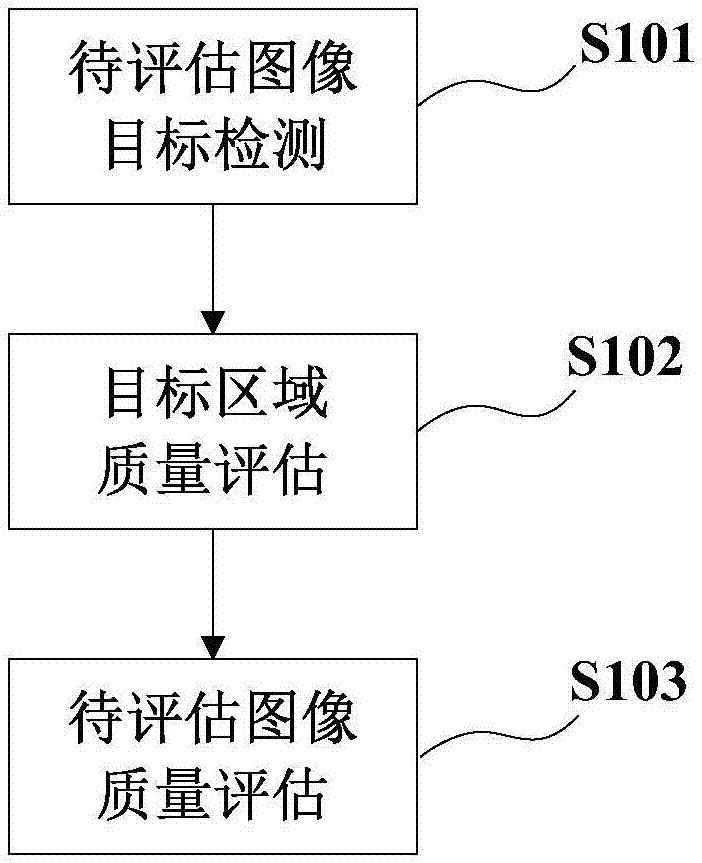

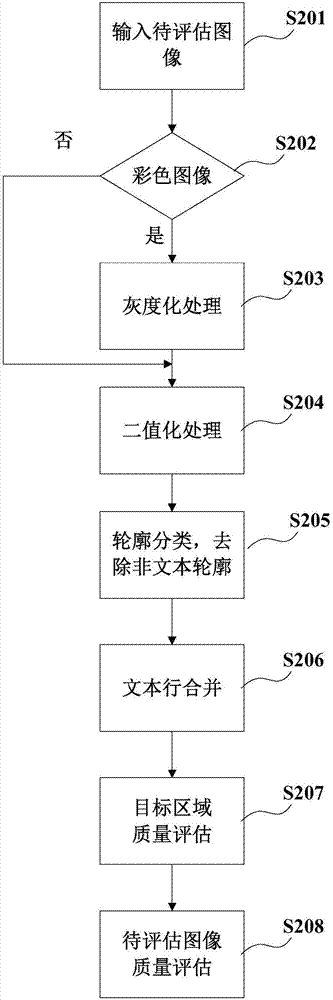

Image quality evaluation method and device

InactiveCN107481238AEvaluation is objective and effectiveFast evaluationImage enhancementImage analysisEvaluation resultImaging quality

The invention provides an image quality evaluation method and device. The method comprises the steps: carrying out the target detection of a to-be-estimated image, so as to determine at least one target region; carrying out the quality evaluation of at least one target region, so as to determine the quality evaluation result of each of the target regions; and carrying out the quality evaluation of the to-be-estimated image based on the determined quality evaluation result of each of the target regions. The method provided by the invention enables an image quality evaluation process to focus on an AOI, and neglects the image quality of an inessential region, thereby achieving the quality evaluation of the to-be-estimated image. The method is high in evaluation speed, is higher in evaluation precision, and achieves the objective and effective evaluation of the quality of the to-be-estimated image.

Owner:ZHONGAN INFORMATION TECH SERVICES CO LTD

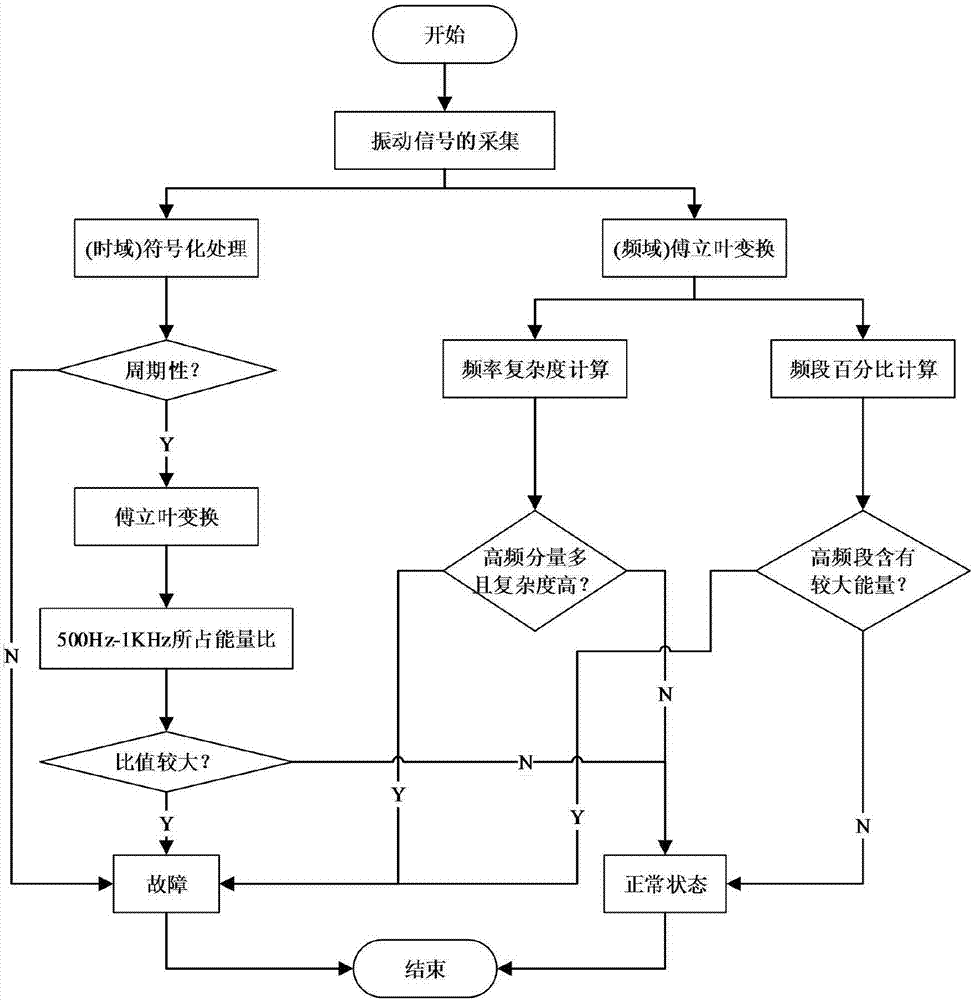

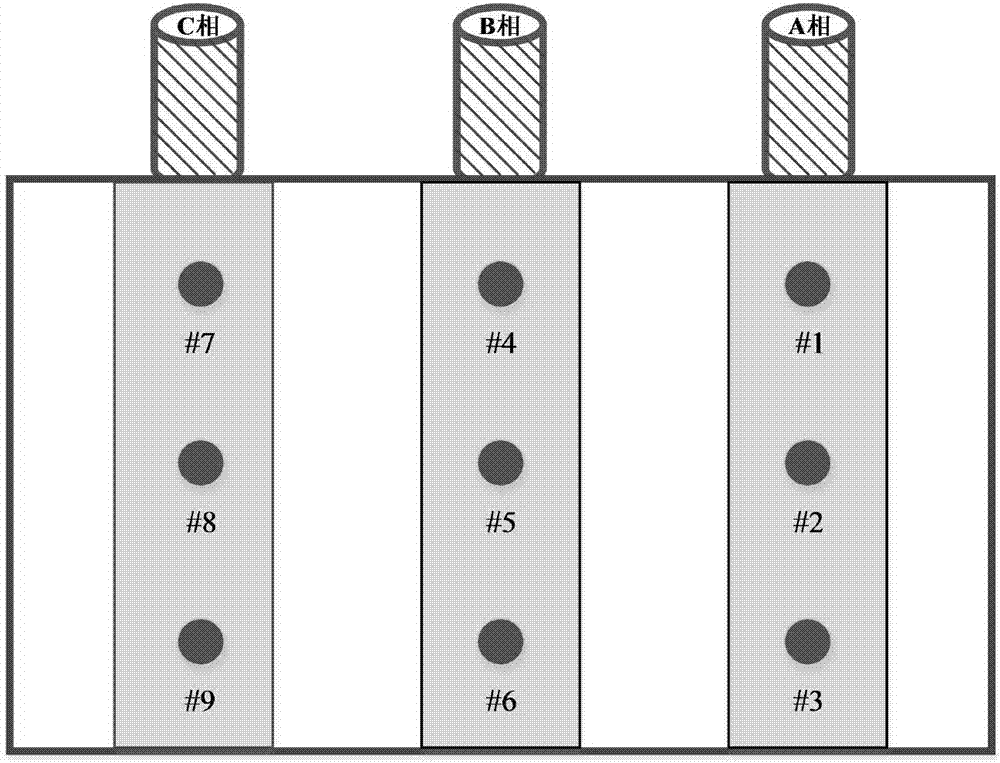

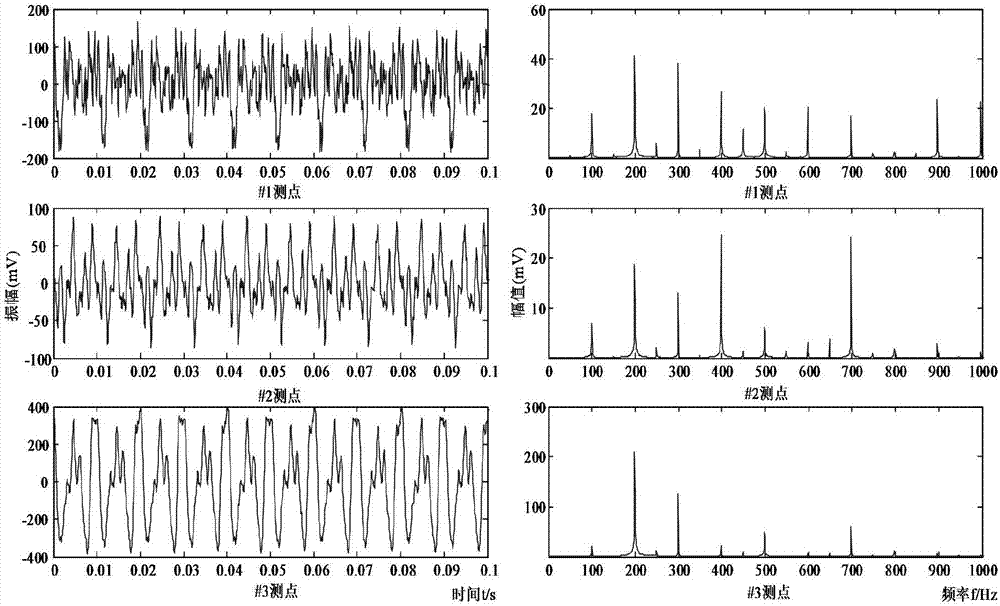

Method for evaluating health state of transformer based on vibration signal characteristics of multiple measuring points

InactiveCN107101714AEffectively assess health statusThe method is simple and feasibleSubsonic/sonic/ultrasonic wave measurementTime domainFrequency spectrum

The invention provides a method for evaluating the health state of a transformer based on vibration signal characteristics of multiple measuring points. The method evaluates the health state of the transformer by selecting vibration signal frequency complexity, vibration signal frequency spectrum energy percentage, and vibration signal certainty as characteristic quantity, and comprises steps of: firstly, analyzing the certainty of the vibration time-domain signal of each measuring point, determining whether the vibration signal is periodical, and preliminary evaluating the health state of each measuring point of the transformer; then analyzing the frequency-domain signal characteristic of each measuring point, selecting the frequency complexity and the vibration signal frequency spectrum energy percentage as characteristic indexes, wherein the greater the frequency complexity is, the more complex the vibration signal frequency components are, and the greater the high-band frequency spectrum energy percentage is, the more the radio-frequency components are; and finally, evaluating the health state of the transformer according to the time-domain and frequency-domain characteristics of the vibration signal.

Owner:NORTH CHINA ELECTRIC POWER UNIV (BAODING)

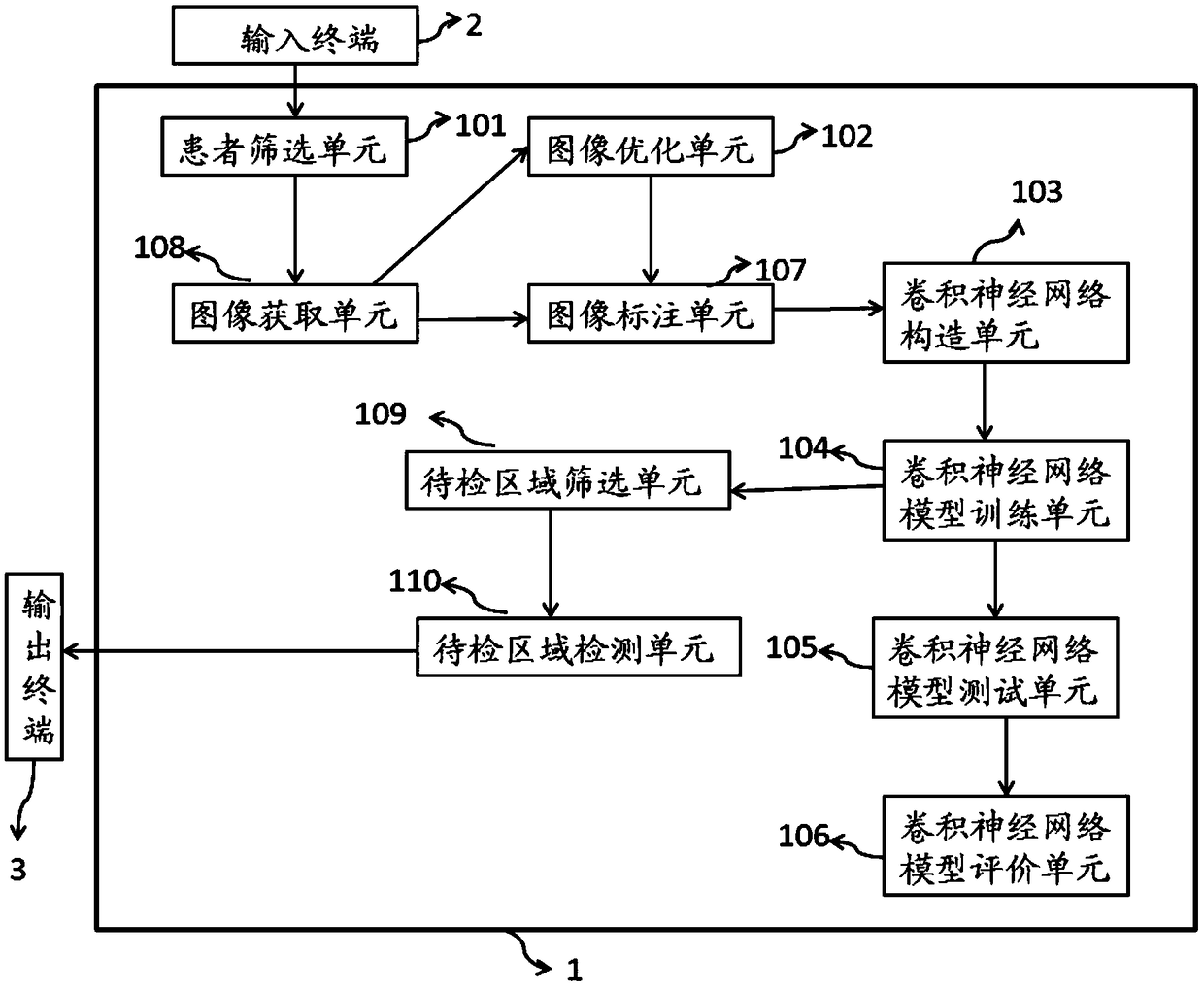

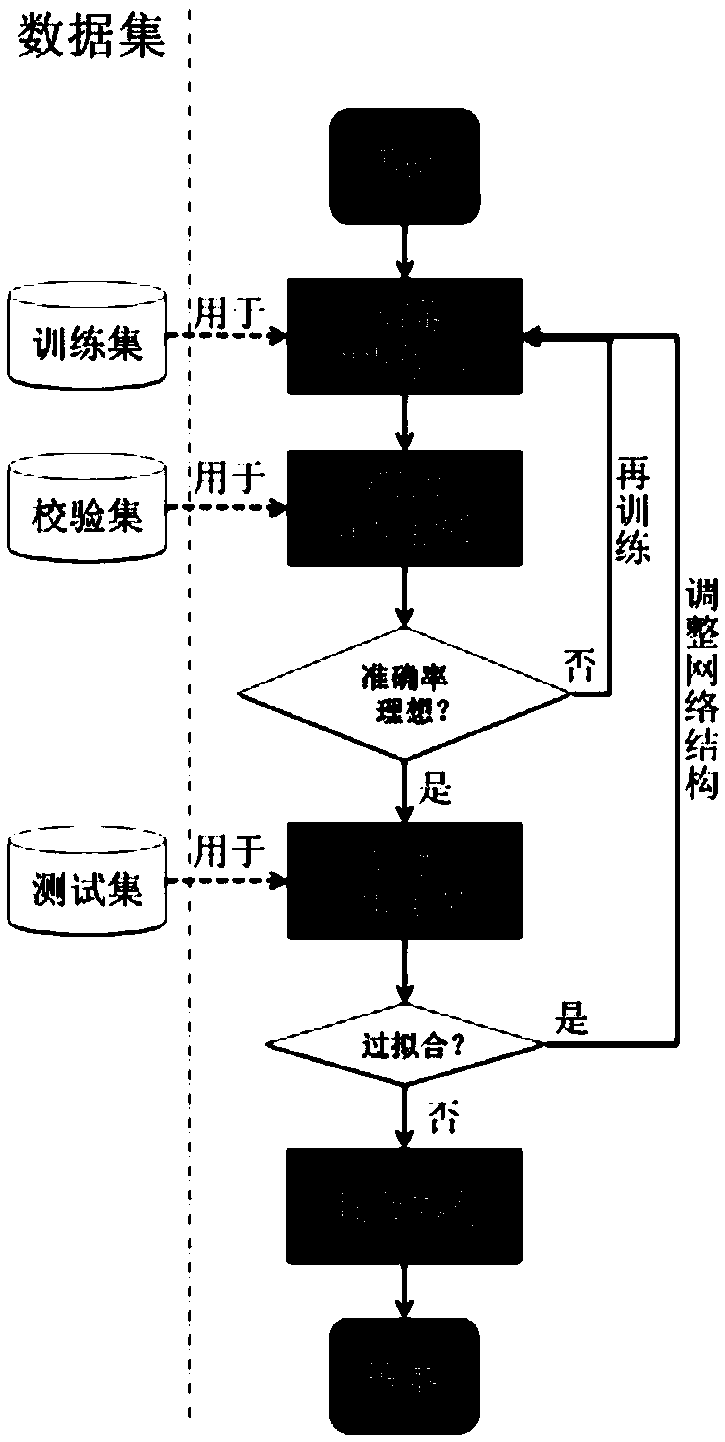

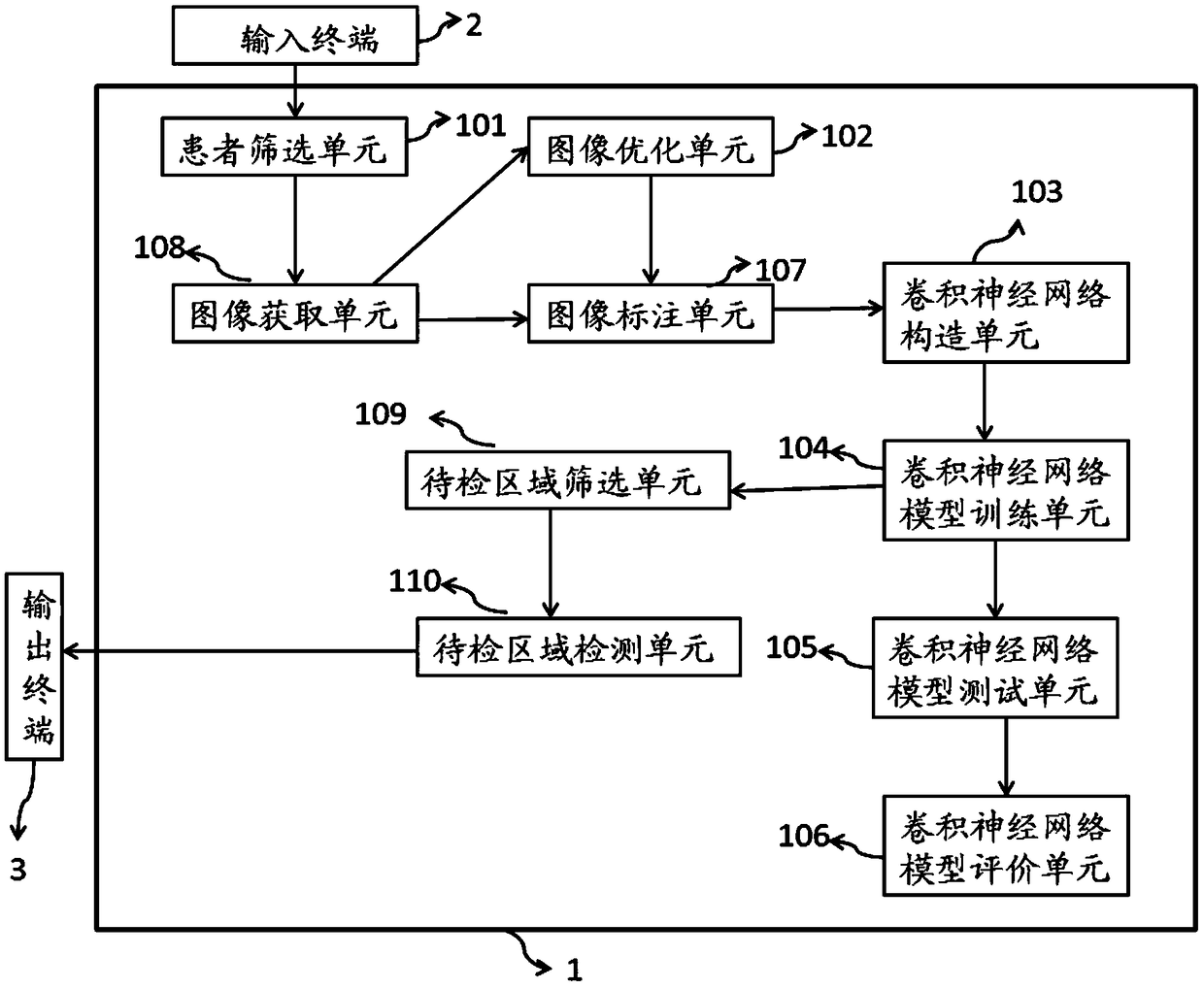

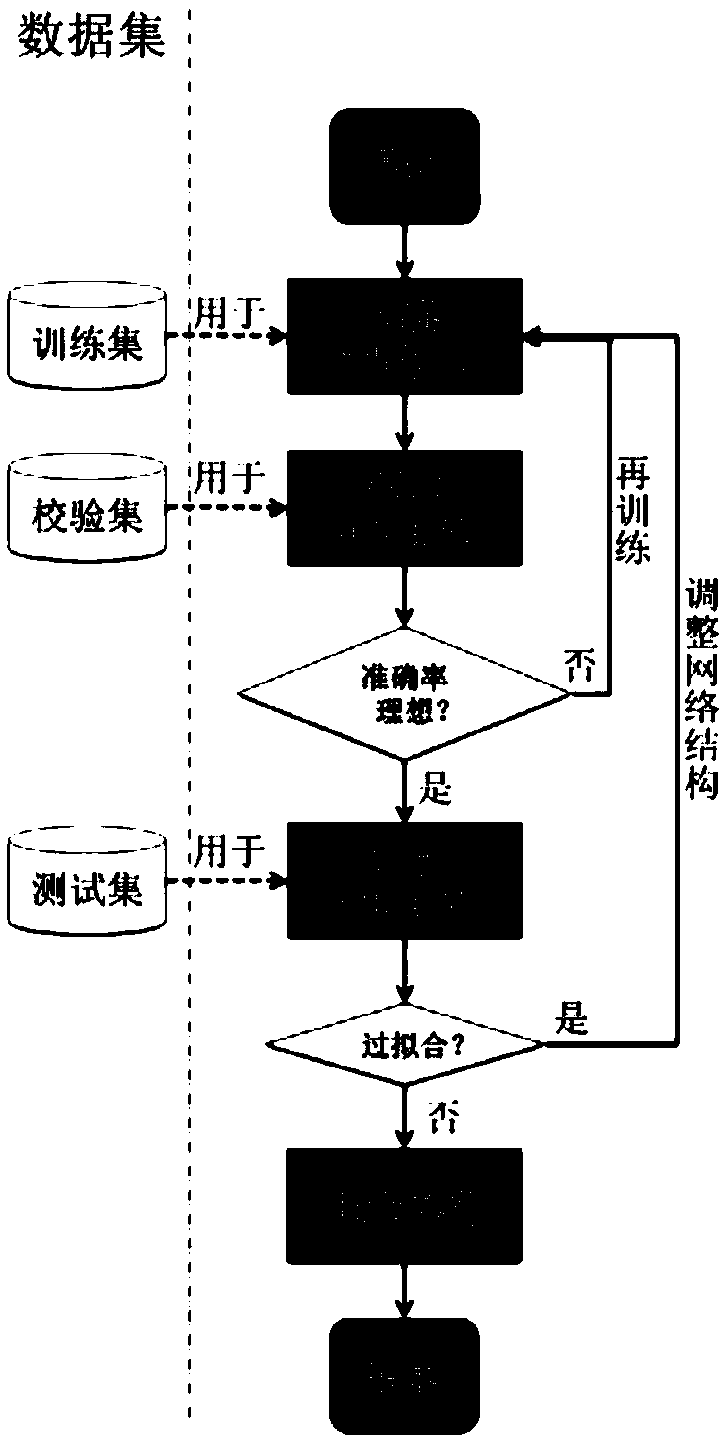

Evaluation system and method for efficacy of synchro-neoadjuvant chemoradiotherapy before rectal cancer surgery

InactiveCN108694718AReduce the need for consultationsFast evaluationImage enhancementImage analysisNewly diagnosedSynchro

The invention relates to an evaluation system and method for the efficacy of synchro-neoadjuvant chemoradiotherapy before the rectal cancer surgery. The evaluation system comprises an image acquisition unit used for acquiring pathological biopsy slice scan images and neoadjuvant chemoradiotherapy treatment pre-MRI images of newly diagnosed locally advanced rectal cancer patients, and classifying the rectal cancer patients into a training set, a check set and a test set, to serve as input image data, an image labeling unit used for respectively labeling the pathological biopsy slice scan imagesand the MRI images of the training set, the check set and the test set, a convolutional neural network constructing unit used for constructing a first convolutional neural network model, and a convolutional neural network model training unit used for obtaining a second convolutional neural network model for evaluating the efficacy of synchro-neoadjuvant chemoradiotherapy before the rectal cancersurgery. The evaluation system for the efficacy of synchro-neoadjuvant chemoradiotherapy before the rectal cancer surgery has multiple advantages such as being high in accuracy, short in time consumption, long in working duration, objective and three-dimensional.

Owner:THE SIXTH AFFILIATED HOSPITAL OF SUN YAT SEN UNIV

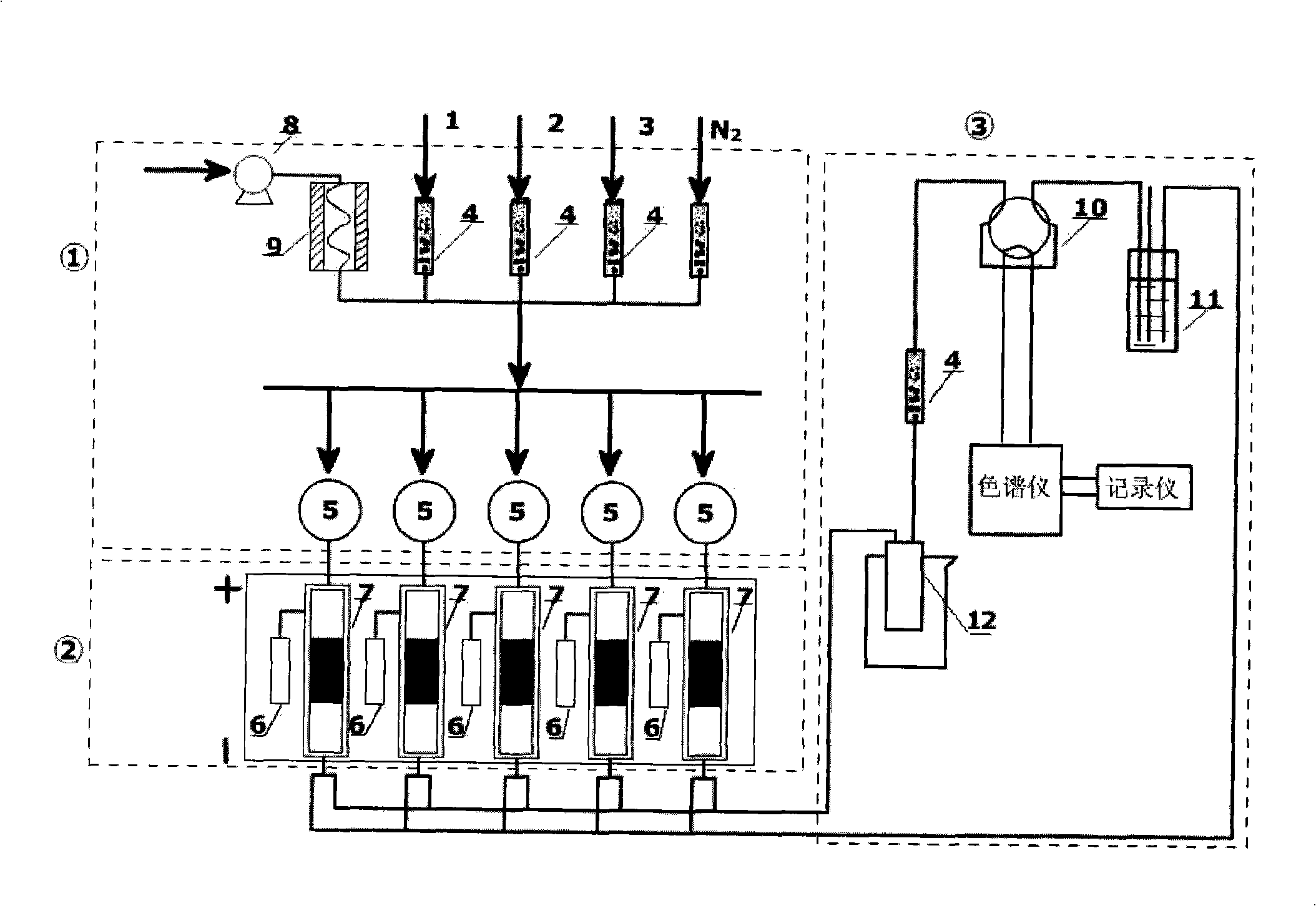

Reaction system for quickly evaluating Claus unit tail gas hydrodesulphurization catalyst

The present invention provides a Claus unit tail gas hydrodesulphurization catalyst fast evaluation reaction system which consists of an air distributing device, a multicenter reaction device and a tail gas detecting and processing device, wherein, the air distributing device consists of an air source, a current divider, a drying pipe (4), a flowmeter (5), a constant flow pump (8) and a preheater (9) which are connected by a pipeline; the multicenter reaction device is a parallel reactor consisting of a plurality of fixed bed reactors (7) in parallel connection; the front end of each reactor is connected with the flowmeter by a pipeline with a valve; the tail end is connected with the tail gas detecting and processing device by the pipeline with the valve, and the reaction temperature of each reactor can be controlled independently by a program temperature controller. The present invention uses the same air source and the parallel operation of a plurality of fixed bed reactors (7) to realize the fast evaluation on the sulfur dioxide hydrogenation activity and / or the organic sulfur hydrolysis activity of the Claus unit tail gas hydrodesulphurization catalyst.

Owner:WUHAN UNIV OF TECH

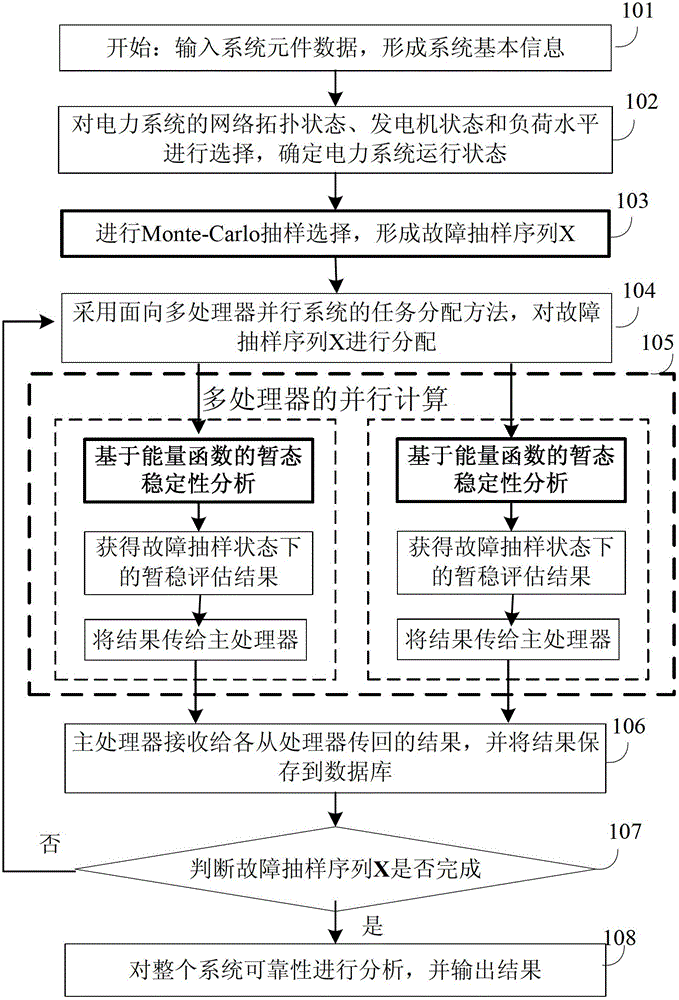

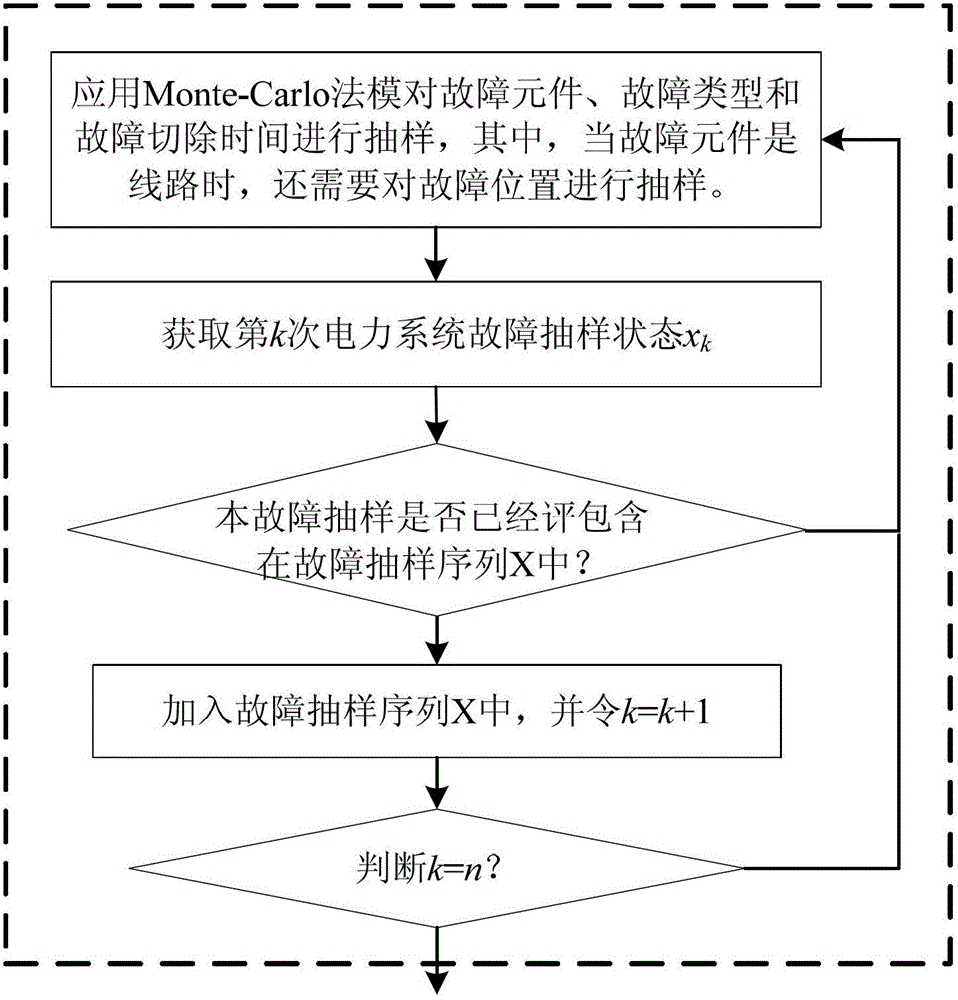

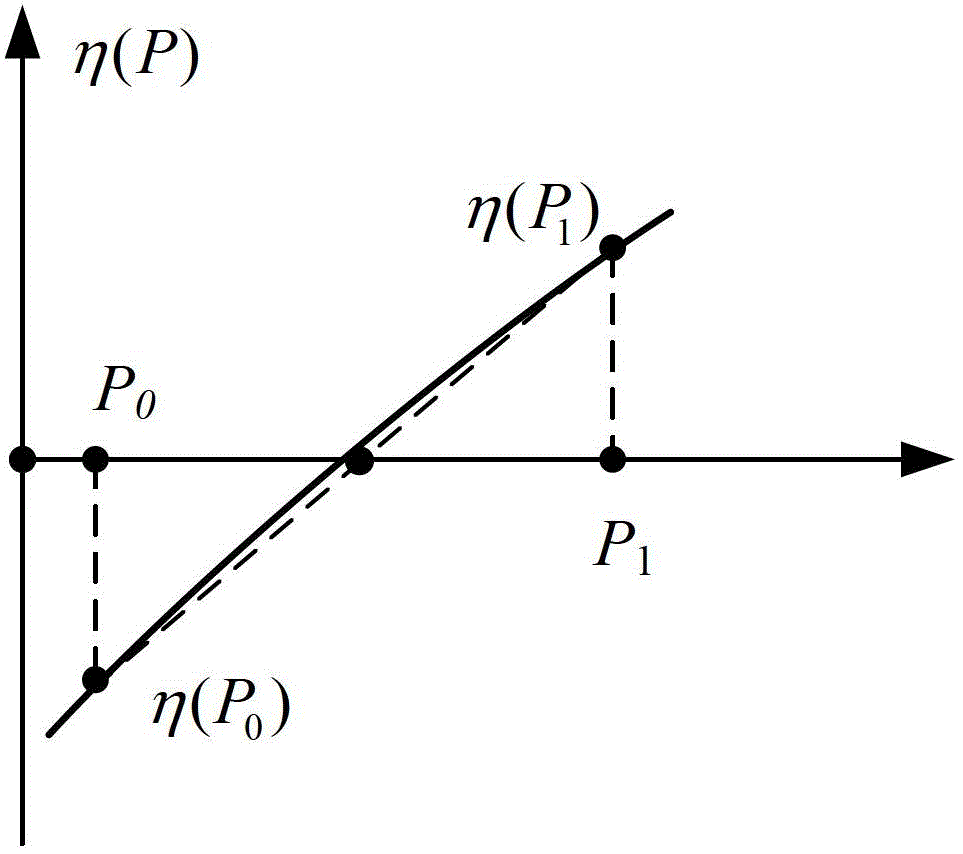

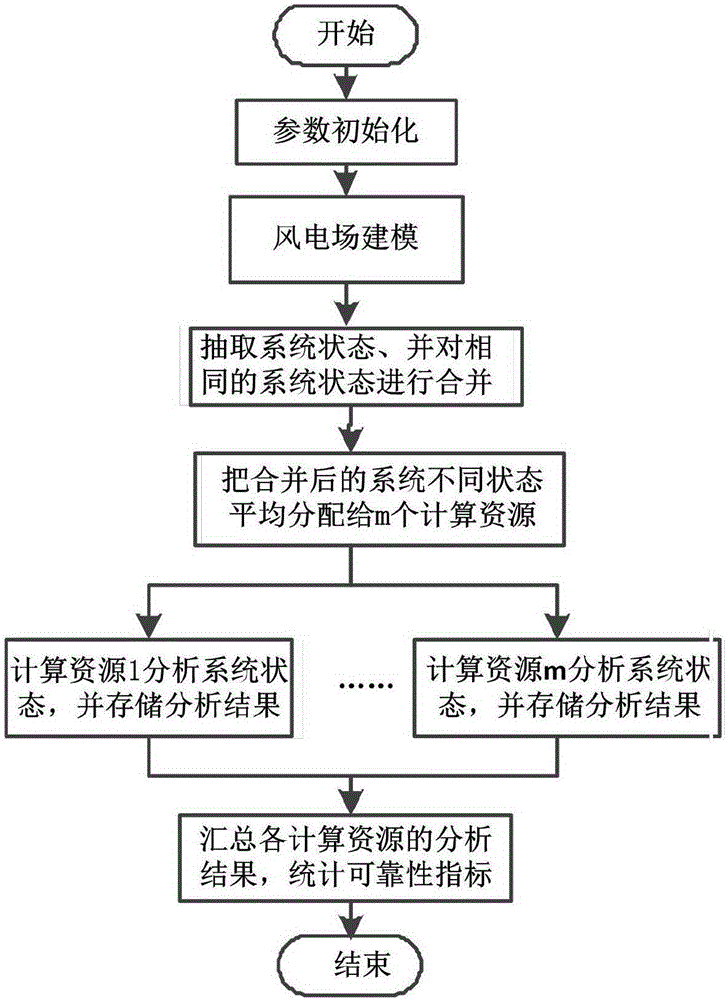

Method for improving transient stability analysis efficiency of electric power system

ActiveCN102723712AFast evaluationStable levelAc network circuit arrangementsTransient stateDistribution method

The invention discloses a method for improving a transient stability analysis efficiency of an electric power system and relates to the field of the electric power system. The method comprises the following steps of: initializing element parameters of the electric power system and inputting data of the electric power system; selecting a network topology state, a generator state and a load level of the electric power system, and determining an operation state of the electric power system; carrying out Monte Carlo sampling selection on the operation state of the electric power system to form a fault sampling sequence; utilizing a task distribution method facing to a multiprocessor parallel system and distributing the fault sampling sequence; carrying out transient stability analysis on a fault sample based on an energy function method by each processor; receiving a result returned by a processor by a main processor and storing the result into a database; and when the fault sampling sequence X is finished, calculating the possibility index of the transient stability of the electric power system and outputting the result. The method disclosed by the invention meets the requirements of instantaneity of information of the electric power system and improves the analysis efficiency and the safety of the electric power system.

Owner:TIANJIN UNIV

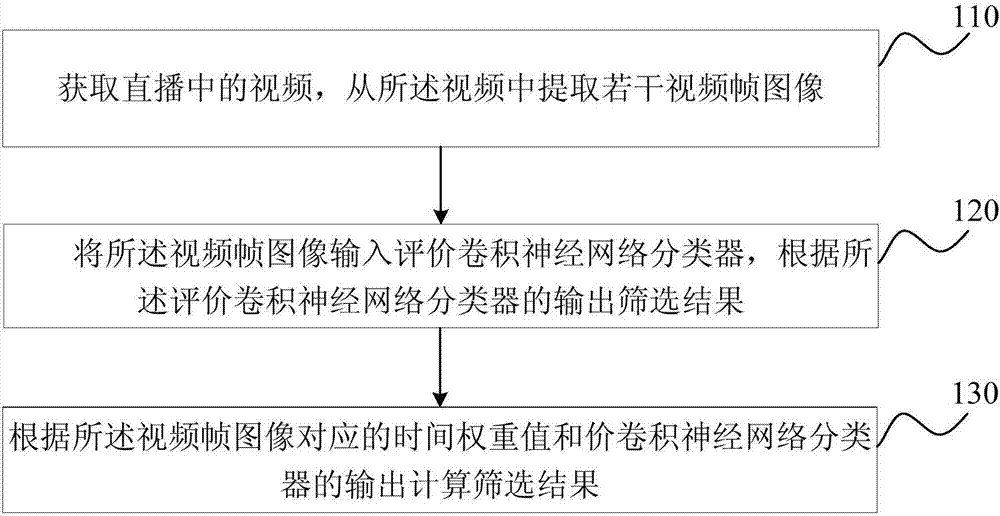

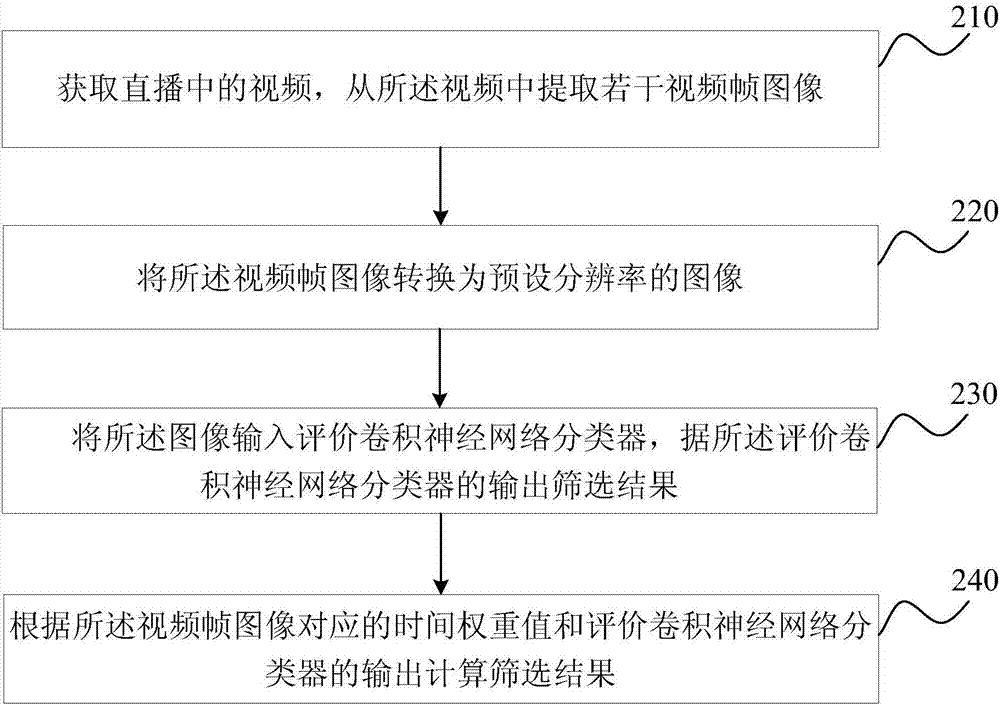

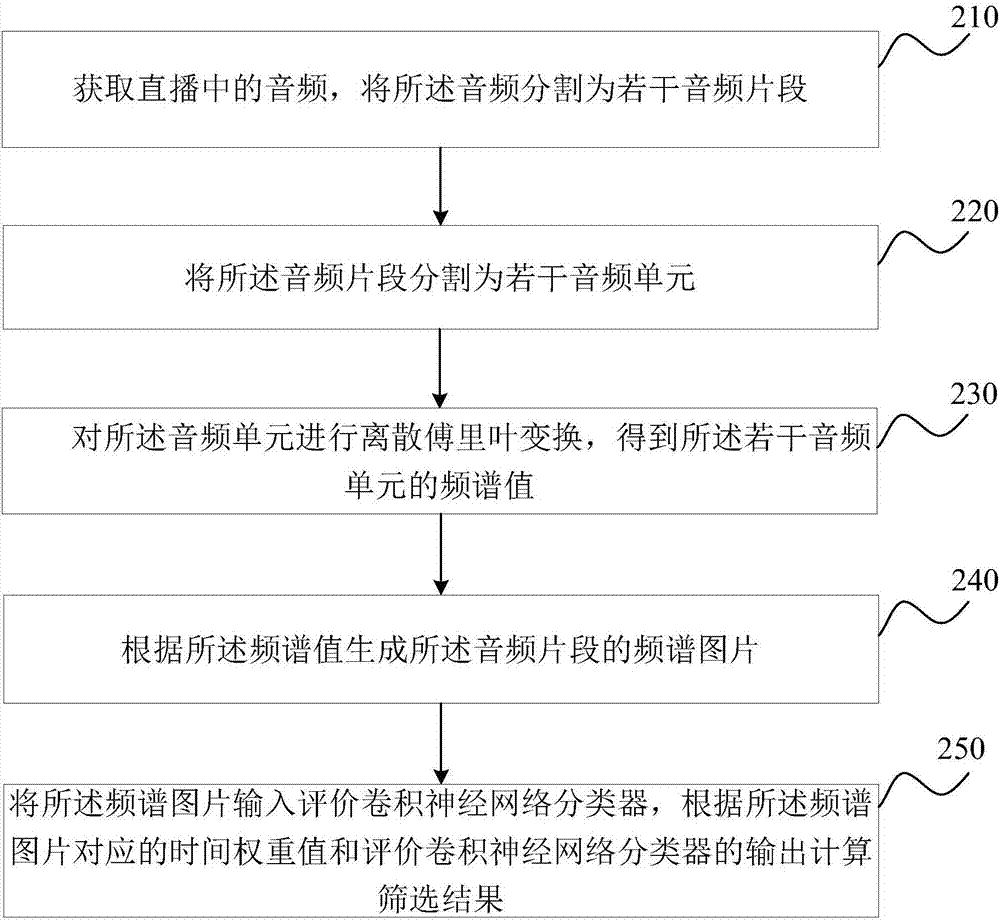

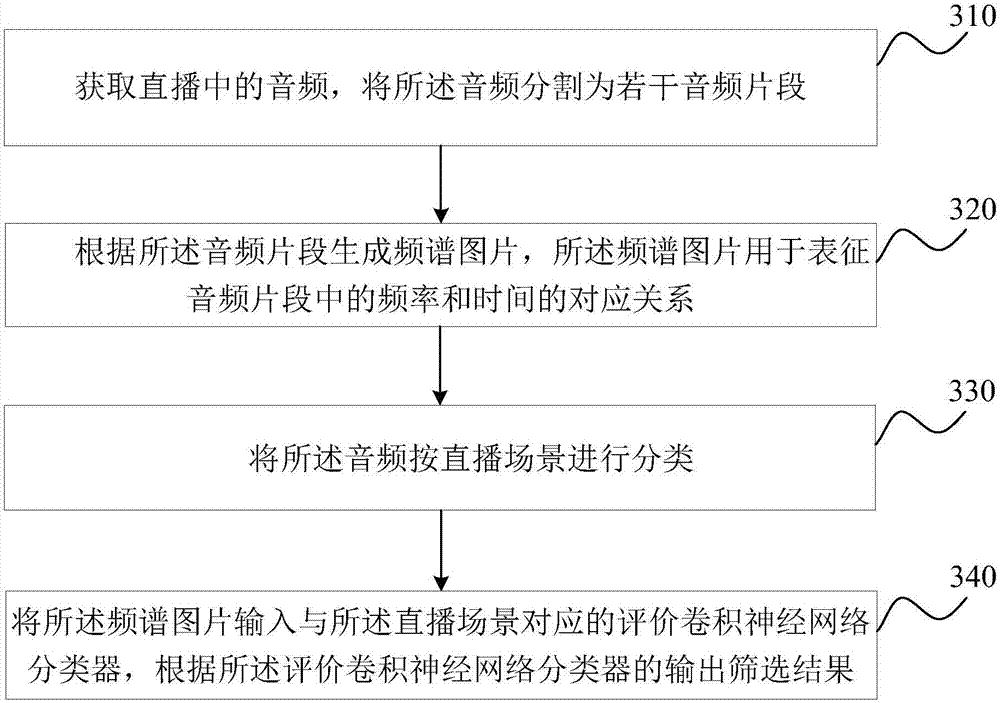

Live broadcast content screening method based on image, apparatus, equipment and storage medium thereof

ActiveCN107295362AUnified evaluation criteriaHigh precisionCharacter and pattern recognitionSelective content distributionNerve networkComputer graphics (images)

Embodiments of the invention disclose a live broadcast content screening method based on an image, an apparatus, equipment and a storage medium thereof. The method comprises the following steps of acquiring a video during live broadcast and extracting several video frame images from the video; inputting the video frame images into an evaluation convolution nerve network classifier so as to acquire output of the evaluation convolution nerve network classifier; according to a time weight value corresponding to the video frame images and the output of the evaluation convolution nerve network classifier, calculating a screening result. The convolution nerve network classifier is used to automatic acquire the screening result with high accuracy, an evaluation standard of a live broadcast content can be unified, an evaluation speed is fast and efficiency is high.

Owner:上海六界信息技术有限公司

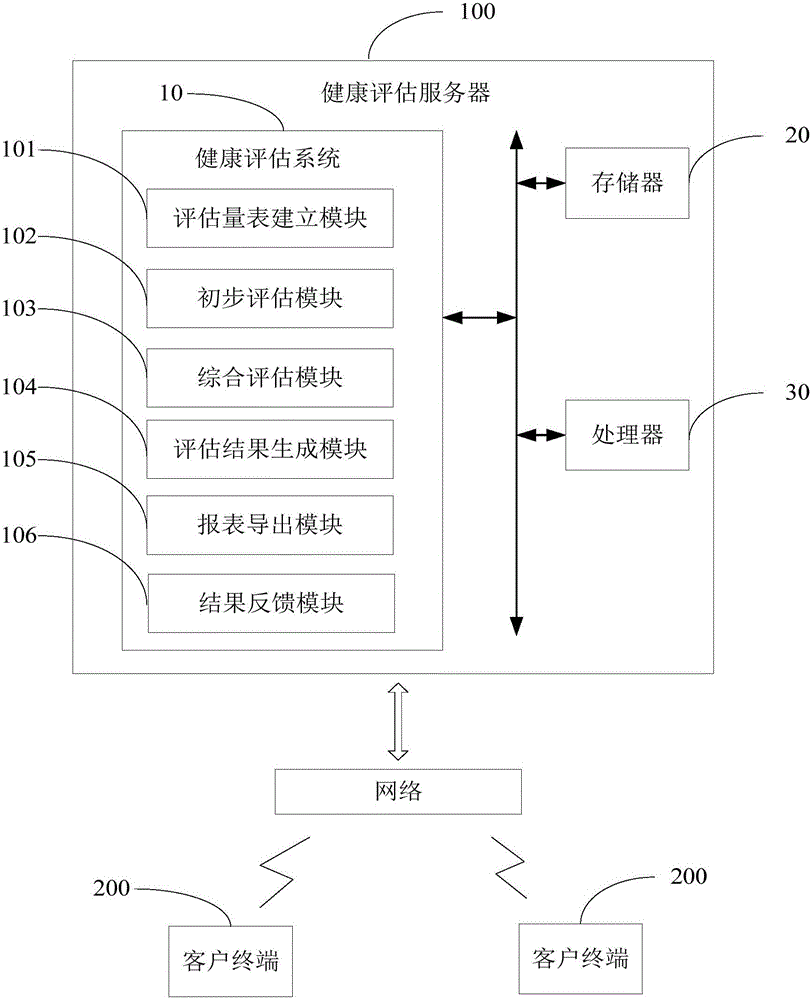

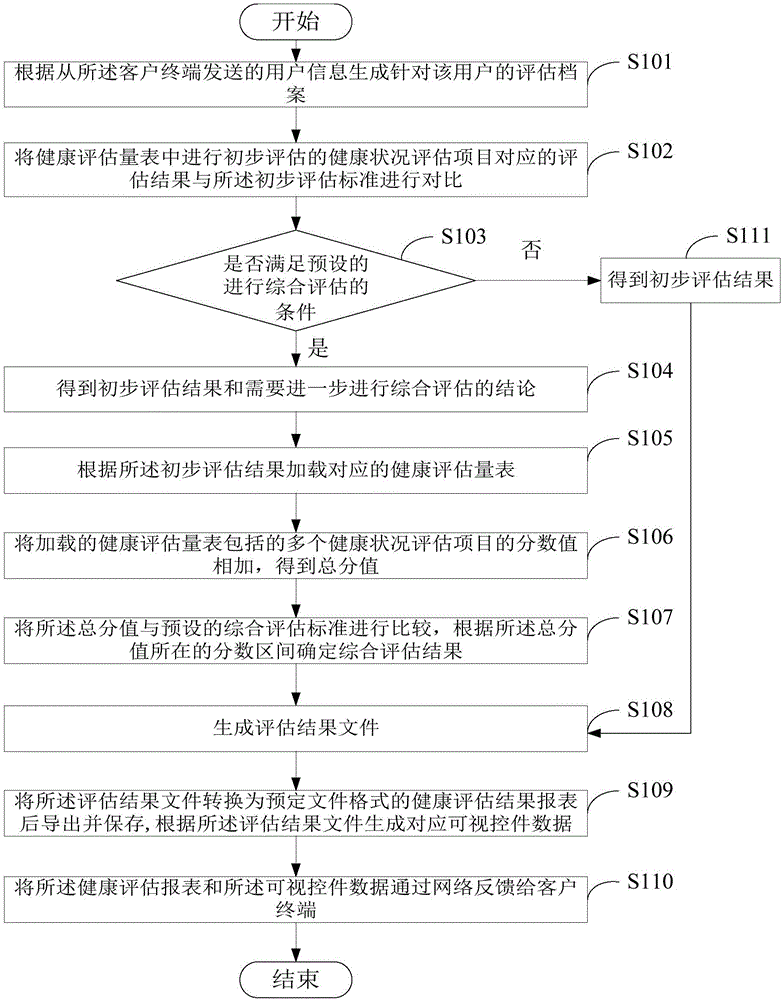

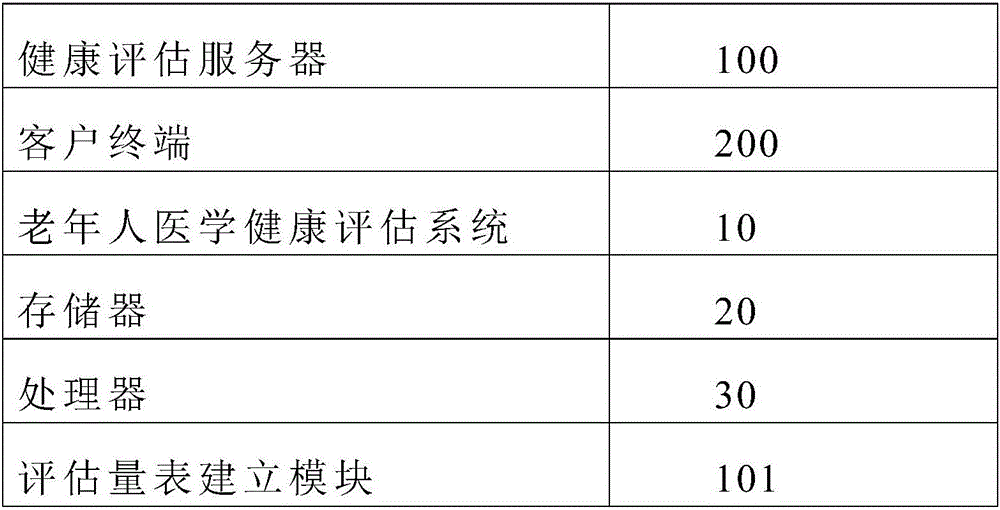

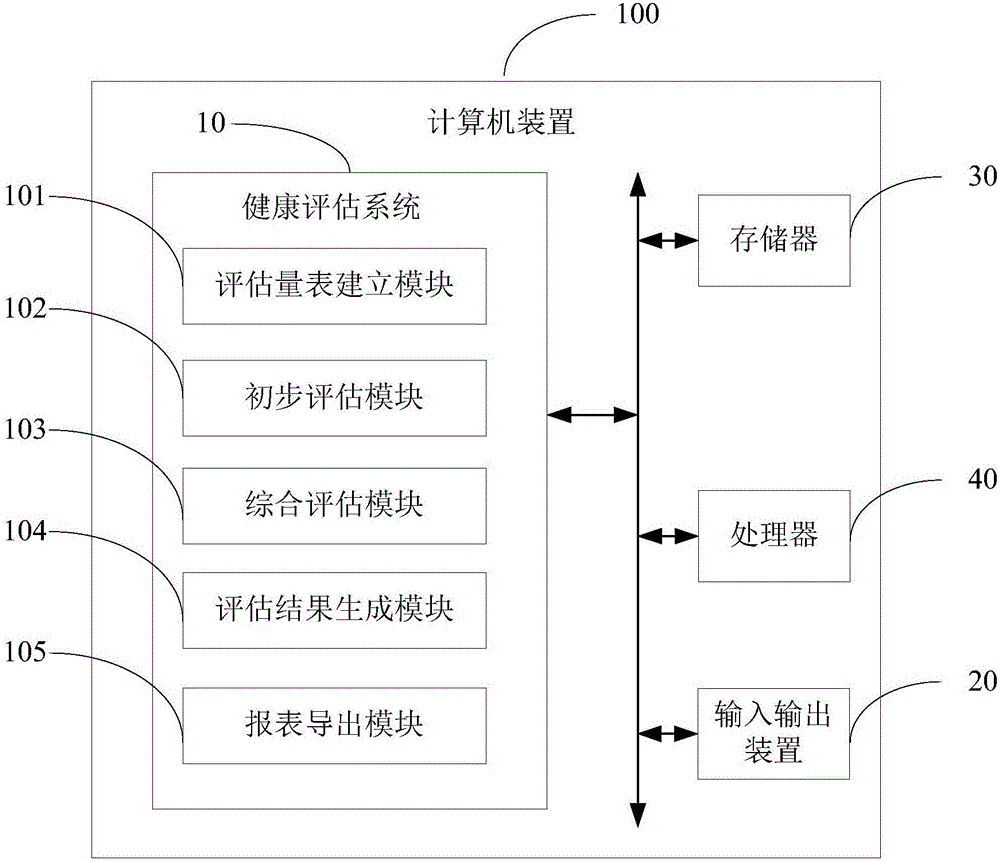

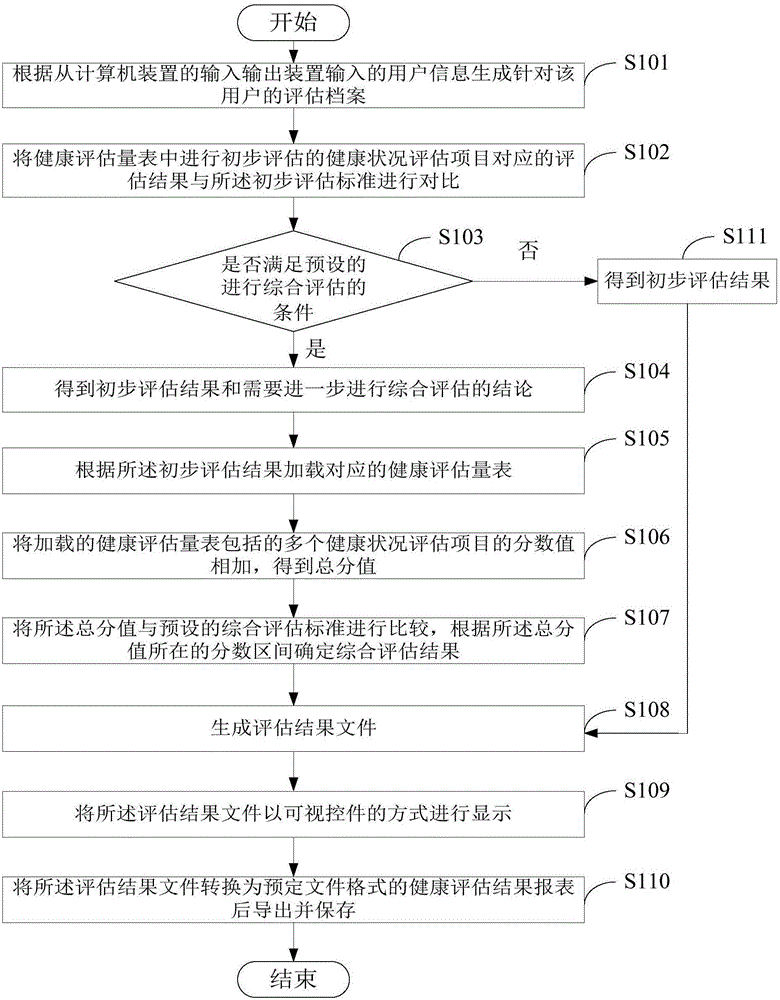

Elderly medical health assessment system and method based on cloud

InactiveCN106169031AHealth assessment is simple and convenientFast evaluationHealth-index calculationSpecial data processing applicationsThe InternetComputer science

The invention provides an elderly medical health assessment system and method based on a cloud, and relates to the internet medical field. The method comprises the steps that a health assessment server receives user information sent by a client terminal through a network, an assessment archive comprising multiple health assessment scales is generated according to the user information, assessment is conducted on the health assessment scales according to a preset assessment standard, and after an assessment result file is obtained and a corresponding report is generated, the report file is fed back to the client terminal. The whole health assessment process is completed through the health assessment server arranged on the cloud, a user can remotely complete health assessment simply by establishing communication with the health assessment server through the client terminal, the assessment speed is high, the efficiency is high, and health assessment on the user is easier and more convenient.

Owner:董碧蓉 +1

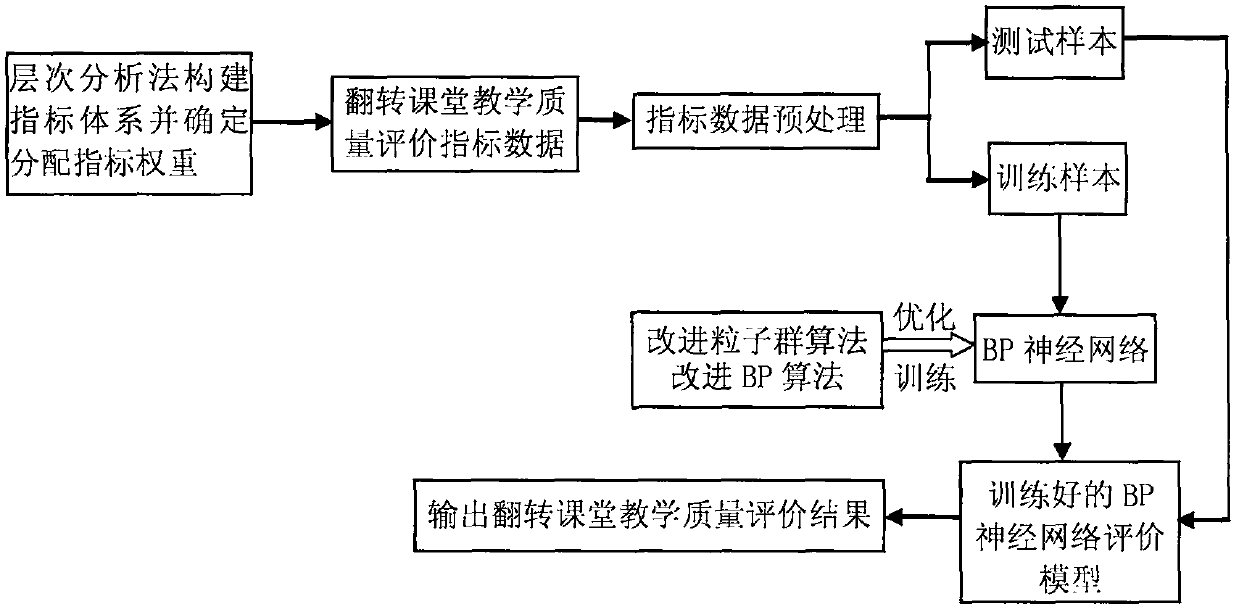

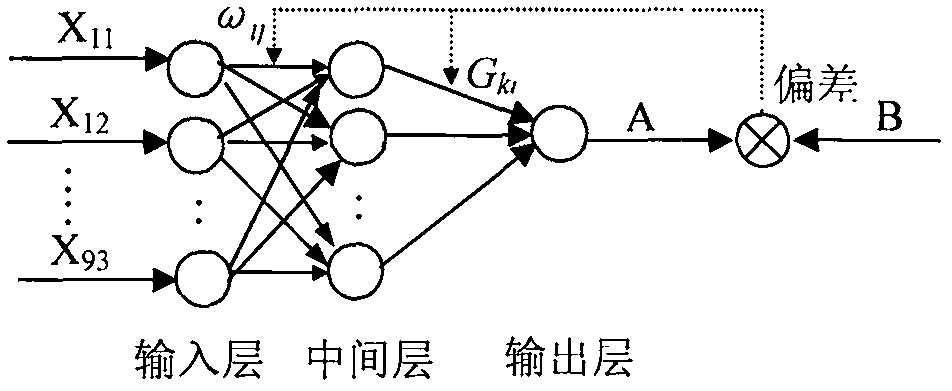

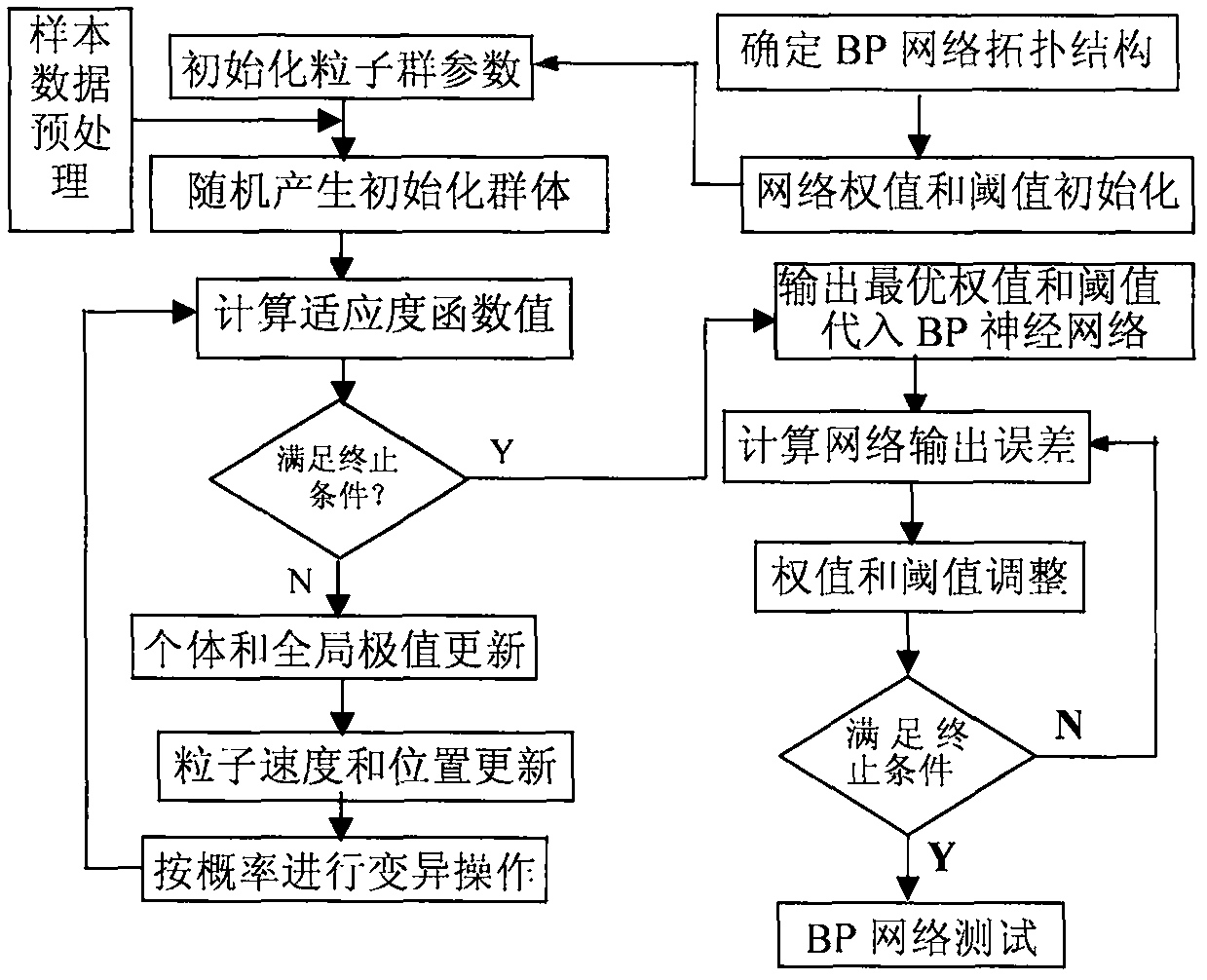

Teaching quality evaluation model for flipped classrooms

ActiveCN107862970AImprove teaching qualityFast evaluationEducational modelsNetwork modelIndex system

The invention discloses a teaching quality evaluation model for flipped classrooms. The teaching quality evaluation model for flipped classrooms based on analytic hierarchy process and BP (back-propagation) neural network is established in order to solve the problems in existing teaching evaluation processes for flipped classrooms. The analytic hierarchy process is used to establish a flipped classroom teaching quality evaluation index system and determine allocation of its index weights; modified particle swarm optimization is used to optimize initial network weigh and threshold; the modifiedBP algorithm is used to train a BP neural network model. Experimental analysis shows that the model of the invention can be used in teaching quality evaluation for flipped classrooms to increase evaluation objectivity, speed and precision.

Owner:WUXI OPEN UNIV

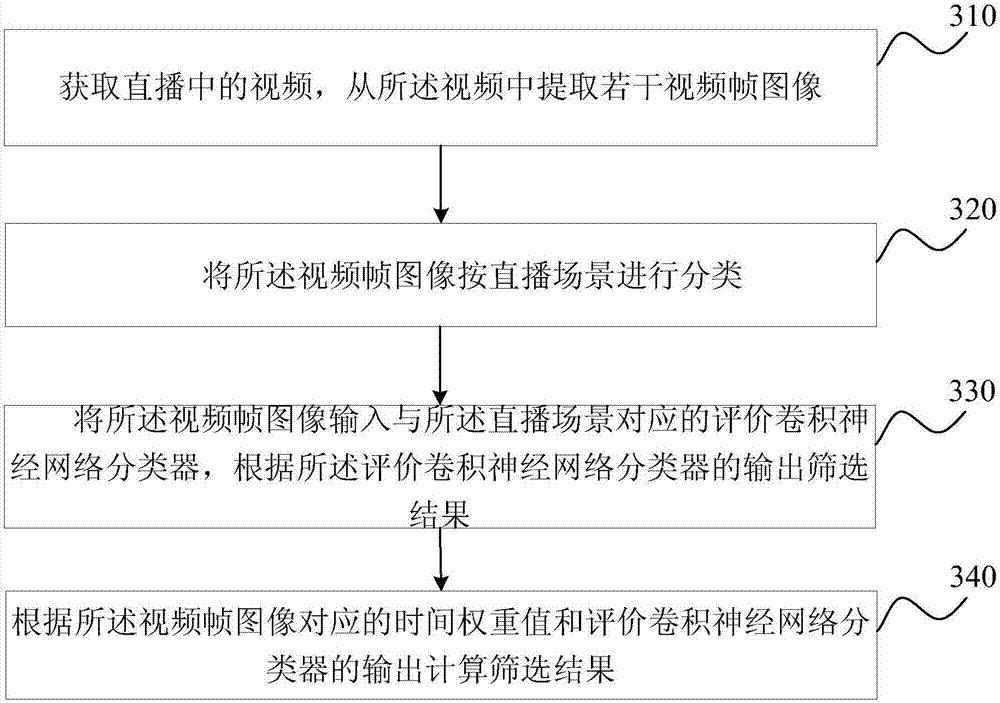

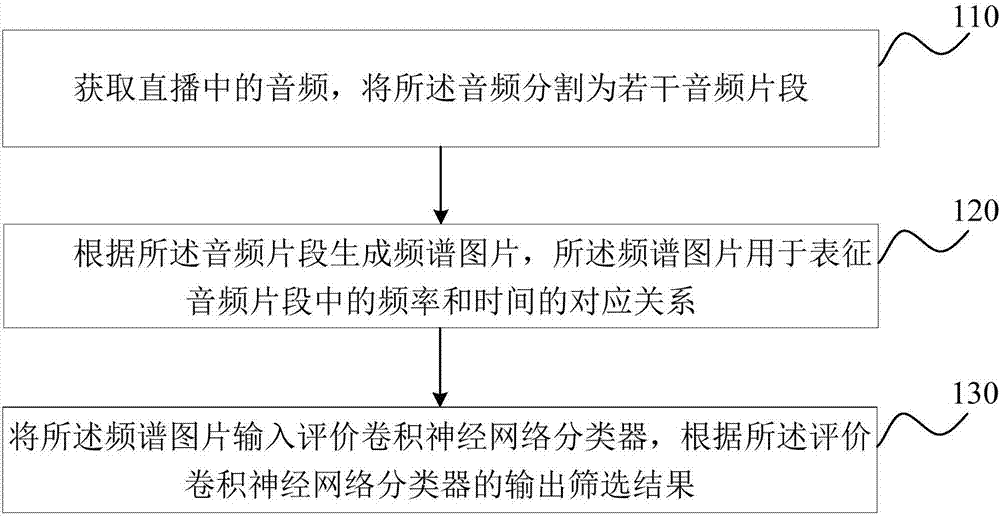

Screening method, device and equipment of live broadcast content and storage medium

ActiveCN107492383AUnified evaluation criteriaHigh precisionSpeech recognitionSpecial data processing applicationsFrequency spectrumAlgorithm

The embodiment of the present invention discloses a screening method, device and equipment of live broadcast content and a storage medium. The method comprises a step of obtaining audio in live broadcast and dividing the audio into a plurality of audio segments, a step of generating a spectral picture according to the audio segments, wherein the spectral picture is used for characterizing corresponding relations between frequencies and times in the audio segments, a step of inputting the spectral picture into an evaluation convolutional neural network classifier and obtaining a screening result according to the output of the evaluation convolutional neural network classifier. The evaluation convolutional neural network classifier can be used to automatically obtain the screen result with high precision, the evaluation criteria of the live broadcast content can be unified, the evaluation speed is faster, and the efficiency is higher.

Owner:上海六界信息技术有限公司

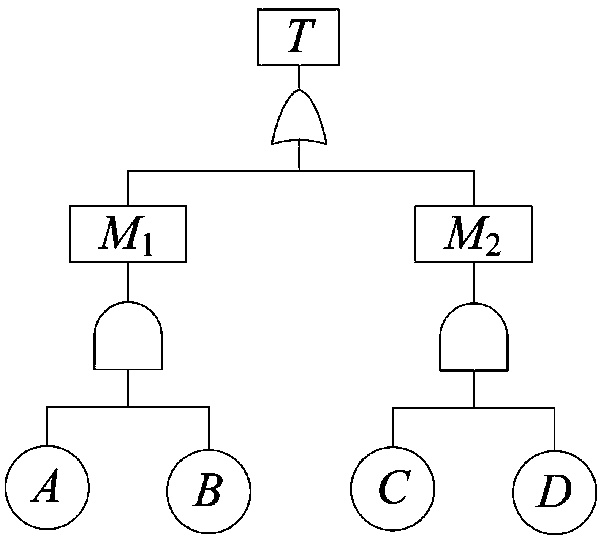

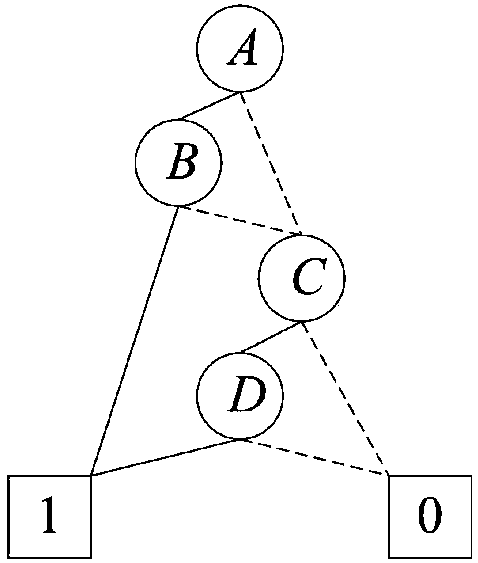

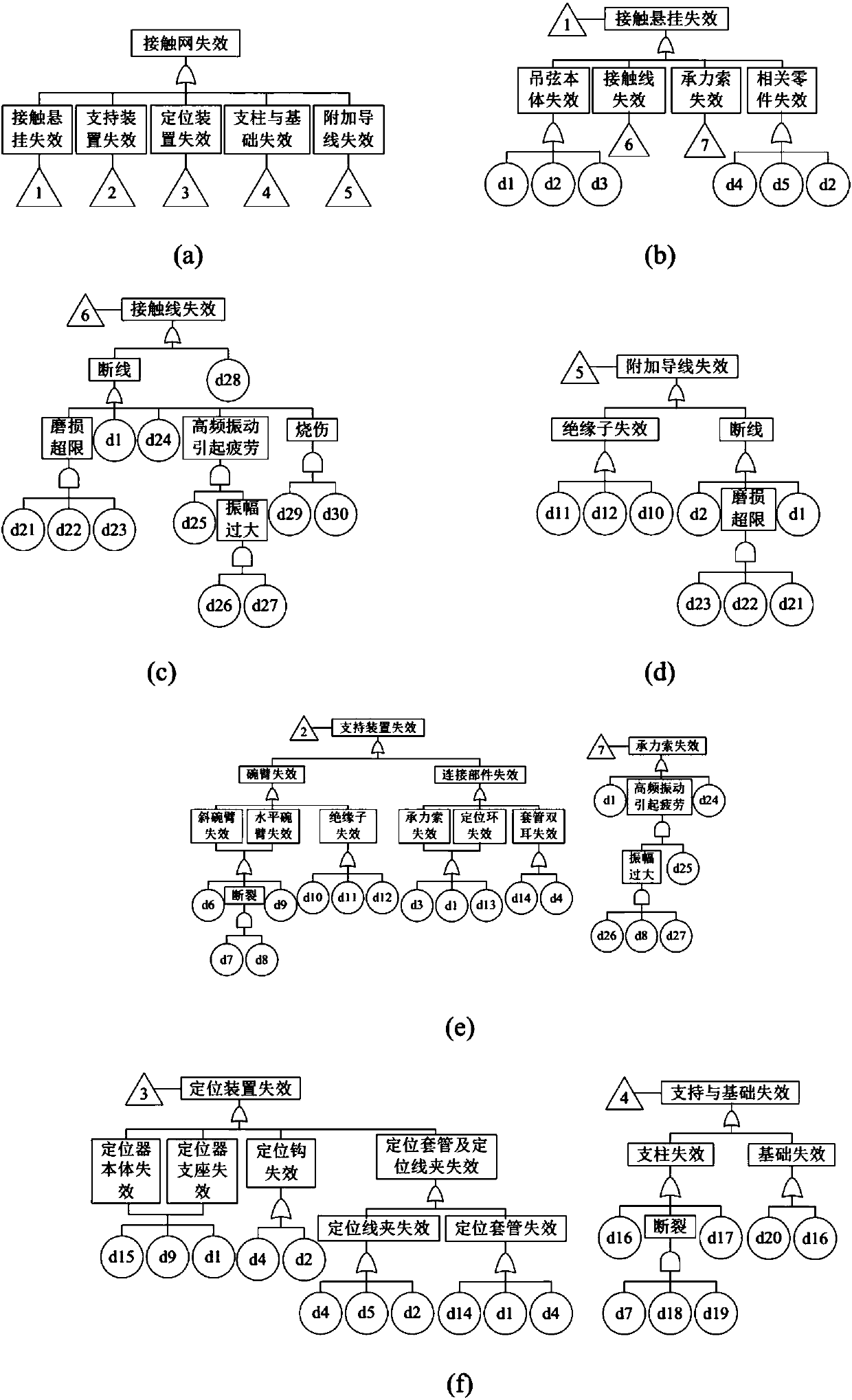

Contact network failure risk assessment method based on binary decision graph algorithm

PendingCN108596511ASolving combinatorial explosionsSolve complexityResourcesComplex mathematical operationsContact networkDecision graph

The invention discloses a contact network failure risk assessment method based on a binary decision graph algorithm, comprising the steps of: (1) generating a BDD structure, determining system boundaries, basic events and top events, establishing and normalizing a fault tree, and generating a BDD structure, wherein the corresponding BDD nodes may be directly created by ITE operations for basic events; and ITE operations may be performed on basic events or other intermediate events to obtain the BDD structure of the original intermediate event for intermediate events; (2) calculating the accident rate of the contact network failure risk, generating a Boolean logic expression by the fault tree, and generating a Boolean logic function corresponding to the fault tree top event, wherein when the true value is obtained, the probability of occurrence of the top event or any intermediate event may be obtained; and (3) measuring the event importance. The invention applies the BDD method to thefailure risk assessment of the contact network, which simplifies the calculation process, and solves the problems such as the combined explosion and the complicated solving process encountered by thecut set method in the contact network failure fault tree analysis.

Owner:CHINA RAILWAYS CORPORATION +1

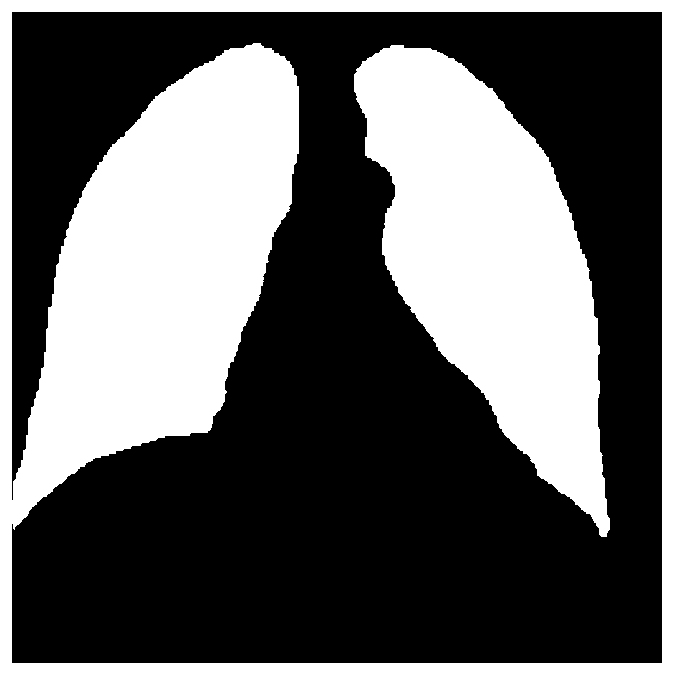

Rectal cancer preoperative concurrent neoadjuvant radiotherapy and chemotherapy effect evaluation system and method based on big data analysis MRI images

InactiveCN108922602AFast evaluationLong working hoursImage enhancementImage analysisNerve networkAdjuvant chemoradiotherapy

The invention relates to a rectal cancer preoperative concurrent neoadjuvant radiotherapy and chemotherapy effect evaluation system and method. The evaluation system comprises: an image acquisition unit for acquiring MRI images before neoadjuvant radiotherapy and chemotherapy for patients with the locally advanced rectal cancer, and dividing the rectal cancer patients into a training set, a checkset and a test sets as input image data; an image annotation unit for performing data annotation on MRI images of the training set, the check set and the test set; a convolutional neural network construction unit for constructing a first convolutional neural network model; and a convolutional neural network model training unit for acquiring a second convolutional neural network model for evaluating the rectal cancer preoperative concurrent neoadjuvant radiotherapy and chemotherapy effect. The rectal cancer preoperative concurrent neoadjuvant radiotherapy and chemotherapy effect evaluation system has many advantages such as high accuracy, short time-consuming, long working duration, objective and three-dimensional result.

Owner:THE SIXTH AFFILIATED HOSPITAL OF SUN YAT SEN UNIV

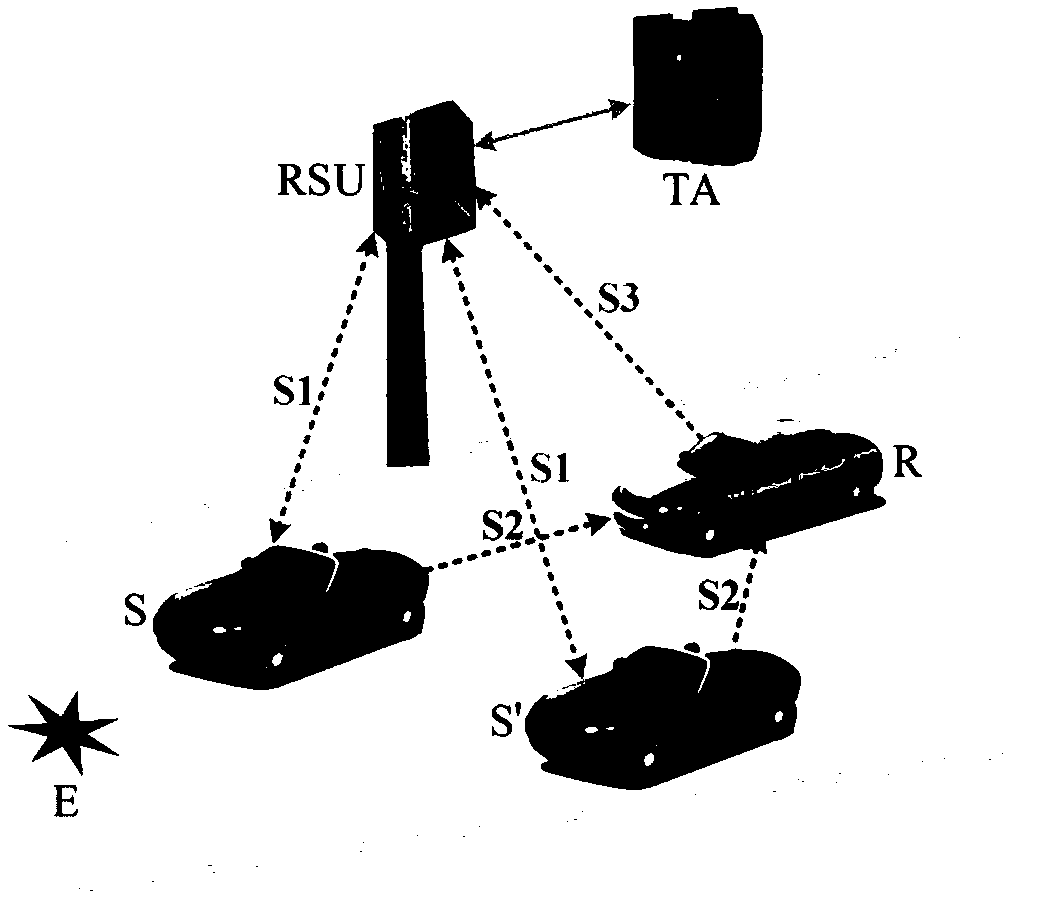

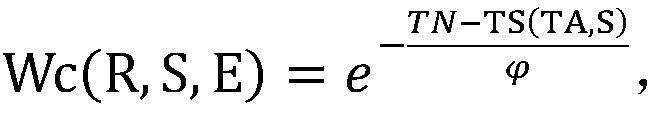

Message reliability evaluation method for aggregation of two trust evaluations in car networking

ActiveCN109195162AThe assessment results are accurateFast evaluationUser identity/authority verificationLocation information based serviceDynamic featureTrustworthiness

The present invention discloses a message reliability evaluation method for aggregation of two trust evaluations in car networking. A trust center is configured to maintain trust information of vehicles, and the vehicles require the newest trust certificates themselves at a fixed period, message publishers carry the newest trust certificates when sending the messages to prove the trustworthiness themselves; a message receiver extracts the trust certificates and integrally considers the message of the plurality of message publishers to determine the reliability after receiving each message, generate one trust feedback for each message publisher and send the trust feedbacks to the trust center, and then the trust center updates the trust feedbacks and locally store the trust feedbacks. The message reliability evaluation method for aggregation of two trust evaluations in car networking can effectively aggregate the two trust evaluations with no need for requiring the trust center by the message receivers in real time so that the evaluation result is more accurate and the evaluation speed is faster, the condition that the vehicles cannot be connected with the trust center in a short time can be compatible, and the message reliability evaluation method for aggregation of two trust evaluations in car networking more accord with the high dynamic features of the car networking.

Owner:JINAN UNIVERSITY

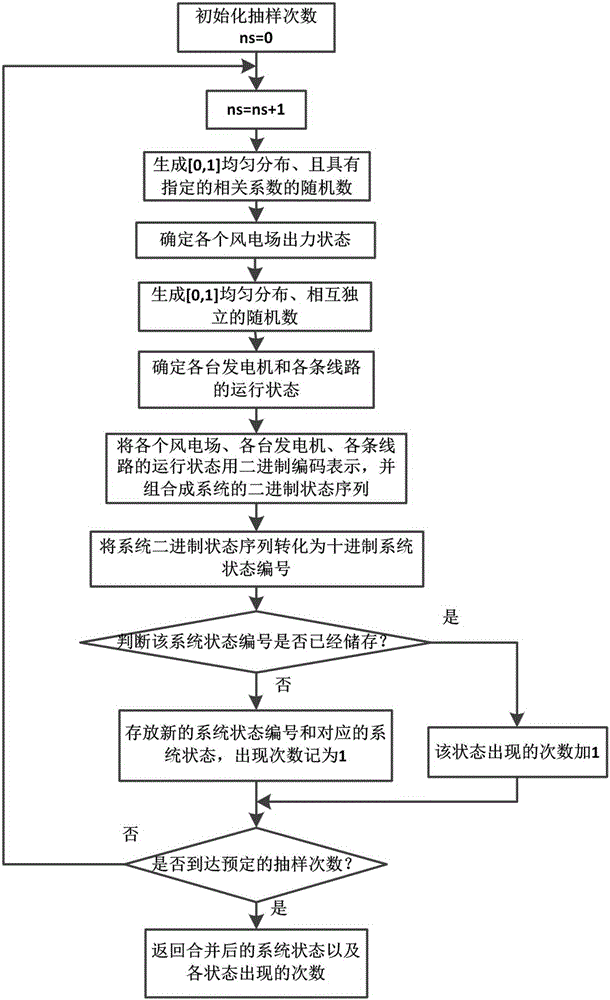

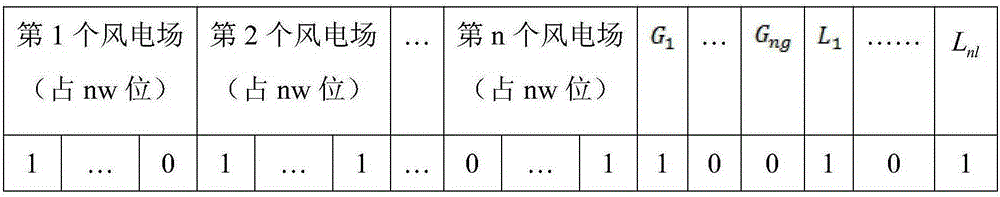

Reliability evaluation method for electric power system containing wind power plant

ActiveCN105207197AAccelerate the speed of reliability assessmentAvoid Duplicate State AnalysisResourcesAc network circuit arrangementsPeaking power plantElectric power system

The invention provides a reliability evaluation method for an electric power system containing a wind power plant, which comprises the steps of initializing parameters; carrying out modeling on the wind power plant, extracting the state of the wind power plant by adopting correlated random variable simulation technologies, converting the state into a binary state sequence, and then combining the binary state sequence with extracted binary state sequences of a generator and circuit elements so as to form a binary state of the system; carrying out decimal coding on system states, and recognizing and combining the identical system states; carrying out parallel computation on the stored different system states; and collecting a parallel computation result, and calculating an index of the system reliability. According to the invention, through marking the system states by using decimal numbers, the identical system sampling states can be recognized quickly, and the total number of the system states to be evaluated is reduced; and parallel computation is combined on the basis, and the evaluation speed of the system reliability is improved.

Owner:永春县产品质量检验所福建省香产品质量检验中心国家燃香类产品质量监督检验中心福建

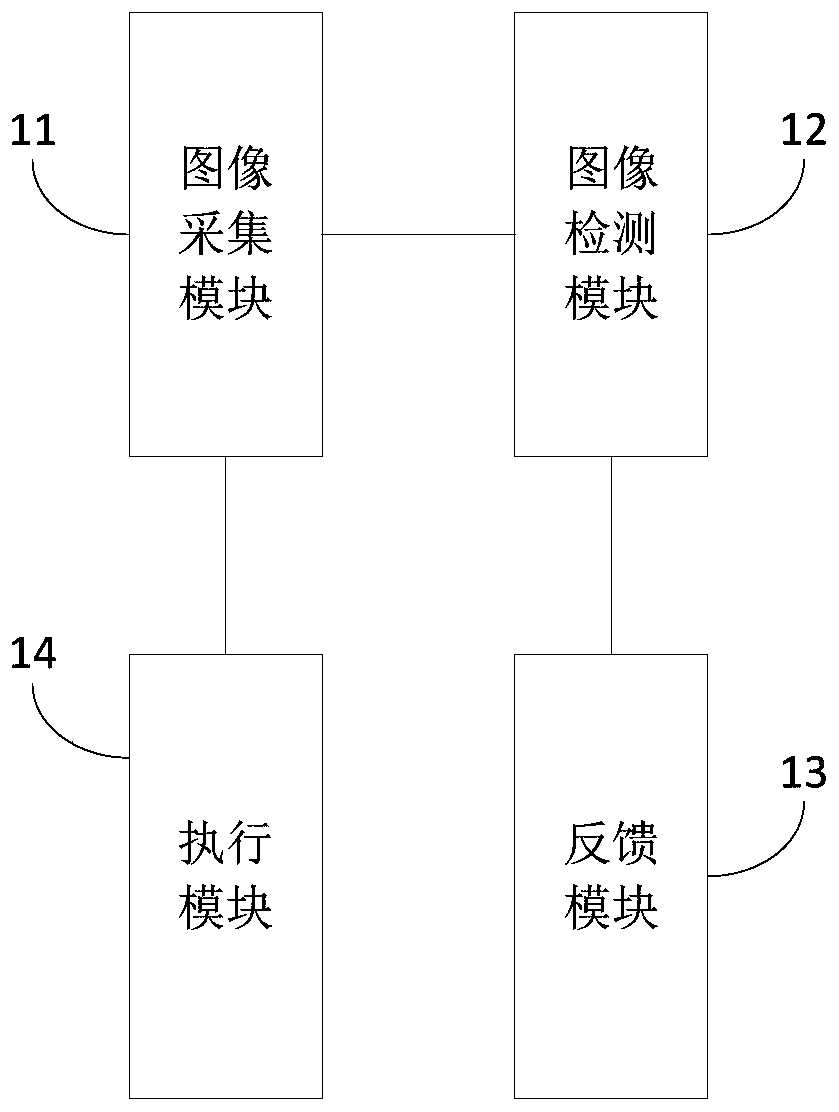

Medical imaging system and method, computer equipment and readable storage medium

ActiveCN110232688AReduce mistakesFast learningImage enhancementImage analysisEvaluation resultUser input

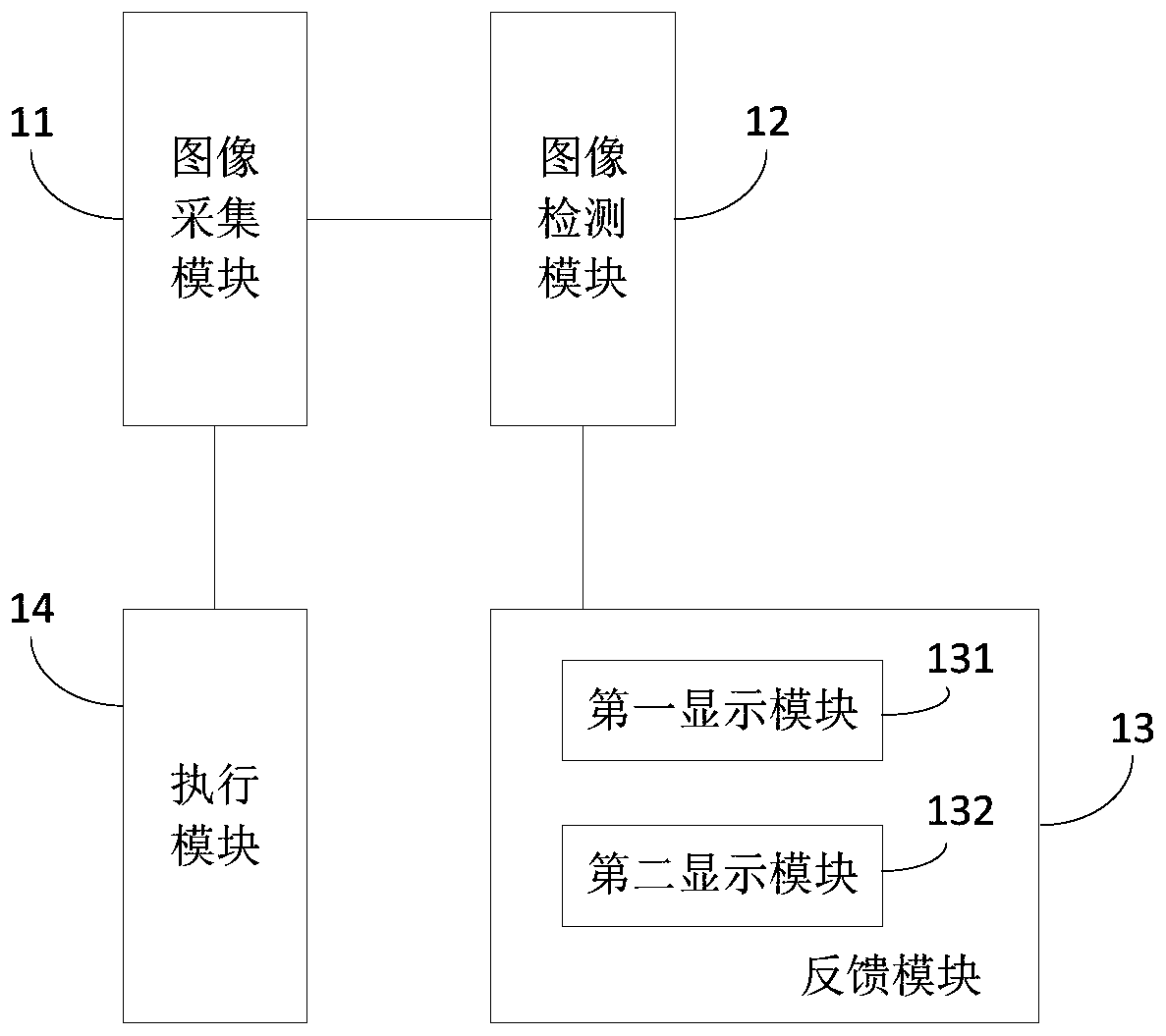

The invention relates to a medical imaging system and method, computer equipment and a readable storage medium. The system comprises an image acquisition module configured to acquire a medical image of a tested object; an image detection module configured to perform quality evaluation processing on the medical image according to a preset quality evaluation algorithm to obtain a quality evaluationresult; a feedback module configured to display the quality evaluation result of the medical image in real time; and an execution module configured to receive the re-acquisition instruction input by the user in real time and control the image acquisition module to re-acquire the medical image of the tested object. A preset quality assessment algorithm is used for carrying out quality assessment onmedical images, the assessment process is high in speed, the quality assessment efficiency is improved, manual participation is not needed, and errors of assessment results are reduced. The quality evaluation result can be displayed in real time, and a re-acquisition instruction input by a user can be received in real time, so that the efficiency of the medical imaging process is further improved.

Owner:SHANGHAI UNITED IMAGING INTELLIGENT MEDICAL TECH CO LTD

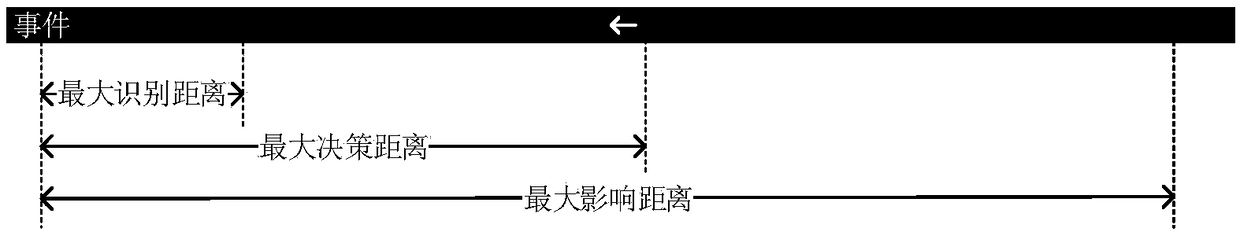

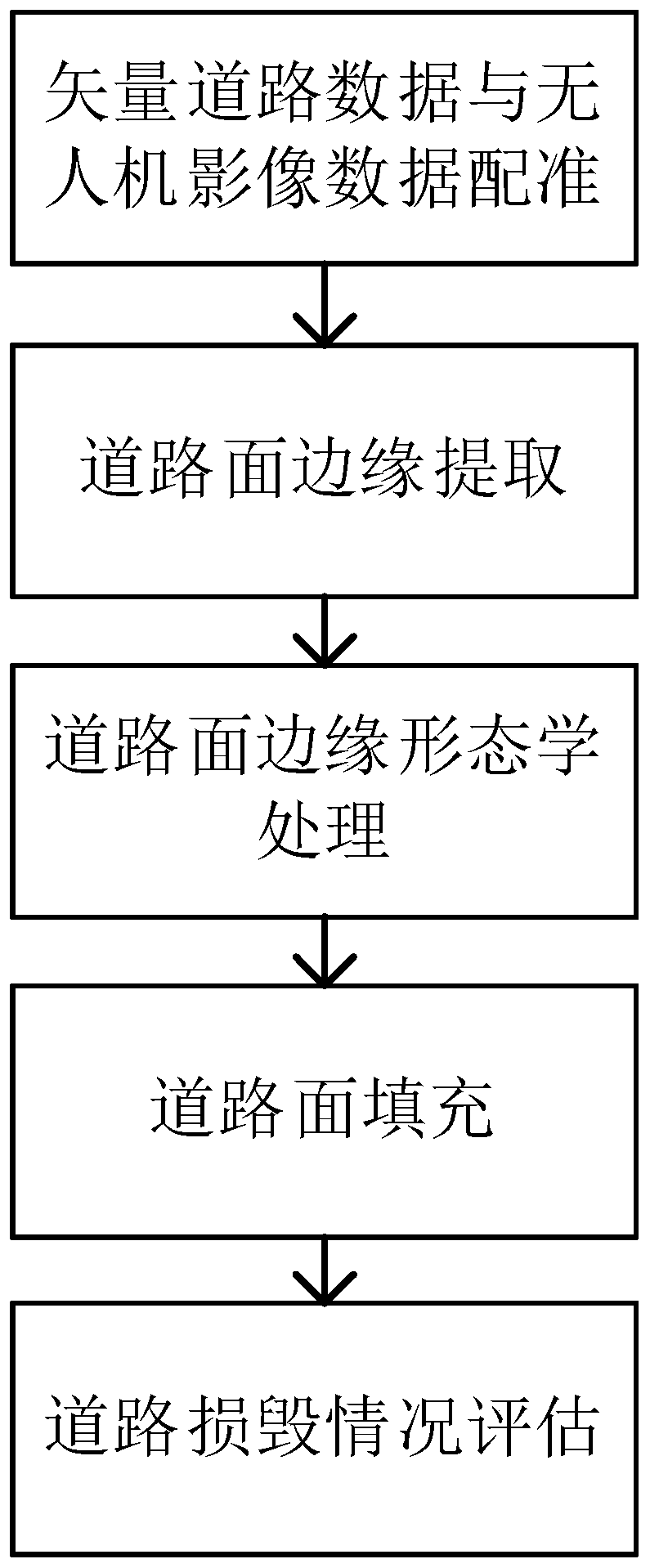

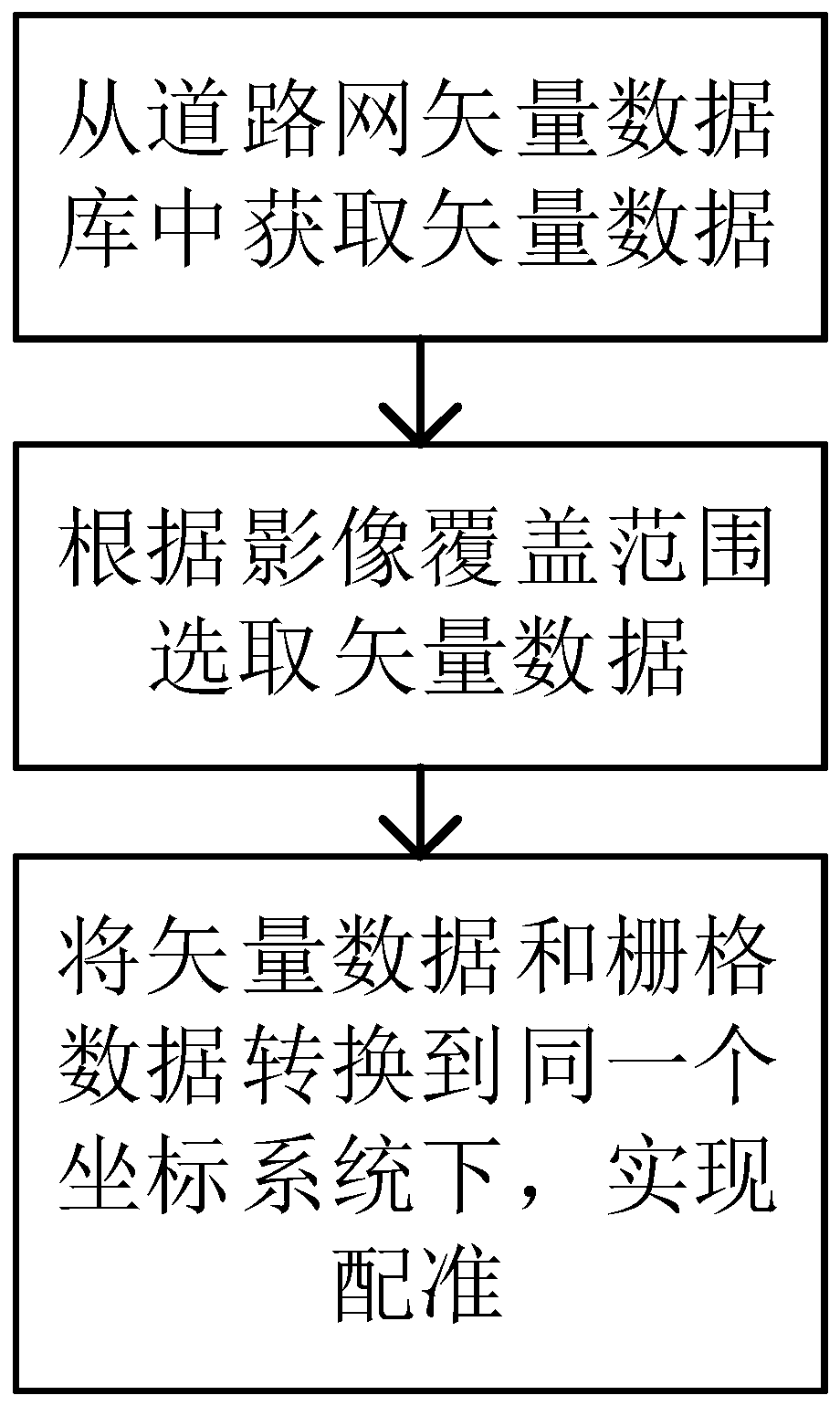

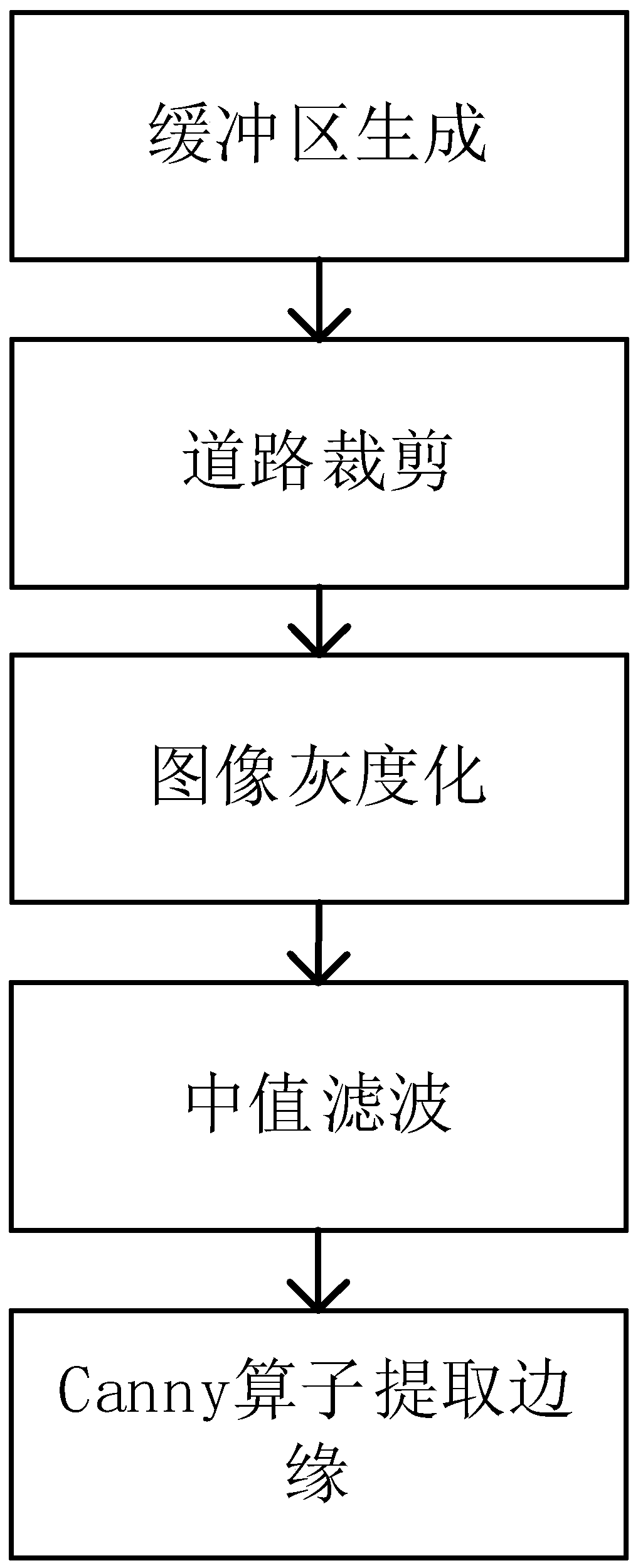

Unmanned aerial vehicle image road damage assessment method based on vector guidance

ActiveCN109785307AHigh degree of automationFast evaluationImage analysisUncrewed vehicleRoad networks

The invention provides an unmanned aerial vehicle image road damage assessment method based on vector guidance, and the method comprises the steps: registering the collected unmanned aerial vehicle image data by using the existing road network vector data, and cutting an image by using a registered road as a buffer region. And edge information of the image is obtained by using an edge detection operator, and then connection and refinement processing are performed on the edges by using a morphological algorithm; and then generating seed points by using the vector data, and carrying out floodingfilling on the road surfaces from the seed points to sequentially generate a plurality of road surfaces; and finally, counting the number and area of road surfaces, and comparing the number and areawith the area of a complete road to realize objective assessment of road damage.

Owner:WUHAN UNIV

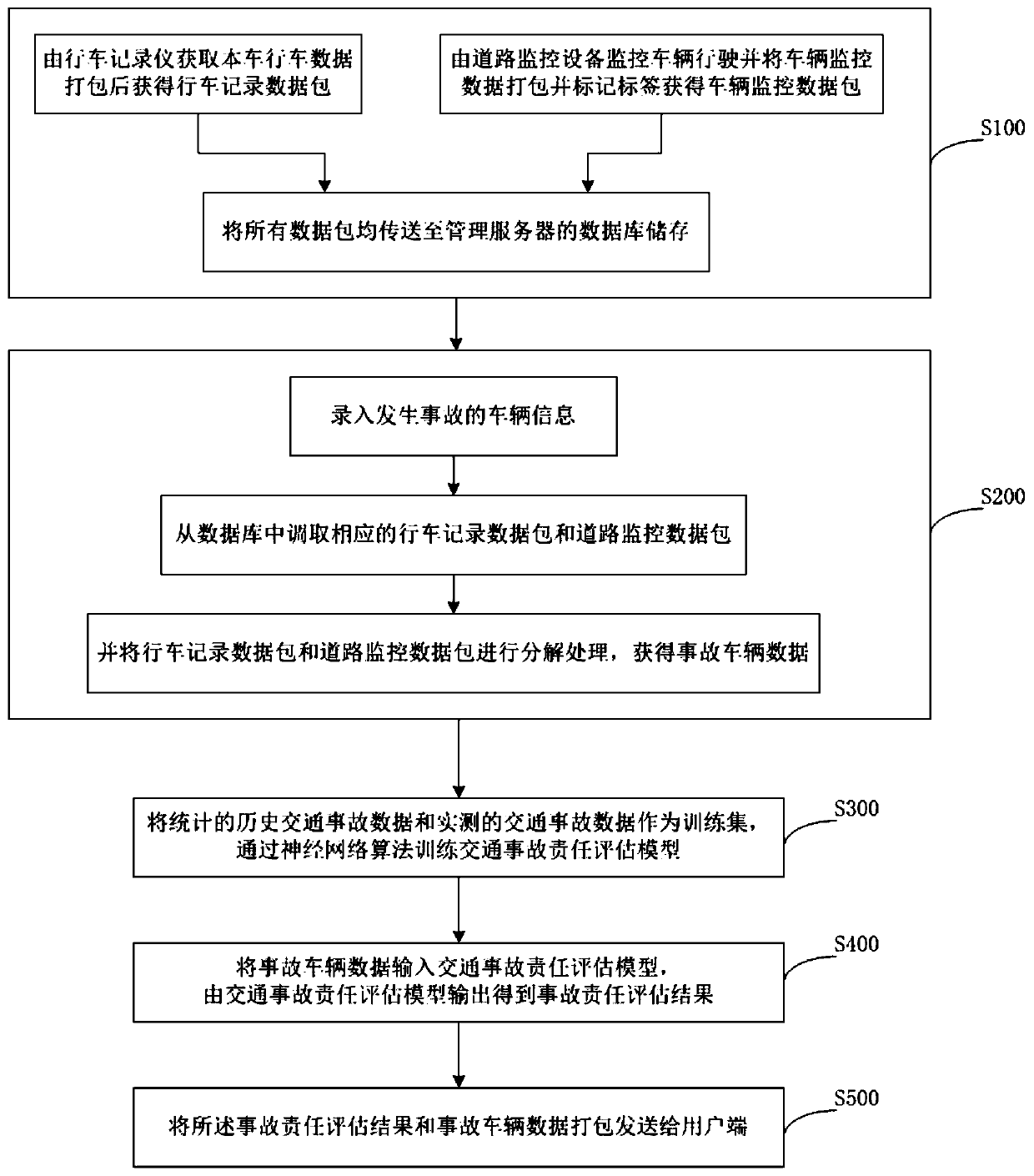

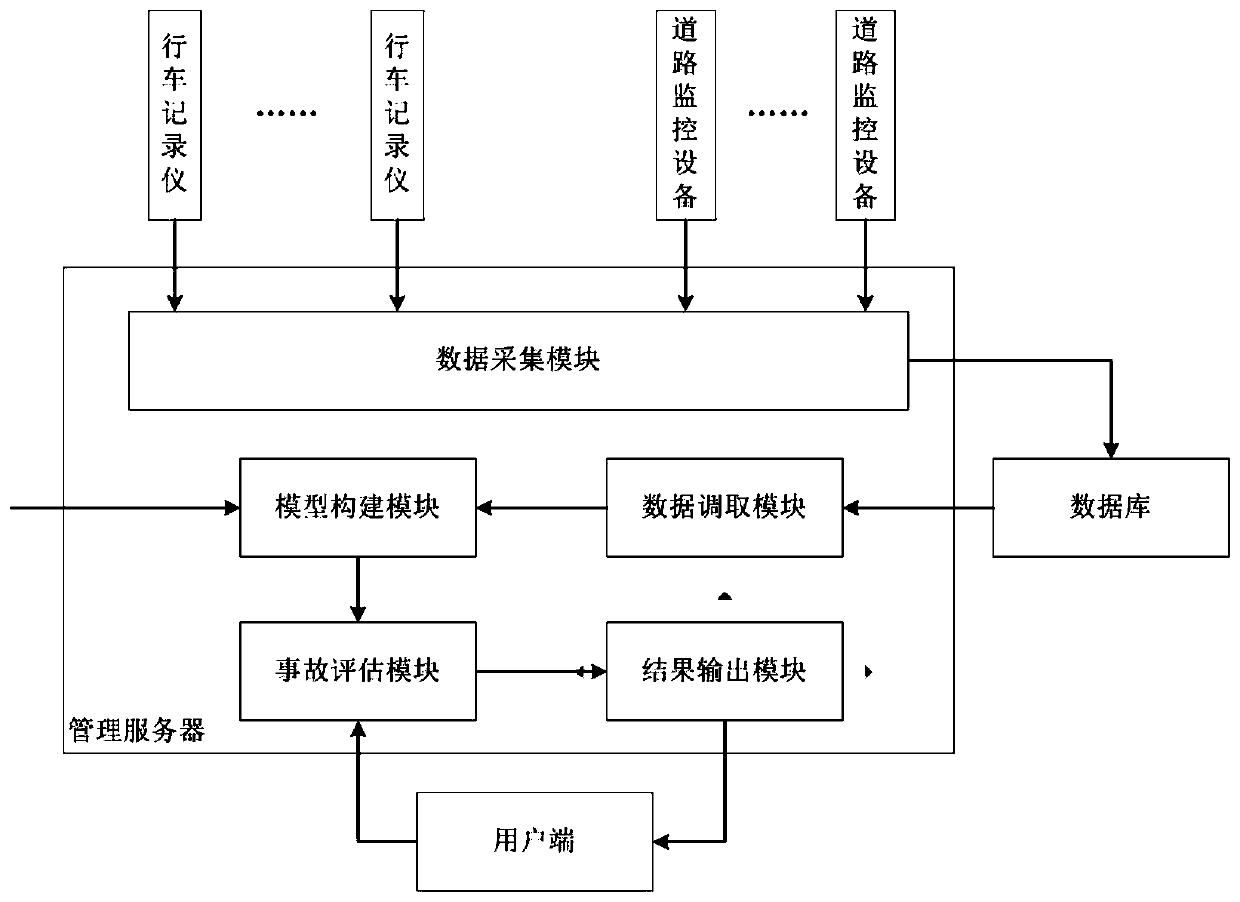

Traffic accident responsibility assessment method and device based on deep learning

InactiveCN110070642ARealize centralized managementReal and reasonable acquisitionRegistering/indicating working of vehiclesDetection of traffic movementCar drivingSimulation

The invention discloses a traffic accident responsibility assessment method and device based on deep learning. The method comprises the following steps: acquiring driving data of a current car througha car driving recorder, and monitoring car driving through road monitoring equipment; inputting information of cars involved in an accident, and retrieving and obtaining data of the cars involved inthe accident from a database; training a traffic accident responsibility assessment model through the neural network algorithm; and inputting the data of the cars involved in the accident into the traffic accident responsibility assessment model, obtaining an accident responsibility assessment result output by the traffic accident responsibility assessment model, and sending the accident responsibility assessment result to user terminals. The method and device disclosed by the invention has the advantages that centralized management of traffic accident evidences can be achieved, and traffic accident responsibility assessment can be automatically and efficiently carried out; the assessment result is accurate and has a sound legal basis; the assessment speed is high, so that the traffic accident handling efficiency can be greatly improved, and waste of manpower and material resources can be avoided; and evidence analysis and judgment can be carried out in an all-around manner, so that the responsibility assessment result is fair and reasonable.

Owner:TIANJIN UNIV

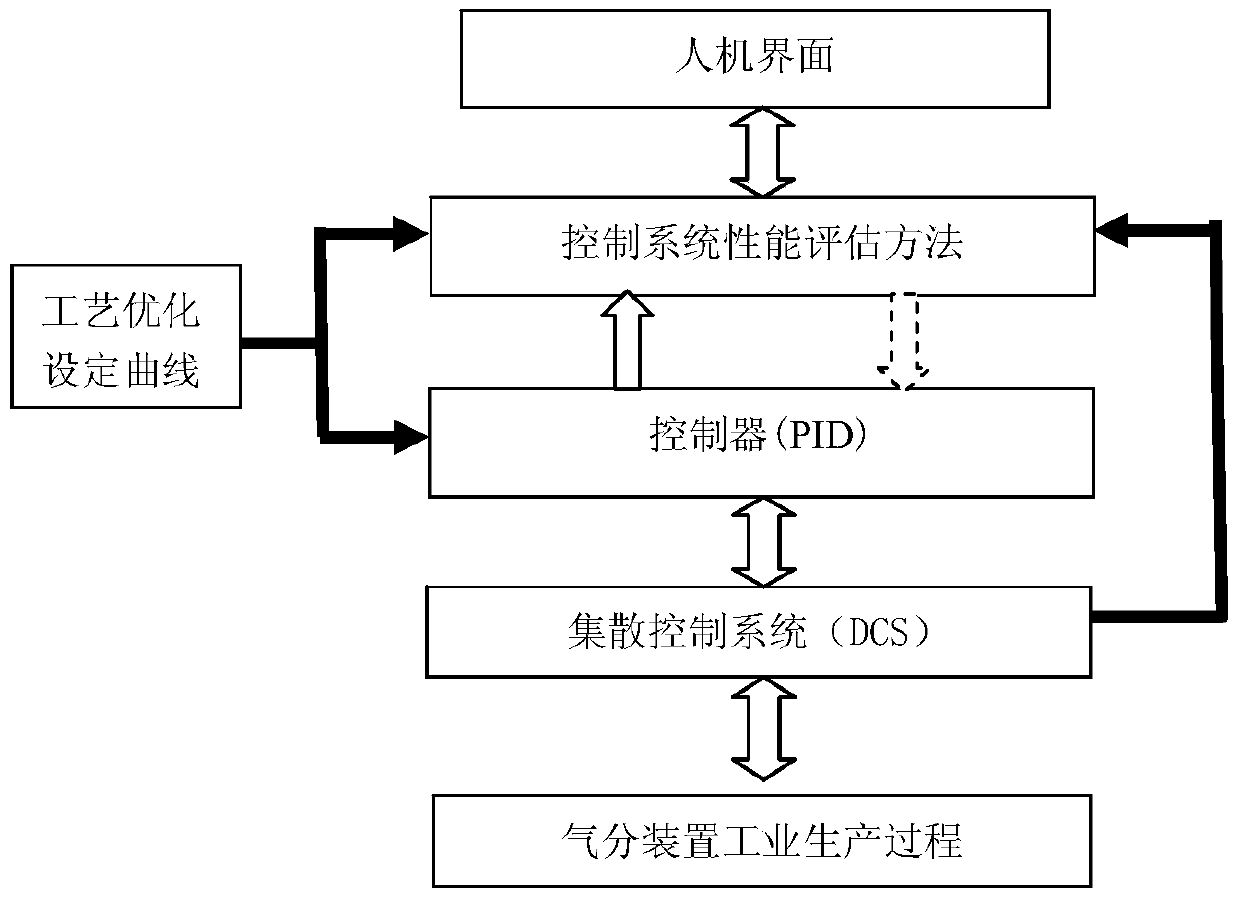

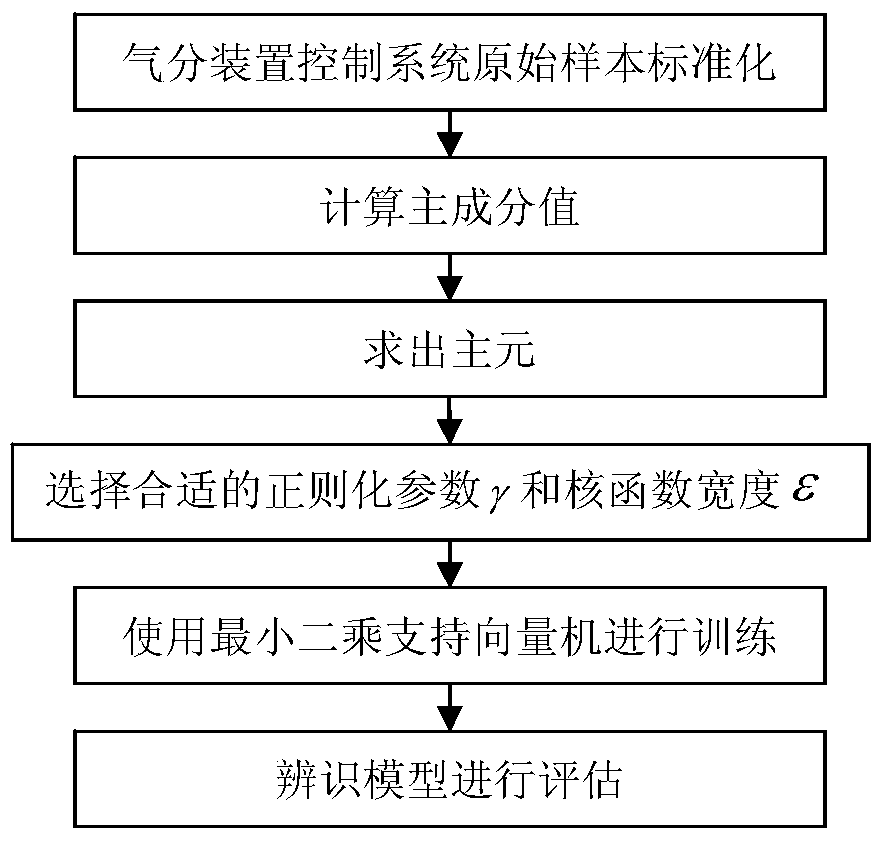

Gas fractionation device control system performance evaluation method based on PCA (Principle Component Analysis)-LSSVM (Least Squares Support Vector Machine)

ActiveCN104865944AReduce operational complexityFast evaluationElectric testing/monitoringEvaluation resultComputation complexity

The invention relates to a gas fractionation device control system performance evaluation method based on PCA (Principle Component Analysis)-LSSVM (Least Squares Support Vector Machine), which comprises the following steps: a PCA method is adopted for carrying out dimension reduction processing on data; acquired main component values are trained via the LSSVM, and a model is built; and a performance index value calculated through the obtained model serves as an evaluation result. The PCA-LSSVM method is used for building the system model, the model is used for control system performance evaluation, a correlation matrix of the control system does not need to be obtained, computation complexity is reduced, and the evaluation speed is enhanced.

Owner:LIAONING UNIVERSITY OF PETROLEUM AND CHEMICAL TECHNOLOGY

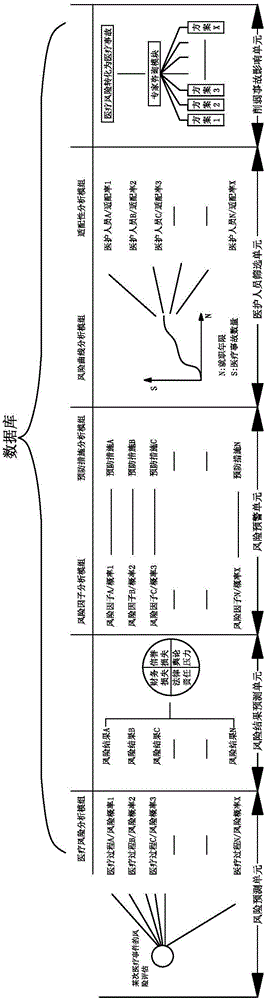

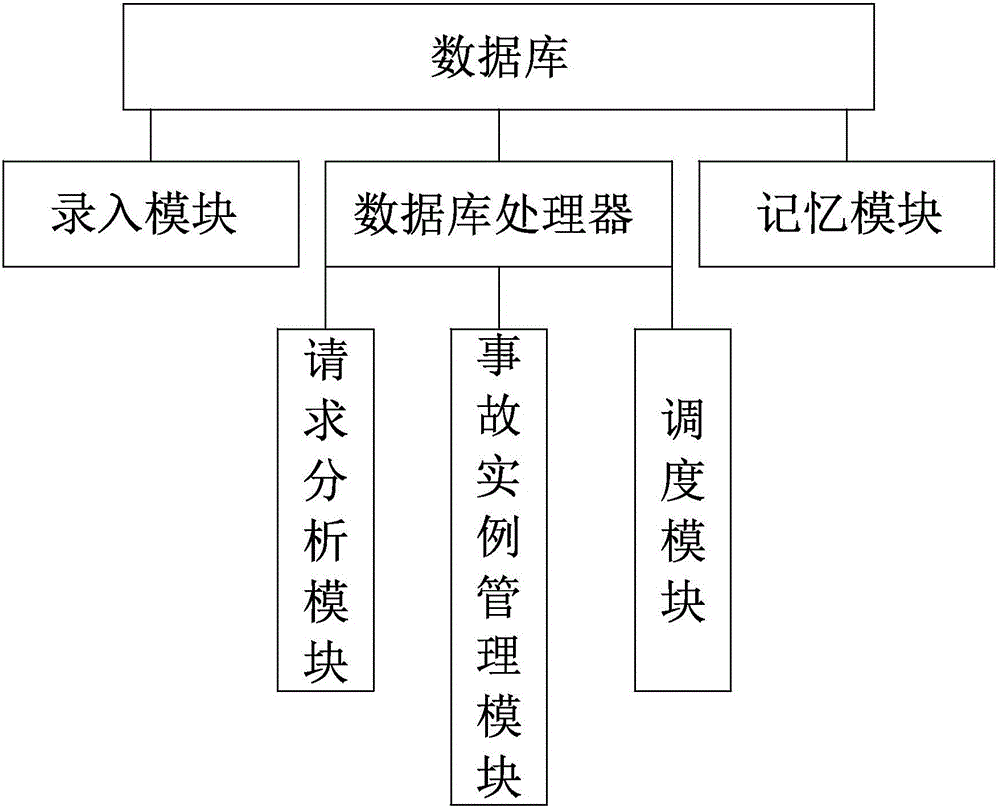

Hospital medical risk assessment system and method

InactiveCN105740992AEasy to operateEvaluation takes less timeForecastingResourcesLong term monitoringEmergency medicine

The invention discloses a hospital medical risk assessment system. The hospital medical risk assessment system comprises a database and an assessment system, the database comprises a database processor, and the assessment system comprises a risk prediction unit, a risk result prediction unit, a risk early-warning unit, a medical care personnel screening unit and an accident influence weakening unit. The risk assessment system having a novel mode is constructed on the basis of the structure, the risk prediction unit, the risk result prediction unit, the risk early-warning unit, the medical care personnel screening unit and the accident influence weakening unit successively analyze a medical practice in the assessment process. Compared with the prior art, the risk assessment system has the advantages of convenient operation, a concise and reasonable operation standard, a concise and reasonable operation flow, short assessment-consumed time, the high response speed and obviously raised risk assessment efficiency. In the test process, long-term monitoring for hospital medical risks is achieved, the medical risks are substantially reduced, and the generation probability of medical accidents is reduced.

Owner:ZHEJIANG UNIV

Dispatching optimization method based on two-layer nest structure

InactiveCN104460594AFast evaluationThe evaluation result is accurateTotal factory controlProgramme total factory controlHigh probabilityManufacturing enterprises

The invention relates to a dispatching optimization method based on a two-layer nest structure and belongs to the technical field of industrial automation. A nest optimization algorithm structure is adopted for the problem of mixed integral non-linear programming (MINLP) existing in the production dispatching of most of manufacturing enterprises, global search is conducted by means of continuous updating of multiple solutions without the gradient information of a solution space, a feasible coarse judgment model is added and constructed, the feasibility of a solution is coarsely and fast judged before the solution evaluation, so that it is ensured that the true satisfactory solution of the dispatching model is obtained with a high probability, the calculated amount is small, the optimizing process is simple, and the application range is wide.

Owner:TSINGHUA UNIV

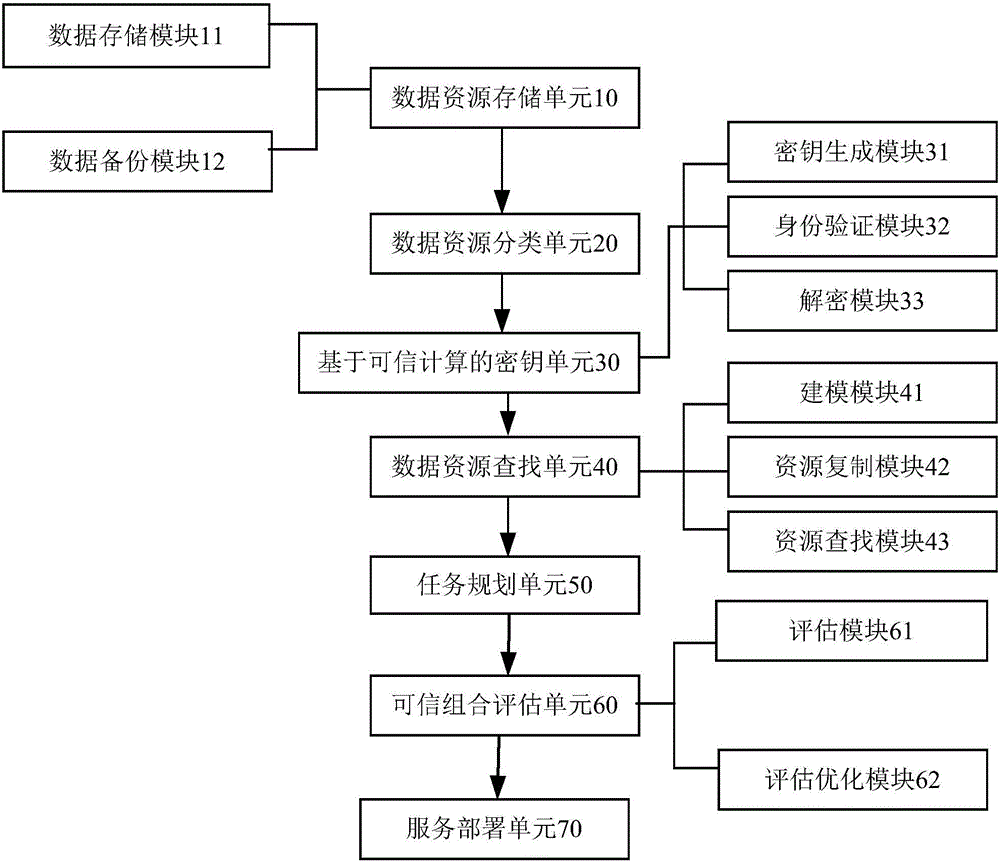

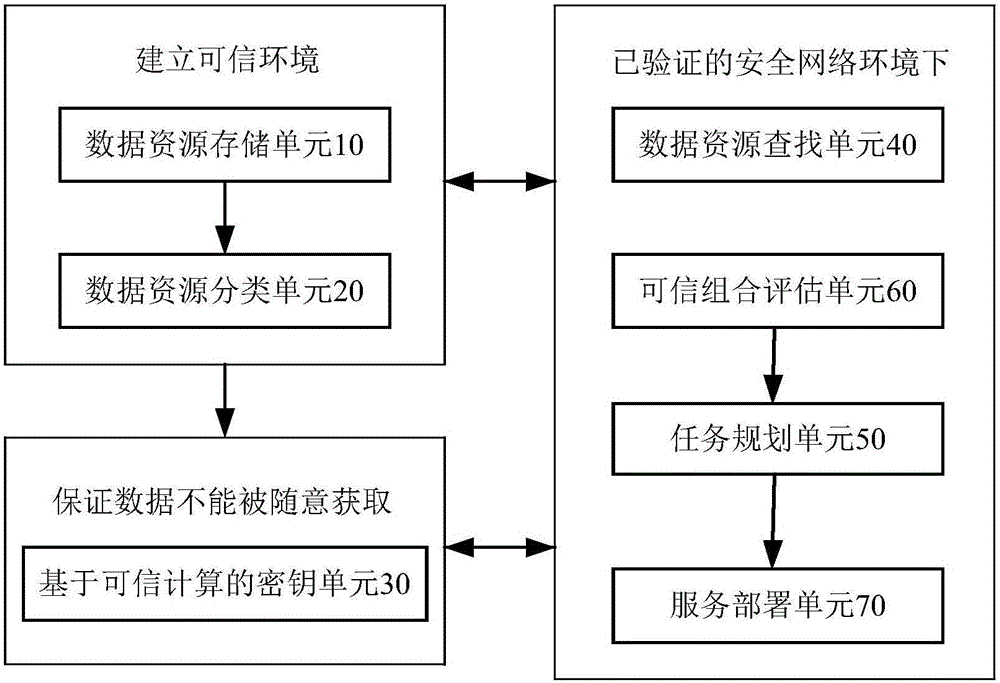

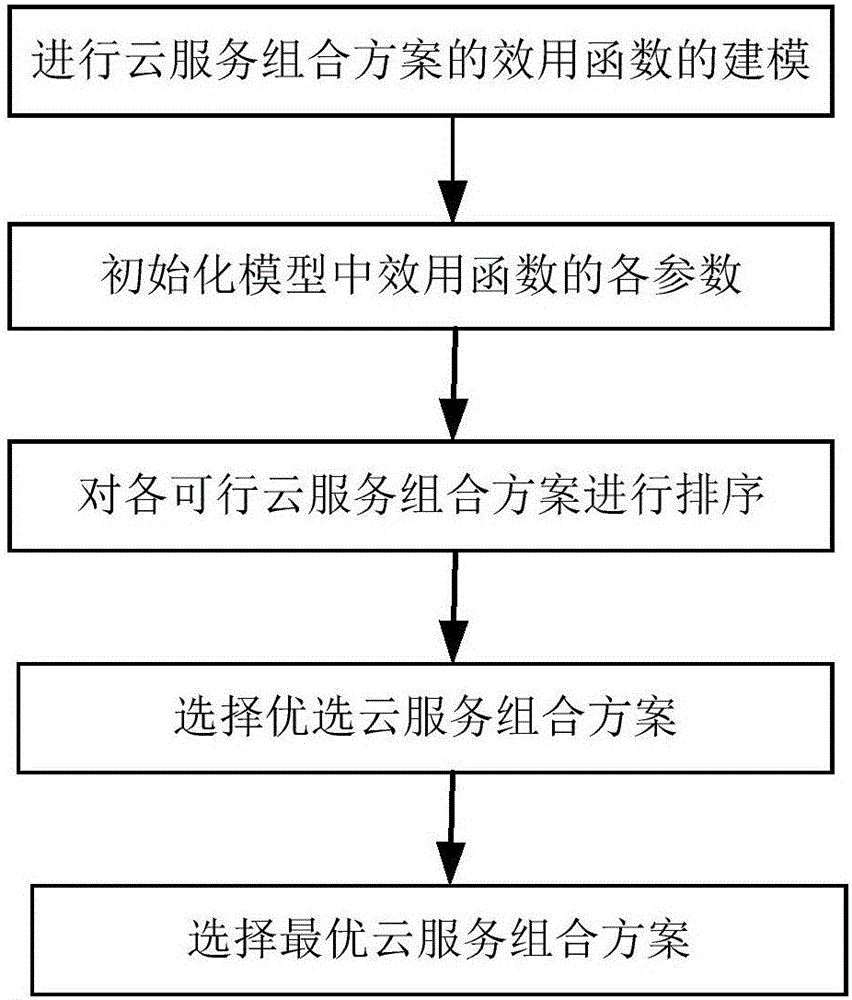

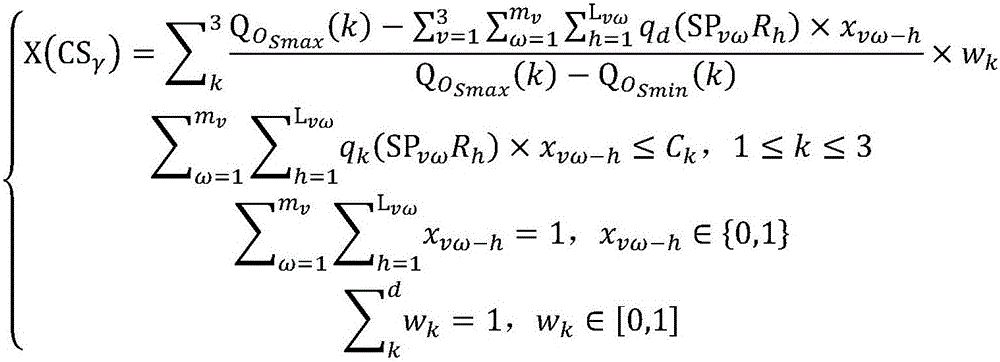

Information security big-data resource management system based on trusted computing and cloud computing

ActiveCN106203164AIncrease credibilityProcessing speedDigital data protectionResource Management SystemTrust relationship

The invention discloses an information security big-data resource management system based on trusted computing and cloud computing. The information security big-data resource management system comprises a data resource storage unit, a data resource classification unit, a key unit based on trusted computing, a data resource searching unit, a task planning unit, a trusted combination evaluation unit and a service deployment unit. A system architecture is that a credibility evaluation mechanism and a trusted relationship transmission mechanism are constructed on the basis of characteristic foundation including a protective function, authentication and integrity measurement, so that a trusted chain from data resource storage, data resource searching to data resource service distribution is established. By means of the information security big-data resource management system disclosed by the invention, effective management of big-data resources is realized; and the security and the creditability of the system are improved.

Owner:上海宽惠网络科技股份有限公司

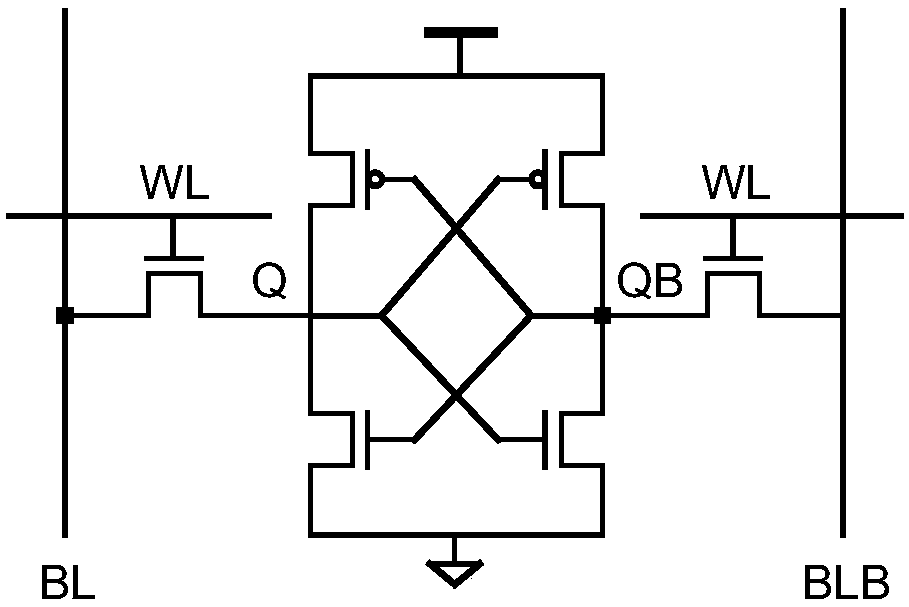

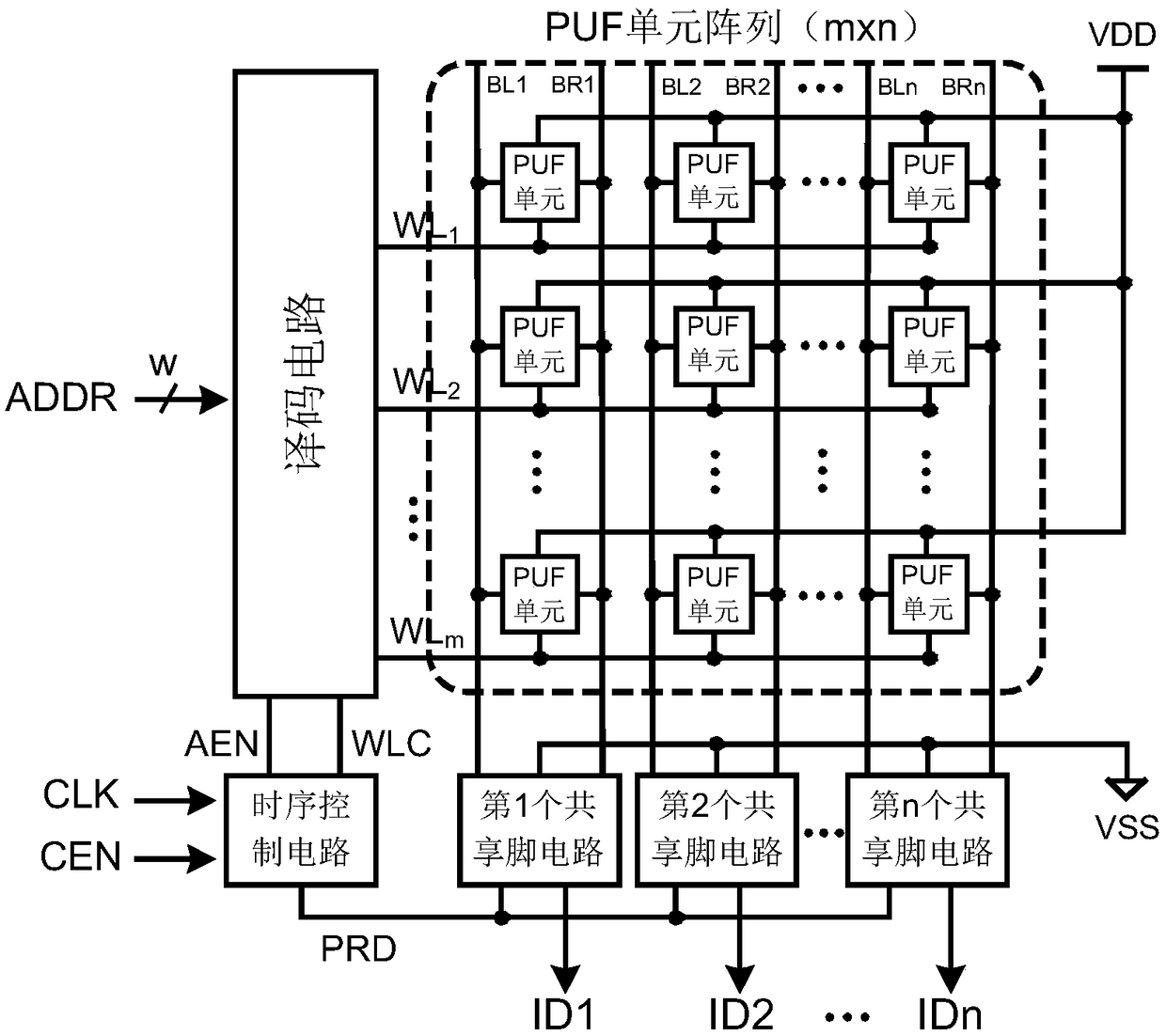

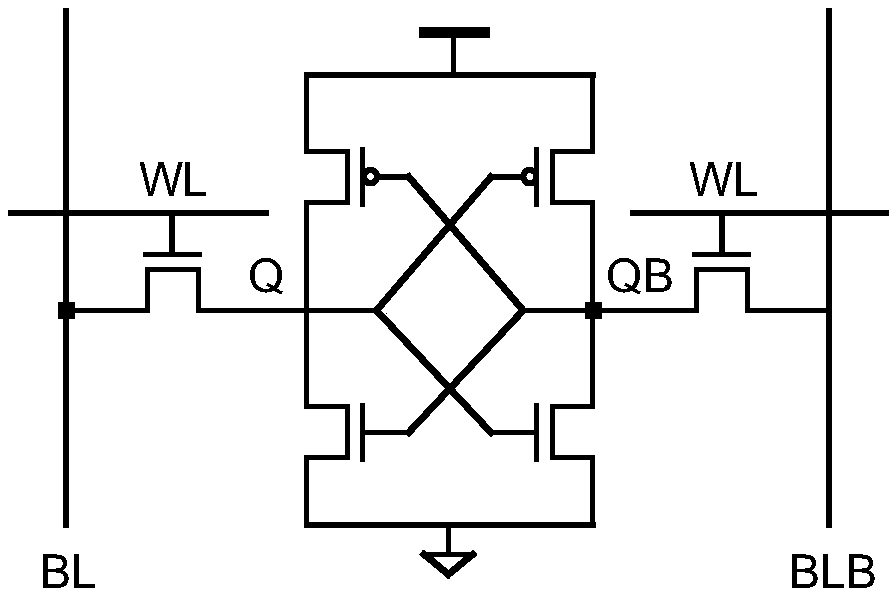

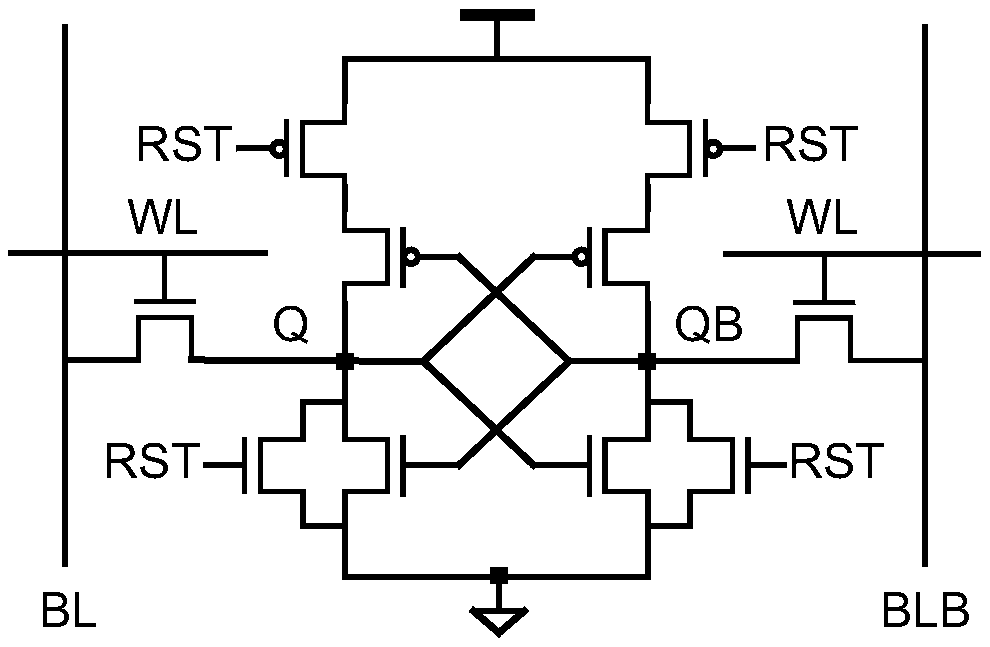

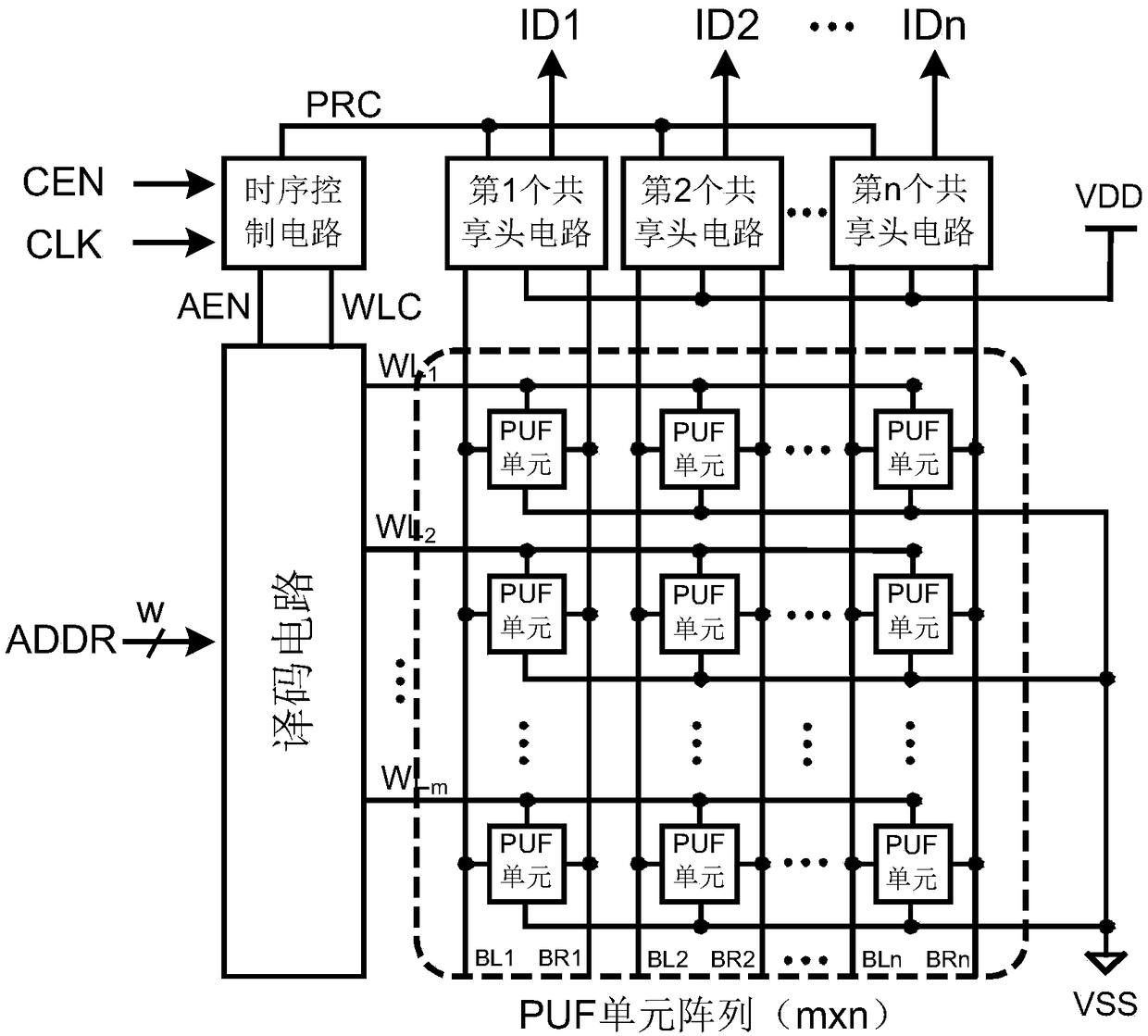

A weakly physically non-clonable function circuit utilizing PMOS process deviations

ActiveCN109241782AReduce power consumptionReduce latencyReliability increase in field effect transistorsInternal/peripheral component protectionProcess deviationsNAND gate

The invention discloses a weak physical non-clone function circuit utilizing PMOS process deviation, including a decoding circuit, a sequencing circuit, an array of PUF cells and n shared pin circuits, The PUF cell array is formed by arranging m * n PUF cells in m rows and n columns, the PUF unit includes a first PMOS transistor, second PMOS transistor, third PMOS transistor and fourth PMOS transistor and the width-to-length ratios of the four PMOS transistors are all minimum sizes in the TSMC 65 nm process: 120 nm / 60 nm, each share pin circuit comprises a first NMOS transistor, a second NMOStransistor, a third NMOS transistor, a fourth NMOS transistor, a first two-input NAND gate and a second two-input NAND gate, and that width-to-length ratio of the four NMOS transistor ranges from 2 mum / 60 nm to 8 mum / 60 nm; The circuit has the advantages of small area, low power consumption, small delay and high speed on the basis of the reset function.

Owner:NINGBO UNIV

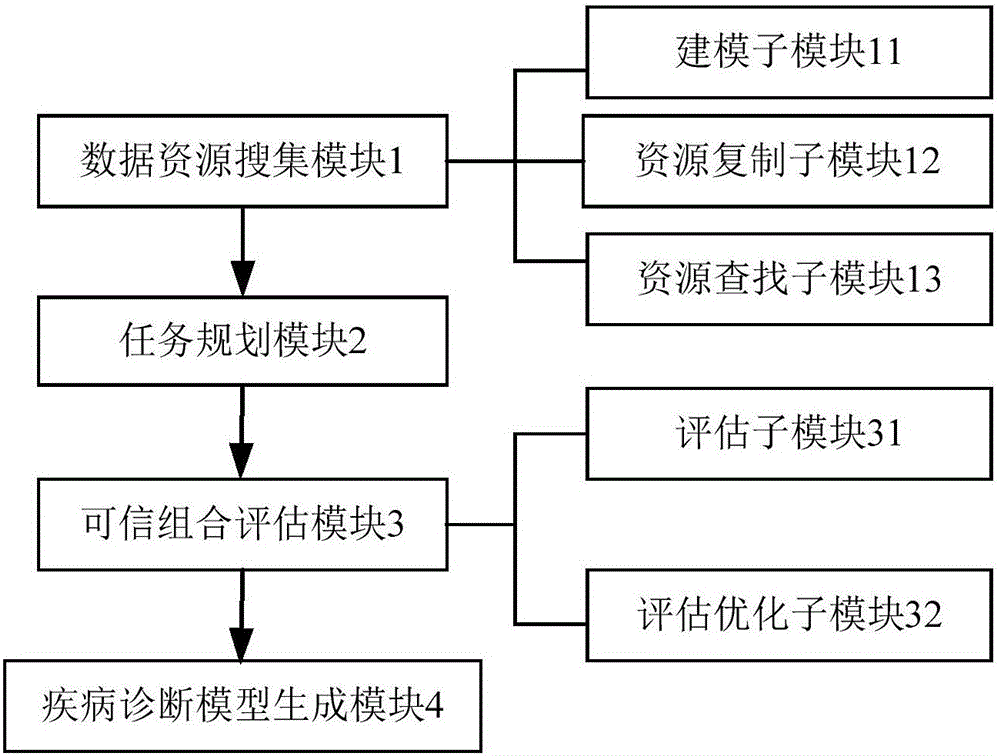

Cloud computing based disease self-diagnosis service construction system

InactiveCN105933172AImplement the buildEasy to findData processing applicationsWeb data indexingMedical recordDisease

The invention discloses a cloud computing based disease self-diagnosis service construction system, which comprises a data resource collection module, a task planning module, a credible combination assessment module and a disease diagnosis model generation module, wherein the data resource collection module comprises a modeling submodule, a resource replication submodule and a resource search submodule, and the credible combination assessment module comprises an assessment submodule and an assessment optimization submodule. The cloud computing based disease self-diagnosis service construction system is provided with the data resource collection module, thereby facilitating users to use data resources through matching service description information, further increasing the coverage rate of data resource information in the network, and improving the search efficiency of medical record data resources; and the cloud computing based disease self-diagnosis service construction system is provided with the credible combination assessment module in order to efficiently realize low-cost disease self-diagnosis services, the credibility of a big data service supporting cloud service combination scheme is improved, and storage and computing resources of the cloud are utilized in a maximum benefit manner. In addition, the assessment time is saved, and the assessment speed is improved.

Owner:吴本刚

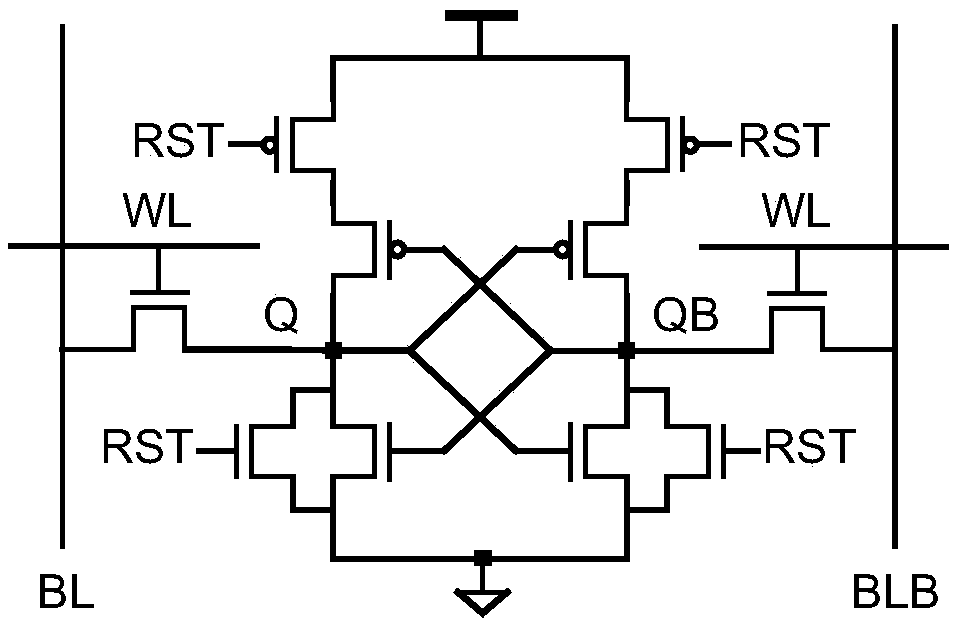

A weakly physically non-clonable function circuit utilizing NMOS process deviations

ActiveCN109067552AReduce power consumptionReduce latencyUser identity/authority verificationProcess deviationsNAND gate

The invention discloses a weak physical non-clone function circuit utilizing NMOS process deviation, including a decoding circuit, sequencing circuit, an array of PUF cells and n shared head circuits,the PUF cell array is formed by arranging m plus n PUF cells in m rows and n columns, a PUF unit includes a first NMOS transistor, second NMOS transistor, the third NMOS transistor and the fourth NMOS transistor and the aspect ratios of the four PMOS transistors are all minimum sizes in the TSMC 65 nm process: 120nm / 60nm, each shared head circuit includes a first PMOS transistor, a second PMOS transistor, a third PMOS transistor, a fourth PMOS transistor, a first two-input NAND gate and a second two-input NAND gate. The aspect ratios of the four NMOS transistors range from 2um / 60nm to 16um / 60nm. The utility model has the advantages of small area, low power consumption, small delay and high speed on the basis of the reset function.

Owner:WENZHOU UNIVERSITY

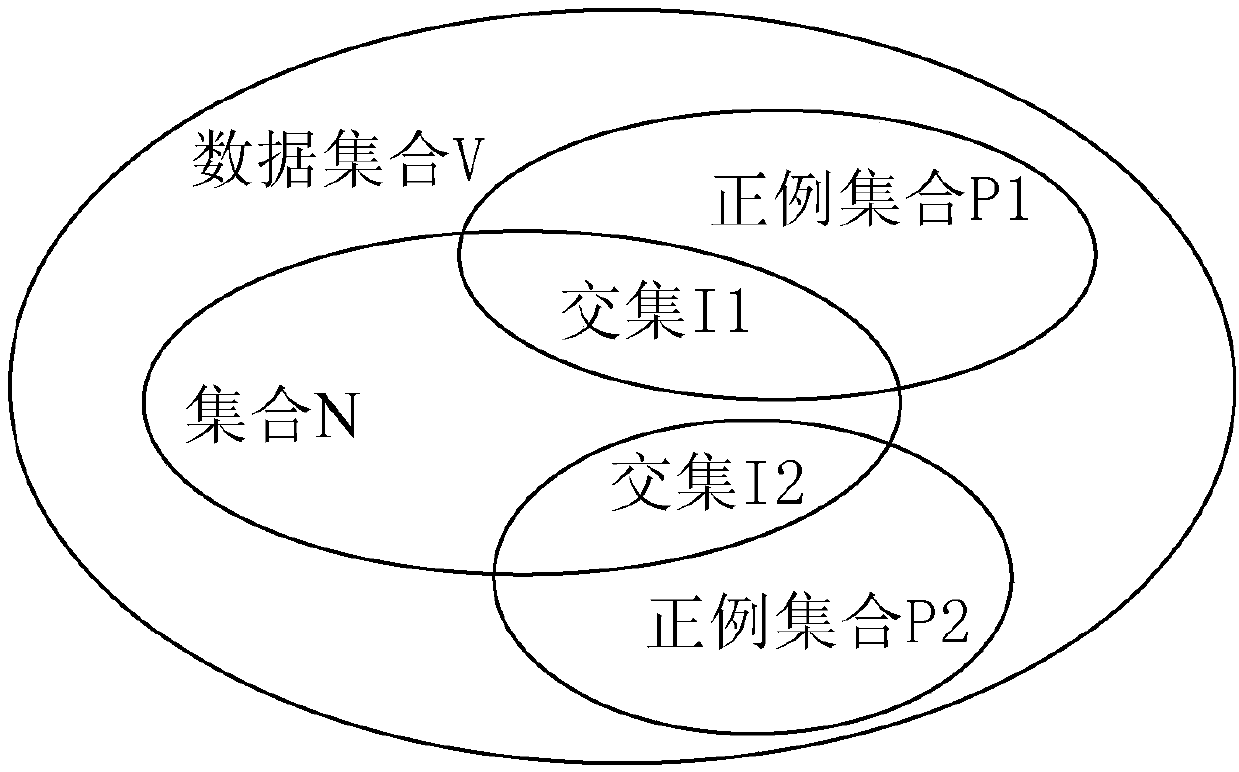

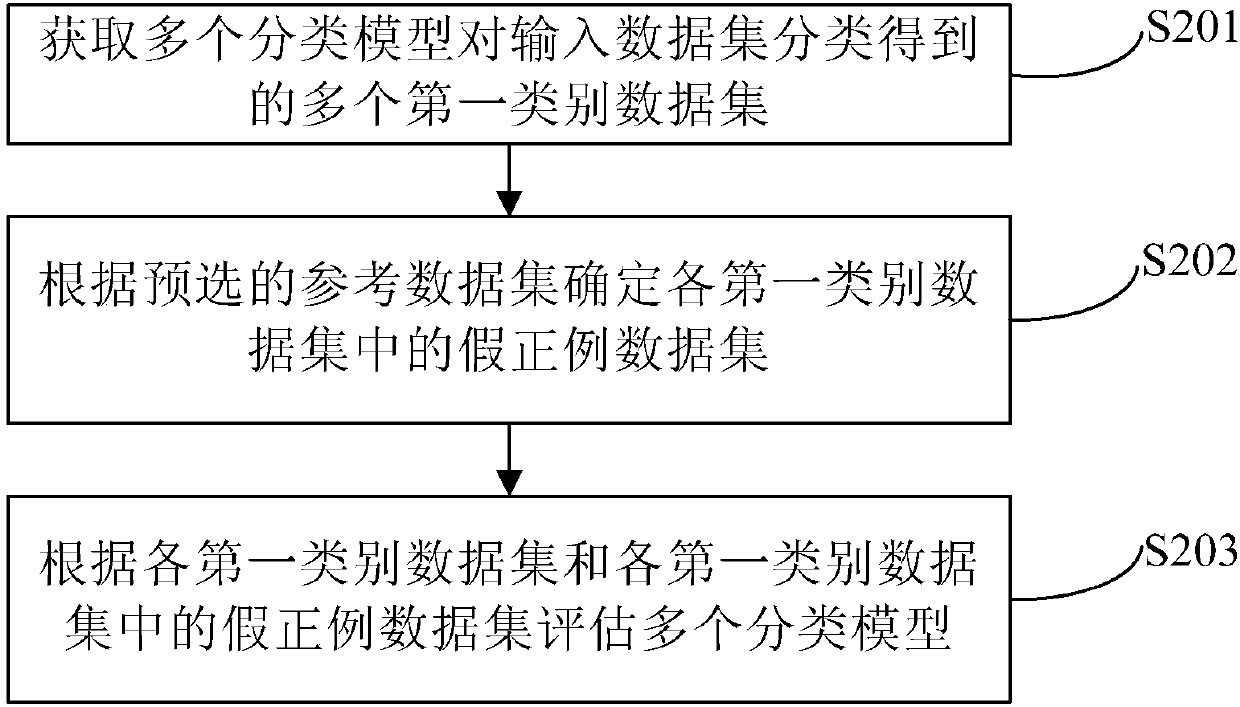

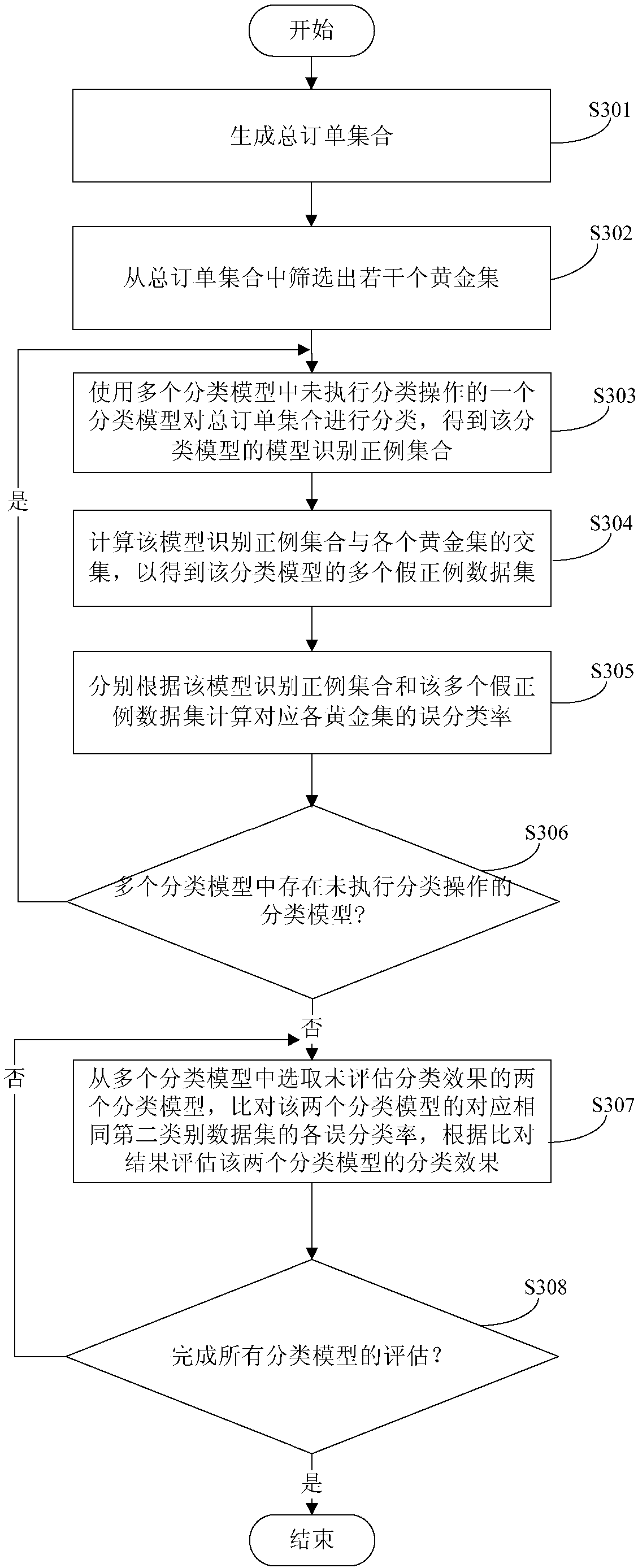

A method and device for evaluating a classification model

InactiveCN109784352AImprove development efficiencyGet rid of the dependence of manual labelingCharacter and pattern recognitionData setDependability

The invention discloses a method and device for evaluating a classification model, and relates to the technical field of computers. A specific embodiment of the method comprises the steps of obtaininga plurality of first category data sets obtained by classifying an input data set by a plurality of classification models, wherein each first category data set corresponds to one classification model; Determining a false positive example data set in each first type of data set according to the pre-selected reference data set; And evaluating the plurality of classification models according to thefirst category data sets and the false positive example data sets in the first category data sets. The implementation mode can completely get rid of dependence on manual marking, the operation processcan be fully automatically operated, the evaluation cost is reduced, the evaluation speed is increased, the evaluation range is expanded, the evaluation reliability is improved, and the model development efficiency is improved.

Owner:BEIJING JINGDONG SHANGKE INFORMATION TECH CO LTD +1

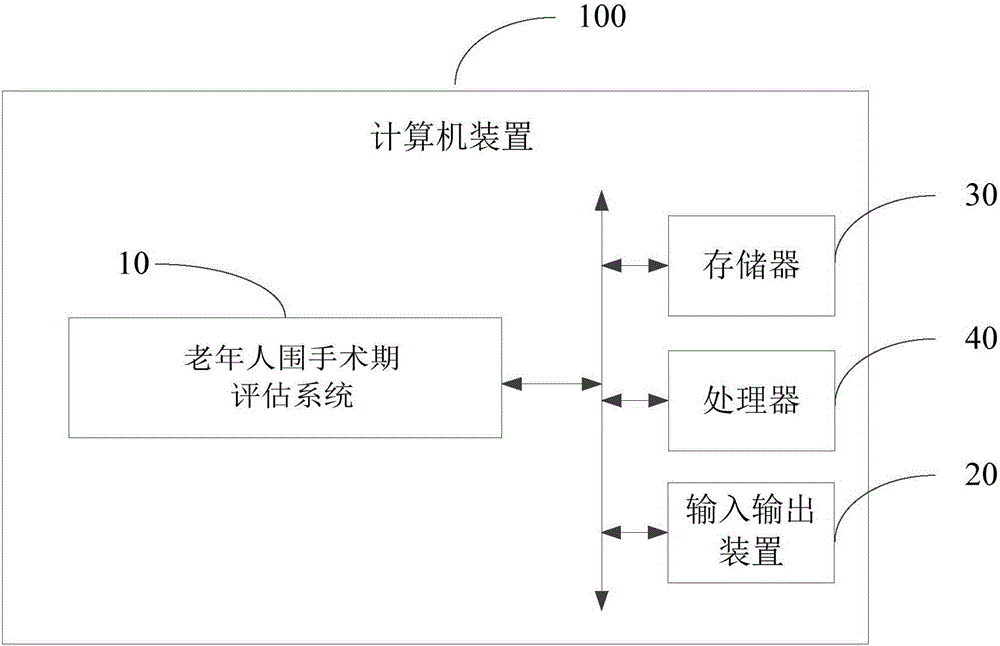

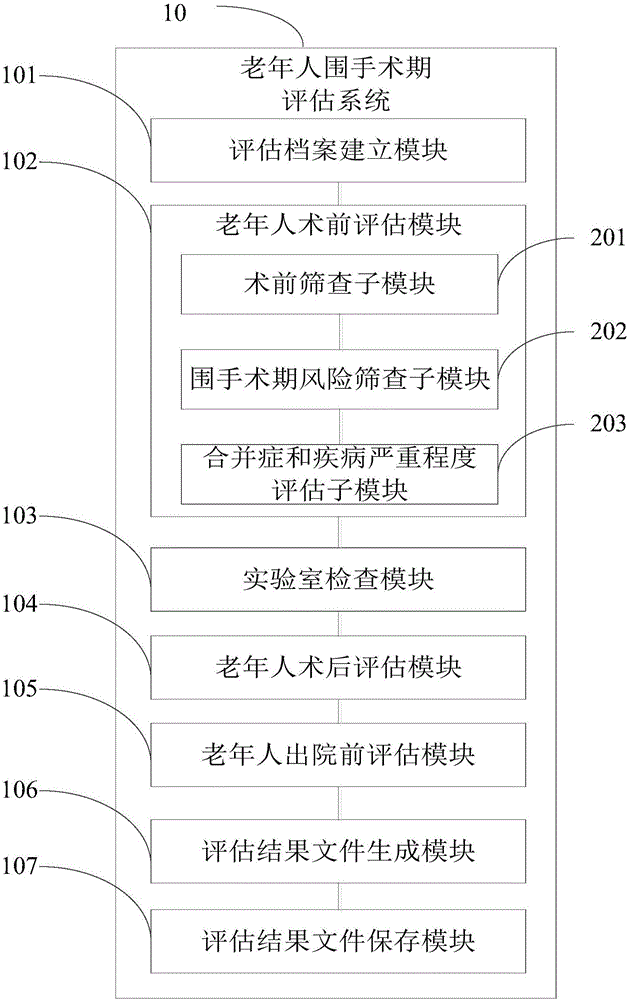

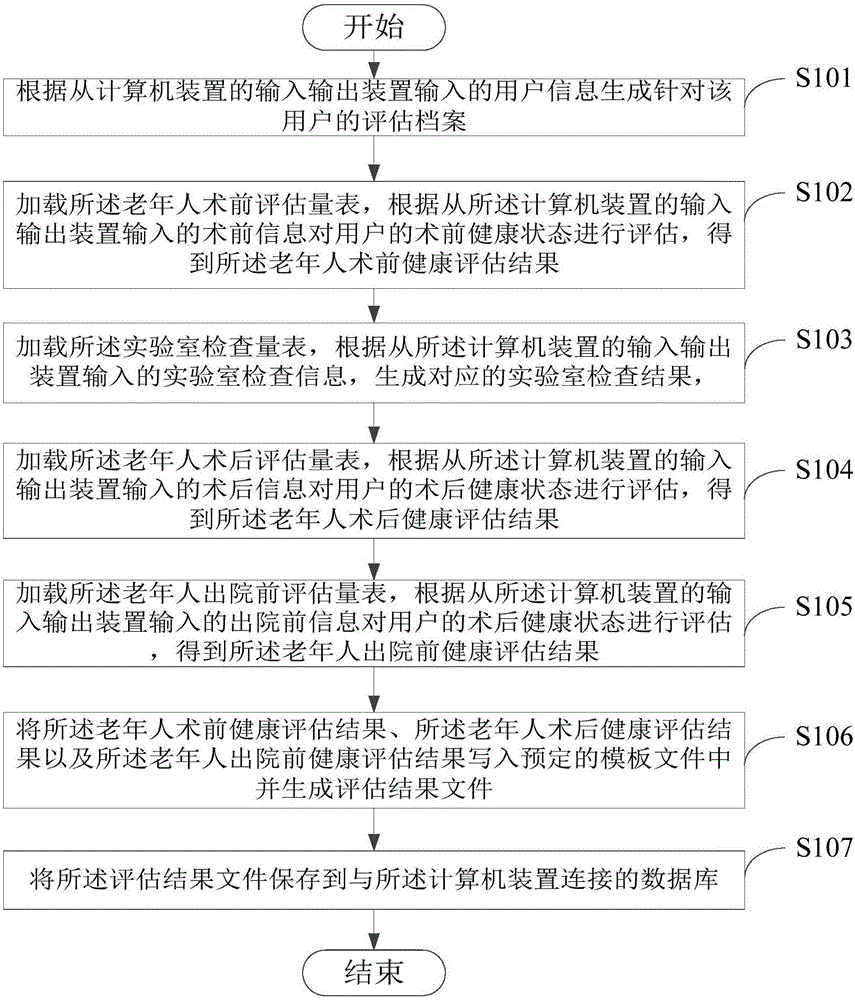

Assessment system and method for perioperative period of old people

InactiveCN106295157AFast evaluationImprove efficiencyMedical simulationHealth-index calculationOlder peopleThe Internet

The embodiment of the invention provides an assessment system and method for the perioperative period of old people, and relates to the field of internet medical treatment. In different stages of the perioperative period of the old people, health assessment results in the different stages are generated according to input information of input and output devices in combination with corresponding assessment scales, and the health states of the old people in the whole perioperative period are integrally assessed. The whole assessment process is automatically accomplished by a computer, and the assessment speed is high, so that the health assessment of the perioperative period of the old people is simpler and more convenient.

Owner:董碧蓉 +2

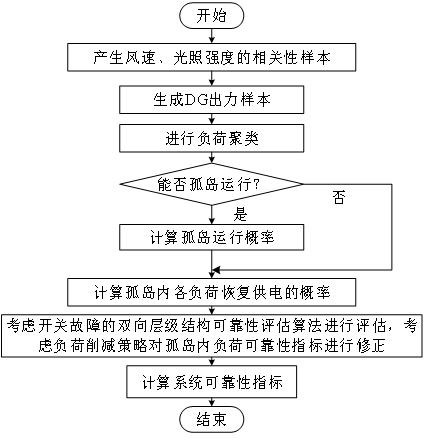

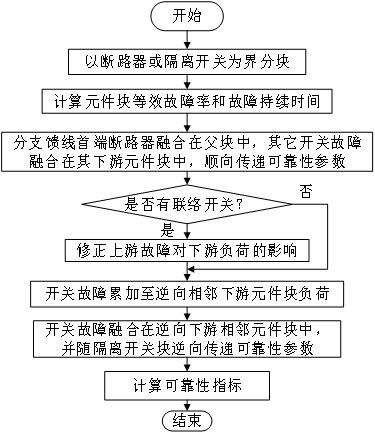

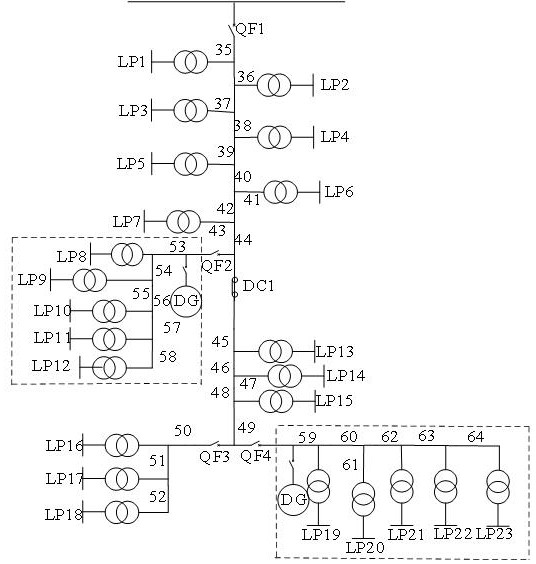

Power distribution system reliability evaluation method considering distributed power supply correlation

ActiveCN111753397AAdapt to engineering realityFast evaluationDesign optimisation/simulationResourcesSolar powerPeak load

The invention relates to a power distribution system reliability evaluation method considering distributed power supply correlation. The method comprises the following steps of S1, considering uncertainty of a distributed power supply and correlation between wind power and illumination intensity, analyzing a wind-solar power generation output law, and based on Latin hypercube sampling, combining aSpearman rank correlation coefficient and Cholesky decomposition to obtain a distributed power supply output sample of a specified correlation coefficient; S2, based on the peak load percentage modelof the IEEE reliability test system, clustering by adopting a load clustering technology to obtain the load condition of each load point; s3, evaluating the reliability of the system based on a powerdistribution system reliability evaluation algorithm considering the bidirectional hierarchical structure of the switch fault; and S4, considering the island operation mode of the power distributionnetwork after the distributed power supply is connected, proposing an improved heuristic load reduction strategy with the maximum load shedding amount, and correcting the reliability index of the loadin the island. The reliability calculation efficiency of the system is improved.

Owner:STATE GRID FUJIAN ELECTRIC POWER CO LTD +1

Medical health assessment system and method for old people

InactiveCN106295154AHealth assessment is simple and convenientFast evaluationHealth-index calculationSpecial data processing applicationsOlder peopleThe Internet

The embodiment of the invention provides a medical health assessment system and method for old people, and relates to the internet medical field. According to input user information, an assessment archive which comprises a plurality of health assessment scales is generated; and then, according to a preset assessment standard, the health assessment scales are assessed to obtain an assessment result file and generate a corresponding statement. The whole health assessment process is automatically finished by a computer device, assessment speed is high, efficiency is high, and therefore, the user health assessment is simple and convenient.

Owner:董碧蓉 +1

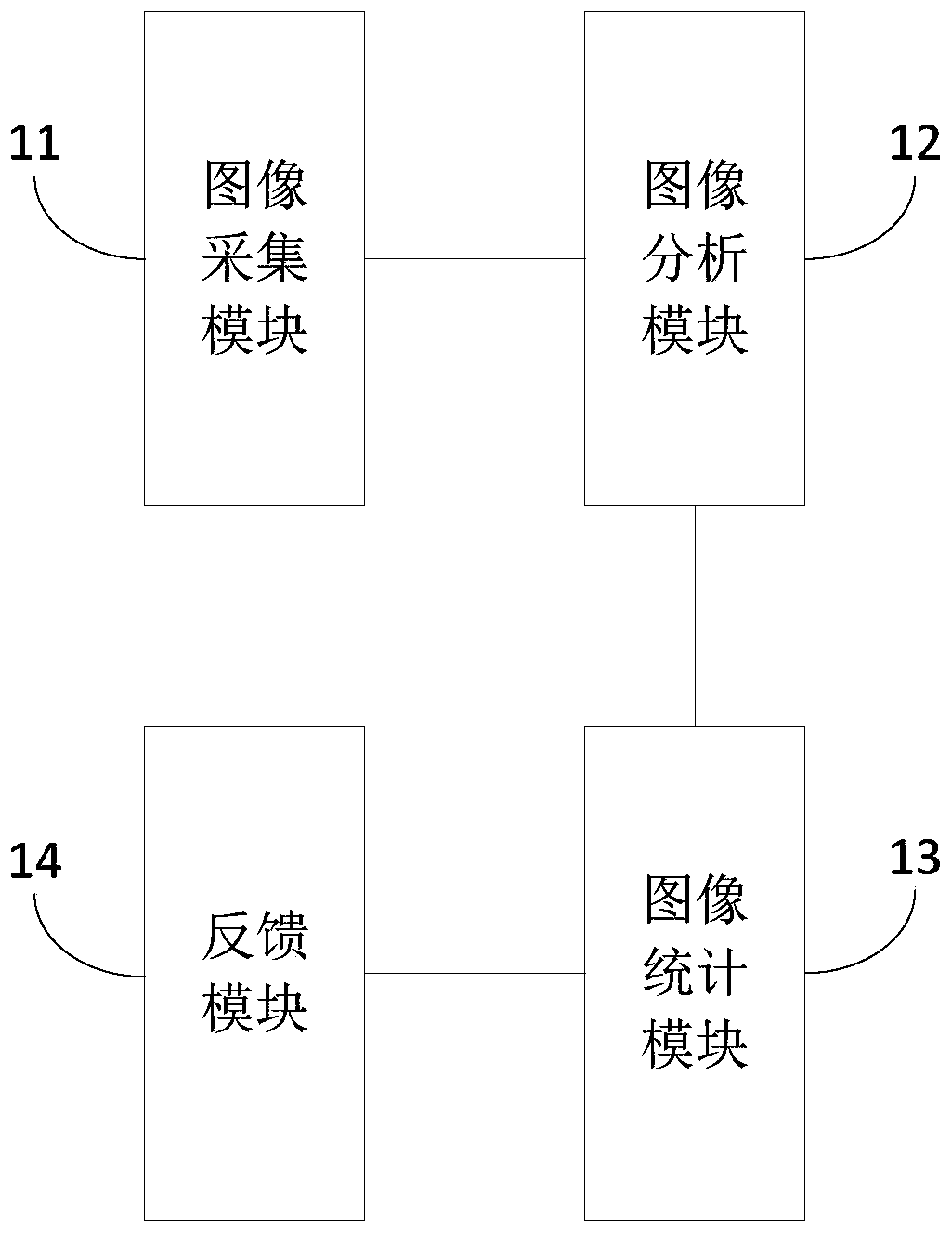

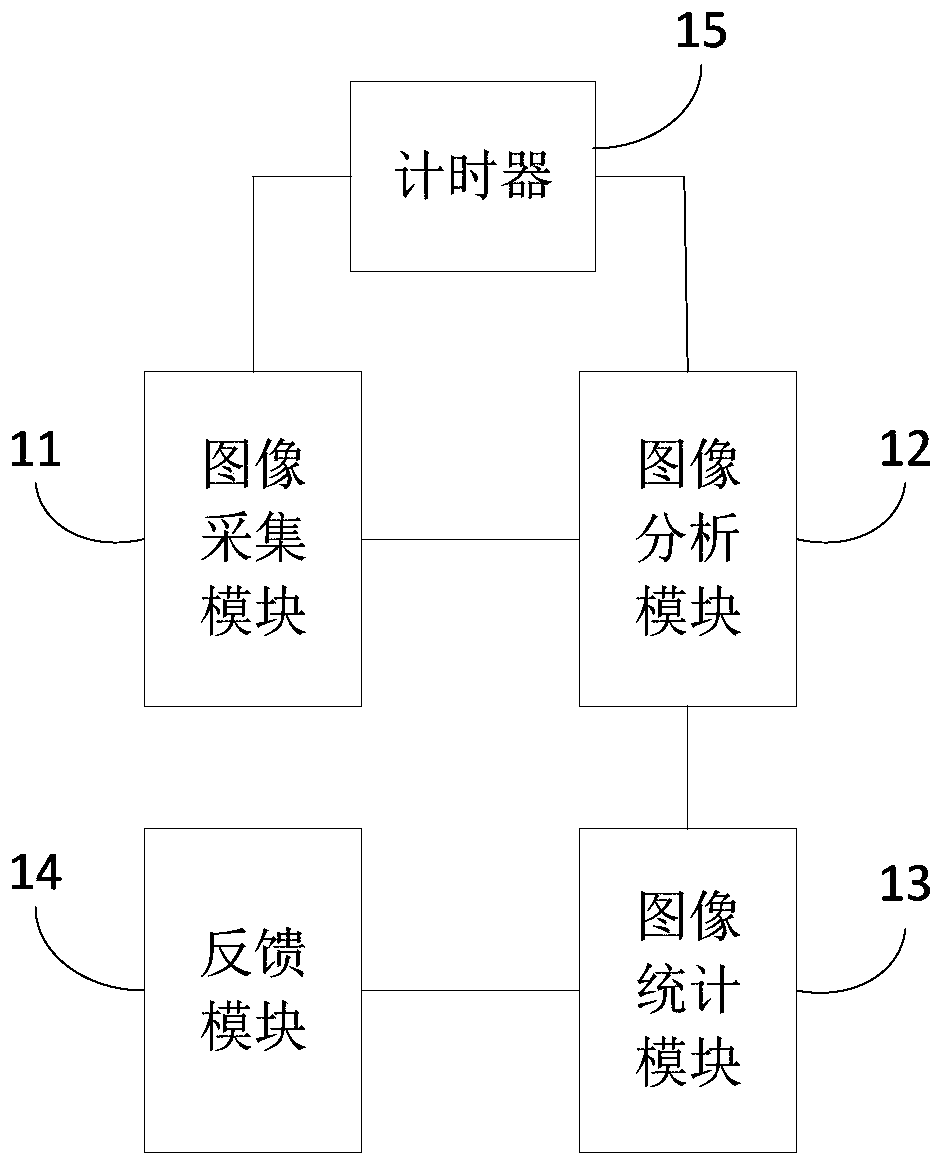

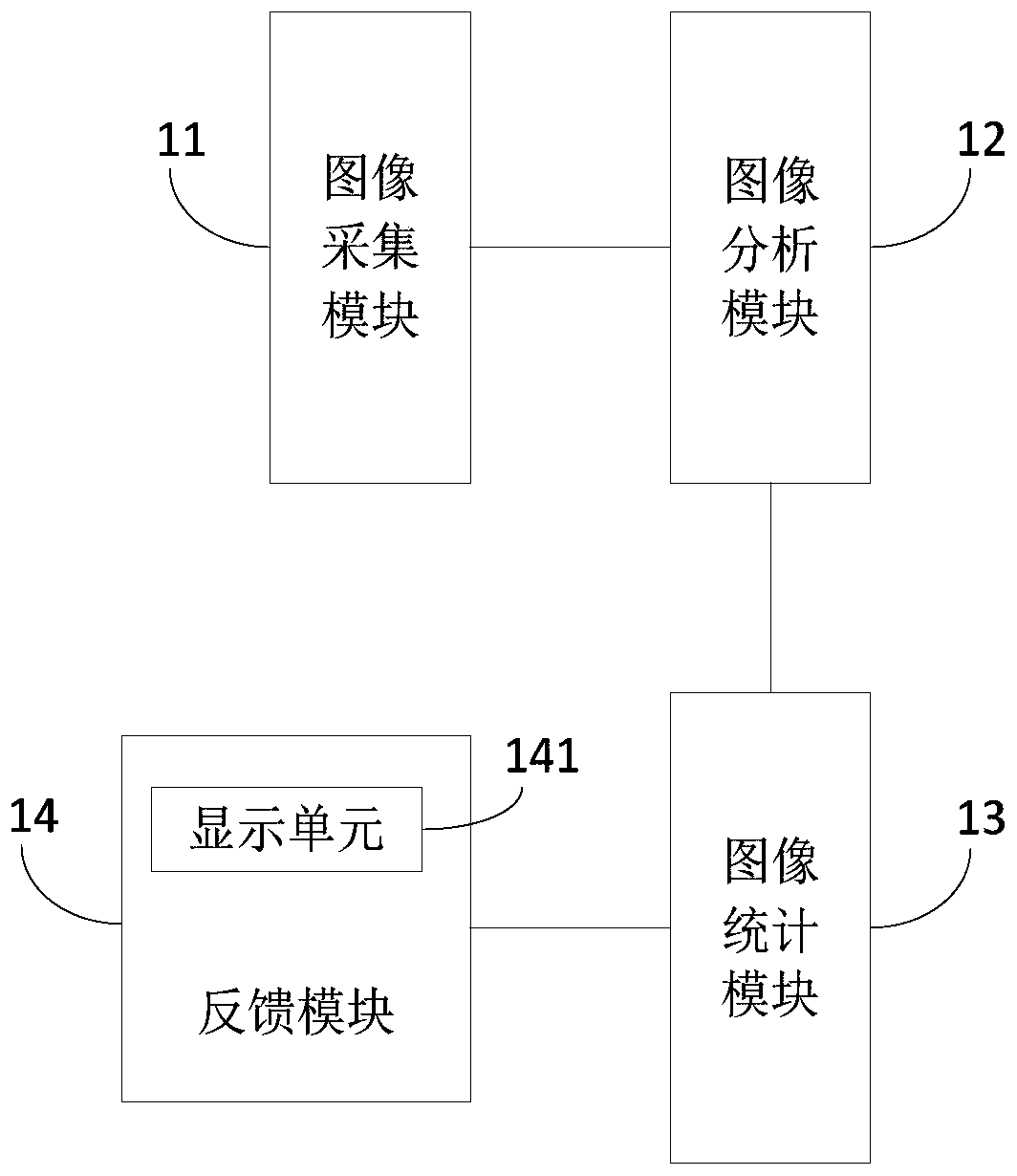

Medical image quality control system and method, computer equipment and readable storage medium

PendingCN110717912AImprove image qualityReduce mistakesImage enhancementImage analysisImaging qualityEngineering

The invention relates to a medical image quality control system and method, computer equipment and a readable storage mediumThe system comprises an image collection module which is configured to collect a medical image of a tested object according to a collection instruction inputted by a collection user, and the medical image comprises a collection user recognition; the image analysis module is configured to perform quality evaluation on the medical image according to a preset quality evaluation algorithm to obtain a quality evaluation result; the image statistics module is configured to perform statistics on the quality evaluation result of the medical image at a preset time interval to obtain a statistics result, and the statistics result comprises a corresponding relationship between the medical image and the collected user identifier and the quality evaluation result; and the feedback module is configured to display the statistical result. The system can automatically perform statistics on the quality evaluation result of the medical image, improves the quality statistics efficiency and reduces the error of the statistics result, thereby realizing the accurate and efficient quality control process of the medical image.

Owner:SHANGHAI UNITED IMAGING INTELLIGENT MEDICAL TECH CO LTD