Patents

Literature

292 results about "Process deviations" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Process Deviation is a measure of variance that tells 1) whether a given process differs from an agreed-upon requirement or course of action and 2) how much the variance is.

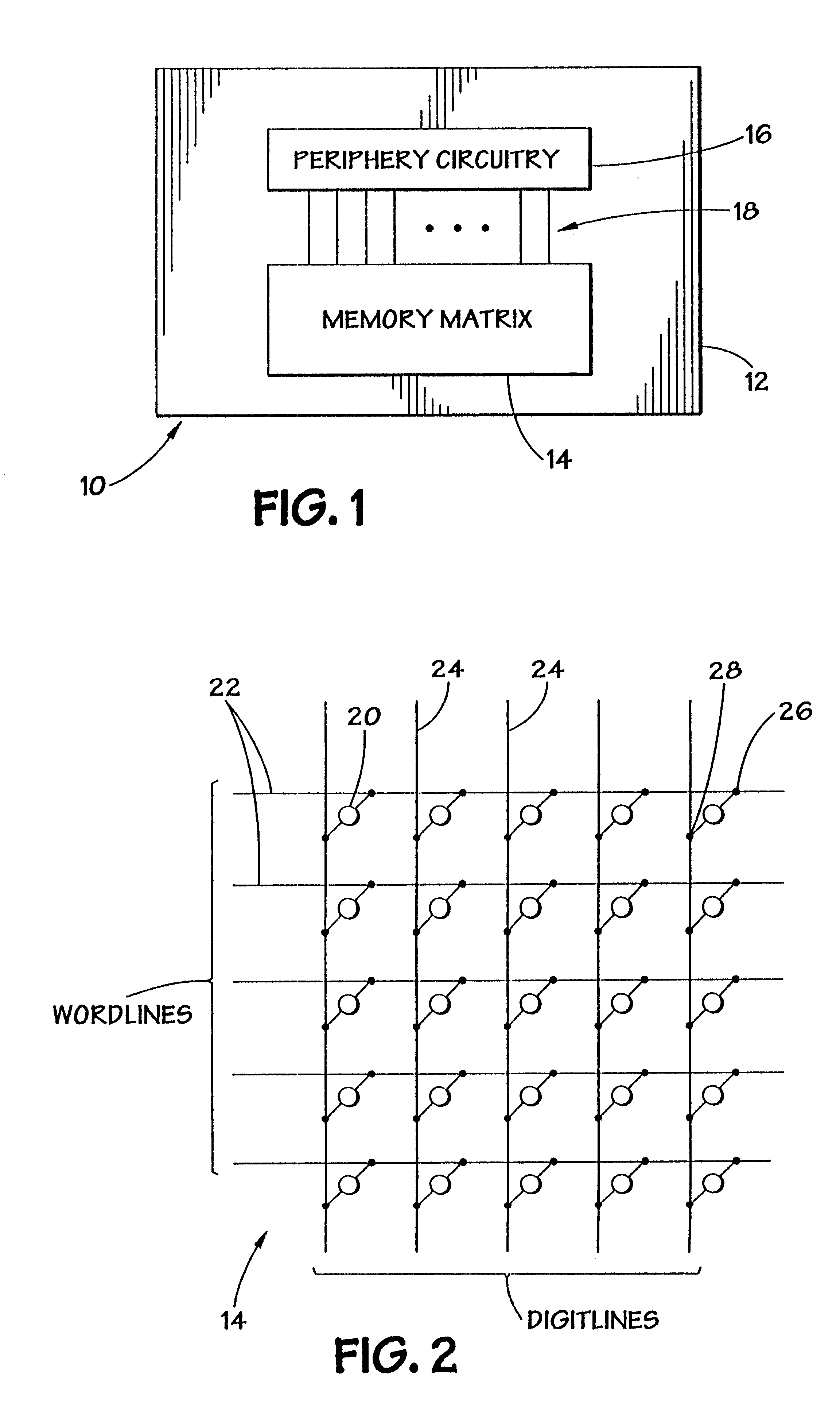

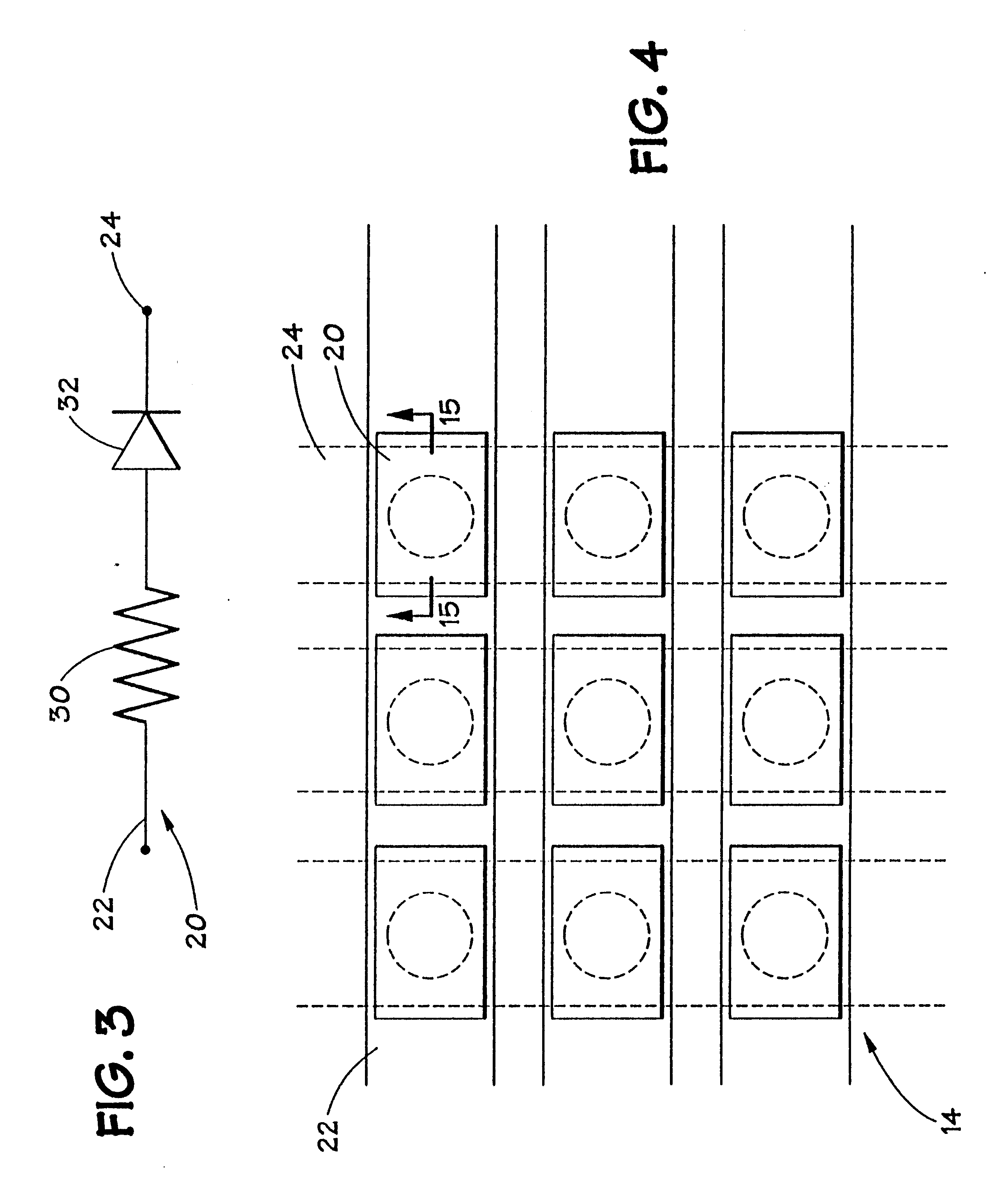

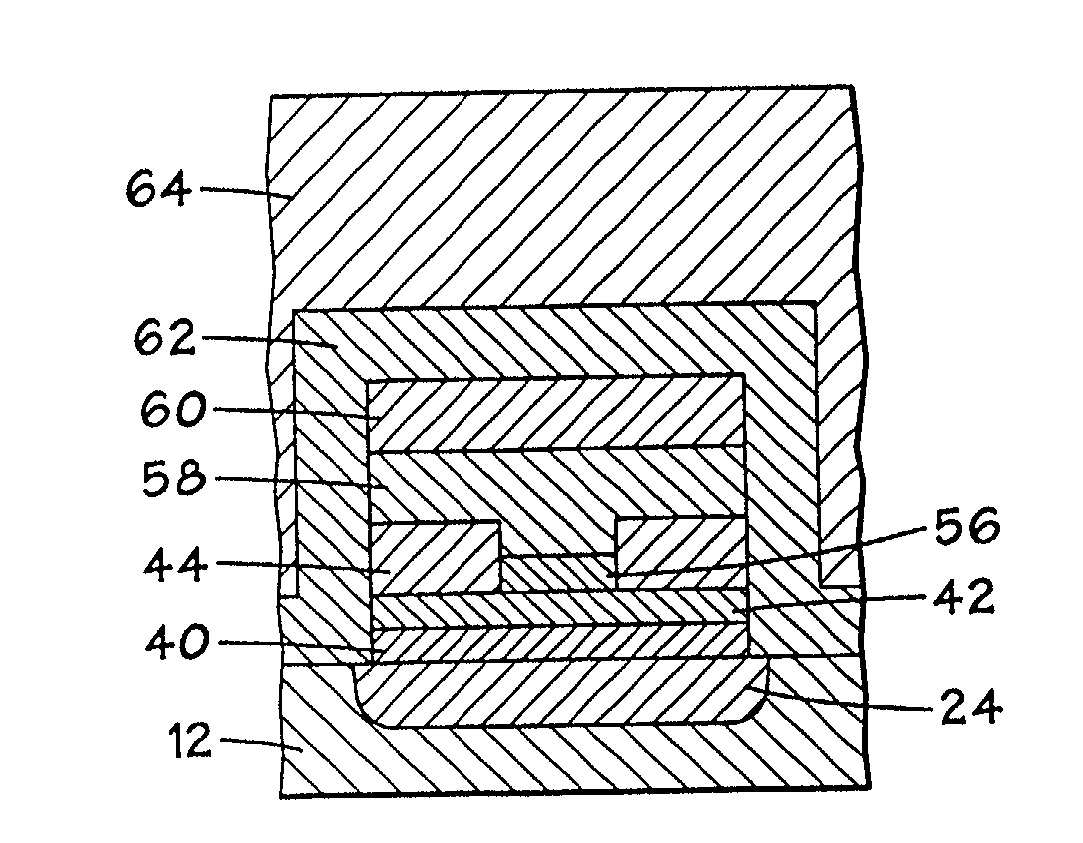

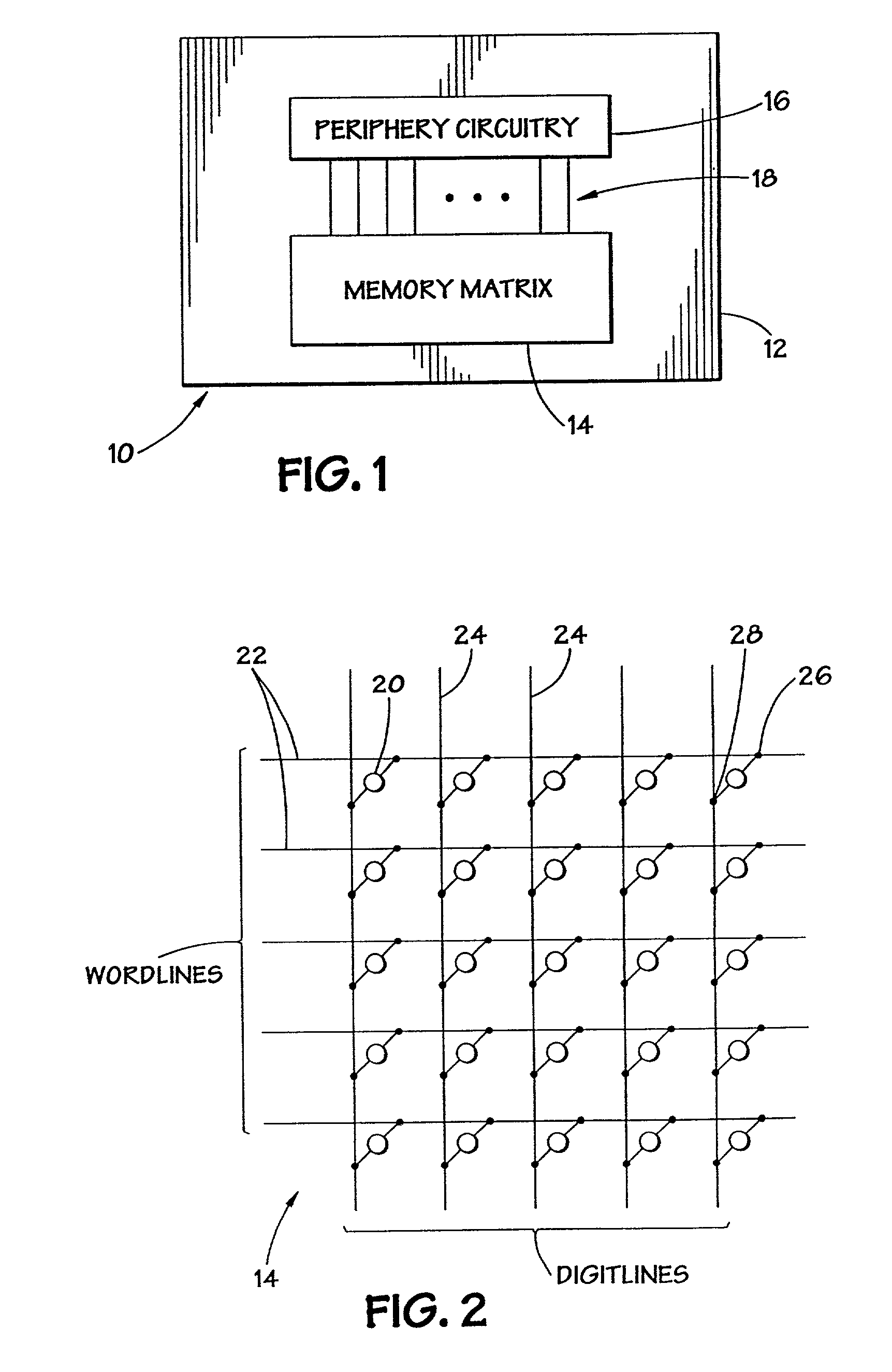

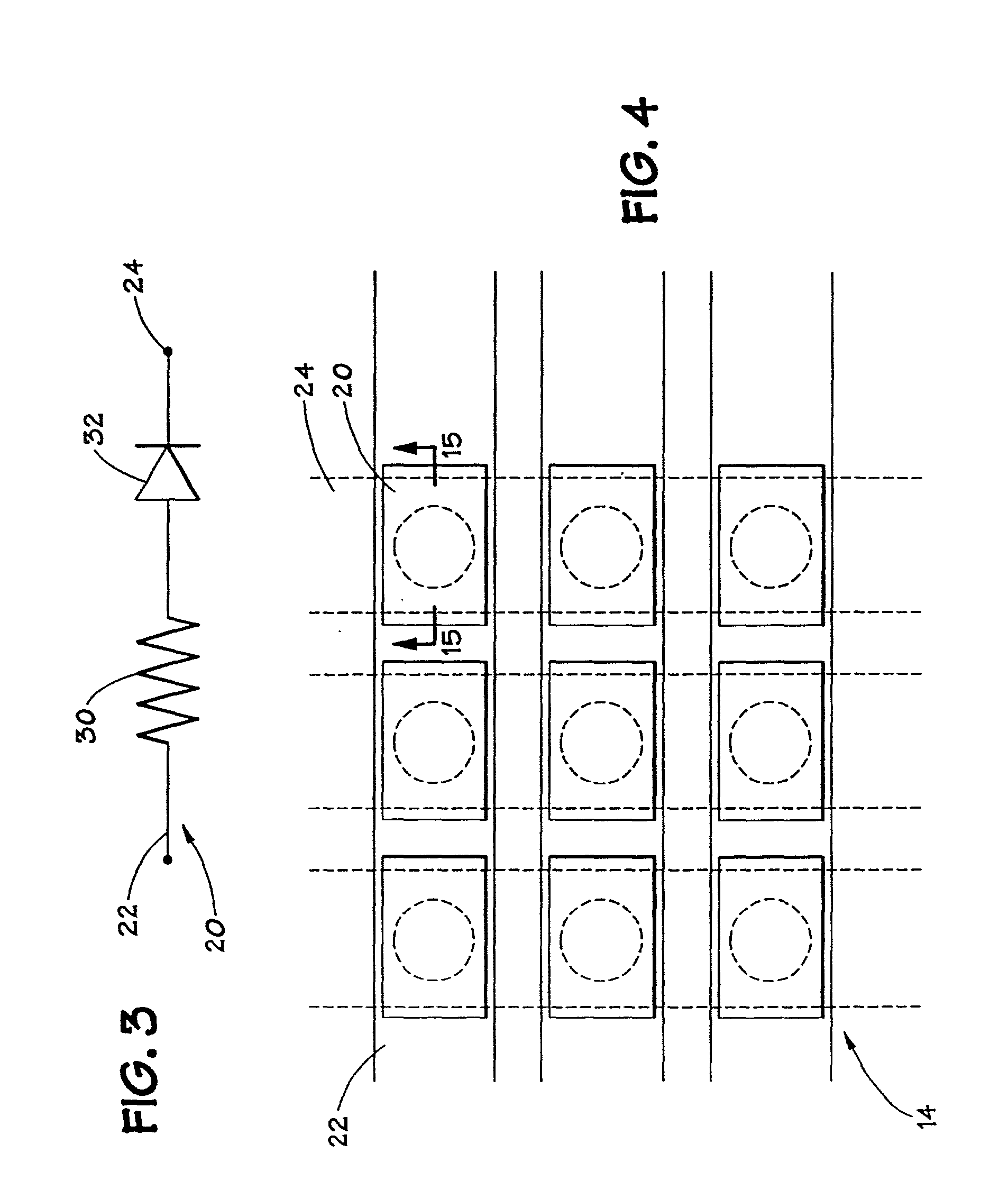

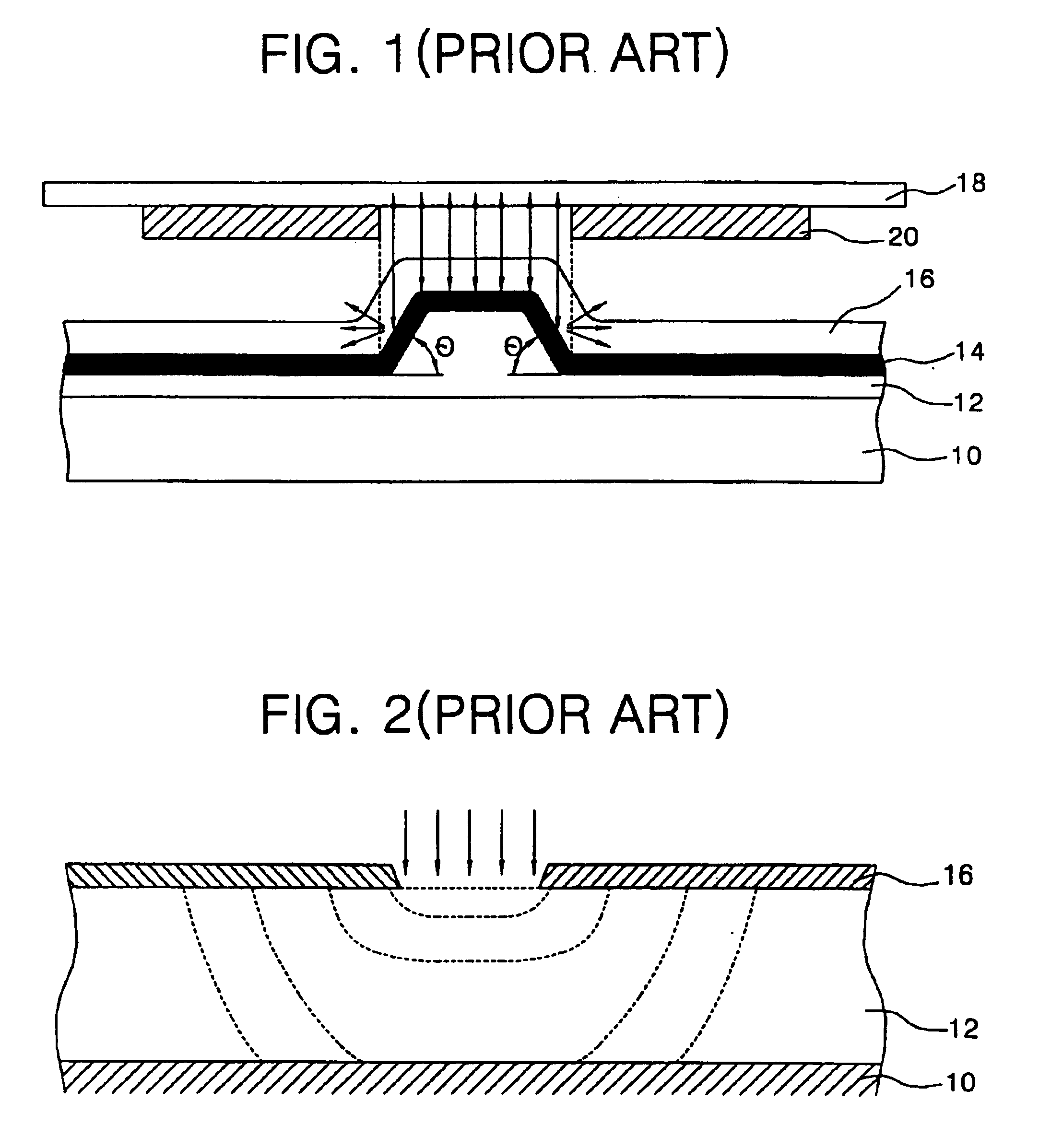

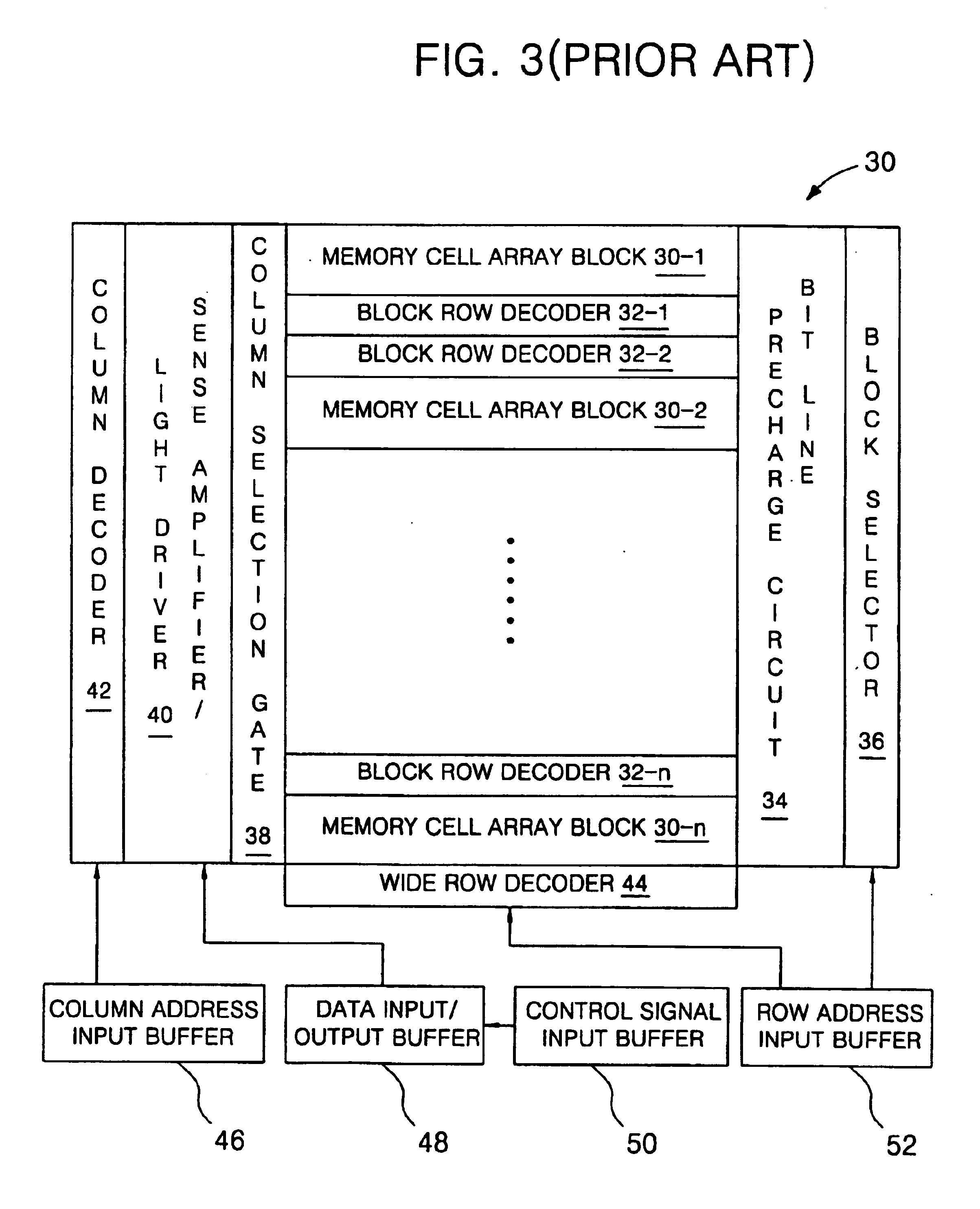

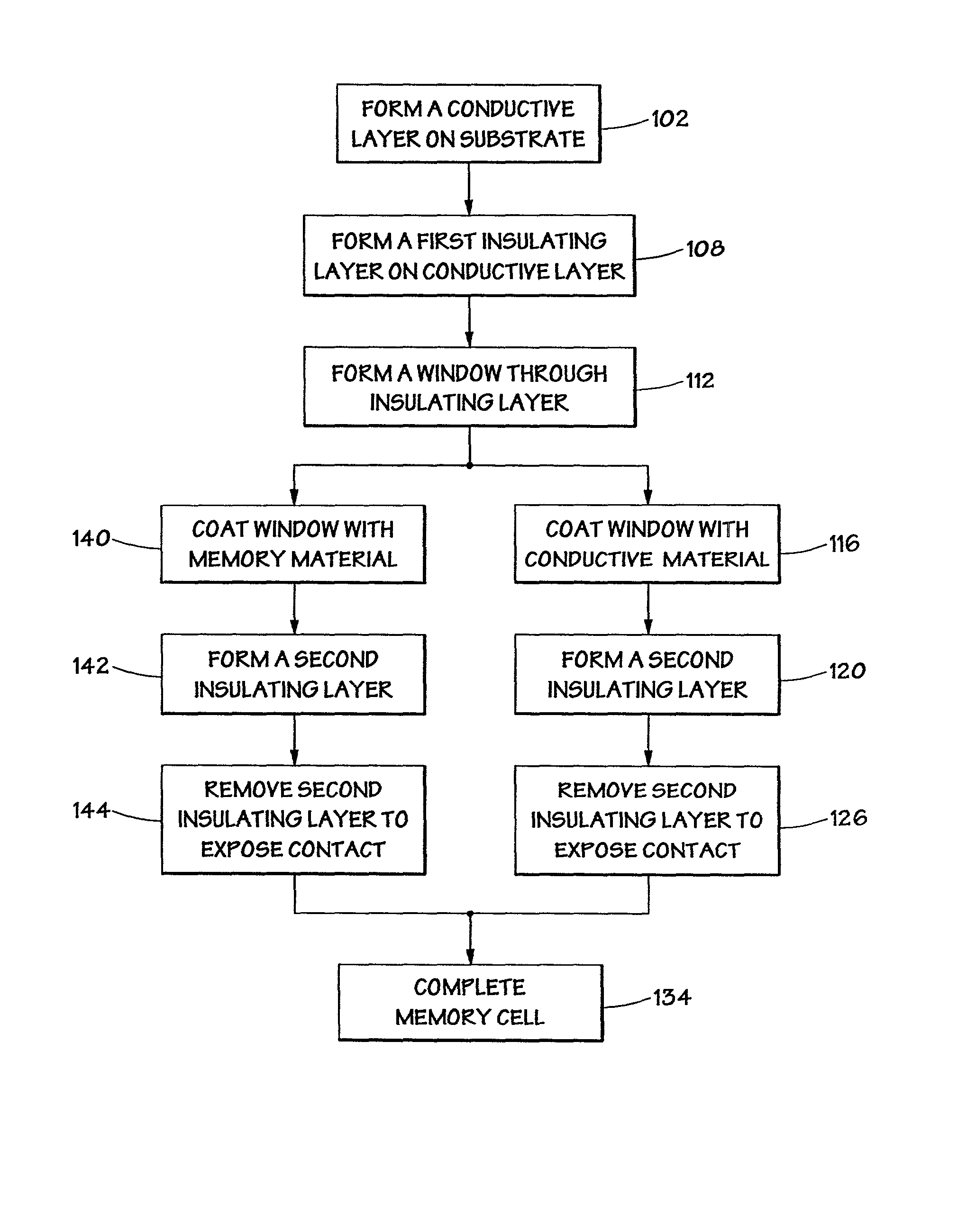

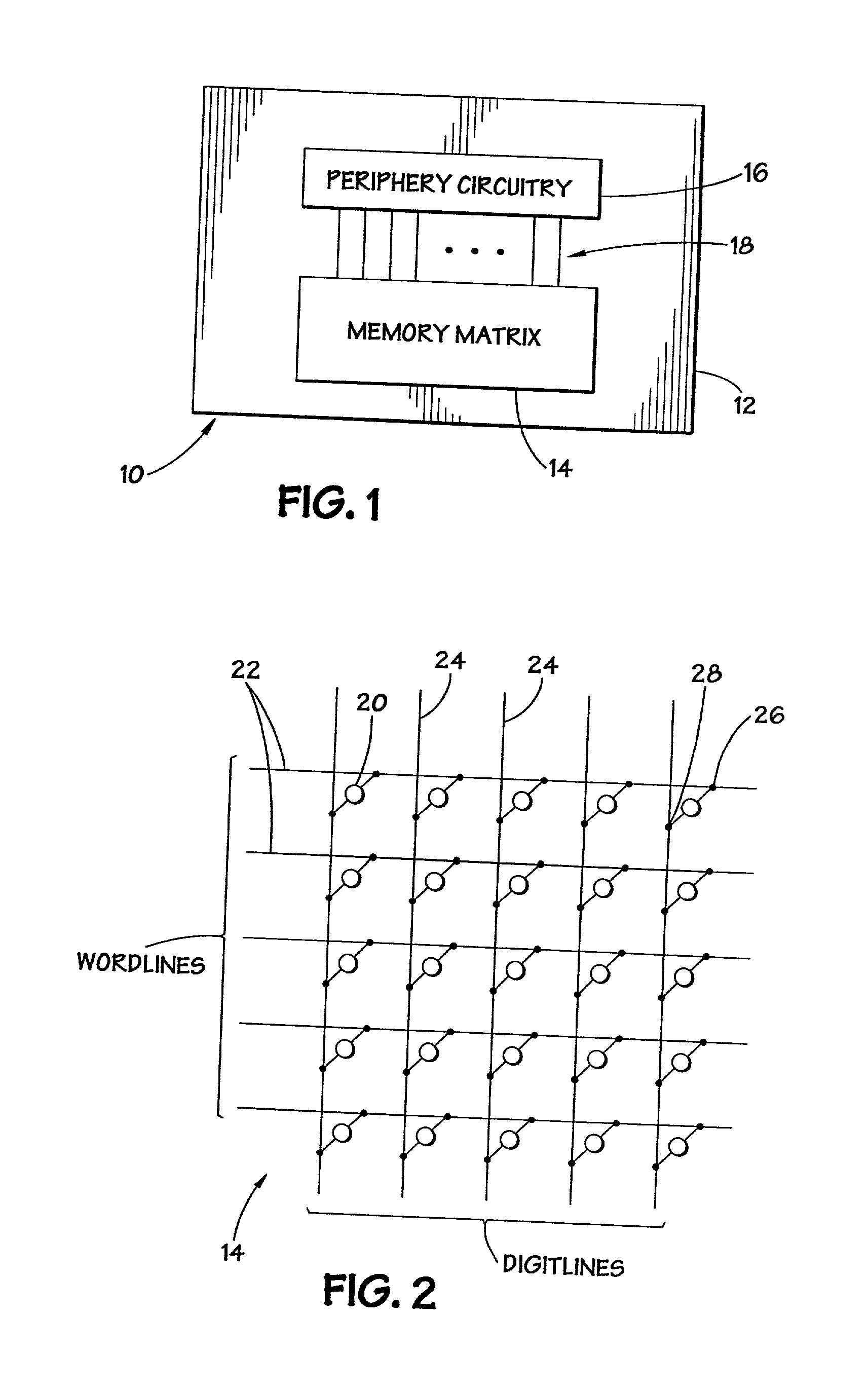

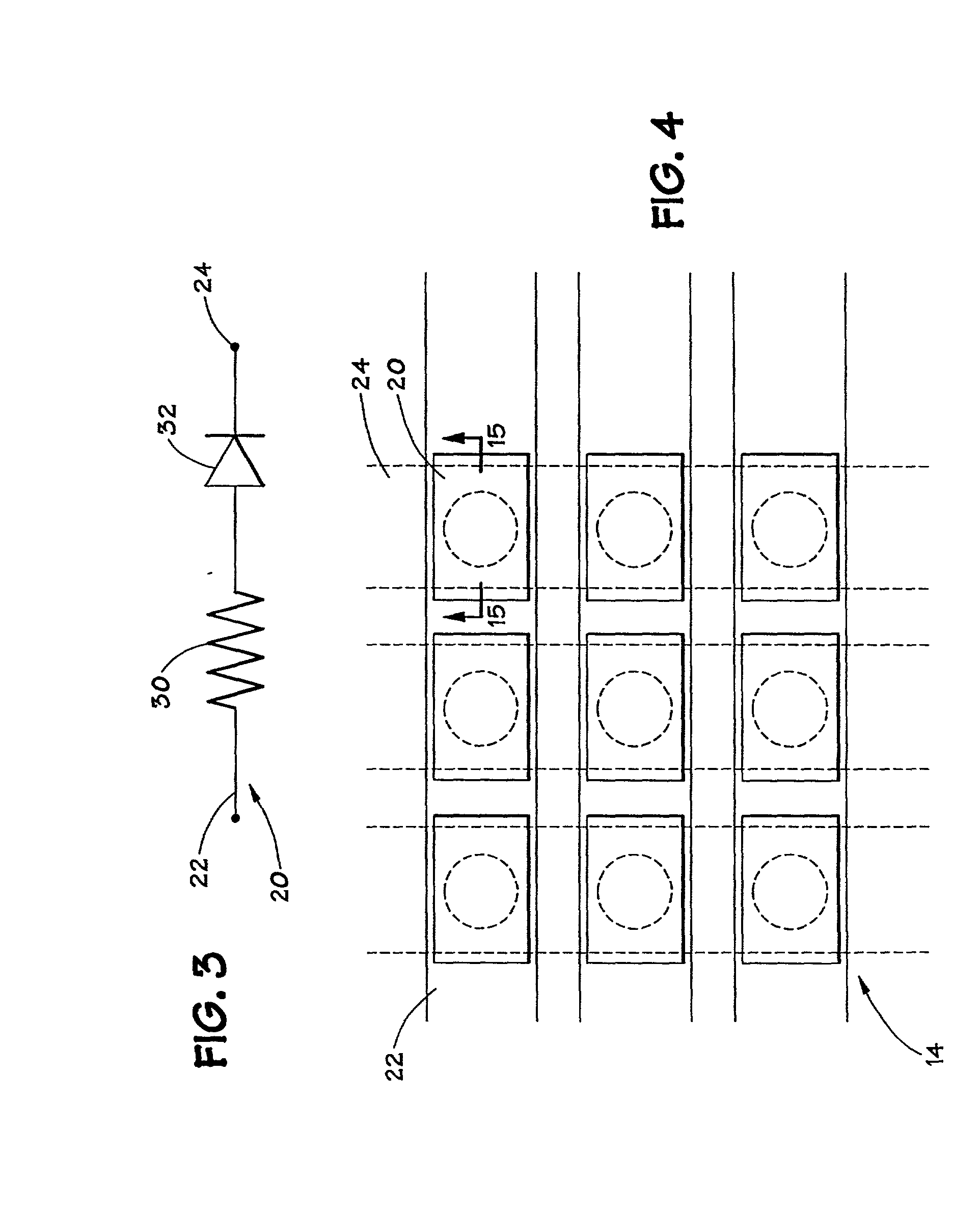

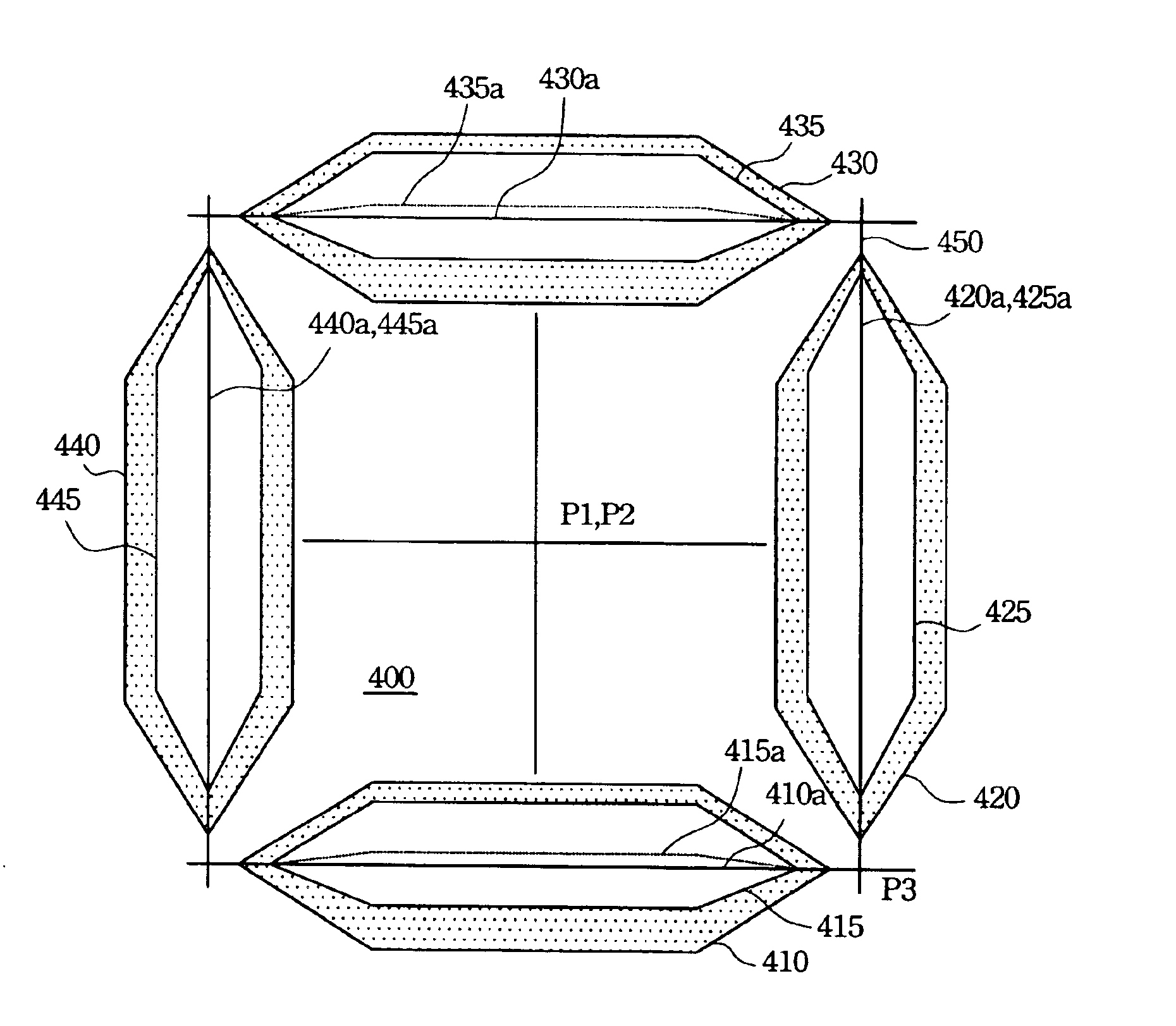

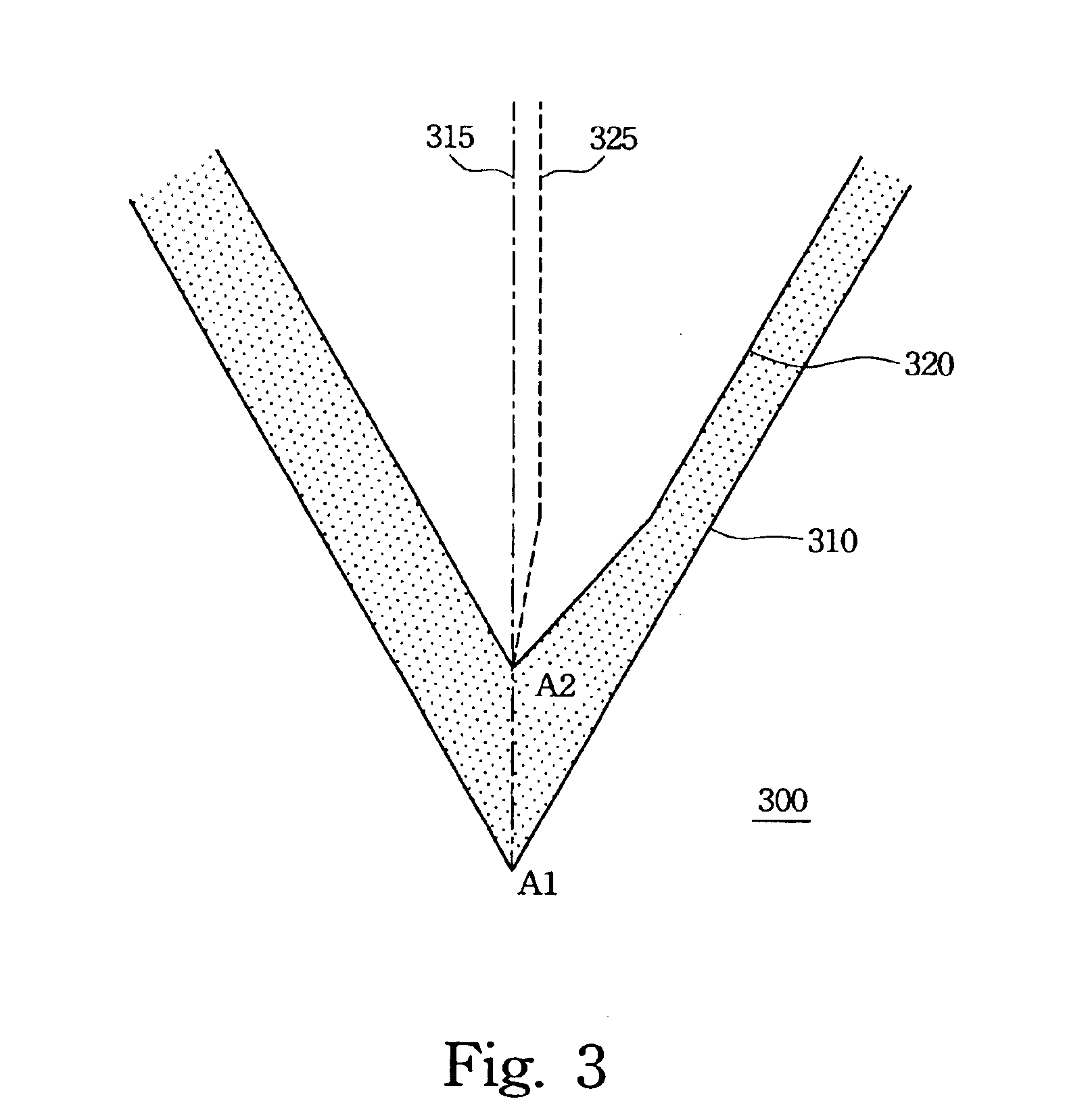

Memory elements and methods for making same

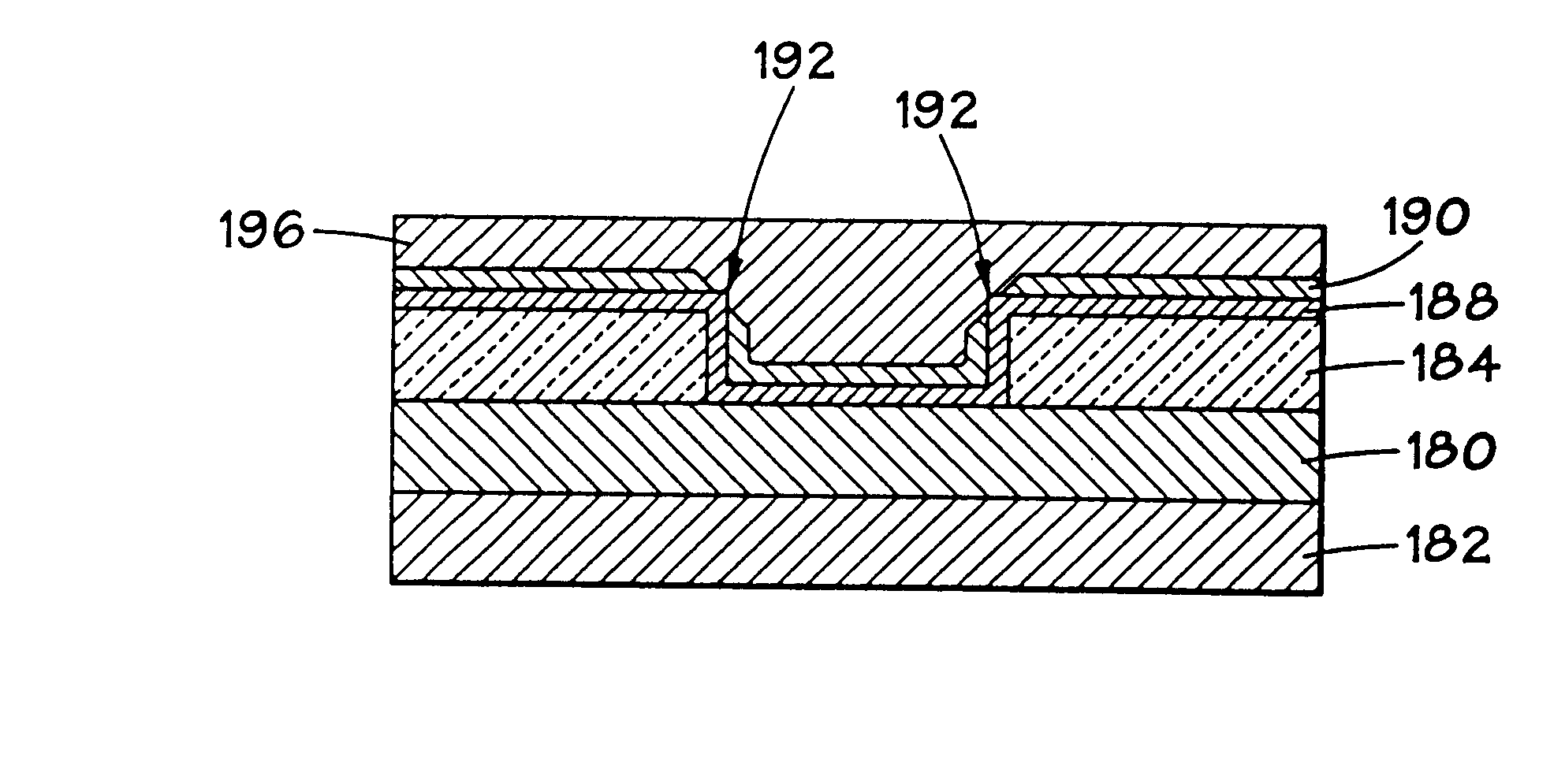

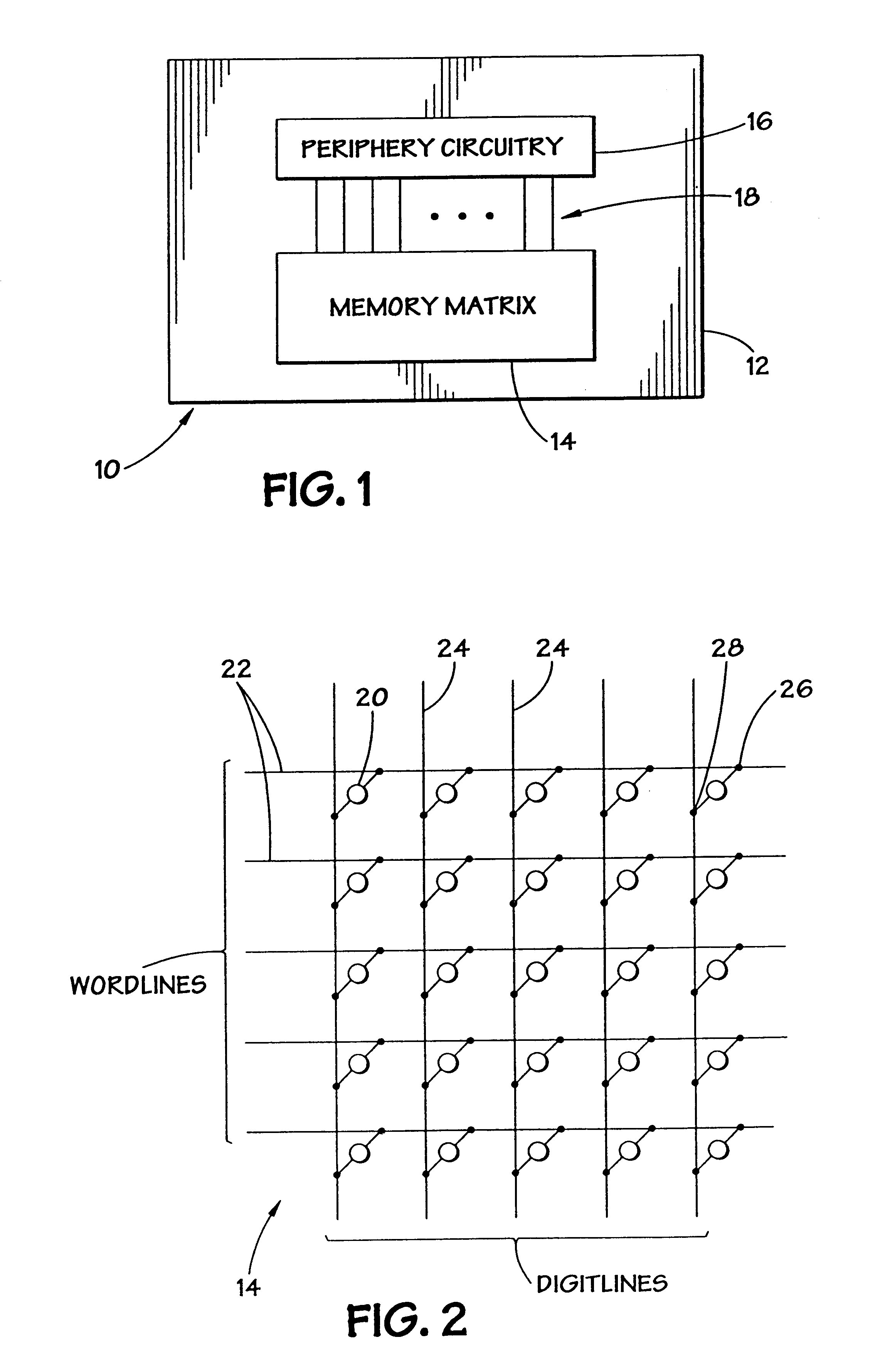

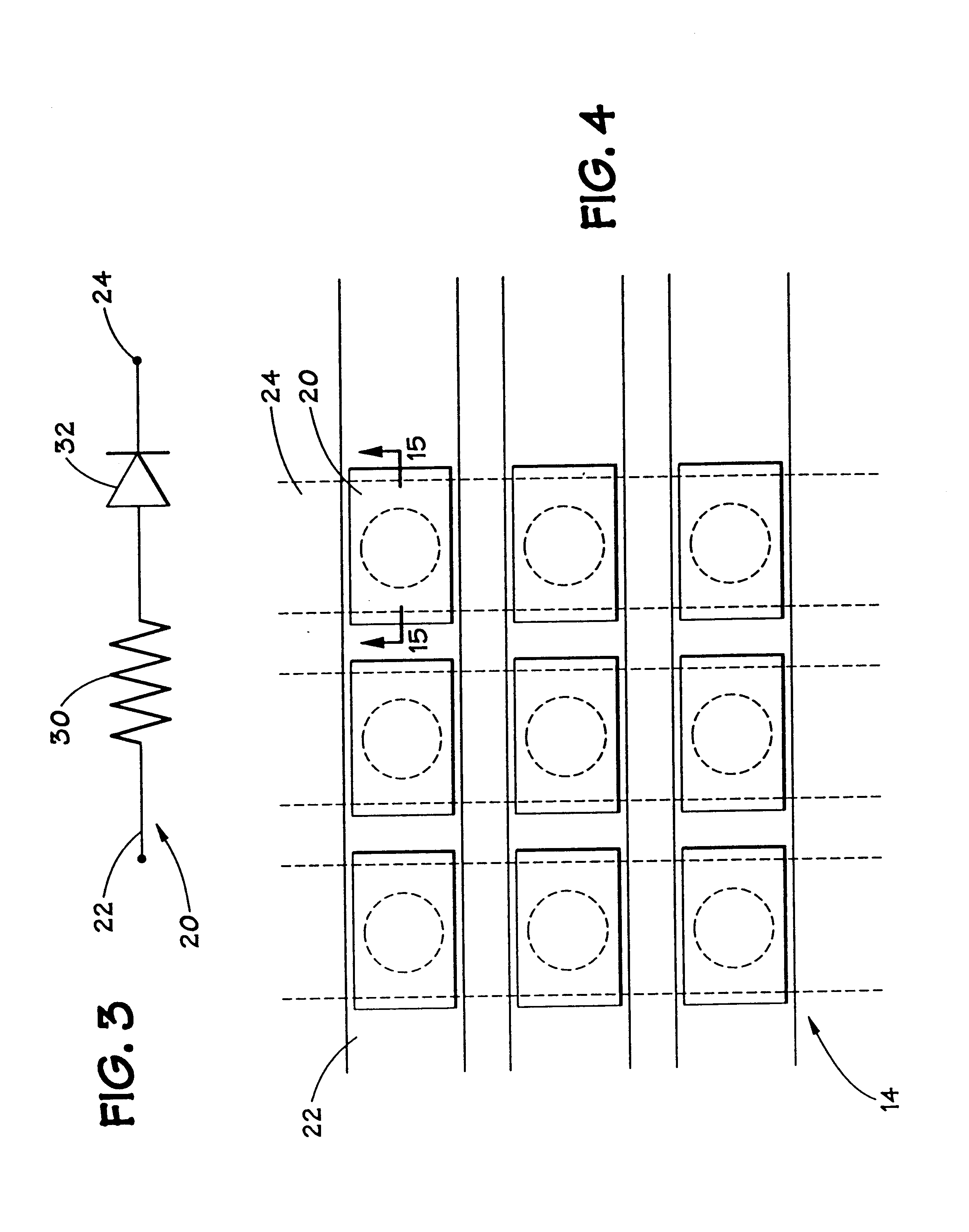

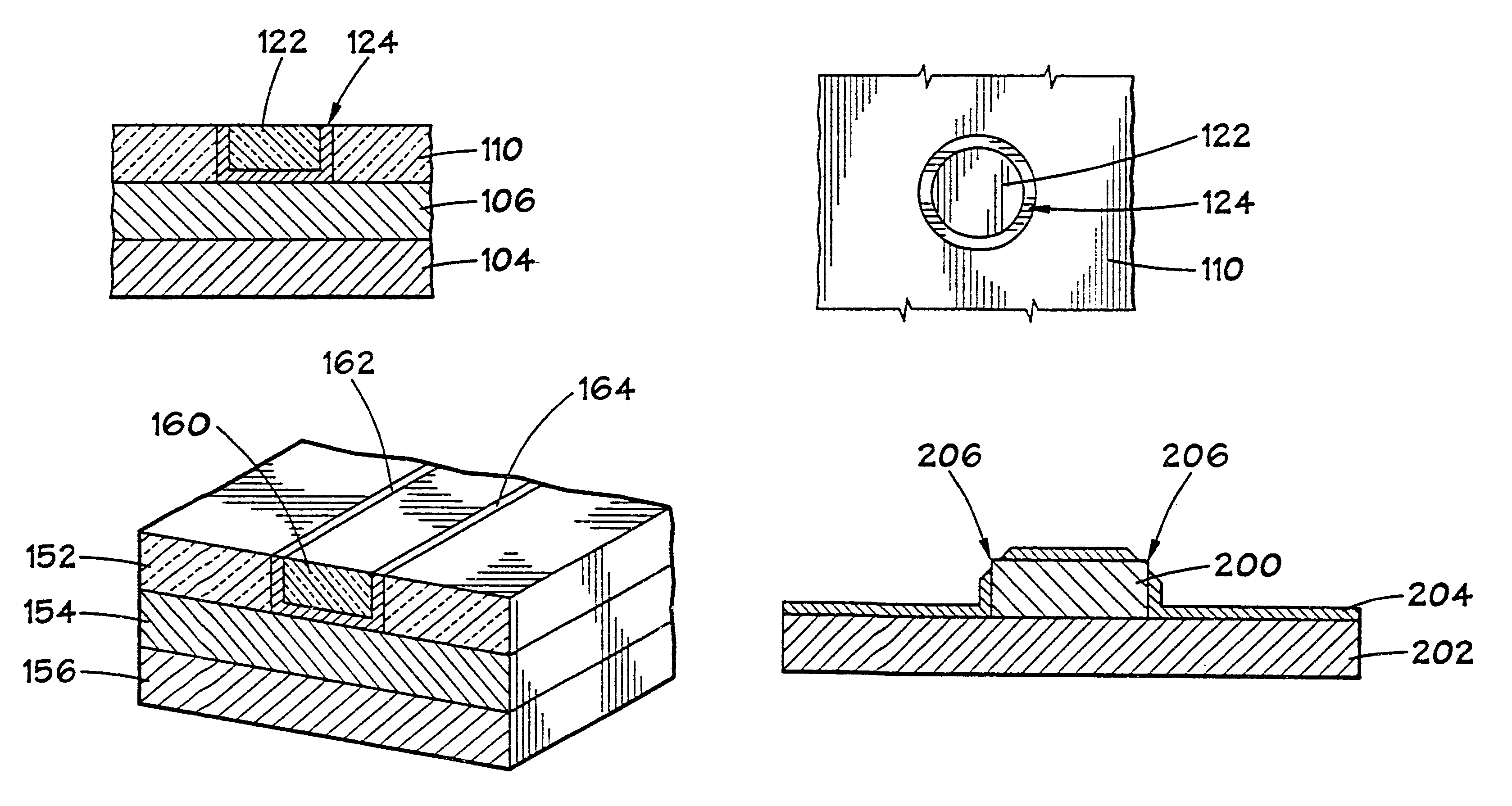

Annular, linear, and point contact structures are described which exhibit a greatly reduced susceptibility to process deviations caused by lithographic and deposition variations than does a conventional circular contact plug. In one embodiment, a standard conductive material such as carbon or titanium nitride is used to form the contact. In an alternative embodiment, a memory material itself is used to form the contact. These contact structures may be made by various processes, including chemical mechanical planarization and facet etching.

Owner:ROUND ROCK RES LLC

Method of forming a contact structure in a semiconductor device

InactiveUS6440837B1Solid-state devicesSemiconductor/solid-state device manufacturingProcess deviationsEtching

Annular and linear contact structures are described which exhibit a greatly reduced susceptibility to process deviations caused by lithographic and deposition variations than does a conventional circular contact plug. In one embodiment, a standard conductive material such as carbon or titanium nitride is used to form the contact. In an alternative embodiment, a memory material itself is used to form the contact. These contact structures may be made by various processes, including chemical mechanical planarization and facet etching.

Owner:ROUND ROCK RES LLC

Memory elements and methods for making same

InactiveUS20020160551A1Solid-state devicesSemiconductor/solid-state device manufacturingProcess deviationsEtching

Annular, linear, and point contact structures are described which exhibit a greatly reduced susceptibility to process deviations caused by lithographic and deposition variations than does a conventional circular contact plug. In one embodiment, a standard conductive material such as carbon or titanium nitride is used to form the contact. In an alternative embodiment, a memory material itself is used to form the contact. These contact structures may be made by various processes, including chemical mechanical planarization and facet etching.

Owner:ROUND ROCK RES LLC

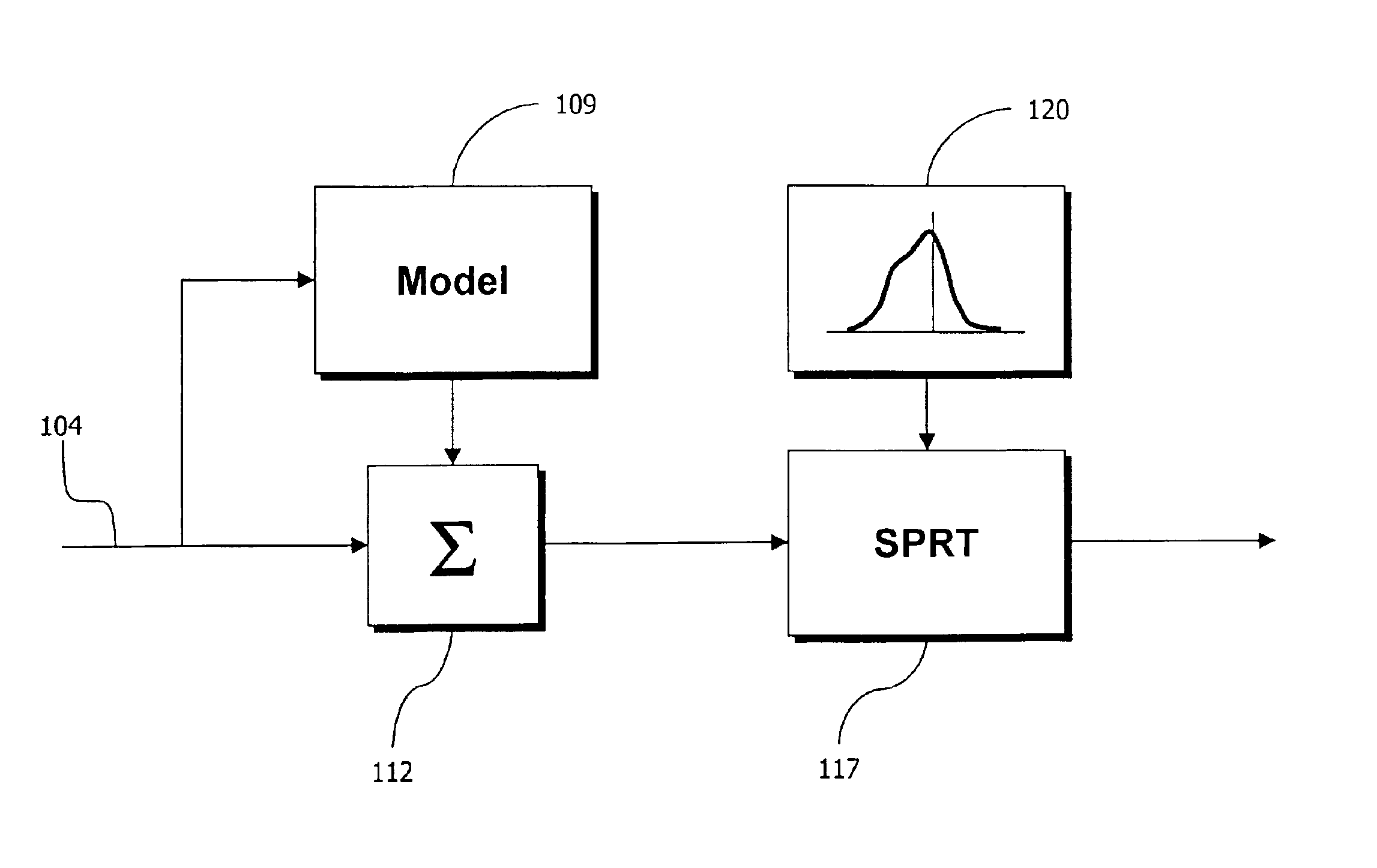

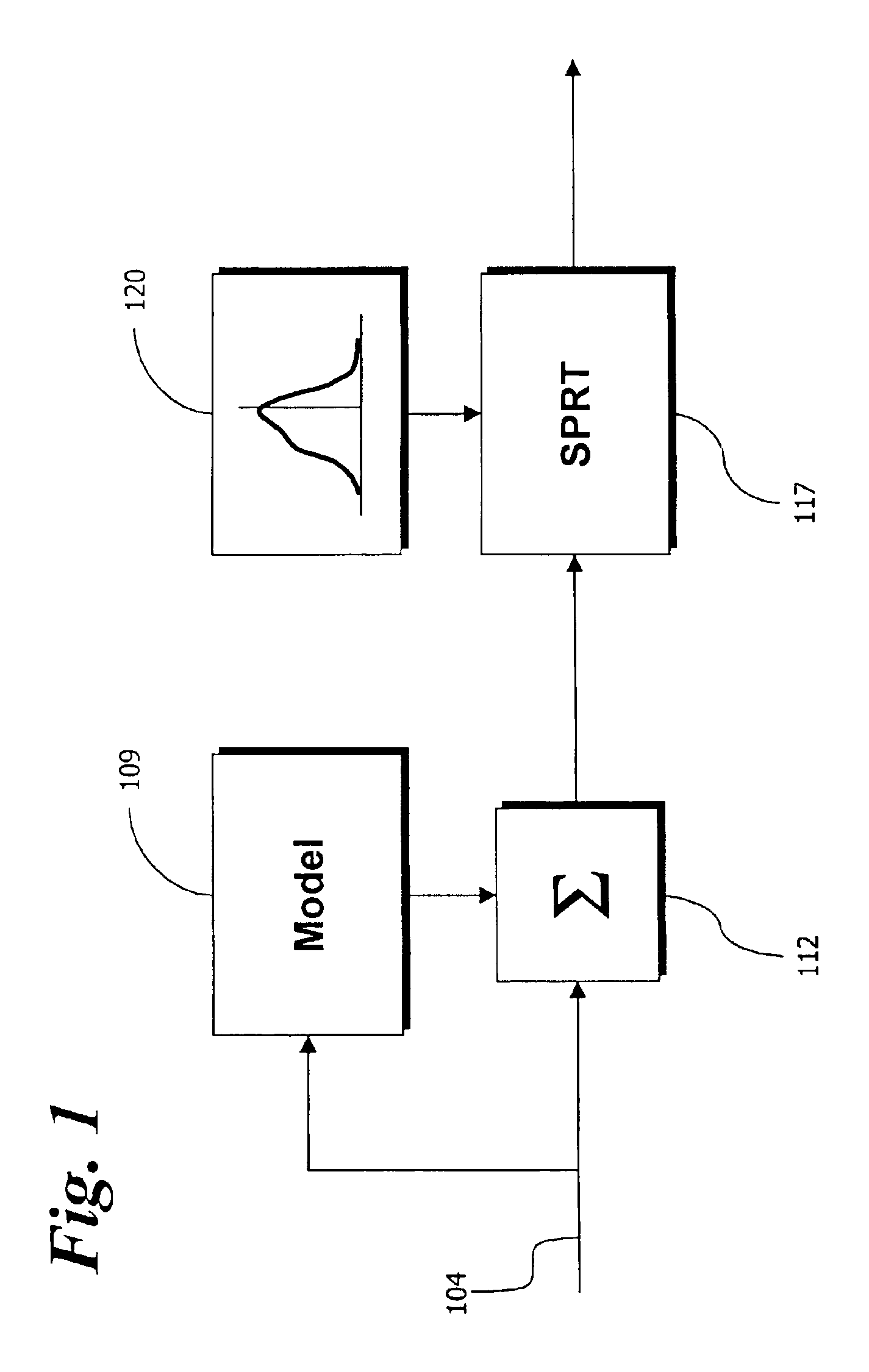

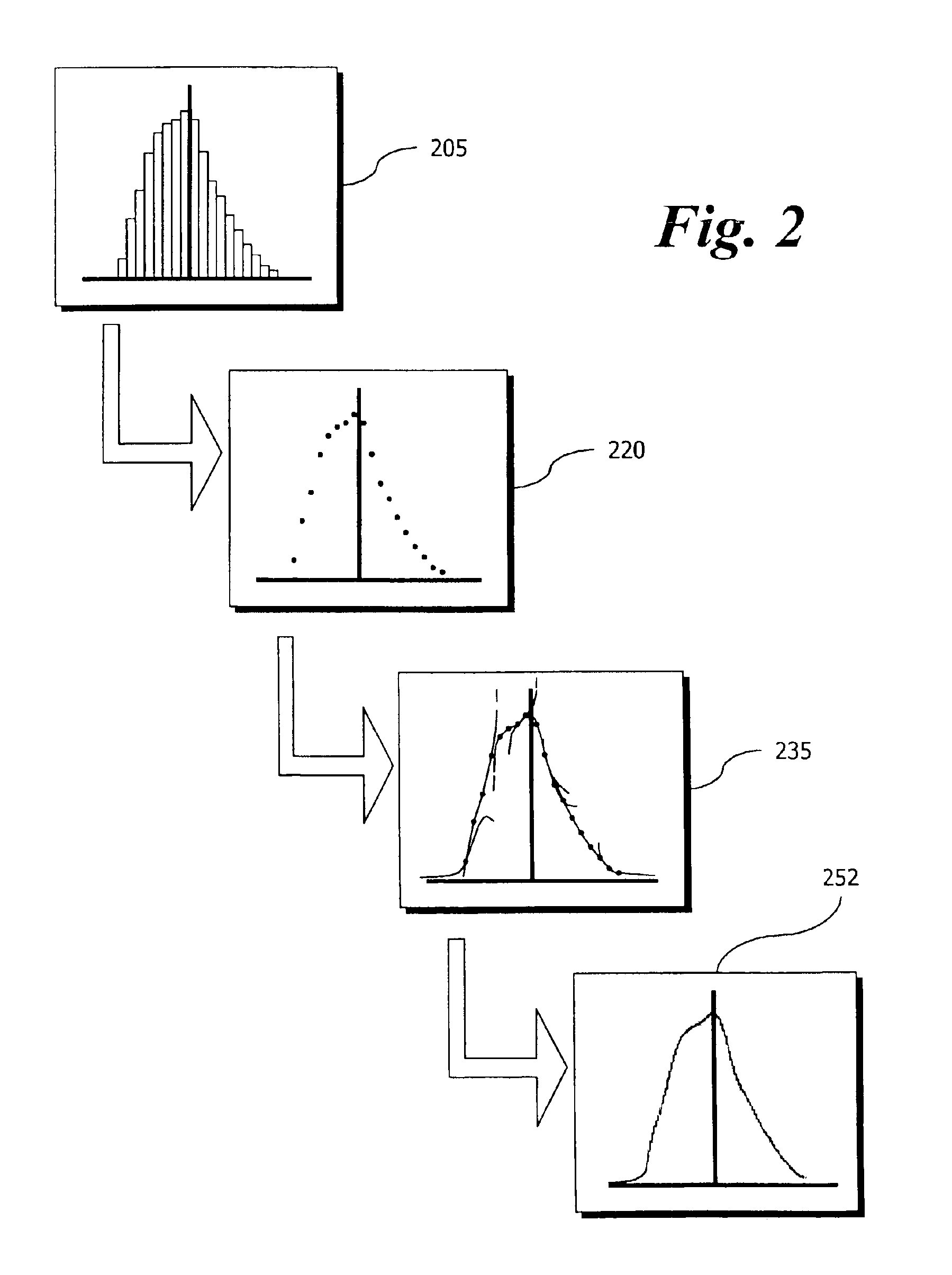

Residual signal alert generation for condition monitoring using approximated SPRT distribution

InactiveUS6975962B2Registering/indicating working of machinesDigital computer detailsProcess deviationsMonitoring system

A system and method for monitoring a condition of a monitored system. Estimates of monitored parameters from a model of the system provide residual values that can be analyzed using a sequential probability ratio test (“SPRT”). The invention employs empirically derived distributions in the SPRT to provide more accurate and sensitive alerts of impending faults, breakdowns and process deviations. The distributions can be generated from piecewise continuous approximation or spline functions based on the actual distribution of residual data to provide improved computational performance. The distributions can be provided before monitoring, or can be updated and determined during monitoring in an adaptive fashion.

Owner:SMARTSIGNAL CORP

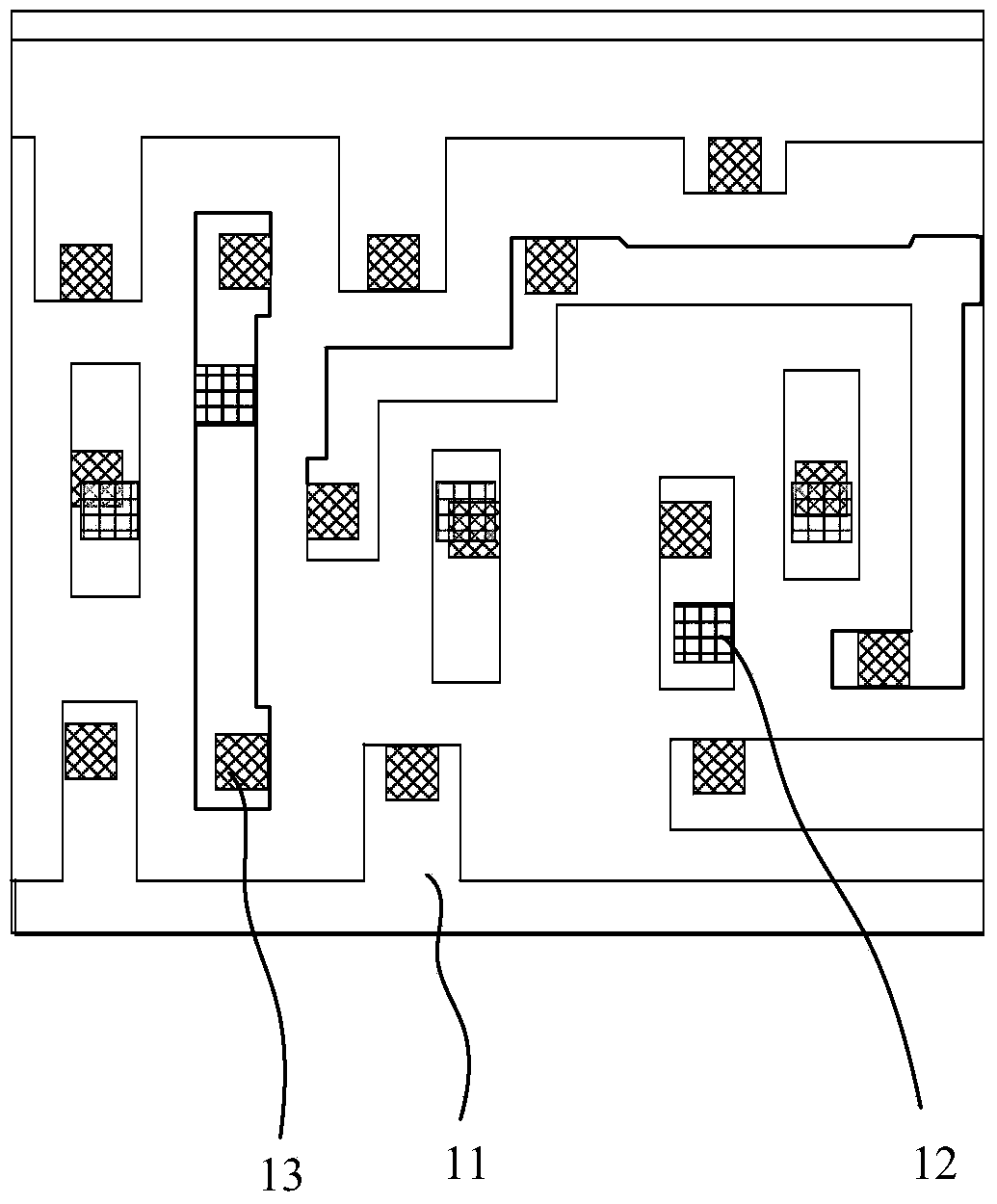

Layout method of semiconductor device

InactiveUS6872990B1Minimizing varianceTransistorSolid-state devicesProcess deviationsDevice material

Owner:SAMSUNG ELECTRONICS CO LTD

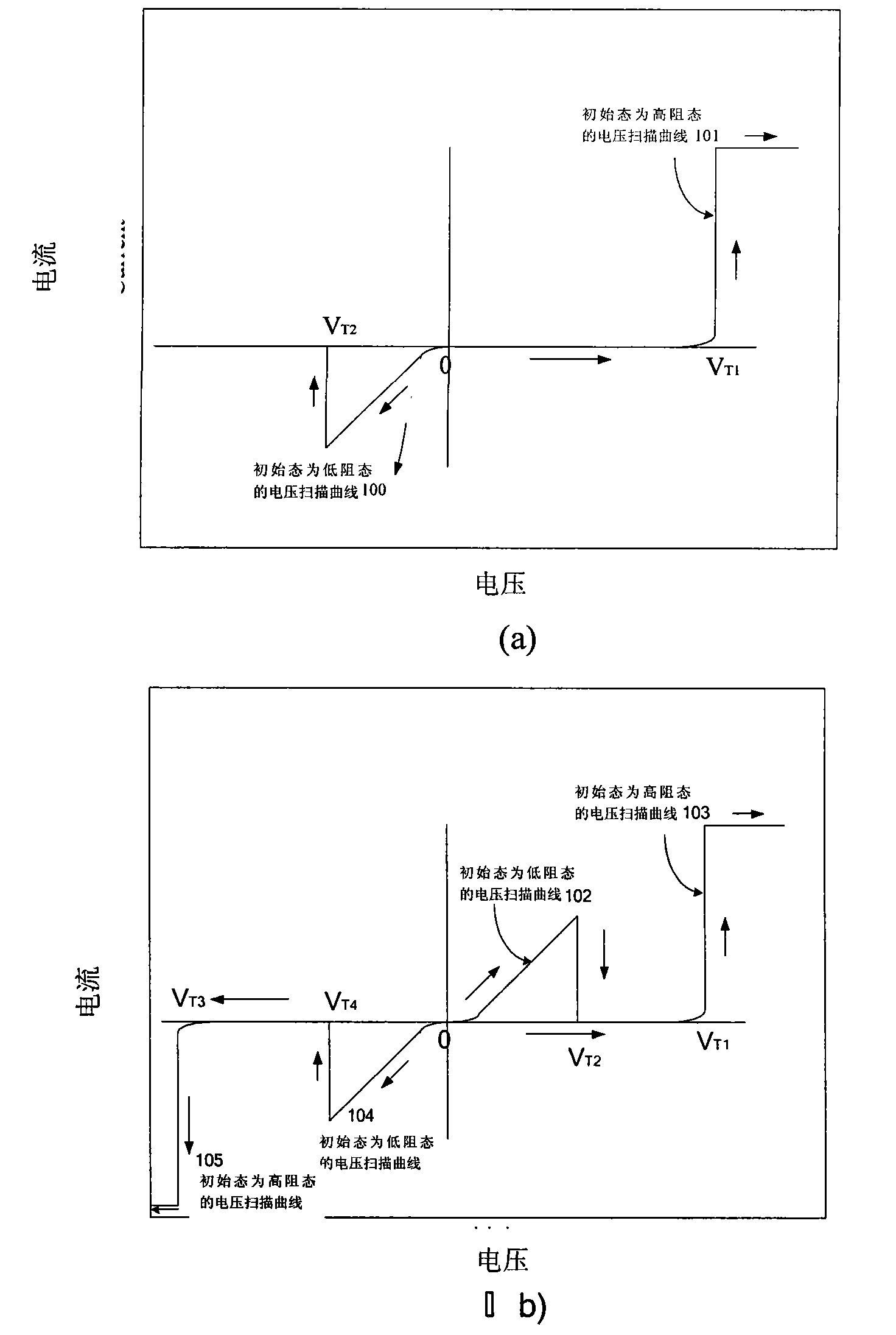

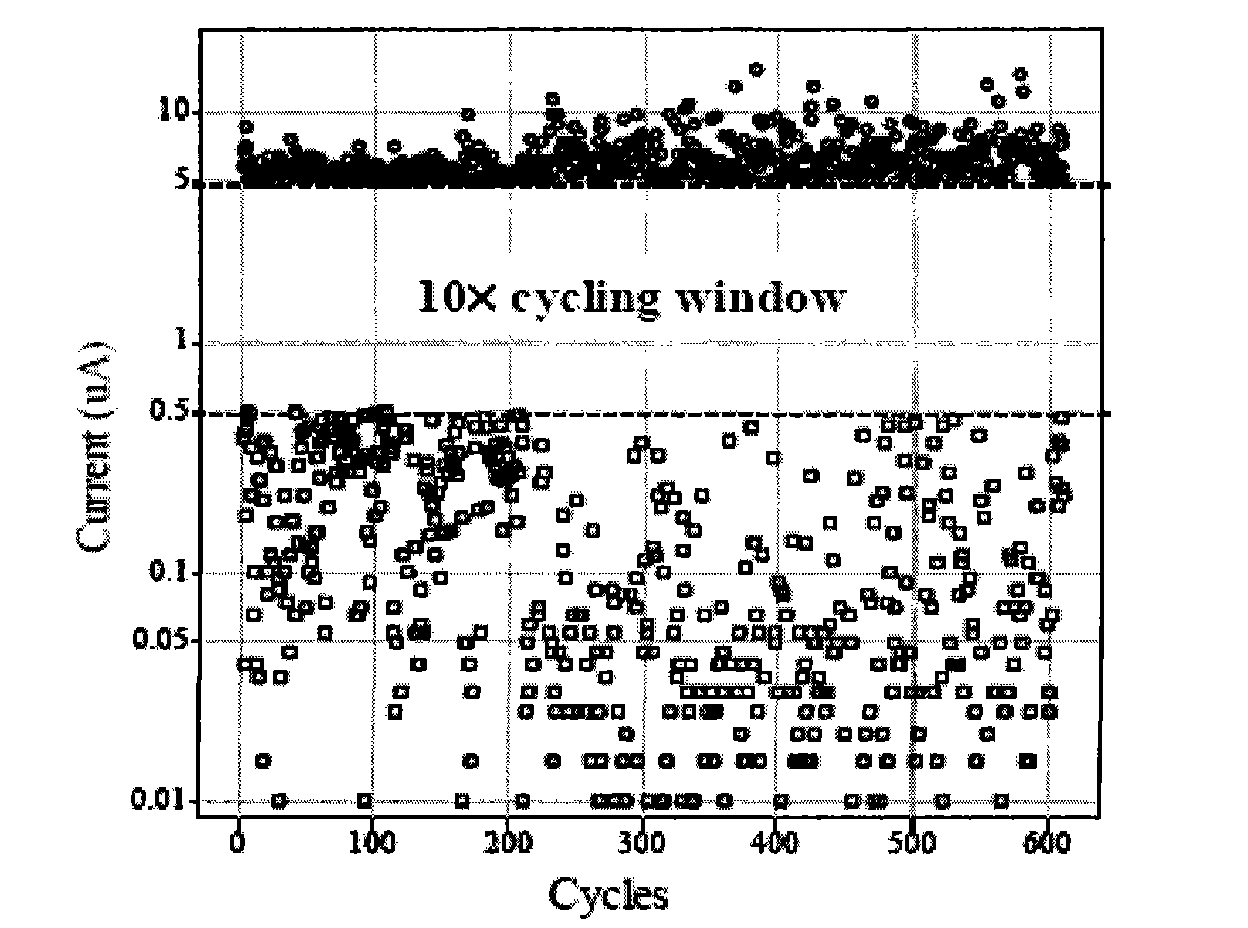

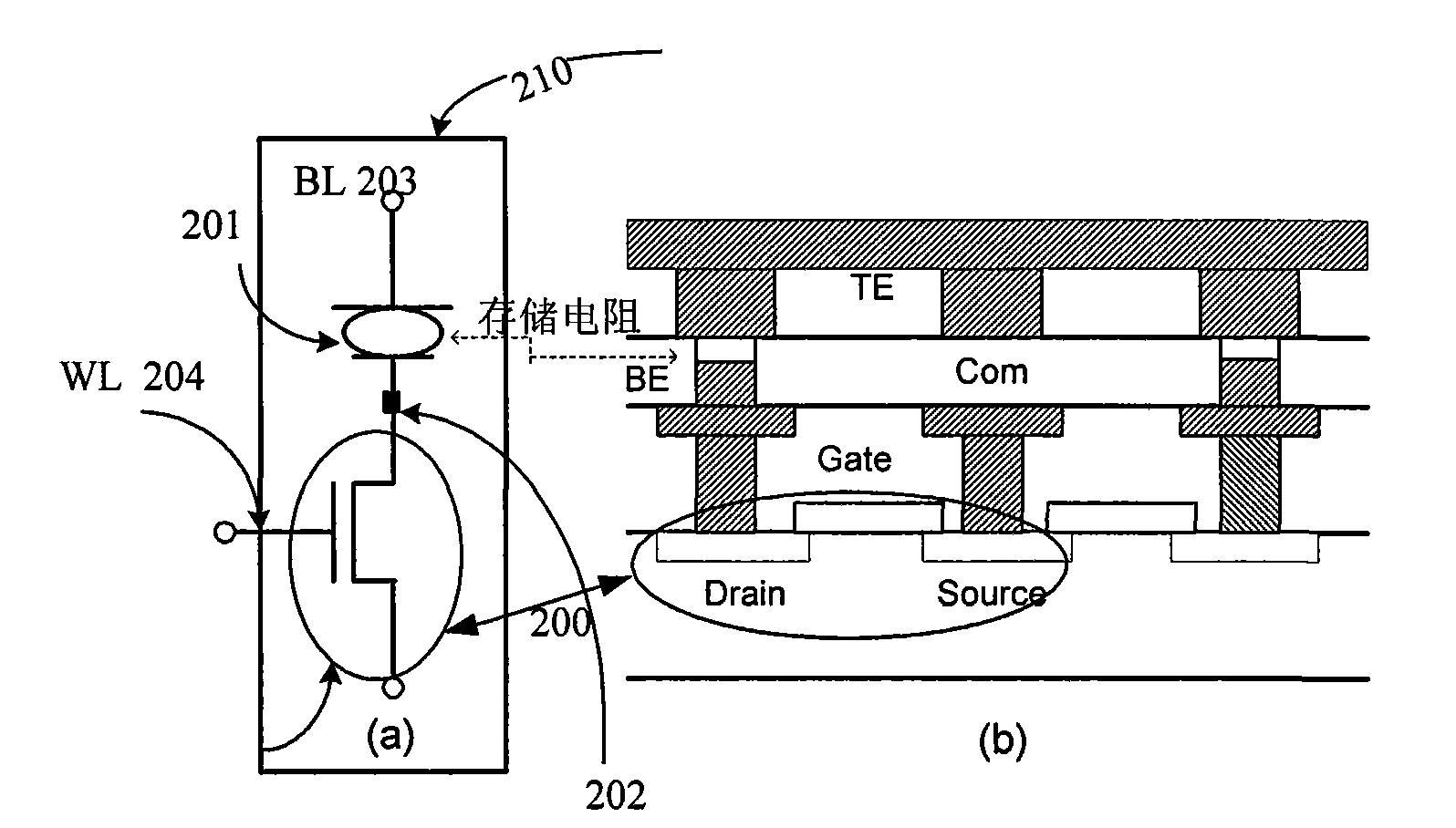

One-time programming resistance random memory unit, array, memory and operation method thereof

InactiveCN101872647AFast and accurate readoutImprove reading speedRead-only memoriesProcess deviationsComputer hardware

The invention belongs to the technical field of the memory, and relates to a one-time programming resistance random memory unit, an array, a memory and an operation method thereof. The one-time programming resistance random memory unit utilizes binary or multi-variant metal oxide which has the structural characteristic of 2T2R, and represents the memory state 1 and 0 through the state combination difference of a first memory resistance and a second memory resistance. The one-time programming resistance random memory unit, array and memory are not easy to be influenced by the process deviation, and have the advantages of fast reading speed, high read-write tolerance and nonvolatility.

Owner:FUDAN UNIV

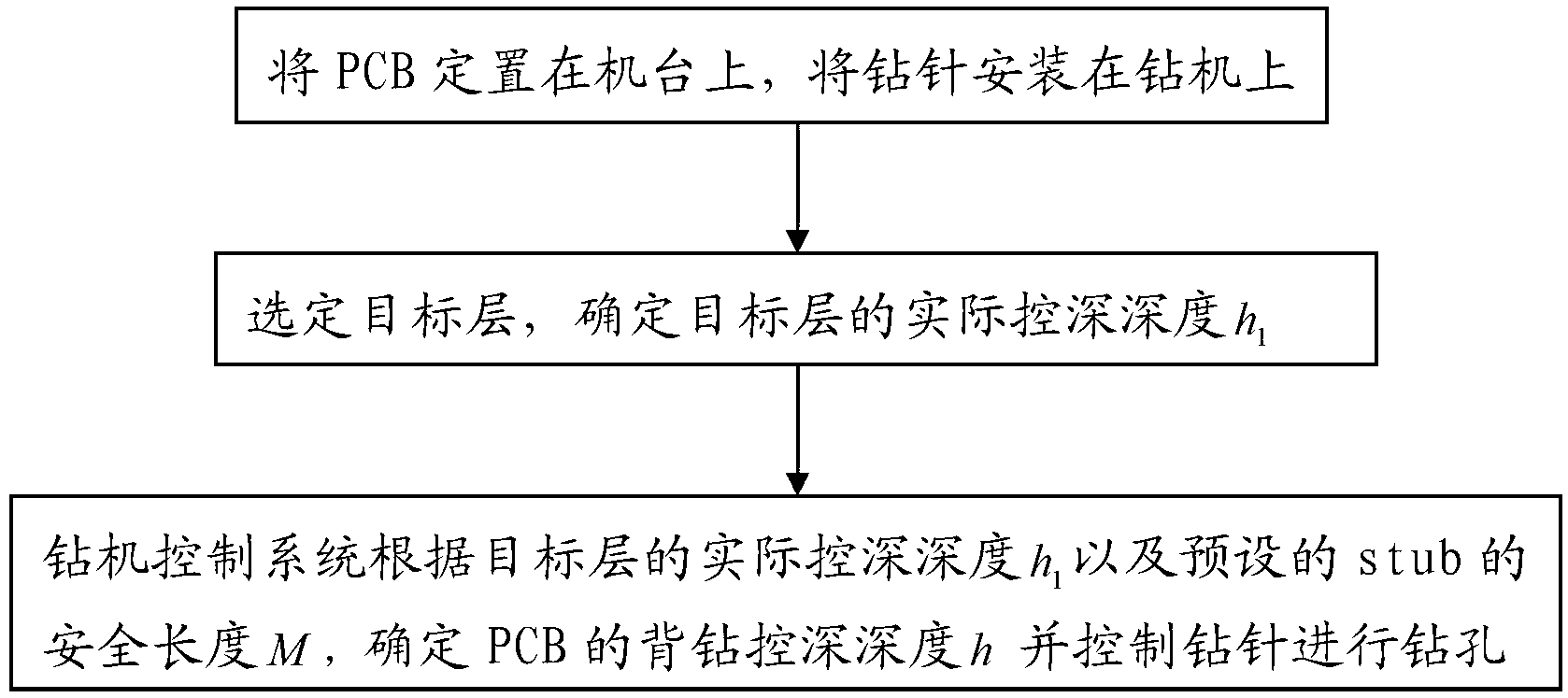

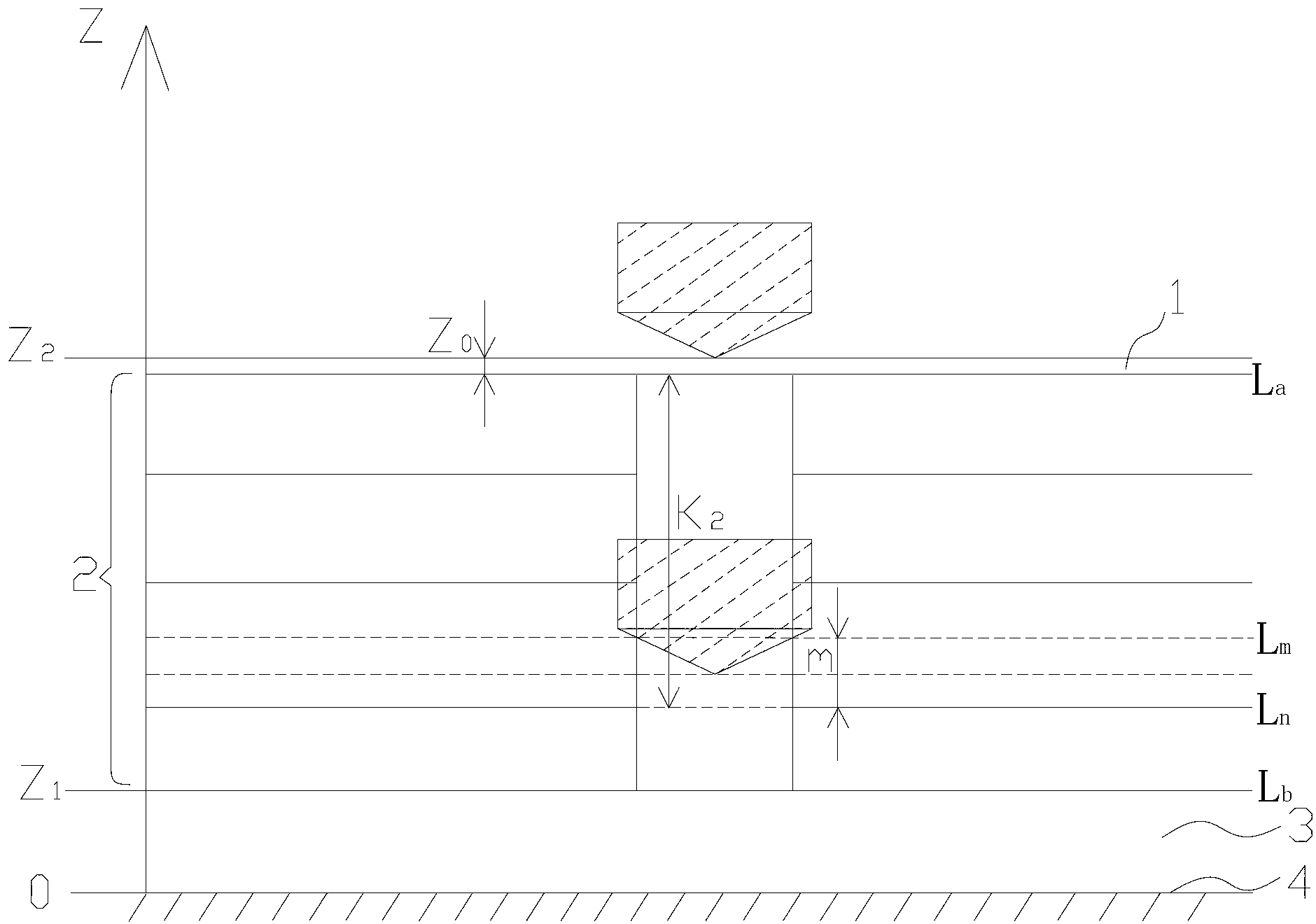

PCB (printed circuit board) back drilling method

The invention relates to a PCB (printed circuit board) back drilling method. The PCB back drilling method comprises the following steps: fixing a PCB on a machine table, and mounting a drill bit on a drilling machine; selecting a target layer, and determining an actual control depth h1 of the target layer; and determining a back drilling control depth h of the PCB according to the actual control depth h1 of the target layer and a preset safety length M of a stub and controlling the drill bit to drill a hole drilling machine control system. According to the PCB back drilling method, influence of thickness uniformity of the board, cone height of a drill tip and copper / tin-plating process variation on the accuracy of the control depth can be reduced; and through introduction of the safety length M of the stub, the precision of the PCB back drilling control depth h can be effectively controlled, thus achieving precision control of the stub and eliminating adverse effects of the stub on a signal.

Owner:GUANGZHOU FASTPRINT CIRCUIT TECH

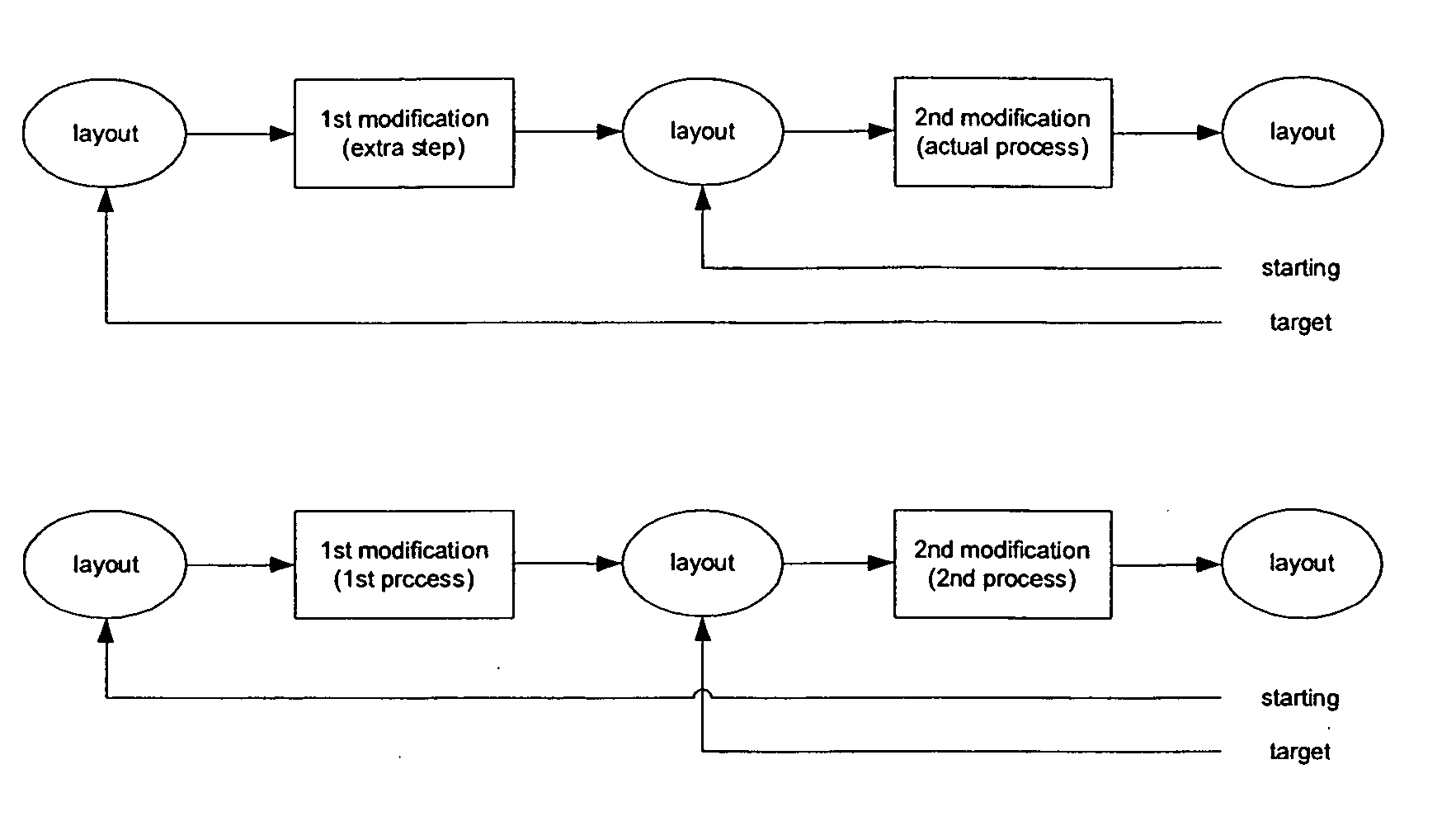

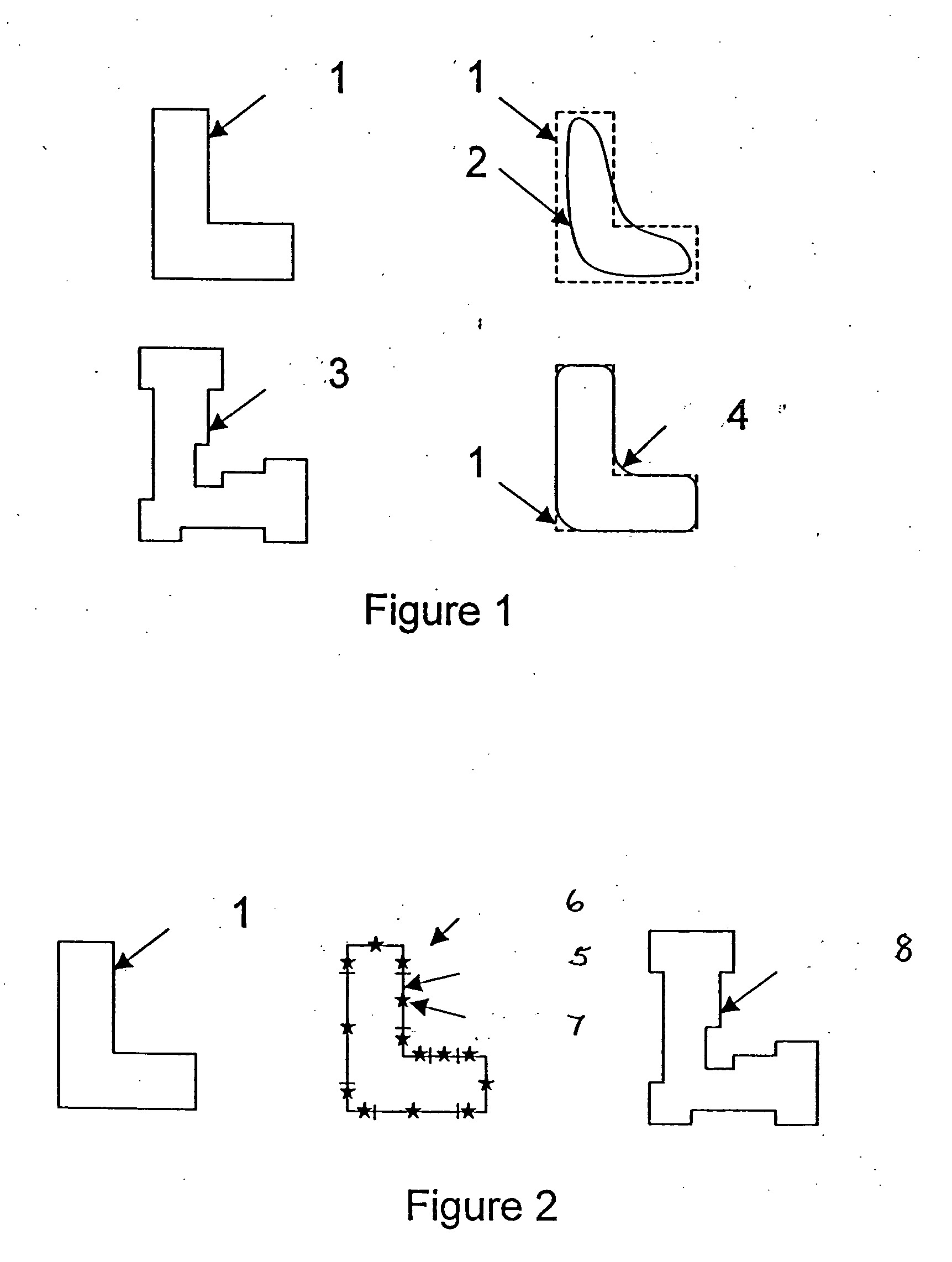

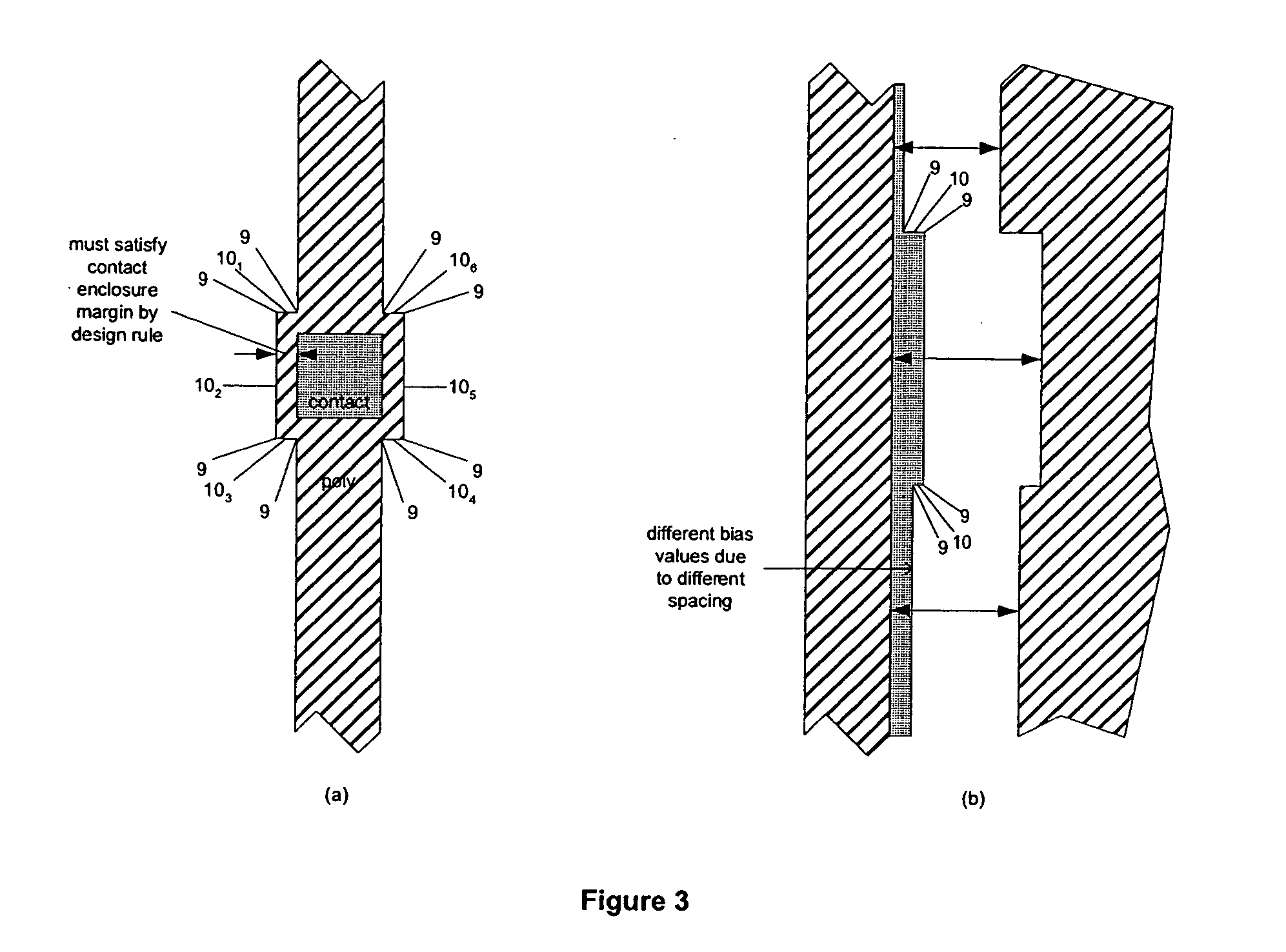

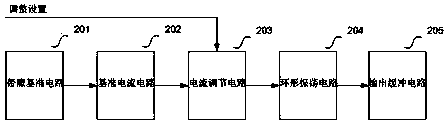

System for simplifying layout processing

ActiveUS20050223350A1Promote generationImprove manufacturabilityComputer aided designTotal factory controlProcess deviationsEngineering

A system and method for integrated circuit design are disclosed to enhance manufacturability of circuit layouts by applying layout processing to handle imperfections such as jogs in integrated circuit design layouts. The layout processing may be applied to jogs in the original integrated circuit design layout or jogs created post-design by process biases, as well as design rule check and Boolean processes or process compensation.

Owner:APPLIED MATERIALS INC

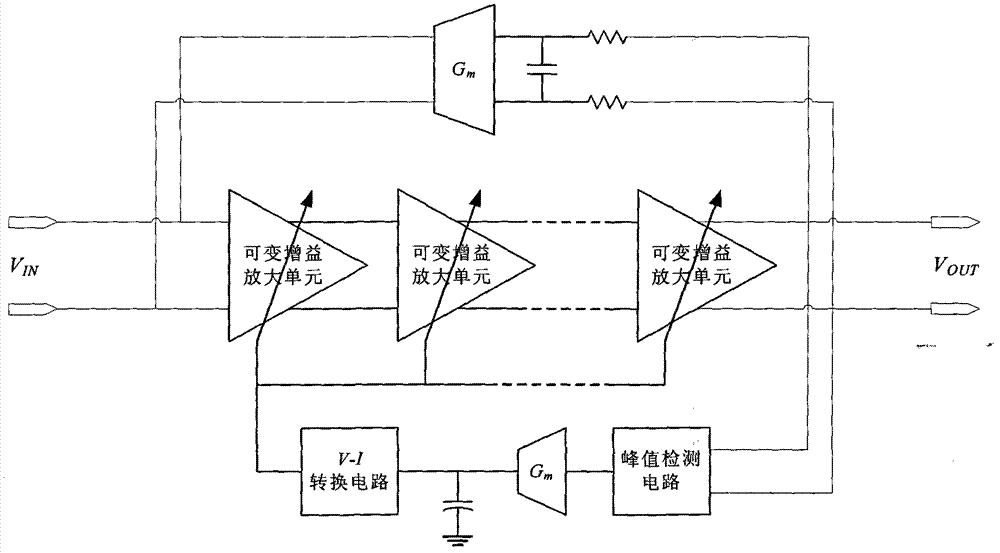

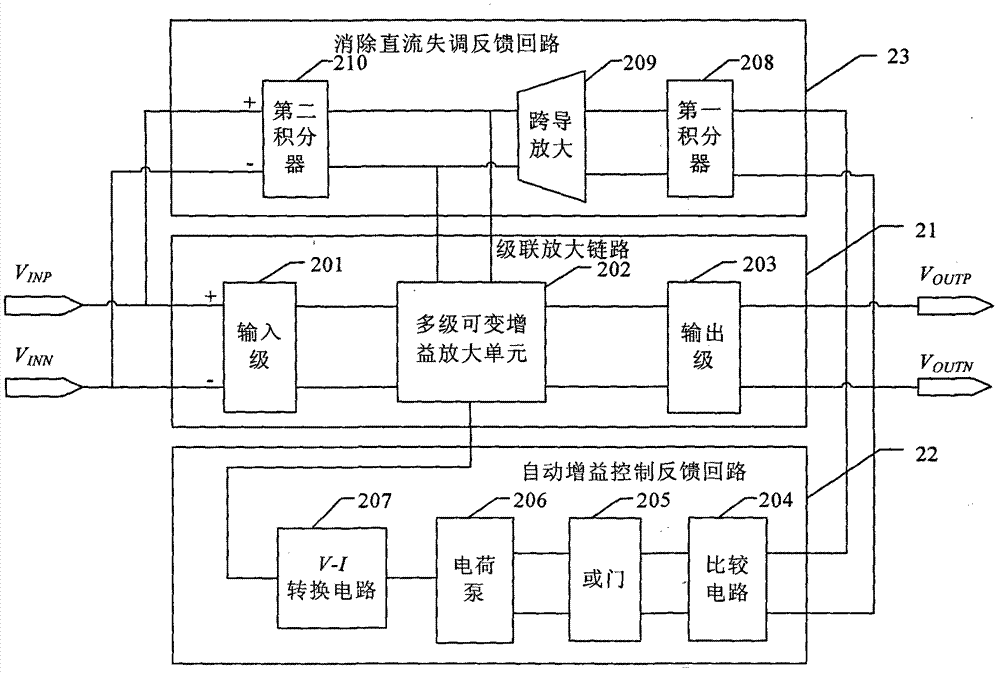

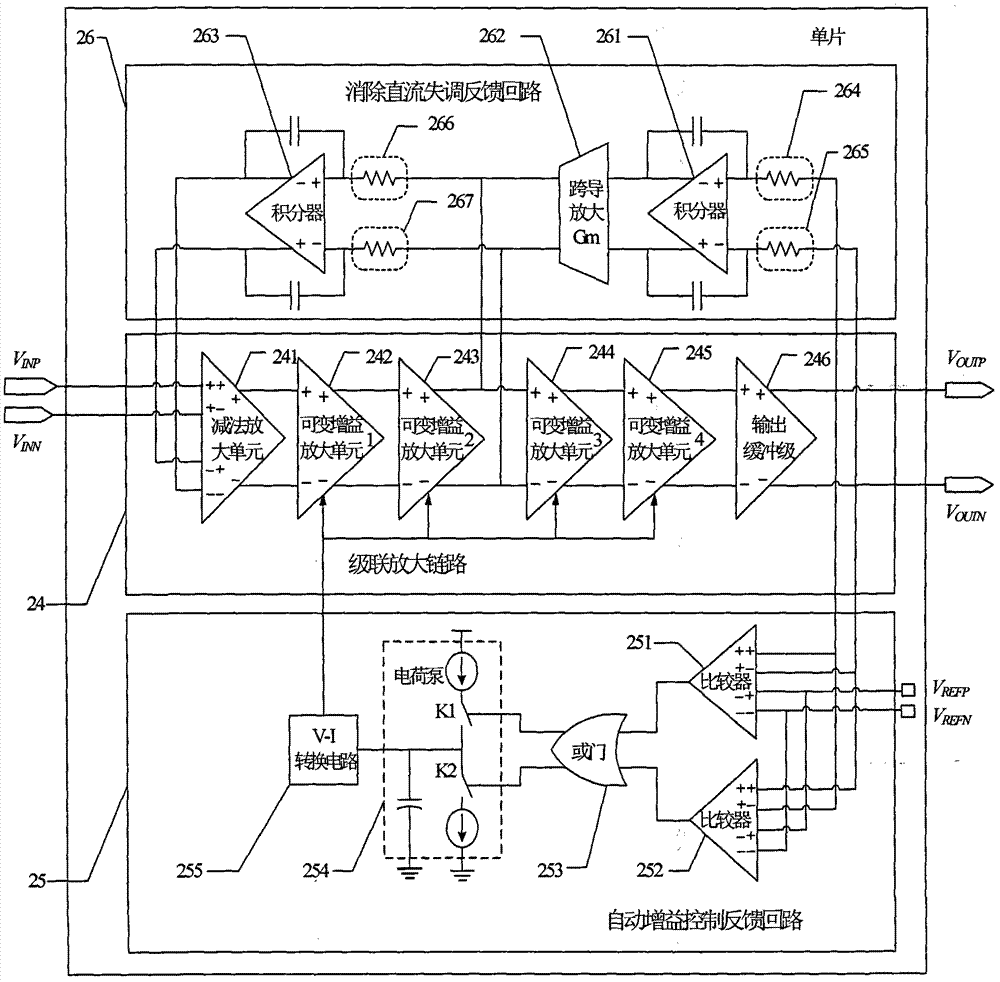

Automatic gain control amplifier for canceling direct current offset

ActiveCN102790596AThe process deviation and other factors have little influenceSimple structureGain controlCapacitanceProcess deviations

The invention discloses a complementary metal oxide semiconductor (CMOS) automatic gain control amplifier for canceling direct current offset. The CMOS automatic gain control amplifier comprises a cascade amplification link, an automatic gain control feedback loop and a direct current offset canceling feedback loop. The cascade amplification link uses multistage variable gain amplification units for cascading and can achieve high gain and enlarge high gain dynamic ranges. The automatic gain control feedback loop uses a charge pump structure and has the advantages that the automatic gain control feedback loop is less influenced by process deviation and temperature deviation, is capable of accurately detecting narrow-band and wide-band signal amplitude and is suitable for achieving CMOS processes. The direct current offset canceling feedback loop uses two-stage negative feedback loops, and each of the two-stage negative feedback loops uses an integrator as low-pass negative feedback; an active device is used as an integrator input resistor, and an equivalent resistor is provided with characteristics of temperature compensation; and the automatic gain control amplifier for canceling the direct current offset is capable of effectively canceling the direct current offset superposed by a preceding stage circuit and the direct current offset of the amplification link and is provided with a lower high pass corner frequency and a higher integrated level, and the automatic gain control amplifier for canceling the direct current offset is small in low-frequency signal loss and requires no off-chip passive devices (high value resistors or capacitors and the like). The automatic gain control amplifier is applicable to wireless communication receivers with zero intermediate frequency structures in the CMOS processes.

Owner:杭州中科微电子有限公司

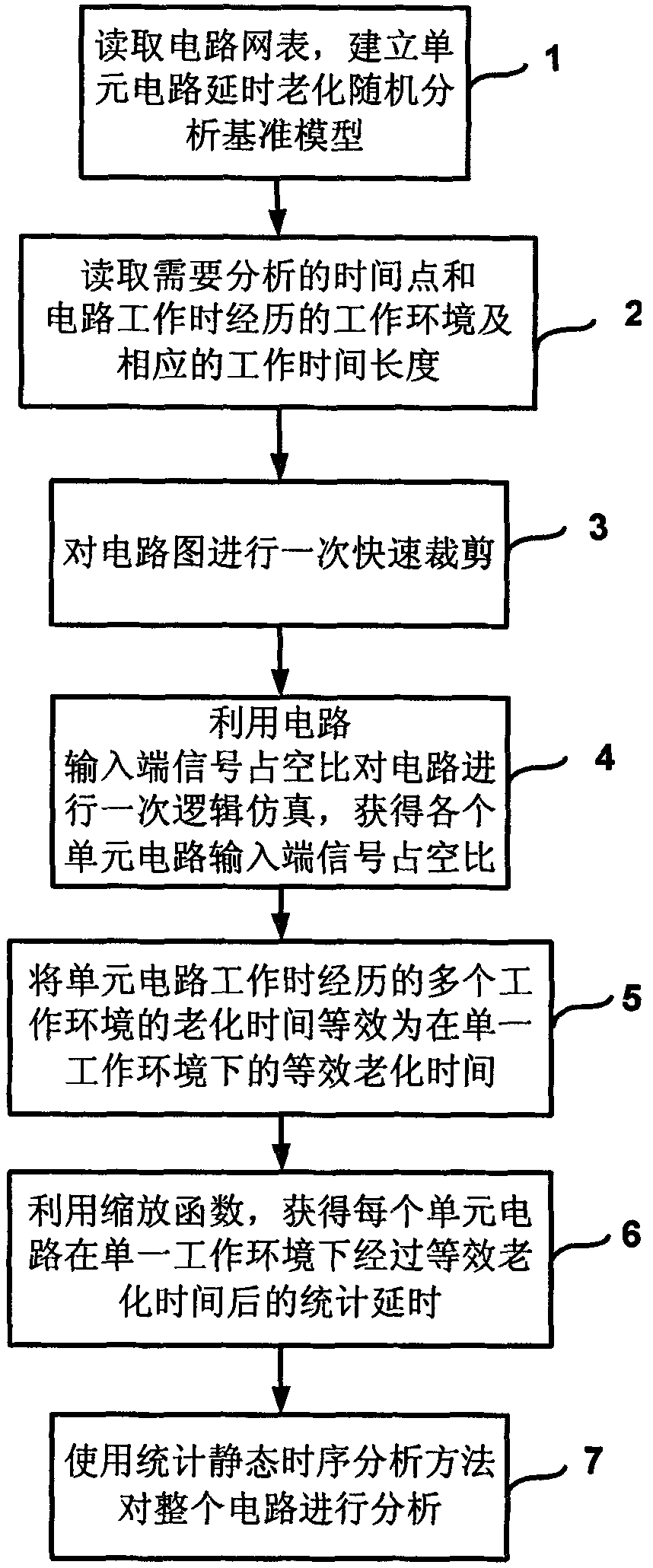

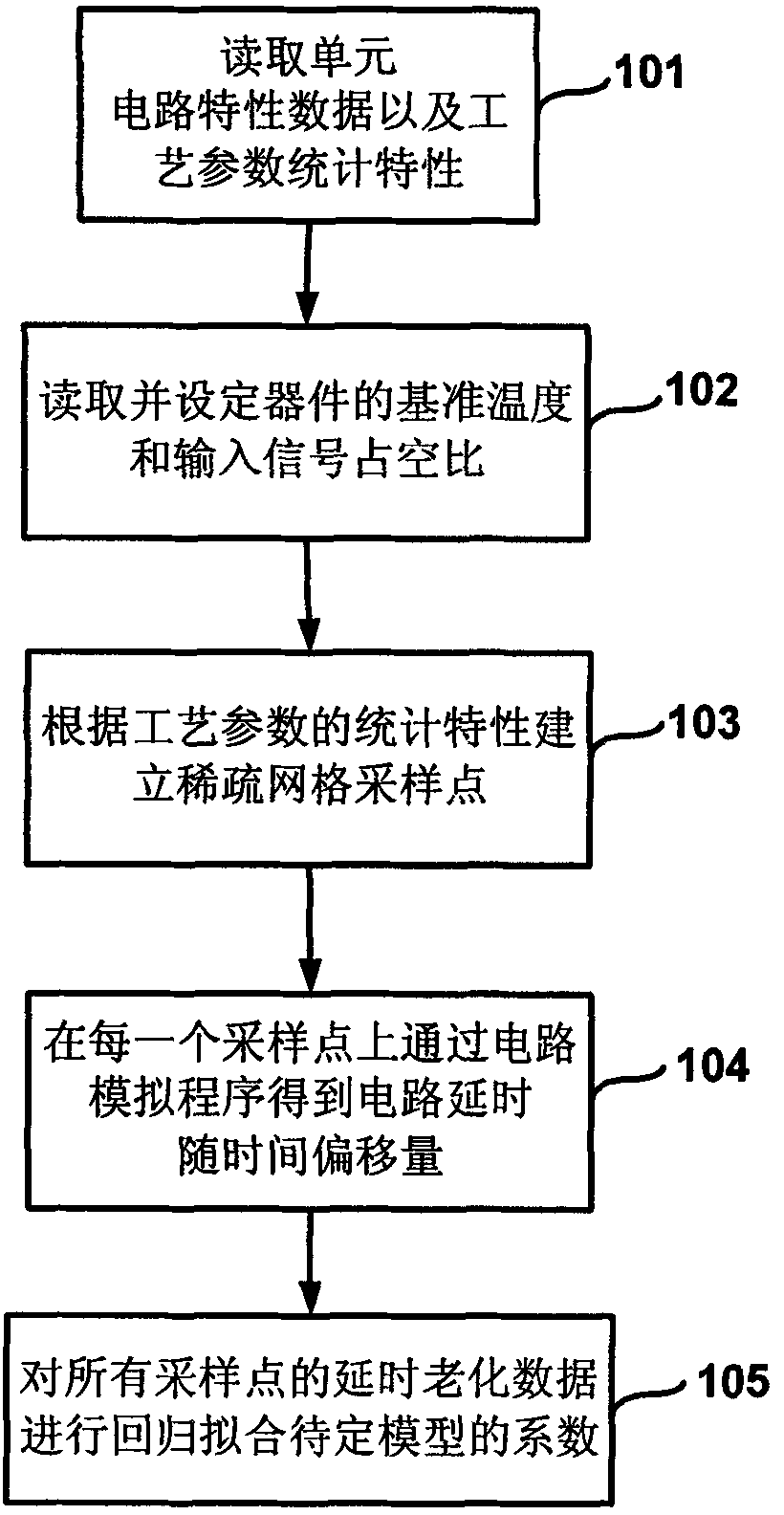

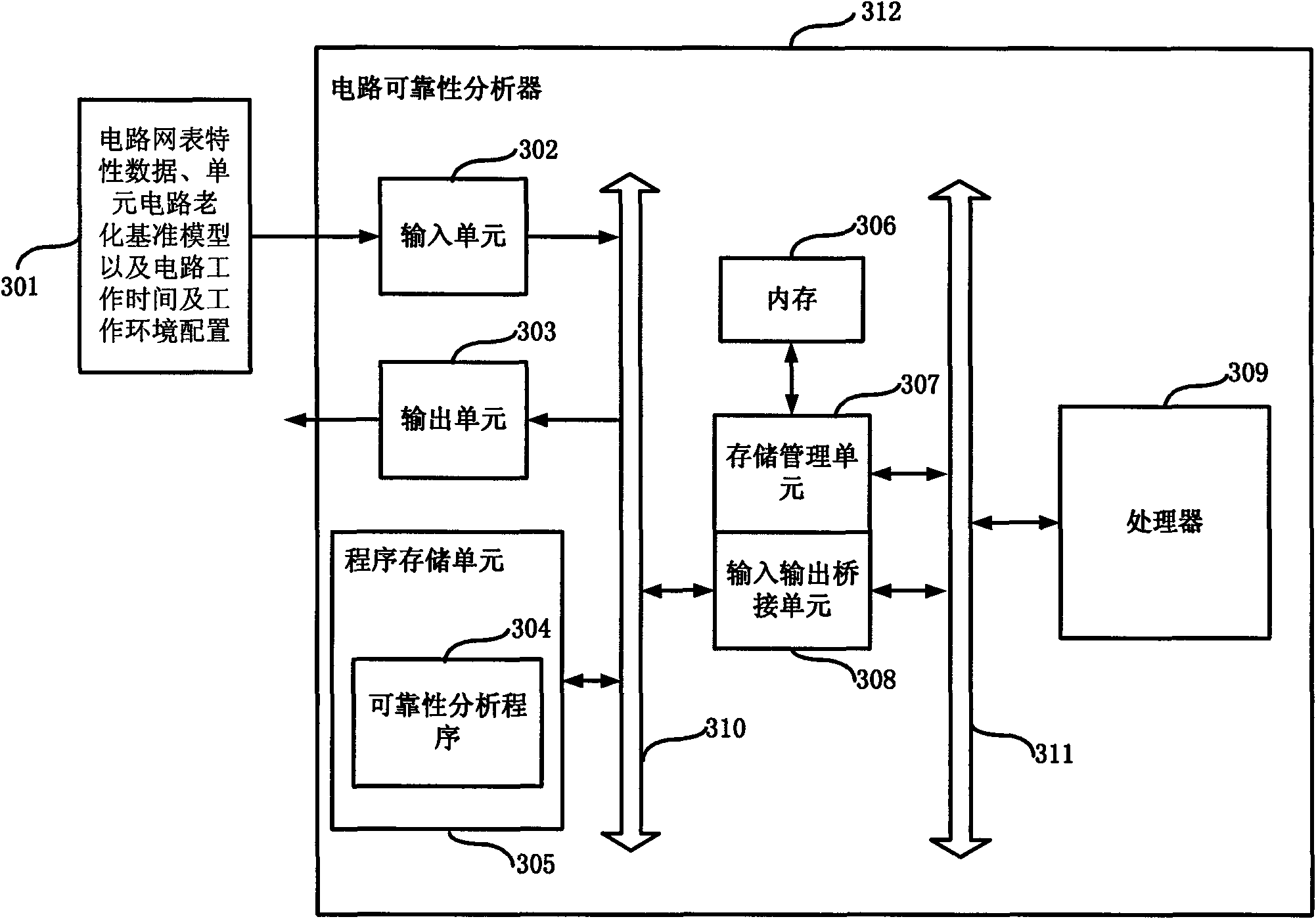

Method and device for analyzing reliability of integrated circuit

ActiveCN101964003AMeet analysis needsExtension of timeSpecial data processing applicationsProcess deviationsCircuit delay

The invention relates to a method and a device for analyzing the reliability of an integrated circuit. In the analytical method, a unit circuit delayed aging stochastic analysis reference model in consideration with both negative bias temperature instability (NBTI) effect and process parameter perturbation is established, a scaling function and an equivalent aging time concept are provided to solve the delayed statistical distribution of a unit circuit under the actual work environment quickly from the reference model, and the pre-clipping process of the circuit is provided to reduce the complexity of reliable analysis. The device of the invention comprises an input unit, an output unit, a program storage unit, an external bus, a memory, a storage administration unit, an input / output bridging unit, a system bus and a processor. In the method and the device, the effect of the process parameter perturbation, the NBTI effect and the work environment of the circuit on reliability are considered simultaneously, and the complexity of the reliable analysis can be reduced effectively by utilizing the scaling function, equivalent aging time and the pre-clipping technology so as to realize the quick analysis on the reliability of super-large-scale integrated circuits in consideration with process deviation.

Owner:FUDAN UNIV

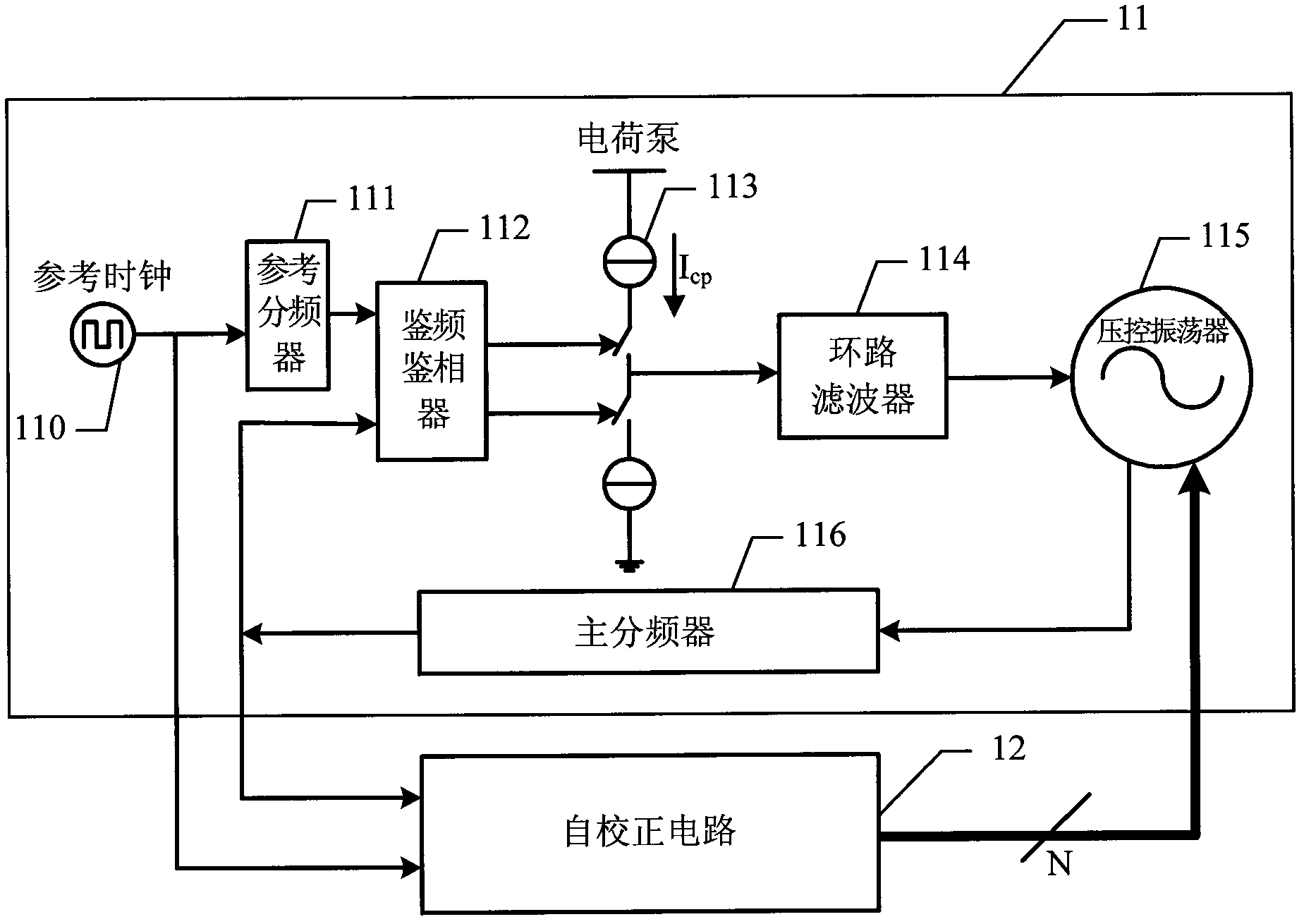

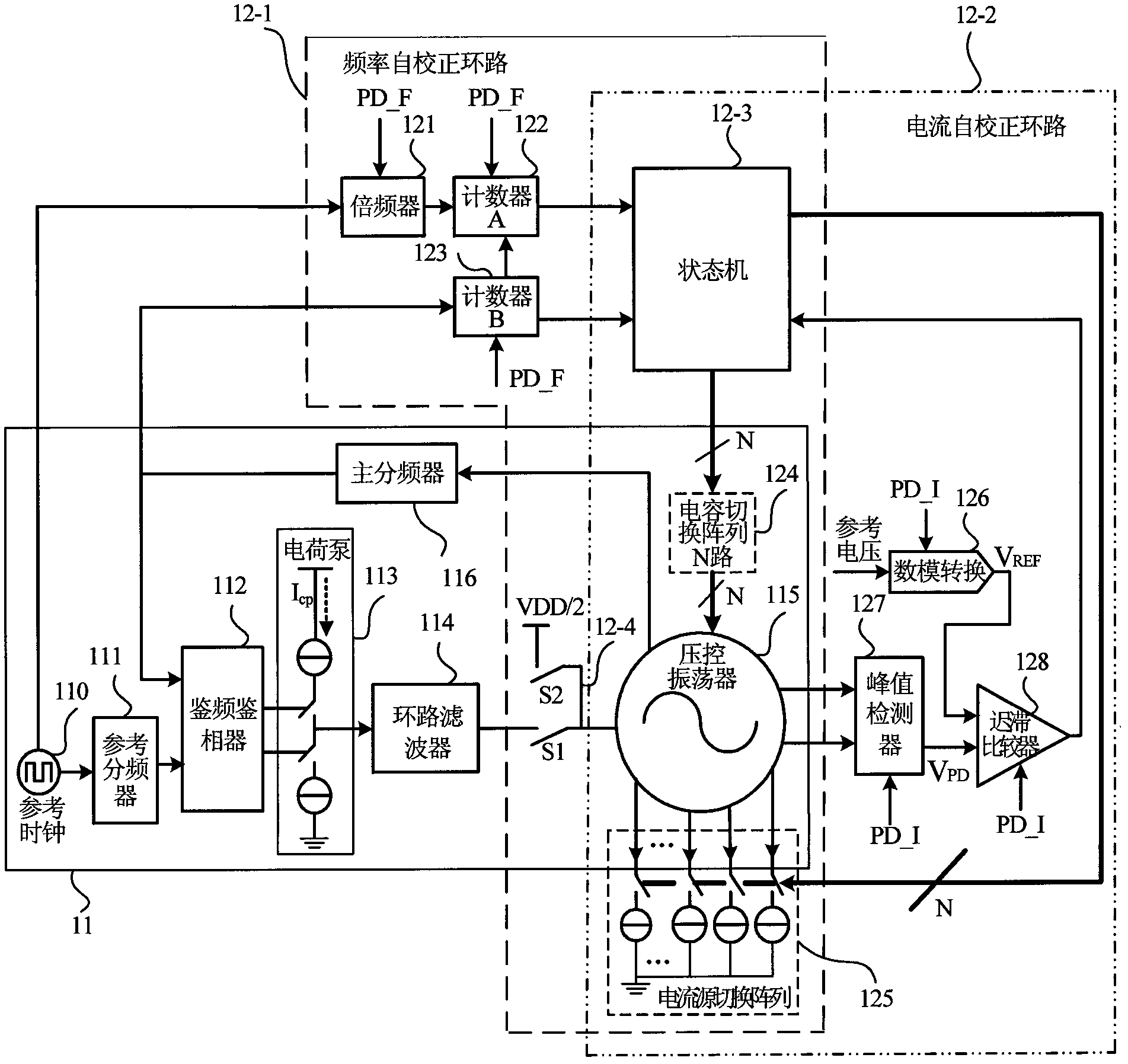

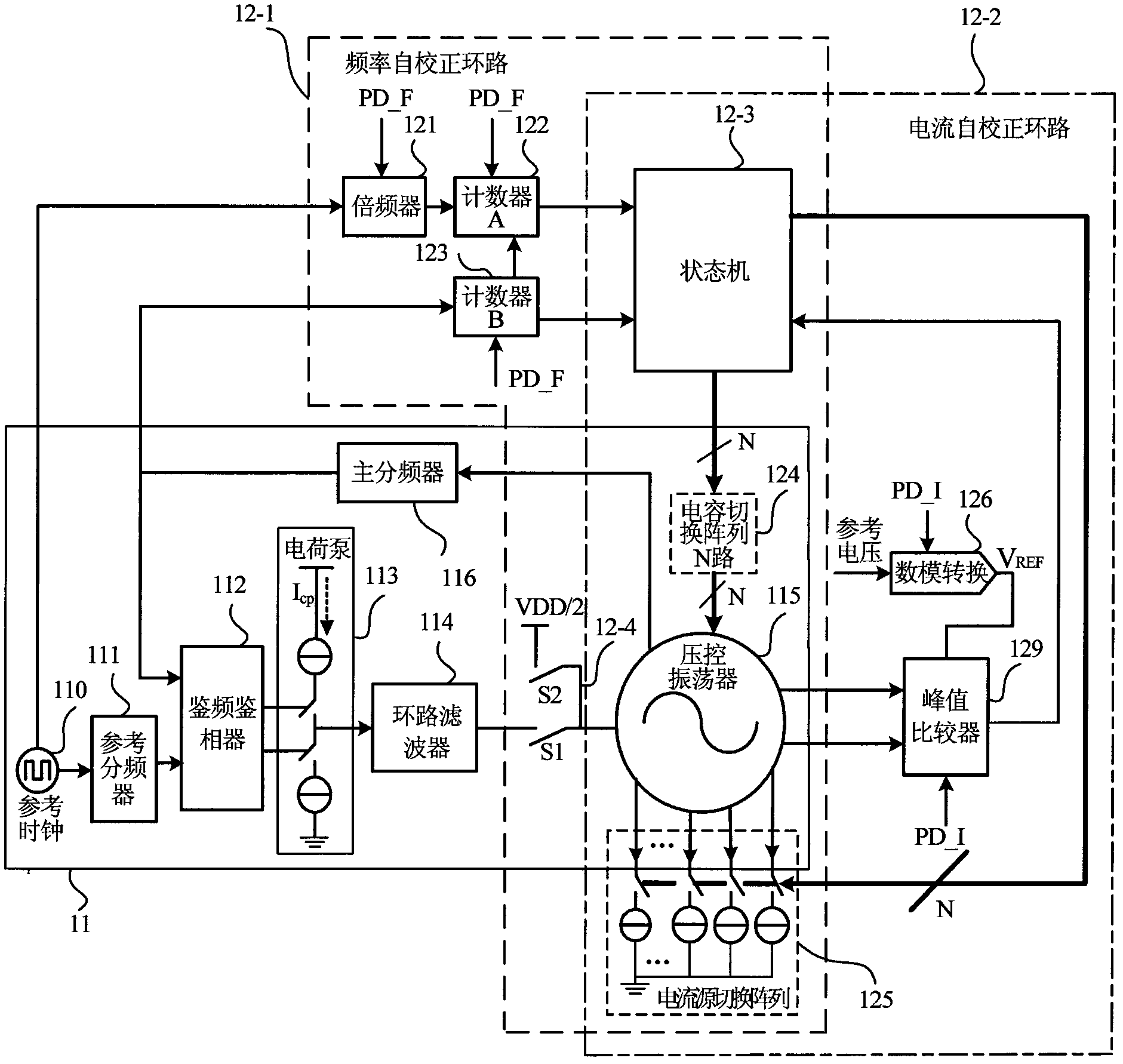

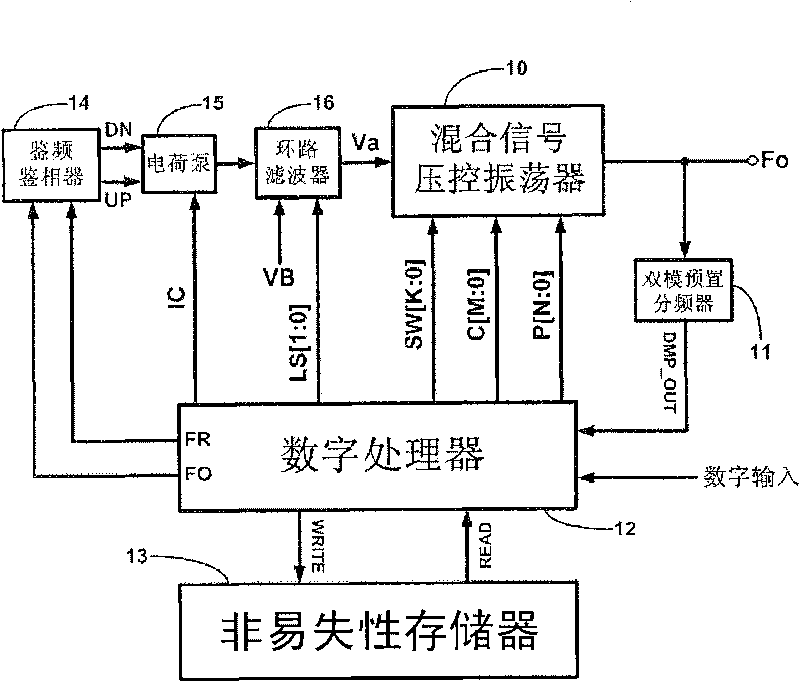

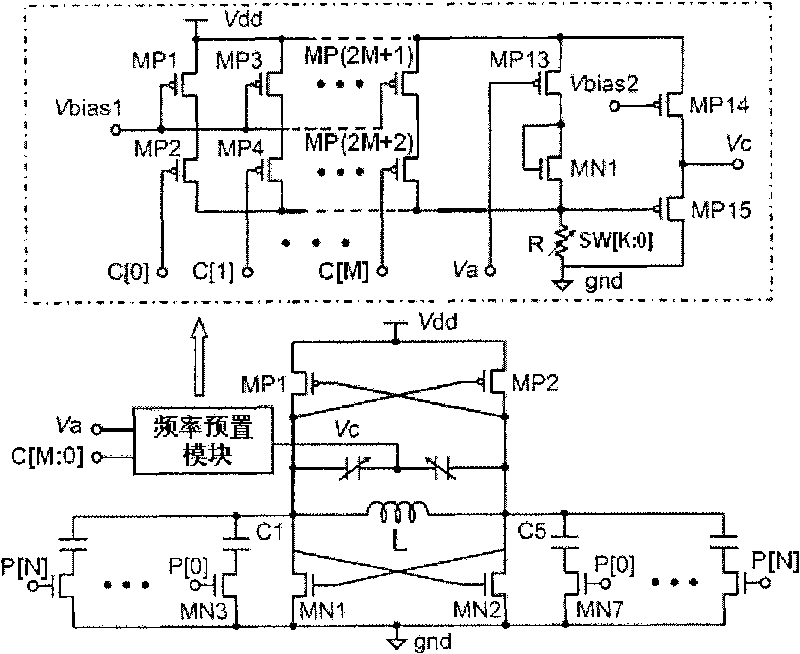

Self-correcting frequency synthesizer capable of optimizing properties of voltage-controlled oscillator and optimizing method of self-correcting frequency synthesizer

ActiveCN102868397ALarge frequency adjustment rangeFulfil requirementsPulse automatic controlProcess deviationsMulti band

The invention discloses an optimizing method of a self-correcting frequency synthesizer capable of optimizing properties of a voltage-controlled oscillator. The method comprises the following steps that: when a chip is electrified or a channel is changed each time, a frequency self-correcting loop in a synthesizer self-correcting circuit is started firstly, and a frequency sub-wave band code necessary for the voltage-controlled oscillator is searched; secondly a current self-correcting loop in the synthesizer self-correcting circuit is started, and a current sub-wave band code that an output amplitude of the voltage-controlled oscillator achieves an appointed amplitude is searched, so that the voltage-controlled oscillator works in a minimum power consumption, a good phase noise property is obtained, and at the same time the properties of the voltage-controlled oscillator are not changed when process deviation and temperature change occur; after the accomplishment of frequency correction and current correction is judged by a state machine, a synthesizer enters into the frequency self-locking process of a phase-locked loop; and the optimization and correction process is ended. The invention further discloses the self-correcting frequency synthesizer capable of optimizing the properties of the voltage-controlled oscillator. A wider frequency adjustment range can be obtained, and good local oscillator spectrum purity is obtained through small power consumption; and the optimizing method is suitable for the self-correcting frequency synthesizer of a transceiver with low power consumption, multiple modes and multi-band frequency.

Owner:杭州中科微电子有限公司

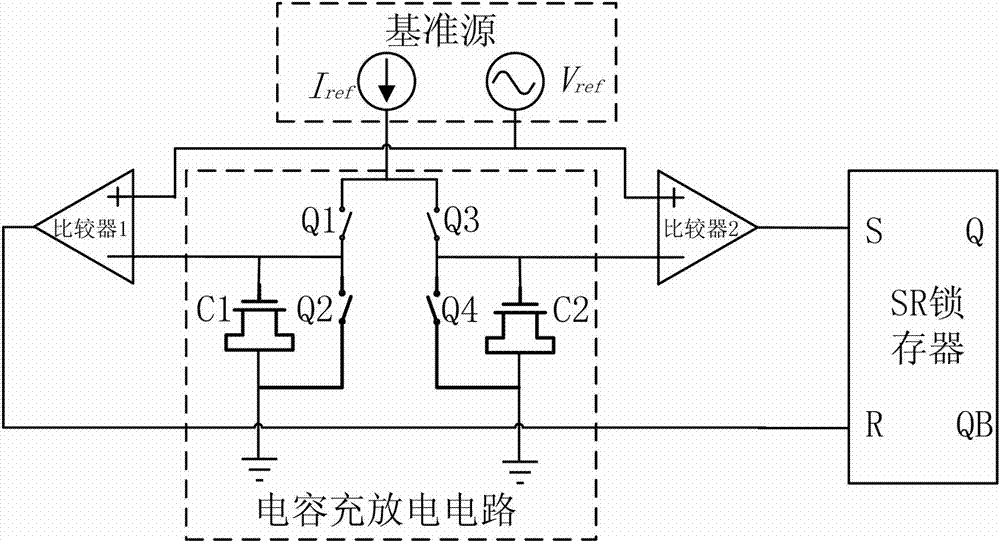

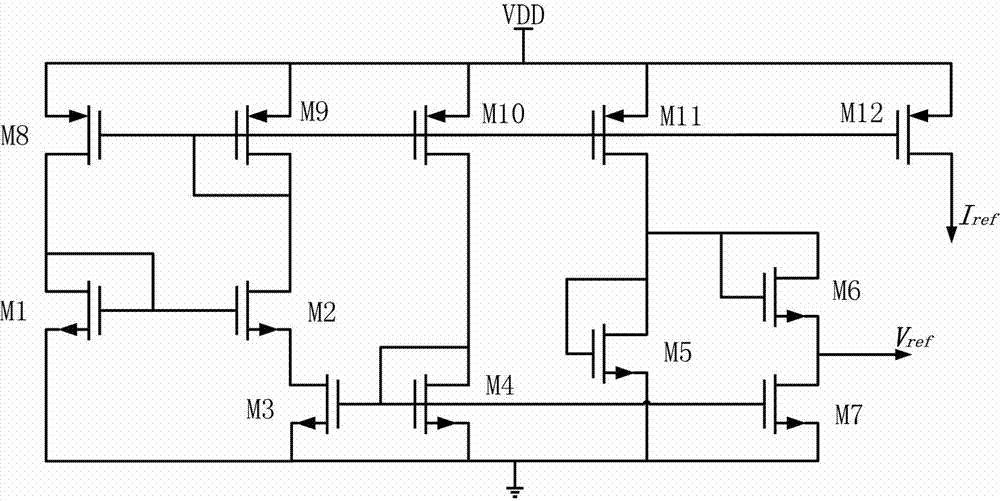

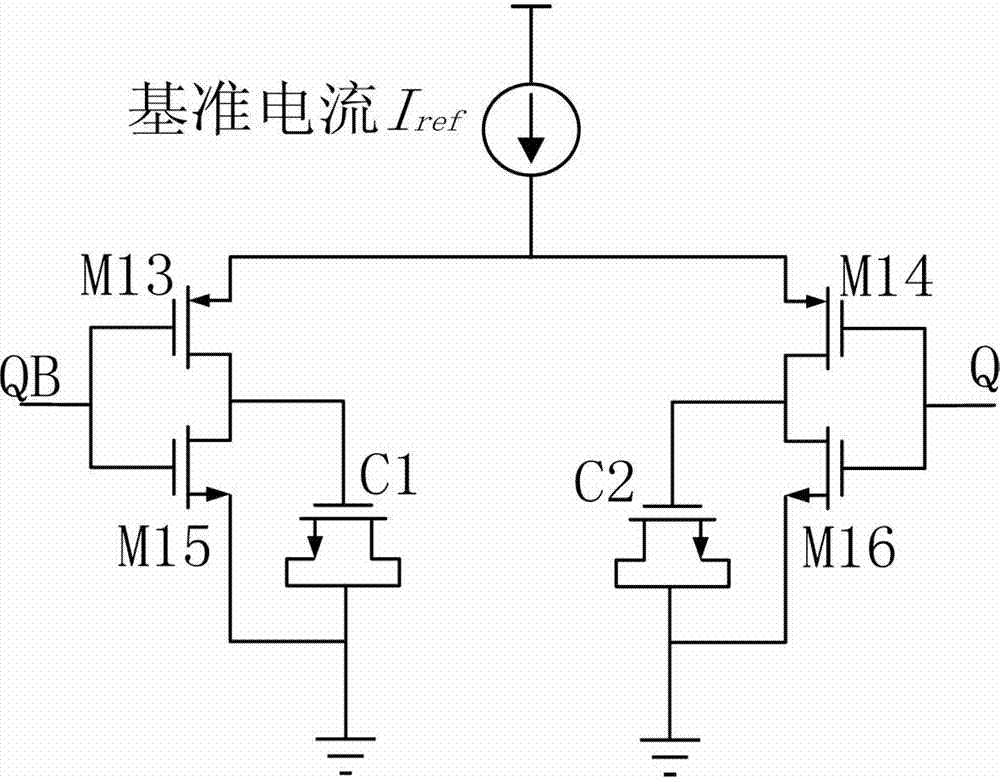

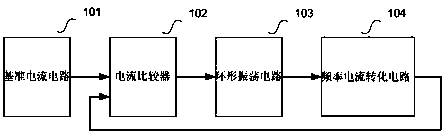

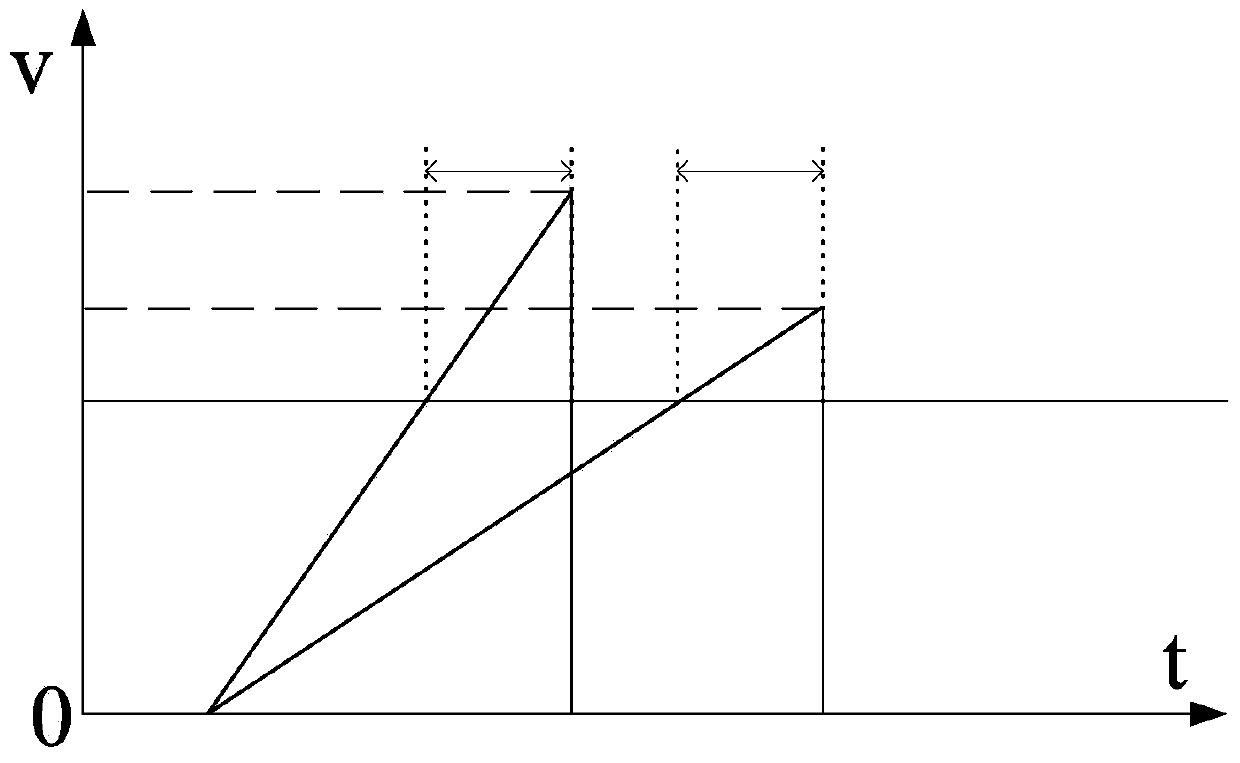

CMOS (complementary metal oxide semiconductor) relaxation oscillator with temperature and process self-compensating characteristics

ActiveCN103701411ASolve temperature problemsSolve process problemsOscillations generatorsCapacitanceProcess deviations

The invention discloses a CMOS (complementary metal oxide semiconductor) relaxation oscillator with temperature and process self-compensating characteristics. The CMOS relaxation oscillator comprises a reference source, a capacitor charge and discharge circuit, a first comparator, a second comparator and an SR (set reset) latch, wherein the reference current of the reference source is connected with the capacitor charge and discharge circuit, the reference voltage of the reference source is respectively connected with the same-phase input end of the first comparator and the same-phase input end of the second comparator, the reverse-phase input end of the first comparator and the reverse-phase input end of the second comparator are respectively connected with the capacitor charge and discharge circuit, the output end of the first comparator is connected with the R end of the SR latch, and the output end of the second comparator is connected with the S end of the SR latch. The CMOS relaxation oscillator with temperature and process self-compensating characteristics can overcome the defects of high cost, low reliability, great process deviation and the like in the prior art for realizing the advantages of low cost, high reliability and small process deviation.

Owner:四川电子科技大学教育发展基金会

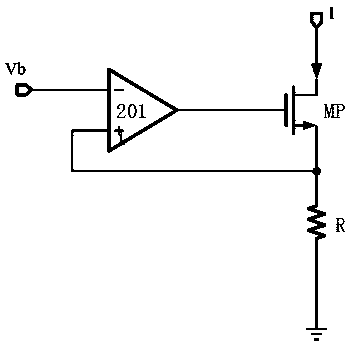

High-precision annular oscillator, and frequency calibration circuit and method thereof

InactiveCN103441760AAvoid nonlinearityAvoid errorsPulse automatic controlProcess deviationsReference current

The invention discloses a high-precision annular oscillator, and a frequency calibration circuit and method thereof. The high-precision annular oscillator comprises a band gap reference circuit, a reference current circuit, a current adjusting circuit, an annular oscillation circuit and an output buffer circuit. The frequency calibration circuit comprises a frequency divider, a counter, a comparator, a register and a nonvolatile memory. The frequency calibration circuit can rapidly position the adjusting current needed by the high-precision annular oscillator and store an adjustment arrangement in the nonvolatile memory. According to the invention, the high-precision annular oscillator cooperates with the frequency calibration circuit so that the effects of temperature deviations, voltage deviations and technology deviations on oscillation frequencies can be compensated, and thus the high precision of the oscillation frequencies can be realized. Through the cooperation between the high-precision annular oscillator and the frequency calibration circuit, high-precision oscillation frequencies are obtained, at the same time a complex circuit is avoided, the area and power consumption of a chip are reduced, the non-linearity, error and noise of a simulation comparison circuit are avoided, the frequency precision is improved, and the testing time and cost of the chip are saved.

Owner:BRITE SEMICON SHANGHAI CORP

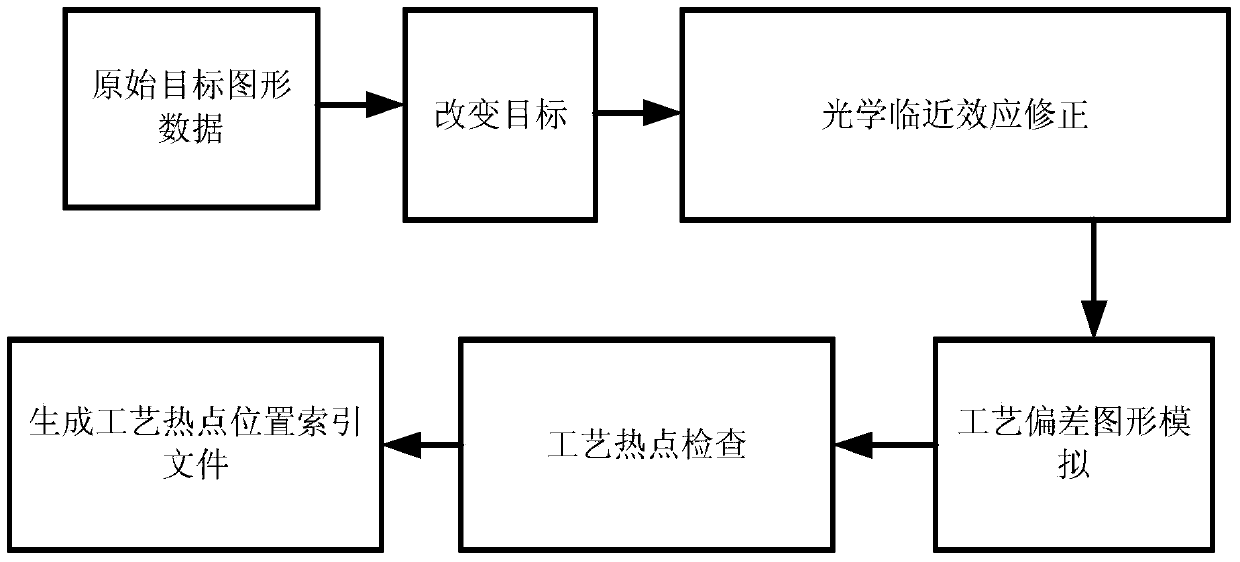

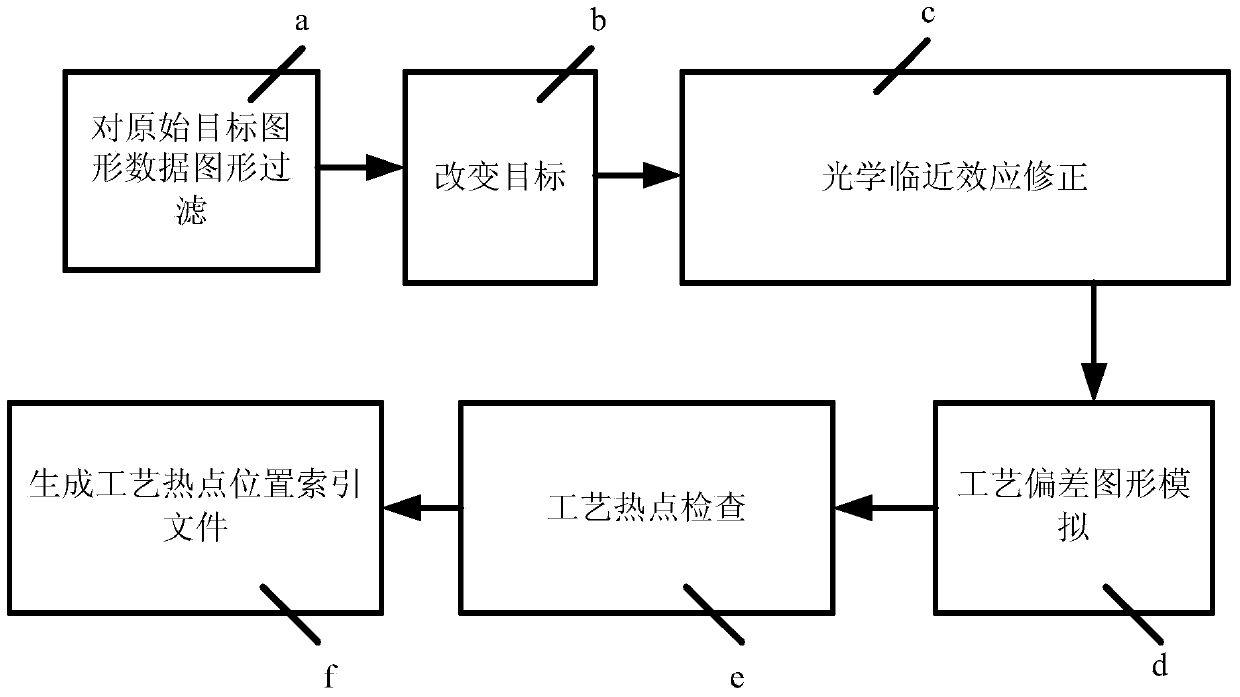

Layout design photoetching technology friendliness detection method based on regular figure filtering

ActiveCN103744267AAdded filtering stepsReduce use costPhotomechanical exposure apparatusMicrolithography exposure apparatusProcess deviationsAlgorithm

The invention provides a layout design photoetching technology friendliness detection method based on regular figure filtering. According to the layout design photoetching technology friendliness detection method based on regular figure filtering, by adding a step of filtering original object figure data before steps of performing optical proximity effect correction and technological error figure simulation, the time consumption of layout design photoetching technology friendliness detection is shortened, the usage cost of software and hardware is reduced, and also the extremely good matching between a detection result and a method of prior art can be realized, and thus the rapid accurate search for technological hot-spot areas in layout design is realized.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

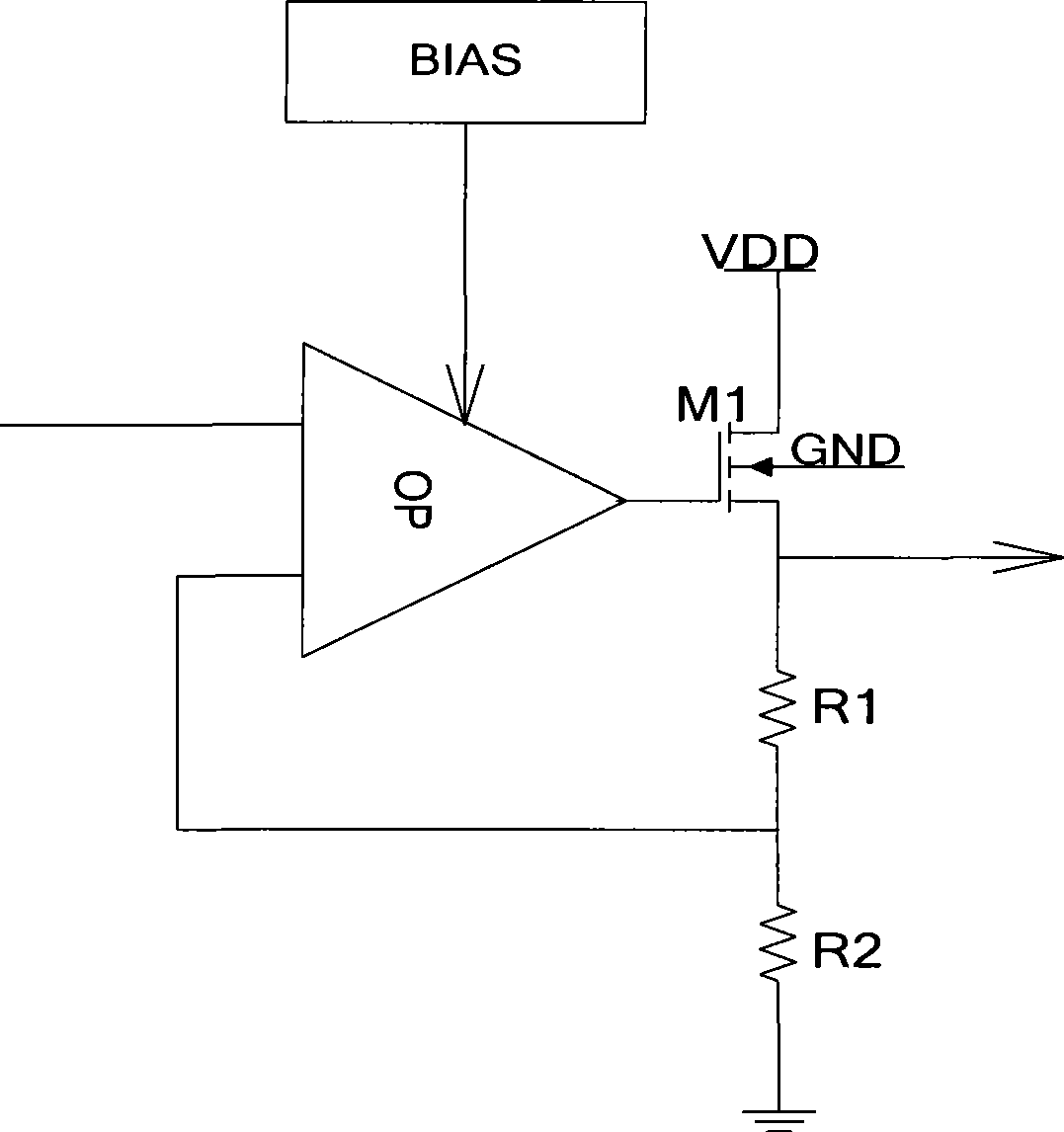

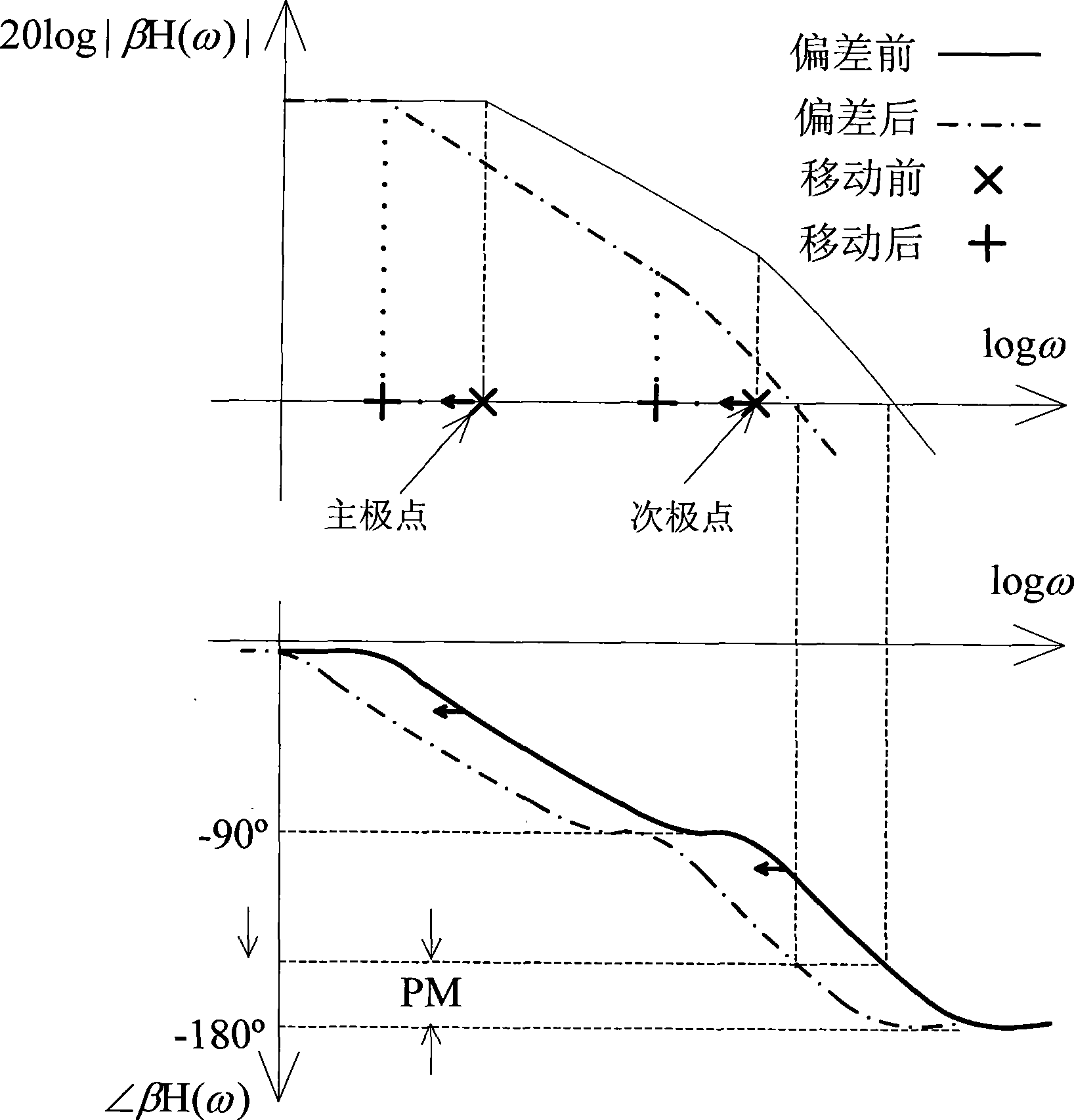

Voltage regulator circuit and resistance deviation compensation method

ActiveCN101458537AReduce gainReduce the impact of phaseElectric variable regulationProcess deviationsElectrical resistance and conductance

The invention discloses a voltage adjuster circuit, which includes an operational amplifier. A positive direction inputting terminal of the operational amplifier receives input signal, an outputting terminal of the operational amplifier connects with a source follower composed of NMOS pipe, the operational amplifier also connect with a biasing circuit, the biasing circuit provides biasing signal to the operational amplifier. The invention also discloses a resistor tolerance compensation method, the circuit pole point is proportional to corresponding resistor, the resistor uses same technique variable direction resistor or same resistor, when resistor changes, the pole point moves towards to same direction on coordinate for compensating increase biasing and phase biasing caused by resistor variable. The circuit provided by the invention can reduce effect to the circuit increase and phase caused by factors such as technique biasing or temperature biasing efficiently, ensures the circuit property.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

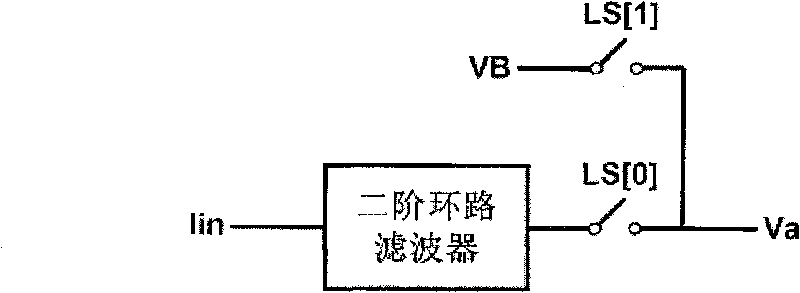

Frequency complex for fast locking phaselocked loop

ActiveCN101741379AAvoid correctionRealize automatic correctionPulse automatic controlProcess deviationsLoop filter

The invention discloses a frequency complex for fast locking phaselocked loop. The frequency complex comprises a mixed signal voltage-controlled oscillator, a bimodule preset frequency divider, a digital processing unit, a nonvolatile memory, a phase-frequency detector, a charge pump and a loop filter. By using the invention, the processing of correcting the phaselocked loop in every charging can be avoided, the presetting on the output frequency of the mixed signal voltage-controlled oscillator can be carried out precisely with small difference between the preset frequency and the target frequency under process variation, and the phaselocked loop can finish locking in an extremely short time. In addition, the modules comprising the nonvolatile memory can be manufactured by standard CMOS process and conveniently applied in fast frequency hopping communication systems.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

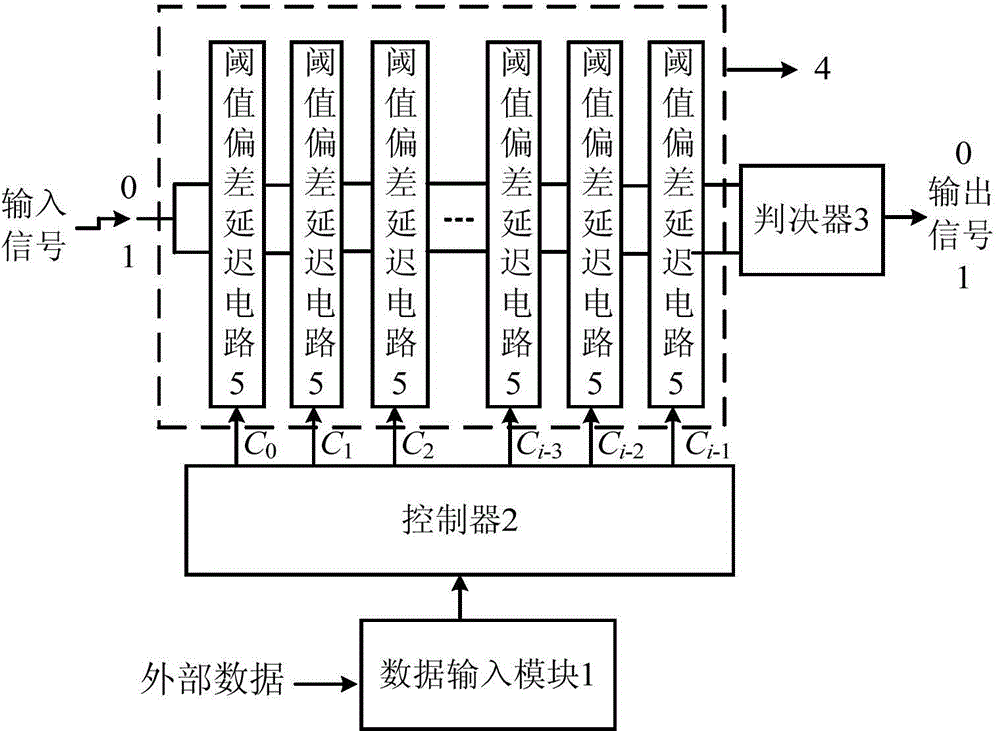

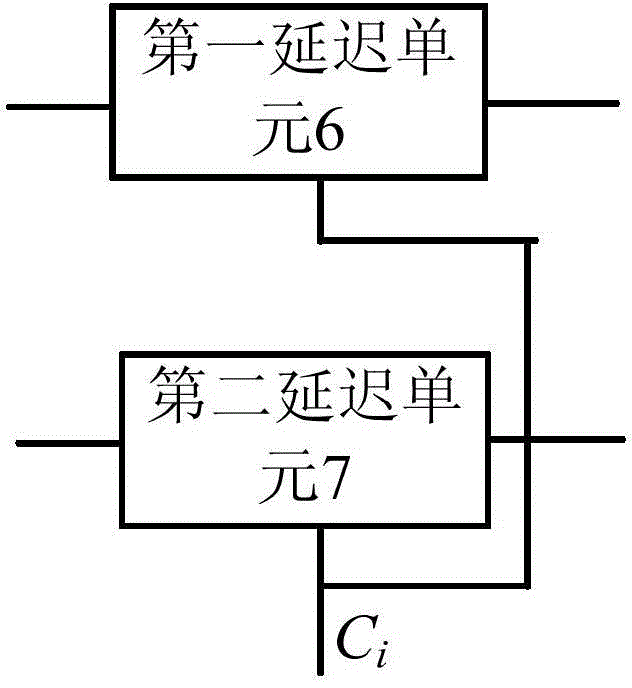

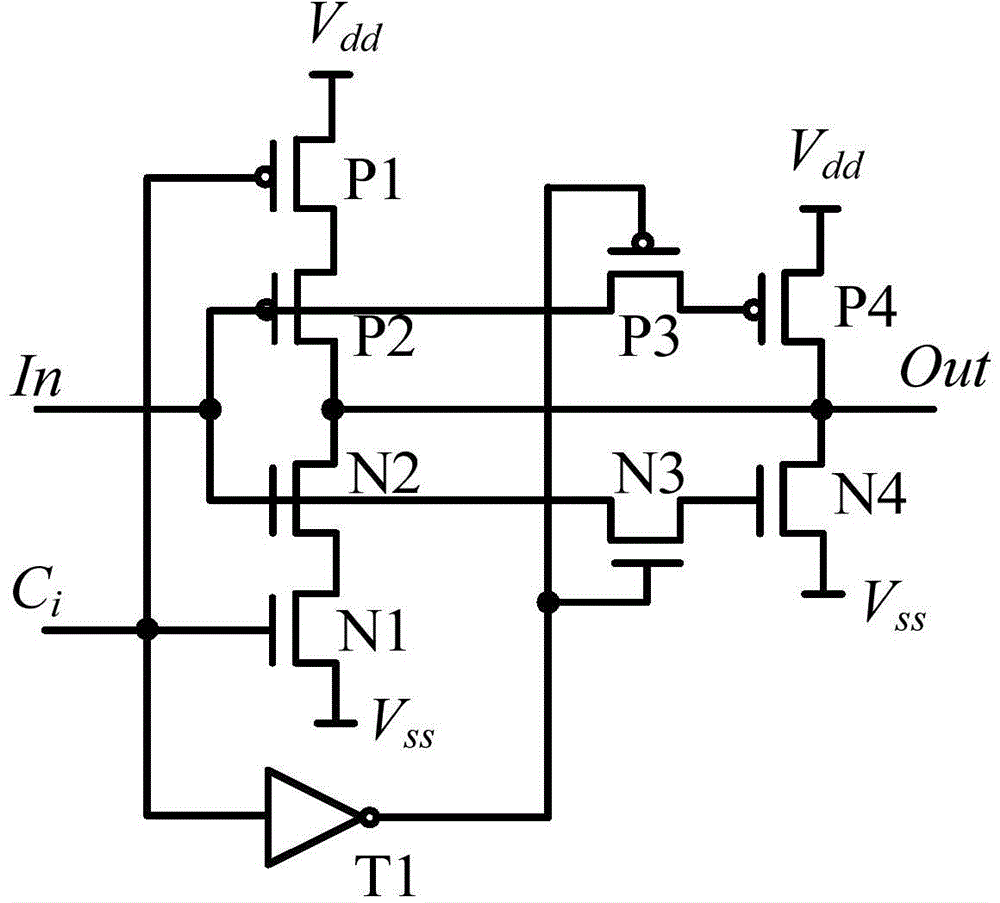

PUF circuit based on threshold deviation delay

ActiveCN104318181AAchieve changeRun fastInternal/peripheral component protectionProcess deviationsControl signal

The invention discloses a PUF (Physical Unclonable Functions) circuit based on threshold deviation delay. The PUF circuit comprises a data input module, a controller, a decision device and a PUF unit circuit, wherein external data is accessed into the input end of the data input module; the output end of the data input module is connected with the input end of the controller; the PUF unit circuit comprises an i-bit threshold deviation delay circuit; the threshold deviation delay circuit consists of two delay units; and the two delay units are respectively a first delay unit and a second delay unit. The PUF circuit has the advantages that the threshold deviation delay circuit is configured through control signals, so that a plurality of pieces of extractible process deviation exist in the PUF circuit; output signals (secret keys) of the PUF circuit can be reconstructed; and the output secret key change can be realized without replacing hardware.

Owner:NINGBO UNIV

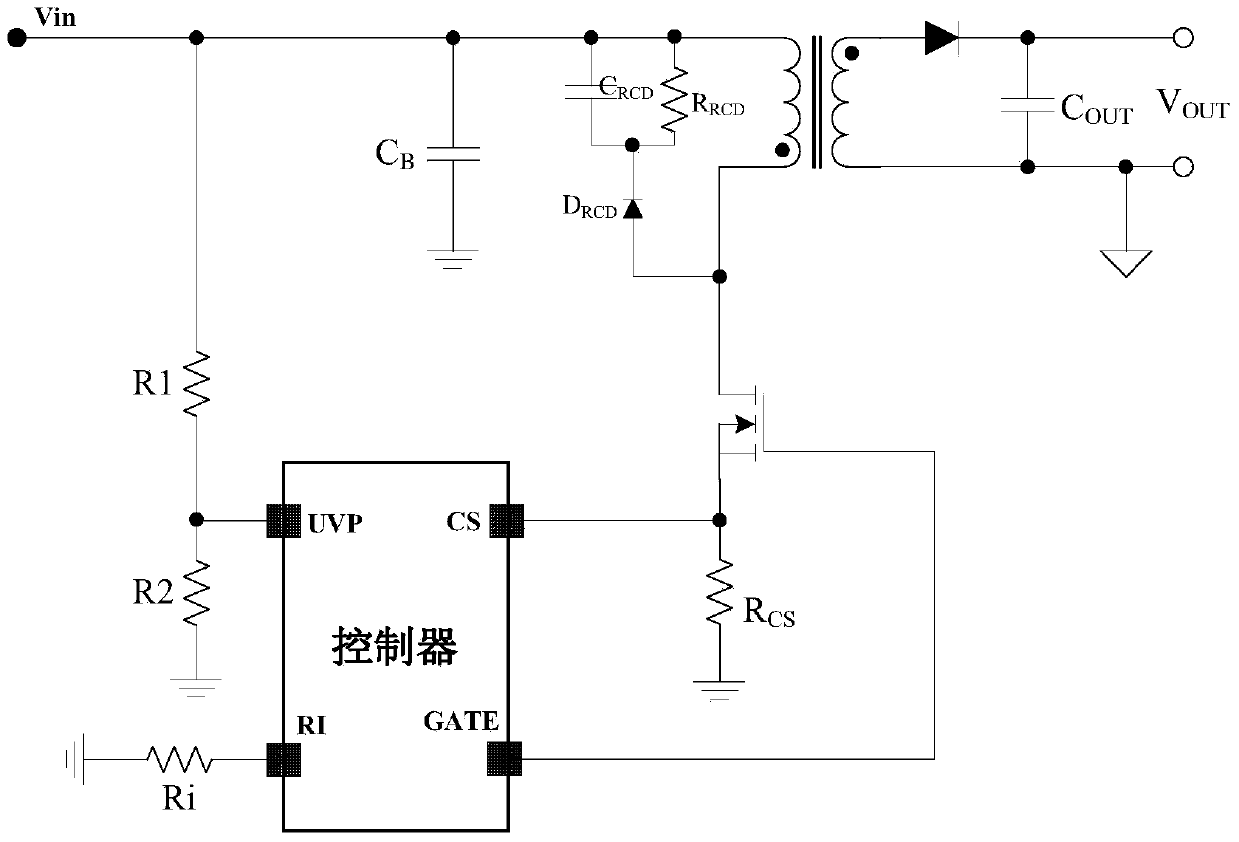

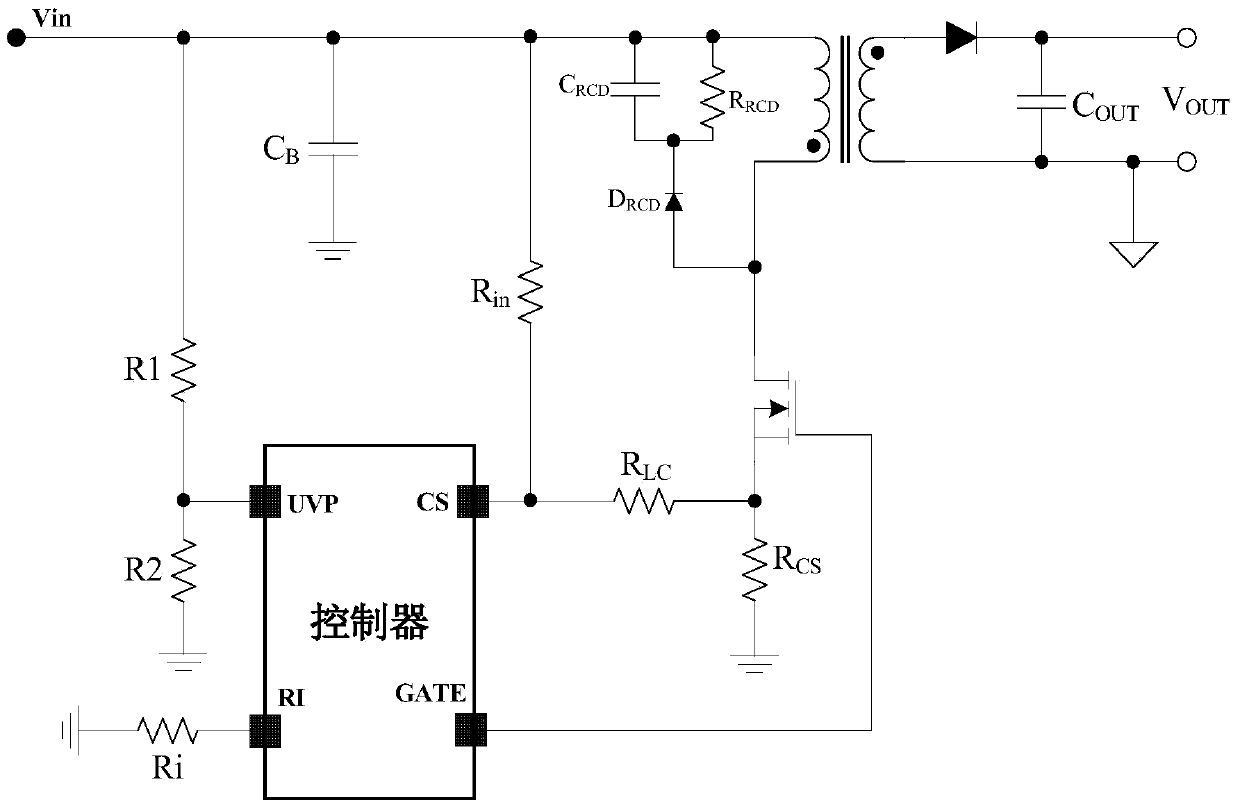

Input undervoltage protecting circuit of switching power supply controller

ActiveCN103795036ASmall temperature coefficientHigh precisionEmergency protective circuit arrangementsPower conversion systemsProcess deviationsPower controller

The invention provides an input undervoltage protecting circuit of a switching power supply controller. The input undervoltage protecting circuit of the switching power supply controller comprises a current detection circuit, a reference voltage generating circuit, an undervoltage protecting signal generating circuit and a pulse outputting control circuit. The current detection circuit comprises a controller internal resistor R2 and a controller external resistor R1, and the resistance value of the R2 is far smaller than that of the R1. The reference voltage generating circuit comprises an internal resistor R3 and a reference current source Iref, and the R3 and the R2 are resistors of the same type in the controller. The undervoltage protecting signal generating circuit comprises a comparator comp. A protecting point input voltage Vin(p) meets the formula (please see the formula in the specification). When the input voltage Vin of a switching power supply drops to be lower than the protecting point input voltage Vin(p), the output end UVP of the comparator comp generates undervoltage protecting signals to control the pulse outputting control circuit to cut off pulse output of GATE pins of the controller. According to the input undervoltage protecting circuit of the switching power supply controller, the peripheral circuits of the controller are simplified, the loss is small, meanwhile, the precision of input undervoltage protecting is high, and process bias is small. The invention further provides an input undervoltage protecting circuit with feed-forward compensation, the feed-forward compensation current Icom is in proportion to input voltages, the precision is high, and the process bias is small.

Owner:MORNSUN GUANGZHOU SCI & TECH

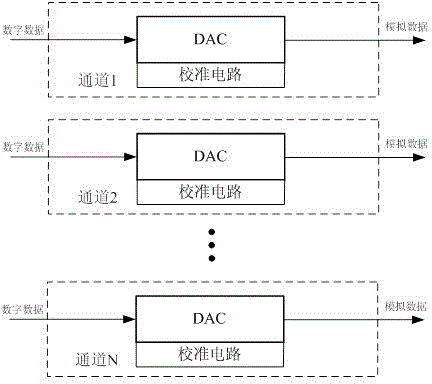

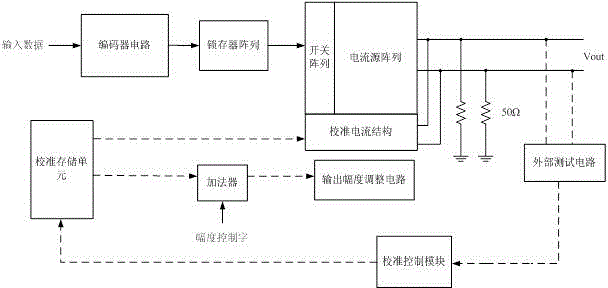

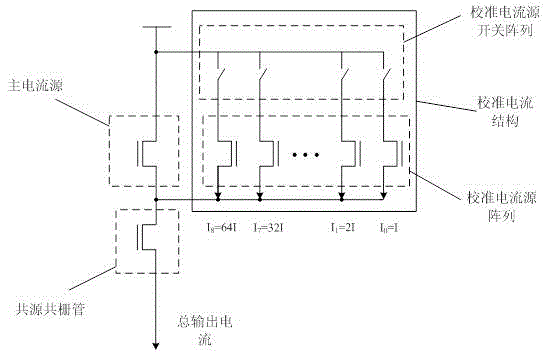

Calibration system and method suitable for current source array in multichannel sectional type current steering DAC (digital to analog converter)

ActiveCN104617953AImprove linearityIncrease the number of effective digitsAnalogue/digital conversion calibration/testingProcess deviationsBit field

The invention discloses a calibration system and a calibration method suitable for a current source array in a multichannel sectional type current steering DAC (digital to analog converter). The calibration method suitable for the current source array in the multichannel sectional type current steering DAC includes steps: firstly, calibrating a channel, and then sequentially calibrating other channels, and enabling output among all the channels to tend to be uniform, wherein when the channels are calibrated, switches in a current source switch array are by selectively closed and calibrated, and an output amplitude adjustment circuit is adjusted so as to sequentially calibrate a low data bit segment and a high data bit segment of the current source array segment by segment. The calibration method suitable for the current source array in the multichannel sectional type current steering DAC can calibrate each current source at the low data bit segment of the sectional type current steering DAC, and thereby achieves high calibration accuracy, remedies deviation and a mismatch, among the current sources in the current source array of the sectional type current steering DAC, improves linearity of the single DAC, and then improves performance indexes such as the significant number of digits of the DAC and a spurious free dynamic range, and improves linear performance of the multichannel sectional type current steering DAC and amplitude consistency among all the channels.

Owner:CHENGDU CORPRO TECH CO LTD

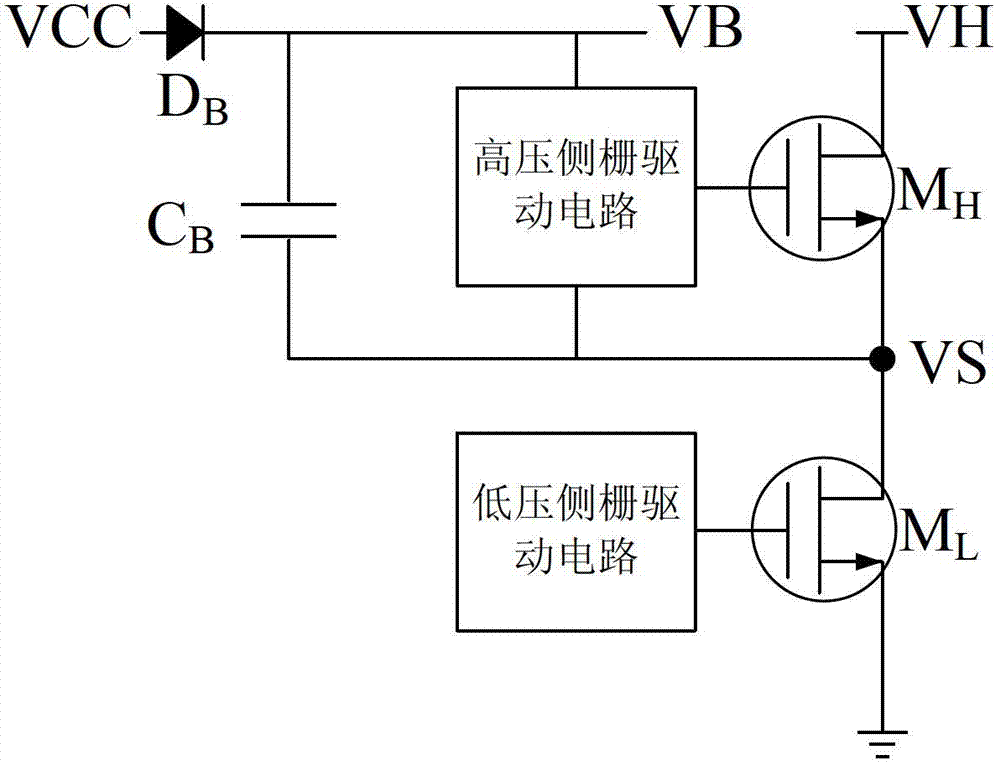

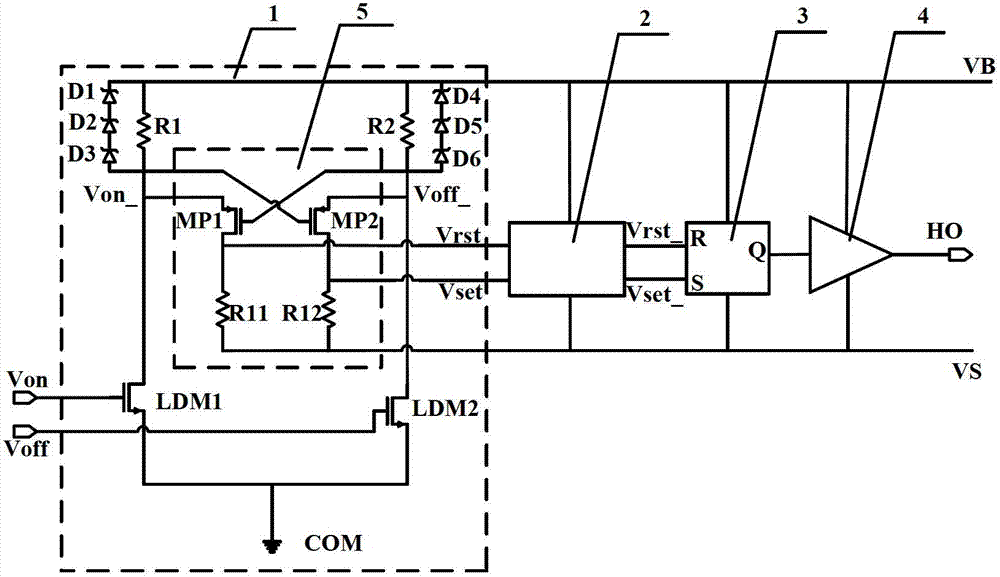

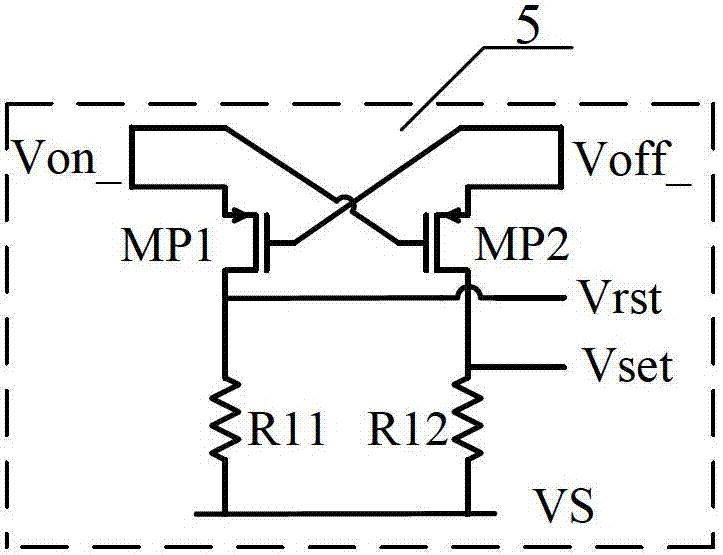

High-voltage side gate drive circuit capable of resisting noise interference

ActiveCN102769453AEliminate the effects of working statusDoes not affect deliveryReliability increasing modificationsProcess deviationsHigh voltage pulse

The invention provides a high-voltage side gate drive circuit capable of resisting noise interference. The high-voltage side gate drive circuit comprises a high-voltage level shift circuit, a differential-mode noise elimination circuit, an RS trigger and an output drive level circuit, wherein a low-side pulse signal is converted into a high-voltage pulse signal for output through the high-voltage level shift circuit; a common mode noise elimination circuit is connected between the output of the high-voltage level shift circuit and the input of the differential-mode noise elimination circuit; the common mode noise elimination circuit is used for eliminating a common mode noise signal generated in application; and the differential-mode noise elimination circuit eliminates the differential-mode noise introduced by process variations, outputs a normal pulse signal, reduces the normal pulse signal into a normal square signal through the RS trigger, outputs the square signal from the output drive level circuit and drives an external high-side power tube.

Owner:SOUTHEAST UNIV

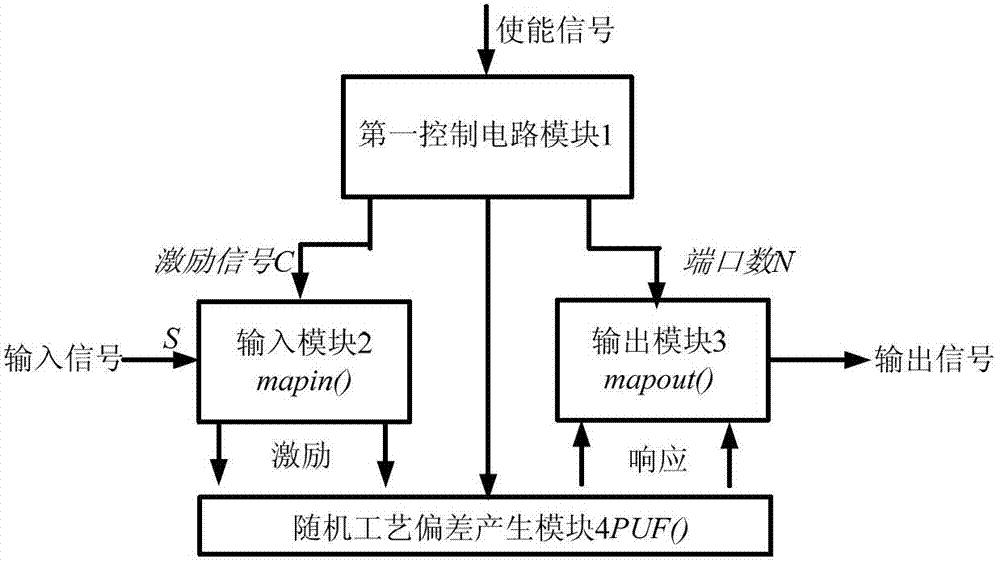

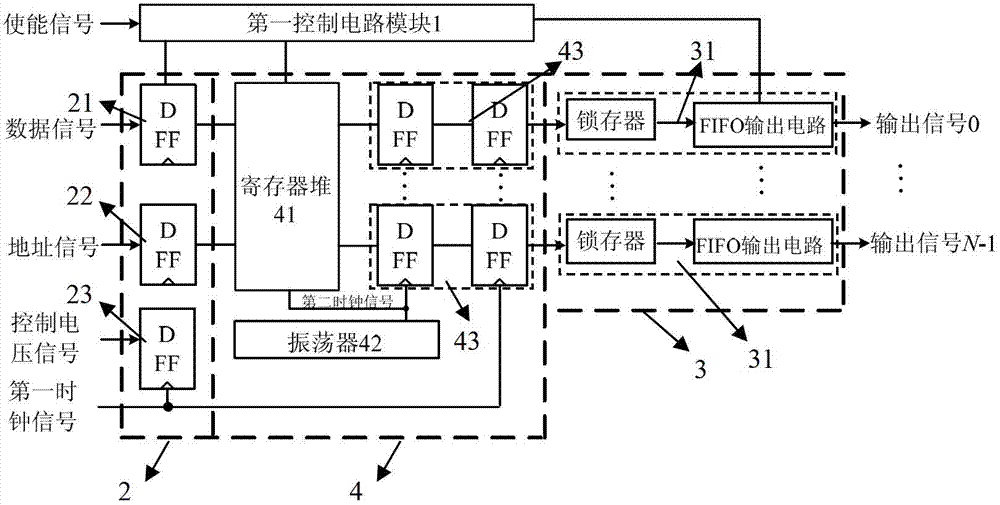

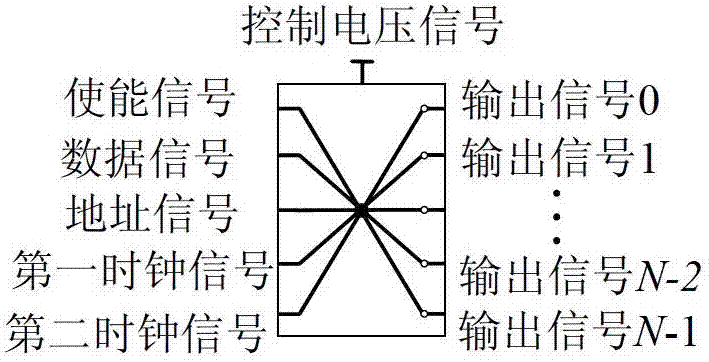

Reconfigurable multi-port physical unclonable functions (PUF) circuit unit

ActiveCN103198267AFlexible replacementImplement refactoringInternal/peripheral component protectionProcess deviationsComputer module

The invention discloses a reconfigurable multi-port physical unclonable functions (PUF) circuit unit. The reconfigurable multi-port PUF circuit unit comprises a first control circuit module, an input module, an output module and a random process deviation generation module, wherein the first control circuit module is connected with the input module, the output module and the random process deviation generation module respectively; the input module is connected with the random process deviation generation module; and the random process deviation generation module is connected with the output module. The reconfigurable multi-port PUF circuit unit has the advantages that the number of output secret keys and ports can be reconfigured; the number of output secret keys and ports can be exchanged flexibly; a plurality of secret keys can be generated within one clock period; the cost is low; and the running speed is high.

Owner:NINGBO UNIV

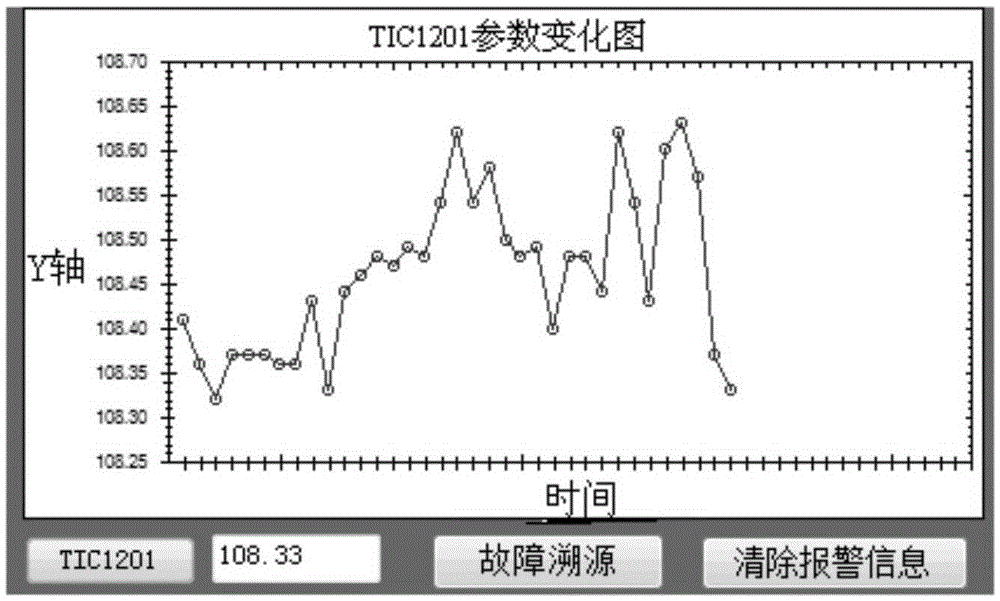

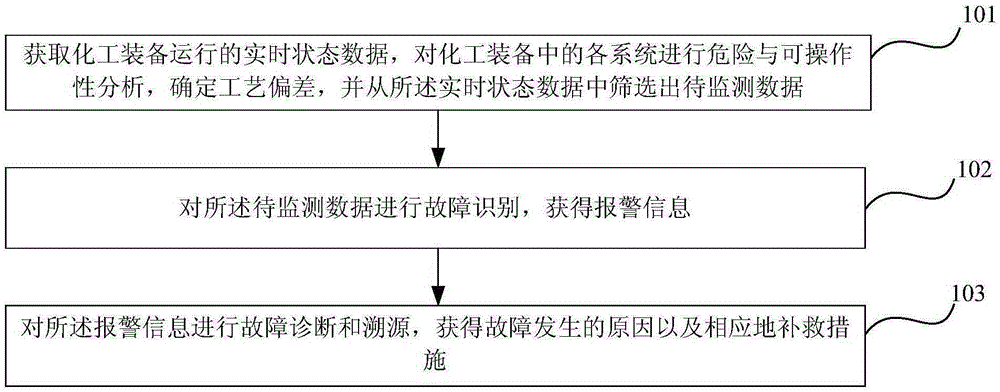

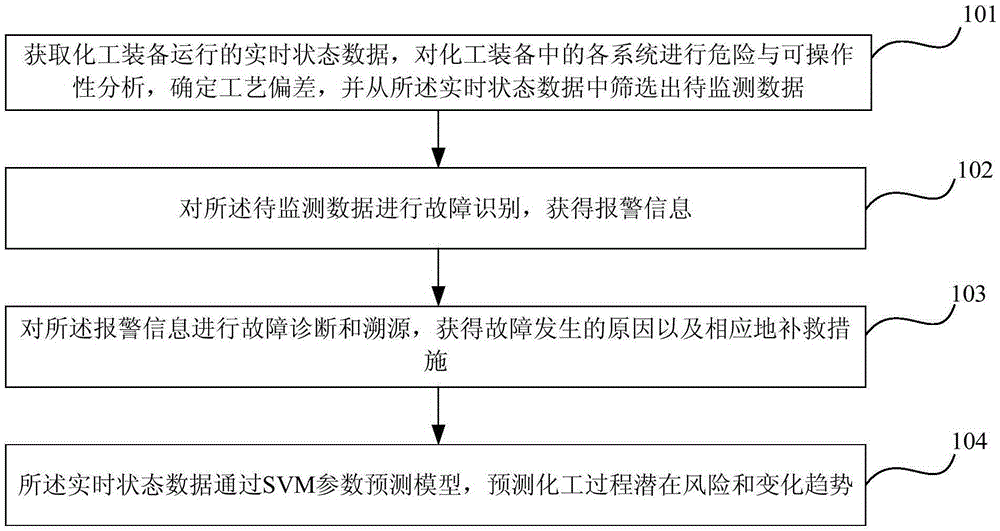

Radar monitoring method and device for long-term security risk of chemical equipment

InactiveCN105389595AGuaranteed uptimeMonitor potential risksCharacter and pattern recognitionProcess deviationsRadar

The invention relates to a radar monitoring method and device for the long-term security risk of chemical equipment. The method comprises that real-time operation state data of the chemical equipment is obtained, the risk and operability of each system of the chemical equipment are analyzed, technical deviation is determined, and data to be monitored is screened from the real time state data; fault identification is carried out on the data to be monitored to obtain alarming information; and fault diagnosis and tracing are carried out on the alarming information to obtain the reason and corresponding remedial measures of the fault.

Owner:CHINA UNIV OF PETROLEUM (BEIJING)

Memory elements and methods for making same

InactiveUS20020086524A1Solid-state devicesSemiconductor/solid-state device manufacturingProcess deviationsEtching

Annular and linear contact structures are described which exhibit a greatly reduced susceptibility to process deviations caused by lithographic and deposition variations than does a conventional circular contact plug. In one embodiment, a standard conductive material such as carbon or titanium nitride is used to form the contact. In an alternative embodiment, a memory material itself is used to form the contact. These contact structures may be made by various processes, including chemical mechanical planarization and facet etching.

Owner:ROUND ROCK RES LLC

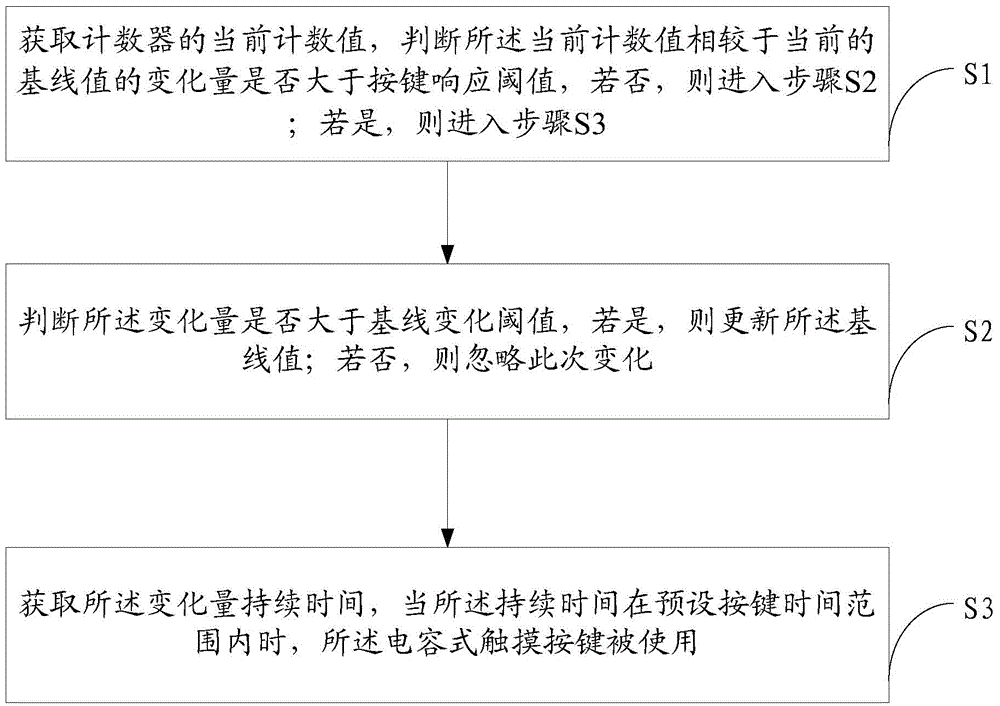

Method for detecting state of capacitive touch key

InactiveCN104935320AEliminate the effects ofStrong interference abilityElectronic switchingProcess deviationsValue set

The invention discloses a method for detecting a state of a capacitive touch key, compares a current count value of a counter with a baseline value, and judges whether the capacitive touch key is effectively touched by analyzing the variable quantity of the current count value relative to the baseline value and time of duration. In addition, when the variable quantity of the current count value relative to the baseline value is larger than a baseline variation threshold and is smaller than a key response threshold, the baseline value needs to be updated, i.e., by setting the baseline variation threshold and the key response threshold, that environment temperature variation influences the baseline value is reflected, thereby updating the baseline value when environment temperature varies, improving a capability of being resistant to interference of environment temperature, and improving detection precision. In addition, the baseline value is not a numerical value set in a unified manner, but varies at any time according to the environment temperature, and thus influence of technological deviations of different chips on detection of the state of the capacitive touch key is also eliminated.

Owner:ANYKA (GUANGZHOU) MICROELECTRONICS TECH CO LTD

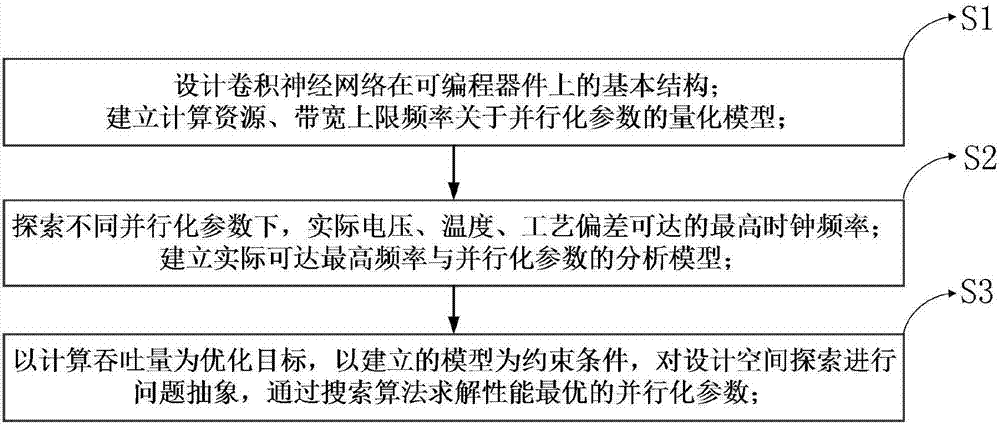

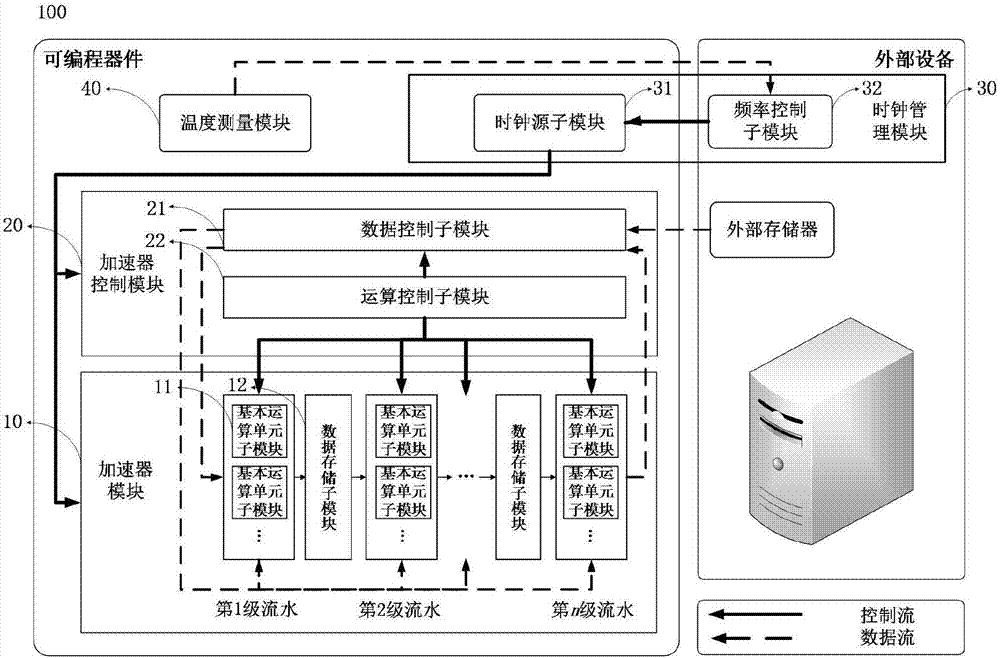

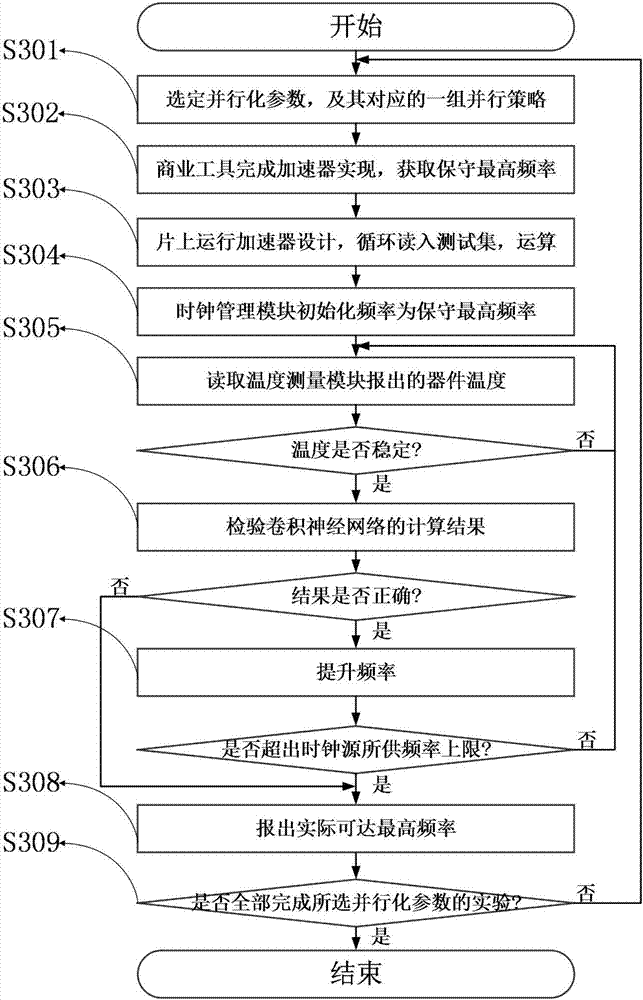

Programmable device-based convolutional neural network acceleration method and system

ActiveCN107392308AReduce complexityStreamlined Design ParametersPhysical realisationProcess deviationsDelay margin

The present invention relates to a programmable device-based convolutional neural network acceleration method and system. The method comprises: designing a basic structure of a convolution neural network on the programmable device, and establishing the quantification model of the computing resource and the frequency about the parallelization parameter respectively; under different parallelization parameters, exploring the highest reachable clock frequency of the actual voltage, temperature, process deviation, establishing an analysis model of the actual highest reachable frequency and the parallelization parameter; and taking throughput calculation as an optimization purpose, according to the established quantitative model and analysis model, carrying out problem abstract on the convolutional neural network design space exploration, and using a certain search algorithm to solve the parallelization parameters with optimal performance. According to the method and system provided by the present invention, the delay margin reserved by the commercial design tools for the voltage, the temperature and the process deviation can be used while ensuring the stability and reliability of the accelerator, so that the performance of the convolutional neural network accelerator can be further improved.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

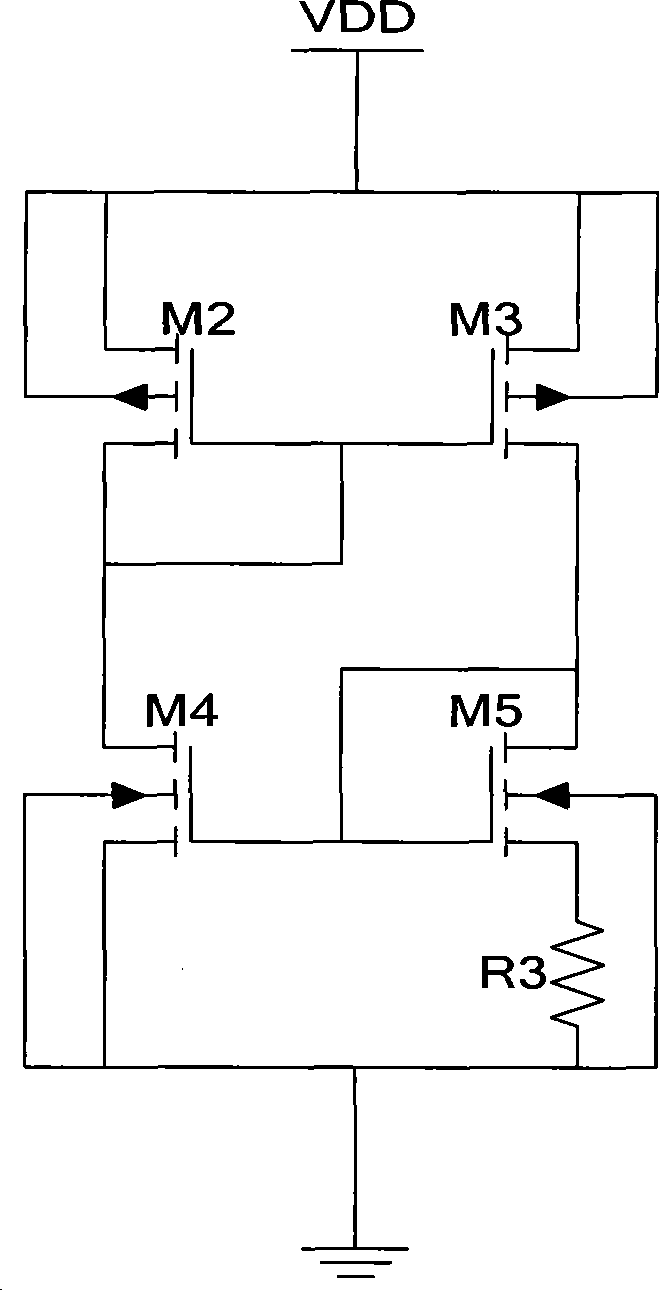

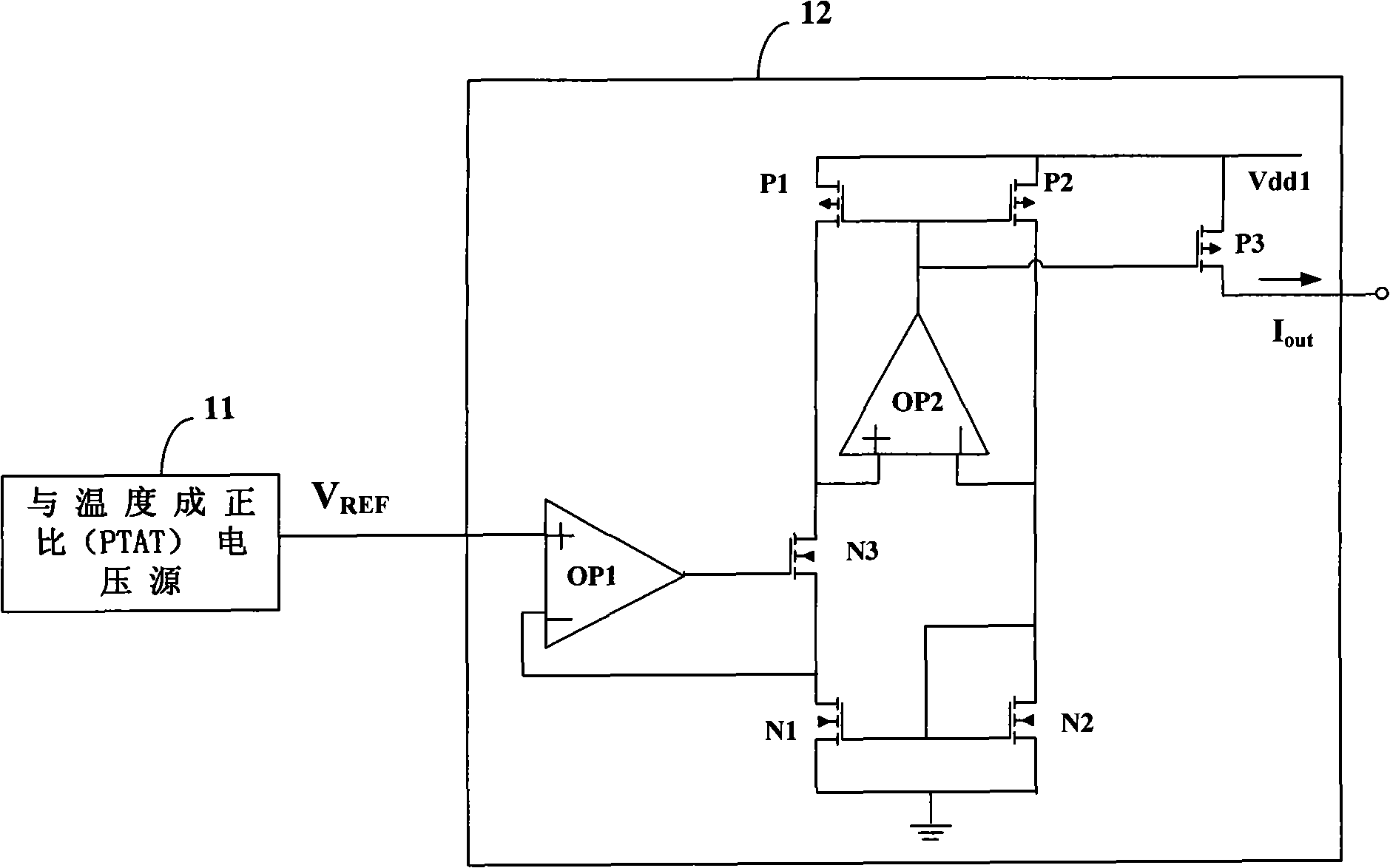

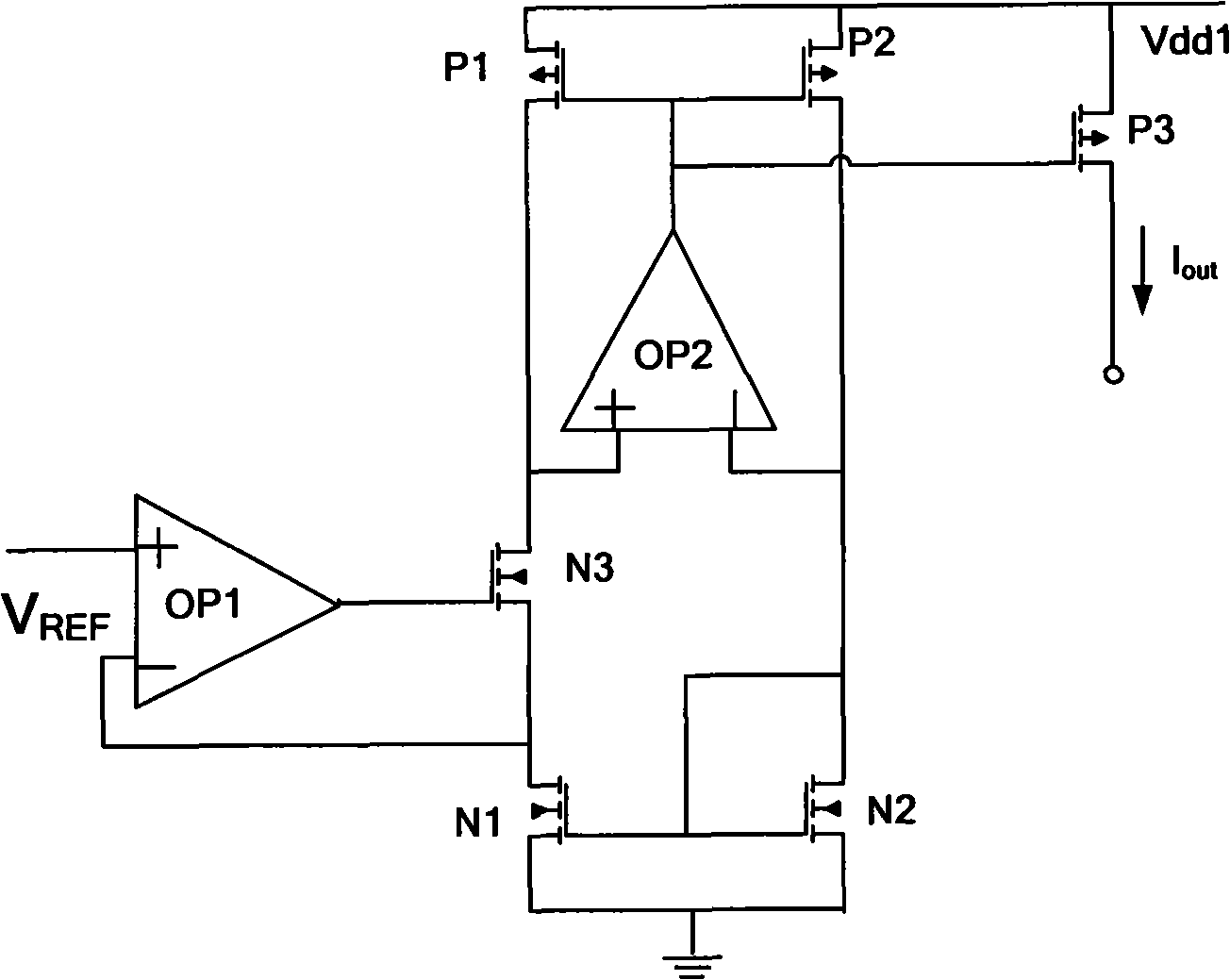

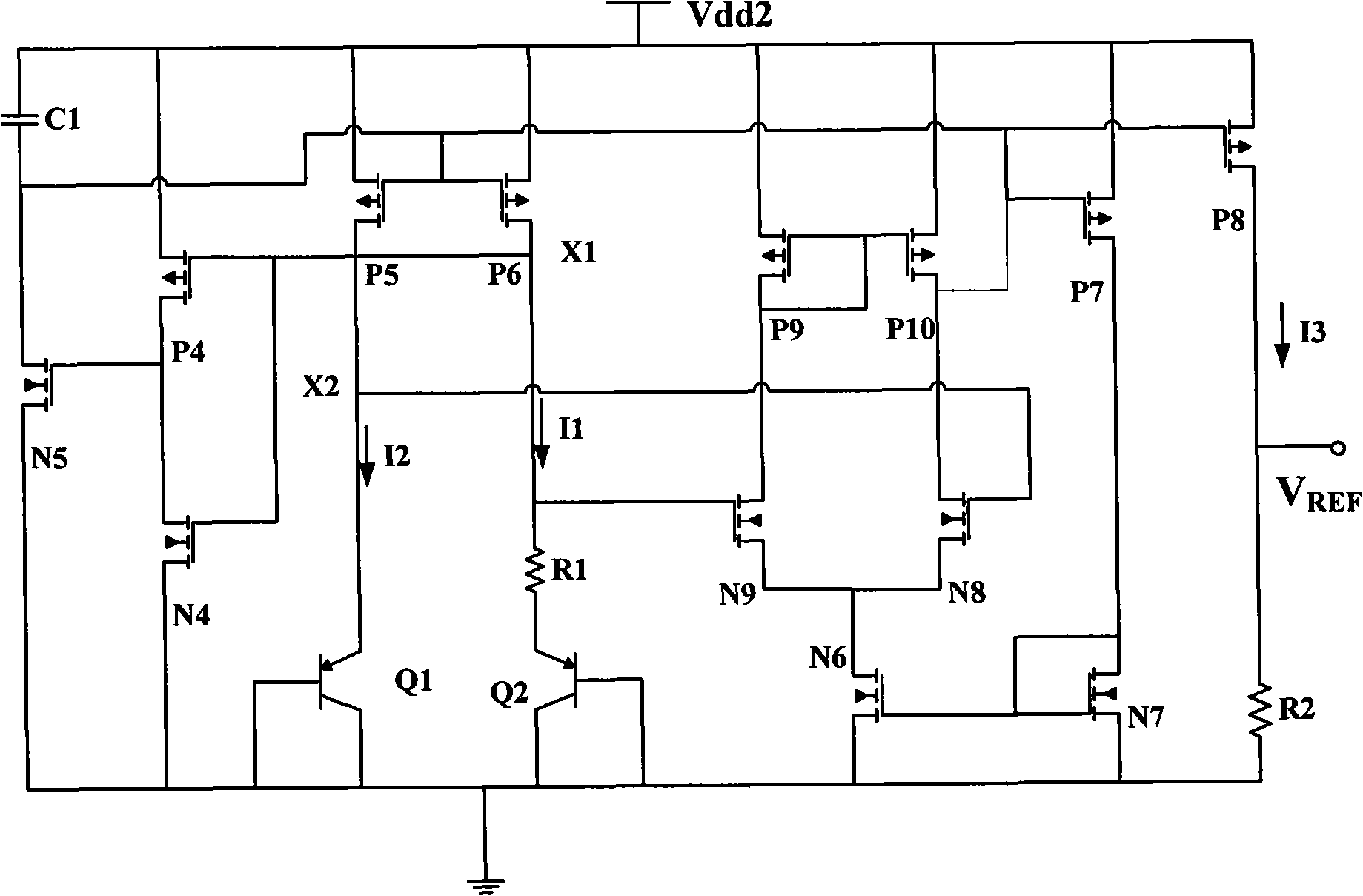

Low voltage CMOS current source

ActiveCN101561689AImprove featuresGood temperature characteristicsElectric variable regulationProcess deviationsCMOS

The invention discloses a low voltage CMOS current source, and belongs to the field of analog integrated circuit. The low voltage CMOS current source comprises a PTAT voltage source, a current converting circuit and a mirror image circuit which are connected with the PTAT voltage source, wherein, the PTAT voltage source is used for generating a reference voltage V[REF] with a positive temperature coefficient; and the current converting circuit and the mirror image circuit are used for converting the reference voltage V[REF] into a reference current, and outputting the reference current by a current mirror relation. The low voltage CMOS current source has good power supply property and temperature property, and process deviation of the CMOS current source has little influence on an output current value of the CMOS current source.

Owner:陕西光电子先导院科技有限公司

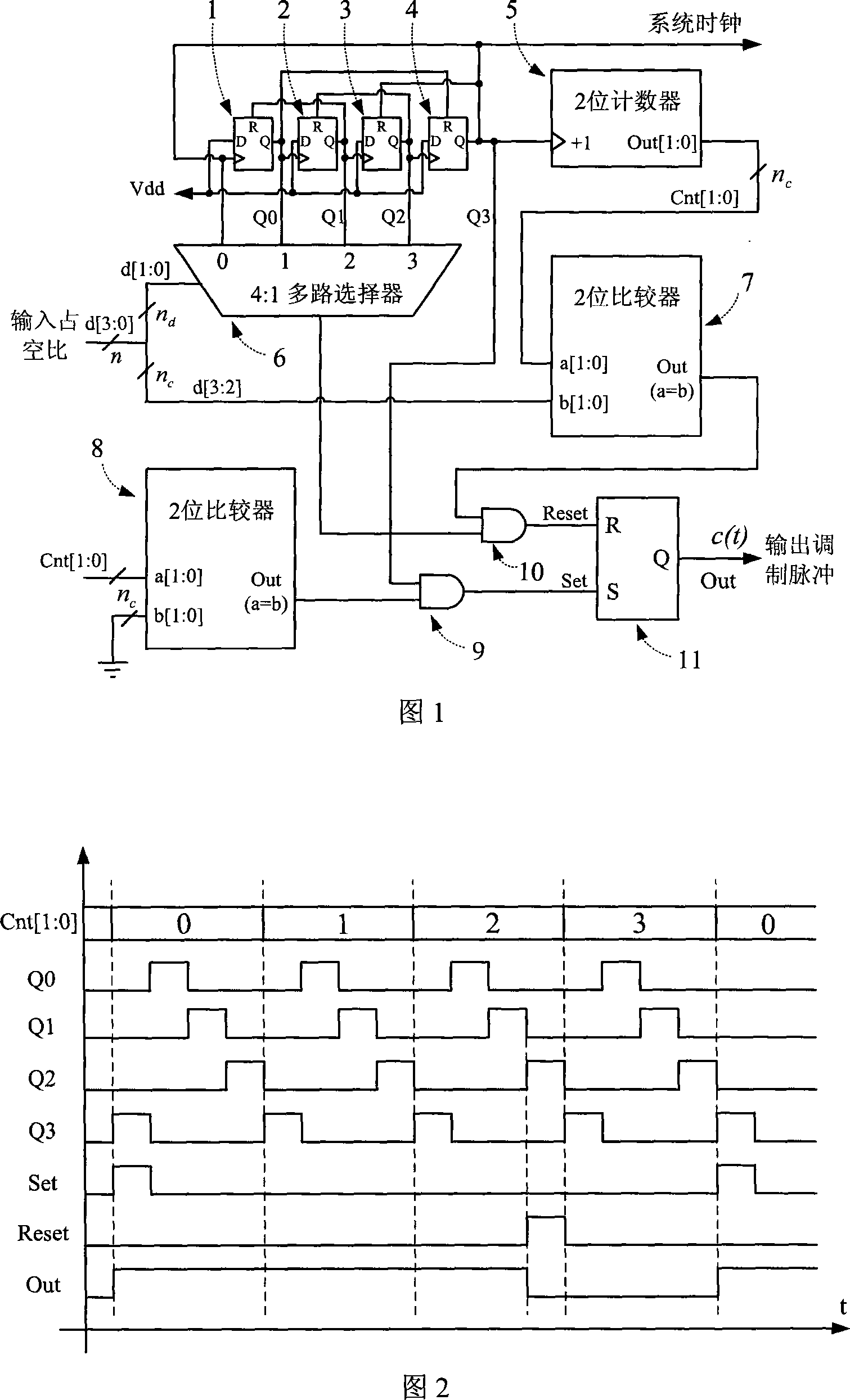

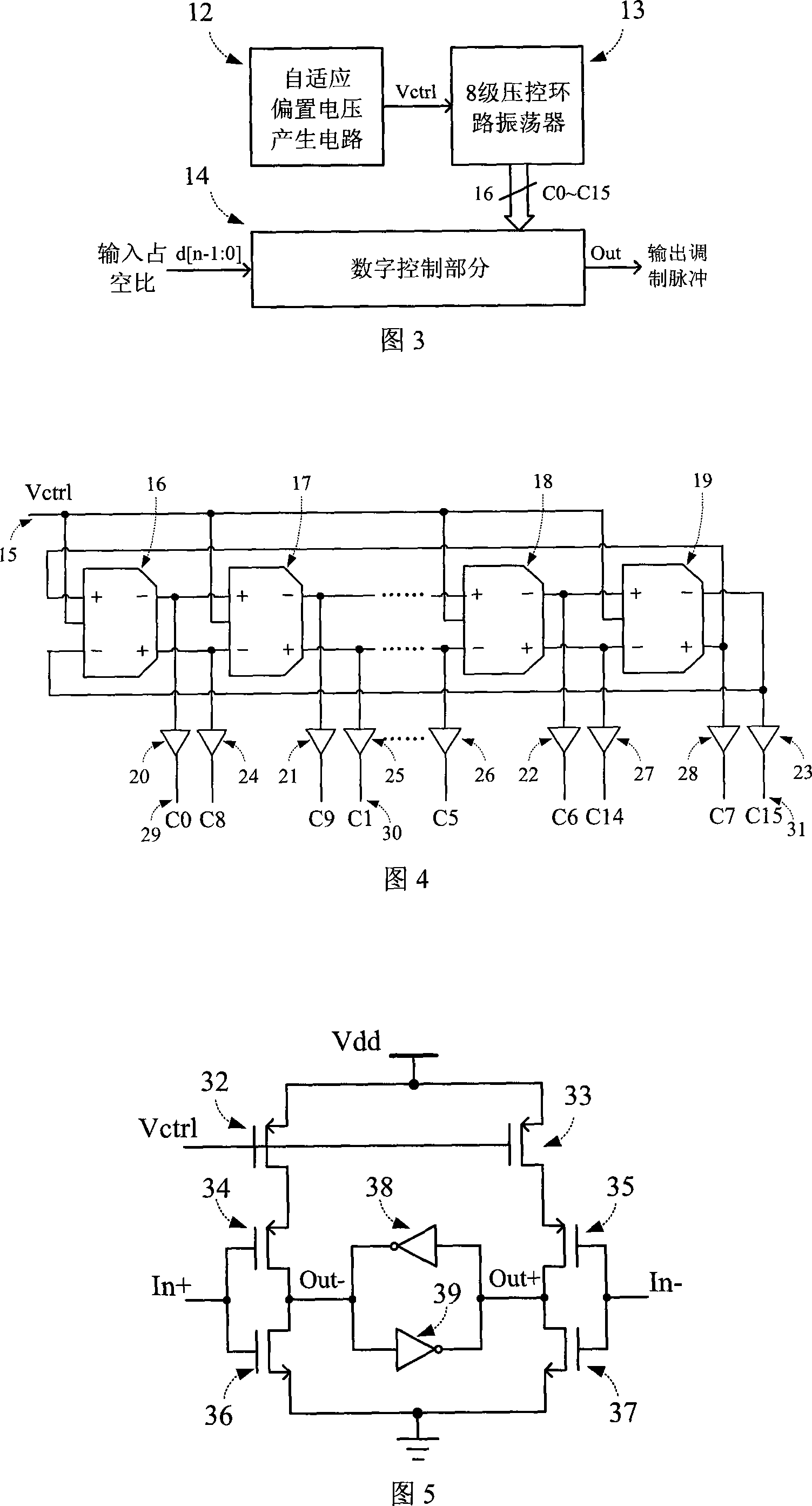

Mixed digital pulse duration modulater suitable for digital power supply controller

InactiveCN101090272AGuaranteed stabilityHigh speedDifferential modulationProcess deviationsEngineering

This invention relates to a mixed digital pulse modulator used in digital supply controllers composed of an adaptive offset voltage generation circuit, a 8-stage voltage-controlled loop oscillator and a digital control part, in which, the adaptive offset voltage generation circuit generates an offset voltage compensated by temperature technology to control the loop oscillator and a 16-phase clock C0-C15 not influenced by outside temperature or technical offset, and the digital control part generates a modulated pulse with the resolution of n-bit according to the clock staggered for 1 / 16 period orderly and n-bit duty ratio input from outside d[n-1 :0].

Owner:HEBEI ZHAORI OPTOELECTRONICS TECH

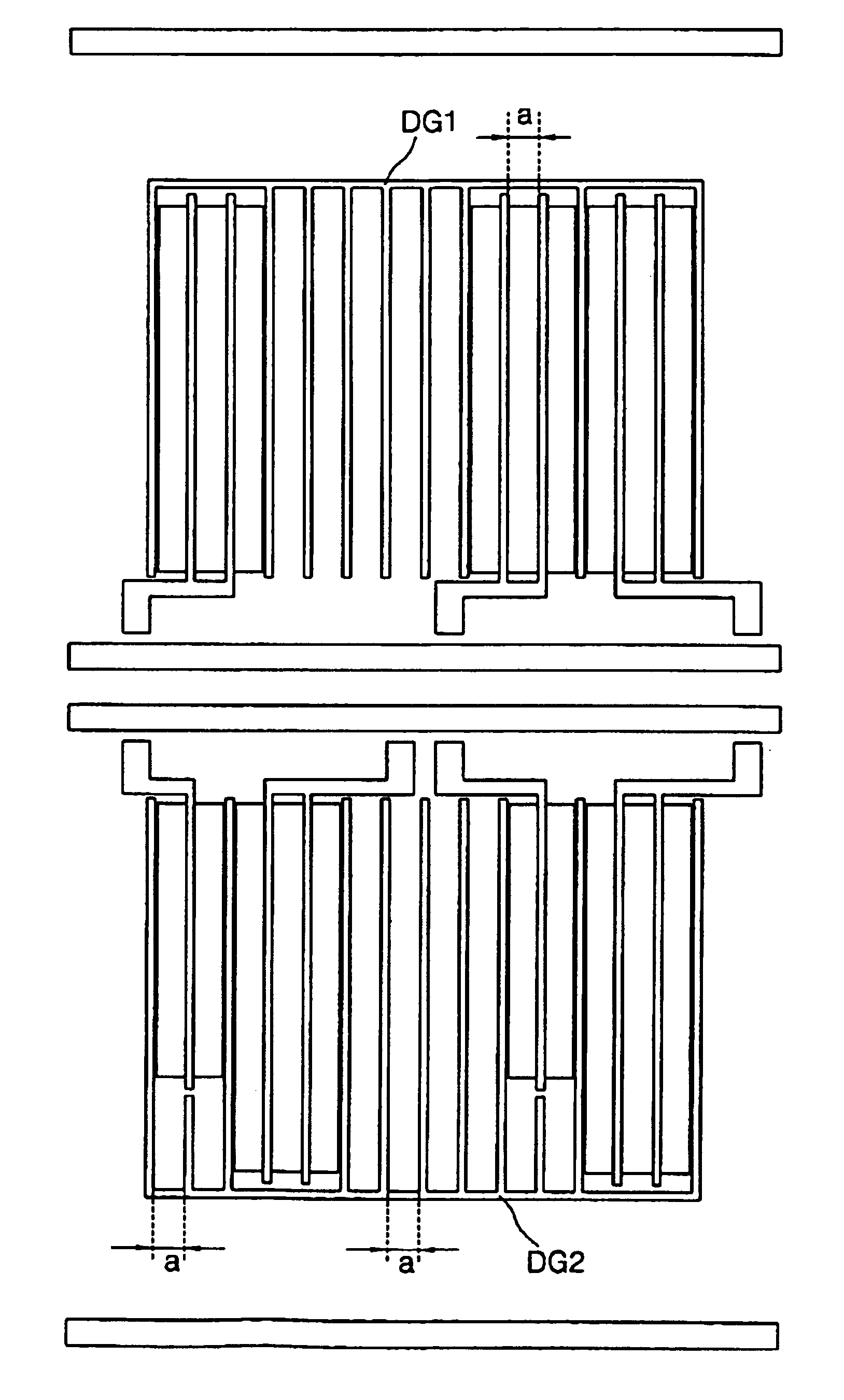

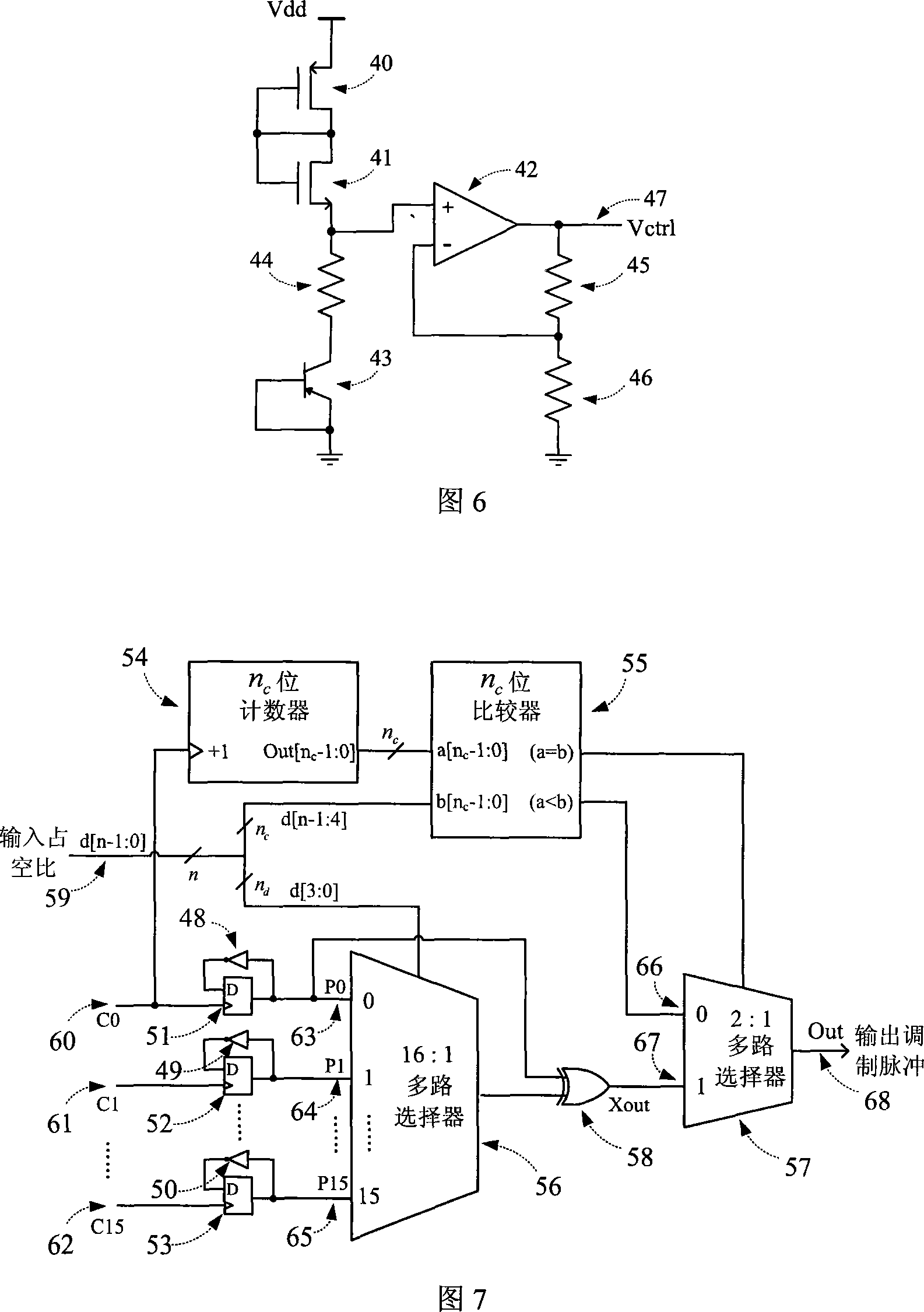

Alignment mark and alignment method using the same for photolithography to eliminating process bias error

InactiveUS6936521B2Eliminate biasStable positionSemiconductor/solid-state device detailsSolid-state devicesProcess deviationsPhotolithography

Owner:PROMOS TECH INC

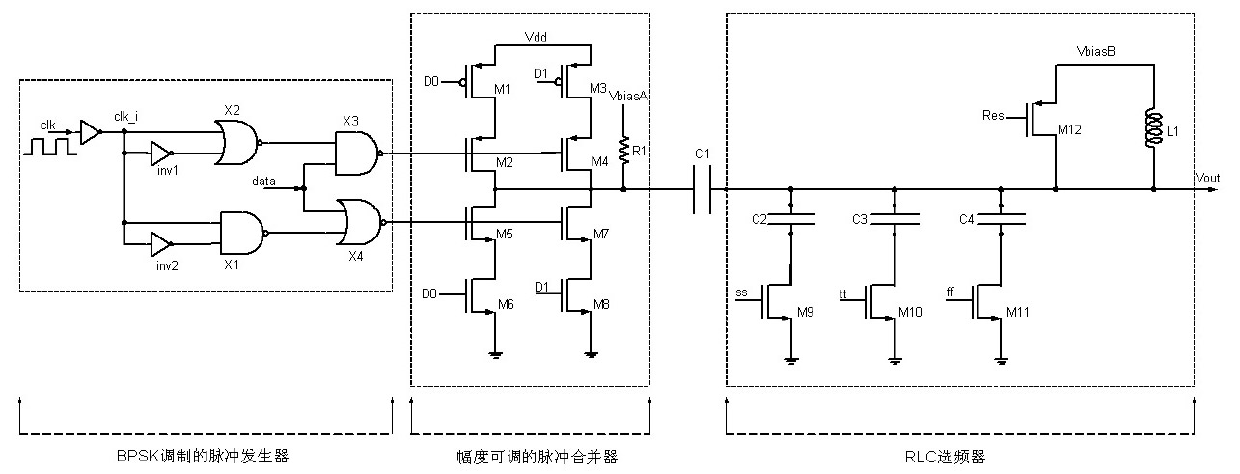

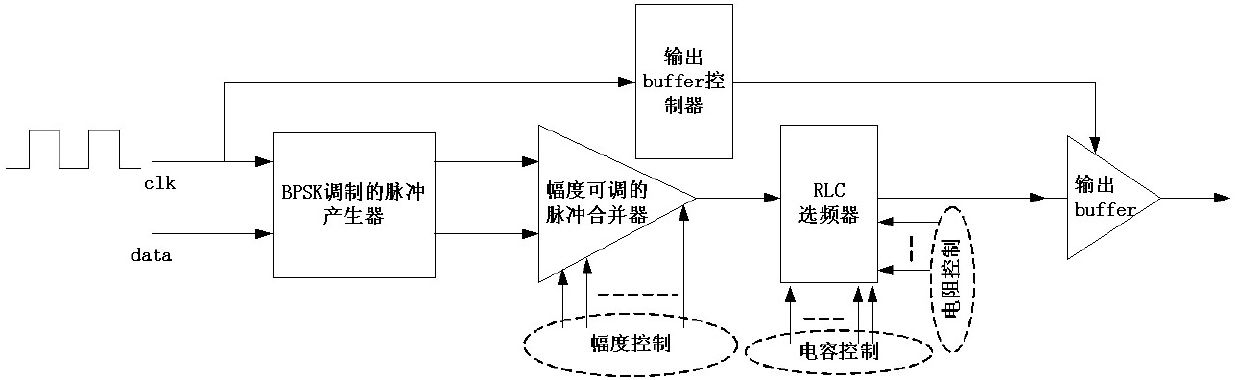

Pulse ultra-wideband transmitter with adjustable amplitude and spectrum

InactiveCN101924574AReduce power consumptionSimple structureTransmissionProcess deviationsUltra-wideband

The invention belongs to the ultra-wideband communication technical field, and in particular relates to a pulse ultra-wideband transmitter with adjustable amplitude and spectrum. The transmitter is composed of four-stage modules which are sequentially connected together, wherein, the former two-stage modules generate pulse signals modulated by BPSK, an intermediate RLC frequency-selective network realizes adjustment of amplitude, length and spectrum of pulse, and finally the pulse is output by an ultra-wideband output buffer. The transmitter is modulated by adopting the BPSK, and an RLC network is taken as a core module of the whole system to realize adjustment of pulse parameters and compensation of process variation. By virtue of the characteristics of low duty cycle of an IR-UWB transmission signal, the output buffer is switched off in the case of no pulse to lower power consumption. The transmitter has the advantage of adjustable pulse parameters, thus meeting the requirements of UWB standards in different countries for spectrum and transmission power.

Owner:FUDAN UNIV

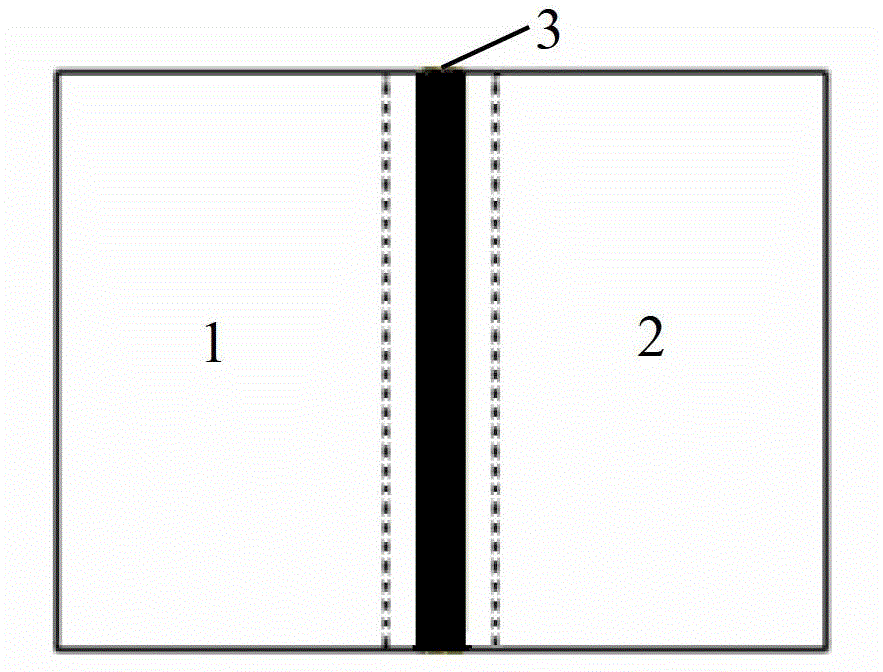

Method for reducing mask board splicing errors

InactiveCN102981356AReduce Stitching ErrorsAnti-aliasingOriginals for photomechanical treatmentProcess deviationsGraphics

The invention discloses a method for reducing mask board splicing errors. According to the result of a graph formed by etching an exposed graph after repeated exposure on a splicing area of two adjacent mask boards, the structural compensation is carried on the exposed graph on the splicing area on the mask boards reversely. By utilizing the method, the distortion treatment to the exposed graph at the splicing area caused by repeated exposure and process deviation can be eliminated through compensation design of the mask boards, the consistency of an etched graph at the splicing area and an etched graph at a non-splicing area is ensured, and the yield of products is increased.

Owner:BOE TECH GRP CO LTD