Patents

Literature

314 results about "Simics" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Simics is a full-system simulator used to run unchanged production binaries of the target hardware at high-performance speeds. Simics was originally developed by the Swedish Institute of Computer Science (SICS), and then spun off to Virtutech for commercial development in 1998. Virtutech was acquired by Intel in 2010 and Simics is now marketed through Intel's subsidiary Wind River Systems.

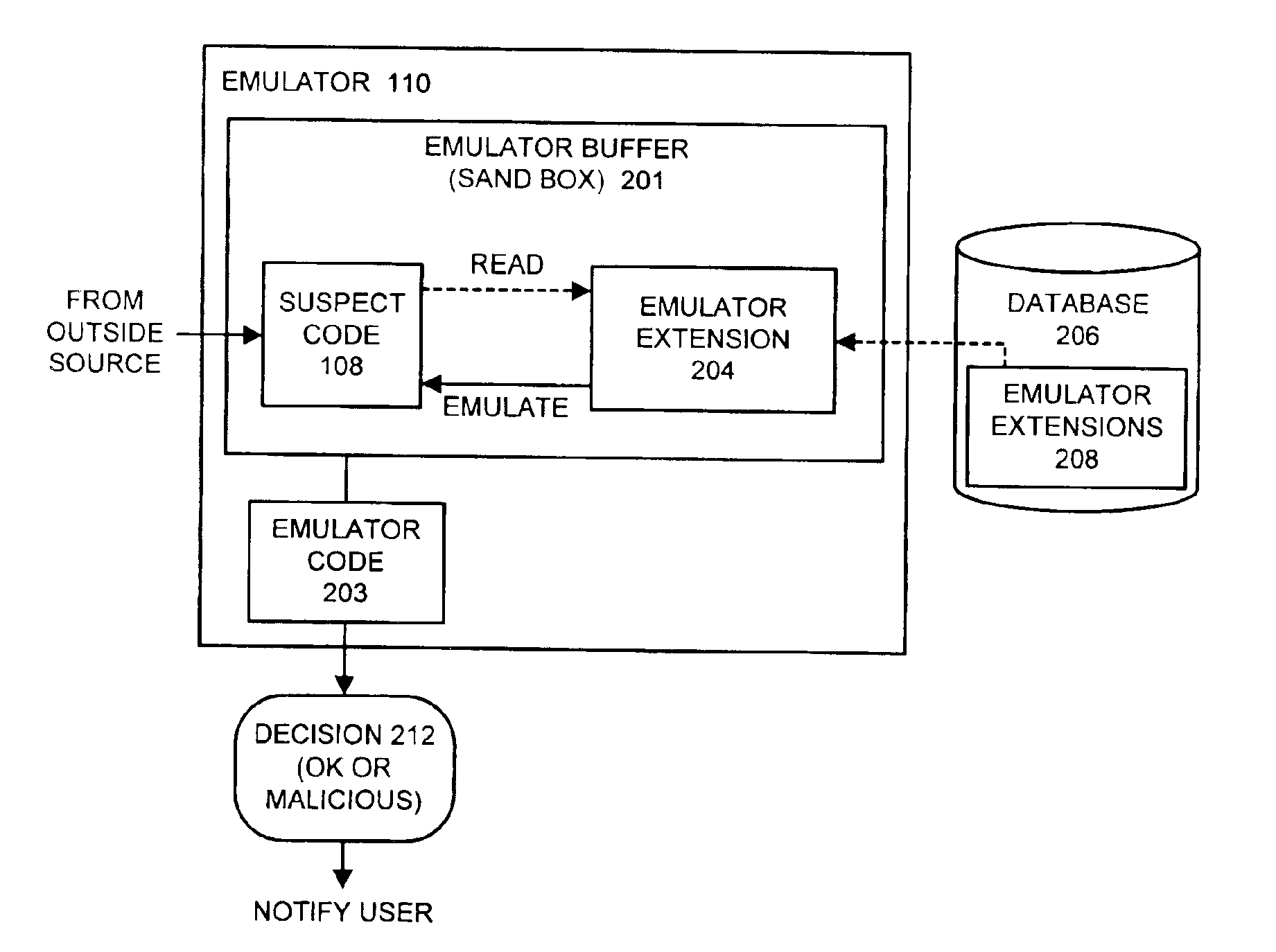

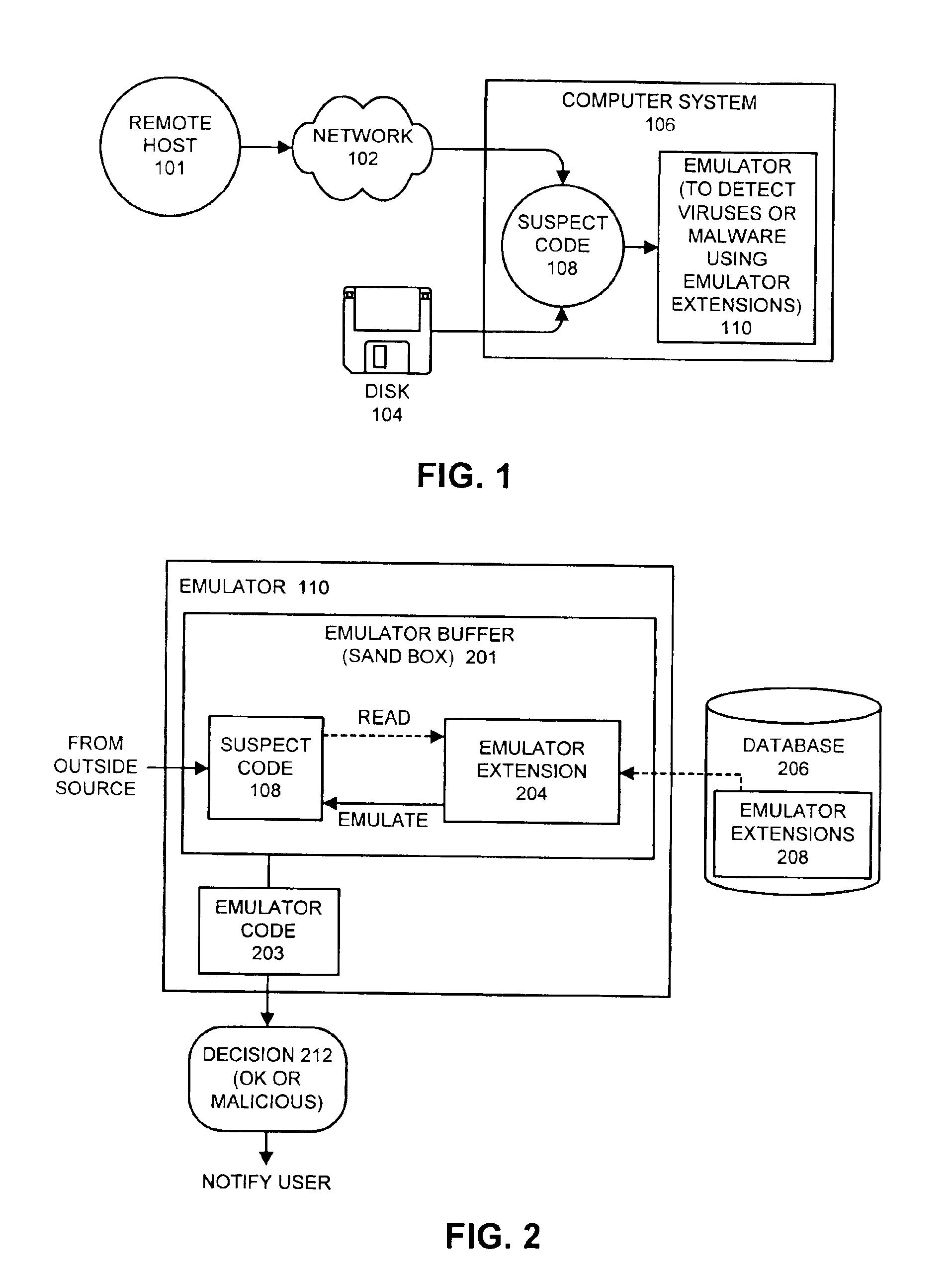

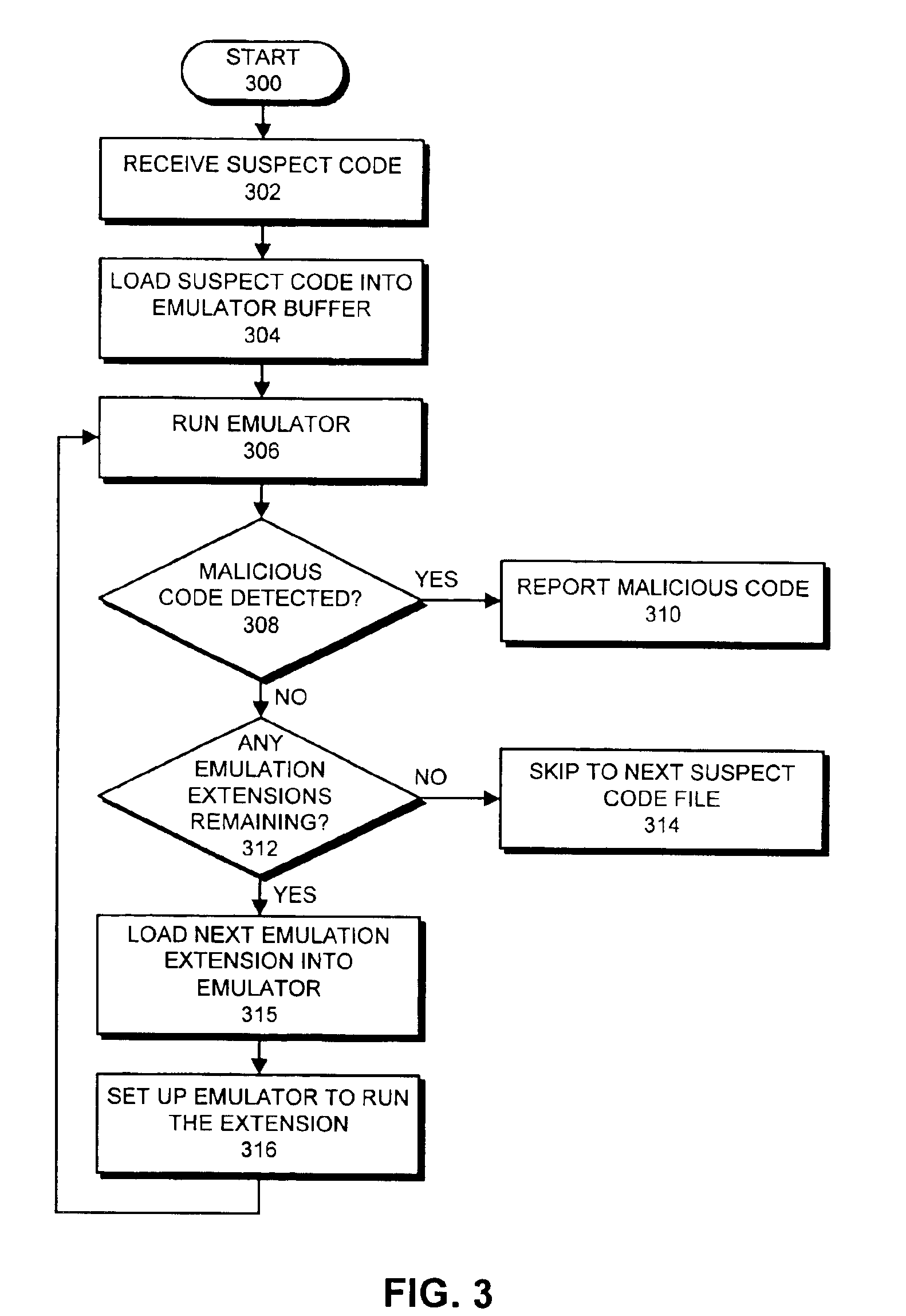

Detecting computer viruses or malicious software by patching instructions into an emulator

InactiveUS6907396B1High simulationPlatform integrity maintainanceTransmissionProgram instructionAnalog computer

One embodiment of the present invention provides a system for emulating computer viruses and / or malicious software that operates by patching additional program instructions into an emulator in order to aid in detecting a computer virus and / or malicious software within suspect code. During operation, the system loads a first emulator extension into the emulator. This first emulator extension includes program instructions that aid in the process of emulating the suspect code in order to detect a computer virus and / or malicious software. The system also loads the suspect code into an emulator buffer. Next, the system performs an emulation using the first emulator extension and the suspect code. This emulation is performed within an insulated environment in a computer system so that the computer system is insulated from malicious actions of the suspect code. During this emulation, the system determines whether the suspect code is likely to exhibit malicious behavior. In one embodiment of the present invention, loading the first emulator extension into the emulator involves loading the first emulator extension into the emulator buffer within the emulator. In this embodiment, performing the emulation involves emulating the program instructions that comprise the first emulator extension.

Owner:MCAFEE LLC

Digital system simulation

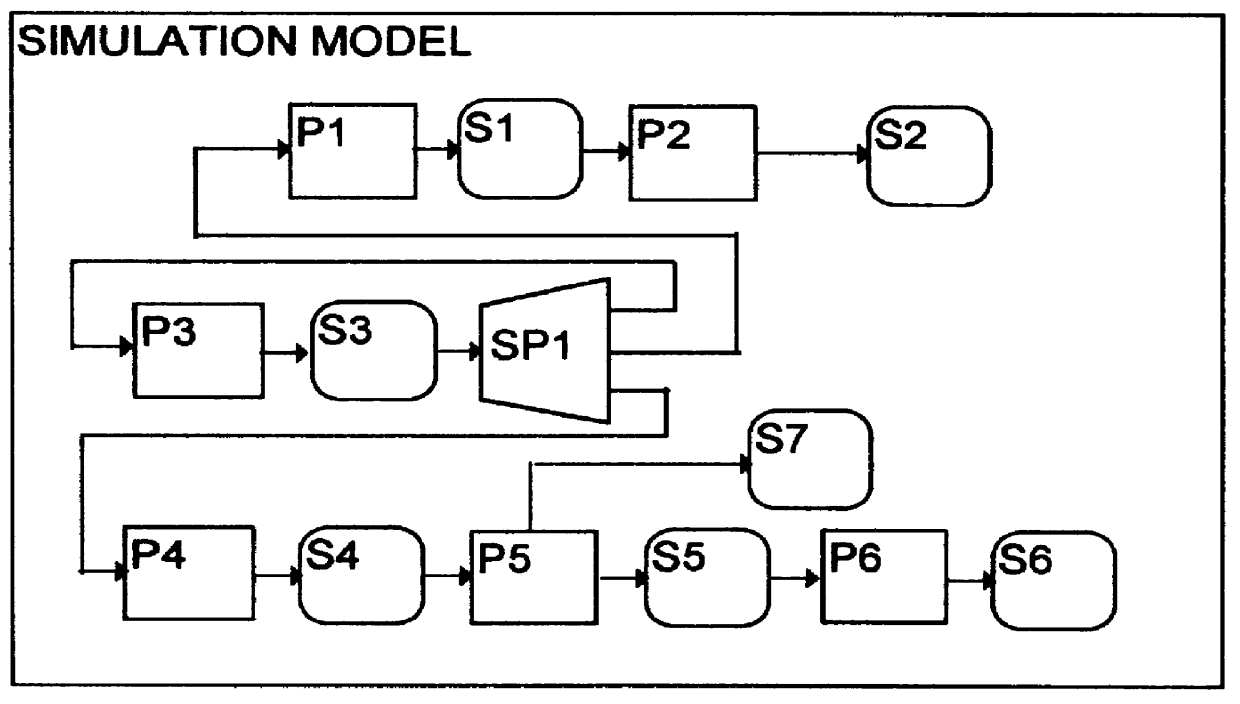

InactiveUS6097885AAnalogue computers for electric apparatusCAD circuit designSystems simulationDistributed computing

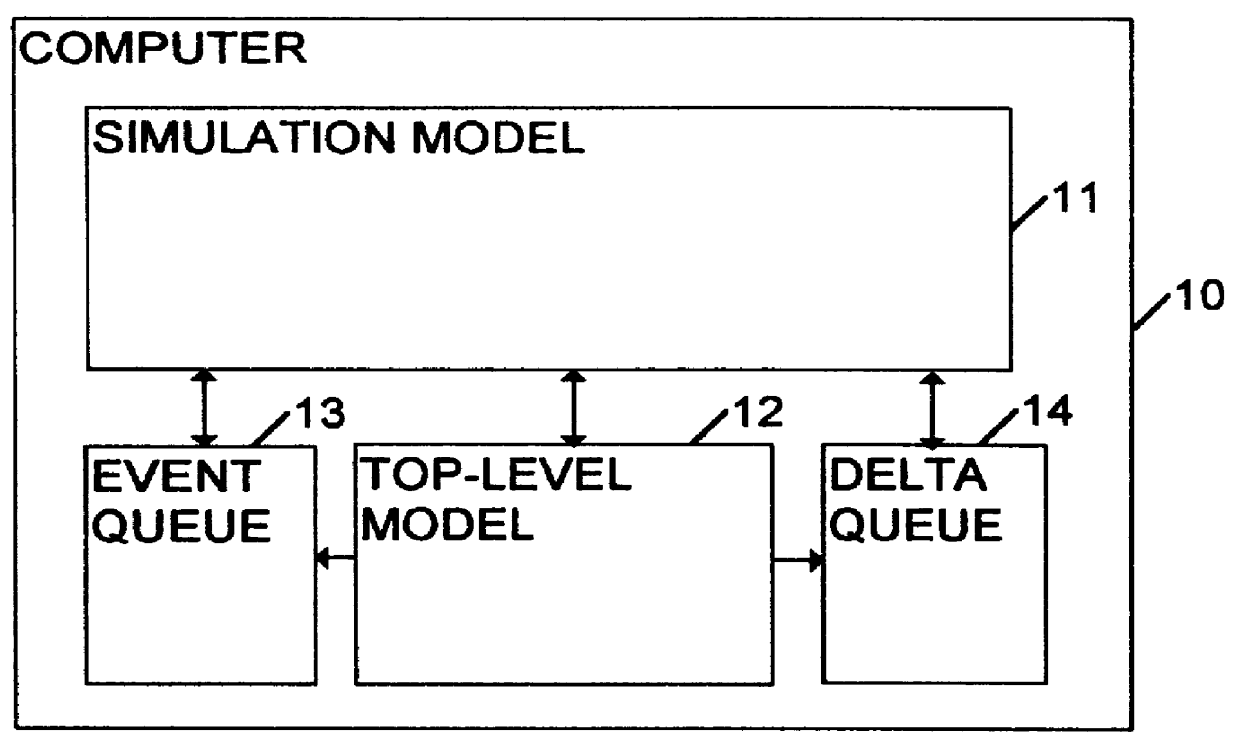

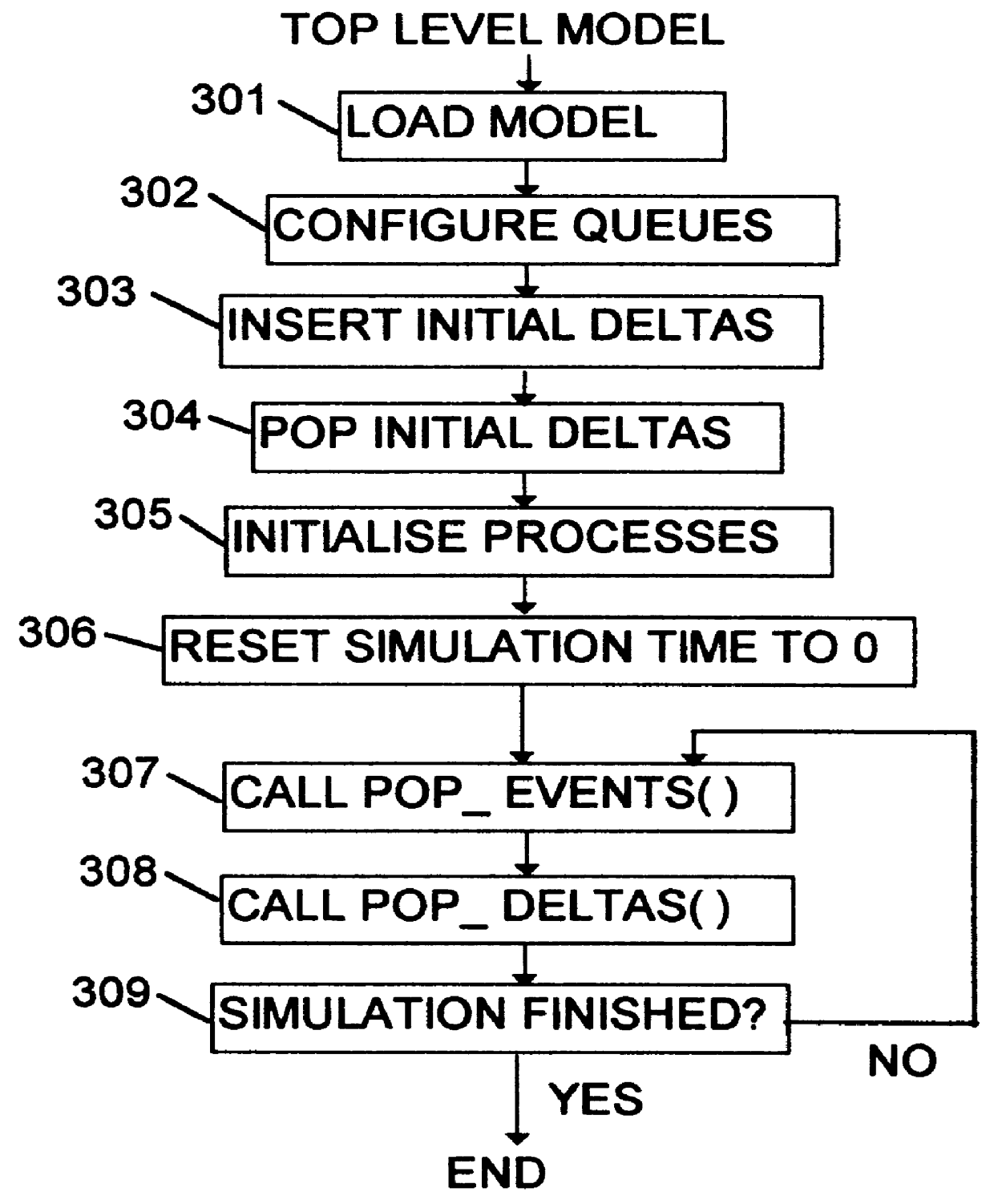

A simulator for a digital system comprises a simulation model, an event queue for scheduling changes to the state of the simulation model at specified times, and a separate delta queue, for scheduling changes to the state of the simulation model that are to take place instantaneously. The use of separate event and delta queues facilitates optimization of the queuing. The simulation model comprises a number of replaceable parts, each of which contains and is responsible for managing its own state information. The event and delta queues contain references to the parts of the model for which changes of state are scheduled, without containing the actual values of those changes of state.

Owner:INT COMP LTD

Simulation model using object-oriented programming

InactiveUS6053947AIncrease execution speedEfficiency and flexibilityAnalogue computers for electric apparatusCAD circuit designComputer basedPriority scheduling

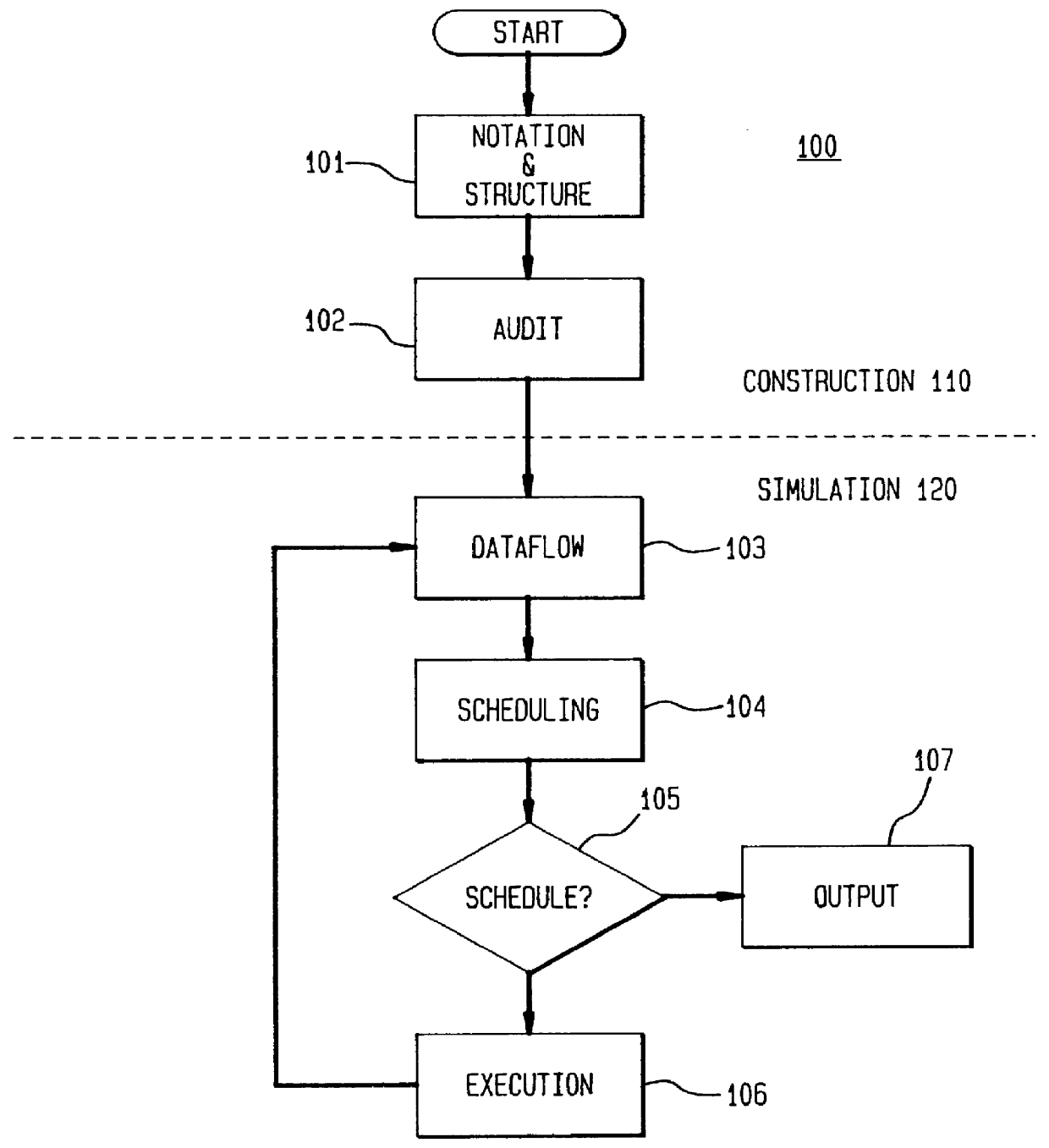

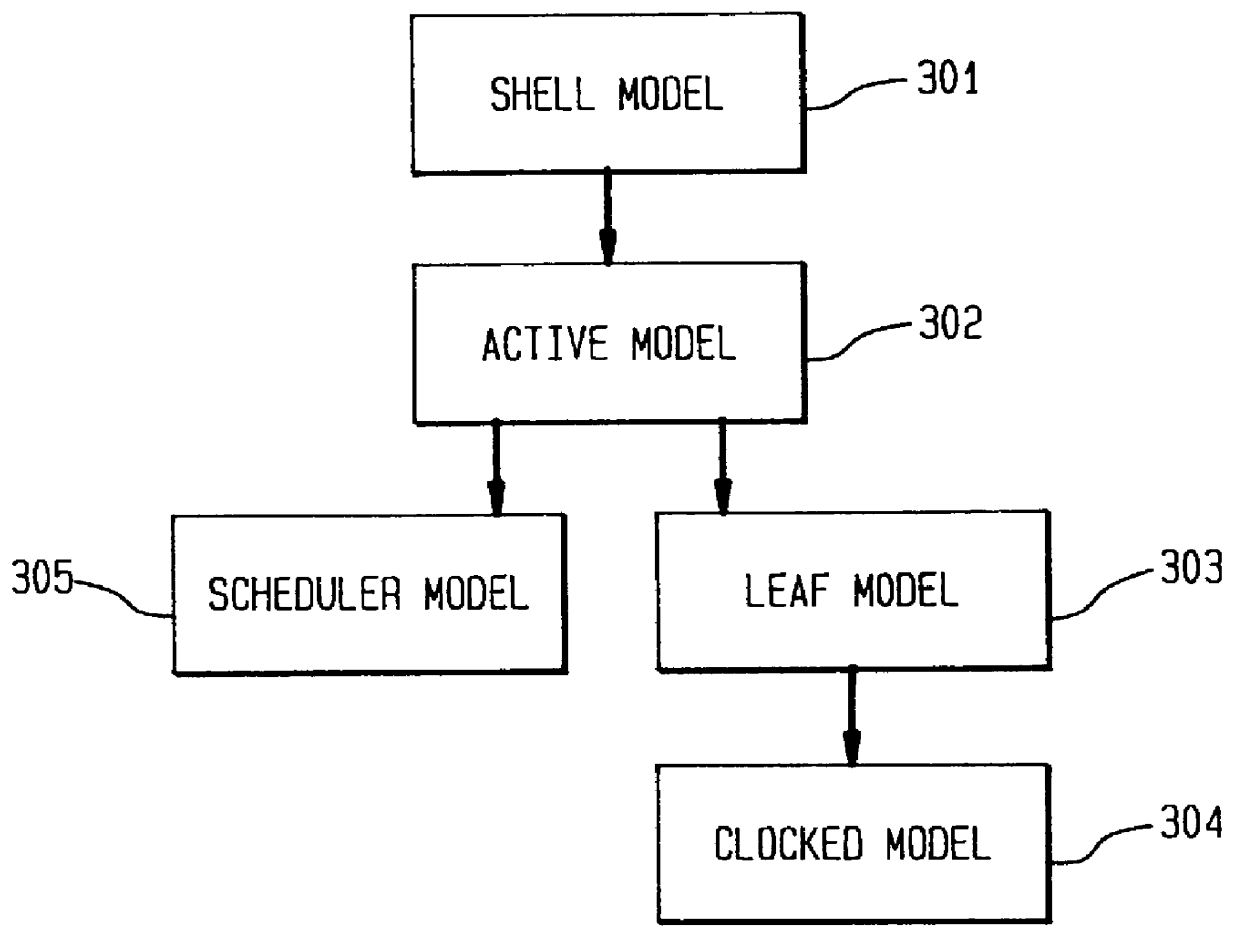

A method, apparatus and system for simulating the operation of a circuit using a computer-based simulator comprising: (a) distributing at least one signal upon to one or more simulation model subcircuit functions, which use the signal, upon a change in the signal; (b) scheduling one or more subcircuit functions that use the signal for execution according to a priority assigned to each subcircuit function; and (c) providing an output value to the simulator when no subcircuit functions are scheduled, otherwise, executing one or more subcircuit functions with the highest priority and returning to step (a) to repeat the process.

Owner:BELL SEMICON LLC

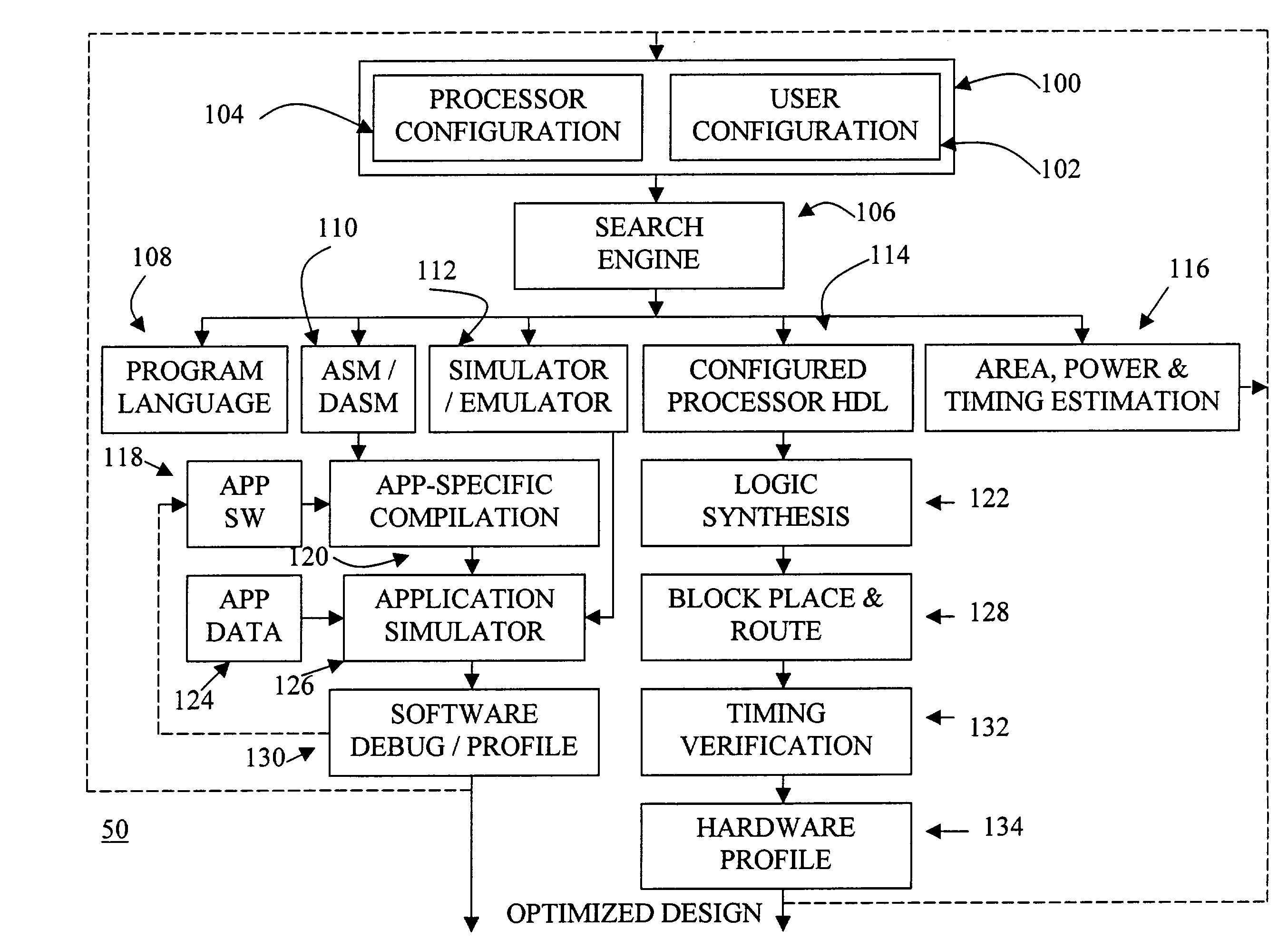

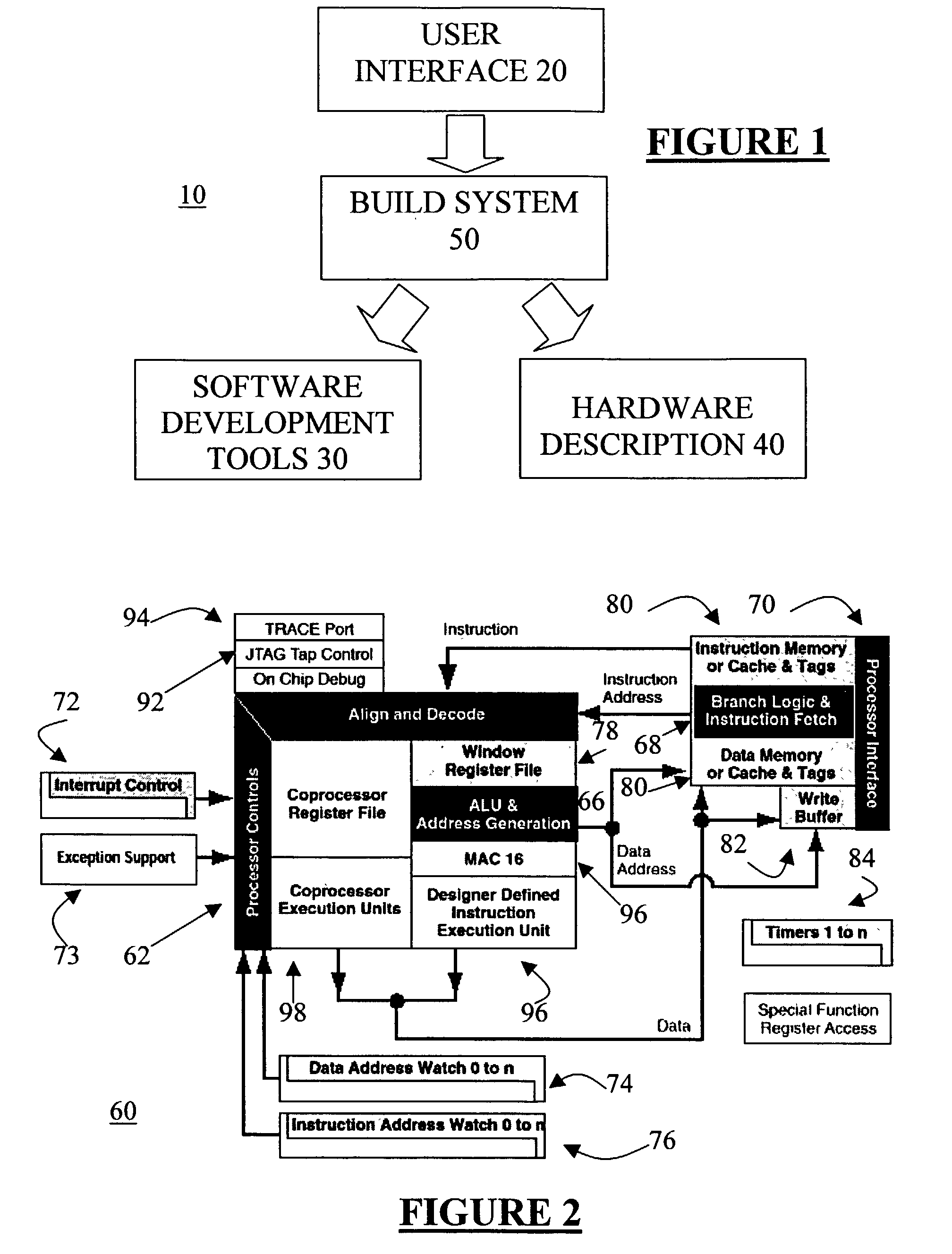

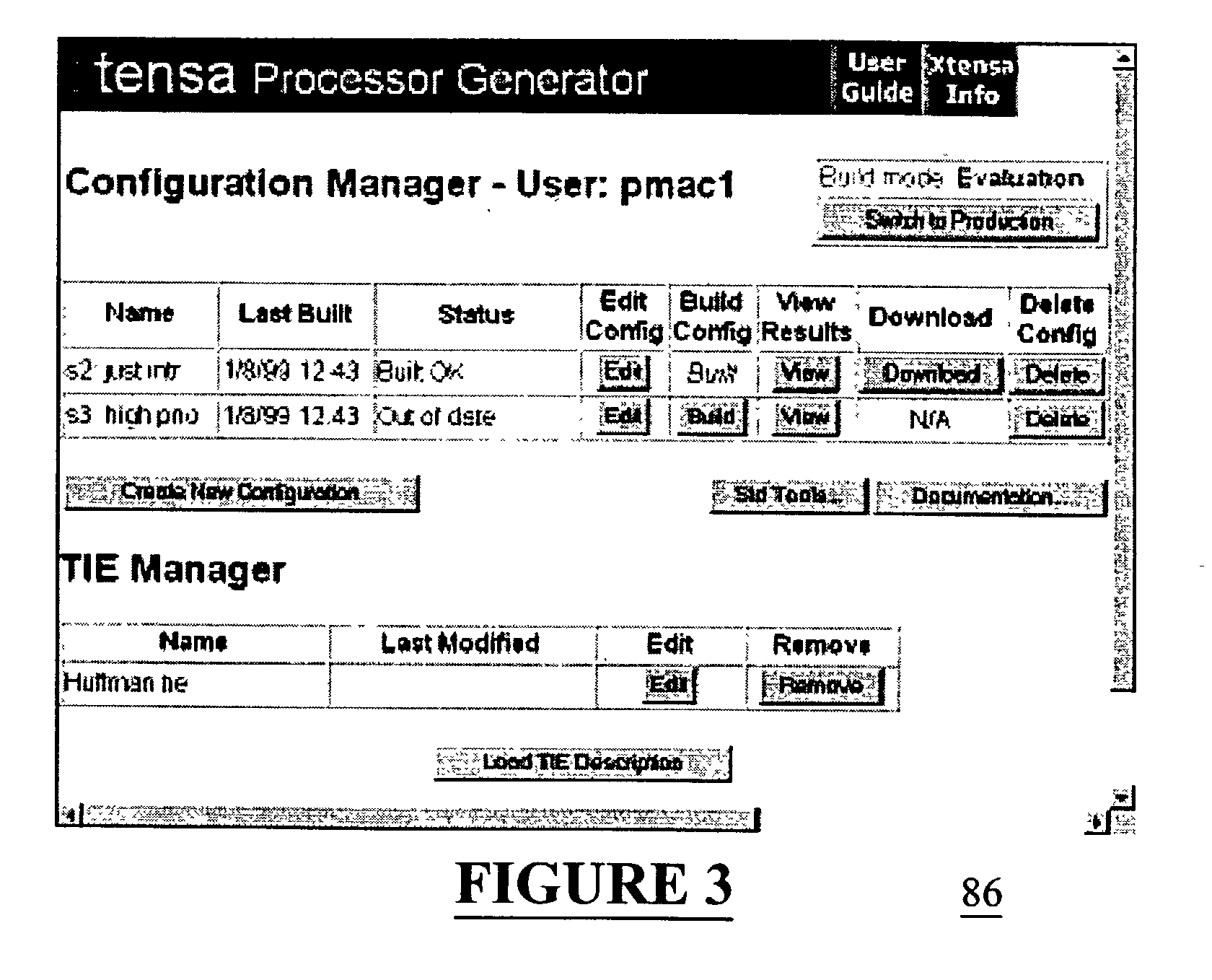

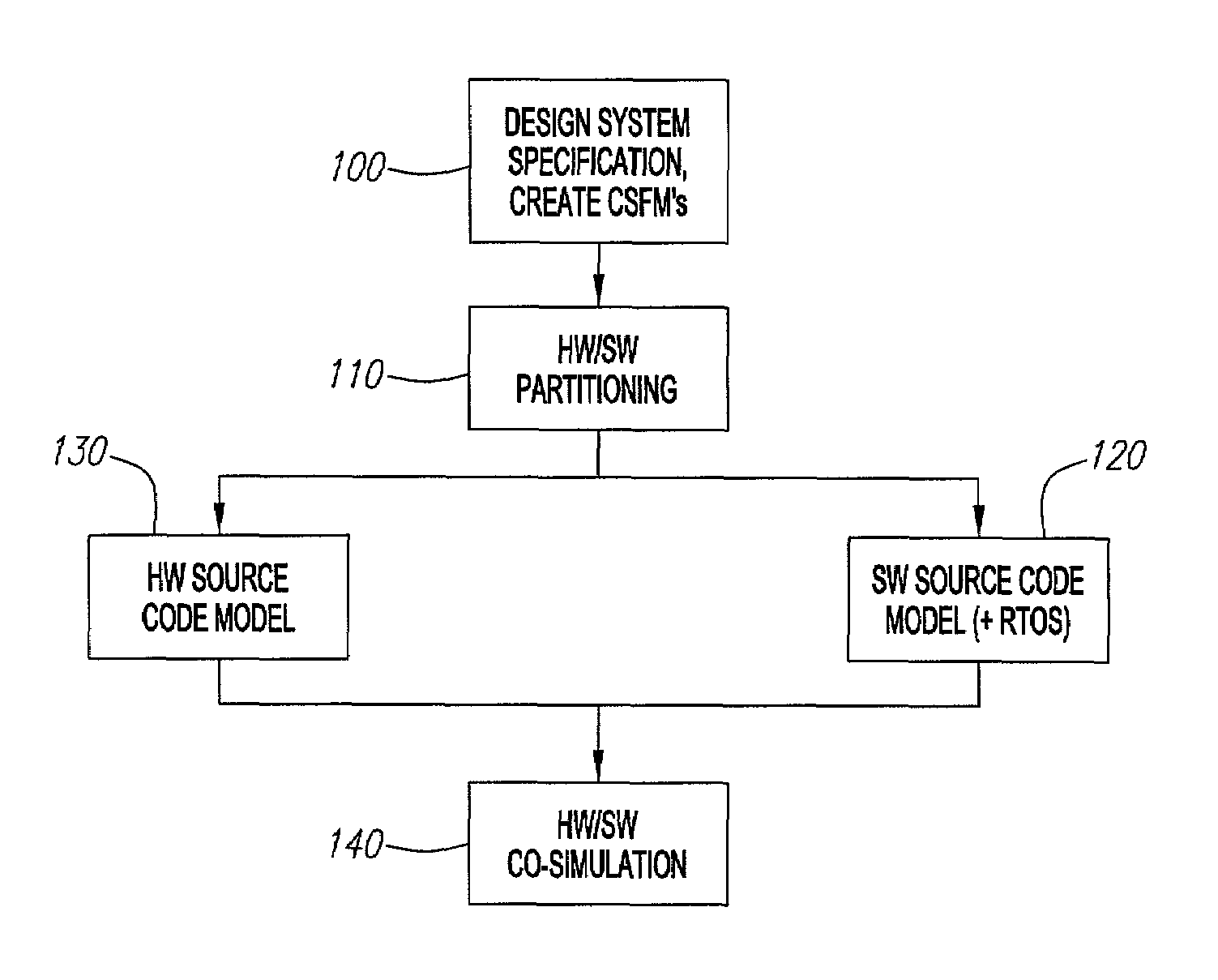

Automated processor generation system for designing a configurable processor and method for the same

InactiveUS20030208723A1Decompilation/disassemblyGeneral purpose stored program computerApplication softwareProcessor design

An automated processor design tool uses a description of customized processor instruction set extensions in a standardized language to develop a configurable definition of a target instruction set, a Hardware Description Language description of circuitry necessary to implement the instruction set, and development tools such as a compiler, assembler, debugger and simulator which can be used to develop applications for the processor and to verify it. Implementation of the processor circuitry can be optimized for various criteria such as area, power consumption, speed and the like. Once a processor configuration is developed, it can be tested and inputs to the system modified to iteratively optimize the processor implementation. By providing a constrained domain of extensions and optimizations, the process can be automated to a high degree, thereby facilitating fast and reliable development.

Owner:TENSILICA

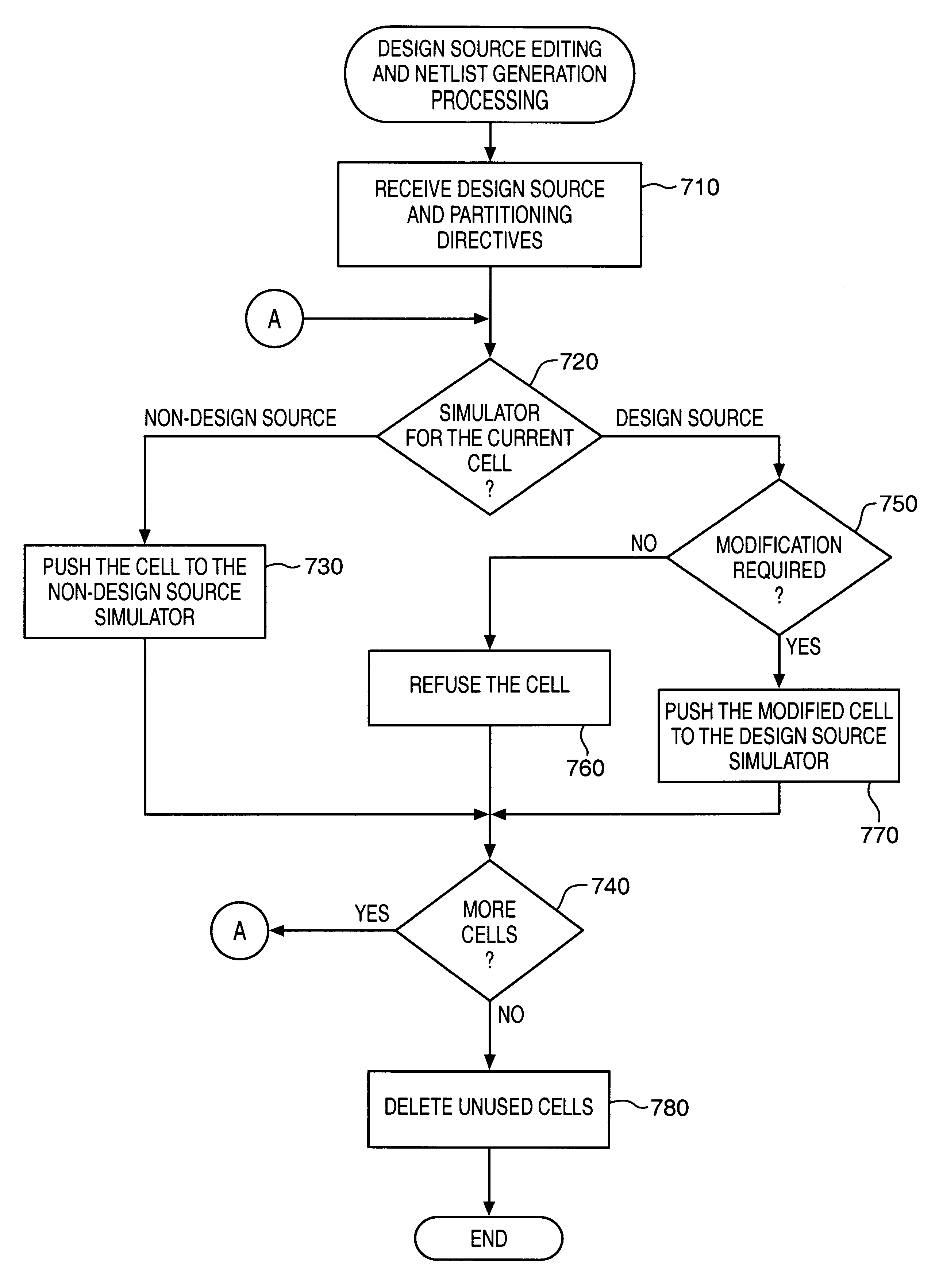

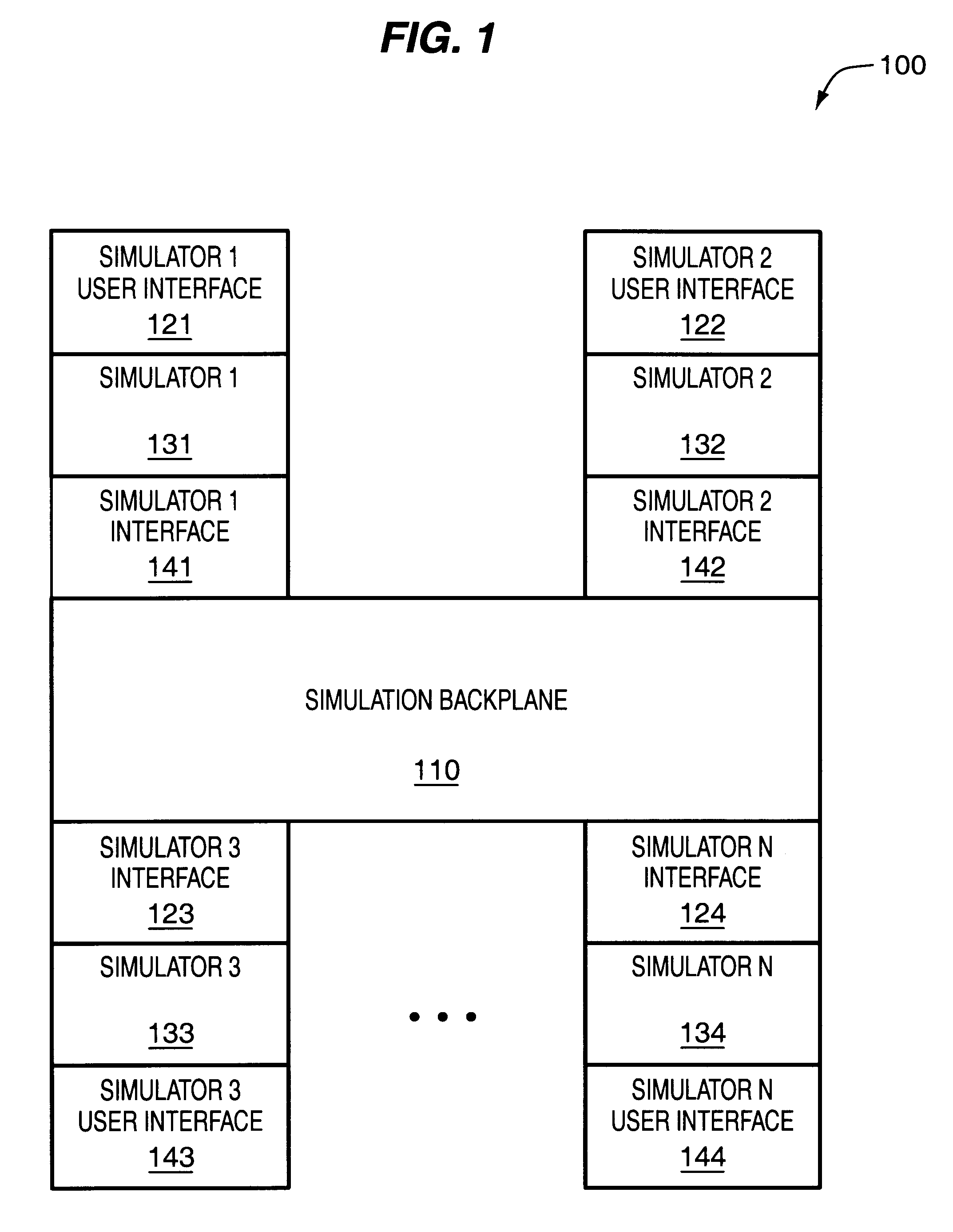

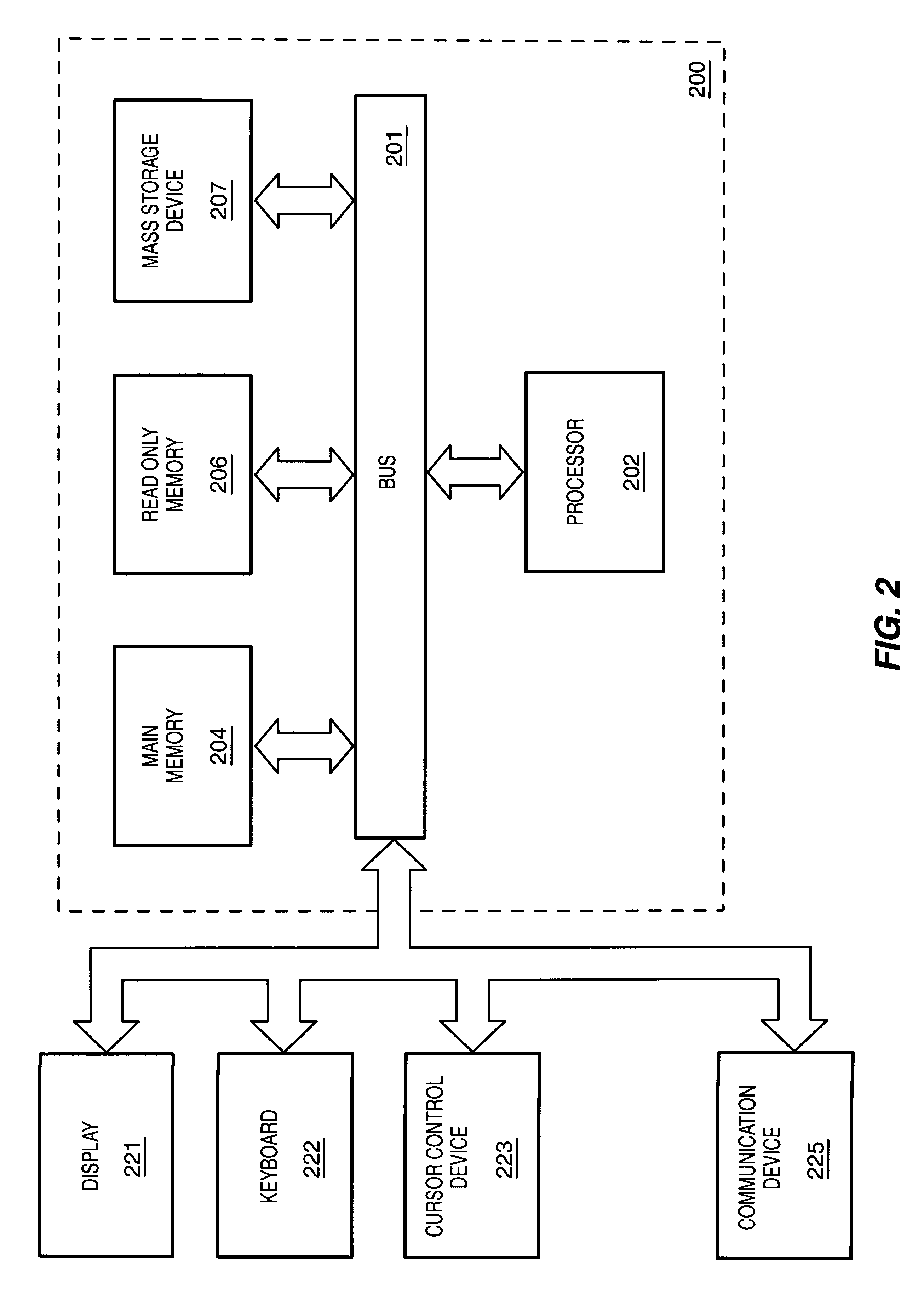

Automated design partitioning

InactiveUS6339836B1Detecting faulty computer hardwareCAD circuit designTheoretical computer scienceNetlist

A flexible and extensible automated design partitioning mechanism that facilitates simulation sessions employing two or more simulators is provided. A simulation backplane includes partitioning logic that identifies the design blocks of an overall design pertaining to each of a plurality of simulators. Once the partitions have been identified, nets that cross simulator boundaries (e.g., mixed nets) are determined and inter-simulator connectivity information is generated for the simulators. According to one aspect of the present invention, the partitioning logic is able to accomodate arbitrary (e.g., instance-based) partitioning. A design source expressed in a design representation upon which a first simulator may operate is received. Design blocks to be partitioned to each of a plurality of solvers are identified based upon one or more partitioning directives and the design source. A first instance of a cell is assigned to a first solver and a second instance of the cell is assigned to a second solver. Netlist like information is generated for those of the design blocks that are partitioned to a non-design source solver. To accomodate a folded representation of a design block containing the first or second instance of the cell, one or more additional cells are created. According to another aspect of the present invention, name space mapping is retained across all simulators. A design source upon which a first simulator may operate is read. Based upon a set of rules, a primary partition that is to be simulated by a first solver is identified. The primary partition includes a top cell of the design representation. Additionally, a secondary partition that is to be simulated by a second solver is identified. Subsequently, netlist information is generated for the second solver while retaining name space mapping in the secondary partition by adding one or more levels of hierarchy so as to include information about the top cell in the secondary partition.

Owner:MENTOR GRAPHICS CORP

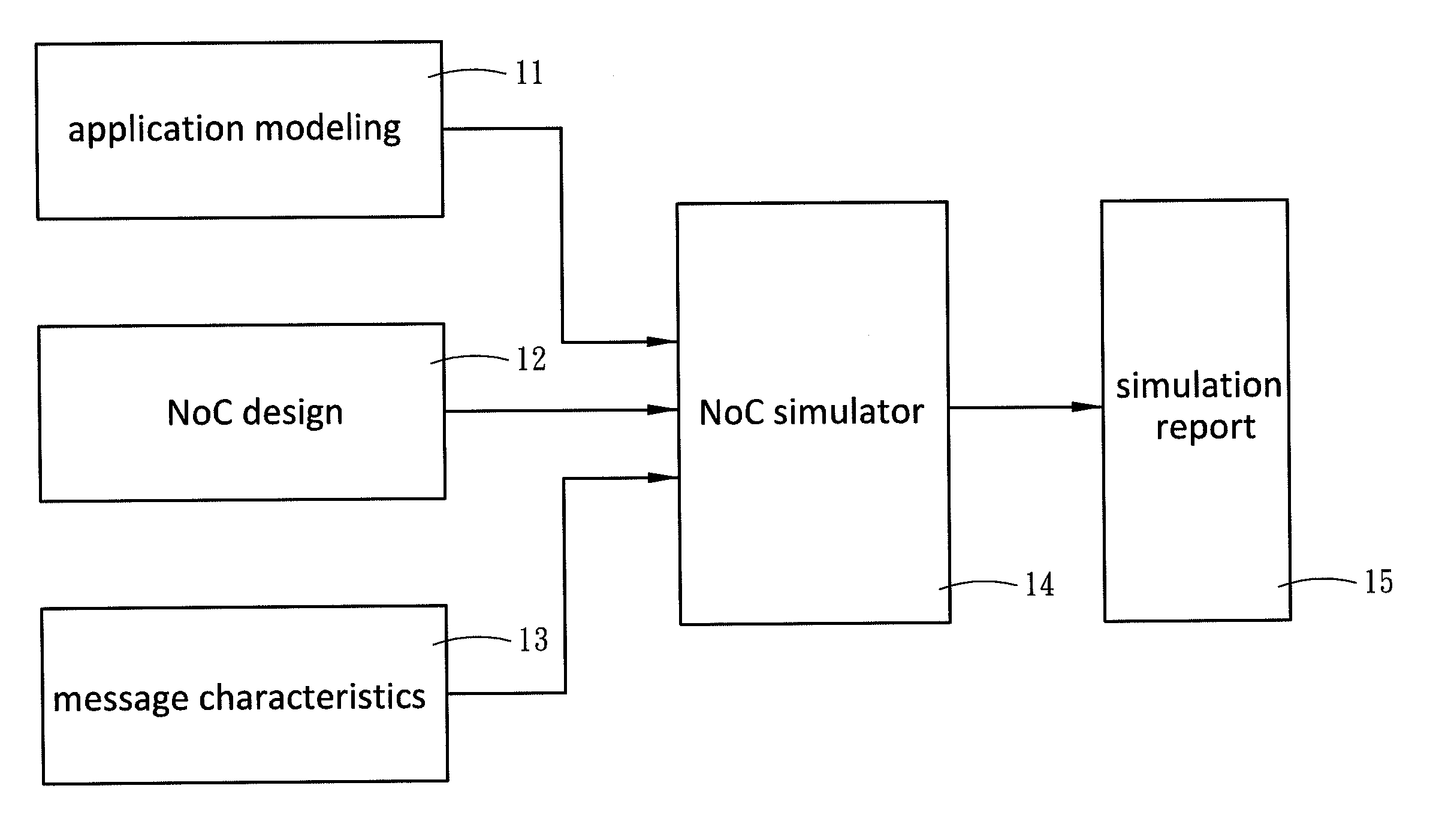

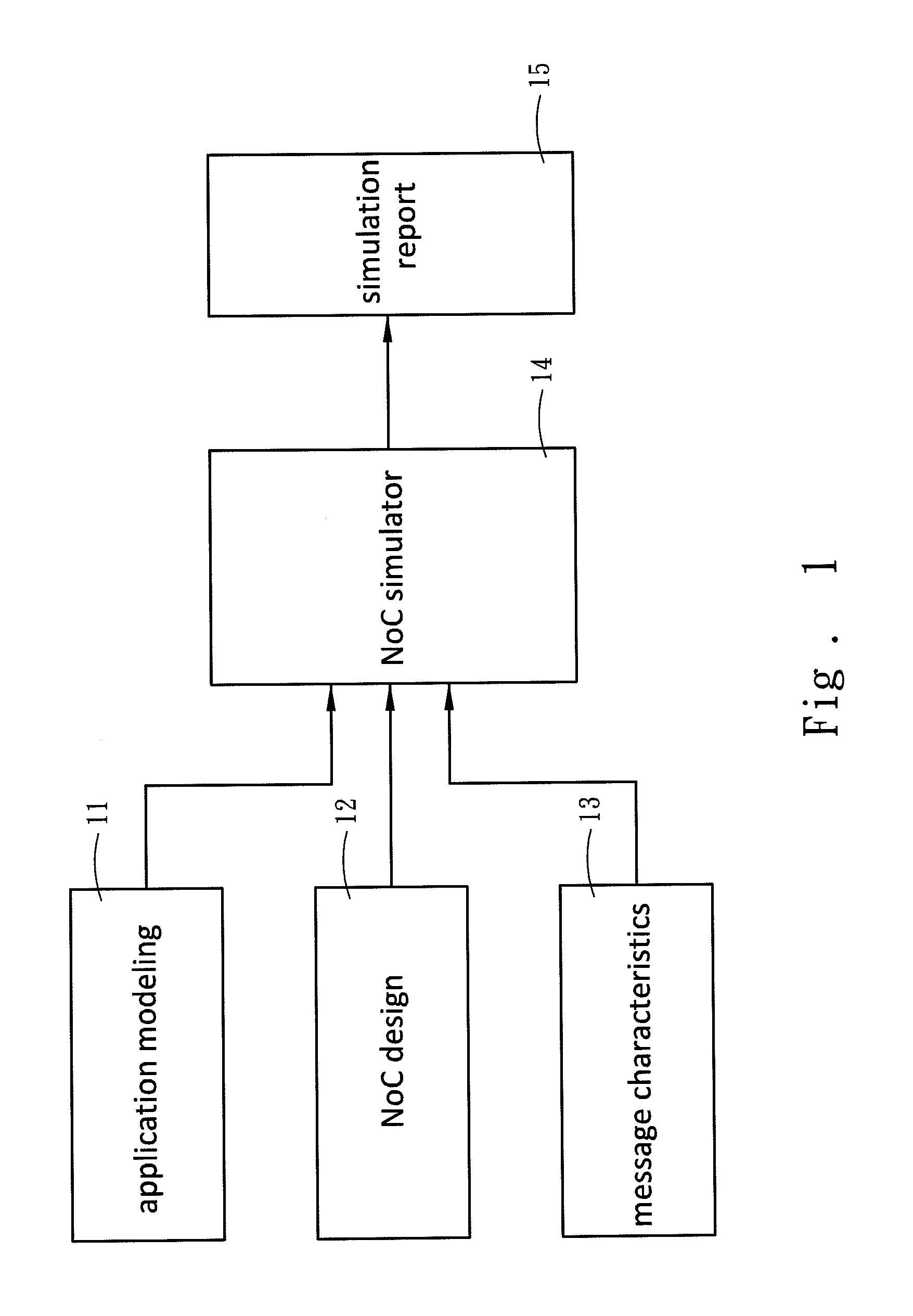

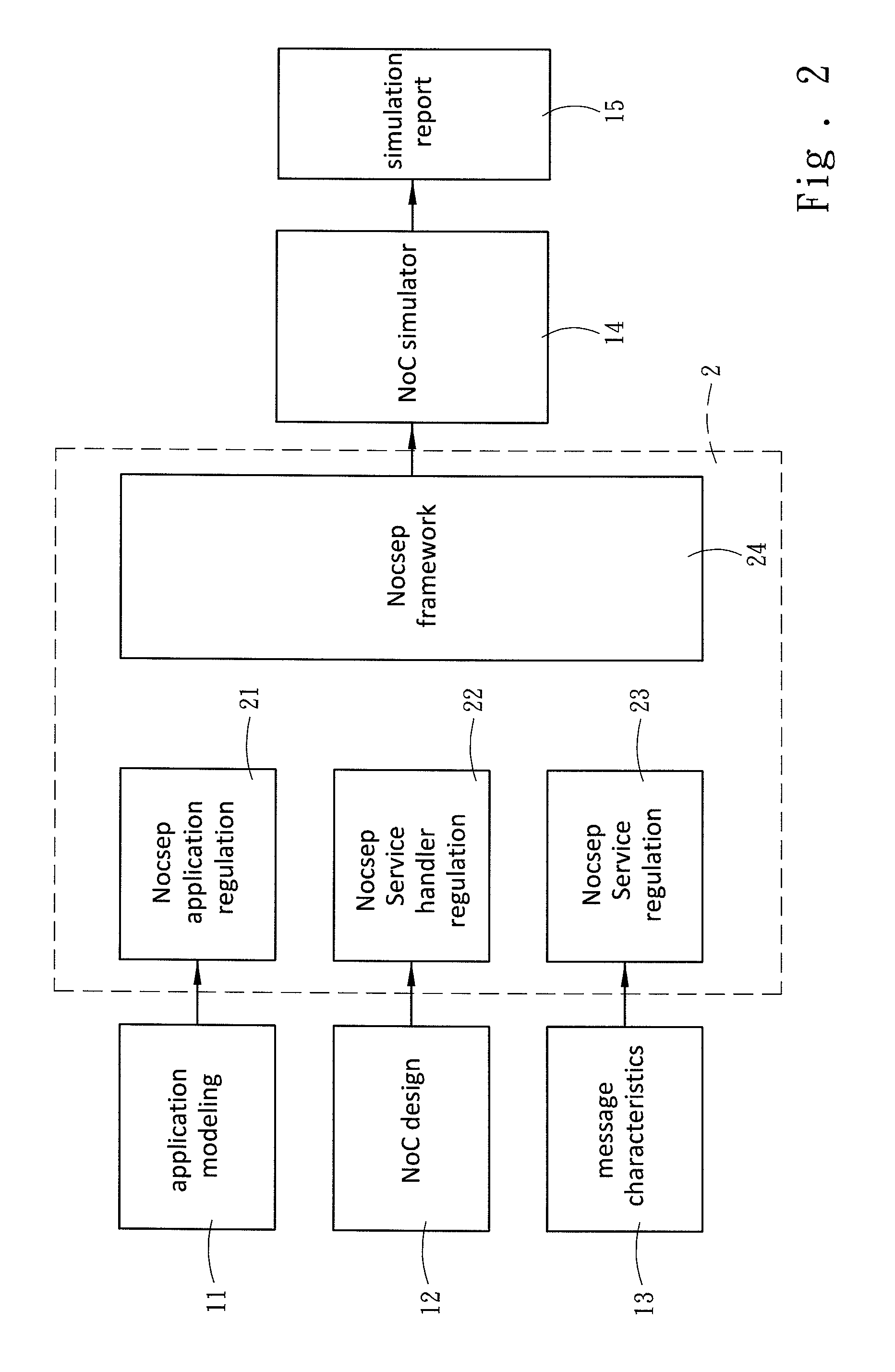

Noc-centric system exploration platform and parallel application communication mechanism description format used by the same

InactiveUS20110191774A1Fast simulationSimplifies some non-critical detailsMultiprogramming arrangementsTransmissionDescription formatComputer architecture

Network-on-Chip (NoC) is to solve the performance bottleneck of communication in System-on-Chip, and the performance of the NoC significantly depends on the application traffic. The present invention establishes a system framework across multiple layers, and defines the interface function behaviors and the traffic patterns of layers. The present invention provides an application modeling in which the task-graph of parallel applications is described in a text method, called Parallel Application Communication Mechanism Description Format. The present invention further provides a system level NoC simulation framework, called NoC-centric System Exploration Platform, which defines the service spaces of layers in order to separate the traffic patterns and enable the independent designs of layers. Accordingly, the present invention can simulate a new design without modifying the framework of simulator or interface designs. Therefore, the present invention increases the design spaces of NoC simulators, and provides a modeling to evaluate the performance of NoC.

Owner:NATIONAL TSING HUA UNIVERSITY

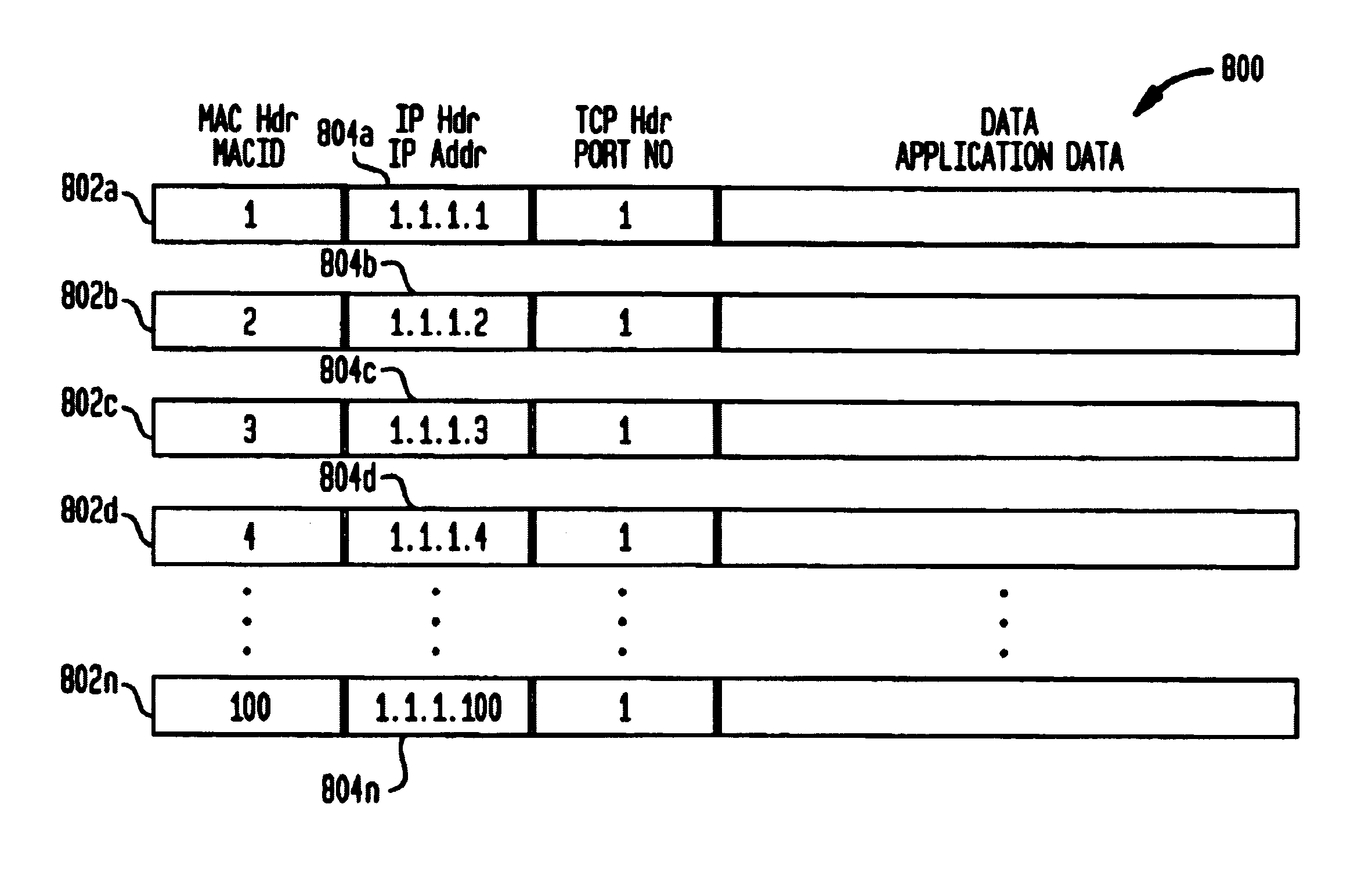

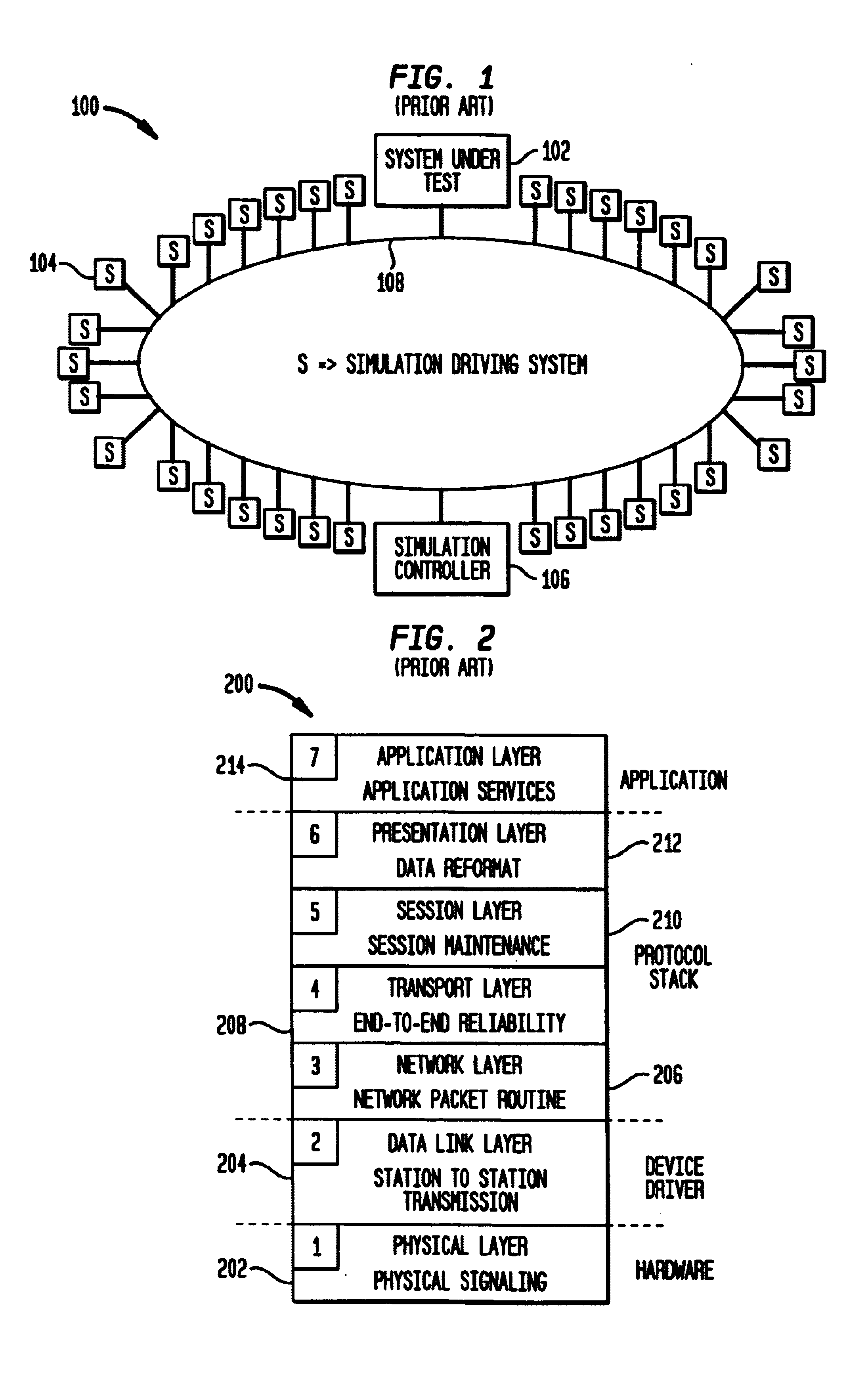

Intelligent workstation simulation-simulation at protocol stack level 2

InactiveUS7006963B1Improve fidelitySimulate the realDigital computer detailsNuclear monitoringGeneral purposeParallel computing

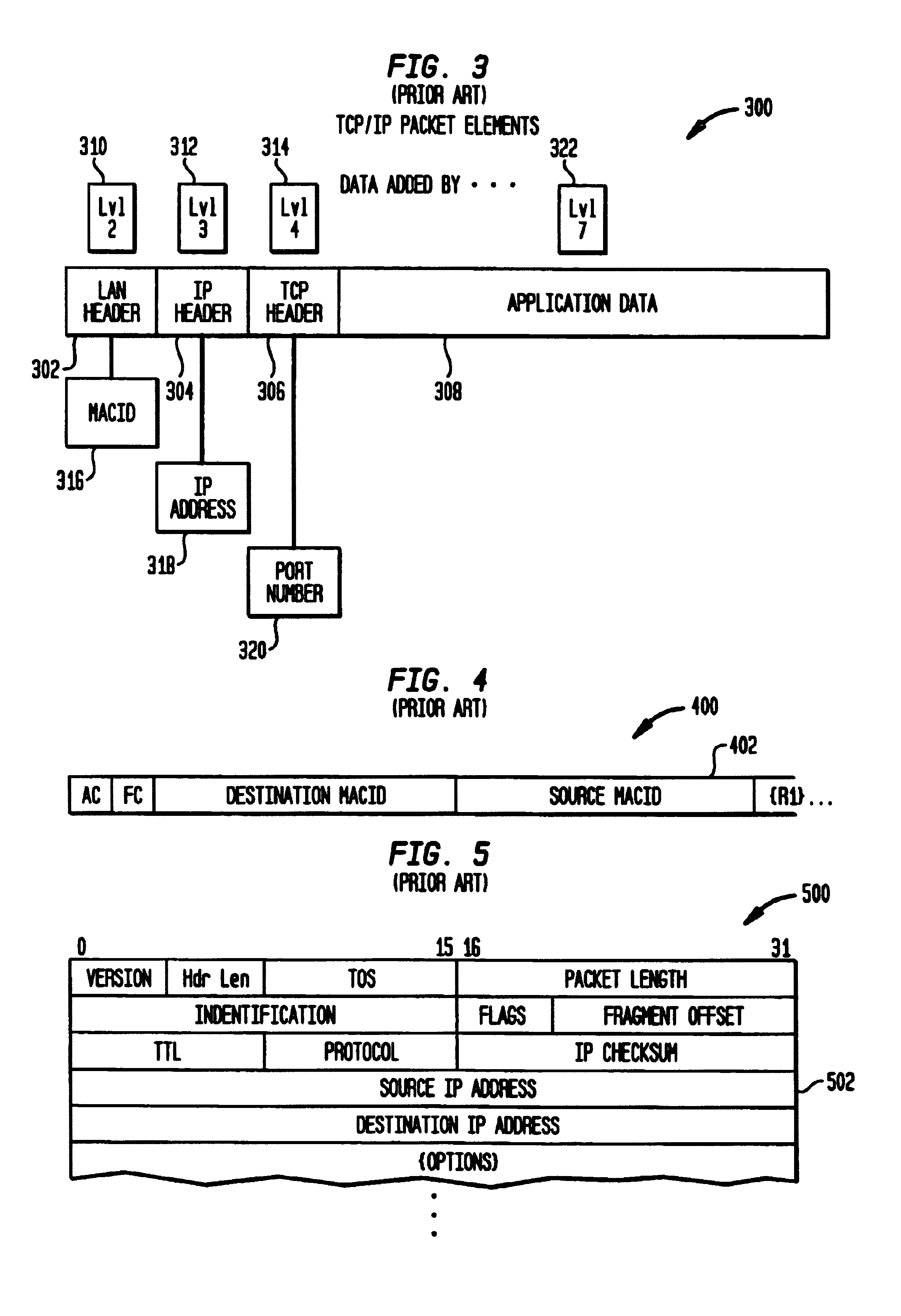

A general purpose simulator providing a high fidelity simulation performs the simulation at level 2, the data link layer of the protocol stack level where each individual client has a unique client address. The unique client address emulated by the simulator is inserted into a data frame at the data link layer of a protocol stack before the data frame is transmitted on the communications channel. Simulation at level 3 is also performed by inserting level 3 network identifier to emulated remote multiple clients. The simulator of the present invention may be run at a workstation residing connected to a server servicing the simulated client requests. The simulator also may be run on a host computer connected to a server via a communications device. Additionally, the simulator may also be run on the same system as the server.

Owner:IBM CORP

Hybrid system combining TLM simulators and HW accelerators

InactiveUS20110307847A1Simple designLow costCAD circuit designProgram controlHybrid systemComputer architecture

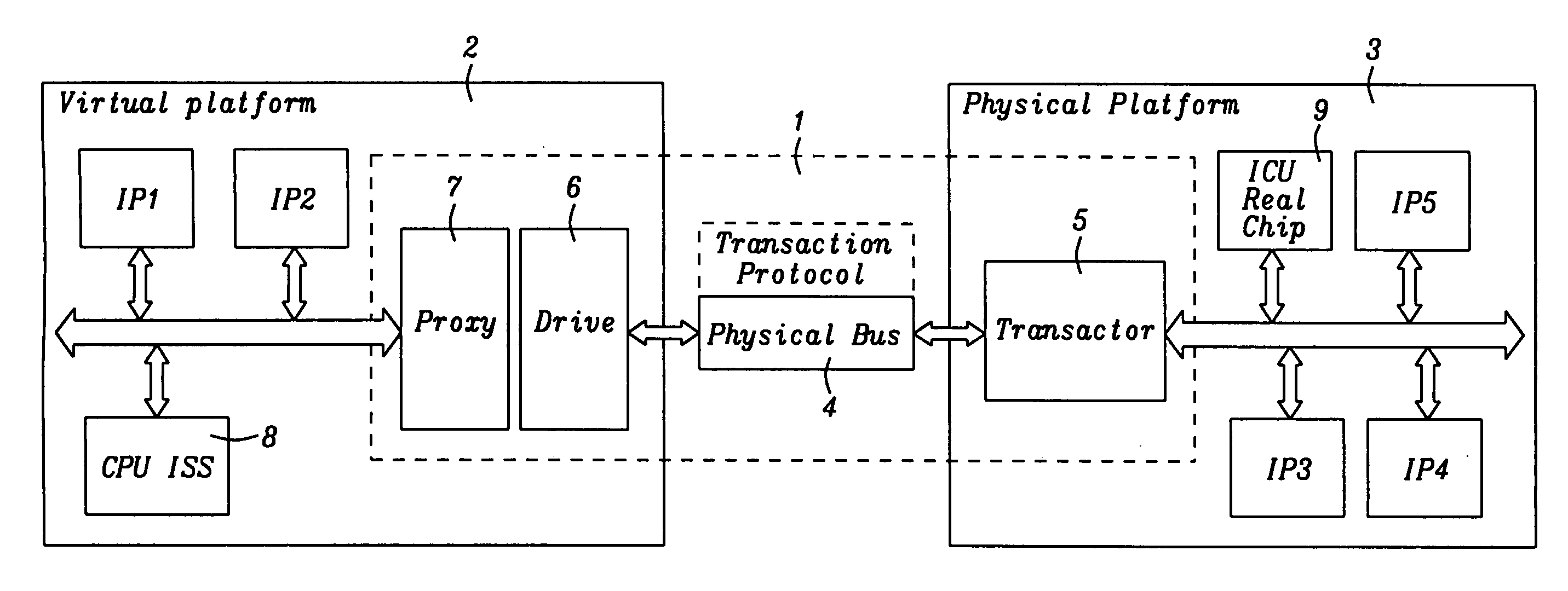

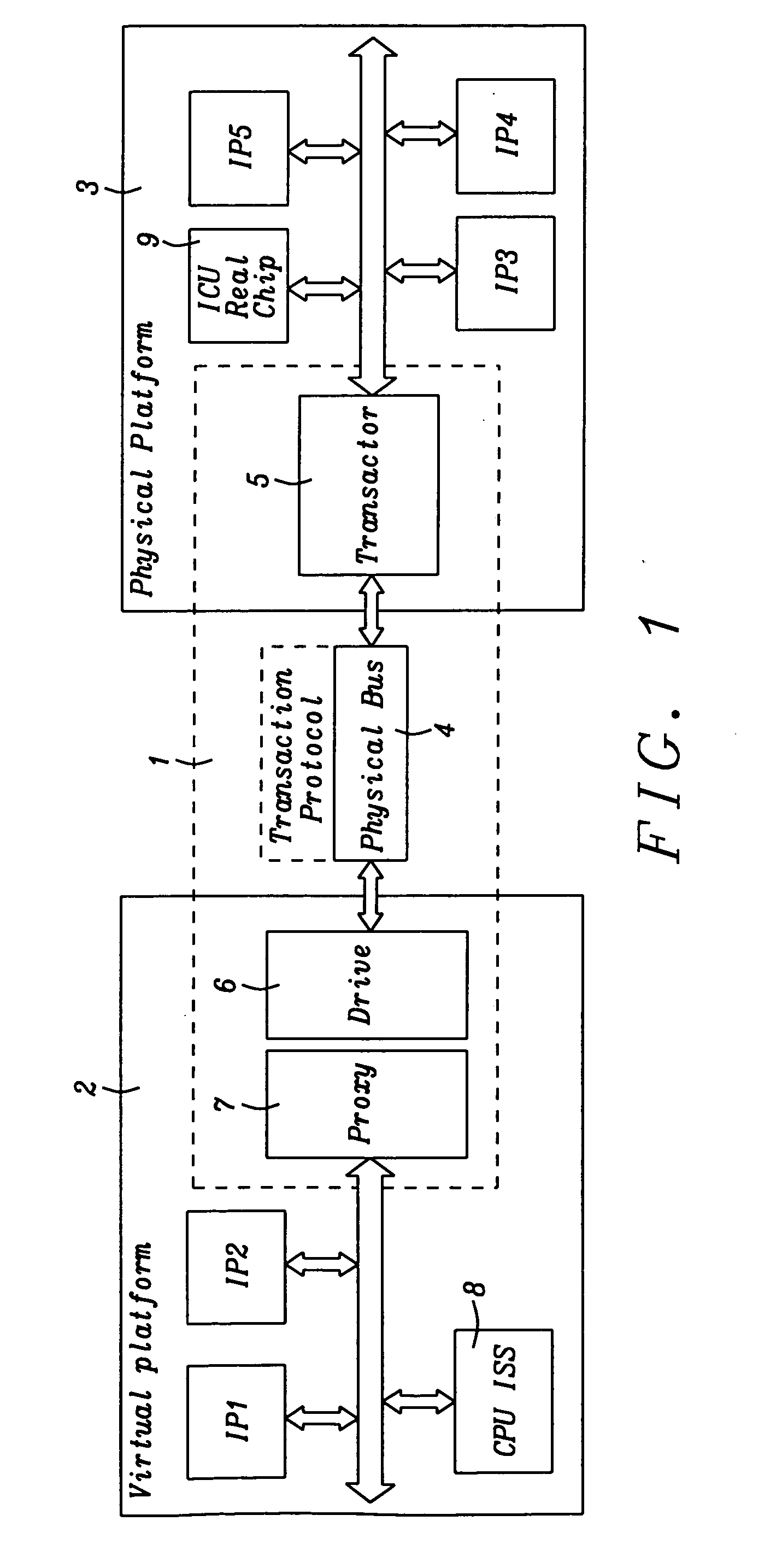

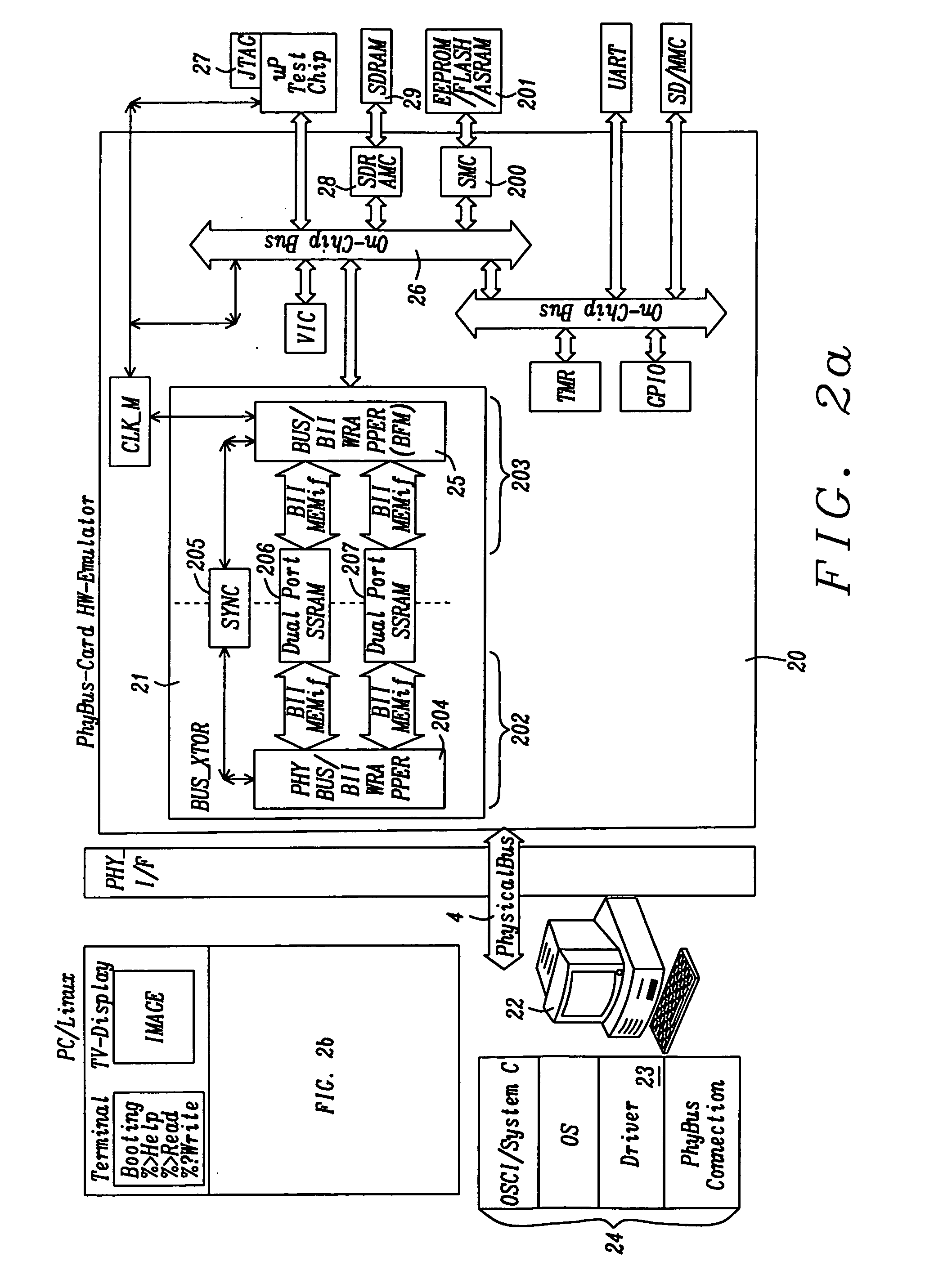

A hybrid system is combining transaction level modeling (TLM) simulators and hardware accelerators so that new system-on chip (SoC) designs are integrated in a virtual platform (VP) to run TLM simulation and existent semiconductor intellectual properties (IP) are added to physical platform (PP) to run hardware accelerator. A new circuit design with TLM is easier to be performed than with register transfer language (RTL) and it is integrated in a virtual platform and existent IP doesn't have to be redesigned to be integrated in a virtual platform.

Owner:GLOBAL UNICHIP CORPORATION

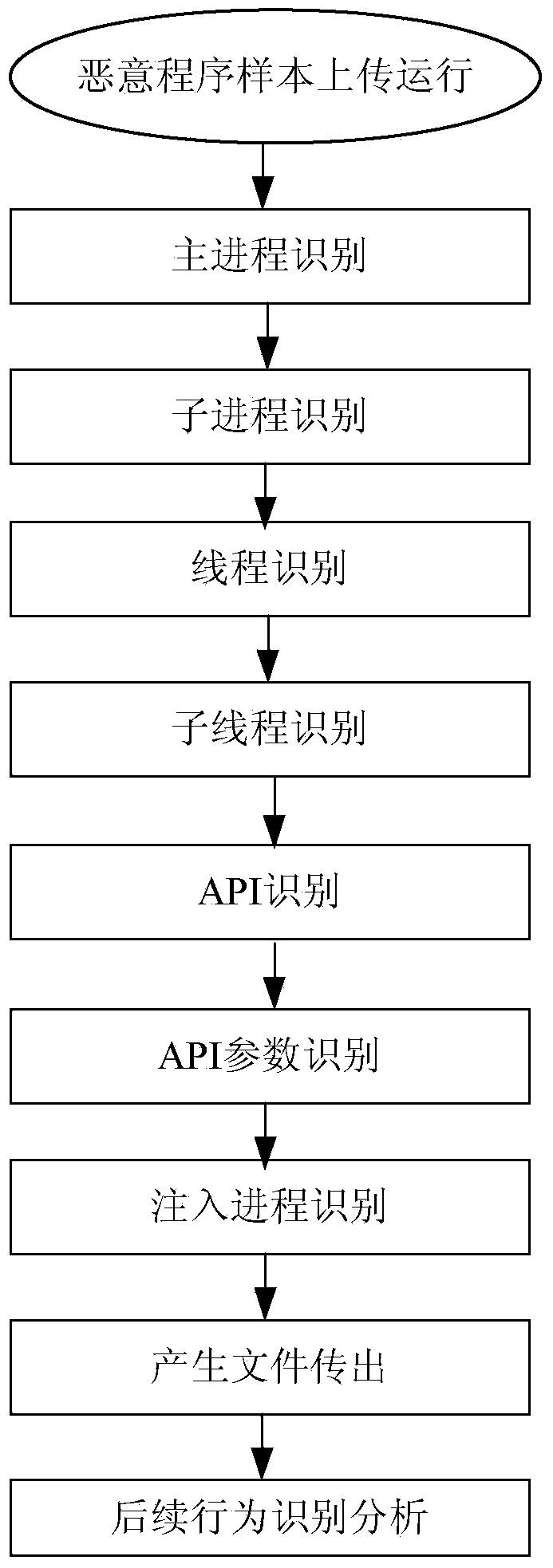

Malicious program behavior capture method based on Qemu

InactiveCN103927484AAchieve captureNo omission semanticsPlatform integrity maintainanceSource codeProgram behavior

The invention relates to a malicious program behavior capture method based on the Qemu. The method is characterized in that a malicious program behavior capture module is directly inserted into a source code of the Qemu, a client operating system is installed on the Qemu, and then behavior capture is carried out on malicious program samples on the client operating system through the malicious program behavior capture module running in the Qemu. The method has the advantages that the malicious program behavior capture module is directly inserted into the source code of the Qemu, completely isolated from the samples running on the client operating system and located on the lower layer of the operating system, and in theory, the malicious program samples can not detect or escape the malicious program behavior capture module easily.

Owner:XIDIAN NINGBO INFORMATION TECH INST

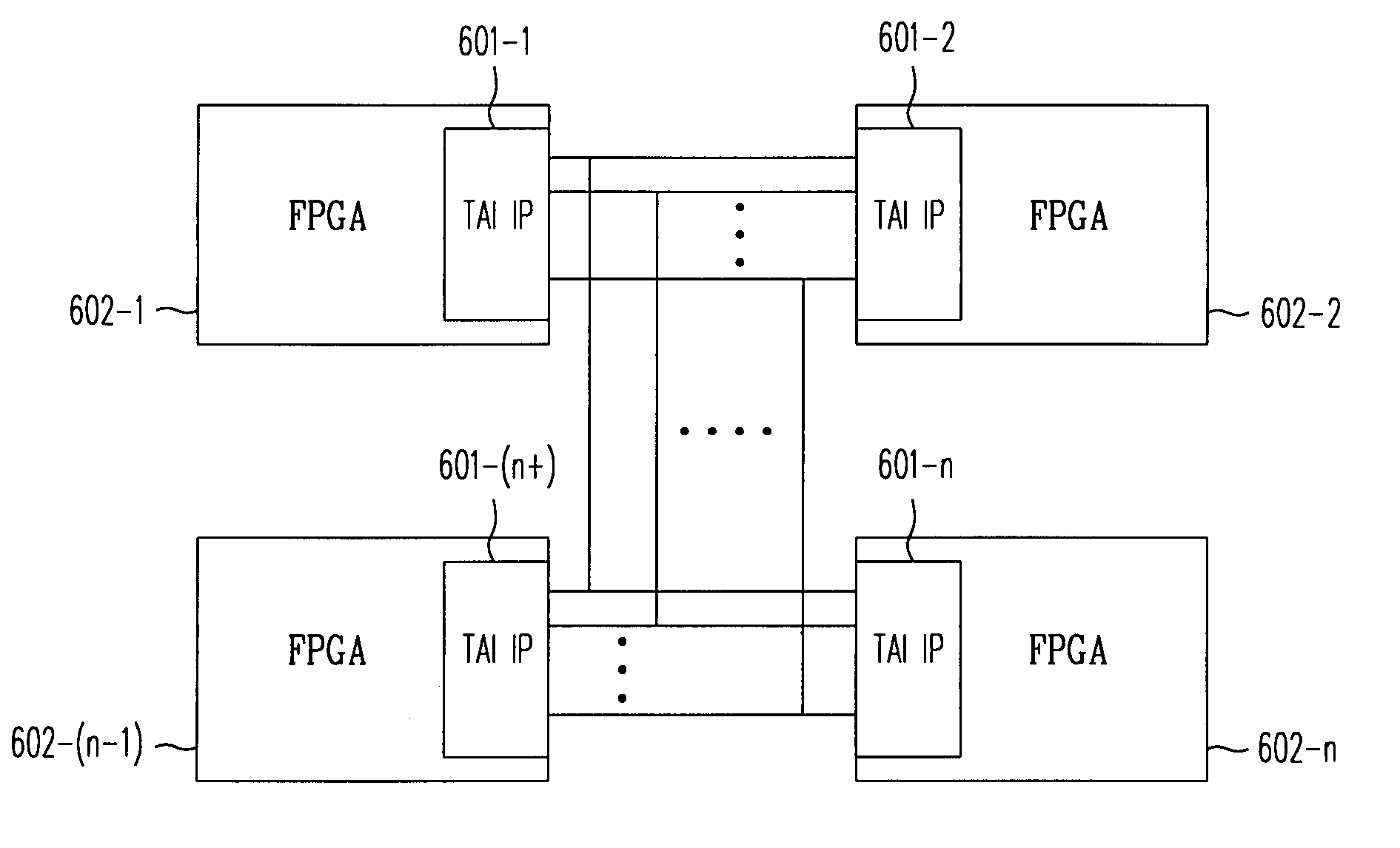

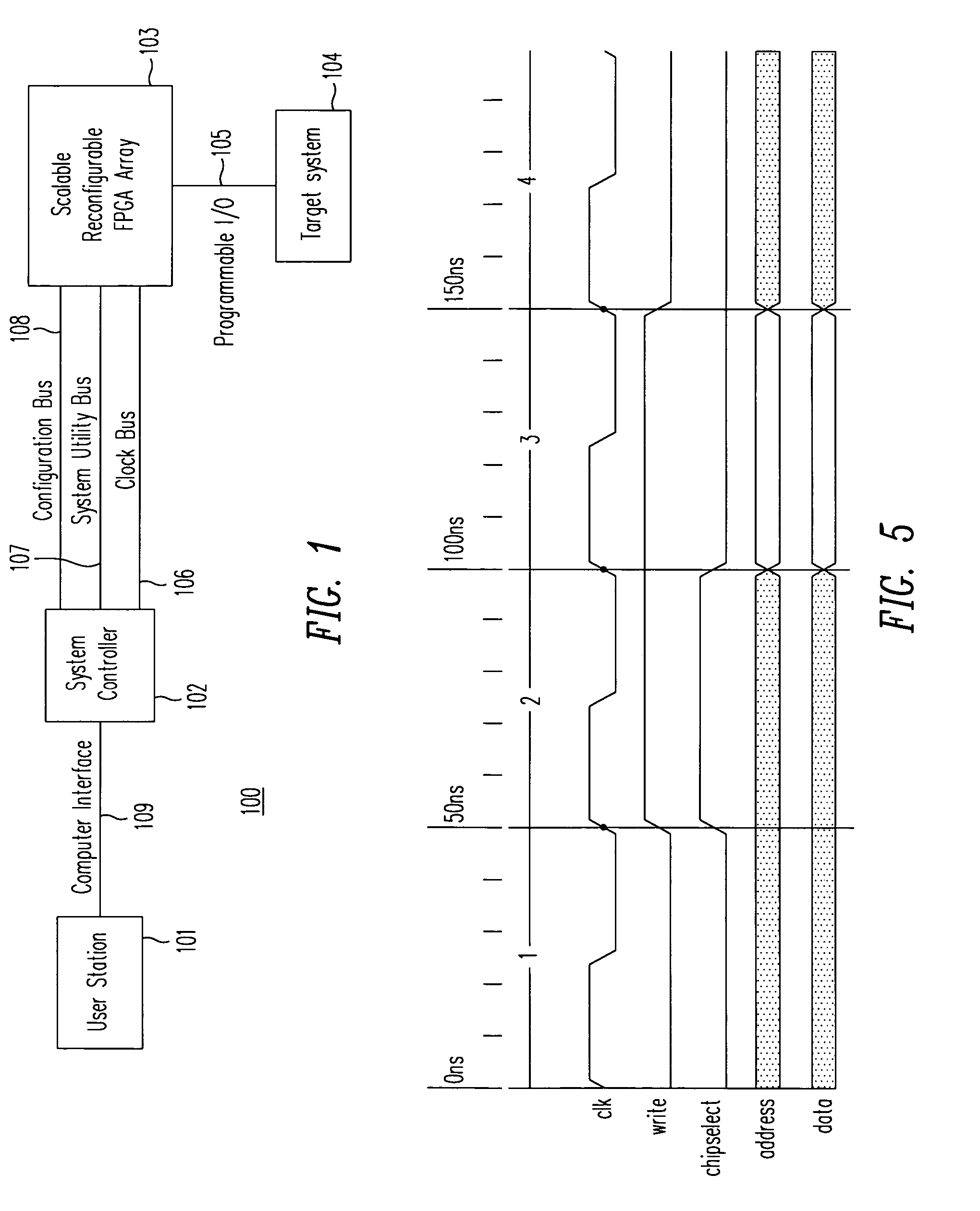

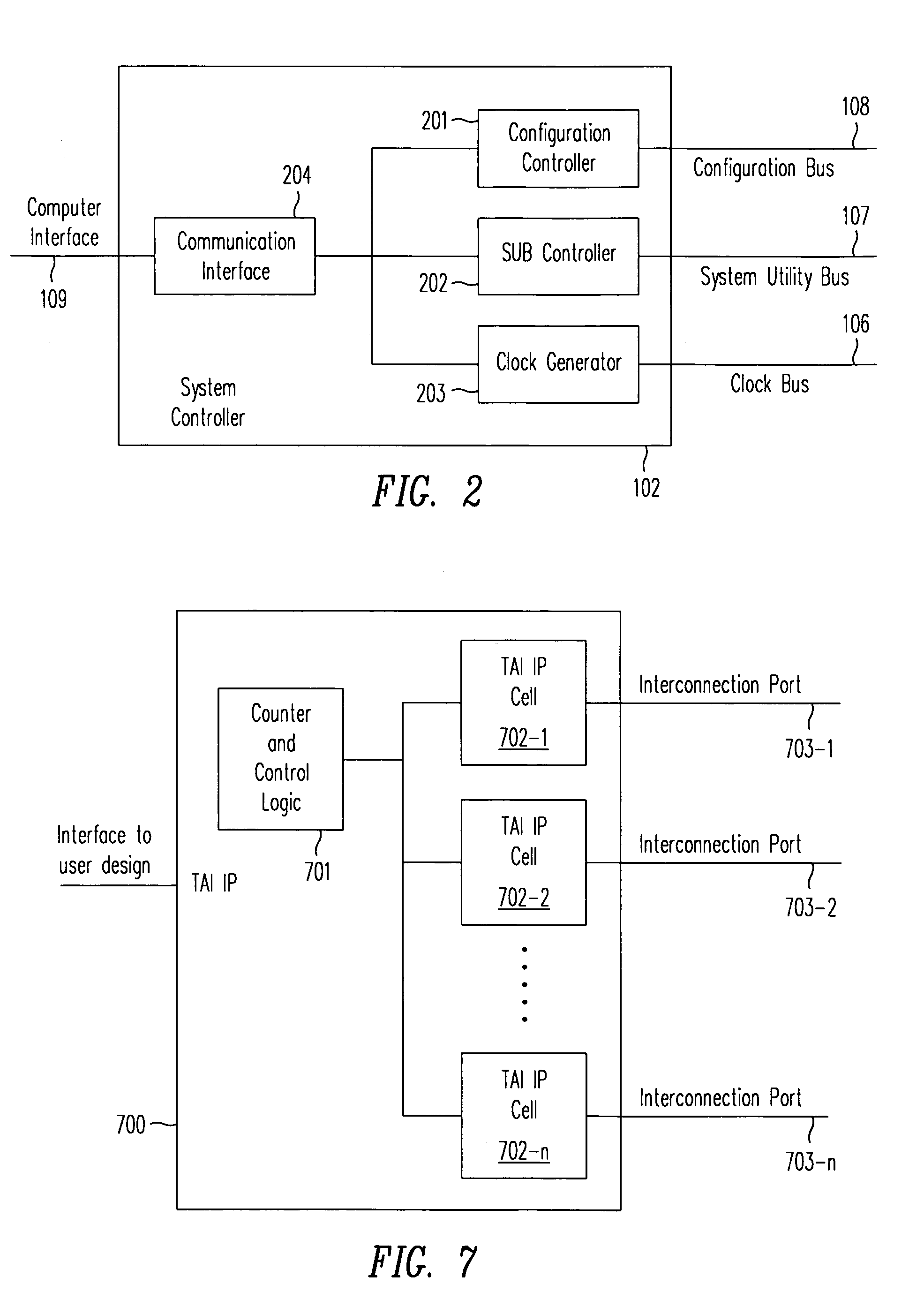

Scalable reconfigurable prototyping system and method

ActiveUS7353162B2Electronic circuit testingAnalogue computers for electric apparatusThird partyComputer architecture

A method and a system provide a reconfigurable platform for designing and emulating a user design. The method and system facilitates design and emulation of a system-on-a-chip type user design. The netlist of a user design may be included with netlists from customized or optimized third party circuits in an emulation using a platform including a number of field programmable devices. Various customized circuits for specific development activities, such as debugging, performance analysis, and simulator linkage may be configured to interact with the user design.

Owner:S2C LTD

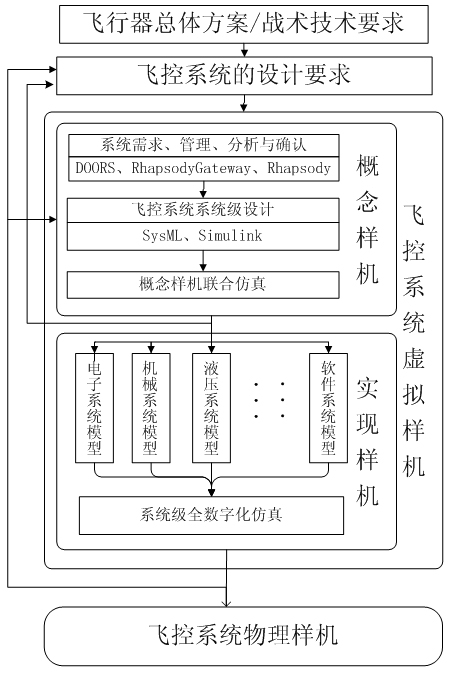

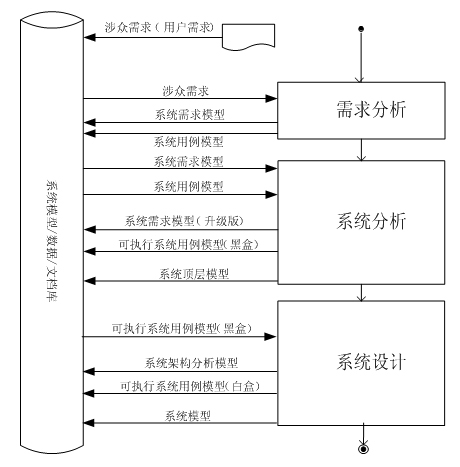

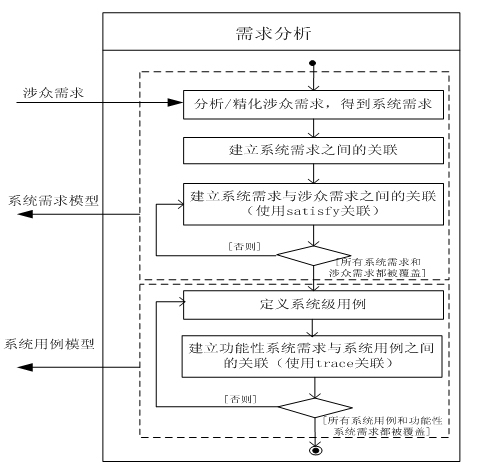

Design method of concept prototype of flight control system

InactiveCN101986318ADesign Method AdvantagesImprove verificationSpecial data processing applicationsSystems analysisControl system design

The invention discloses a design method of a concept prototype of a flight control system, which belongs to the technical field of design of the control systems. The method comprises the following steps: step 1) carrying out demand analysis, management and confirmation on the flight control system; step 2) carrying out system analysis and confirmation on the flight control system, and carrying out structural and functional division on the system; step 3) designing all member simulators of the flight control system; and step 4) carrying out system level design and simulation on the flight control system, and establishing the concept prototype of the flight control system. The seamless butt joint between Rhapsody software and Matlab software can be realized by utilizing the point-to-point way, and design data in the two types of software can be organically combined. Compared with the prior art, by adopting the method, the correctness of the design of the flight control system from a top layer can be ensured, and the design efficiency of the whole flight control system can be greatly improved.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

Systems and methods for performing software performance estimations

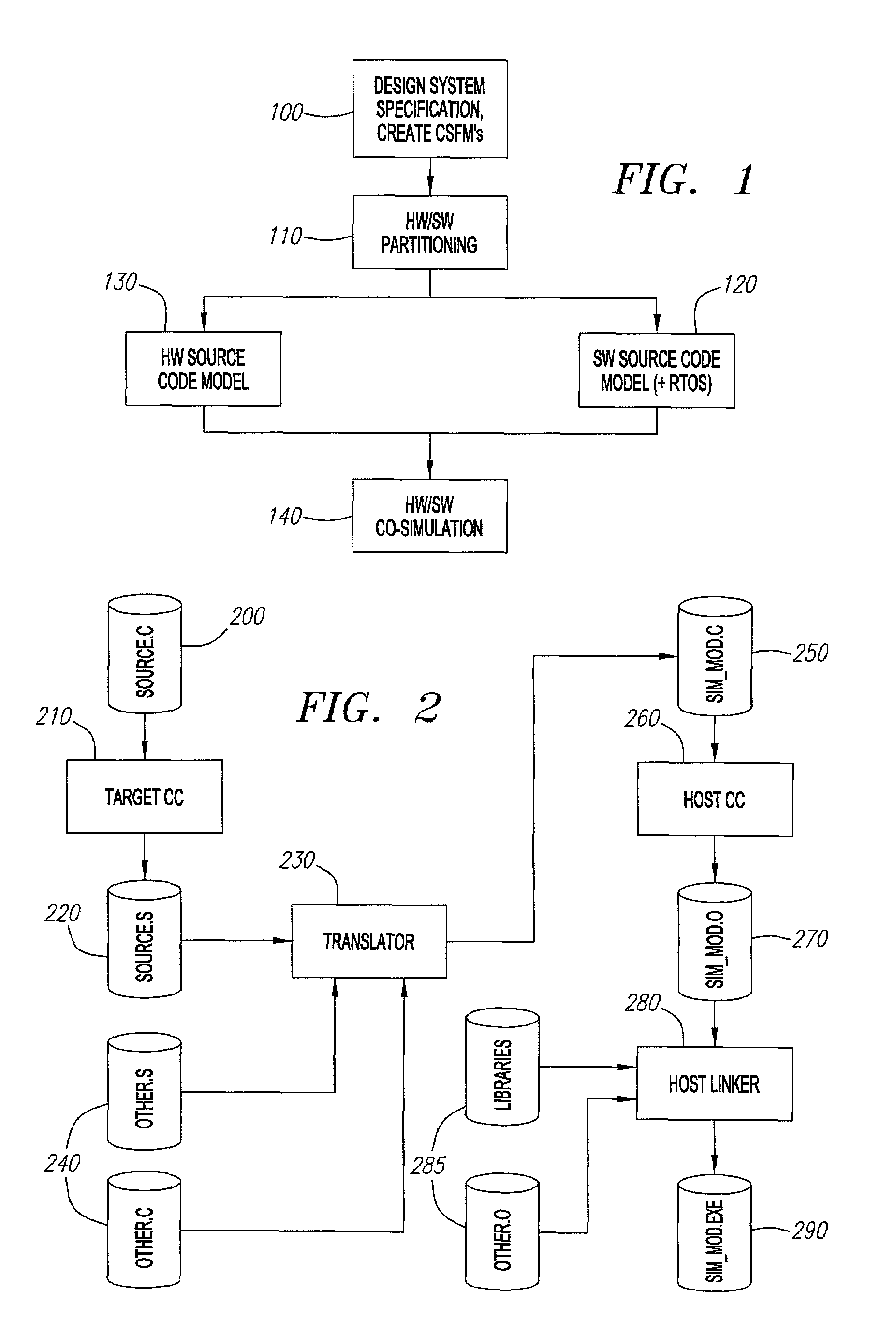

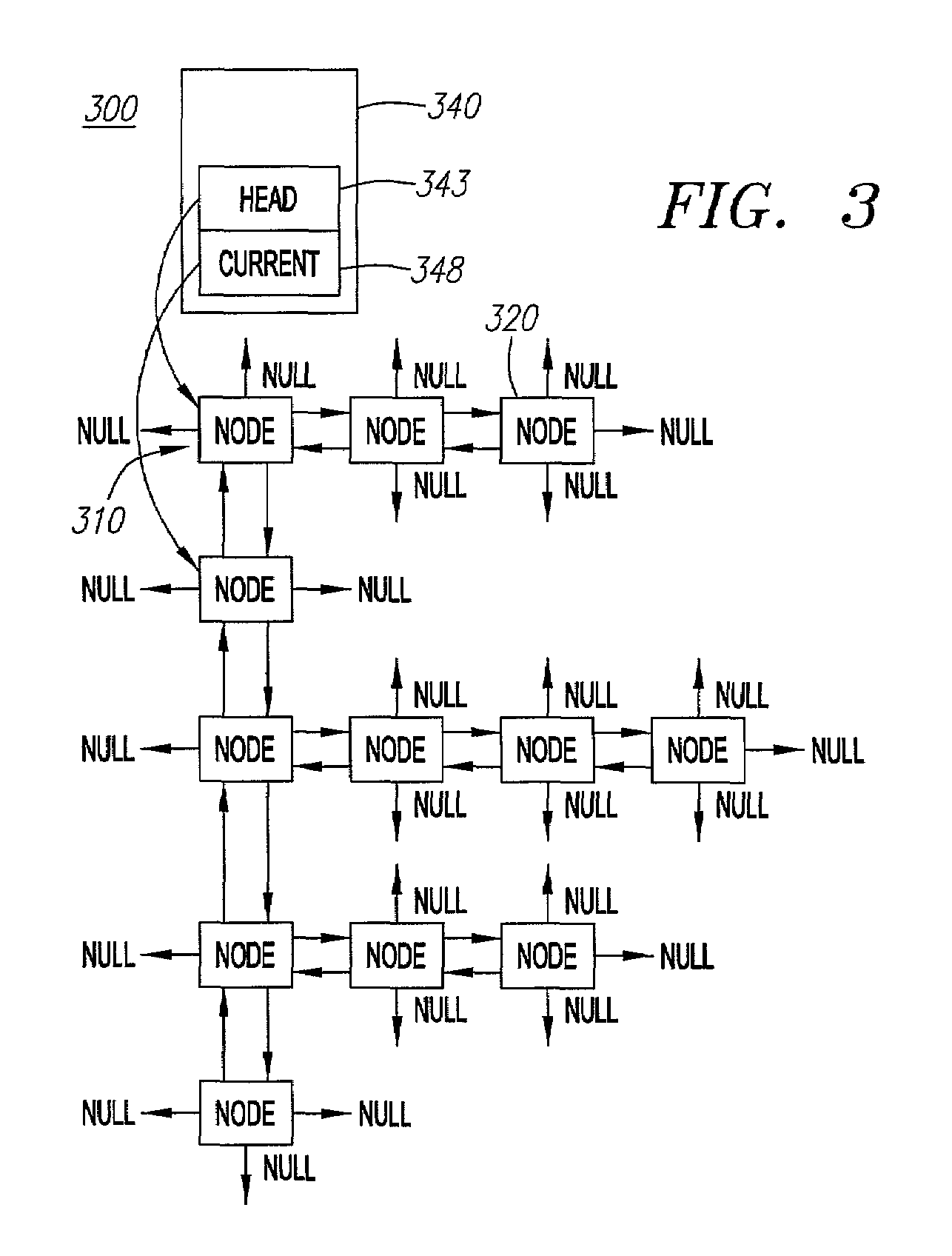

InactiveUS7702499B1Error detection/correctionSoftware simulation/interpretation/emulationParallel computingSource code

Systems and methods are provided for annotating software with performance information. The computer code is compiled into assembler code, the assembler code is translated into a simulation model, expressed in assembler-level source code. The simulation model is annotated with information for calculating various performance parameters of the software, such as timing information, or resource usage information. The simulation model is then re-compiled and executed on a simulator, optionally including a hardware simulation model, and the performance information is computed from the simulation.

Owner:CADENCE DESIGN SYST INC

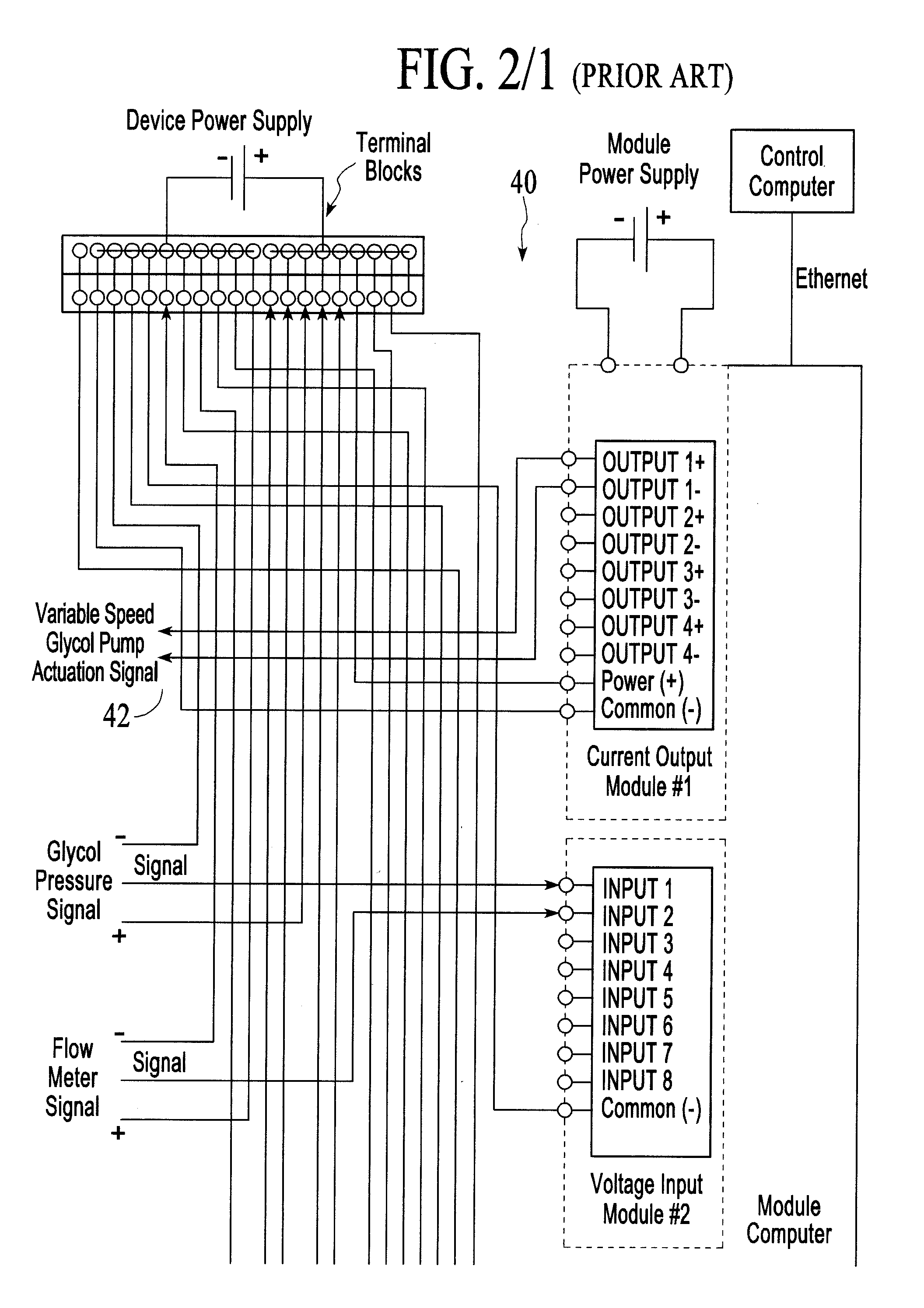

Control system simulator and simplified interconnection control system

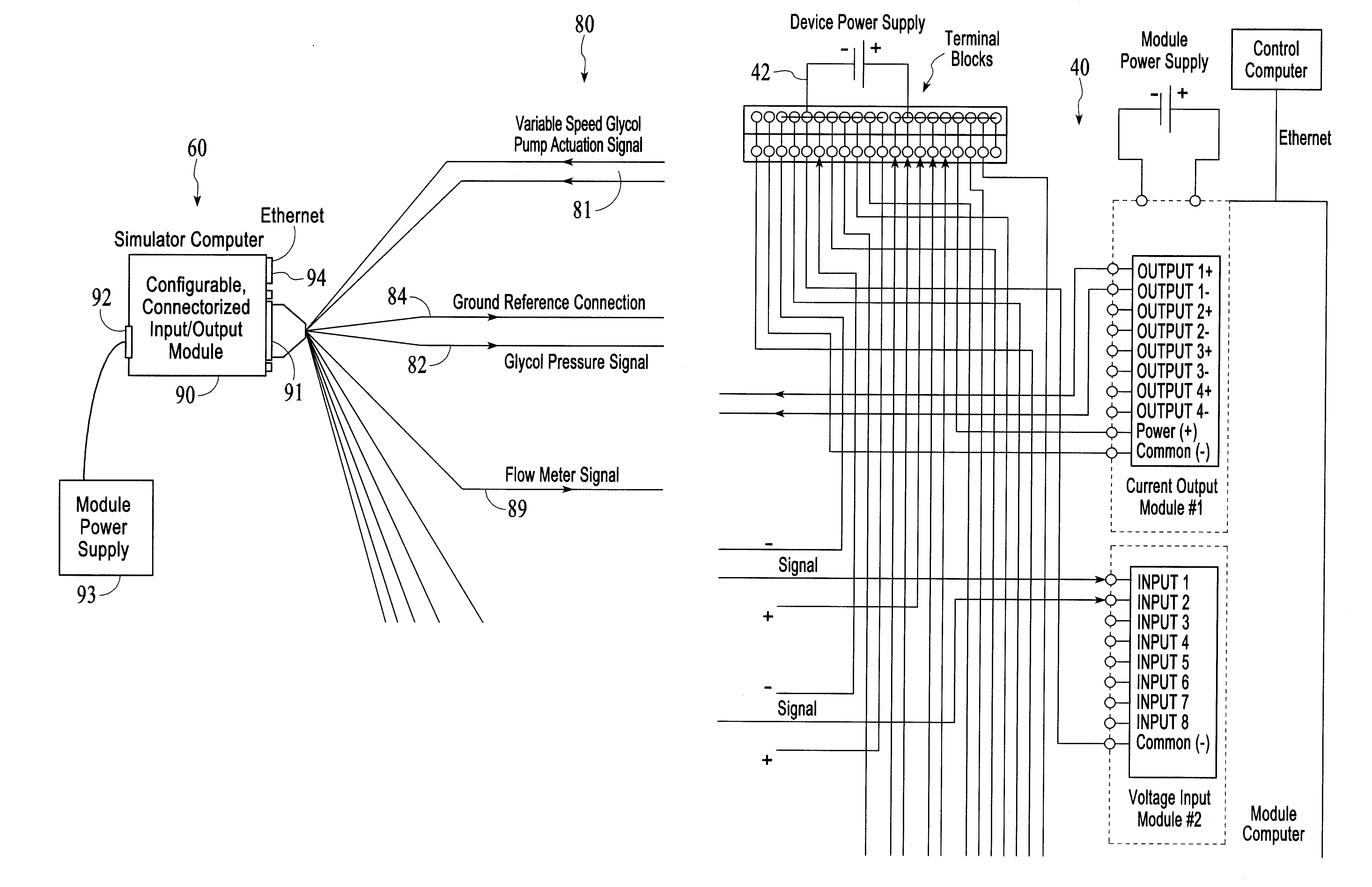

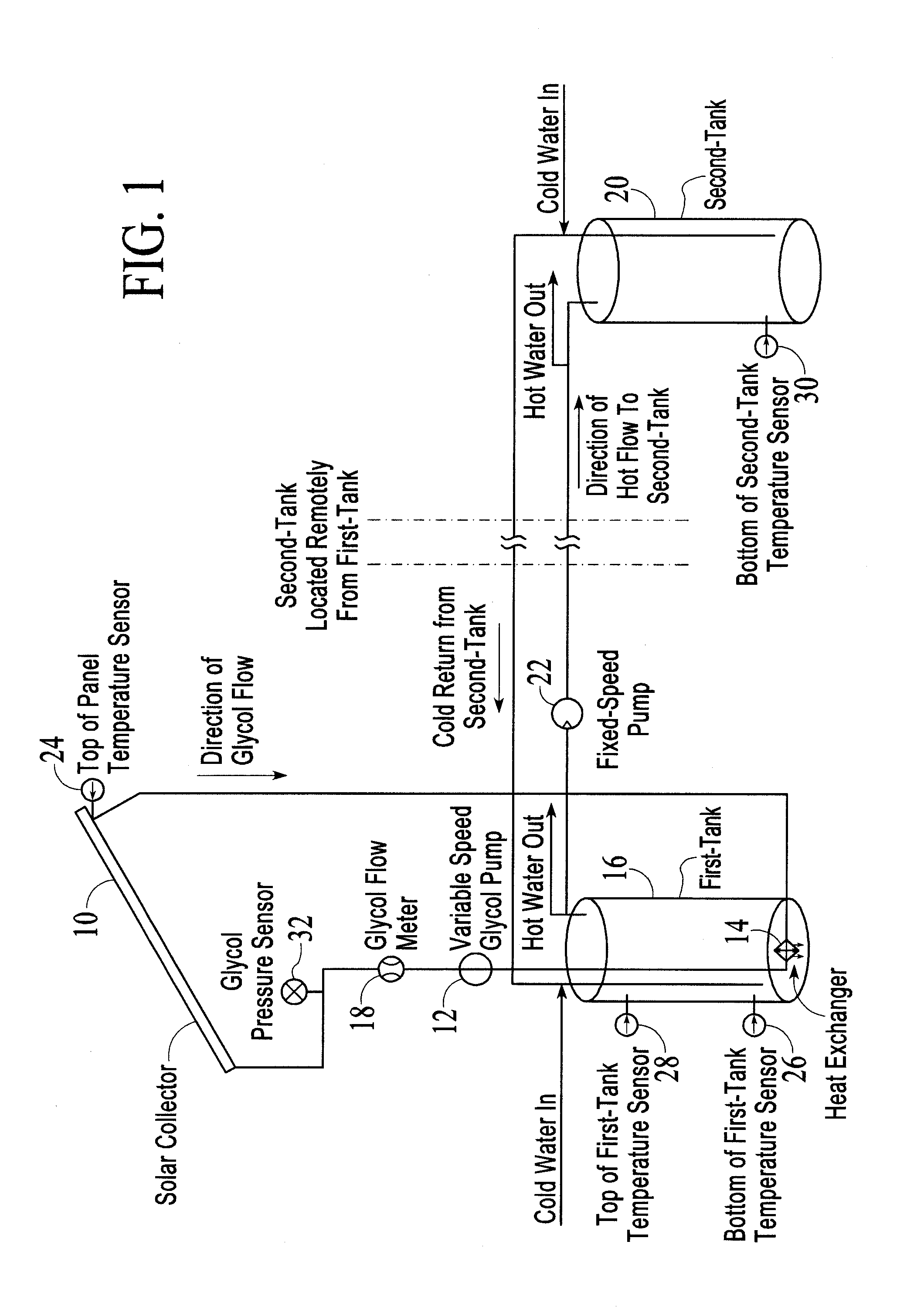

InactiveUS20110231176A1Simplifies electrical interconnectionReduce in quantitySimulator controlAnalogue computers for electric apparatusComputer control systemSimulation

A computer-based simulator, separate from a computer process control system, that simplifies the electrical interconnection of the computer-based simulator to the computer control system and reduces the number of hardware components required to effect a computer-based simulator. The invention also facilitates remote configuration and operation of the control and simulator systems.

Owner:X 10

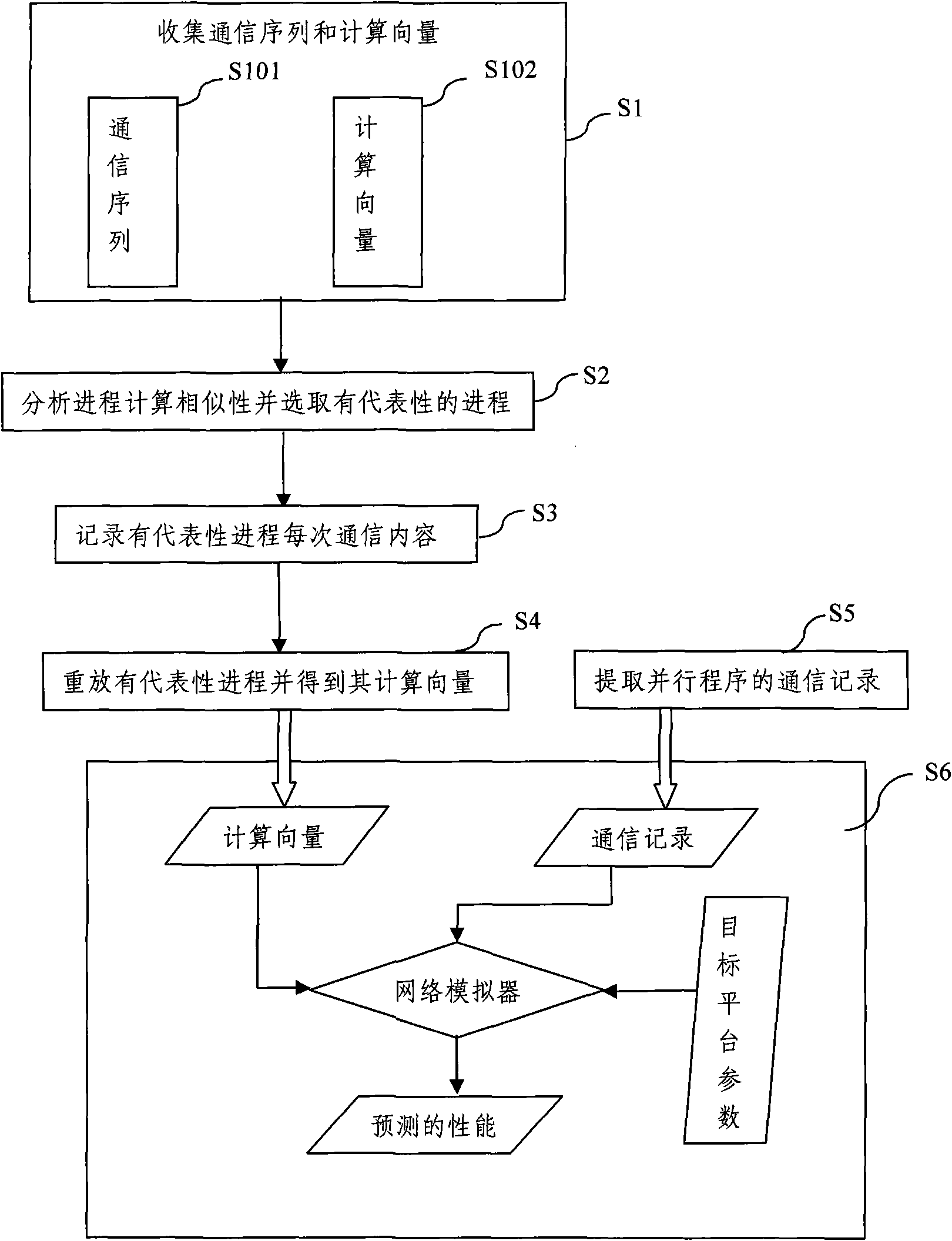

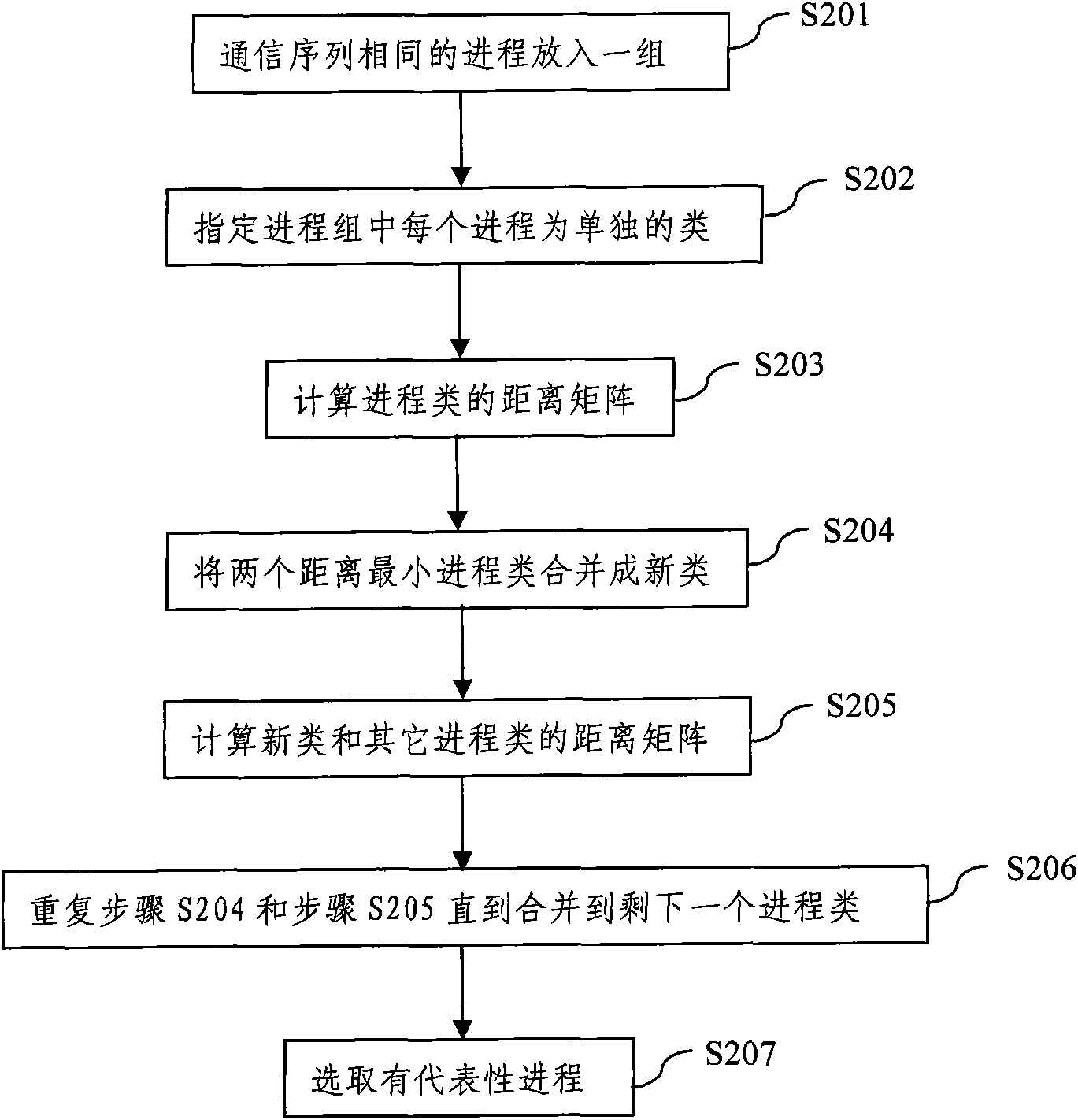

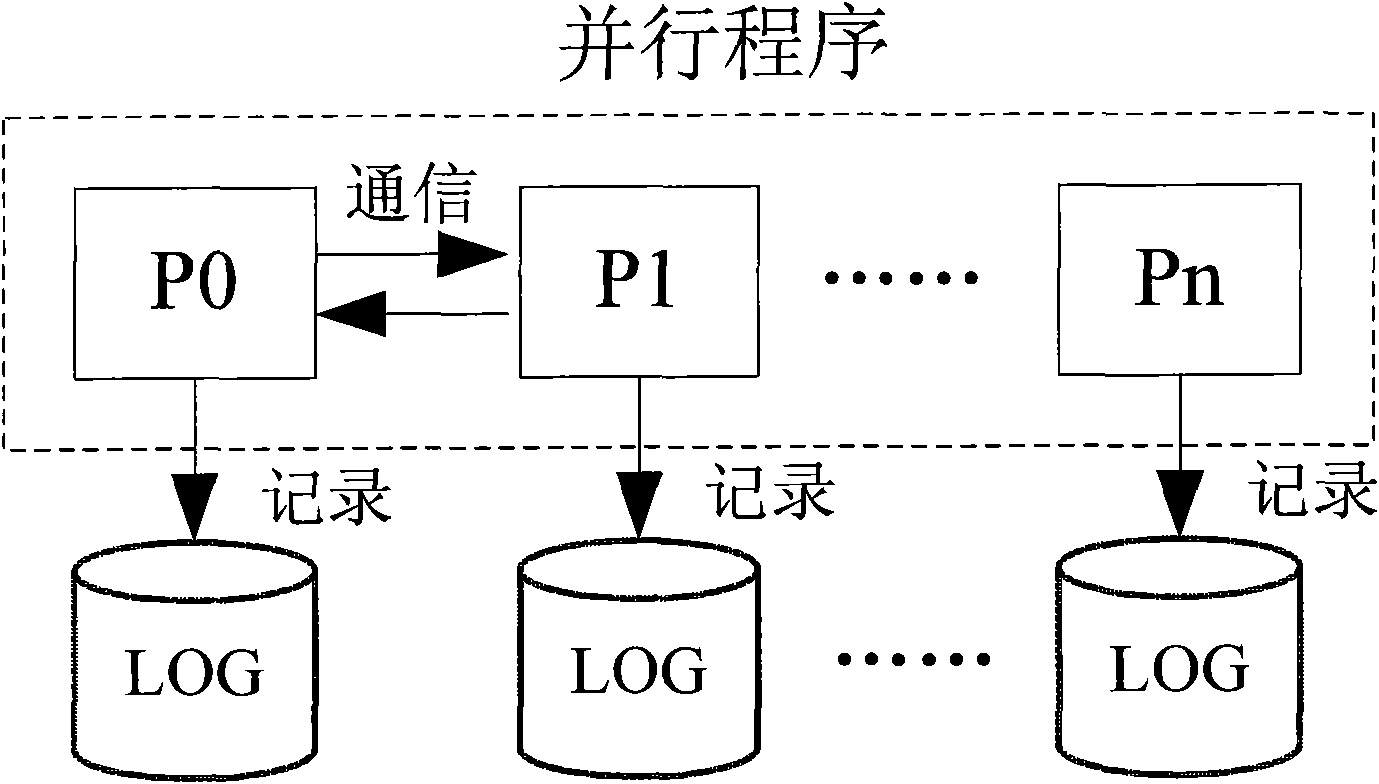

Large-scale parallel program property-predication realizing method

ActiveCN101650687ASave resourcesNo intervention requiredConcurrent instruction executionSoftware testing/debuggingParallel computingSequential computation

Owner:TSINGHUA UNIV

Programming language capable of cross-language reusing

InactiveCN102880452AImprove reusabilityReusableSpecific program execution arrangementsJavaSoftware engineering

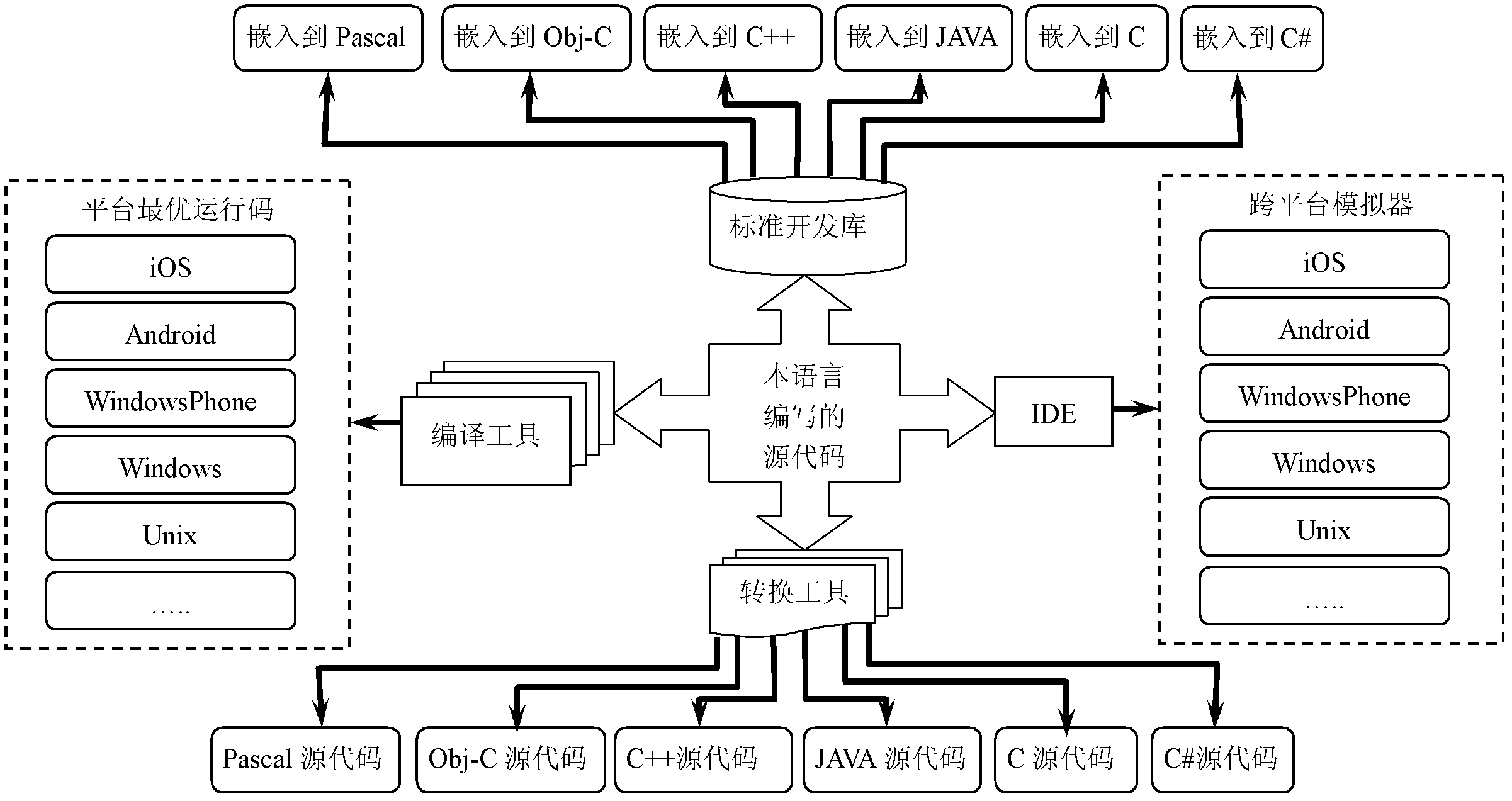

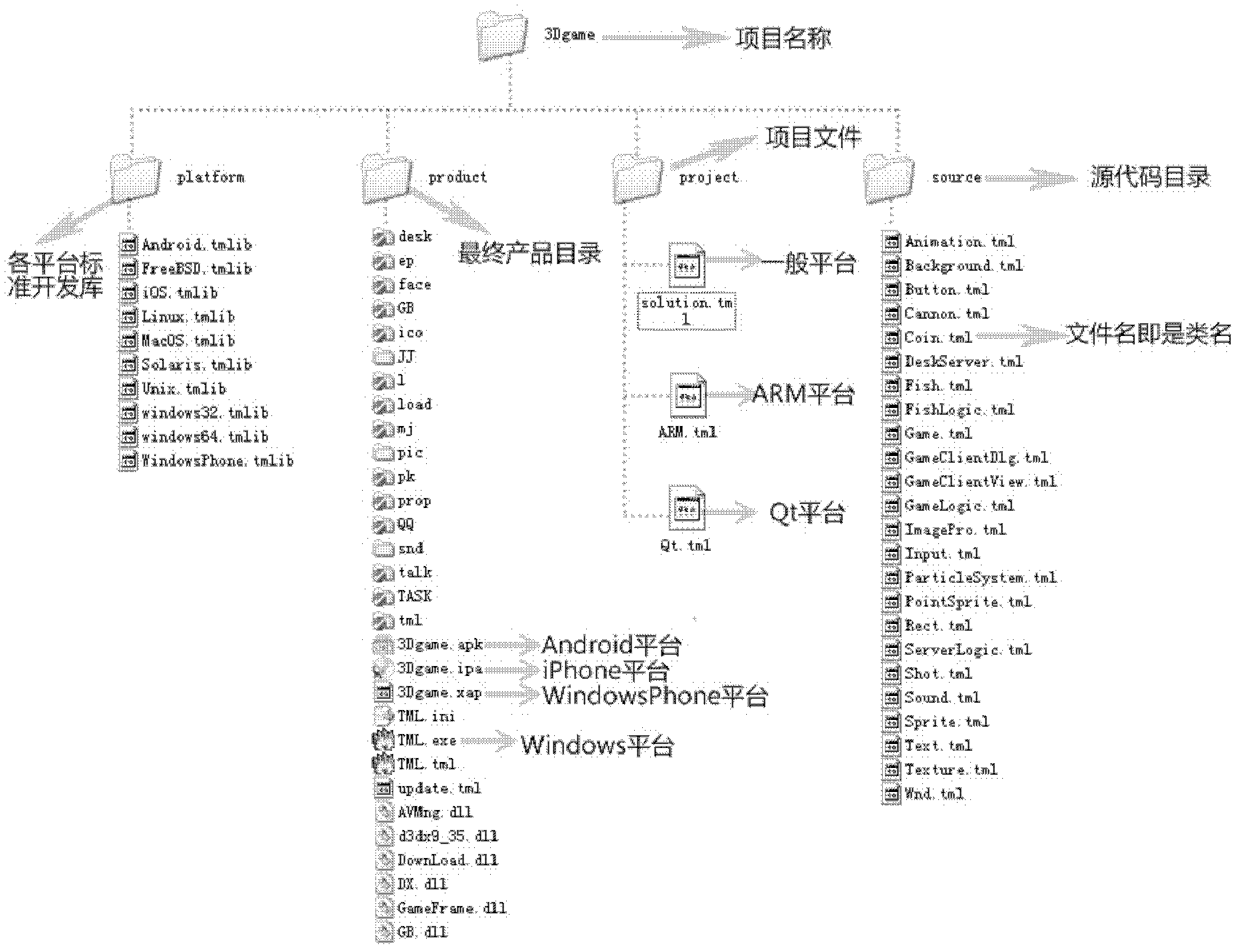

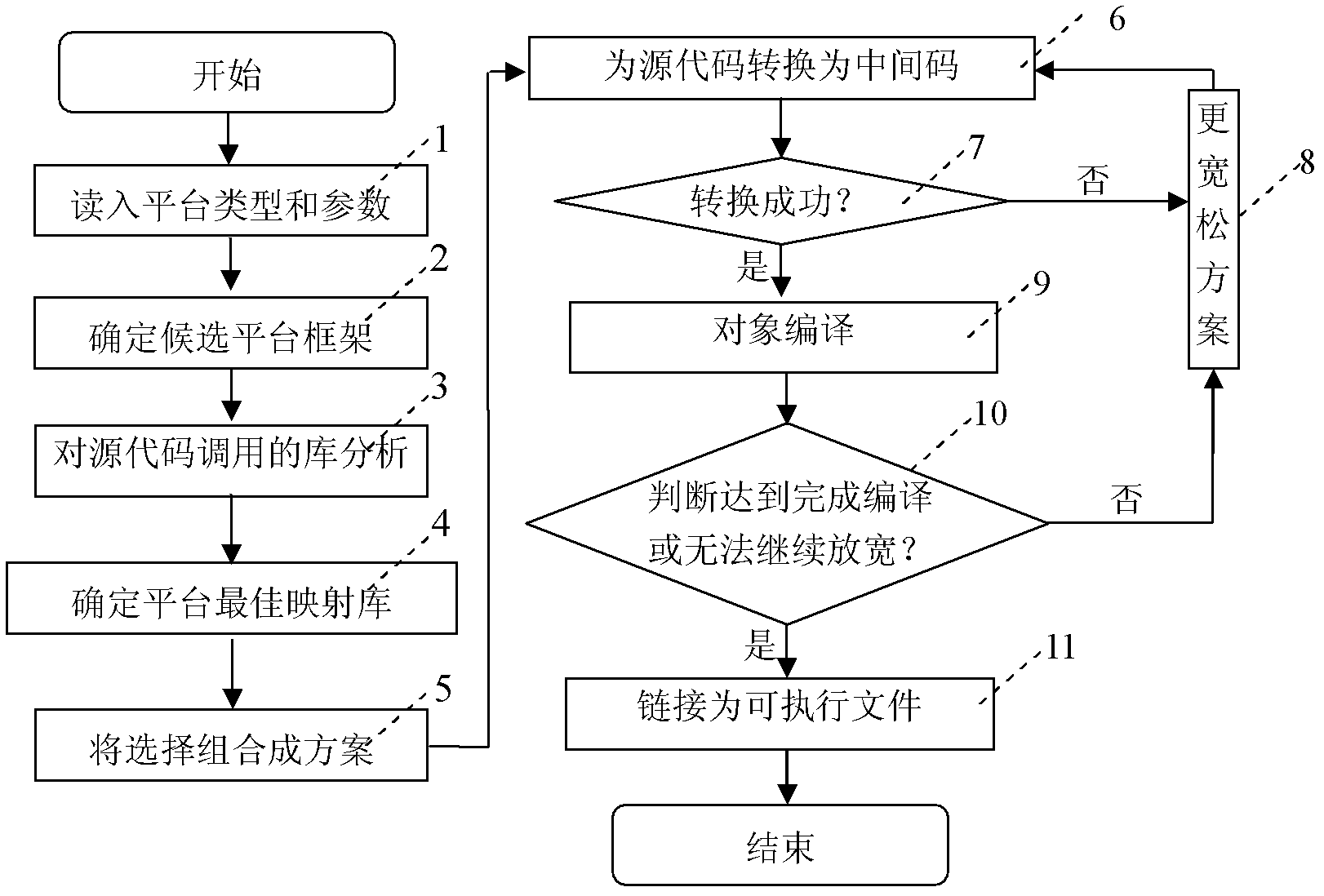

The invention relates to a programming language capable of cross-language reusing, and discloses a method for programming and developing software application programs by using a group of certain brief term and syntax rule with natural language semanteme. Through the description of multiple programming language families and the display method of the same thought realizing parts in multiple language development of certain software with an abstract special function, the cross-platform, cross-compiling, convertible and embeddable unified development is realized. Through the compiling tool disclosed by the invention, the same set of codes programmed by the language can be compiled into the applications with different states under different platforms; and the platform characteristics are realized by corresponding compiling tools. Through the converting tool disclosed by the tool, the codes programmed by the language can be converted into other languages as C++, Java, C#, Pascal and Obj-C, and can also be converted into the codes directly executed by the ARM embedded chip. Through the standard developing library disclosed by the invention, the language can be directly embedded into other languages for mixed programming. Through the IDE and the simulator disclosed by the invention, the cross-platform debugging and simulation can be realized.

Owner:山东国软信息技术有限公司 +1

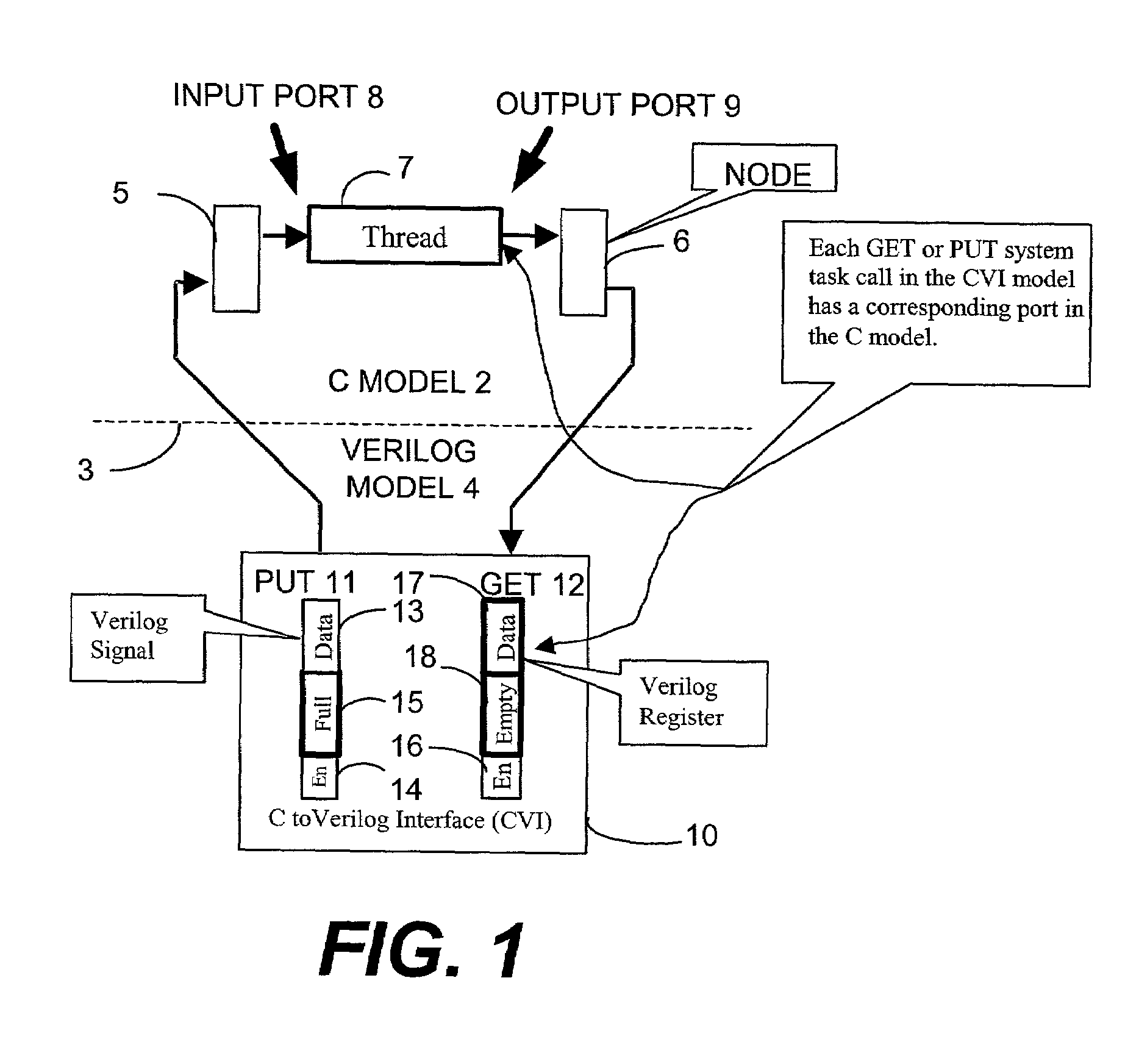

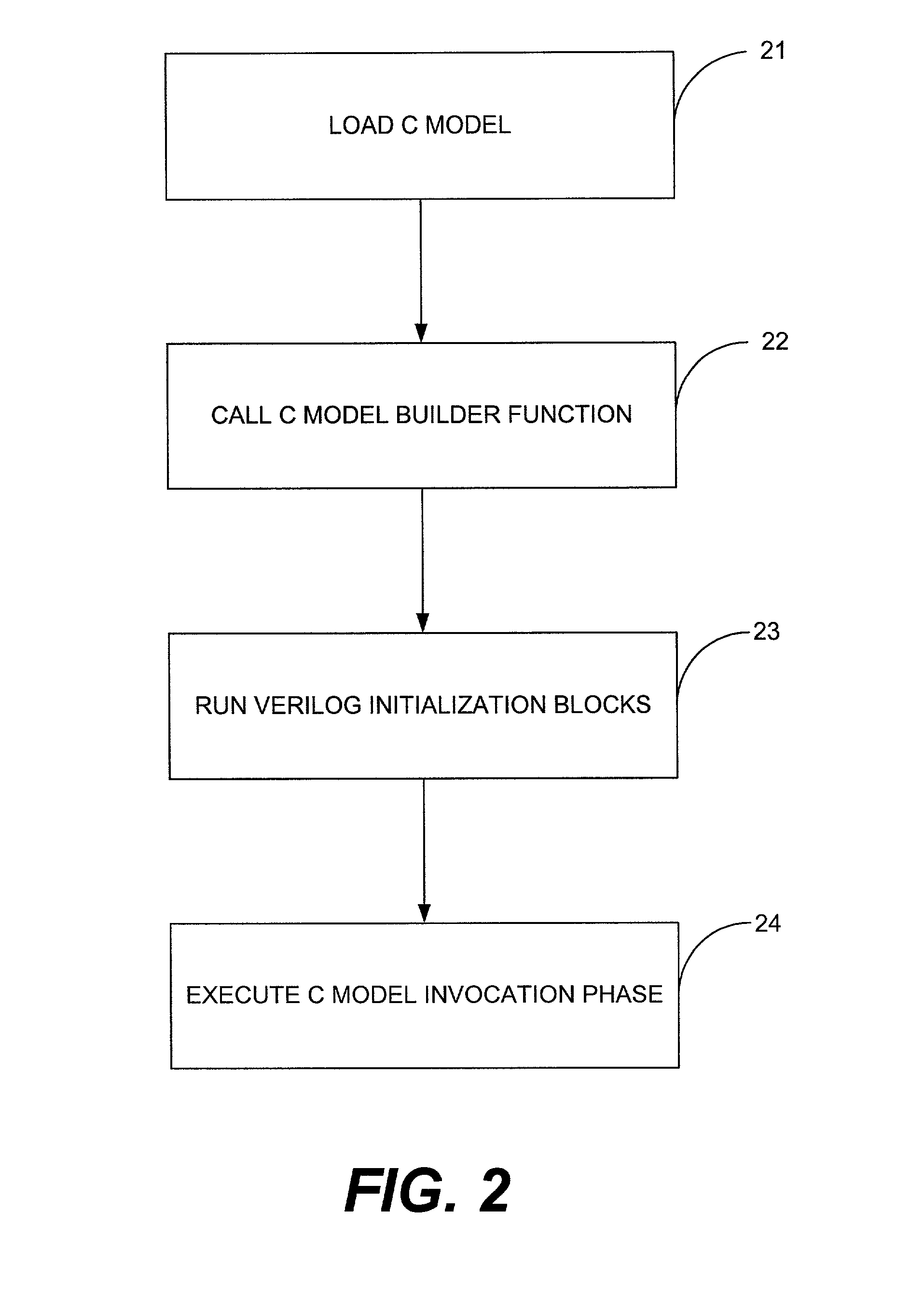

Apparatus and method for performing event processing in a mixed-language simulator

InactiveUS7058562B2Minimizes context switchingAnalogue computers for electric apparatusCAD circuit designComplex event processingTheoretical computer science

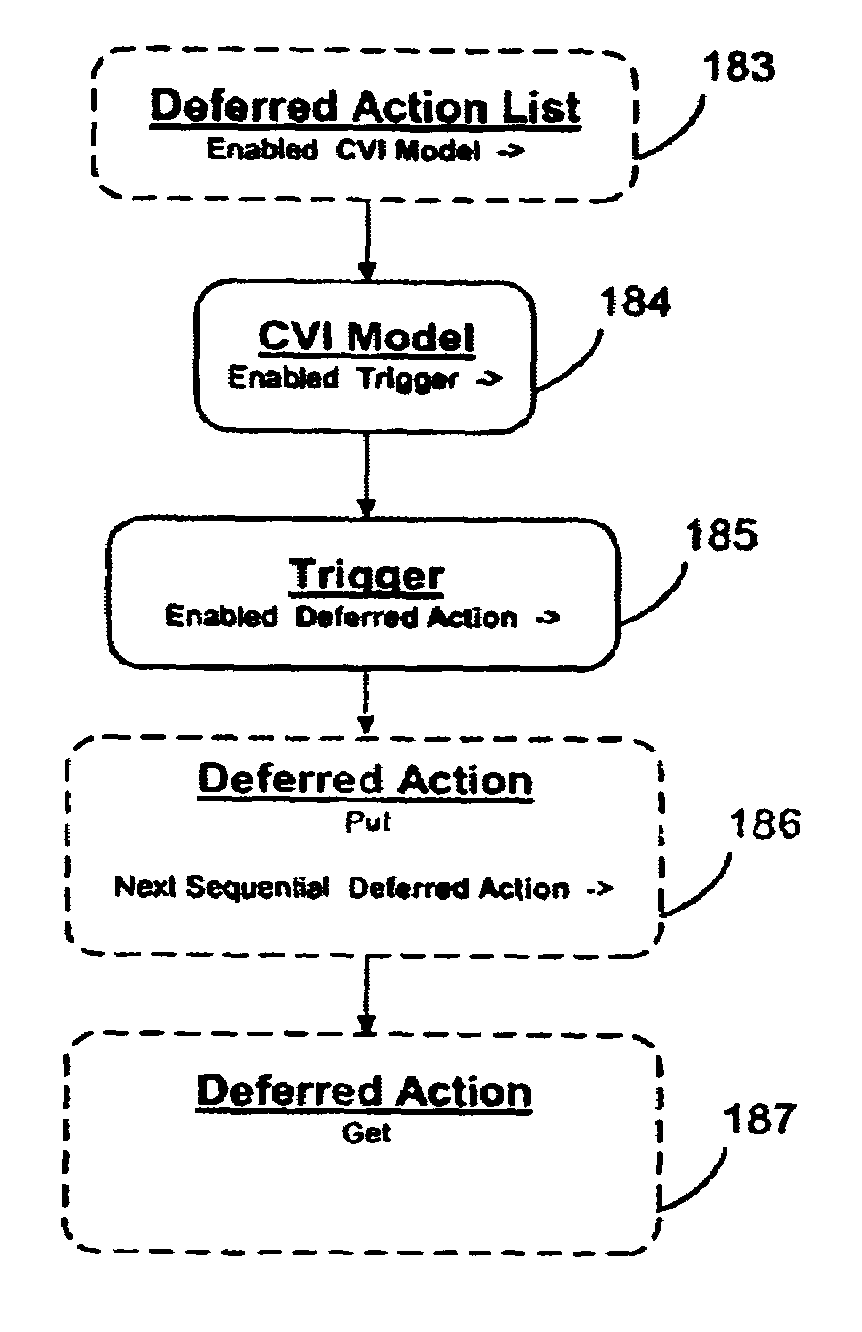

An apparatus performs event processing in a mixed-language simulator. The apparatus comprises logic for generating a list of actions to be performed for a given trigger event occurrence and for processing at least some of the listed actions in a source-code-to-HDL-interface domain before performing a context switch from the source-code-to-HDL-interface domain to a source code model domain. By listing actions to be performed for a given trigger event occurrence and then processing listed actions before switching contexts, the amount of context switching between the HDL model domain and the source code model domain that occurs during the simulation is reduced.

Owner:HEWLETT PACKARD DEV CO LP

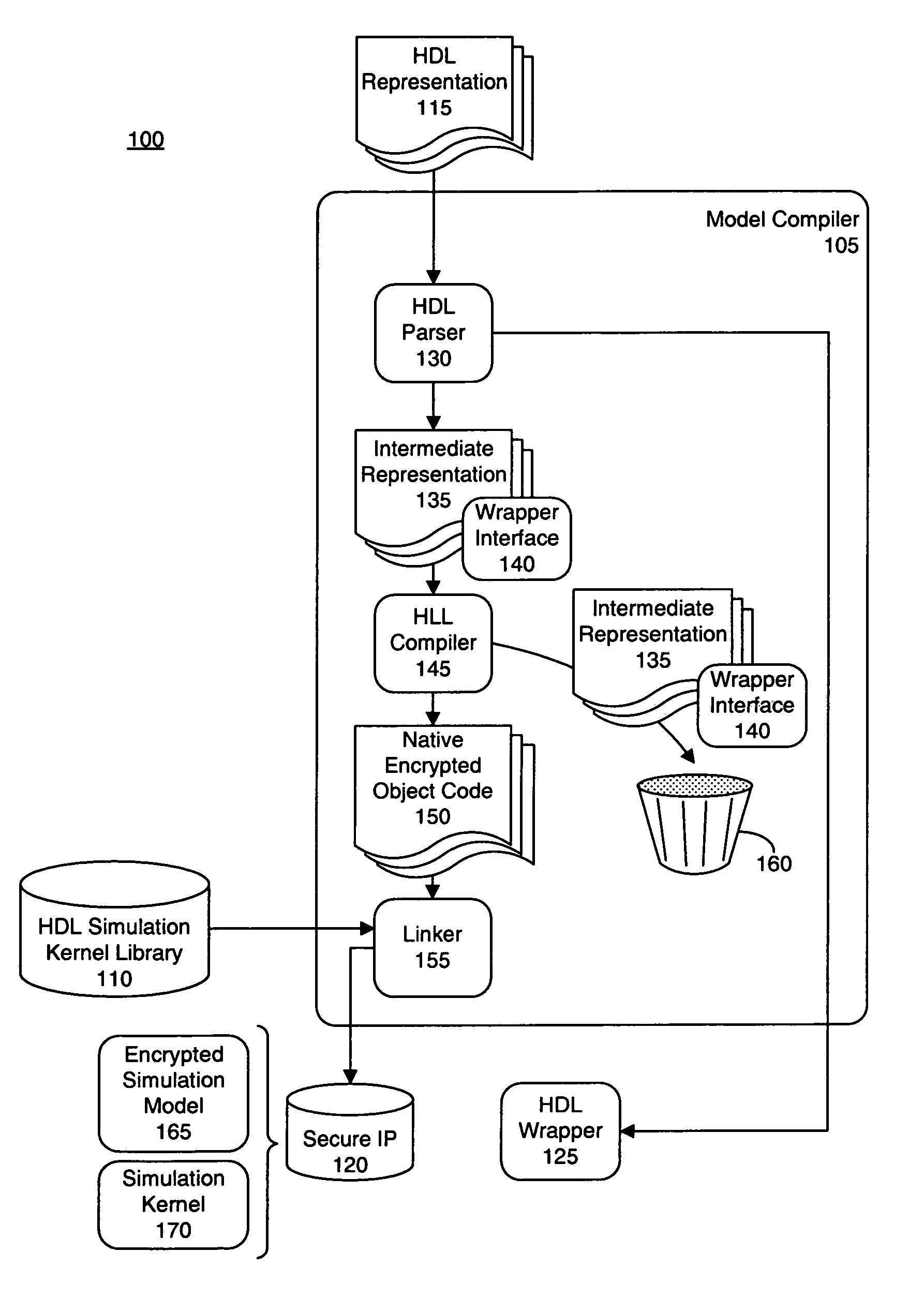

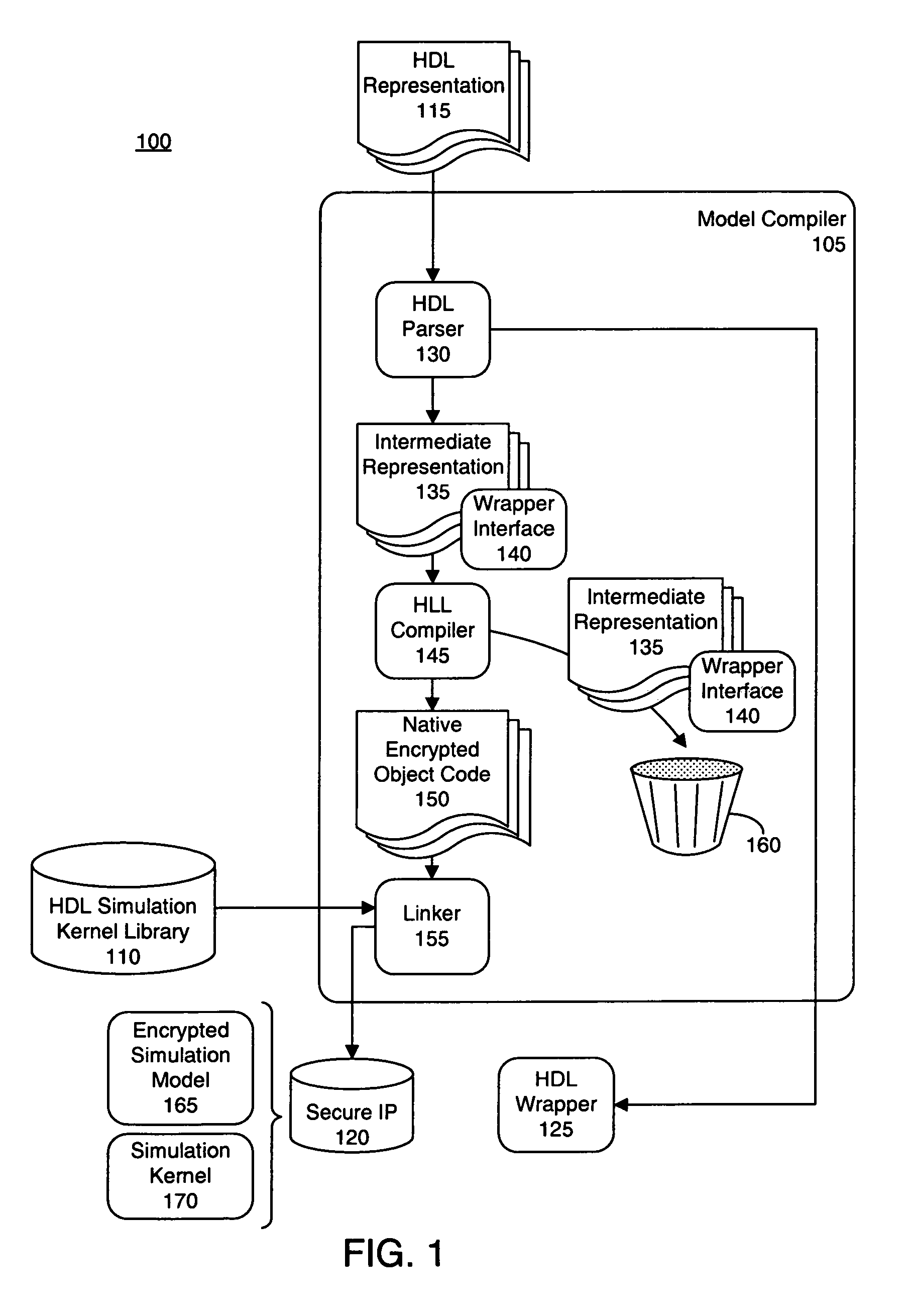

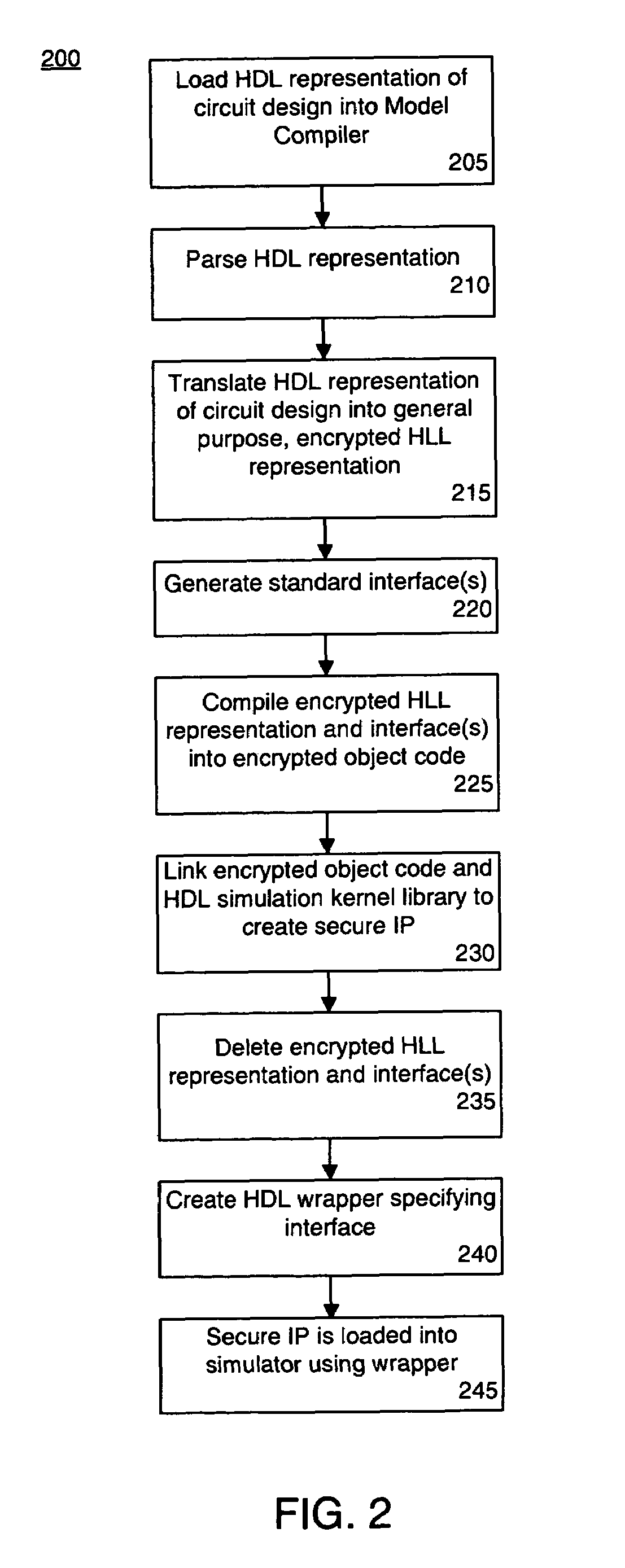

Event-driven simulation of IP using third party event-driven simulators

InactiveUS7721090B1Analogue computers for electric apparatusUnauthorized memory use protectionComputer hardwareThird party

A method of creating a secure intellectual property (IP) representation of a circuit design for use with a software-based simulator can include translating a hardware description language representation of the circuit design into an encrypted intermediate form and compiling the intermediate form of the circuit design to produce encrypted object code. The method further can include linking the encrypted object code with a simulation kernel library thereby creating the secure IP representation of the circuit design. The secure IP can include an encrypted simulation model of the circuit design and a simulation kernel configured to execute the encrypted simulation model.

Owner:XILINX INC

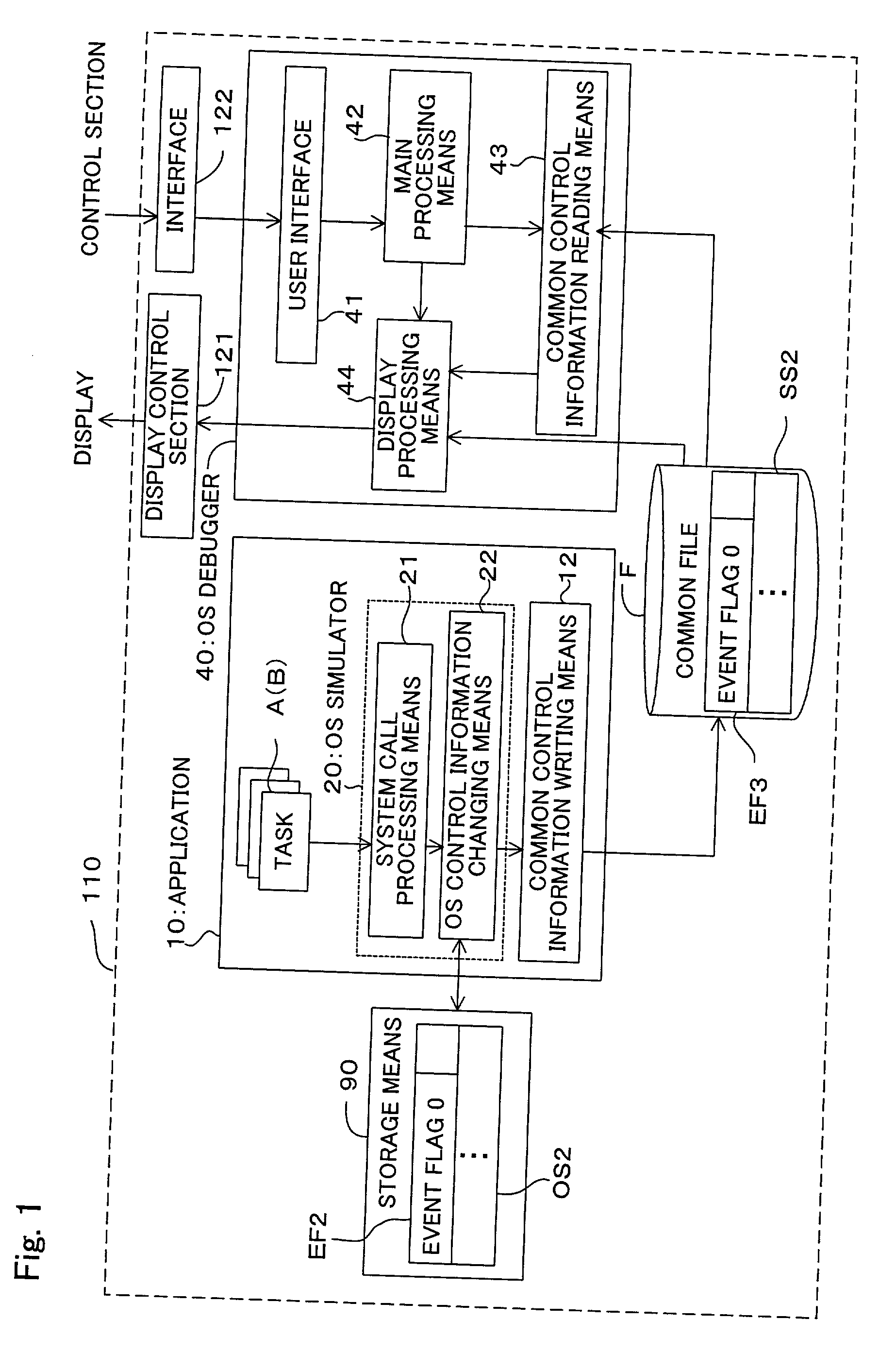

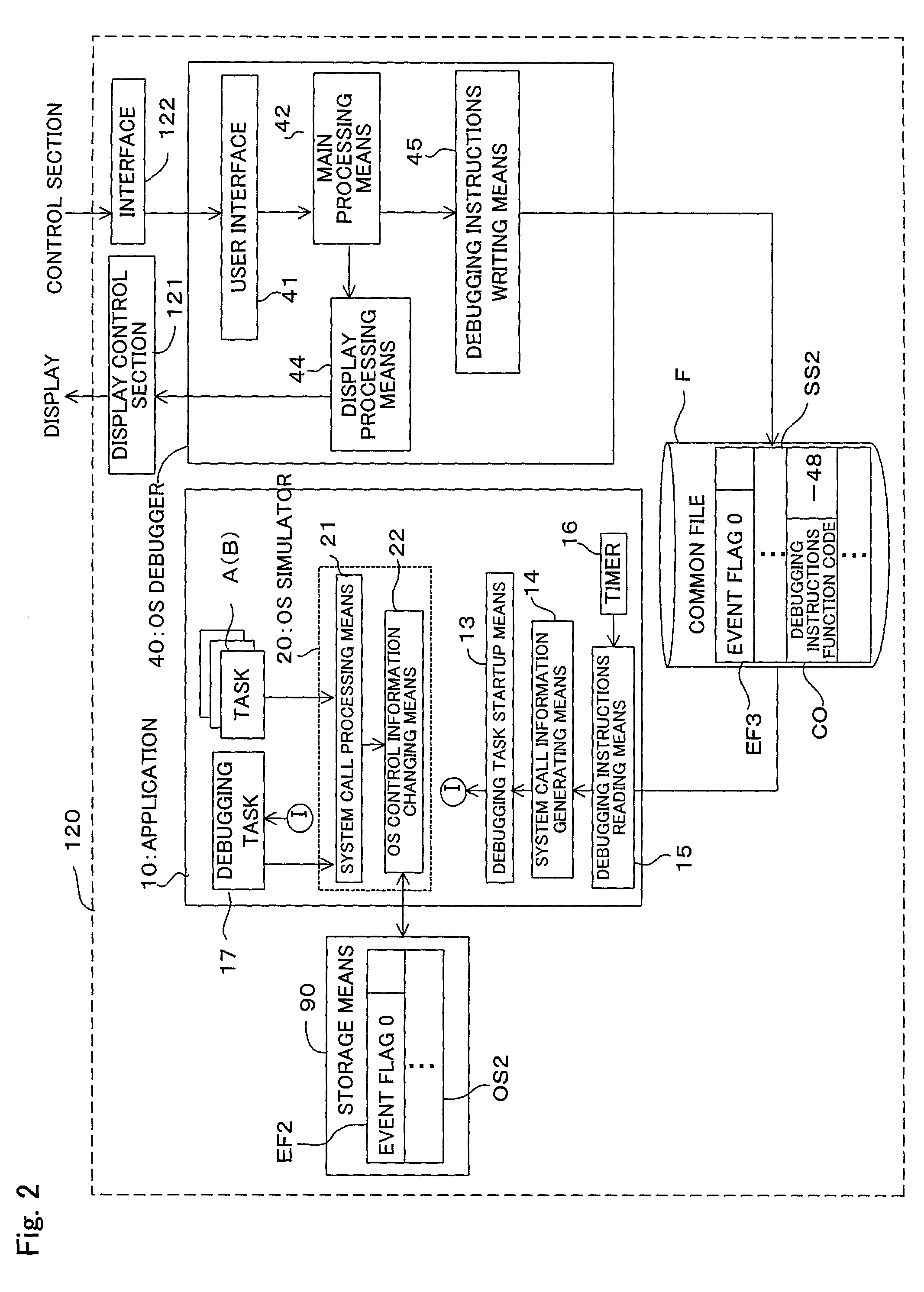

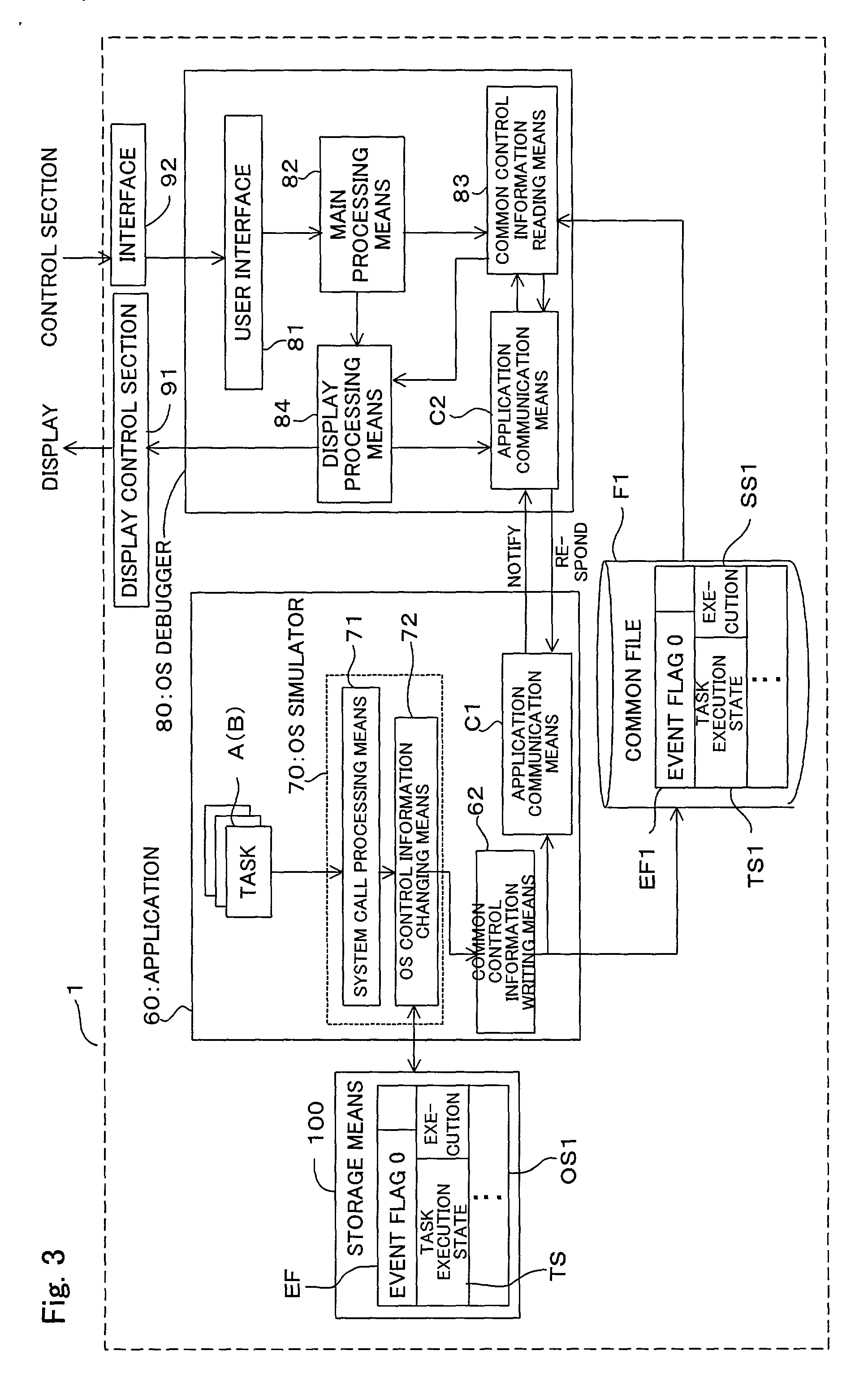

Debugging supporting apparatus, debugging supporting method and recording medium readable by computer with its programs recorded thereon

InactiveUS20010027387A1Efficient debugEfficient debuggingSoftware testing/debuggingProgram controlApplication softwareDebugger

Disclosed are a debugging supporting apparatus, a debugging supporting method and its recording medium so constituted that even if an application developed in a simulation environment by OS simulator stops, OS control information can be referred to at that moment. The debugging supporting apparatus comprises a common file that is shared between the application and the OS debugger and which records common control information including the same data as item forming OS control information, writing means for writing specific item of the OS control information stored in the storage means on the common file as common control information, and reading means for reading out the common control information stored in the common file.

Owner:PANASONIC CORP

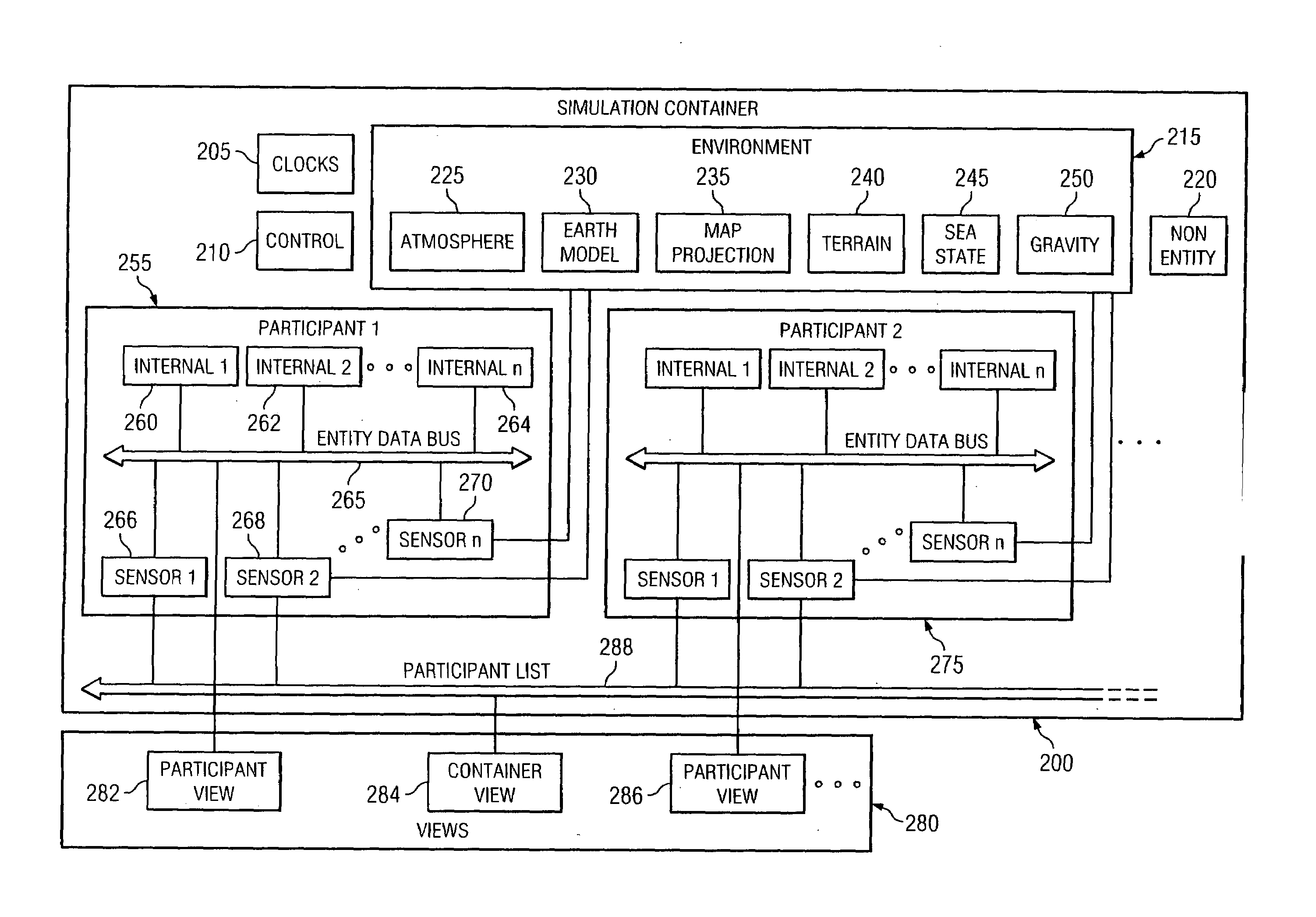

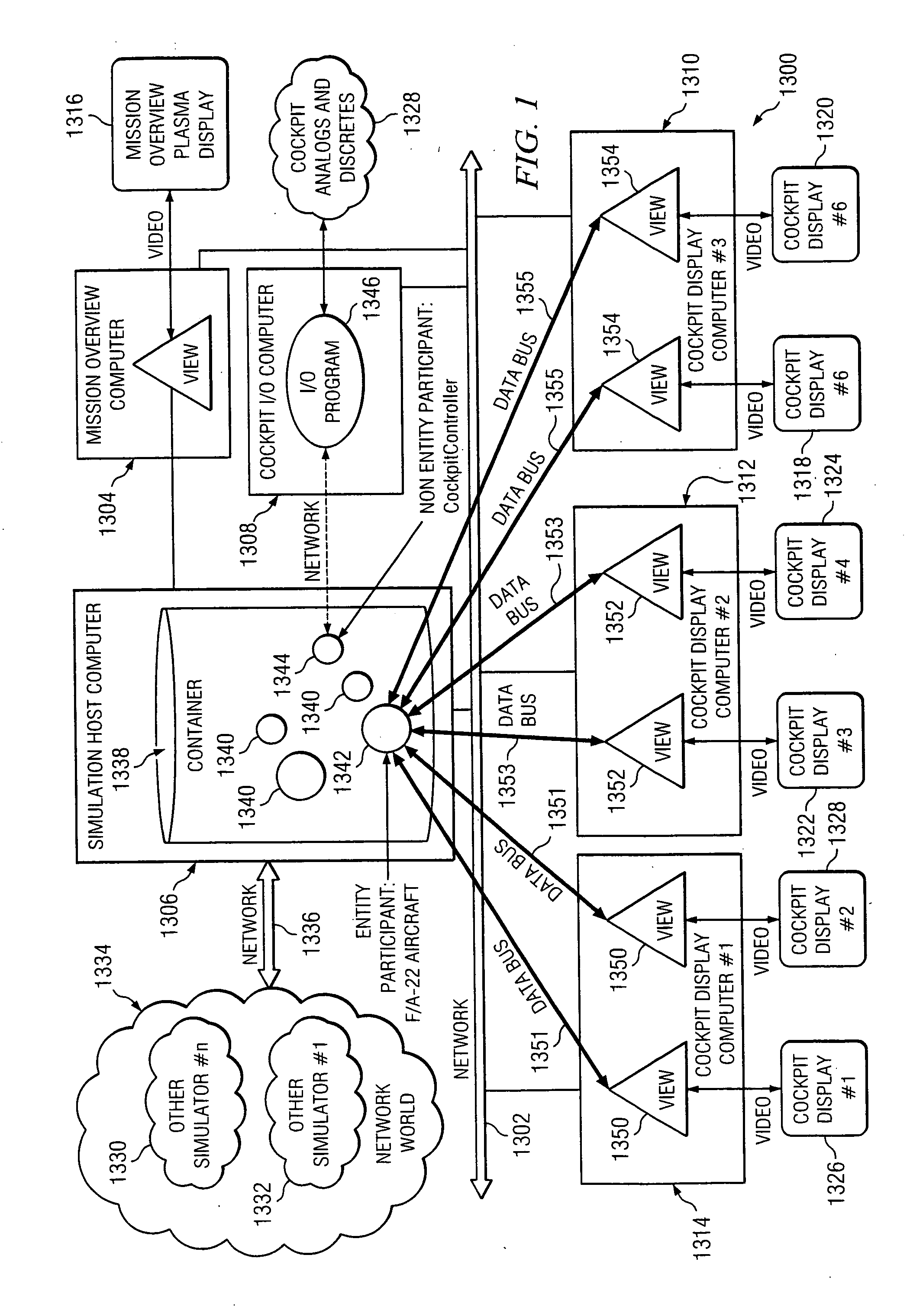

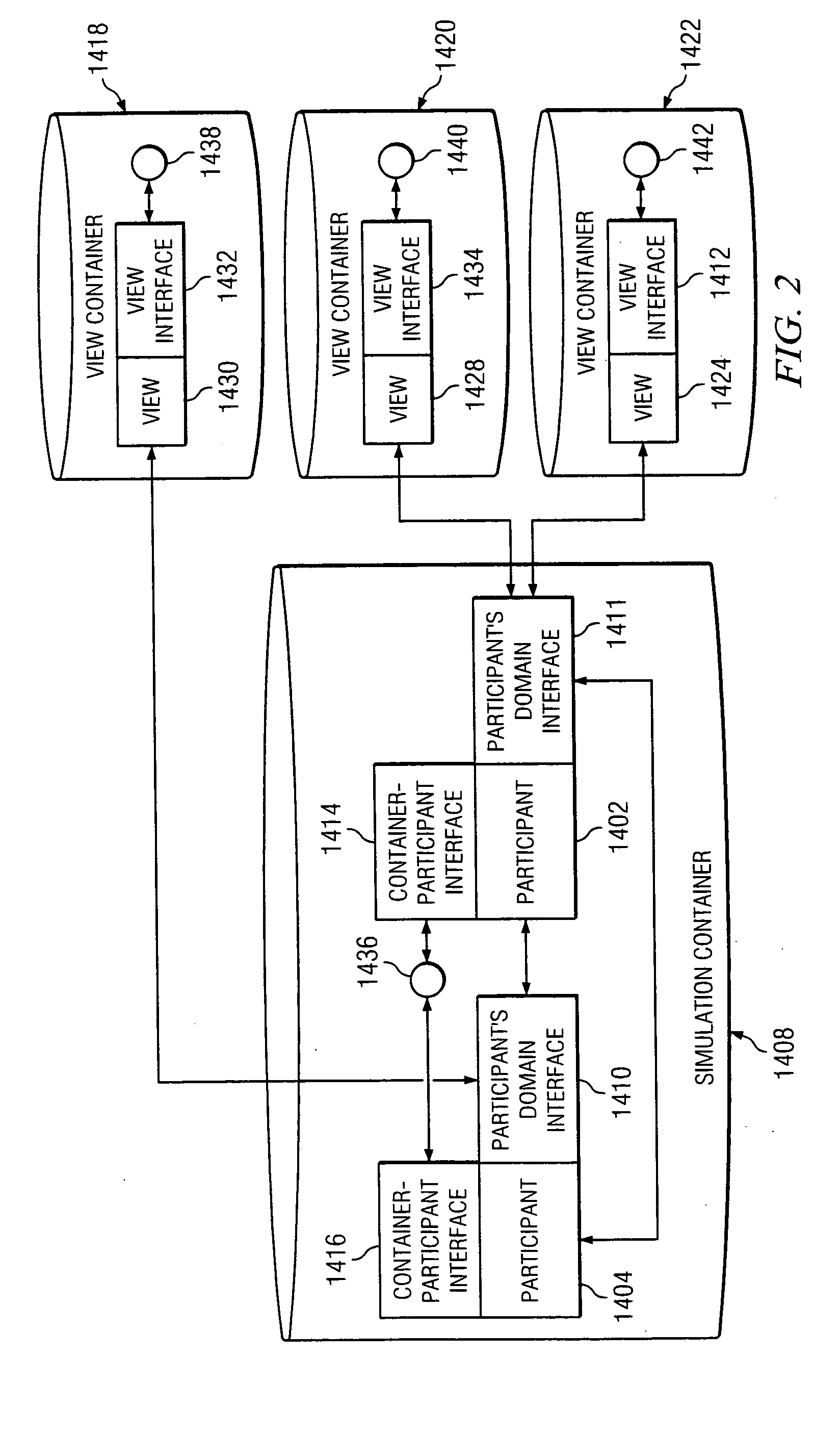

Container-based architecture for simulation of entities in time domain

ActiveUS20100217573A1ExtensibilityInterprogram communicationAnalogue computers for electric apparatusExtensibilityTime domain

The present invention relates generally to a software architecture for simulation of physical entities. The invention provides an object-oriented container based framework architecture for simulator software implementations, methods, and objects in a time domain on a distributed computer network. The invention further provides an interface system and a plug-in definition which allows compartmentalization of participants in the container and easy extensibility of the system.

Owner:ZEDASOFT

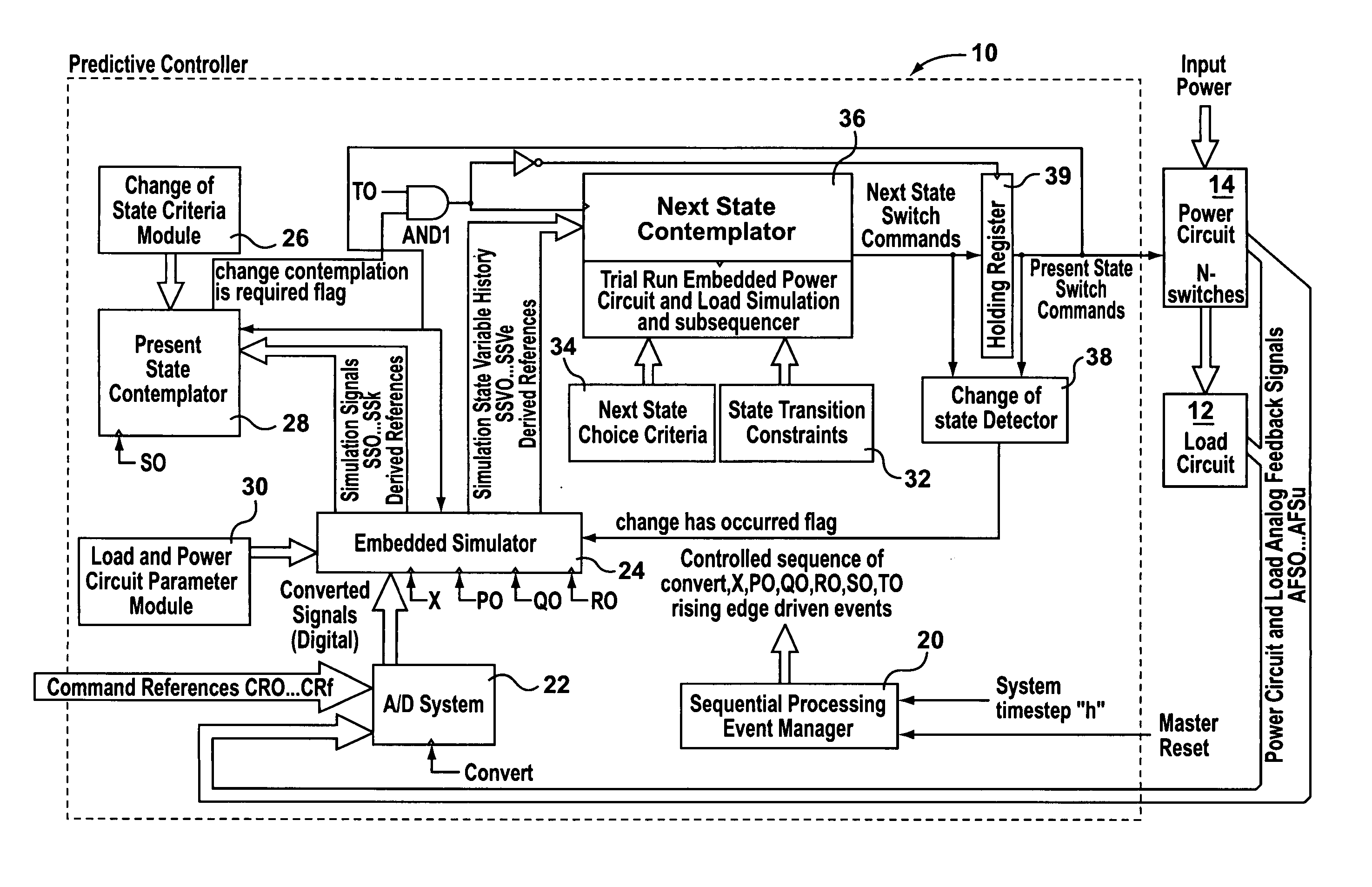

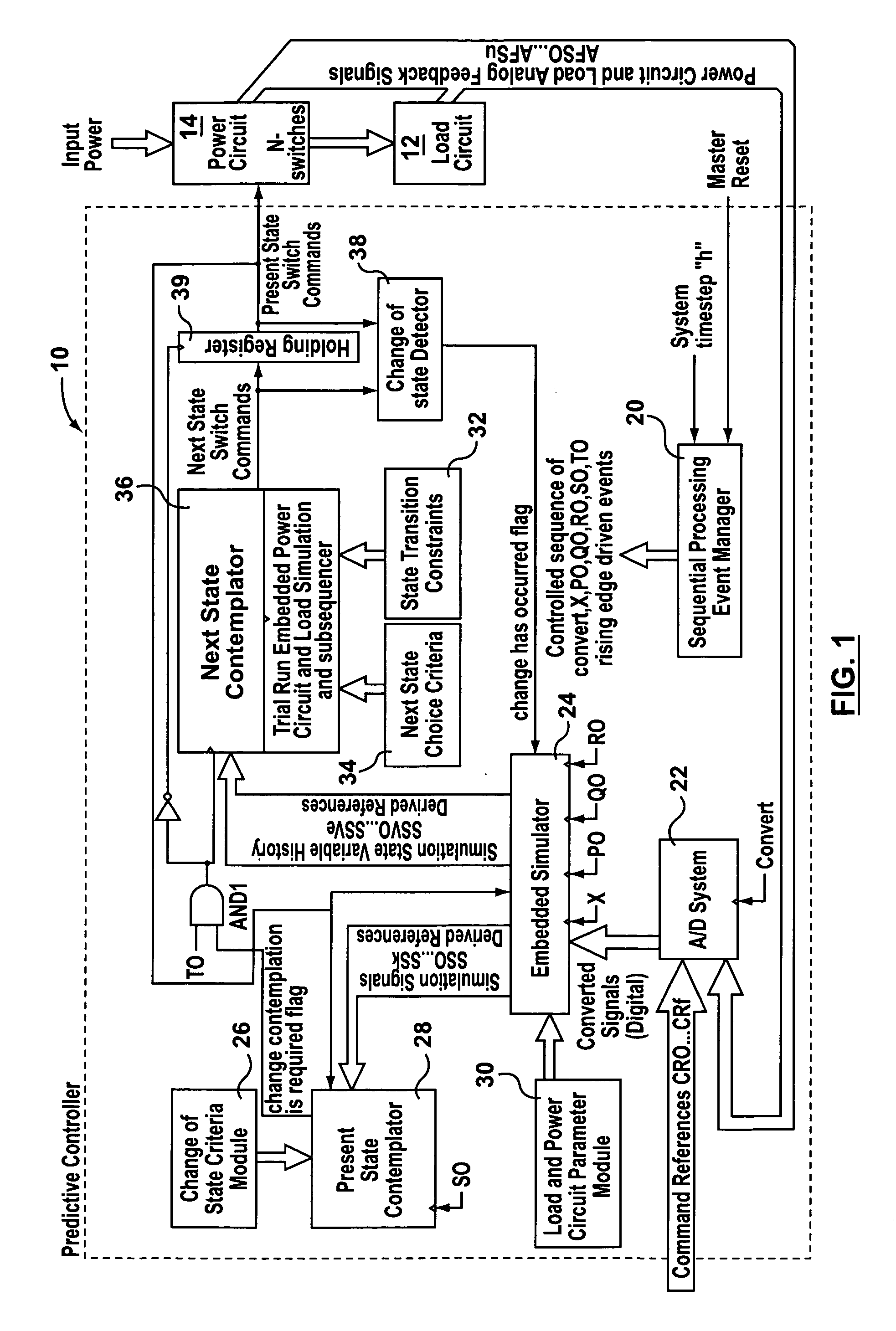

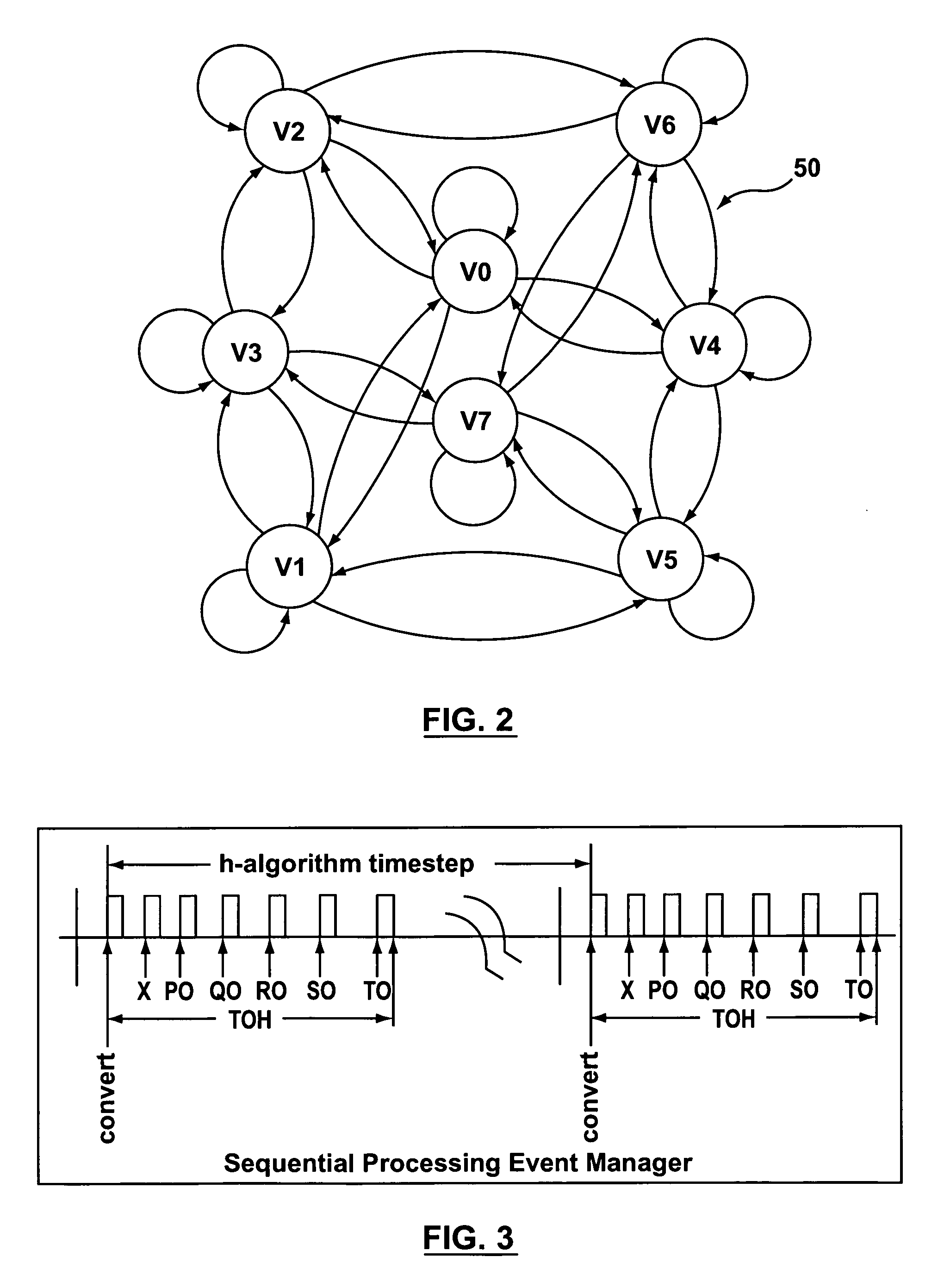

Predictive control system and method

A control system and control method provides improved control of various loads by selecting the switch configuration of an associated power circuit having N binary switches, based in part on a finite state machine. The control system includes an embedded simulator, a present state contemplator and a next state contemplator to predict the operation of the load based on various switch configurations of the power circuit. The various switch states of the power circuit are modeled by the finite state machine (having up to 2N switch states) such that at any time, the power circuit switches are in a Present State and there are a plurality of Next States which are one or more switch transitions away from the Present State. The embedded simulator estimates the operating conditions of the load based on measured operational characteristics and the Present State. The present state contemplator determines, based on the operating conditions, whether a switch state transition should be contemplated. If so, then the next state contemplator determines the optimal next state based on a set of performance criterion and sends a state switch command to the power circuit.

Owner:ZETACON CORP

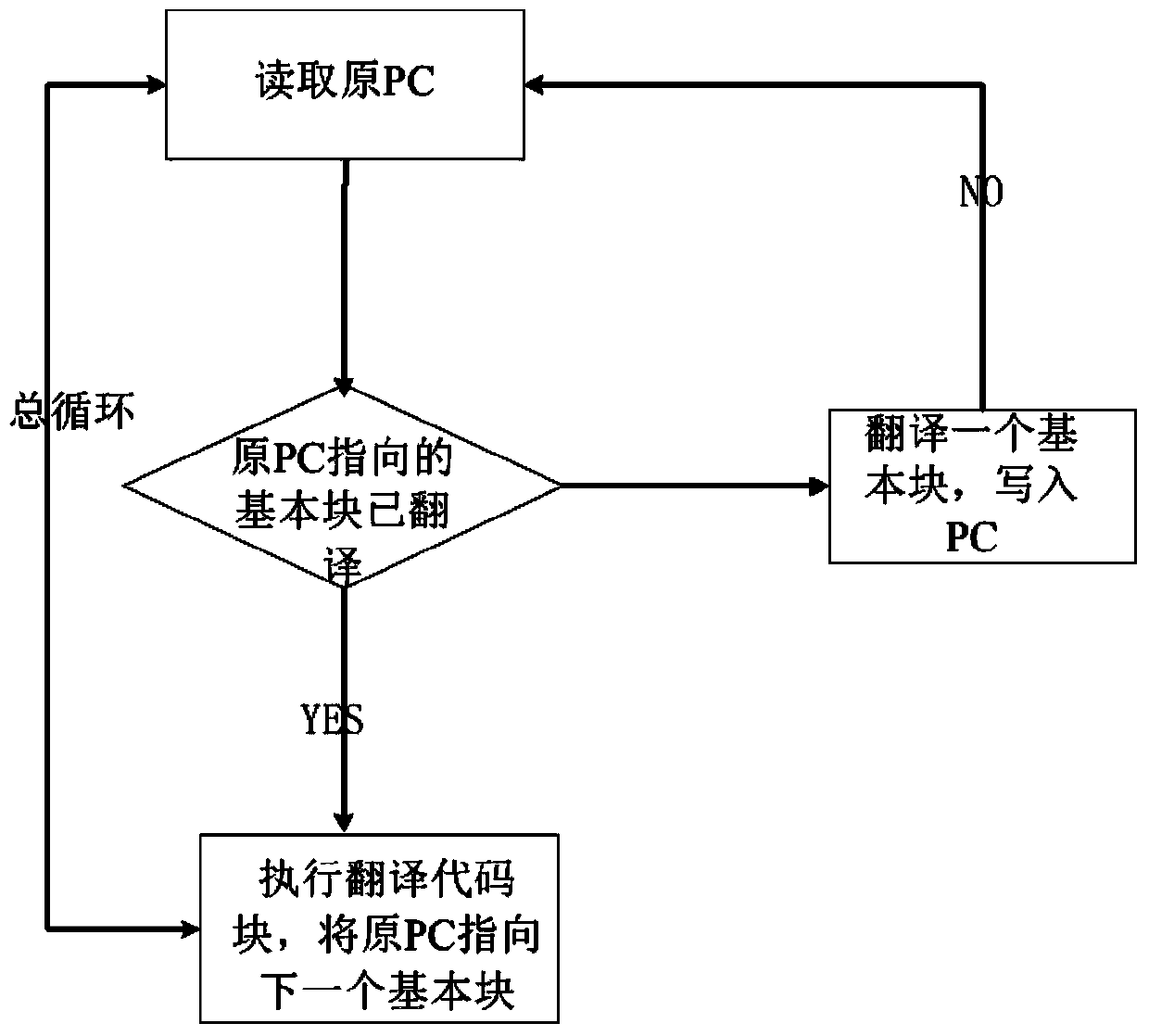

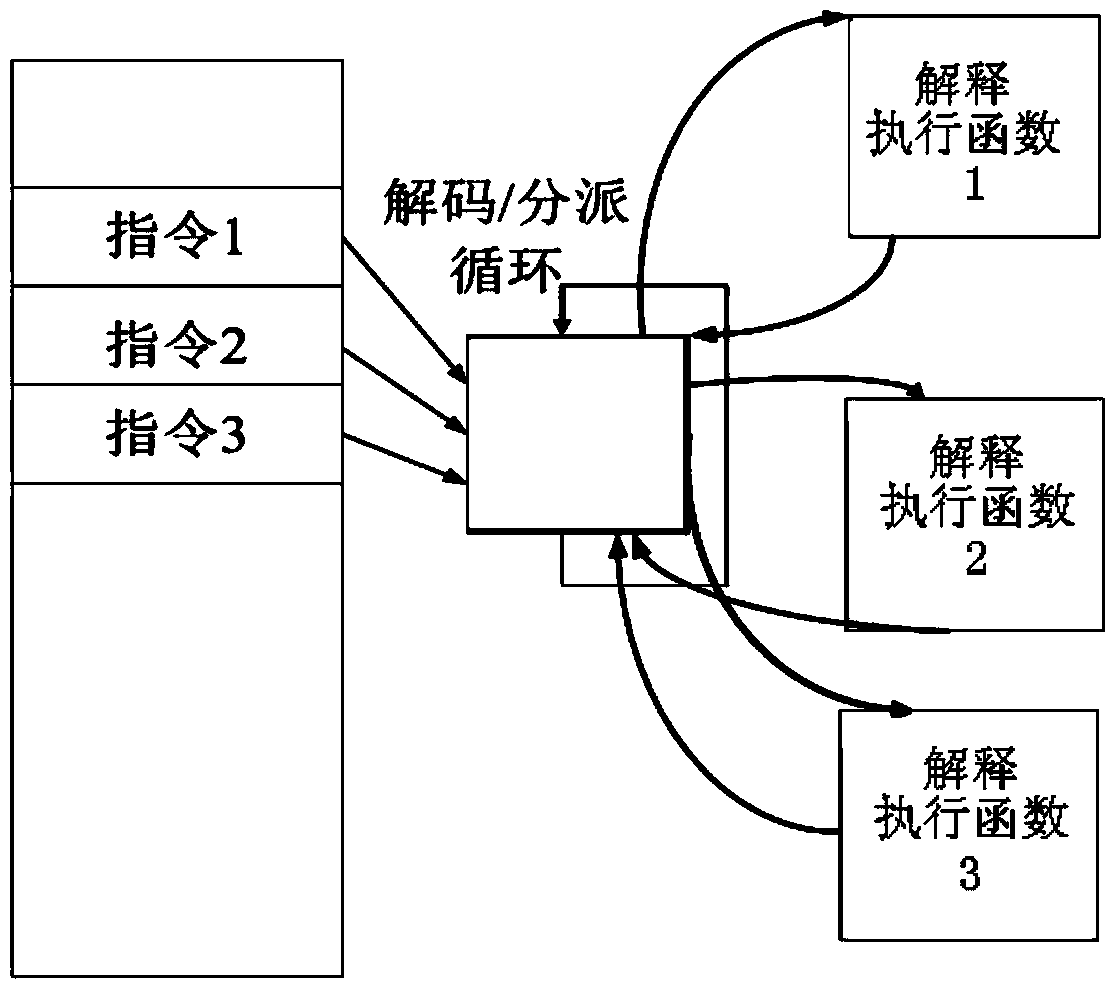

Platform virtualization system

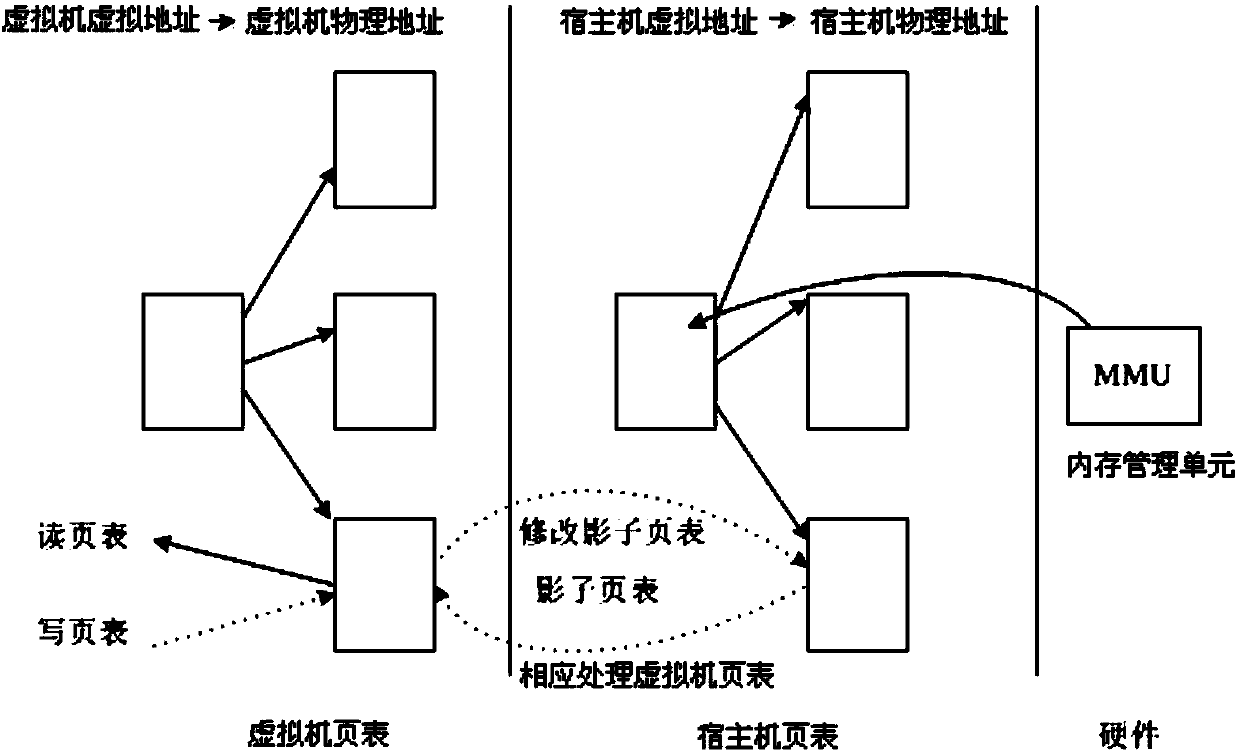

InactiveCN103793260AEase system deploymentRelieve pressureSoftware simulation/interpretation/emulationCode TranslationMemory virtualization

The invention relates to a platform virtualization system comprising a CPU simulator, a memory virtualization module, and an external virtualization module. The CPU simulator reads an X86 architecture code instruction and judges whether an instruction basic block is translated or not; a binary translator is used for translation and comprises a translation engine and an execution engine; the translation engine translates an X86 architecture code into a Loongson platform code; the execution engine prepares the operational context of the Loongson platform code, locates the Loongson platform code corresponding to the X86 architecture code from a Loongson platform code cache and executes the code. The memory virtualization module uses a shadow page-table method. The external virtualization module establishes a corresponding device model for each external device. An X86 architecture virtual machine interacts with the external devices through the device models, thereby discovering and accessing the devices. The platform virtualization system allows information systems not matching with the domestic Loongson hardware platform yet to run in the domestic software-hardware environments in a virtualized manner, and contributions are made for the smooth transition between new and old technical systems in the automatic upgrading process of the information systems.

Owner:INST OF CHINA ELECTRONICS SYST ENG CO +1

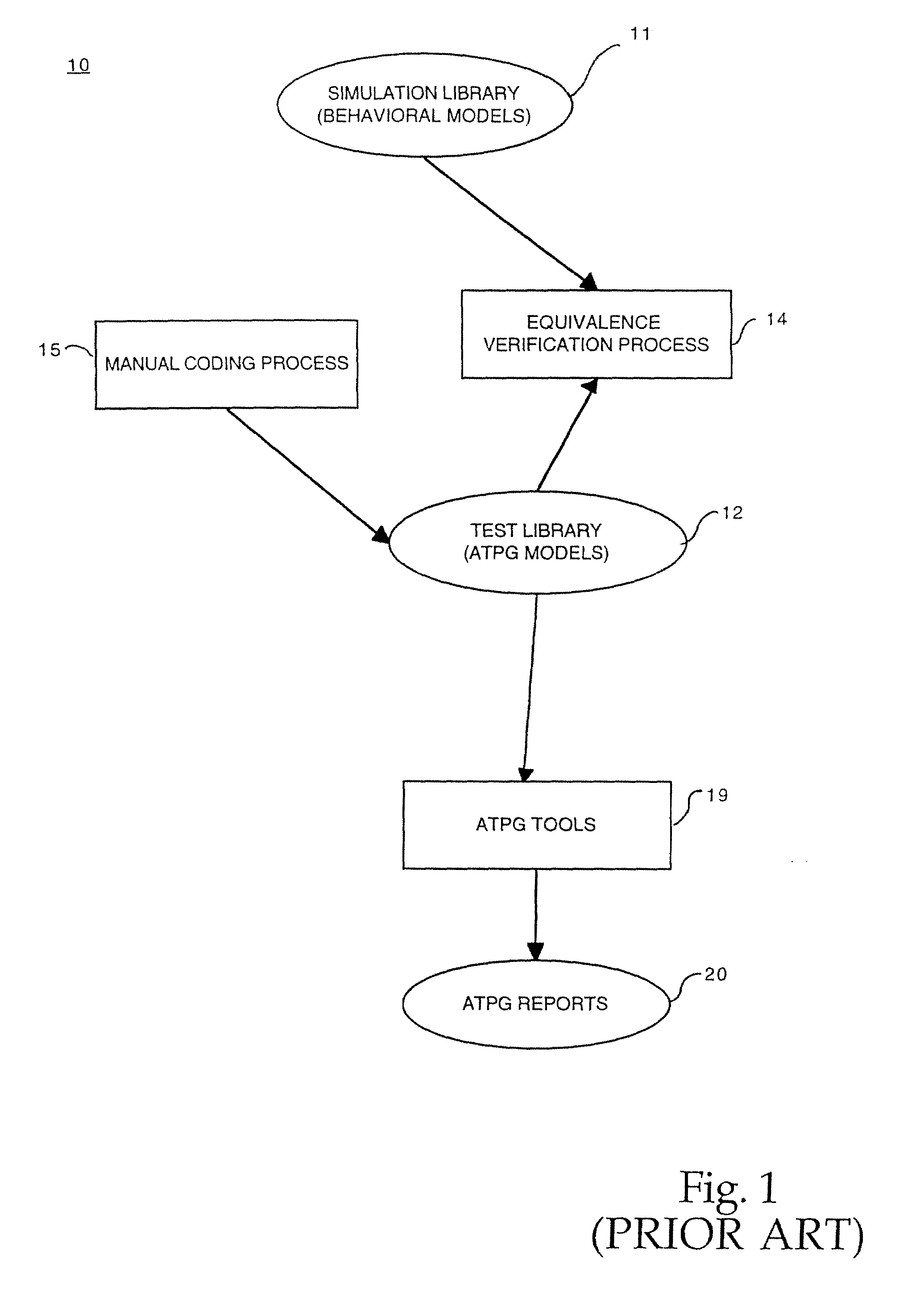

Method and system for generating an atpg model of a memory from behavioral descriptions

InactiveUS20040167764A1Tedious, time-consuming, error-prone and difficult tasksFacilitate the processDigital circuit testingCAD circuit designRandom access memoryTheoretical computer science

Abstract of the Disclosure 42Method and system for constructing a structural model of a memory for use in ATPG (Automatic Test Pattern Generation). Behavioral models of memories of simulation libraries are re-coded into simplified behavioral models using behavioral hardware description language (e.g., Verilog). Simplified behavioral models are automatically converted into structural models that include ATPG memory primitives. Structural models are stored for subsequent access during pattern generation. In another embodiment for modeling random access memories (RAMs), the ATPG memory primitives include memory primitives, data bus primitives, address bus primitives, read-port primitives and macro output primitives. In another embodiment for modeling content addressable memories (CAMs), the ATPG memory primitives include memory primitives, compare port primitives and macro output primitives. Functional equivalence between simplified behavioral models and simulation models can be verified with the same behavioral hardware description language simulator (e.g., Verilog). Another advantage is complicated memories, such as CAMs, can be accurately modeled for ATPG.

Owner:SYNOPSYS INC

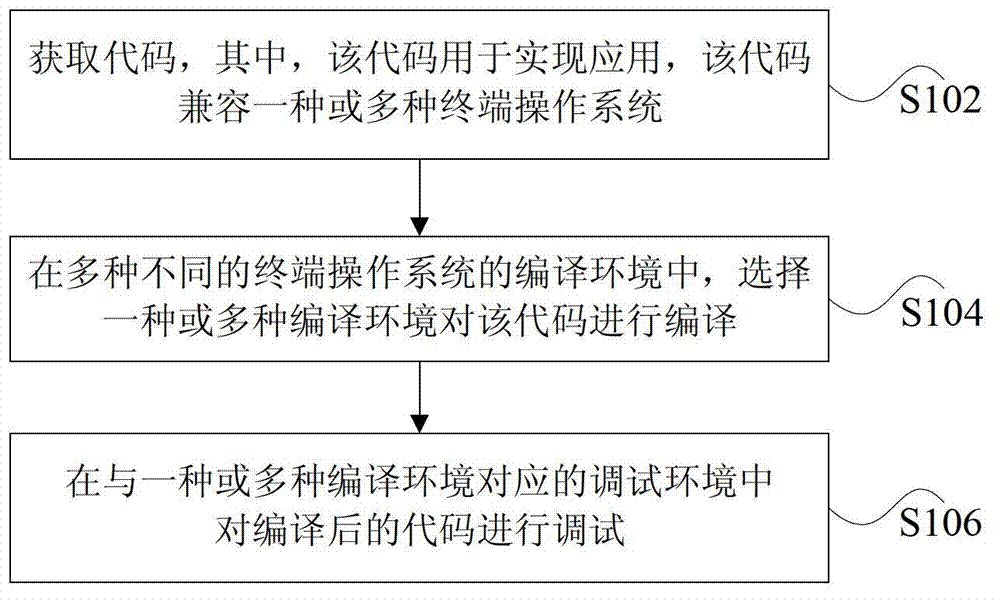

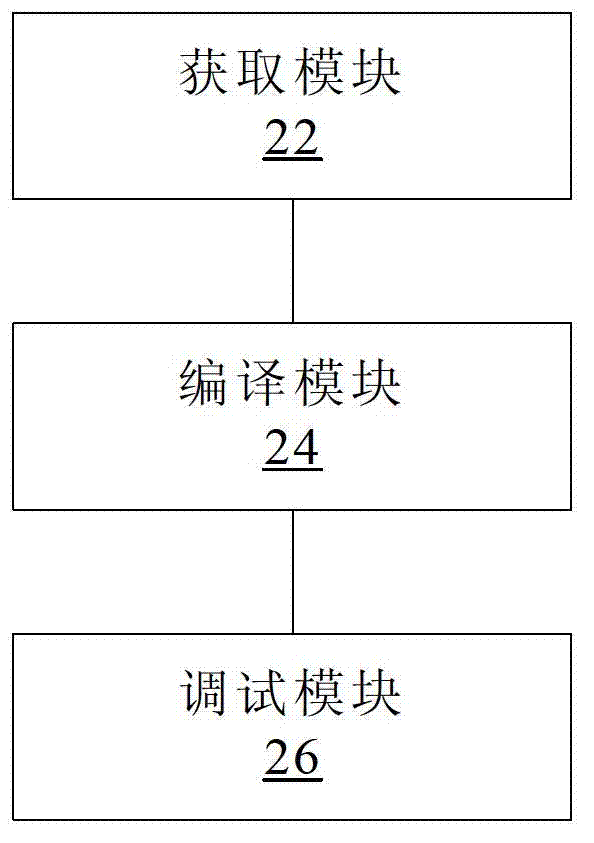

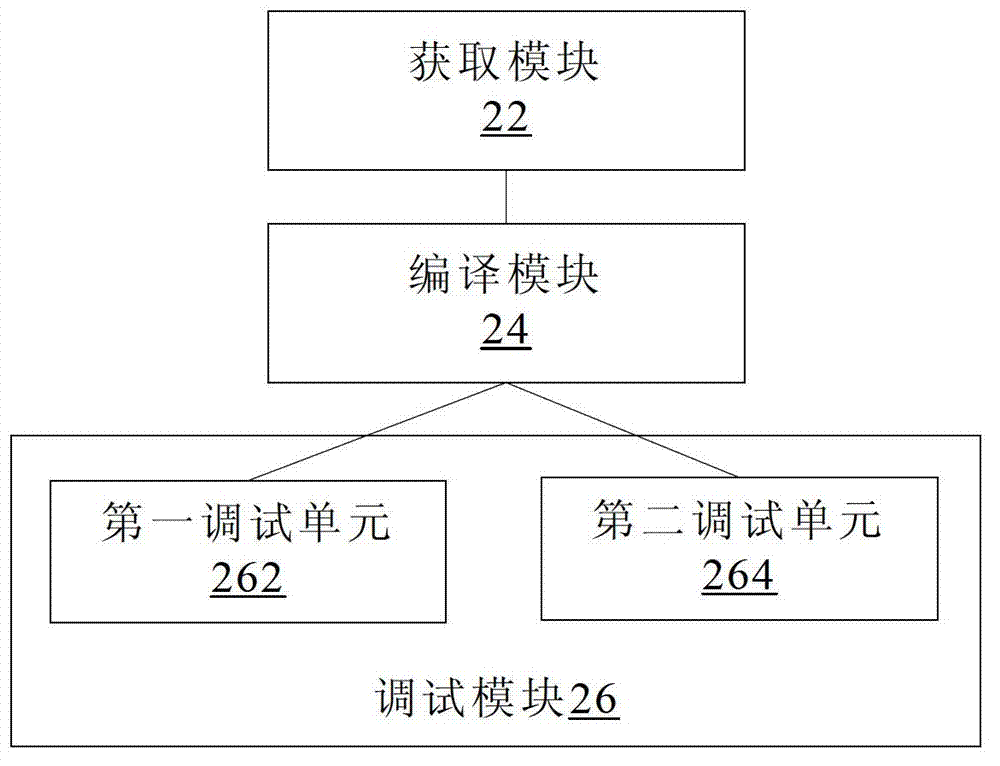

Method and device for developing, compiling and debugging application

ActiveCN103713889ASave time for compilation and debuggingImprove development efficiencyVersion controlSoftware testing/debuggingSoftware engineeringTerminal operation

The invention discloses a method and a device for developing, compiling and debugging an application. The method comprises the following steps of acquiring a code which is used for implementing the application, and is compatible to one or a plurality of terminal operation systems; compiling the code by selecting one or a plurality of compiling environments from compiling environments of a plurality of different terminal operation systems; and debugging the compiled code in debugging environments corresponding to the compiling environments. By using the method and the device, an integrated cross-platform application development environment is provided for a developer; the developer only needs to use an integrated development environment and develop a code which is compatible to one or a plurality of terminal operation systems, the application which can run in the different terminal operation systems can be compiled, the code can be debugged on different terminals and simulators, an effect of running the application code in different terminal environments is achieved, a large amount of time for coding and compiling and debugging in different environments is saved, and on-line developing, on-line compiling and on-line debugging can be carried out by the developer simultaneously.

Owner:三亚中兴软件有限责任公司

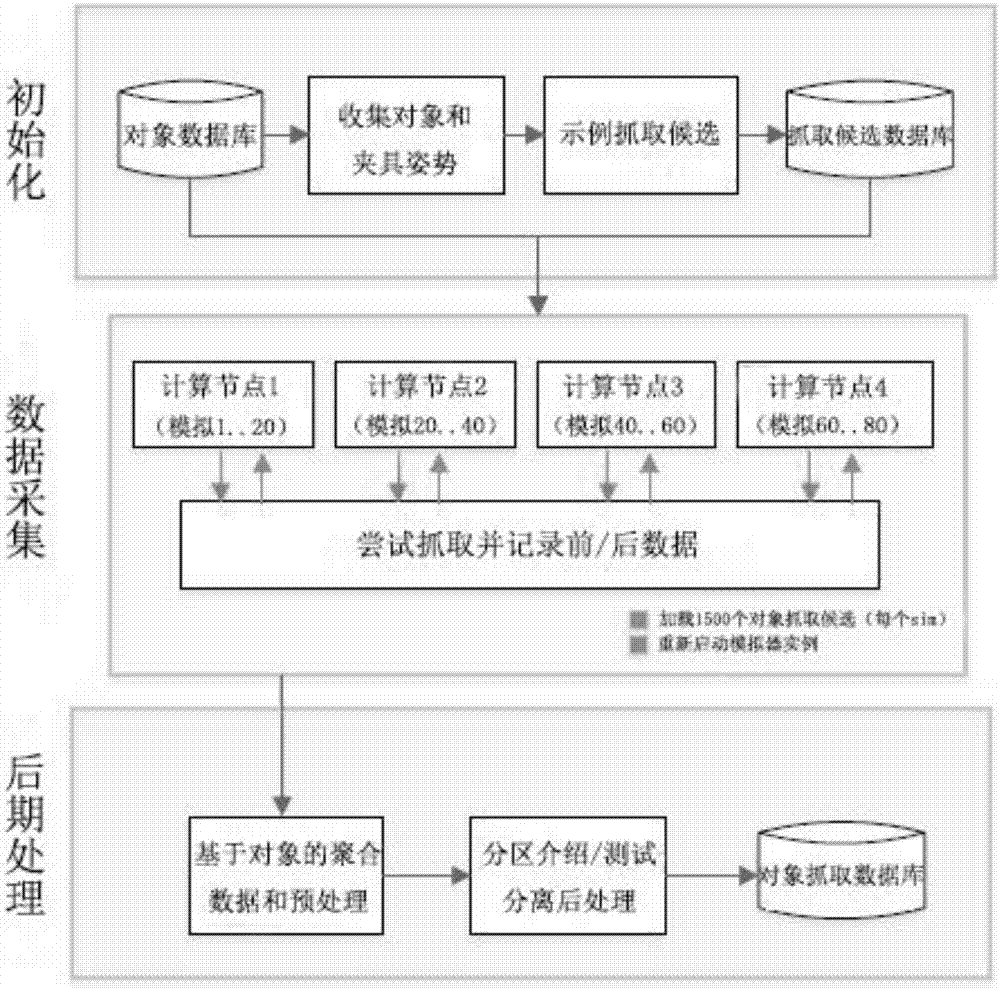

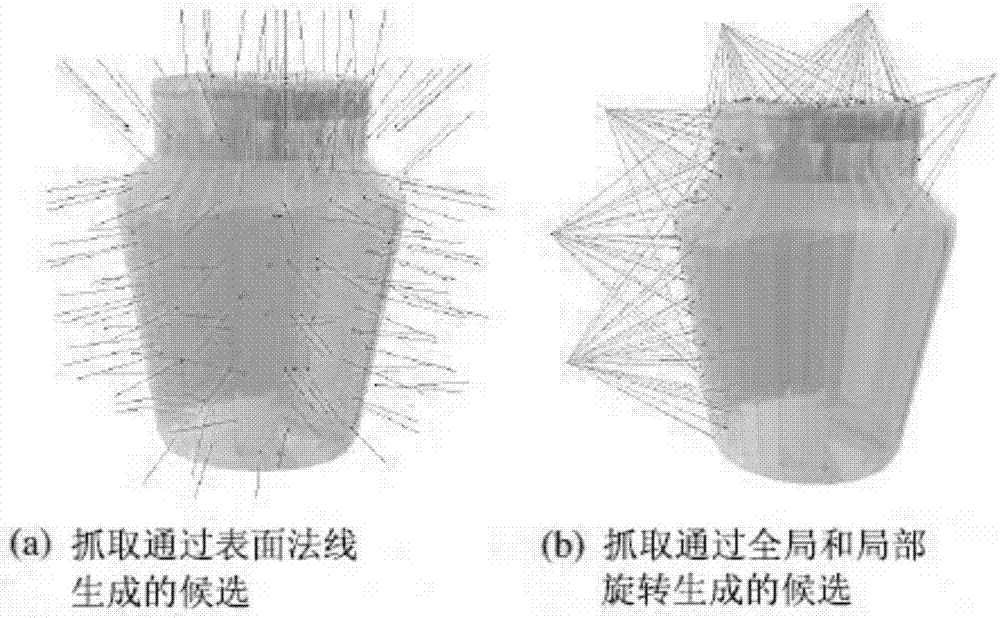

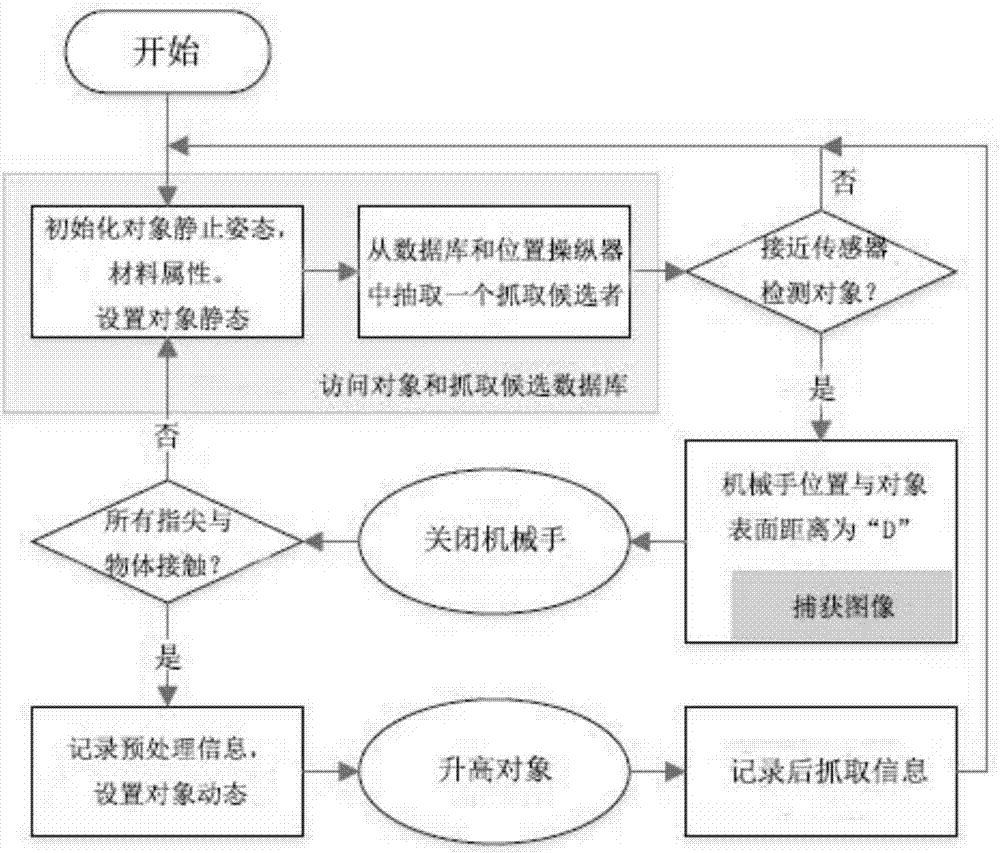

Grabbing and operating method for manipulators based on simulator

A grabbing and operating method for manipulators based on a simulator presented by the invention mainly comprises simulation initialization, simulation task execution and post-processing. First, simulation initialization is carried out based on an initial object, manipulator configuration, attributes and a grab candidate database. Then, a data set is created within a feasible amount of time through grab mapping of different images and through a mode of parallelization to perform simulation tasks and data collection. Finally, an object grab database is formed based on aggregated data of the object and preprocessing, and post-processing is carried out. Through the grabbing and operating method for manipulators based on a simulator of the invention, noise is reduced, and the limitation by sensors is reduced greatly. The flexibility and stability of manipulators are improved, and the accuracy of measurement is improved.

Owner:SHENZHEN WEITESHI TECH

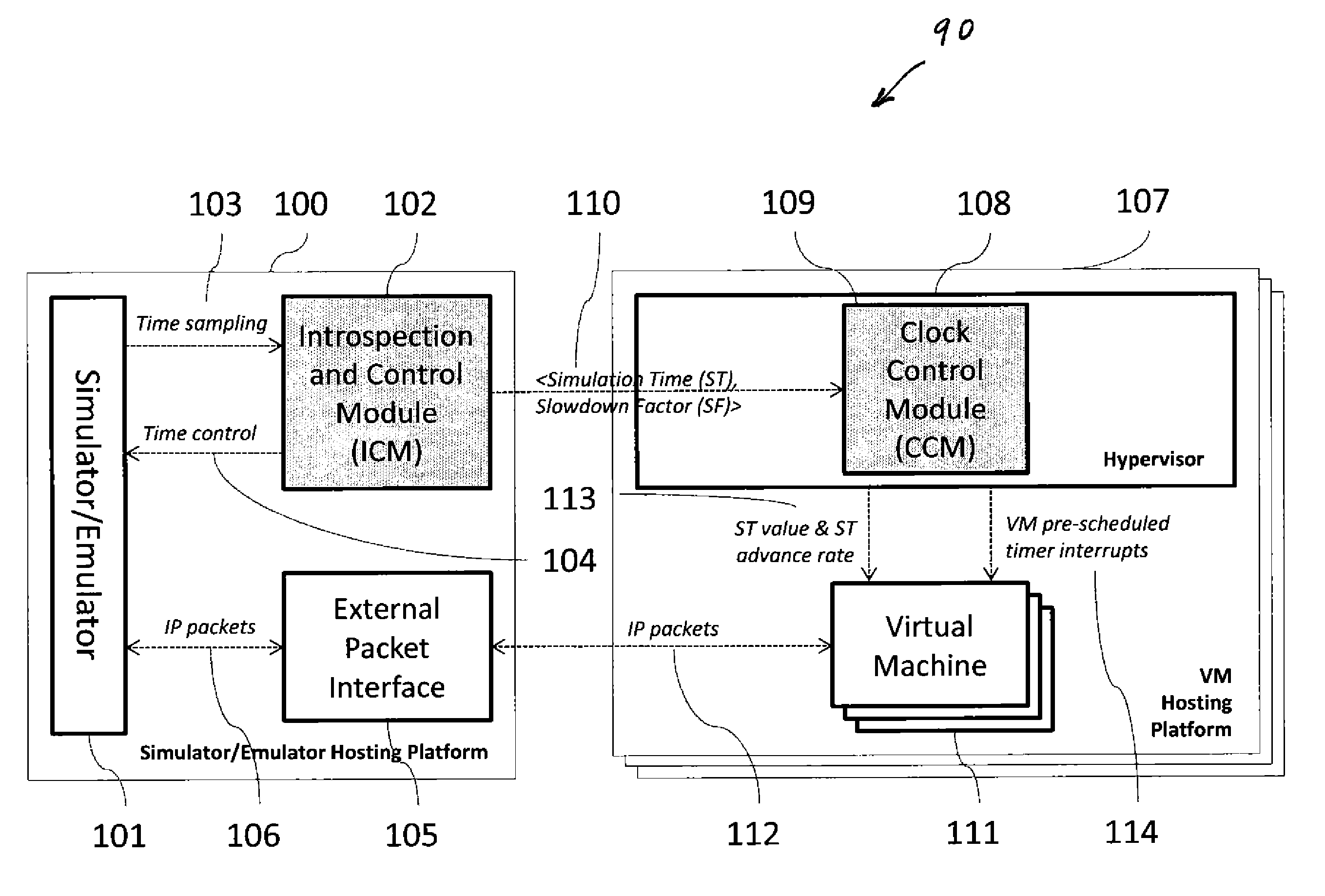

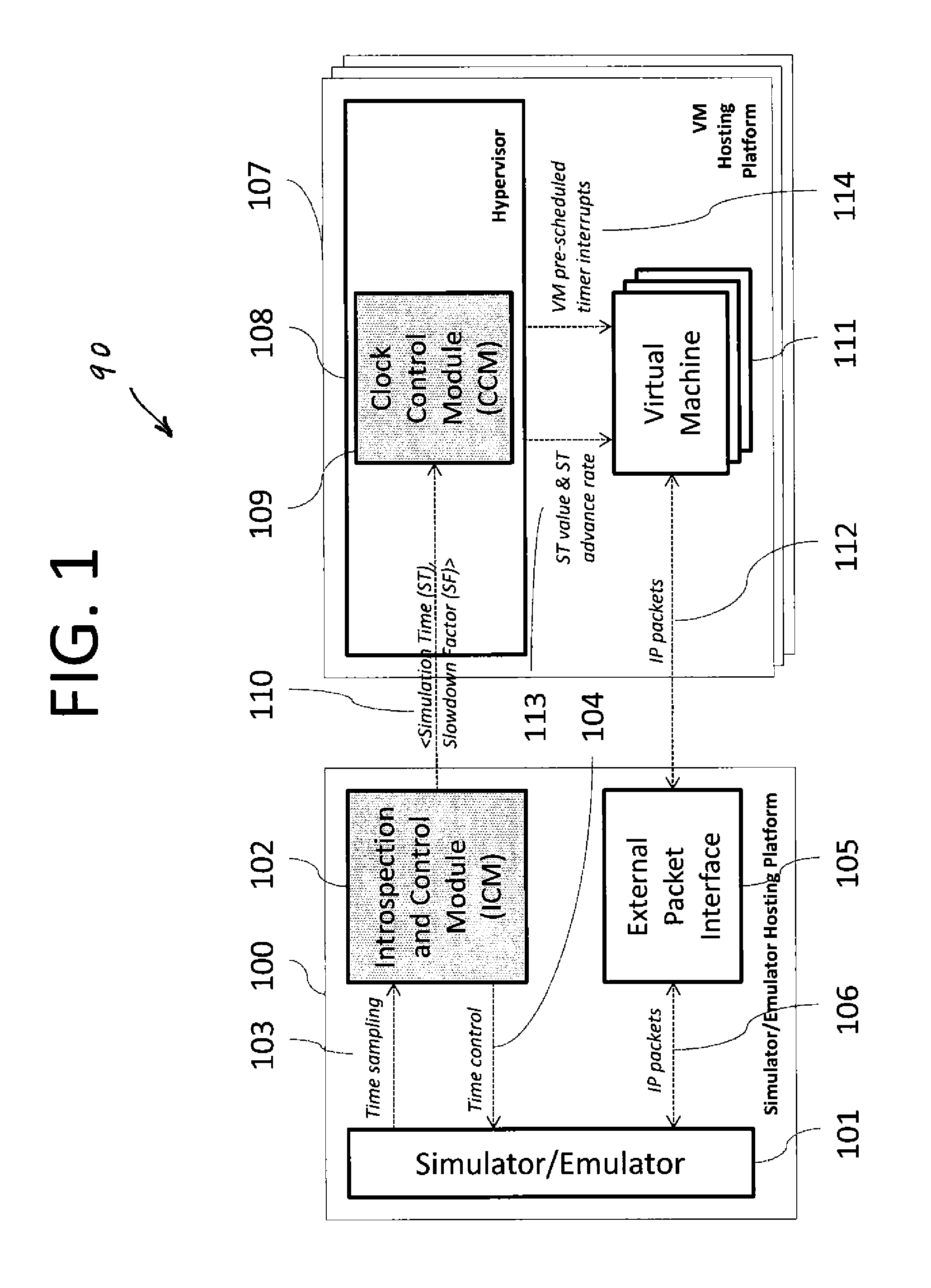

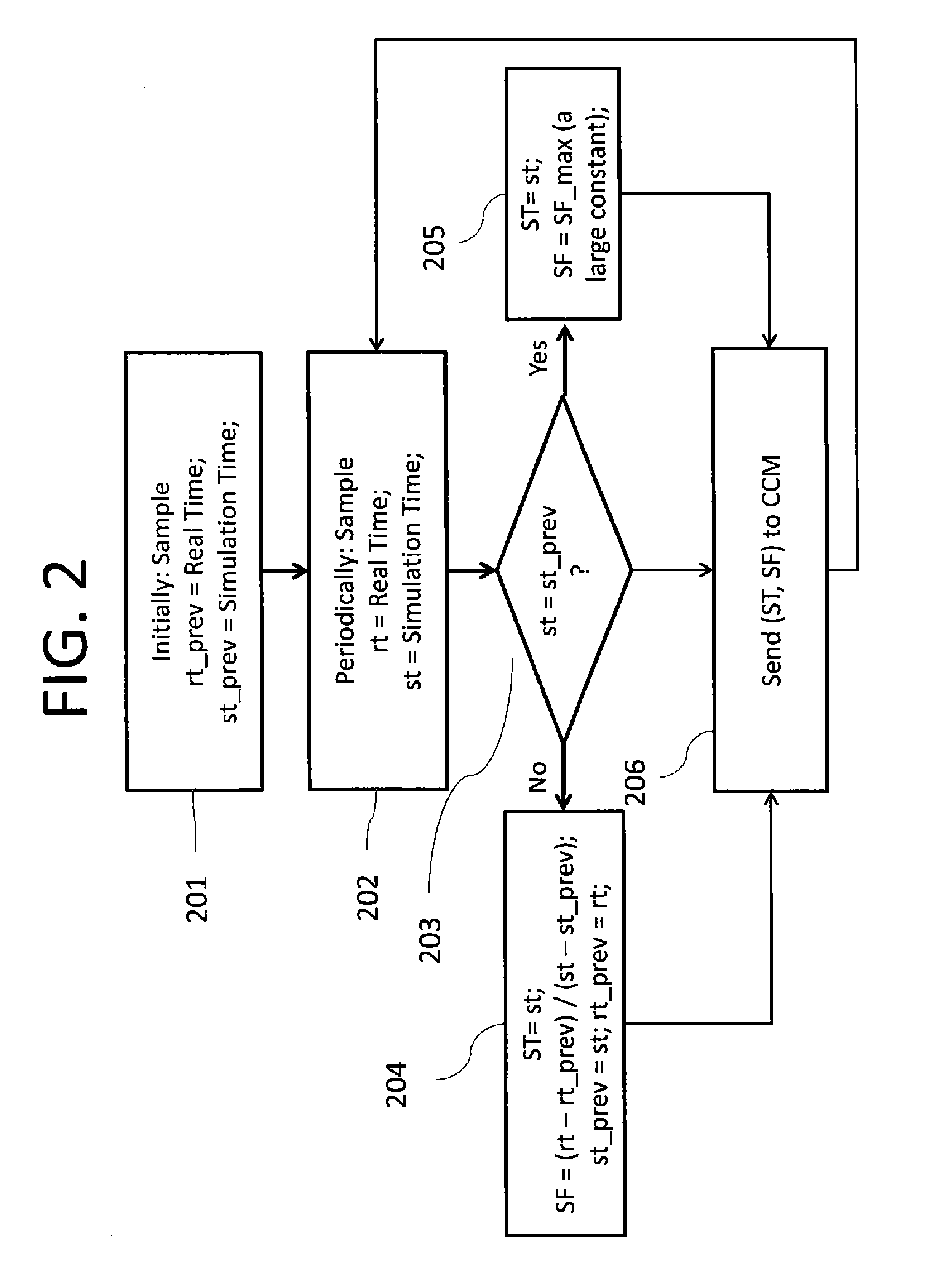

Dynamic time virtualization for scalable and high fidelity hybrid network emulation

InactiveUS20130218549A1Small footprintMaximum fidelitySoftware simulation/interpretation/emulationSpecial data processing applicationsTime informationSmall footprint

A system and method for measurement of the performance of a network by simulation, wherein time divergence is addressed by using discrete event simulation time to control and synchronize time advance or time slow down on virtual machines for large-scale hybrid network emulation, particularly where the loss of fidelity could otherwise be substantial. A dynamic time control and synchronization mechanism is implemented in a hypervisor clock control module on each test bed machine, which enables tight control of virtual machine time using time information from the simulation. A simulator state introspection and control module, running alongside the simulator, enables extraction of time information from the simulation and control of simulation time, which is supplied to the virtual machines. This is accomplished with a small footprint and low overhead.

Owner:PERSPECTA LABS INC

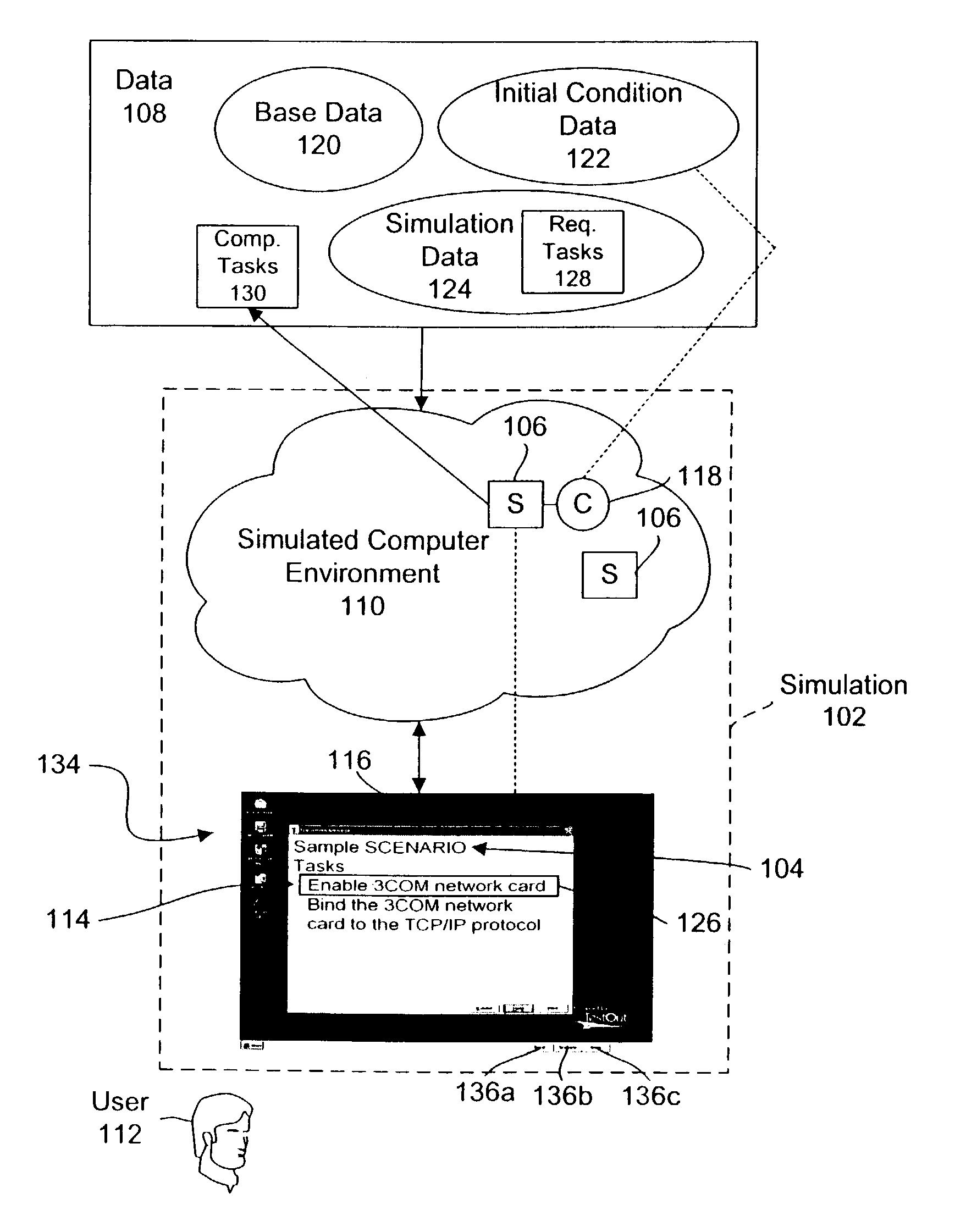

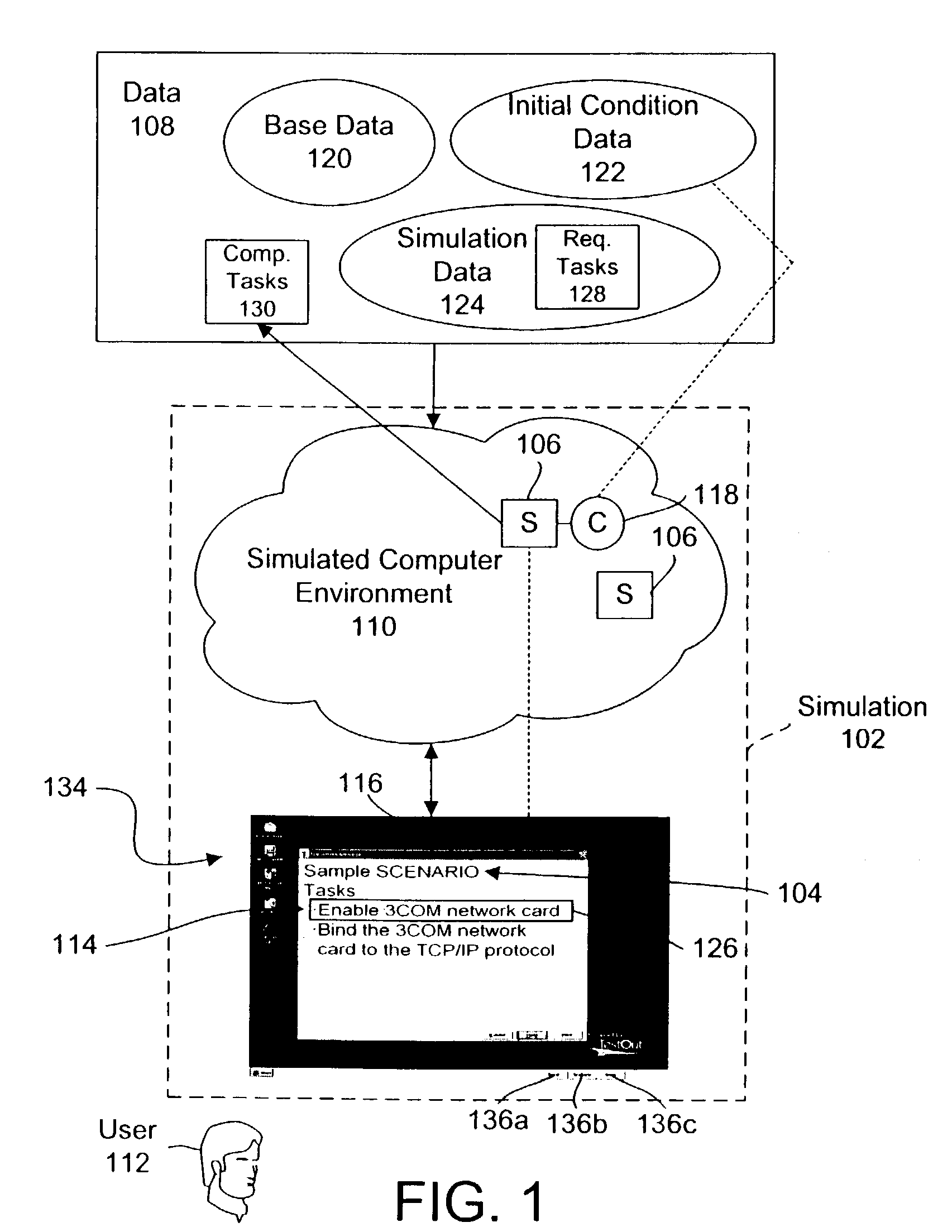

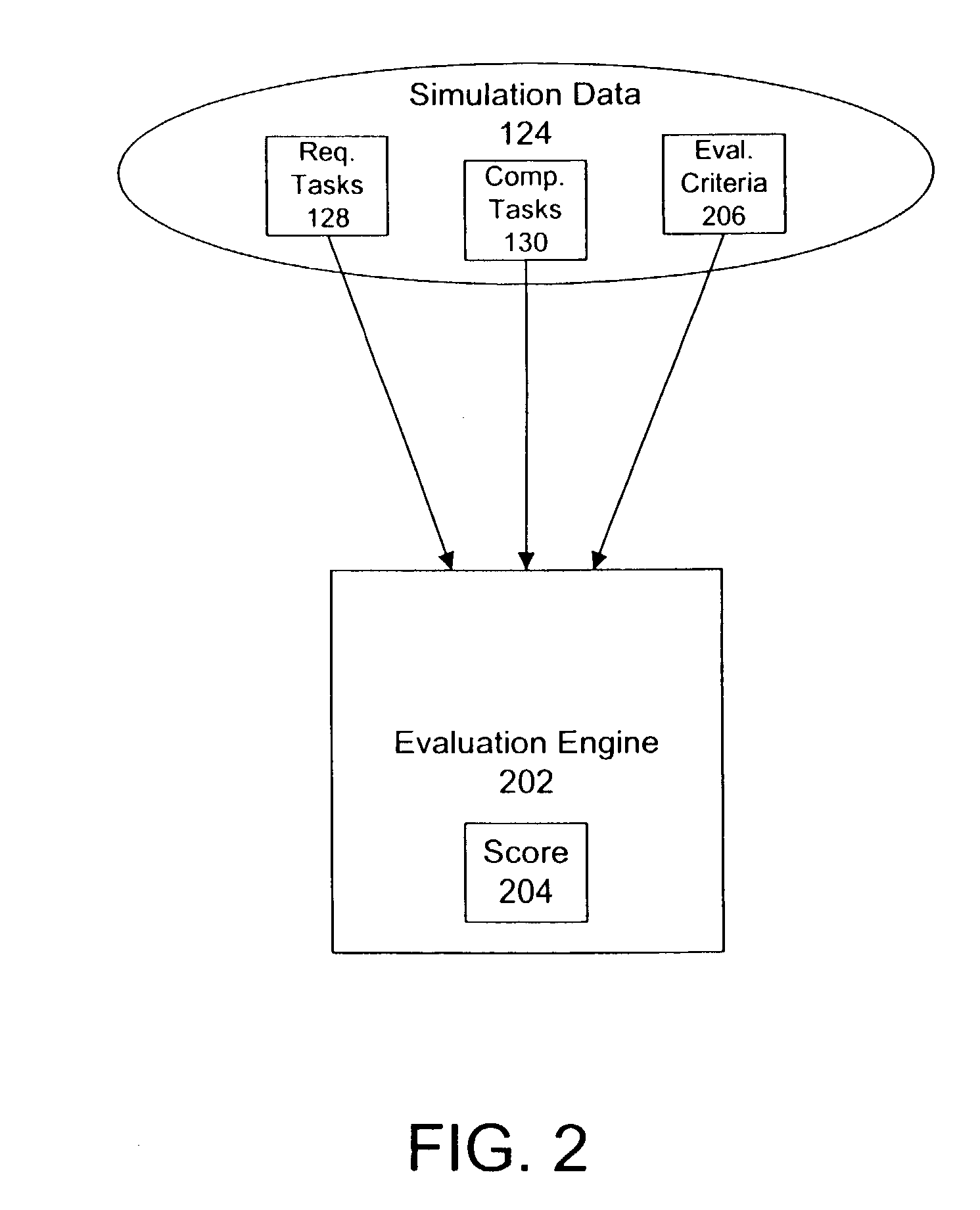

System and method for simulating a computer environment and evaluating a user's performance within a simulation

InactiveUS7089172B2Error detection/correctionSpecific program execution arrangementsAnalog computerSimulation based

A system and method is provided for simulating a computer environment and evaluating a user's performance within a simulation which uses the computer environment. The method reads base data which defines a simulated component within a simulated computer environment. Initial condition data may also be read to modify a simulated component. The simulated computer environment is represented by executing one or more simulators to simulate actual software modules. A simulation is presented to a user. The simulation includes a scenario and a set of tasks to be completed. As the user interacts with the simulators, tasks completed by the user are recorded. Finally, the set of completed tasks are evaluated to determine a user's performance within the simulation. The system and method allows a simulation author to automatically define a set of possible tasks for a simulation by performing the desired tasks in the simulated computer environment. The system and method provides a robust evaluation process for simulations. Partial scores, weighted scores, partially weighted scores, and binary scores are provided, as well as rescoring of simulations and simulation-based exam question seeding.

Owner:TESTOUT CORP

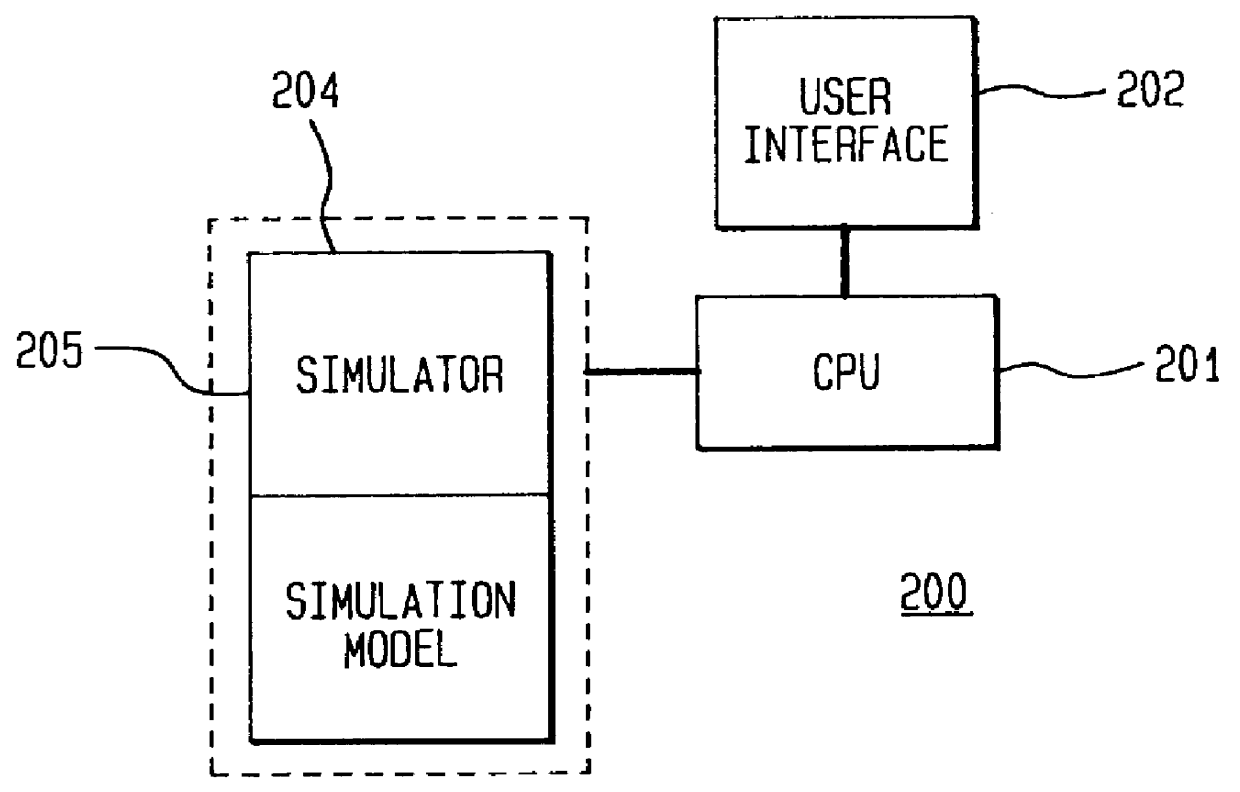

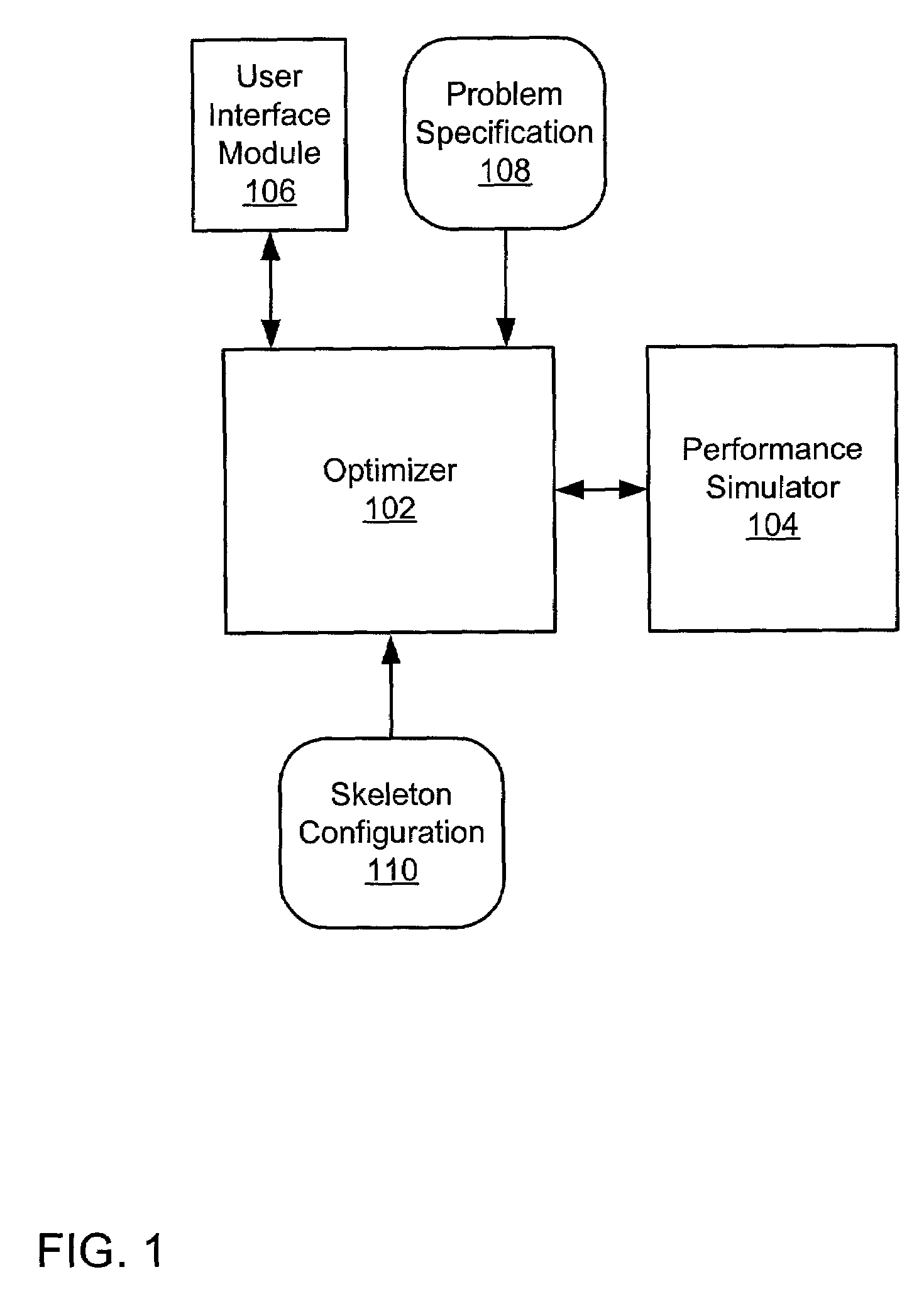

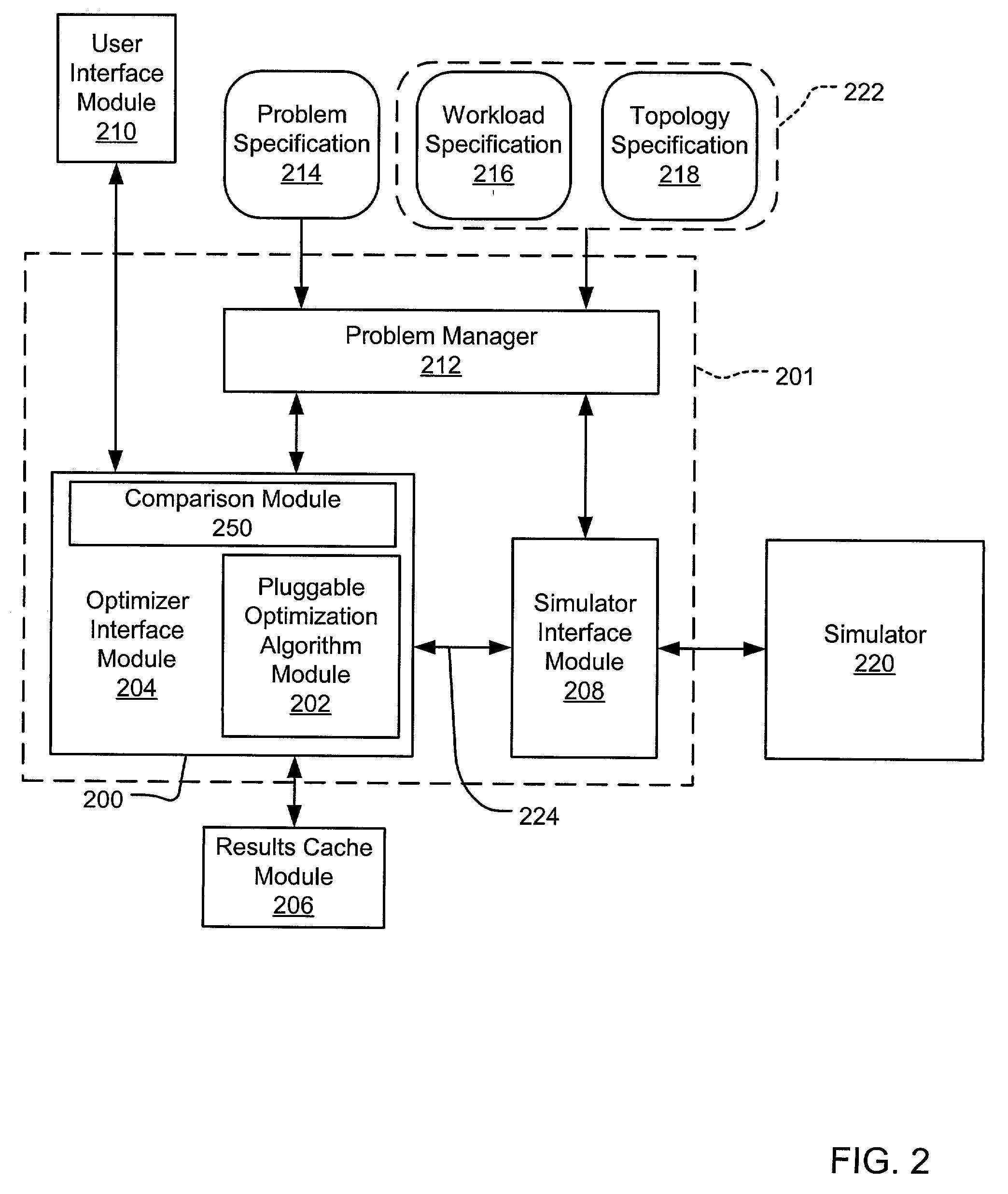

Modular architecture for optimizing a configuration of a computer system

An optimizer optimizes the configuration of a computer system, such as a web farm. The optimizer makes use of a performance simulator that simulates a cluster of machines running a given workload. A modular architecture allows different optimization modules to be plugged into the optimization system. In addition, the modular architecture also interfaces with different simulators through a simulator interface module. The simulator is decoupled from the optimization module. Simulation data may be filtered to provide and store only relevant objective and parameter values. A unique comparison module also guides the optimization module towards the optimum solution, even if no solutions have yet satisfied the objective completely. By caching simulation and / or optimization results (i.e. as opposed to raw simulation output data from the simulator), the simulations from previous simulation runs and different designers may be reused to reduce the time required for each optimization.

Owner:MICROSOFT TECH LICENSING LLC

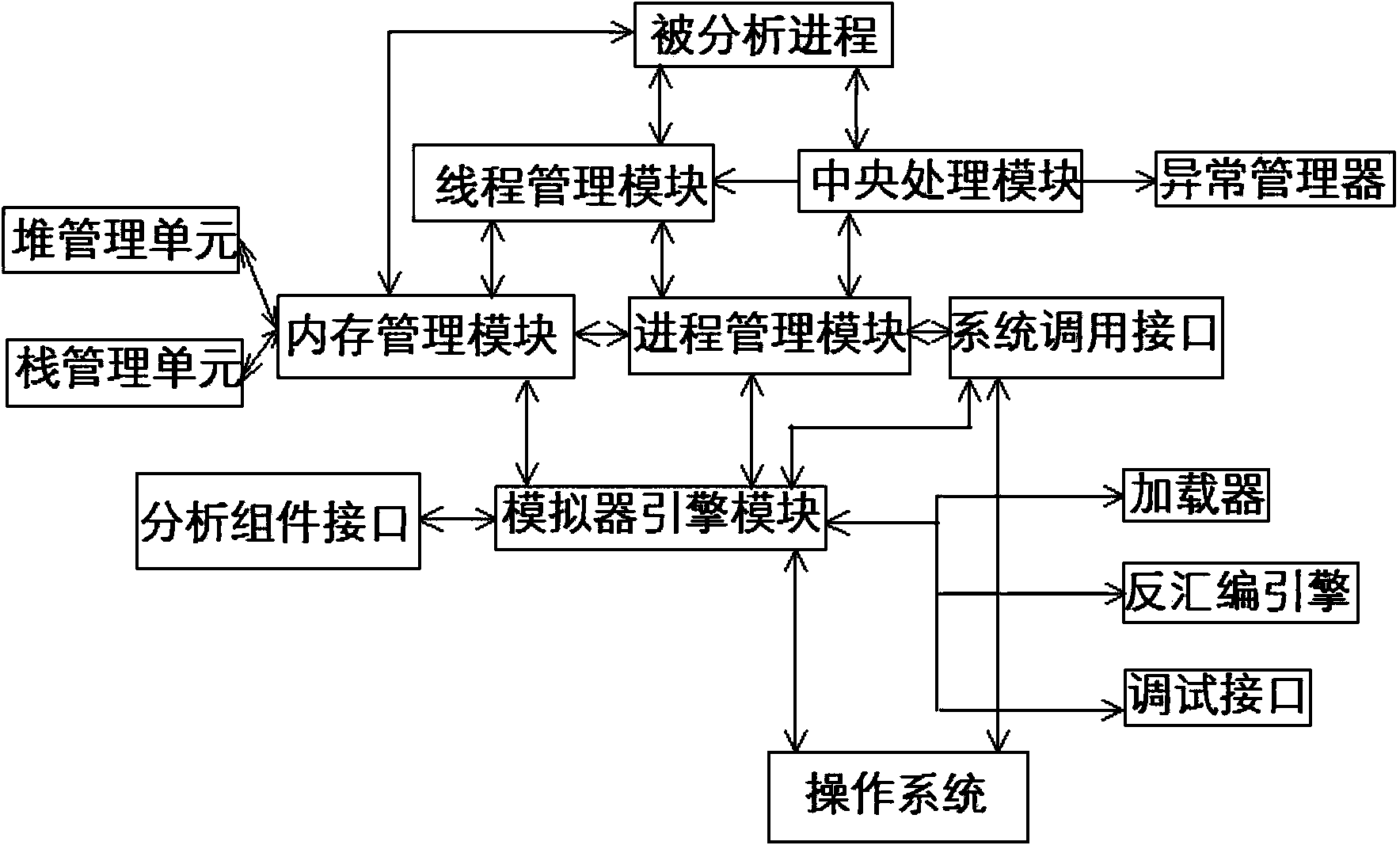

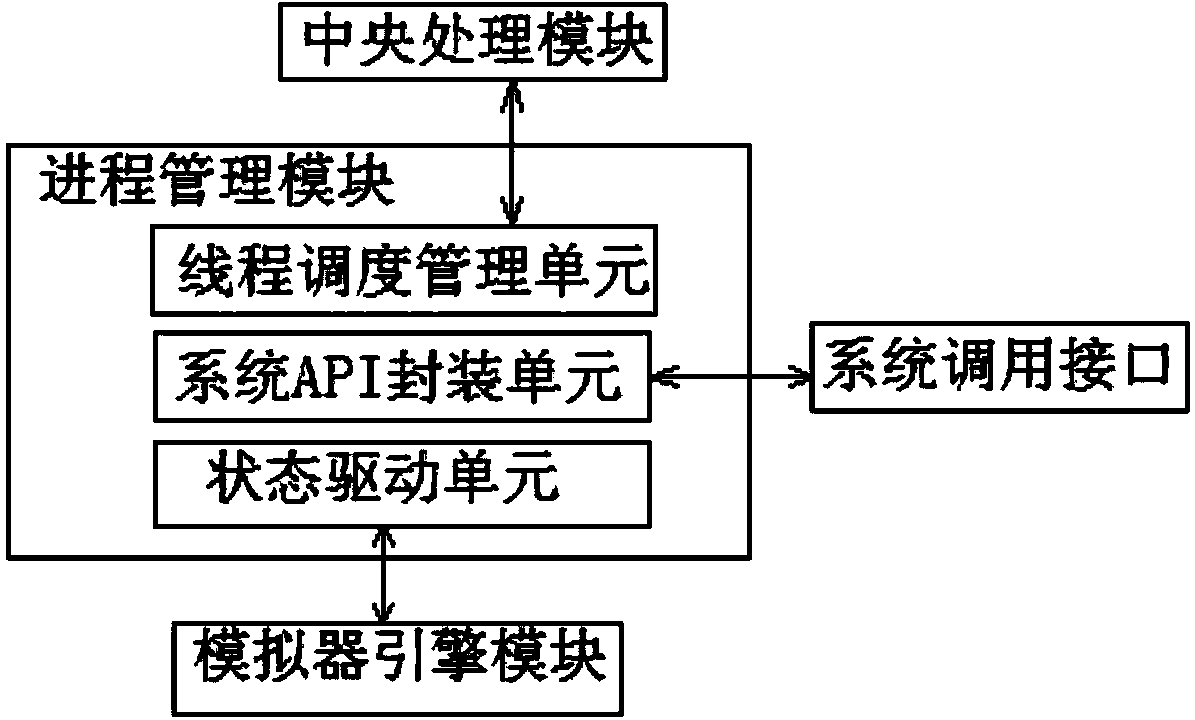

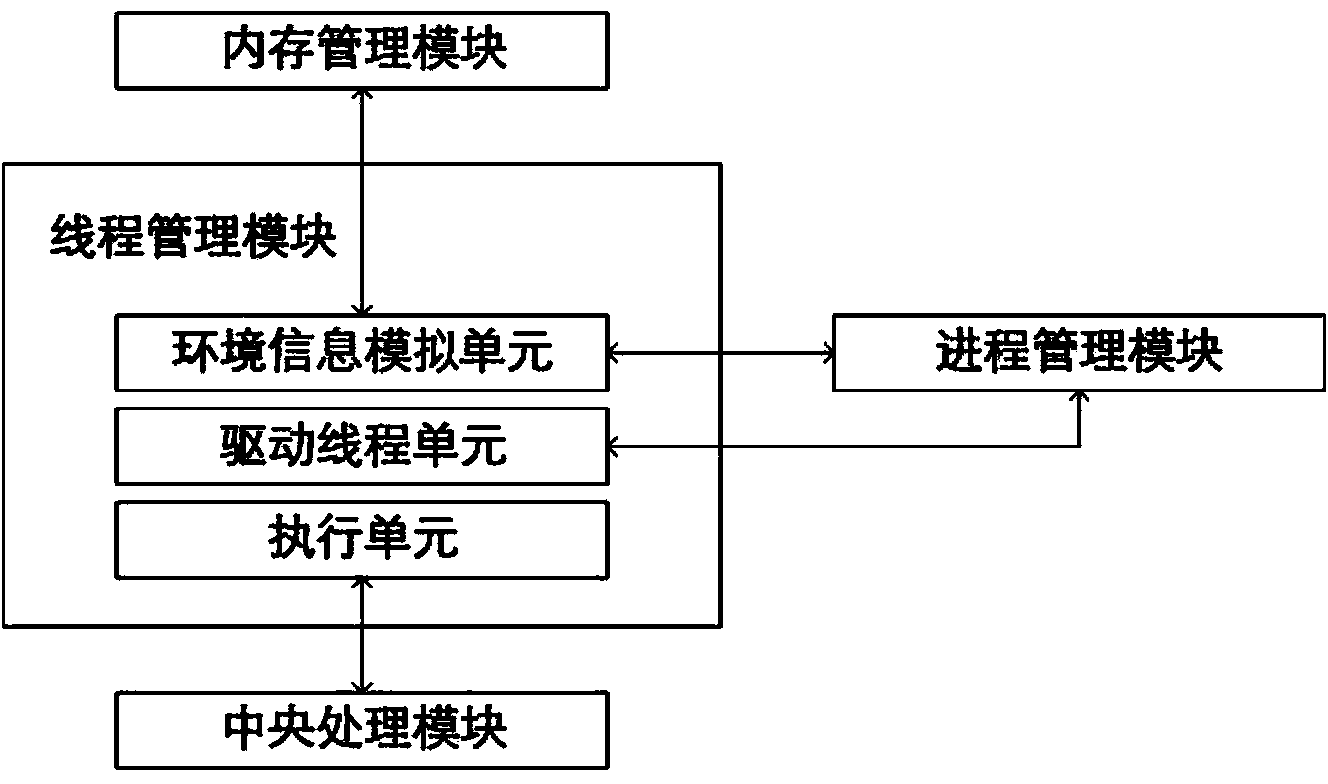

Binary program analytic system based on process simulation

ActiveCN103440457AGuaranteed analytical efficiencySynchronous Efficient Simulation ExecutionSoftware testing/debuggingPlatform integrity maintainanceReverse analysisApplication programming interface

The invention discloses a binary program analytic system based on process simulation, belonging to the technical field of electronic data monitoring. The binary program analytic system comprises a simulator engine module, a memory management module, a process management module, a system call interface, a thread management module, a central processing module and an analytic component interface for providing an application program interface, wherein the simulator engine module is respectively connected with the memory management module, the progress management module, the system call interface and the analytic component interface; the progress management module is respectively connected with the memory management module, the central processing module and the system call interface; and the thread management module is respectively connected with the memory management module, the thread management module and the central processing module. The binary program analytic system does not depend on static reverse analysis carried out on a program, but adopts a completely dynamic analytic method, so that most of influences caused by a program protection technology can be avoided.

Owner:智巡密码(上海)检测技术有限公司

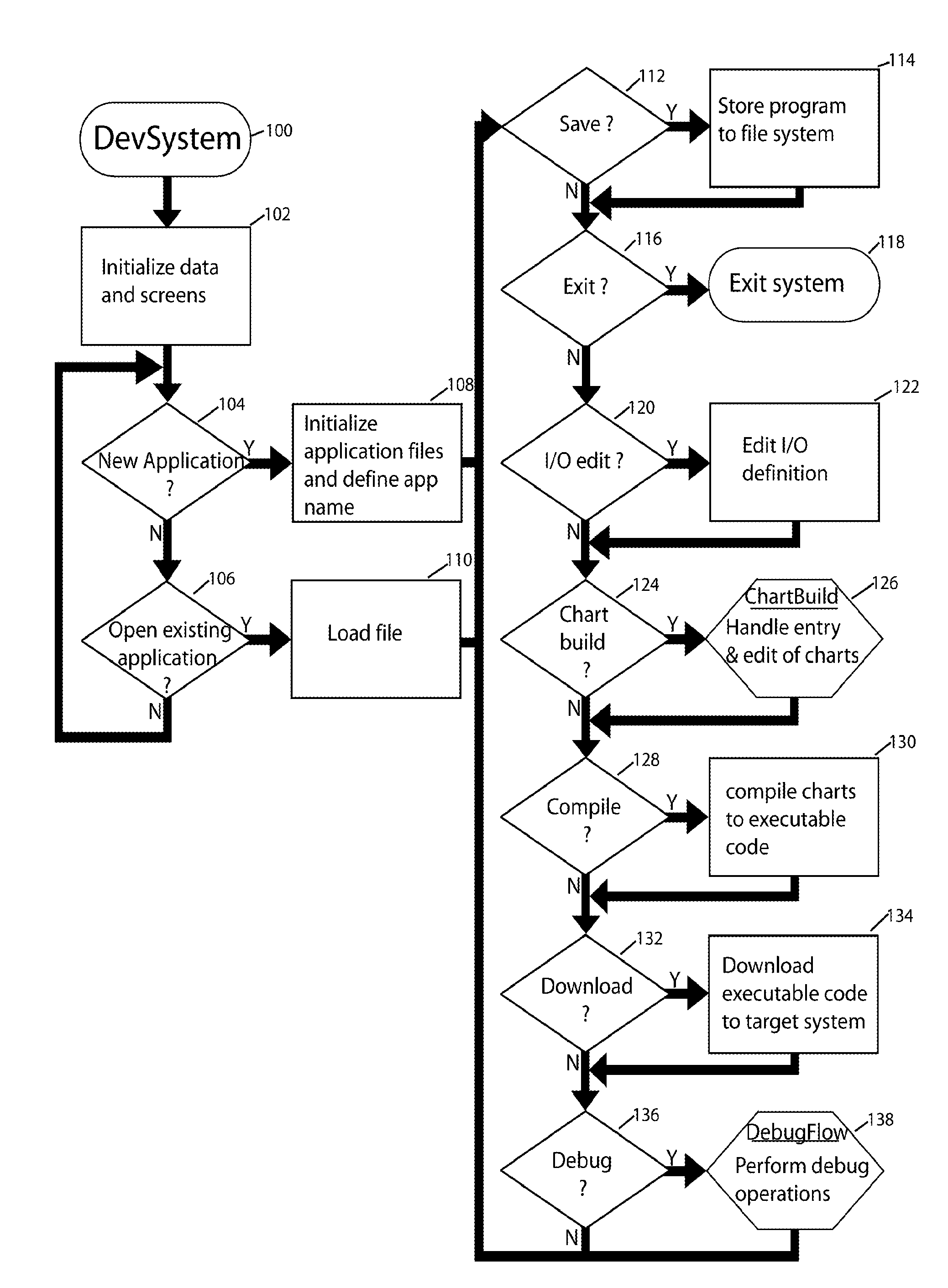

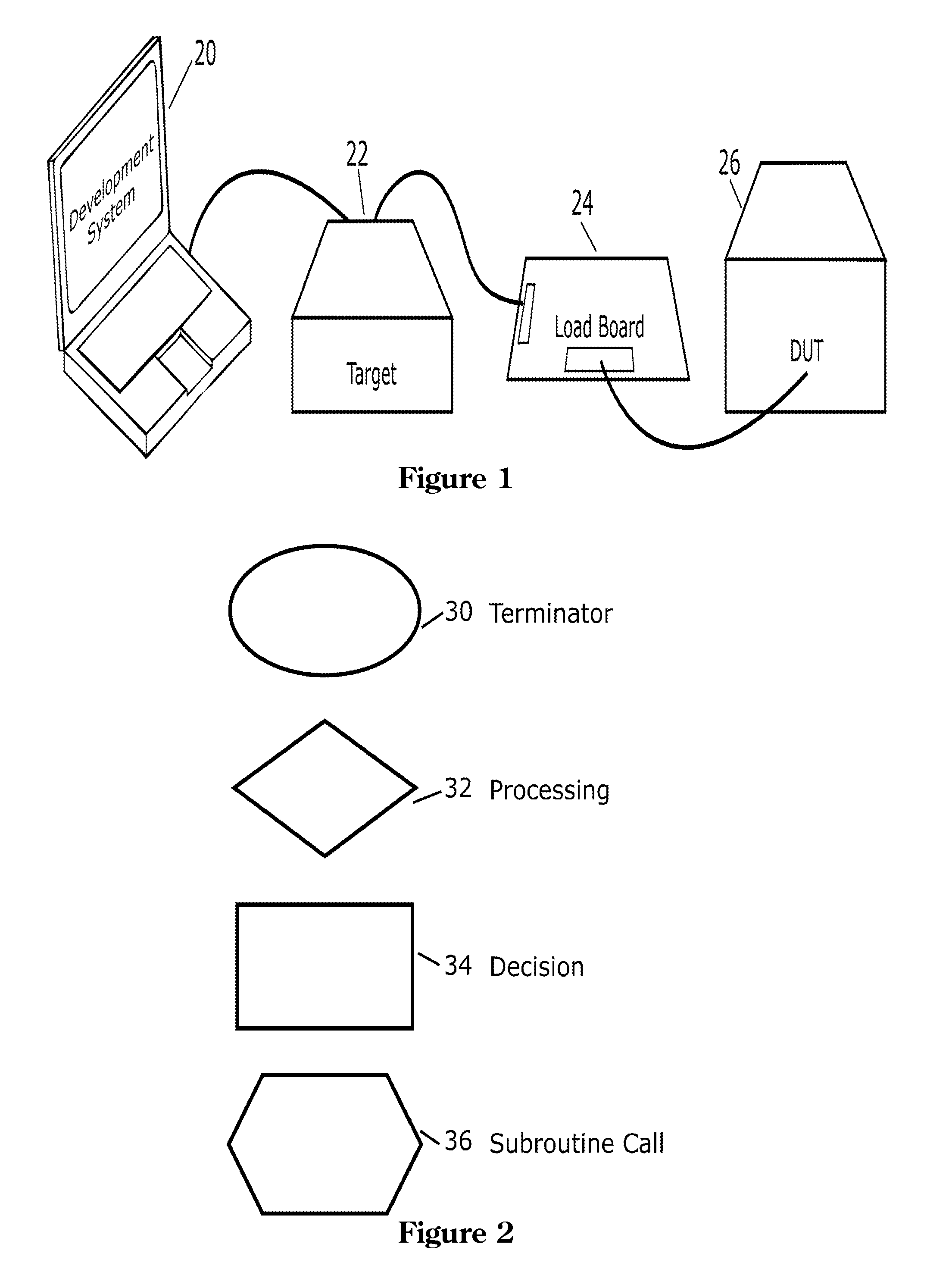

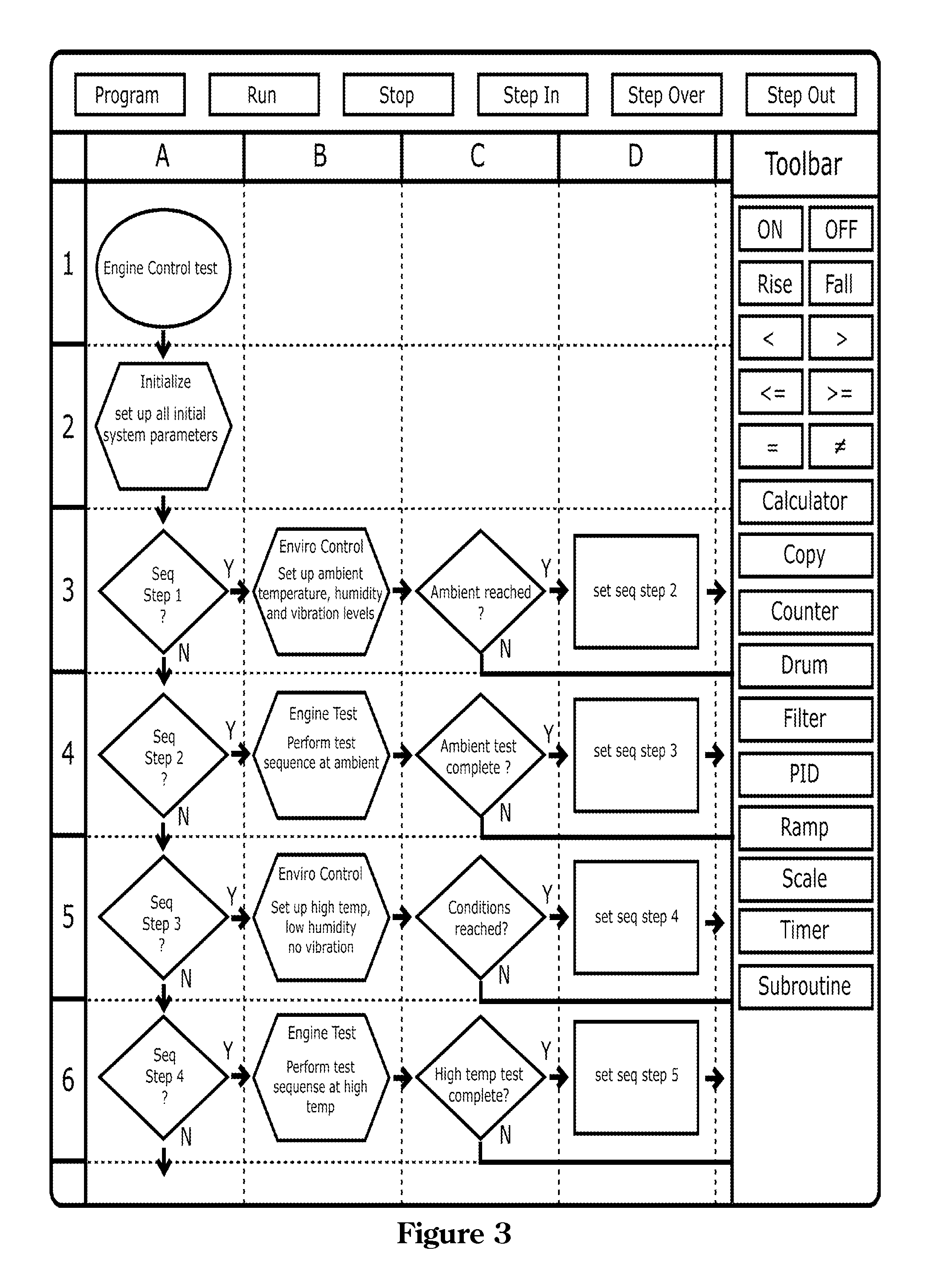

Flow Chart Programming Platform for Testers and Simulators

InactiveUS20120117537A1Low costReduce developmentSugar derivativesVisual/graphical programmingGraphicsParallel computing

A system for the development, compilation, execution, monitoring and debug of automated test and simulation systems in a flow chart programming language. A development and debug system, implemented as software on a computer, which provides an application developer the capability to enter fully defined application programs through the use of graphical flow charts. An executions system, implemented as a program on a device incorporating a central processing unit, memory, communications and necessary interfaces, which executes graphical flow charts compiled by the development and debug system. The development and debug system communicates with the execution system to download programs, control operation, monitor operation and provide a debugging environment.

Owner:VELOCIO NETWORKS

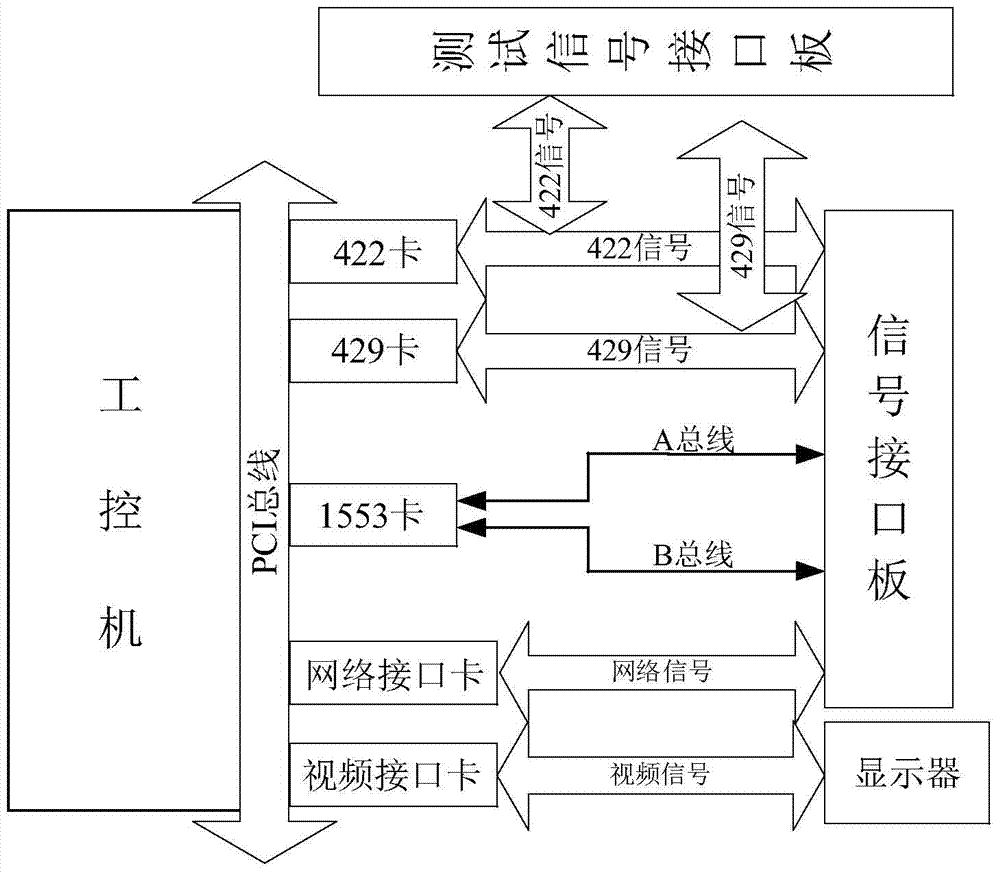

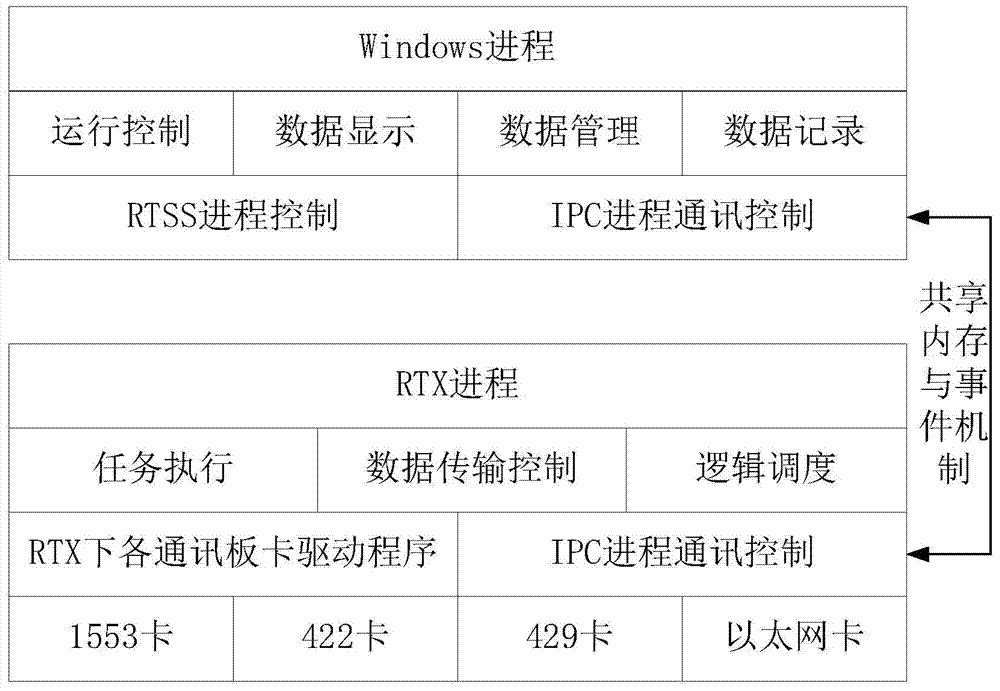

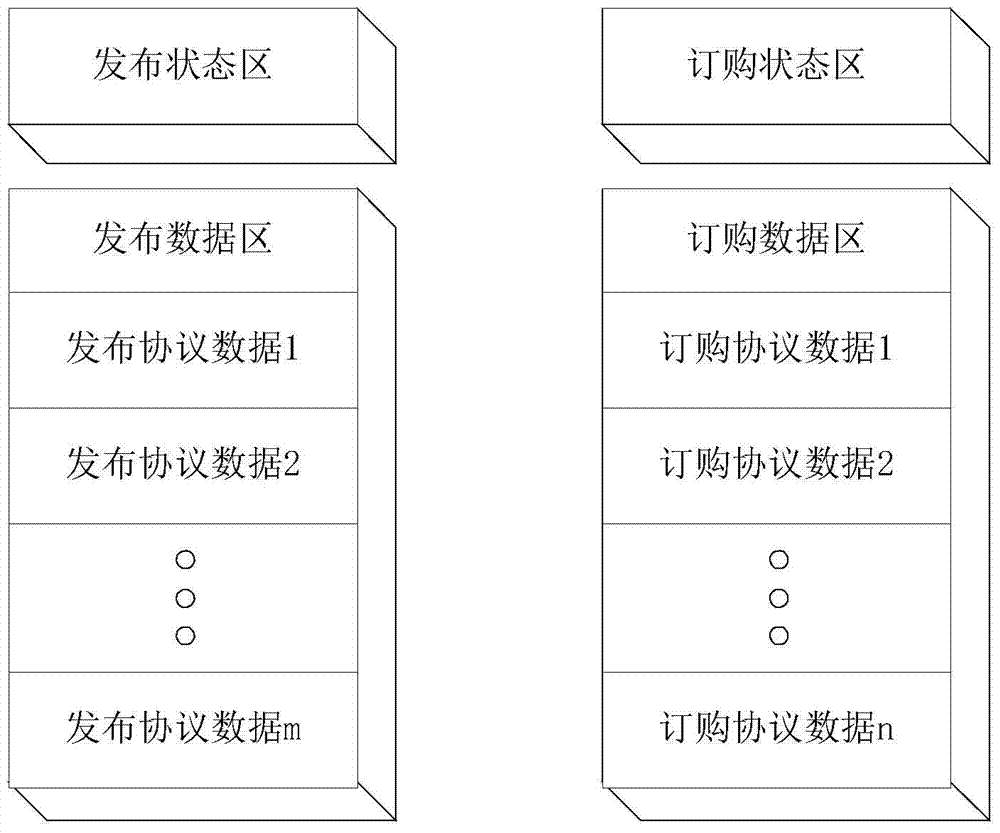

Aircraft mission computer simulator

InactiveCN104750540AAccelerate the development progressShorten the development cycleSoftware simulation/interpretation/emulationData displayData recording

The invention discloses an aircraft mission computer simulator, belongs to the field of aircraft avionic system simulation, and aims to solve the problems of poor real-time property and difficulty of compatibility of the real-time property and an operation state of an existing aircraft mission computer simulator. A Windows+RTX (Real Time eXchange) mechanism is embedded into an industrial personal computer to serve as an internal architecture of the mission computer simulator; the internal architecture comprises a Windows process and an RTX process; the Windows process is communicated with the RTX process by using a shared memory communication mechanism and a mutual exclusion mechanism; the shared memory communication mechanism realizes data exchange is performed between the Windows process and the RTX process through a shared memory; the Windows process is used for realizing operation control, data display, data management and data recording of the mission computer simulator; the RTX process is used for realizing mission execution, data transmission control and logic scheduling of the mission computer simulator. The simulator is applied to an aircraft research process.

Owner:HARBIN INST OF TECH