Patents

Literature

106results about How to "Efficient debugging" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

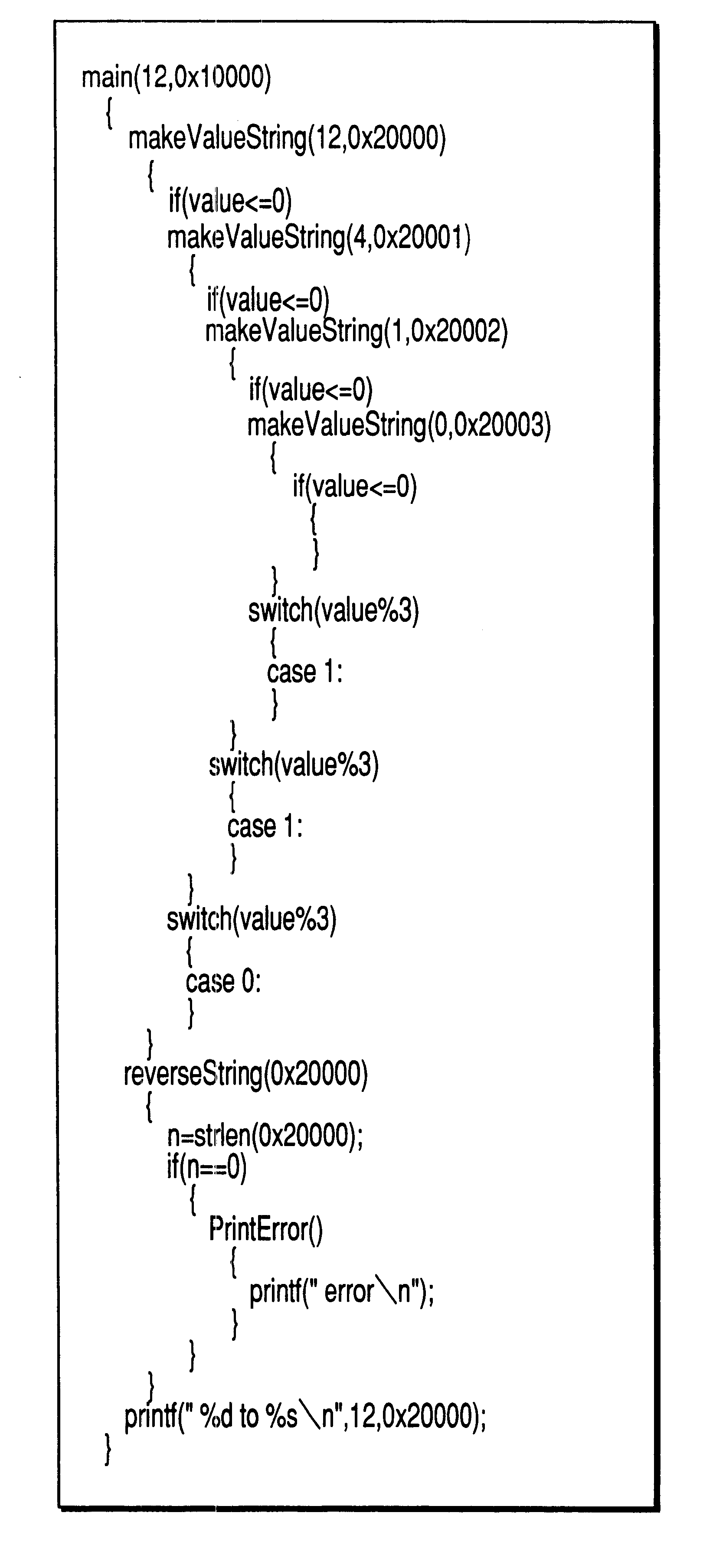

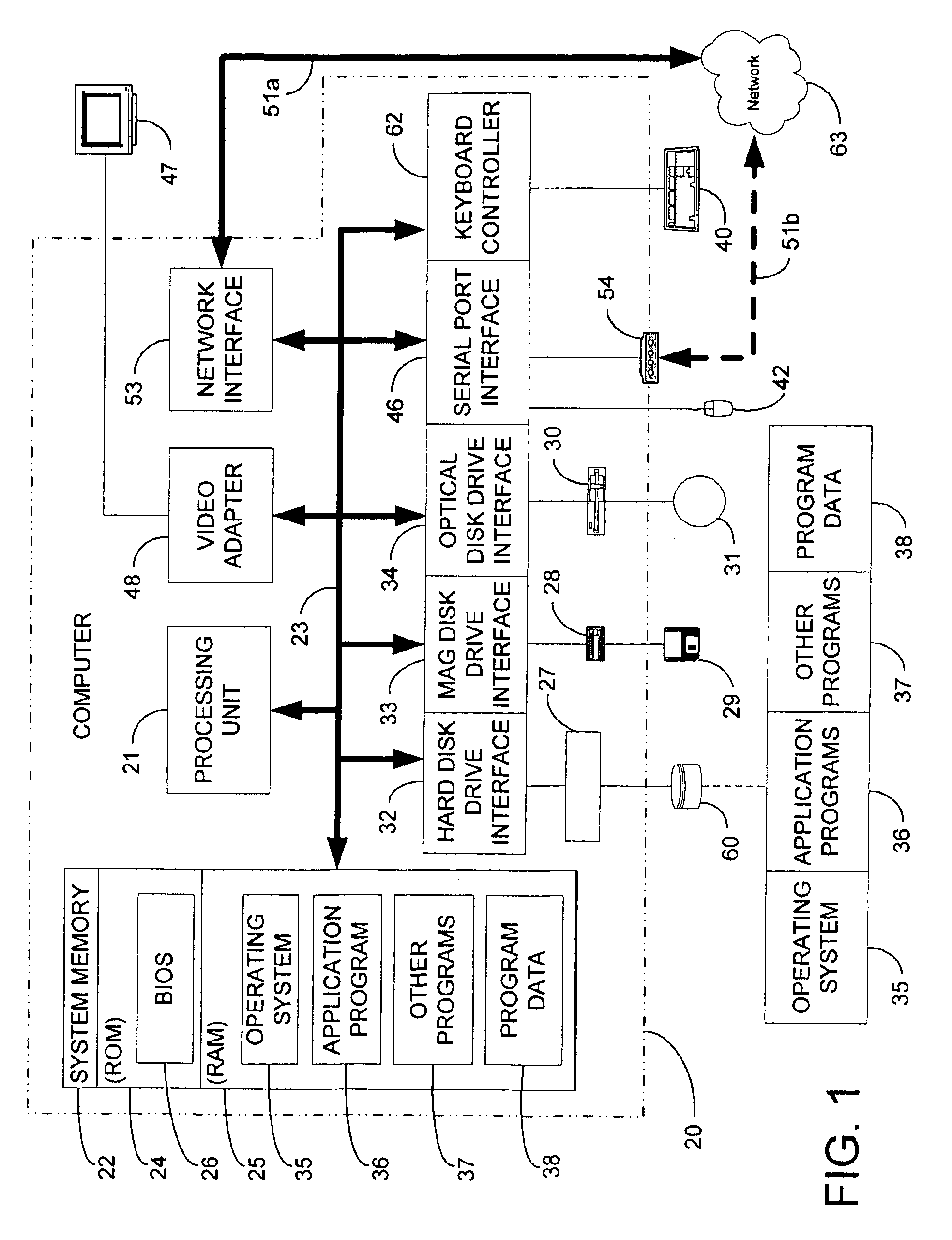

Debugging support device and debugging support method

InactiveUS6345383B1Debugging of object-oriented programs more efficientEfficient debuggingSoftware testing/debuggingSpecific program execution arrangementsComputer hardwareComputer science

Owner:KK TOSHIBA

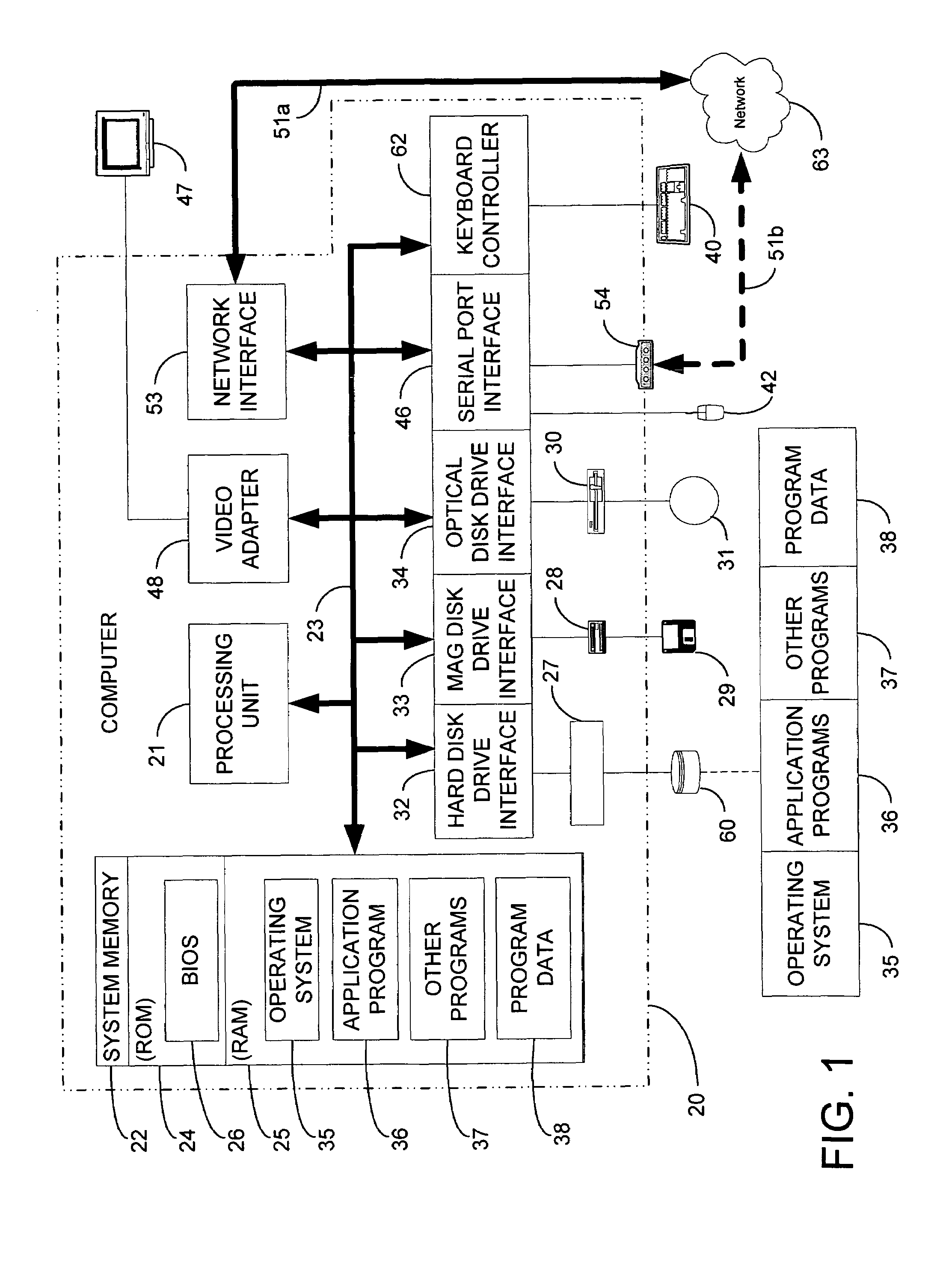

Method and system for debugging a program

InactiveUS6915509B1Efficient debuggingError detection/correctionMultiple digital computer combinationsEmbedded systemDebugger

Owner:MICROSOFT TECH LICENSING LLC

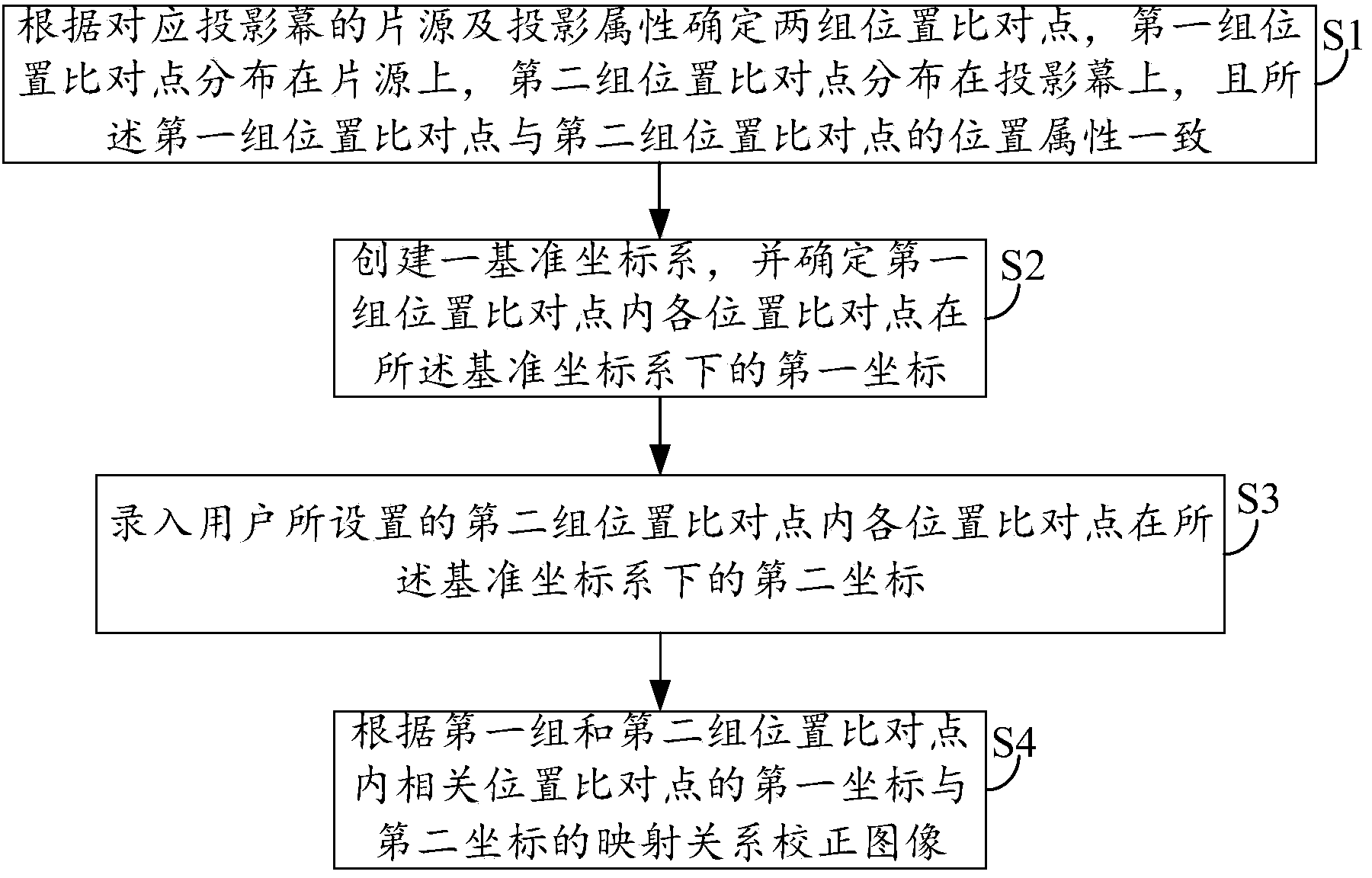

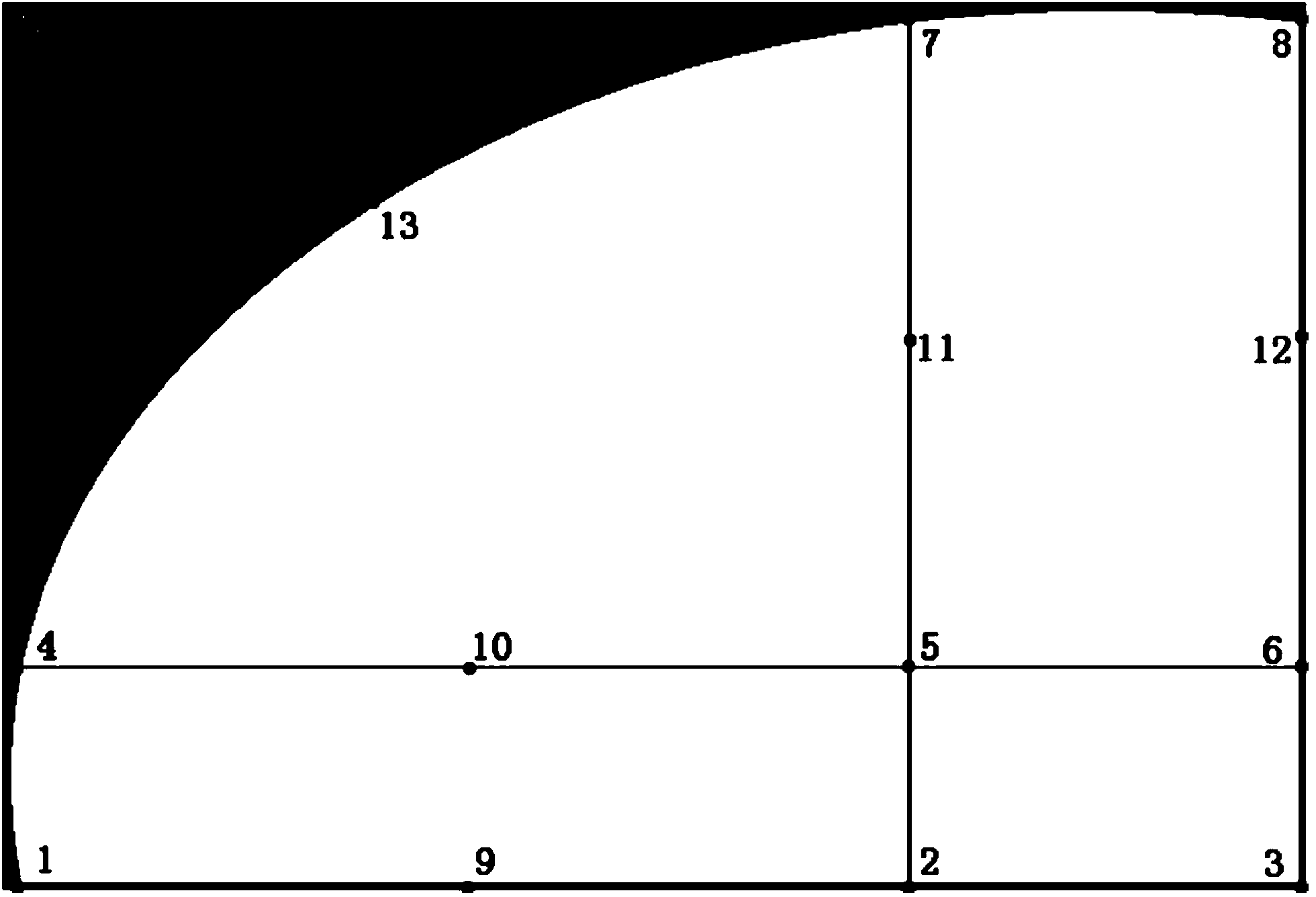

Method, device and system for geometric correction assistance of projected image

ActiveCN103888741APrecise goal orientationEasy to debugTelevision system detailsPicture reproducers using projection devicesPattern recognitionComputer graphics (images)

The invention discloses a method, device and system for geometric correction assistance of a projected image. The method, device and system are used for improving the convenience of correction. The method for geometric correction assistance comprises the steps that two sets of position comparison points are determined according to a film source corresponding to a projection curtain and the projection attribute, the first set of position comparison points are distributed on the film source, the second set of position comparison points are distributed on the projection curtain, and the position attribute of the first set of position comparison points and the position attribute of the second set of position comparison points are consistent; a reference coordinate system is created and a first coordinate of each position comparison point in the first set of position comparison points in the reference coordinate system is determined; a second coordinate, set by a user, of each position comparison point in the second set of position comparison points in the reference coordinate system is input; the image is corrected according to the mapping relationship of the first coordinates and the second coordinates of the relevant position comparison points in the first set and the second set of the position comparison points.

Owner:北京淳德电子有限公司

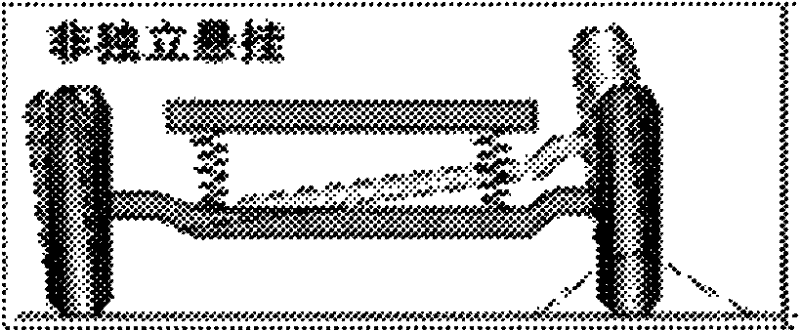

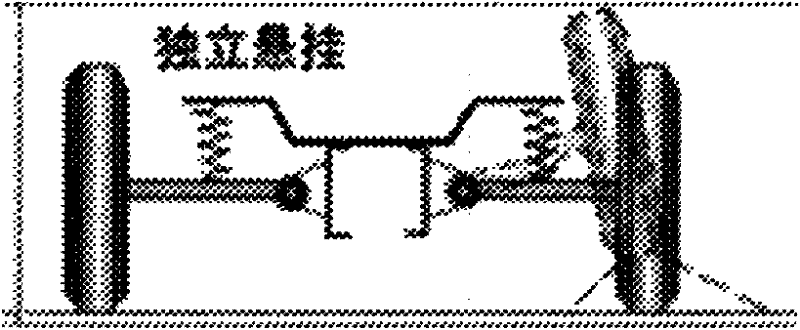

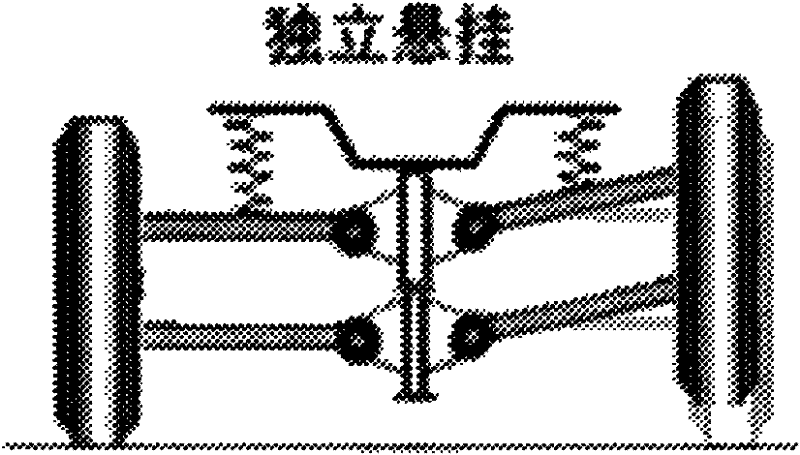

Self compensation floating swing arm independent suspension system

ActiveCN102363408AIdeal handlingIdealized securityInterconnection systemsResilient suspensionsAnti-roll barCamber angle

The invention provides a self compensation floating swing arm independent suspension system, comprising a self compensation floating swing arm independent suspension device and a centrifugal force control scissors-type anti-roll bar device. The two mechanisms can be used in combination or independently and are applicable to both front wheels and rear wheels. The self compensation floating swing arm independent suspension system guarantees that wheels perform line bounce along a vertical direction of a car body on various kinds of road surfaces when a car runs at a low speed or at a high speed or makes turns and guarantees maximum contact area between the wheels and the road surfaces, with the parameters of king pin angle, toe-in angle, camber angle, wheel track, and axle base being maintained the same as original parameters; and, when the car makes turns, the centrifugal force control scissors-type anti-roll bar device works automatically, offsets a roll force with a force equal to the roll force in magnitude and opposite to the roll force in direction, and enables the car body to lower automatically, thereby improving anti-roll capacity and realizing idealization of controllability, safety, stability and comfort of the car. The self compensation floating swing arm independent suspension system has a simple structure, excellent performance, and low cost, and is easy to realize.

Owner:侯贺

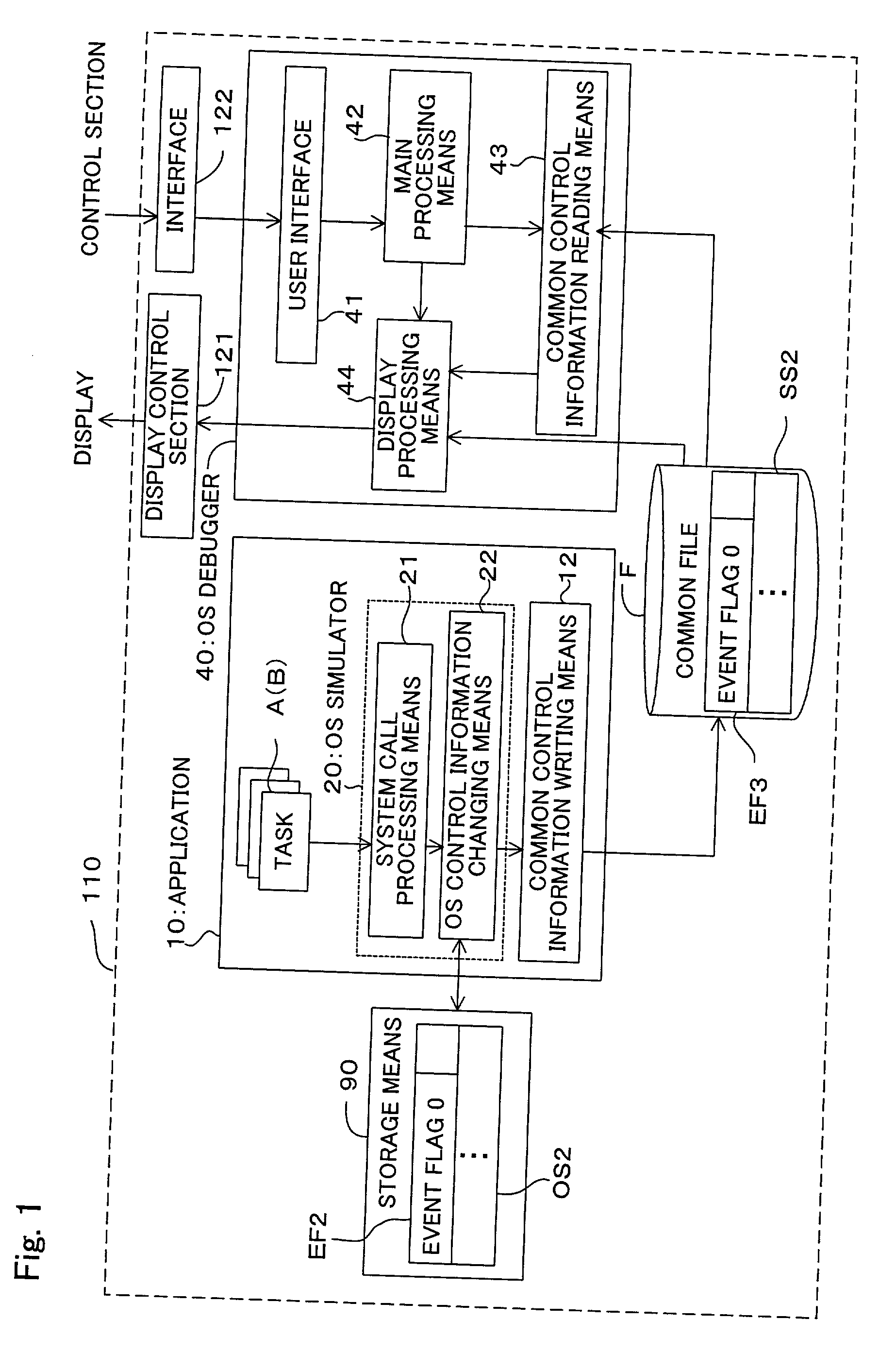

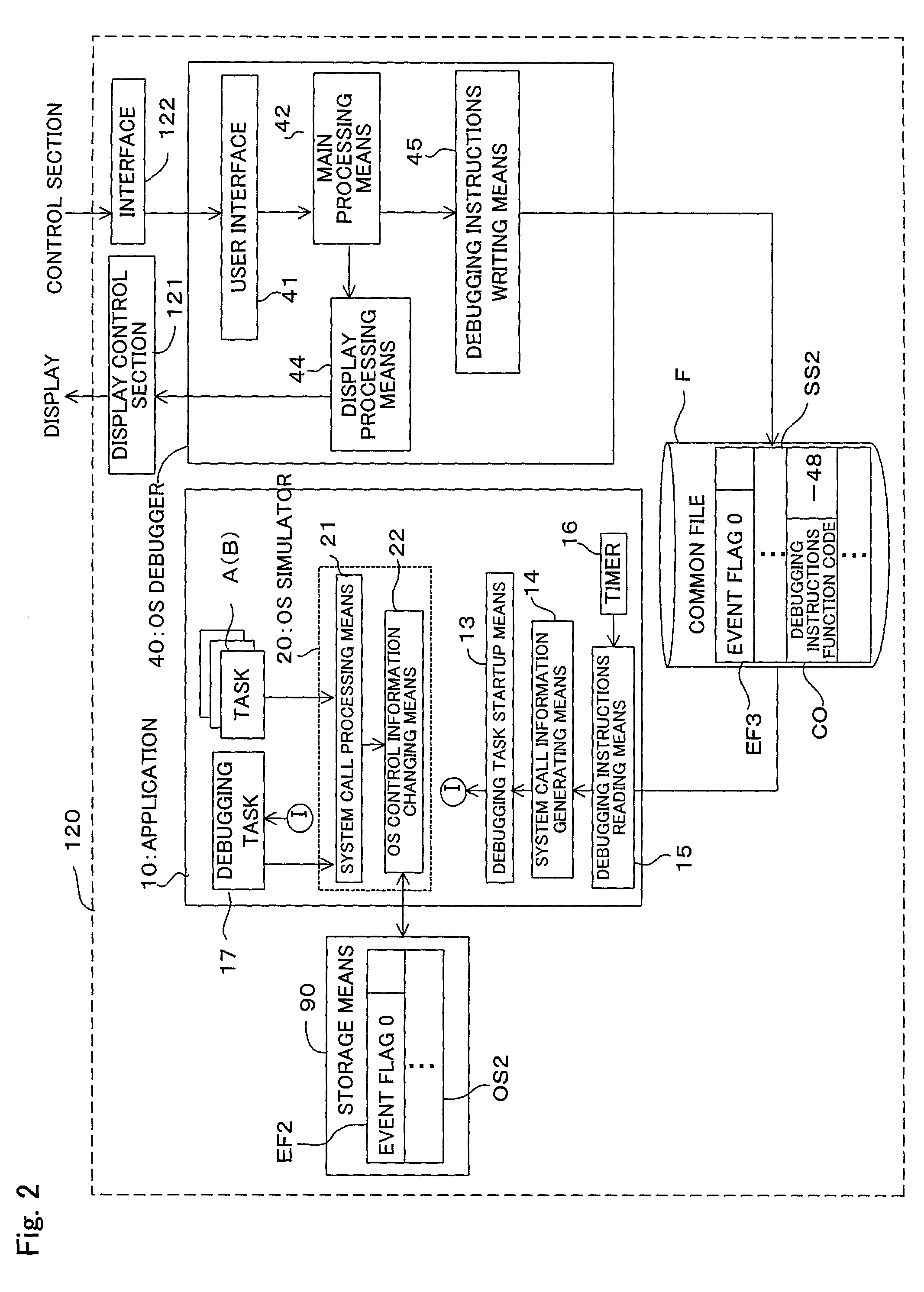

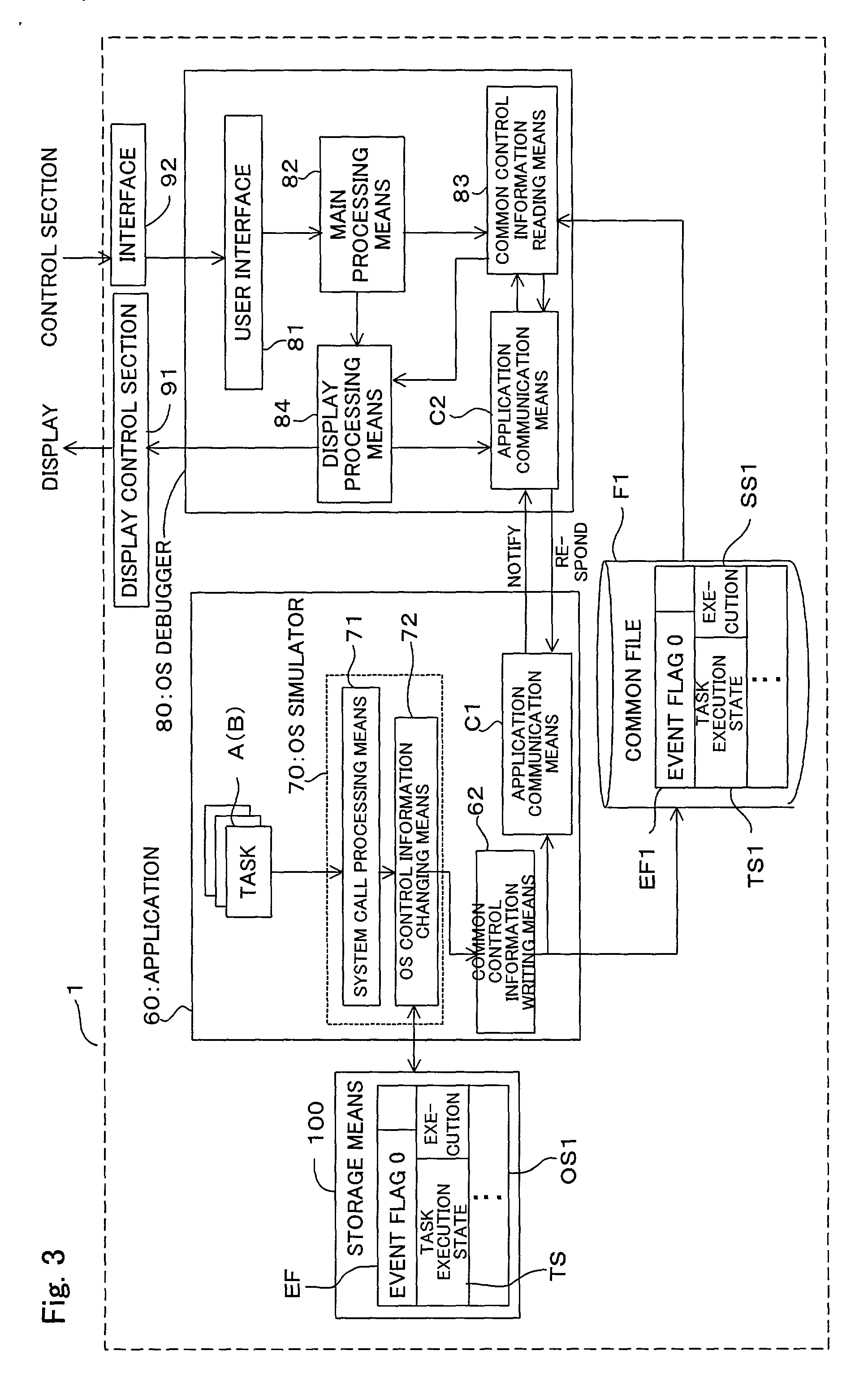

Debugging supporting apparatus, debugging supporting method and recording medium readable by computer with its programs recorded thereon

InactiveUS20010027387A1Efficient debugEfficient debuggingSoftware testing/debuggingProgram controlApplication softwareDebugger

Disclosed are a debugging supporting apparatus, a debugging supporting method and its recording medium so constituted that even if an application developed in a simulation environment by OS simulator stops, OS control information can be referred to at that moment. The debugging supporting apparatus comprises a common file that is shared between the application and the OS debugger and which records common control information including the same data as item forming OS control information, writing means for writing specific item of the OS control information stored in the storage means on the common file as common control information, and reading means for reading out the common control information stored in the common file.

Owner:PANASONIC CORP

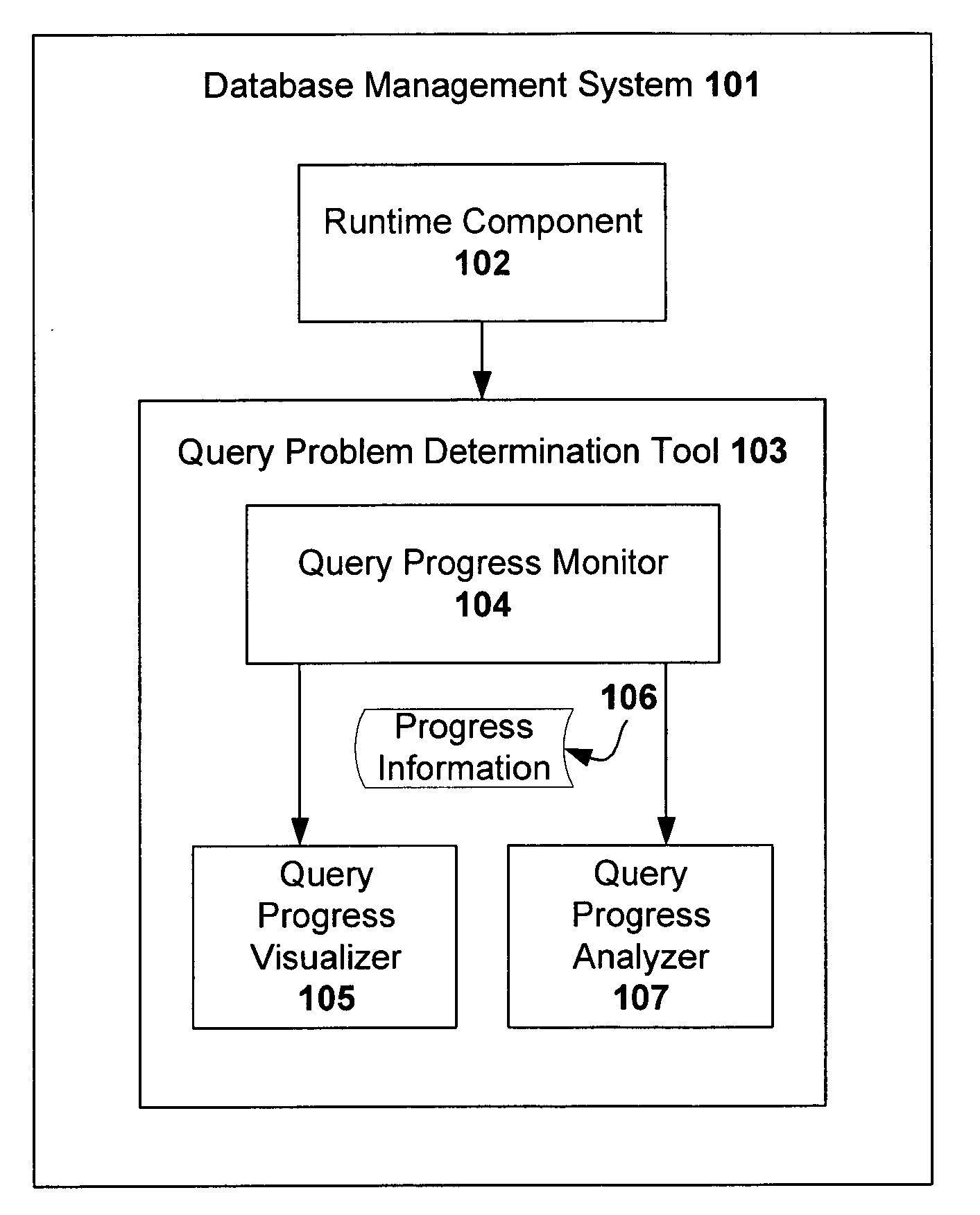

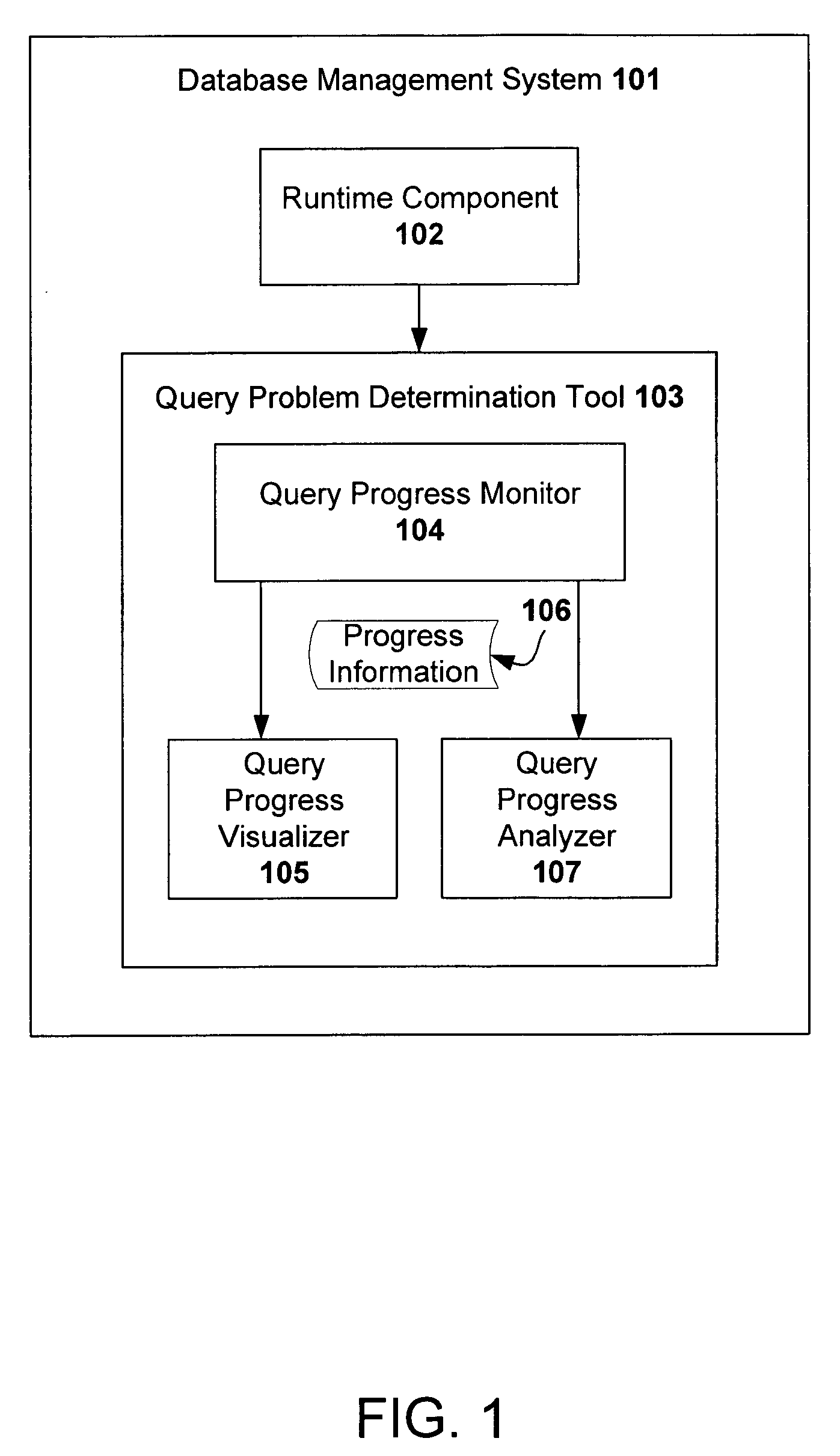

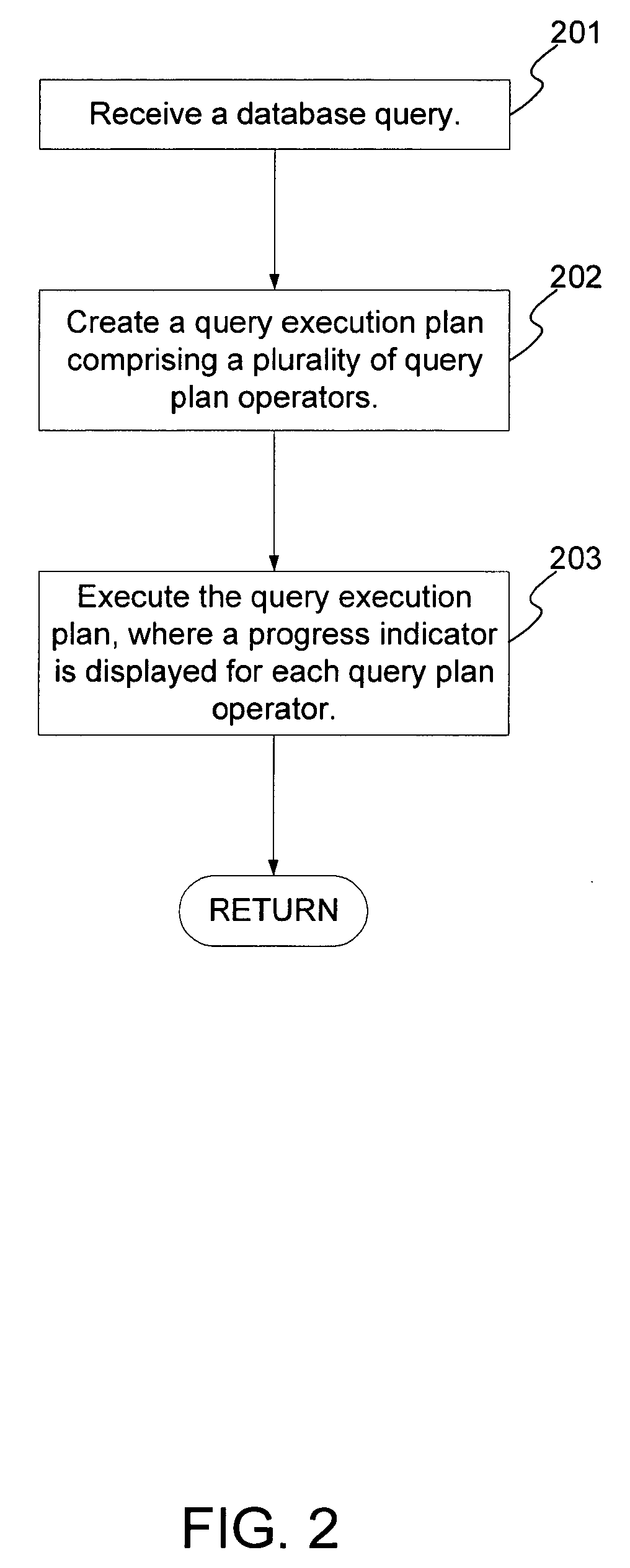

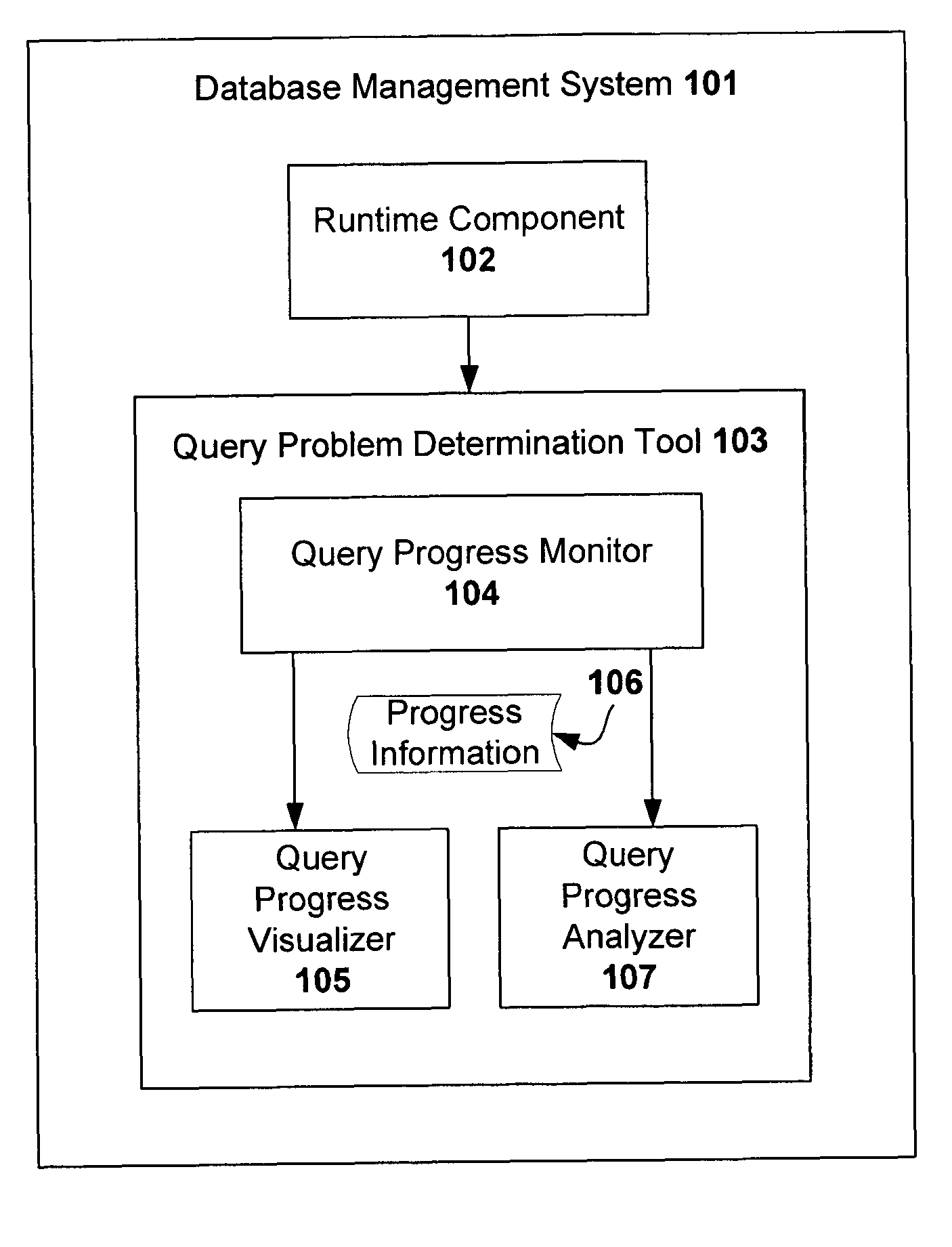

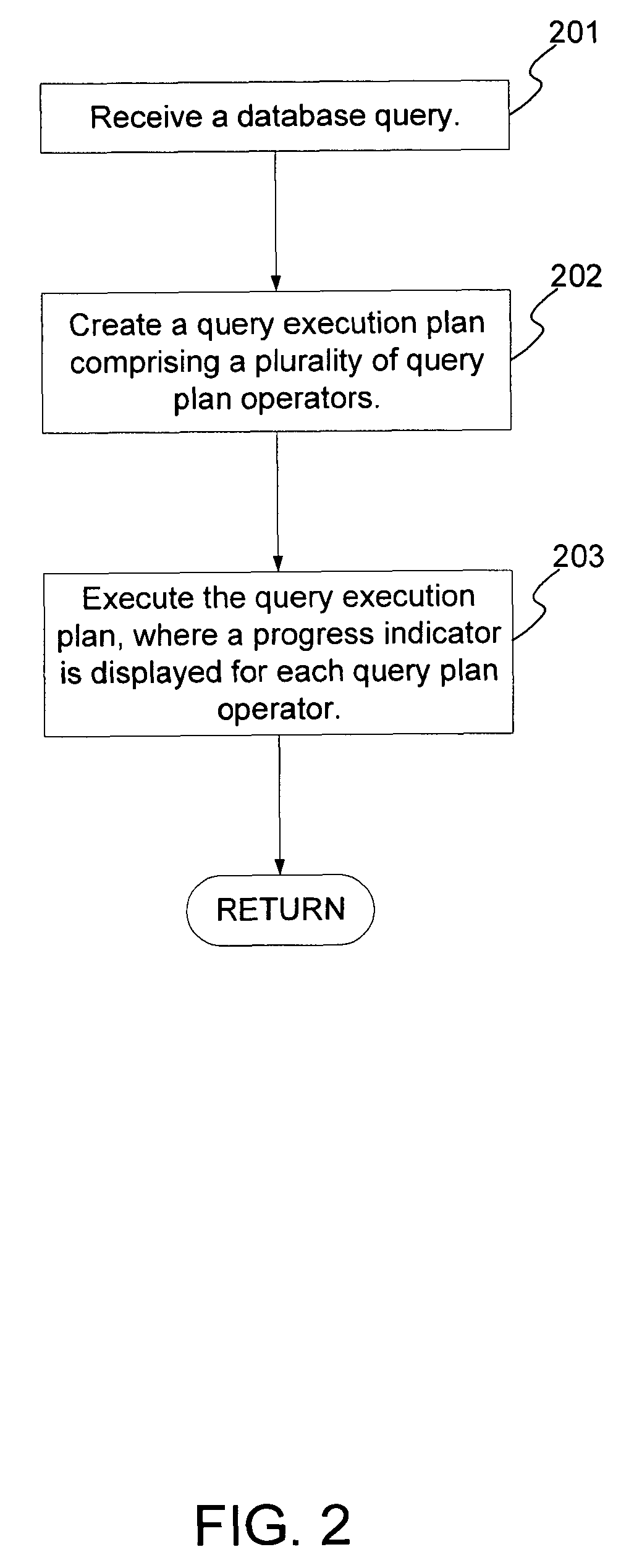

SQL query problem determination tool

InactiveUS20060218125A1Efficiency problemEfficient debuggingDigital data processing detailsError detection/correctionExecution planQuery plan

A method and system for query problem determination have been disclosed. The method includes receiving a database query; creating a query execution plan for the database query comprising a plurality of query plan operators; and executing the query execution plan, wherein a progress indicator is displayed for each query plan operator. The system includes a query progress monitor, which collects progress information for each query plan operator during the execution of the query execution plan. This progress information is then communicated to a query progress visualizer and a query progress analyzer, which graphically displays the progress information as a progress indicator for each query plan operator and performs debugger type operations, respectively. In this manner, information concerning the progress of the query execution is provided at a query operator level, such that the information may be used to more efficiently debug any problems with the query.

Owner:LINKEDIN

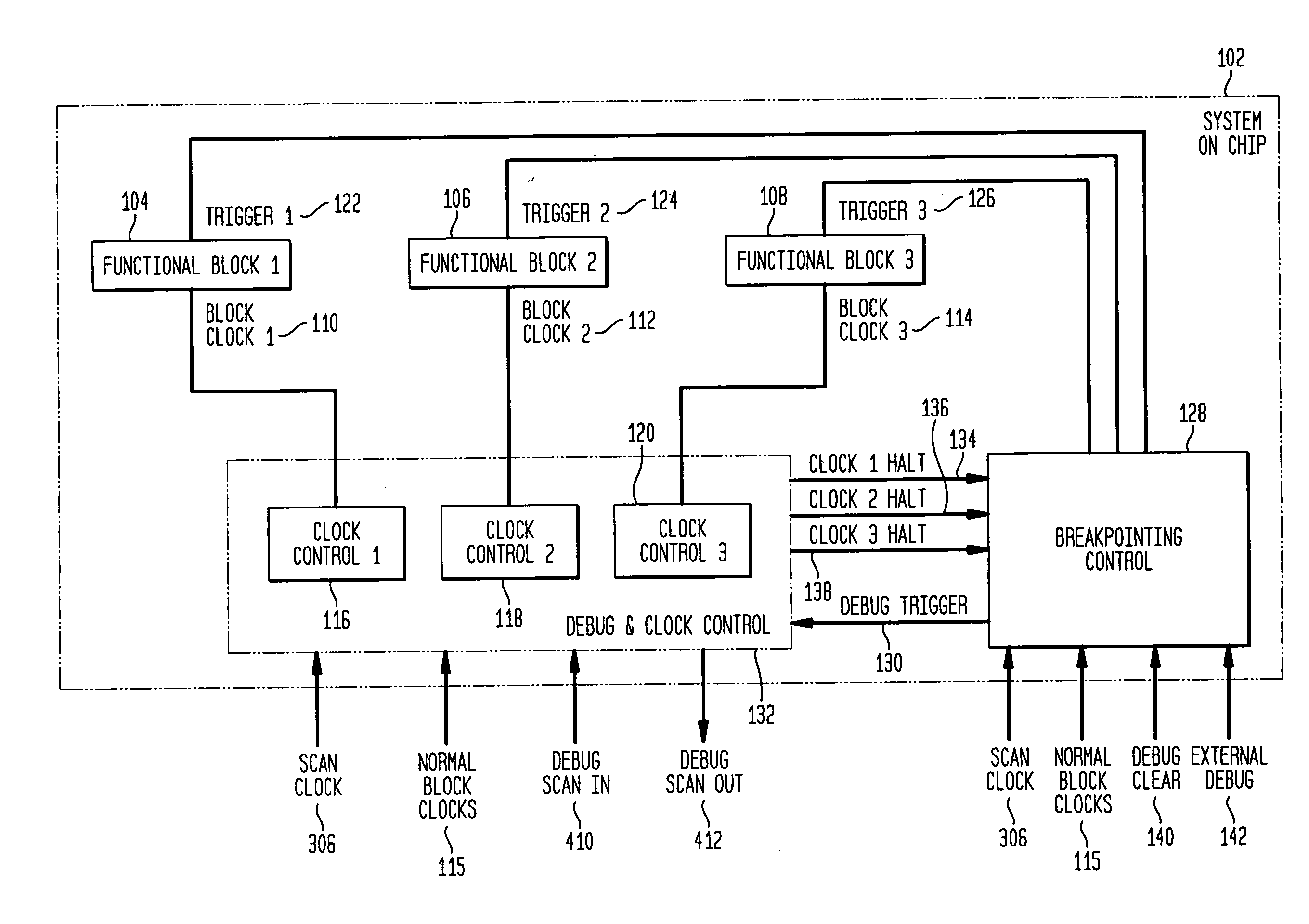

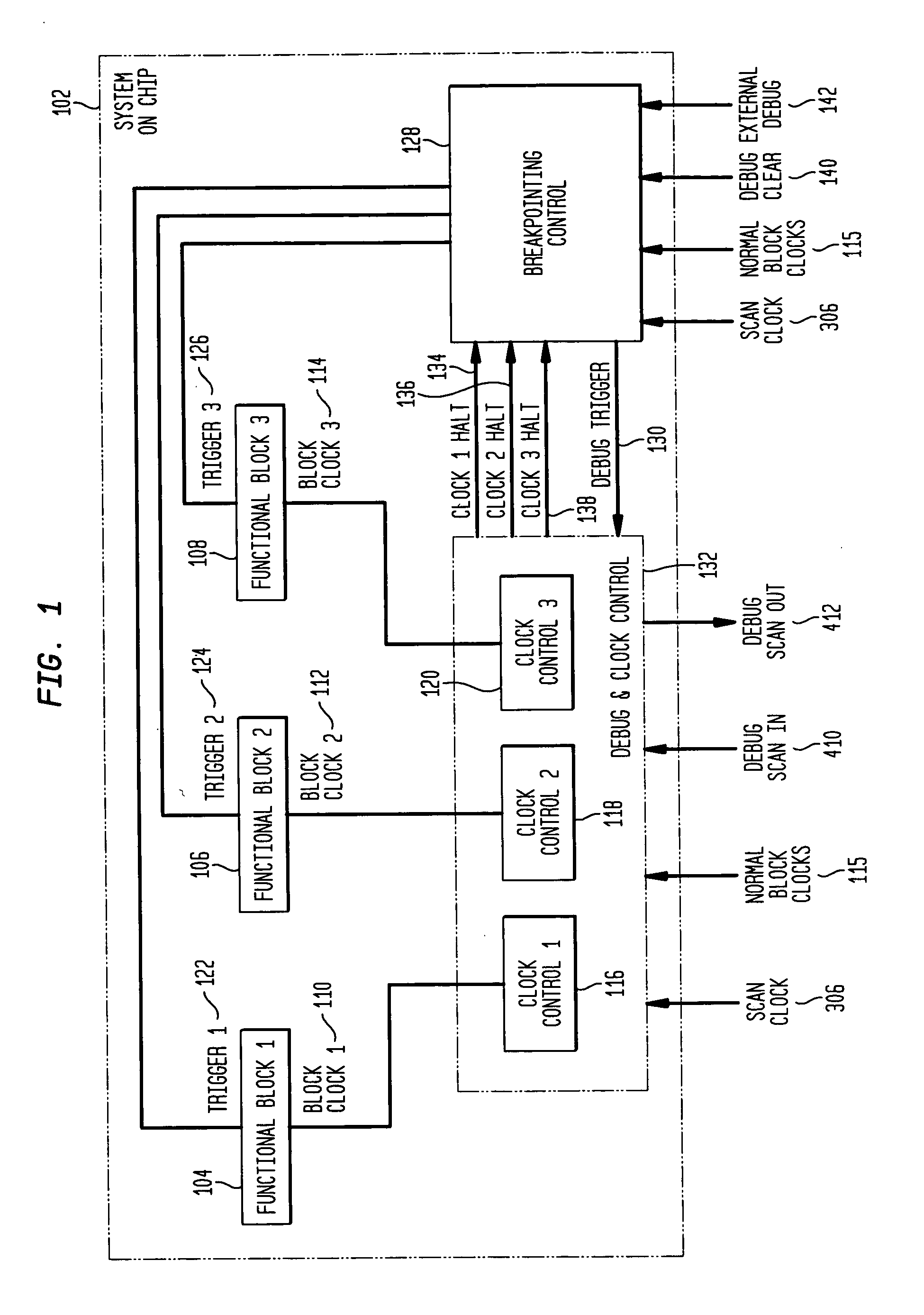

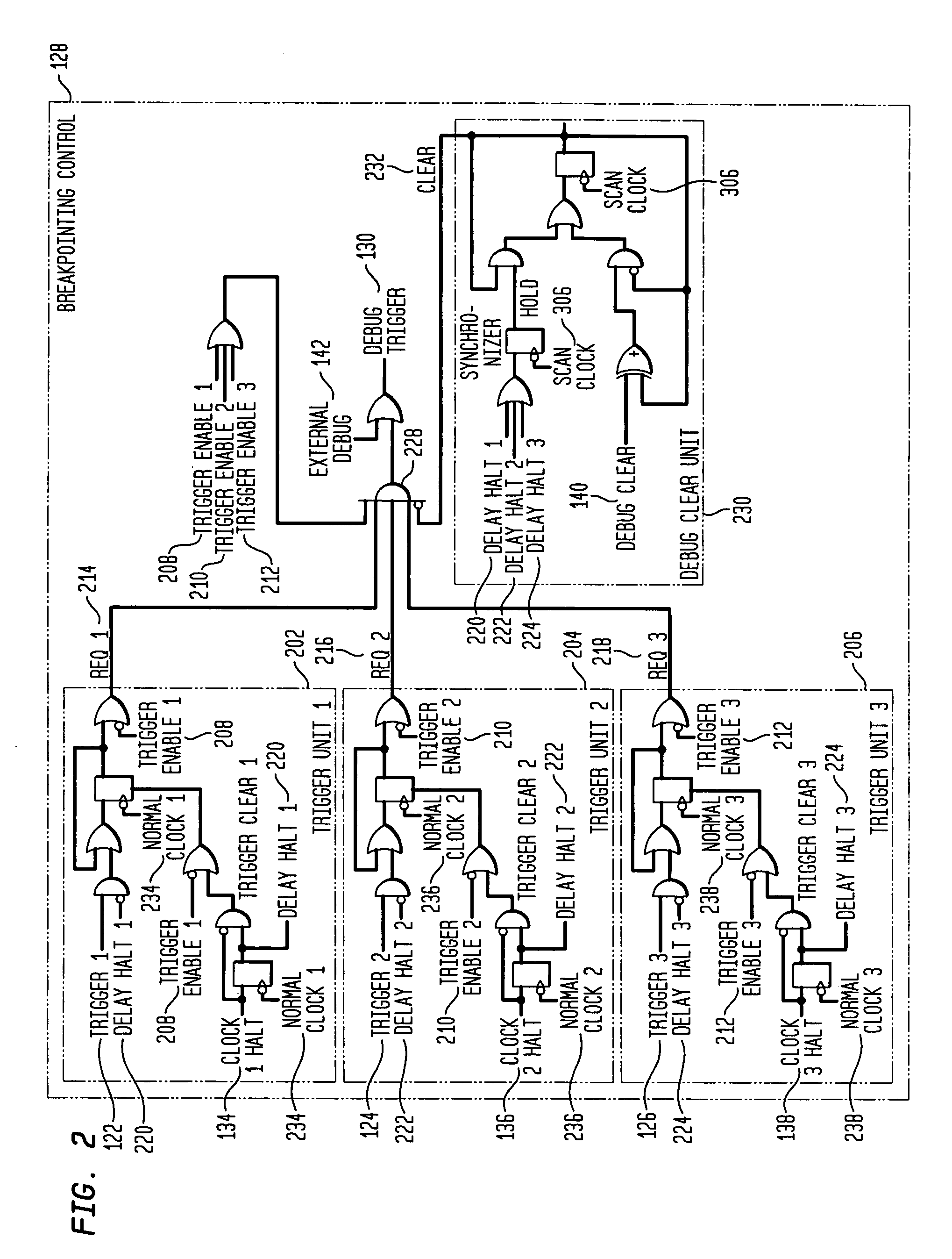

System and method for debugging system-on-chips using single or n-cycle stepping

InactiveUS20050149892A1Efficient debuggingEffective controlDigital circuit testingDetecting faulty computer hardwareReal systemsSoftware design

Large, complex SoCs comprise interconnections of various functional blocks, which blocks frequently running on different clock domains. By effectively controlling the clocks within the SoC, this invention provides a means to halt execution of a SoC and to then single or n-cycle step its execution in a real system environment. Accordingly, the invention provides an effective debugging tool to both the SoC designer and software designers whose code is executed by the SoC as it provides them the capability of studying the cause and effect of interactions between functional blocks. The invention is also applicable to SoCs containing only one functional block while containing complex circuitry operating on a clock different than the block's clock. In particular, the invention permits halting of the block clock and then single or n-cycle stepping its execution to permit analysis of the interactions between the block and the SoC circuitry.

Owner:BELL SEMICON LLC

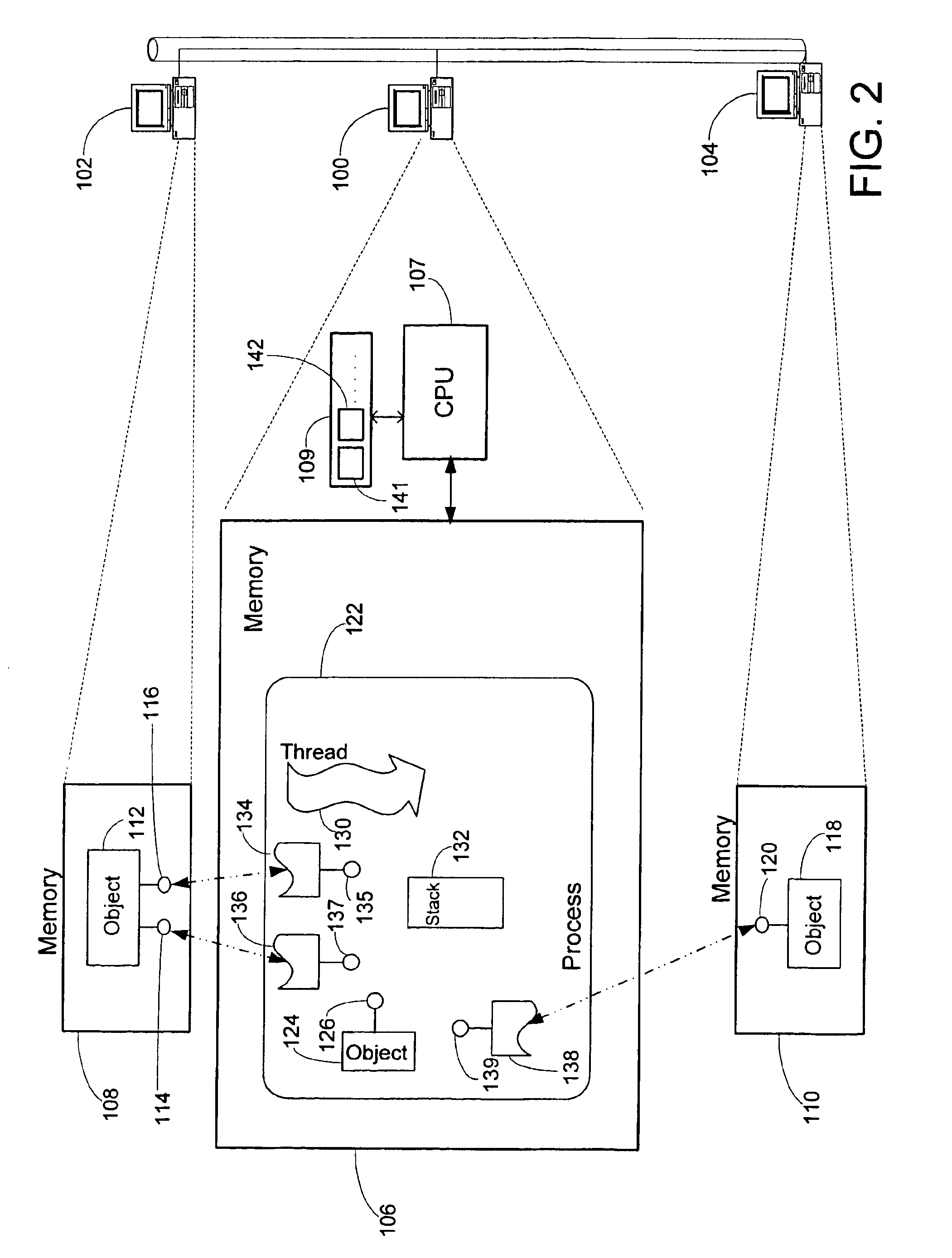

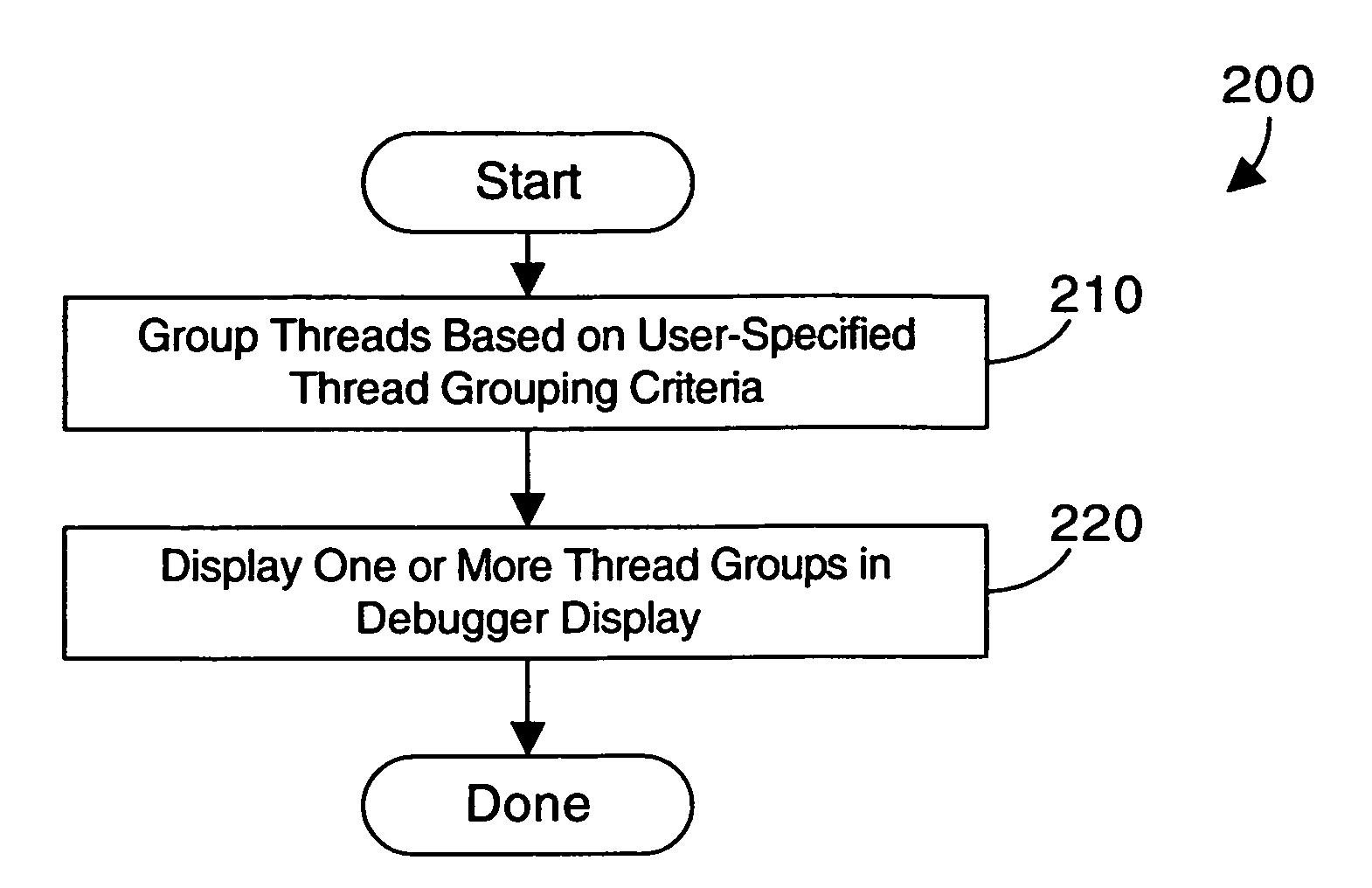

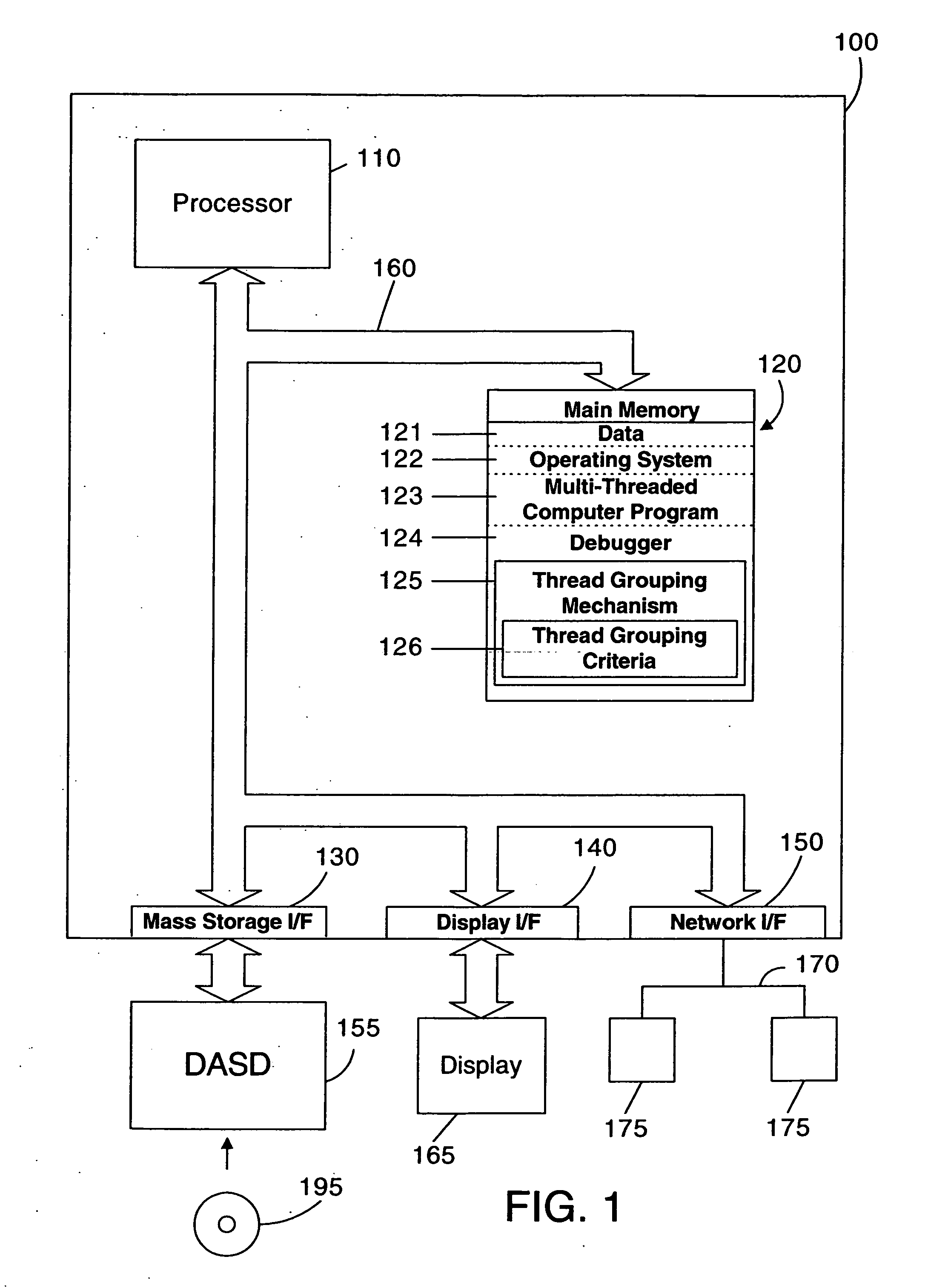

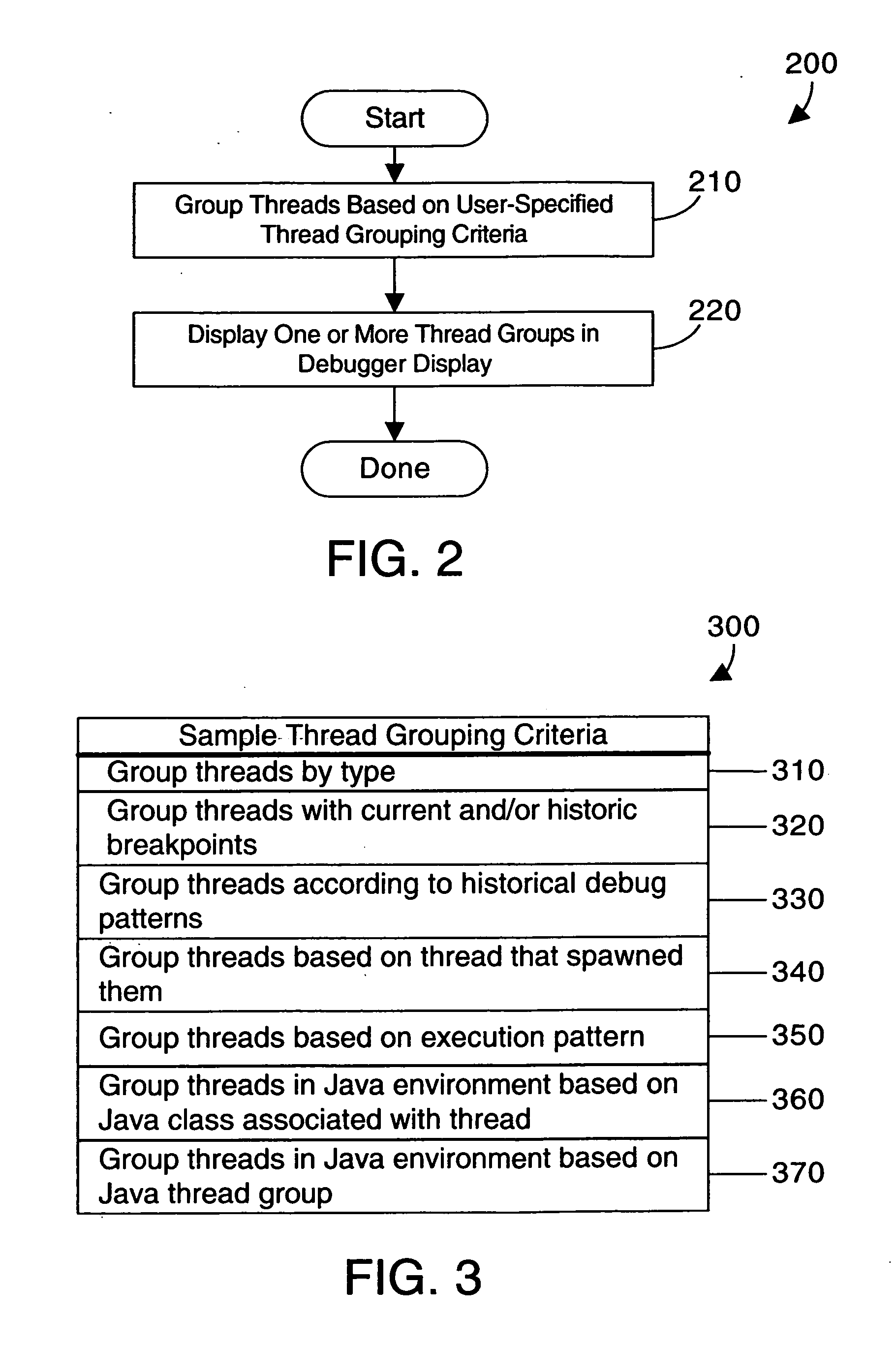

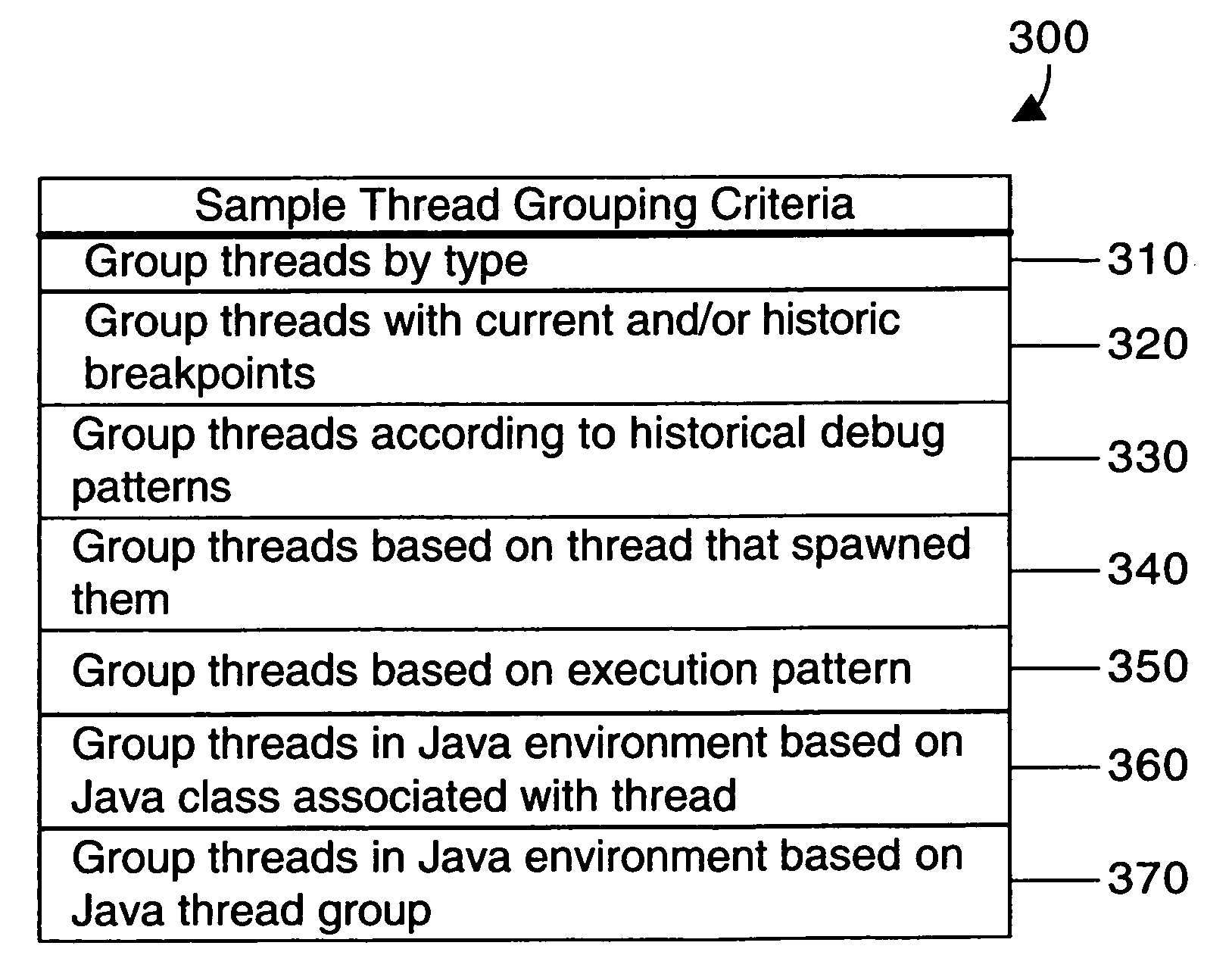

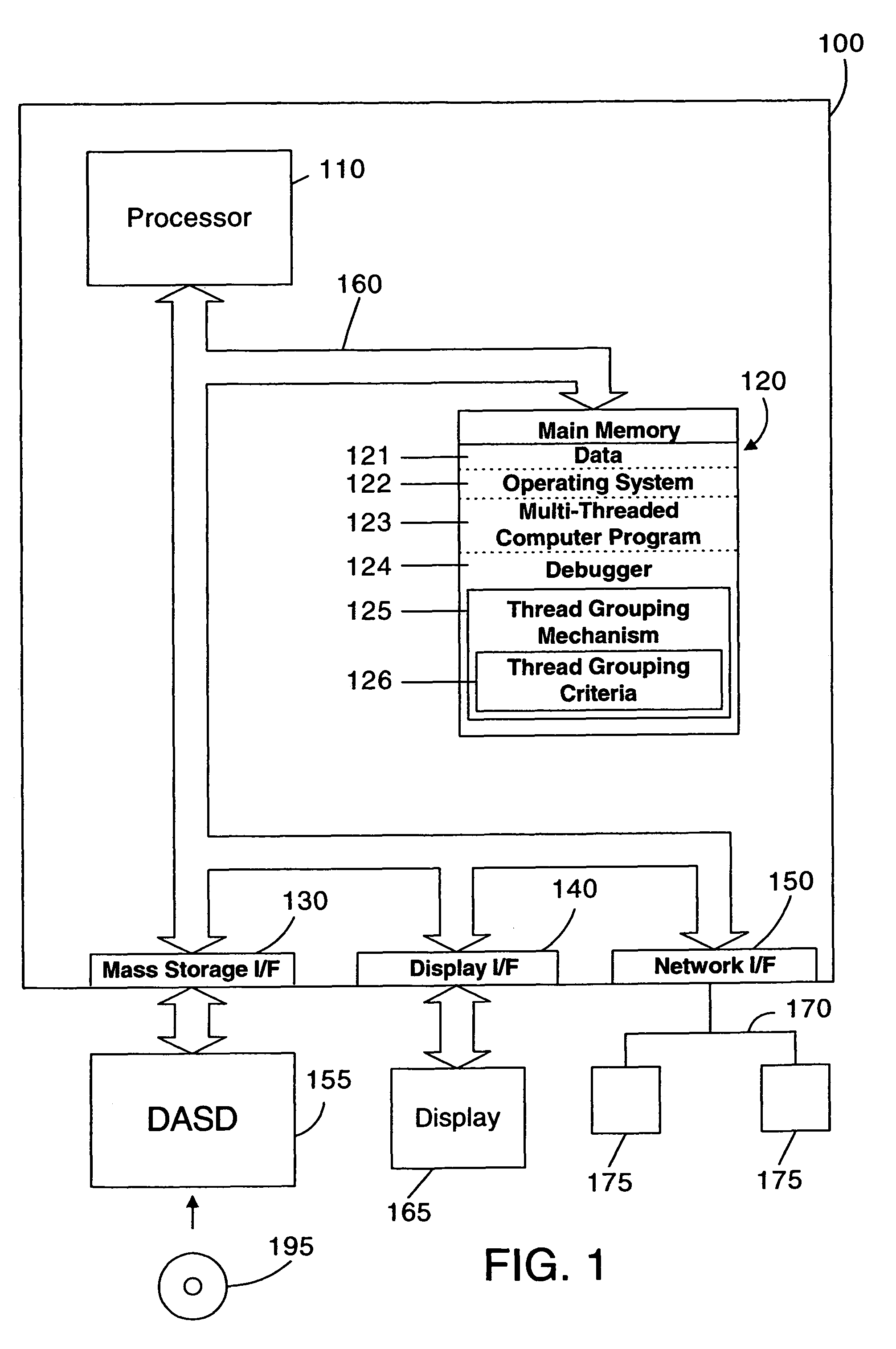

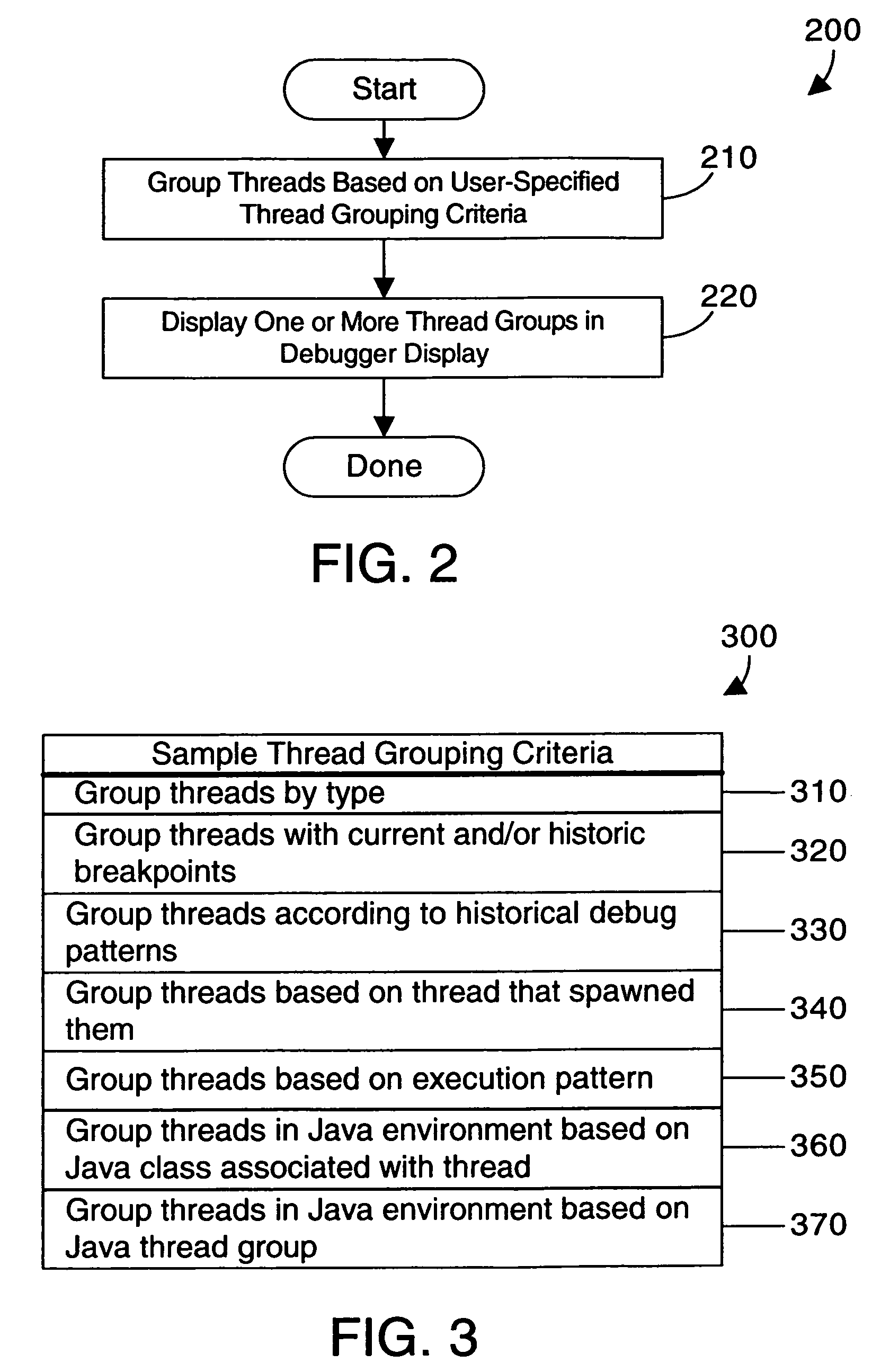

Apparatus and method for grouping threads in a debugger display

InactiveUS20070150867A1Efficient debuggingError detection/correctionSpecific program execution arrangementsGraphicsObject Class

A debugger display groups threads according to user-specified criteria. The threads may be grouped by type, by current or historic breakpoints, according to historical debug patterns, based on what thread spawned the thread, based on execution pattern, based on object class in a Java environment, based on Java thread group in a Java environment, or base on other suitable criteria. The grouping of threads is displayed graphically to a user of the debugger, thereby allowing more efficient debugging of multi-threaded computer programs.

Owner:LINKEDIN

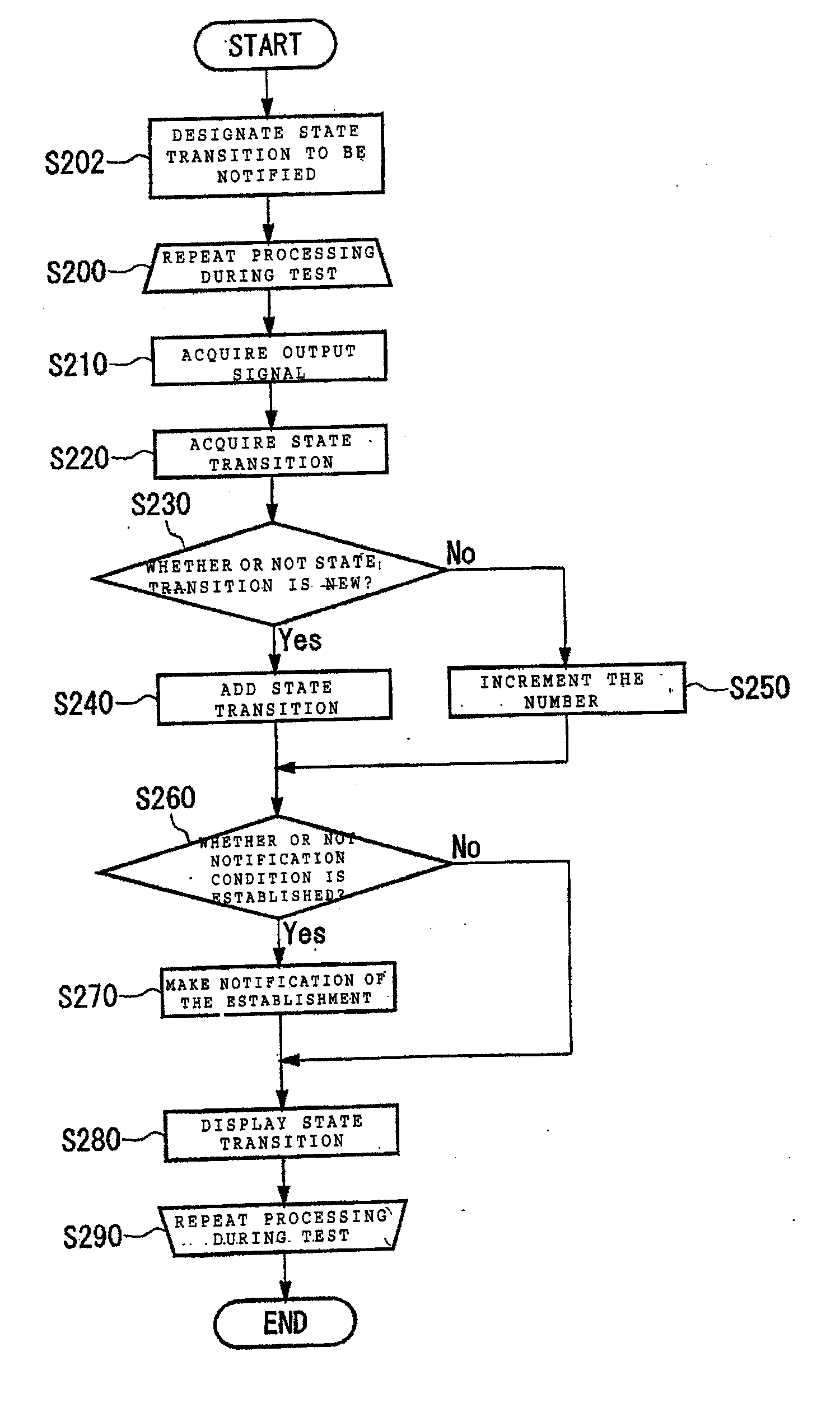

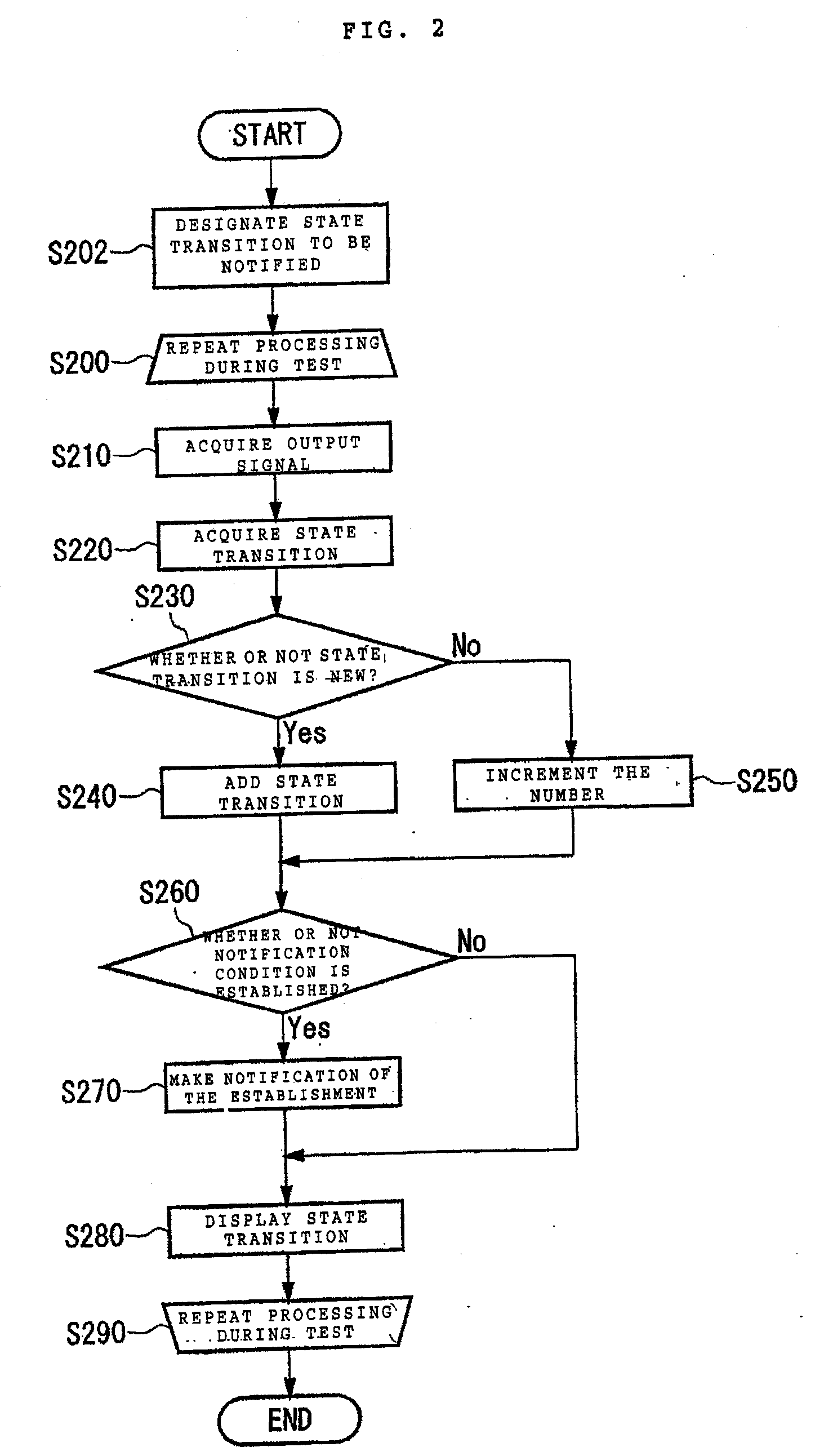

Visualization method and apparatus for logic verification and behavioral analysis

InactiveUS20060080626A1Efficient debuggingError detection/correctionElectrical testingRegression testingElectronic systems

A logic verification tool detects and flags a logic operation with high probability to cause a fault in an electronic system. An efficient logic debug method utilizes a partial sequence of signal outputs and state transitions to extrapolate a verification result with equivalent robustness to full regression testing.

Owner:GLOBALFOUNDRIES INC

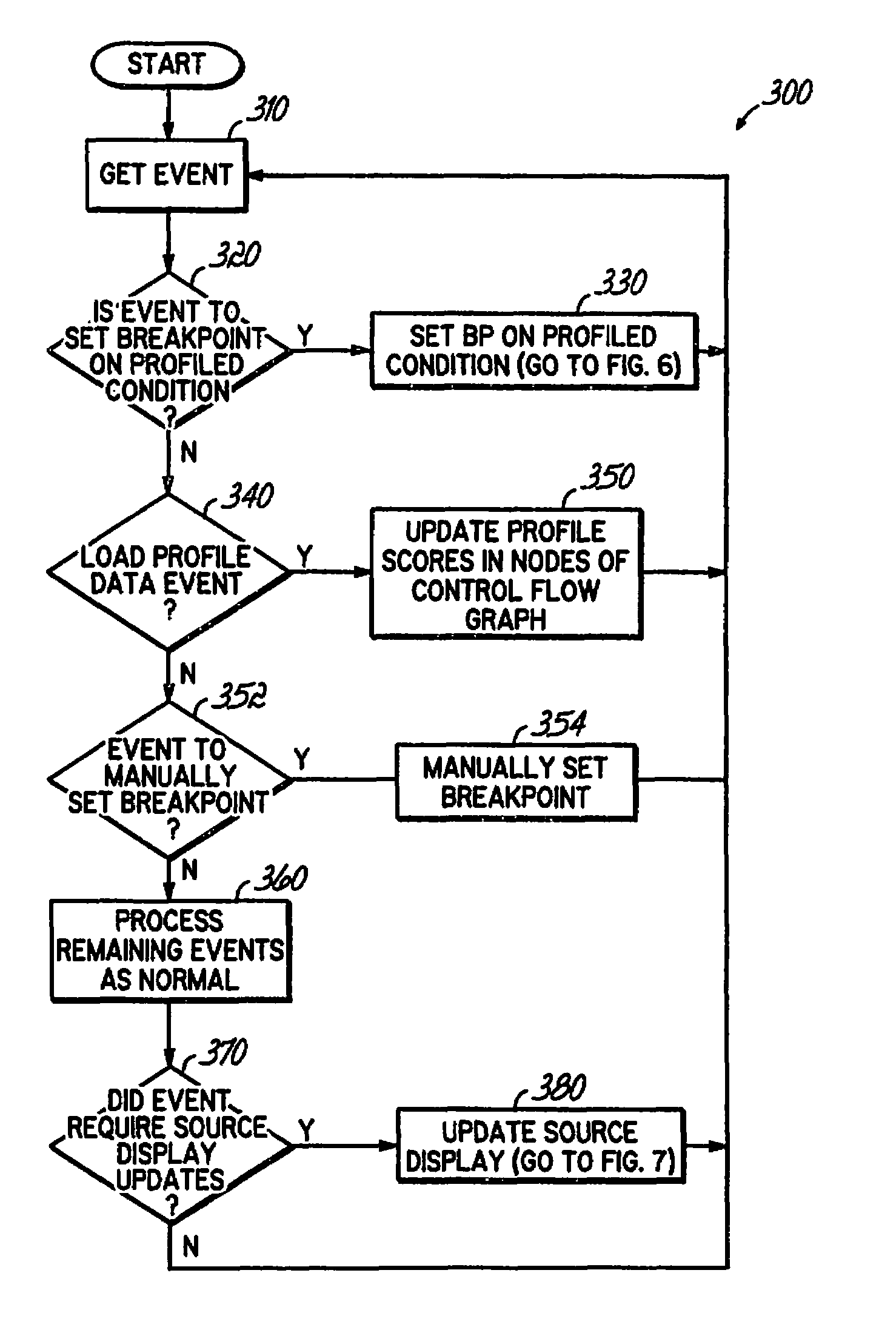

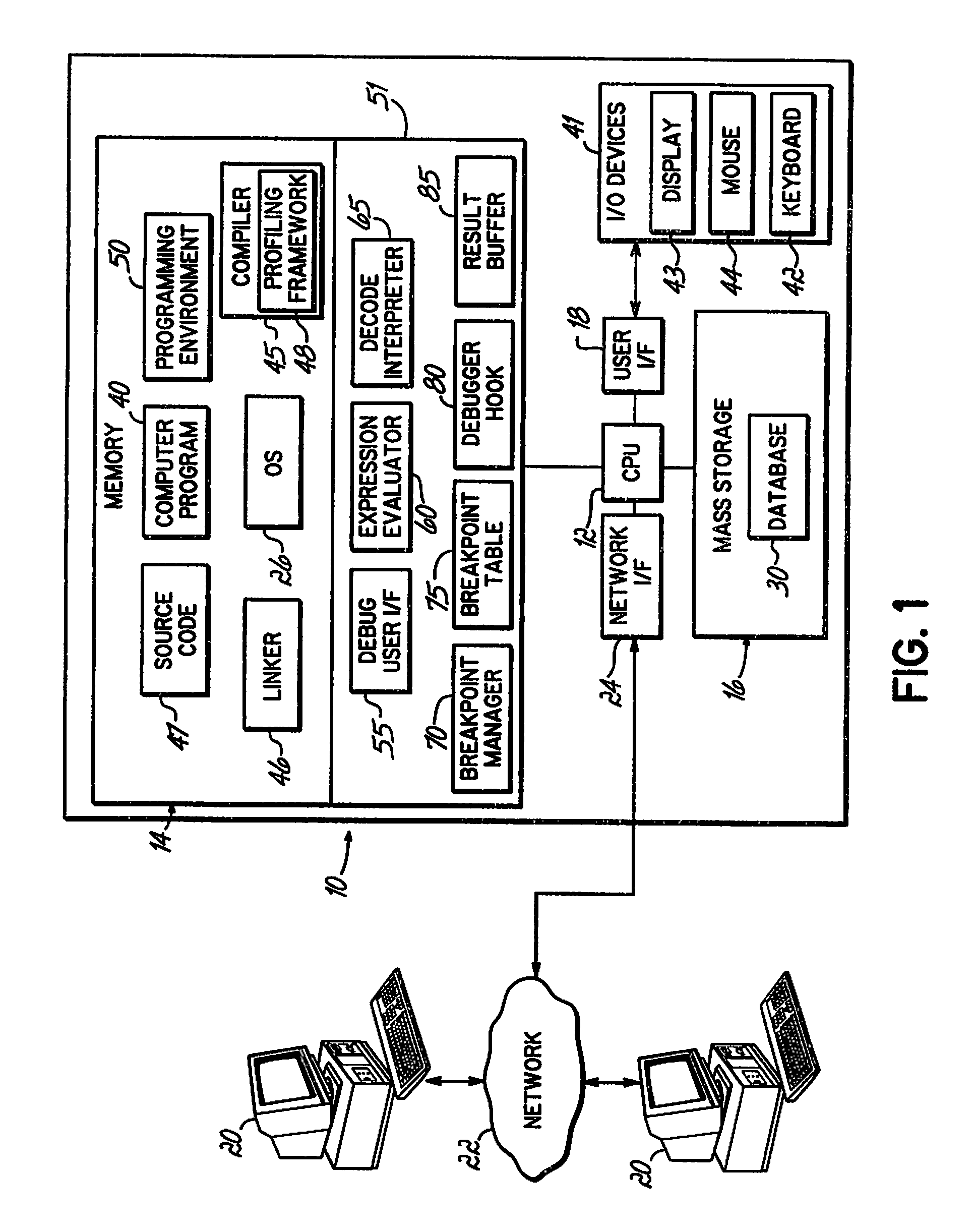

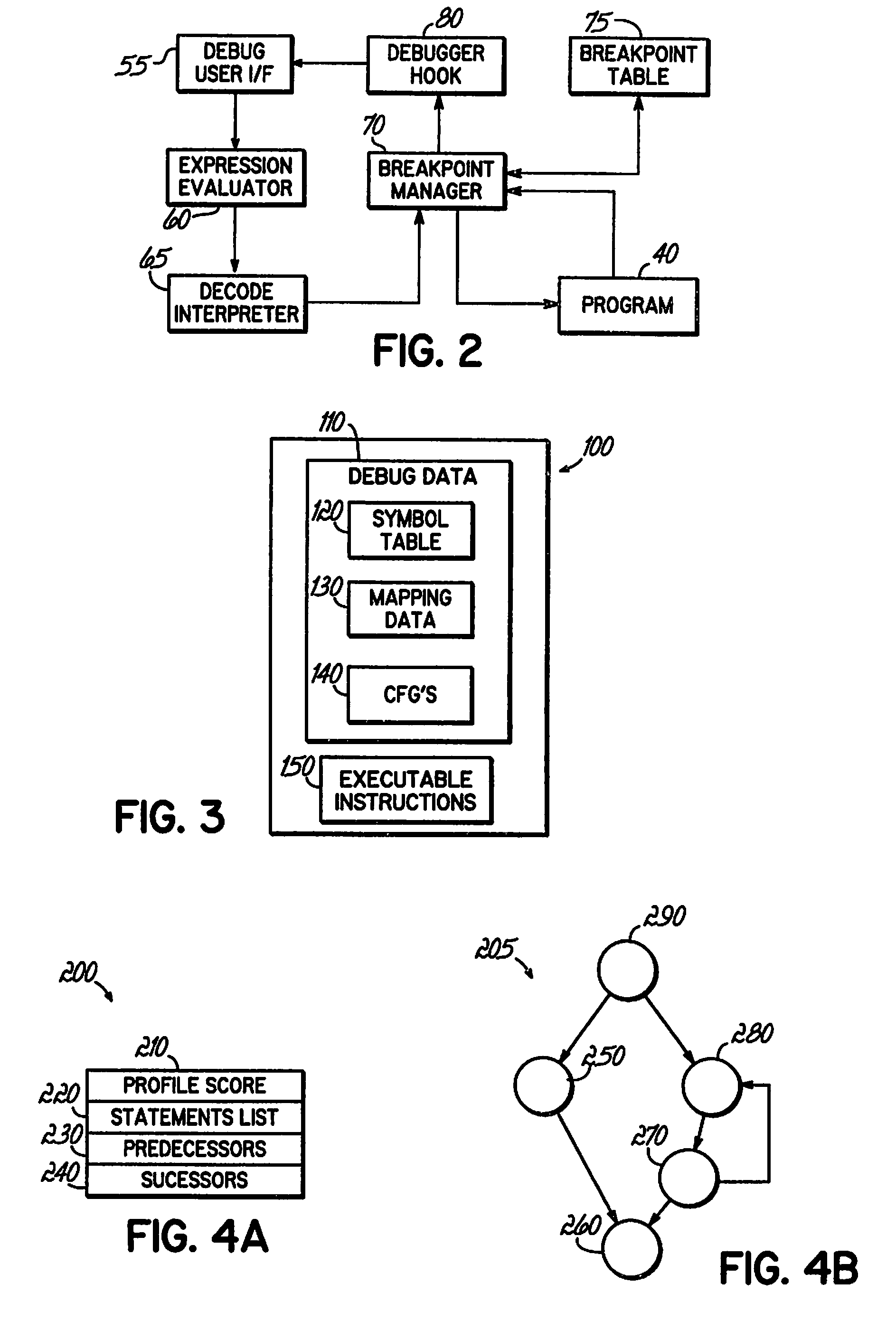

Identifying a potential breakpoint location in a code path in a computer program based upon the frequency of execution of the code path as identified in collected profile data

InactiveUS8219980B2Efficient debuggingError detection/correctionSpecific program execution arrangementsParallel computingComputer program

An apparatus, program product and method identify a potential breakpoint location in a code path in a computer program based upon the frequency of execution of the code path as identified in collected profile data. By doing so, a potential breakpoint location may be identified for an infrequently executed code path and / or a frequently executed code path, and a breakpoint may be set at the identified breakpoint location. As such, breakpoints may be set in locations that may be more likely to assist a user in debugging the computer program and may result in more efficient debugging.

Owner:IBM CORP

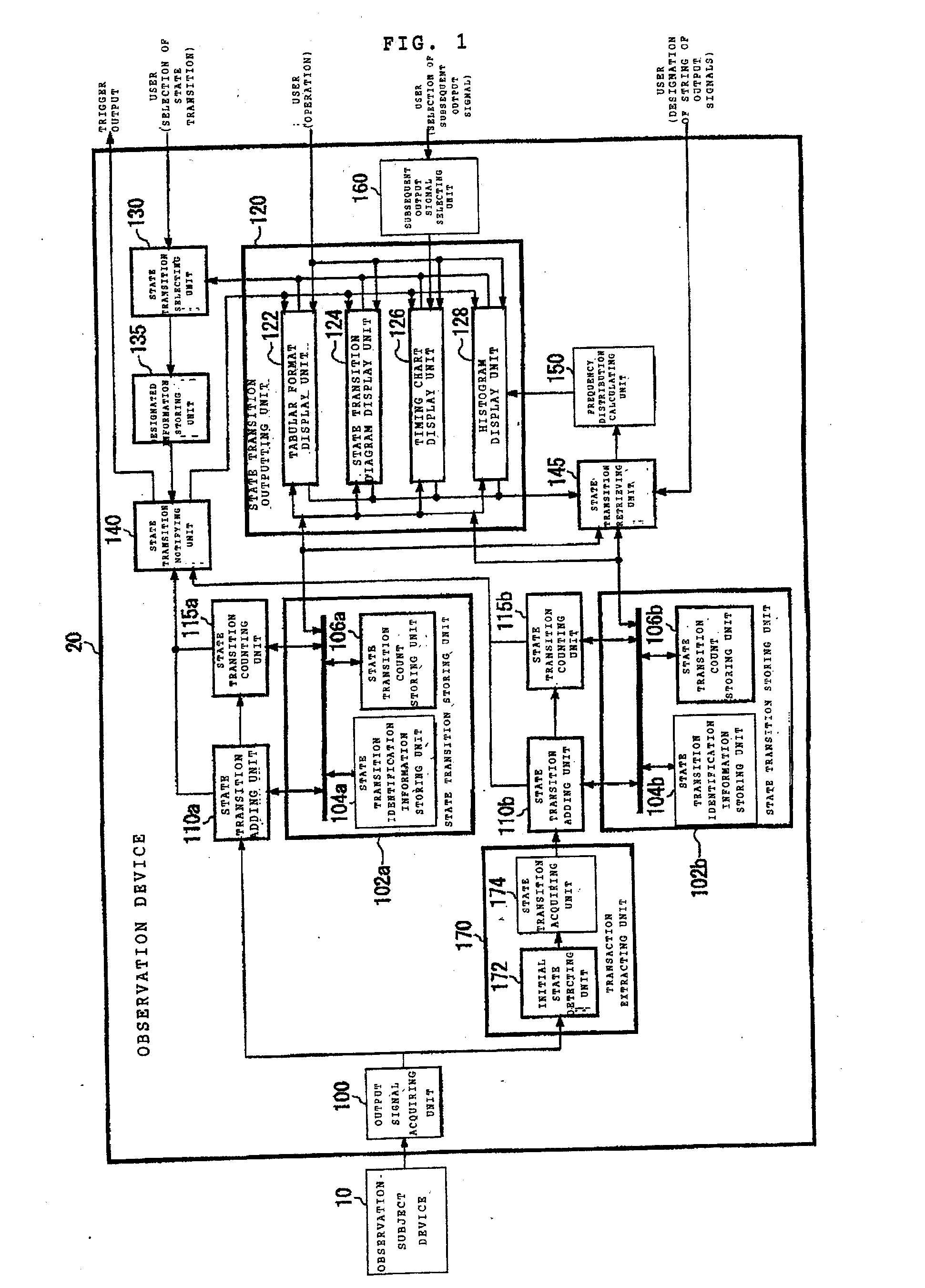

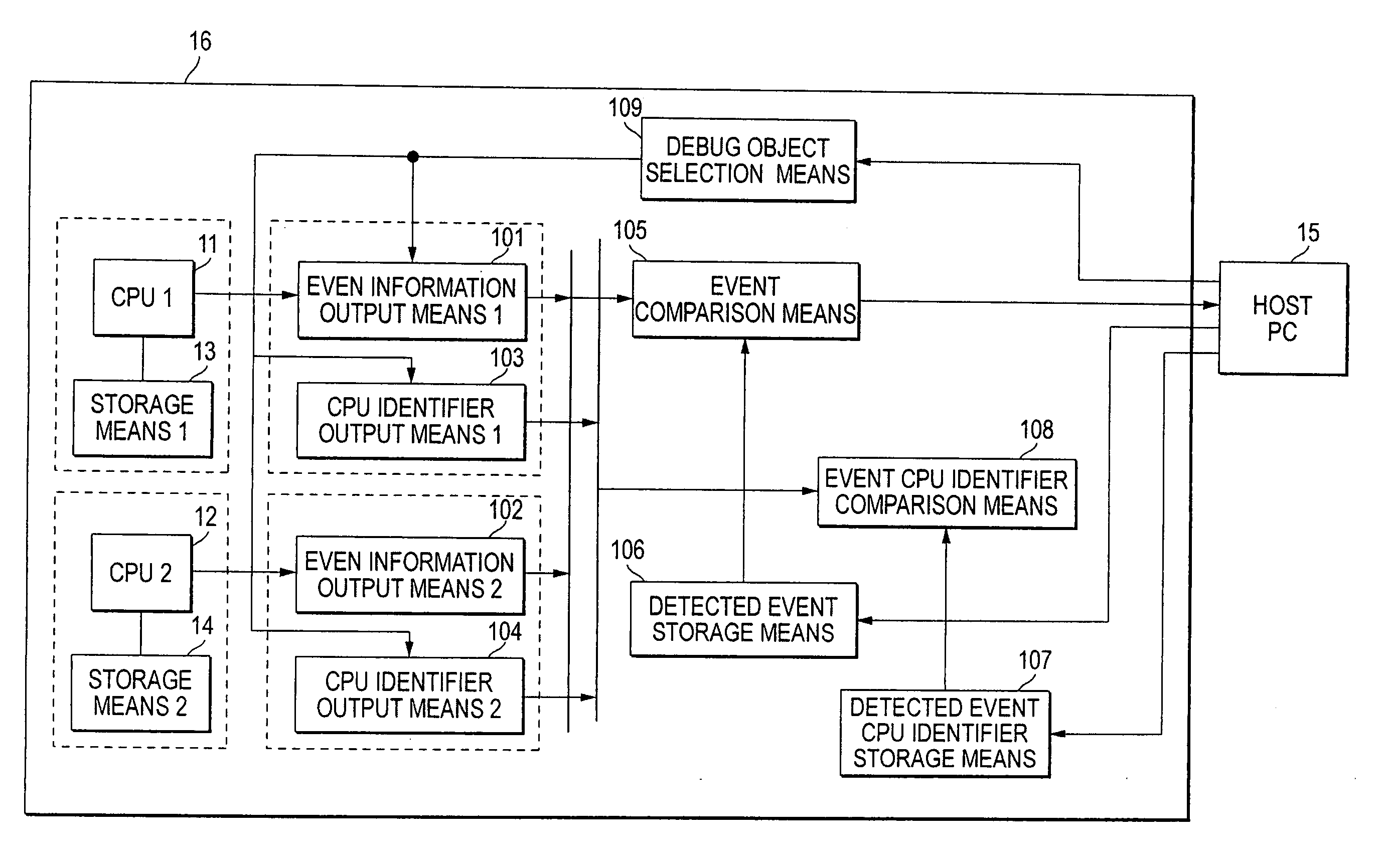

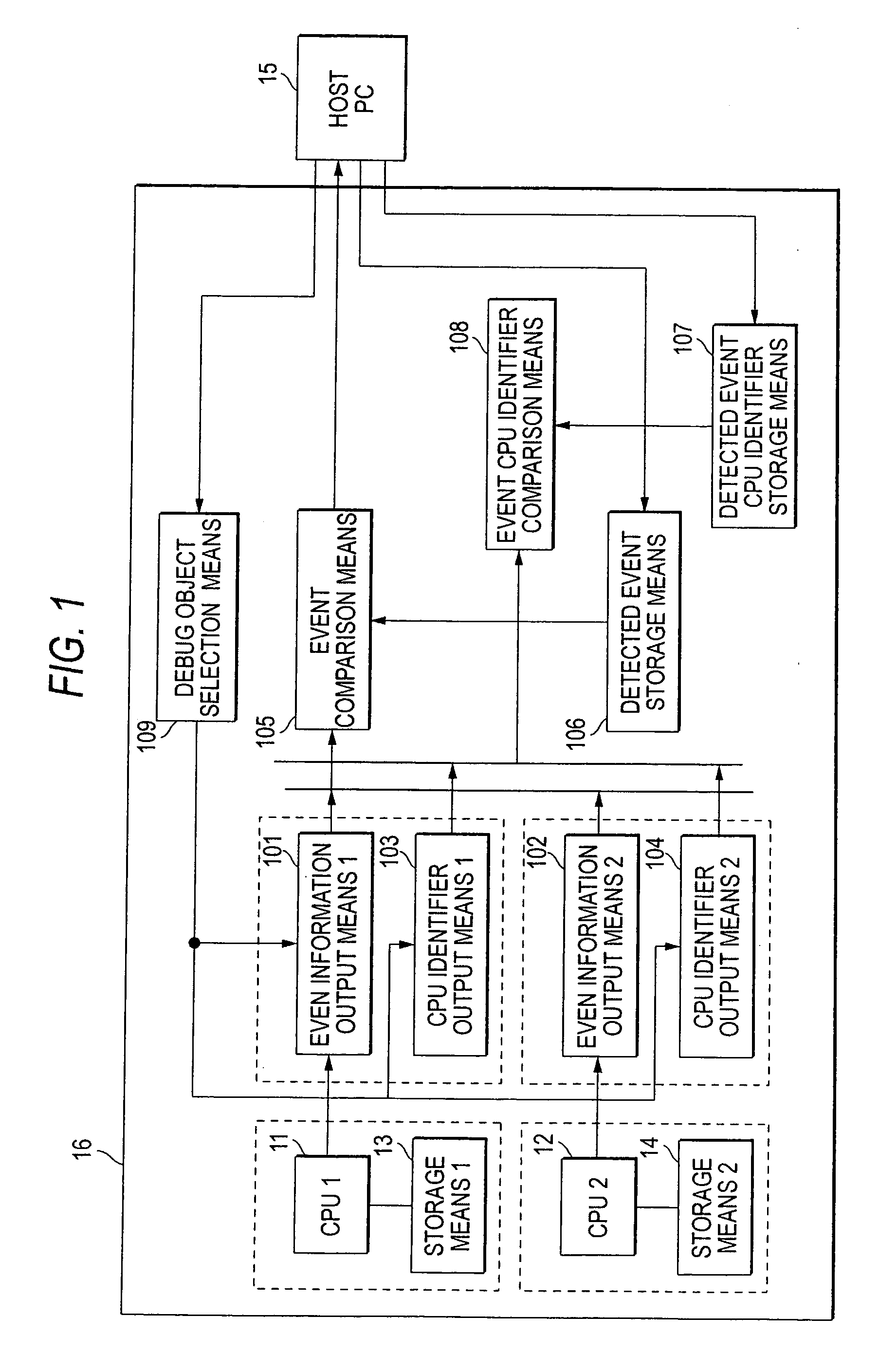

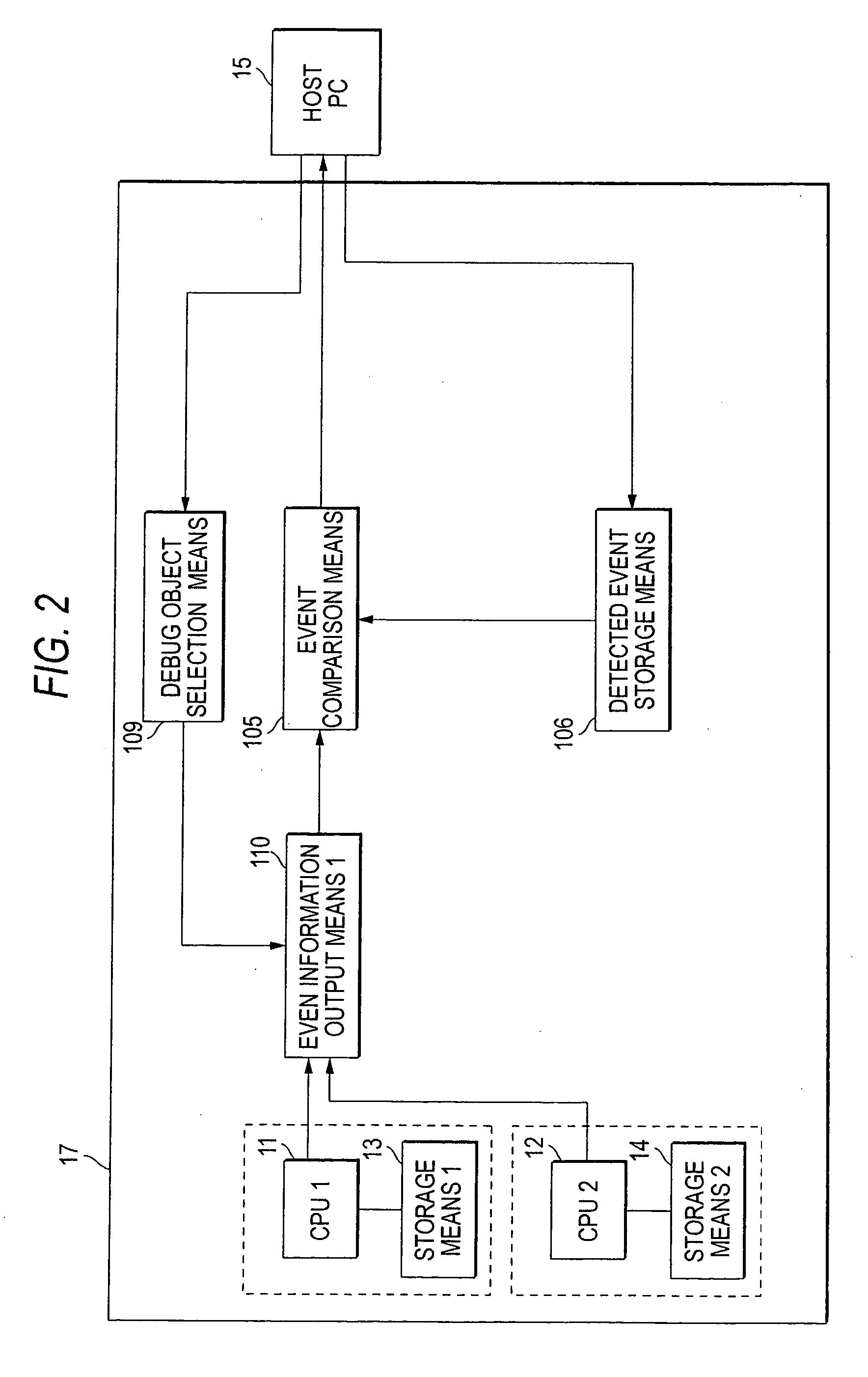

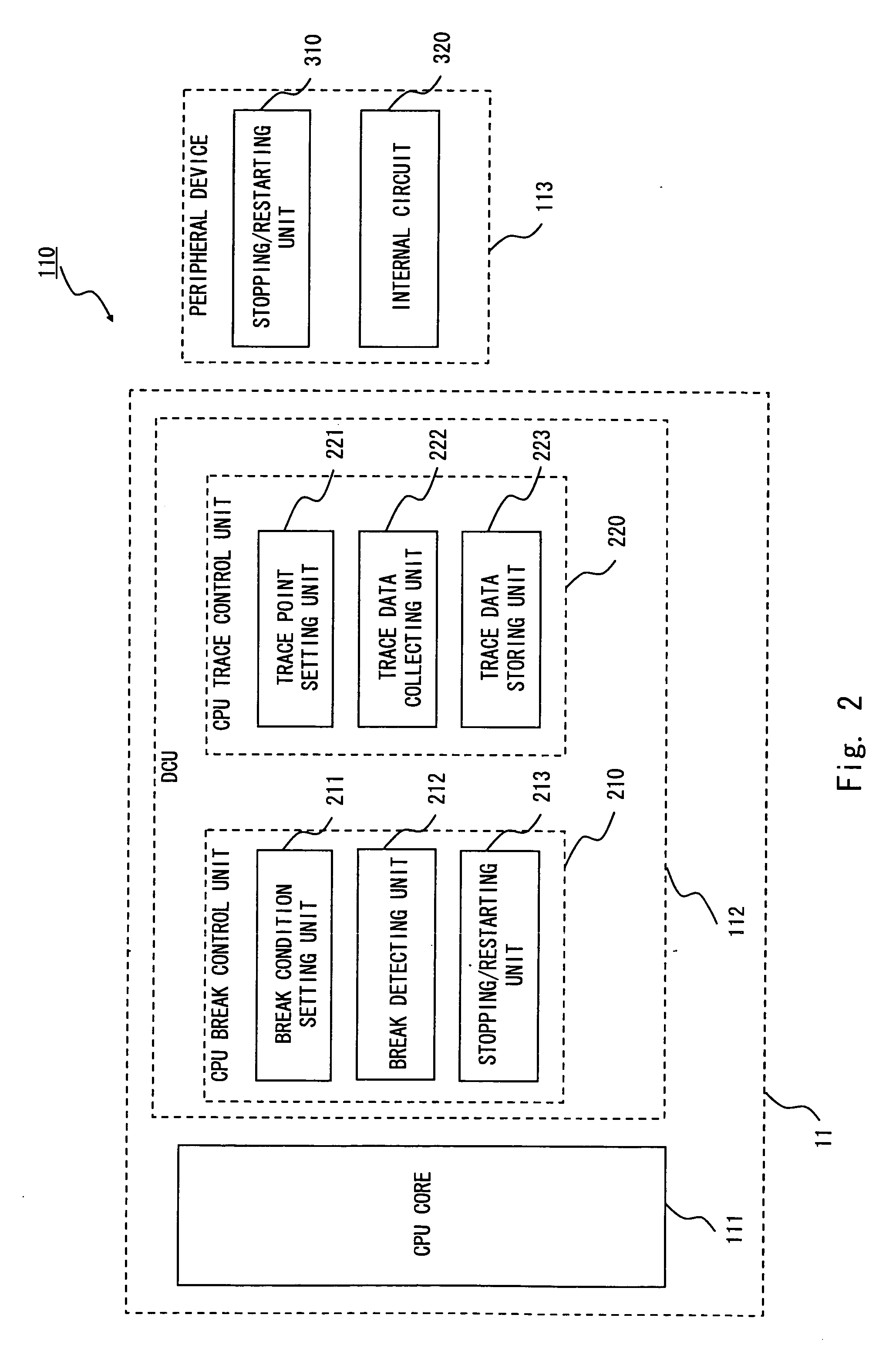

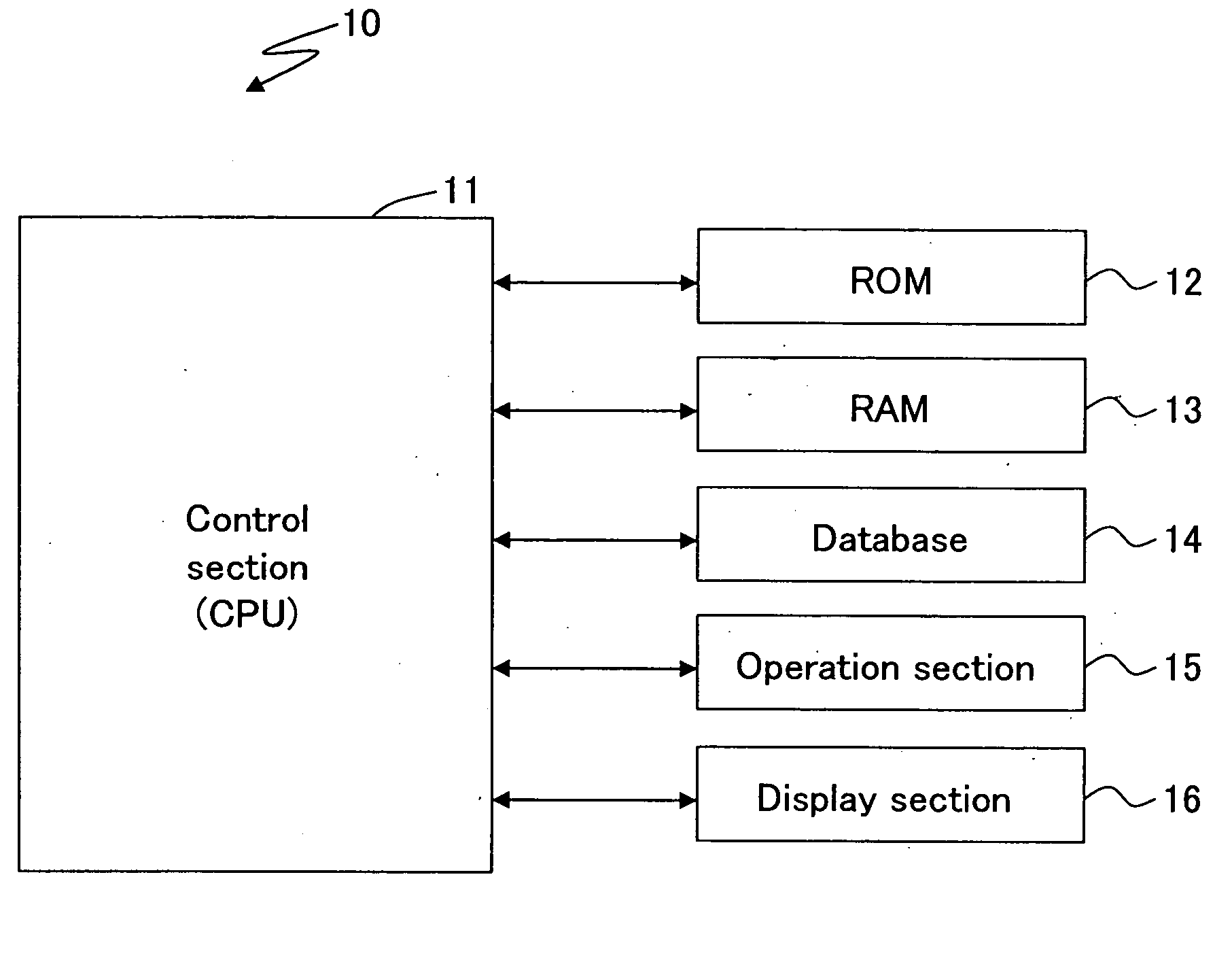

Debugging apparatus

InactiveUS20060150023A1Shorten timeImprove debug efficiencyError detection/correctionElectrical testingComputer hardware

To efficiently debug while reducing a debugging circuit in a system LSI made up of a plurality of CPUs. A debugging apparatus includes debug object selection means 109 for selecting the CPU to be debugged from CPUs 11 and 12 in accordance with a debug object selection request from a host PC 15 connected to a system LSI 17, event information output means 110 for outputting internal event information of one selected CPU to be debugged, detected event storage means 106 for temporarily storing a detected event set by the host PC 15, and event comparison means 105 for making a comparison between the internal event information output from the event information output means 110 and the detected event stored in the detected event storage means 106 to detect a match therebetween. The event comparison means 105 notifies the host PC 15 that an event match is detected.

Owner:PANASONIC CORP

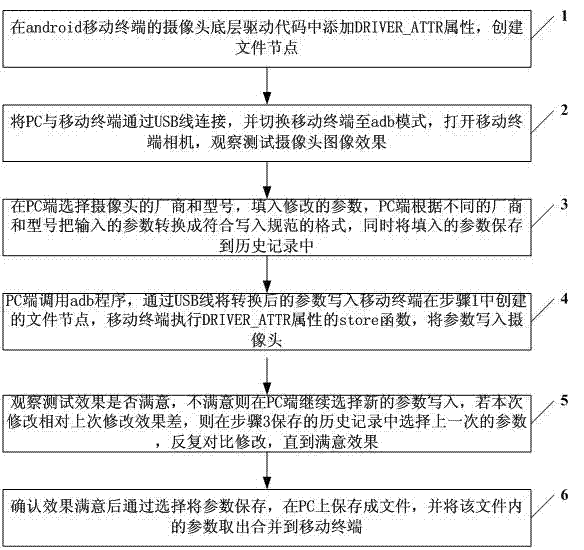

Camera online debugging method

ActiveCN103049375AEfficient debuggingImprove debugging efficiencySoftware testing/debuggingCamera imageComputer terminal

The invention discloses a camera online debugging method. A camera is arranged on a mobile terminal. The camera online debugging method includes the following steps: adding DRIVER_ATTR attributes in a camera bottom driving code at an android mobile terminal, and building document nodes; connecting a person computer (PC) with the mobile terminal through a universal serial bus (USB), switching the mobile terminal to an adb mode, opening the mobile terminal camera, and observing and testing camera image effect; selecting manufacturers and models of the camera at the PC end, and filling modified parameters; calling an adb program through the PC end, writing the switched parameters in the document nodes built in the mobile terminal through the USB, executing a store function of the DRIVER_ATTR attributes through the mobile terminal, and writing the parameters in the camera; contrasting and modifying repeatedly till results are satisfied; and storing the parameters. The camera online debugging method performs online real-time humanized and efficient debugging on the camera, can effectively improve camera debugging efficiency of the android system, and picks up best effect parameters conveniently.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

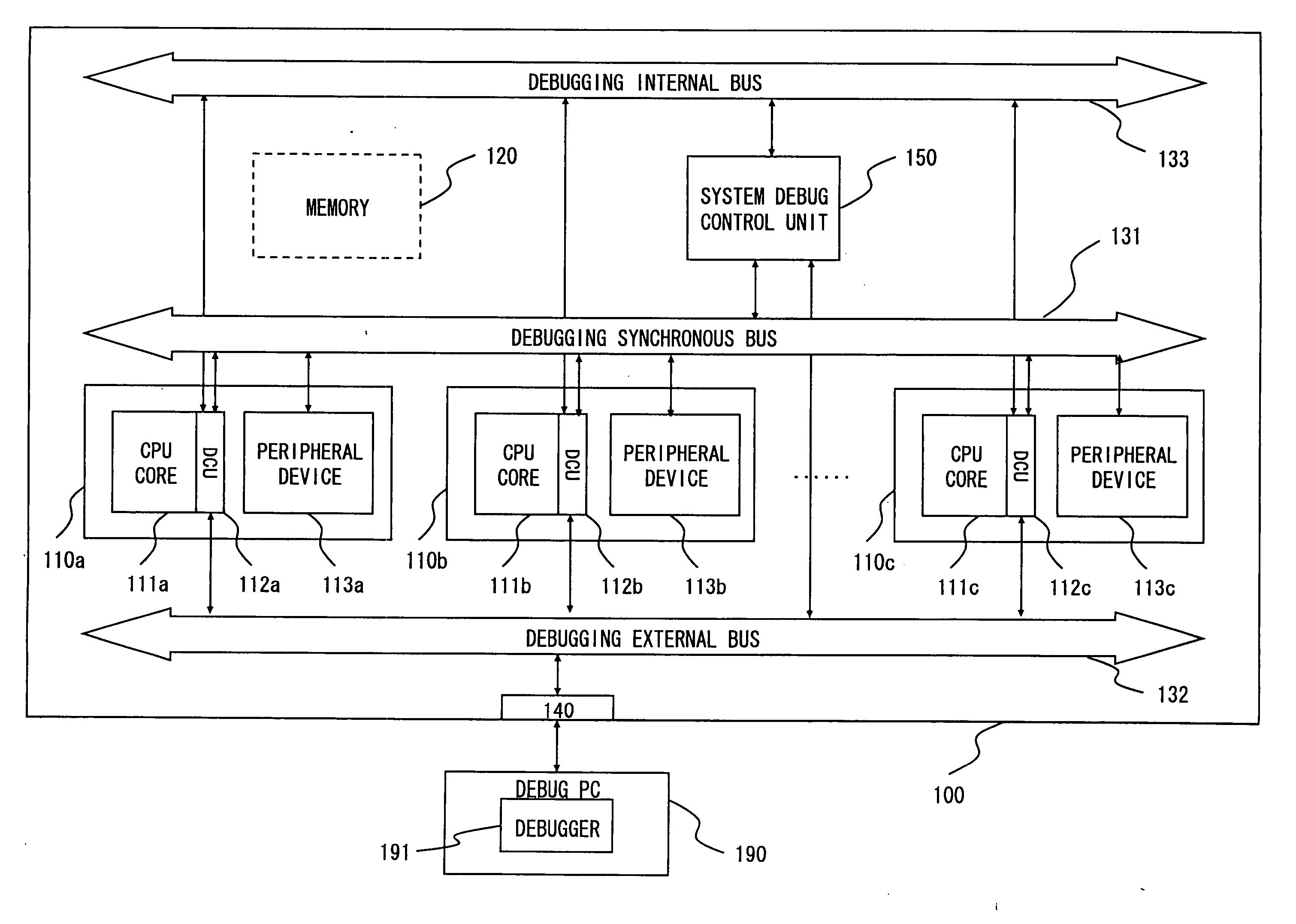

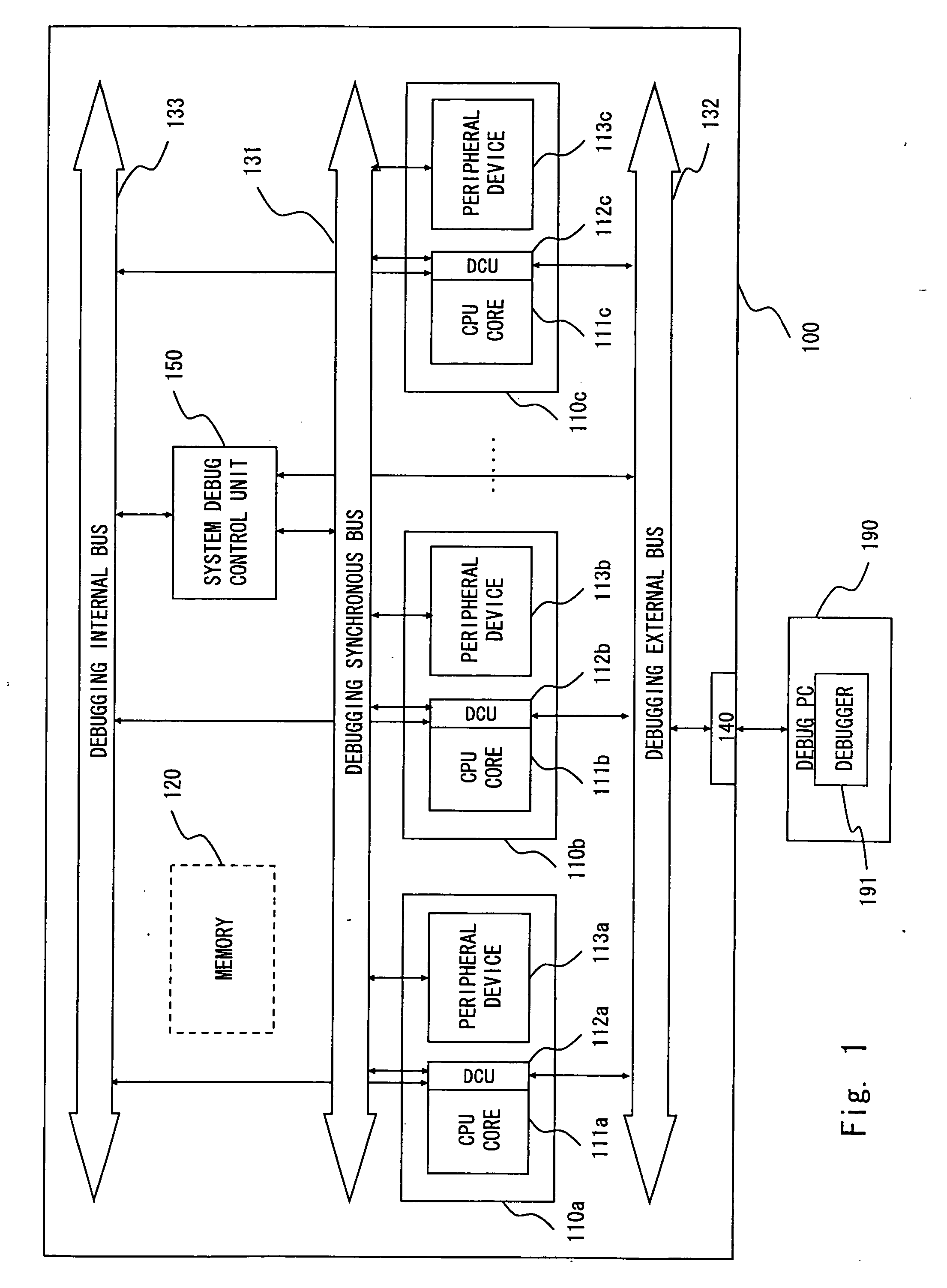

Semiconductor integrated circuit device, and debugging system and method for the semiconductor integrated circuit device

ActiveUS20070101198A1Improve debugging efficiencyEfficient debuggingError detection/correctionEngineeringSemiconductor

To provide a debugging system, debugging method, and a semiconductor integrated circuit device capable of collecting debug-target information with accuracy and improving debug efficiency. A semiconductor integrated circuit device according to an embodiment of the present invention includes: subsystems; a break detecting unit detecting that a program execution of a CPU core in one subsystem satisfies a predetermined break condition; and a break selecting unit stopping operations of one selected from the subsystems in accordance with the detection result of the break detecting unit.

Owner:RENESAS ELECTRONICS CORP

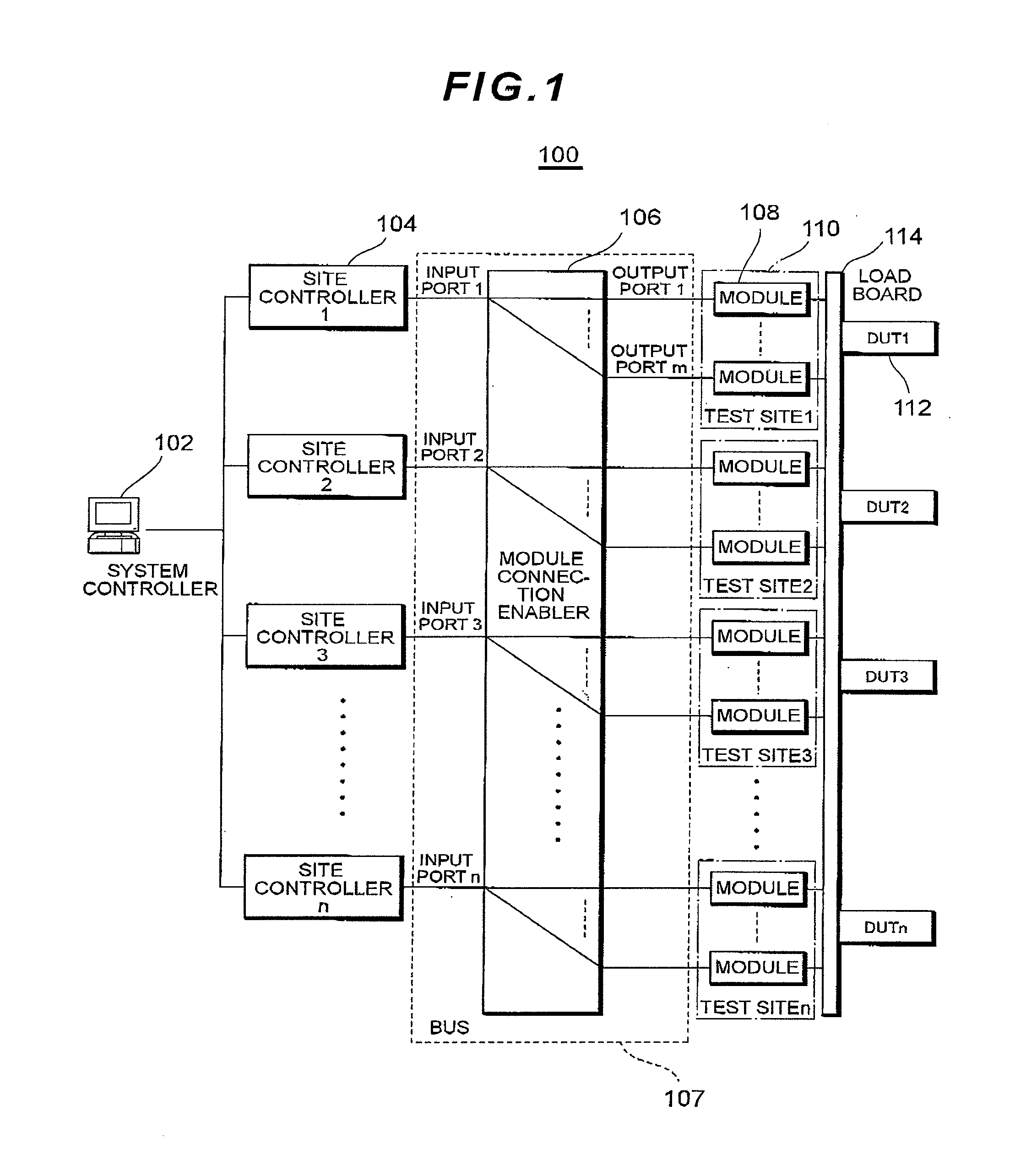

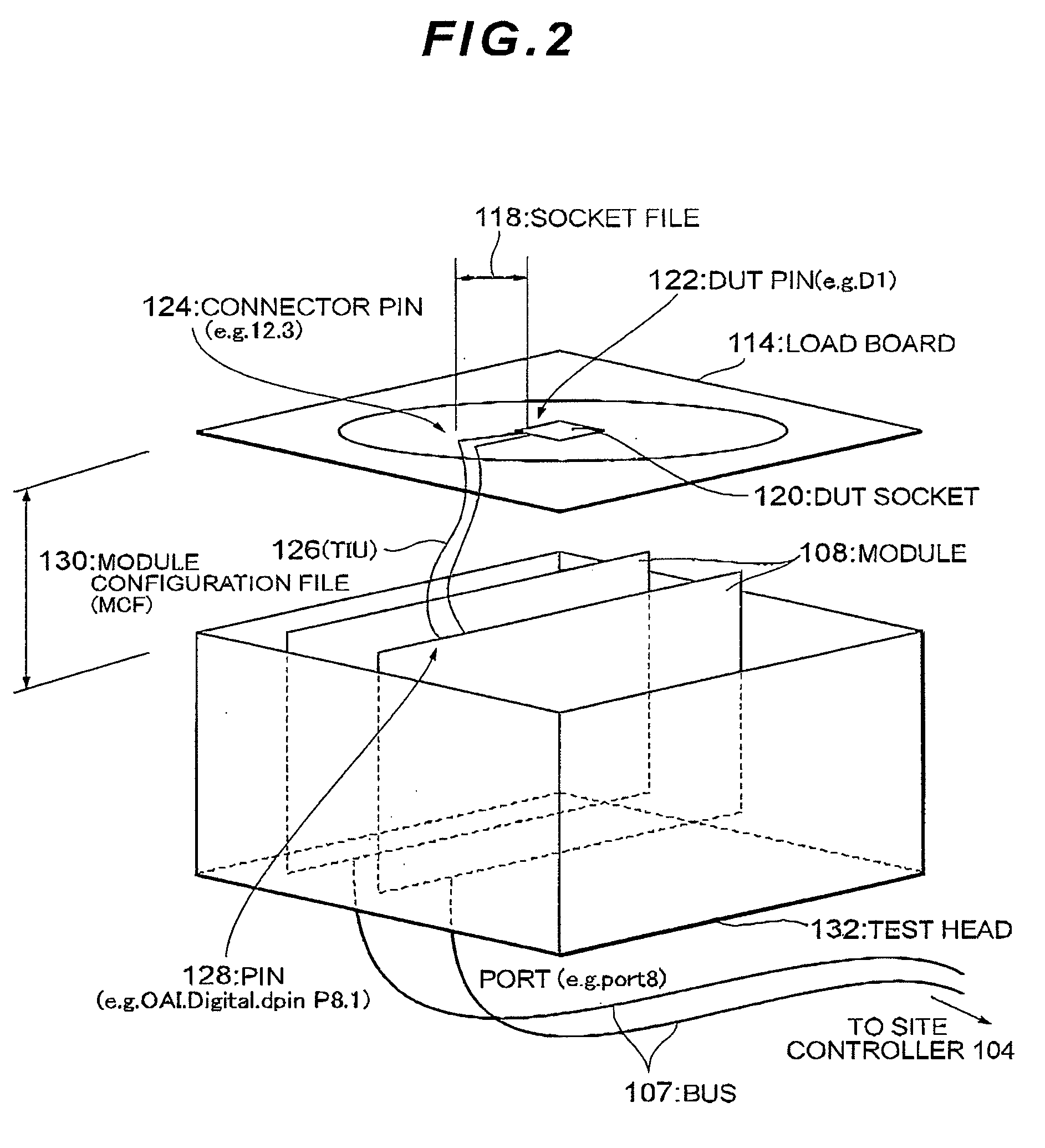

Test system and method which can use tool during debugging

InactiveUS20090204849A1Efficient testingEfficient debuggingFunctional testingProgramming languageTesting equipment

A test process executed by a test system includes a test class thread for executing a test class in which a procedure for testing a device is described, and a tool thread for executing a tool which includes a function that can be used for the test of the device. Then, during debugging of the test class, the test system controls the test class thread so that the test class thread is in a stopped state, and controls the tool thread so that the tool thread is in an operating state.

Owner:ADVANTEST CORP

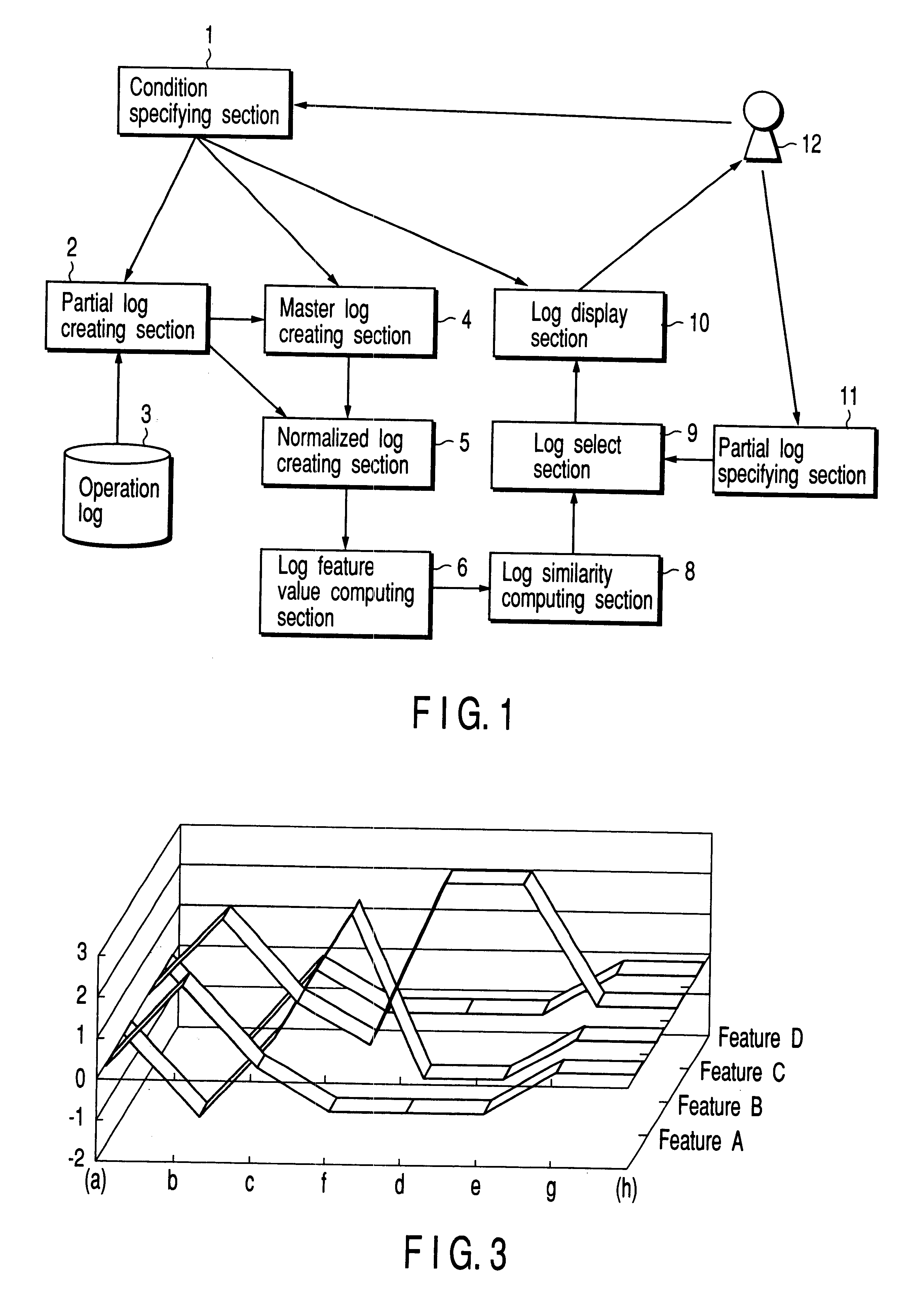

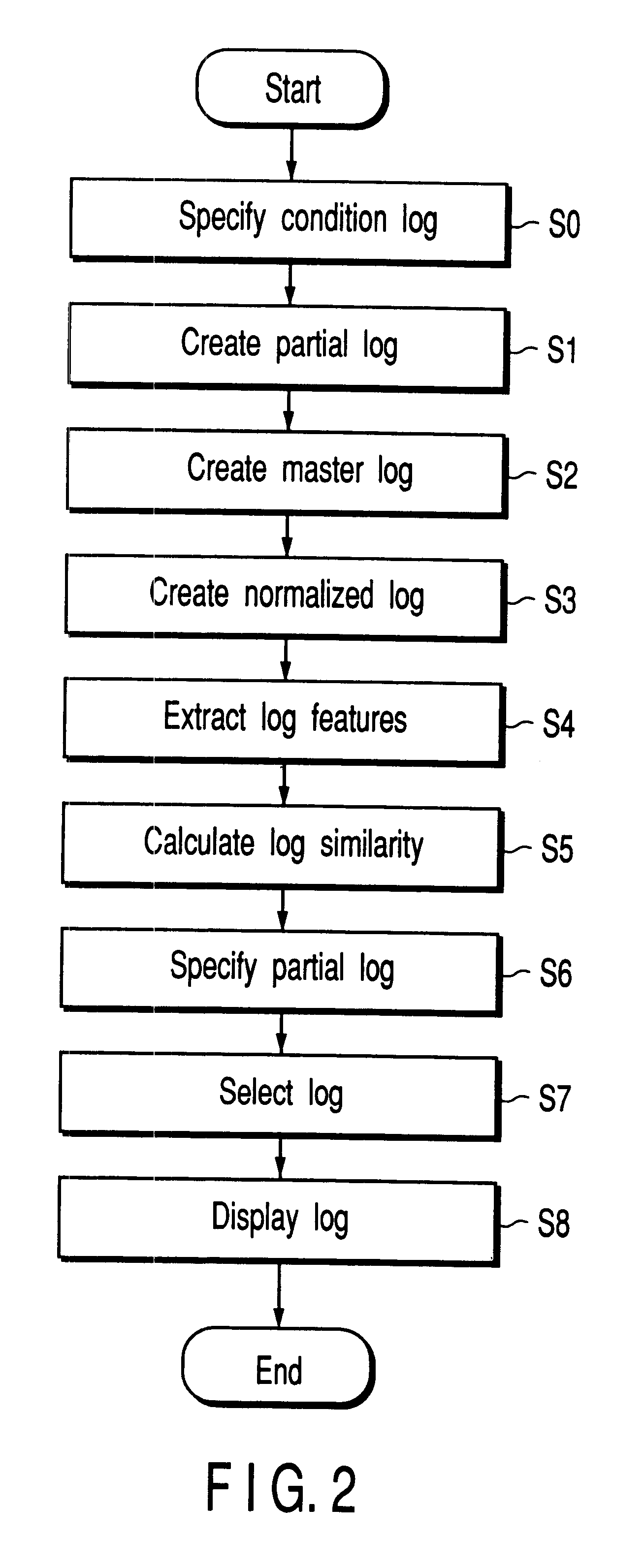

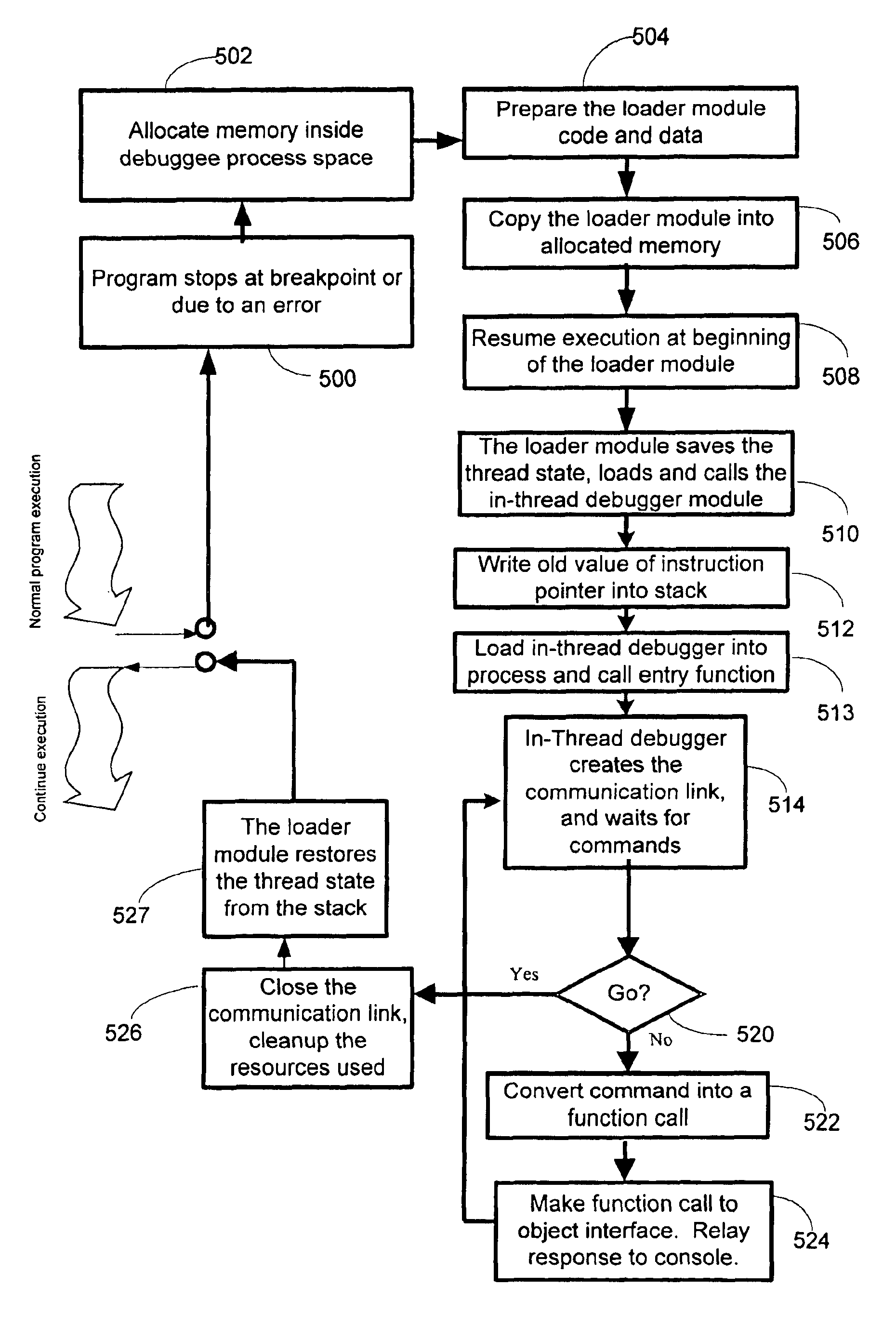

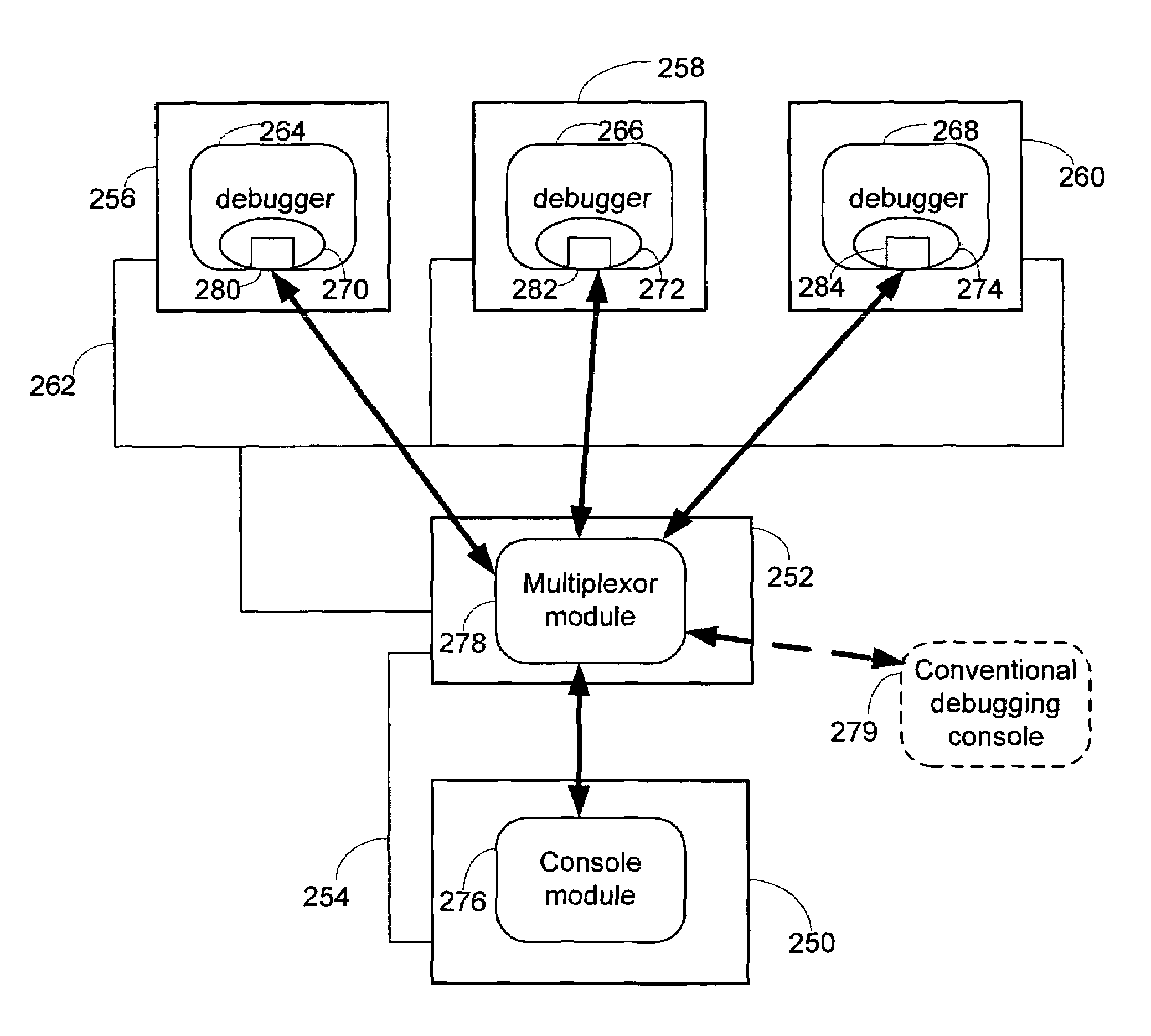

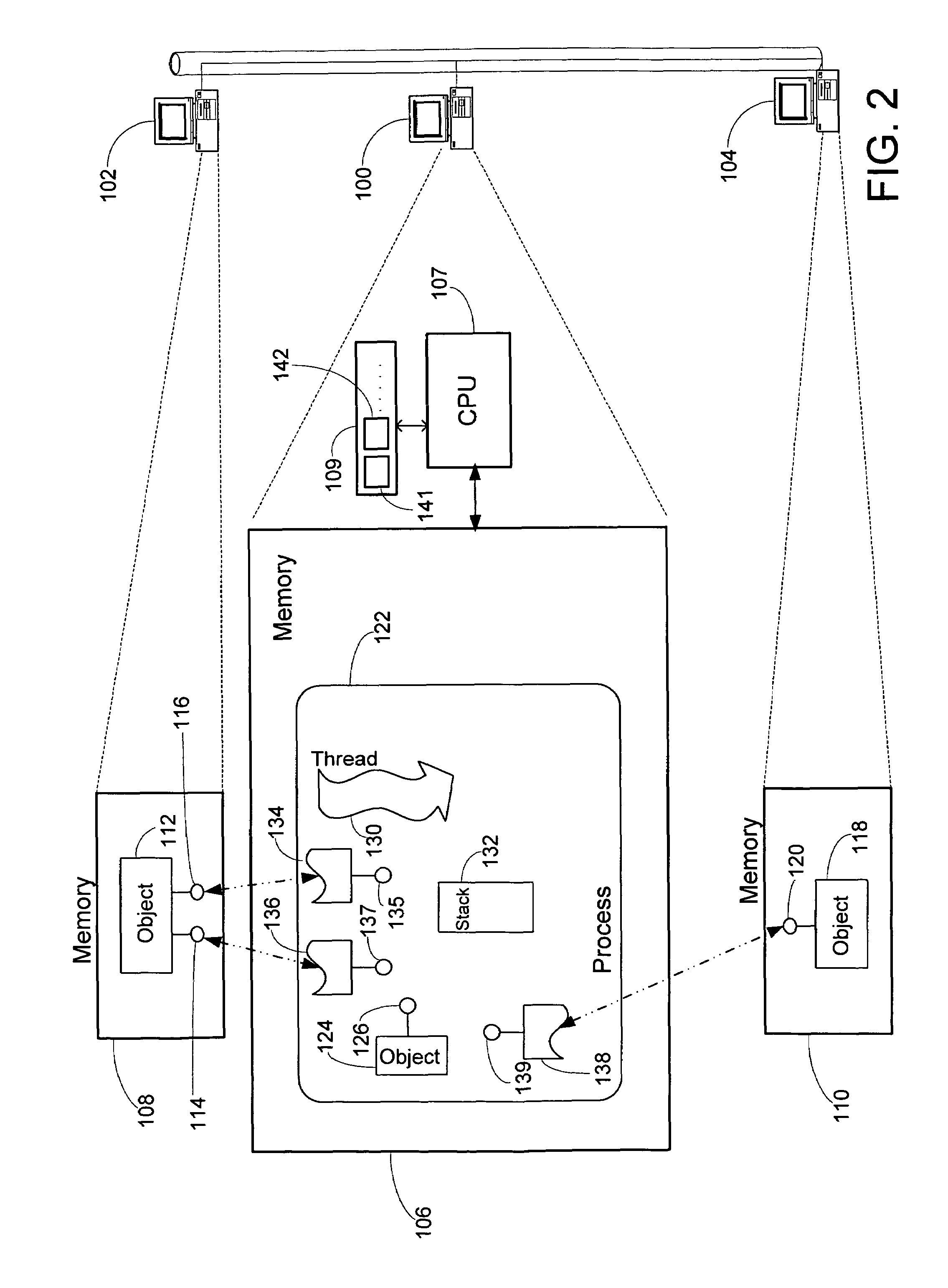

Method and system for debugging a program from within a thread of execution of the program

InactiveUS7555744B2Efficient debuggingError detection/correctionMultiple digital computer combinationsModulaOperating system

In a method and system for debugging a program, a debugging module is loaded into a normal thread of execution of the program. A user may then send commands to the debugger module from a command console module operating in a safe separate process. The debugger module receives the commands and converts them into function calls to objects that are accessible by the program. This allows the user to interact manually with the objects and achieve substantially the same responses from the object as the program itself would have obtained during its normal execution. Thus the user can effectively debug the program without having to know the internal structure of any of its constituent objects.

Owner:MICROSOFT TECH LICENSING LLC

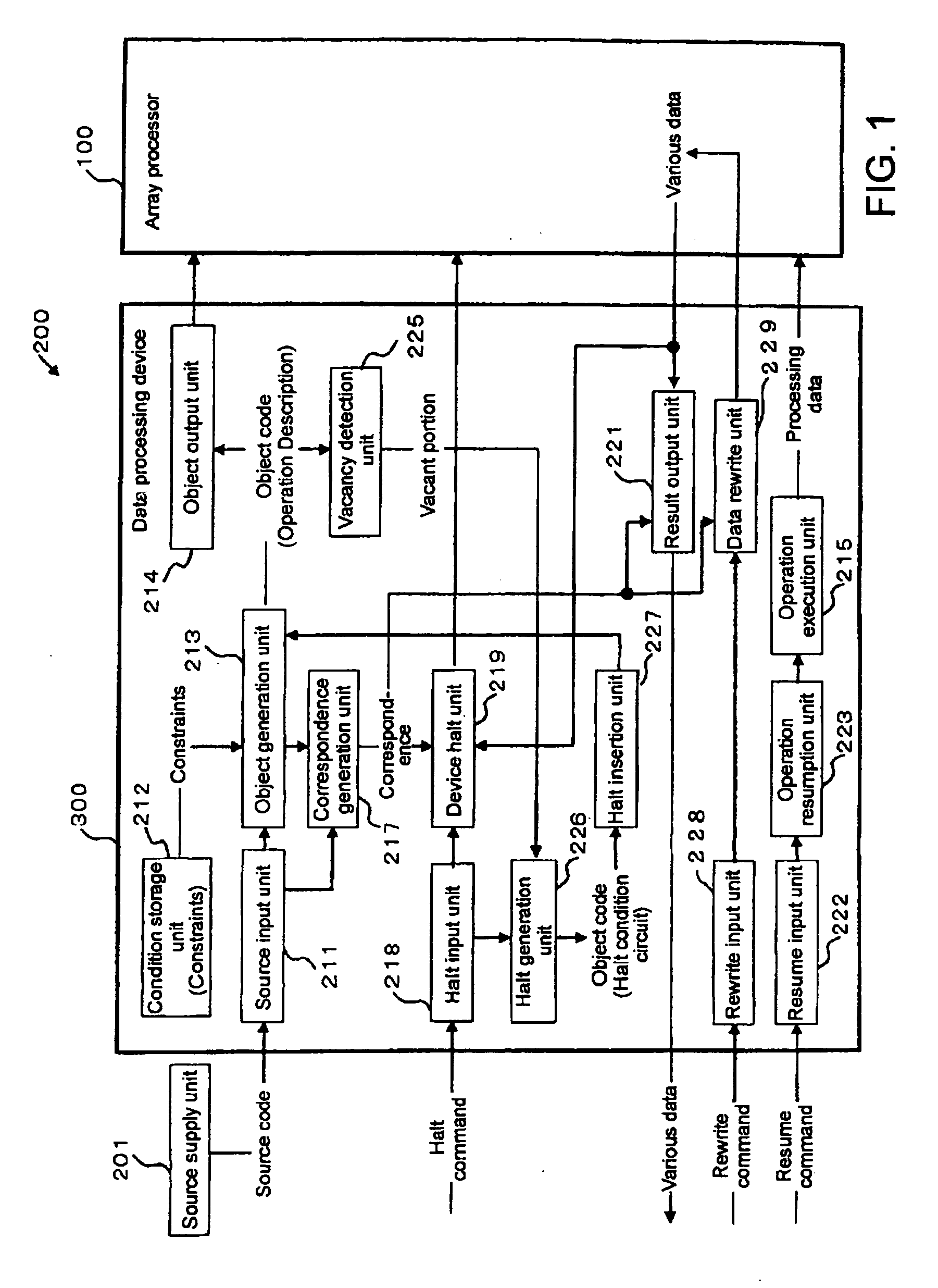

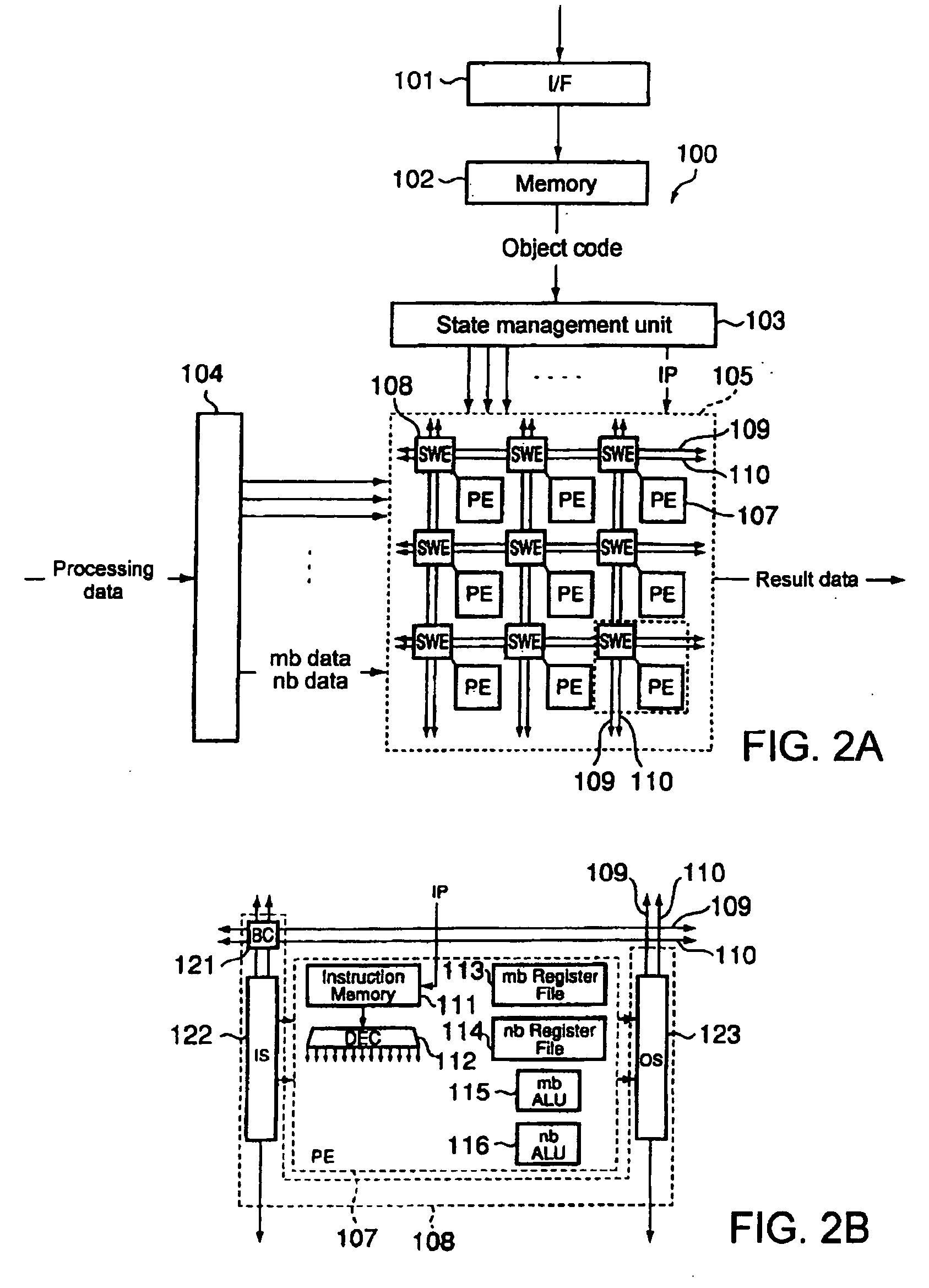

Data processing system

InactiveUS20050050522A1Facilitates taskEfficient debuggingError detection/correctionSpecific program execution arrangementsData processing systemObject code

A data processing device for debugging code for a parallel arithmetic device that includes a plurality of data processing circuits arranged in a matrix and that causes, for each operating cycle, successive transitions of operation states in accordance with object code includes: operation execution means for causing the parallel arithmetic device to execute state transitions by means of the object code; device halt means for temporarily halting the state transitions for each operating cycle; a result output means for reading and supplying as output at least a portion of held data, connection relations, and operation commands of the plurality of data processing circuits of the halted parallel arithmetic device; a resume input means for receiving as input a resume command of the state transitions; and an operation resumption means for causing the operation execution means to resume the state transitions upon input of a resume command.

Owner:NEC CORP +1

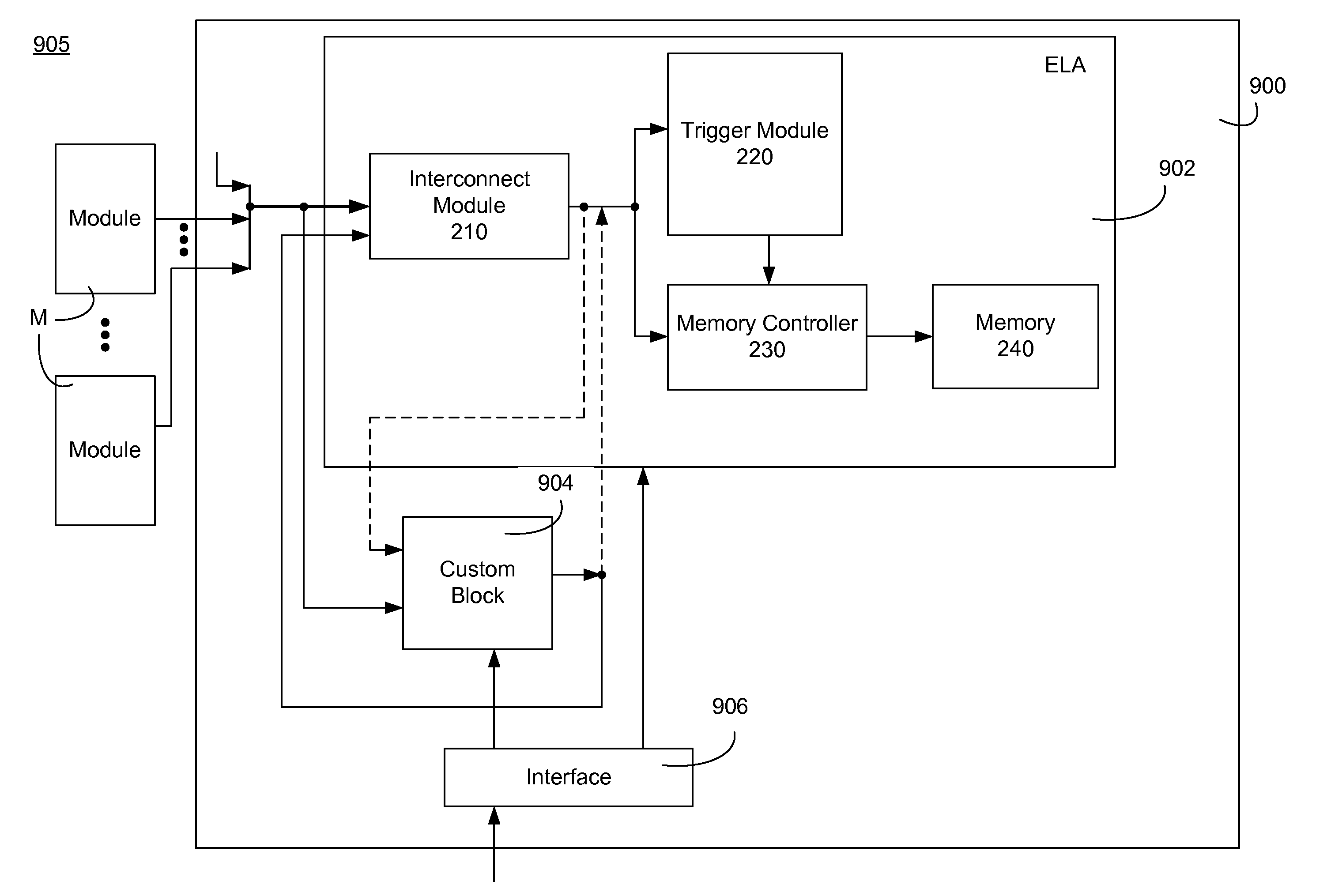

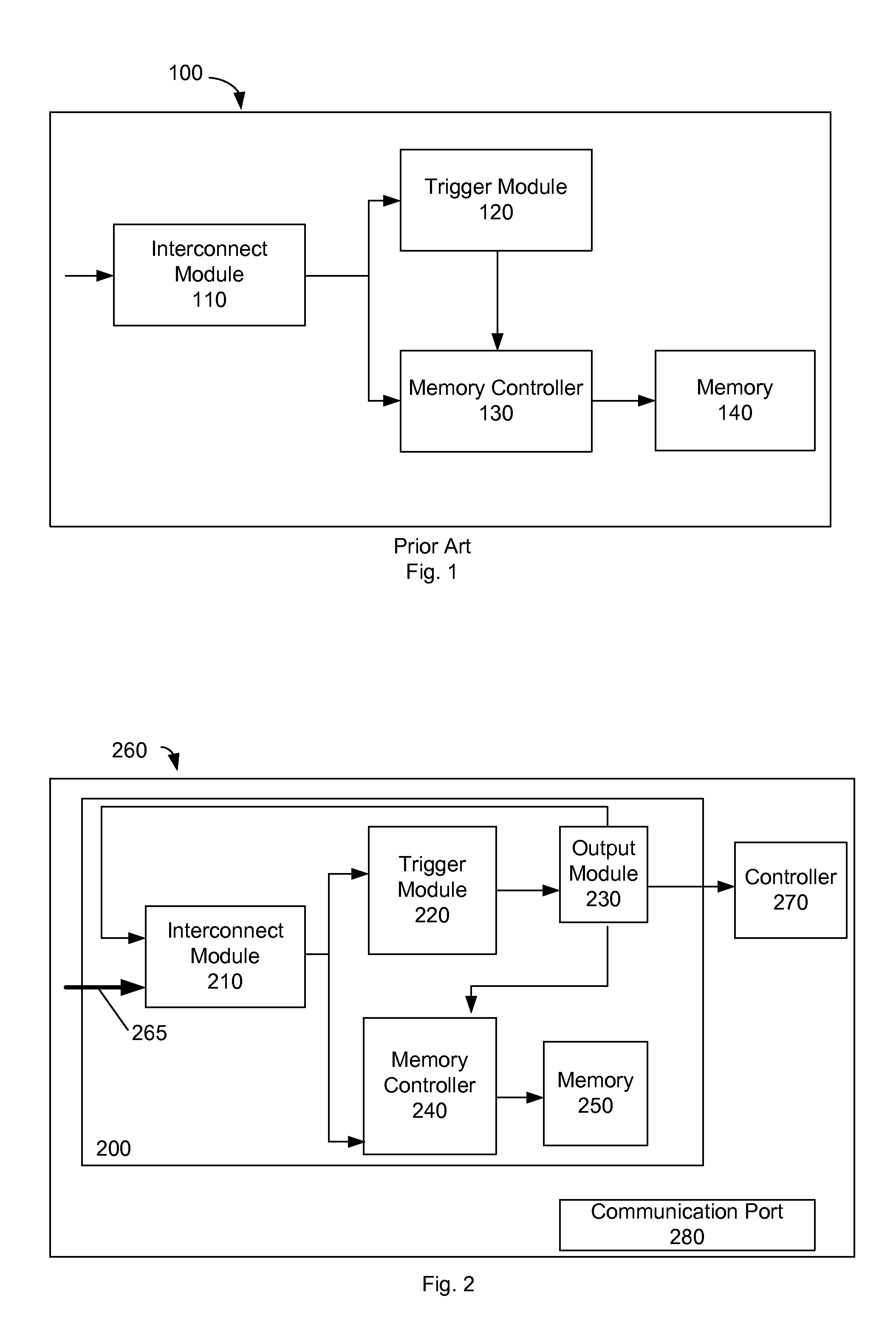

System and Method for Analyzing an Electronics Device Including a Logic Analyzer

ActiveUS20120144256A1Efficient testingEfficient debuggingElectronic circuit testingDetecting faulty hardware by remote testSignal of interestLogic analyzer

A system for testing or debugging a device under test having an embedded logic analyzer. In one embodiment, the system includes software stored in non-transitory memory for testing a device under test having an embedded logic analyzer, the software program product having instructions which, when executed by a computing device associated with the device under test cause the computing device to reconstruct signals of interest in the device under test based at least in part upon signals captured by the embedded logic analyzer during the test or debug session, and cause the computing device to display the reconstructed signals of interest to a user of the computing device.

Owner:LEXMARK INT INC

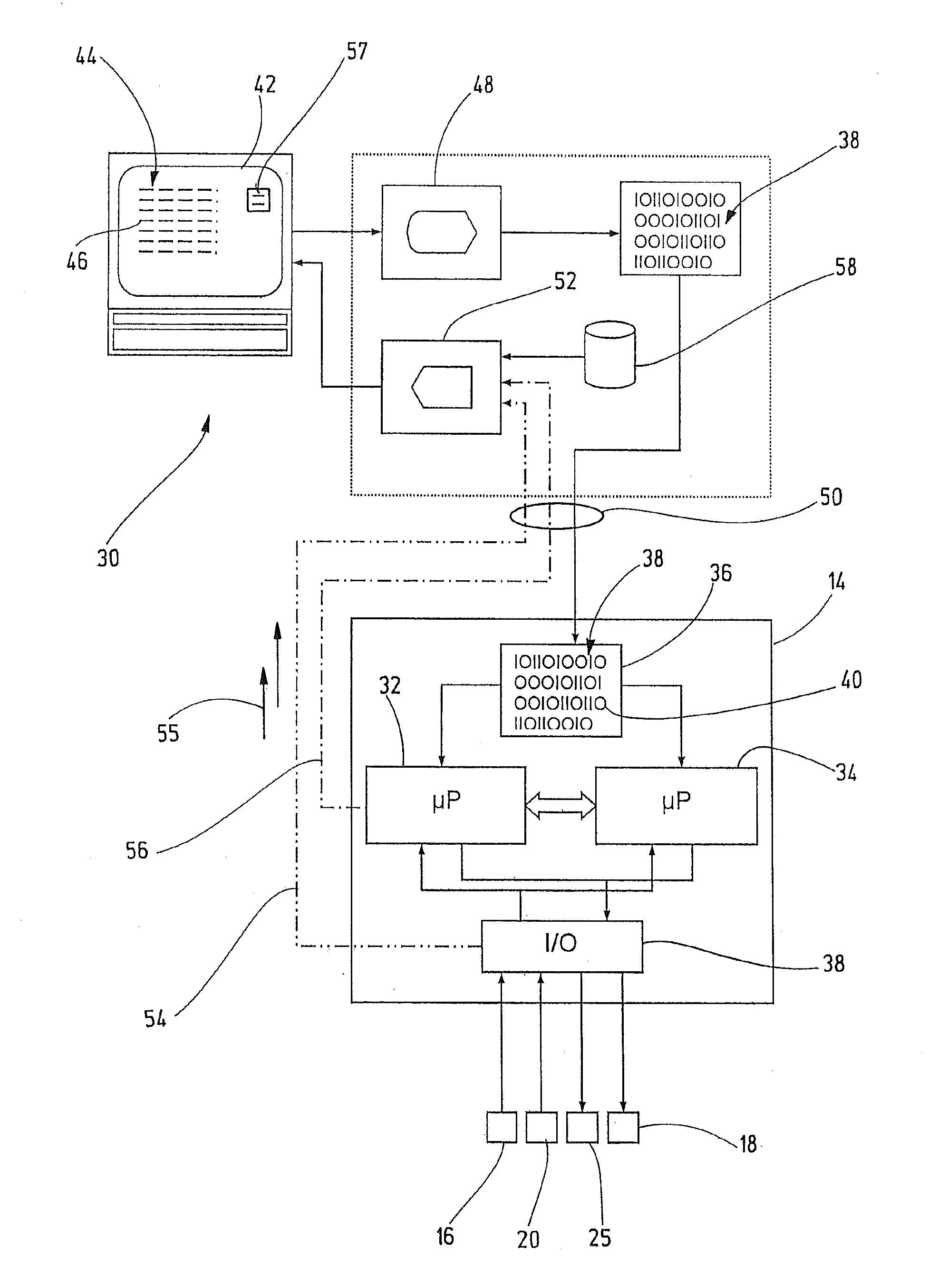

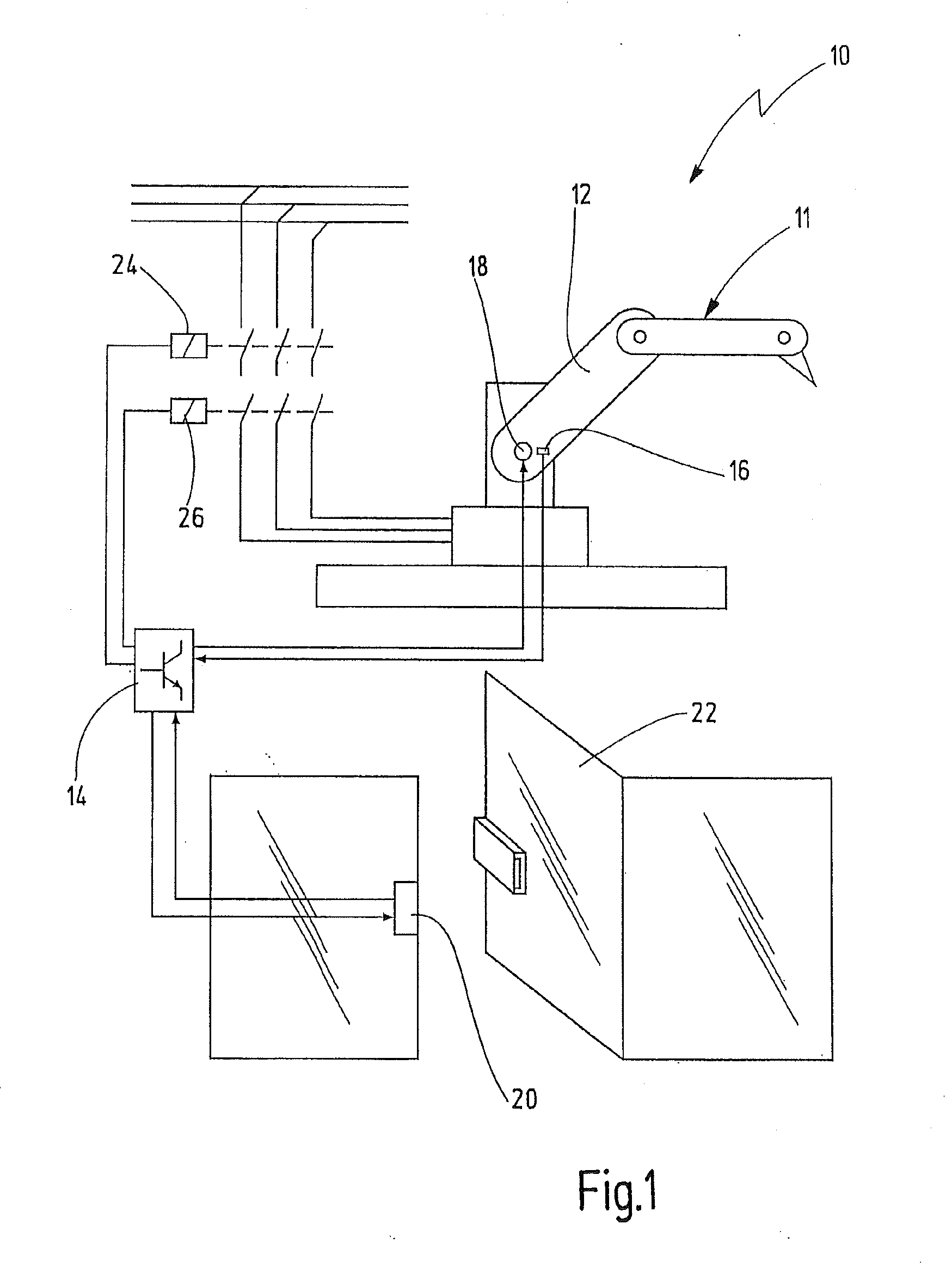

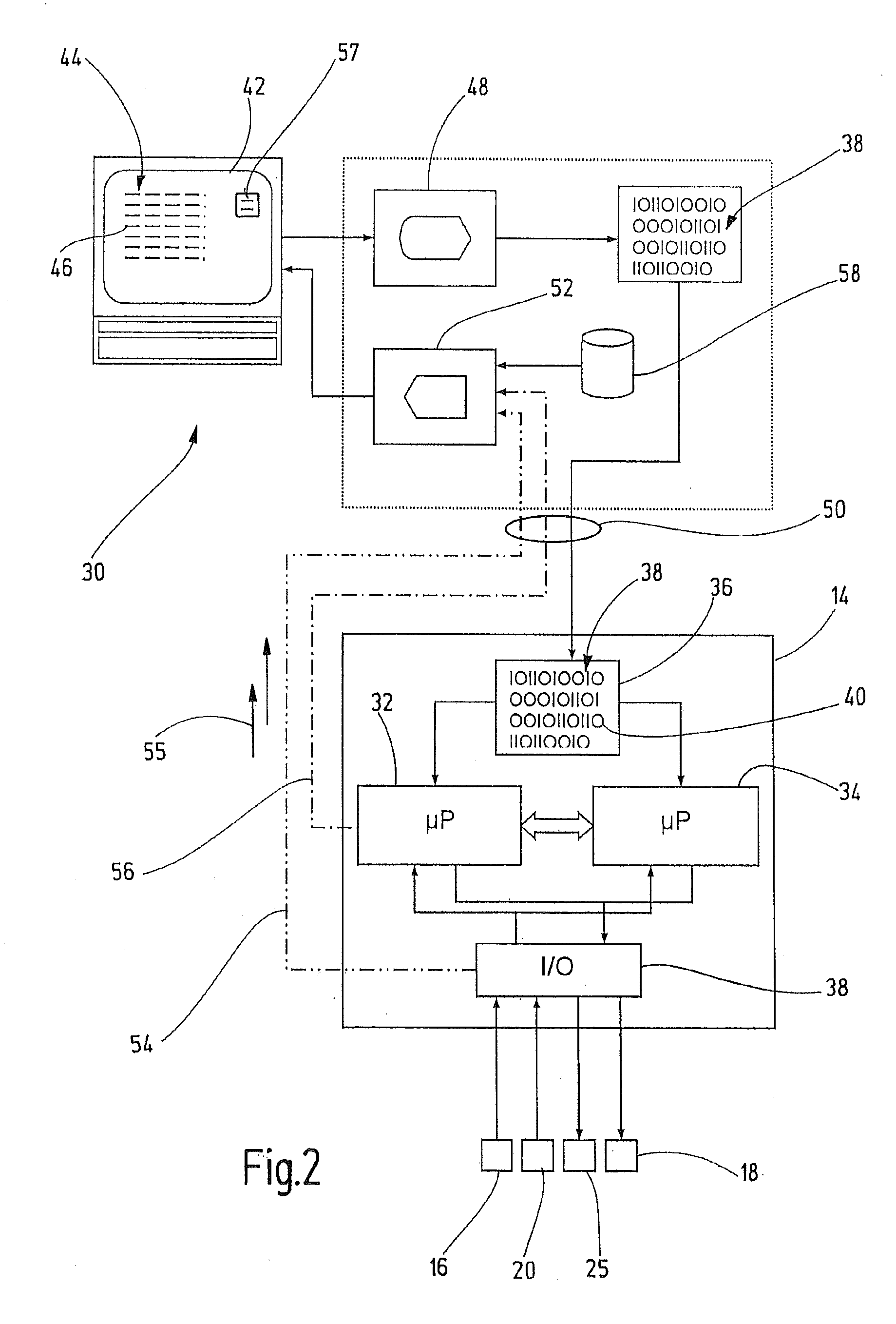

Method and device for programming an industrial controller

ActiveUS20100268358A1Convenient and easy to use interfaceLimit installationComputer controlSimulator controlReal systemsData memory

An installation comprises at least one sensor for providing sensor data representing a real system state of the installation and at least one actuator for acting on the real system state. A controller for controlling the installation comprises a data memory for storing the sensor data and a program memory for storing a machine code program. A programming tool for programming the controller includes a program editor, a debugging tool and a compiler. A machine code program is executed on the controller while the debugging tool is activated, and the debugging tool determines a reverse relationship between the machine code running on the controller and at least one high level control instruction shown in the program editor. The debugging tool reads sensor data from a data memory in the controller and assigns the sensor data to the at least one high level control instruction, thereby linking the at least one high level control instruction to a real system state during the execution of the machine code program.

Owner:PILZ (COMPANY)

Grouping threads in a debugger display

InactiveUS7844952B2Efficient debuggingError detection/correctionSpecific program execution arrangementsObject ClassJava

A debugger display groups threads according to user-specified criteria. The threads may be grouped by type, by current or historic breakpoints, according to historical debug patterns, based on what thread spawned the thread, based on execution pattern, based on object class in a Java environment, based on Java thread group in a Java environment, or base on other suitable criteria. The grouping of threads is displayed graphically to a user of the debugger, thereby allowing more efficient debugging of multi-threaded computer programs.

Owner:LINKEDIN

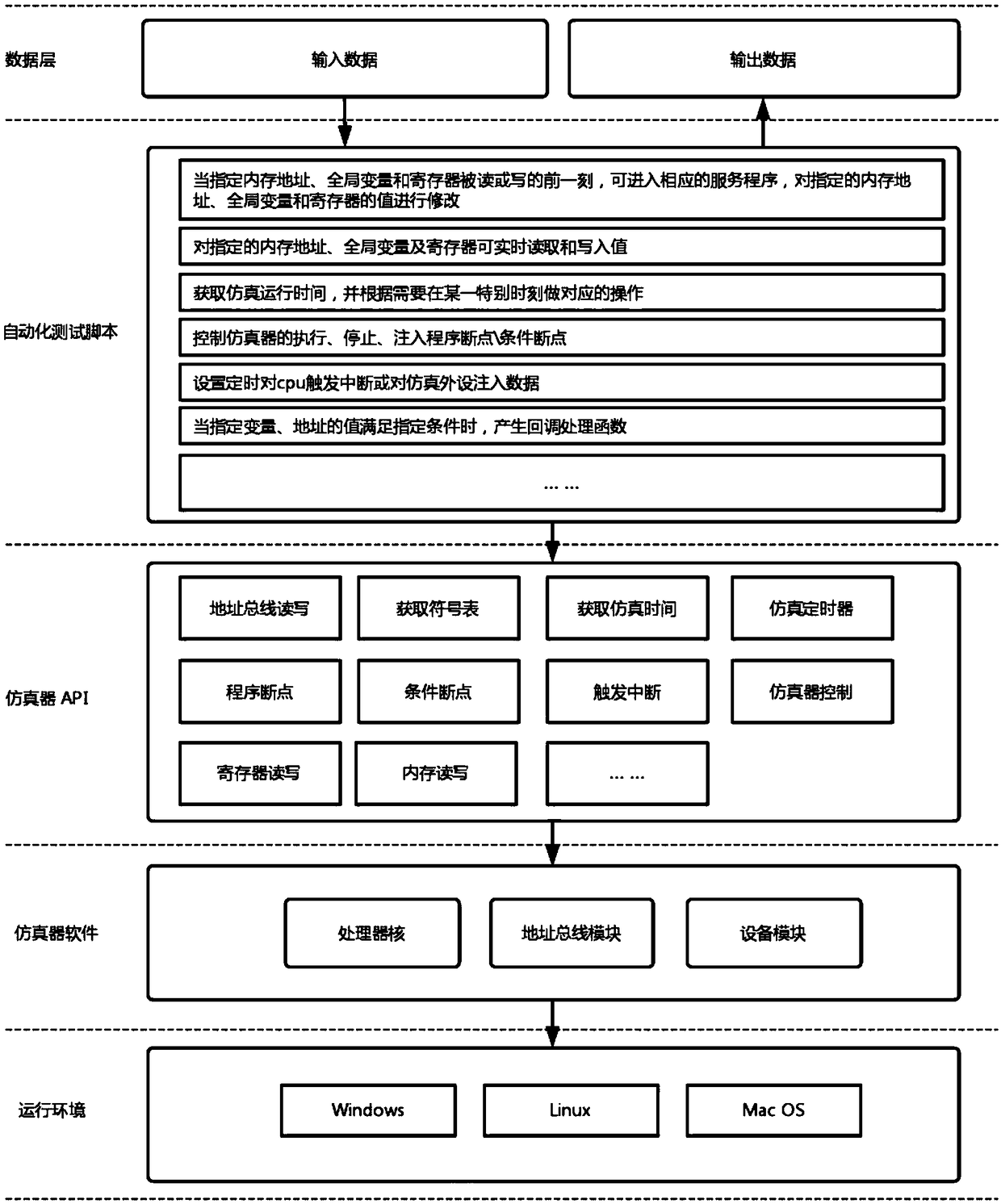

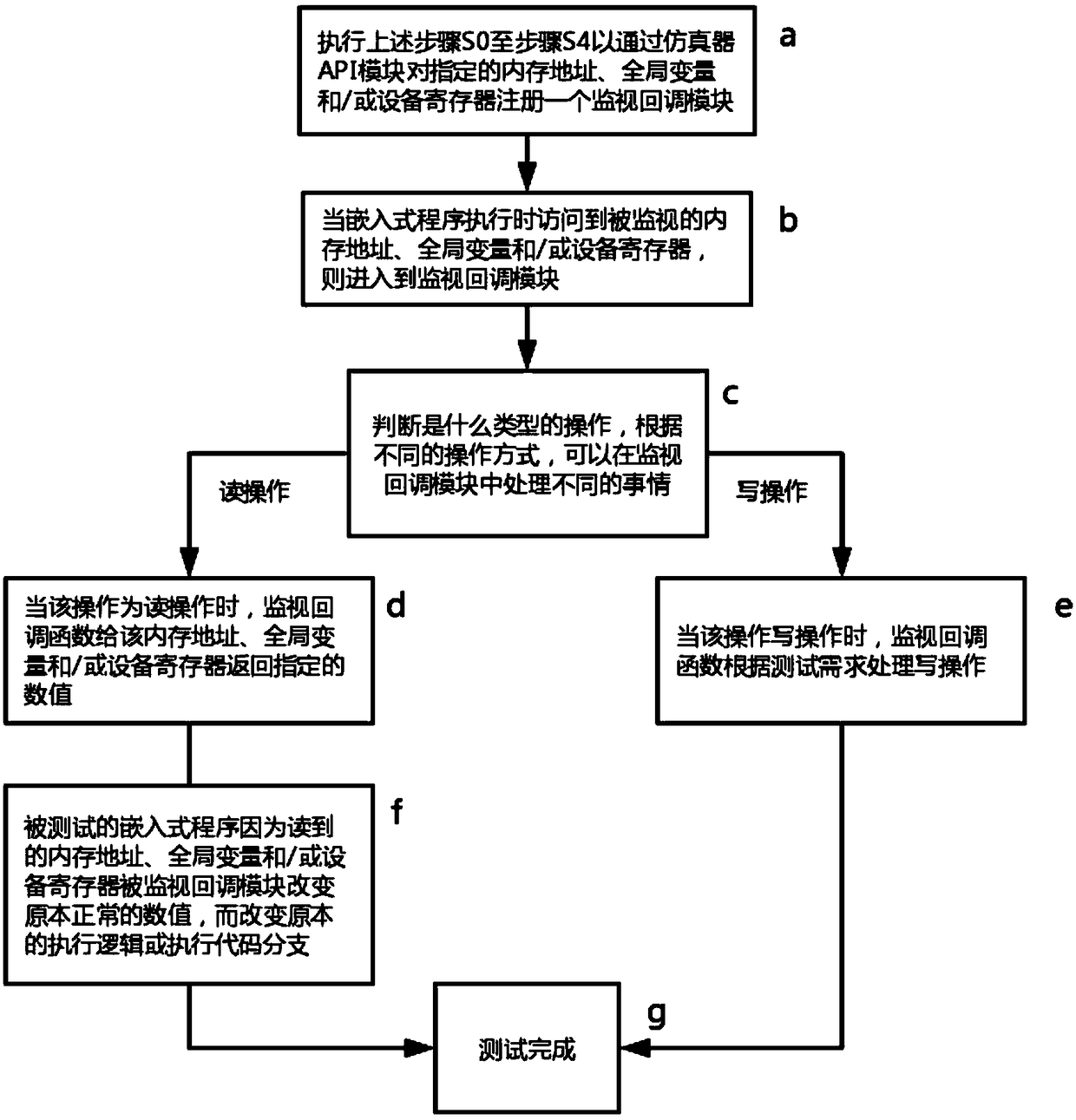

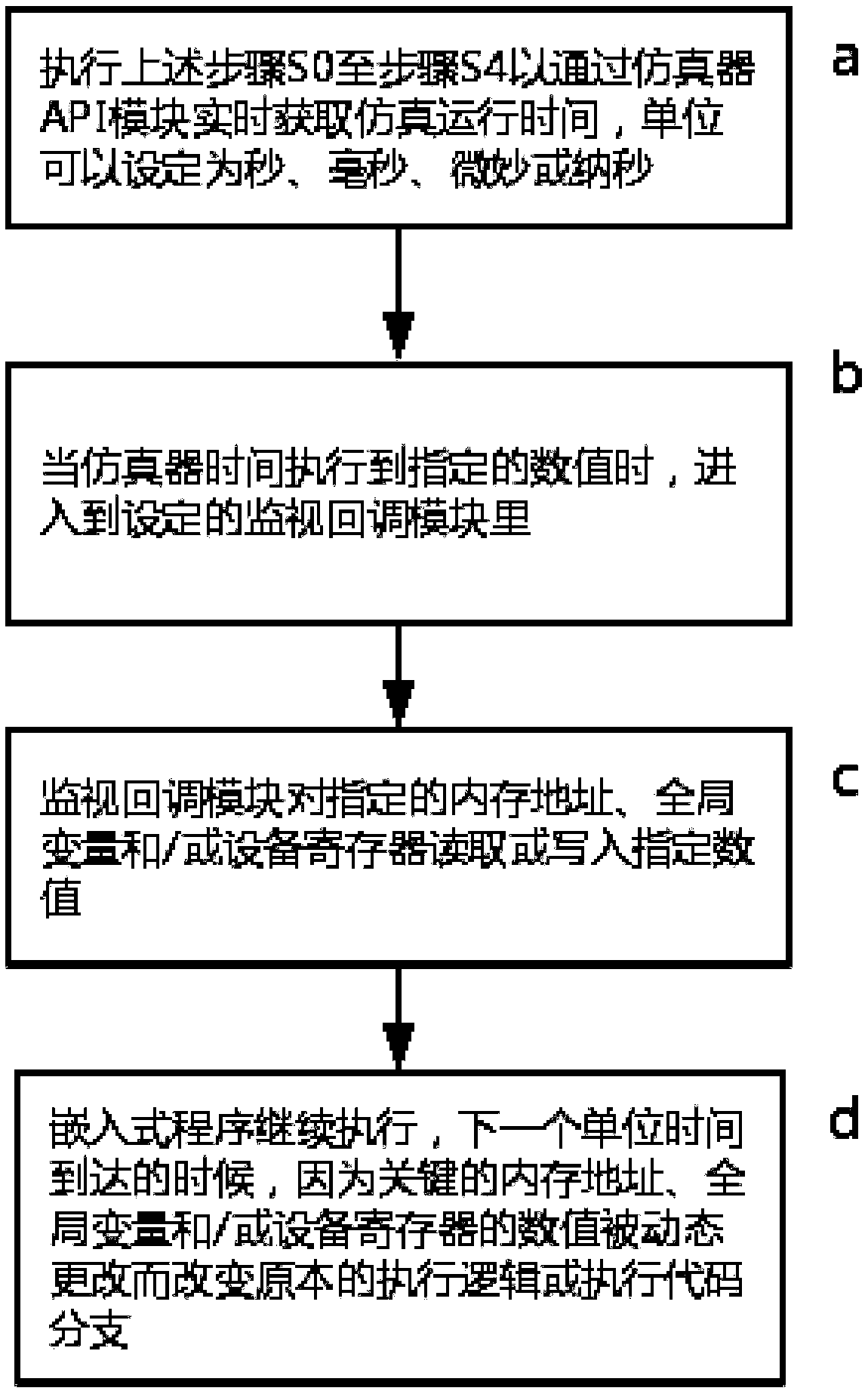

Automatic test method based on embedded software simulator

ActiveCN109213680AQuickly locate logic errorsEfficient testingSoftware testing/debuggingTest scriptAutomatic test equipment

An automated test method based on an embedded software simulator comprises the following steps: step S0, creating an automated test script module to prepare for test requirements; Step S1: according to the function provided by the emulator API module, the test logic conforming to the software under test is written in the automated test script module, the emulator API module includes address bus read and write, register read and write, memory read and write, program breakpoint, conditional breakpoint, symbol table, emulator control, simulation time, simulation timer, and / or trigger interrupt. 2, loading the automated t script module into the simulator software; 3, starting the emulator software and executing the automate test script module; S4, verifying the correctness of the code logic ofthe automated test script module and making adjustment and modification; 5, if that step S4 is passed, executing and operating the embedded software automation test through the automation test scriptmodule; Step S6: the test is complete. Makes program debugging controllable, changeable, and quick to locate program logic errors.

Owner:康烁

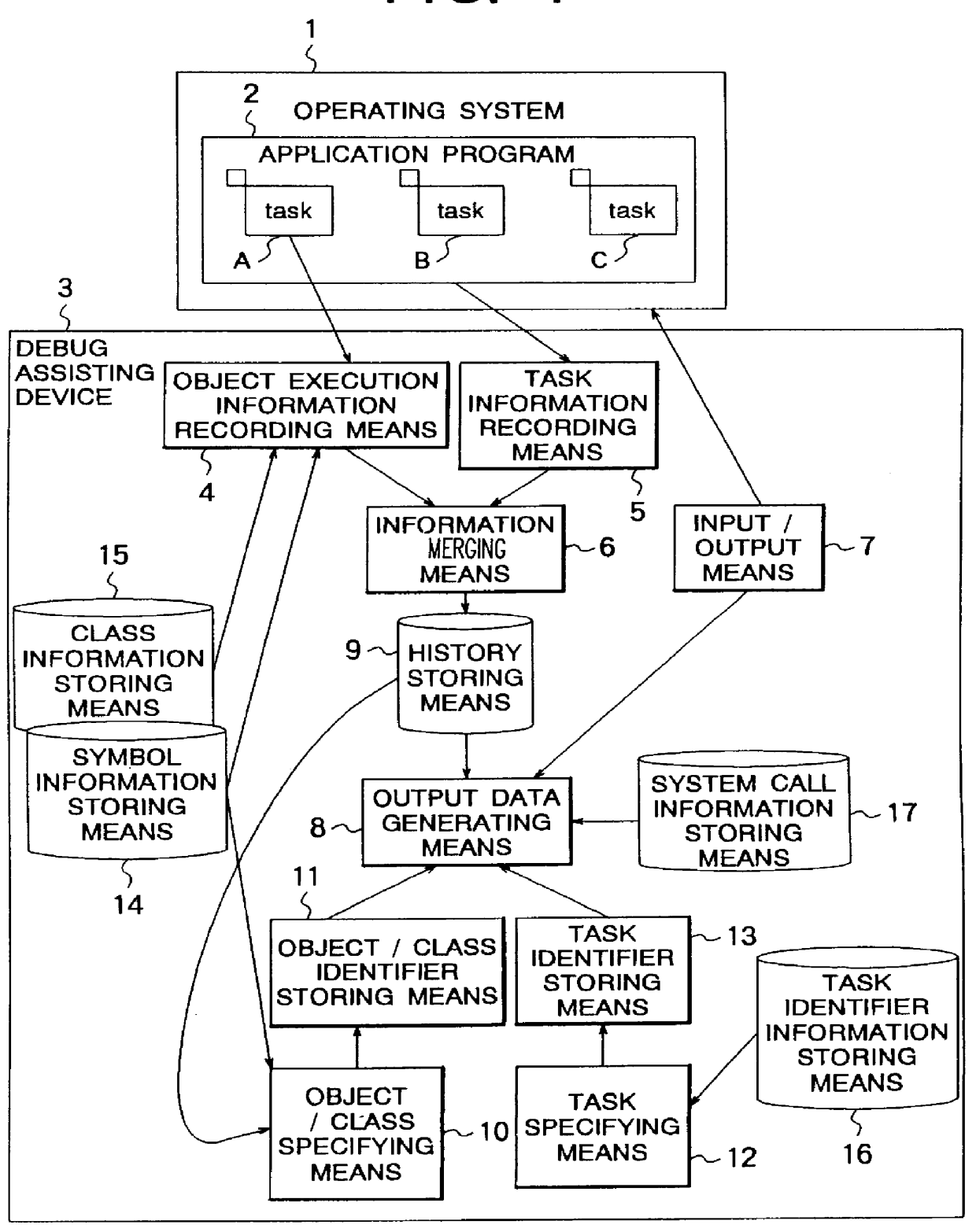

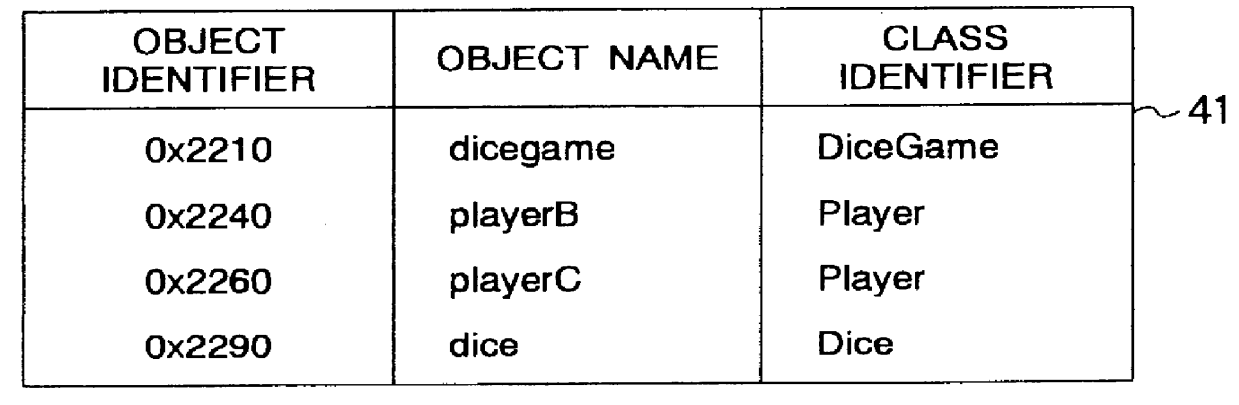

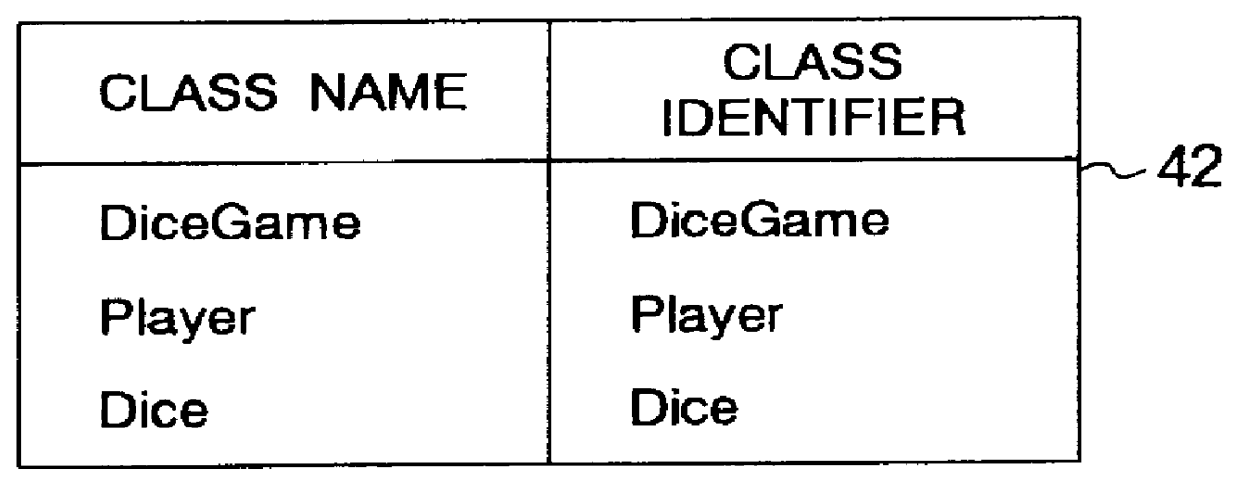

Multitask processor, a multitask processing method, a multitask processing display method and a storage medium for processing by correlating task and object

InactiveUS6131109AEasy to findEfficient debuggingProgram initiation/switchingHardware monitoringInput/outputTime sequence

The debug assisting apparatus comprises a task information recording device to record the execution information of task A, task B, and task C executed by the OS 1 in multitask processing, an object execution information recording device to record the information of the objects operated by the tasks, an information merging device both to chronologically merge the recorded object execution information and execution information of task A, task B, and task C and to store such information as the program operation history in a history storing device, and an output data generating device to generate the output data showing the execution progress of task A, task B, and task C and the operation of the objects in association according to the operation history table in the history storing device and output such data to the input / output device (monitor).

Owner:KK TOSHIBA

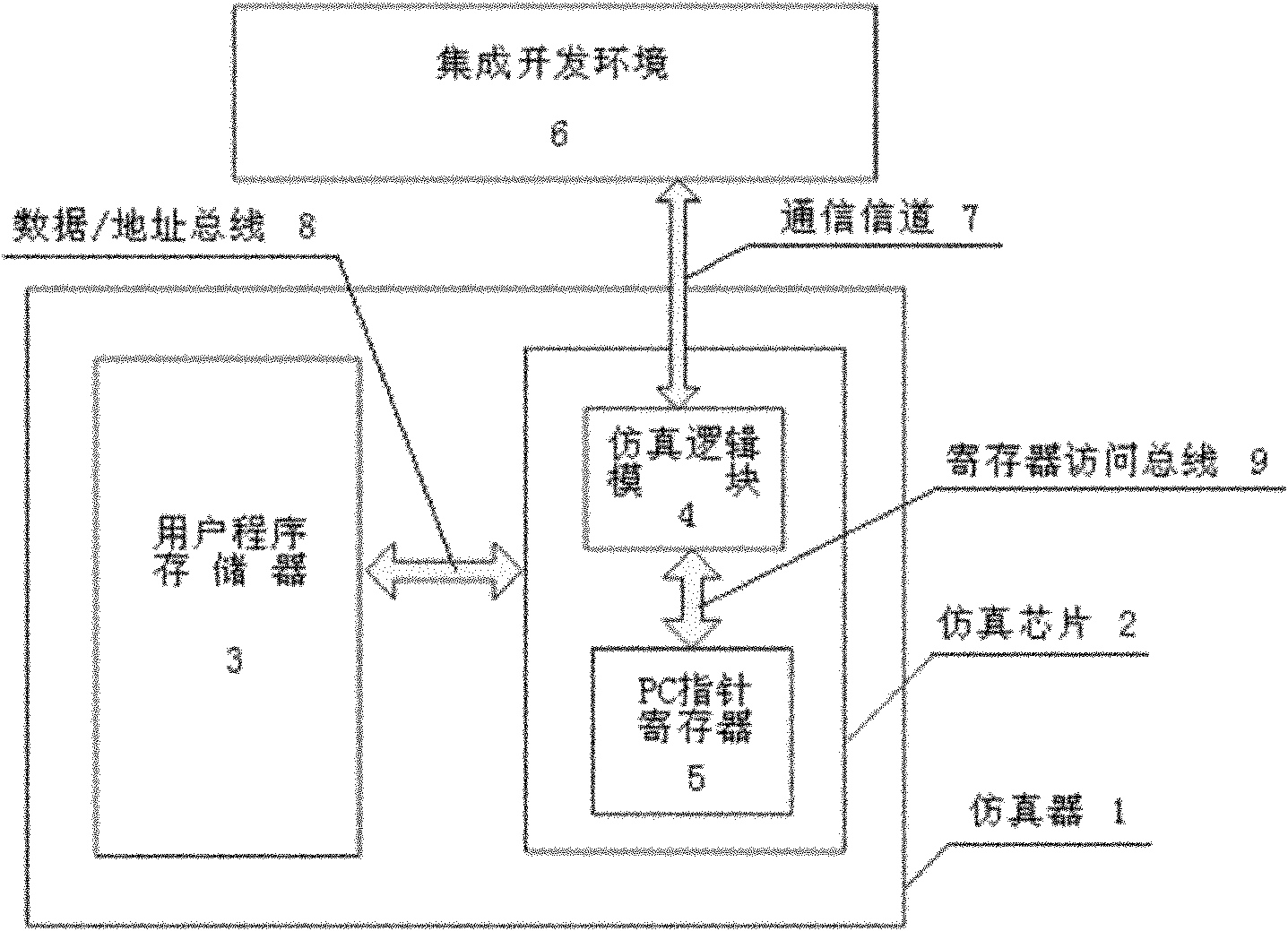

Processor chip emulator capable of setting program pointer value

InactiveCN102467446AEfficient debuggingReliable debuggingSoftware testing/debuggingProcessor registerACCESS.bus

The invention discloses a processor chip emulator capable of setting a program pointer value, which comprises an emulator and integrated development environment debugging software. An emulation chip comprises a PC (personal computer) pointer register and an emulation logic module, wherein the emulation logic module and the PC pointer register are connected through a register access bus; the emulation logic module can execute data write or read operation on the PC pointer register through the register access bus; and the emulation chip can not write data into the PC pointer register by executing a user program. By using the invention, in the user program development process, the user can enable the next program statement to be executed to be executed from the user program statement in the position designated by the user by setting the PC pointer register value in a debugging state; and when the user program is in the operation state, even if a user program miswrites the PC pointer register, no user program execution disorder condition can occur, so that the user can debug the user program efficiently and reliably.

Owner:SHANGHAI HUAHONG INTEGRATED CIRCUIT

SQL query problem determination tool

InactiveUS7765200B2Efficient debuggingError detection/correctionDigital data processing detailsQuery planExecution plan

A method and system for query problem determination have been disclosed. The method includes receiving a database query; creating a query execution plan for the database query comprising a plurality of query plan operators; and executing the query execution plan, wherein a progress indicator is displayed for each query plan operator. The system includes a query progress monitor, which collects progress information for each query plan operator during the execution of the query execution plan. This progress information is then communicated to a query progress visualizer and a query progress analyzer, which graphically displays the progress information as a progress indicator for each query plan operator and performs debugger type operations, respectively. In this manner, information concerning the progress of the query execution is provided at a query operator level, such that the information may be used to more efficiently debug any problems with the query.

Owner:LINKEDIN

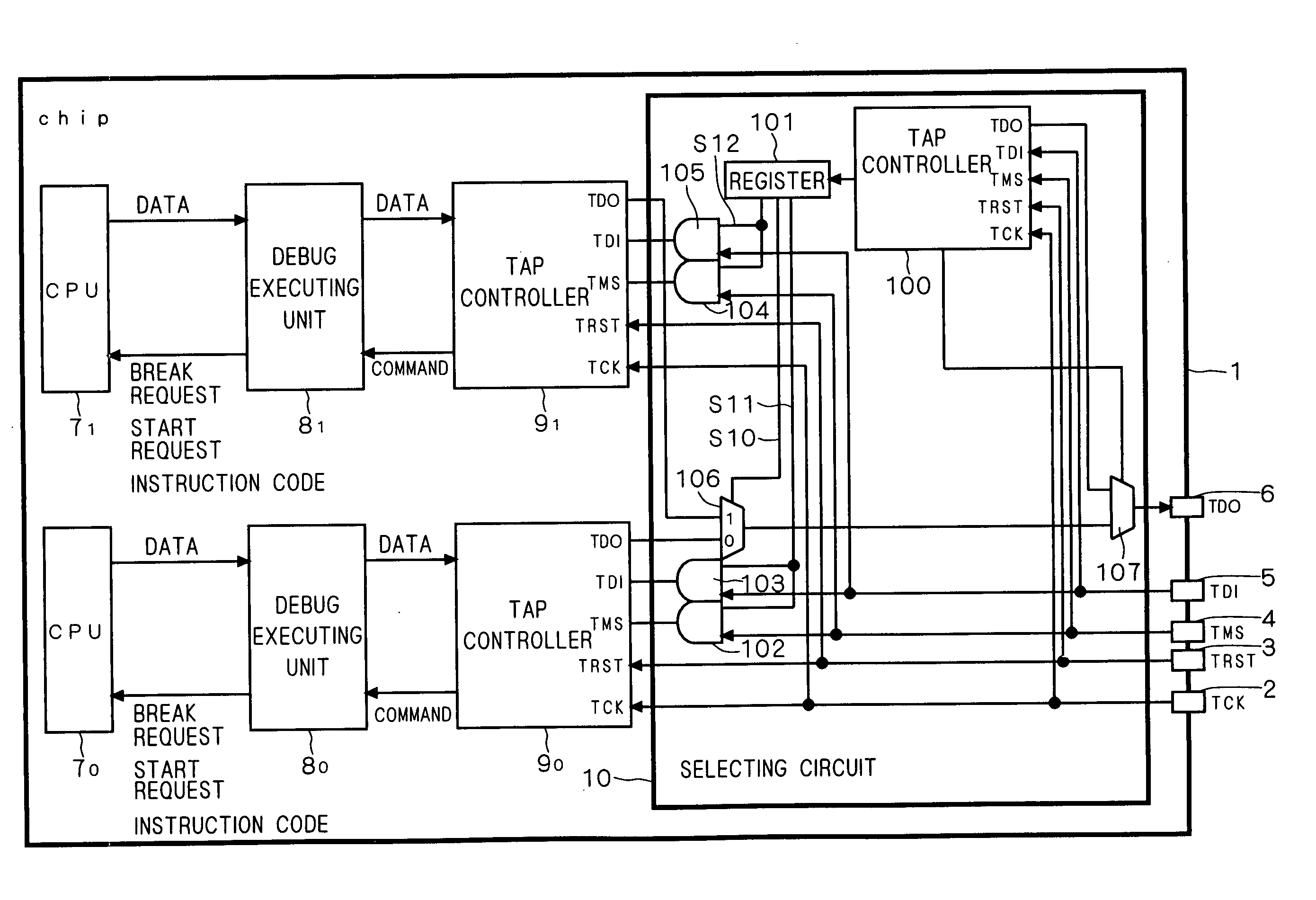

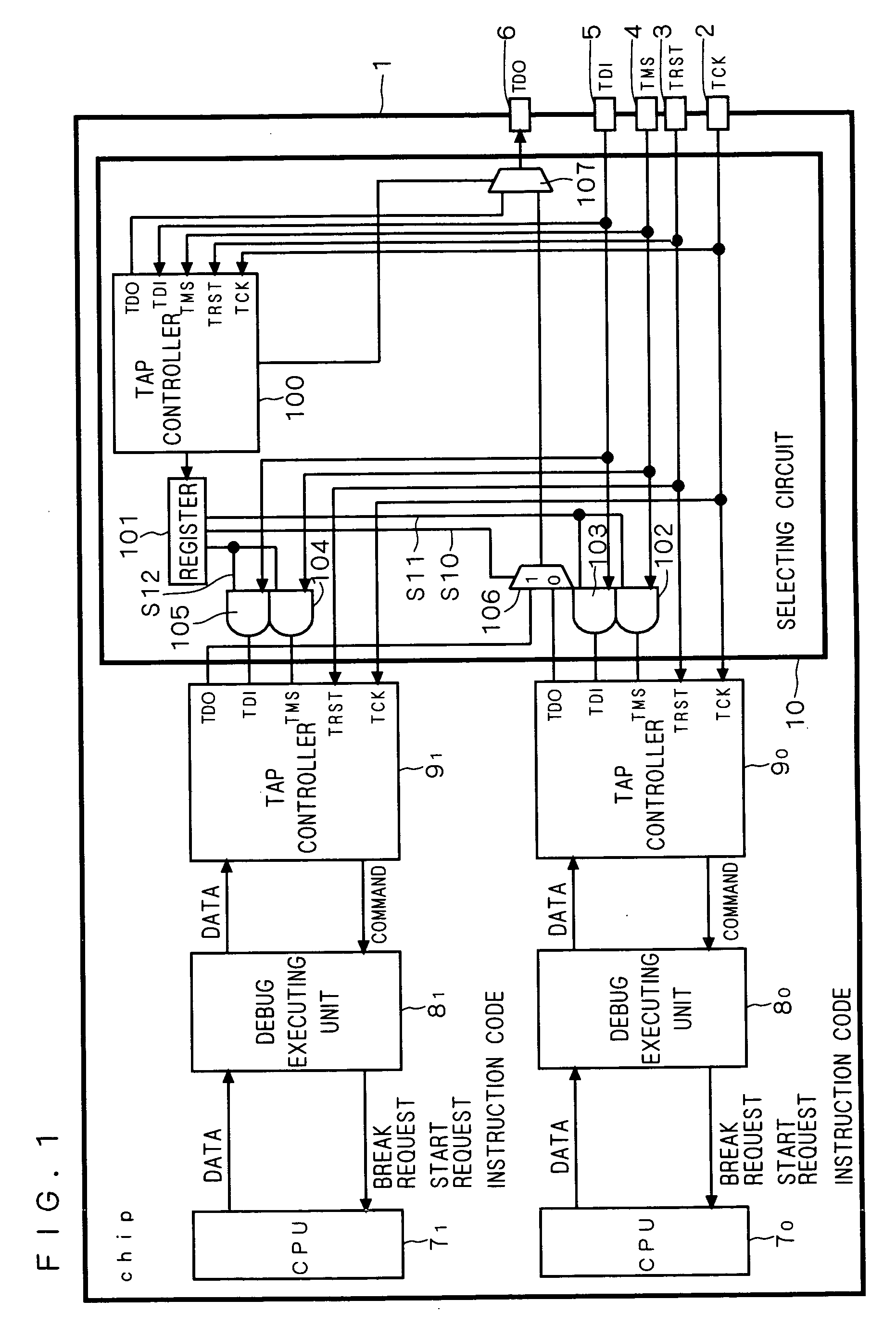

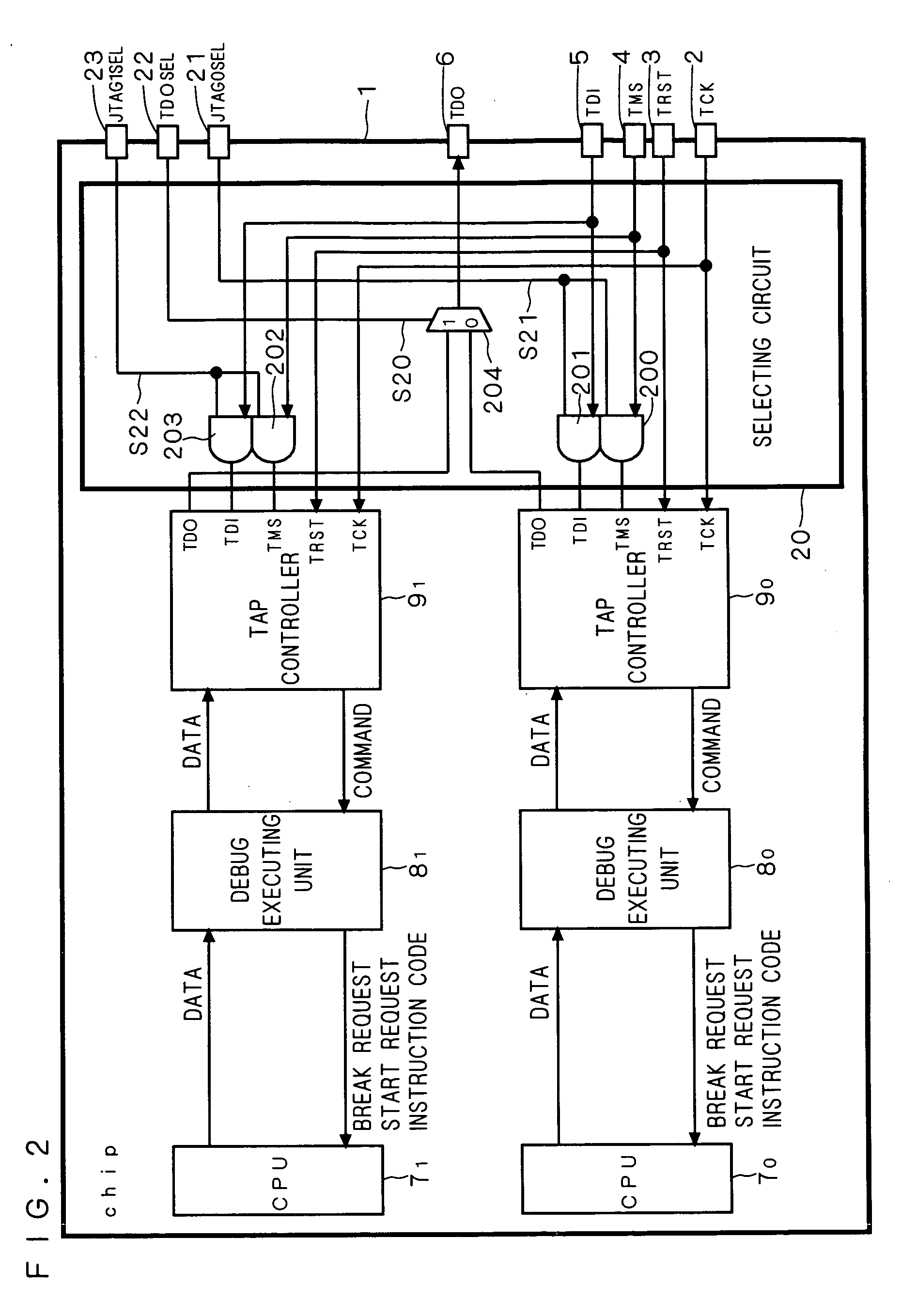

Multiprocessor system capable of efficiently debugging processors

InactiveUS20040163012A1Efficient debuggingLow costDigital computer detailsFunctional testingProcessor registerComputer terminal

A multiprocessor system is obtained which is capable of efficiently debugging a plurality of processors, while allowing cost reduction. A chip (1) has CPUs (70, 71), debug executing units (80, 81), TAP controllers (90, 91), a selecting circuit (10), and a single set of terminals including terminals (2) to (6). When only the CPU (70) is to be debugged, a TAP controller (100) sets a register (101) so that a signal (S11) is "H" and a signal (S12) is "L." When only the CPU (71) is to be debugged, the TAP controller (100) sets the register (101) so that the signal (S11) is "L" and the signal (S12) is "H." When both CPUs (70) and (71) are to be debugged, the TAP controller (100) sets the register (101) so that the signals (S11) and (S12) are both "H."

Owner:RENESAS TECH CORP

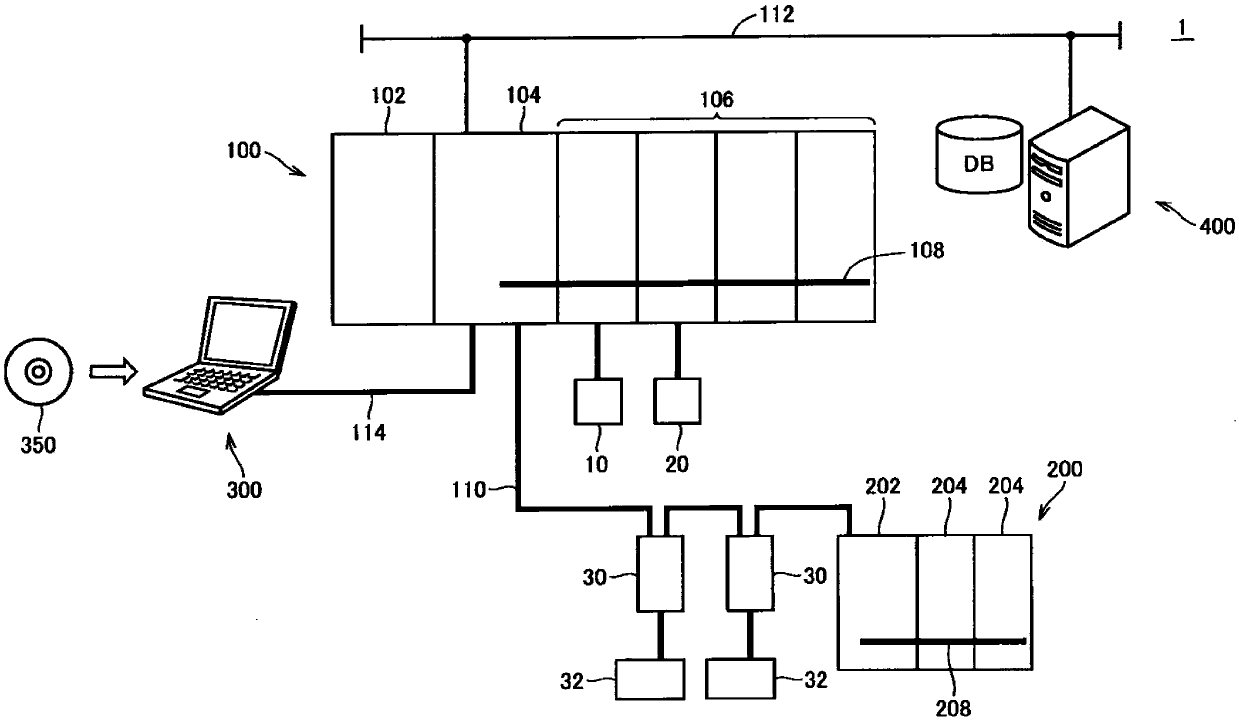

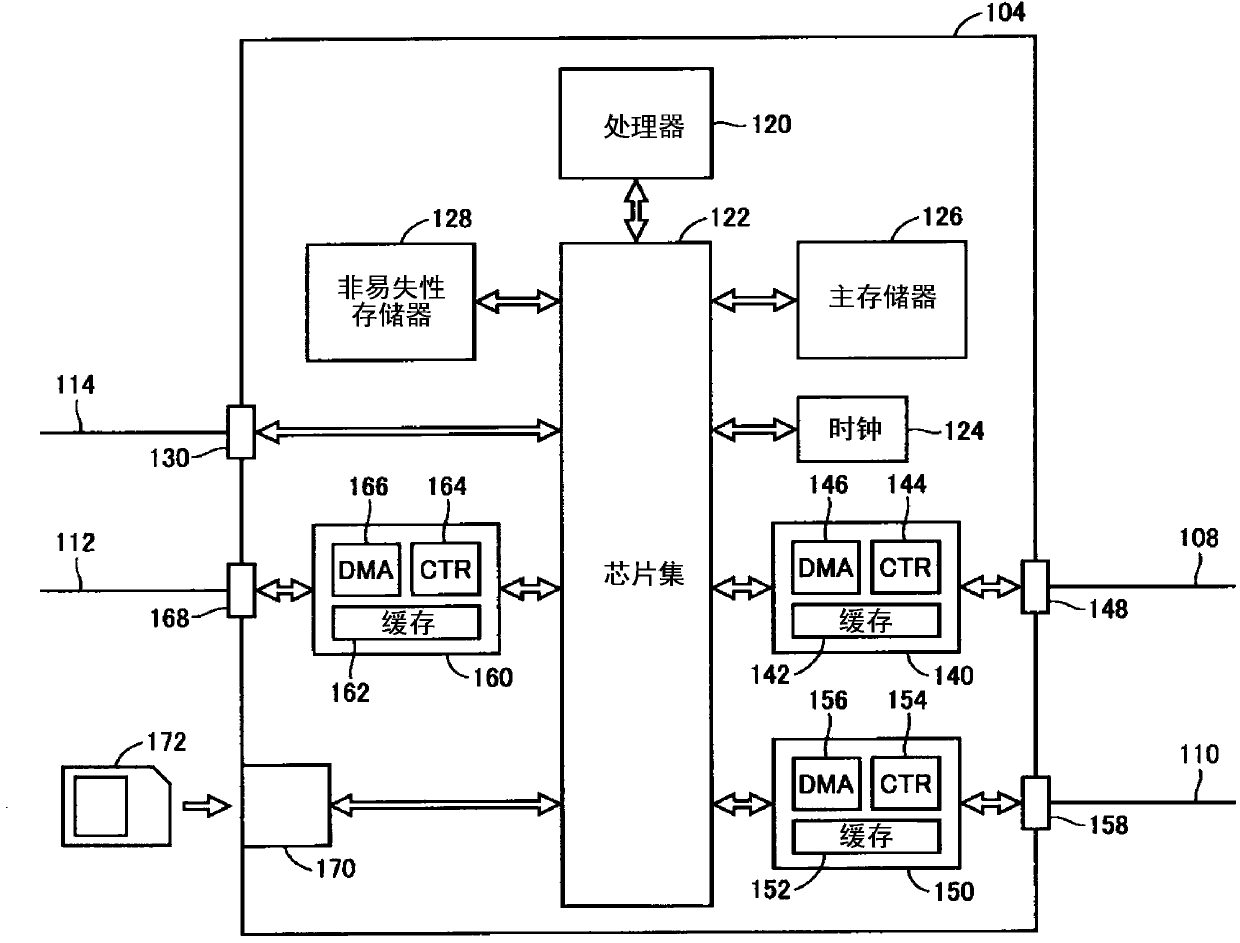

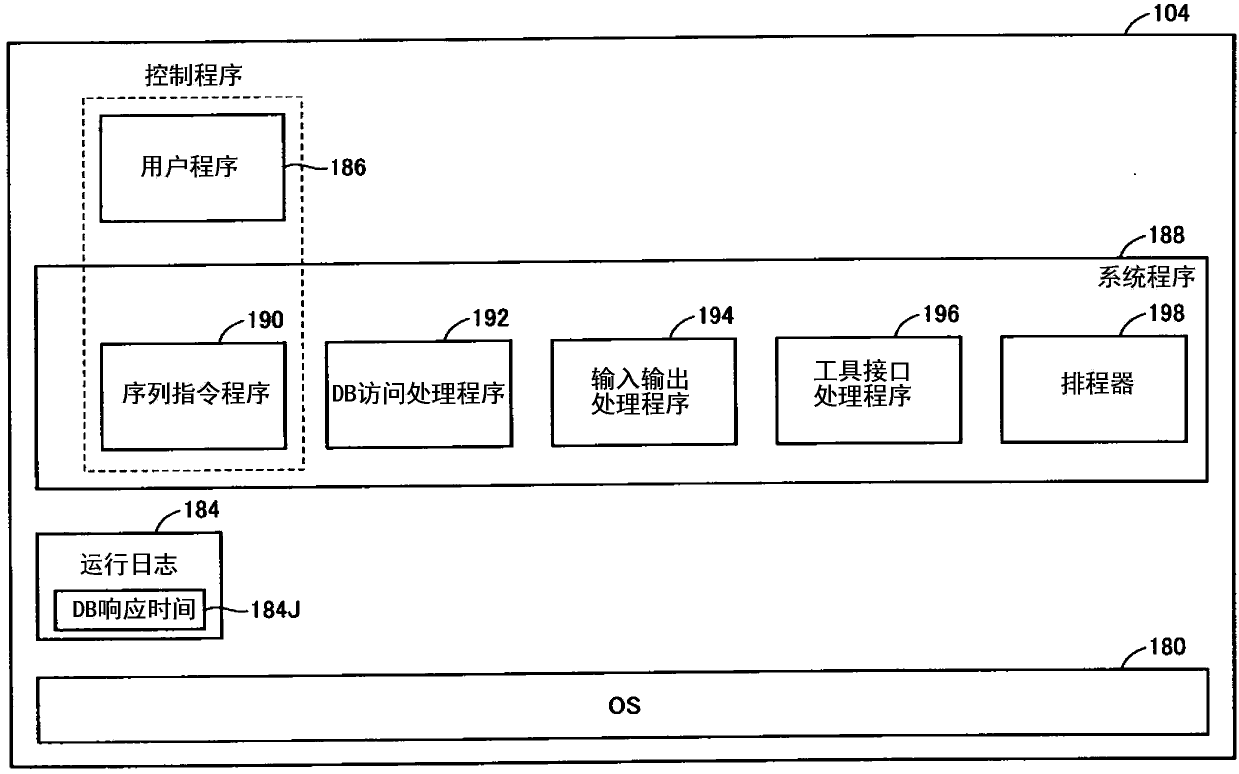

Controller, information processing apparatus, and program

ActiveCN103995500AEfficient debuggingEasy to analyzeDatabase queryingError detection/correctionCommunication interfaceInformation processing

A technique capable of efficiently performing debugging in a program and checking of soundness in a control system including a controller and a database system. A CPU unit has a communication interface for connection to a database device. The CPU unit executes a user program to call a DB connection service in accordance with an instruction included in the user program and generate a statement to access the database device. In the DB connection service, a statement according to an access instruction is generated, and the generated statement is transmitted to a database system. After that, information indicative of time until a response from the database system is received is acquired, and the acquired information is stored as a log into a memory. A support device acquires the information and displays it on a monitor.

Owner:ORMON CORP

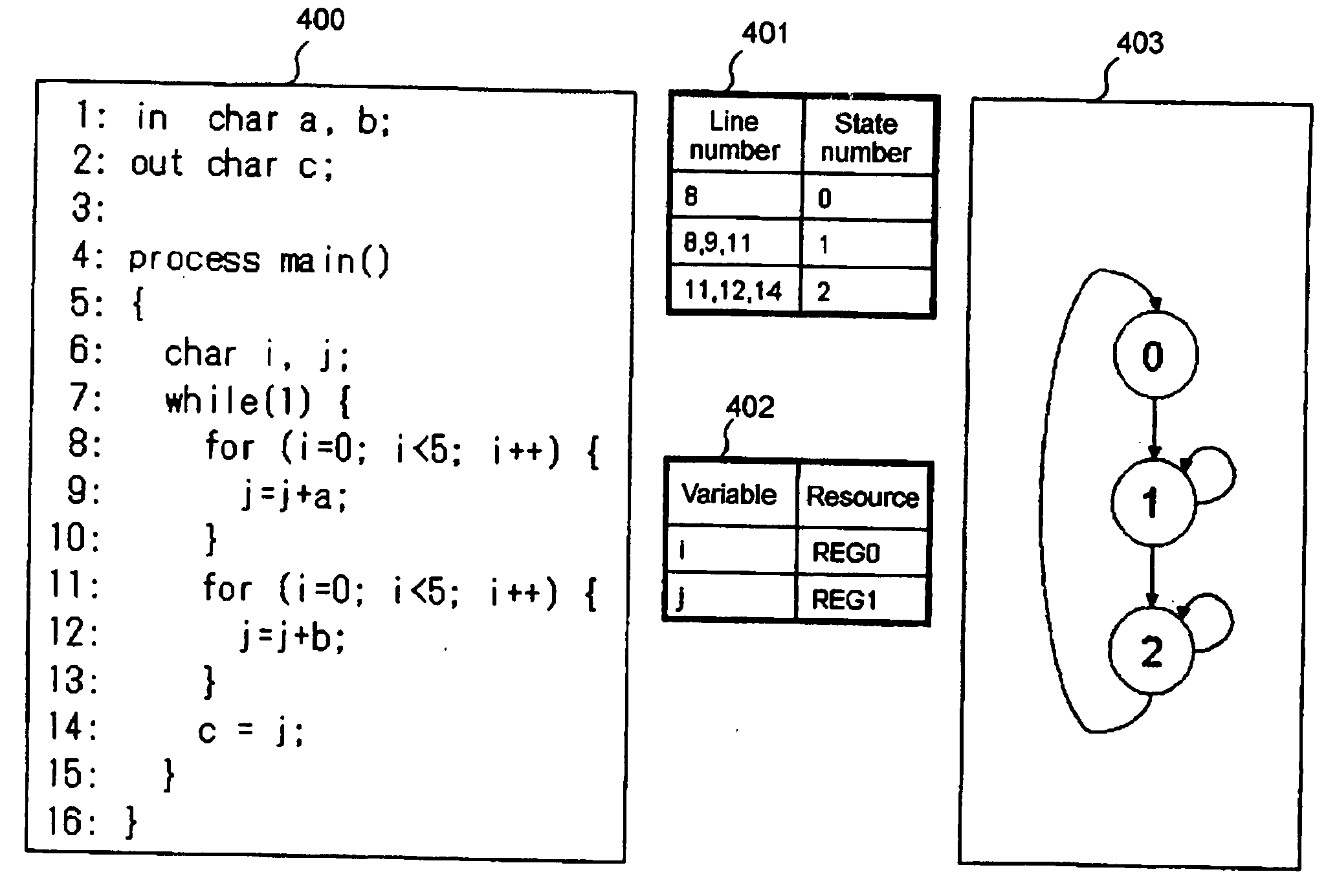

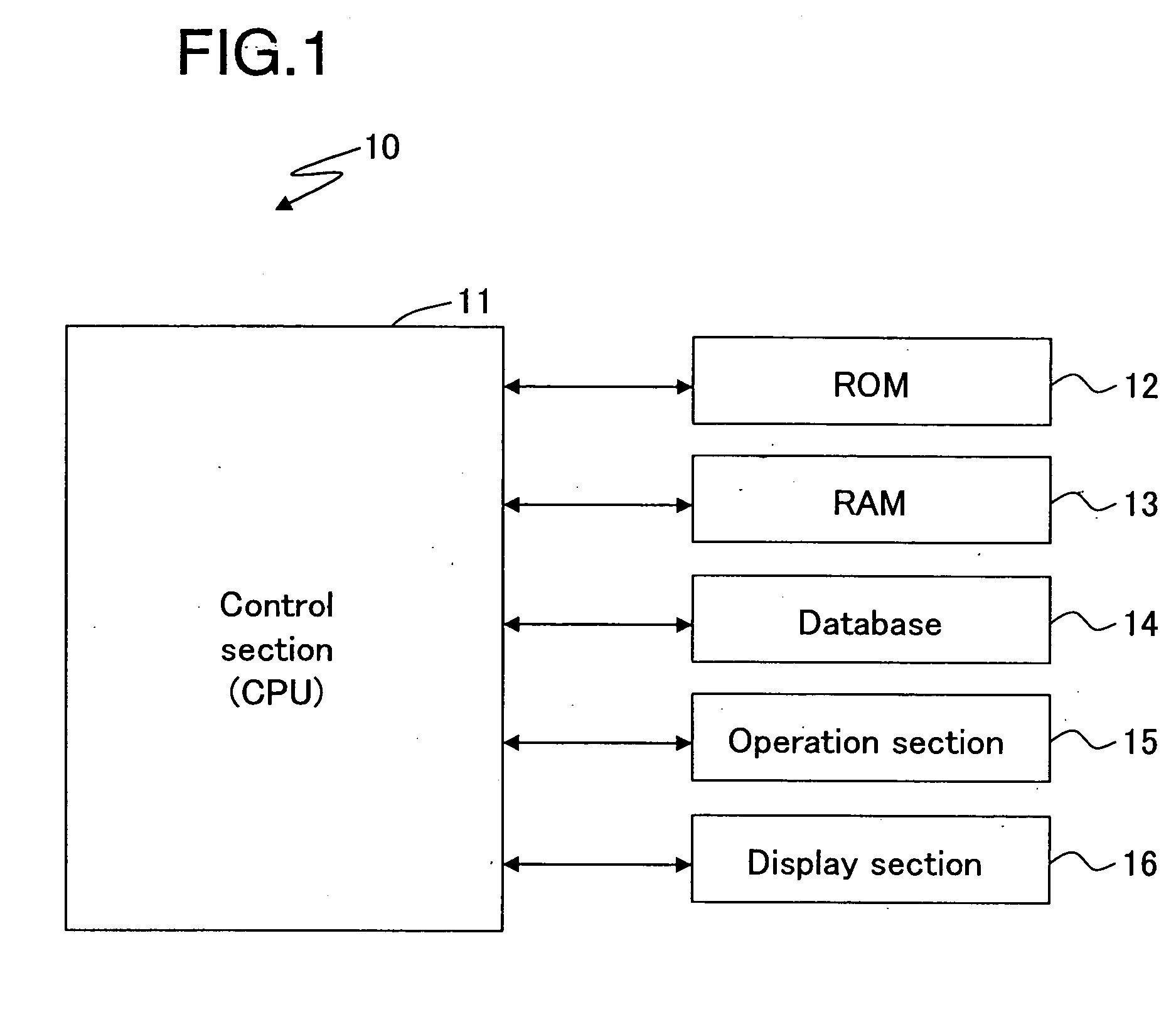

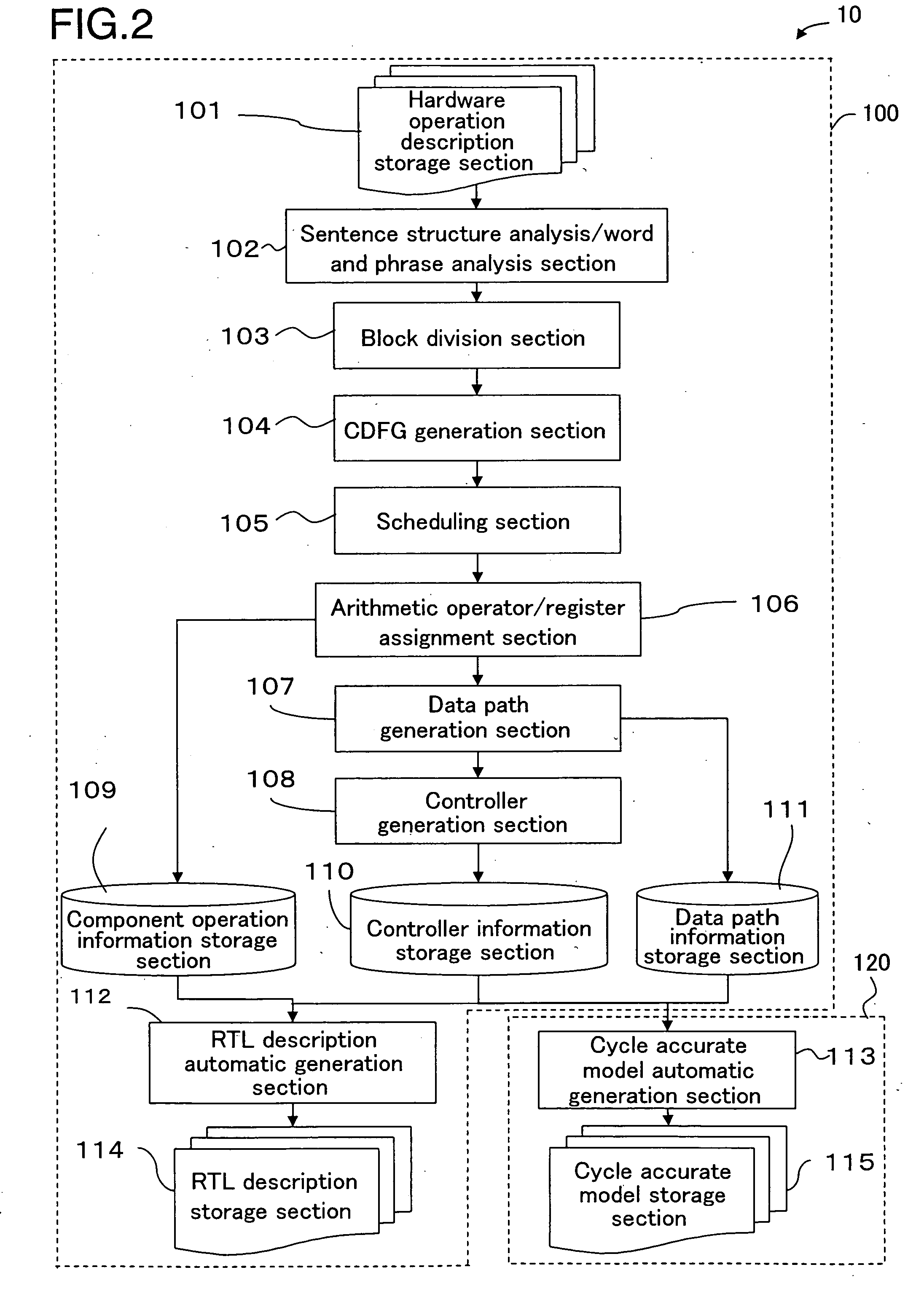

High level synthesis device, method for generating a model for verifying hardware, method for verifying hardware, control program, and readable recording medium

ActiveUS20050010387A1Increase speedSimple designCAD circuit designSoftware simulation/interpretation/emulationComputer hardwareHigh-level synthesis

A high level synthesis device includes a high level synthesis section for performing high level synthesis of hardware including a plurality of components and a controller for controlling the plurality of components; and a cycle accurate model generation section for generating a cycle accurate model, capable of verifying a state of at least one of the plurality of components and the controller at a cycle accurate level, with a general-purpose programming language.

Owner:SHARP KK

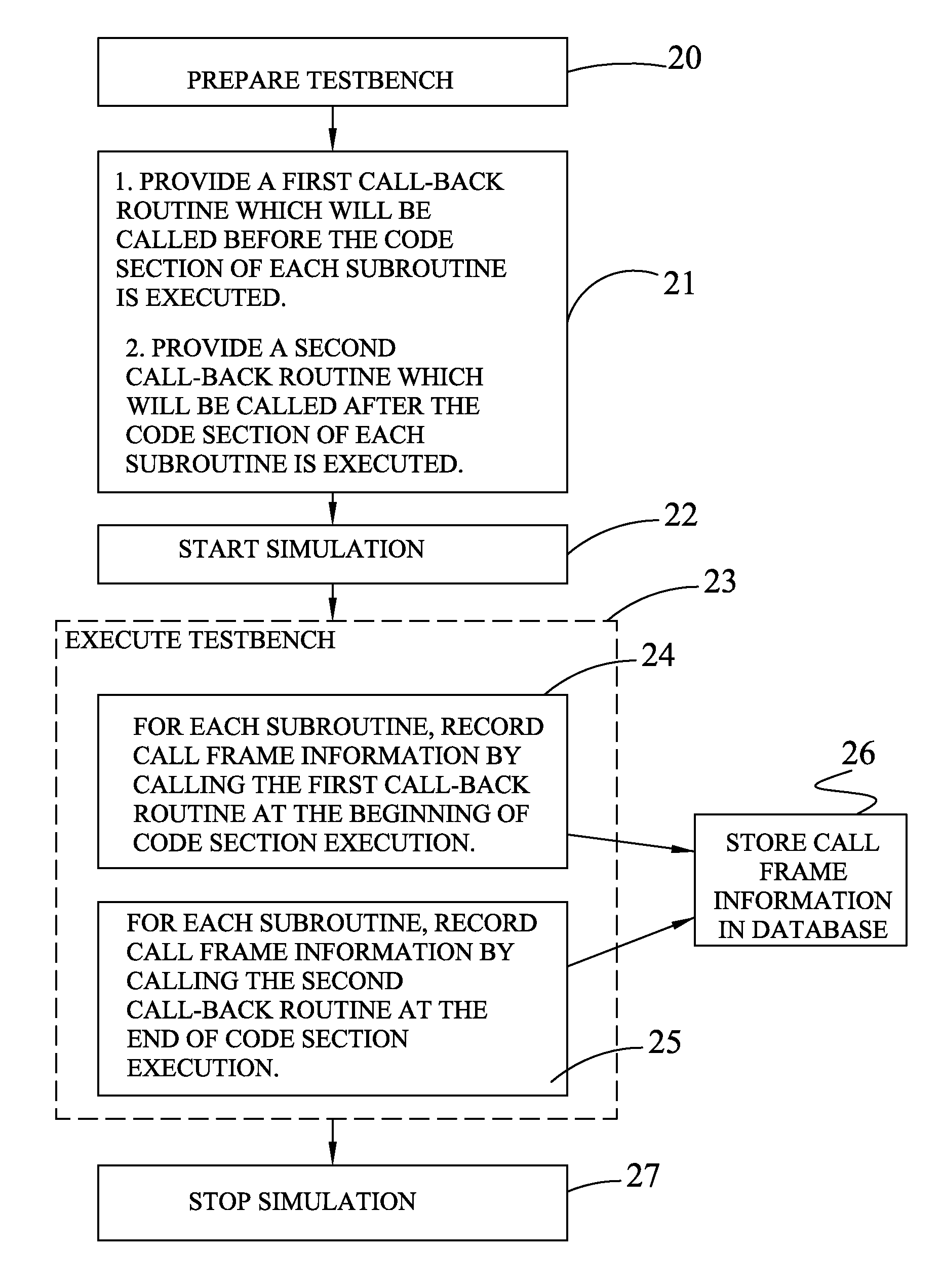

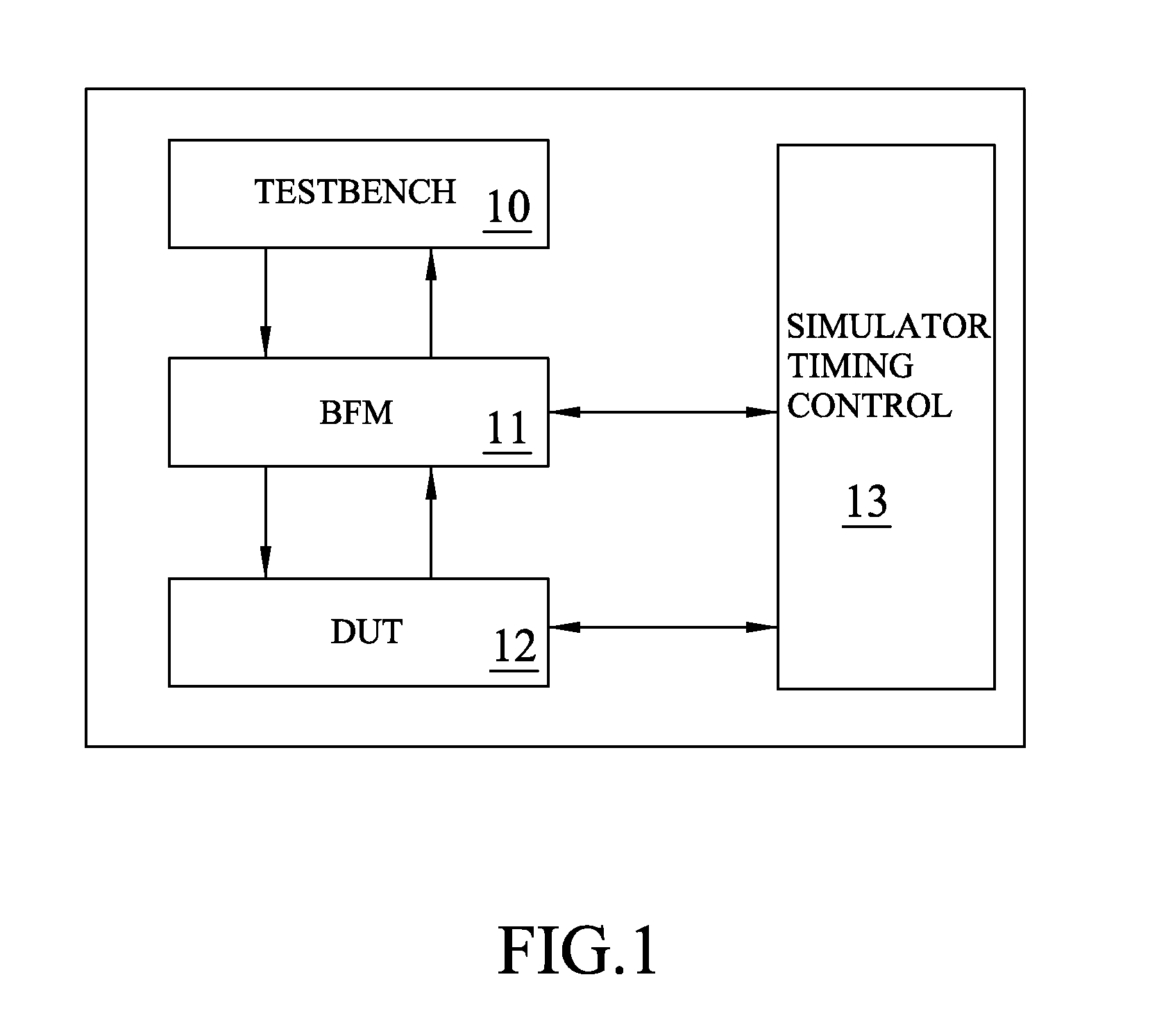

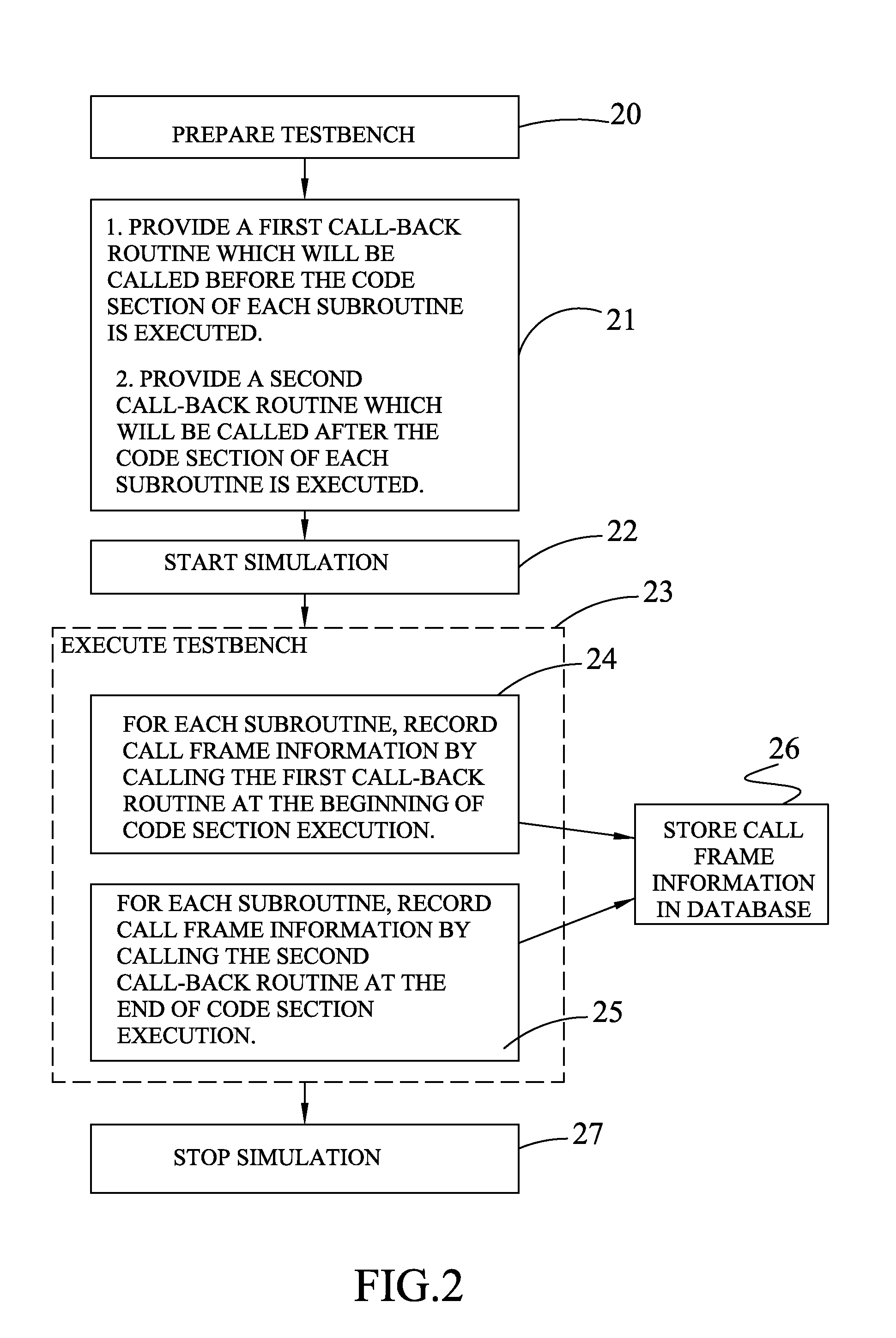

Method of recording and replaying call frames for the testbench

ActiveUS8522176B2Efficient debuggingEasy to getDetecting faulty computer hardwareDesign optimisation/simulationParallel computingSource code

A computer-implemented method to debug testbench code of a testbench associated with a circuit design by recording a trace of call frames along with activities of the circuit design. By correlating and displaying the recorded trace of call frames, the method enables users to easily trace an execution history of subroutines executed by the testbench thereby to debug the testbench code. In addition, users can trace source code of the testbench code by using the recorded trace of call frames. Furthermore, users can debug the testbench code utilizing a virtual simulation, which is done by post-processing records of the virtual simulation stored in a database.

Owner:SYNOPSYS INC

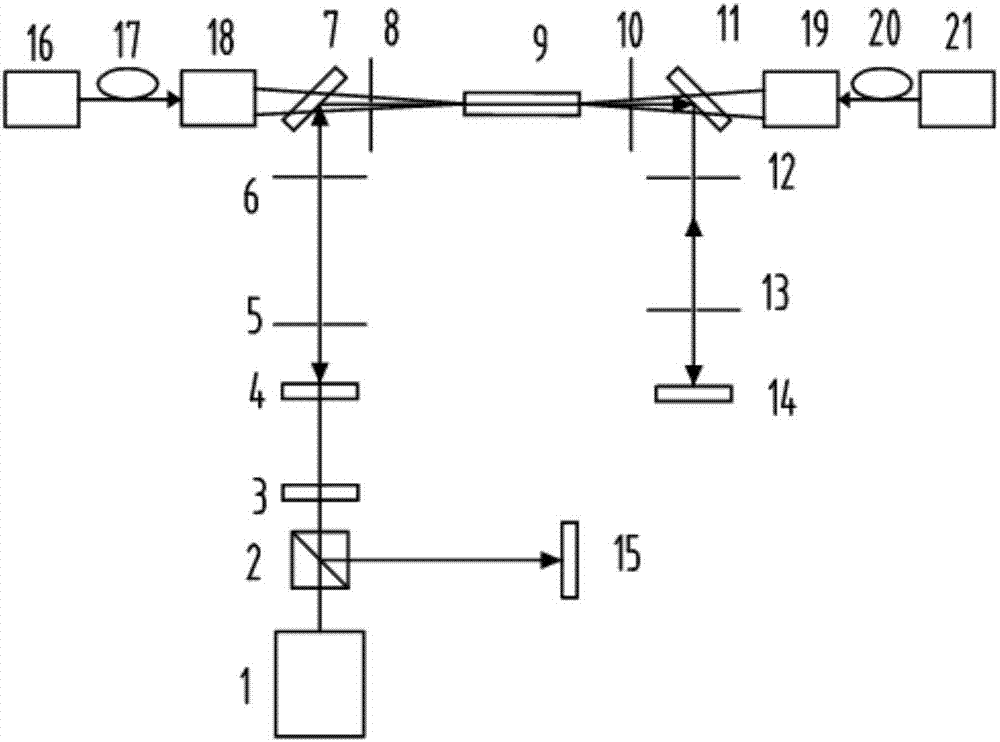

Efficiently-debugged U-type cavity laser and debugging method thereof

PendingCN107221832AGuaranteed parallelism of end facesEfficient debuggingLaser detailsInfraredResonant cavity

The invention discloses an efficiently-debugged U-type cavity laser and a debugging method thereof. A 1064nm infrared laser, a PBS and a quarter-wave plate are used to form a laser debugging device, 1064nm laser is adjusted to be reference light, pairs of apertures are used to adjust the reference light to be collimated; pairs of apertures are then used to adjust a reflection light path to be collimated, and a laser crystal is adjusted to enable the end surface of the laser crystal to be vertical to the reference light; a laser diode and an optical coupling system are adjusted to enable pumping light and the reference light to be overlapped; a total-reflection mirror is adjusted to enable reflection light of the reference light through the PBS and reflection light through the total-reflection mirror to be overlapped; and an output mirror is adjusted to enable the reflection light of the total-reflection mirror and reflection light through the output mirror to be overlapped. The laser debugging device is used for enabling the pumping light and the reference light to be overlapped, reference light reflected by the total-reflection mirror and the output mirror is overlapped, the end surface parallelism of the whole resonant cavity is ensured, the laser U-type cavity can be debugged efficiently, and the debugging method is simple and accurate.

Owner:NANJING INST OF ADVANCED LASER TECH

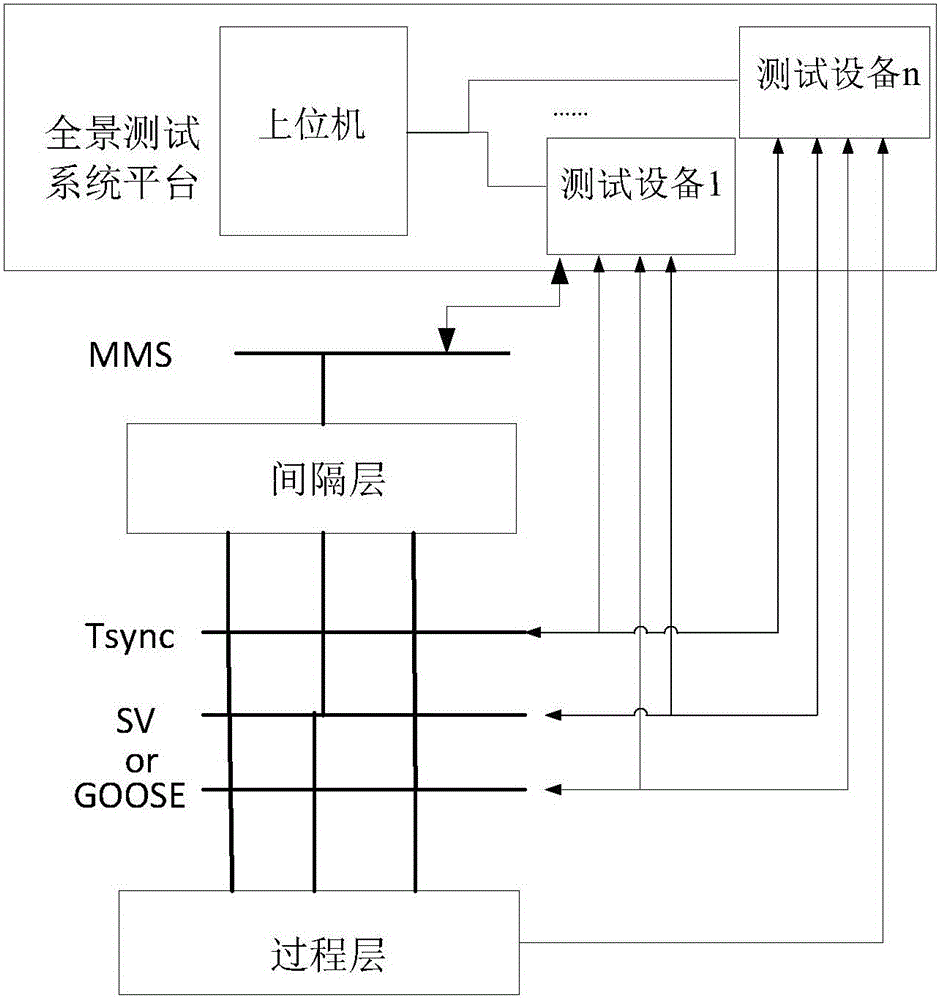

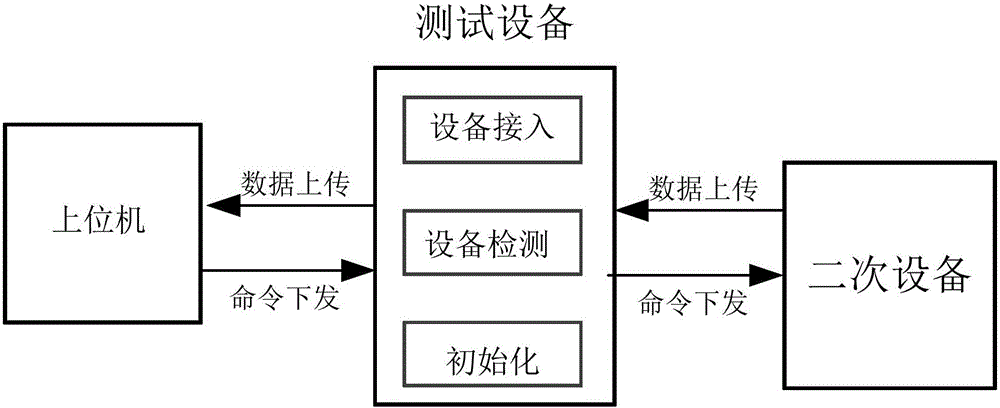

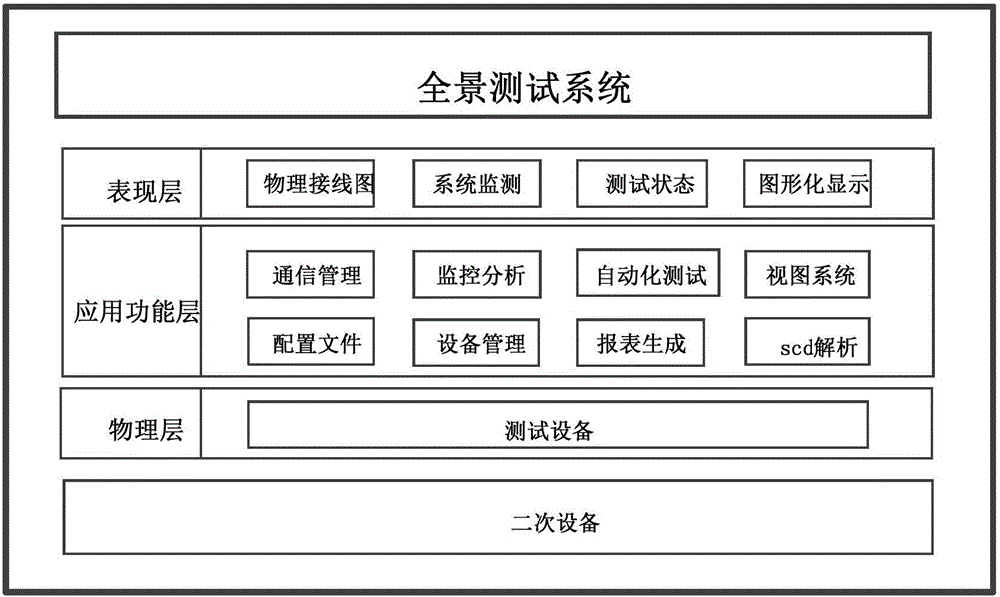

Intelligent transformer substation secondary equipment panorama test system and construction and test method thereof

ActiveCN105738736AComplete efficientlyEfficient debuggingElectrical testingVirtual terminalSmart substation

The embodiment of the present invention discloses an intelligent transformer substation secondary equipment panorama test system and a construction and test method thereof. According to the present invention, by analyzing a transformer substation database configuration file, all intelligent electronic devices and the configuration information of the intelligent electronic devices can be obtained, and by the virtual terminal input and output of the acquisition and control modules between the intelligent electronic devices, the connection between the intelligent electronic devices is realized; a secondary equipment panorama diagram is drawn by taking the intervals as units, the intelligent electronic devices in the panorama diagram are monitored real-timely, and the states and the data flow directions of the intelligent electronic device virtual terminals can be visualized; the connection states of the input and output virtual terminals of the intelligent electronic devices and the correlated devices are displayed, and the connection states of the virtual terminals and the information and the data flow directions of the devices of a transformer substation can be changed directly under the panorama diagram. The test system and the test method provided by the embodiment of the present invention can carry out the integration and visualization test on the functions of a plurality of intelligent electronic devices of the whole transformer substation simultaneously, thereby finishing the overall debugging and verification of the intelligent transformer substation secondary equipment efficiently and reliably.

Owner:YUNNAN POWER GRID CO LTD ELECTRIC POWER RES INST

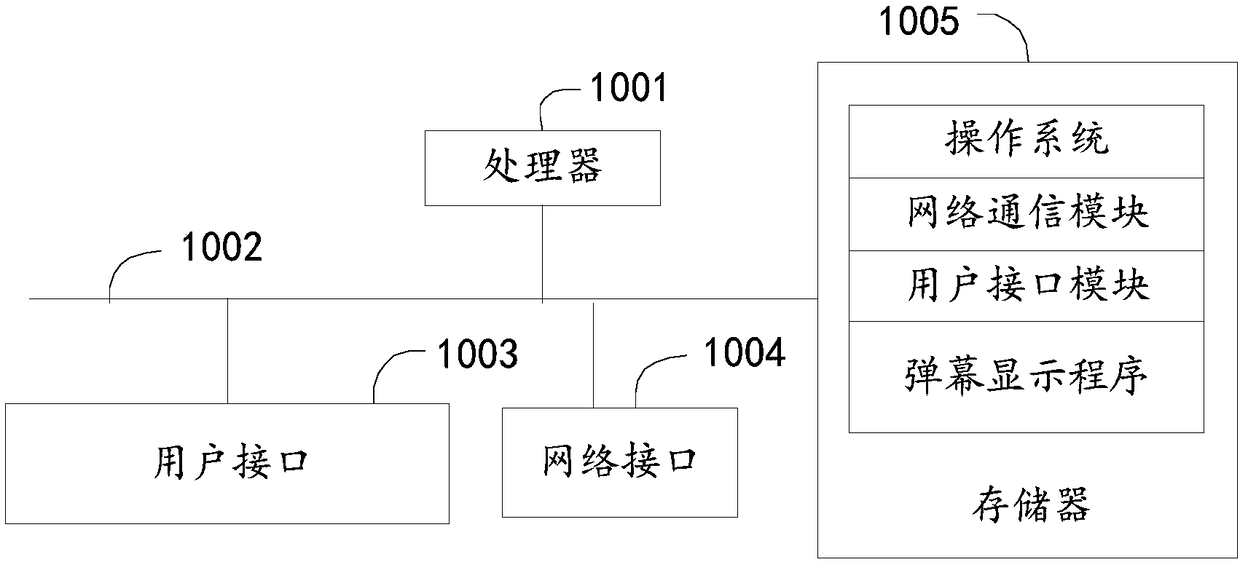

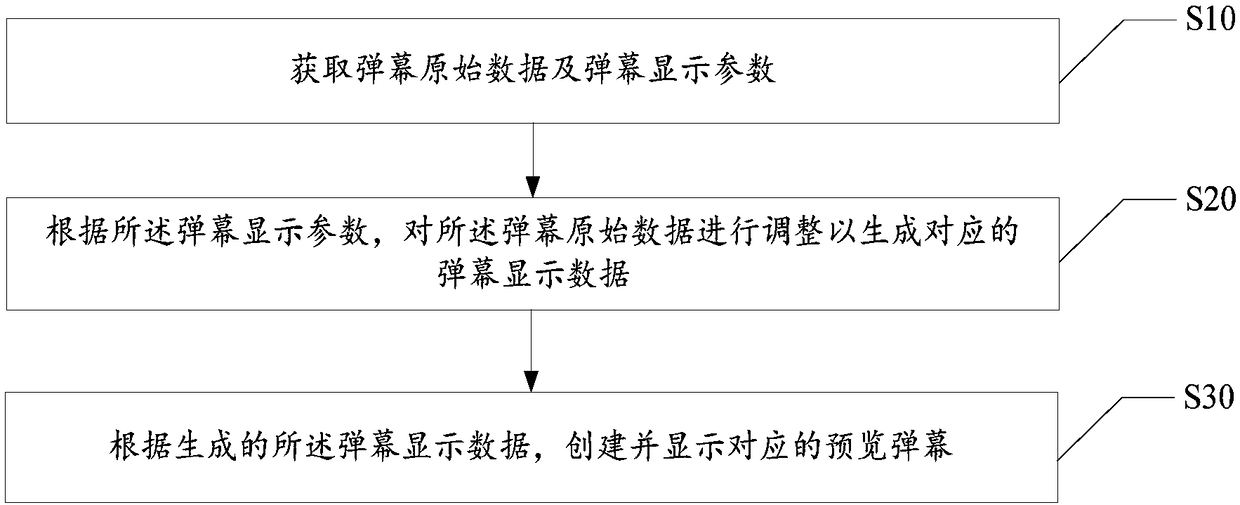

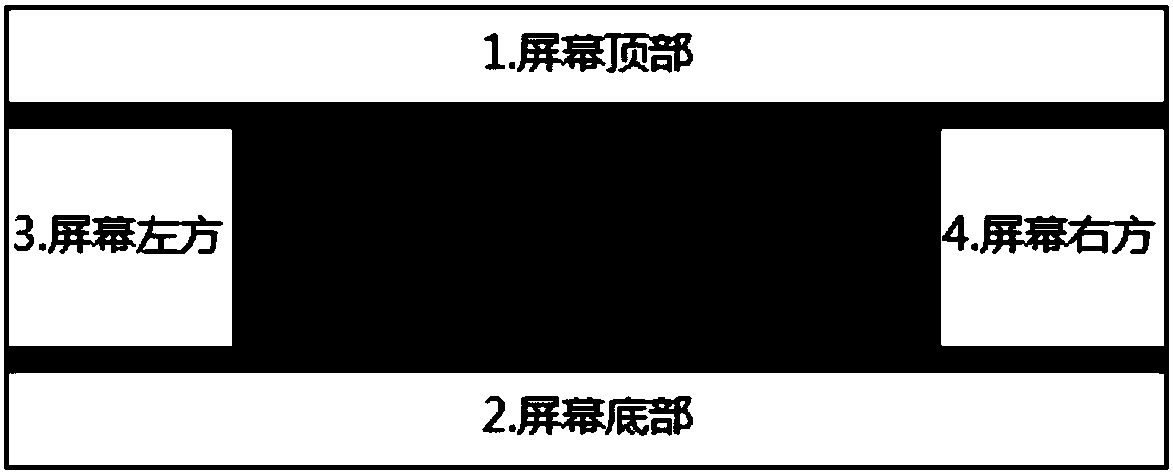

Bullet screen display method and apparatus, and readable storage medium

InactiveCN108260019AEasy to operateEfficient debuggingSelective content distributionComputer graphics (images)Original data

The invention provides a bullet screen display method. The method comprises the following steps: obtaining bullet screen original data and bullet screen display parameters; adjusting the bullet screenoriginal data according to the bullet screen display parameters to generate corresponding bullet screen display data; and creating and displaying corresponding preview bullet screen according to thegenerated bullet screen display data. The invention further provides a bullet screen display data apparatus and a readable storage medium. During bullet screen debugging, the bullet screen display effect can be previewed in real time just by configuring the bullet screen display parameters.

Owner:深圳市瑞致达科技有限公司