Patents

Literature

78 results about "ACCESS.bus" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

ACCESS.bus, or A.b for short, is a peripheral-interconnect computer bus developed by Philips and DEC in the early 1990s, based on Philips' I²C system. It is similar in purpose to USB, in that it allows low-speed devices to be added or removed from a computer on the fly. While it was made available earlier than USB, it never became popular as USB gained in popularity.

Method and system for sharing a computer resource between instruction threads of a multi-threaded process

InactiveUS7131125B2Program initiation/switchingData switching by path configurationComputer resourcesExternal storage

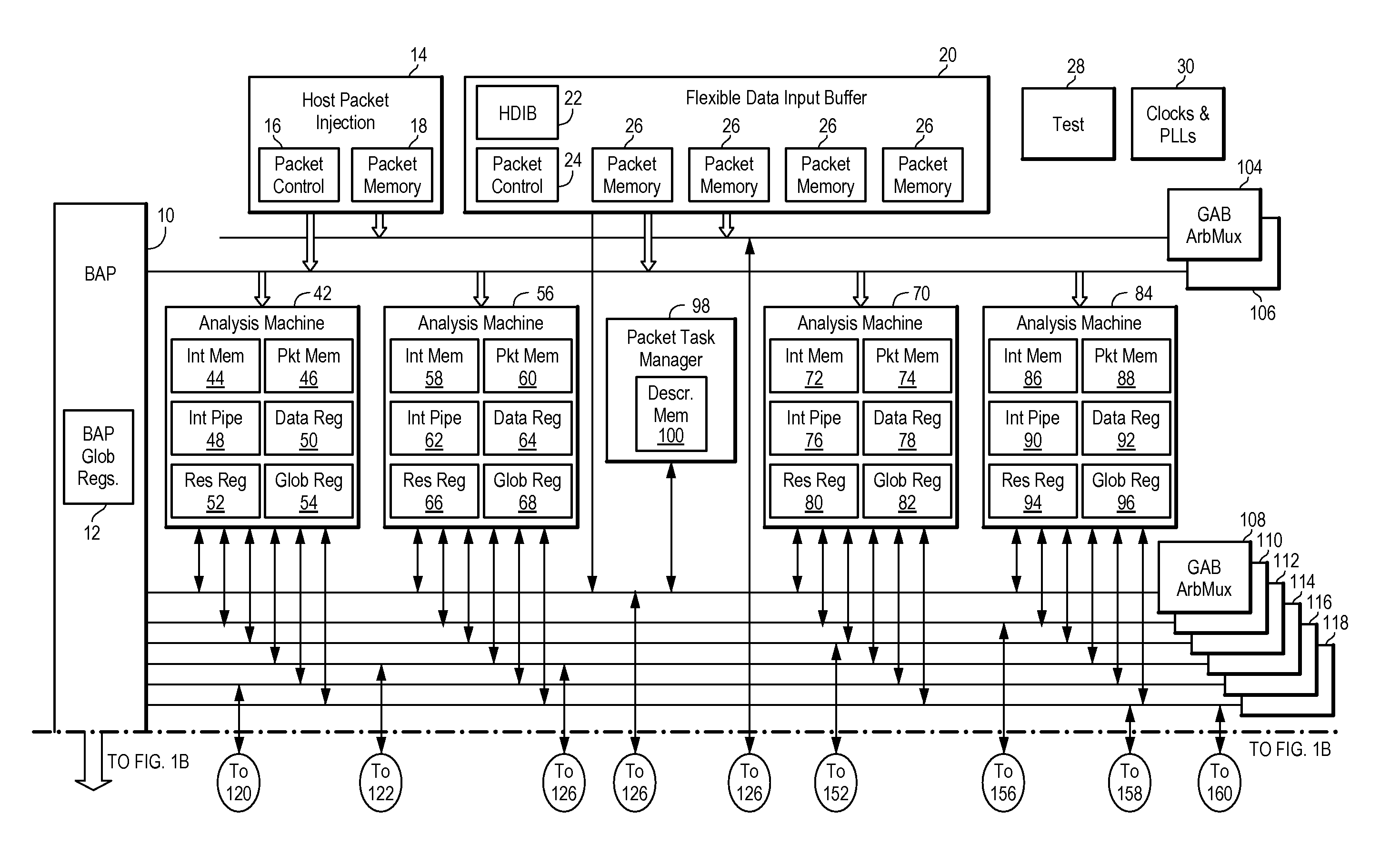

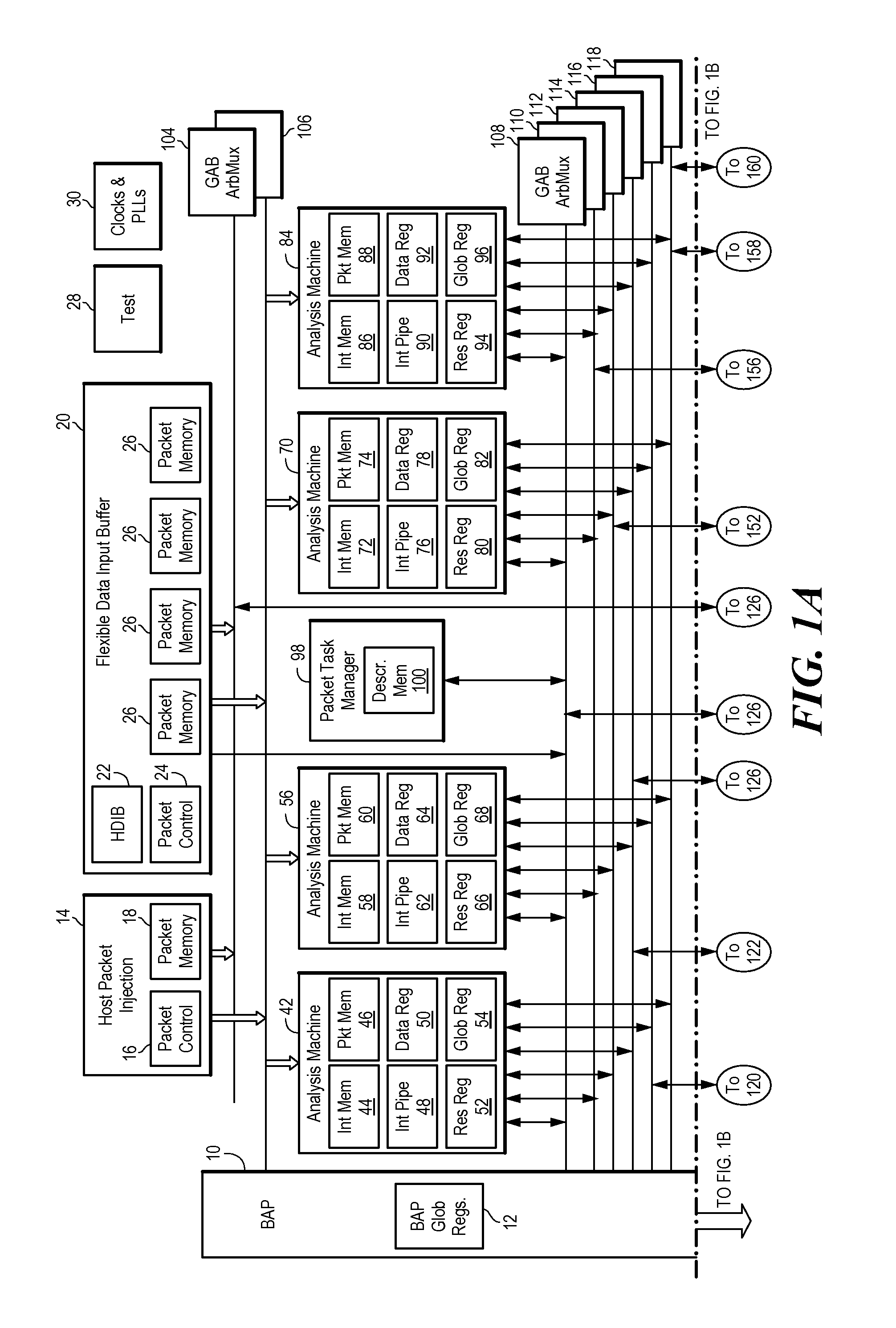

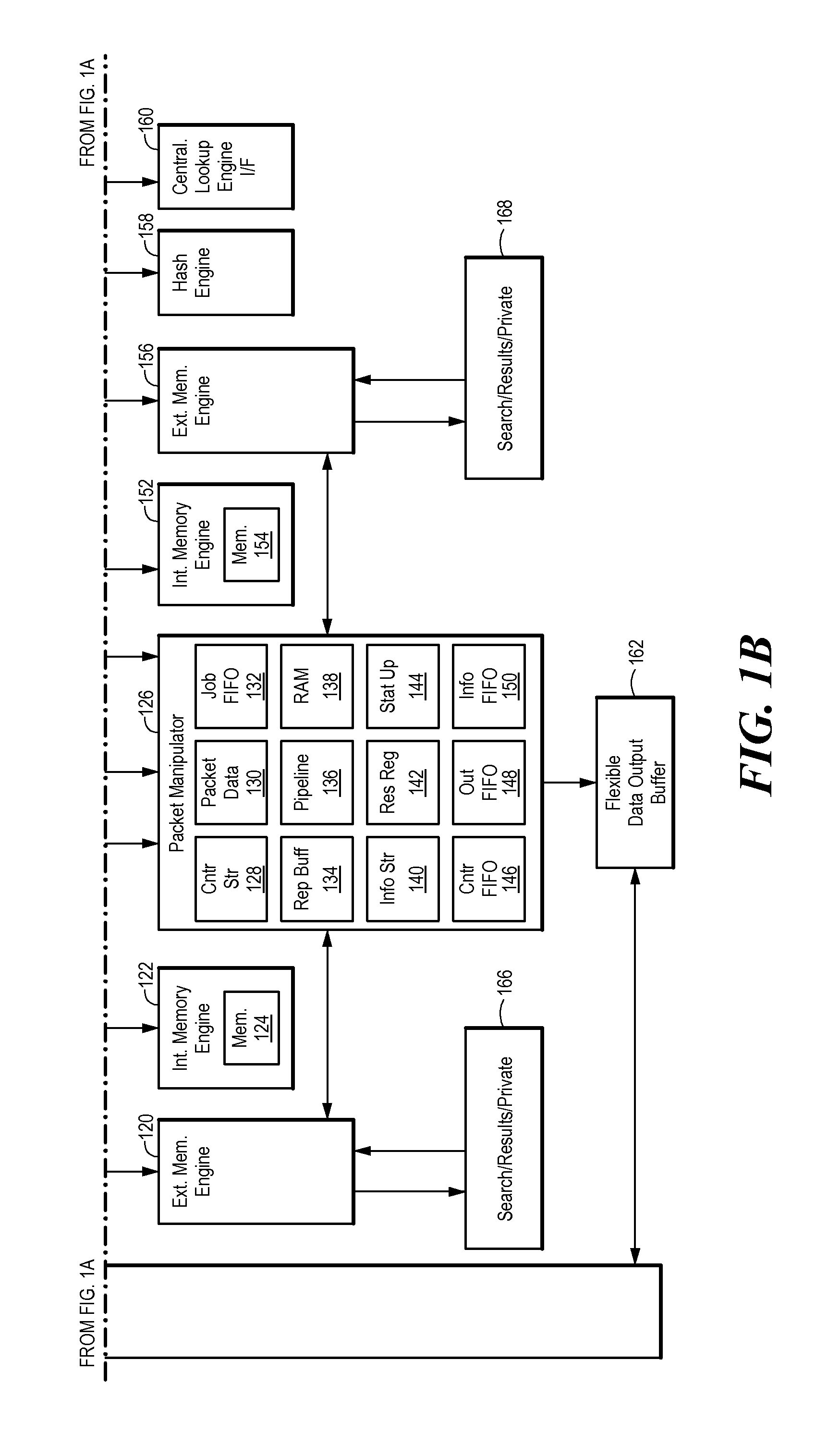

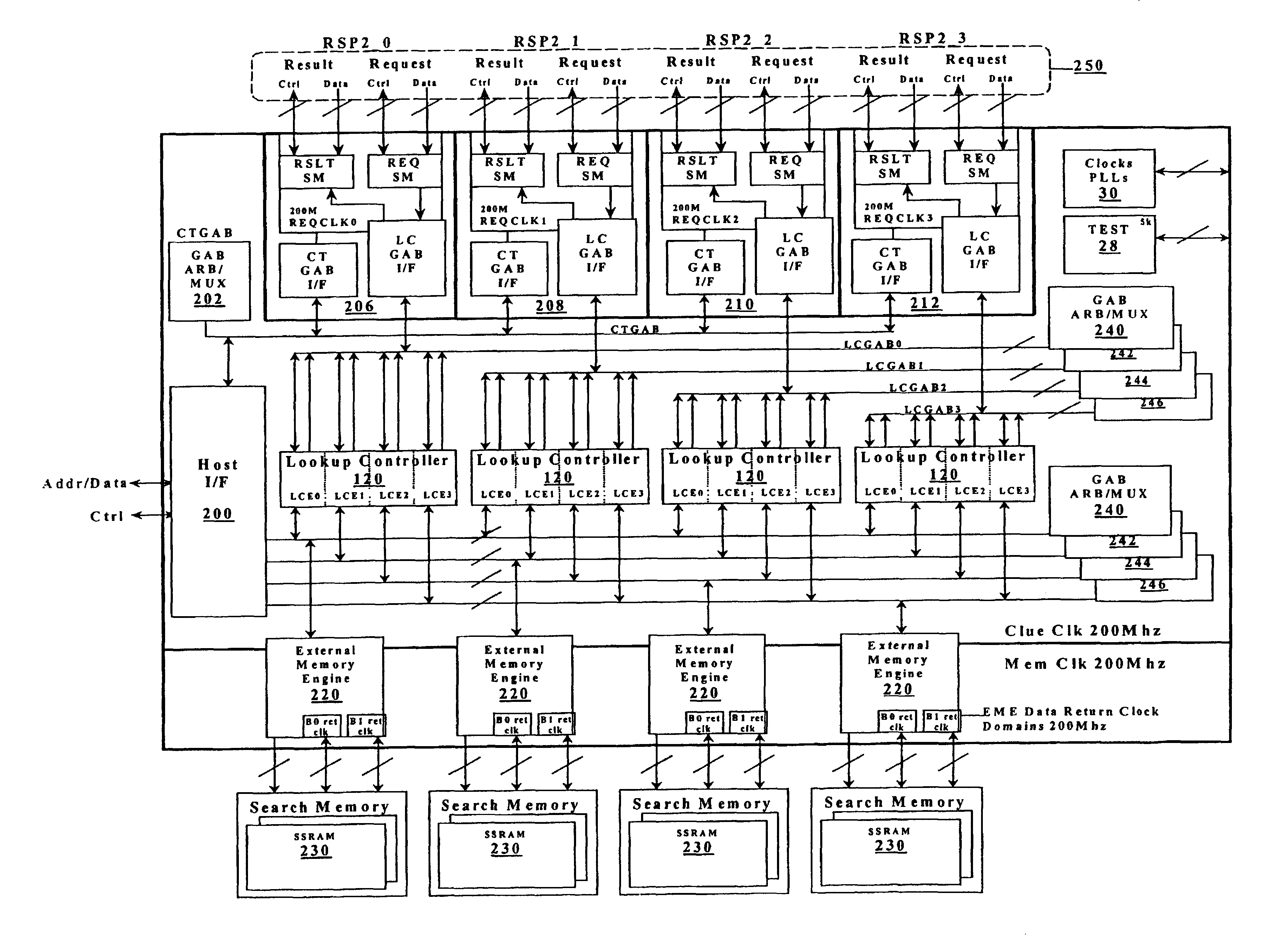

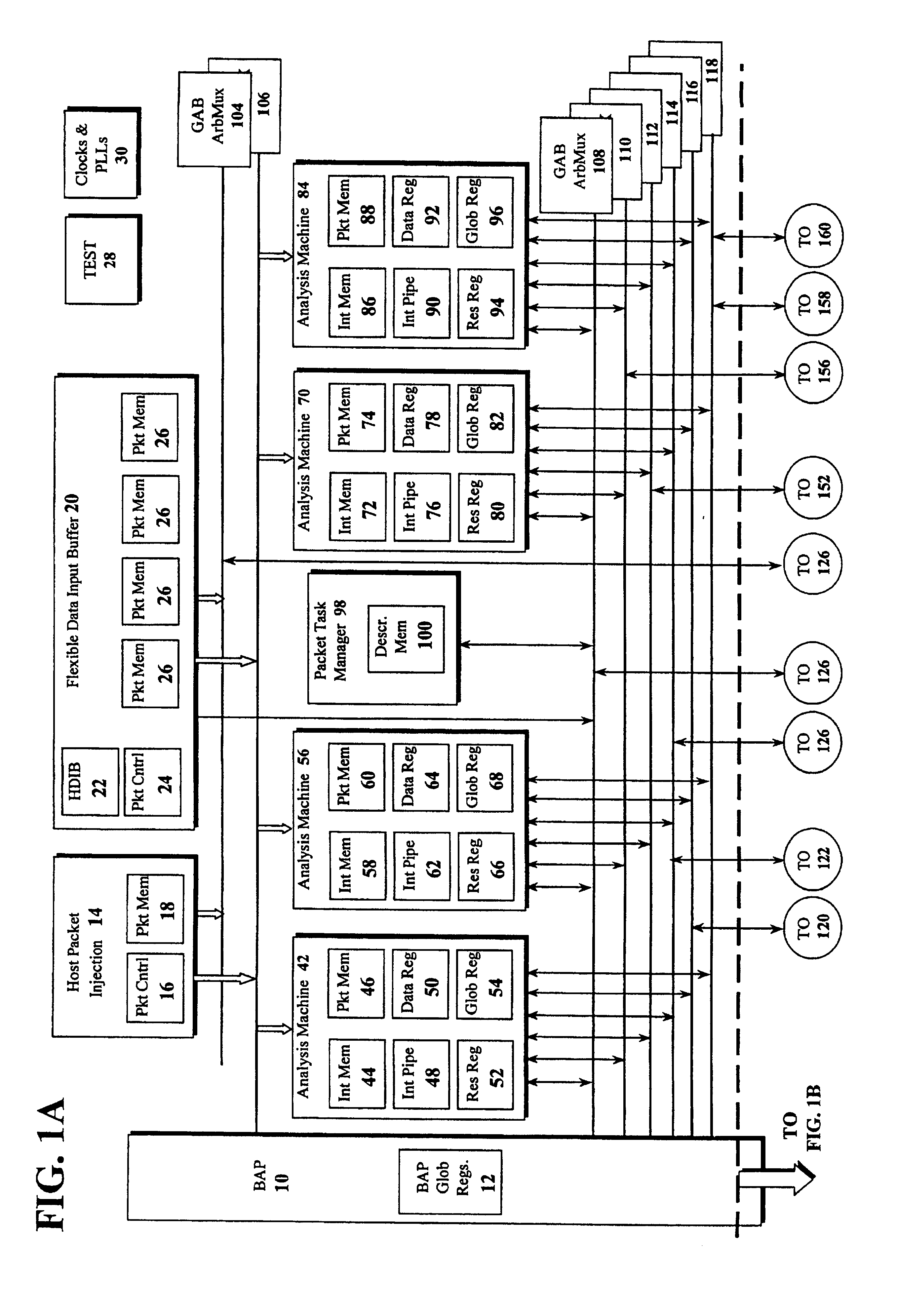

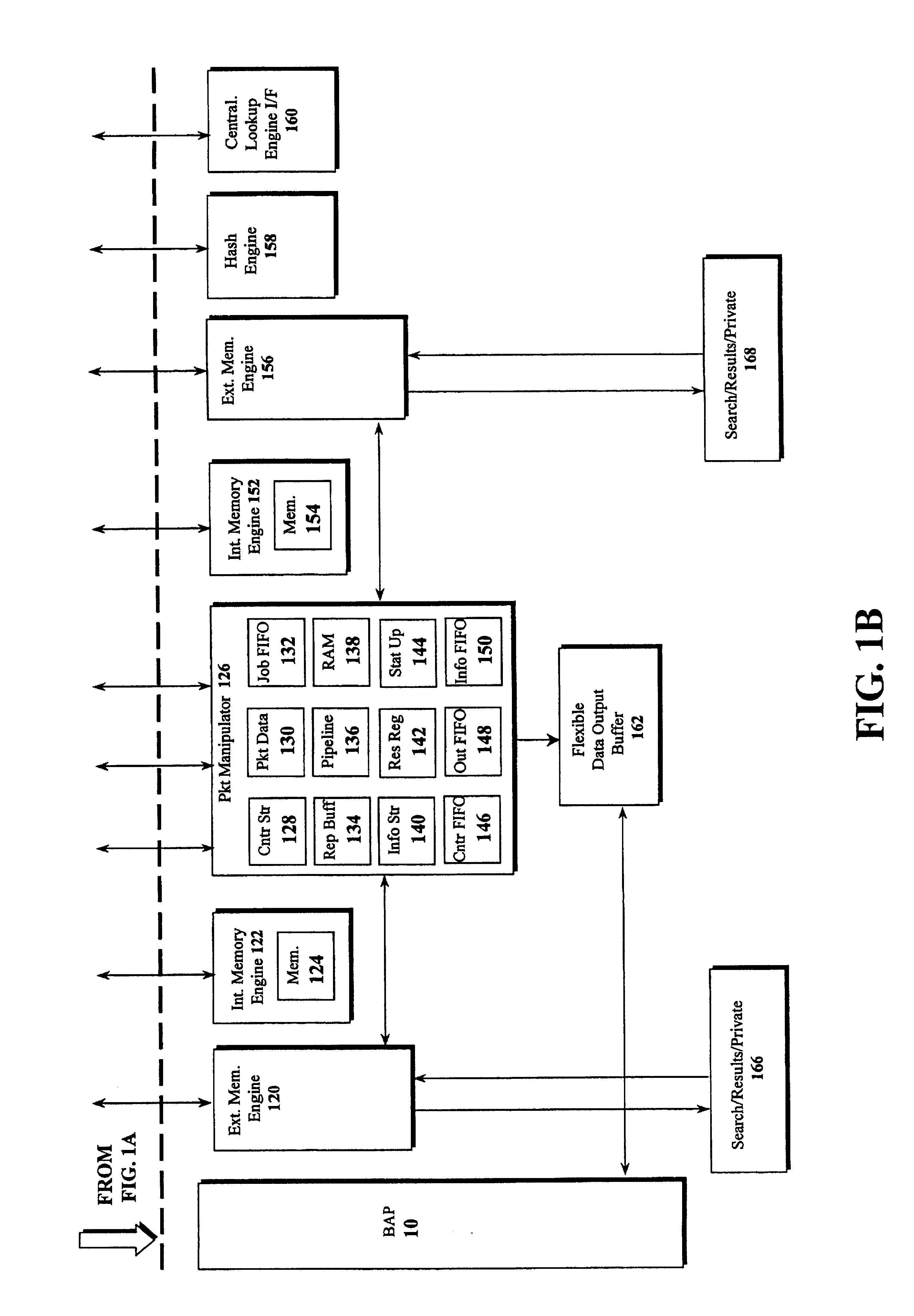

Route switch packet architecture processes data packets using a multi-threaded pipelined machine wherein no instruction depends on a preceding instruction because each instruction in the pipeline is executed for a different thread. The route switch packet architecture transfers a data packet from a flexible data input buffer to a packet task manager, dispatches the data packet from the packet task manager to a multi-threaded pipelined analysis machine, classifies the data packet in the analysis machine, modifies and forwards the data packet in a packet manipulator. The route switch packet architecture includes an analysis machine having multiple pipelines, wherein one pipeline is dedicated to directly manipulating individual data bits of a bit field, a packet task manager, a packet manipulator, a global access bus including a master request bus and a slave request bus separated from each other and pipelined, an external memory engine, and a hash engine.

Owner:AVAYA MANAGEMENT LP

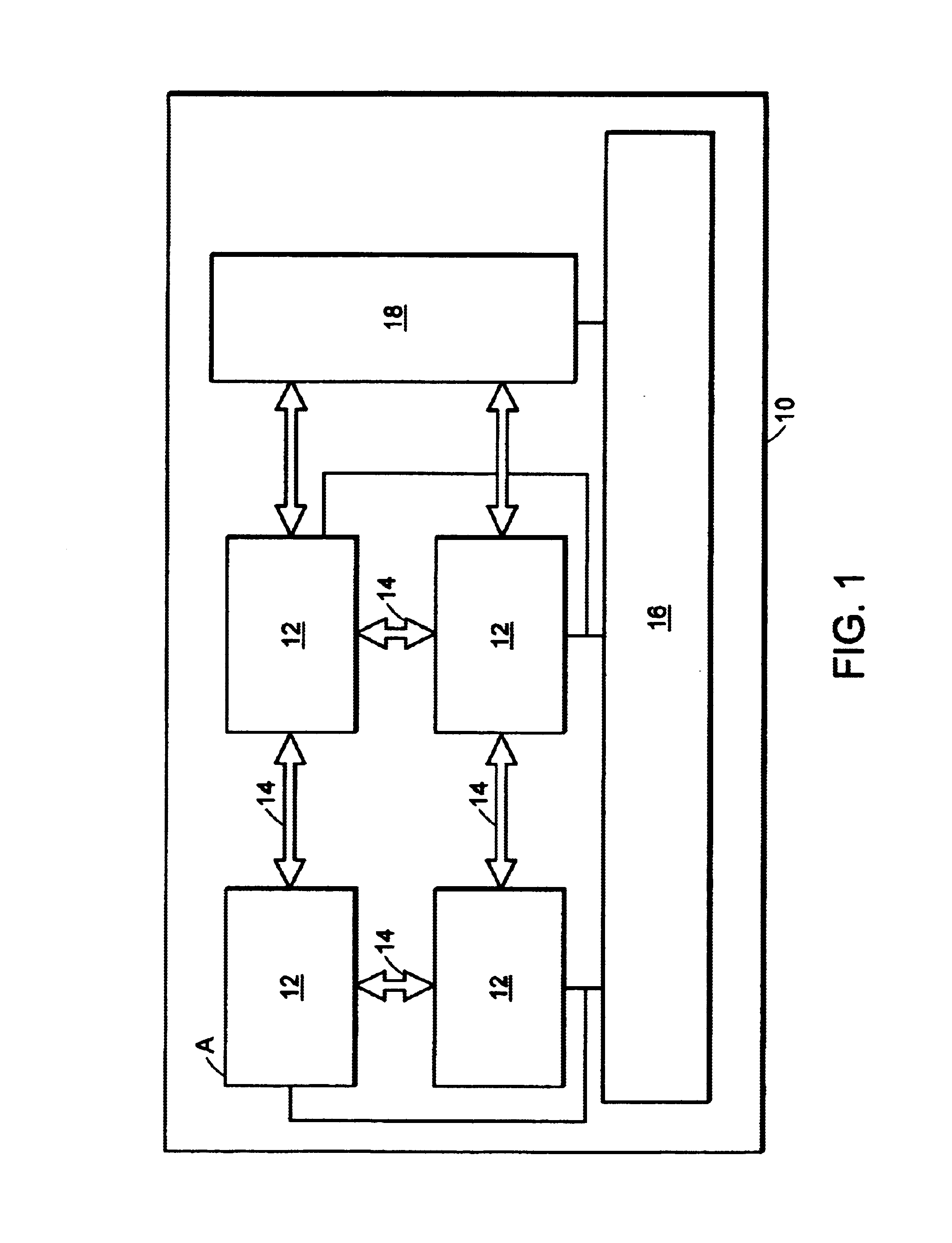

Global access bus architecture

Global access bus architecture includes a master request bus and a slave request bus separated from each other and pipelined. The global access bus architecture includes packet input global access bus software code for flow of data packet information from a flexible input data buffer to an analysis machine, packet data global access bus software code for flow of packet data between a flexible data input bus and a packet manipulator, statistics data global access bus software code for connection of an analysis machine to a packet manipulator, private data global access bus software code for connection of an analysis machine to an internal memory engine, lookup global access bus software code for connection of an analysis machine to an internal memory engine, results global access bus software code for providing flexible access to an external memory, and results global access bus software code for providing flexible access to an external memory.

Owner:AVAYA MANAGEMENT LP

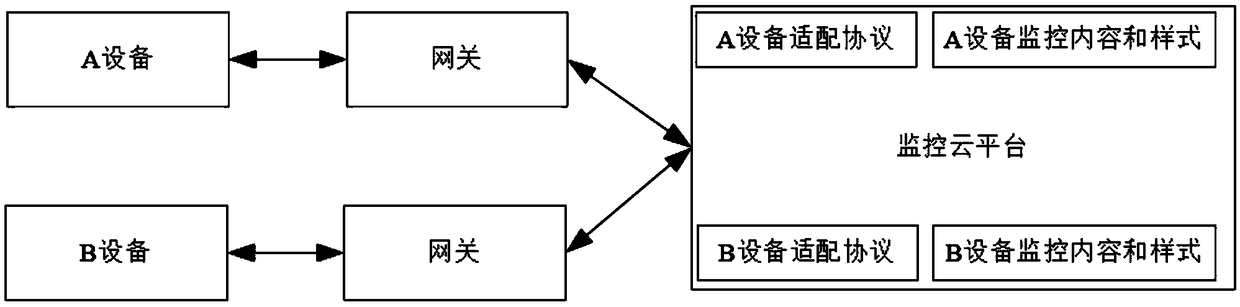

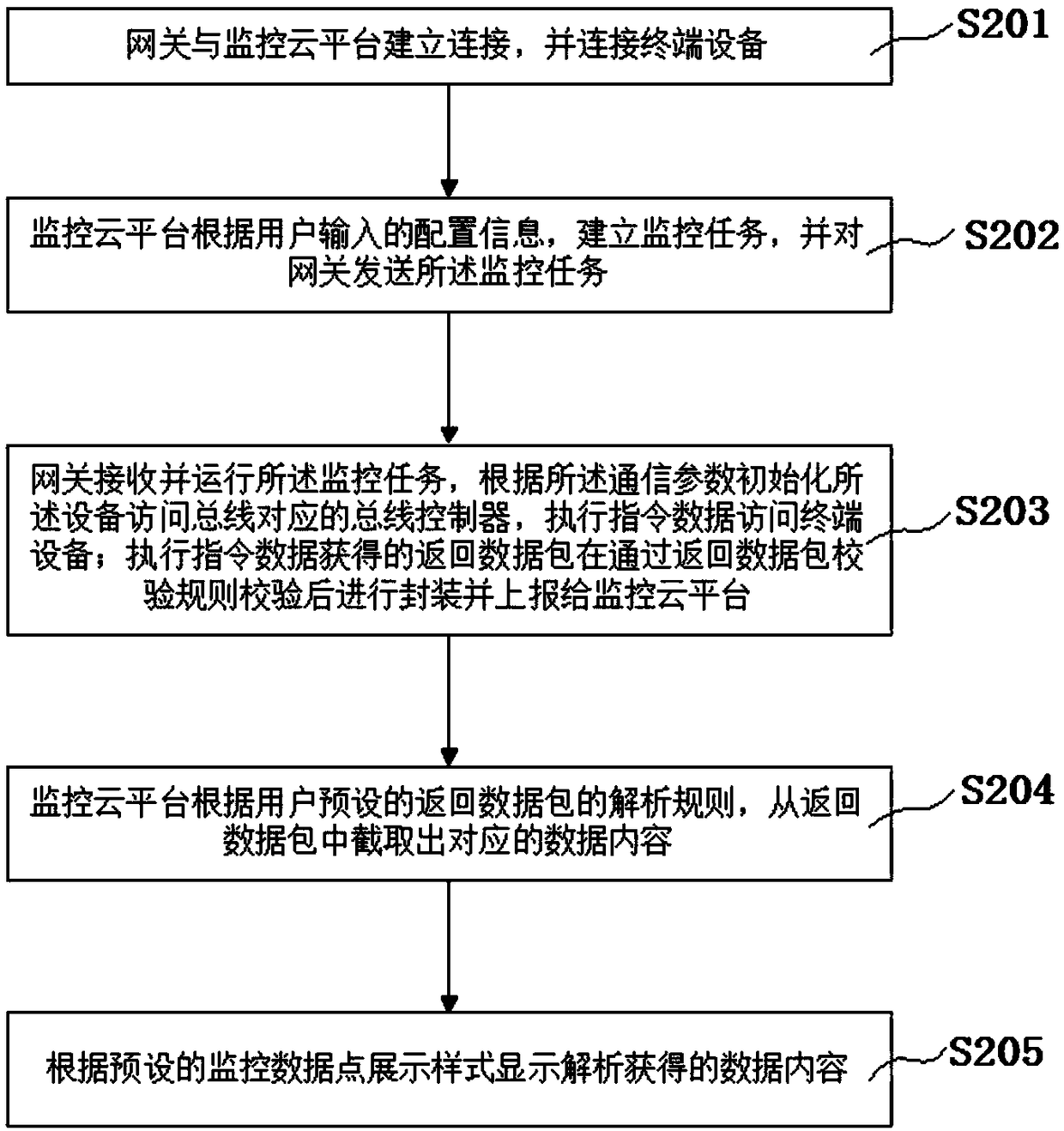

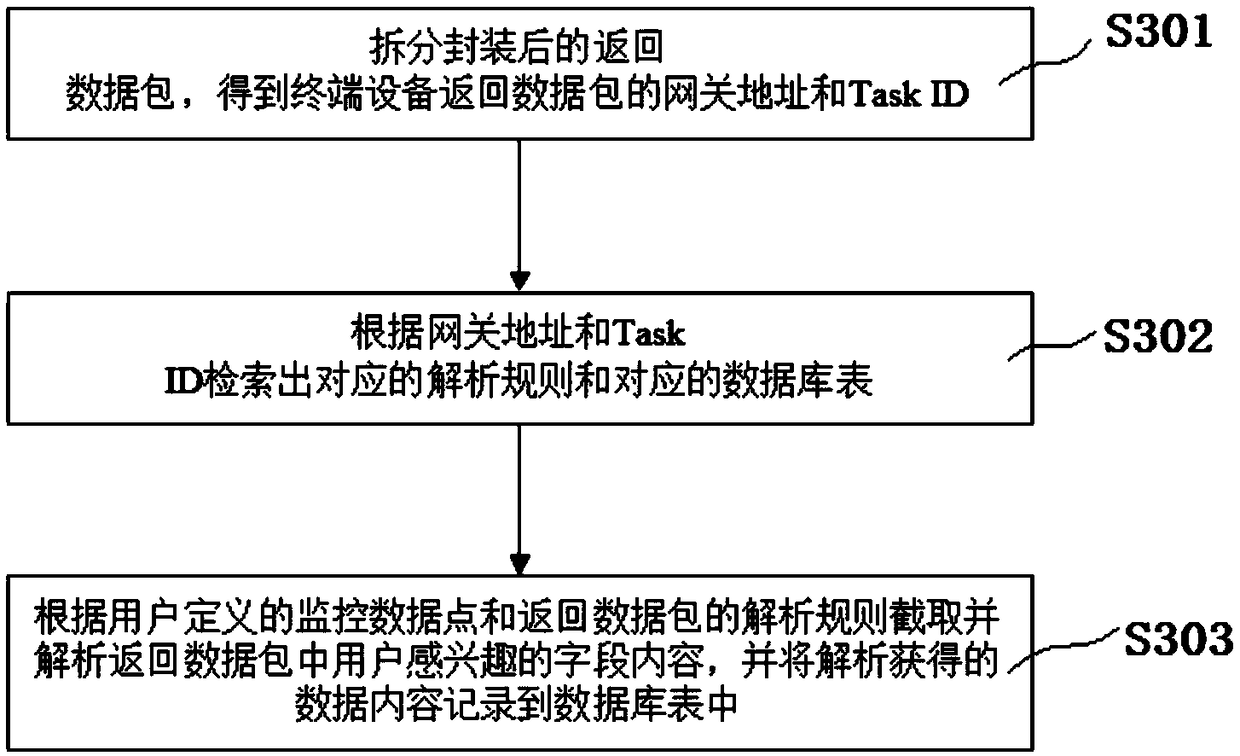

Protocol self-adaptation method and system based on monitoring cloud platform and gateway

ActiveCN108667807ALow costConvenient and flexible accessNetworks interconnectionNetwork connectionsUser inputNetwork packet

The invention relates to a protocol self-adaptation method based on a monitoring cloud platform and a gateway. The method comprises the steps as follows: the gateway and the monitoring cloud platformbuild a connection, and are connected with terminal equipment; the monitoring cloud platform builds a monitoring task according to configuration information input by a user, and sends the monitoring task to the gateway; the gateway receives and runs the monitoring task, initializes a bus controller corresponding to an equipment access bus via a communication parameter, and execution command data accesses the terminal equipment; a return data packet acquired by the execution command data is packaged and reported to the monitoring cloud platform after being verified via a return data packet verification rule; and the monitoring cloud cuts out corresponding data content from the return data packet according to an analysis rule of the return data packet preset by the user. According to the method and system provided by the invention, the protocol self-adaptation method based on the monitoring cloud platform and the gateway can conveniently and flexibly access the different equipment of thedifferent buses without customized development, and thus non-developers can complete self-adaptation configuration.

Owner:SOUTH CHINA NORMAL UNIVERSITY

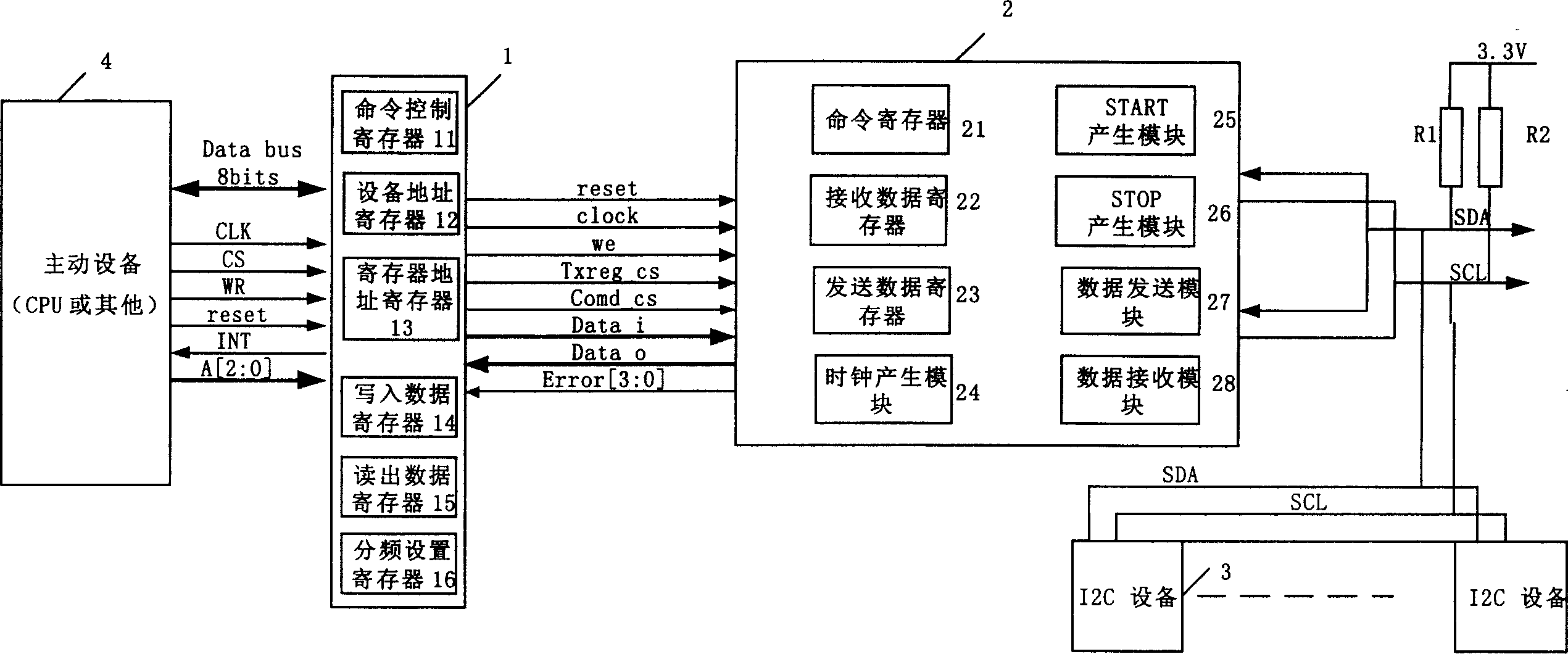

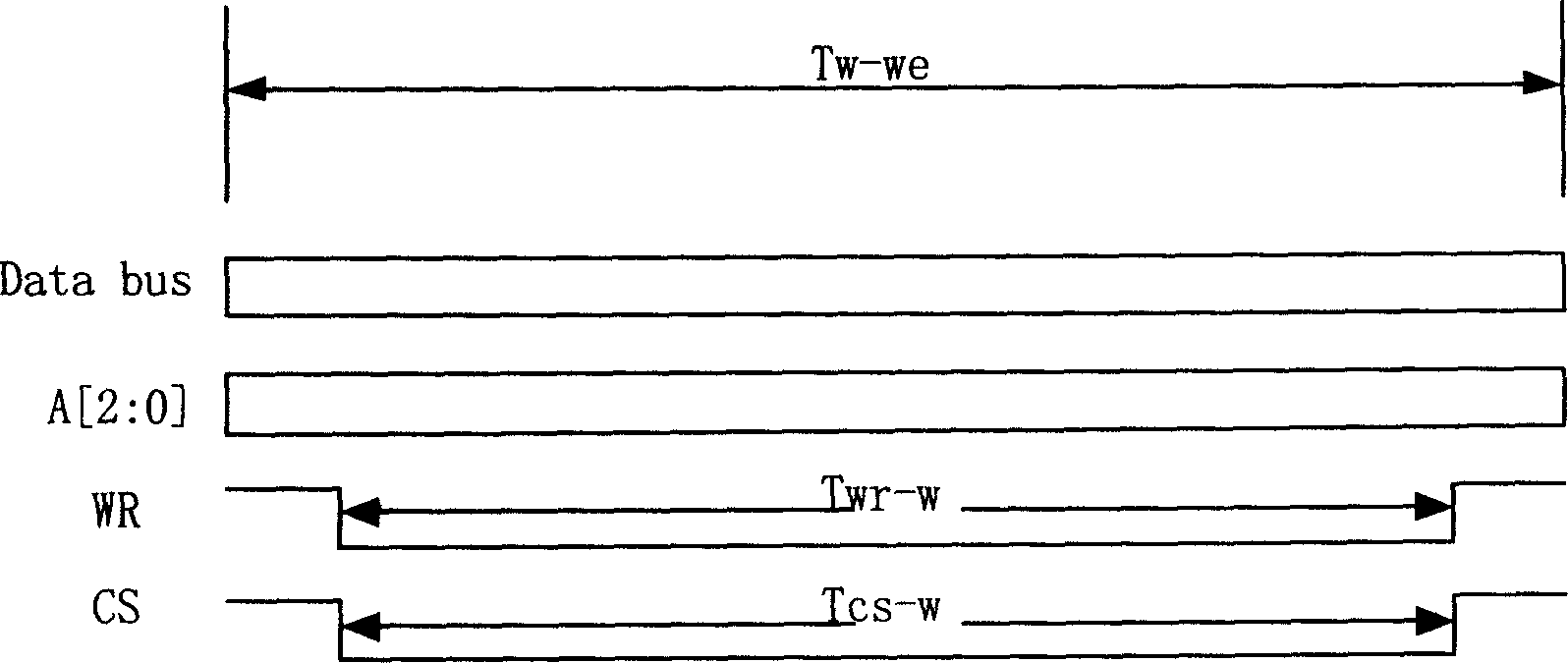

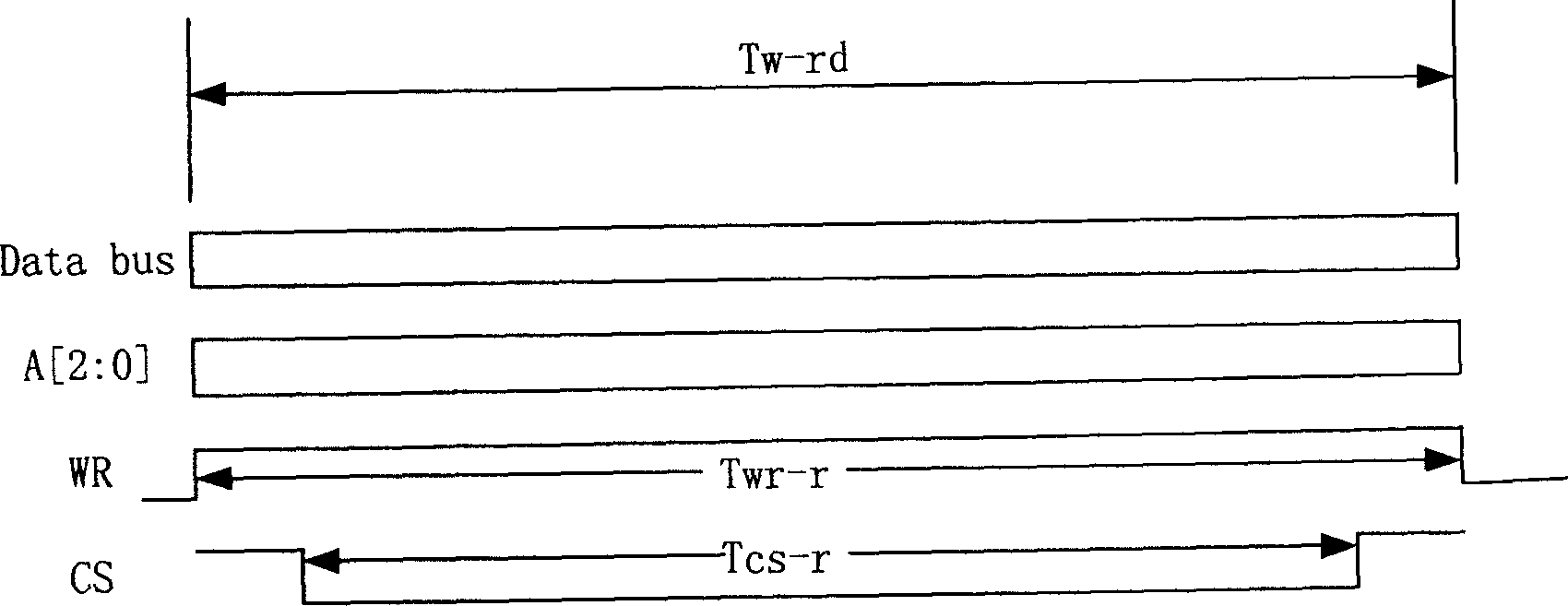

Device and method for implementing automatically reading and writing internal integrated circuit equipment

InactiveCN1558332ASimplify workloadChange this phenomenon of relying on CPUElectric digital data processingProcessor registerACCESS.bus

The present invention discloses equipment and method of automatically reading / writing I2C device. The equipment consists of hardware realized command generating module and write / read operation executing module, the command generating module is connected via the asynchronous access bus with active equipment and the write / read operation executing module, and the write / read operation executing module is connected via the I2C bus with I2C equipment. During write / read, the active equipment provides the starting signal, write / read signal and the address and register address of the I2C equipment and the data to be written; the command generating module generates automatically the commands essential for access of the I2C equipment and sends to write / read operation executing module; and the write / read operation executing module generates the signal time sequence for access of the I2C equipment based on I2C bus protocol and executes the write / read operation to the I2C equipment.

Owner:ZTE CORP

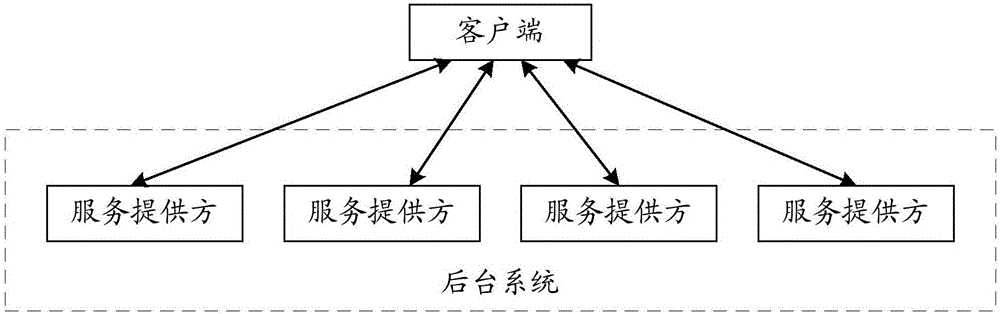

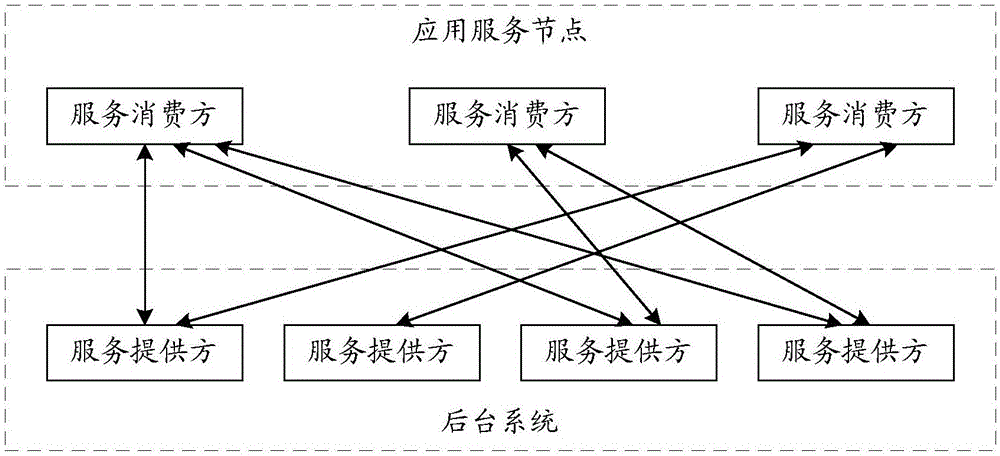

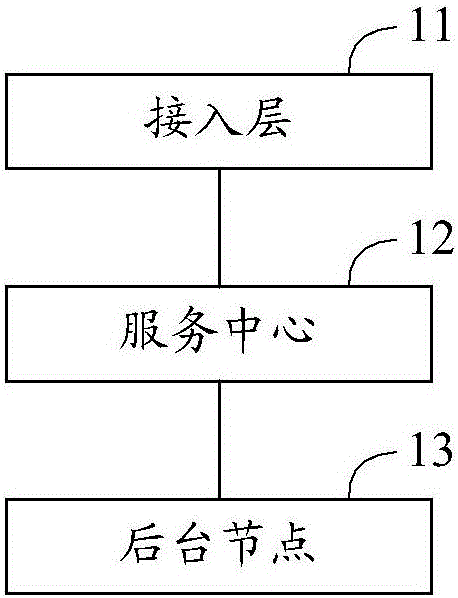

Service management method and system

The invention is applicable to the field of Internet, and provides a service management method and a service management system, and aims at solving the problems that in the prior art, services under a distributed architecture are not managed in a concentrated manner and not high in flexibility. The method comprises the steps of receiving service requests sent by a client via a unified access bus; performing a unified service governance process on the received service requests, and sending service calling requests to a background node according to service governance results; and receiving service responses sent by the background node, and encapsulating the service responses and returning the encapsulated service responses to the clients. According to the technical scheme of the method of the invention, concentrated processing and monitoring of the services are achieved by a service center, a unified interface is provided for the outside, and thus the all service requests interact with service providers of the background node after being processed by the service center in a concentrated manner, reuse and integration of the business are facilitated, and the flexibility of the distributed architecture is enhanced.

Owner:SHENZHEN KINGDOM TECH

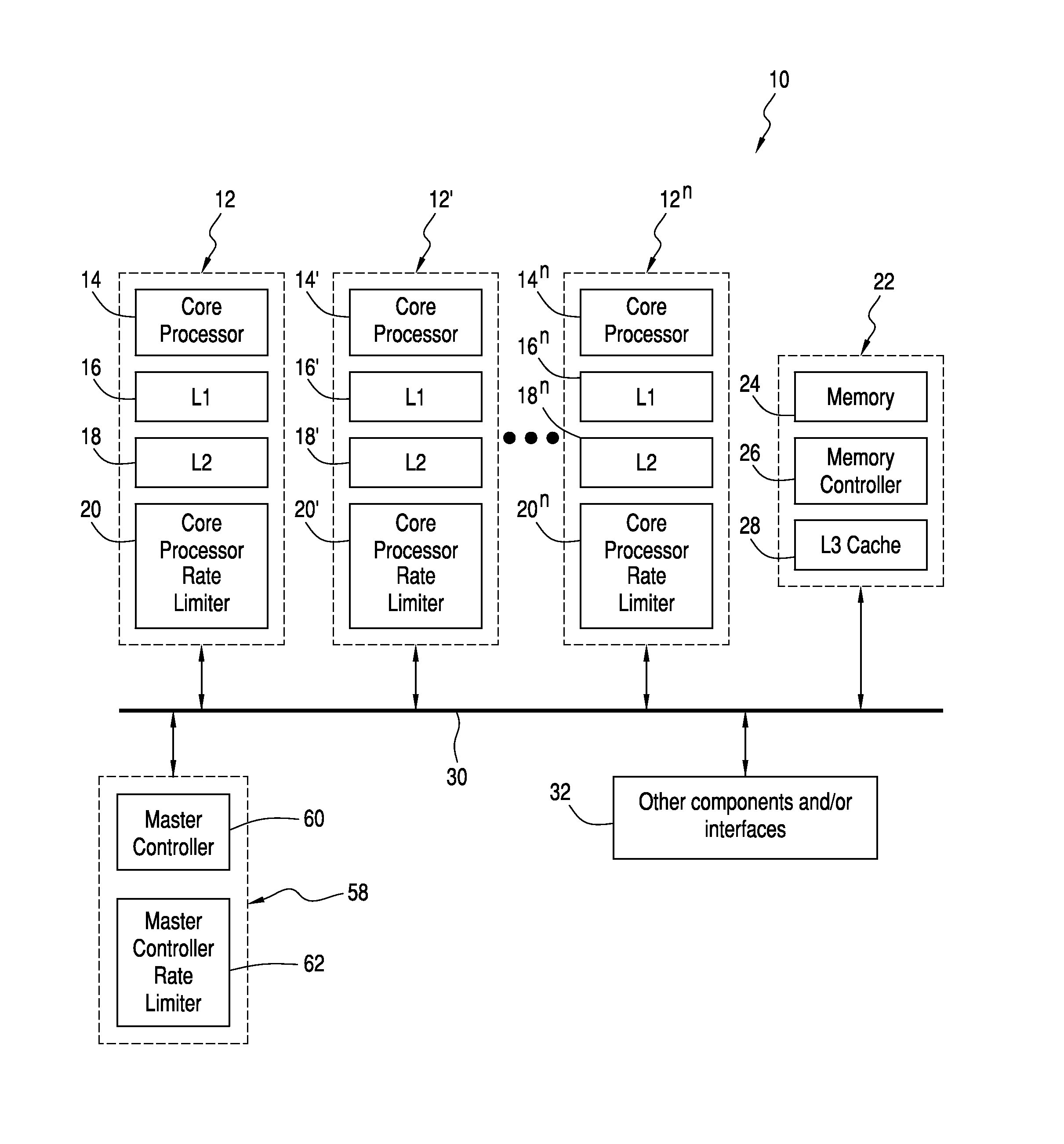

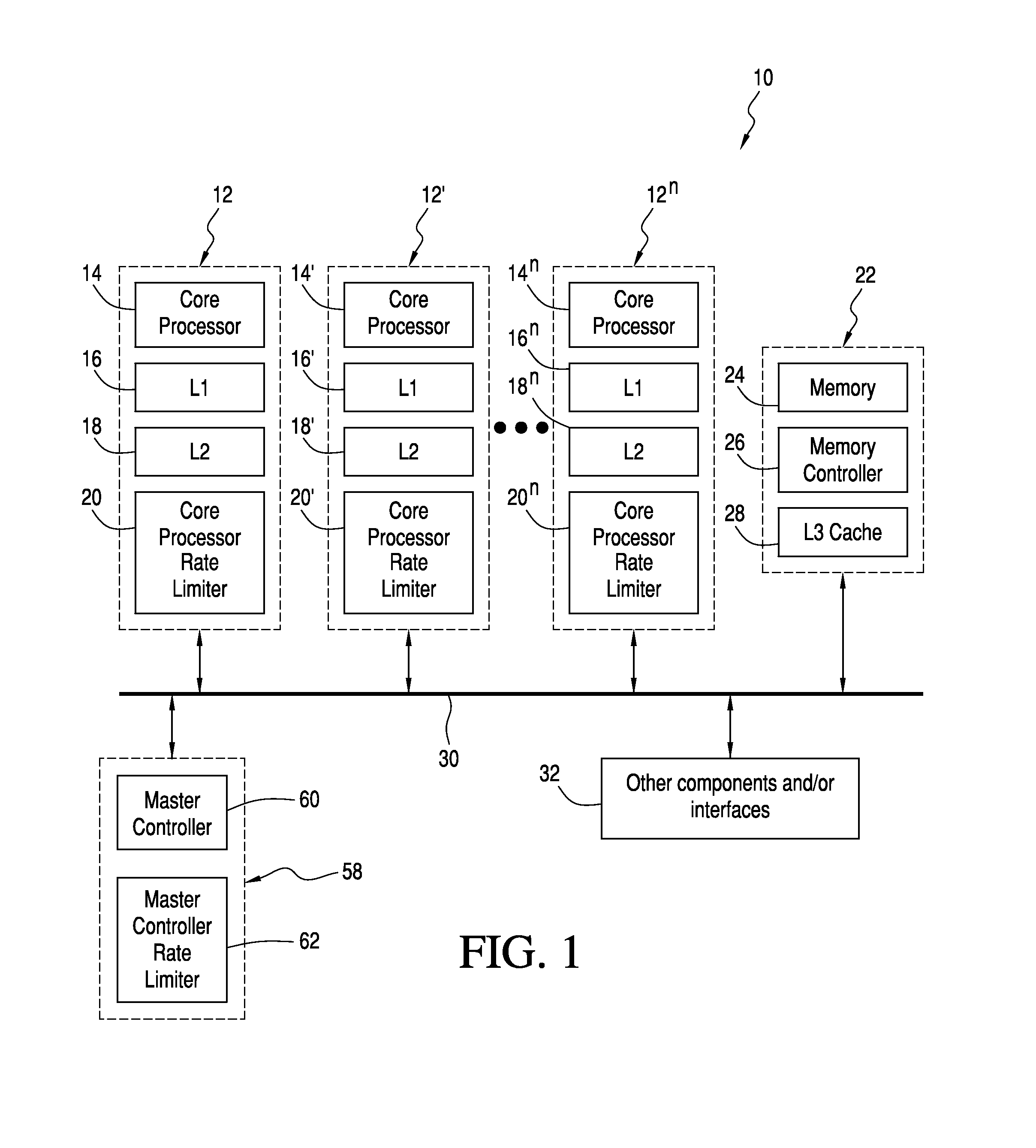

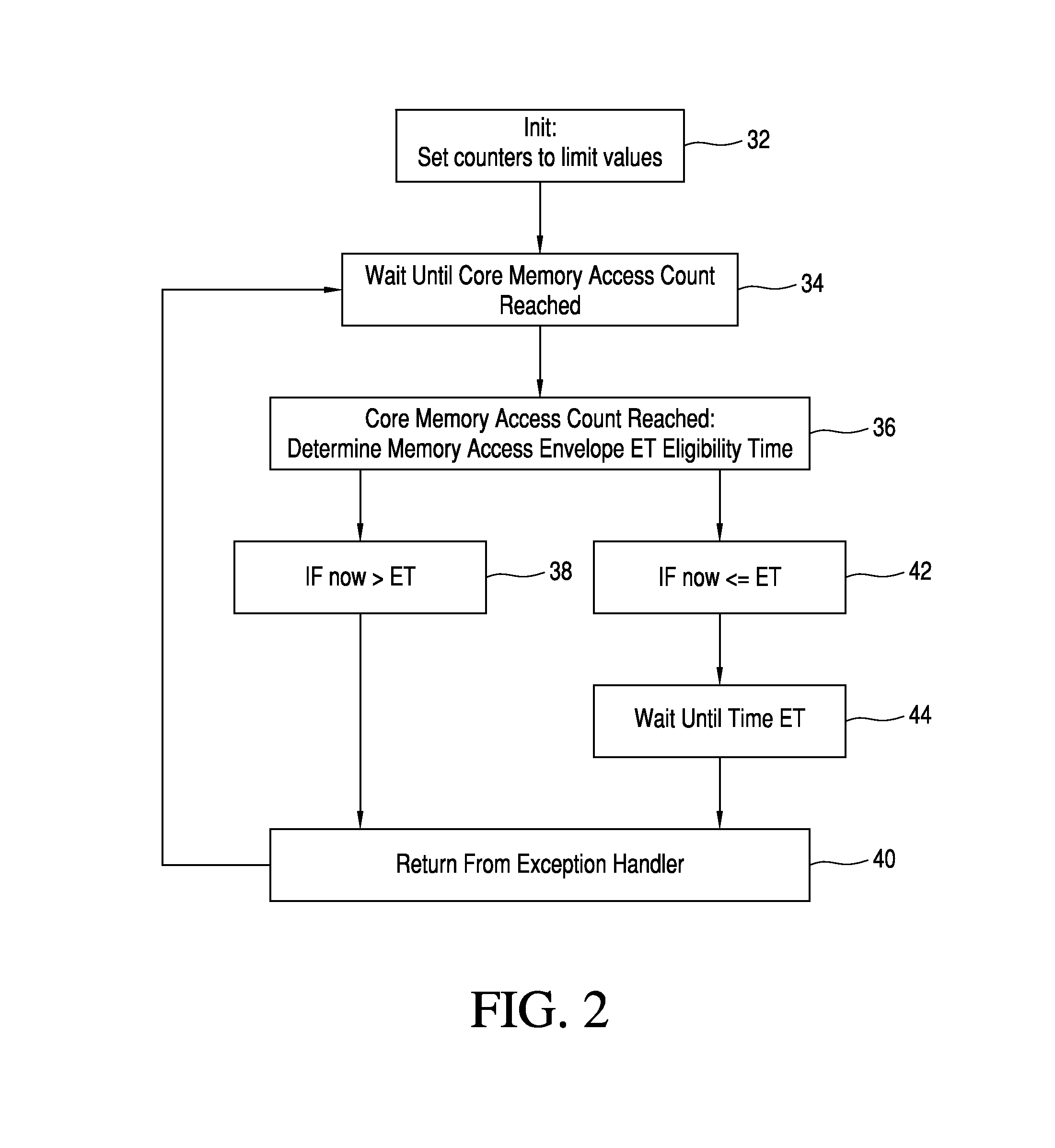

Multi-core processor system configured to constrain access rate from memory

A multi-core processor system includes a number of cores, a memory system, and a common access bus. Each core includes a core processor; a dedicated core cache operatively connected to the core processor; and, a core processor rate limiter operatively connected to the dedicated core cache. The memory system includes physical memory; a memory controller connected to the physical memory; and, a dedicated memory cache connected to the memory controller. The common access bus interconnects the cores and the memory system. The core processor rate limiters are configured to constrain the rate at which data is accessed by each respective core processor from the memory system so that each core processor memory access is capable of being limited to an expected value.

Owner:ROCKWELL COLLINS INC

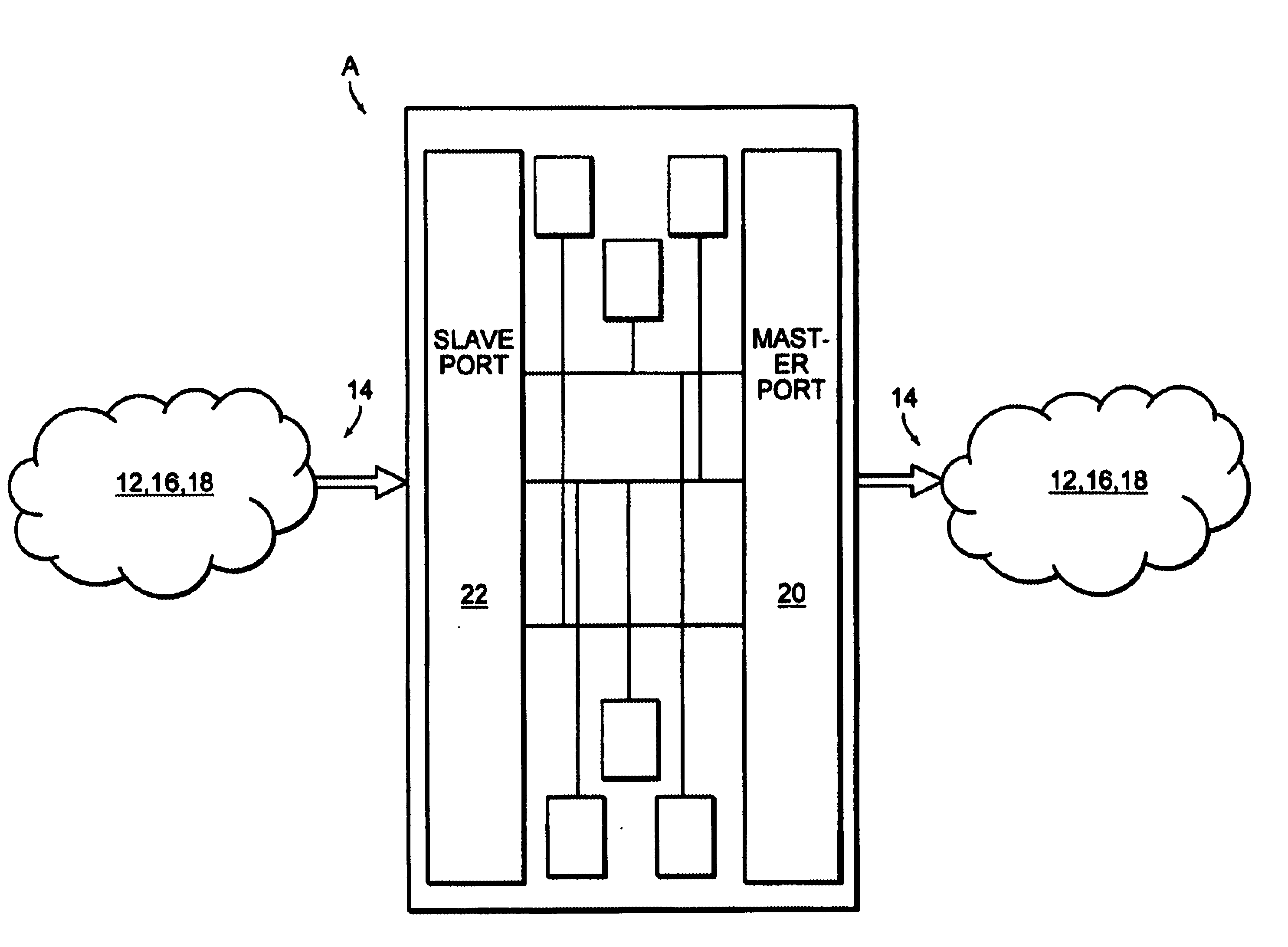

High speed access bus interface and protocol

InactiveUS6778526B1Fast transferSync fastNetworks interconnectionElectric digital data processingData streamBus interface

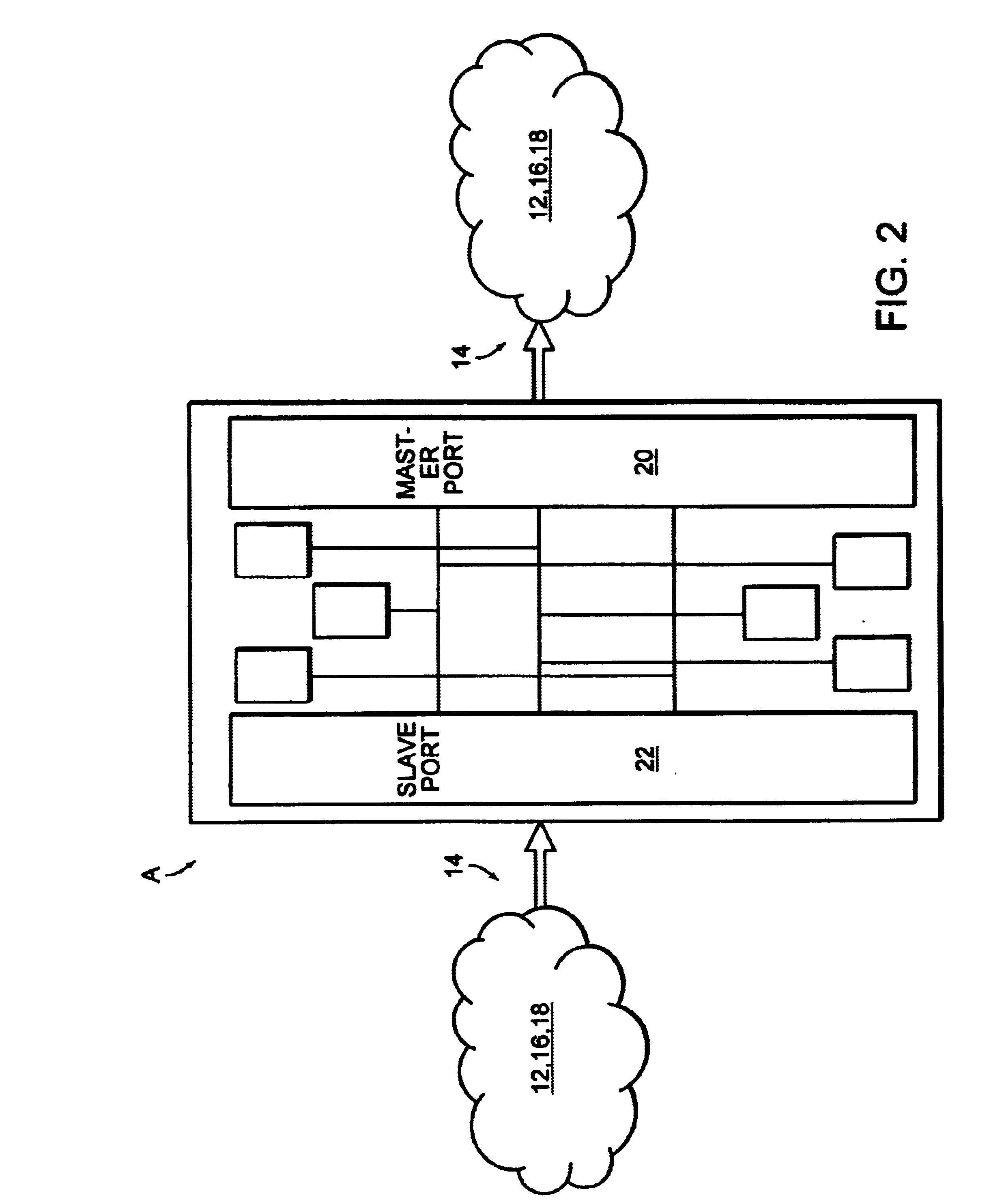

A high speed access bus interface for a communications network. The interface allows uni-directional transfer of data packets at a fast path processing rate of about 10 gigabits per second. The interface uses a master port and a slave port in a chip to chip data transfer scheme. The master and slave ports may have one or more than one data channel for transferring data packets. The master port includes a clock signal for synchronizing the transfer from the master port to the slave port. The slave may send an asynchronous signal to the master port in order to initiate the master port to stop or stall the pipeline transfer of data packets until space is made available in the slave port buffer. In addition to the clock synchronization, the interface utilizes an enable signal, a start of packet signal, an end of packet signal, an error signal (if necessary), a last valid byte signal, and a parity bit signal to identify, address, each data packet in the data stream. If a processing error occurs, the master port error signal to the slave port also initiates the slave port to disregard the previous data packet. The operating frequency of 50 MHz allows the data packet transfer to exceed 10 gigabits per second.

Owner:AVAYA MANAGEMENT LP

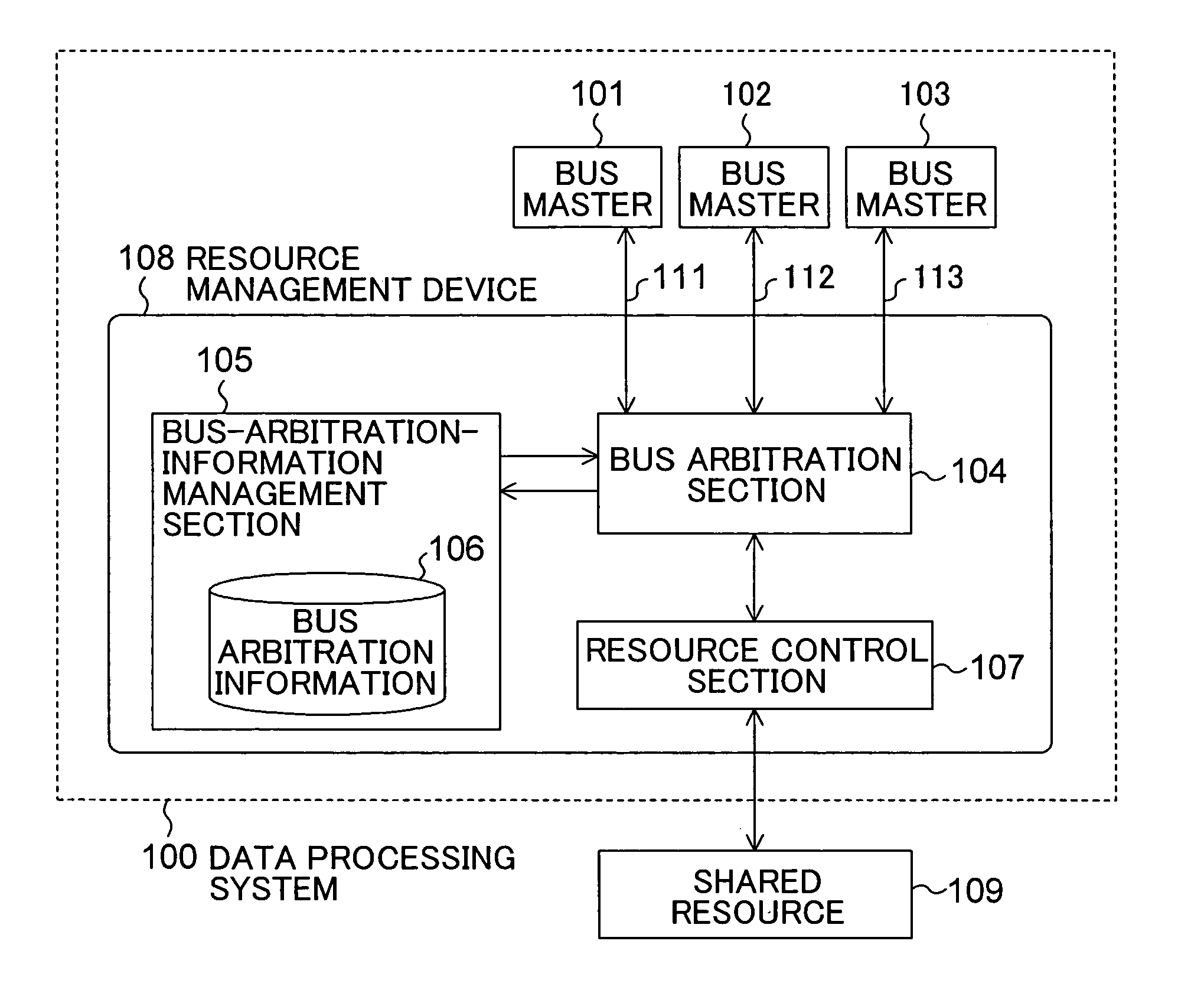

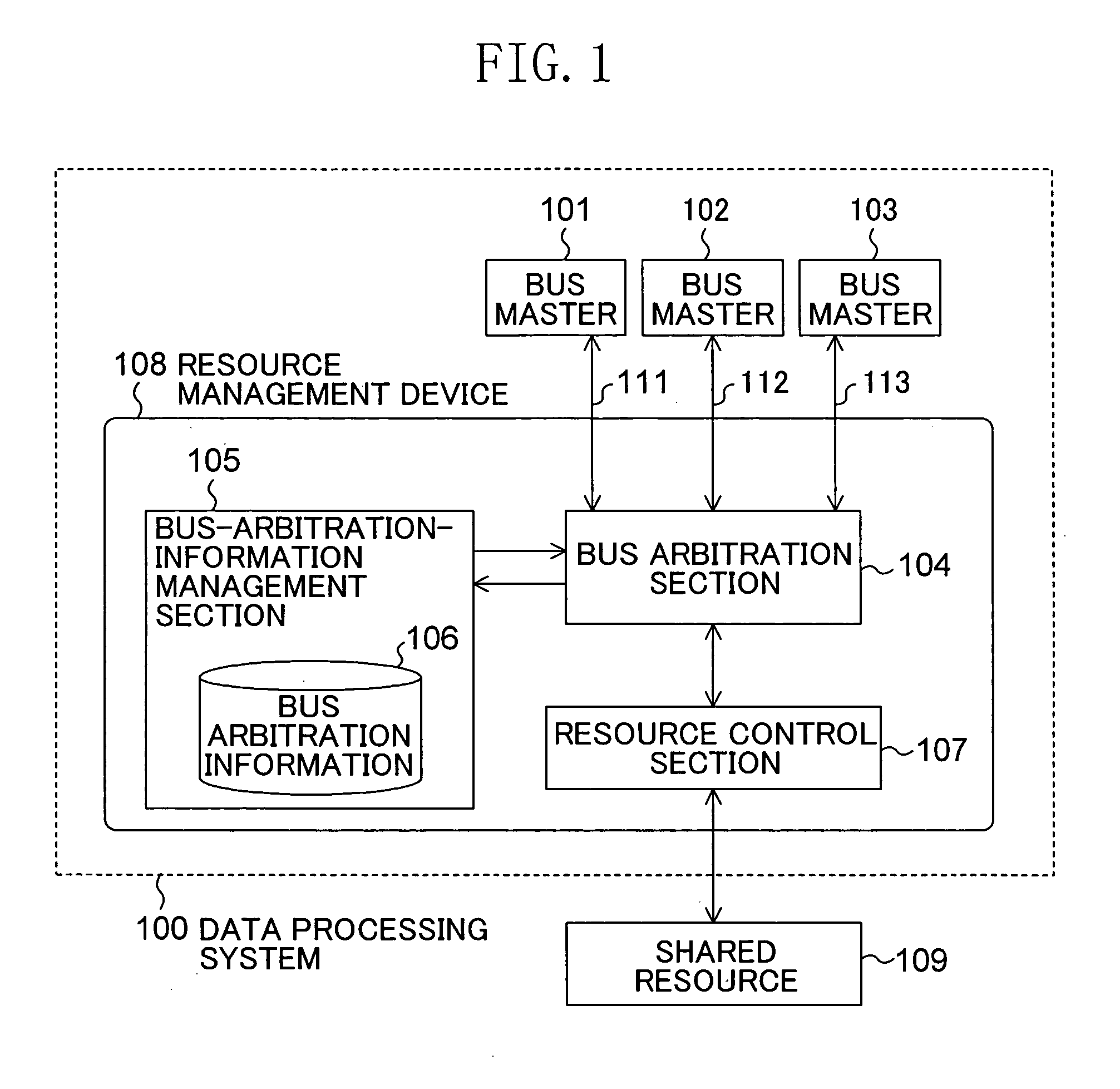

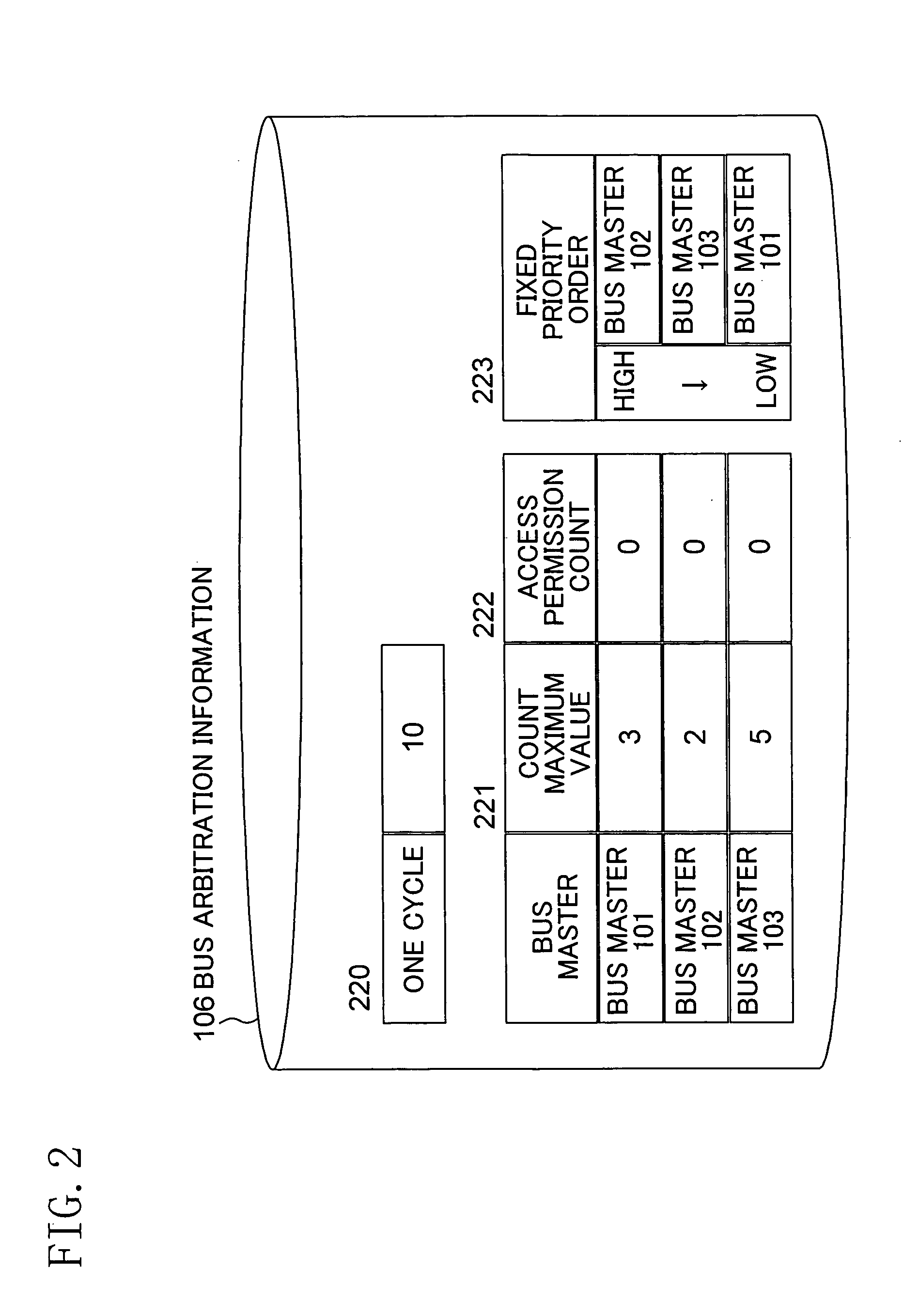

Resource management device

A bus arbitration section and a resource control section are interposed between a shared resource and a plurality of bus masters. The minimum number of receivable access permissions within a given period is set as bus arbitration information for each of the bus masters. If two or more of the bus masters issue access requests at the same time, the bus arbitration section preferentially gives access permission to a bus master which gained access permission a number of times less than a set value in the bus arbitration information within the given period, out of the two or more access bus masters.

Owner:BEIJING ESWIN COMPUTING TECH CO LTD

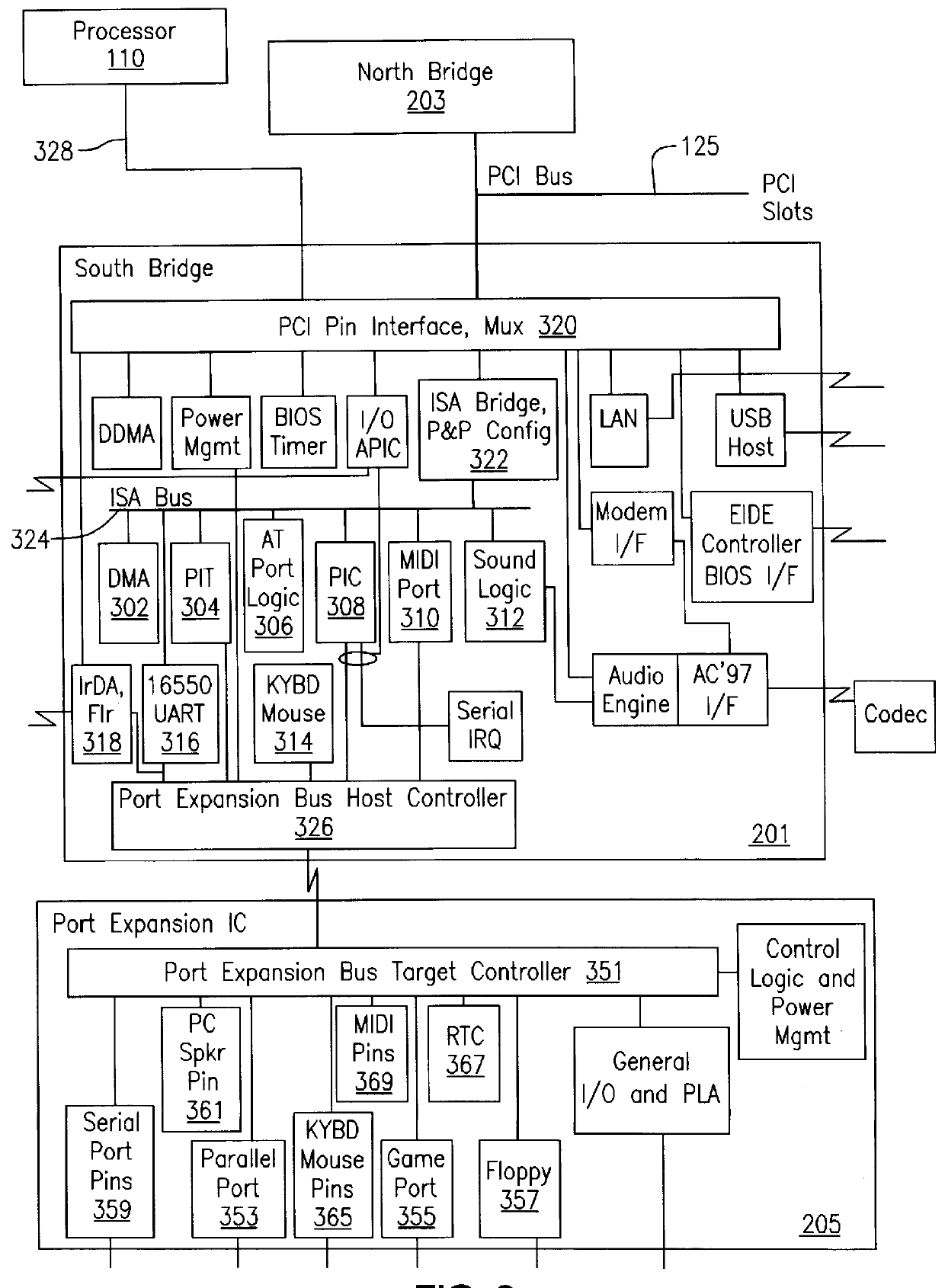

PC core logic chipset comprising a serial register access bus

InactiveUS6032213AGeneral purpose stored program computerGenerating/distributing signalsData informationIntegrated circuit layout

A computer system includes first and second integrated circuits. The first integrated circuit provides a first input / output bus operating in accordance with a first protocol, such as ISA. The first input / output bus includes a plurality of address and data lines respectively providing address and data information. The second integrated circuit includes a plurality of second functional blocks at least some of which interface to legacy devices. The first integrated circuit includes a host controller circuit, coupled to the first input / output bus and for coupling to a register access bus which includes a register data out and a register data in signal line. The register access bus connects the first and second integrated circuits. The host controller circuit receives address and data information from the input / output bus and serially provides the address and data information to the data out line. A target controller circuit on the second integrated circuit is coupled to the register access bus. The target controller circuit receives the serially provided address and data information and provides the address and data information, over a second representation of the input / output bus, the second representation being at least a subset of the first protocol and including a plurality of internal address lines and a plurality of internal data lines coupled to the second functional blocks. Write operations take place to memory locations in the second integrated circuit from a write operation begun on the first integrated circuit and read operations take place from memory locations in the second integrated circuit for read operations begun on the first integrated circuit.

Owner:ADVANCED MICRO DEVICES INC

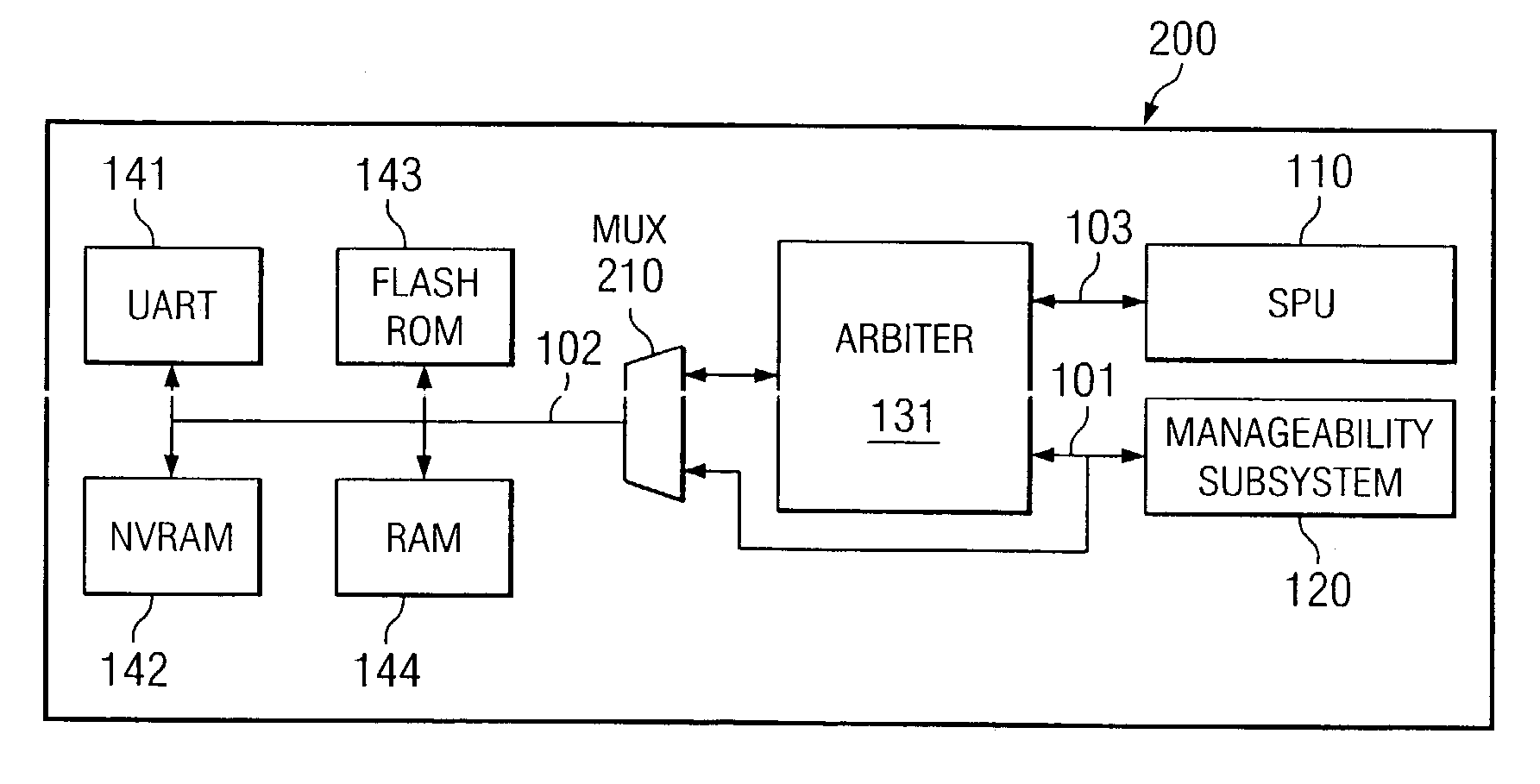

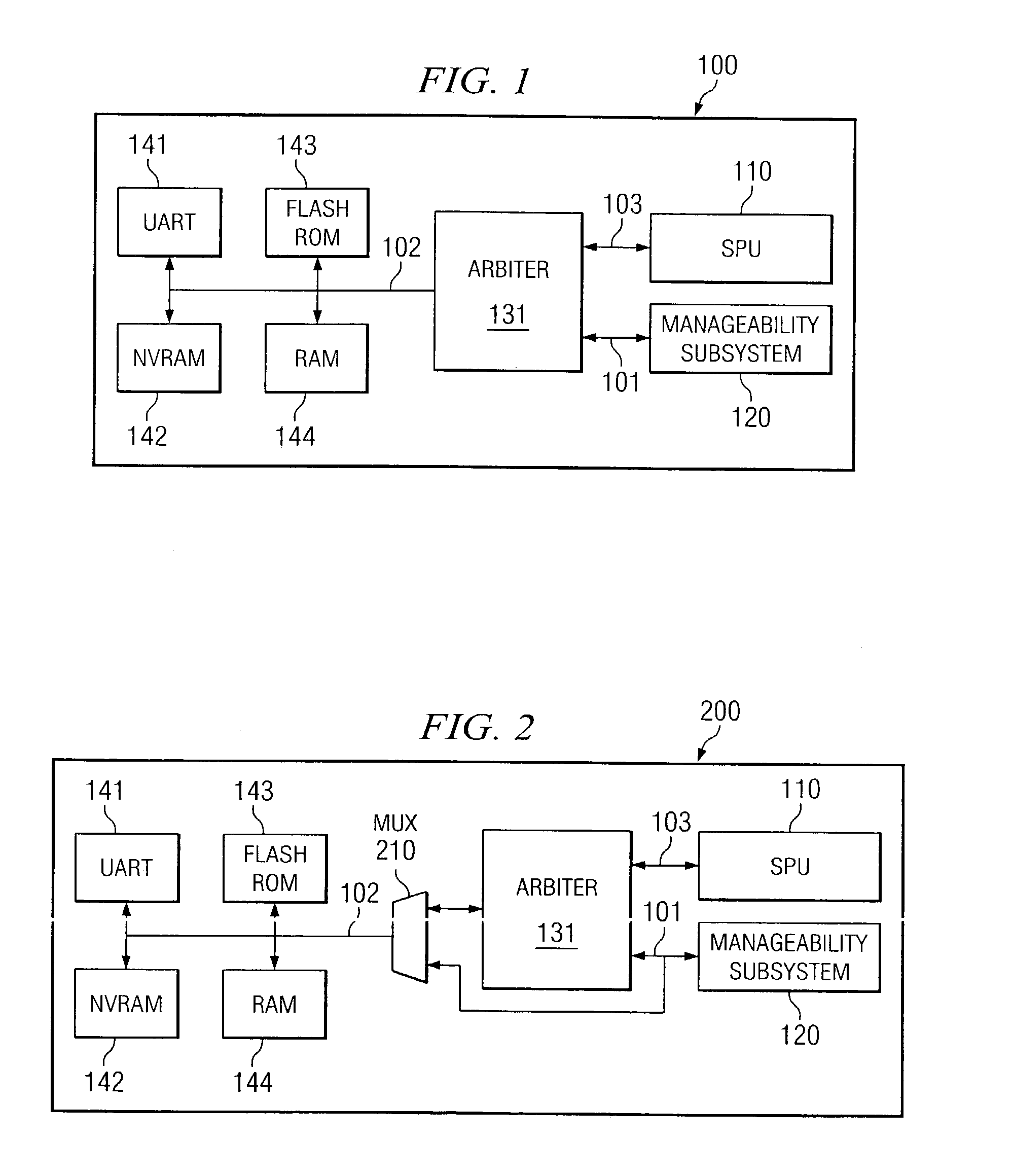

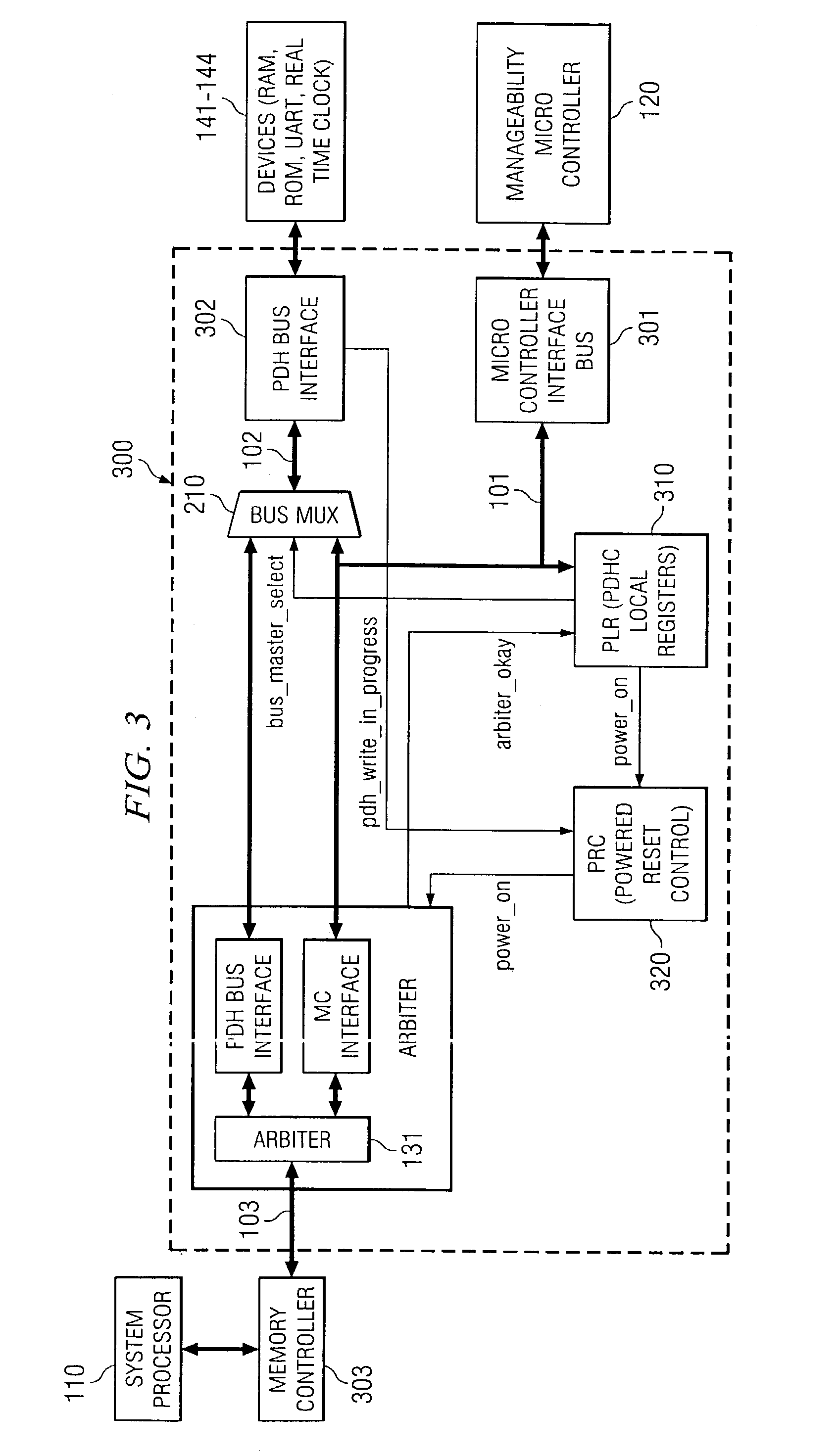

Systems and methods for accessing bus-mastered system resources

Disclosed are systems and methods for providing access to bus-mastered system resources comprising disposing a bus multiplexer between a first bus and a bus access arbiter, wherein the first bus is coupled to at least one system resource for which bus access is arbitrated by the bus access arbiter, and controlling the bus multiplexer to couple a second bus to the first bus thereby providing a link between the first bus and the second bus bypassing the bus access arbiter.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP +1

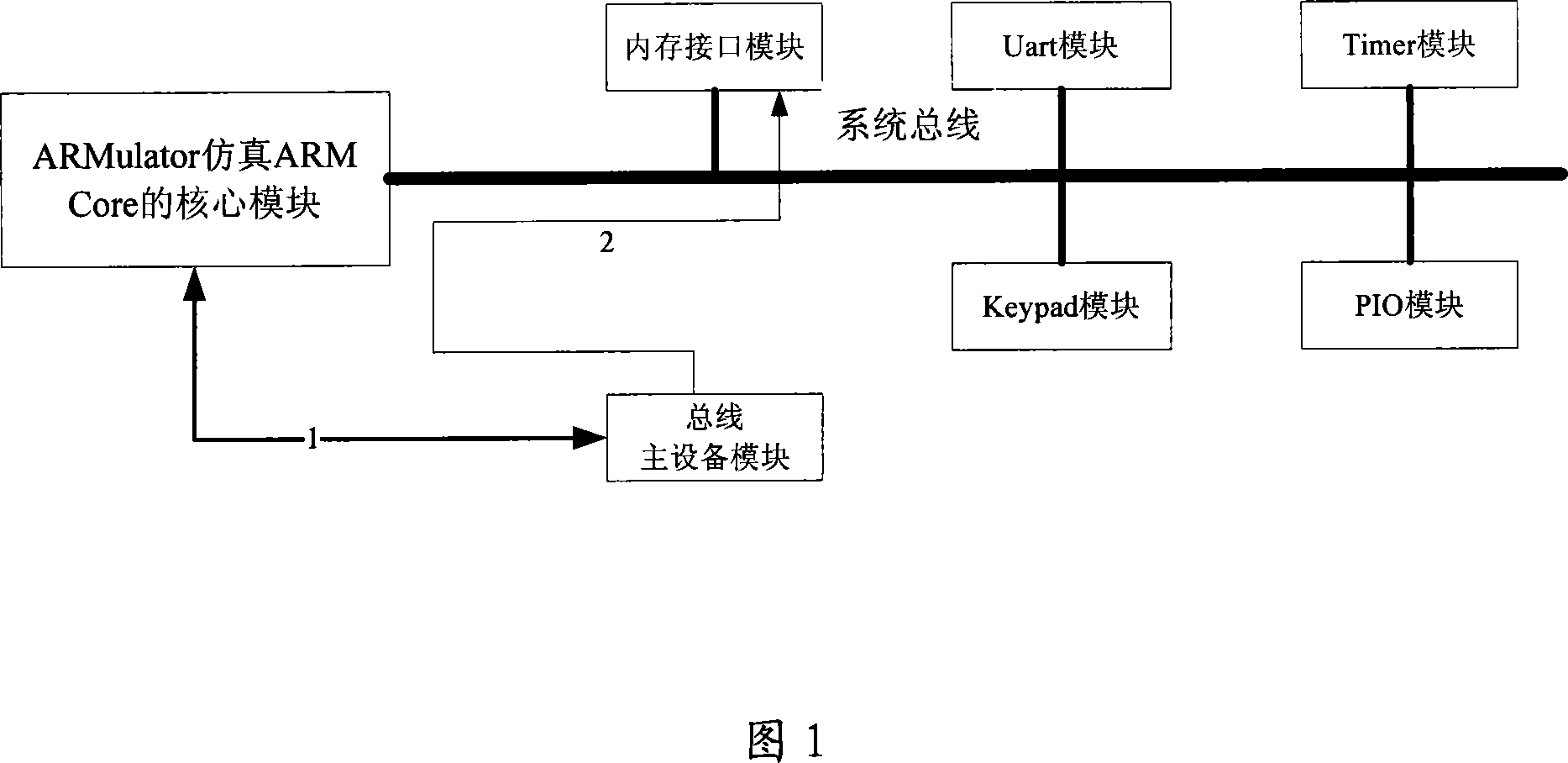

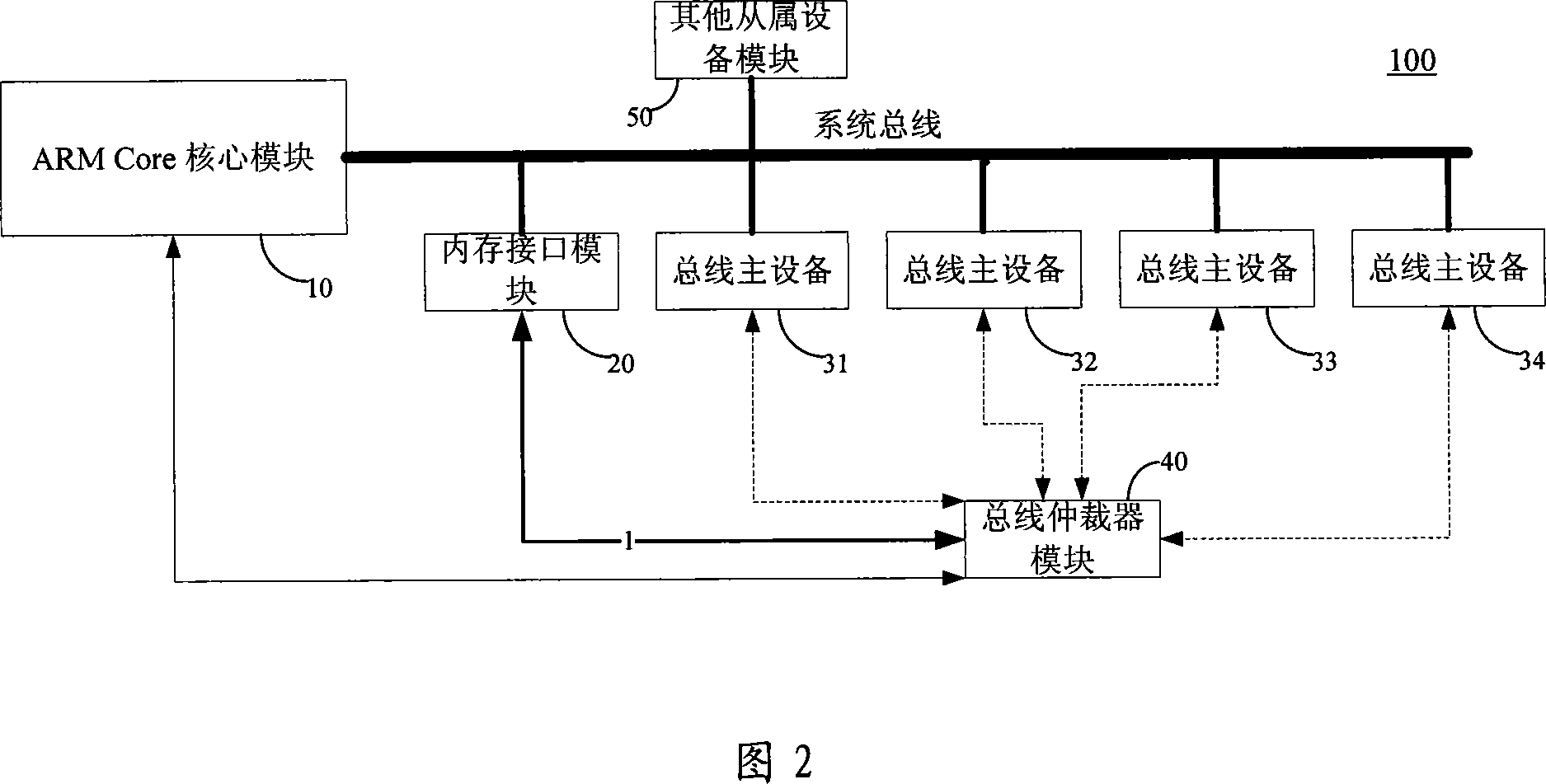

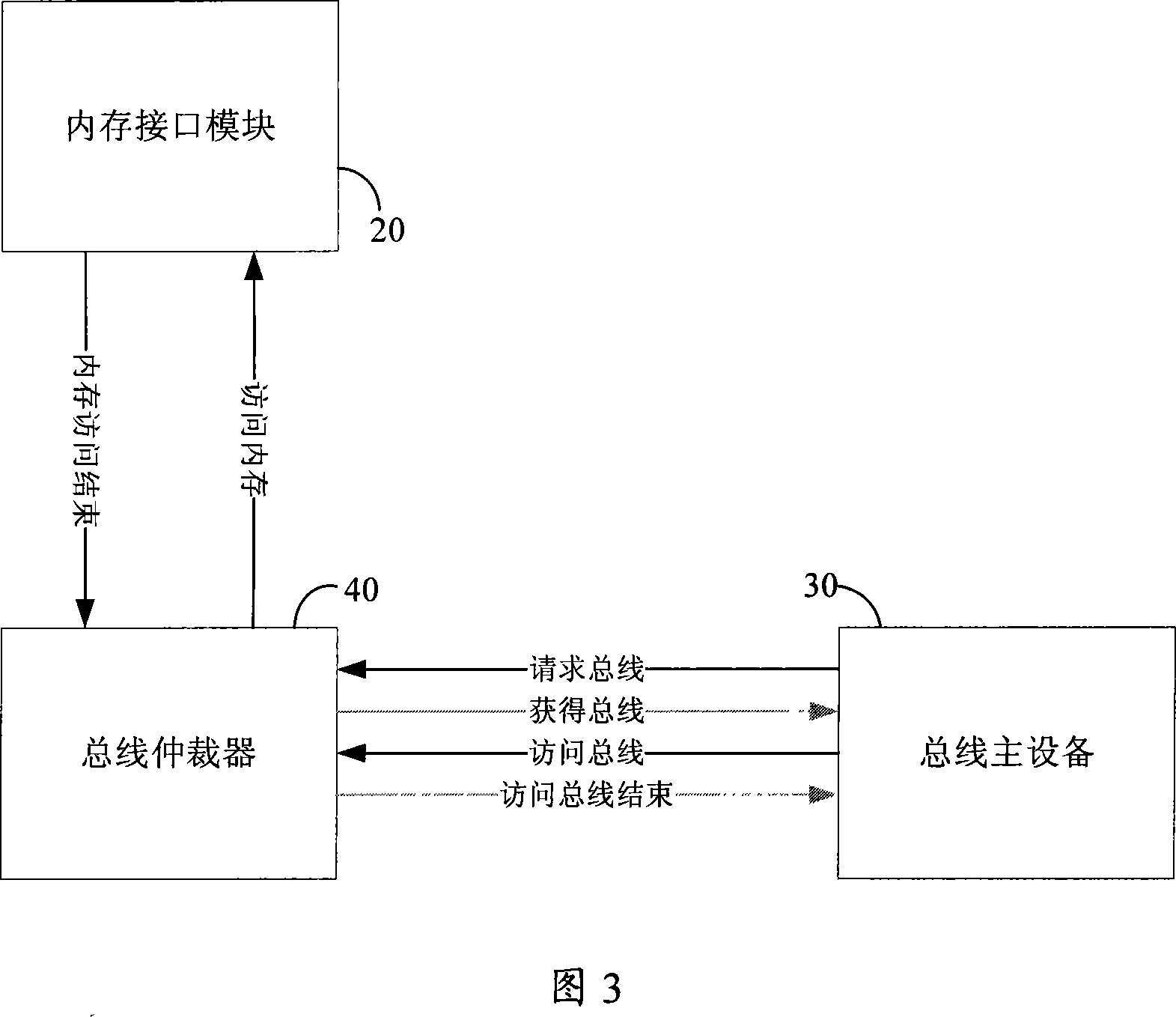

Simulator and method for bus arbitraction

InactiveCN101075220ASimulation is accurateAvoid the disadvantages of bus operationElectric digital data processingACCESS.busEmbedded system

An simulation device of bus arbitration is prepared as adding a bus arbitrator in simulation model of ARMulator to let operation of access bus on all bus master units including ARM Core pass arbitration of said bus arbitrator first, enabling to make access on bus slave unit and to obtain required return-back value only after bus is obtained.

Owner:VIMICRO CORP

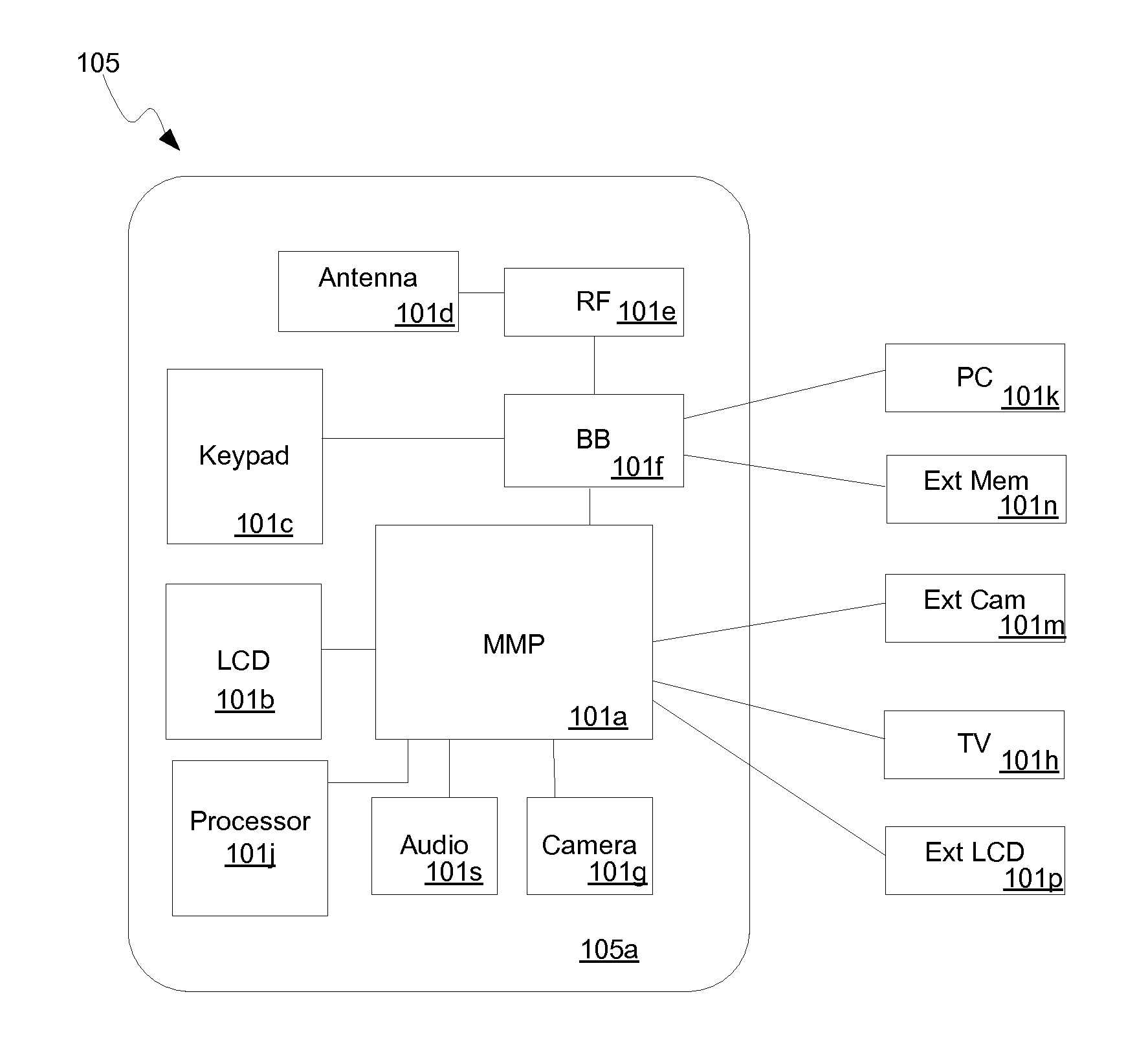

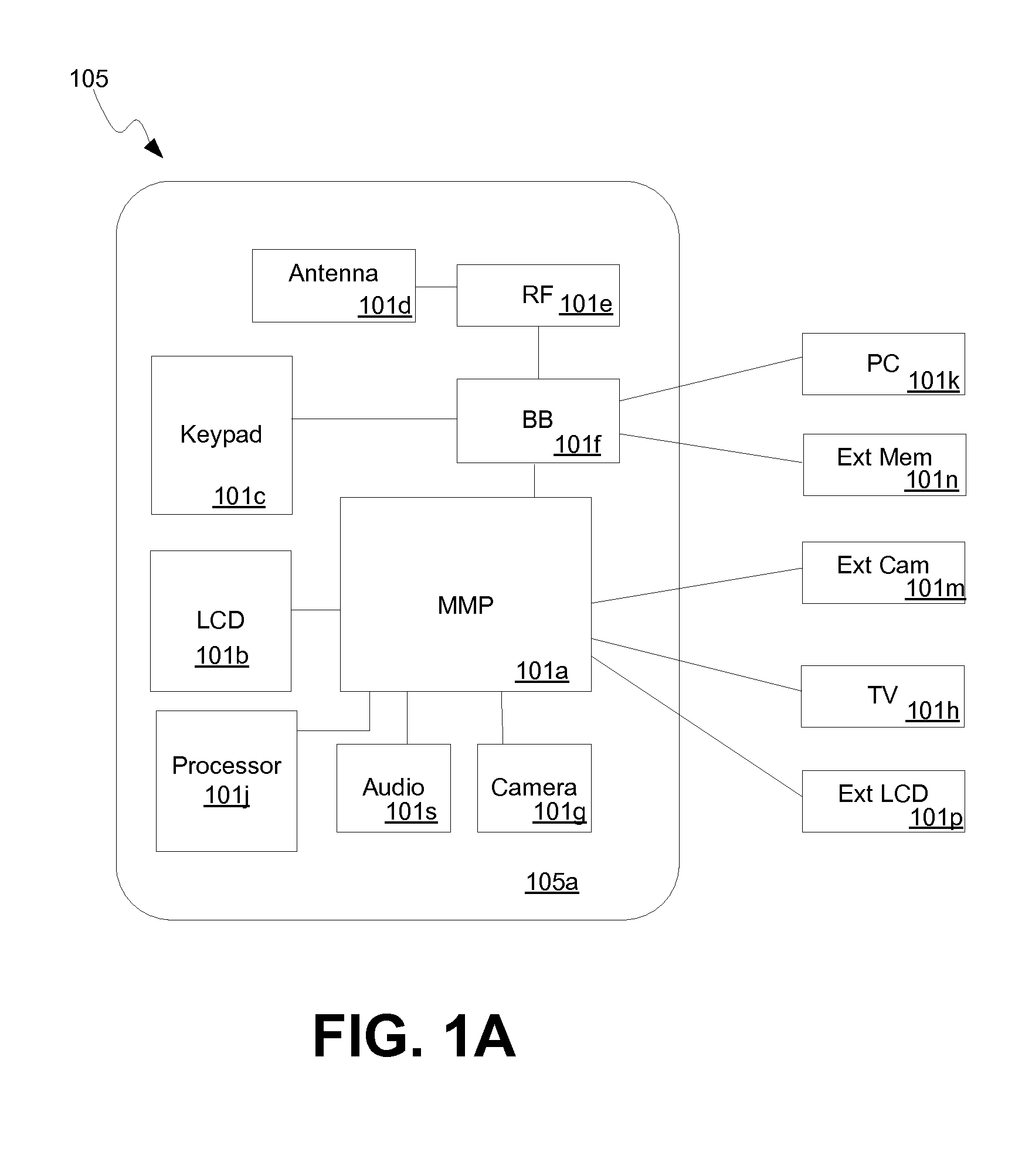

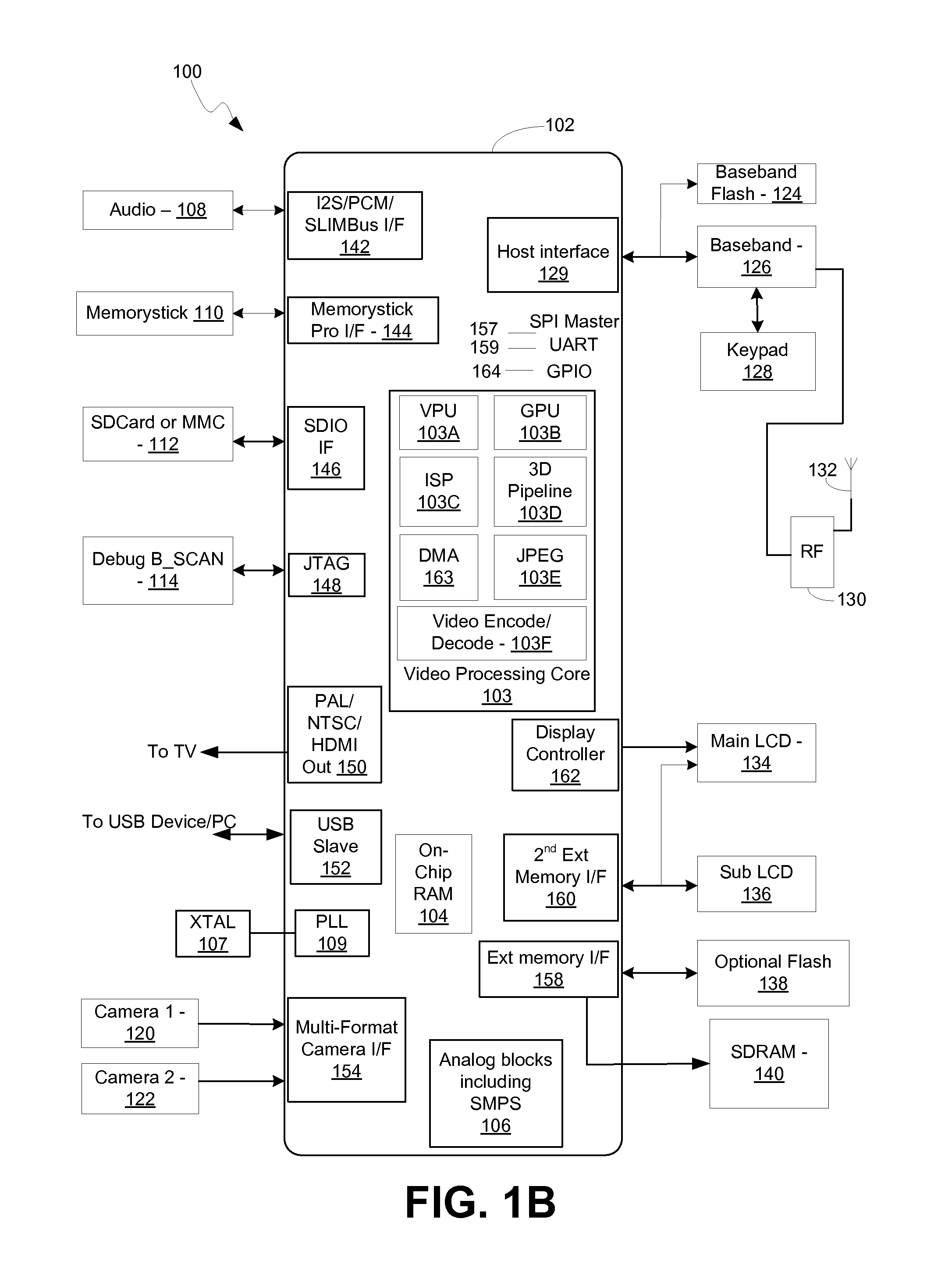

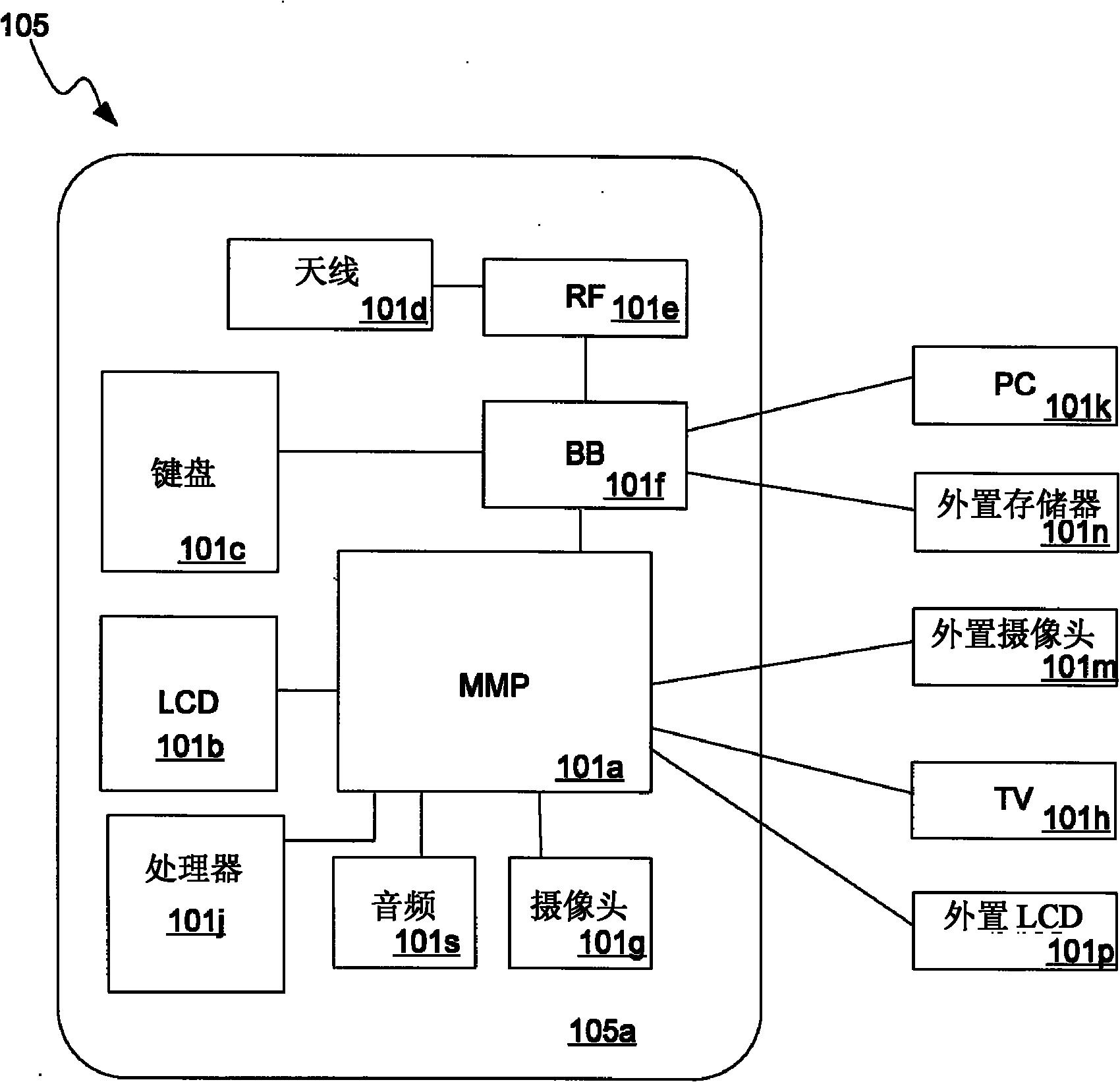

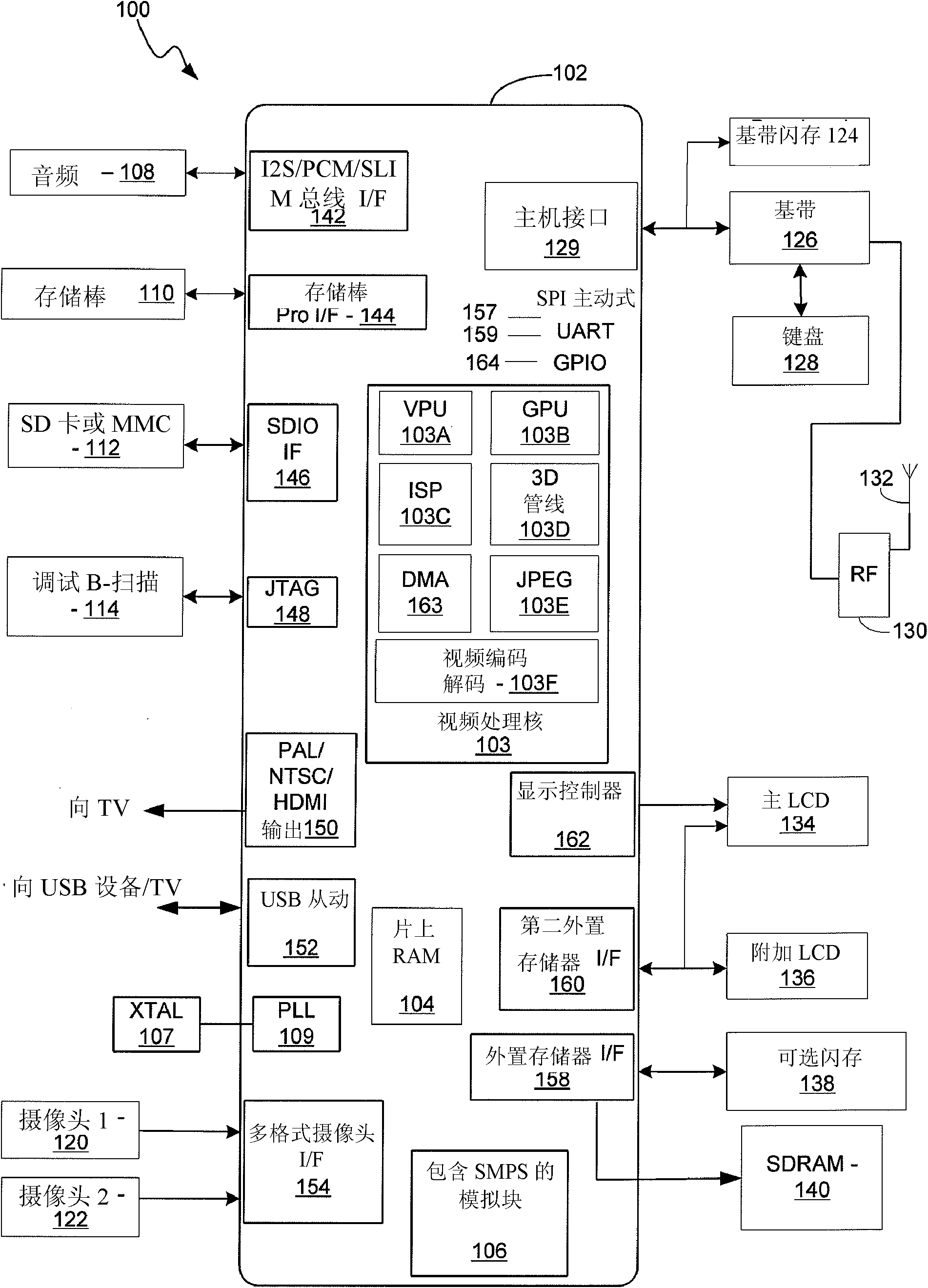

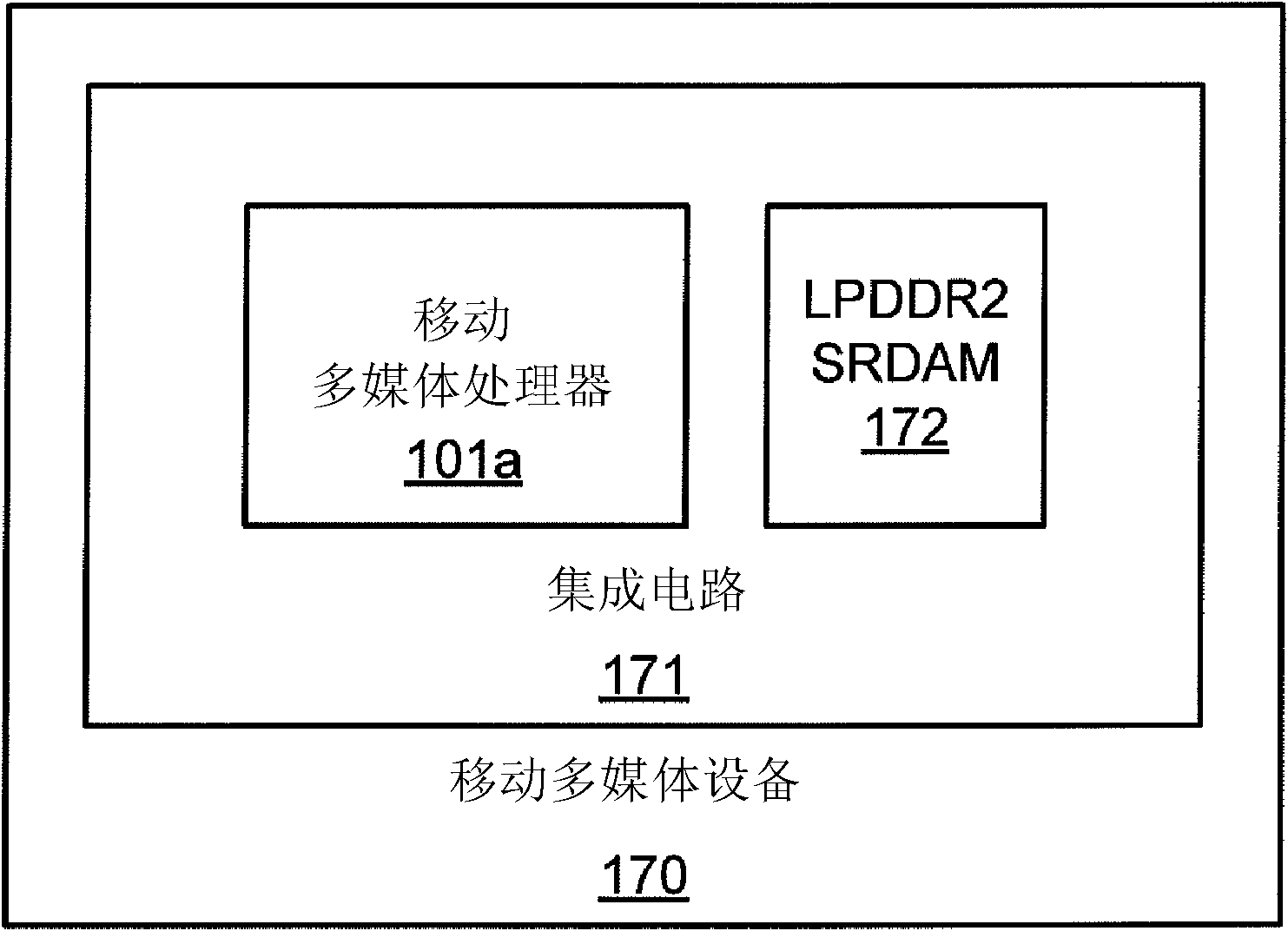

Method and System for Providing 1080P Video With 32-Bit Mobile DDR Memory

InactiveUS20110242427A1Energy efficient ICTColor signal processing circuitsHigh-definition televisionHigh definition tv

A method and system are provided in which a multimedia processor and a single low power double data rate memory 2 (LPDDR2) synchronous dynamic random access memory (SDRAM) coupled to the multimedia processor are disposed in a single package on a single substrate or chip. The single LPDDR2 SDRAM may be accessed by the multimedia processor via a 32-bit wide access bus. The multimedia processor and single LPDDR2 SDRAM may be operable to process video data. The video data may comprise 1080 progressive (1080p) high-definition television (HDTV) formatted data. The multimedia processor and single LPDDR2 SDRAM may be operable to pipeline process video data from an image sensor. The multimedia processor and single LPDDR2 SDRAM may be disposed in a stacked configuration in the single package.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

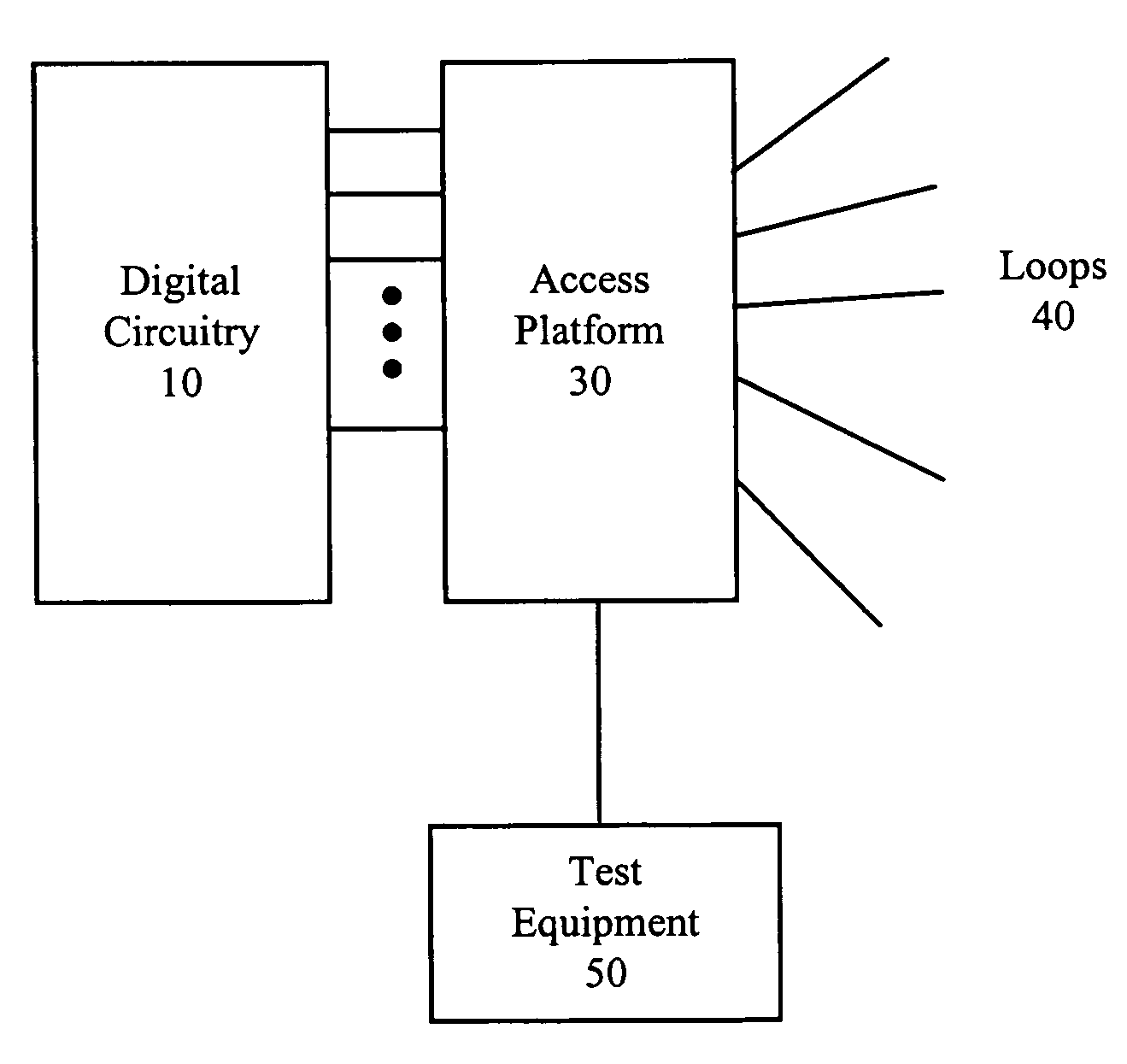

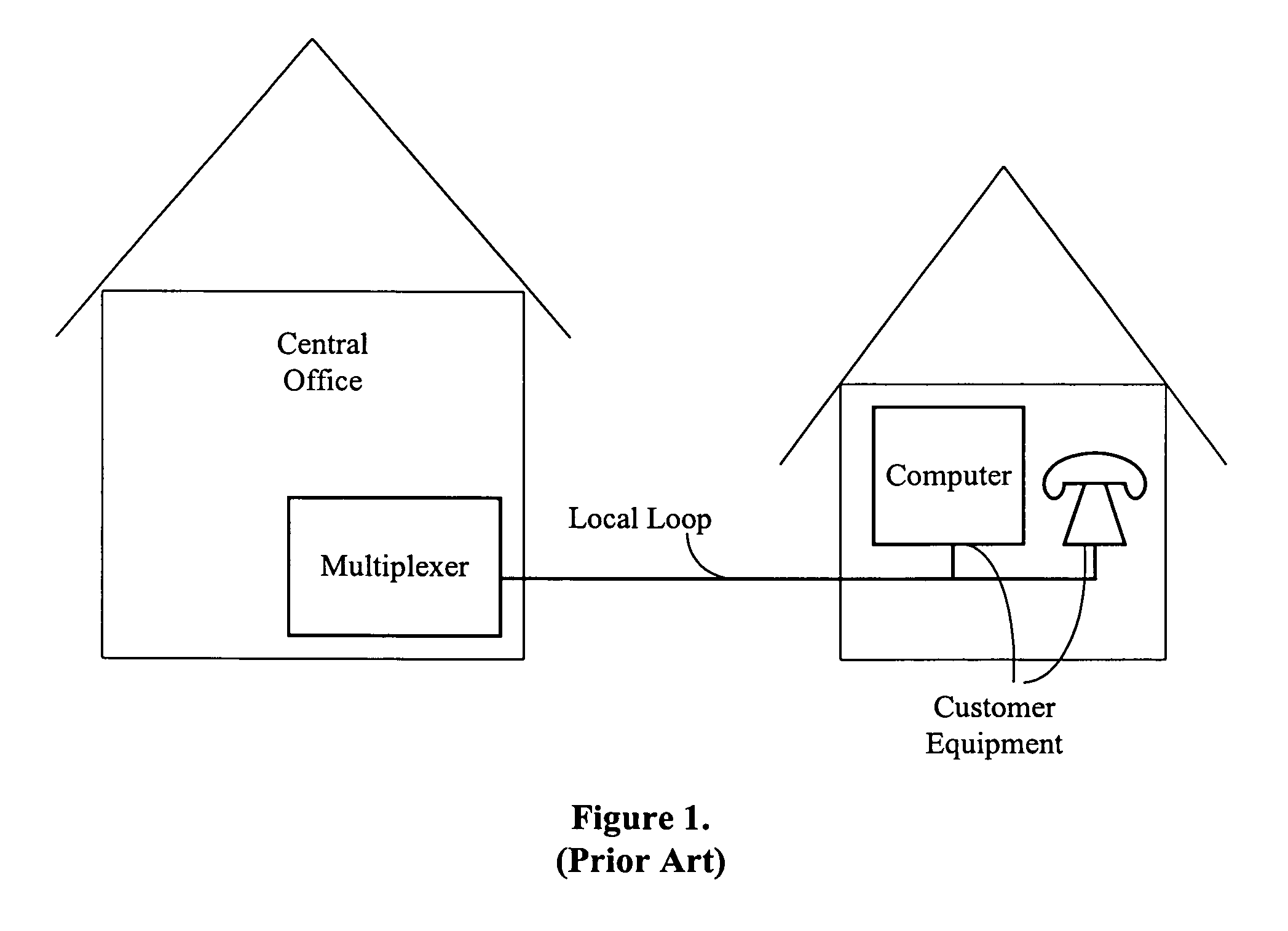

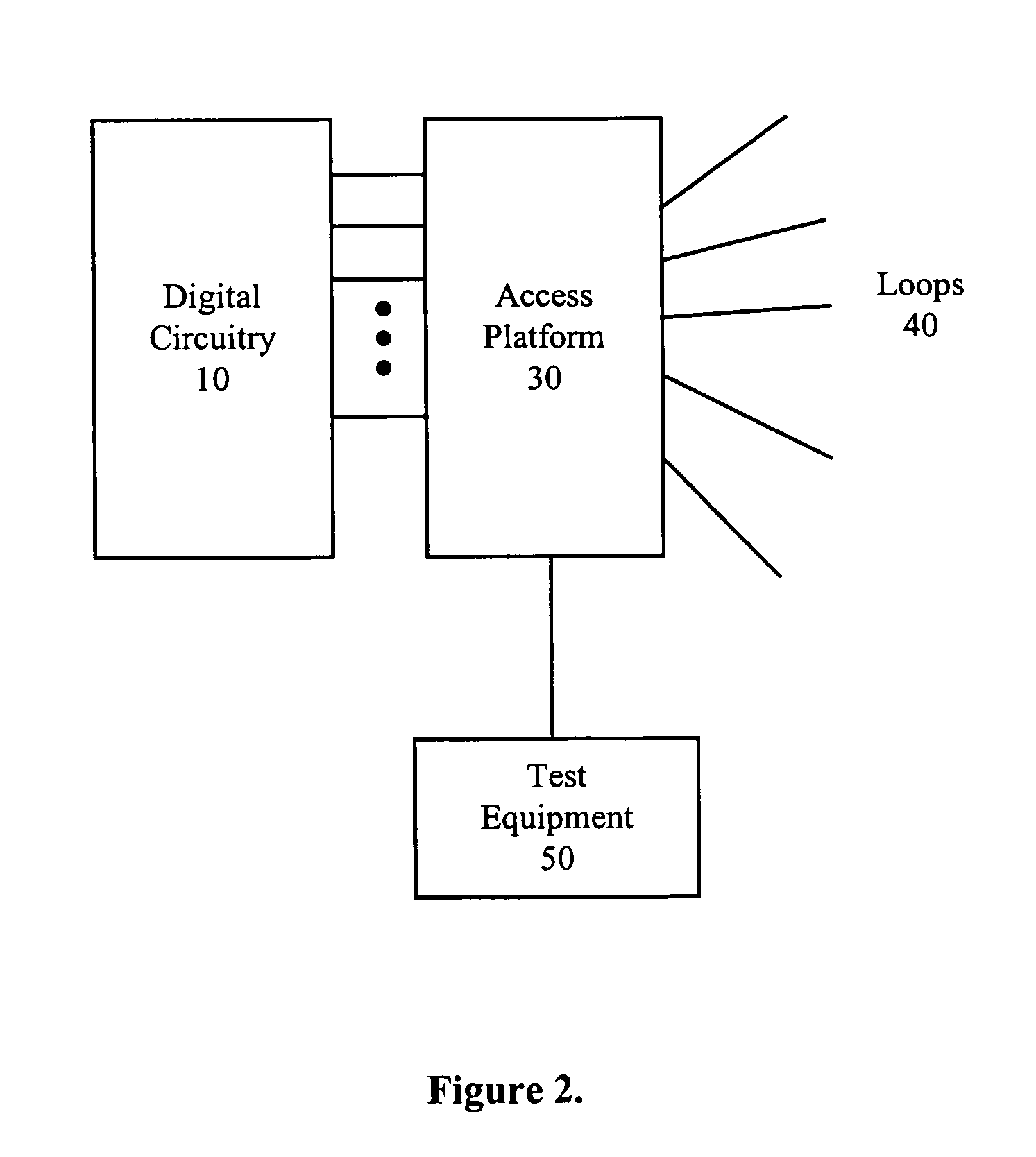

Integrated metallic access for high port density DSLAM

A multi-services access platform is presented for supporting metallic test access in switching or multiplexing devices such as digital subscriber line access multiplexers (DSLAMs). The multi-services access platform includes a chassis within which a predetermined number of card slots are included. Each of the card slots includes a number of input / output ports. A backplane runs along the chassis and includes a metallic test access bus. The metallic test access bus is operable to selectively couple to one or more input / output ports within the line card slots of the chassis to establish one or more metallic test paths. A relay matrix may be used to provide the selective coupling for the metallic test access bus, and the flexibility provided by the configuration of the relay matrix supporting the metallic test access bus allows for a variety of different test access ports (TAPs) to be supported. Specific TAP configurations may be configured that support both a Safety Extra Low Voltage (SELV) rated stimulus and a Telecom Network Voltage (TNV) rated stimulus such that local loops that support a variety of different signaling protocols can be tested using the metallic test access bus either individually or concurrently.

Owner:RPX CORP +1

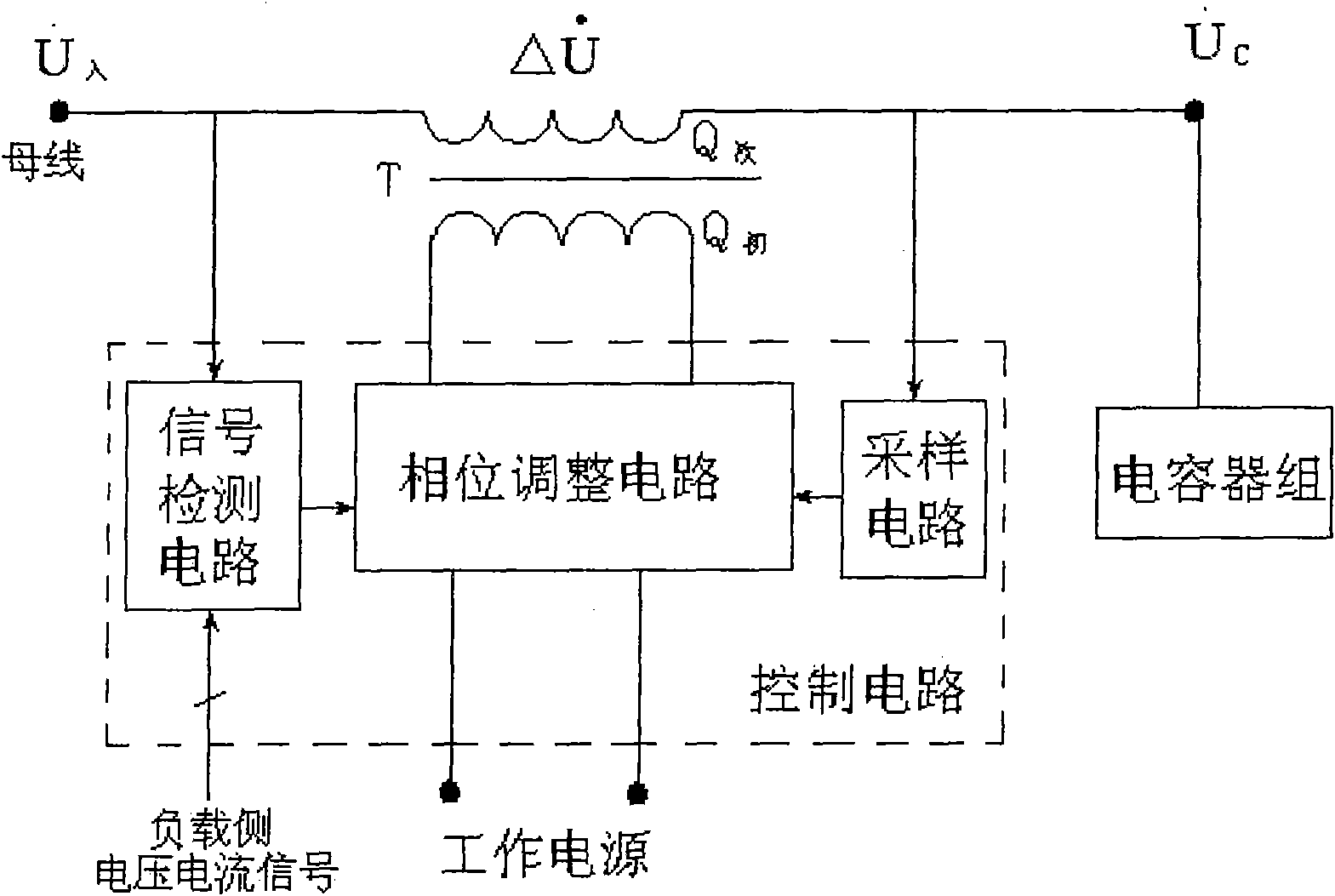

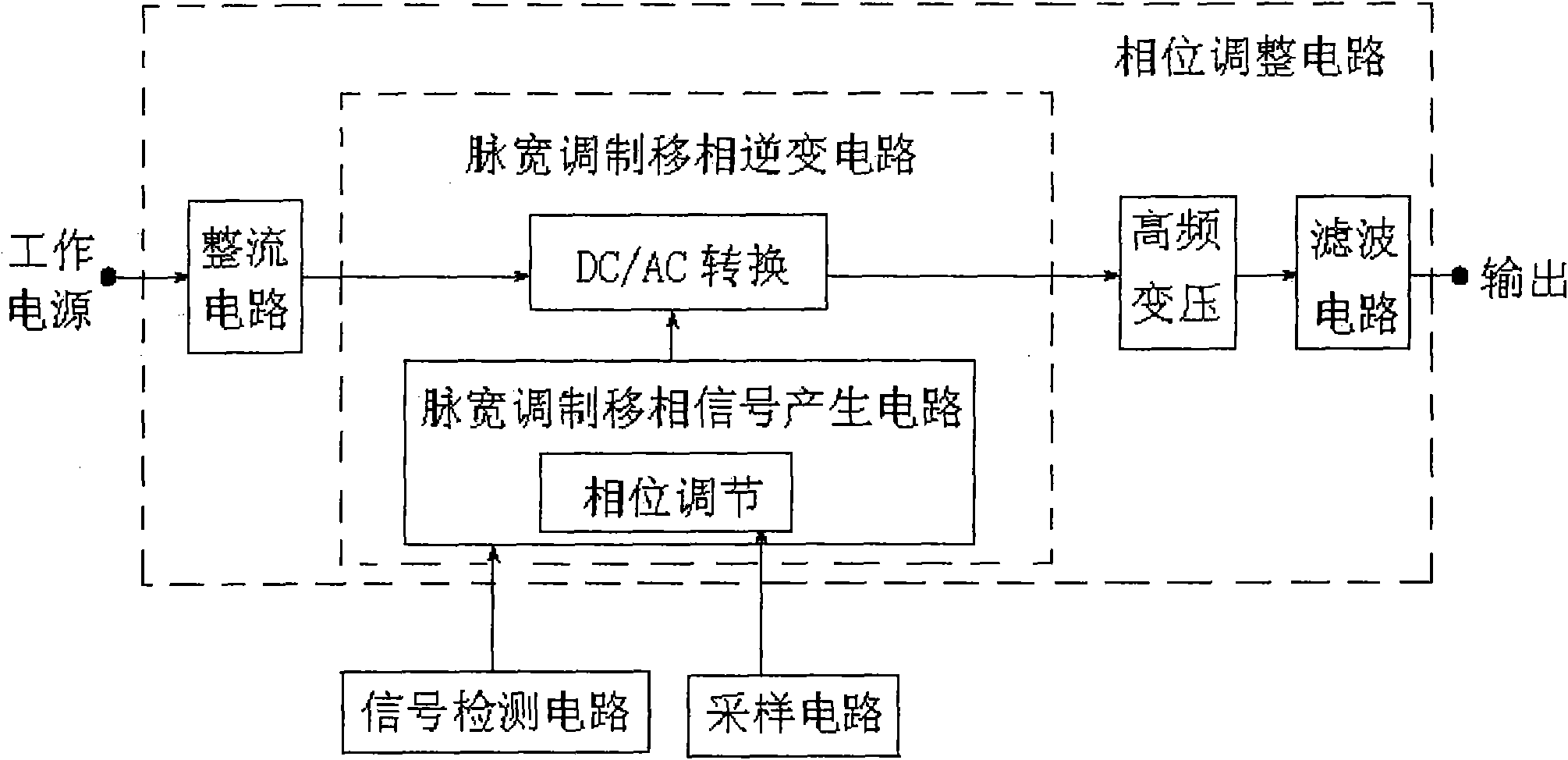

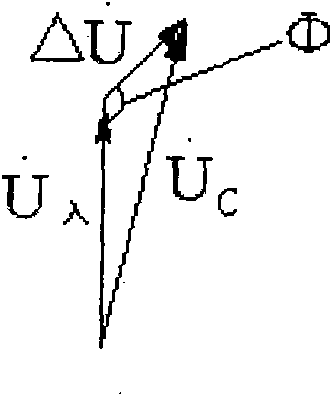

Stepless rapid phase-control reactive power dynamic compensation device and compensation method thereof

InactiveCN101615807AHigh adjustment accuracyImprove efficiencyReactive power adjustment/elimination/compensationReactive power compensationTransformerCompensation effect

The invention discloses a stepless rapid phase-control reactive power dynamic compensation device and a reactive dynamic compensation method. The device comprises a compensation transformer and a control circuit thereof, a capacitor or a capacitor bank; wherein, a secondary winding of the transformer is connected between an access bus and the capacitor in series; a primary winding of the transformer is connected to the output terminal of the control circuit; the control circuit comprises a phase-adjusting circuit adapted with a working power supply, a signal detection circuit connected between the access bus and the phase-adjusting circuit in series and a sampling circuit connected between the phase-adjusting circuit and the output side of the secondary winding of the transformer; the primary winding of the transformer is connected to the output terminal of the phase-adjusting circuit. The reactive compensation of the invention can be realized only by adjusting the output voltage phase of the phase-adjusting circuit, therefore, the invention can realize stepless compensation and has high adjusting accuracy, rapid response, high efficiency and good compensation effect. The compensation device and method of the invention are suitable for all the voltage grades of the existing power grids and various places such as substations, electrified railways and the like.

Owner:NANNING MICRO CONTROL HIGH TECH

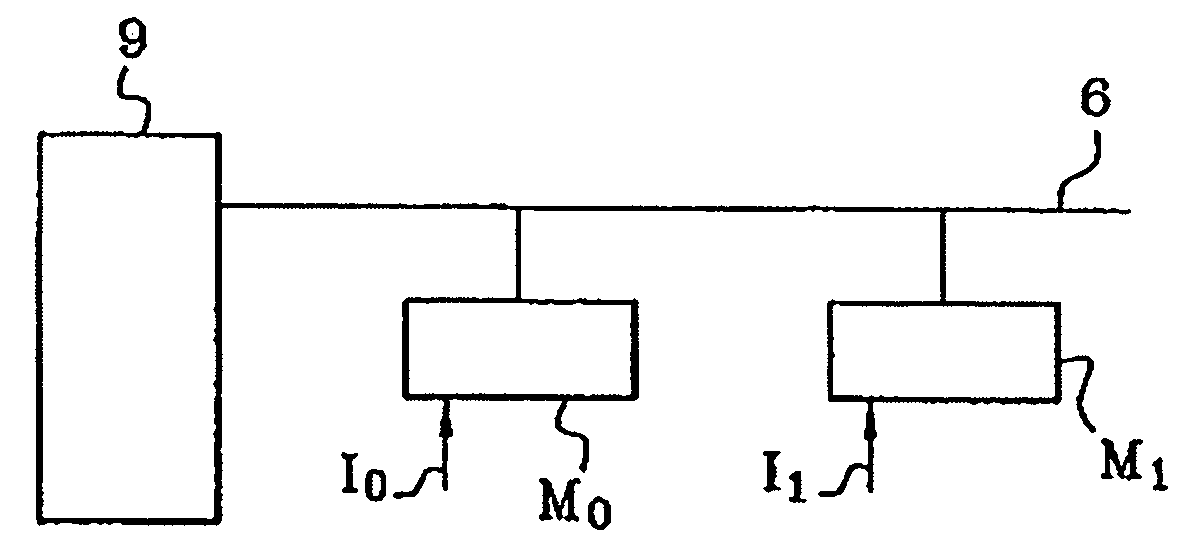

Method for programming/parallel programming of onboard flash memory by multiple access bus

InactiveUS7102383B2Maximum productivityLow costError detection/correctionRead-only memoriesACCESS.busComputer module

Owner:STMICROELECTRONICS SRL

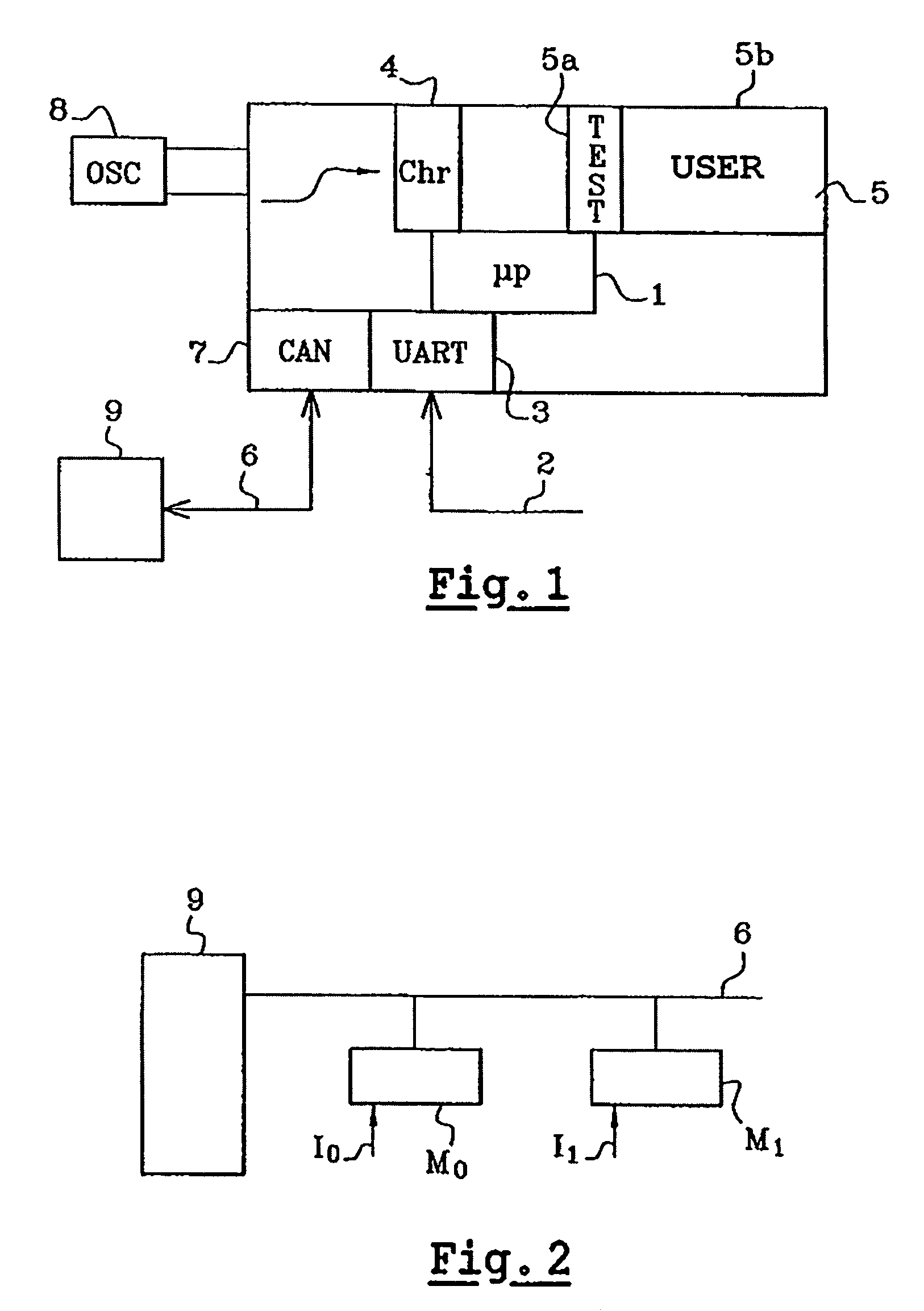

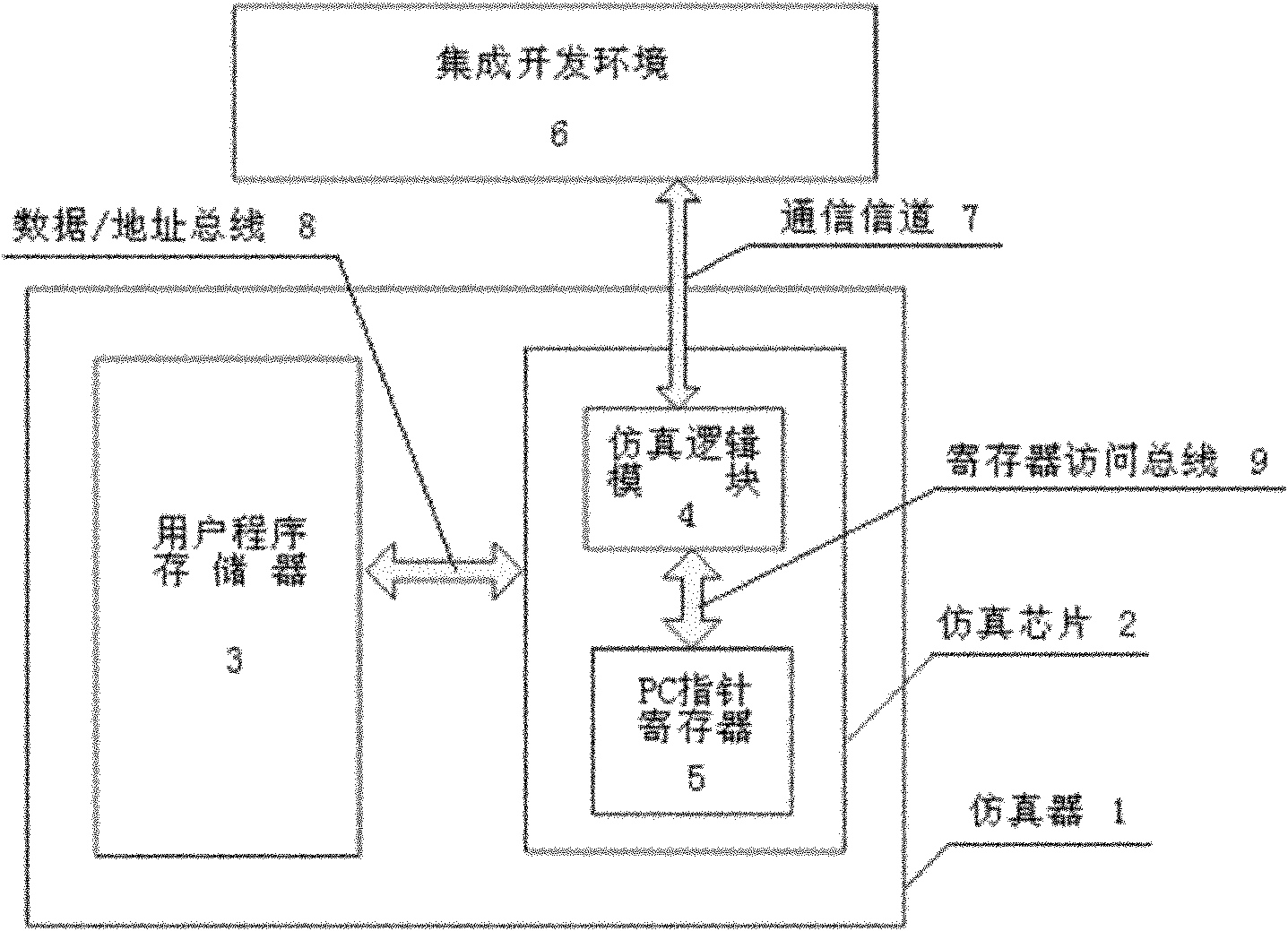

Processor chip emulator capable of setting program pointer value

InactiveCN102467446AEfficient debuggingReliable debuggingSoftware testing/debuggingProcessor registerACCESS.bus

The invention discloses a processor chip emulator capable of setting a program pointer value, which comprises an emulator and integrated development environment debugging software. An emulation chip comprises a PC (personal computer) pointer register and an emulation logic module, wherein the emulation logic module and the PC pointer register are connected through a register access bus; the emulation logic module can execute data write or read operation on the PC pointer register through the register access bus; and the emulation chip can not write data into the PC pointer register by executing a user program. By using the invention, in the user program development process, the user can enable the next program statement to be executed to be executed from the user program statement in the position designated by the user by setting the PC pointer register value in a debugging state; and when the user program is in the operation state, even if a user program miswrites the PC pointer register, no user program execution disorder condition can occur, so that the user can debug the user program efficiently and reliably.

Owner:SHANGHAI HUAHONG INTEGRATED CIRCUIT

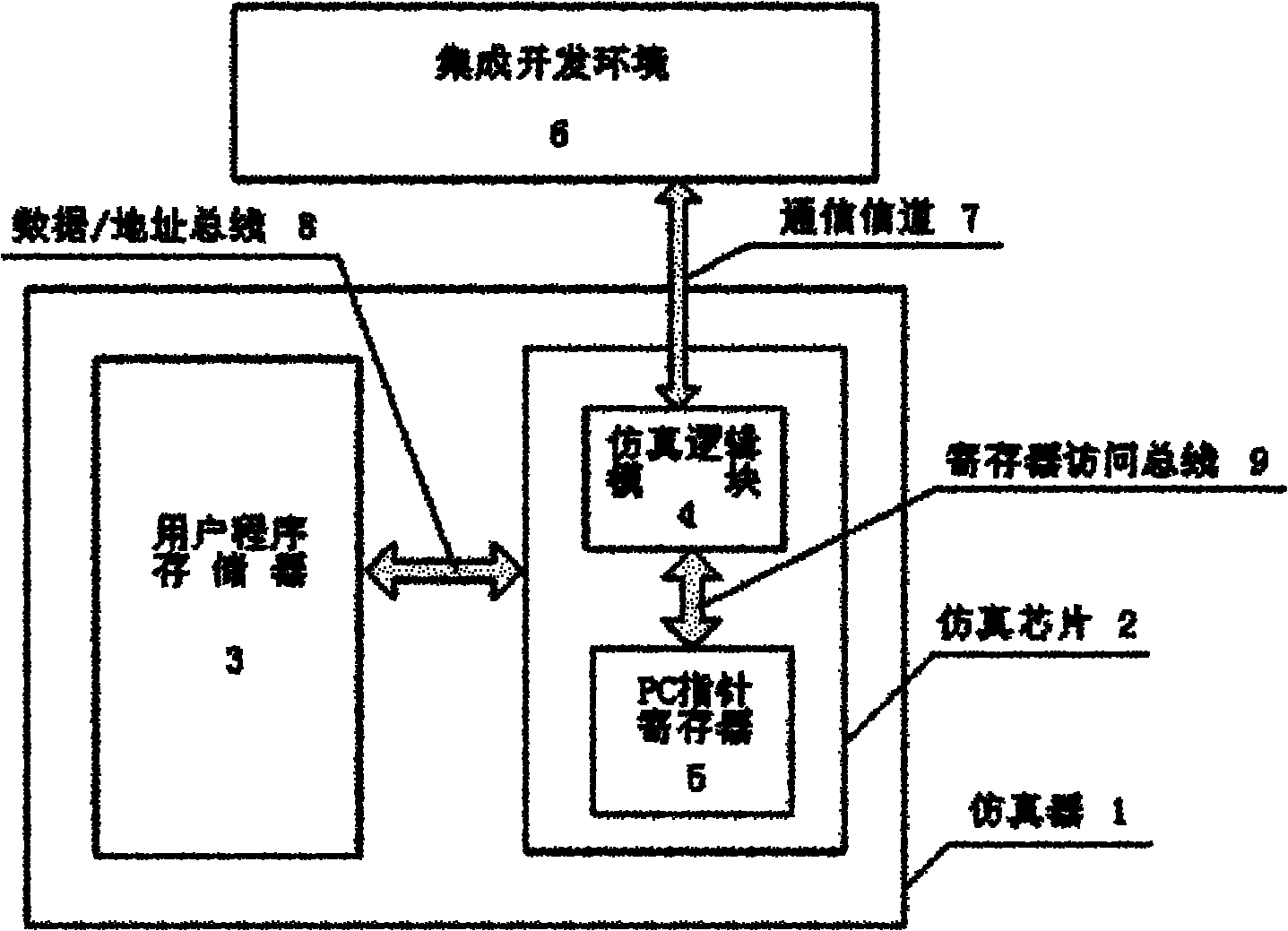

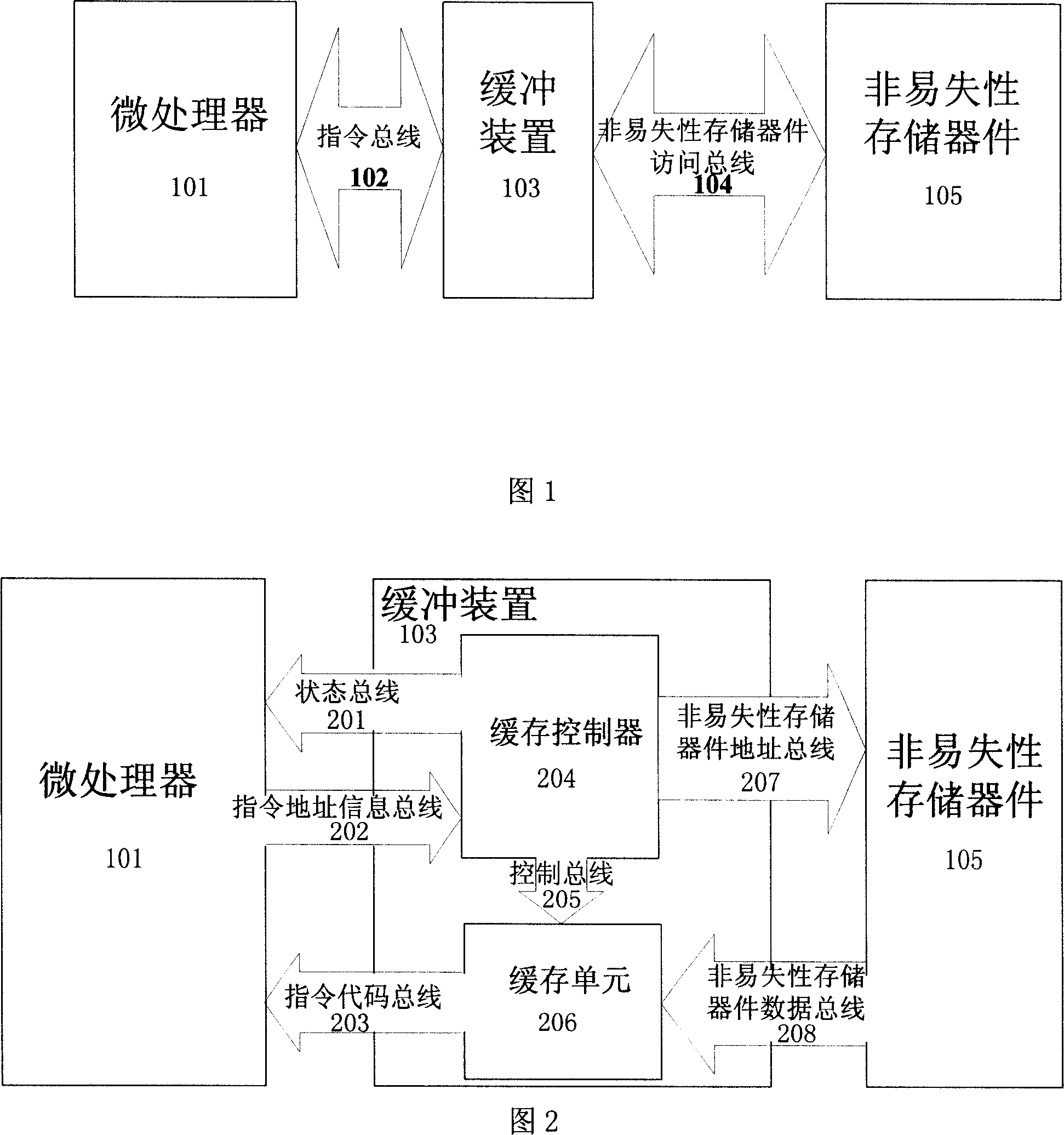

Device for breaking through nonvolatile semiconductor memory member speed bottle-neck

InactiveCN101097562AAvoid complex mechanismsReduce complexityMemory adressing/allocation/relocationACCESS.busBottle neck

A kind of device to breach the speed bottleneck of non-volatile memory is disclosed, which includes buffering device, instruction bus and the access bus of non-volatile memory; the buffering device is mounted between the CPU the non-volatile memory, the buffering device and microprocessor CPU are connected by instruction bus, the buffering device and the non-volatile memory are connected by the access bus of non-volatile memory to expand the bit width of access bus of non-volatile memory connected with buffering device; the instruction bus includes state bus, information bus of instruction address and instruction code bus; the access bus of non-volatile memory includes address bus of non-volatile memory and data bus of non-volatile memory; the buffering device includes buffering controller and buffering unit, and the buffering unit can be controlled by buffering controller via control bus.

Owner:NATIONZ TECH INC

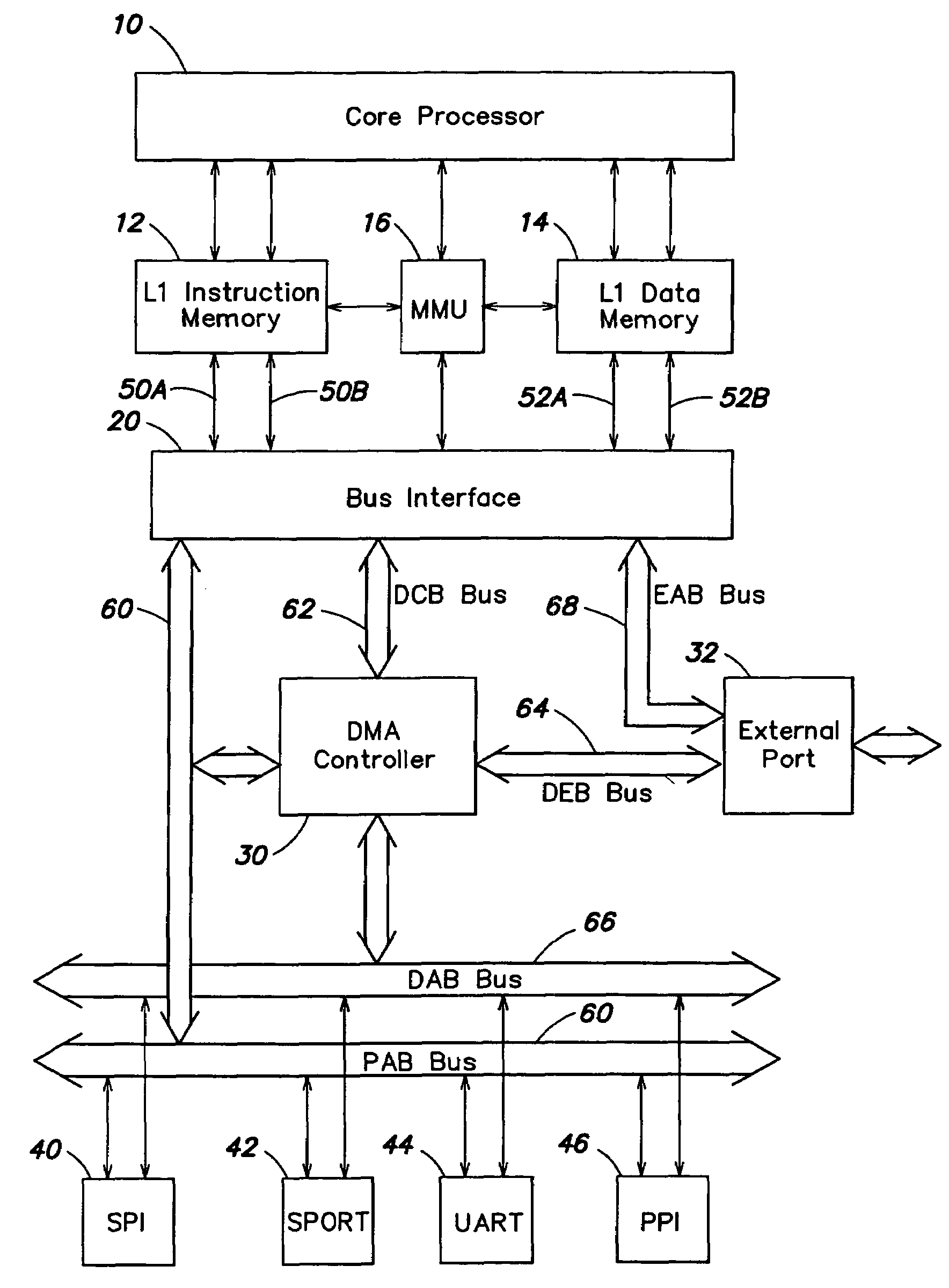

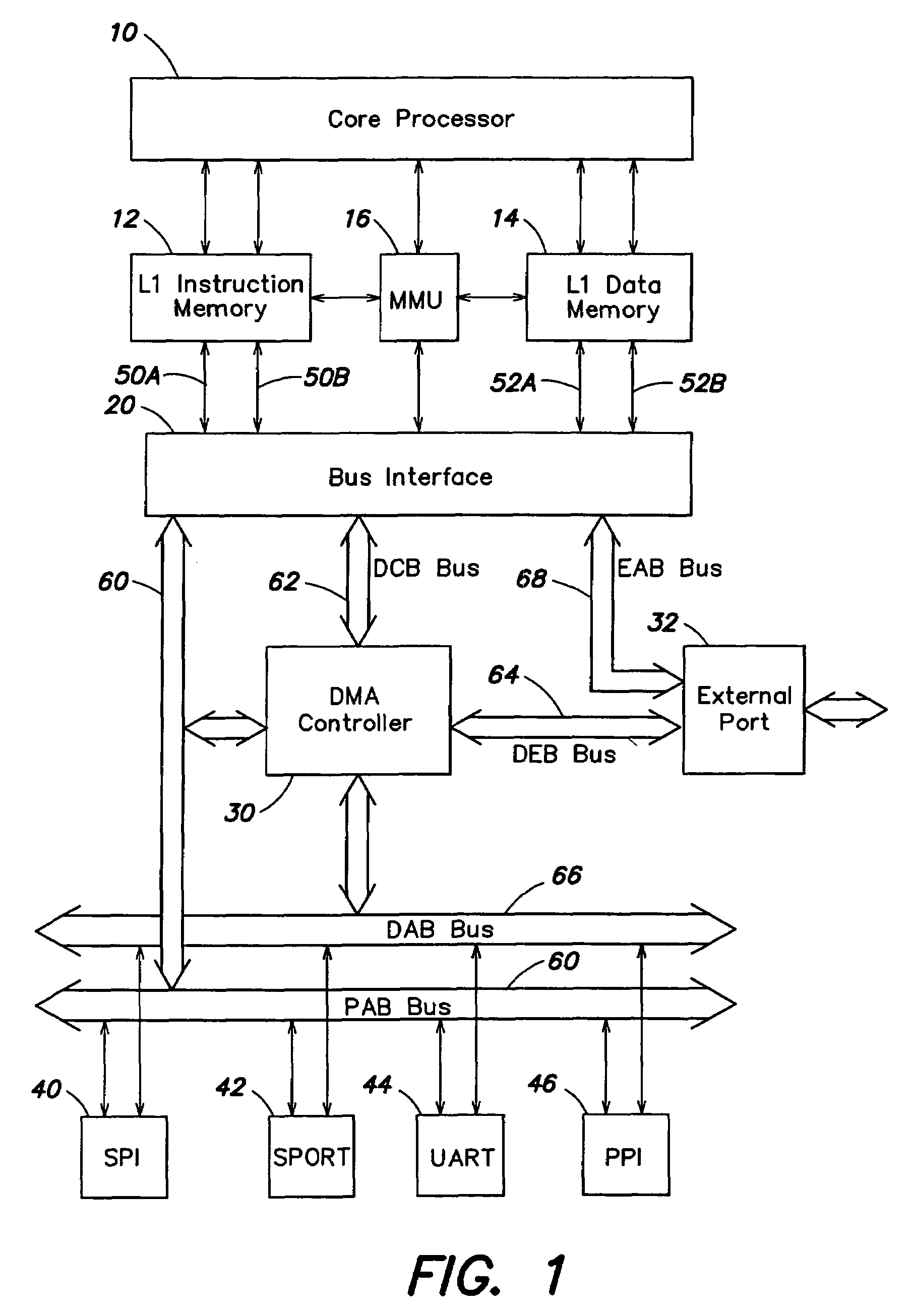

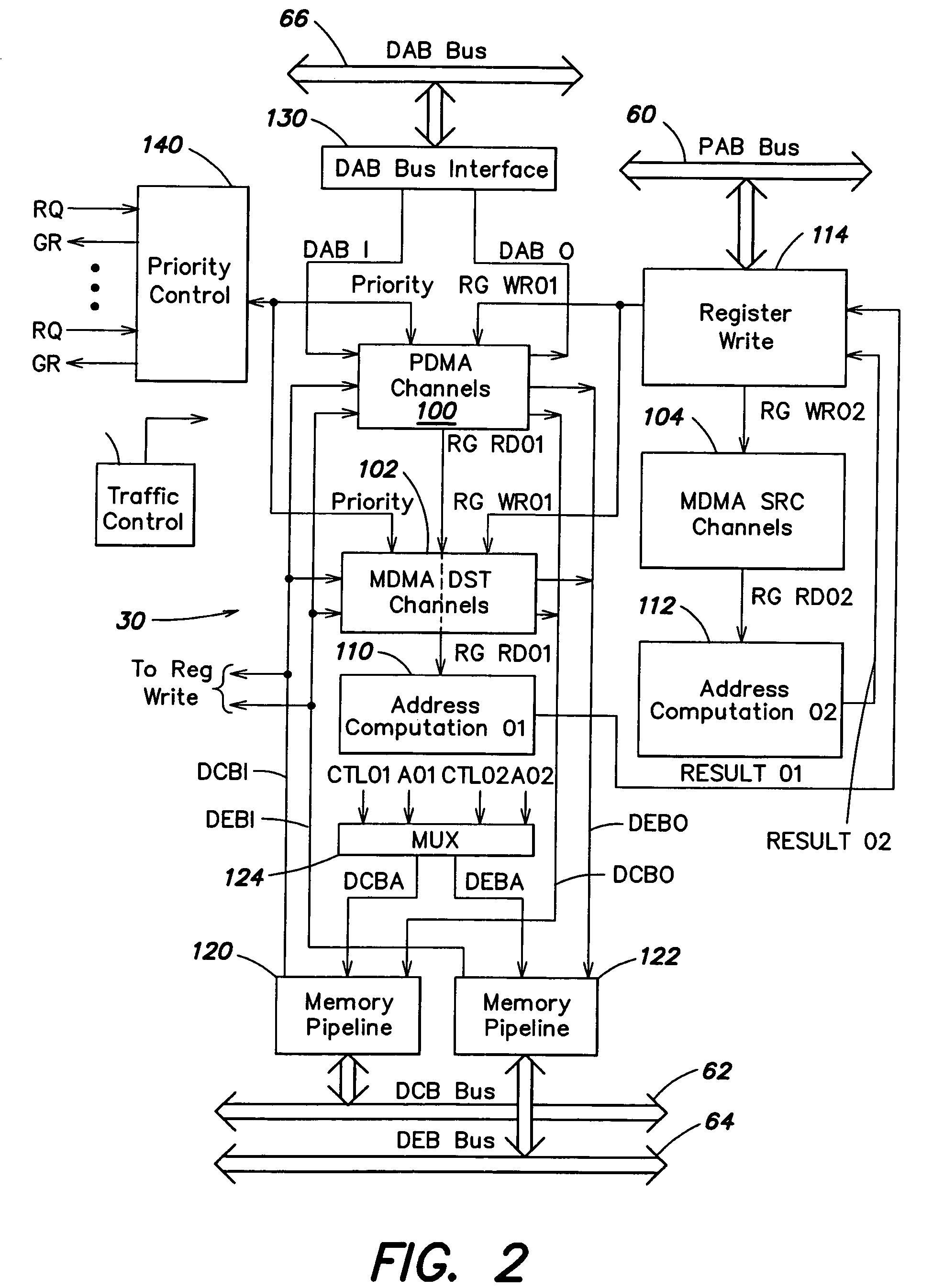

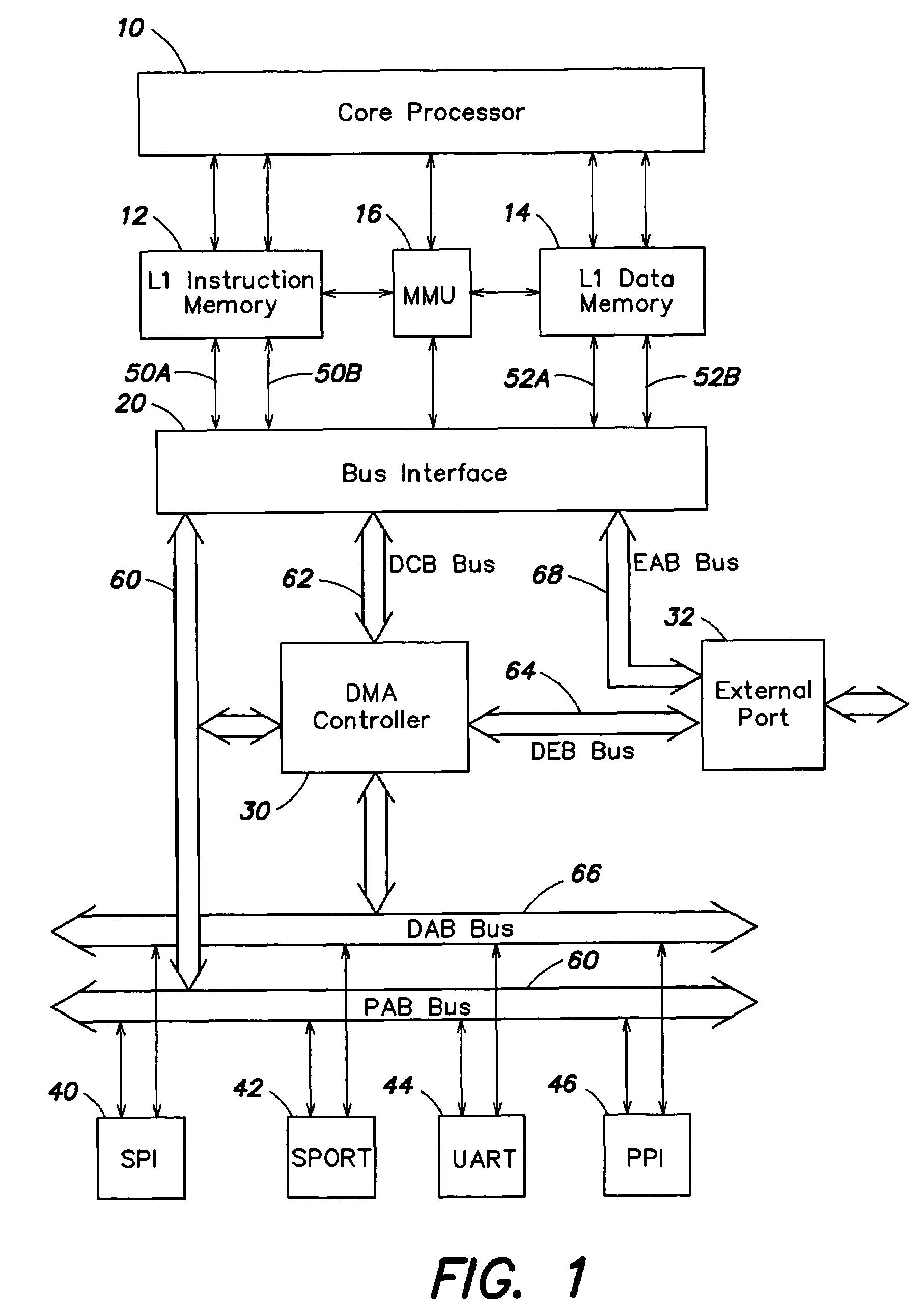

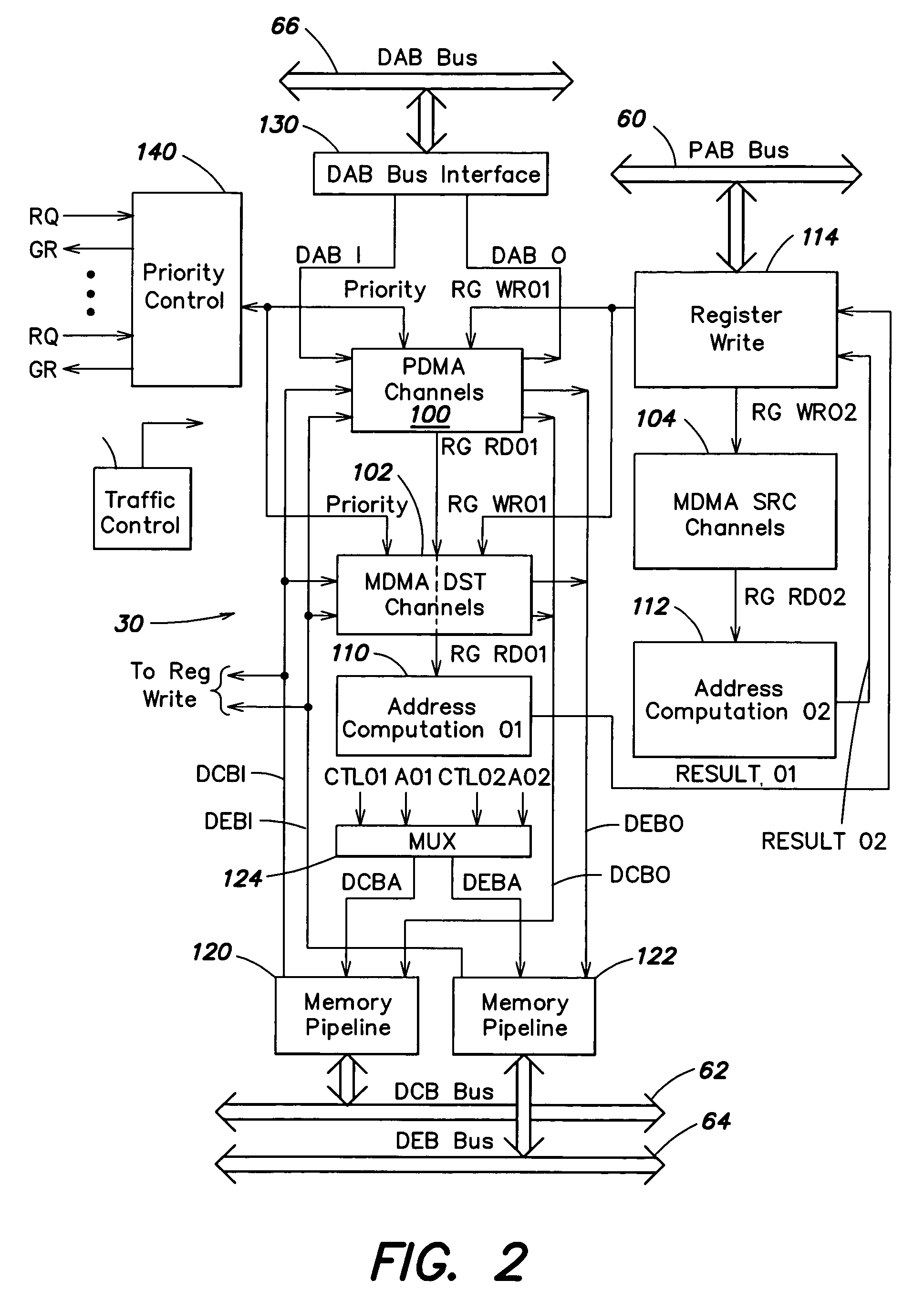

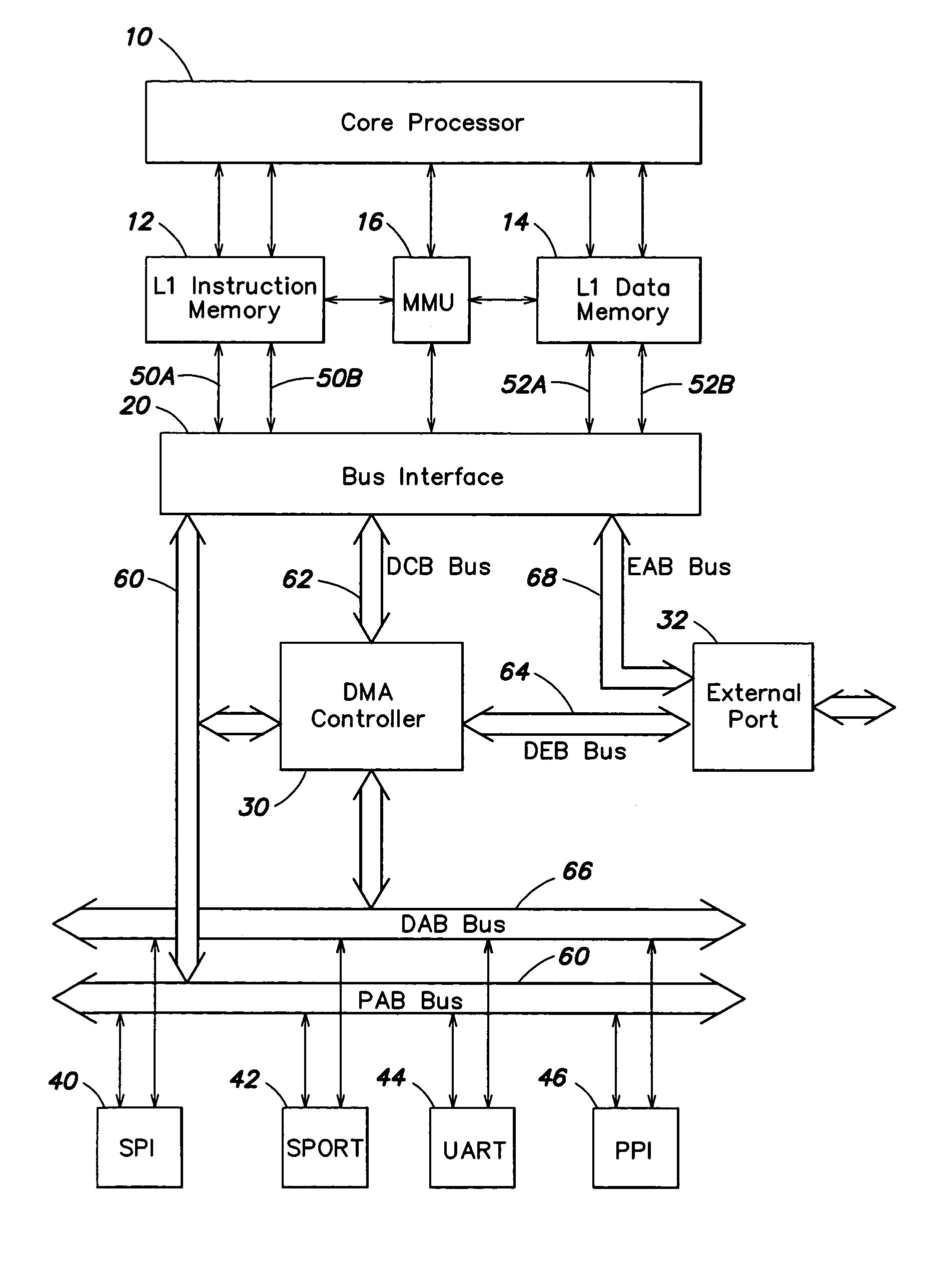

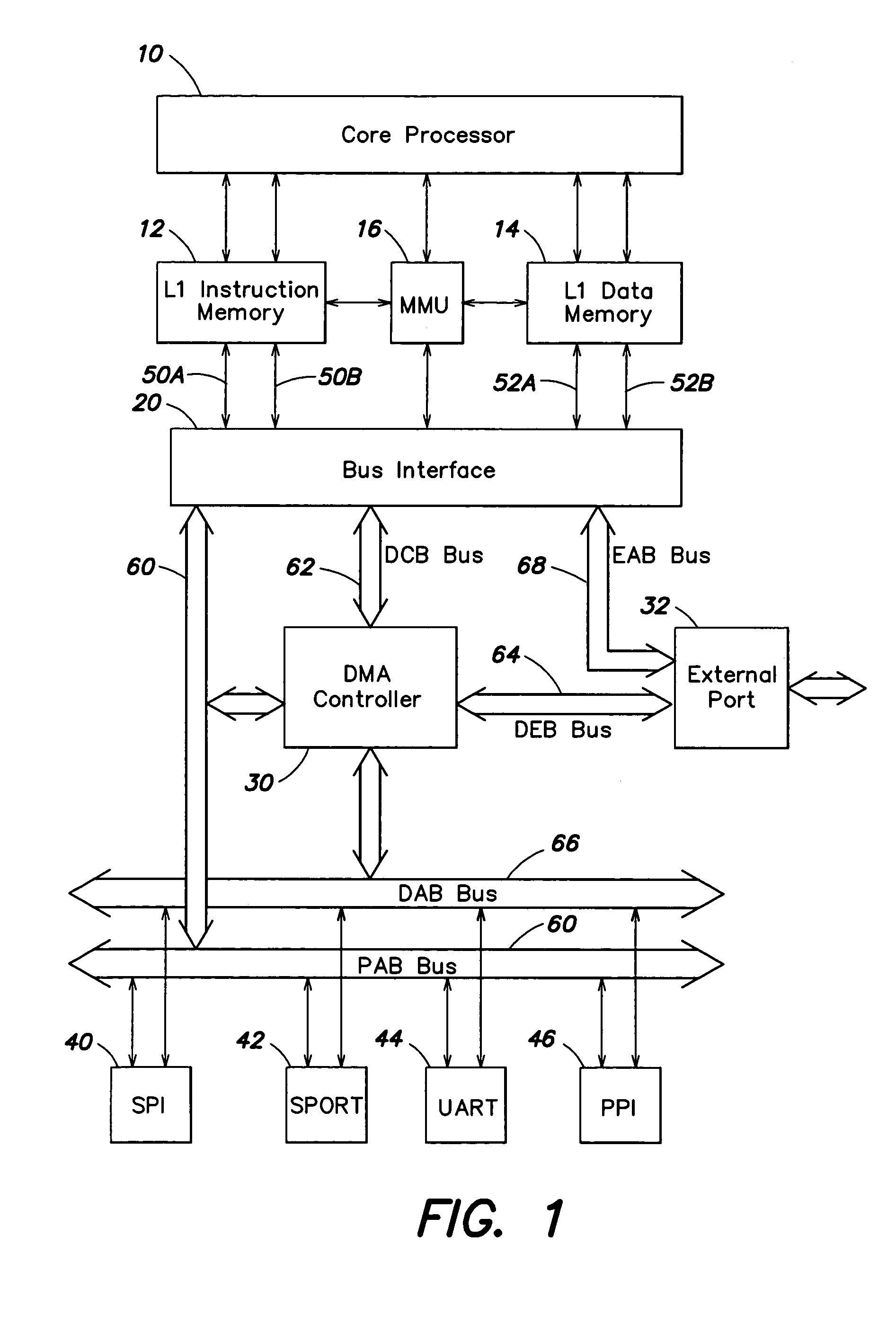

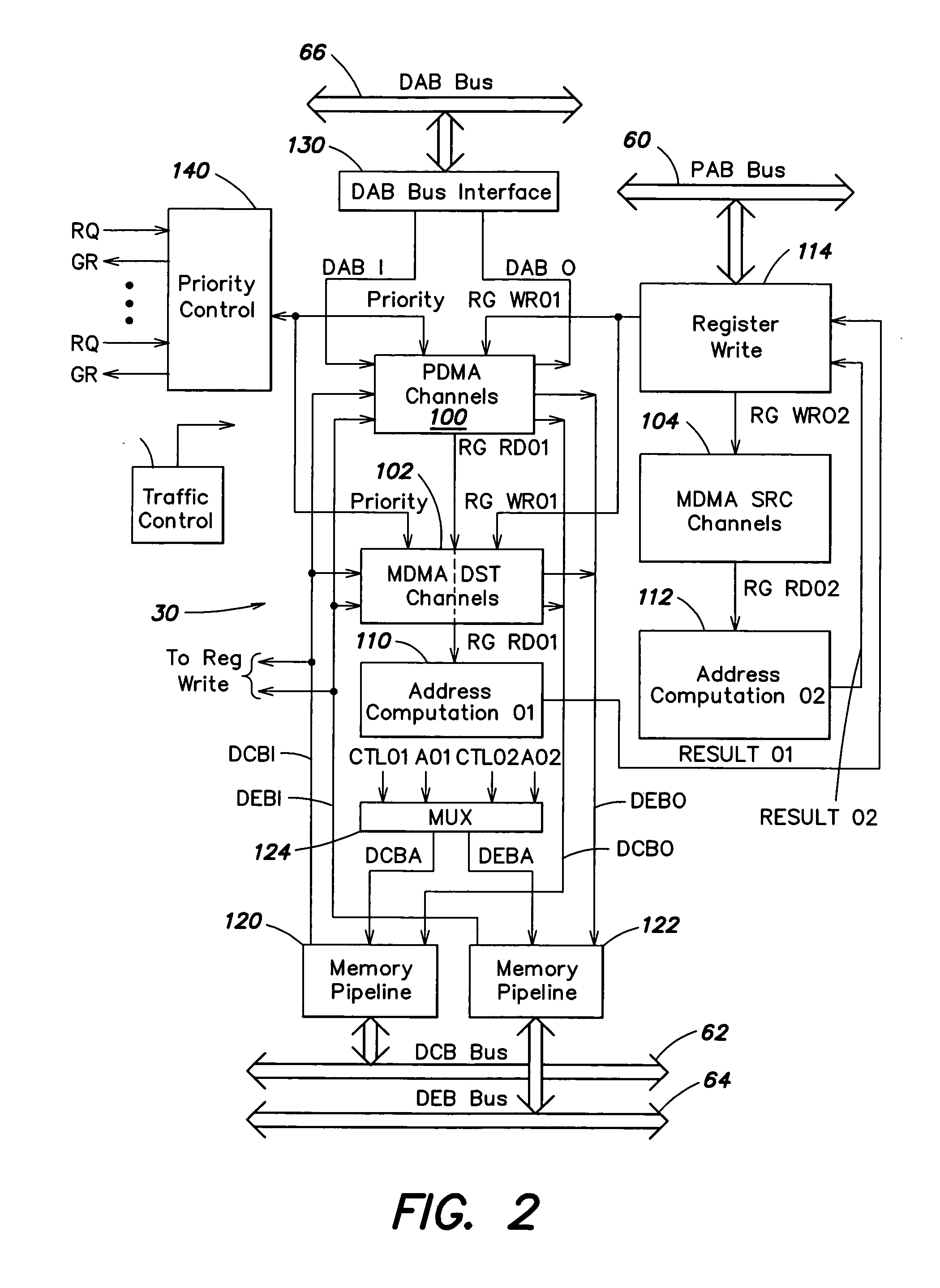

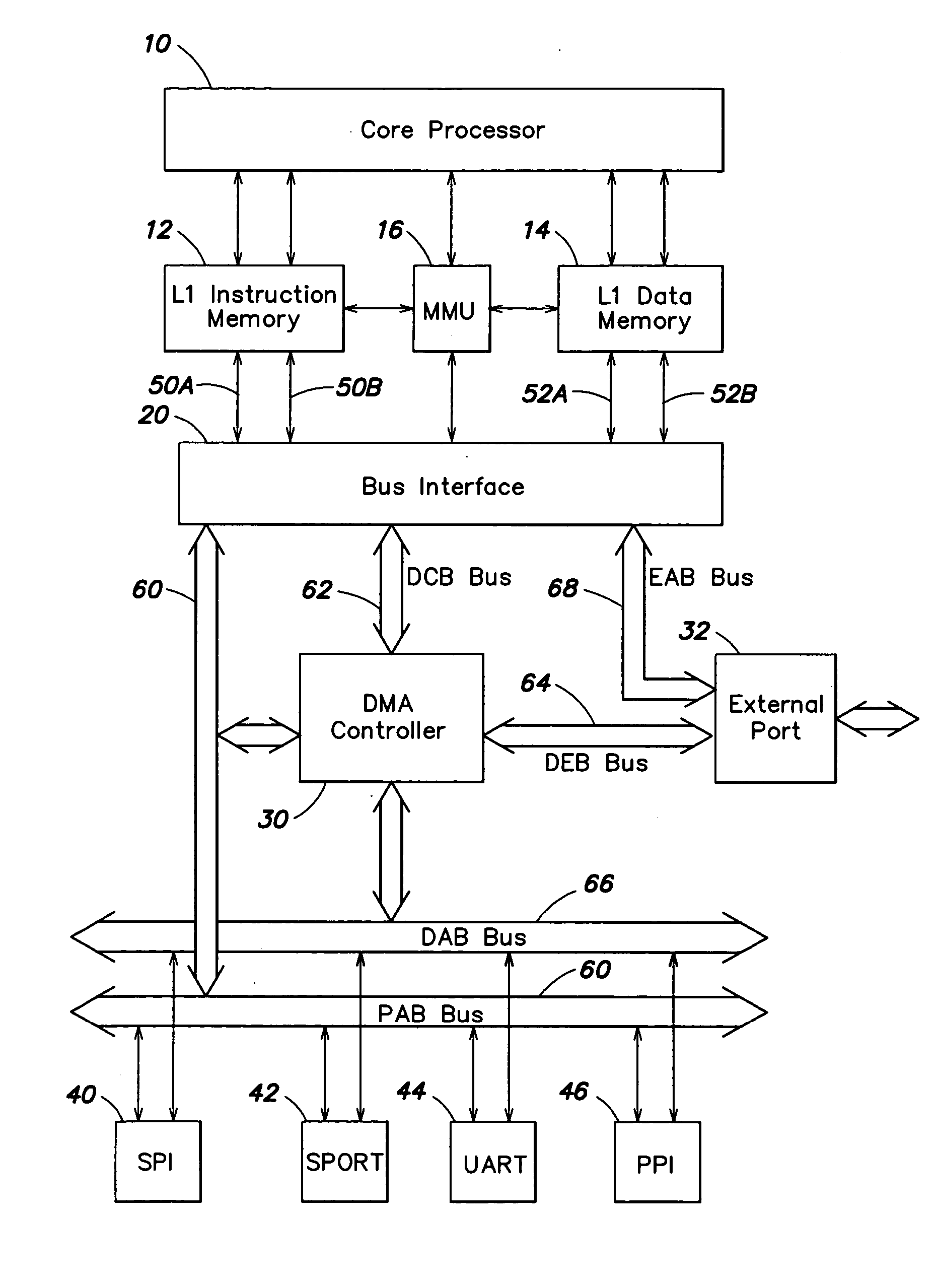

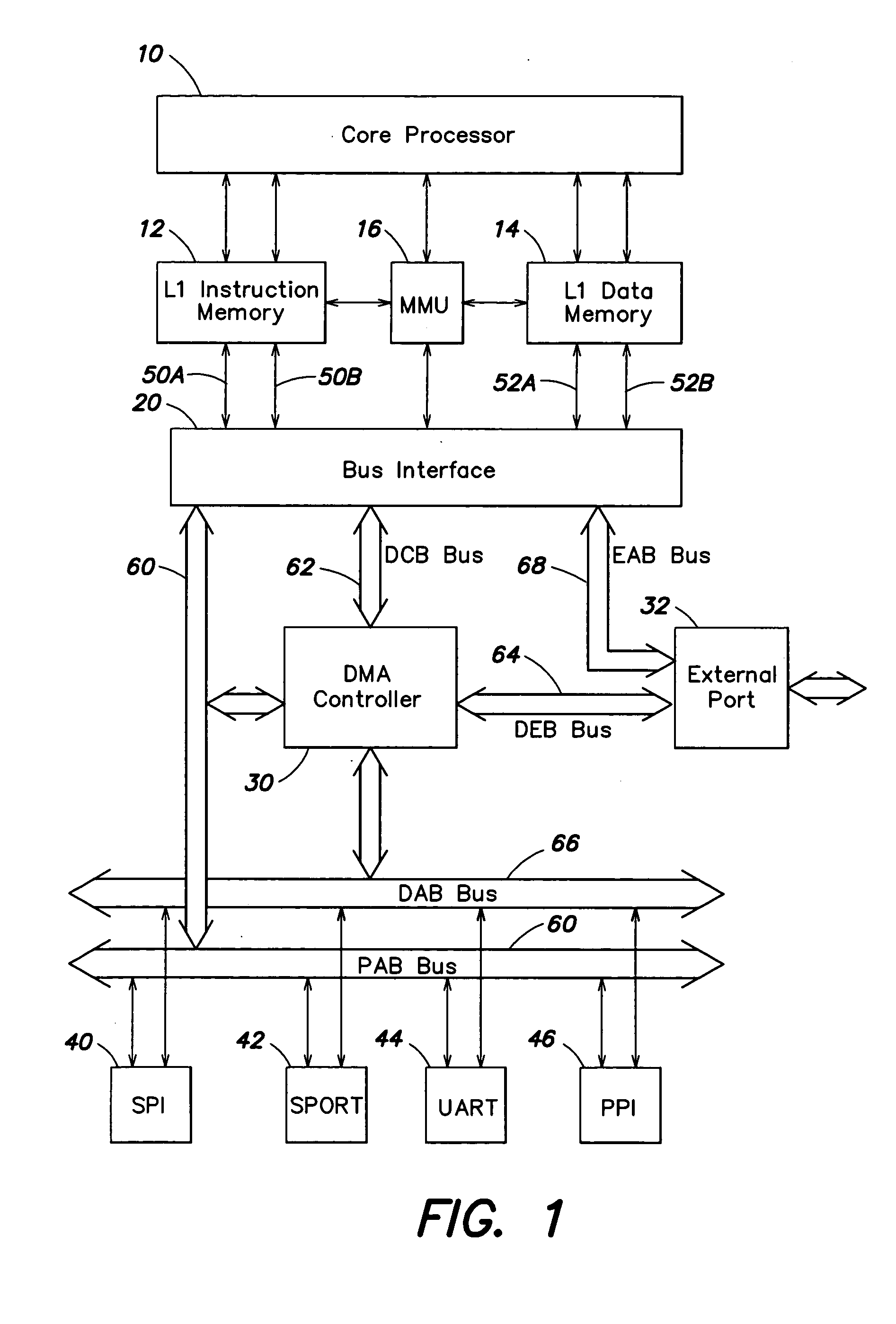

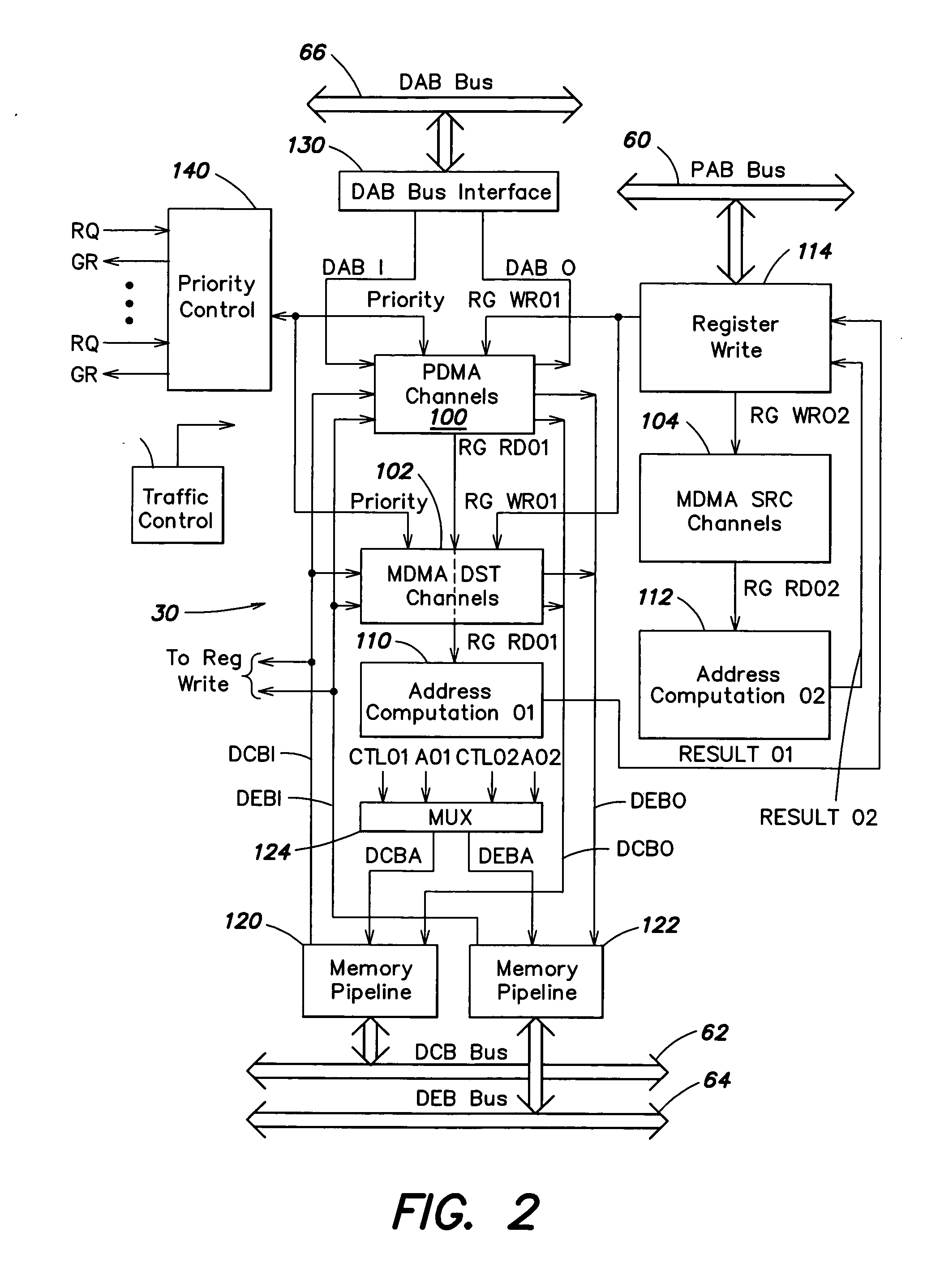

DMA controller for digital signal processors

ActiveUS7533195B2Raise priorityInput/output processes for data processingMemory addressDigital signal processing

A DMA controller includes at least one peripheral DMA channel for handling DMA transfers on a peripheral access bus; at least one memory DMA stream, including a memory destination channel and a memory source channel, for handling DMA transfers on first and second memory access buses; first and second address computation units for computing updated memory addresses for DMA transfers; first and second memory pipelines for supplying memory addresses to the first and second memory access buses, respectively, and for transferring data on the first and second memory access buses; and a multiplexer configured to supply first and second current memory addresses to selected ones of the first and second memory pipelines in response to a control signal.

Owner:ANALOG DEVICES INC

Method and system for video processing

InactiveCN102215401ASolid-state devicesDigital computer detailsHigh-definition televisionDouble data rate

A method and system for video processing are provided in which a multimedia processor and a single low power double data rate memory 2 (LPDDR2) synchronous dynamic random access memory (SDRAM) coupled to the multimedia processor are disposed in a single package on a single substrate or chip. The single LPDDR2 SDRAM may be accessed by the multimedia processor via a 32-bit wide access bus. The multimedia processor and single LPDDR2 SDRAM may be operable to process video data. The video data may comprise 1080 progressive (1080p) high-definition television (HDTV) formatted data. The multimedia processor and single LPDDR2 SDRAM may be operable to pipeline process video data from an image sensor.

Owner:BROADCOM CORP

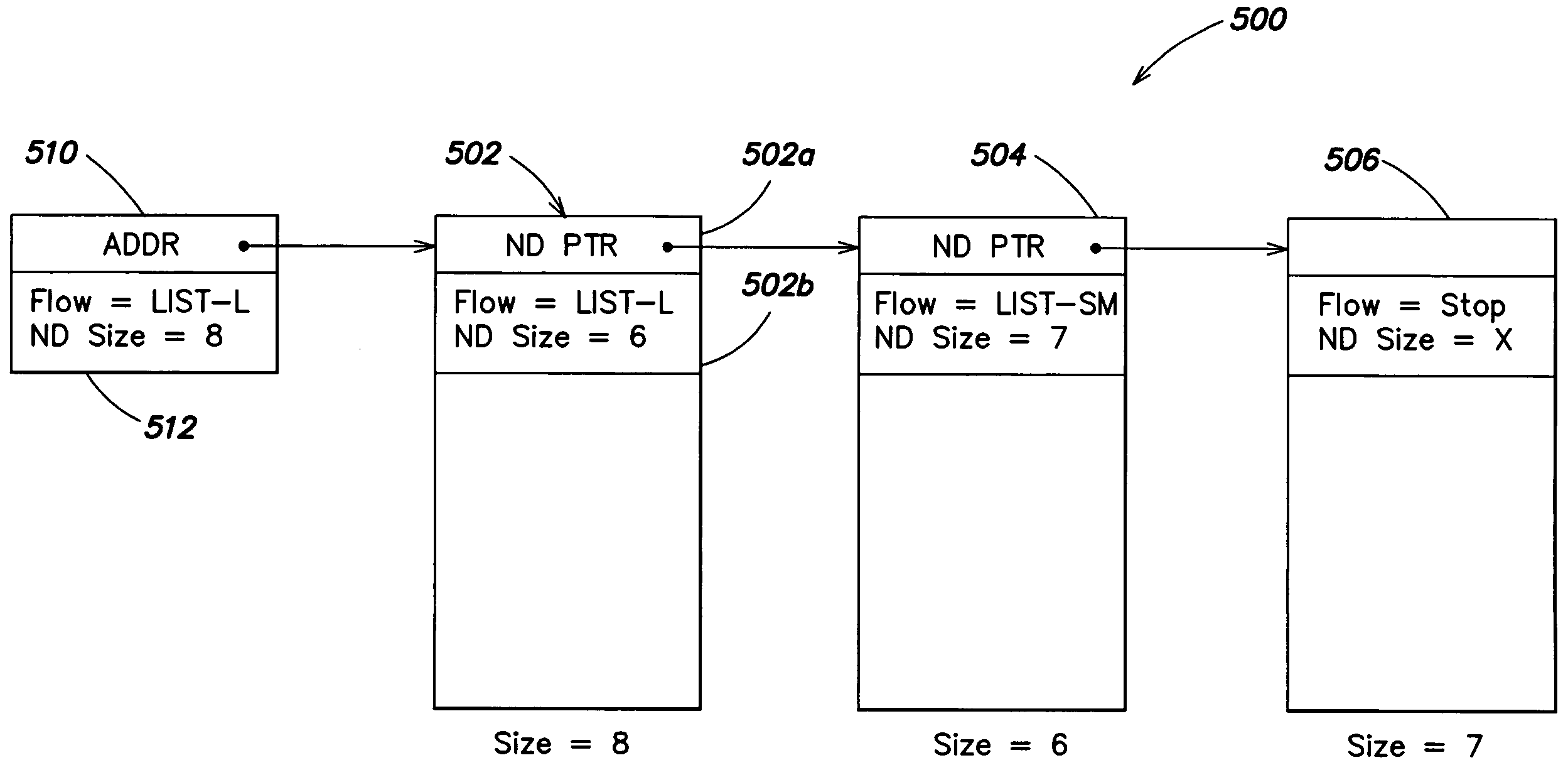

DMA controller utilizing flexible DMA descriptors

A DMA controller includes at least one peripheral DMA channel for handling DMA transfers on a peripheral access bus; at least one memory DMA stream, including a memory destination channel and a memory source channel, for handling DMA transfers on first and second memory access buses; first and second address computation units for computing updated memory addresses for DMA transfers; and first and second memory pipelines for supplying memory addresses to the first and second memory access buses, respectively, and for transferring data on the first and second memory access buses. Channel control logic controls transfer of data through the DMA channels in response to parameters contained in at least one DMA descriptor having a programmable format.

Owner:ANALOG DEVICES INC

DMA controller having programmable channel priority

ActiveUS7240129B2Input/output processes for data processingData conversionMemory addressParallel computing

A DMA controller includes at least one peripheral DMA channel for handling DMA transfers on a peripheral access bus; at least one memory DMA stream, including a memory destination channel and a memory source channel, for handling DMA transfers on first and second memory access buses; first and second address computation units for computing updated memory addresses for DMA transfers; and first and second memory pipelines for supplying memory addresses to the first and second memory access buses, respectively, and for transferring data on the first and second memory access buses. The DMA controller further includes a prioritizer configured to map DMA requests from different DMA requesters to the peripheral channels in response to programmable mapping information.

Owner:ANALOG DEVICES INC

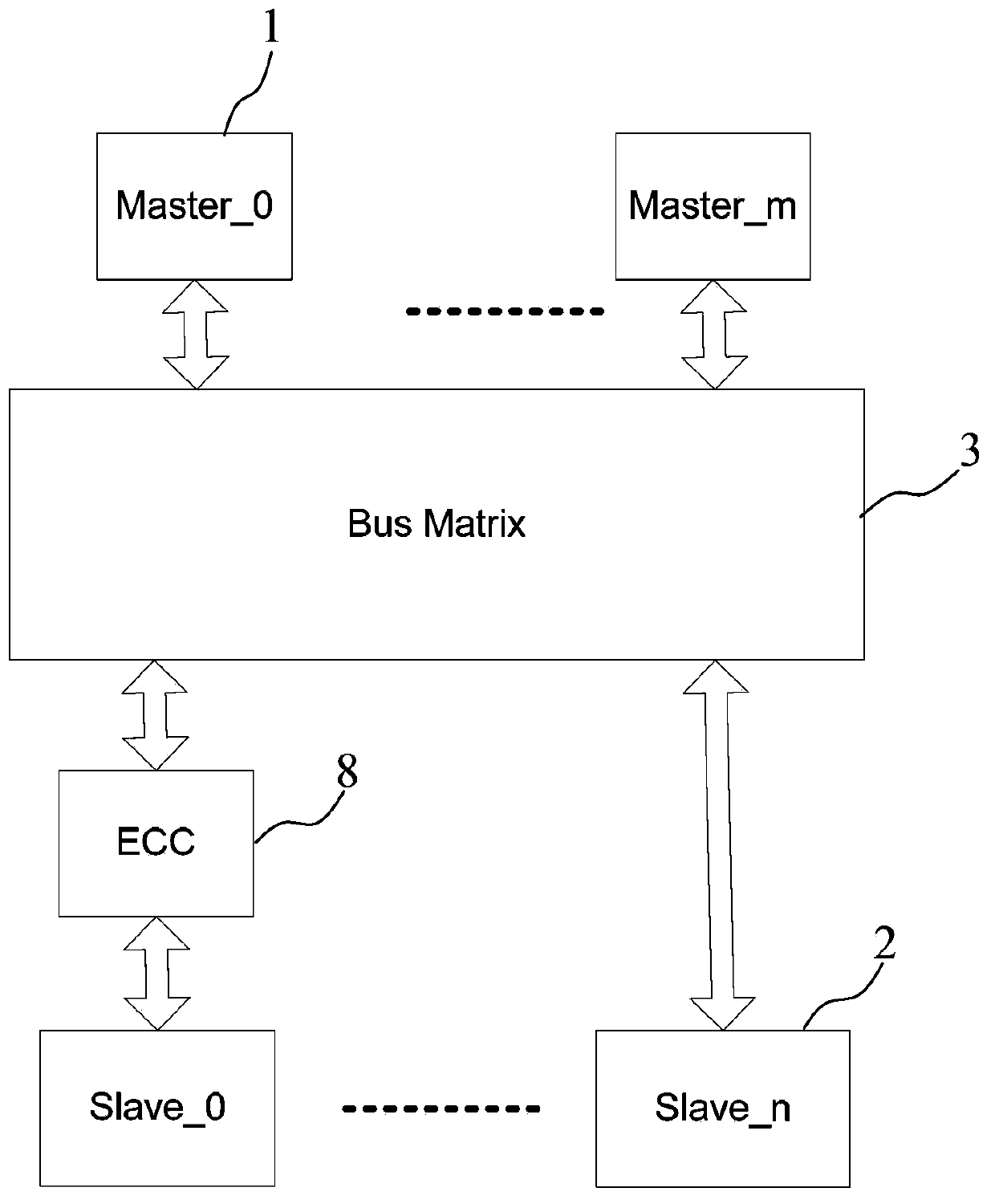

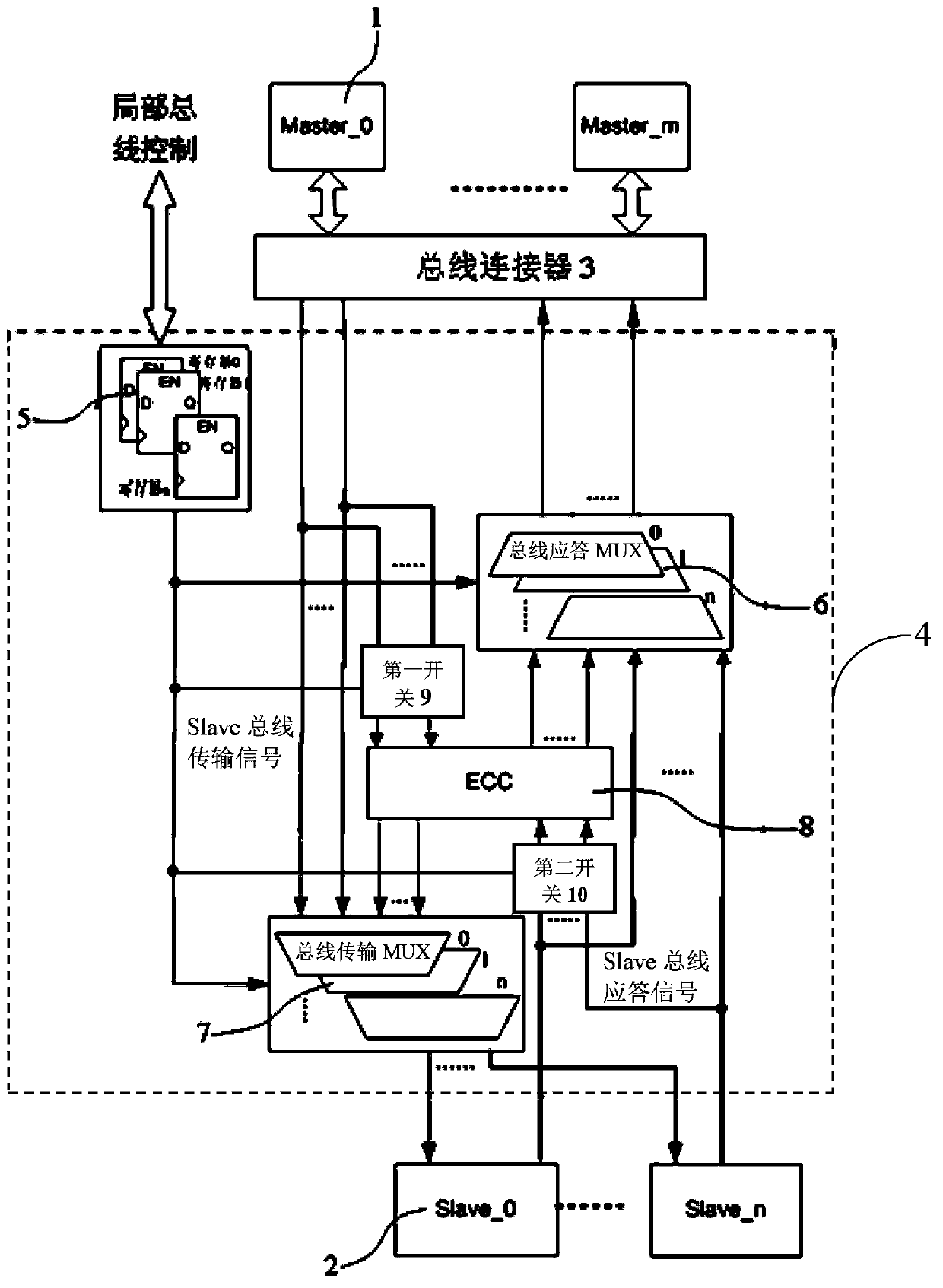

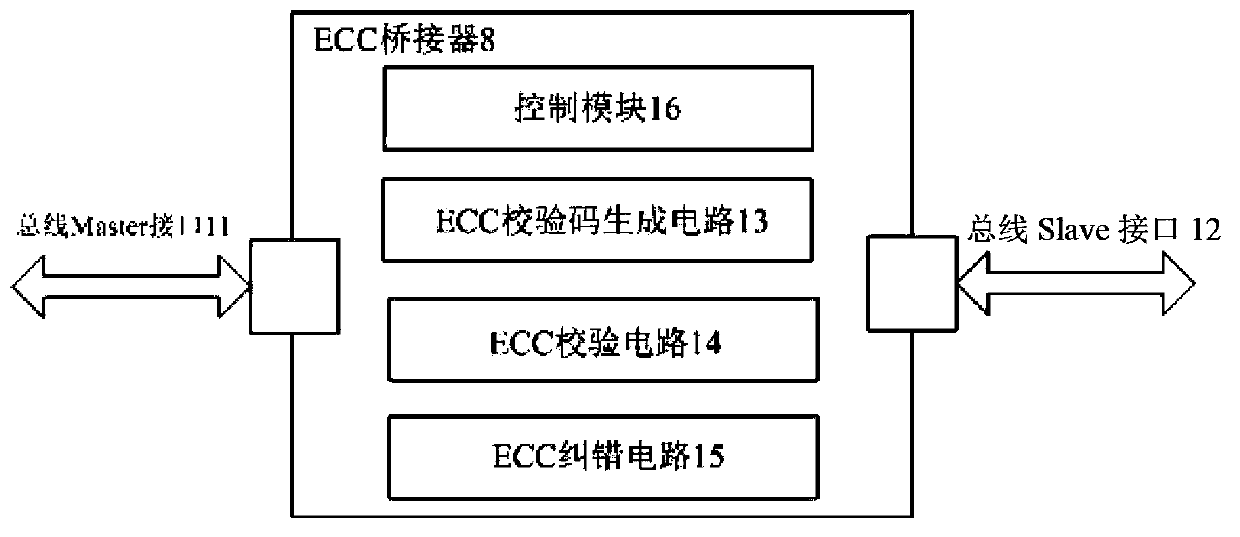

Random access memory access bus ECC (error checking and correcting) verification device

ActiveCN103389923AAvoid normal workEasy to expand applicationRedundant data error correctionError checkTransmission gate

The invention provides a random access memory access bus ECC (error checking and correcting) verification device, which comprises a main equipment module, a random access memory and a bus connector positioned between the main equipment module and the random access memory, wherein a bus ECC bridging module is arranged between the random access memory and the bus connector; the bus ECC bridging module comprises at least two gate control registers, at least two bus response gates, at least two bus transmission gates and an ECC bridge, wherein the first bus input end of each bus transmission gate and the coding input end of the ECC bridge are both connected to the bus connector; the first response input end of each bus response gate and the decoding input end of the ECC bridge are both connected to a random access memory end; a first switch is arranged between the coding input end of the ECC bridge and the bus connector; a second switch is arranged between the random access memory and the decoding input end of the ECC bridge. According to the random access memory access bus ECC verification device disclosed by the invention, whether each random access memory needs ECC verification or whether ECC verification is required in the random access memory is flexibly selected according to different application occasions, thereby being convenient for system expanding application, and improving the integral efficiency.

Owner:苏州国芯科技股份有限公司

DMA controller having programmable channel priority

ActiveUS20050188120A1Input/output processes for data processingData conversionMemory addressParallel computing

A DMA controller includes at least one peripheral DMA channel for handling DMA transfers on a peripheral access bus; at least one memory DMA stream, including a memory destination channel and a memory source channel, for handling DMA transfers on first and second memory access buses; first and second address computation units for computing updated memory addresses for DMA transfers; and first and second memory pipelines for supplying memory addresses to the first and second memory access buses, respectively, and for transferring data on the first and second memory access buses. The DMA controller further includes a prioritizer configured to map DMA requests from different DMA requesters to the peripheral channels in response to programmable mapping information.

Owner:ANALOG DEVICES INC

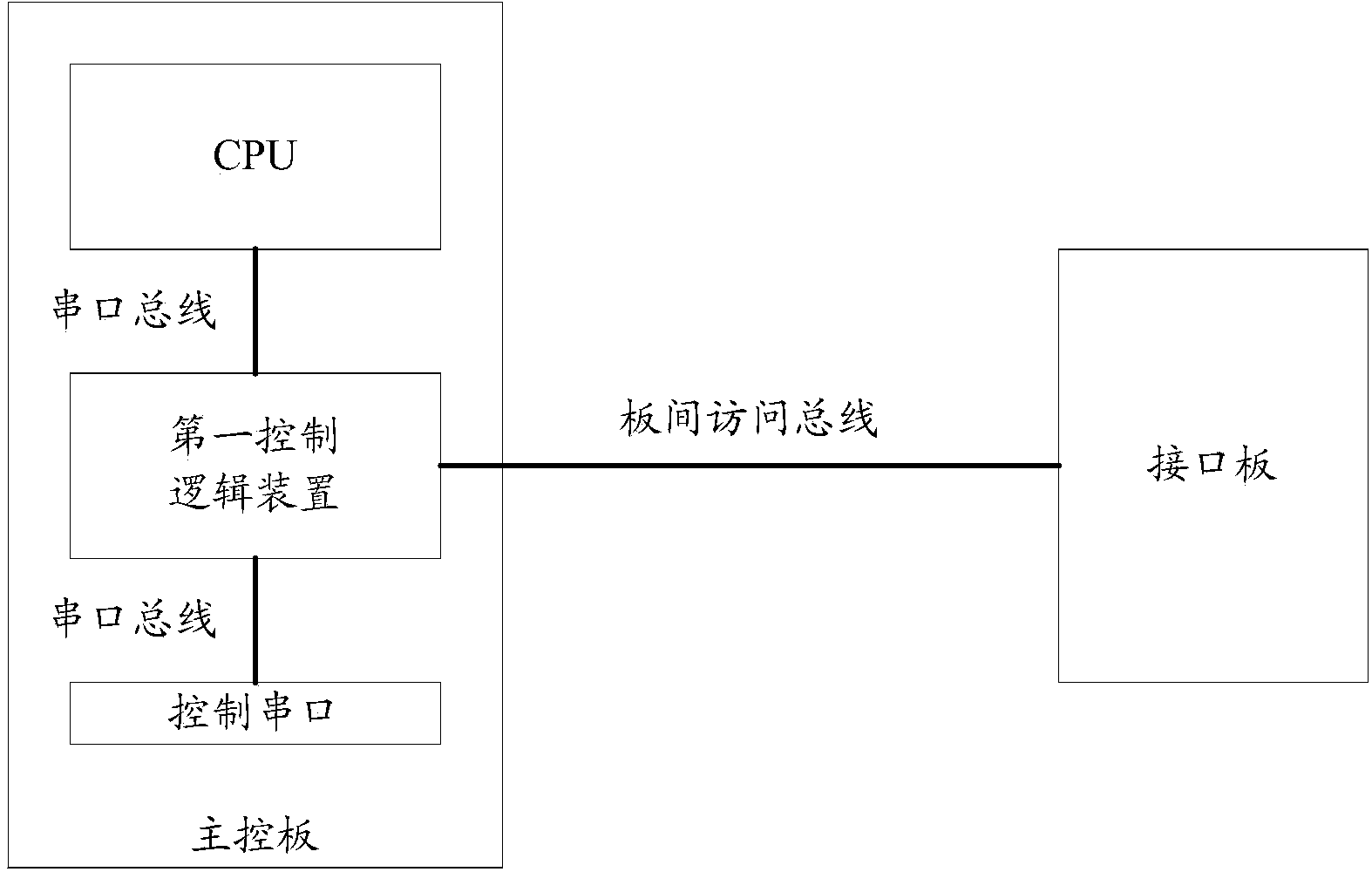

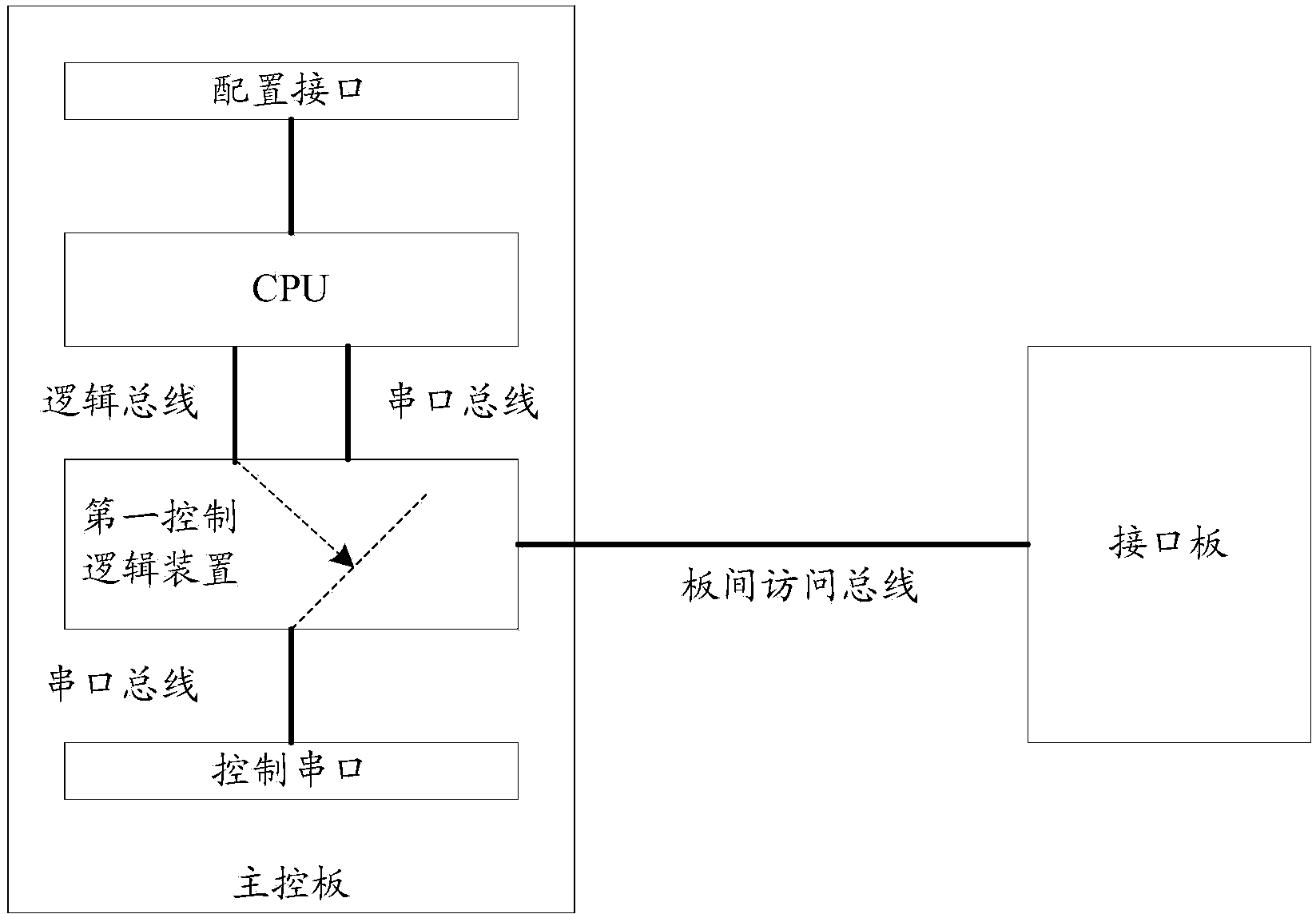

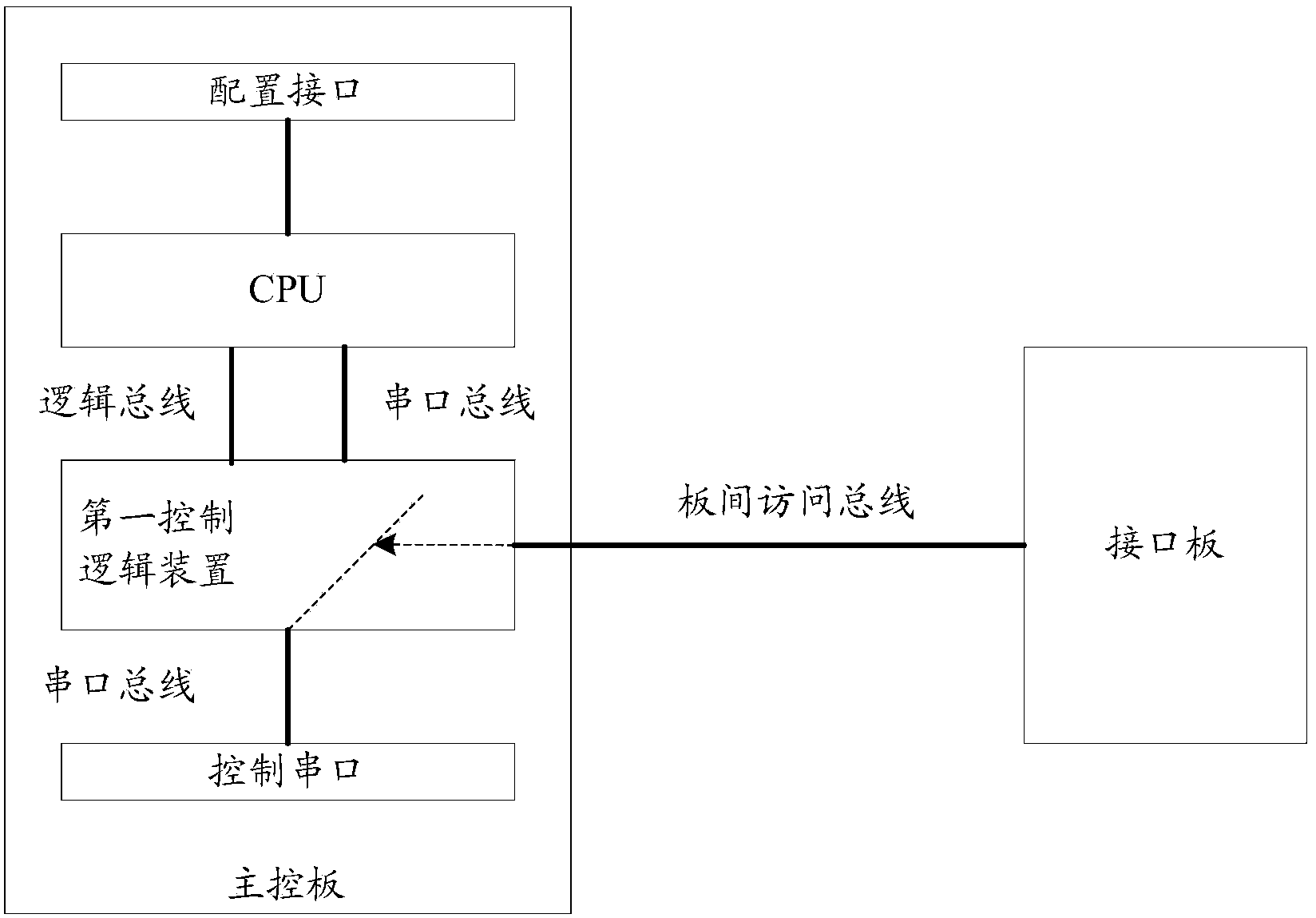

Network device and console configuration method for network device

ActiveCN104301145AMeet the needs of using the control serial portData switching networksACCESS.busSerial port

The invention discloses a network device and a console configuration method for the network device. Based on the network device and the console configuration method for the network device, through switching communication of a console of a main control panel, communication between the console of the main control panel and a CPU of a principle panel can be achieved through an intra-panel serial port bus so that the main control panel can use a console of the principle panel, and the console of the main control panel can also be communicated to an interface panel through an inter-panel access bus so that the interface panel can use the console of the main control panel. Thus, the interface panel in the network device can reuse the console of the main control panel so that the requirement of the interface panel for using the console can be met.

Owner:NEW H3C TECH CO LTD

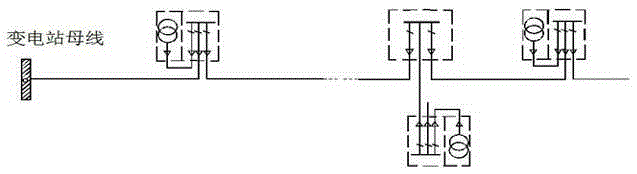

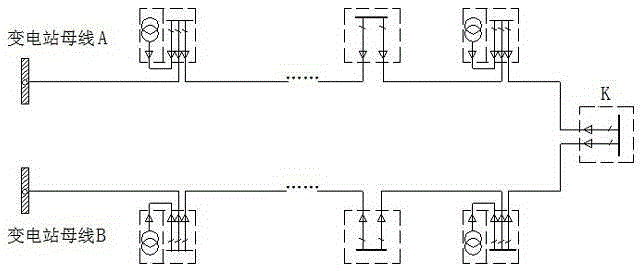

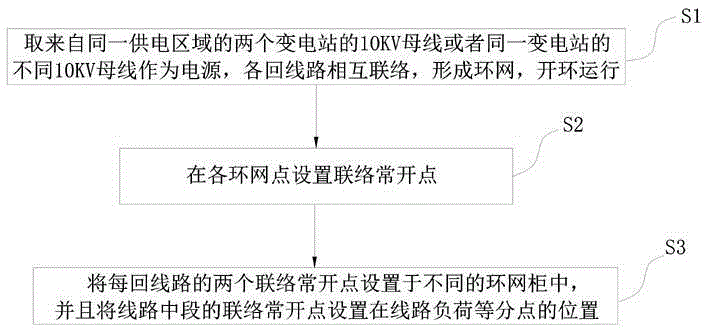

Medium voltage cable network networking method

InactiveCN105244872ASimple wiringFlexible operationAc network circuit arrangementsACCESS.busDouble loop network

The invention provides a medium voltage cable network networking method. The method comprises the steps that 1, a 10KV bus of two substations or different 10KV buses of the same substation in the same power supply area are used as a power supply, wherein lines contact with each other to form a looped network and carry out open-loop operation; 2, a contact normally open point is arranged at each looped network point; and 3, two contact normally open points of each line are arranged in different ring main units, and a contact normally open point in the middle of the line is arranged at the halving point of a line load. When a cable network provided by the invention is in normal operation, each line load is connected with the accessed bus. When a fault occurs, the contact normally open points of the looped network points on both sides of the fault point carry out fault isolation. A load in front of the fault point is connected with an originally accessed bus. A load behind the fault point is connected with a bus which accesses a group line. In a high-reliability power supply area, if a medium voltage cable network networking method is unable to transit to a standard double looped network, the power supply reliability can be improved through the networking method provided by the invention.

Owner:STATE GRID CORP OF CHINA +1

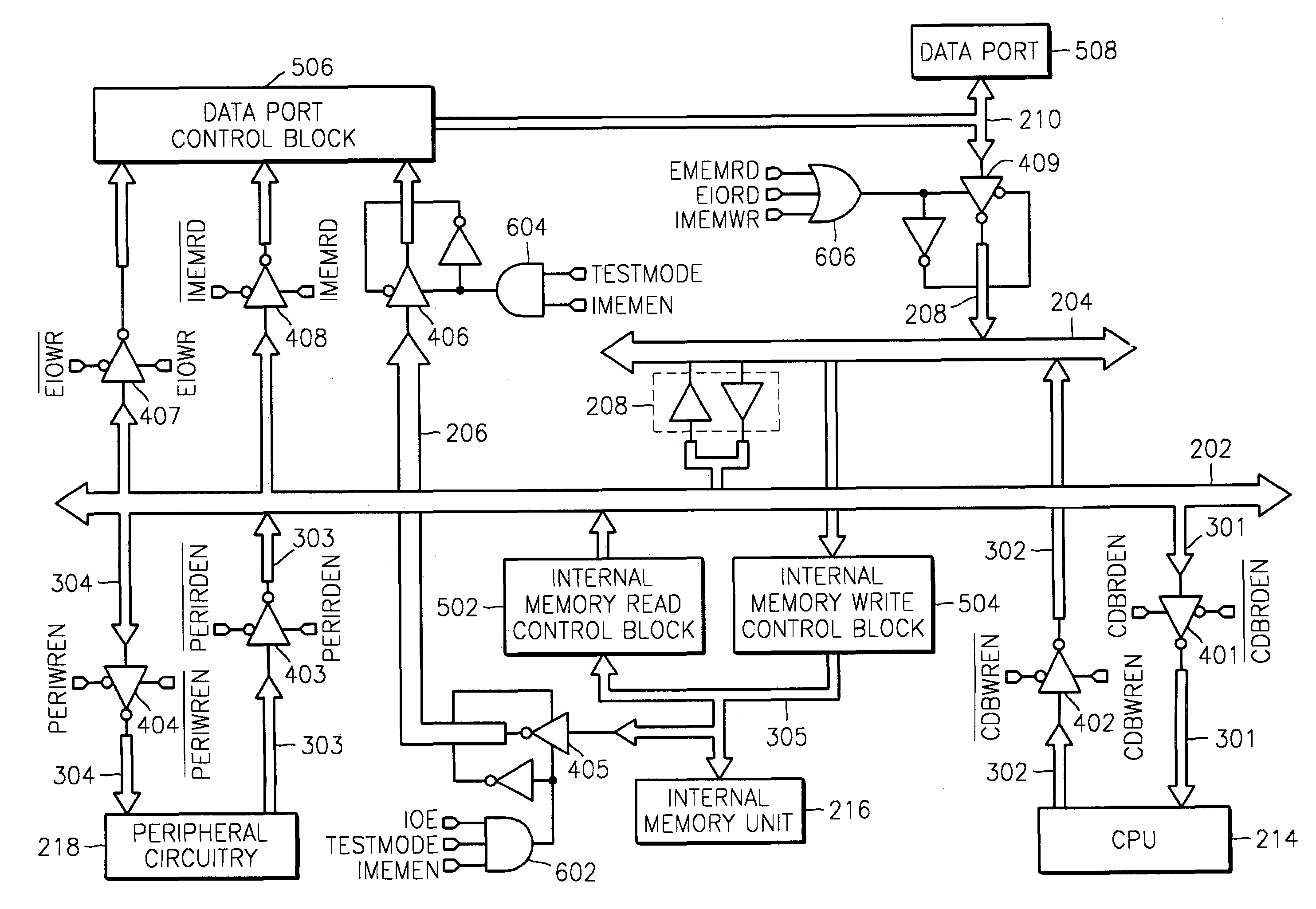

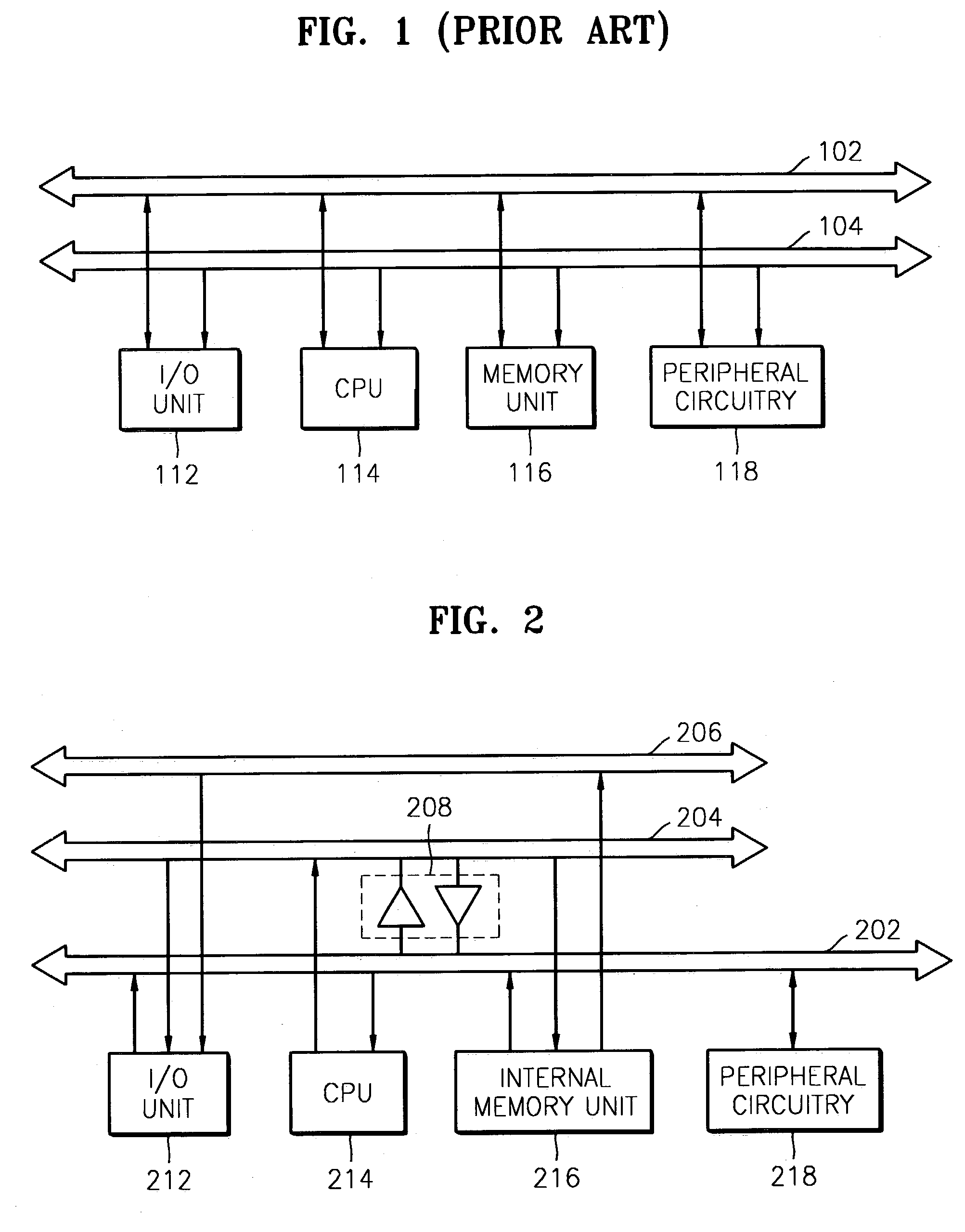

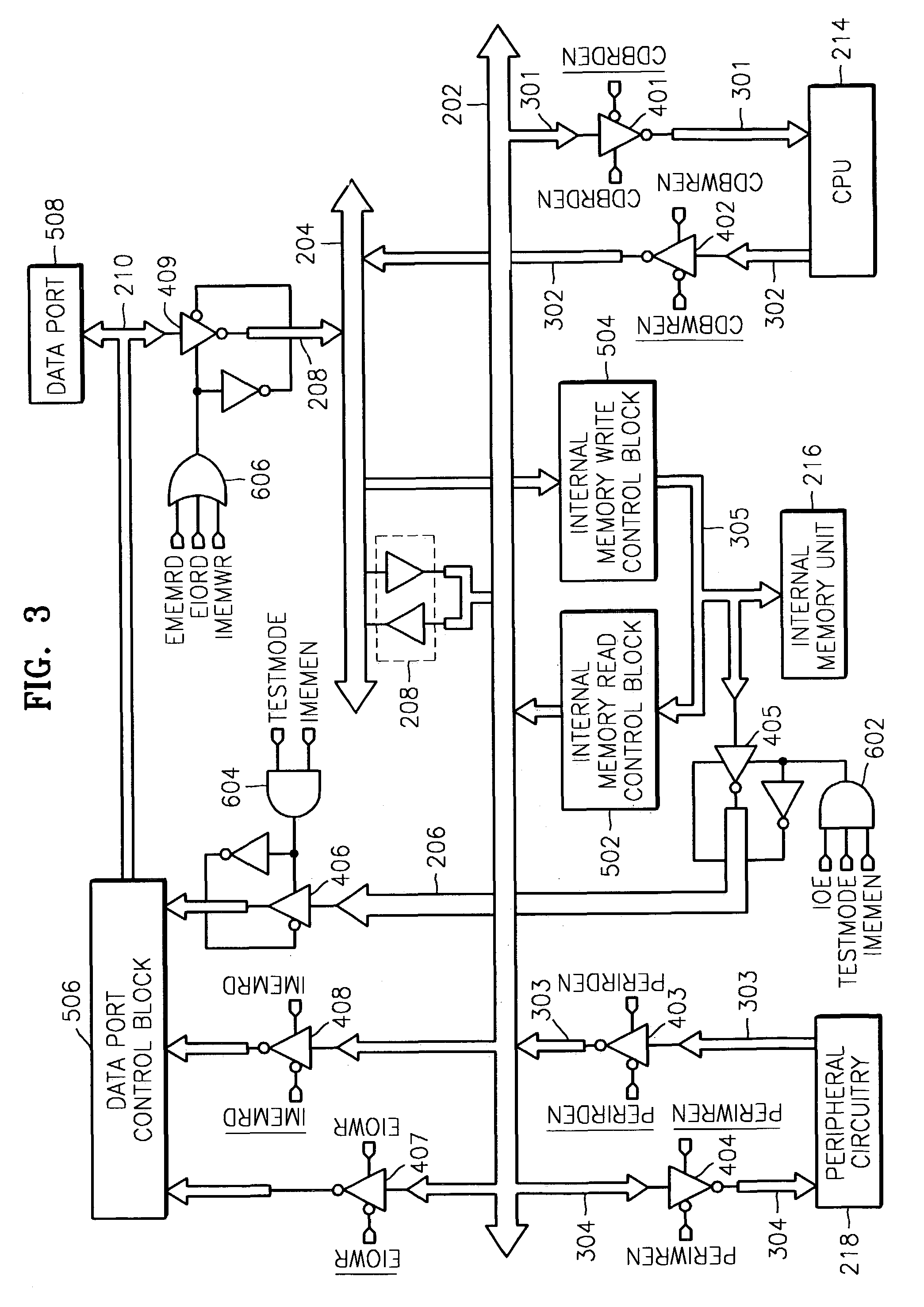

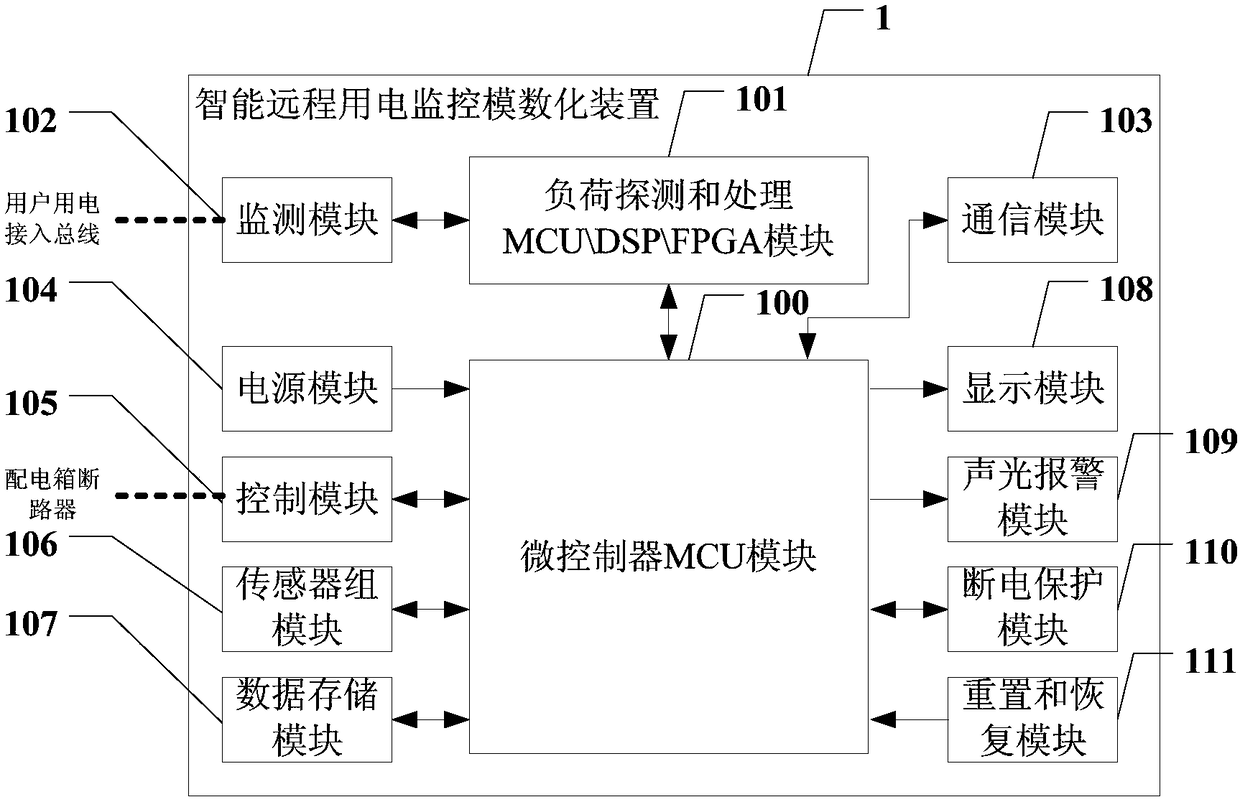

Data bus system for micro controller

ActiveUS7133954B2High speedReduce power consumptionEnergy efficient ICTGeneral purpose stored program computerInternal memoryACCESS.bus

Provided is a data bus system for a micro controller which has an input / output (I / O) unit, a central processing unit (CPU), an internal memory unit, and a peripheral circuitry. The data bus system includes an external access bus used when data is output from the CPU or data is input to the I / O unit or the internal memory unit; an internal access bus used when data is input to the CPU, data is output from the I / O unit or the internal memory unit, or data is input to or output from the peripheral circuitry; and an internal memory test bus used when data is output from the internal memory unit and input to the I / O unit.

Owner:III HLDG 2

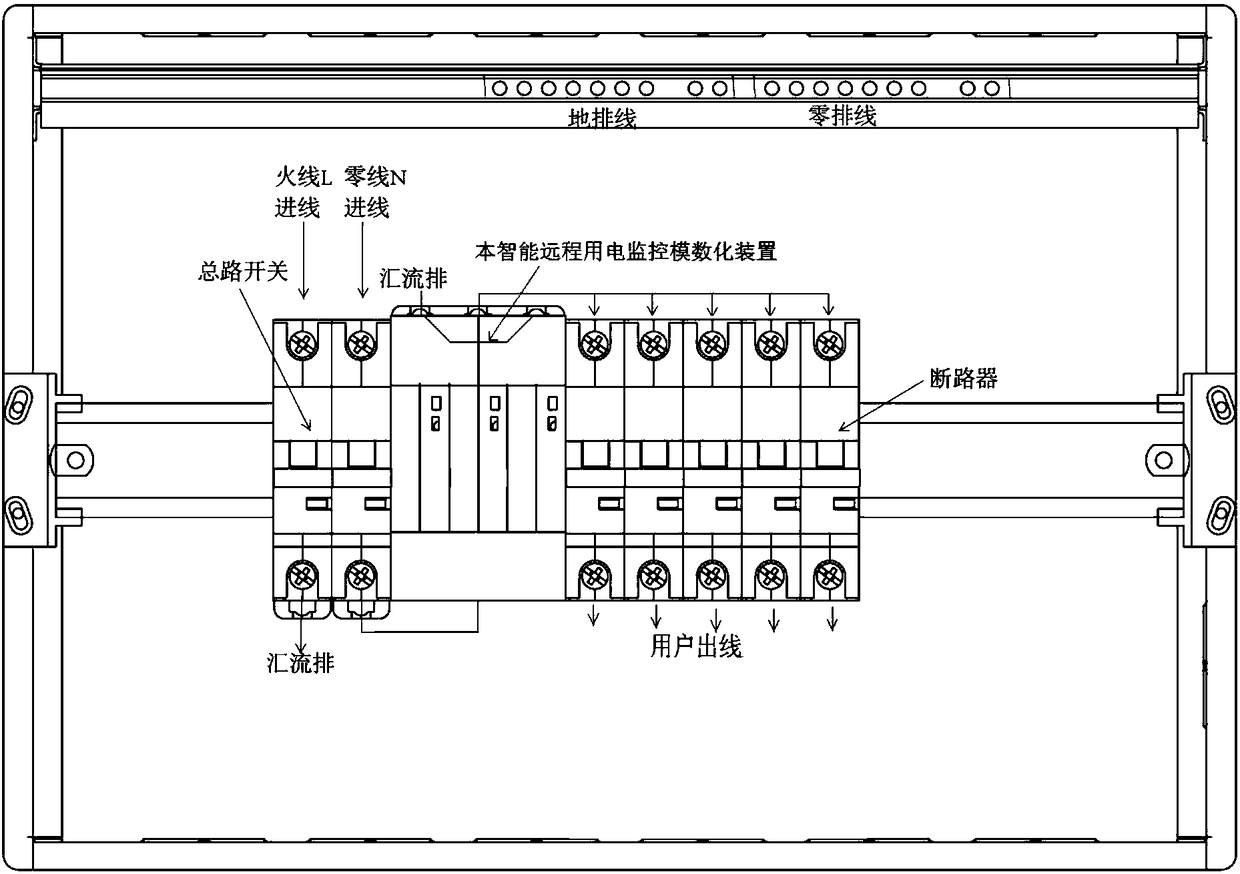

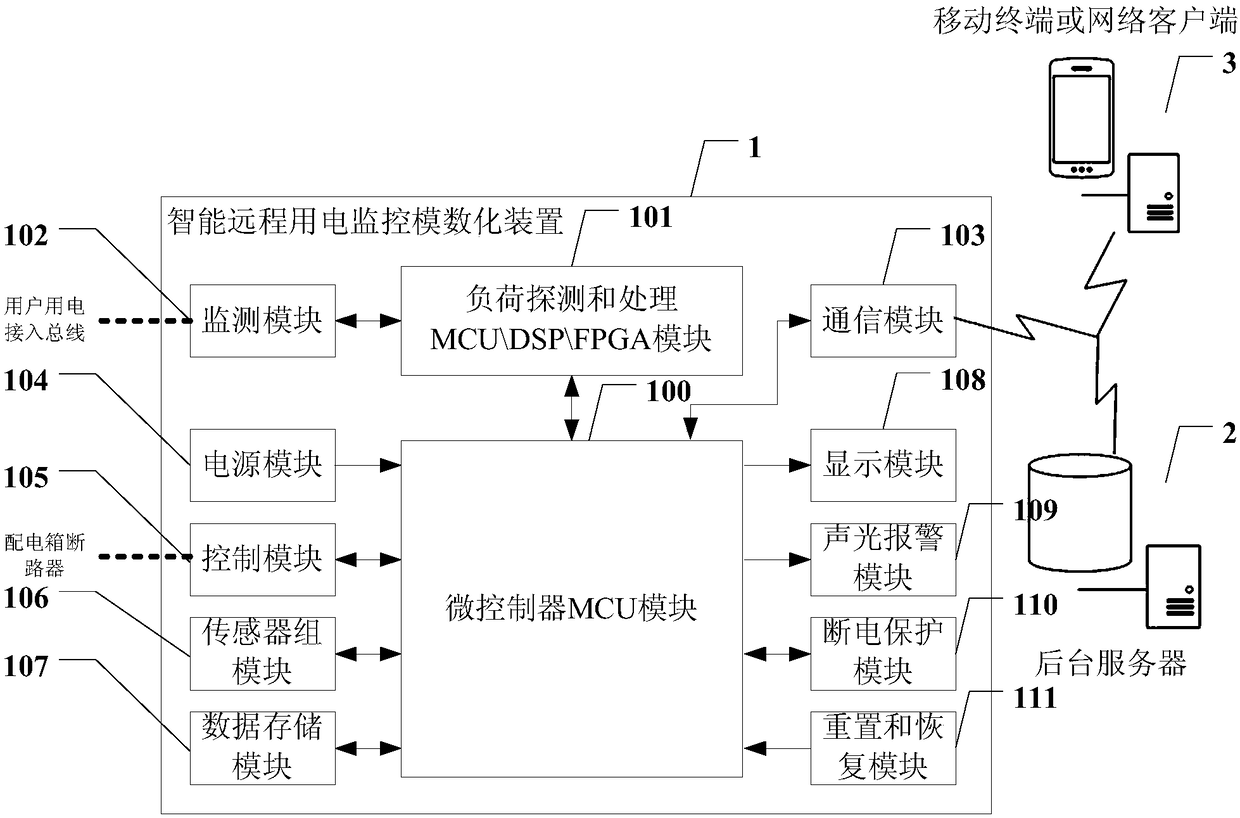

Intelligent remote power utilization monitoring modularization device and system

PendingCN108233529ASimple structureEasy to installPower network operation systems integrationCircuit arrangementsComputer moduleACCESS.bus

The invention provides an intelligent remote power utilization monitoring modularization device and system. The device mainly comprises a monitoring module, a processing module, a micro control moduleand a communication module, wherein the monitoring module is connected with a power utilization access bus and used for collecting power utilization data; the processing module is connected with themonitoring module and used for analyzing the power utilization data according to a preset algorithm; the micro control module is connected with the processing module and used for receiving and executing a control instruction; and the communication module is connected with the micro control module and used for communicating with external equipment. The system mainly comprises the device, a background server and a client. The device provided by the invention adopts a modular design, and has the characteristics of simple structure, convenient installation, easy maintenance and the like. The system provided by the invention can provide detailed power utilization data of electrical appliances or electrical equipment and provide the information such as intelligent energy conservation suggestionsand measures, equipment health inspection or fault early warning through the algorithms such as big data analysis and a neural network.

Owner:上海佳岚智能科技有限公司

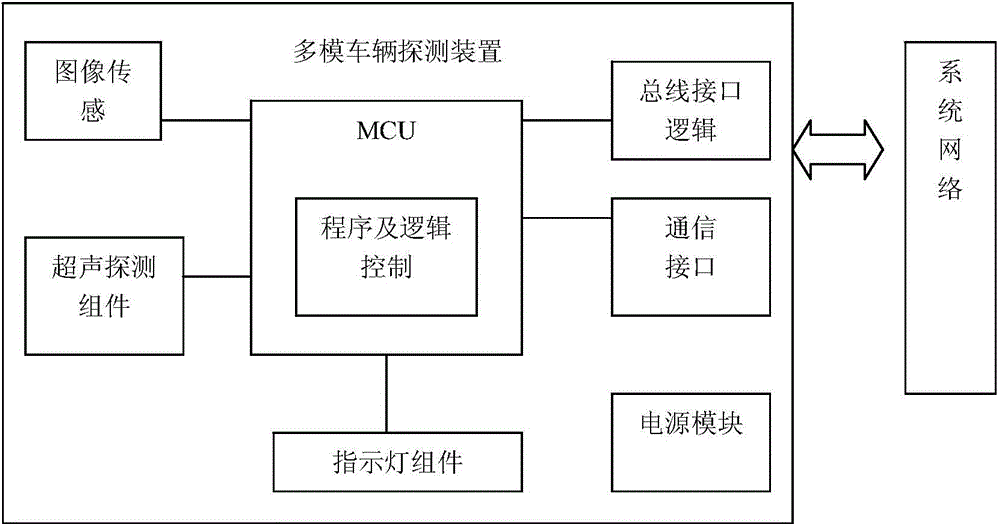

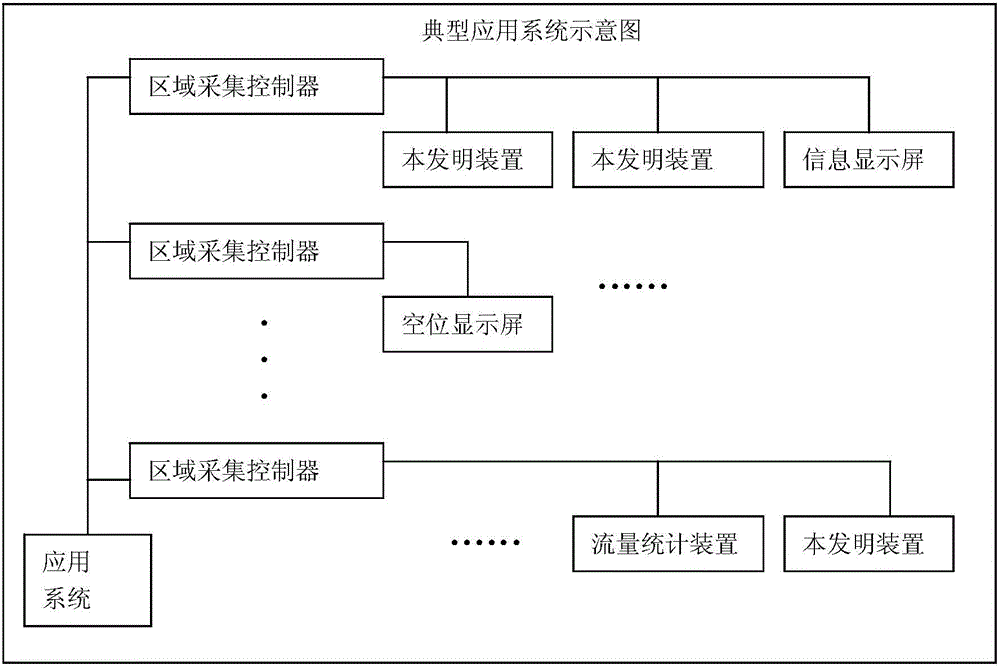

Multi-mode combined vehicle detection apparatus

InactiveCN105096649AEasy to solveReduce in quantityIndication of parksing free spacesSonificationACCESS.bus

The invention relates to a vehicle state and information identification extracting apparatus. The apparatus detects the parking state of vehicles in a detected area and displays the parking state through an indicating lamp, image information is sent to an access bus according to an instruction of a host computer, and a control instruction of the host computer can be received to enable state information to be displayed. The apparatus comprises an MCU, an image sensing assembly, an ultrasonic detection assembly, a logic control module, a communication assembly, an indicating lamp assembly, a power supply module, etc. Ultrasonic reflection is adopted to detect whether vehicles exit in the detected area, a result is displayed by the indicating lamp and also sent as feedback to the host computer through a communication port, and when the host computer orders the apparatus to send image signals to a bus on the basis of task scheduling situations, the MCU enables signals of the image sensing assembly to be accessed to the bus through the logic control module, and the bus is released if a command of the host computer is cancelled. In this way, a parking lot guiding and vehicle tracking comprehensive system can be easily formed. The mode of the apparatus is formed by an ultrasonic mode and an image mode both of which are effective simultaneously, and the bus control is employed, so the comprehensive cost and the reliability are both guaranteed.

Owner:GUANGZHOU TECTRON INTELLIGENT SCI & TECH CO LTD

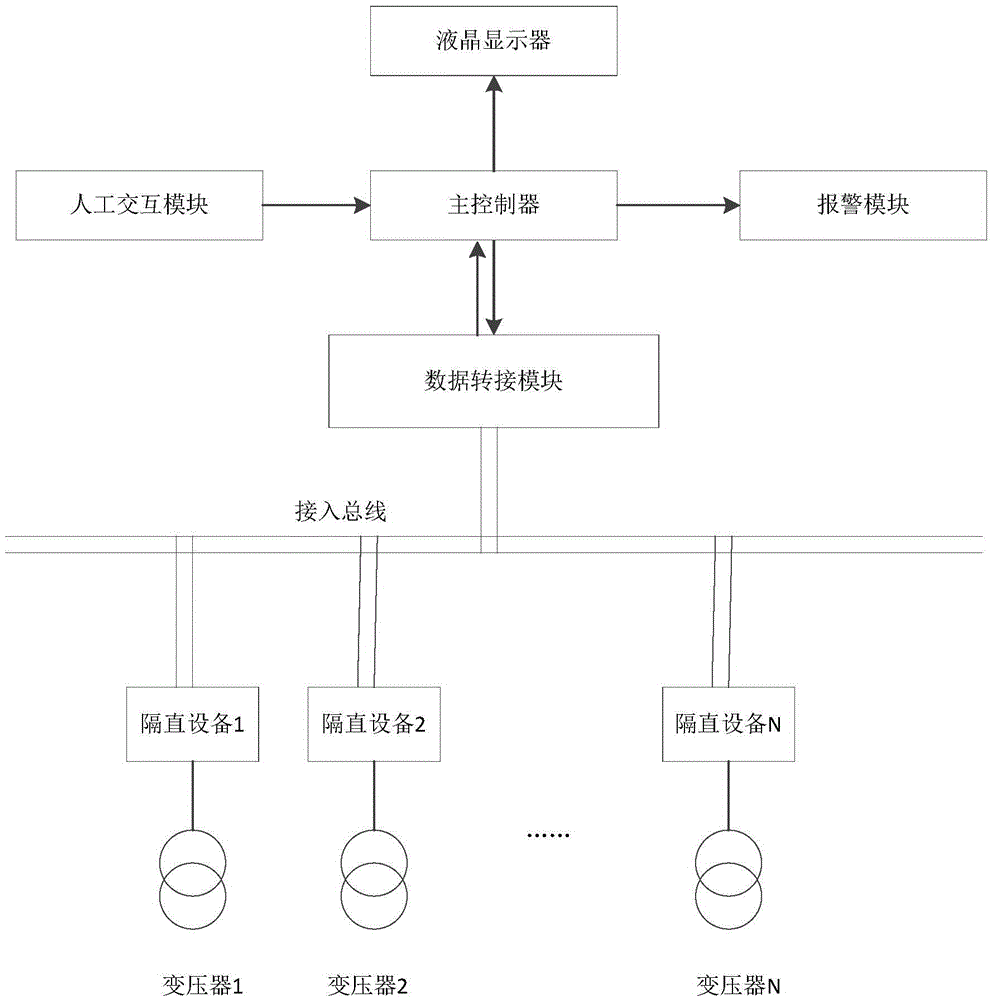

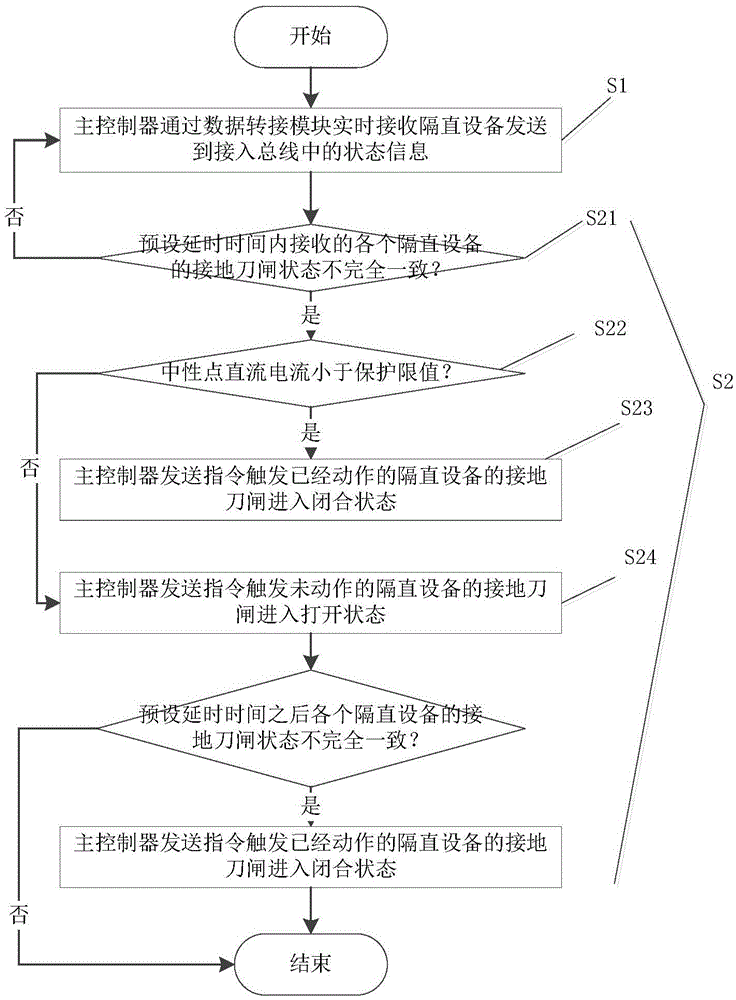

Linkage protection device for transformer neutral point DC blocking equipment and method thereof

ActiveCN105490249ARealize linkageAchieve protectionEmergency protective arrangements for limiting excess voltage/currentElectricityDc current

The invention provides a linkage protection device for transformer neutral point DC blocking equipment and a method thereof. The linkage protection device comprises the components of an access bus which is connected with N sets of DC blocking equipment, wherein N is a positive integer which is larger than or equal with 2; a main controller which is used for monitoring state information of each set of DC blocking equipment and transmitting an instruction for triggering already acted DC blocking equipment to make a corresponding transformer neutral point be grounded when a condition that the states of the DC blocking equipment are not totally same is determined according to the state information of each set of DC blocking equipment; and a data conversion module which is connected with the access bus and the main controller and is used for converting data in the access bus to the data that are readable by the main controller and converting the instruction that is transmitted by the main controller for transmitting to the access bus. When a fault or power failure of certain DC blocking equipment occurs and the DC blocking equipment cannot operate, other sets of DC blocking equipment in normal operation can be shunted, and all transformers directly perform grounded operation, thereby sharing a DC current and preventing bearing of an overlarge DC current by a certain transformer. Furthermore the plurality of sets of equipment share one linkage protection device, thereby realizing cost saving.

Owner:YANGJIANG NUCLEAR POWER

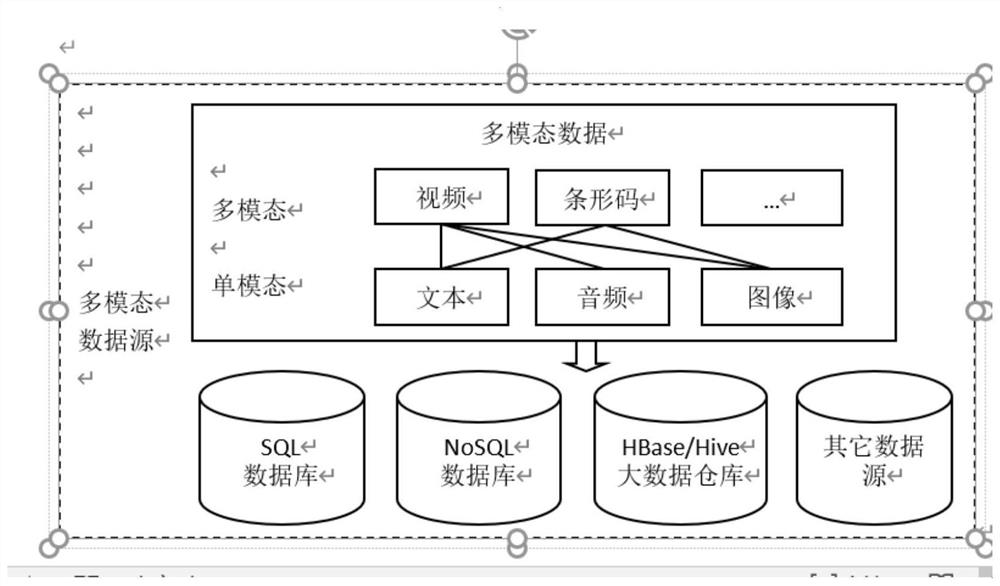

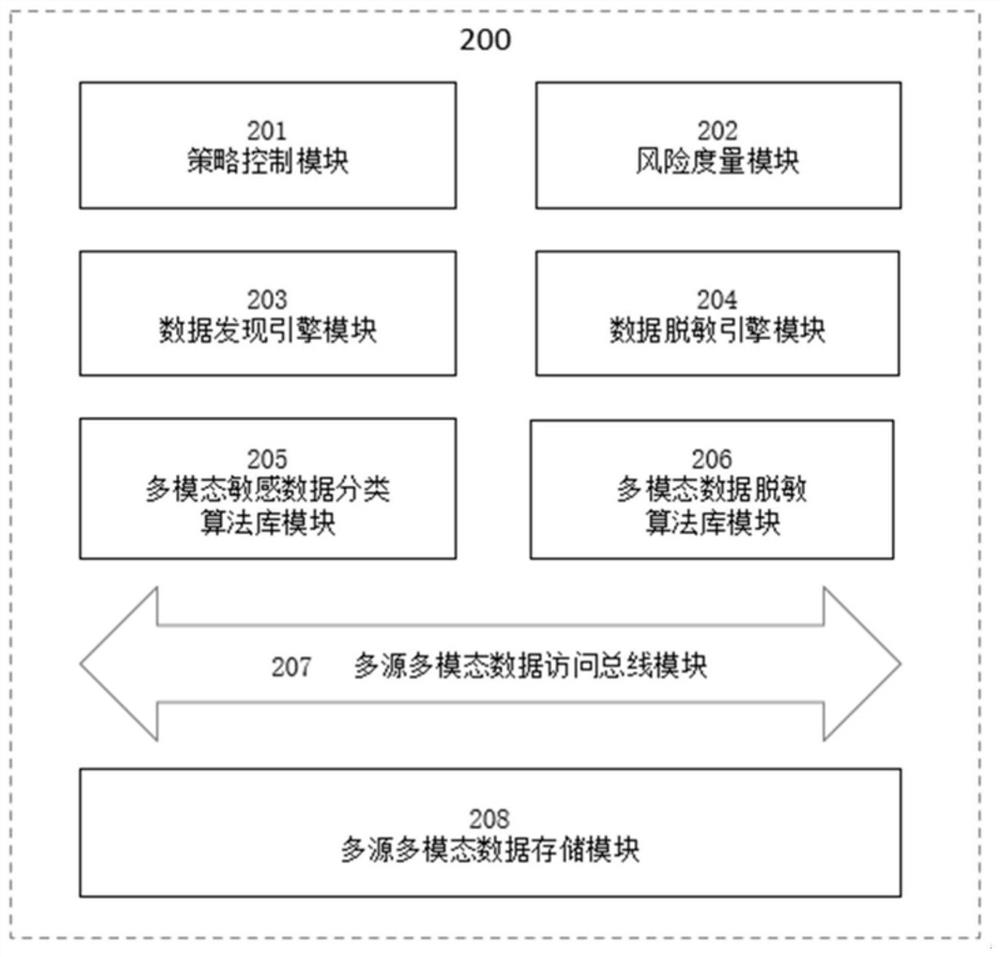

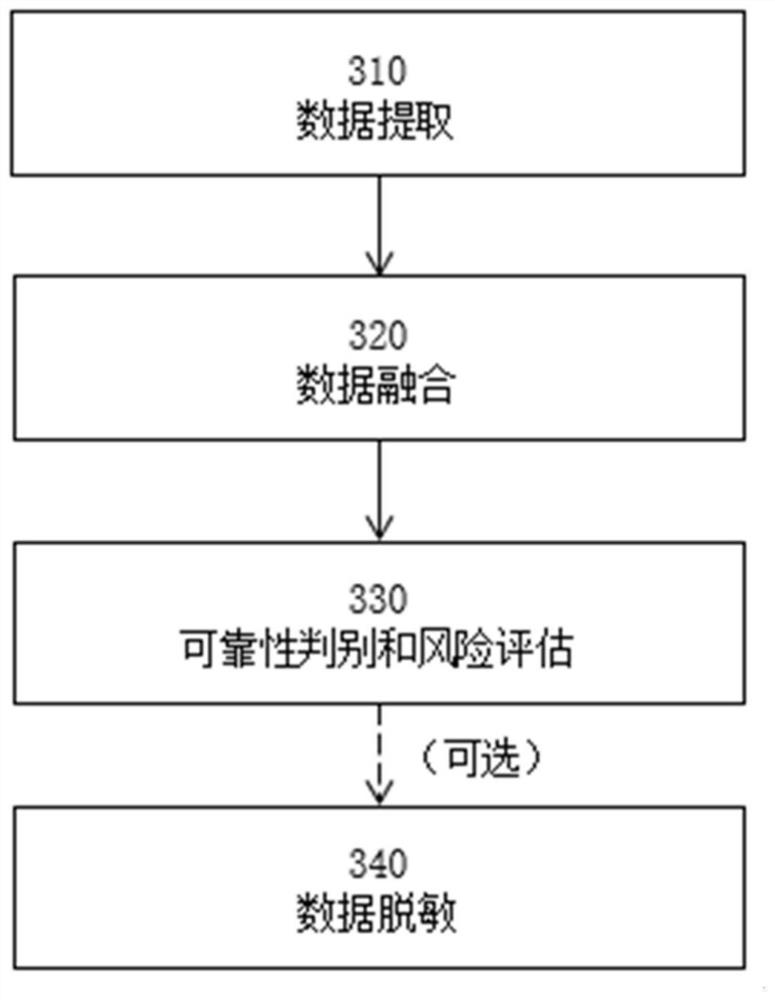

Multi-source multi-modal data processing system and method for applying system

PendingCN111859451ACompliance with Policy Control RequirementsResolve identifiabilityDigital data protectionData processing systemData access

The invention provides a multi-source multi-modal data processing system and a method using the system. The processing system comprises a multi-source multi-modal data storage module, a strategy control module, a risk measurement module, a data discovery engine module, a data desensitization engine module, a multi-modal sensitive data classification algorithm library module, a multi-modal data desensitization algorithm library module and a multi-source multi-modal data access bus module. The multi-source and multi-mode data access bus module provides an interface for accessing the multi-sourceand multi-mode data storage module for other modules, and multi-source and multi-mode data reading, analyzing and writing are achieved. According to the system method, the problems that sensitive information in multi-source and multi-mode data is missed or mistakenly recognized, and the sensitive information is not desensitized or insufficient in desensitization in the prior art are solved.

Owner:北京尚隐科技有限公司