Simulator and method for bus arbitraction

A bus arbitration and simulation device technology, applied in the direction of instruments, electrical digital data processing, etc., can solve problems such as inability to accurately simulate SOC systems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

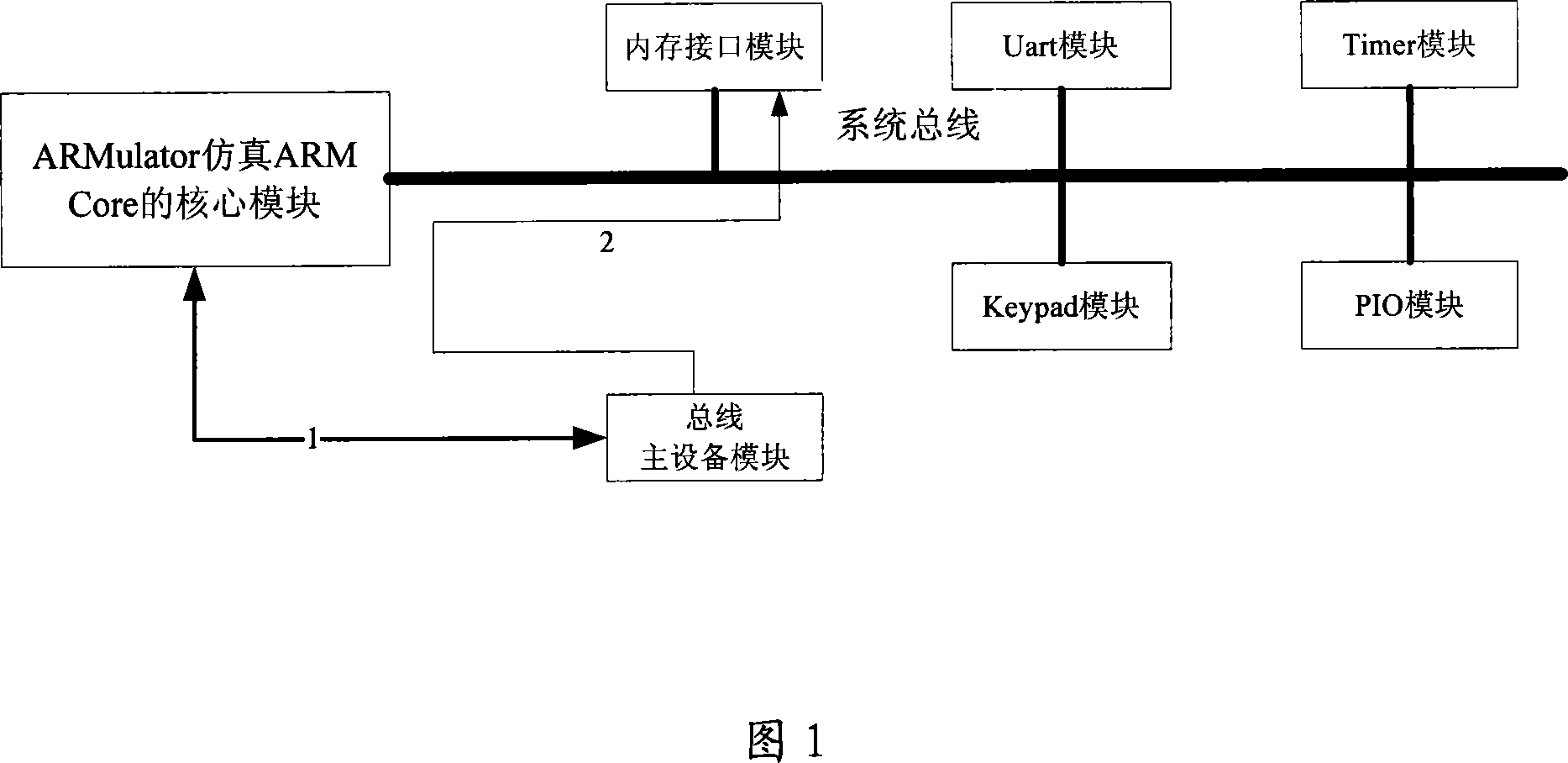

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

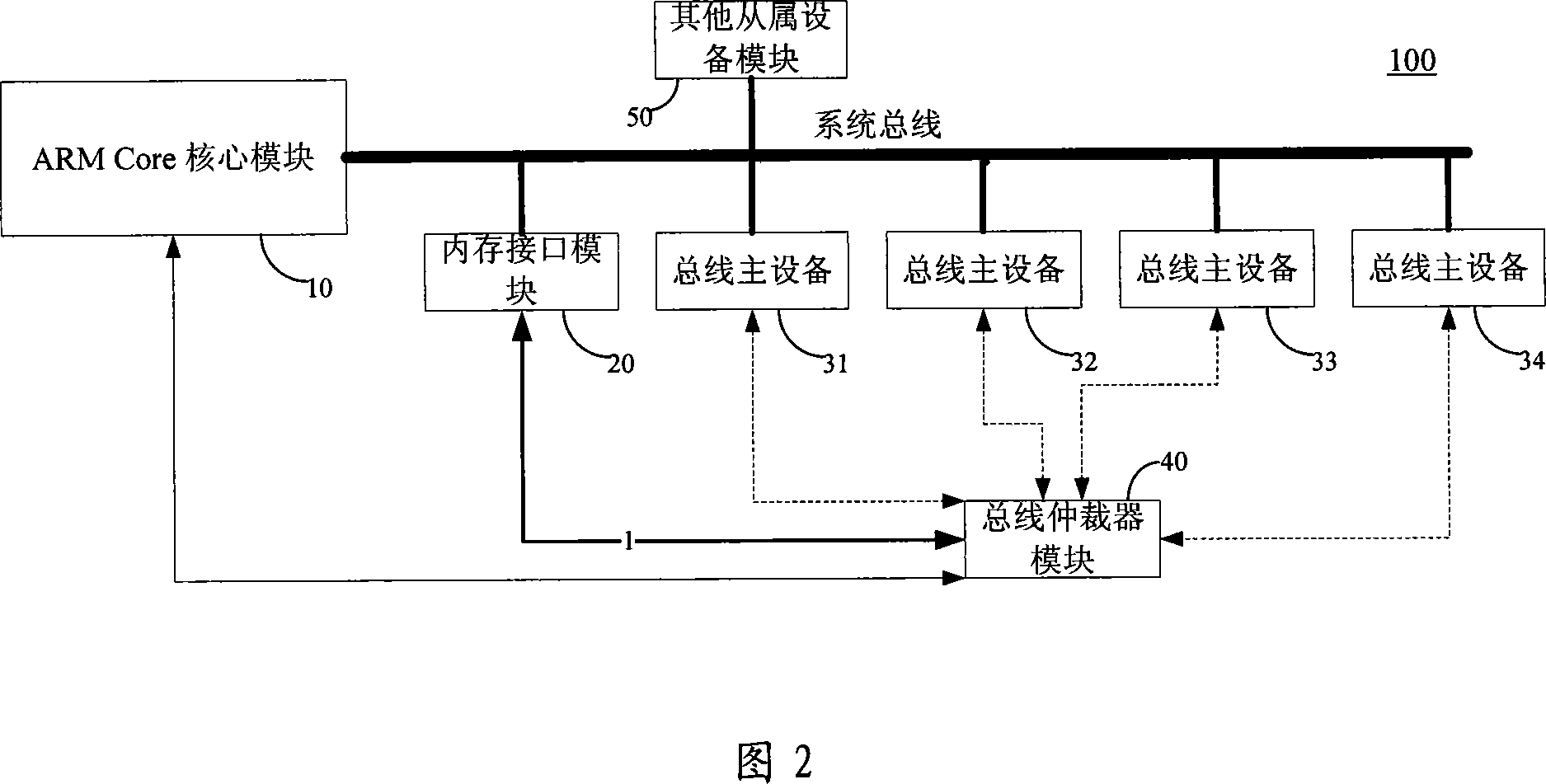

[0033] Please refer to shown in Fig. 2, the present invention provides a kind of bus arbitration simulation device 100, and it comprises ARMCore core module 10, system bus, bus master such as DMA, bus arbitration module 40 and bus slave module such as memory interface module 20. As shown in the figure, one end of all bus masters and ARM Core is connected to the bus arbiter module 40, and the other end is connected to the bus. They may access the bus arbiter and operate the bus at any time. One end of all bus slave modules is connected to the bus arbiter 40 and the other end is connected to the bus, and all bus slaves will not actively access the bus arbiter. Now take a bus master 31 accessing memory as an example to specifically explain the working process of the bus arbitration simulation device of the present invention.

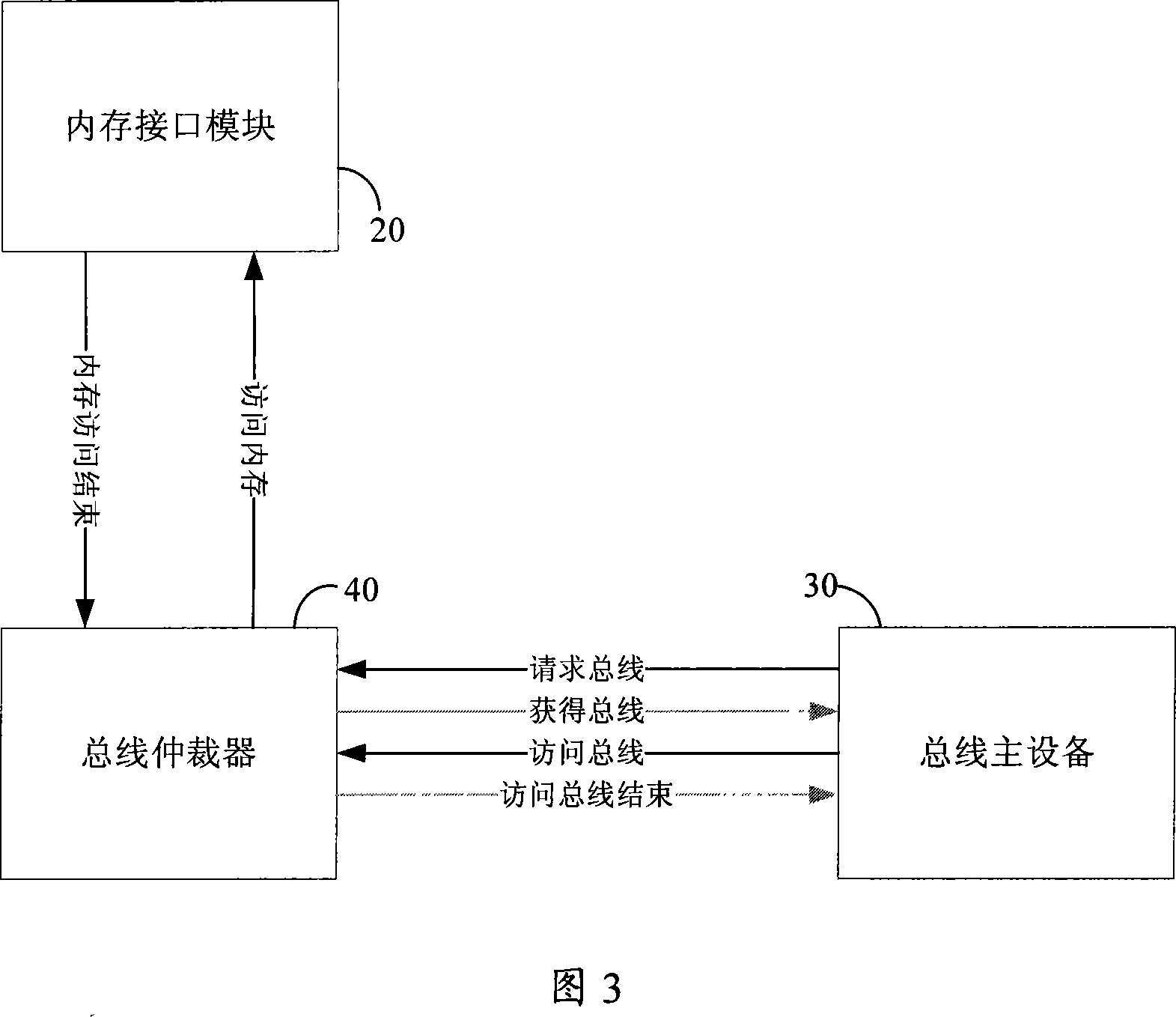

[0034] The specific information interaction process is as follows: please refer to as shown in Figure 3, when the bus master device needs to access the bus...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More