Patents

Literature

2007 results about "System bus" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

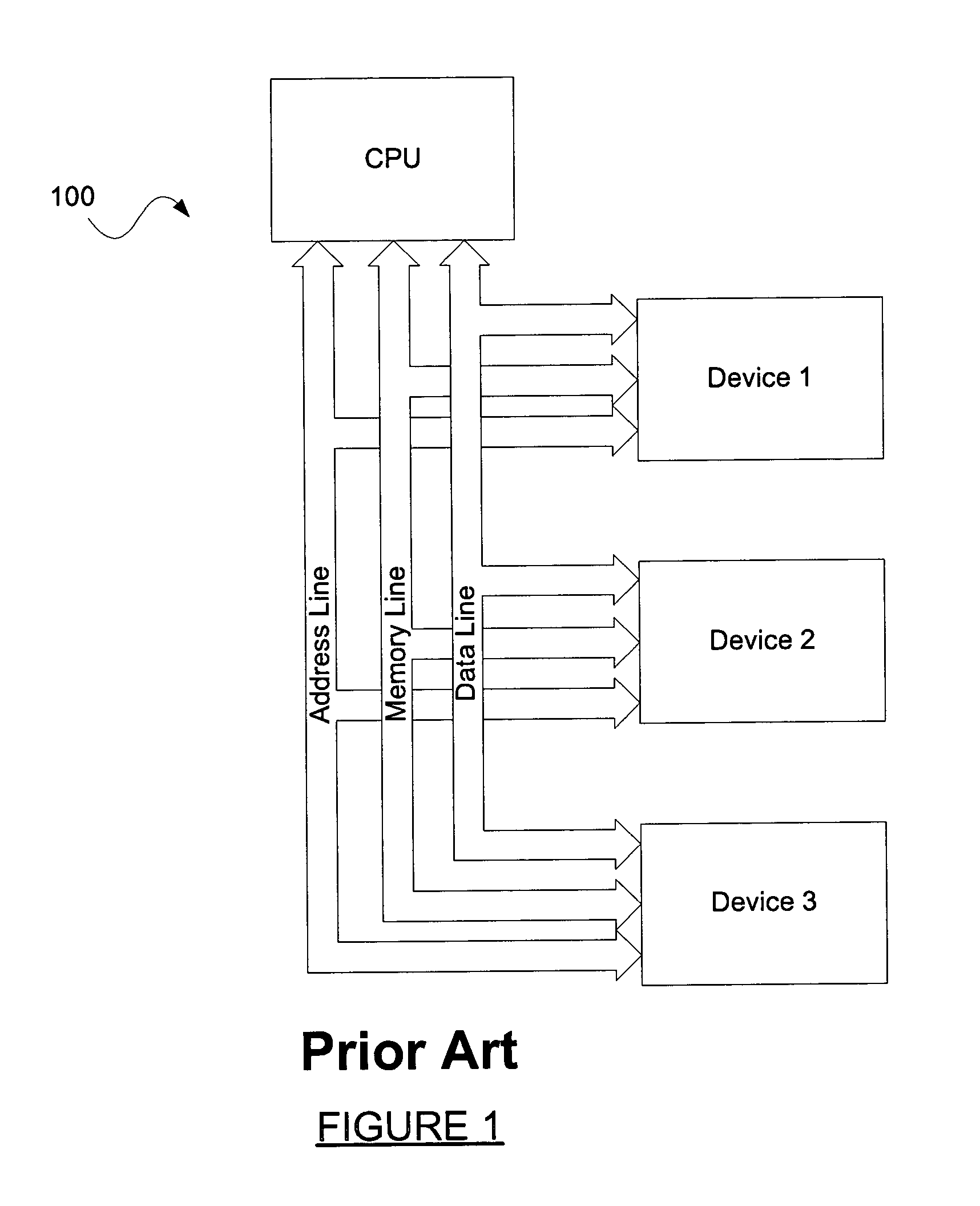

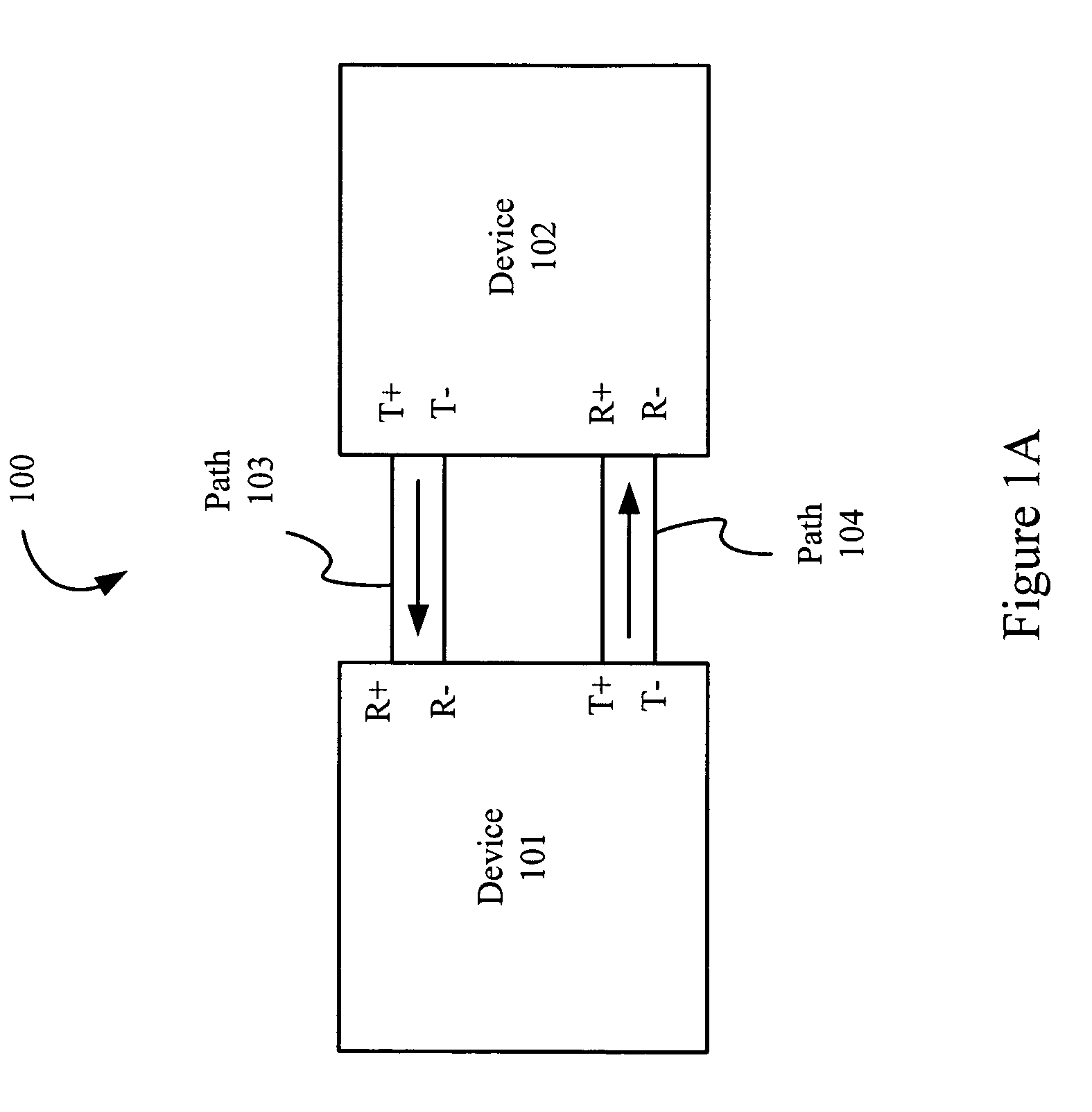

A system bus is a single computer bus that connects the major components of a computer system, combining the functions of a data bus to carry information, an address bus to determine where it should be sent, and a control bus to determine its operation. The technique was developed to reduce costs and improve modularity, and although popular in the 1970s and 1980s, more modern computers use a variety of separate buses adapted to more specific needs.

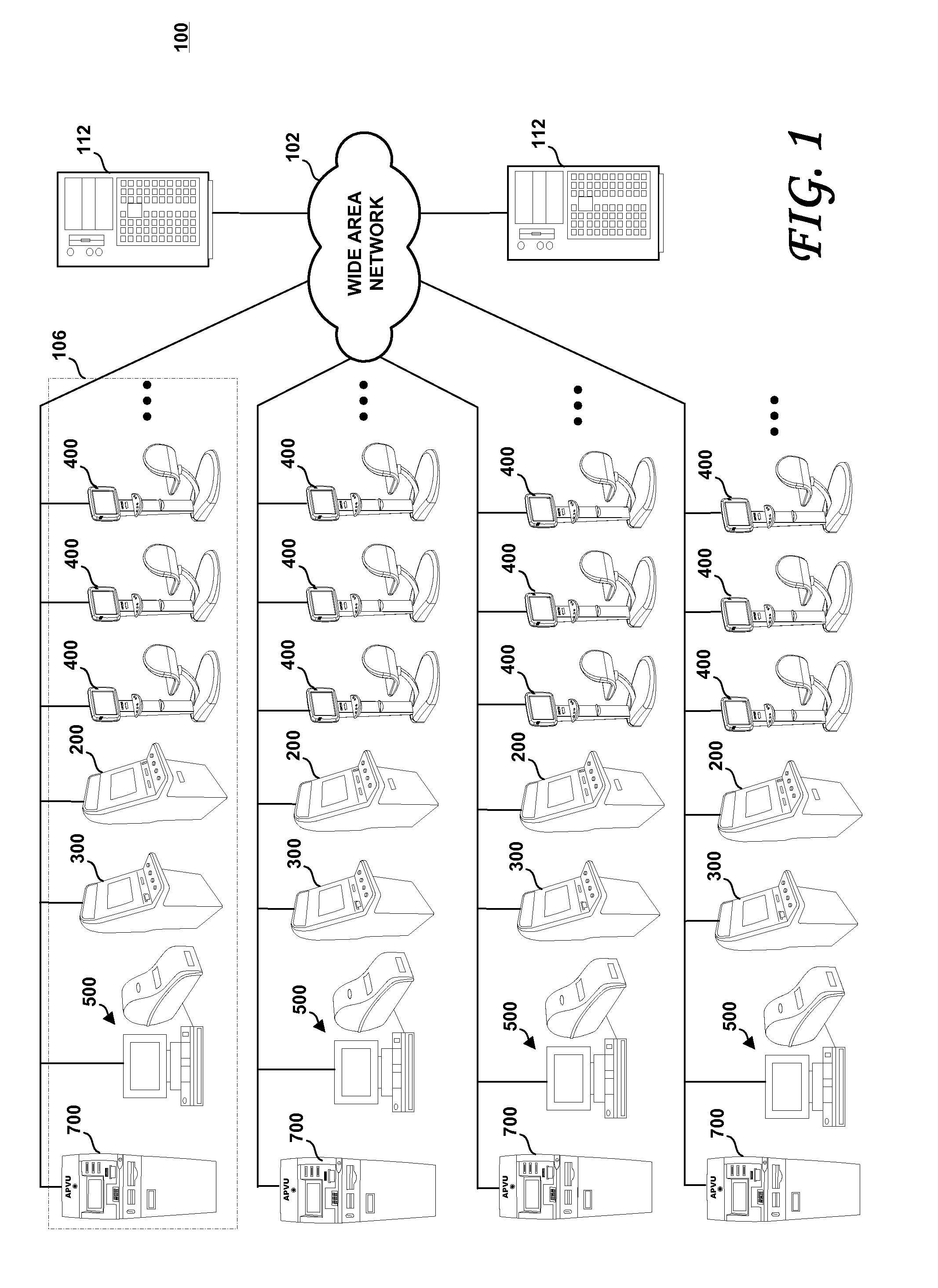

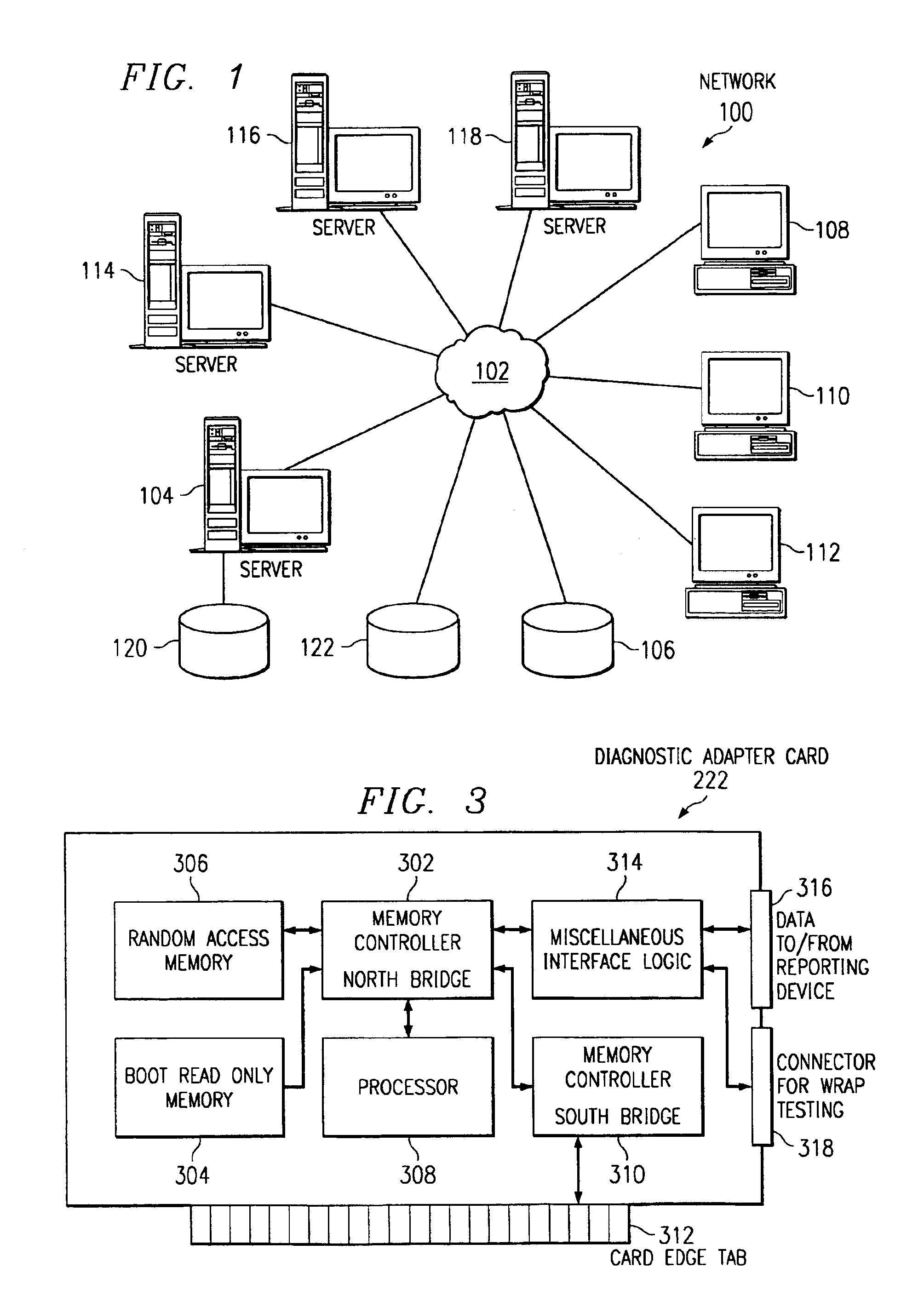

Remote device management system and method

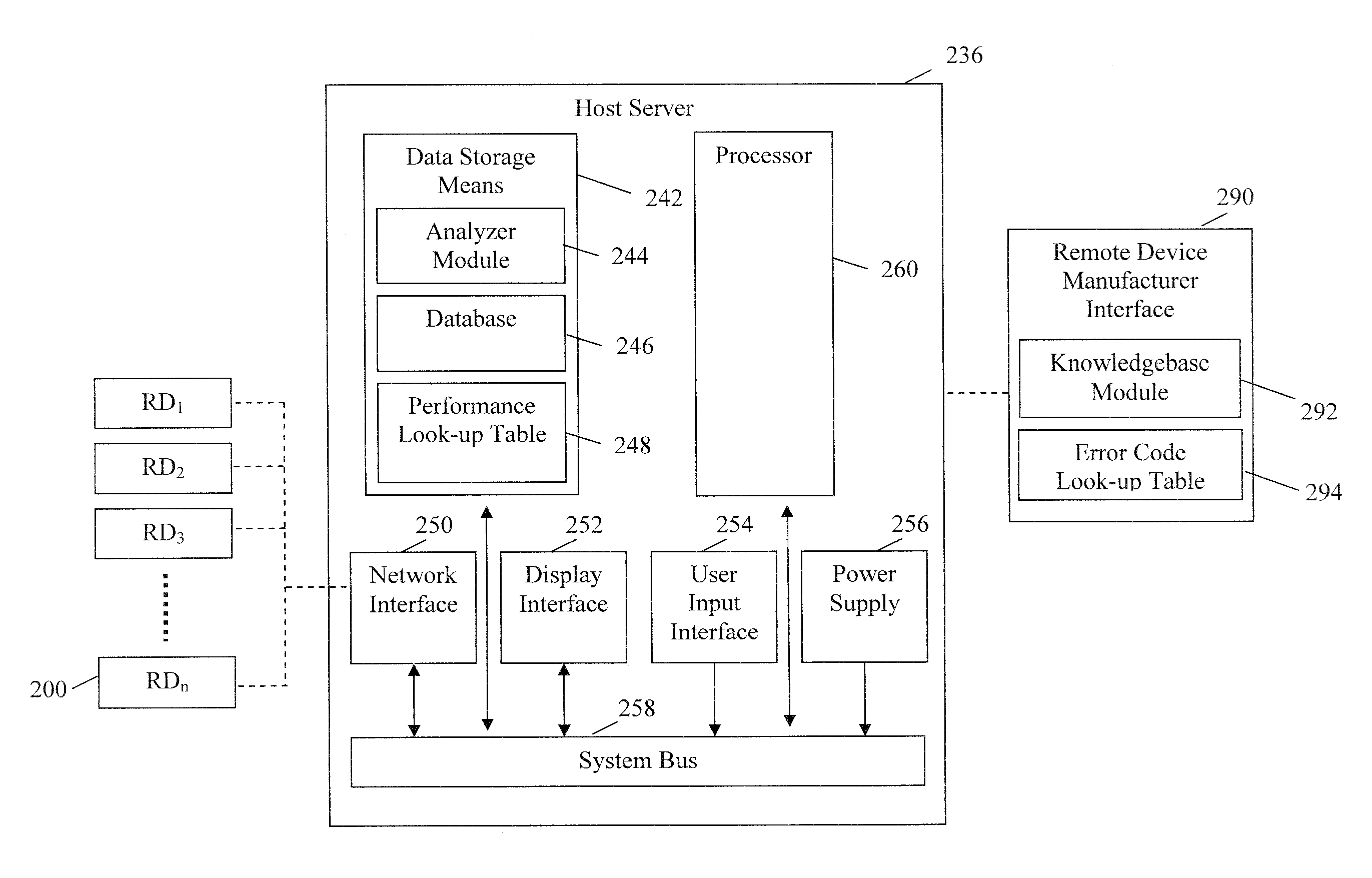

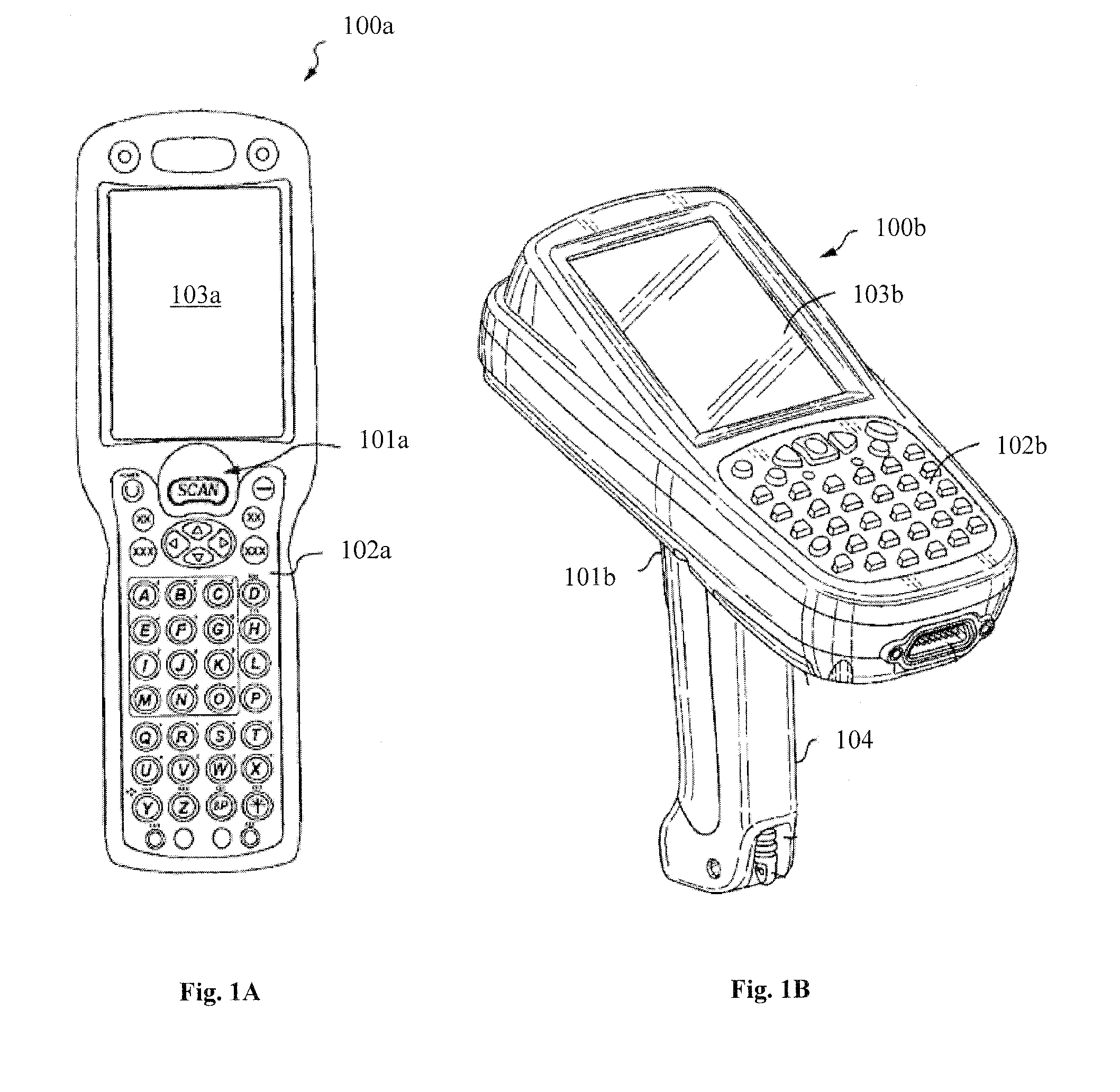

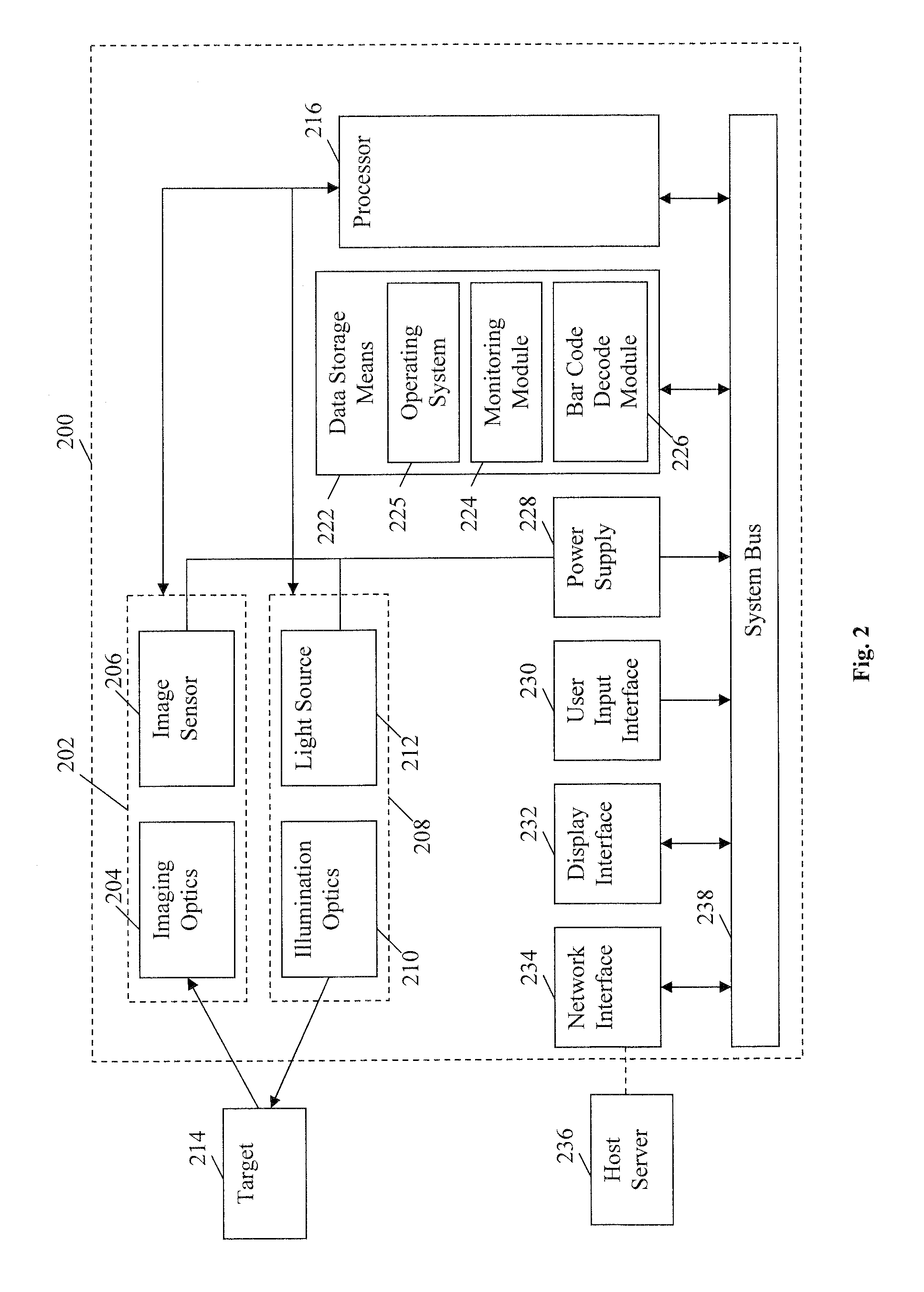

A remote device monitoring system including a host server including at least a processor, system bus, user input interface configured to communicate with a user input device, display interface configured to communicate with a display, network interface configured to communicate with at least one remote device and at least one data storage means including a database, a performance look-up table and at least one analyzer module including program instructions that, when implemented by the processor, receive at least one performance parameter value from at least one remote device and query the performance look-up table.

Owner:HAND HELD PRODS

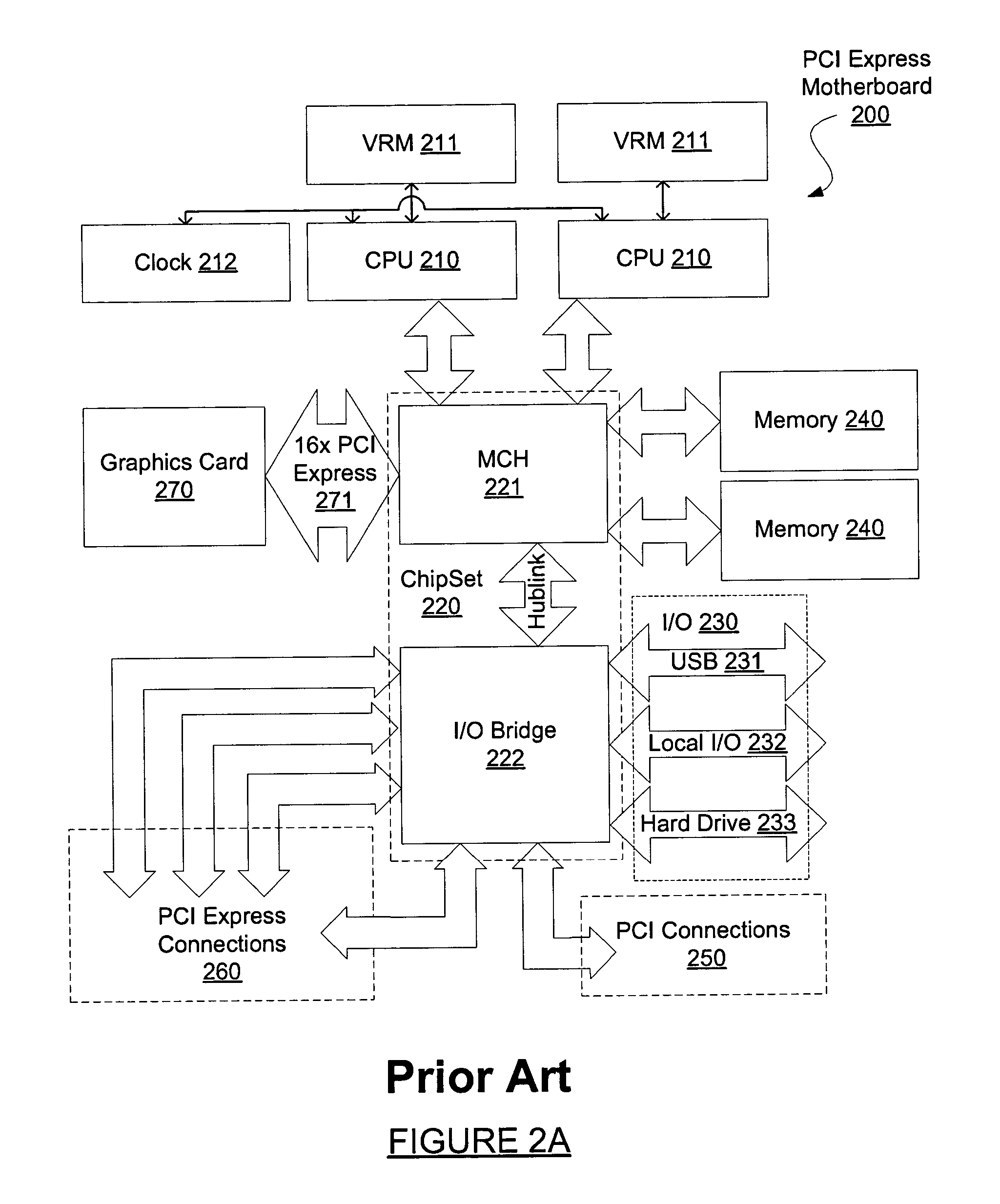

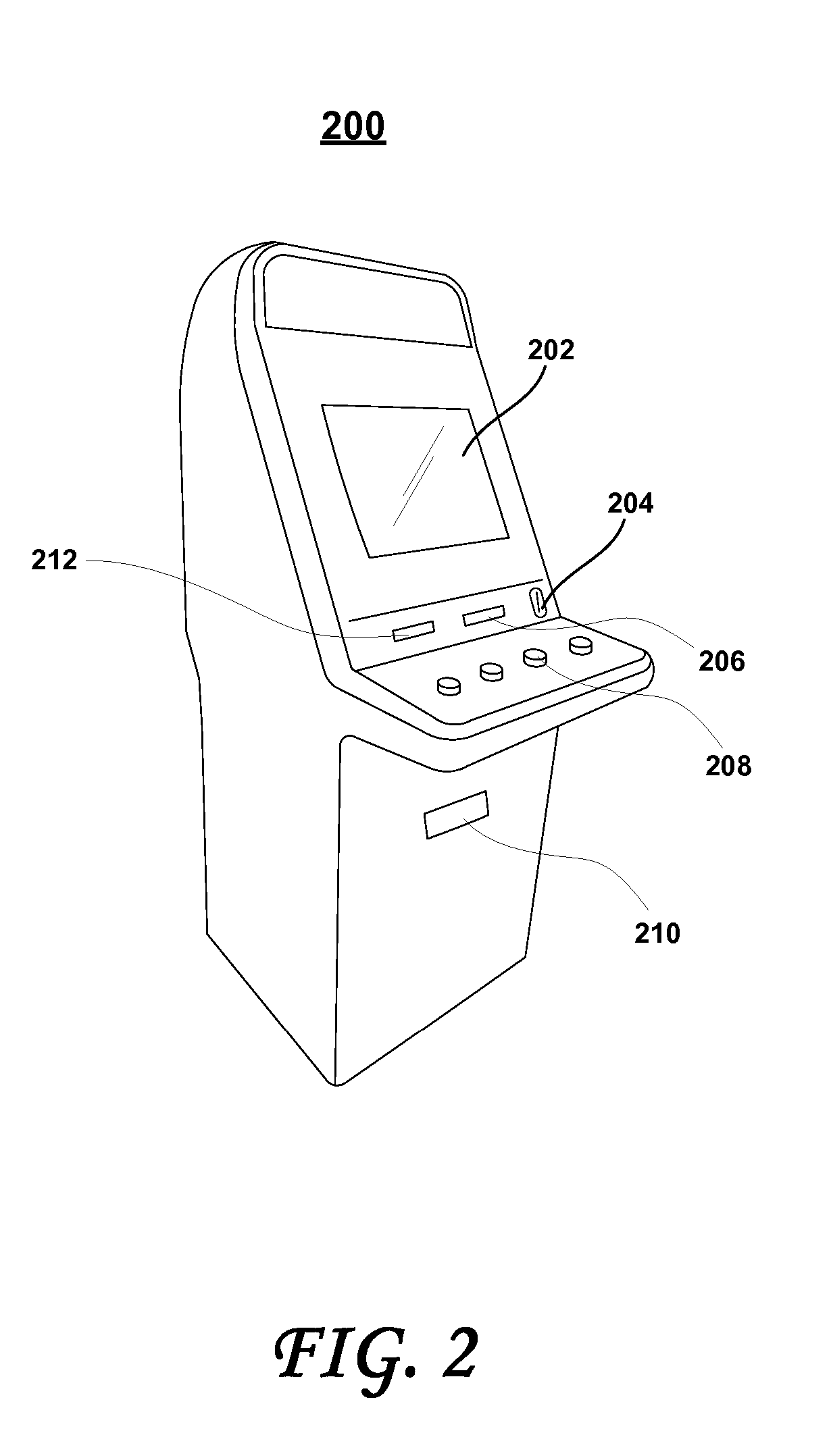

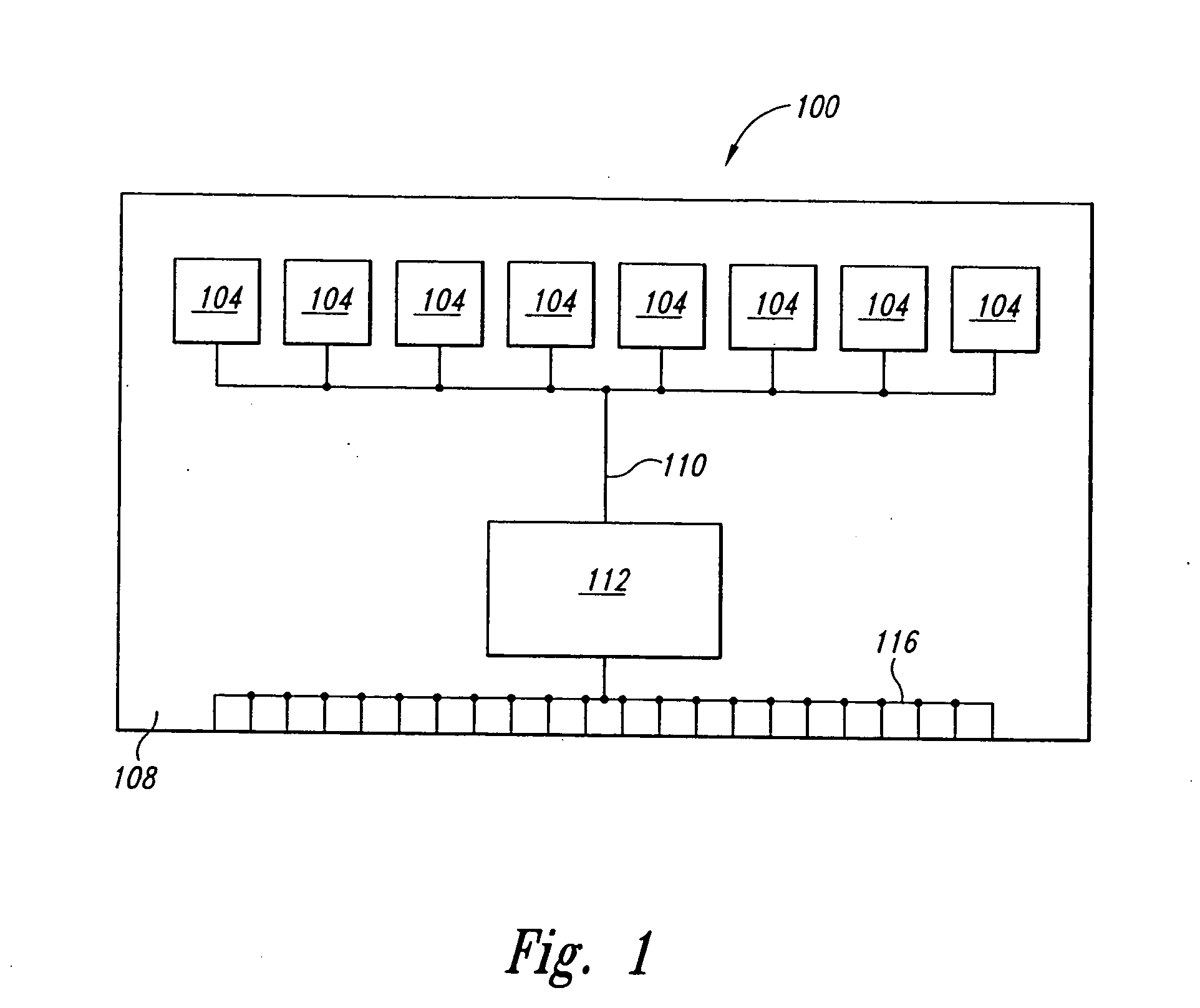

Motherboard for supporting multiple graphics cards

ActiveUS20050088445A1Cathode-ray tube indicatorsMultiple digital computer combinationsGraphicsScalable system

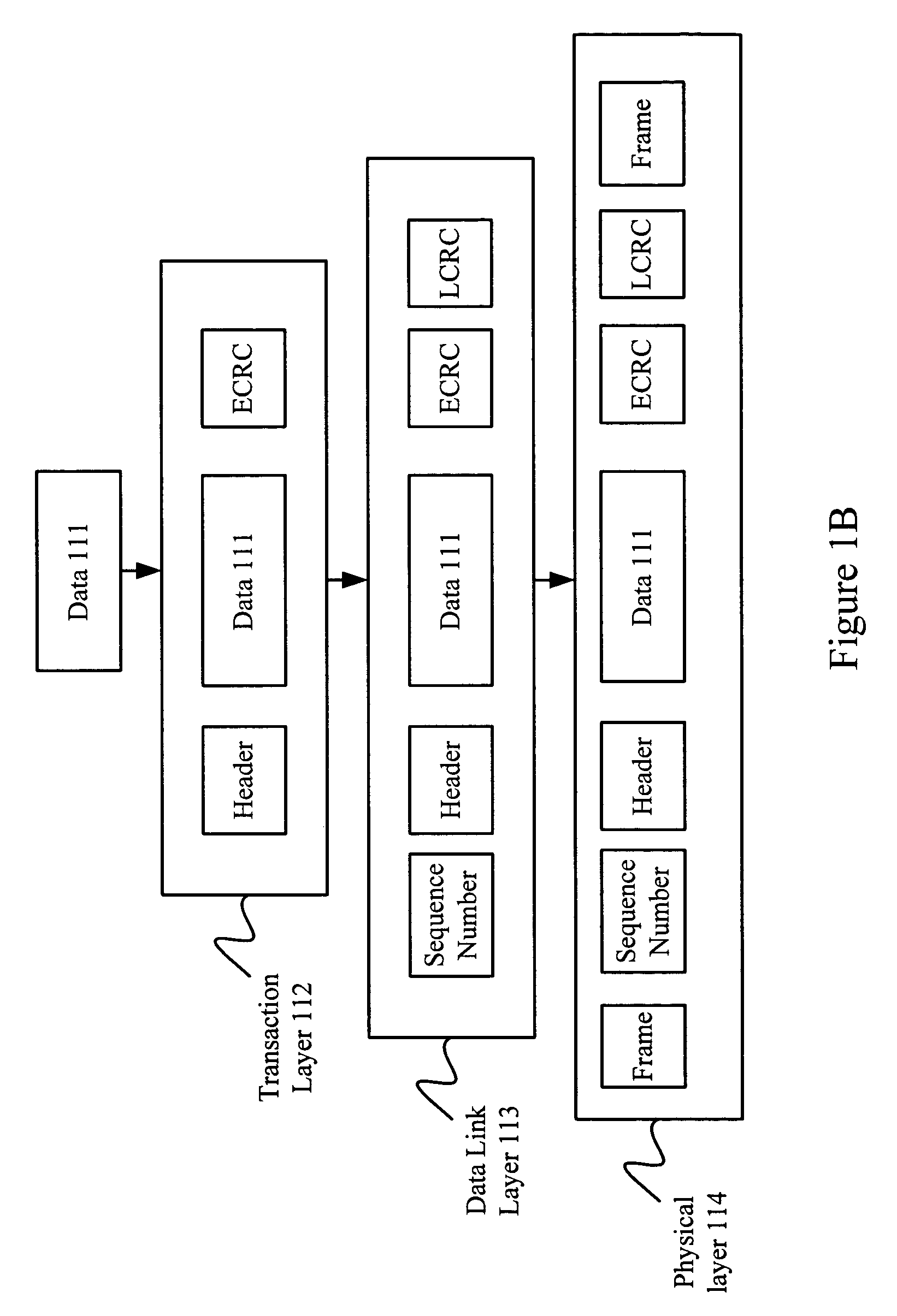

The present invention provides a motherboard that uses a high-speed, scalable system bus such as PCI Express® to support two or more high bandwidth graphics slots, each capable of supporting an off-the-shelf video controller. The lanes from the motherboard chipset may be directly routed to two or more graphics slots. For instance, the chipset may route (1) thirty-two lanes into two ×16 graphics slots; (2) twenty-four lanes into one ×16 graphics slot and one ×8 graphics slot (the ×8 slot using the same physical connector as a ×16 graphics slot but with only eight active lanes); or (3) sixteen lanes into two ×8 graphics slots (again, physically similar to a ×16 graphics slot but with only eight active lanes). Alternatively, a switch can convert sixteen lanes coming from the chipset root complex into two ×16 links that connect to two ×16 graphics slots. Each and every embodiment of the present invention is agnostic to a specific chipset.

Owner:DELL MARKETING

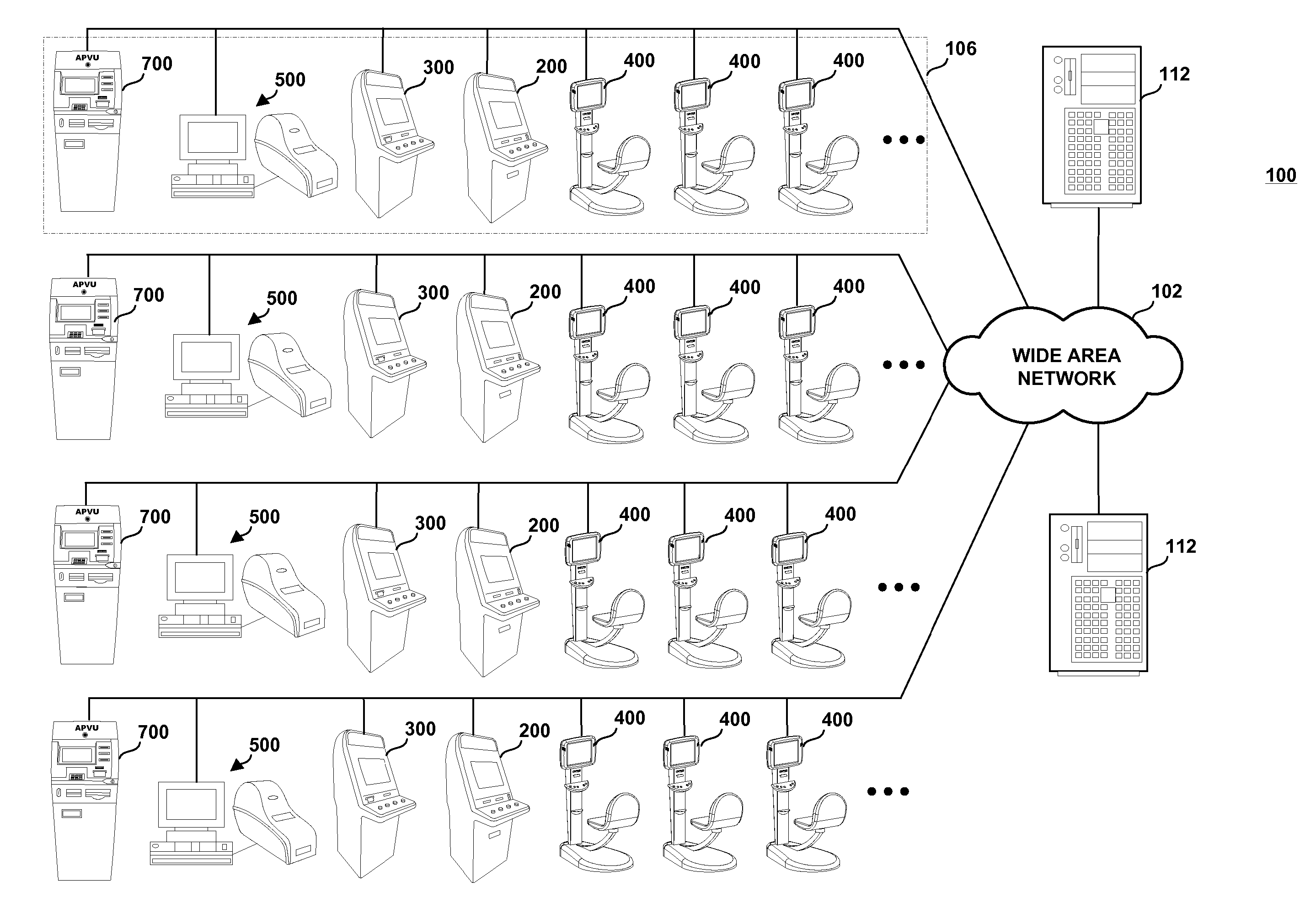

Game talk service bus

InactiveUS20080032801A1Overcomes rapid obsolescenceMultiple digital computer combinationsApparatus for meter-controlled dispensingThird partyPrivate network

A service-oriented bus for distributed gaming systems allowing gaming machines, servers, workstations, mobile PCs, handheld devices and automatic telling machines to talk together over a network. The game service bus provides a publish-and-subscribe message bus over a private network within a gaming property and / or over the public Internet across several properties. The service bus framework allows participating communicating end points to publish services or subscribe to services in a simple and standardized high level fashion, thereby enabling the devices to understand one-another, thus“talk” together. The “talking together” paradigm is rather appropriate, as it emphasizes the value that the service bus brings to a complex distributed casino gaming system that may include thousands of devices manufactured by dozens of vendors. Gaming machines may talk together in a peer-fashion over the service bus, which is well suited for multiplayer gaming. The service-oriented bus allows third party ultra-specialized vendors to offer dazzling plug-in services directly on the casino floor, such as automated geo-localized logistic support and other geo-localized services.

Owner:IGT

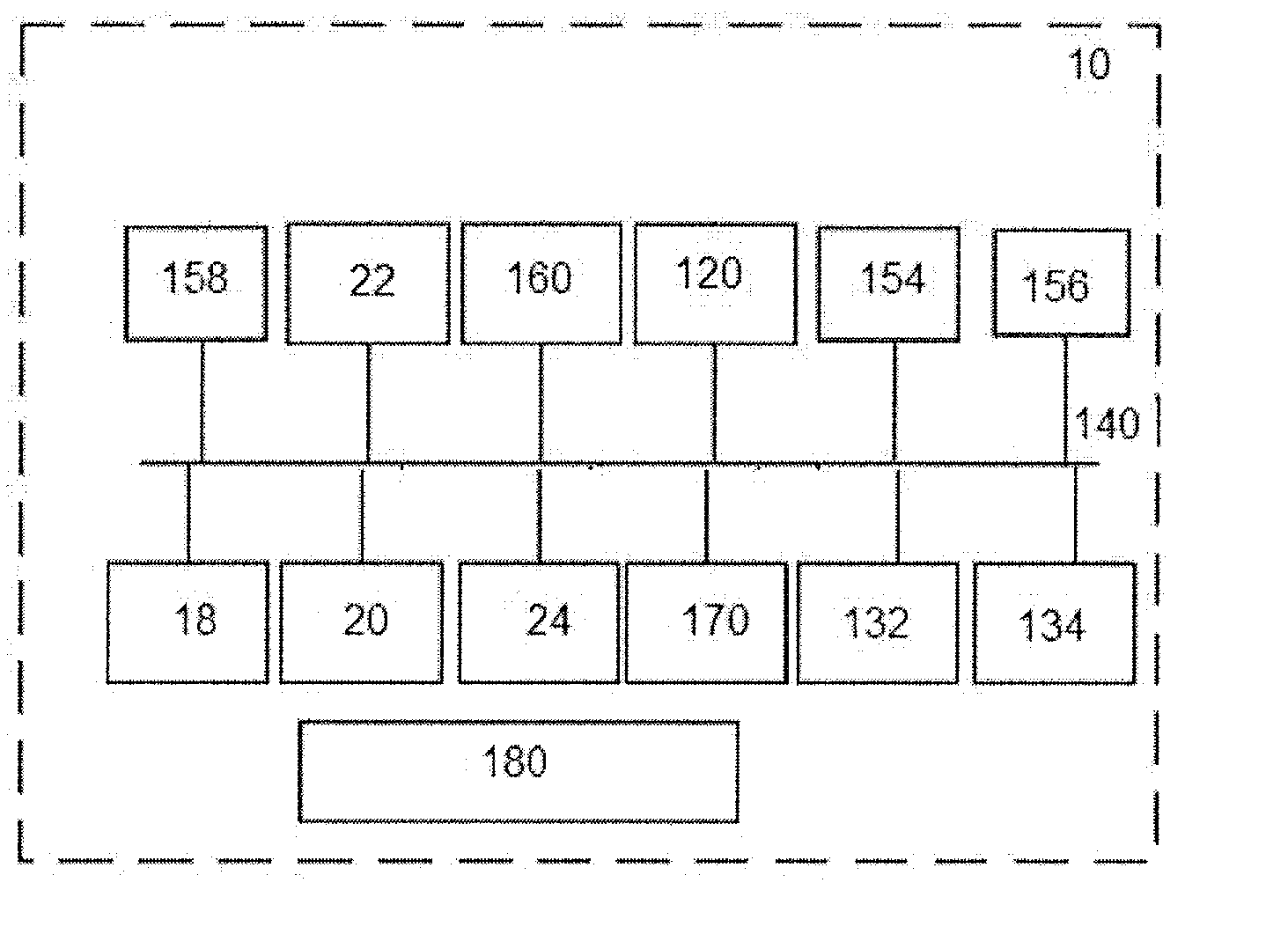

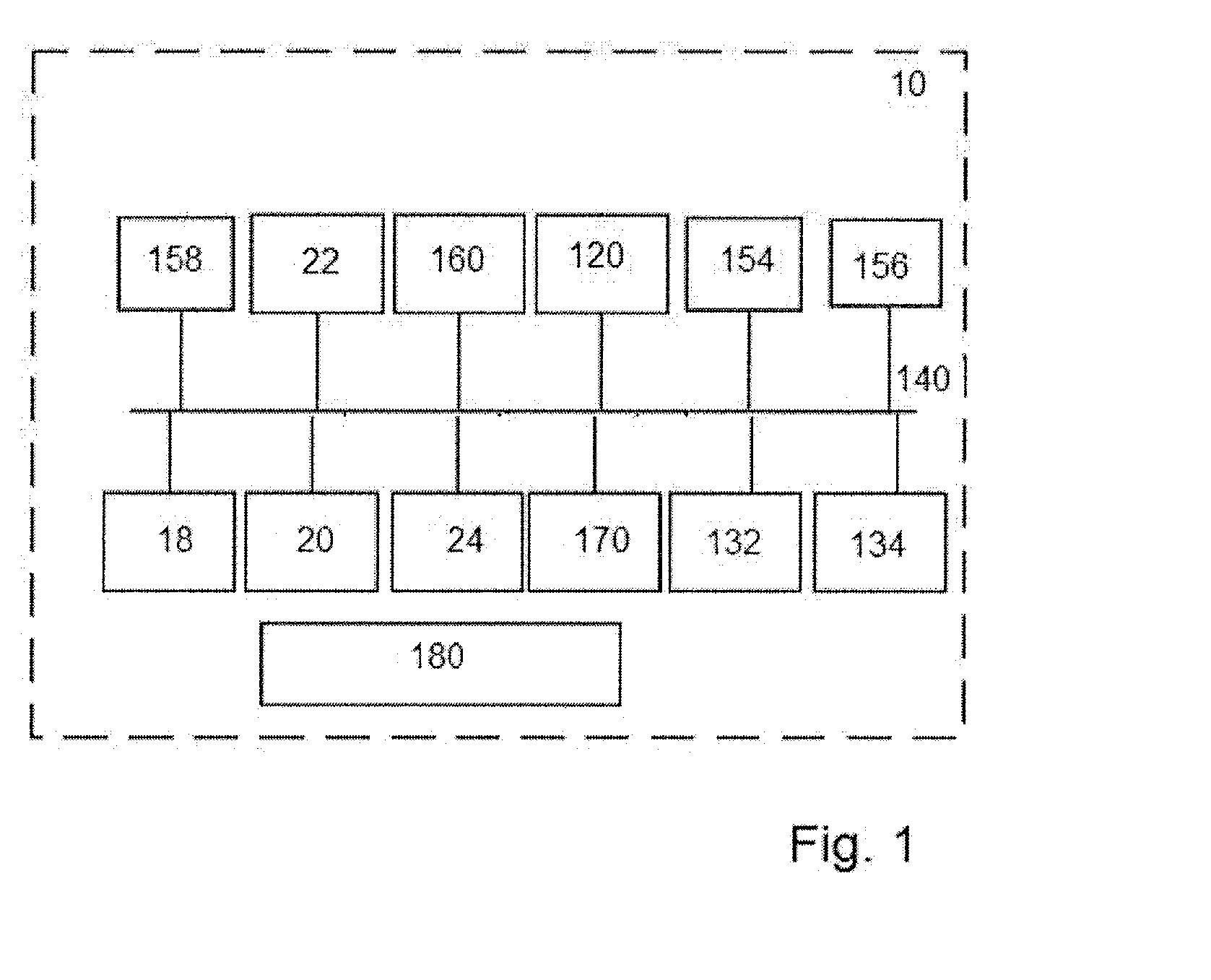

Situation aware security system and method for mobile devices

InactiveUS20120309354A1Unauthorised/fraudulent call preventionEavesdropping prevention circuitsTransceiverAccelerometer

A mobile communication device can comprise a microprocessor, a memory, and one or more sensors, all coupled to a system bus. A sensor can be provided by a GPS receiving device, an accelerometer, an image sensor, a radio frequency transceiver, or a magnetic card reading device. The mobile communication device can be configured, responsive to receiving sensor data from one or more sensors, to select a corresponding security alert level. The mobile communication device can be further configured to perform at least one security-related action corresponding to the selected security alert level.

Owner:SYRACUSE UNIVERSITY

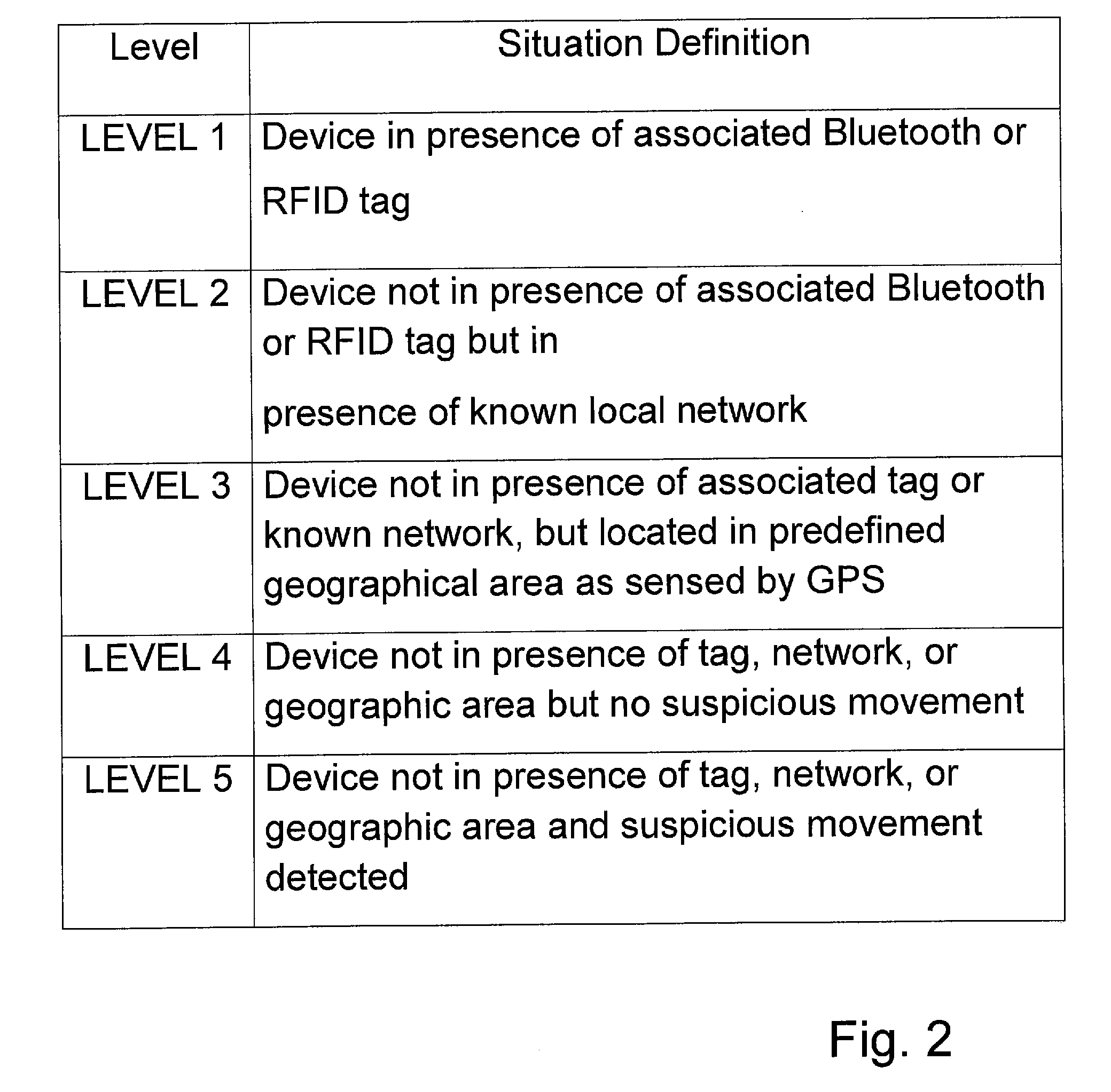

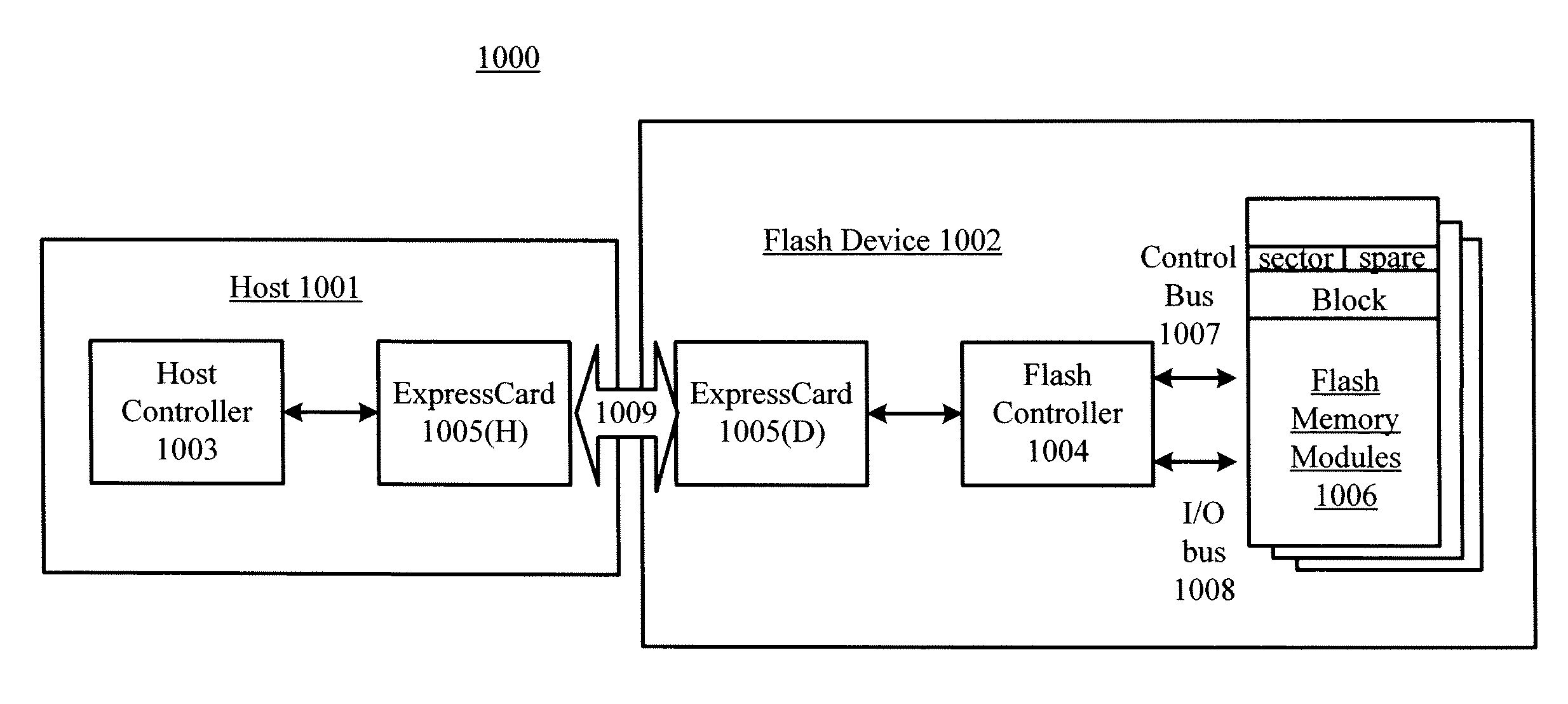

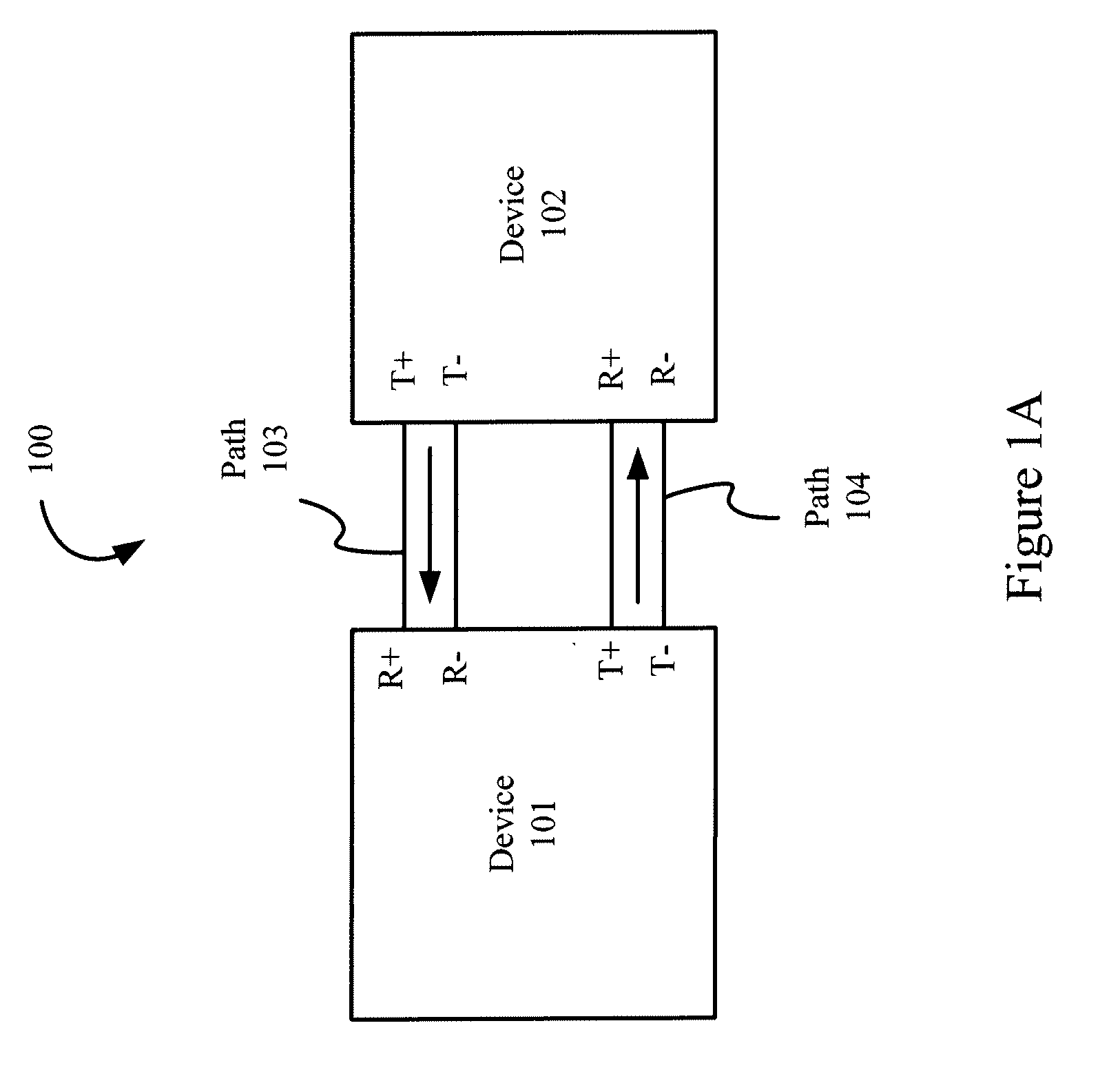

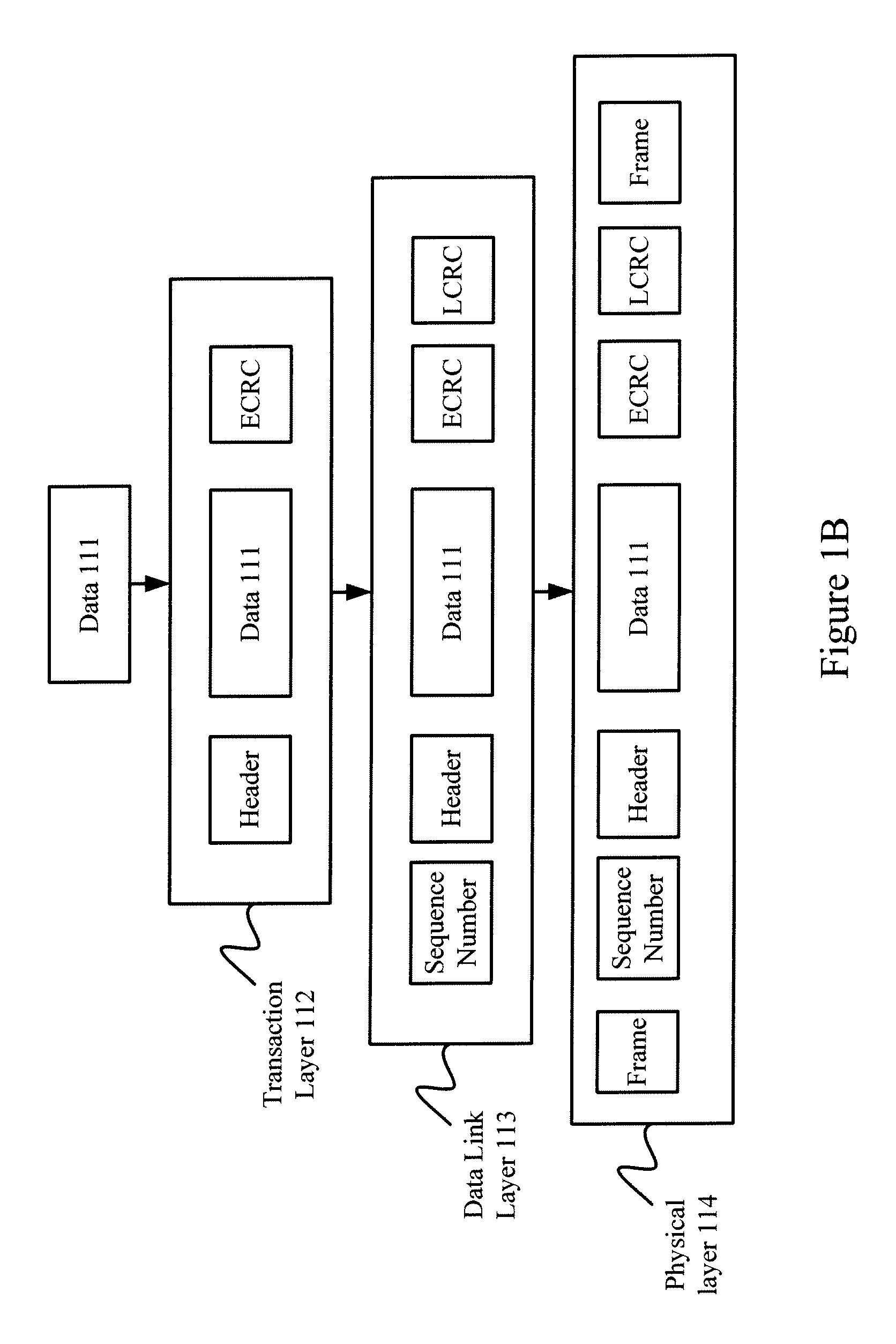

PCI express-compatible controller and interface for flash memory

InactiveUS7457897B1Improve performanceFacilitates optimal serviceabilityRead-only memoriesDigital storagePCI ExpressSystem bus

A PCI Express-compatible flash device can include one or more flash memory modules, a controller, and an ExpressCard interface. The controller can advantageously provide PCI Express functionality as well as flash memory operations, e.g. writing, reading, or erasing, using the ExpressCard interface. A PIO interface includes sending first and second memory request packets to the flash device. The first memory request packet includes a command word setting that prepares the flash device for the desired operation. The second memory request packet triggers the operation and includes a data payload, if needed. A DMA interface includes sending the second memory request from the flash device to the host, thereby triggering the host to release the system bus for the DMA operation.

Owner:SUPER TALENT TECH CORP

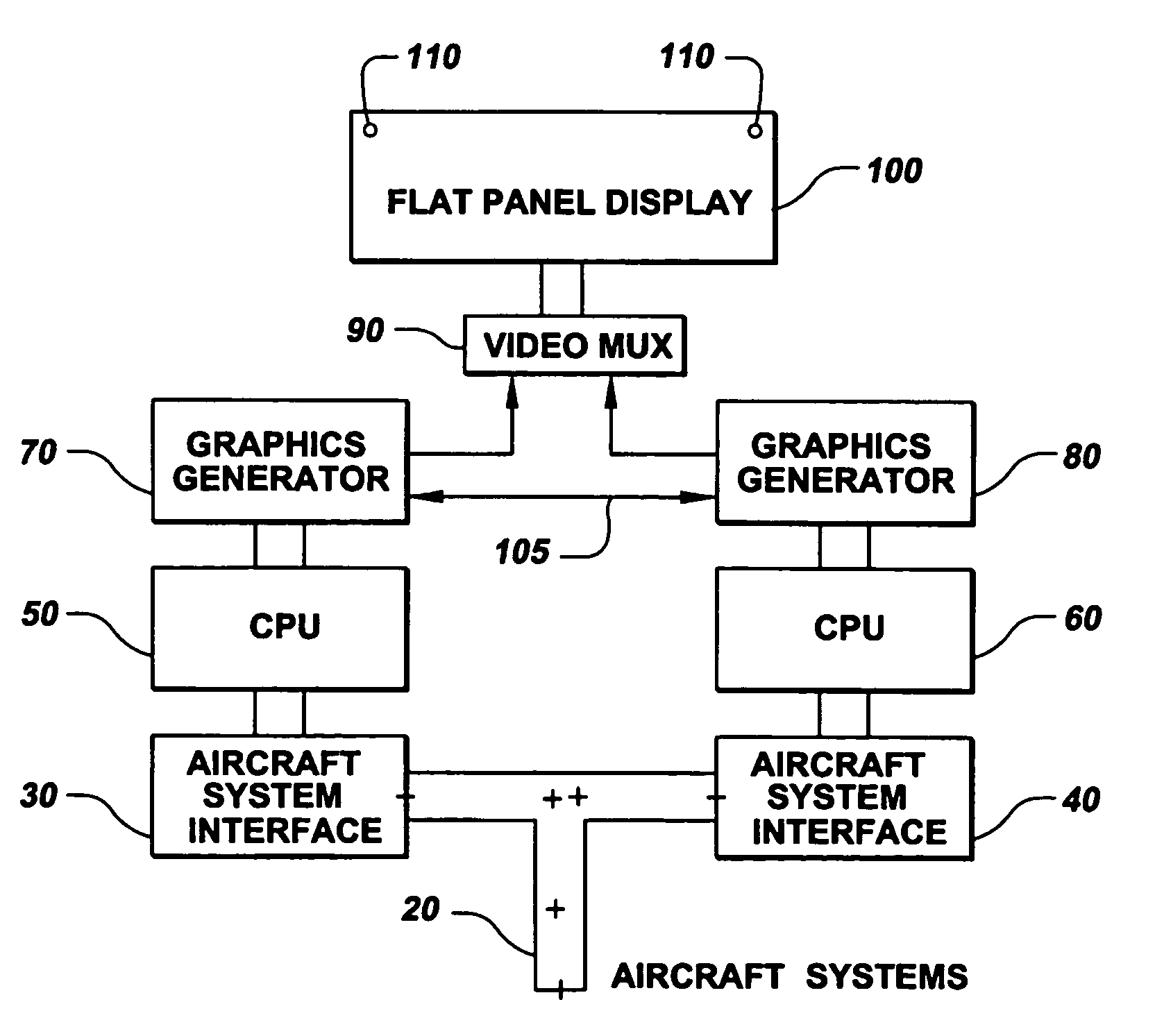

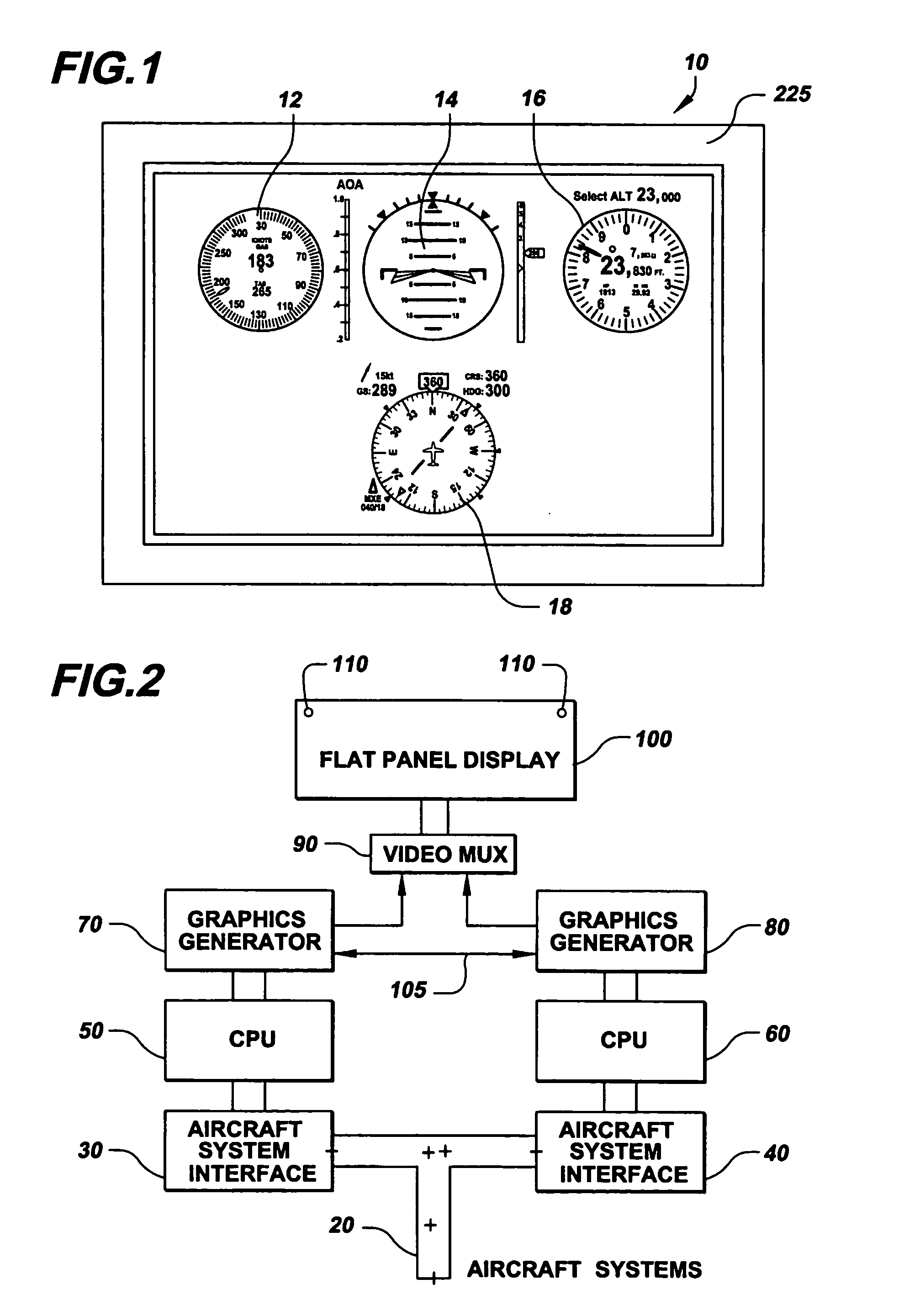

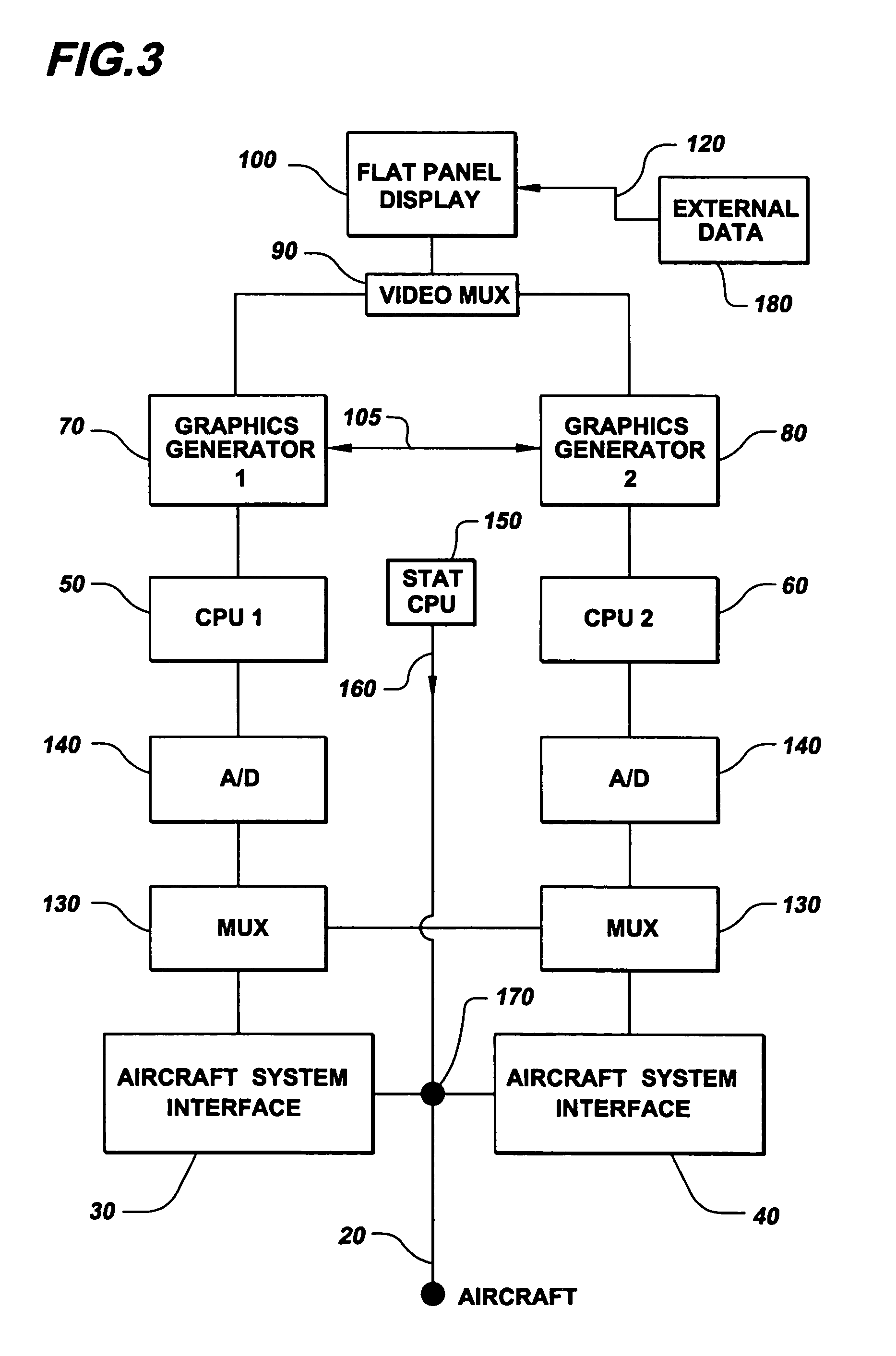

Flat panel display using dual CPU's for an aircraft cockpit

InactiveUS6977666B1Easy to testAnalogue computers for vehiclesAnalogue computers for trafficGraphicsExternal storage

A thin flat panel display for aircraft cockpits. These displays use a dual CPU / graphics generator system to produce simulated aircraft instrumentation displays which are color coded to indicate when one of the graphic generators has not correctly received data from the aircraft system bus. The displays use standard graphic generators and CPUs, and do not require additional software. The displays also allow the aircraft systems to be continuously tested while the aircraft is on the ground. Moreover, the inventive systems include input touch devices which access external memories to display necessary flight and landing information which allow the cockpit crew to expand in detail the external information for display on the flat panels.

Owner:INNOVATIVE SOLUTIONS & SUPPORT

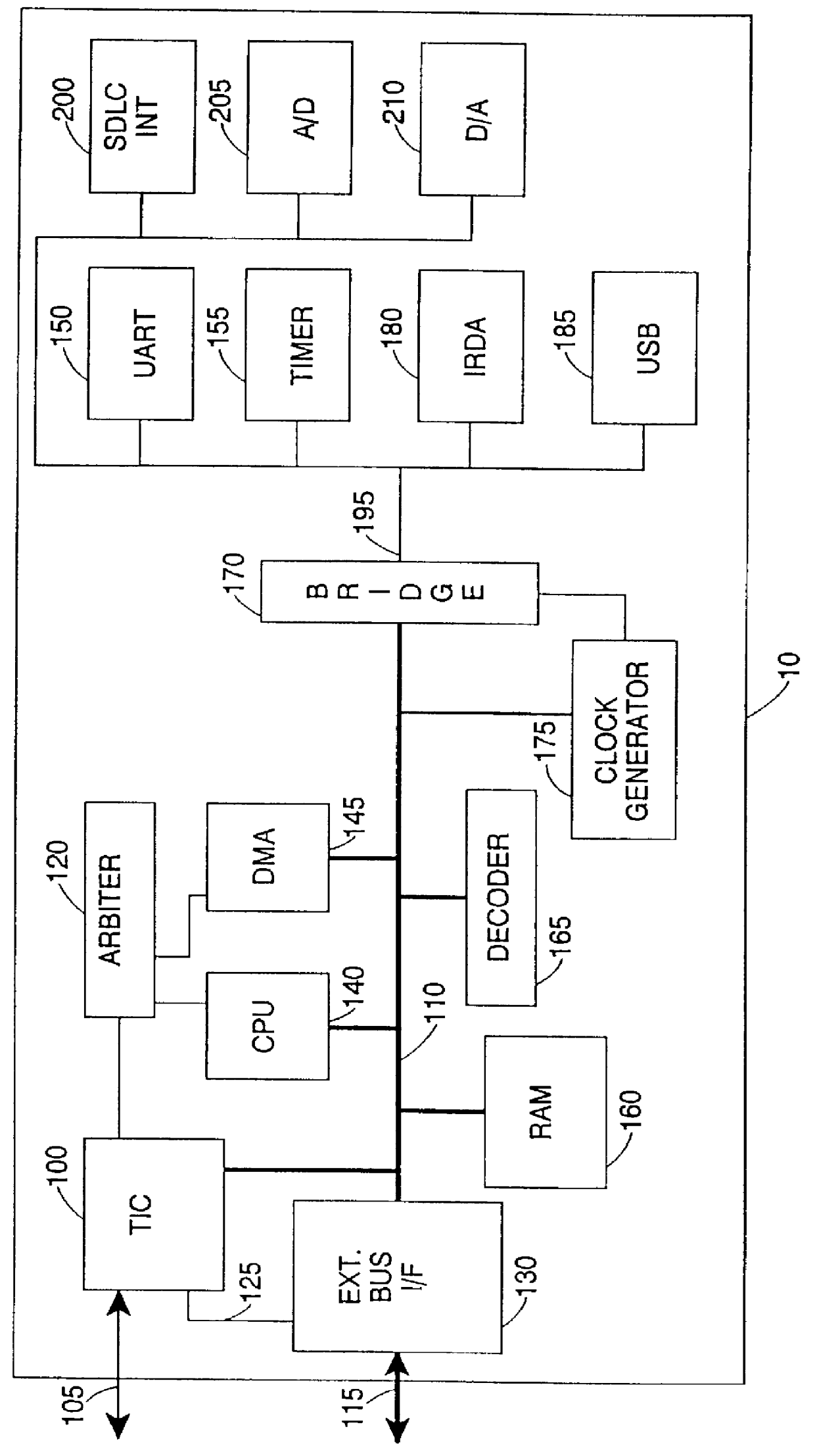

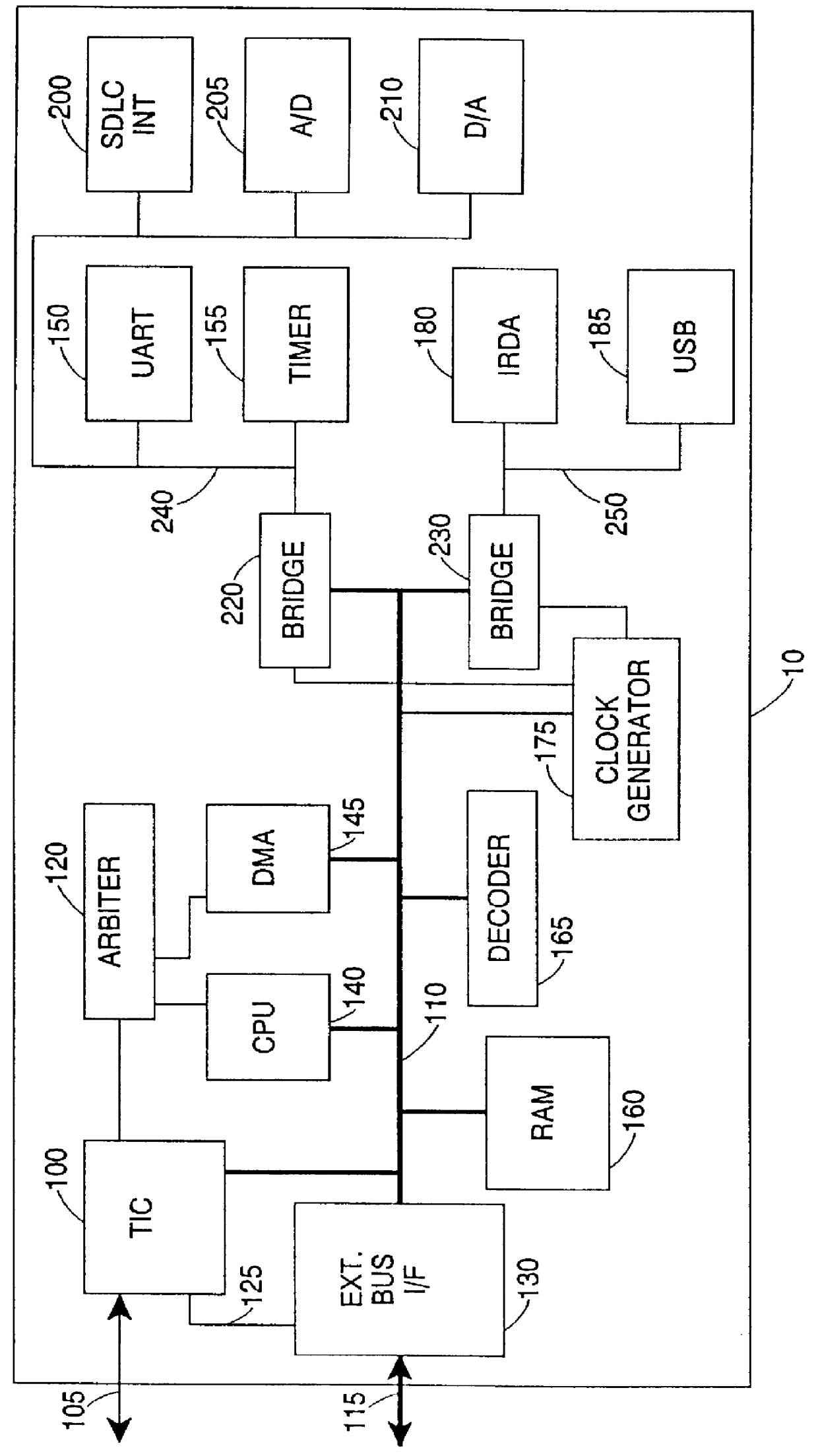

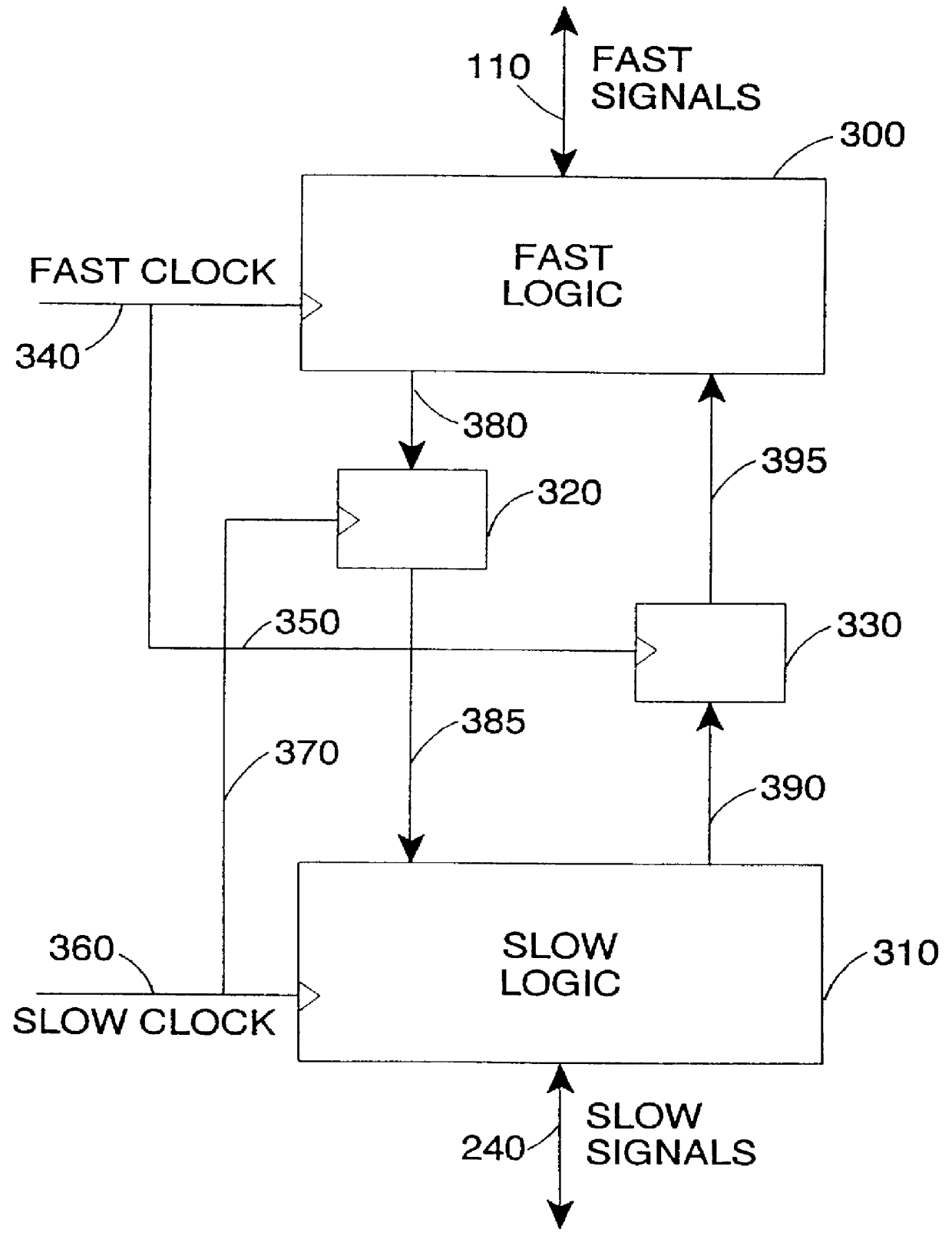

Peripheral buses for integrated circuit

InactiveUS6064626AReduce power consumptionAverage power consumptionEnergy efficient ICTDigital storageCapacitanceClock rate

The present invention provides an integrated circuit comprising a system bus to which a processor is connectable, and first and second peripheral buses to which peripheral units used by said processor are connected, the first peripheral bus operating at a higher clock speed than the second peripheral bus. Further, the integrated circuit comprises bridge logic for providing an interface between the system bus and the peripheral buses to enable signals to be passed between the system bus and the peripheral buses, the bridge logic comprising clock resynchronisation logic for synchronising the system bus and the peripheral buses. Through the provision of first and second peripheral buses operating at different clock speeds, the integrated circuit of the present invention provides a great deal of flexibility for reducing the power consumption of the integrated circuit as compared with a similar integrated circuit having only one peripheral bus. Since the power consumption of each peripheral bus is proportional to the clock frequency and capacitance, significant power consumption savings can be realised by ensuring that each peripheral unit is connected to the slowest peripheral bus appropriate for that peripheral unit.

Owner:ARM LTD

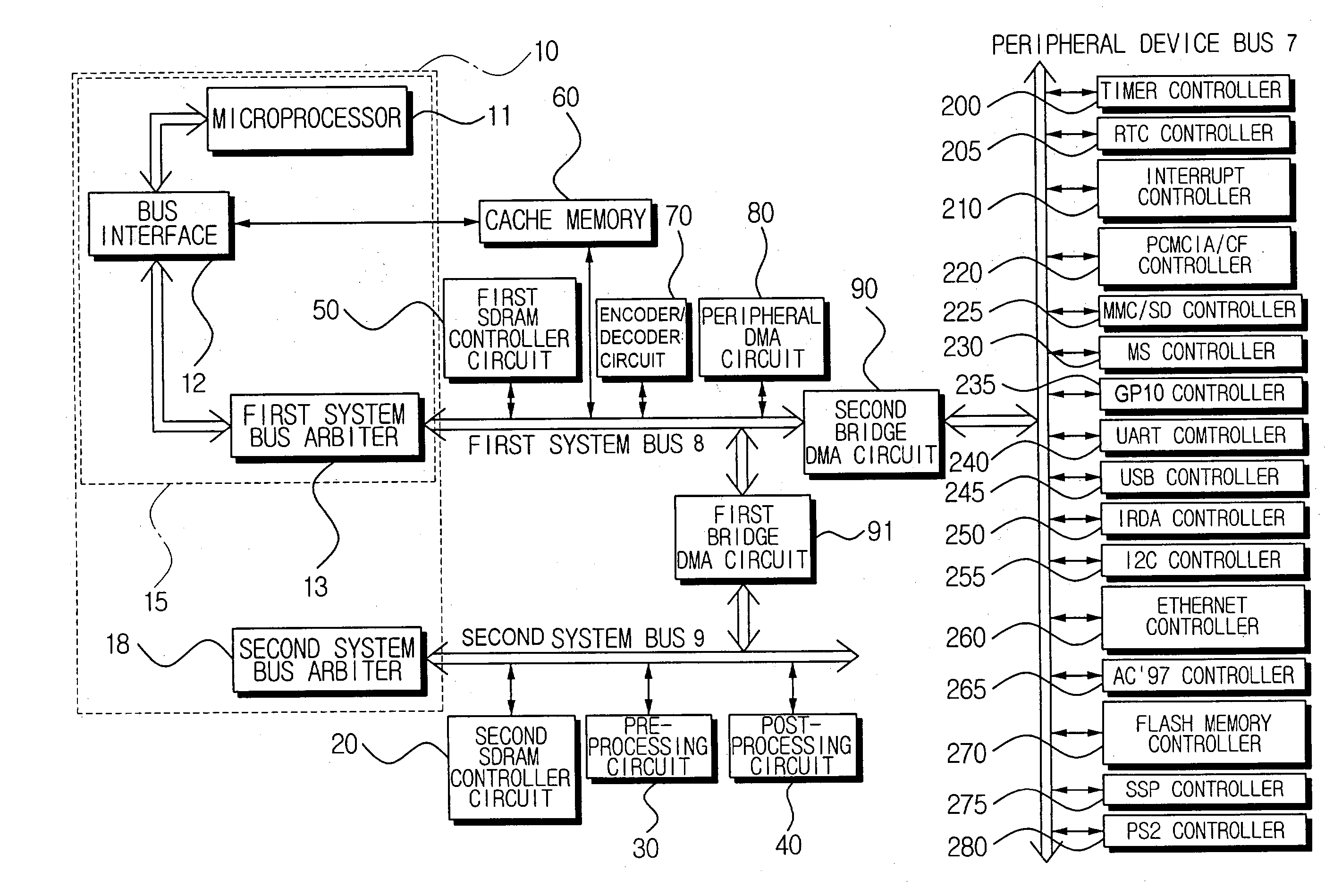

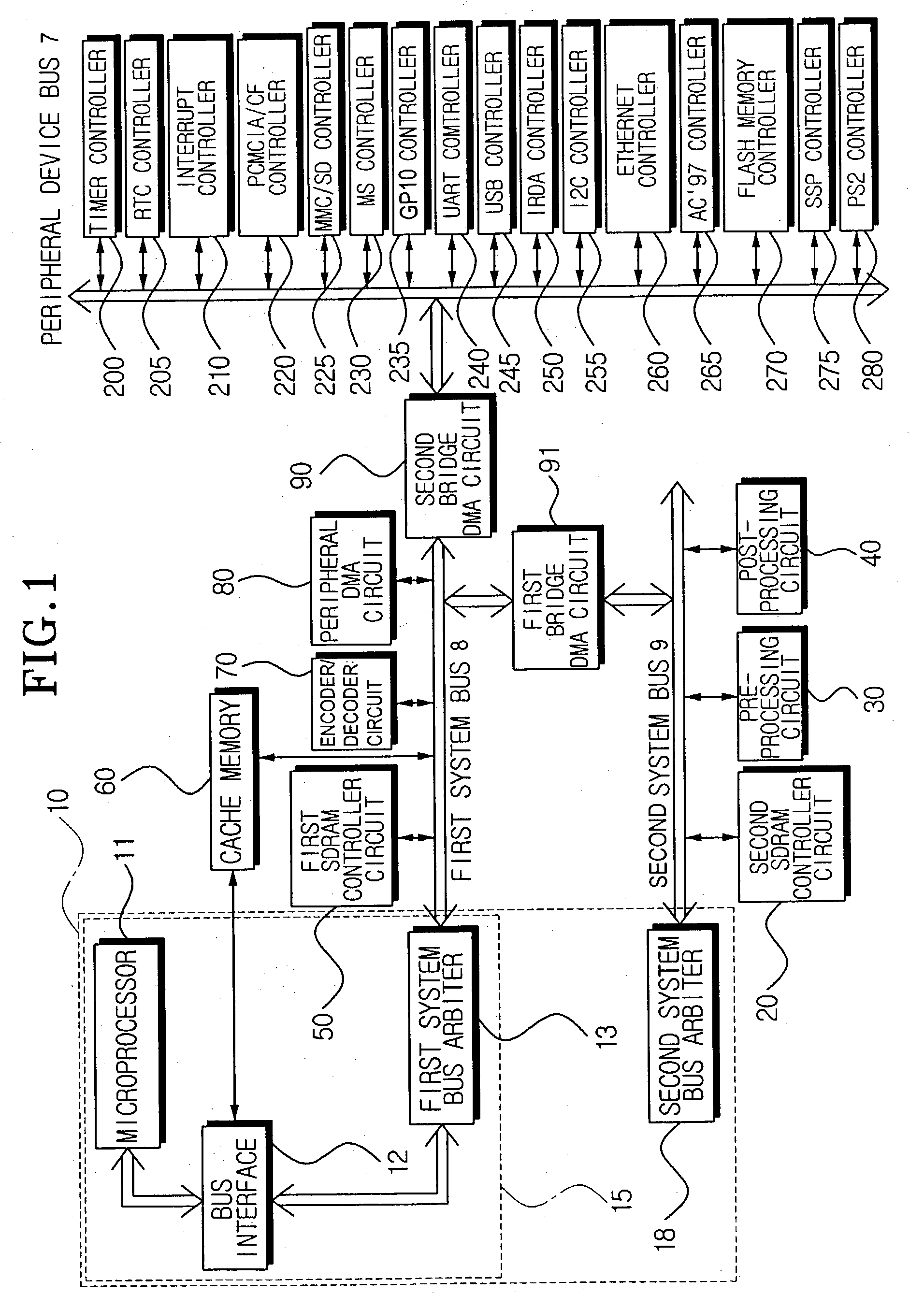

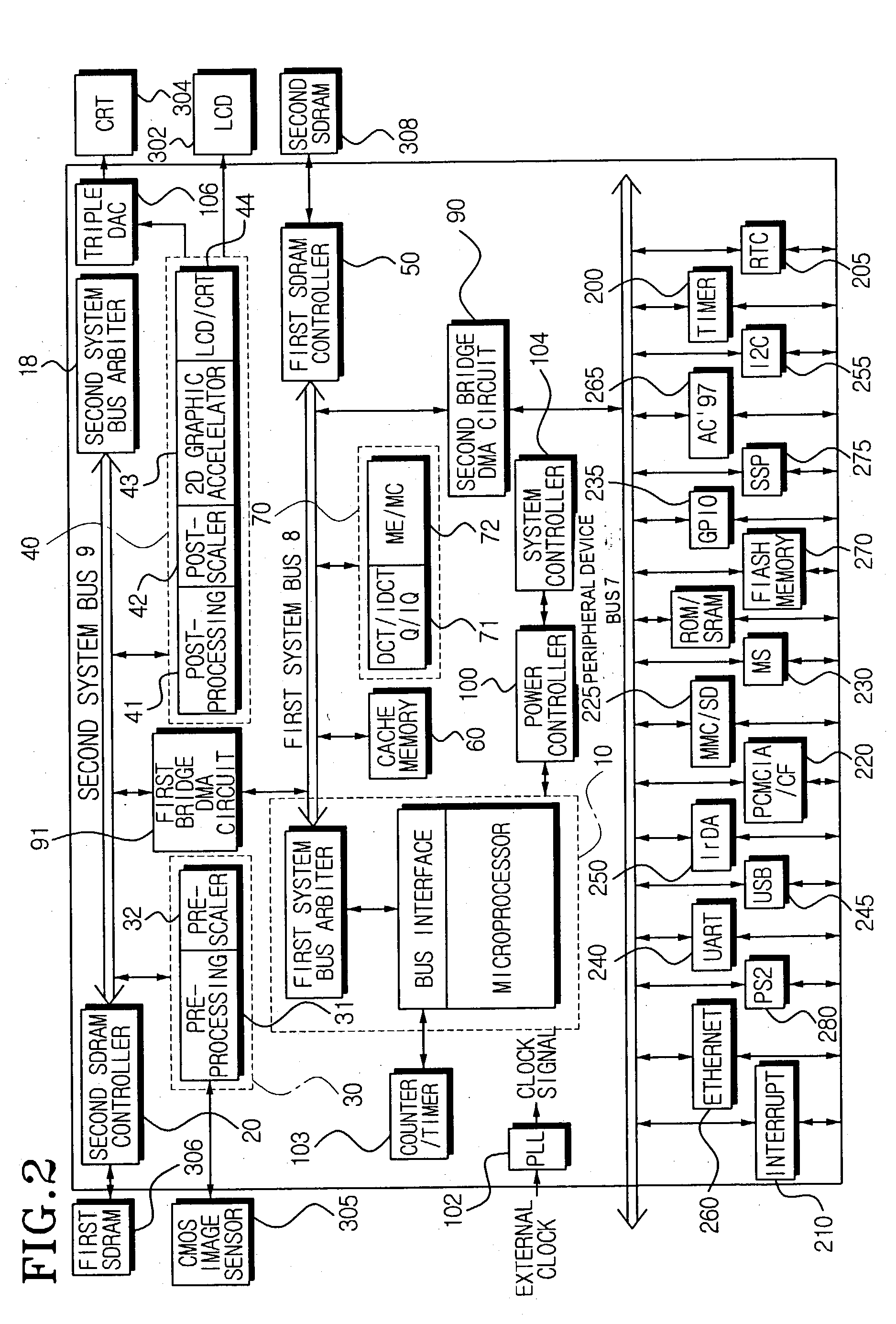

System on chip processor for multimedia devices

InactiveUS7171050B2Advantage in of performance and power consumptionImprove processing speedEnergy efficient ICTCharacter and pattern recognitionEncoder decoderComputer science

A system on chip processor for a multimedia device includes: a pre-processing circuit to convert an external image signal into a compressed input signal for compressing; an encoder / decoder circuit to generate compressed data by compressing the compressed input signal and outputting a coded image signal by decompressing the compressed data; a post-processing circuit to convert the coded image signal into a signal that can be used by an image displaying device; a first system bus connected with pre-processing circuit and post-processing circuit; a second system bus connected with the encoder / decoder circuit; a first bridge DMA circuit to mutually transmit data between first system bus and second system bus; and a controller to control the operation of the circuits.

Owner:SAMSUNG ELECTRONICS CO LTD

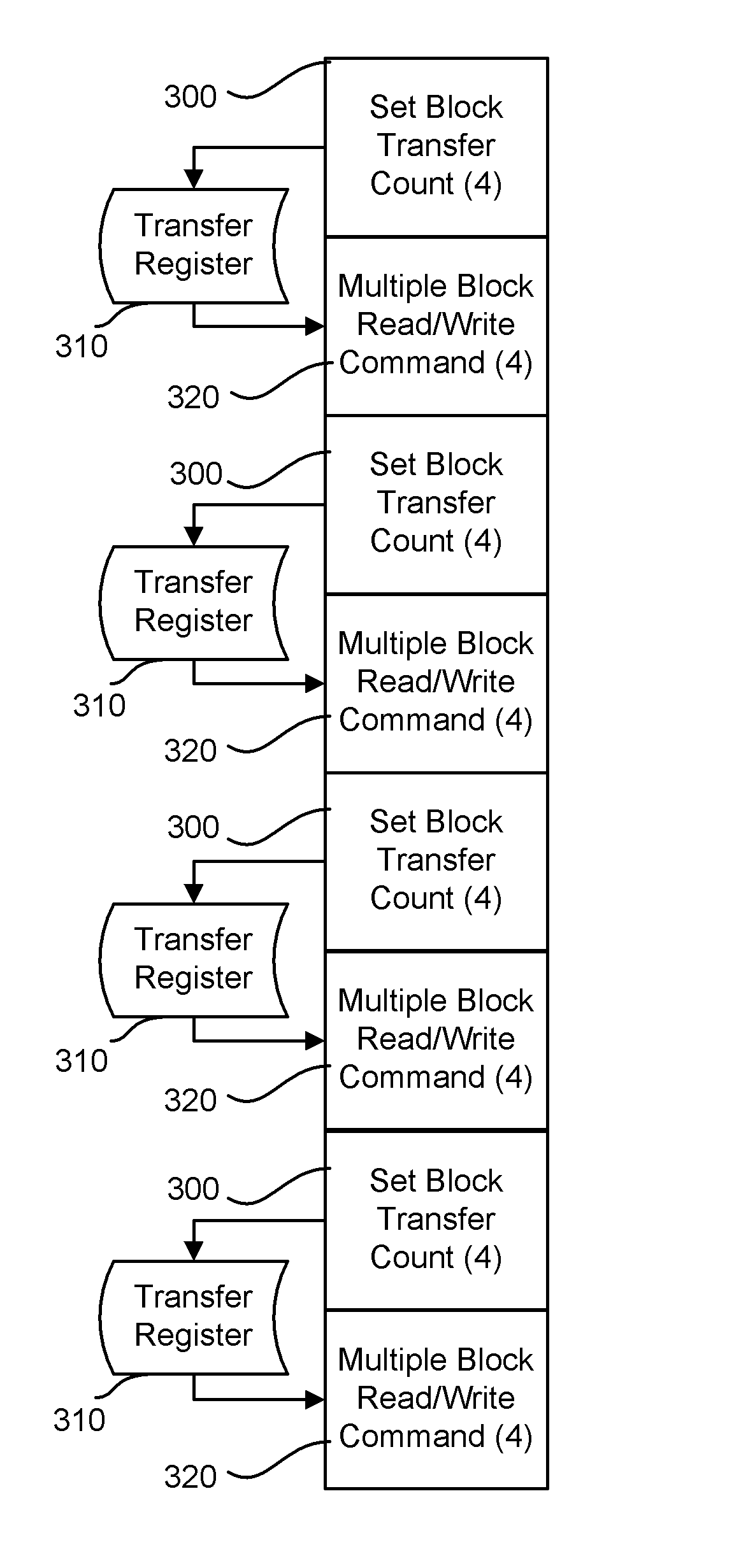

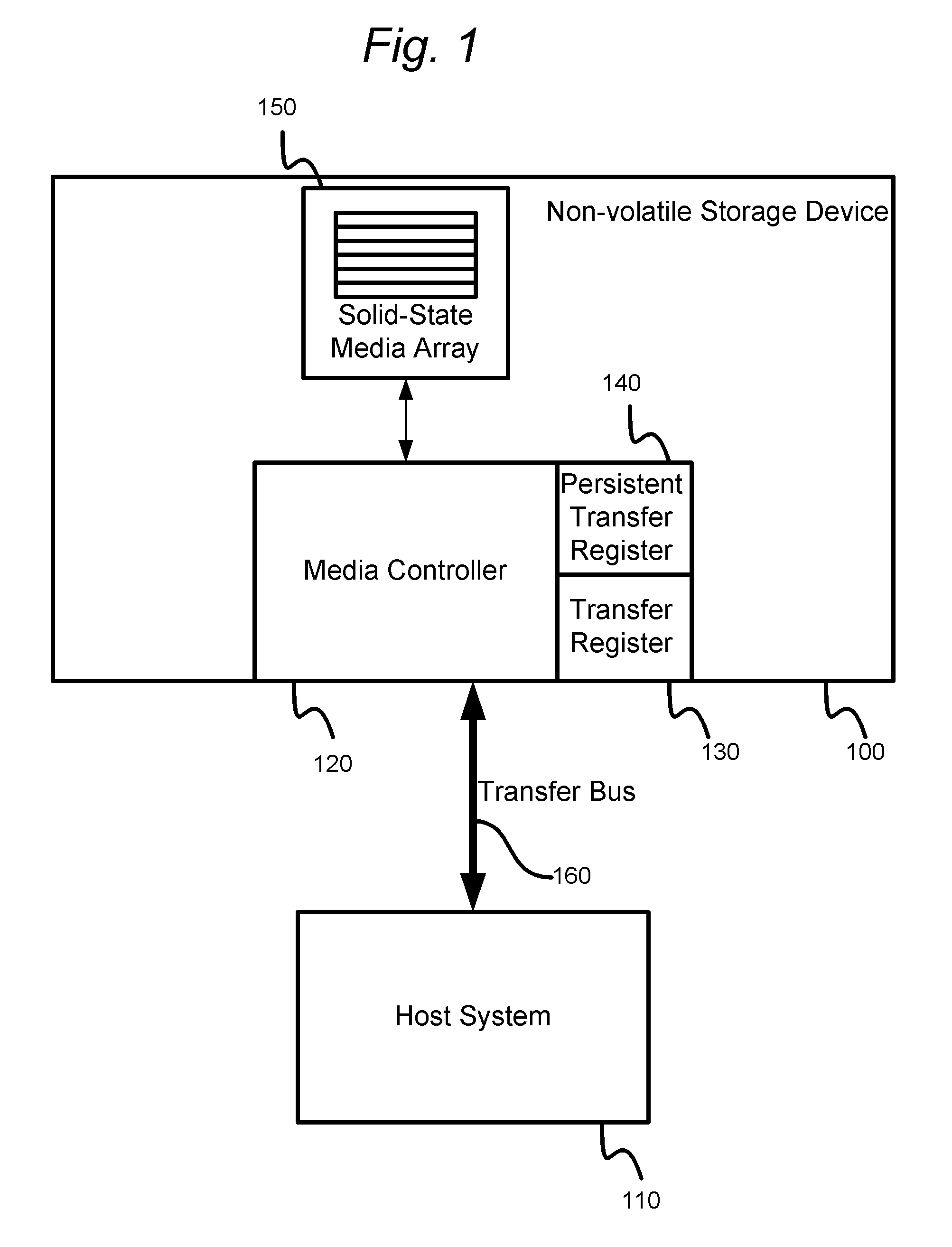

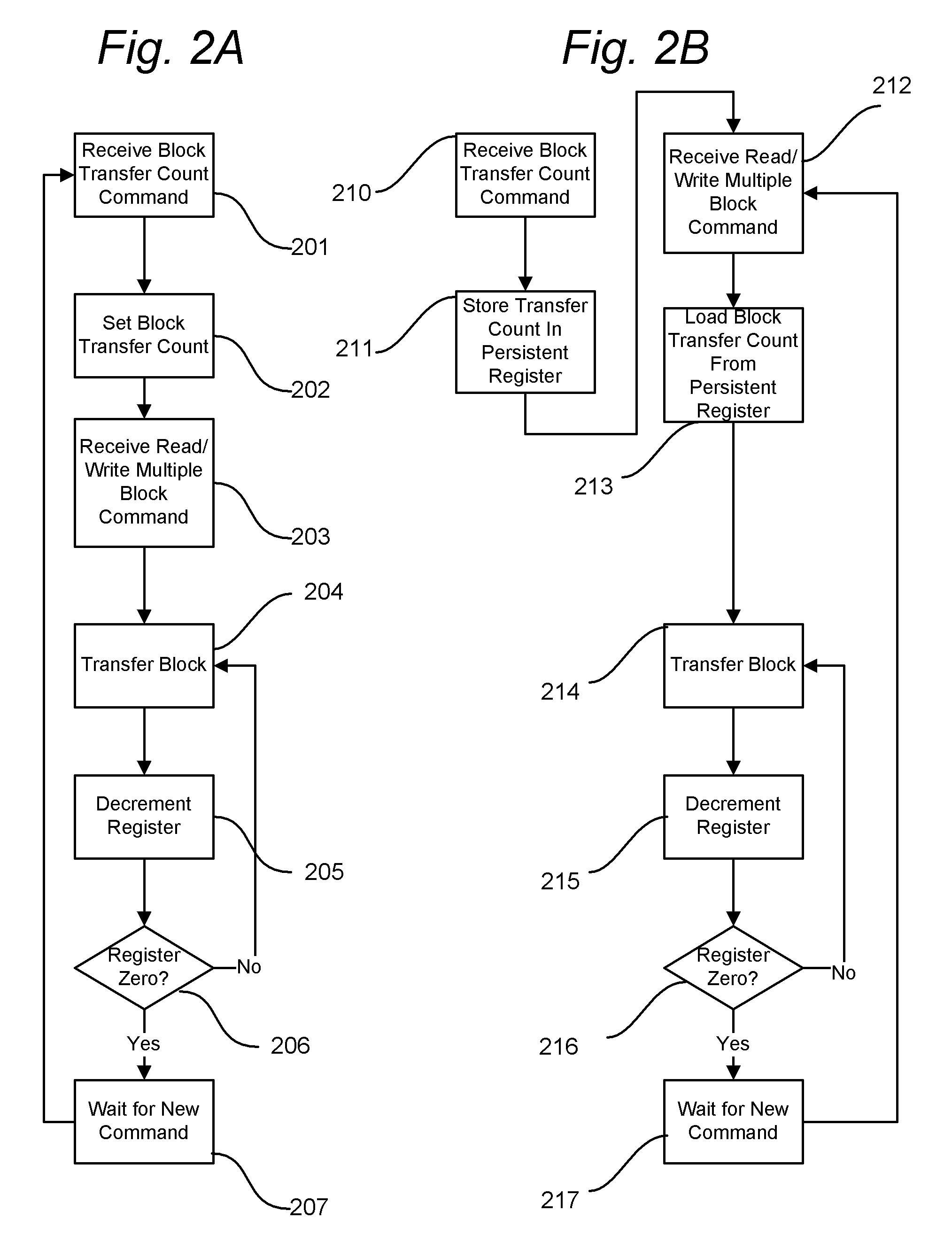

Storage system bus transfer optimization

ActiveUS8751728B1Reduce bus activityInput/output to record carriersConcurrent instruction executionSystem busBlock transfer

Embodiments of the invention include systems and methods for reducing bus transfers for a storage device. In particular, these systems and methods reduce bus transfers by modifying an interface transfer protocol which designates the size of a multiple block read or write command is transmitted in a separate block transfer size command. Separate block transfer size commands can be omitted where the storage device maintains a record of a previously used block transfer size and reuses the size for subsequent multiple block read or write commands.

Owner:WESTERN DIGITAL TECH INC

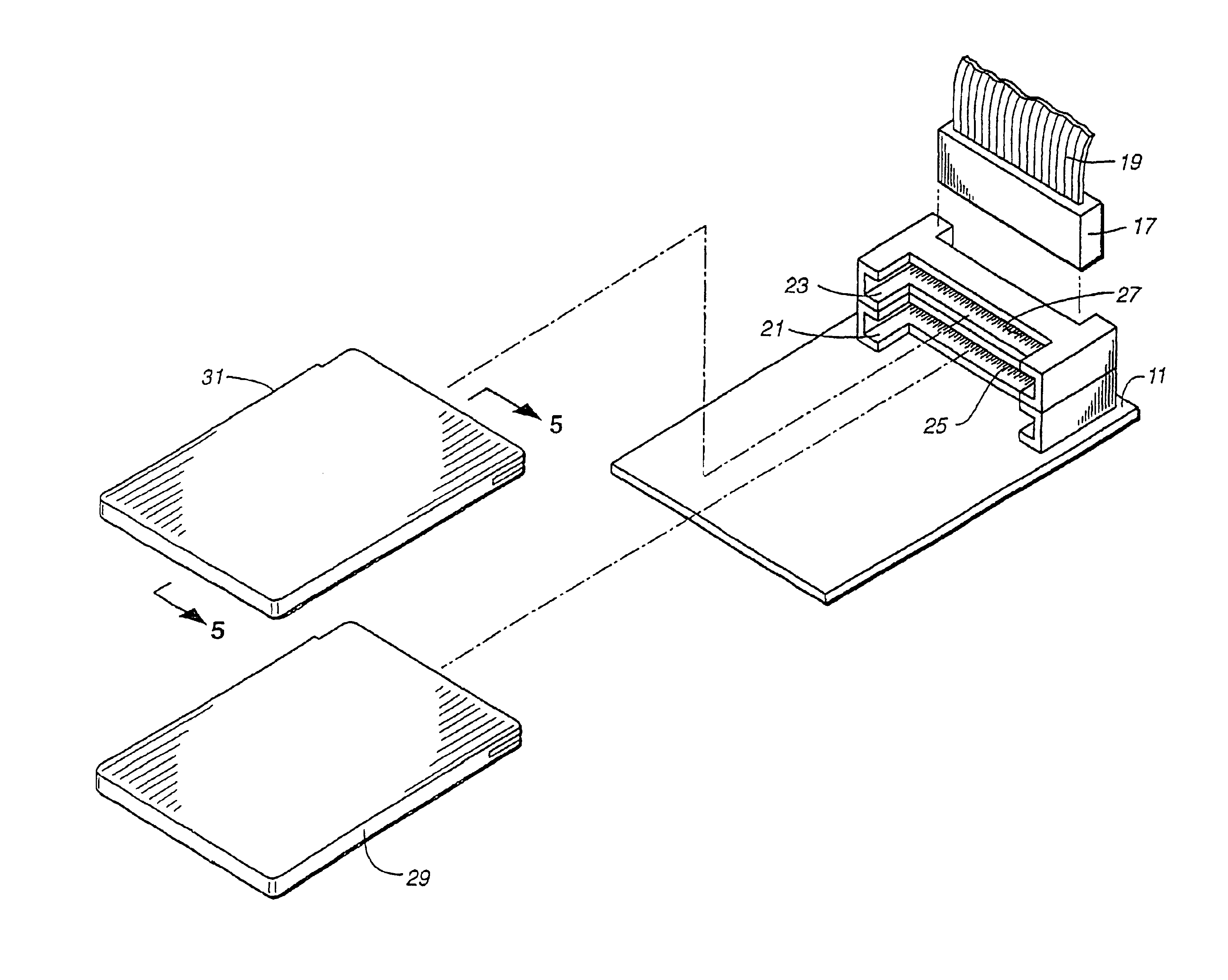

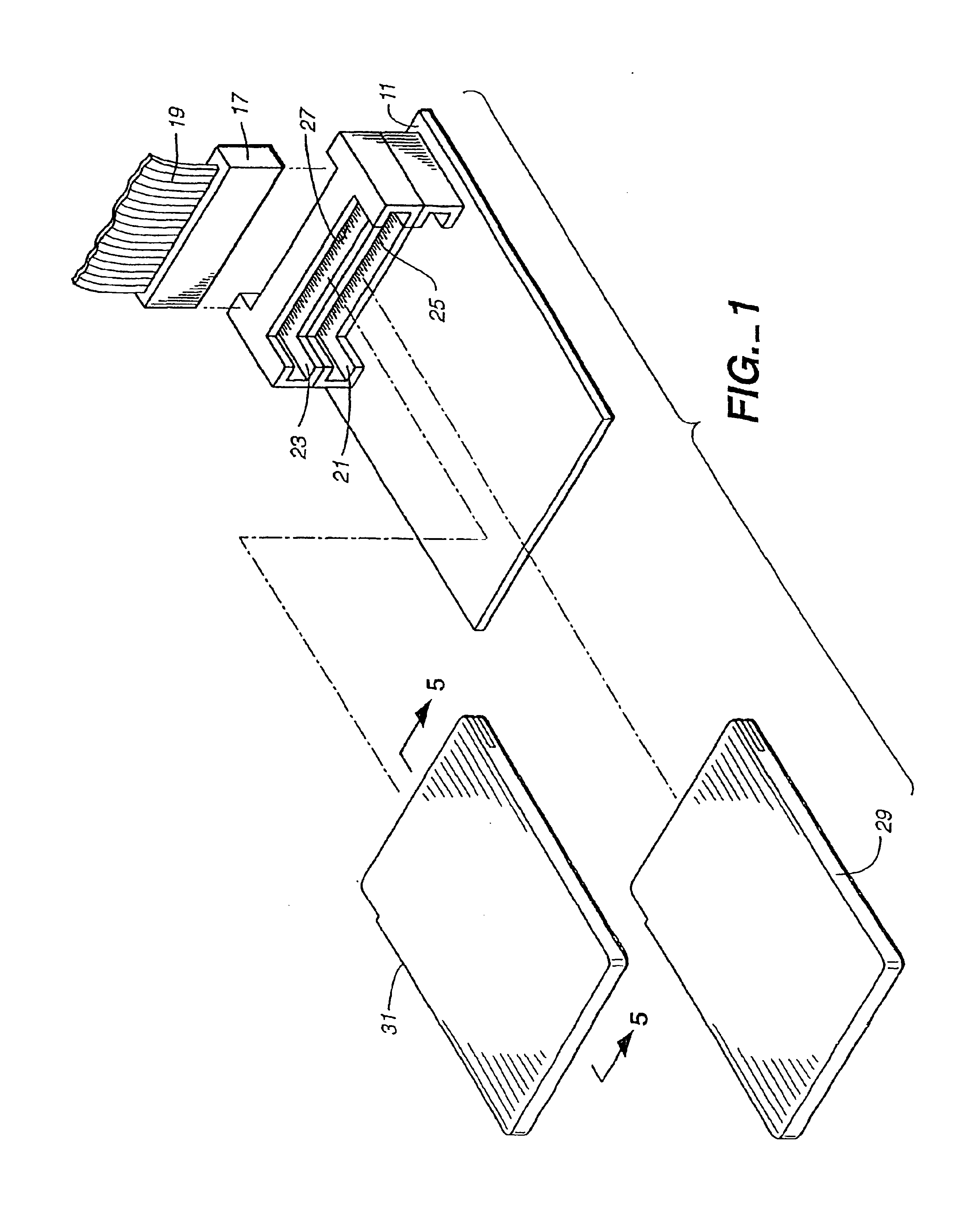

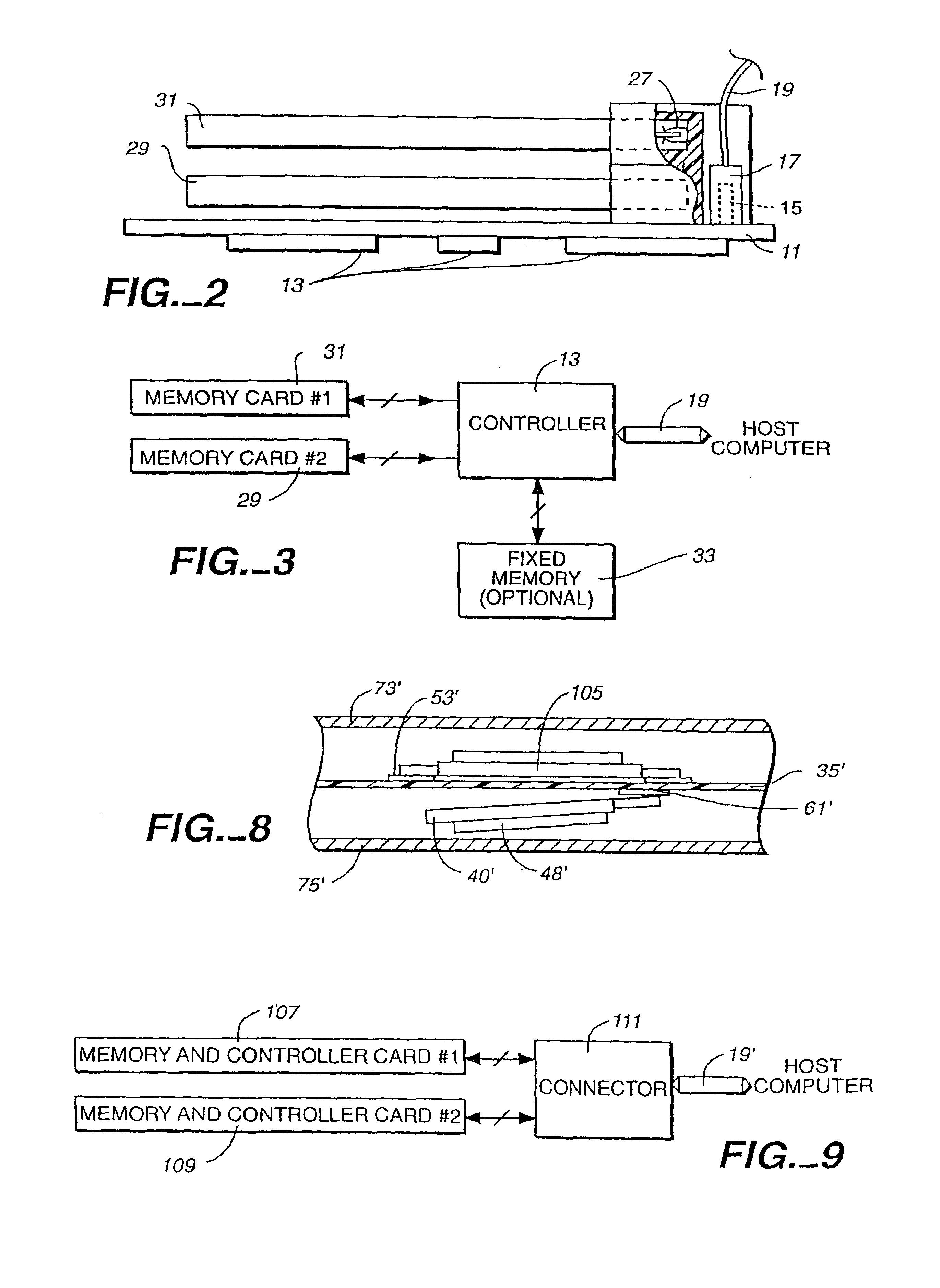

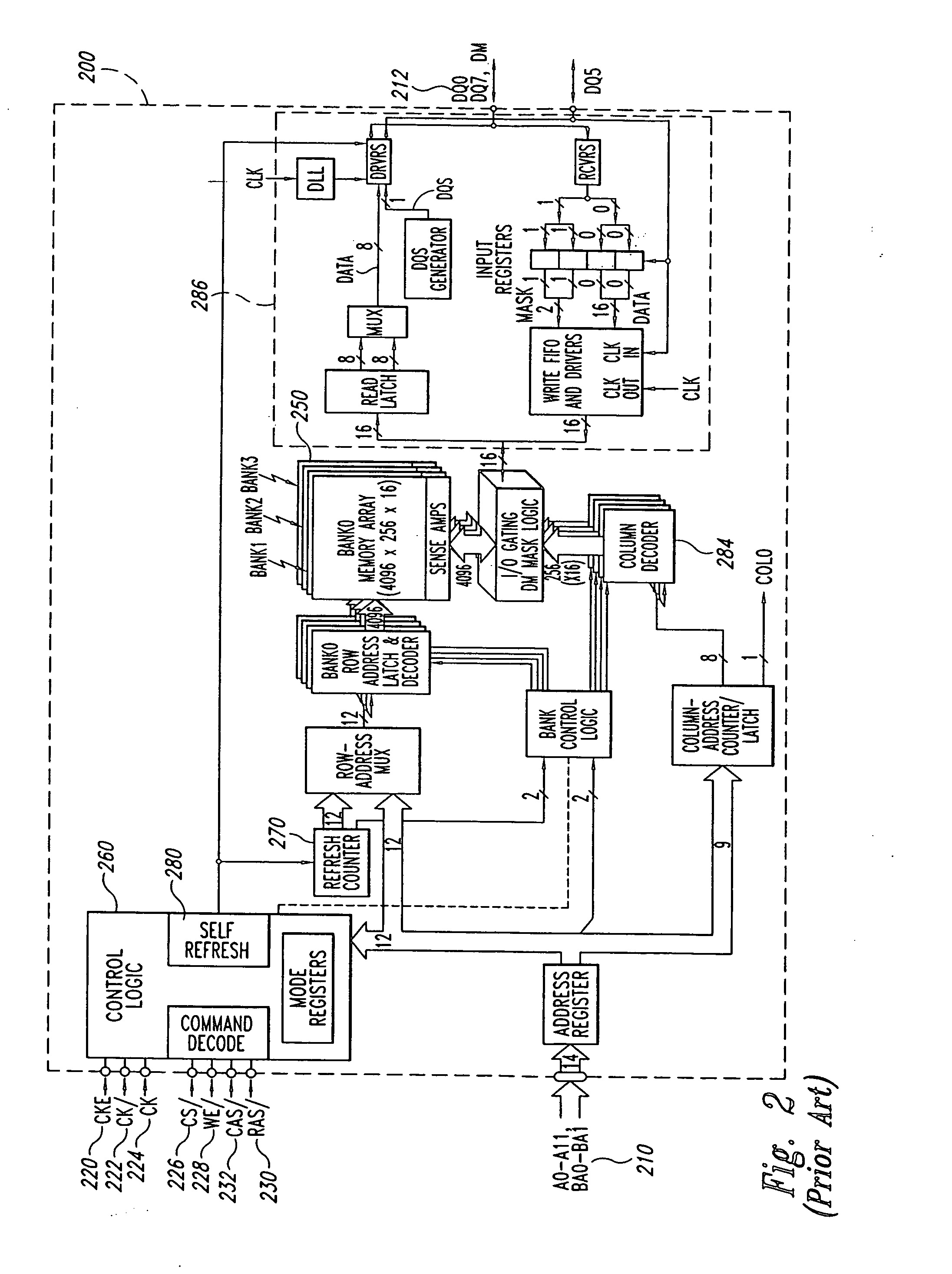

Computer memory cards using flash EEPROM integrated circuit chips and memory-controller systems

InactiveUS6947332B2Easy to useInput/output to record carriersPrinted circuit aspectsElectronic systemsComputerized system

A very small computer memory card is densely packed with a large number of flash EEPROM integrated circuit chips. A computer memory system provides for the ability to removably connect one or more of such cards with a common controller circuit that interfaces between the memory cards and a standard computer system bus. Alternately, each card can be provided with the necessary controller circuitry and thus is connectable directly to the computer system bus. An electronic system is described for a memory system and its controller within a single memory card. In a preferred physical arrangement, the cards utilize a main circuit board with a plurality of sub-boards attached thereto on both sides, each sub-board carrying several integrated circuit chips.

Owner:SANDISK TECH LLC

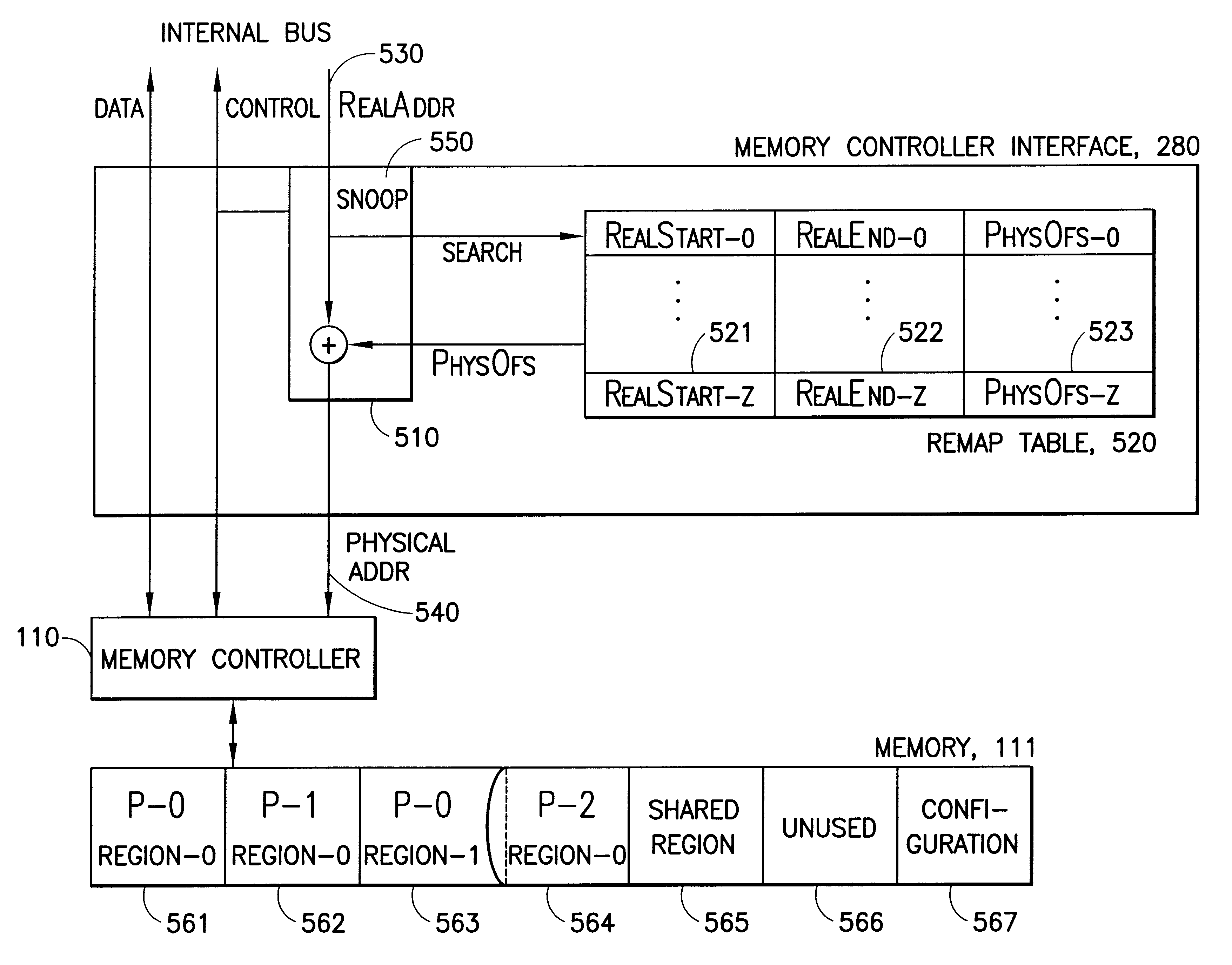

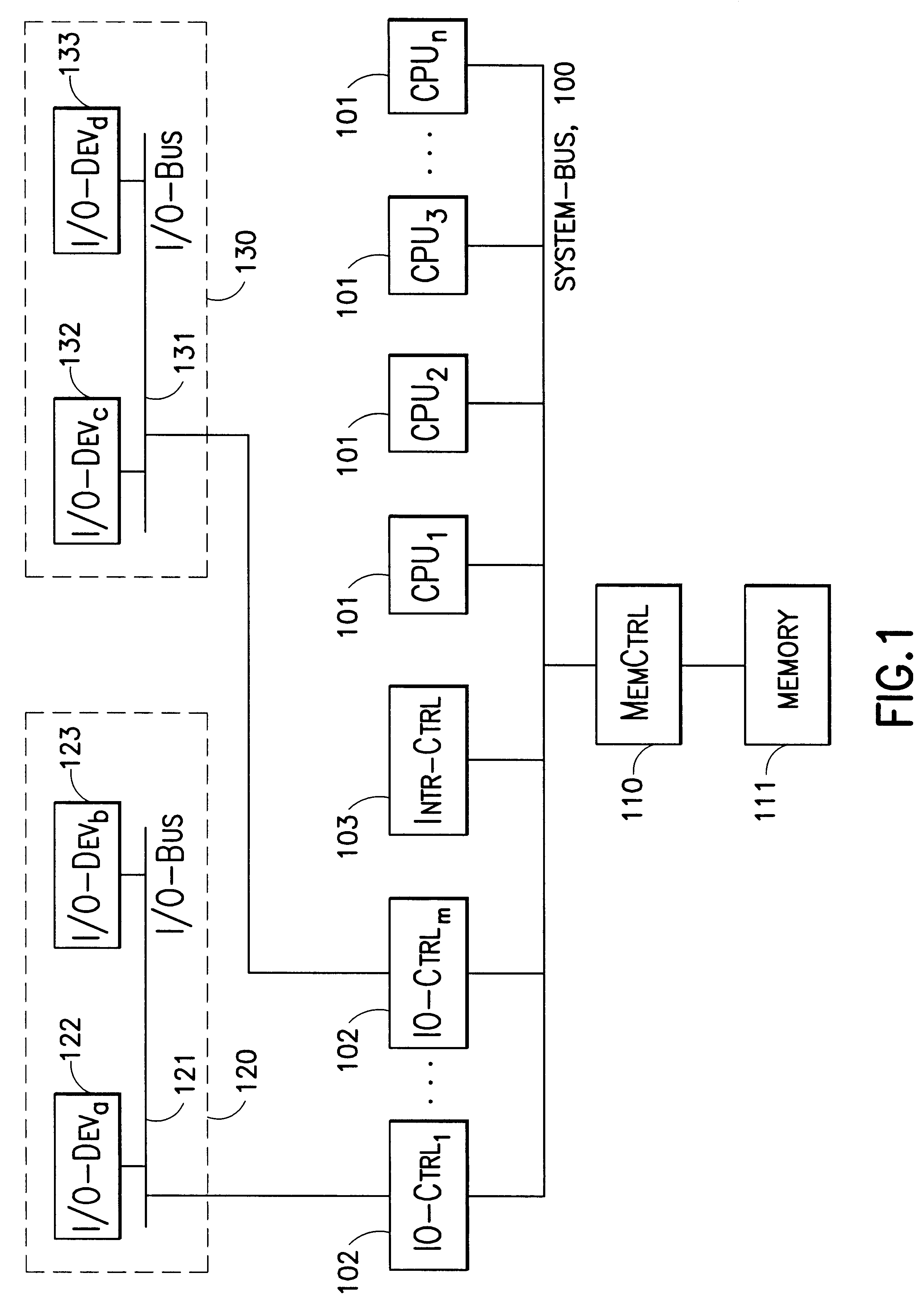

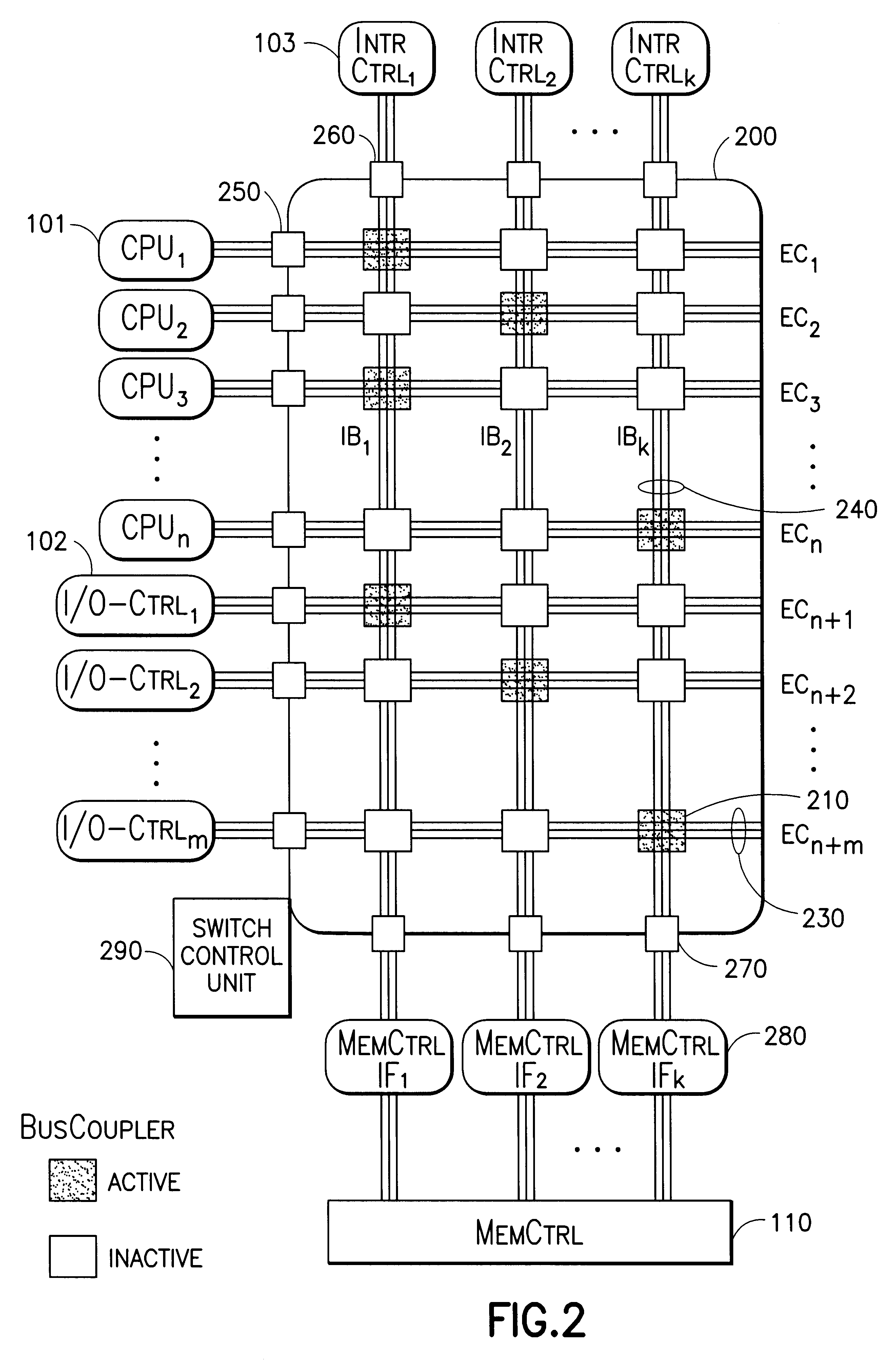

Secure partitioning of shared memory based multiprocessor system

InactiveUS6480941B1Flexible and secure partitioningMemory adressing/allocation/relocationMulti processorPhysical address

A method and apparatus for sharing memory in a multiprocessor computing system. More specifically, this invention provides a number of system buses with each bus being connected to a respective memory controller which controls a corresponding partition of the memory. Any one of the processors can use any one of the system buses to send real addresses to the connected memory controller which then converts the real addresses into physical addresses corresponding to the partition of memory that is controlled by the receiving memory controller. The processors can be dynamically assigned to different partitions of the memory by via a switching mechanism.

Owner:IBM CORP

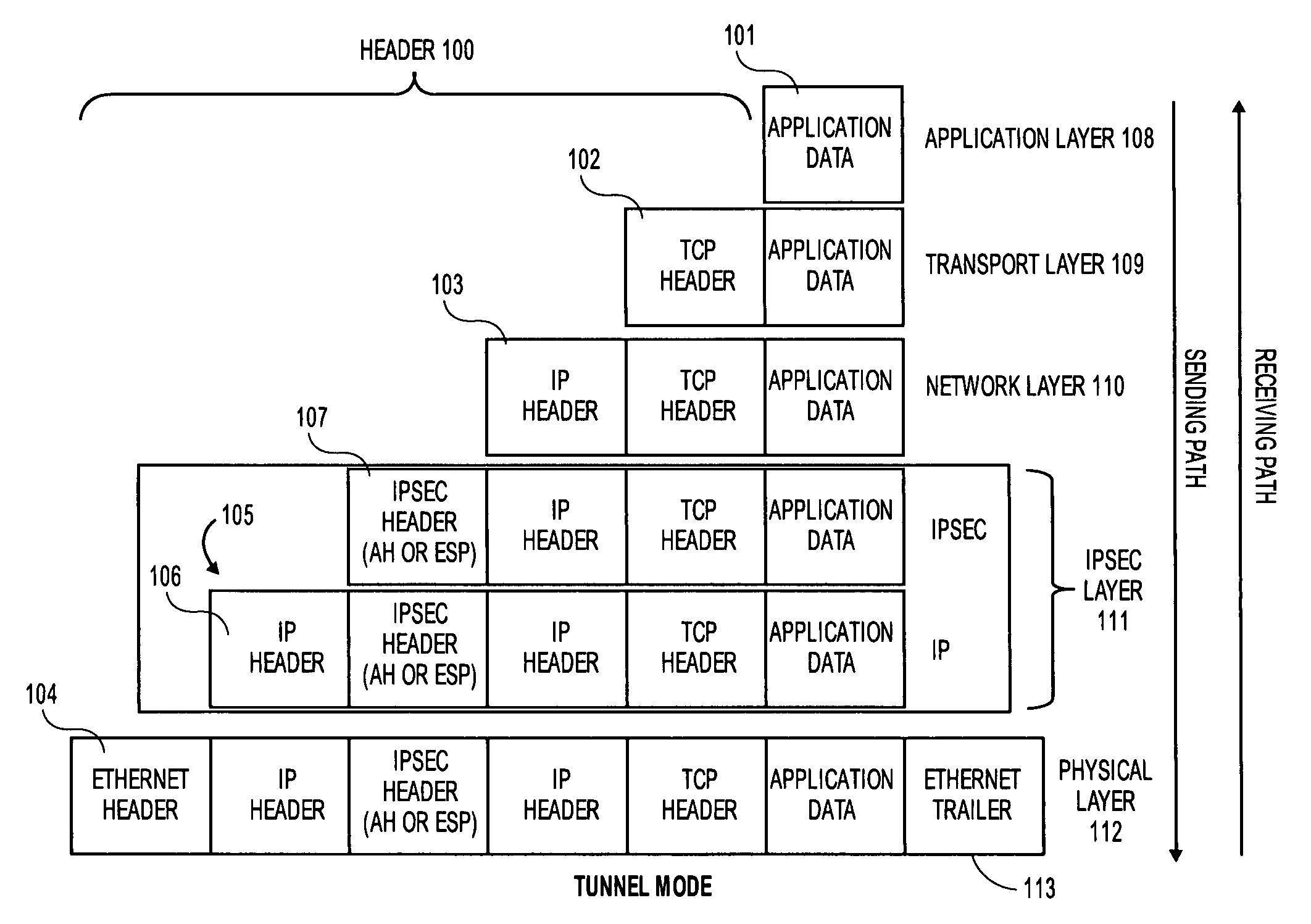

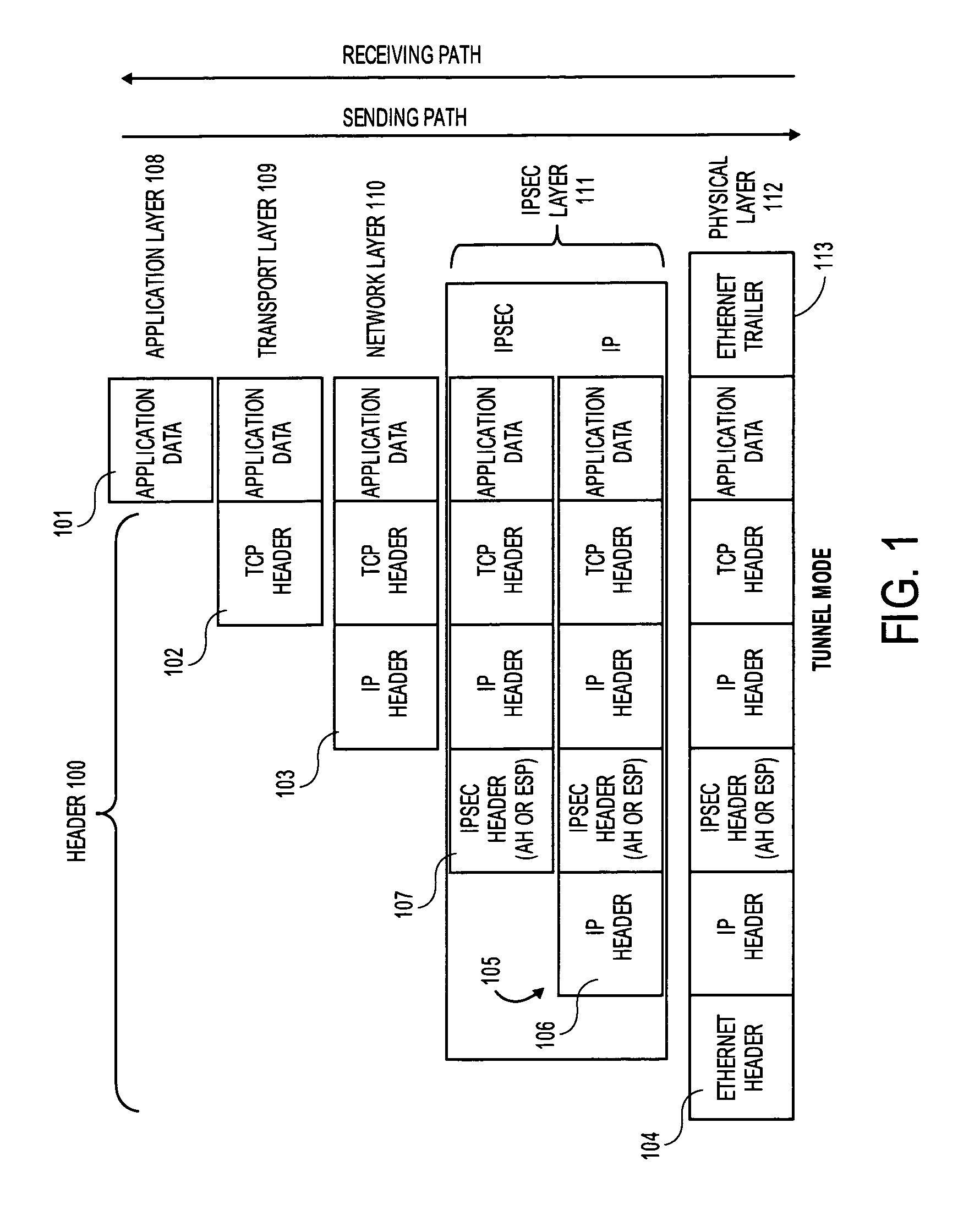

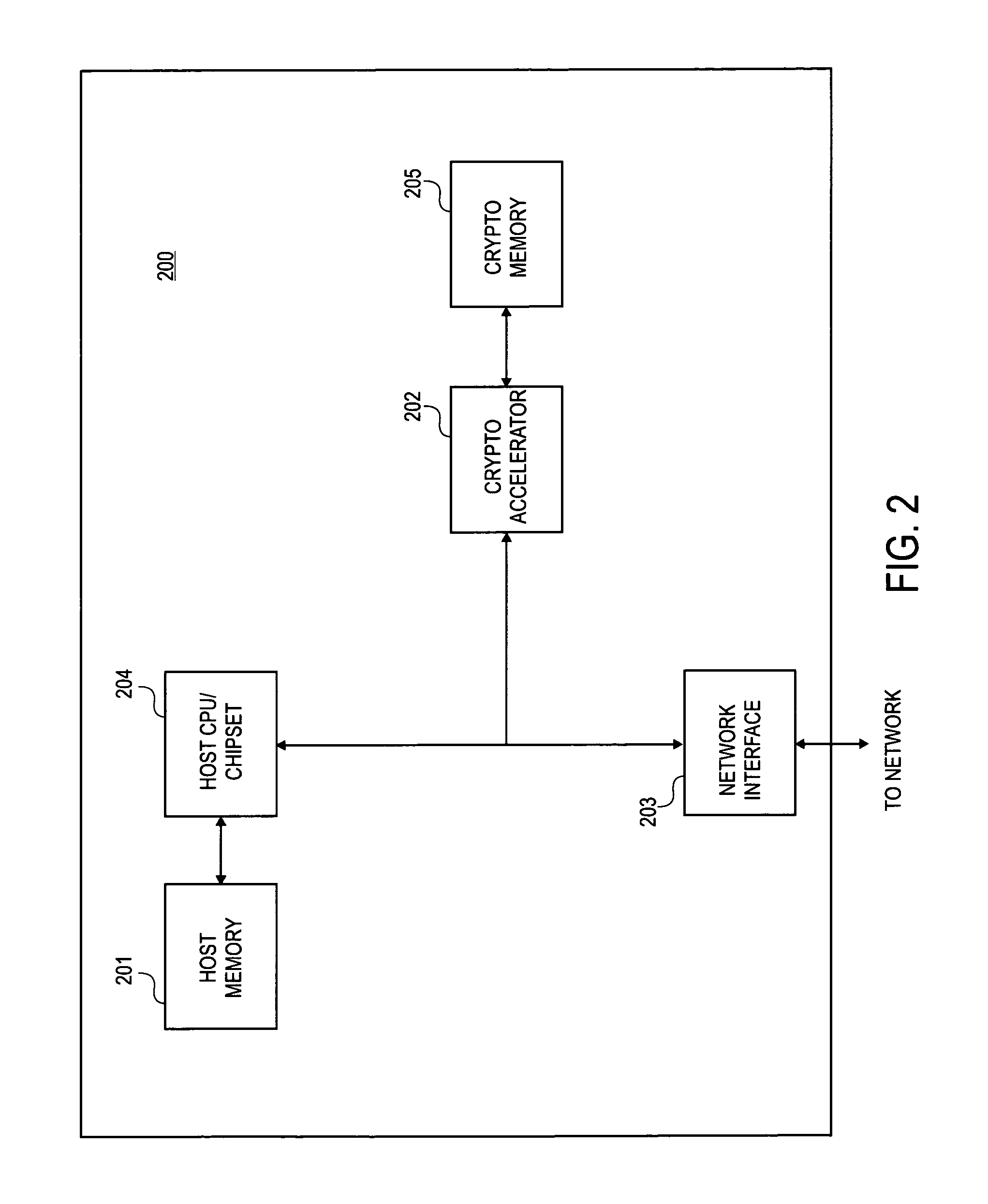

Method and circuit to accelerate IPSec processing

ActiveUS7017042B1Unauthorized memory use protectionHardware monitoringNetwork packetSecurity association

Methods and apparatus' for performing IPSec processing on an IP packet being transmitted onto a network and being received from a network are described. The methods and apparatus' further described perform IPSec processing inline which results in a reduced number of transfers over the system bus, reduced utilization of system memory, and a reduced utilization of the system CPU. An IP packet which requires IPSec processing enters an acceleration device. In one embodiment, the acceleration device is coupled to a security policy database (SPD) and security association database (SAD). IPSec processing is performed at the acceleration device without sending the IP Packet to system memory for processing.

Owner:DIGITAL ARCHWAY +1

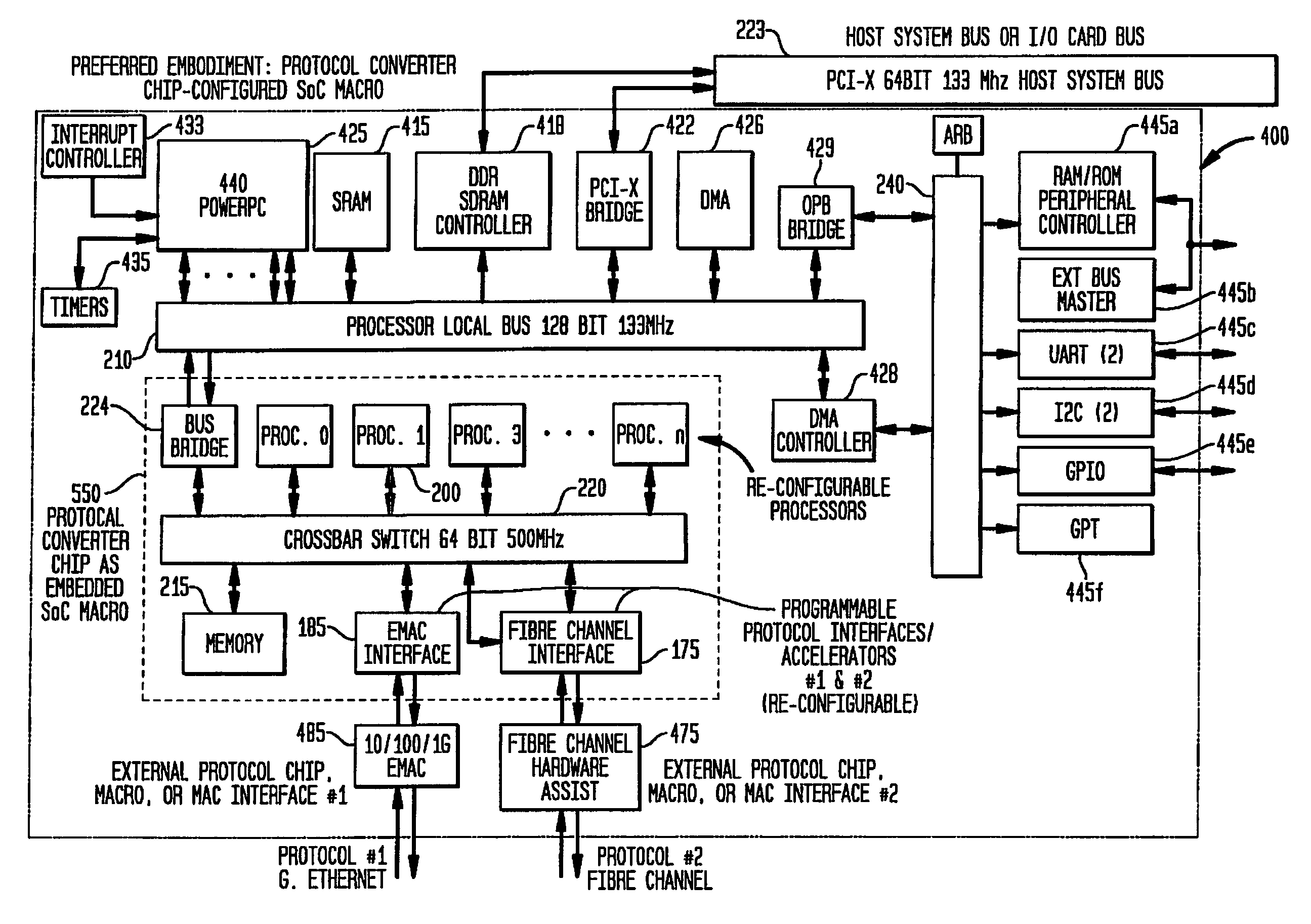

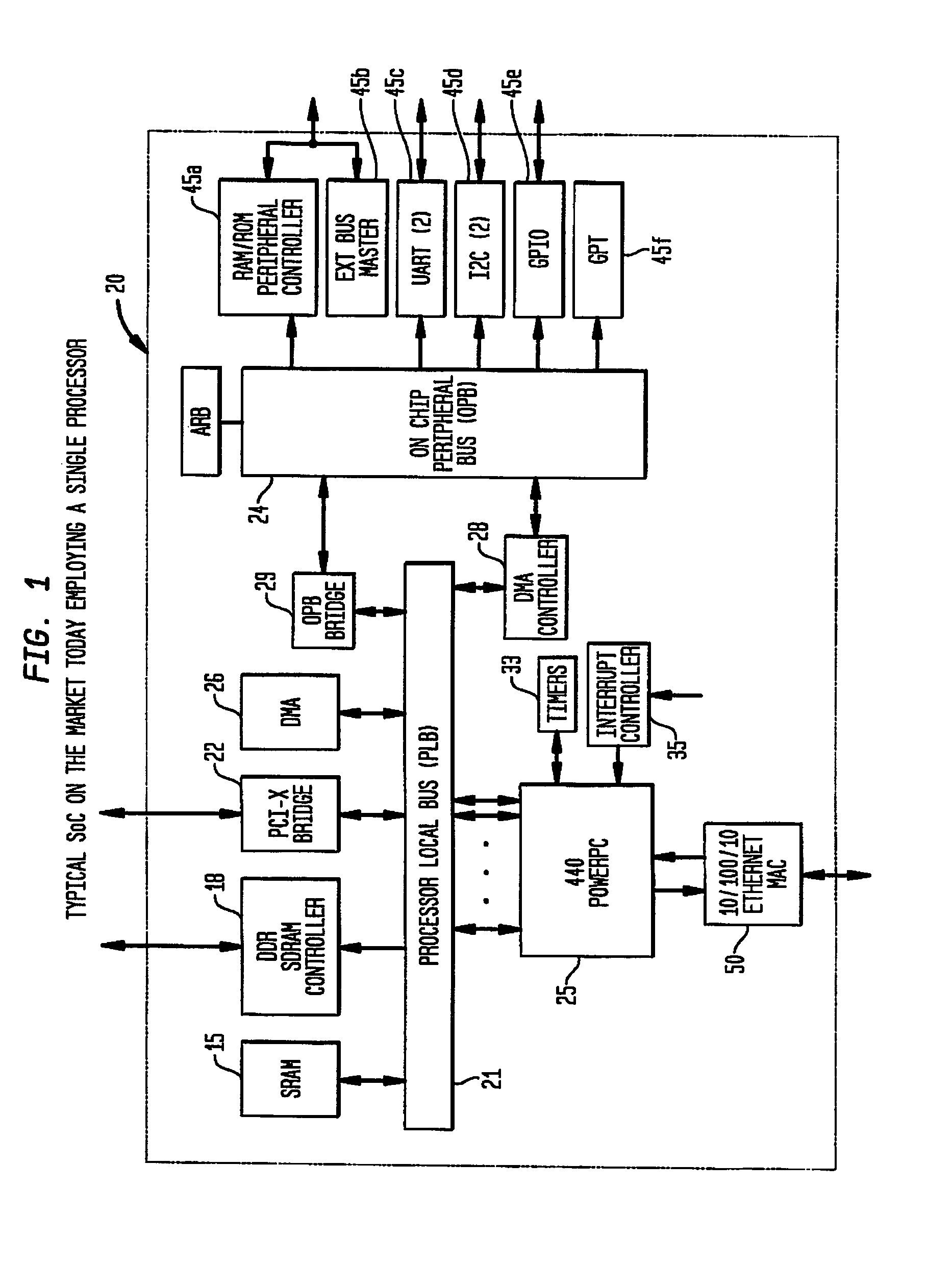

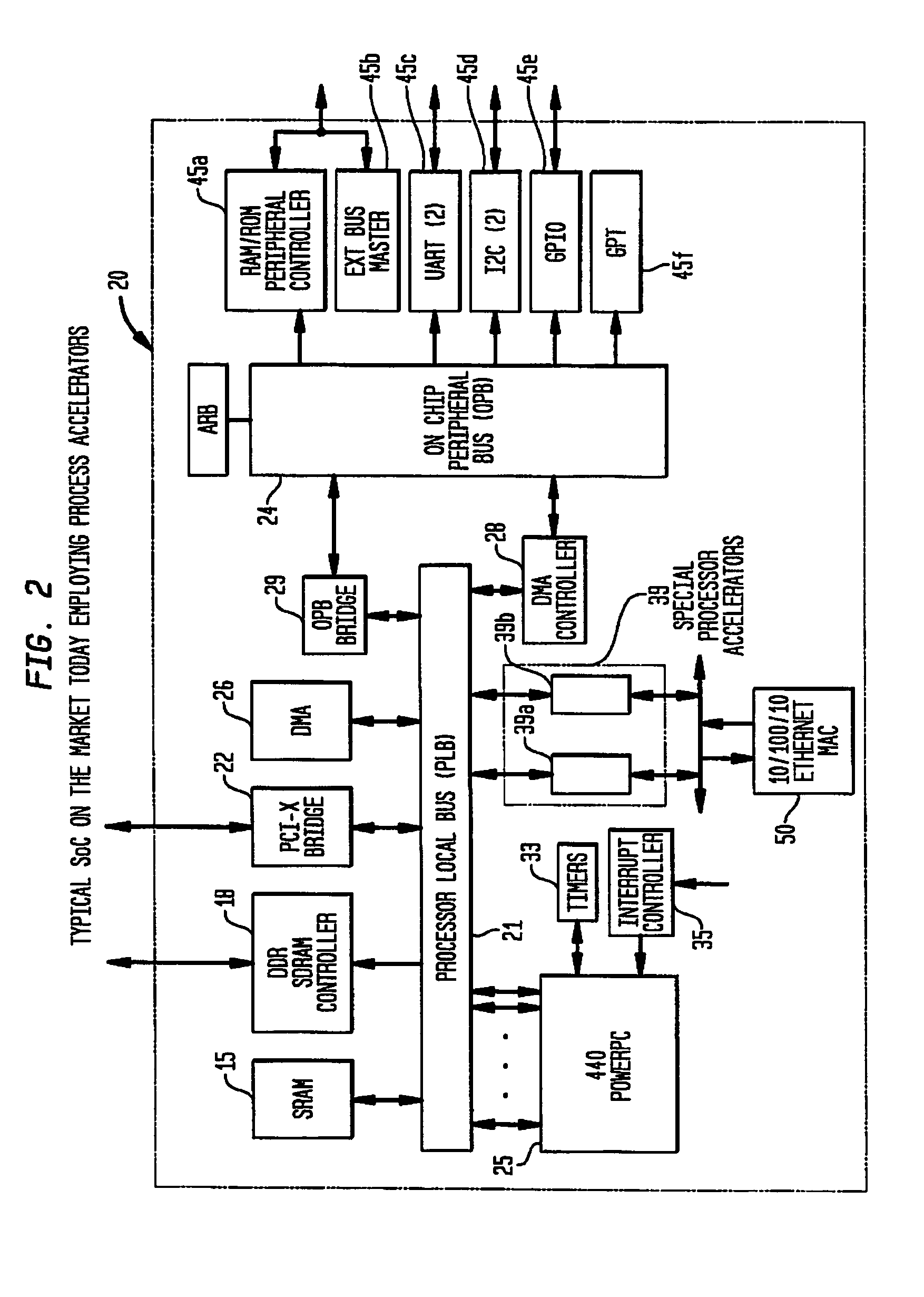

Network processor system on chip with bridge coupling protocol converting multiprocessor macro core local bus to peripheral interfaces coupled system bus

ActiveUS7412588B2Increase the number ofHigh bandwidthMultiple digital computer combinationsConcurrent instruction executionMulti processorCoupling system

A network processor includes a system-onchip (SoC) macro core and functions as a single chip protocol converter that receives packets generating according to a first protocol type and processes the packets to implement protocol conversion and generates converted packets of a second protocol type for output thereof, the process of protocol conversion being performed entirely within the SoC macro core. The process of protocol conversion contained within the SoC macro core does not require the processing resources of a host system. The system-on chip macro core includes a bridge device for coupling a local bus in the protocol converting multiprocessor SoC macro core local bus to peripheral interfaces coupled to a system bus.

Owner:MICROSOFT TECH LICENSING LLC

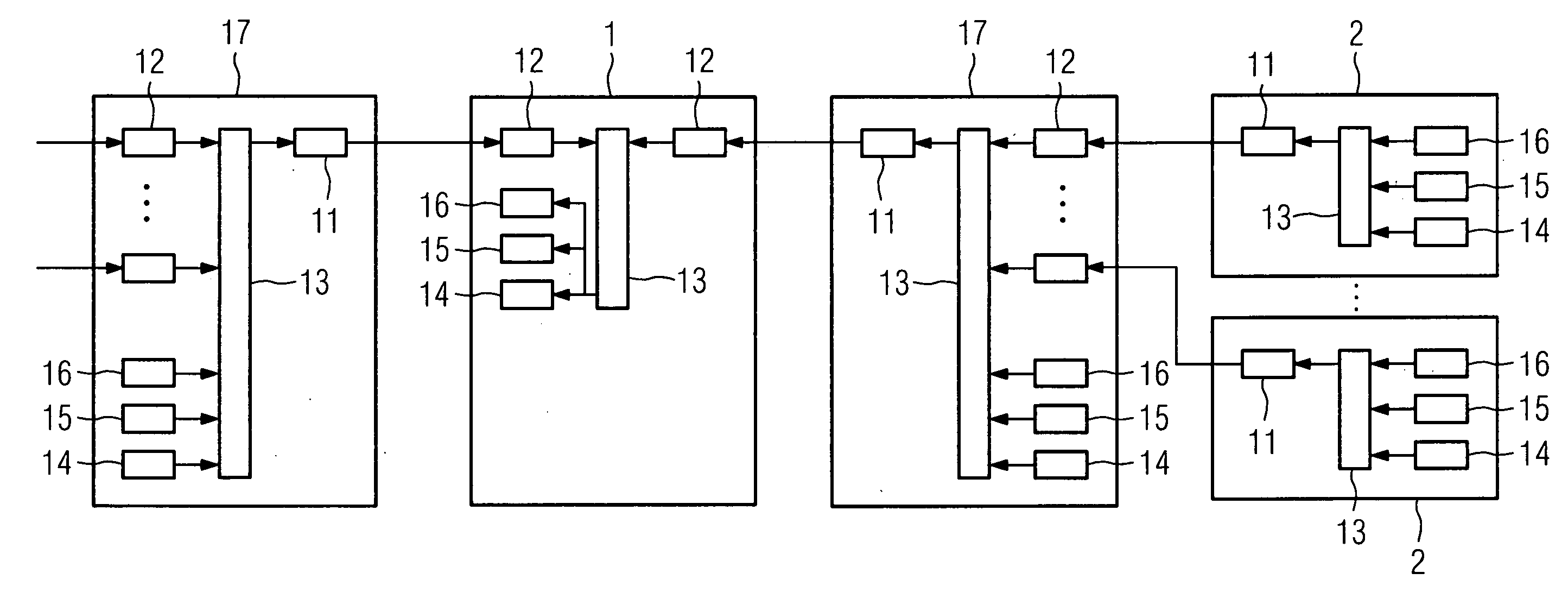

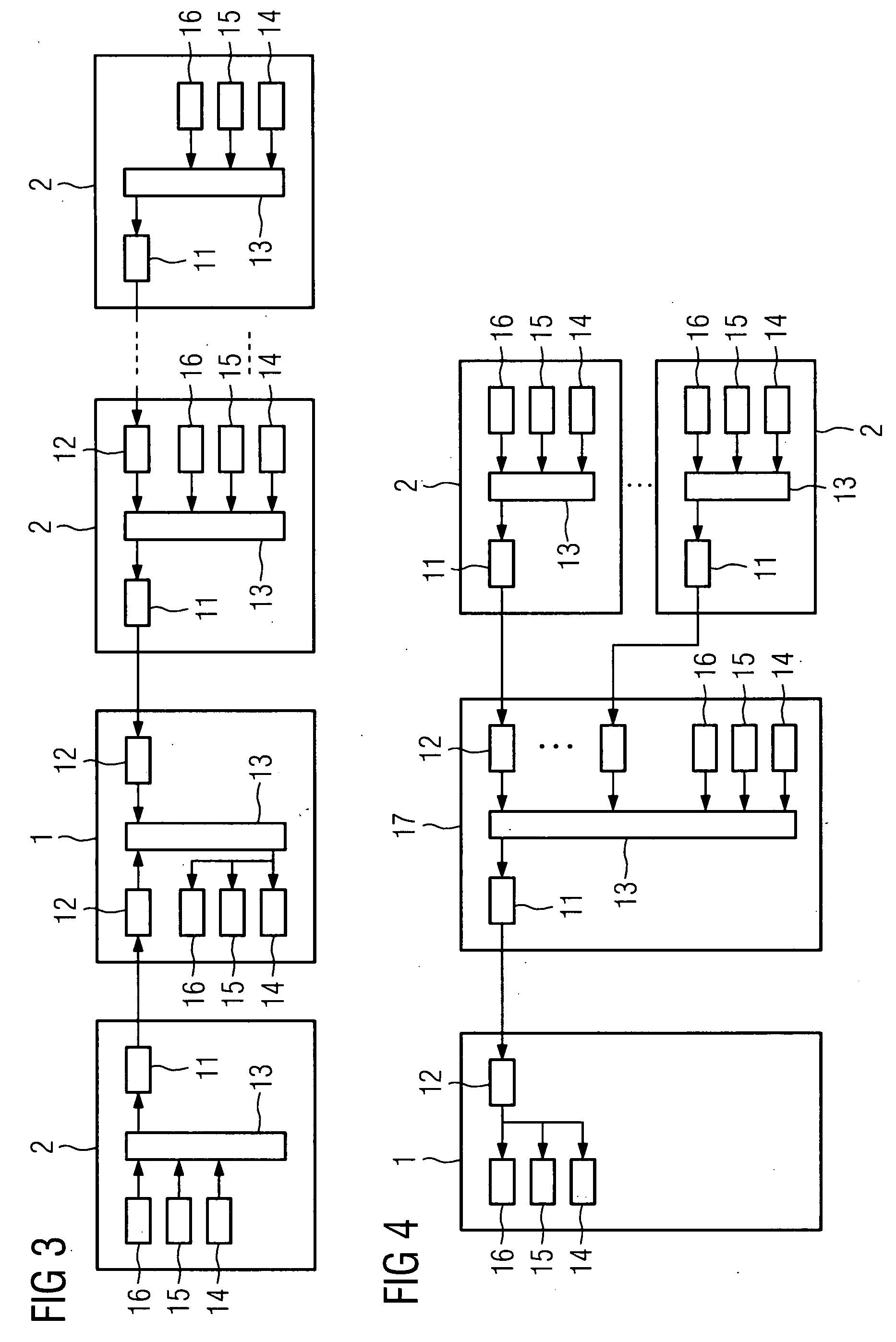

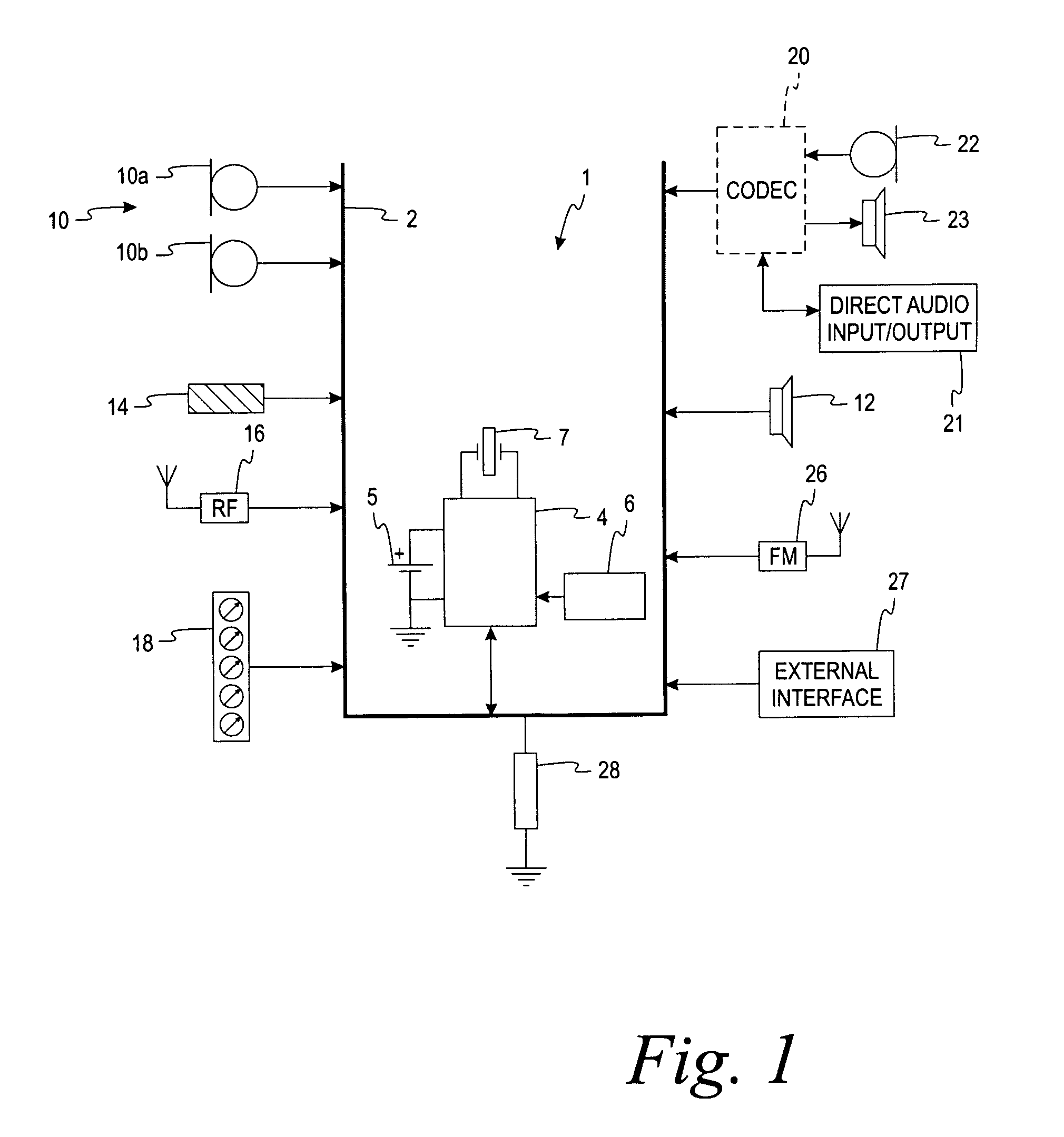

Event signaling between peripheral modules and a processing unit

InactiveUS20080005428A1Reduce loadAvoids possible conflictsTransmission systemsFrequency-division multiplex detailsProcessing elementTransmitter

There is described a method, a bus protocol, a peripheral module, a processing unit, a hub and also to a system consisting of said components, for event signaling between at least one peripheral module and a processing unit by means of a system bus. In this case the data to be transmitted data is encoded into a larger symbol space, from which a standard idle symbol is used in telegram pauses for synchronizing a connection between transmitter and receiver. A message present at the peripheral modules is enabled to be signaled to the processing unit independently of the telegram traffic initiated by the processing unit. This is achieved by a peripheral module wishing to signal an event to the processing unit sending to the processing unit in a telegram pause, instead of the standard idle character, a signaling sequence consisting of an alarm idle symbol and an alarm identifier which contain information about the relevant event as well as the module address of the peripheral module at which the event is present, with the information about the event also being transcoded into the larger symbol space.

Owner:SIEMENS AG

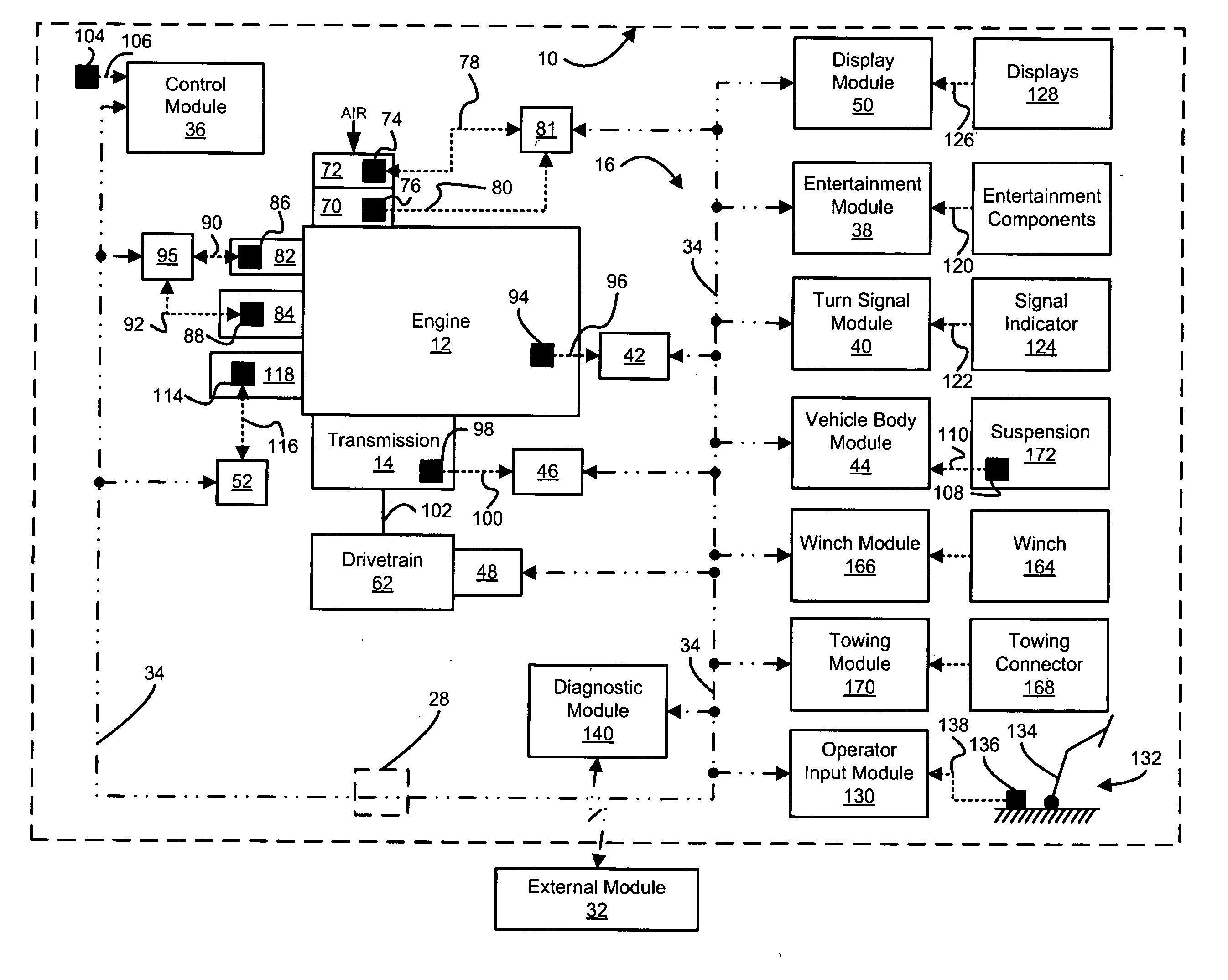

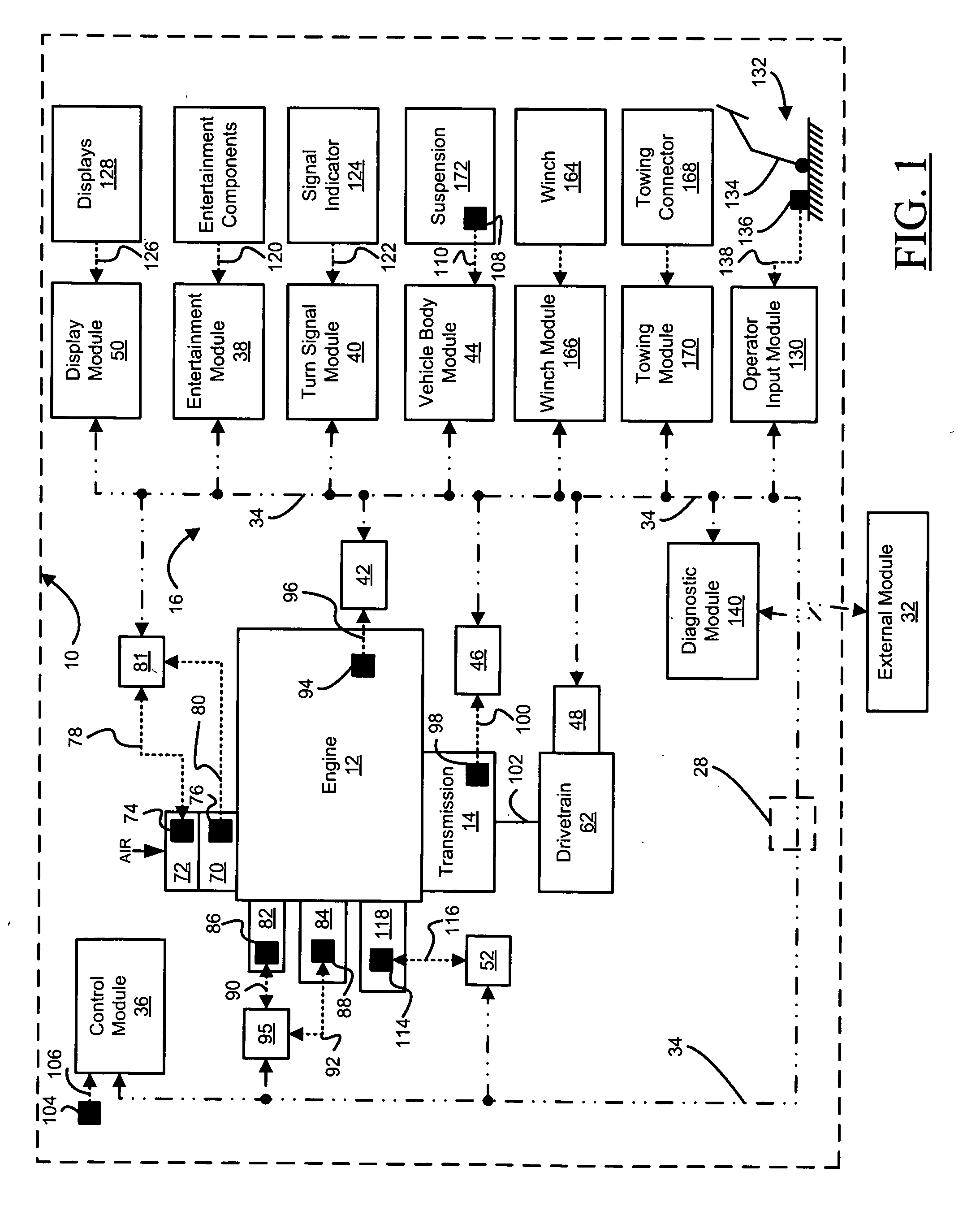

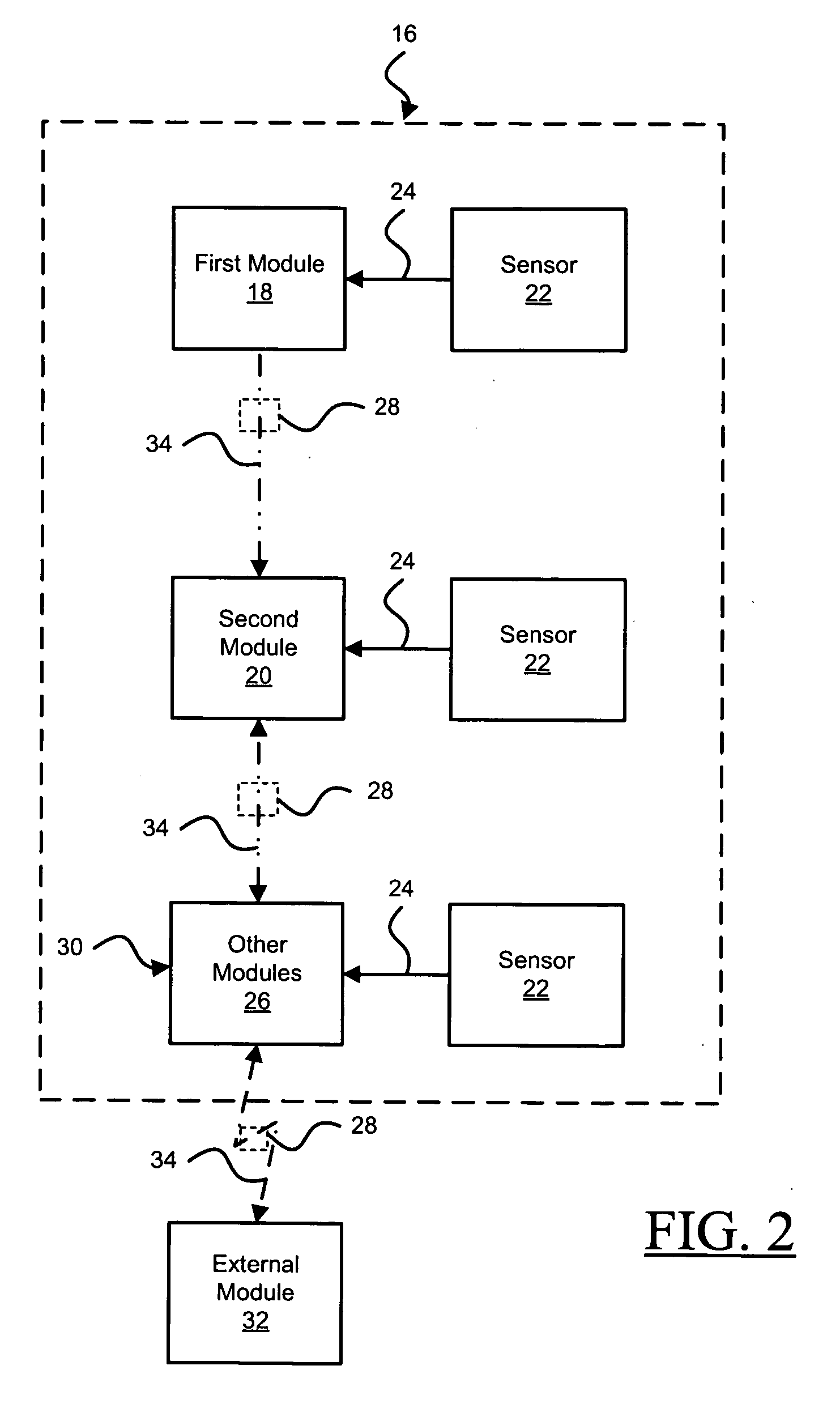

Controller area network based self-configuring vehicle management system and method

A vehicle management system includes a first module having a plurality of functions. The vehicle management system also includes a second module and a system bus. At least the first module and the second module communicate on the system bus. The vehicle management system further includes an identifier based on one of a plurality of vehicle types. When a first vehicle type is identified, a first set of the plurality of functions is utilized based on the identifier associated with the first vehicle type. When a second vehicle type is identified, a second set of the plurality of functions is utilized based on the identifier associated with the second vehicle type.

Owner:POLARIS IND INC

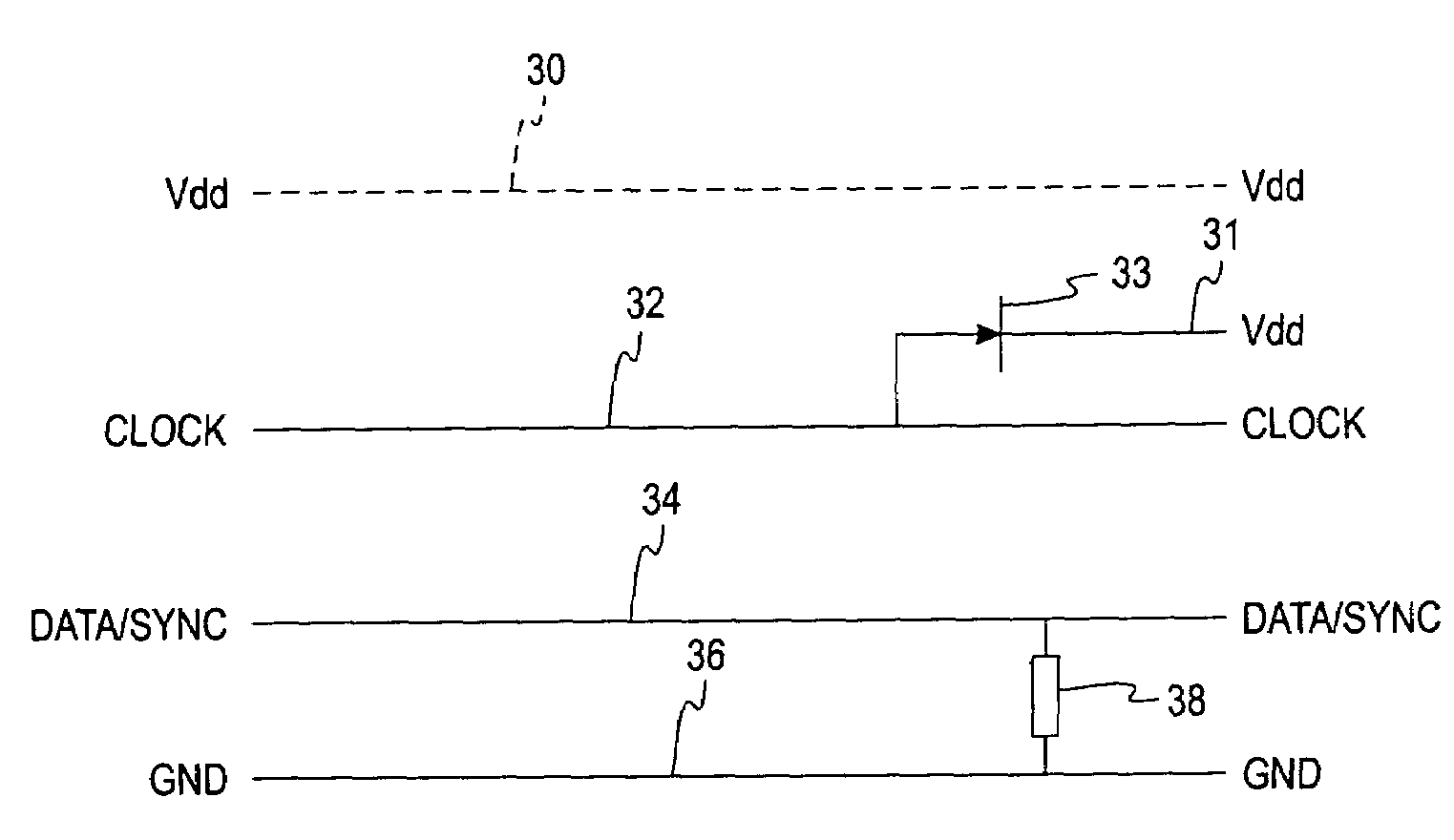

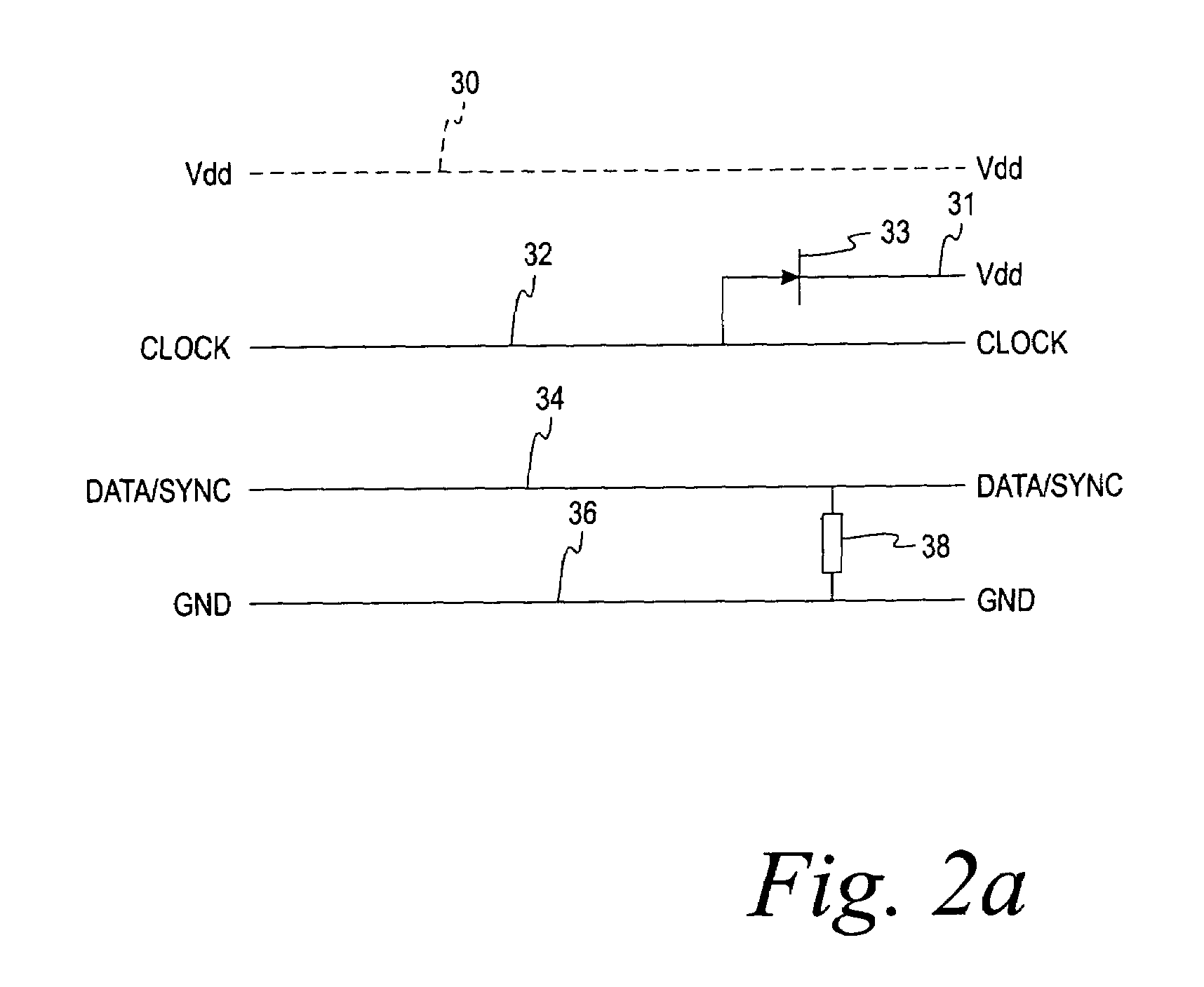

Digital system bus for use in low power instruments such as hearing aids and listening devices

InactiveUS7292876B2Avoids compromising bus speedReduce power consumptionEar supported setsSubstation equipmentScalable systemLow voltage

A low-voltage, low-power, synchronous, bidirectional, time-multiplexed, serial communication, scalable system bus carrying a number of signals over a fewer number of wires between a master device and peripheral devices or between peripheral devices. One of the wires carries a composite digital signal that includes a data signal and a synchronizing signal, though other combinations are contemplated. The system bus can support more peripheral devices than there are available time slots, and supports interrupt polling and servicing. In addition, peripheral devices that include an electro-mechanical or electro-acoustical component connected to the system bus can also communicate directly to each other without using the system bus. The system bus can be implemented in low voltage, low power devices, including listening devices such as hearing instruments and headsets, portable telephones, and personal digital assistants.

Owner:SONION NEDERLAND

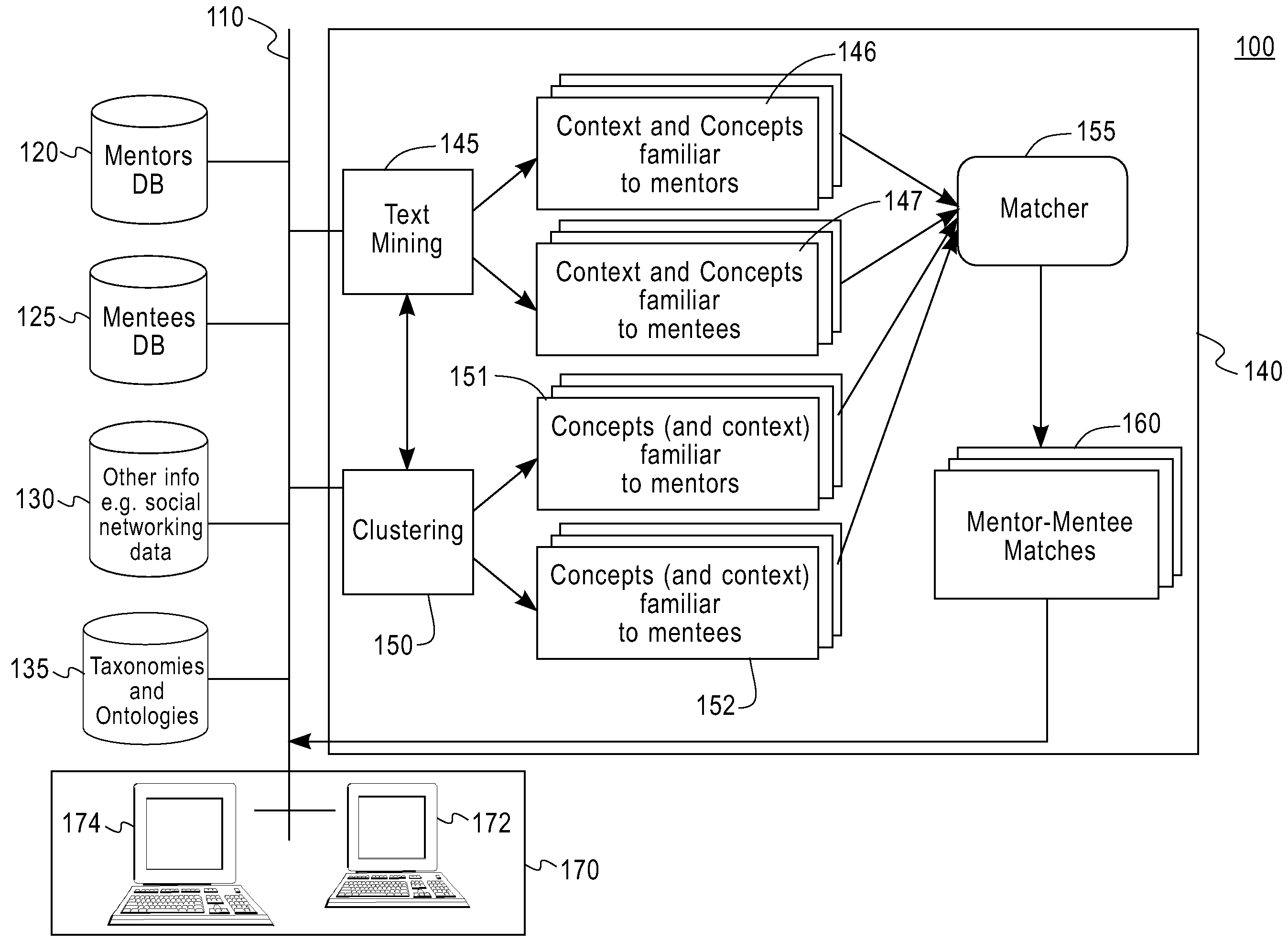

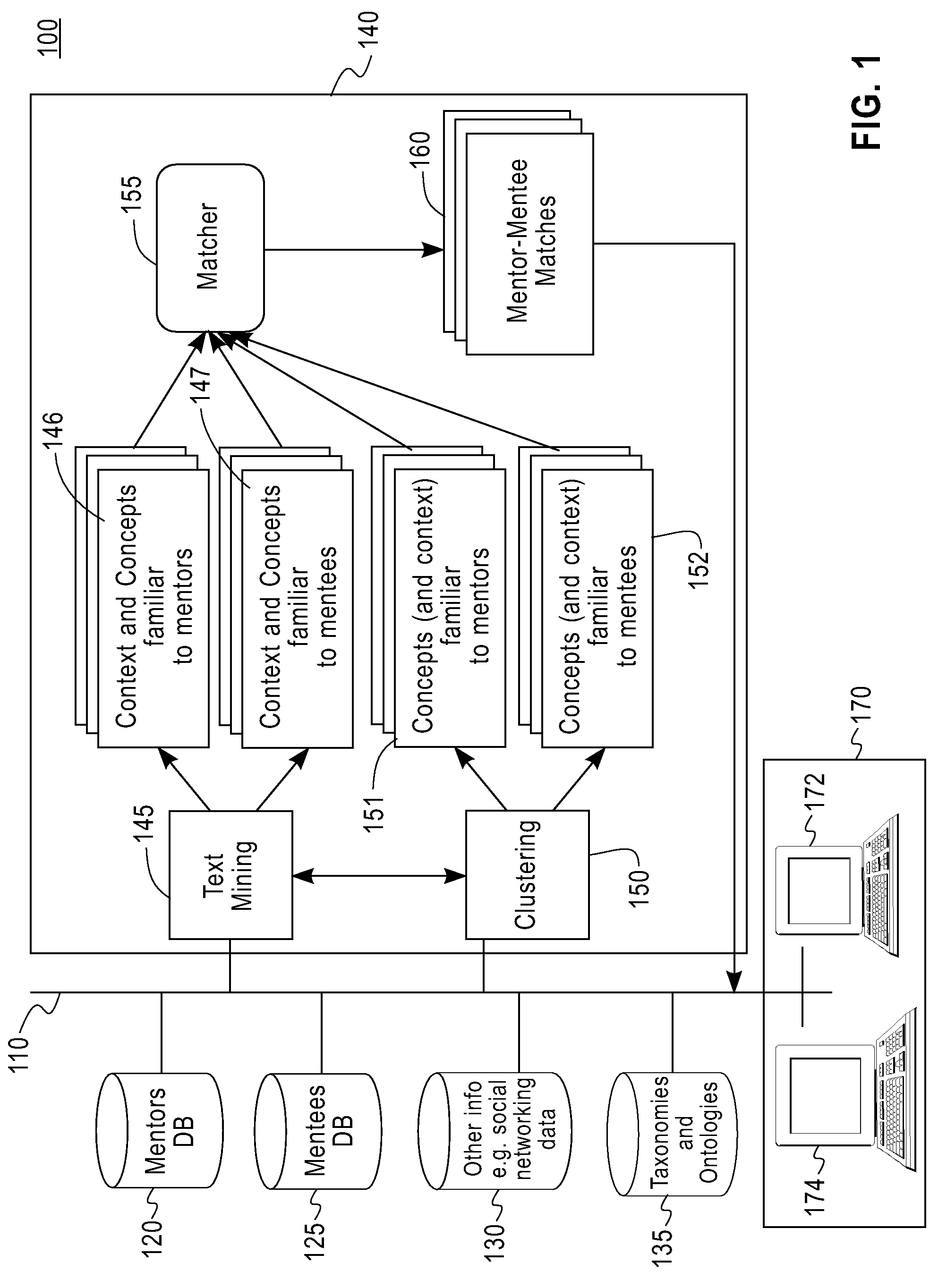

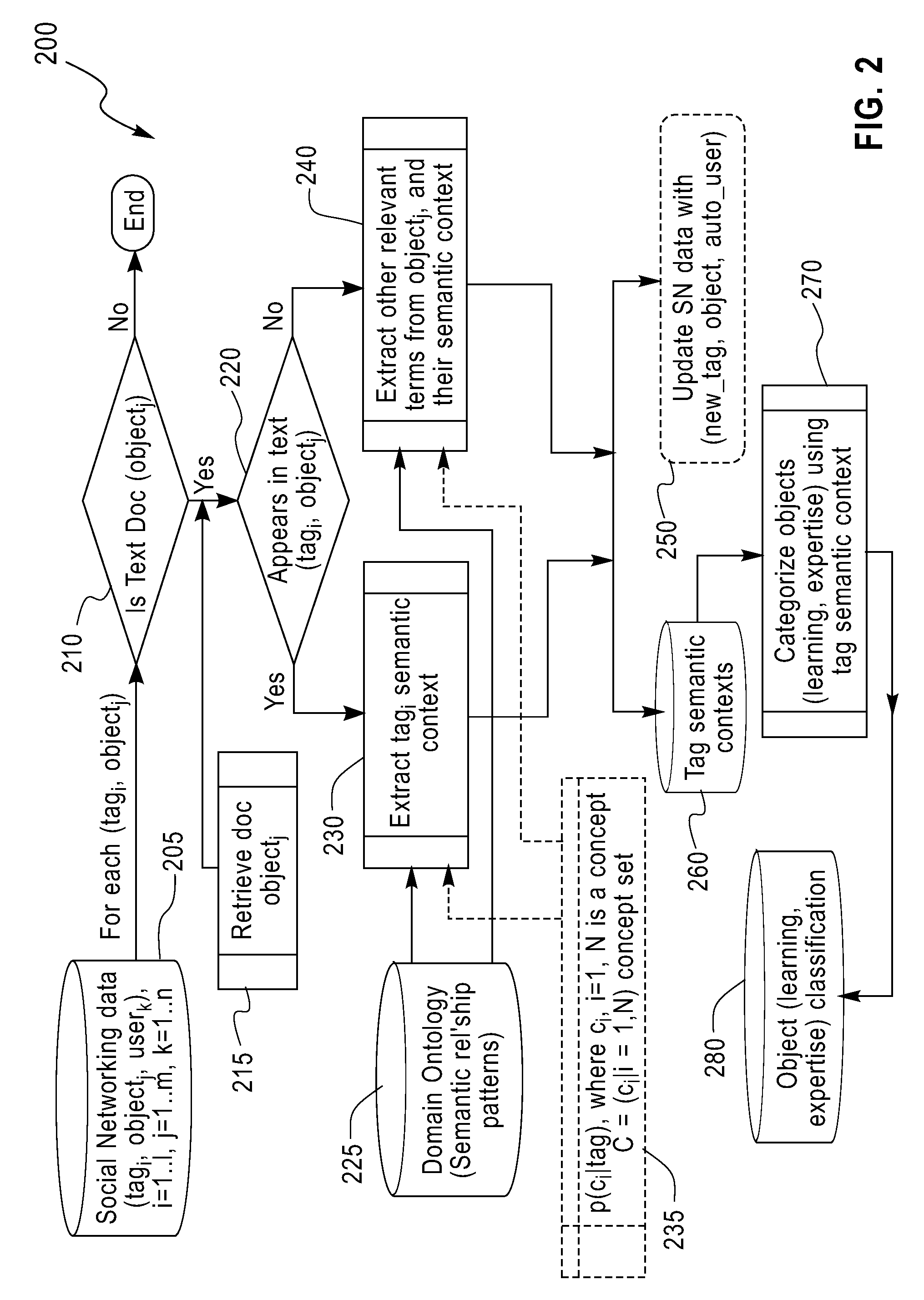

System and method for facilitating skill gap analysis and remediation based on tag analytics

InactiveUS20080313000A1Improve matchMultiprogramming arrangementsOffice automationText miningUser input

This invention includes a workforce management system having a system bus, at least one database in communication with the system bus that includes data representative of workforce employees, and social networking data associated with the employees. A matching functional unit includes a text mining function for mining contextual information from the at least one database to generate context labels for an employee, a clustering function for generating concept labels for an employee, and a matching function that sorts and matches employees by the labels in accordance with a matching criteria. A user interface provides user input to the support operation of the workforce management system.

Owner:IBM CORP

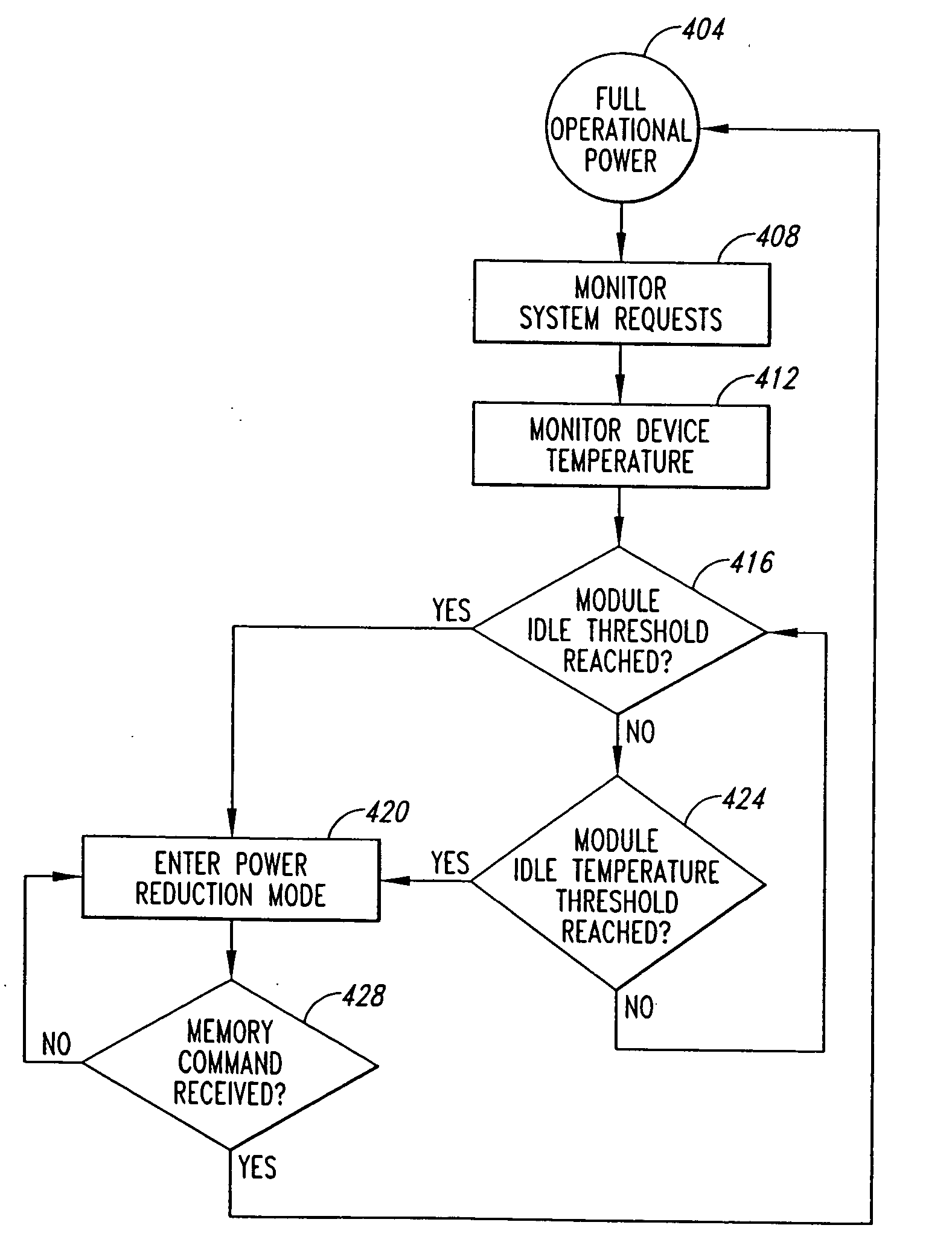

System and method for selective memory module power management

InactiveUS20060206738A1Reduced responsivenessReduce usageEnergy efficient ICTVolume/mass flow measurementActivity levelSystem usage

A memory module includes a memory hub that monitors utilization of the memory module and directs devices of the memory module to a reduced power state when the module is not being used at a desired level. System utilization of the memory module is monitored by tracking system usage, manifested by read and write commands issued to the memory module, or by measuring temperature changes indicating a level of device activity beyond normal refresh activity. Alternatively, measured activity levels can be transmitted over a system bus to a centralized power management controller which, responsive to the activity level packets transmitted by remote memory modules, direct devices of those remote memory modules to a reduced power state. The centralized power management controller could be disposed on a master memory module or in a memory or system controller.

Owner:ROUND ROCK RES LLC

PCI Express-Compatible Controller And Interface For Flash Memory

InactiveUS20090049222A1Improve performanceImprove scalabilityRead-only memoriesDigital storageFlash memory controllerPCI Express

A PCI Express-compatible flash device can include one or more flash memory modules, a controller, and an ExpressCard interface. The controller can advantageously provide PCI Express functionality as well as flash memory operations, e.g. writing, reading, or erasing, using the ExpressCard interface. A PIO interface includes sending first and second memory request packets to the flash device. The first memory request packet includes a command word setting that prepares the flash device for the desired operation. The second memory request packet triggers the operation and includes a data payload, if needed. A DMA interface includes sending the second memory request from the flash device to the host, thereby triggering the host to release the system bus for the DMA operation.

Owner:SUPER TALENT TECH CORP

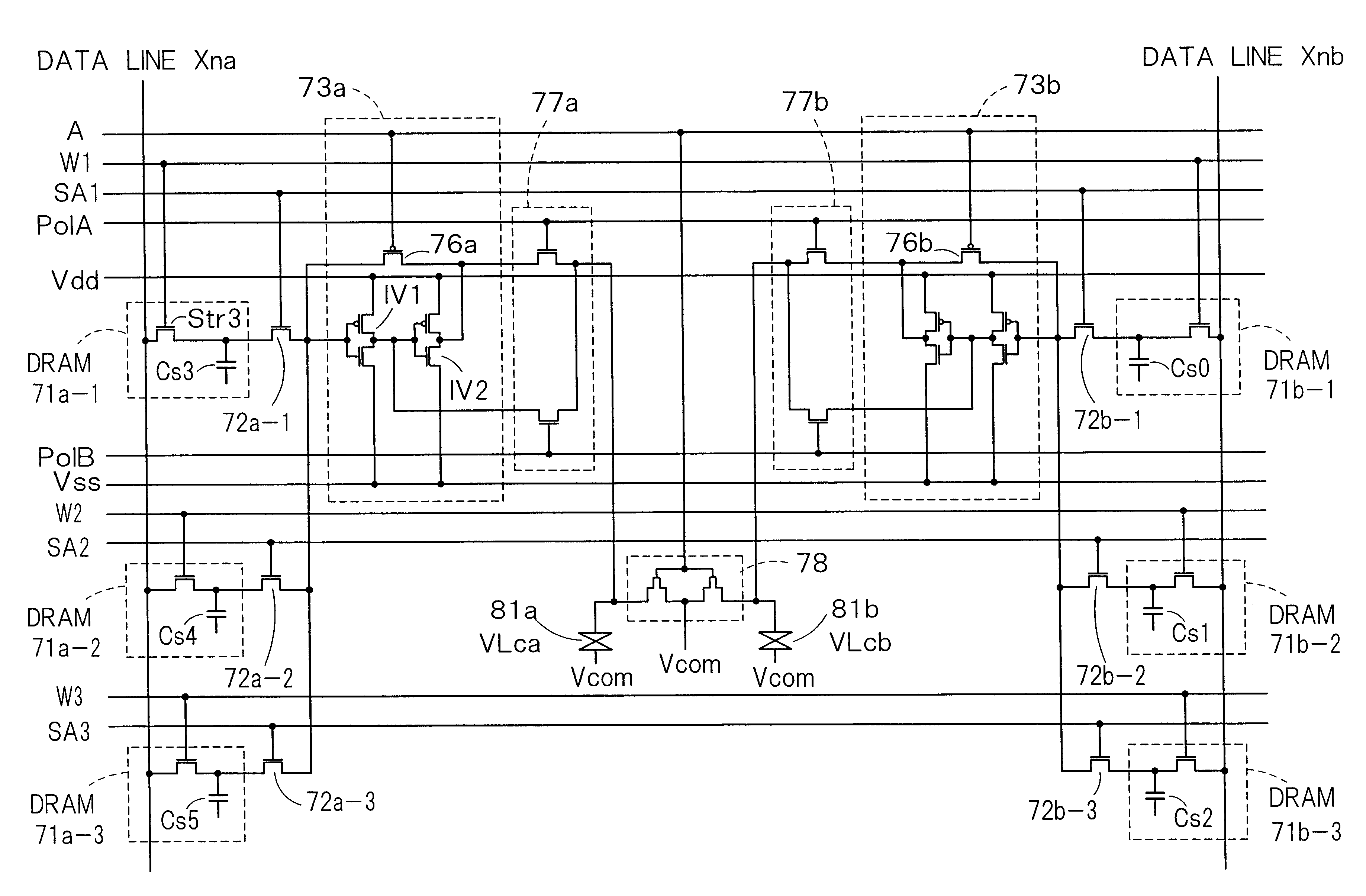

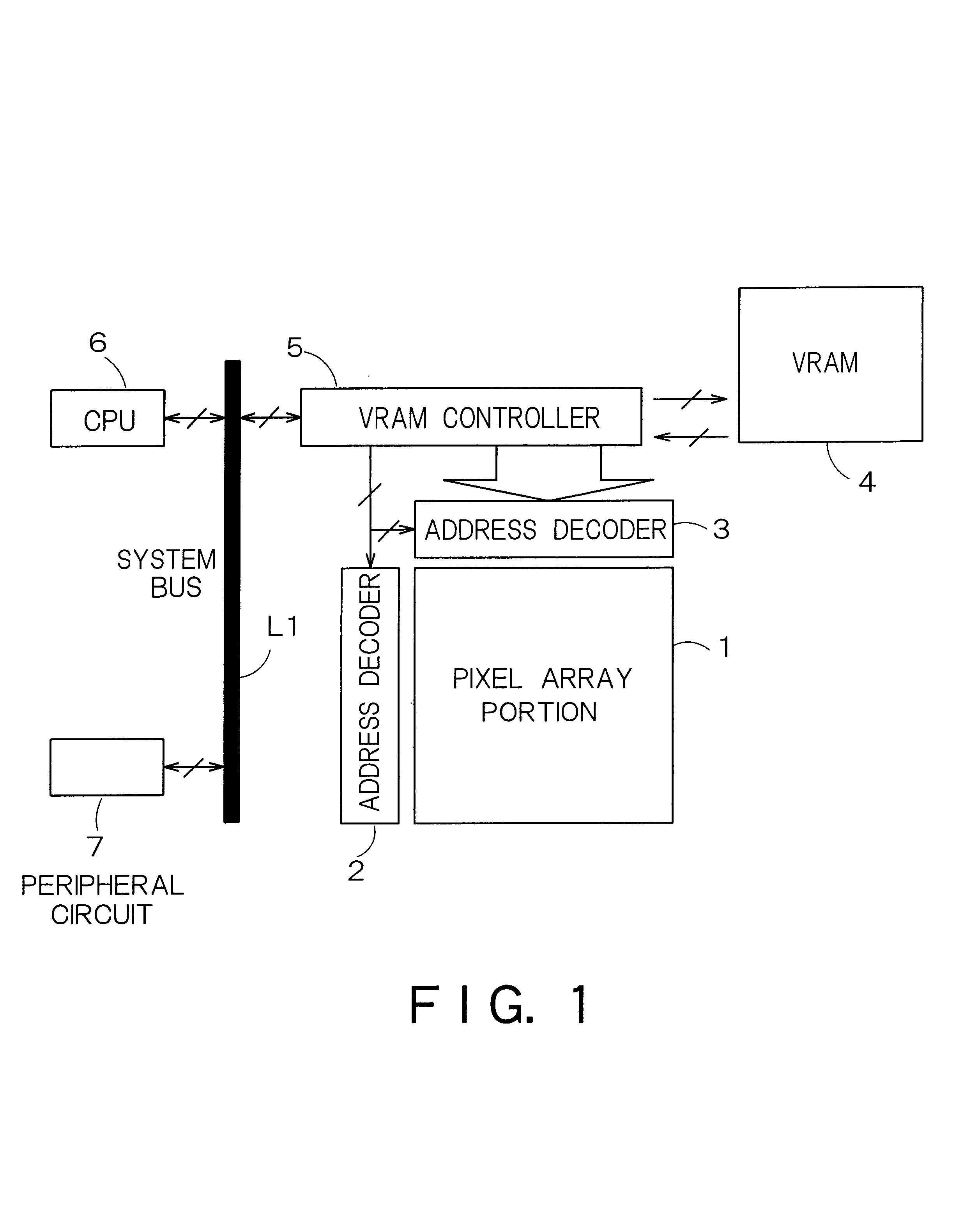

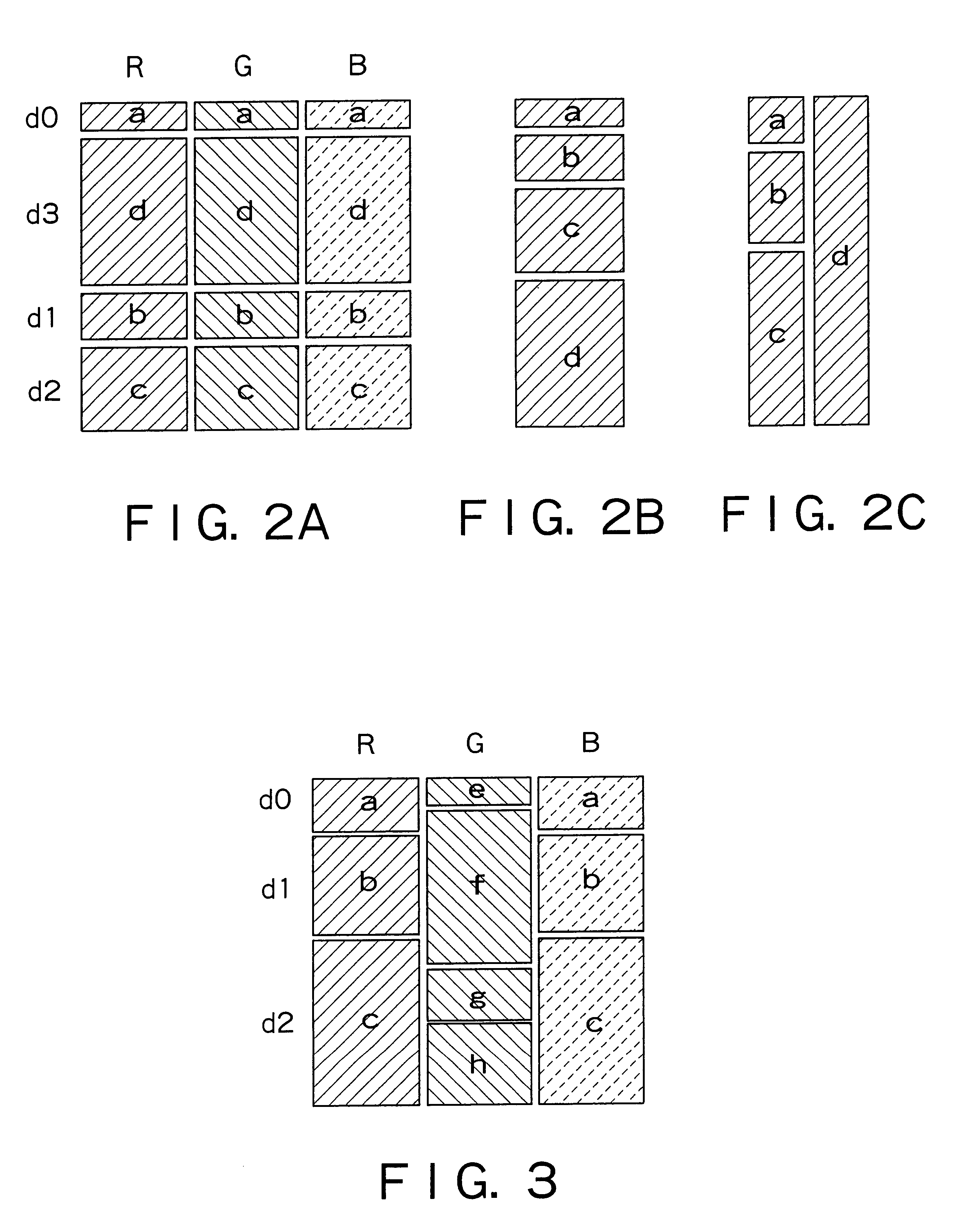

Display apparatus and driving method thereof

InactiveUS20020075211A1Static indicating devicesNon-linear opticsAddress decoderLiquid-crystal display

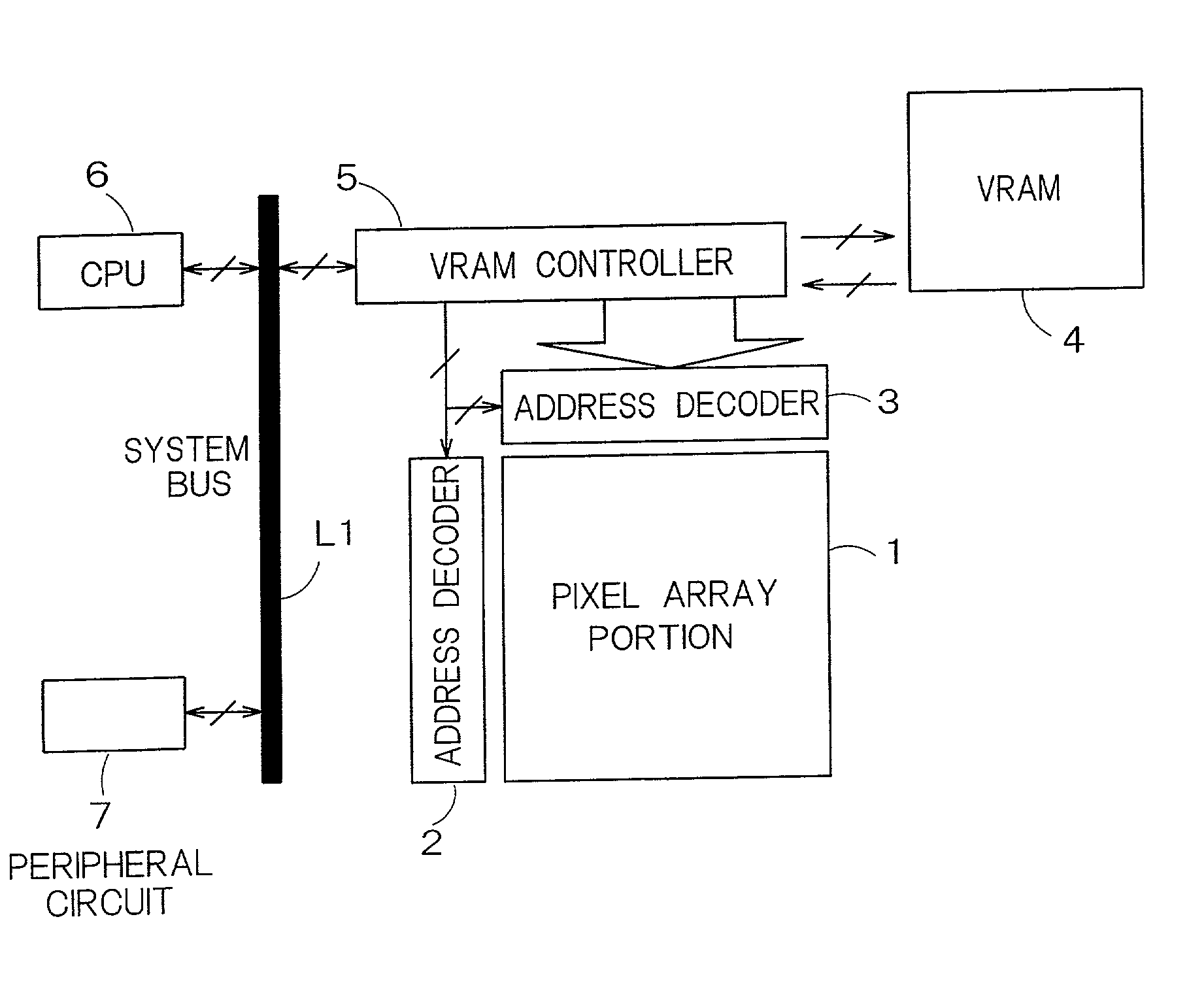

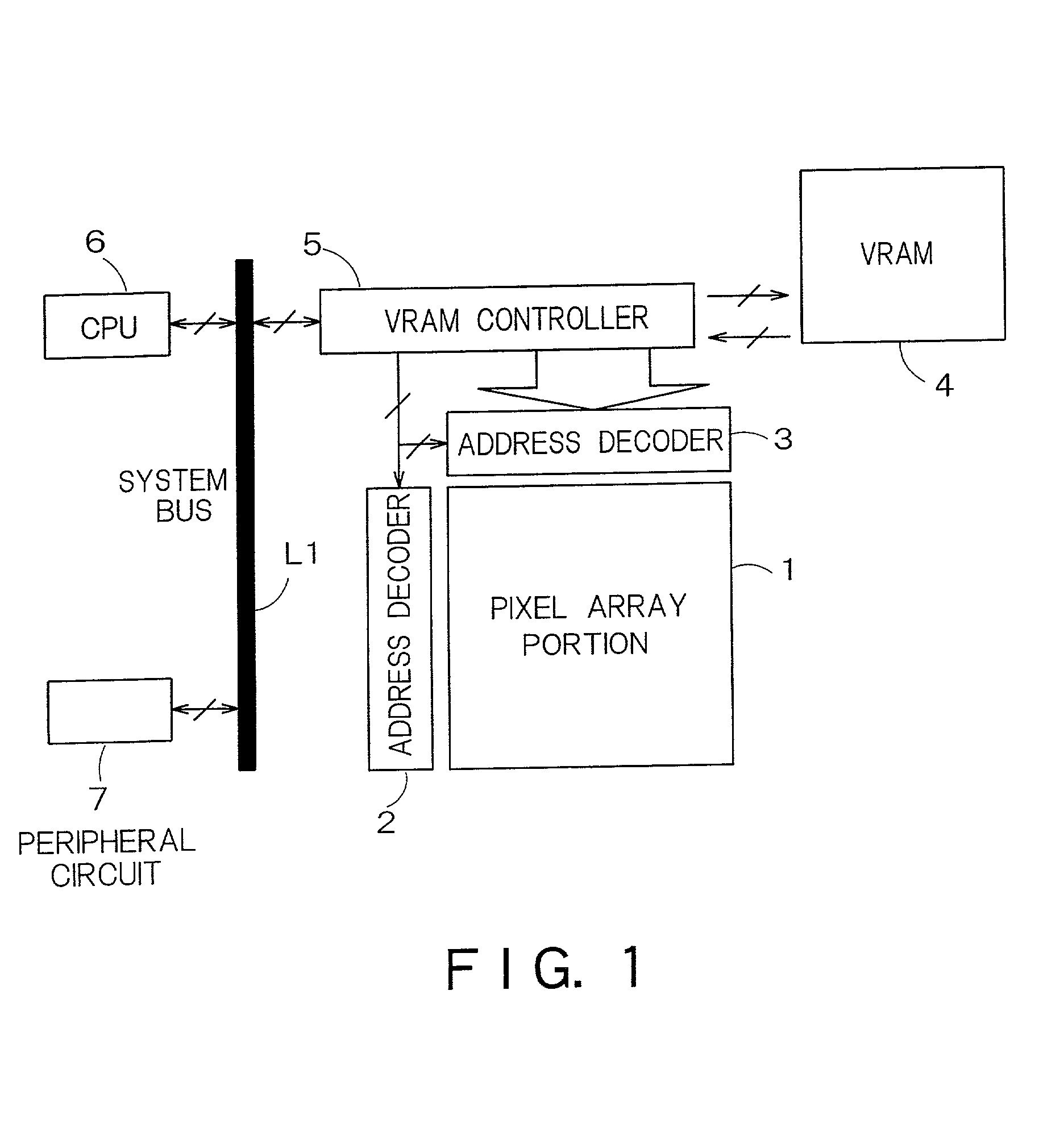

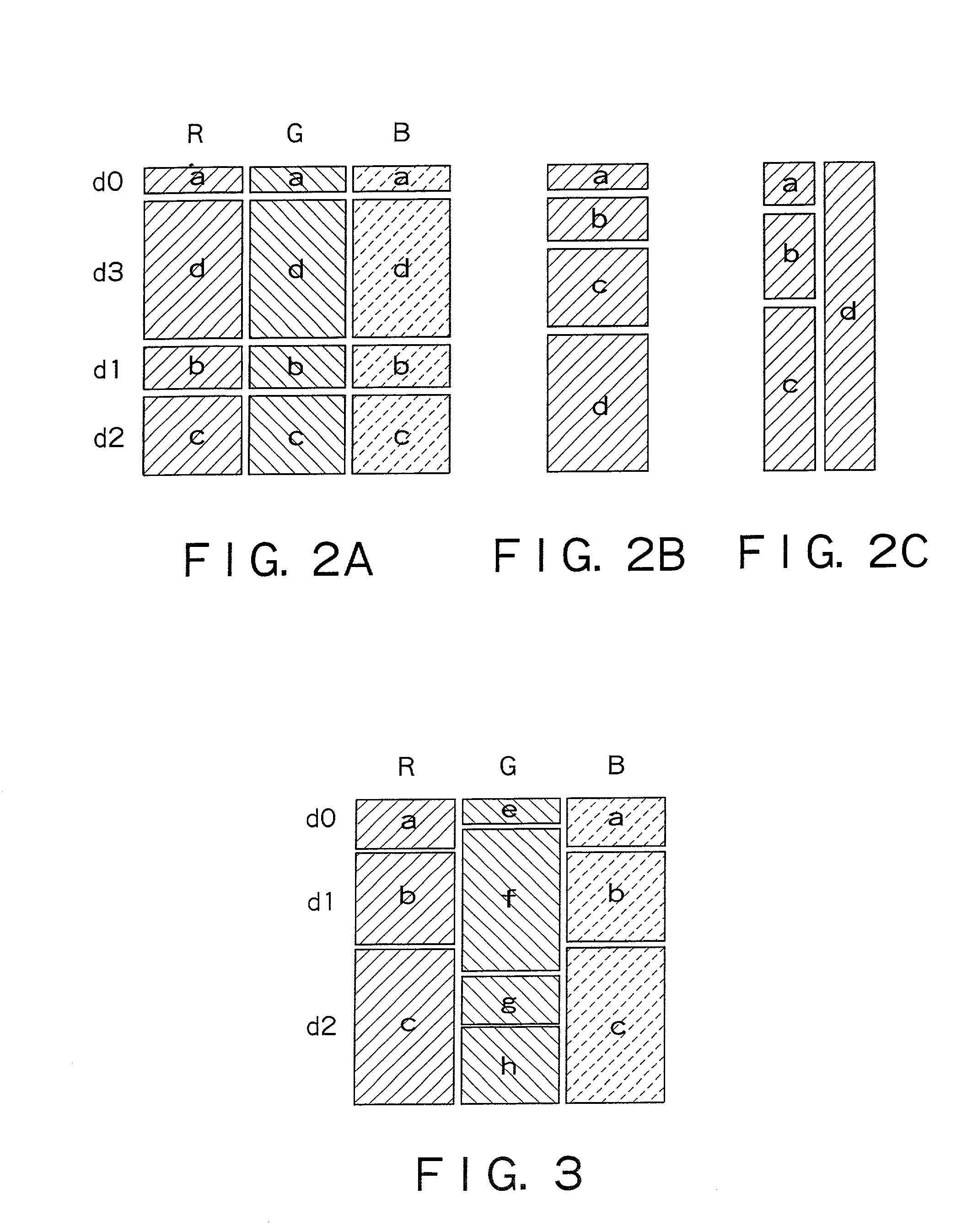

A liquid crystal display device which can reduce power consumption and can be miniaturized. The liquid crystal display device according to the present invention includes a pixel array portion, an address decoder, a display memory (VRAM), and a VRAM controller, and transmits / receives a signal to / from a CPU and a peripheral circuit through a system bus. The pixel array portion has an area gradation pixel structure in which each pixel is composed of a plurality of one-bit memories. The entire pixel array portion is divided into pixel blocks each of which consists of a plurality of pixels, and the one-bit memory is rewritten in units of block. The one-bit memory has a double-word line structure.

Owner:JAPAN DISPLAY CENTRAL CO LTD

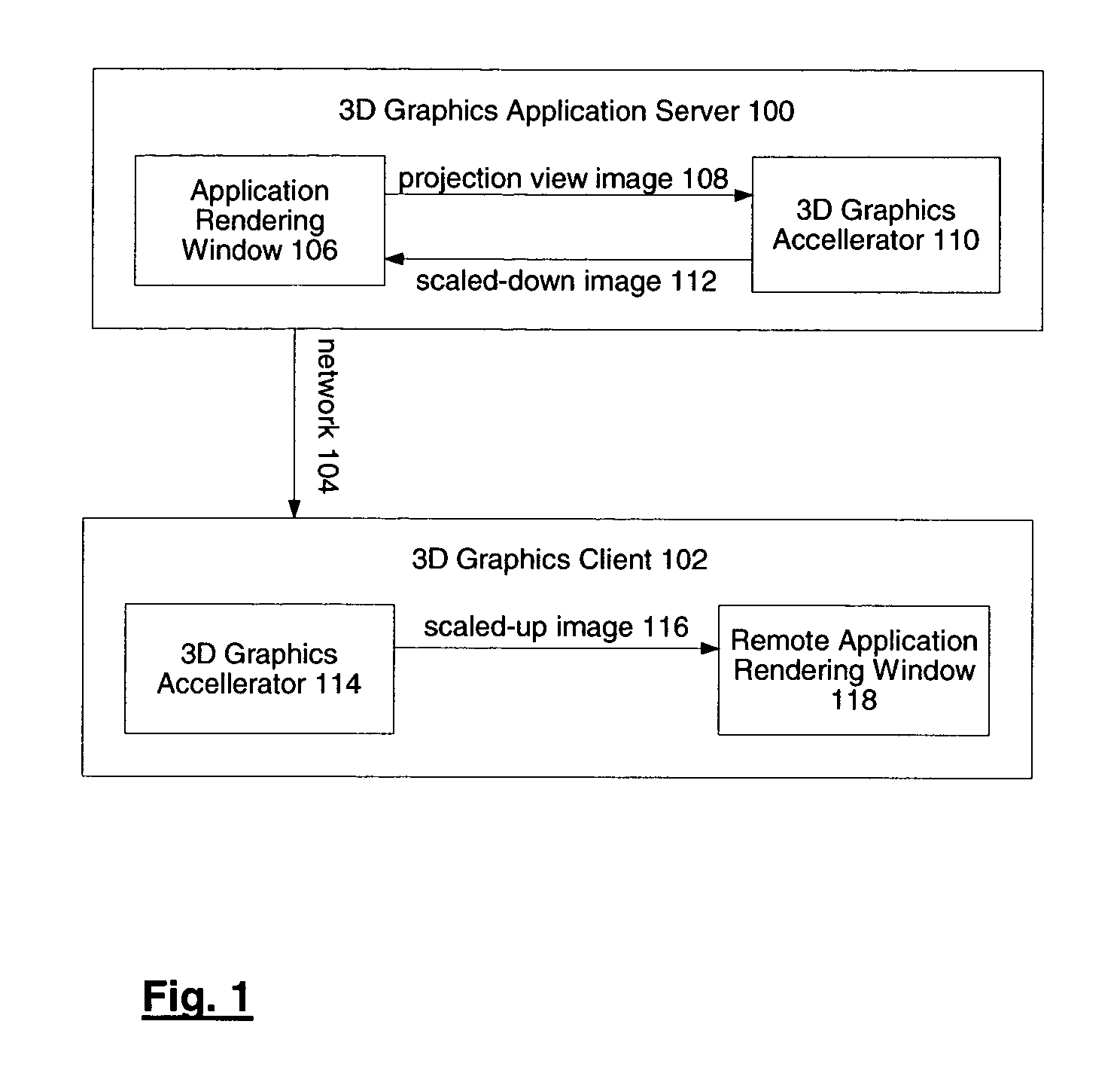

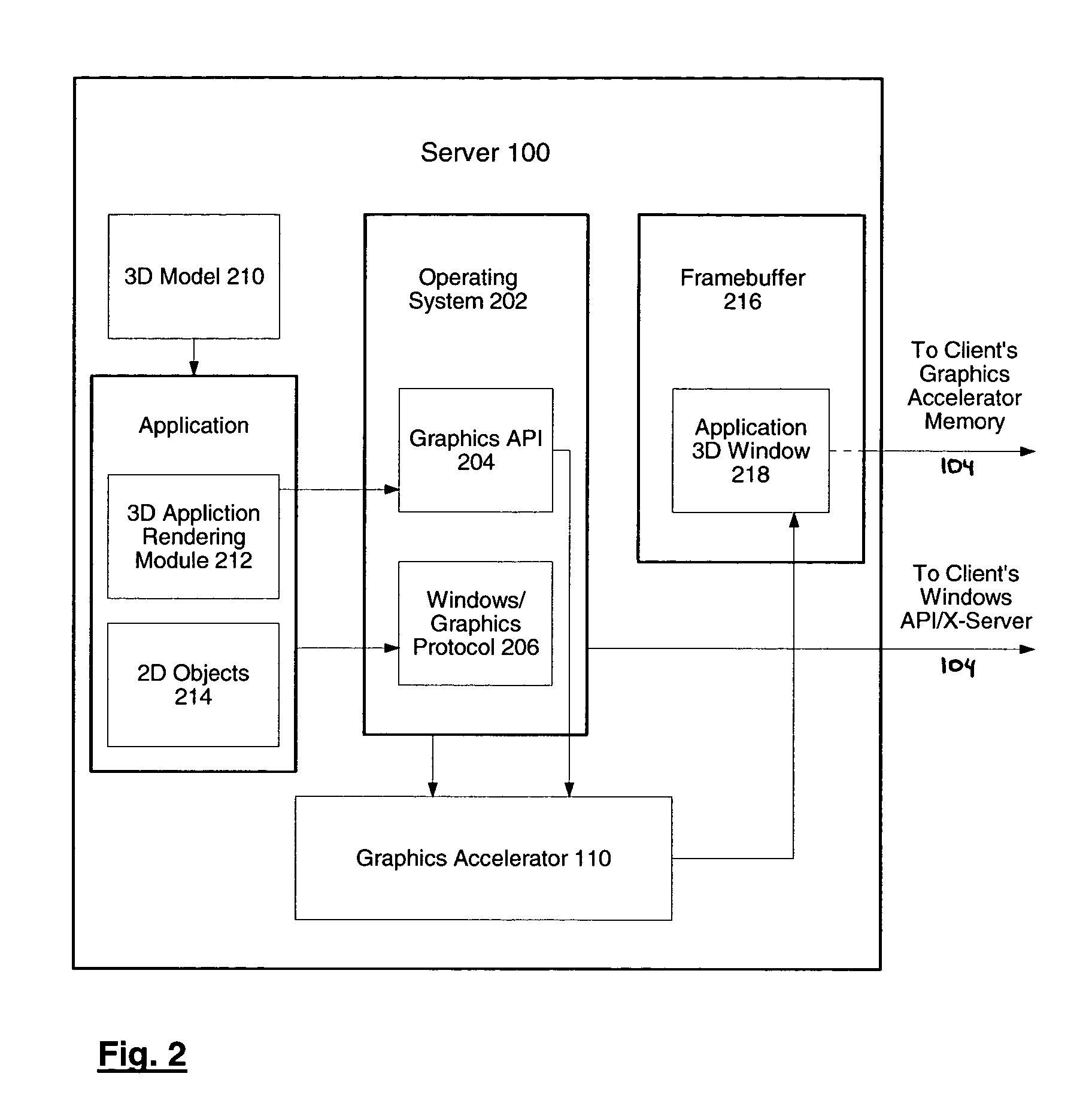

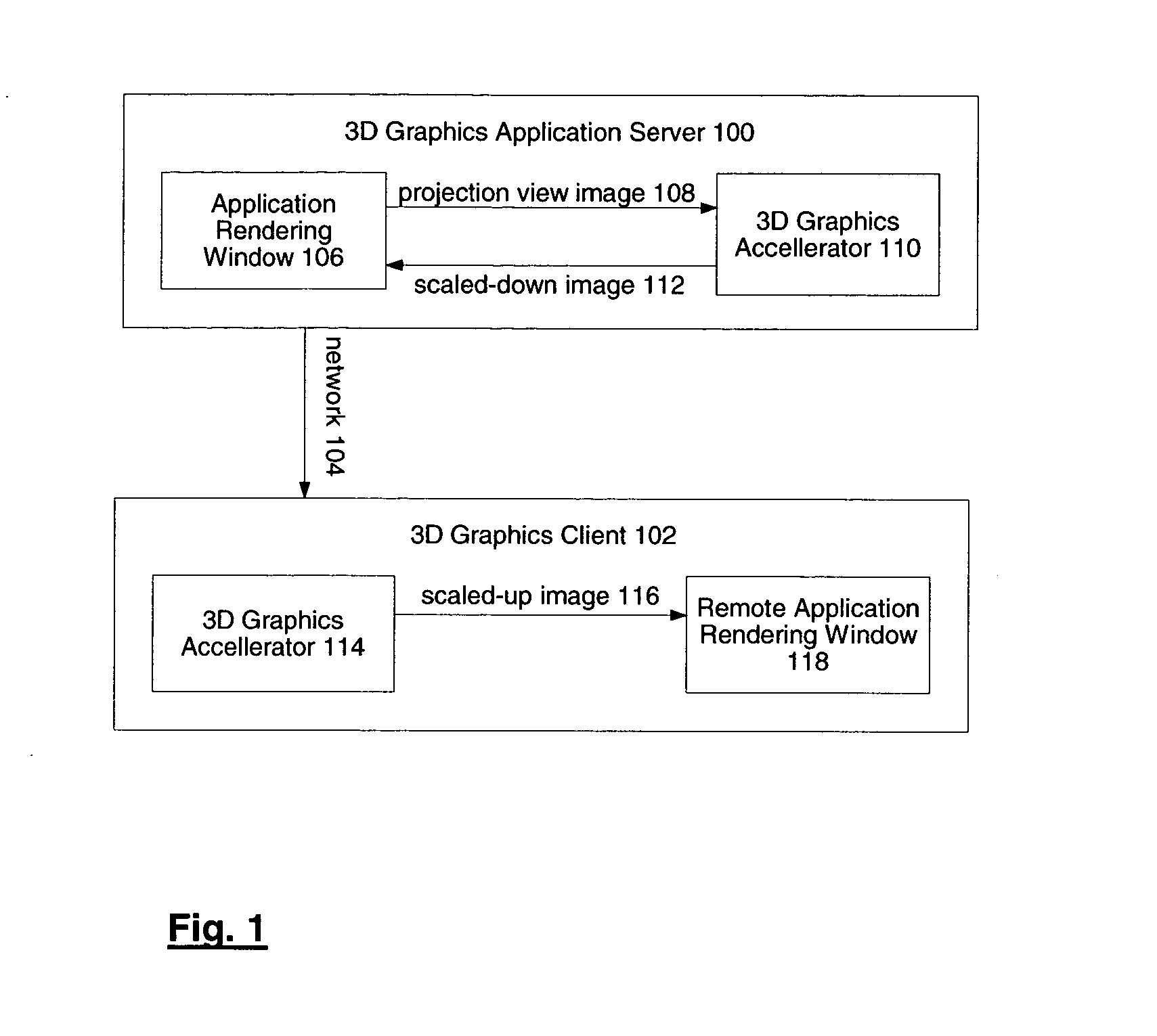

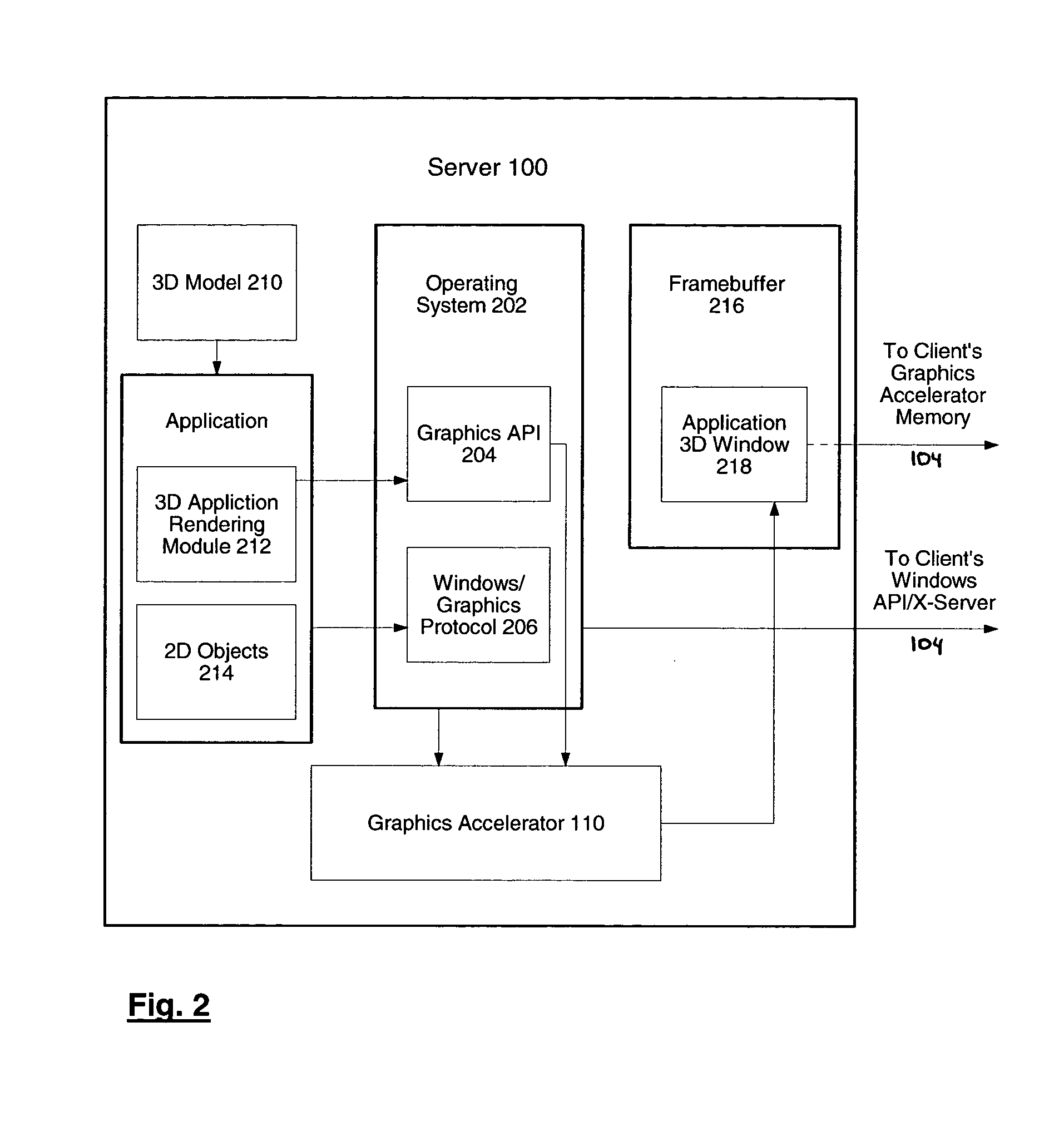

System and method for network transmission of graphical data through a distributed application

InactiveUS7076735B2Reduce network bandwidth requirementsCathode-ray tube indicatorsImage data processing detailsGraphic cardNetworked Transport of RTCM via Internet Protocol

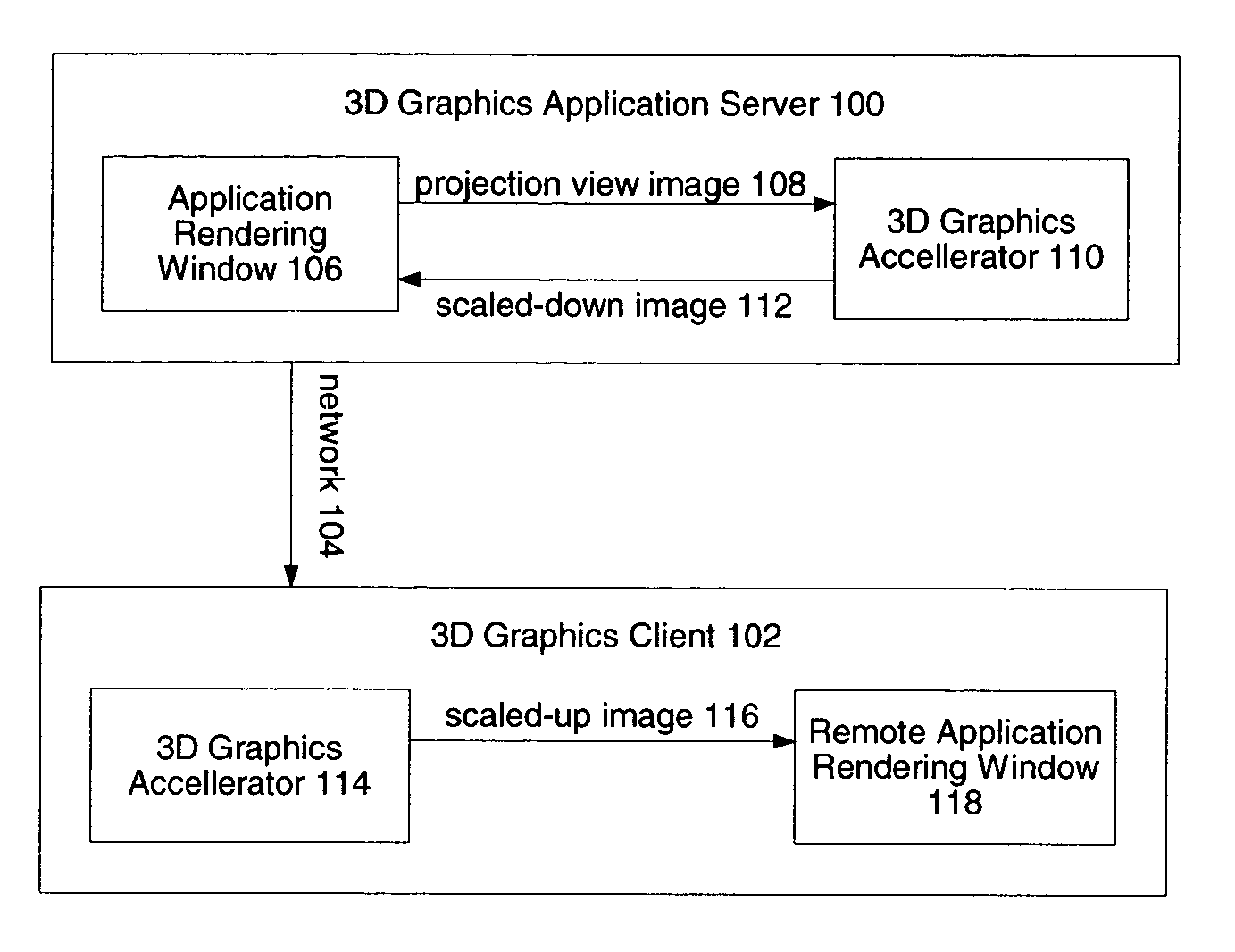

Systems and methods for network transmission of three-dimensional graphical data are disclosed. A single graphical application instance can virtually and efficiently exist on multiple local or remote display systems by directly sharing its raw rendered framebuffer memory information among all local or remote graphics accelerators, thus avoiding the need to re-render any application information again on each node. An internal graphics card is used to scale the rendered data prior to transmission. This graphics scaling eliminates the need for data compression or image compression and achieves an adaptive, hardware-accelerated reduction in network bandwidth. Furthermore, since all memory and remote processing support tasks are performed within the graphics card, the CPU, system bus, and memory bandwidth remain available to the system and other applications.

Owner:LANDMARK GRAPHICS CORP

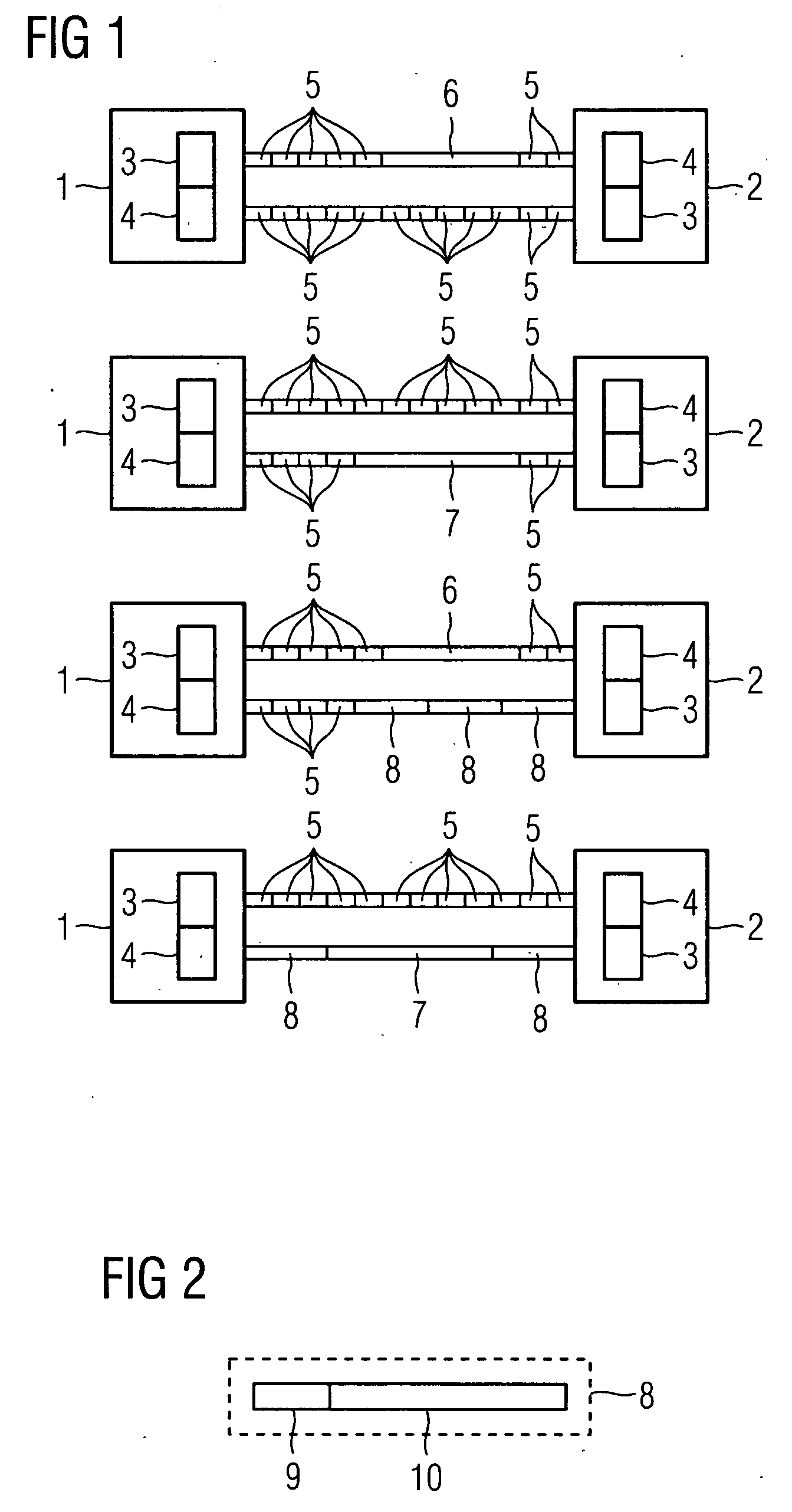

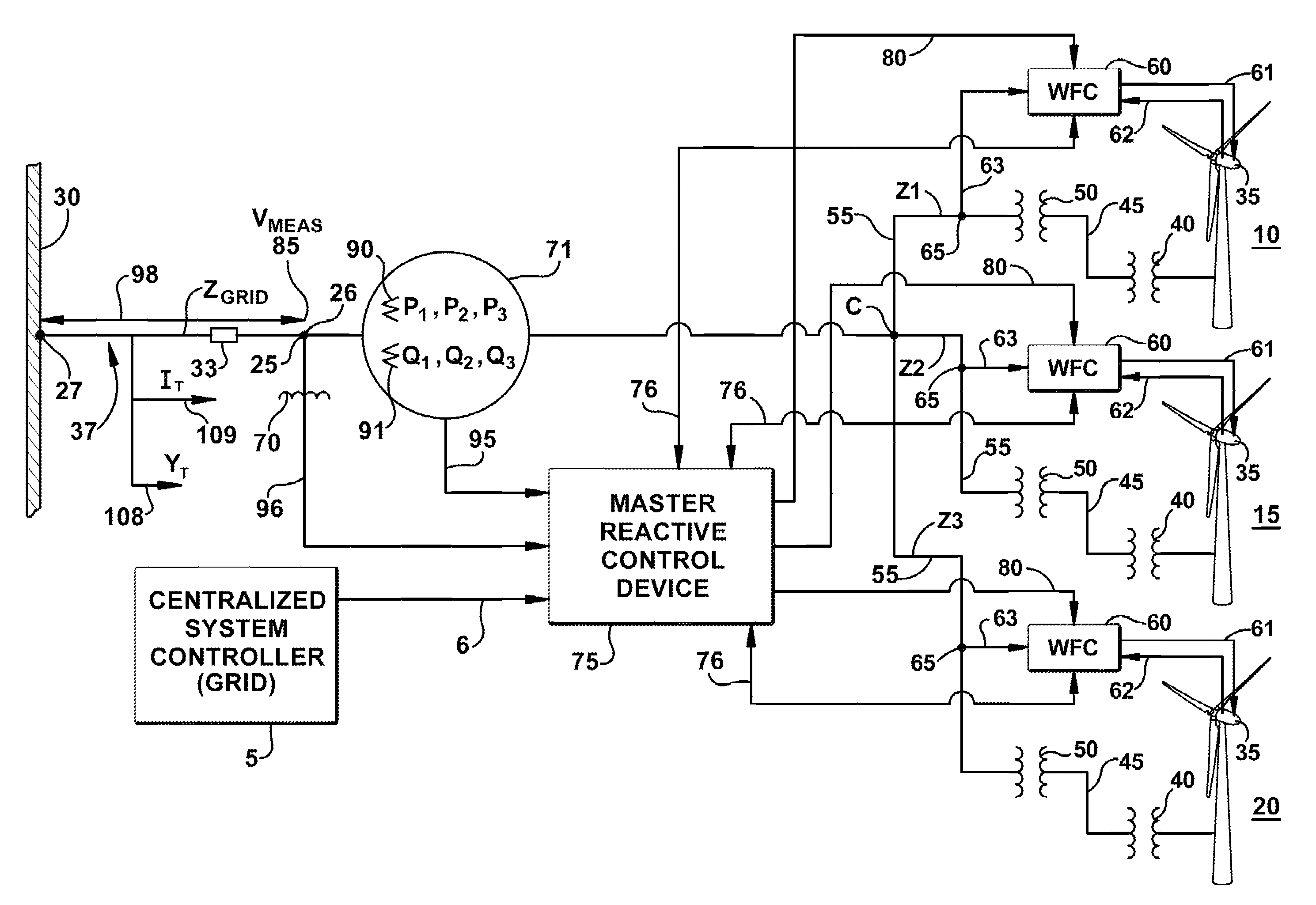

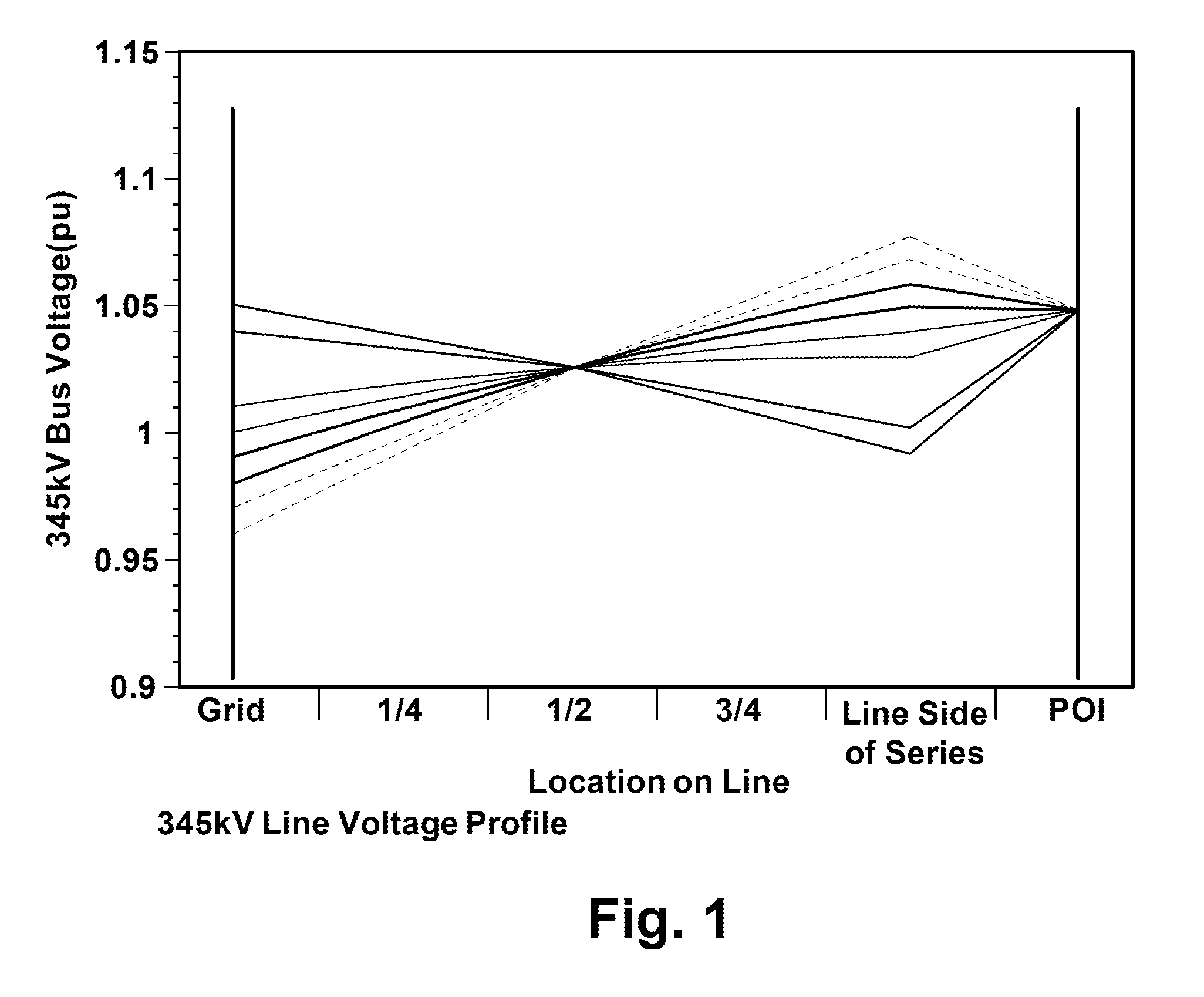

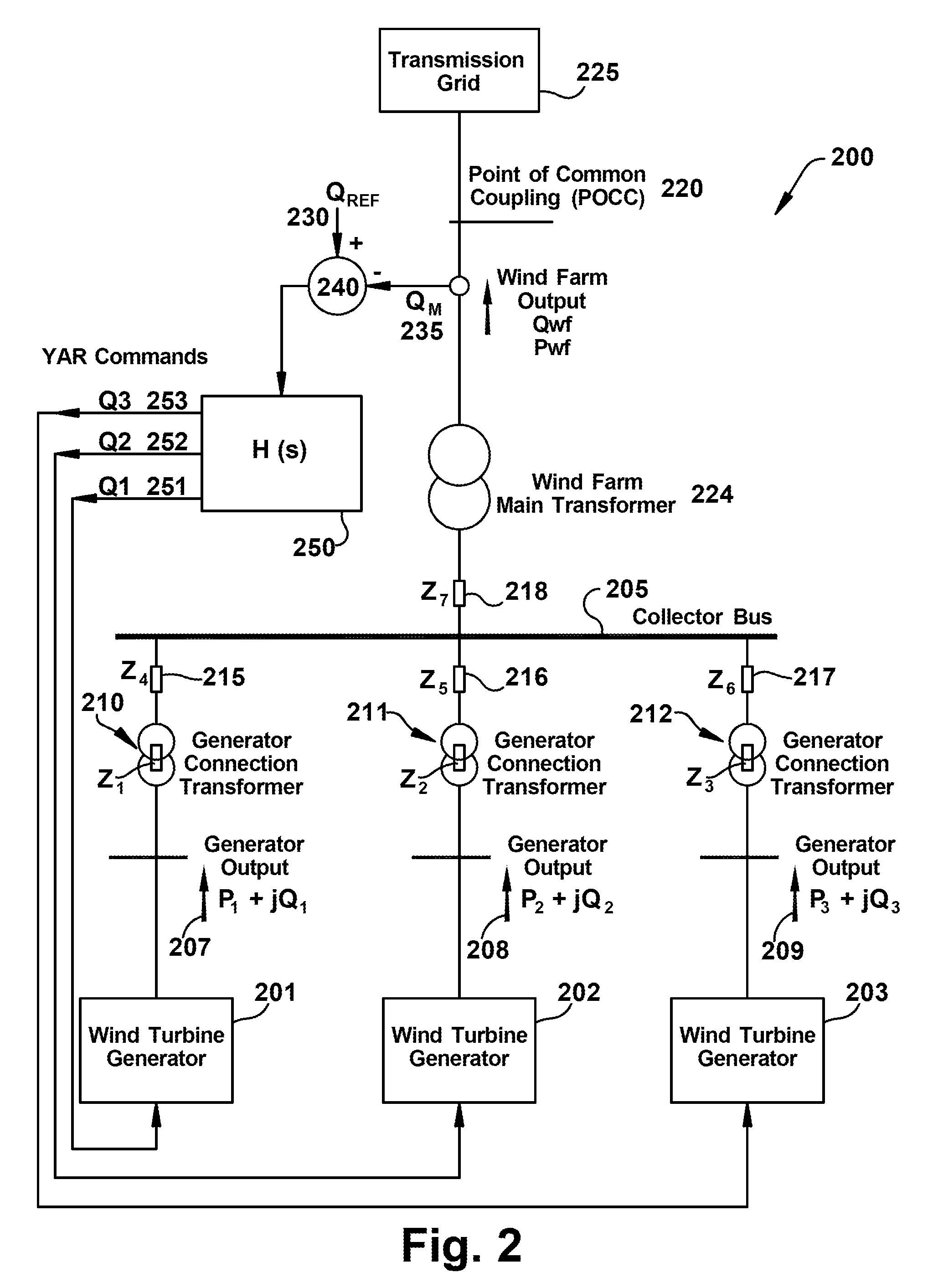

Voltage control at windfarms

A voltage control arrangement for a system of multiple windfarms with transmission lines. Voltage is regulated at a point of regulation on the system, such as a high voltage substation or other system bus. Regulation is achieved at the point of regulation by sensing the voltage, comparing to a reference voltage, and adjusting the reactive power output of the wind turbines and other equipment in the system. The regulation point may be shifted to another point if needed to respect voltage limits at that points of the system after attempting to shift reactive load to restore voltage within limits at the other points in the system. The reference voltage may be adjusted to minimize losses for the system of multiple windfarms and transmission lines. A loss optimizing algorithm is applied to the combined multiple windfarm and transmission line to shift reactive load among local windfarms to minimize losses and to shift reactive load among individual wind turbines within an individual windfarm.

Owner:GENERAL ELECTRIC CO

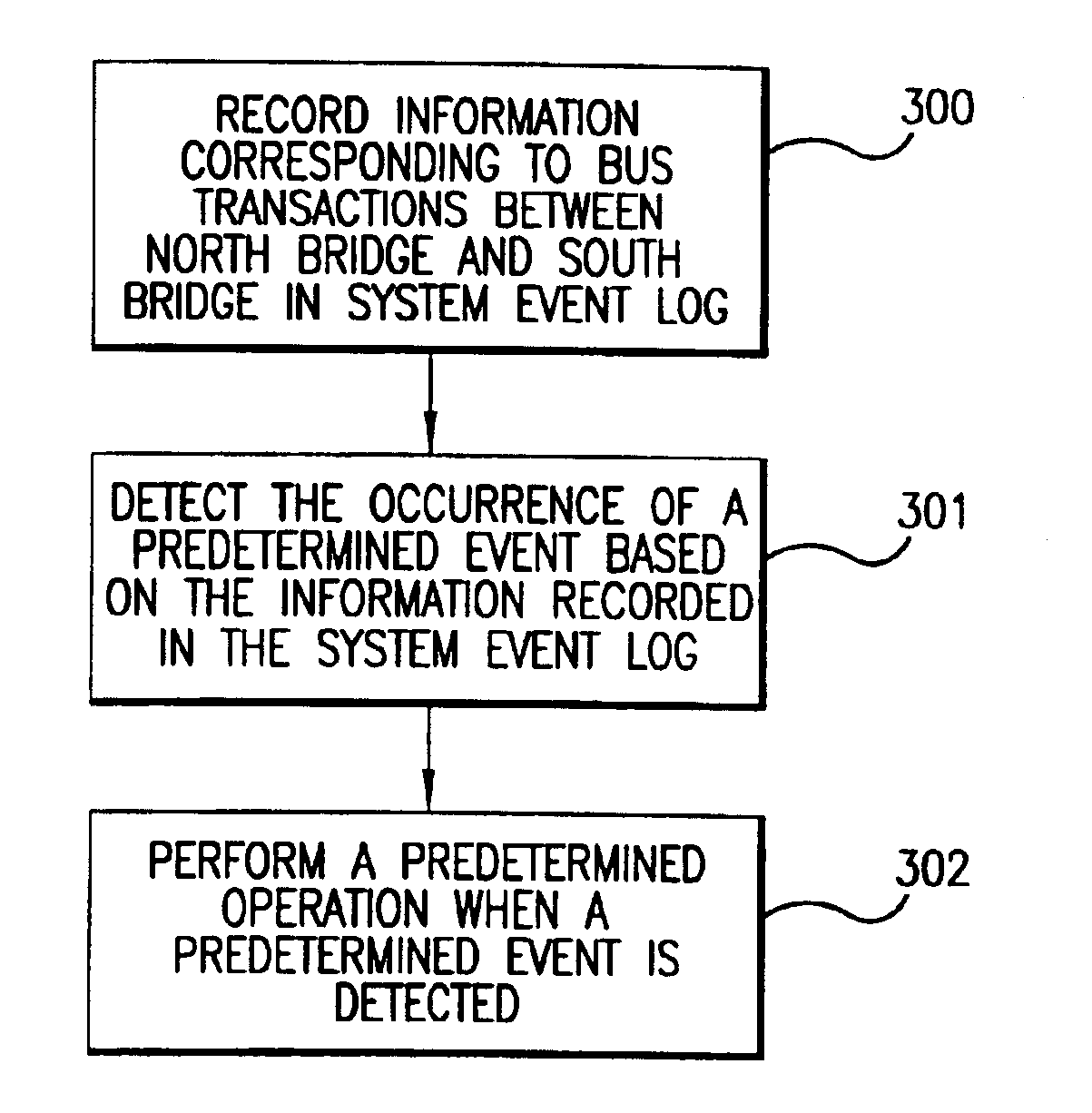

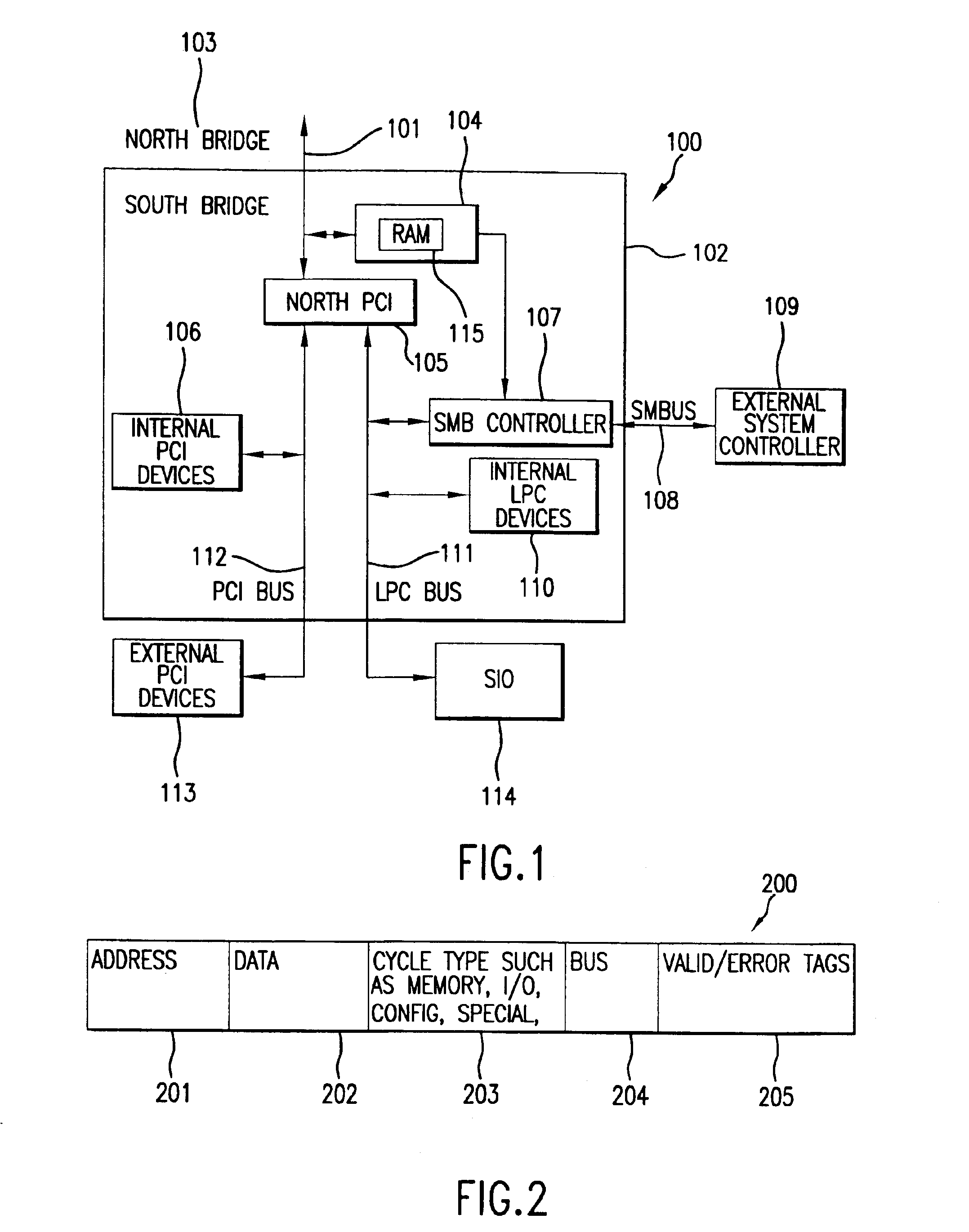

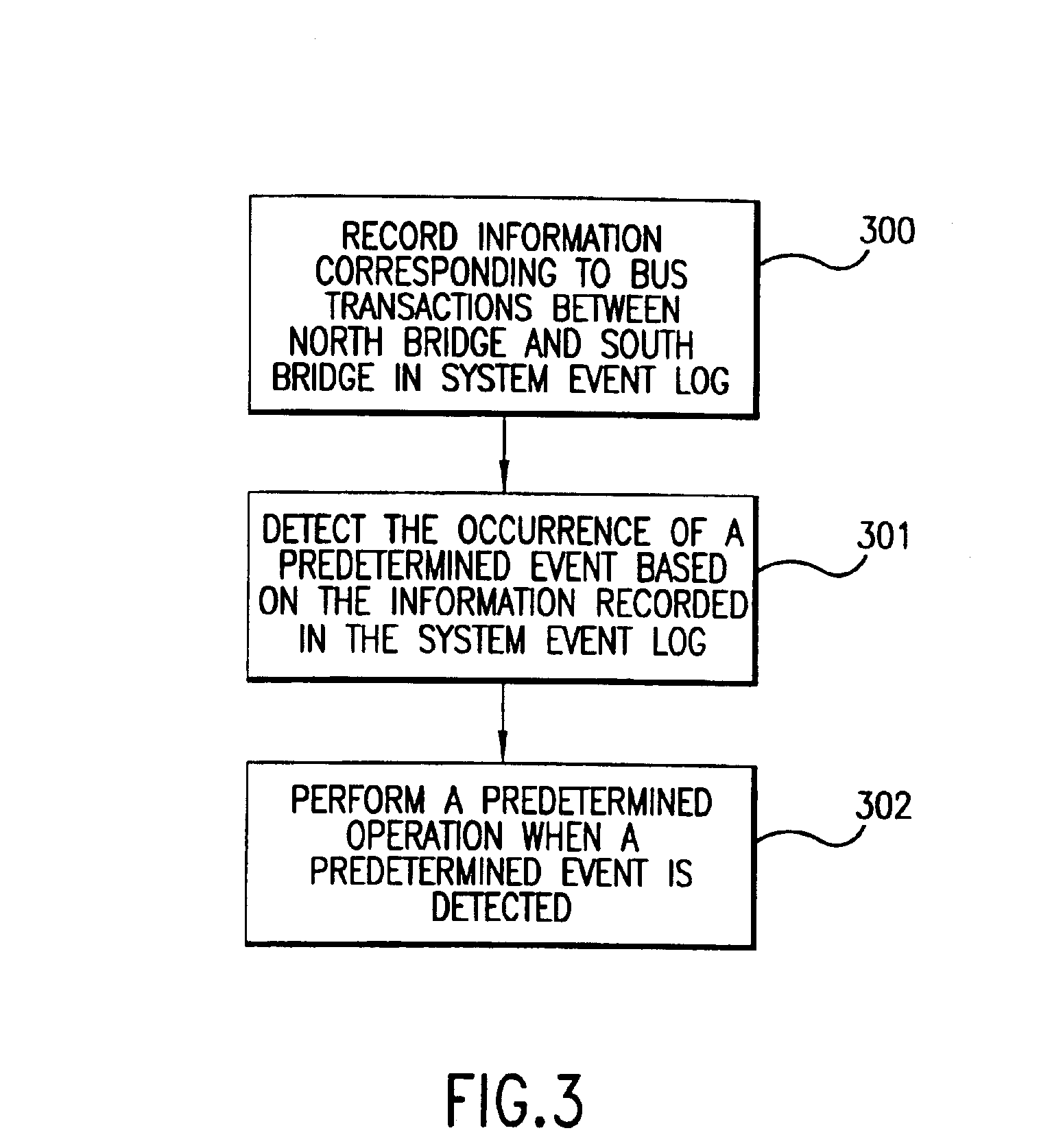

Method and system to implement a system event log for system manageability

Embodiments of the present invention provide a system event log for a computer system. The system event log may comprise a RAM coupled to a system bus. The system event log may be configured to record information in the RAM corresponding to bus transactions on the system bus. The information may be used to de-bug system problems.

Owner:INTEL CORP

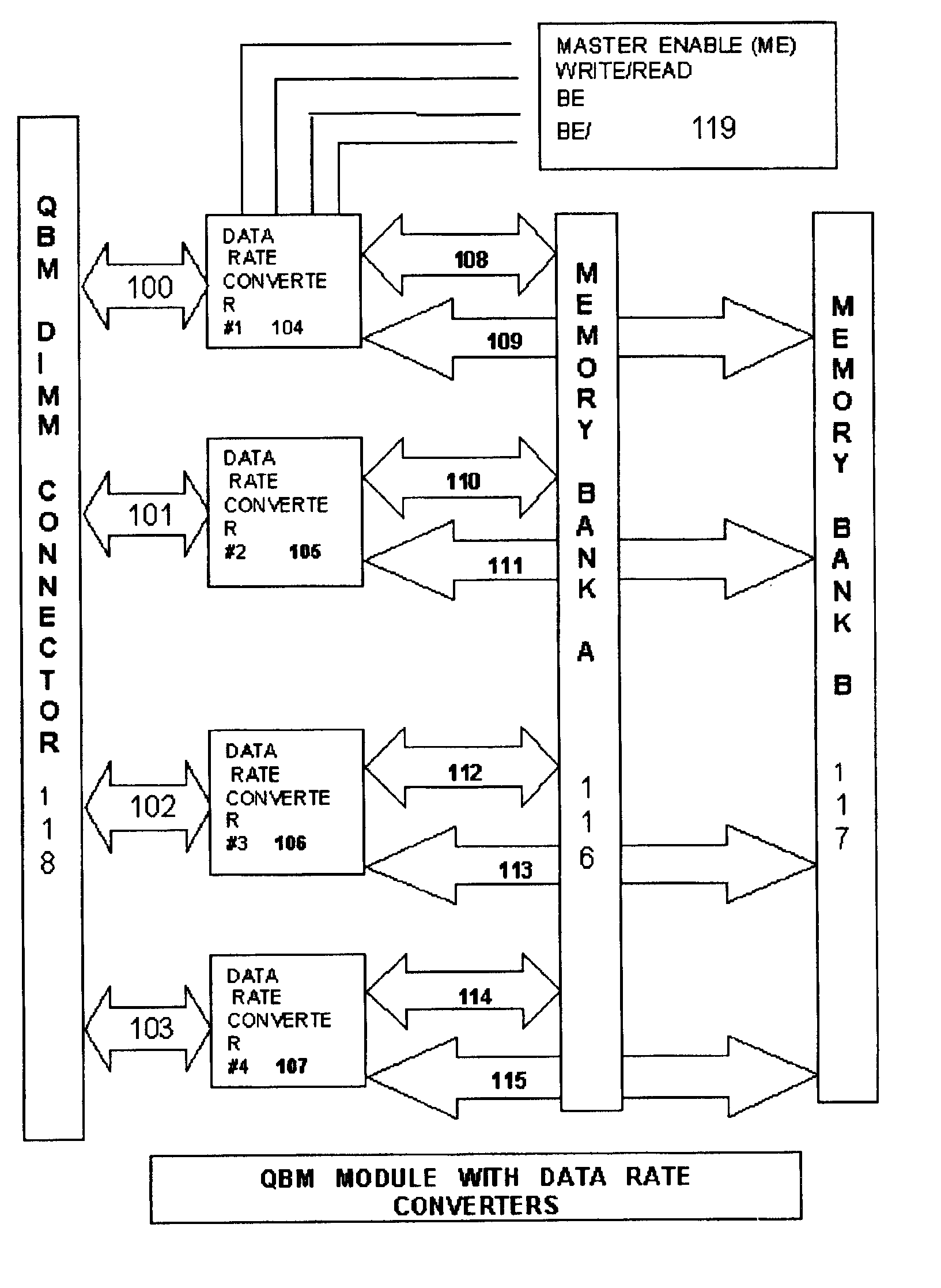

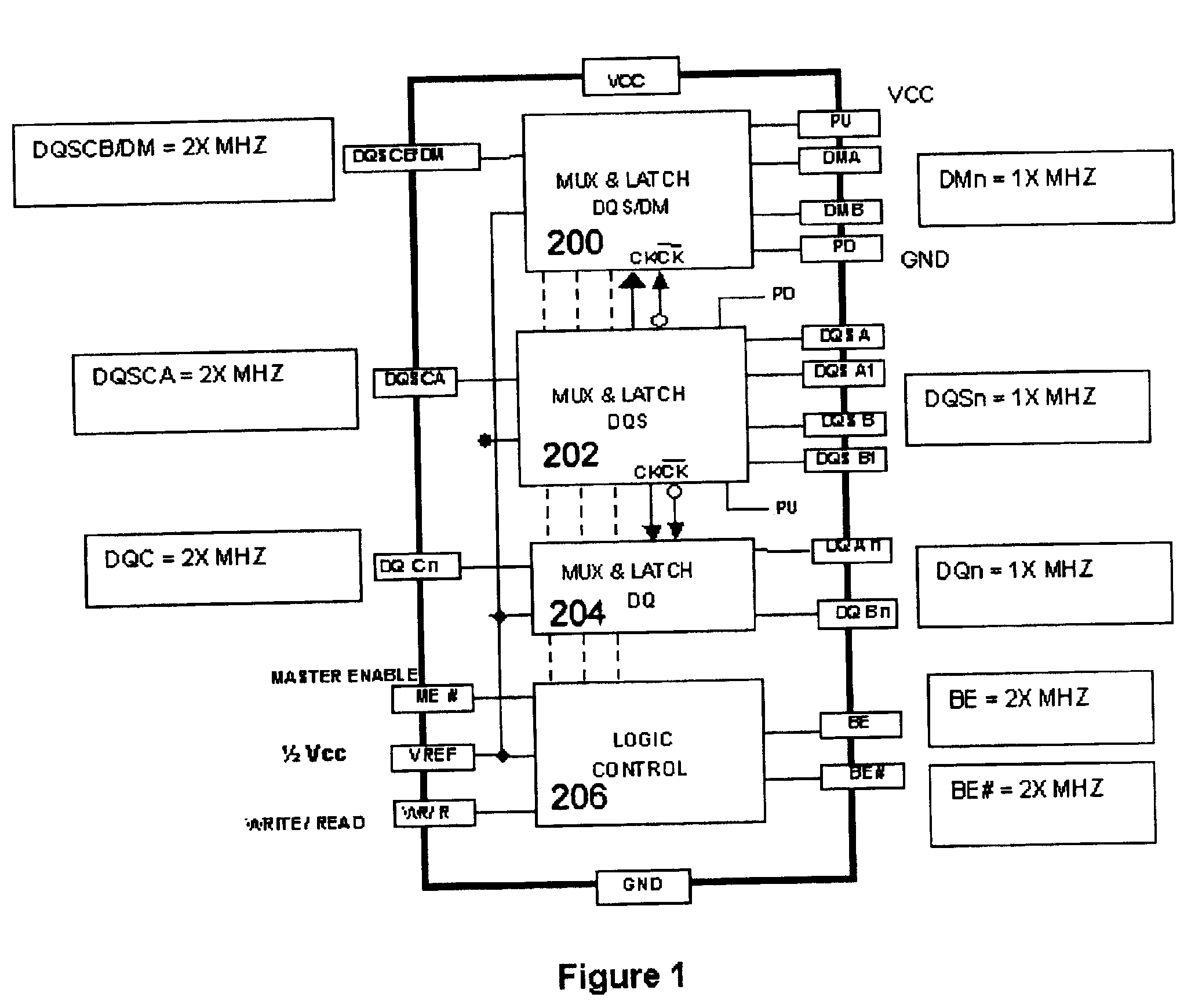

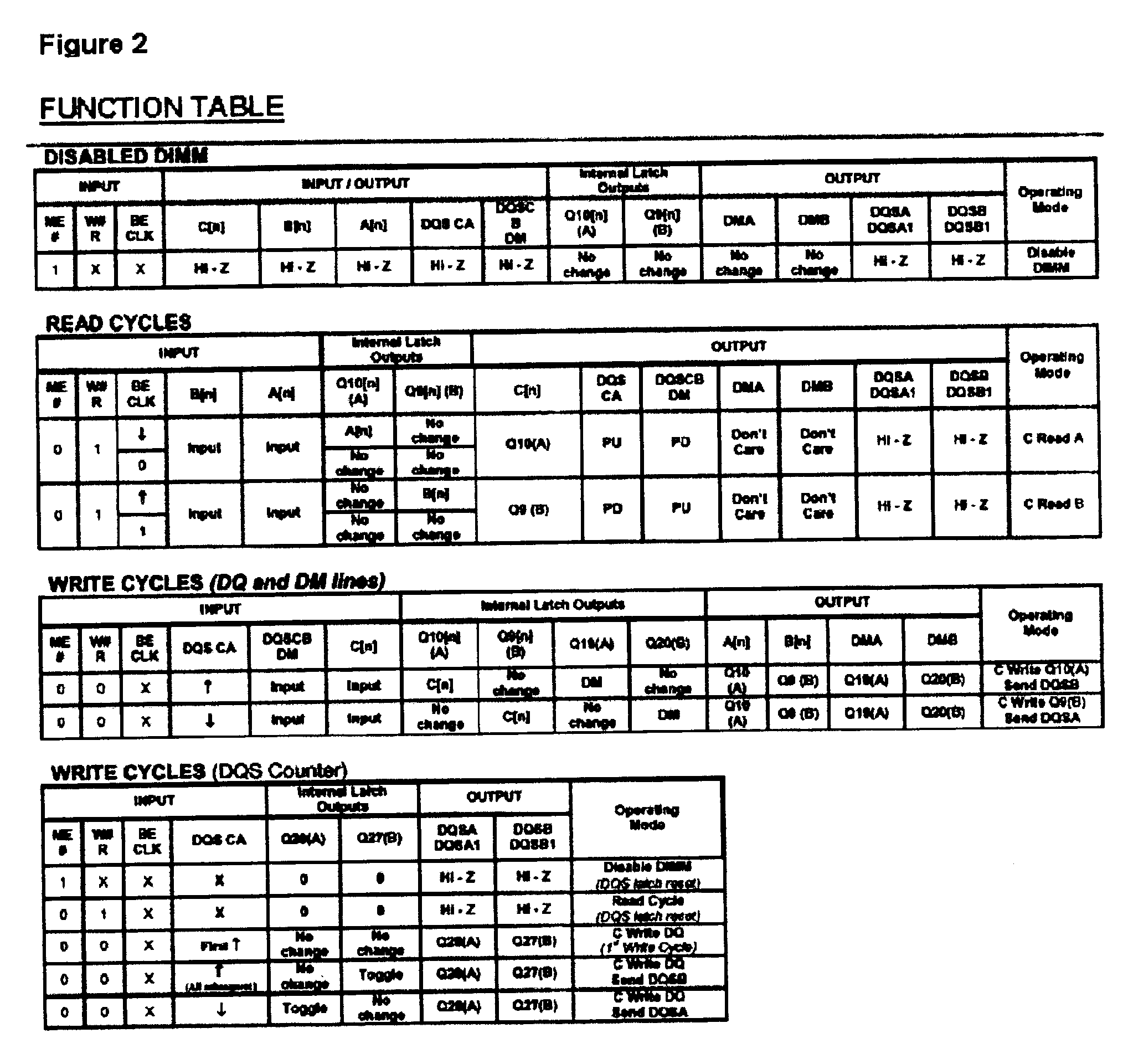

High-speed data-rate converting and switching circuit

InactiveUS6854042B1Extended durationMemory adressing/allocation/relocationDigital storageSignal onMemory bus

A high speed bidirectional data rate conversion circuit converts 1× data rate signals from attached devices on port A and port B to 2× data rate signals on bus C and further converts 2× high speed data rate signals on bus C to 1× data rate signals on ports A and B for memory devices attached to ports A and B. The usage of pass gate switches and combination of latches and counters is used to permit proper synchronization of the data signals, and to further generate strobe signals at both system bus and memory bus sides, and to further generate data mask signals for writing to the memory bus side of the circuit. The collection of such switching elements and latches are provided on a single silicon chip which includes of the functions of the invention.

Owner:URENSCHI ASSETAB LIABILITY

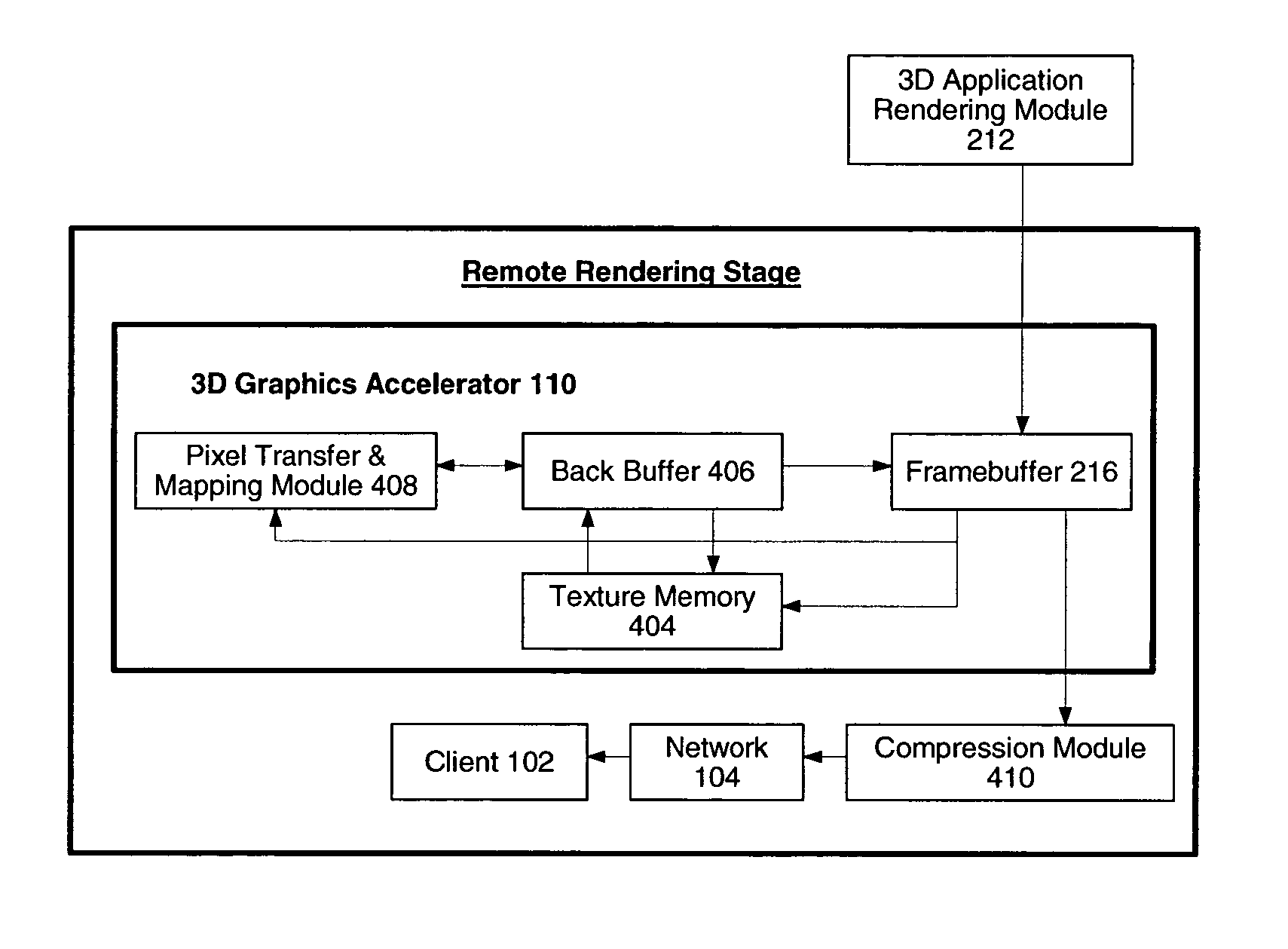

System and method for network transmission of graphical data through a distributed application

InactiveUS20050021656A1Reduce network bandwidth requirementsCathode-ray tube indicatorsMultiple digital computer combinationsGraphicsGraphic card

Systems and methods for network transmission of three-dimensional graphical data are disclosed. A single graphical application instance can virtually and efficiently exist on multiple local or remote display systems by directly sharing its raw rendered framebuffer memory information among all local or remote graphics accelerators, thus avoiding the need to re-render any application information again on each node. An internal graphics card is used to scale the rendered data prior to transmission. This graphics scaling eliminates the need for data compression or image compression and achieves an adaptive, hardware-accelerated reduction in network bandwidth. Furthermore, since all memory and remote processing support tasks are performed within the graphics card, the CPU, system bus, and memory bandwidth remain available to the system and other applications.

Owner:LANDMARK GRAPHICS

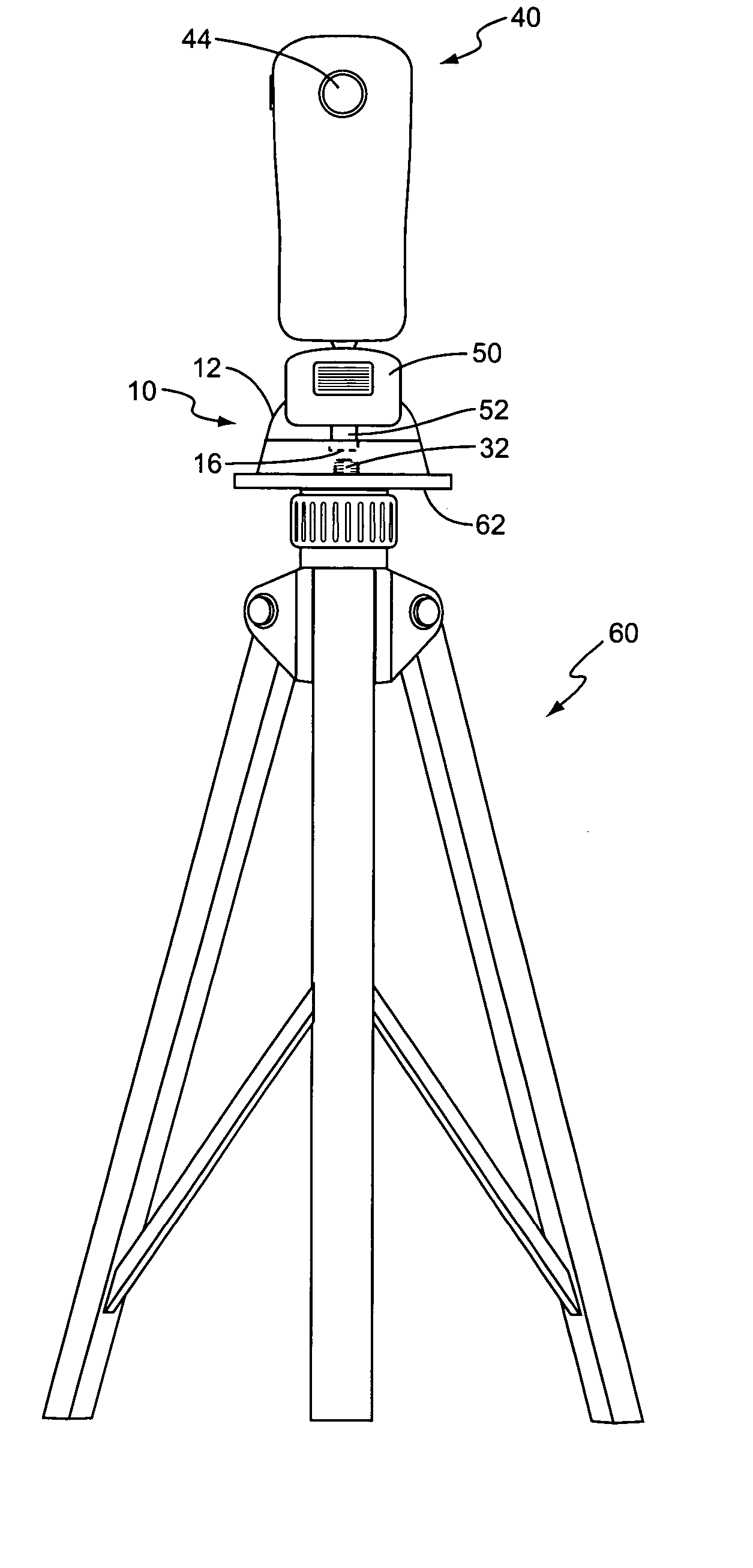

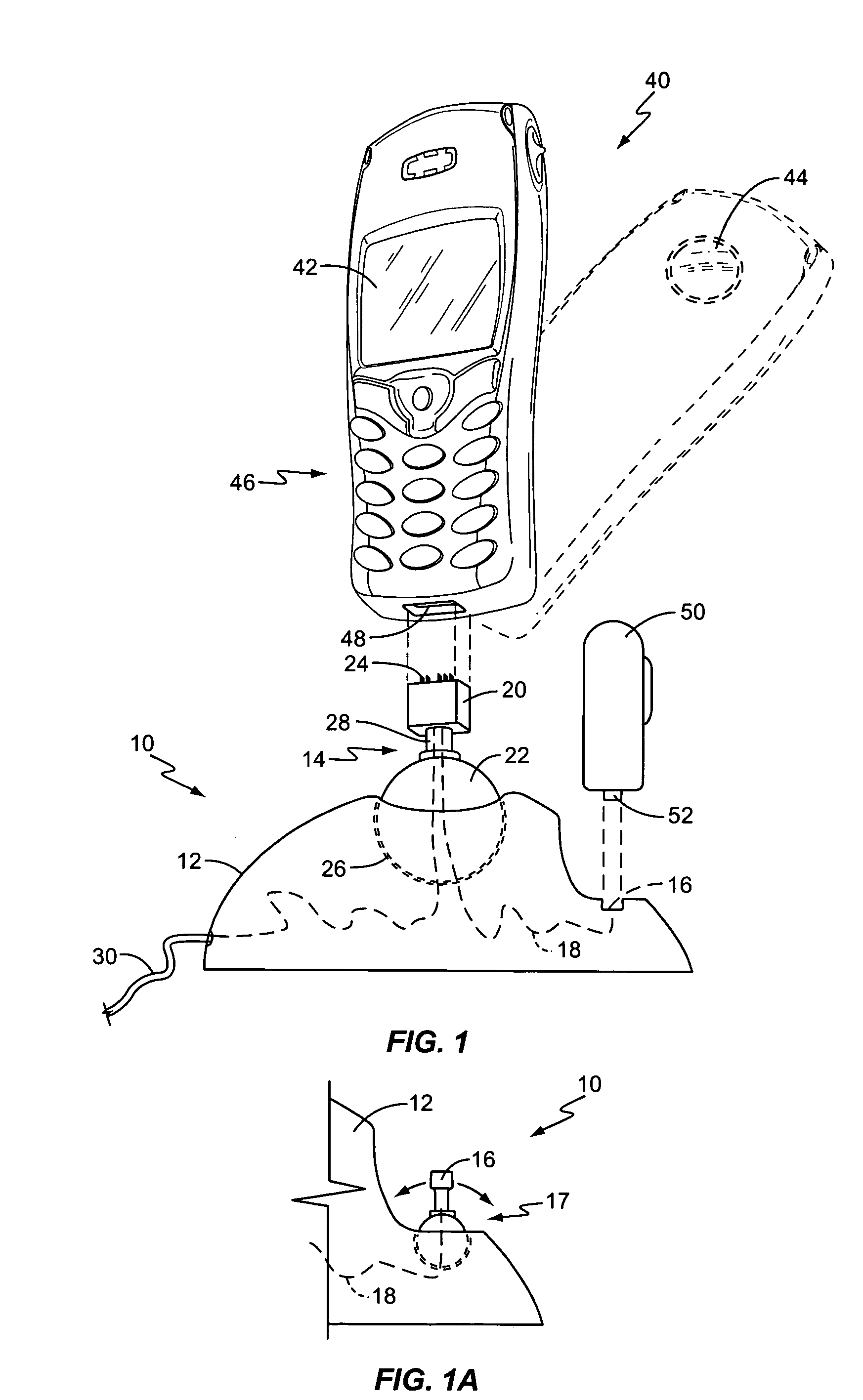

Positioning accessory for camera-equipped wireless terminals

InactiveUS20050122424A1Television system detailsColor television detailsCommunication deviceAuxiliary system

A stand for a camera-equipped wireless communications device comprises a base, an adjustable terminal support movably mounted to the base, and an auxiliary system connector mounted to the base. The adjustable terminal support includes a system plug that connects to a system interface on the camera-equipped wireless communications device. The auxiliary system connector connects a peripheral device associated with the camera-equipped wireless communications device to the base. The system plug and the auxiliary system connector are interconnected by a system bus that extends through the base.

Owner:SONY CORP

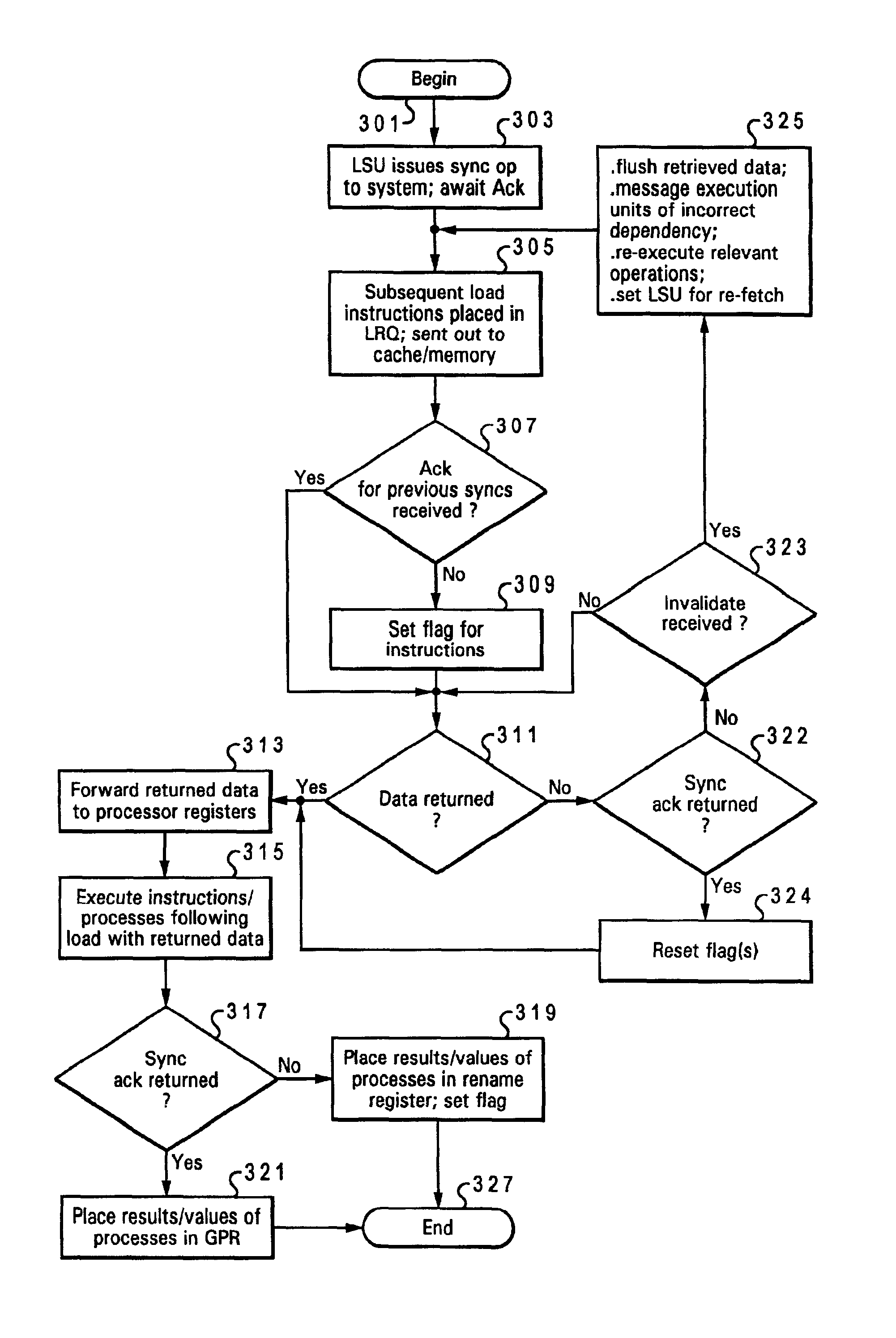

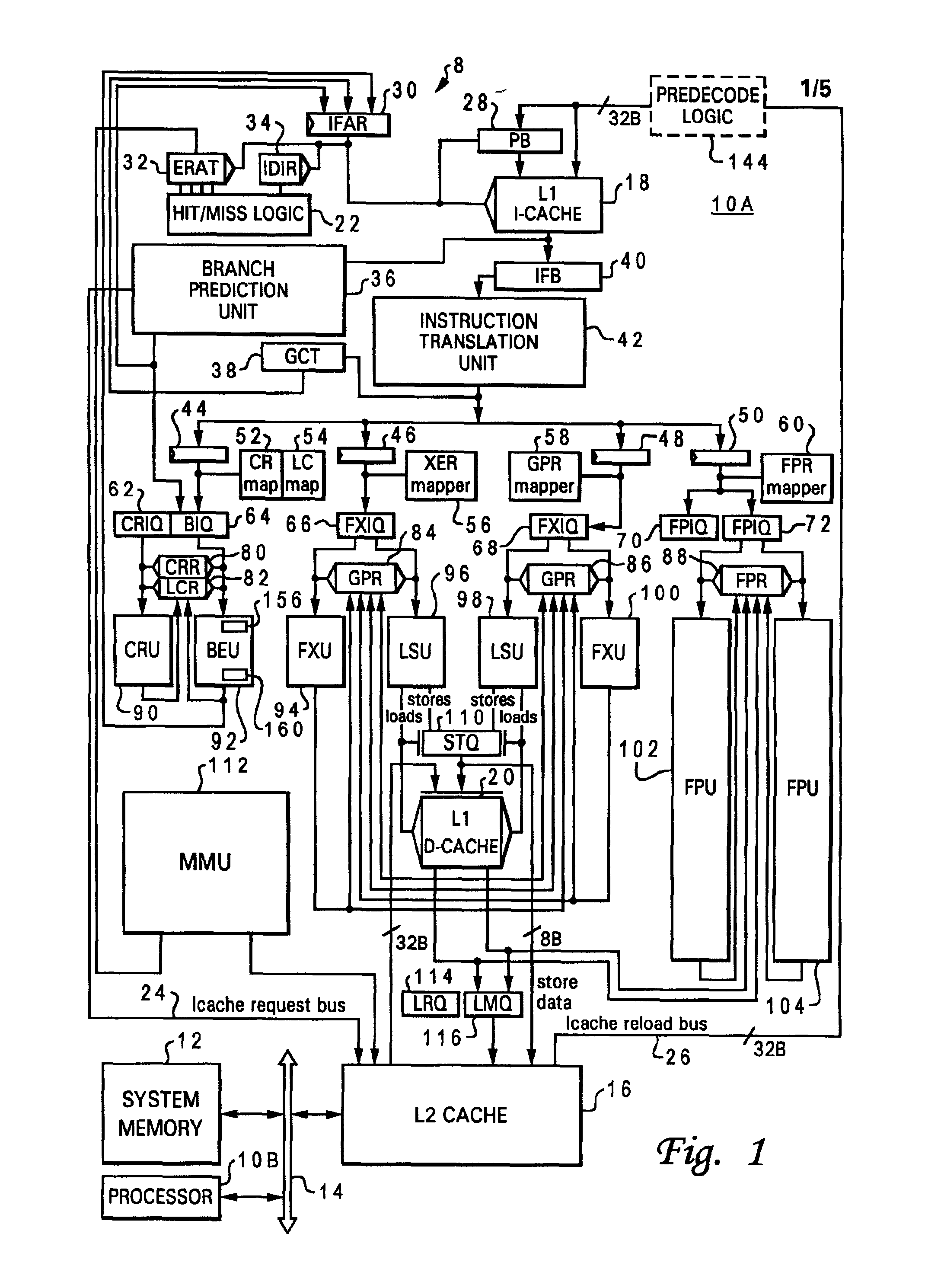

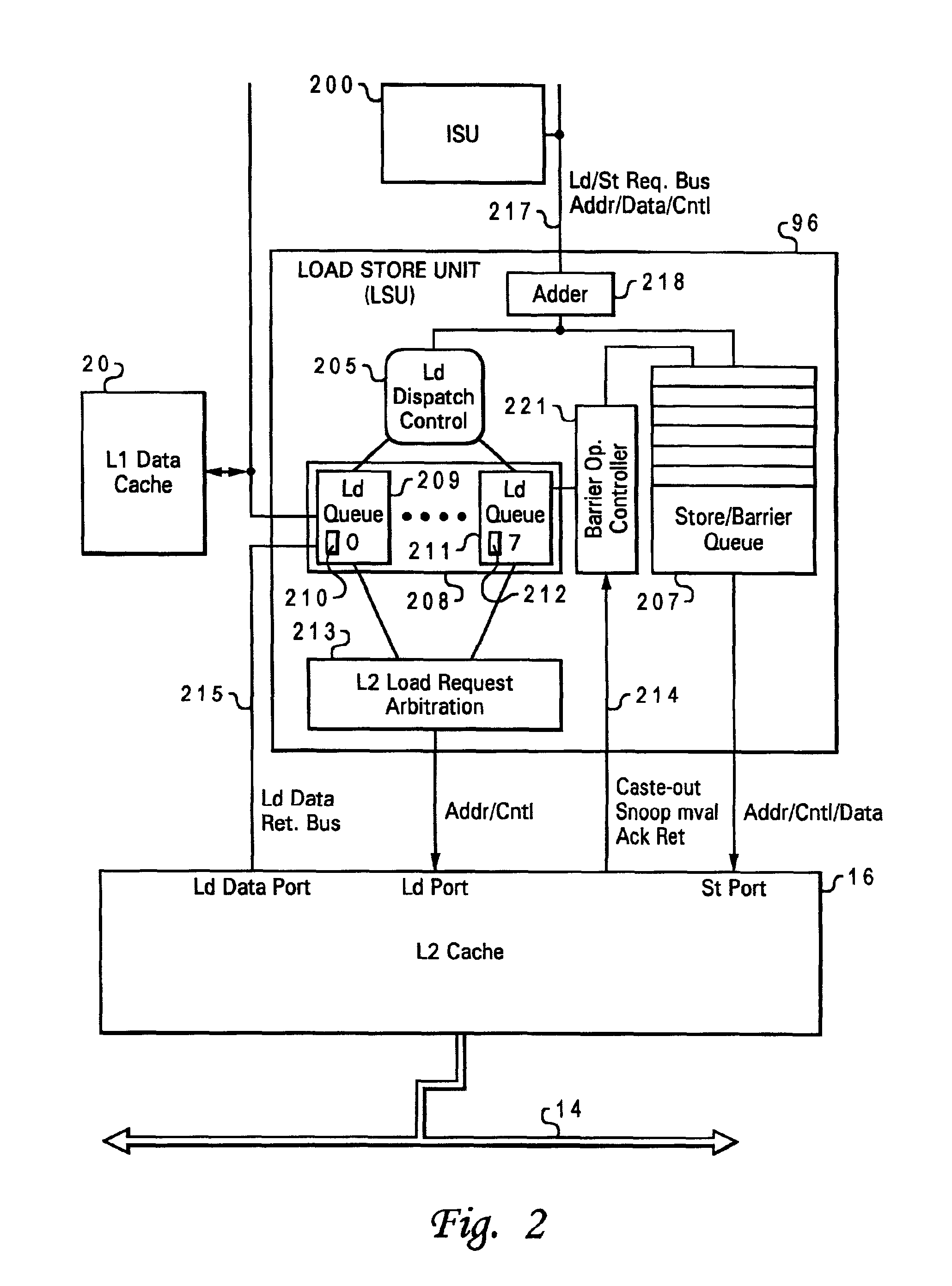

Speculative execution of instructions and processes before completion of preceding barrier operations

InactiveUS6880073B2Digital computer detailsConcurrent instruction executionData processing systemSpeculative execution

Described is a data processing system and processor that provides full multiprocessor speculation by which all instructions subsequent to barrier operations in a instruction sequence are speculatively executed before the barrier operation completes on the system bus. The processor comprises a load / store unit (LSU) with a barrier operation (BOP) controller that permits load instructions subsequent to syncs in an instruction sequence to be speculatively issued prior to the return of the sync acknowledgment. Data returned is immediately forwarded to the processor's execution units. The returned data and results of subsequent operations are held temporarily in rename registers. A multiprocessor speculation flag is set in the corresponding rename registers to indicate that the value is “barrier” speculative. When a barrier acknowledge is received by the BOP controller, the flag(s) of the corresponding rename register(s) are reset.

Owner:IBM CORP

Display device and driving method thereof

InactiveUS6873320B2Reduce consumptionSmall sizeCathode-ray tube indicatorsNon-linear opticsAddress decoderLiquid-crystal display

A liquid crystal display device which can reduce power consumption and can be miniaturized. The liquid crystal display device according to the present invention includes a pixel array portion, an address decoder, a display memory (VRAM), and a VRAM controller, and transmits / receives a signal to / from a CPU and a peripheral circuit through a system bus. The pixel array portion has an area gradation pixel structure in which each pixel is composed of a plurality of one-bit memories. The entire pixel array portion is divided into pixel blocks each of which consists of a plurality of pixels, and the one-bit memory is rewritten in units of block. The one-bit memory has a double-word line structure.

Owner:KK TOSHIBA

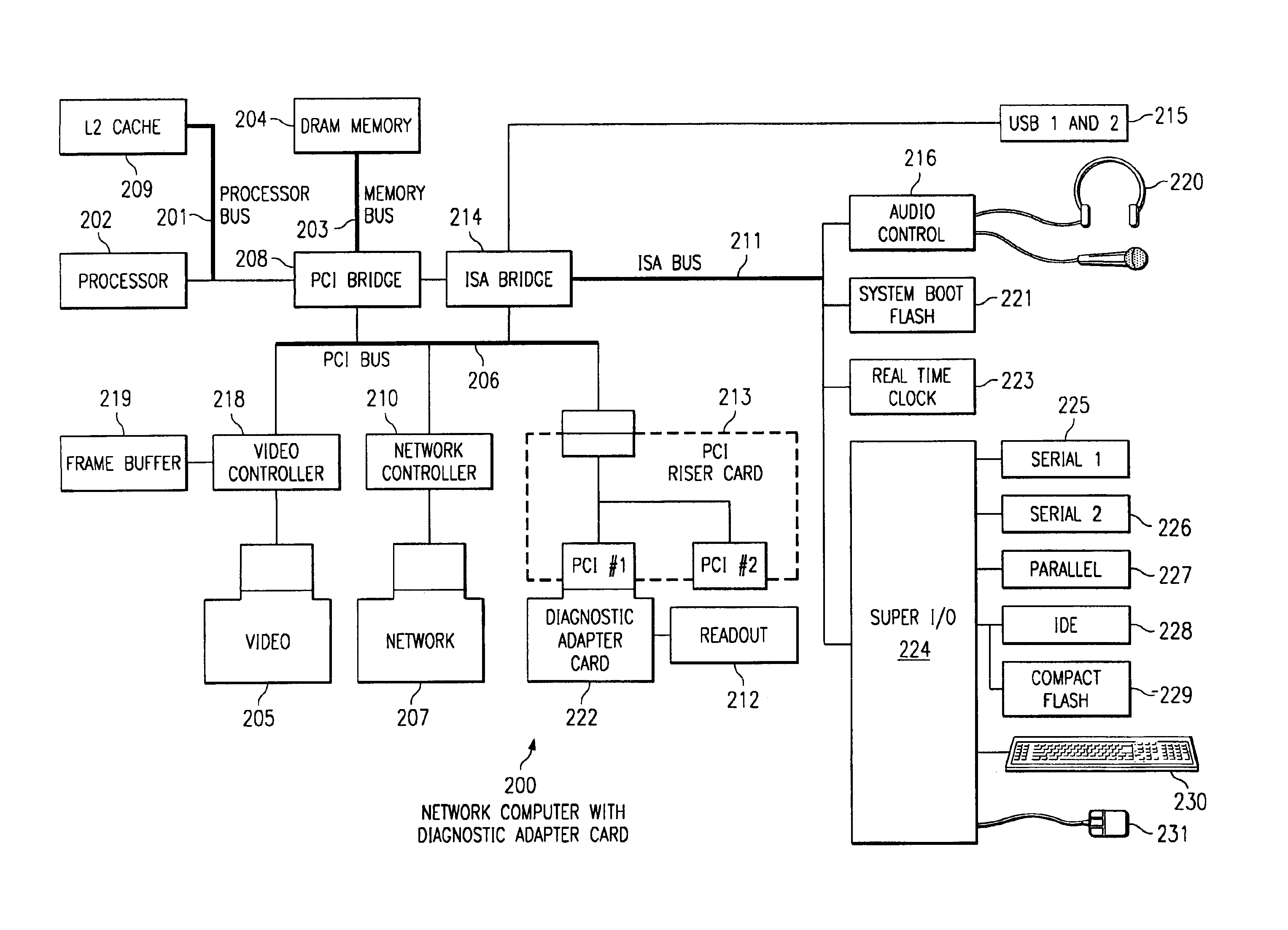

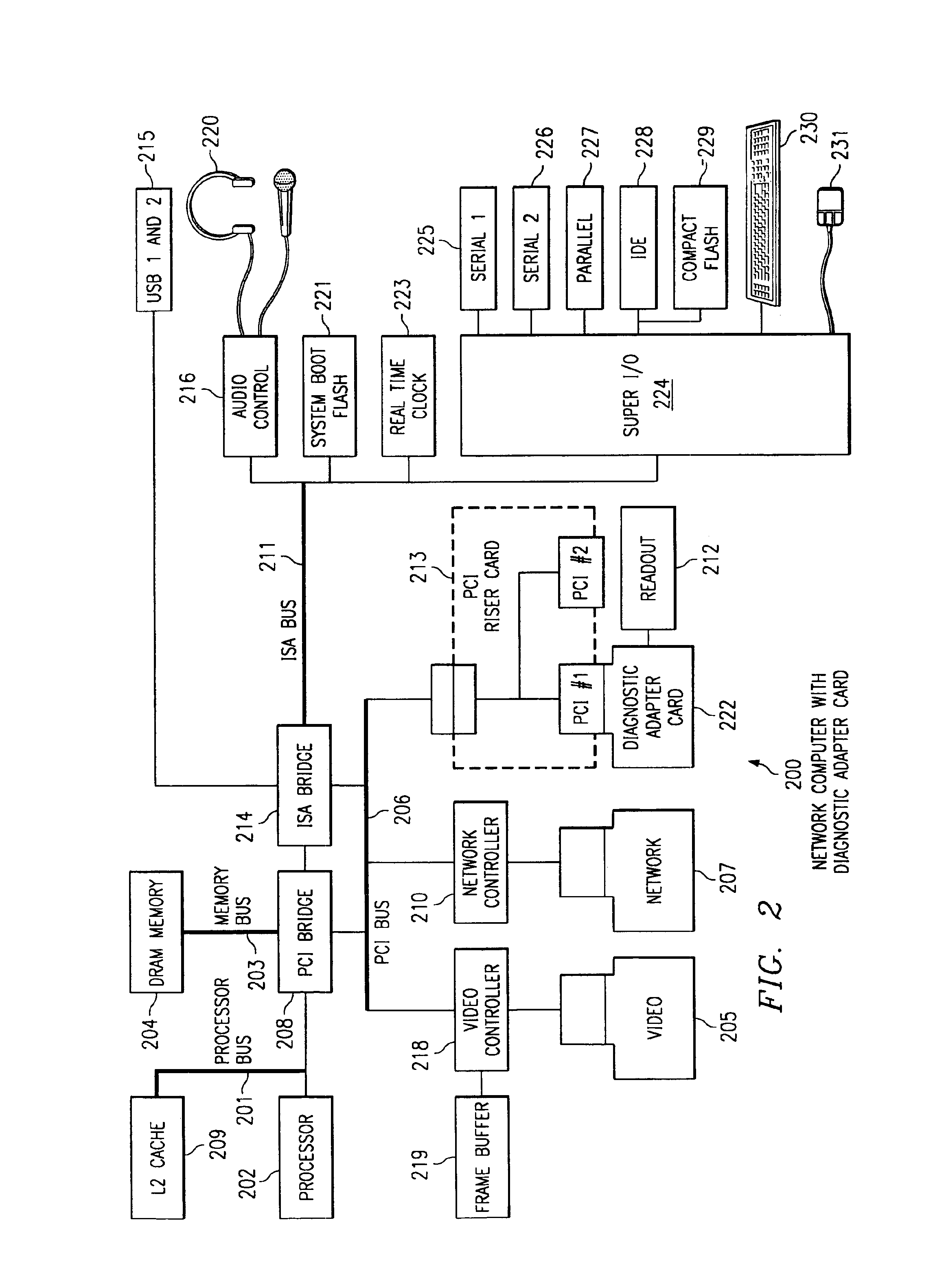

System and method of running diagnostic testing programs on a diagnostic adapter card and analyzing the results for diagnosing hardware and software problems on a network computer

InactiveUS6915343B1Monitor performanceEasy to detectError detection/correctionMultiple digital computer combinationsDiagnostic programRandom access memory

An computer program product and a method is presented for diagnosing hardware and software problems on a network computer through the use of a diagnostic adapter card. The diagnostic adapter card is installed in an open slot in the system bus and thus has access to all the network computer electronics and peripherals. Diagnostic programs are run and the results are logged. By analyzing these results, the source of the problem can be determined and reported for service or repair. The diagnostic adapter card contains its own processor, read only memory, random access memory, and interface logic for connecting to the system bus, a set of external wrap cables for peripheral connector testing, and an external reporting device. Some tests require use of a wrap cable to connect two or more ports together. Other tests, such as system bus timing or memory integrity, do not require the use of wrap cables.

Owner:LENOVO (SINGAPORE) PTE LTD

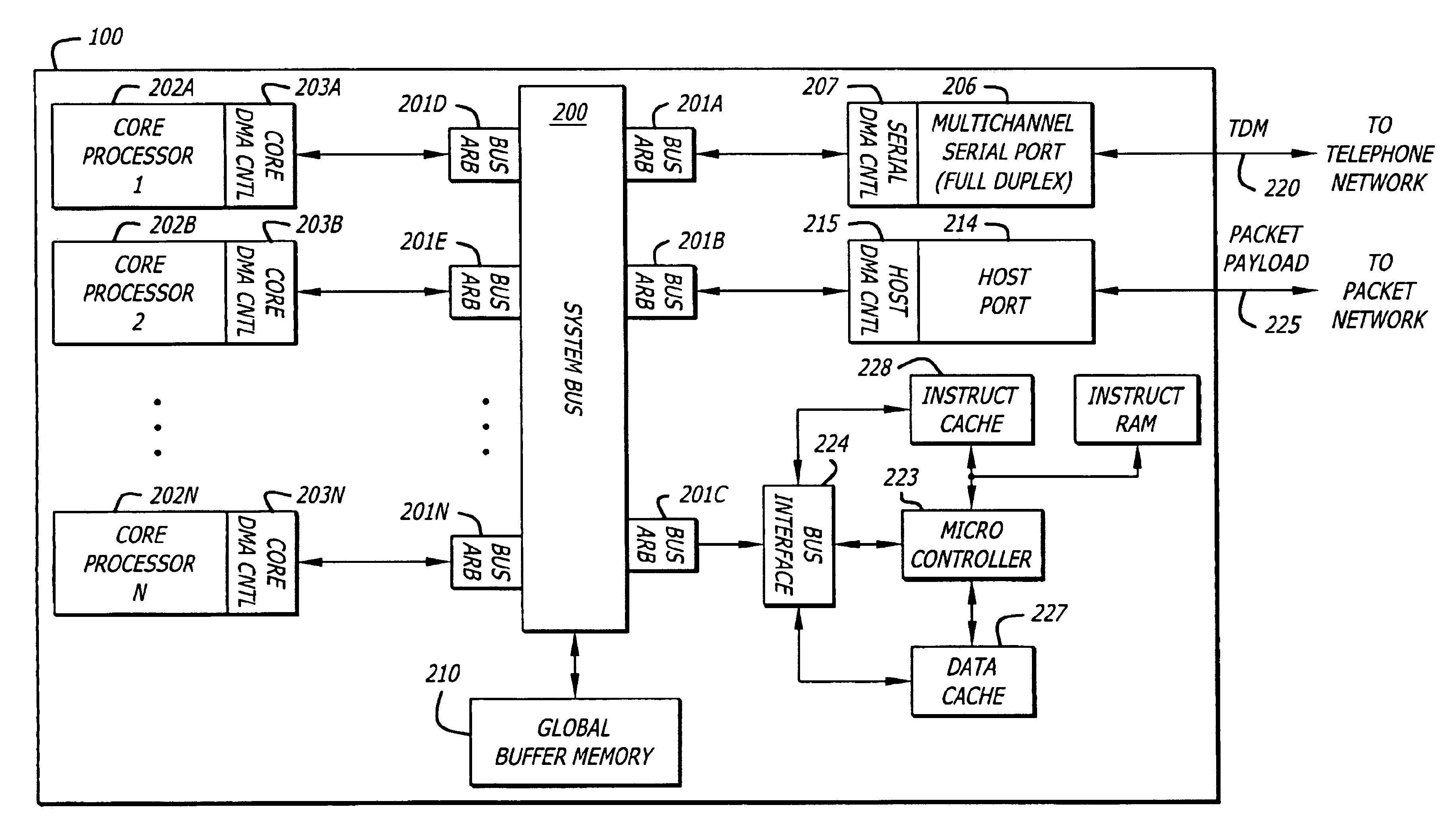

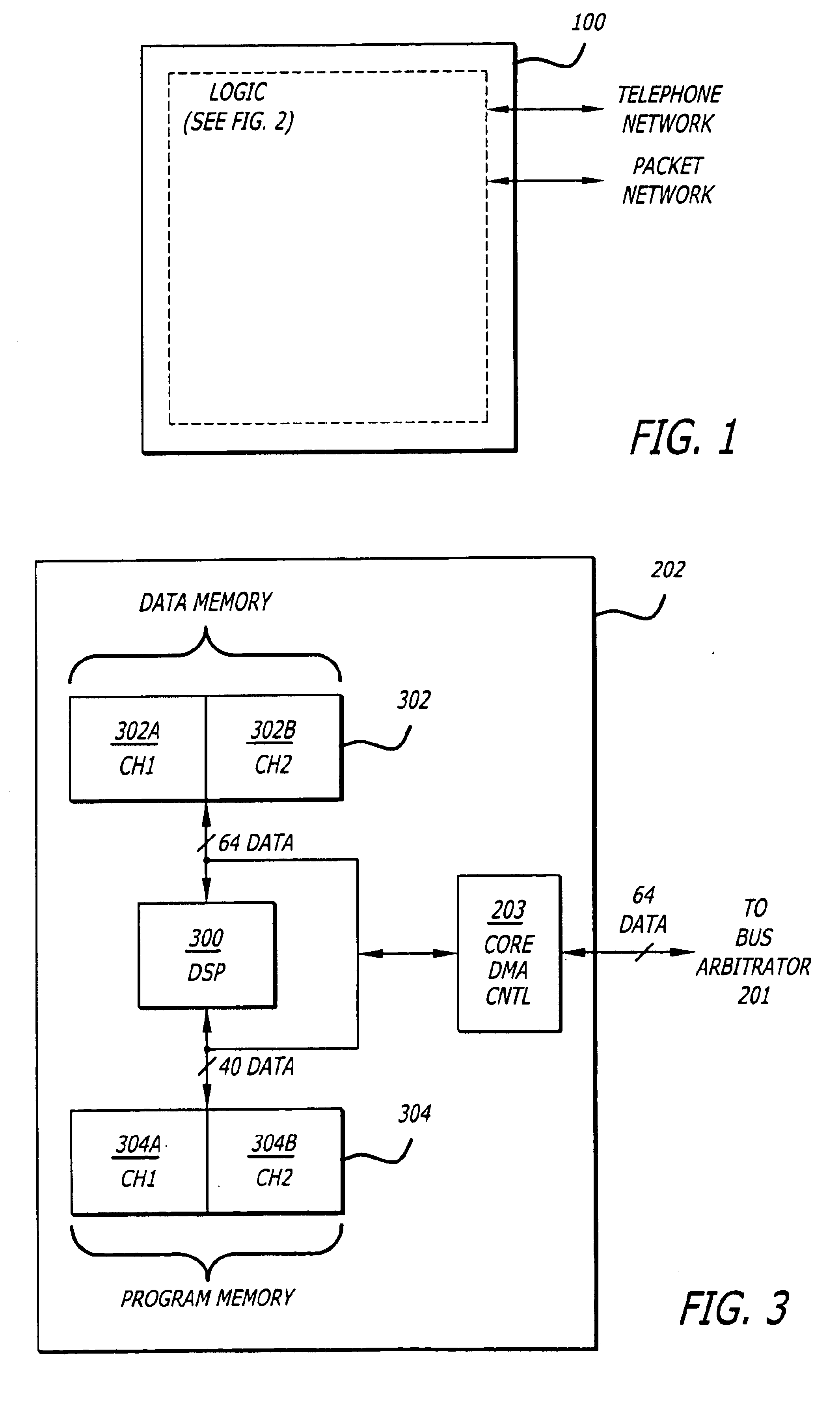

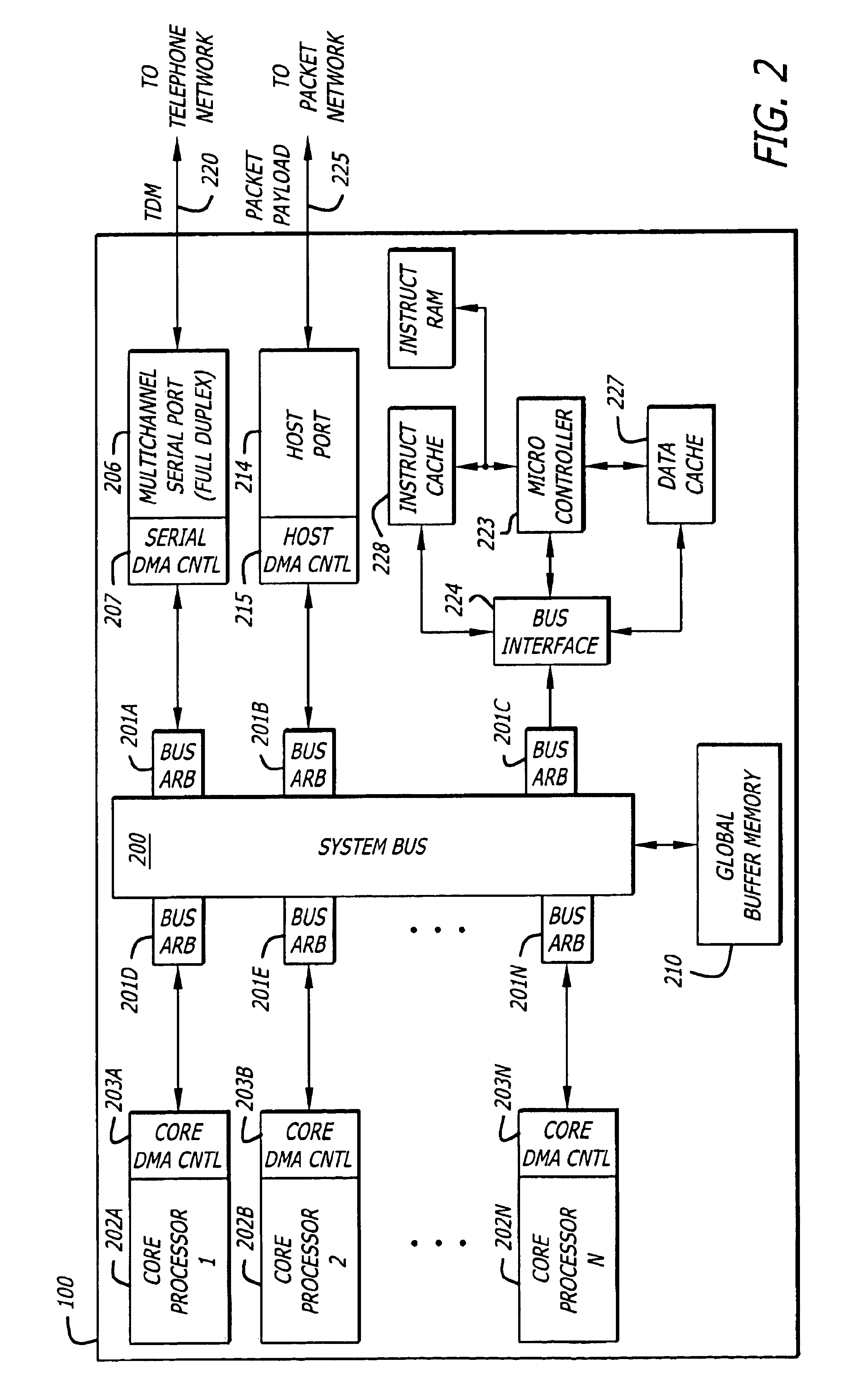

Method and apparatus for distributed direct memory access for systems on chip

InactiveUS6874039B2High bandwidthArbitration is simplifiedMemory adressing/allocation/relocationDigital storageDirect memory accessRemote direct memory access

A distributed direct memory access (DMA) method, apparatus, and system is provided within a system on chip (SOC). DMA controller units are distributed to various functional modules desiring direct memory access. The functional modules interface to a systems bus over which the direct memory access occurs. A global buffer memory, to which the direct memory access is desired, is coupled to the system bus. Bus arbitrators are utilized to arbitrate which functional modules have access to the system bus to perform the direct memory access. Once a functional module is selected by the bus arbitrator to have access to the system bus, it can establish a DMA routine with the global buffer memory.

Owner:INTEL CORP