Patents

Literature

440 results about "Pass gate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

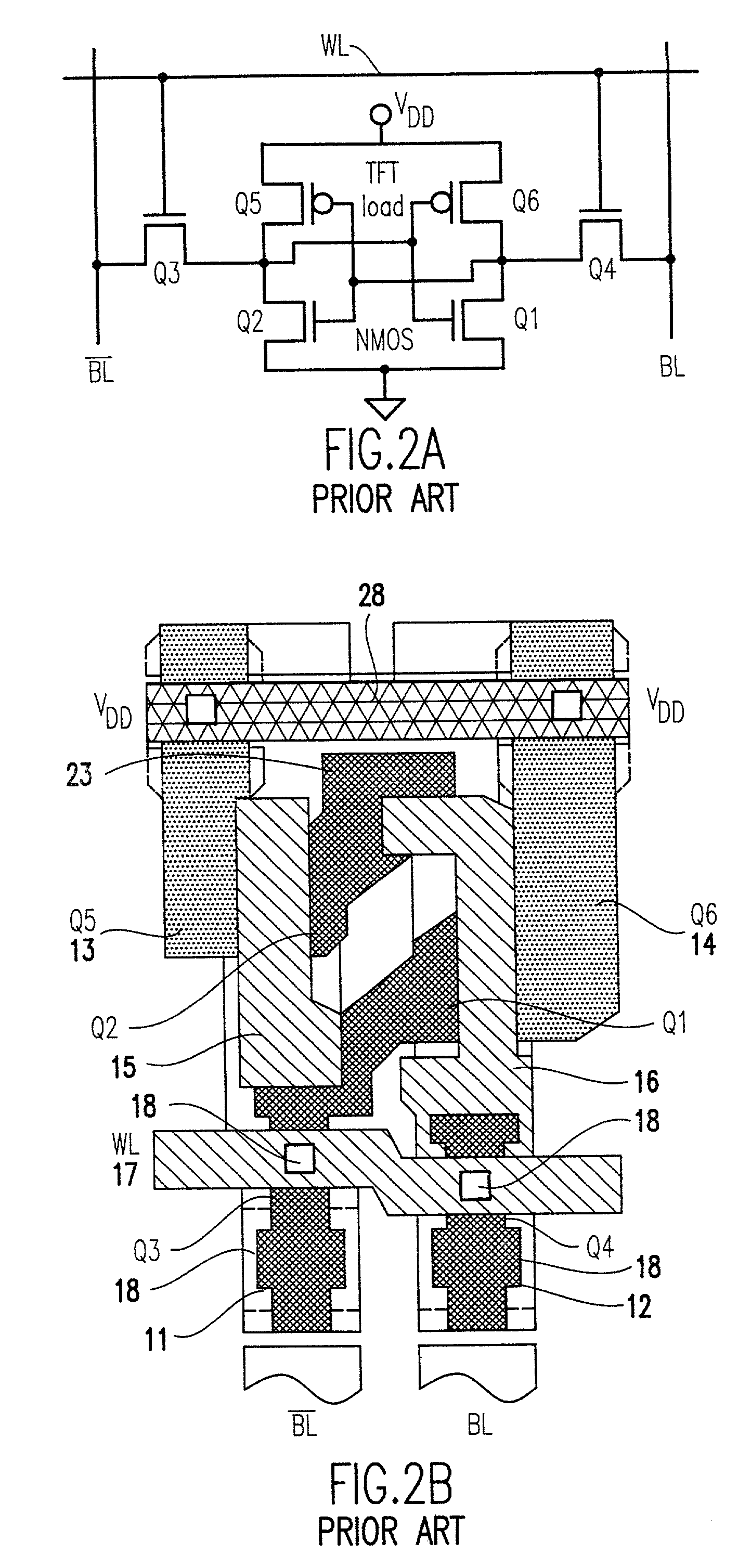

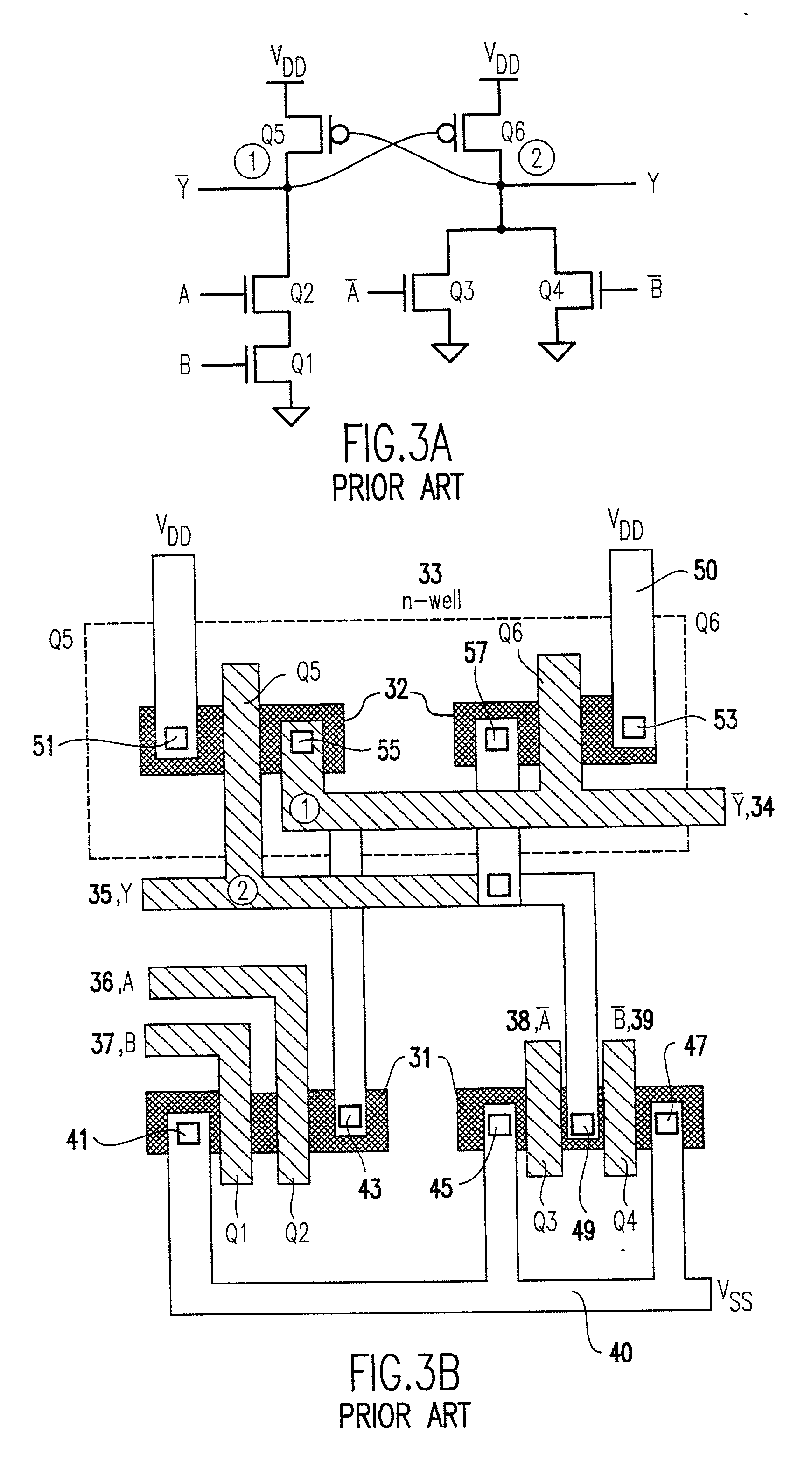

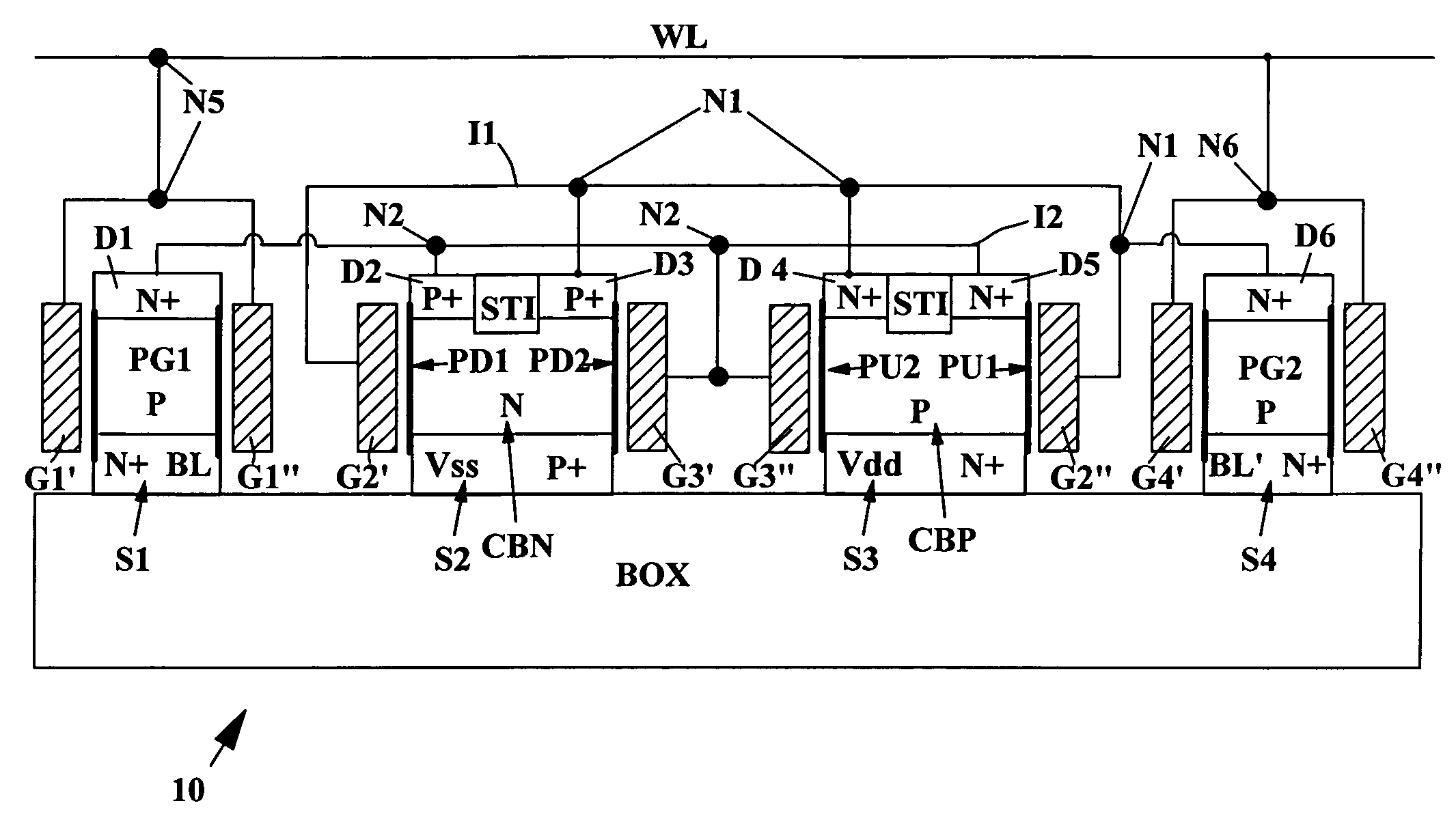

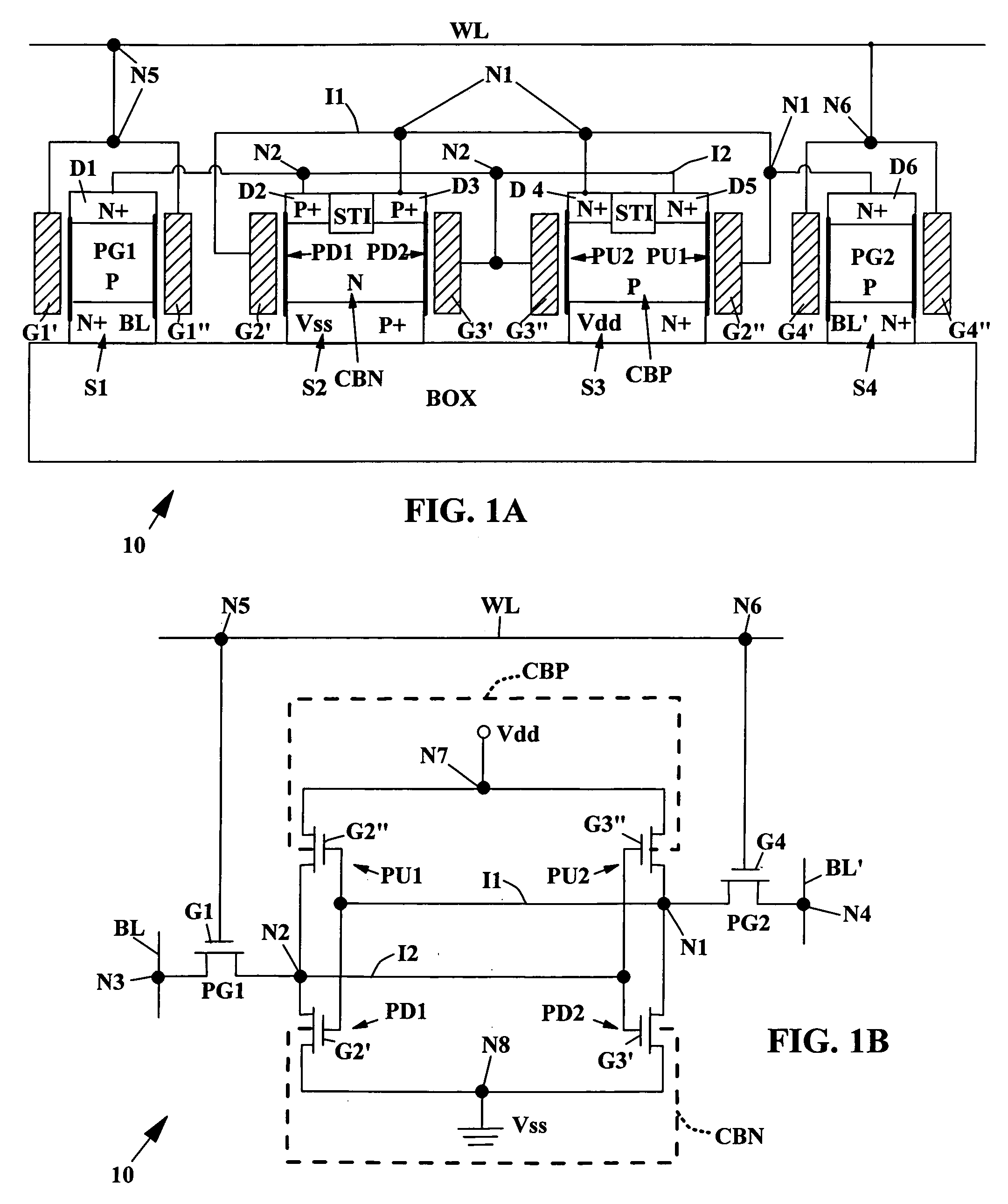

Merged logic and memory combining thin film and bulk Si transistors

InactiveUS20010028059A1Compact and economicalTransistorSolid-state devicesHigh densitySingle process

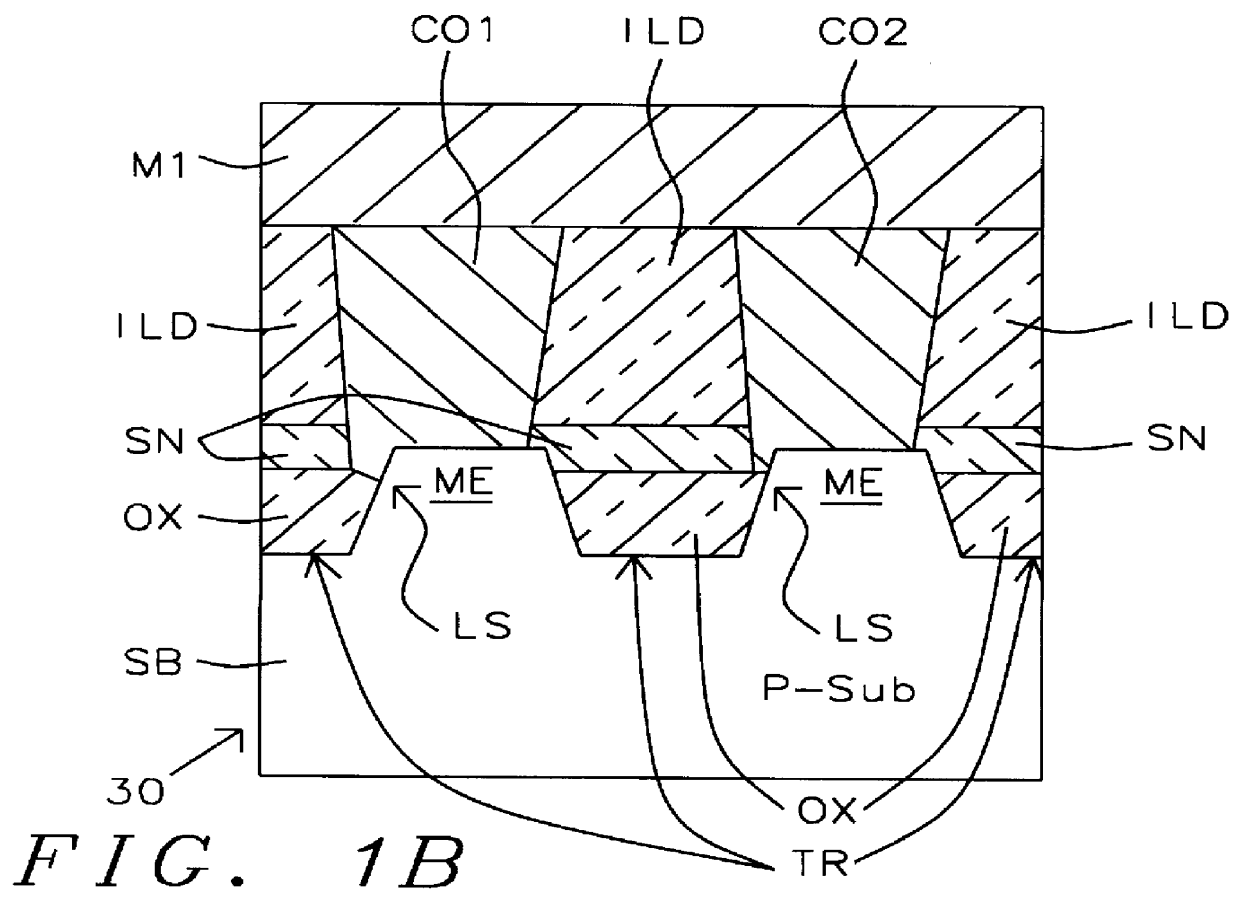

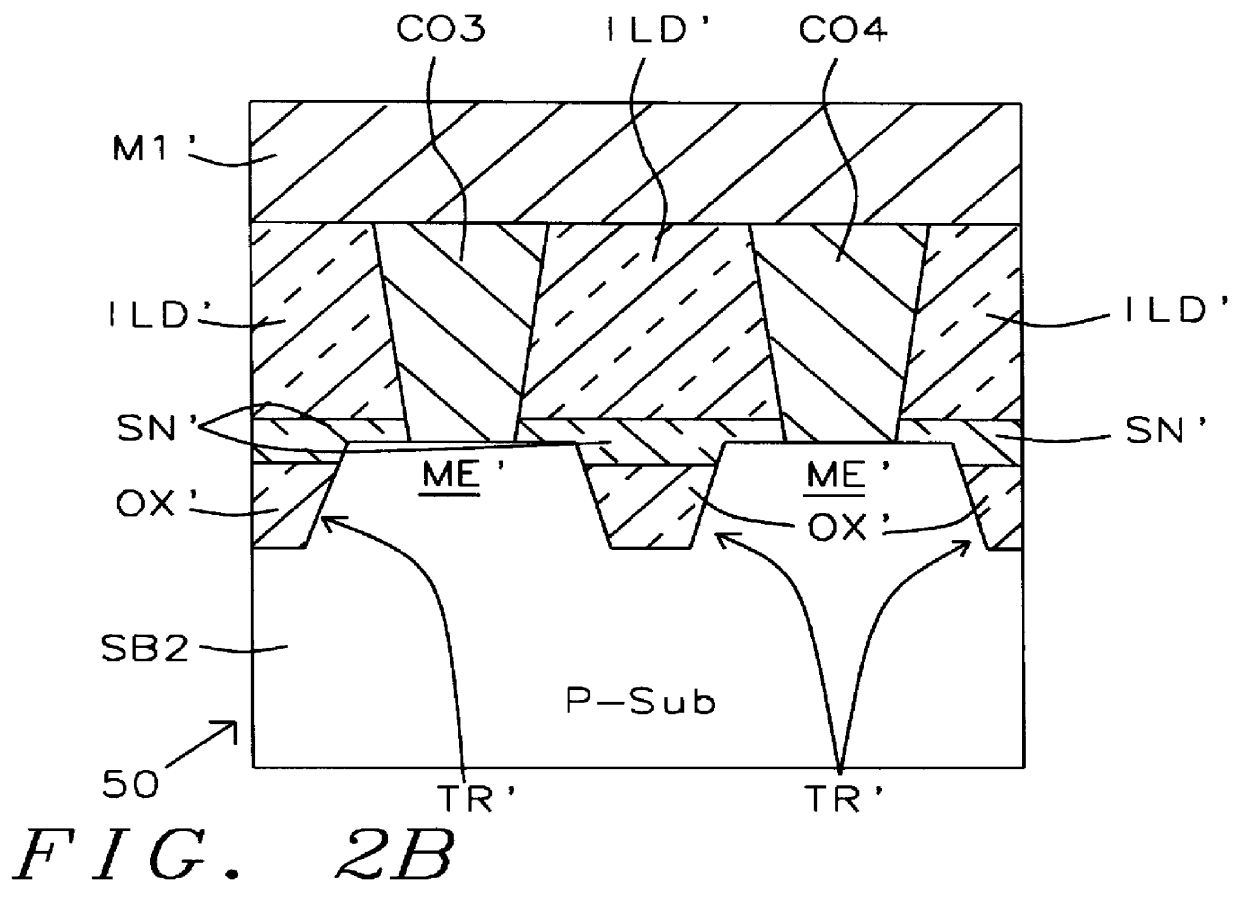

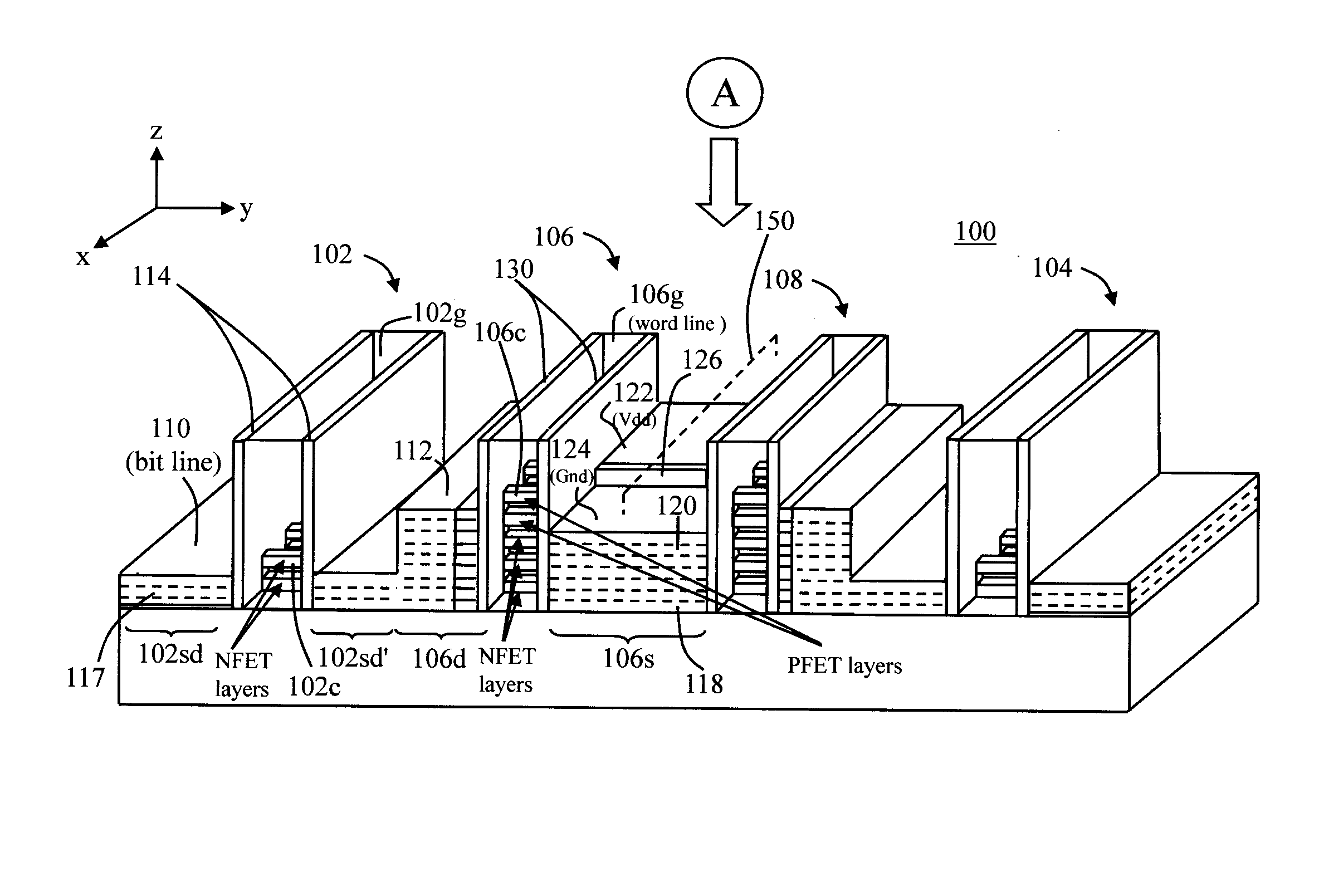

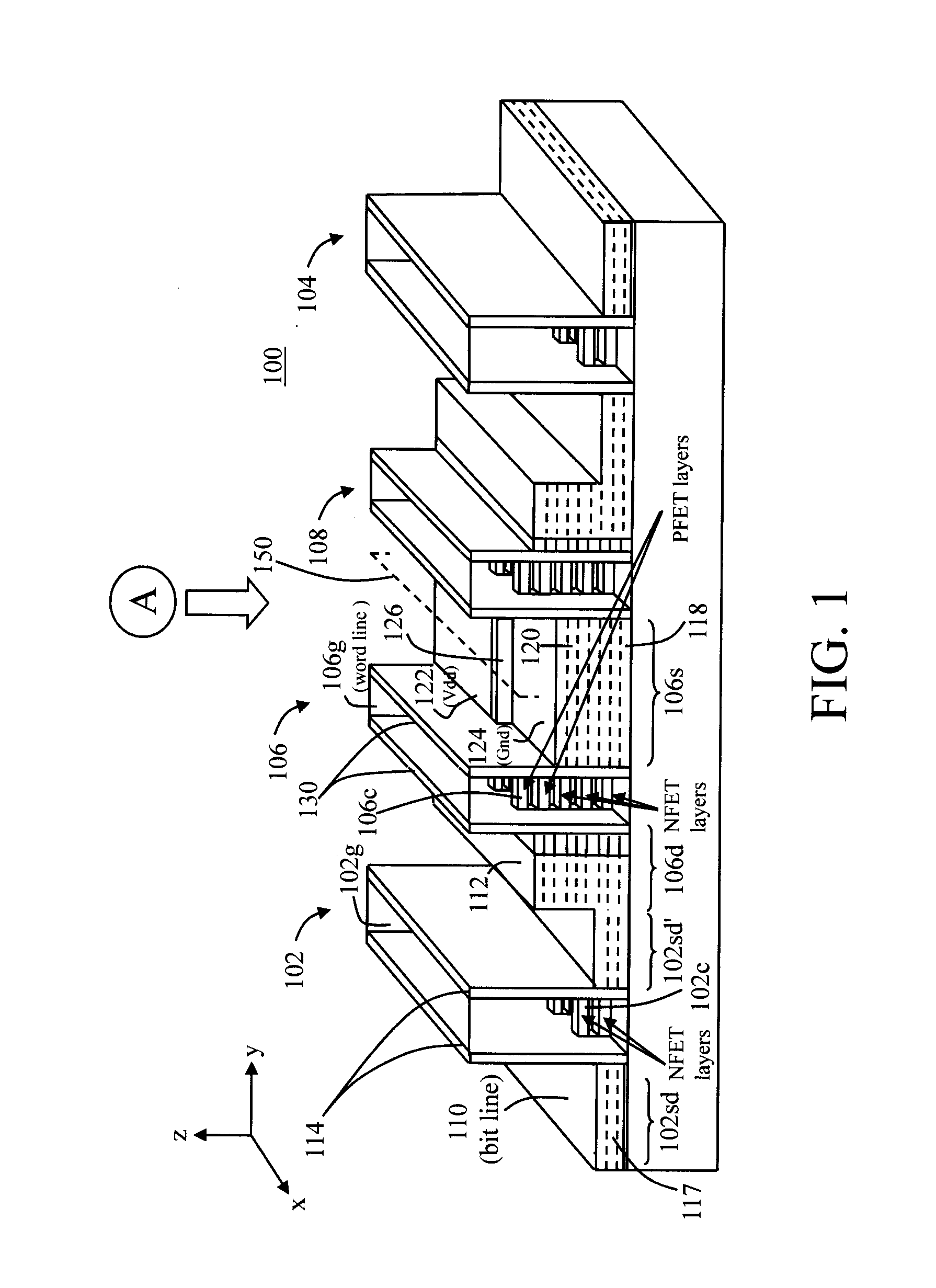

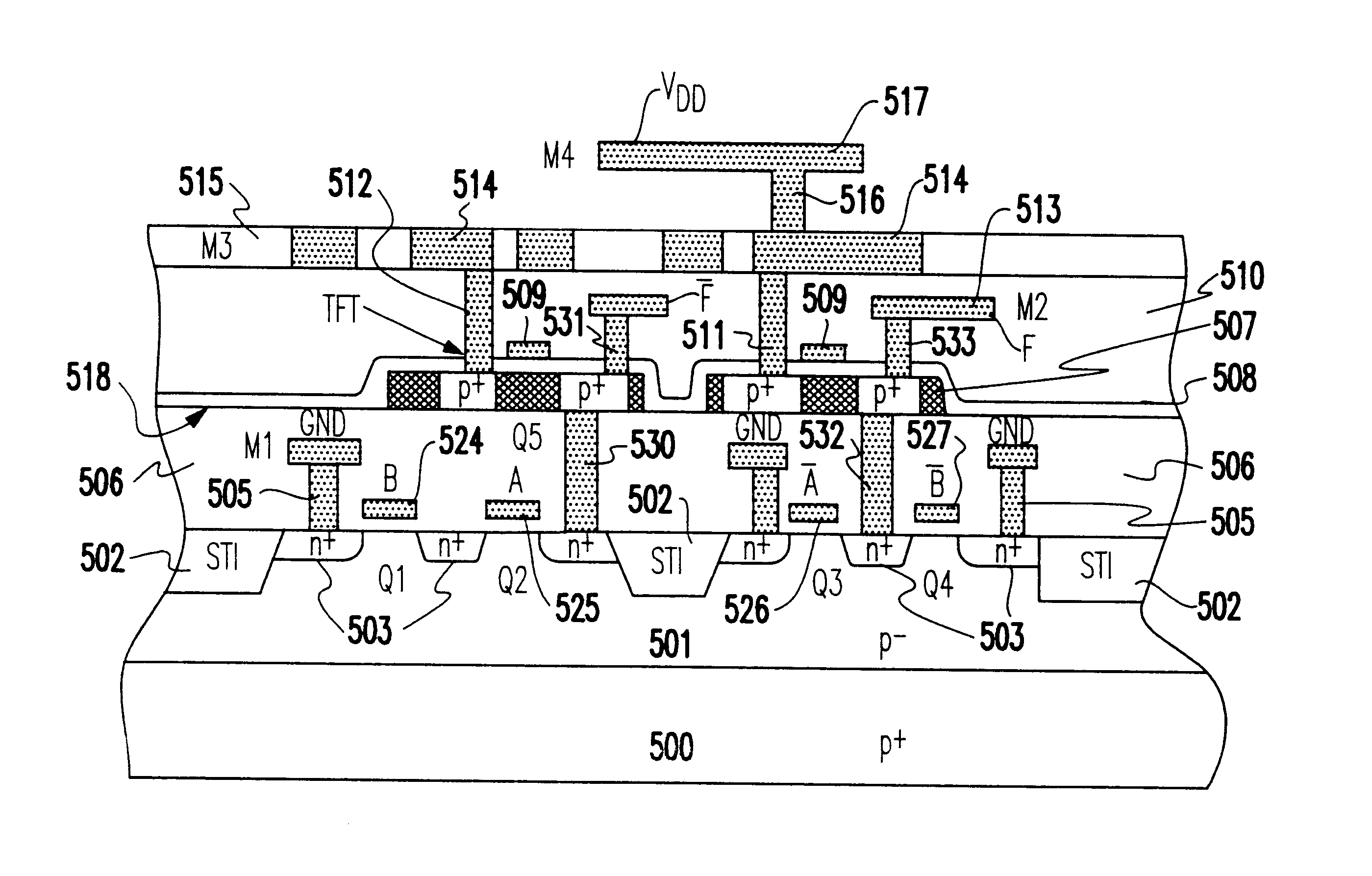

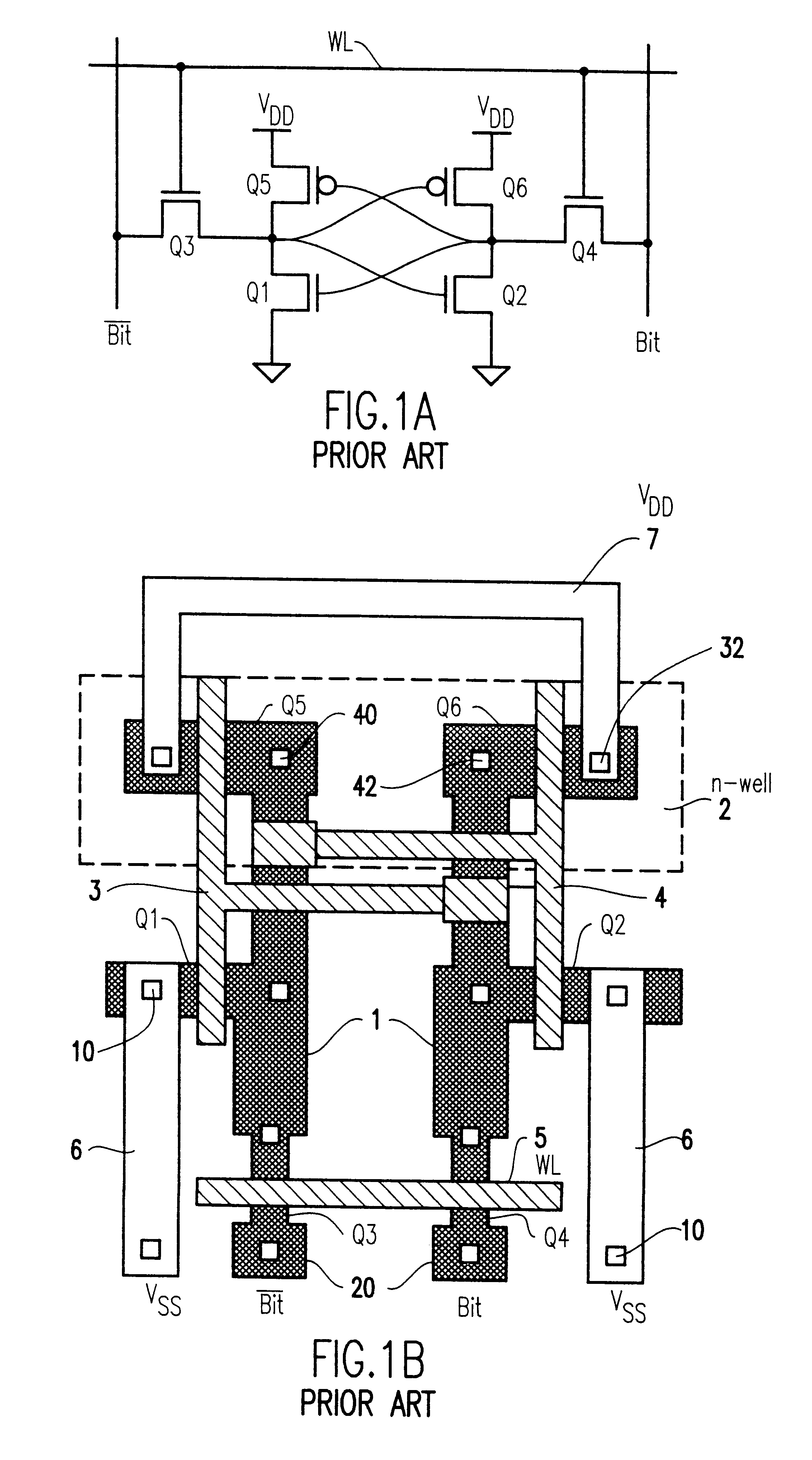

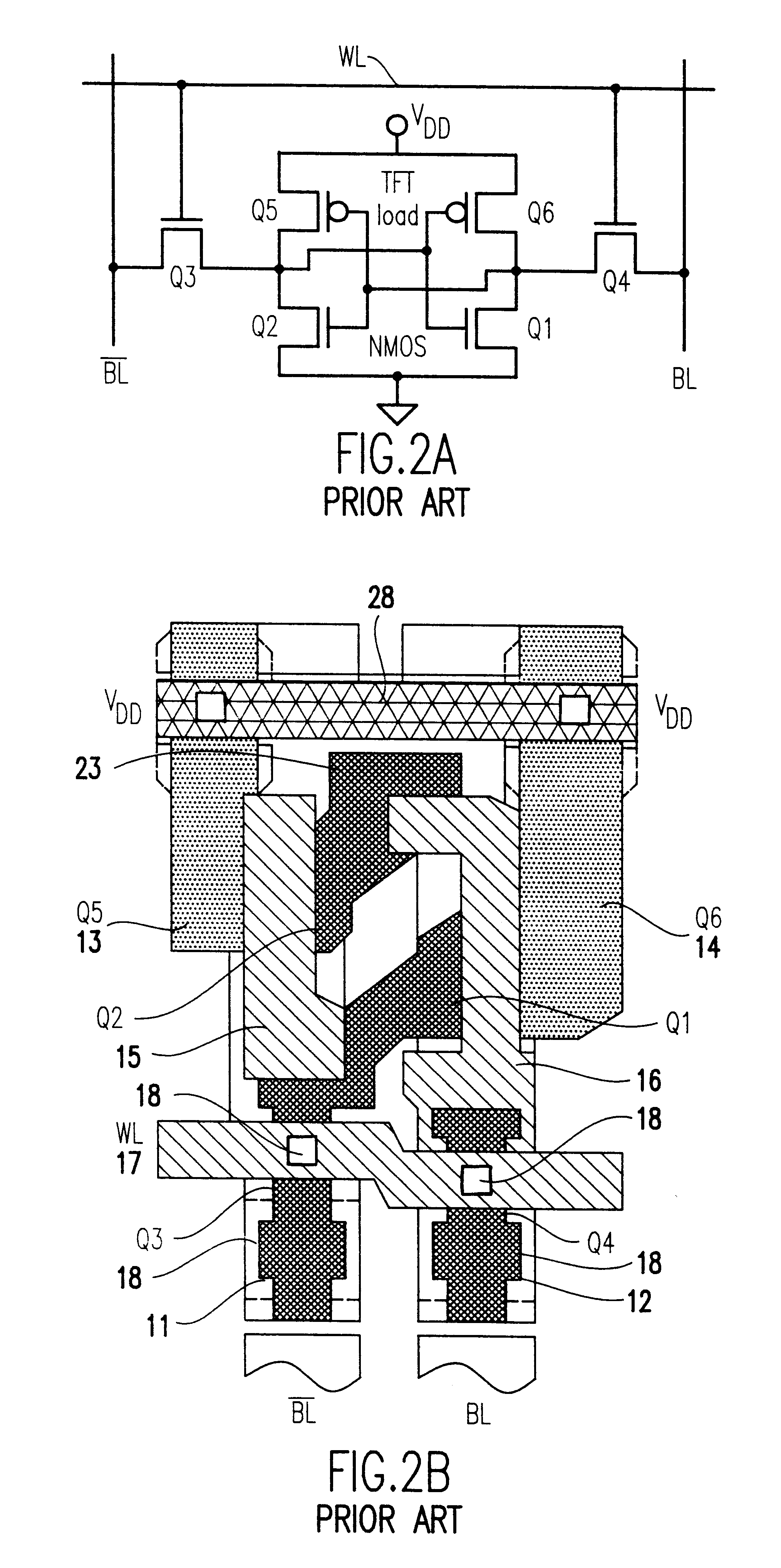

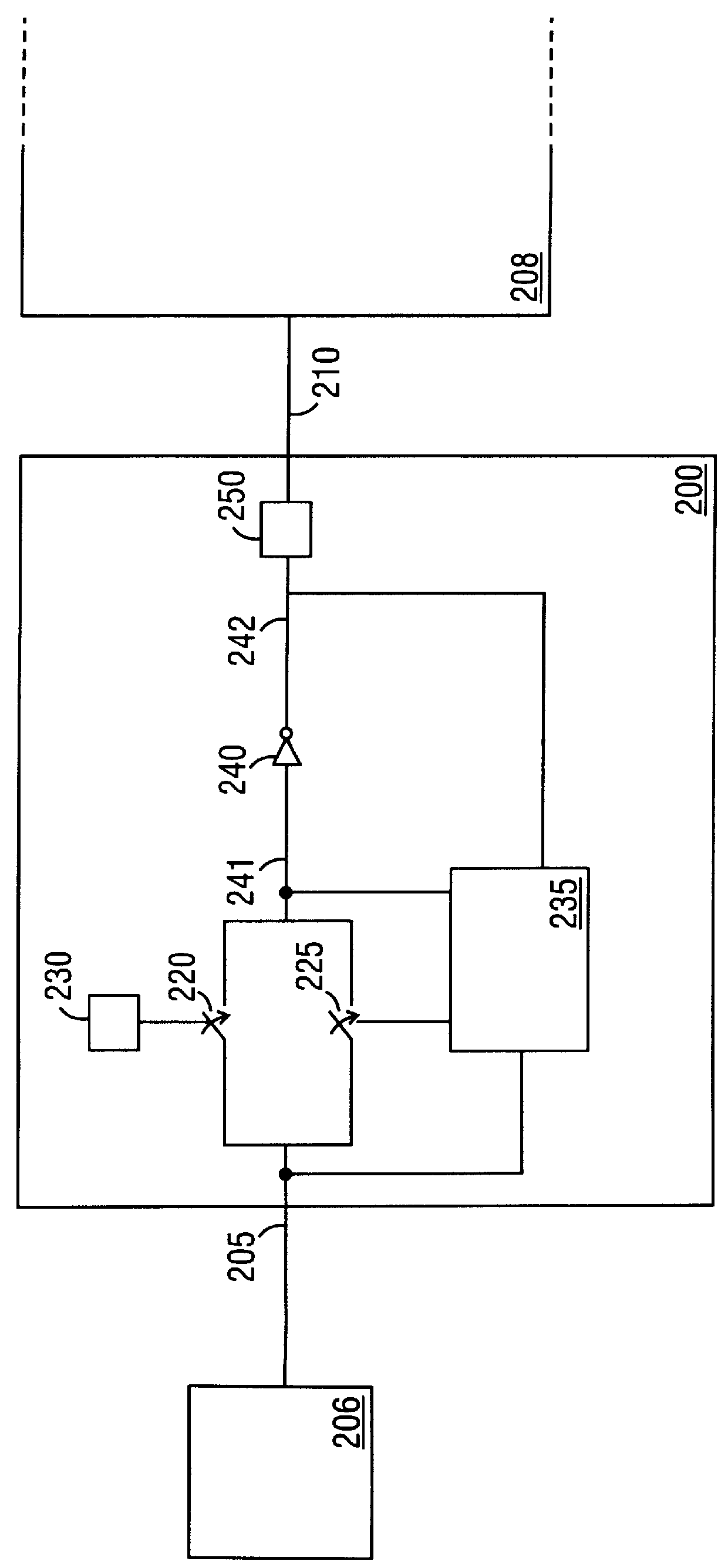

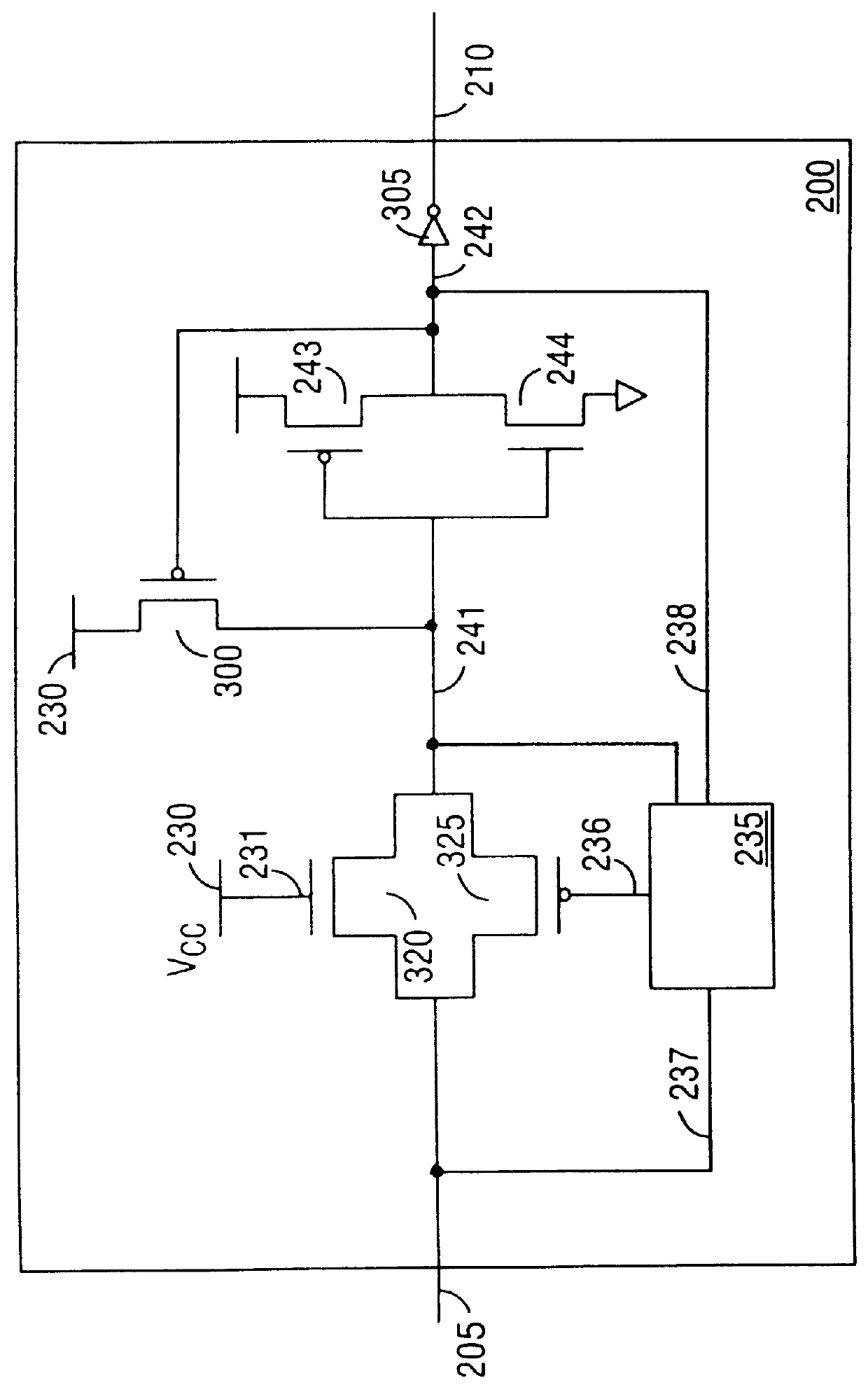

The present invention describes the use of two semiconductor layers, a thin film (TF) layer and a bulk Si wafer layer, to make high density and high speed merged logic and memory IC chips. The memory cells use three-dimensional (3D) SRAM structures. Two kinds of 3D logic cells are disclosed. 3D form of the differential cascode voltage switch (DCVS) architecture, and a 3D form of the DCVS with pass gate (DCVSPG) logic architecture. A high density "system on chip" architecture is described. The high density is achieved by locating large PMOS transistors in the TF Si layer, and the fast NMOS transistors in a bulk Si wafer layer. A single process sequence to simultaneously make the logic and memory circuits on the IC chip is also described.

Owner:GLOBALFOUNDRIES INC

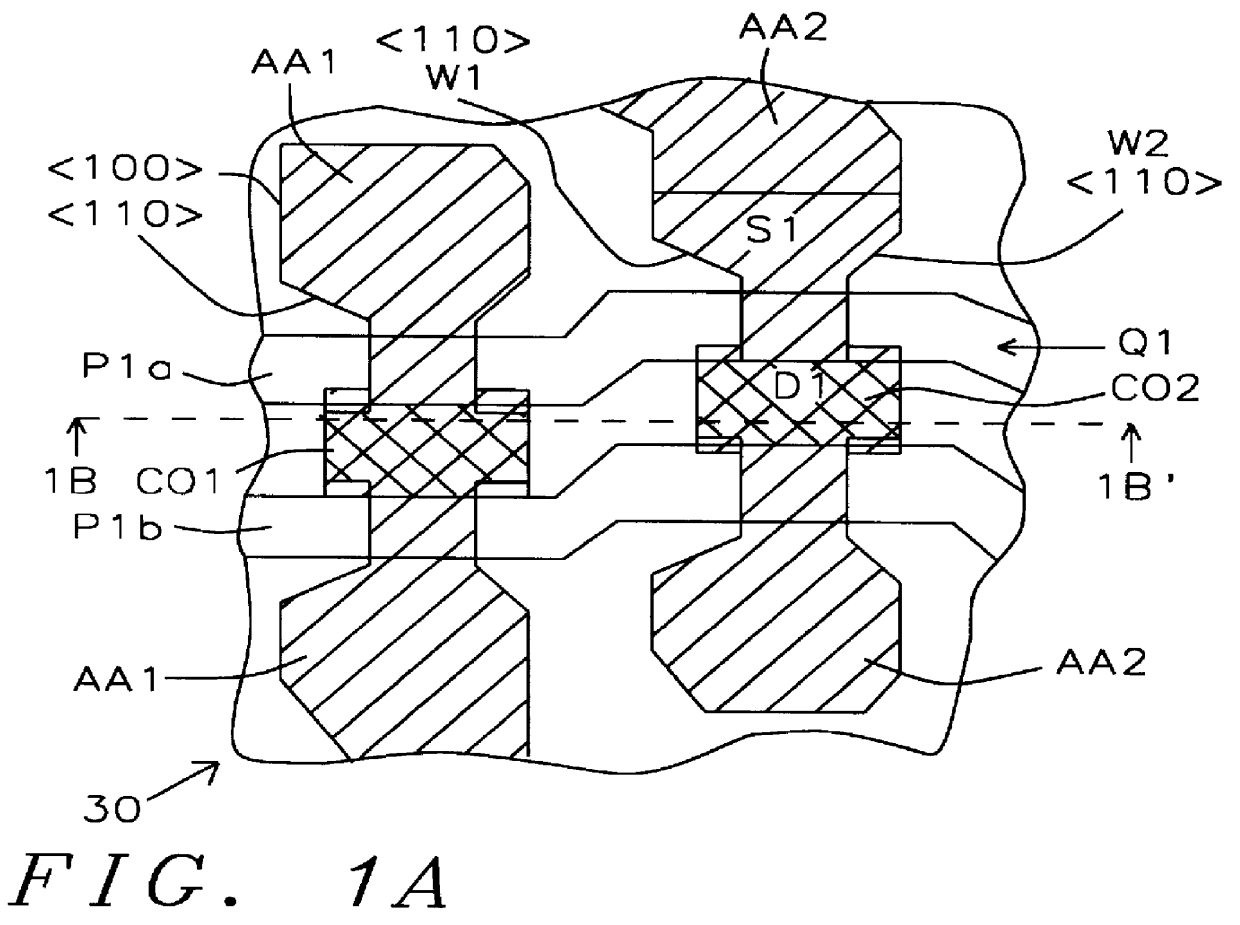

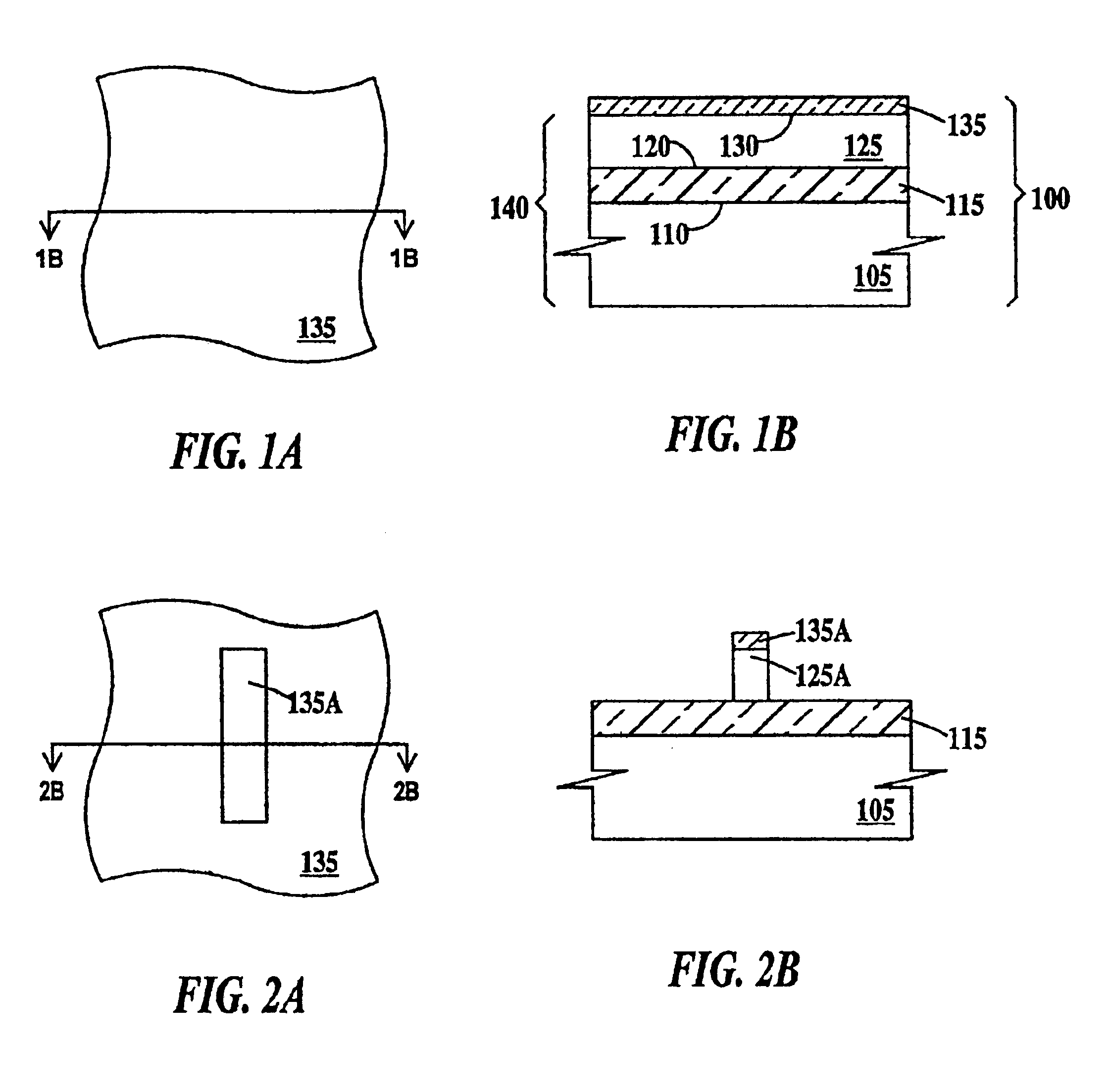

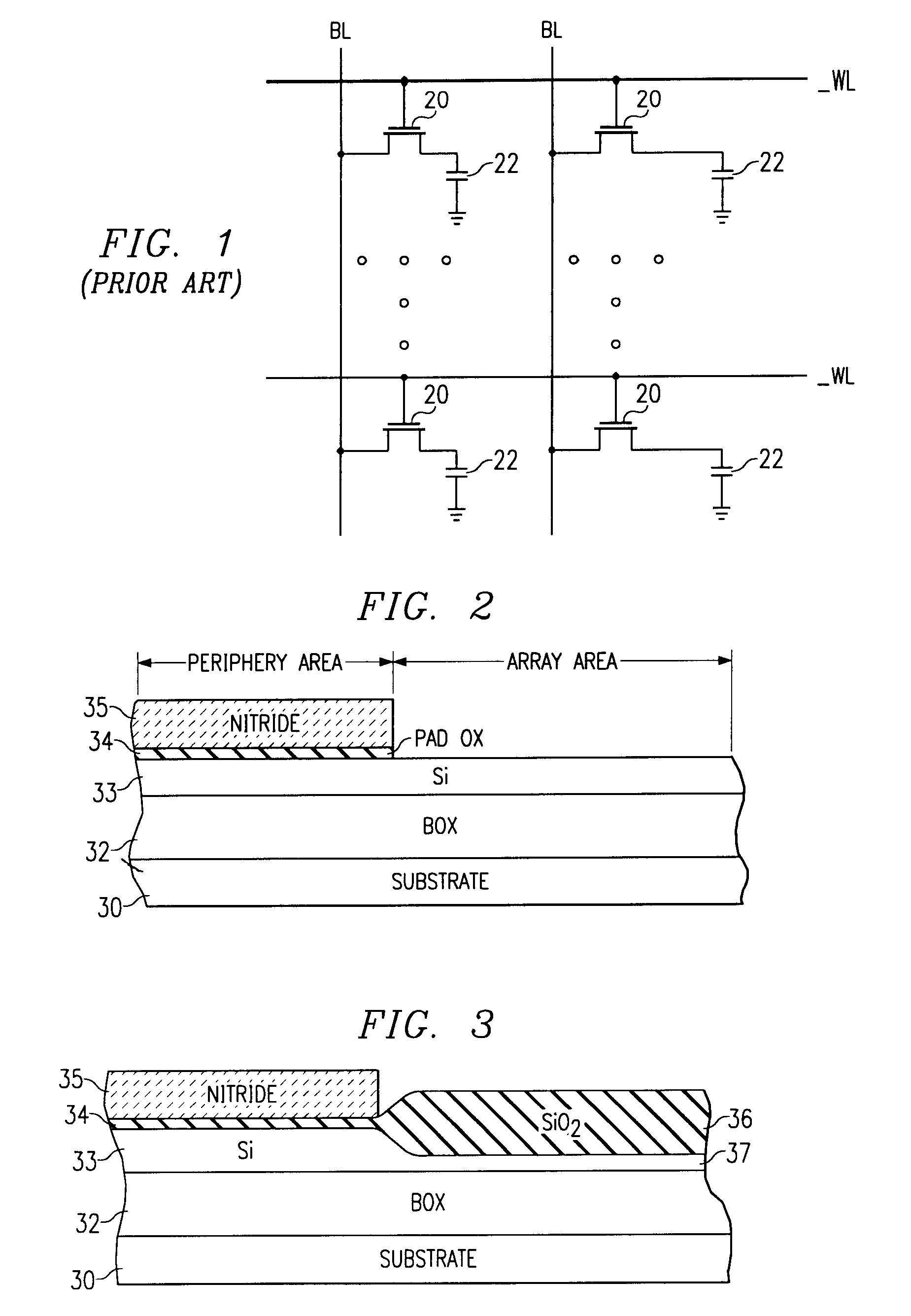

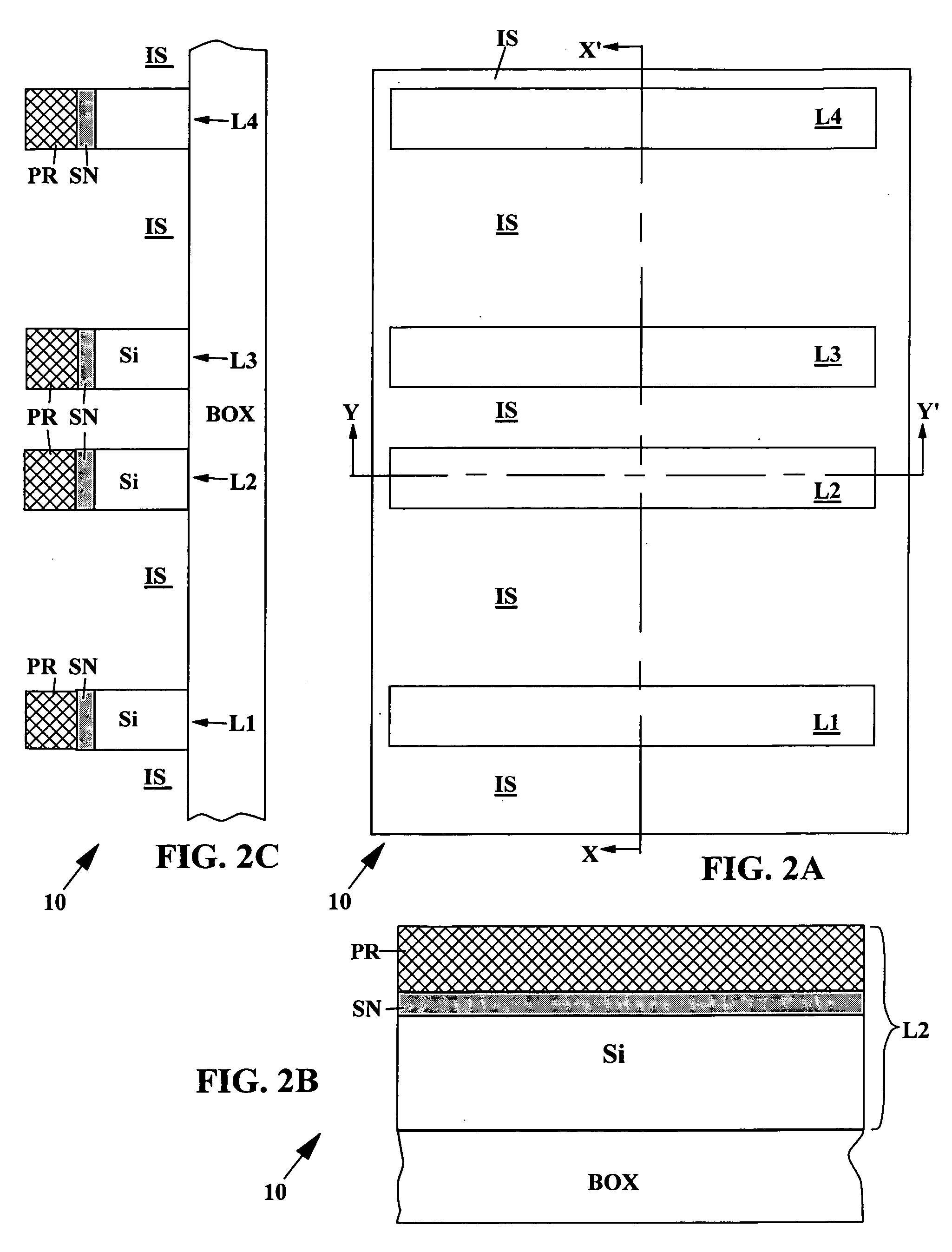

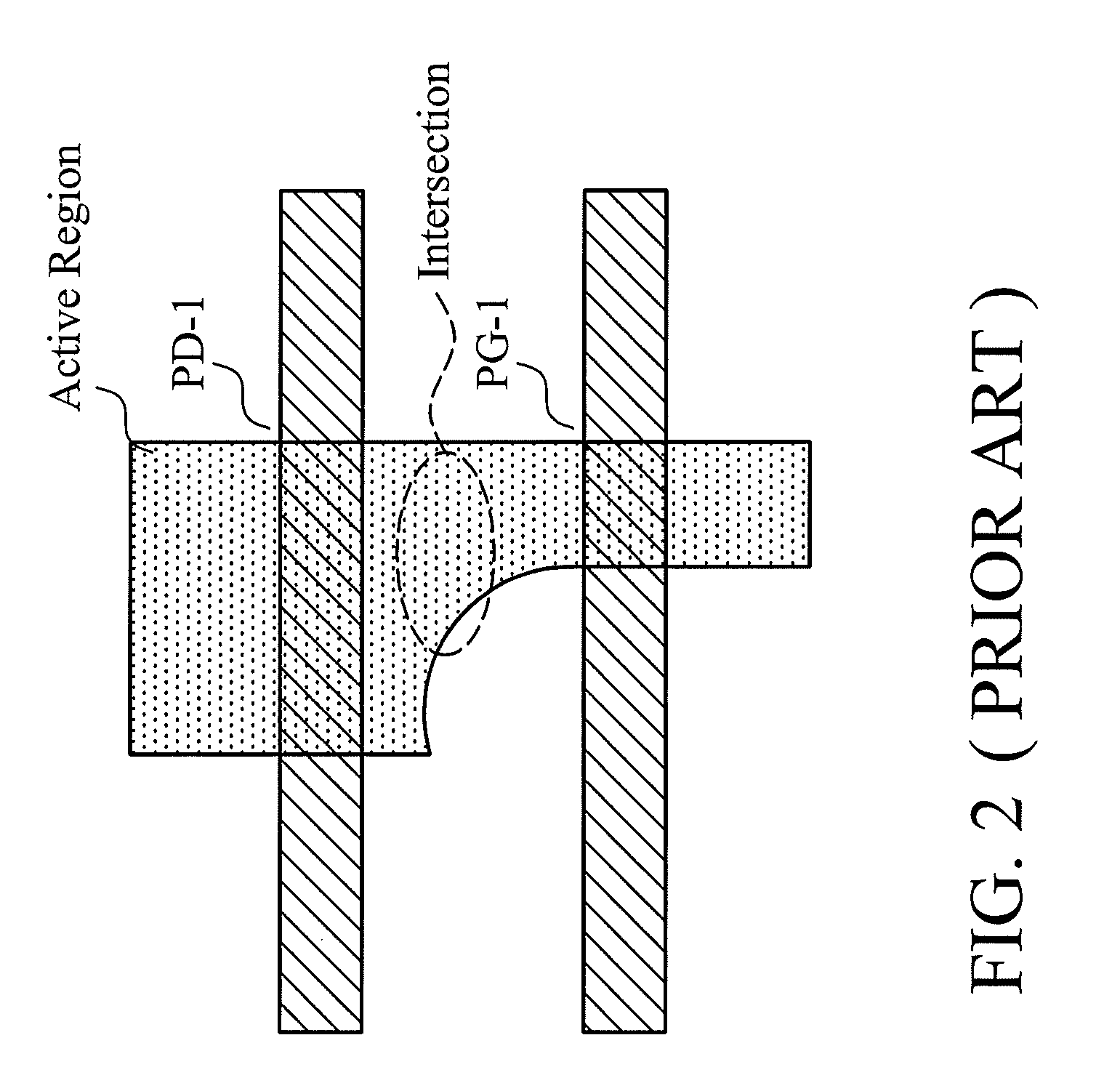

SRAM layout for relaxing mechanical stress in shallow trench isolation technology and method of manufacture thereof

InactiveUS6117722ARelieve pressureSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorCrystal plane

An SRAM device has STI regions separated by mesas and doped regions including source / drain regions, active areas, wordline conductors and contacts in a semiconductor substrate is made with a source region has 90 DEG transitions in critical locations. Form a dielectric layer above the active areas. Form the wordline conductors above the active areas transverse to the active areas. The source and drain regions of a pass gate transistor are on the opposite sides of a wordline conductor. Form the sidewalls along the <100> crystal plane. Form the contacts extending down through to the dielectric layer to the mesas. Substrate stress is reduced because the large active area region formed in the substrate assures that the contacts are formed on the <100> surfaces of the mesas are in contact with the mesas formed on the substrate and that the <110> surfaces of the silicon of the mesas are shielded from the contacts.

Owner:TAIWAN SEMICON MFG CO LTD

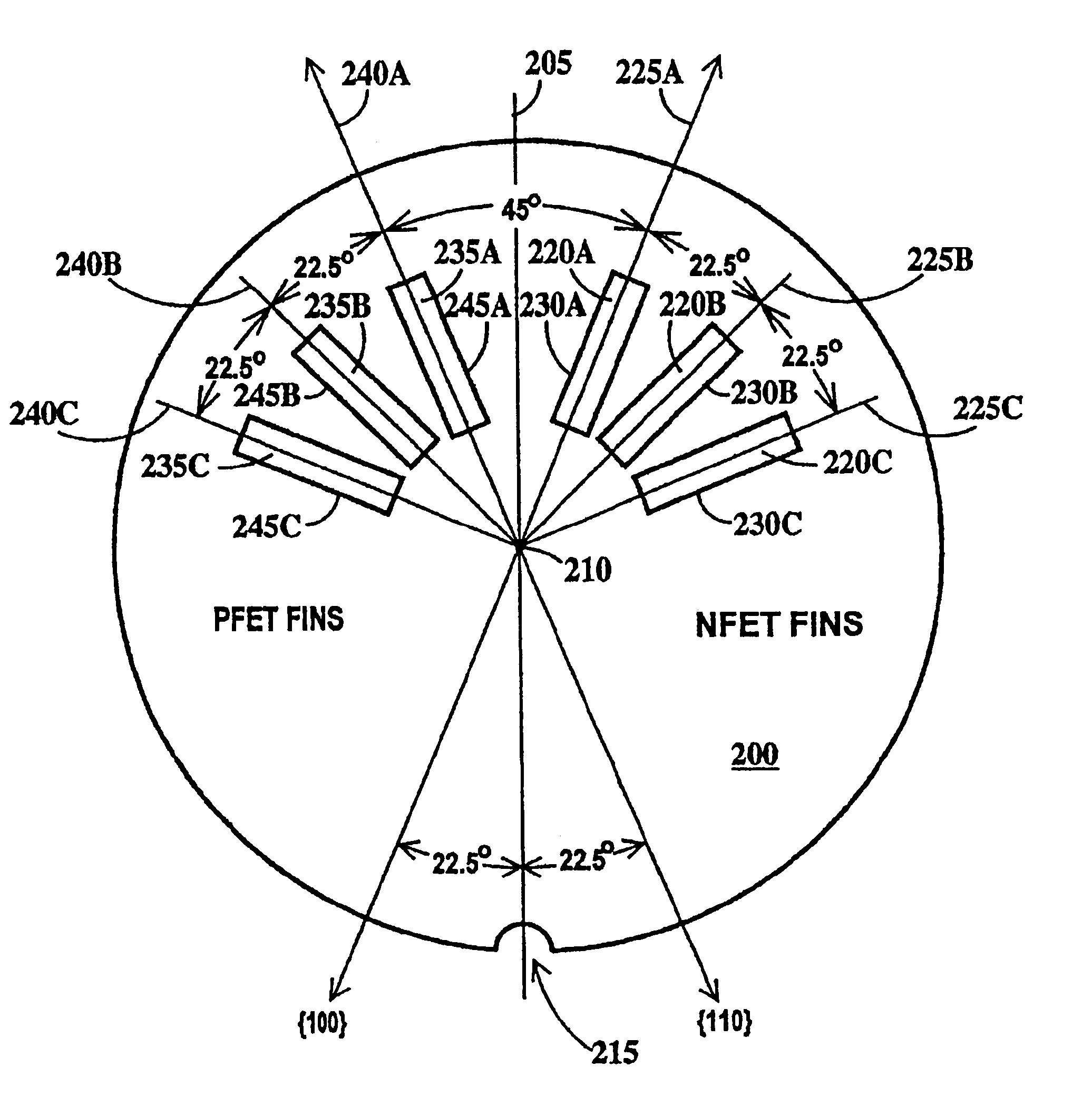

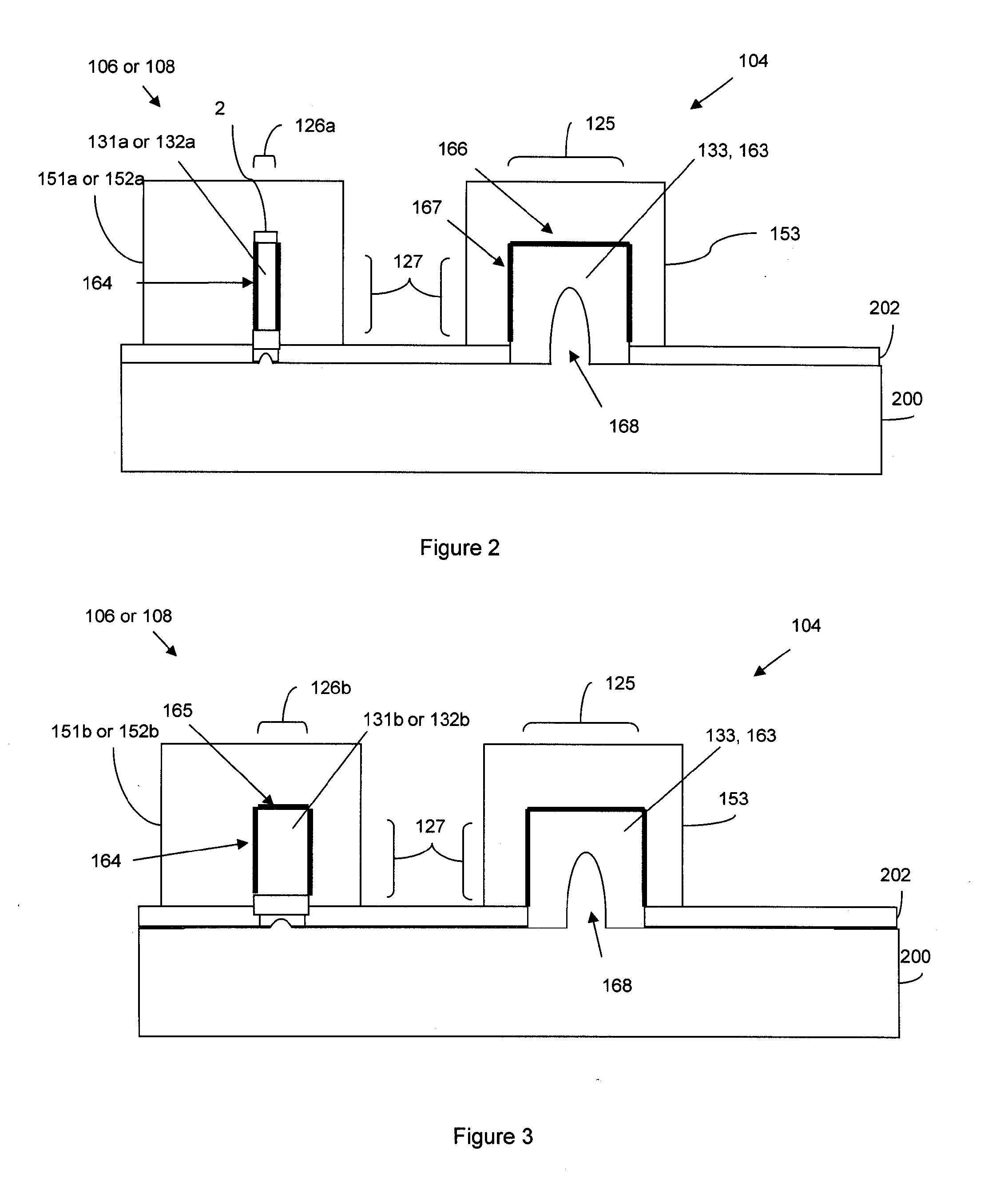

FinFET SRAM cell with chevron FinFET logic

An electronic device, and SRAM and a method of forming the electronic device and SRAM. The semiconductor device including: a pass gate transistor having a fin body having opposing sidewalls aligned in a first direction and having a first majority carrier mobility and a gate adjacent to both sidewalls of the fin body; a pull down latch transistor having a fin body having opposing sidewalls aligned in a second direction and having a second majority carrier mobility and a gate adjacent to both sidewalls of thc fin body; a pull up latch transistor having a fin body having opposing sidewalls aligned in a third direction and having a third majority carrier mobility and a gate adjacent to both sidewalls of the fin body; and CMOS chevron logic circuits, wherein crystal planes of each fin body and of CMOS transistor of the chevron logic are co-aligned.

Owner:IBM CORP

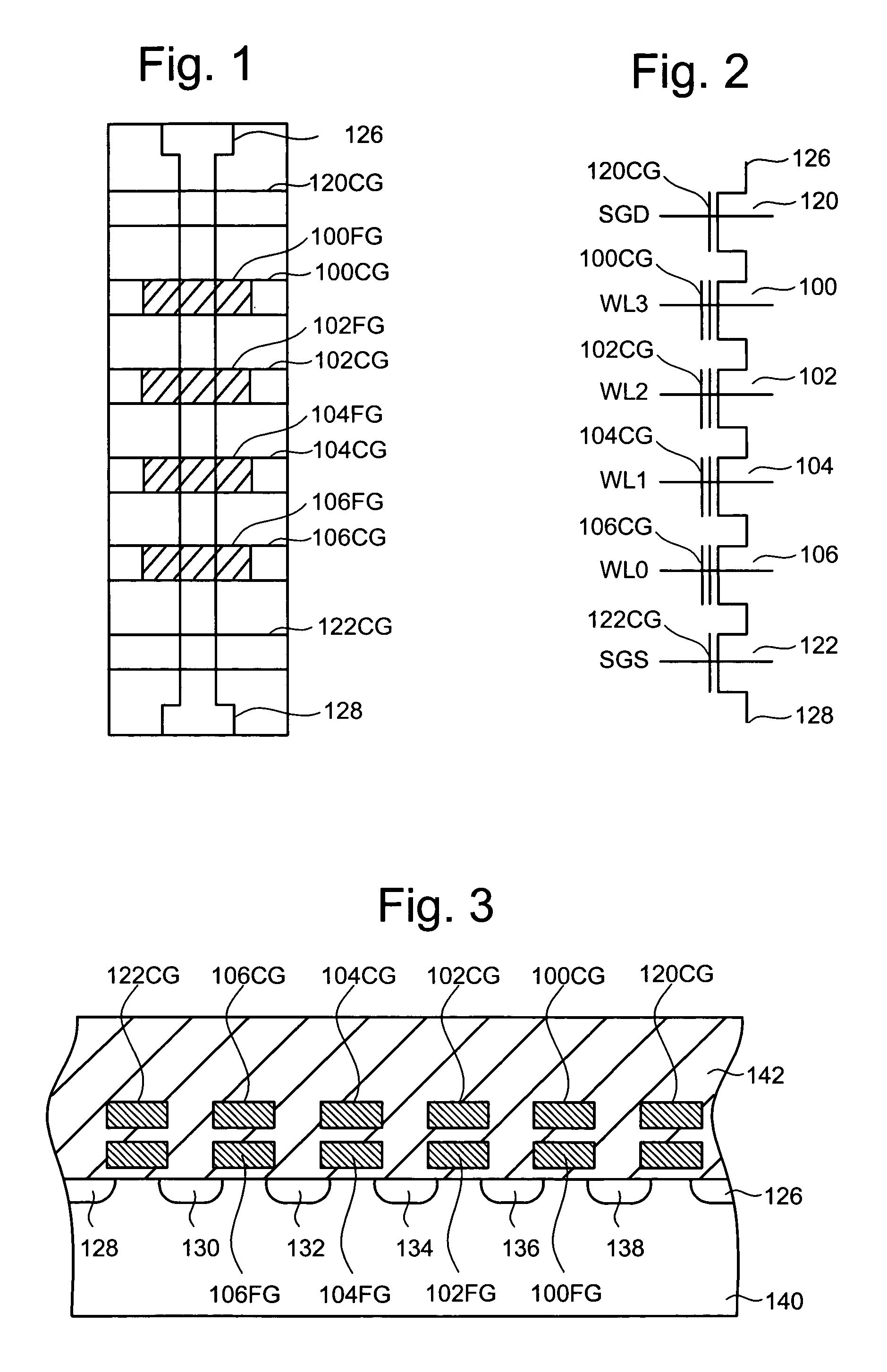

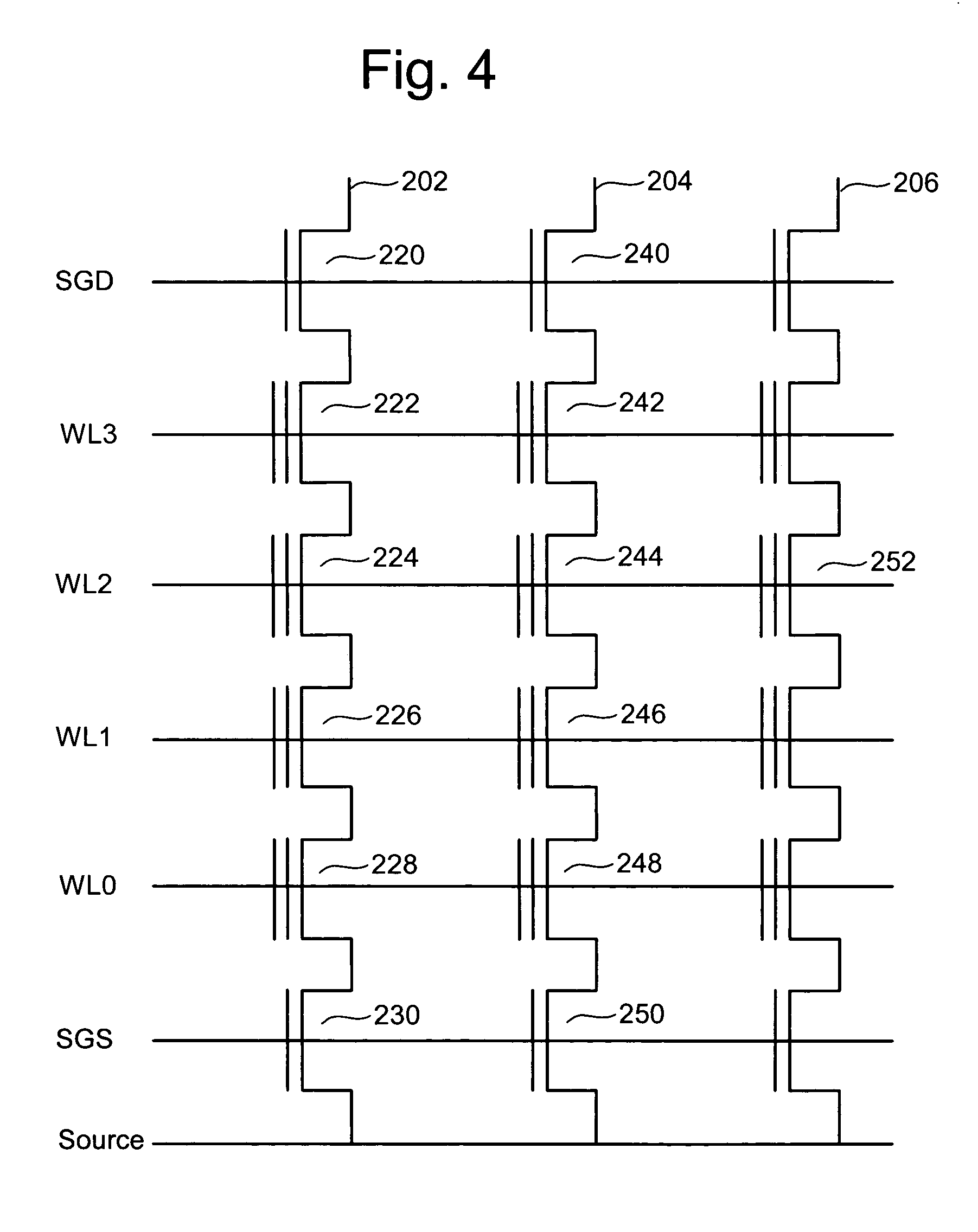

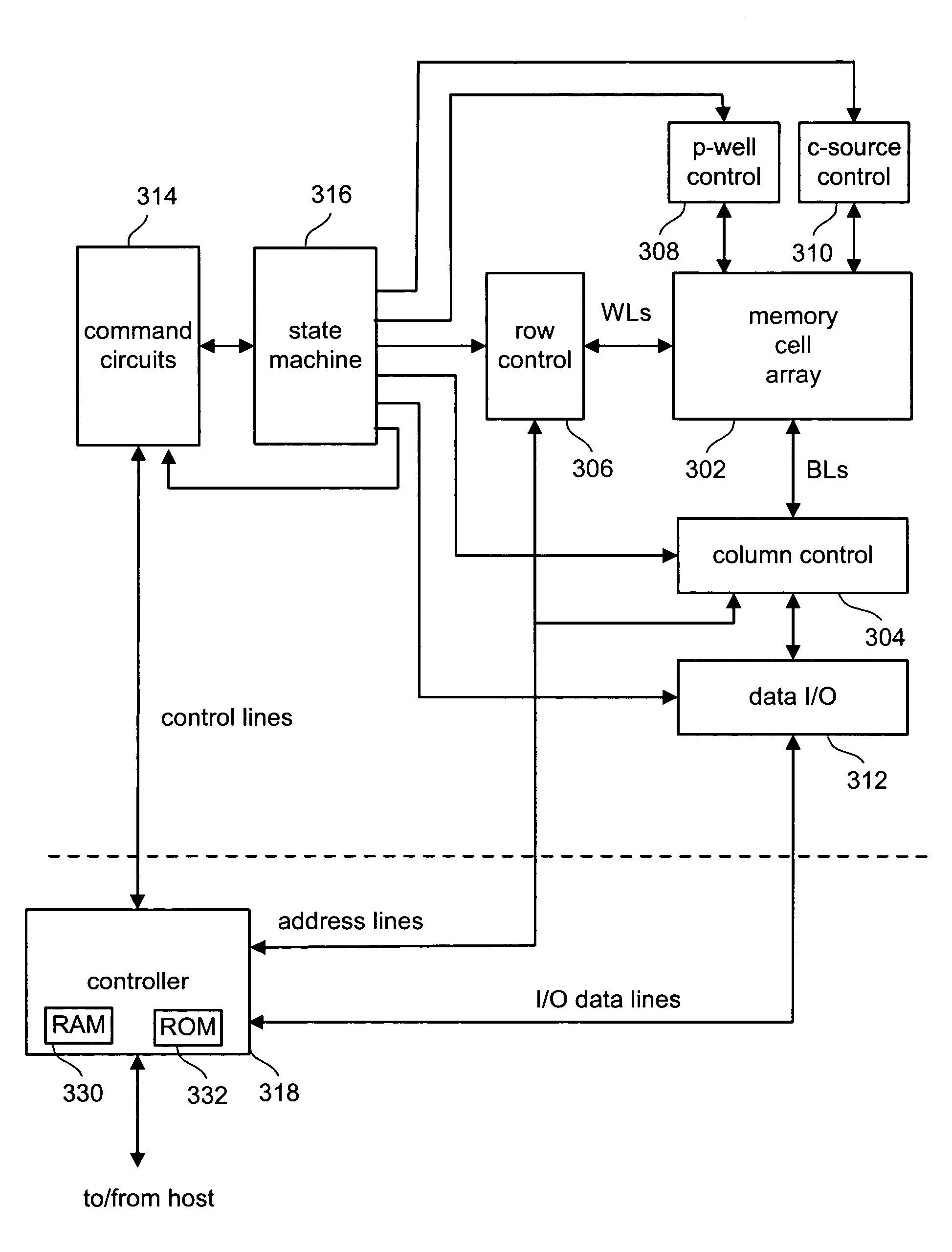

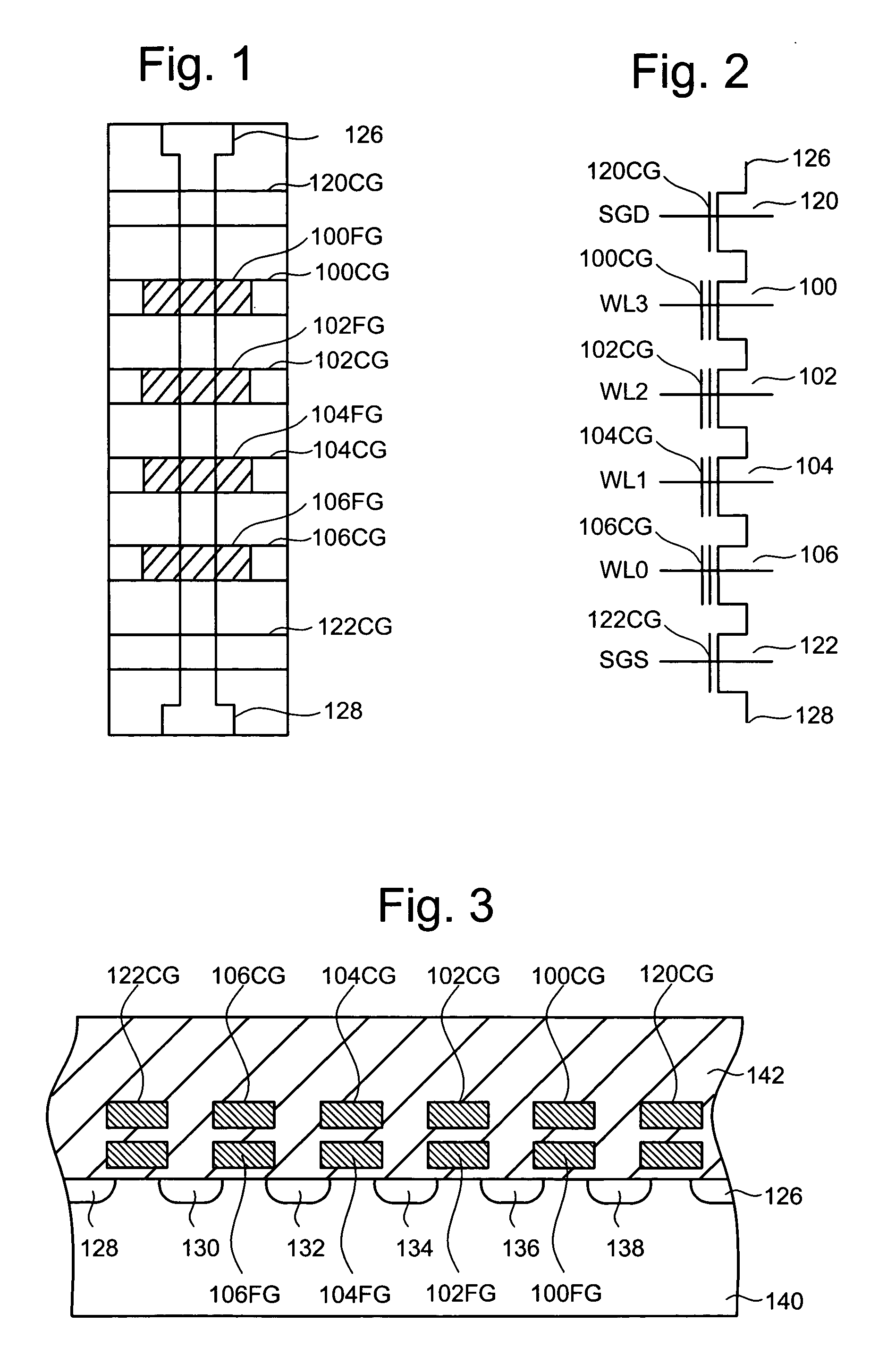

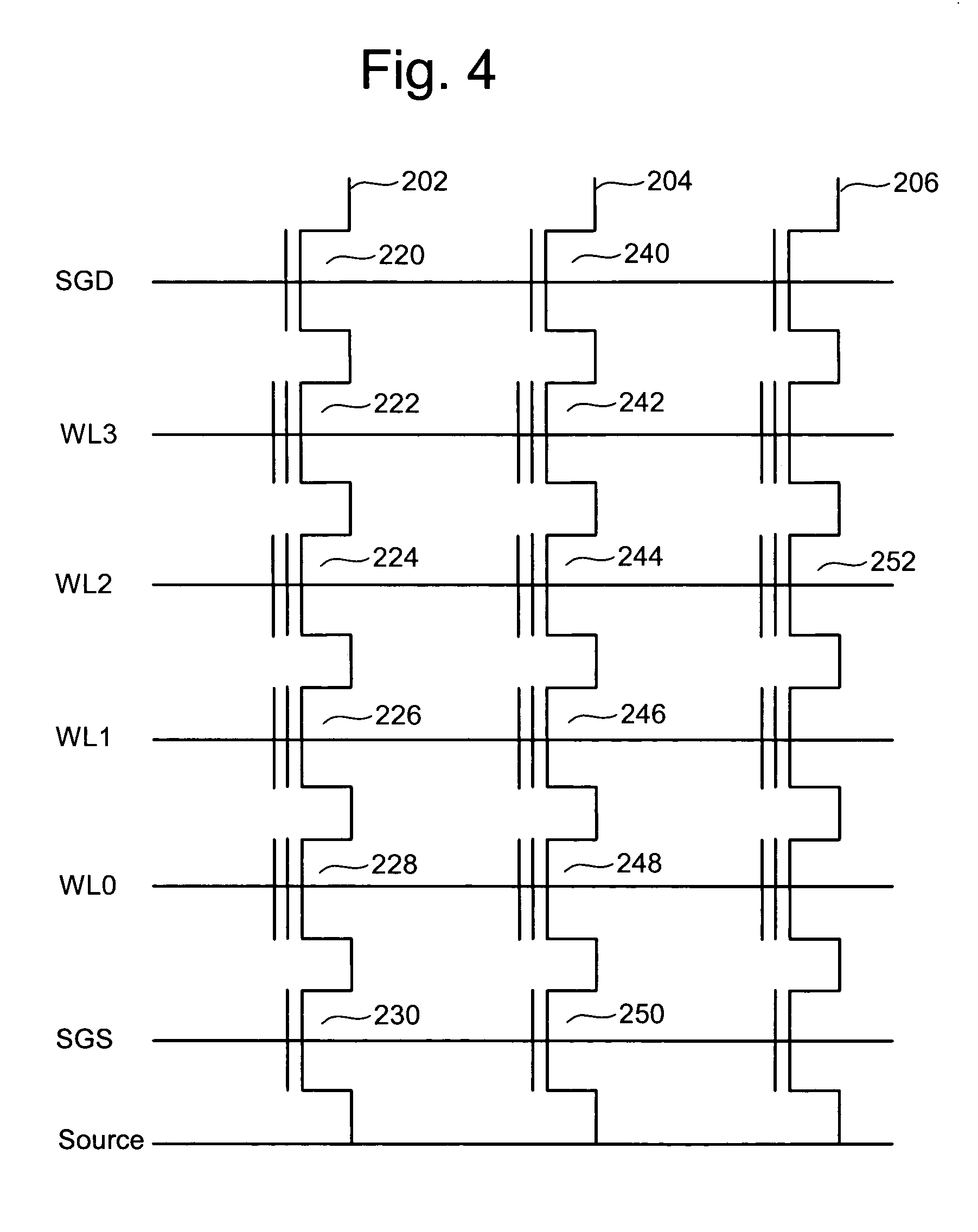

Operating non-volatile memory without read disturb limitations

When reading a memory cell on a NAND string, the word lines for the memory cells not being read will receive a voltage so that those memory cells operate as pass gates. Over time, if there are a lot of read operations without any program operations, the cells not being read may suffer from Read Disturb because the voltage applied to the word lines may cause electrons to accumulate in the floating gates of the non-selected cells. The accumulation of charge in the floating gates raises the threshold voltage. To avoid the limitations of Read Disturb, only one word line of a block (or other grouping) is used to program and read data. In a system using NAND flash memory, the word line being read is not typically subjected to read disturb. Thus, a NAND flash memory that restricts programming and reading to one word line of a block is not likely to exhibit read disturb in that block.

Owner:SANDISK TECH LLC

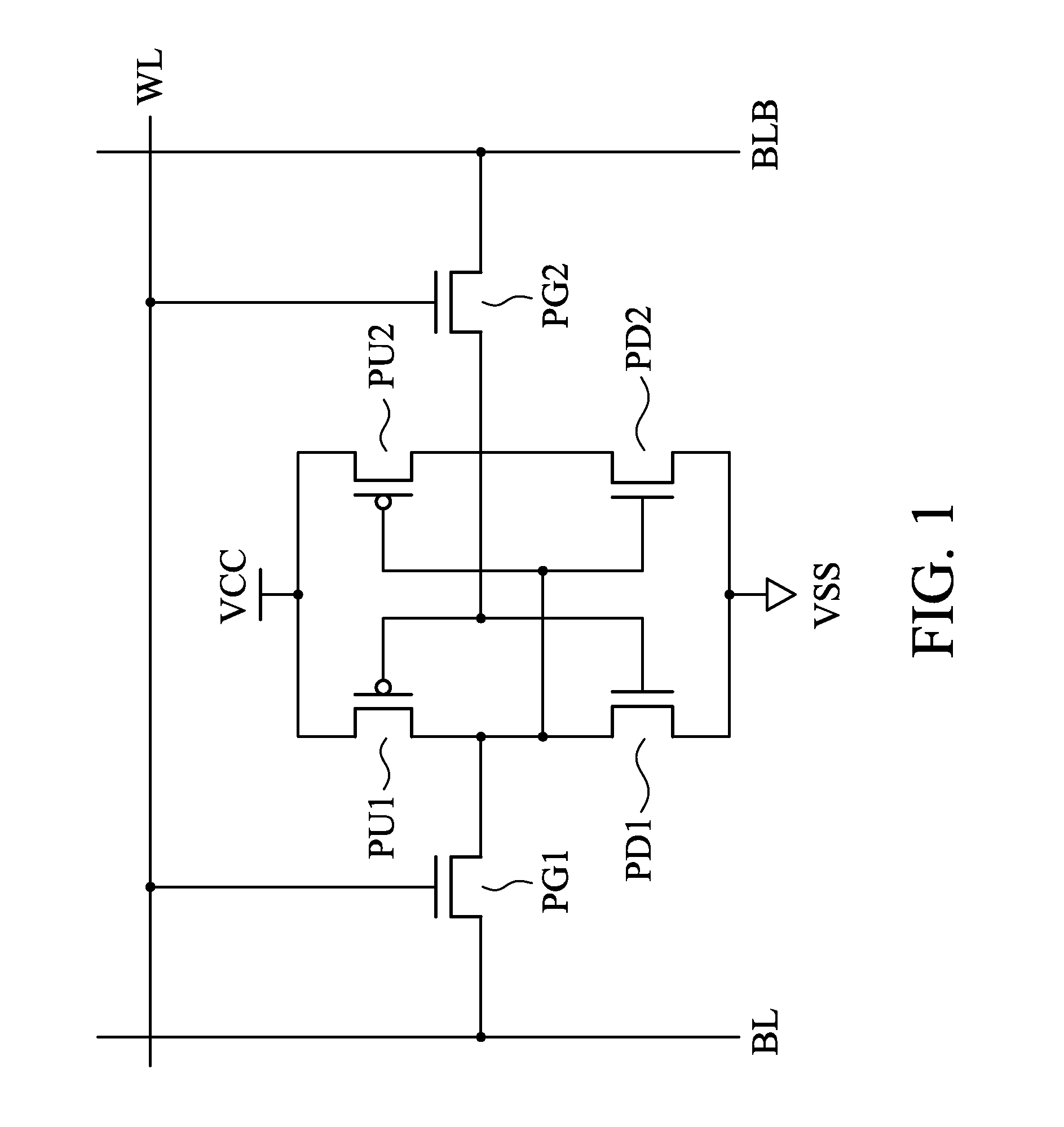

Static random access memory (SRAM) cell and method for forming same

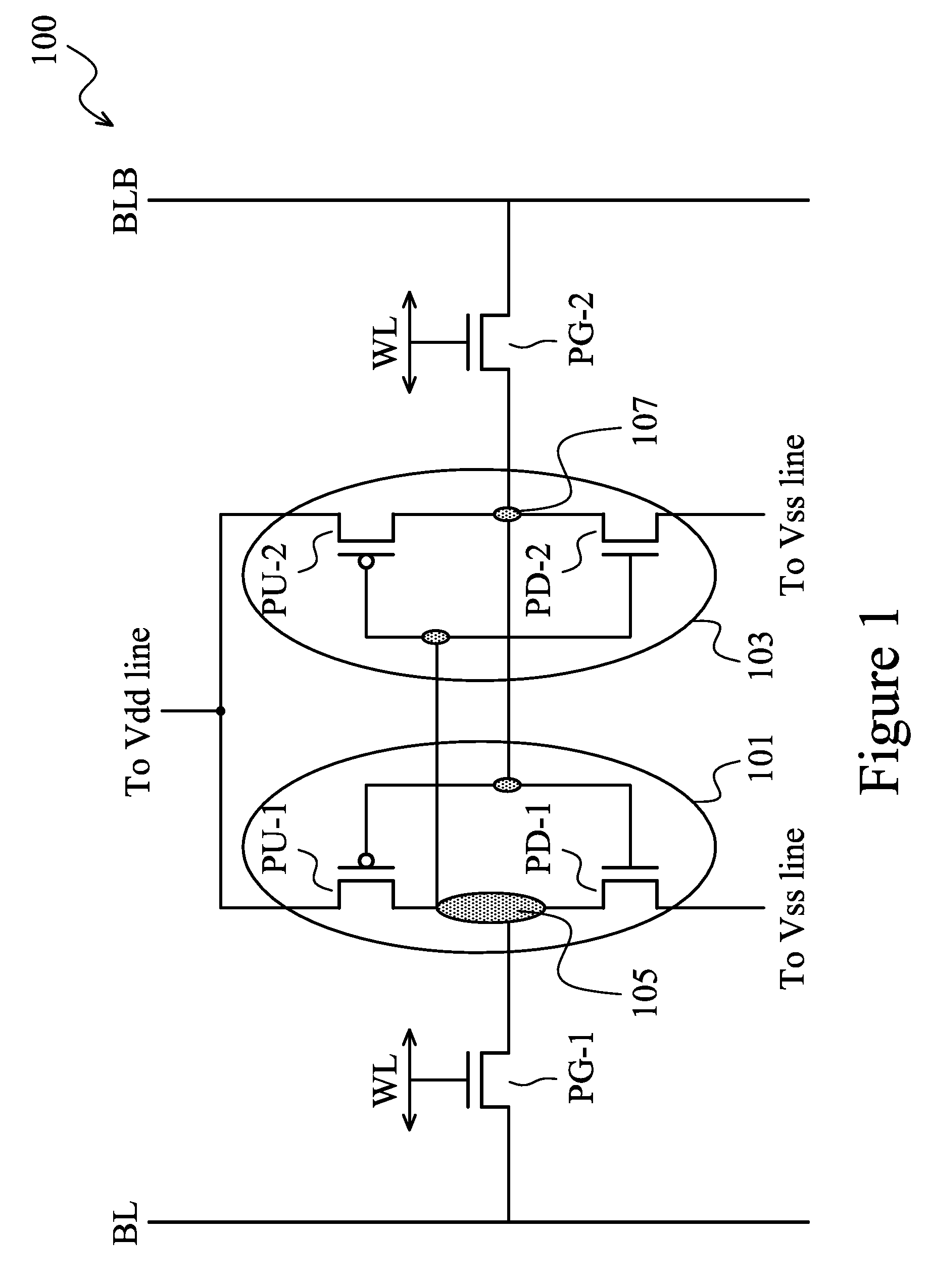

InactiveUS8004042B2High densitySmall sizeTransistorSolid-state devicesStatic random-access memoryRandom access memory

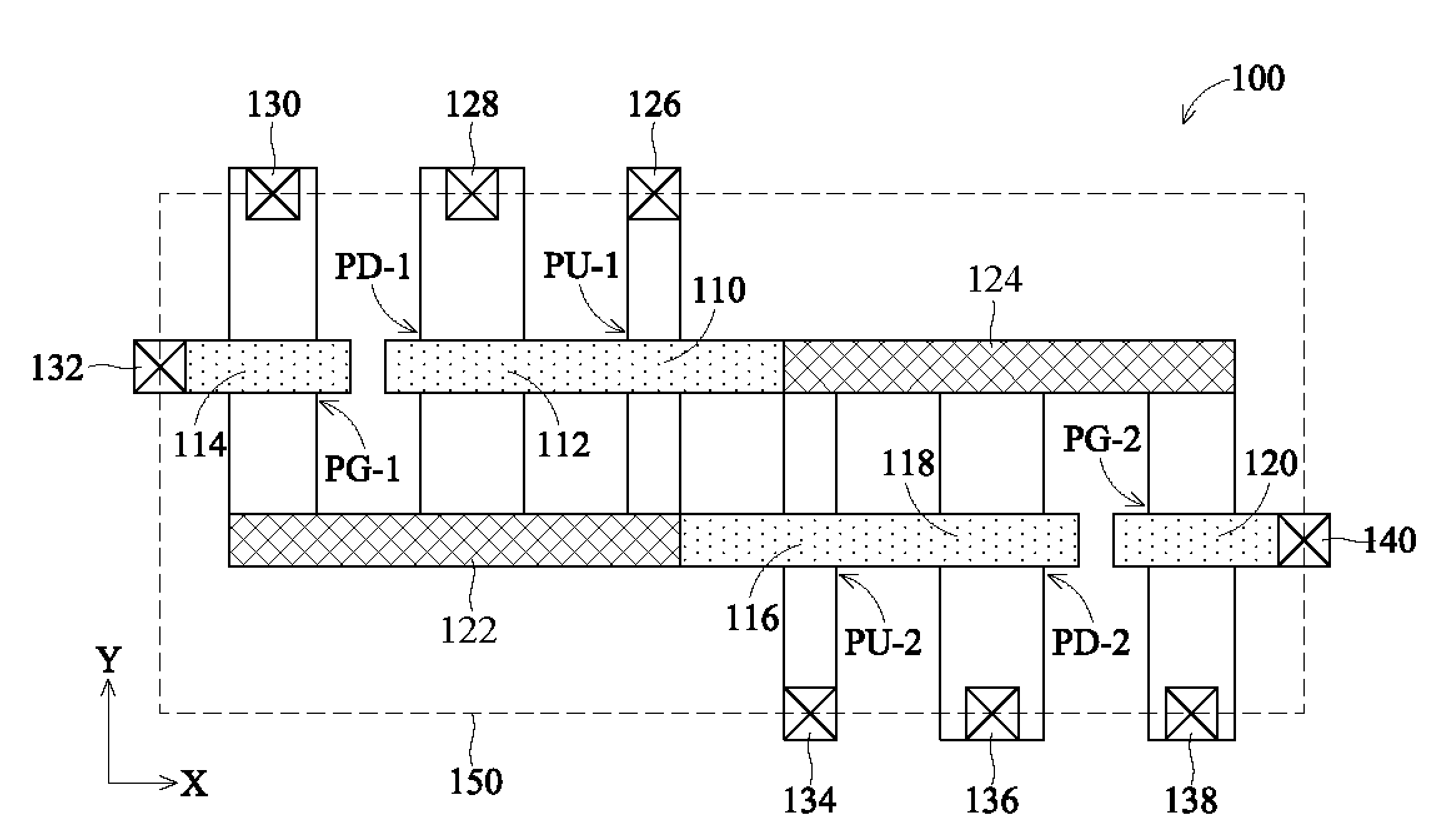

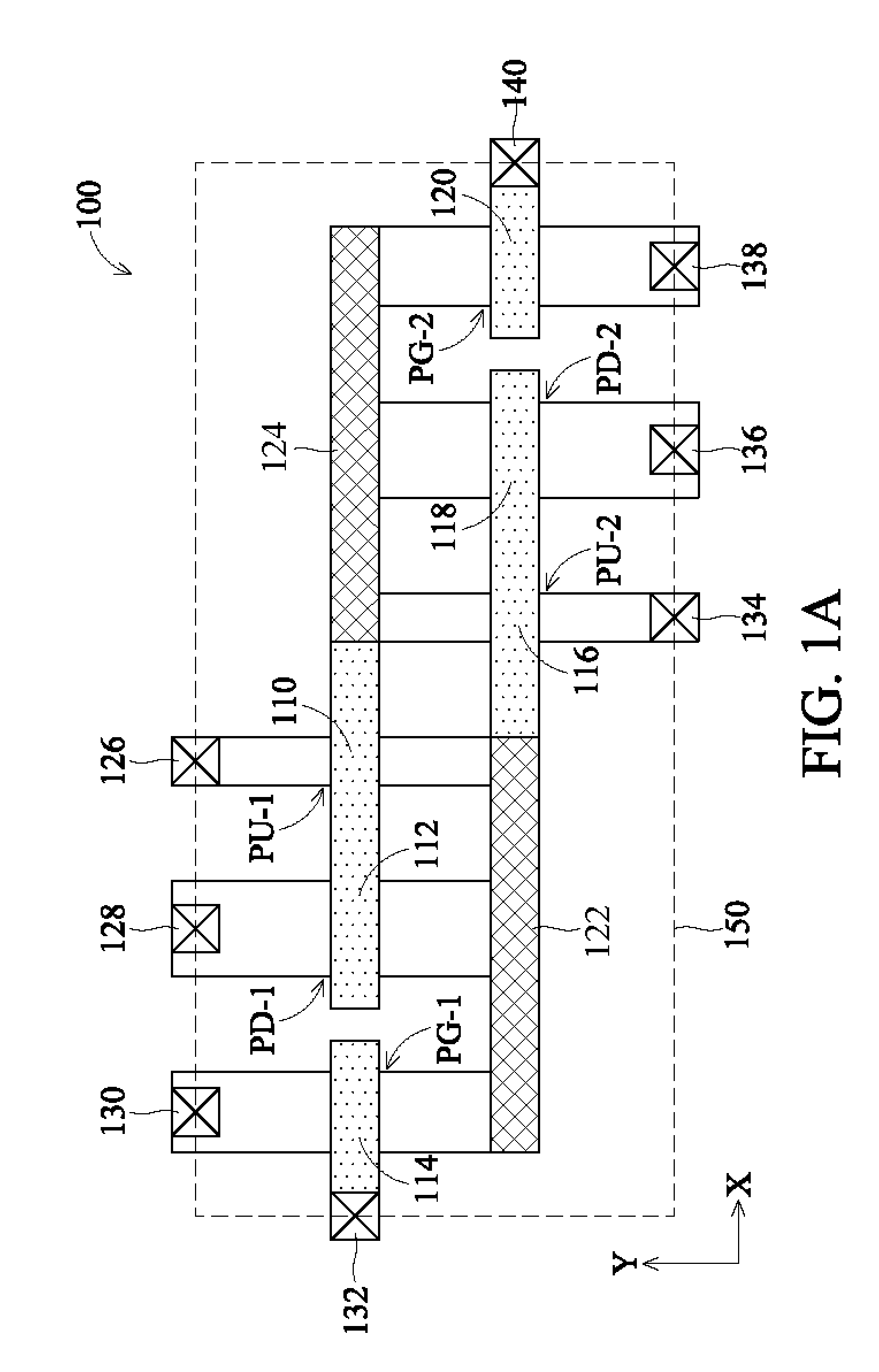

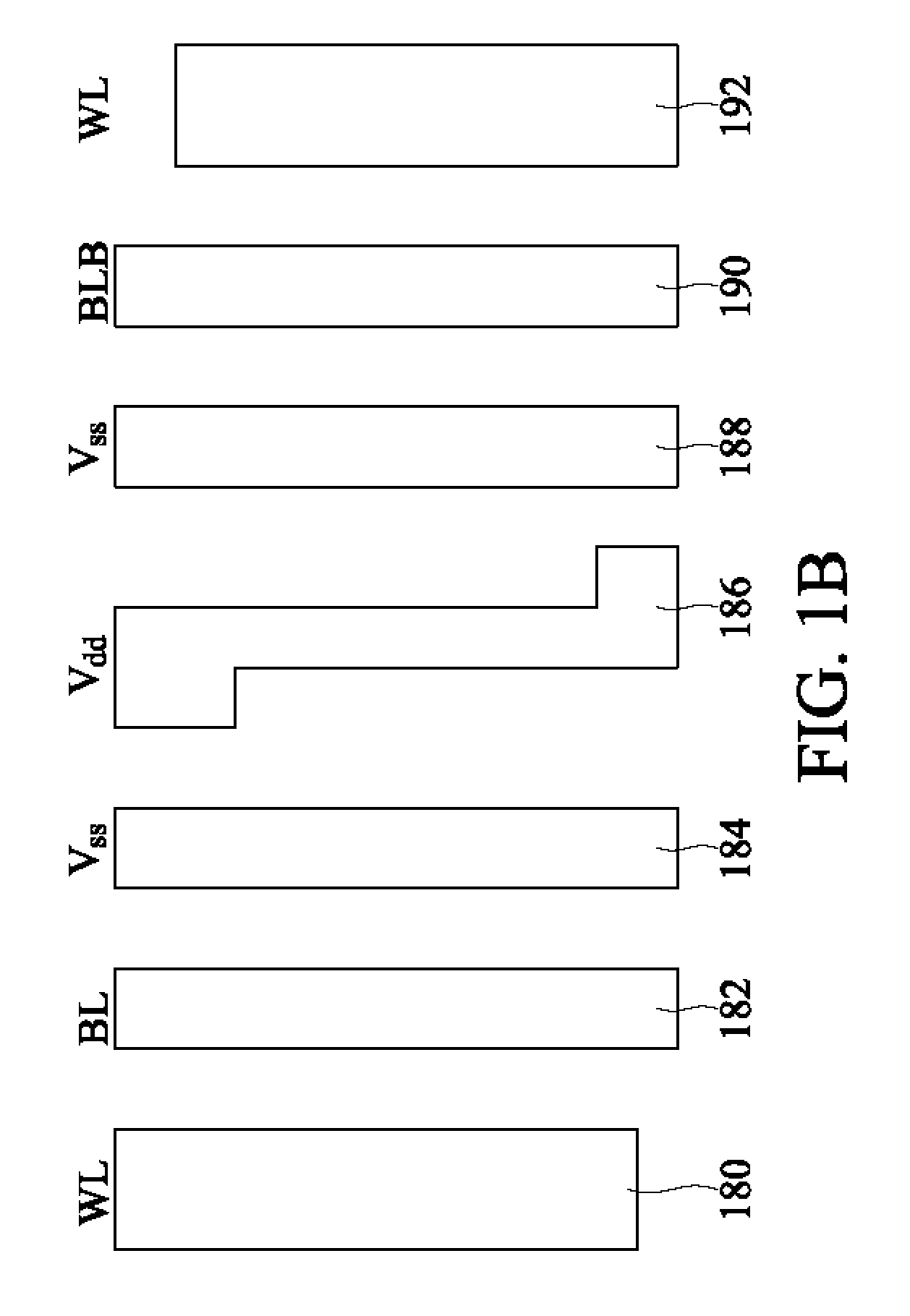

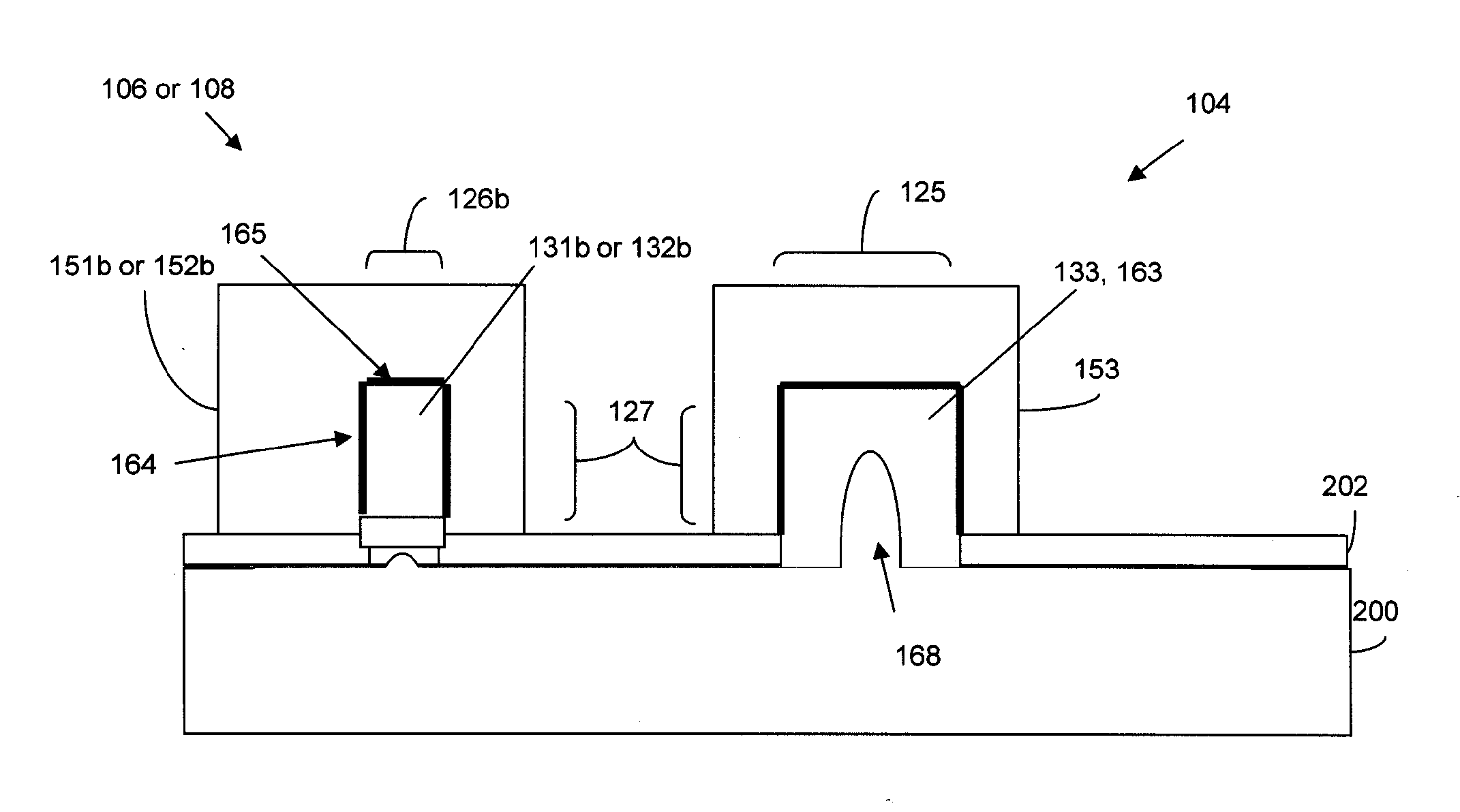

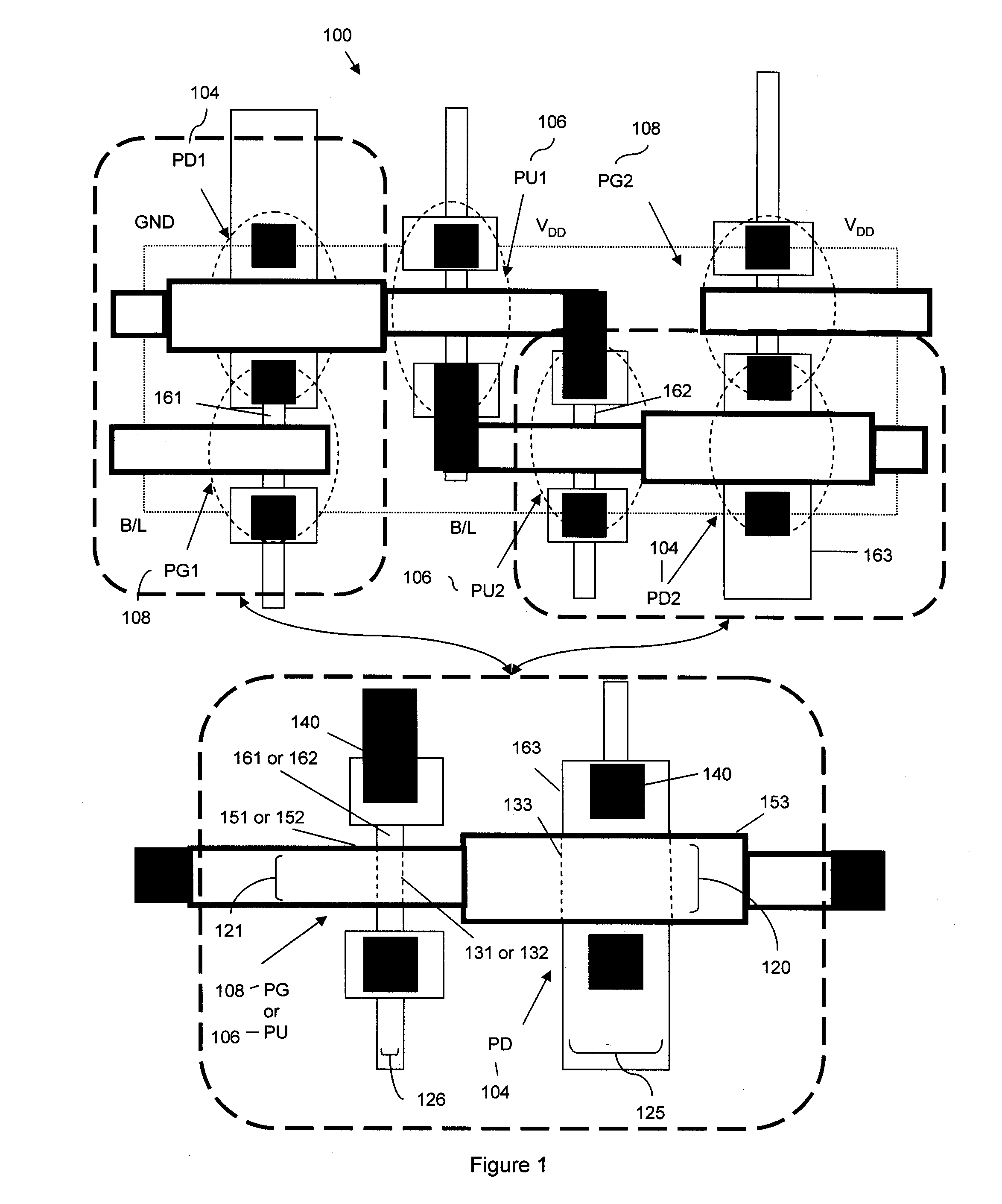

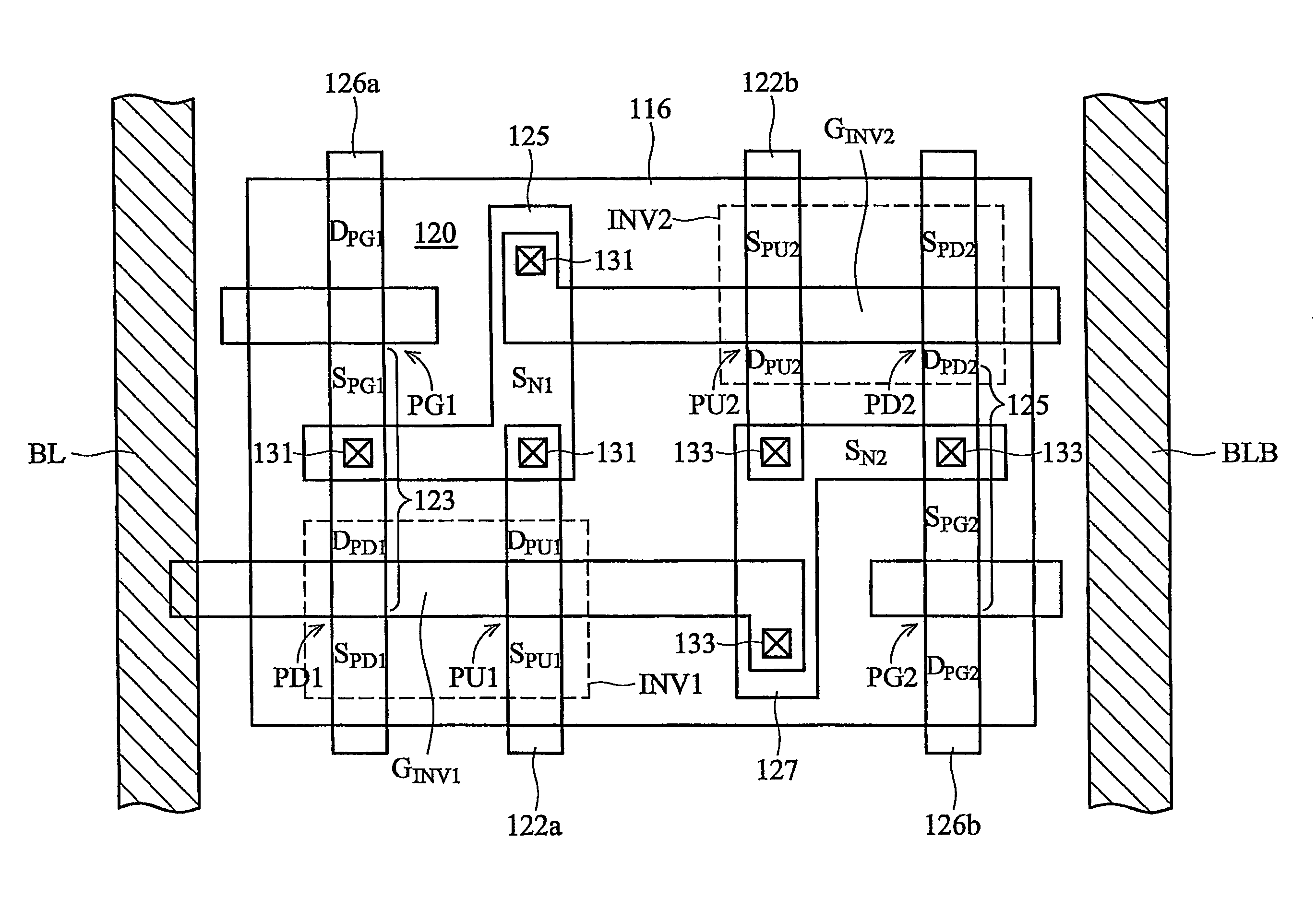

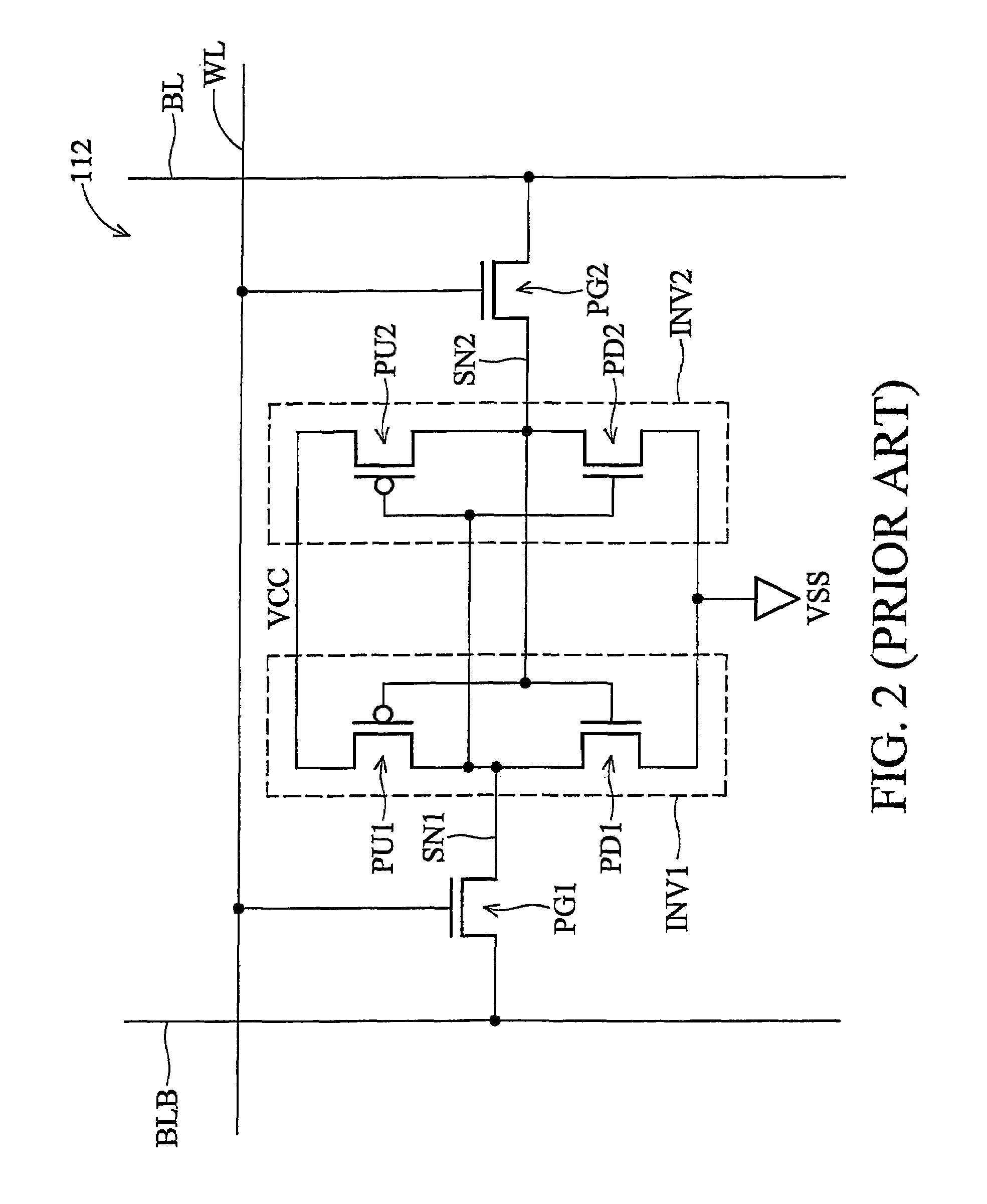

In accordance with an embodiment of the present invention, a static random access memory (SRAM) cell comprises a first pull-down transistor, a first pull-up transistor, a first pass-gate transistor, a second pull-down transistor, a second pull-up transistor, a second pass-gate transistor, a first linear intra-cell connection, and a second linear intra-cell connection. Active areas of the transistors are disposed in a substrate, and longitudinal axes of the active areas of the transistors are all parallel. The first linear intra-cell connection electrically couples the active area of the first pull-down transistor, the active area of the first pull-up transistor, and the active area of the first pass-gate transistor to a gate electrode of the second pull-down transistor and a gate electrode of the second pull-up transistor. The second linear intra-cell connection electrically couples the active area of the second pull-down transistor, the active area of the second pull-up transistor, and the active area of the second pass-gate transistor to a gate electrode of the first pull-down transistor and a gate electrode of the first pull-up transistor.

Owner:TAIWAN SEMICON MFG CO LTD

SRAM cell

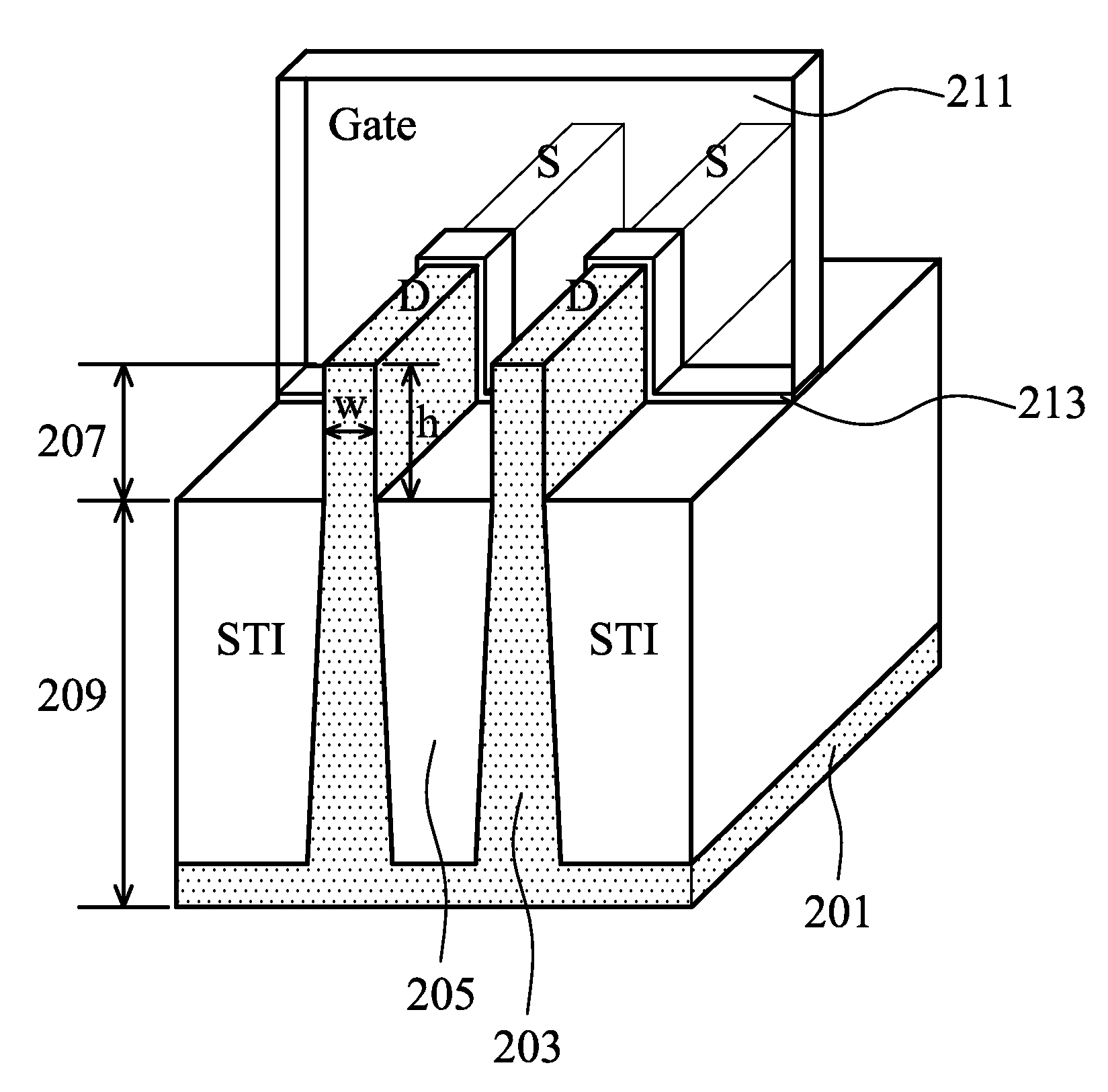

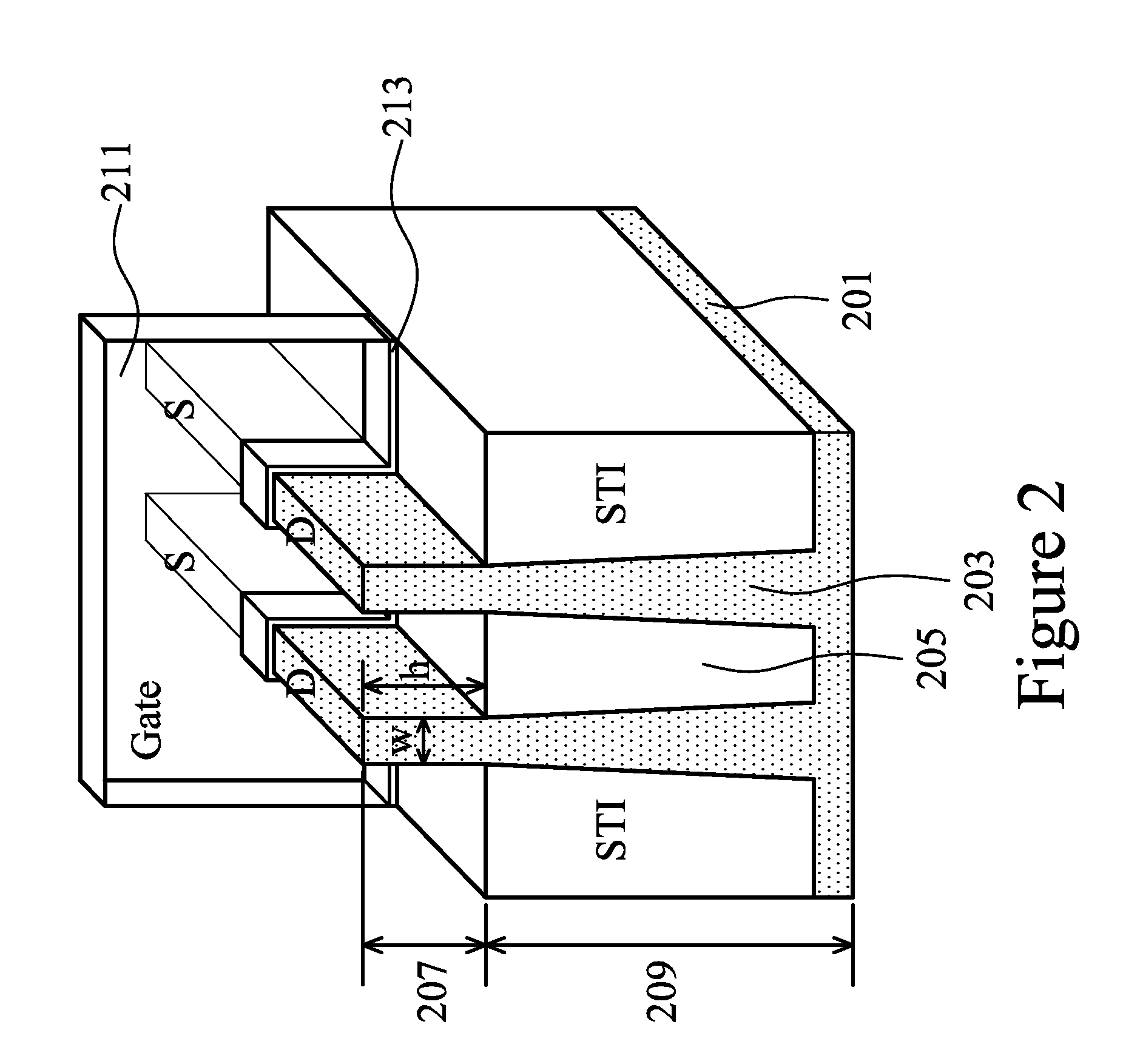

InactiveUS20070108528A1Increase effective widthImprove carrying capacityTransistorSolid-state devicesDriving currentEngineering

Disclosed is an SRAM cell on an SOI, bulk or HOT wafer with two pass-gate n-FETs, two pull-up p-FETs and two pull-down n-FETs and the associated methods of making the SRAM cell. The pass-gate FETs and pull-down FETs are non-planar fully depleted finFETs or trigate FETs. The pull-down FETs comprise non-planar partially depleted three-gated FETs having a greater channel width and a greater gate length and, thus, a greater drive current relative to the pass-gate and pull-up FETs. Additionally, for optimal electron mobility and hole mobility, respectively, the channels of the n-FETs and p-FETs can comprise semiconductors with different crystalline orientations.

Owner:IBM CORP

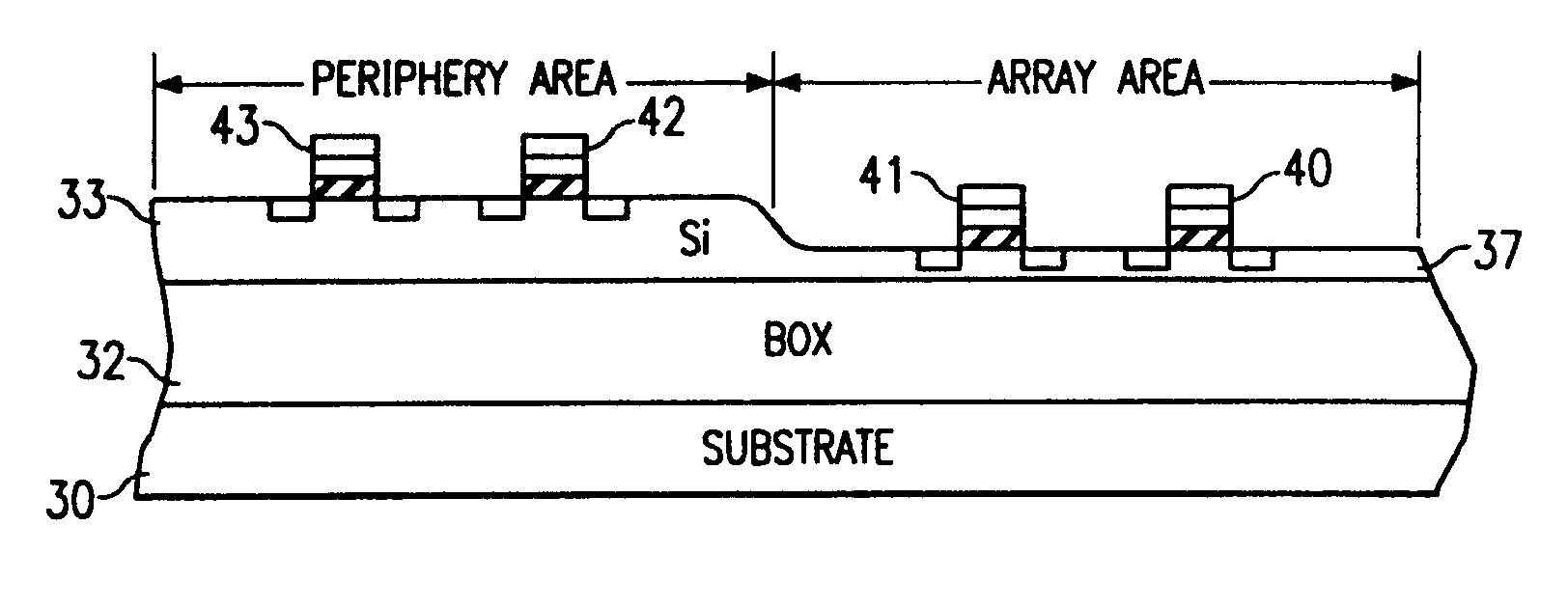

SOI DRAM having P-doped poly gate for a memory pass transistor

An integrated circuit including a DRAM is disclosed, wherein the DRAM includes a memory array including a plurality of pass gate transistors and a plurality of memory elements. The pass gate transistors include a gate material selected to provide a substantially near mid-gap work function or greater. The DRAM also includes a peripheral area including a plurality of logic transistors. In a preferred embodiment the pass gate transistors are silicon-on-insulator transistors.

Owner:TEXAS INSTR INC

Nanomesh SRAM Cell

Nanowire-based devices are provided. In one aspect, a SRAM cell includes at least one pair of pass gates and at least one pair of inverters formed adjacent to one another on a wafer. Each pass gate includes one or more device layers each having a source region, a drain region and a plurality of nanowire channels connecting the source region and the drain region and a gate common to each of the pass gate device layers surrounding the nanowire channels. Each inverter includes a plurality of device layers each having a source region, a drain region and a plurality of nanowire channels connecting the source region and the drain region and a gate common to each of the inverter device layers surrounding the nanowire channels.

Owner:GLOBALFOUNDRIES INC

Merged logic and memory combining thin film and bulk Si transistors

The present invention describes the use of two semiconductor layers, a thin film (TF) layer and a bulk Si wafer layer, to make high density and high speed merged logic and memory IC chips. The memory cells use three-dimensional (3D) SRAM structures. Two kinds of 3D logic cells are disclosed. 3D form of the differential cascode voltage switch (DCVS) architecture, and a 3D form of the DCVS with pass gate (DCVSPG) logic architecture. A high density "system on chip" architecture is described. The high density is achieved by locating large PMOS transistors in the TF Si layer, and the fast NMOS transistors in a bulk Si wafer layer. A single process sequence to simultaneously make the logic and memory circuits on the IC chip is also described.

Owner:GLOBALFOUNDRIES INC

Overvoltage/undervoltage tolerant transfer gate

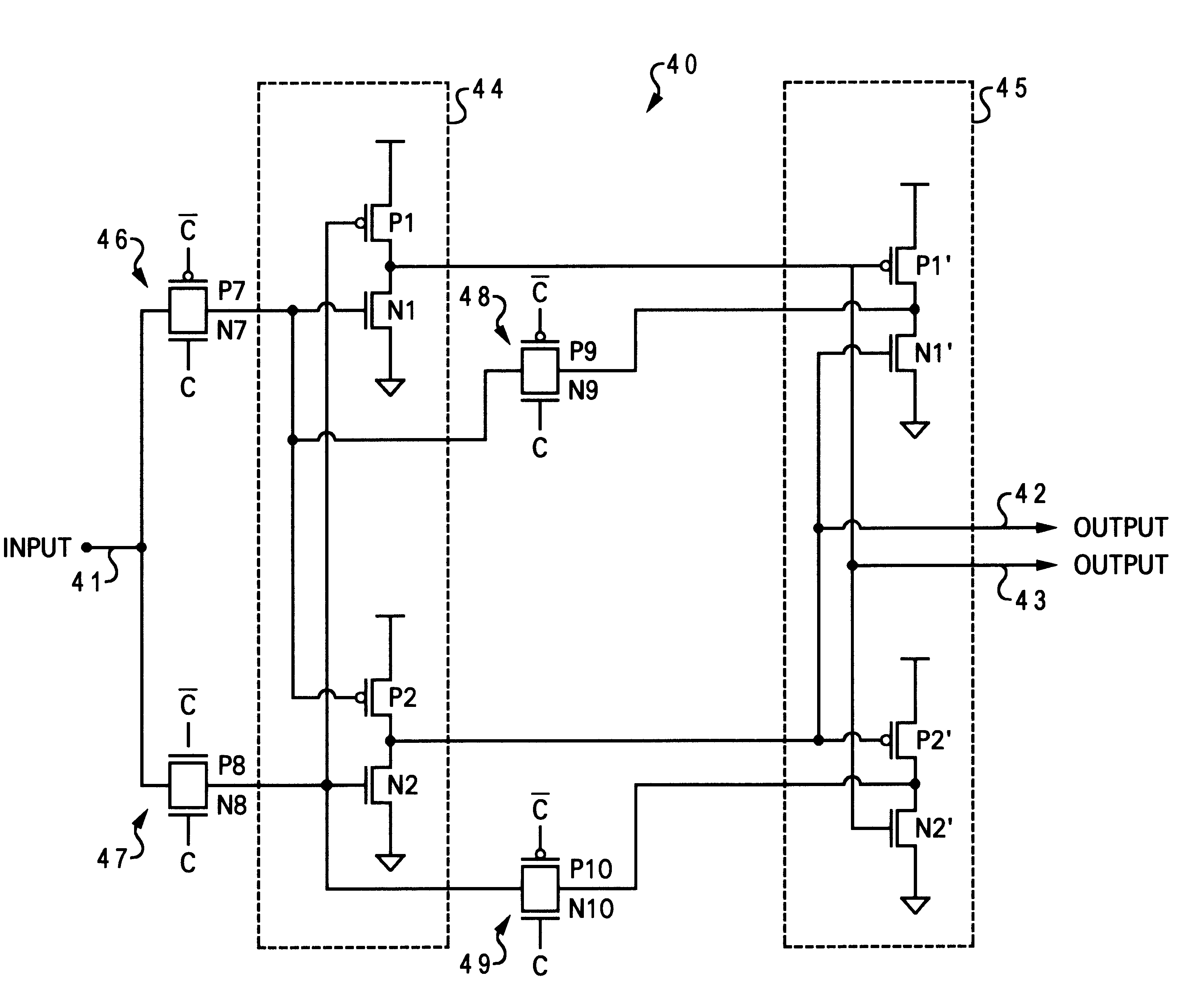

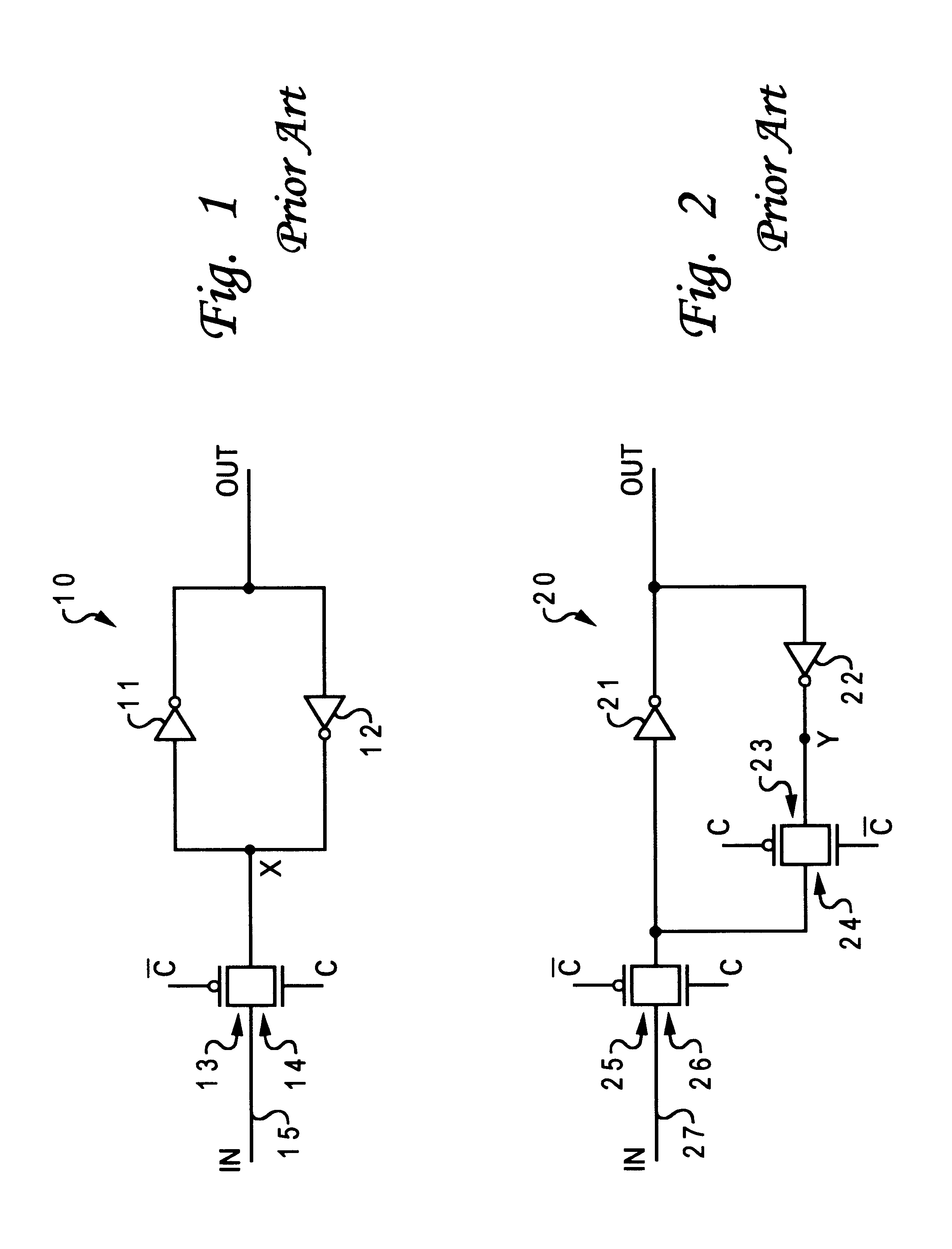

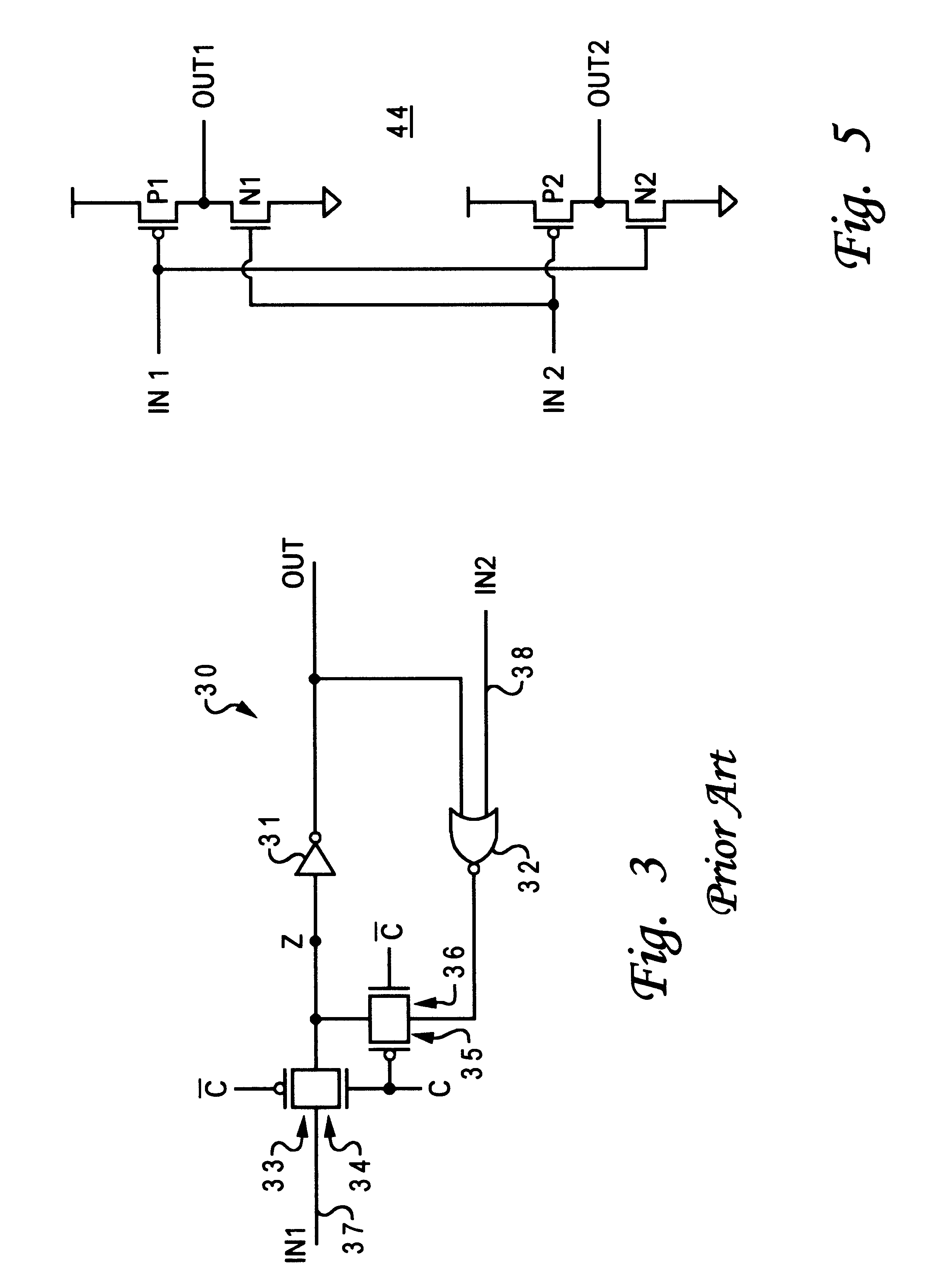

InactiveUS6163199AMassage combsLogic circuits characterised by logic functionOvervoltageComplementary pair

A transfer gate or pass gate circuit for transferring logic signals between nodes for a range of available high-potential supply levels. The primary transfer gate is designed to protect against potentials that either exceed either a high-potential or a low-potential level or that undershoot such potential levels. For overshoot (overvoltage) tolerance, this is achieved by coupling a NMOS transistor in parallel with a pair of PMOS transistors that are coupled in series. All three transistors are located between two nodes, either of which can be the input or the output of the transfer gate. The NMOS transistor is designed to be larger than the PMOS transistors and carries most of the transfer capability. The smaller PMOS transistors are designed to eliminate potential drops that would otherwise occur with a single NMOS transistor or with a complementary pair of transistors. For undershoot (undervoltage) tolerance, a PMOS transistor is coupled in parallel with a pair of NMOS transistors that are coupled in series.

Owner:SEMICON COMPONENTS IND LLC

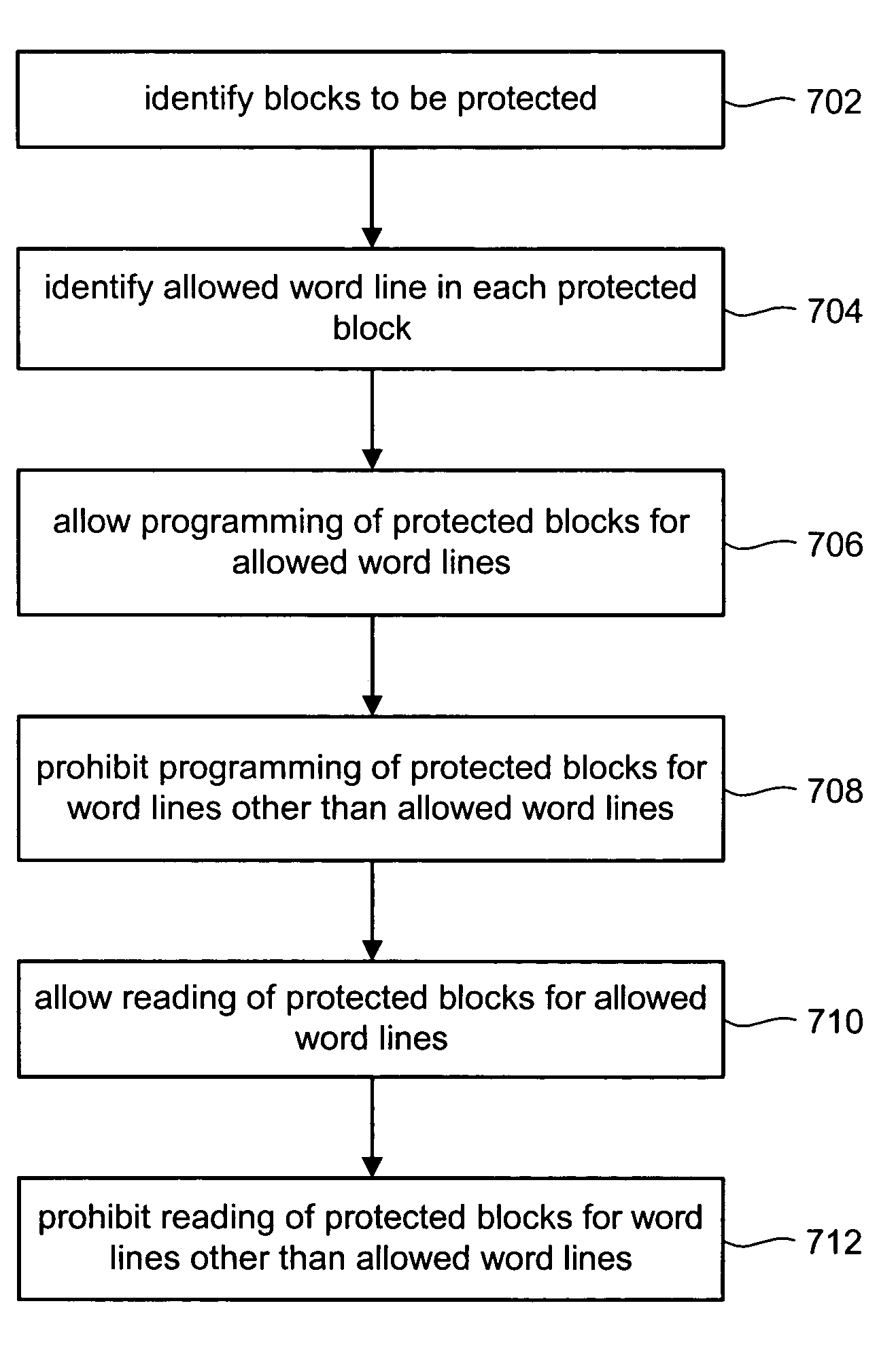

Operating non-volatile memory without read disturb limitations

ActiveUS20050210184A1Without limitationAvoid restrictionsRead-only memoriesDigital storageComputer architecturePass gate

When reading a memory cell on a NAND string, the word lines for the memory cells not being read will receive a voltage so that those memory cells operate as pass gates. Over time, if there are a lot of read operations without any program operations, the cells not being read may suffer from Read Disturb because the voltage applied to the word lines may cause electrons to accumulate in the floating gates of the non-selected cells. The accumulation of charge in the floating gates raises the threshold voltage. To avoid the limitations of Read Disturb, only one word line of a block (or other grouping) is used to program and read data. In a system using NAND flash memory, the word line being read is not typically subjected to read disturb. Thus, a NAND flash memory that restricts programming and reading to one word line of a block is not likely to exhibit read disturb in that block.

Owner:SANDISK TECH LLC

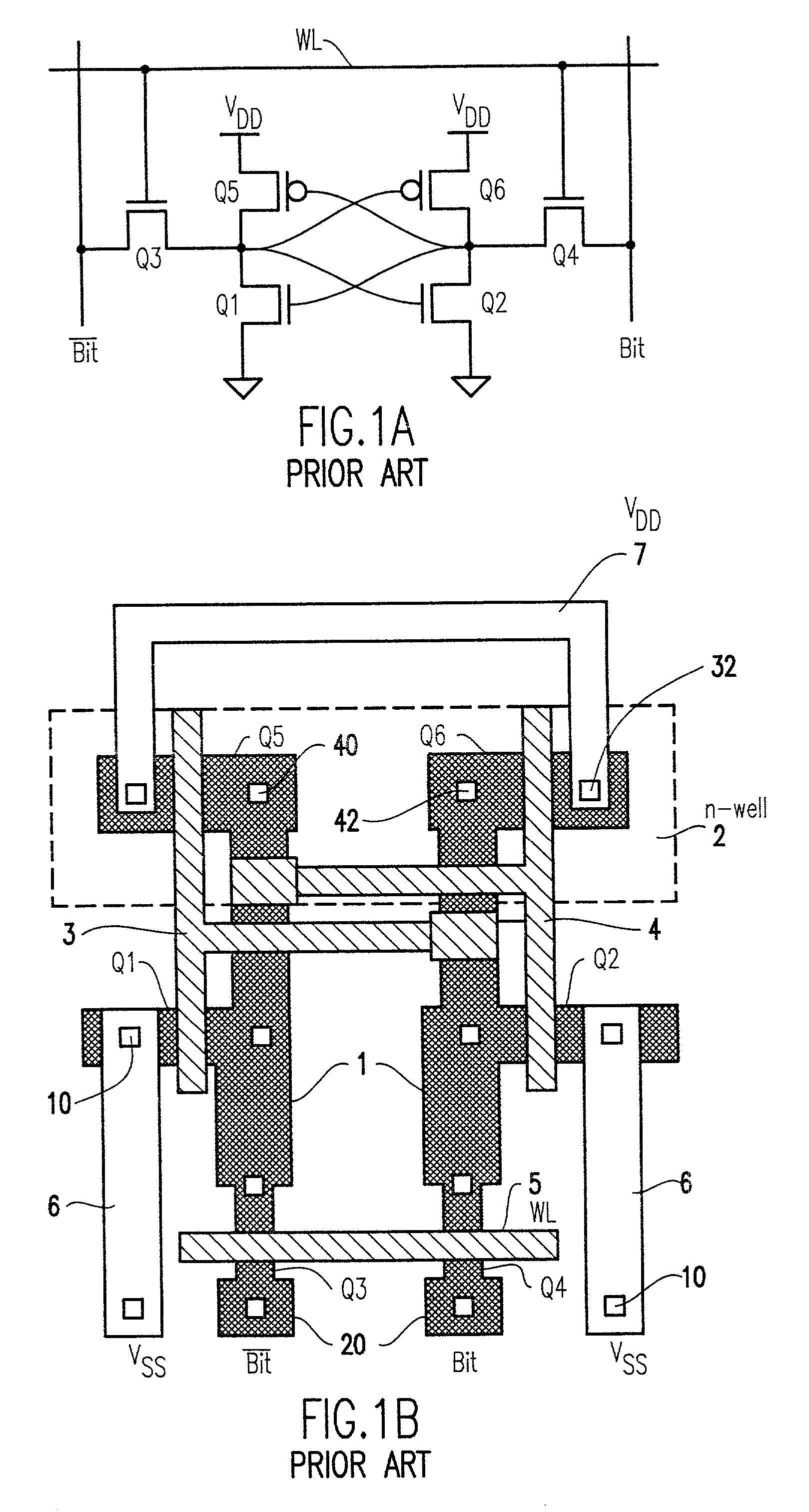

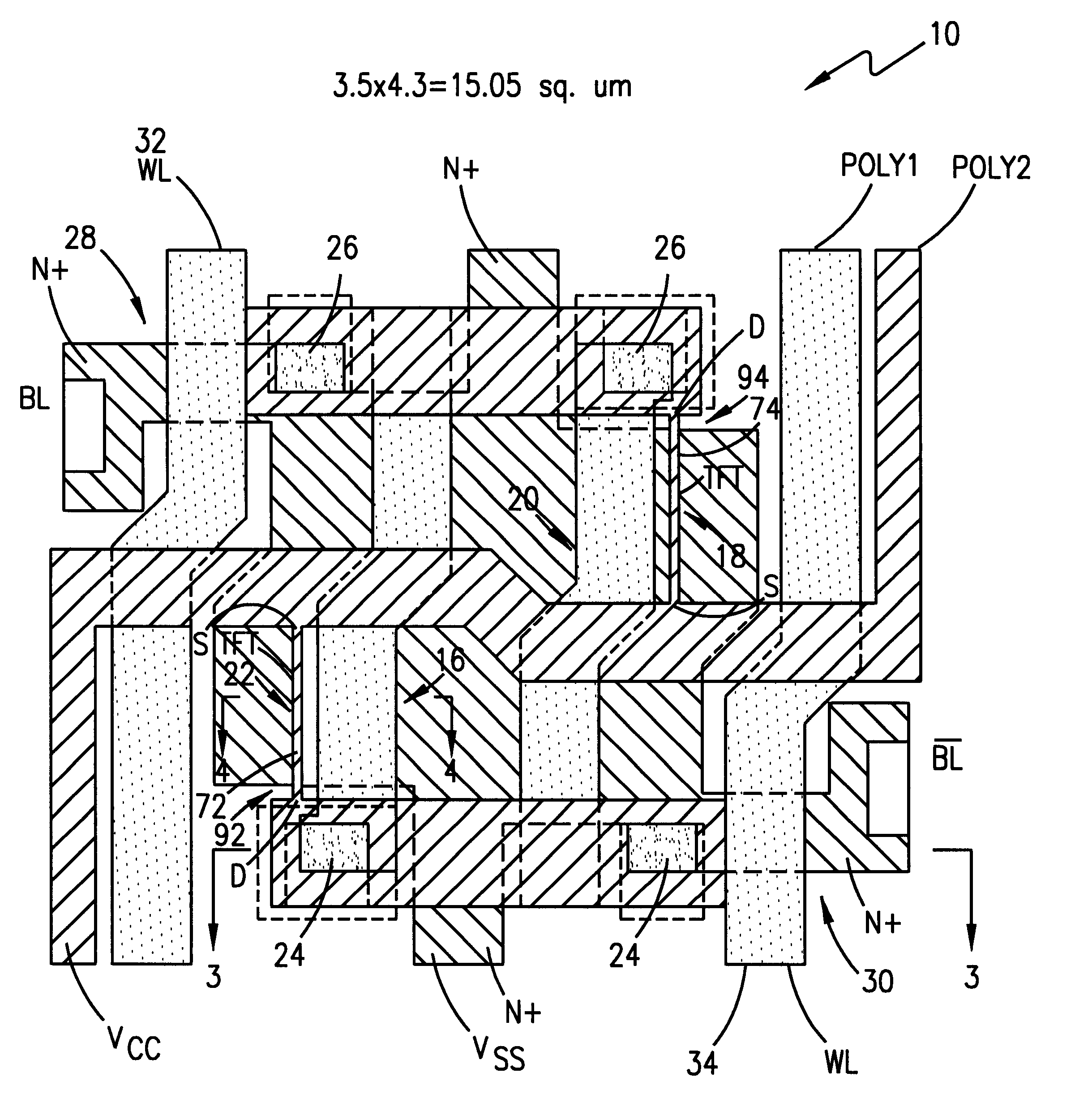

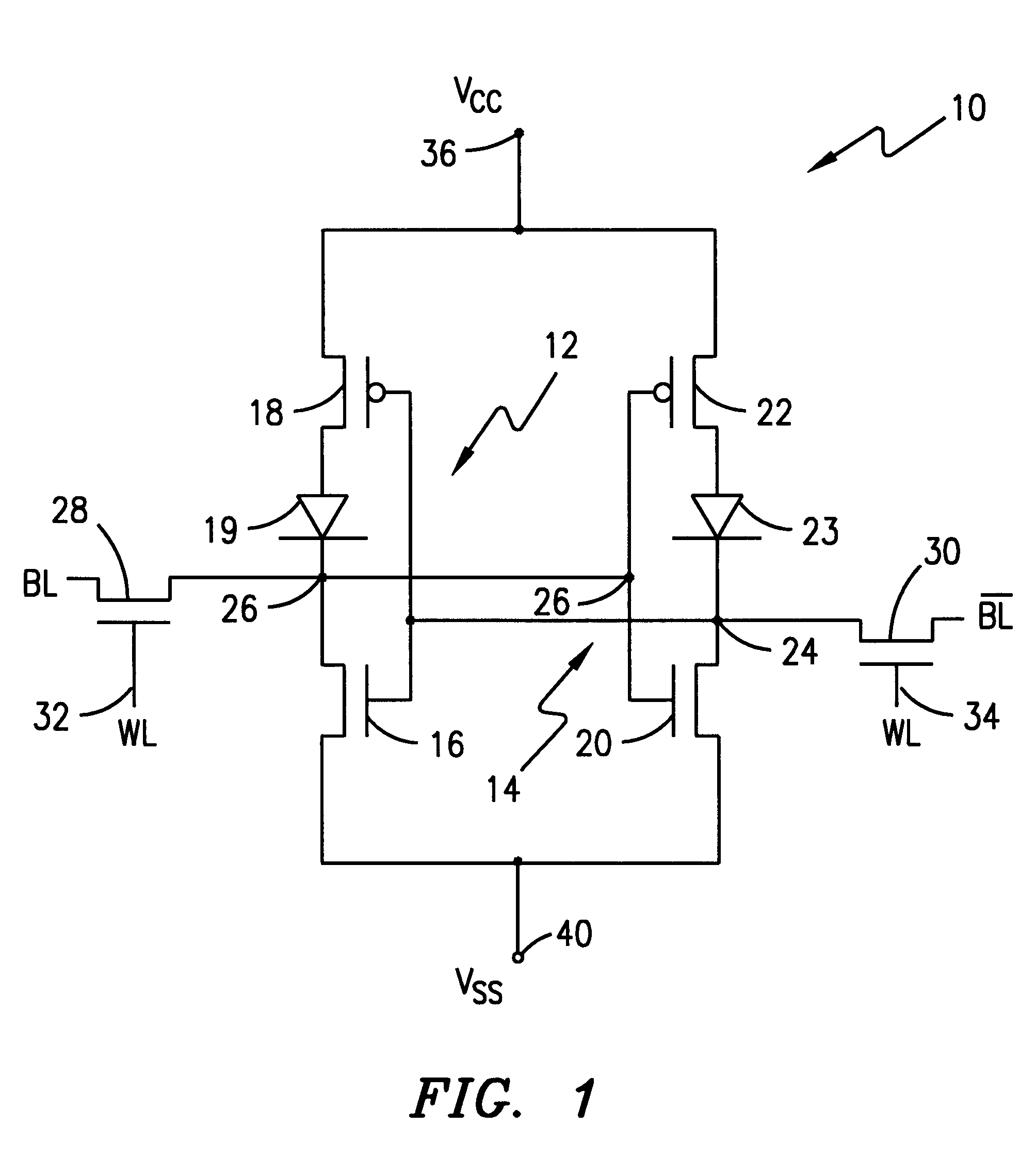

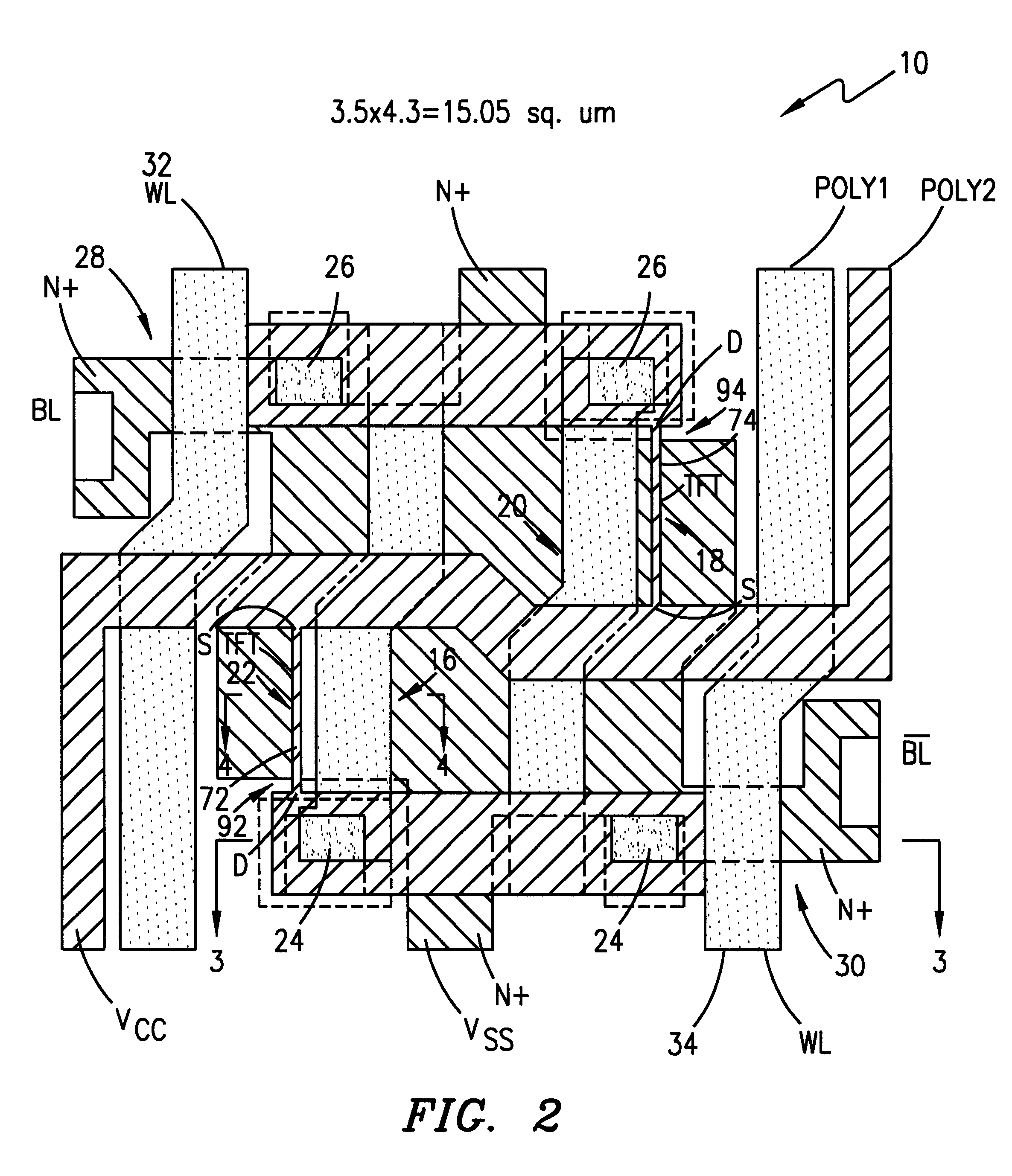

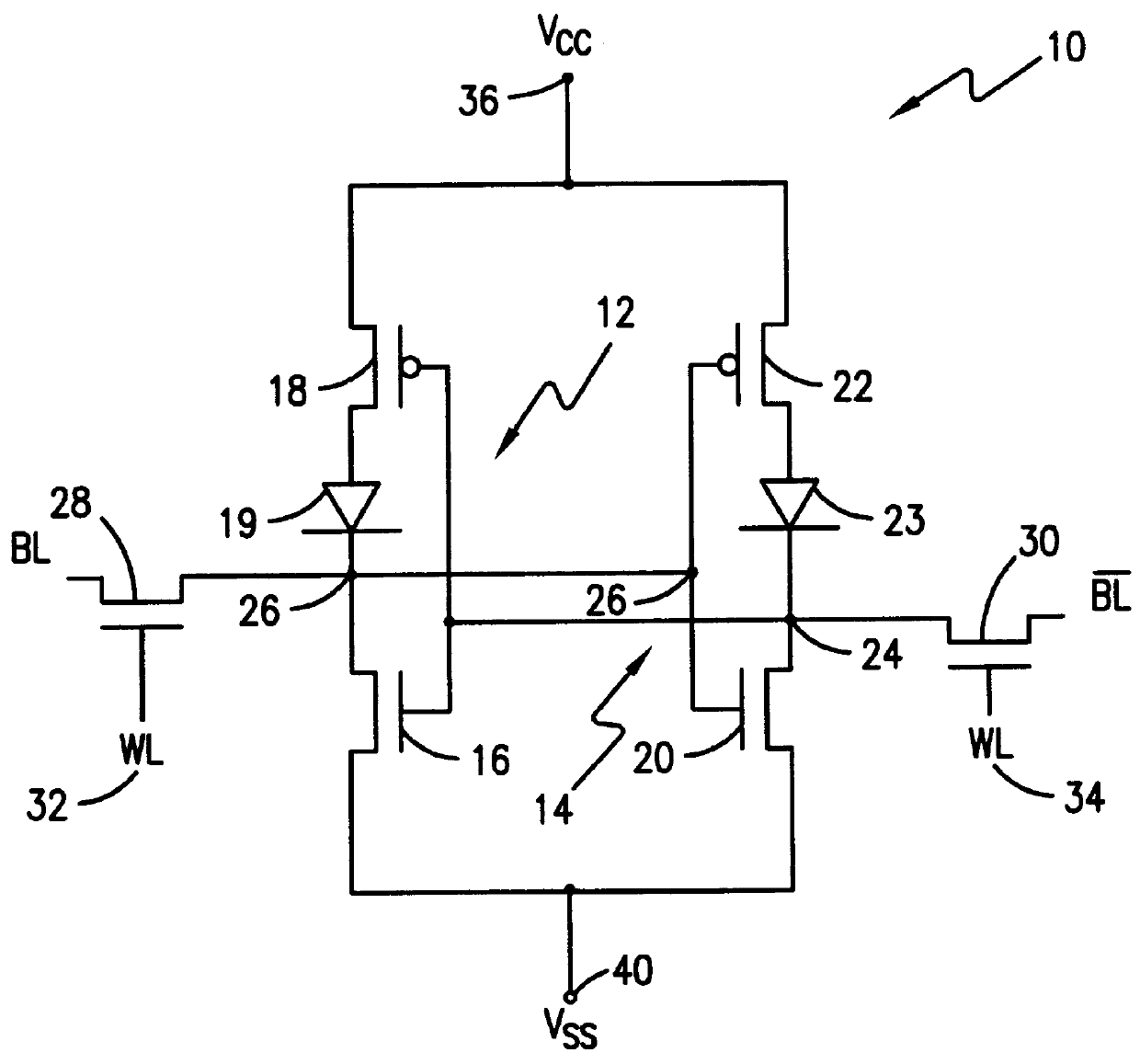

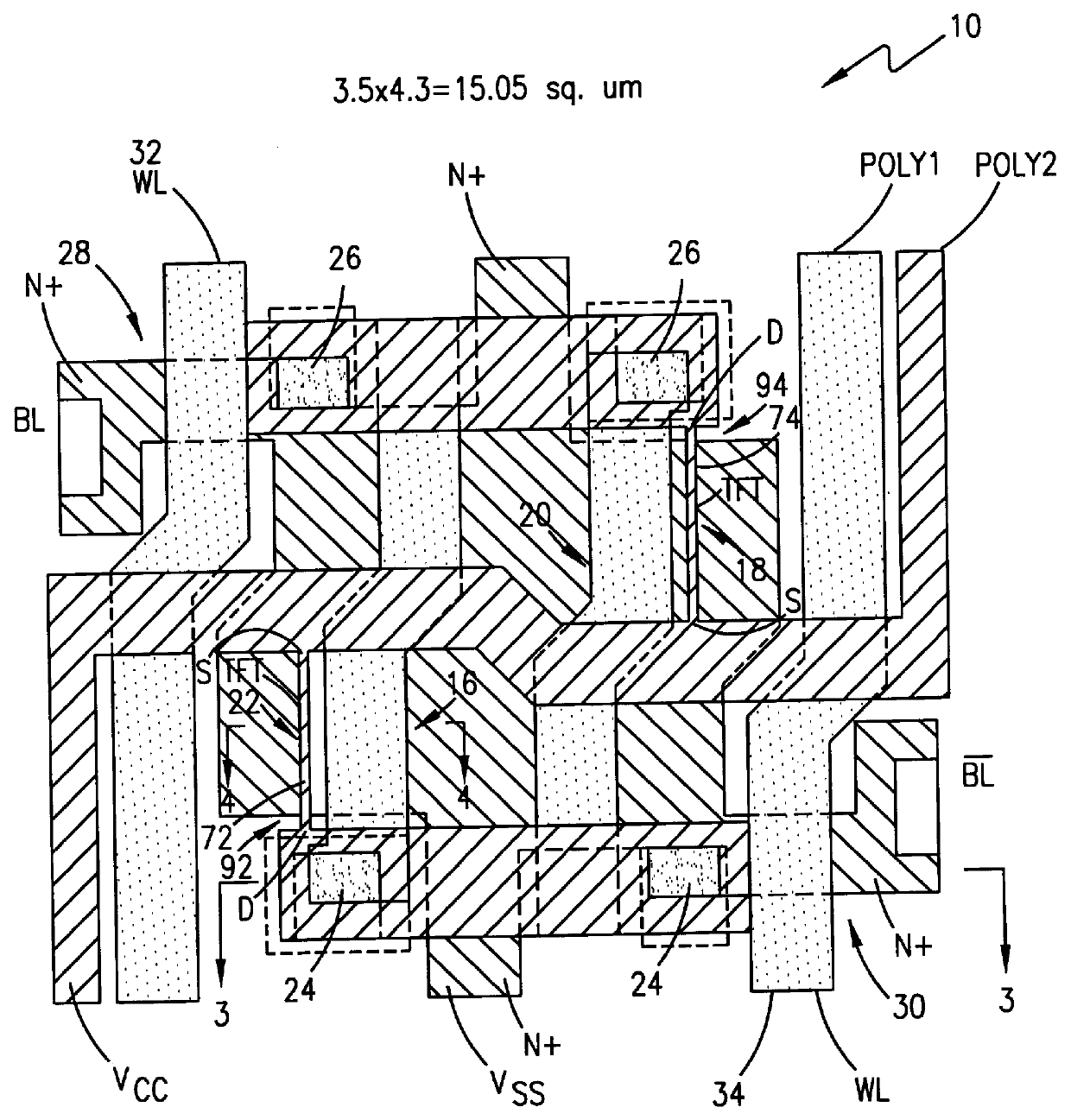

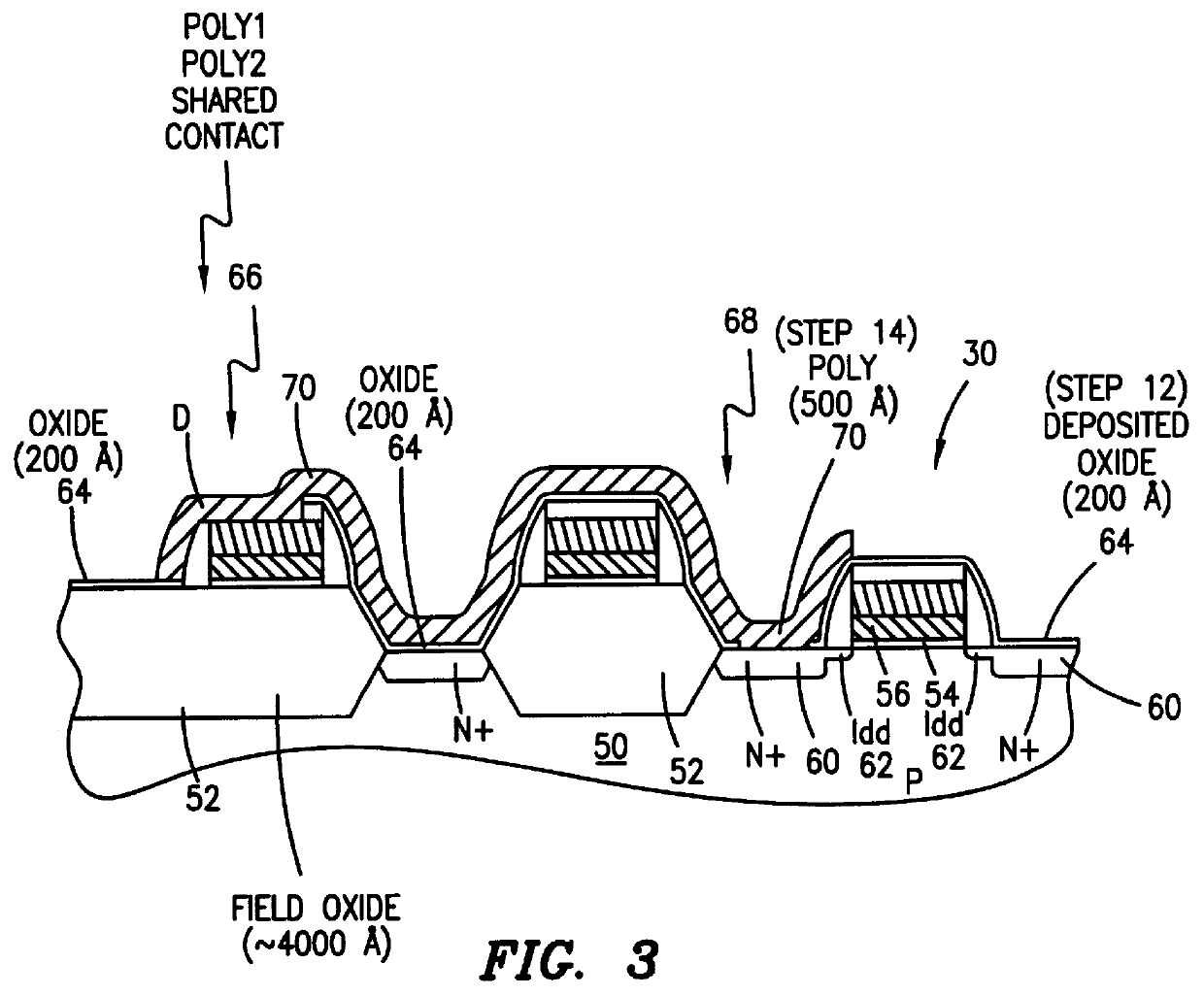

Method of making an SRAM cell and structure

A six transistor static random access memory (SRAM) cell with thin-film pull-up transistors and method of making the same includes providing two bulk silicon pull-down transistors of a first conductivity type, two active gated pull-up thin-film transistors (TFTs) of a second conductivity type, two pass gates, a common word line, and two bit line contacts. The bulk silicon pull-down transistors, two active gated pull-up TFTs, and two pass gates are connected at four shared contacts. In addition, the two bulk silicon pull-down transistors and the two active gated pull-up TFTs are formed with two polysilicon layers, a first of the polysilicon layers (poly1) is salicided and includes poly1 gate electrodes for the two bulk silicon pull-down transistors. A second of the polysilicon layers (poly2) includes desired poly2 stringers disposed along side edges of the poly1 gate electrodes, the desired poly2 stringers forming respective channel regions of the pull-up TFTs.

Owner:STMICROELECTRONICS SRL

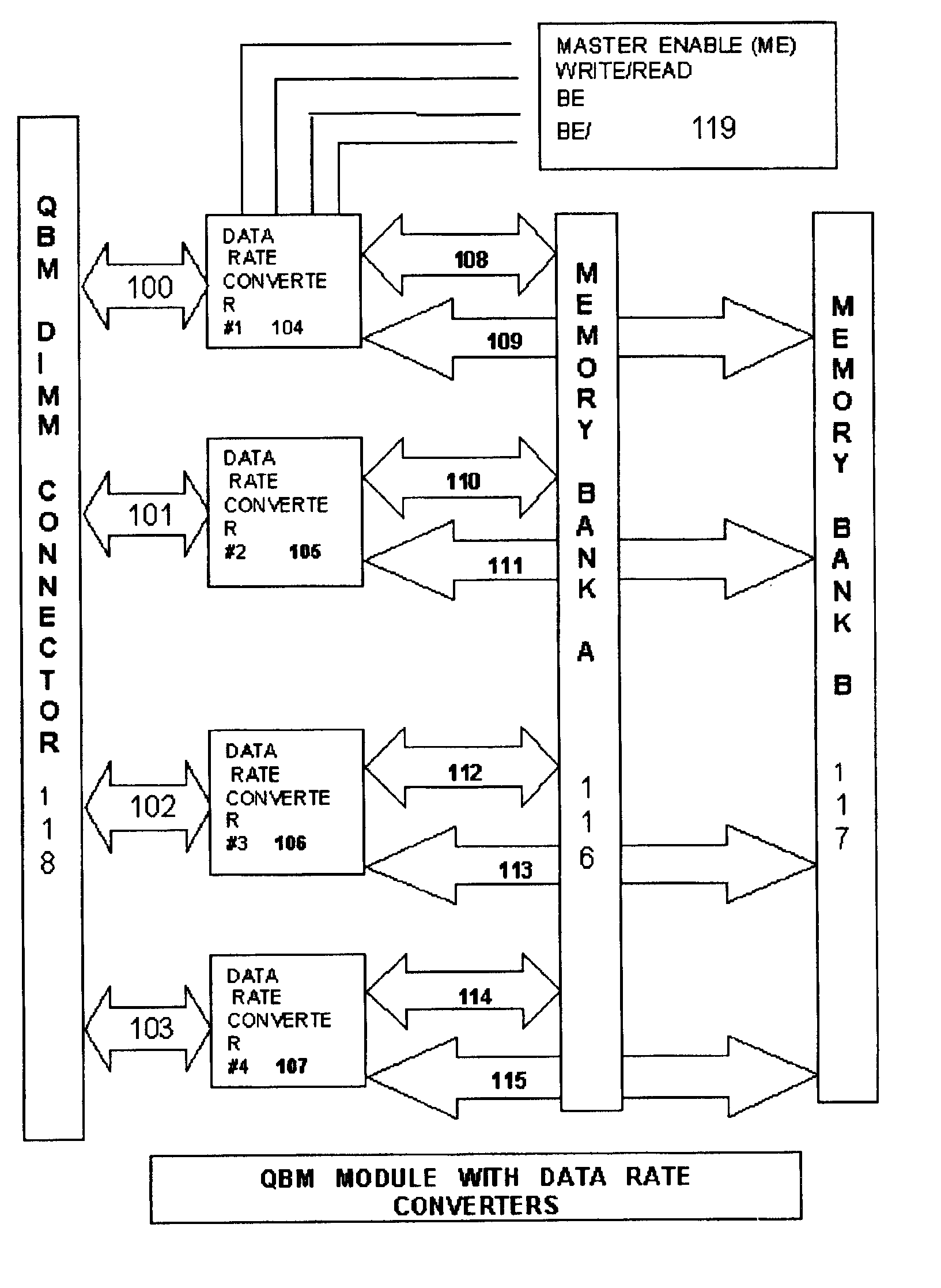

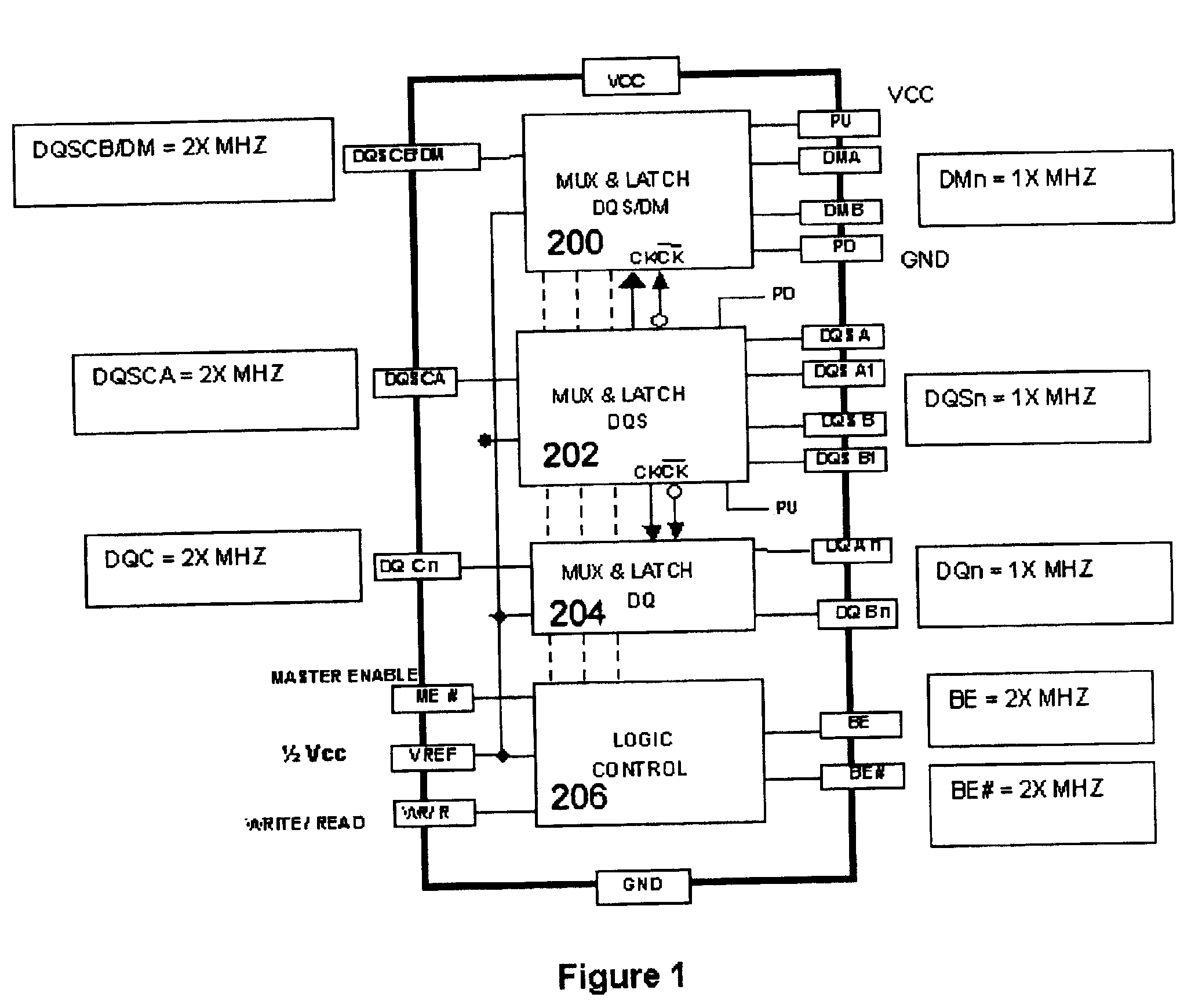

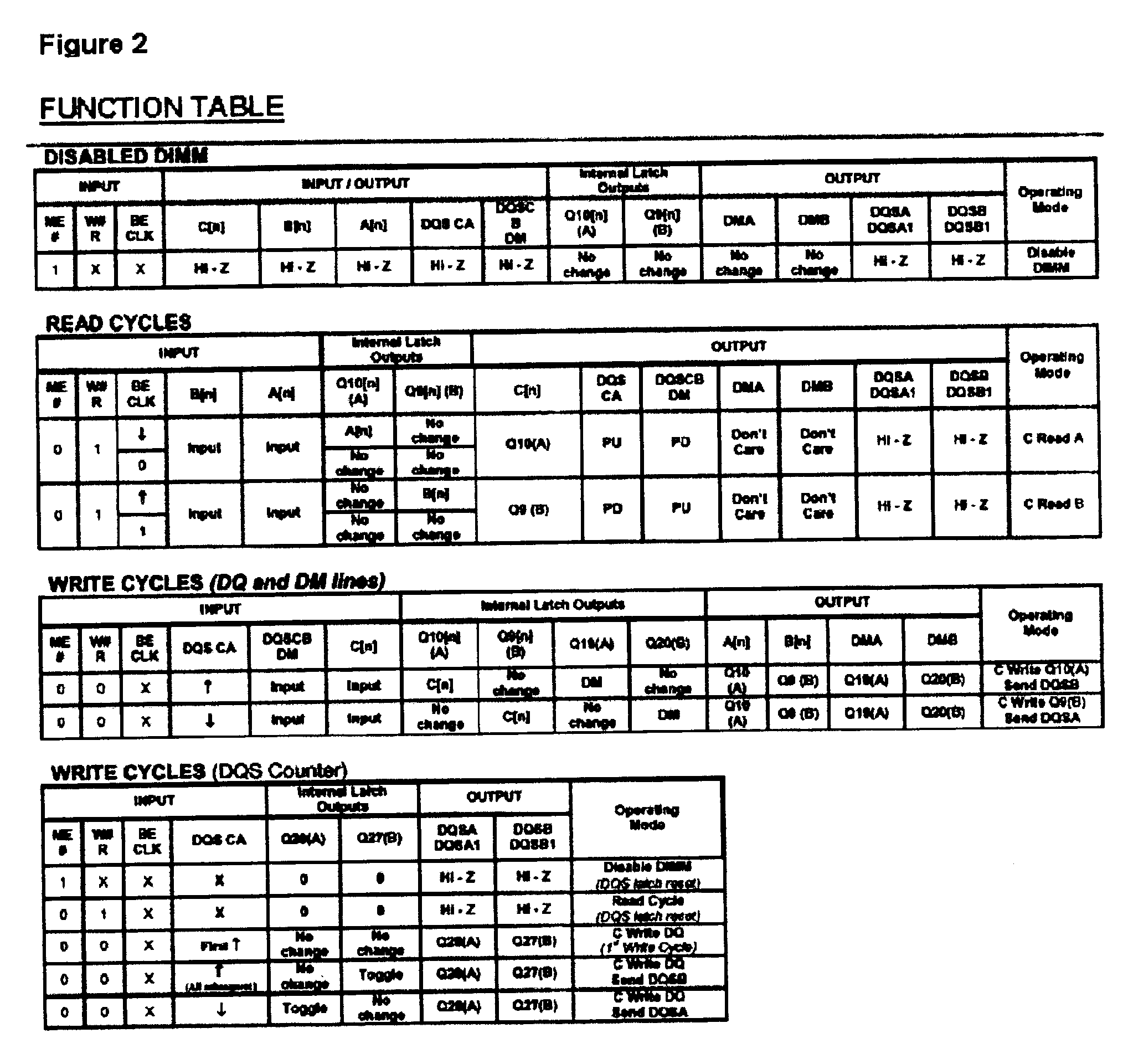

High-speed data-rate converting and switching circuit

InactiveUS6854042B1Extended durationMemory adressing/allocation/relocationDigital storageSignal onMemory bus

A high speed bidirectional data rate conversion circuit converts 1× data rate signals from attached devices on port A and port B to 2× data rate signals on bus C and further converts 2× high speed data rate signals on bus C to 1× data rate signals on ports A and B for memory devices attached to ports A and B. The usage of pass gate switches and combination of latches and counters is used to permit proper synchronization of the data signals, and to further generate strobe signals at both system bus and memory bus sides, and to further generate data mask signals for writing to the memory bus side of the circuit. The collection of such switching elements and latches are provided on a single silicon chip which includes of the functions of the invention.

Owner:URENSCHI ASSETAB LIABILITY

Single event upset (SEU) hardened latch circuit

A single event upset hardened latch circuit is disclosed. The single event hardened latch circuit includes a first dual-port inverter and a second dual-port inverter. An input is coupled to the first dual-port inverter via a first set of pass gates. The first dual-port inverter is coupled to the second dual-port inverter via a second set of pass gates. The output is connected to the first and second dual-port inverters.

Owner:BAE SYST INFORMATION & ELECTRONICS SYST INTERGRATION INC

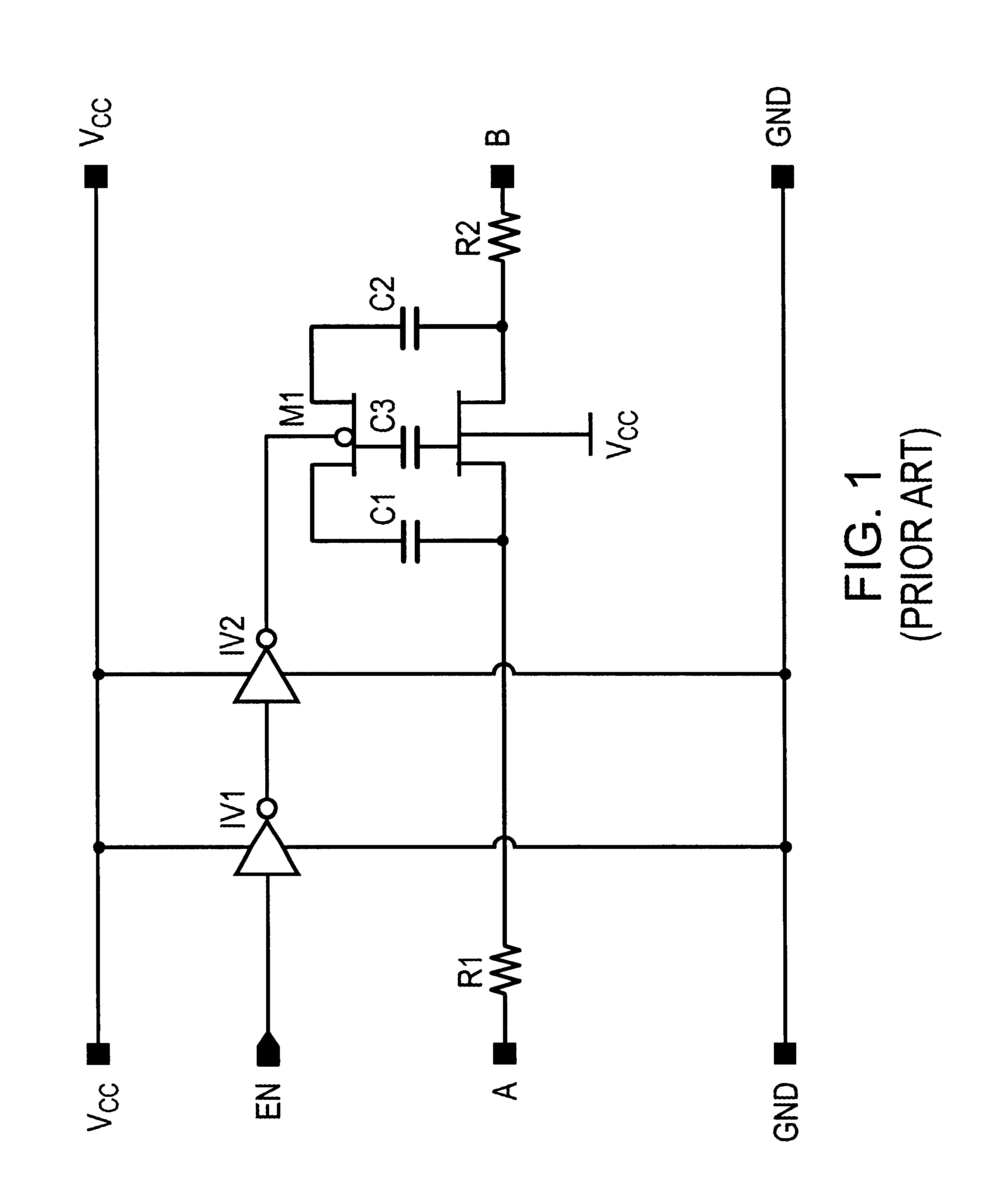

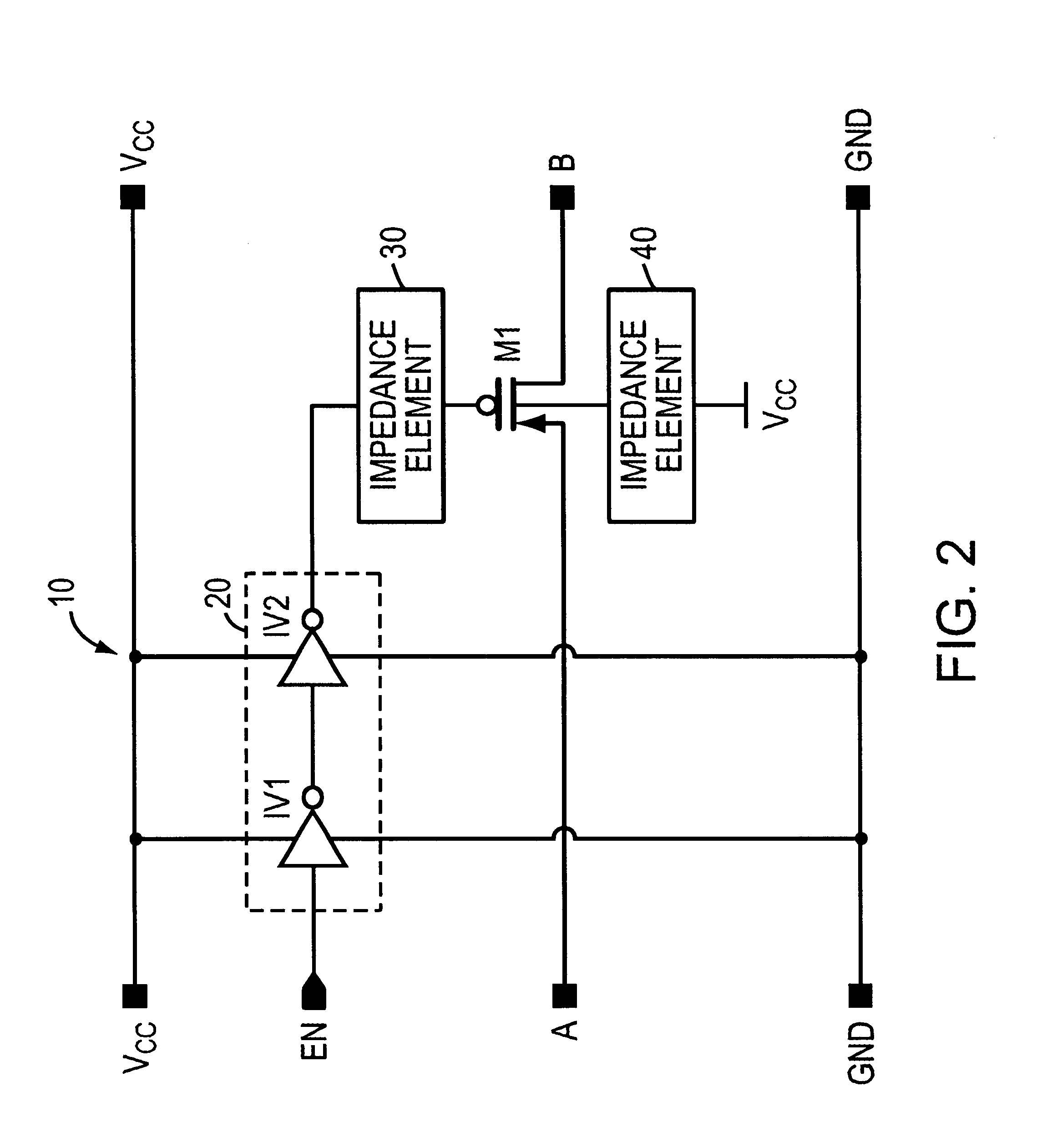

High frequency MOSFET switch

A high-frequency switch circuit having an MOS pass gate or transfer transistor. The switch circuit of the invention includes a first impedance element coupled to the gate of the transfer transistor and, preferably, an alternative second impedance element coupled to the bulk of the transfer transistor. One or both of the impedance elements substantially negates the low-parasitic shunt capacitance associated with the transfer transistor that controls signal attenuation under high frequency operation. The impedance element is coupled in series with that parasitic capacitance to increase substantially the impedance of that pathway, thereby increasing substantially the passable bandwidth. The impedance element may simply be a resistor. The switch circuit is suitable for use in an array of applications, including signal propagation in computing systems, routers, and flat panel screen displays.

Owner:SEMICON COMPONENTS IND LLC

SRAM Structure with FinFETs Having Multiple Fins

A static random access memory (SRAM) cell includes a straight fin and a bended fin physically disconnected from the straight fin. The bended fin has a first portion and a second portion parallel to the straight fin. The distance between the first portion of the bended fin and the straight fin is smaller than the distance between the second portion of the bended fin and the straight fin. The SRAM cell includes a pull-down transistor including a portion of a first gate strip, which forms a first and a second sub pull-down transistor with the straight fin and the first portion of the bended fin, respectively. The SRAM cell further includes a pass-gate transistor including a portion of a second gate strip, which forms a first sub pass-gate transistor with the straight fin. The pull-down transistor includes more fins than the pass-gate transistor.

Owner:TAIWAN SEMICON MFG CO LTD

Vertical MOSFET SRAM cell

InactiveUS20070007601A1Improve transconductanceMore drivabilityTransistorSolid-state devicesMOSFETEngineering

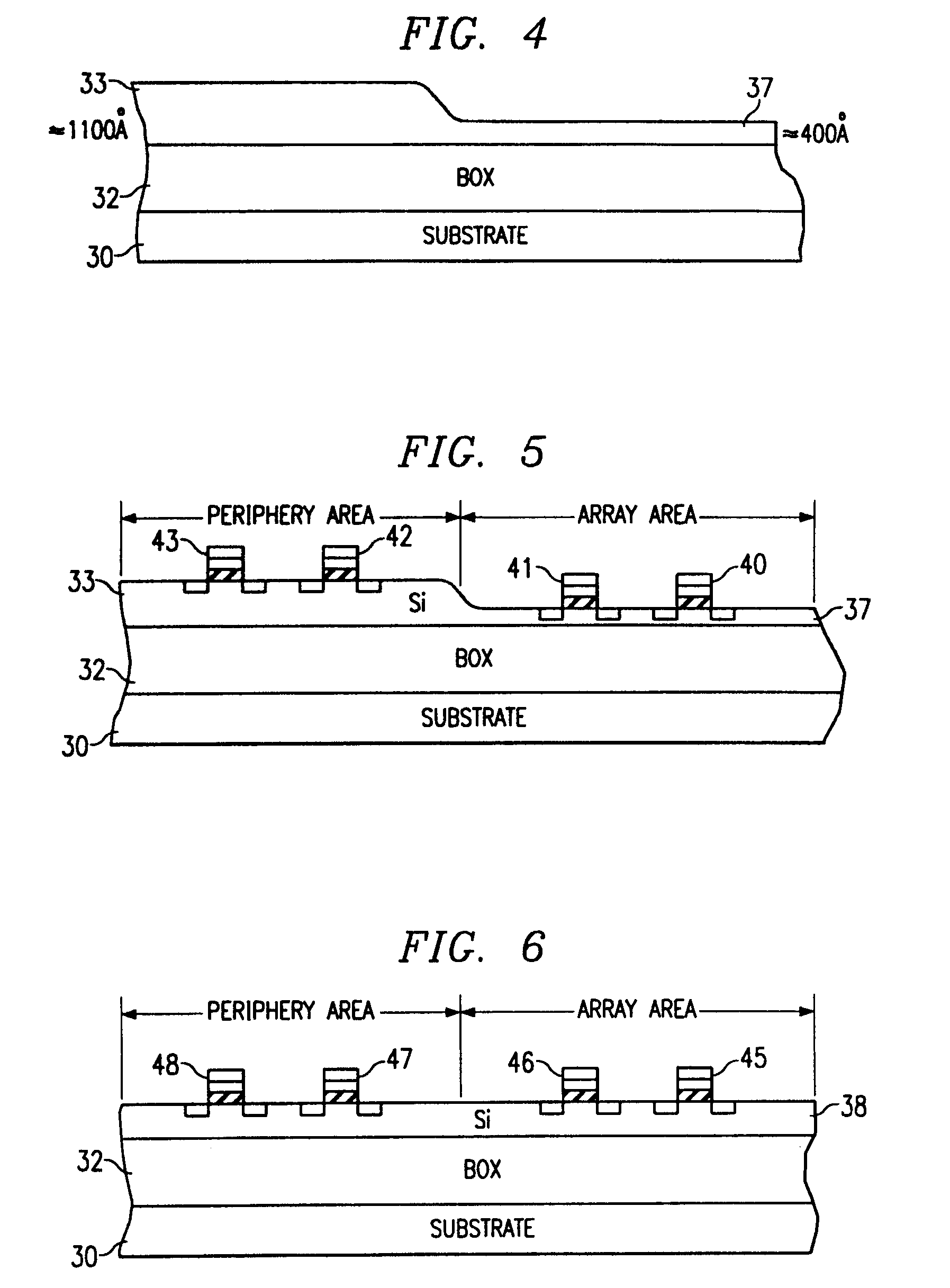

A method of forming an SRAM cell device includes the following steps. Form pass gate FET transistors and form a pair of vertical pull-down FET transistors with a first common body and a first common source in a silicon layer patterned into parallel islands formed on a planar insulator. Etch down through upper diffusions between cross-coupled inverter FET transistors to form pull-down isolation spaces bisecting the upper strata of pull-up and pull-down drain regions of the pair of vertical pull-down FET transistors, with the isolation spaces reaching down to the common body strata. Form a pair of vertical pull-up FET transistors with a second common body and a second common drain. Then, connect the FET transistors to form an SRAM cell.

Owner:HSU LOUIS L +3

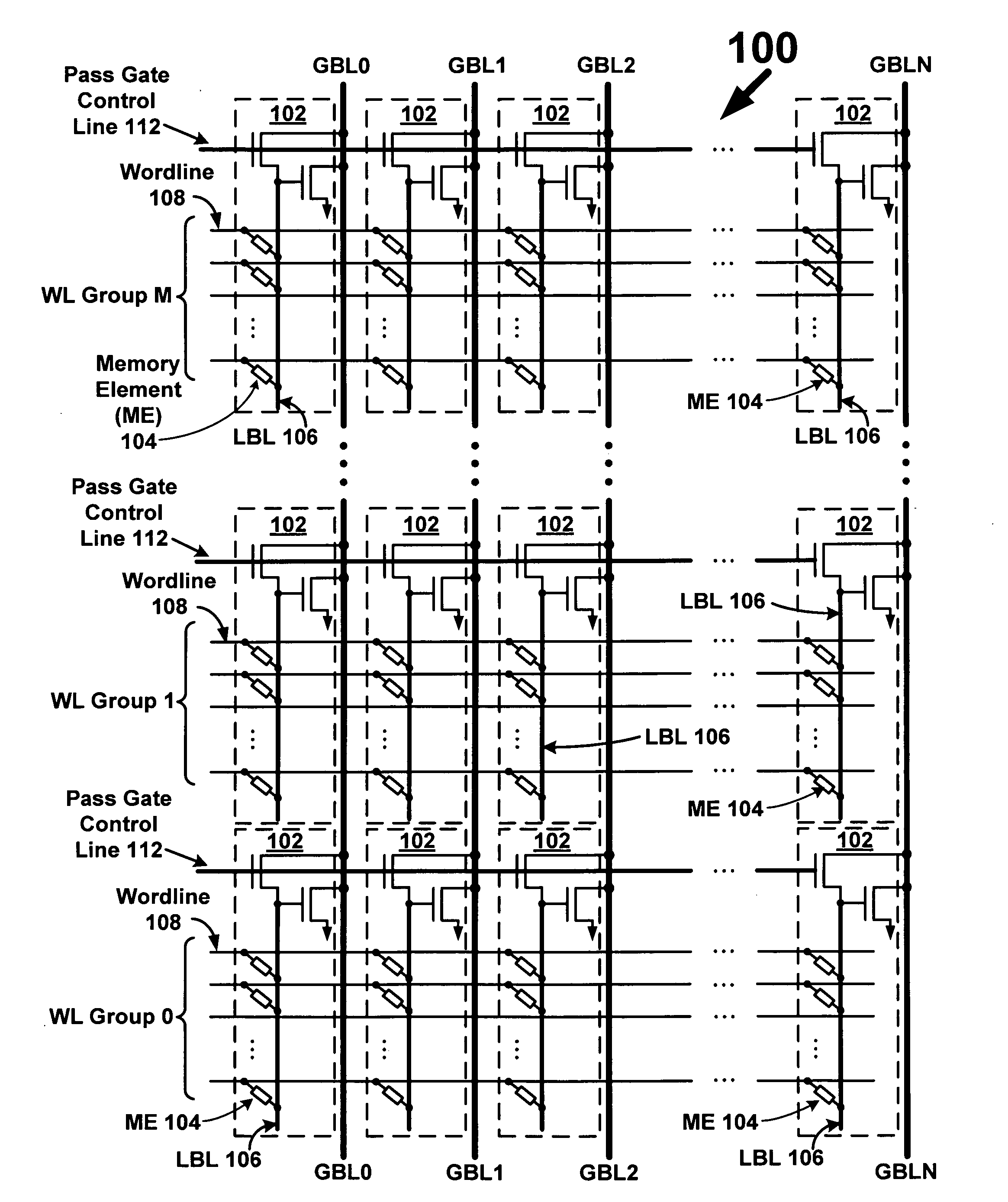

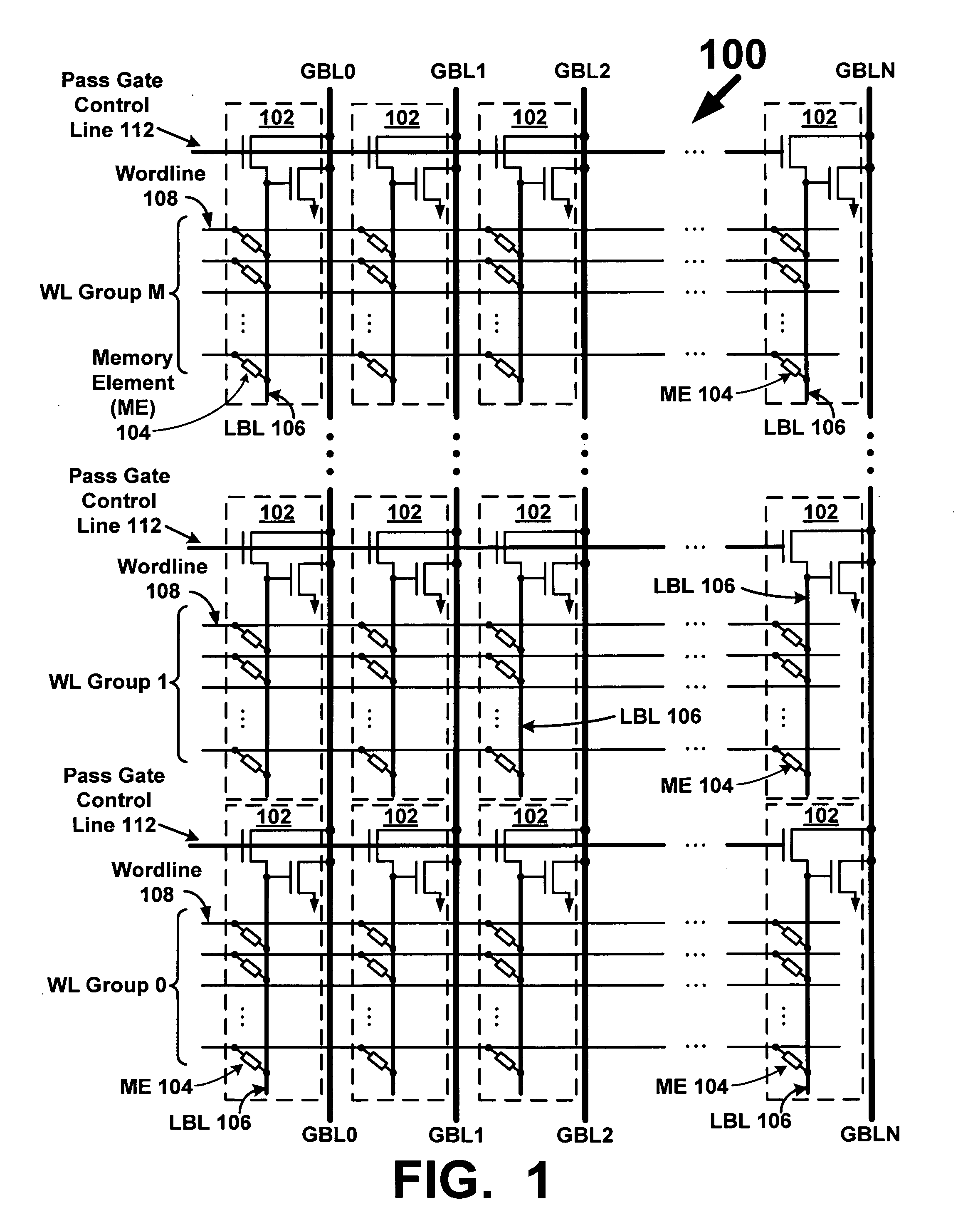

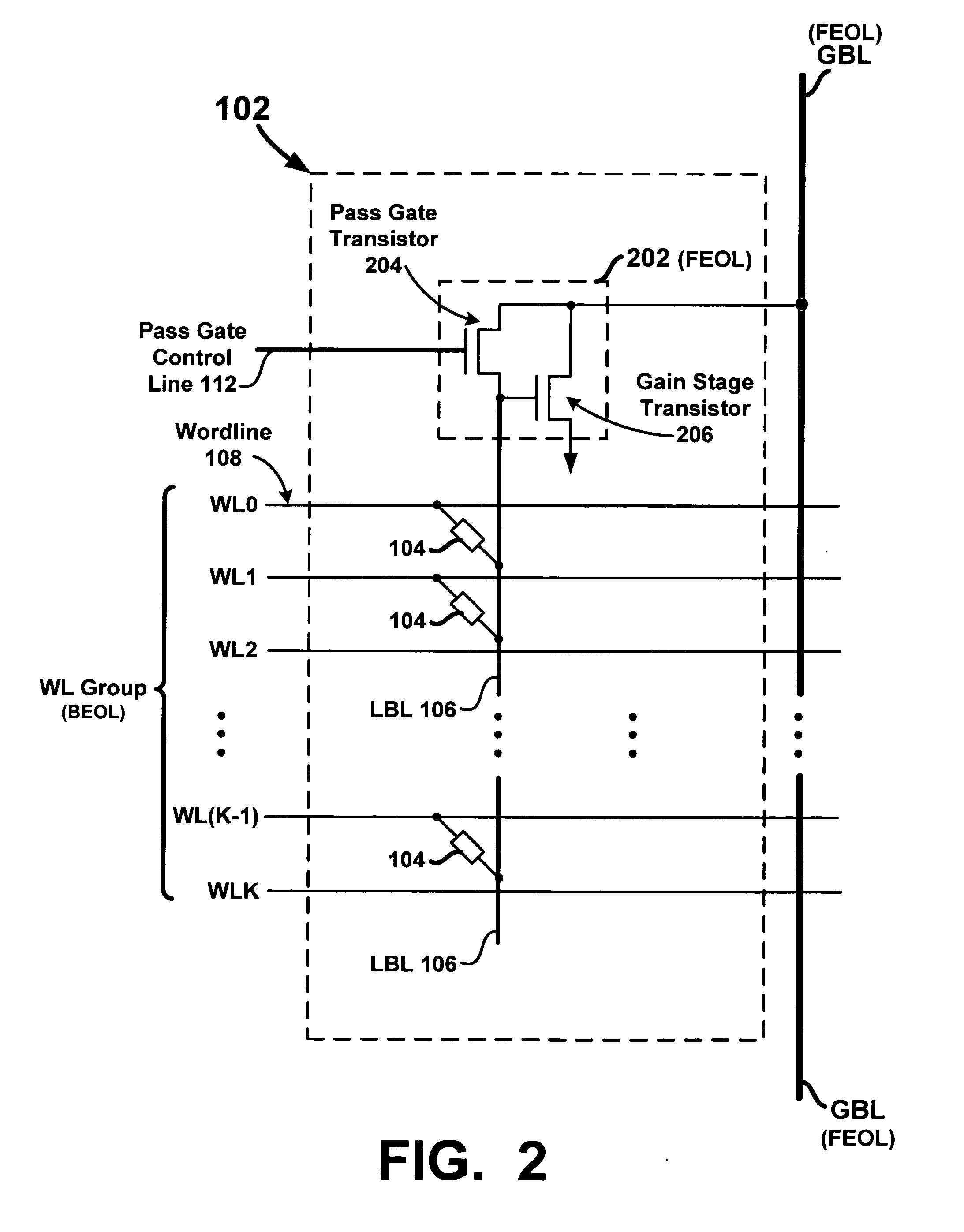

Memory array with local bitlines and local-to-global bitline pass gates and gain stages

ActiveUS20120314468A1Increase chanceCompact integrationNanoinformaticsRead-only memoriesSignal onComputer science

A memory array includes wordlines, local bitlines, two-terminal memory elements, global bitlines, and local-to-global bitline pass gates and gain stages. The memory elements are formed between the wordlines and local bitlines. Each local bitline is selectively coupled to an associated global bitline, by way of an associated local-to-global bitline pass gate. During a read operation when a memory element of a local bitline is selected to be read, a local-to-global gain stage is configured to amplify a signal on or passing through the local bitline to an amplified signal on or along an associated global bitline. The amplified signal, which in one embodiment is dependent on the resistive state of the selected memory element, is used to rapidly determine the memory state stored by the selected memory element.

Owner:UNITY SEMICON

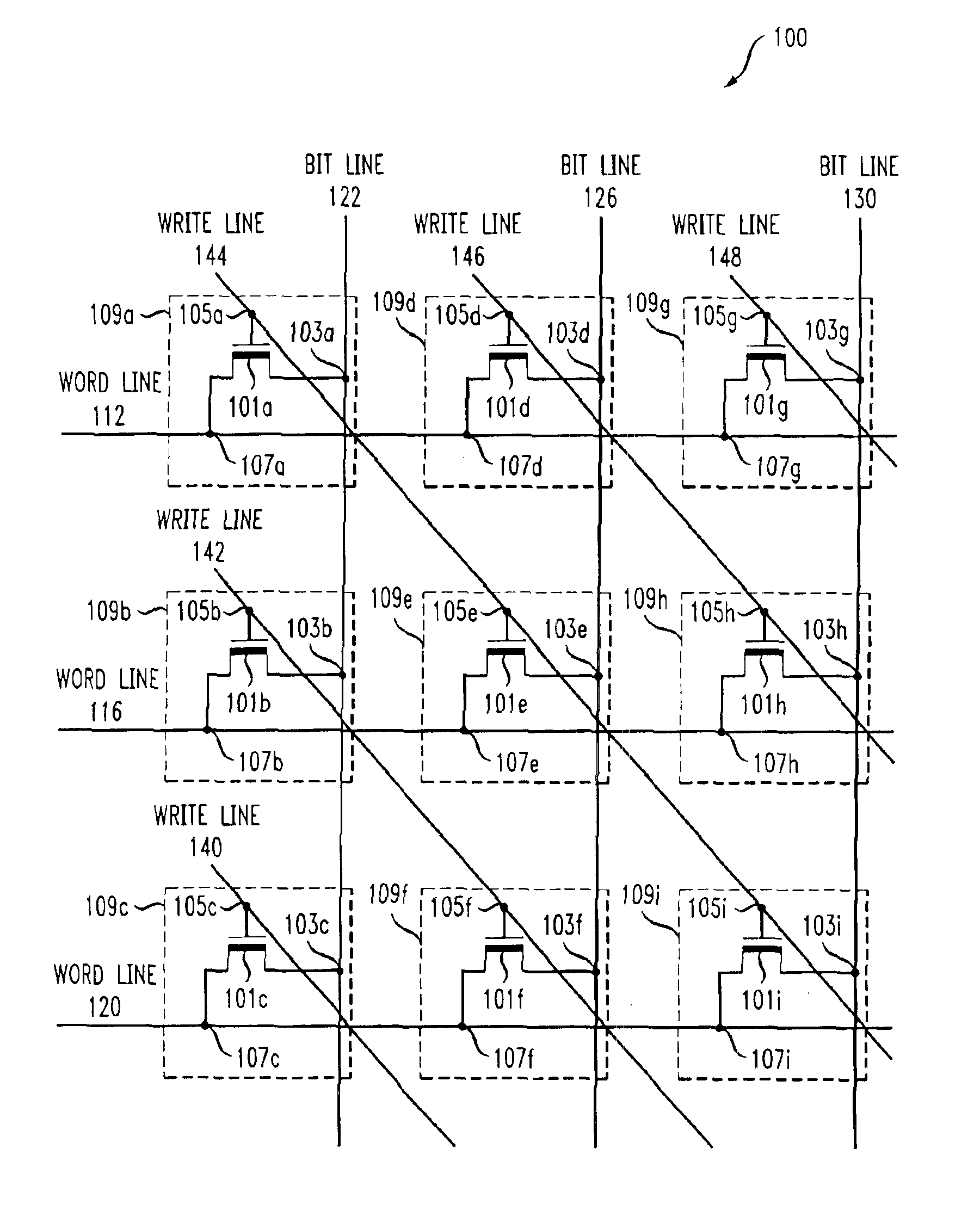

Memory array employing single three-terminal non-volatile storage elements

InactiveUS6894916B2Easy to optimizeDenser memory arrayTransistorSolid-state devicesBit lineComputer architecture

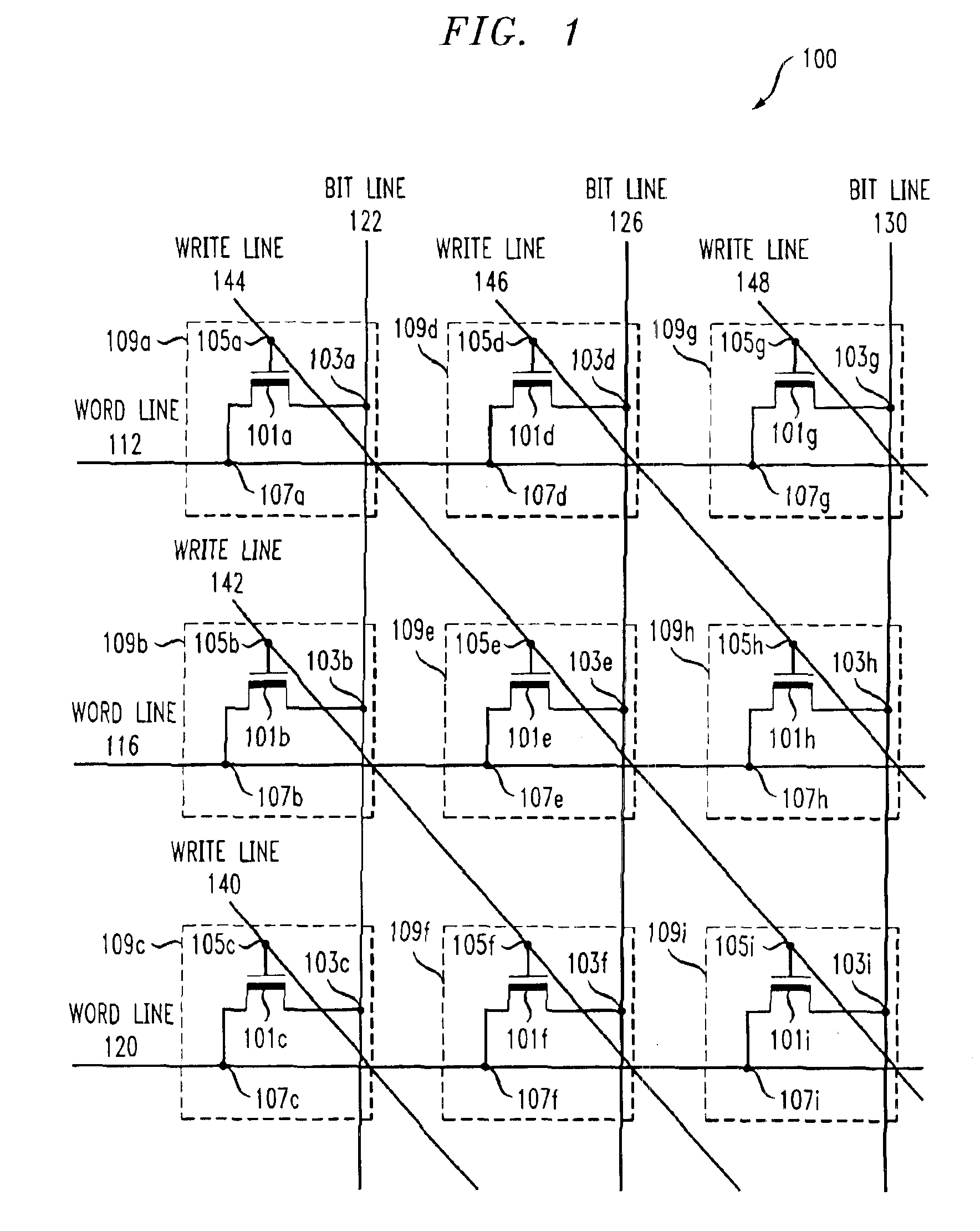

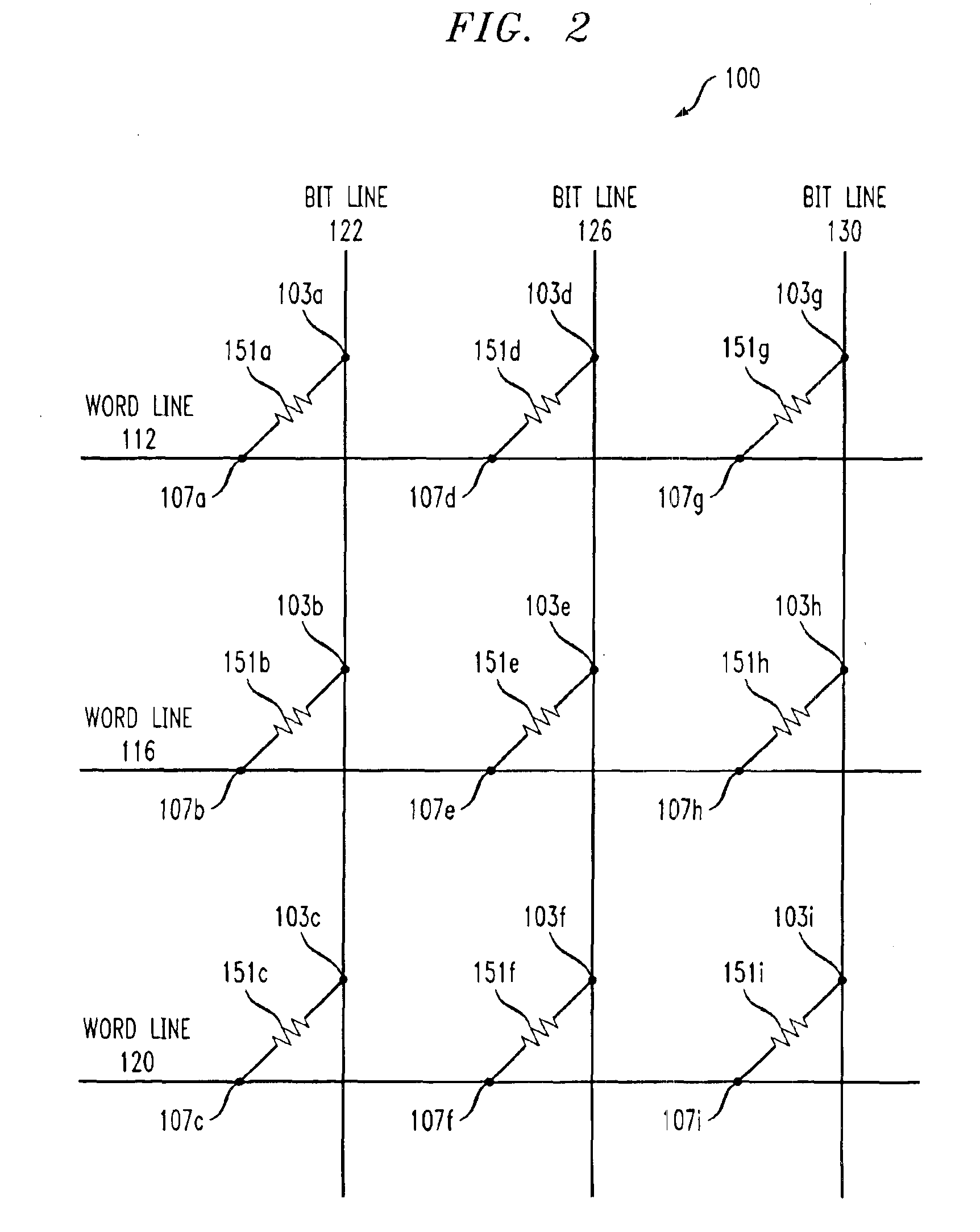

An improved non-volatile memory array comprises a plurality of memory cells, at least one of the memory cells comprising a three-terminal non-volatile storage element for storing a logical state of the at least one memory cell. The memory array further comprises a plurality of write lines operatively coupled to the memory cells for selectively writing the logical state of one or more memory cells in the memory array, and a plurality of bit lines and word lines operatively coupled to the memory cells for selectively reading and writing the logical state of one or more memory cells in the memory array. The memory array is advantageously configured so as to eliminate the need for a pass gate being operatively coupled to a corresponding non-volatile storage element in the at least one memory cell.

Owner:IBM CORP

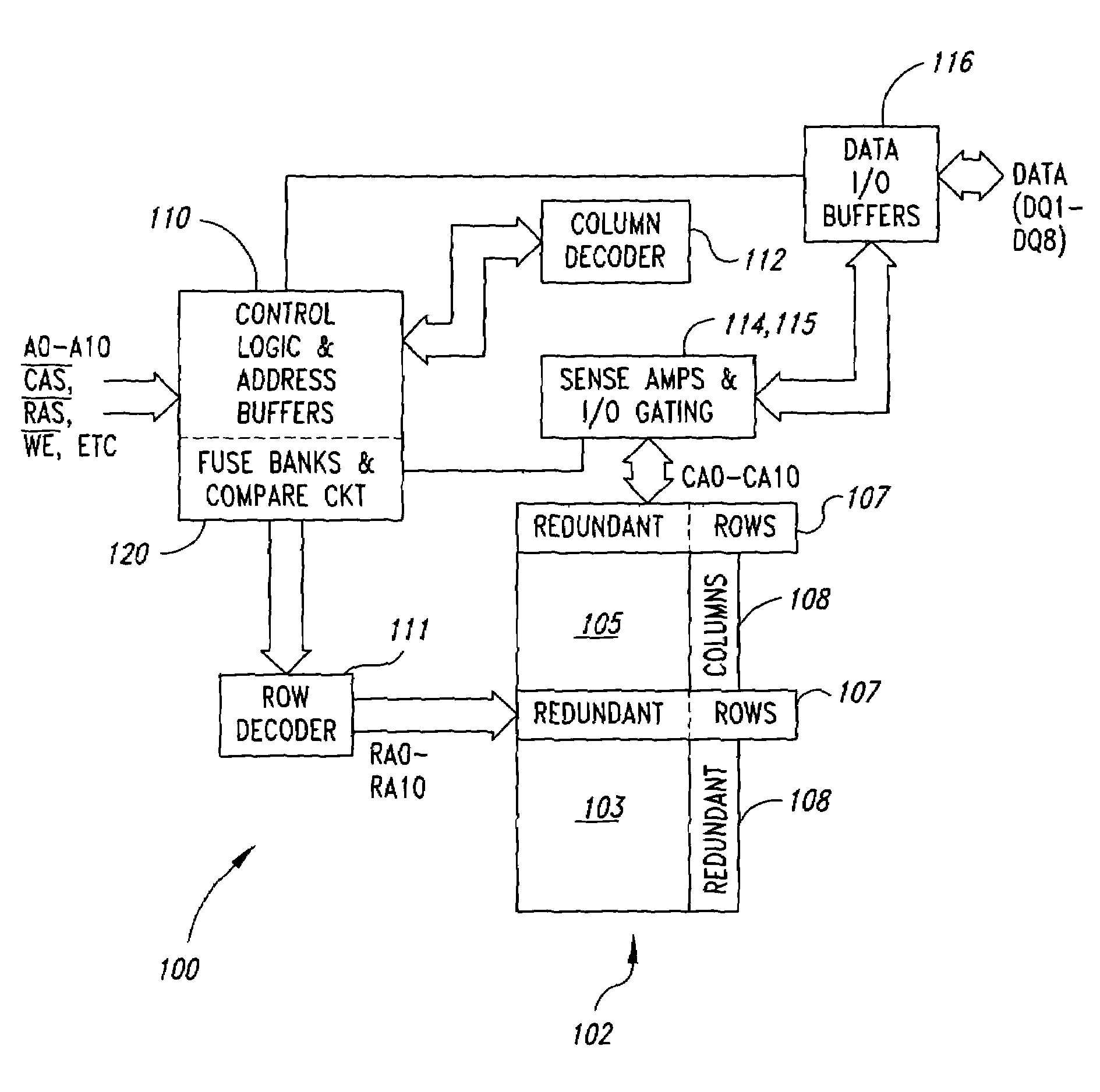

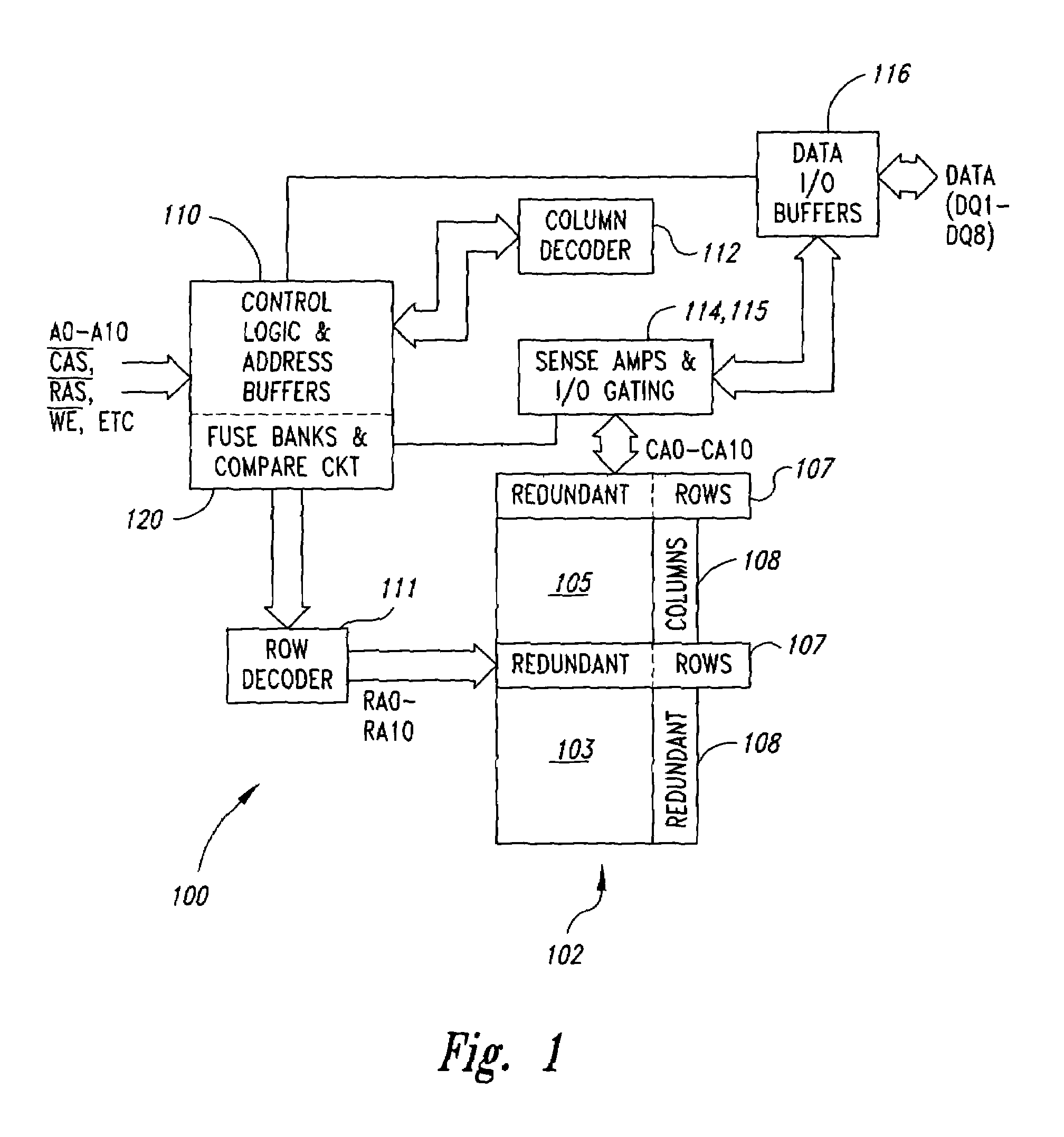

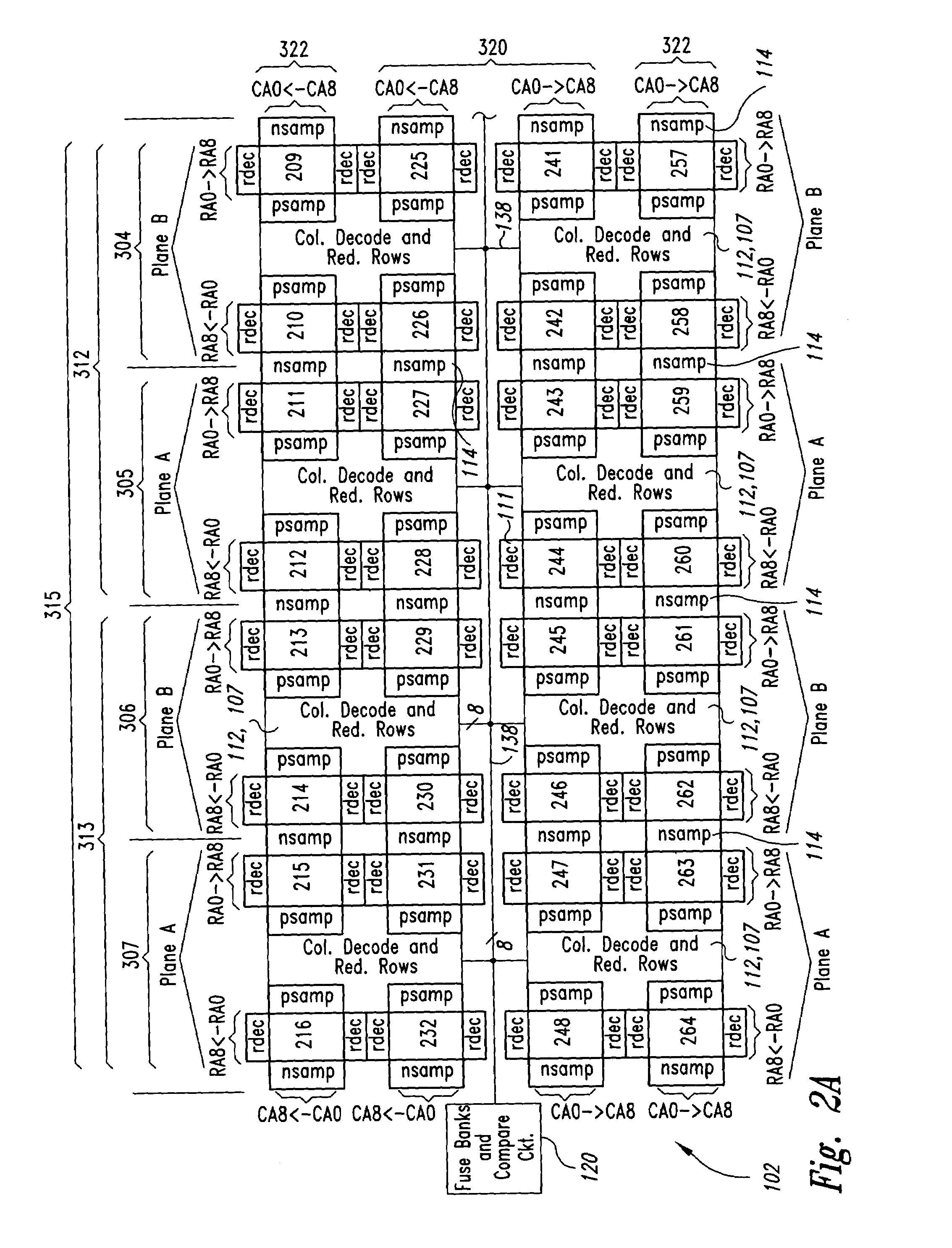

Layout for a semiconductor memory device having redundant elements

InactiveUS7043672B2Reduce areaReduce in quantityMemory loss protectionSemiconductor/solid-state device manufacturingComputer architectureAudio power amplifier

The present invention reduces the area on a die required for rows and columns of redundant memory cells by sharing compare circuitry with banks of redundant memory cells based on division of the primary memory array into two or more “planes.” Pass gates or multiplexers coupled between at least two banks of fuses and one compare circuit selectively couple the appropriate fuse bank to the compare circuit. Preferably, a bit in the address (e.g., address bit RA9 in a row address word having address bits A0-RA9) is received by and controls the multiplexer to select between the two banks of fuses. Additionally, the planes span blocks of memory in the memory array, where each block is divided by shared sense amplifiers. As a result, while eight lines are coupled to 16 rows or columns, only eight rows or columns will be active at any one time because isolation gates will enable only eight of the 16 rows or columns within two planes of memory. As a result, the present invention saves on the number of lines required to intercouple the compare circuits to the redundant rows / columns.

Owner:MICRON TECH INC

SRAM cell structure with dielectric sidewall spacers and drain and channel regions defined along sidewall spacers

A six transistor static random access memory (SRAM) cell with thin-film pull-up transistors and method of making the same includes providing two bulk silicon pull-down transistors of a first conductivity type, two active gated pull-up thin-film transistors (TFTs) of a second conductivity type, two pass gates, a common word line, and two bit line contacts. The bulk silicon pull-down transistors, two active gated pull-up TFTs, and two pass gates are connected at four shared contacts. In addition, the two bulk silicon pull-down transistors and the two active gated pull-up TFTs are formed with two polysilicon layers, a first of the polysilicon layers (poly1) is salicided and includes poly1 gate electrodes for the two bulk silicon pull-down transistors. A second of the polysilicon layers (poly2) includes desired poly2 stringers disposed along side edges of the poly1 gate electrodes, the desired poly2 stringers forming respective channel regions of the pull-up TFTs.

Owner:STMICROELECTRONICS SRL

SRAM cell for soft-error rate reduction and cell stability improvement

Owner:TAIWAN SEMICON MFG CO LTD

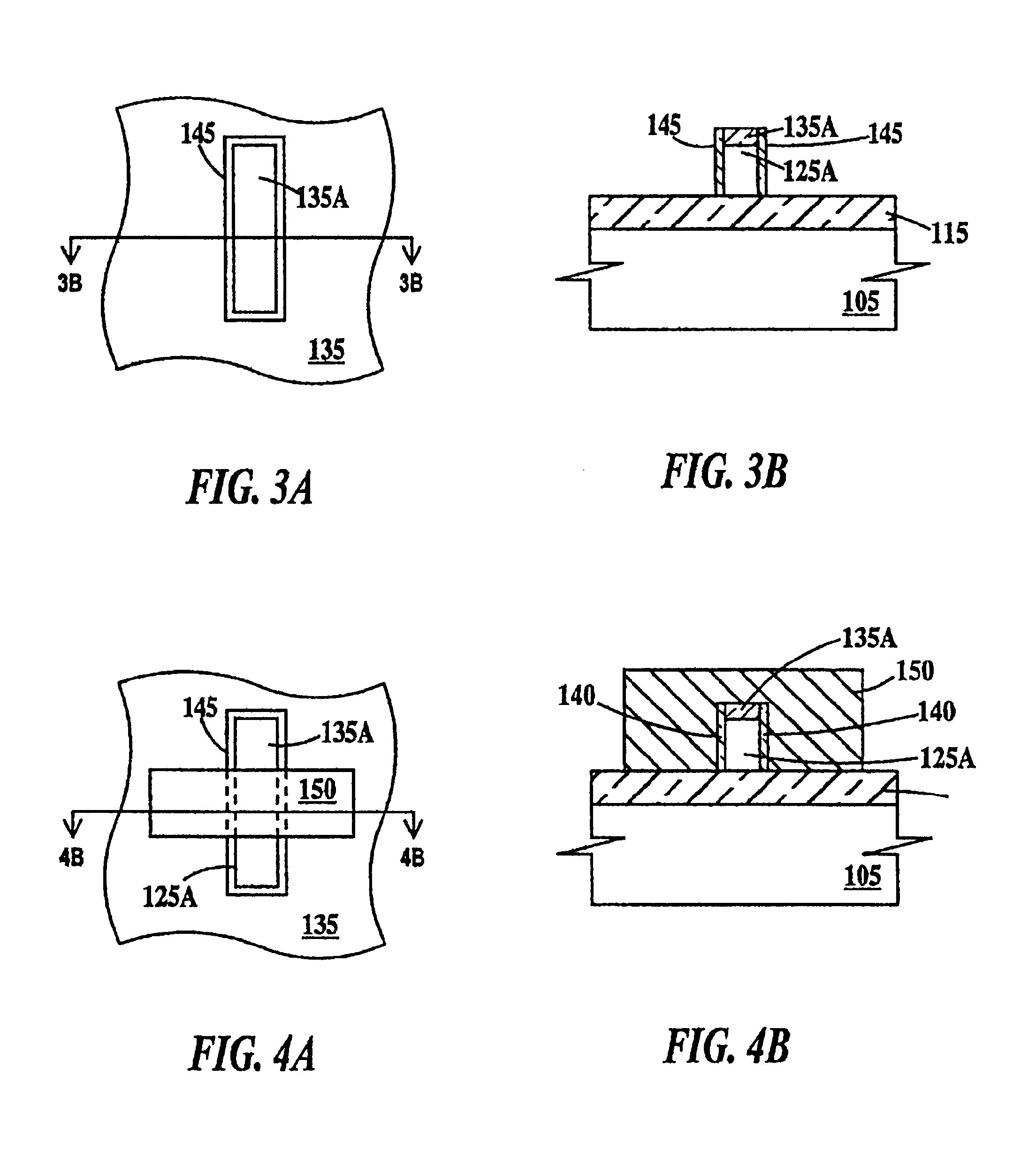

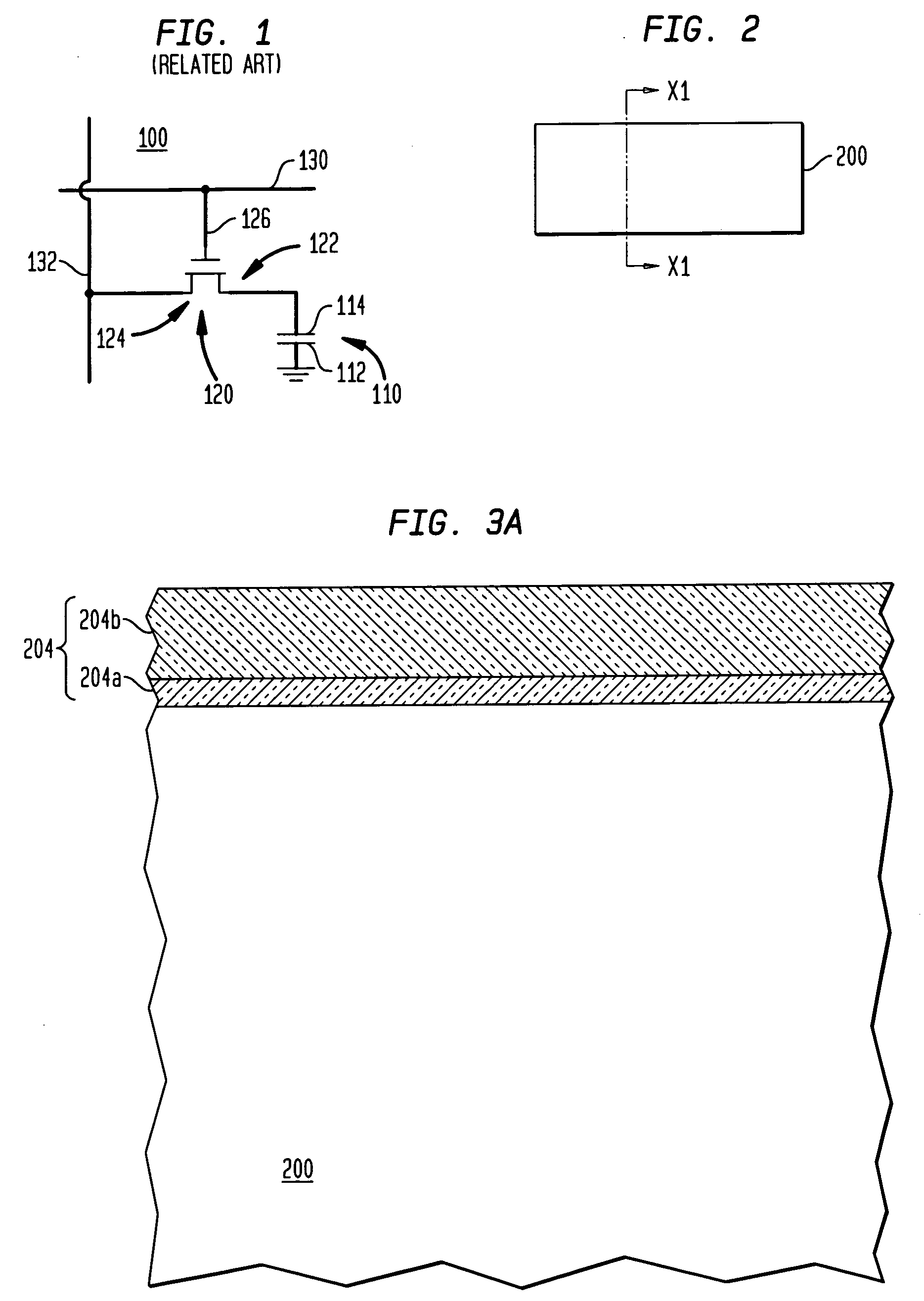

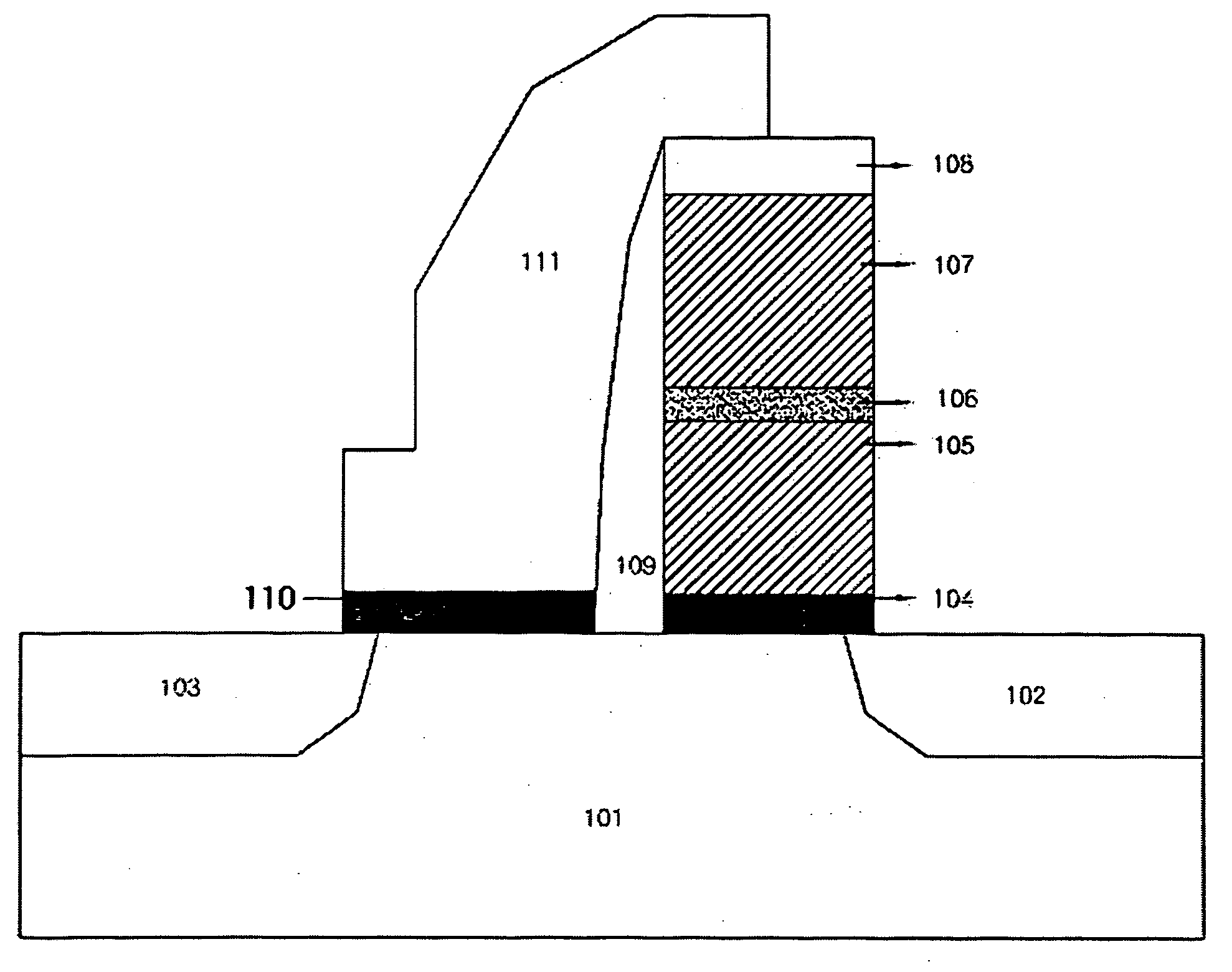

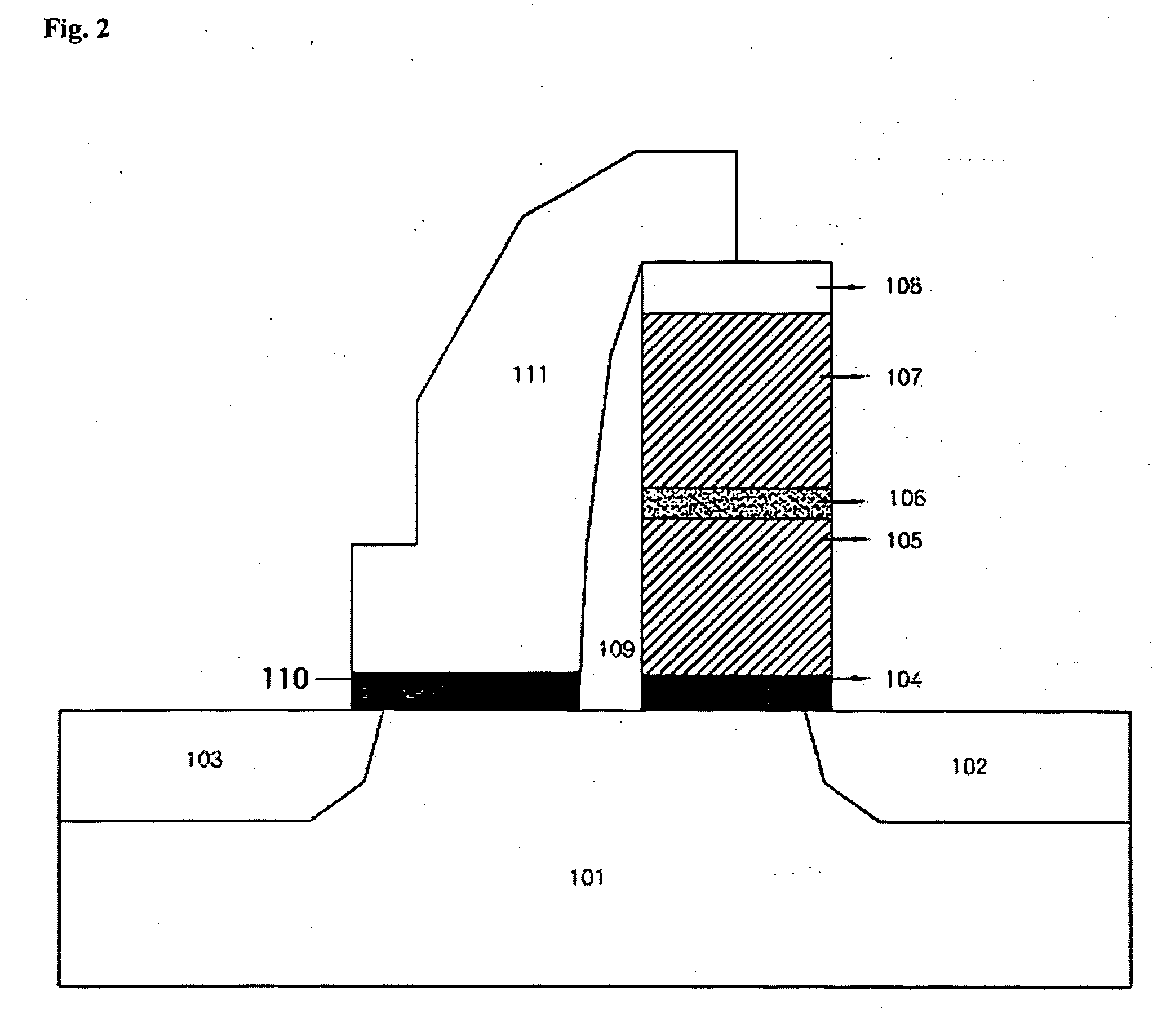

Encapsulated spacers in vertical pass gate dram and damascene logic gates

InactiveUS20050167741A1Improves Structural IntegrityTransistorSolid-state devicesDevice materialEngineering

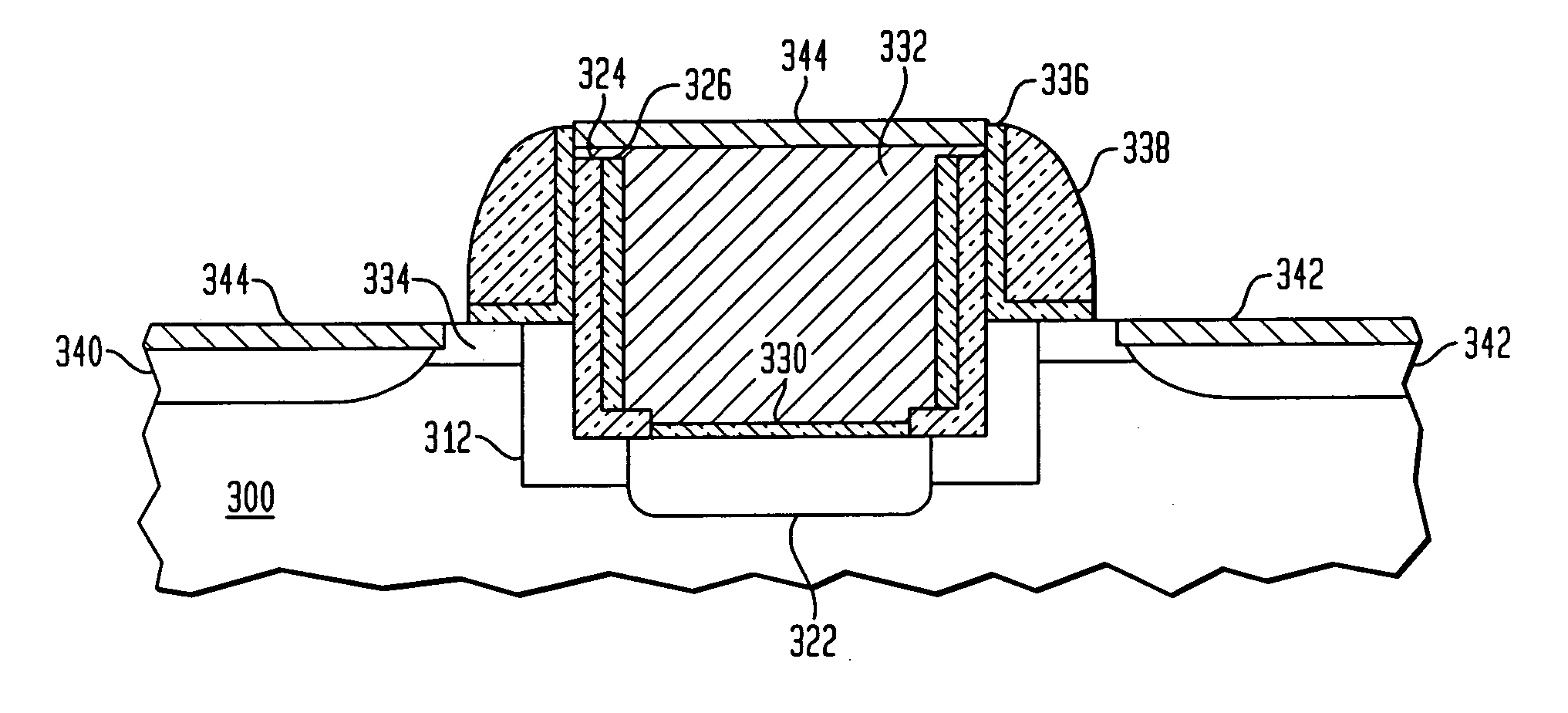

Semiconductor devices having improved isolation are provided along with methods of fabricating such semiconductor devices. The improved isolation includes an encapsulated spacer formed within a gate region of a device.

Owner:INFINEON TECH AG +1

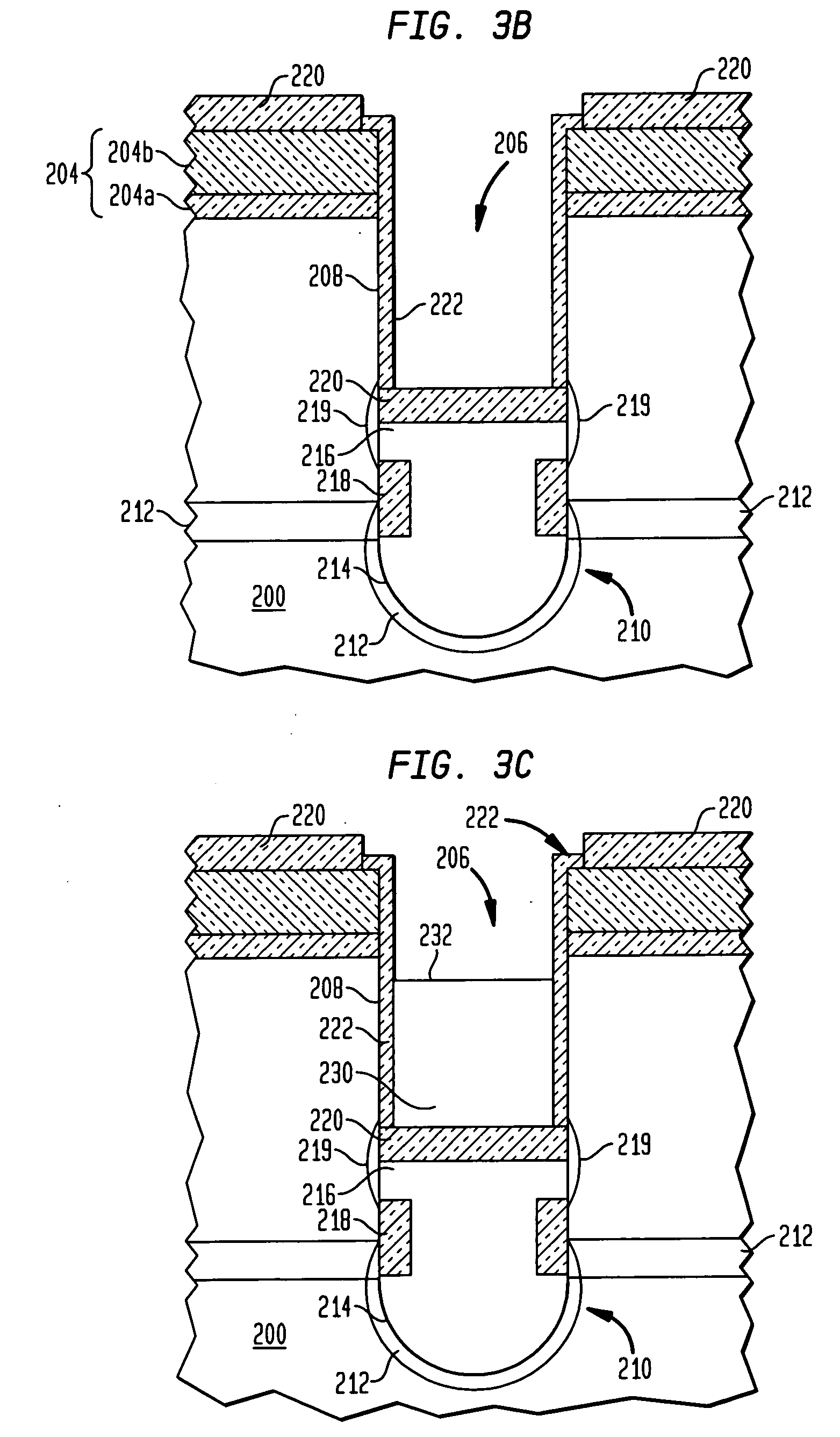

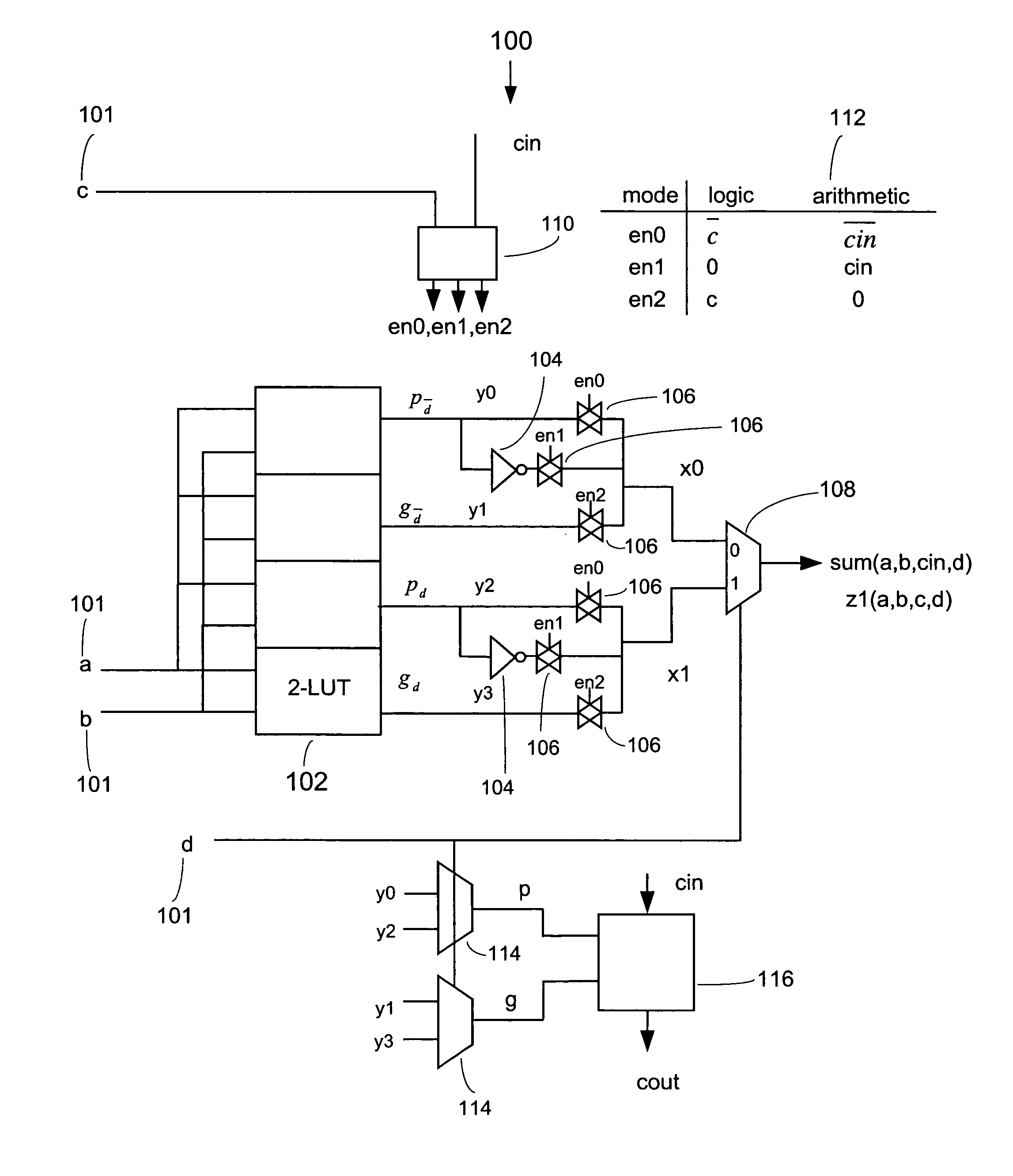

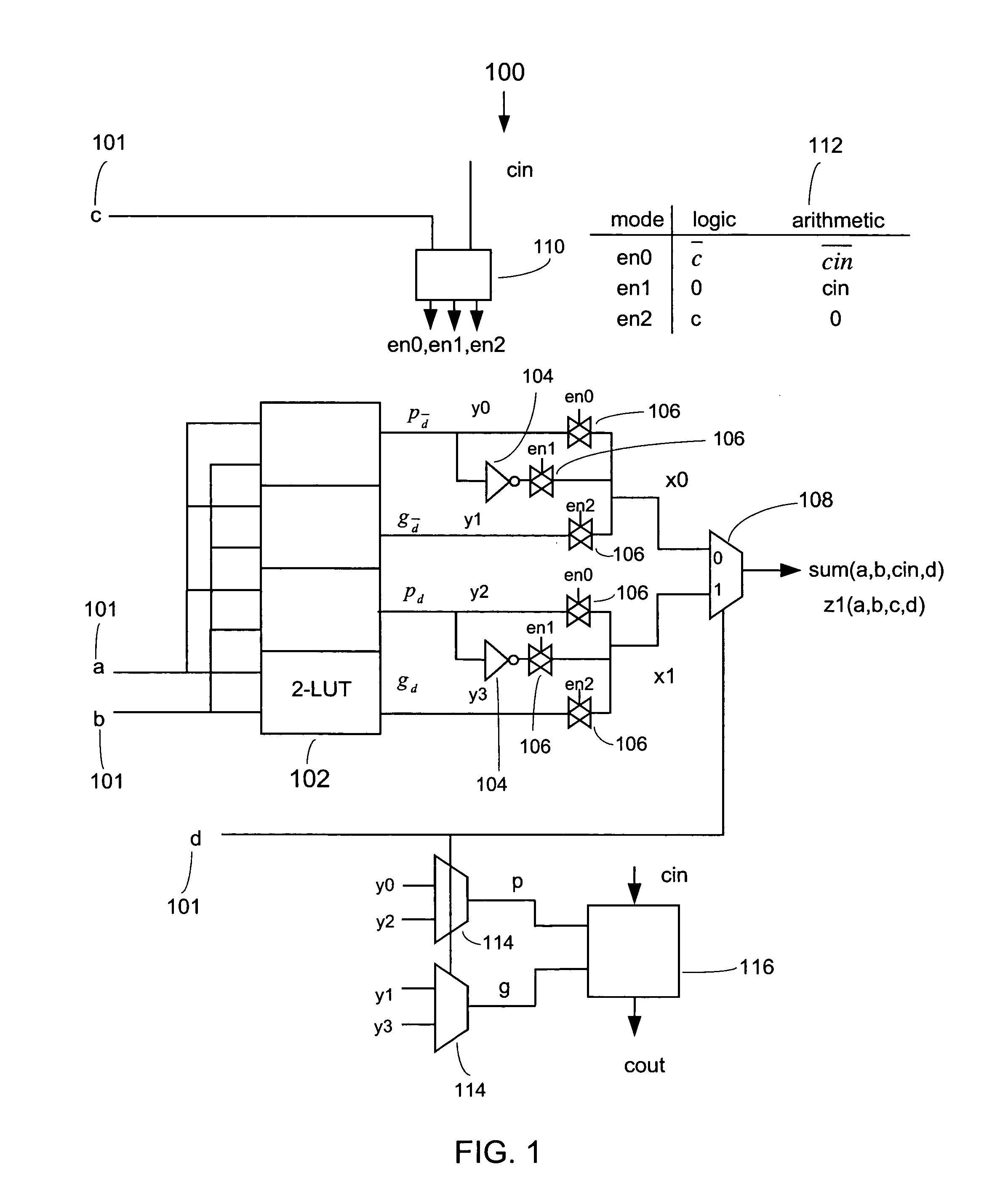

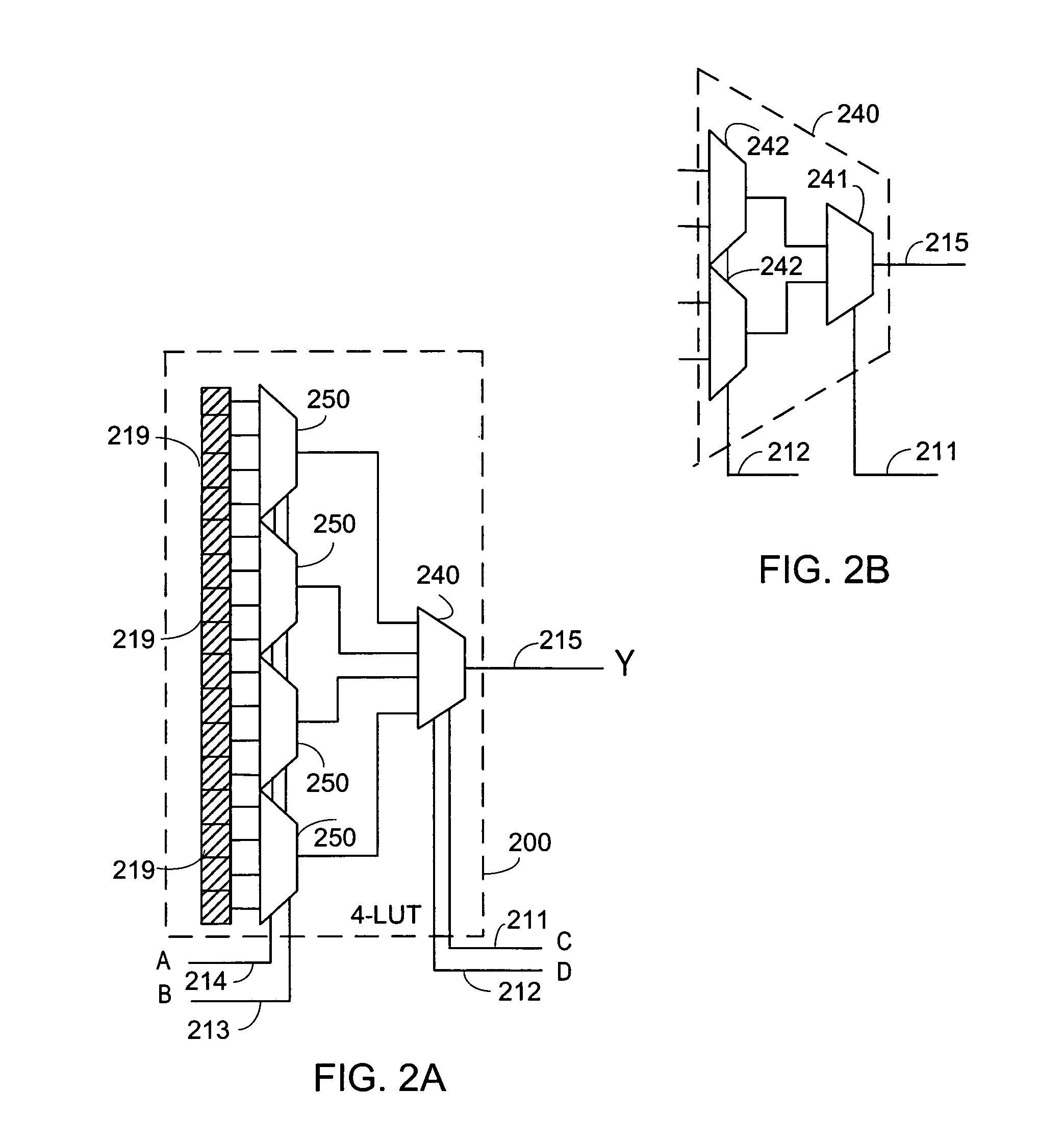

Arithmetic structures for programmable logic devices

According to some embodiments, arithmetic structures in logic elements result from combining inverters and pass gates (or other multiplexing hardware) with LUT hardware. According to other embodiments, arithmetic structures in logic elements result from combining dedicated adder hardware (e.g., including XOR units) and fracturable LUT hardware. According to other embodiments, arithmetic structures in logic elements result from providing complementary input connections between multiplexers and LUT hardware. In this way, the present invention enables the incorporation of arithmetic structures with LUT structures in a number of ways.

Owner:ALTERA CORP

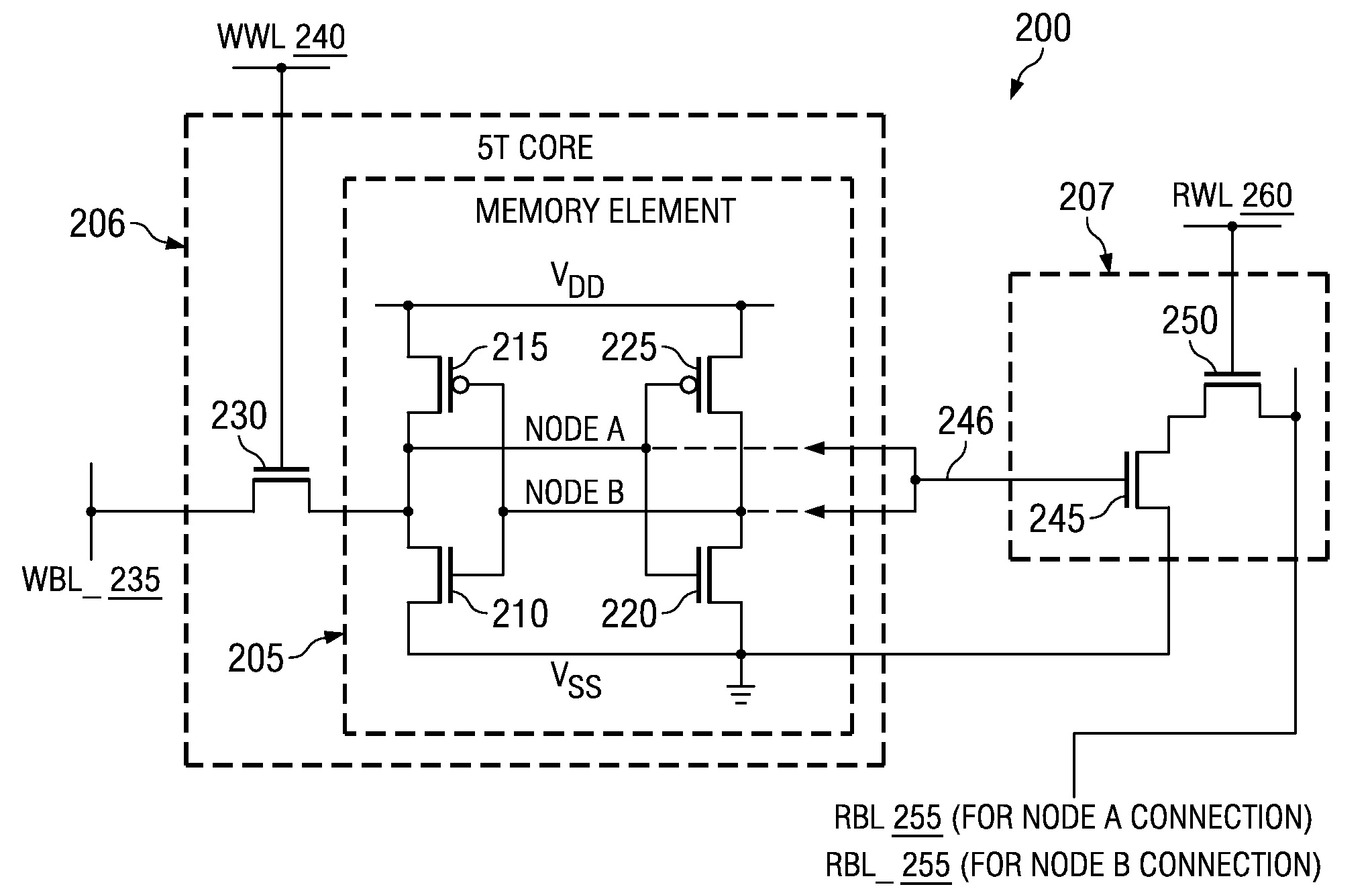

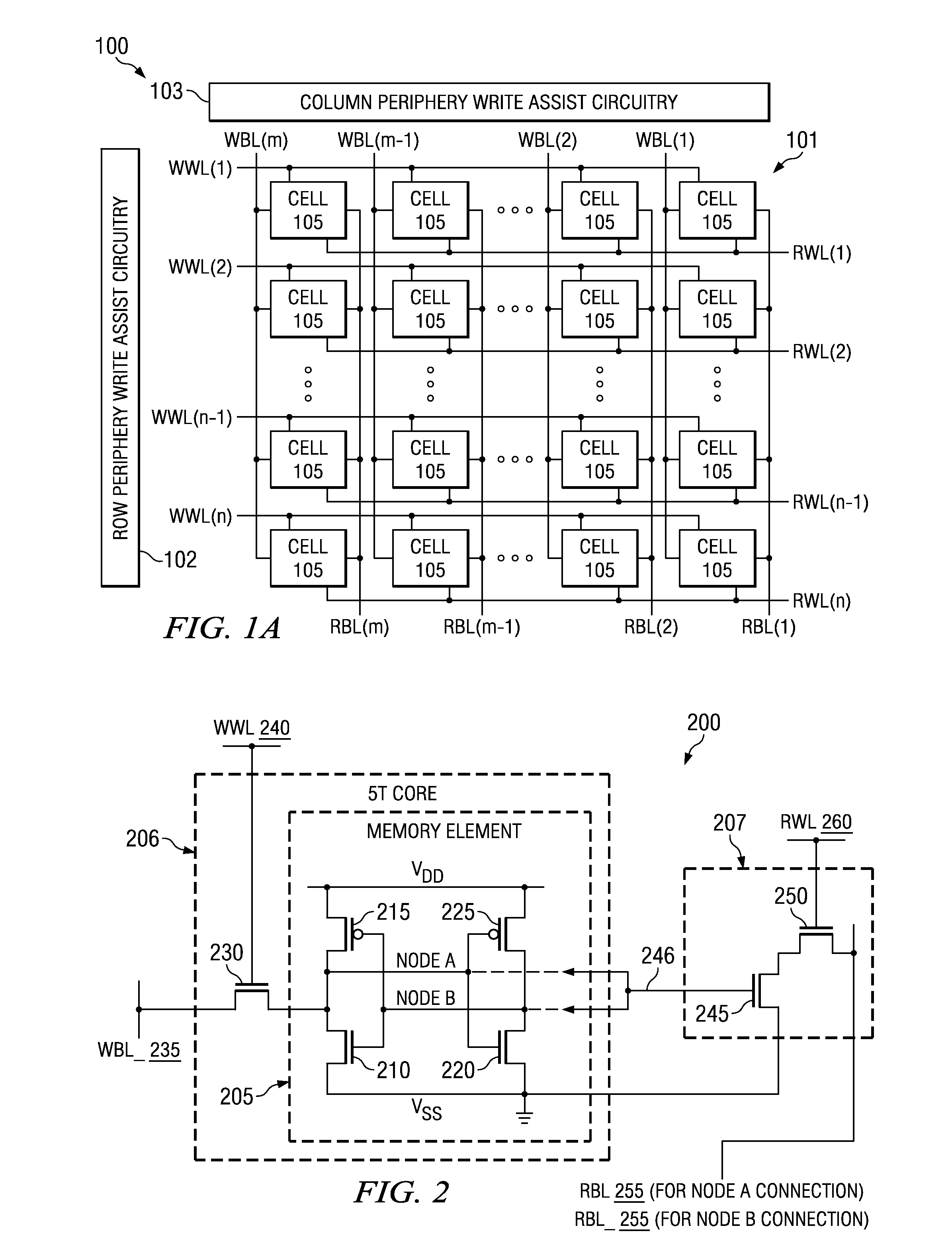

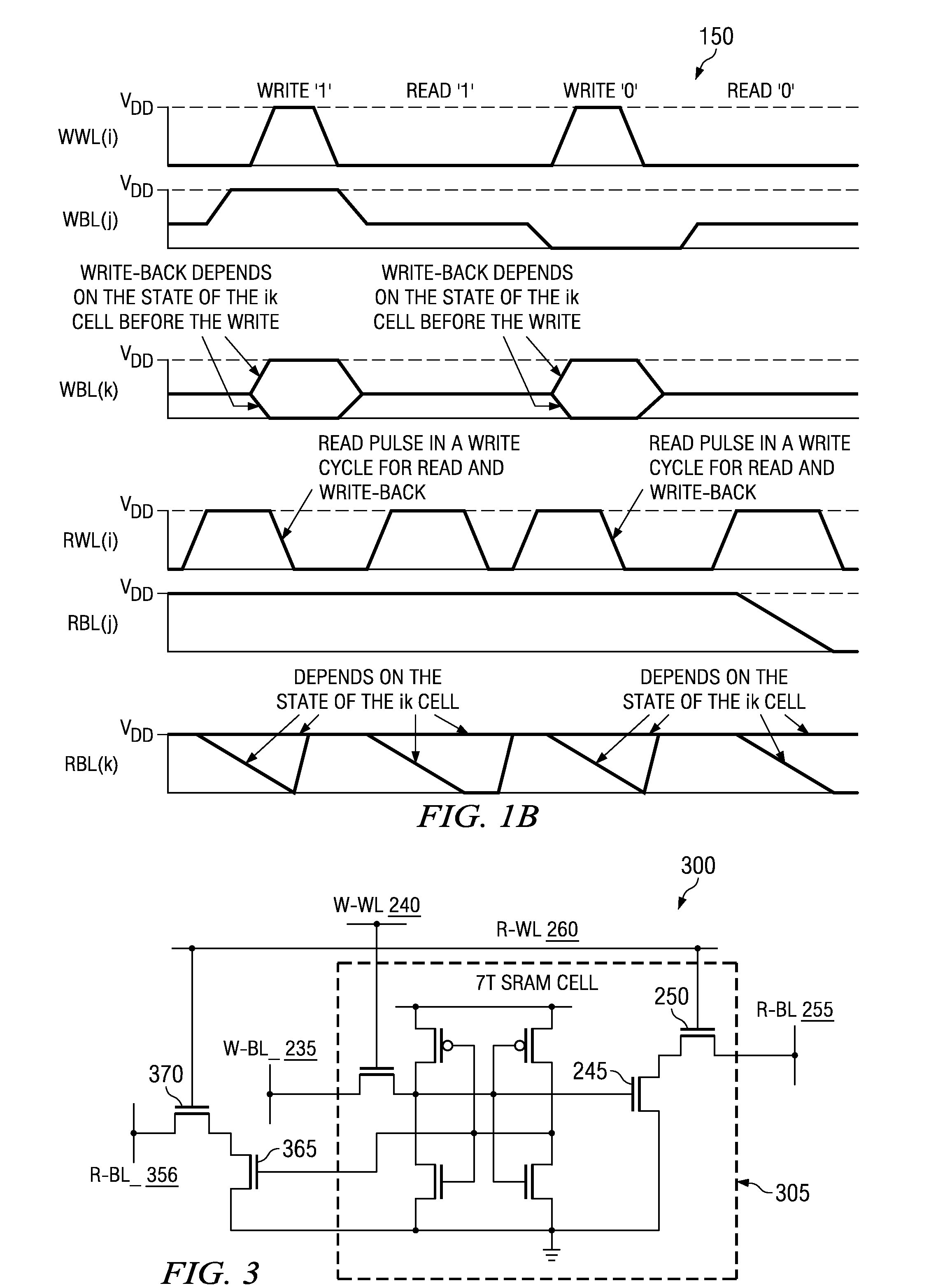

Seven transistor SRAM cell

Owner:TEXAS INSTR INC

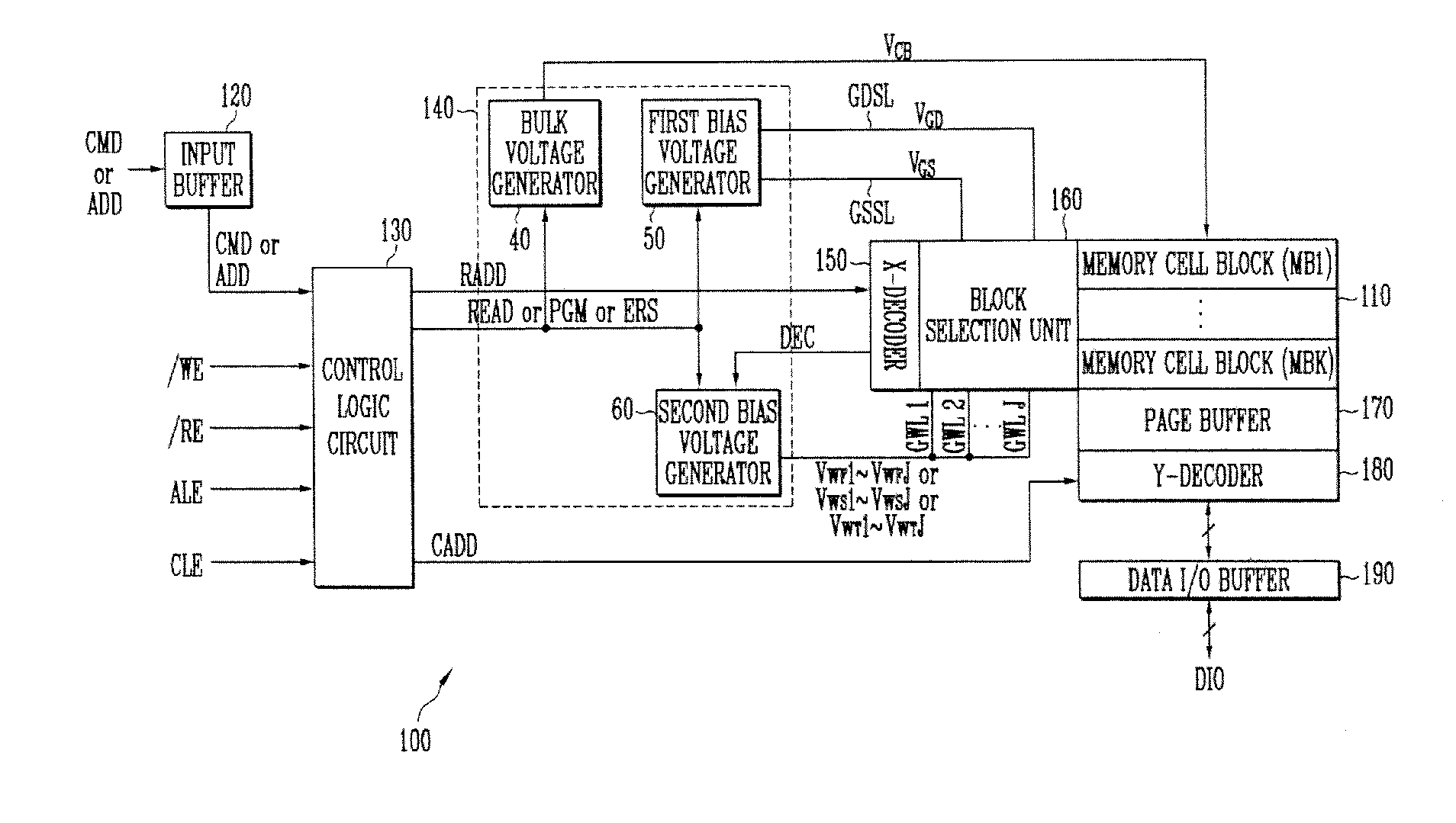

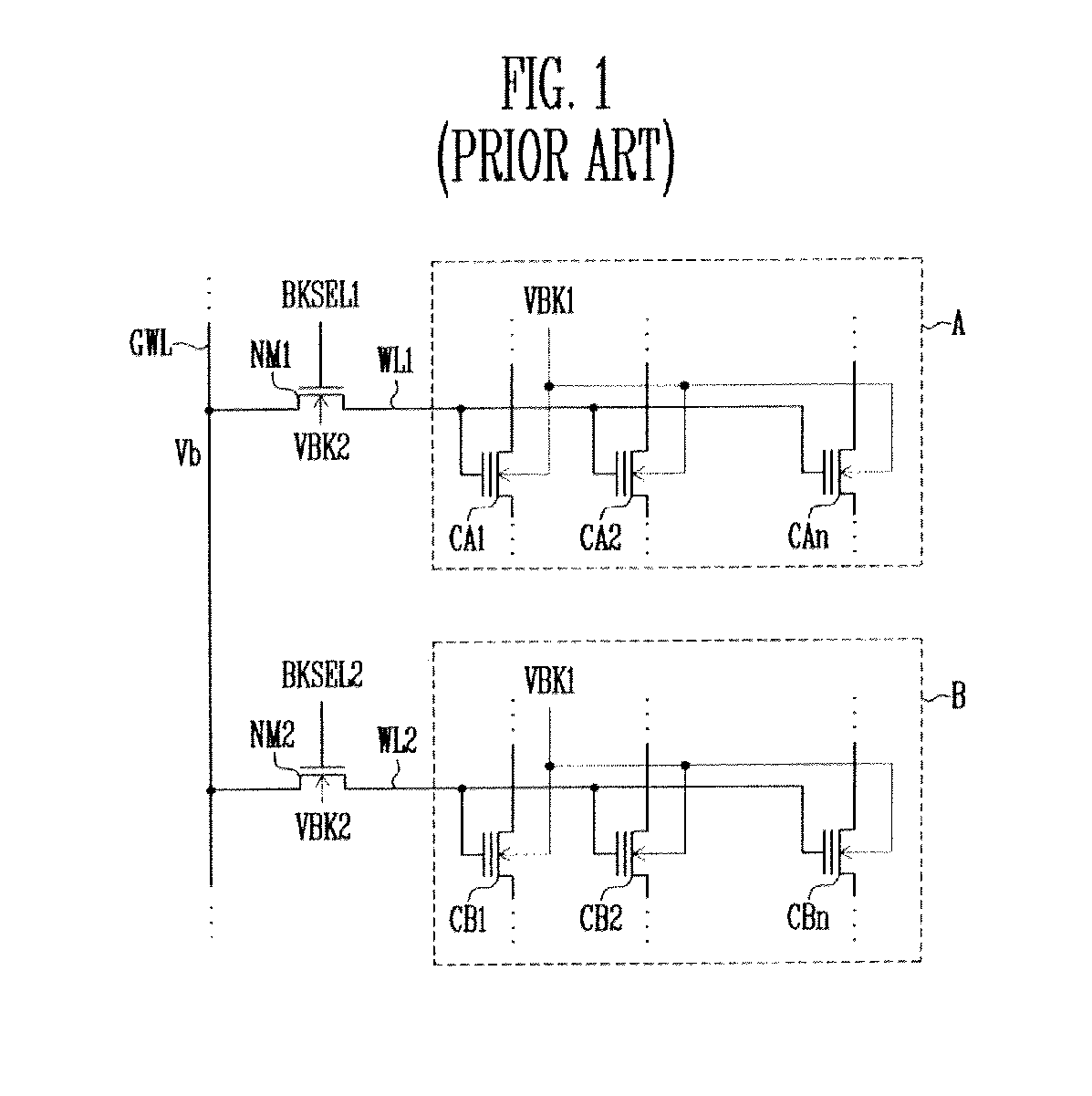

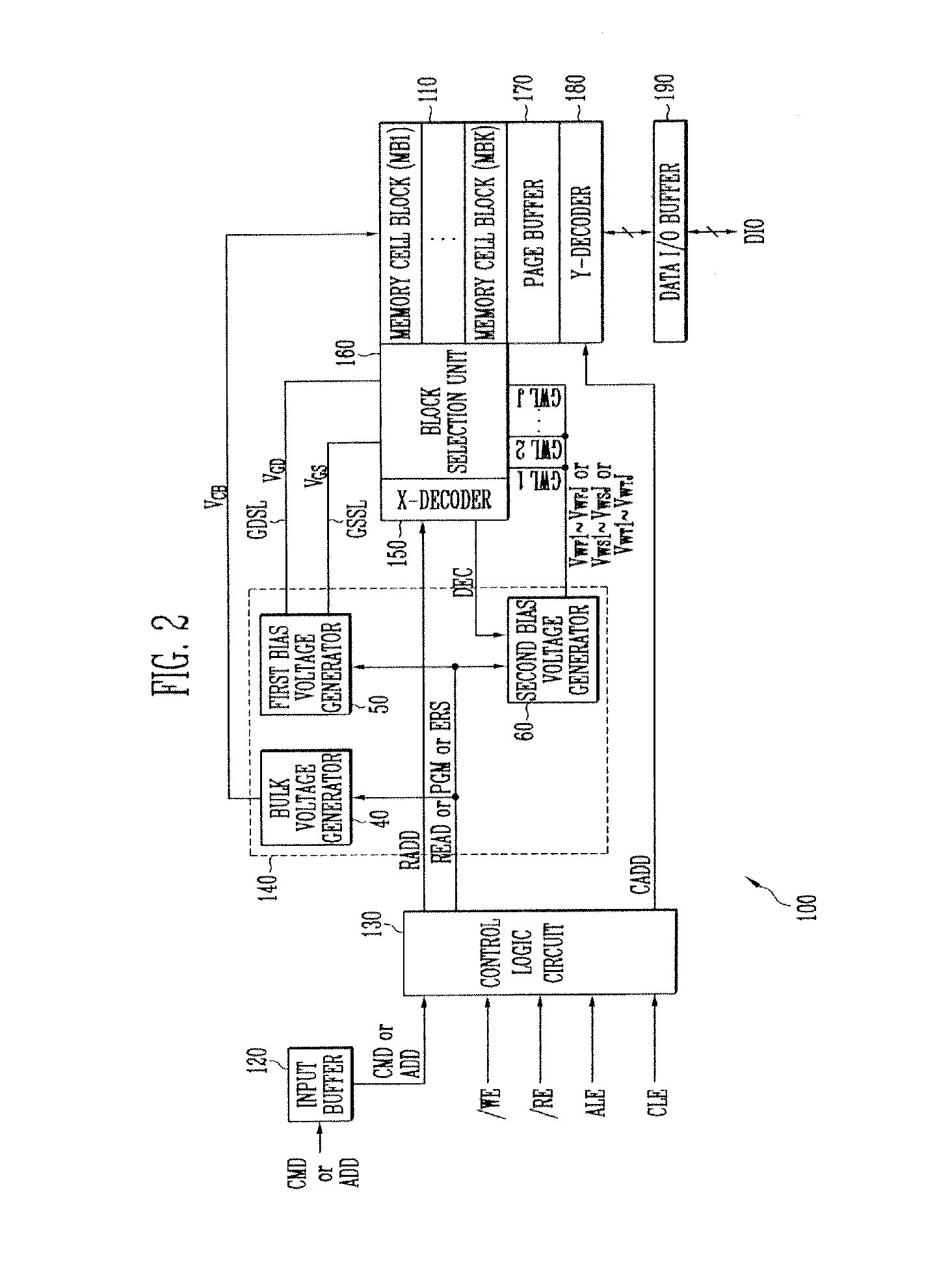

Flash Memory Device with Improved Erase Function and Method for Controlling Erase Operation of the Same

The present patent relates to flash memory devices with improved erase function, and method of controlling an erase operation of the same. According to the present patent, the flash memory device includes memory cell blocks, each having a plurality of memory cells sharing local word lines and bit lines, an X-decoder which decodes a row address signal and outputs the decoded signal, a block selection unit, which selects some of the memory cell blocks in response to the decoded signal, and connects local word lines of the selected memory cell blocks to corresponding global word lines, respectively, and a high voltage generator, which generates word line bias voltages in response to one of a read command, a program command and an erase command, and supplies the generated word line bias voltages to the global word lines in response to the decoded signal, respectively, wherein the word line bias voltages, which are generated by the high voltage generator in response to the erase command, have a positive value, respectively. Accordingly, a positive bias voltage is applied to a global word line in an erase operation. It is thus possible to prevent a shallow erase phenomenon of non-selected memory cell blocks due to the leakage current of pass gates.

Owner:SK HYNIX INC

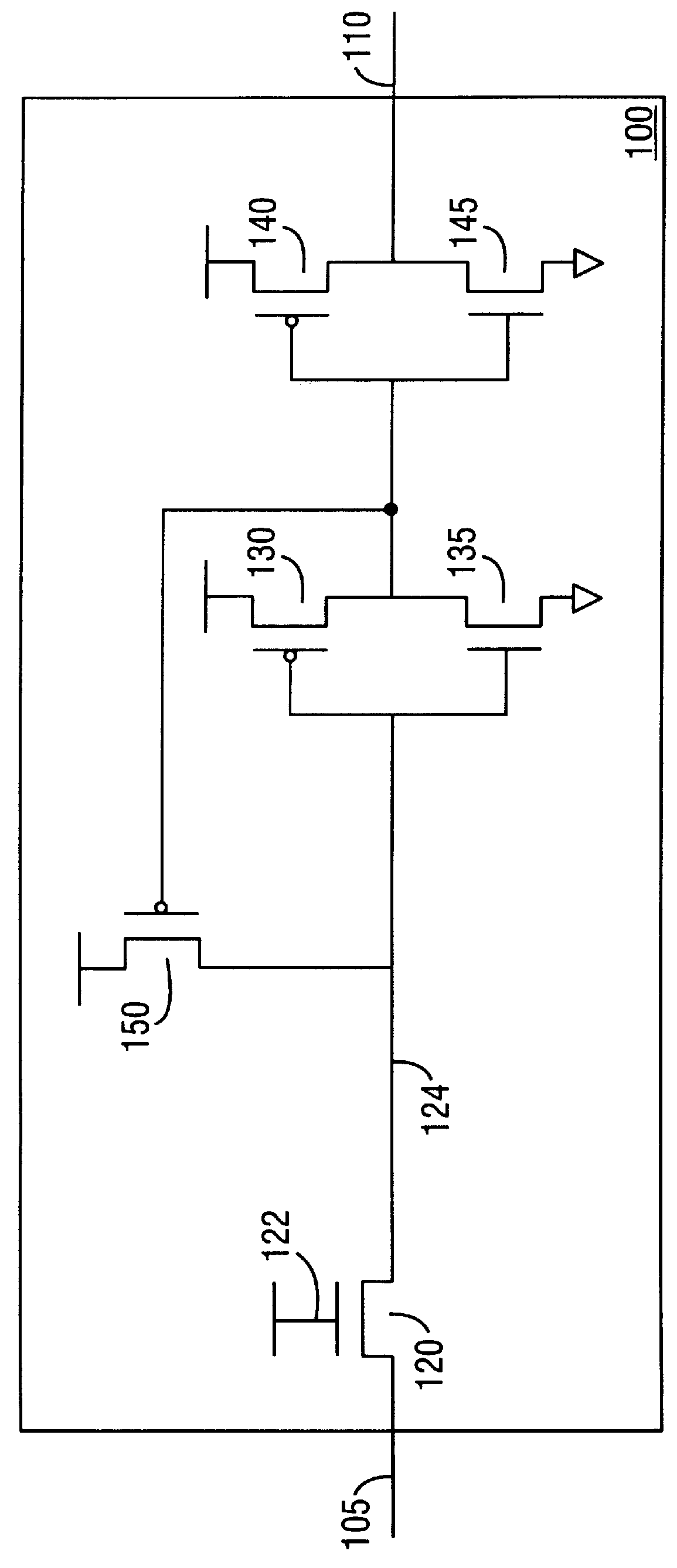

Pass gate input buffer for a mixed voltage environment

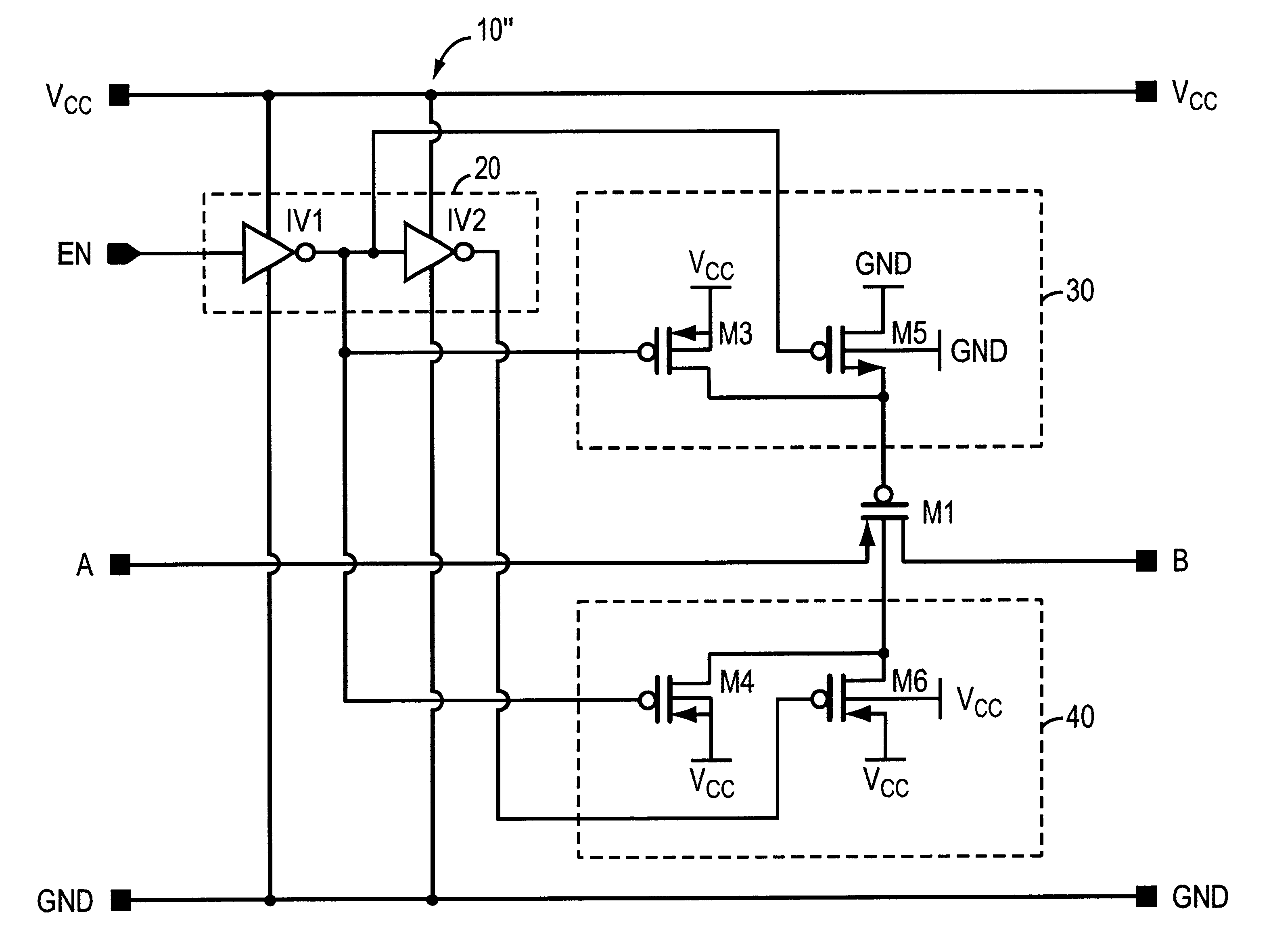

InactiveUS6031393AReliability increase in field effect transistorsLogic circuit coupling/interface arrangementsEngineeringVoltage source

An input buffer to interface among devices on a main circuit board is described. The input buffer includes a first transistor coupled between a first terminal and an input terminal of an inverter. The first transistor has an enable terminal adapted to be coupled to a first voltage supply. A second transistor that is coupled between the first terminal and the input terminal is also included. The input buffer further includes a control circuit to enable the second transistor. The control circuit is coupled to the first terminal, an enable terminal of the second transistor, the input terminal, and an output terminal of the inverter. A method for buffering signals among devices on a main circuit board comprises receiving a first signal in a first state from a first device. A first portion of the first signal is transmitted through a first transistor. A second portion of the first signal is transmitted through a second transistor. A second signal is generated by applying the first signal to the enable terminals of the third and fourth transistors. The second signal is then transmitted to a second device.

Owner:INTEL CORP

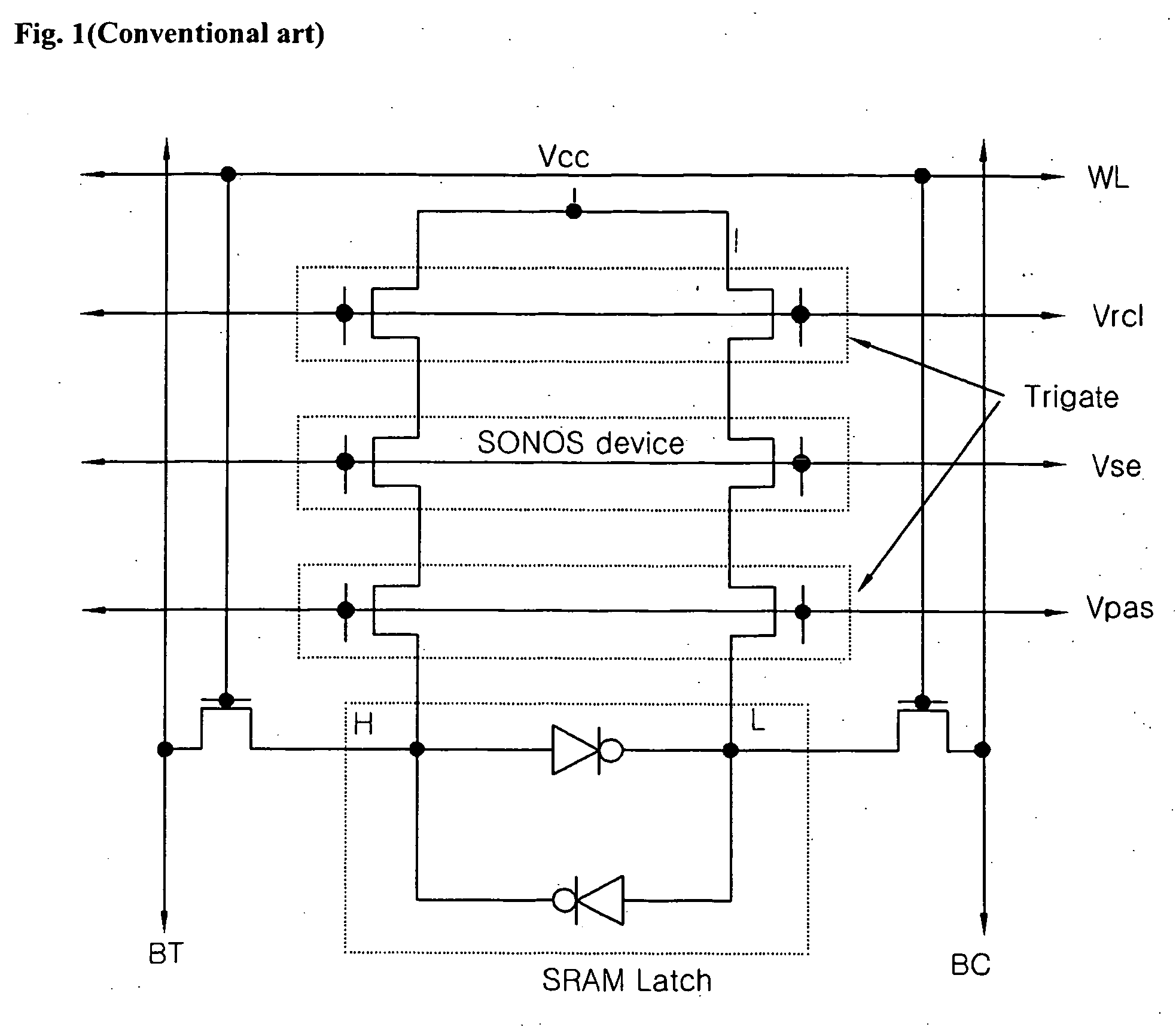

Semiconductor device

An nvSRAM having a stacked oxide layer is disclosed. A disclosed device comprises: two NMOS transistors and two PMOS transistors for an SRAM latch; two NMOS pass gates for reading and writing a HIGH condition and a LOW condition that are formed in the SRAM latch; and two floating gate NVM devices of split gate structure for storing the HIGH condition and the LOW condition that are stored in the SRAM latch when the power is off.

Owner:DONGBU ELECTRONICS CO LTD

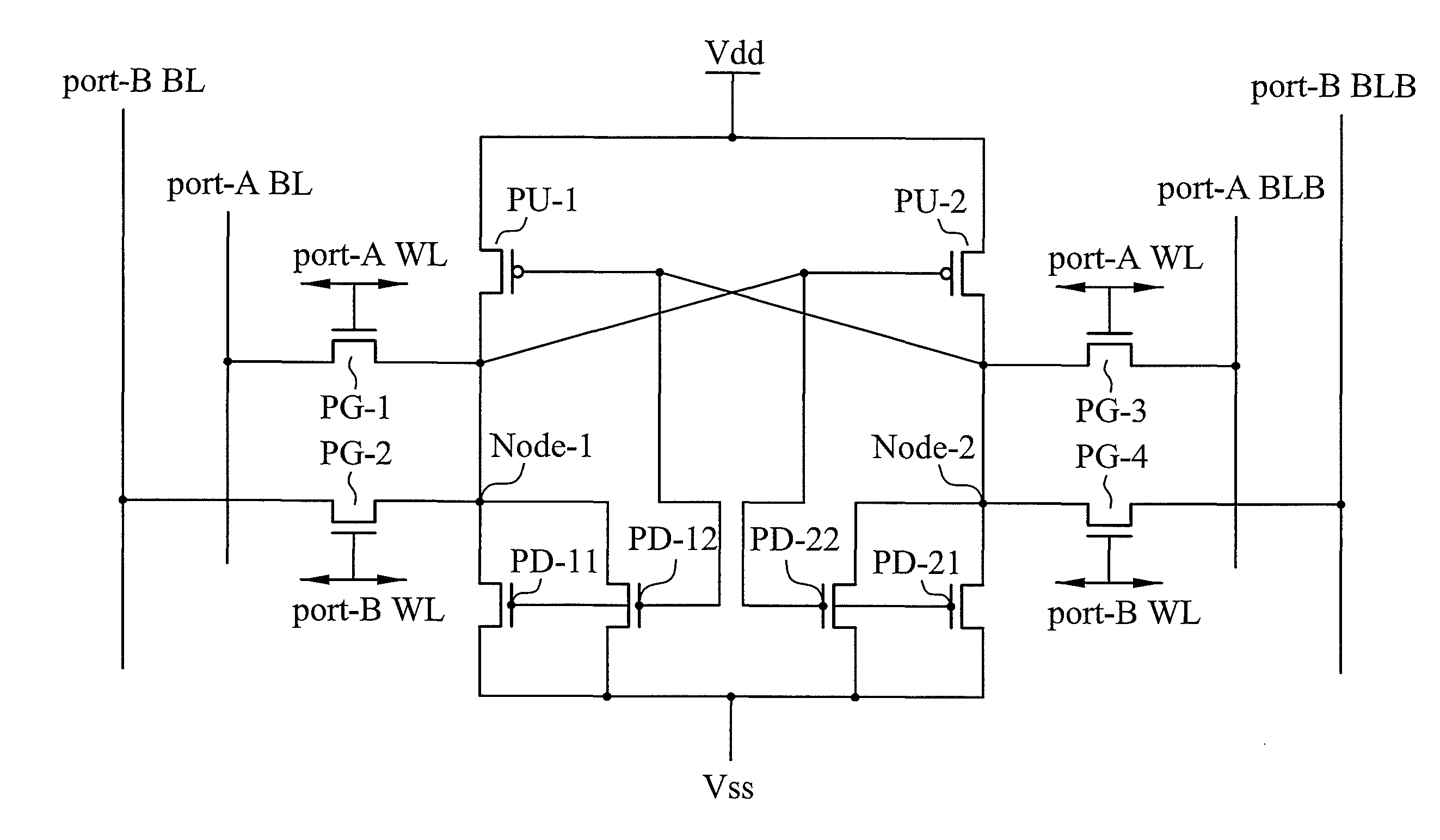

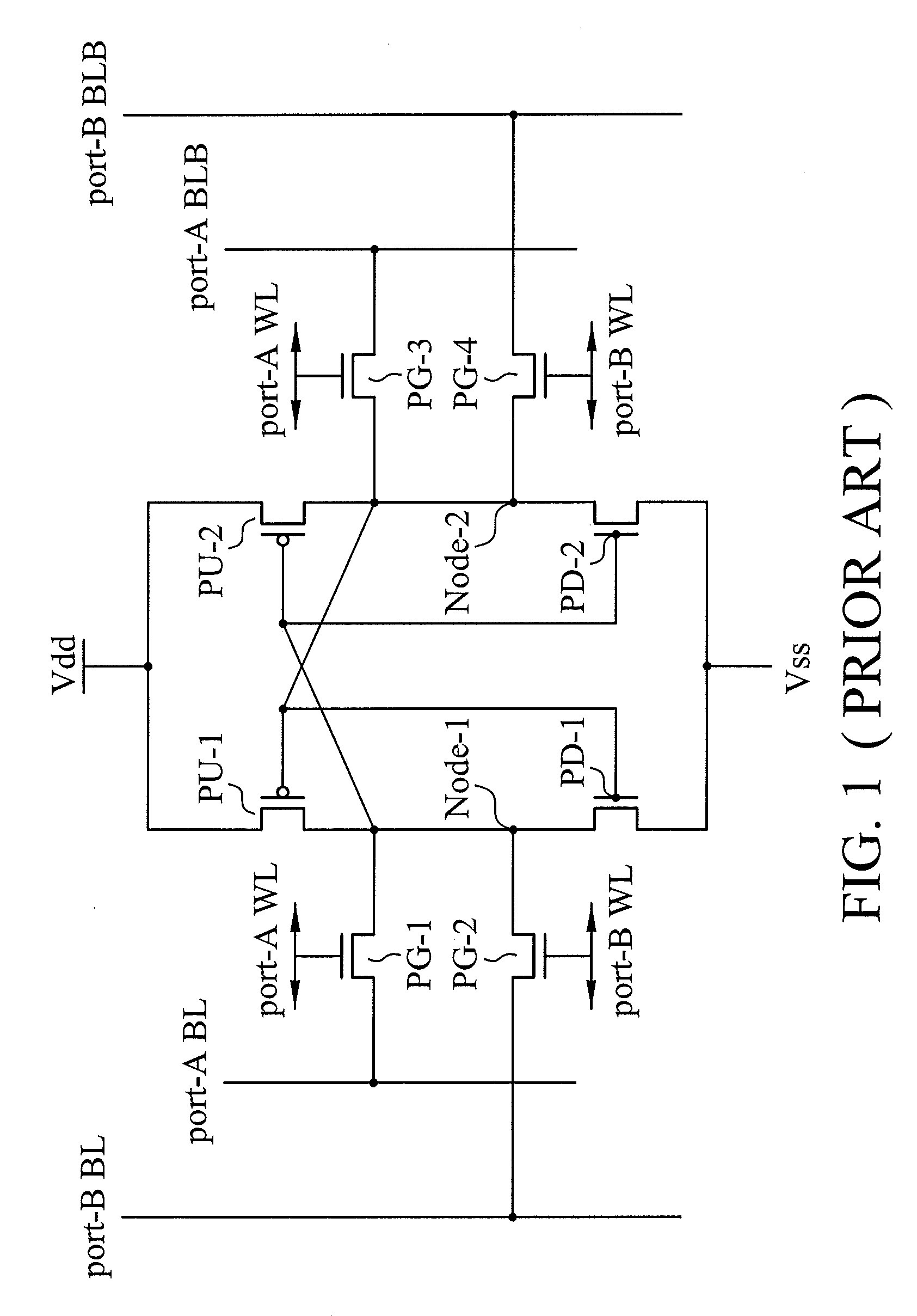

Cell structure for dual port SRAM

A multi-port SRAM cell includes cross-coupled inverters each including a pull-up transistor and at least a pair of pull down transistors. The SRAM cell includes first and second access ports coupled to first and second word line conductors, each access port including a first pass gate transistor coupled to the data storage node and a second pass gate transistor coupled to the data bar storage node, each pass gate transistor being coupled to a respective bit line conductor, wherein the pull down transistors of the first inverter are formed in a first active region, the pull down transistors of the second inverter are formed in a second active region, the pass gate transistors coupled to the data storage node are formed in a third active region and the pass gate transistors coupled to the data bar storage node are formed in a fourth active region.

Owner:TAIWAN SEMICON MFG CO LTD

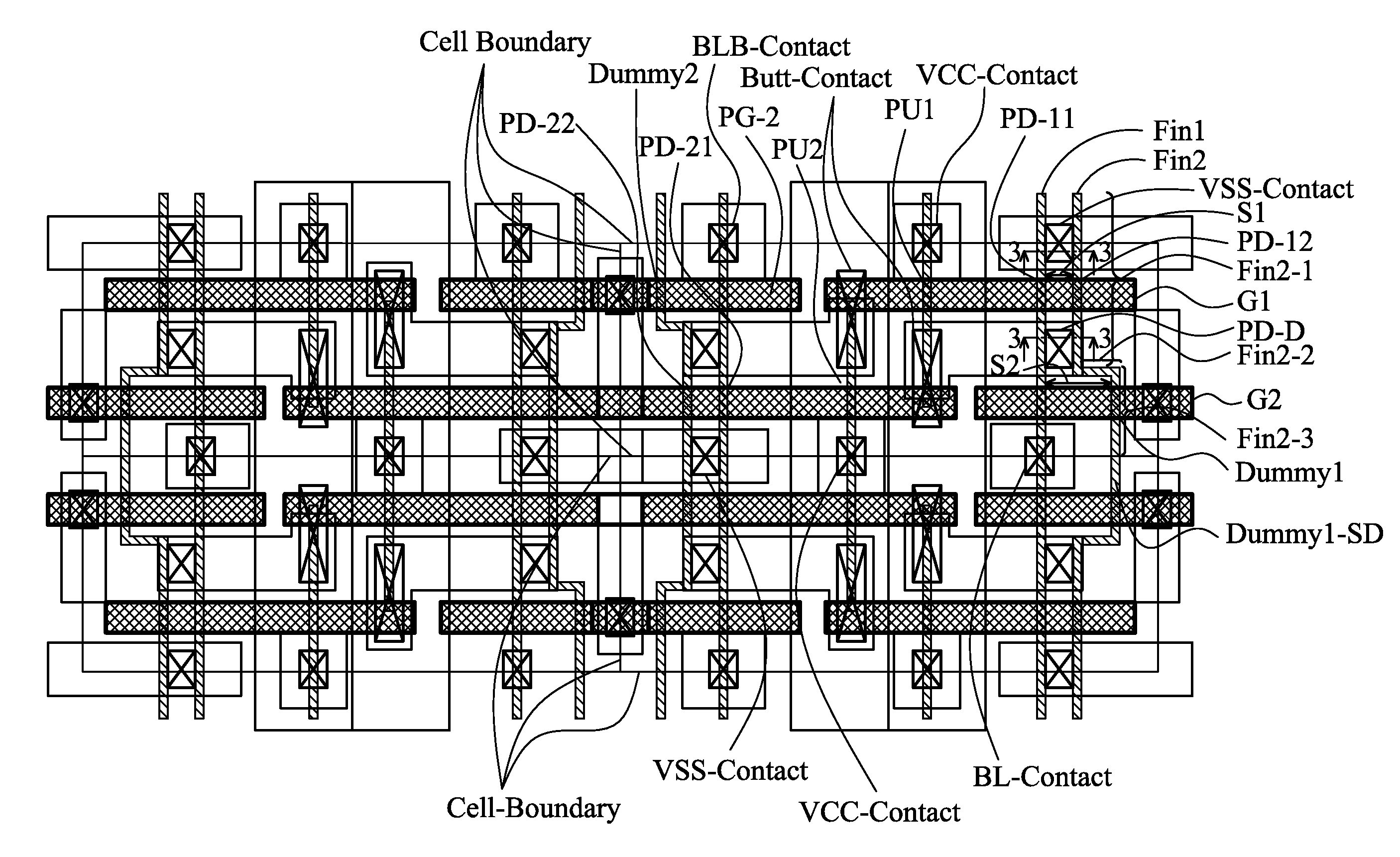

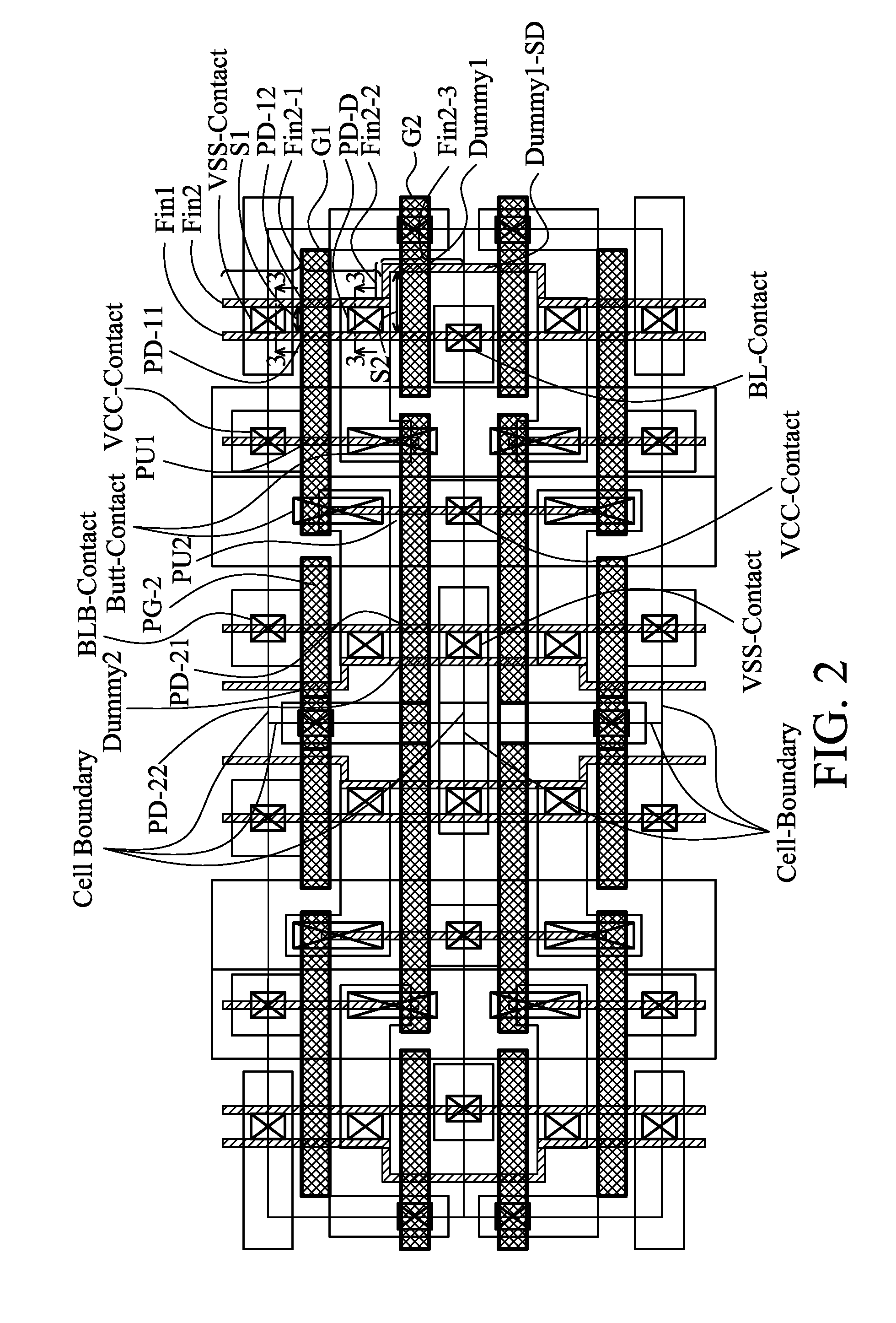

Cell Layout for SRAM FinFET Transistors

An SRAM array and method of making is disclosed. Each SRAM cell comprises two pull-up (PU), two pass-gate (PG), and two pull-down (PD) FinFETs. The PU transistors are adjacent to each other and include one active fin having a first fin width. Each PG transistor shares at least one active fin with a PD transistor. The active fin shared by a PG and a PD transistor has a second fin width smaller than the first fin width. The method includes patterning a plurality of fins including active fins and dummy fins and patterning and removing at least a portion of the dummy fins. No dummy fin is disposed between PU FinFETs in a memory cell. One dummy fin is disposed between a PU FinFET and the at least one active fin shared by a PG and a PD transistor. At least one dummy fin is disposed between adjacent memory cells.

Owner:TAIWAN SEMICON MFG CO LTD