Patents

Literature

232 results about "Common drain" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In electronics, a common-drain amplifier, also known as a source follower, is one of three basic single-stage field effect transistor (FET) amplifier topologies, typically used as a voltage buffer. In this circuit (NMOS) the gate terminal of the transistor serves as the input, the source is the output, and the drain is common to both (input and output), hence its name. The analogous bipolar junction transistor circuit is the common-collector amplifier. This circuit is also commonly called a "stabilizer."

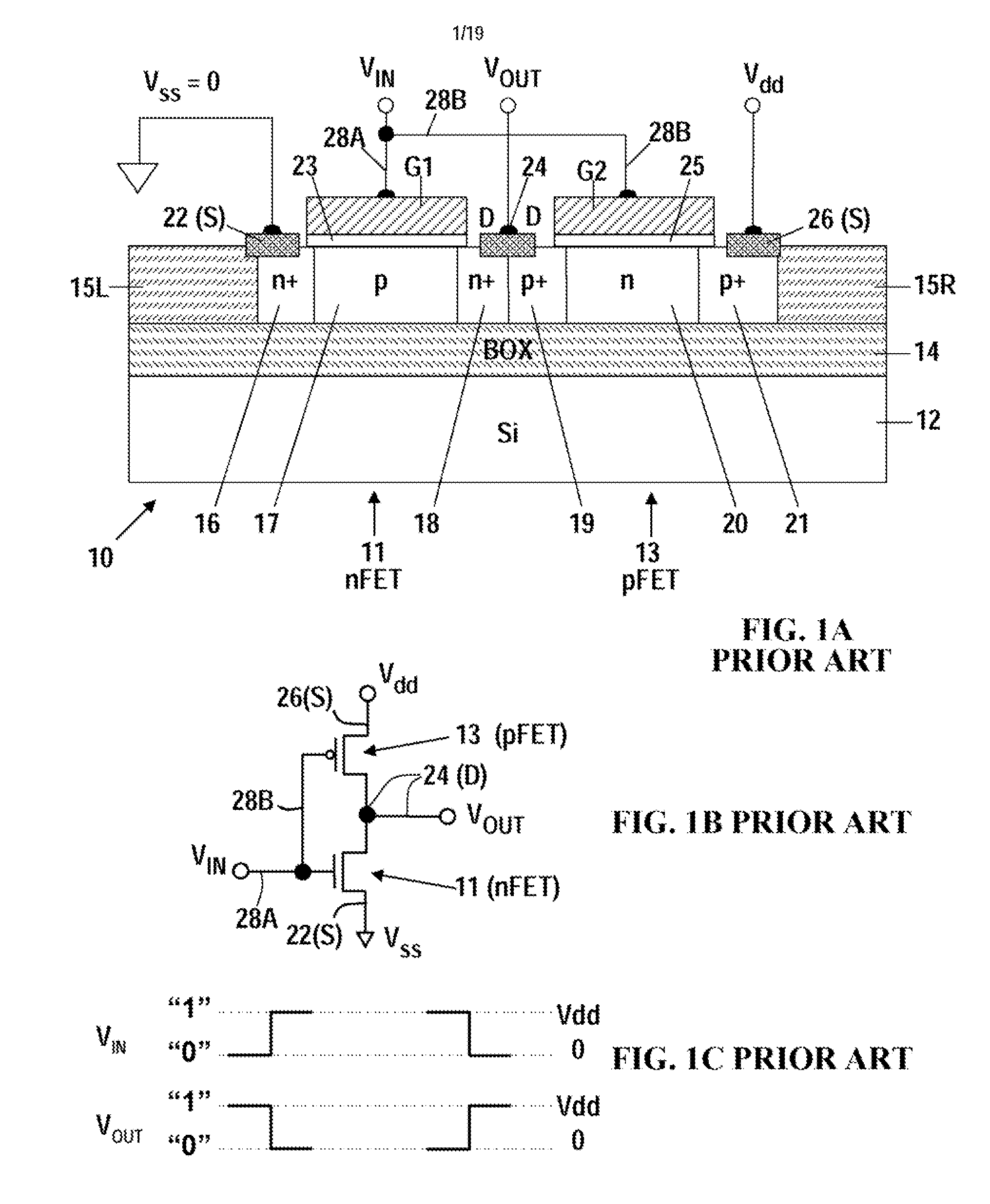

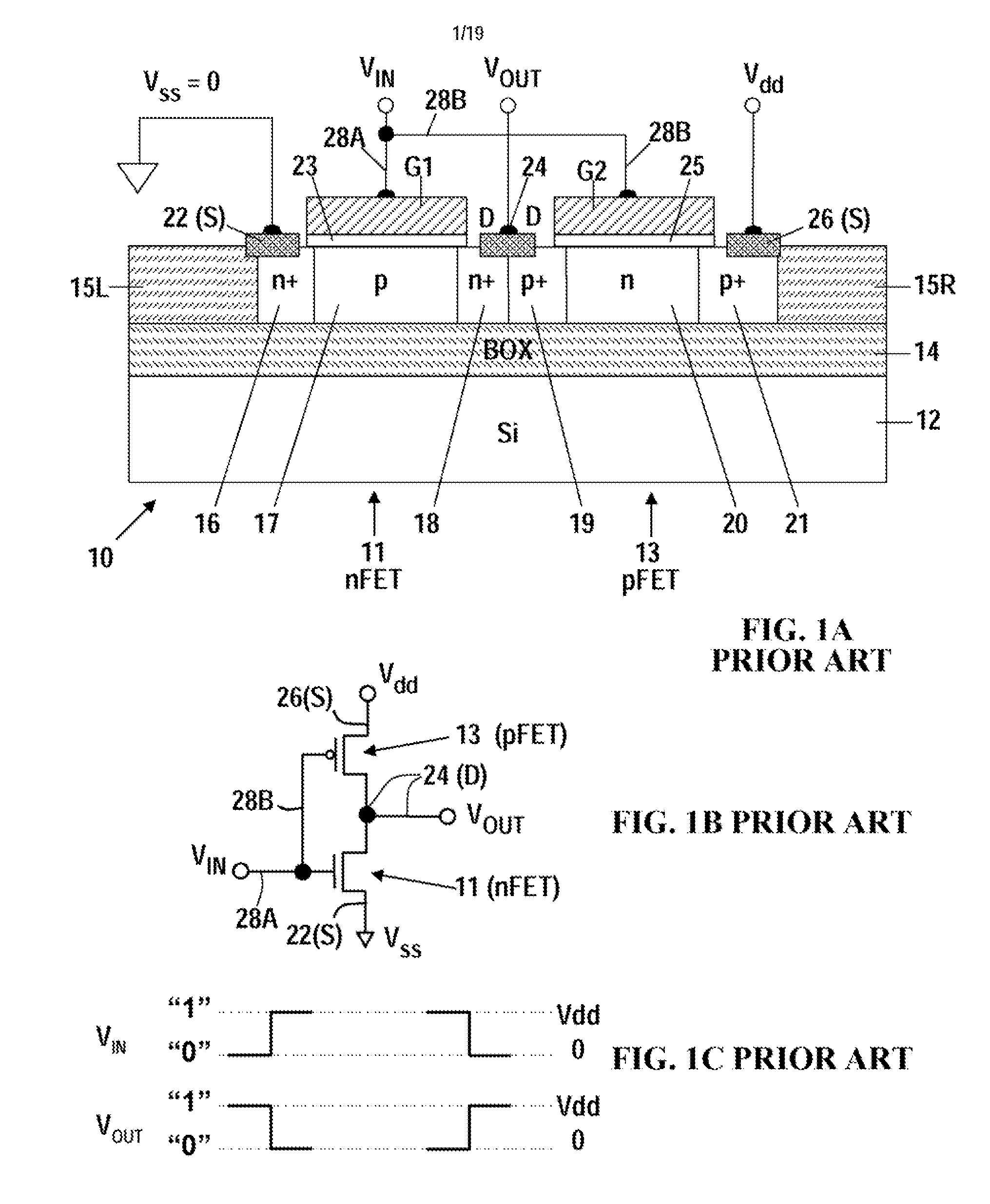

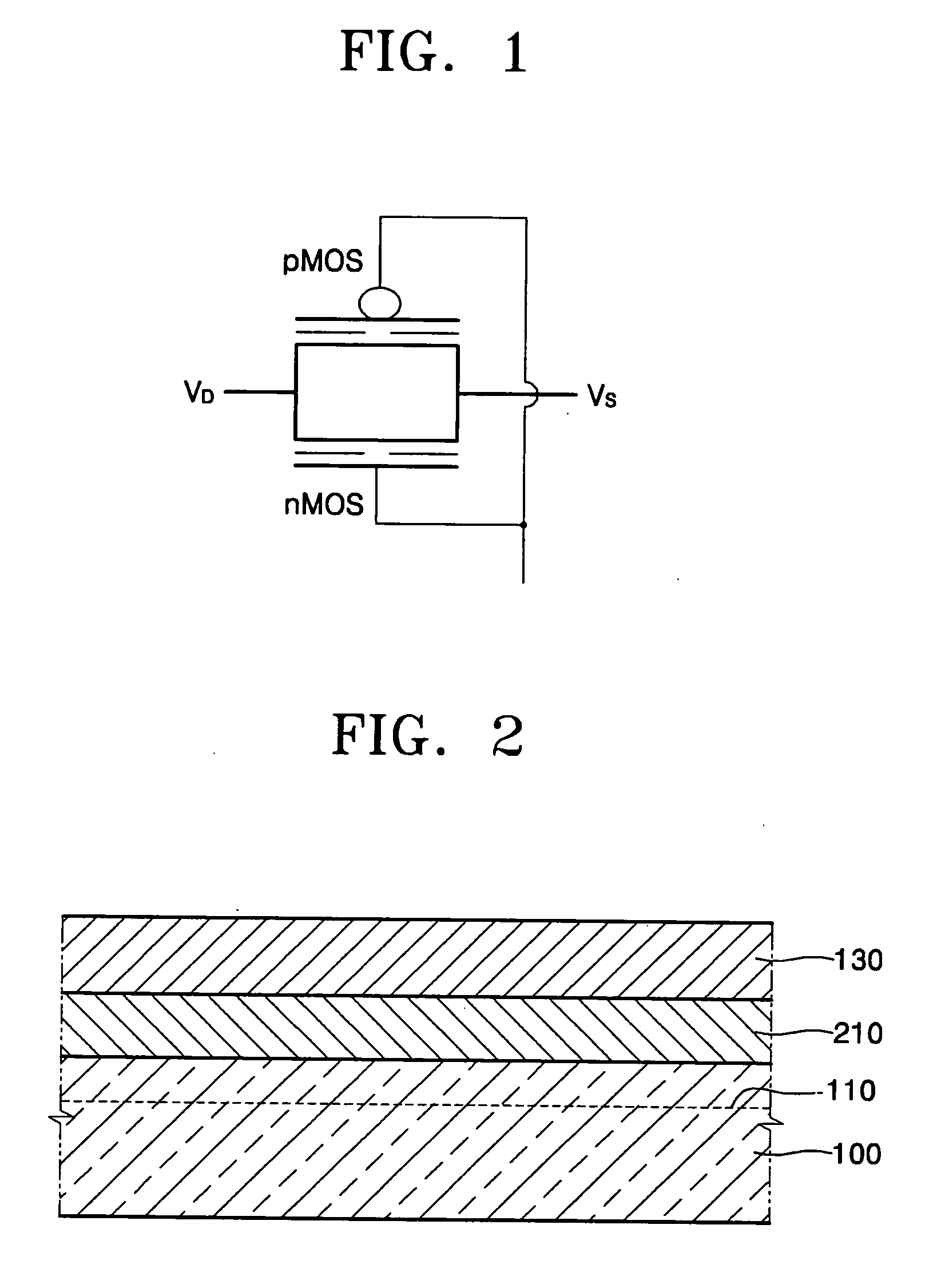

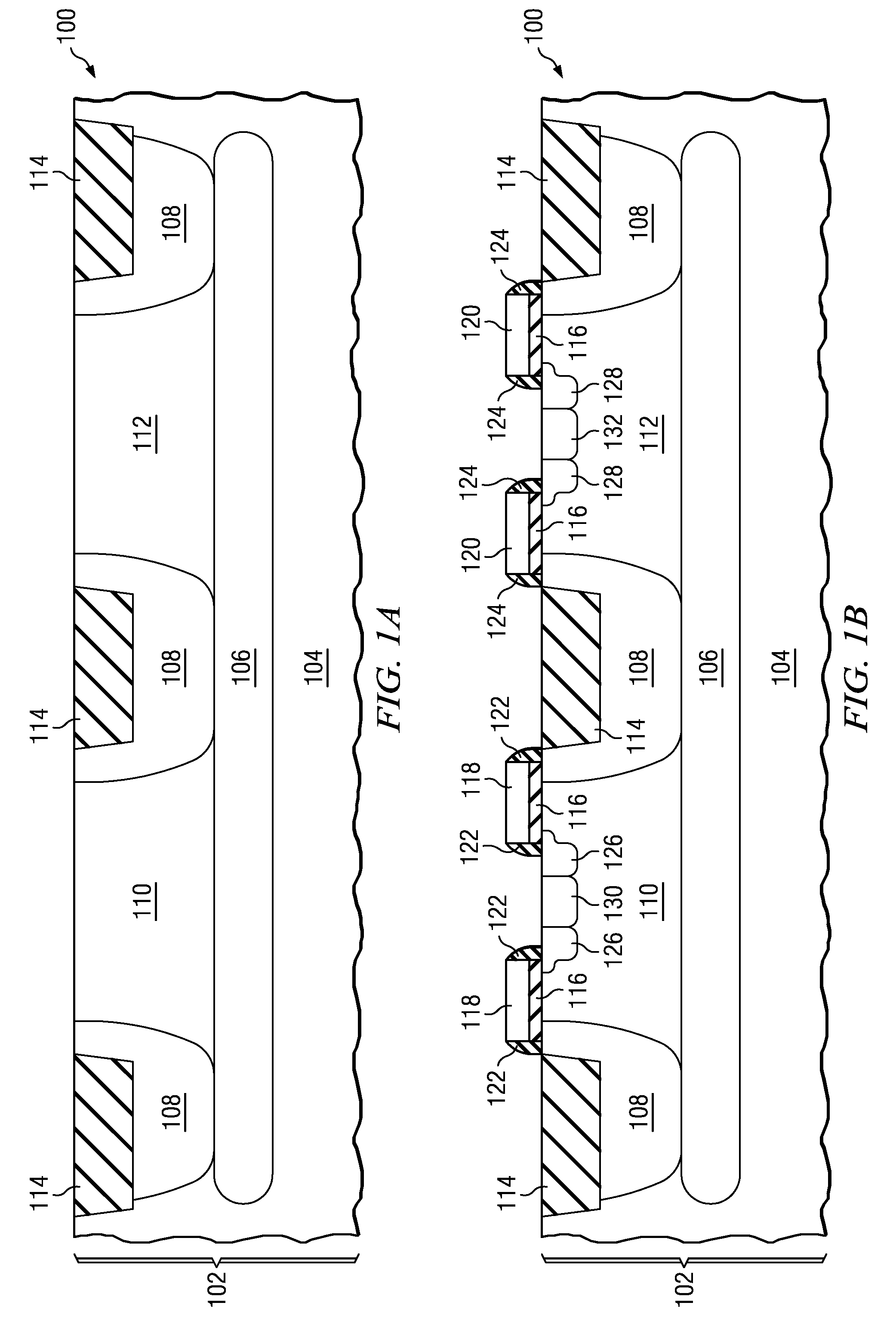

CMOS eprom and eeprom devices and programmable CMOS inverters

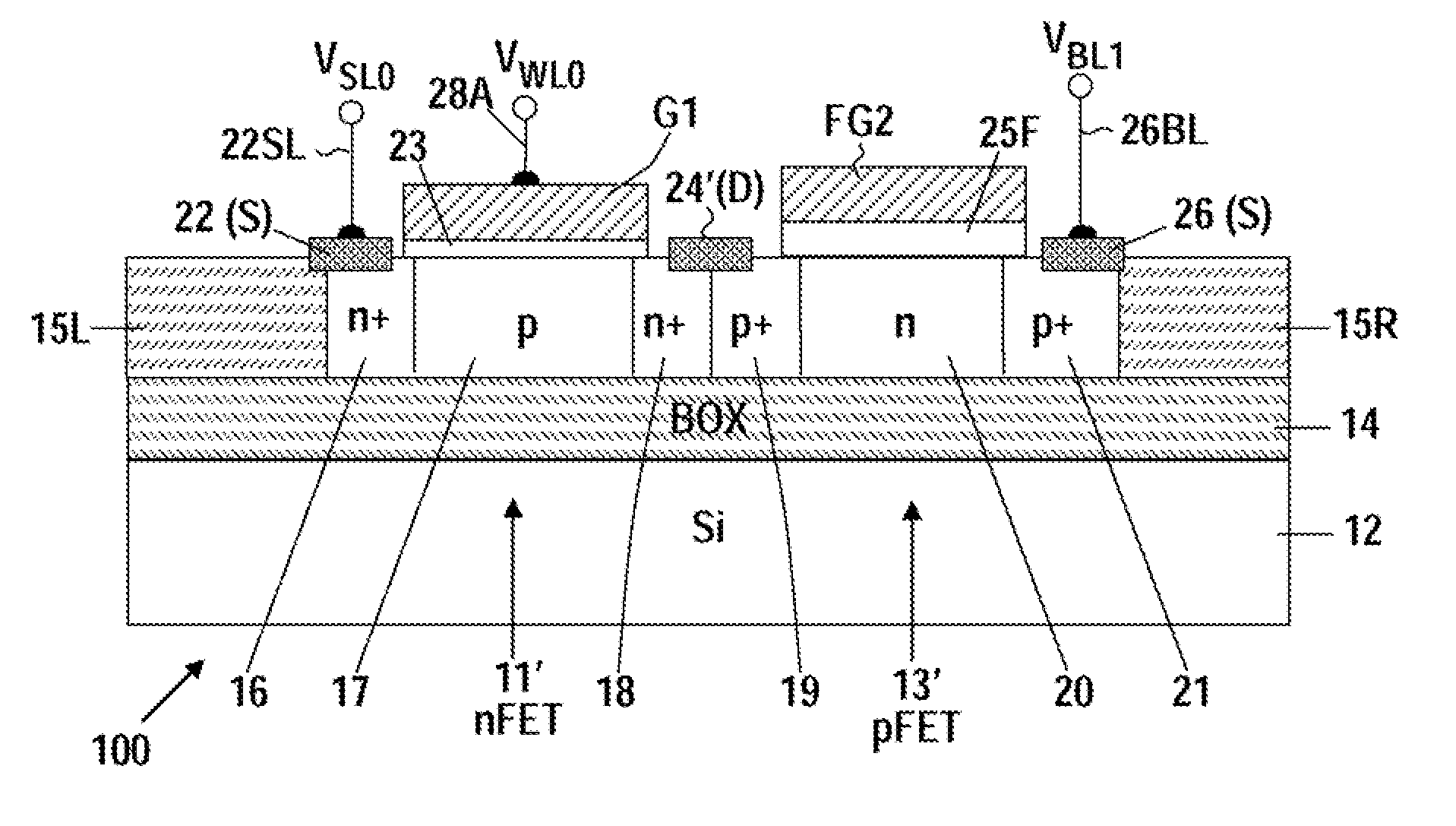

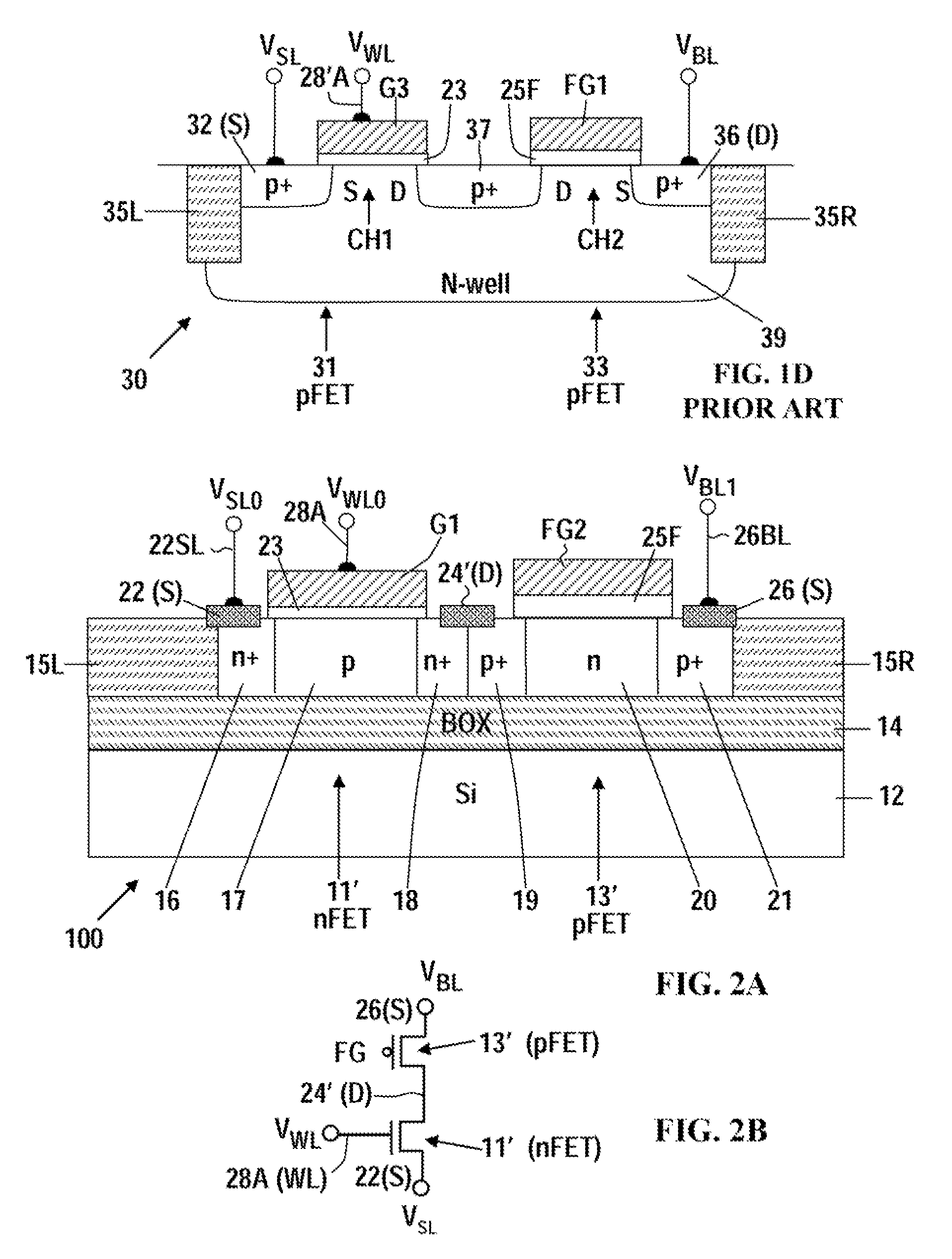

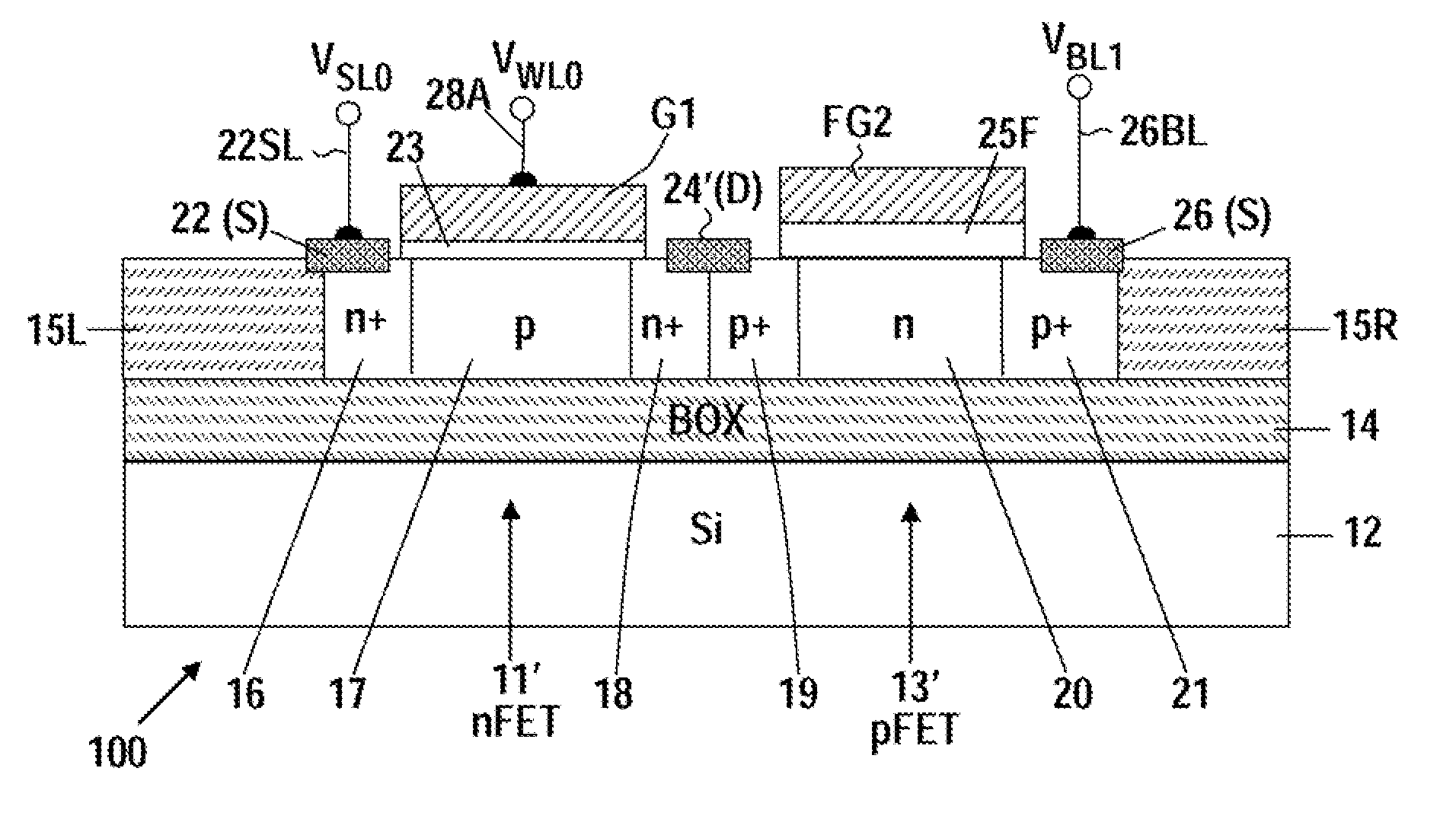

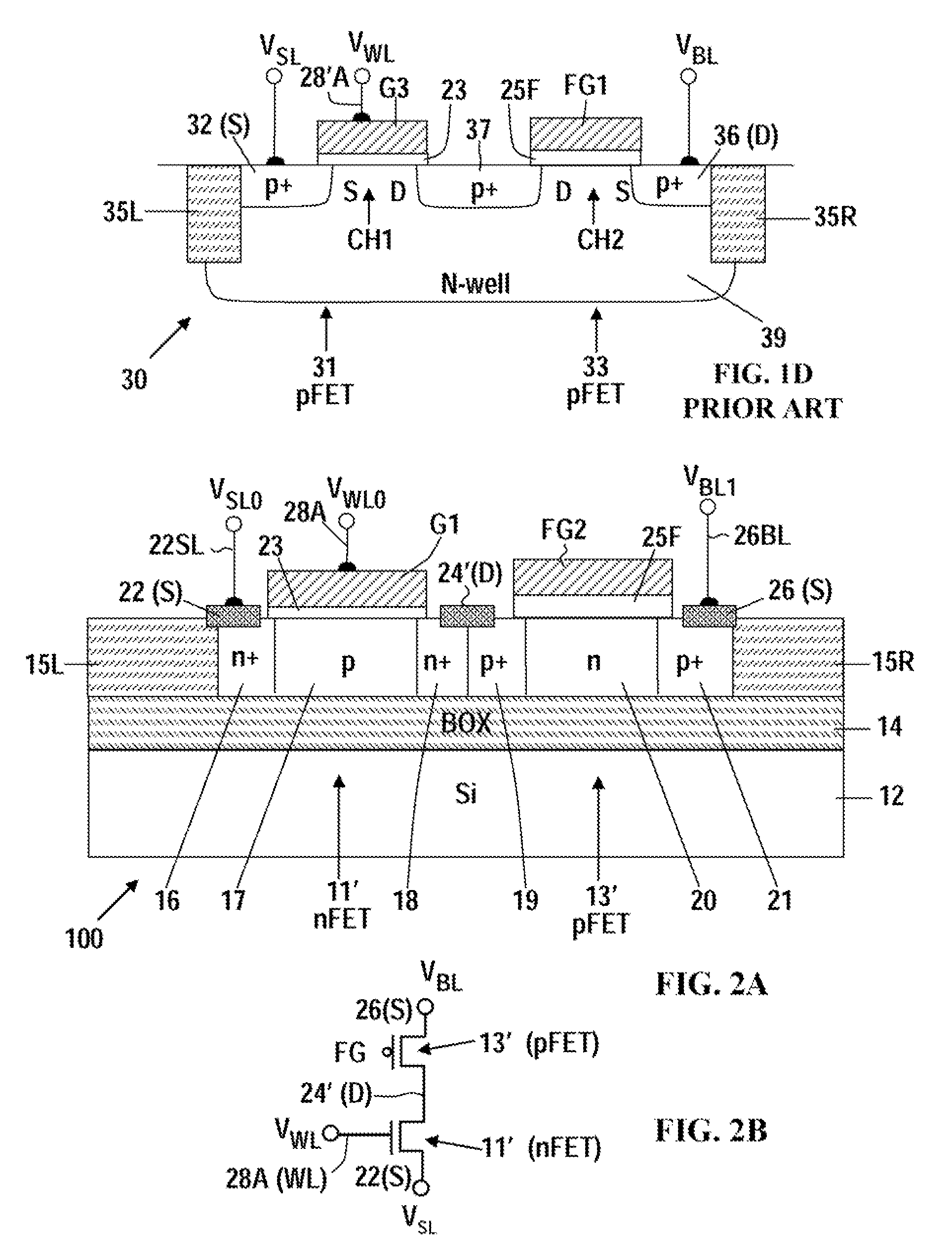

A CMOS EPROM, EEPROM or inverter device includes an nFET device with a thin gate dielectric layer and a pFET device juxtaposed with the nFET device with a thick gate dielectric layer and a floating gate electrode. The thick gate dielectric layer is substantially thicker than the thin gate dielectric layer. A common drain node connected both FET devices has no external connection in the case of a memory device and has an external connection in the case of an inverter. There are external circuit connections to the source regions of both FET devices and to the gate electrode of the nFET device. The pFET and nFET devices can be planar, vertical or FinFET devices.

Owner:MARVELL ASIA PTE LTD

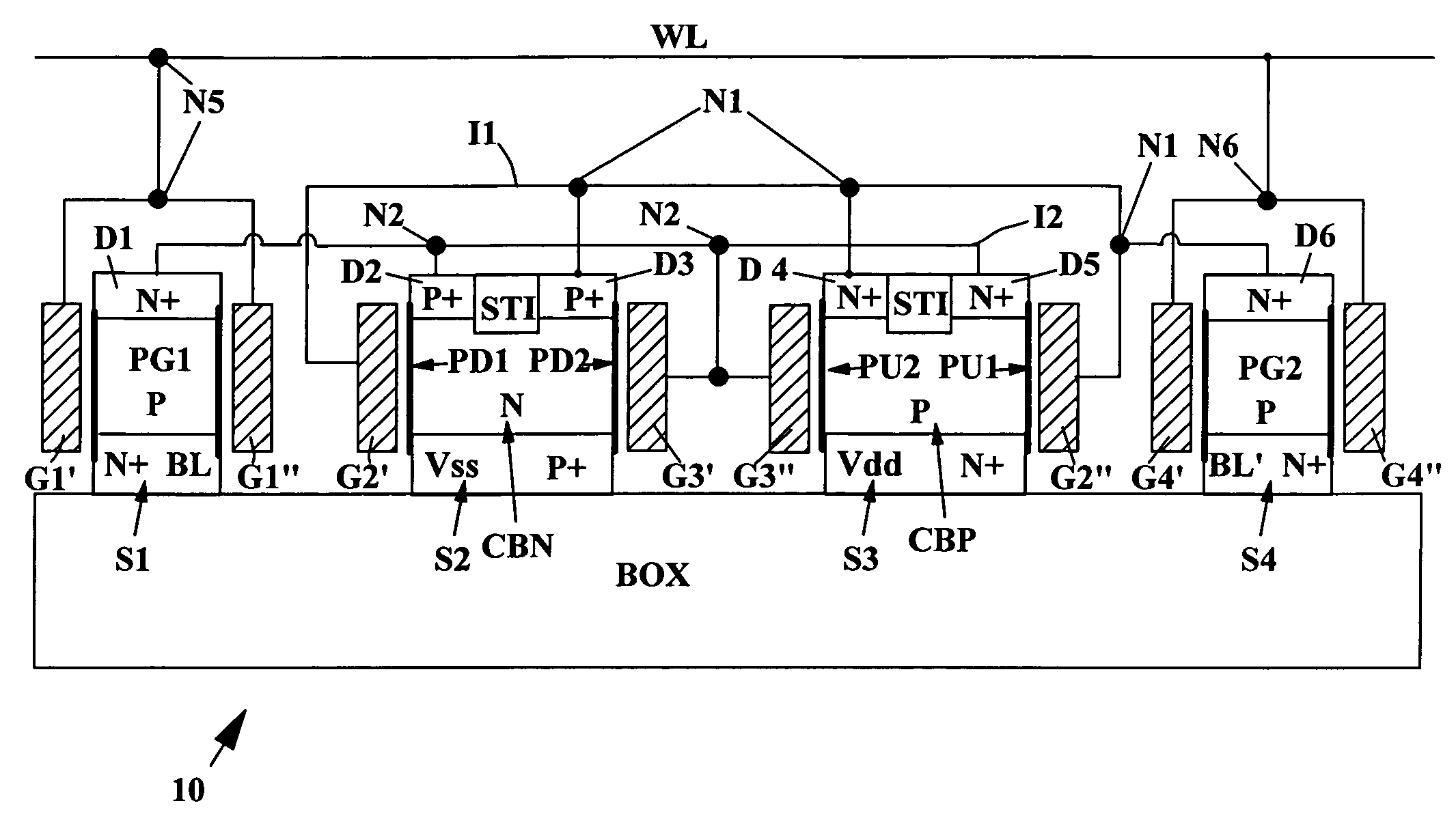

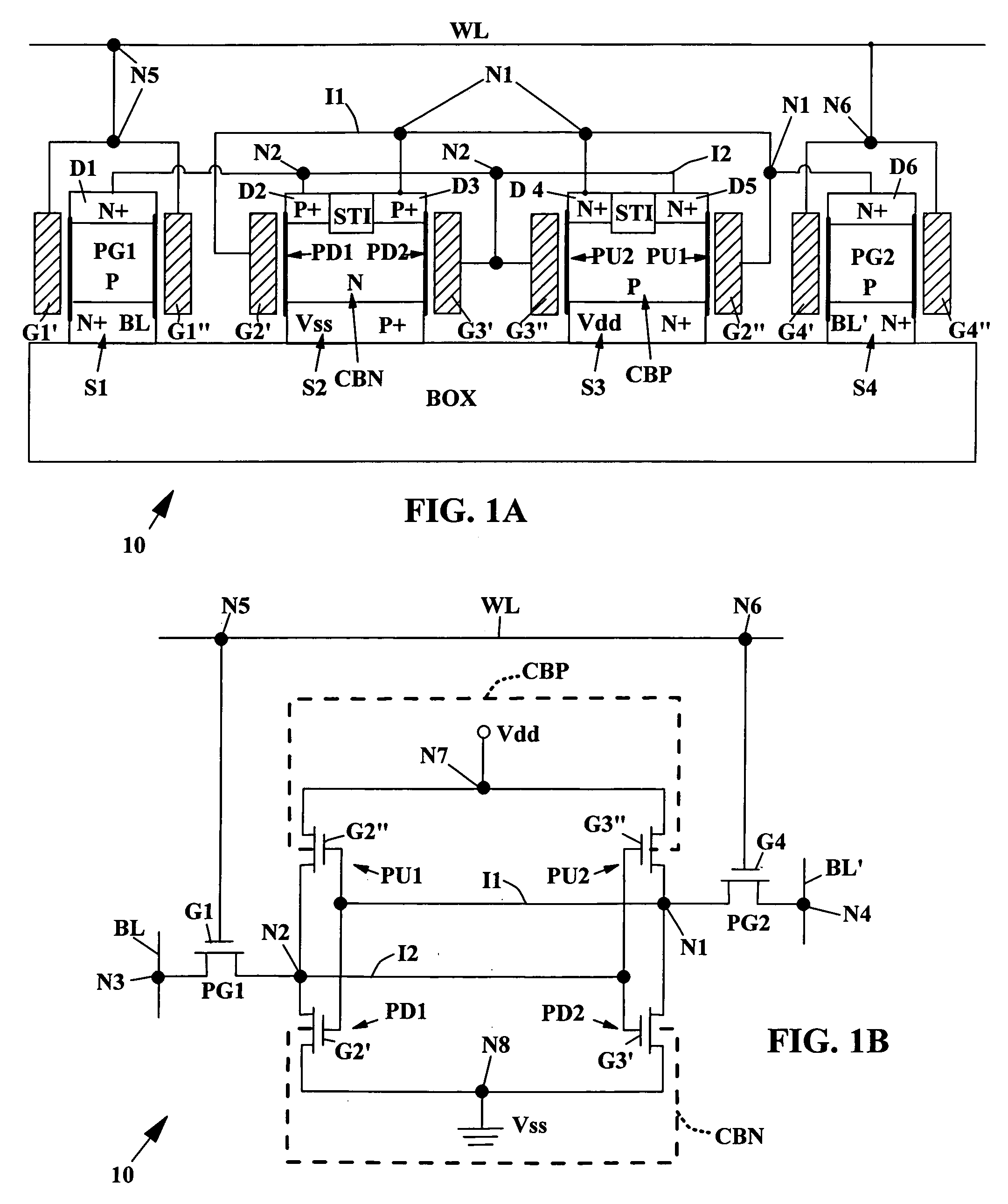

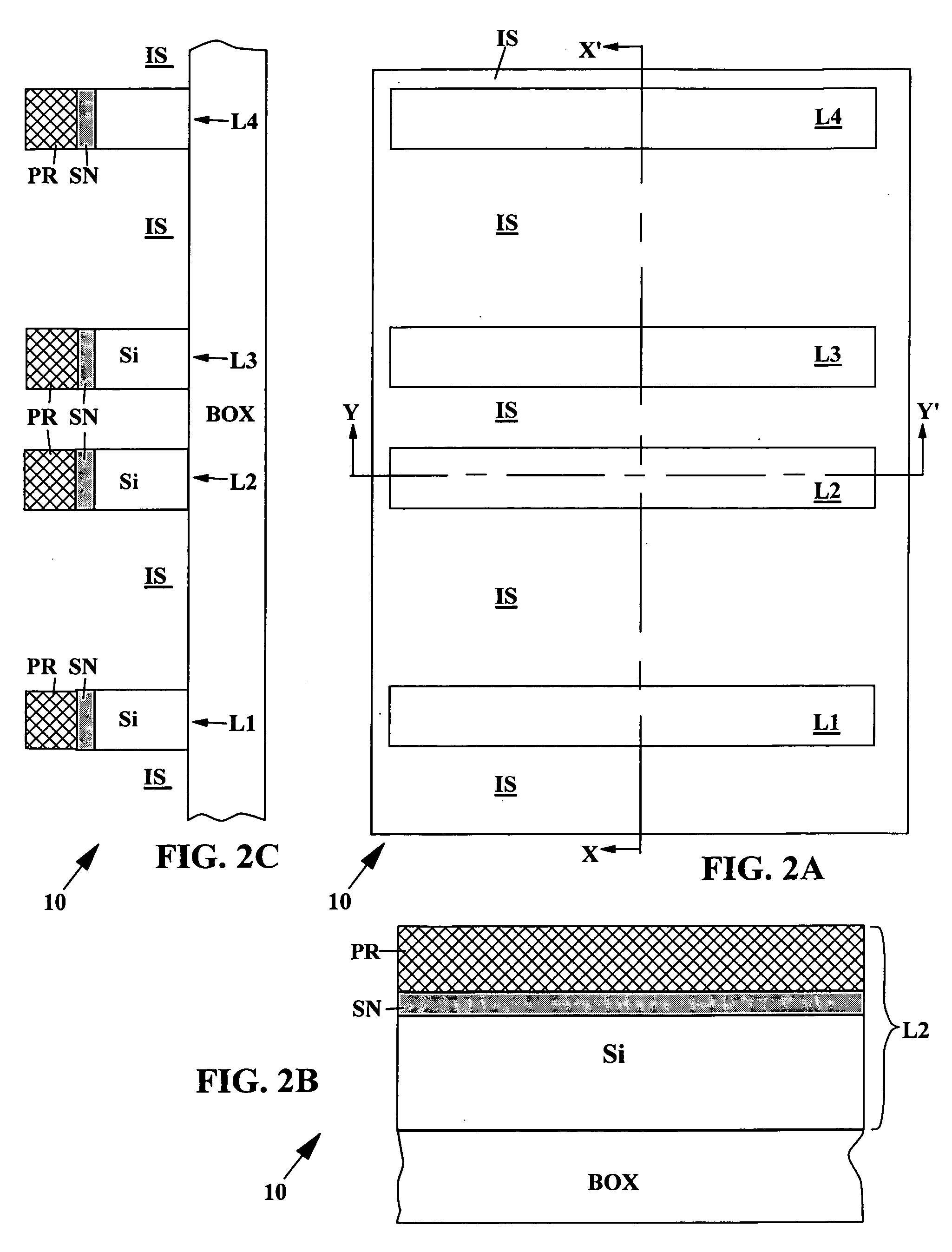

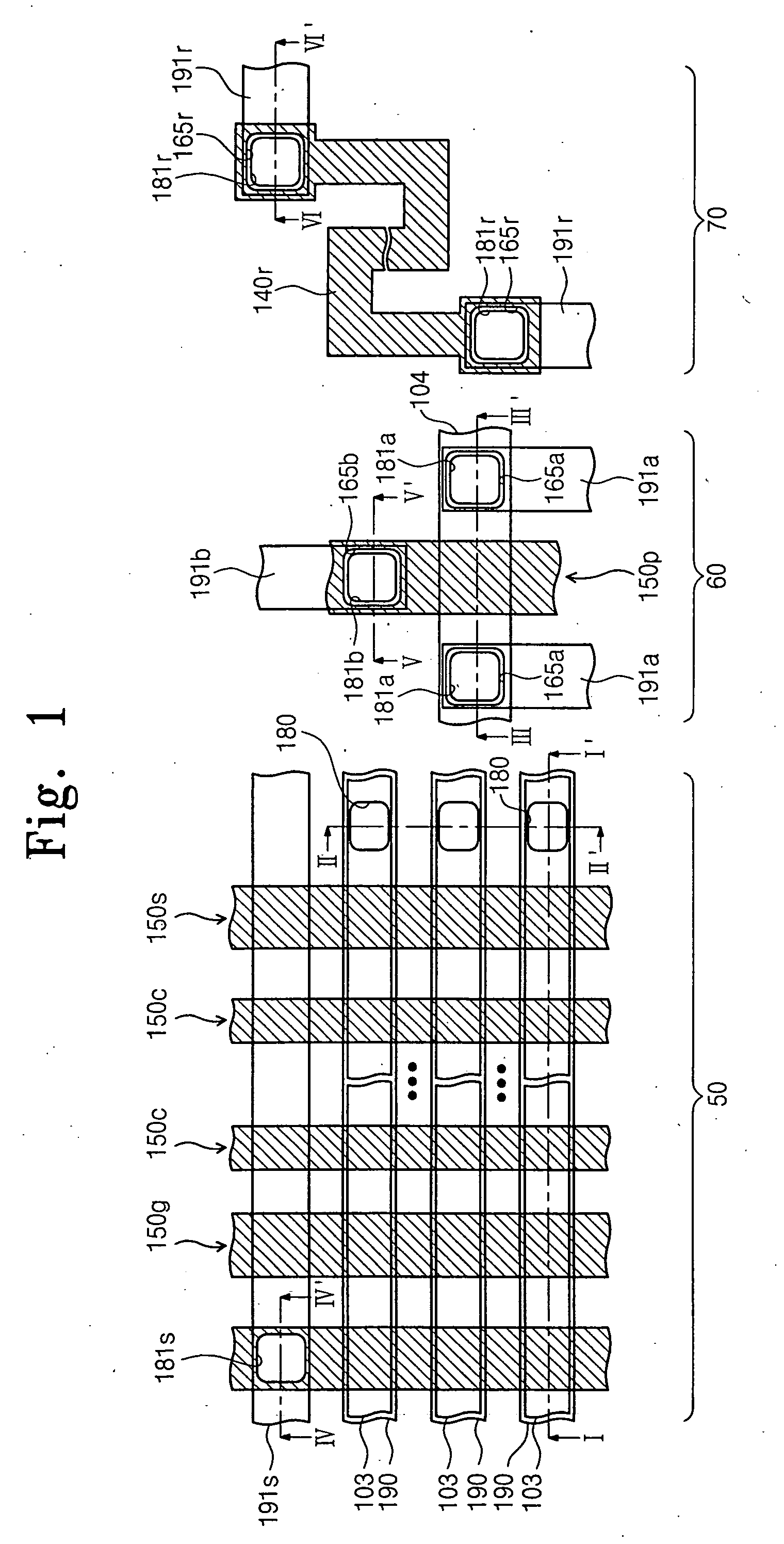

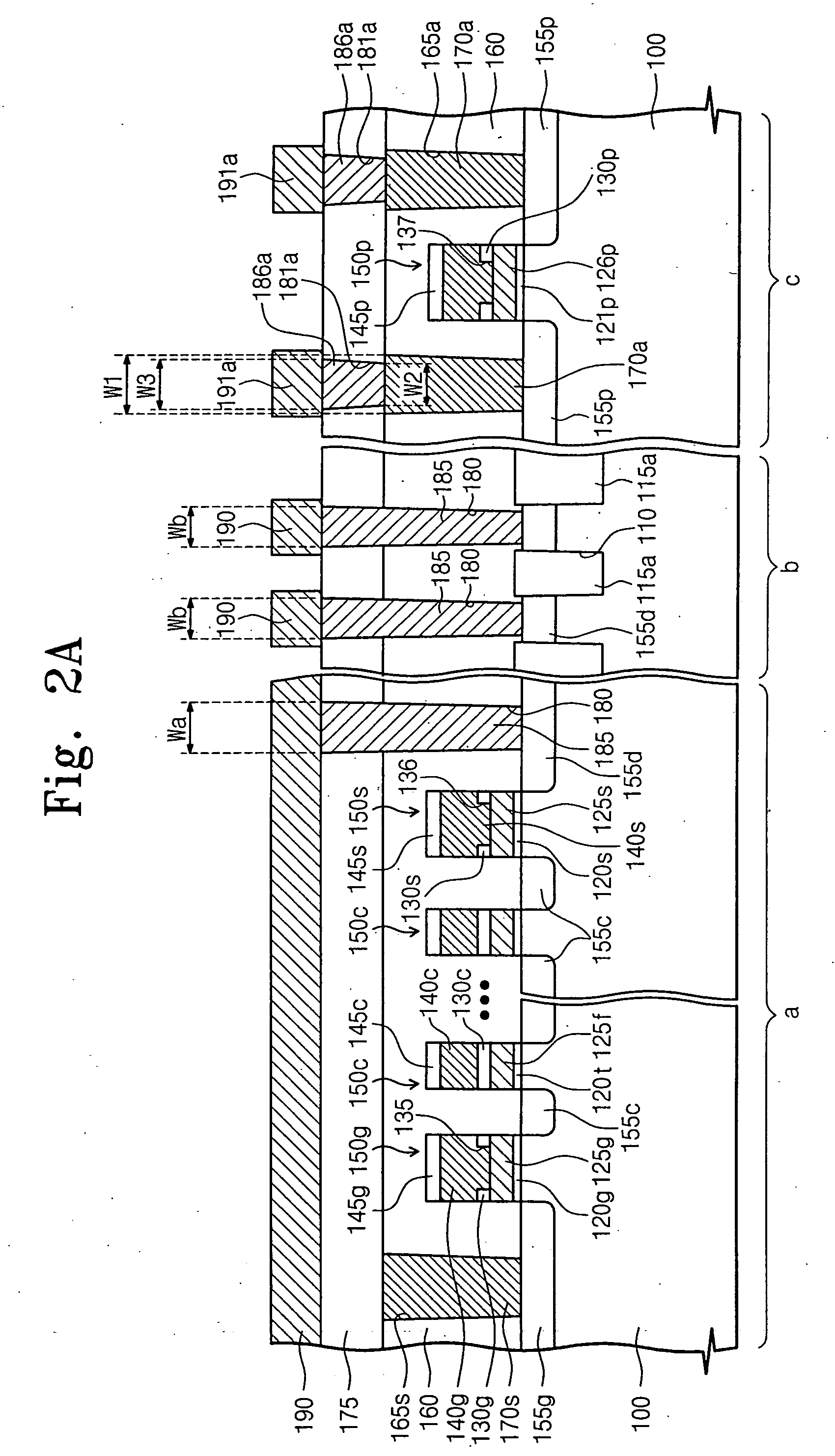

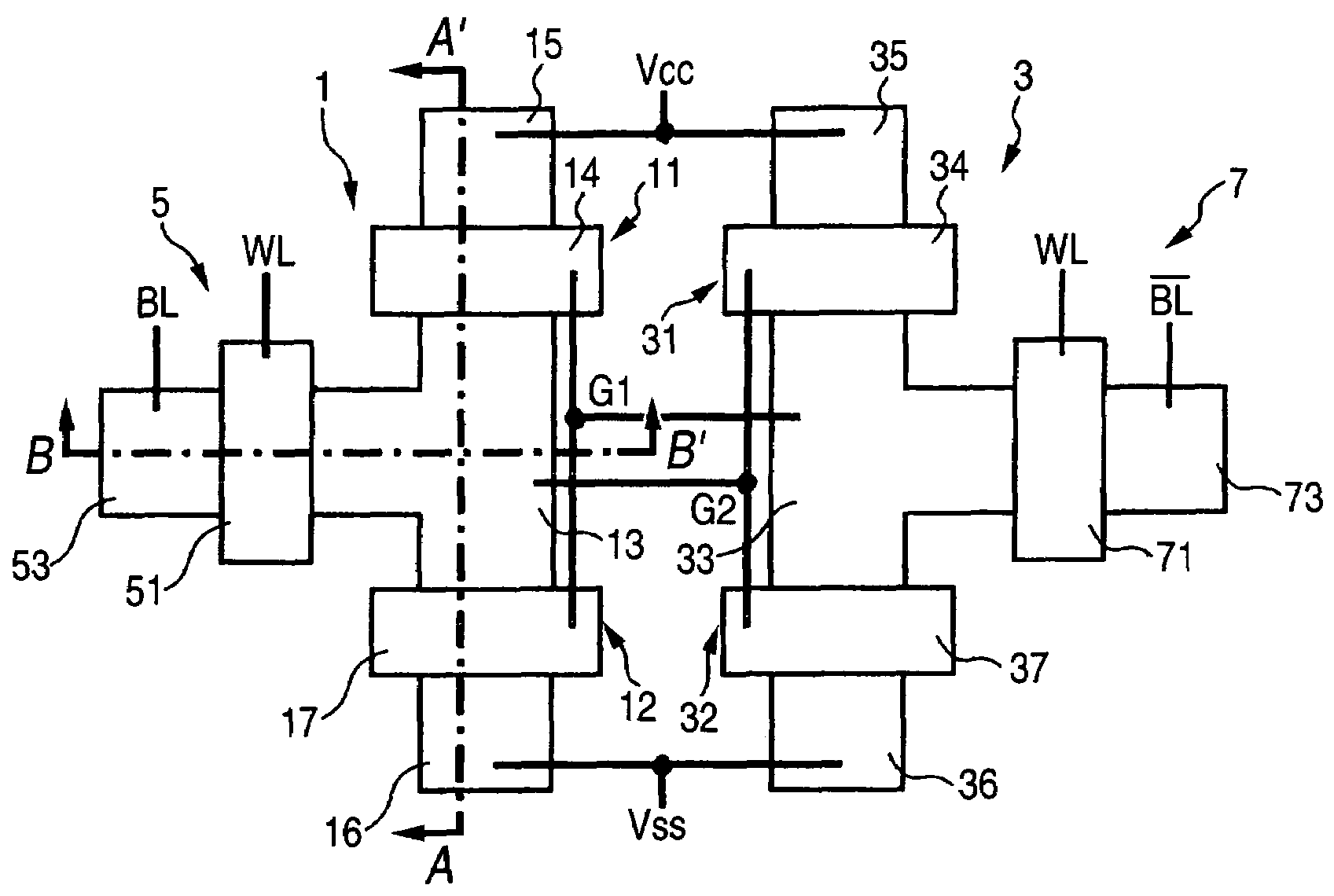

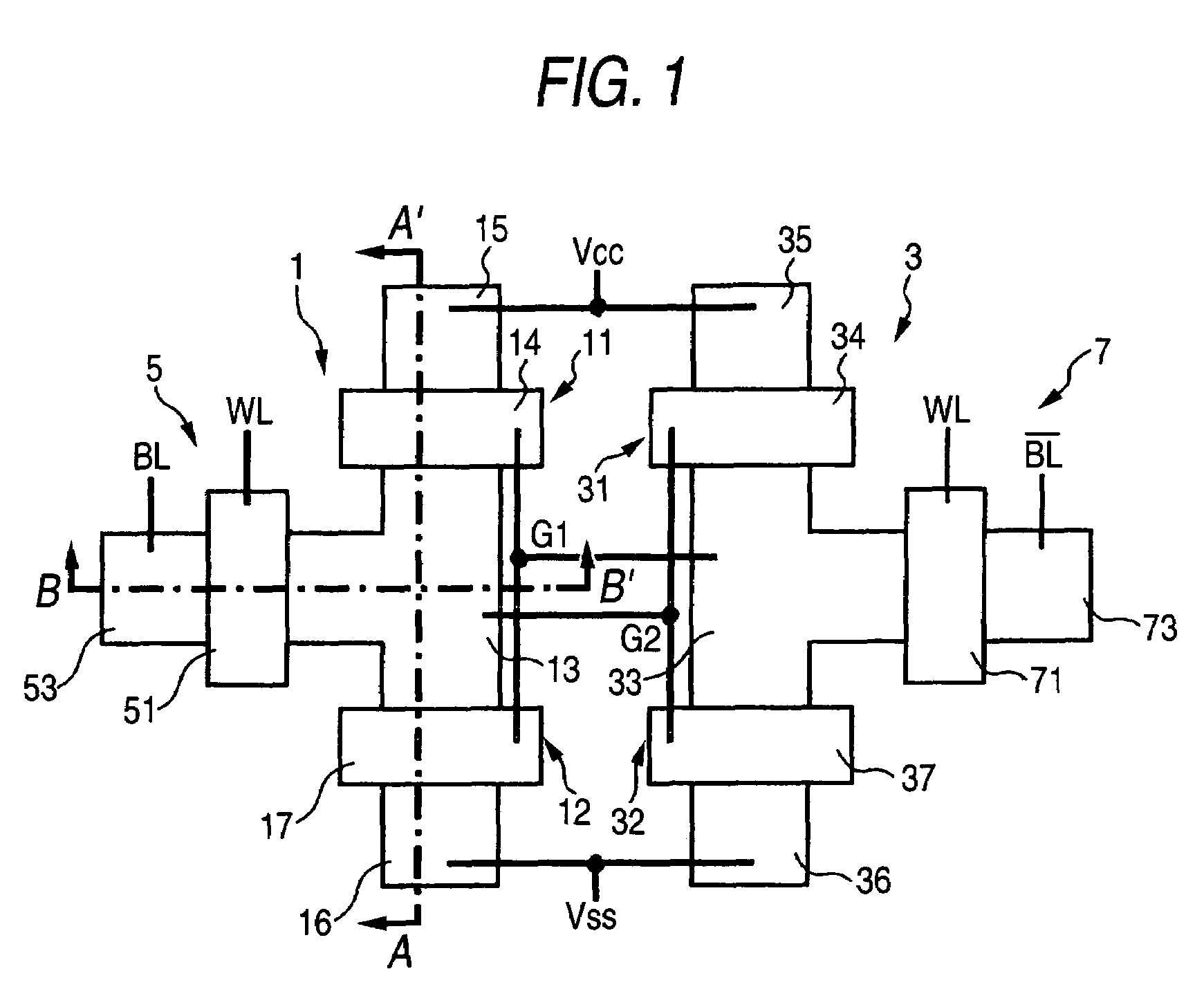

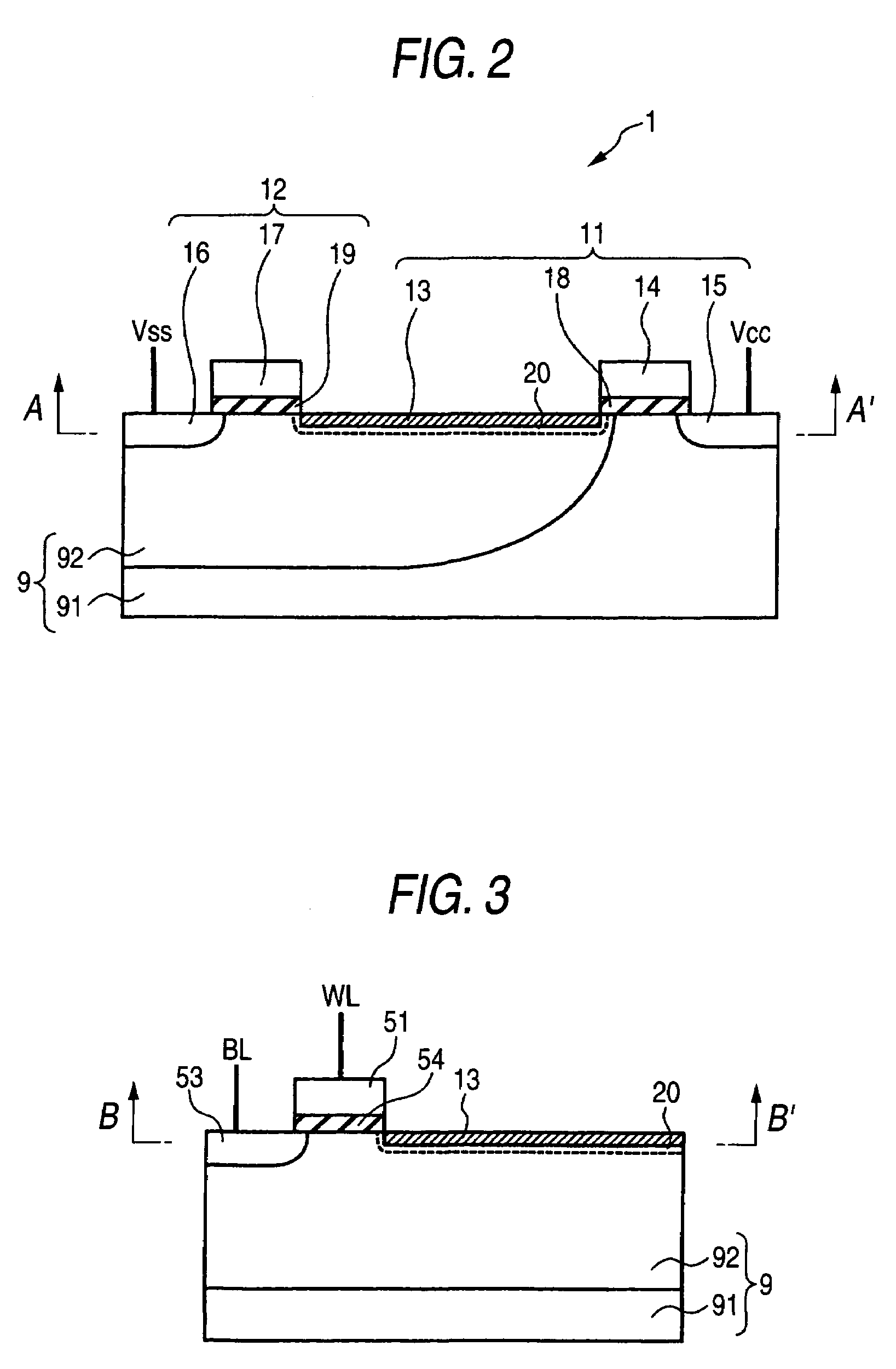

Vertical MOSFET SRAM cell

InactiveUS20070007601A1Improve transconductanceMore drivabilityTransistorSolid-state devicesMOSFETEngineering

A method of forming an SRAM cell device includes the following steps. Form pass gate FET transistors and form a pair of vertical pull-down FET transistors with a first common body and a first common source in a silicon layer patterned into parallel islands formed on a planar insulator. Etch down through upper diffusions between cross-coupled inverter FET transistors to form pull-down isolation spaces bisecting the upper strata of pull-up and pull-down drain regions of the pair of vertical pull-down FET transistors, with the isolation spaces reaching down to the common body strata. Form a pair of vertical pull-up FET transistors with a second common body and a second common drain. Then, connect the FET transistors to form an SRAM cell.

Owner:HSU LOUIS L +3

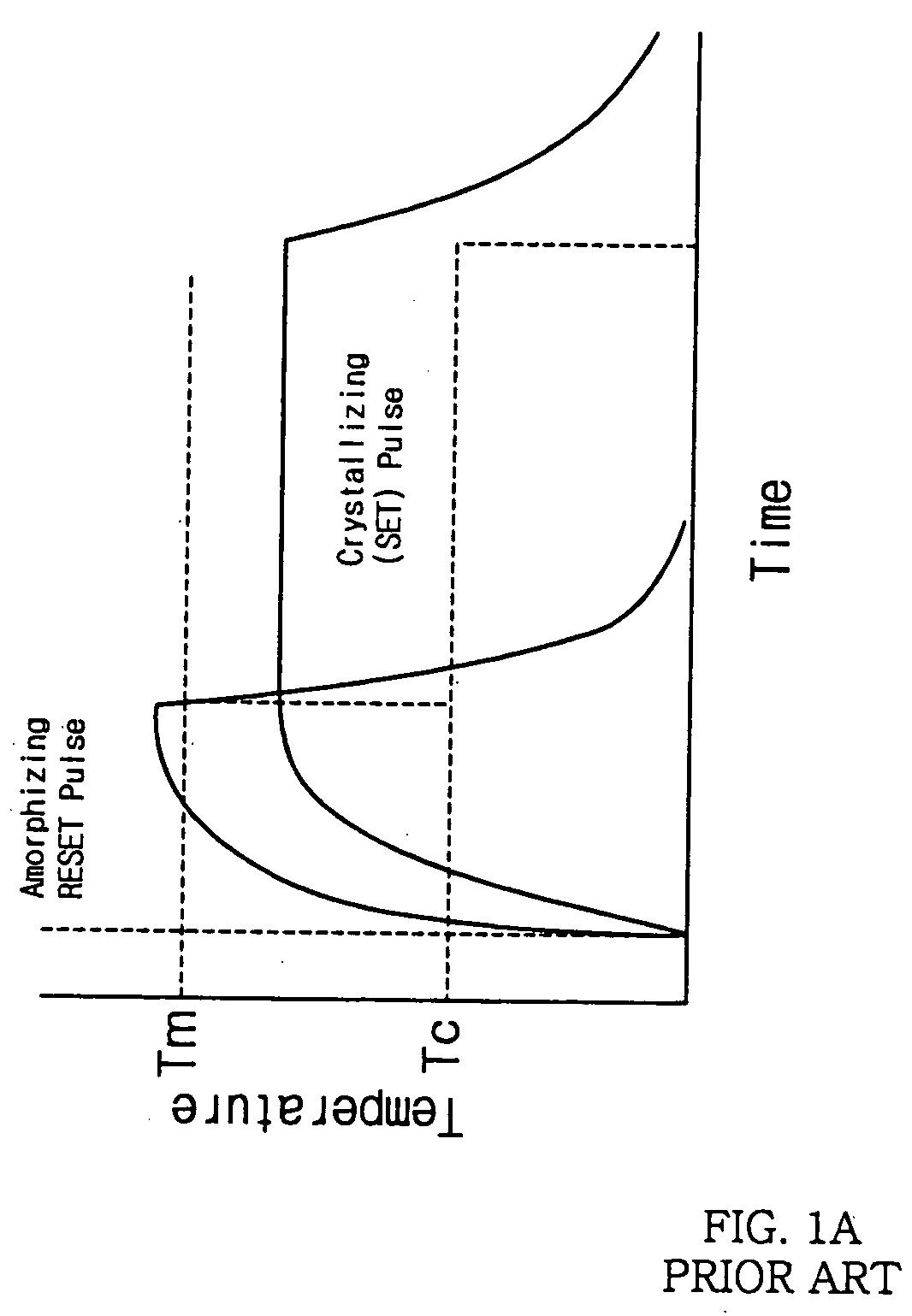

High-density phase change cell array and phase change memory device having the same

InactiveUS20050270832A1Suitable for implementationSolid-state devicesRead-only memoriesContact formationPhase-change memory

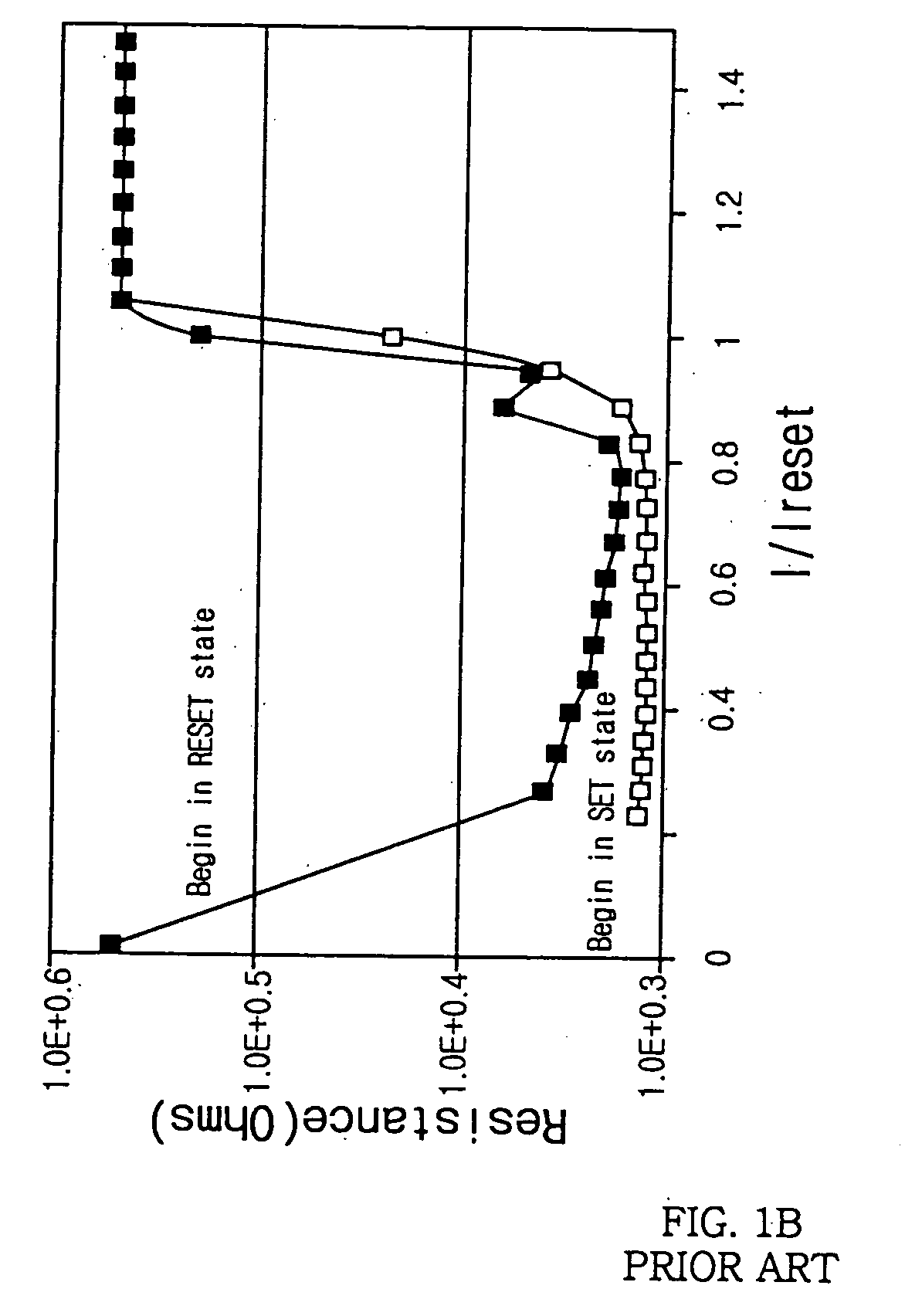

The present invention relates generally to a phase change memory device and, more particularly, to a phase change memory cell array suitable for the implementation of a high-density memory device. The phase change memory cell array includes a first access transistor pair and a second access transistor pair formed on a semiconductor substrate to be adjacent to each other while each of the first and second access transistor pairs having a common drain, phase change resistance elements formed on source regions of the access transistors, respectively, and a semiconductor region formed on the same plane as the common drains to electrically connect the common drains of the first and second transistor pairs. The phase change memory cell array and the memory device of the present invention are suitable for the implementation of a high-density semiconductor device, and capable of improving the reliability of a contact forming process by securing a sufficient space for the contact forming process.

Owner:EROMTECH

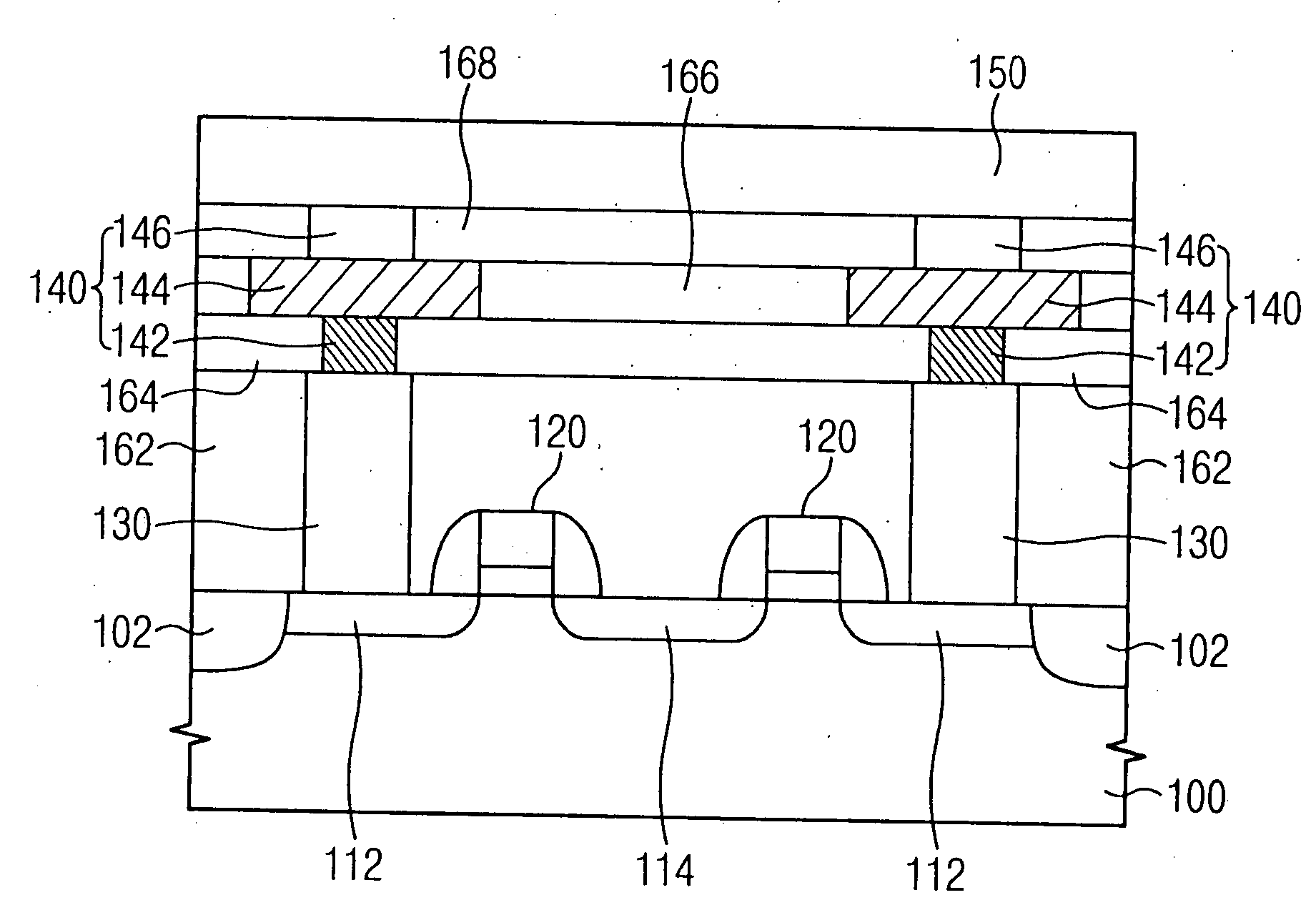

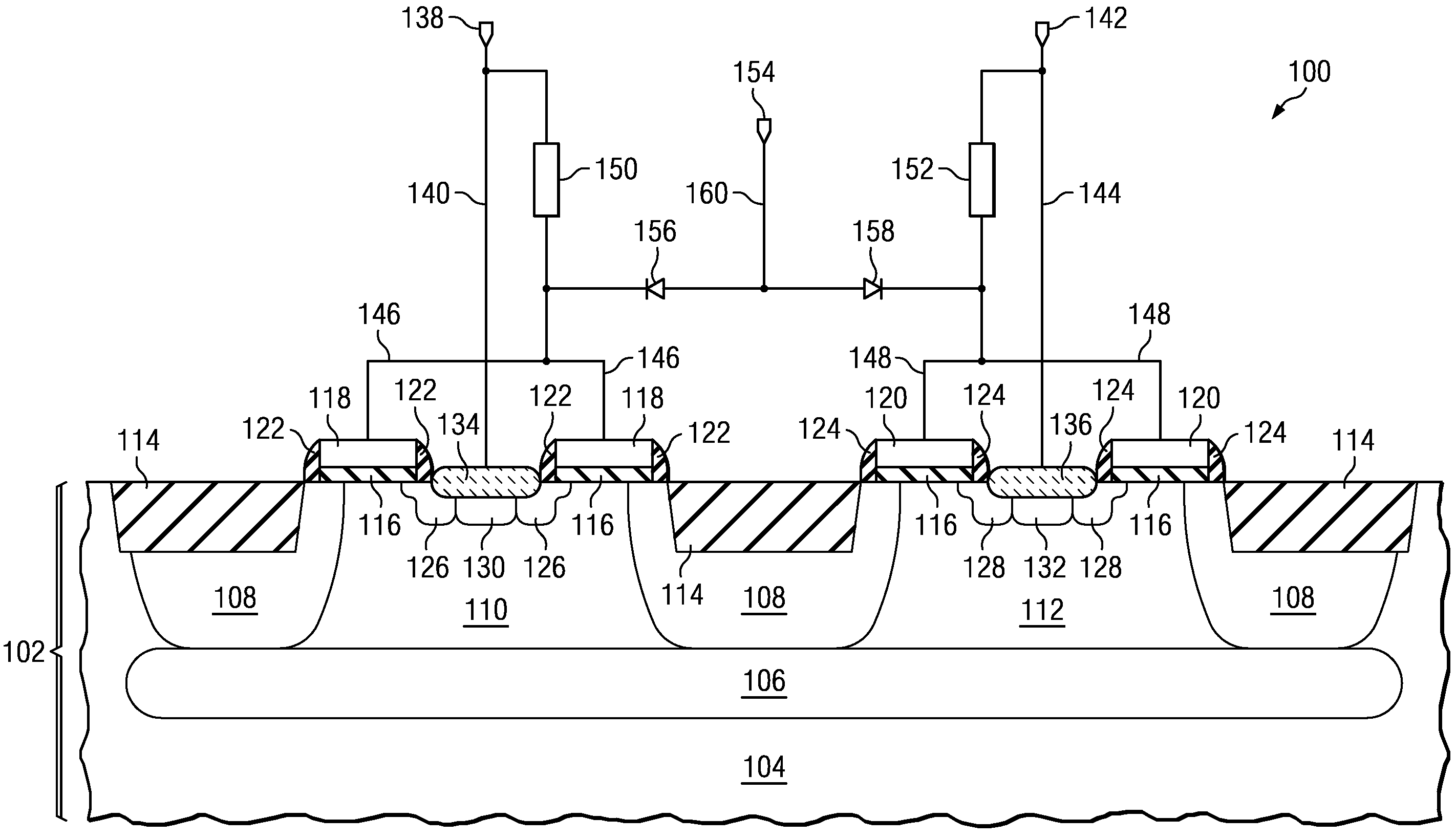

Methods for fabricating a stressed MOS device

InactiveUS20070026599A1Semiconductor/solid-state device manufacturingSemiconductor devicesStress inducedSemiconductor materials

Methods are provided for fabricating a stressed MOS device. The method comprises the steps of forming a plurality of parallel MOS transistors in and on a semiconductor substrate. The parallel MOS transistors having a common source region, a common drain region, and a common gate electrode. A first trench is etched into the substrate in the common source region and a second trench is etched into the substrate in the common drain region. A stress inducing semiconductor material that has a crystal lattice mismatched with the semiconductor substrate is selectively grown in the first and second trenches. The growth of the stress inducing material creates both compressive longitudinal and tensile transverse stresses in the MOS device channel that enhance the drive current of P-channel MOS transistors. The decrease in drive current of N-channel MOS transistors caused by the compressive stress component is offset by the tensile stress component.

Owner:GLOBALFOUNDRIES INC

CMOS EPROM and EEPROM devices and programmable CMOS inverters

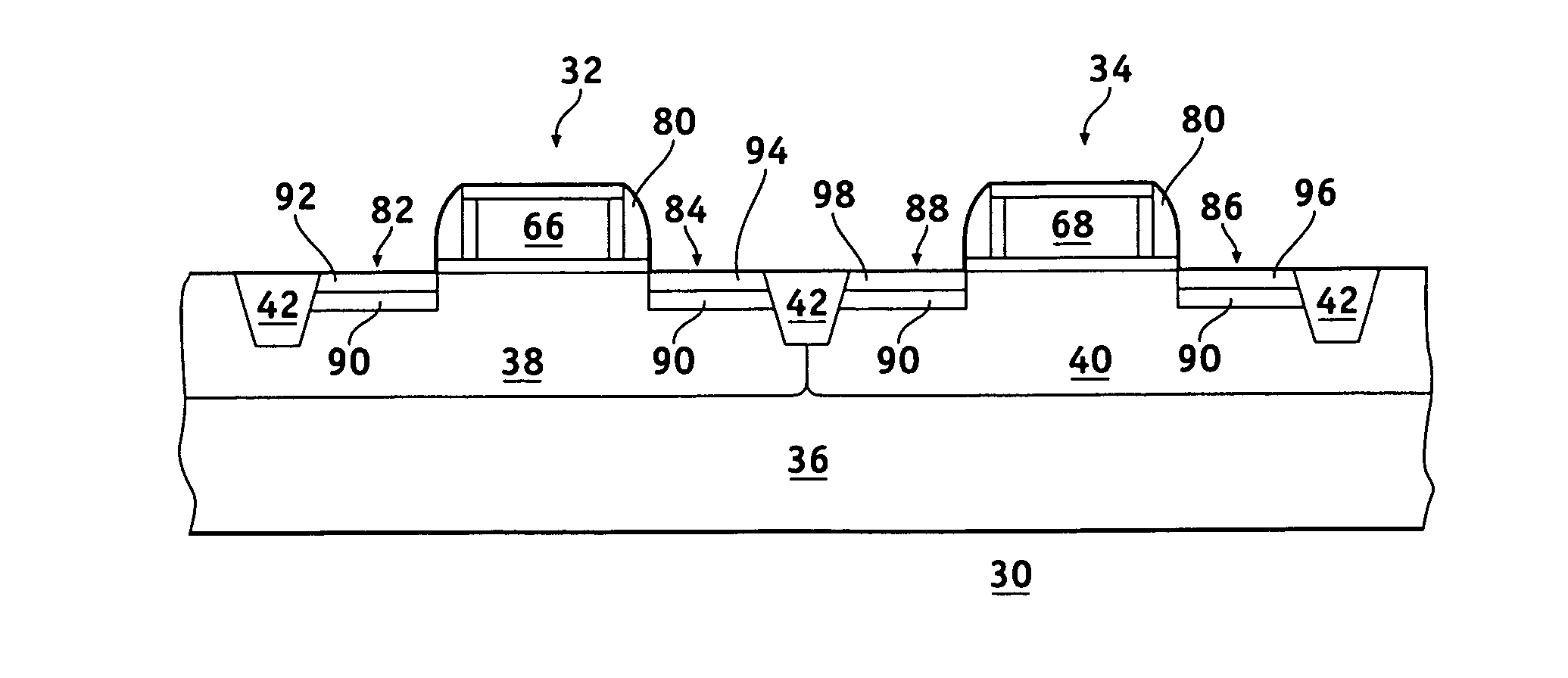

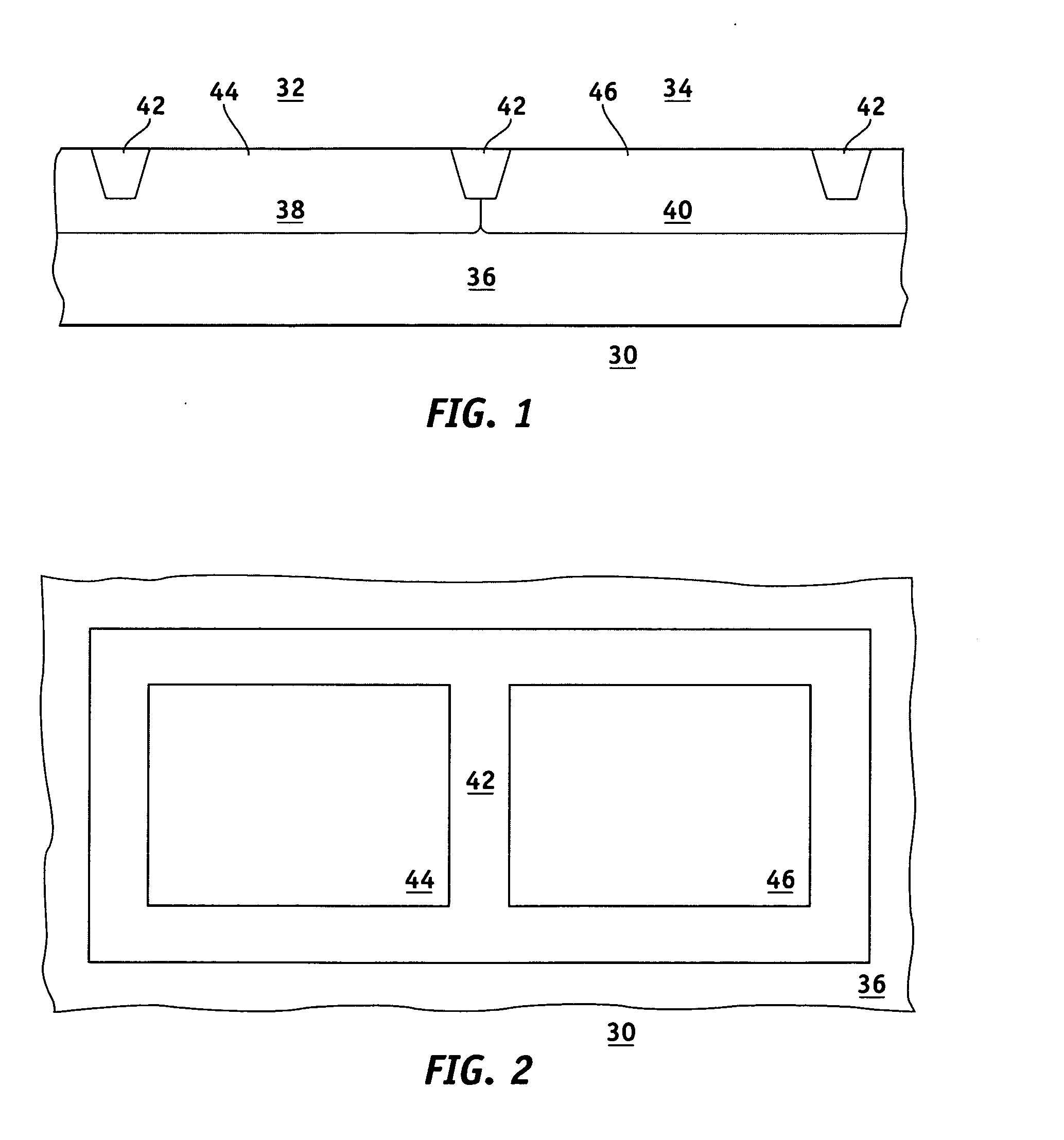

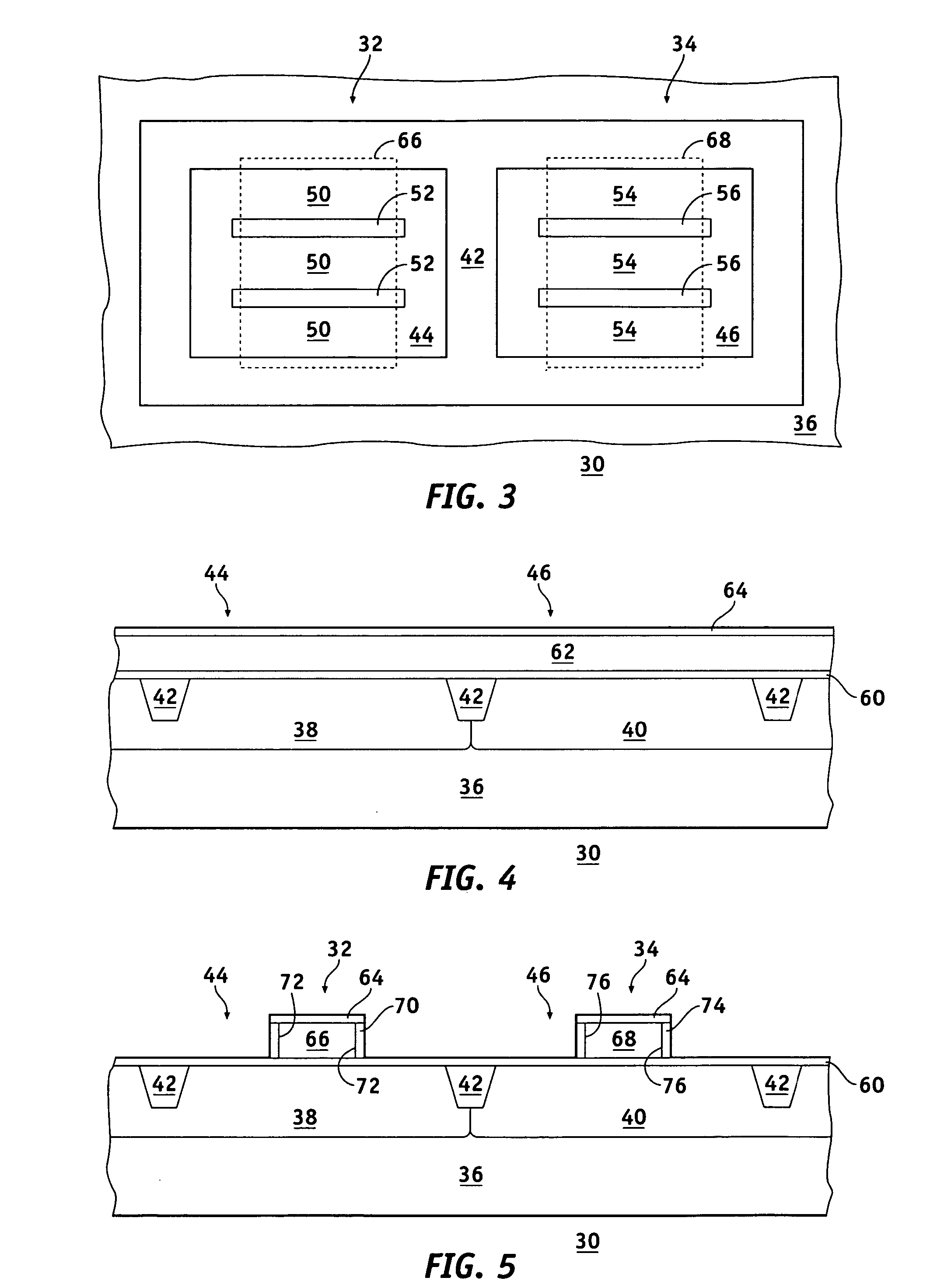

A CMOS EPROM, EEPROM or inverter device includes an nFET device with a thin gate dielectric layer and a pFET device juxtaposed with the nFET device with a thick gate dielectric layer and a floating gate electrode. The thick gate dielectric layer is substantially thicker than the thin gate dielectric layer. A common drain node connected both FET devices has no external connection in the case of a memory device and has an external connection in the case of an inverter. There are external circuit connections to the source regions of both FET devices and to the gate electrode of the nFET device. The pFET and nFET devices can be planar, vertical or FinFET devices.

Owner:MARVELL ASIA PTE LTD

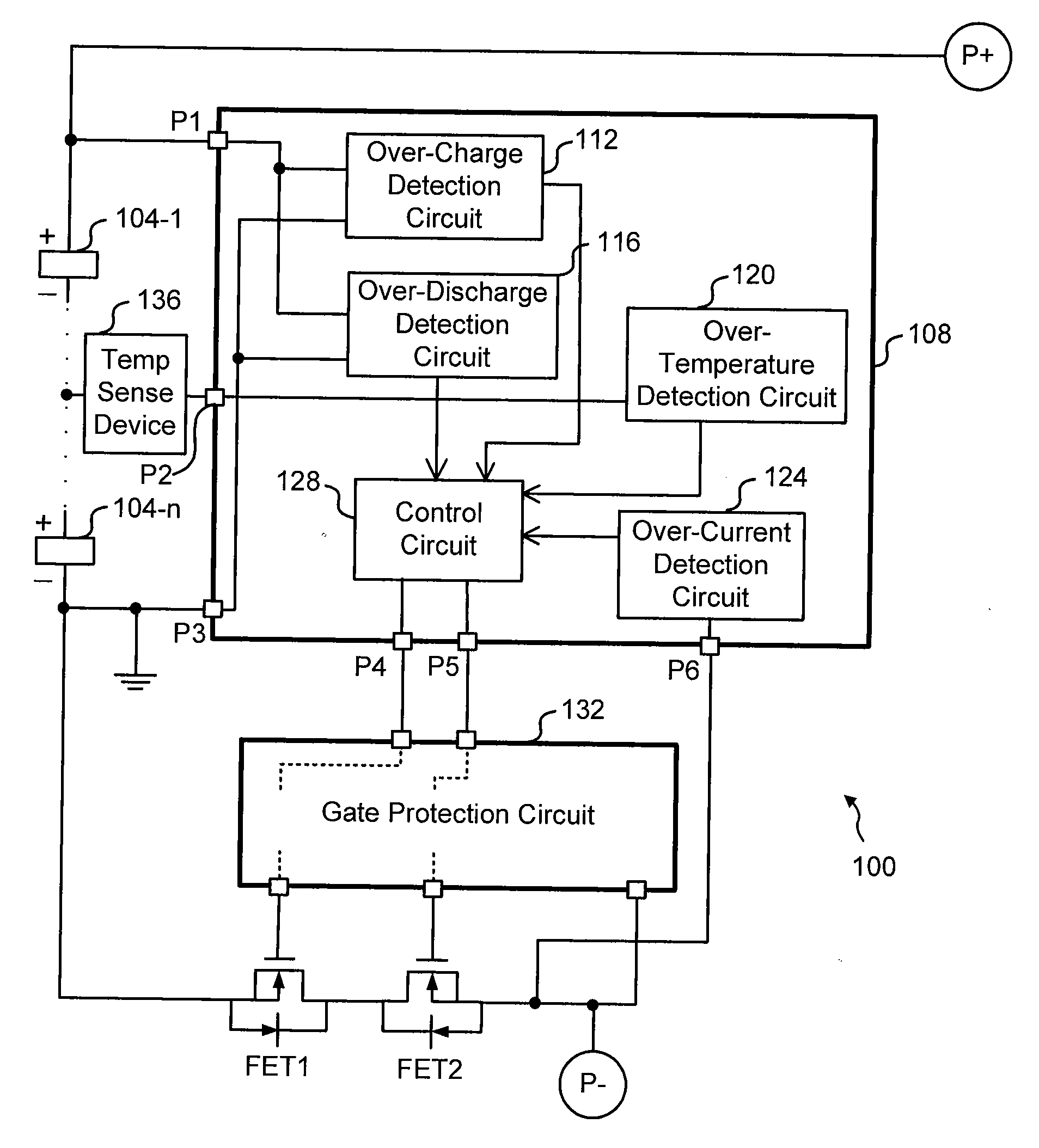

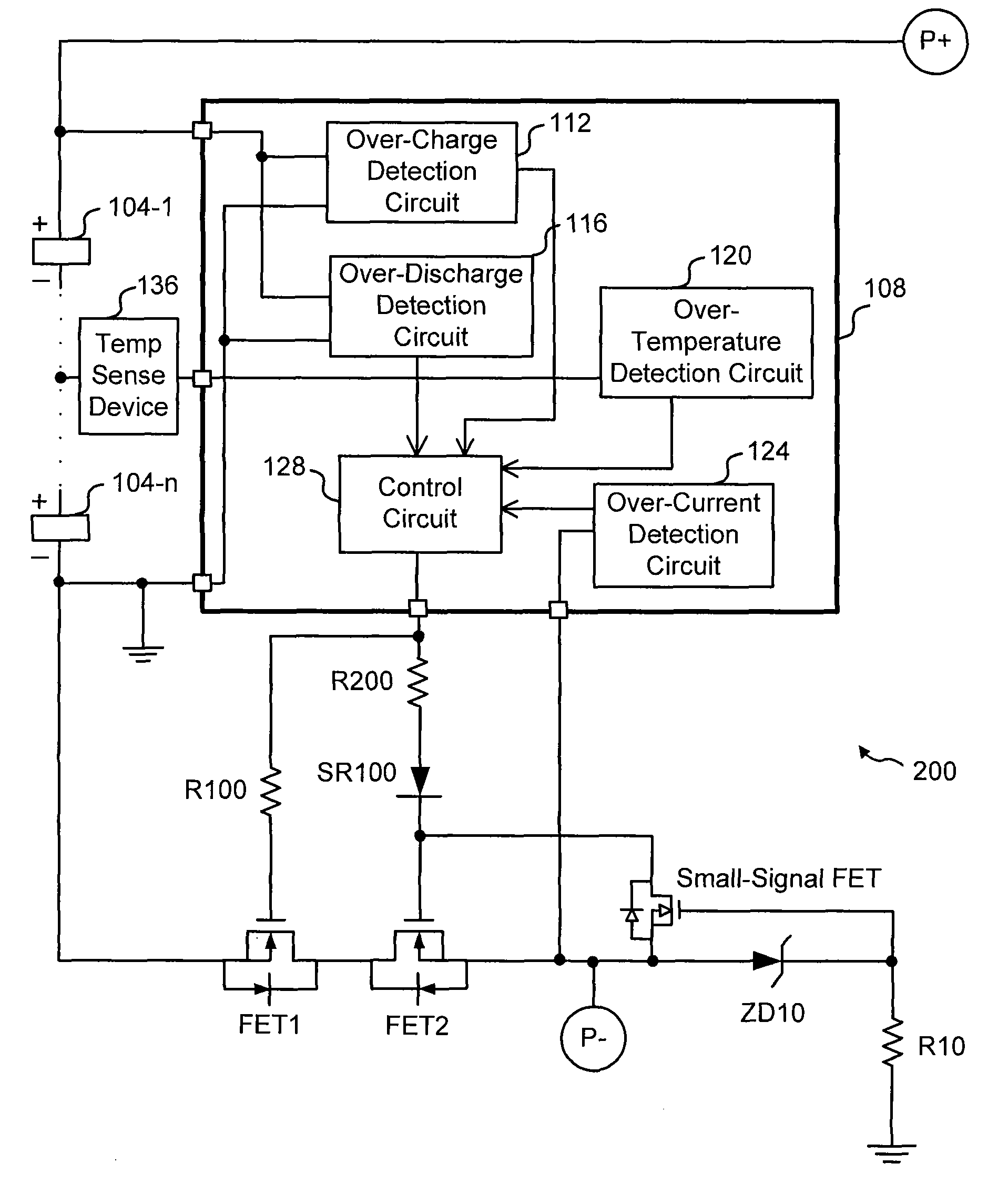

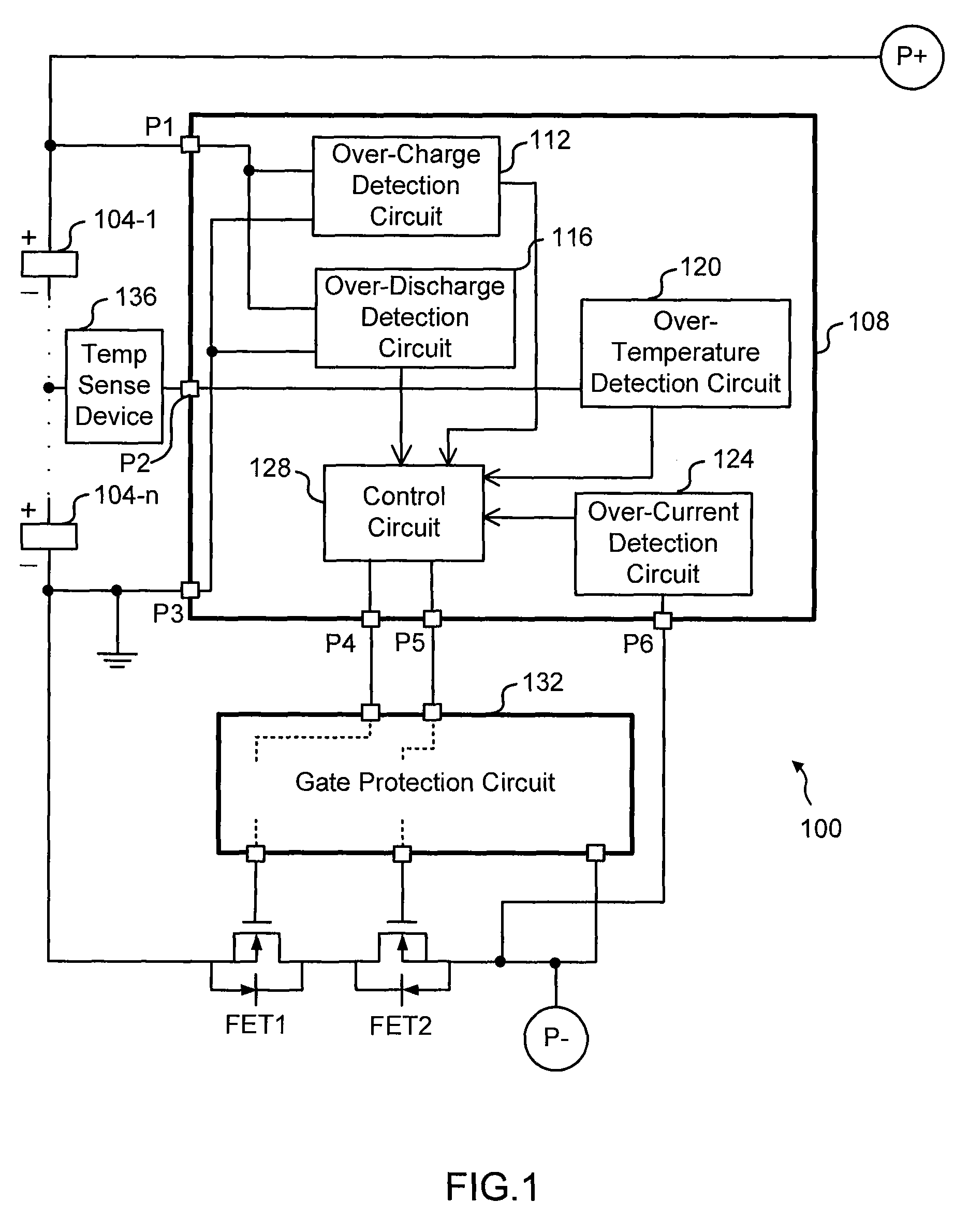

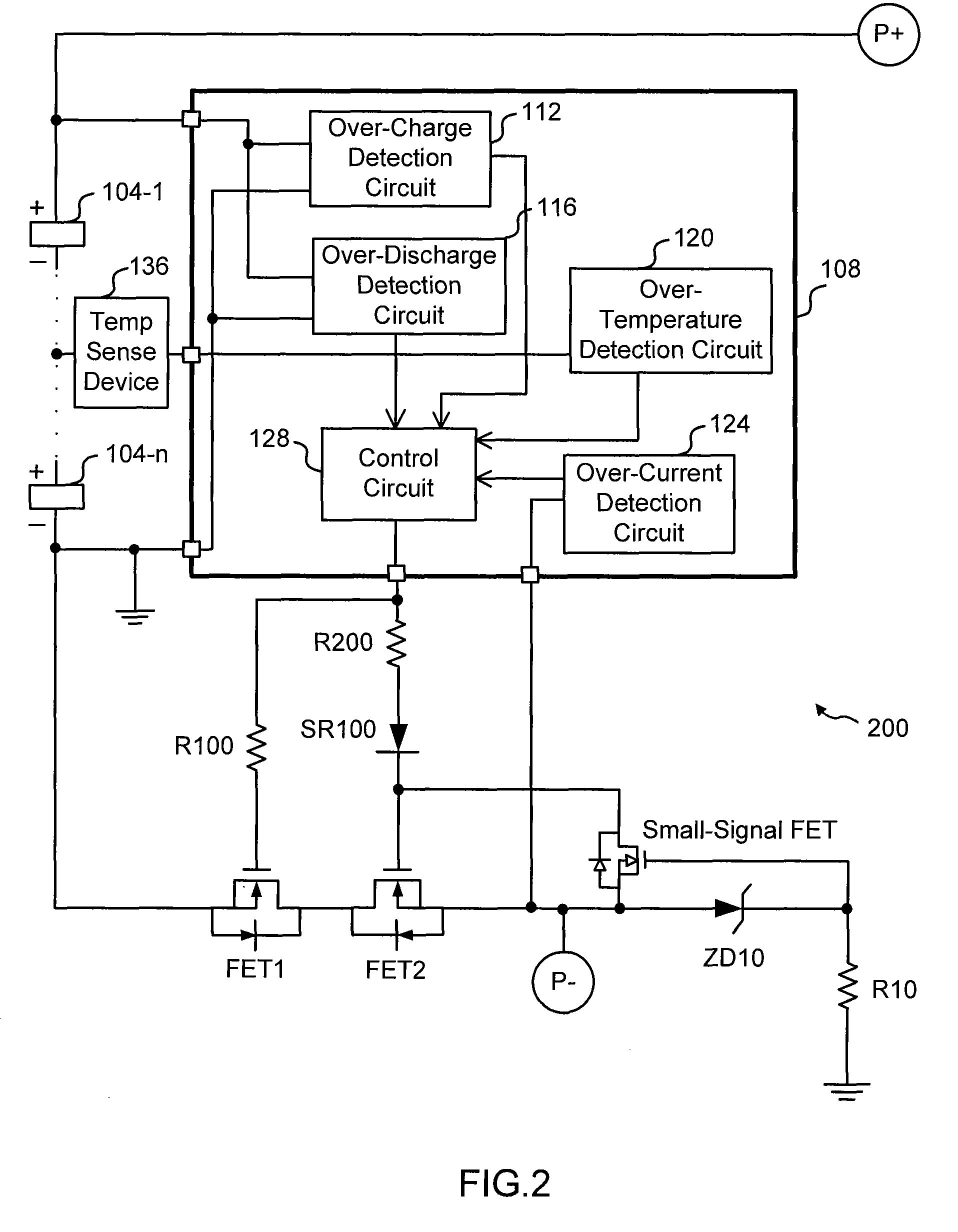

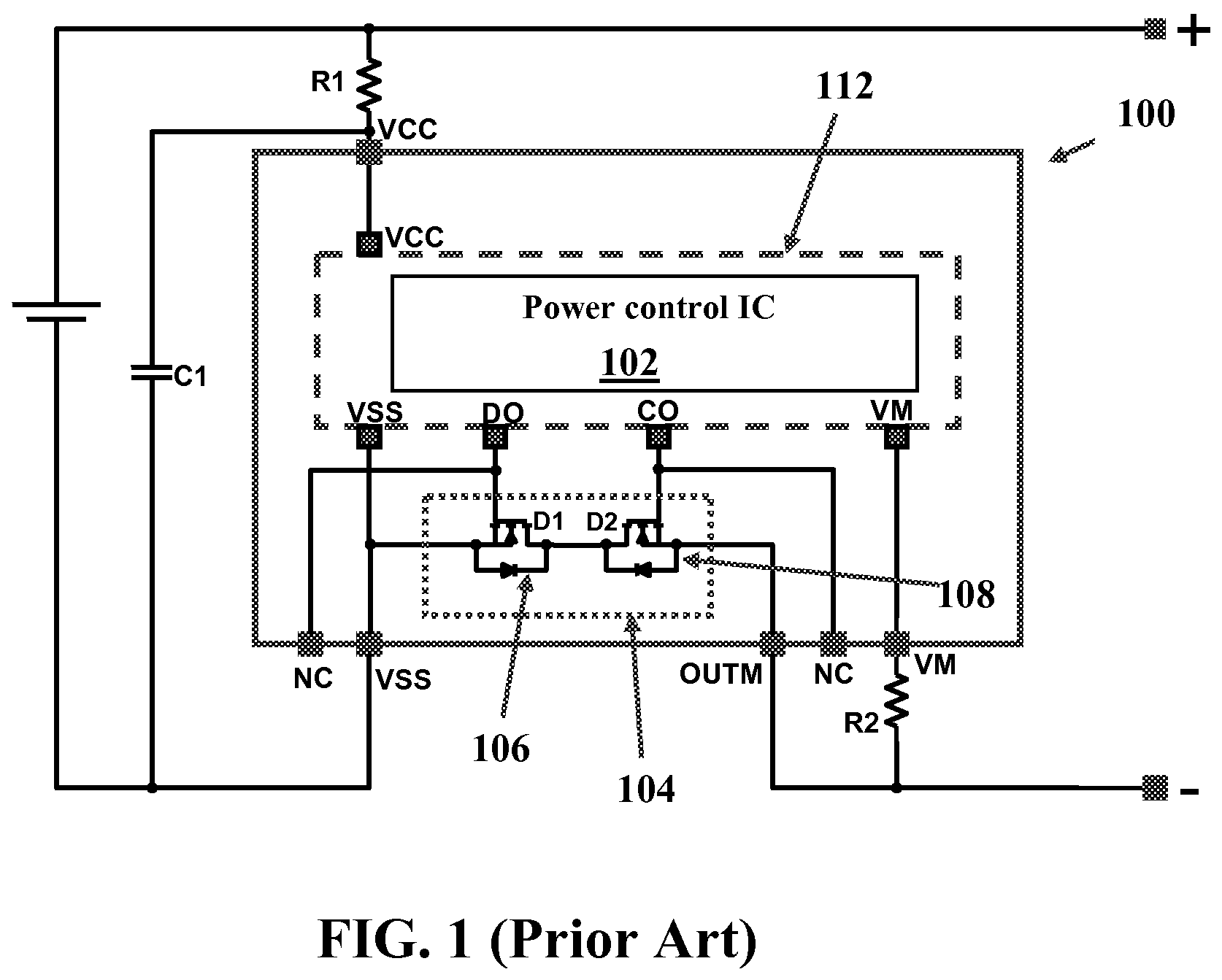

Low side n-channel fet protection circuit

ActiveUS20090072790A1Material analysis by electric/magnetic meansManual exchangesMOSFETControl signal

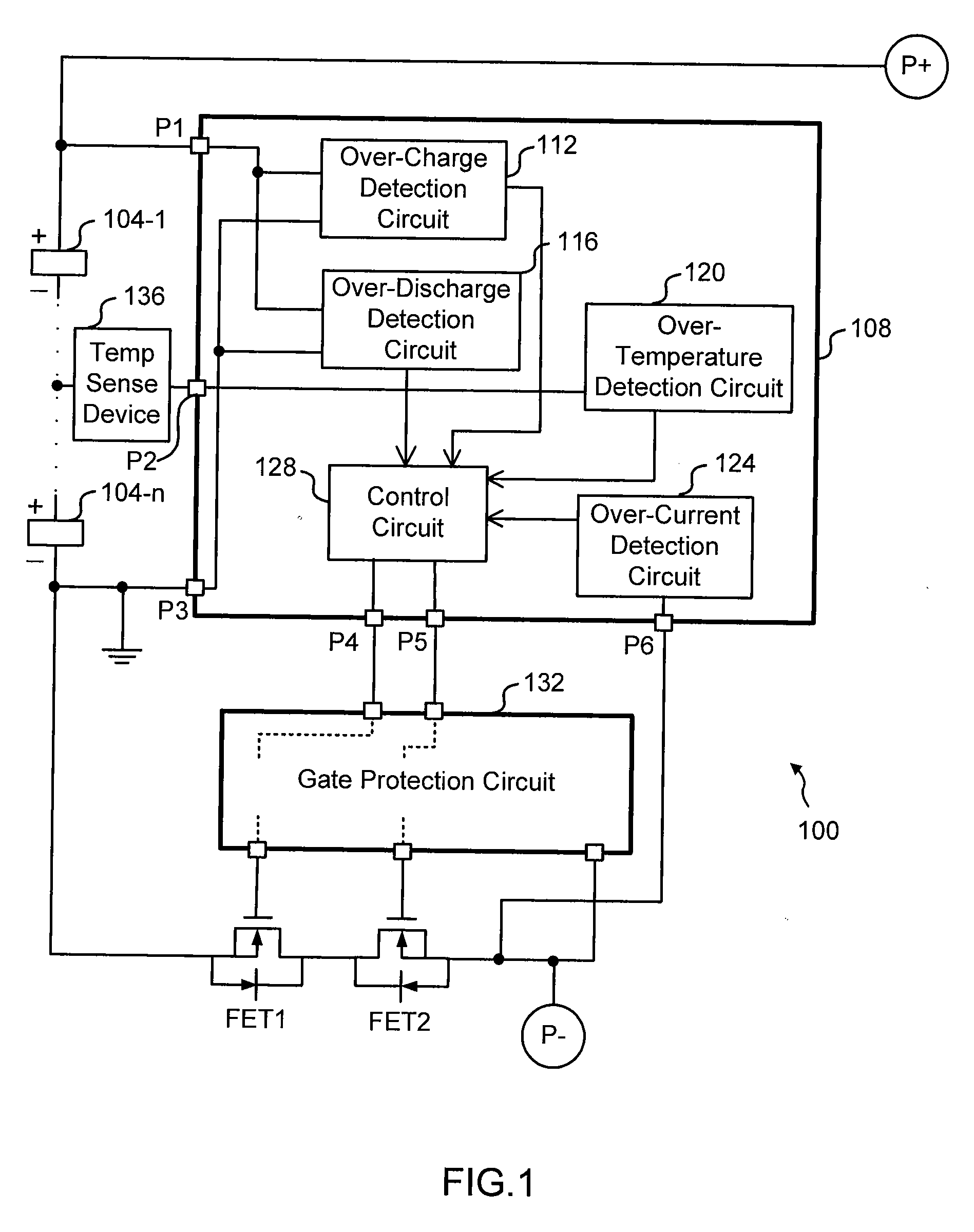

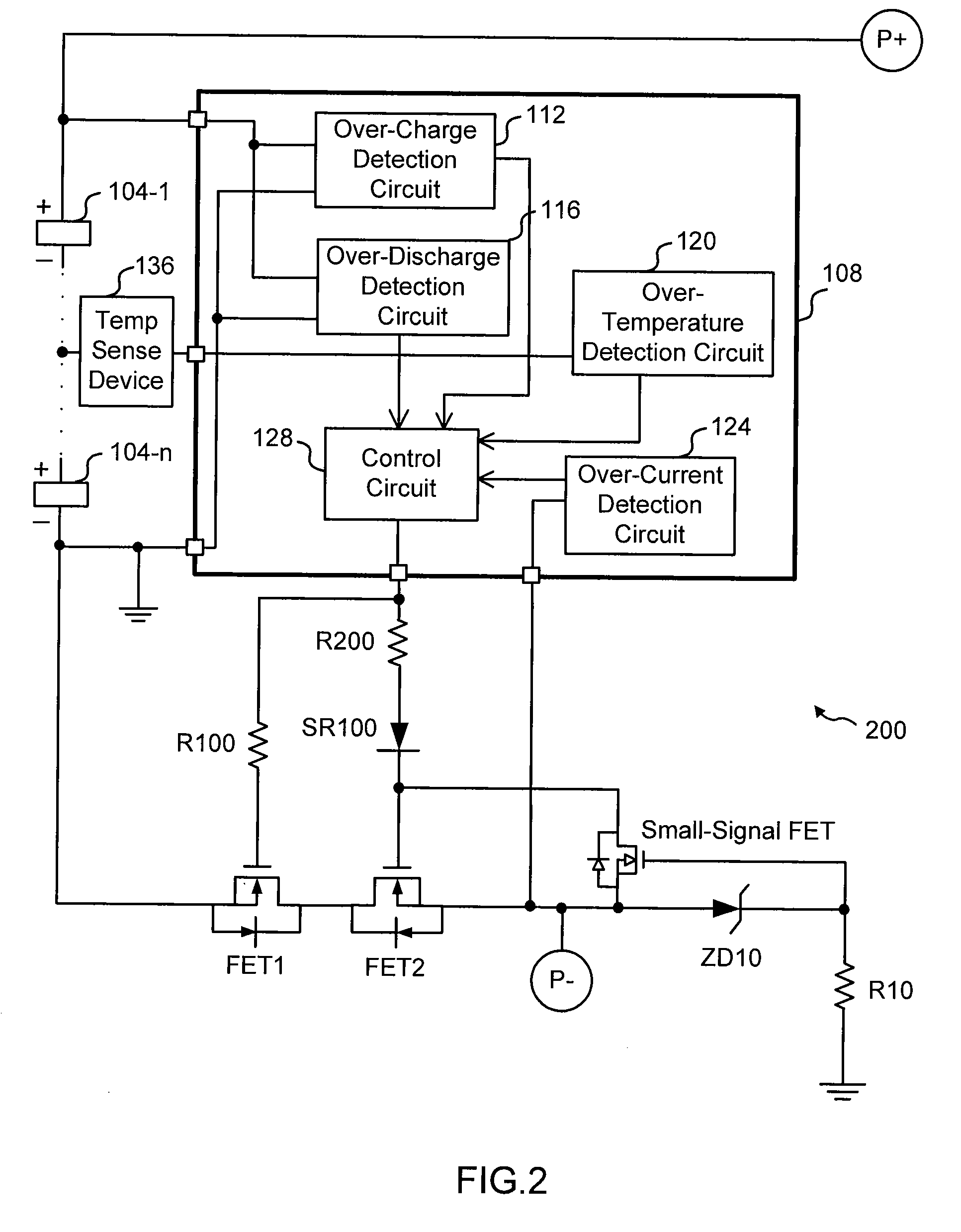

The present invention relates to a battery protection circuit for protecting a plurality of batteries connected in series. The battery protection circuit includes: a controller for monitoring the batteries and outputting control signals based on predetermined conditions associated with the batteries; a first N-channel MOSFET and a second N-channel MOSFET coupled in a common-drain configuration in a low-side path, wherein at least one of the first and second N-channel MOSFETs turns off in response to the control signal received from the controller when at least one of the predetermined conditions is detected; and a gate protection circuit for preventing gate-to-source voltages of the first and second N-channel MOSFETs from exceeding a predetermined gate-to-source voltage level.

Owner:INT COMPONENTS

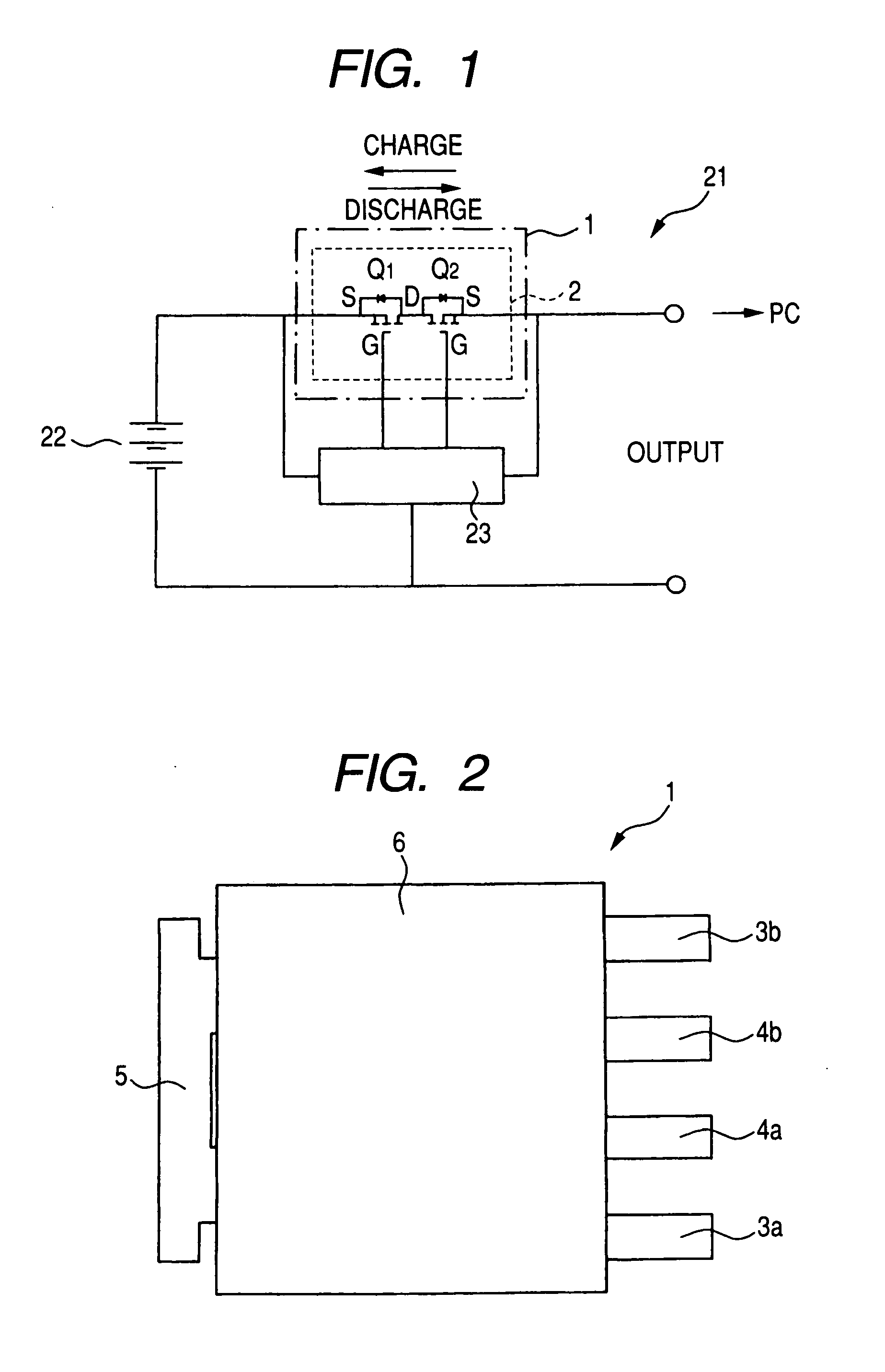

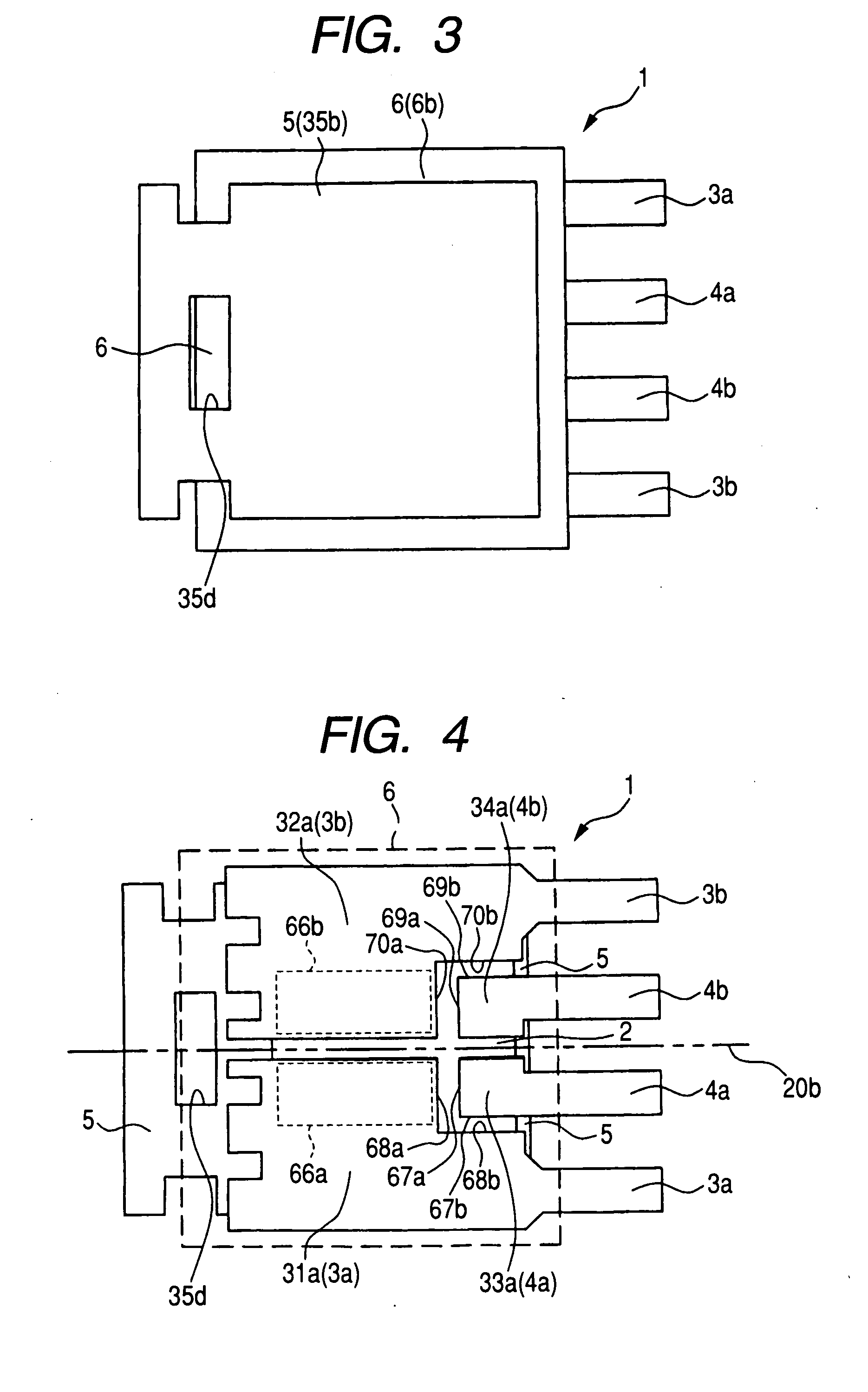

Semiconductor device

InactiveUS20060263988A1Substrate wiring resistant is increasedImprove the immunityTransistorSemiconductor/solid-state device detailsDevice materialSemiconductor chip

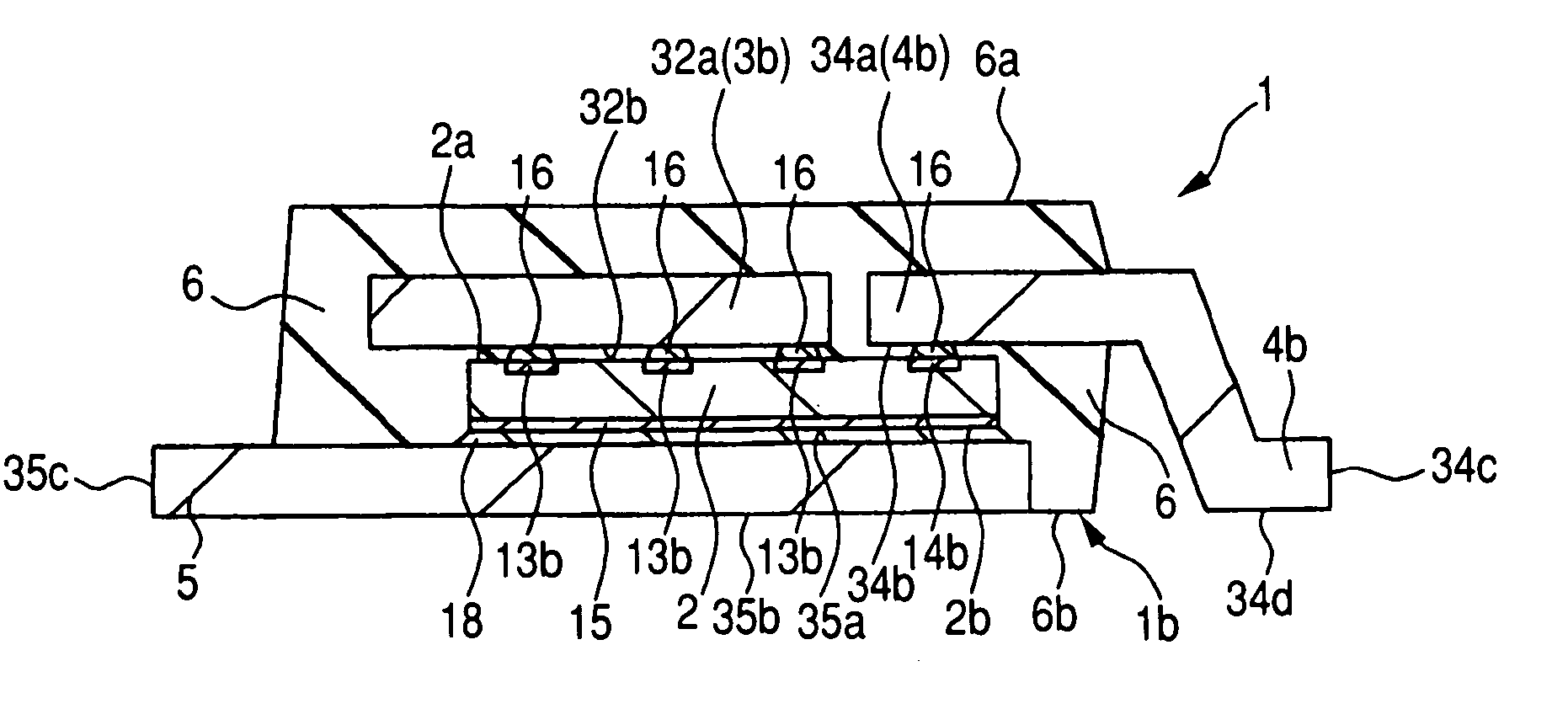

Two vertical-type power MISFETs are formed over a semiconductor chip, a common drain electrode formed over a back surface of the semiconductor chip is electrically connected with a drain terminal via a conductive bonding material, source electrodes and gate electrodes formed over a surface of the semiconductor chip are respectively electrically connected with source terminals and gate terminals via bump electrodes, and these components are sealed by a resin sealing portion. The exposed portions of the gate terminals are arranged inside the resin sealing portion, and the exposed portions of the source terminals are arranged outside the resin sealing portion. The source terminals extend over the surface of the semiconductor chip and are connected with the source electrodes which are uniformly arranged over regions of the surface of the semiconductor chip except for gate electrode forming regions and the vicinities of these regions via the bump electrodes.

Owner:RENESAS ELECTRONICS CORP

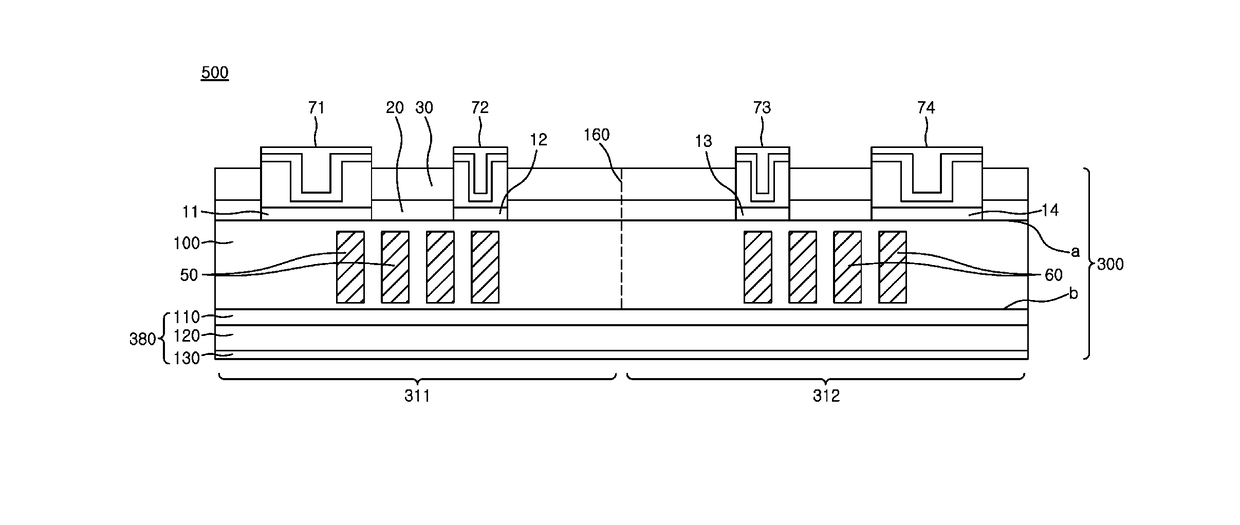

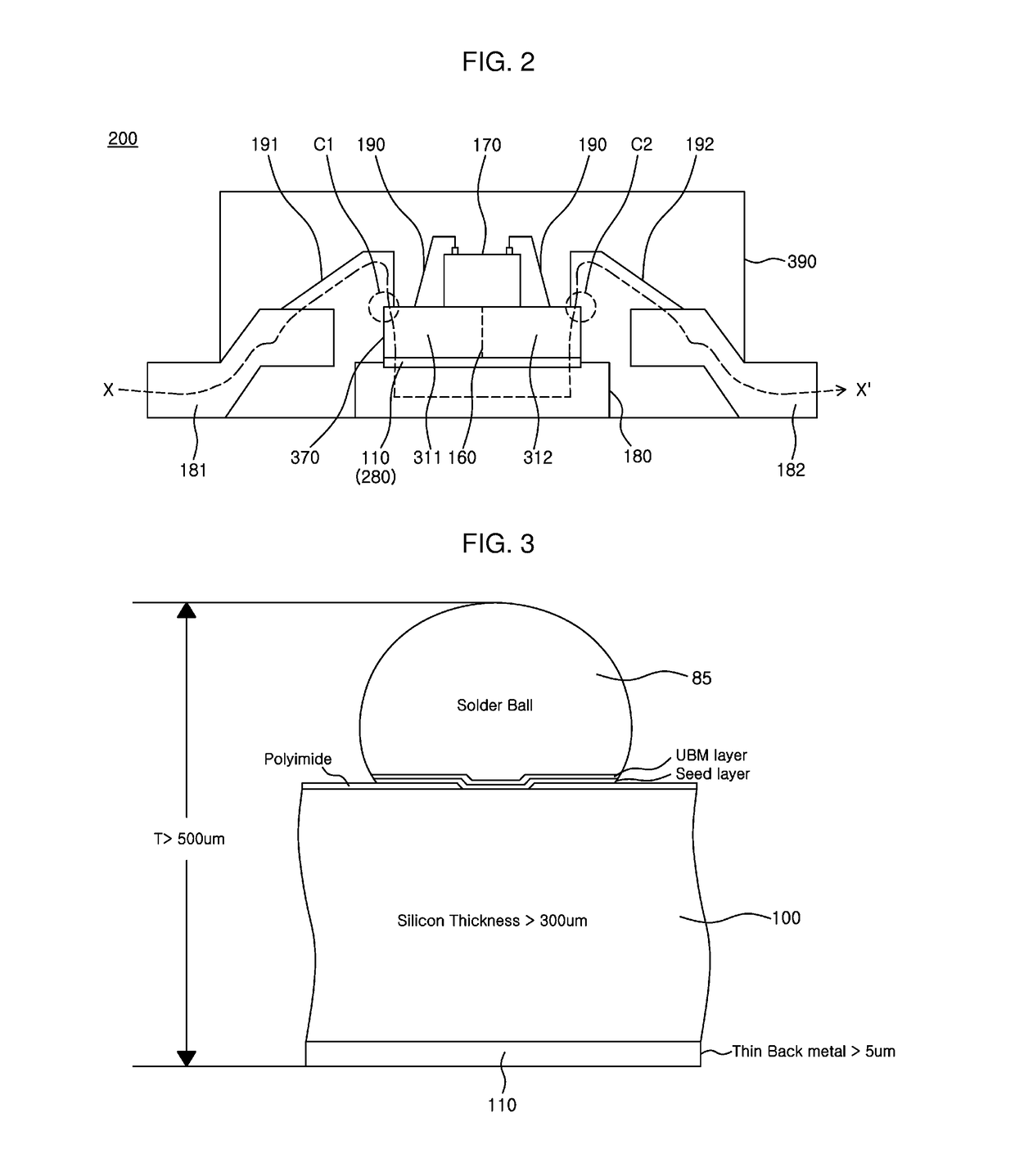

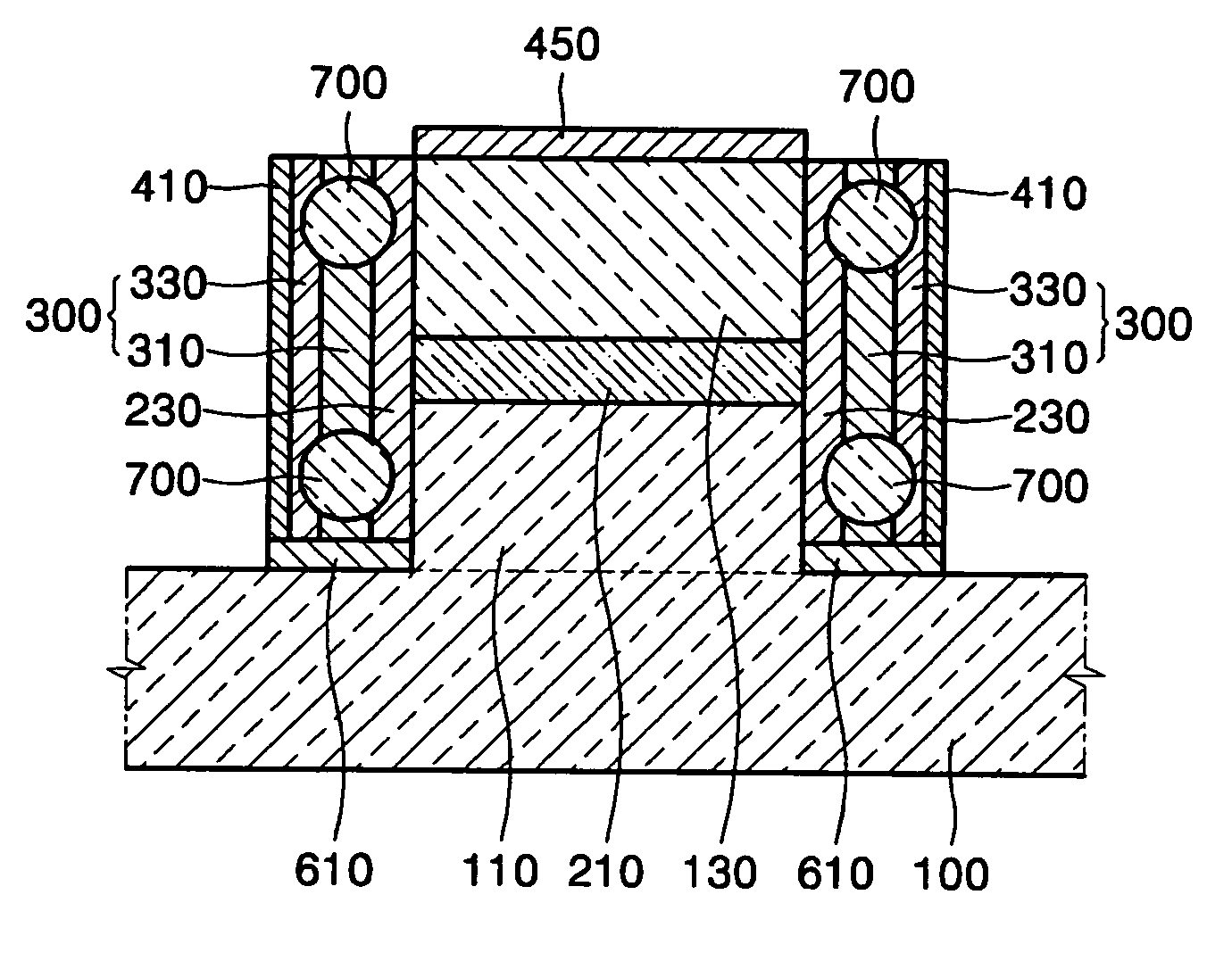

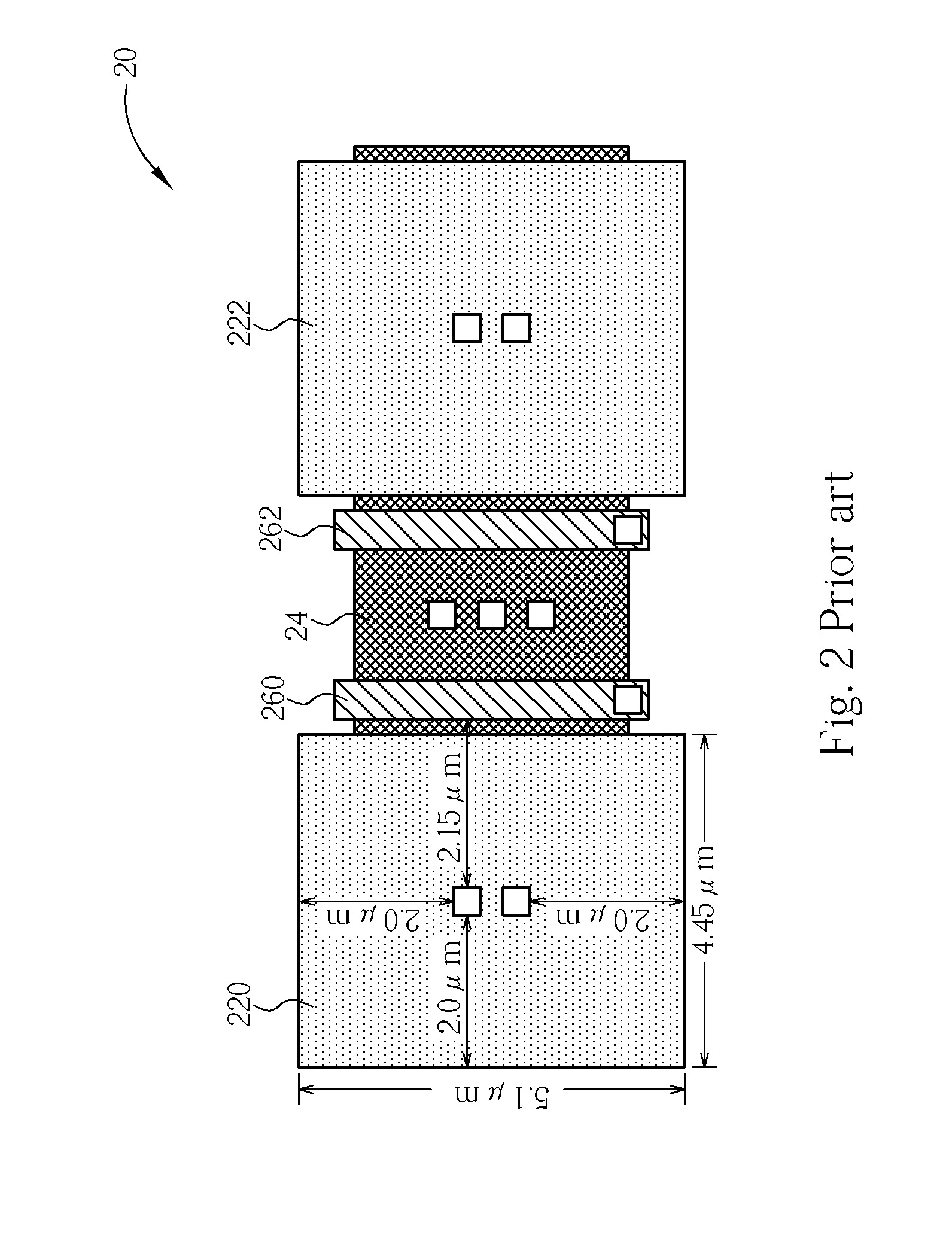

Wafer-level chip-scale package including power semiconductor and manufacturing method thereof

ActiveUS20170358510A1TransistorSemiconductor/solid-state device testing/measurementPower semiconductor devicePower flow

A wafer-level chip-scale package includes: a power semiconductor comprising a first semiconductor device formed on a semiconductor substrate, and a second semiconductor device formed on the semiconductor substrate; a common drain electrode connected to the first semiconductor device and the second semiconductor device; a first source metal bump formed on a surface of the first semiconductor device; and a second source metal bump formed on the surface of the second semiconductor device; wherein the first source metal bump, the common drain electrode, and the second source metal bump form a current path in an order of the first source metal bump, the common drain electrode, and the second source metal bump.

Owner:MAGNACHIP SEMICONDUCTOR LTD

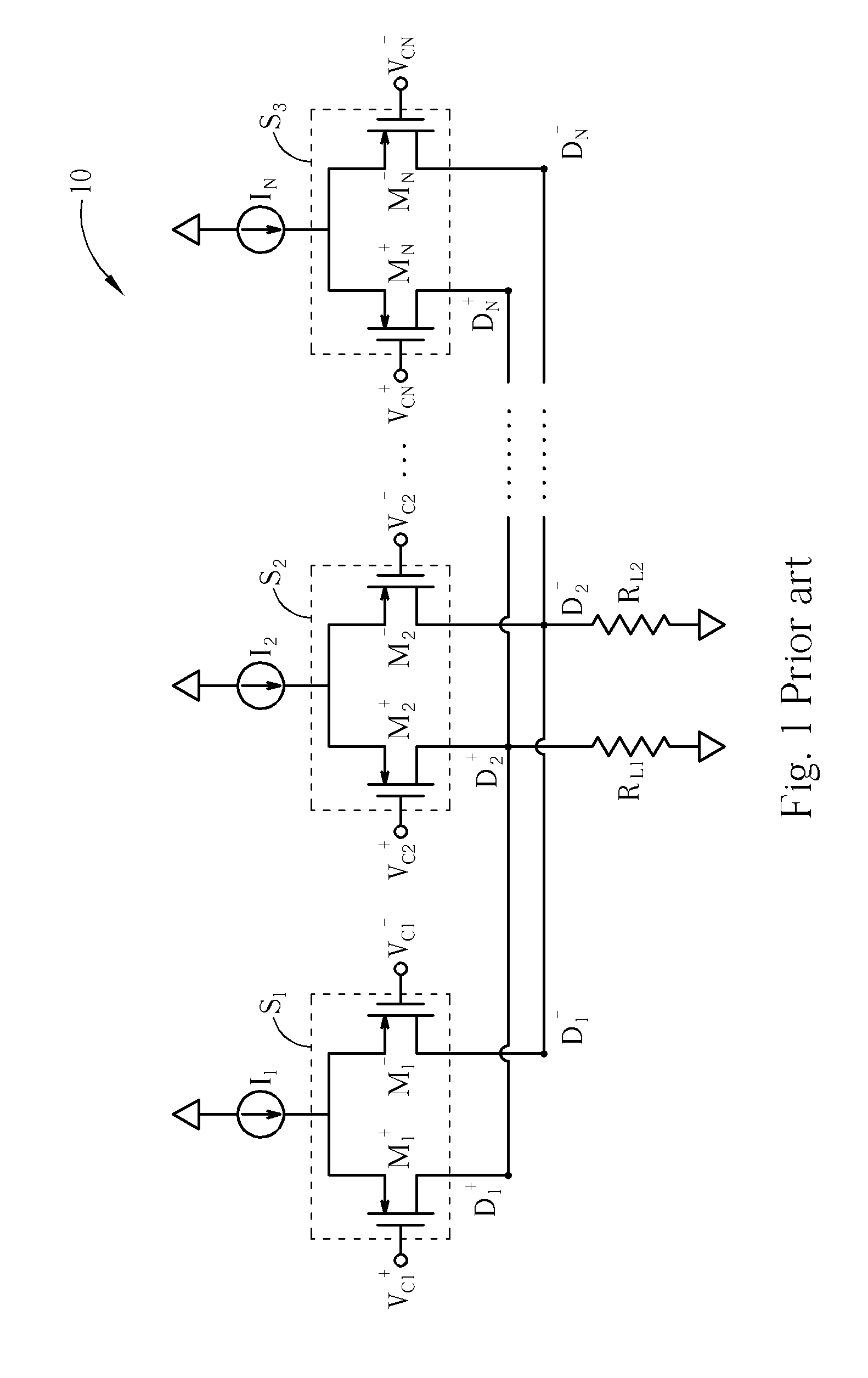

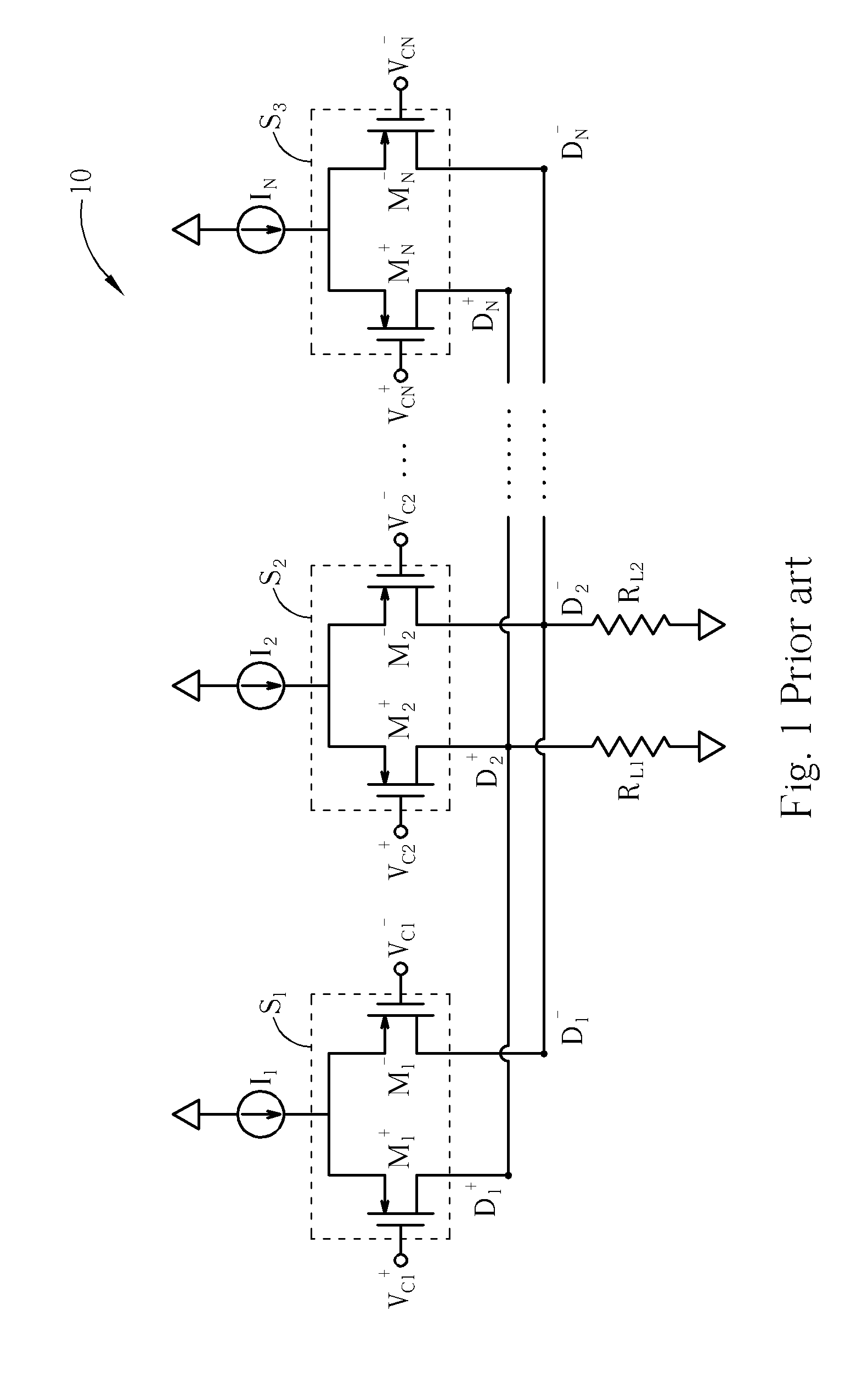

Current limited bilateral MOSFET switch with reduced switch resistance and lower manufacturing cost

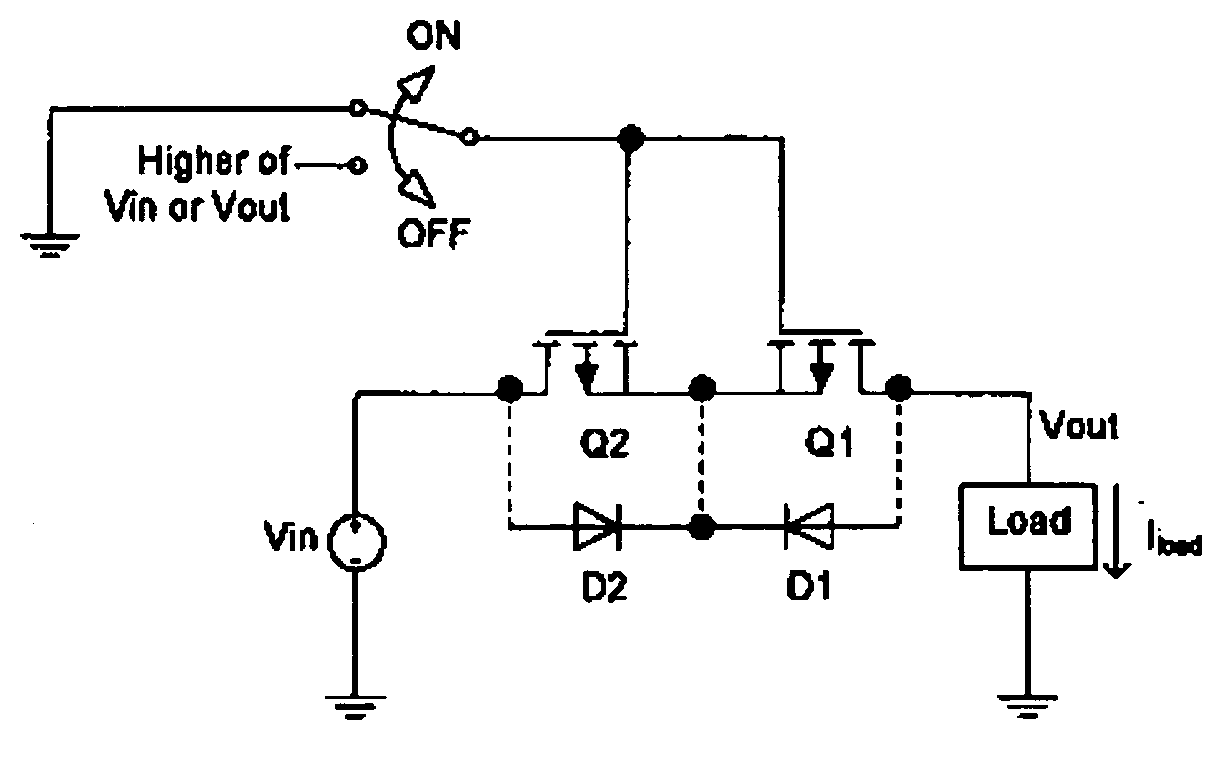

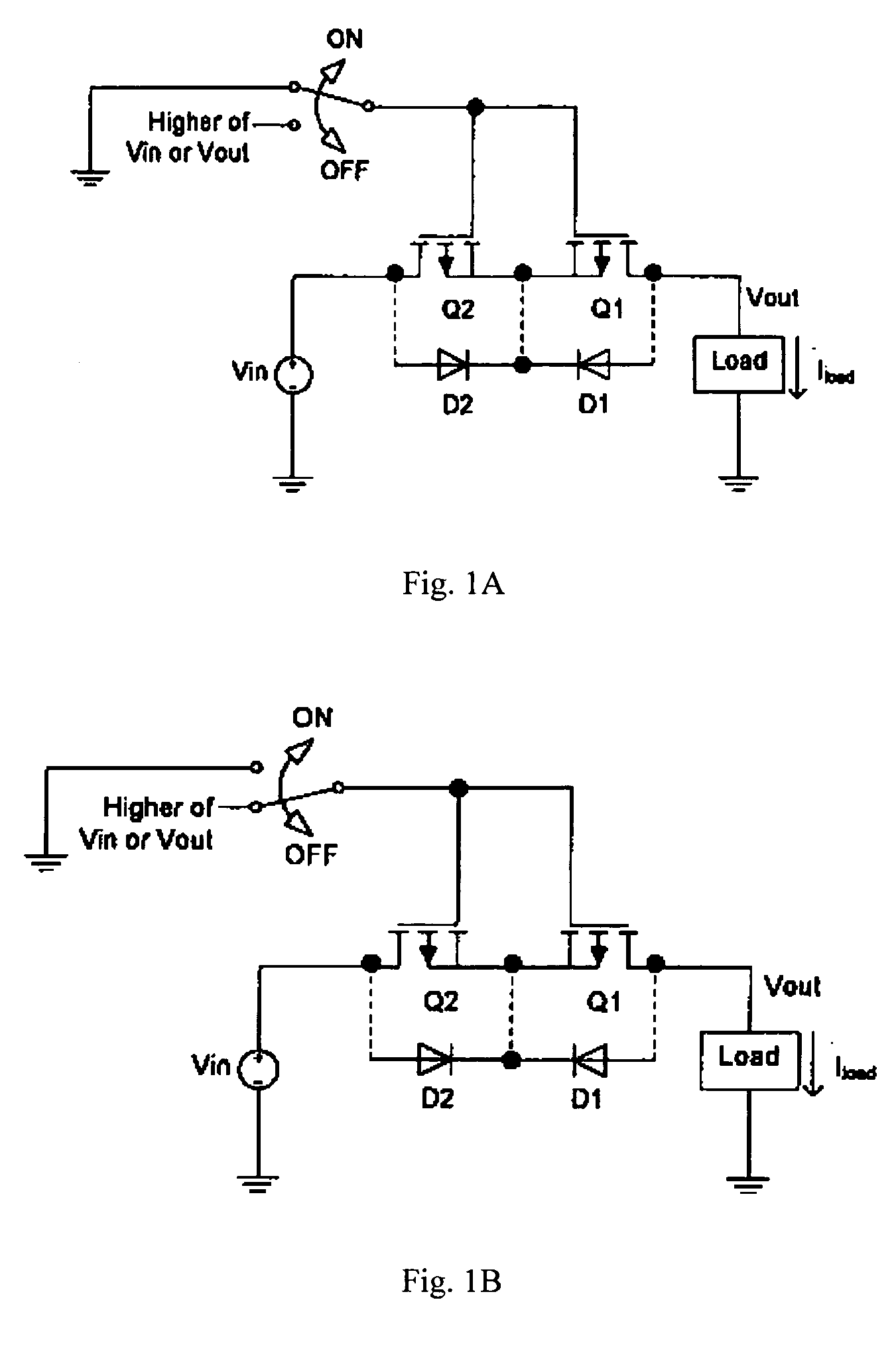

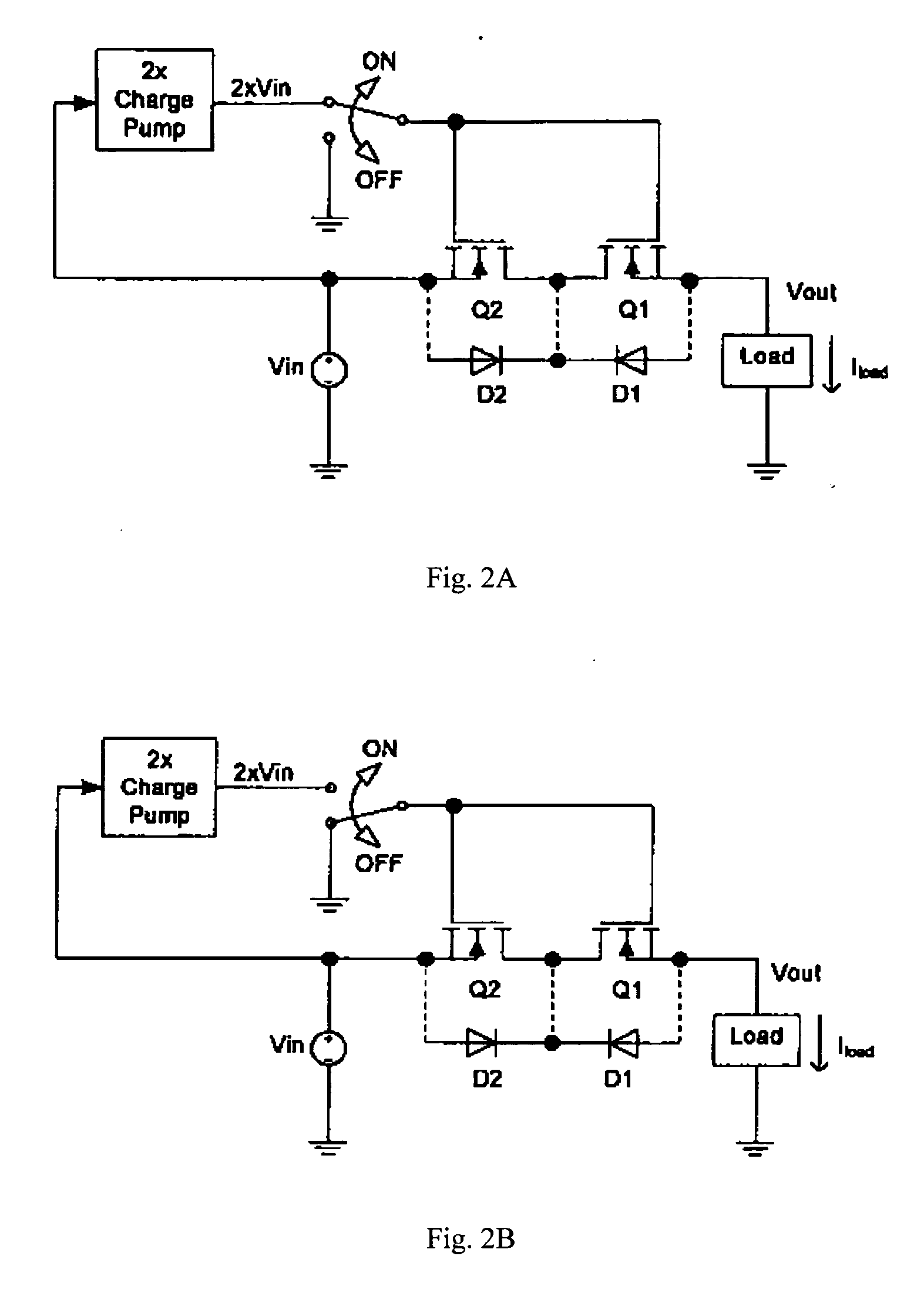

ActiveUS20070127182A1Reduce resistanceEliminate requirementsTransistorElectronic switchingMOSFETElectrical resistance and conductance

A circuit and method for controlling a MOSFET based switch that includes two back-to-back FET to block current flow in the OFF state irrespective of the polarity of the voltage differential across the switch. The MOSFET based switch further has a built-in current limit function by sensing the current flow through one of the two MOSFET switches. Furthermore, the bilateral current-limited switch further includes circuitry required for controlling both P type and N type FET in either common drain or common source configuration.

Owner:ALPHA & OMEGA SEMICON LTD

NAND-type nonvolatile memory device and related method of manufacture

ActiveUS20080079091A1Solid-state devicesSemiconductor/solid-state device manufacturingBit lineCommon drain

In a NAND type nonvolatile memory device, a first insulating layer covers a common drain region formed in a string active region and a peripheral active region. A second insulating layer covers the first insulating layer. A bit line plug penetrates the first and second insulating layers and is connected to the common drain region. A peripheral lower plug penetrates the first insulating layer and is connected to the peripheral active region. A peripheral upper plug penetrates the second insulating layer and is stacked on the peripheral lower plug.

Owner:SAMSUNG ELECTRONICS CO LTD

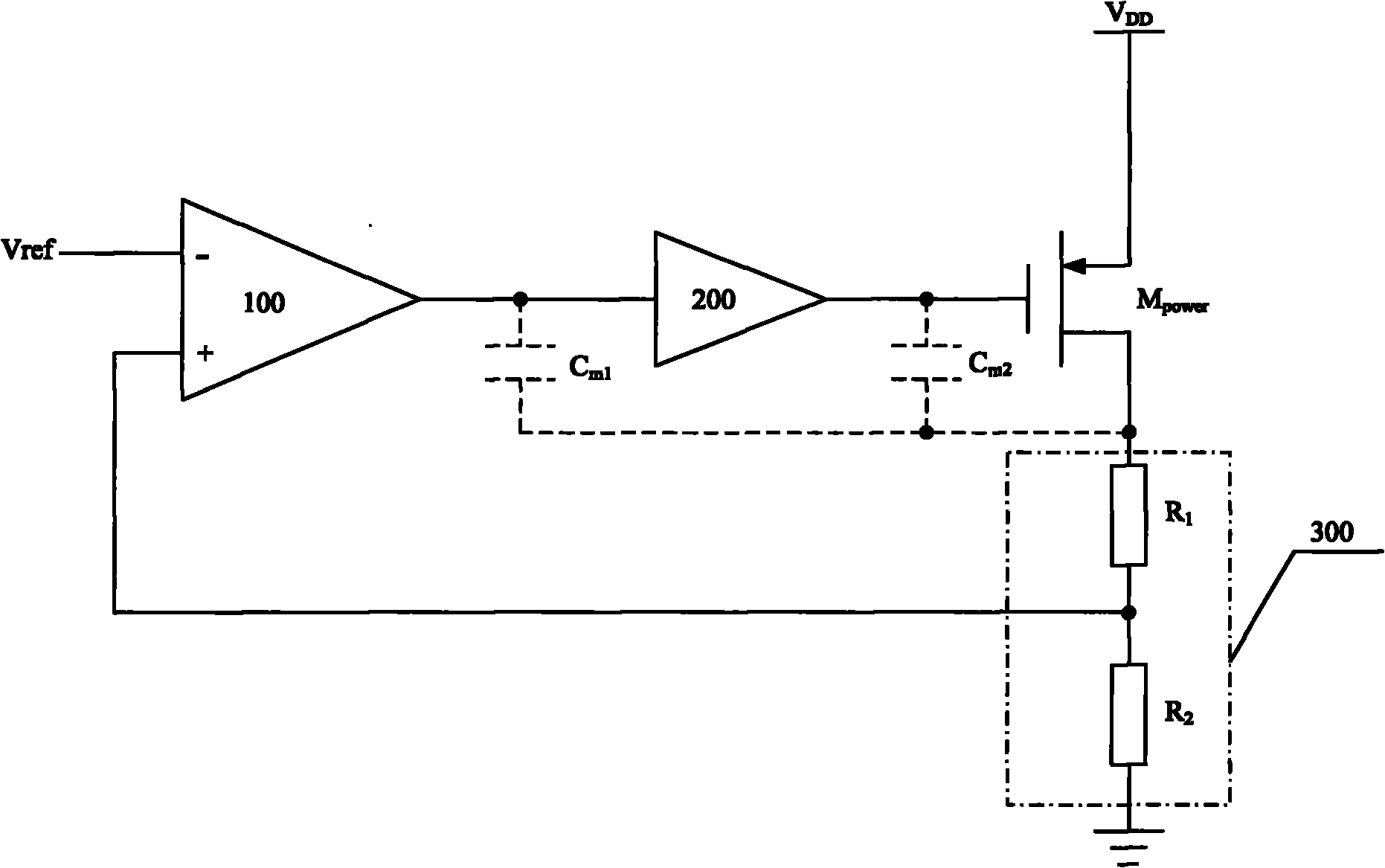

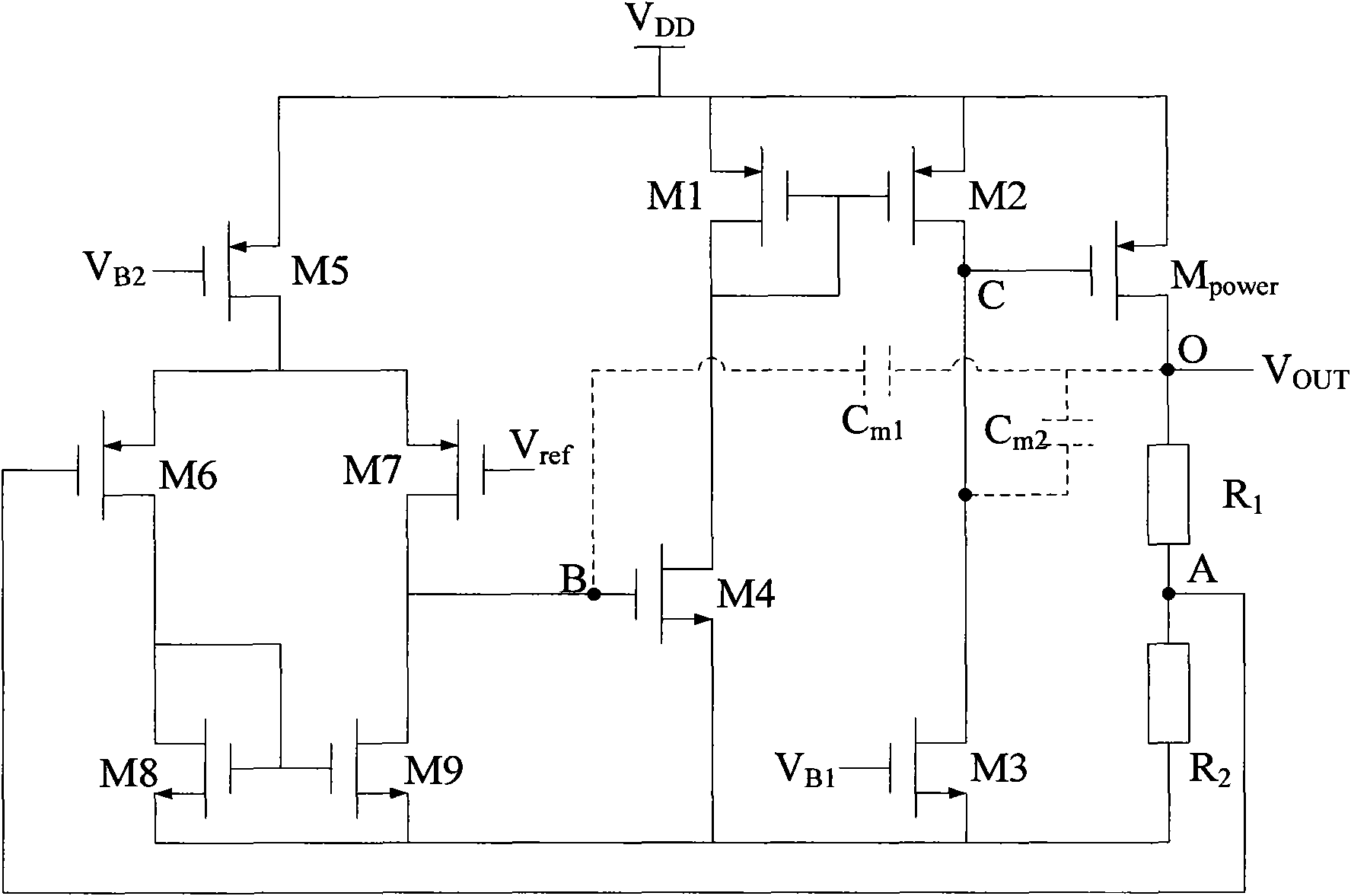

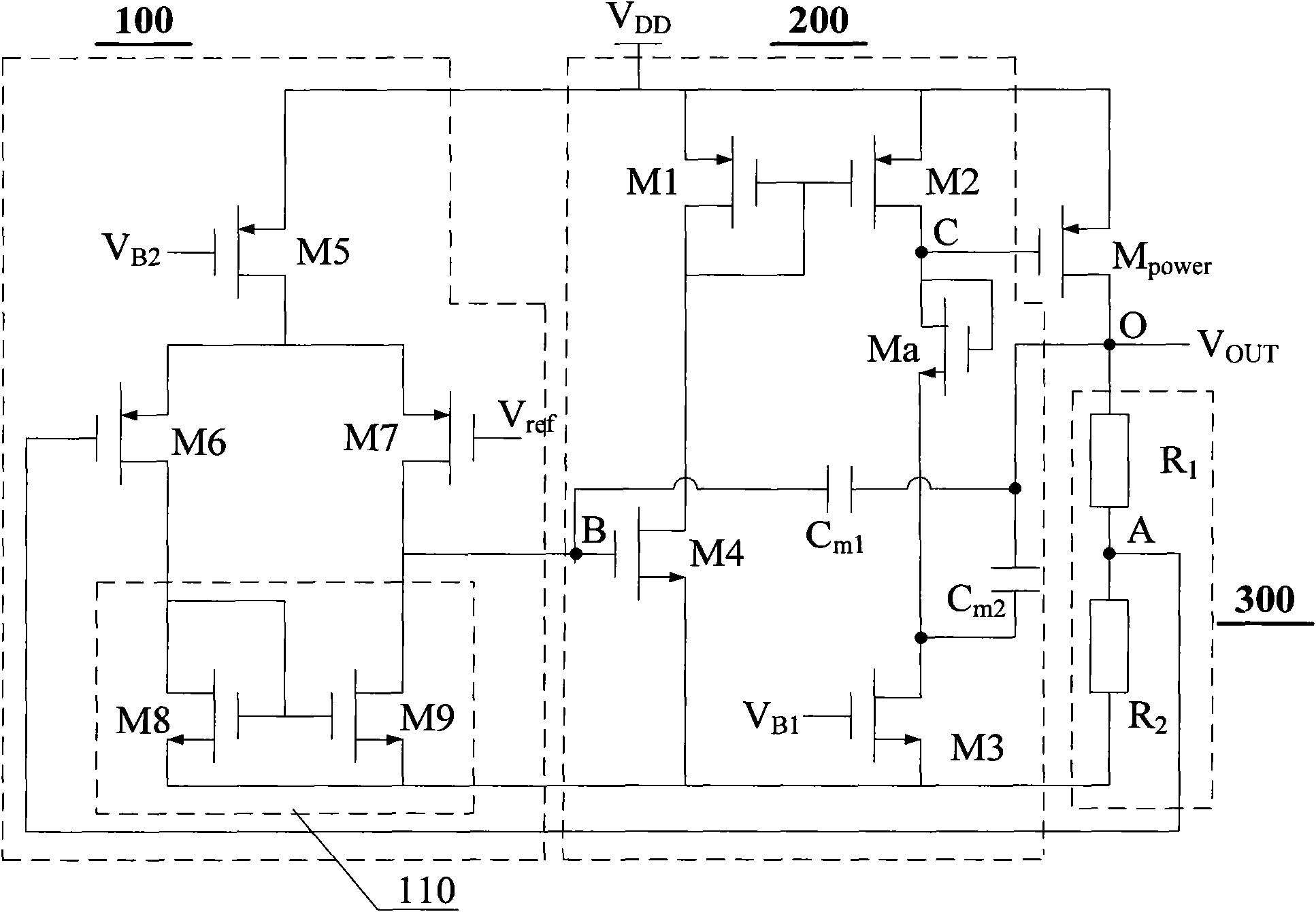

Capacitor-less low dropout regulator structure

ActiveCN102385406AControl damping coefficientIncrease the damping factorElectric variable regulationCapacitanceDamping factor

The invention relates to a capacitor-less low dropout regulator, which comprises a first-stage amplifier, a second-stage buffer, a voltage division circuit and an output transistor, wherein an impedance device is introduced between an output end of a common drain amplification circuit of the second-stage buffer and the ground, the impedance device is an active resistor device or a passive resistor device which is used for increasing the output resistance of the second-stage buffer, effectively controlling the damping coefficient of the capacitor-less low dropout regulator and reducing the influence of complex poles on dominant poles. Frequency compensation of the capacitor-less low dropout regulator is realized, and under the condition that a capacitor device does not need to be increasedadditionally, low-dropout output voltage is ensured to be precise and stable and have low noise, and the capacitor-less low dropout regulator can be used in a circuit capable of realizing monolithic integration and driving larger capacitive load.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

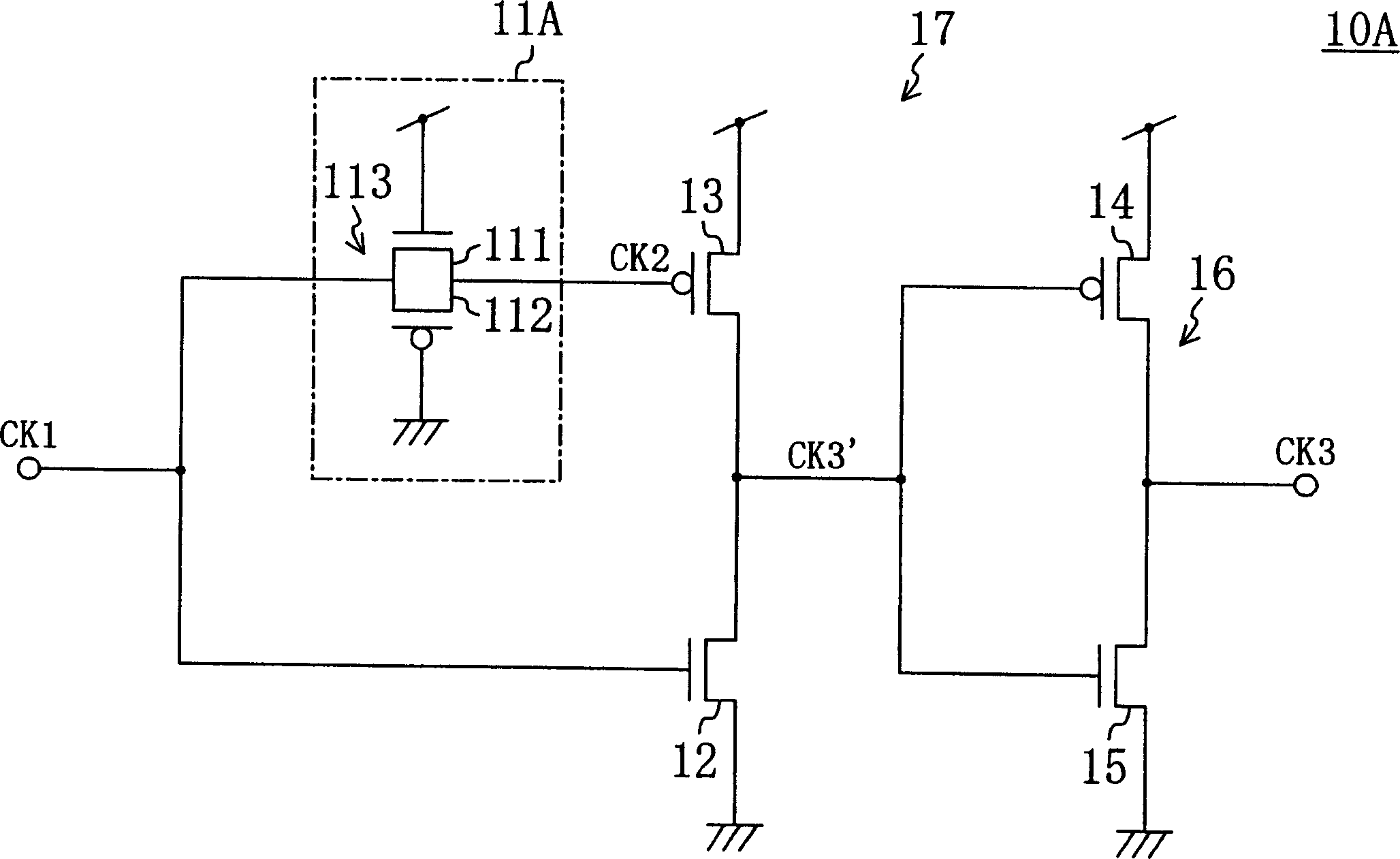

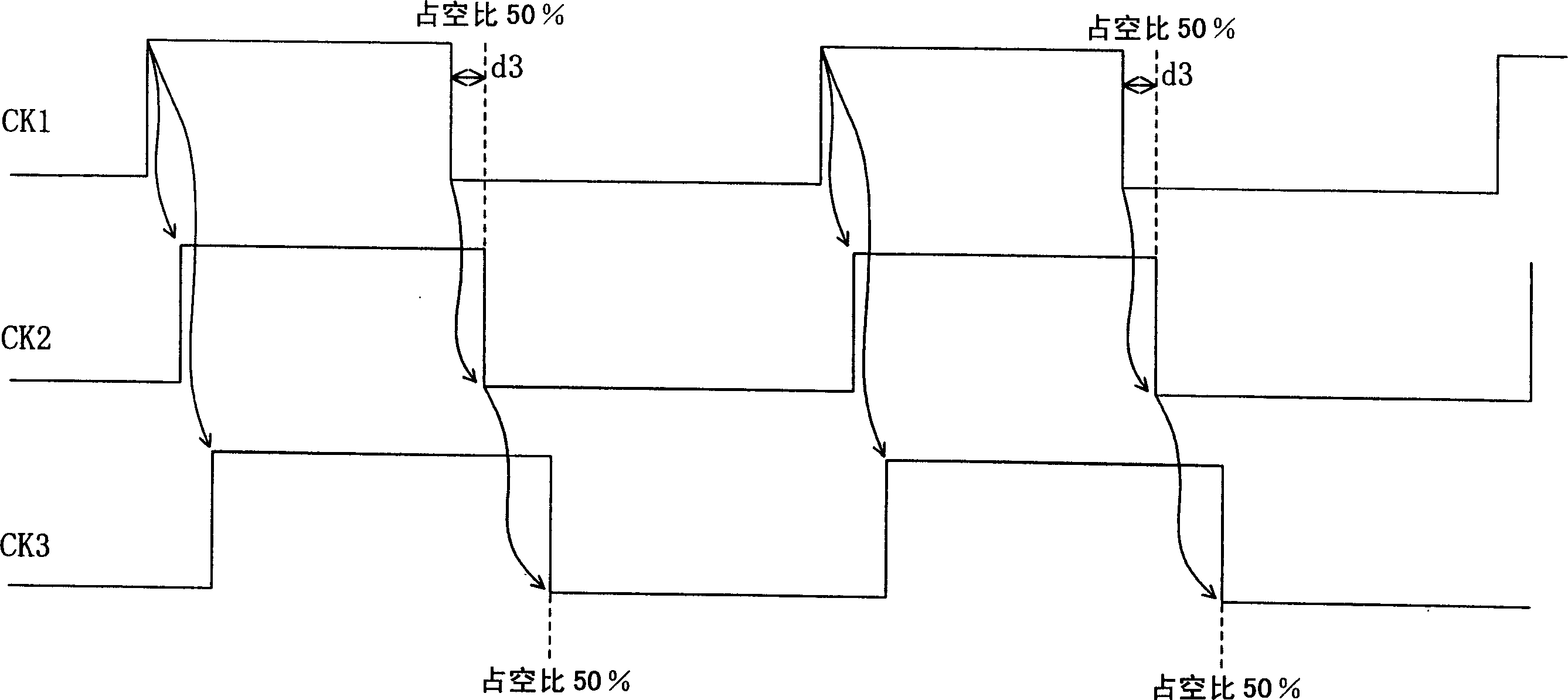

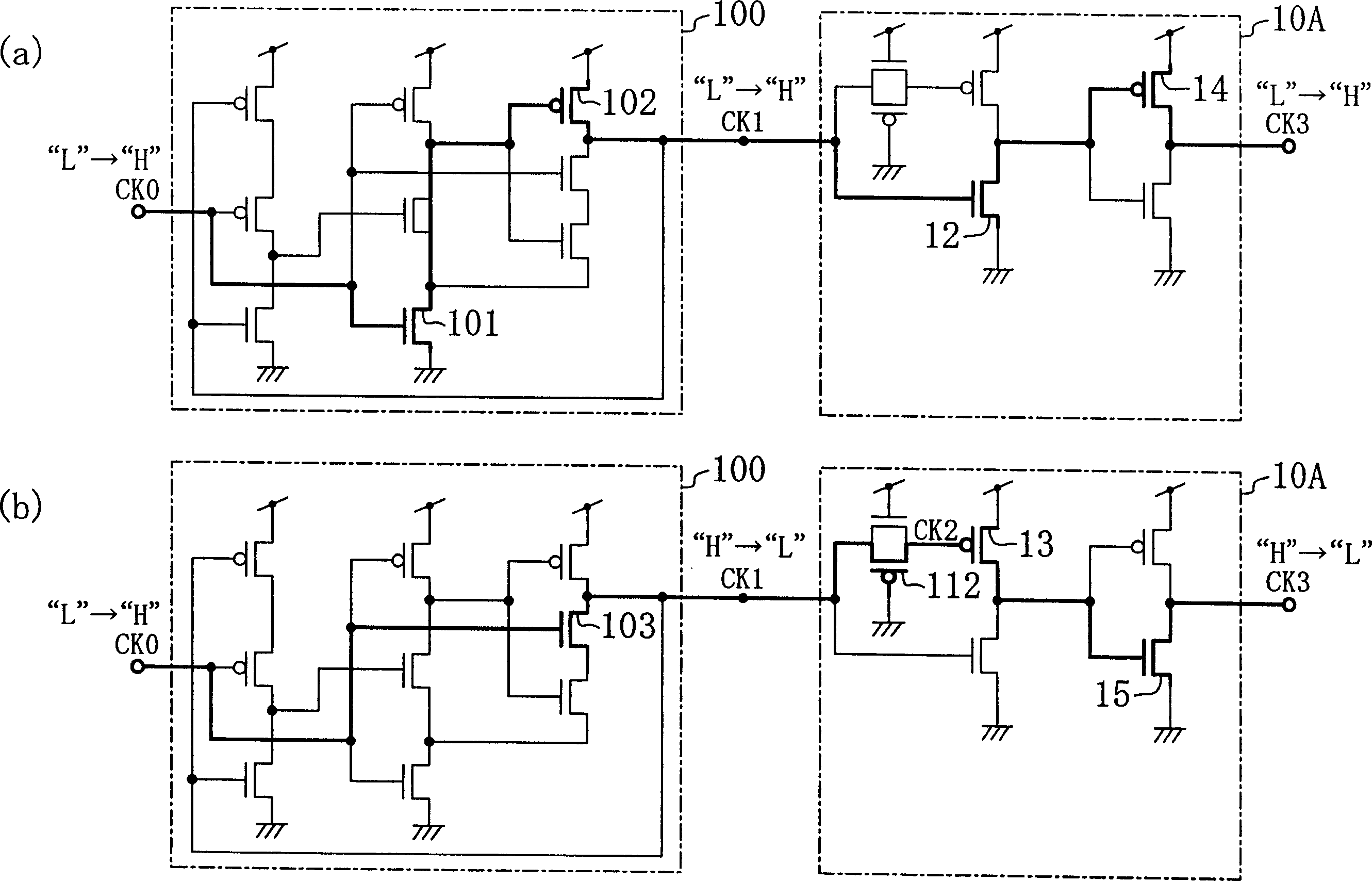

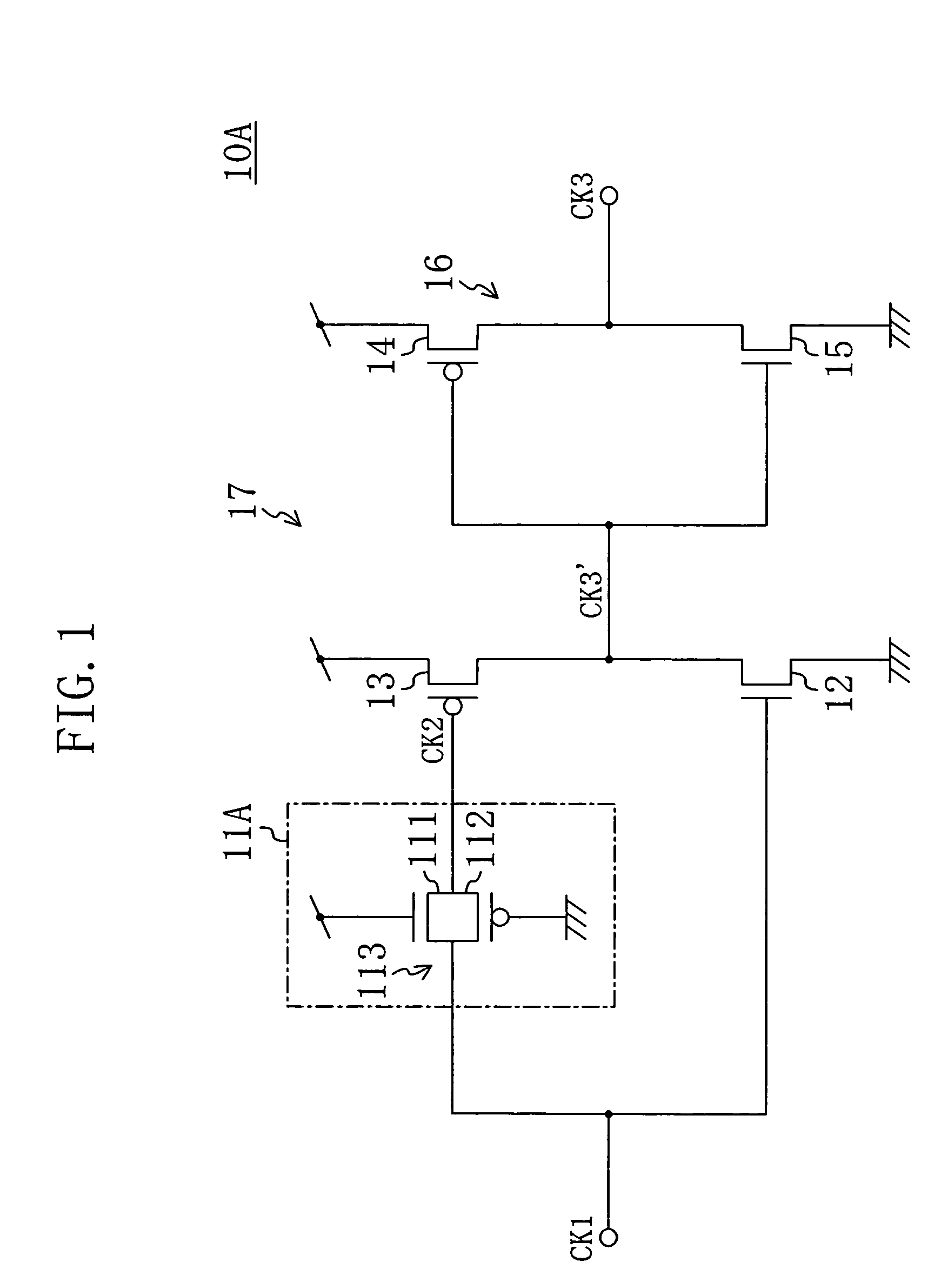

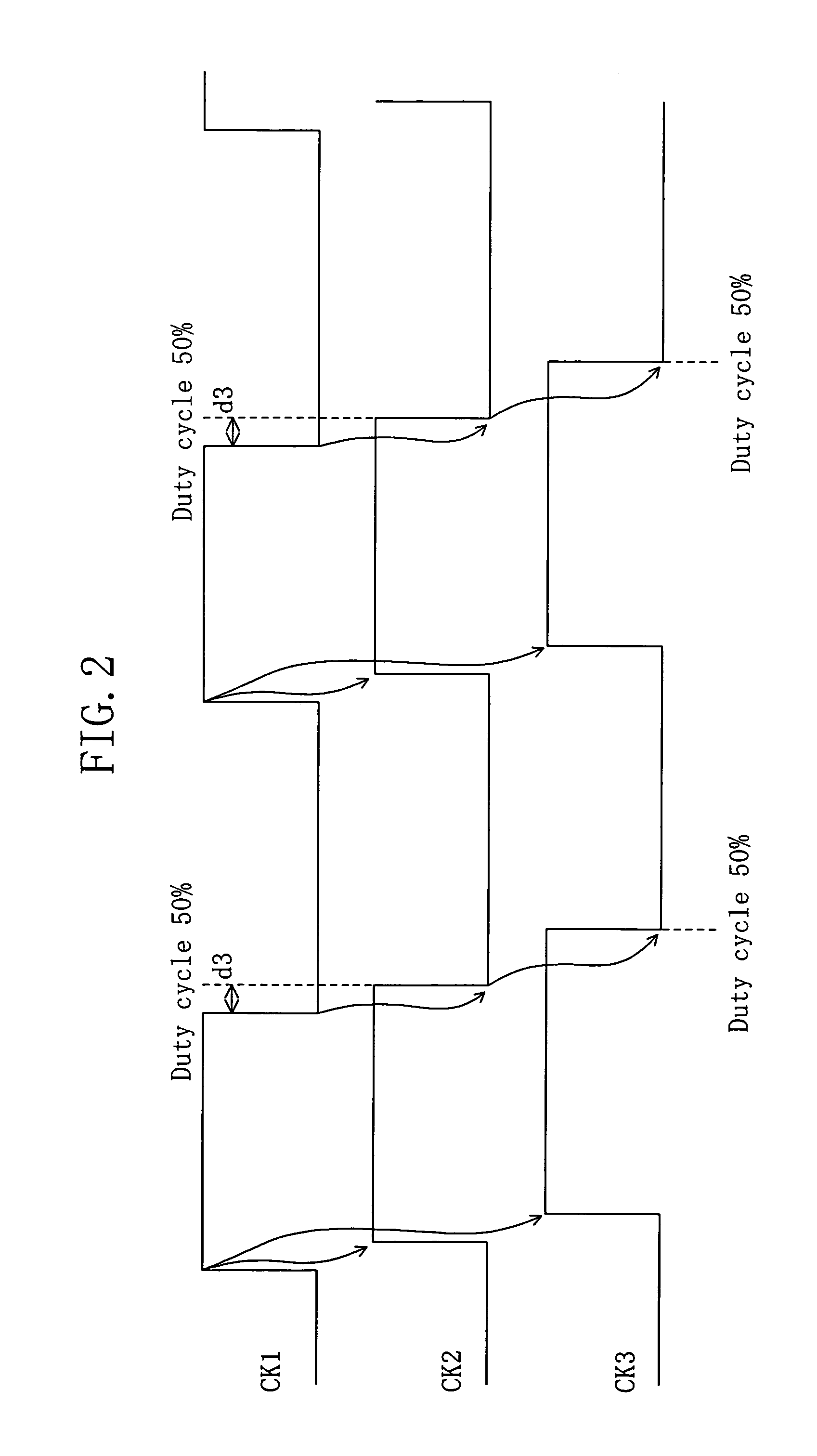

Duty ratio correction circuit

InactiveCN1507156APulse automatic controlContinuous to patterned pulse manipulationCommon drainEngineering

Provided is a duty cycle correction circuit for correcting a duty cycle of an imparted clock to obtain a clock whose duty cycle is 50%. A duty cycle correction circuit is provided with: a delay part 11A for delaying a clock CK1 to output a clock CK2; and a clock output part 17 composed of transistors 12, 13 with the clocks CK1, CK2 as respective gate inputs, and an inverter circuit 16 for inverting a signal CK3' which is a common drain output of the transistors to output a clock CK3. The delay part 11A delays the clock CK1 so that the falling change of the clock CK1 may appear at a timing of duty cycle 50%. The transistors 12, 13 output a ground voltage and a power supply voltage from their common drain in accordance with the rising change of the clock CK1 and the falling change of the clock CK2 (signal CK3'). The clock CK3 whose duty cycle is finally corrected to about 50% is then obtained.

Owner:PANASONIC CORP

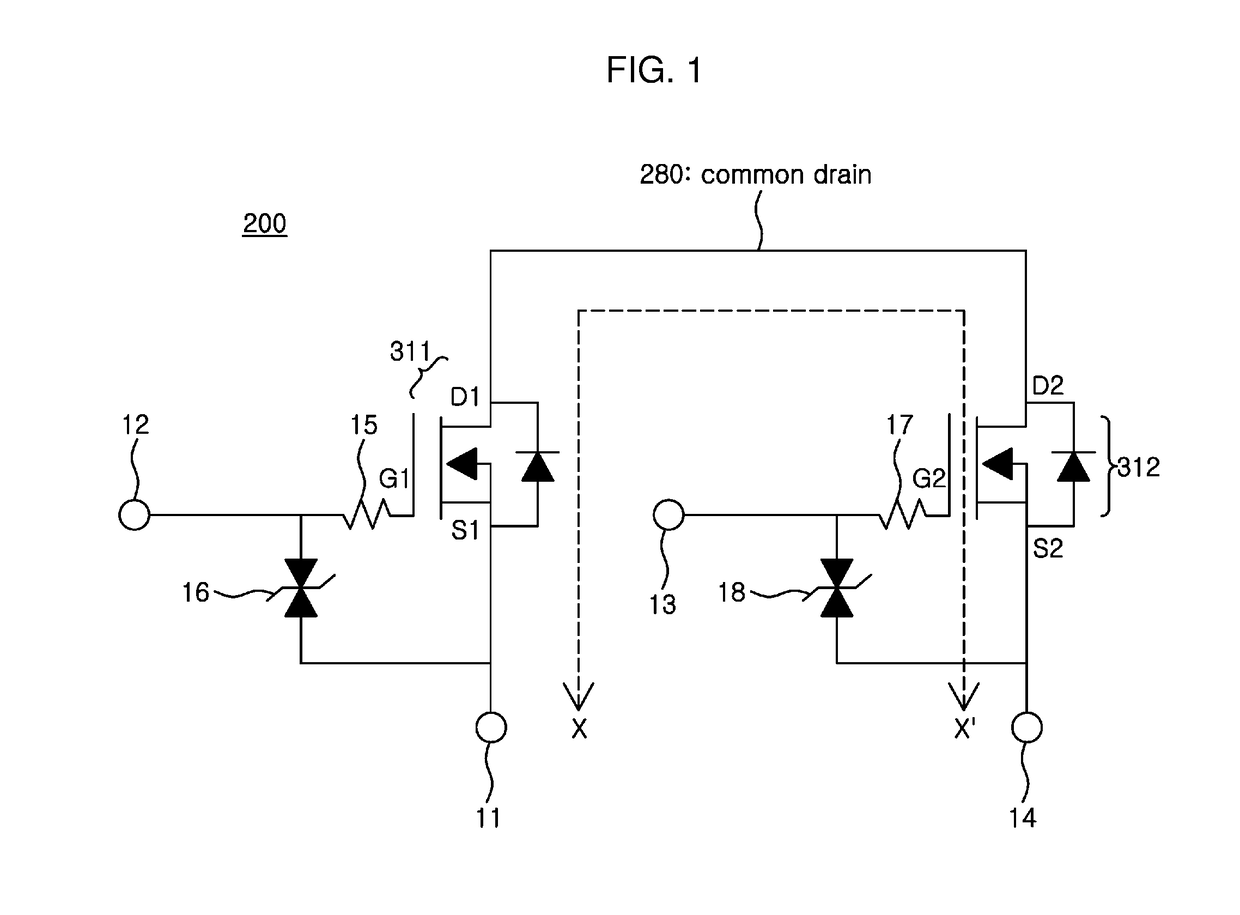

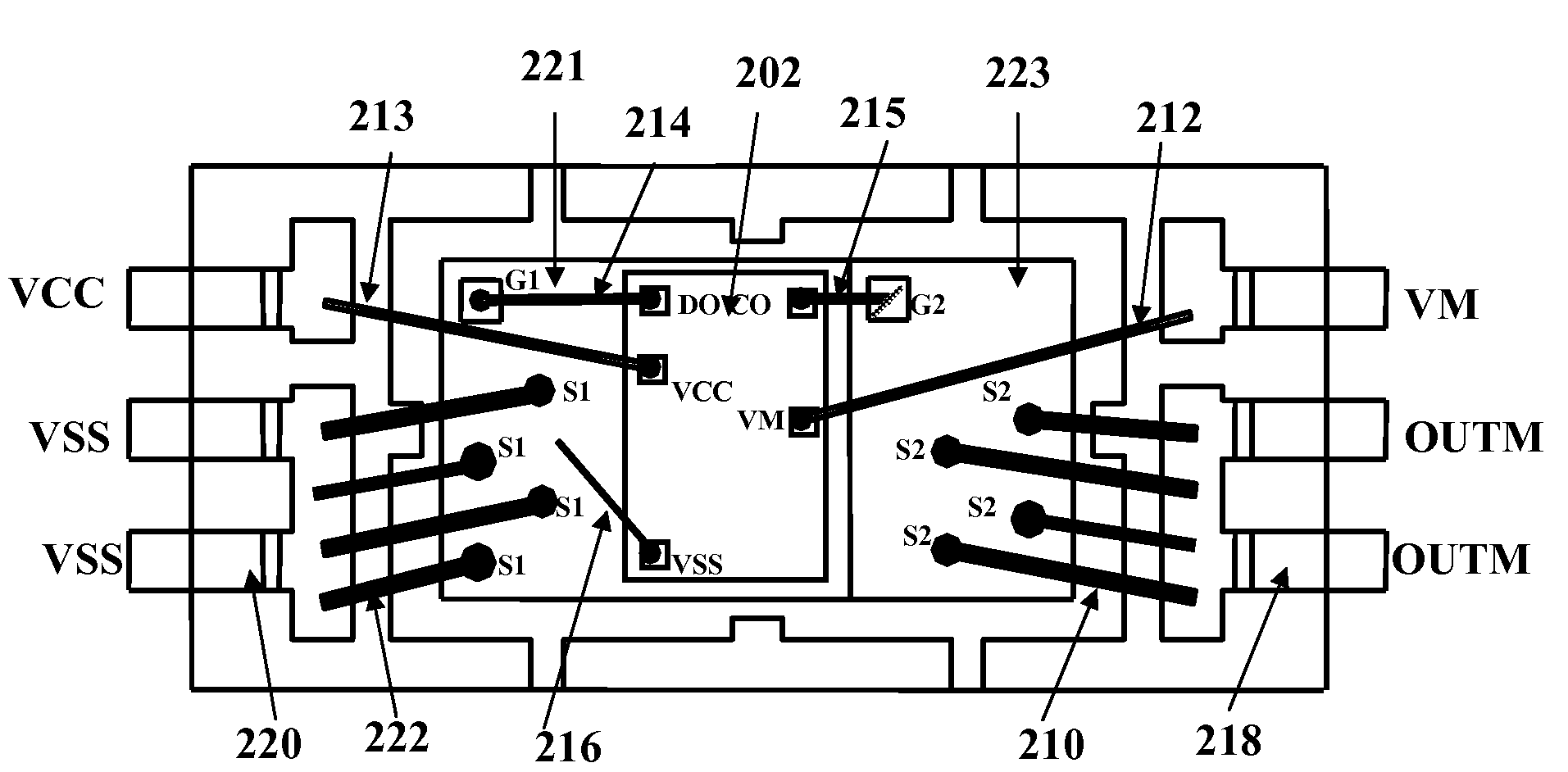

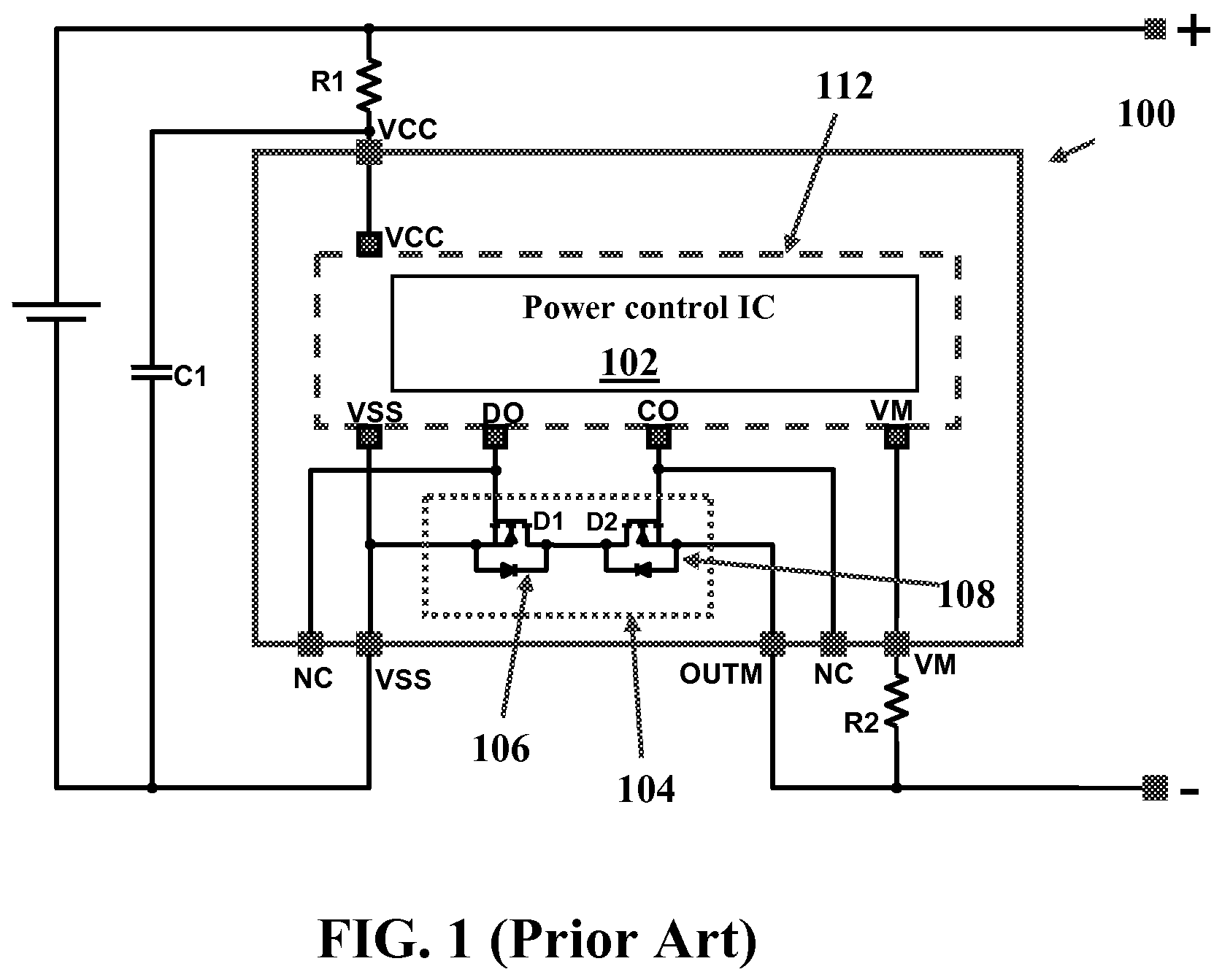

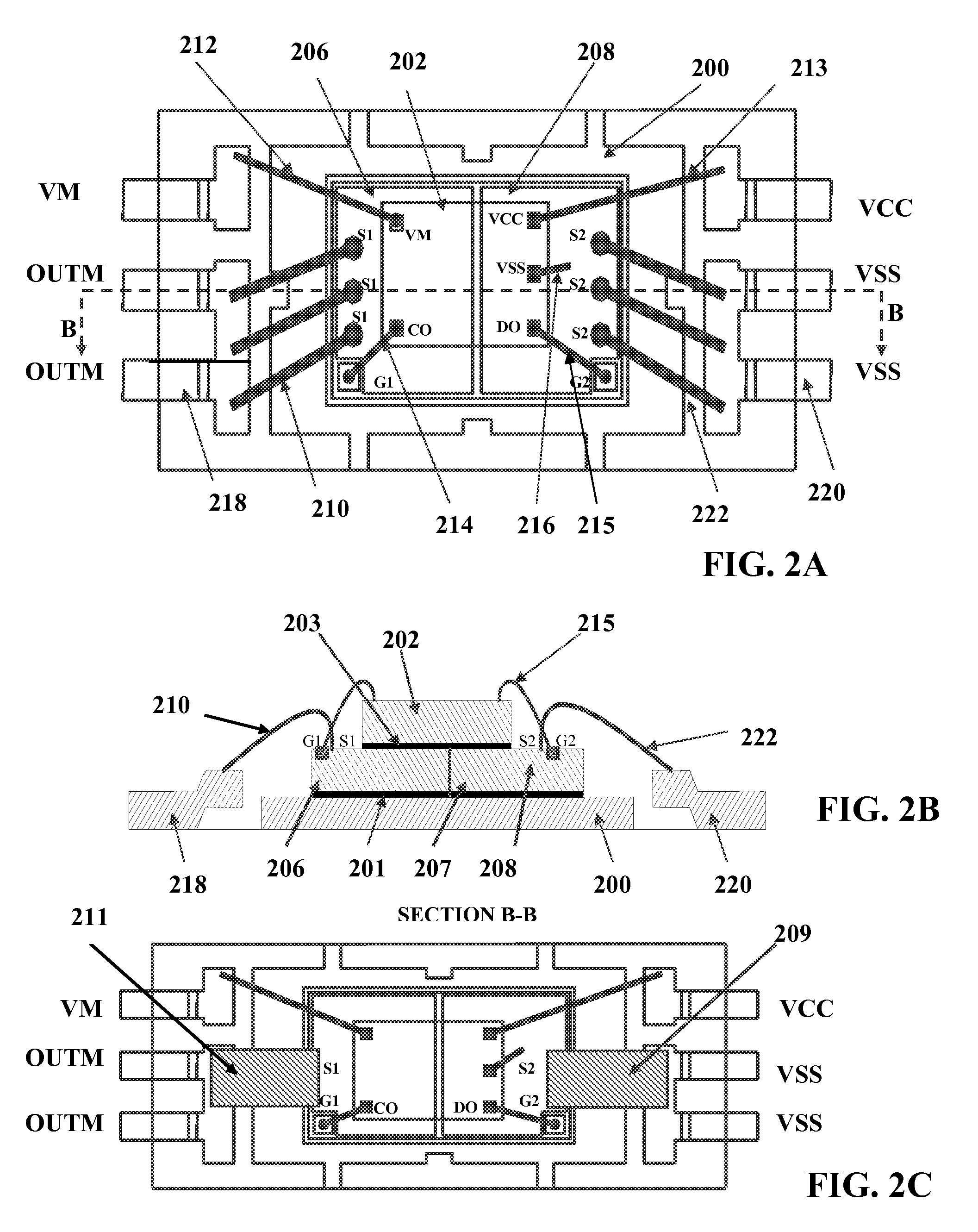

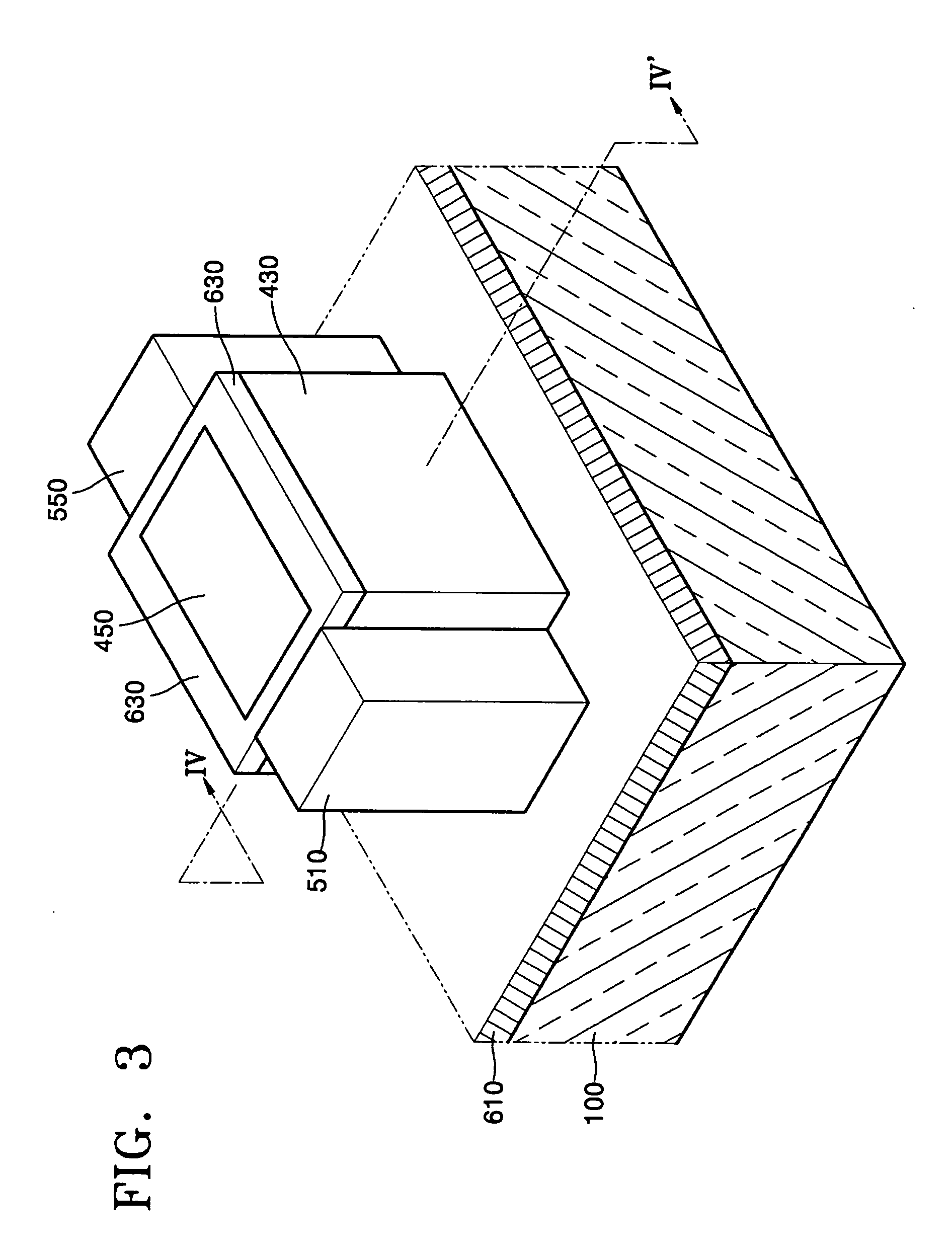

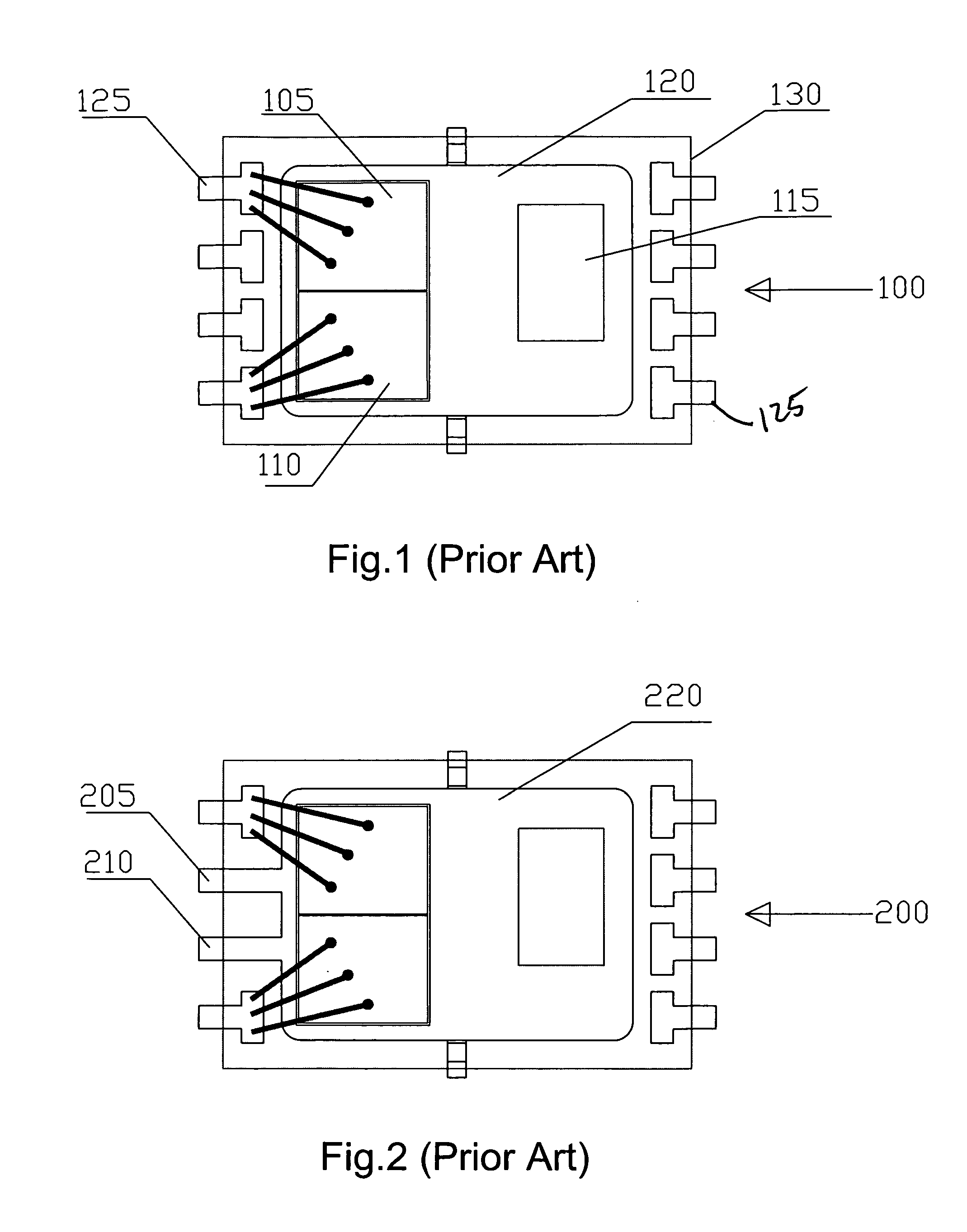

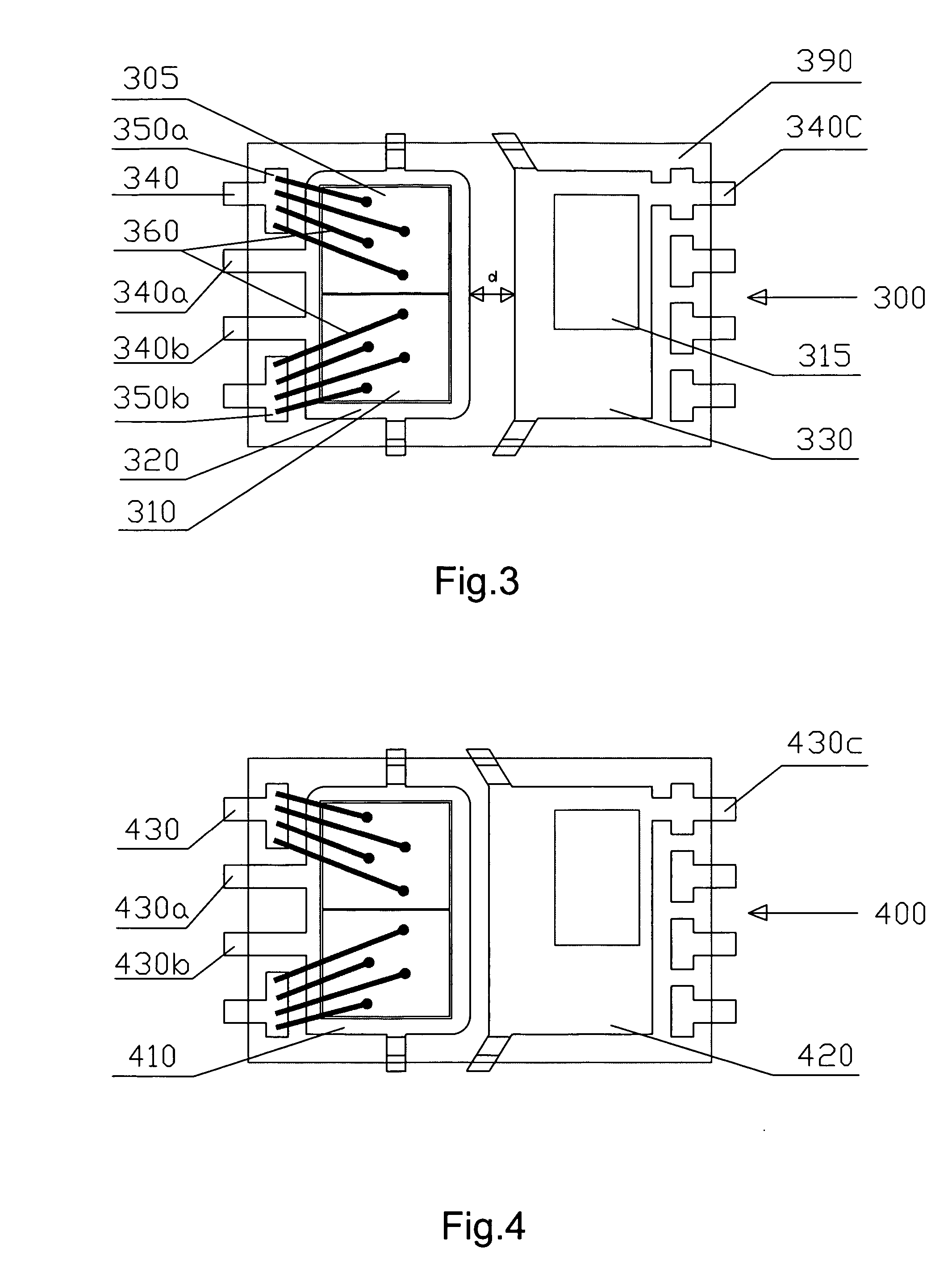

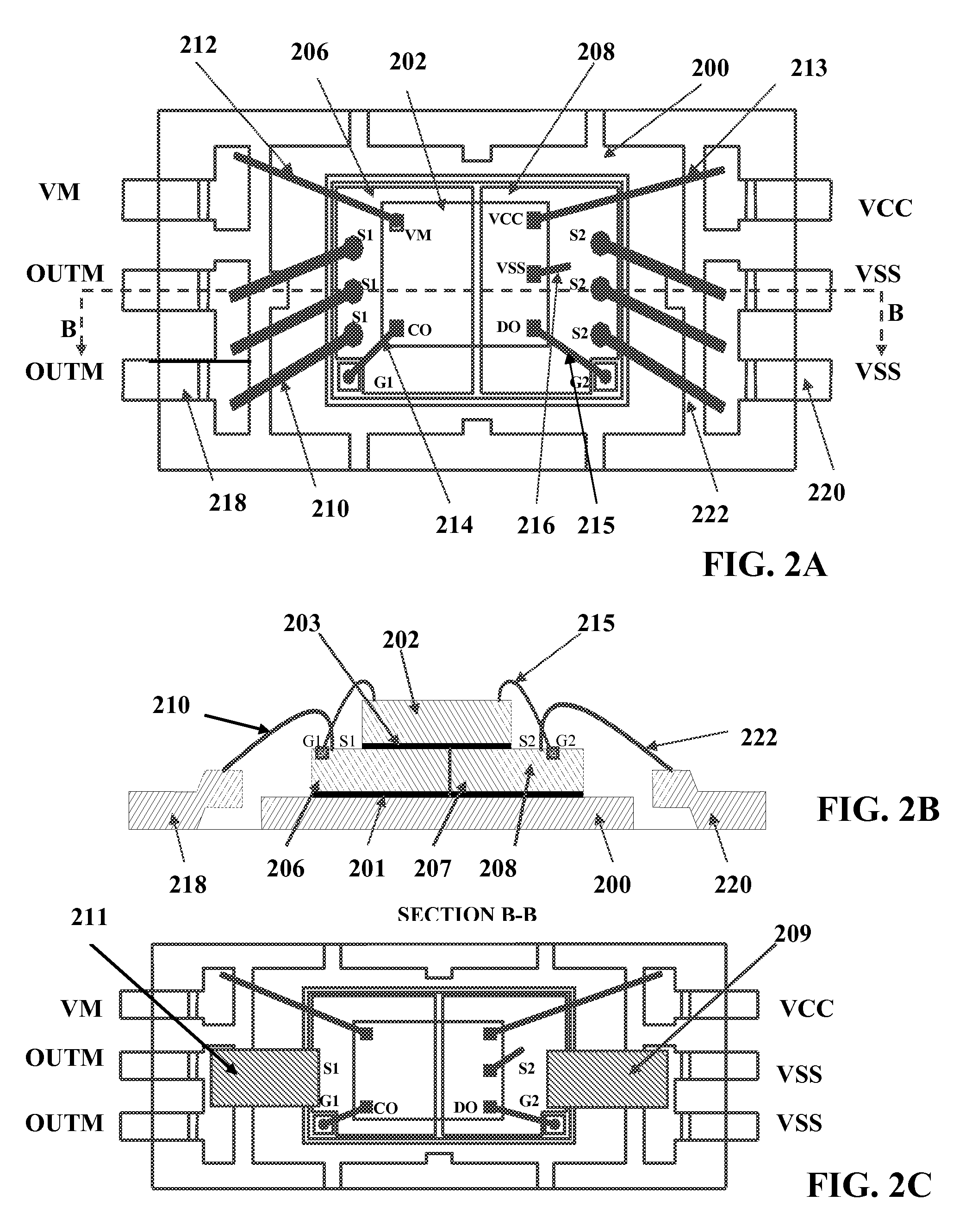

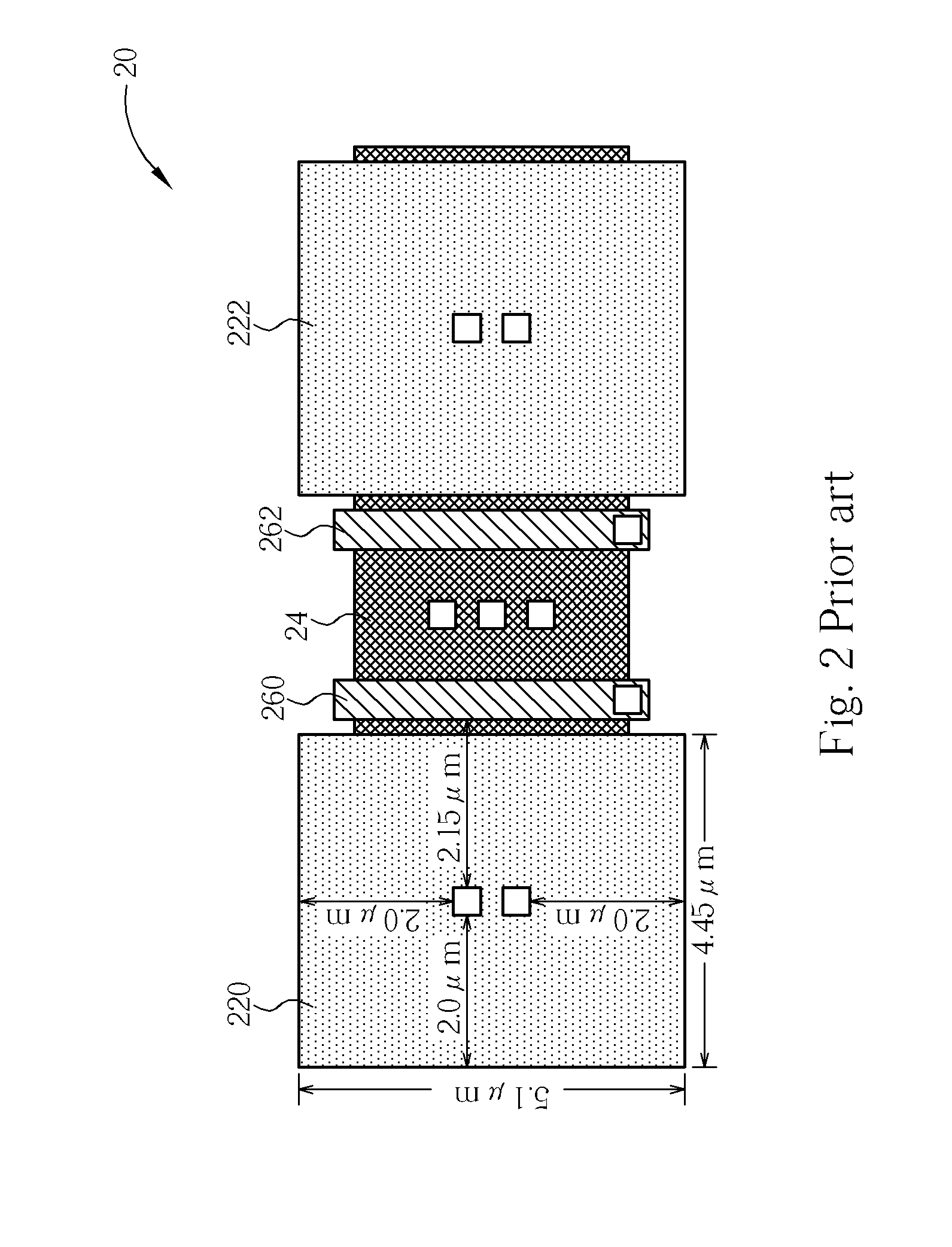

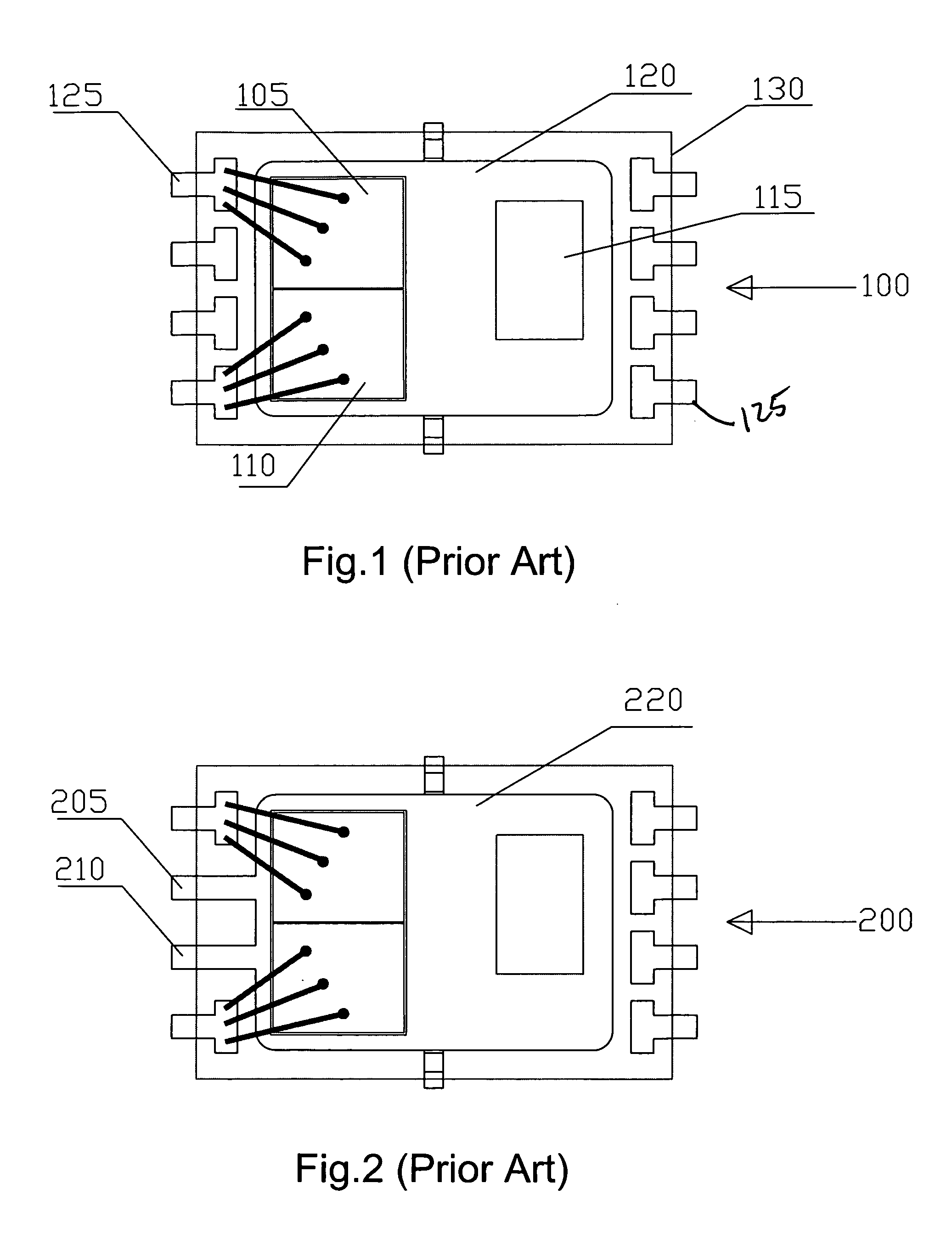

Stacked-die package for battery power management

ActiveUS20090128968A1Reduce thicknessLower turn-on resistanceSemiconductor/solid-state device detailsSolid-state devicesMOSFETCommon drain

A stacked-die package for battery protection is disclosed. The battery protection package includes a power control integrated circuit (IC) stacked on top of integrated dual common-drain metal oxide semiconductor field effect transistors (MOSFETs) or two discrete MOSFETs. The power control IC is either stacked on top of one MOSFET or on top of and overlapping both two MOSFETs.

Owner:ALPHA & OMEGA SEMICON LTD

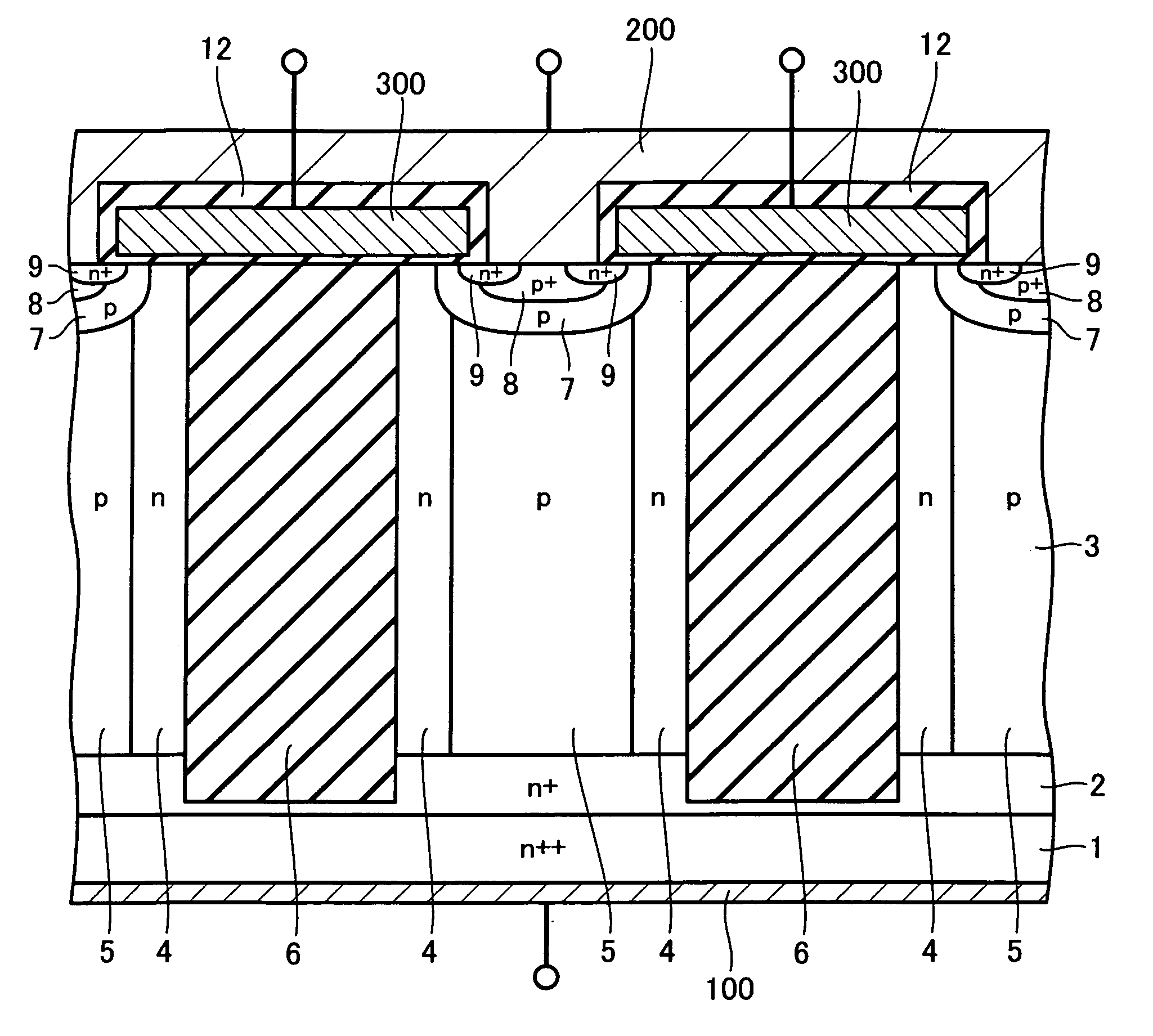

Semiconductor device and method of manufacturing the same

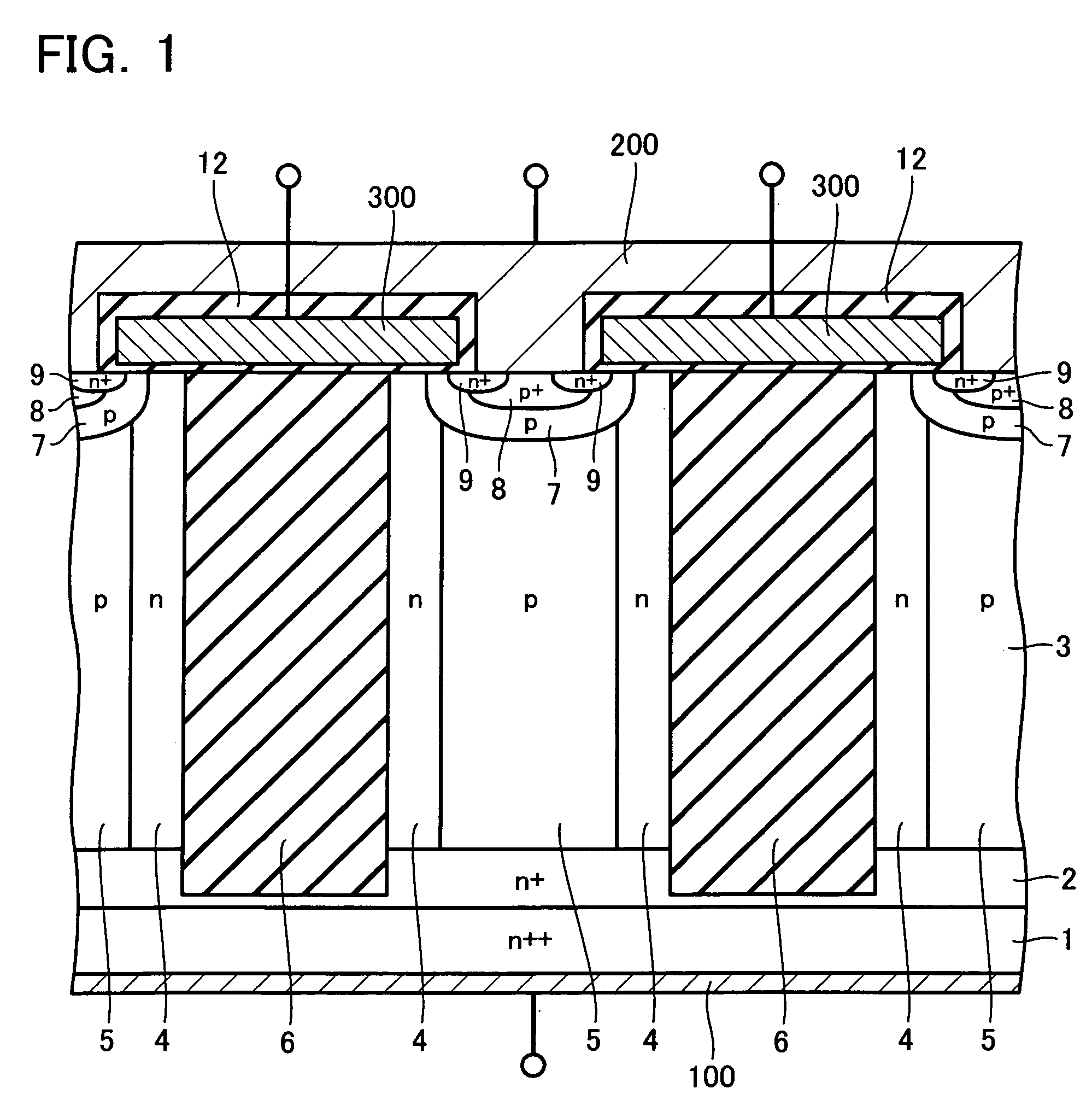

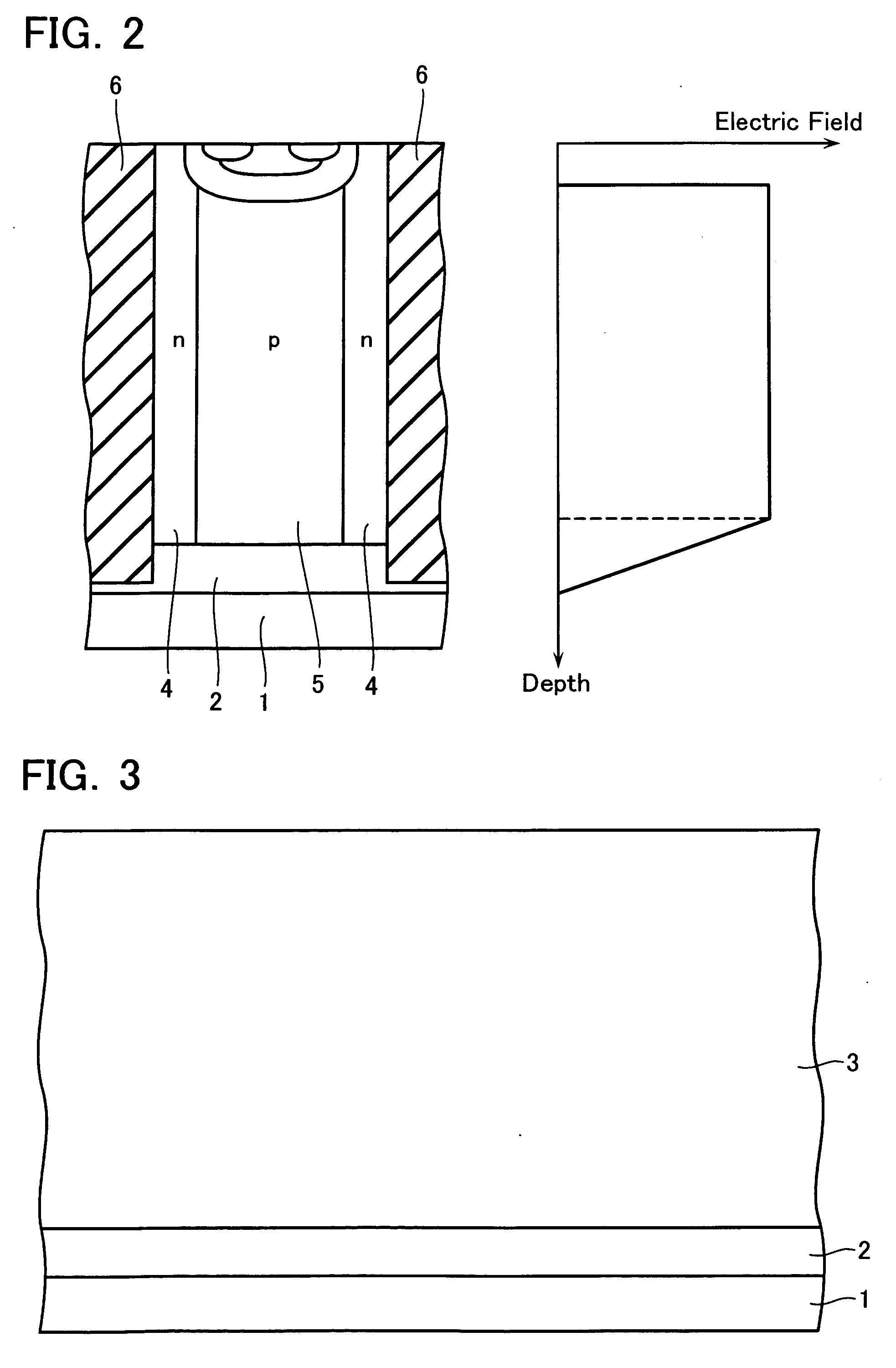

A semiconductor substrate of a first conduction type is provided for serving as a common drain to a plurality of power MISFET cells. A middle semiconductor layer is formed on the semiconductor substrate and has a lower impurity concentration than that of the semiconductor substrate. Pillar regions are formed on the middle semiconductor layer and include semiconductor regions of the first conduction type having a lower impurity concentration than that of the middle semiconductor layer.

Owner:KK TOSHIBA

Multi bits flash memory device and method of operating the same

A multi bits flash memory device and a method of operating the same are disclosed. The multi bits flash memory device includes: a stacked structure including: a first active layer with a mesa-like form disposed on a substrate; a second active layer, having a different conductivity type from the first active layer, formed on the first active layer; an active interlayer isolation layer interposed between the first active layer and the second active layer such that the first active layer is electrically isolated from the second active layer; a common source and a common drain formed on a pair of opposite side surfaces of the stacked structure; a common first gate and a common second gate formed on the other pair of opposite side surfaces of the stacked structure; a tunnel dielectric layer interposed between the first and second gates and the first and second active layers; and a charge trap layer, storing charges that tunnel through the tunnel dielectric layer, interposed between the tunnel dielectric layer and the first and second gates.

Owner:SAMSUNG ELECTRONICS CO LTD

Low side N-channel FET protection circuit

The present invention relates to a battery protection circuit for protecting a plurality of batteries connected in series. The battery protection circuit includes: a controller for monitoring the batteries and outputting control signals based on predetermined conditions associated with the batteries; a first N-channel MOSFET and a second N-channel MOSFET coupled in a common-drain configuration in a low-side path, wherein at least one of the first and second N-channel MOSFETs turns off in response to the control signal received from the controller when at least one of the predetermined conditions is detected; and a gate protection circuit for preventing gate-to-source voltages of the first and second N-channel MOSFETs from exceeding a predetermined gate-to-source voltage level.

Owner:INT COMPONENTS

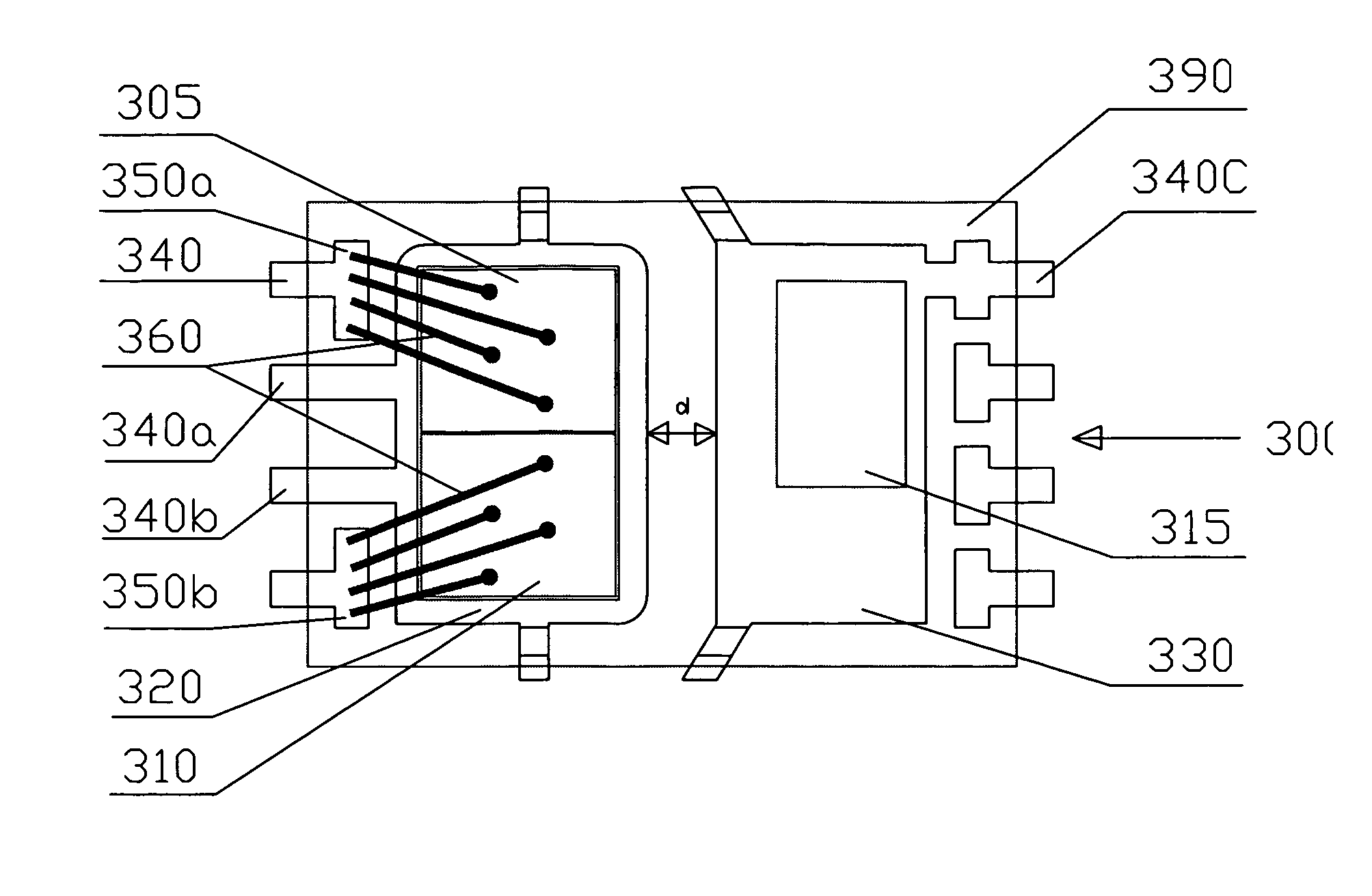

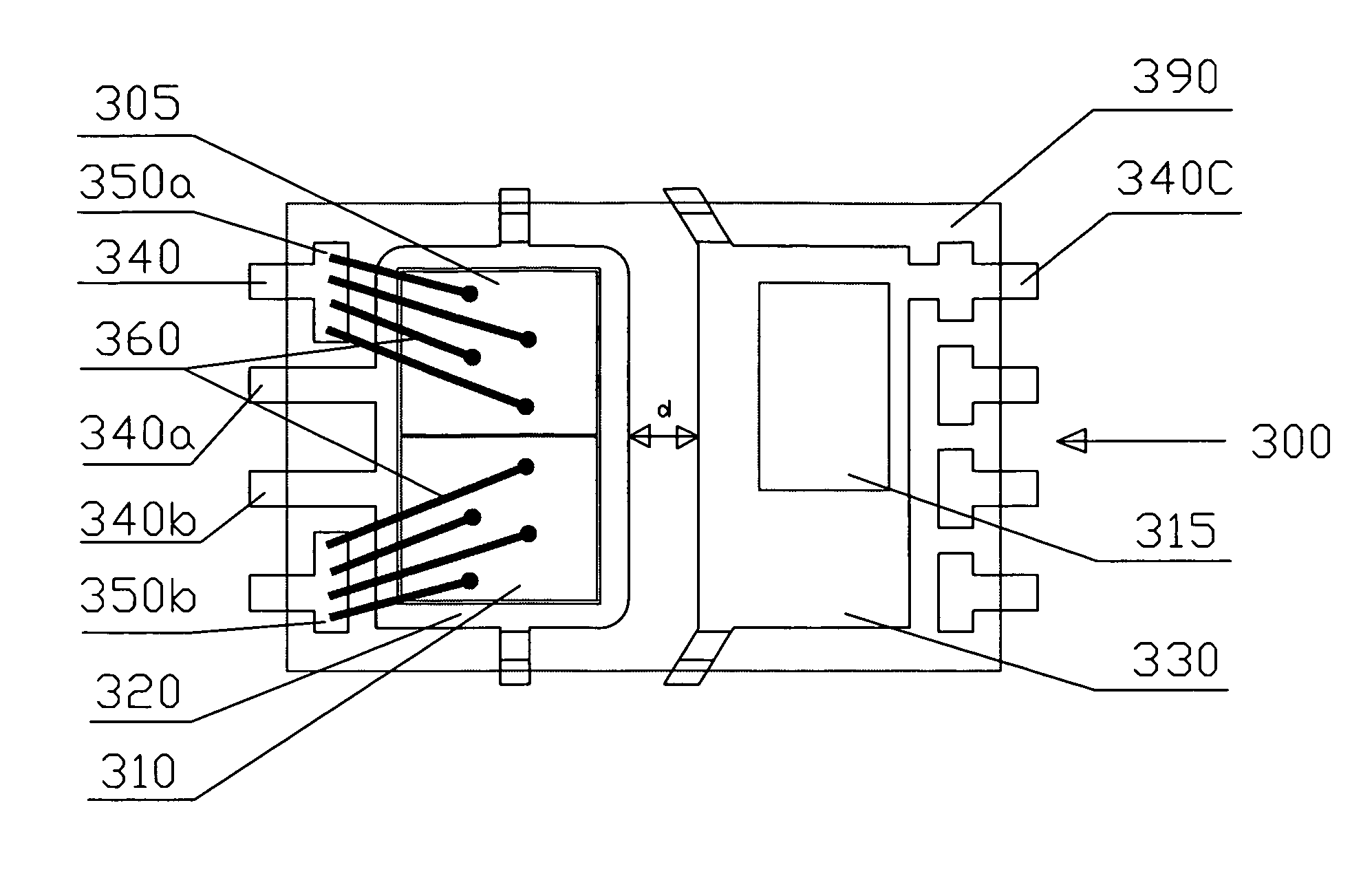

Semiconductor package having improved thermal performance

ActiveUS20070145609A1Reduce the amount of solutionImprove thermal efficiencySemiconductor/solid-state device detailsSolid-state devicesMOSFETSemiconductor package

A composite semiconductor package is disclosed. The package includes a lead frame having first and second die bonding pads, the first and second die bonding pads having a large lateral separation therebetween, a first device bonded to the first die bonding pad, a second device bonded to the second die bonding pad, a plurality of first leads coupled to the first die bonding pad, a plurality of second leads coupled to the second die bonding pad, and an encapsulant covering the lead frame, the first and second devices and at least a portion of the first and second pluralities of leads. The package may be a TSSOP-8 composite package having a common drain MOSFET pair and an IC.

Owner:ALPHA & OMEGA SEMICON LTD

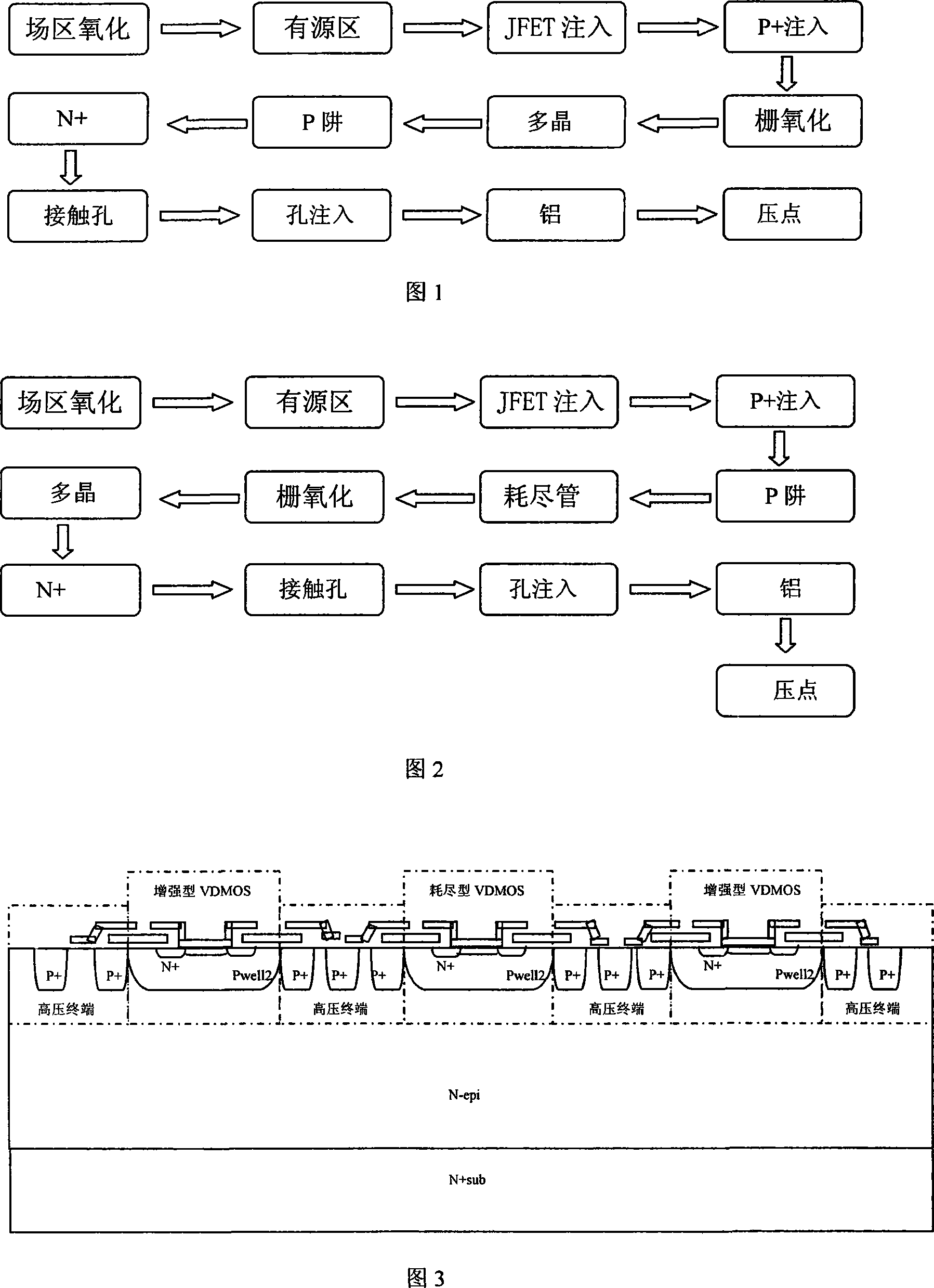

Bi-directional DMOS with common drain

ActiveUS20100032757A1Reduced series resistanceWithout adding fabrication cost and complexitySolid-state devicesSemiconductor/solid-state device manufacturingOxide semiconductorCommon drain

A three terminal bi-directional laterally diffused metal oxide semiconductor (LDMOS) transistor which includes two uni-directional LDMOS transistors in series sharing a common drain node, and configured such that source nodes of the uni-directional LDMOS transistors serve as source and drain terminals of the bi-directional LDMOS transistor. The source is shorted to the backgate of each LDMOS transistor. The gate node of each LDMOS transistor is clamped to its respective source node to prevent source-gate breakdown, and the gate terminal of the bi-directional LDMOS transistor is connected to the gate nodes of the constituent uni-directional LDMOS transistors through blocking diodes. The common drain is a deep n-well which isolates the two p-type backgate regions. The gate node clamp can be a pair of back-to-back zener diodes, or a pair of self biased MOS transistors connected source-to-source in series.

Owner:TEXAS INSTR INC

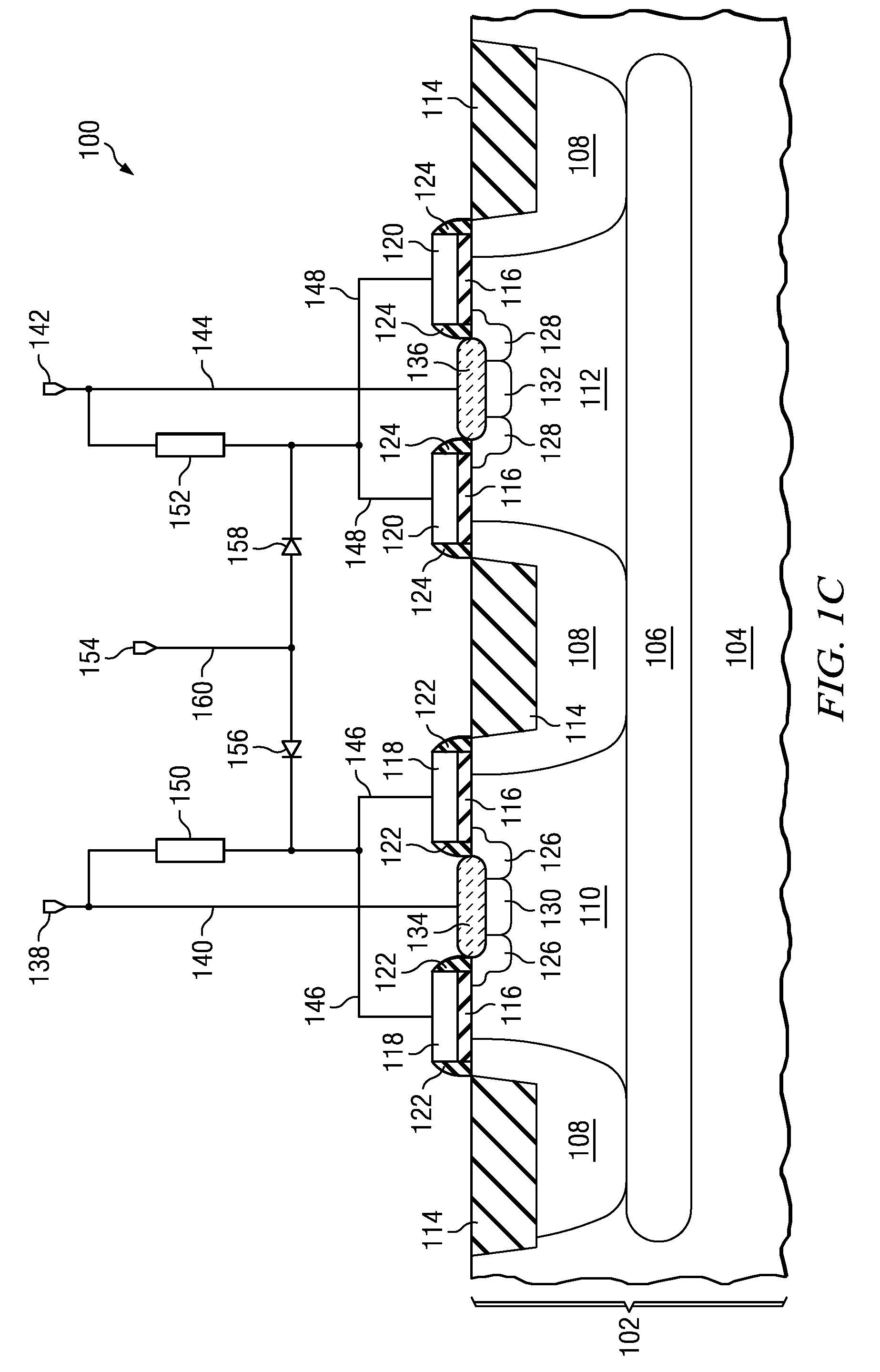

Single chip integration making technology for enhanced and consumption-up vertical dual diffusion field effect pipe

ActiveCN101127327AImprove compatibilityIncreased photolithographic injectionSemiconductor/solid-state device manufacturingBiochemical engineeringVoltage regulation

The utility model relates to a monolithic fabrication technology for the enhanced and depletion VDMOS, belonging to a technology applying for fabricating a enhanced and a depletion VDMOS with a high voltage (650V) common drain in one IC, which is characterized in that the material of the VDMOS adopting a N(100) substrate doped arsenic, which has a resistivity below 0.005 Omega-CM, the thickness of the epitaxy is 55Mum, the resistivity of the epitaxy is 24 Omega-CM. The withstand voltage can be stable on 650V, and up to 700V. To add a depletion VDMOS on the surface of the enhanced VDMOS, the depletion area needs a individual switching voltage adjustment, which is adding once more VT impurity, while adjusting the pre-and post process. The utility model has the advantages of fewer photoetching, low cost and simple fabricating control.

Owner:WUXI CRYSTAL SOURCE MICROELECTRONICS CO LTD

Stacked-die package for battery power management

ActiveUS7898092B2Improve performanceSmall sizeSemiconductor/solid-state device detailsSolid-state devicesMOSFETCommon drain

A stacked-die package for battery protection is disclosed. The battery protection package includes a power control integrated circuit (IC) stacked on top of integrated dual common-drain metal oxide semiconductor field effect transistors (MOSFETs) or two discrete MOSFETs. The power control IC is either stacked on top of one MOSFET or on top of and overlapping both two MOSFETs.

Owner:ALPHA & OMEGA SEMICON LTD

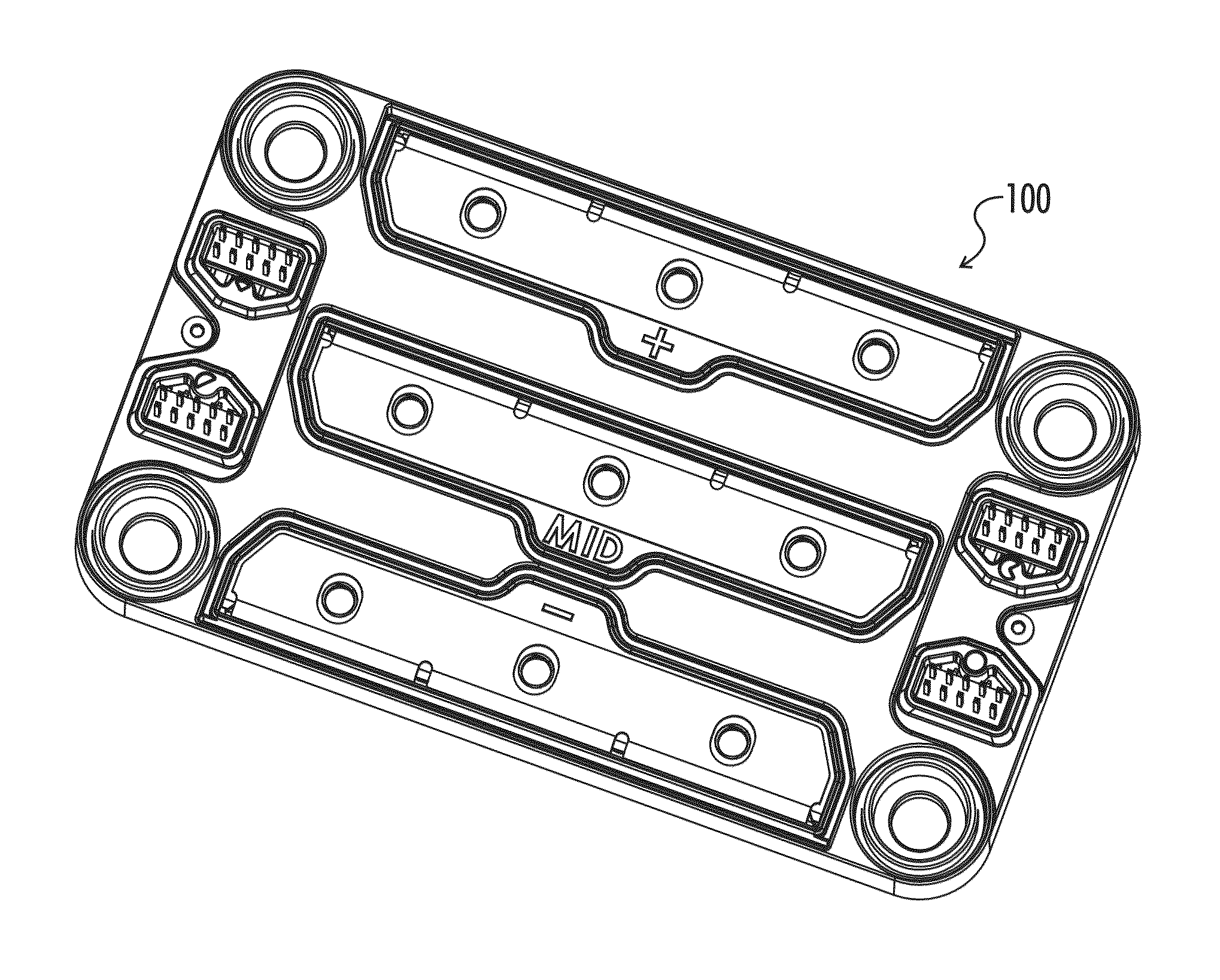

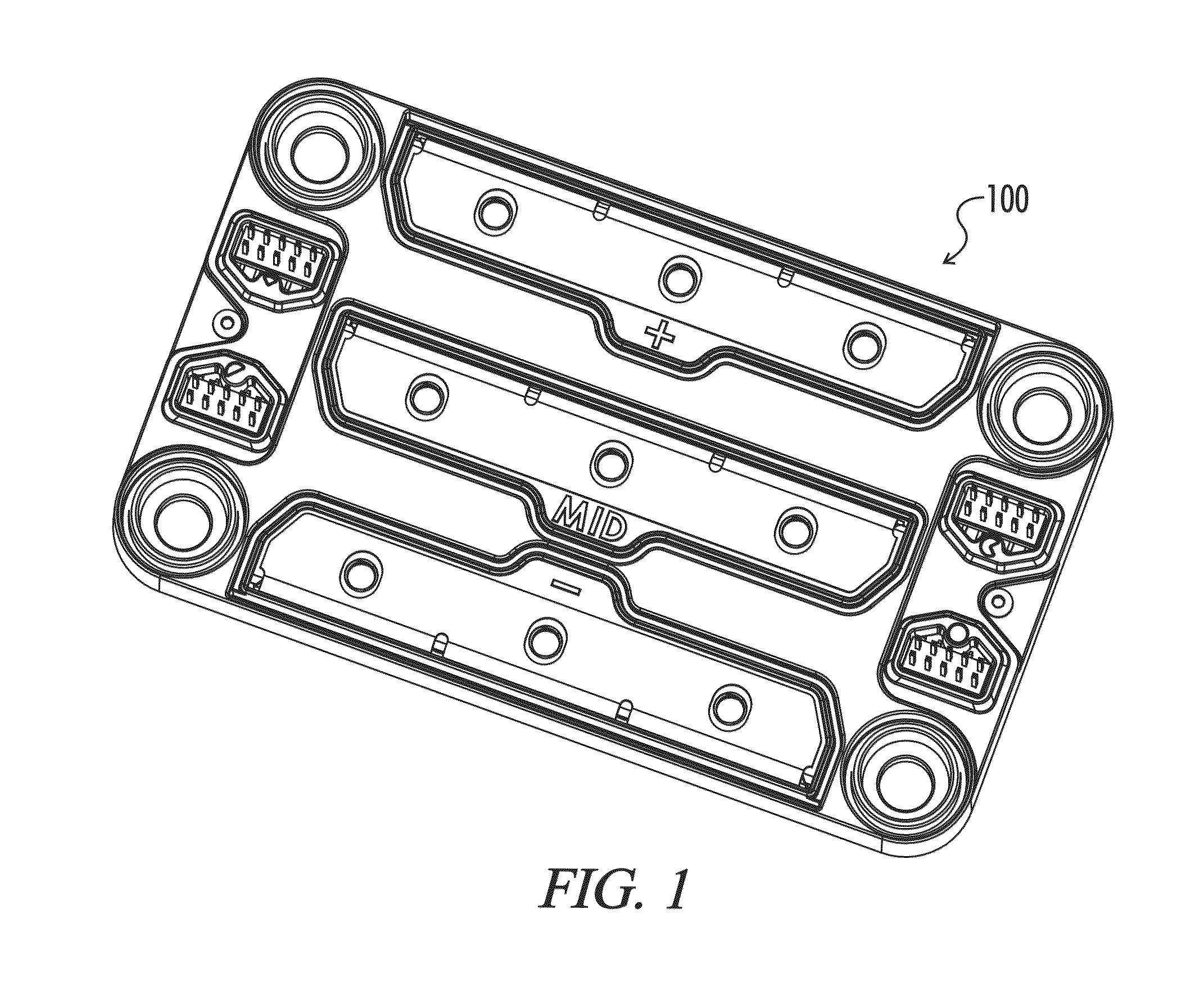

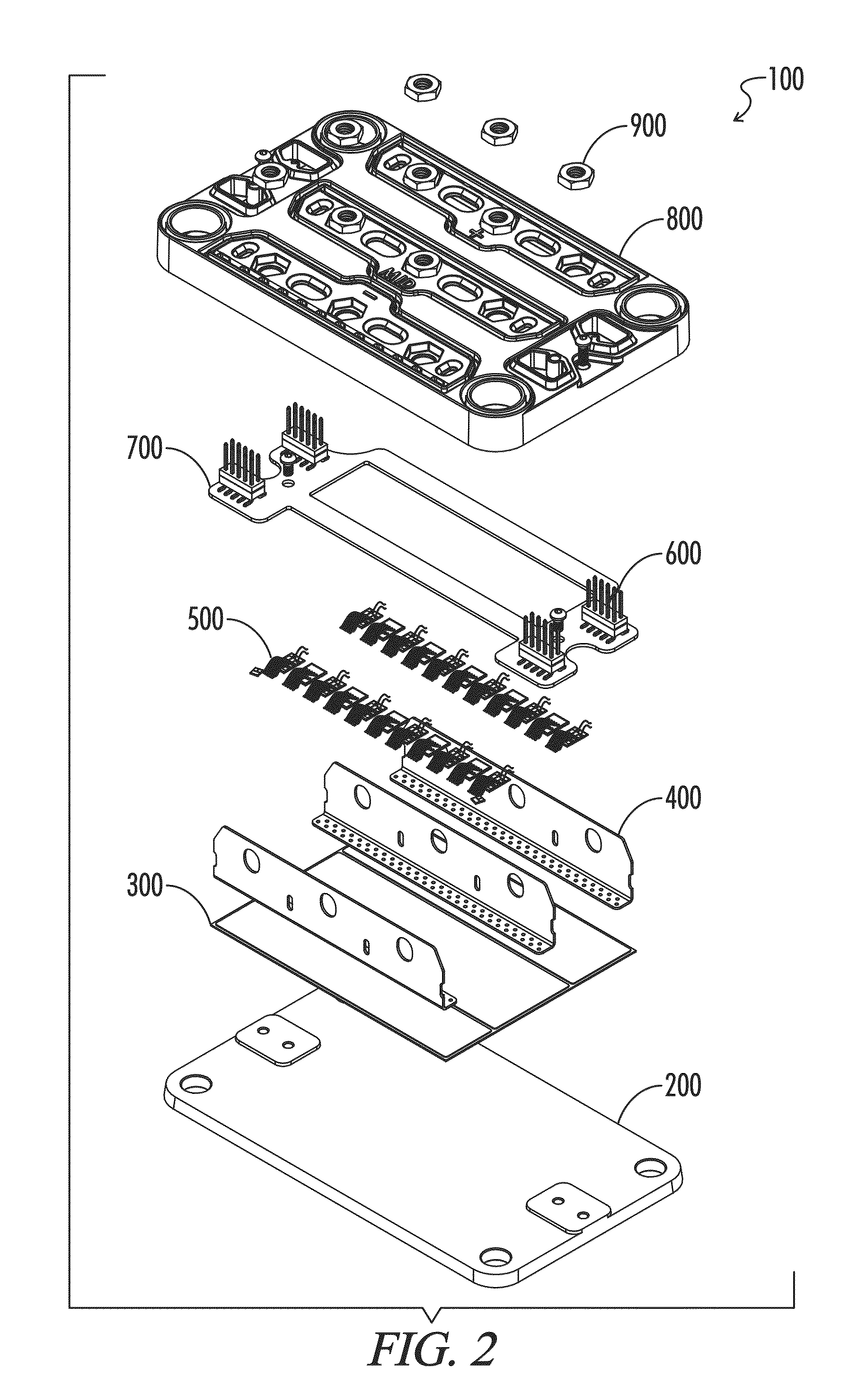

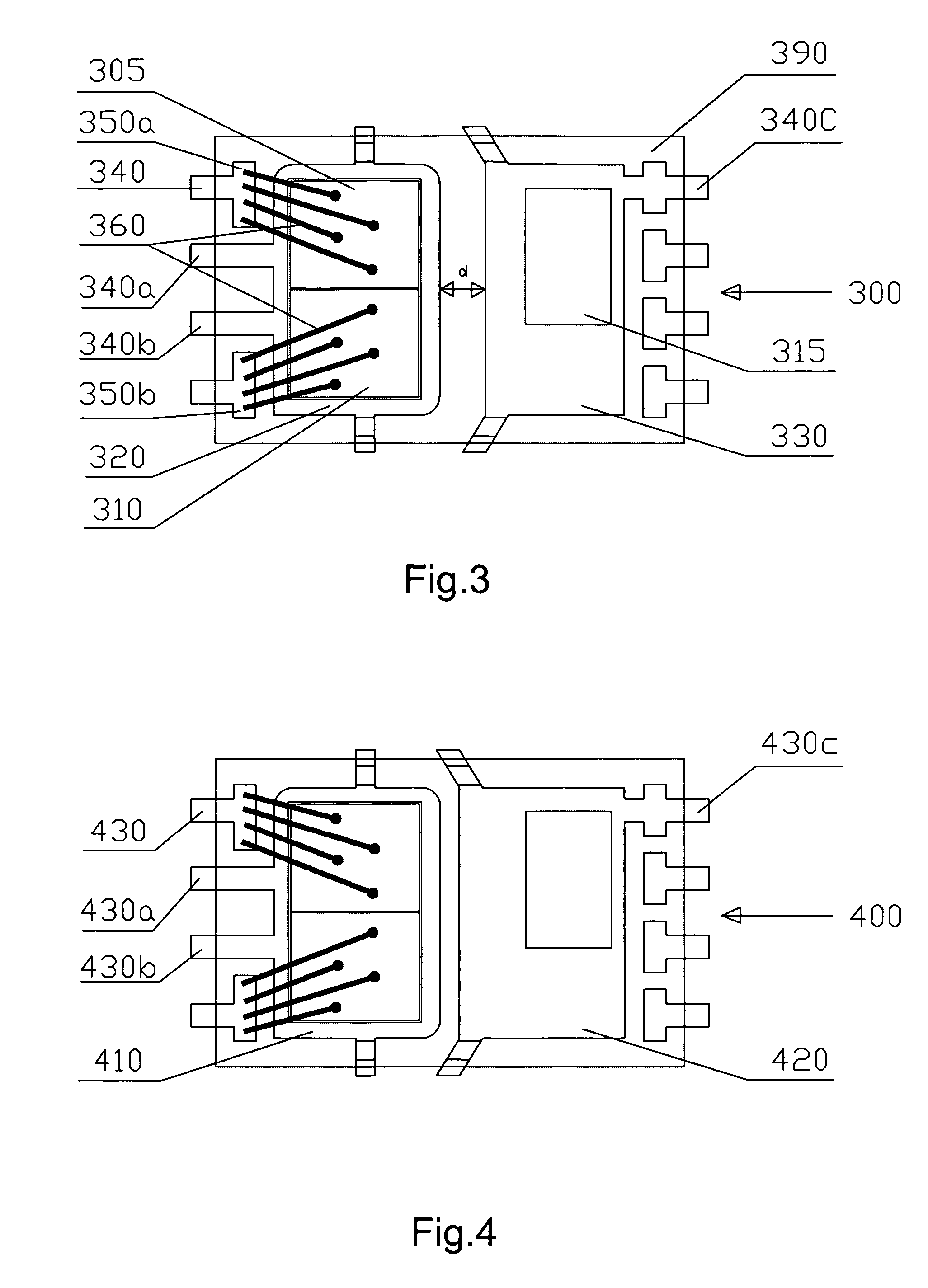

Low profile, highly configurable, current sharing paralleled wide band gap power device power module

ActiveUS9426883B2Closed casingsSemiconductor/solid-state device detailsElectrical conductorFull bridge

Owner:WOLFSPEED INC

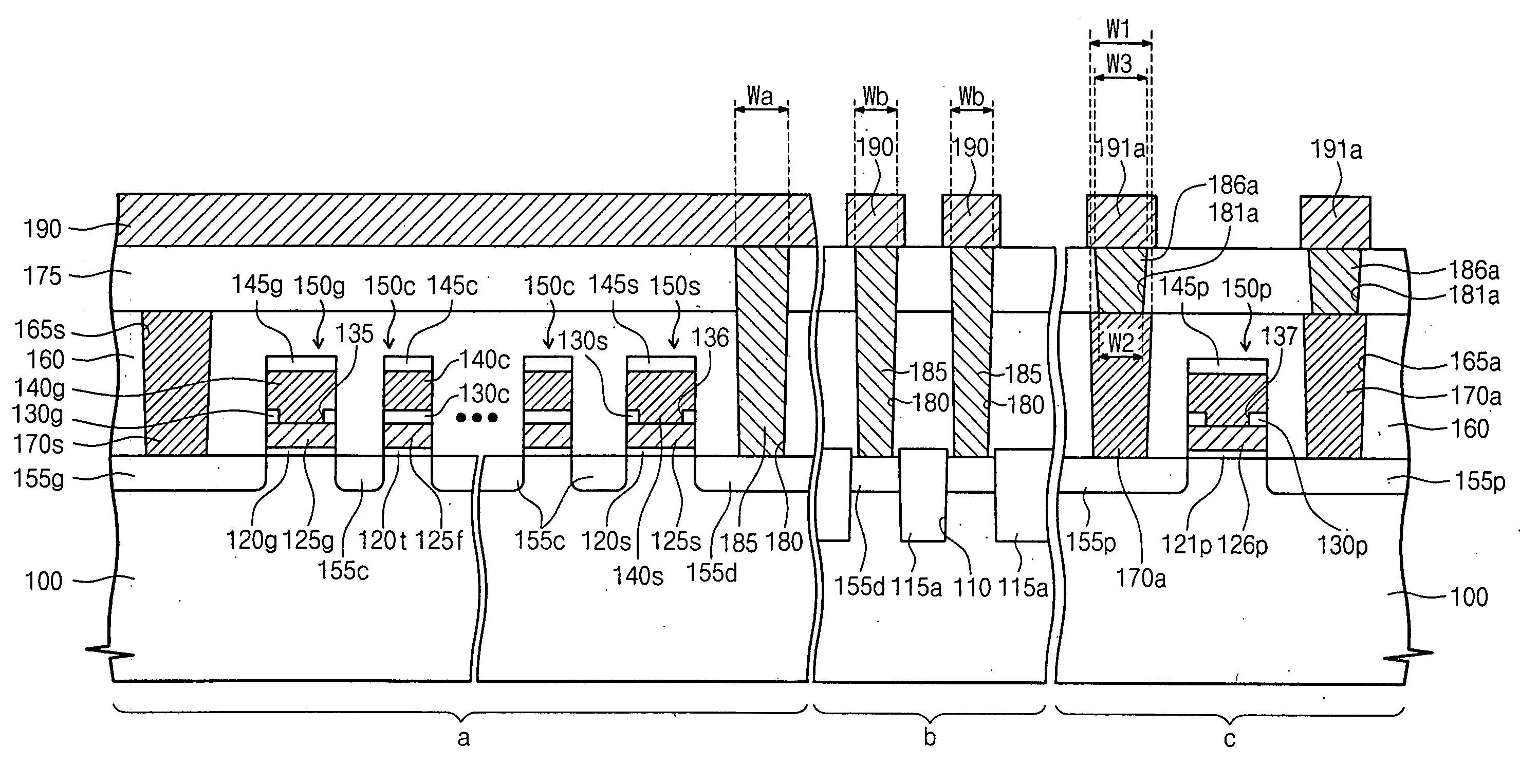

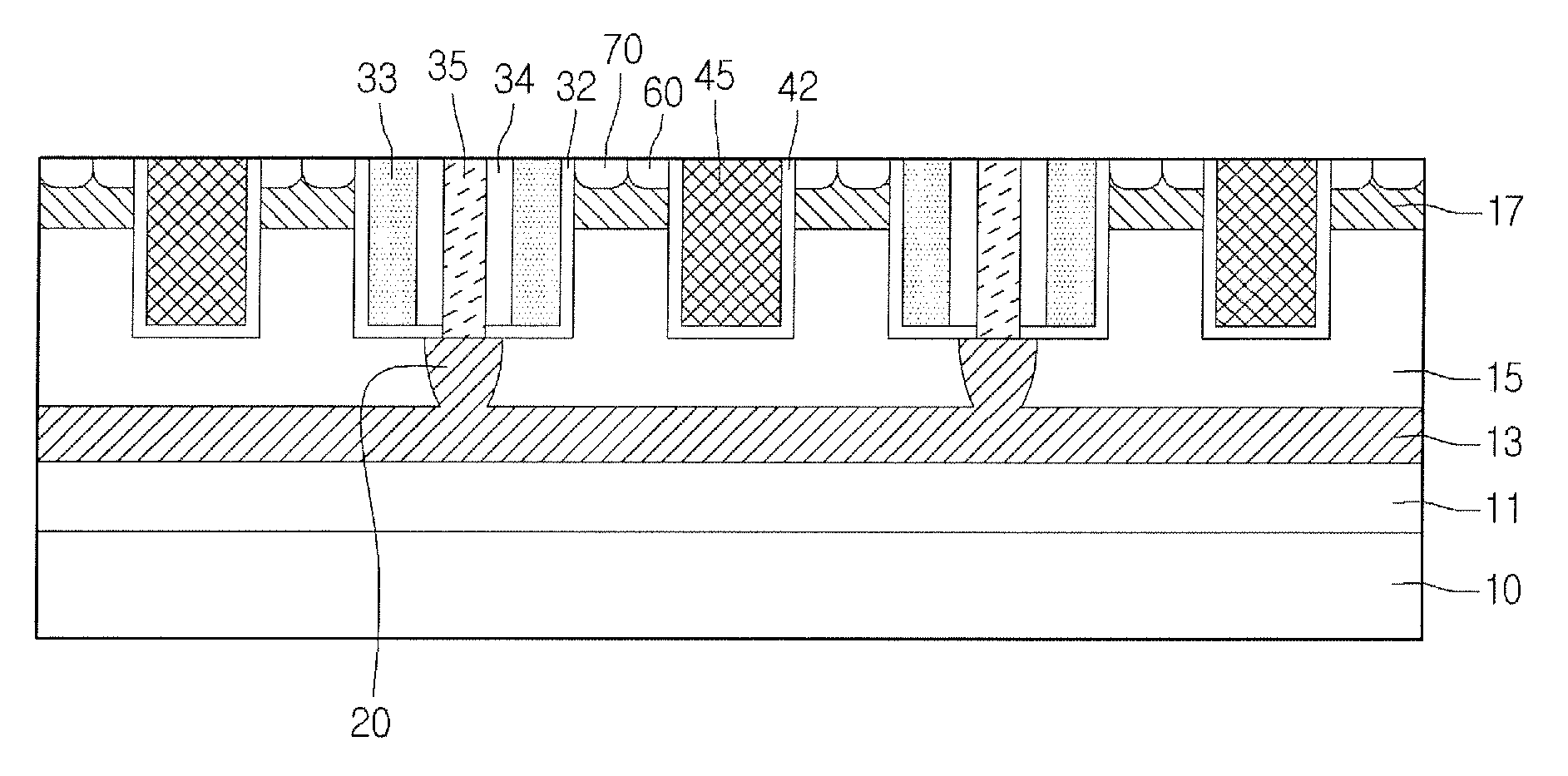

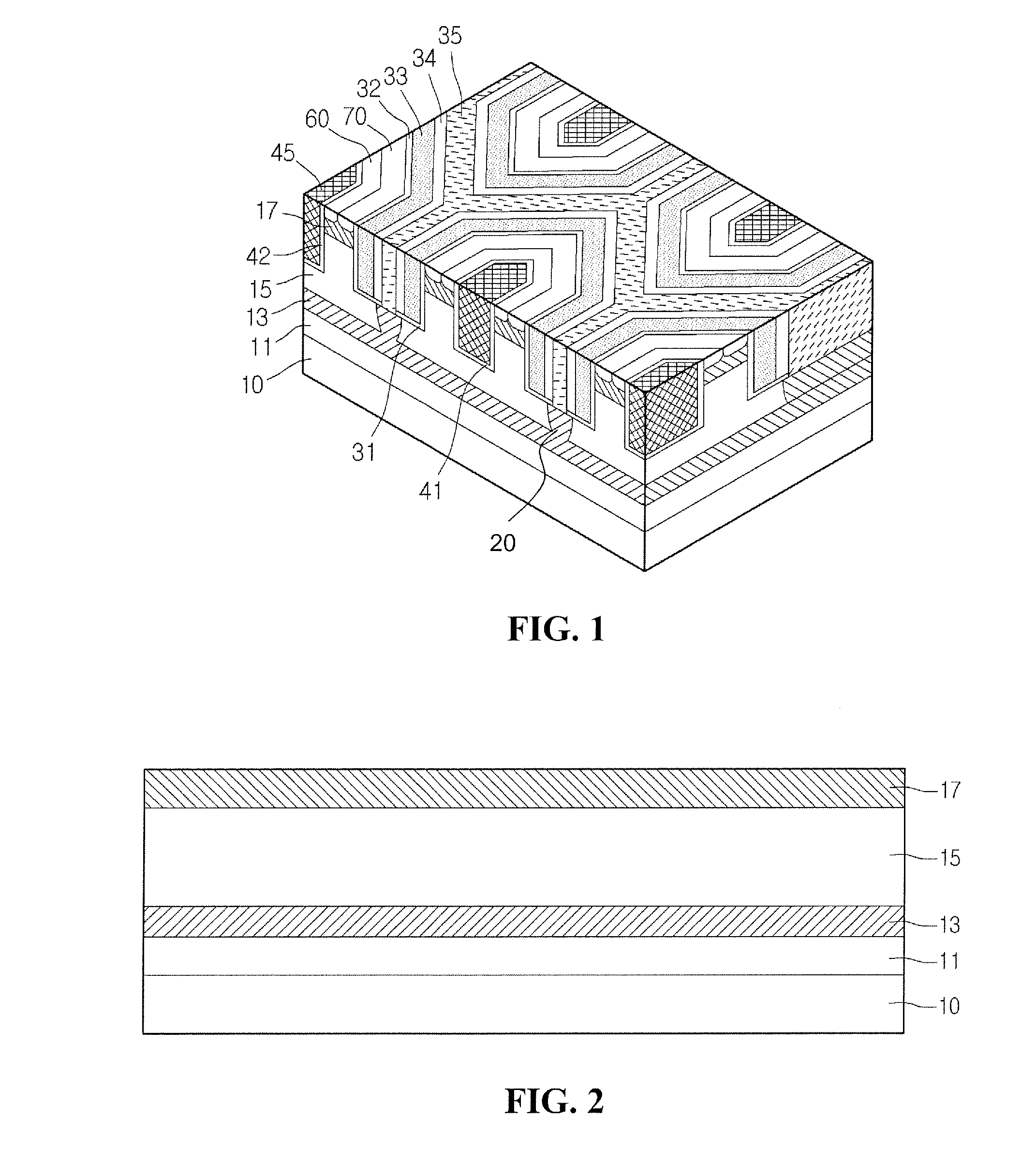

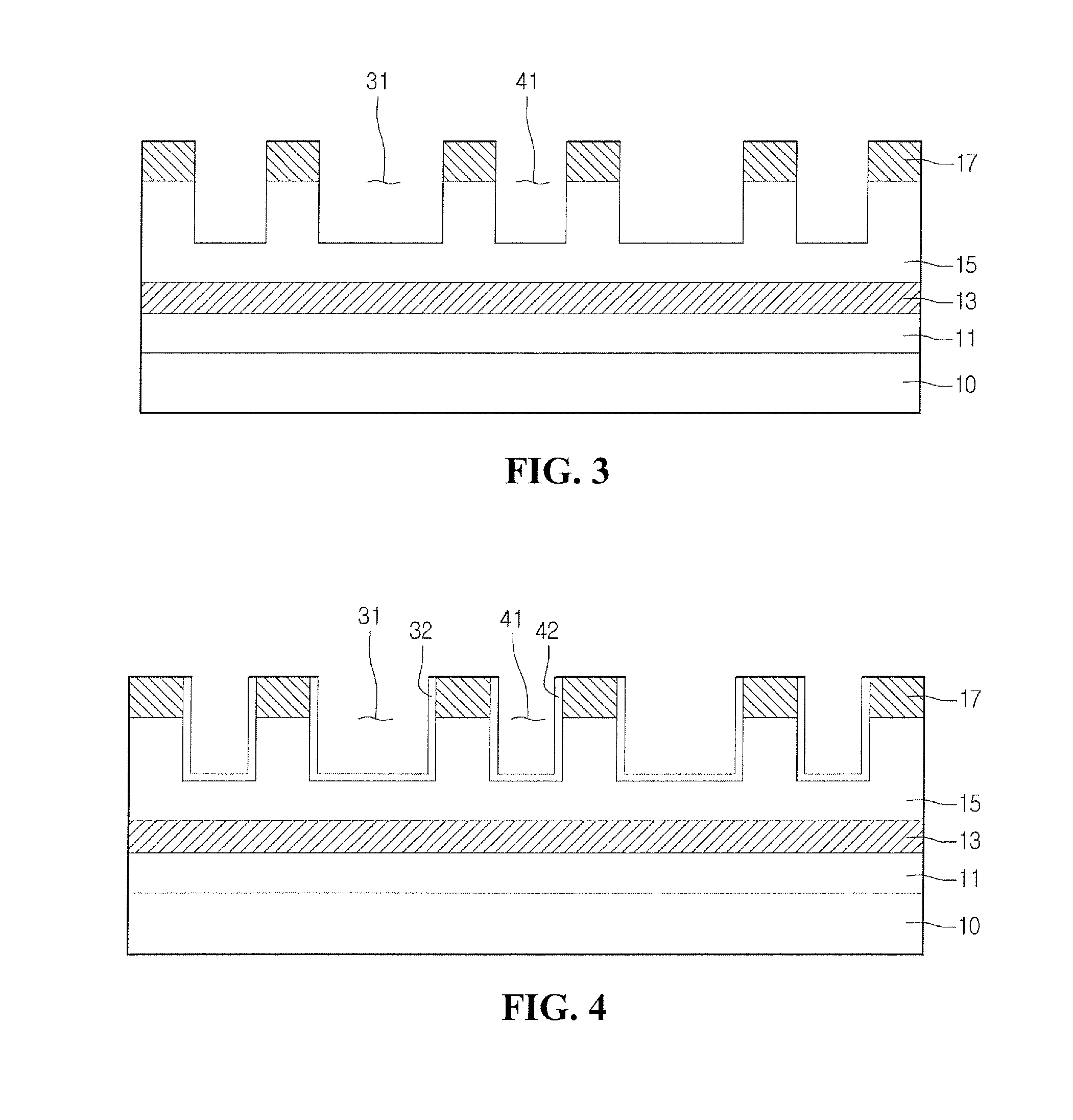

Semiconductor Device and Method of Fabricating the Same

ActiveUS20080258214A1Semiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricCommon drain

Provided are a semiconductor device and a method of fabricating the semiconductor device. The semiconductor device can provide a trench MOS transistor having an up-drain structure. The semiconductor device can include a first conductive type well in a semiconductor substrate, a second conductive type well on the first conductive type well, trenches formed by removing portions of the second conductive type well and the first conductive type well; gates provided in the trenches with a gate dielectric being between each gate and the walls of the trench, a first conductive type source region and a second conductive type body region on the second conductive type well, the first conductive type source region surrounding a lateral surface of the gate, and a common drain between the gates, the common drain being connected to the first conductive type well.

Owner:MARVELL ASIA PTE LTD

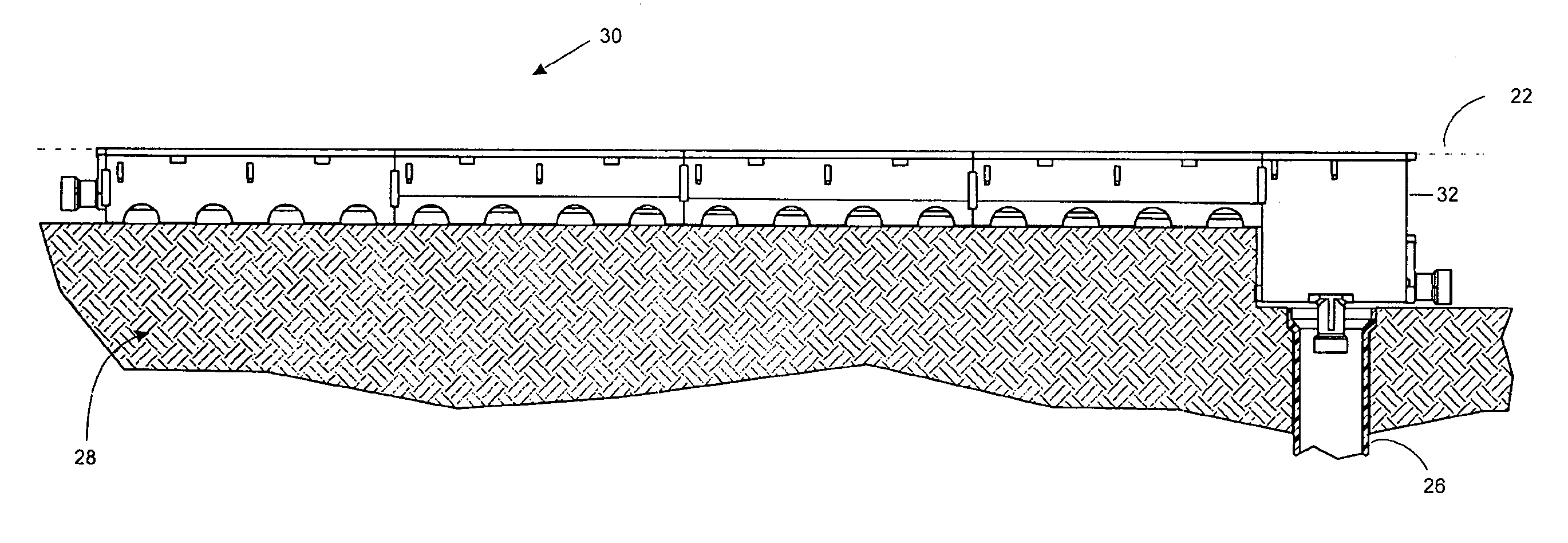

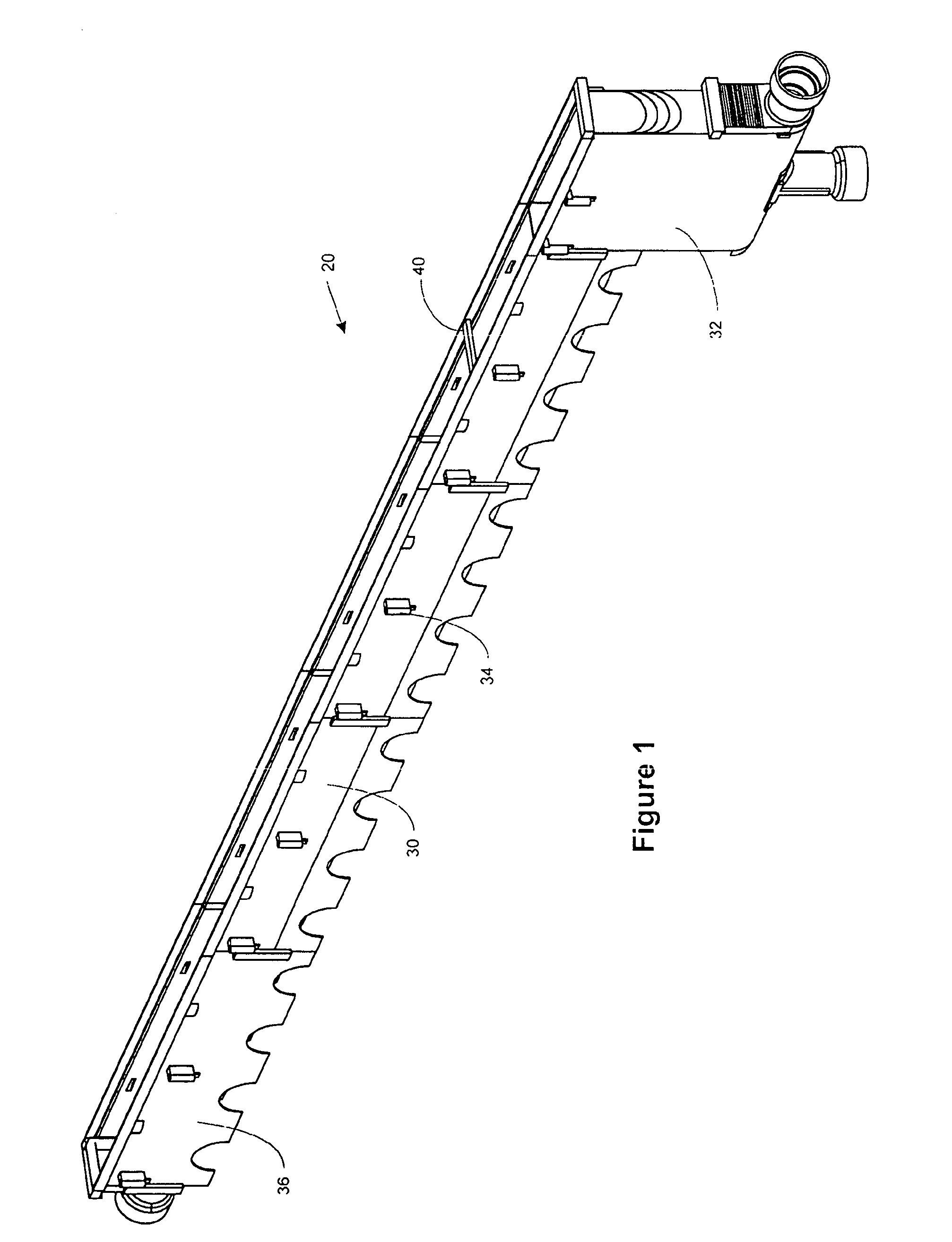

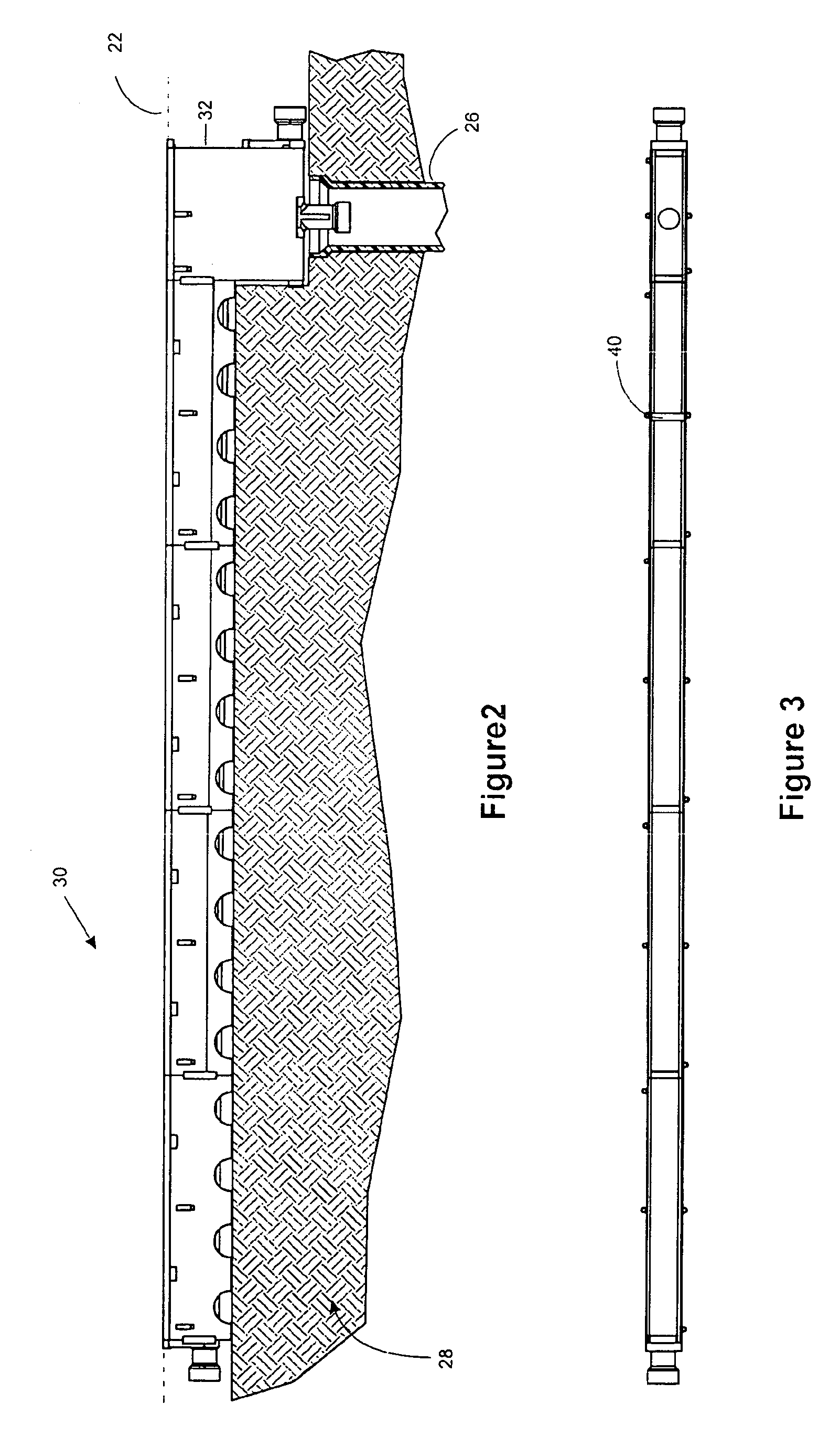

Pre-sloped trench drain system

ActiveUS7507054B2Easy to installImprove system flexibilityGround-workPaving gutters/kerbsCommon drainTube drain

A below grade trench drain system and a method for making the trench drain system is disclosed which does not rely on the contractor's prowess to dig a trench with a proper slope. The trench drain system, in accordance with the present invention, includes a plurality of modular trench sections formed with a uniform exterior height and an interior fluid channel formed with a pre-sloped floor. As such, the trench drain system, in accordance with the present invention, can be installed in a level trench, which greatly simplifies installation by the contractor and ensures that the trench drain will be installed with the proper slope. The modular trench sections can be coupled together forming a trench drain with a continuous slope or alternatively coupled with modular trench sections with no slope to form a stepped slope. The configuration of the modular trench sections allows the modular trench sections to form a trench drain system sloped in different directions to enable connections to the common drain in the center as well at both ends. As such, the trench drain system provides more configurations for connections to the common drain system thus improving the flexibility of the system and at the same time provide a trench drain system which does not depend on the installation prowess of the installation contractor.

Owner:LIGHTHOUSE INDS

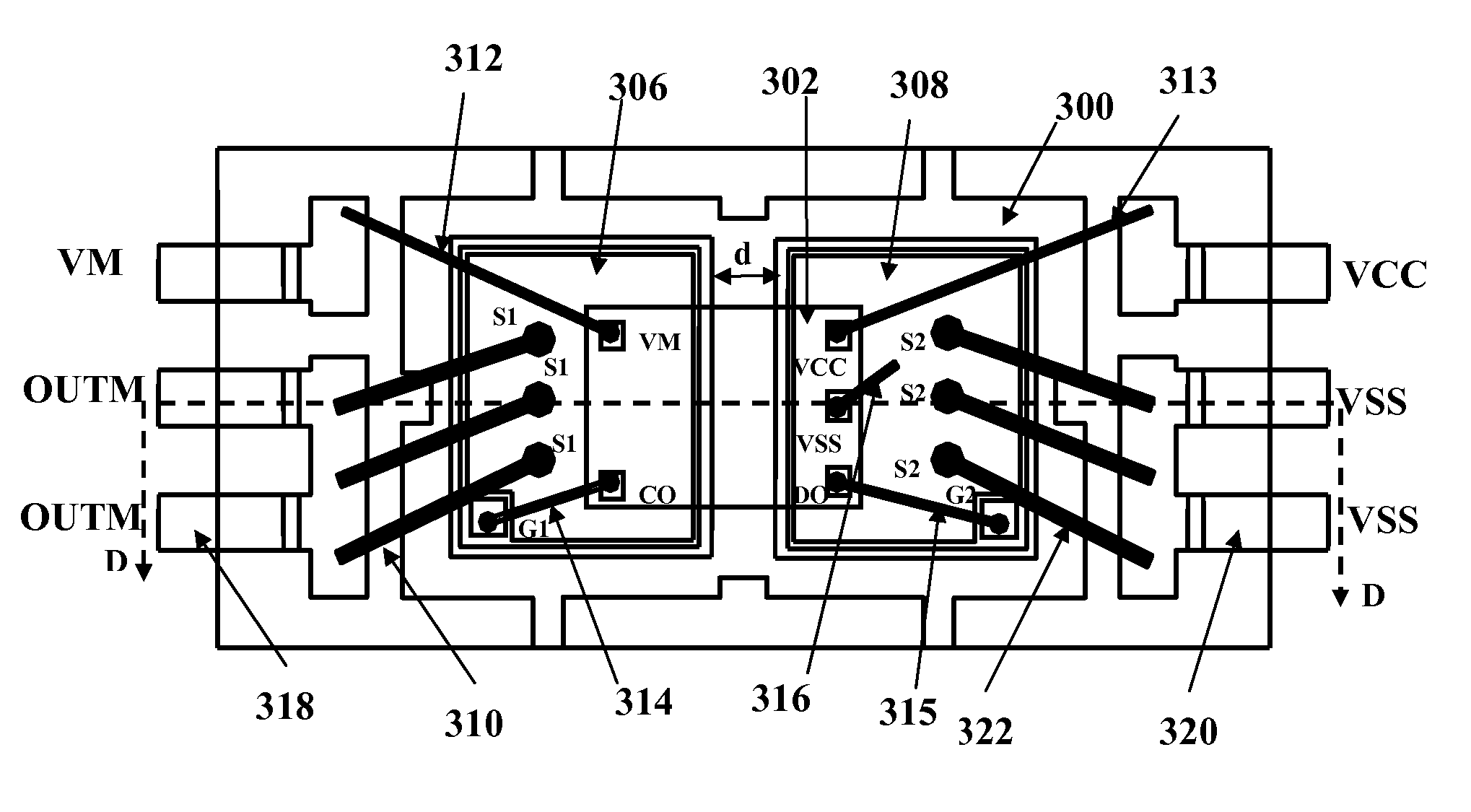

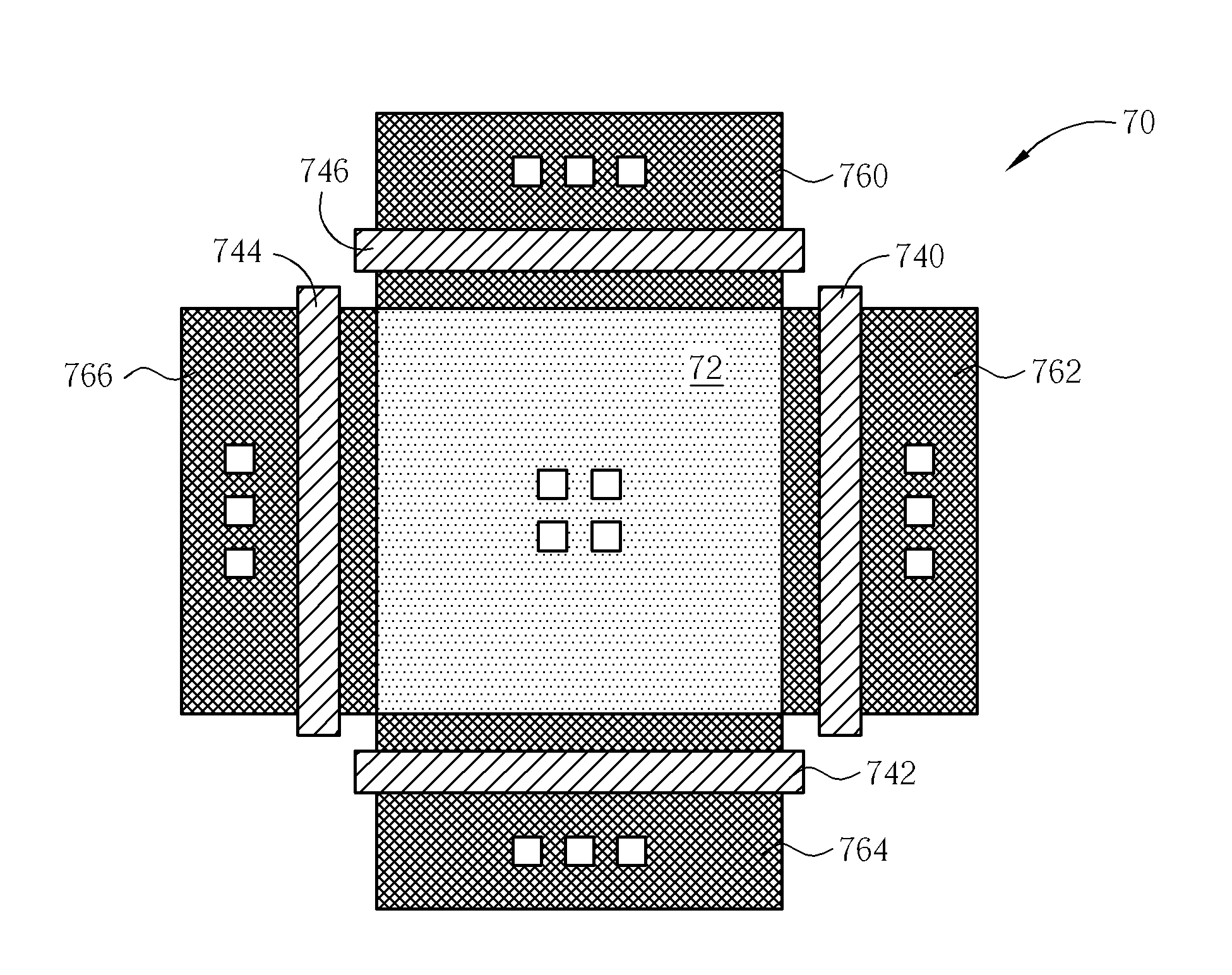

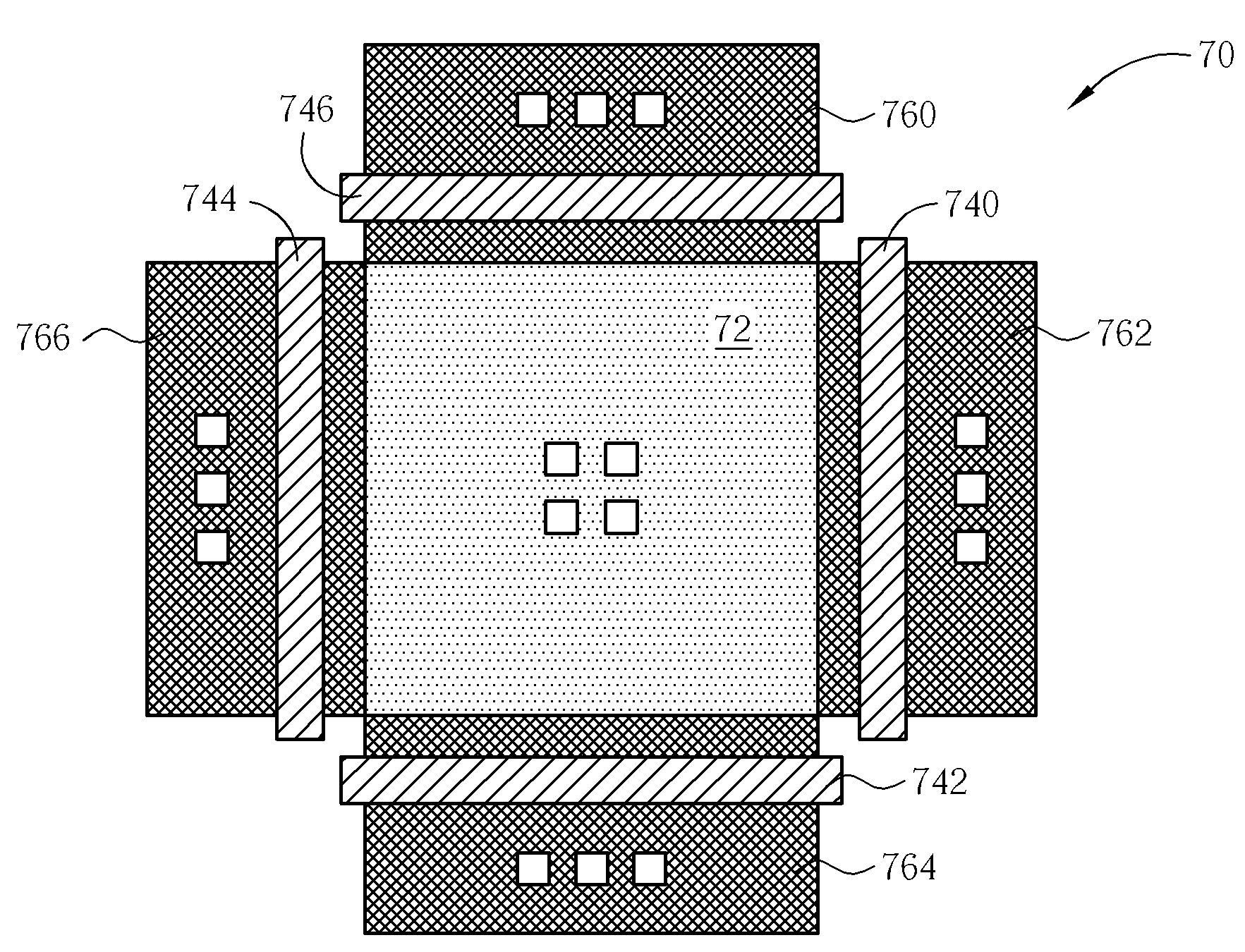

Multi-Transistor Layout Capable Of Saving Area

ActiveUS20060267110A1Save extra spaceTransistorSemiconductor/solid-state device detailsEngineeringCommon drain

A multi-transistor layout capable of saving area includes a substrate; a common drain comprising four sides formed over the substrate; four gates formed over the four sides of the common drain; and four sources formed over outer sides of the four gates corresponding to the common drain.

Owner:FARADAY TECH CORP

Static random access memory

InactiveUS7057302B2Improve error resistanceTransistorSolid-state devicesStatic random-access memoryRandom access memory

A static random access memory has first and second complementary field-effect transistors. The first complementary field-effect transistor includes a semiconductor substrate, a first field-effect transistor of electron conduction type which has a first drain region constituting a Schottky junction and a gate electrode, and a first field-effect transistor of positive hole conduction type which shares the first drain region and has a shared gate electrode. The second complementary field-effect transistor includes a second field-effect transistor of electron conduction type which has a second drain region and a gate electrode, a second field-effect transistor of positive hole conduction type which shares the second drain region and has a shared gate electrode. The gate electrode shared by the first and second complementary field-effect transistors is connected to the common drain region of the mutually opposing complementary field-effect transistors, and the static random access memory has superior resistance to software errors.

Owner:KK TOSHIBA

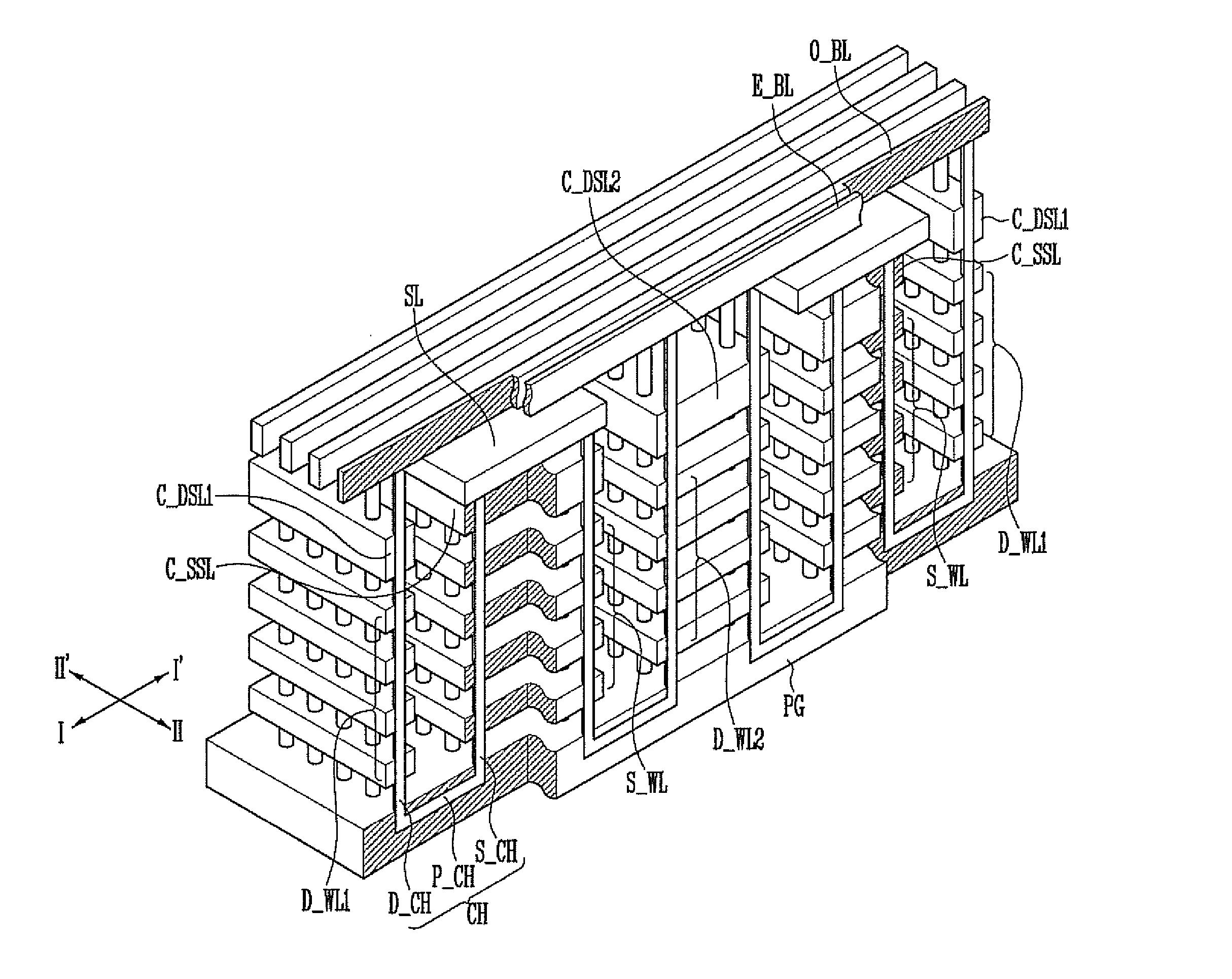

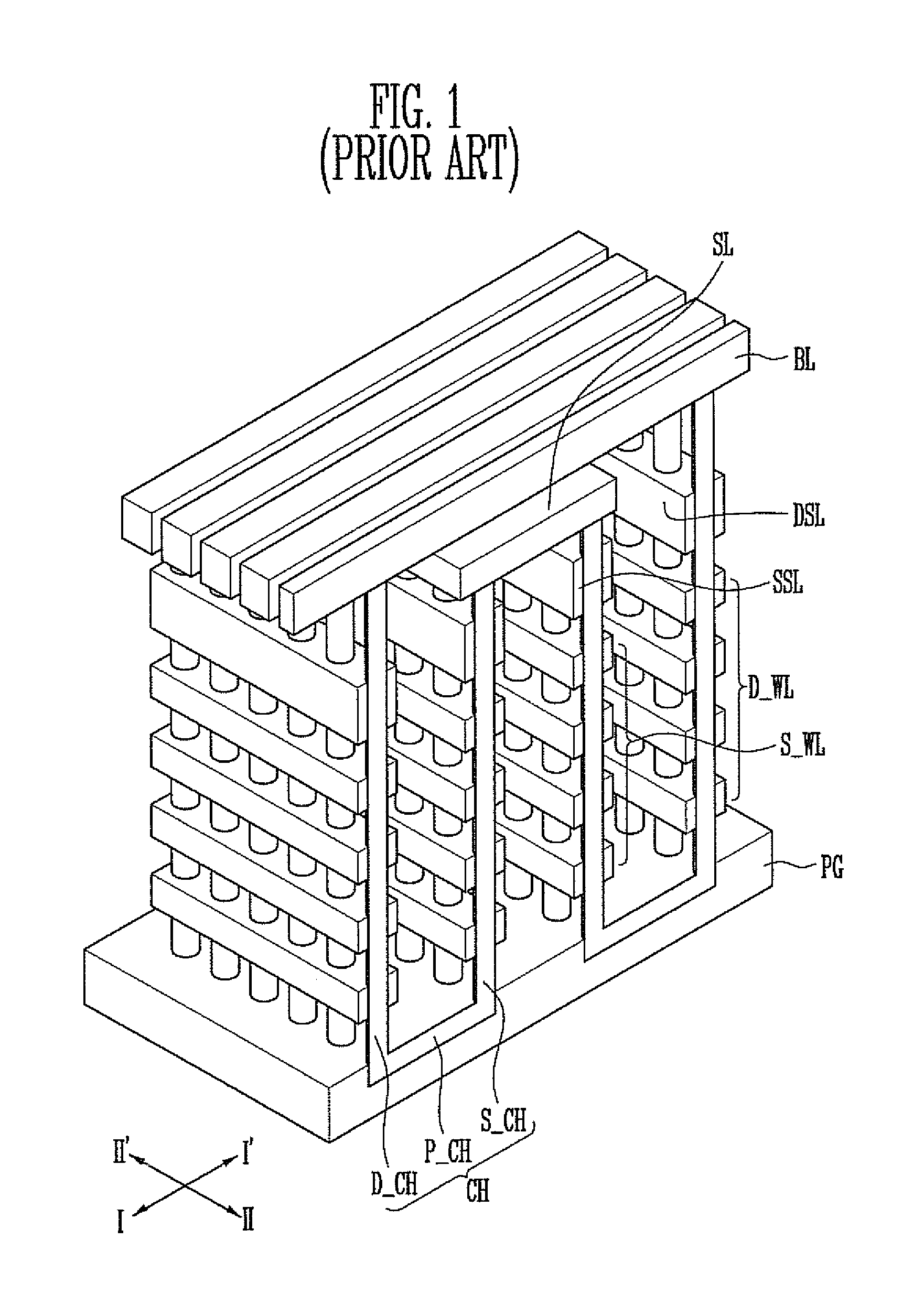

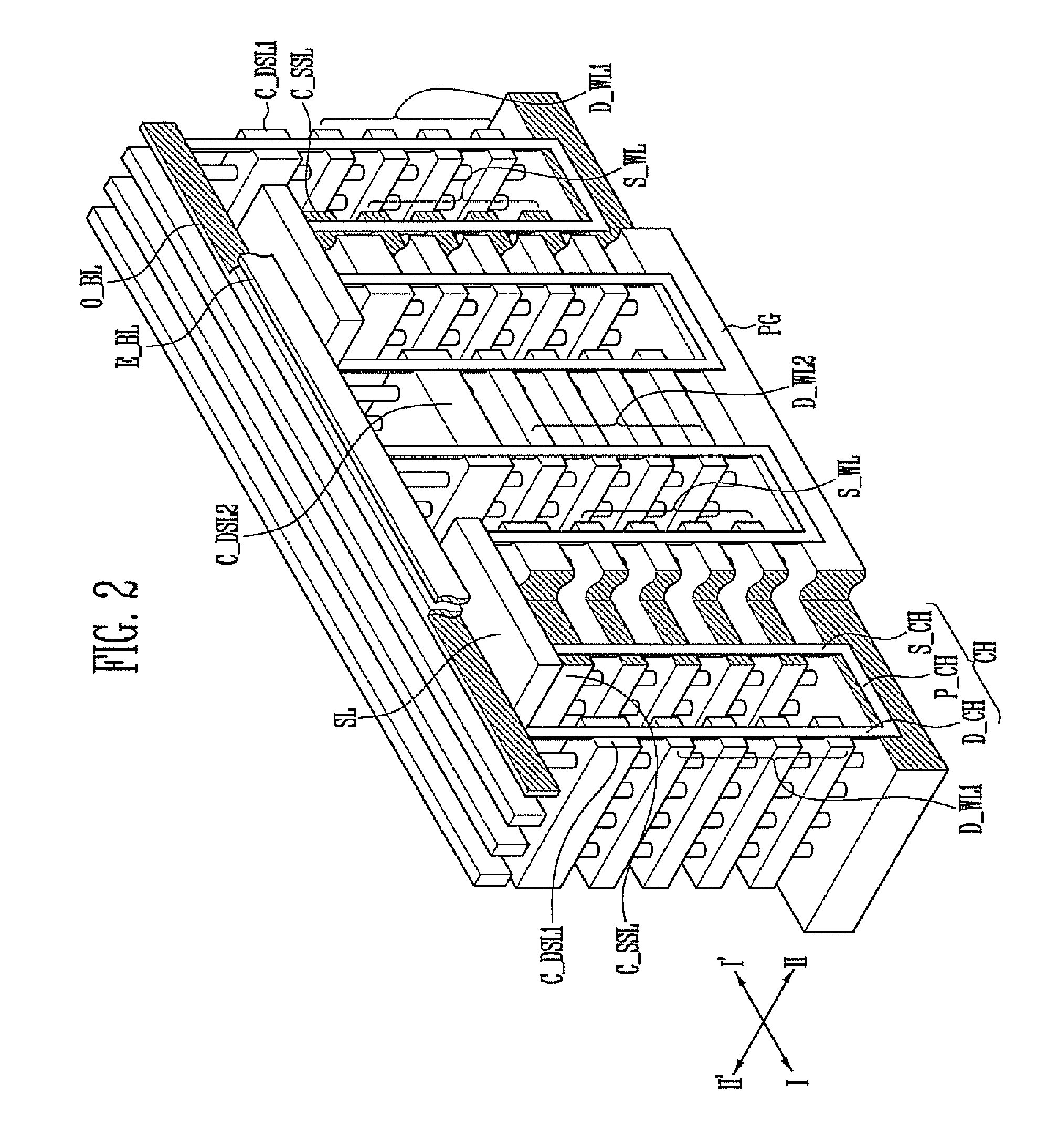

Three-dimensional non-volatile memory device

A three-dimensional (3-D) non-volatile memory device according to embodiment of the present invention includes a plurality of bit lines, at least one string row extending in a first direction coupled to the bit lines and including 2N strings, wherein the N includes a natural number, a common source selection line configured to control source selection transistors of the 2N strings included in a memory block, a first common drain selection line configured to control drain selection transistors of a first string and a 2N-th string among the 2N strings included in a memory block, and N−1 second common drain selection lines configured to control drain selection transistors of adjacent strings in the first direction among remaining strings other than the first string and the 2N-th string.

Owner:SK HYNIX INC

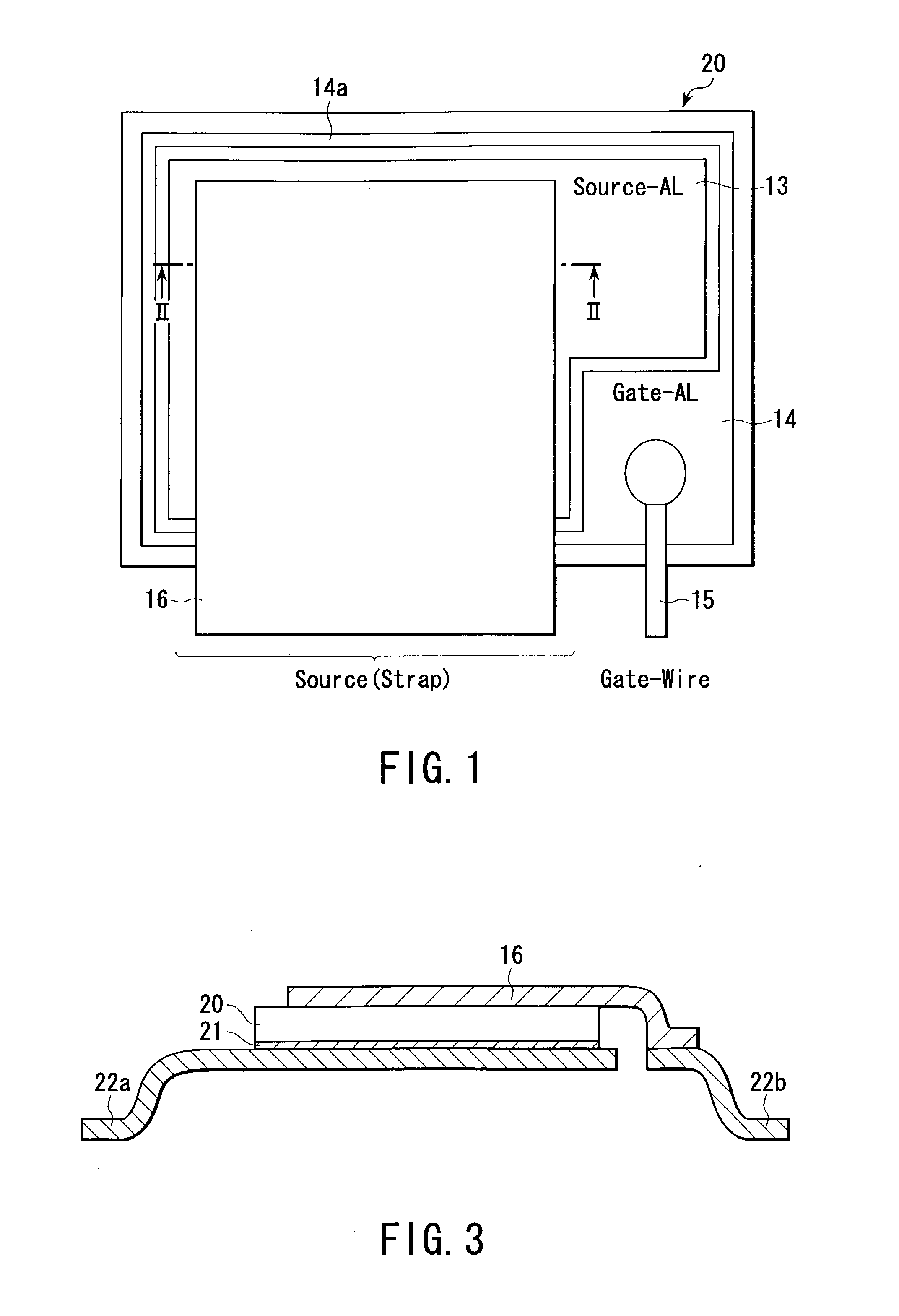

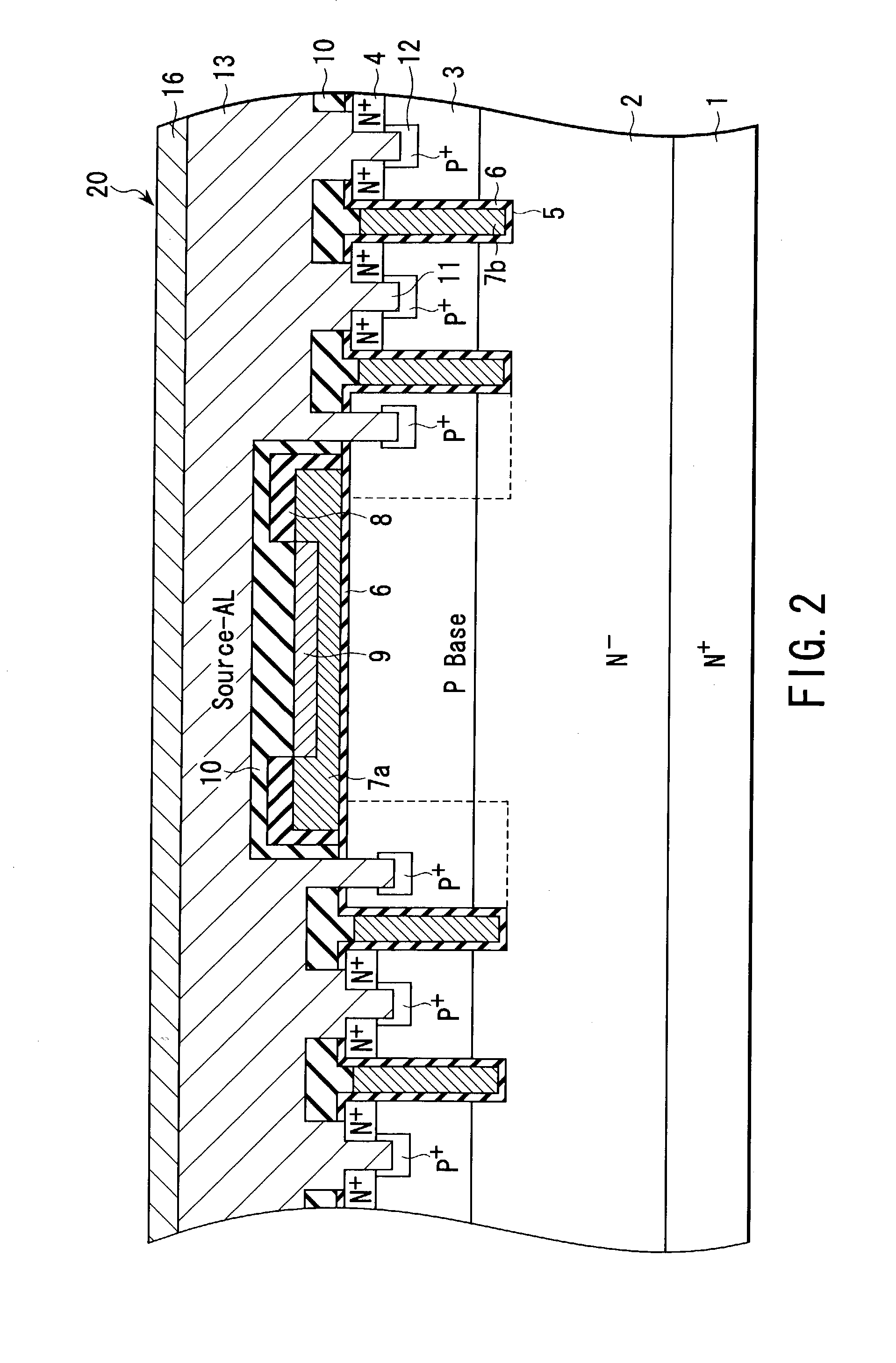

Semiconductor device

InactiveUS20040026753A1Semiconductor/solid-state device detailsSolid-state devicesCommon drainSemiconductor

A semiconductor device comprising a semiconductor substrate having first and second surfaces opposing each other, the substrate including a plurality of cells sharing a common drain region, each of the cells having source and gate regions, a surface source electrode connected to the source region of each of the cells and provided on the first surface, a strap member coupled with the surface source electrode by ultrasonic waves, a gate polysilicon wiring layer connecting the gate region of each of the cells and having a silicide layer in at least a portion of a surface thereof, a surface gate electrode connected to the gate polysilicon wiring layer and provided on the first surface, and a drain electrode provided on the second surface and shared by the cells.

Owner:KK TOSHIBA

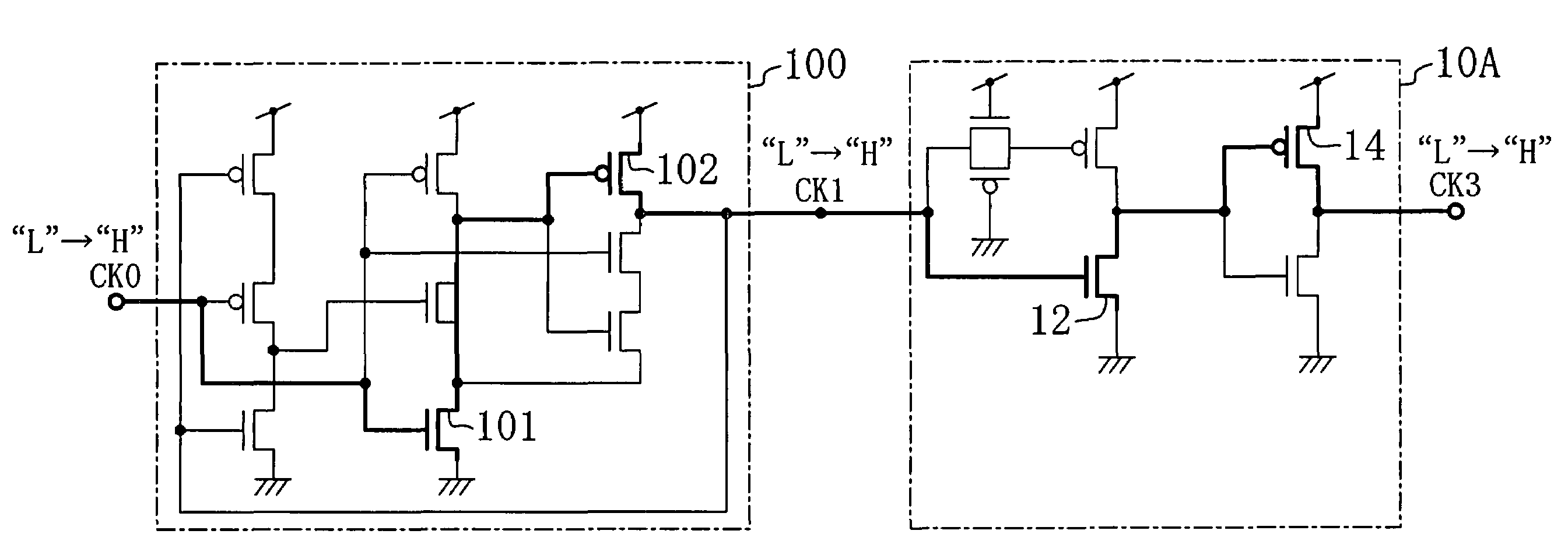

Duty cycle correction circuit

InactiveUS6982581B2Reliability increasing modificationsPulse automatic controlCommon drainDelay unit

In order to correct the duty cycle of a given clock signal to produce a clock signal with a 50% duty cycle, a duty cycle correction circuit includes a delay unit for delaying a first clock signal to output a second clock signal and a clock-signal output unit. The clock-signal output unit includes two transistors which use the first and second clock signals as the inputs of respective gates and an inverter circuit for inverting a signal output from a common drain of the transistors to output a third clock signal. The delay unit delays the first clock signal so that the first clock signal falling appears at a timing at which the duty cycle thereof becomes 50%. The two transistors in the clock-signal output unit output, as the third clock signal, a ground voltage and a source voltage as the signal from the common drain in response to the rising of the first clock signal and the falling of the second clock signal, respectively.

Owner:PANASONIC CORP

Multi-transistor layout capable of saving area

ActiveUS7294892B2Save extra spaceTransistorSemiconductor/solid-state device detailsCommon drainEngineering

A multi-transistor layout capable of saving area includes a substrate; a common drain comprising four sides formed over the substrate; four gates formed over the four sides of the common drain; and four sources formed over outer sides of the four gates corresponding to the common drain.

Owner:FARADAY TECH CORP