Single chip integration making technology for enhanced and consumption-up vertical dual diffusion field effect pipe

A vertical double diffusion and manufacturing process technology, applied in the field of semiconductor manufacturing, can solve problems such as corrosion of aluminum, and achieve the effect of simple process steps, high compatibility and low cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

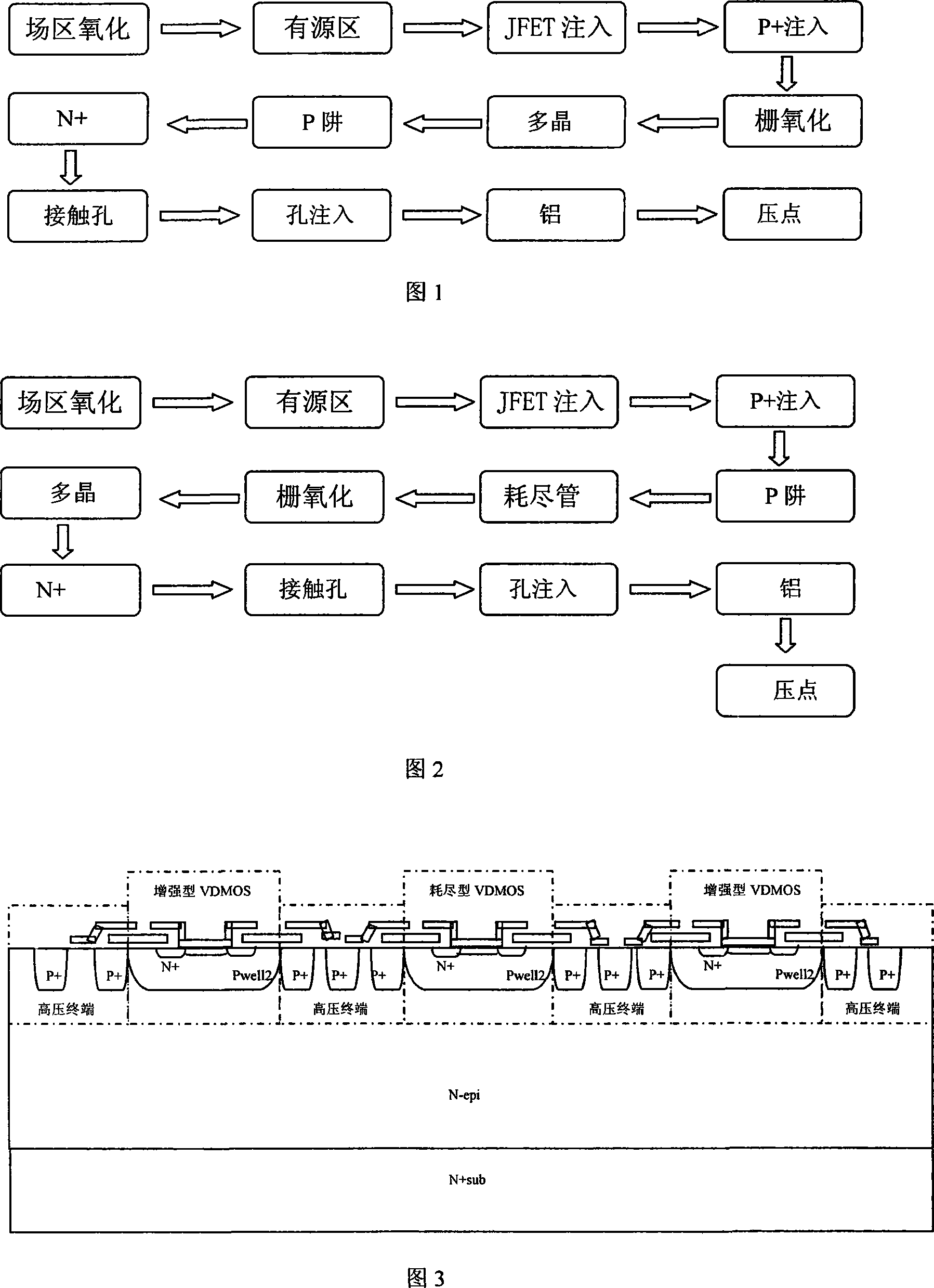

Method used

Image

Examples

Embodiment Construction

[0039] The N(100) arsenic-doped substrate VDMOS material sheet used has a resistivity of less than 0.005Ω·CM, an epitaxial thickness of 55 μm, and an epitaxial resistivity of 24Ω·CM. On the chip area of 2000*2500μm, the strip primitive cell design is adopted, the polycrystalline gate width is 11μm, and the layout method of the enhanced tube surrounds the depletion area, and the corresponding experimental layout design is carried out. According to the adjusted process flow of VDMOS with depletion, the specific implementation method of successfully making enhancement mode and depletion mode VDMOS on the same IC at the same time is as follows:

[0040] 1.) Field region oxidation, the thickness of the oxide layer is 9900-11000 Ȧ.

[0041] 2.) Active area photolithography, etching. Remove the oxide layer in the active area.

[0042] 3.) JFET implantation: implantation energy 100kev; implantation dose 1.2E12; impurity type is phosphorus. The purpose of this injection is mainly ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More