Duty ratio correction circuit

A duty cycle correction, circuit technology, applied in electrical components, generation of electrical pulses, automatic control of power, etc., can solve problems such as can not be ignored

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

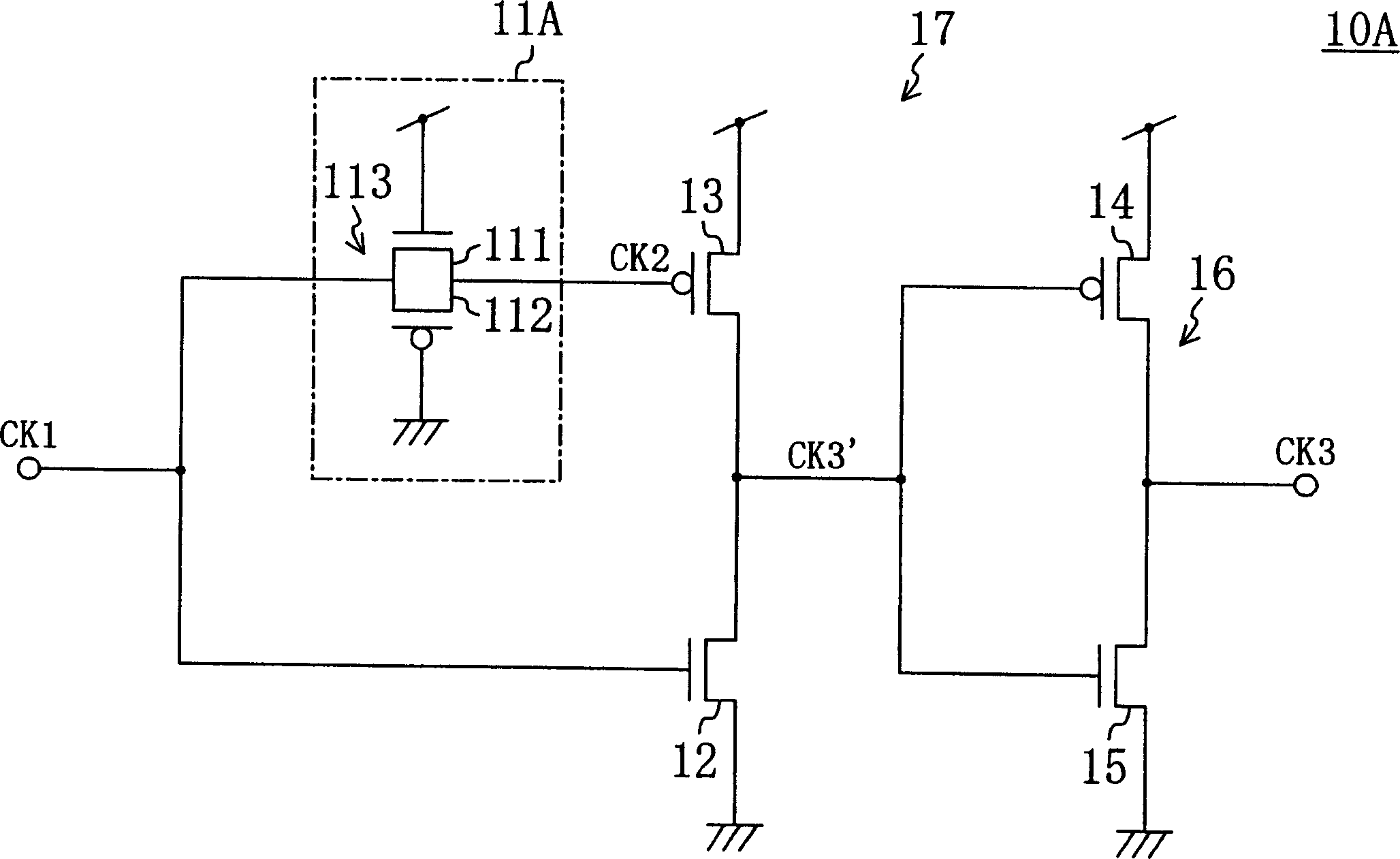

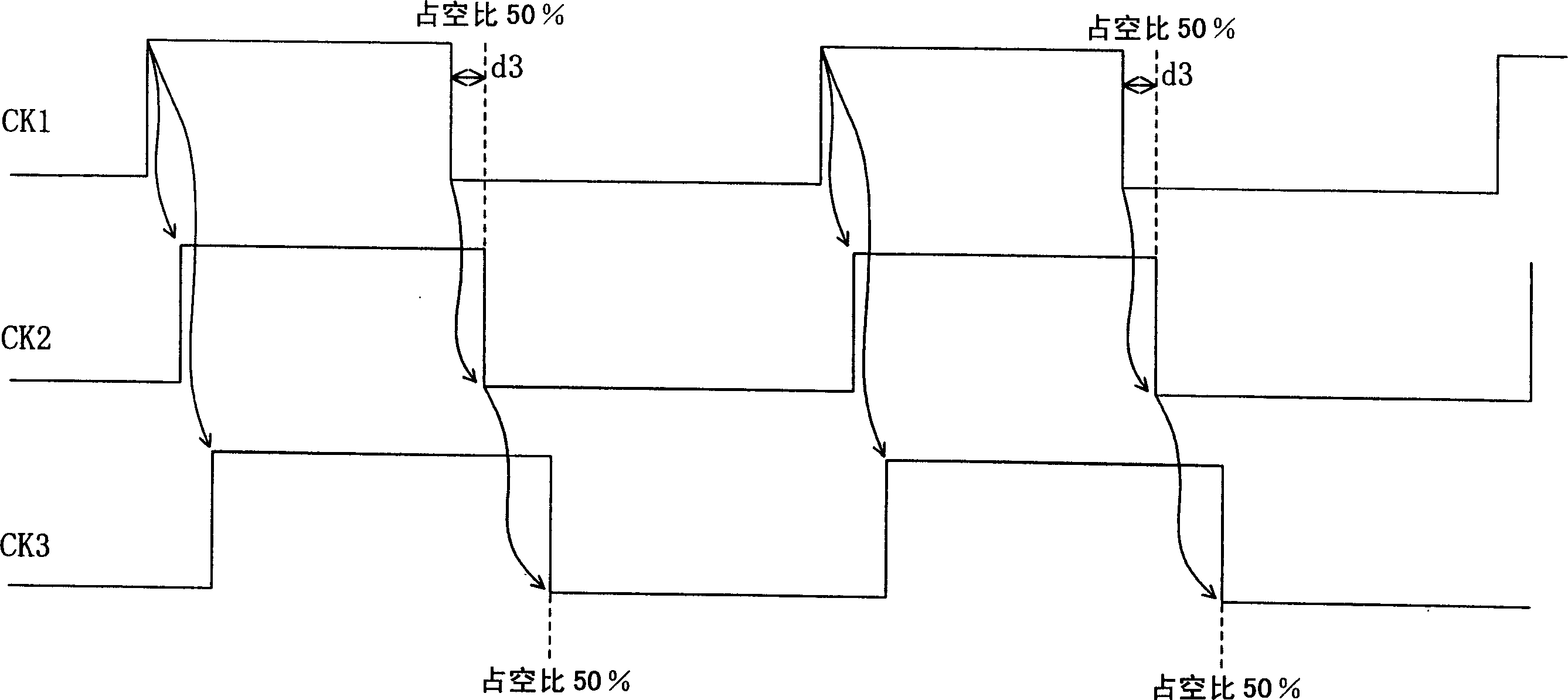

[0032] figure 1 The circuit configuration of the duty ratio correction circuit according to the first embodiment of the present invention is shown. The duty cycle correction circuit 10A of this embodiment includes: a delay unit 11A, which delays the clock CK1 (equivalent to the first clock of the present invention) input to the duty cycle correction circuit 10A and then outputs the clock CK2 (equivalent to the second clock of the present invention). ); n-channel transistor 12, whose source is supplied with ground voltage, and whose gate is supplied with clock CK1; p-channel transistor 13, whose source is supplied with supply voltage, and whose gate is supplied with clock CK2; and an inverter The circuit 16 is composed of transistors 14 and 15, and outputs the clock CK3 (equivalent to the third clock of the present invention) after the signal CK3' output from the connected drains of the transistors 12 and 13 is inverted. A clock output unit 17 is constituted by transistors 12...

no. 2 example

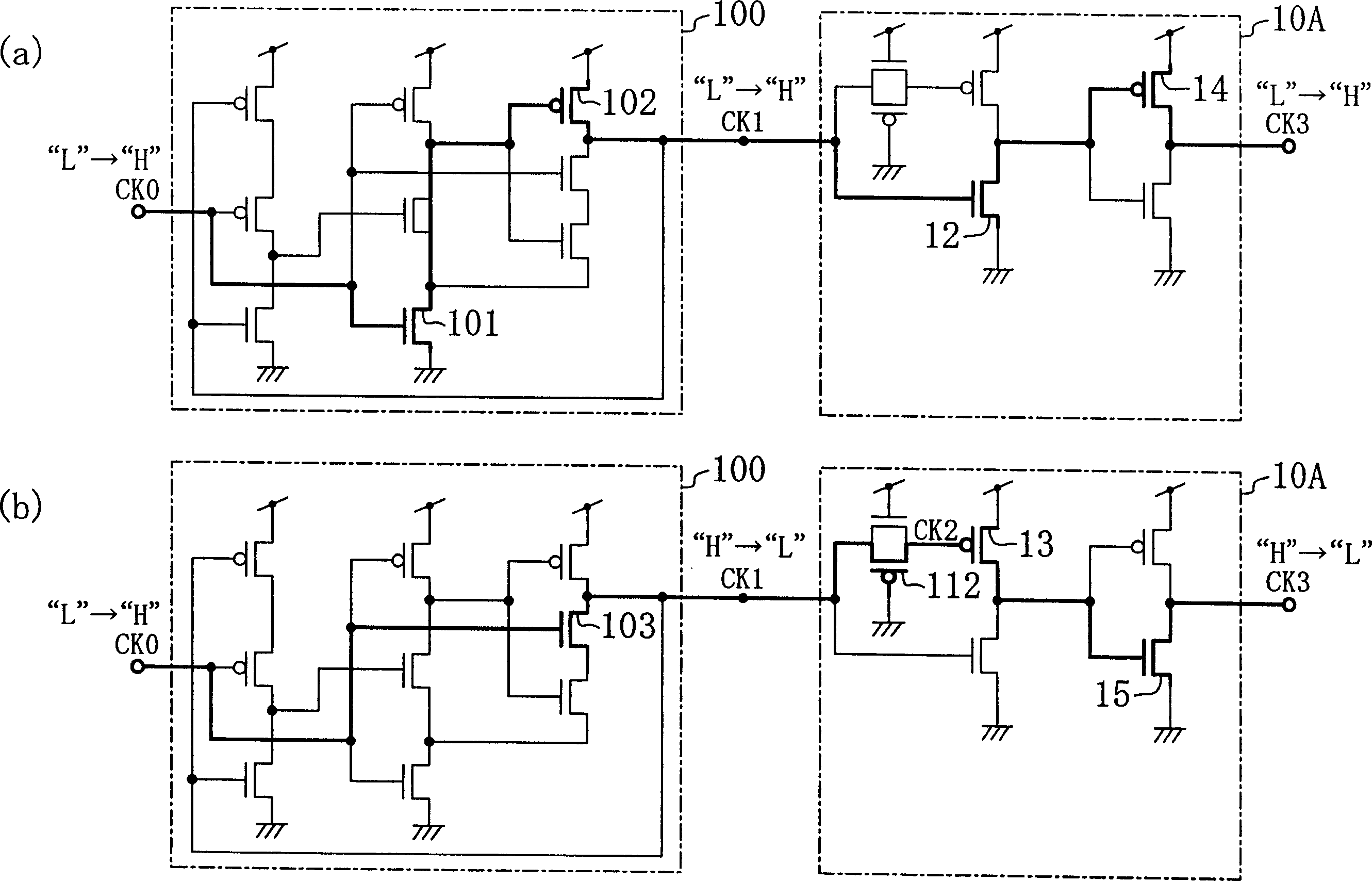

[0049] Figure 4 A circuit configuration of a duty ratio correction circuit according to a second embodiment of the present invention is shown. The duty ratio correction circuit 10B of the present embodiment has a circuit configuration in which the delay unit 11A in the duty ratio correction circuit 10A of the first embodiment is replaced with a delay unit 11B having a different configuration. And includes the output section 18 after omitting the inverter circuit 16 in the duty ratio correction circuit 10A, and the figure 1 The signal CK3' shown is output as a clock CK3. Moreover, in Figure 4 in, with figure 1 Components that are the same as those shown are denoted by the same symbols, and descriptions thereof are omitted. Next, the delay unit 11B will be described.

[0050] The delay unit 11B has a transmission gate 113 composed of an n-channel transistor 111 and a p-channel transistor 112 . The gate of the transistor 111 is supplied with a power supply voltage. On ...

no. 3 example

[0055] Figure 5 A circuit configuration of a duty cycle correction circuit according to a third embodiment of the present invention is shown. The duty ratio correction circuit 10C of the present embodiment is constituted by replacing the delay unit 11B in the duty ratio correction circuit 10B of the second embodiment with a delay unit 11C having a different configuration. Moreover, in Figure 5 in, with Figure 4 Components that are the same as those shown are denoted by the same symbols, and descriptions thereof are omitted. Next, the delay unit 11C will be described.

[0056] The delay unit 11C has a p-channel transistor 112 . The gate threshold voltage Vth of the transistor 112 is applied to the gate of the transistor 112 . Here, since the transistor 112 is a p-channel transistor, a voltage lower than the ground voltage is applied. Thus, by applying the gate threshold voltage Vth to the gate of the transistor 112, the transistor 112 can be turned into a switching ope...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More