Patents

Literature

990 results about "Frequency compensation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

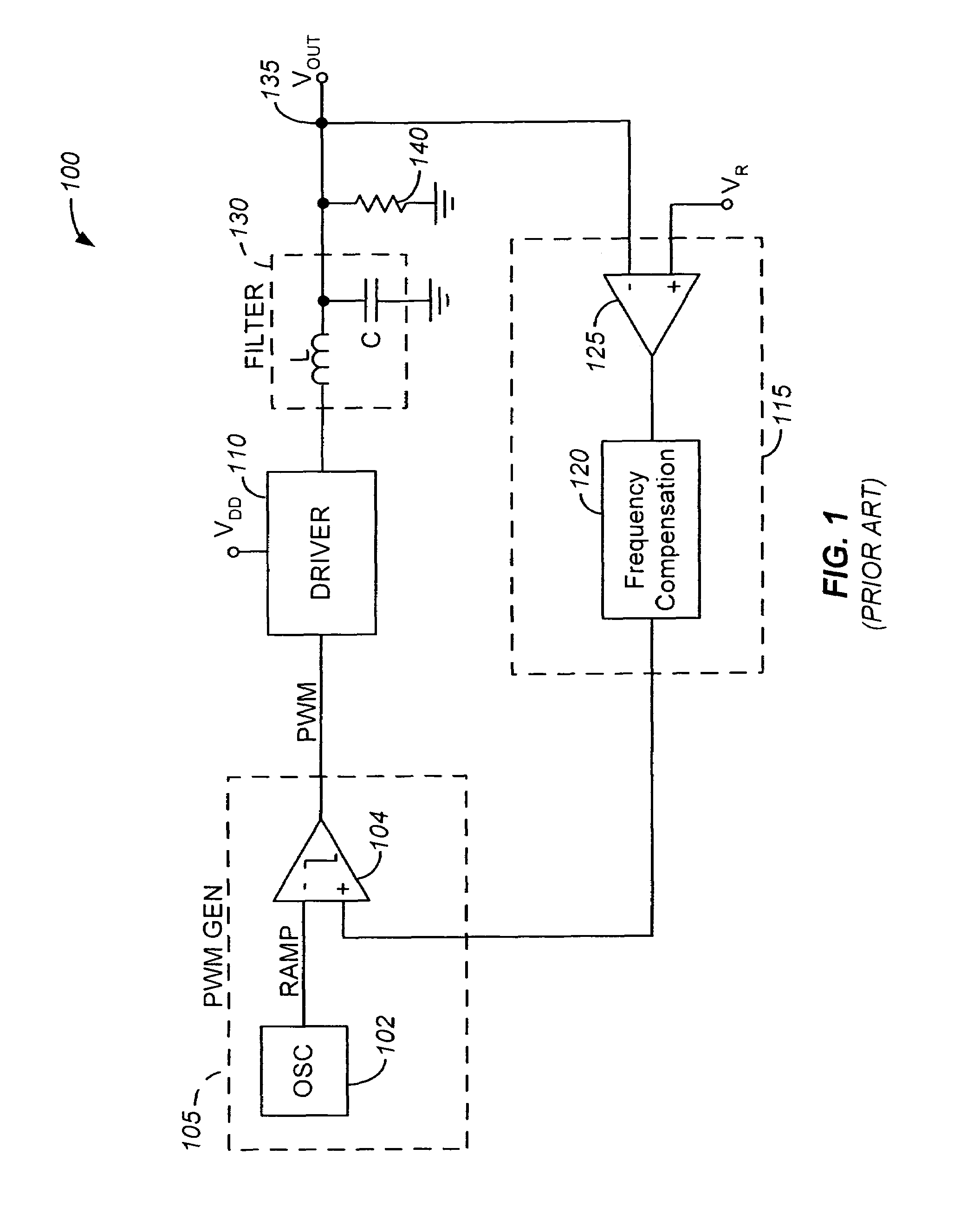

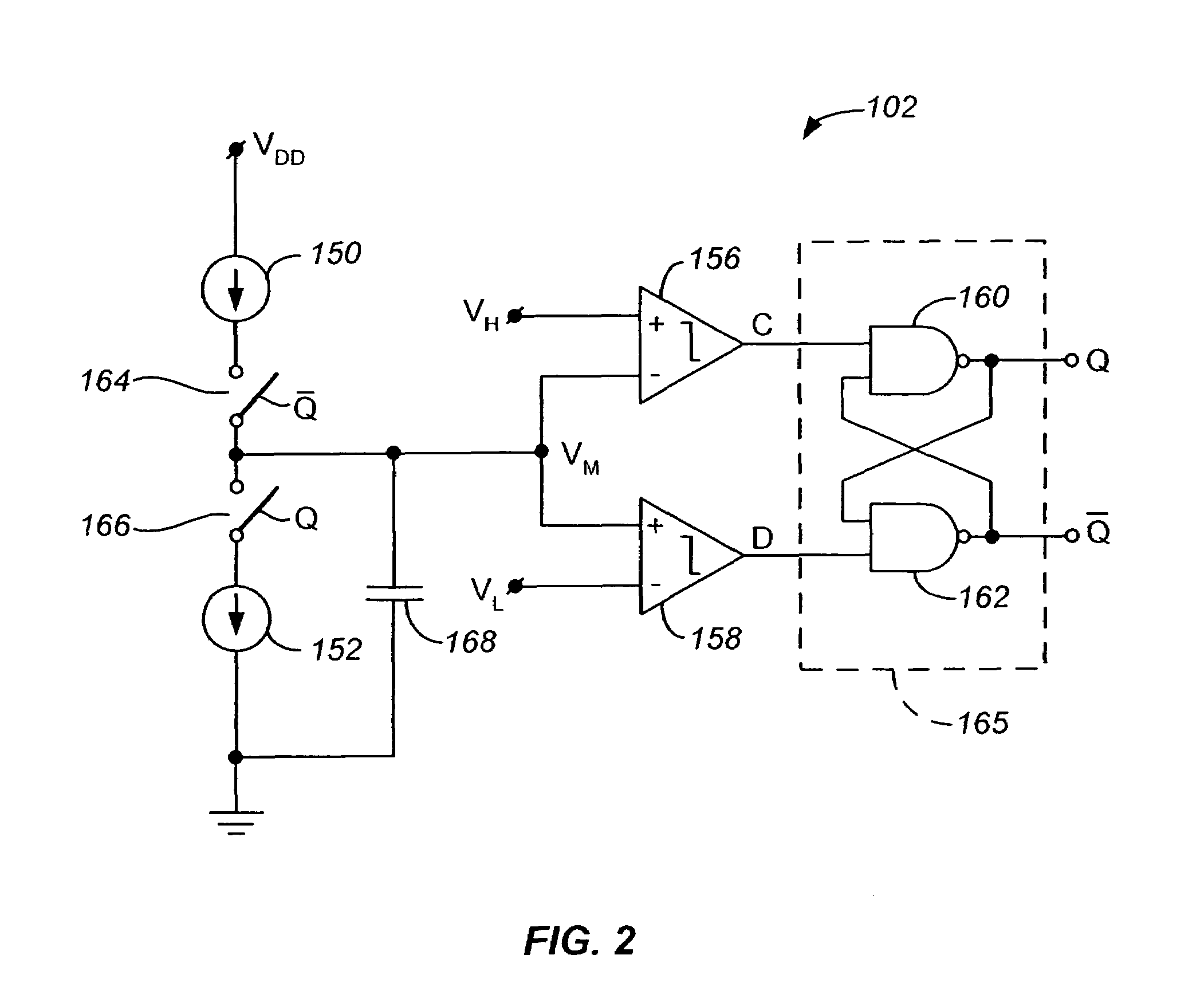

In electronics engineering, frequency compensation is a technique used in amplifiers, and especially in amplifiers employing negative feedback. It usually has two primary goals: To avoid the unintentional creation of positive feedback, which will cause the amplifier to oscillate, and to control overshoot and ringing in the amplifier's step response. It is also used extensively to improve the bandwidth of single pole systems.

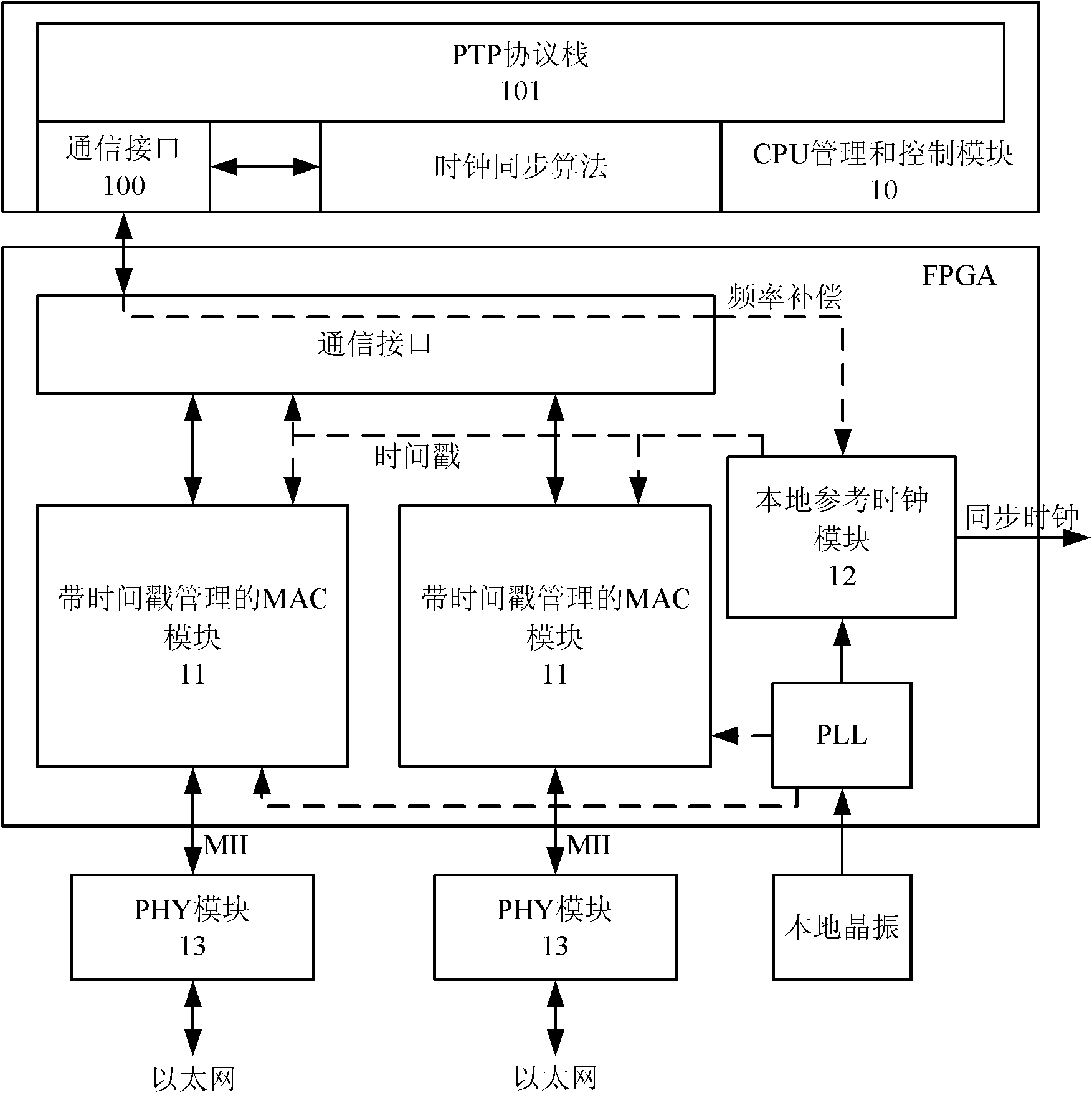

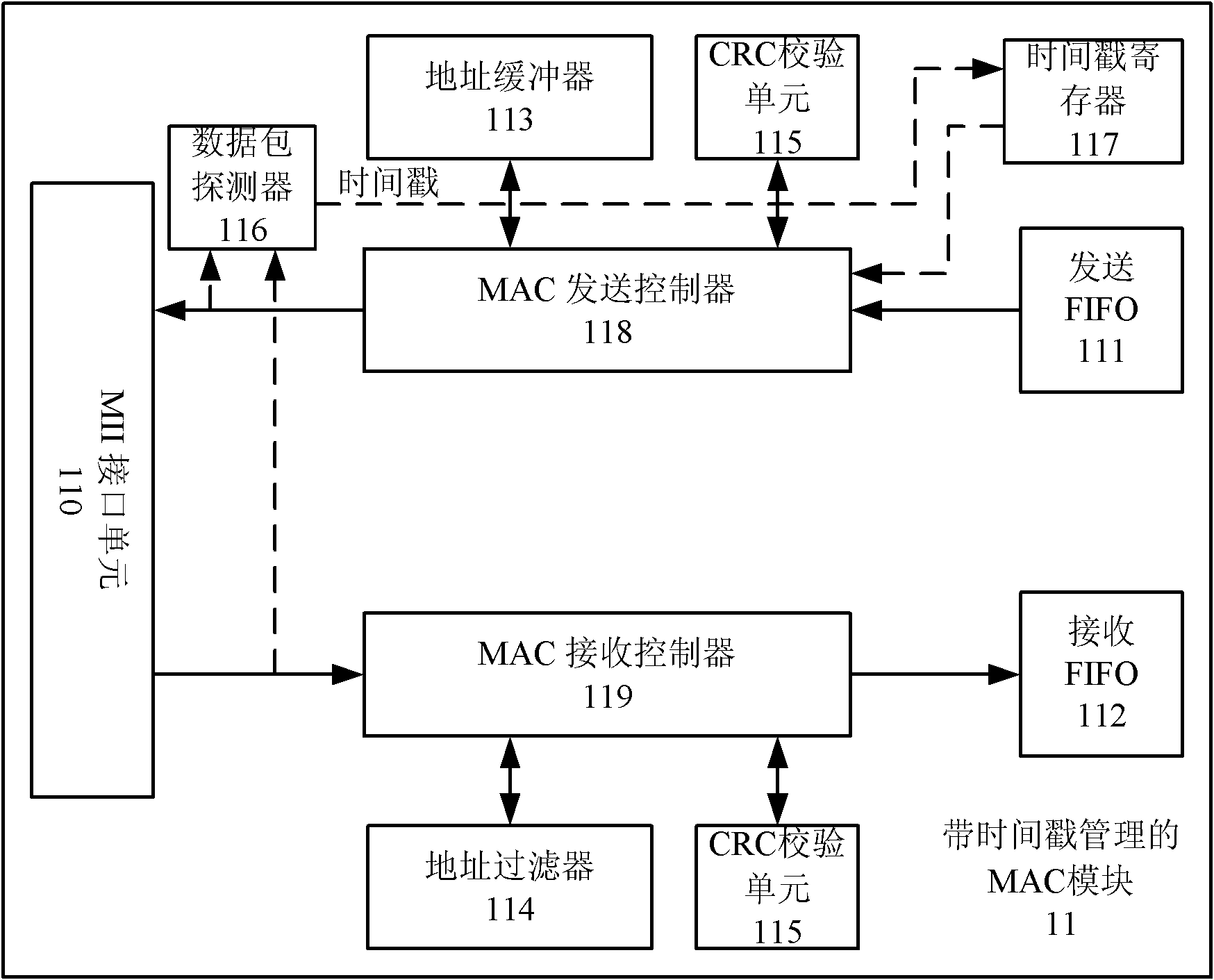

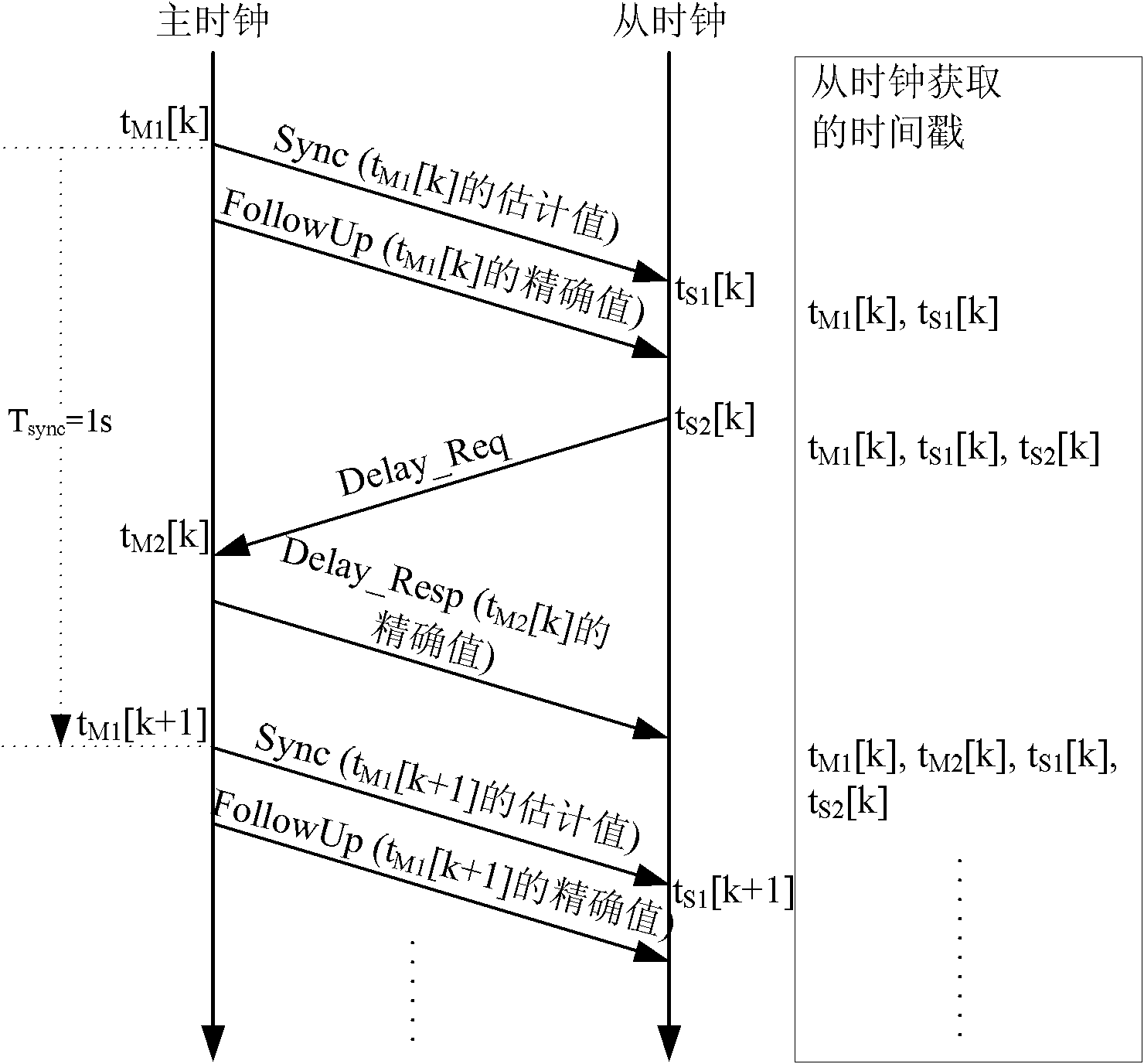

IEEE1588 based accurate clock synchronization protocol system and synchronization method thereof

ActiveCN101977104ASave communication bandwidthImprove real-time performanceSynchronising arrangementBus networksInformation transmissionTimestamp

The invention relates to an IEEE 1588 based accurate clock synchronization protocol system and a synchronization method thereof, belonging to the technical field of network information transmission. By adopting the invention, a main clock carries an accurate timestamp while sending a synchronization message, and a follow message is not required to be sent, thus greatly reducing communication bandwidth required for realizing clock synchronization. Meanwhile a frequency adjustable clock counter is constructed, and clock synchronization algorithm is combined, so as to realize frequency compensation function and achieve high accuracy clock synchronization requirement.

Owner:SHANGHAI JIAO TONG UNIV

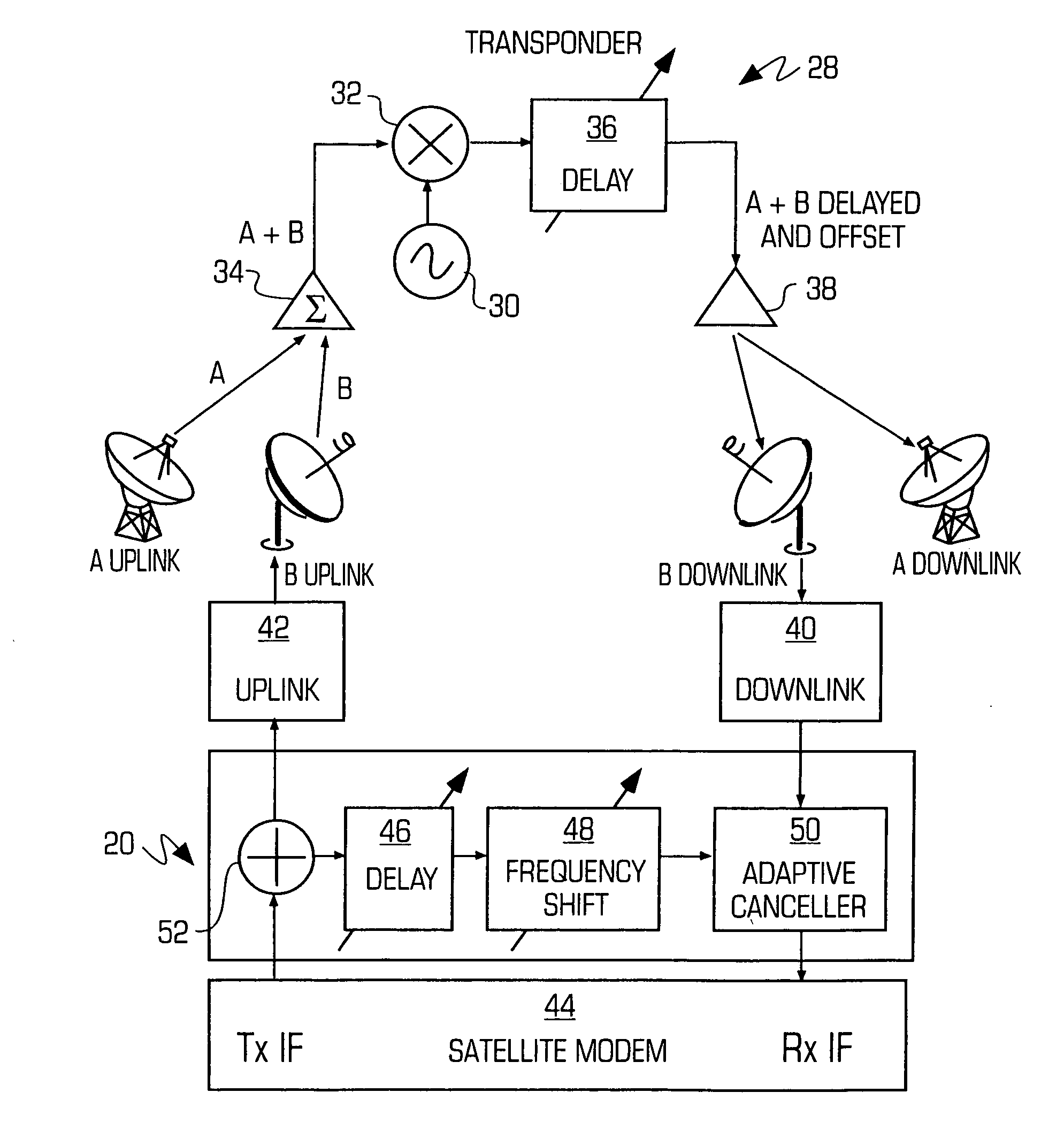

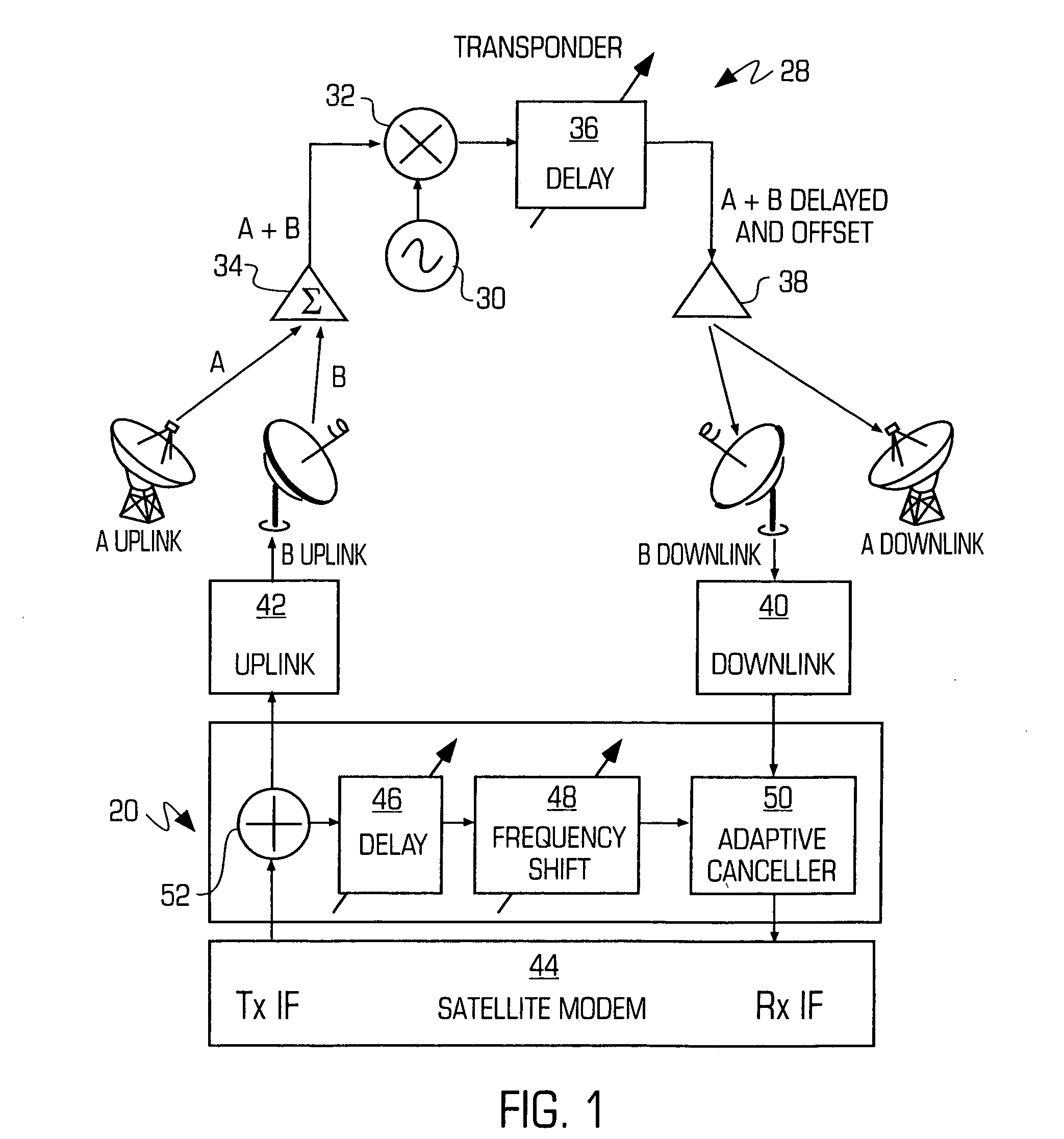

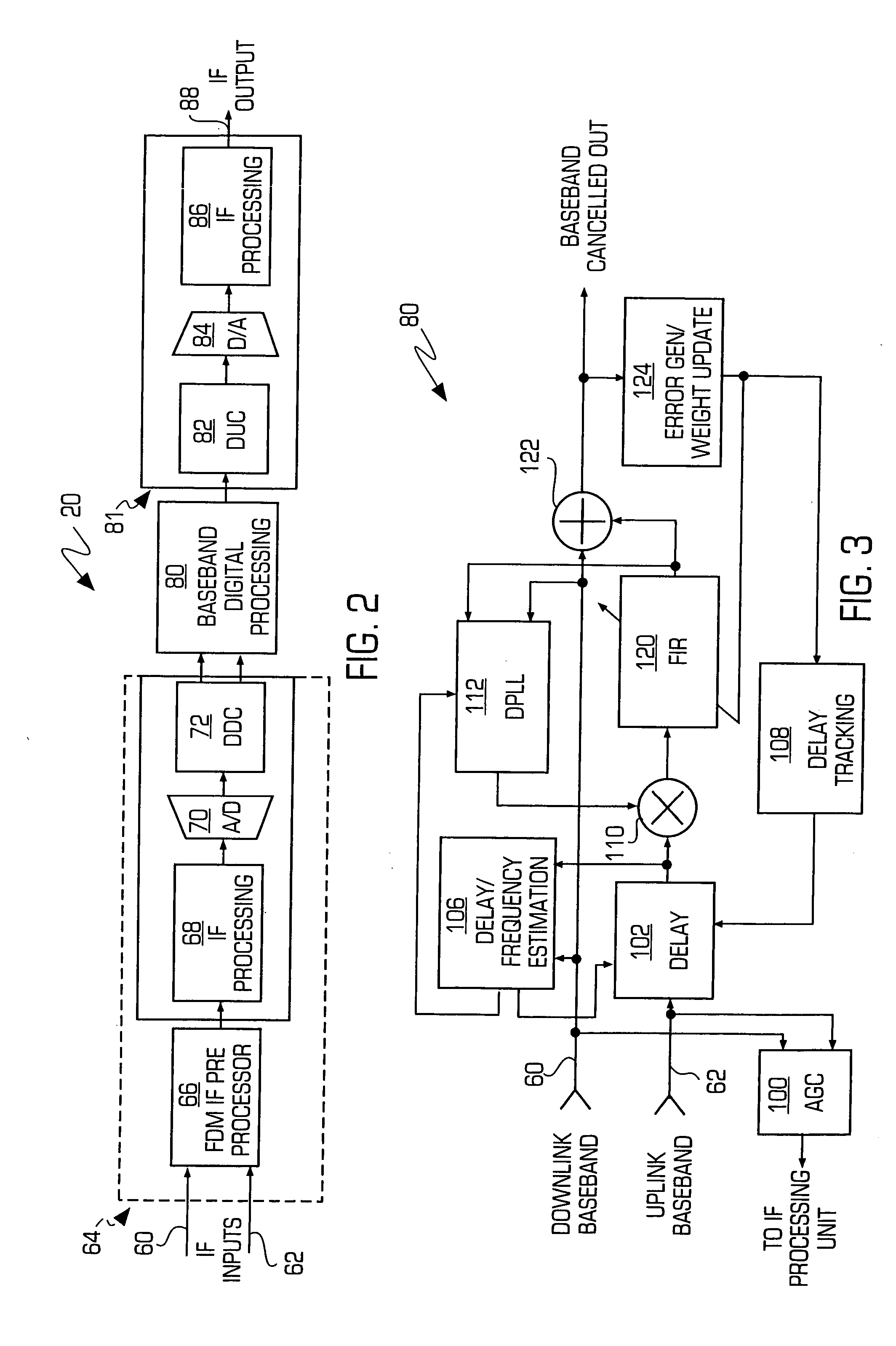

Adaptive canceller for frequency reuse systems

InactiveUS20050159128A1Easy to useHighly effectiveRadio transmissionTransmission noise suppressionFinite impulse responseAdaptive filter

An adaptive interference canceller for canceling an interfering signal corresponding to a delayed, frequency translated, amplitude and phase offset version of a transmitted signal contained in a composite received signal relayed through a relay system such as a satellite transponder. The canceller digitally downconverts the received signal and a local replica of the transmitted signal from IF to baseband, applies a variable delay and frequency compensation to the replica as a coarse delay and frequency correction, and tracks fine delay, amplitude and phase differences using an adaptive finite impulse response filter to generate a cancellation signal corresponding to the delayed and frequency shifted version. A minimum output power process produces an error signal that drives the variable delay and adaptive filter to minimize the power in the signal of interest to maximize cancellation of the interfering signal.

Owner:RAYTHEON APPLIED SIGNAL TECH

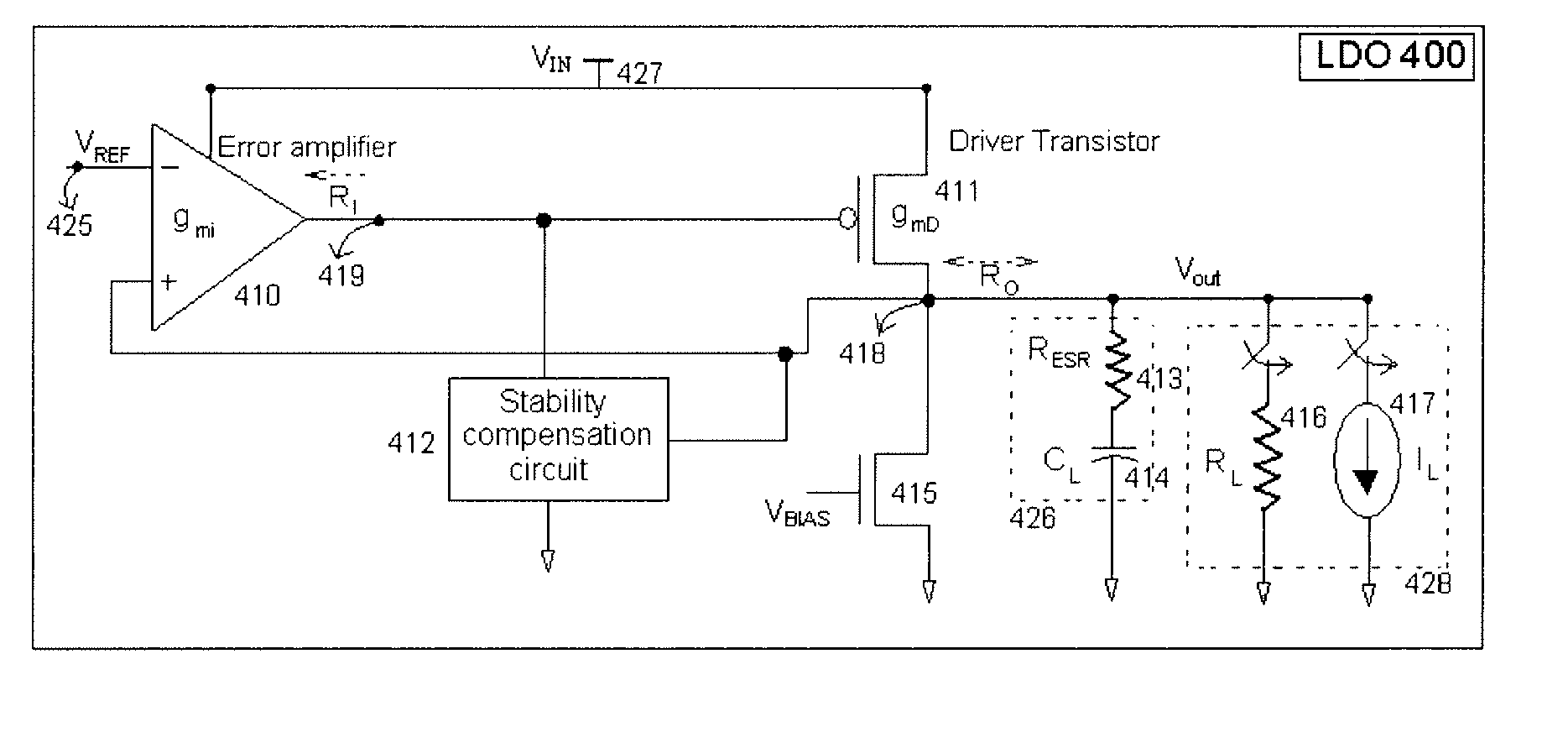

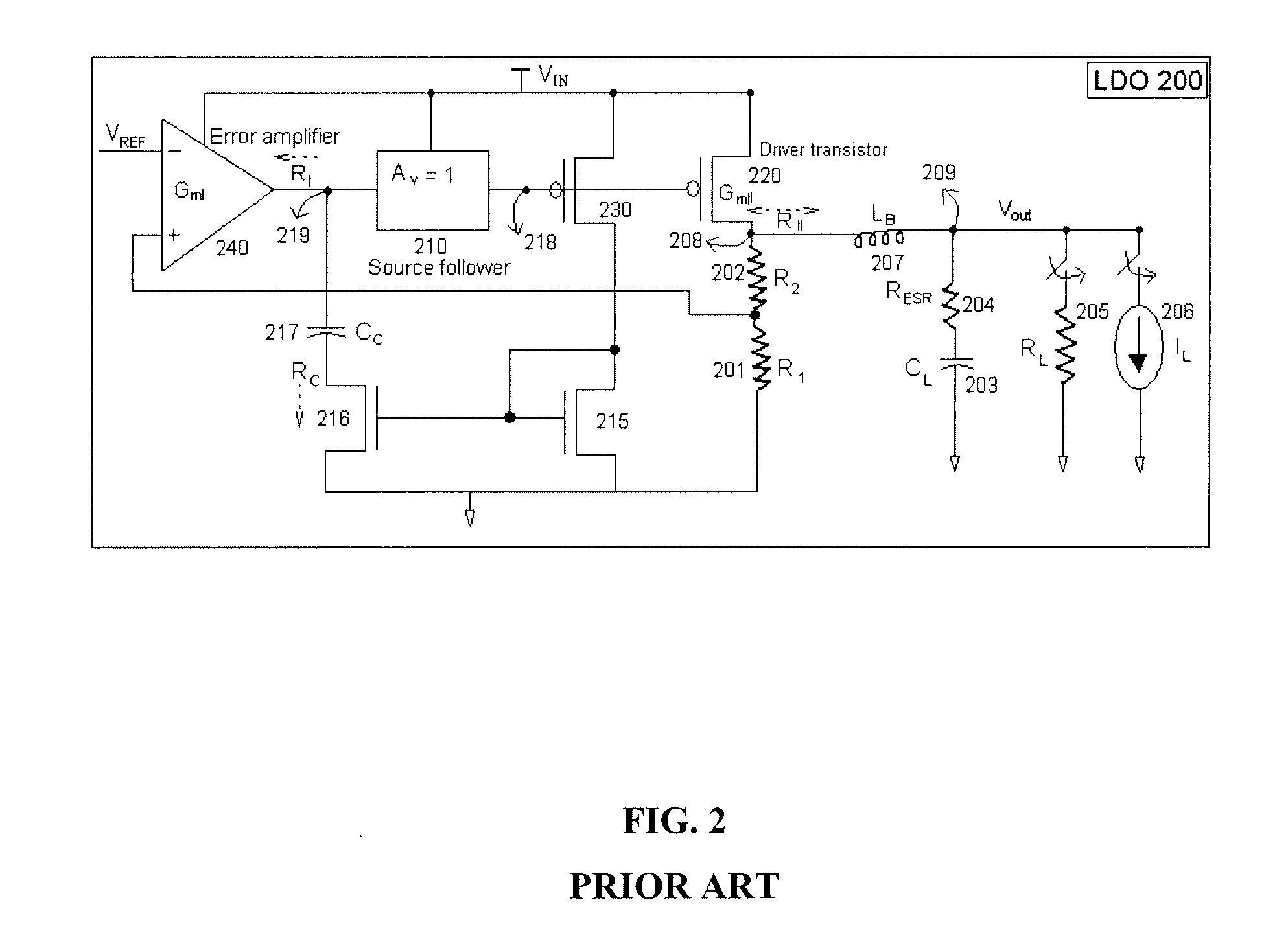

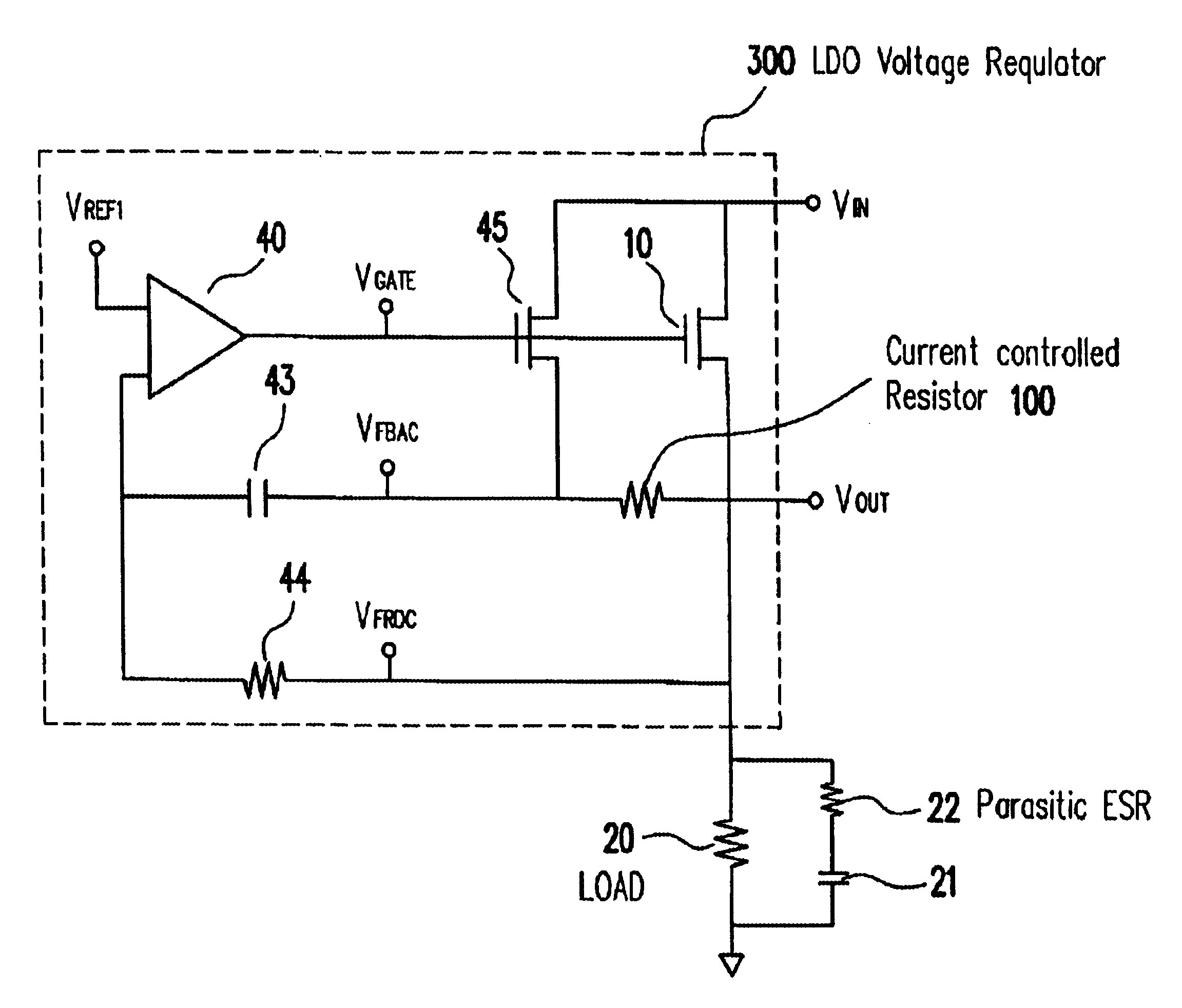

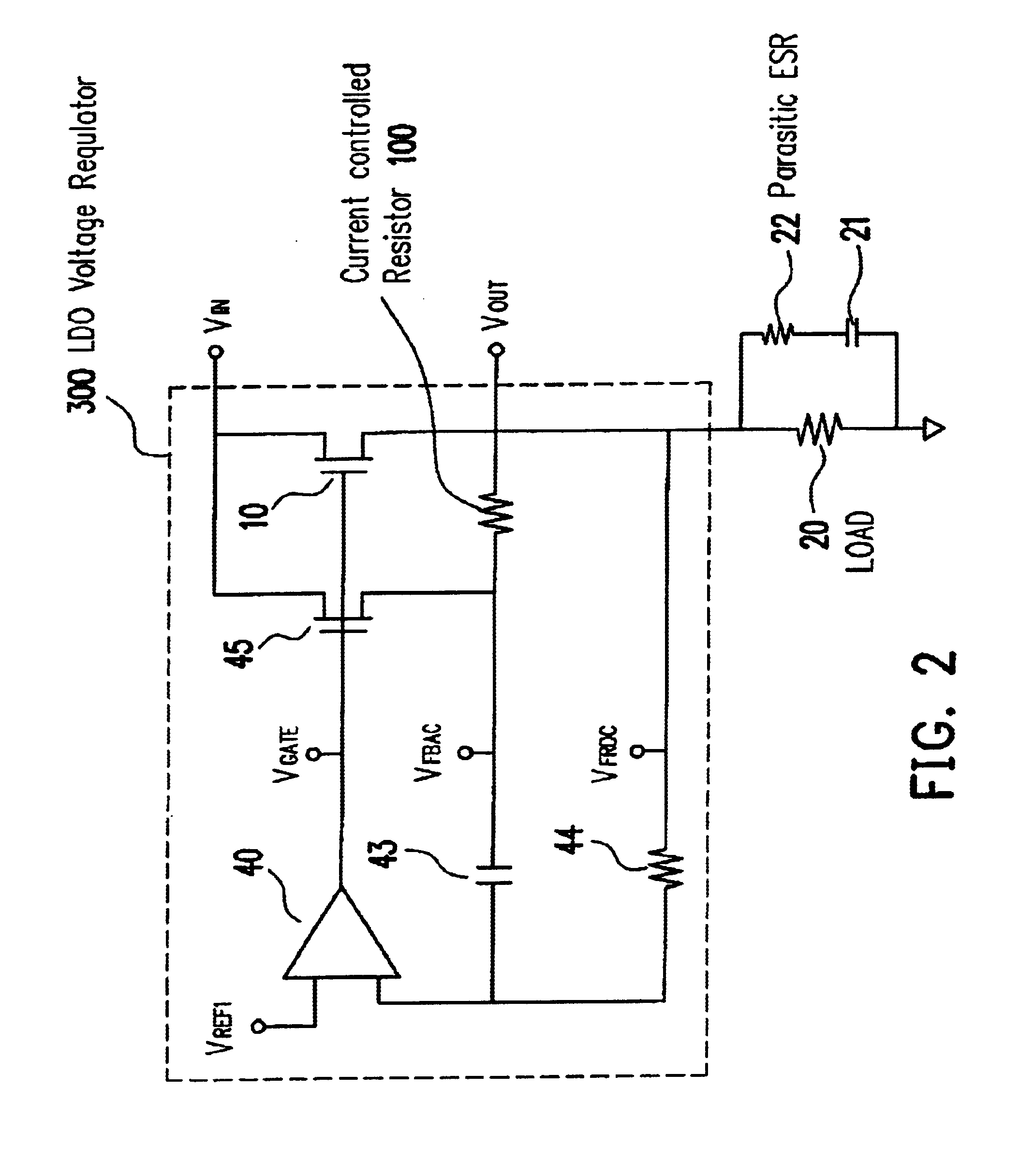

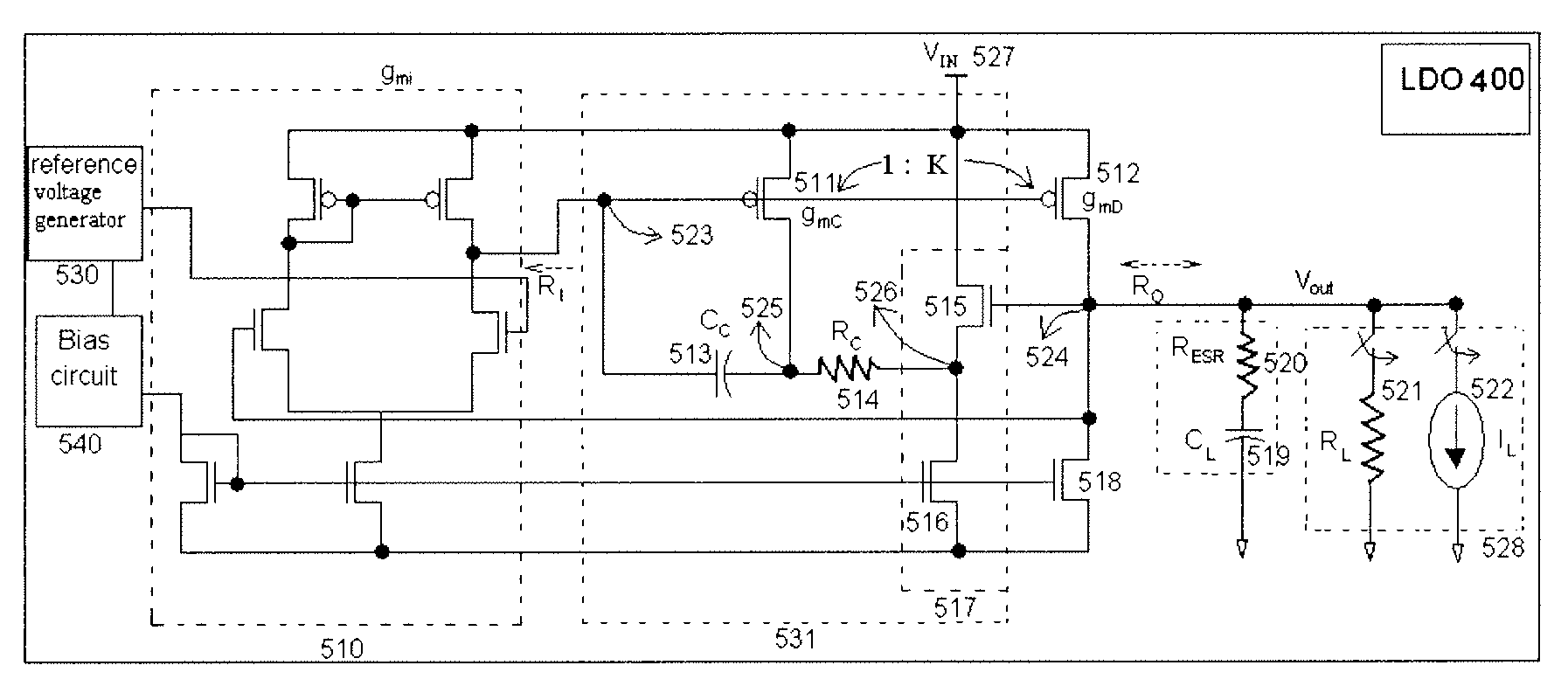

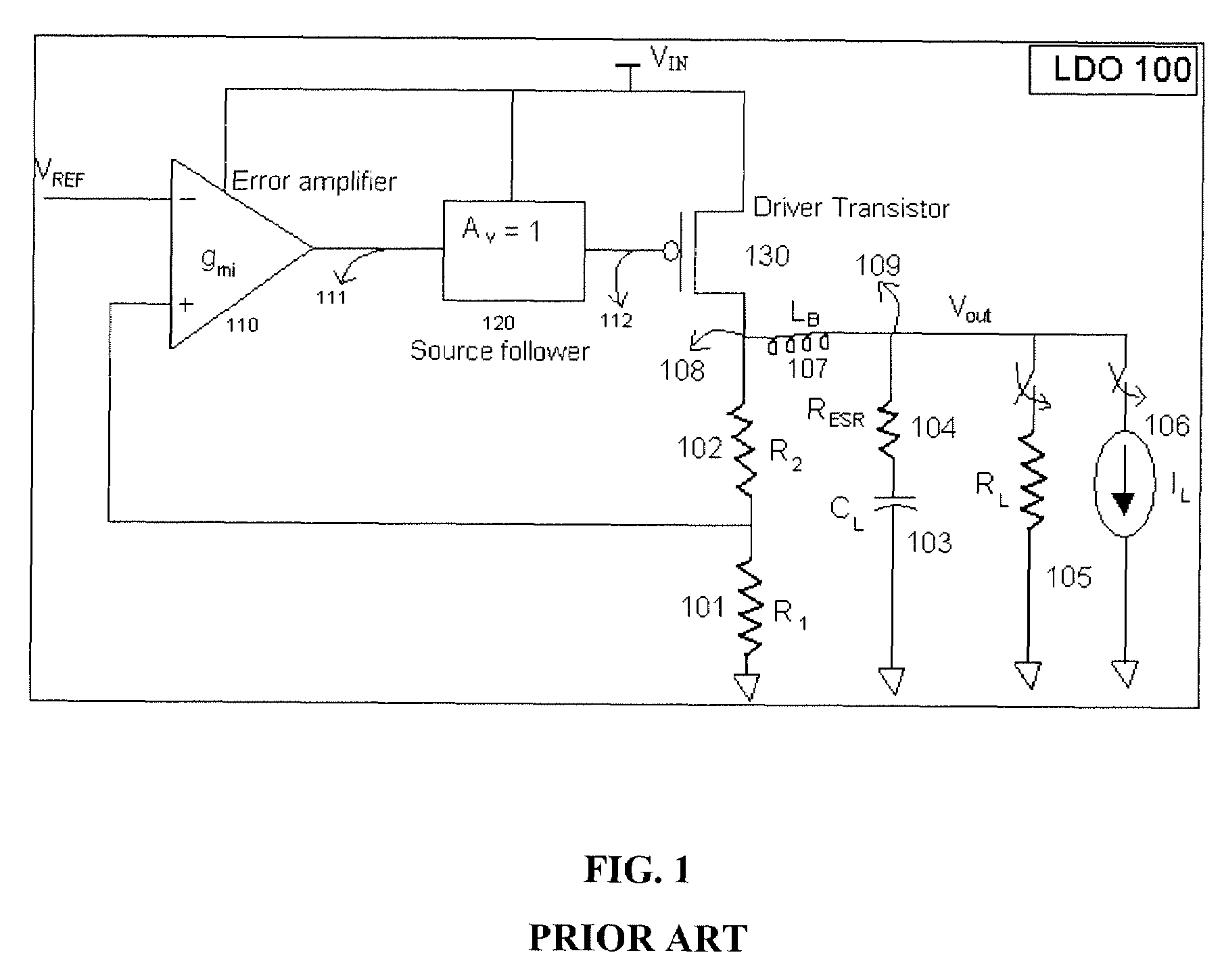

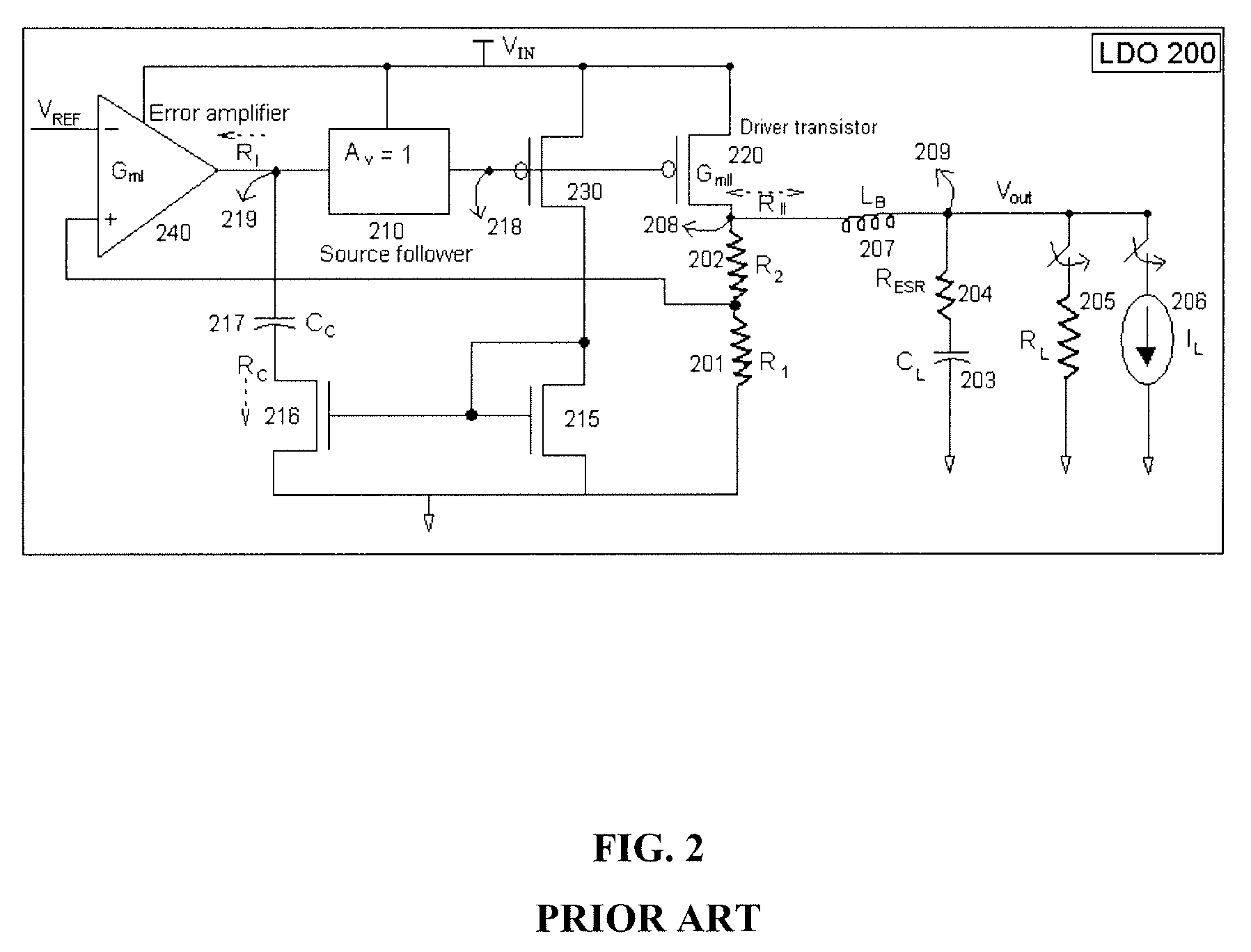

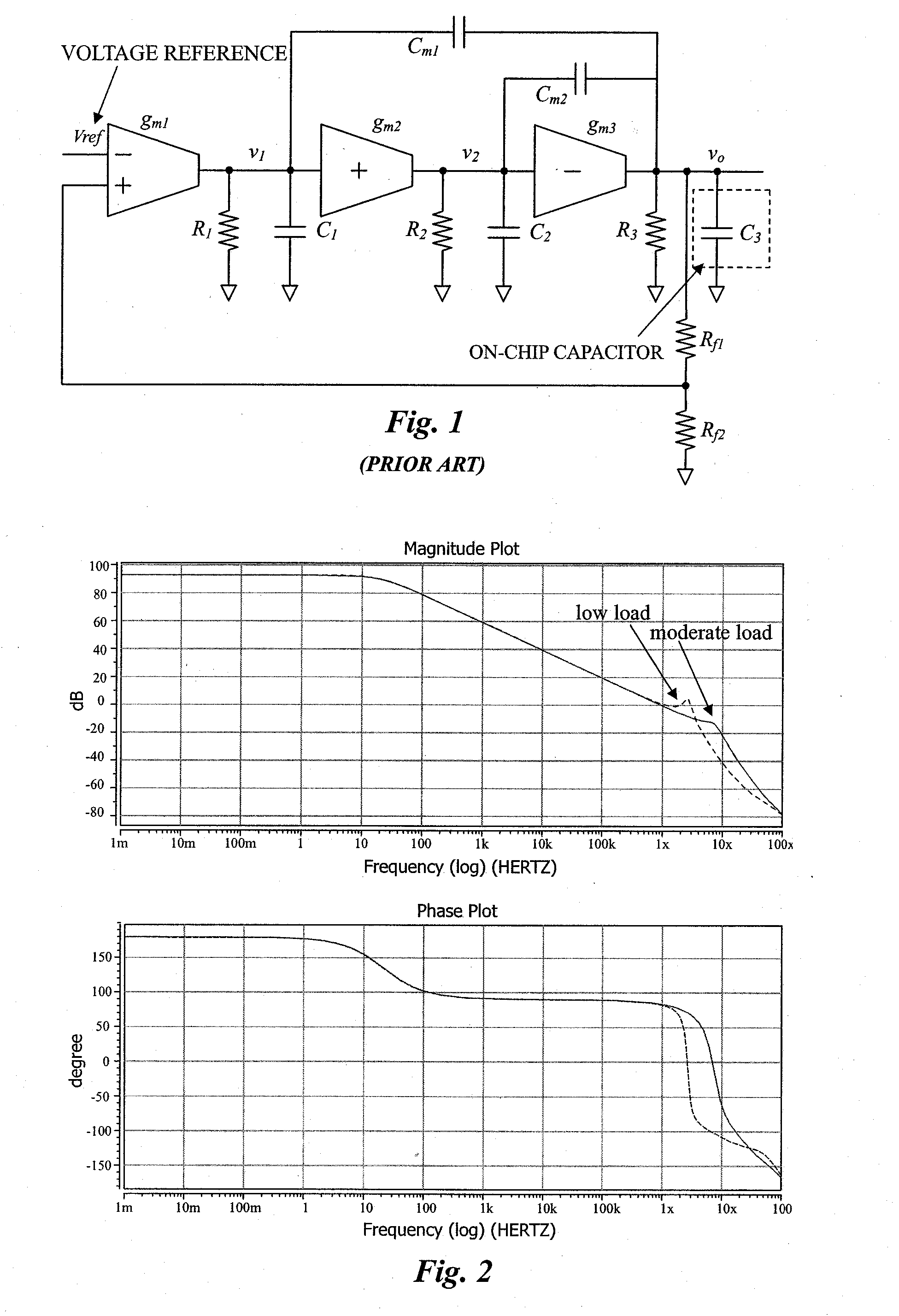

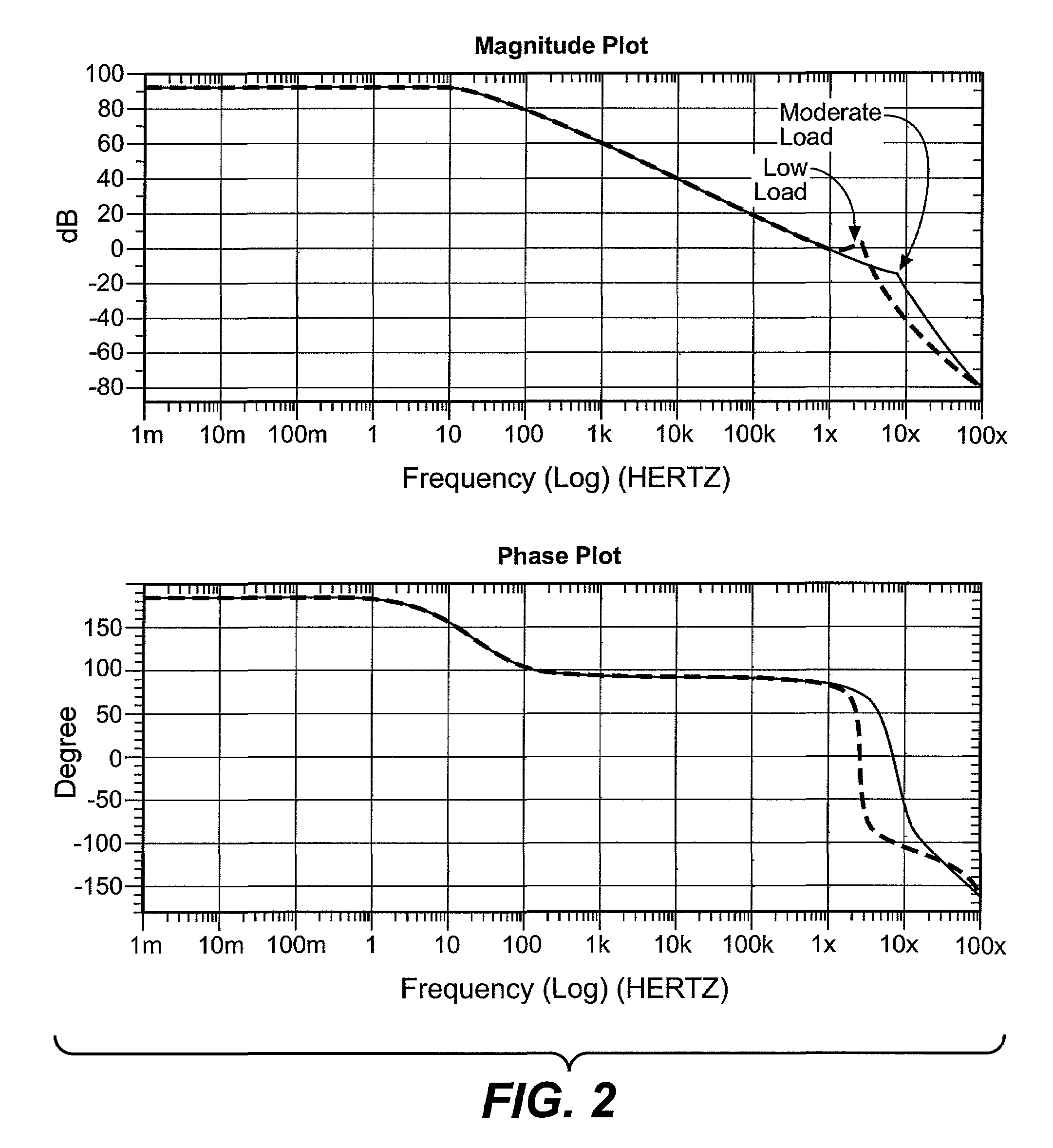

Low dropout regulator

InactiveUS20070159146A1Good phase marginMinimize power consumptionElectric variable regulationLow loadEngineering

The present invention provides a low dropout (LDO) regulator with a stability compensation circuit. A “zero frequency” tracking as well as “non-dominant parasitic poles' frequency reshaping” are performed to achieve a good phase margin for the LDO by means of the compensation circuit. In this compensation method neither a large load capacitor nor its equivalent series resistance is needed to stabilize a regulator. LDO regulators, in system on chip application, having load capacitors in the range of few nano-Farads to few hundreds of nano-Farads can be efficiently compensated with this compensation method. A dominant pole for the regulator is realized at an internal node and the second pole at an output node of the regulator is tracked with a variable capacitor generated zero over a range of load current to cancel the effect of each other. A third pole of the system is pushed out above the unity gain frequency of the open loop transfer function with the help of the frequency compensation circuit. The compensation technique is very effective in realizing a low power, low-load-capacitor LDO desirable for system on chip applications.

Owner:ST ERICSSON SA

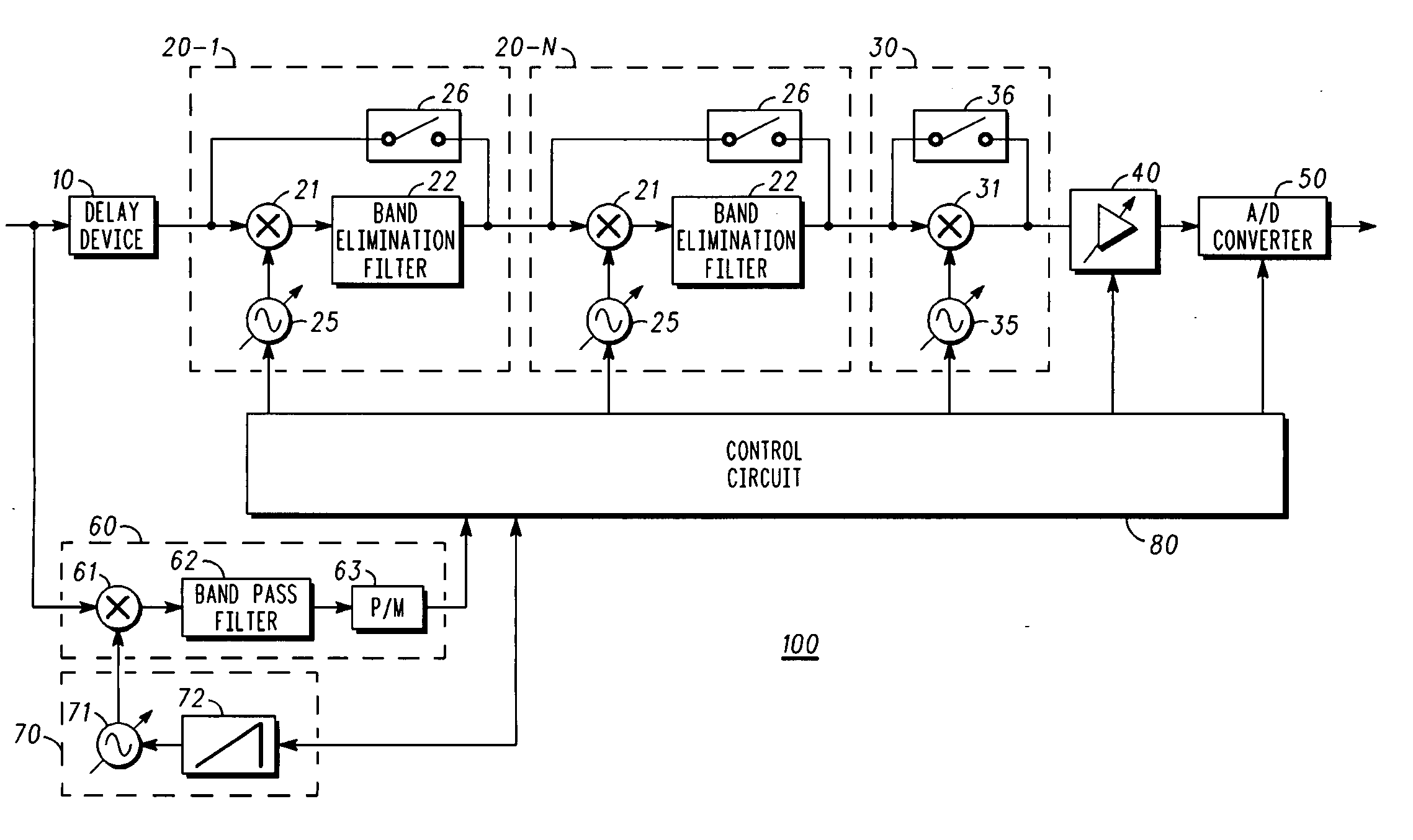

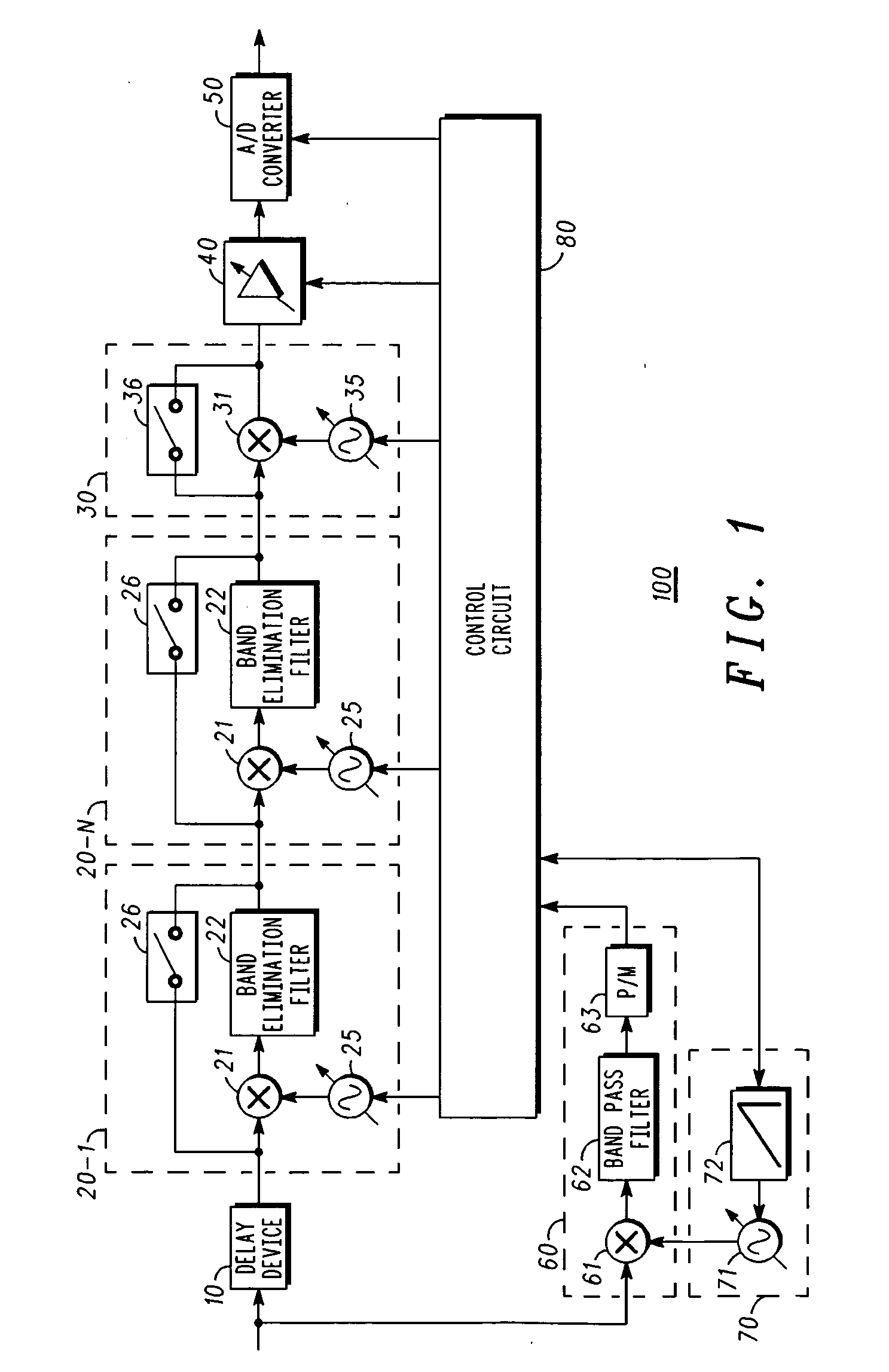

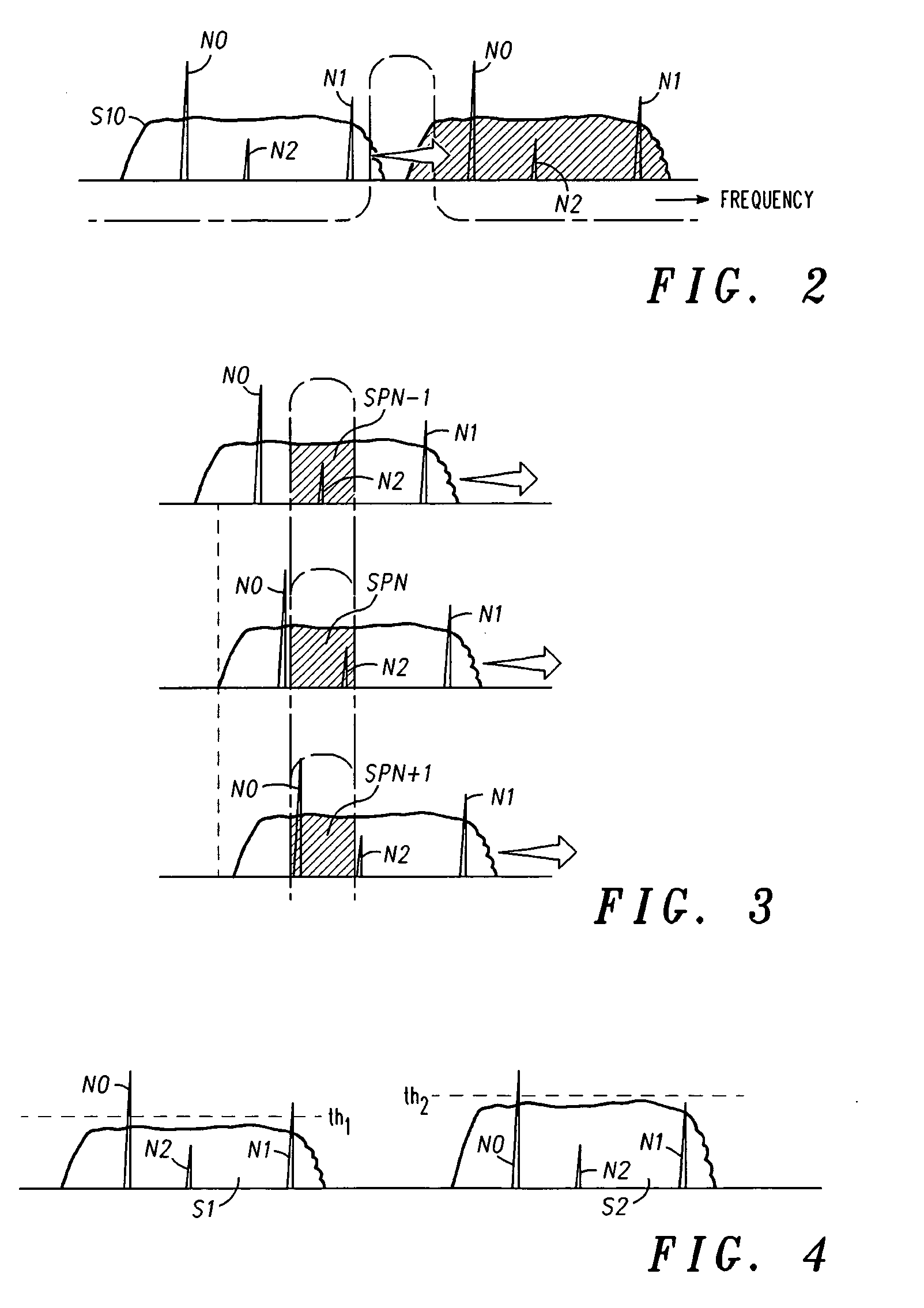

Narrow band interference supressor

InactiveUS20050201498A1Error preventionLine-faulsts/interference reductionFrequency compensationAudio power amplifier

A compact narrow band interference suppressor. The narrow band interference suppressor includes a plurality of interference signal elimination circuits, a frequency compensation circuit, an AGC amp, and an AD converter that are connected in series. Each interference signal elimination circuit includes a mixer for synthesizing a local oscillation signal of a variable frequency oscillator to eliminate an interference signal with a band elimination filter. The frequency compensation circuit includes a mixer for synthesizing a signal having a frequency generated by the variable frequency oscillator to restore the signal to the frequency band of the signal input to the narrow band interference suppressor by the variable frequency oscillator. The AD converter converts the polarity of the signal in accordance with the number of times the signal passes through the mixer.

Owner:MOTOROLA INC

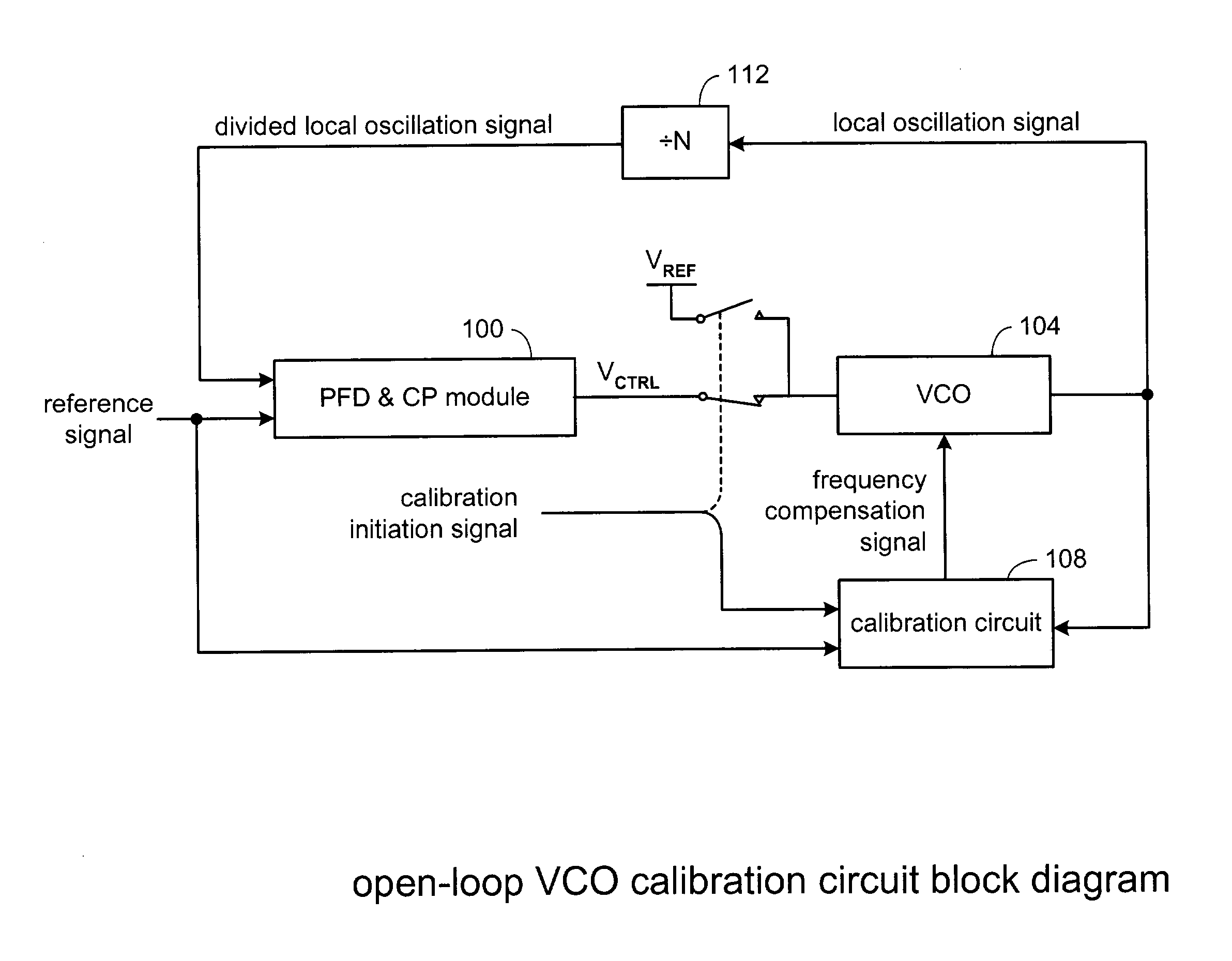

Analog open-loop VCO calibration method

InactiveUS7099643B2Quick calibrationQuick correctionAutomatic scanning with simultaneous frequency displayPulse automatic controlFrequency compensationEngineering

An analog open-loop voltage controlled oscillator (VCO) calibration circuit and method for selecting the frequency of the VCO for a phase locked loop (PLL).A frequency divider module produces a 50% duty cycle divided local oscillation and a 50% duty cycle divided reference signal, wherein the divided signals are substantially equal. A period-to-voltage conversion module converts the divided local oscillation signal and the divided reference signal to voltages proportional to the divided signals. A comparator module produces a frequency adjustment signal based on a comparison of the proportional voltages and couples the frequency adjustment signal to a logic module which produces a frequency compensation signal based on the frequency adjustment signal. The frequency compensation signal functions to adjust the configuration of switched capacitors in a capacitor bank, coupled to the VCO tuned circuit, until the divided local oscillation signal is substantially equal to the divided reference signal.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

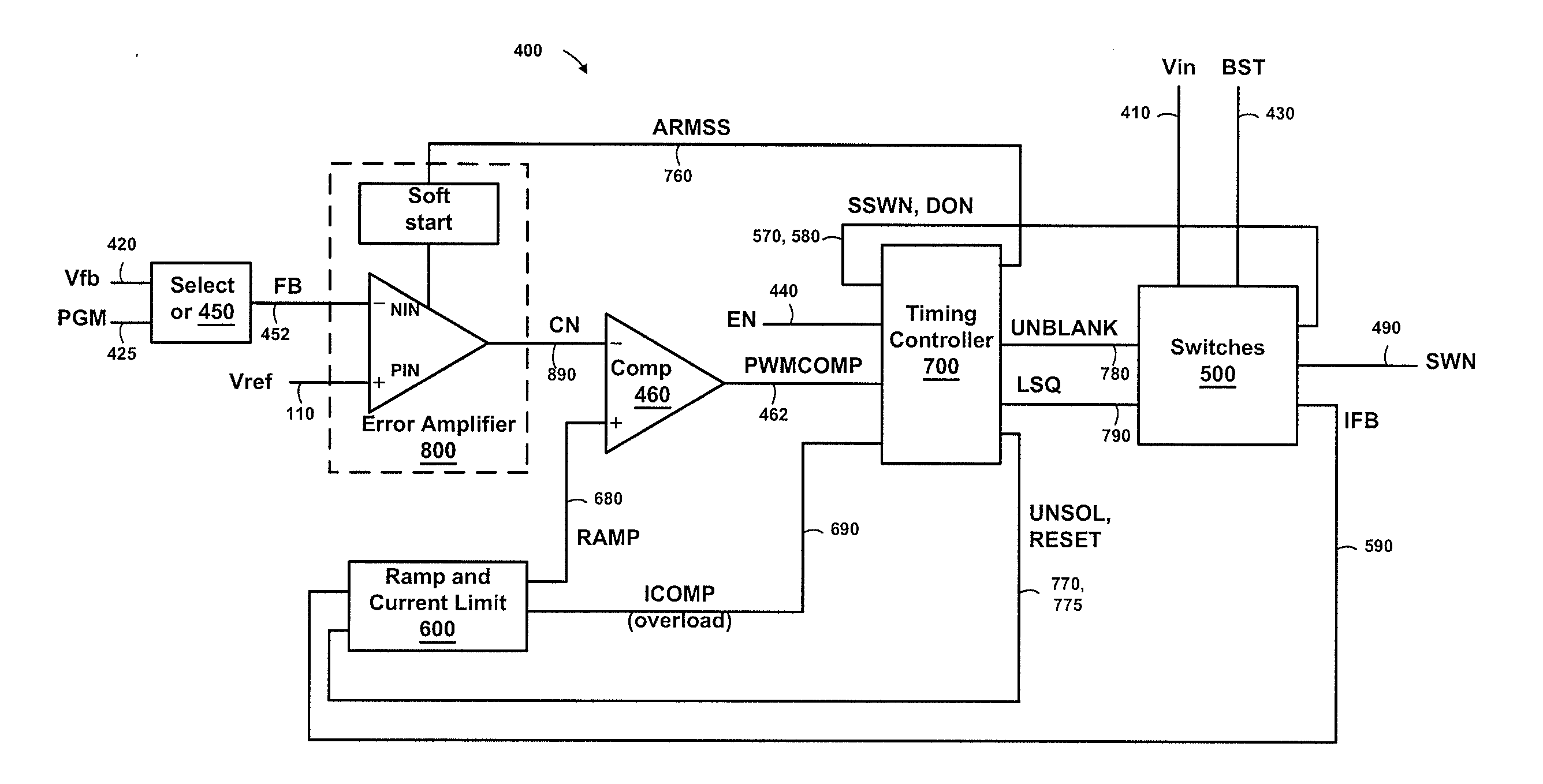

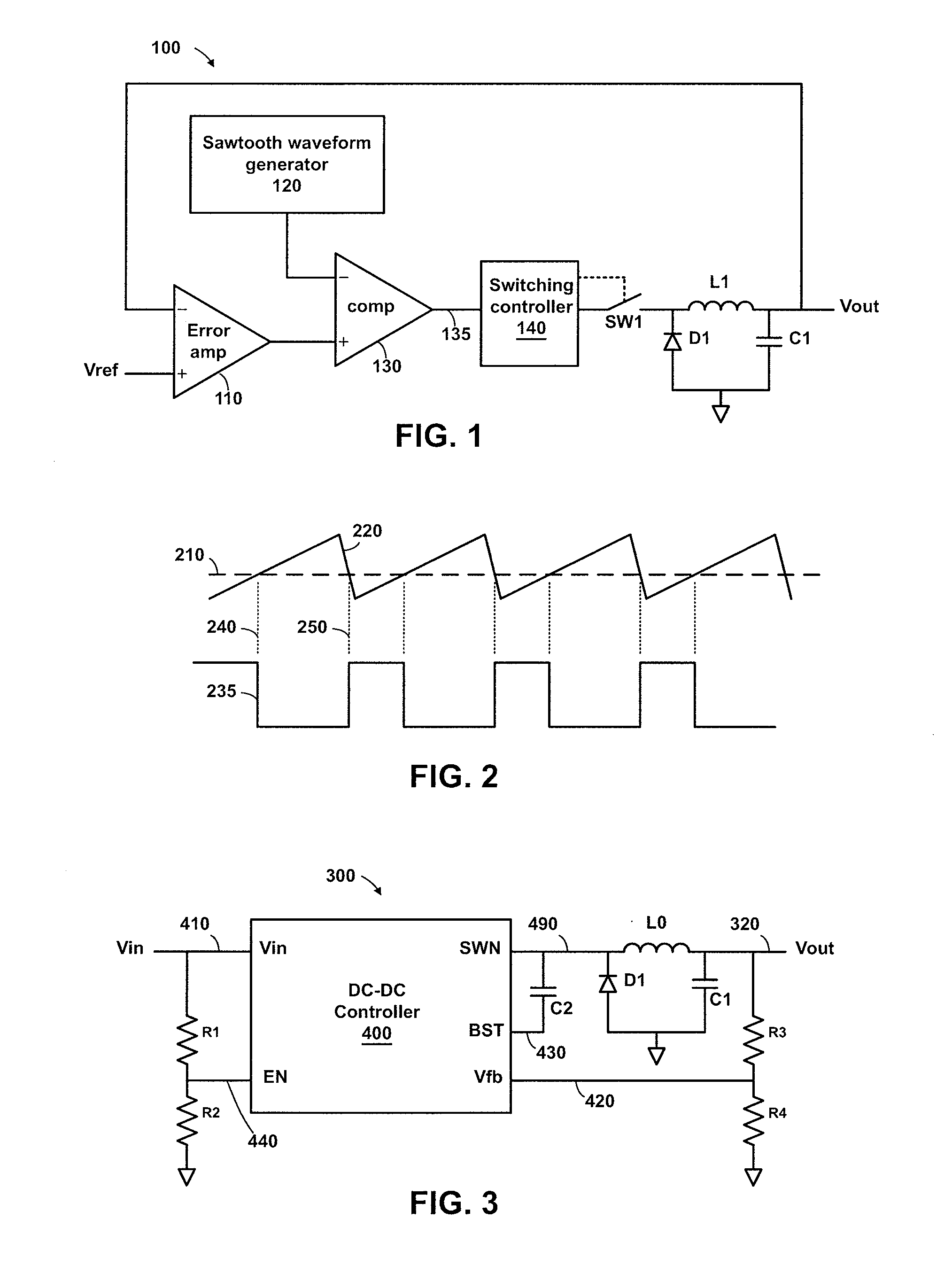

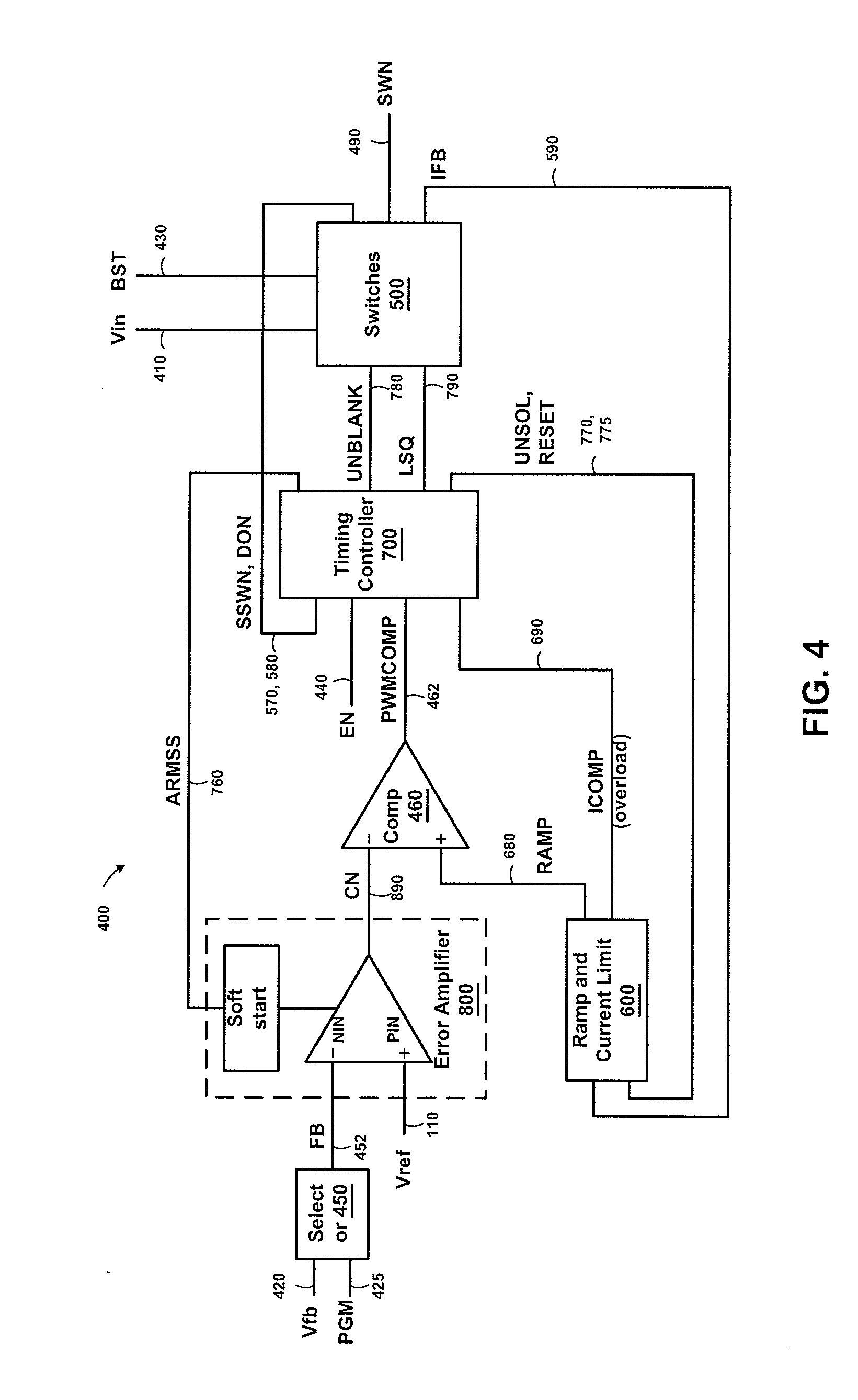

Methods and apparatuses for combinations of current feedback for frequency compensation, overload detection, and super overload detection in switching power conversion

ActiveUS20120153921A1Dc-dc conversionEmergency protective arrangements for limiting excess voltage/currentFrequency compensationEngineering

A single replica current is proportional to current through a main switch of a switching power converter. This replica current may be used for current compensation, detection and response to an overload, detection and response to a super-overload, and combinations thereof. An input voltage is switchably coupled to an output signal generating a load current responsive to a switch control. A replica switch generates a replica current proportional to the load current. A ramp modulation signal may be generated. A voltage ramp of the ramp modulation signal may be adjusted in response to the replica current. A feedback difference signal is compared to the ramp modulation signal to generate a comparison output. Comparison of an overload reference voltage to a replica voltage proportional to the replica current generates an overload signal. The switch control is generated responsive to the comparison output and may be modified responsive to the overload signal.

Owner:INTEGRATED DEVICE TECH INC

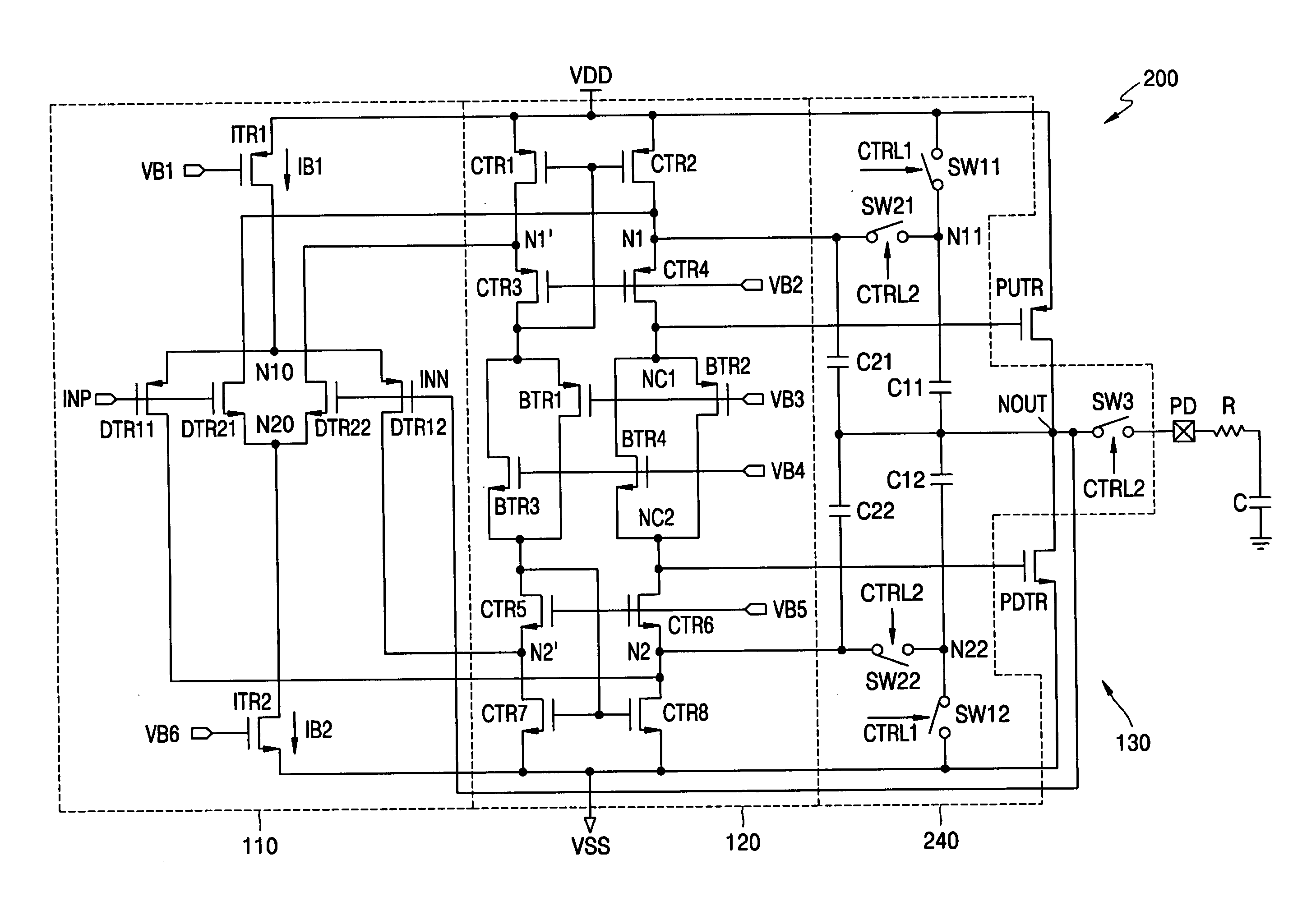

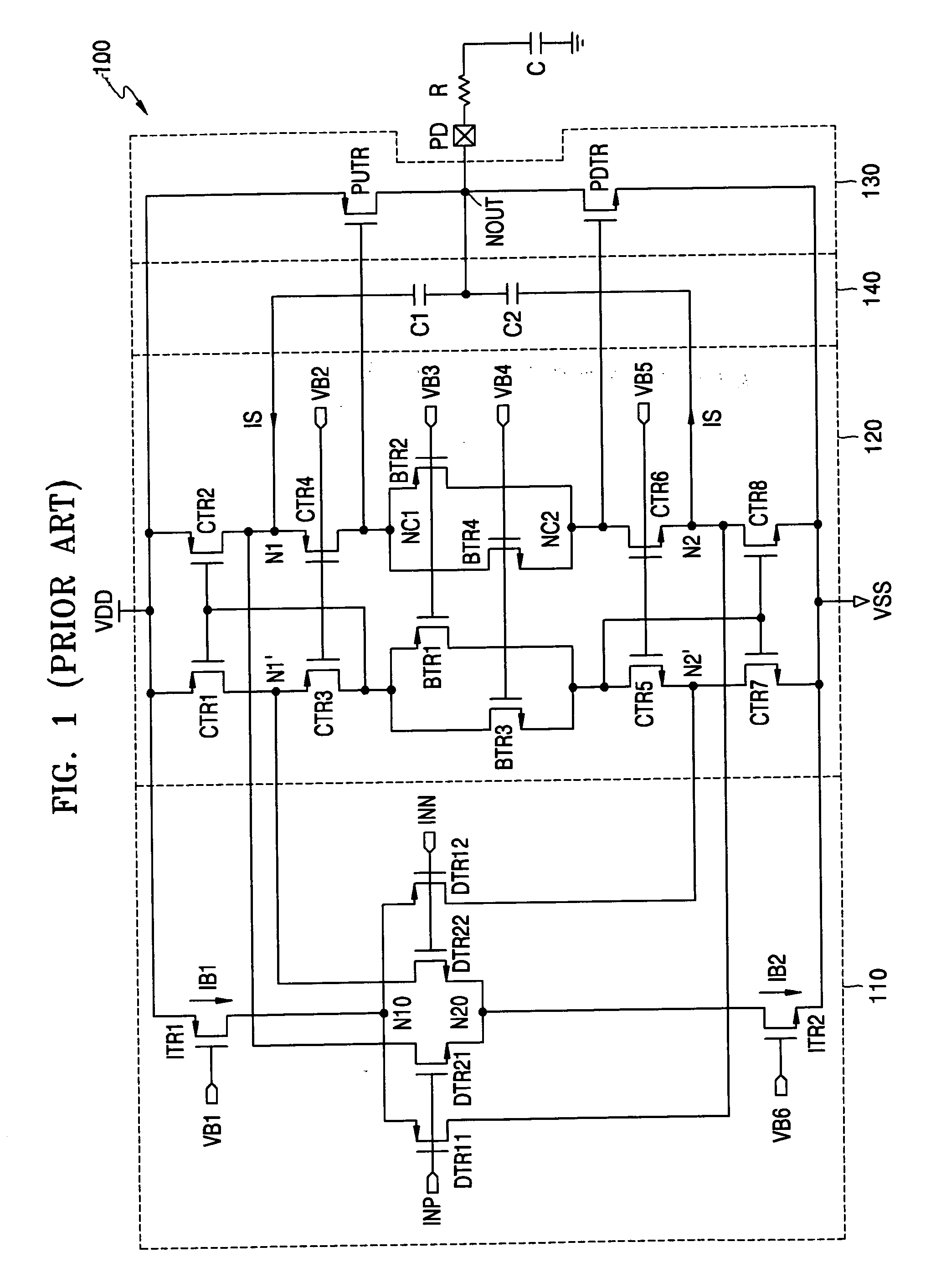

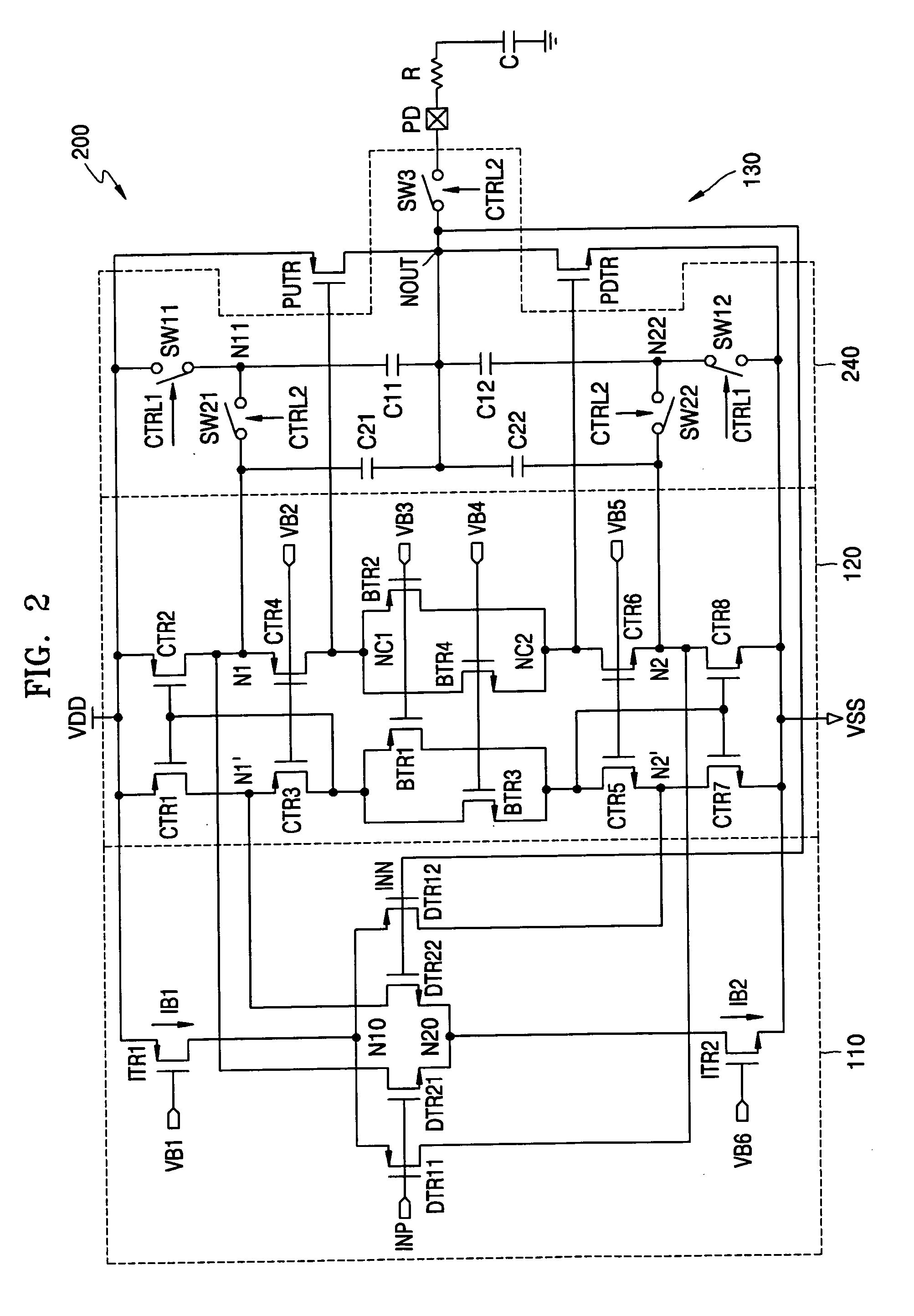

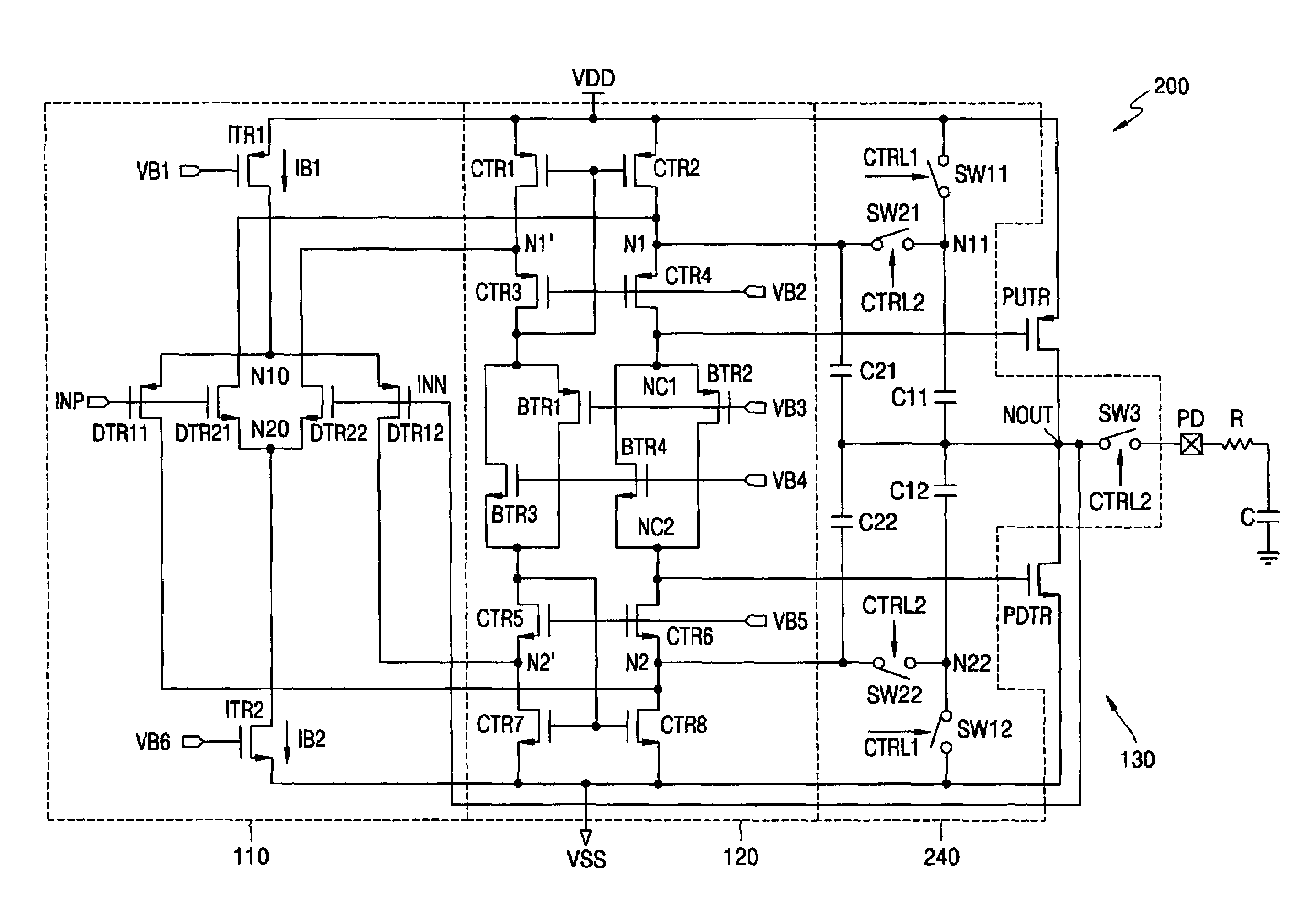

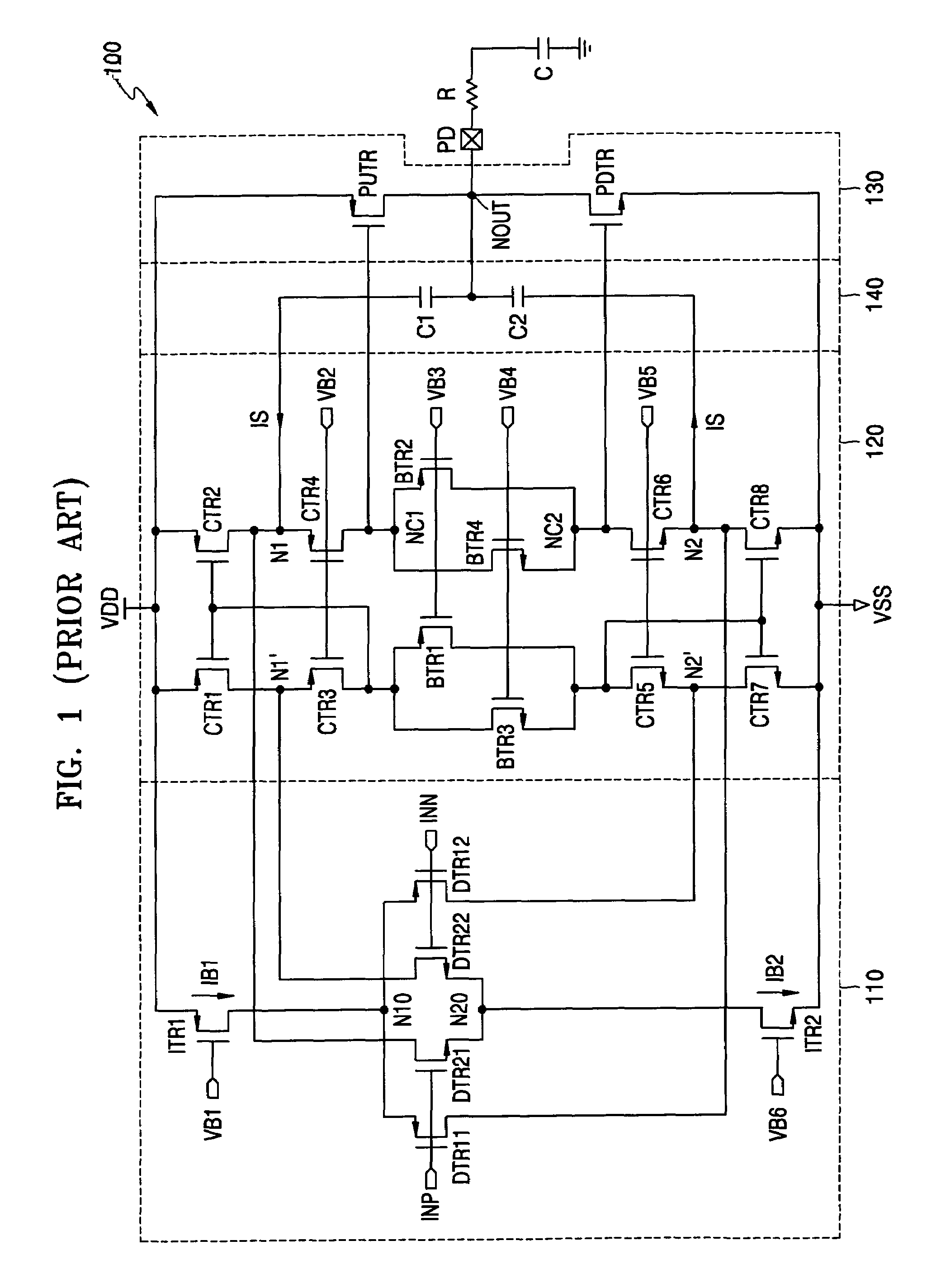

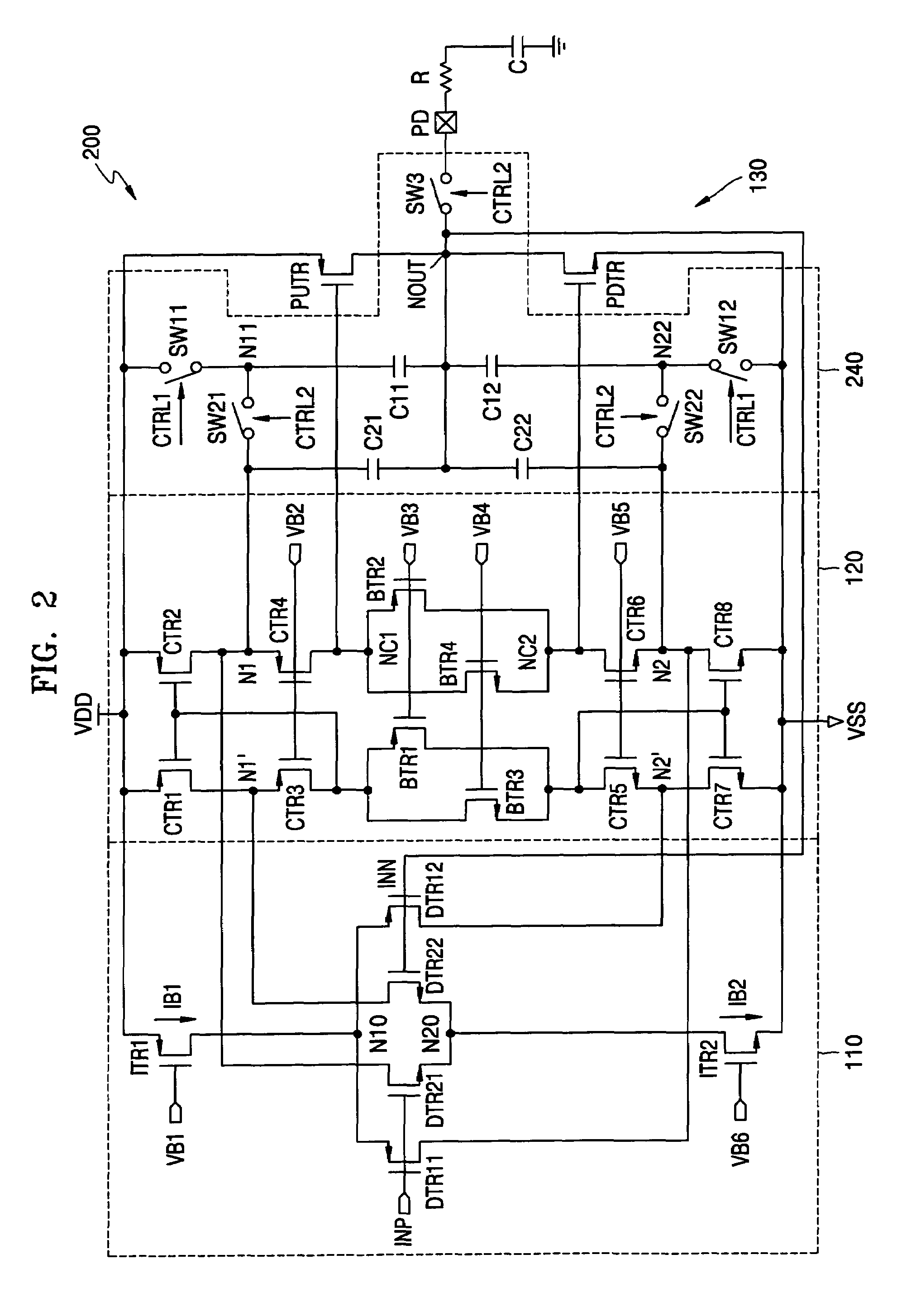

Circuits and methods for improving slew rate of differential amplifiers

ActiveUS20060091955A1Increase conversion rateReduce power consumptionNegative-feedback-circuit arrangementsAmplifier modifications to reduce detrimental impedenceElectricityFrequency compensation

Circuits and methods are provided for providing high speed operational amplifiers and, in particular, operational amplifiers having frequency compensation circuits that provide improved slew rates with low power dissipation when configured with feedback. Frequency compensation schemes are provided to enable dynamic configuration of frequency compensation circuits implementing miller compensation whereby nodal connections of compensation capacitors are changed during driver setup and driving periods such that compensation capacitors are connected to source voltages to rapidly charge / discharge compensation capacitors using supply source currents during setup period, while providing frequency compensation during the setup and driving periods to maintain circuit stability and prevent oscillation of an output voltage due to the feedback.

Owner:SAMSUNG ELECTRONICS CO LTD

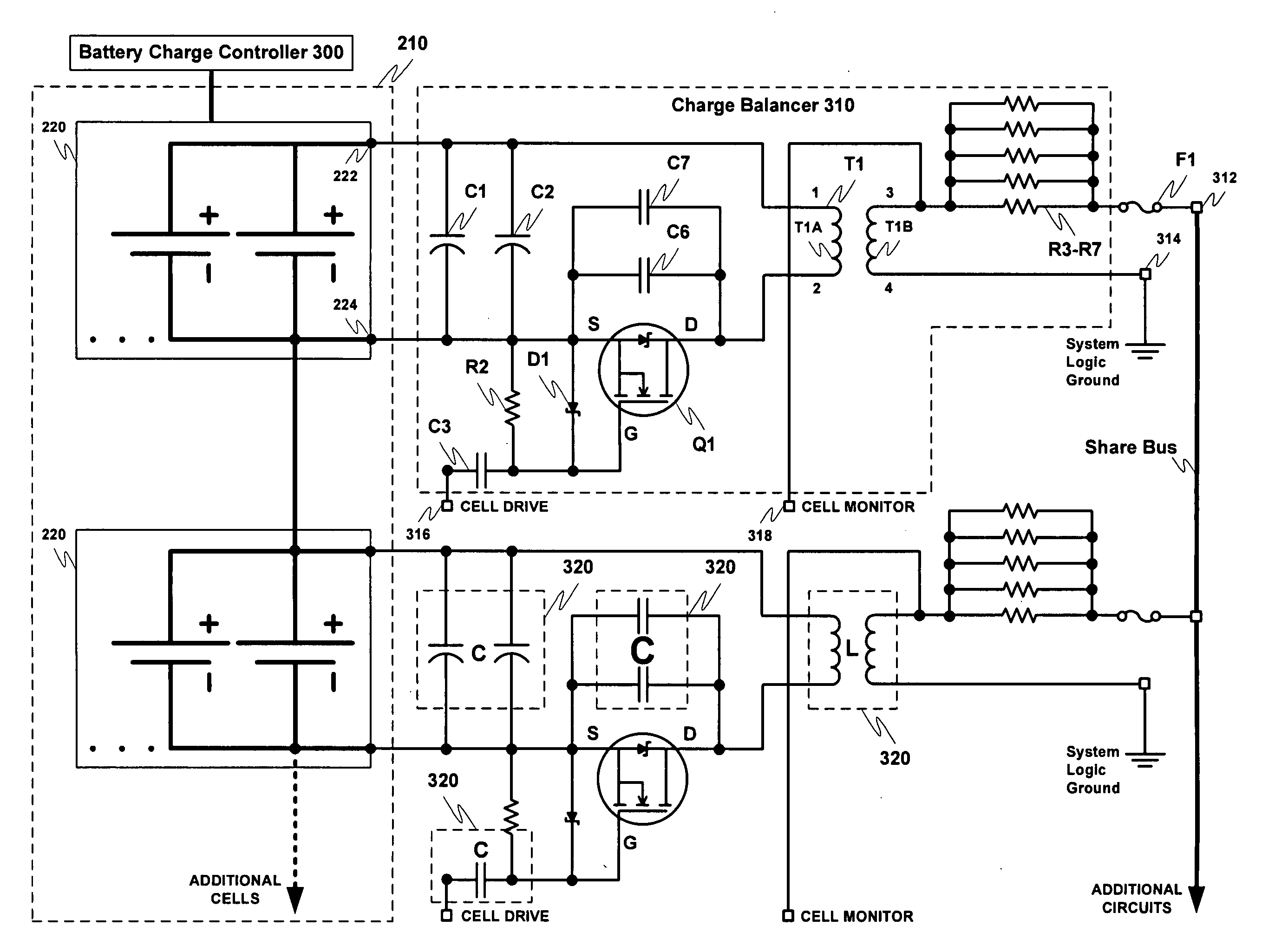

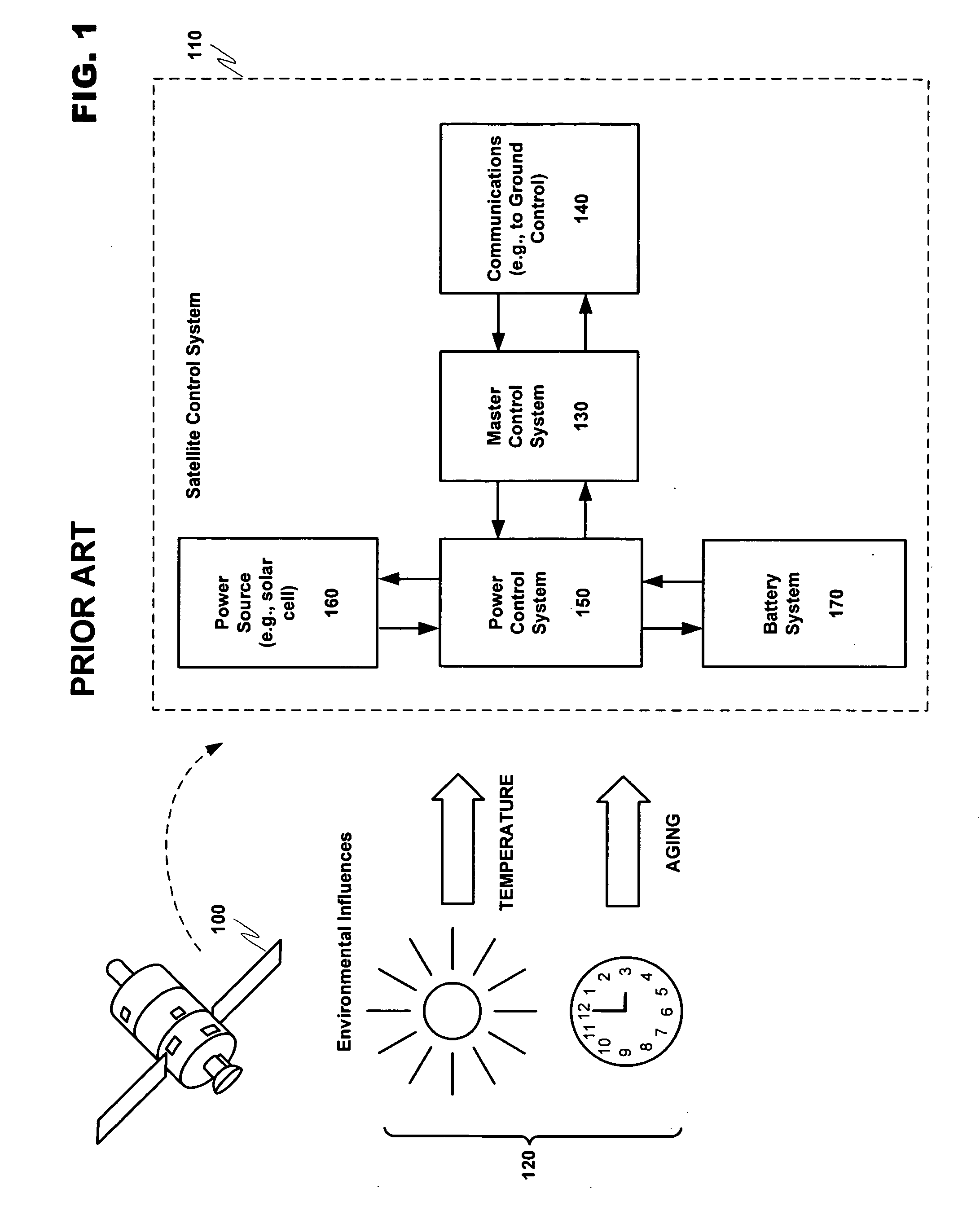

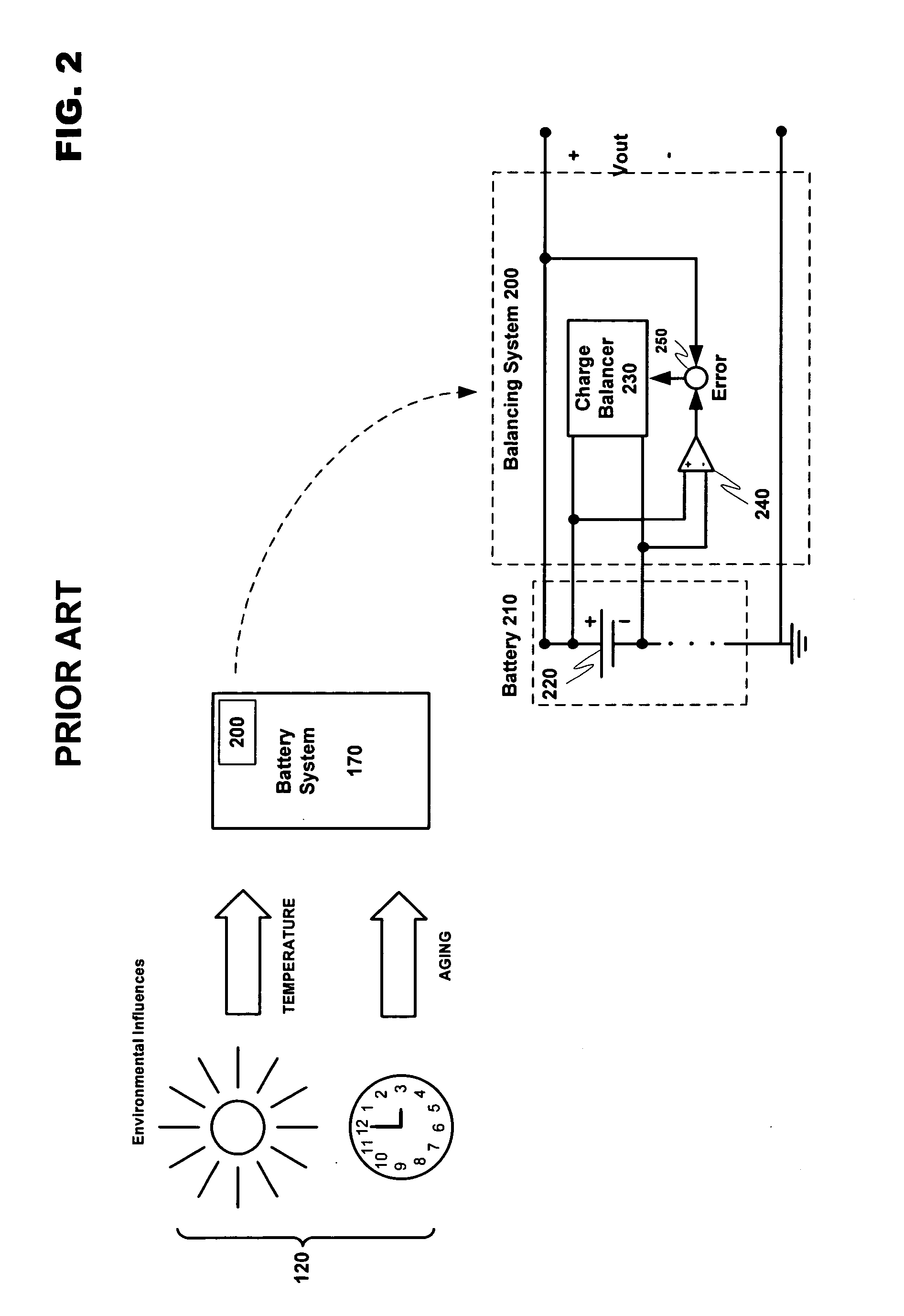

Battery balancing including resonant frequency compensation

ActiveUS20070279003A1Balance levelImprove performanceCharge equalisation circuitEfficient power electronics conversionFrequency compensationFrequency matching

A system for balancing charge between a plurality of storage battery cells within a storage battery. The battery balancing system sense changes, possibly caused by environmental influences, in the overall resonant frequency of charge balancing circuits contained within the battery balancing system. Using a phase locked loop based controller, the battery balancing system compensates for the change in resonant frequency by driving the battery balancing circuits at a frequency that matches the actual sensed resonant frequency of the battery balancing circuits.

Owner:COBHAM ADVANCED ELECTRONICS SOLUTIONS

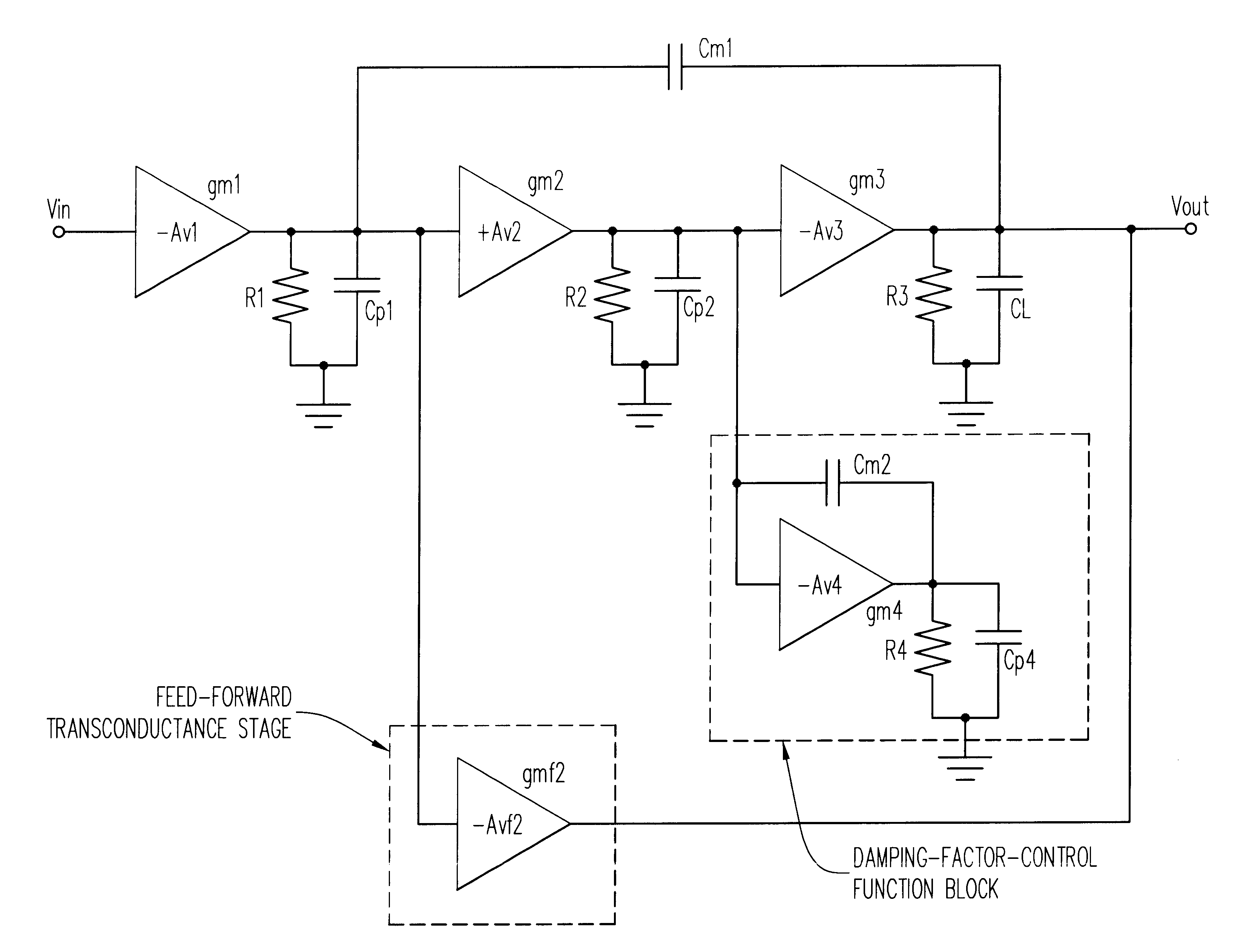

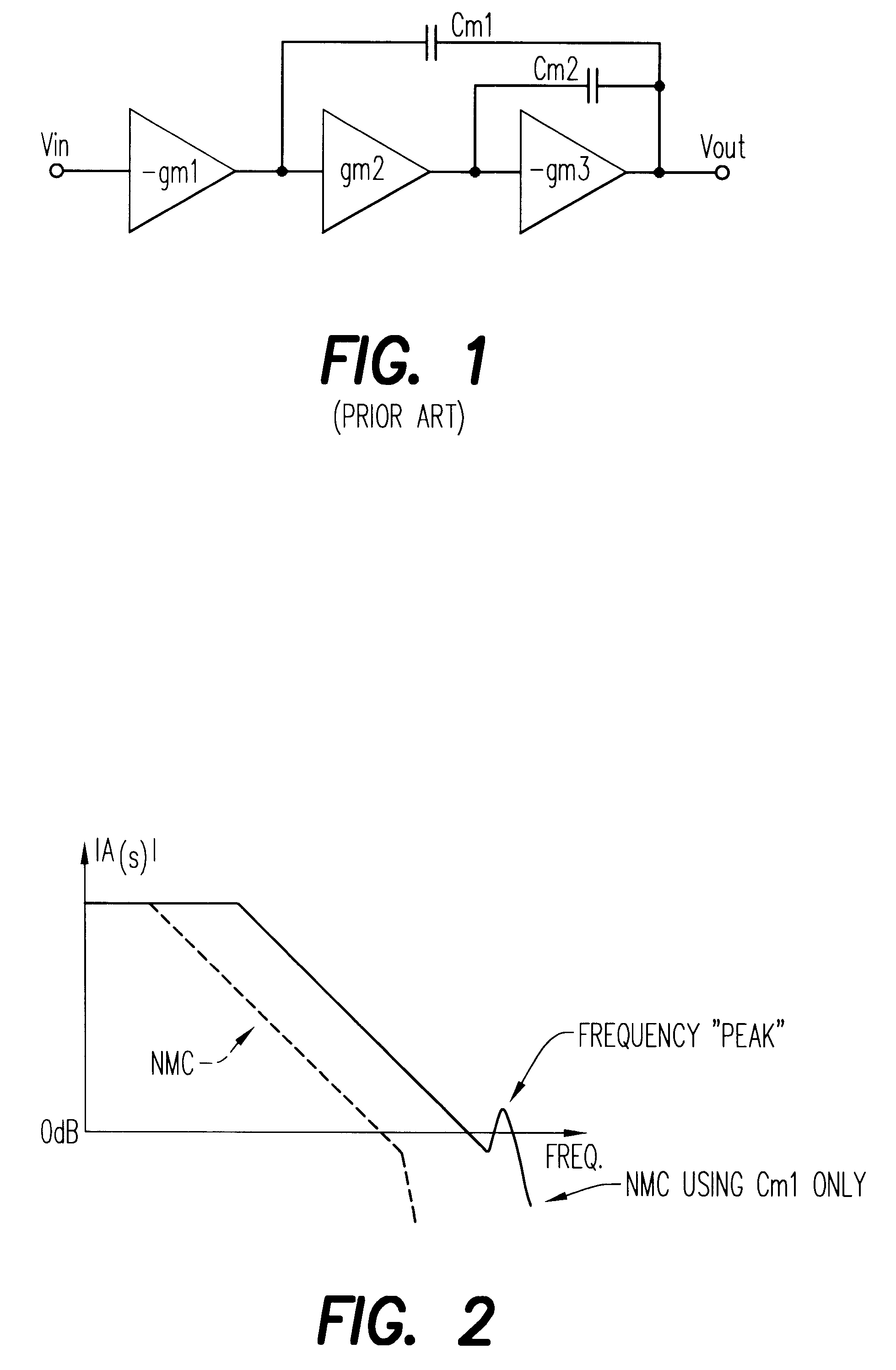

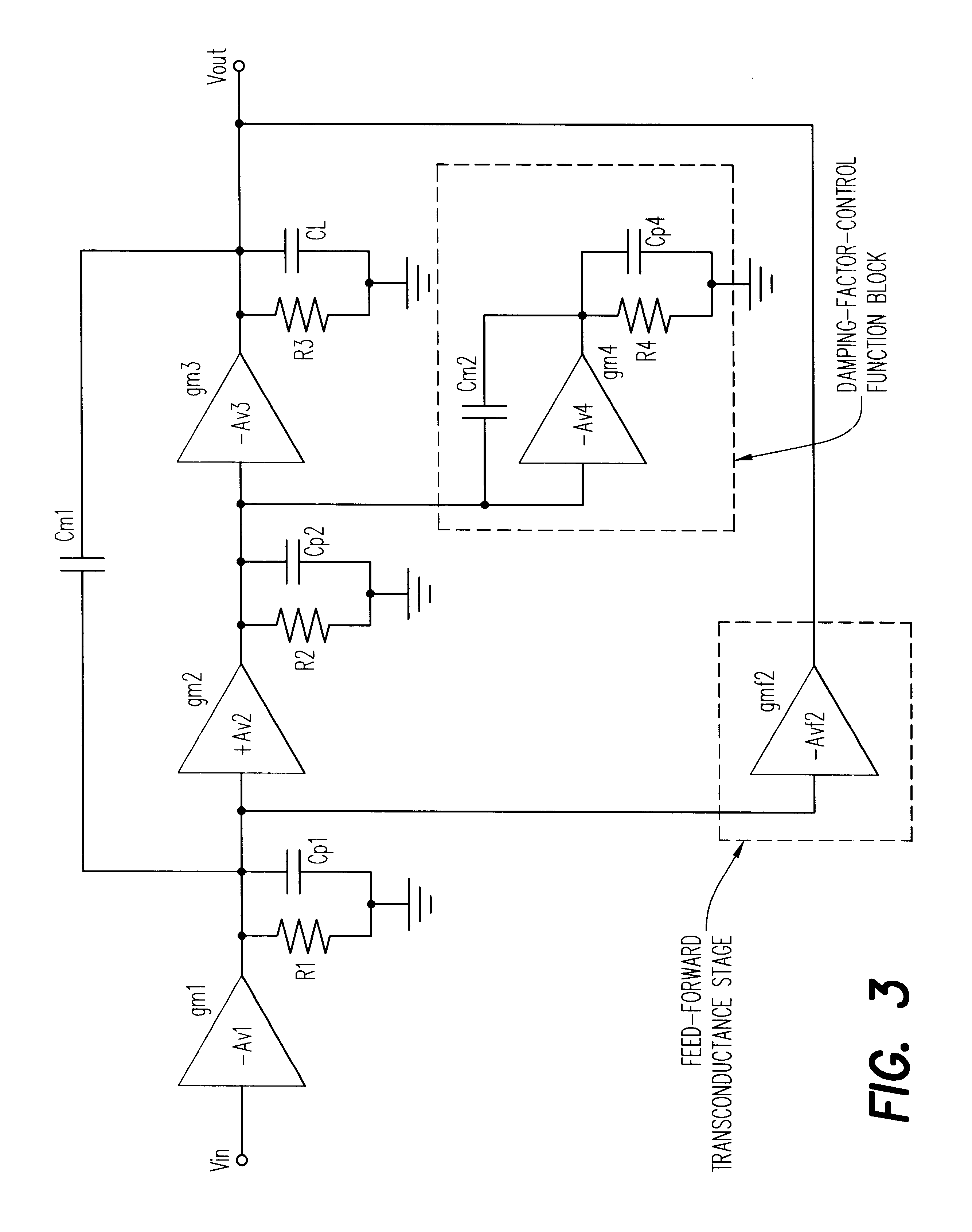

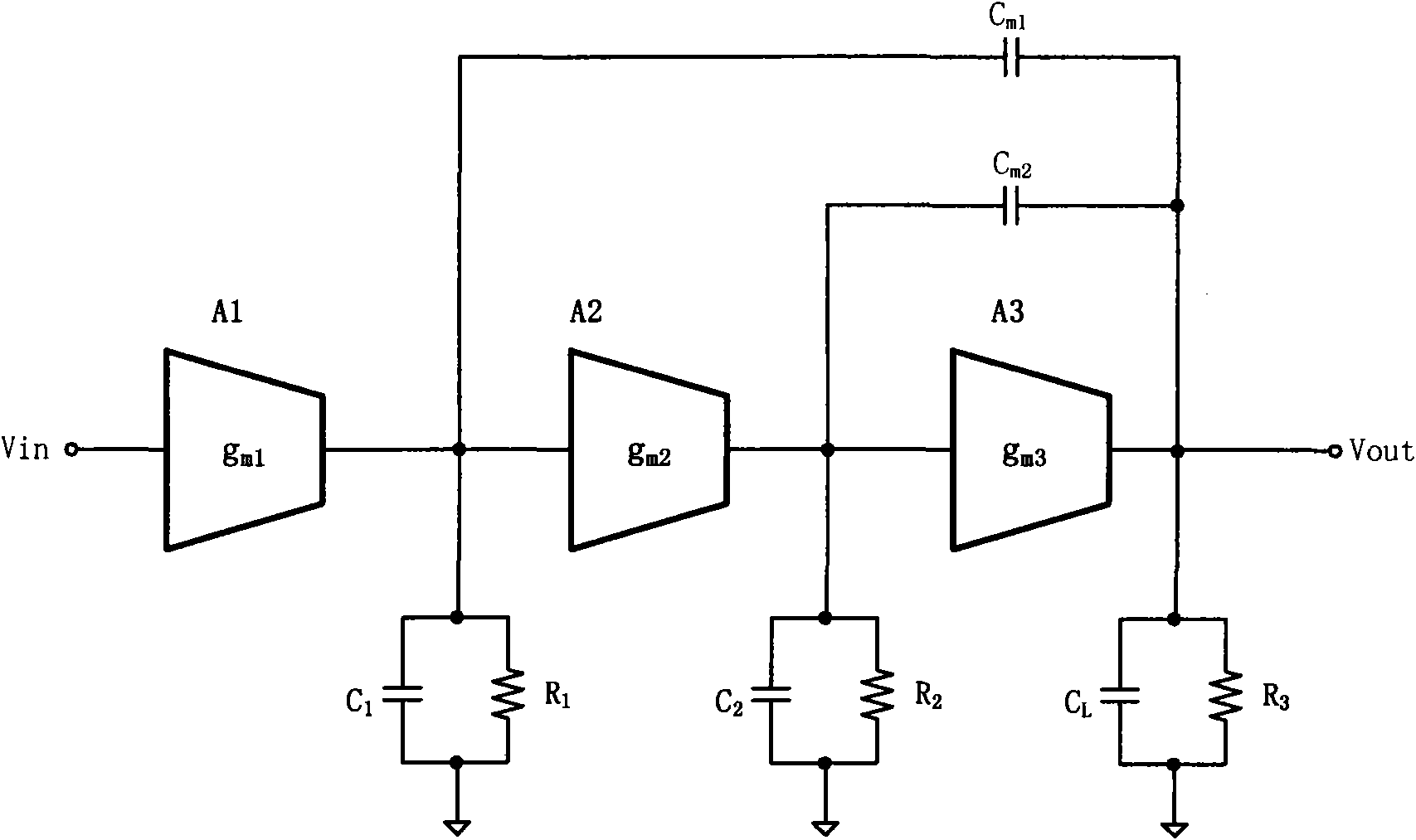

Frequency compensation techniques for low-power multistage amplifiers

InactiveUS6208206B1Negative-feedback-circuit arrangementsAmplifier modifications to reduce detrimental impedenceDamping factorCapacitance

A three stage amplifier is disclosed provided with a novel frequency compensation technique. Only a single feedback loop with a single compensation capacitance is provided. Instead of a conventional nested compensation technique, damping factor control is provided by means of a fourth gain stage in order to stabilize the amplifier. The resulting amplifier is particularly useful to drive large capacitive loads for low-voltage low-power applications.

Owner:THE HONG KONG UNIV OF SCI & TECH

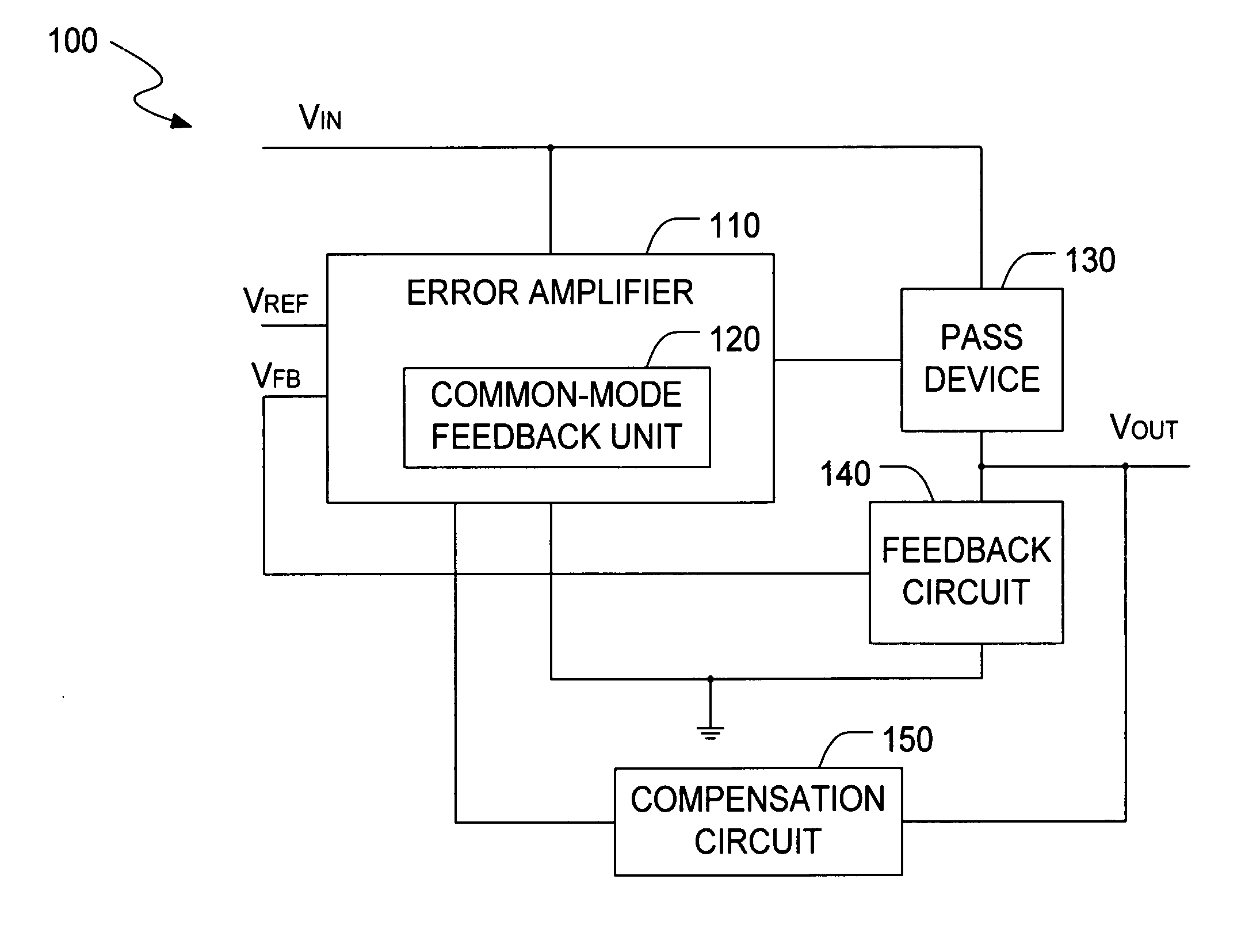

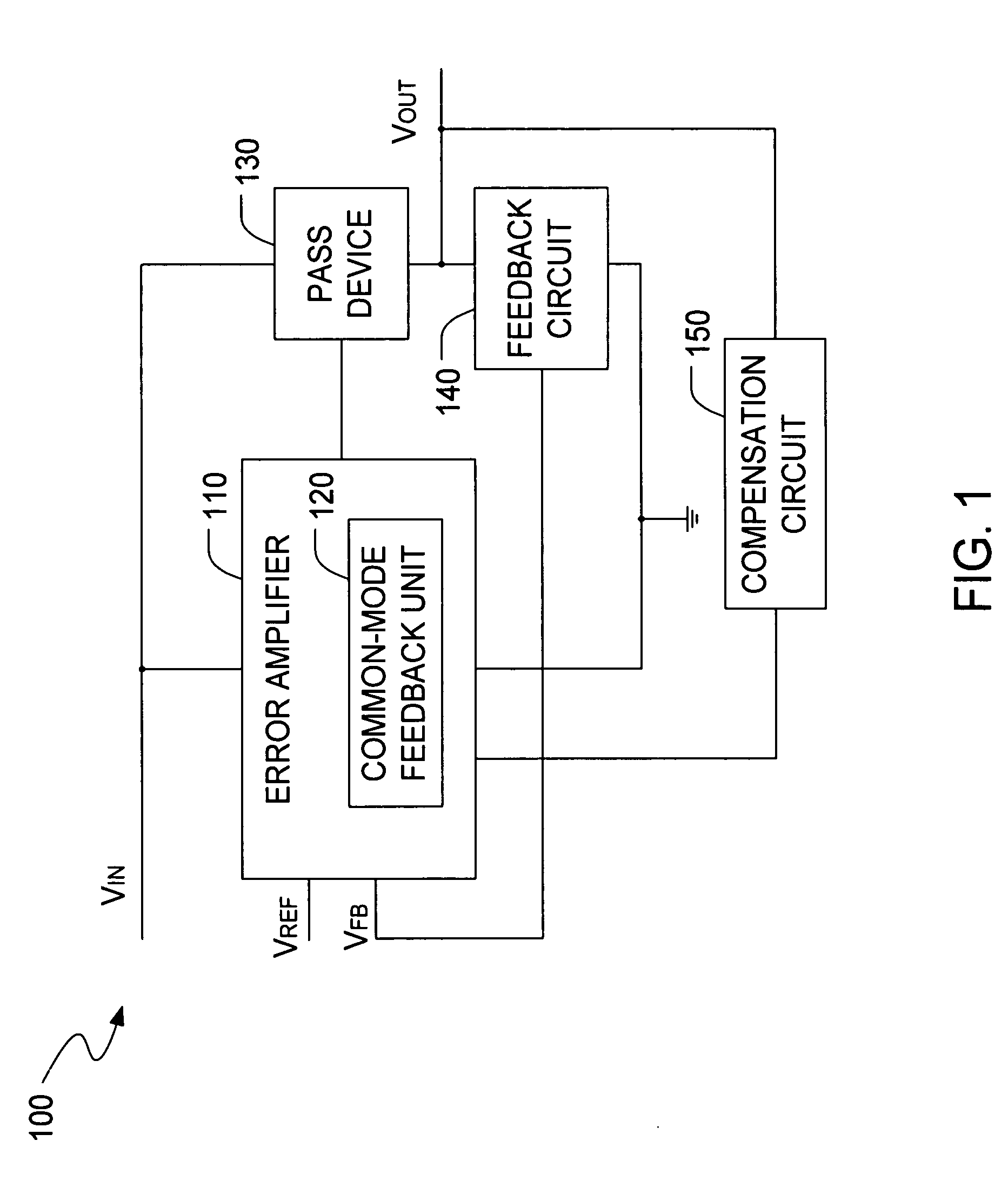

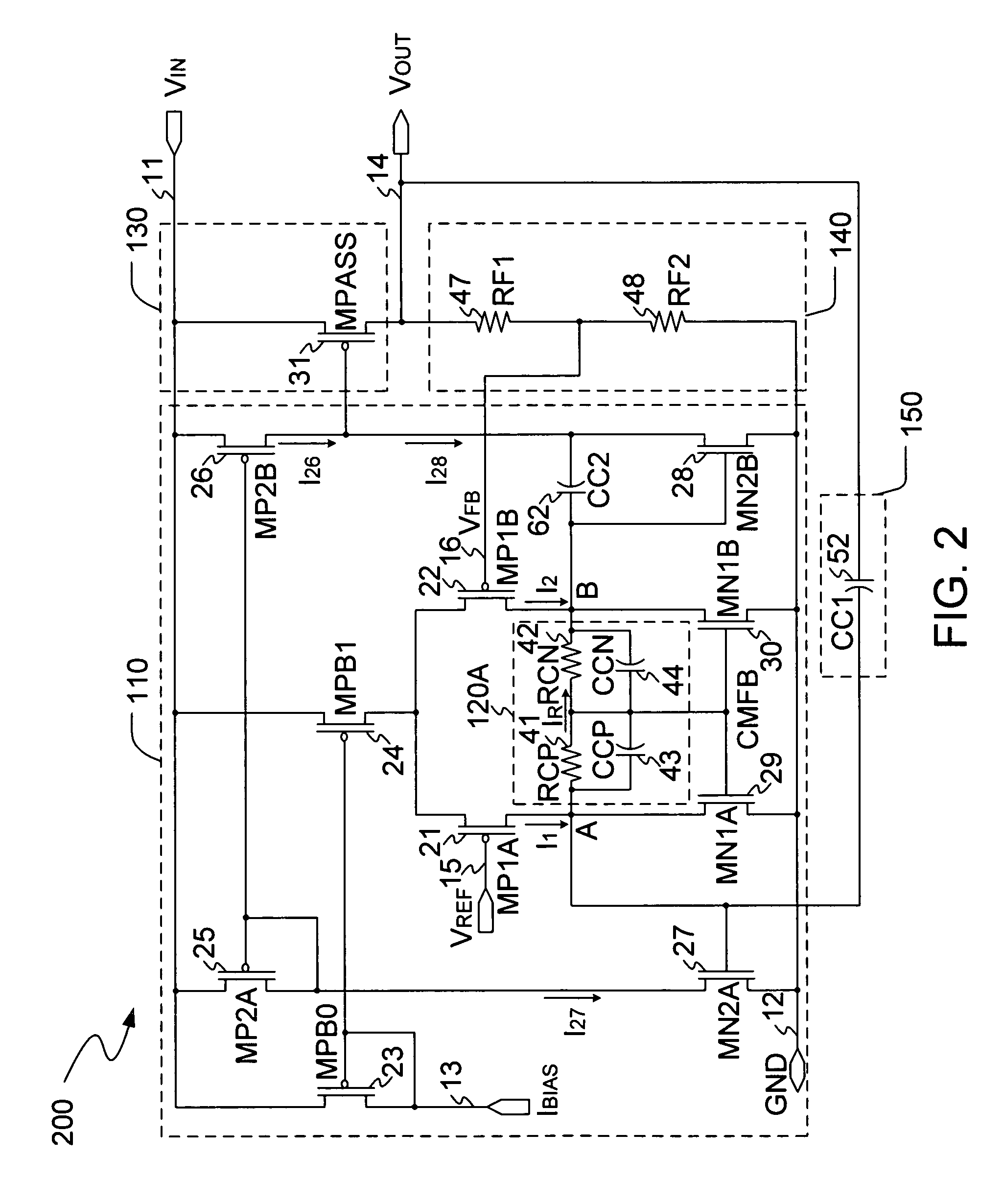

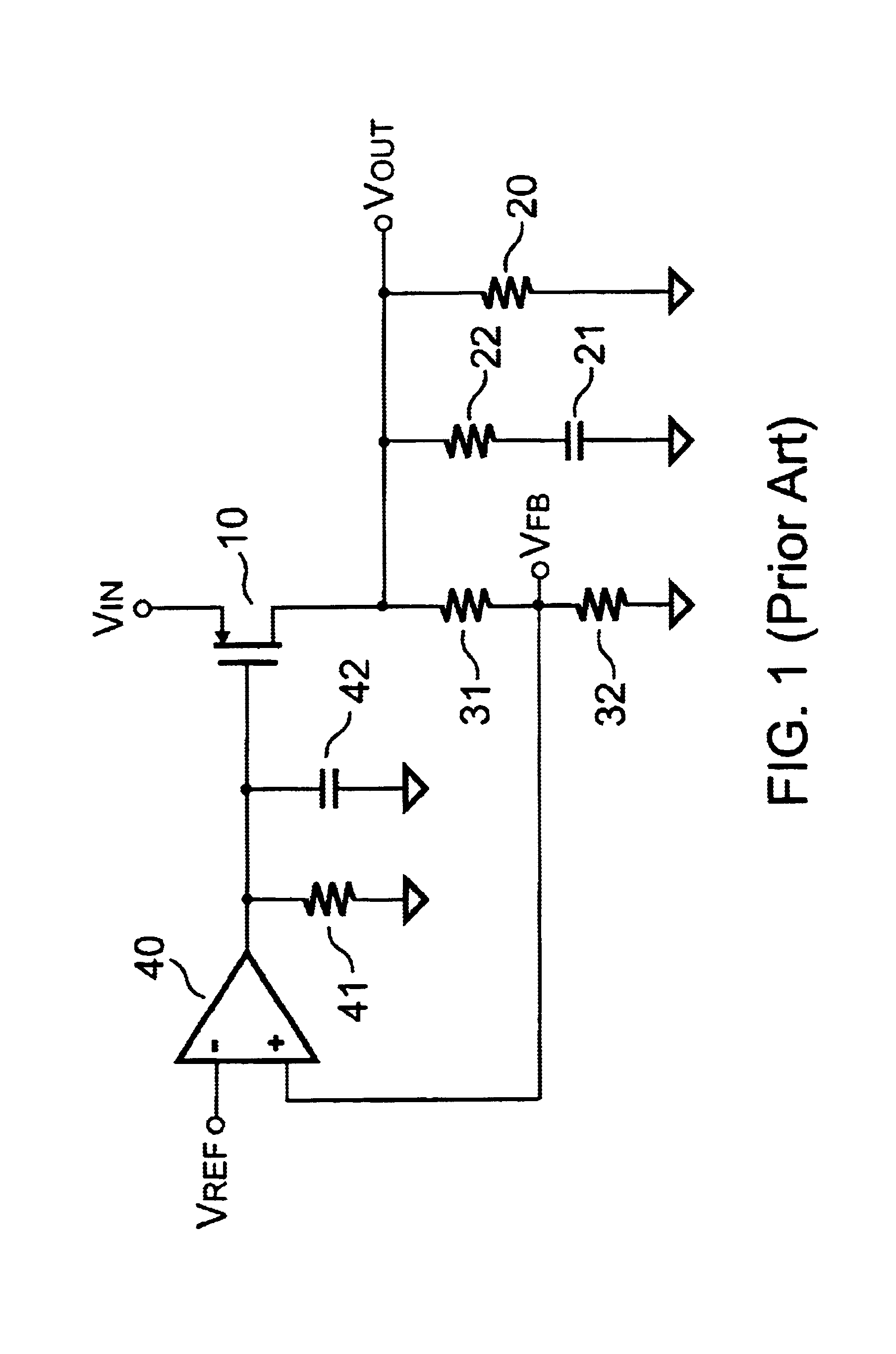

Low drop-out voltage regulator with common-mode feedback

InactiveUS20060197513A1Increase conversion rateStable output voltageAmplifier with semiconductor-devices/discharge-tubesElectric variable regulationFrequency compensationAudio power amplifier

The present invention is a LDO voltage regulator circuit with common-mode feedback. The LDO voltage regulator includes an error amplifier with a common-mode feedback unit, a pass device and a compensation circuit. A signal from the pass device acts as an input signal to the error amplifier and is compared with another input signal, producing a differential signal. The differential signal is amplified and then provided to the pass device. A capacitor in the compensation unit provides frequency compensation to the LDO voltage regulator. The common-mode feedback unit incorporated into the error amplifier greatly improves a slew rate of a gate voltage of the pass device.

Owner:O2 MICRO INT LTD

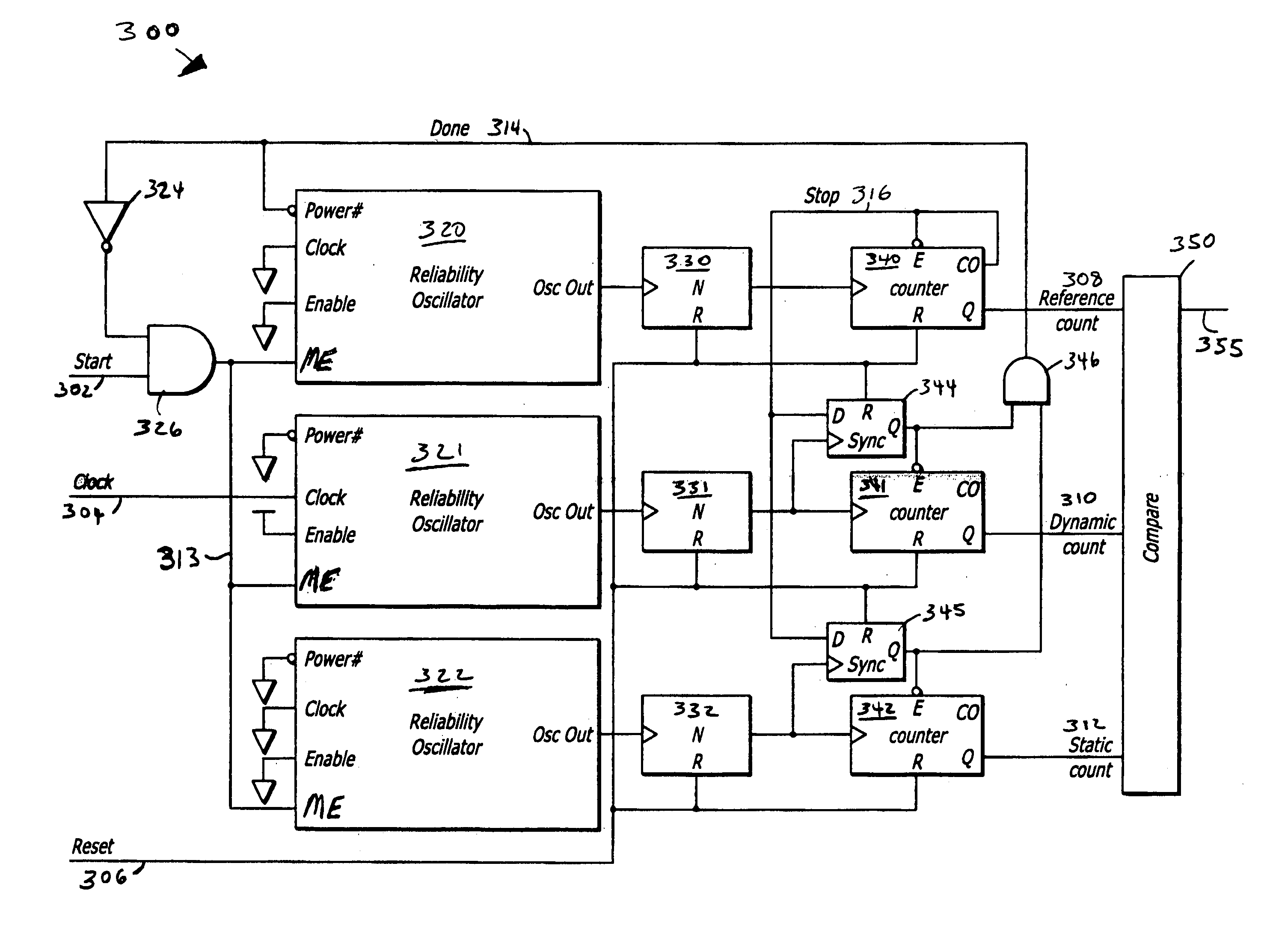

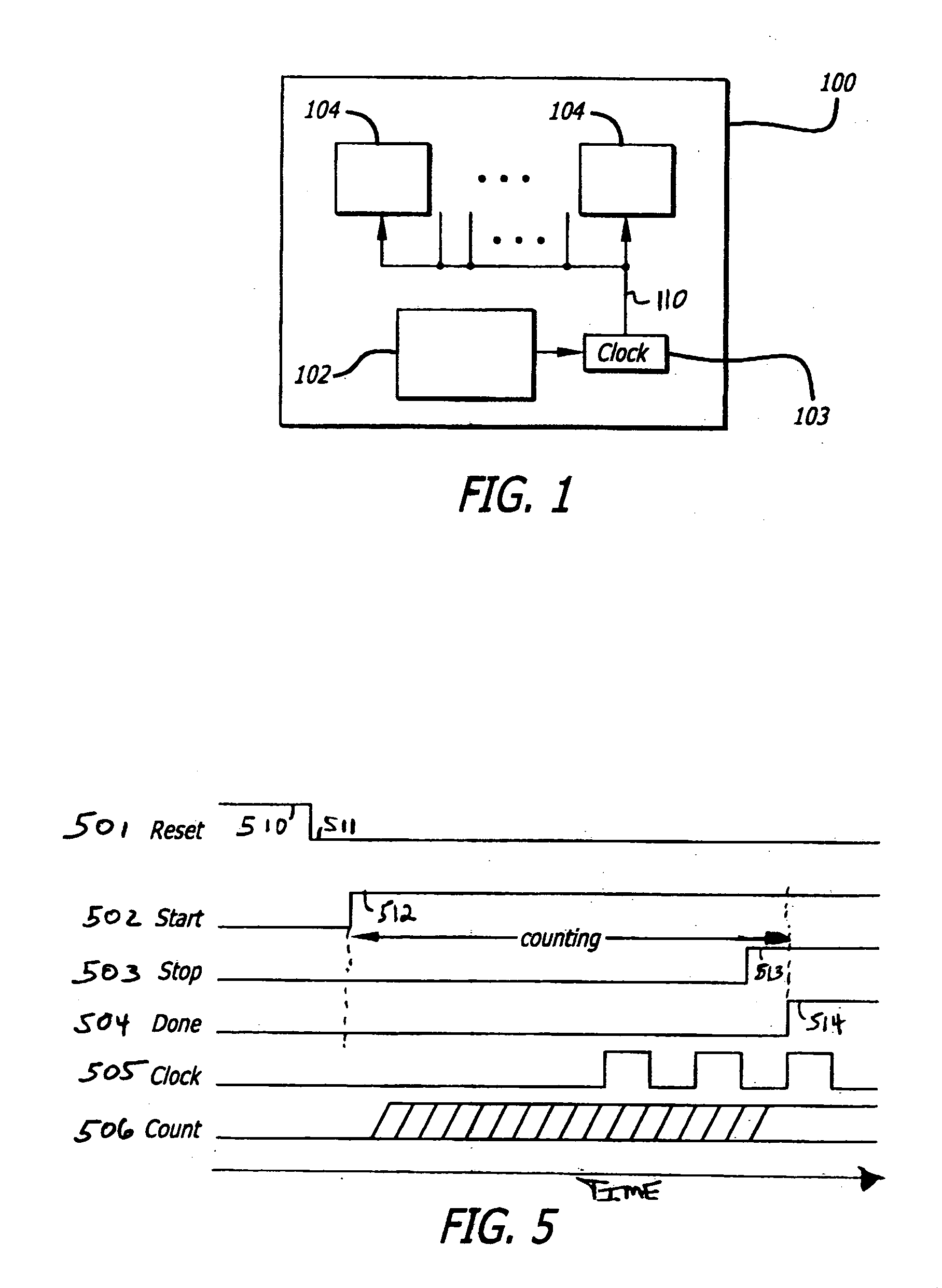

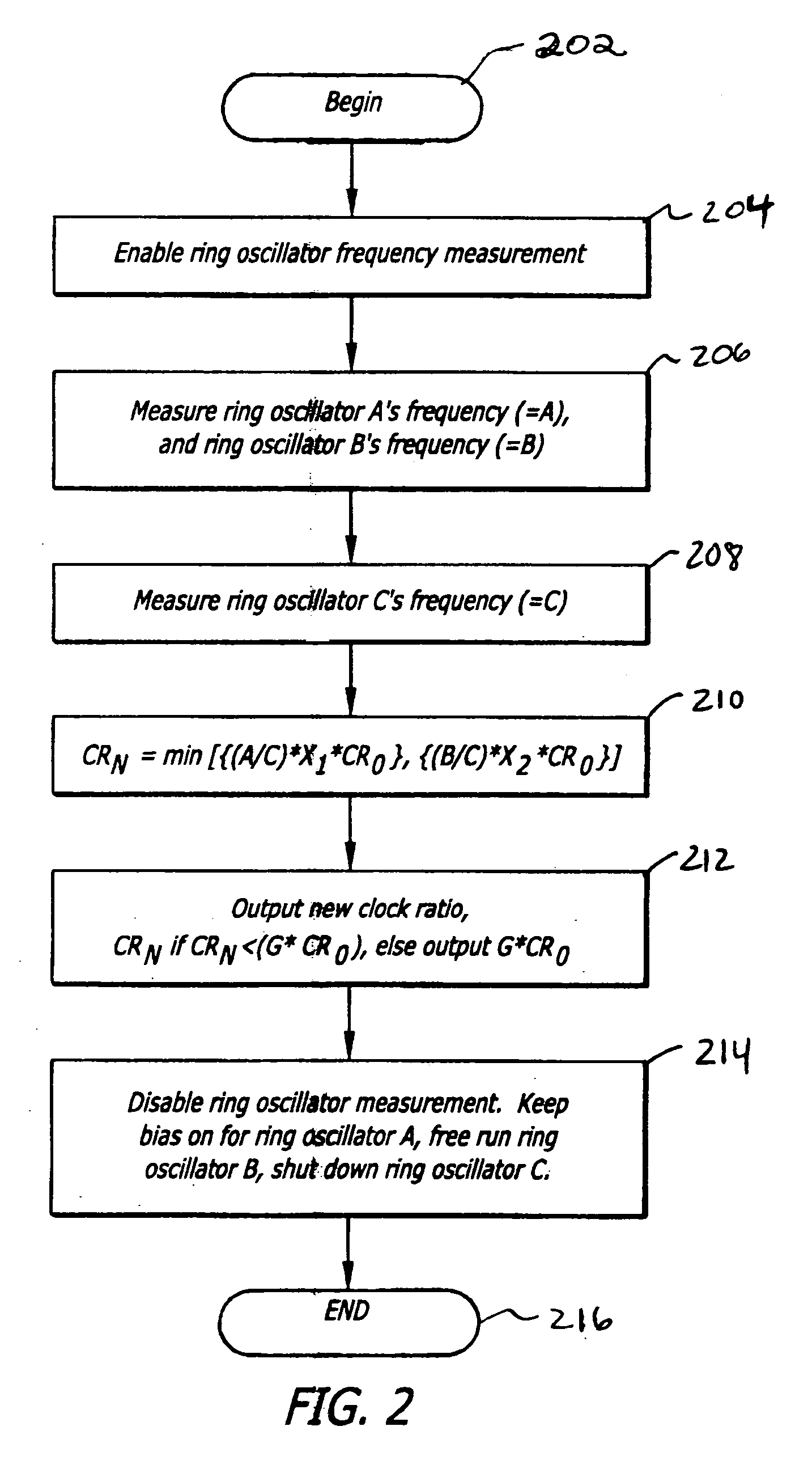

On-chip frequency degradation compensation

ActiveUS20050140418A1Electrical testingElectric pulse generatorFrequency compensationElectrical and Electronics engineering

Embodiments of the invention include a trio of reliability oscillators. In one embodiment, an on-chip frequency compensation circuit includes a selectively enabled reliability oscillator to generate a reference oscillating signal, a clocked reliability oscillator to generate an AC degraded oscillating signal, and a static reliability oscillator to generate a DC bias degraded oscillating signal. A compare circuit coupled to the reliability oscillators compares the oscillating signals and generates a frequency compensation signal if the comparison determines that there is frequency degradation greater than a predetermined threshold.

Owner:INTEL CORP

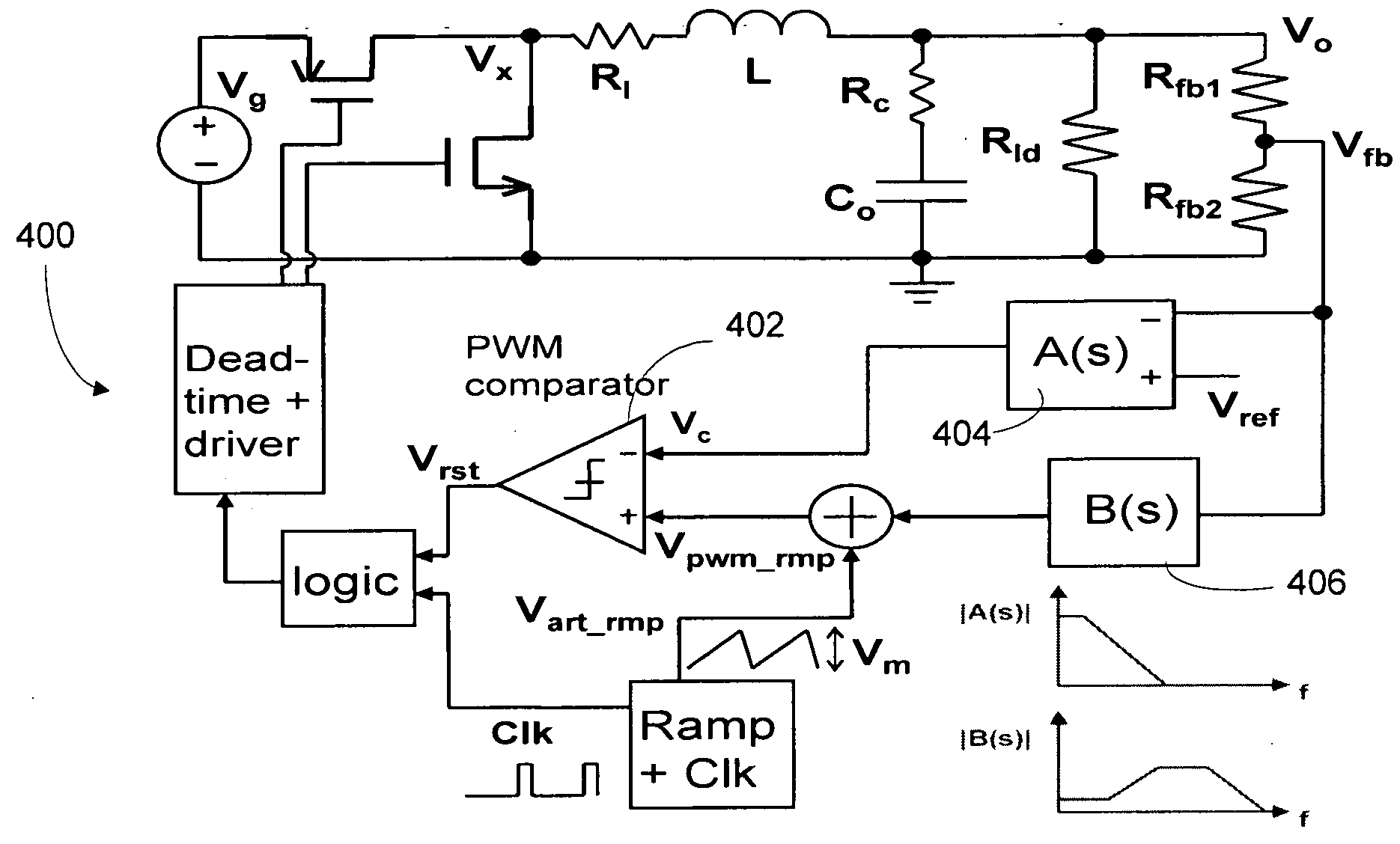

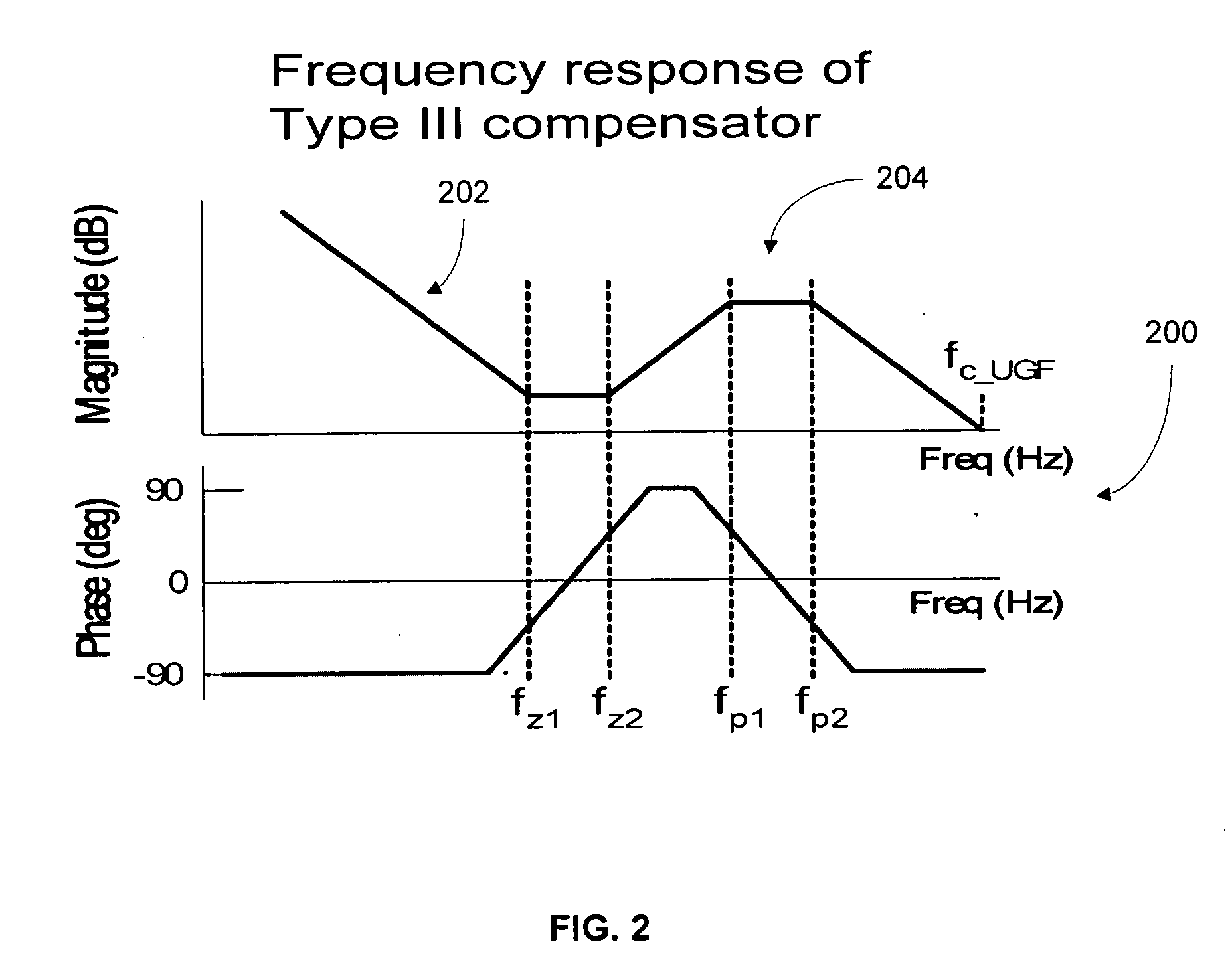

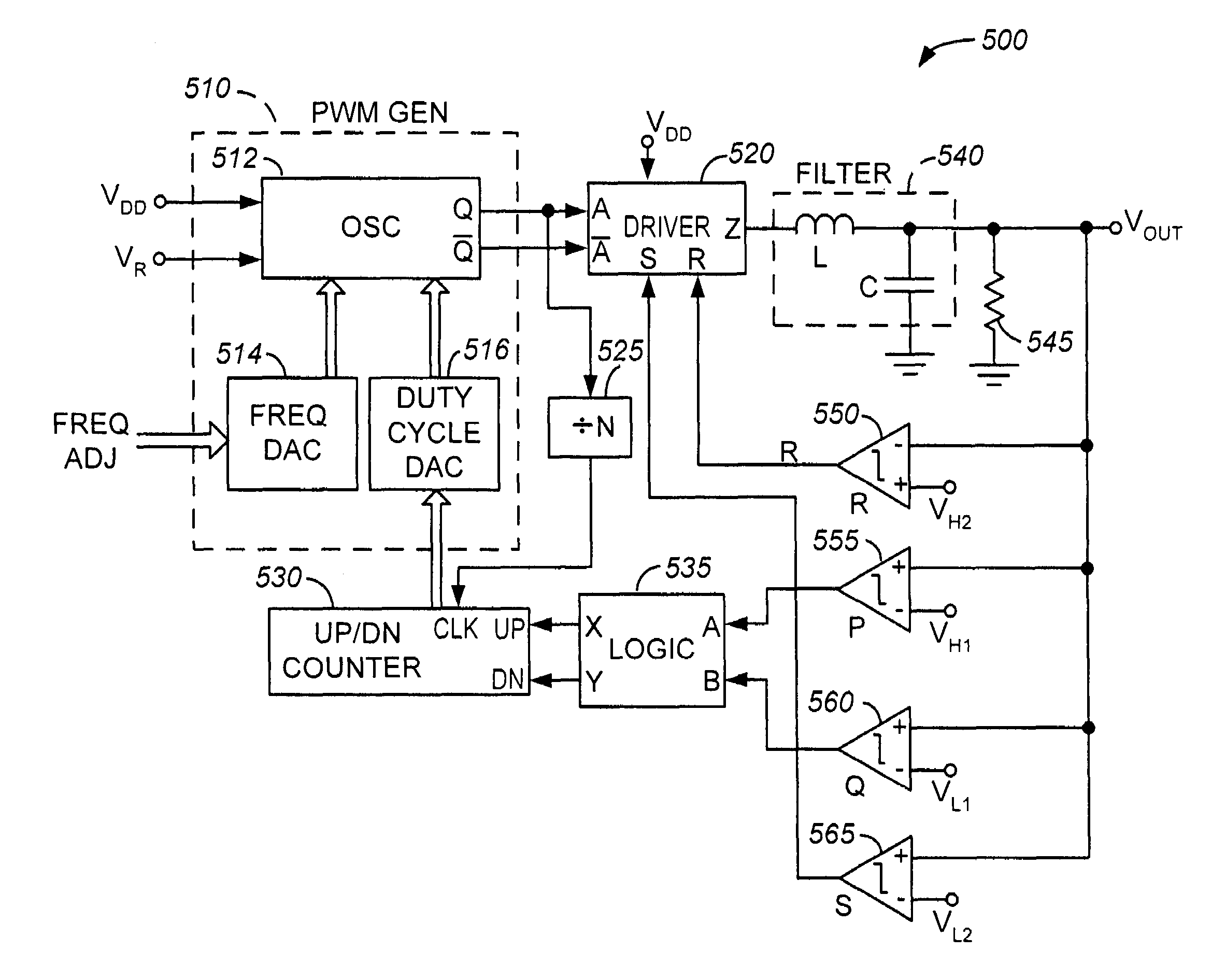

Frequency compensation based on dual signal paths for voltage-mode switching regulators

ActiveUS20090174383A1Advantage in circuit designCircuit can be designedEfficient power electronics conversionDc-dc conversionBandpass filteringFrequency compensation

A frequency compensation method for voltage-mode switching regulators is disclosed. A lowpass filter and a bandpass filter are employed in the two signal paths into the dual inputs of PWM comparators. In one embodiment, two zeros are generated to compensate for the L-C output filter poles. Stable operation, low output voltage ripple and fast load transient response are achieved; while the power consumption of error amplifier and the area for implementing on-chip passive components are greatly reduced.

Owner:THE HONG KONG UNIV OF SCI & TECH

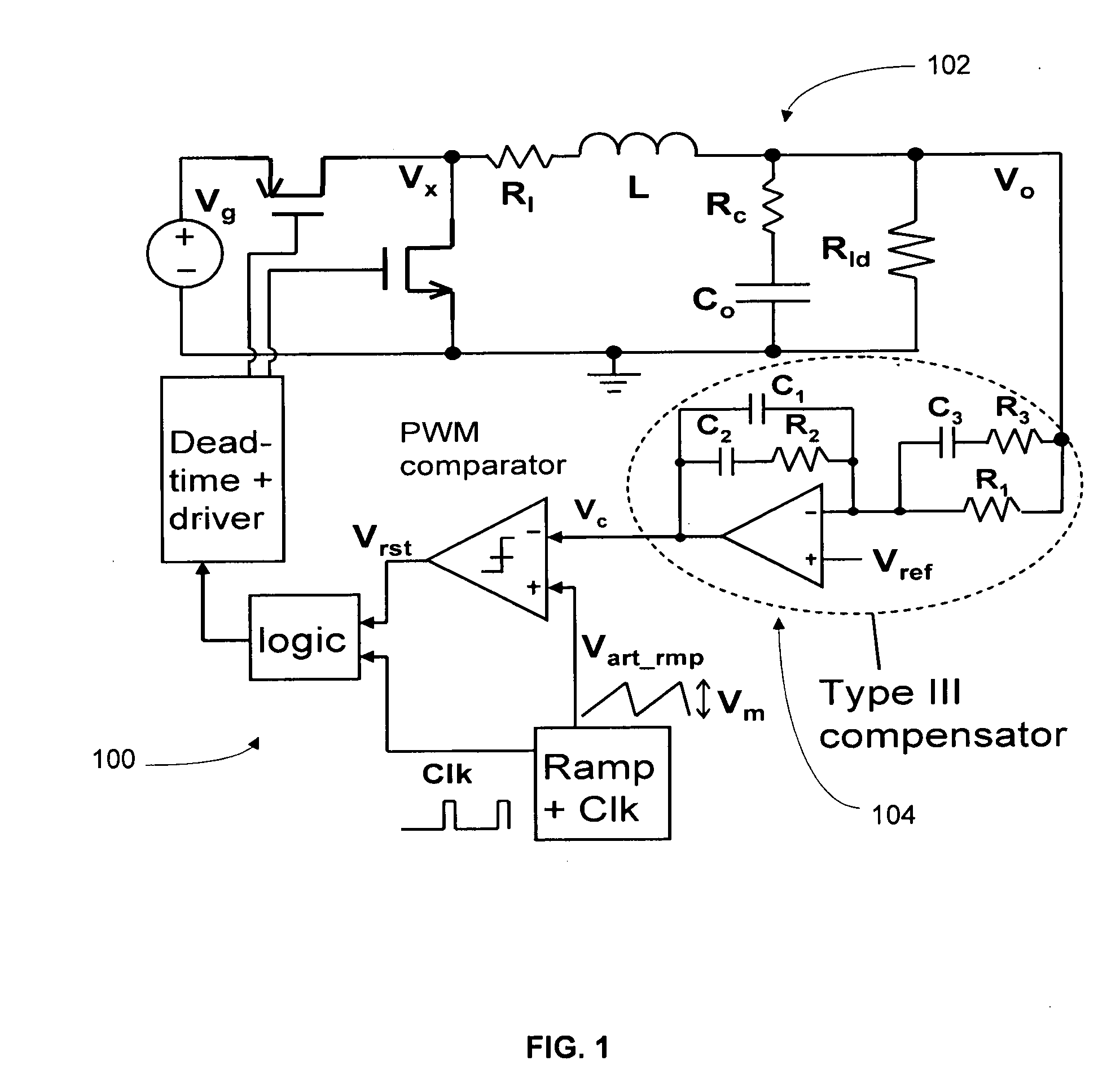

Pulse width modulated buck voltage regulator with stable feedback control loop

ActiveUS7548047B1Minimizing hardwareMinimize the ringing of the filterDc-dc conversionElectric variable regulationFrequency compensationVoltage reference

A pulse-width modulated buck regulator includes a feedback control without having any external frequency compensation components to stabilize the feedback control loop irrespective of the reactive component of its load impedance. Additionally, the output voltage is maintained constant not only with feedback but also using a power supply voltage compensation scheme. Thus, the feedback control compensates for resistive losses, thus minimizing hardware. The output voltage is compared with first and second reference voltages. If the output voltage is greater than the first reference voltage, a counter's count is decremented. If the output voltage is less than the second reference voltage, the counter's count is incremented. The counter is disabled if the output voltage is smaller than the first reference voltage and greater than the second reference voltage. The duty cycle of the output voltage is varied in accordance with the counter's count.

Owner:MARVELL ASIA PTE LTD

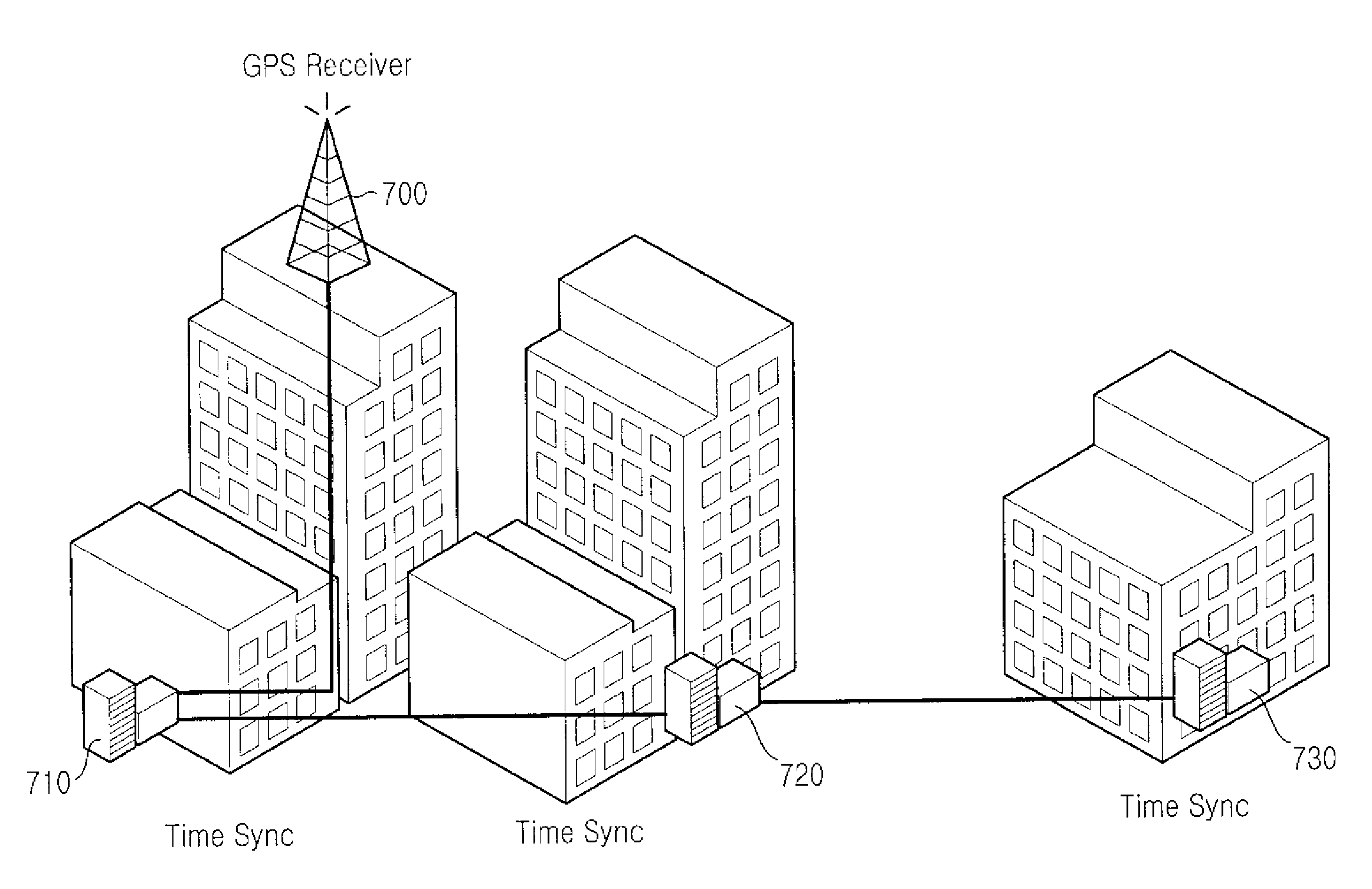

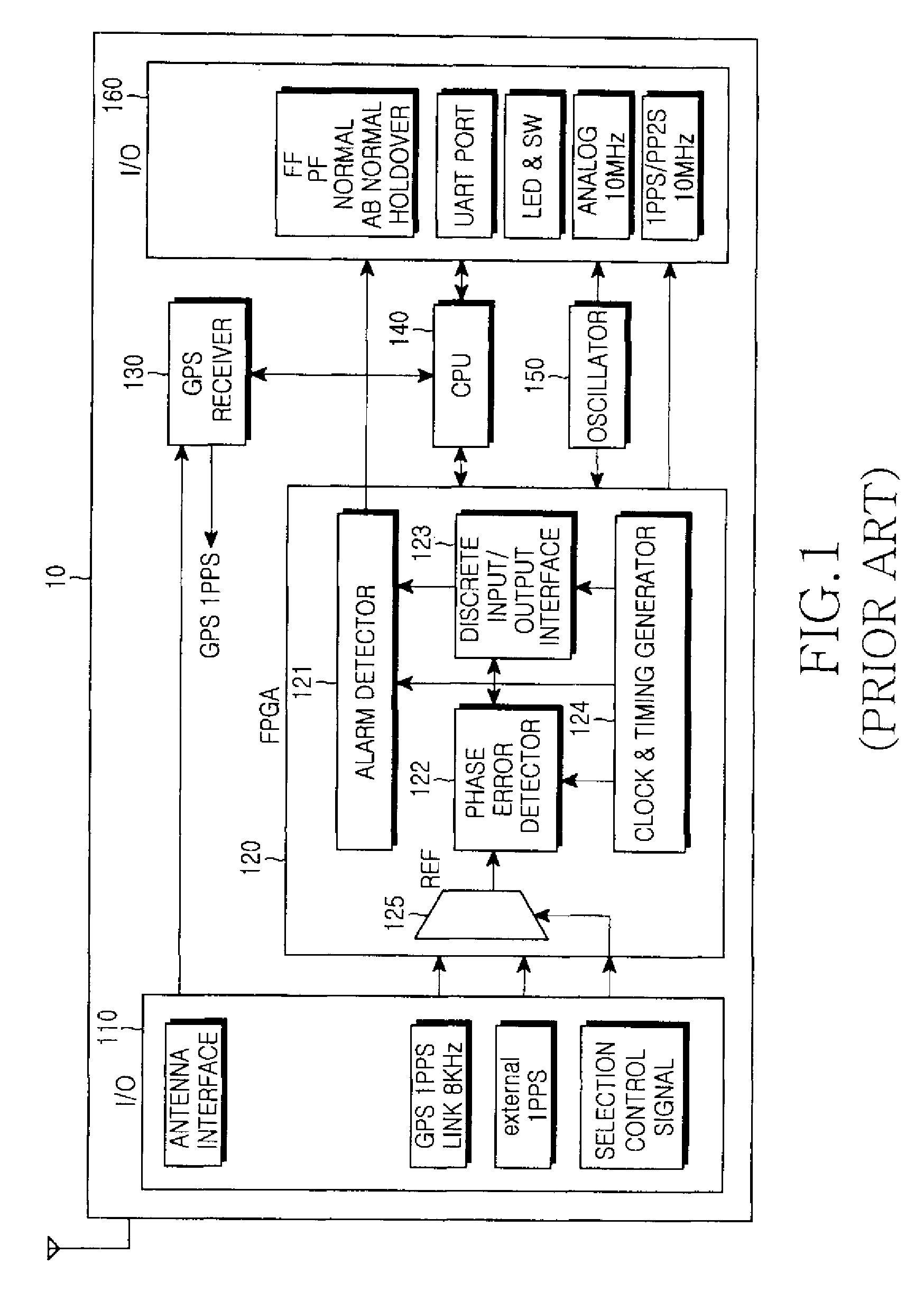

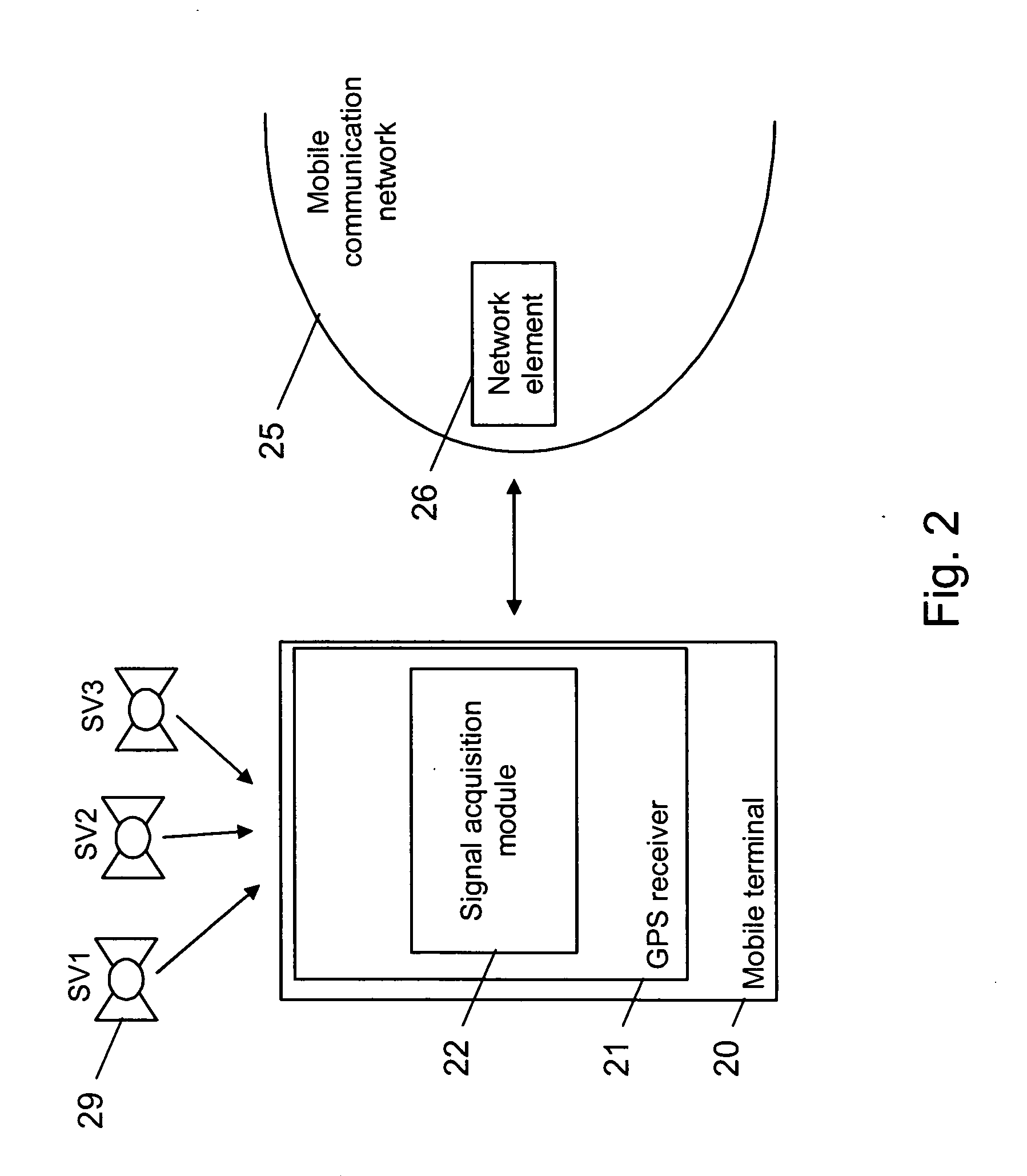

Apparatus and method for performing time synchronization using GPS information in communication system

InactiveUS20090168808A1Synchronisation information channelsTime-division multiplexTemporal informationCommunications system

Disclosed is an apparatus and a method for performing time synchronization by using Global Positioning System (GPS) information in a communication system. The apparatus comprises a grand-master node having a GPS receiver, for generating a synchronizing message required to synchronize time on slave nodes by using Time Of Day (TOD) information received from the GPS receiver and at least one slave node for receiving the synchronizing message required to synchronize time from the grand-master node or from another slave node, for carrying out time synchronization operation by using an Offset and Frequency Compensation Clock (OFCC) synchronization process supporting time offset and frequency separation compensation, and for generating a synchronizing message required to synchronize time on other slave nodes.

Owner:SAMSUNG ELECTRONICS CO LTD

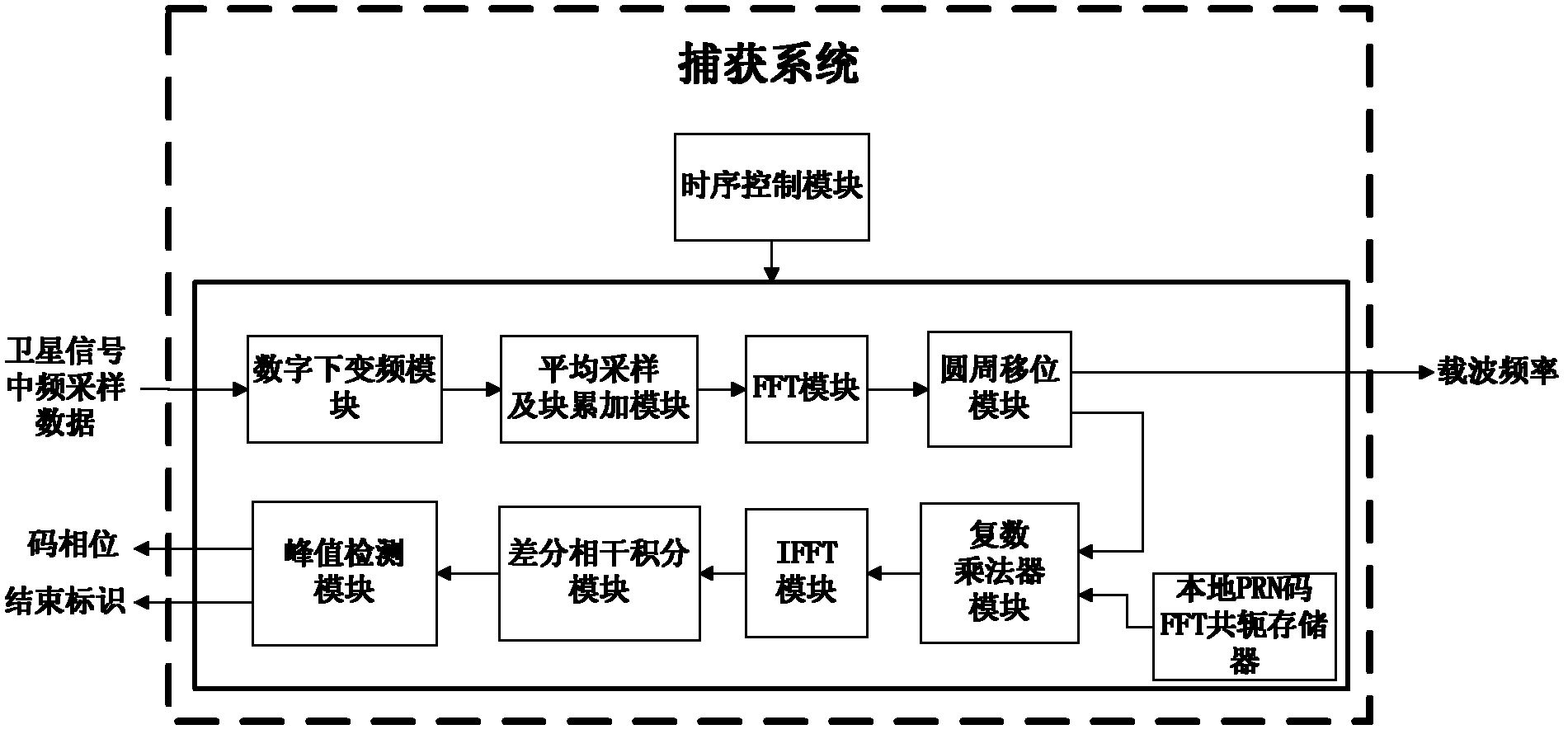

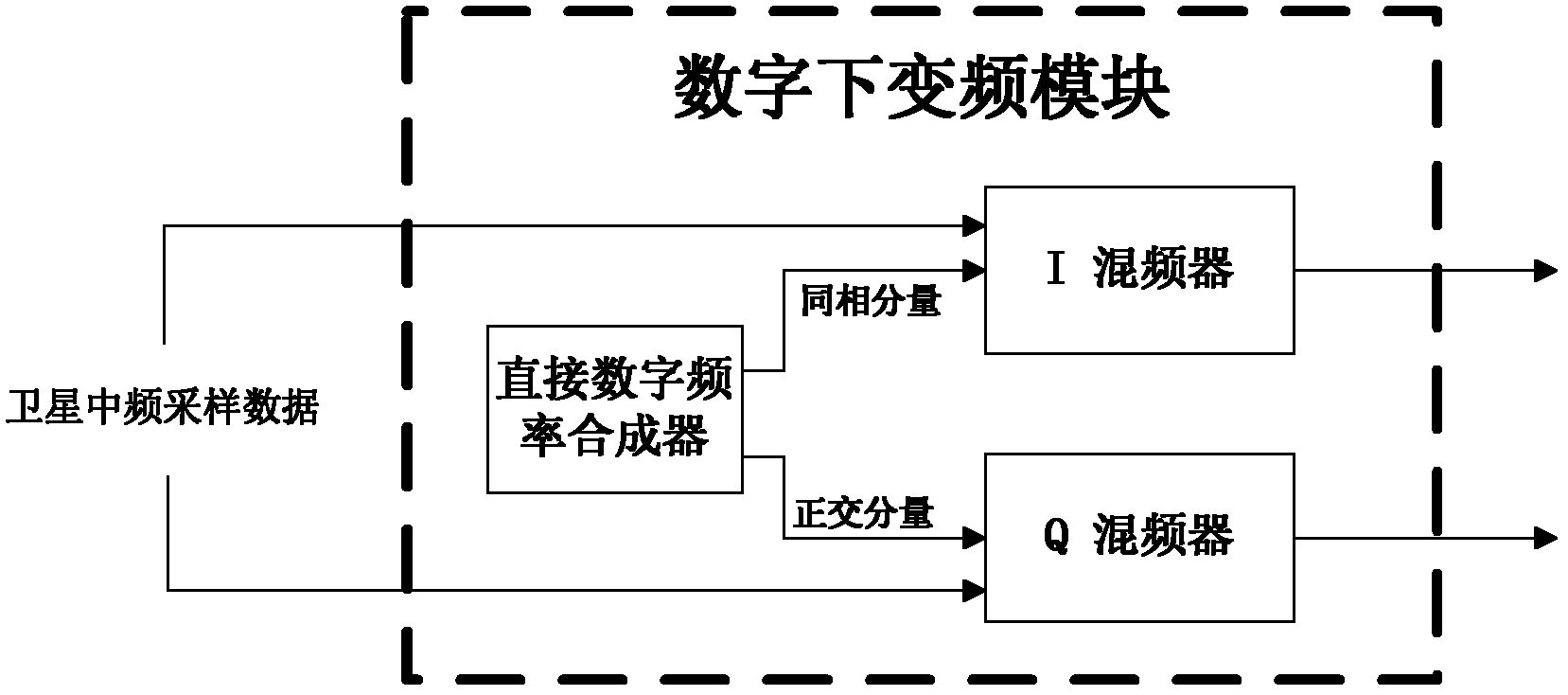

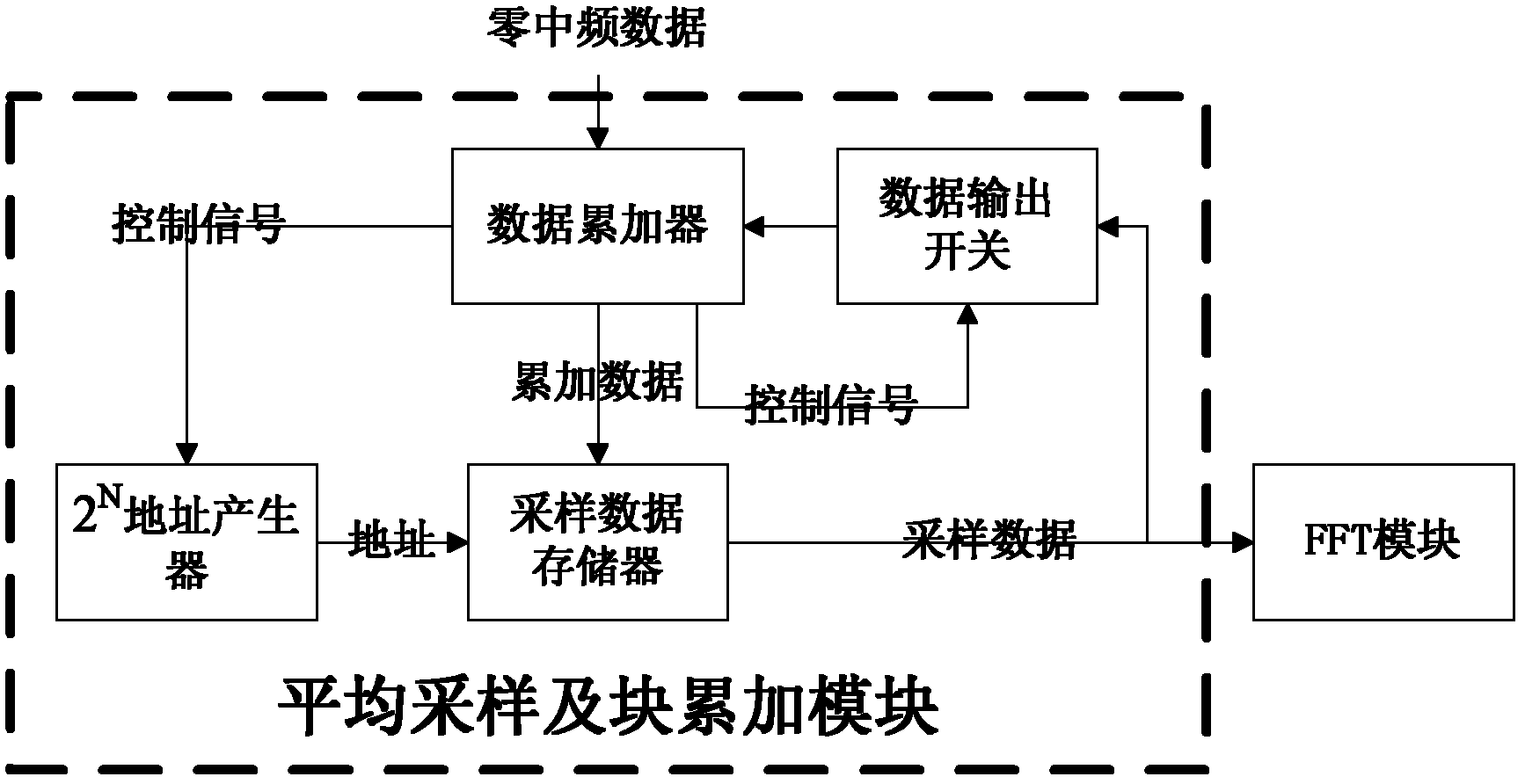

High-sensitivity satellite navigation signal capturing method and system

The invention discloses a high-sensitivity satellite navigation signal capturing method and a system. The system comprises a digital down-conversion module, an average sampling and block accumulation module, an FFT (fast Fourier transform) module, a circumference shifting module, a local PRN (pseudo random noise) code FFT conjugate memory, a complex multiplier module, an IFFT (inverse fast Fourier transform) module, a differential coherence integration module, a peak detection module and a sequential control module. The digital down-conversion module realizes digital down-conversion operation for satellite digital intermediate frequency signals; the average sampling and block accumulation module averagely samples satellite data and completes a block accumulation function; the FFT module searches code phase frequency domains; the circumference shifting module utilizes Doppler circumference shifting search to replace frequency compensation; the local PRN code FFT conjugate memory stores a local PRN code FFT conjugate result; the complex multiplier module realizes signal de-spreading; the IFFT module calculates different code phase coherence results; the differential coherence integration module accumulates differential coherence energy of de-spread satellite signals; the peak detection module realizes signal capturing output; and the sequential control module controls timing sequence of the various modules of the system. Weak signal capturing speed and sensitivity of a satellite navigation receiver are improved, and parameters can be configured flexibly.

Owner:JINAN UNIVERSITY

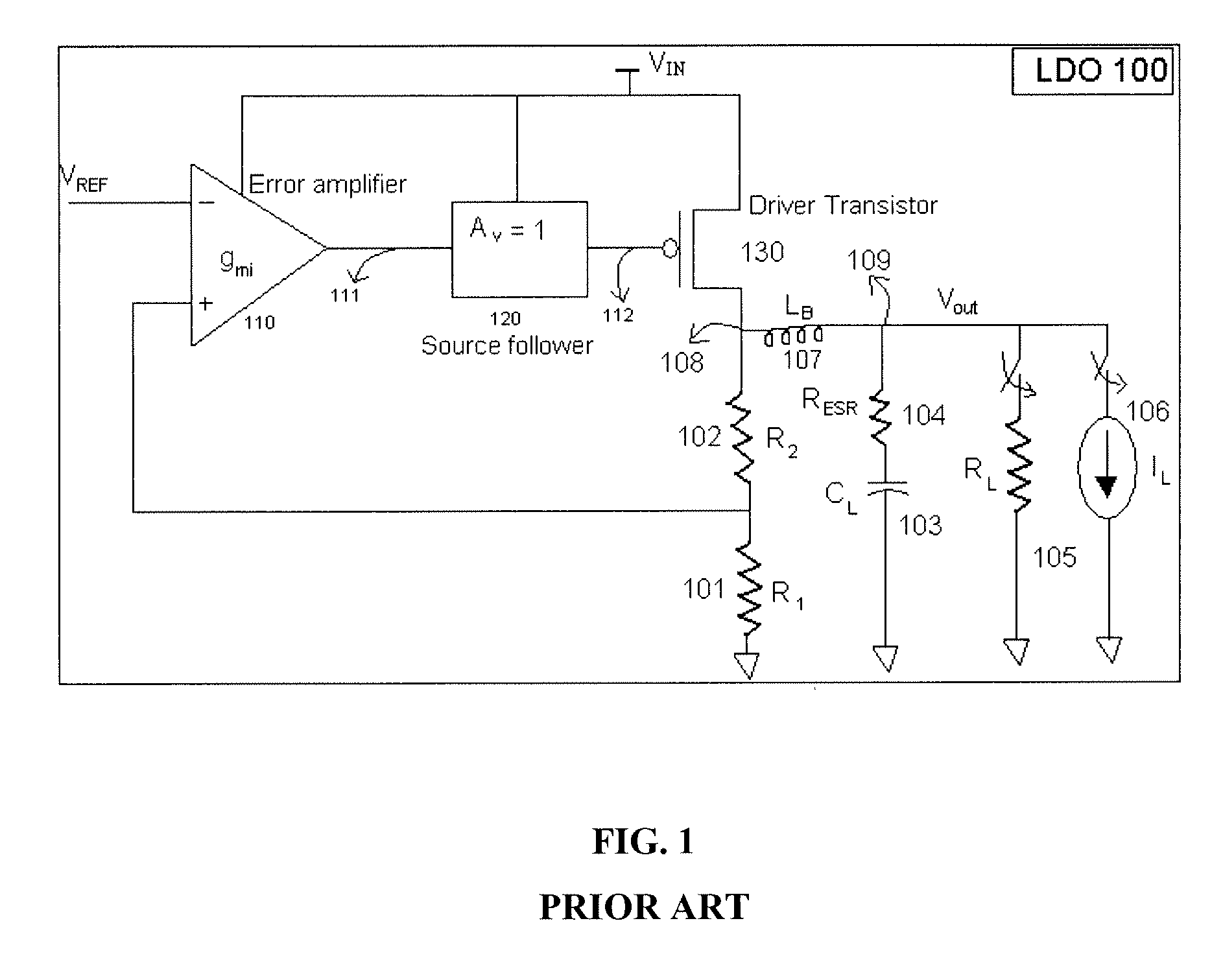

Low drop-out voltage regulator and an adaptive frequency compensation

InactiveUS6861827B1Lower overall pressure dropTight output controlElectric variable regulationCapacitanceFrequency compensation

A method and apparatus to dynamically modify the internal compensation of a low drop-out (LDO) voltage regulator is presented. The process involves creating an additional equivalent series resistance (ESR) from an internal circuit. The additional ESR of the internal circuit is sufficient to ensure the DC output stability. This allows the ESR of the output capacitance to be reduced to zero if desired, for improved transient response.

Owner:FAIRCHILD TAIWAN

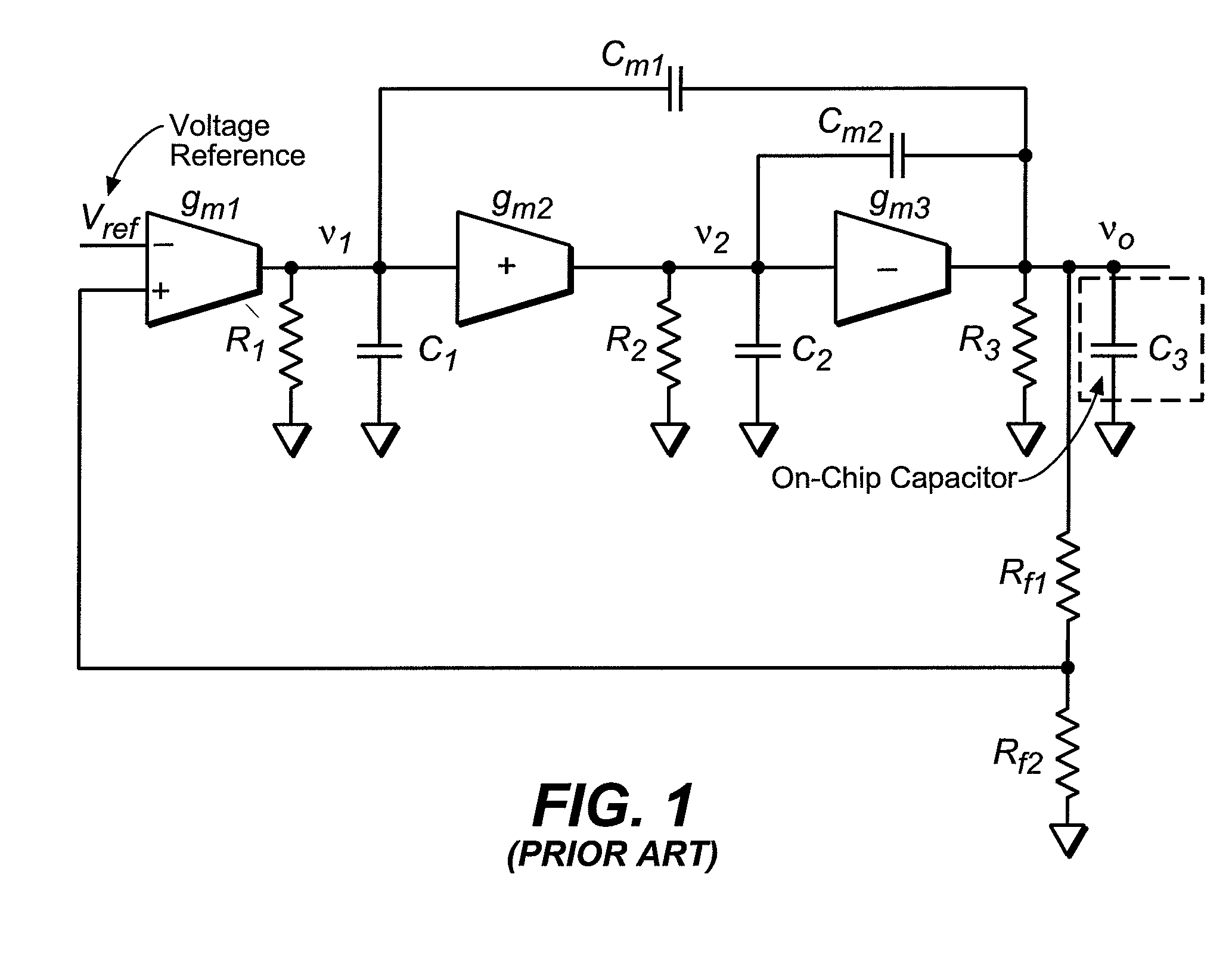

Low dropout regulator with stability compensation

InactiveUS7589507B2Good phase marginMinimize power consumptionElectric variable regulationLow loadEngineering

The present invention provides a low dropout (LDO) regulator with a stability compensation circuit. A “zero frequency” tracking as well as “non-dominant parasitic poles' frequency reshaping” are performed to achieve a good phase margin for the LDO by means of the compensation circuit. In this compensation method neither a large load capacitor nor its equivalent series resistance is needed to stabilize a regulator. LDO regulators, in system on chip application, having load capacitors in the range of few nano-Farads to few hundreds of nano-Farads can be efficiently compensated with this compensation method. A dominant pole for the regulator is realized at an internal node and the second pole at an output node of the regulator is tracked with a variable capacitor generated zero over a range of load current to cancel the effect of each other. A third pole of the system is pushed out above the unity gain frequency of the open loop transfer function with the help of the frequency compensation circuit. The compensation technique is very effective in realizing a low power, low-load-capacitor LDO desirable for system on chip applications.

Owner:ST ERICSSON SA

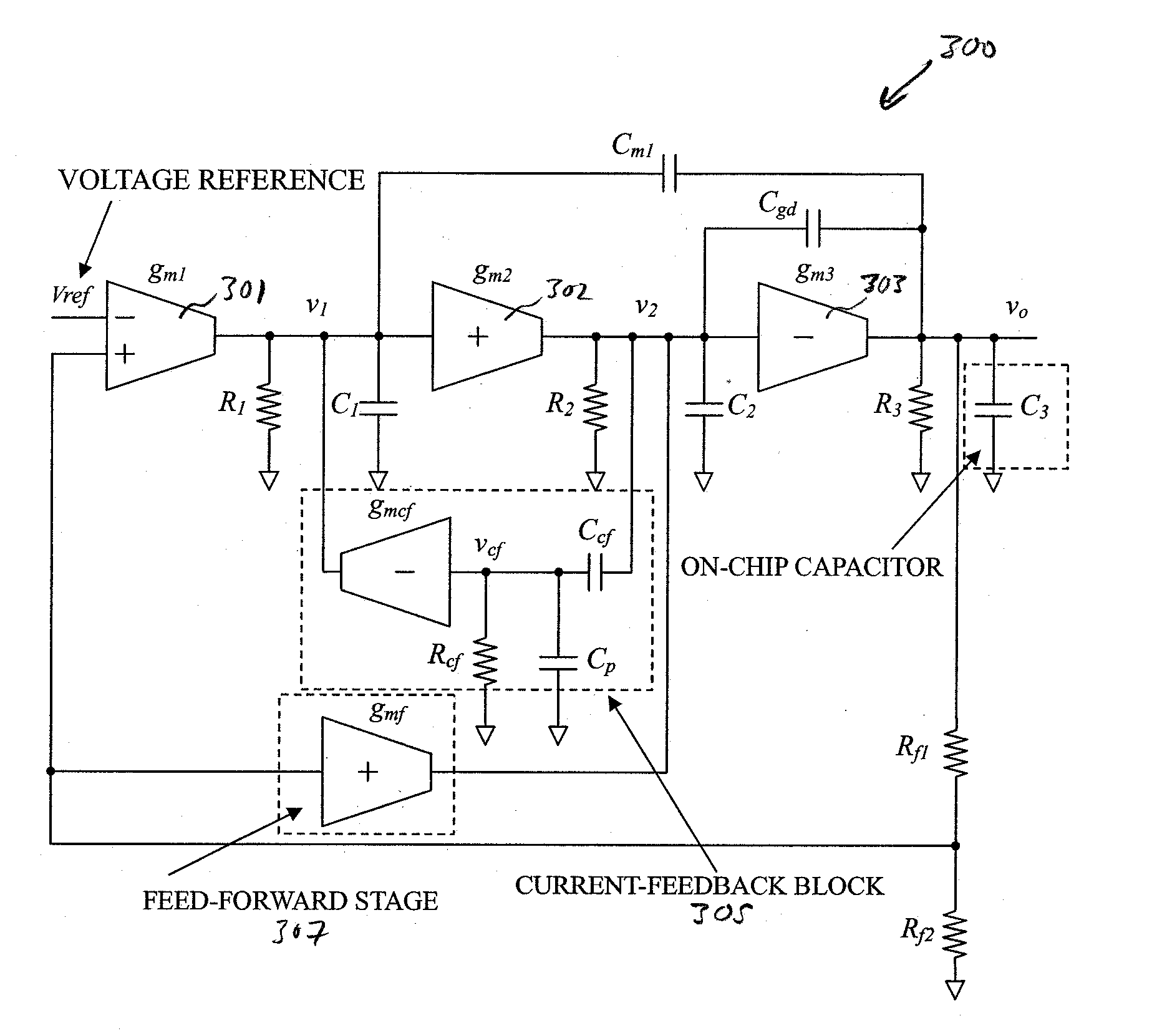

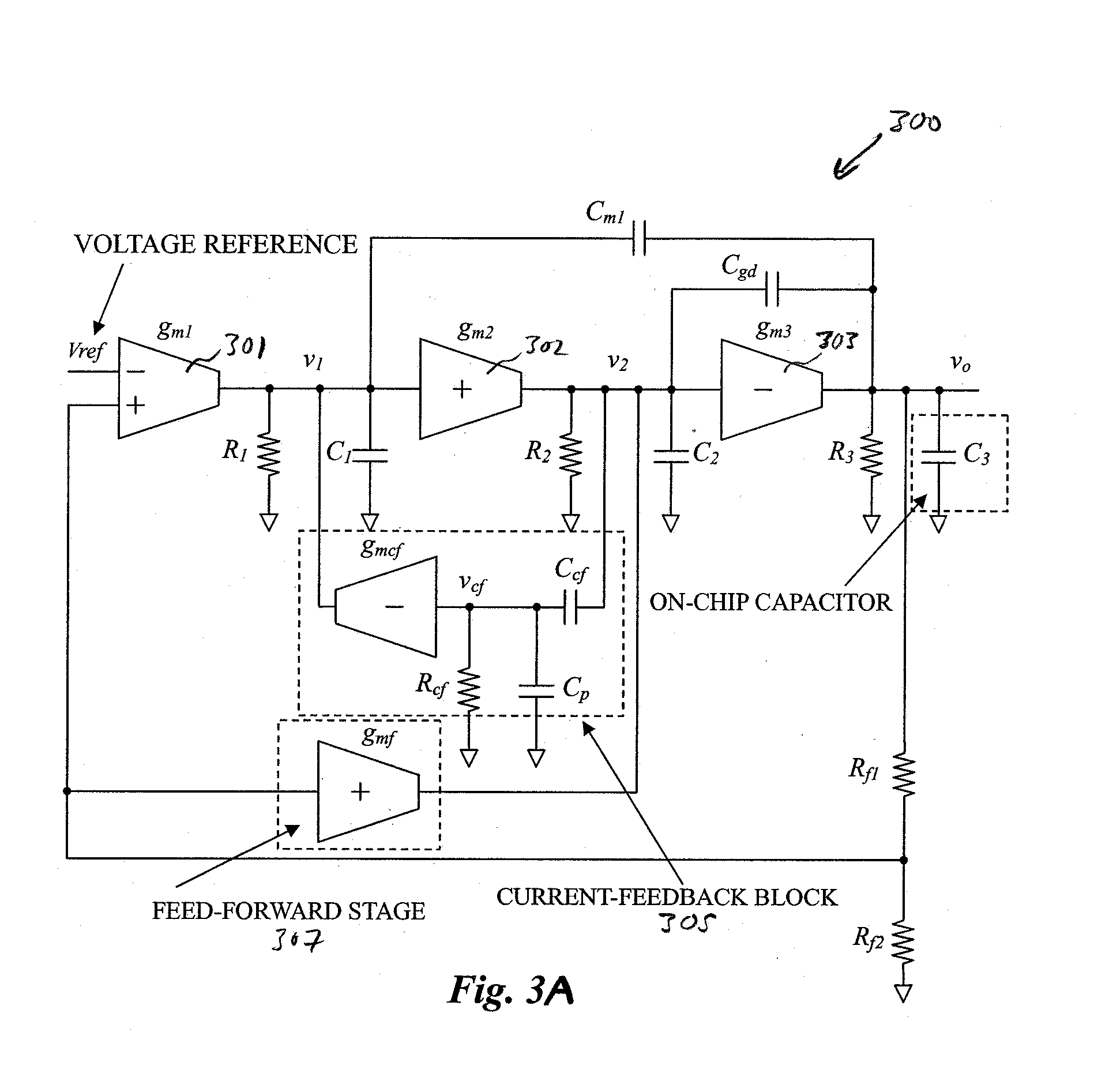

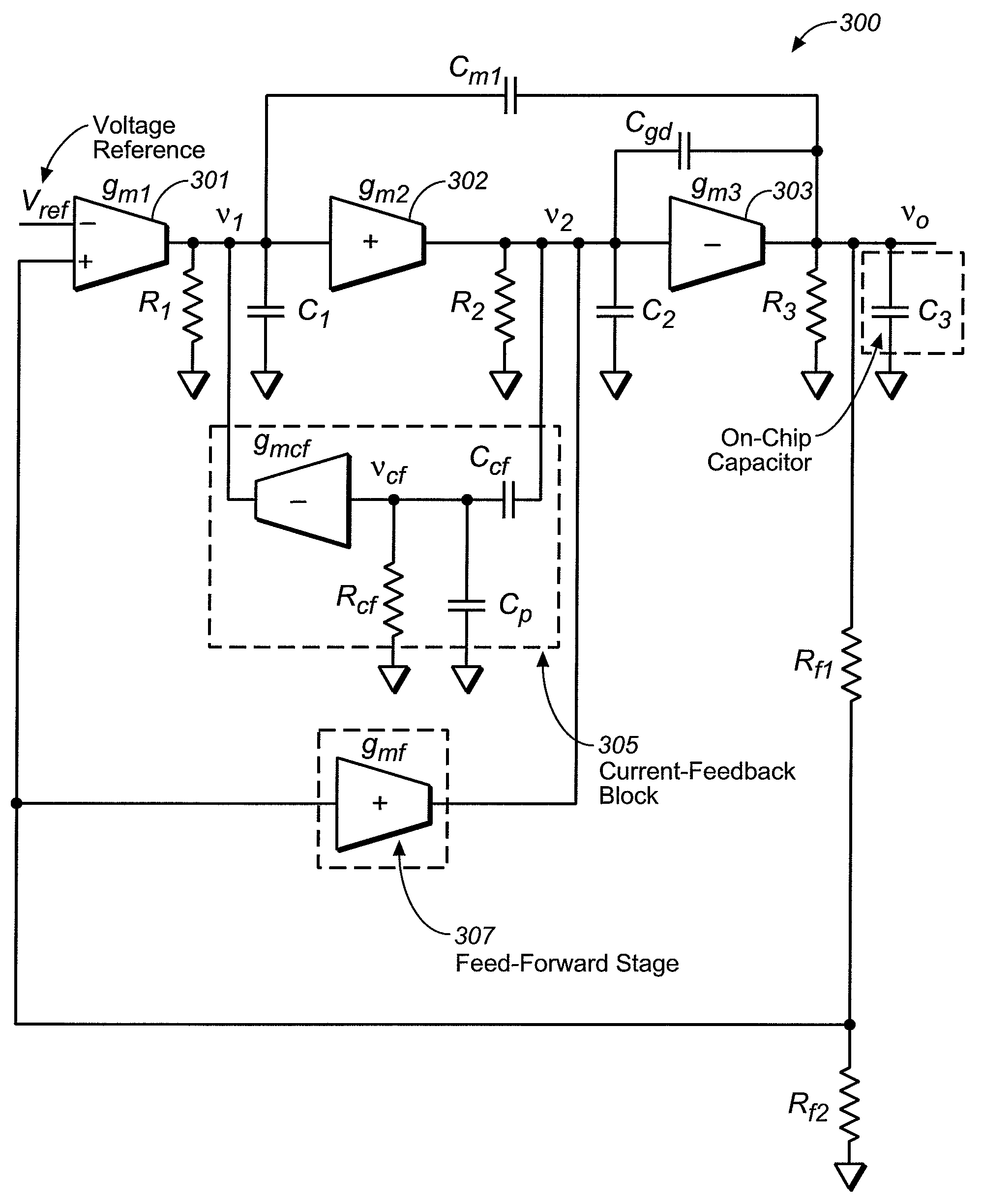

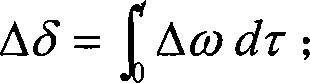

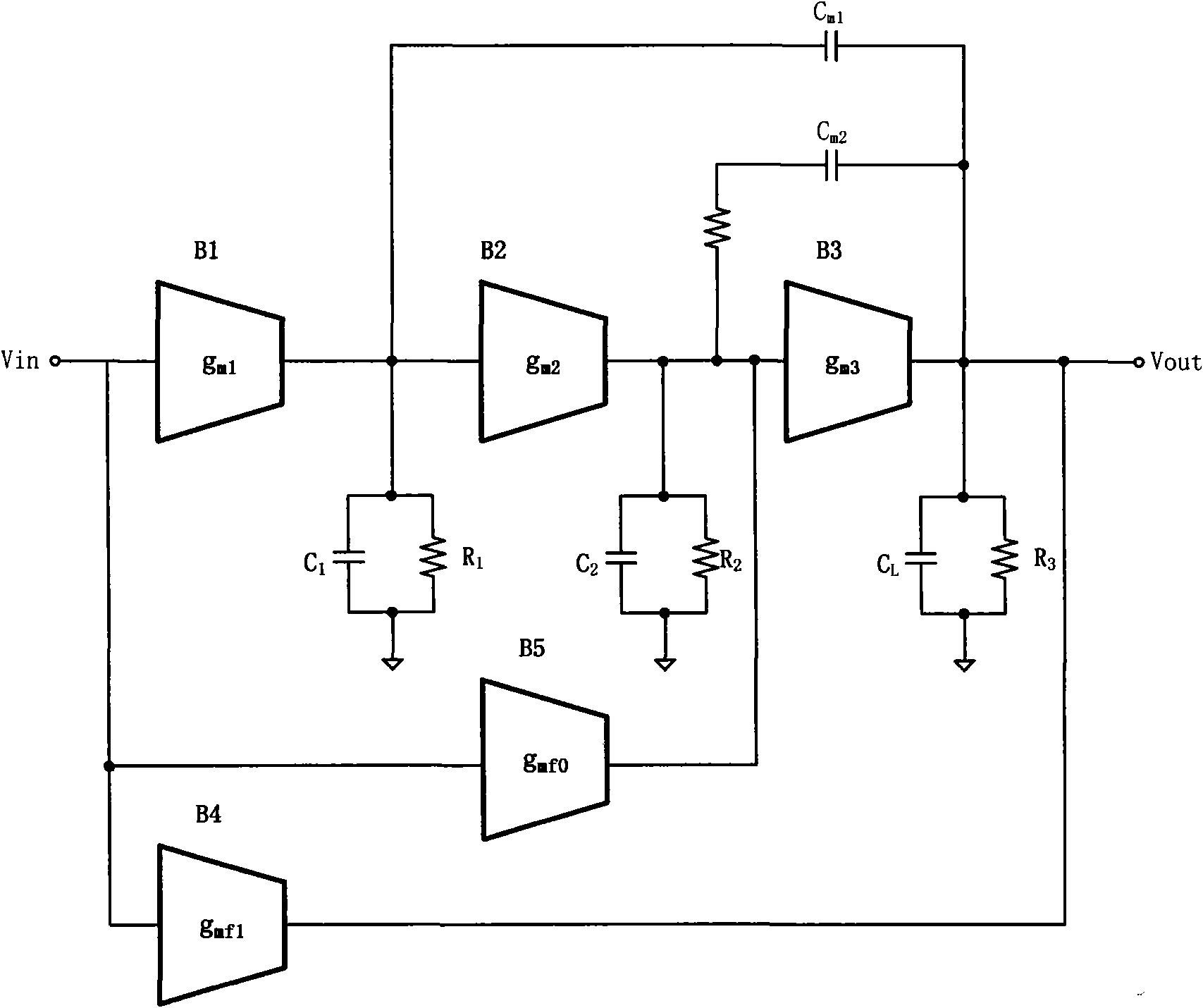

Area-Efficient Capacitor-Free Low-Dropout Regulator

ActiveUS20070018621A1Improve stabilitySacrificing performanceElectric variable regulationCapacitanceFrequency compensation

An area-efficient capacitor-free low-dropout regulator based on a current-feedback frequency compensation technique is disclosed. An implementation of a current feedback block with a single compensation capacitor is used to enable capacitance reduction. The resultant low-dropout regulator does not generally require an off-chip capacitor for stability and is particularly useful for system-on-chip applications.

Owner:THE HONG KONG UNIV OF SCI & TECH

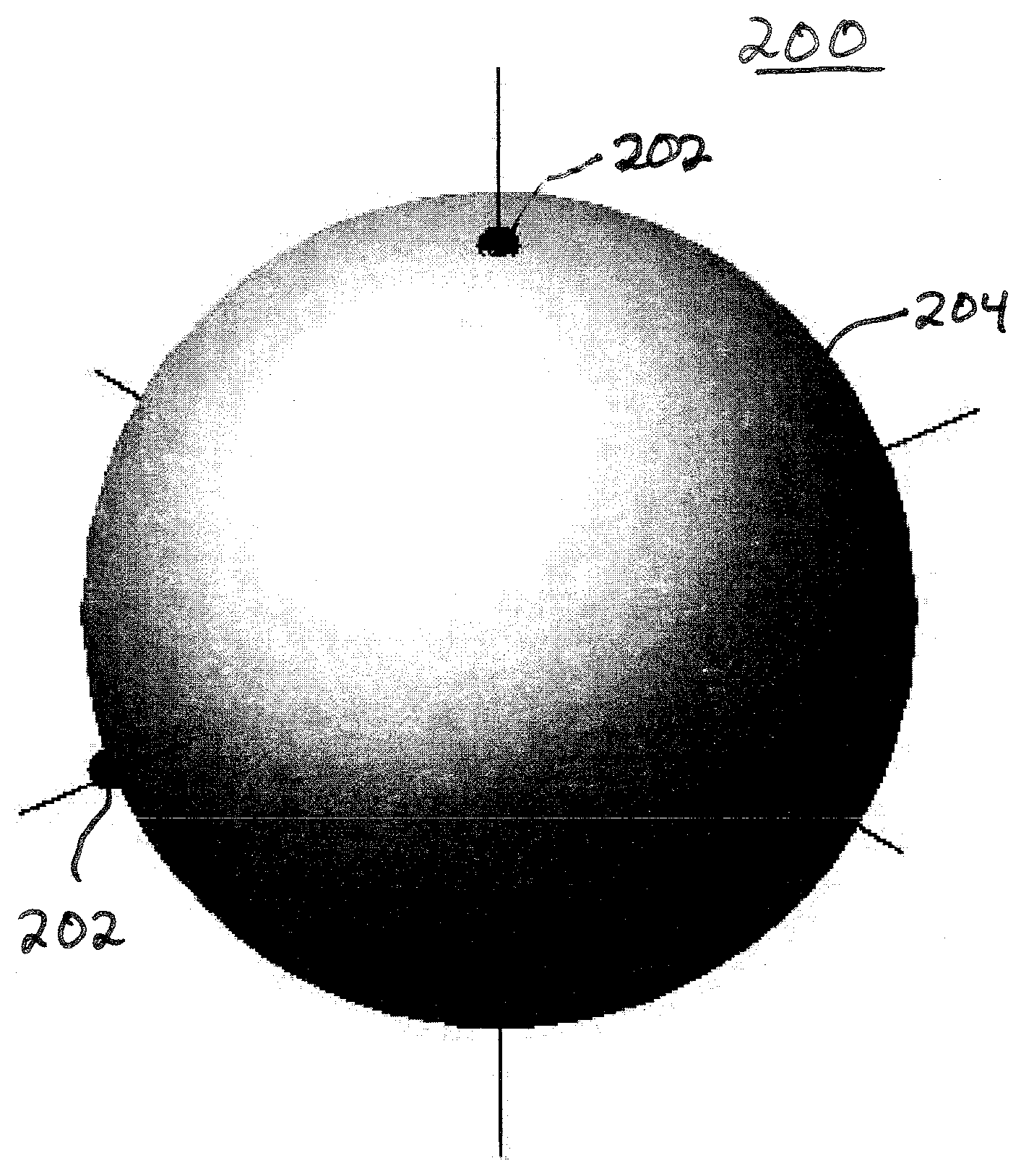

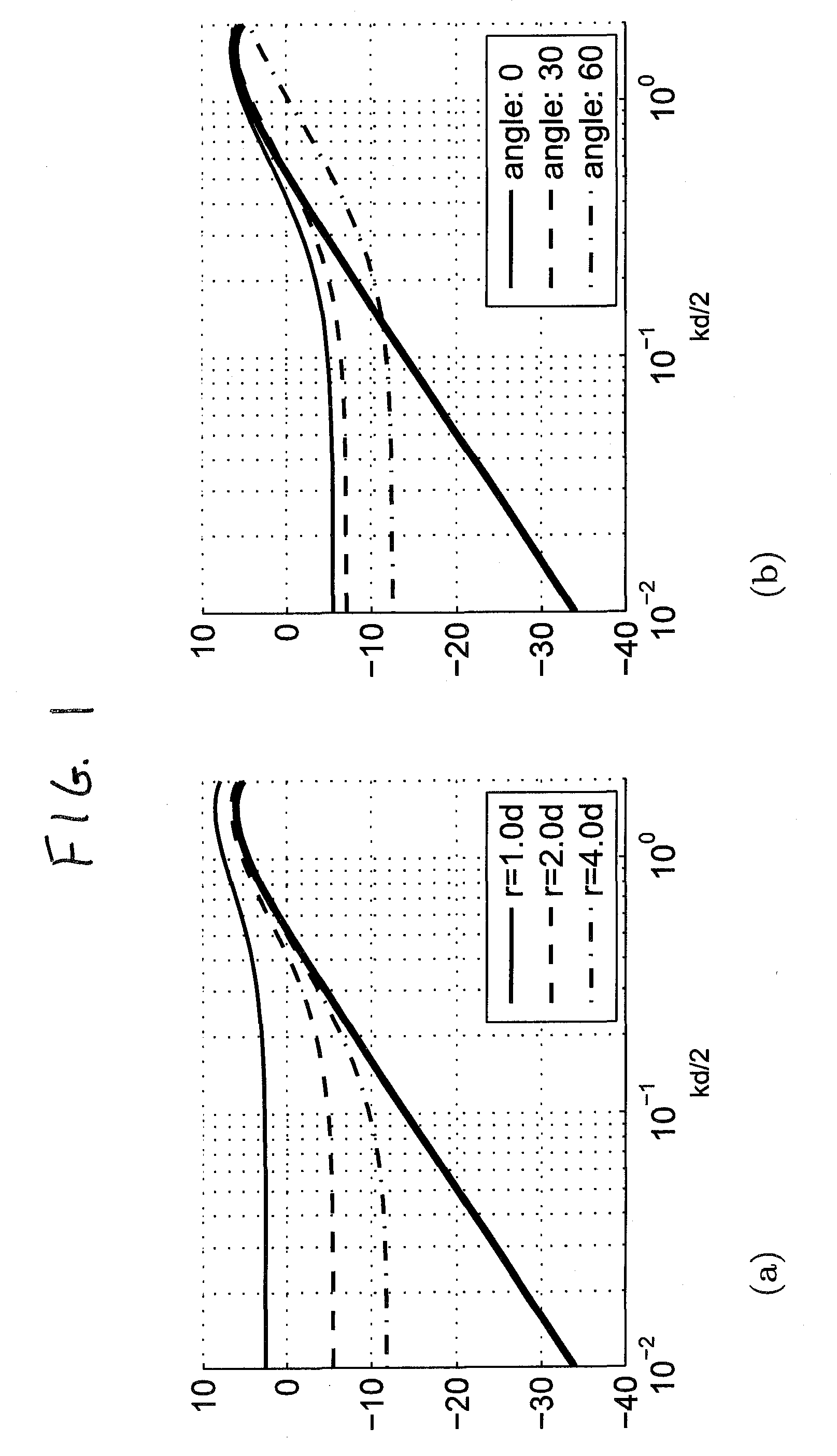

Position-Independent Microphone System

ActiveUS20080247565A1Microphones signal combinationSpecial data processing applicationsSound sourcesFrequency compensation

An audio system generates position-independent auditory scenes using harmonic expansions based on the audio signals generated by a microphone array. In one embodiment, a plurality of audio sensors are mounted on the surface of a sphere. The number and location of the audio sensors on the sphere are designed to enable the audio signals generated by those sensors to be decomposed into a set of eigenbeam outputs. Compensation data corresponding to at least one of the estimated distance and the estimated orientation of the sound source relative to the array are generated from eigenbeam outputs and used to generate an auditory scene. Compensation based on estimated orientation involves steering a beam formed from the eigenbeam outputs in the estimated direction of the sound source to increase direction independence, while compensation based on estimated distance involves frequency compensation of the steered beam to increase distance independence.

Owner:MH ACOUSTICS

Area-efficient capacitor-free low-dropout regulator

ActiveUS7495422B2Improve stabilitySacrificing performanceElectric variable regulationCapacitanceFrequency compensation

An area-efficient capacitor-free low-dropout regulator based on a current-feedback frequency compensation technique is disclosed. An implementation of a current feedback block with a single compensation capacitor is used to enable capacitance reduction. The resultant low-dropout regulator does not generally require an off-chip capacitor for stability and is particularly useful for system-on-chip applications.

Owner:THE HONG KONG UNIV OF SCI & TECH

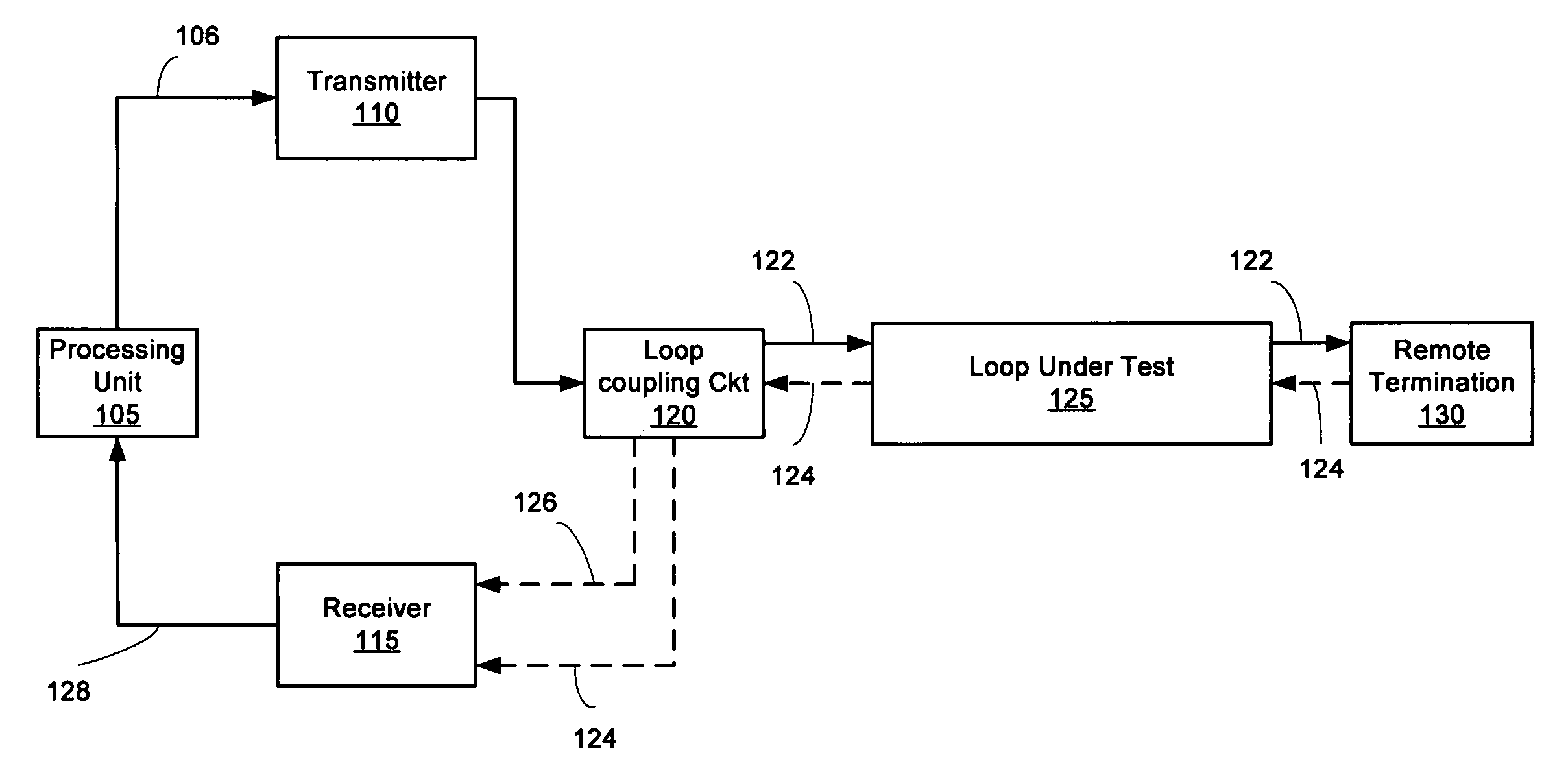

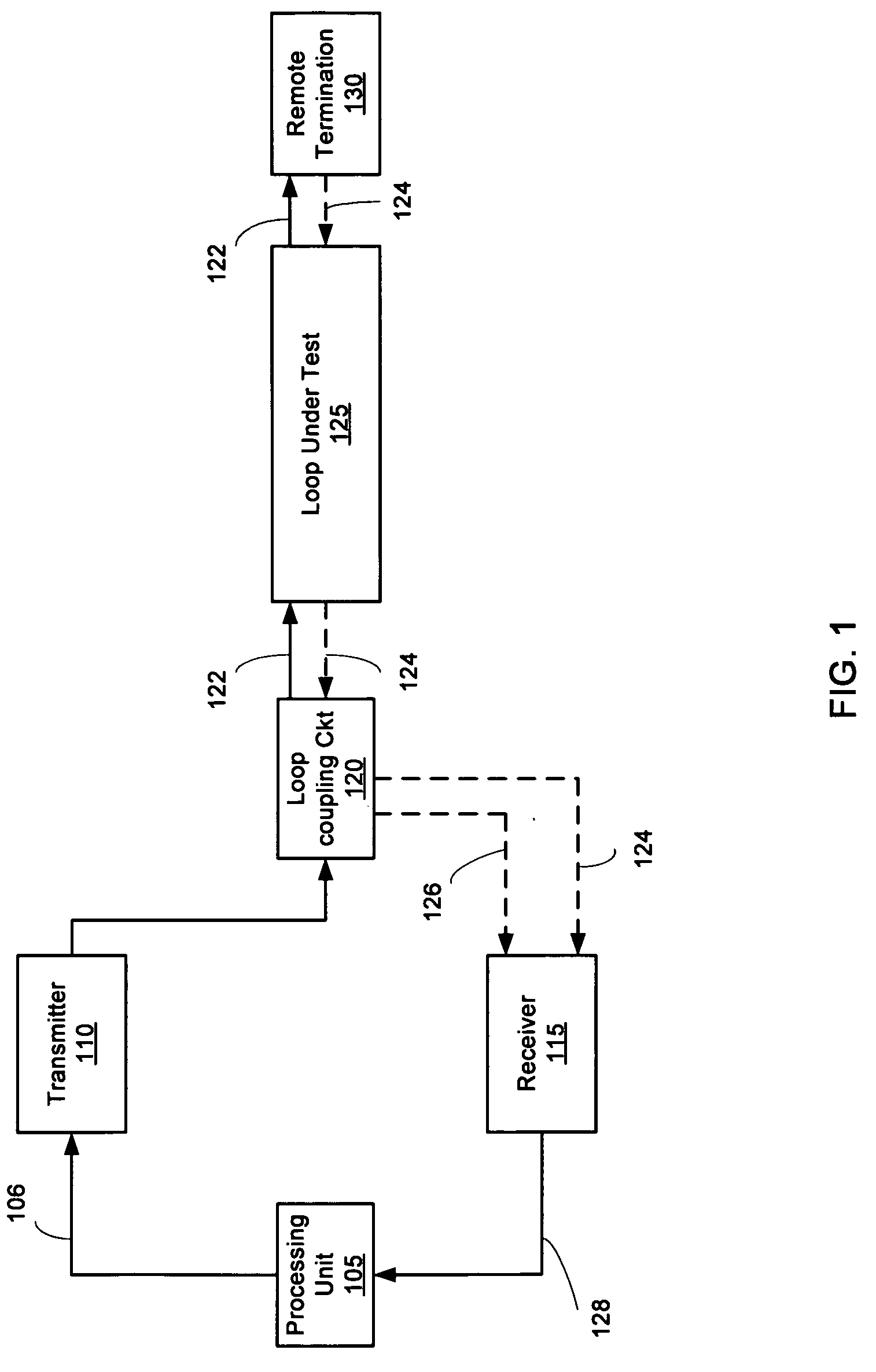

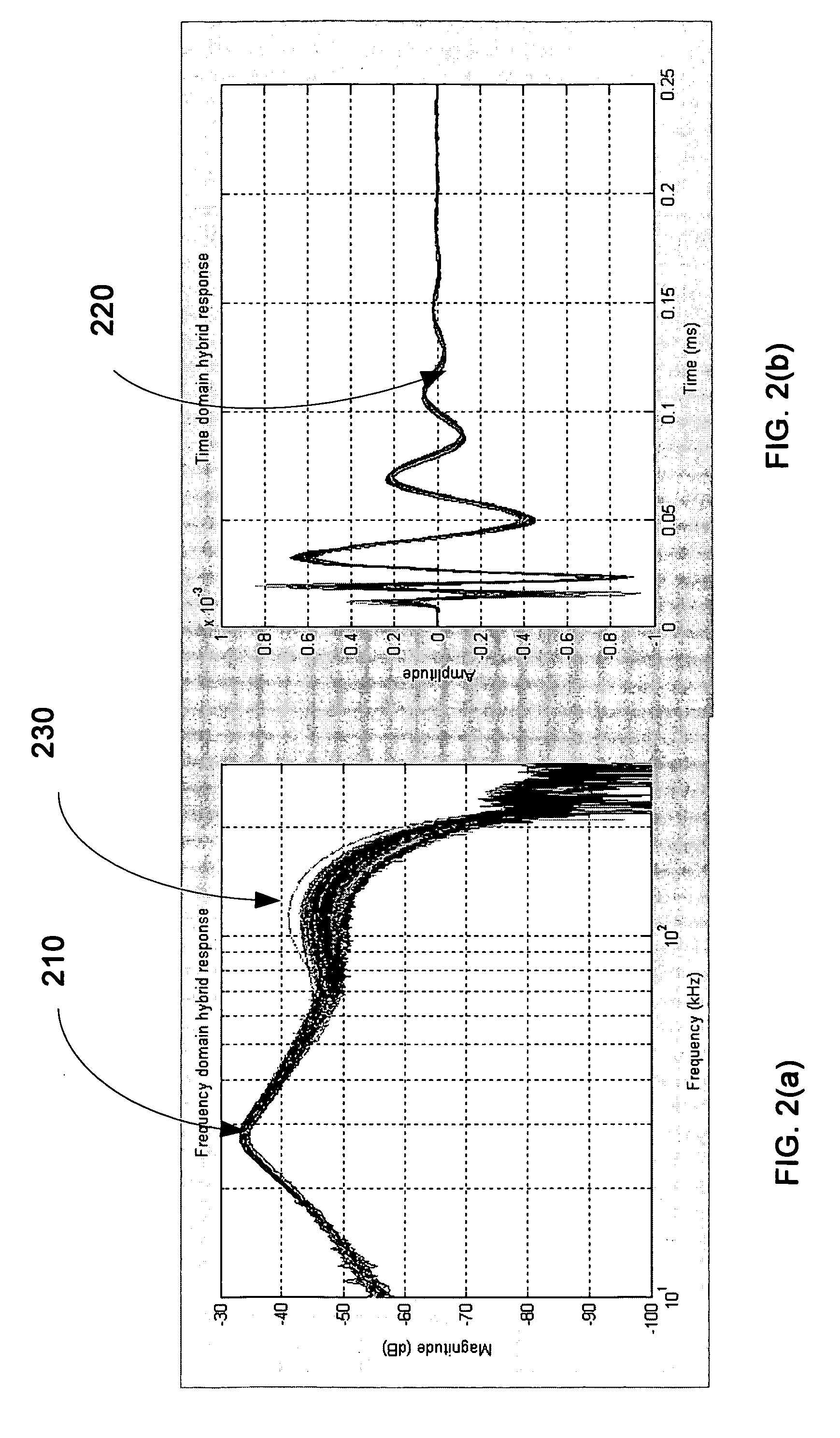

Method and apparatus for single end loop testing for DSL provisioning and maintenance

InactiveUS20050163287A1Simple and robust in applicationReduce near-end echoSupervisory/monitoring/testing arrangementsSubstation equipmentDigital signal processingLoop length

A method and apparatus for single end loop testing for DSL provisioning and maintenance provides testing of the DSL loop using digital techniques including frequency compensation, matched filtering and median filtering, to remove strong background and enhance desired signal for peak detection. The SELT system allows DSL providers to extract loop information from reflective measurements at the central office (CO) so as to determine loop capability of supporting different DSL services. The method and apparatus acquires the desired signal (the far-end echo) which is submerged in the correlated background noise (the near-end echo) by providing a process for detecting loop length and termination types with high accuracy for loops up to 12 kft for 24 AWG and up to 9 kft for 26 AWG by exploiting several digital signal processing techniques including frequency.

Owner:IKANOS COMMUNICATIONS

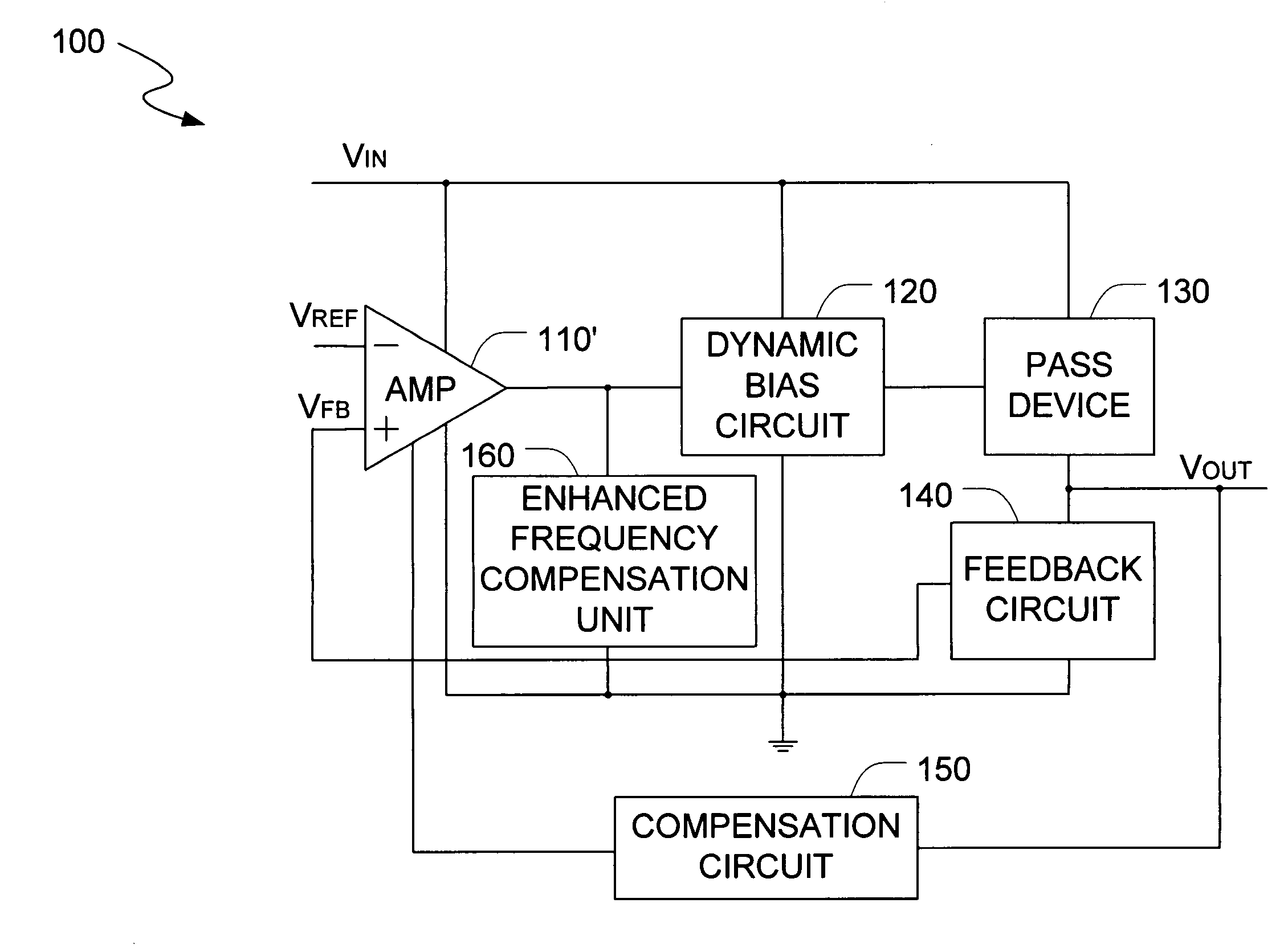

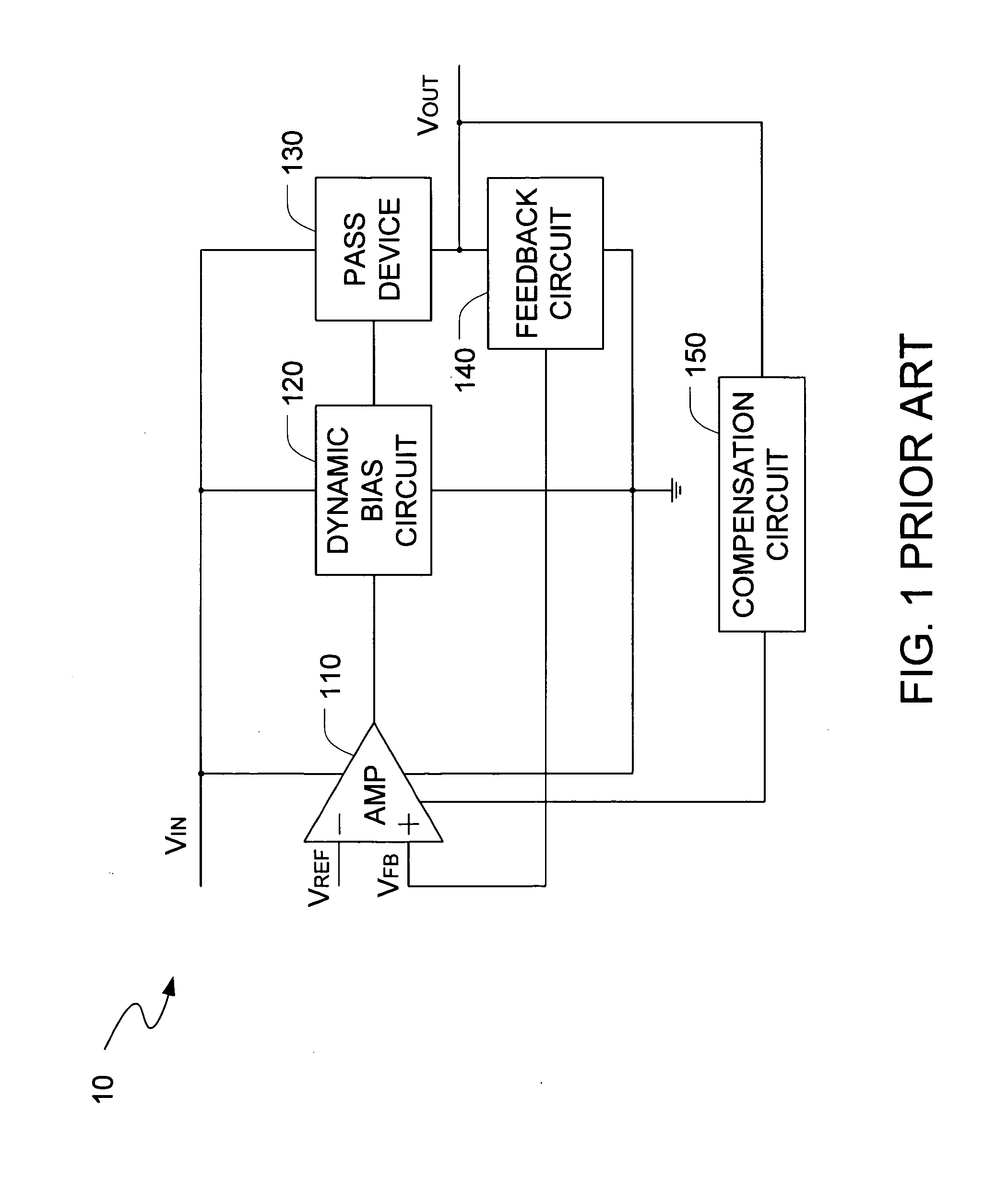

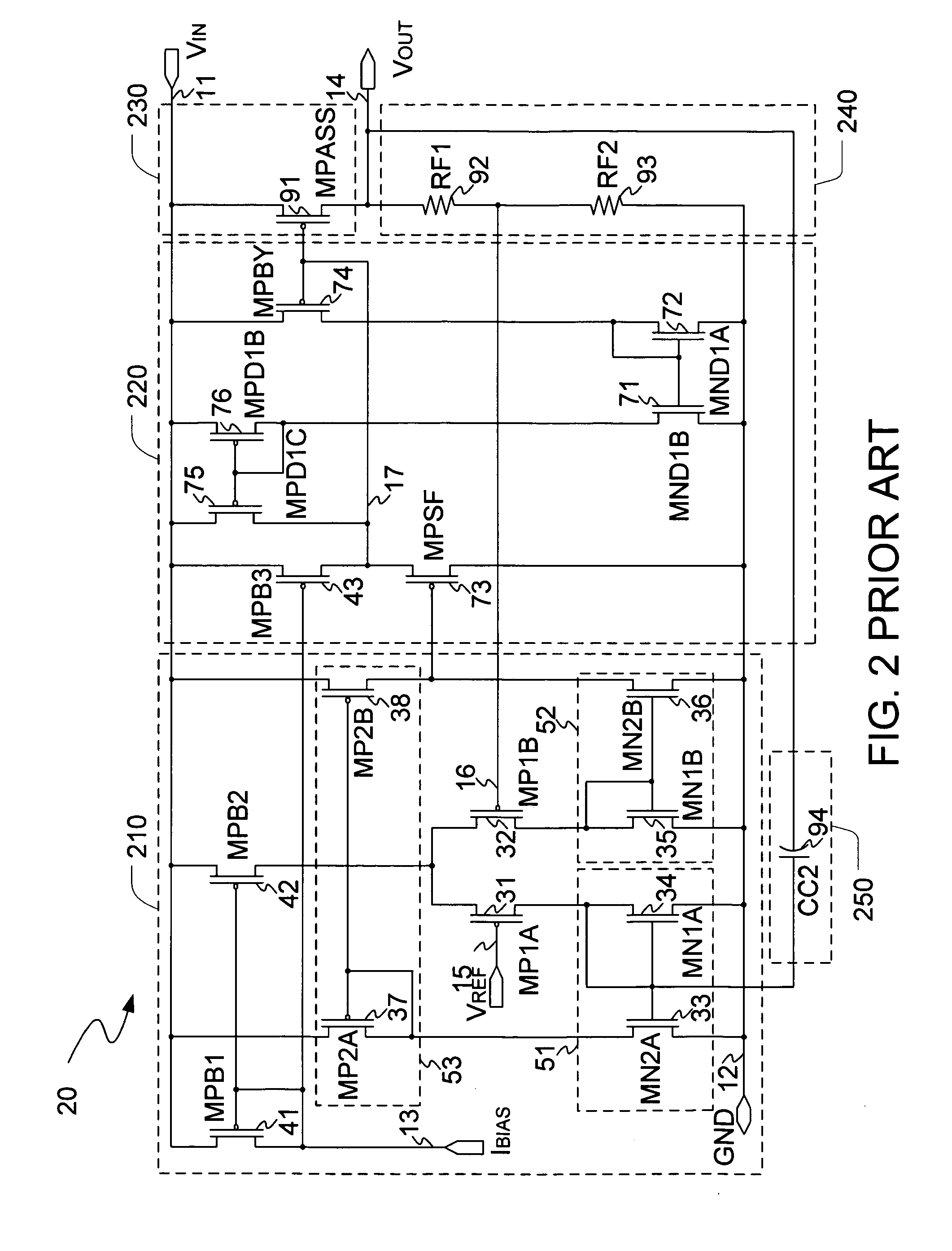

Low drop-out voltage regulator with enhanced frequency compensation

InactiveUS20060192538A1Enhanced frequency compensation capacityIncrease conversion rateElectric variable regulationFrequency compensationAudio power amplifier

The present invention is a voltage regulator circuit with enhanced frequency compensation. The voltage regulator includes an error amplifier, a dynamic bias circuit, an enhanced frequency compensation unit, a pass device and a compensation circuit. A signal from the pass device acts as an input signal of the error amplifier and is compared with another input signal, producing a differential signal. The differential signal is amplified and then provided to the dynamic circuit and the enhanced frequency compensation unit. The enhanced frequency compensation unit is provided such that a zero reference value in a left-hand plane can be generated to optimize the compensation for the voltage regulator circuit. The error amplifier includes a capacitor for compensating an output voltage of the voltage regulator circuit.

Owner:O2 MICRO INT LTD

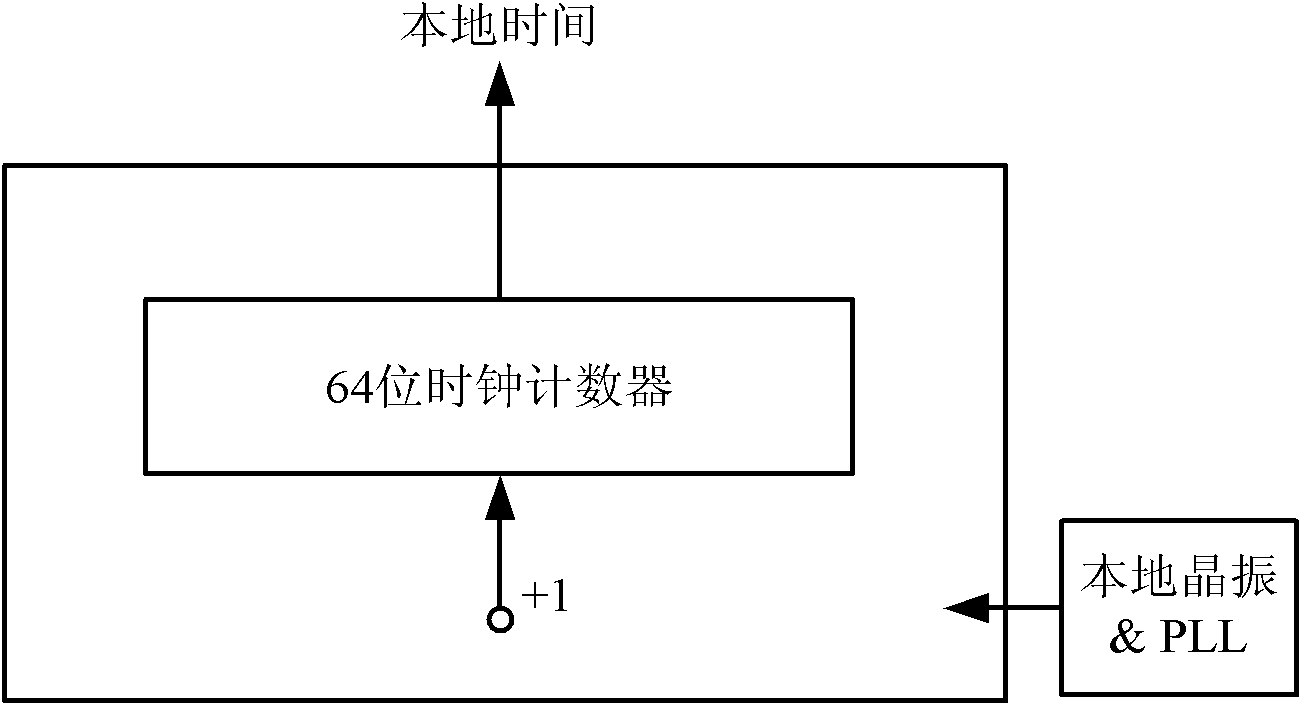

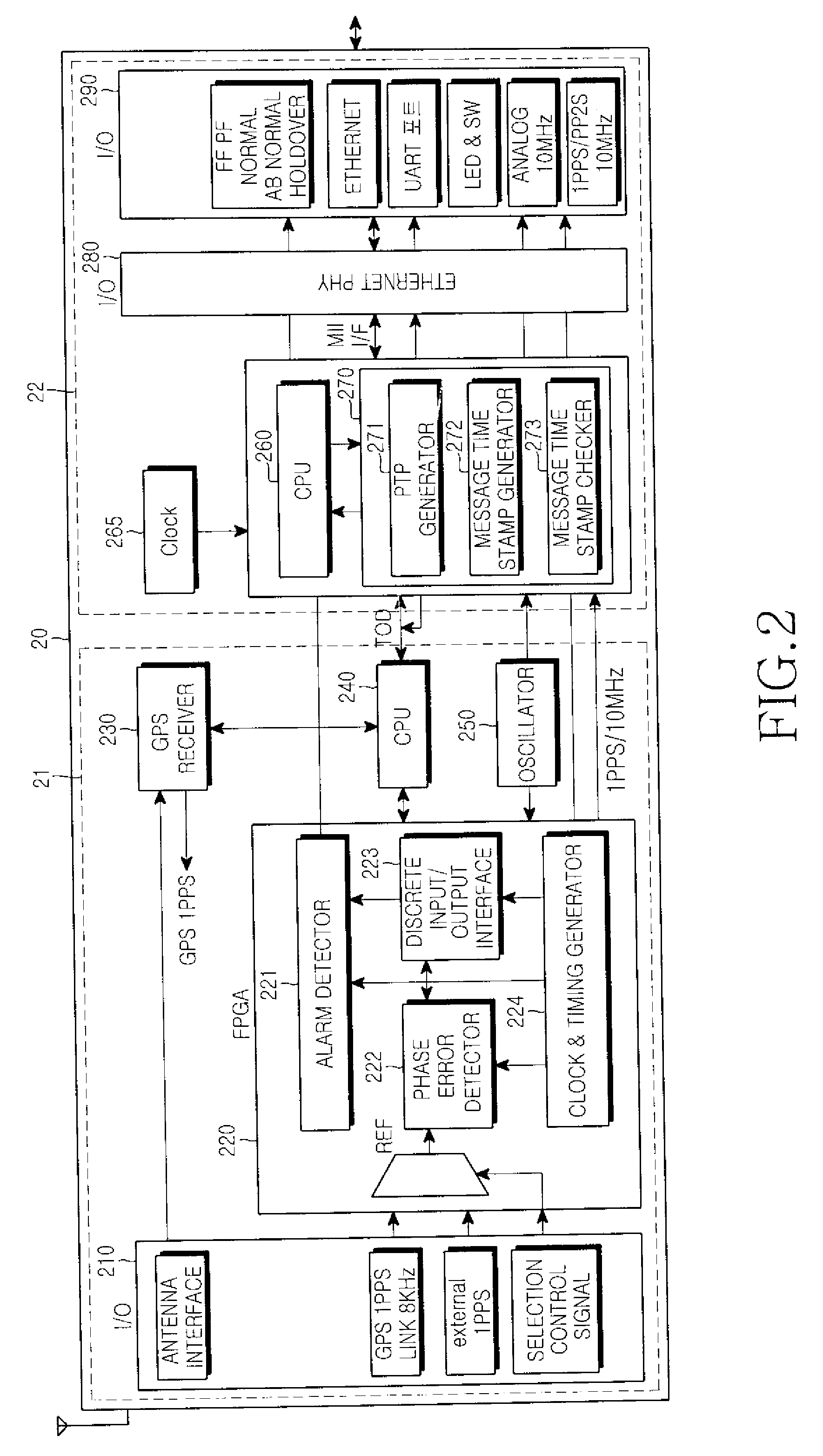

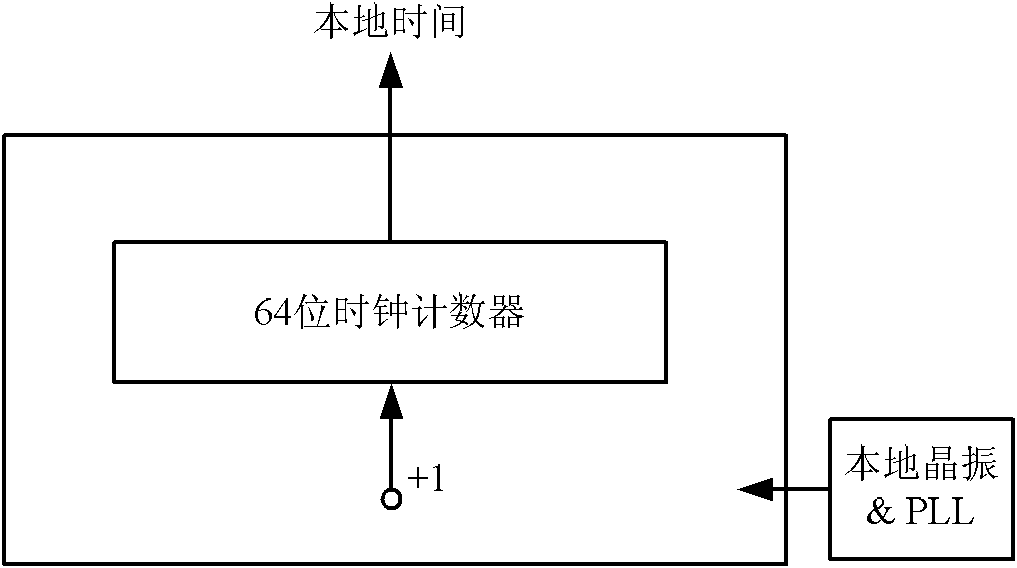

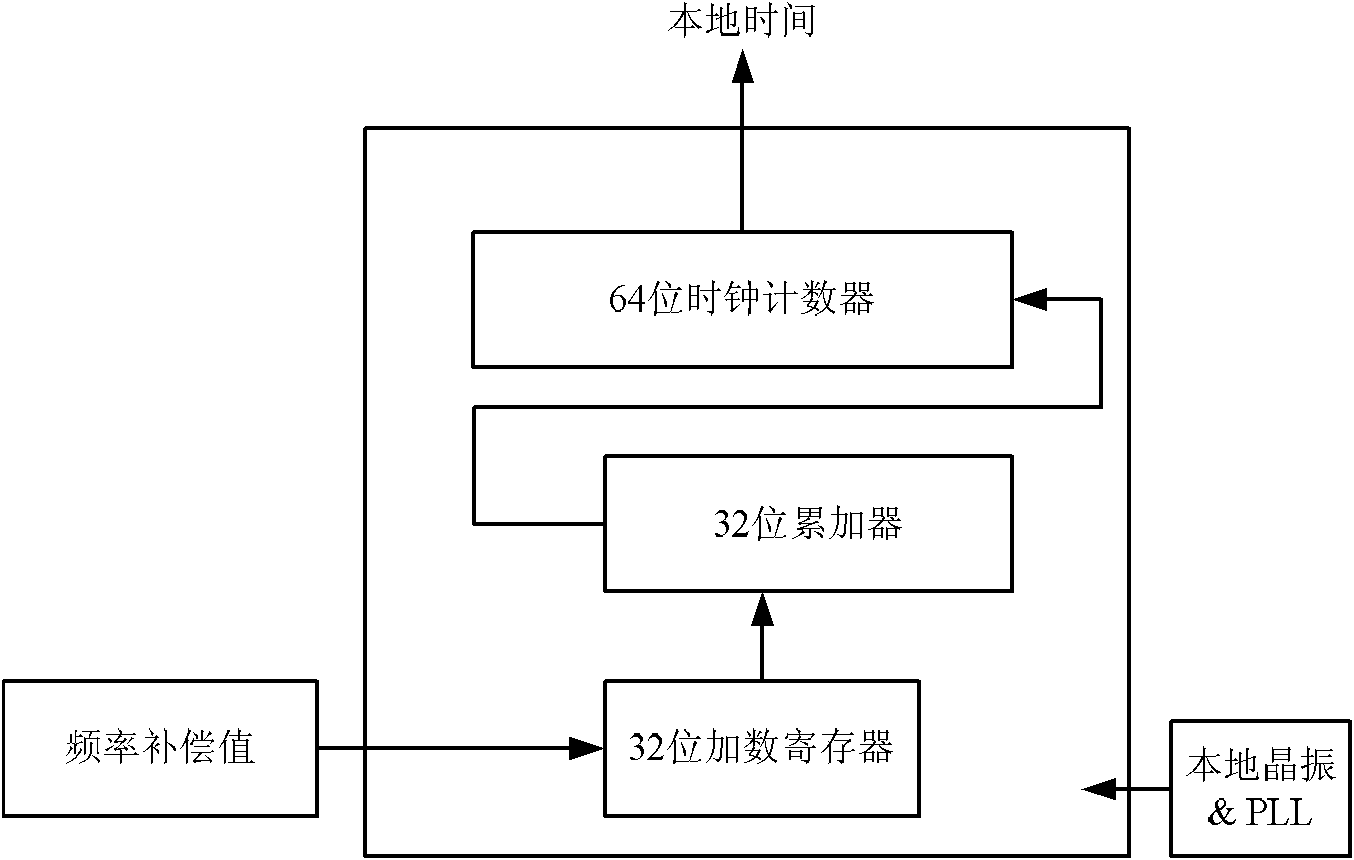

IEEE 1588-based synchronization system and synchronization method thereof

ActiveCN102104475ARealize the function of frequency compensationImprove Clock Synchronization AccuracyTime-division multiplexData switching networksData synchronizationFrequency compensation

The invention discloses an IEEE 1588 accurate clock synchronization protocol-based synchronization system and a synchronization method thereof in the technical field of wireless communication. The system consists of master equipment and slave equipment which are connected through a network, wherein the master equipment comprises a main clock module and a central processing unit (CPU) management control module; and the slave equipment comprises a slave clock module and a CPU management control module. Due to the adoption of a frequency compensation clock provided by Balasubramanian and the like, a frequency adjustable clock counter is constructed and the frequency compensation function is realized; and an improved clock synchronization method is adopted, the limited machine precision of anembedded system, namely influence brought by truncation errors is considered; therefore, higher clock synchronization accuracy is achieved.

Owner:SHANGHAI JIAO TONG UNIV

Circuits and methods for improving slew rate of differential amplifiers

ActiveUS7652538B2Increase conversion rateReduce power consumptionNegative-feedback-circuit arrangementsAmplifier modifications to reduce detrimental impedenceElectricityFrequency compensation

Owner:SAMSUNG ELECTRONICS CO LTD

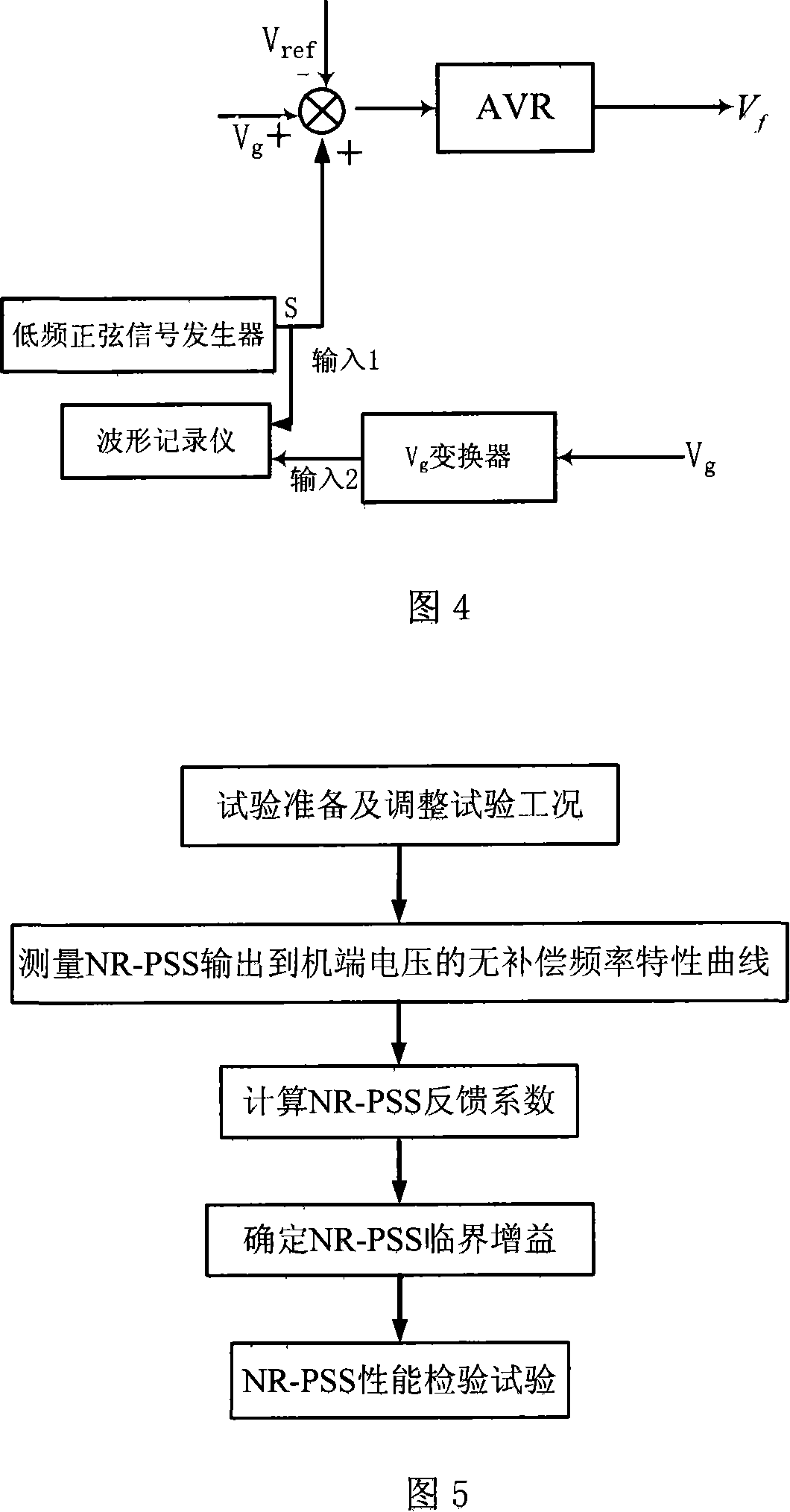

Method for regulating frequency domain based nonlinear power system stabilizer parameter

ActiveCN101119094AClear thinkingSimple stepsFrequency analysisDynamo-electric machine testingGain coefficientEngineering

Owner:TSINGHUA UNIV

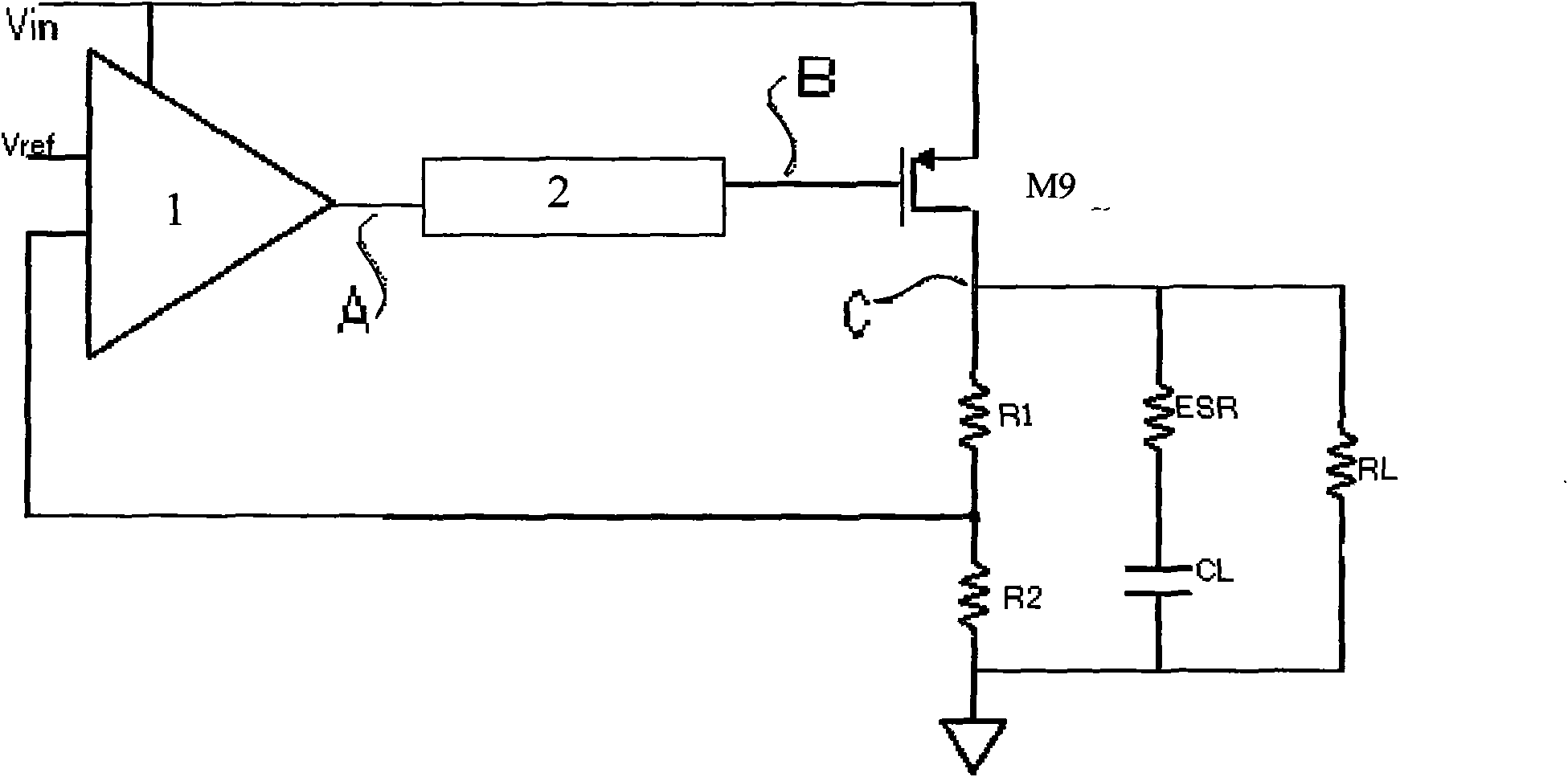

Self-adaption zero-frequency compensation circuit in low-voltage difference linear voltage regulator

ActiveCN101957628ALower resistanceFix stability issuesElectric variable regulationCapacitanceLow voltage

The invention relates to a self-adaption zero-frequency compensation circuit in a low-voltage difference linear voltage regulator. The output end of a transconductance amplifier is connected with a voltage regulation pipe by a voltage bumper, a current detection circuit is connected with the voltage bumper and the common end of the voltage regulation pipe, and the other end is connected with a variable-resistance circuit connected with the compensation end of the transconductance amplifier. In the invention, when a load is higher and current is lower, the current detection circuit can detect the load and the current and the load and the current act on the variable-resistance circuit at the moment to ensure that the resistance is enlarged, and the zero position is also relatively lower; on the contrary, when the load is reduced and the current is enlarged, the resistance value of the variable-resistance circuit is reduced, and the zero position is higher. Therefore, the self-adaption zero can change along with the change of a pole so that the compensation circuit takes the effect of compensation and effectively ensures the stable state of system operation. The compensation circuit successfully solves the problem of poor stability of a low-voltage difference linear voltage regulator so that a load capacitance equivalent series resistance is not really important to the influence on system stability, transient response and ripple waves.

Owner:江西芯世达微电子有限公司

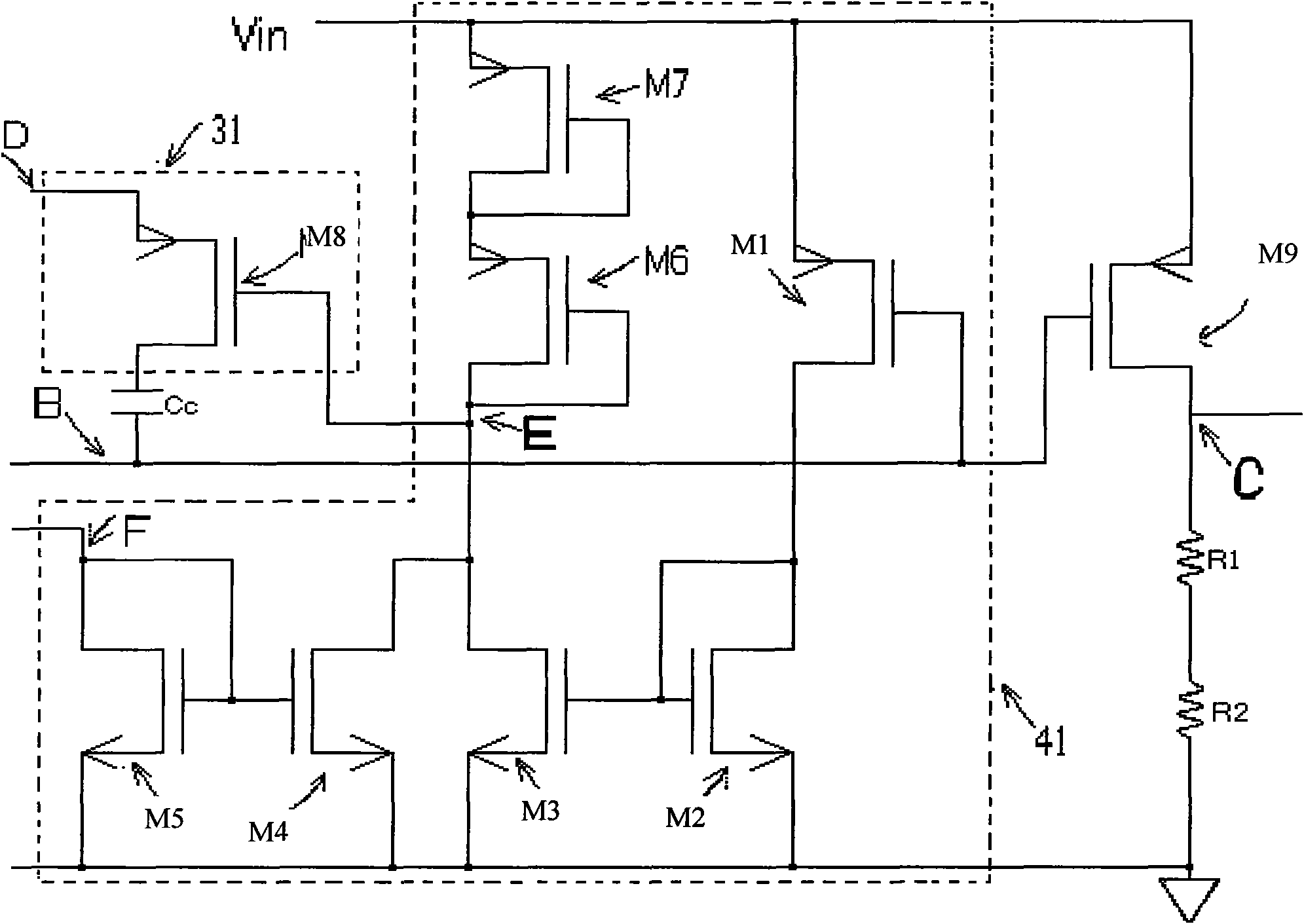

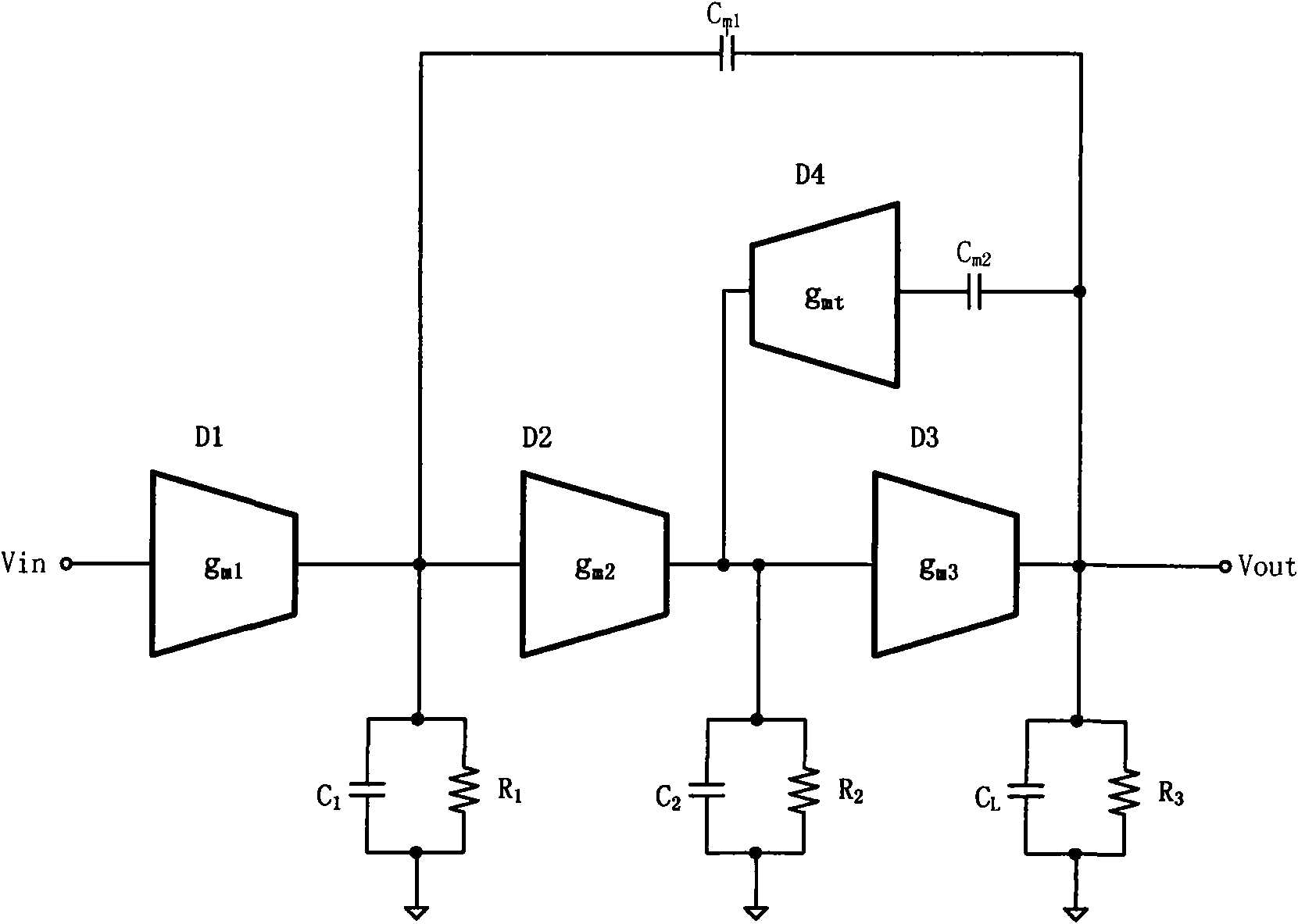

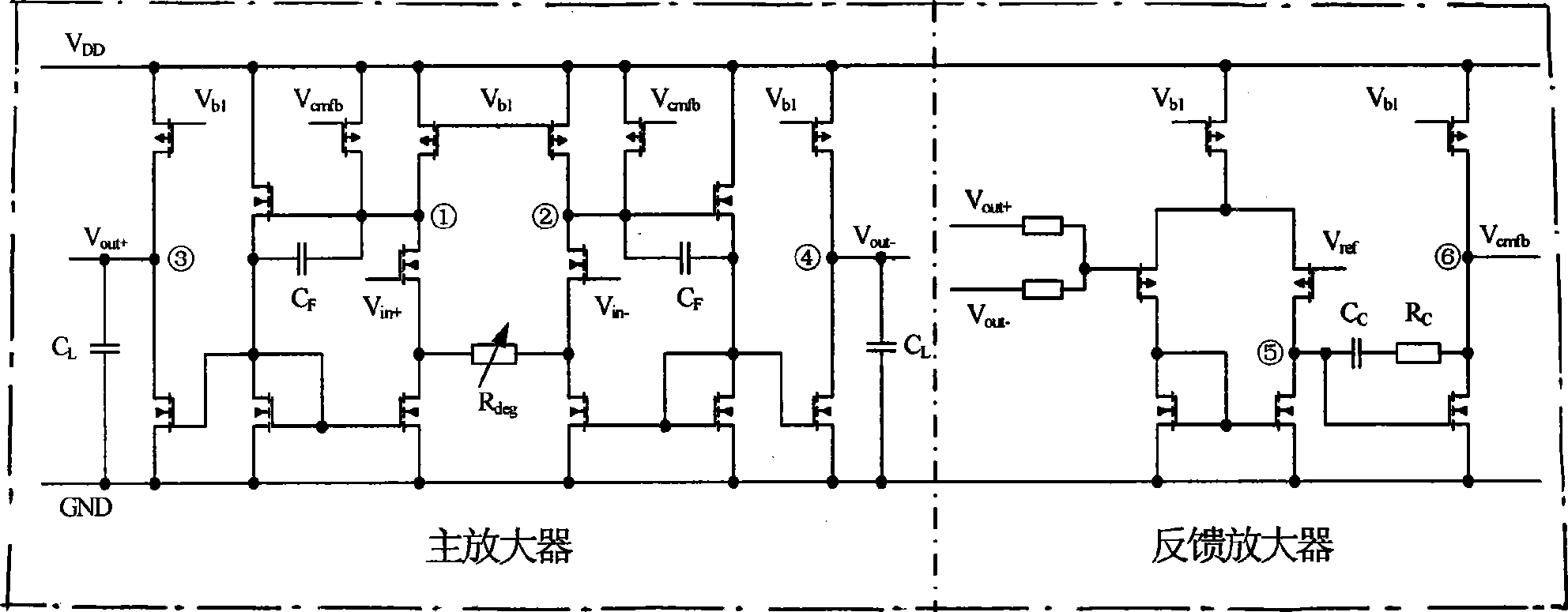

High-bandwidth low-power consumption frequency-compensation three-stage operational amplifier

InactiveCN101917169AGood compensationIncrease separation resistanceEnergy efficient ICTAmplifier modifications to raise efficiencyLoad circuitWireless communication protocol

The invention belongs to the technical field of analog IC (Integrated Circuit) design, in particular to a high-bandwidth low-power consumption frequency-compensation three-stage operational amplifier. The amplifier comprises an input stage, a second stage, an output stage, a common mode feedback stage, a comprehension circuit, an internal feedforward circuit, wherein the second stage is connectedwith the input stage, the output stage is connected with the second stage and used for amplifying a signal output by the second stage and driving an external load circuit, the common mode feedback stage extracts the common mode level of the differential output stage and stabilizes the common mode level, the comprehension circuit comprises a traditional trsanscondutance comprehension circuit, a miller comprehension circuit and a resistor for separating a high-frequency zero pole, and the internal feedforward circuit is used for comprehending an internal additional pole and forming a push-pull circuit together with the output stage to reduce static power consumption. The three-stage operational amplifier realizes high gain, high bandwidth and high stability under the condition of little DC power consumption and can be used in a high-speed analog-digital conversion circuit, such as a sigma-delta modulator suitable for the bandwidth of an LTE (Line Terminator Equipment) wireless communication protocol.

Owner:FUDAN UNIV

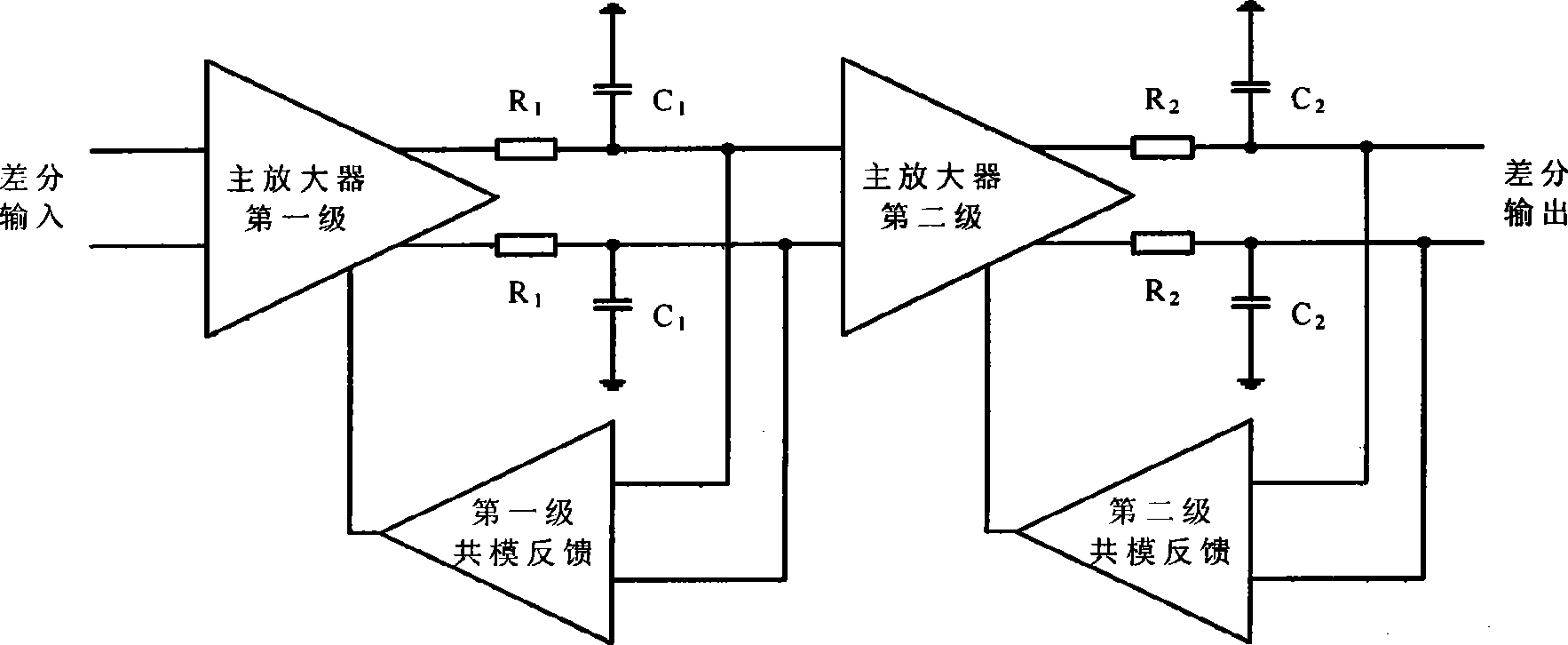

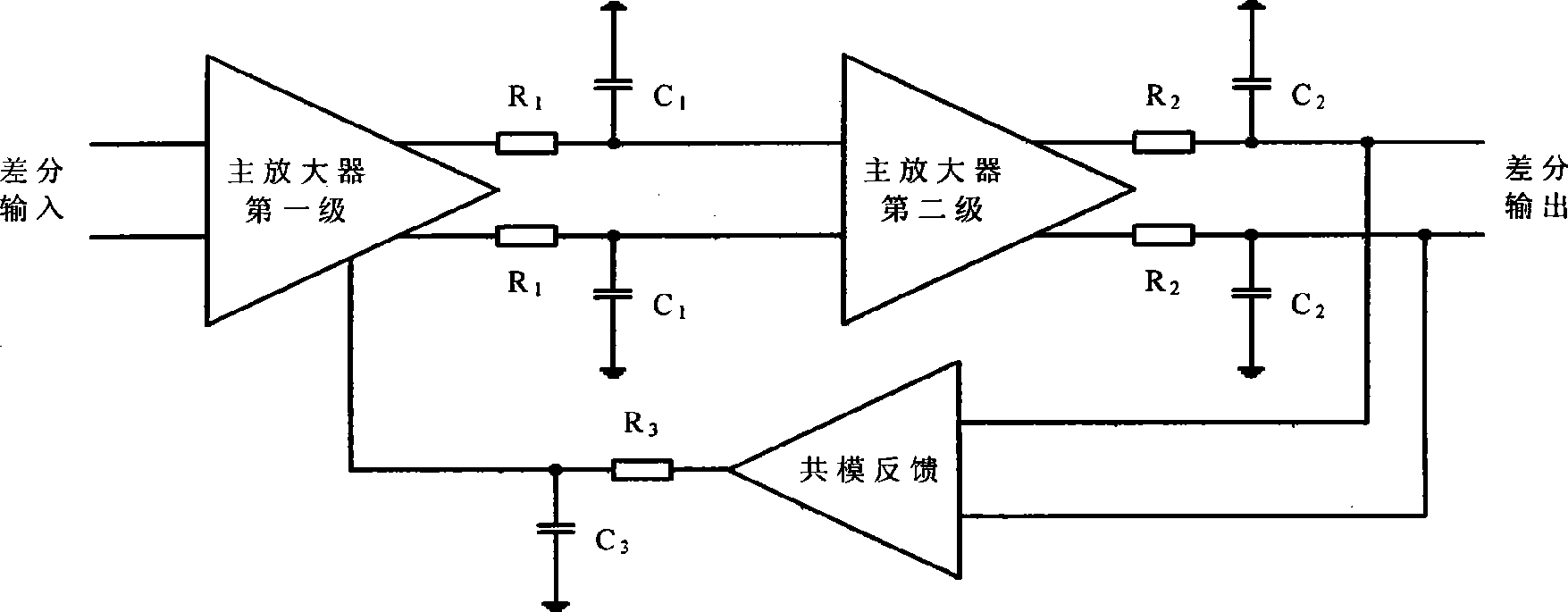

Method for compensating common mode feedback circuit frequency of two-stage amplifier

InactiveCN101373956AImprove phase marginImprove stabilityDifferential amplifiersDc-amplifiers with dc-coupled stagesDual stageControl signal

The invention discloses a common-mode feedback circuit frequency compensation method of a dual-stage amplifier, which belongs to the analog integrated circuit design field. One common-mode feedback circuit is adopted in the dual-stage amplifier to reduce the area and the power consumption of the feedback circuit; the dual-stage amplifier adopts a fully-differential input / output structure; a differential output terminal is used for sampling the common-mode output level; a first-stage amplifying circuit thereof comprises a controllable biasing circuit; a common-mode feedback control signal controls the first-stage common-mode output level and the second-stage common-mode output level of the amplifier at the same time through the controllable biasing circuit; a feedback amplifier is realized by adopting a dual-stage operational amplifier with miller compensation. The left half plane zero point generated by the feedback amplifier in a loop circuit counteracts a certain left half plane pole in a prime amplifier, thereby forming a stable compensation loop circuit. The common-mode feedback circuit frequency compensation method has the advantages of less feedback circuit elements, lower feedback circuit power consumption, high low-frequency loop gain and better compensation phase margin.

Owner:RESEARCH INSTITUTE OF TSINGHUA UNIVERSITY IN SHENZHEN

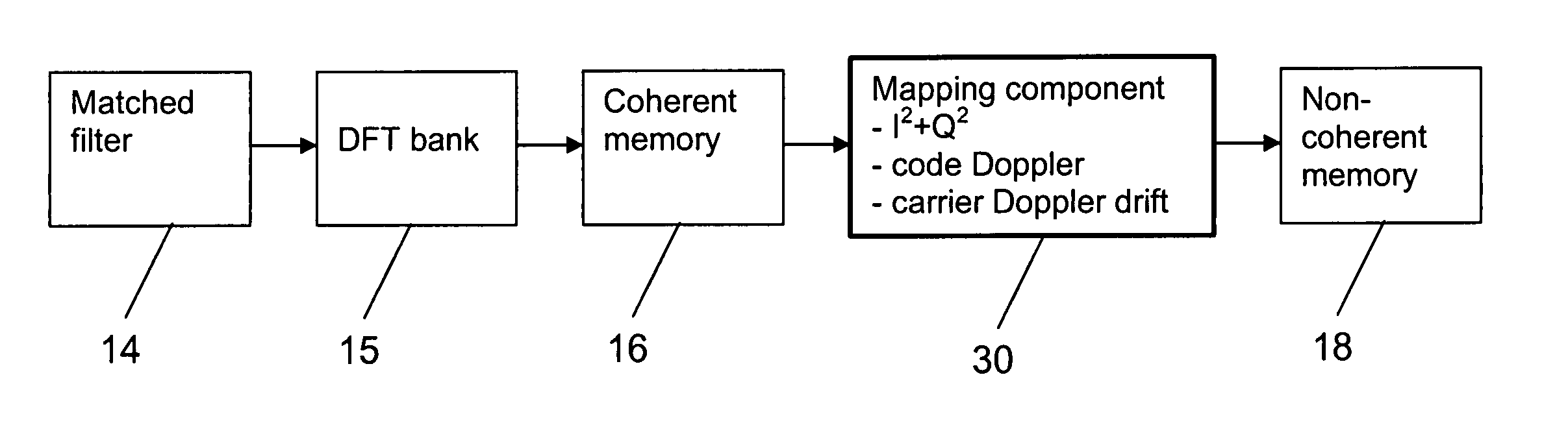

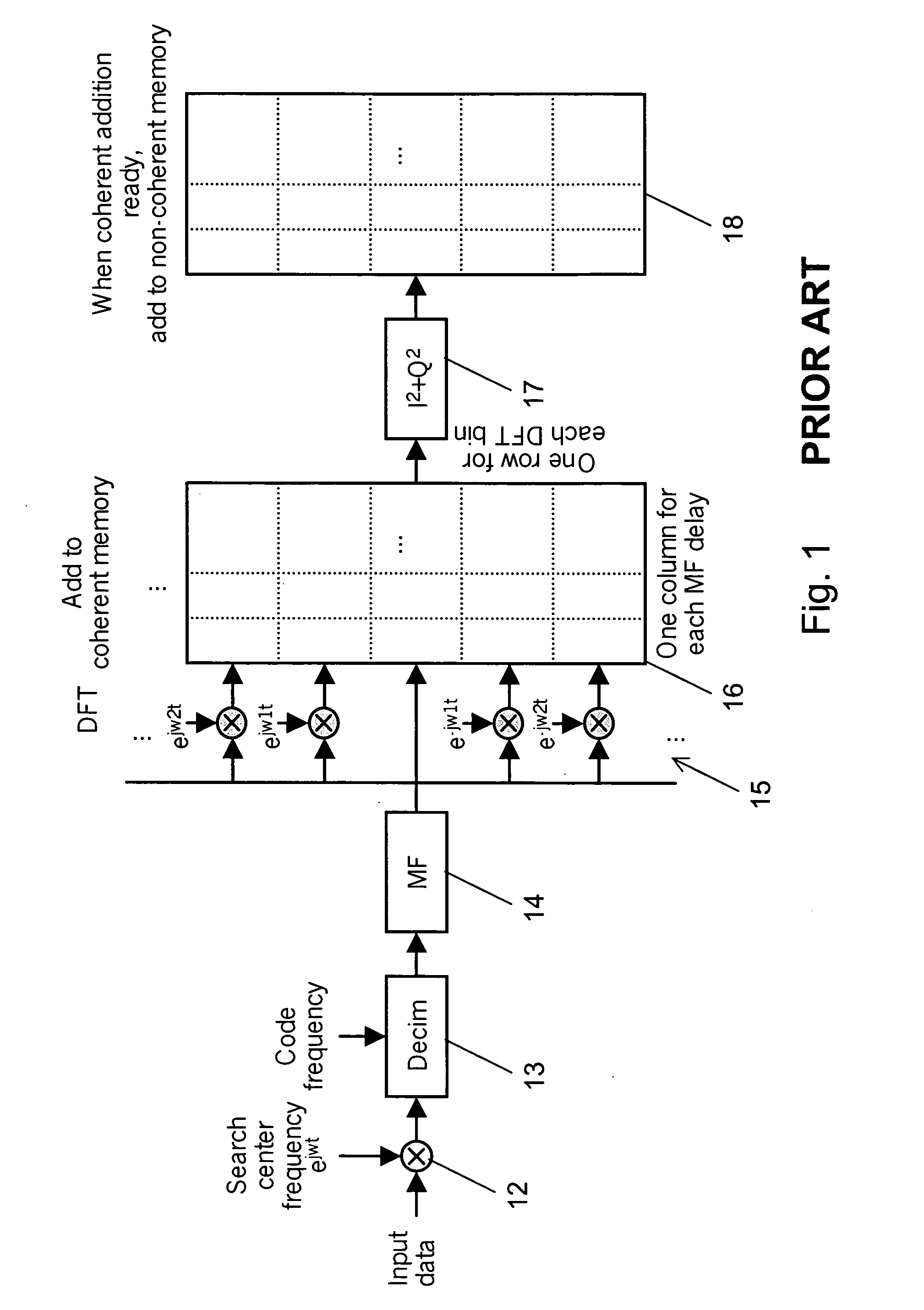

Determination of a code phase

InactiveUS20060133463A1Long integration timeHigh sensitivityAmplitude-modulated carrier systemsSatellite radio beaconingFrequency compensationCarrier signal

The invention relates to determining a correct code phase of a received, code modulated carrier signal using a correlation portion, a frequency compensation portion, a coherent memory and a non-coherent memory. In order to compensate for a code Doppler effect and / or a carrier Doppler drift effect, a mapping portion maps correlation values either to the coherent memory or to the non-coherent memory. Alternatively, the mapping portion maps correlation values stored in the coherent memory or in the non-coherent memory to new positions. The mapping depends on a frequency compensation applied by the frequency compensation portion and elapsed integration time, and / or on a drift of a frequency offset in correlation values output by said correlation portion.

Owner:NOKIA TECHNOLOGLES OY

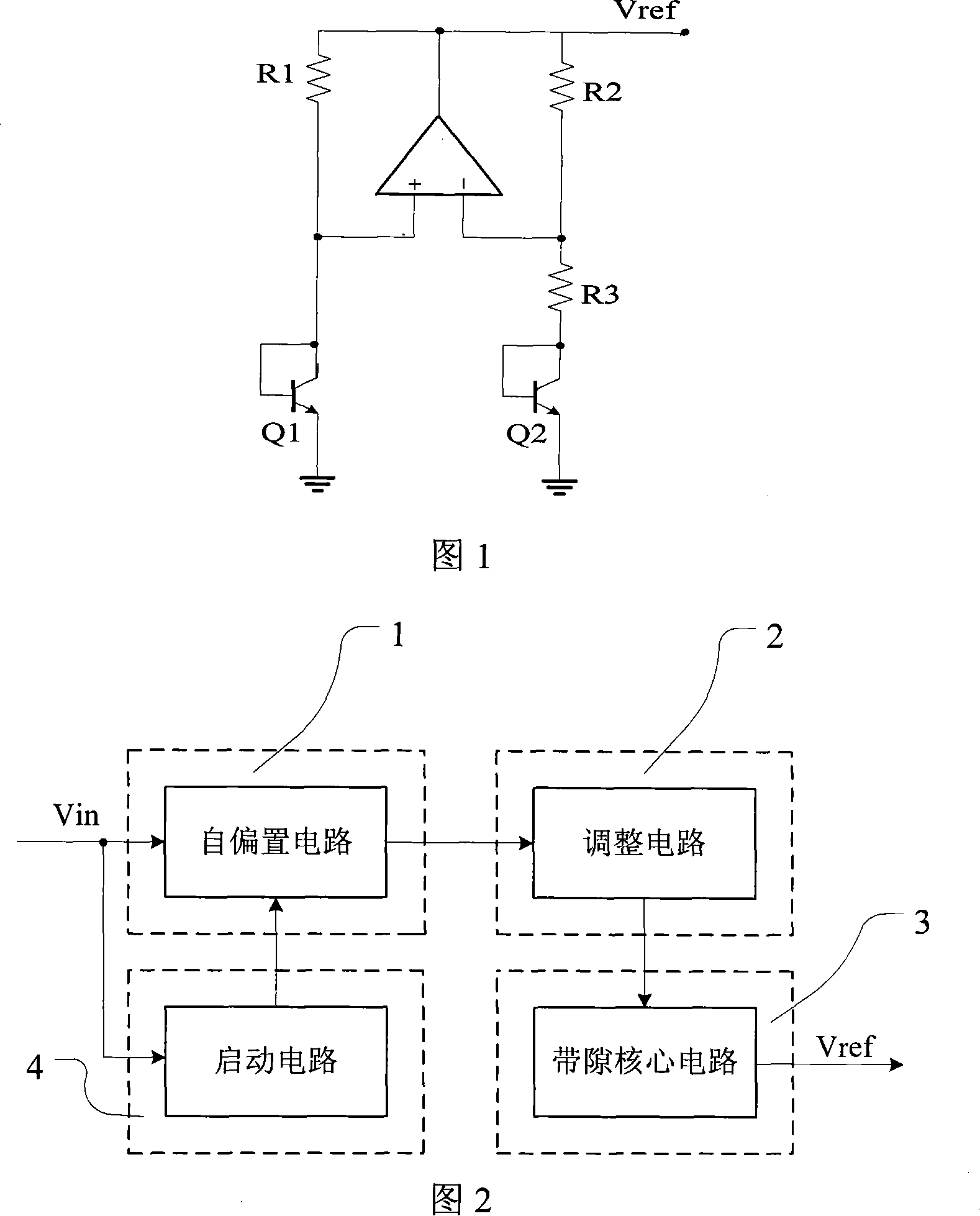

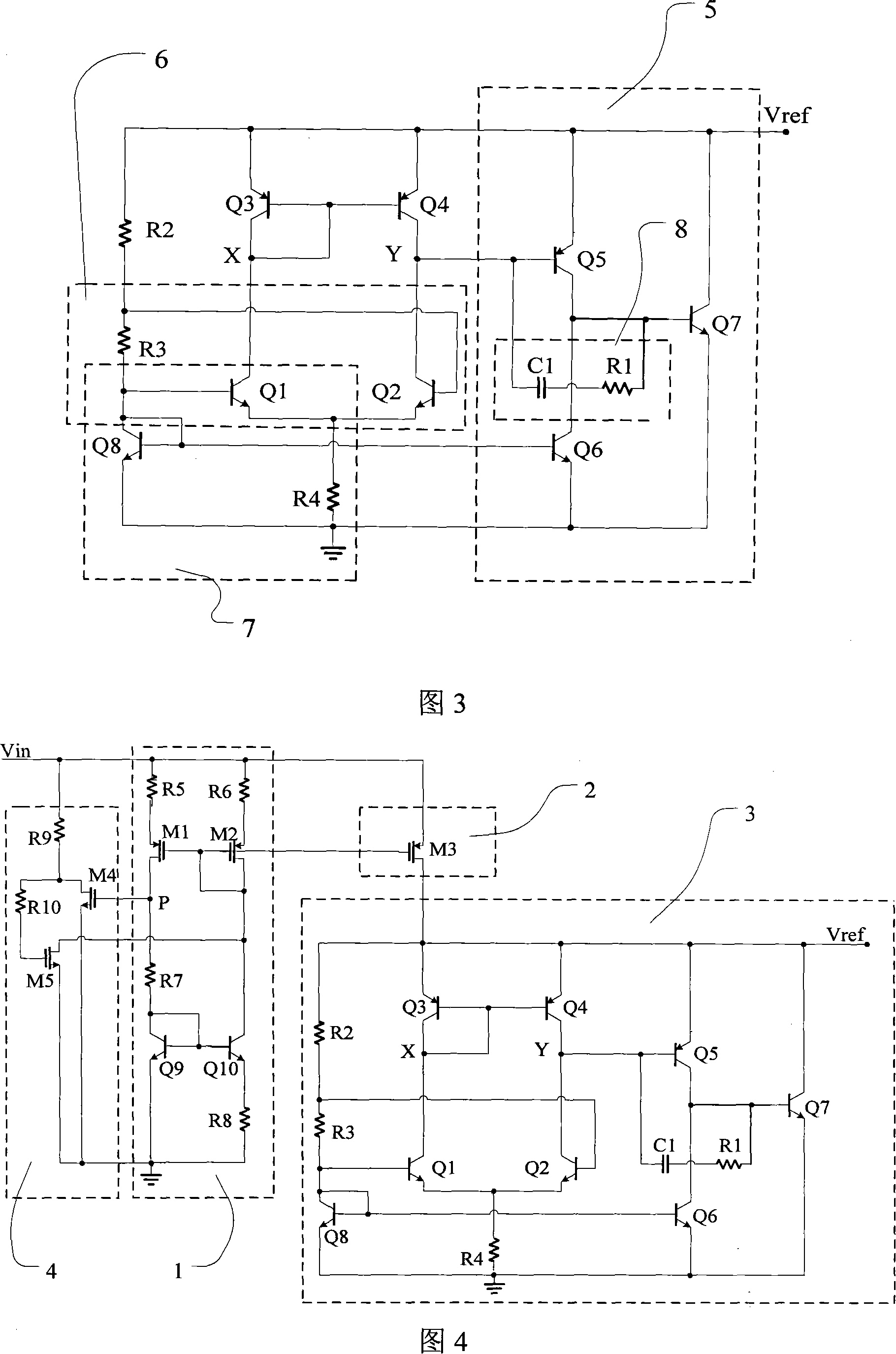

Band-gap reference source with high power supply restraint

InactiveCN101131592ASimple structureReduce power consumptionElectric signal transmission systemsDigital-analogue convertorsNegative feedbackFrequency compensation

There is a sort of reference source which has the crack by checking the high electrical source, and it consists of the self-polarization circuit, the regulating circuit, the kernel circuit which has the crack, and the startup circuit. The IPTAT generating circuit of the kernel circuit which has the crack makes the collector current of the Q1 and Q2 of the NPN pipe to equal by that the degenerative feedback which is magnified adjusts its quiescent point, the IPTAT current and the VBE of the Q8 of the NPN transistor which has the negative temperature coefficient in the constant-current circuit are progressed the first compensation of the temperature, at the same time they debase the temperature coefficient. The constant-current circuit produces the polarization by itself, and provides the polarization current to the IPTAT generating current. The operational amplifier circuit advances the plus for the two-stage operational amplifier, the compensation current progresses the frequency compensation for the two-stage operational amplifier. The generating circuit removes the dependency of the reference export VREF to supply voltage by negative feedback effect in order advance the PSRR. The startup circuit removes the degeneration polarization point and it drives the self-polarization circuit to work. The self-polarization circuit provides the polarization voltage for the regulating circuit. The circuit configuration of this invention is simple and new, it does not need the external polarization, the area of this circuit is small, and it has the good temperature coefficient.

Owner:HUAZHONG UNIV OF SCI & TECH