Patents

Literature

134 results about "Loop length" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

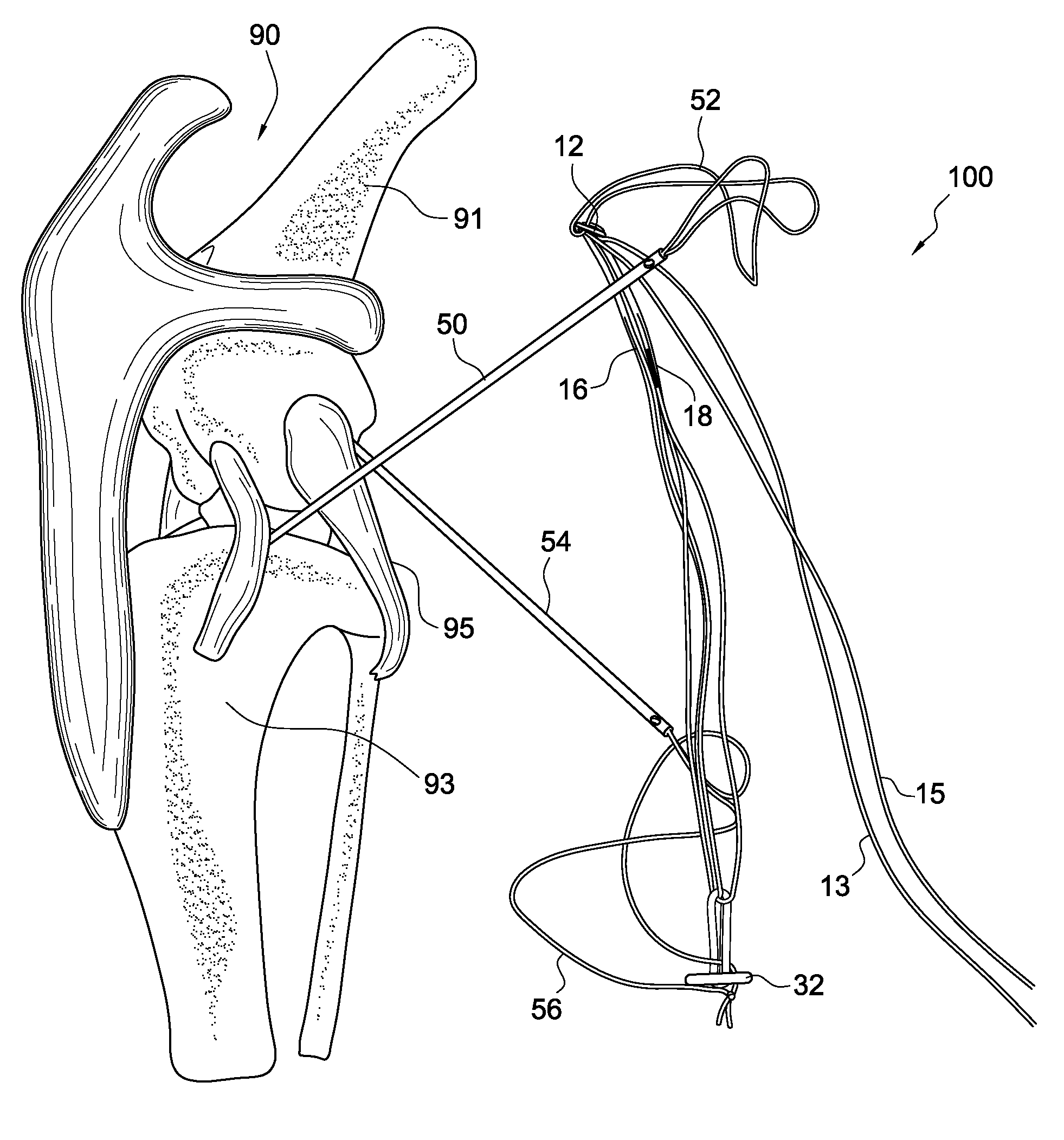

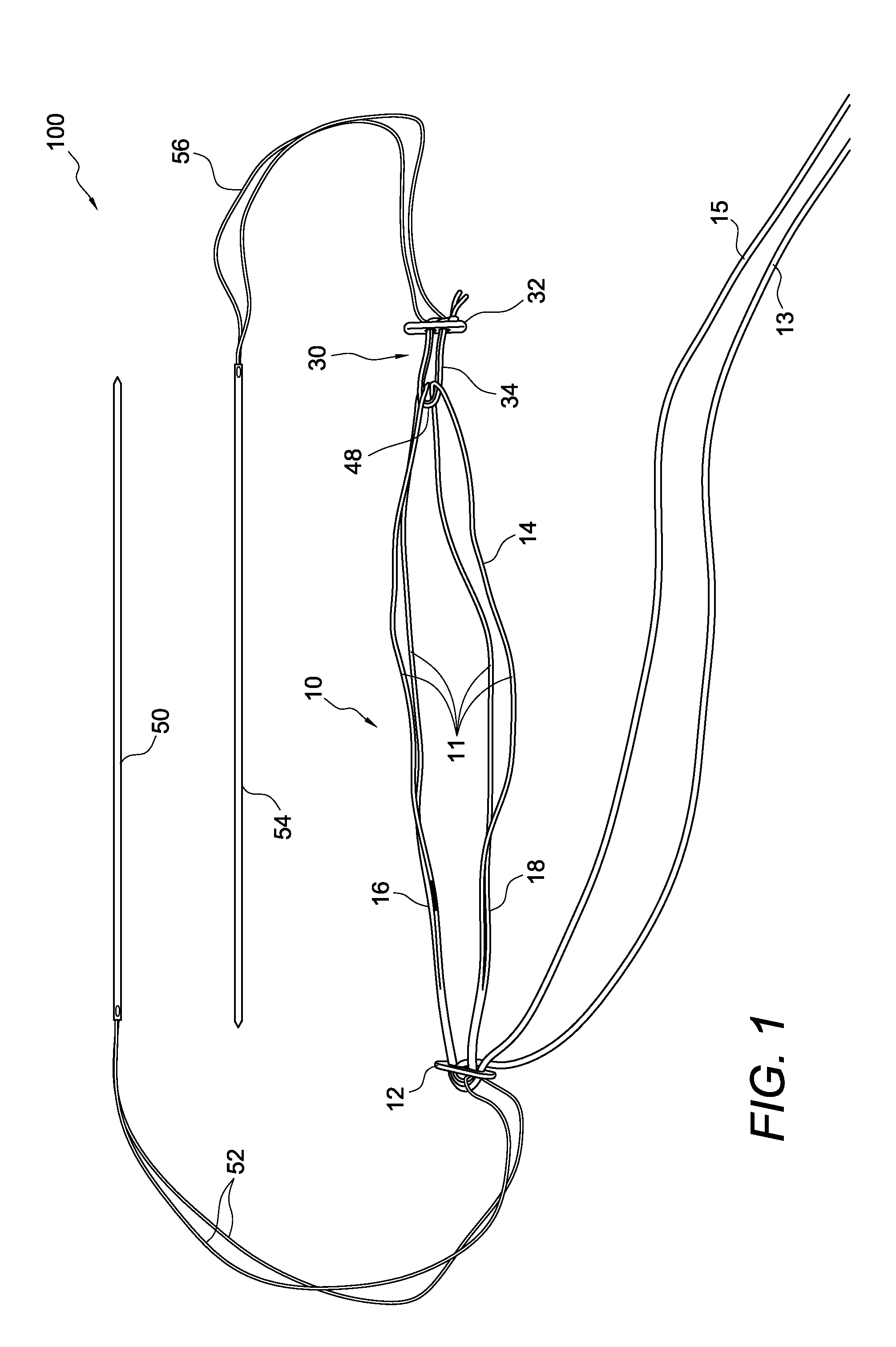

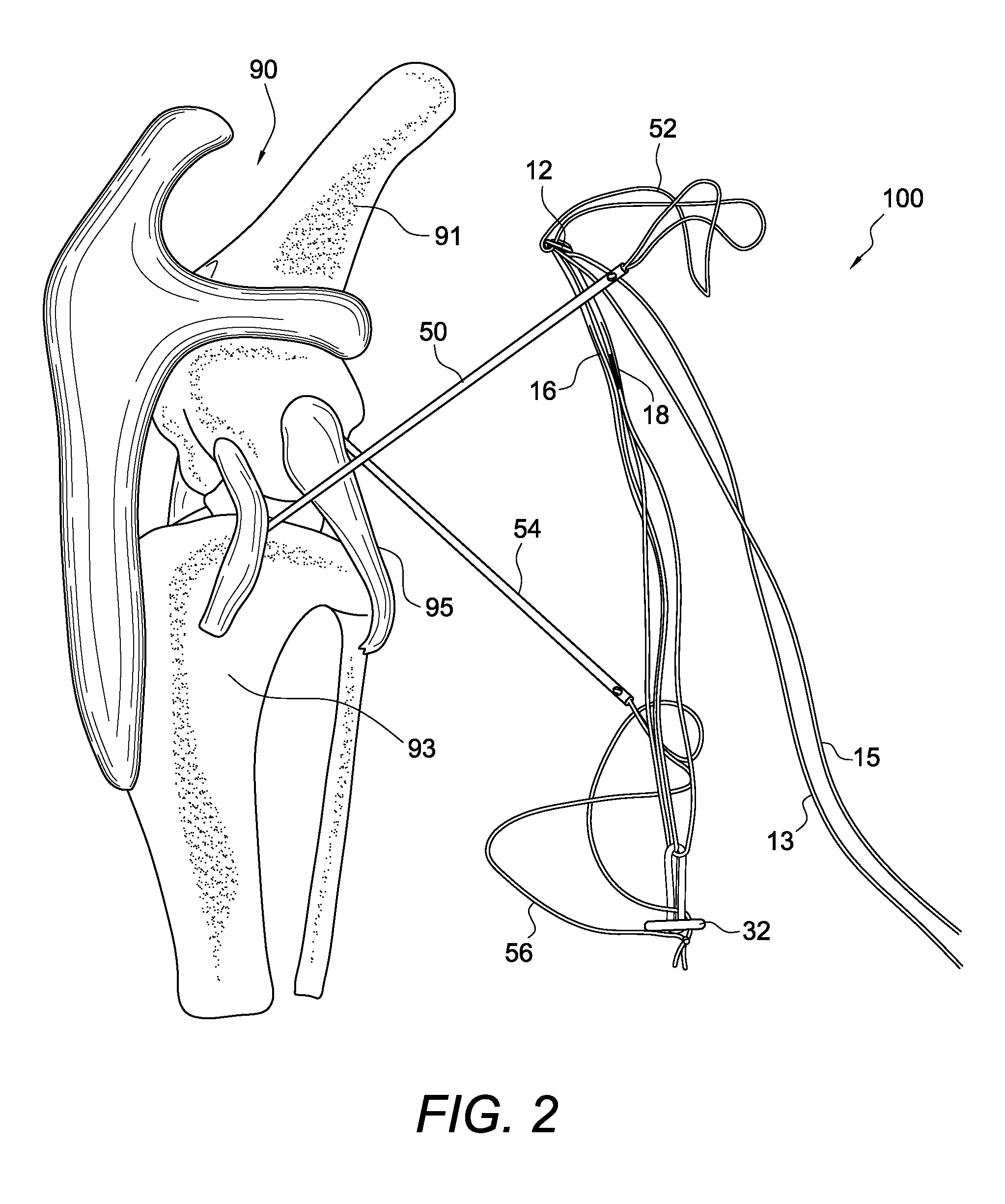

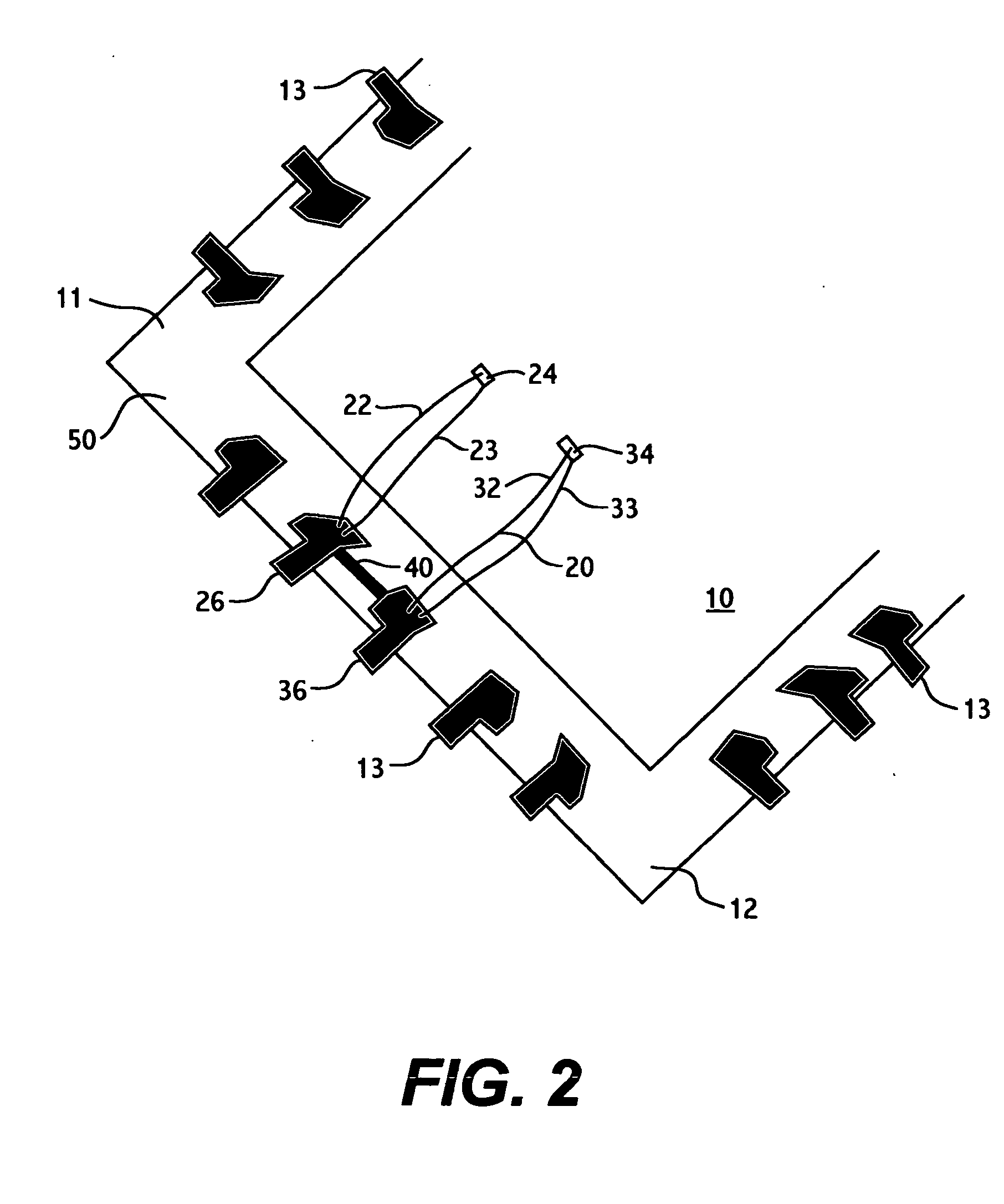

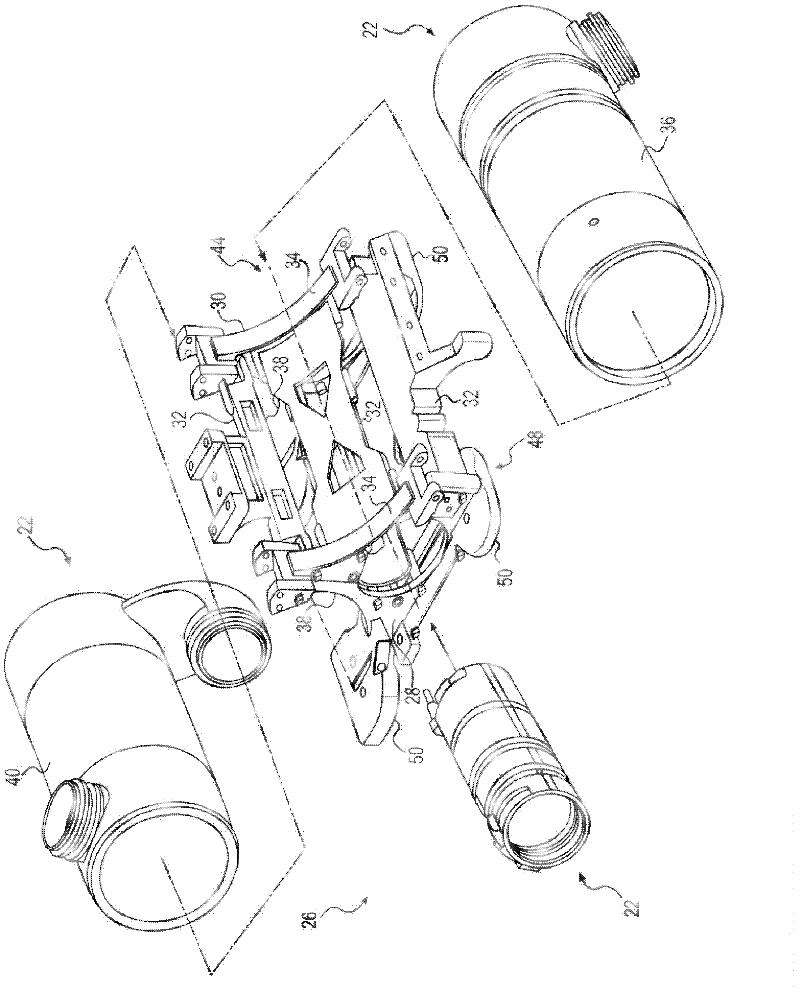

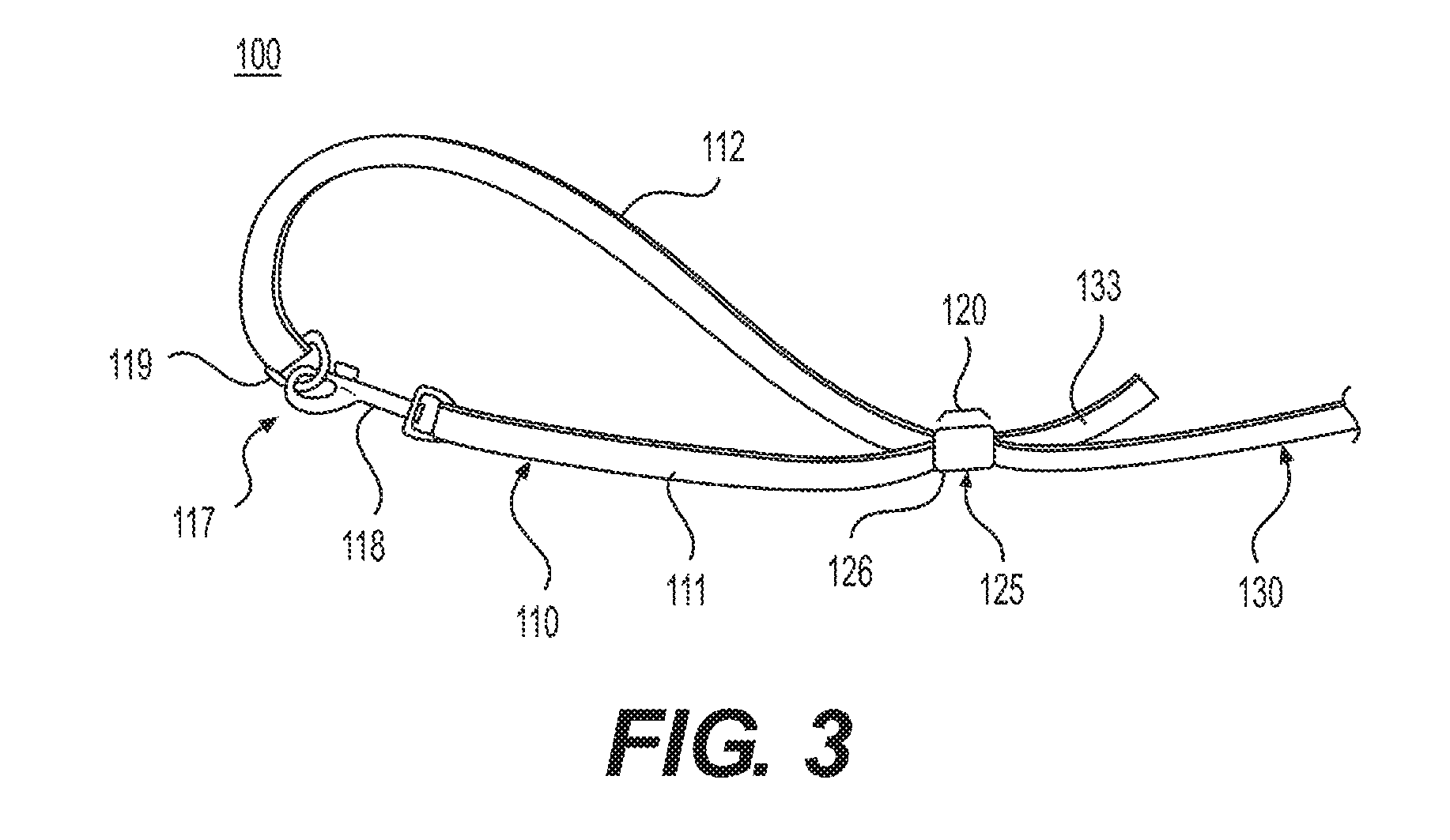

Adjustable suture-button construct for knotless stabilization of cranial cruciate deficient ligament stifle

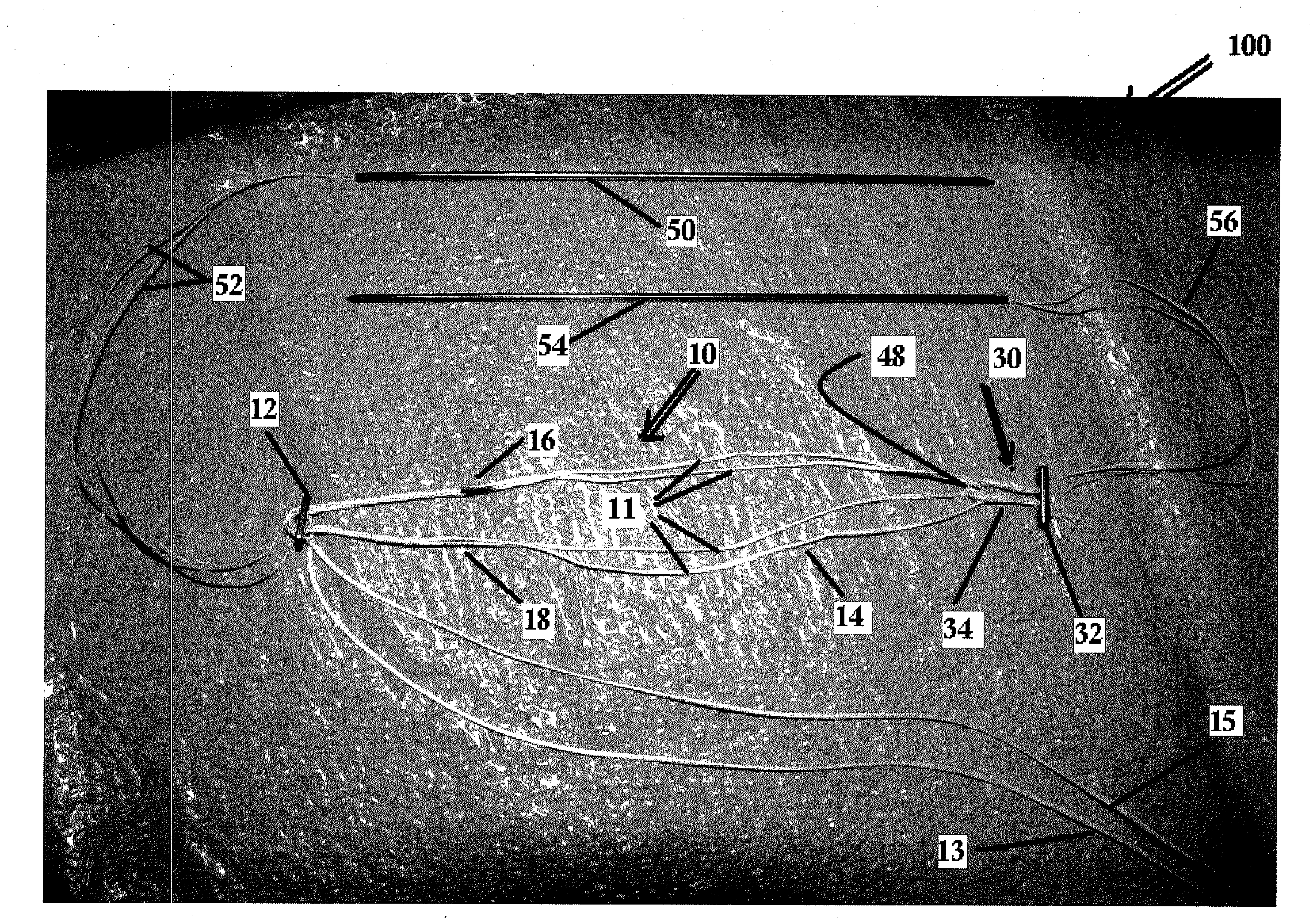

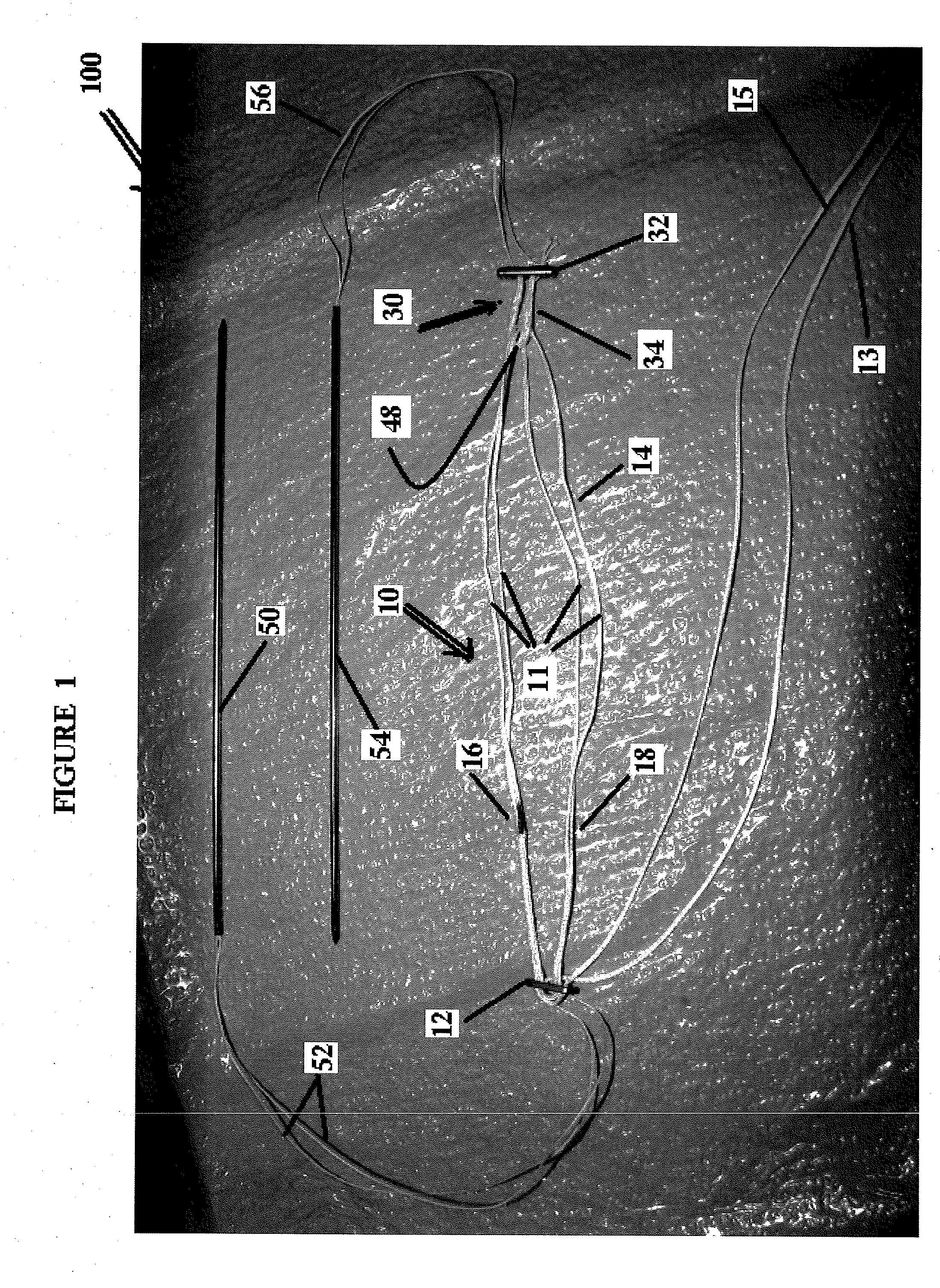

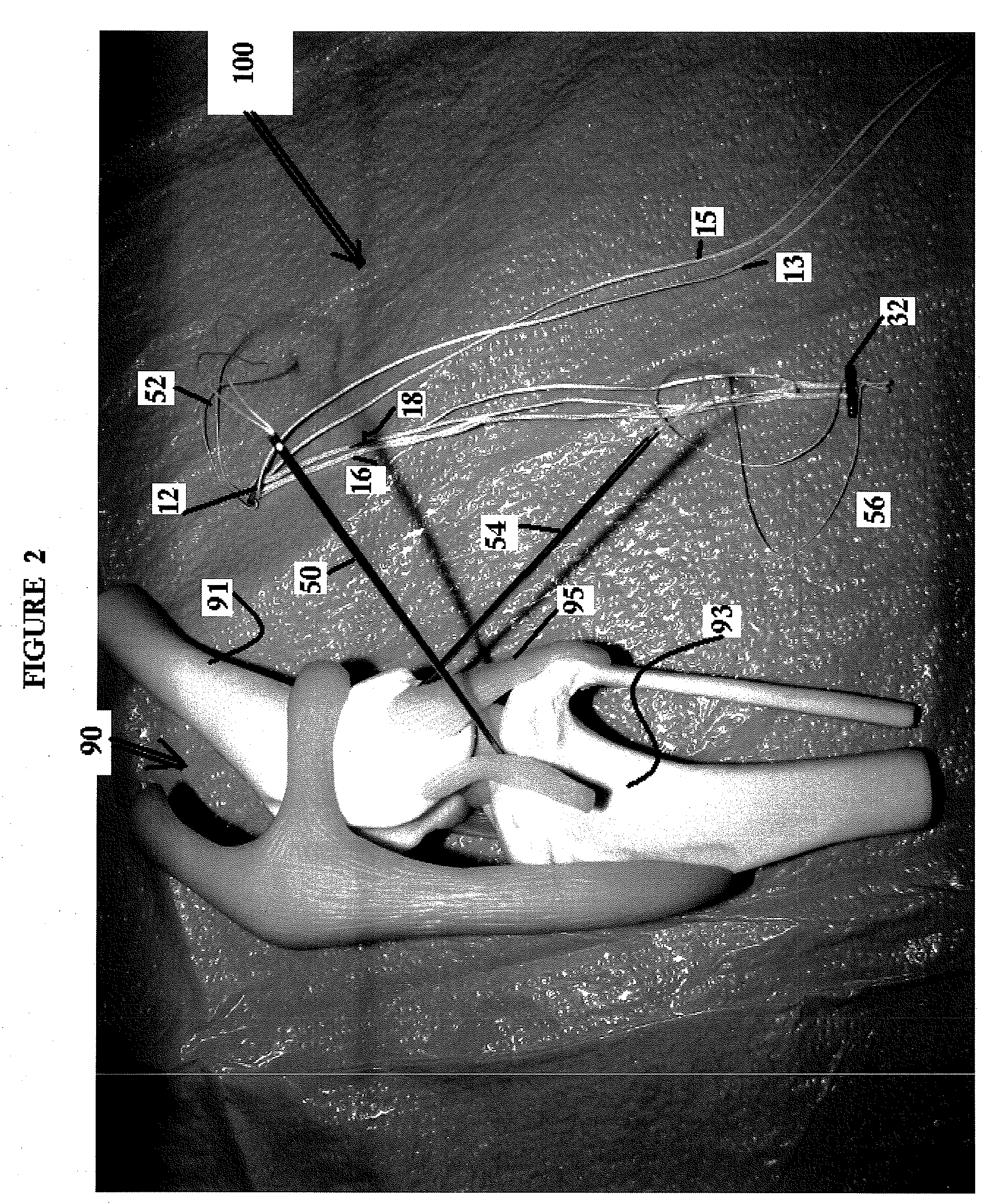

An adjustable, knotless button / loop / needle construct for fixation of cranial cruciate ligament deficient stifle. The adjustable, knotless construct includes two fixation devices (for example, two buttons), at least one flexible, adjustable loop attached to at least one of the fixation devices (e.g., the buttons), and two needles (each needle being attached to one fixation device, e.g., the buttons). The adjustable, knotless construct has an adjustable loop length and allows adjustment in one direction while preventing or locking the construct from loosening in the opposite direction, due to applied tensile forces. The construct and technique of the present invention provides an improved knotless system for cruciate ligament repair.

Owner:ARTHREX

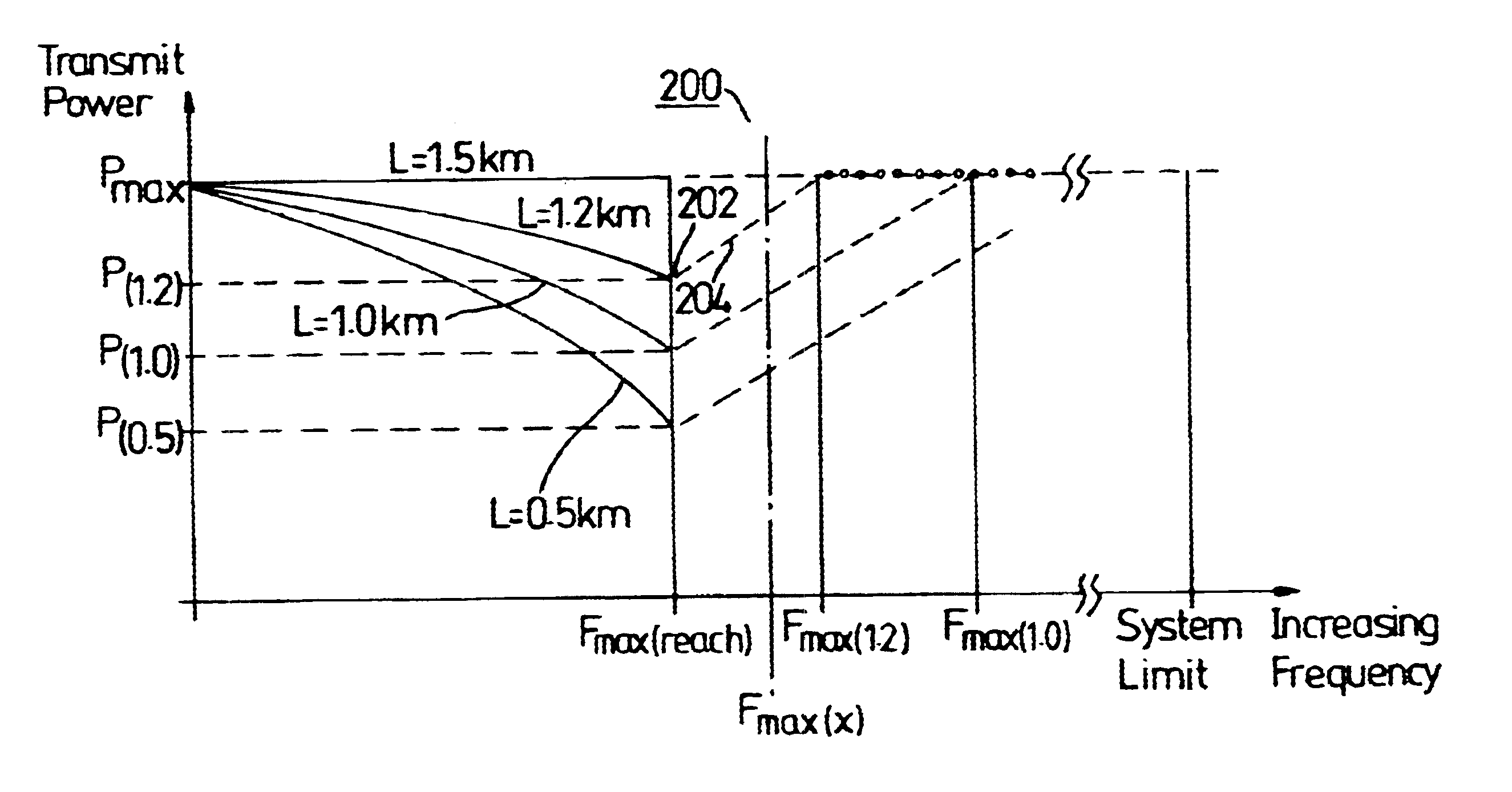

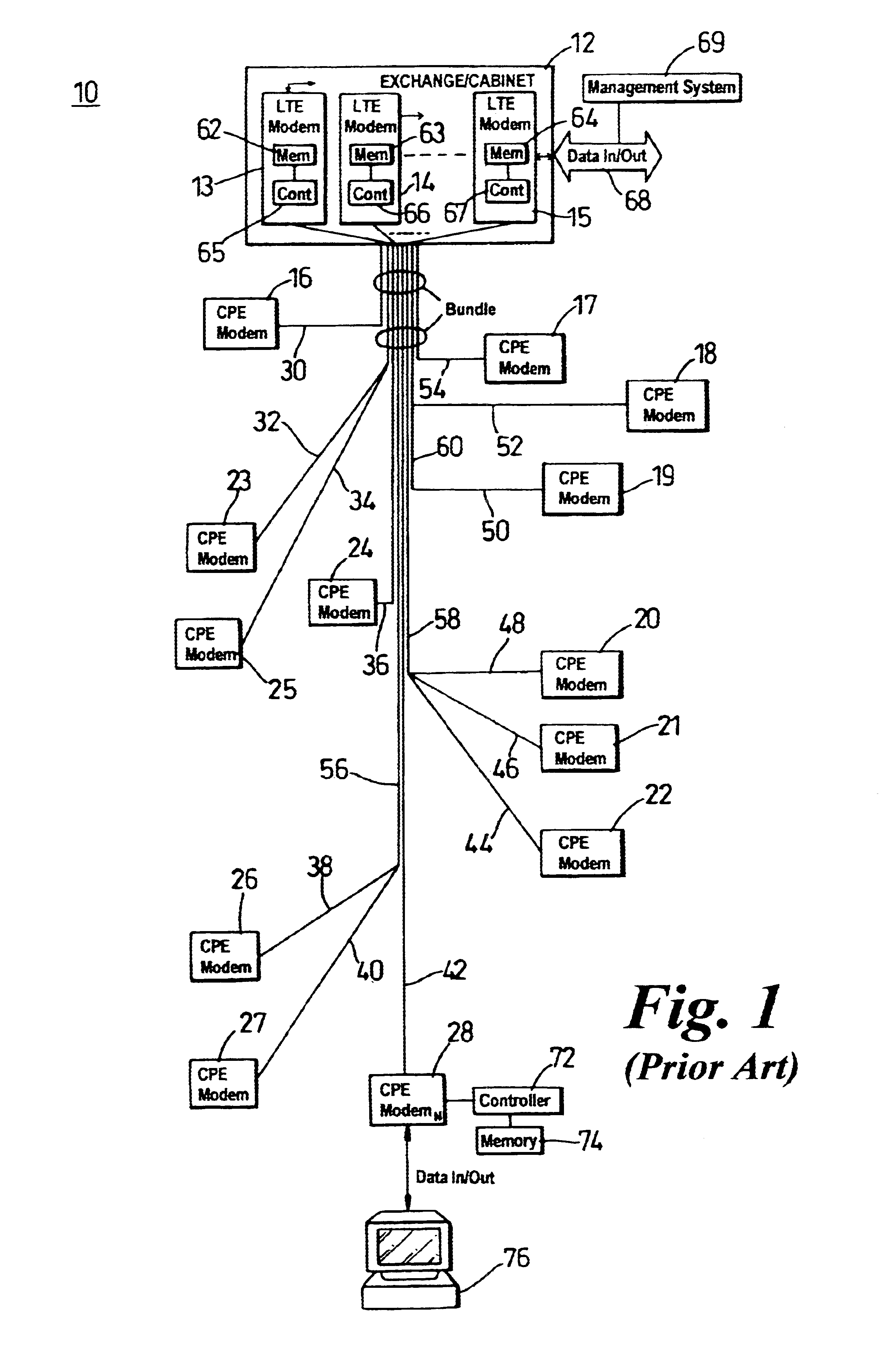

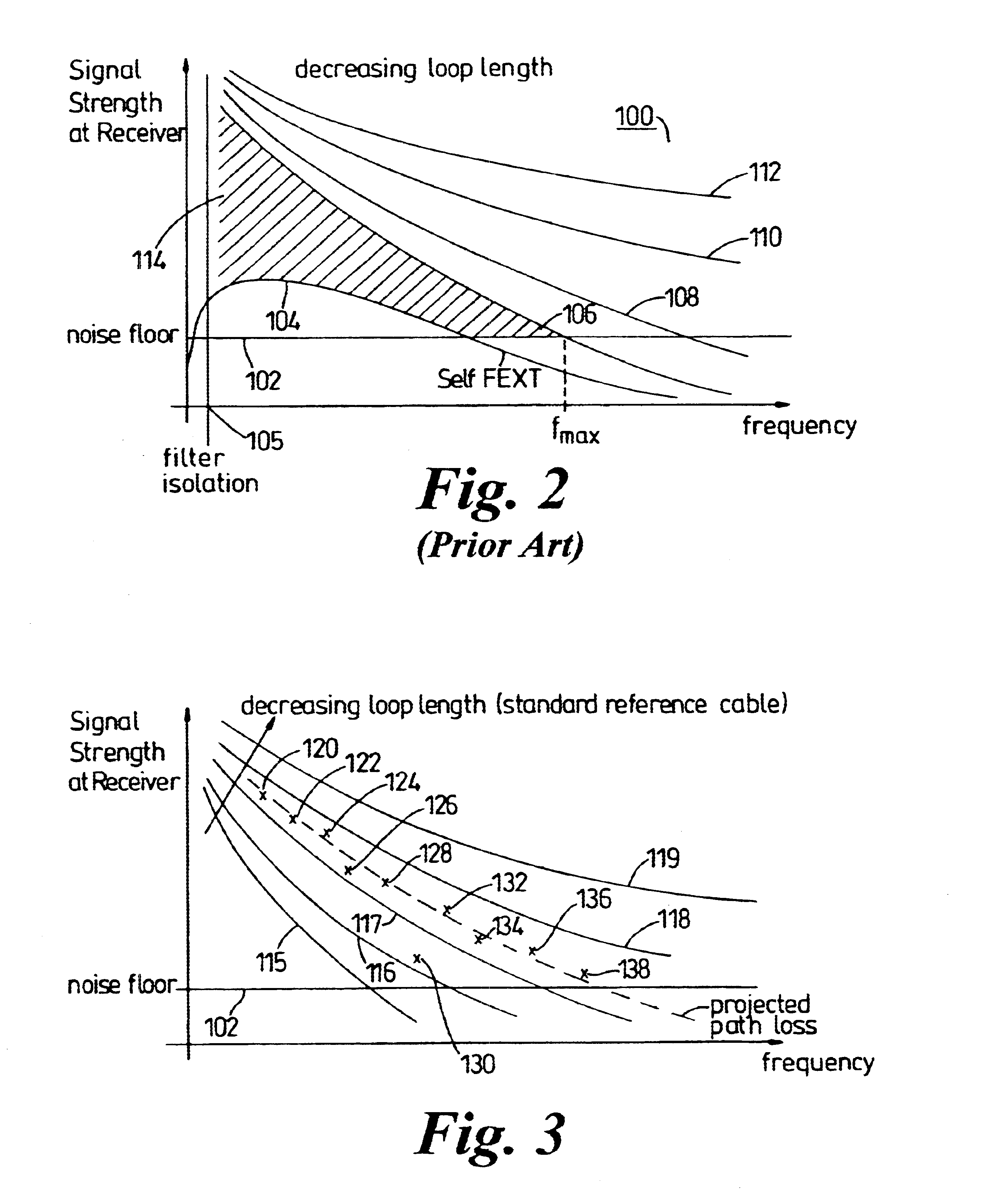

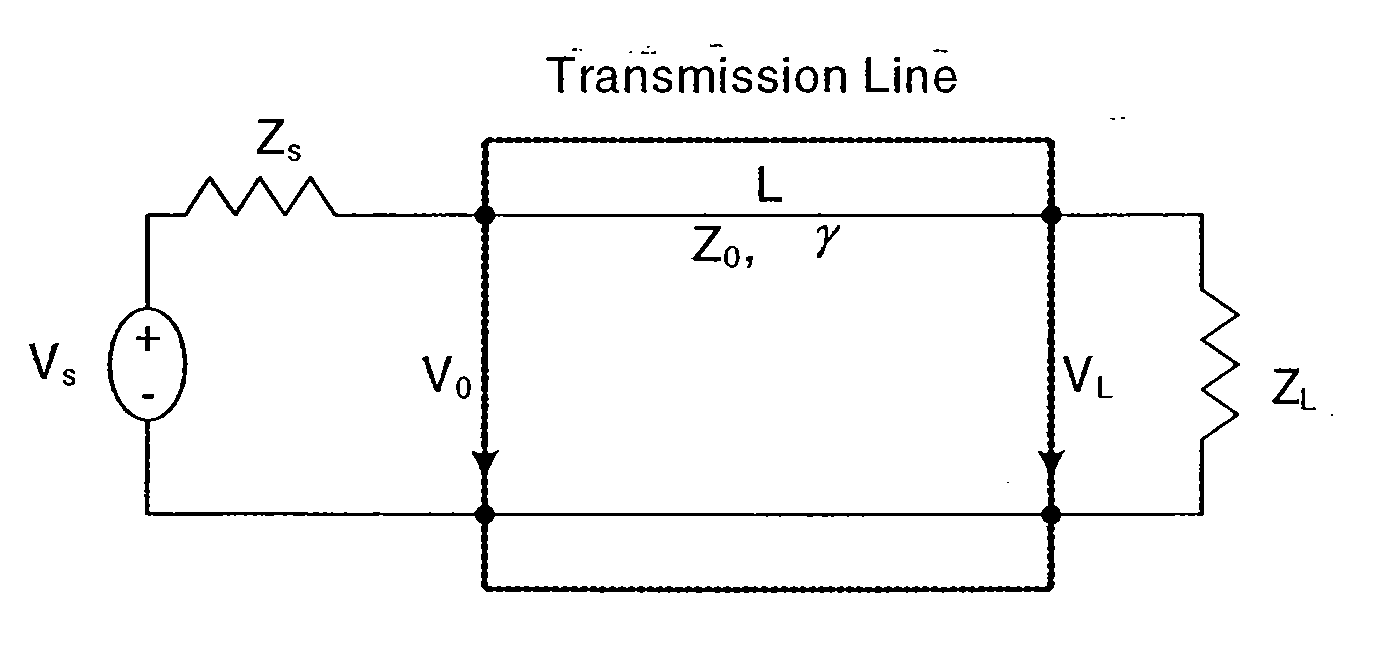

Wireline communication system and method of frequency allocation therein

InactiveUS6650697B1Reduce impactImprove performanceTelephonic communicationLink quality based transmission modificationModem deviceFrequency spectrum

To alleviate the requirement to back-off all up-link performance, such as by limiting power spectral density, to overcome far-end cross-talk problems otherwise associated with relatively short loop-length wireline links, the present invention partitions the frequency spectrum based on an estimate of the loop length of a subscriber unit (CPE) modem from an exchange (LTE) modem. Up to a threshold frequency (fmax) at which received transmissions from a subscriber having a longest loop length (115) become indistinguishable by the LTE modem from a noise floor (102), up-link performance on all loop lengths is limited to correspond to that of the longest loop. At frequencies above the threshold frequency (fmax), subsets of subscribers (152-154) having relatively short loop lengths (116-119) use high frequency carriers that have signal to noise ratios sufficient to support information transmission in these elevated frequency bands.

Owner:NORTEL NETWORKS LTD

Adjustable suture-button construct for knotless stabilization of cranial cruciate deficient ligament stifle

An adjustable, knotless button / loop / needle construct for fixation of cranial cruciate ligament deficient stifle. The adjustable, knotless construct includes two fixation devices (for example, two buttons), at least one flexible, adjustable loop attached to at least one of the fixation devices (e.g., the buttons), and two needles (each needle being attached to one fixation device, e.g., the buttons). The adjustable, knotless construct has an adjustable loop length and allows adjustment in one direction while preventing or locking the construct from loosening in the opposite direction, due to applied tensile forces. The construct and technique of the present invention provides an improved knotless system for cruciate ligament repair.

Owner:ARTHREX

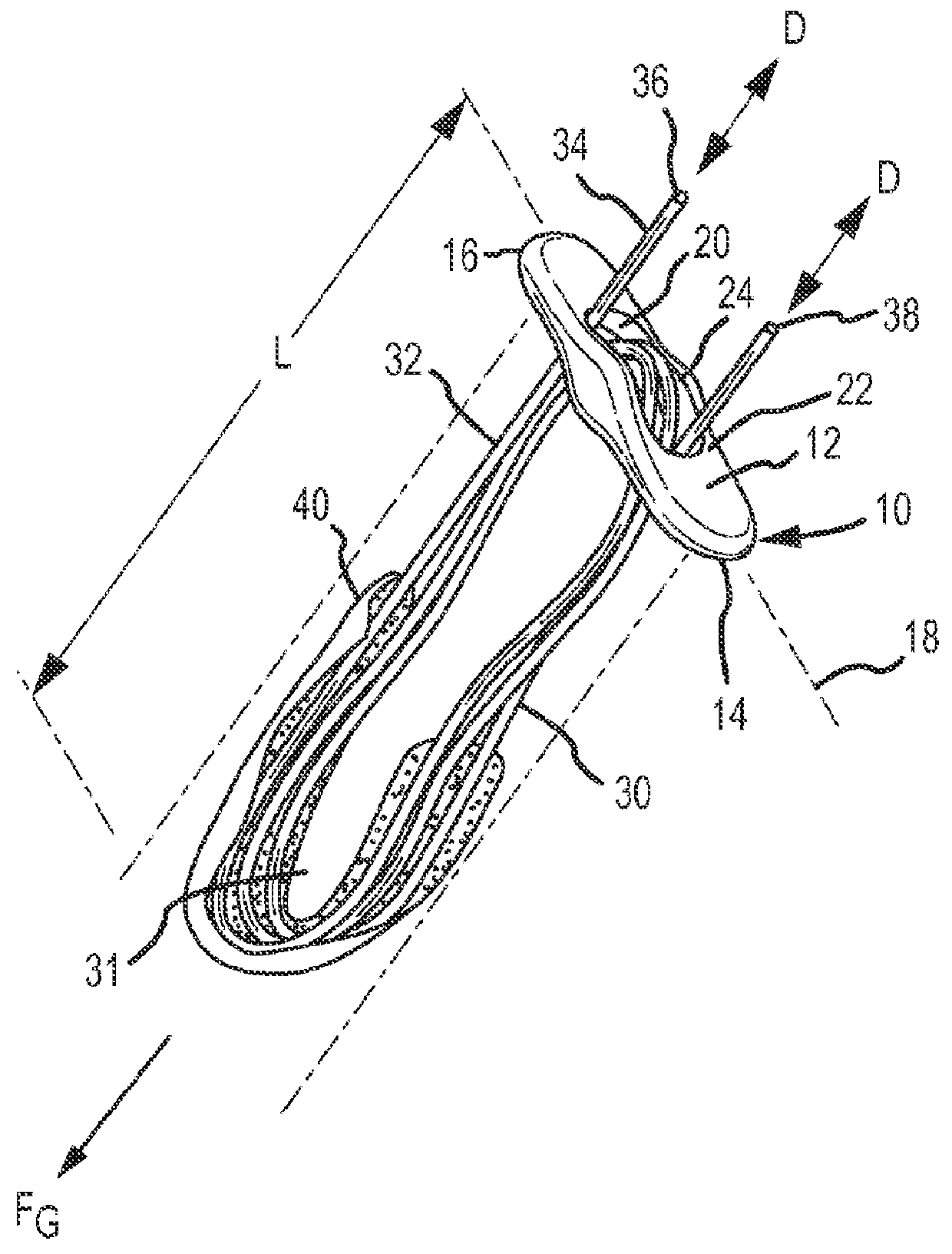

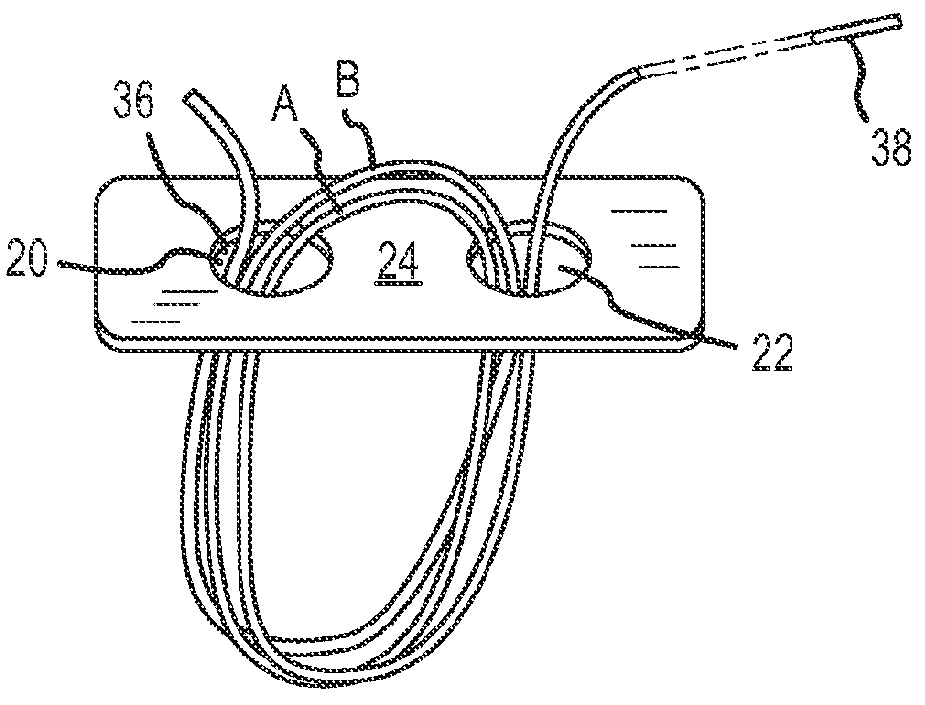

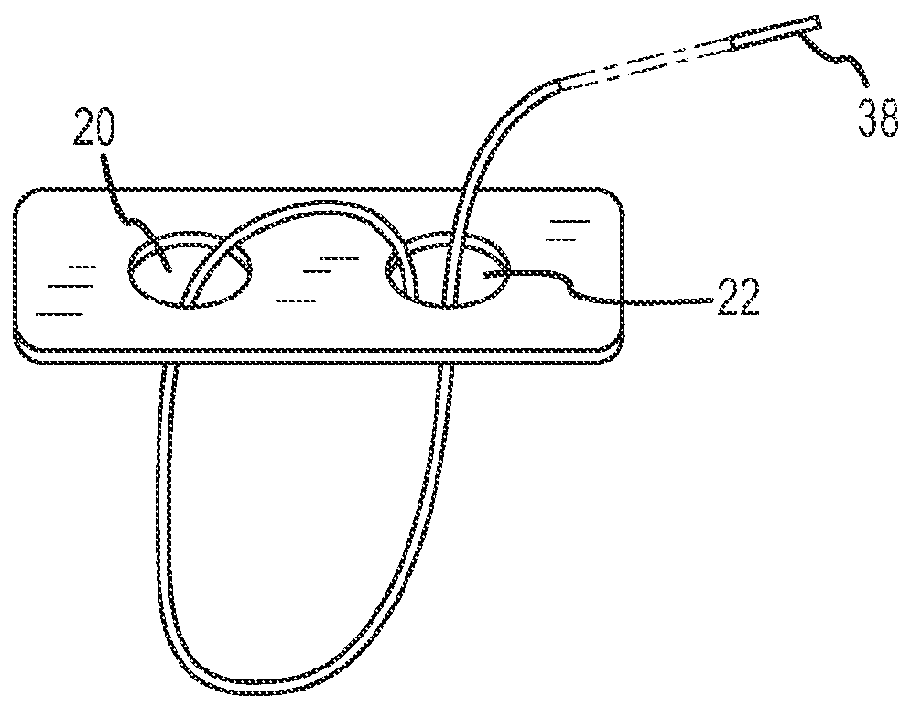

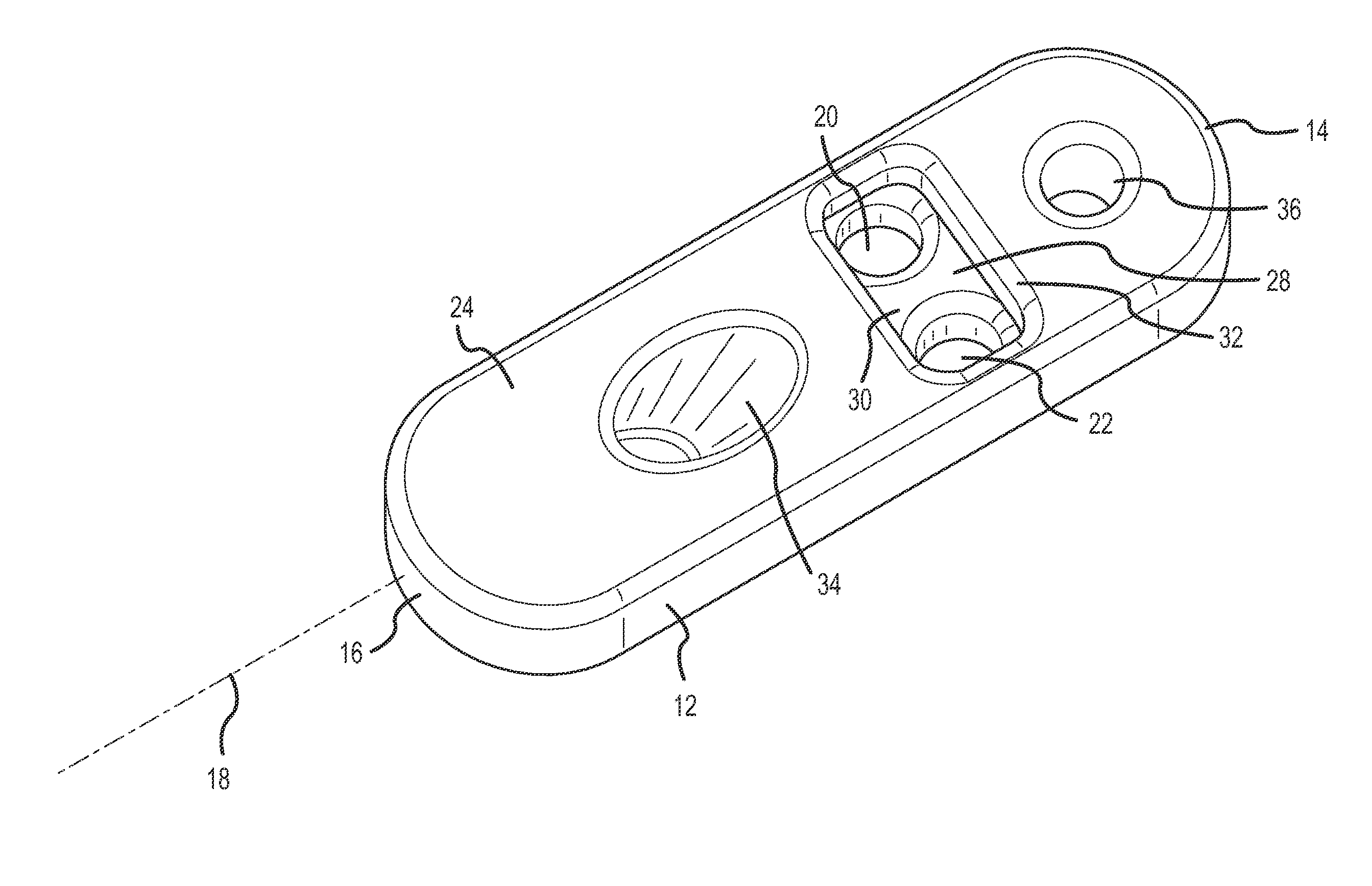

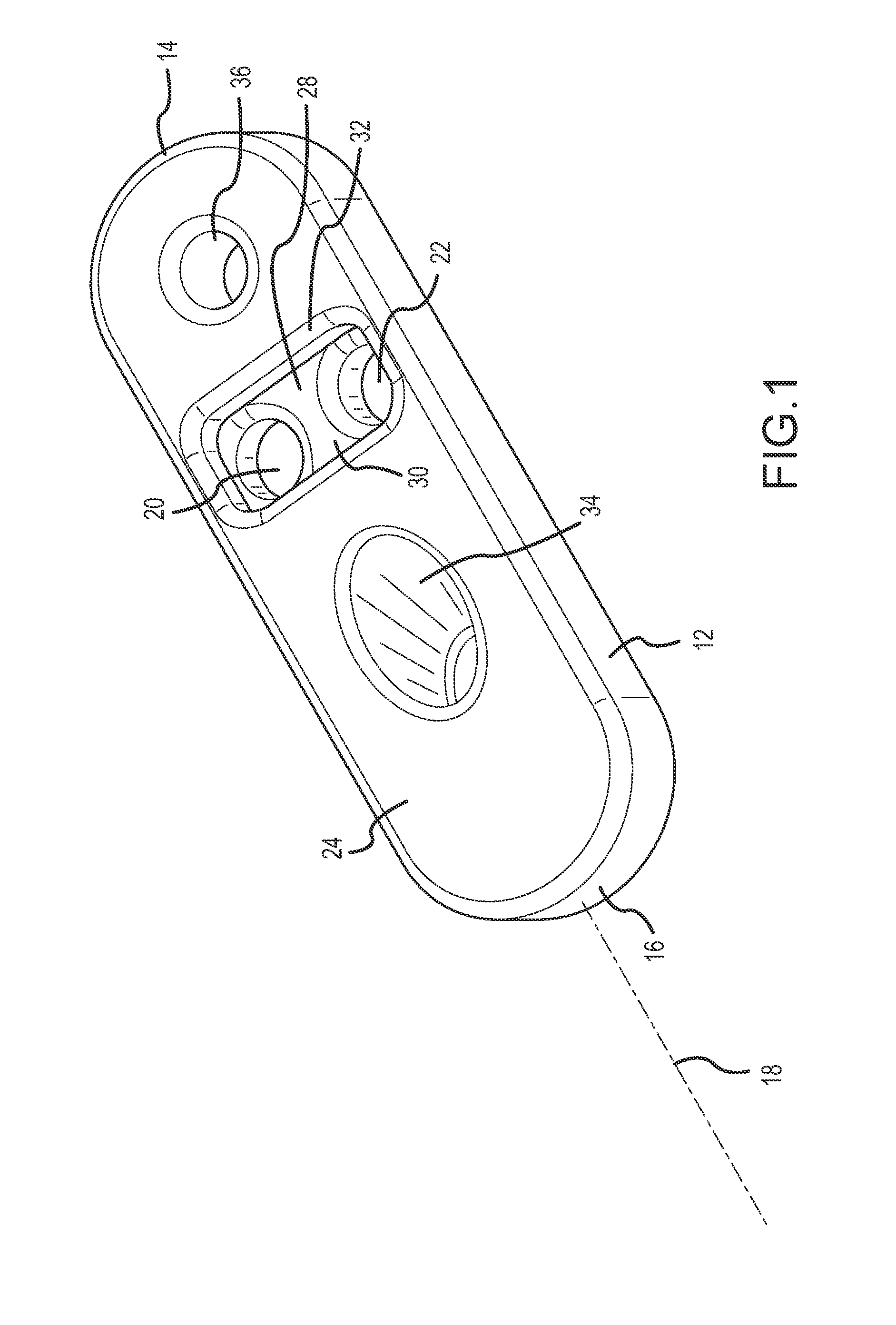

Suspensory graft fixation with adjustable loop length

InactiveUS20120109194A1Reduce loop lengthShorten the lengthSuture equipmentsLigamentsBone tunnelLoop length

A suspensory graft ligament fixation device is shown to be particularly suitable for maximizing the contact between a soft tissue graft and the bone tunnel prepared to receive the graft. The suspensory fixation device has an elongated anchor member adapted to be transversely situated at the exit of the bone tunnel. A loop member is suspended transversely from the anchor member and has a loop length which is adjustable. When a graft ligament is attached to the saddle end of the loop, the length of the loop member may be shortened to pull the graft member into the bone tunnel until it bottoms out at the floor of the bone tunnel.

Owner:LINVATEC

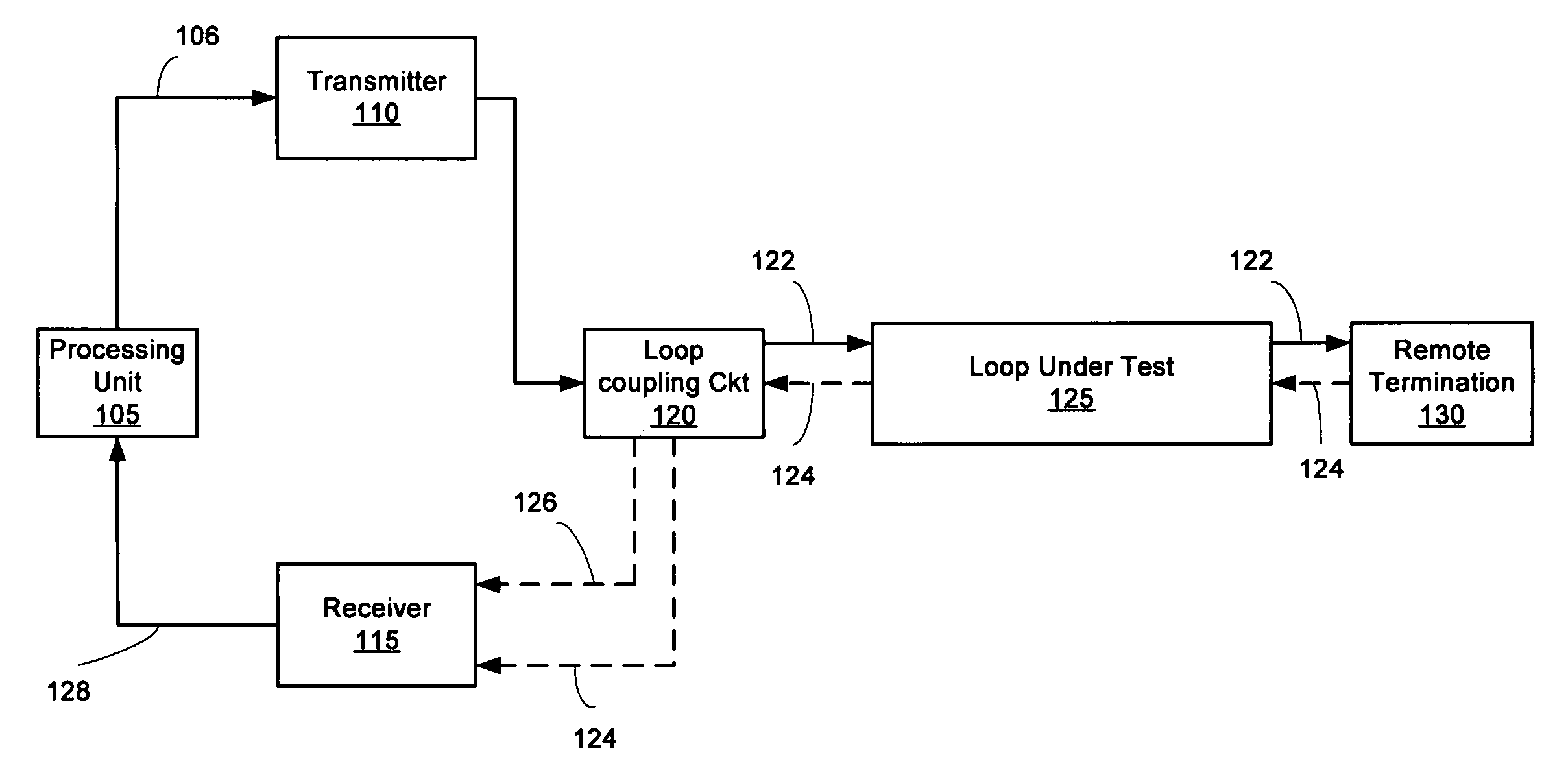

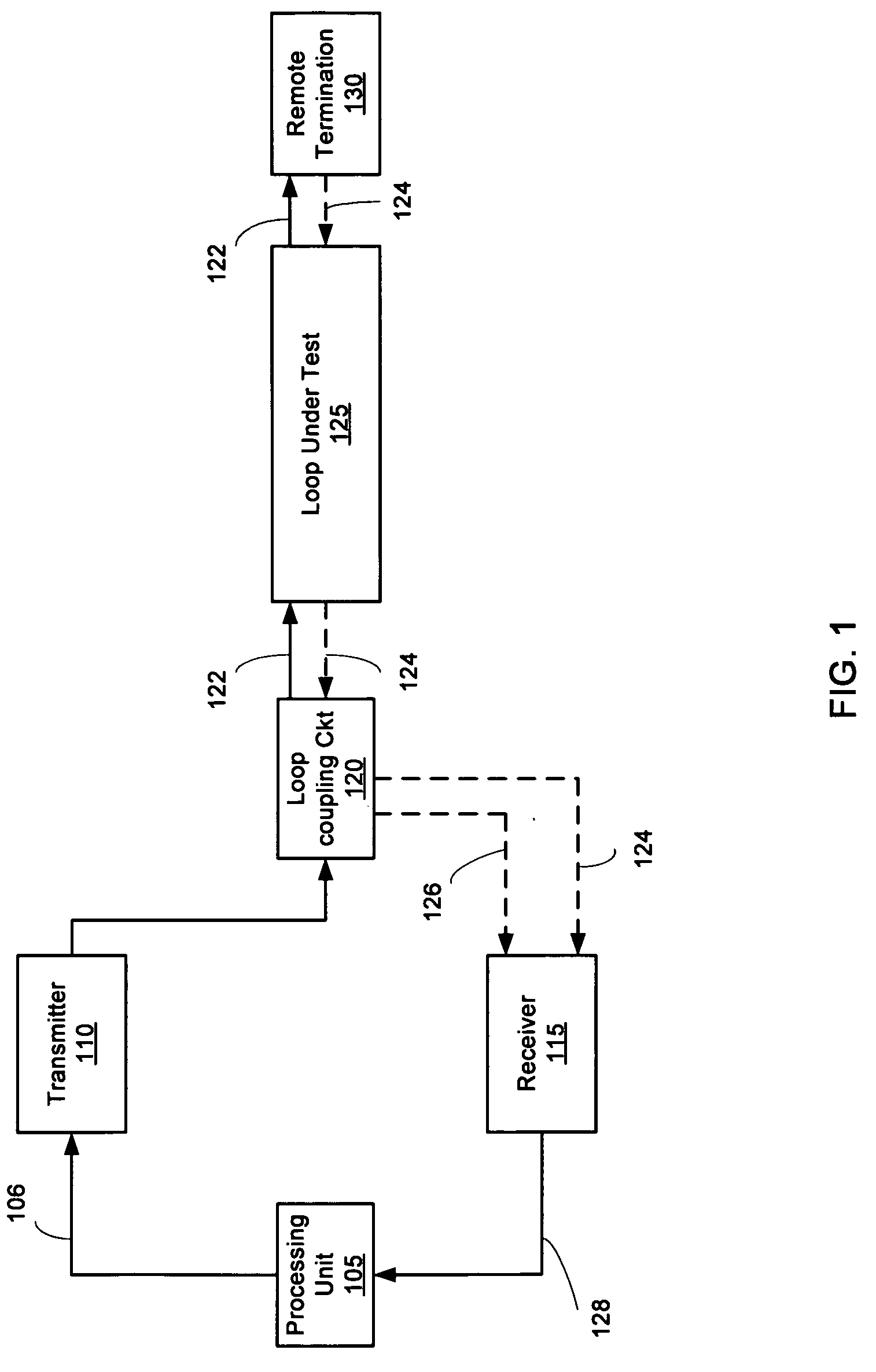

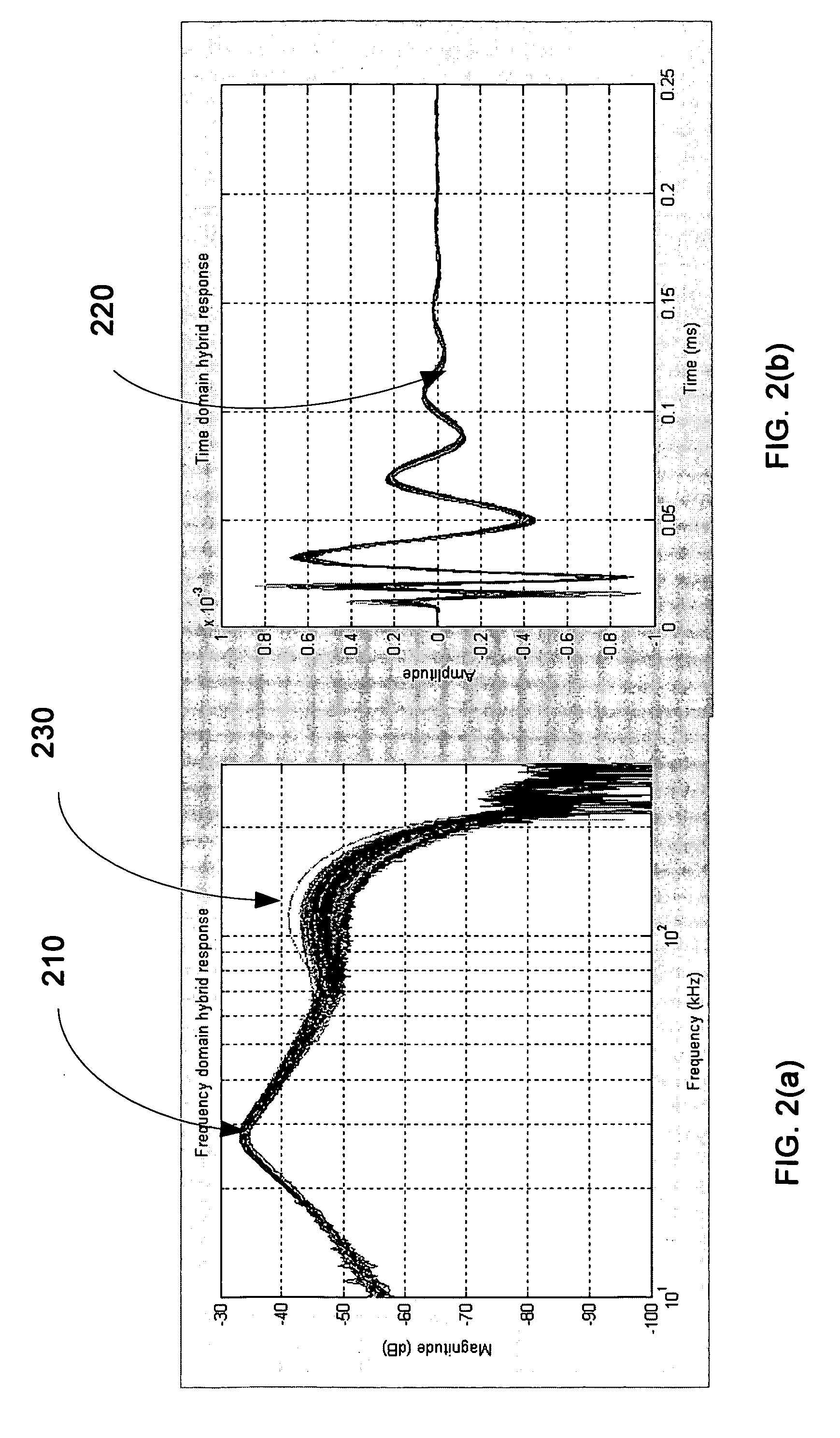

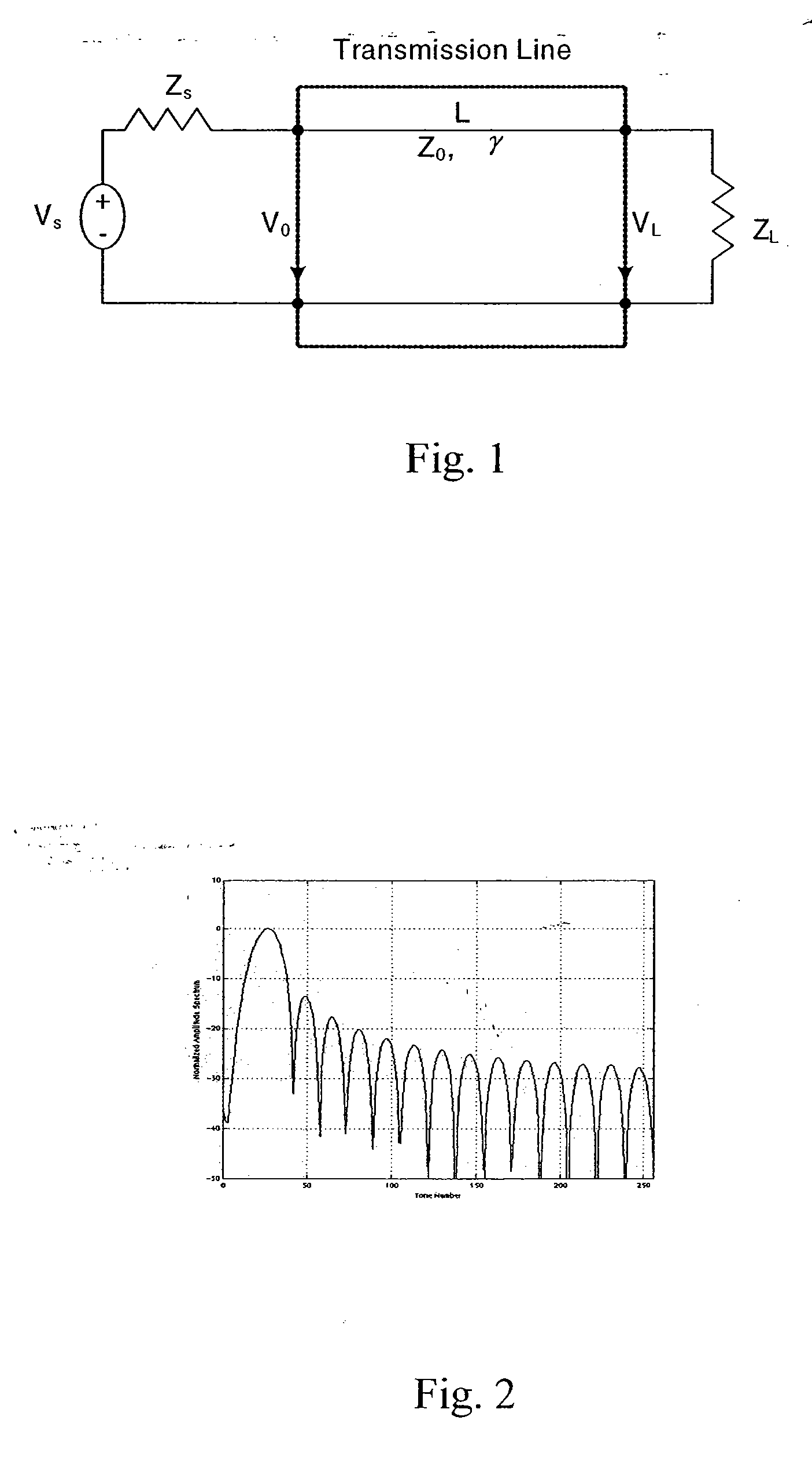

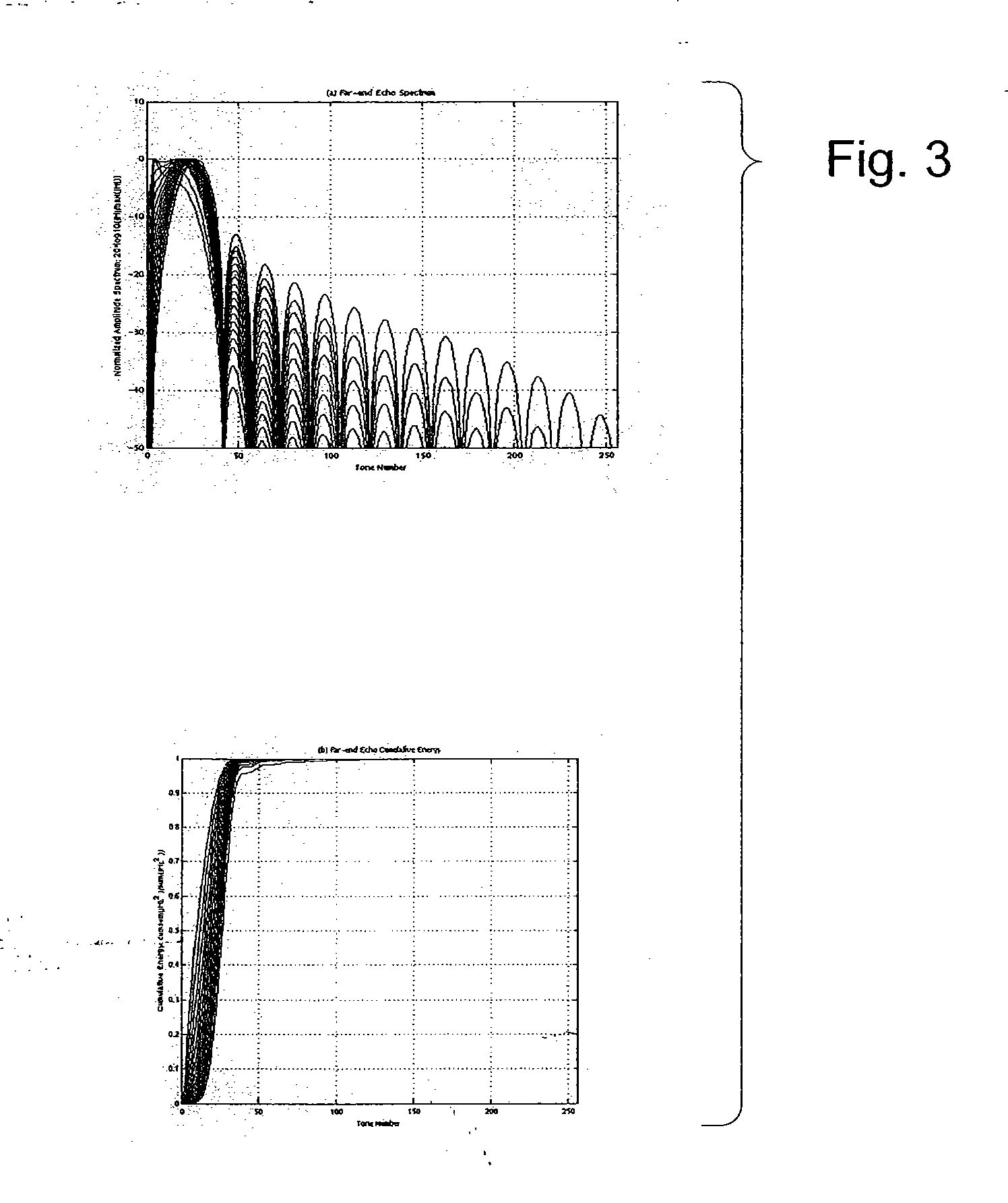

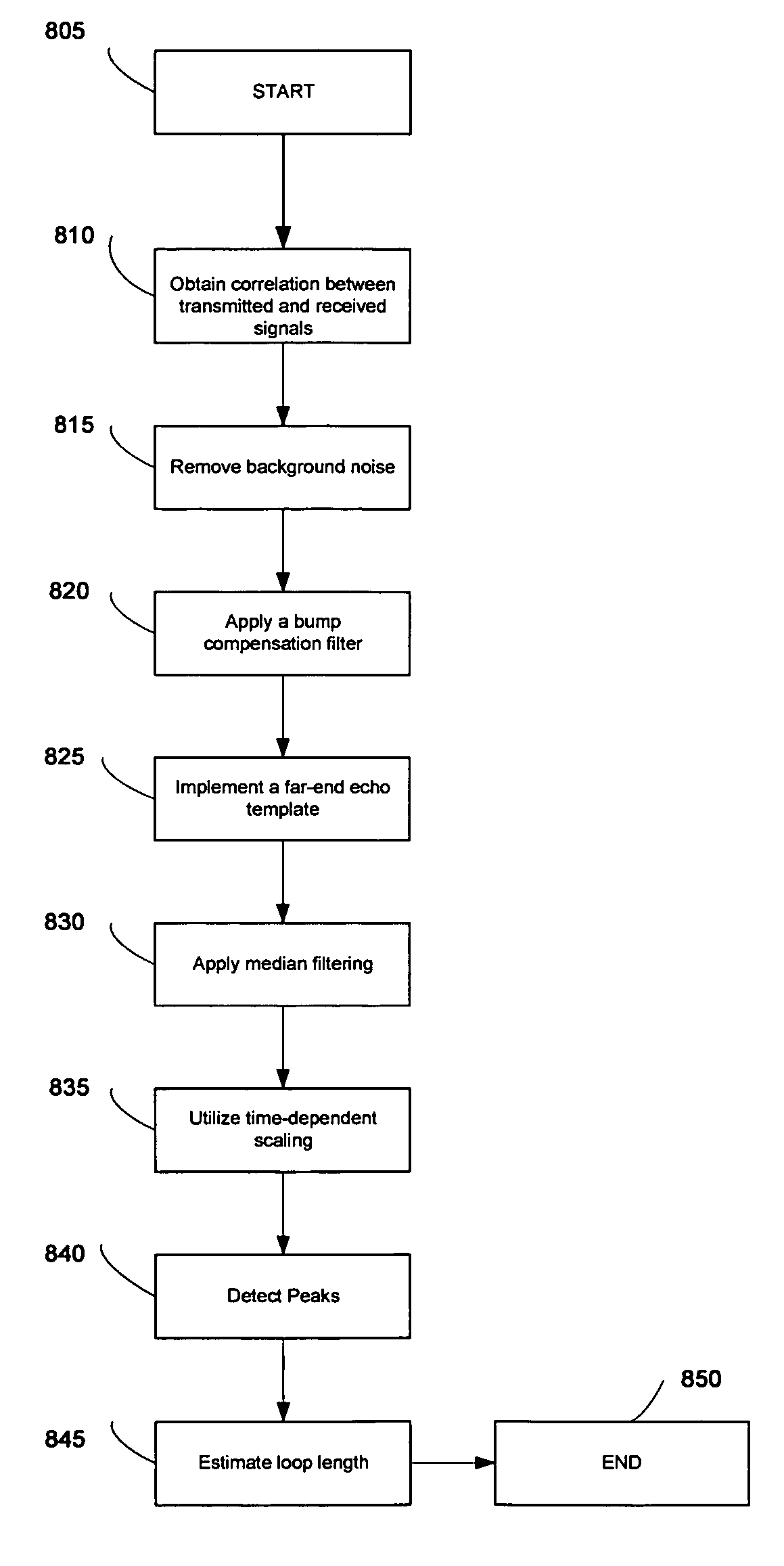

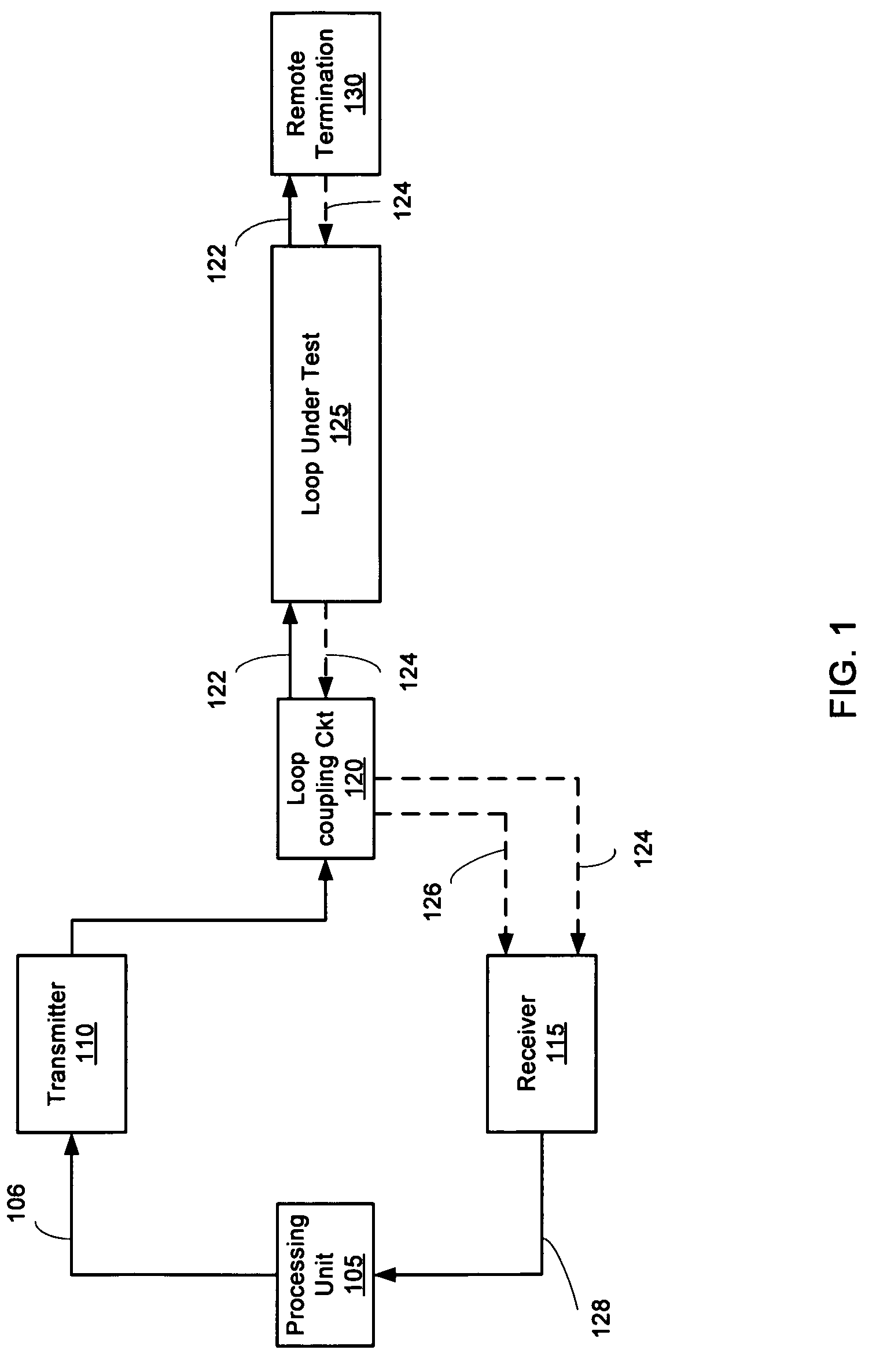

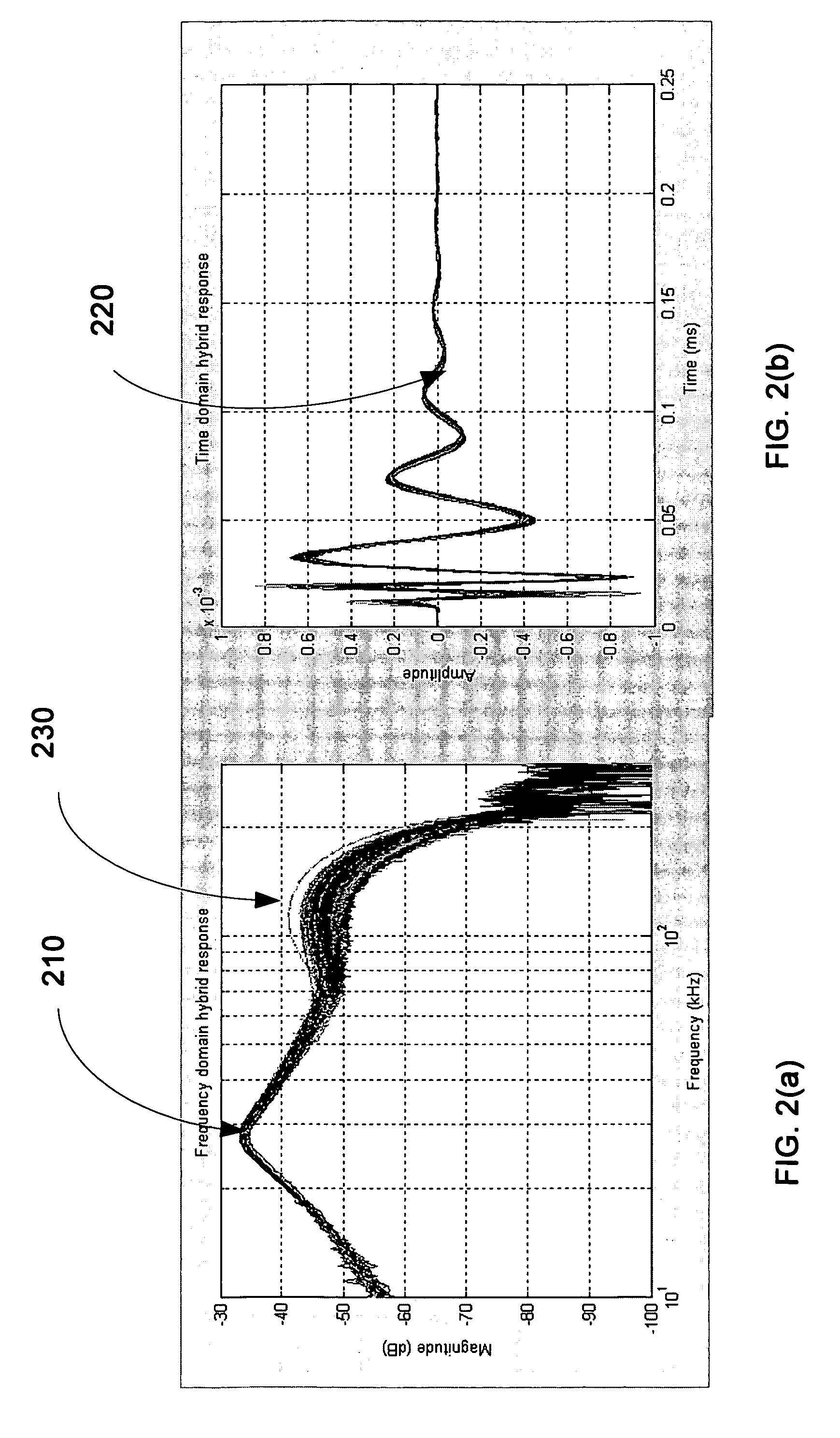

Method and apparatus for single end loop testing for DSL provisioning and maintenance

InactiveUS20050163287A1Simple and robust in applicationReduce near-end echoSupervisory/monitoring/testing arrangementsSubstation equipmentDigital signal processingLoop length

A method and apparatus for single end loop testing for DSL provisioning and maintenance provides testing of the DSL loop using digital techniques including frequency compensation, matched filtering and median filtering, to remove strong background and enhance desired signal for peak detection. The SELT system allows DSL providers to extract loop information from reflective measurements at the central office (CO) so as to determine loop capability of supporting different DSL services. The method and apparatus acquires the desired signal (the far-end echo) which is submerged in the correlated background noise (the near-end echo) by providing a process for detecting loop length and termination types with high accuracy for loops up to 12 kft for 24 AWG and up to 9 kft for 26 AWG by exploiting several digital signal processing techniques including frequency.

Owner:IKANOS COMMUNICATIONS

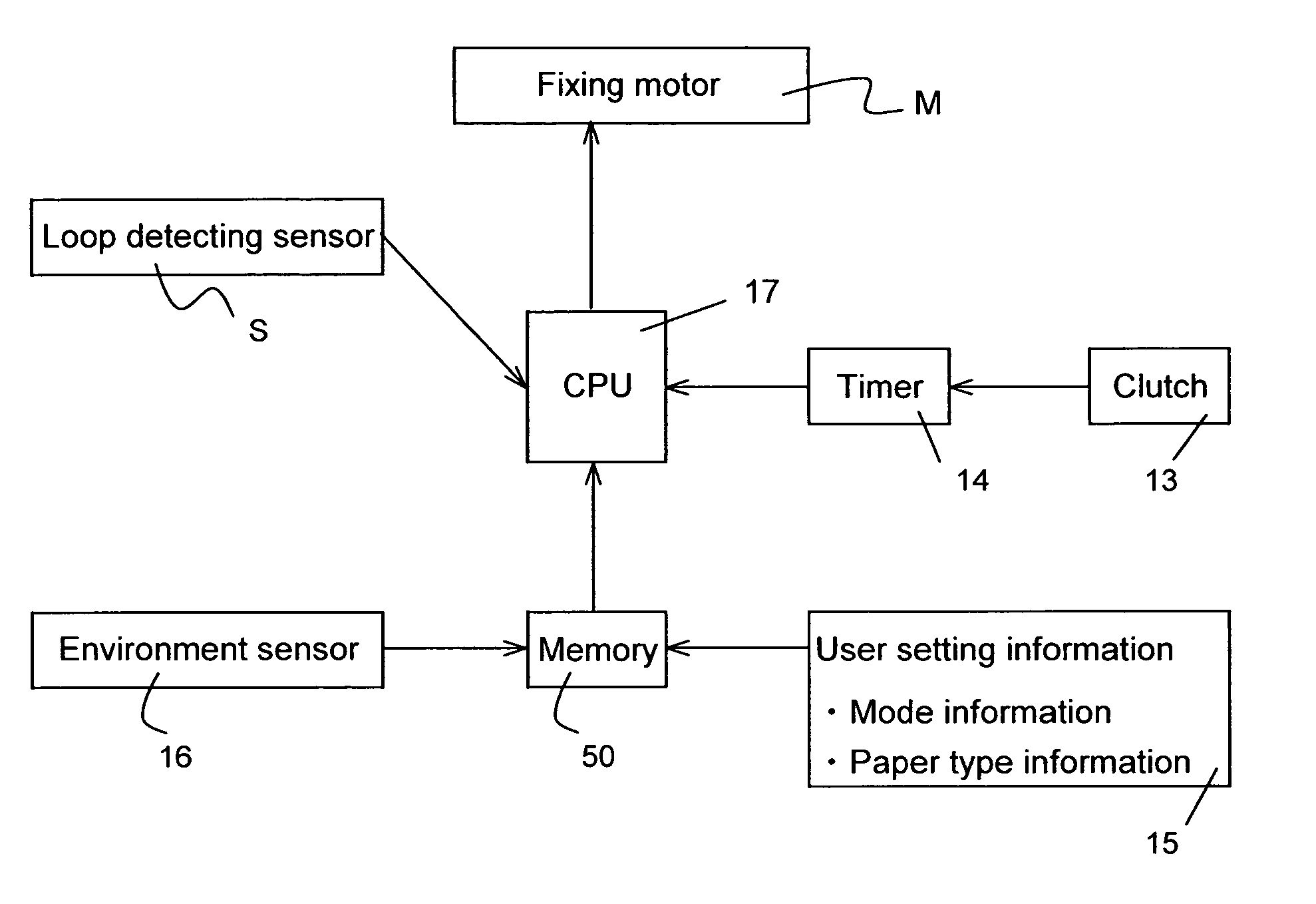

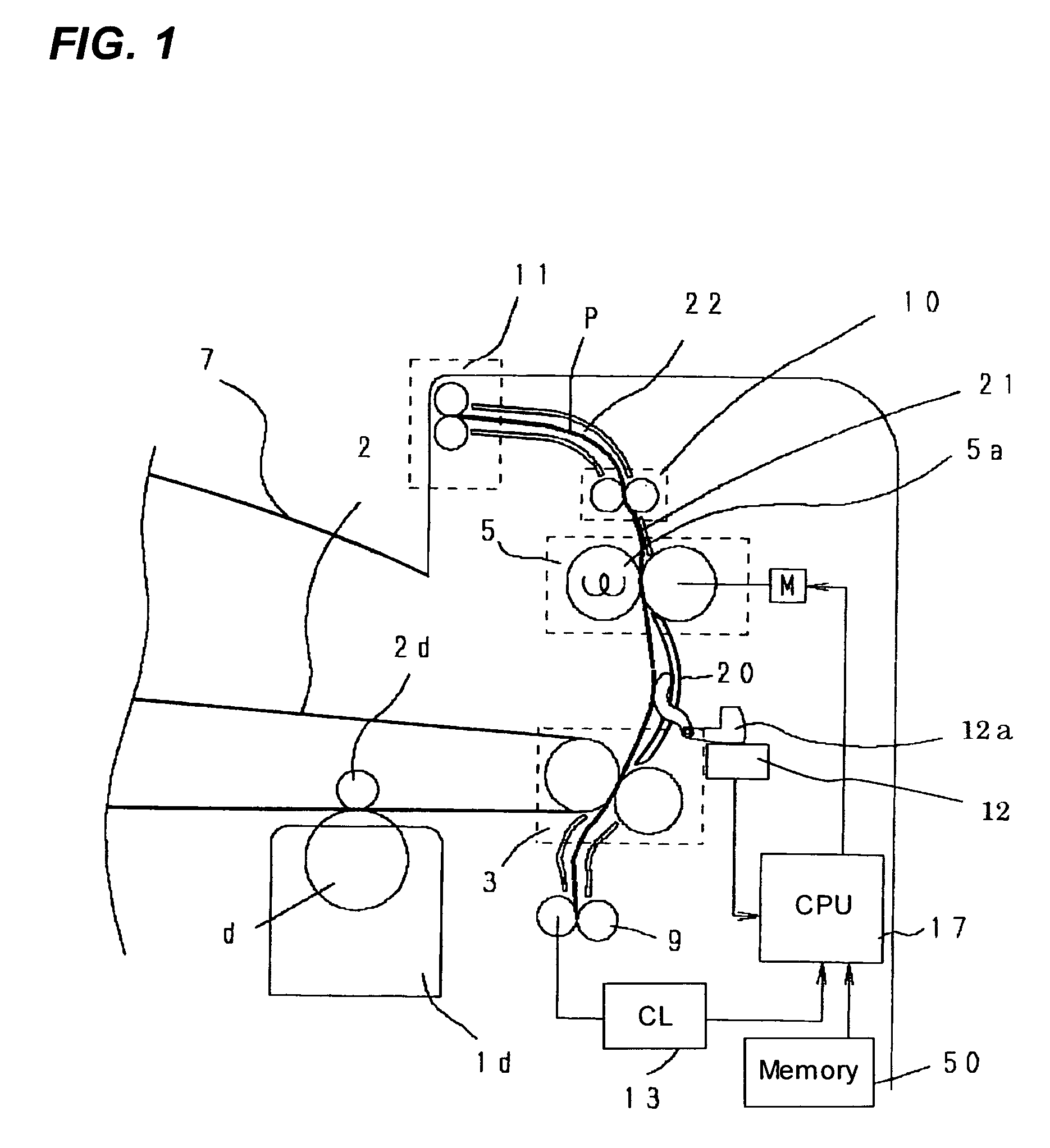

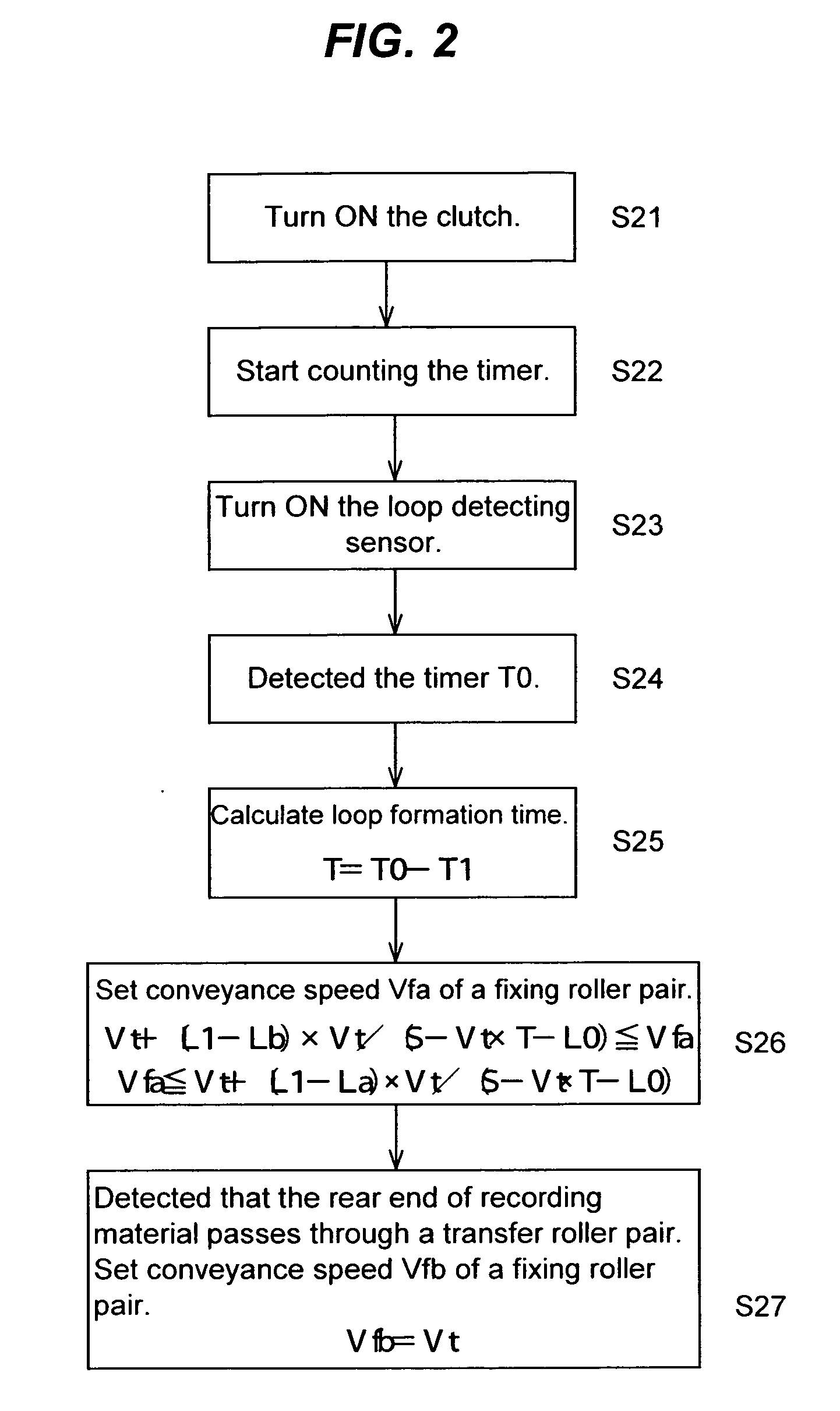

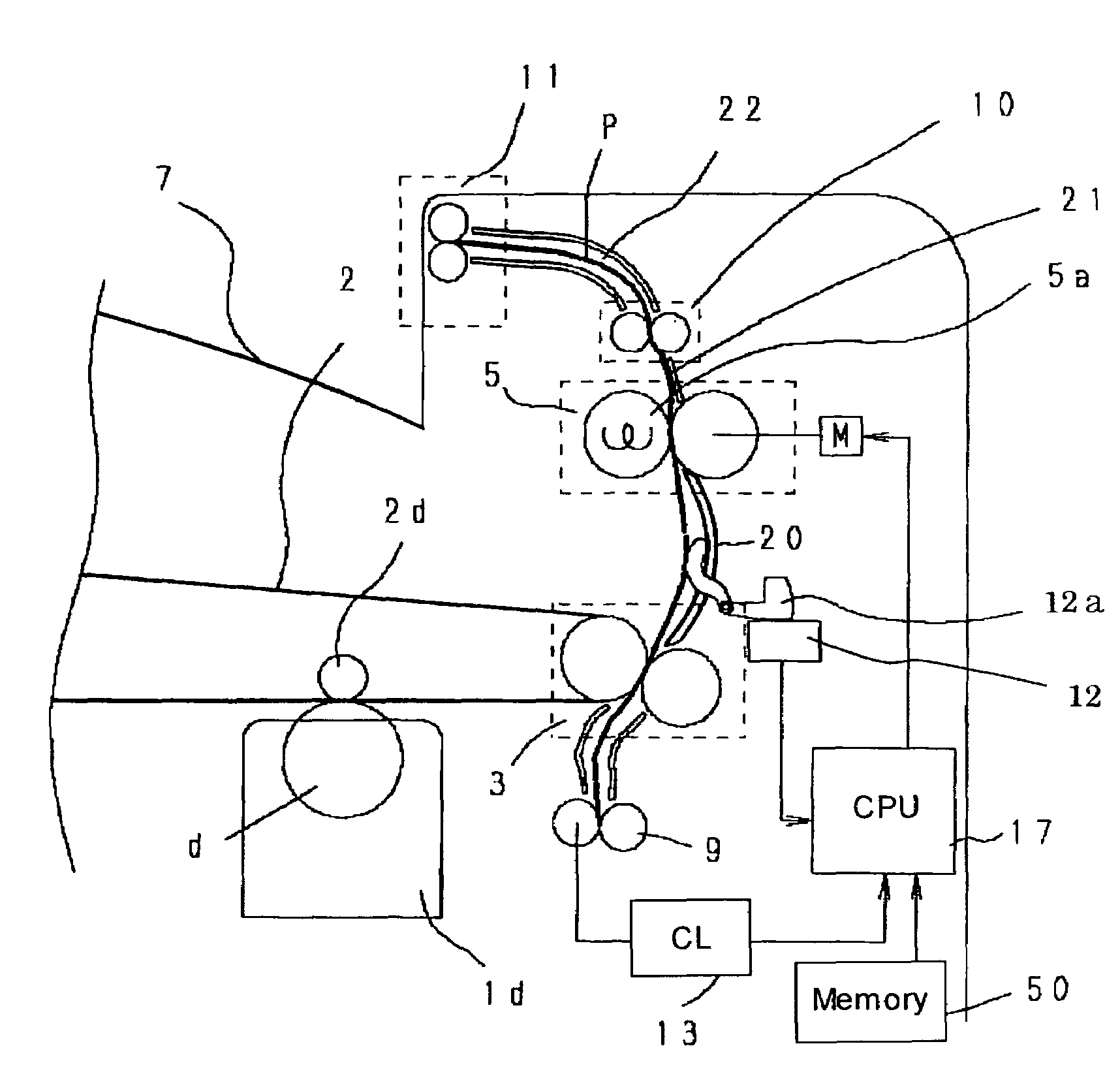

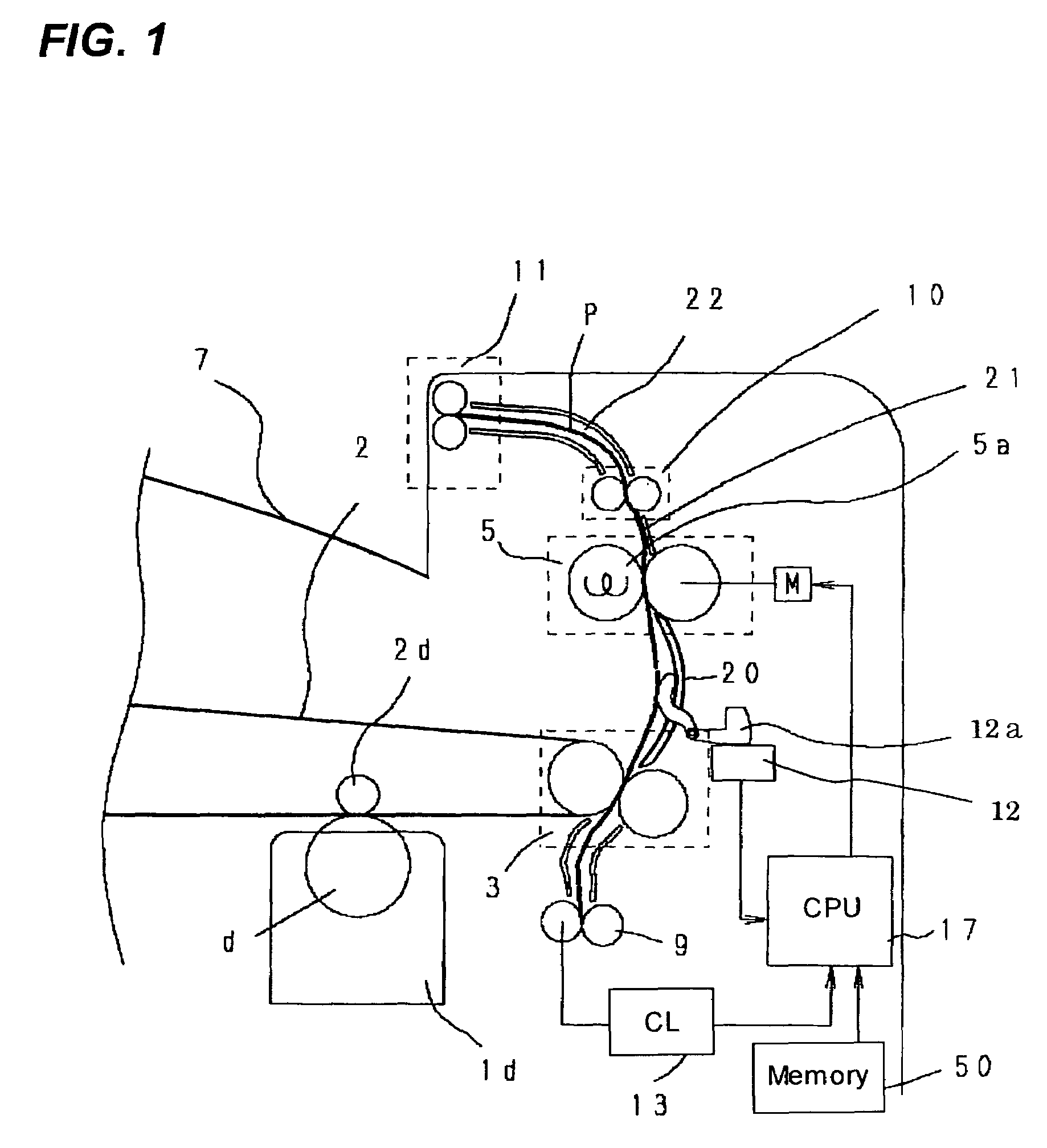

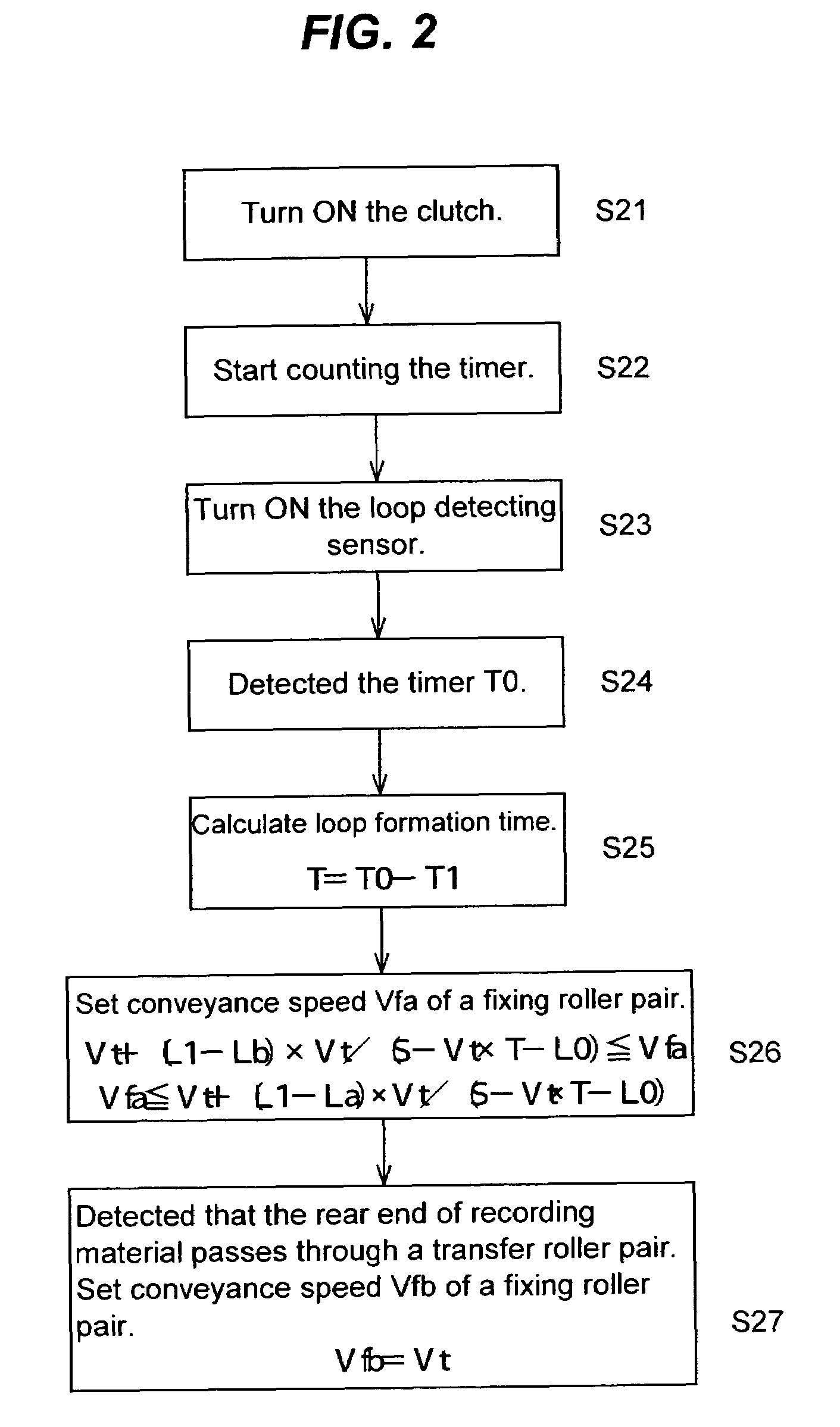

Image forming apparatus

InactiveUS20060222386A1Reduce generationPrevent image deteriorationElectrographic process apparatusLower limitLoop length

Conveyance speed of recording materials by a fixing roller pair can be set to conveyance speed based on detected results of a recording material detection means and a loop detecting sensor, and information on the recording material that has been stored in a memory in advance, wherein the conveyance speed of the fixing roller pair is set so that loop length of the recording material will be a lower limit length, after the loop detecting sensor detects a loop of the recording material, and before the rear end of the recording material passes through the transfer roller pair.

Owner:CANON KK

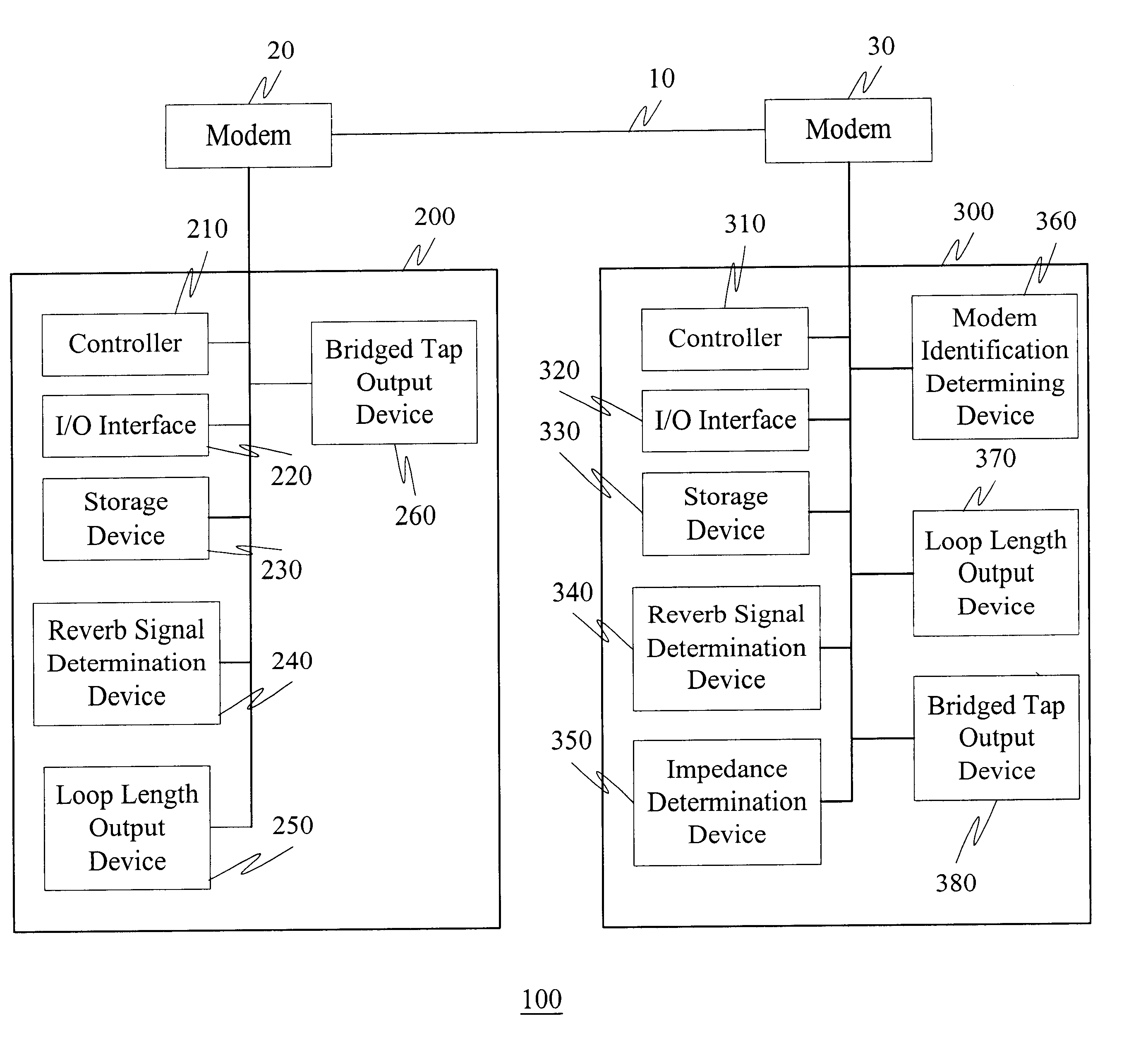

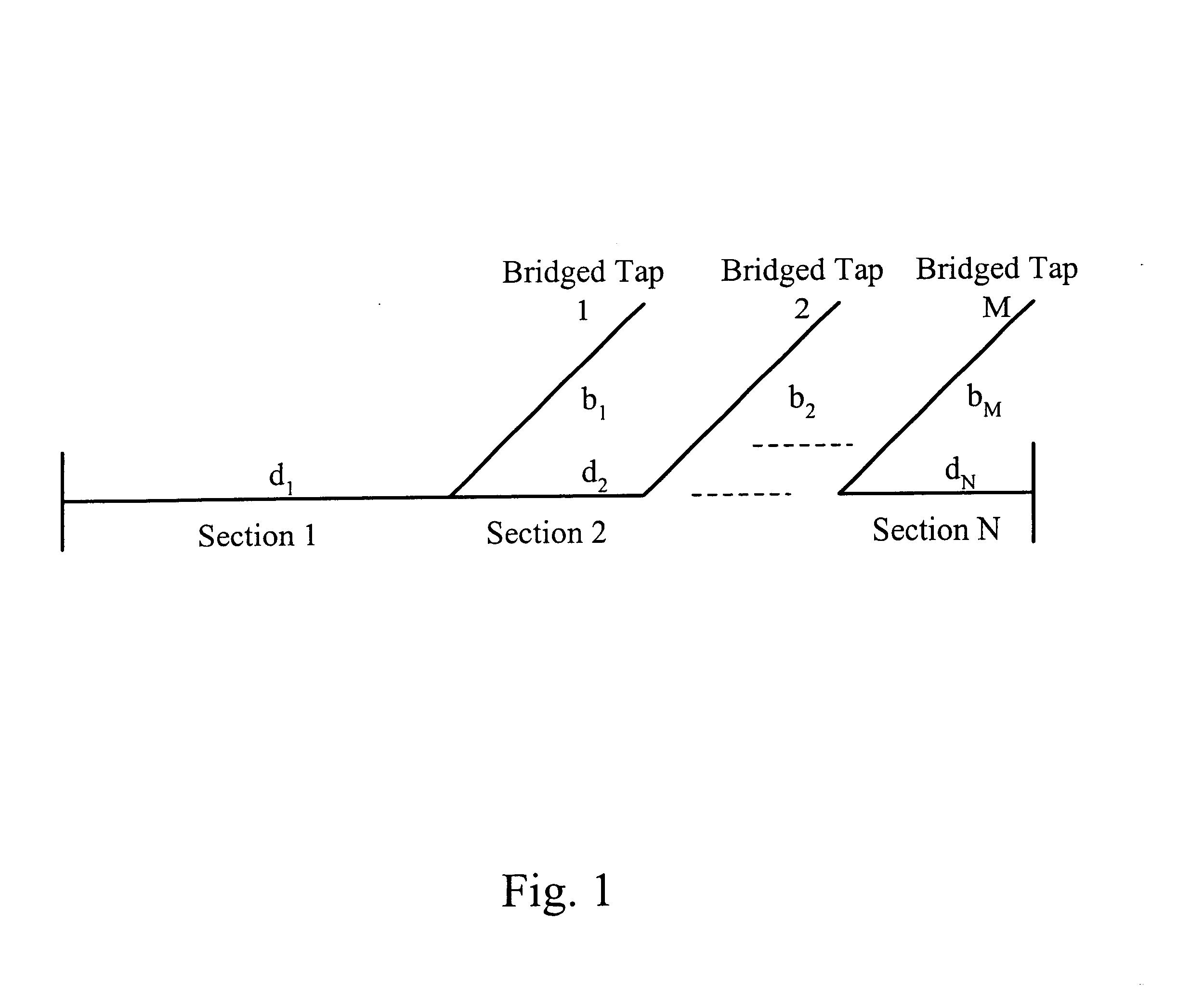

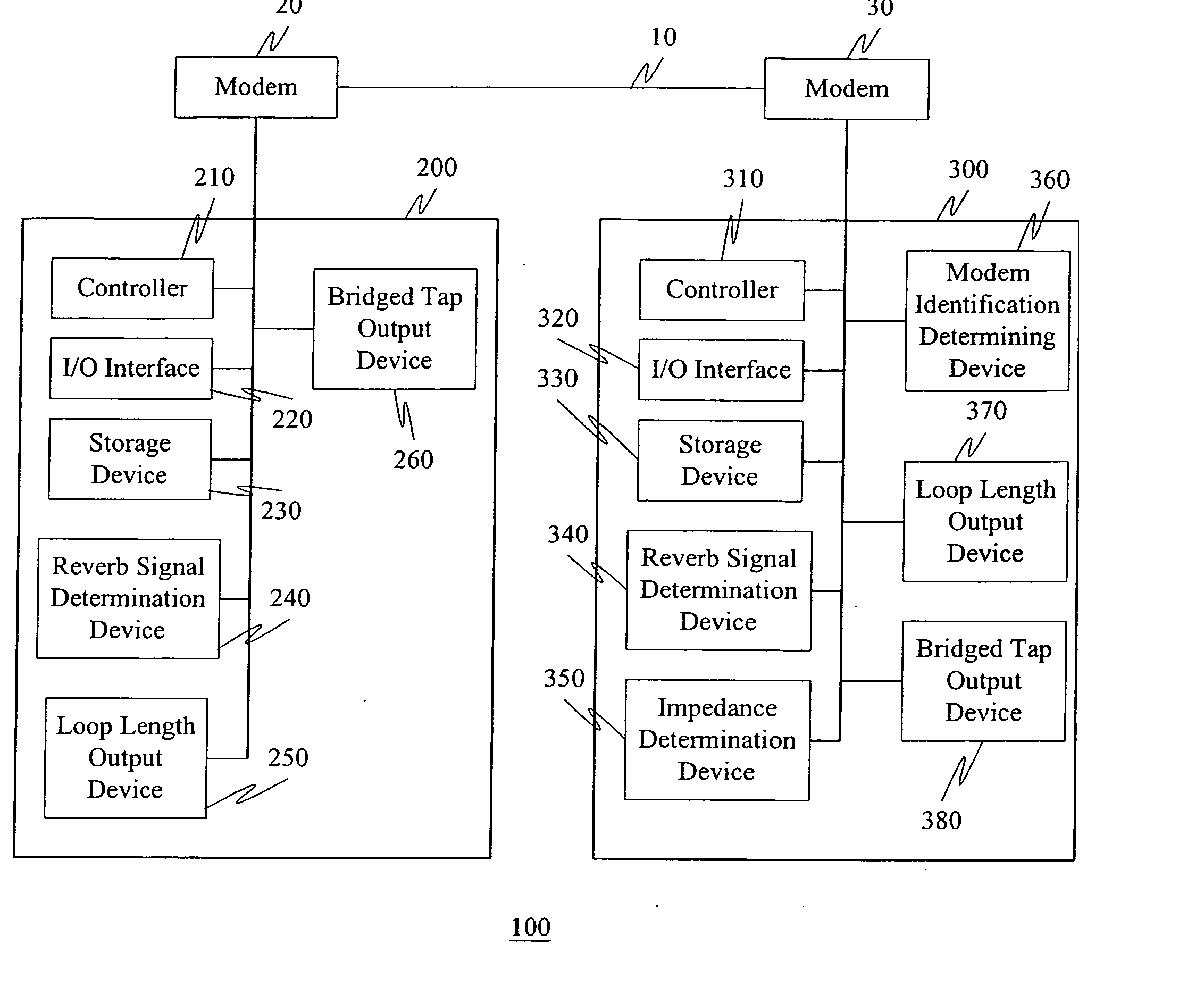

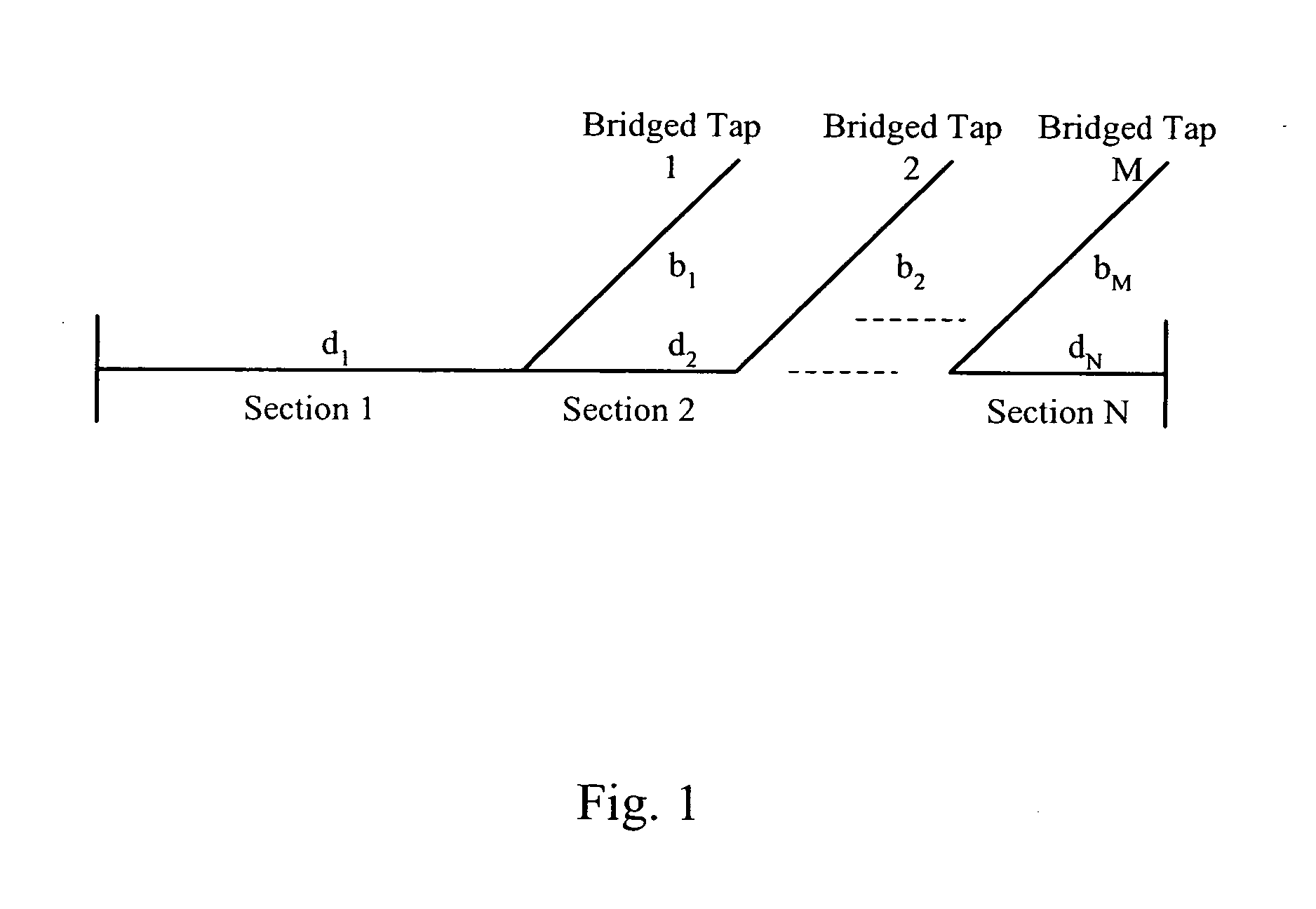

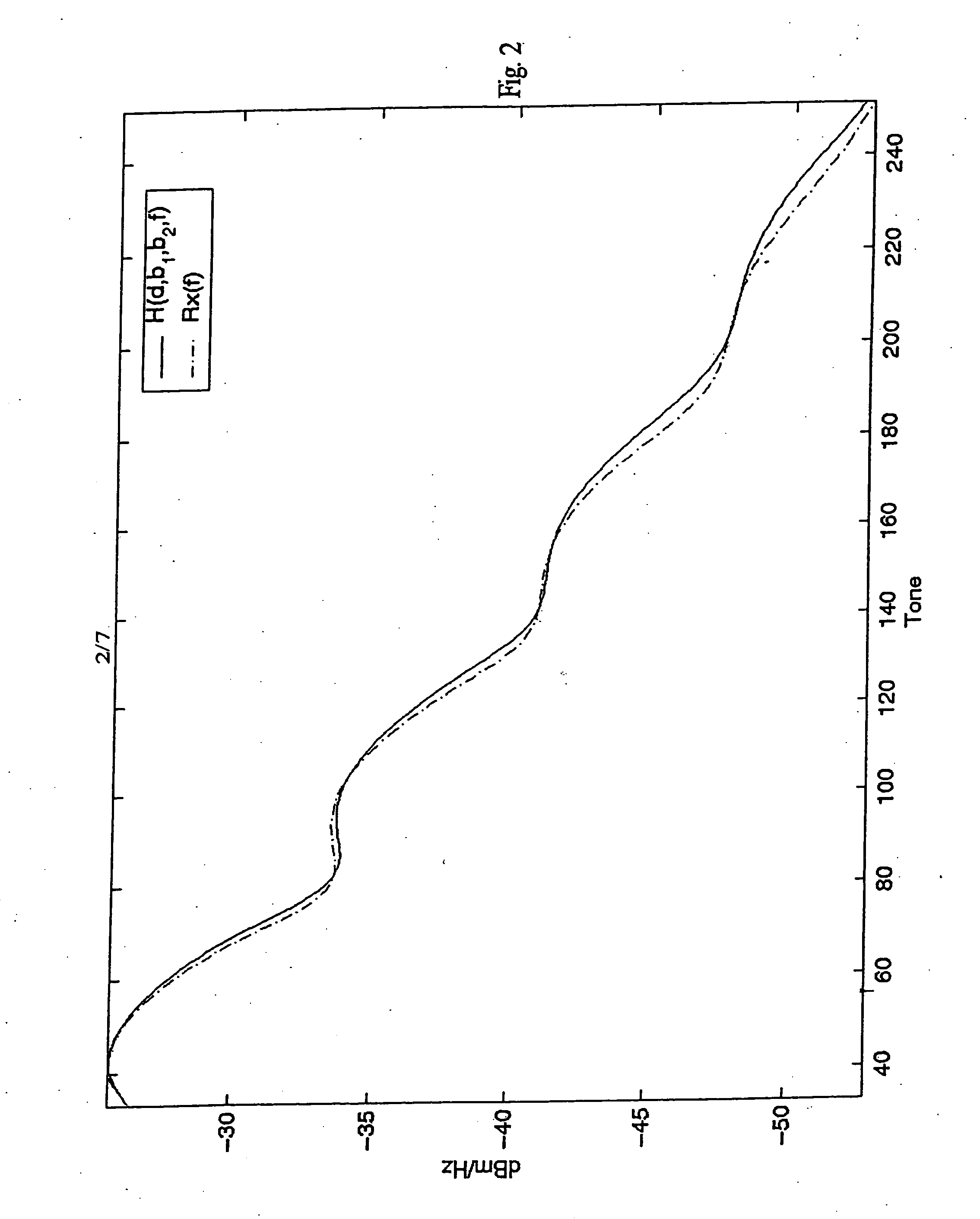

Systems and methods for loop length and bridged tap length determination of a transmission line

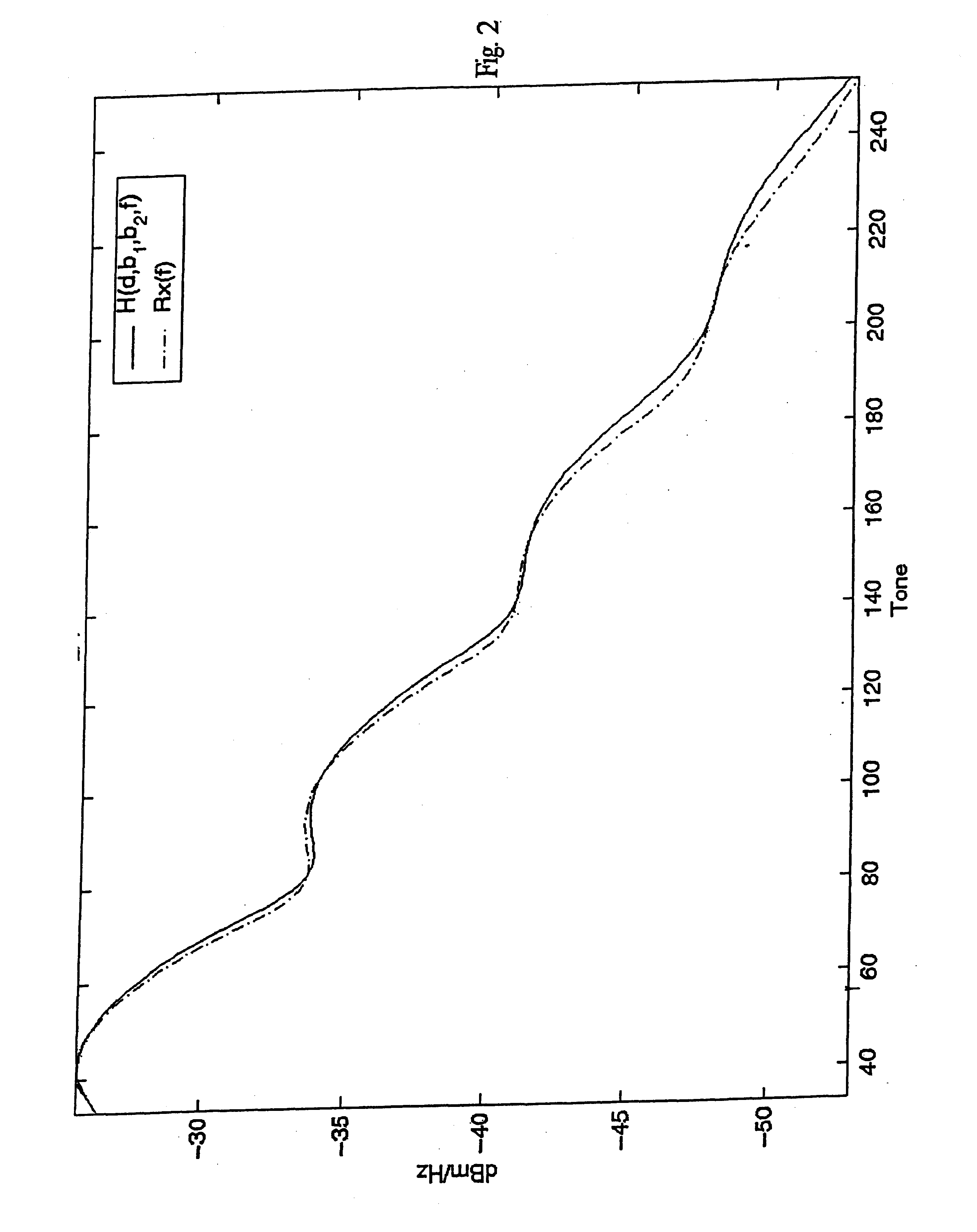

InactiveUS6865221B2Error prevention/detection by using return channelCorrect operation testingModem deviceChannel impulse response

Through the use of a least squares minimization concept, the loop length, the number of bridged taps and length of the bridged taps on a transmission line can be determined from readily available modem data. In particular, the loop length, the number of bridge taps and the length of bridged taps can be estimated by comparing a measured frequency domain channel impulse response of the transmission line to a model of a loop that is comprised of multiple sections and multiple bridge taps.

Owner:AVAGO TECH INT SALES PTE LTD

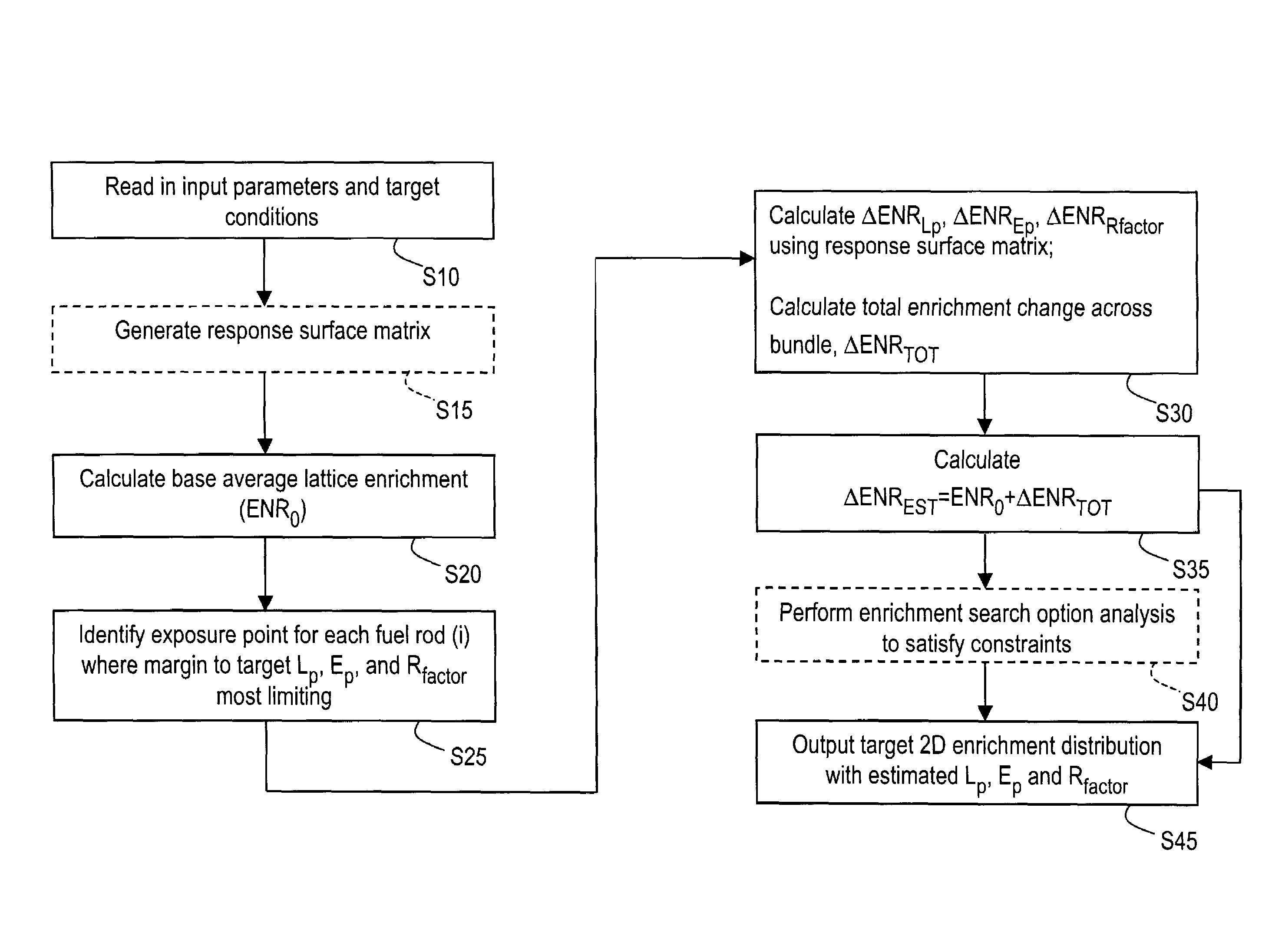

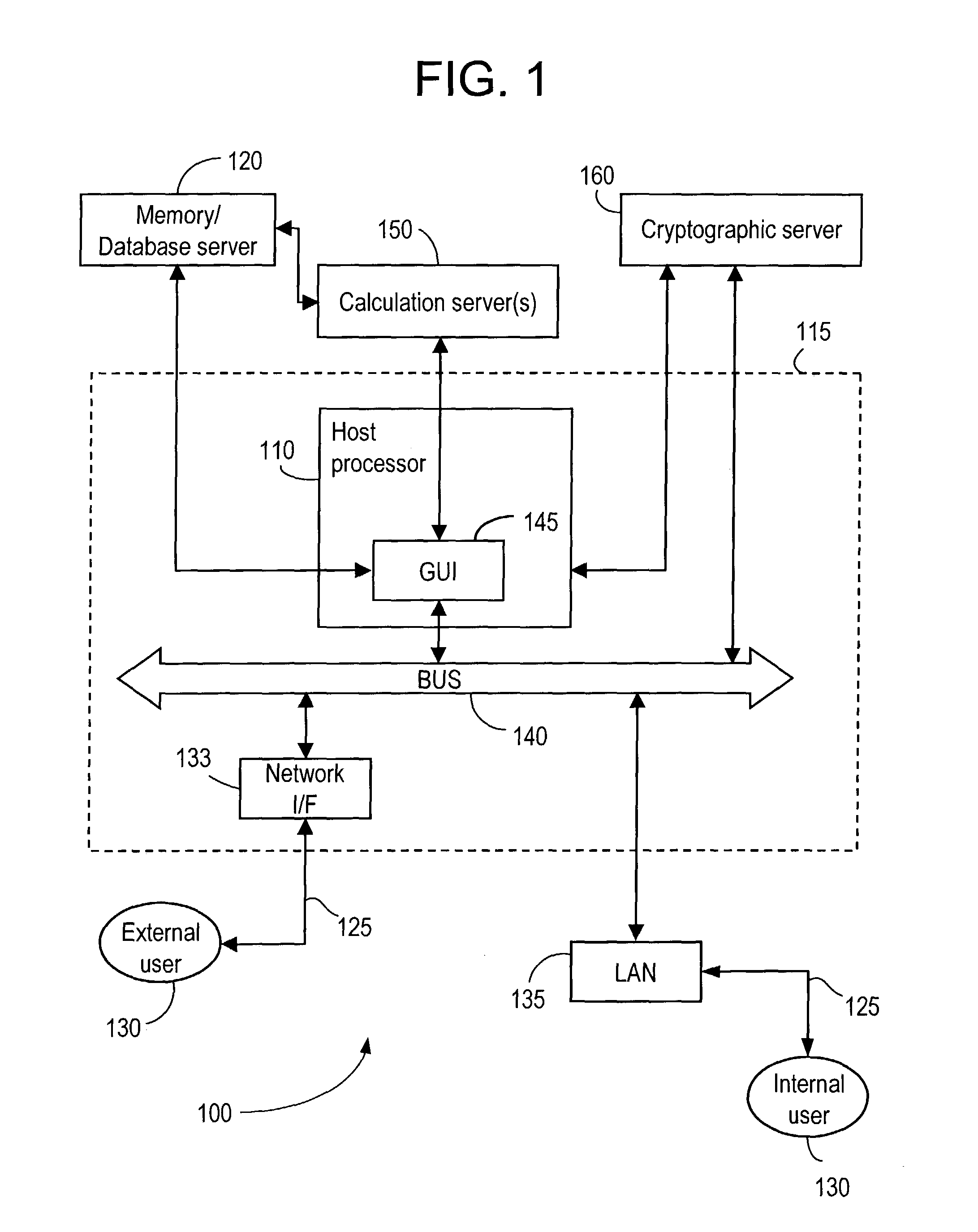

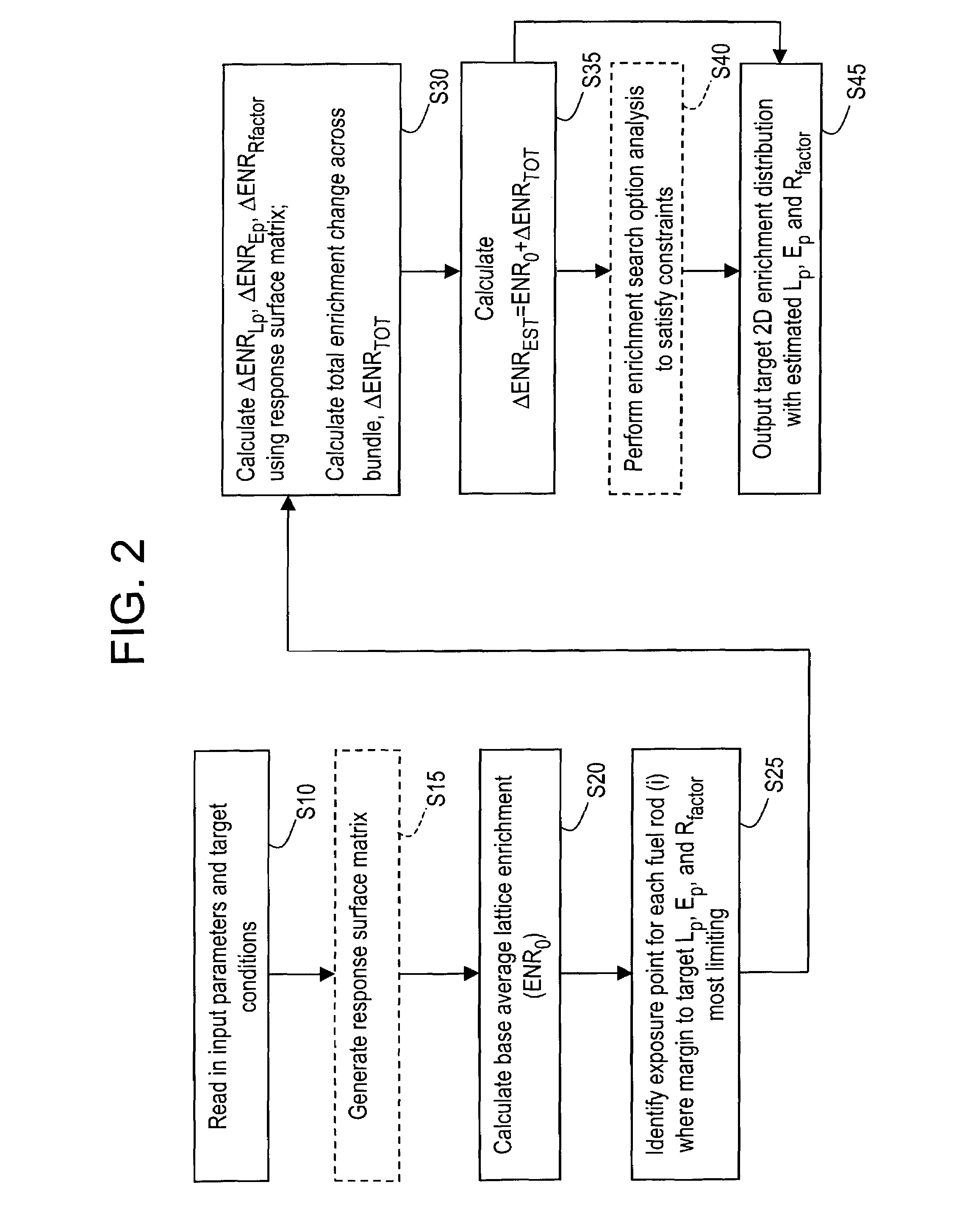

Method and arrangement for determining pin enrichments in fuel bundle of nuclear reactor

A method and arrangement of determining pin enrichments for a fuel bundle of a nuclear reactor, where a plurality of input parameters and target conditions may be input and enrichment changes, to be made across the fuel bundle, may be calculated using response matrix technology. Fuel bundle pin enrichment data may be output that satisfies the target conditions. The method and arrangement may enable production of fuel bundles having a desired local peaking, exposure peaking and R-factor performance. Consequently, given fuel cycles typically may be loaded and operated such that less fuel may be needed for identical cycle lengths, potentially resulting in improved fuel cycle economics. Additionally, because fuel bundle development may require fewer iterations, there may be a substantial cycle time reduction in the bundle design process, potentially reducing cost and enhancing profitability.

Owner:GLOBAL NUCLEAR FUEL -- AMERICAS

Communication channel capacity estimation

InactiveUS20070025548A1Less computation complexitySimple topologyTwo-way loud-speaking telephone systemsError preventionLoop lengthAlgorithm

Owner:AVAGO TECH INT SALES PTE LTD

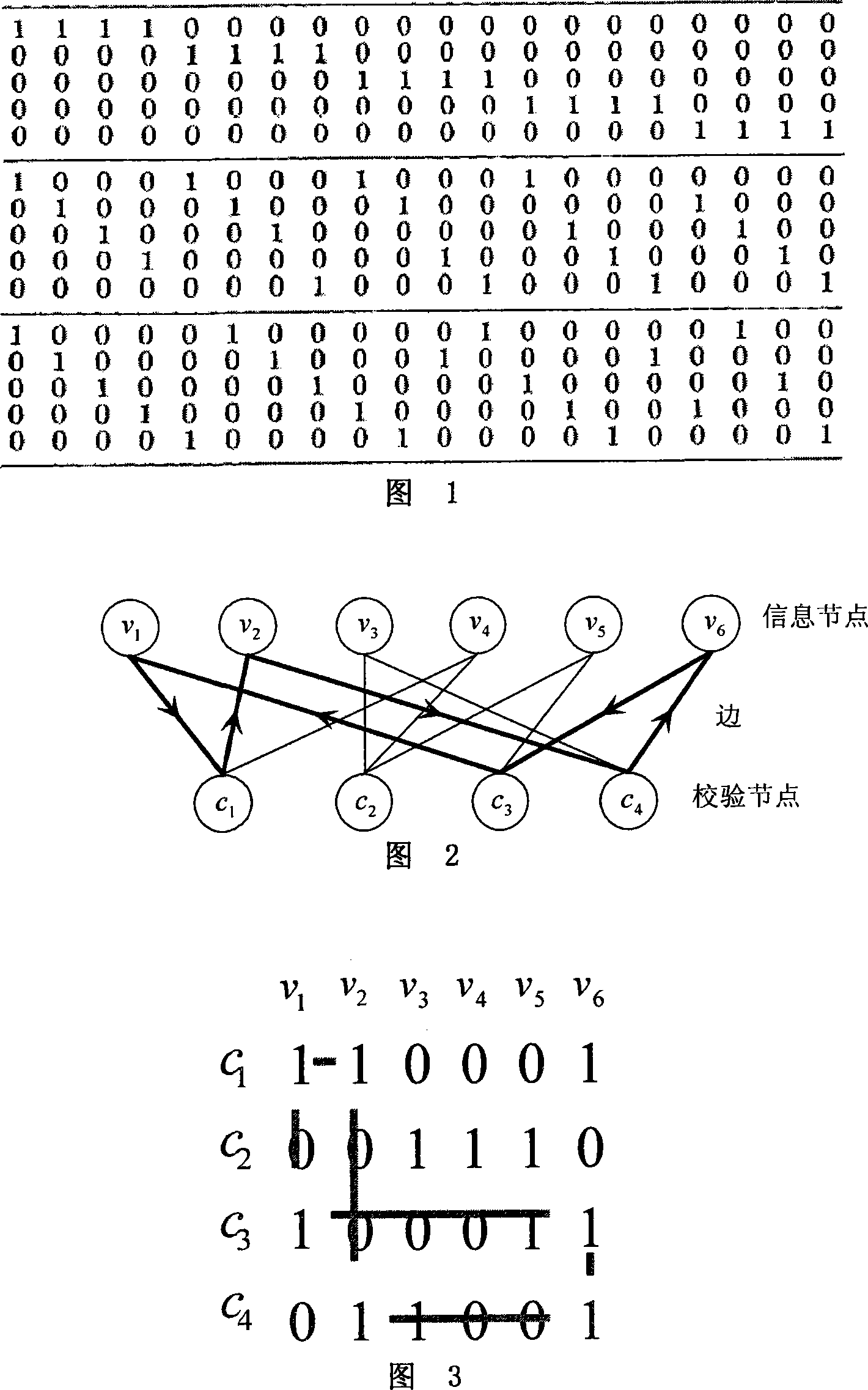

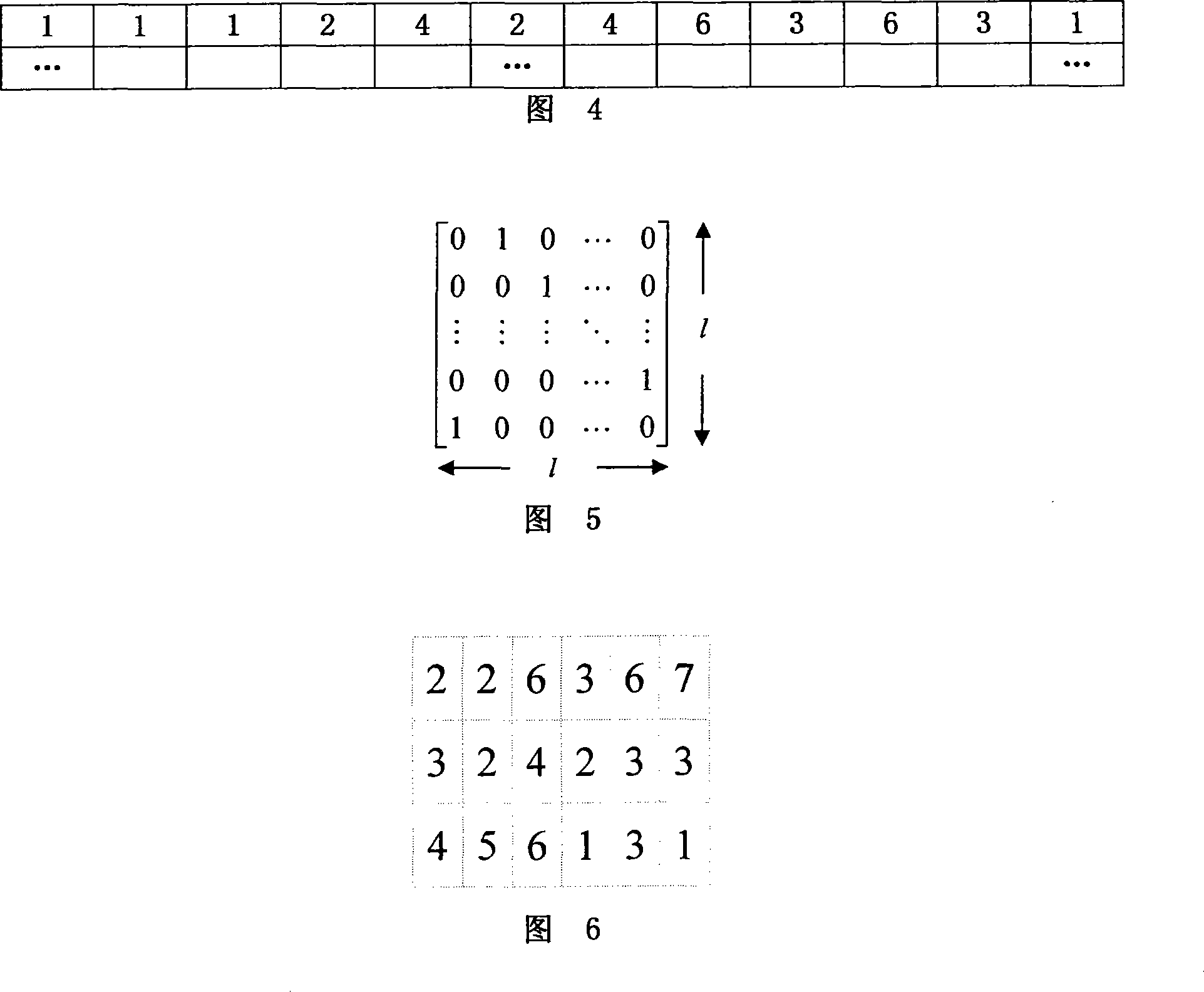

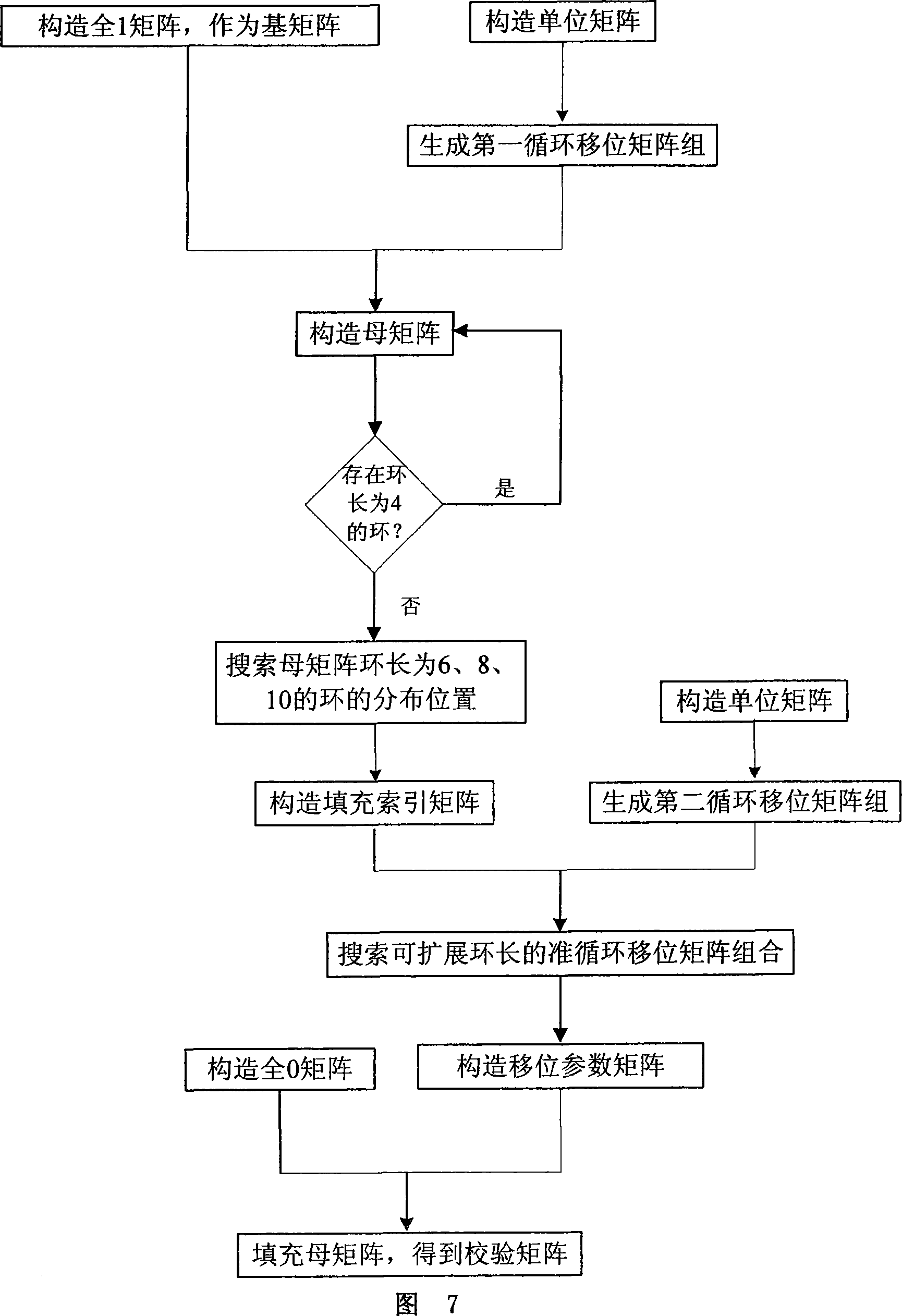

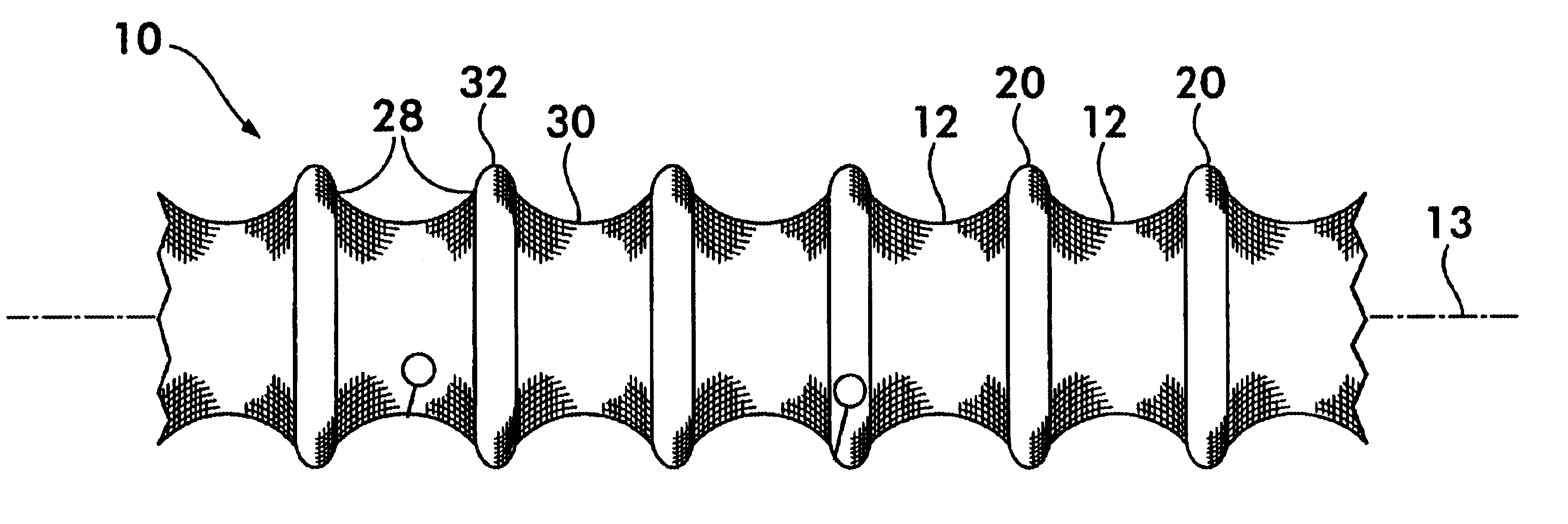

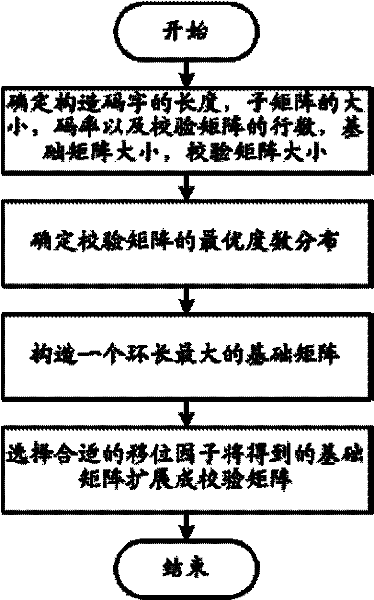

Low density check code check matrix constructing method based on shift matrix classified extension

InactiveCN101159435AFind quickly and efficientlyEffectively foundError correction/detection using multiple parity bitsLoop lengthLow density

A method for LDPC check matrix configuration based on circular shift matrix grading extension, which comprises configuring a master matrix exclusive of loops with the length of 4, then searching the distribution of loop 6, 8 and 10 in the master matrix, adopting grading expansion method to fill the displacement parameters of the circular shift matrix in the position of 1 element in the master matrix, and finally using circular shift matrix and all 0 matrix to fill the master matrix expansion according to the positions of displacement parameter matrix and 0 element so as to generate check matrix. For timely and effective discovery of good codes with secondarily maximized minimum loop length and average minimum loop length, the invention only requires graded optimization of the combination of the master matrix with very small code length and the circular shift matrix; compared with the method of random circular shift configuration check matrix followed by comparing average minimum loop length, the search volume is significantly reduced. The check matrix not only has excellent performance, but also further reduces average iteration times. The invention is suitable for all methods that adopt circular shift matrix to constitute check matrix.

Owner:PLA UNIV OF SCI & TECH

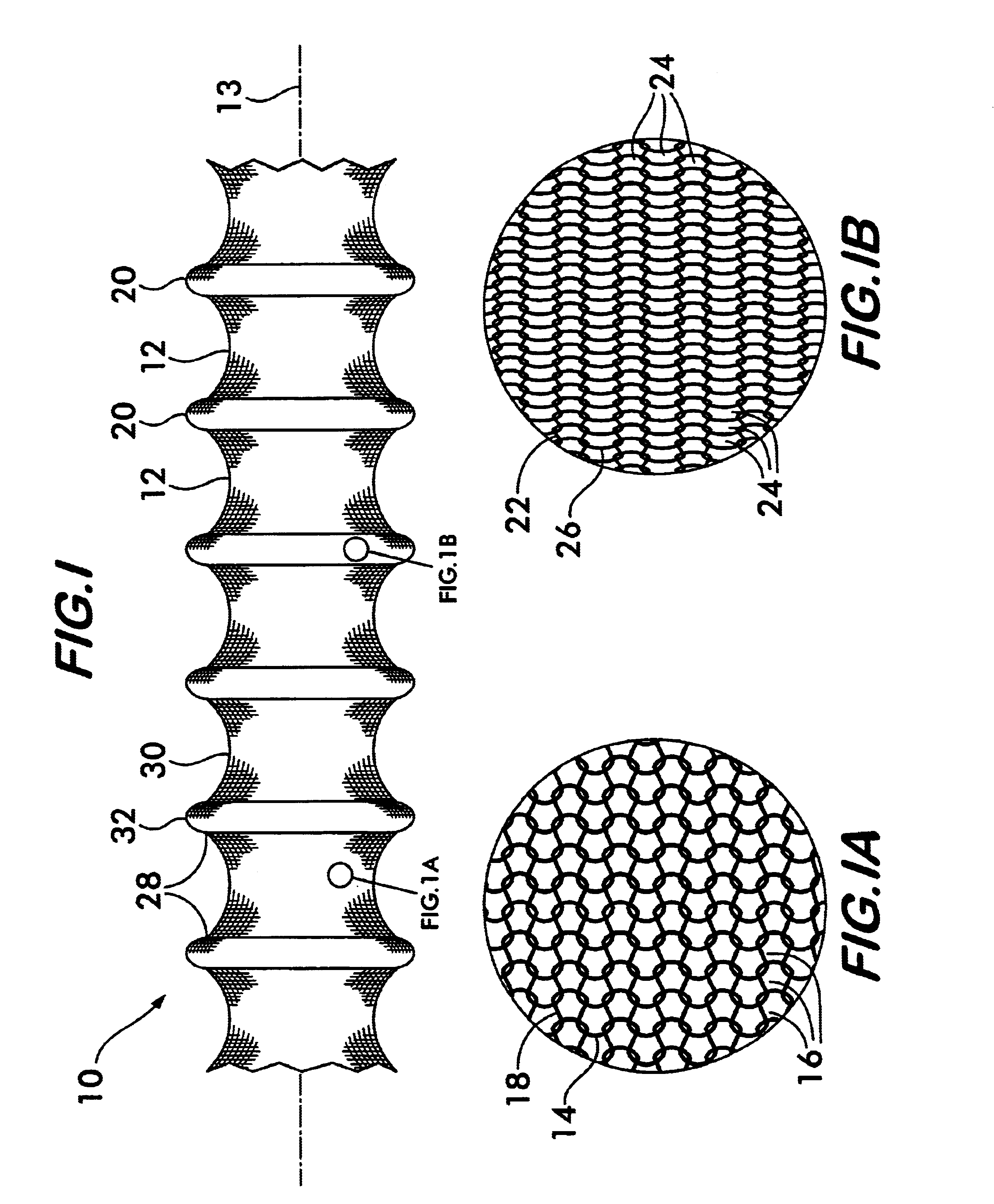

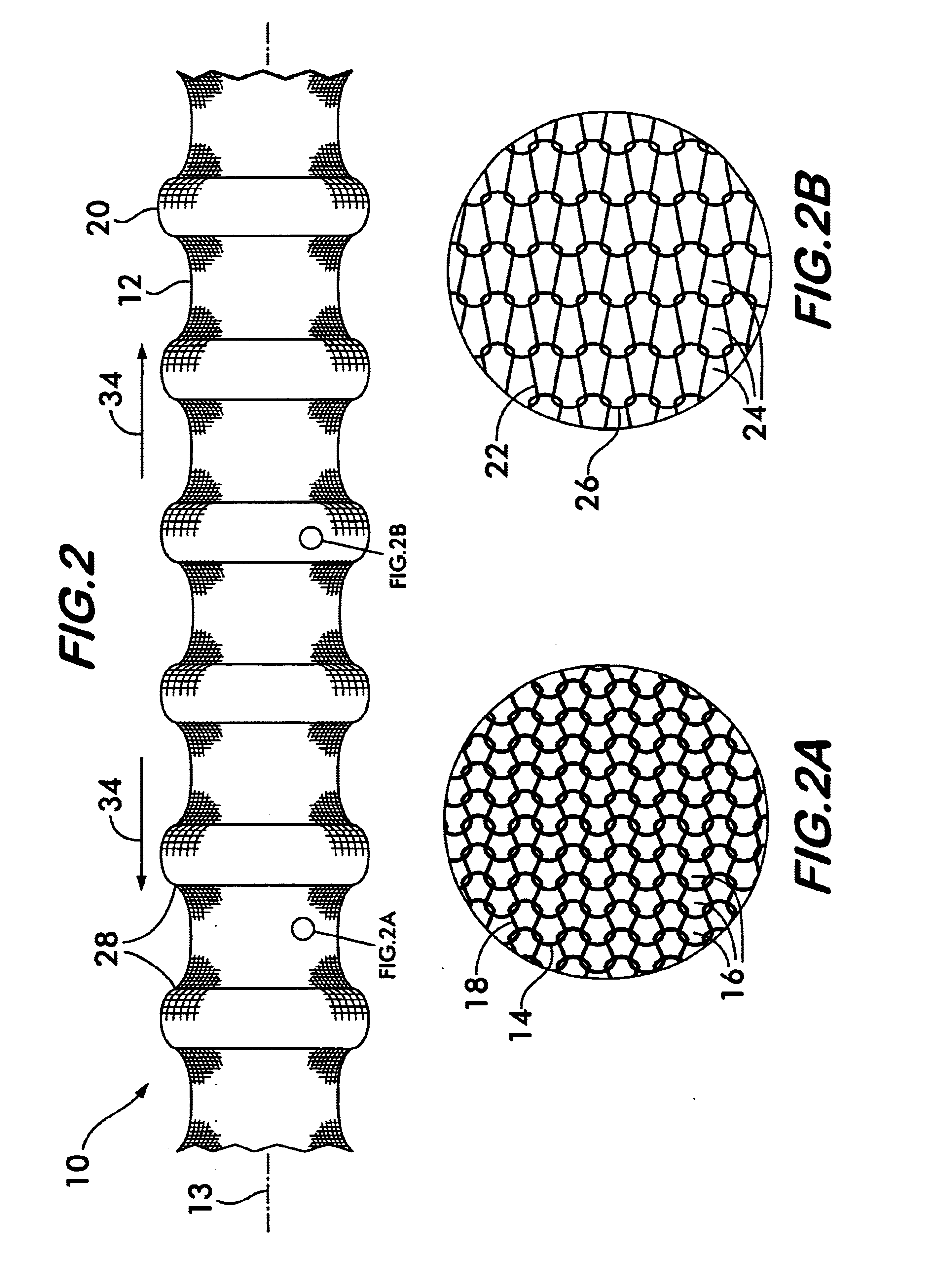

Knit convolute protective sleeve

InactiveUS6711920B2Ornamental textile articlesSemiconductor/solid-state device detailsLoop lengthEngineering

A knitted convolute protective sleeve is disclosed. The sleeve is knitted from filamentary members to form alternating crests and troughs lengthwise along the sleeve. The crests and troughs may be formed by alternatingly knitting segments from relatively stiff and relatively flexible filamentary members, by interlacing stiffening hoops at spaced intervals lengthwise along a knitted sleeve having a smaller nominal diameter than the hoops, or by varying the knitting parameters, such as loop density and loop length as a function of length along the sleeve.

Owner:FEDERAL MOGUL WORLD WIDE LLC

Suspensory graft fixation with adjustable loop length

A suspensory fixation device has an elongated anchor member adapted to be transversely situated at the exit of a bone tunnel. A graft supporting loop member formed of a pair of parallel suture limbs extending from a bight portion is suspended transversely from the anchor member and has a loop length which is adjustable so the graft ligament can be supported in the bone tunnel at varying distances from the anchor member. When a graft ligament is attached to the saddle end of the loop member, the length of the loop member may be shortened by simply pulling distally on the pair of limbs at one end of the loop member to pull the graft ligament into the bone tunnel a predetermined distance or until it bottoms out at the floor of the bone tunnel. When tension is applied to the loop member by the graft pulling the loop proximally, the bight portion of the suture automatically locks the graft supporting loop member in place.

Owner:LINVATEC

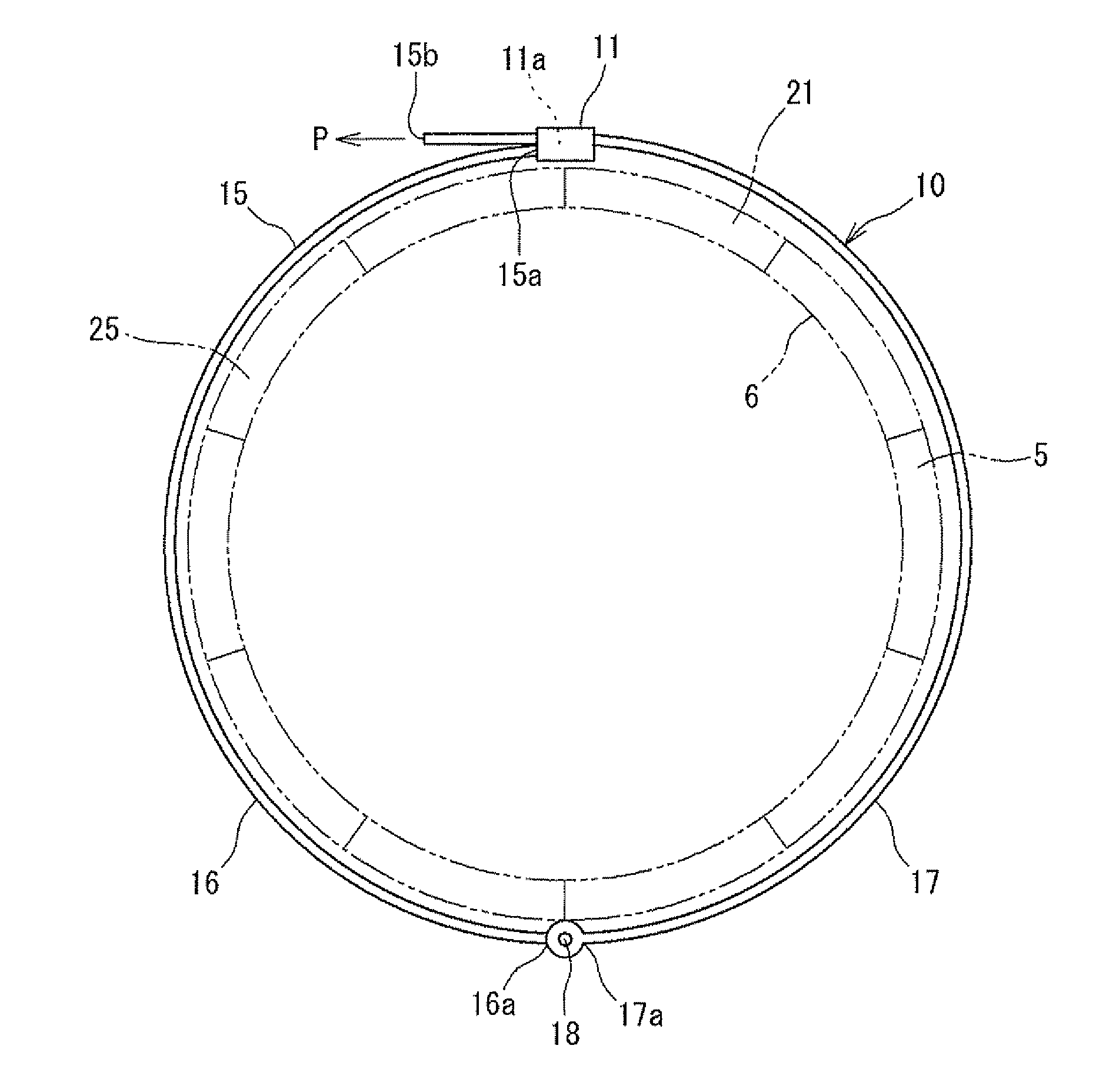

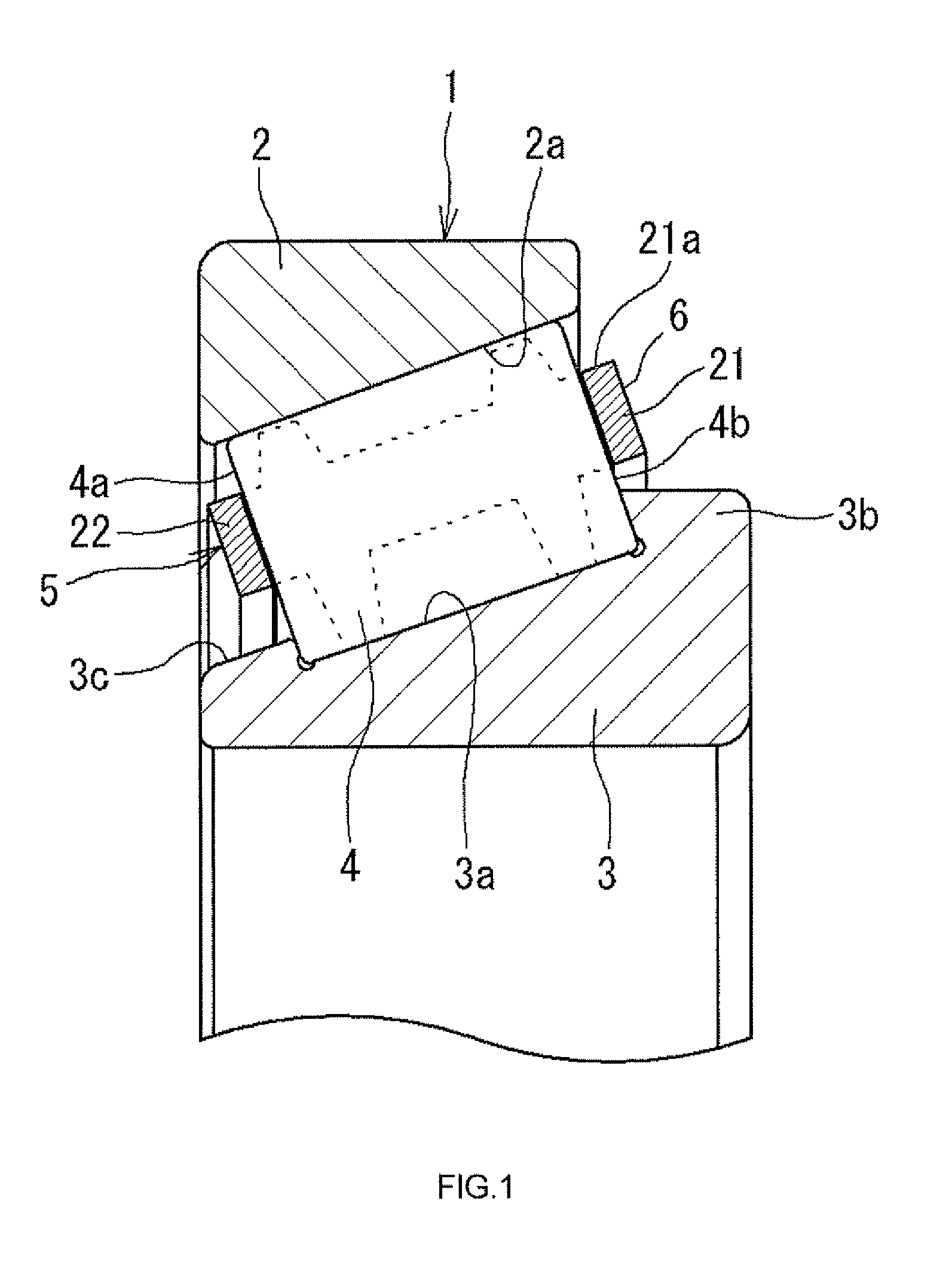

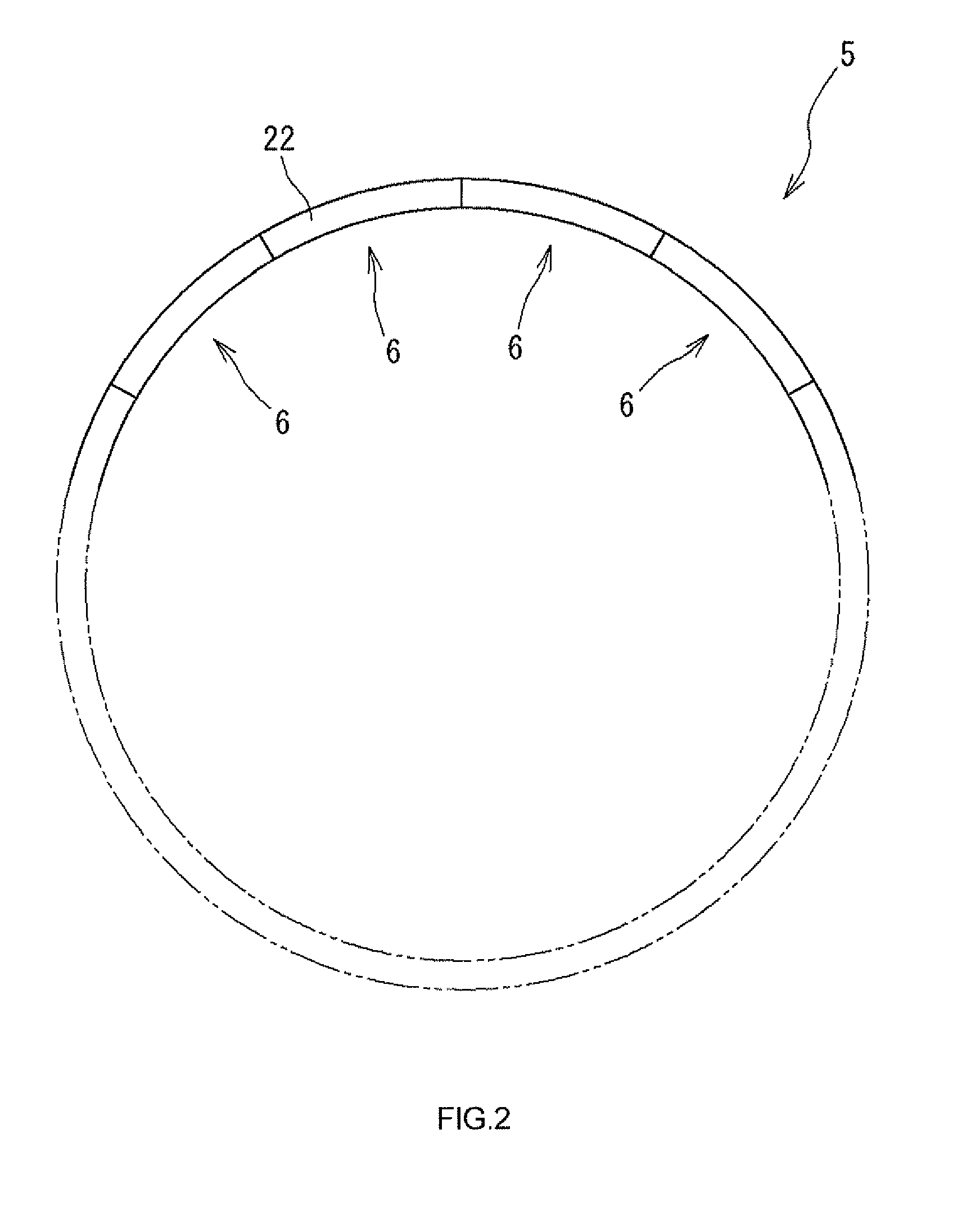

Jig for split cage and method of assembling rolling bearing

InactiveUS20140013603A1Easy to assembleRolling contact bearingsBearing assemblyLoop lengthEngineering

A split cage is configured by annularly arranging cage segments in a circumferential direction. Each cage segment includes a pair of first and second rim portions spaced from each other by a predetermined interval and facing each other, and bar portions extending from the first rim portion to the second rim portion. Spaces, each of which is surrounded by the adjacent bar portions and the first and second rim portions, are formed as pockets that house rolling elements. A jig for the split cage includes a looped band wound on an outer peripheral side of the first or second rim portions of the cage segments annularly arranged. The band includes a lock portion that is able to adjust a loop length of the band with respect to an outer peripheral length of the first or second rim portions, and that is able to fix the adjusted loop length.

Owner:JTEKT CORP

Systems and methods for loop length and bridged tap length determination of a transmission line

InactiveUS20050123030A1Error prevention/detection by using return channelCorrect operation testingLoop lengthChannel impulse response

Through the use of a least squares minimization concept, the loop length, the number of bridged taps and length of the bridged taps on a transmission line can be determined from readily available modem data. In particular, the loop length, the number of bridge taps and the length of bridged taps can be estimated by comparing a measured frequency domain channel impulse response of the transmission line to a model of a loop that is comprised of multiple sections and multiple bridge taps.

Owner:AVAGO TECH INT SALES PTE LTD

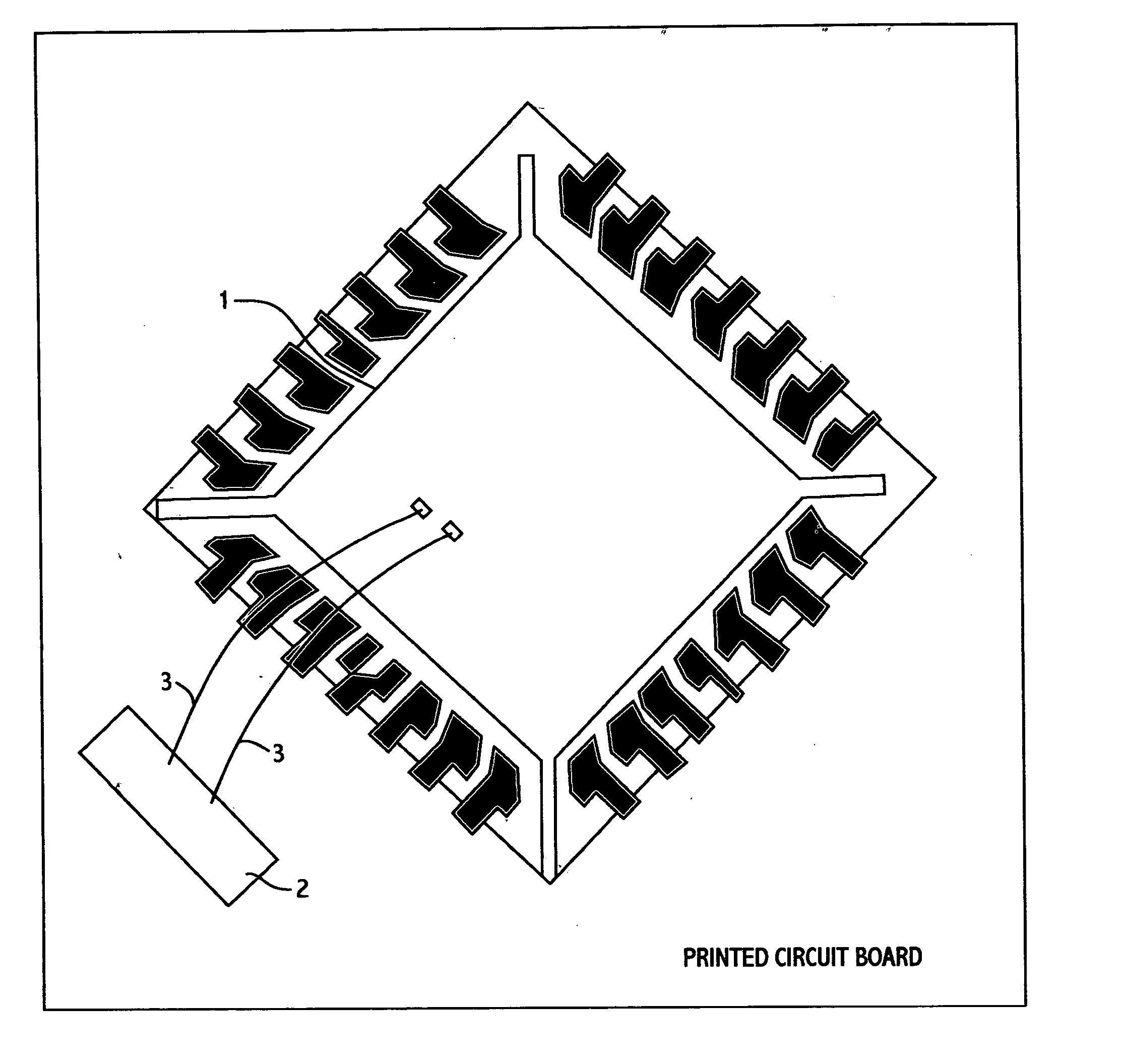

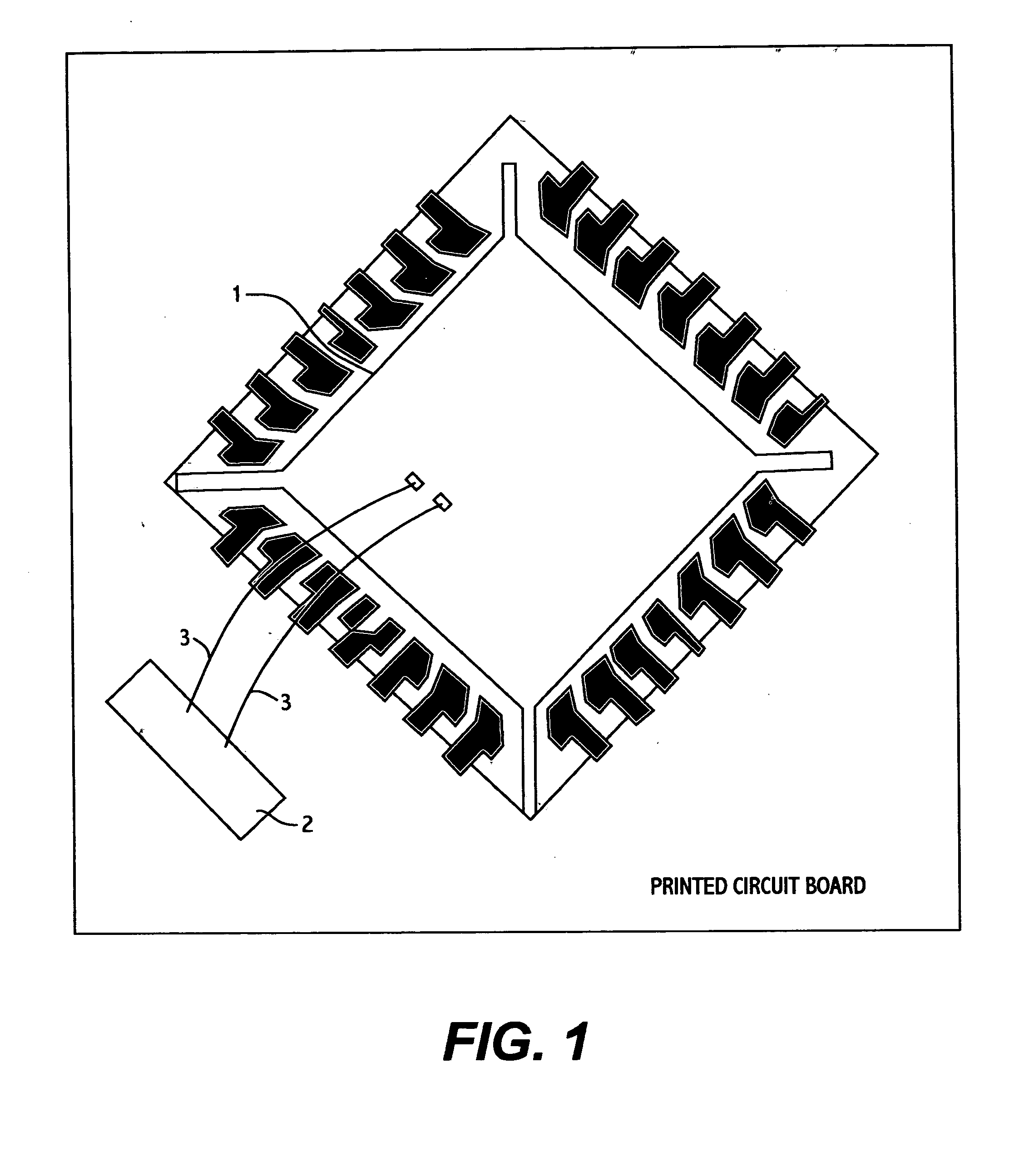

Integrated circuit package having an inductance loop formed from a multi-loop configuration

InactiveUS20050045986A1Process economyFew process stepsSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorLoop length

An integrated circuit package includes an inductance loop formed from a connection of lead wires and one or more input / output (I / O) package pins. In one embodiment, the inductance loop is formed from first and second wires which connect a first bonding pad on the integrated circuit chip to a first I / O pin of the package and a third and fourth wires which connect a second bonding pad on the chip to a second I / O pin of the package. To complete the inductor loop, the first and second I / O pins are connected by a third conductor between the pins. The third conductor may include one or more bonding wires and the I / O pins are preferably ones which are adjacent one another. However, the loop may be formed from non-adjacent connections of I / O pins based, for example, on loop-length requirements, space considerations, and / or other design or functional factors. In another embodiment, connection between the first and second I / O pins is established by making the I / O pins have a unitary construction. In another embodiment, connection between the first and second I / O pins is established by a metallization layer located either on the surface of the package substrate or within this substrate. By forming the inductor loop within the limits of the integrated circuit package, a substantial reduction in space requirements is realized, which, in turn, promotes miniaturization. Also, the integrated circuit may be implemented in any one of a variety of systems, at least one parameter of which is controlled by the length of the inductor loop of the package.

Owner:GCT SEMICONDUCTOR INC

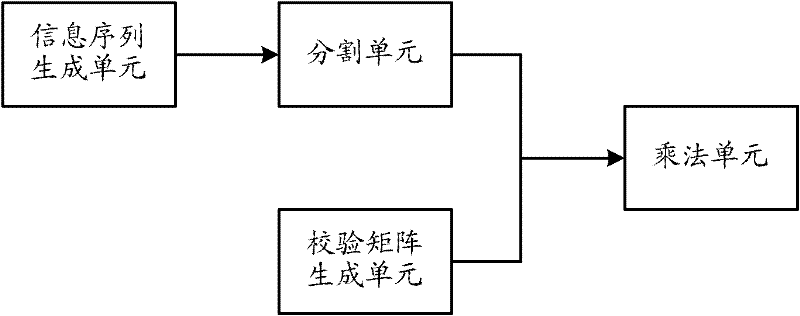

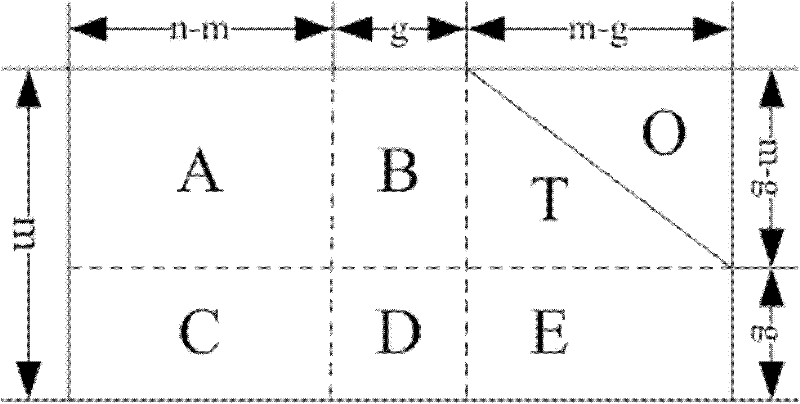

Low density parity check (LDPC) code check matrix construction method and corresponding matrix multiply operation device

ActiveCN102394659AGood code wordReduce implementation complexityError correction/detection using multiple parity bitsError checkTheoretical computer science

The invention relates to a low density parity check (LDPC) code check matrix construction method and a corresponding matrix multiply operation device. The method comprises the following steps that: determining the length n*L of a code word, the size L of a circulating replacement sub-matrix, a code rate L and number of rows m*L of a check matrix, wherein the size Hb of a basic matrix is m*n, the size H of the check matrix is mL*nL; determining best distribution of the check matrix H; constructing a basic matrix Hb with maximal loop length; exapdning the obtain basic matrix Hb to a quasi-cyclic-low density parity check (QC-LDCP) code with the loop length being maximized by selecting an appropriate movement factor, and determining the entire check matrix H by selecting the movement factor with element of a 1 position in the basic matrix Hb. The device comprises a check parity generating unit, an information sequence generating unit, a segmenting unit and a multiply unit. Due to the adoption of the method and the device, the coding complexity is reduced, the LDPC code with an error check performance being very approximate to a random structure is obtained, and simultaneously the realization complexity of the LDPC code is reduced.

Owner:上海新微科技发展有限公司

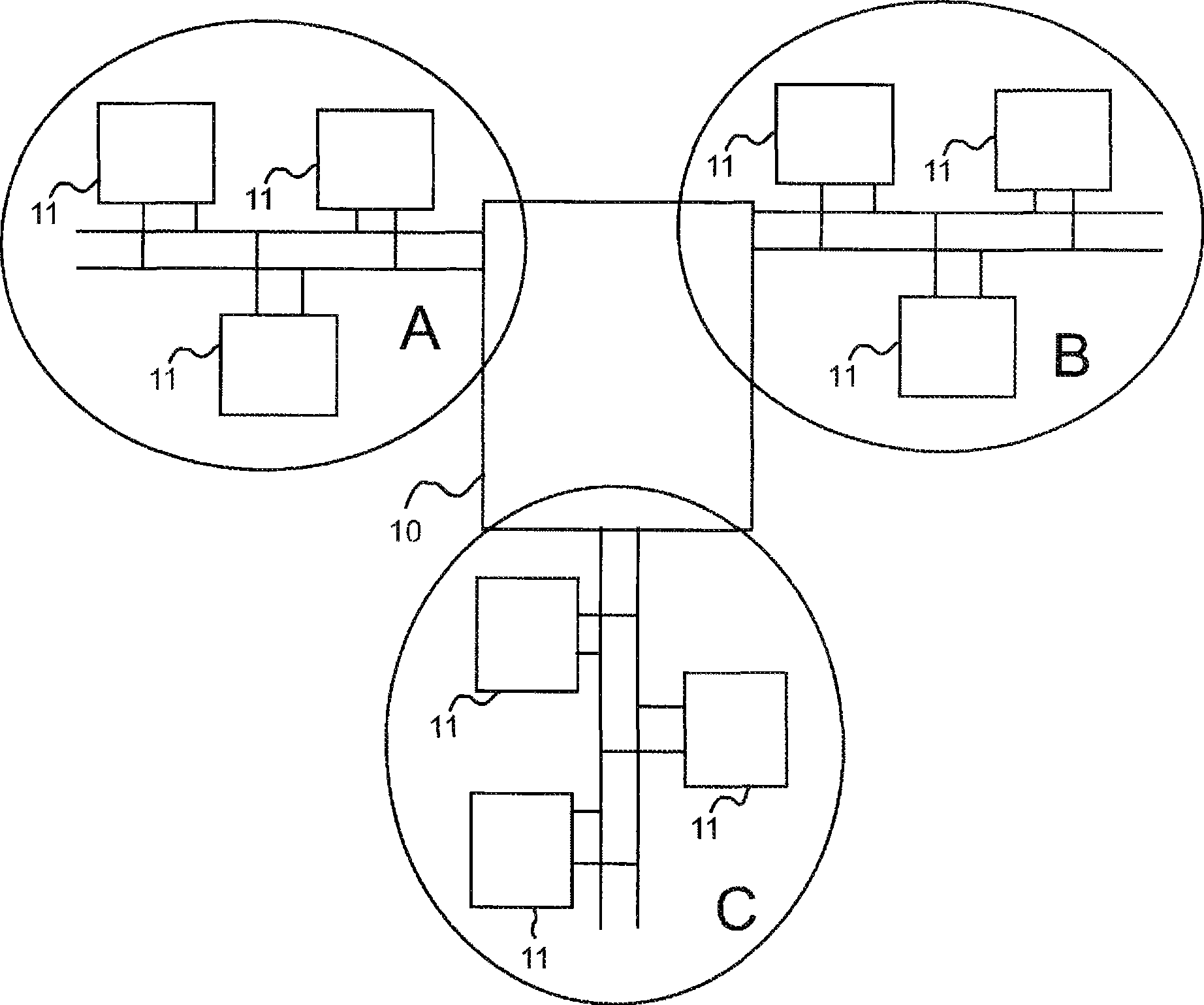

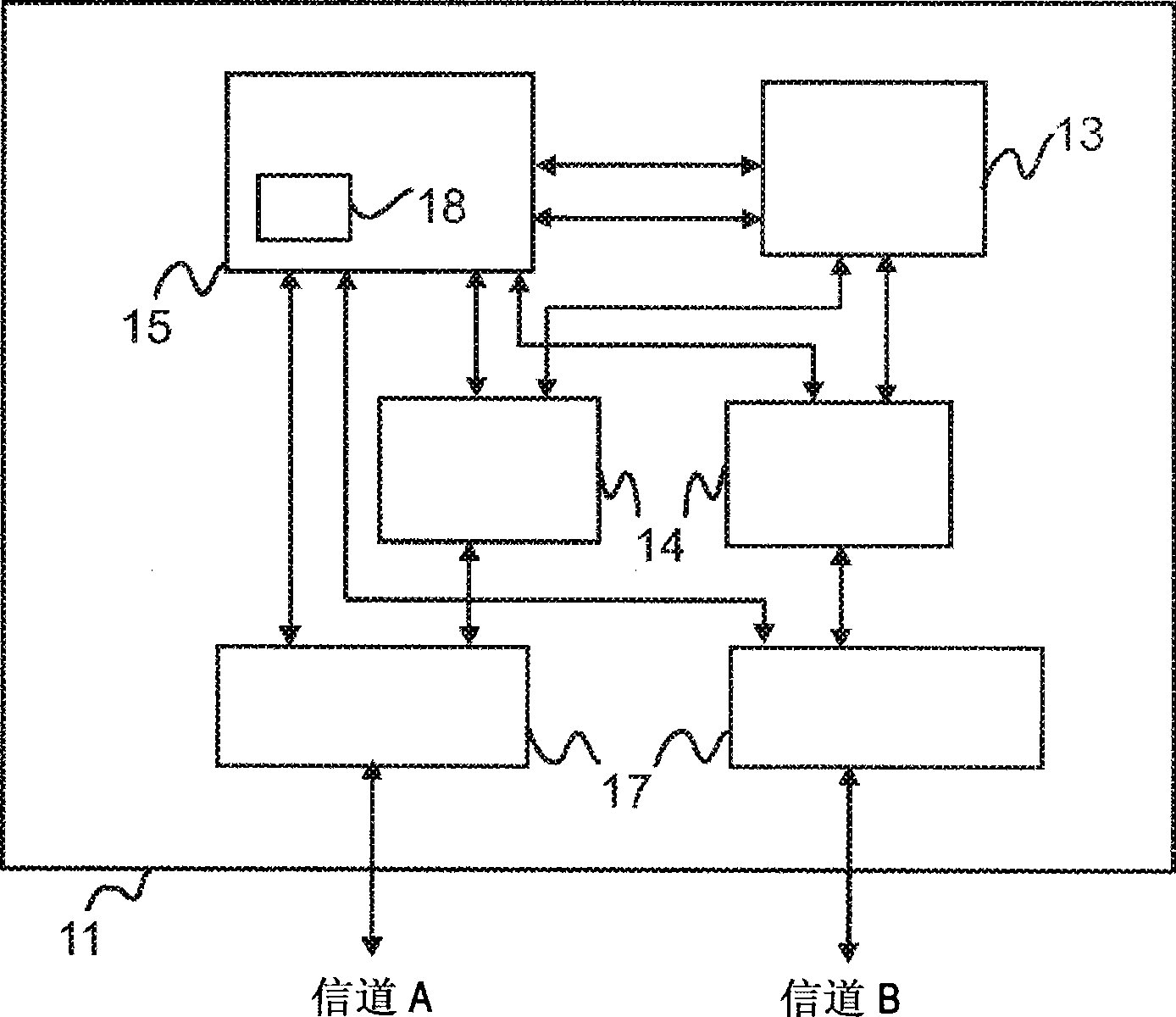

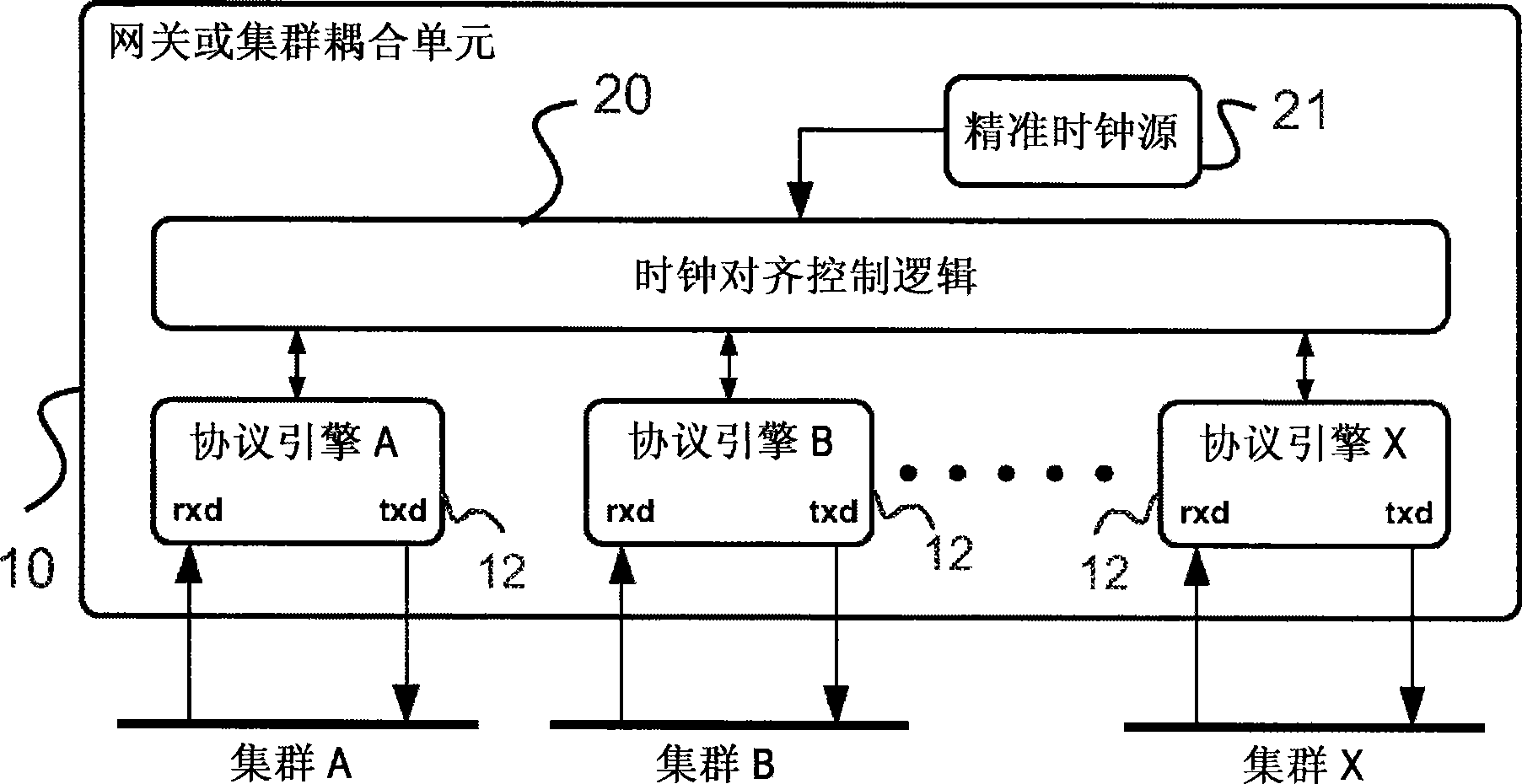

Network and method for clock synchronization of clusters in a time triggered network

InactiveCN101512944ASynchronization speed is fastReduce demandSynchronisation arrangementTime-division multiplexLoop lengthCommunication control

The invention relates to a network operating on a time triggered protocol using time slots, wherein at least two clusters are included in the network, each cluster includes at least a node. Further, it relates to a method for clock synchronization within a time triggered network. To provide a network and a method reducing the amount of time needed for aligning multiple communication clusters as much as possible it is proposed to provide a network operating on a time triggered protocol using time slots, wherein at least two clusters (A, B, X) are included in the network, each cluster (A, B, X) includes at least a node (11), wherein the node (11) includes a communication controller (15) having a node clock source (18) for determining a timing for the node (11), wherein the clusters (A, B, X) are connected to a coupling unit (10) having a clock alignment control logic (20) comprising a coupling unit clock source (21) which is more accurate than the node clock source (18), wherein the coupling unit clock source (21) is used for aligning the timing between the at least two clusters (A, B, X). Further it is proposed to provide a method for clock synchronization within a time triggered network using time slots, having at least two clusters (A, B, X), wherein each cluster includes at least one node (11), each node (11) comprises a node clock source (18) and a communication controller (15) and the clusters (A, B, X) are connected to a coupling unit (10) having a clock alignment control logic (20) comprising a coupling unit clock source (21) which is more accurate than the node clock source (18), the method comprising the steps of: monitoring the timing of the connected clusters (A, B, X) within the coupling unit (10); increasing or decreasing a cycle length of the timing within the clusters by use of the coupling unit clock source (21).

Owner:NXP BV

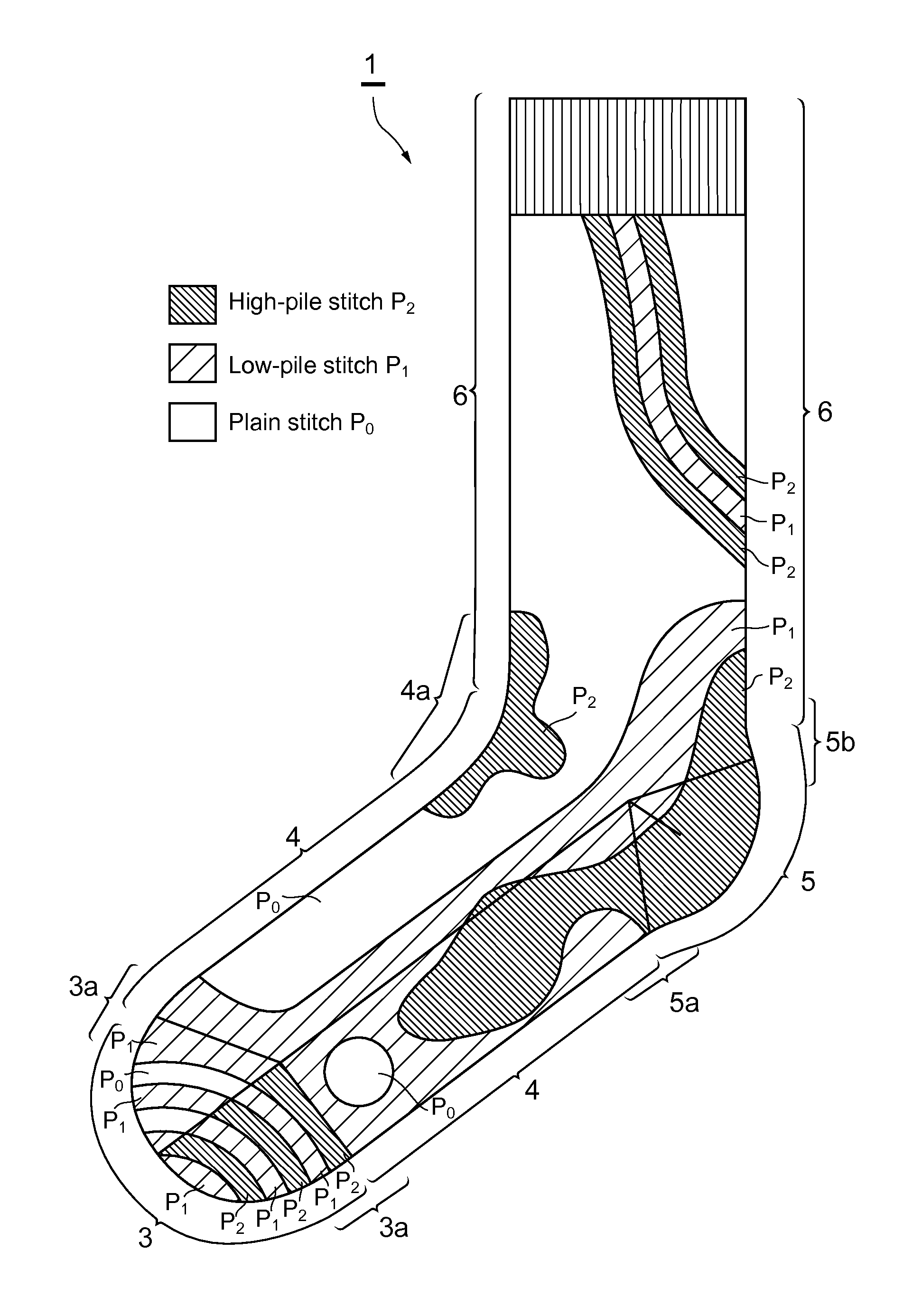

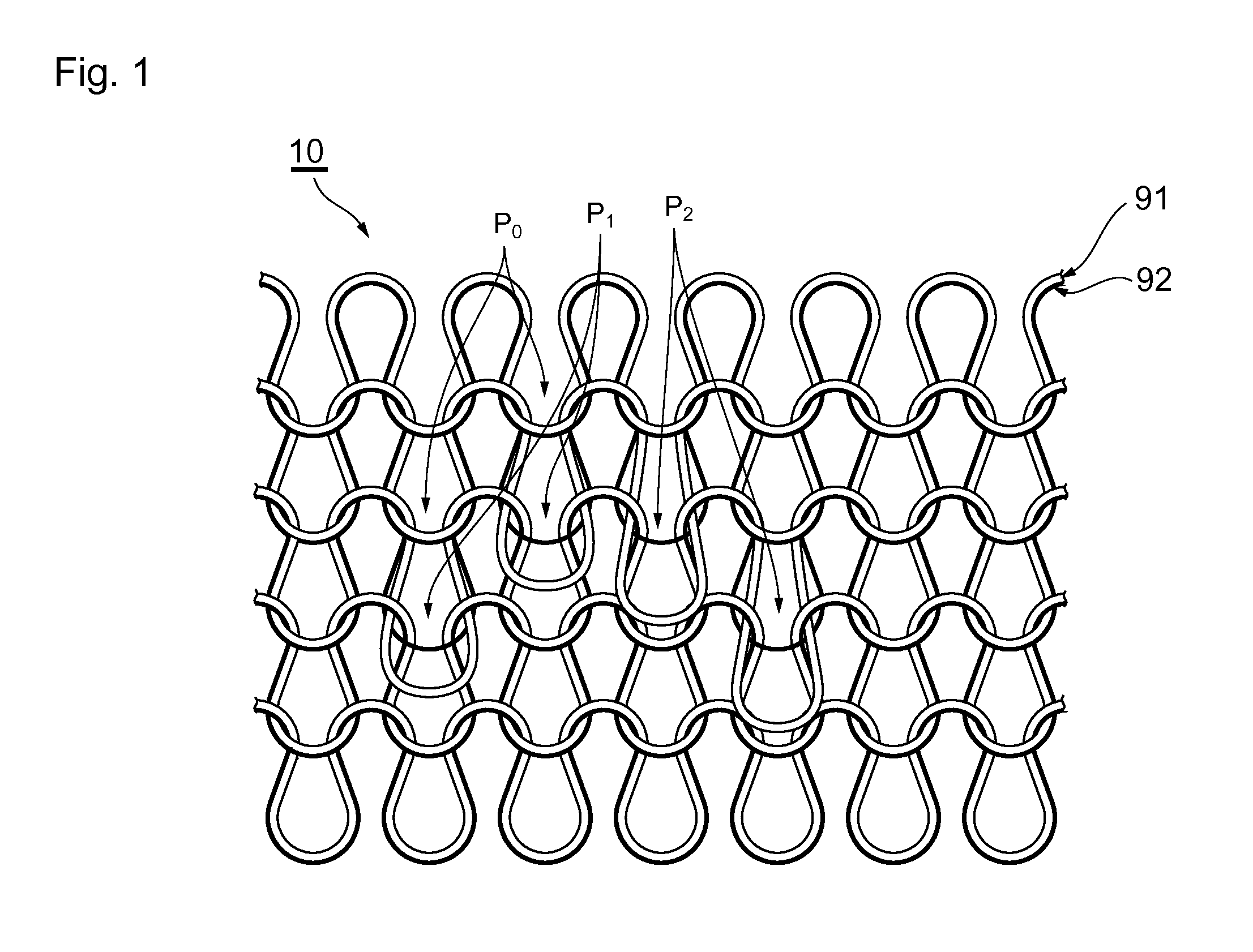

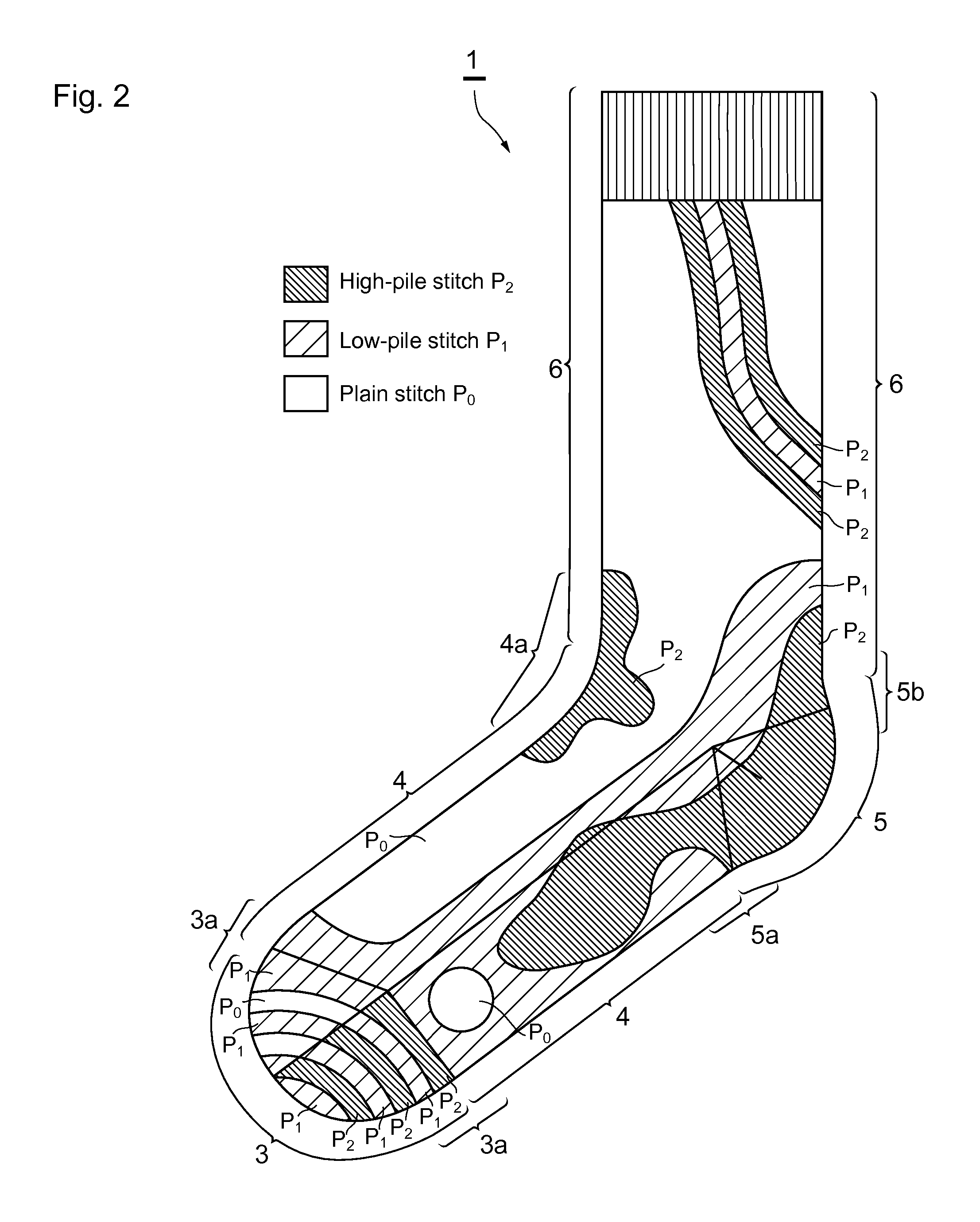

Knitted fabric with different pile lengths, knit product and socks using the same

InactiveUS20130205839A1Textile/flexible product manufactureCircular knitting machinesYarnLoop length

A knitted fabric that has a three-dimensional appearance includes a plurality of knitting structures of different pile lengths. The knitting structures include a plain stitch of ground yarn and pile yarn, a low-pile stitch in which a sinker-loop length of the pile yarn is longer than that of ground yarn, and a high-pile stitch in which the sinker-loop length of the pile yarn is longer than that in the low-pile stitch. A pile motif is formed by selectively arranging, in the same course, the low-pile stitch and the high-pile stitch in a region of the plain stitches on a stitch-by-stitch basis or by selectively arranging, in the same course, the high-pile stitch in a region of the low-pile stitches on a stitch-by-stitch basis.

Owner:OKAMOTO INDS

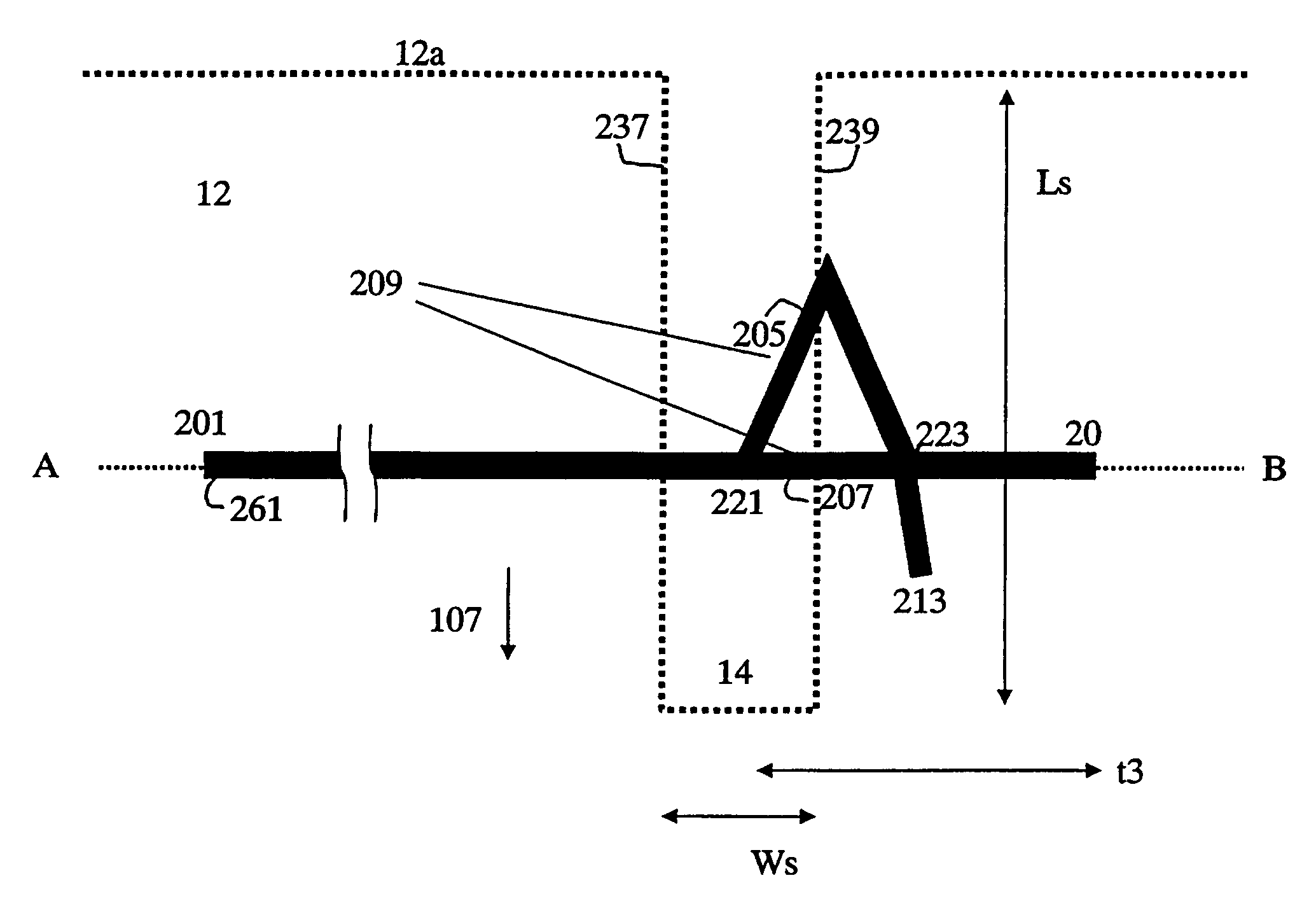

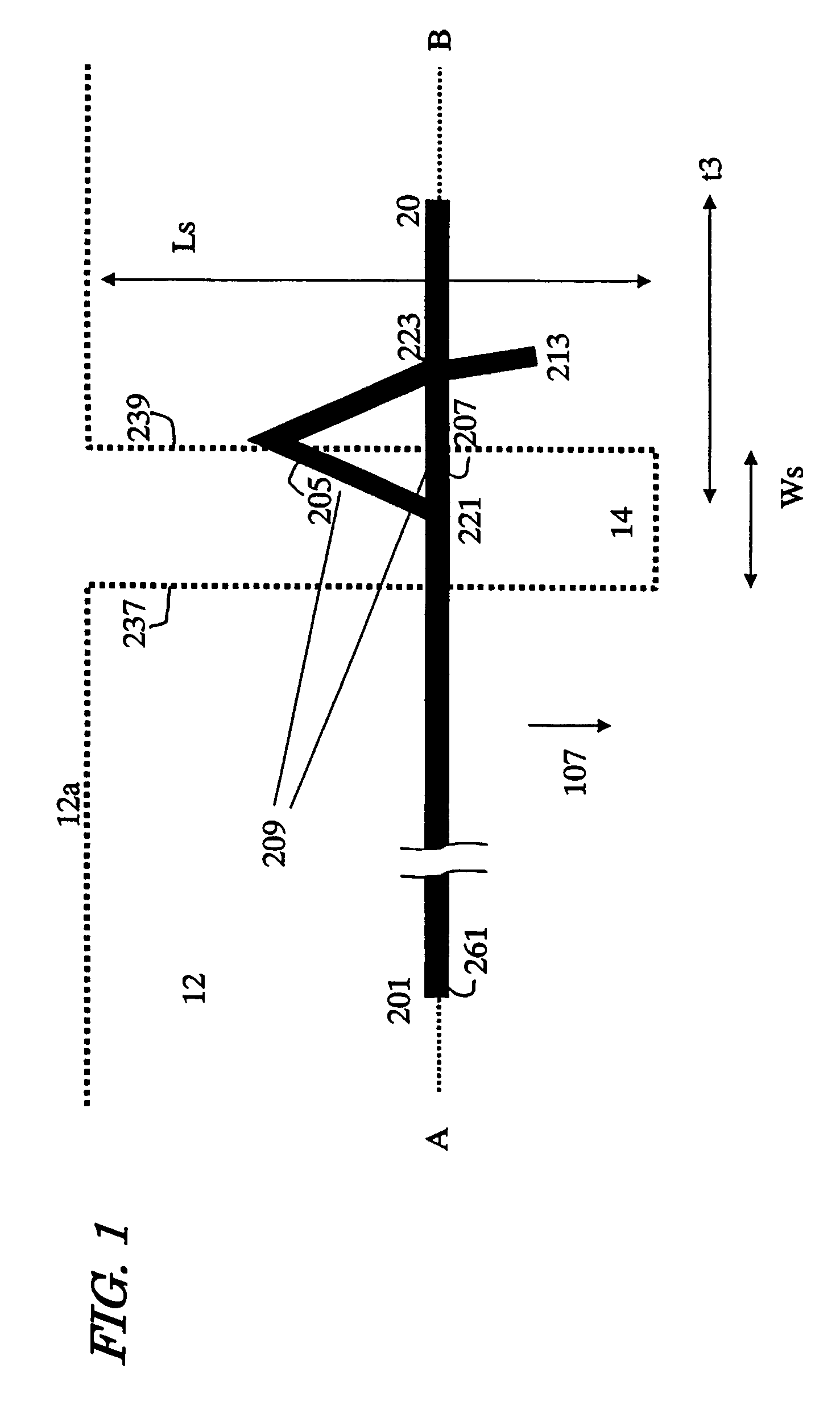

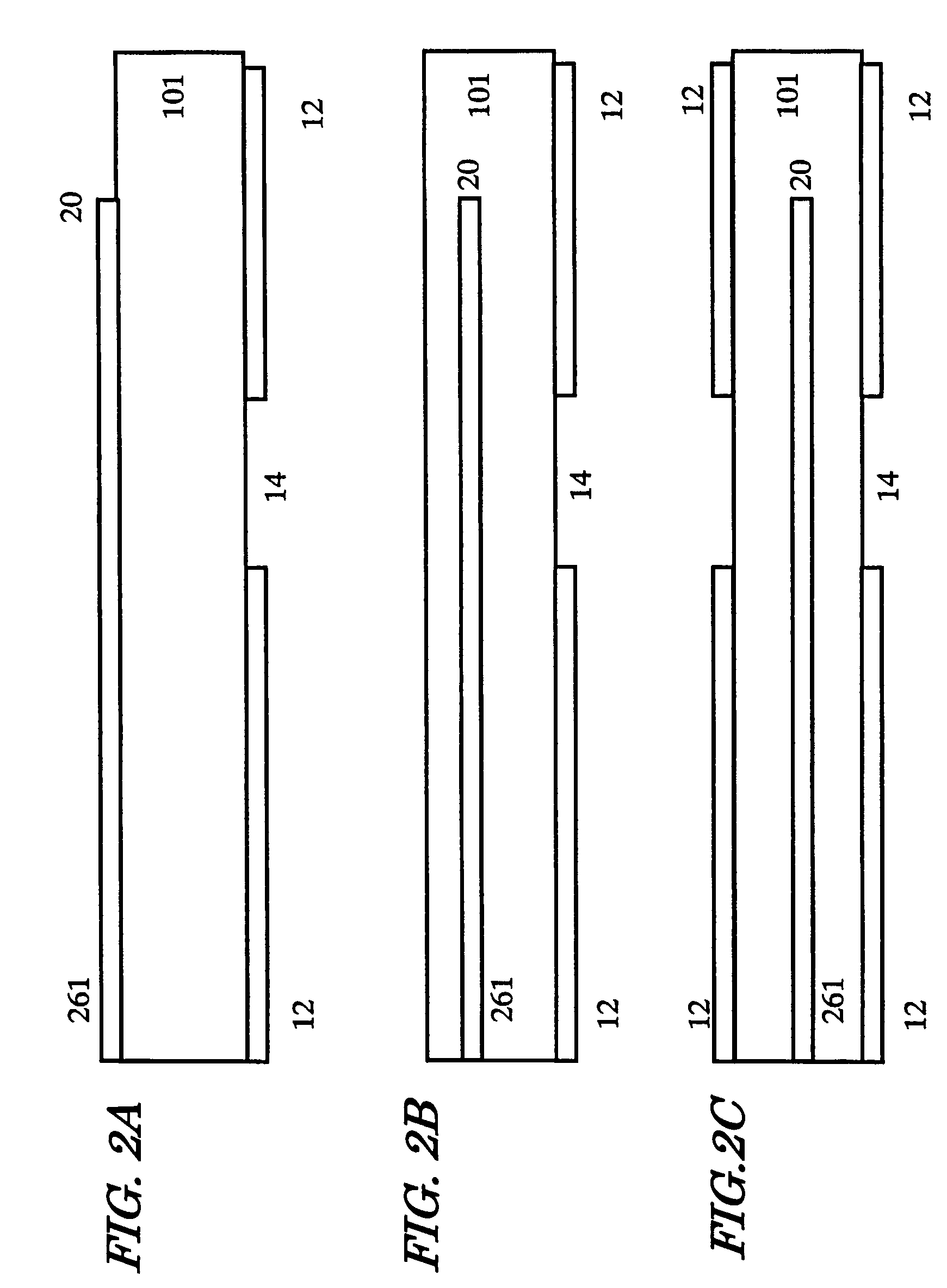

Slot antenna

InactiveUS7397439B2Simultaneous aerial operationsAntenna supports/mountingsElectrical conductorLoop length

A slot antenna according to the present invention includes: a ground conductor 12 provided on a rear face side of a dielectric substrate 101, the ground conductor having a finite area; a slot 14 which recesses into the ground conductor 12, beginning from an open-end point on a side edge of the ground conductor 12; and a feed line 261 for supplying a high-frequency signal to the slot 14, the feed line 261 intersecting the slot 14. At a first point near the slot, the feed line 261 branches into a group of branch lines including at least two branch lines, such that at least two branch lines in the group of branch lines are connected to each other at a second point near the slot to form at least one loop line 209. A maximum value of a loop length of each loop line 209 is prescribed to be less than 1× effective wavelength at an upper limit frequency of an operating band of the slot antenna. In the group of branch lines, any branch line that does not constitute a part of the loop line 209 but terminates with a leading open-end point has a branch length which is less than a ¼ effective wavelength at the upper limit frequency of the operating band.

Owner:PANASONIC CORP

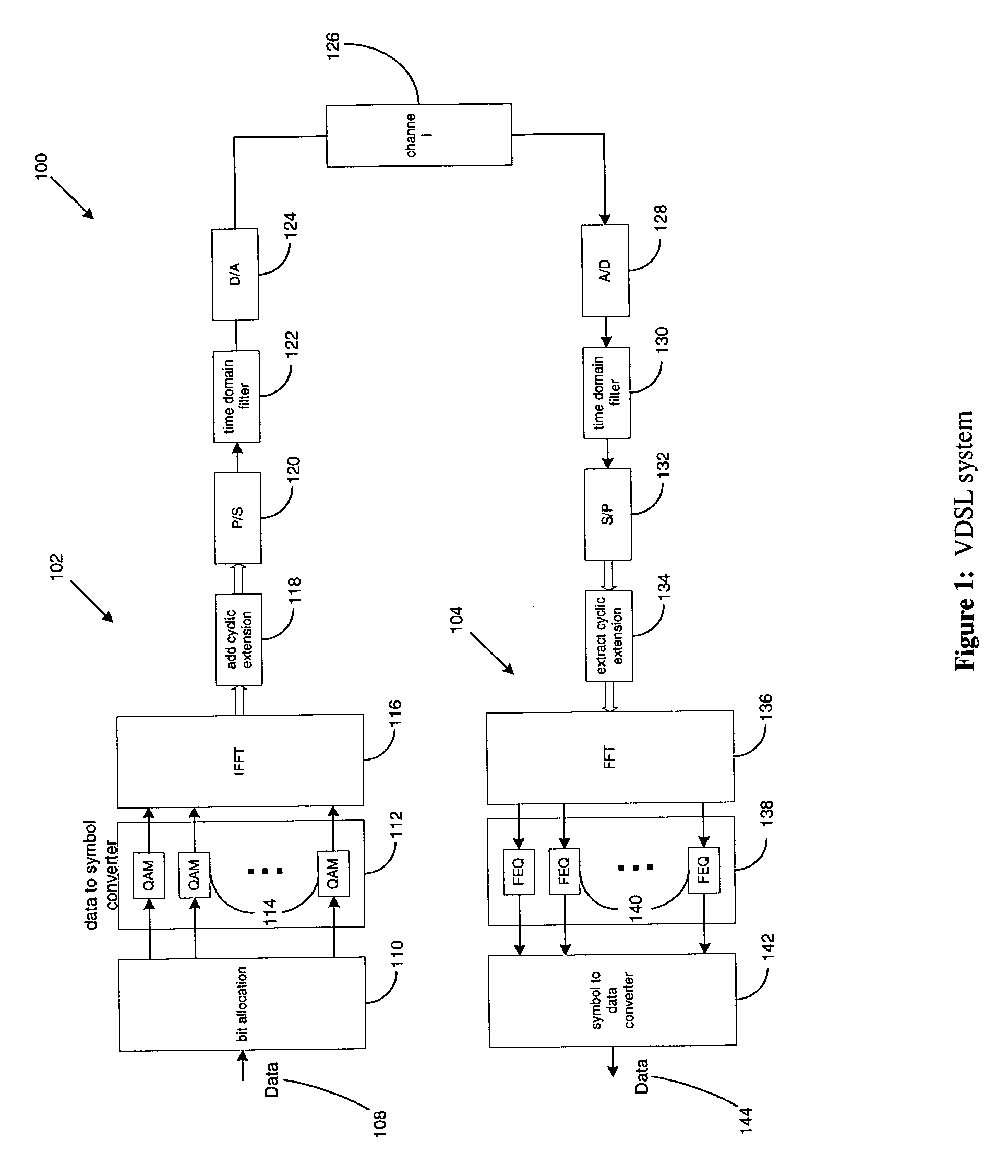

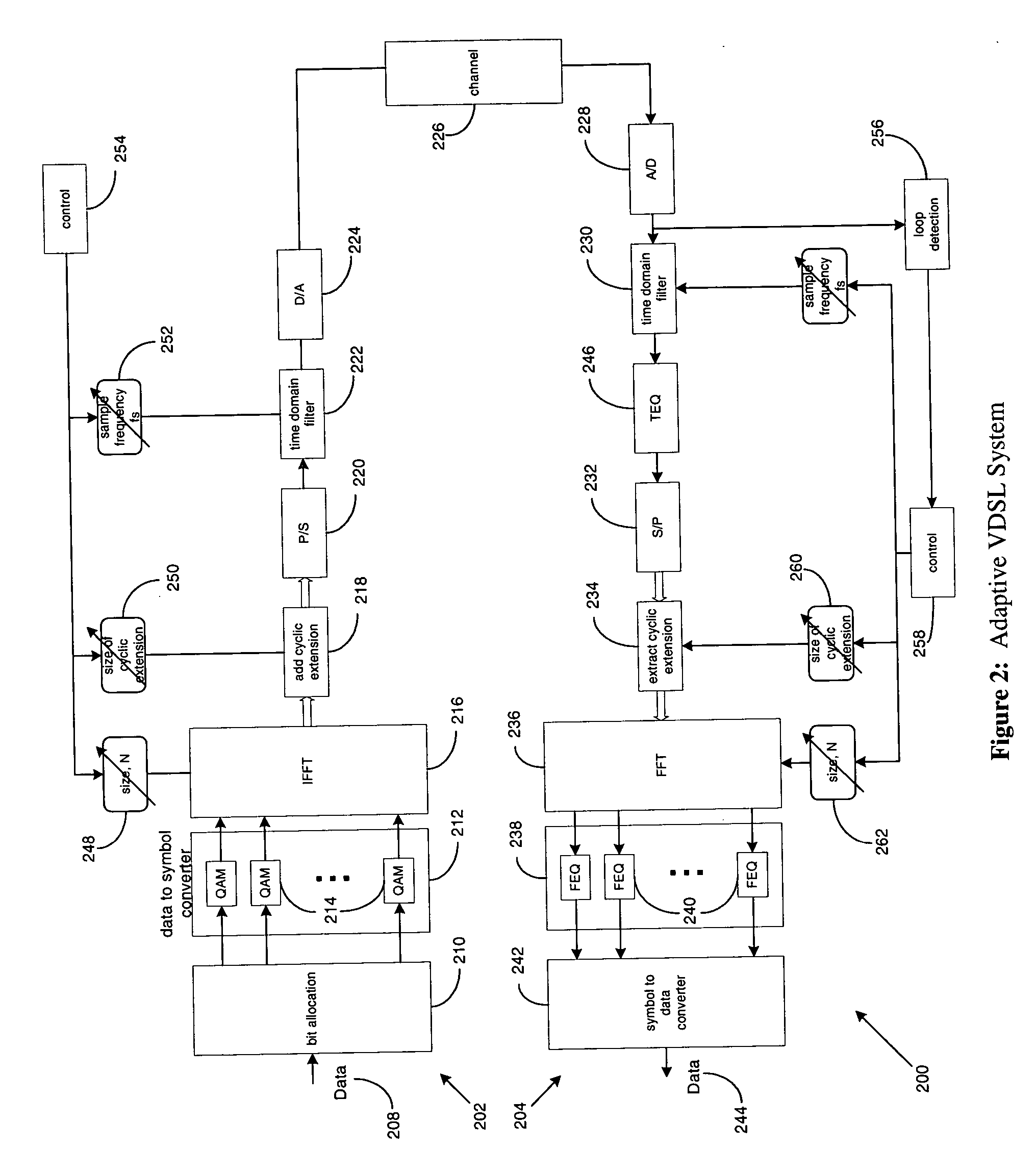

Systems and methods for adaptive VDSL with variable sampling frequency and time-domain equalizer

InactiveUS20060104339A1Lighten the computational burdenImprove system performanceMultiple-port networksDelay line applicationsLoop lengthTime domain equalization

A method and system for enhancing reach-performance of a multi-carrier VDSL System estimates loop length, estimates maximum available bandwidth that can be utilized at that particular loop length, optimally selects an FFT size and sampling rate, and decides whether to apply a time domain equalization to its receiver and if so, selects a cyclic extension size. To minimize the implementation complexity, the sampling frequencies at receiver and transmitter are lowered to match the actual usable bandwidth. The FFT / IFFT sizes in the implementation are also required to set appropriately accordingly.

Owner:IKANOS COMMUNICATIONS

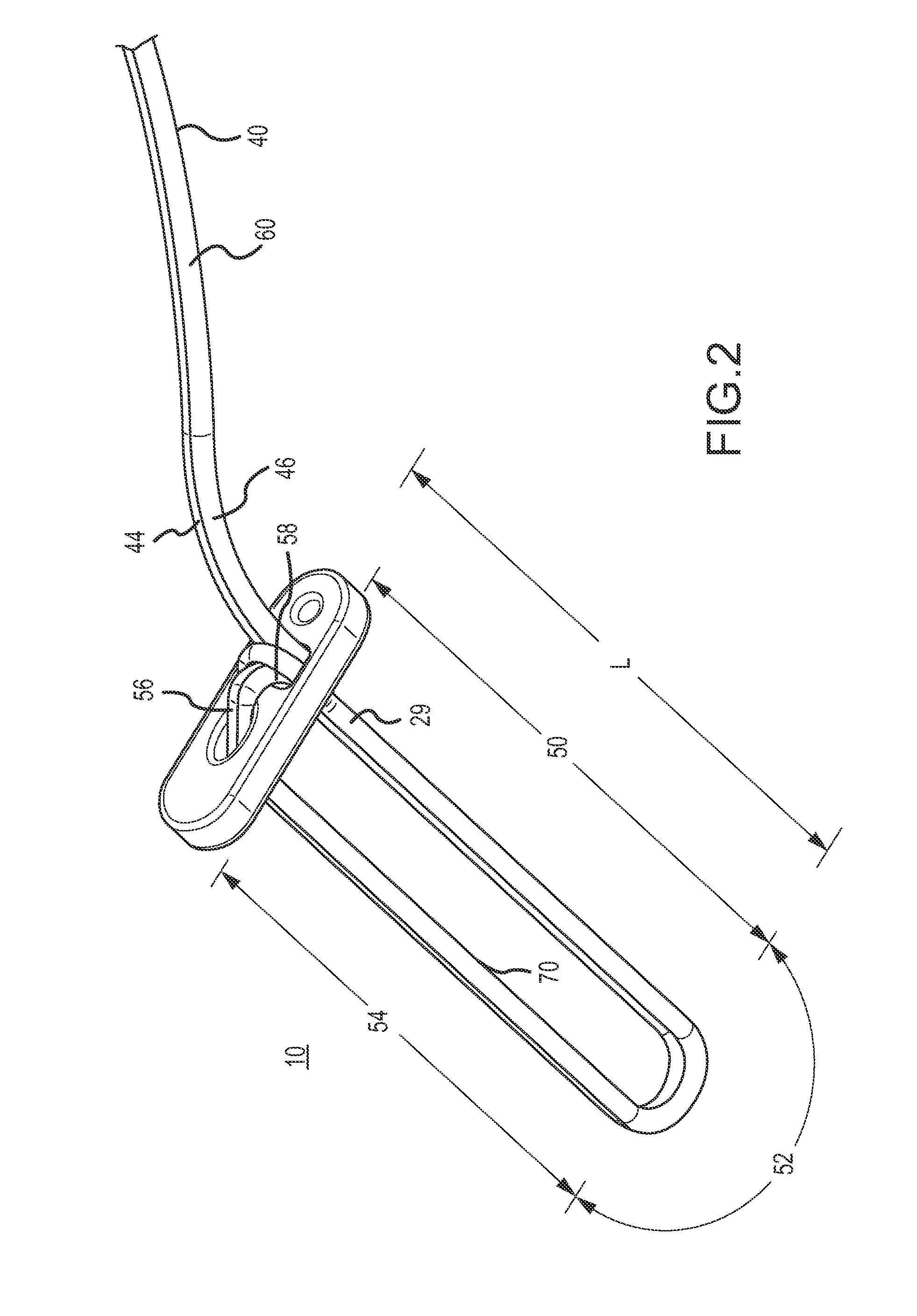

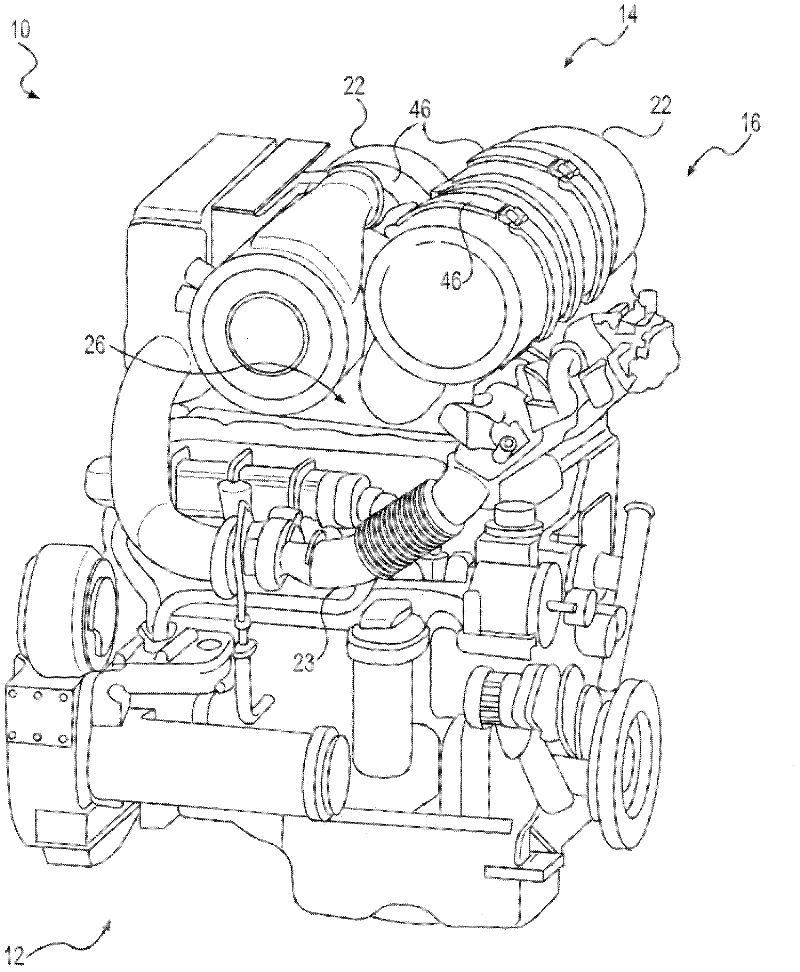

Strap for securing exhaust treatment device

A strap for securing an exhaust treatment device is disclosed. The strap has a first strap member that includes a coupler on a first end and a loop on a second end. The strap has a second strap member that is provided with the coupler on the first end. The coupler is configured to link with the coupler of the first strap member. The second strap member is provided with the loop on the second end. The loop includes a flexible material strap which forms the loop and is fixed on a point of securement. A loop length is not smaller than one third of the effective length of the strap. The effective length is defined as a distance from an end of the loop of the first strap member to an end of the loop of the second strap member when the coupler of the first strap member is coupled to the coupler of the second strap member. The loop length is defined as a distance from an end of the loop of the second strap member to the point of securement.

Owner:CATERPILLAR INC

Image forming apparatus with conveyance speed control based in part on loop detection

InactiveUS7398027B2Reduce generationPrevent image deteriorationElectrographic process apparatusLower limitLoop length

Conveyance speed of recording materials by a fixing roller pair can be set to conveyance speed based on detected results of a recording material detector and a loop detecting sensor, and information on the recording material that has been stored in a memory in advance, and the conveyance speed of the fixing roller pair is set so that loop length of the recording material will be a lower limit length, after the loop detecting sensor detects a loop of the recording material, and before the rear end of the recording material passes through the transfer roller pair.

Owner:CANON KK

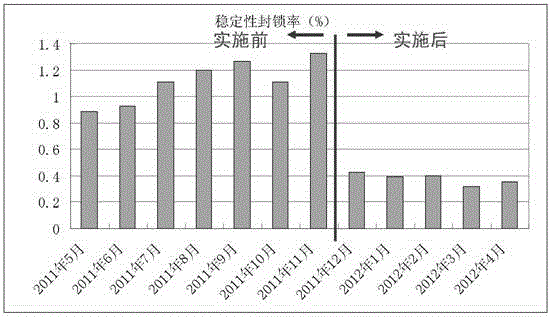

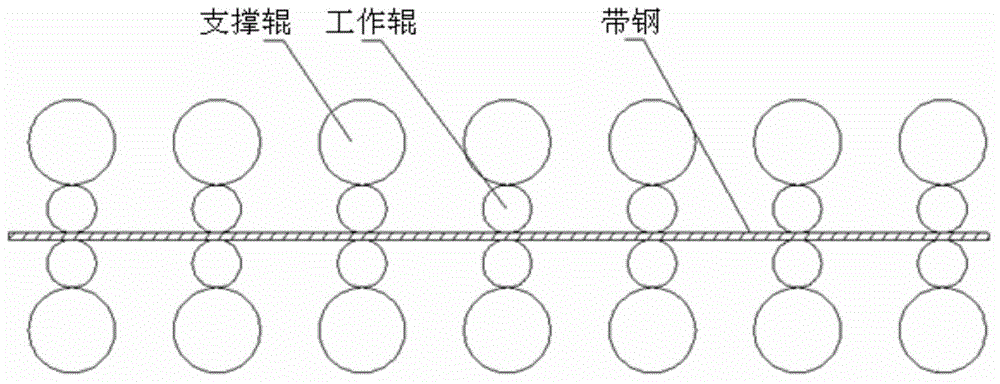

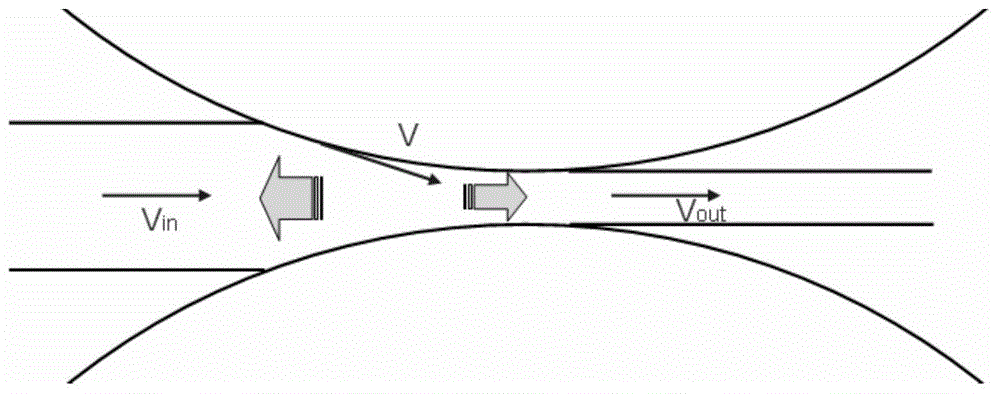

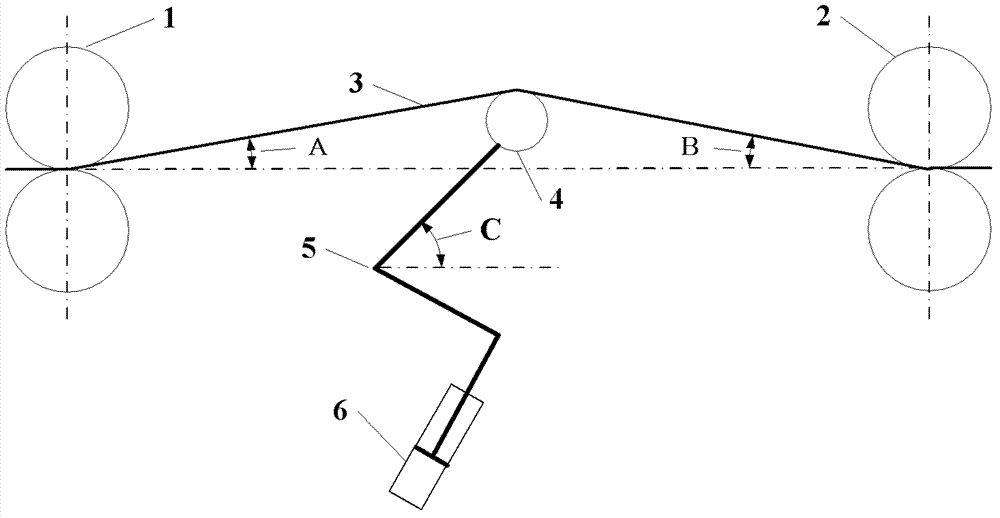

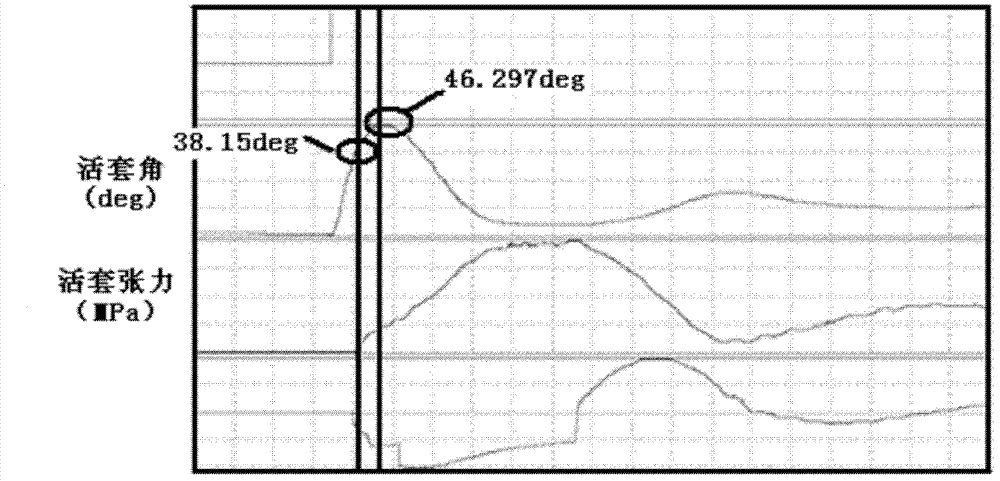

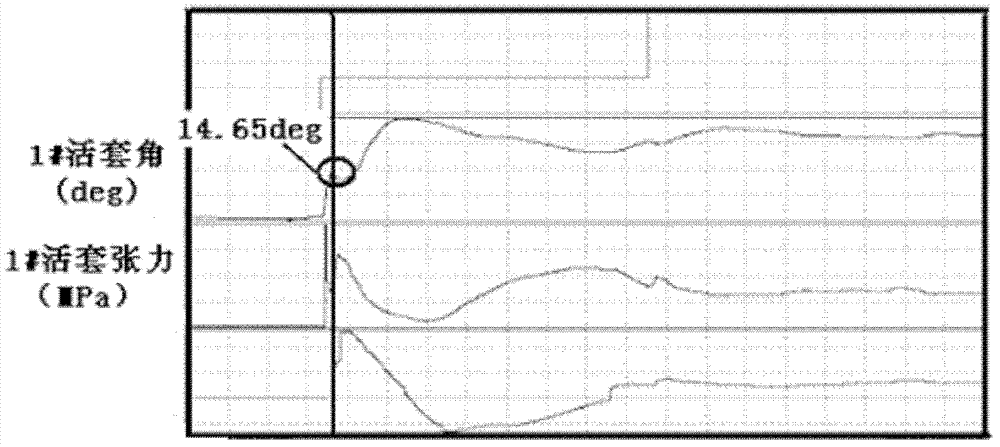

Method for automatically improving per-second flow balance of strip steel in hot continuous rolling strip threading process

ActiveCN104801548AIntelligent adjustment of speed ratioAdapt to changes in external working conditionsFlexible work arrangmentsMass flow control deviceLoop lengthEngineering

The invention provides a method for automatically improving per-second flow balance of strip steel in the hot continuous rolling strip threading process. Due to the fact that 'later' intervention of an operator is basically correct, the per-second flow balance can be changed more reasonable, an ideal rack speed matching value of a piece of steel is calculated by analysis the loop length and manual invention amount of the operator in the strip threading process and used for correcting setting of a next piece of same-specification steel. Compared with routine techniques, the method is characterized in that 'later intervention' is converted into accurate 'advanced correction', accordingly a complicated and tedious forward slip formula is omitted, and racks can have an 'intelligent learning' function on the speed aspect. According to the method, the complicated and tedious forward slip formula is omitted, and a method for automatically adjusting per-second flow matching between racks is found. The method is used for improving the per-second flow balance in the hot continuous rolling strip threading process and improving rolling stability so as to decrease strip steel head rolling breakage times and width decrease times. In addition, automation degree of strip threading is improved, and the working load of the operator is decreased.

Owner:BAOSHAN IRON & STEEL CO LTD

Method and apparatus for single end loop testing for DSL provisioning and maintenance

InactiveUS7460649B2Simple and robust in applicationReduce near-end echoSupervisory/monitoring/testing arrangementsSubstation equipmentDigital signal processingLoop length

A method and apparatus for single end loop testing for DSL provisioning and maintenance provides testing of the DSL loop using digital techniques including frequency compensation, matched filtering and median filtering, to remove strong background and enhance desired signal for peak detection. The SELT system allows DSL providers to extract loop information from reflective measurements at the central office (CO) so as to determine loop capability of supporting different DSL services. The method and apparatus acquires the desired signal (the far-end echo) which is submerged in the correlated background noise (the near-end echo) by providing a process for detecting loop length and termination types with high accuracy for loops up to 12 kft for 24 AWG and up to 9 kft for 26 AWG by exploiting several digital signal processing techniques including frequency.

Owner:IKANOS COMMUNICATIONS

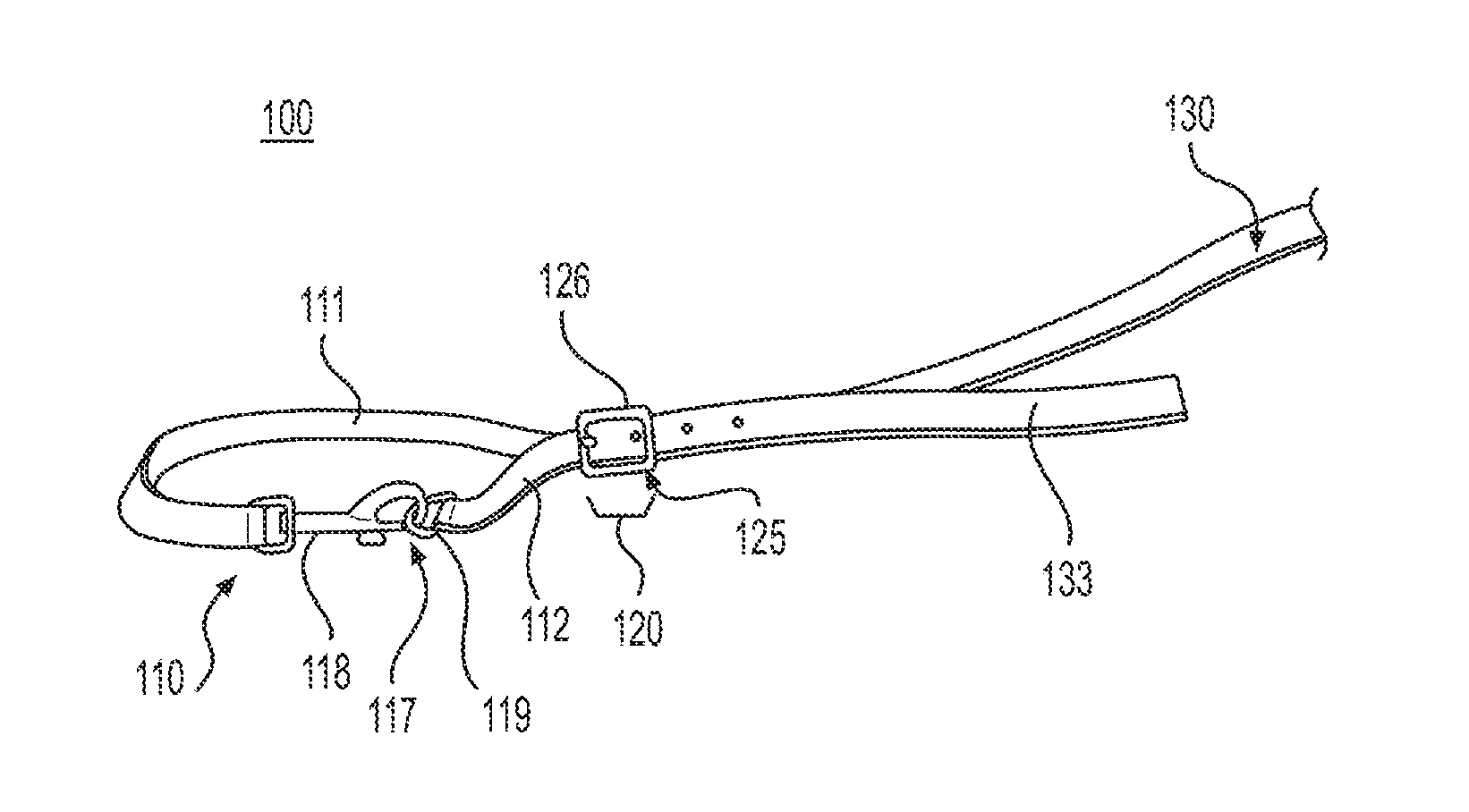

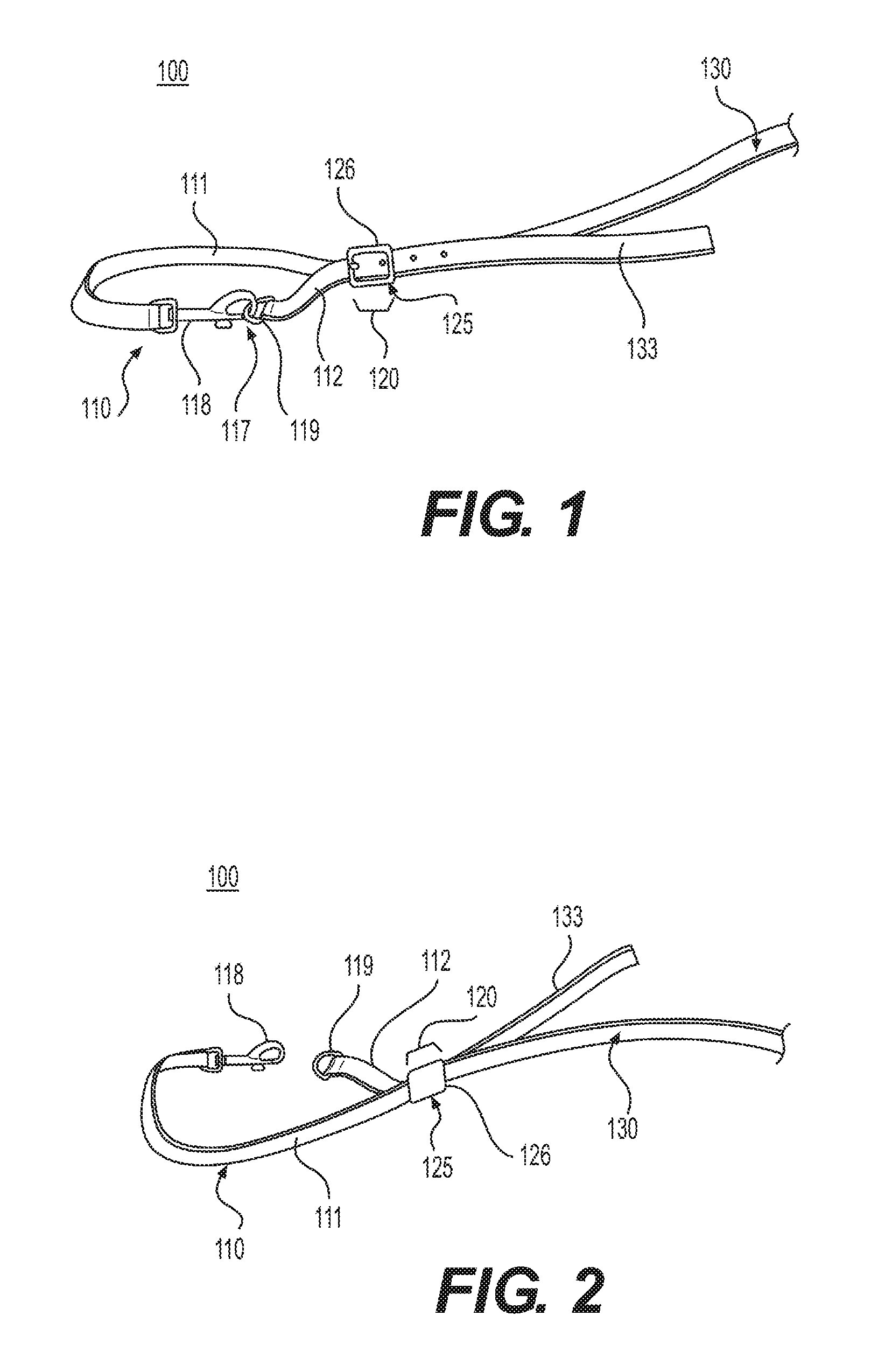

Leash Having Length-Adjustable Loop-Shaped Handle Portion and Method of Using Same

InactiveUS20160165849A1Easy to useEasily be restrained/tiedSafety beltsTaming and training devicesLoop lengthEngineering

A leash and method of securing an animal or person to an object using a leash are disclosed. Embodiments provide a leash that includes a handle portion having a handle portion fastening system, the handle portion being formed in a loop while the handle portion fastening system is releasably secured. The loop has a length which may be adjustable via an adjustment device. The adjustments to the loop length may be made via the adjustment device while the animal or person is secured to the object. Embodiments foster easy and quick restraint of an animal or human to an object without having to disconnect the leash from the animal's or human's collar or harness.

Owner:LEWIS BRANDON L

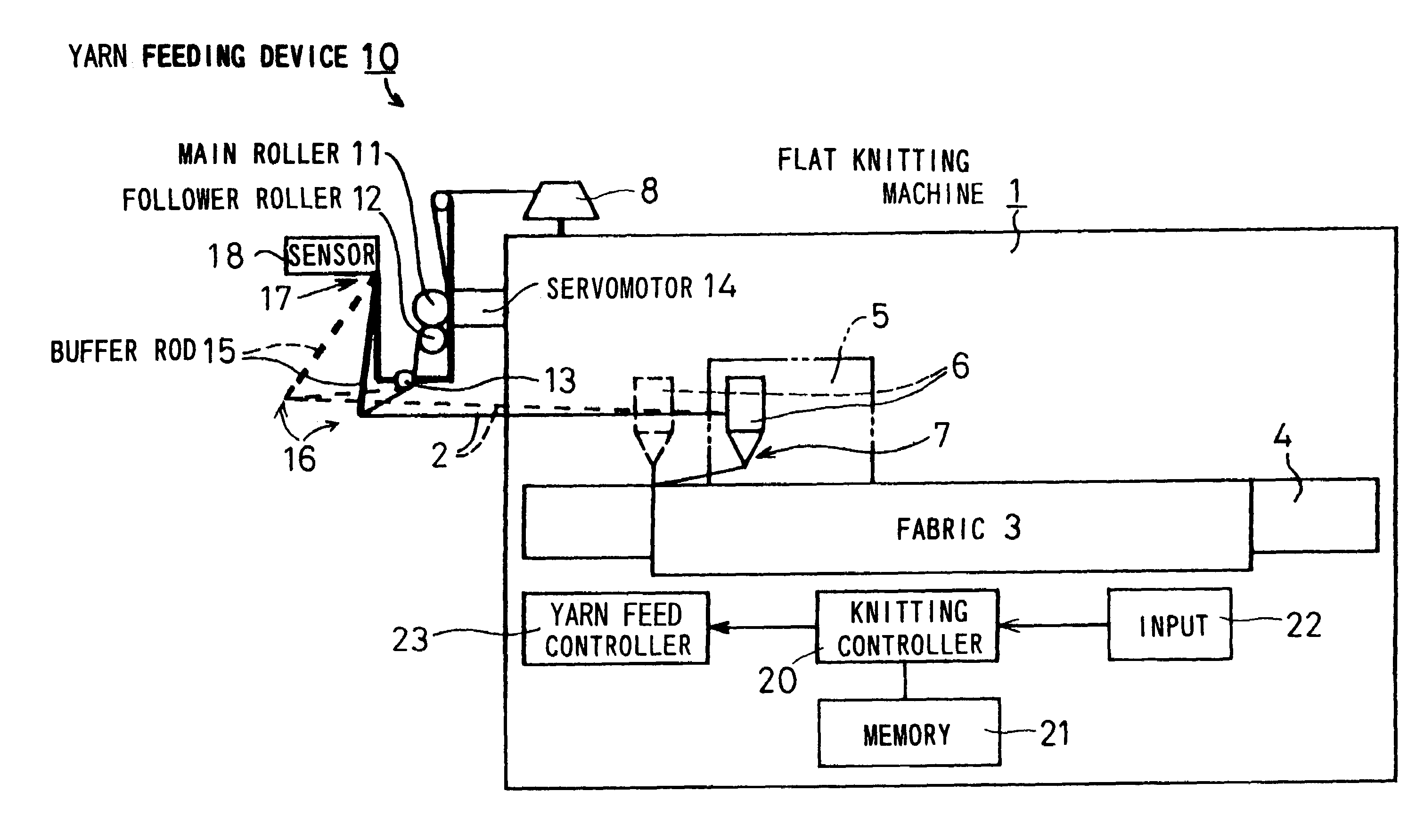

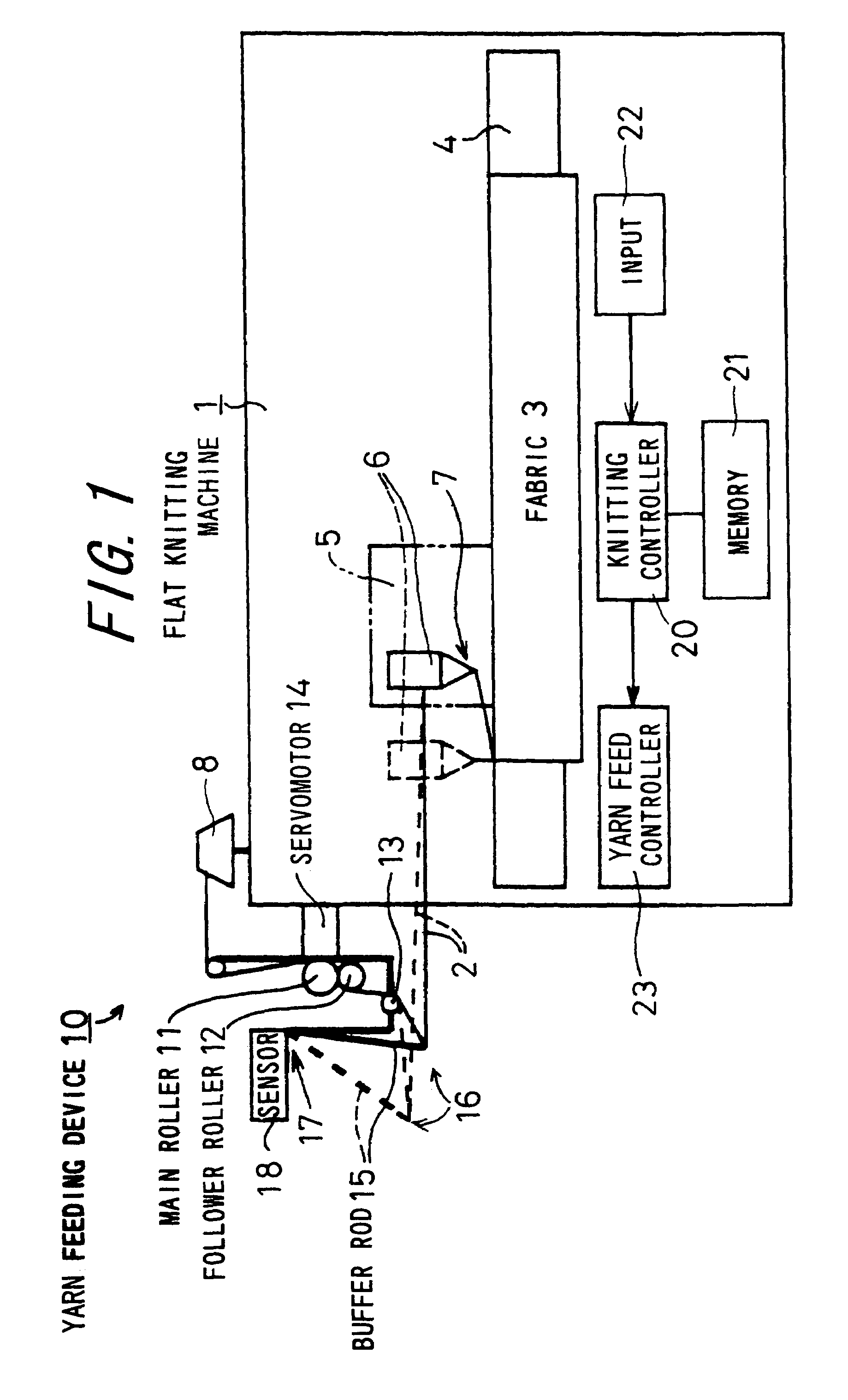

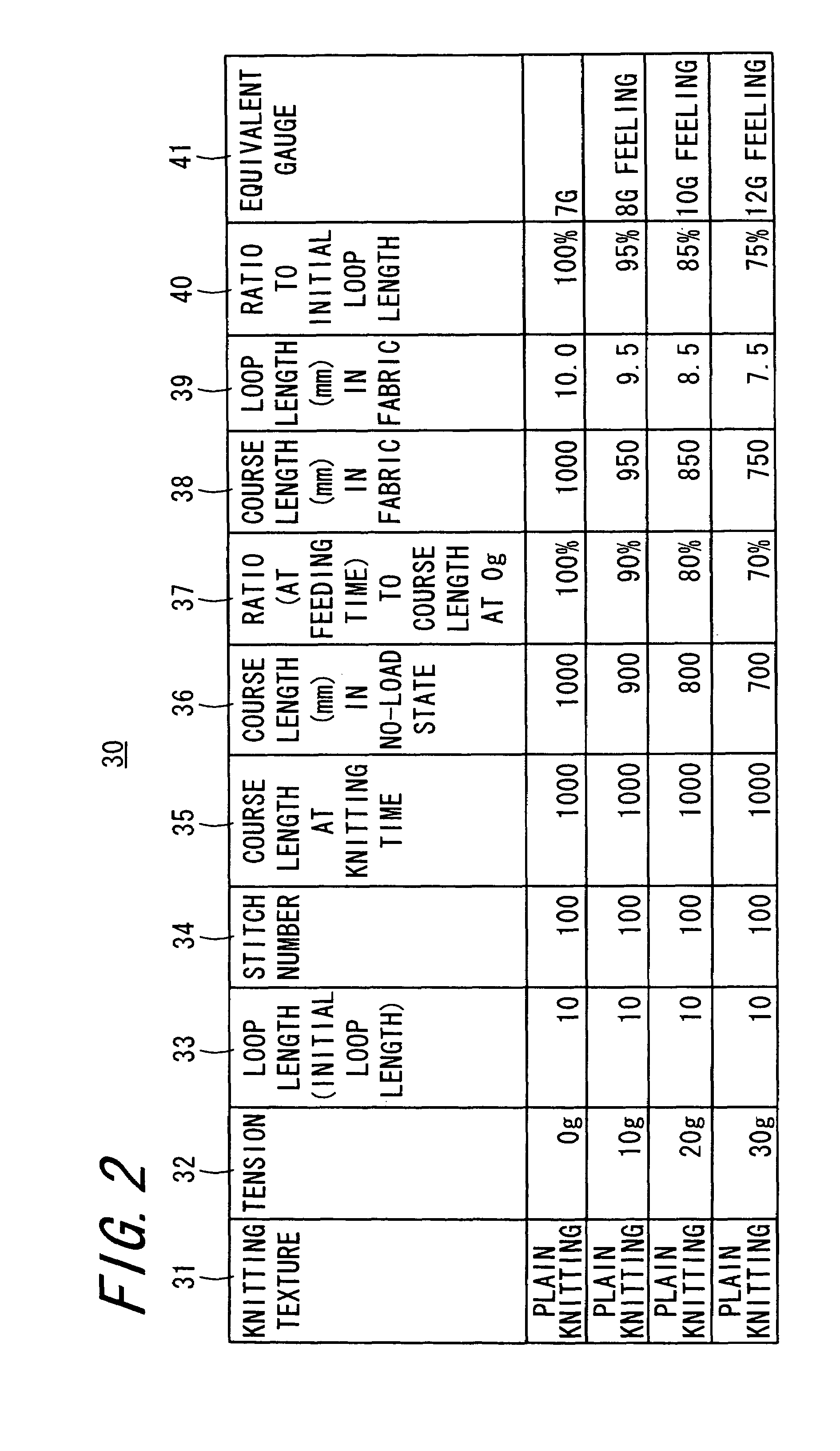

Knitting method and system using stretch yarn

An object of the invention is to be capable of easily acquiring a fabric having a desired feeling using a stretch yarn. A knitting controller (20) controls a carriage (5), and the like, according to knitting data and control data stored in a memory (21). Data representing relationships between a gauge texture and a stitch loop length being obtained after knitting and the relationships between these gauge texture and stitch loop length and the length and tension of the stretch yarn (2) being fed at the time of knitting are collected previously and stored in the memory (21) in the form of table data. The knitting controller (20) sets control target values of the length and tension of the stretch yarn (2) for a yarn feed controller (23) such that a gauge texture and a stitch loop length being specified by an input unit (22) can be attained, with reference to the table data stored in the memory (21).

Owner:SHIMA SEIKI MFG LTD

Forecasting method for loop length of hot continuous rolling mill

ActiveCN103191934AStable wearingFlexible work arrangmentsTension/compression control deviceLoop lengthStrip steel

The invention provides a forecasting method for loop length of a hot continuous rolling mill, which is used for forecasting all loop lengths between racks of hot continuous rolling before strip steel threading. According to the invention, the speed of anti-loop opening or anti-narrowing of the hot continuous rolling mill the loop corresponding to each loop can be obtained through the loop length generated at the moment of strip steel biting and speed drop compensation valve in order to prevent loop opening or loop narrowing, so as to obtain a loop length coefficient. The more is the loop length coefficient close to zero, the more stable threading of the strip steel can be realized, and accordingly, loop opening and narrowing can be avoided.

Owner:BAOSHAN IRON & STEEL CO LTD

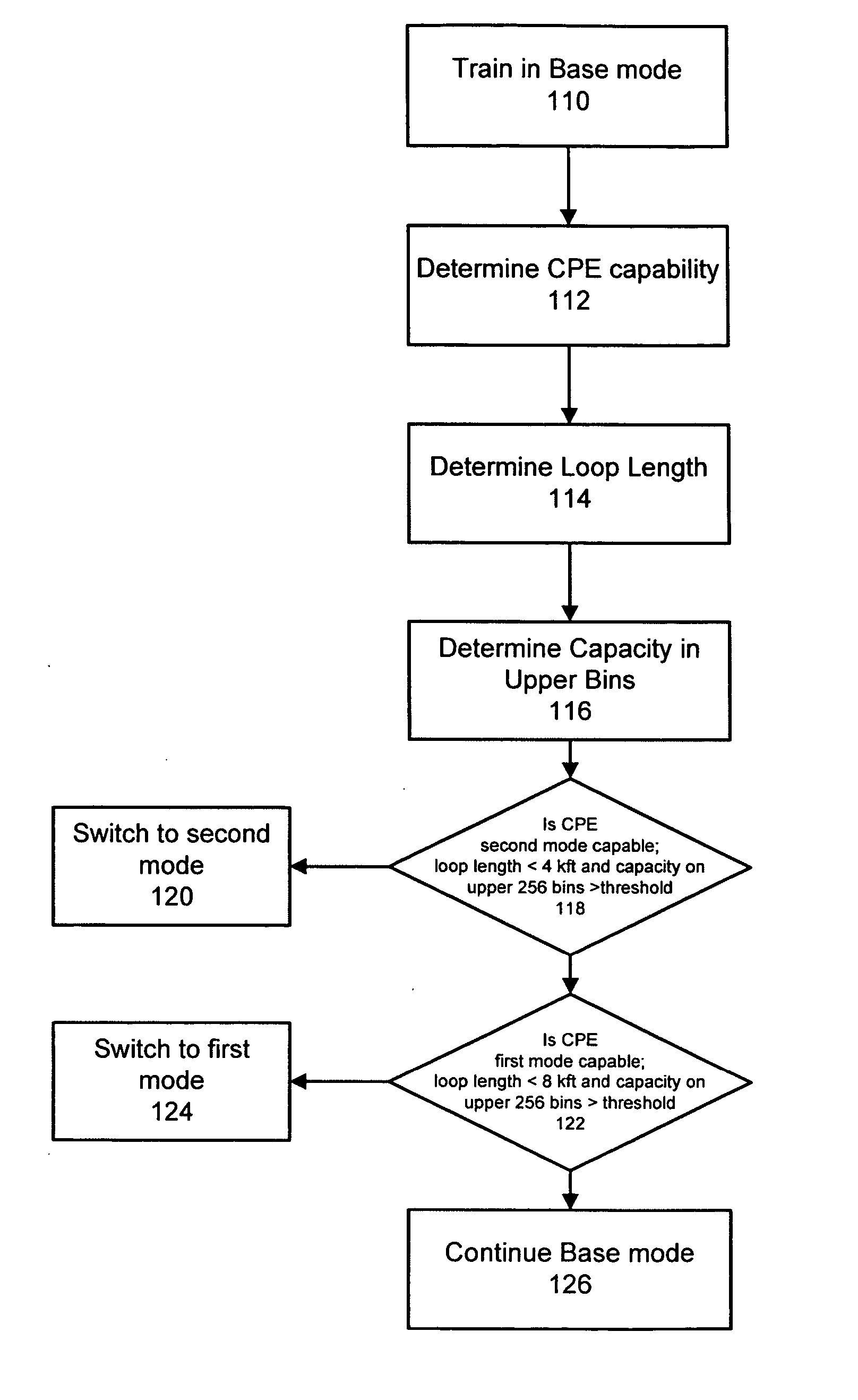

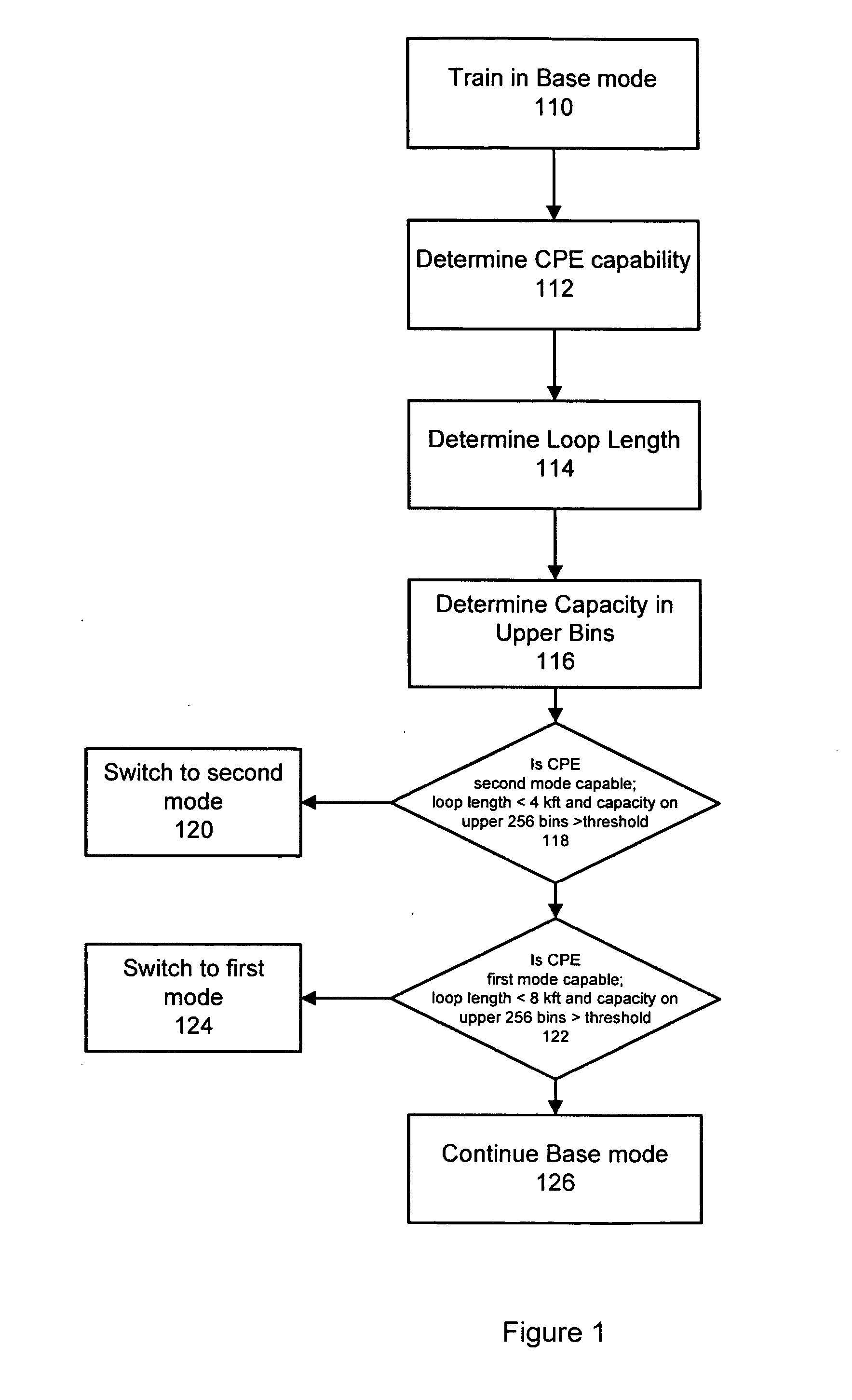

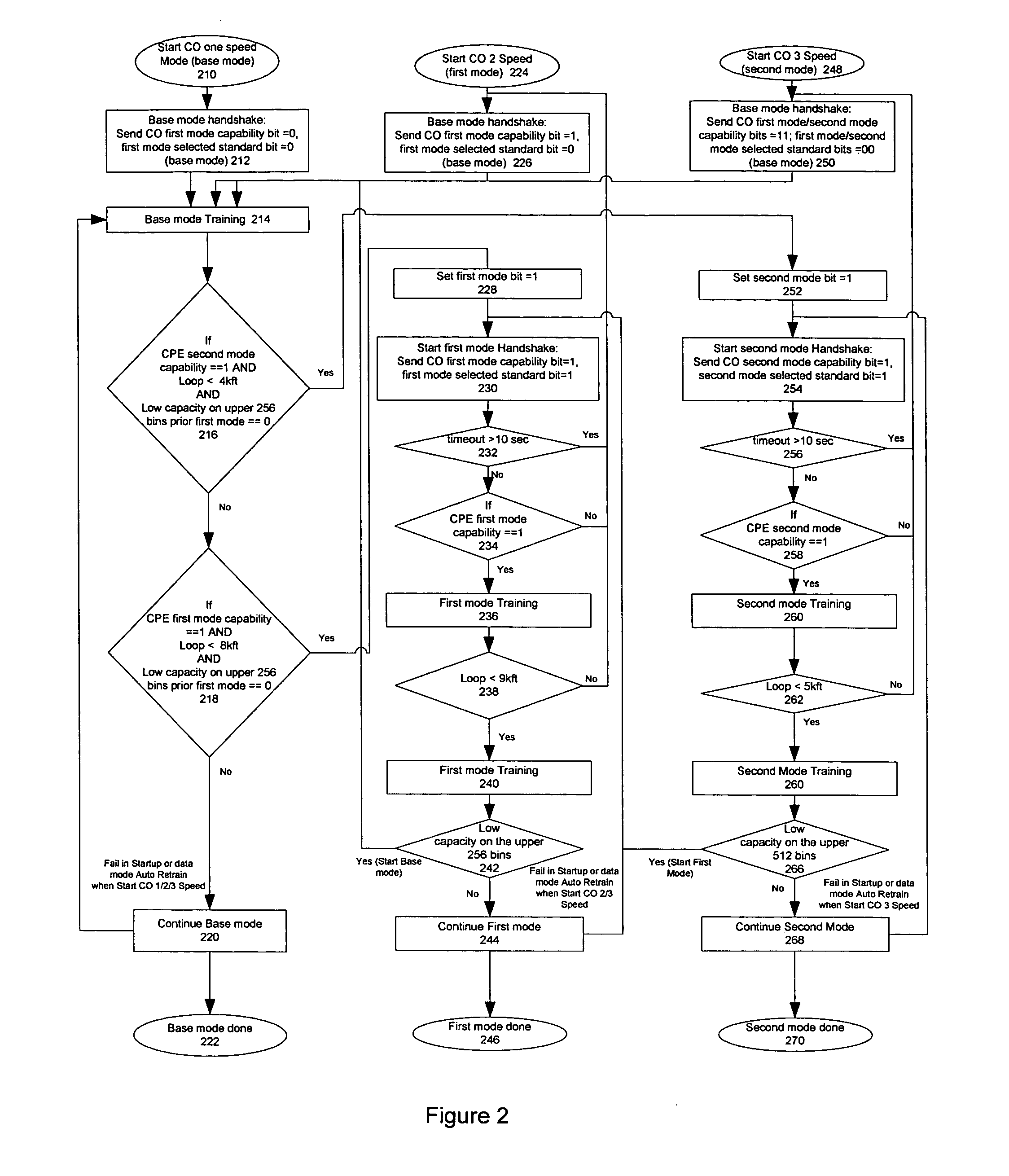

Method and system for selecting an optimal asymmetric digital subscriber line mode

A method and system of the present inventions are directed to selecting an optimal mode for ADSL operation based near / far end modem capability, loop length and capacity in the upper bands of modes of operation. A method for switching among a plurality of modes for ADSL modem operation may include the steps of determining a far end modem's capability for supporting one or more of a base mode, a first mode and a second mode; determining a loop length between a near end modem and the far end modem; determining a capacity in an upper band of the first mode and the second mode; and selecting an appropriate mode based on a combination of the far end modem's capability, the loop length and the capacity in the upper band.

Owner:IKANOS COMMUNICATIONS

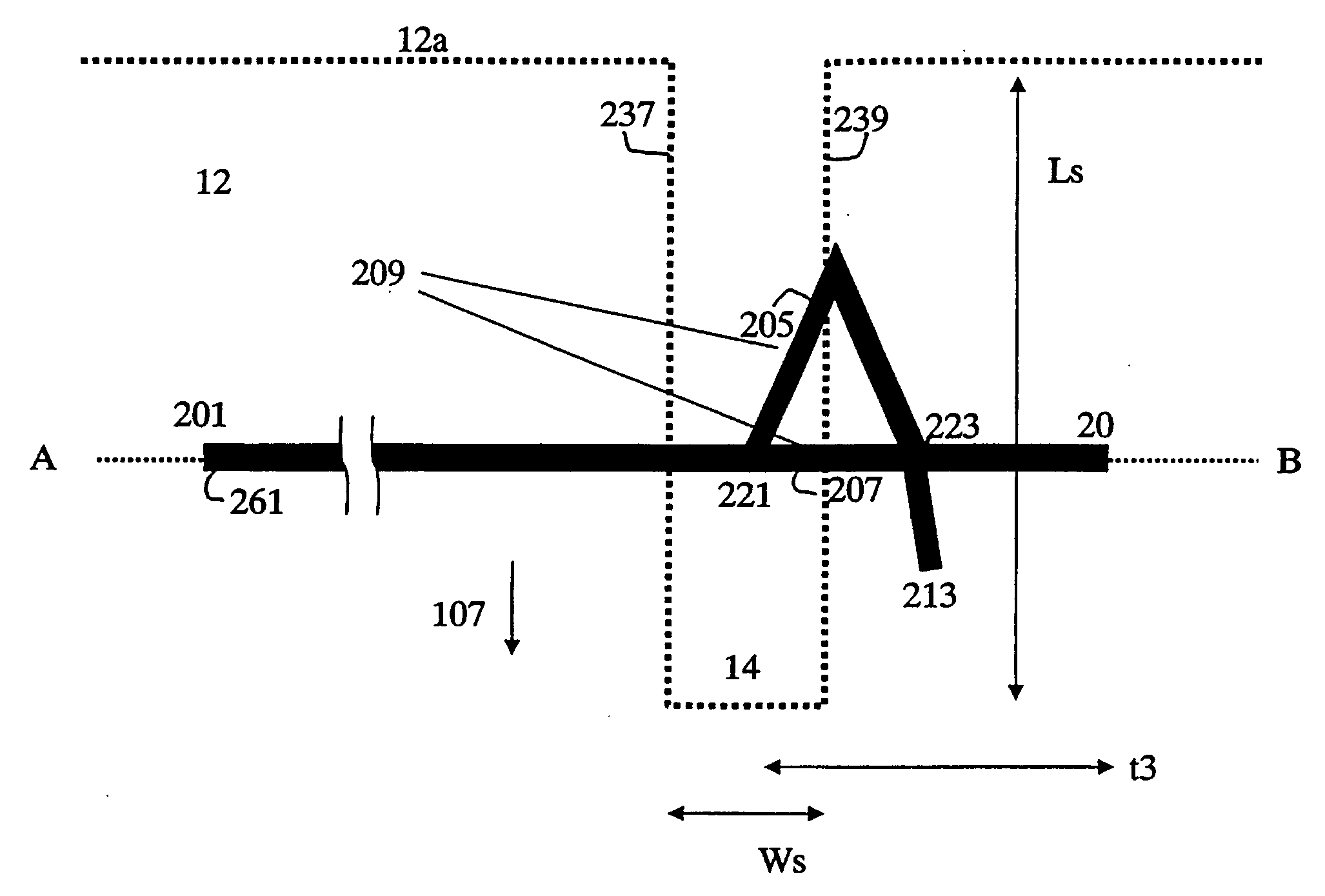

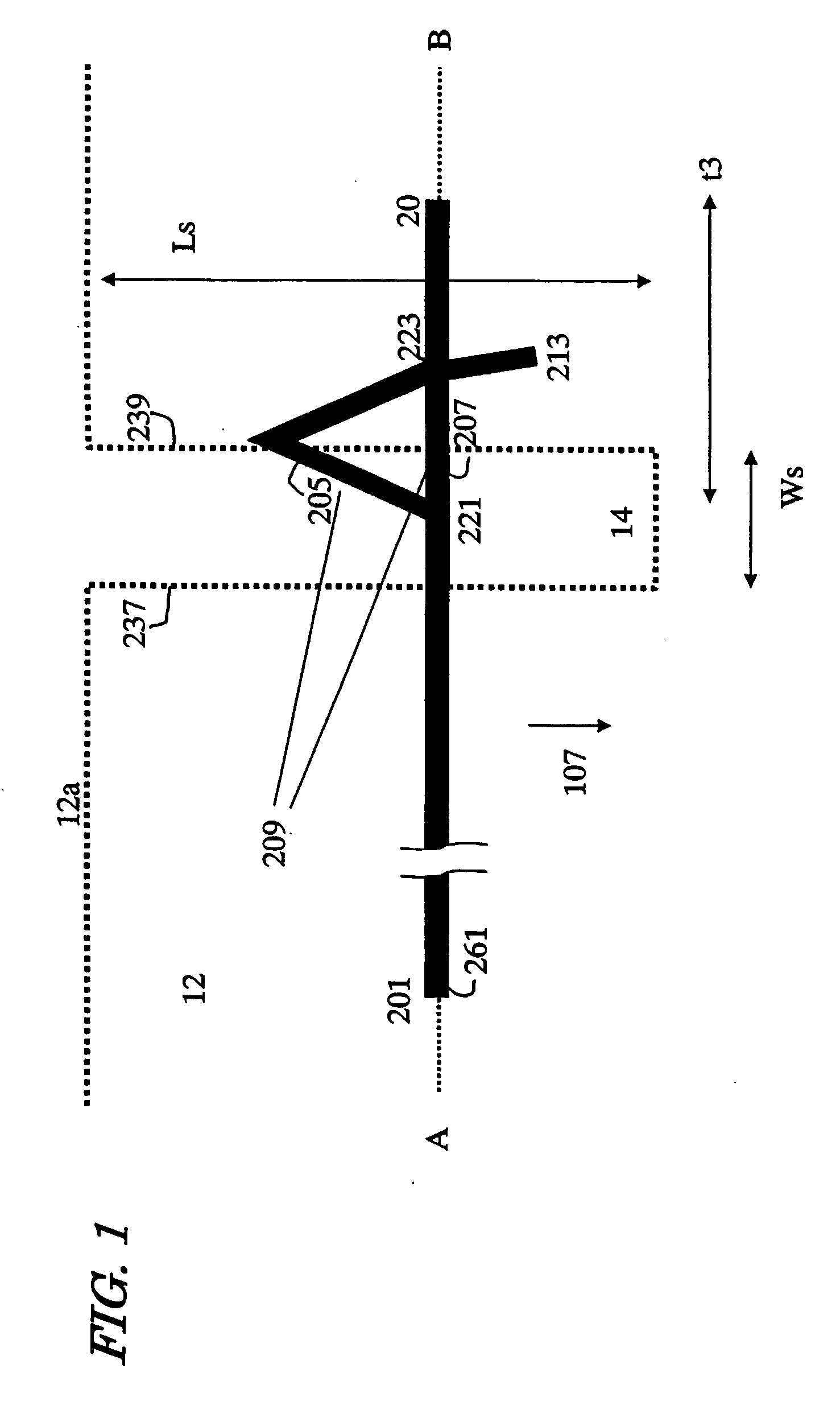

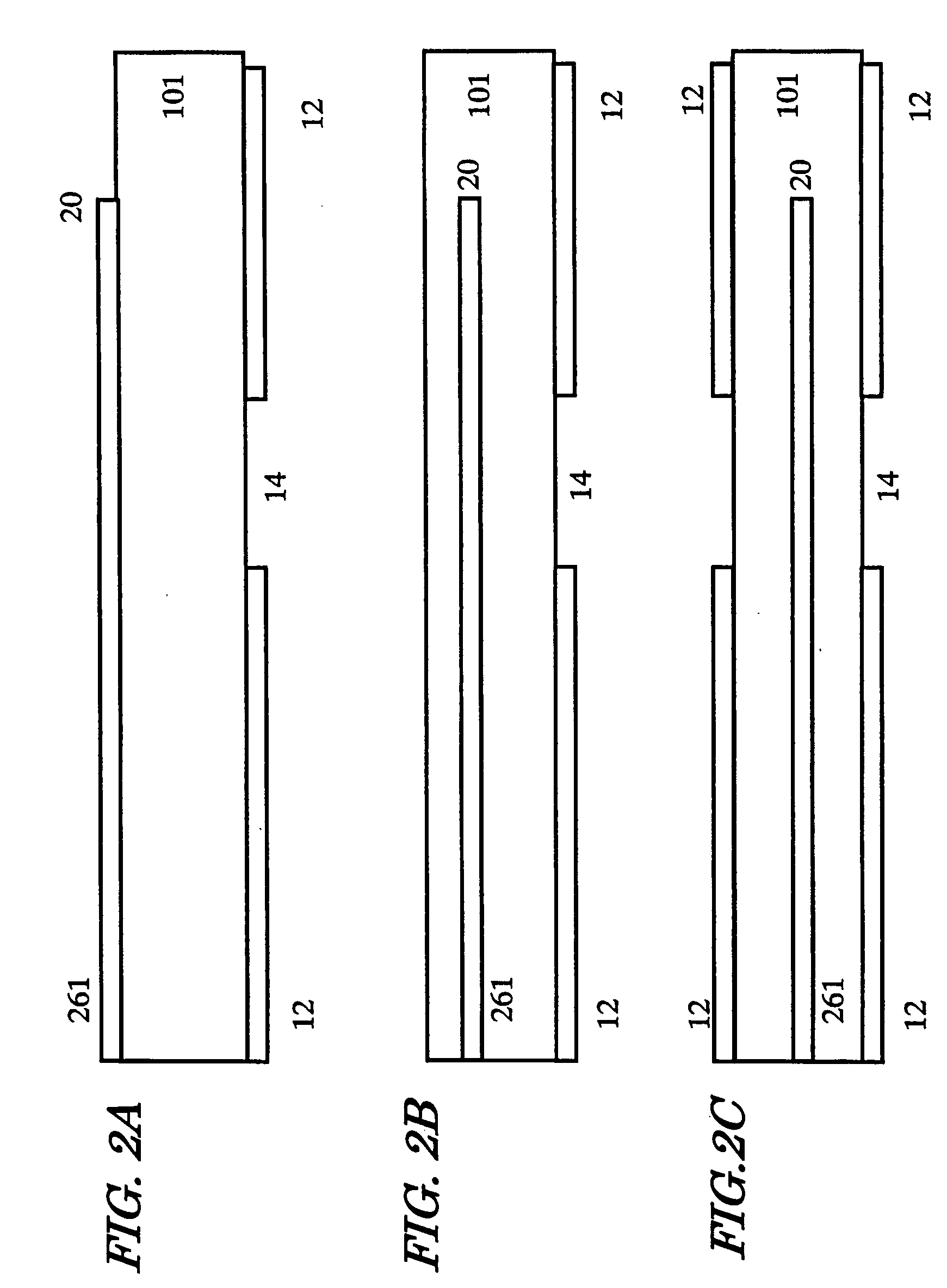

Slot antenna

InactiveUS20070164918A1Simultaneous aerial operationsAntenna supports/mountingsElectrical conductorLoop length

A slot antenna according to the present invention includes: a ground conductor 12 provided on a rear face side of a dielectric substrate 101, the ground conductor having a finite area; a slot 14 which recesses into the ground conductor 12, beginning from an open-end point on a side edge of the ground conductor 12; and a feed line 261 for supplying a high-frequency signal to the slot 14, the feed line 261 intersecting the slot 14. At a first point near the slot, the feed line 261 branches into a group of branch lines including at least two branch lines, such that at least two branch lines in the group of branch lines are connected to each other at a second point near the slot to form at least one loop line 209. A maximum value of a loop length of each loop line 209 is prescribed to be less than 1×effective wavelength at an upper limit frequency of an operating band of the slot antenna. In the group of branch lines, any branch line that does not constitute a part of the loop line 209 but terminates with a leading open-end point has a branch length which is less than a ¼ effective wavelength at the upper limit frequency of the operating band.

Owner:PANASONIC CORP

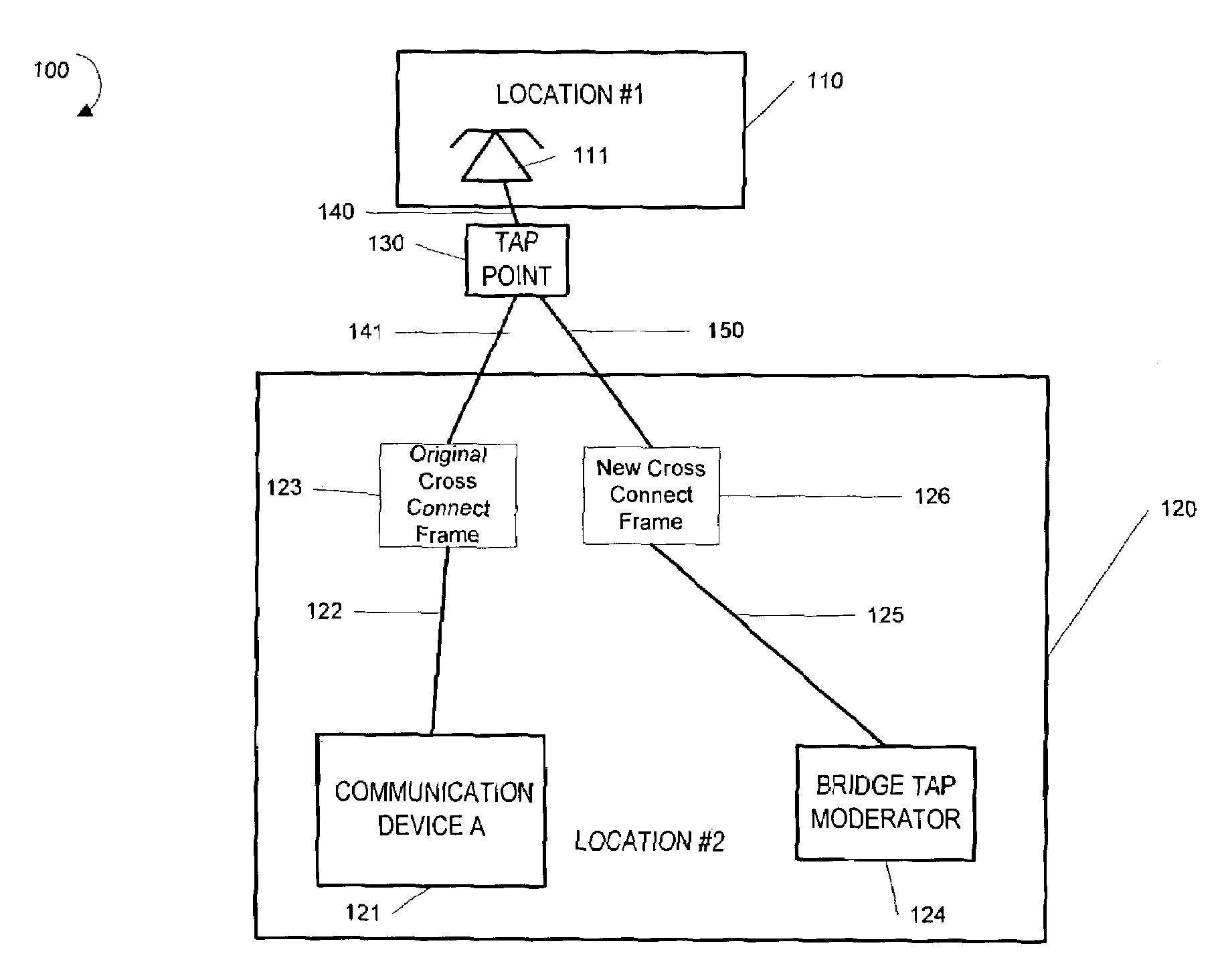

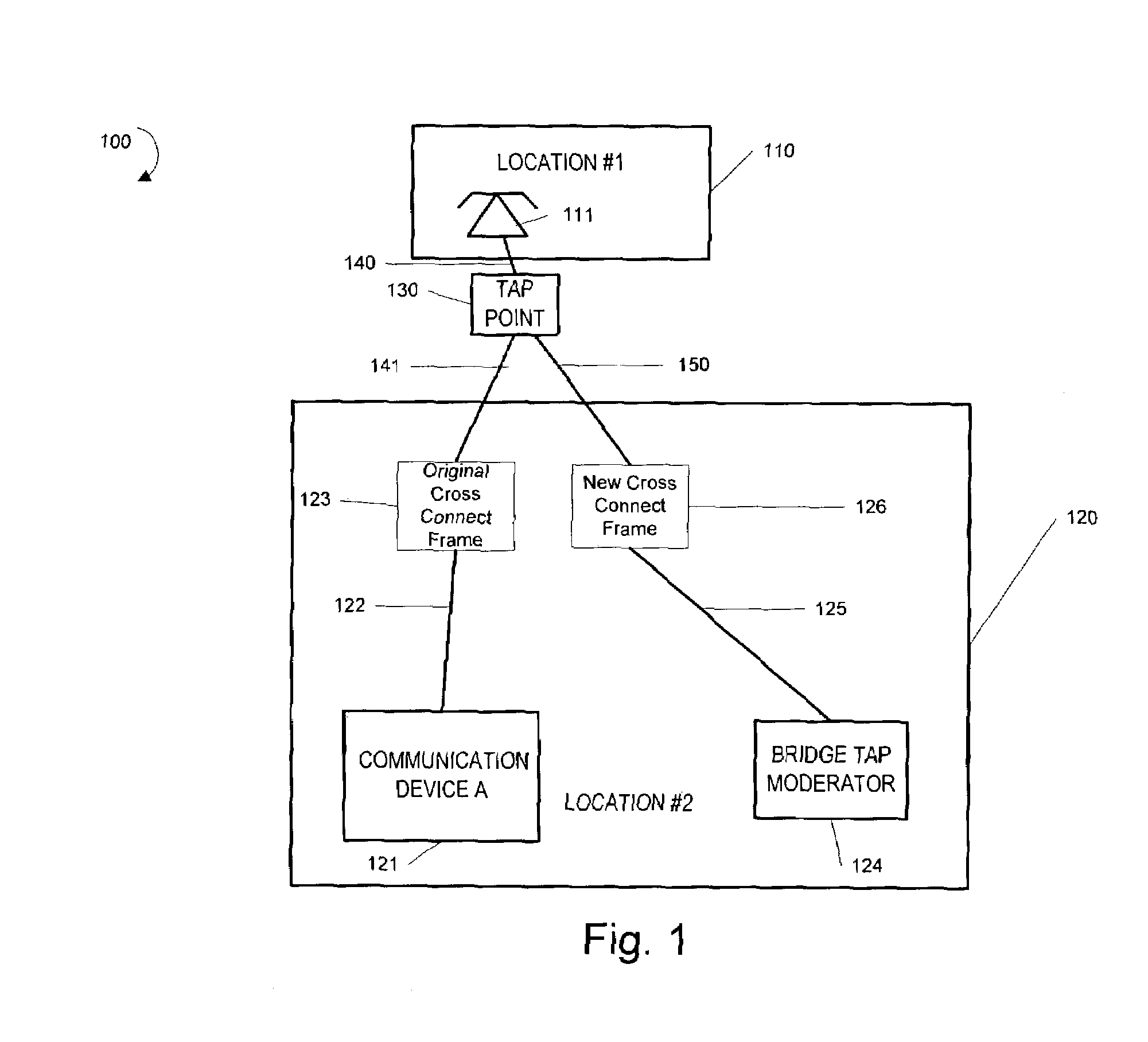

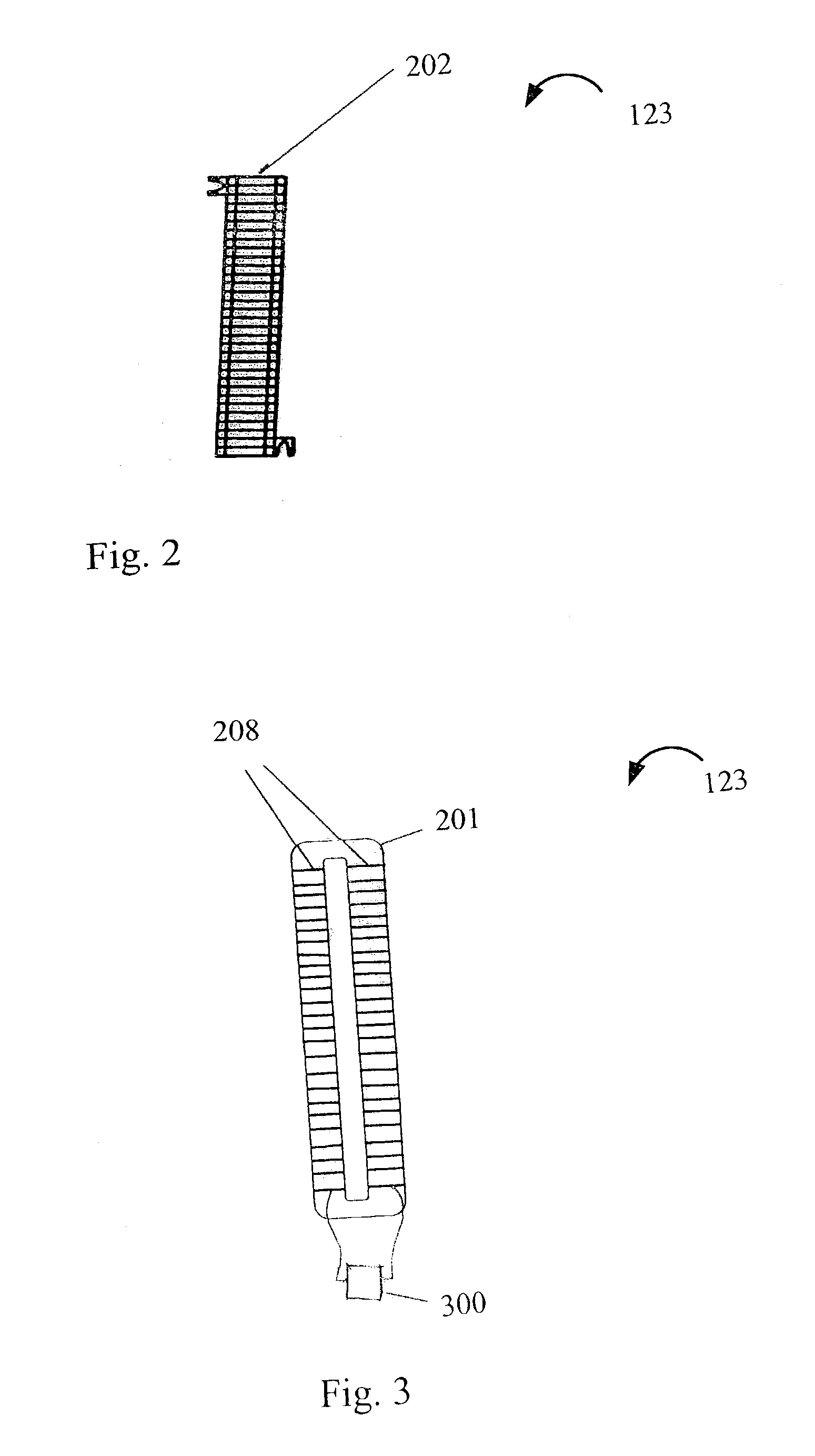

Methods and apparatus for a bridge tap moderator

InactiveUS7076056B1Shorten the durationEliminate the effects ofInterconnection arrangementsSubstation equipmentQuality of serviceLoop length

Methods and apparatus for protecting quality of service during a process involving bridge tap in a communications system are described. Bridge tap may occur during system construction, central office re-concentration, replacement projects, upgrade projects, expansion projects, and installation of back-up cables, etc. Cables, with one end connected to a point in the system, and the other end left unterminated, result in bridge tap. In the bridge tap moderator of the present invention, a plurality of termination networks are attached to a modular connector such that a separate termination load is placed across each connector terminal pair for each corresponding wire pair of the cable. Communication lines can be easily attached to the moderator thereby easily, quickly, and efficiently eliminating bridge tap on a large number of wire pairs. The bridge tap modulator apparatus and method of use also minimize the amount of time bridge tap exists during cable and / or communication device installation. The use of bridge tap moderator results in improved overall system performance reflected in an improvement in attainable sync rate and increase in allowable loop length.

Owner:VERIZON PATENT & LICENSING INC