Patents

Literature

6584results about How to "Reduce demand" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

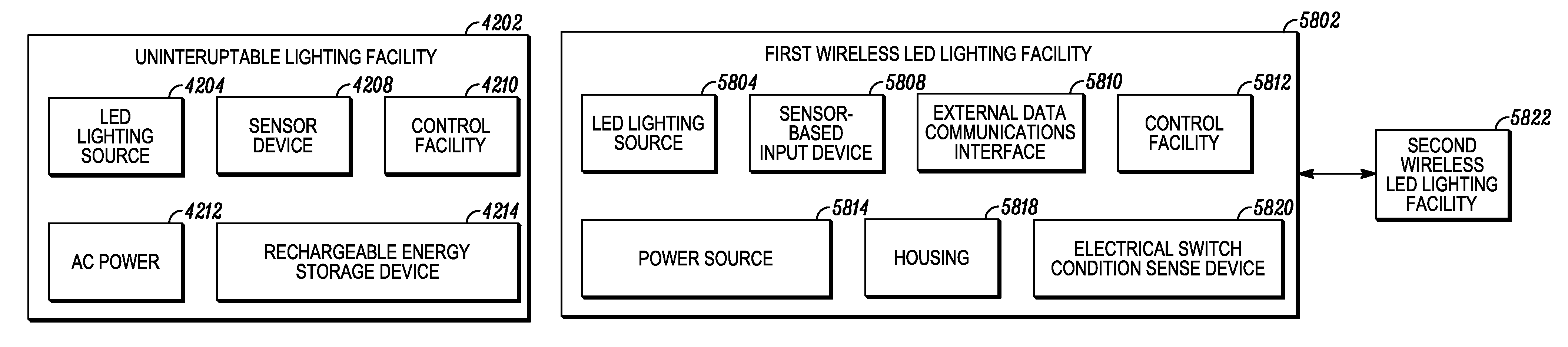

Autonomous grid shifting lighting device

InactiveUS20110133655A1Advantage in easeLow costElectroluminescent light sourcesSemiconductor lamp usageElectricityEffect light

In embodiments of the present invention improved capabilities are described for autonomous shifting of at least a portion of a lighting load off an energy distribution grid, comprising electrically connecting a lighting device to the energy distribution grid; causing the lighting device to interpret information obtained from an information source proximate the lighting device; and causing the lighting device to select from at least two different power sources based on the interpretation, where selecting may include a sharing of the load between the two different power sources, and where one power source may be the energy distribution grid.

Owner:RING LLC

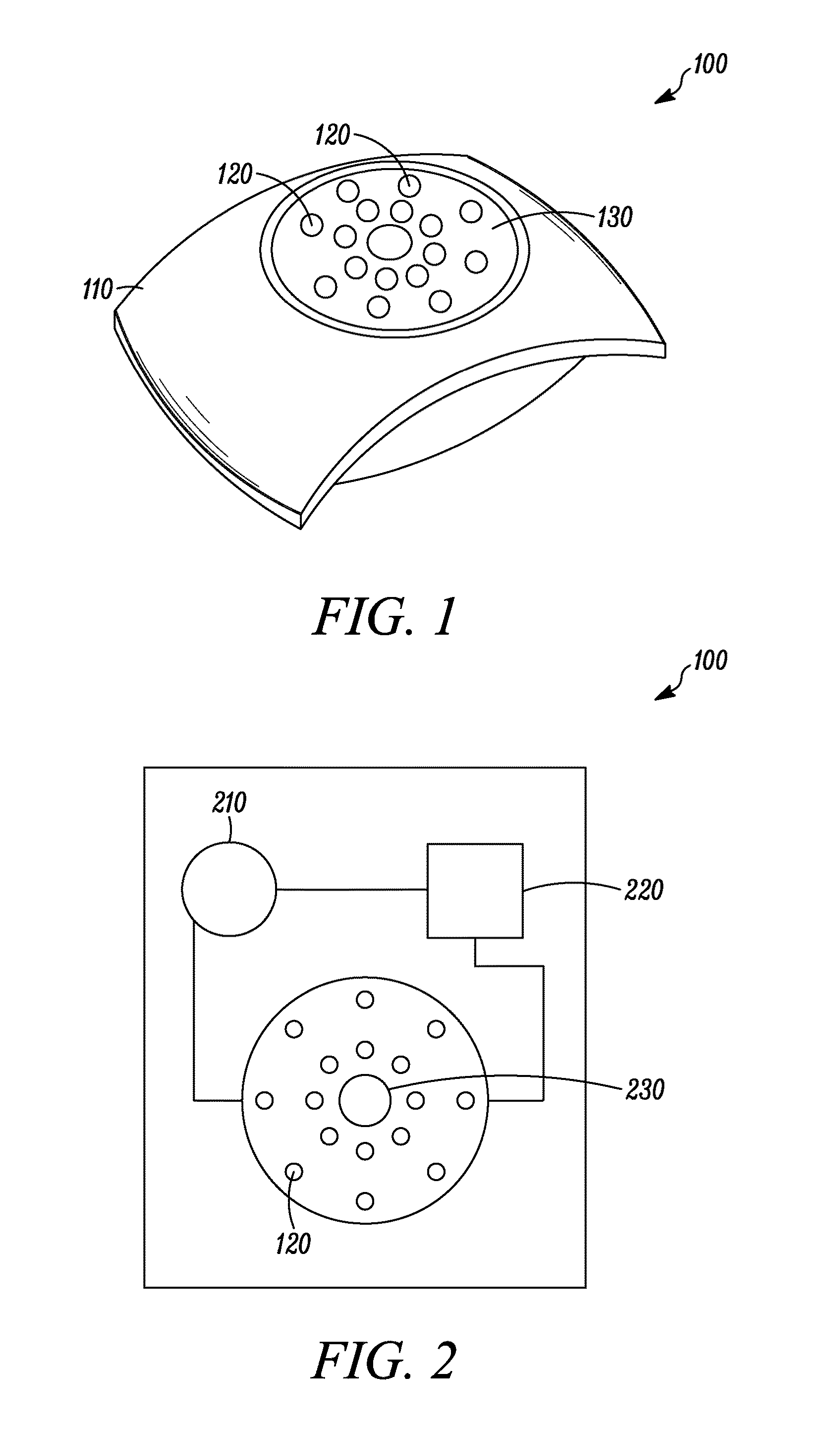

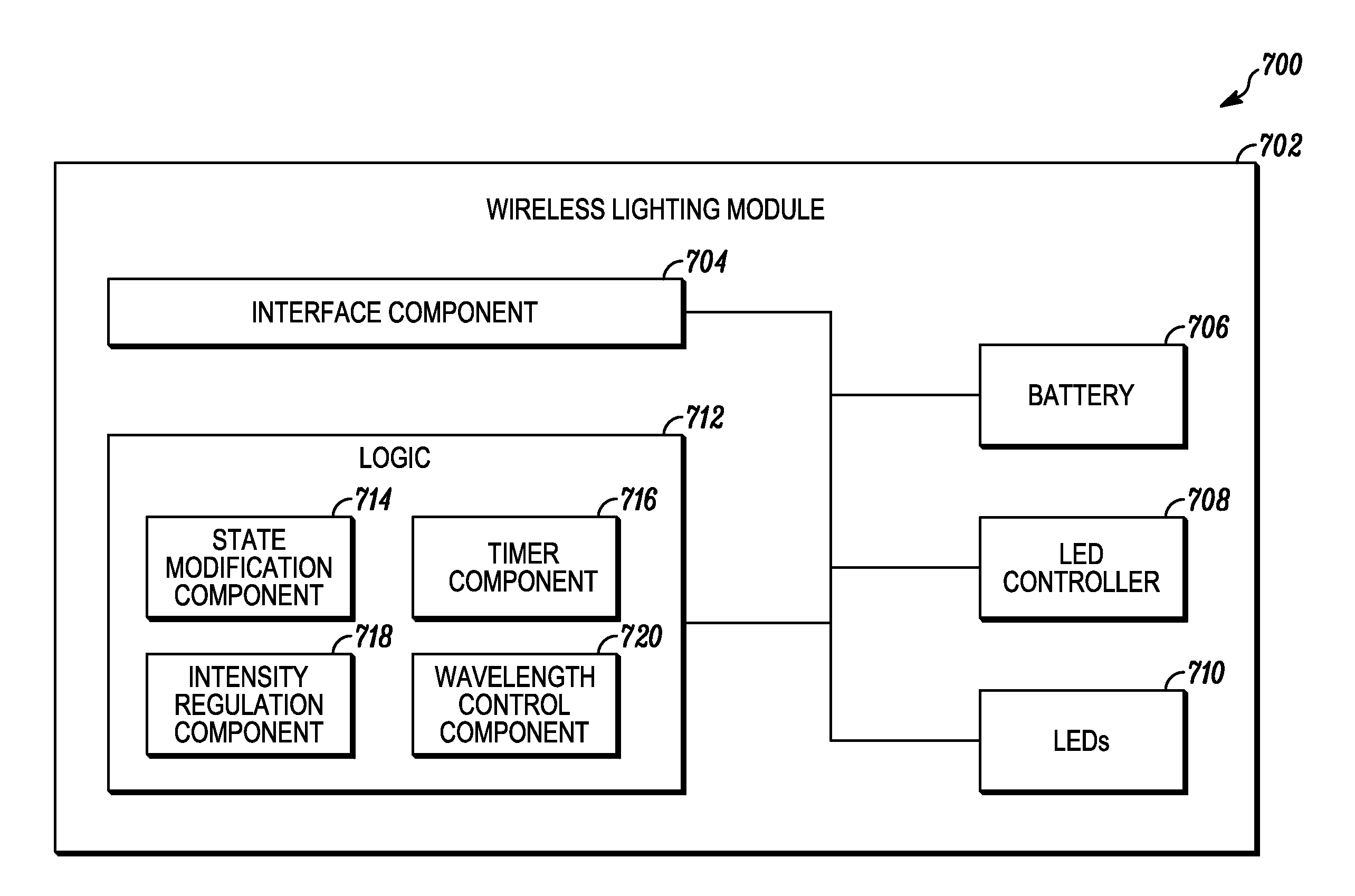

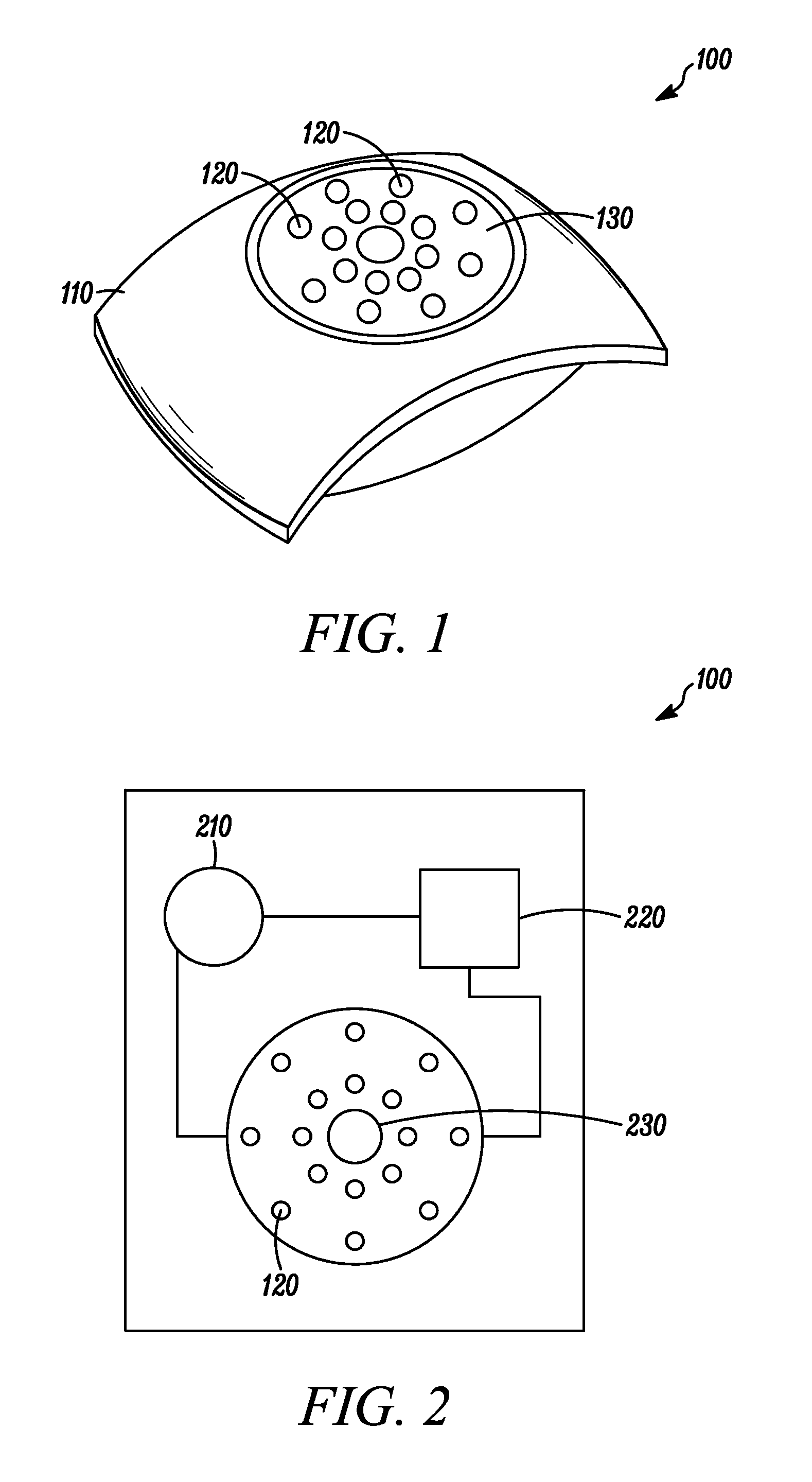

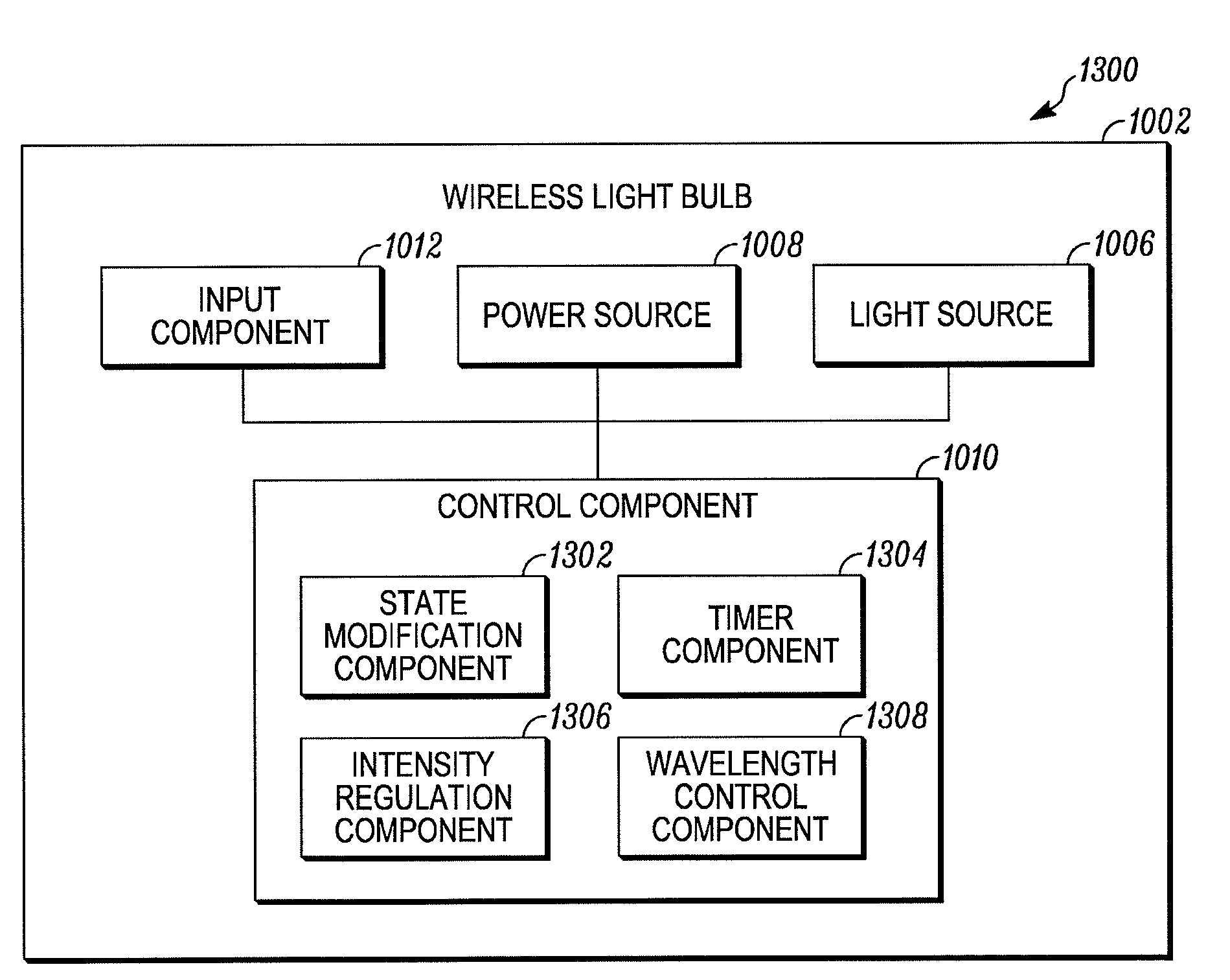

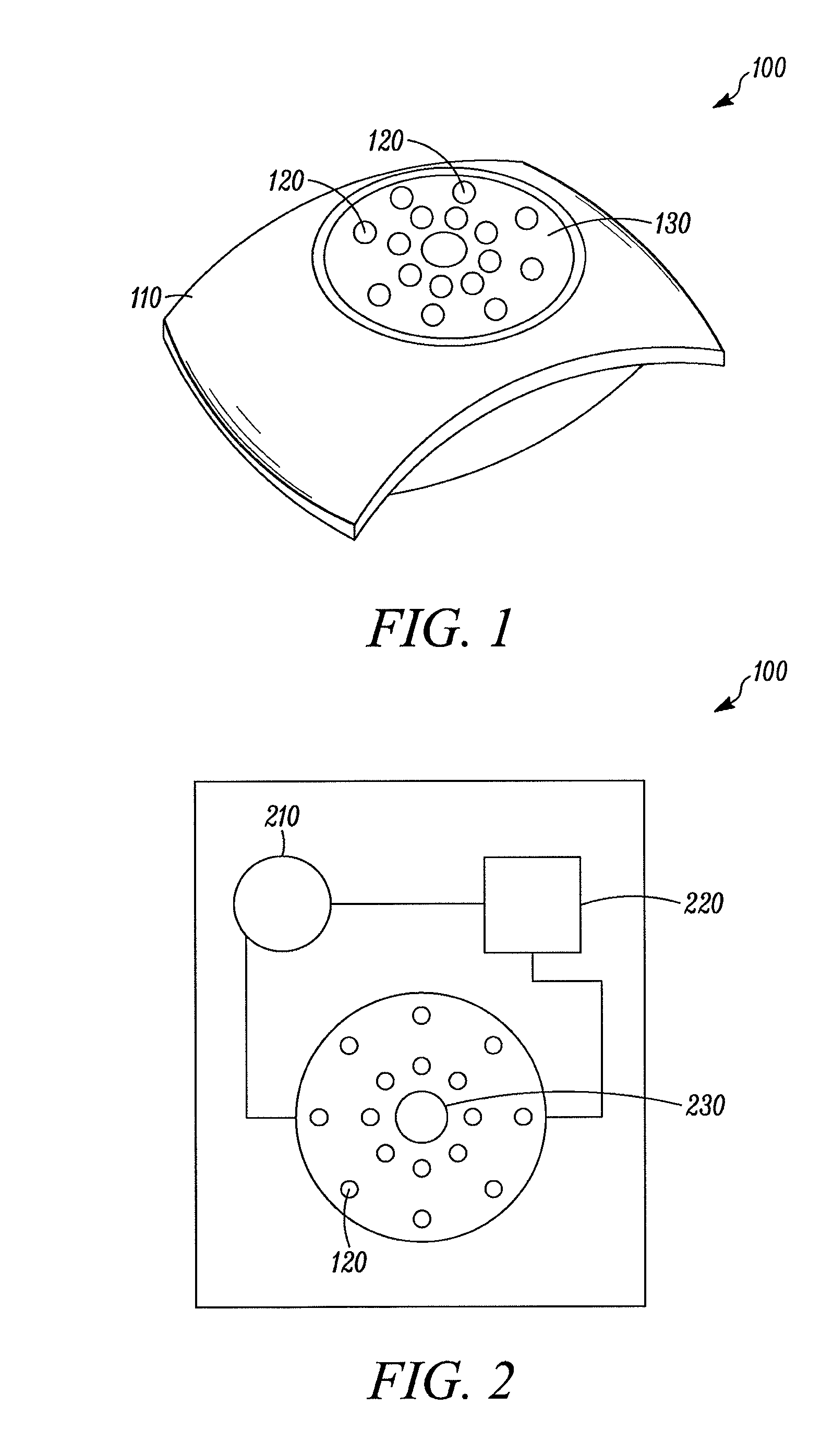

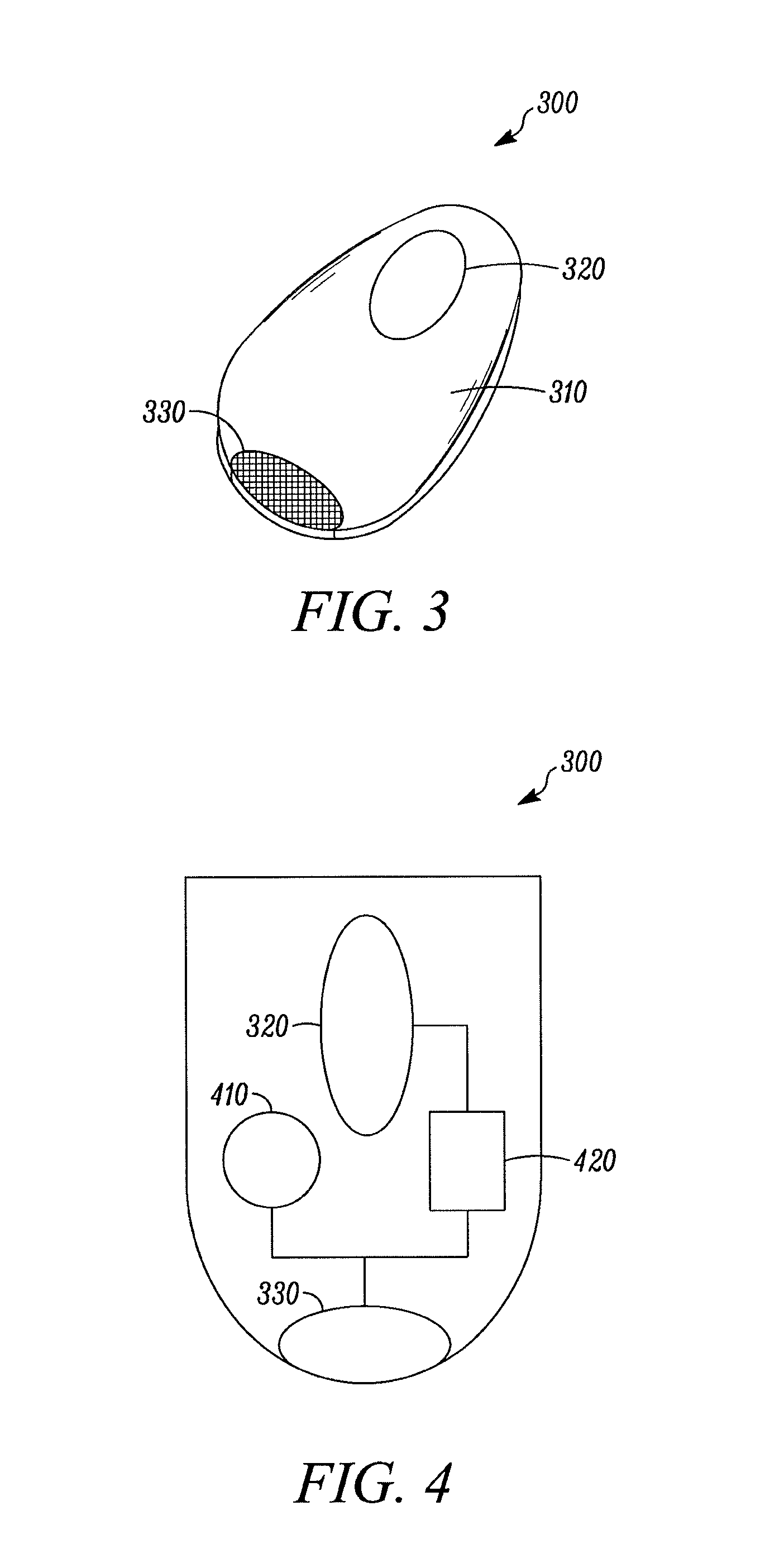

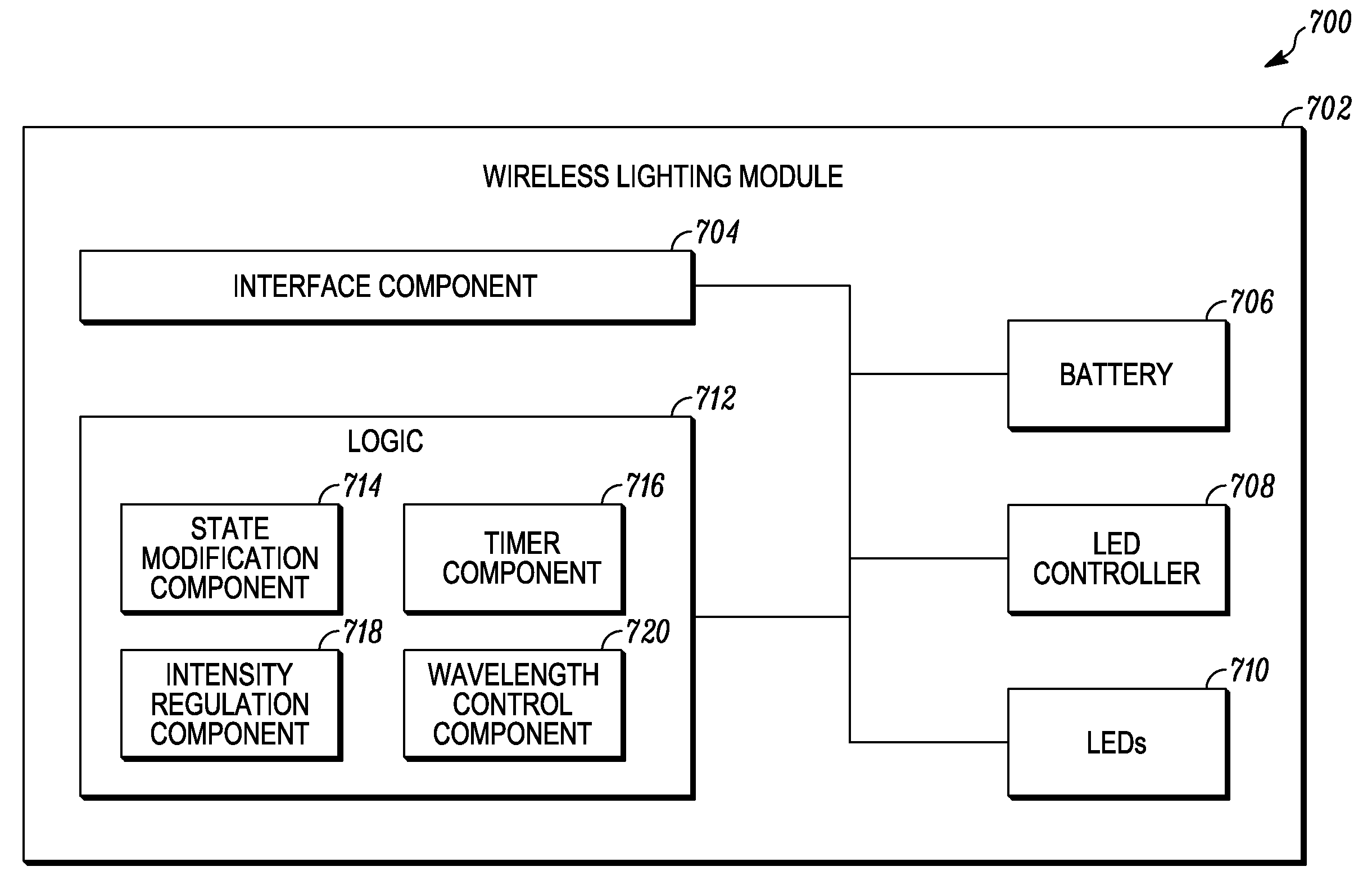

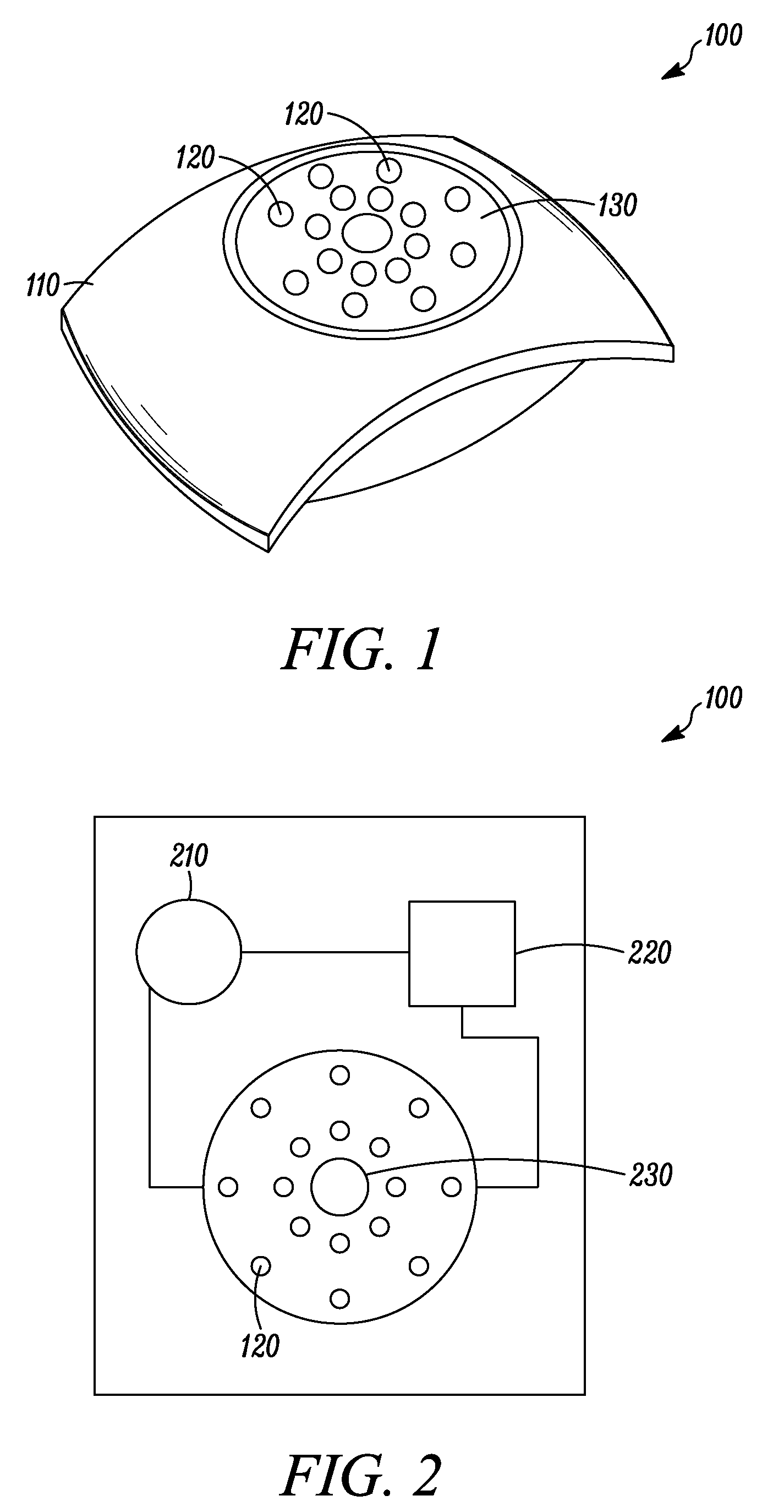

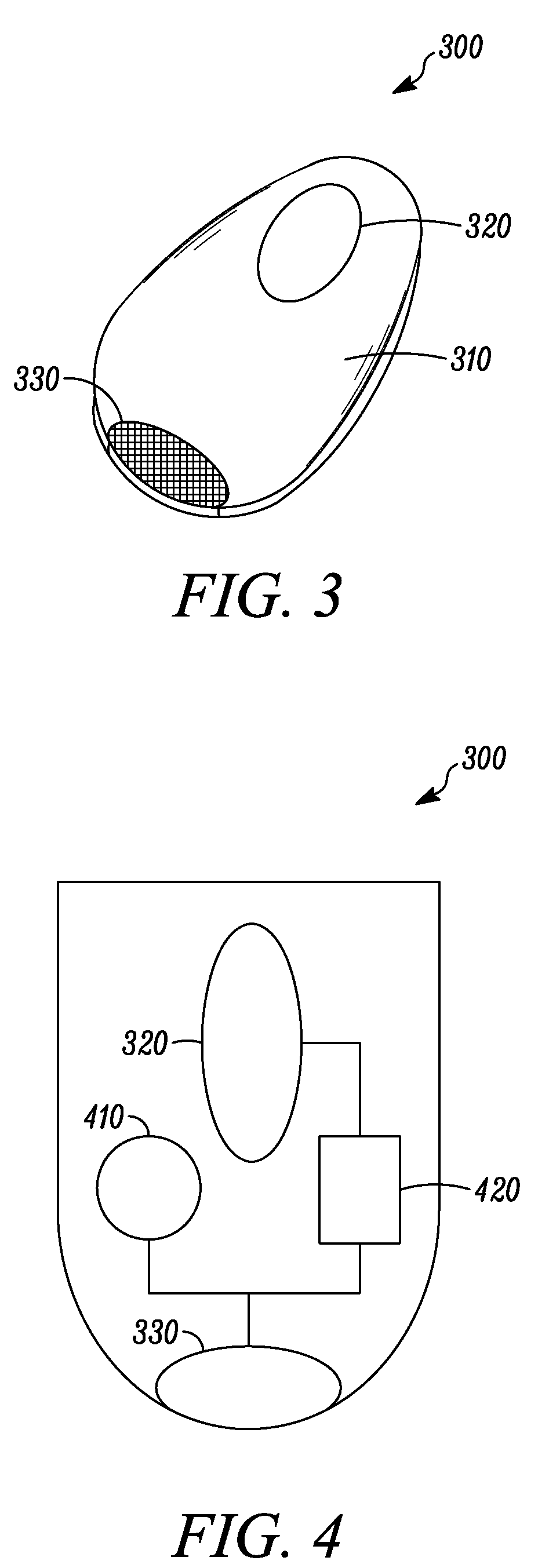

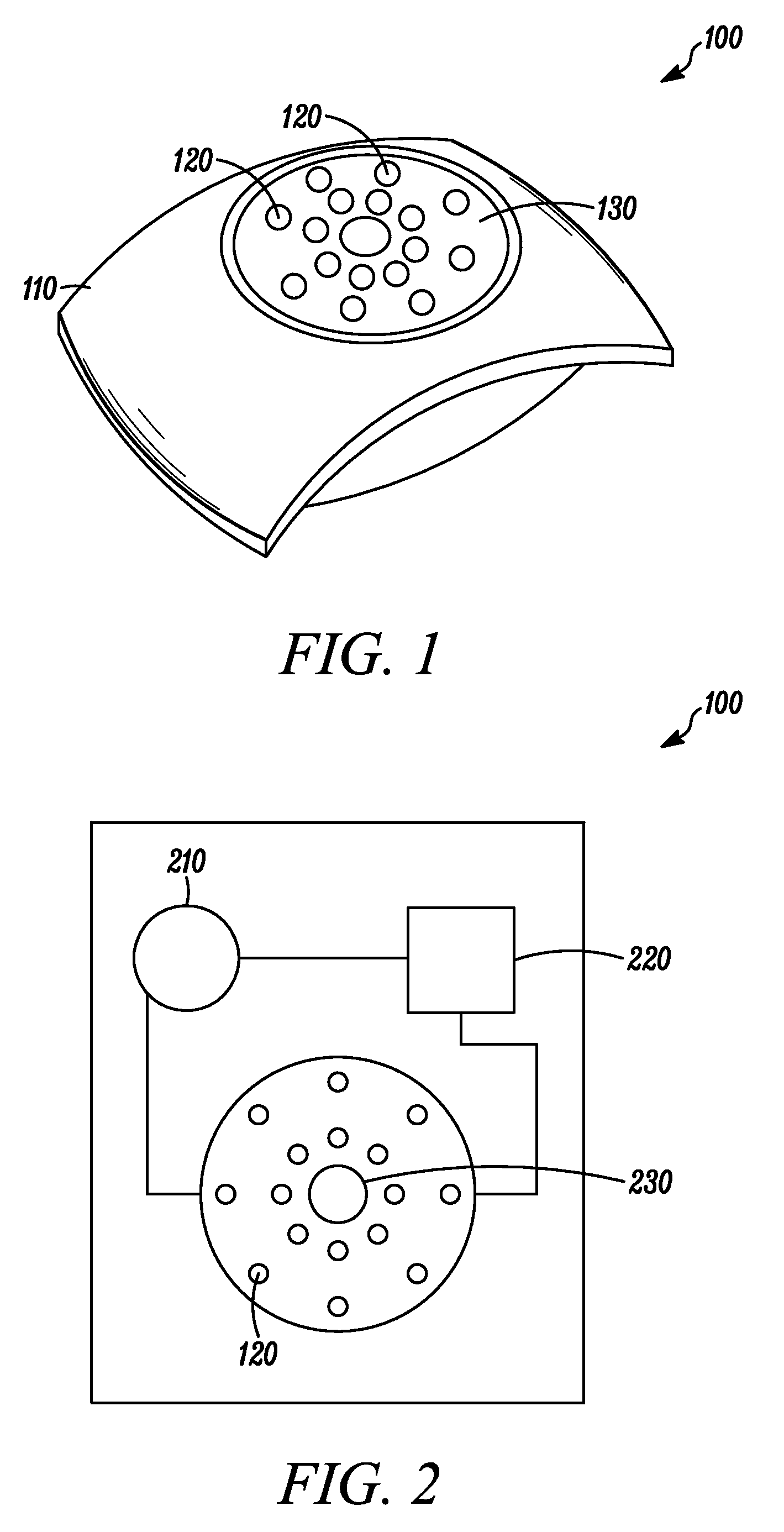

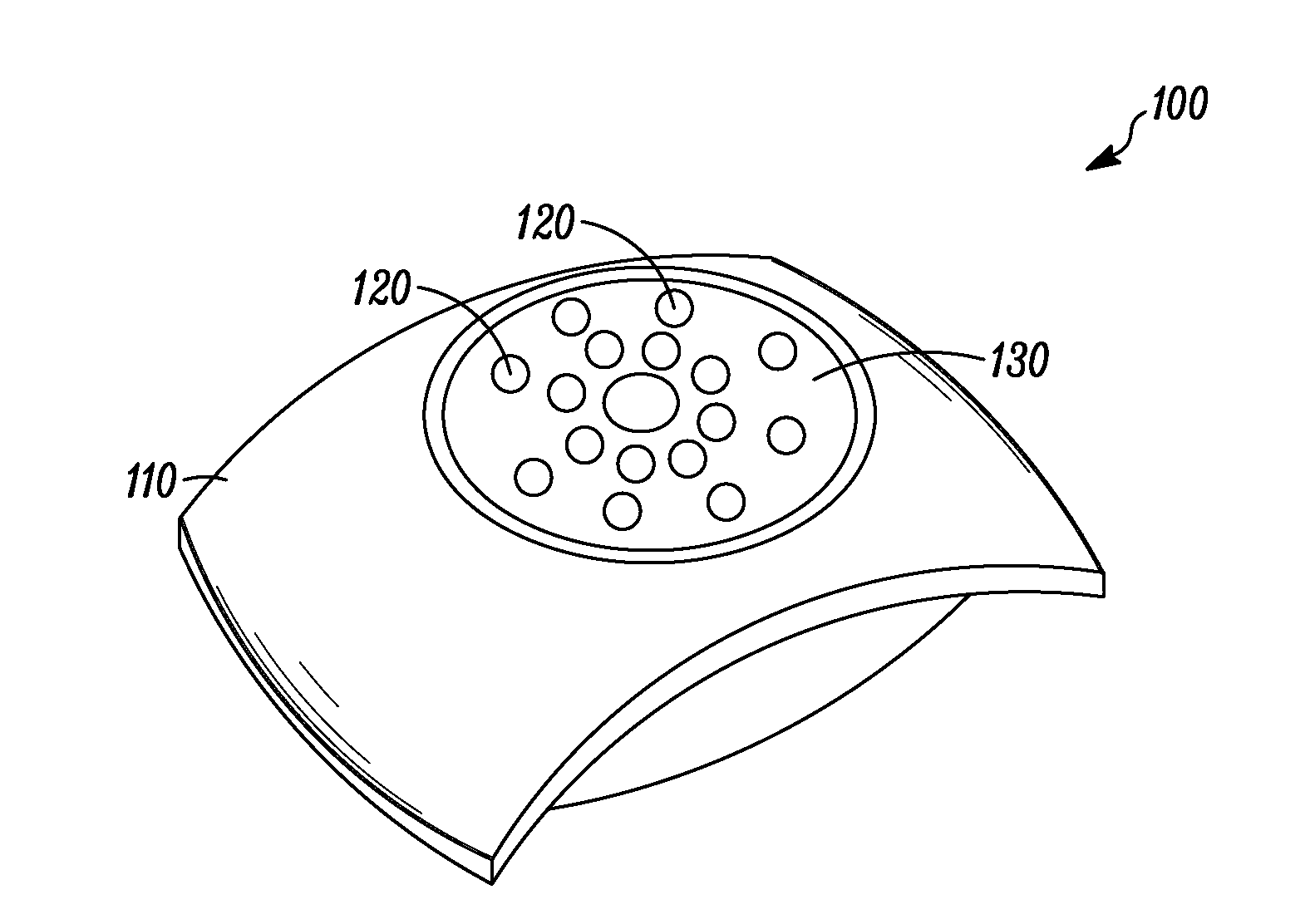

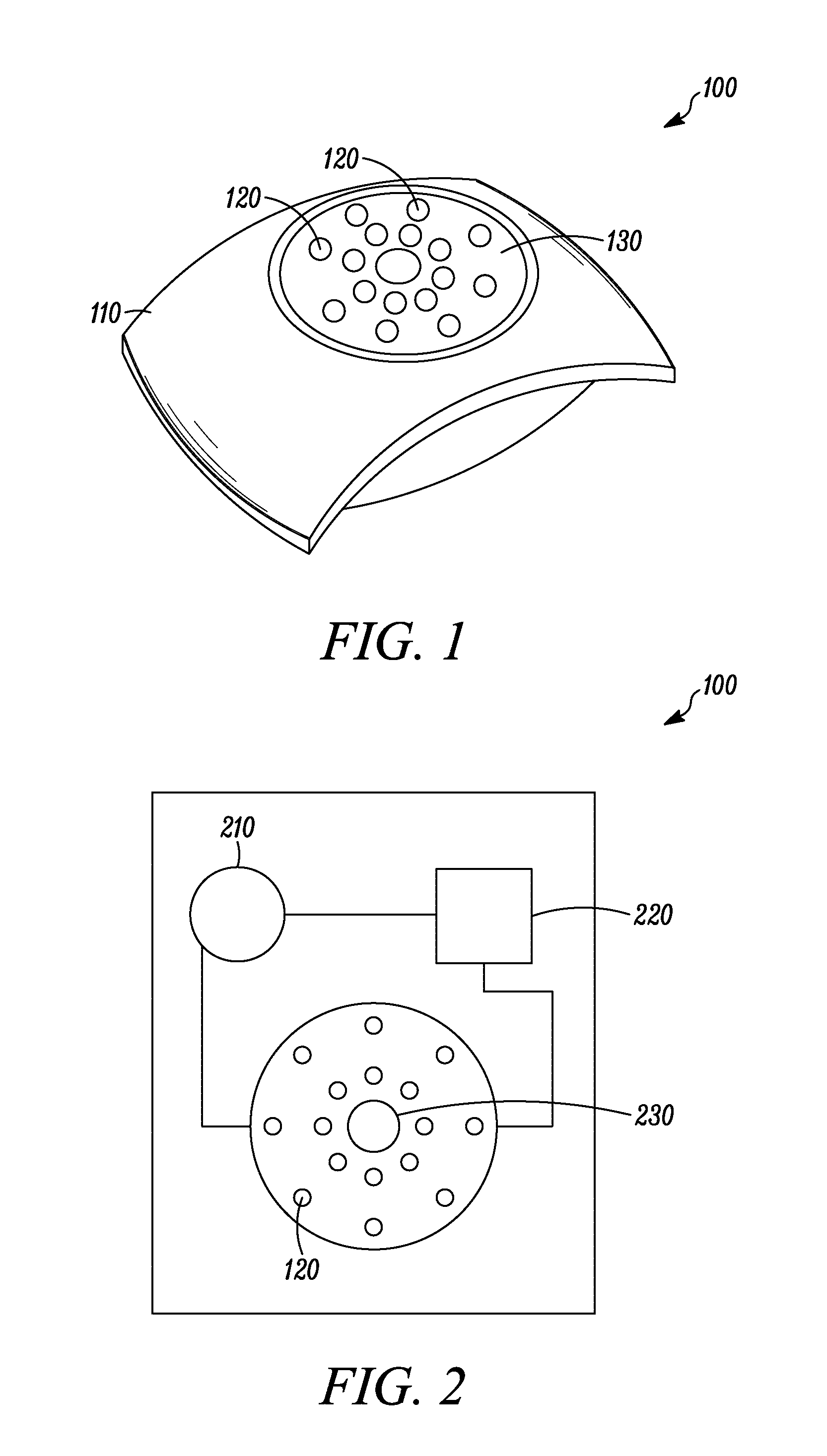

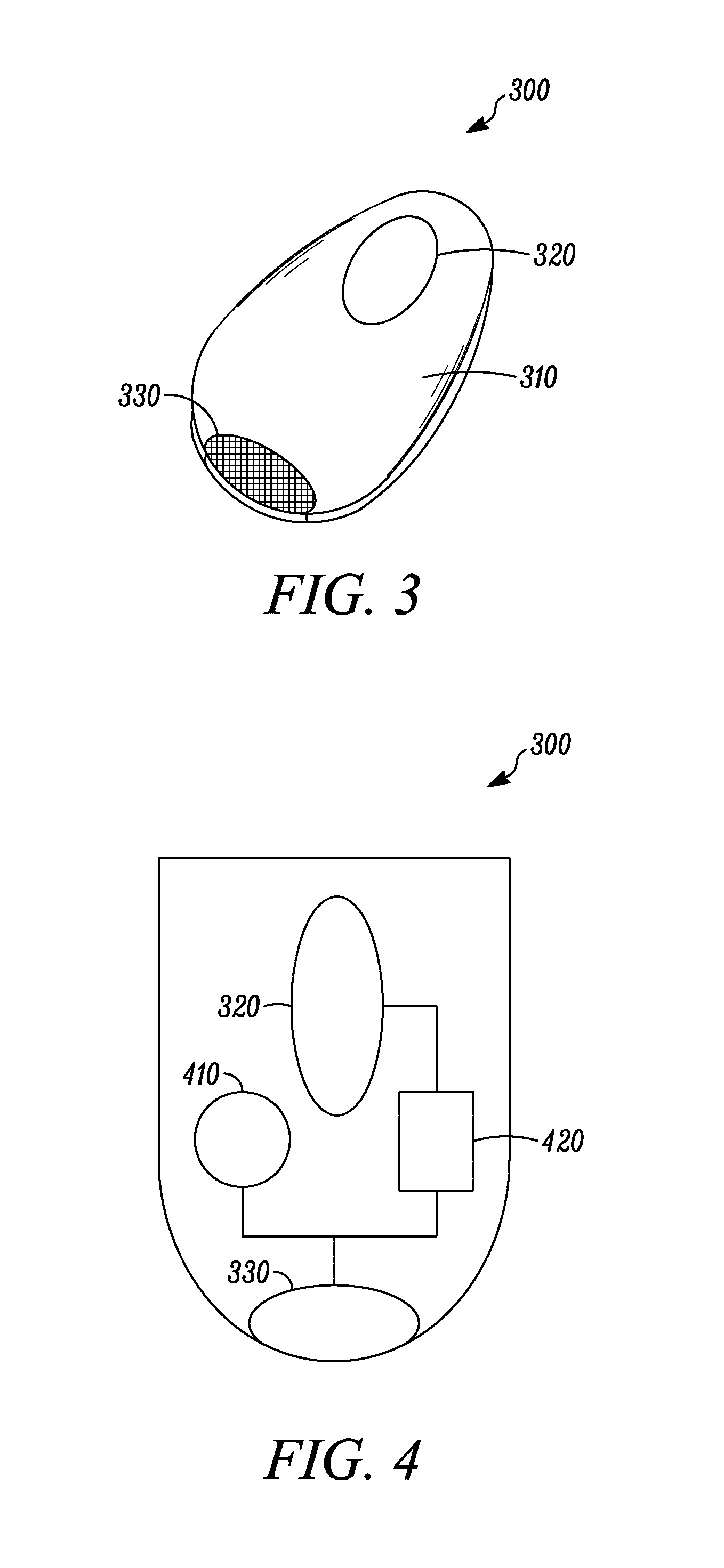

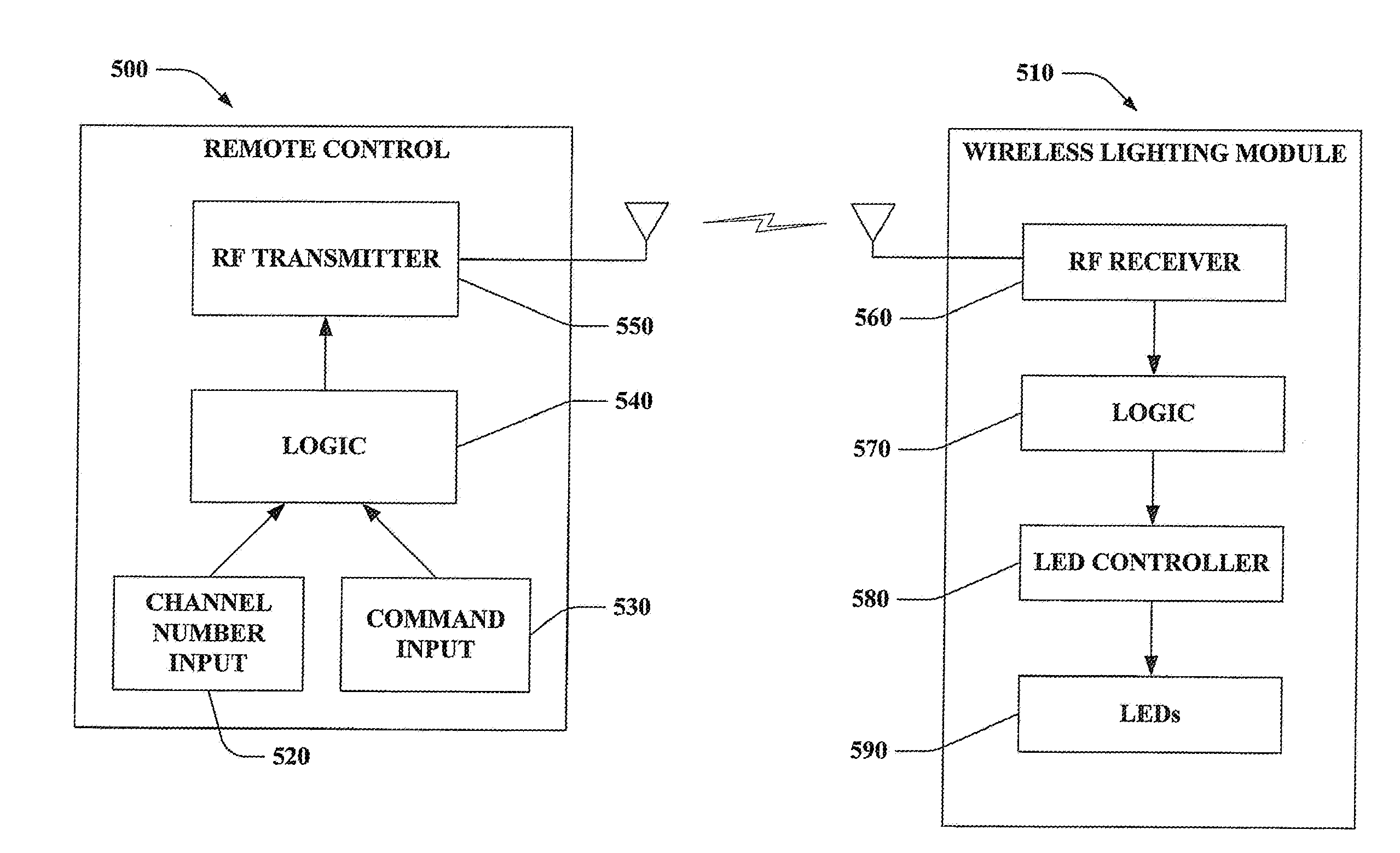

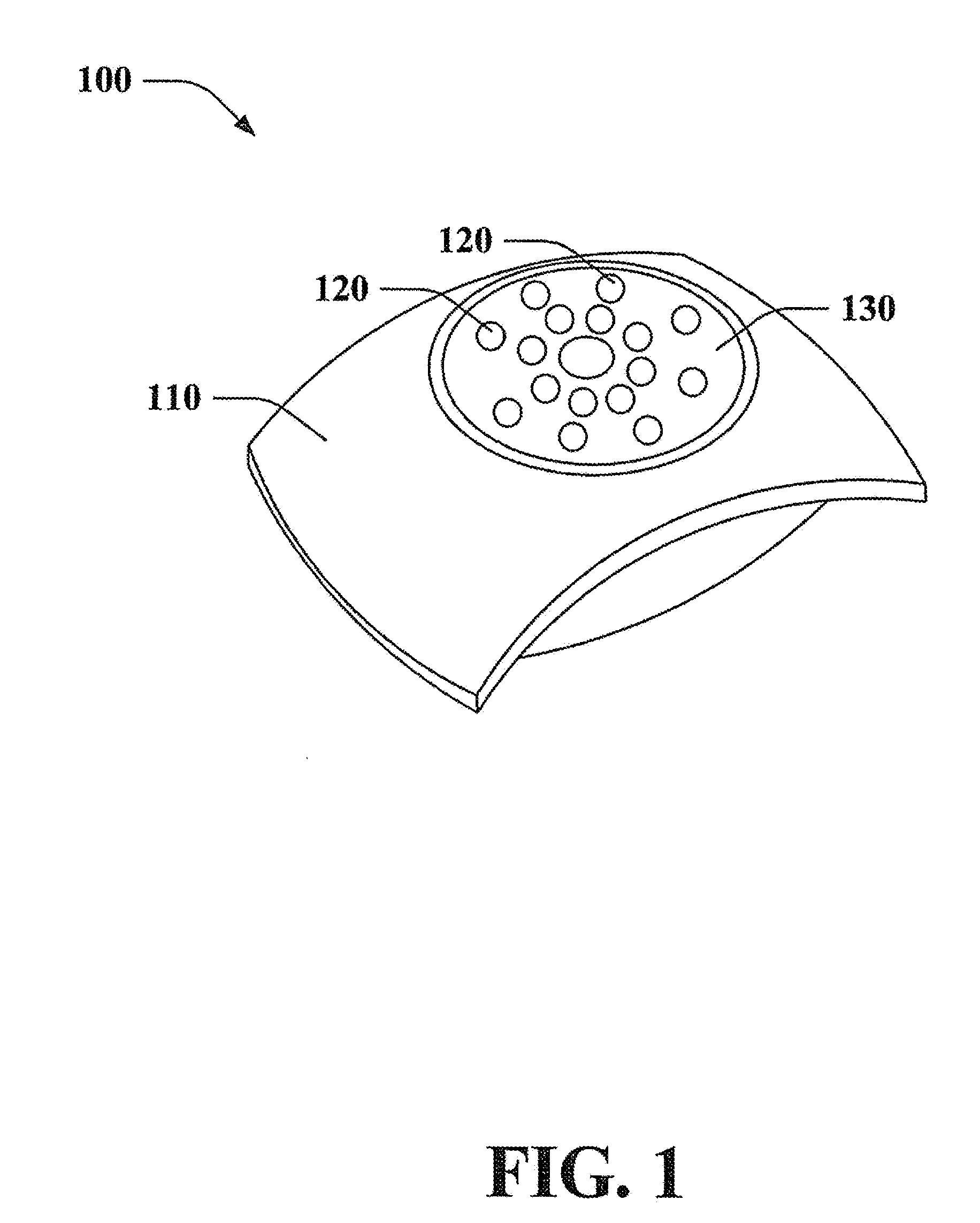

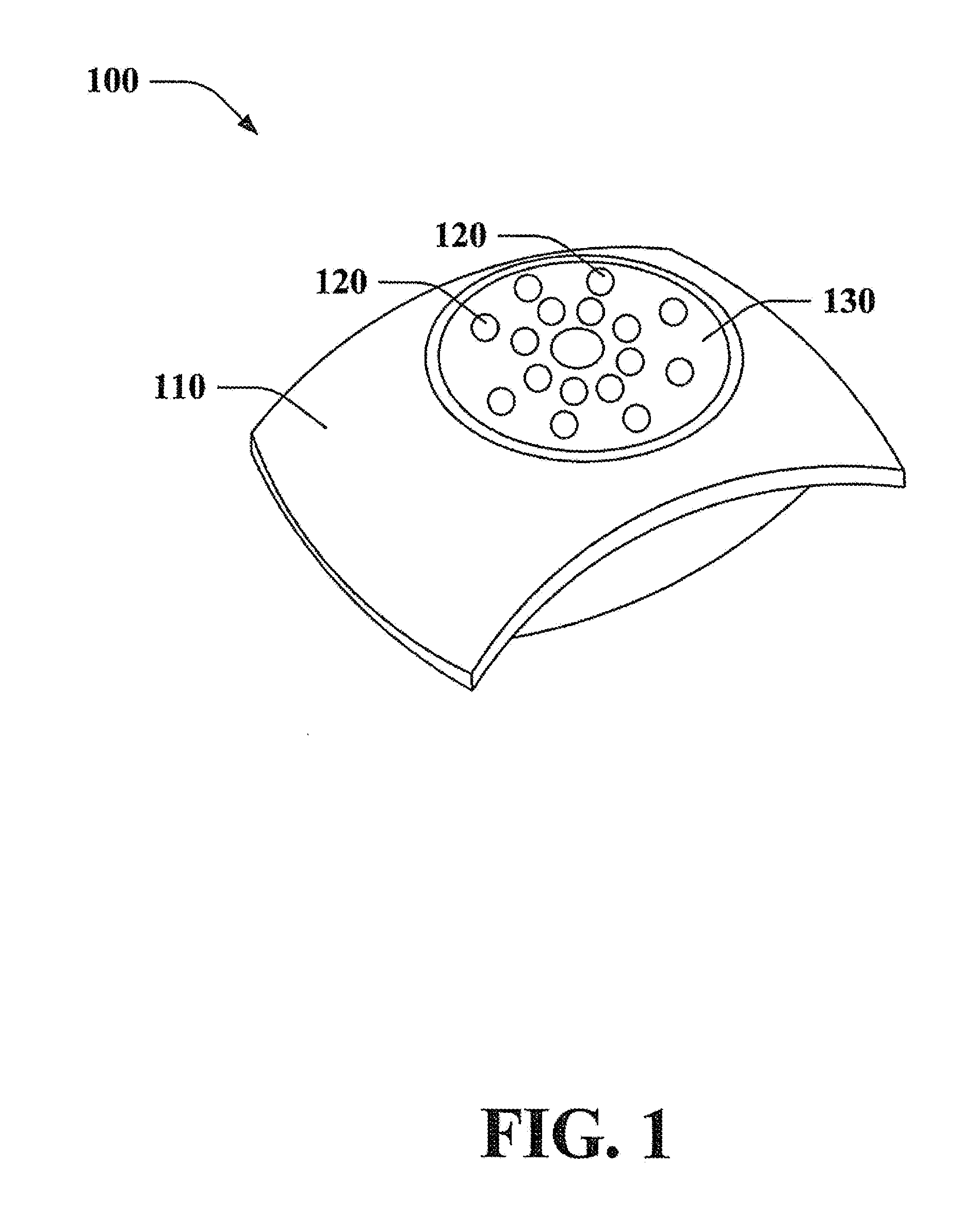

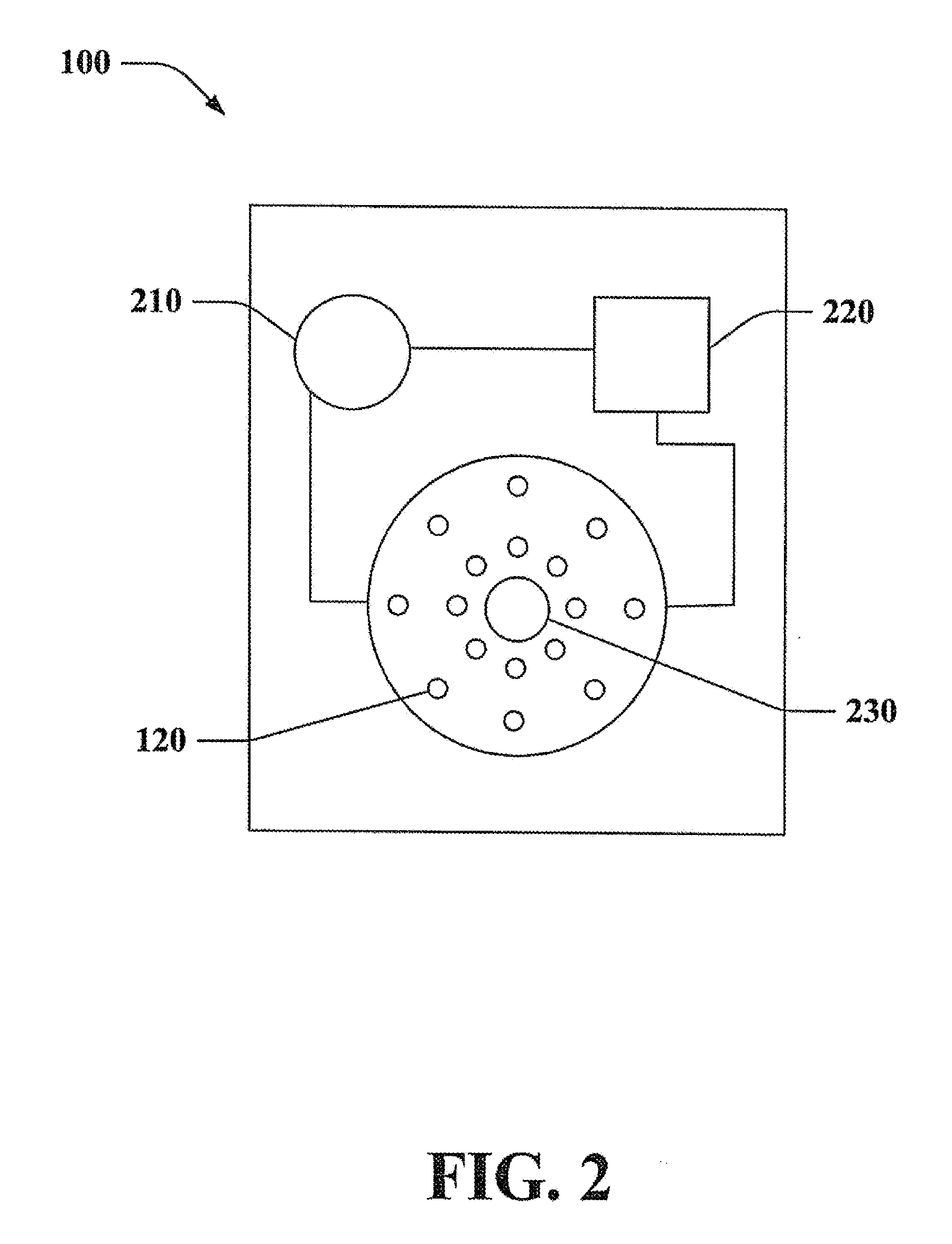

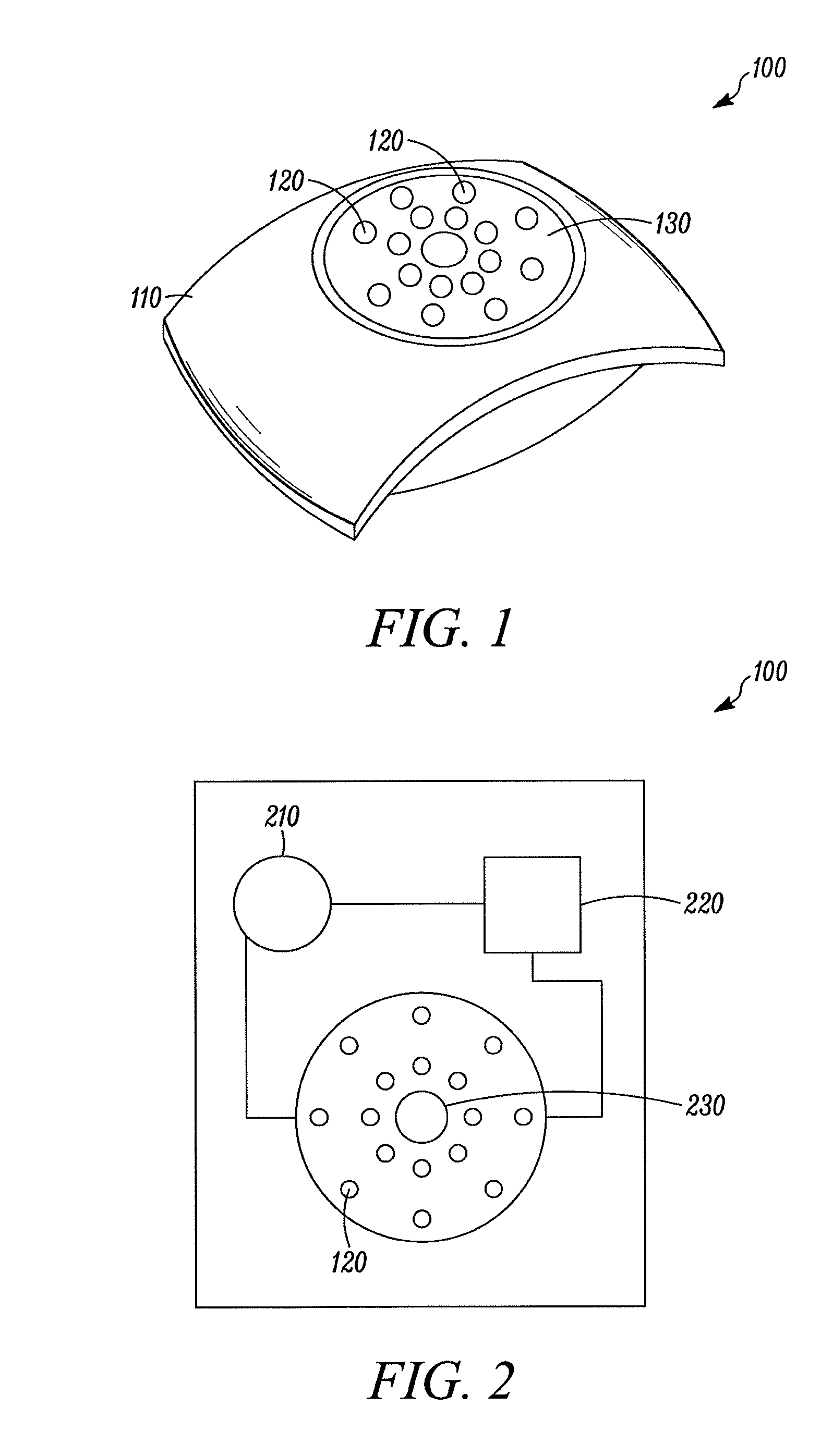

Wireless lighting devices and applications

ActiveUS20100141153A1Advantage in easeLow costPoint-like light sourceElectric circuit arrangementsEffect lightEngineering

In embodiments of the present invention improved capabilities are described for systems and methods that employ a control component and / or power source integrated in an LED based light source to control and / or power the LED light source wirelessly. In embodiments, the LED based light source may take the form of a standard light bulb that plugs into a standard lighting socket or fixture.

Owner:RING LLC

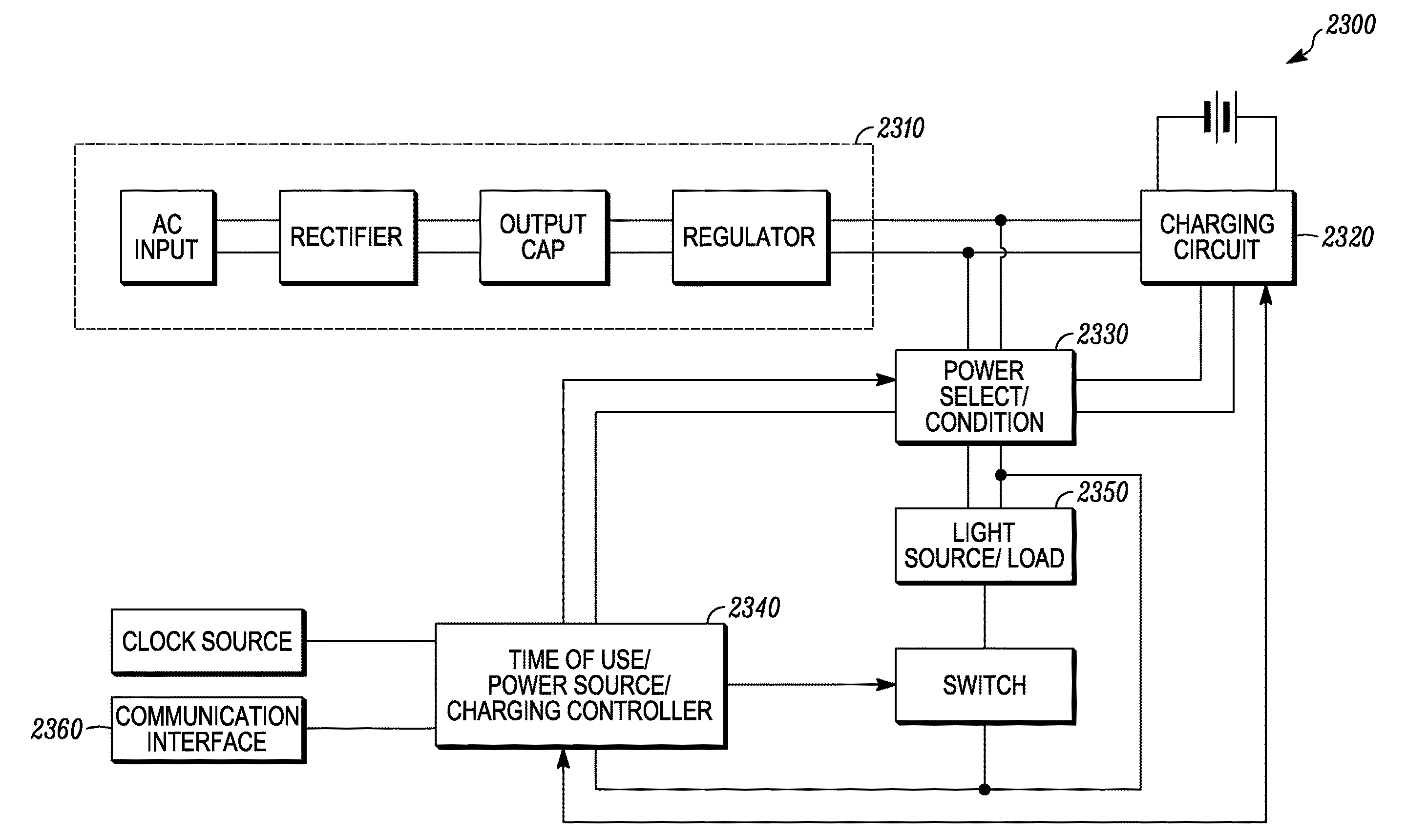

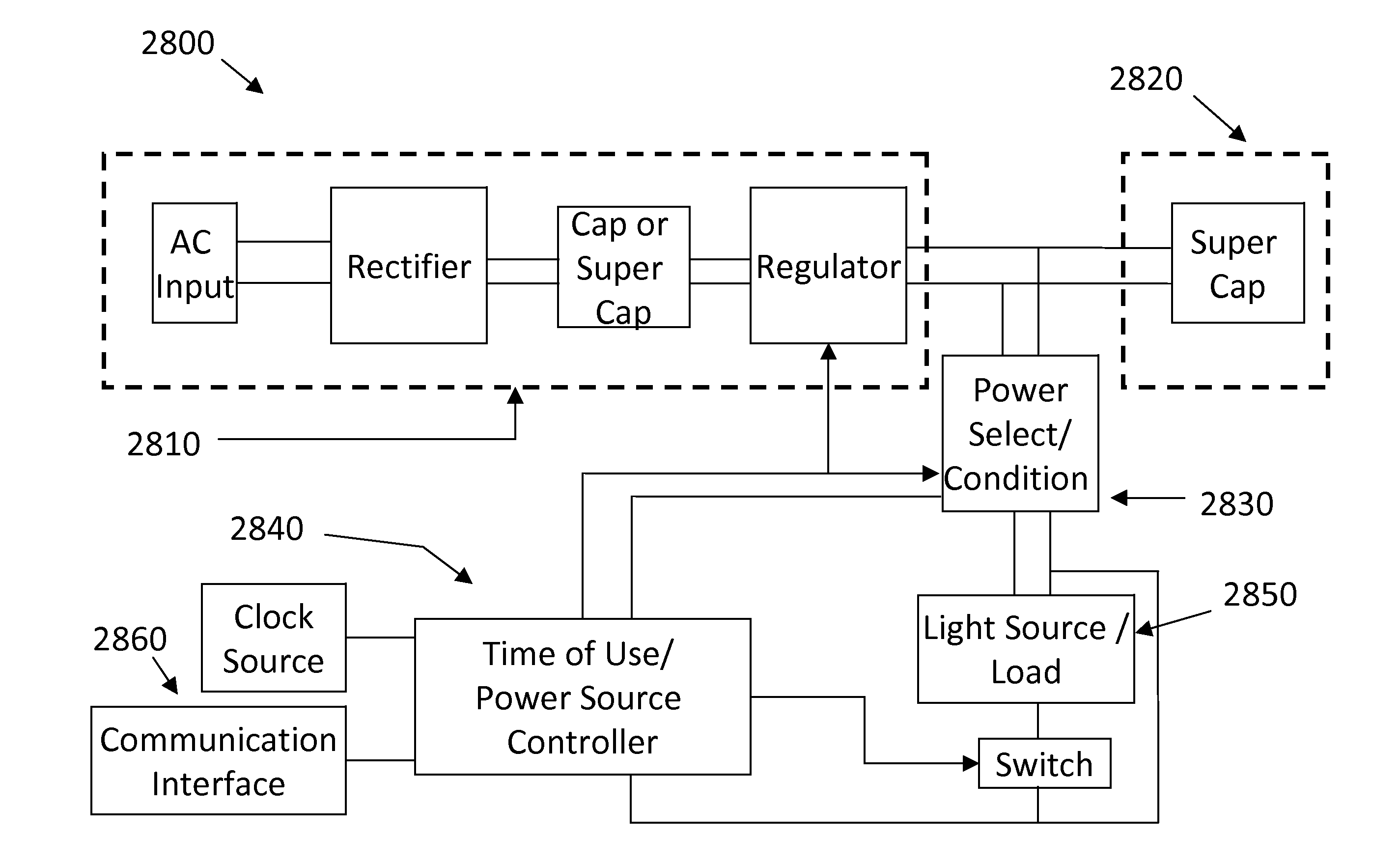

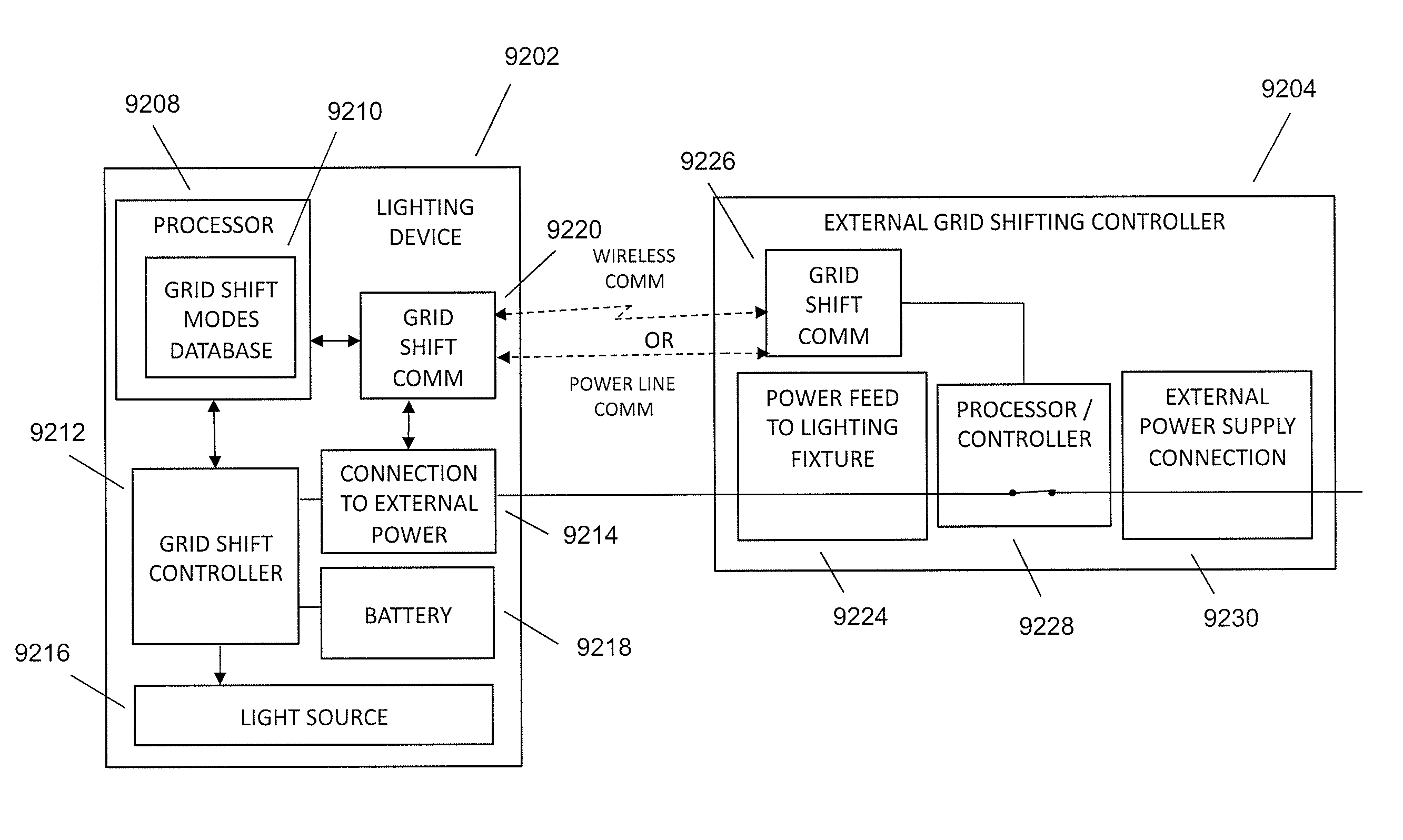

Grid Shifting System for a Lighting Circuit

ActiveUS20120080944A1Advantage in easeLow costBatteries circuit arrangementsElectroluminescent light sourcesCommunication interfacePower grid

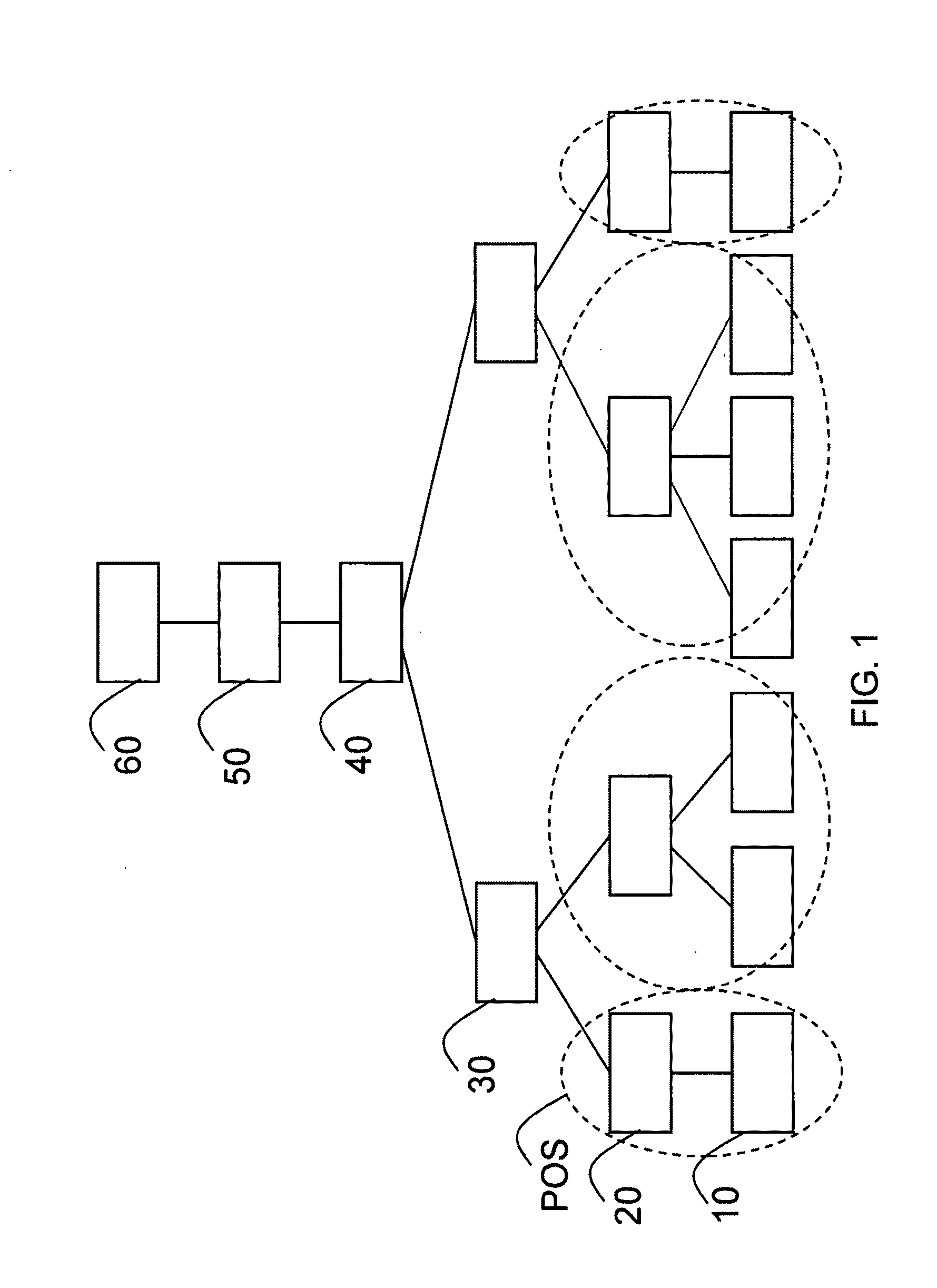

A power management system for a lighting circuit may include a grid shifting controller that includes a processor and a connection to an external power source. The power management system may also include a communication interface associated with the grid shifting controller. The grid shifting controller may be configured to provide control information to a processor of at least one grid shifting electrical fixture over the communication interface, the control information being configured to direct the at least one grid shifting electrical fixture on the use of power from the external power source and an energy storage device associated with the at least one grid shifting electrical fixture.

Owner:RING LLC

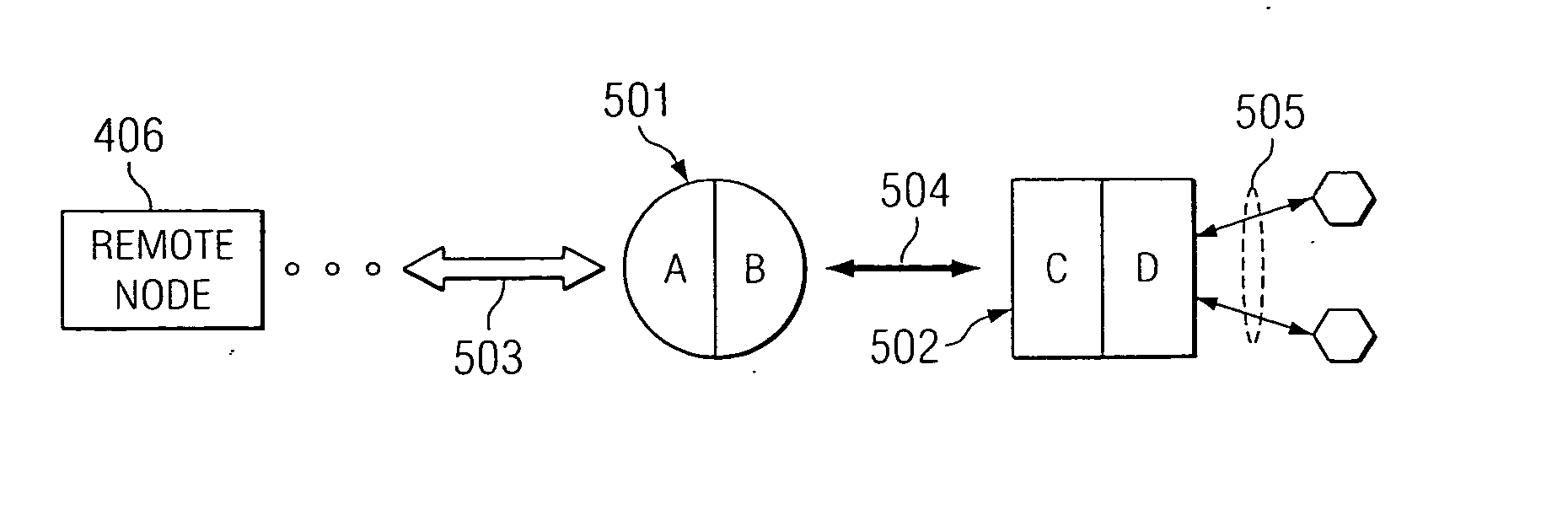

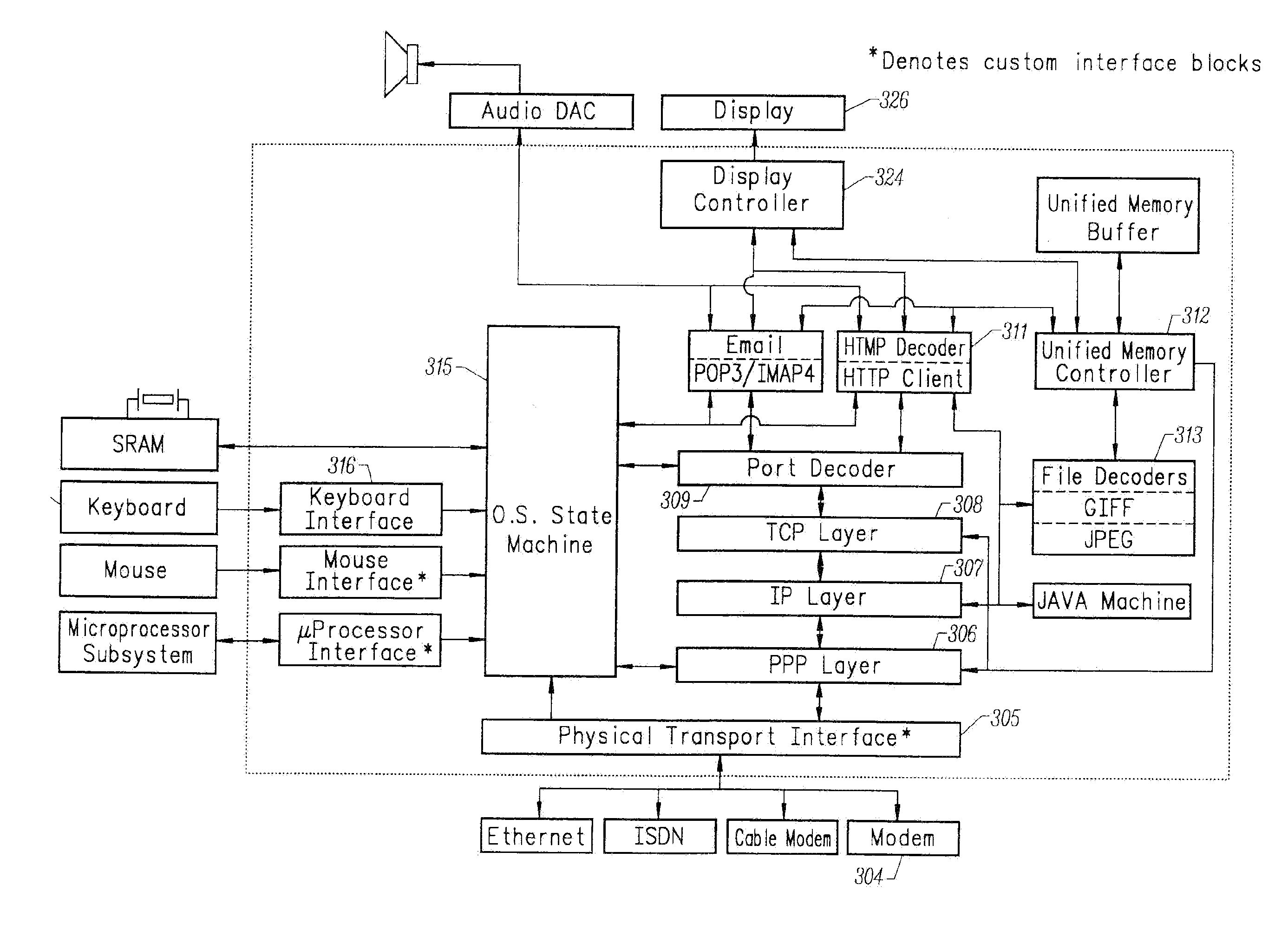

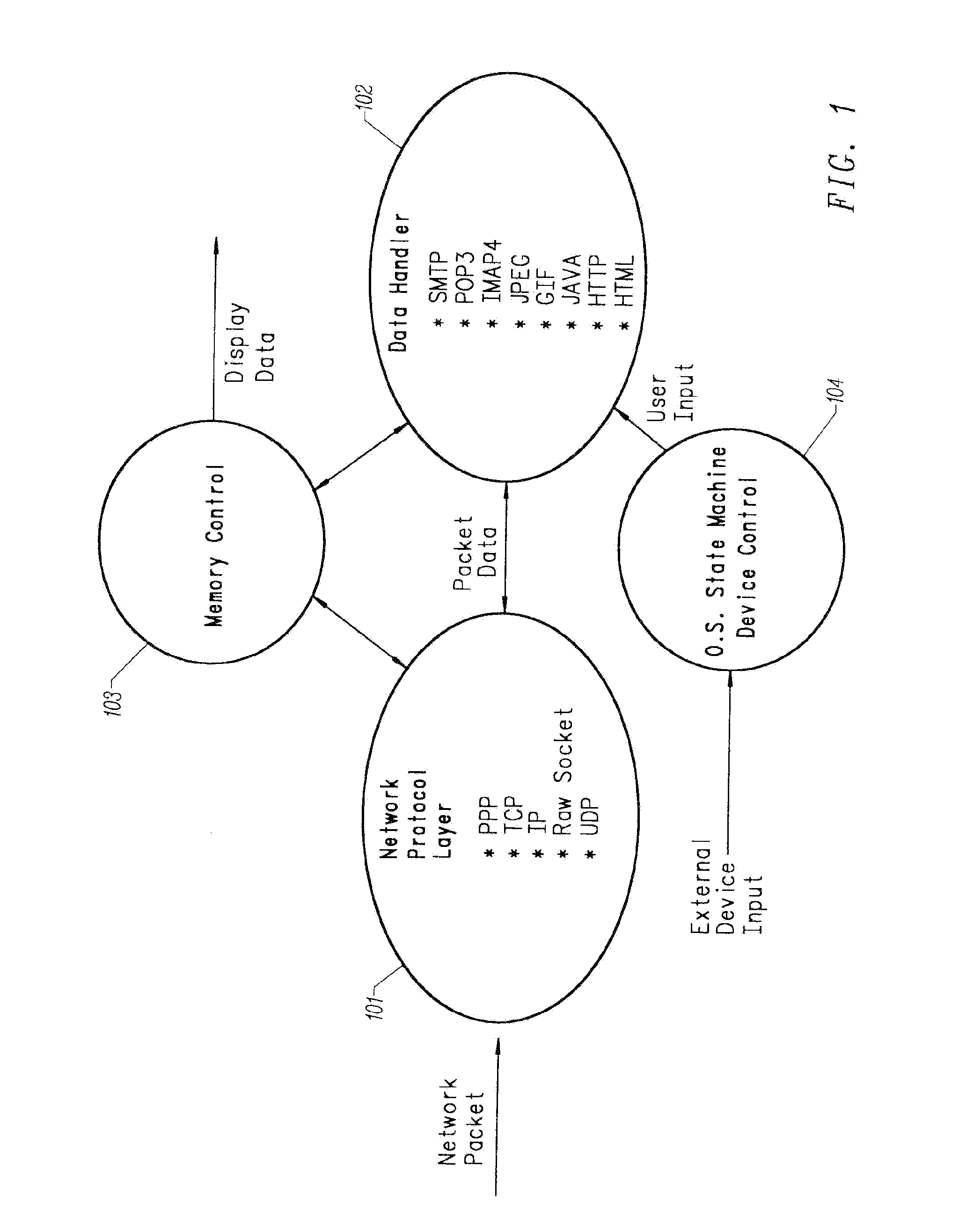

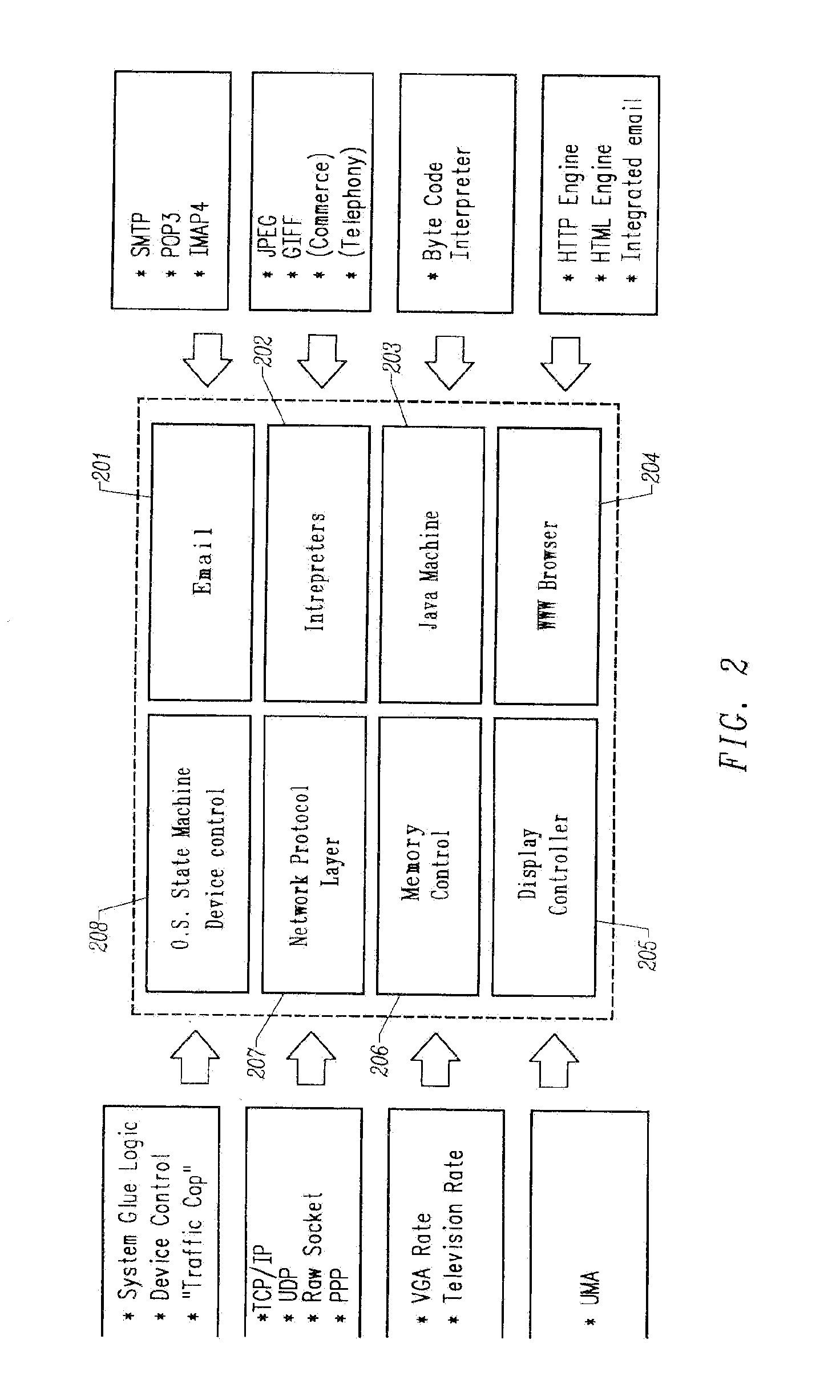

Multiple network protocol encoder/decoder and data processor

InactiveUS6034963AReduce system costLow costTime-division multiplexData switching by path configurationRaw socketByte

A multiple network protocol encoder / decoder comprising a network protocol layer, data handler, O.S. State machine, and memory manager state machines implemented at a hardware gate level. Network packets are received from a physical transport level mechanism by the network protocol layer state machine which decodes network protocols such as TCP, IP, User Datagram Protocol (UDP), PPP, and Raw Socket concurrently as each byte is received. Each protocol handler parses and strips header information immediately from the packet, requiring no intermediate memory. The resulting data are passed to the data handler which consists of data state machines that decode data formats such as email, graphics, Hypertext Transfer Protocol (HTTP), Java, and Hypertext Markup Language (HTML). Each data state machine reacts accordingly to the pertinent data, and any data that are required by more than one data state machine is provided to each state machine concurrently, and any data required more than once by a specific data state machine, are placed in a specific memory location with a pointer designating such data (thereby ensuring minimal memory usage). Resulting display data are immediately passed to a display controller. Any outgoing network packets are created by the data state machines and passed through the network protocol state machine which adds header information and forwards the resulting network packet via a transport level mechanism.

Owner:NVIDIA CORP

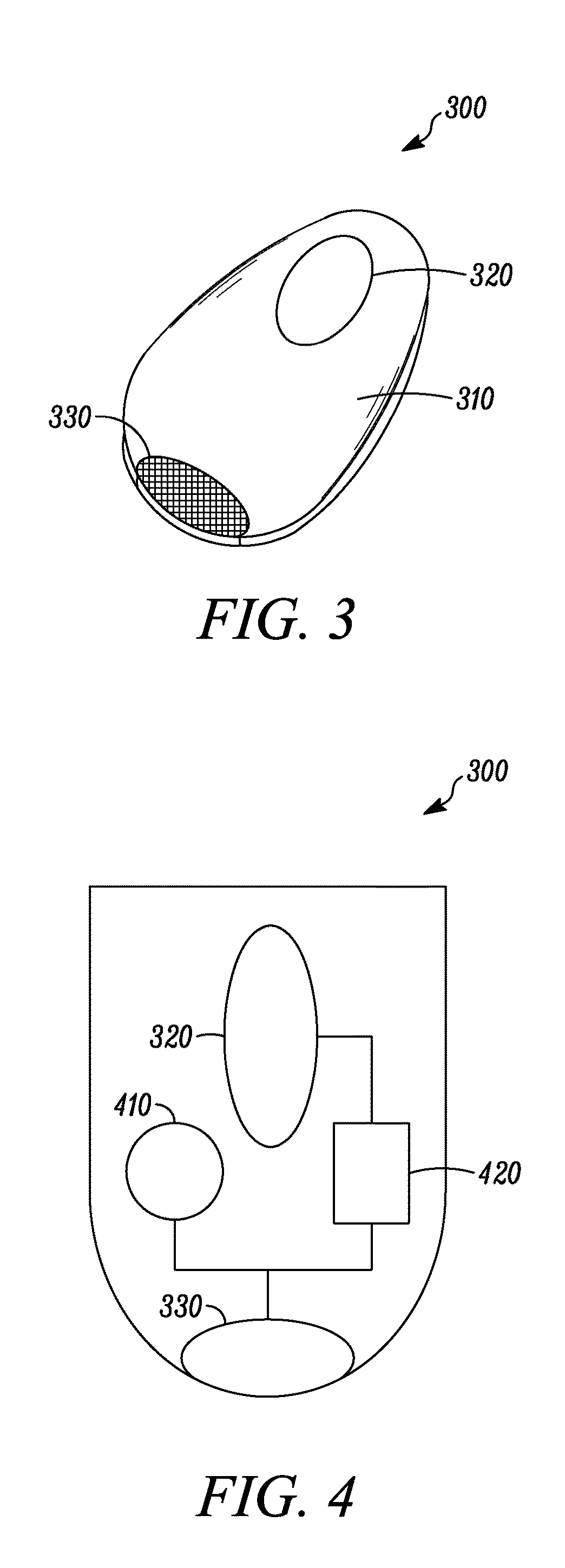

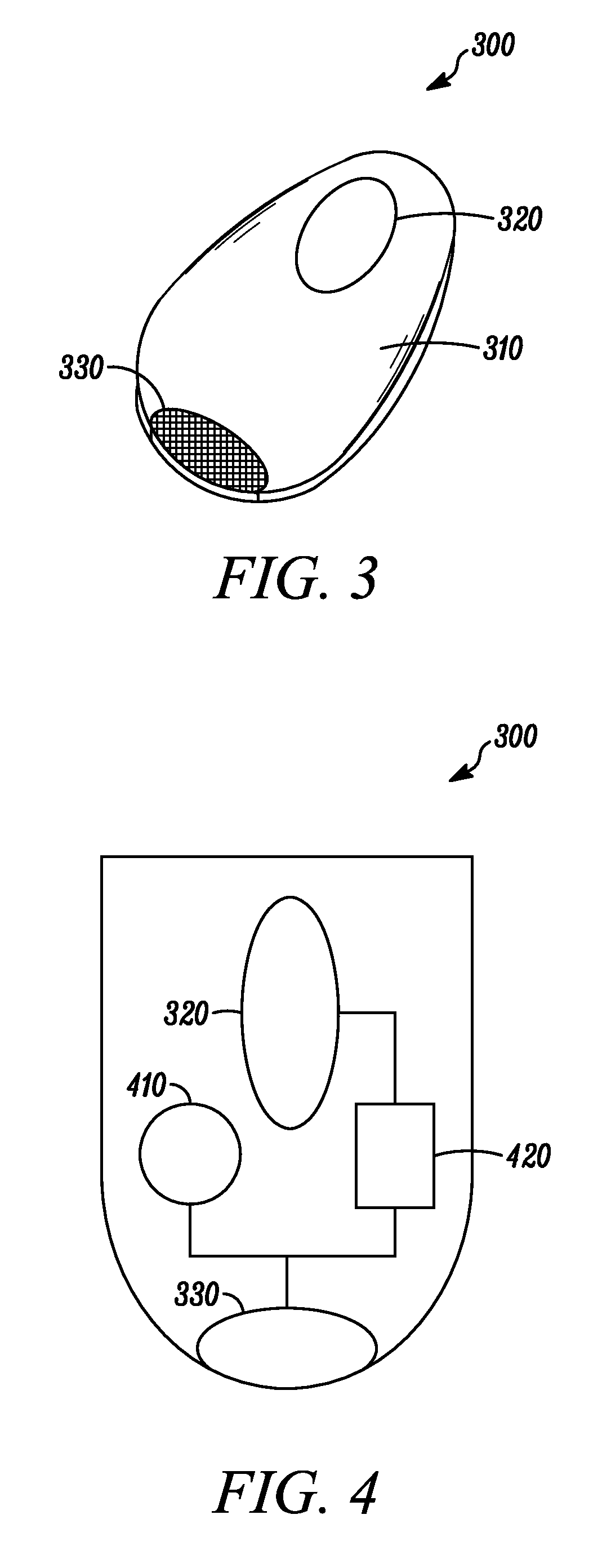

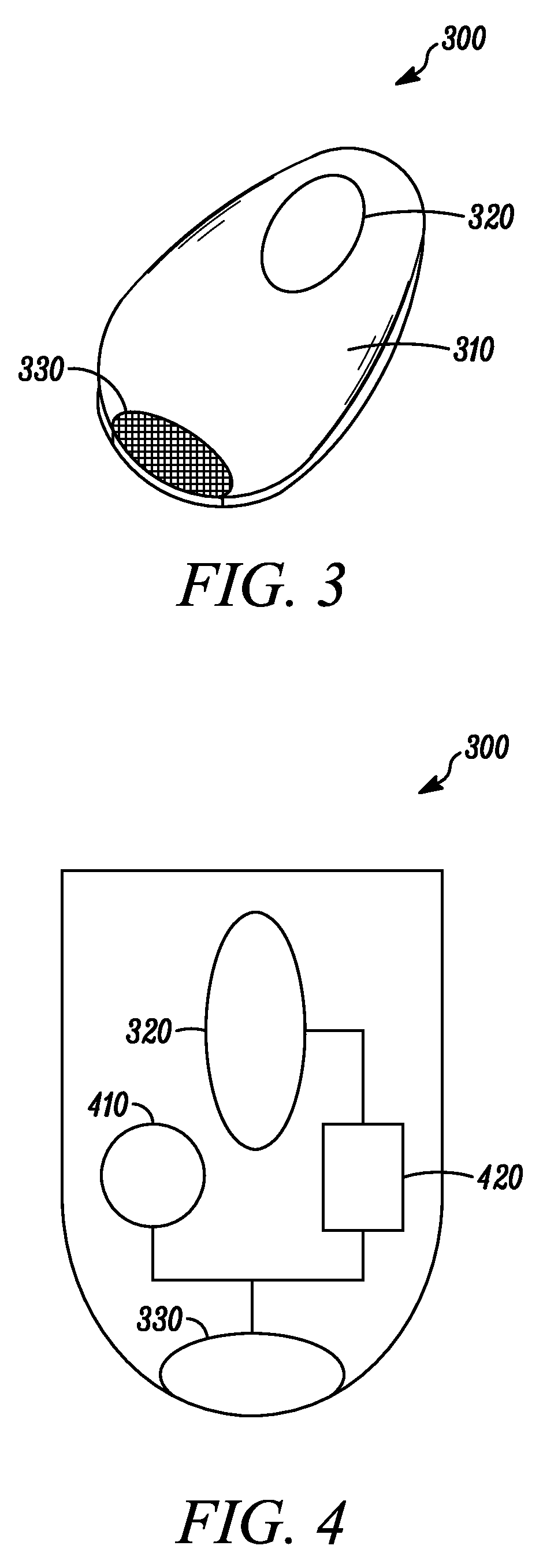

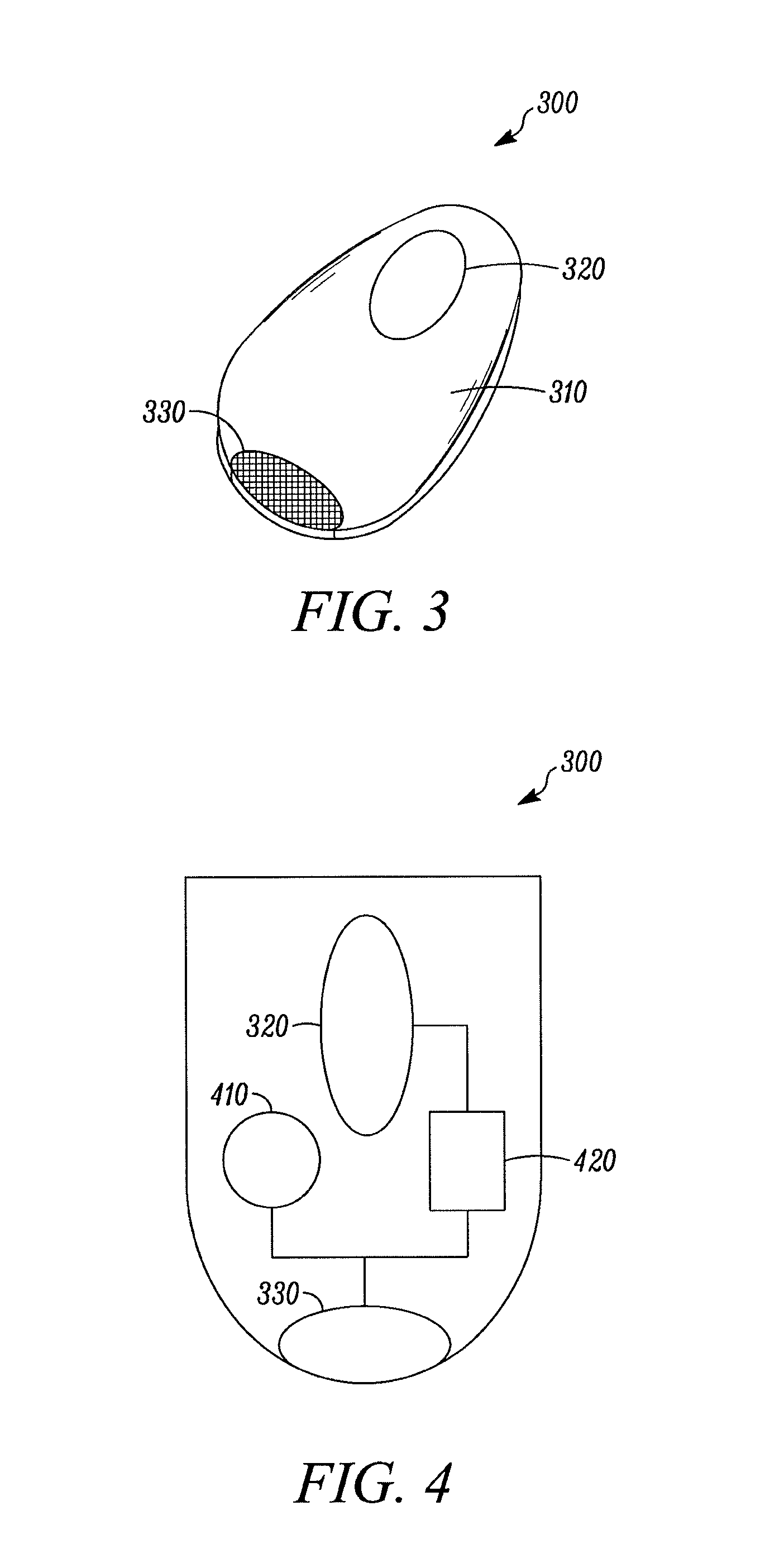

Remote switch sensing in lighting devices

InactiveUS20110121654A1Advantage in easeLow costPoint-like light sourceElectric circuit arrangementsLight equipmentStandby power

In embodiments of the present invention improved capabilities are described for providing intelligent power control in response to an external power interruption, causing a processor is in an electrical fixture to interrogate an external power control switch to gain an understanding of the switch's state, where prior to the external power interruption the electrical fixture may be powered by external power and where external power may be connected and disconnected by a user of the switch. In the event that the switch's state is determined to be such that it would normally pass power to the electrical fixture, the processor causes the electrical fixture to operate using a backup power supply. In the event that the switch's state is determined to be such that it would normally not pass power to the electrical fixture, the processor causes the electrical fixture to act as if the user of the switch has intentionally removed power. In response to a return of external power, powering the electrical fixture is then through external power where the user of the switch switches external power.

Owner:RING LLC

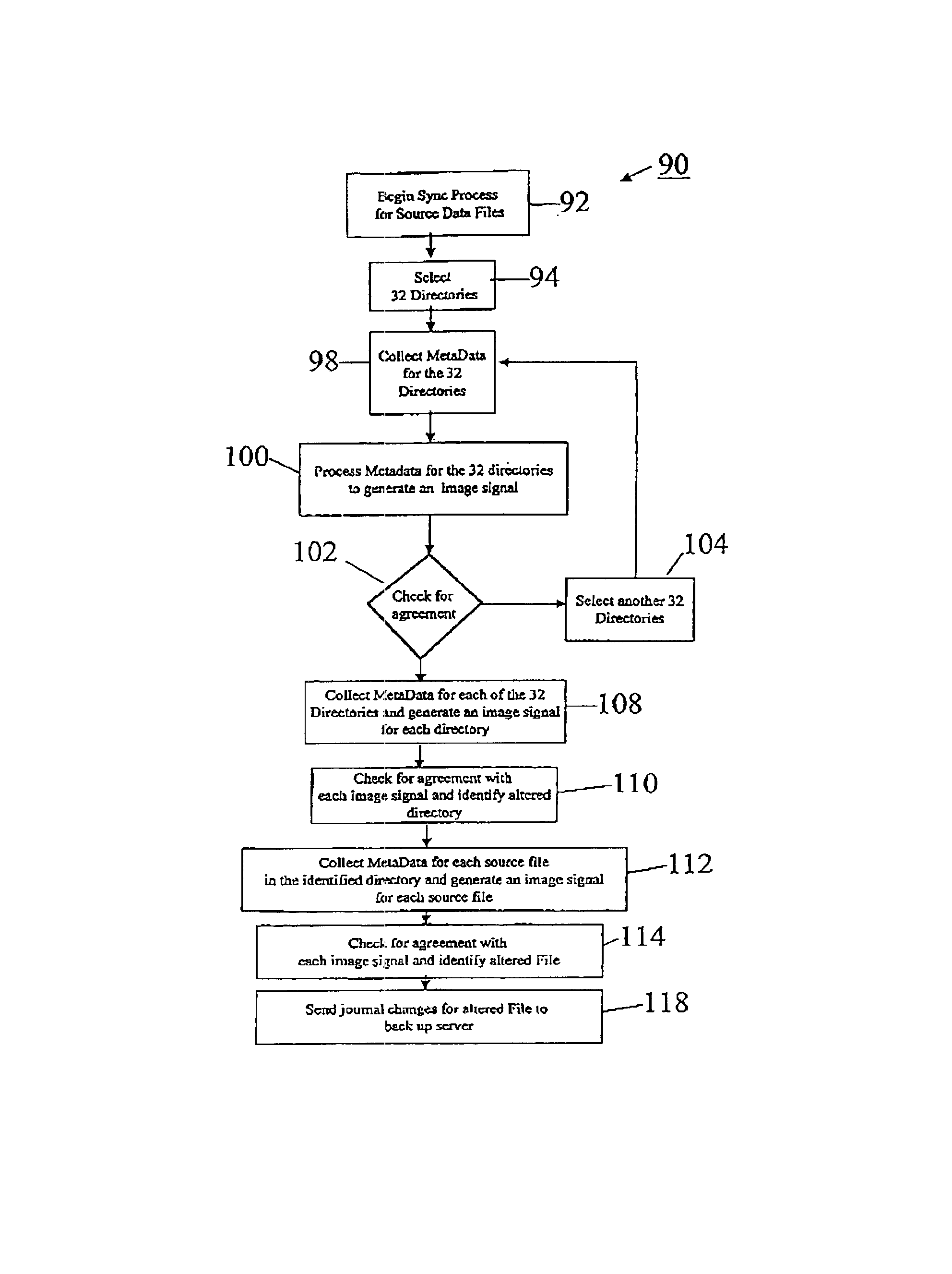

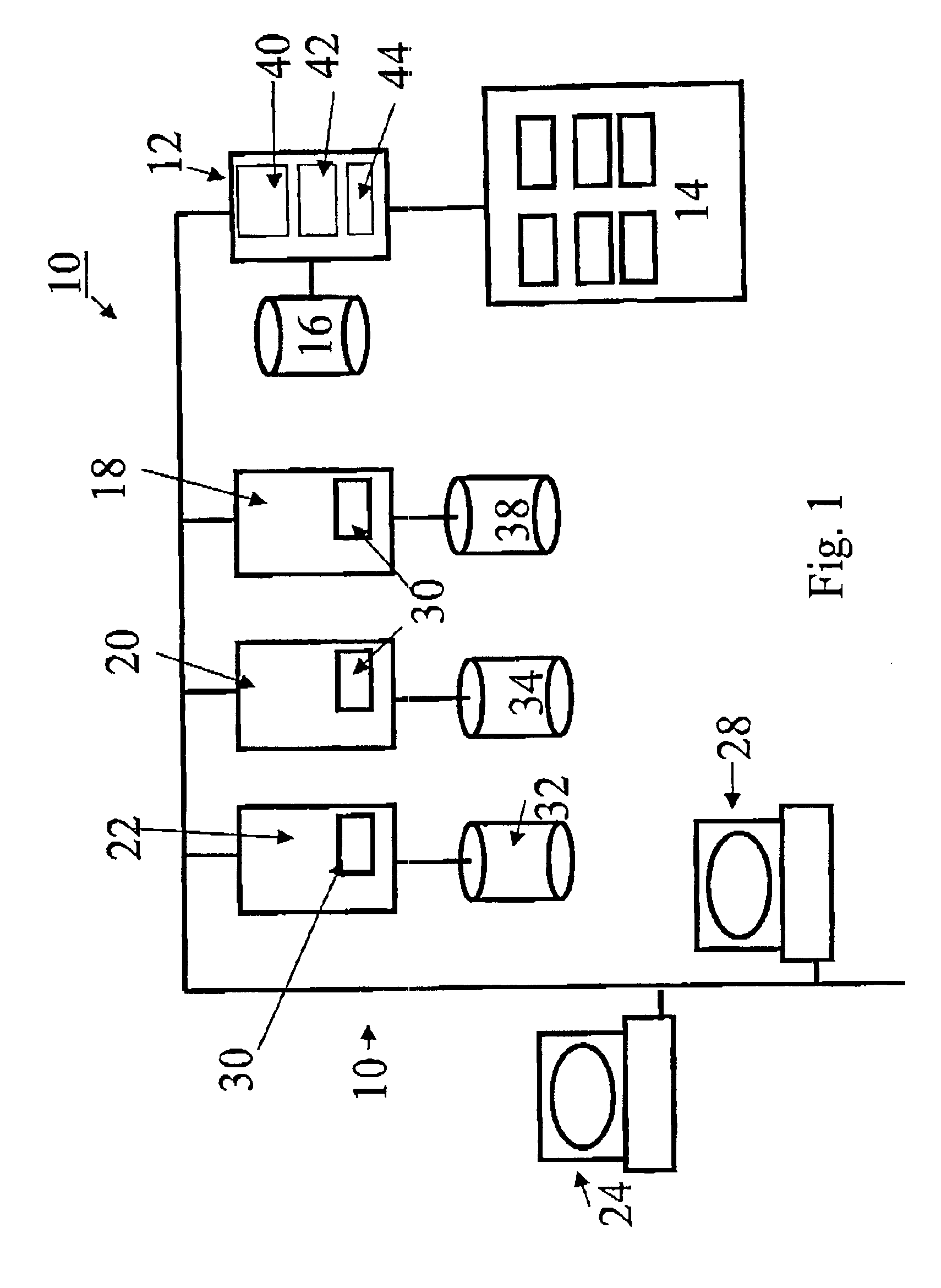

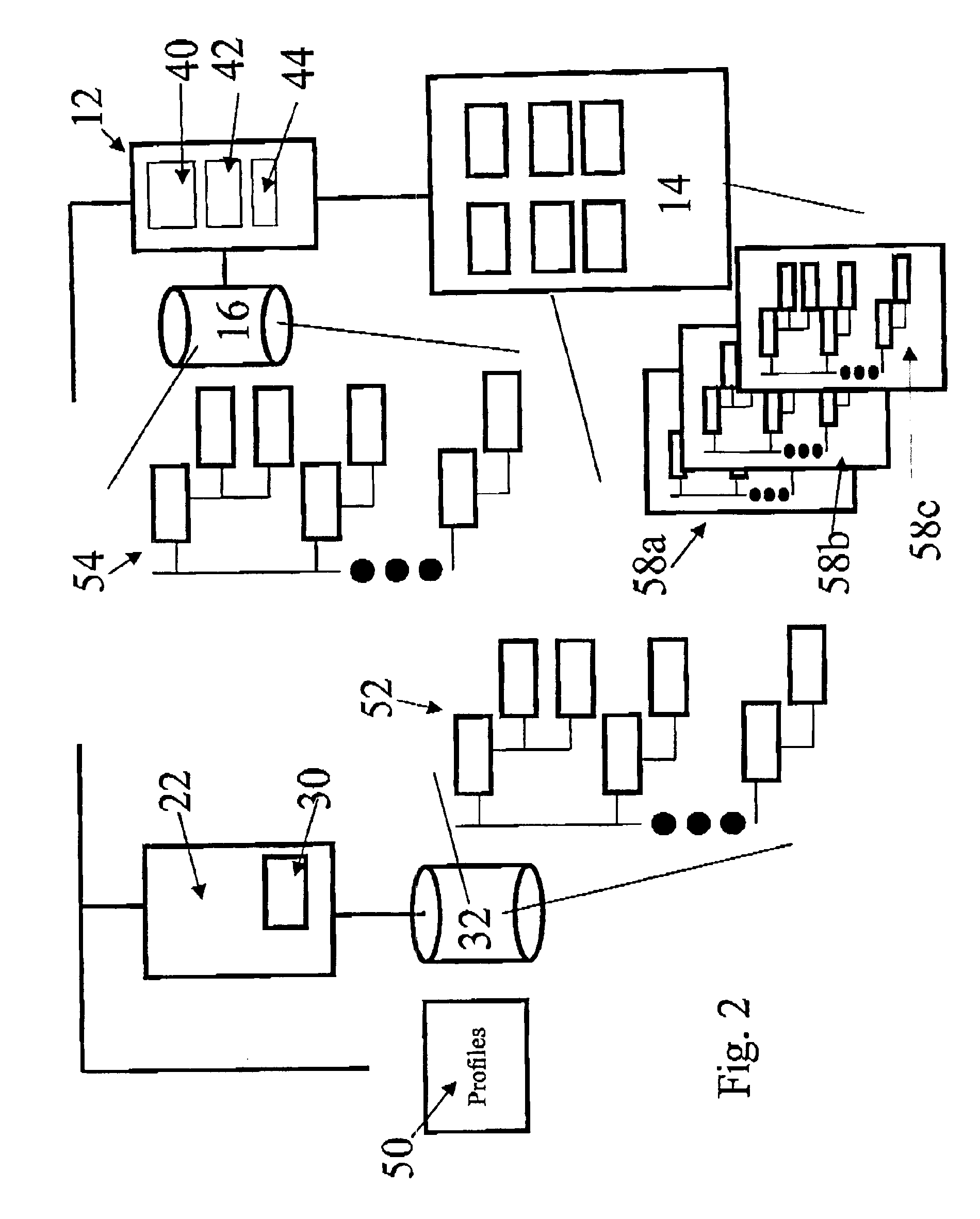

Systems and methods for backing up data files

InactiveUS6847984B1Provide integrityReduce demandData processing applicationsError detection/correctionBaseline dataData file

The invention provides systems and methods for continuous back up of data stored on a computer network. To this end the systems of the invention include a synchronization process that replicates selected source data files data stored on the network and to create a corresponding set of replicated data files, called the target data files, that are stored on a back up server. This synchronization process builds a baseline data structure of target data files. In parallel to this synchronization process, the system includes a dynamic replication process that includes a plurality of agents, each of which monitors a portion of the source data files to detect and capture, at the byte-level, changes to the source data files. Each agent may record the changes to a respective journal file, and as the dynamic replication process detects that the journal files contain data, the journal files are transferred or copied to the back up server so that the captured changes can be written to the appropriate ones of the target data files.

Owner:KEEPITSAFE INC

Wireless lighting devices and applications

InactiveUS8033686B2Advantage in easeLow costPoint-like light sourceLighting support devicesLight equipmentEffect light

In embodiments of the present invention improved capabilities are described for systems and methods that employ a control component and / or power source integrated in an LED based light source to control and / or power the LED light source wirelessly. In embodiments, the LED based light source may take the form of a standard light bulb that plugs into a standard lighting socket or fixture.

Owner:RING LLC

Wireless lighting devices and grid-shifting applications

ActiveUS20100271802A1Advantage in easeCost saving and in energy efficiencyBatteries circuit arrangementsElectroluminescent light sourcesMesh gridPower management

In embodiments of the present invention improved capabilities are described for systems and methods that provide a method of power management of a lighting source, including providing a lighting facility, wherein the lighting facility includes the lighting source, an external control device for communicating between the lighting facility and an external control source, an internal control facility, an energy storage device, and a connection to external power; and shifting power usage between the external power and the energy storage device as controlled by the internal control facility and as a result of information received from the external control source.

Owner:RING LLC

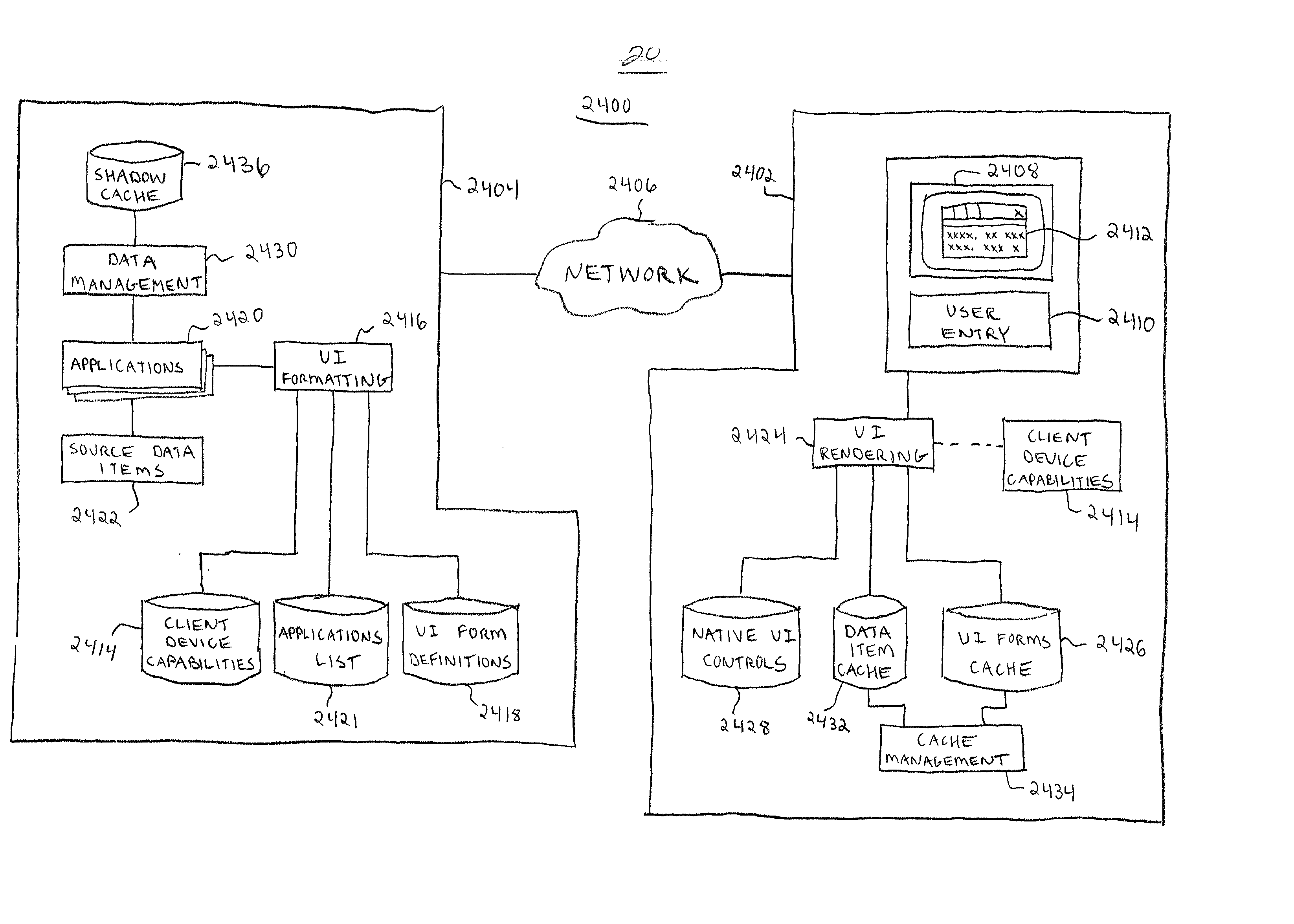

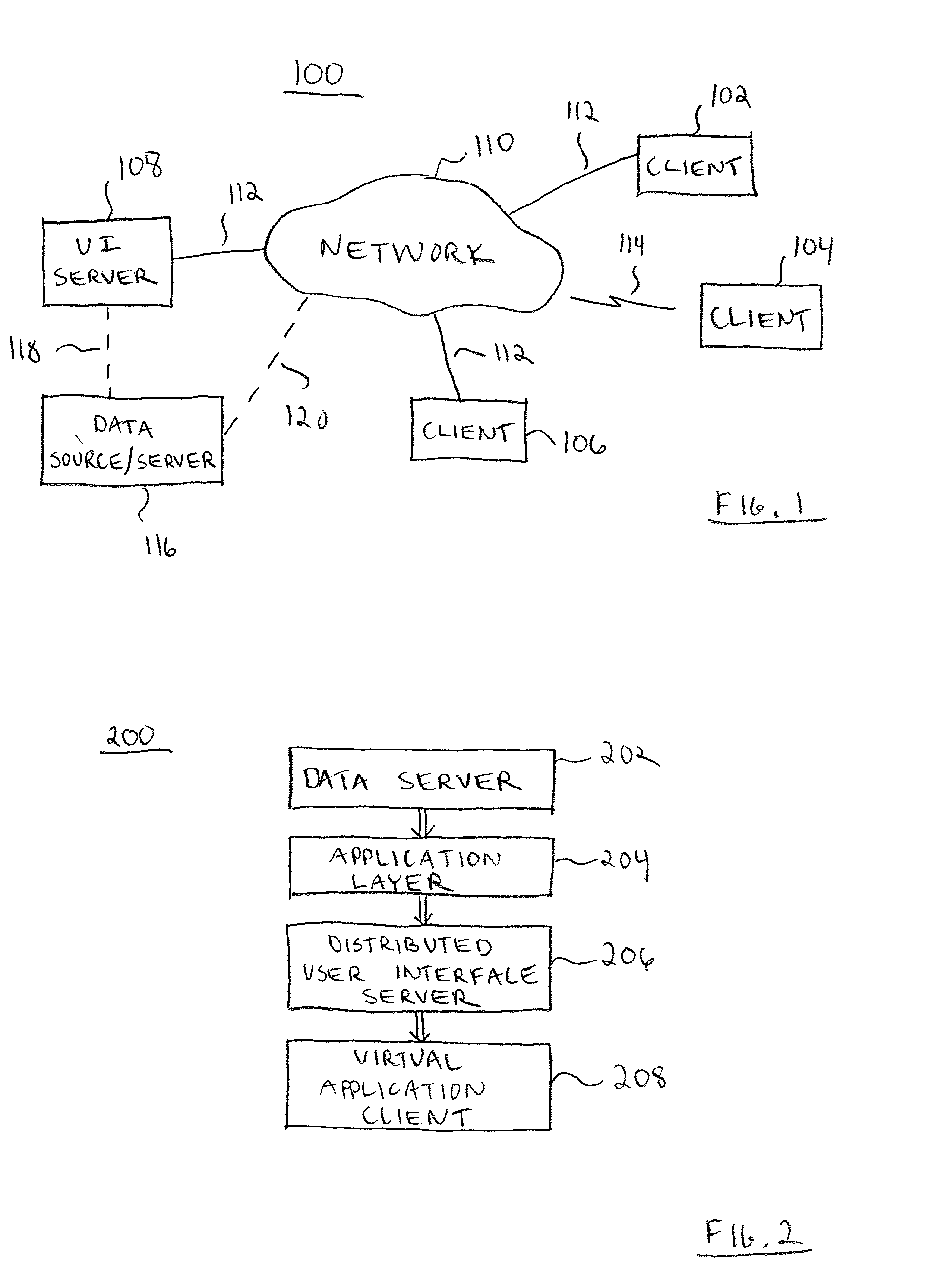

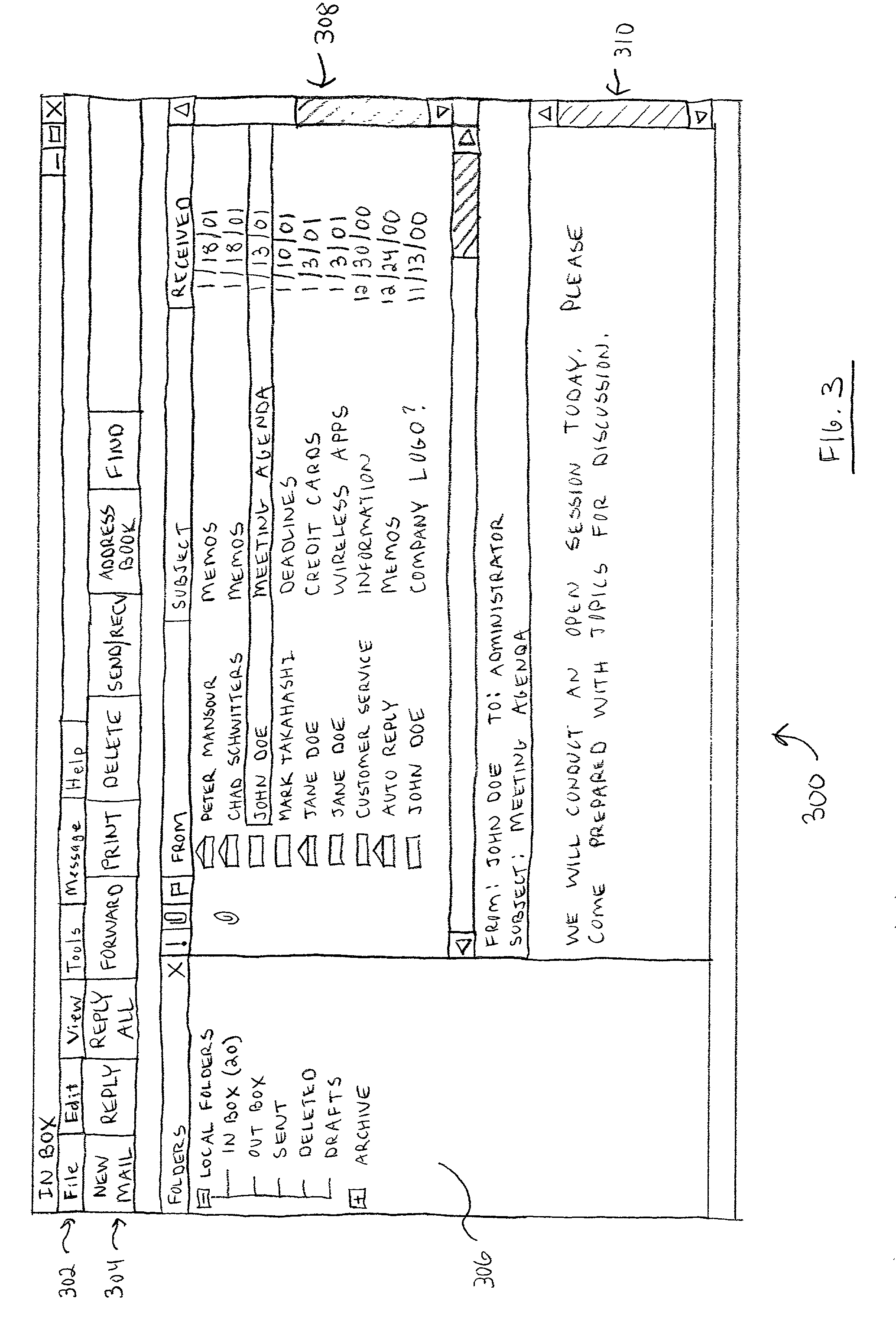

Platform-independent distributed user interface client architecture

InactiveUS20020129096A1Reduce demandLower-bandwidthCathode-ray tube indicatorsMultiple digital computer combinationsDistributed user interfaceThe Internet

A distributed user interface (UI) system includes a client device configured to render a UI for a server-based application. The client device communicates with a UI server over a network such as the Internet. The UI server performs formatting for the UI, which preferably utilizes a number of native UI controls that are available locally at the client device. In this manner, the client device need only be responsible for the actual rendering of the UI. The source data items are downloaded from the UI server to the client device when necessary, and the client device populates the UI with the downloaded source data items. The client device employs a cache to store the source data items locally for easy retrieval.

Owner:SPROQIT TECHNOLGIES

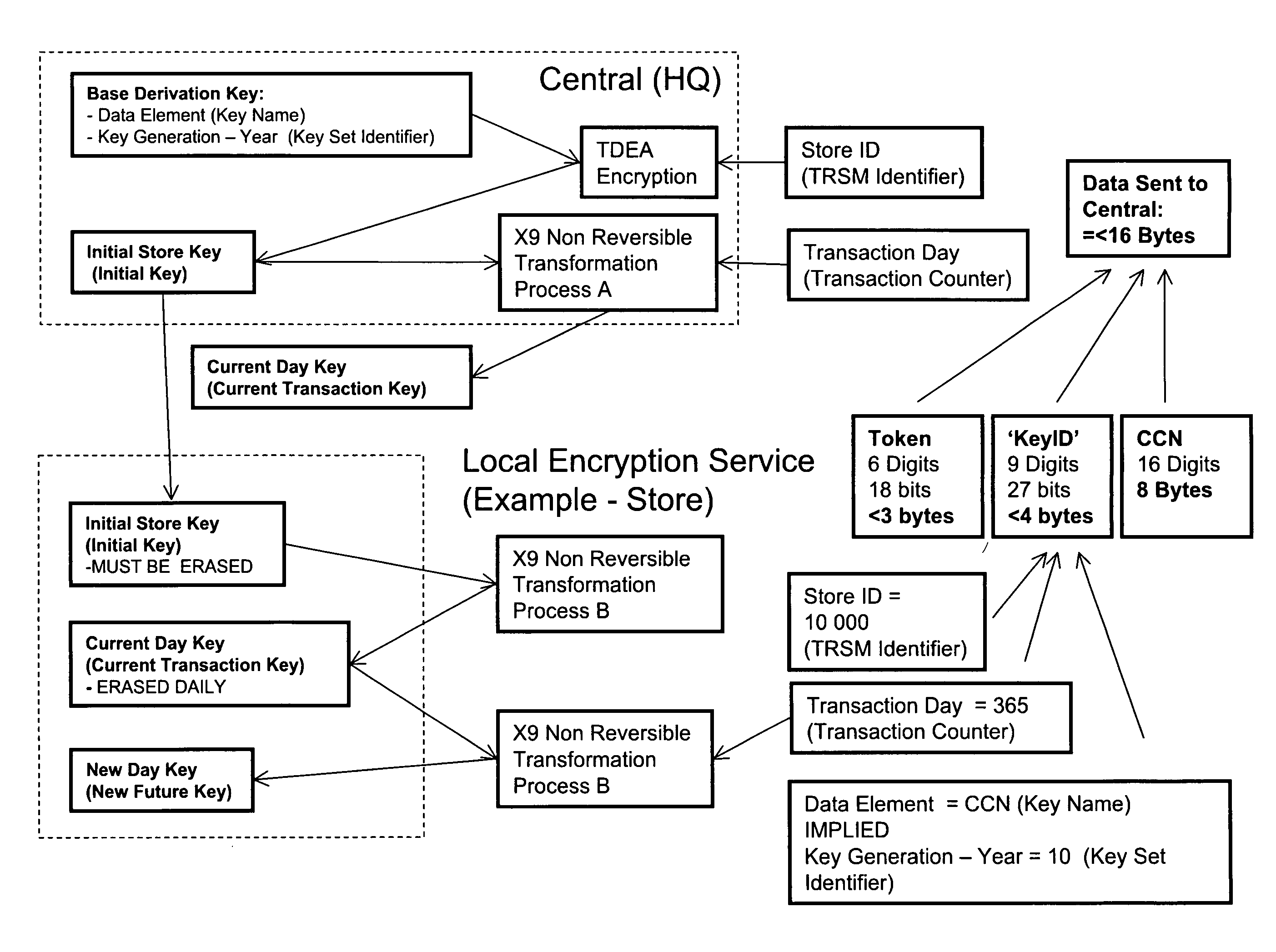

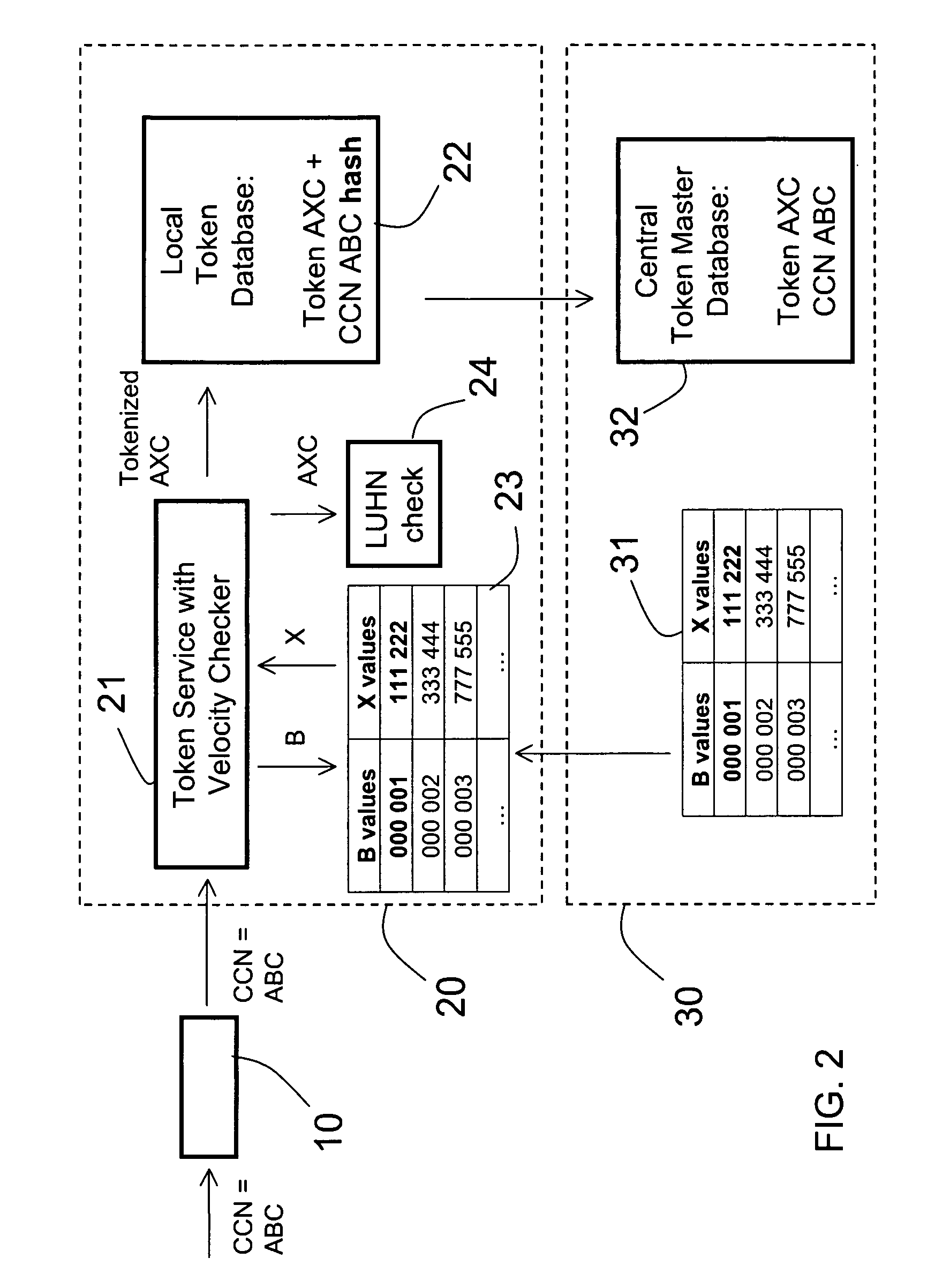

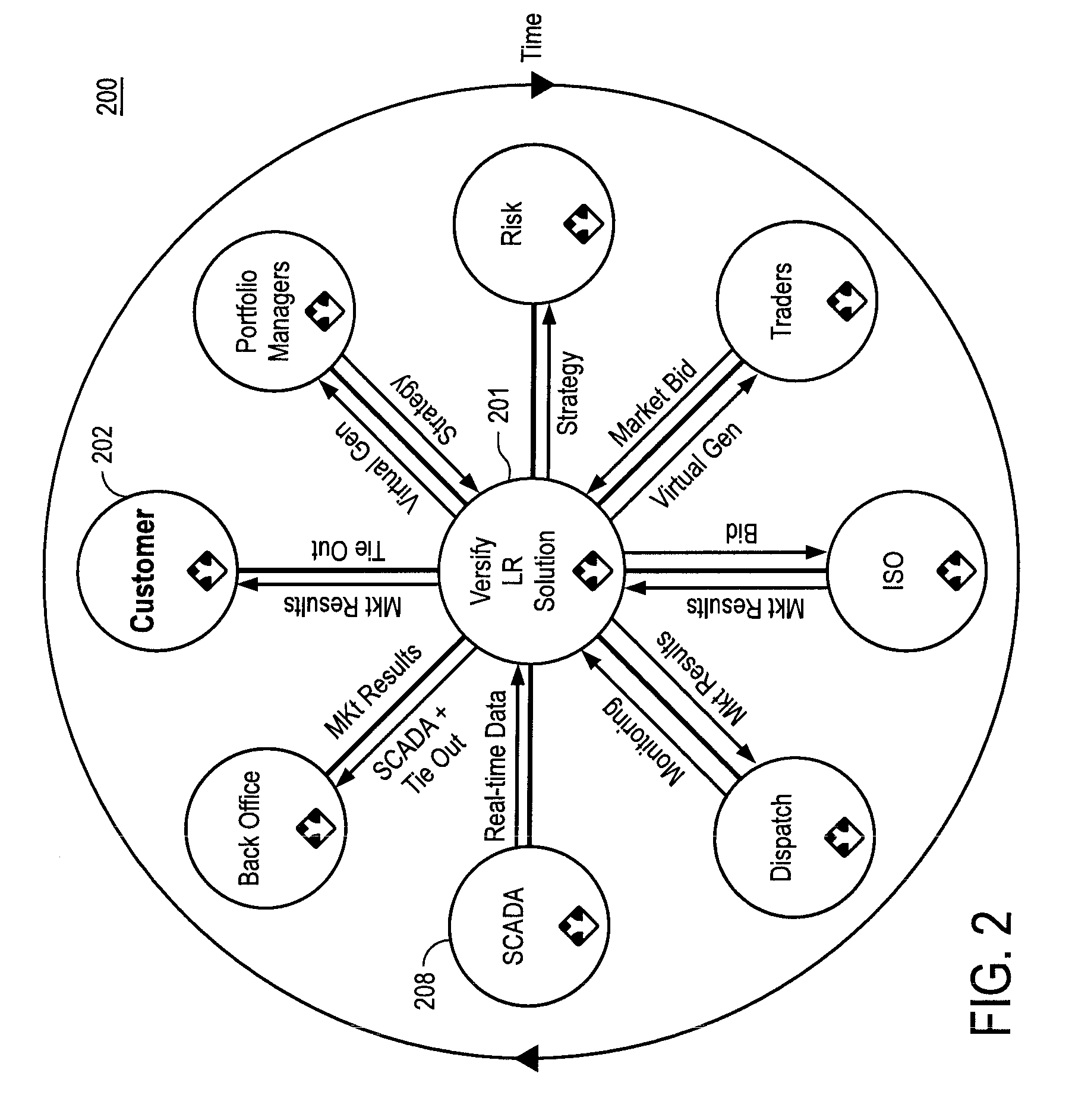

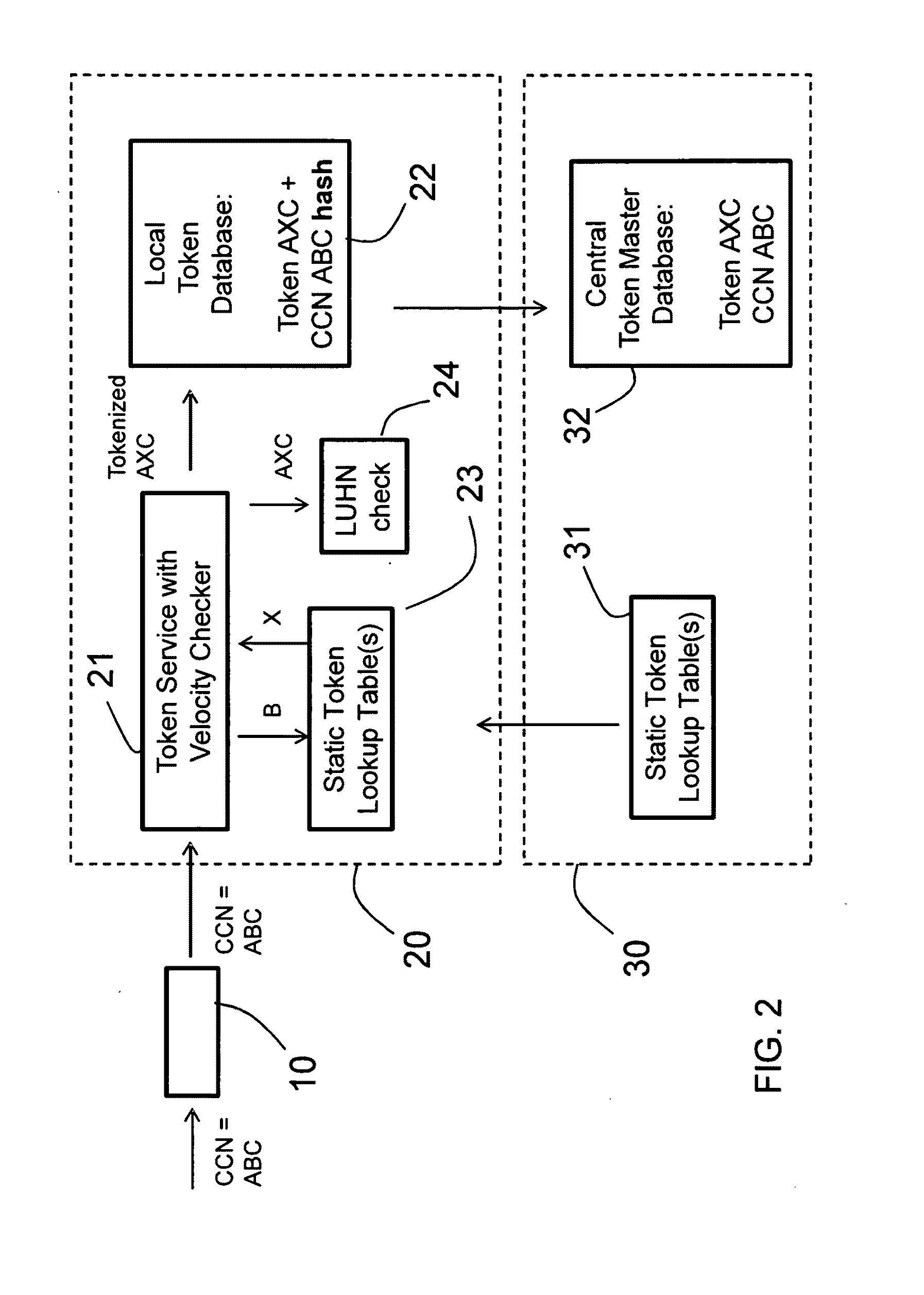

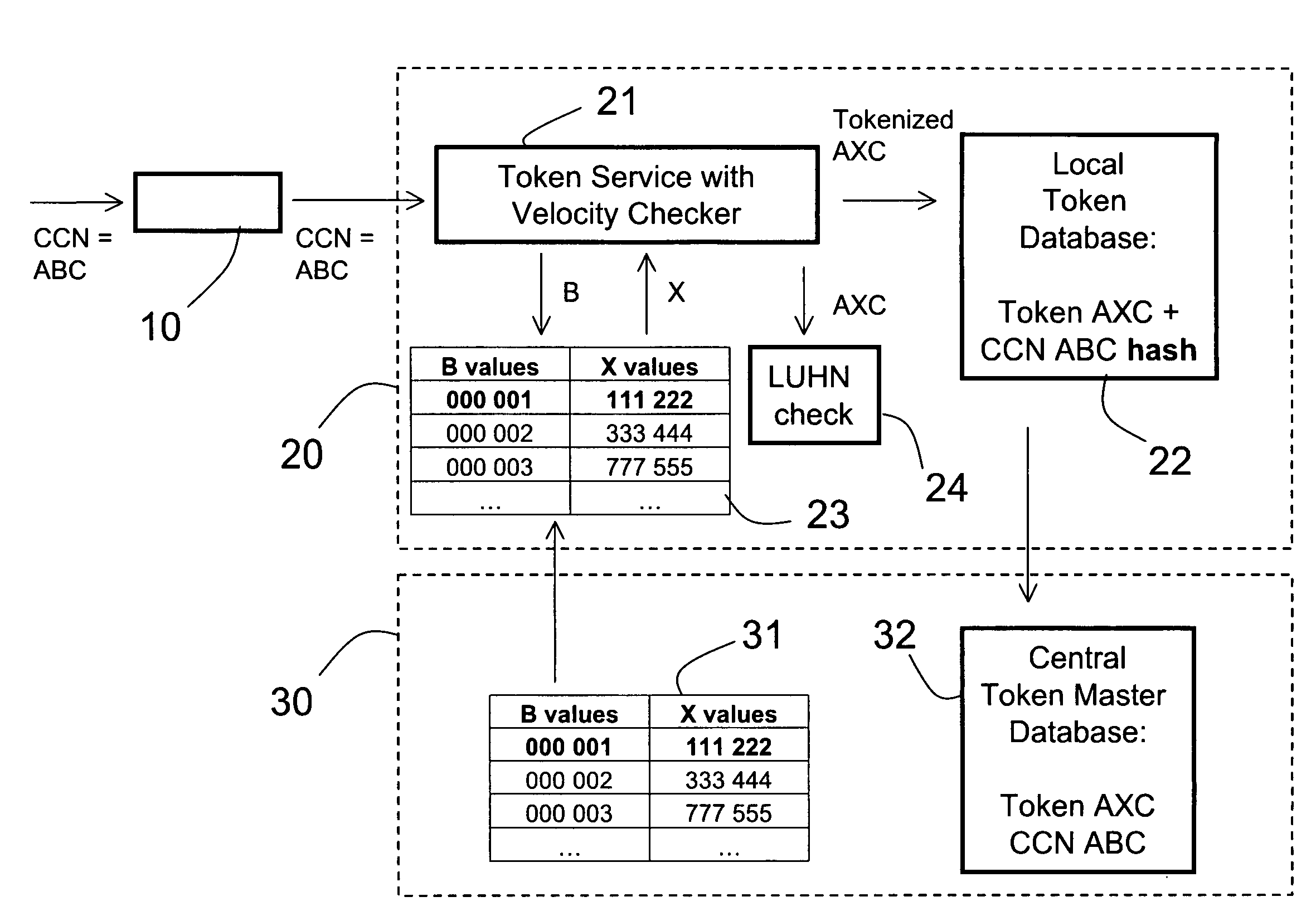

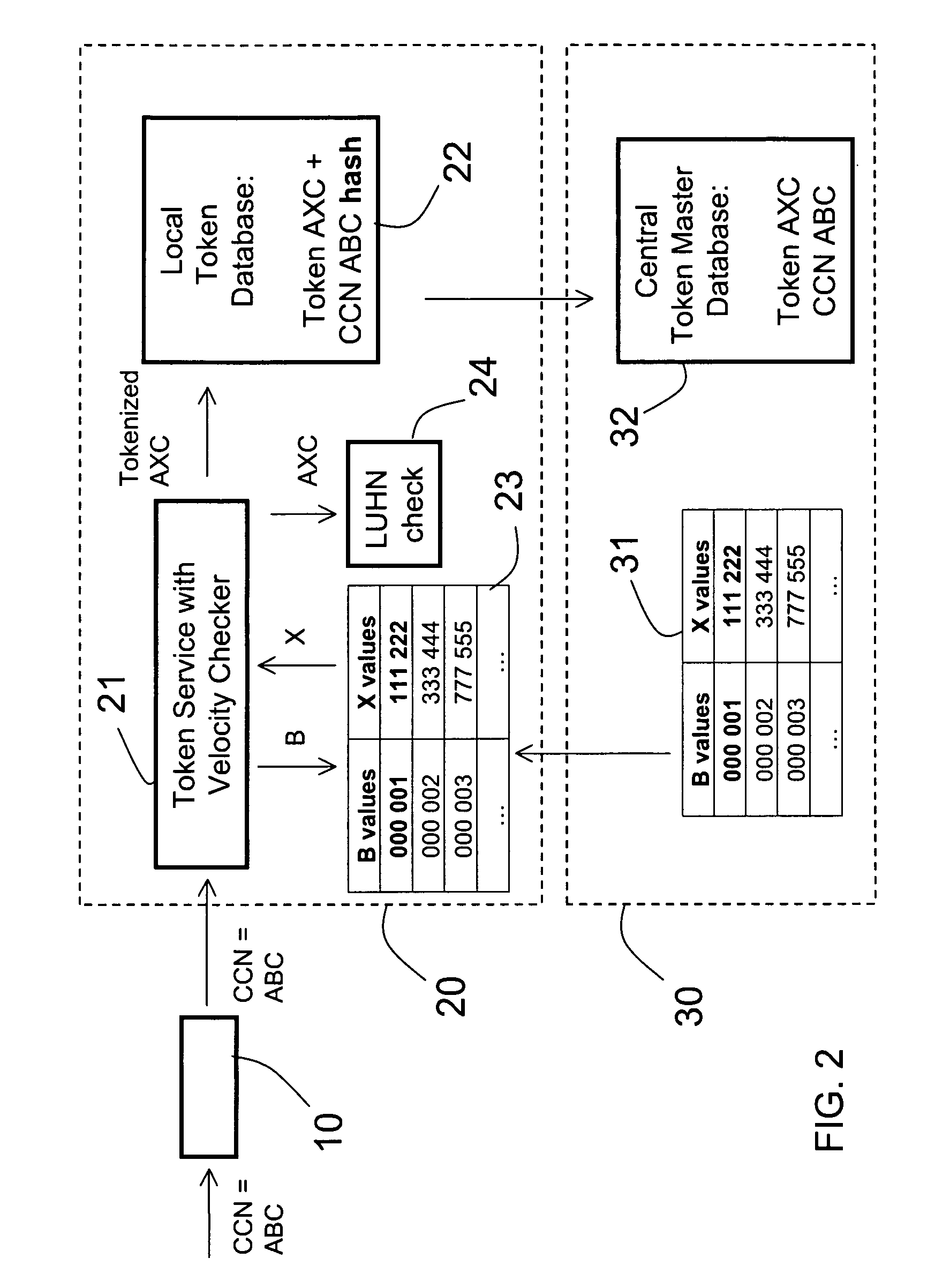

Method and apparatus for tokenization of sensitive sets of characters

ActiveUS8578176B2Reduce demandImprove forecastAcutation objectsUnauthorized memory use protectionComputer networkSafe handling

A method and system for secure handling of sensitive sets of characters in a distributed hierarchical system are disclosed, comprising at least one local server on a lower hierarchic level and at least one central server at a higher hierarchic level. The method comprises the steps: receiving a sensitive set of characters in said local server; replacing a part of said sensitive set of characters with a token to form a tokenized set of characters, said token belonging to a subset of possible tokens assigned to the local server by the central server; transferring at least one of said sensitive set of characters and said tokenized set of characters to the central server; and canceling said sensitive set of characters from said local server within a limited time from said transferring, while maintaining said tokenized set of characters in a local database connected to said local server.

Owner:PROTEGRITY CORP

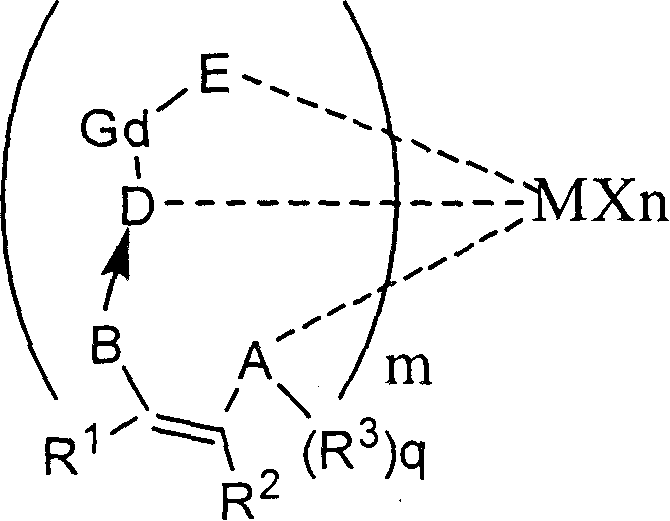

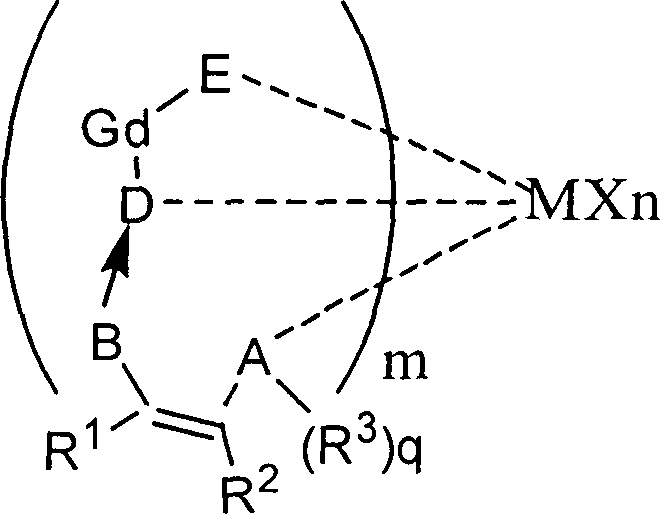

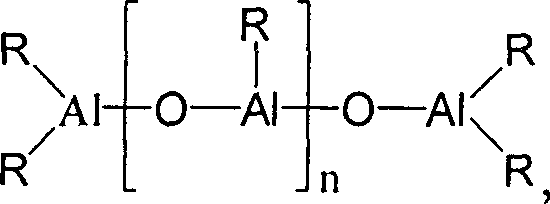

Application of supported non-metallocene catalyst in ethene polymerization process by slurry method

The invention discloses an application of load non- metallocene catalyst in the slurry process for vinyl polymerying, the load non- metallocene catalyst and catalyst promoter forming the catalytic system, the alkene polymerization comprising: vinyl homopolymerization, combined polymerization of vinyl with propylene, butylenes, hexane, octane or norbornene; the catalyst carrier being chosen from: inorganic oxide of metallic oxide from IIA, IIIA, IVA, and IVB groups, or oxided mixture and mixing oxide; the catalyst promoter being chosen from: methylaluoxane, ethylaluoxane, isobutylaluoxane, trimethylaluminum,triethylaluminum,triisobutylaluminum,methylaluoxane-trimethylaluminum or methylaluoxane-triethylaluminum; the mole proportion between the catalyst promoter and catalyst being Al / Ti= 1:1-500. The inventioin is characterized by the less methylaluoxane consumption, stable reaction, easy-to-control polymerization temperature and non still-sticking phenomenon. The produced polyolefine possesses perfect granual shape, and the maximum polymer clamp density can reach 0.385 g / ml.

Owner:SINOPEC YANGZI PETROCHEM

Power outage detector and transmitter

ActiveUS20120026726A1Advantage in easeLow costPoint-like light sourceLighting support devicesEngineeringTransmitter

In embodiments of the present invention improved capabilities are described for systems and methods that employ a control component and / or power source integrated in an LED based light source to control and / or power the LED light source wirelessly. In embodiments, the LED based light source may take the form of a standard light bulb that plugs into a standard lighting socket or fixture.

Owner:RING LLC

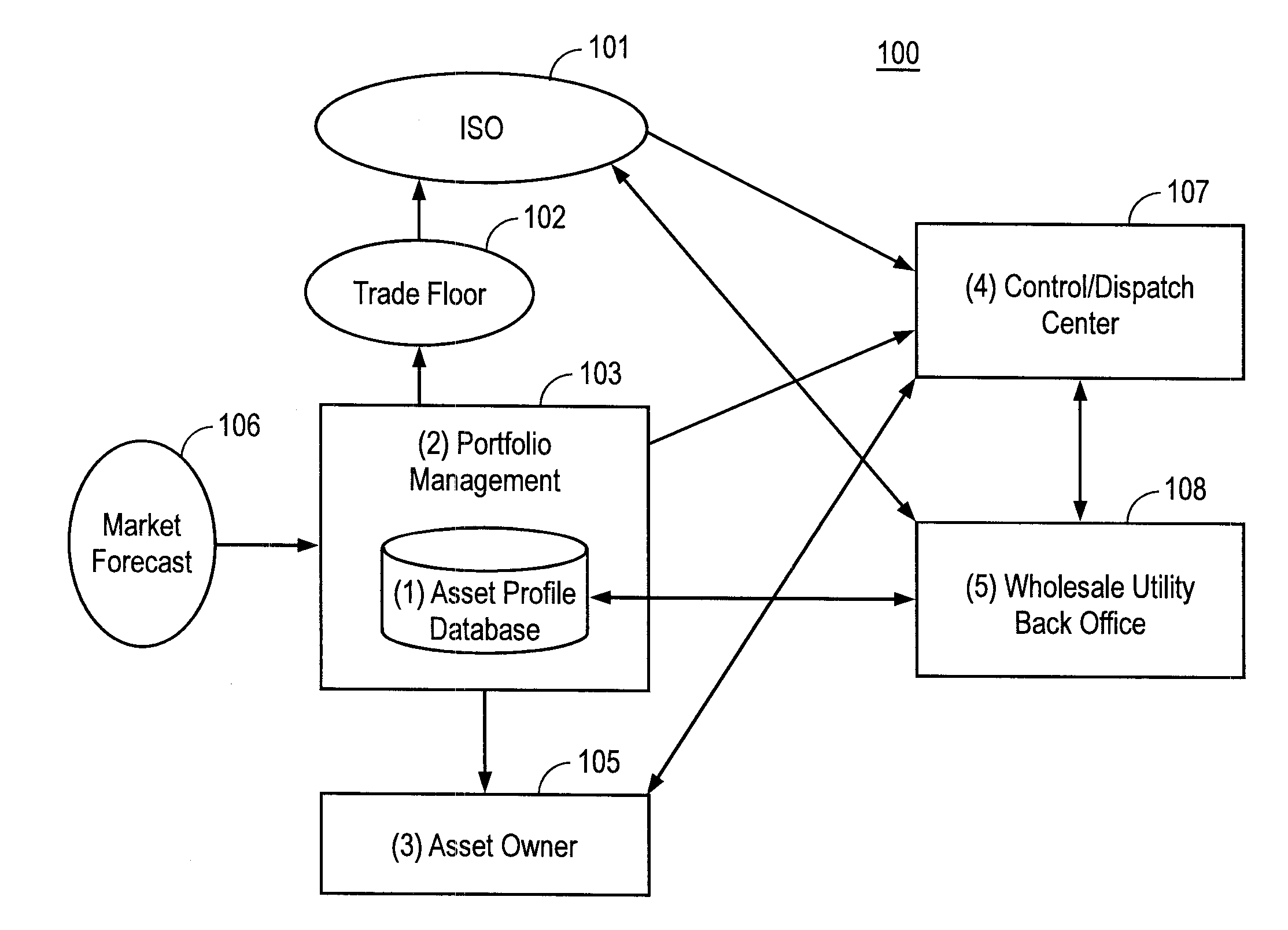

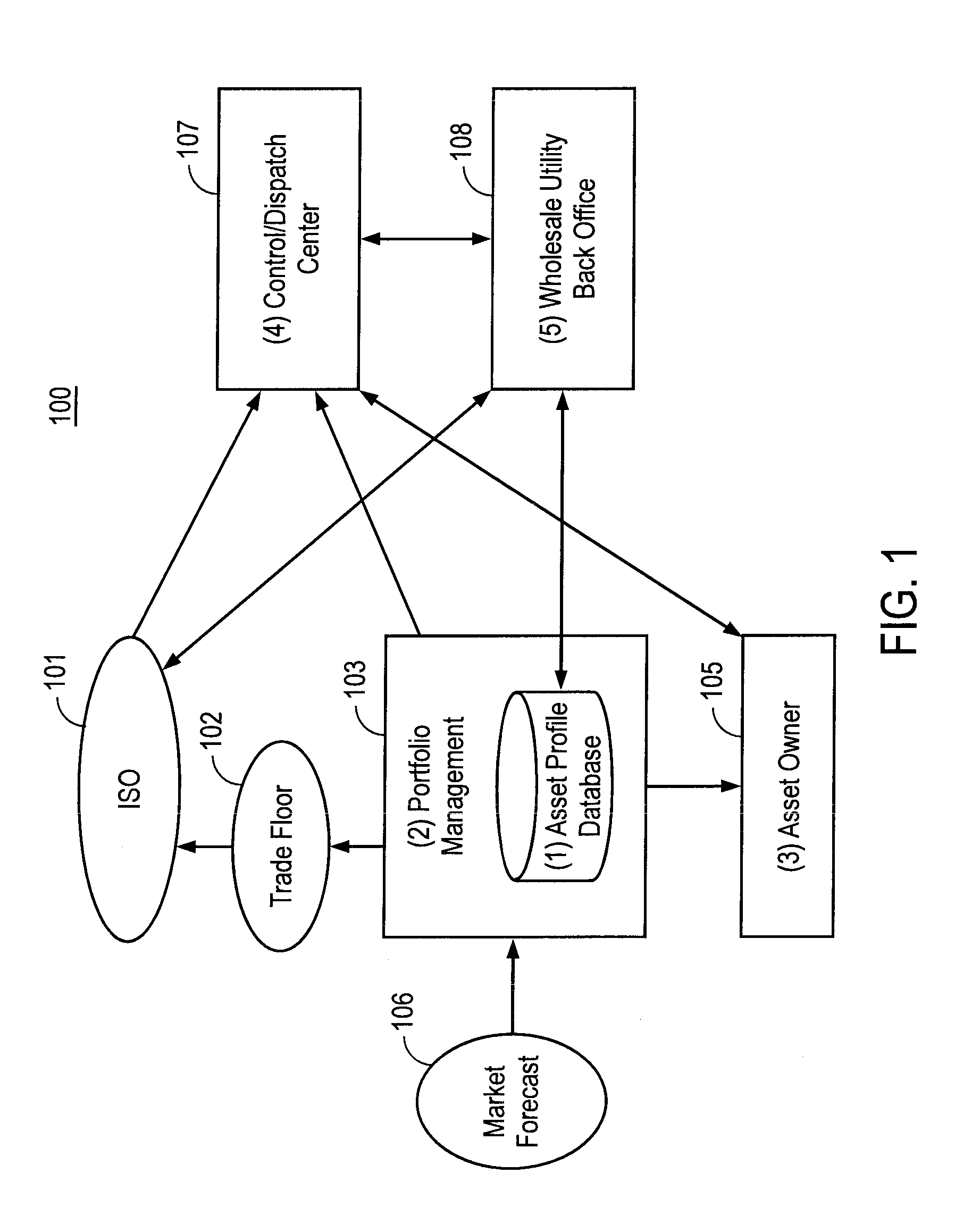

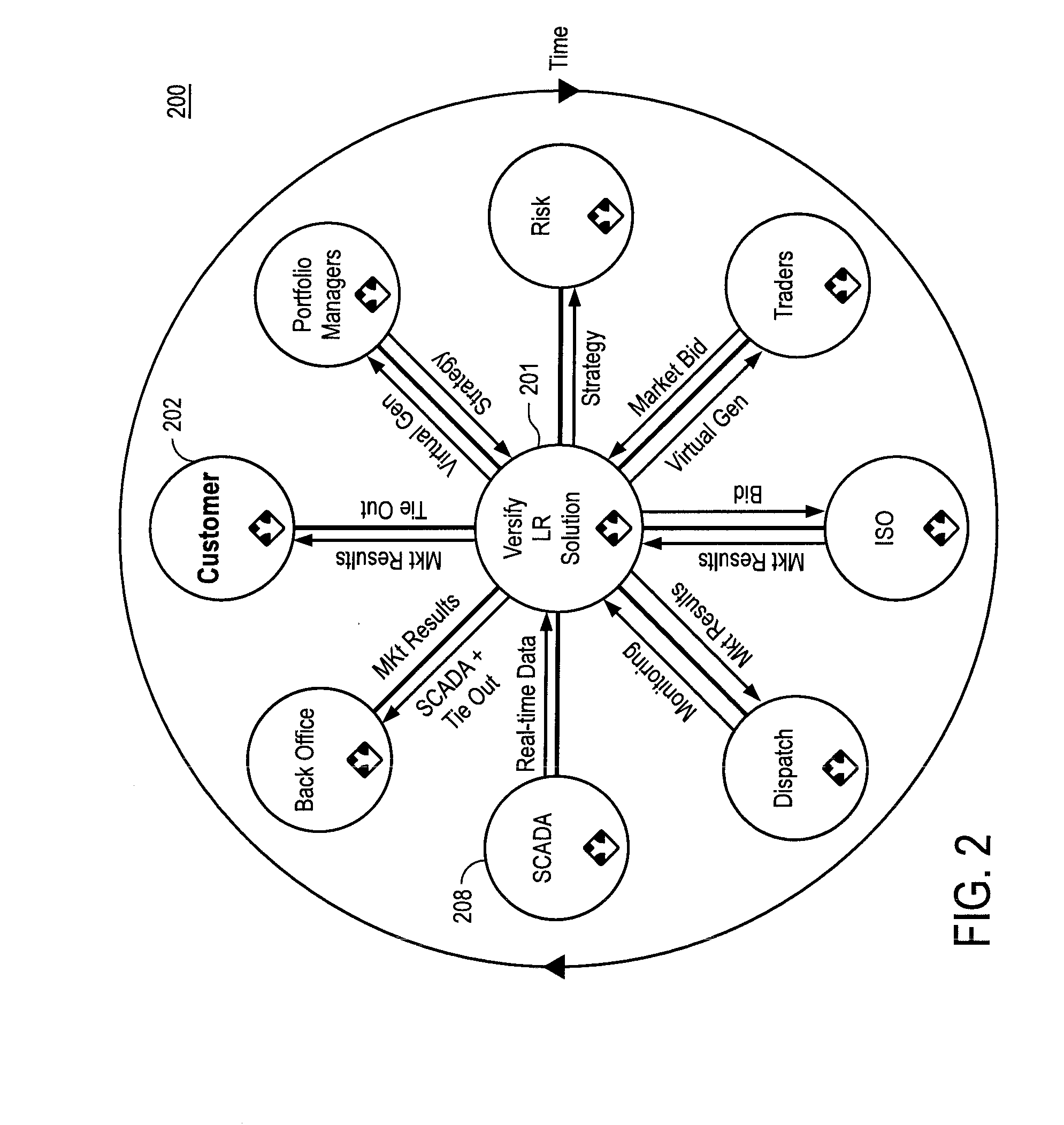

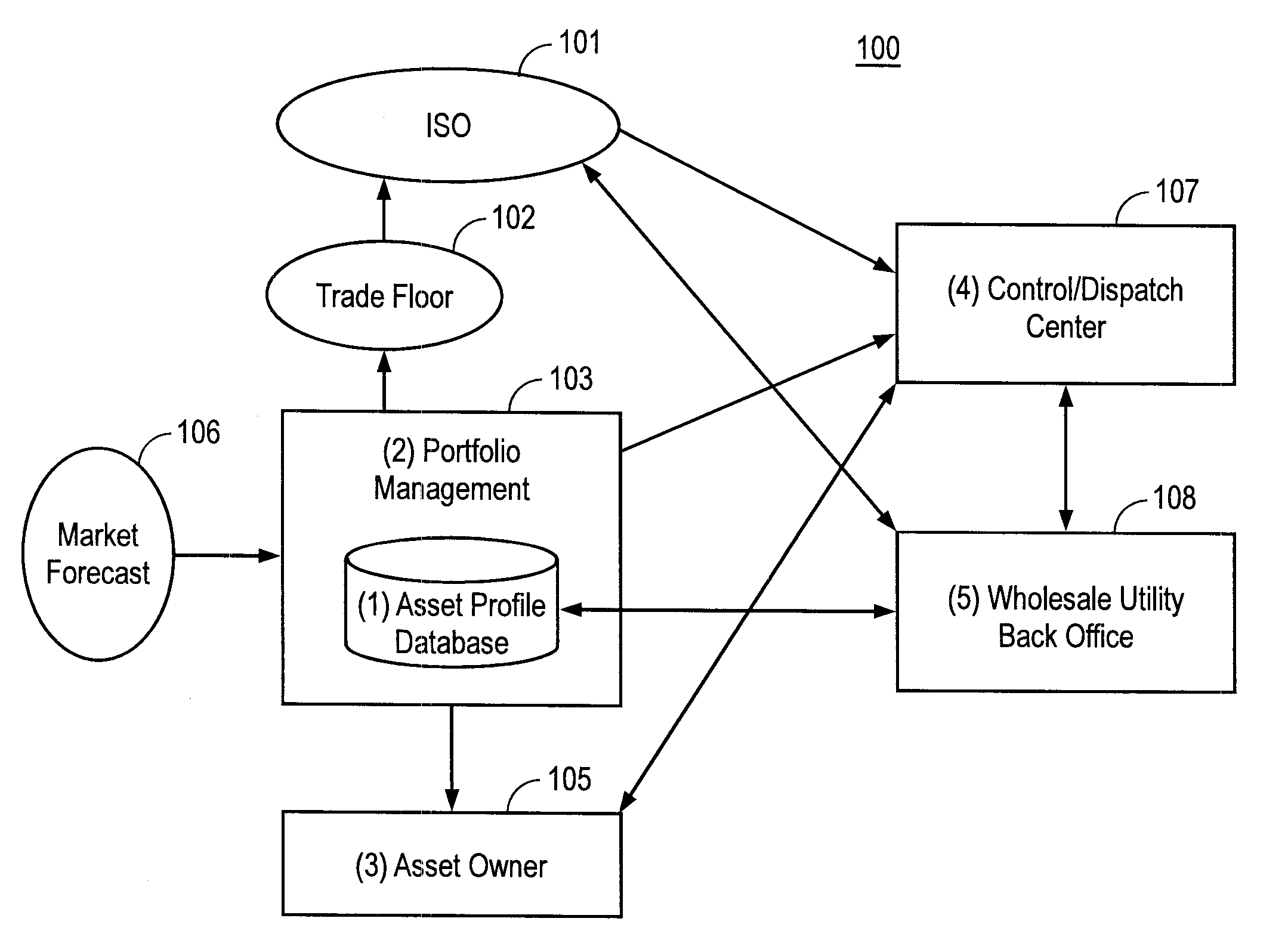

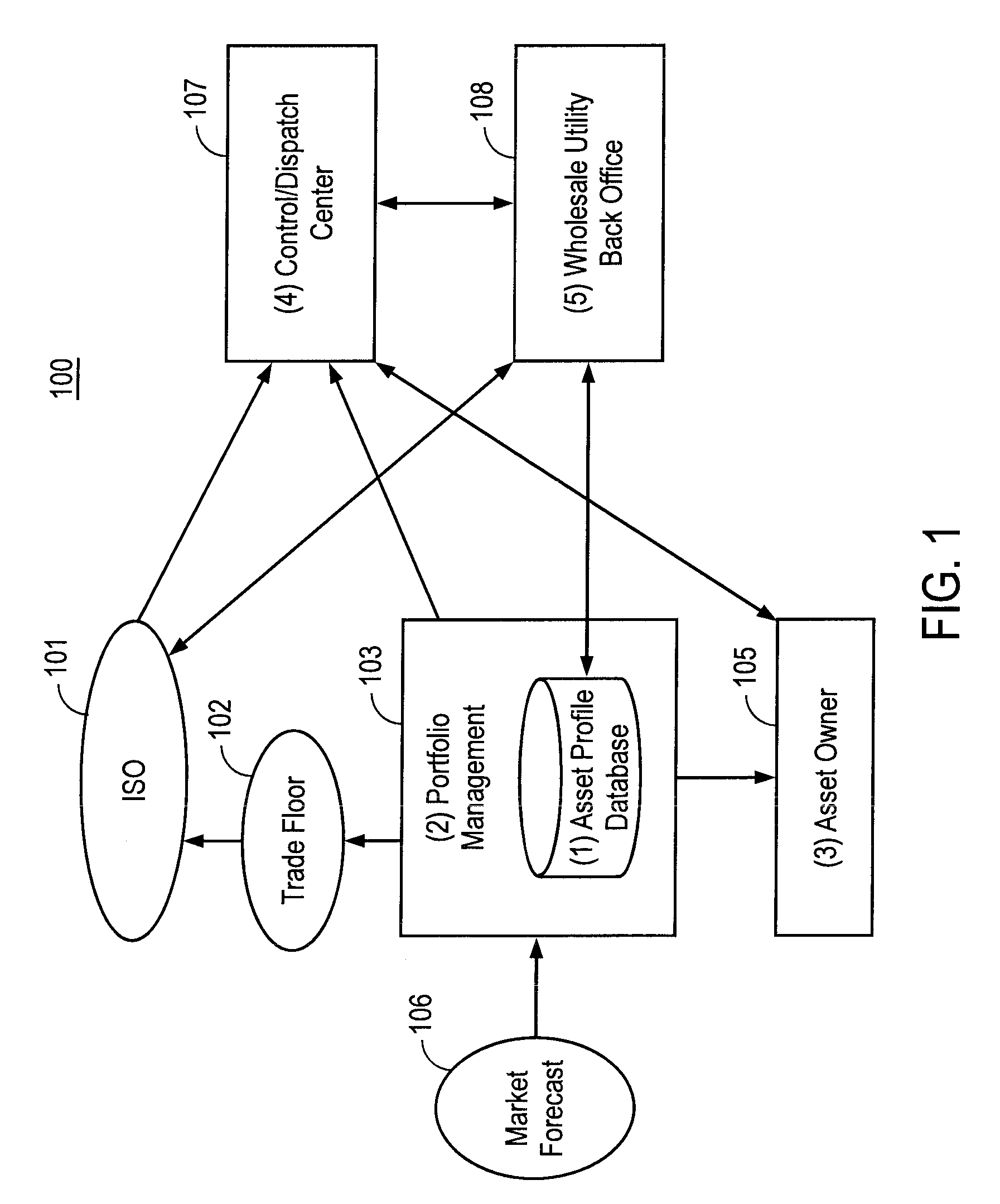

Aggregator, monitor, and manager of distributed demand response

ActiveUS20090326726A1Facilitate power capacity to powerReduce loadMarket predictionsLevel controlPower gridMesh grid

The invention broadly encompasses a system including a database to store demand response data, the demand response data including demand response agreement parameters, demand response load and energy demand characteristics of one or more demand response customers, the demand response load characteristics including power consumption capacity of each of one or more demand response loads, an aggregator to aggregate the demand response loads based on the demand response data and forecast data into a demand response portfolio, a monitor to monitor power demand of one or more demand response customers and one or more power grids, and a dispatcher to notify the one or more demand response customers of the demand response portfolio and to notify a utility of a response from the one or more demand response customers whether to control the demand response load to return the power consumption capacity of the demand response load back to the one or more power grids.

Owner:MCG VERSIFY ACQUISITION LLC

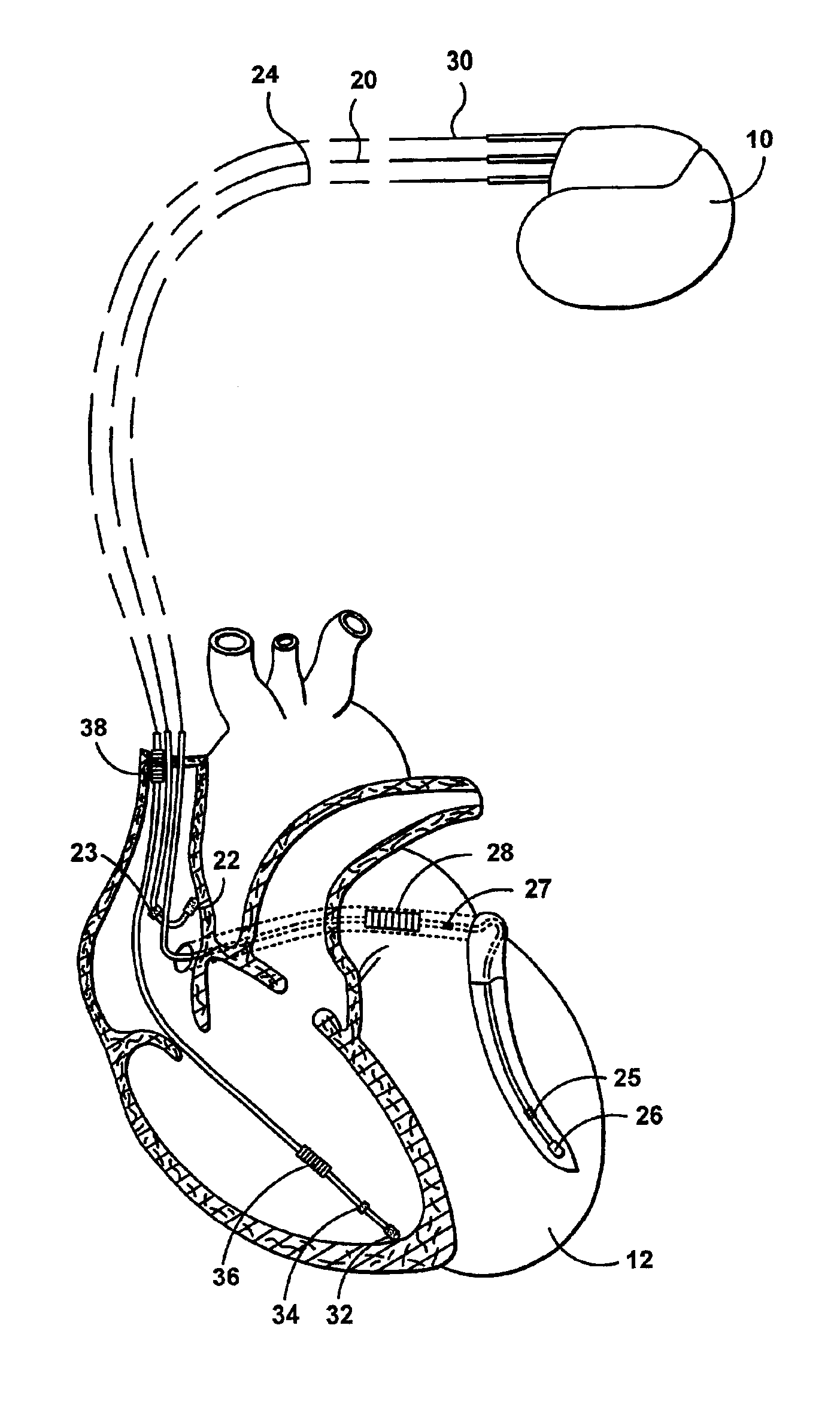

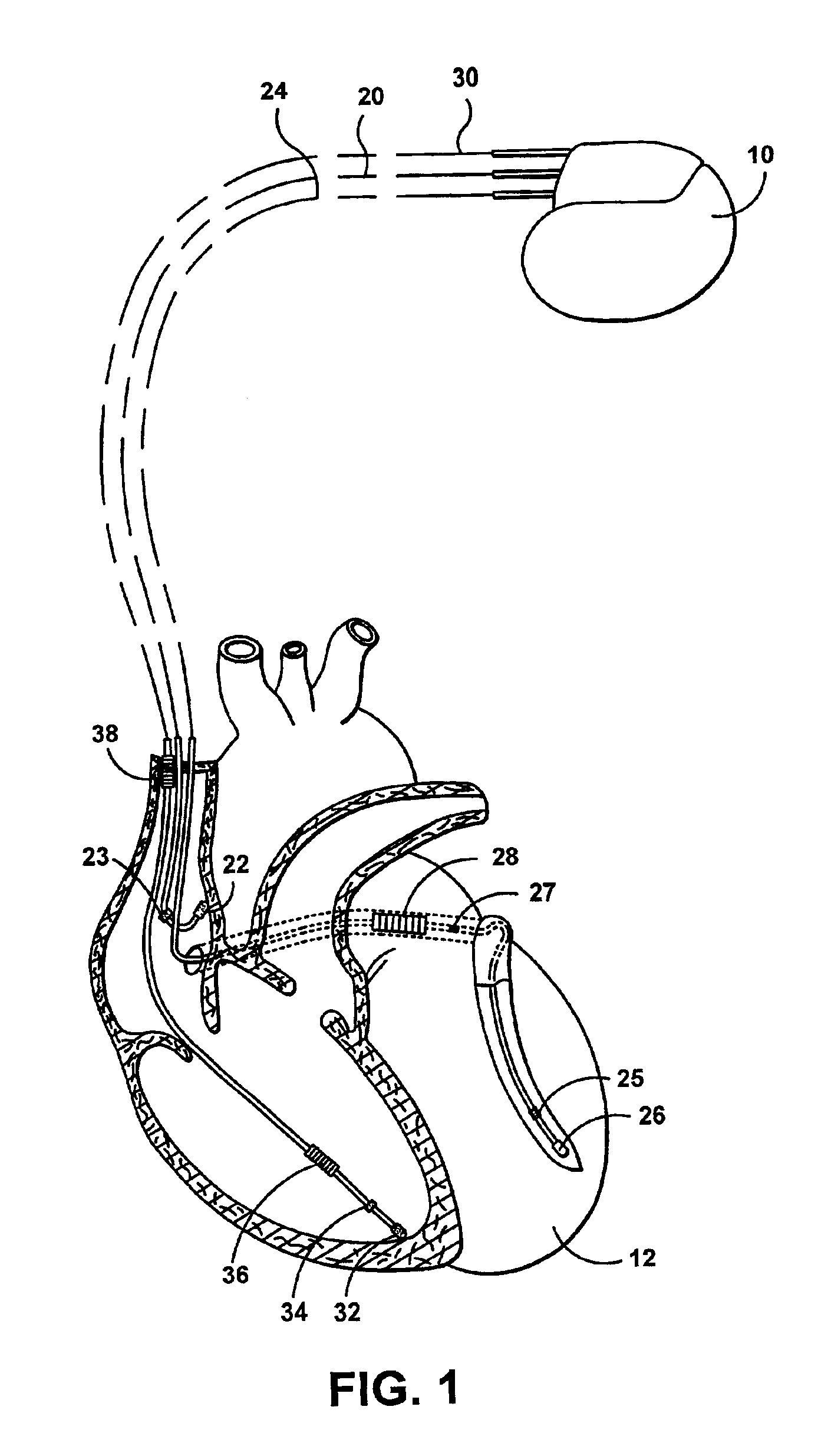

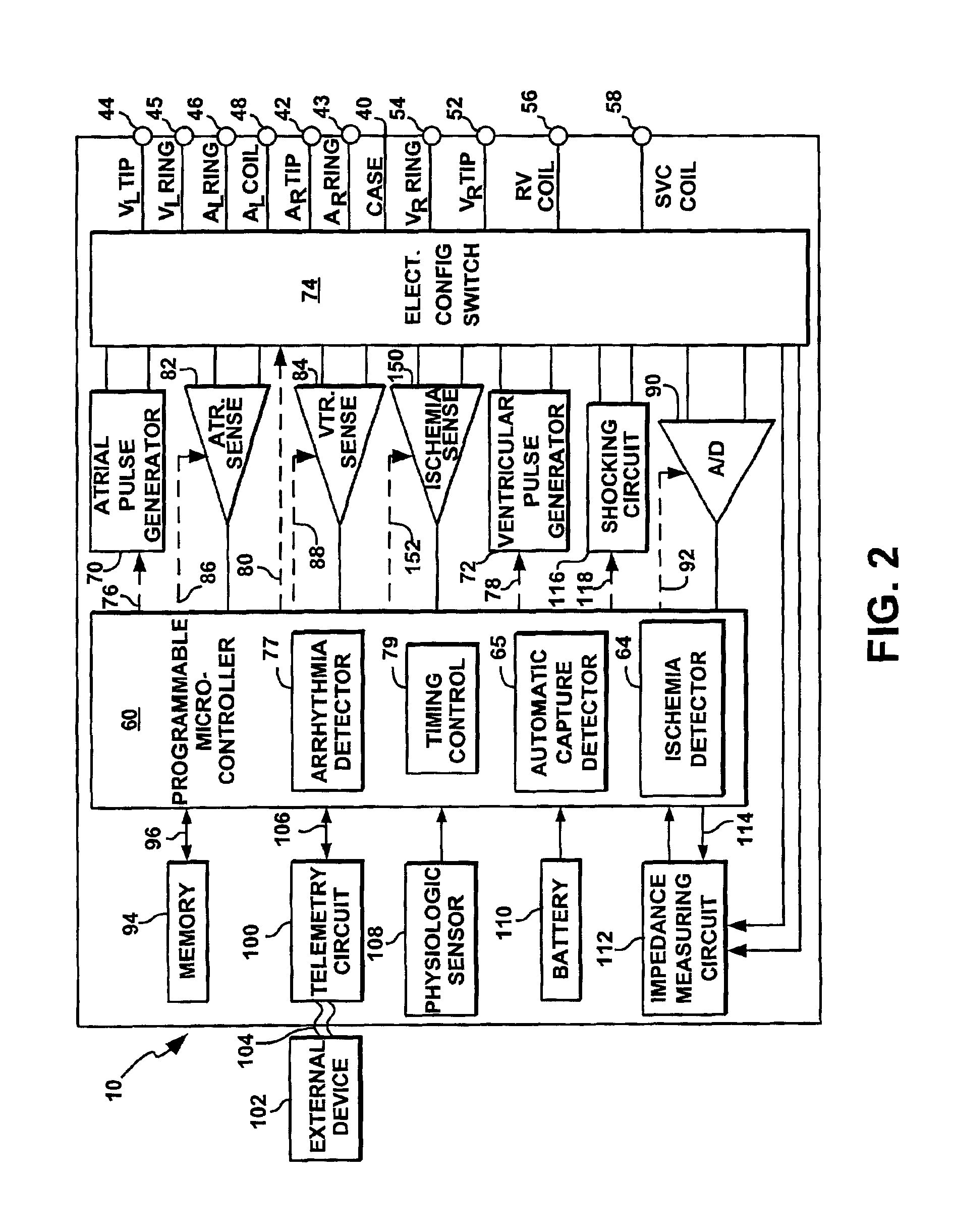

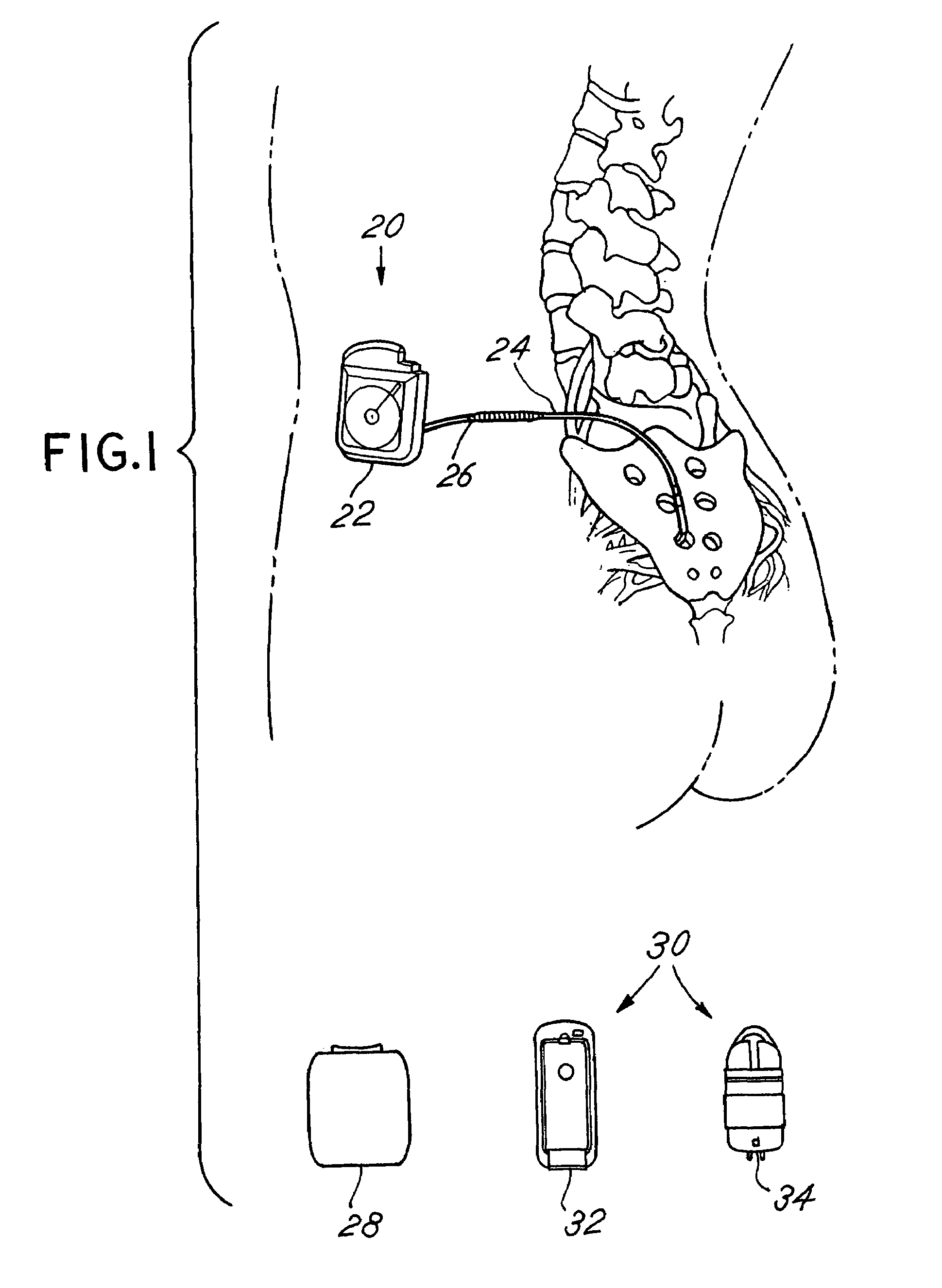

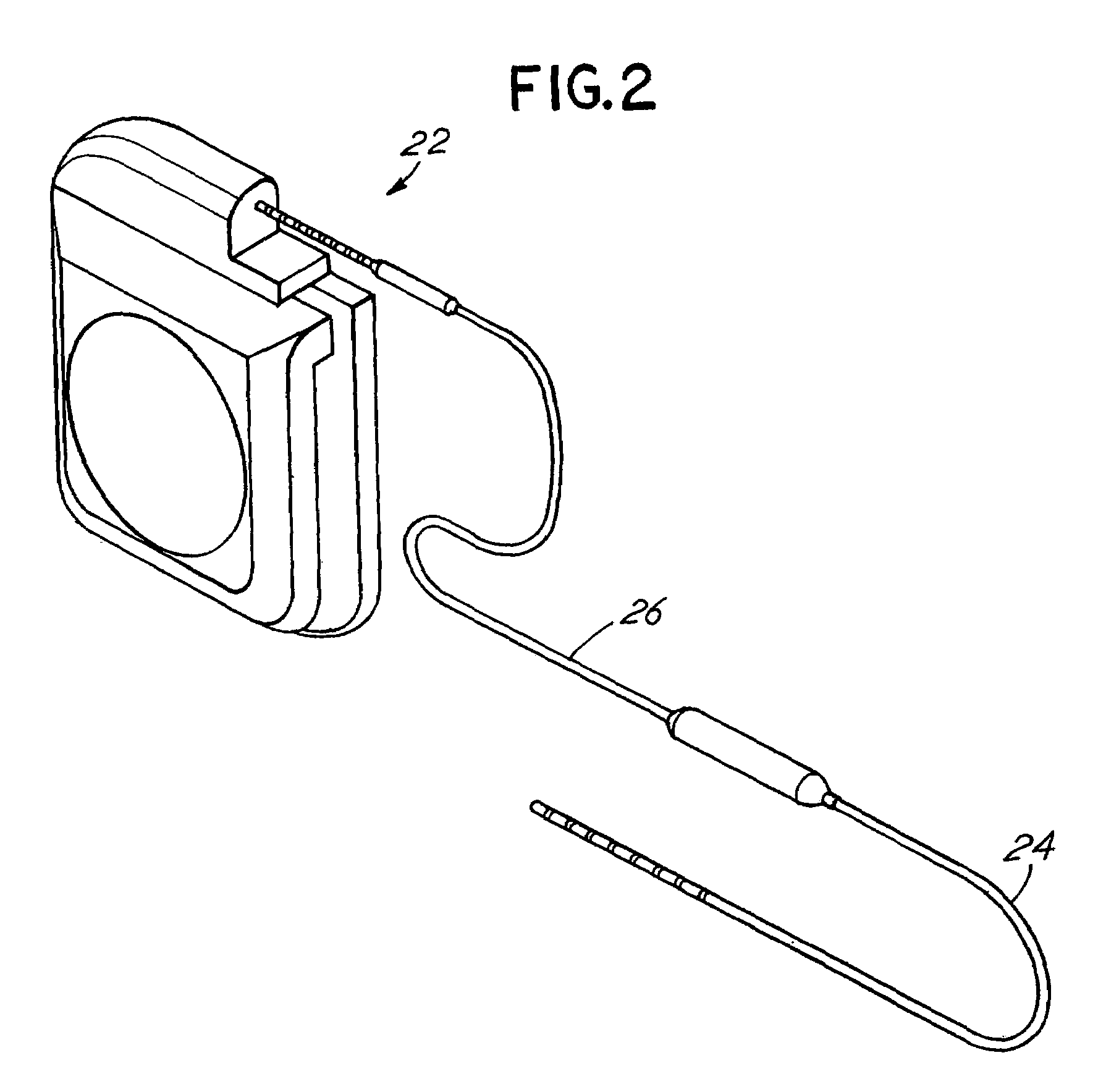

Cardiac stimulation device for optimizing cardiac output with myocardial ischemia protection

InactiveUS6865420B1Reduce demandReduce detectionHeart stimulatorsCardiac muscleIntracardiac Electrogram

A cardiac stimulation device and method detect myocardial ischemia and provide a response for alleviating the ischemia. Myocardial ischemia is detected by identifying changes in the ST-segment of the intracardiac electrogram (EGM) sensed using large sensing electrode surfaces created by electrically coupling one or more cardiac electrodes or by using larger surface area shocking coils. Myocardial ischemia monitoring is performed when stimulation parameters are adjusted for increasing cardiac output, causing an increased metabolic demand to be placed on the myocardium itself. When myocardial ischemia is detected, stimulation parameters are re-adjusted to reduce the demand placed on the myocardium and thereby alleviate the ischemia.

Owner:PACESETTER INC

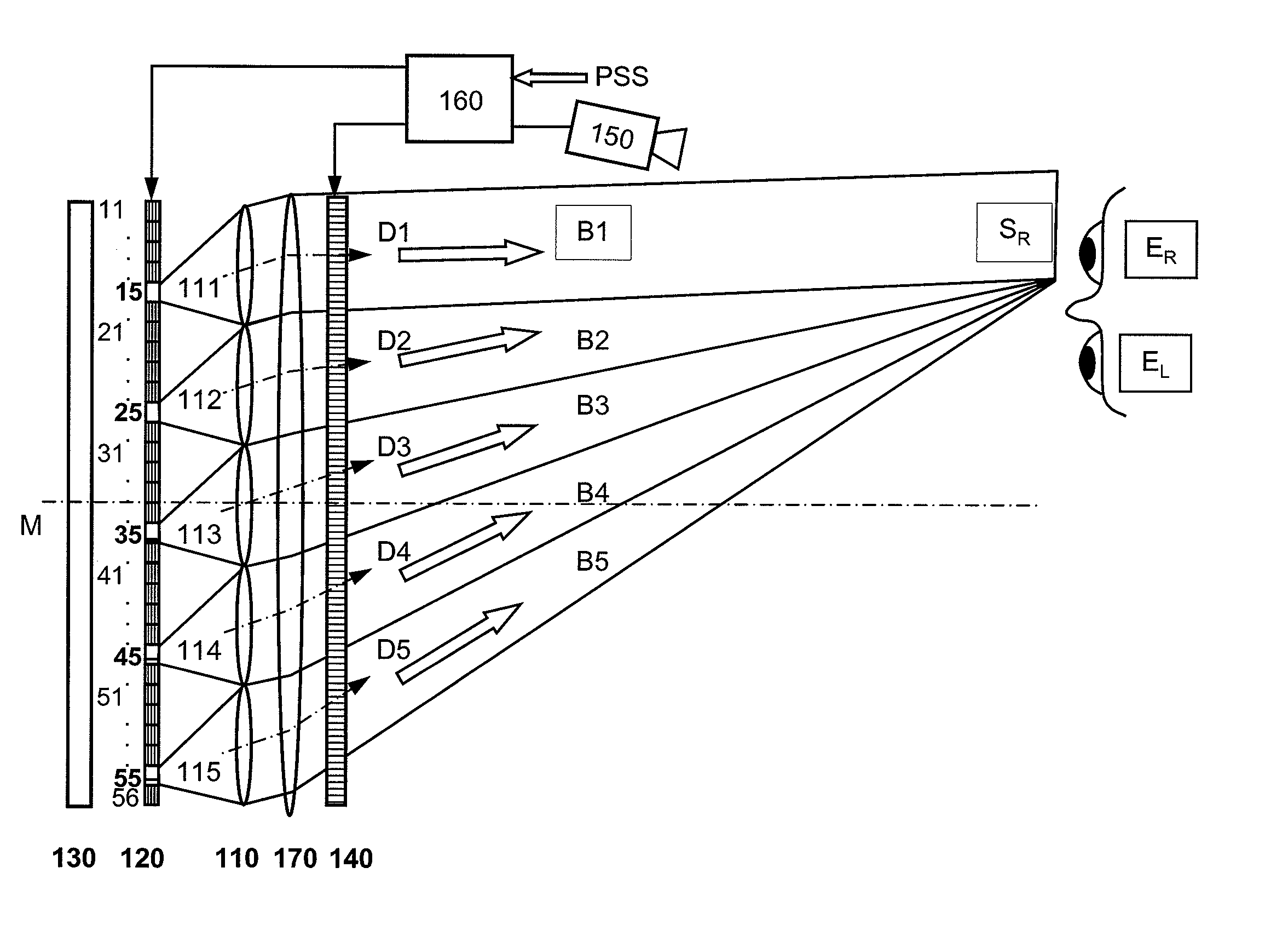

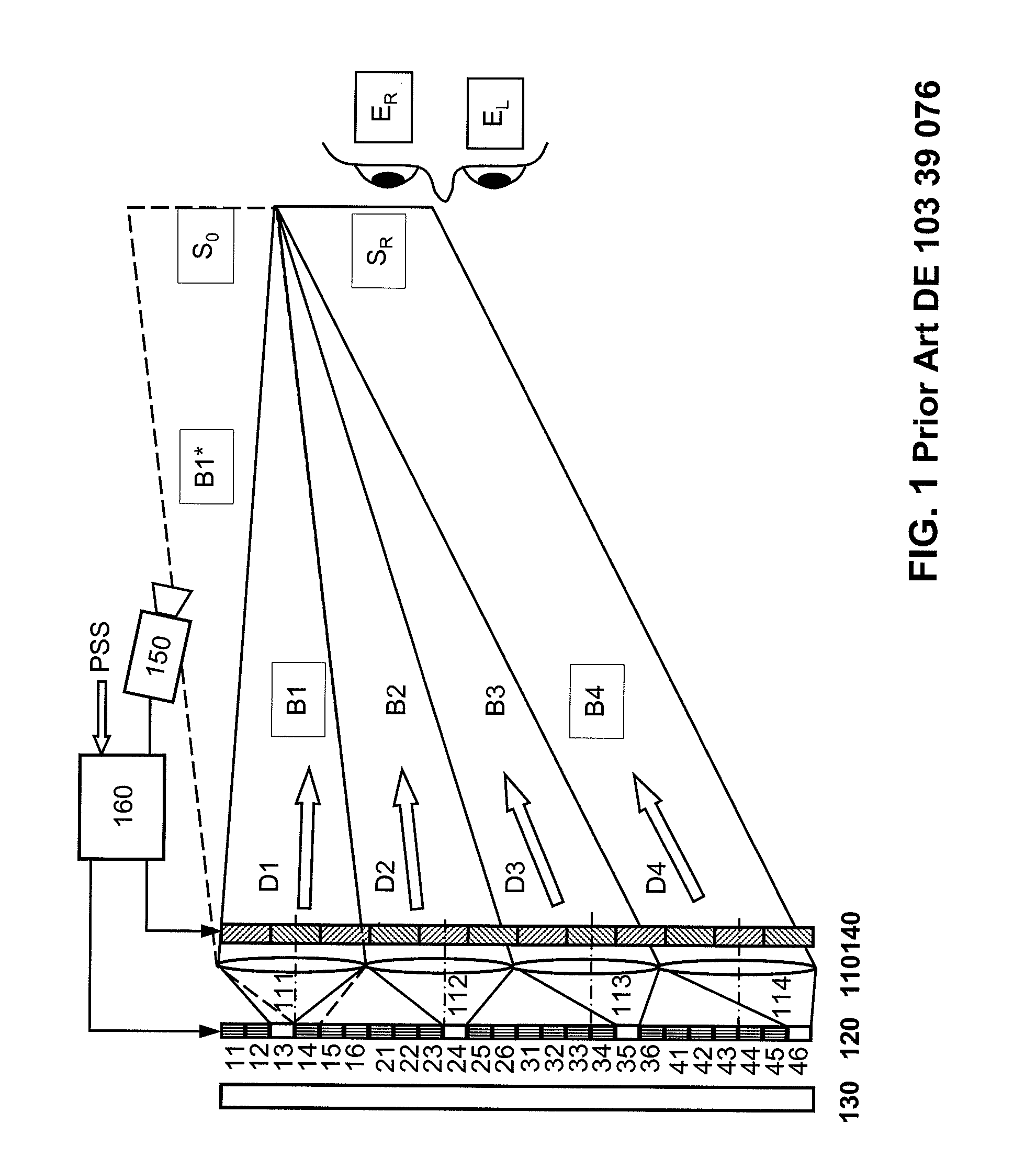

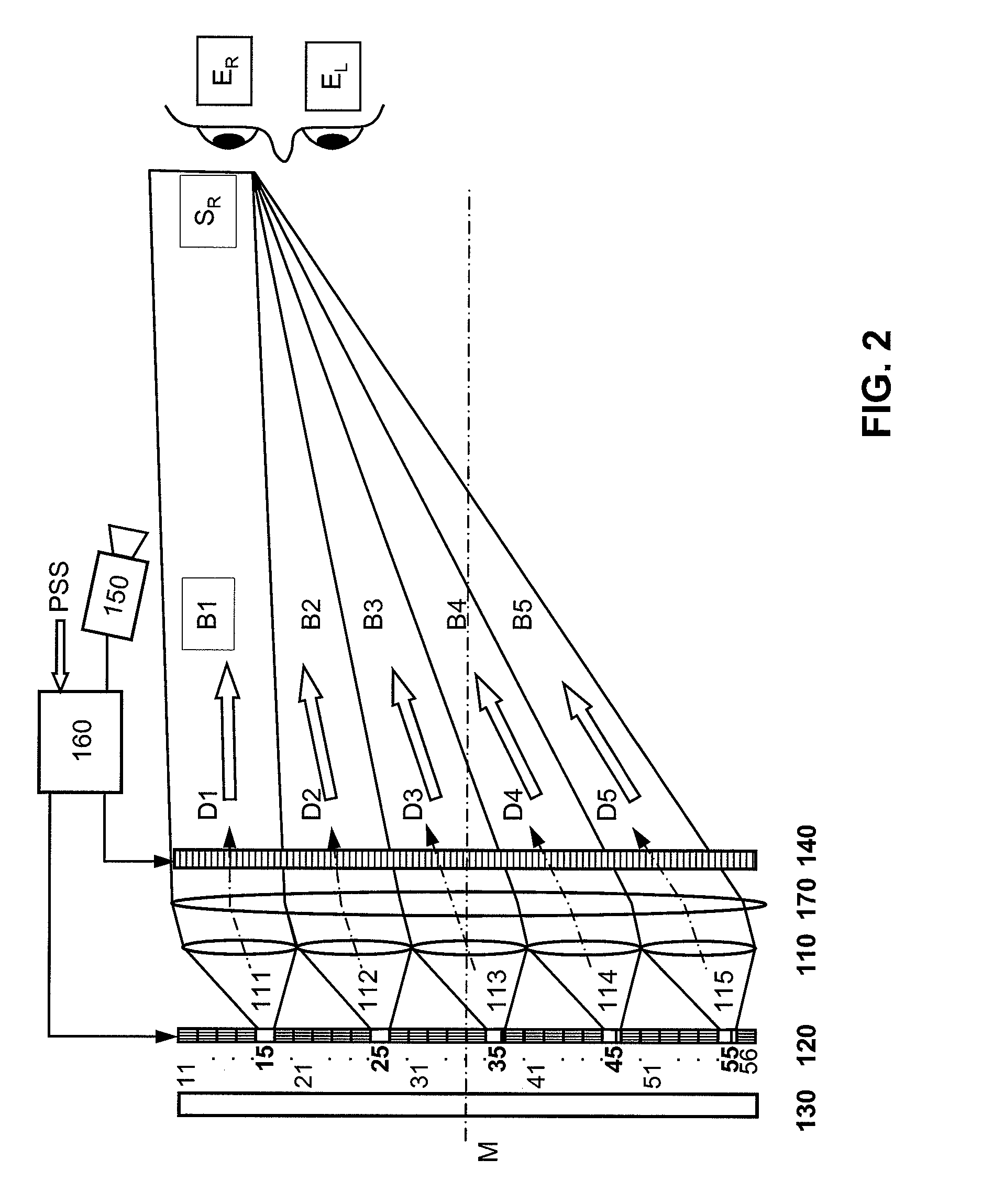

Multi-user autostereoscopic display with position tracking

InactiveUS20070188667A1Low costLittle laborOptical rangefindersMicroscopesDisplay deviceImaging equipment

An autostereoscopic multi-user display comprising a sweet-spot unit which is directionally controlled by a tracking and image control device (160), wherein an illumination matrix (120) is provided with separately activatable illuminating elements (11 . . . 56), in addition to an imaging device used to alternatingly image active illuminating elements, for making expanded sweet spots (SRI / SR2) visible to various eye positions (EL1 / ERI, EL2 / ER2) of viewers observing alternating images or a stereoscopic image sequence on a transmissive image matrix (140) with the aid of directed beams (B1R . . . B5L). According to the invention, the imaging device comprises an imaging matrix (110) provided with a plurality of lens elements (111 115) whose focal length is small in order to image the active illuminating elements in an enlarged manner onto the sweet spots (SRI / SR2), and a field lens (171), which follows the imaging matrix (110), in order to keep the distances of the activated illuminating elements between adjacent beams (B1, B2,B4, B5) as constant as possible and in order to assist selection of the directions (D1. . . D5) with the illumination matrix (120) for the beams.

Owner:SEEREAL TECHNOLOGIES

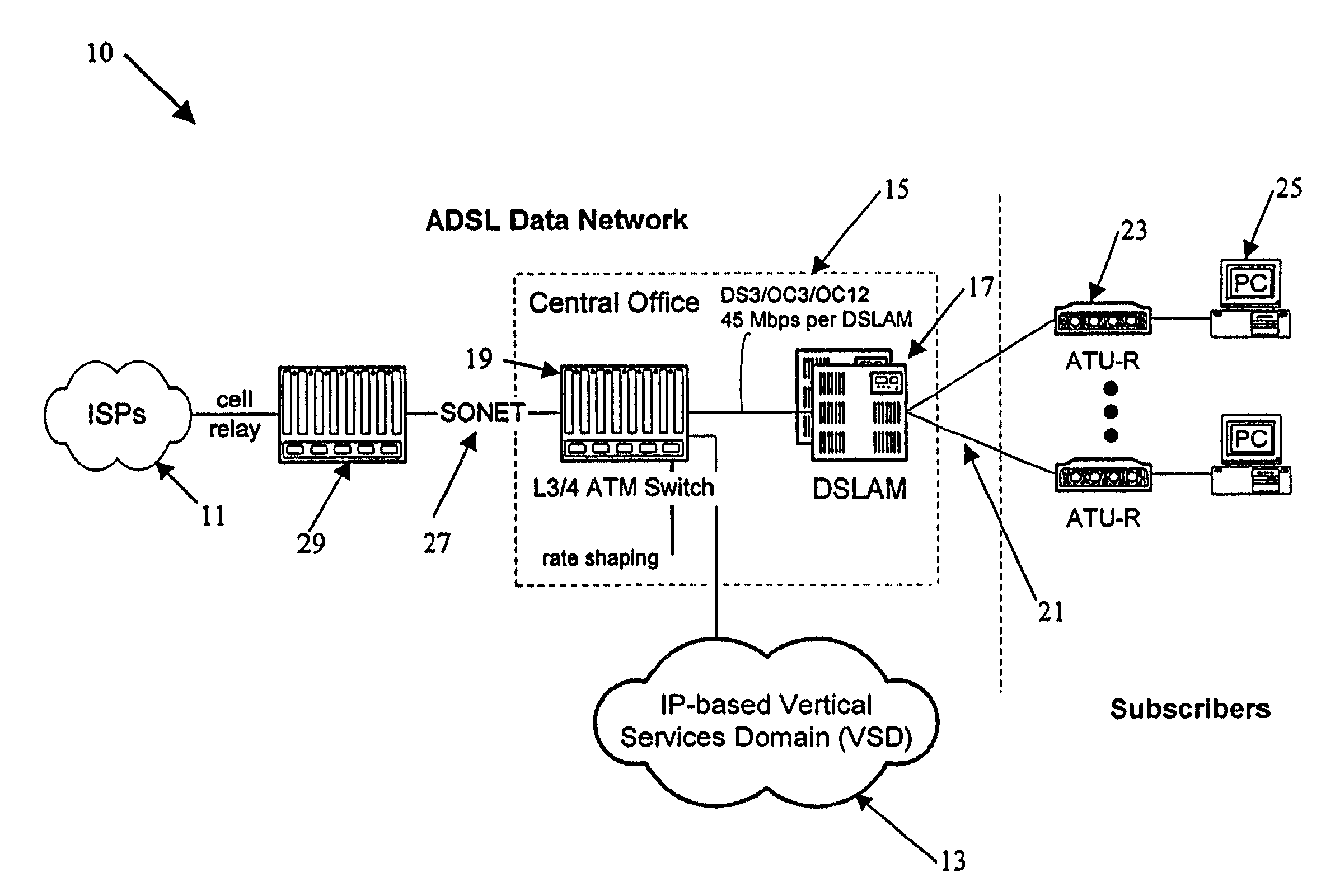

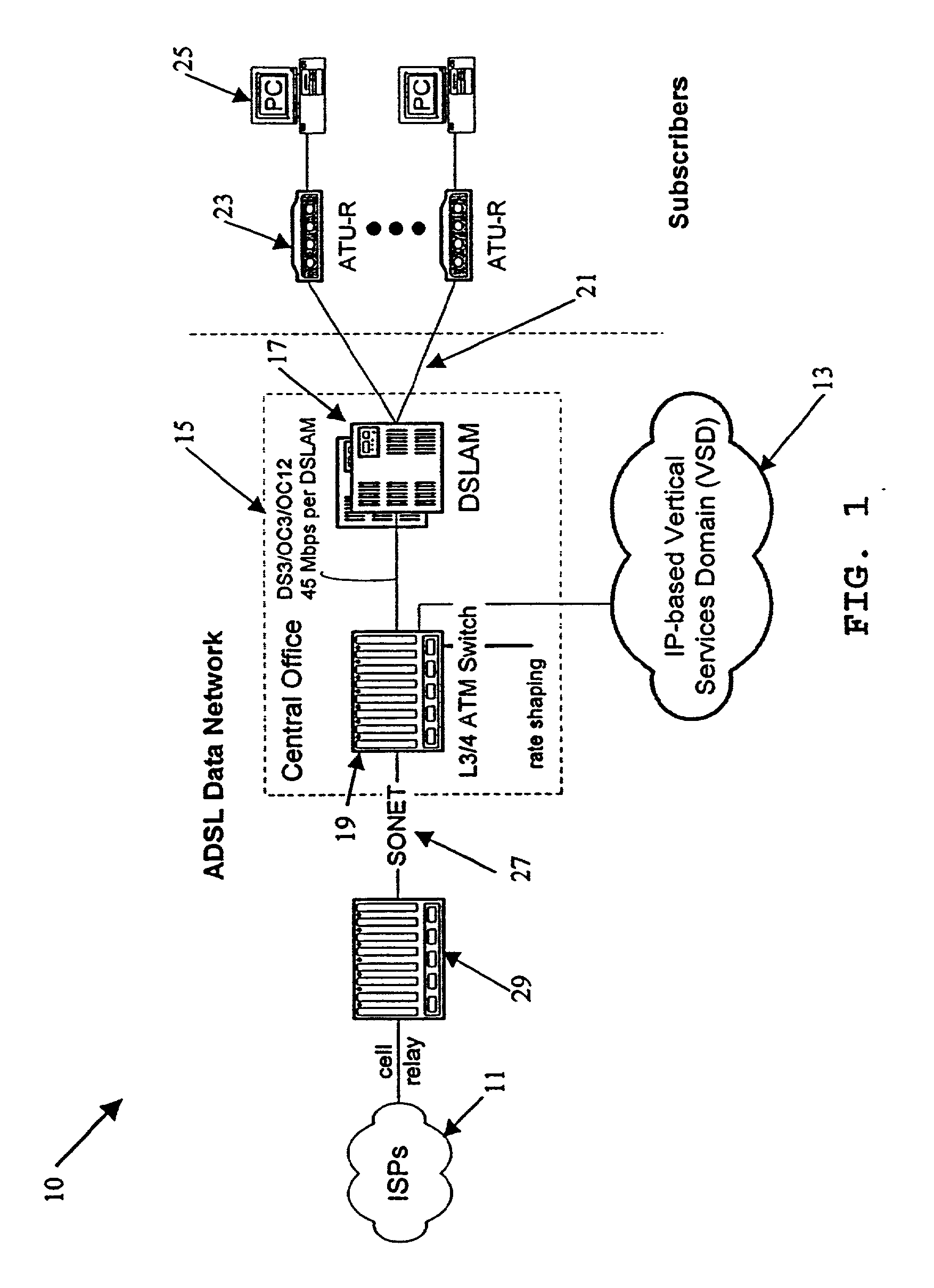

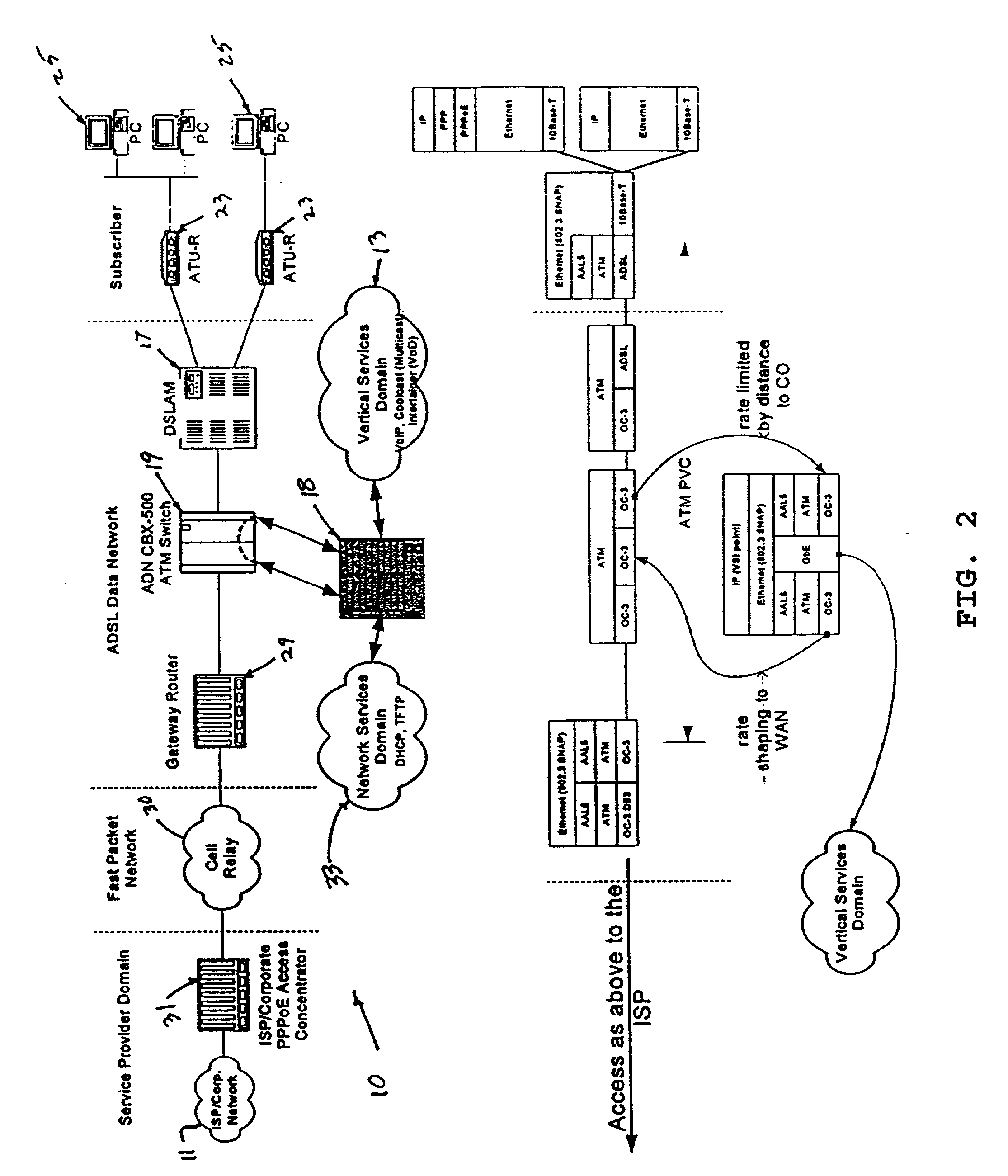

Vertical Services Integration Enabled Content Distribution Mechanism

InactiveUS20070124488A1Increased cost-effectivenessHigh bandwidthMultiple digital computer combinationsData switching networksContent distributionNetwork link

The invention relates to an enhanced ADSL Data Network (ADN) with vertical services capabilities. In general, vertical services capabilities are data services offered directly from a central office to an end user, without compromising the integrity of the user's guaranteed bit rate to the Internet through the ADN. One such vertical service is content downloadable at a high data rate from a content server located in or proximate to a central office that serves the end user. The content of the local server is updated and upgraded periodically and systematically from a central content server that distributes content to a number of remote central offices. The content is distributed between the central content server and the respective local content servers using available bandwidth, that is to say bandwidth on at least certain network links that is unused by subscriber traffic.

Owner:VERIZON PATENT & LICENSING INC

Off-Grid LED Power Failure Lights

ActiveUS20120043889A1Advantage in easeLow costDc network circuit arrangementsElectroluminescent light sourcesLight sourceEngineering

In embodiments of the present invention improved capabilities are described for systems and methods that employ a control component and / or power source integrated in an LED based light source to control and / or power the LED light source wirelessly. In embodiments, the LED based light source may take the form of a standard light bulb that plugs into a standard lighting socket or fixture.

Owner:RING LLC

Grid shifting system for a lighting circuit

ActiveUS8994276B2Advantage in easeLow costElectroluminescent light sourcesElectric light circuit arrangementCommunication interfacePower grid

A power management system for a lighting circuit may include a grid shifting controller that includes a processor and a connection to an external power source. The power management system may also include a communication interface associated with the grid shifting controller. The grid shifting controller may be configured to provide control information to a processor of at least one grid shifting electrical fixture over the communication interface, the control information being configured to direct the at least one grid shifting electrical fixture on the use of power from the external power source and an energy storage device associated with the at least one grid shifting electrical fixture.

Owner:RING LLC

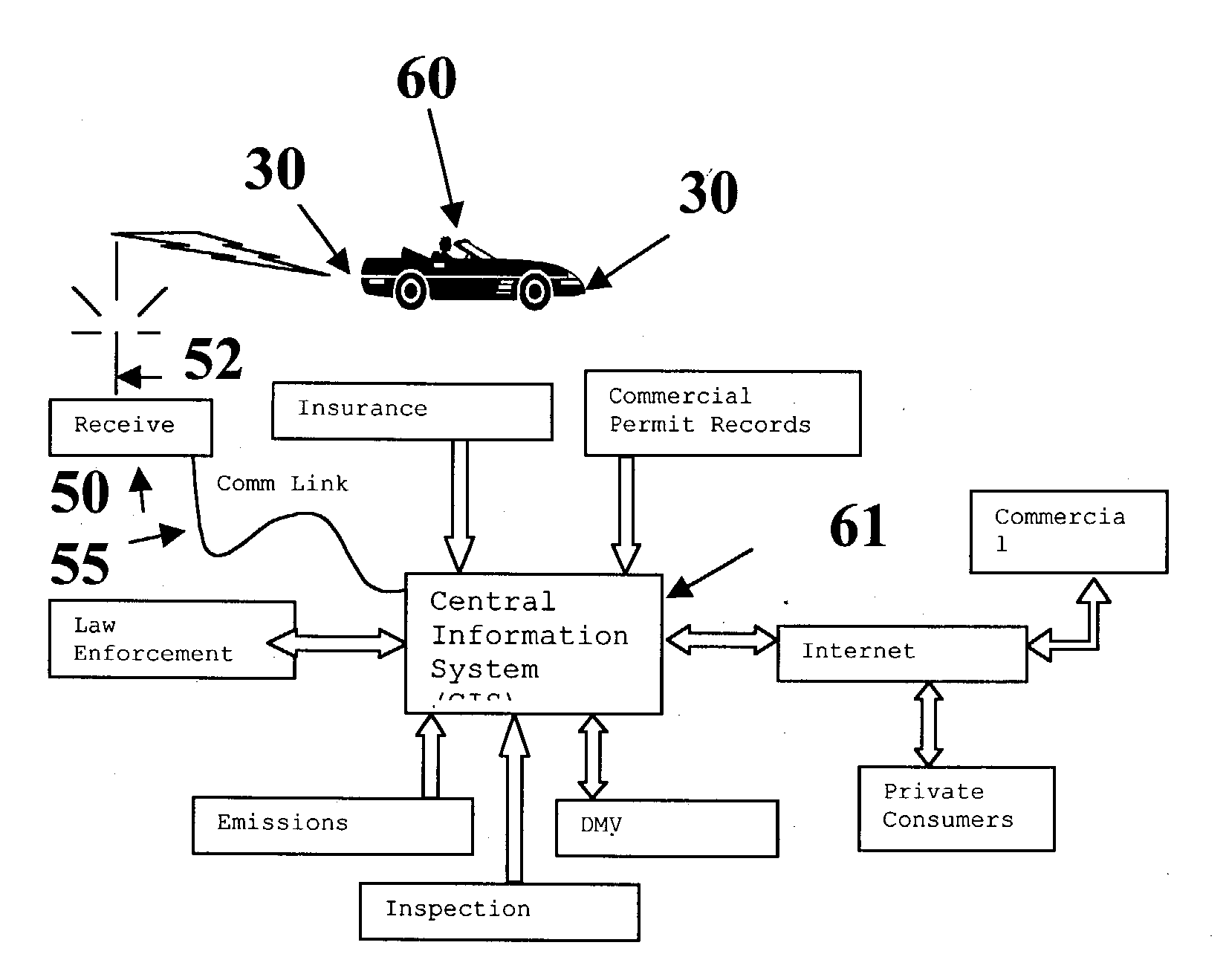

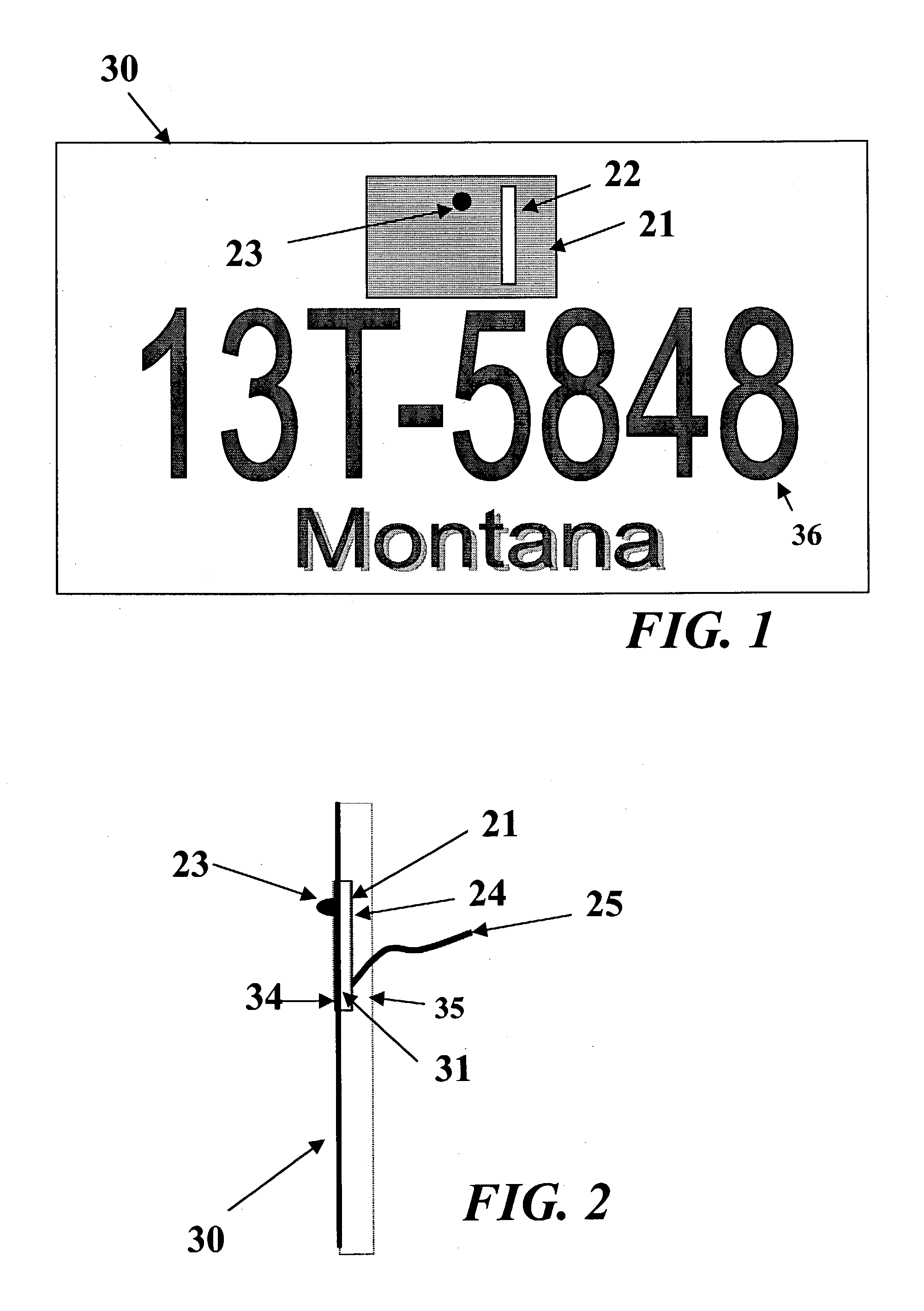

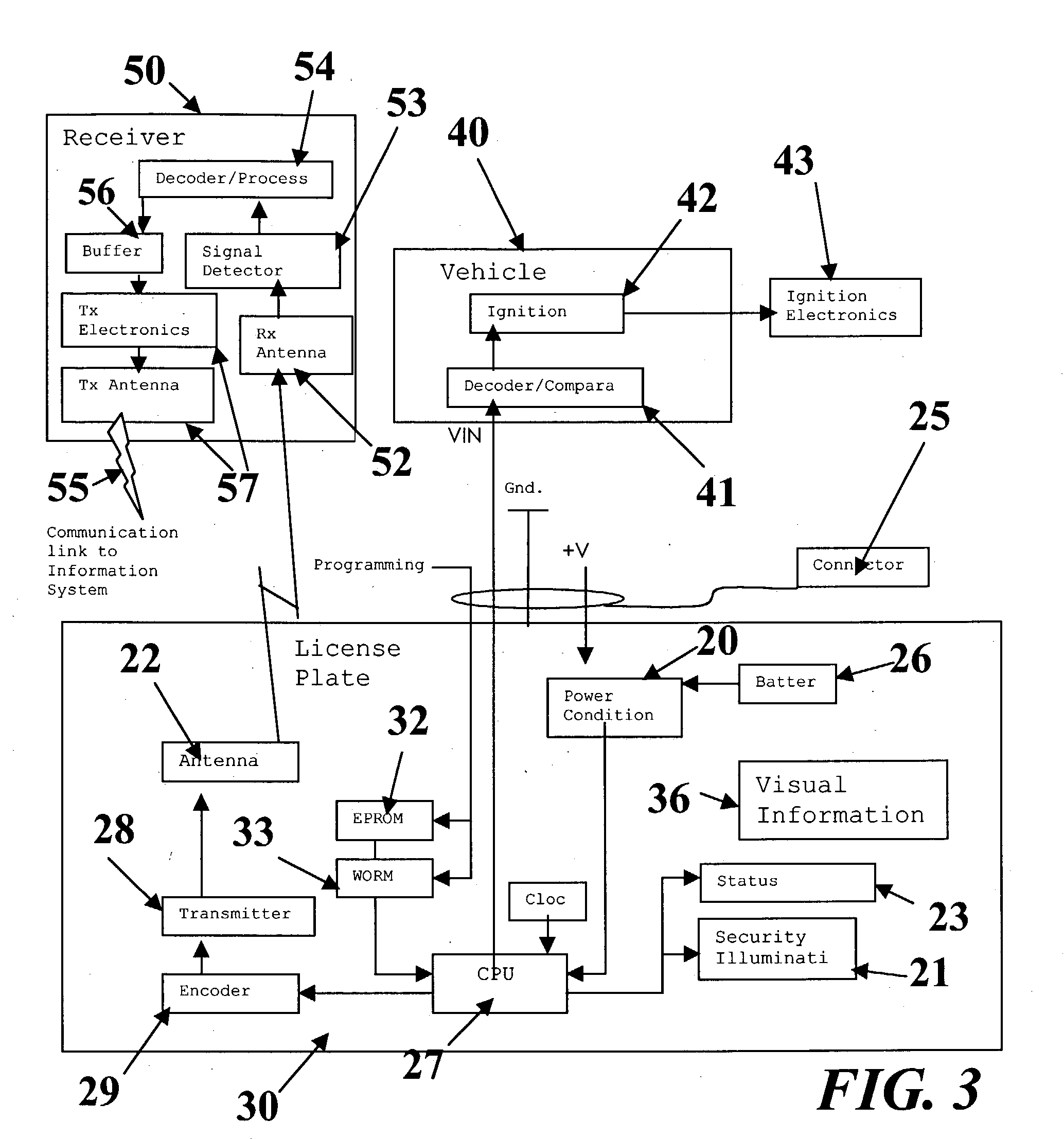

RF electronic license plate and information system for vehicle tracking

InactiveUS20040189493A1Accurately determineReduce demandRoad vehicles traffic controlVehicle componentsMobile vehicleRadio frequency

A motor vehicle tracking and information system that uses a radio-frequency electronic vehicle license plate in conjunction with roadside receivers and an information system architecture. The system is used to identify and track vehicles, detecting vehicles operating in violation of the law, and automatically issuing citations.

Owner:ESTUS JAY M +2

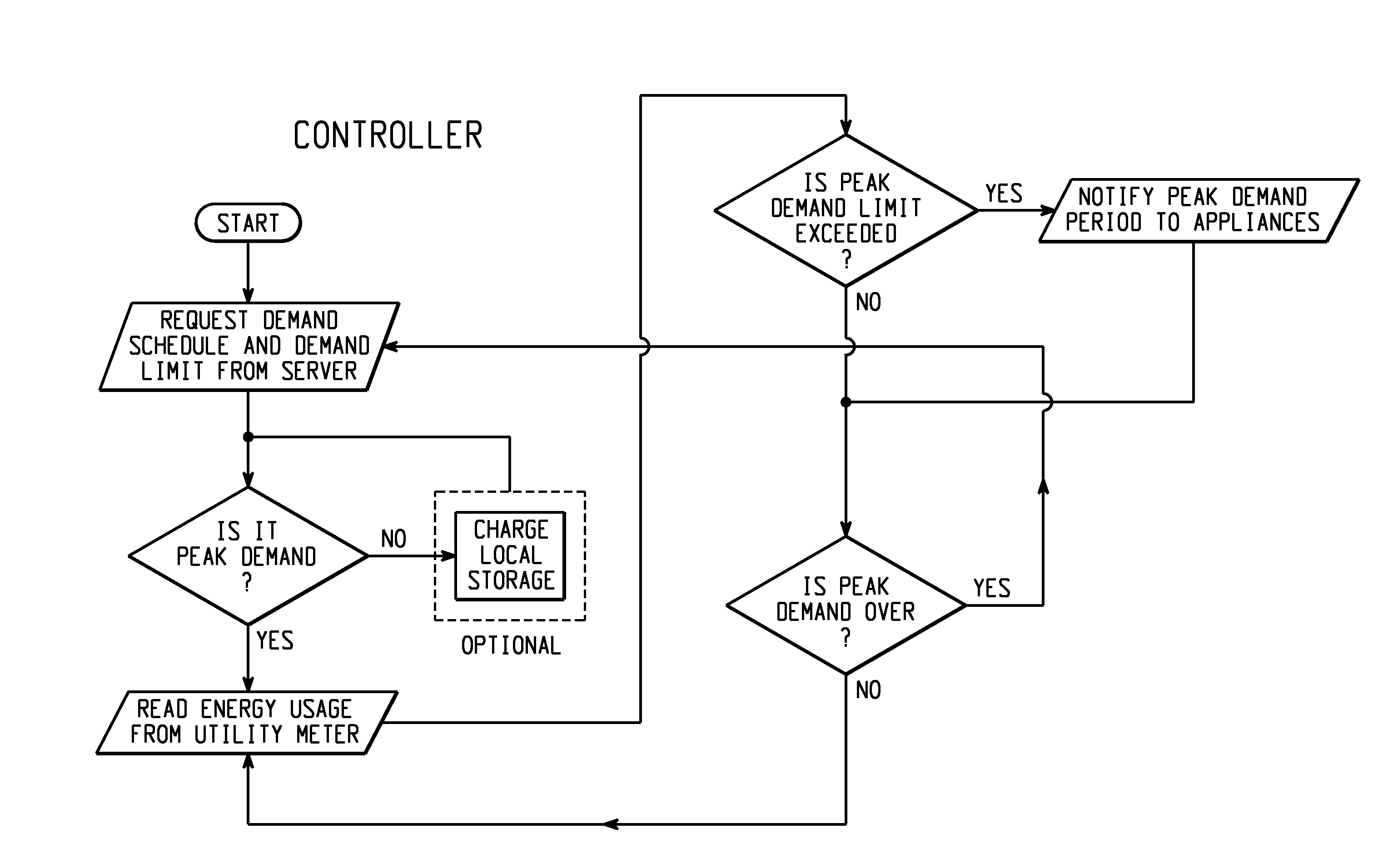

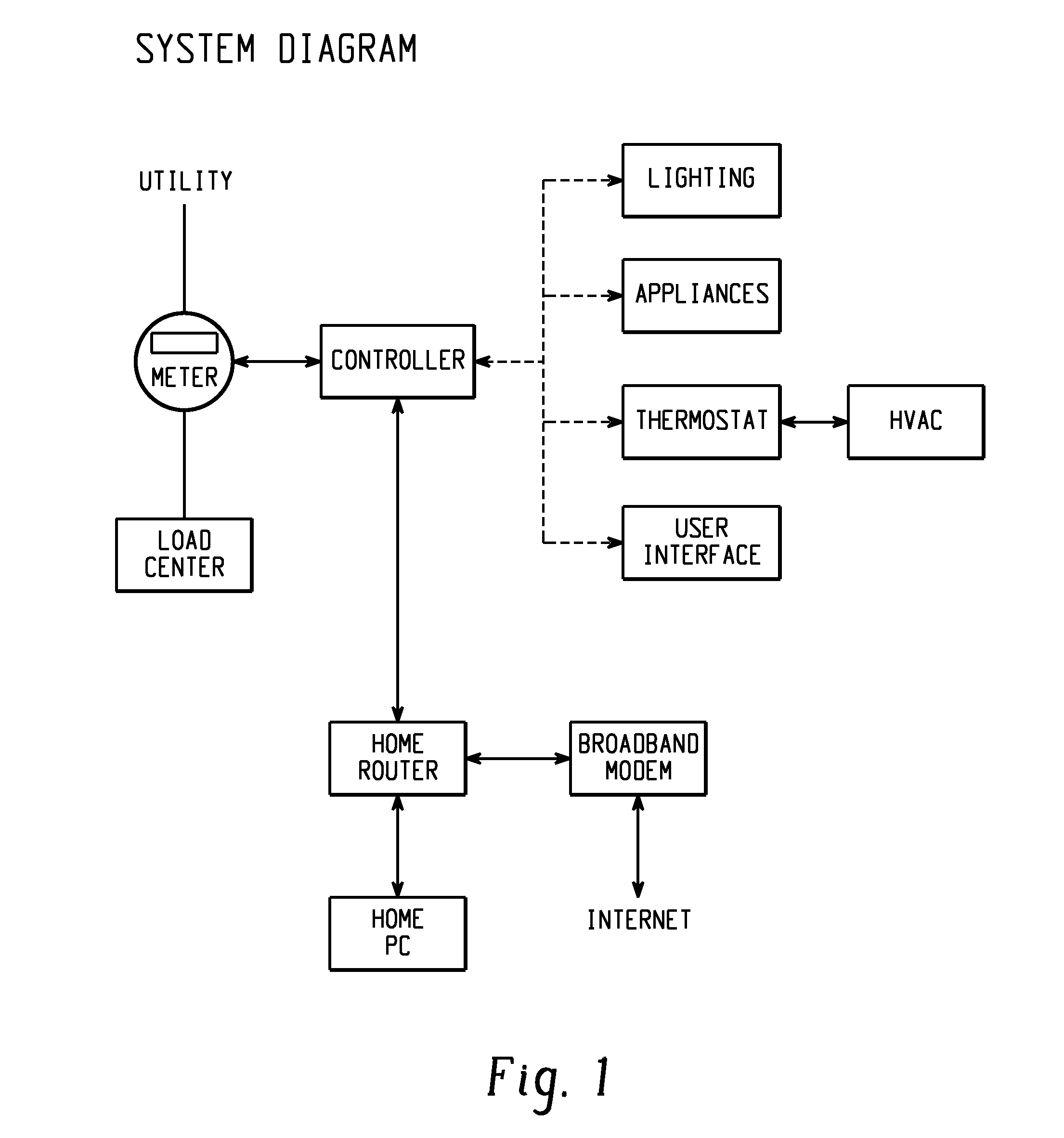

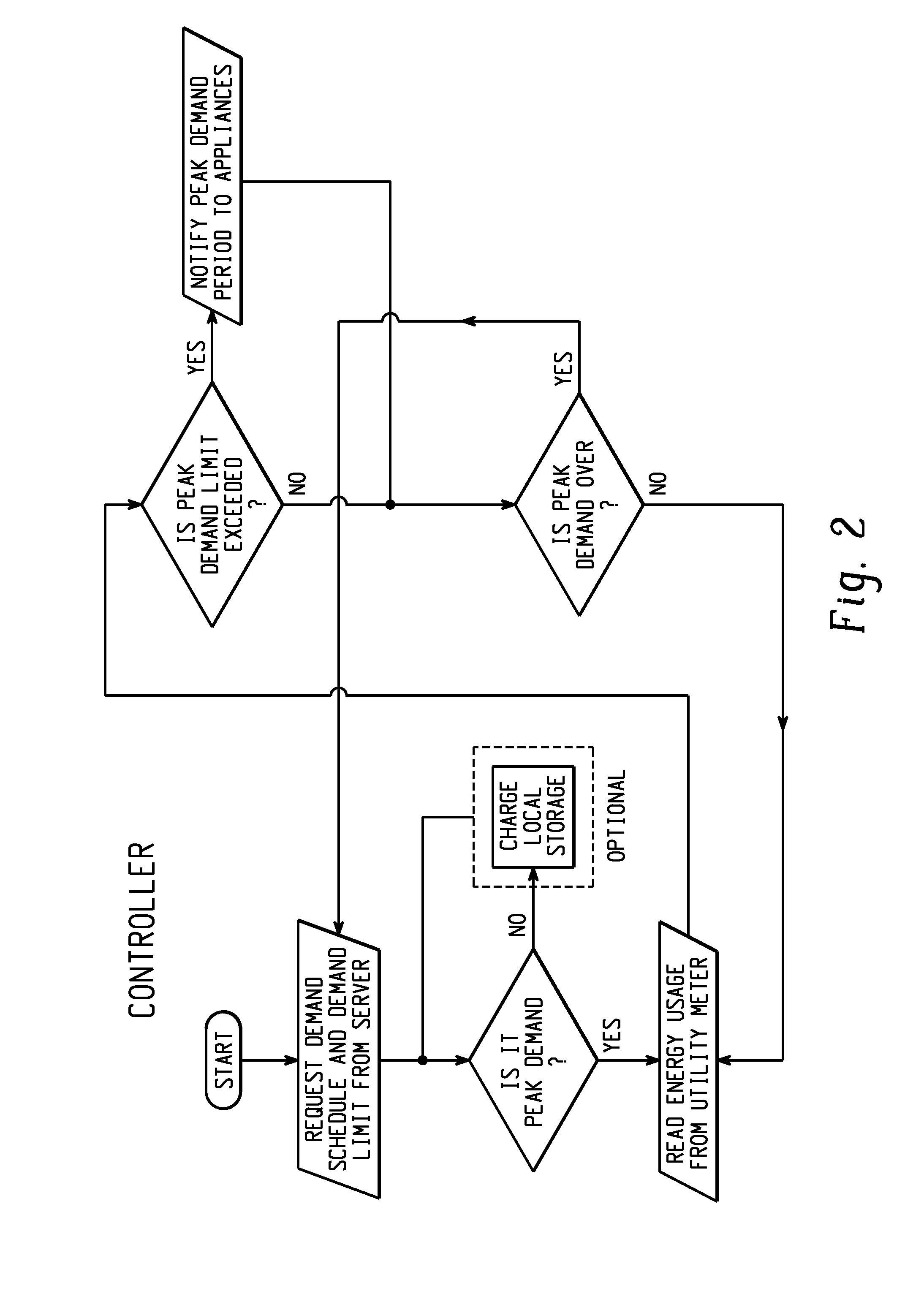

Demand side management module

ActiveUS20100070099A1Easy to manageLess inconvenienceLevel controlLighting and heating apparatusControl systemEngineering

A household appliance system and method include an appliance control system having a common appliance interface provided on an appliance and a demand side management module connected to the common appliance interface. The module corresponds to one select utility of a plurality of utilities and is adapted to communicate with the one select utility of the plurality of utilities. The appliance control system operates the appliance based on communications with the one select utility through the module.

Owner:HAIER US APPLIANCE SOLUTIONS INC

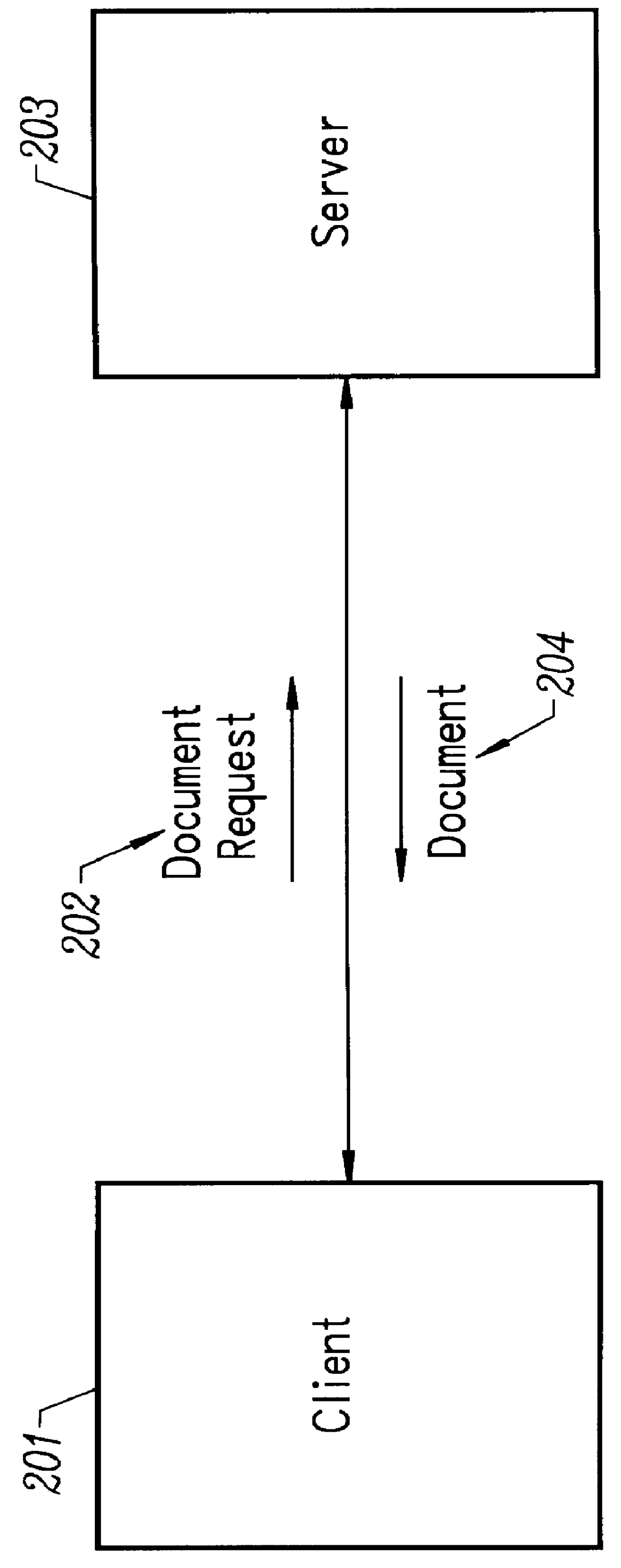

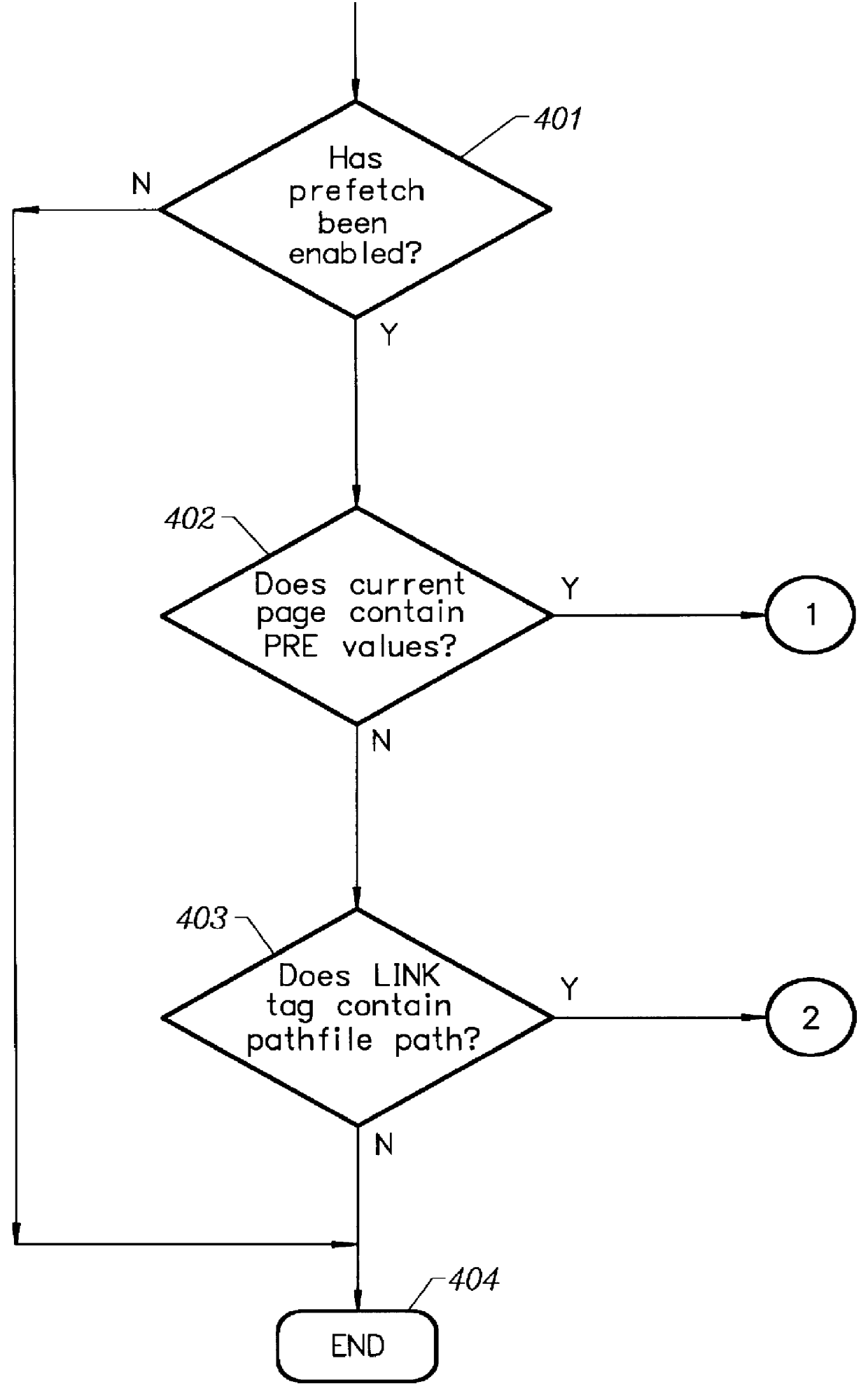

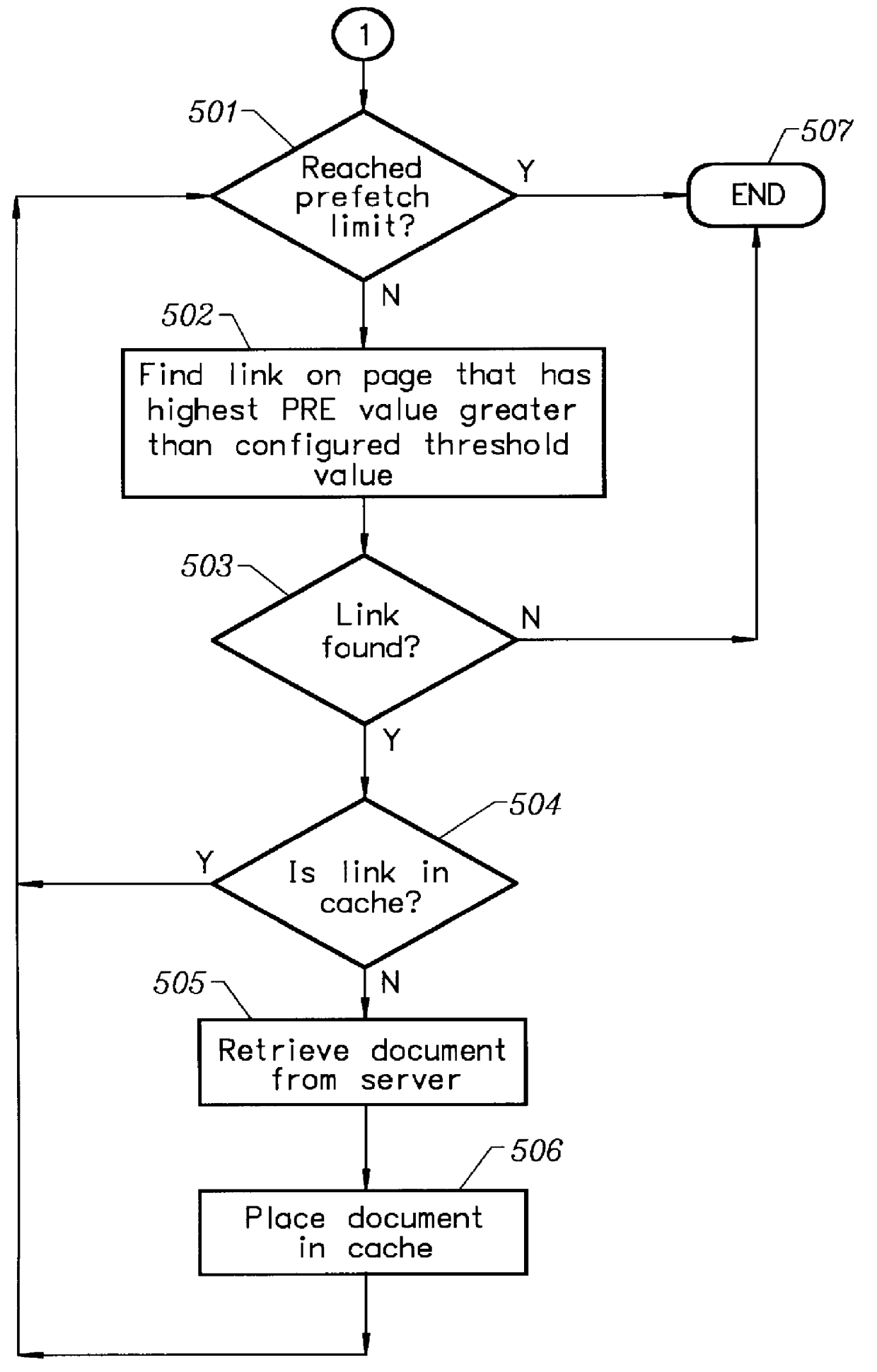

System and method for creating pathfiles for use to predict patterns of web surfaces

InactiveUS6055572AEfficiently uses its free bandwidthReduce demandDigital data information retrievalMultiple digital computer combinationsControl systemServer allocation

A prefetching and control system for a computer network environment. The user configures the client's prefetch parameters which are: enabling / disabling prefetching, prefetch threshold value, and the maximum number of documents to prefetch. A prefetch value or weight is contained in the Hypertext Markup Language (HTML) page or prefetch file, called a pathfile, for each link. The HTML page contains the prefetch values for each of its links, while pathfile contains the weights for every link on the HTML page associated with the Universal Resource Locator (URL). The client compares the prefetch or weight values of each link with its threshold value to decide if the link should be prefetched and placed in the local cache as long as the maximum number of documents to prefetch is not exceeded. Pathfiles reside on the server and are created by the server or web administrator / author. The server automatically creates the pathfiles from its log files which are filtered to retain all of the valid document requests and average paths are derived from the filtered results. Weights are assigned to each path in the URL by the server and inserted into the pathfile along with the associated paths. If no log files exist on the server, then the web administrator / author may manually enter in the weights for each path.

Owner:META PLATFORMS INC

Aggregator, monitor, and manager of distributed demand response

ActiveUS8260468B2Facilitate power capacity to powerReduce loadMarket predictionsLevel controlPower gridNews aggregator

The invention broadly encompasses a system including a database to store demand response data, the demand response data including demand response agreement parameters, demand response load and energy demand characteristics of one or more demand response customers, the demand response load characteristics including power consumption capacity of each of one or more demand response loads, an aggregator to aggregate the demand response loads based on the demand response data and forecast data into a demand response portfolio, a monitor to monitor power demand of one or more demand response customers and one or more power grids, and a dispatcher to notify the one or more demand response customers of the demand response portfolio and to notify a utility of a response from the one or more demand response customers whether to control the demand response load to return the power consumption capacity of the demand response load back to the one or more power grids.

Owner:MCG VERSIFY ACQUISITION LLC

System and method for distributed tokenization using several substitution steps

ActiveUS20110213807A1Reduce disadvantagesReduce problemsAcutation objectsDigital data processing detailsCredit cardSocial Security number

A method for distributed tokenization of sensitive strings of characters, such as social security numbers, credit card numbers and the like, in a local server is disclosed. The method comprises the steps of receiving from a central server at least one, and preferably at least two, static token lookup tables, and receiving a sensitive string of characters. In a first tokenization step, a first substring of characters is substituted with a corresponding first token from the token lookup table(s) to form a first tokenized string of characters, wherein the first substring of characters is a substring of the sensitive string of characters. Thereafter, in a second step of tokenization, a second substring of characters is substituted with a corresponding second token from the token lookup table(s) to form a second tokenized string of characters, wherein the second substring of characters is a substring of the first tokenized string of characters. Optionally, one or more additional tokenization steps is / are used.

Owner:PROTEGRITY CORP

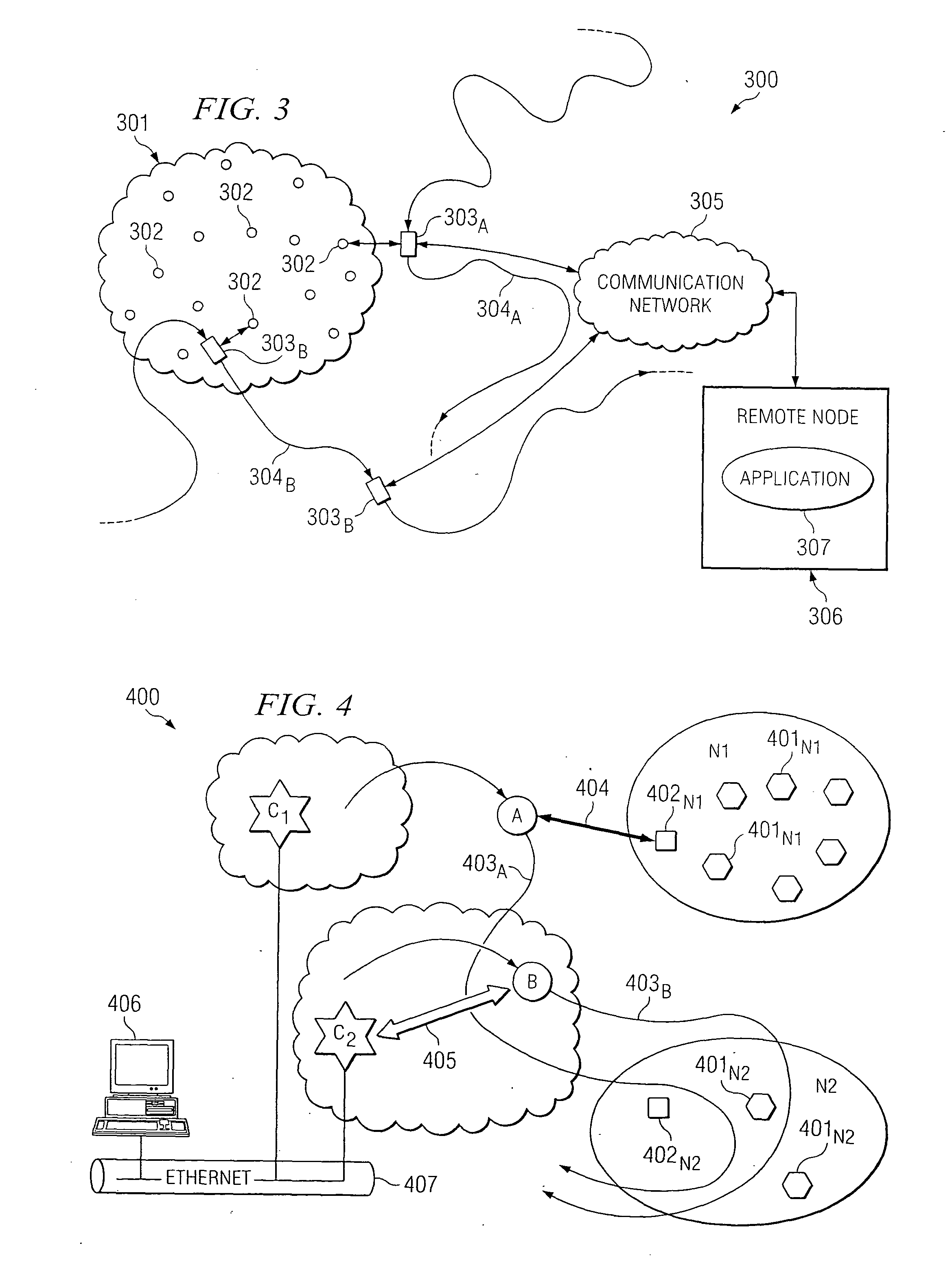

System and method for using mobile collectors for accessing a wireless sensor network

ActiveUS20050057370A1Flexible deploymentReduce demandPower managementElectric signal transmission systemsLine sensorWireless sensor networking

A system and method are provided that use mobile collectors for accessing a wireless sensor network. In certain embodiments, one or more mobile collectors having mobility that is unpredictable to a wireless sensor network are deployed for use in accessing the wireless sensor network. Thus, rather than relying on an access technique having certainty designed therein with regard to the access of a wireless sensor network, certain embodiments utilize an access technique that relies on statistical probability for accessing the wireless sensor network. For instance, by deploying a plurality of mobile collectors that are operable for accessing a wireless sensor network, a statistical probability exists that at some point (or at various points in time) at least one of the mobile collectors will travel within range of the wireless sensor network to enable access thereof.

Owner:KEYSIGHT TECH

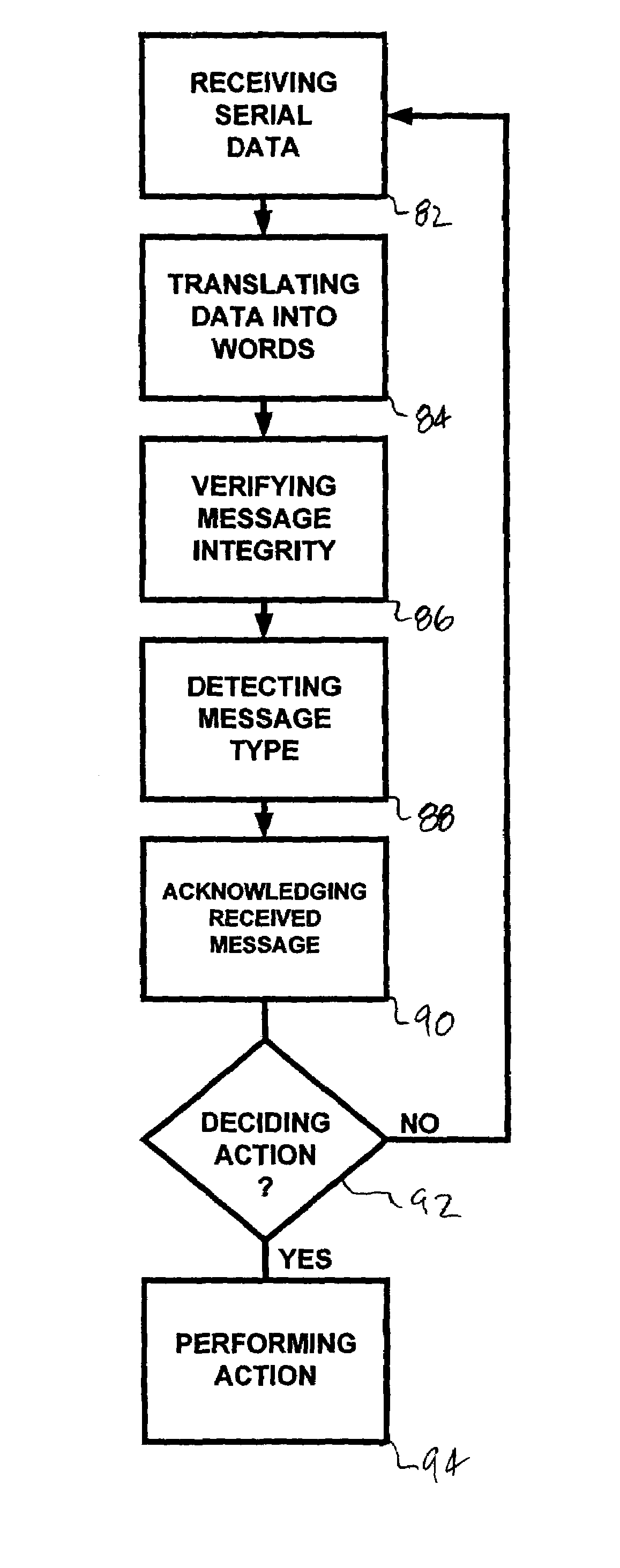

Method of operating an implantable medical device telemetry processor

An implantable medical device with a main processor also has a telemetry processor to perform some telemetry processing functions resulting under some circumstances in reducing demands on the main processor, conserving energy, increasing telemetry processing speed, and many other advantages. A wide variety of implantable medical devices can be configured with a telemetry processor including neuro stimulators, pacemakers, defibrillators, drug delivery pumps, diagnostic recorders, and cochlear implants. The telemetry processor includes control logic, a data decoder, a receive buffer, a data encoder, and a transmit buffer. Methods of receiving messages and transmitting messages with a telemetry processor are also disclosed.

Owner:MEDTRONIC INC

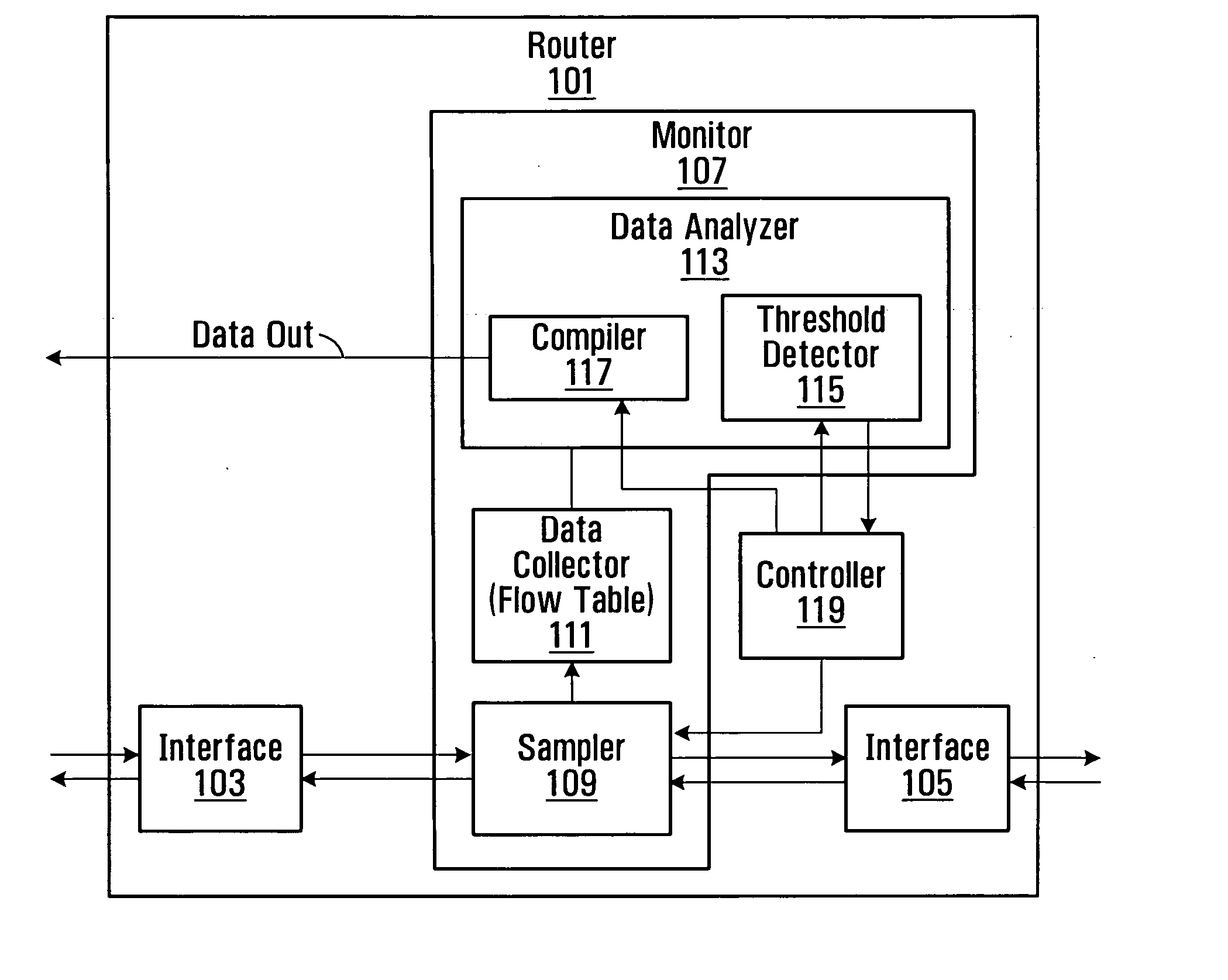

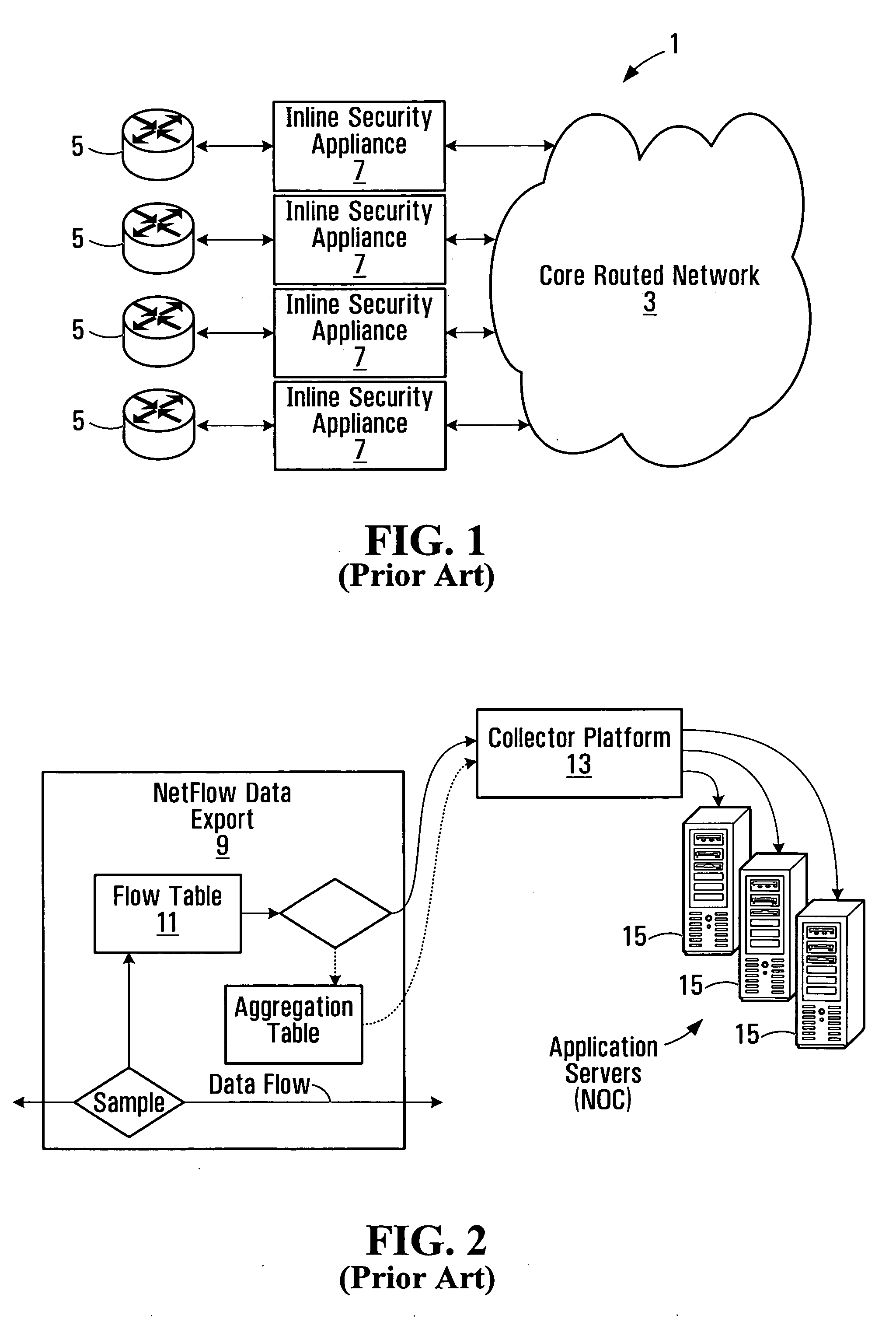

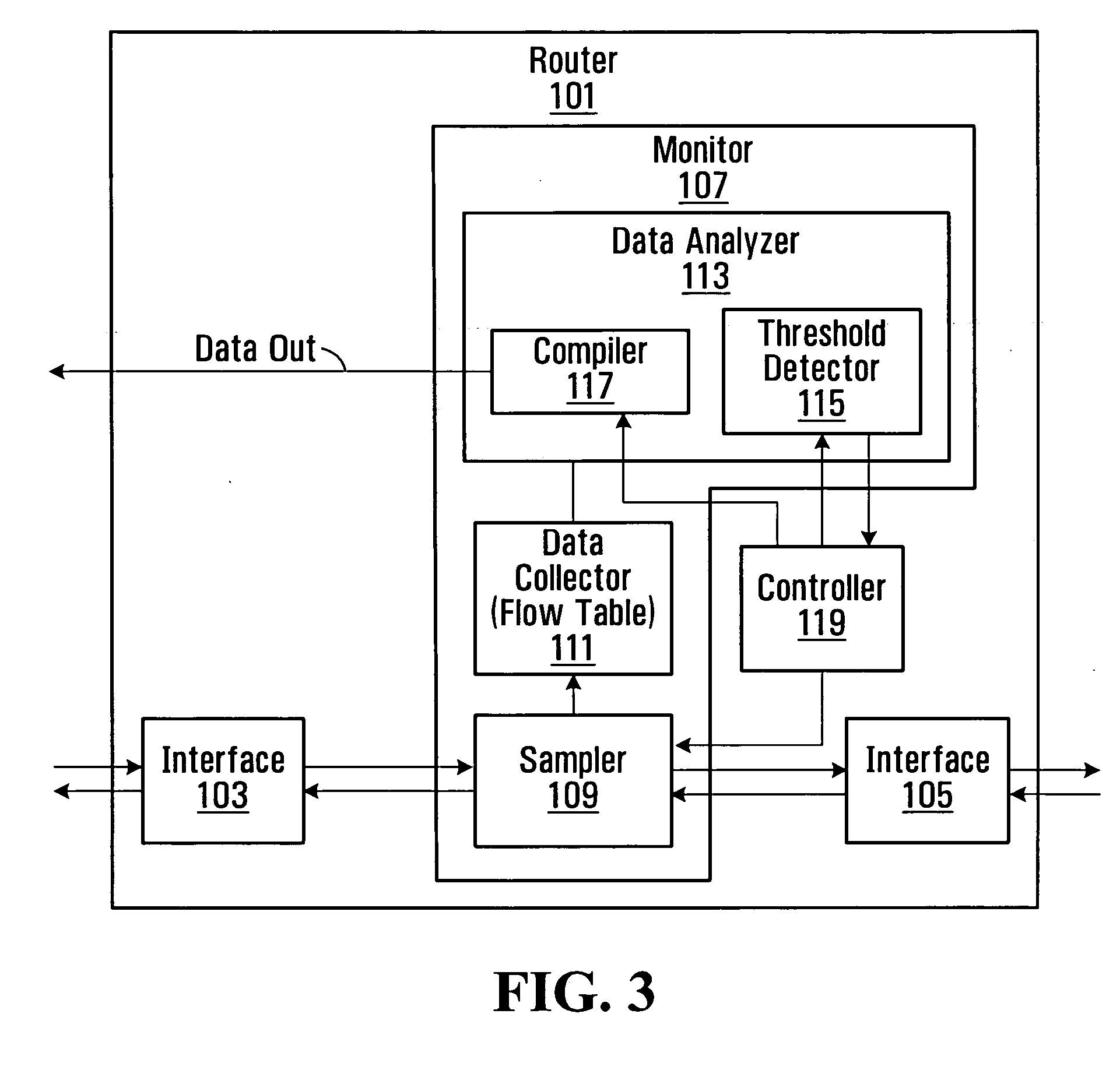

Method and apparatus for monitoring malicious traffic in communication networks

ActiveUS20070153689A1Reduce demandReduce amount of dataError preventionTransmission systemsTraffic volumeMonitoring data

A method and apparatus for monitoring data traffic in a communication network are provided. A router connected to the communication network monitors information contained in the data traffic, and based on the information determines whether data in the traffic is indicative of a malicious threat to one or more resources connected to the network. Parameters which control monitoring of traffic at the router, such as the sampling rate and what information is to be extracted from the data is varied according to the condition of the network so that the monitoring can be adapted to focus on traffic which relates to a particular suspected or detected threat.

Owner:RPX CORP

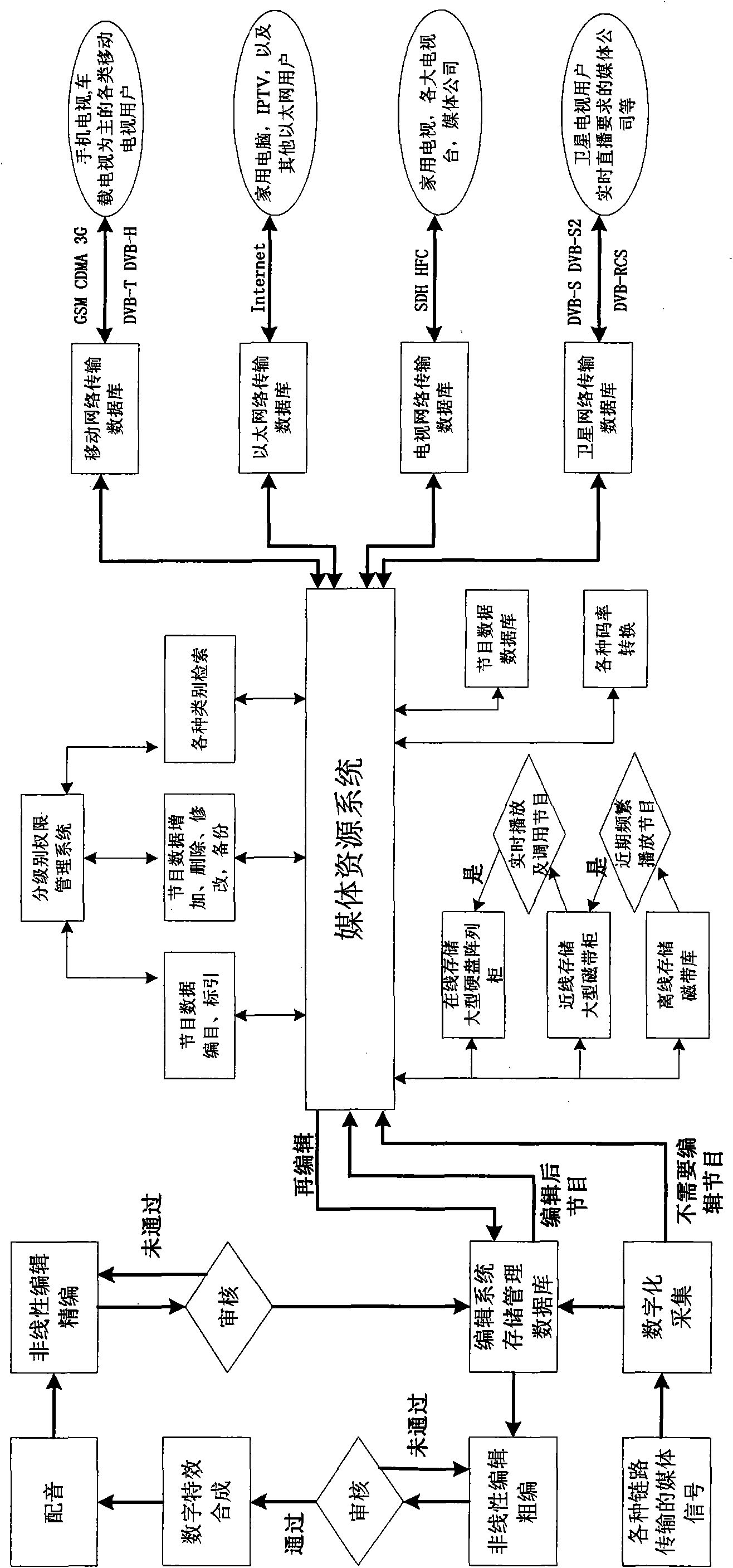

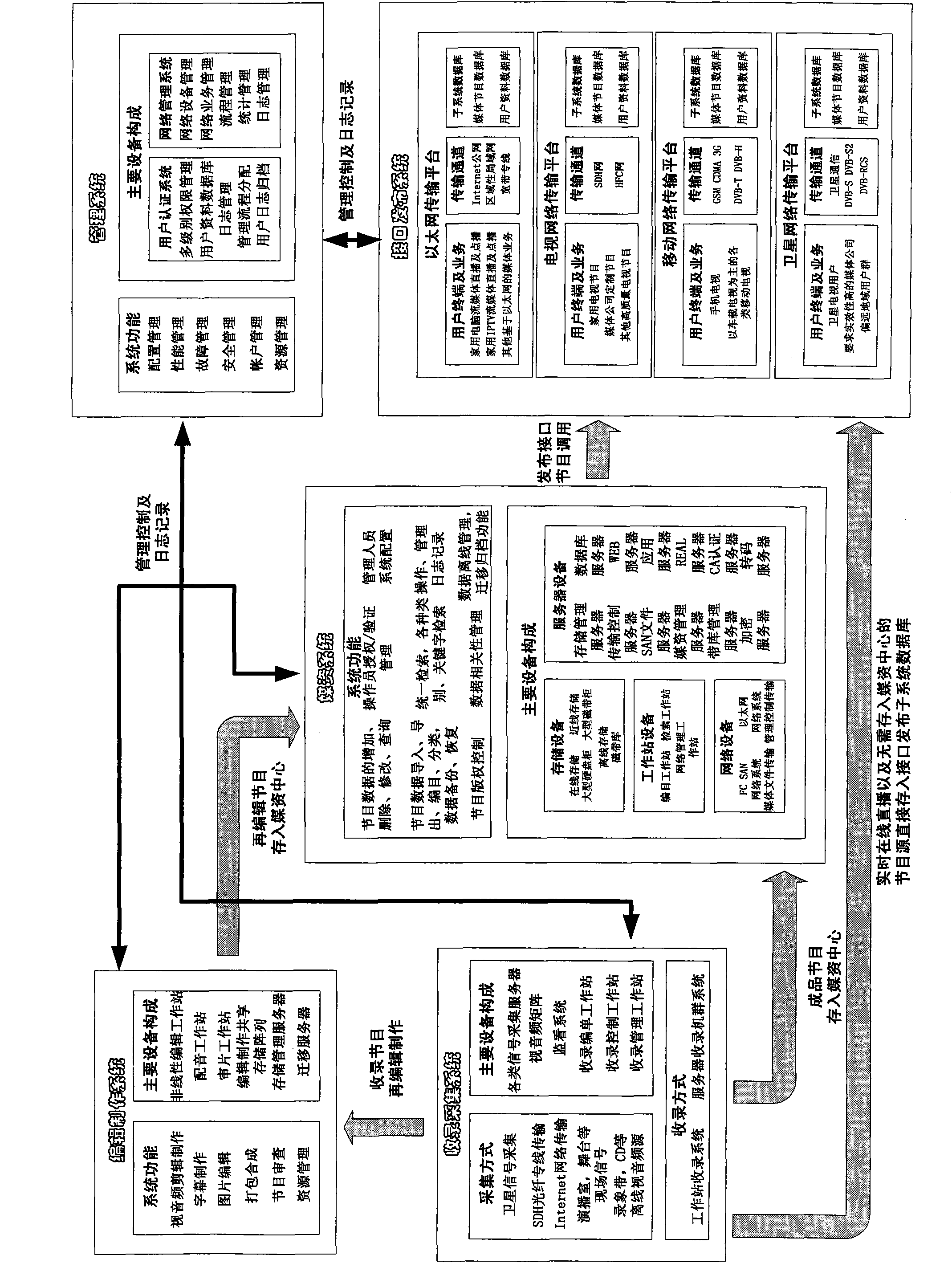

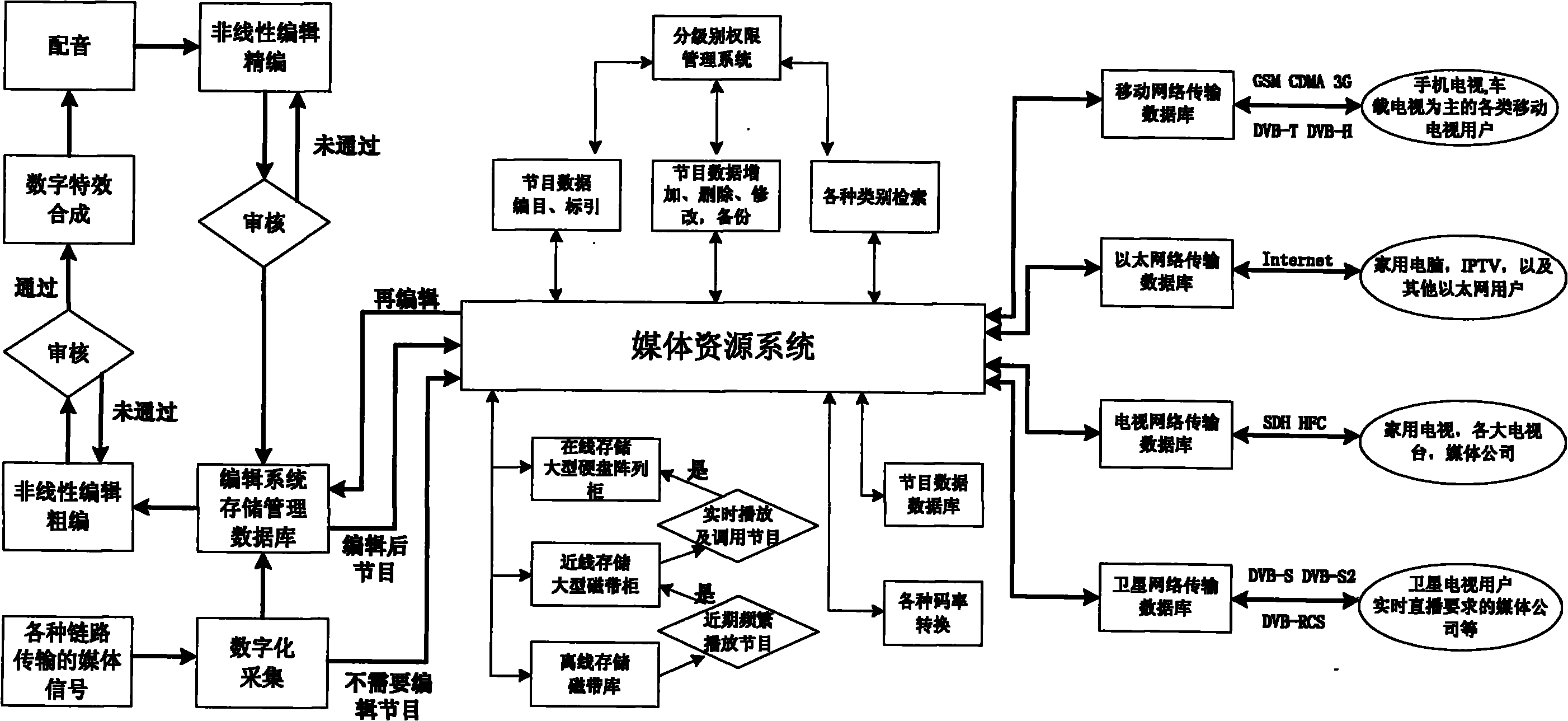

Digital multimedia information transmission platform

InactiveCN101783873ASupport automatic technical review functionImprove review efficiencyTelevision system detailsColor television detailsSystems managementCataloging

The invention discloses a digital multimedia information transmission platform, which comprises an acquisition system, a manufacturing system, a media resource system, a management system and a release system, wherein the acquisition system consists of control equipment, outside network material receiving server and an foreign signal, studio signal and magnet tape material acquisition and collection subsystem; the manufacturing system consists of a program editing system, a program examination system, a background packing and synthesizing system and a resource manager; the media resource system consists of a media resource cataloging and searching work station, a transcoding server, a database server, a storage management and migration server and a system management working station; the management system consists of a uniform user identification system and a network management system; the release system serving as an external interface module of a multimedia center encrypts finished products in multiple formats and executes related release according to outside service demands; and the platform is an integrated production line of digital media contents and also a digital media resource comprehensive service system platform and can realize overall media resource sharing.

Owner:BEIJING INFV MEDIA TECH

Method and apparatus for tokenization of sensitive sets of characters

ActiveUS20090249082A1Simple methodSafe handlingAcutation objectsUnauthorized memory use protectionComputer networkServer allocation

A method and system for secure handling of sensitive sets of characters in a distributed hierarchical system are disclosed, comprising at least one local server on a lower hierarchic level and at least one central server at a higher hierarchic level. The method comprises the steps: receiving a sensitive set of characters in said local server; replacing a part of said sensitive set of characters with a token to form a tokenized set of characters, said token belonging to a subset of possible tokens assigned to the local server by the central server; transferring at least one of said sensitive set of characters and said tokenized set of characters to the central server; and canceling said sensitive set of characters from said local server within a limited time from said transferring, while maintaining said tokenized set of characters in a local database connected to said local server.

Owner:PROTEGRITY CORP

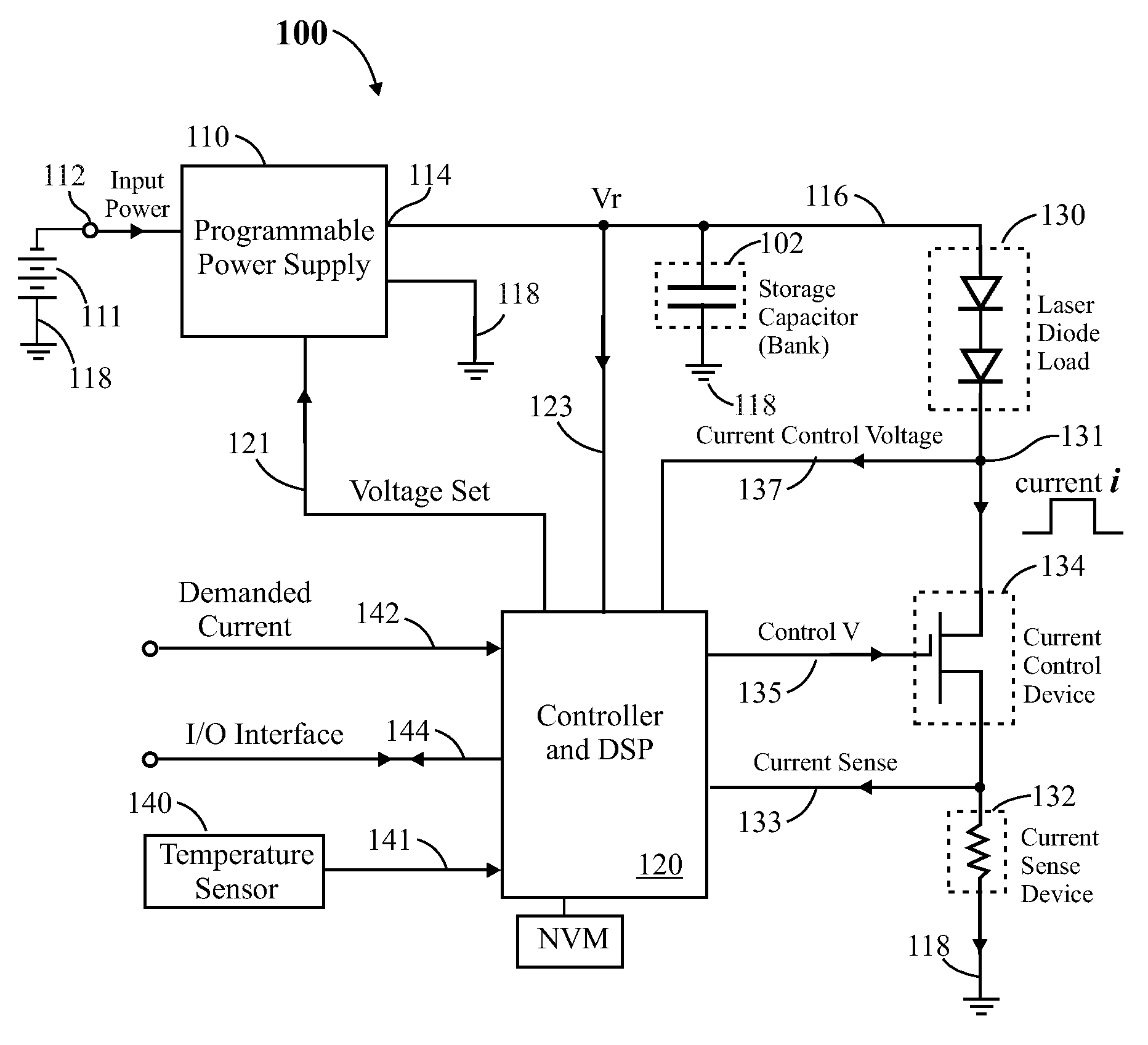

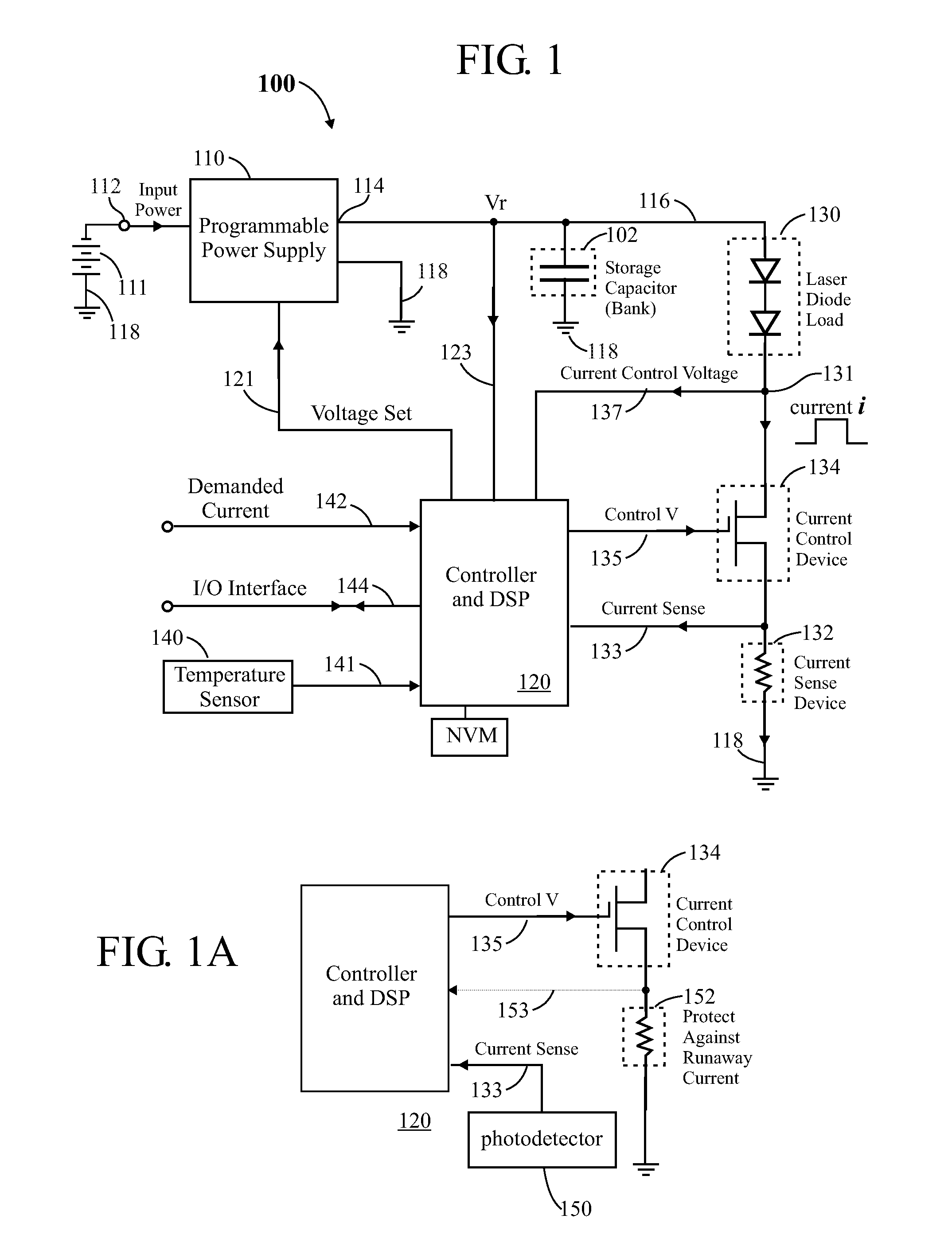

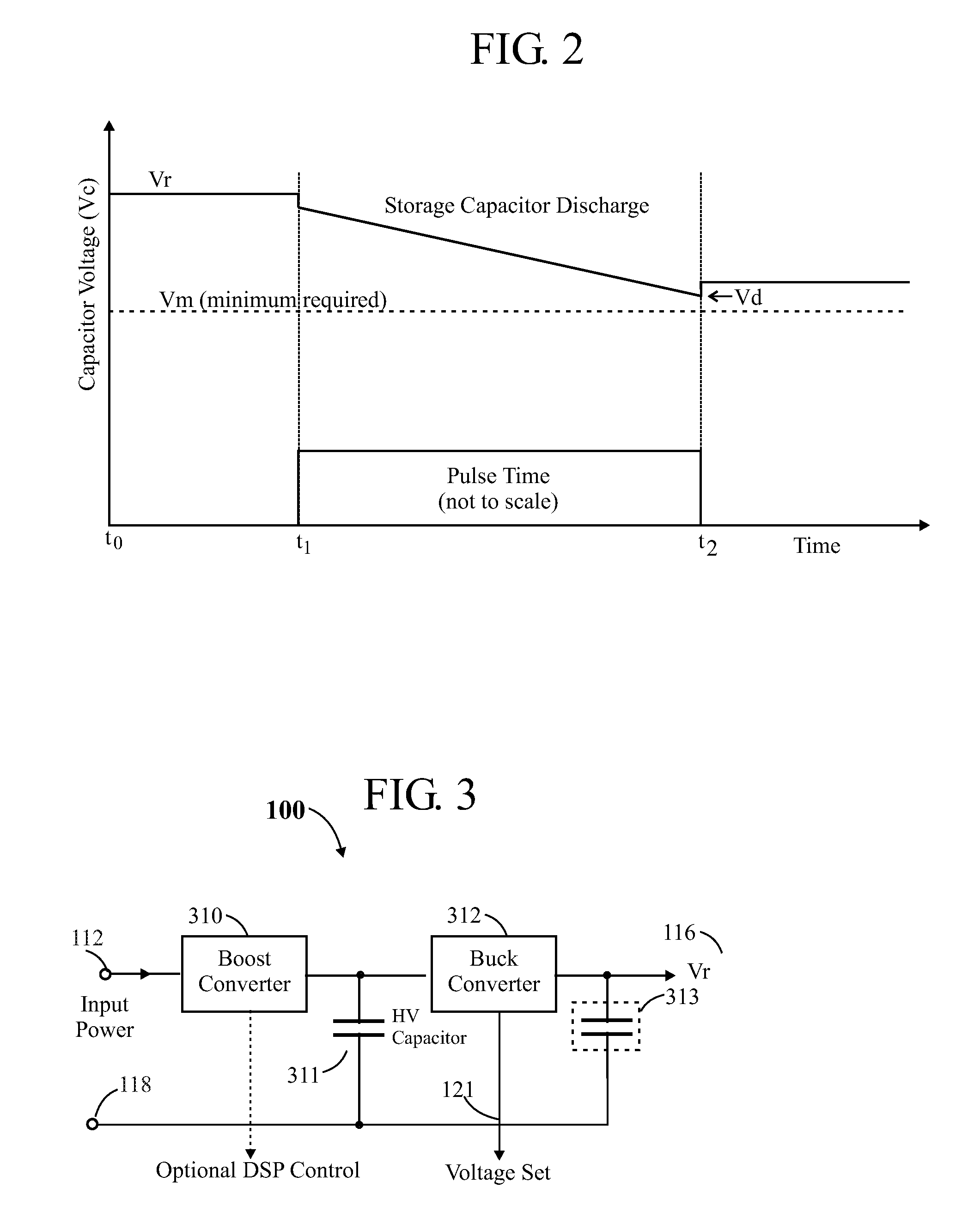

Smart linear pulsed laser diode driver, and method

ActiveUS20110085576A1Improve efficiencySmall sizeLaser detailsElectroluminescent light sourcesCapacitor voltageEngineering

In a pulsed laser diode driver an energy storage capacitor is continuously being charged to a supply voltage Vr. When a pulse is initiated, energy stored in the capacitor is delivered to the laser diode load. The capacitor voltage Vd at the end of a pulse is used to control Vr to ensure that Vd is maintained above a minimum voltage Vm required to ensure operation of a current control device (such as FET) just above saturation. Test pulses (such as with attenuated currents or reduced pulsewidth) may be fired to determine an initial optimum value for Vr. After a test pulse, a slightly high estimate for Vr may be used and may be iterated (incremented) down to an optimum value Vm during a firing burst. A digital processor may be used to calculate and store data to optimize the performance. Various embodiments are disclosed.

Owner:ANALOG MODULES

Gigabit Ethernet Adapter

InactiveUS20070253430A1Fast communication speedCompact solutionWide area networksRaw socketSmall form factor

A gigabit Ethernet adapter provides a provides a low-cost, low-power, easily manufacturable, small form-factor network access module which has a low memory demand and provides a highly efficient protocol decode. The invention comprises a hardware-integrated system that both decodes multiple network protocols byte-streaming manner concurrently and processes packet data in one pass, thereby reducing system memory and form factor requirements, while also eliminating software CPU overhead. A preferred embodiment of the invention comprises a plurality of protocol state machines that decode network protocols such as TCP, IP, User Datagram Protocol (UDP), PPP, Raw Socket, RARP, ICMP, IGMP, iSCSI, RDMA, and FCIP concurrently as each byte is received. Each protocol handler parses, interprets, and strips header information immediately from the packet, requiring no intermediate memory. The invention provides an internet tuner core, peripherals, and external interfaces. A network stack processes, generates and receives network packets. An internal programmable processor controls the network stack and handles any other types of ICMP packets, IGMP packets, or packets corresponding to other protocols not supported directly by dedicated hardware. A virtual memory manager is implemented in optimized, hardwired logic. The virtual memory manager allows the use of a virtual number of network connections which is limited only by the amount of internal and external memory available.

Owner:NVIDIA CORP