Patents

Literature

1956results about How to "Good compensation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

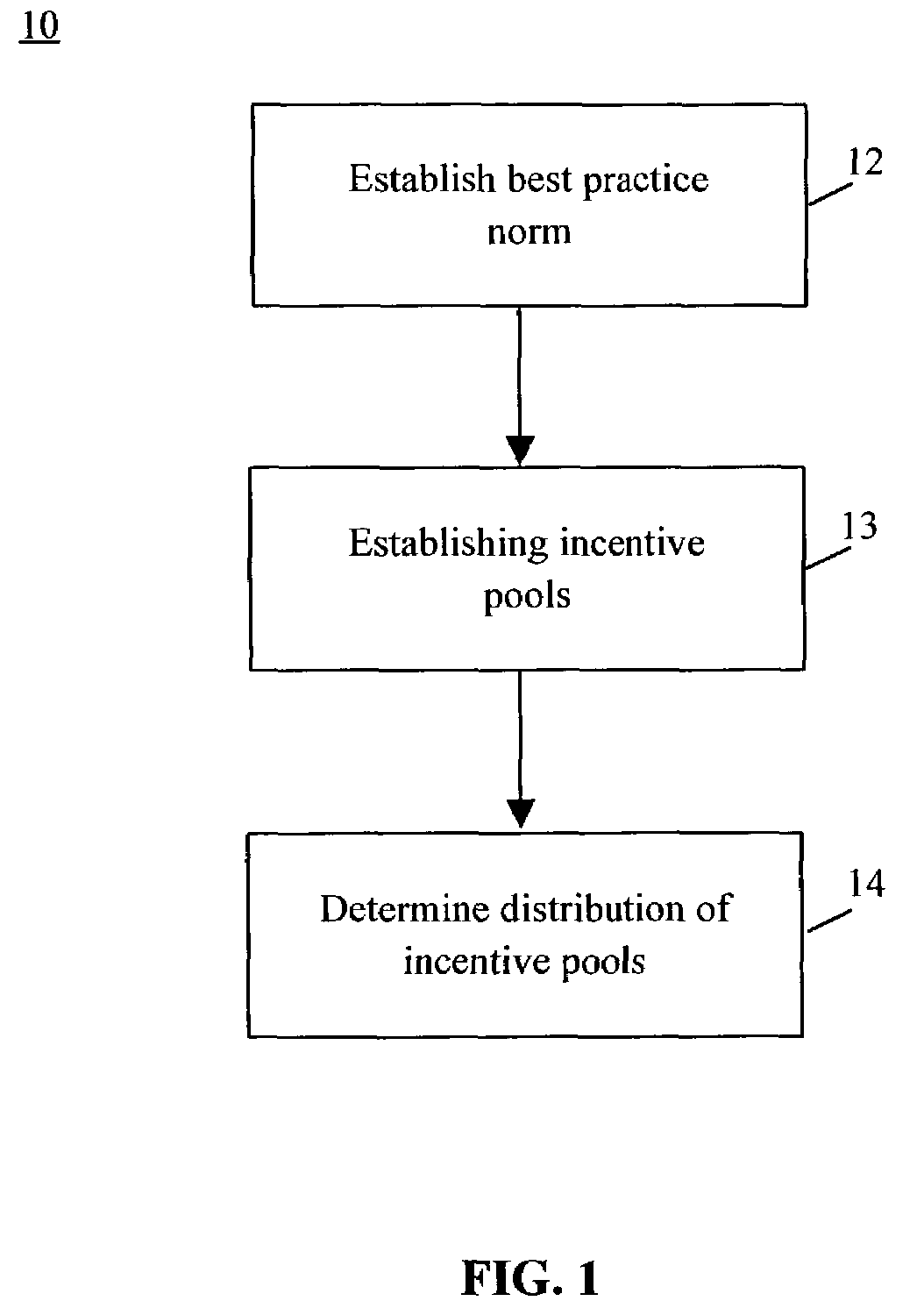

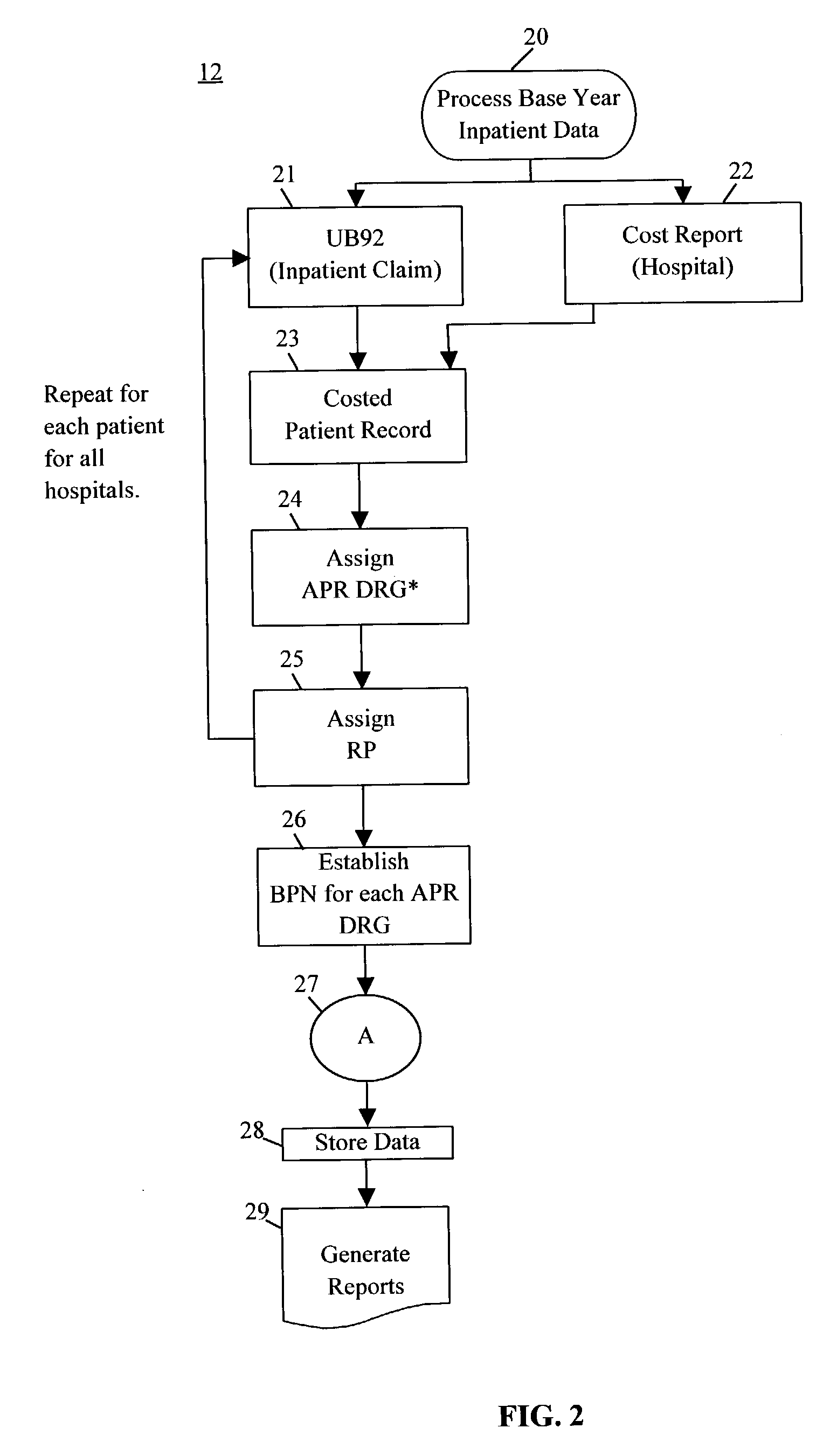

Method and system for evaluating a physician's economic performance and gainsharing of physician services

InactiveUS20080195417A1Impose significant, additional data collection burdens on providersEfficient and inexpensiveFinanceOffice automationPaymentDisease

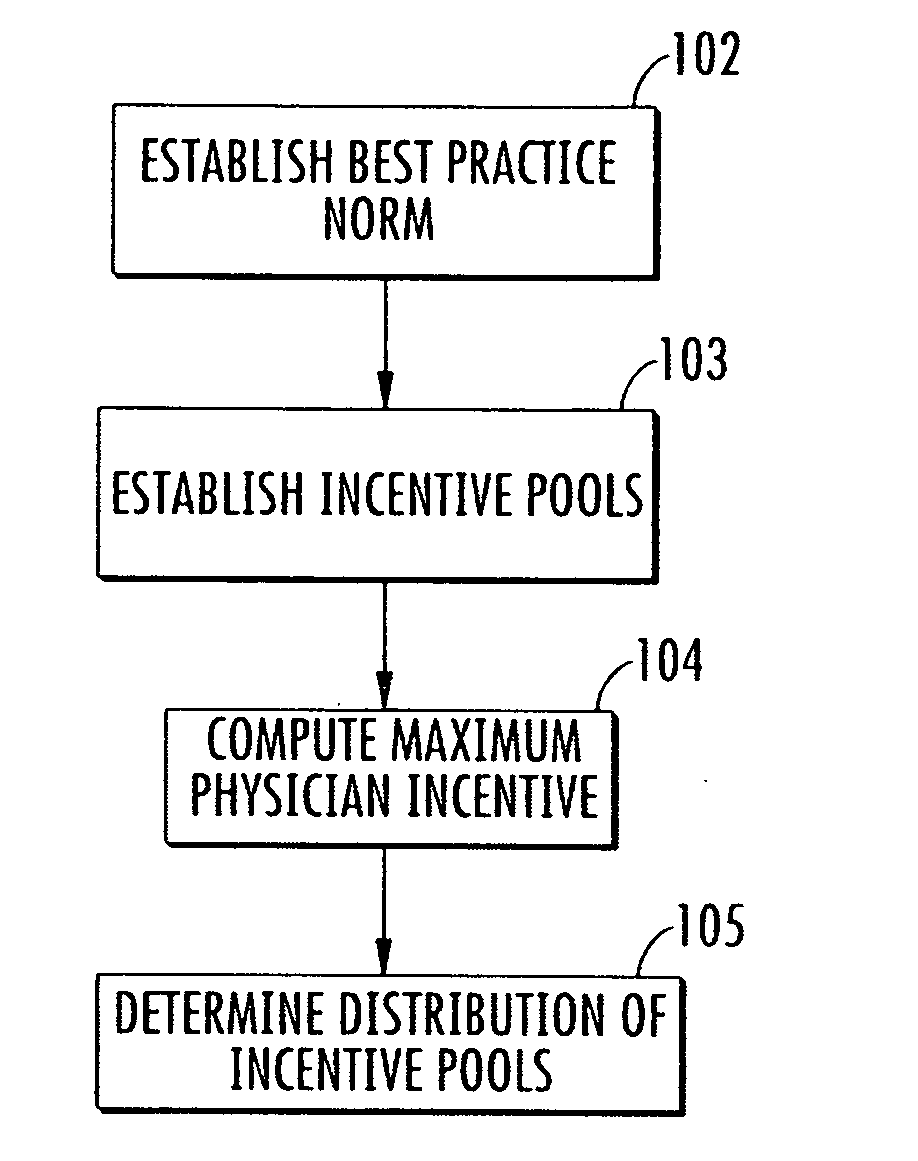

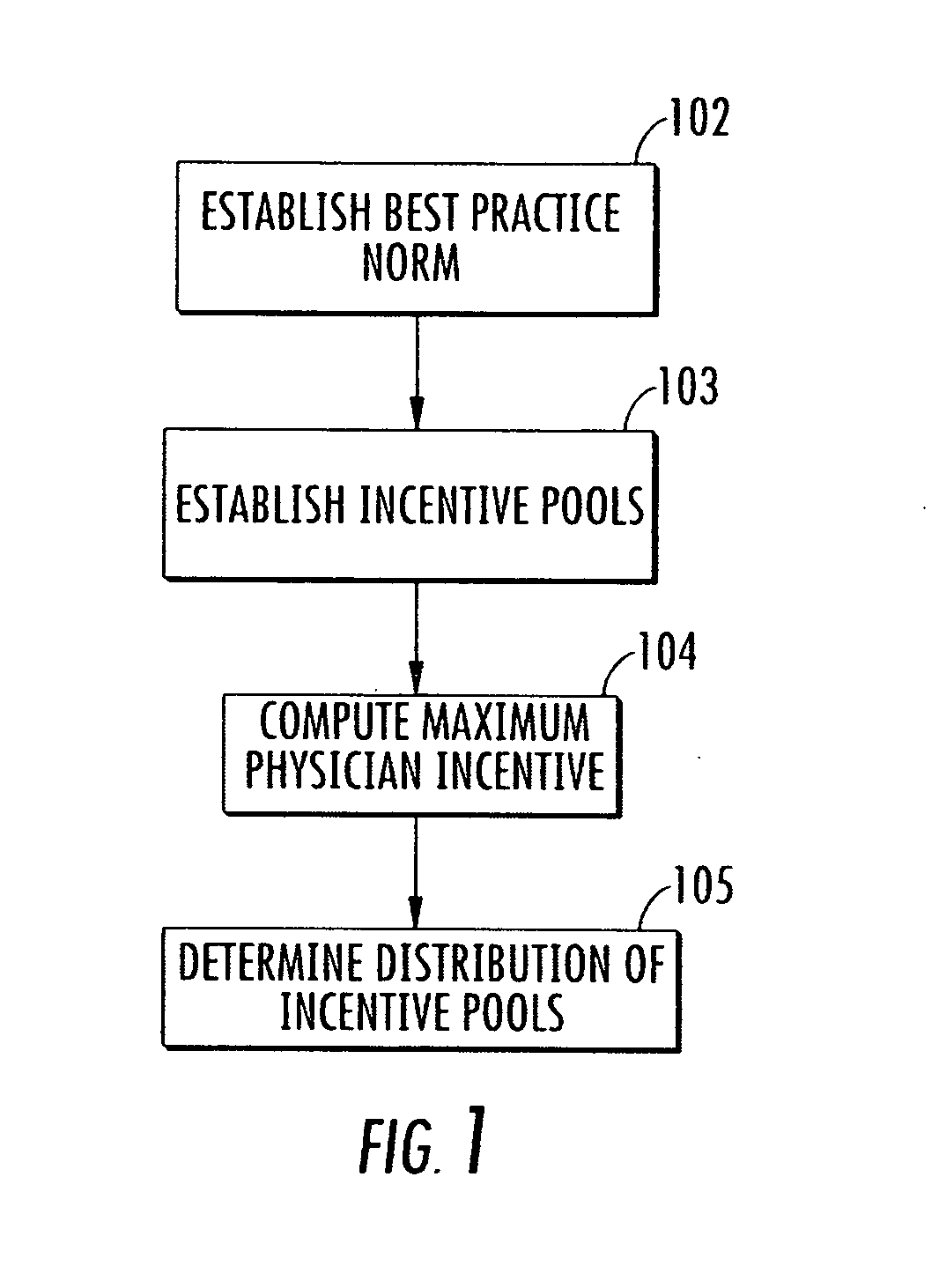

The invention relates to a method and system of physician economic performance evaluation in which the relative medical difficulty associated with patients admitted by a particular physician is determined and, given that measurement, judgments made concerning the relative amount of inpatient resources that the physician required. Also, one application of the present invention relates to a method for gainsharing of physician services using a surplus allocation methodology for rewarding physicians in relation to their performance. An incentive pool is determined from previous patient claims and payments made to physicians in advance, such as in a base year. Best practice norms are established for a plurality of classified diagnosis groups. In one embodiment of the present invention, the classified diagnosis related groups are adjusted for severity of illness to compensate for actual clinical challenges faced by individual physicians. The best practice norms can be used in the surplus allocation method for determining physician performance. The incentive is established proportional to the relationship between a physician's individual performance and the best practice norm.

Owner:AMS APPLIED MEDICAL SOFTWARE

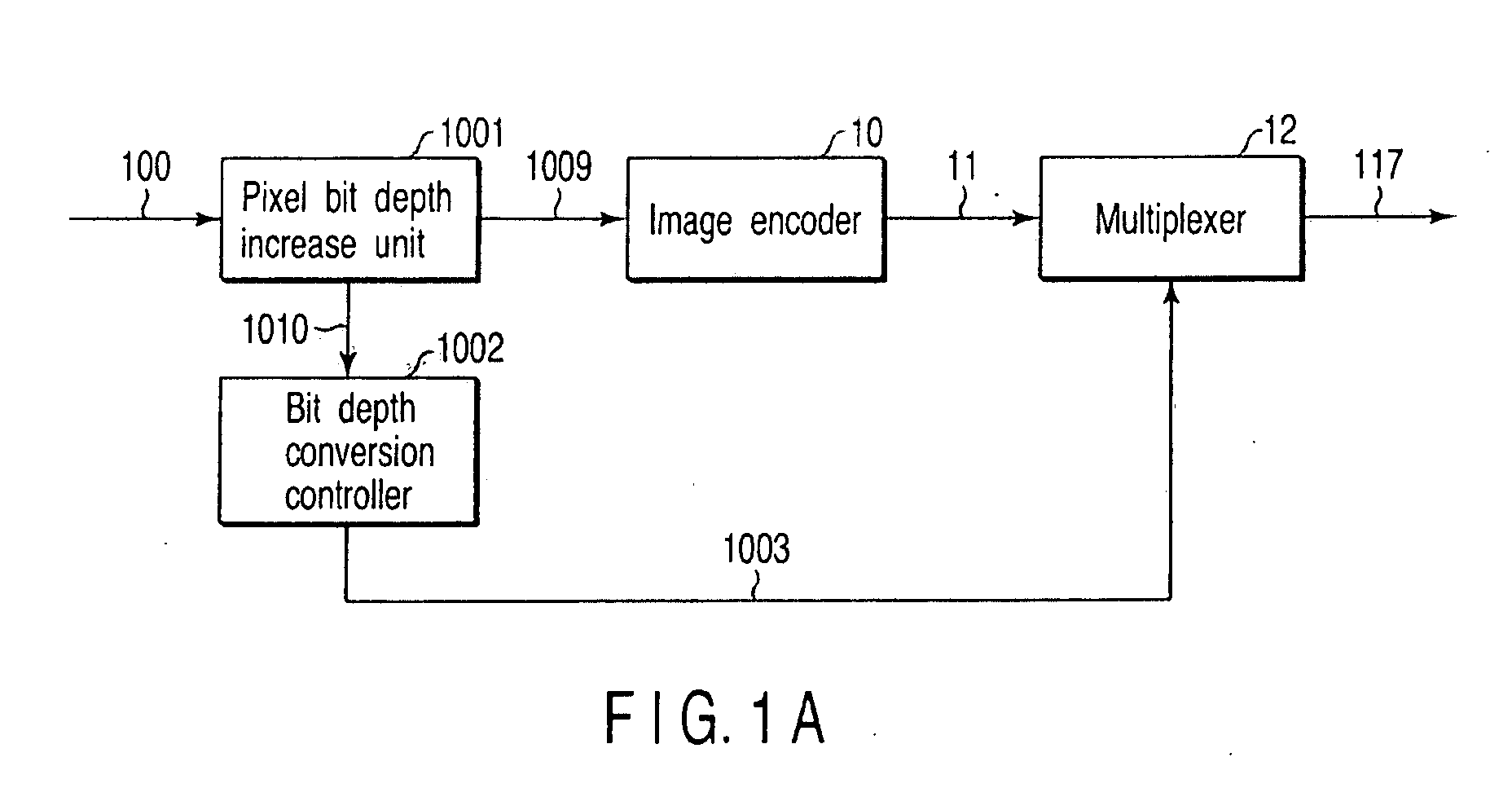

Image encoding apparatus and method for the same and image decoding apparatus and method for the same

ActiveUS20090087111A1Increase bit depthDecrease bit depthCharacter and pattern recognitionDigital video signal modificationComputer visionMuxponder

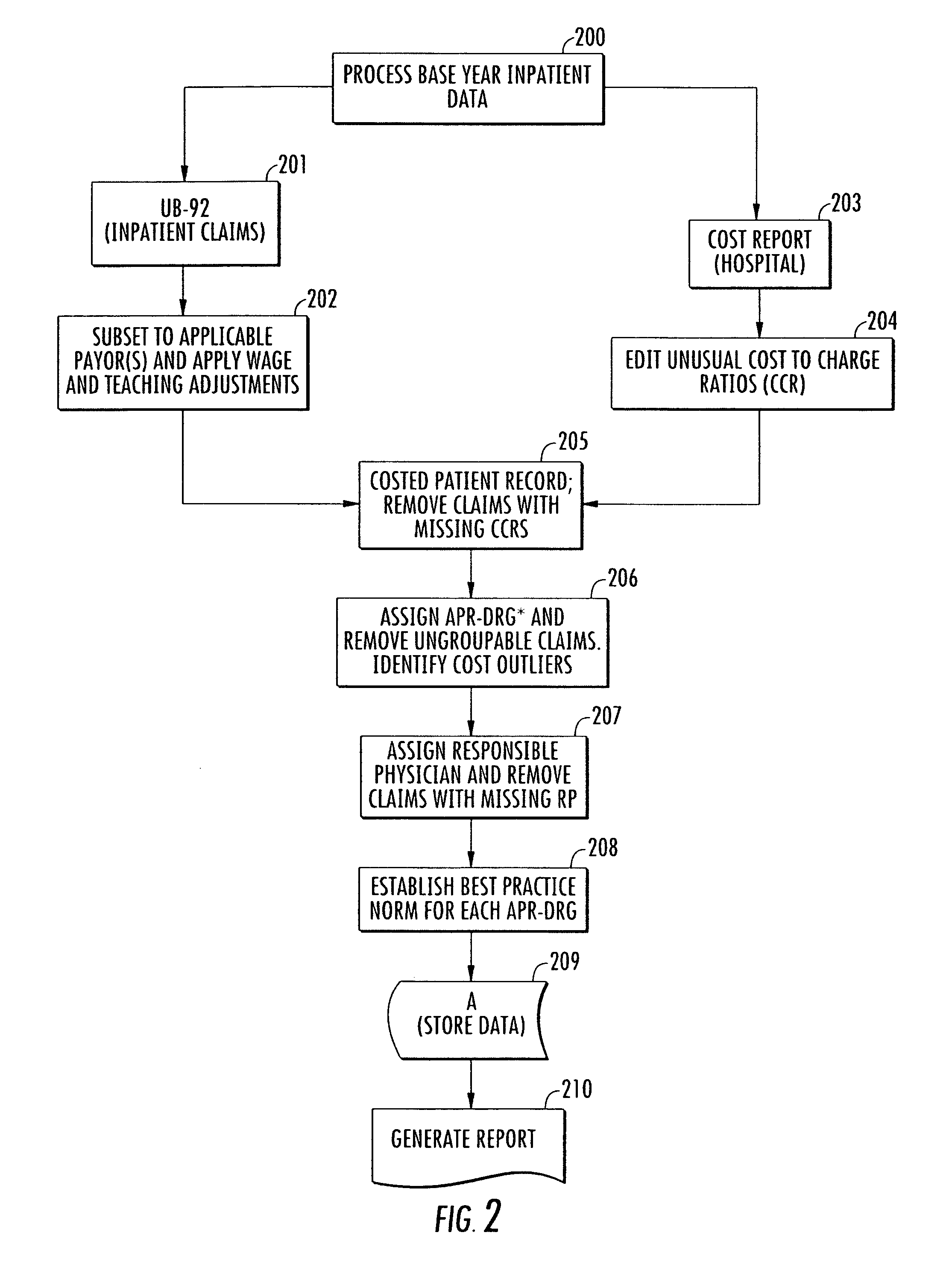

An image encoding apparatus includes a pixel bit depth increase converter to convert bit depth of each pixel of an input image to output a converted input image and output bit conversion information indicating the number of bits changed by conversion, an image encoder to encode the input converted input image to output encoded image information, and a multiplexer to multiplexes the bit conversion information and encoded image information.

Owner:KK TOSHIBA

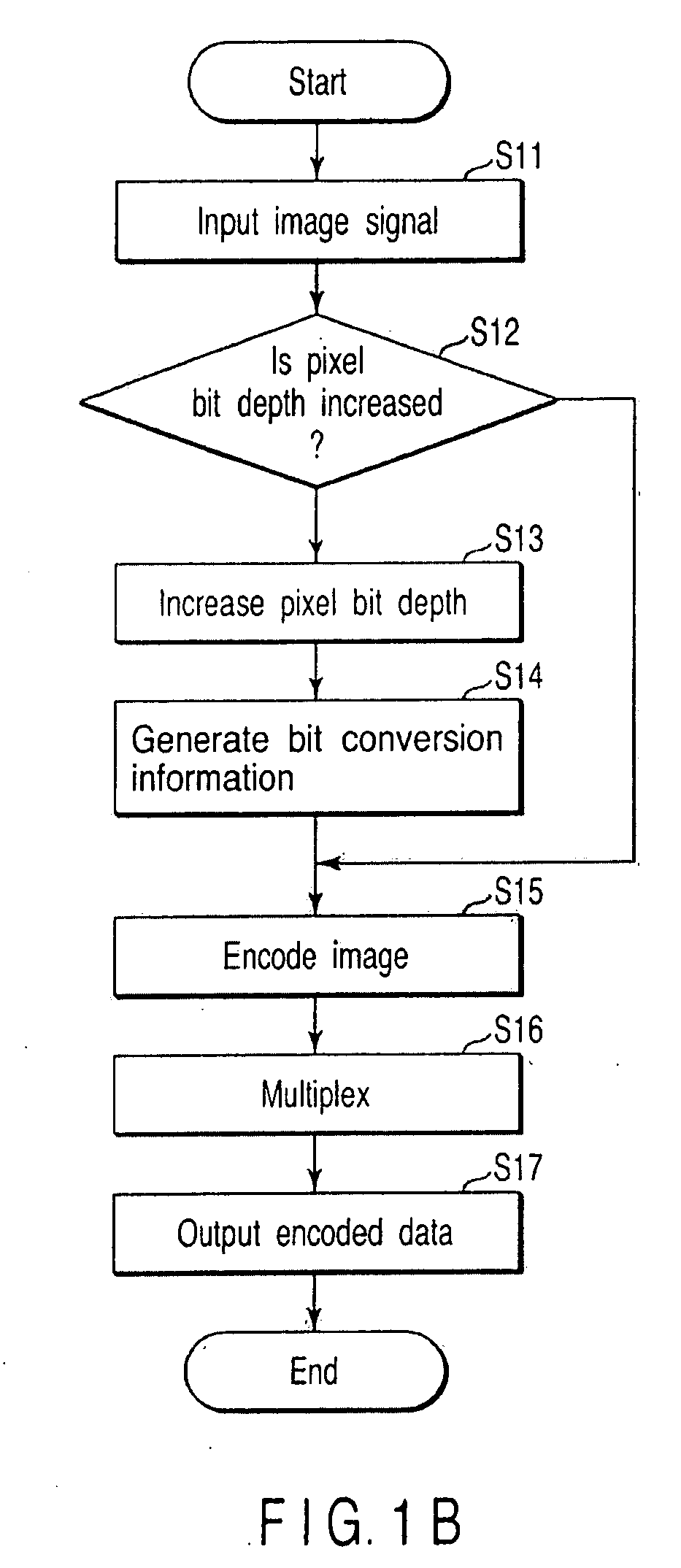

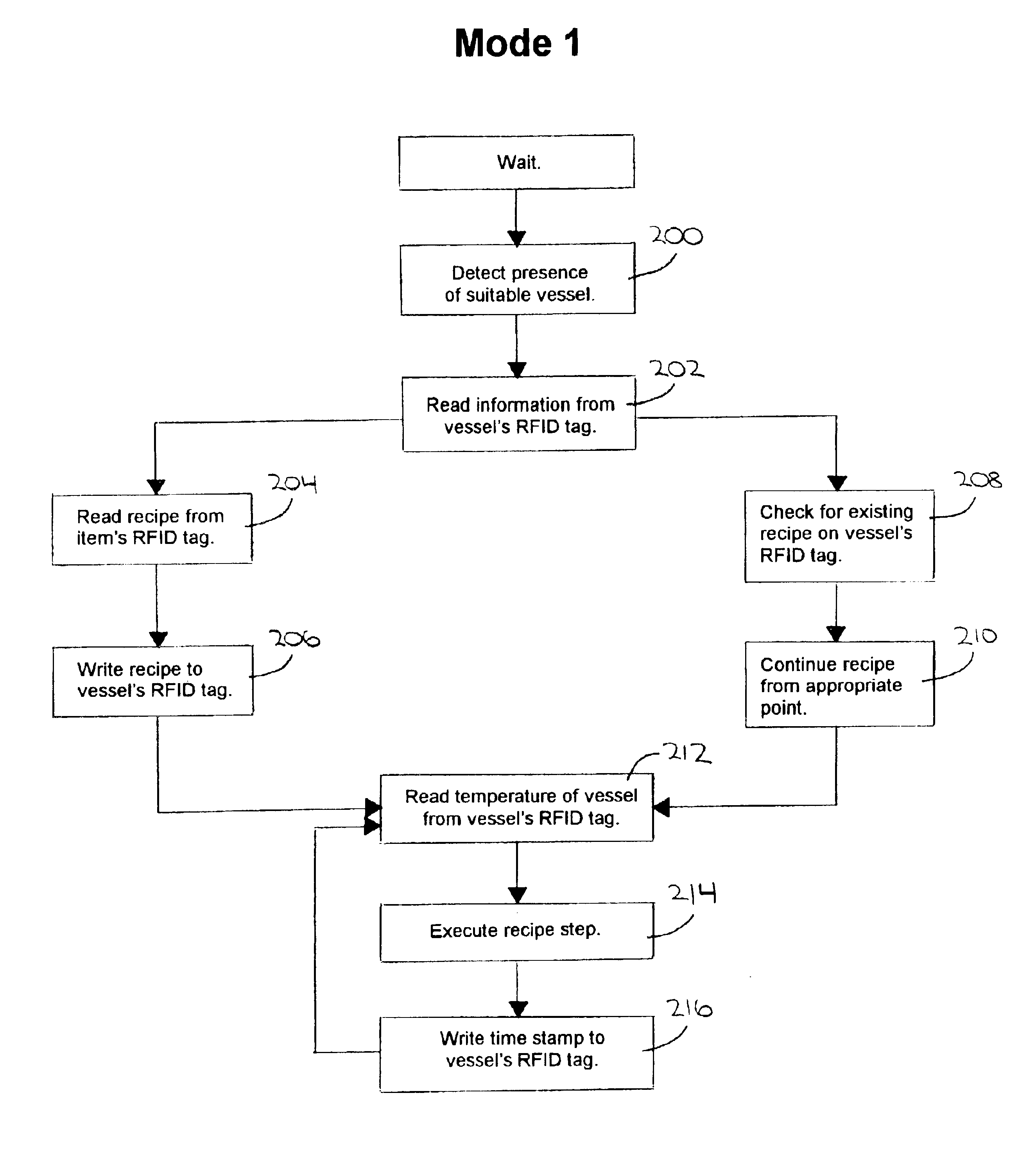

RFID-controlled smart range and method of cooking and heating

InactiveUS6953919B2Facilitate communicationFacilitates informationCooking vesselsDeep fat fryersAdditive ingredientEngineering

A system and method for providing multiple cooking modes and an ability to automatically heat cooking vessels and other objects using RFID technology, and an ability to read and write heating instructions and to interactively assist in their execution. An induction heating range is provided with two antennas per hob, and includes a user interface display and input mechanism. The vessel includes an RFID tag and a temperature sensor. In a first cooking mode, a recipe is read by the range and the range assists a user in executing the recipe by automatically heating the vessel to specified temperatures and by prompting the user to add ingredients. The recipe is written to the RFID tag so that if the vessel is moved to another hob, into which the recipe has not been read, the new hob can read the recipe from the RFID tag and continue in its execution.

Owner:HR TECH

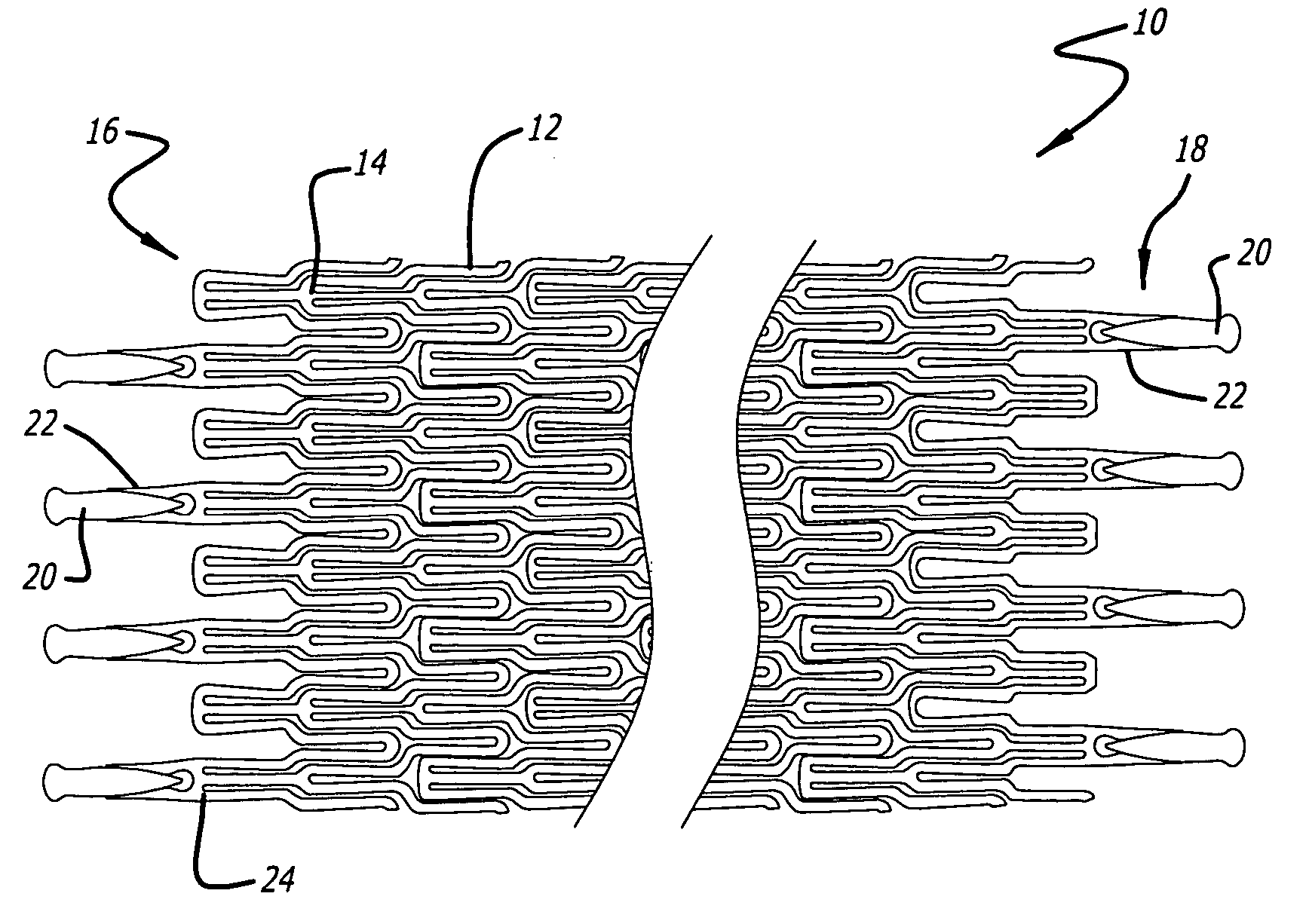

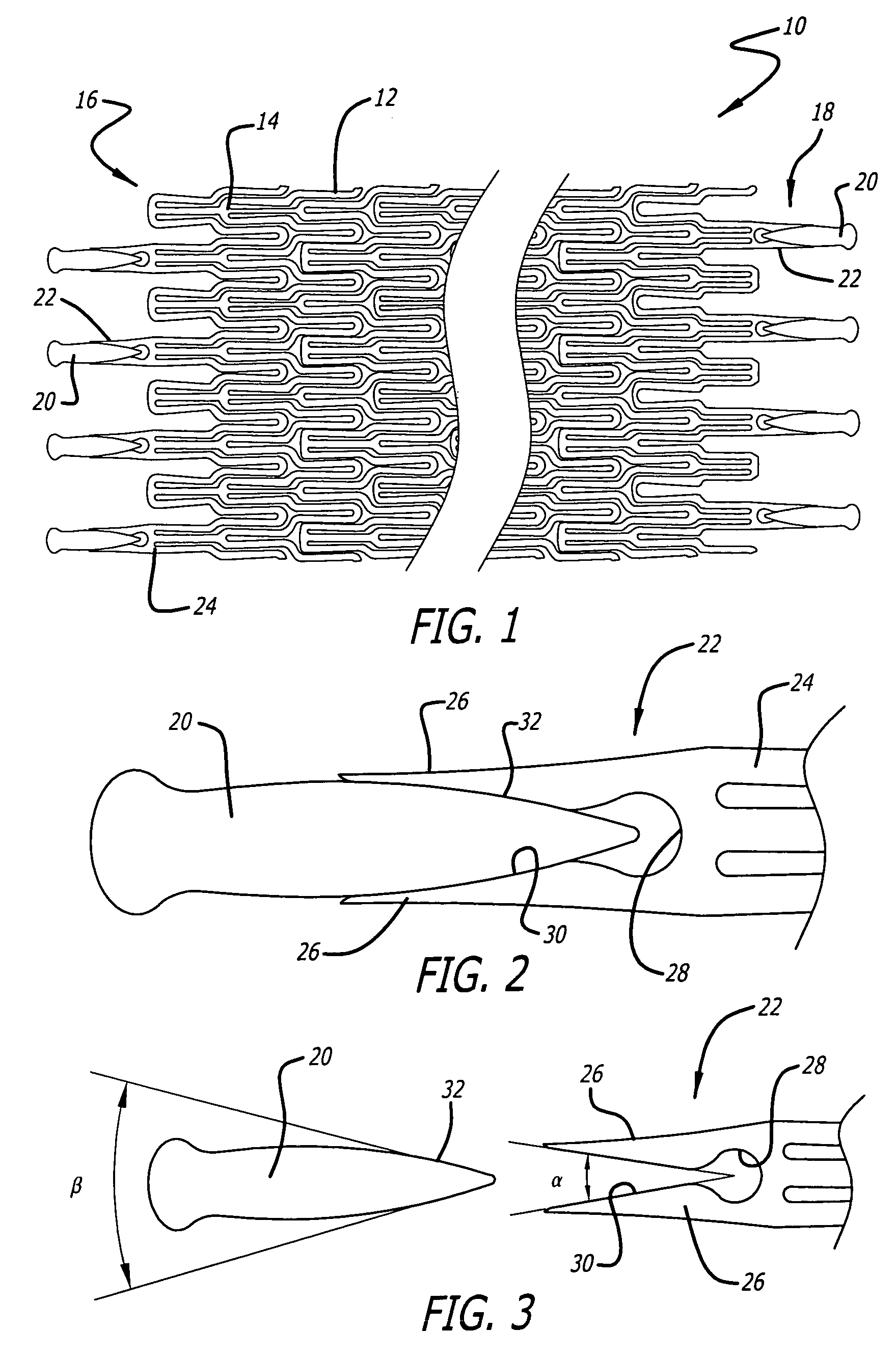

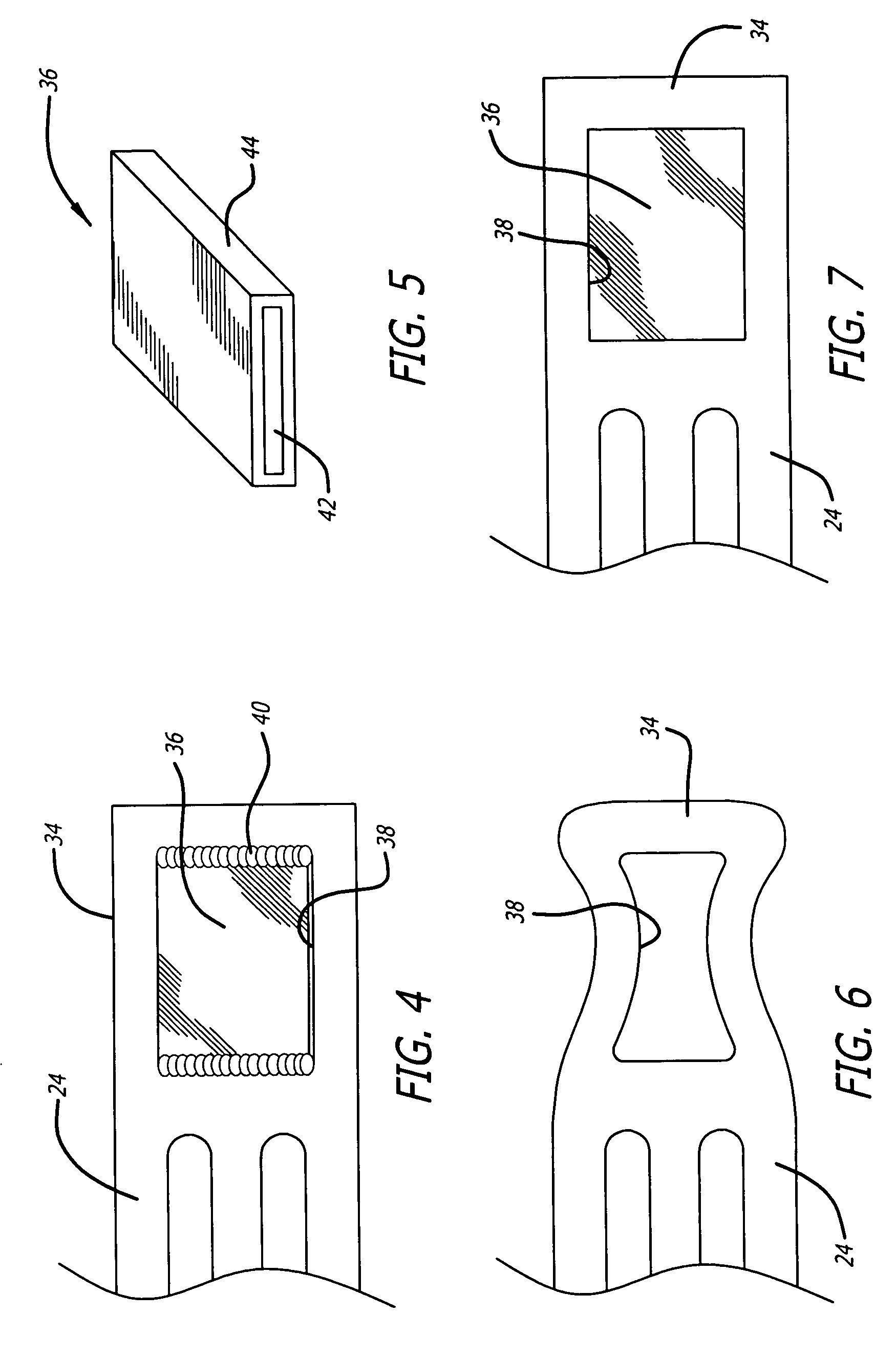

Radiopaque markers for medical devices

InactiveUS20050060025A1High level of radiopacitySufficient radiopacityStentsBlood vesselsIridiumRhenium

An implantable medical device includes a structural body made from a superelastic material and includes one or more marker holders integrally formed on the structural body. Each marker holder is designed to hold a radiopaque marker which has a level of radiopacity greater than the superelastic material. The radiopaque marker can be made from a nickel-titanium alloy which includes a ternary element. The ternary element can be selected from the group of elements consisting of iridium, platinum, gold, rhenium, tungsten, palladium, rhodium, tantalum, silver, ruthenium, and hafnium. In one form, the marker holder includes a pair of projecting fingers connected together at a notched region to cooperatively create a particular-shaped opening. This opening, in turn, is adapted to receive a similarly shaped portion formed on the radiopaque marker. In one form, the radiopaque marker includes an inner core which is partially, or completely, encased by an outer layer. This inner core can be made from a highly radiopaque material while the outer layer is formed from a material that is easier to weld to the marker.

Owner:ABBOTT VASCULAR SOLUTIONS

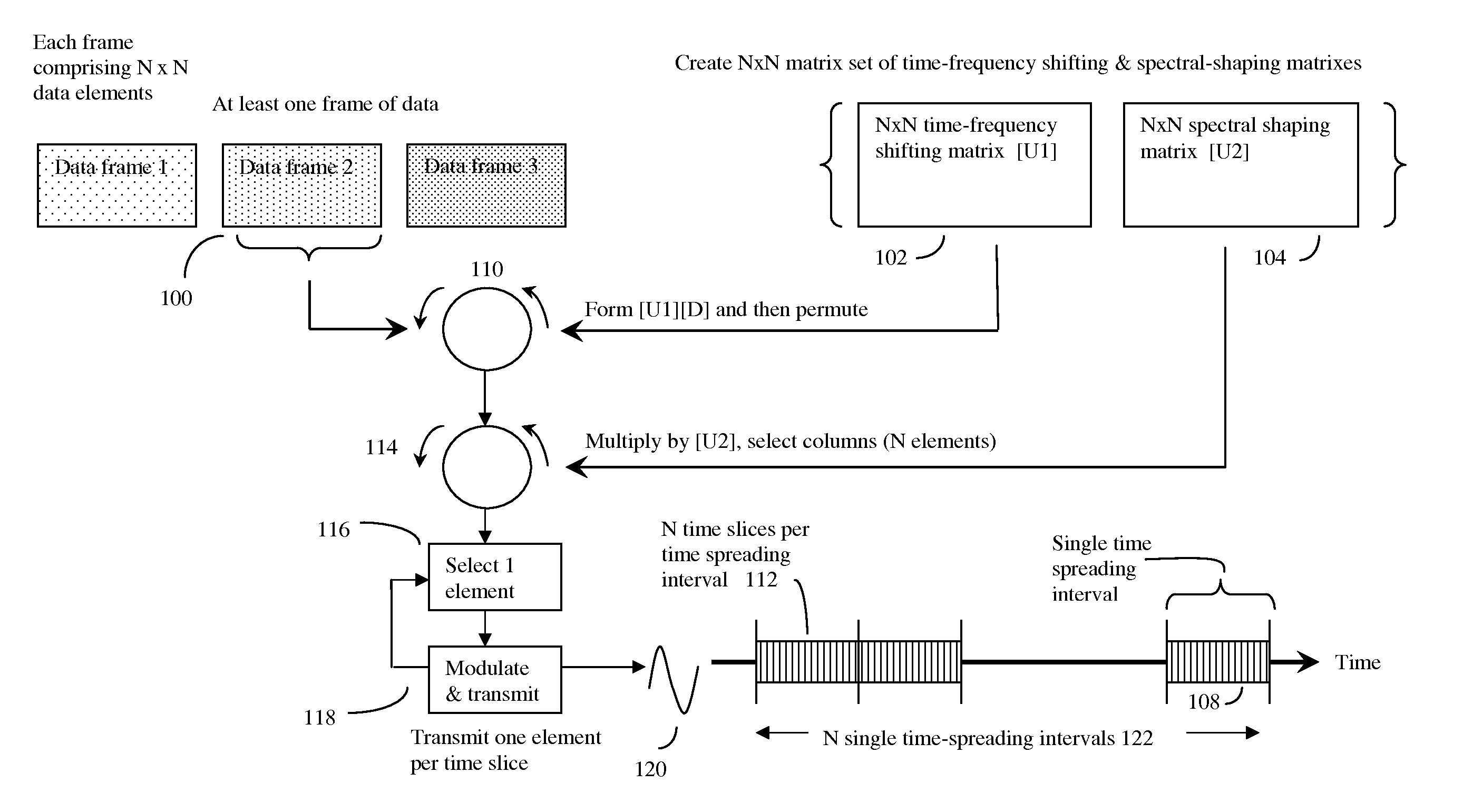

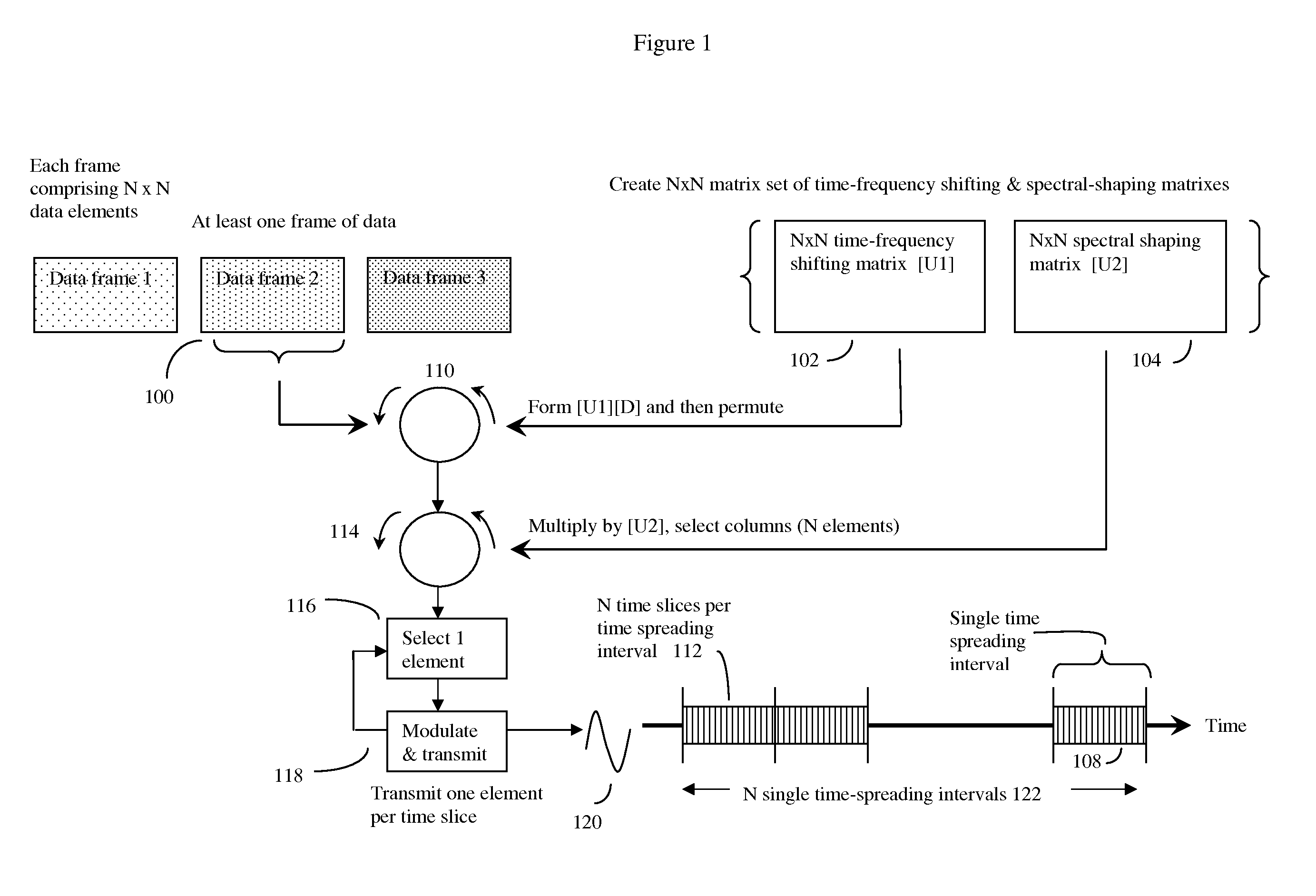

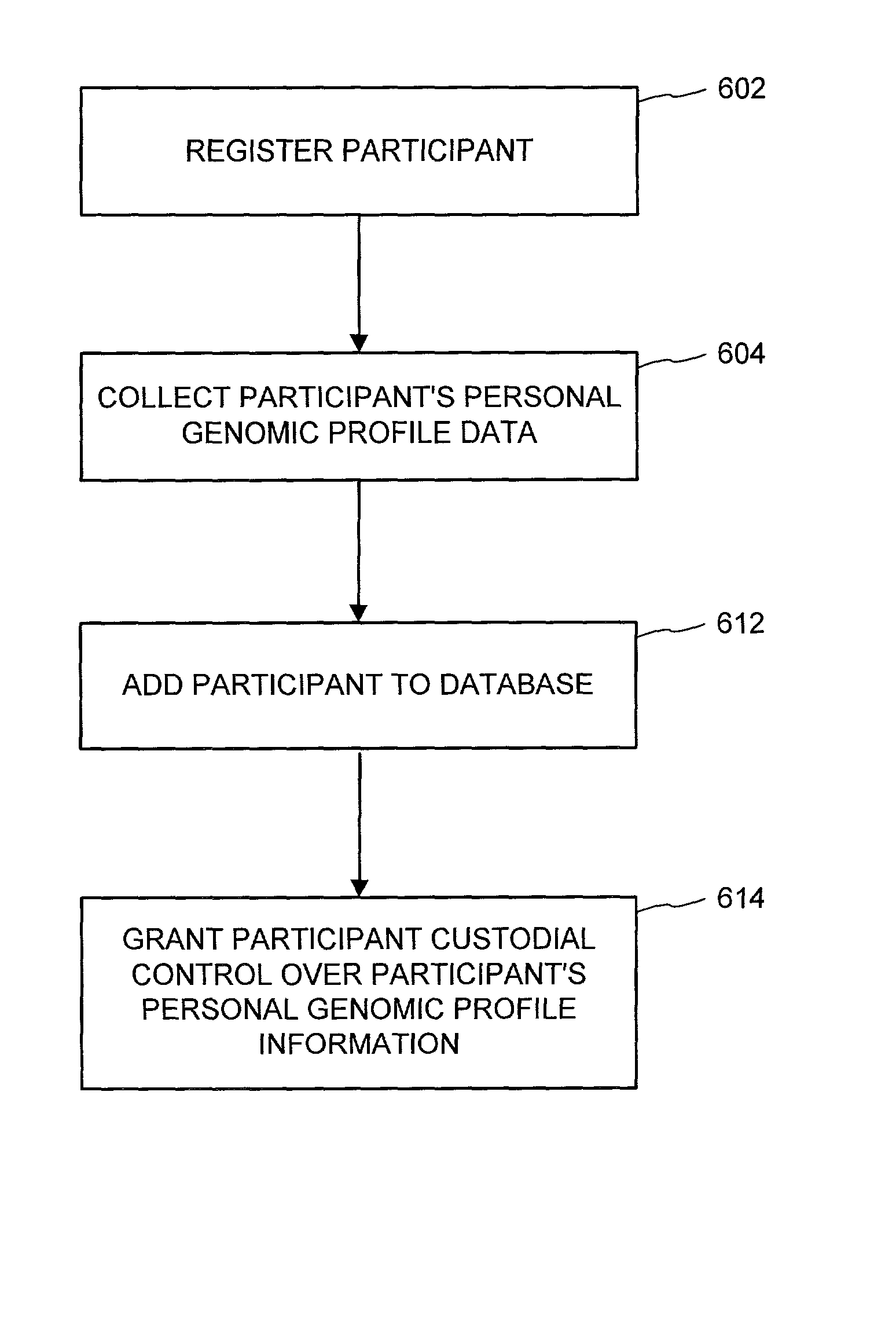

Orthonormal time-frequency shifting and spectral shaping communications method

ActiveUS20110293030A1Long to transmitGood compensationNetwork traffic/resource managementModulated-carrier systemsFrequency spectrumEngineering

A wireless combination time, frequency and spectral shaping communications method that transmits data in convolution unit matrices (data frames) of N×N (N2), where generally either all N2 data symbols are received over N spreading time intervals (each composed of N time slices), or none are. To transmit, the N2 sized data frame matrix is multiplied by a first N×N time-frequency shifting matrix, permuted, and then multiplied by a second N×N spectral shaping matrix, thereby mixing each data symbol across the entire resulting N×N matrix (TFSSS data matrix). Columns from this N2 TFSSS data matrix are selected, modulated, and transmitted, on a one element per time slice basis. At the receiver, the replica TFSSS matrix is reconstructed and deconvoluted, revealing the data. The method can accommodate multiple users at once, can adapt to changing channel conditions, and is particularly useful for coping with channel impairments such as Doppler shifts.

Owner:COHERE TECH

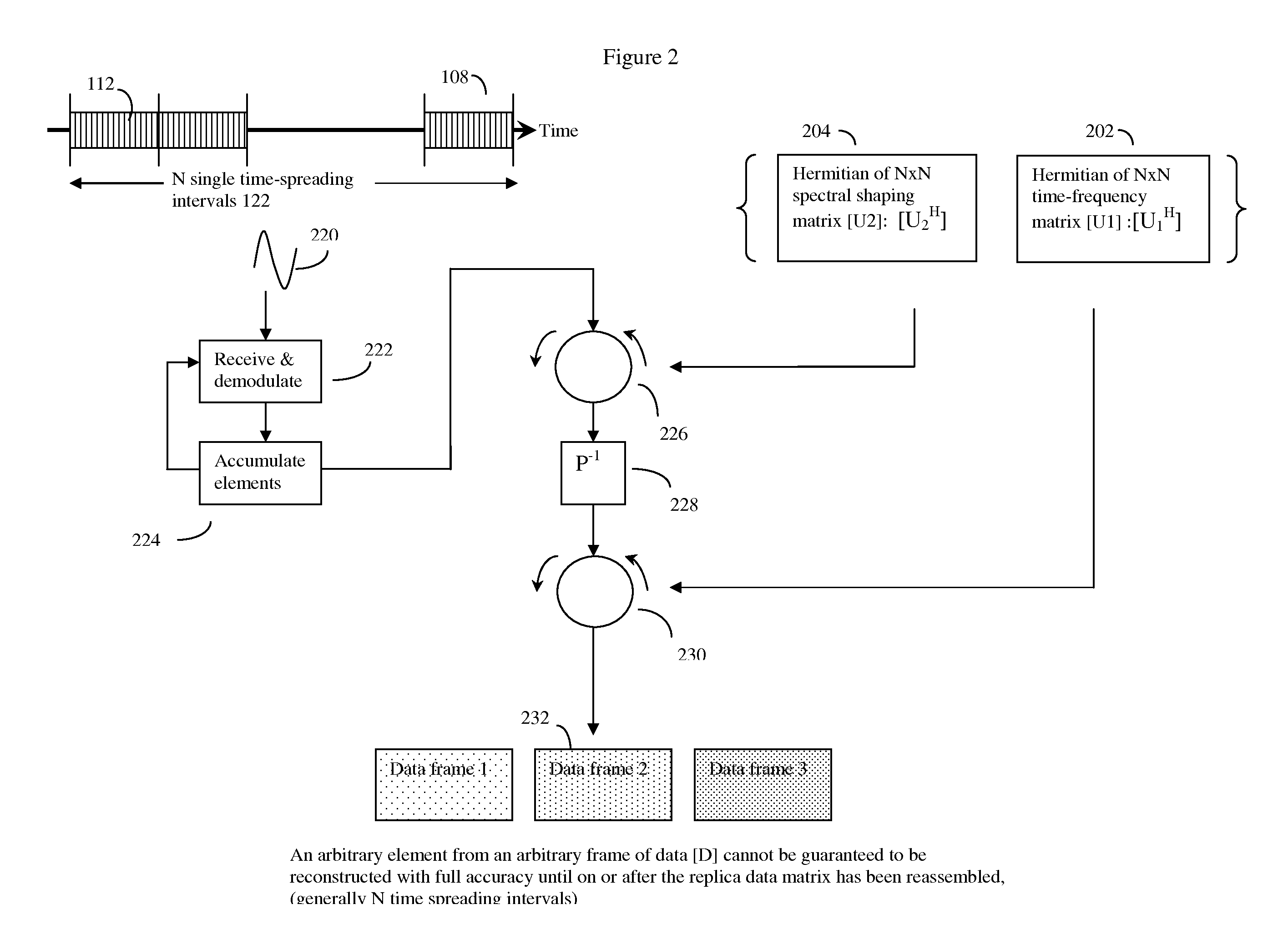

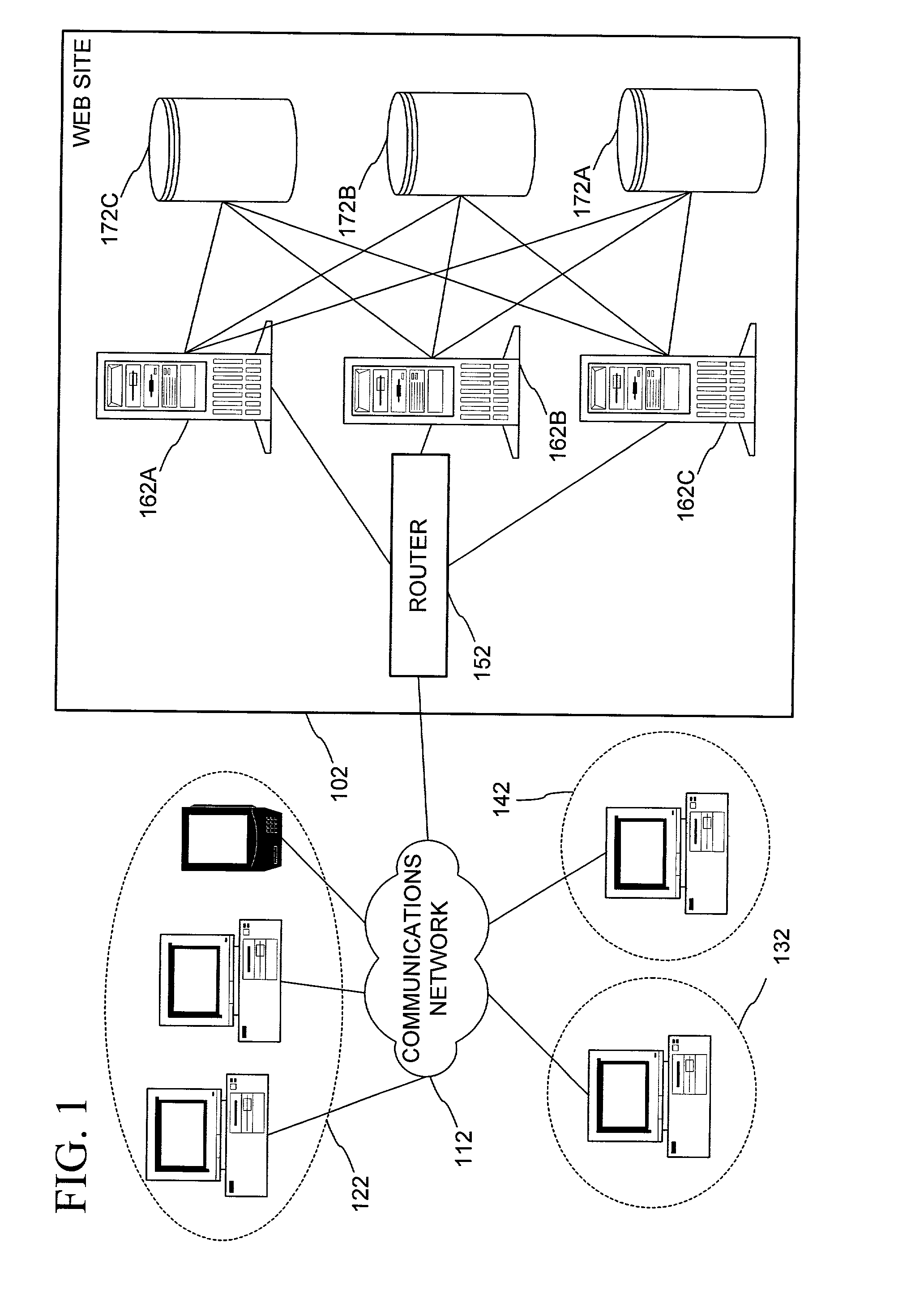

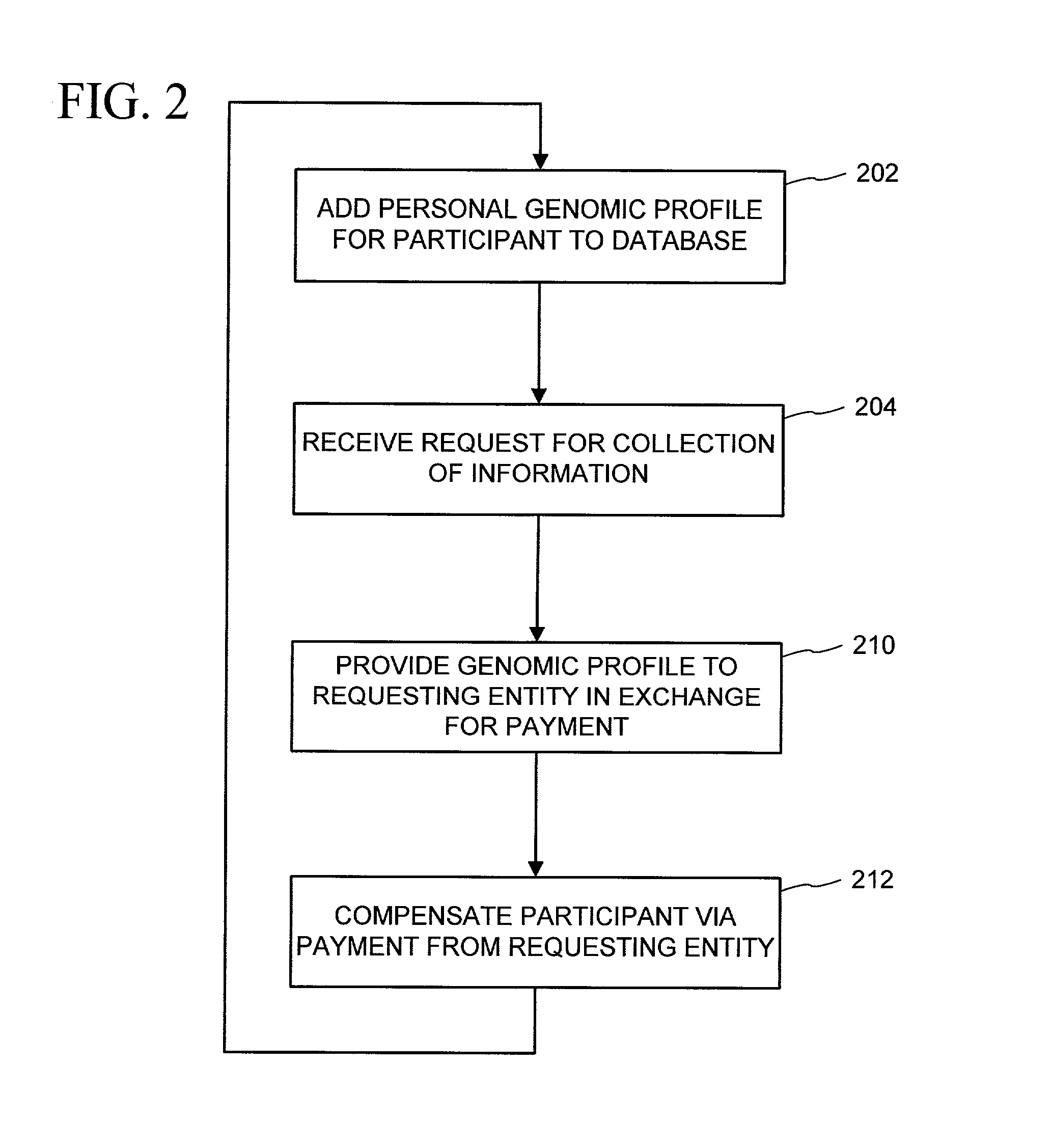

Genomic profile information systems and methods

InactiveUS20020095585A1Increase valueSignificant compensationComputer security arrangementsProteomicsInformation networksAnonymity

A variety of methods and systems related to genomic profile information and related participants are described. Participants can be encouraged to allow access to their genomic profile information in a variety of ways. A peer-to-peer genomic profile information network can be implemented. A collection of genomic profile information for a large number of participants can be built, and anonymity of the participants can be maintained. Participants can maintain custodial control over their genomic profile information. Comparative tools and groups can help participants identify and communicate with other participants having similar information.

Owner:GENOMIC HEALTH INC

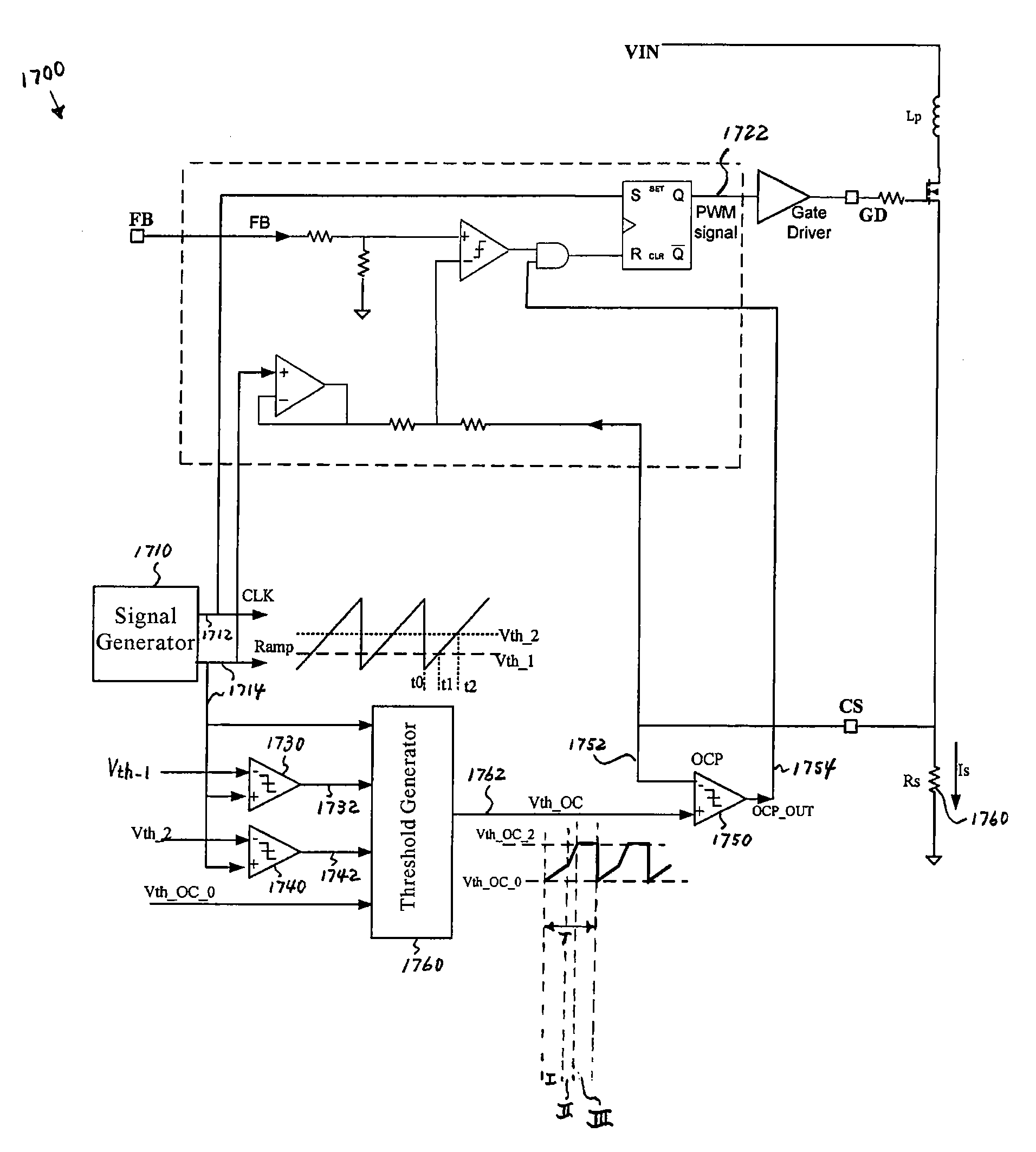

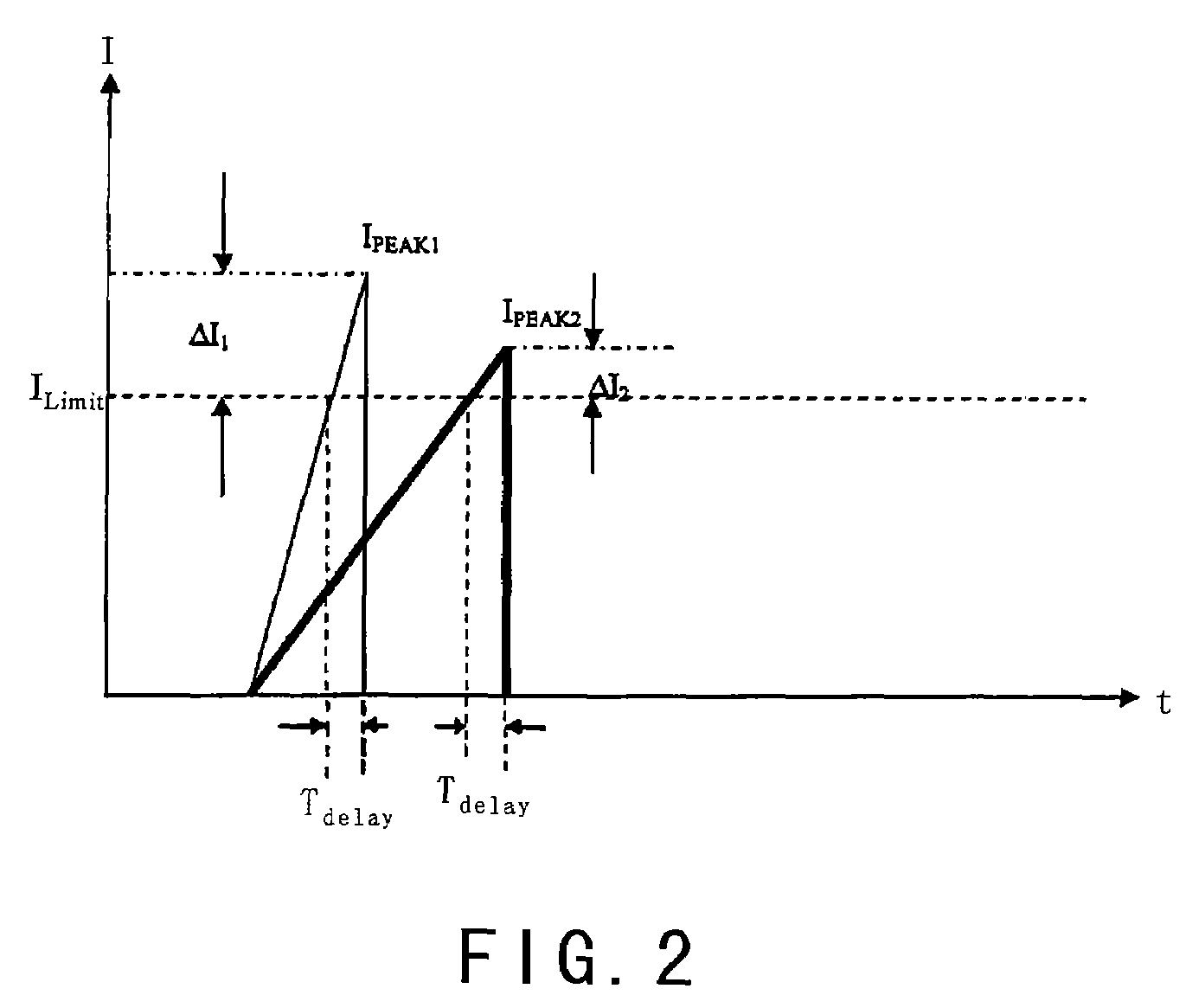

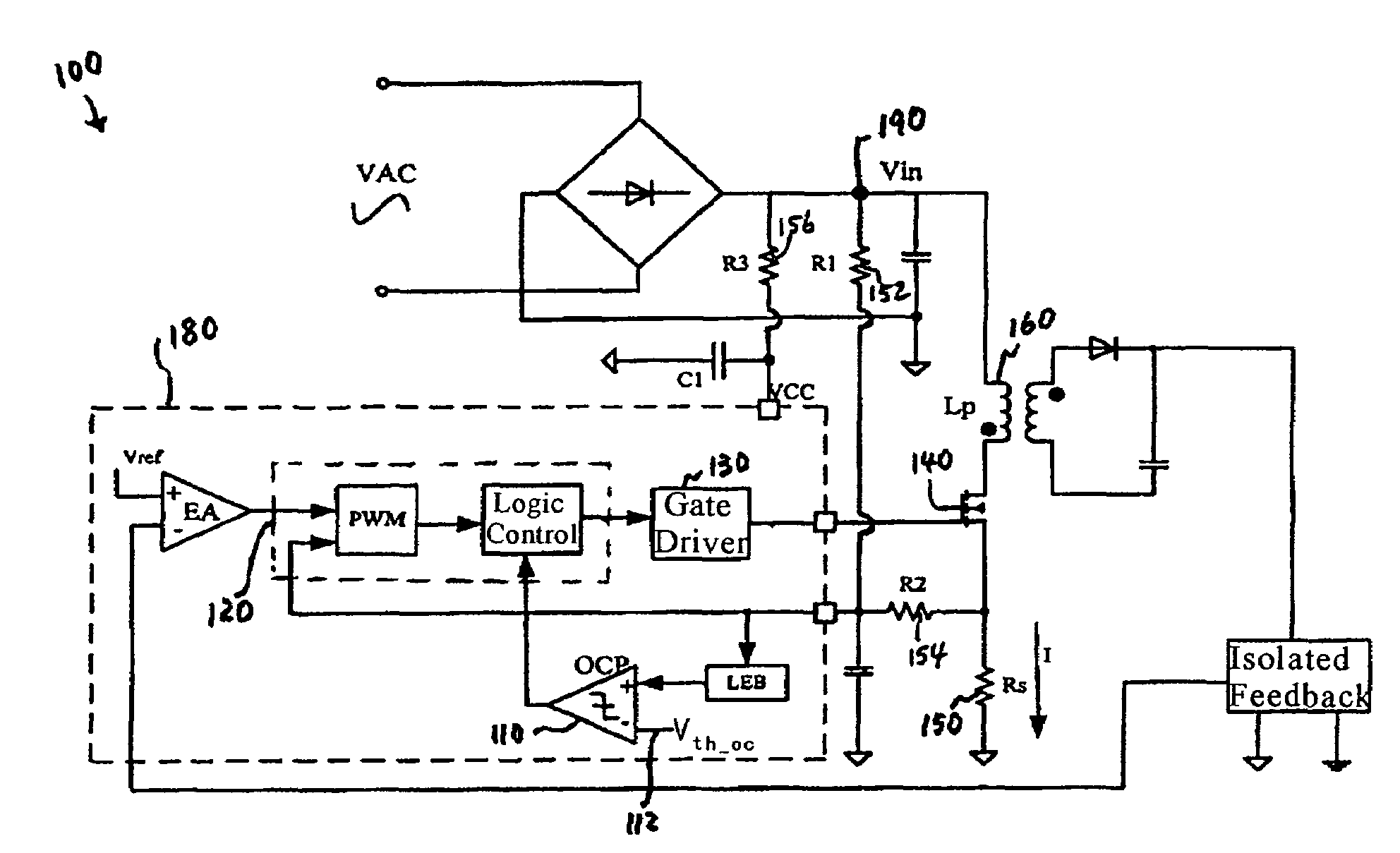

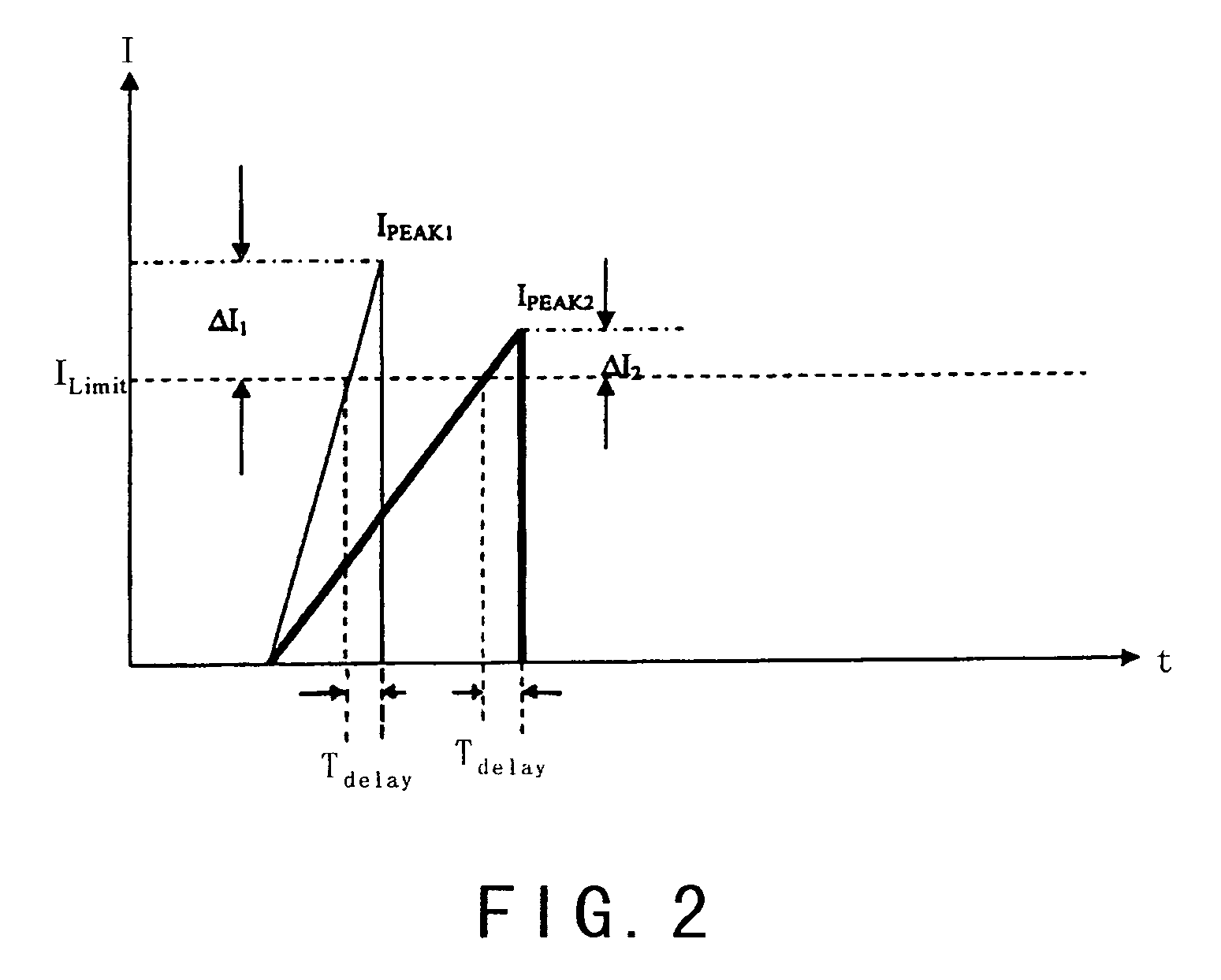

System and method providing over current and over power protection for power converter

ActiveUS7684220B2Good compensationEasy to adjustArrangements responsive to excess currentEmergency protective arrangements for limiting excess voltage/currentEngineeringComparator

System and method for protecting a power converter. A system includes a threshold generator configured to generate a threshold signal, and a first comparator configured to receive the threshold signal and a first signal and to generate a comparison signal. The first signal is associated with an input current for a power converter. Additionally, the system includes a pulse-width-modulation generator configured to receive the comparison signal and generate a modulation signal in response to the comparison signal, and a switch configured to receive the modulation signal and adjust the input current for the power converter. The threshold signal is associated with a threshold magnitude as a function of time. The threshold magnitude increases with time at a first slope during a first period, and the threshold magnitude increases with time at a second slope during a second period. The first slope and the second slope are different.

Owner:ON BRIGHT ELECTRONICS SHANGHAI

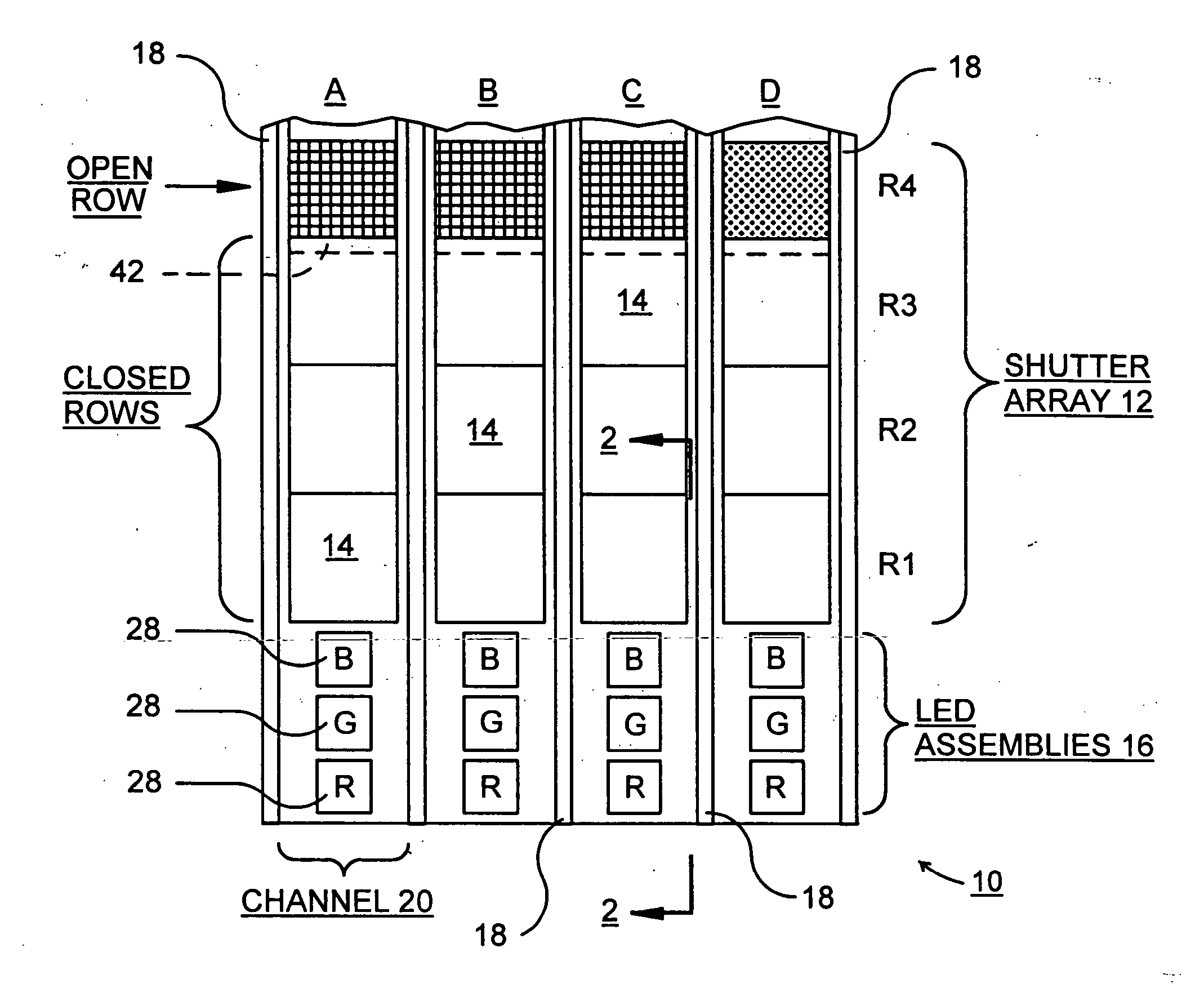

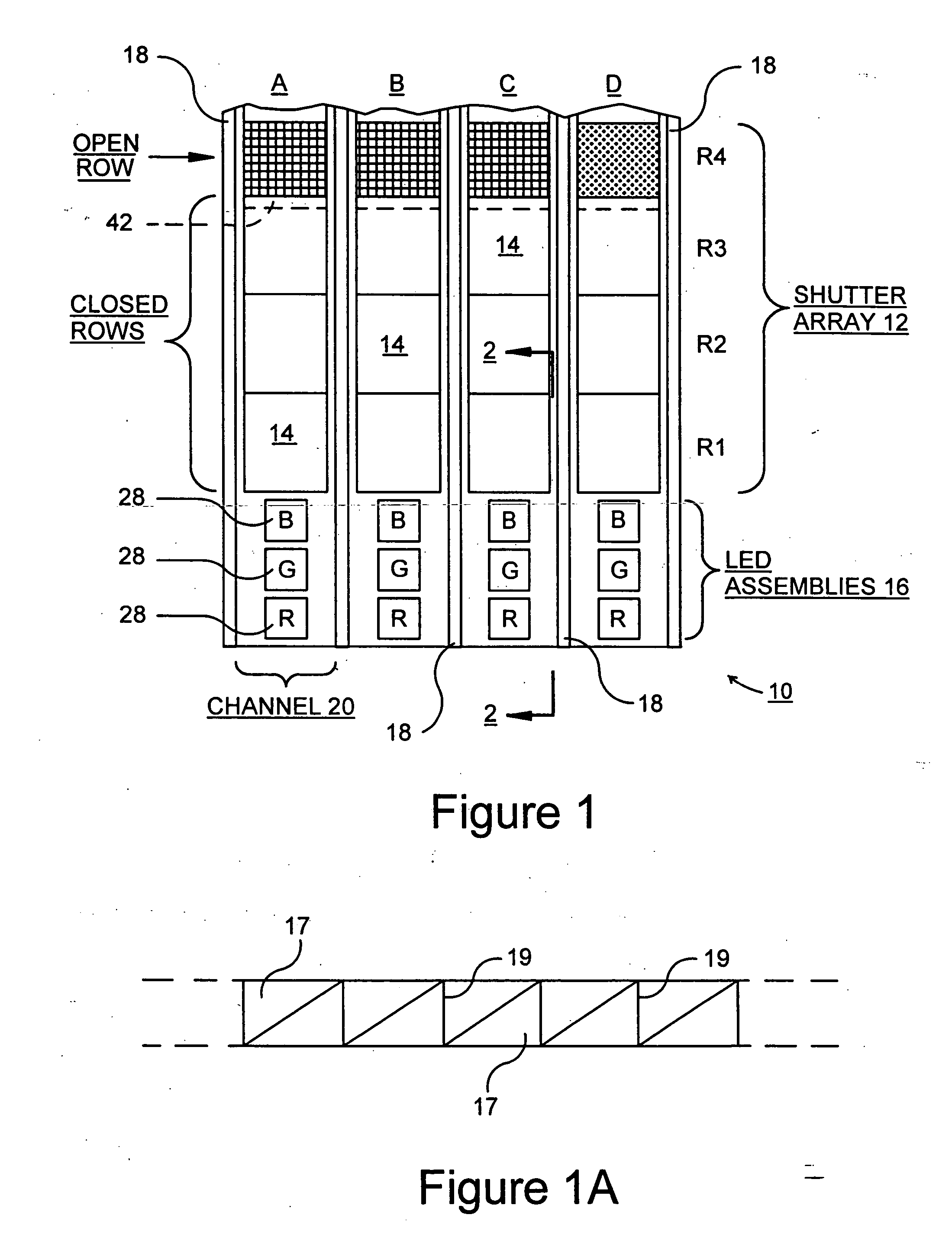

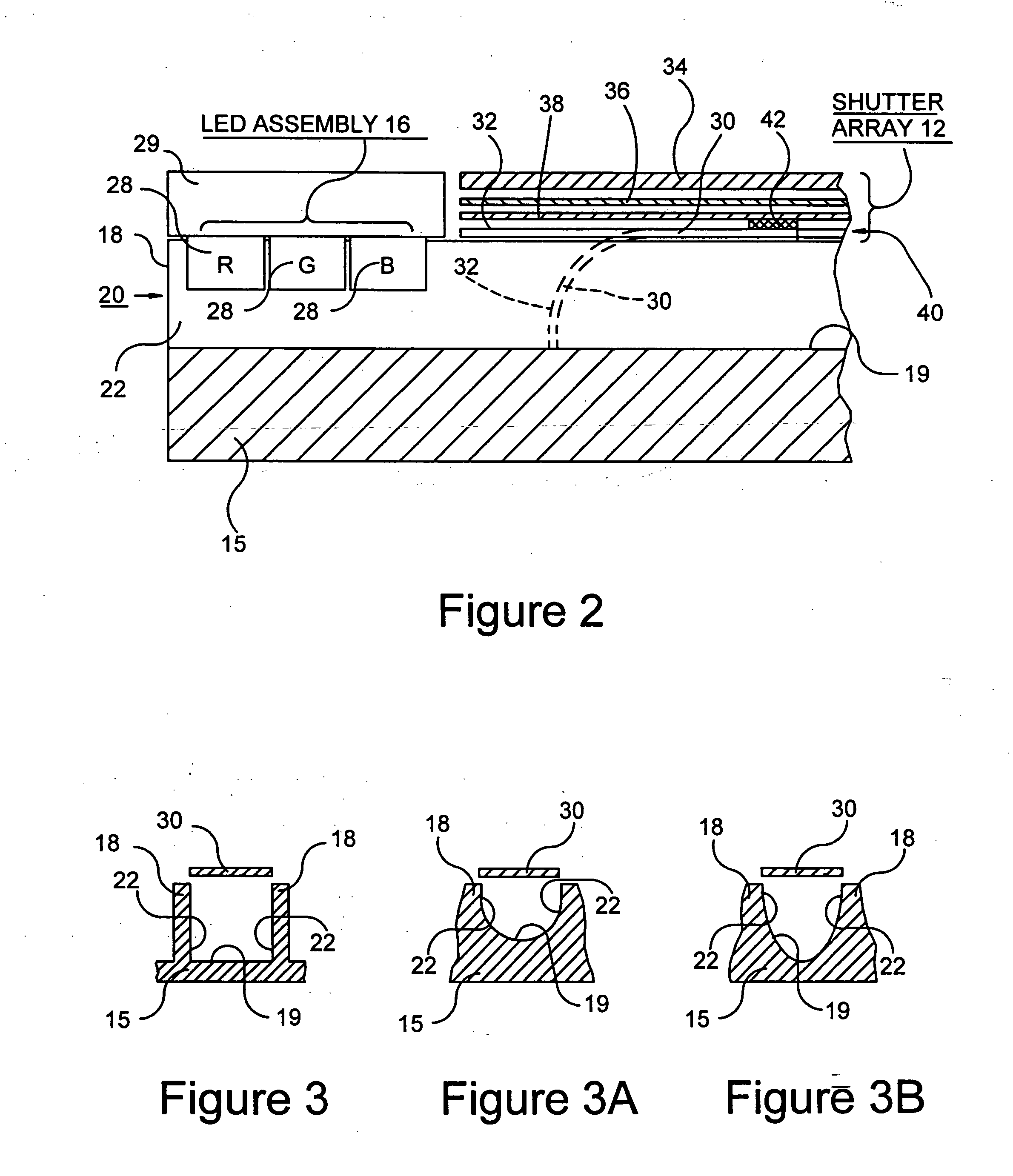

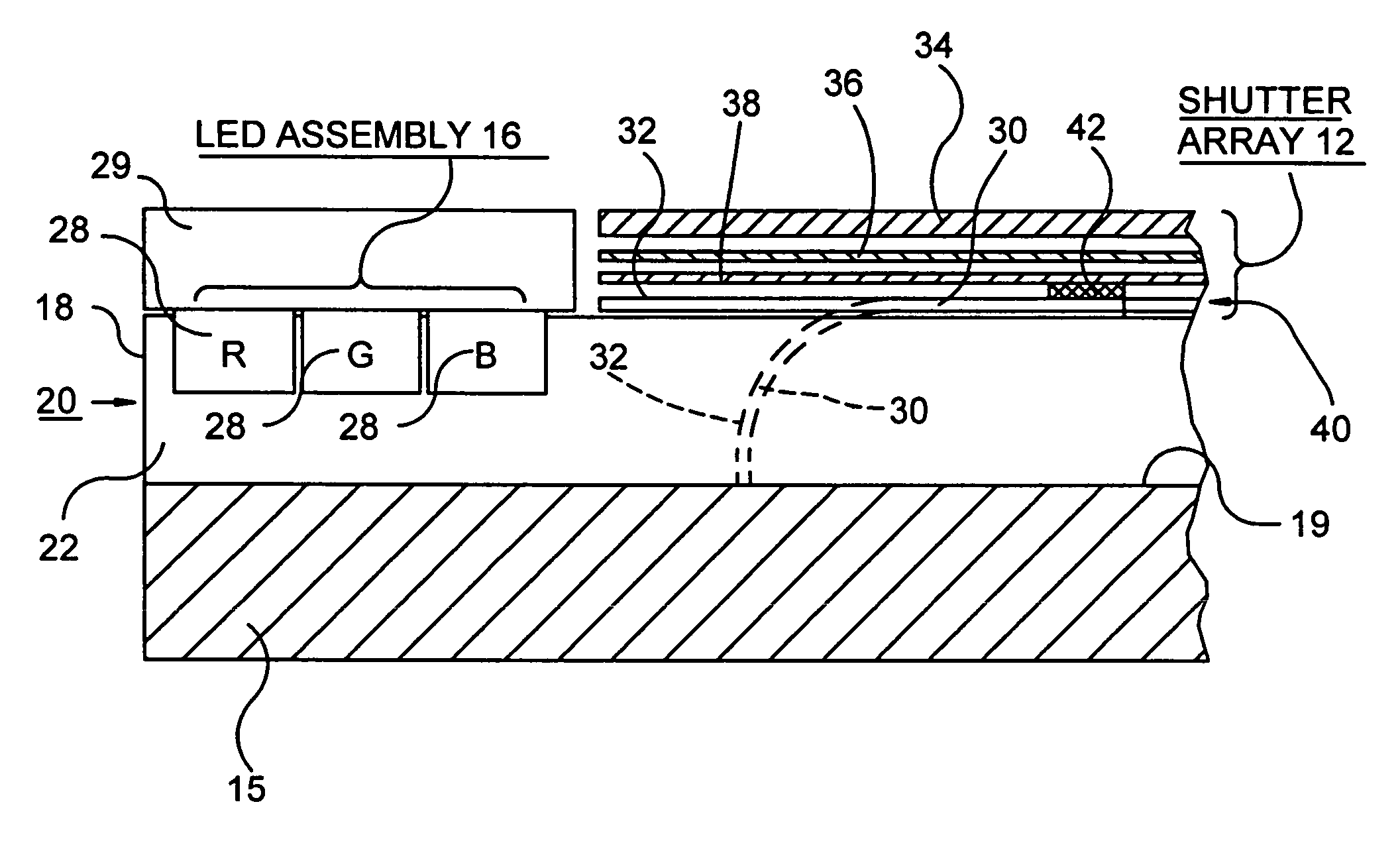

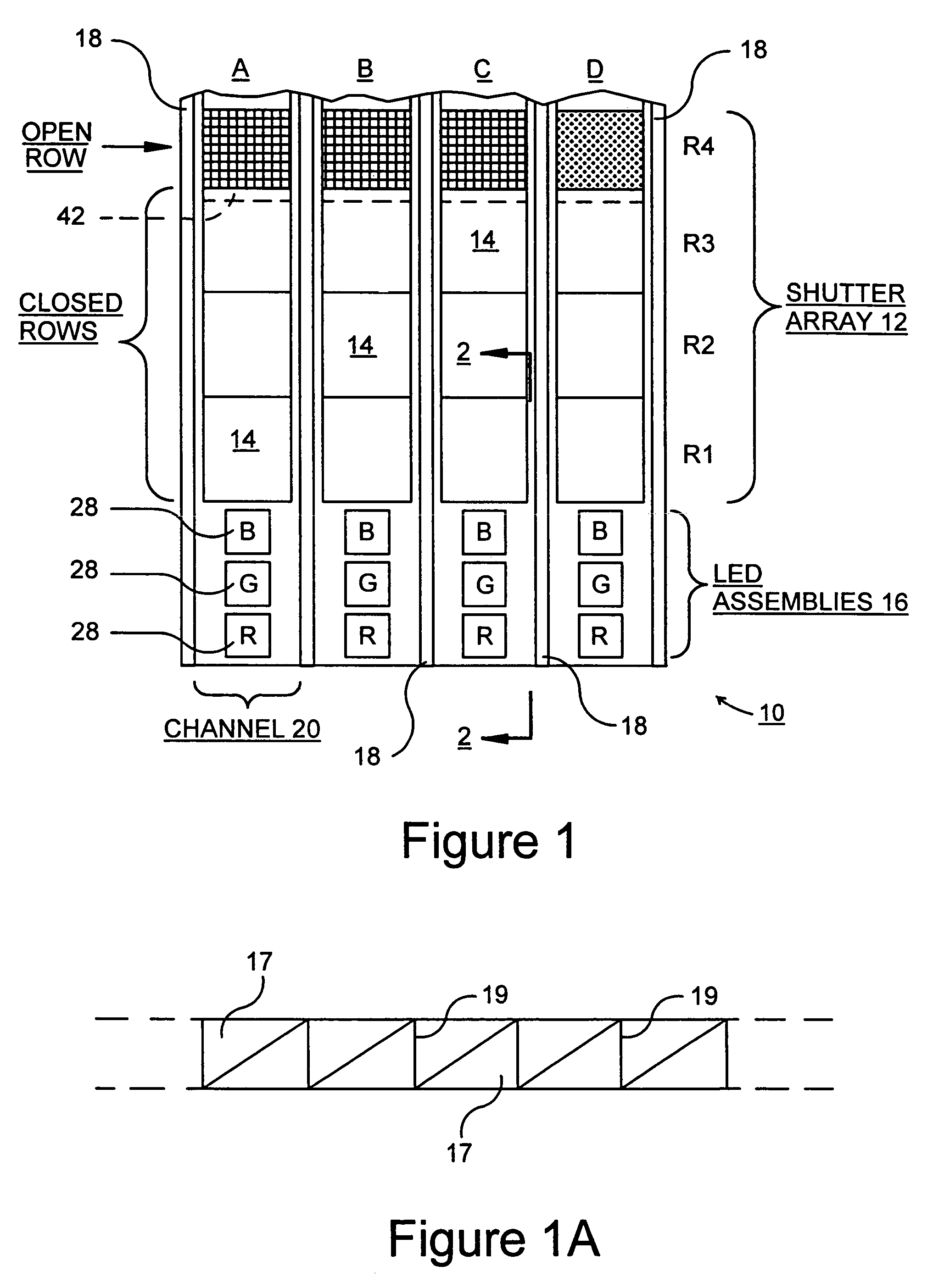

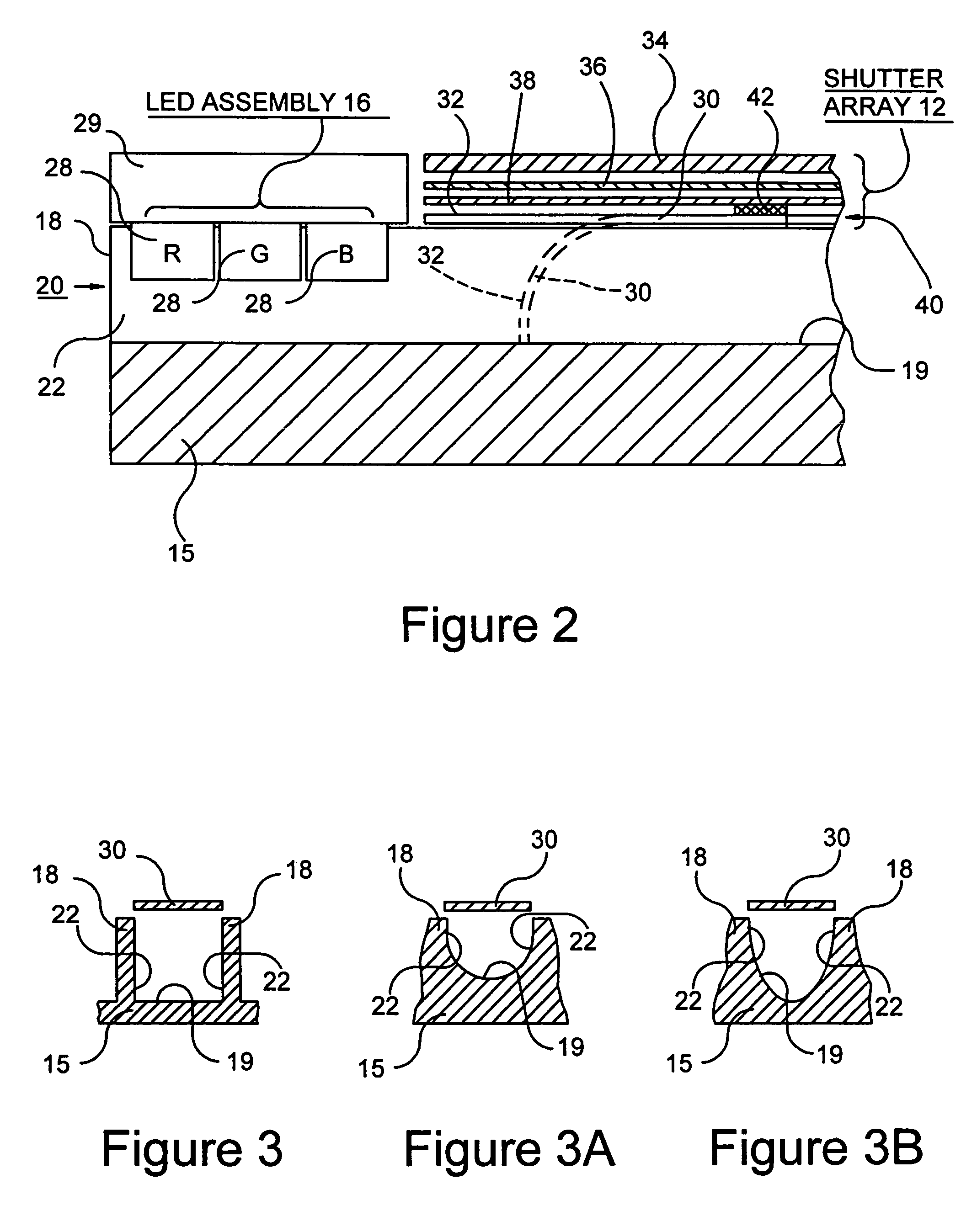

Flexible video displays and their manufacture

ActiveUS20070052636A1Need can be simplifiedSimple configurationStatic indicating devicesNon-linear opticsPhysicsFlat panel display

A high performance flexible, thin, flat panel display, has a linear array of switchable light emitting diodes (“LEDs”) to emit bands of light across the display, providing a light pattern programmable at video frequencies and a two-dimensional electropolymeric shutter array to convert the light pattern into a video image. In preferred embodiments, the light pattern can be varied or controlled spatially, with respect to both hue and intensity, by suitable drive signals, at points along the array determined by the location of individual LEDs, or groups of LEDs, and temporally as the shutters in the array are opened and closed, to provide a pleasing full color gamut for every pixel in the display. Closed shutters, displaying a reflective appearance, can be employed for background or other effects. The shutter array can be flexibly constructed and supported on a flexible substrate to provide a flexible display. Methods of manufacturing the display and displaying video images are also disclosed. Benefits include low cost, low energy consumption, good luminosity, freedom from exotic materials or manufacturing methods, configurability into rolls and other shapes and simplified drive electronics.

Owner:NEW VISUAL MEDIA GROUP

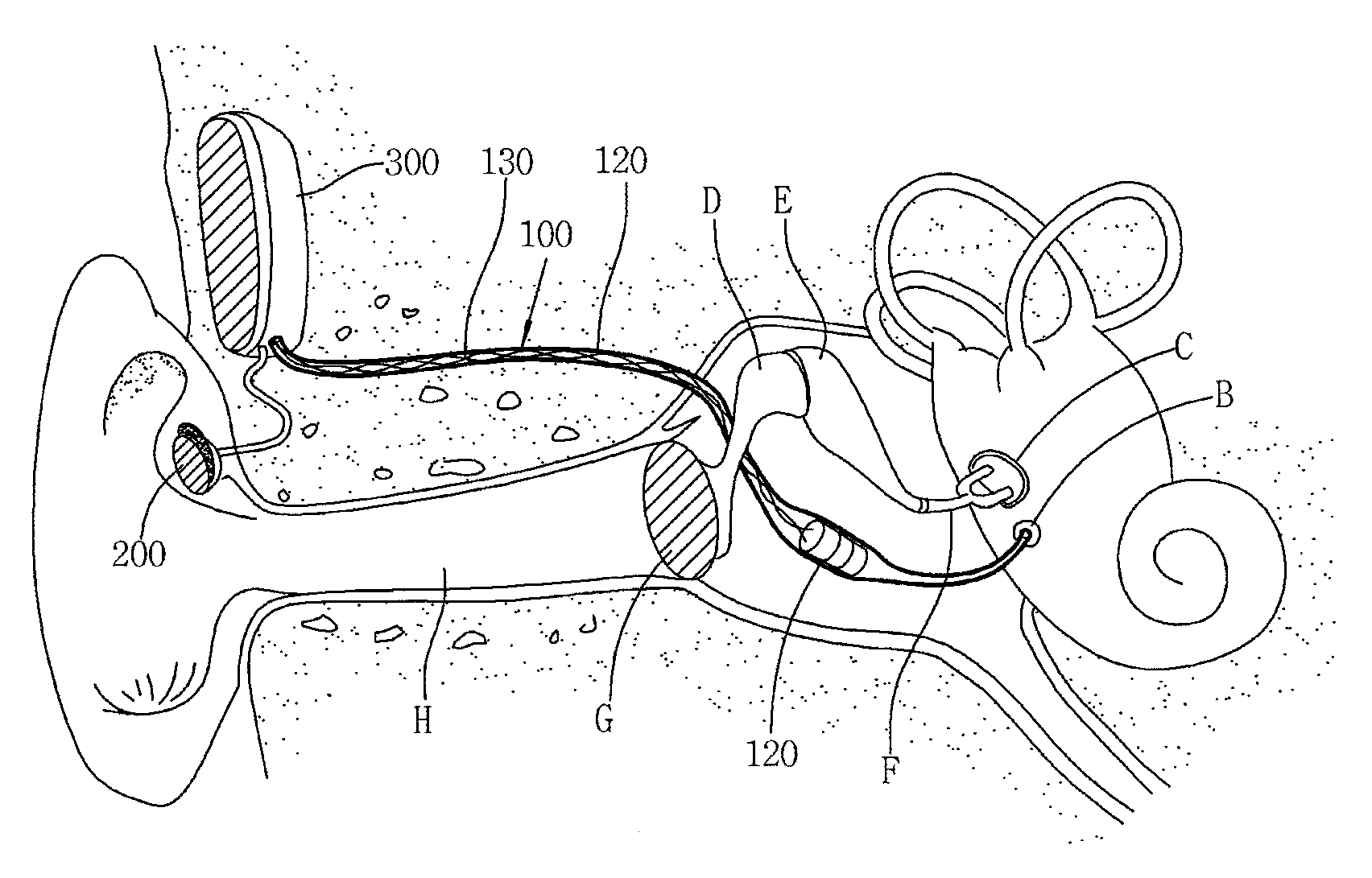

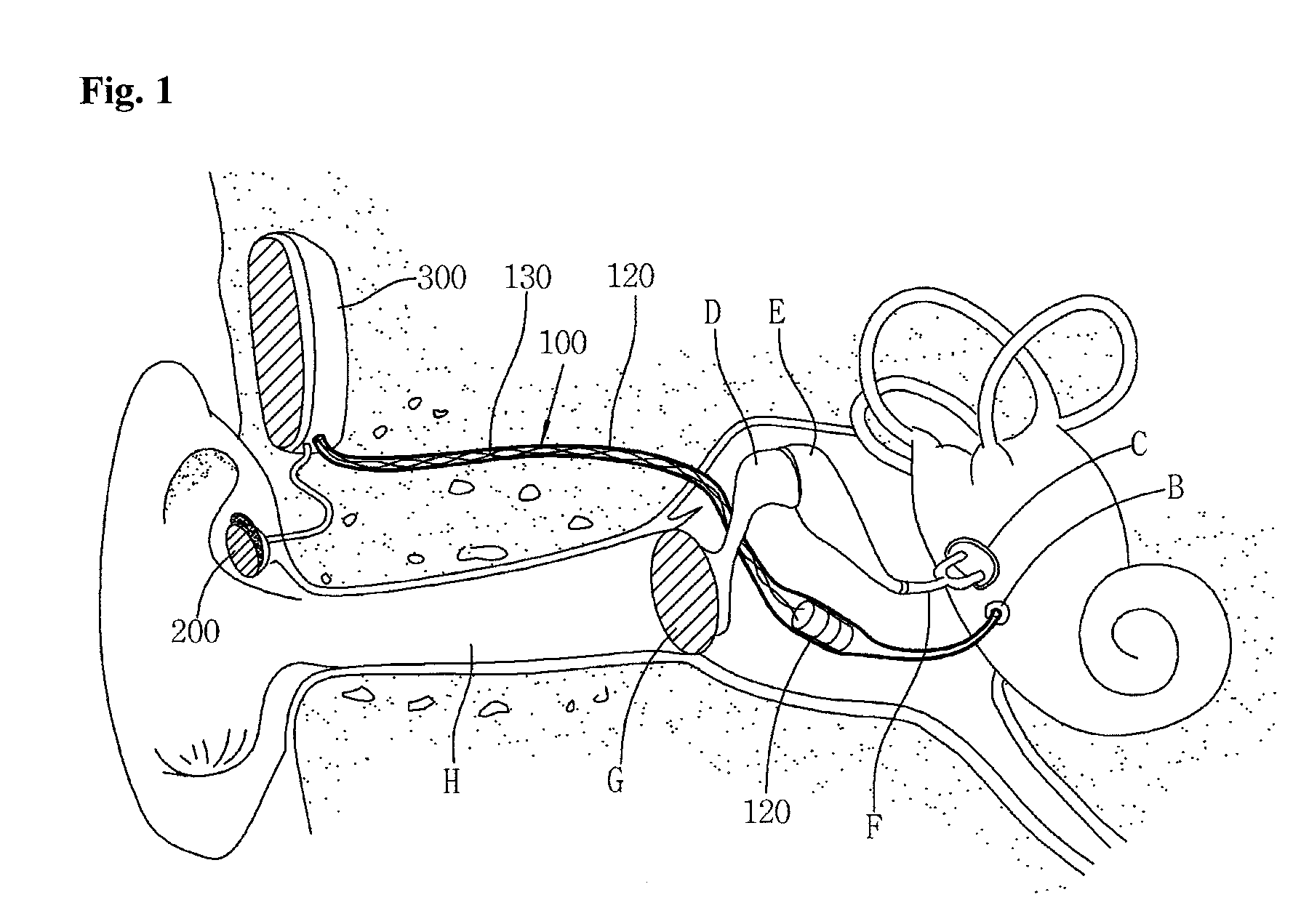

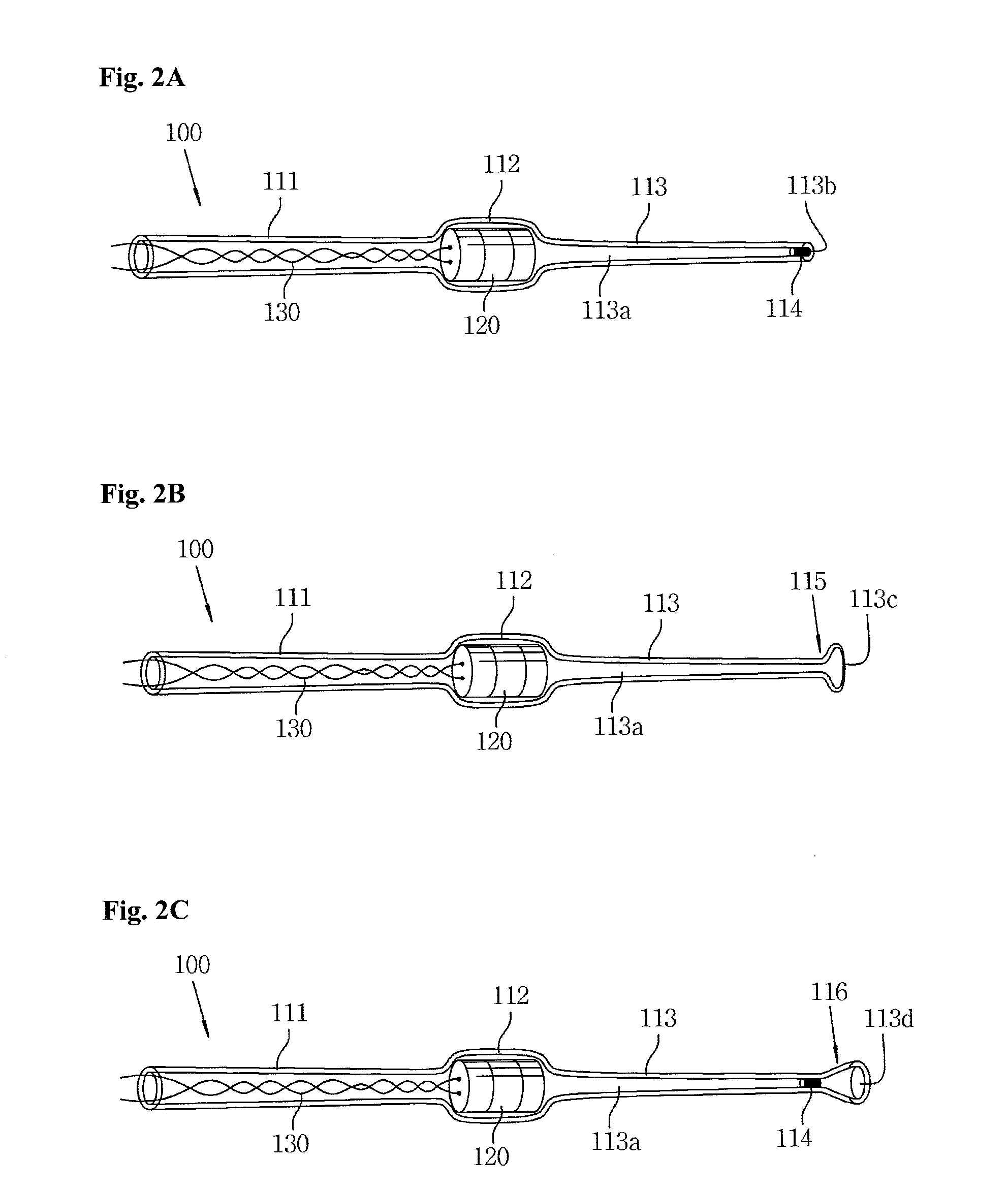

Implantable middle ear hearing device having tubular vibration transducer to drive round window

ActiveUS20090023976A1Reduce deliveryGood compensationEar treatmentDeaf-aid setsMiddle ear functionSensorineural hearing loss

An implantable middle ear hearing device having a tubular vibration transducer to drive a round window is designed to input sound to a round window opposite an oval window in an inner ear. The tubular vibration transducer has a unique structure that does not attenuate the magnitude of a signal, particularly, in a high frequency band. Sound delivery effect is much higher than those of conventional schemes. It is also possible to minimize difficulties associated with and problems resulting from the operation, which the conventional methods would have. Further, the transducer can have a relatively less compact than ossicle contact type transducers, and thus be easily fabricated. The hearing device can be applied to a sensorineural hearing loss patient with the ossicle damaged. Moreover, since sound is directly transmitted without through the ear drum and the ossicle, high efficiency sound delivery is achievable and hearing loss compensation are easy.

Owner:KYUNGPOOK NAT UNIV IND ACADEMIC COOP FOUND

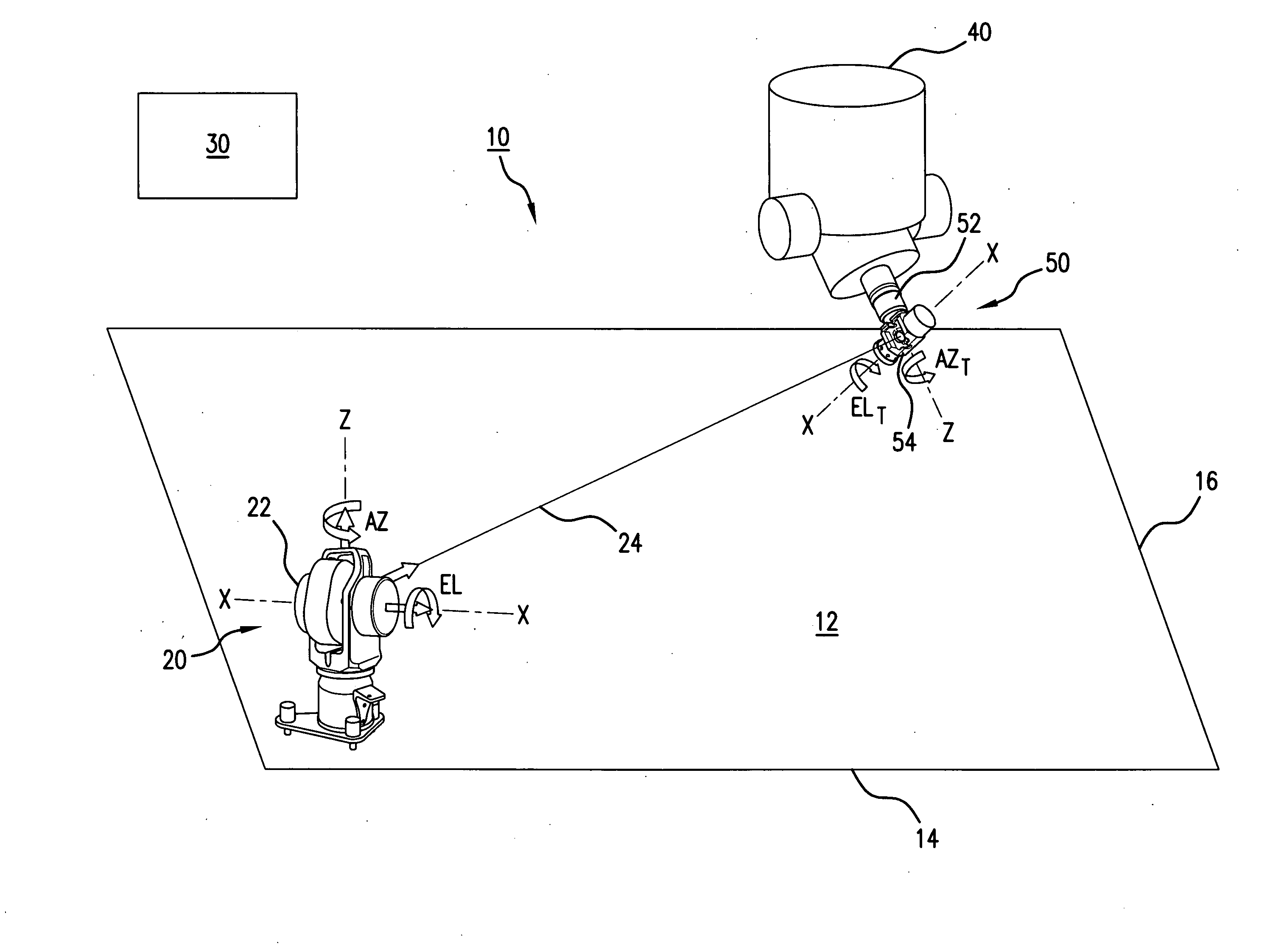

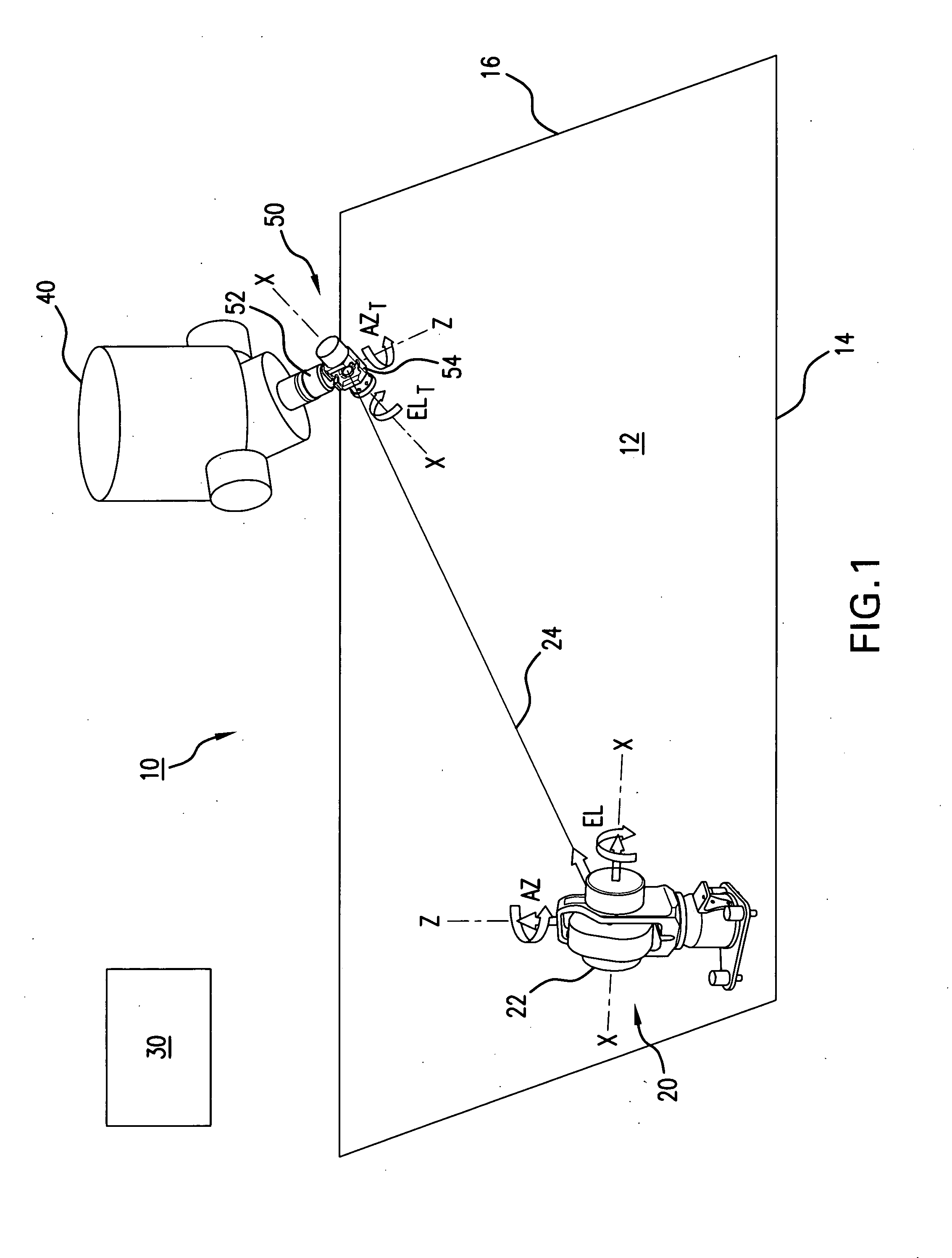

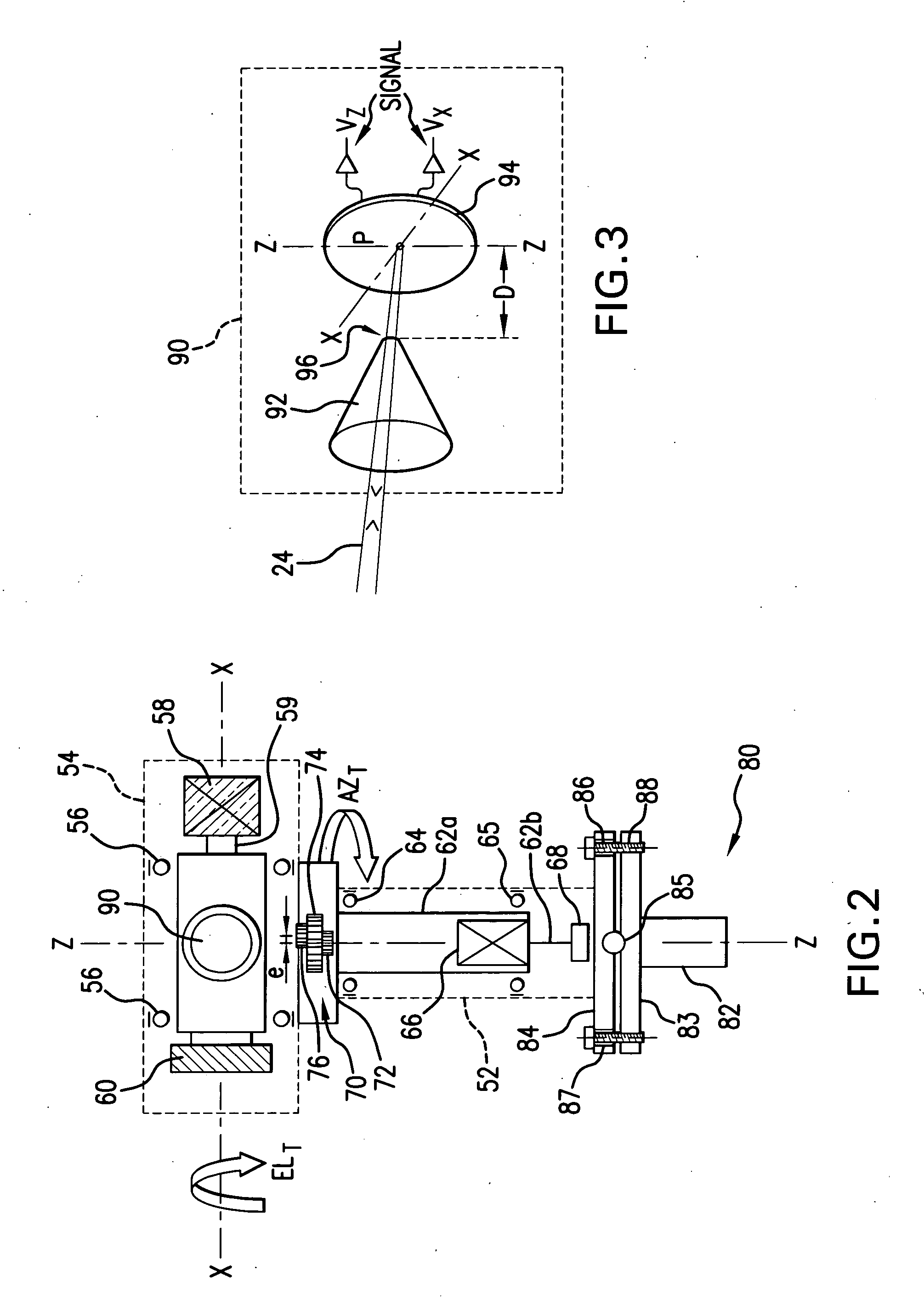

Volumetric error compensation system with laser tracker and active target

ActiveUS20100176270A1Accurate rotational axis alignmentAccurate repeatabilityProgramme-controlled manipulatorPhotometry using reference valueRotational axisLight beam

A volumetric error compensation measurement system and method are disclosed wherein a laser tracker tracks an active target as the reference point. The active target has an optical retroreflector mounted at the center of two motorized gimbals to provide full 360 degree azimuth rotation of the retroreflector. A position sensitive detector is placed behind an aperture provided at the apex of the retroreflector to detect the relative orientation between the tracker laser beam and the retroreflector by measuring a small portion of the laser beam transmitted through the aperture. The detector's output is used as the feedback for the servo motors to drive the gimbals to maintain the retroreflector facing the tracker laser beam at all times. The gimbals are designed and the position of the retroreflector controlled such that the laser tracker always tracks to a pre-defined single point in the active target, which does not move in space when the gimbals and / or the retroreflector makes pure rotations. Special mechanism and alignment algorithm are used in the gimbal design and retroreflector centering alignment to achieve accurate rotational axis alignment and repeatability.

Owner:AUTOMATED PRECISION INC

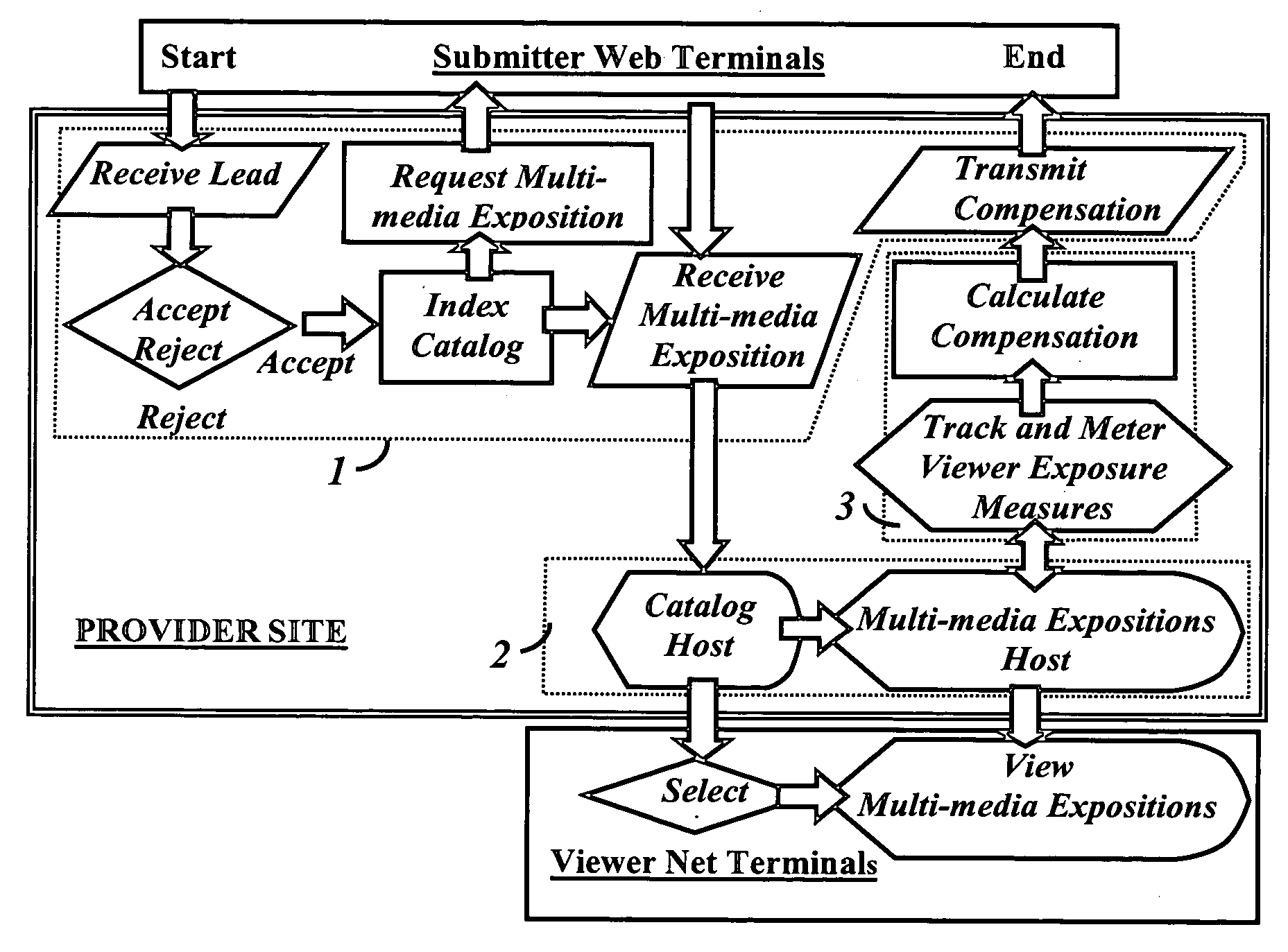

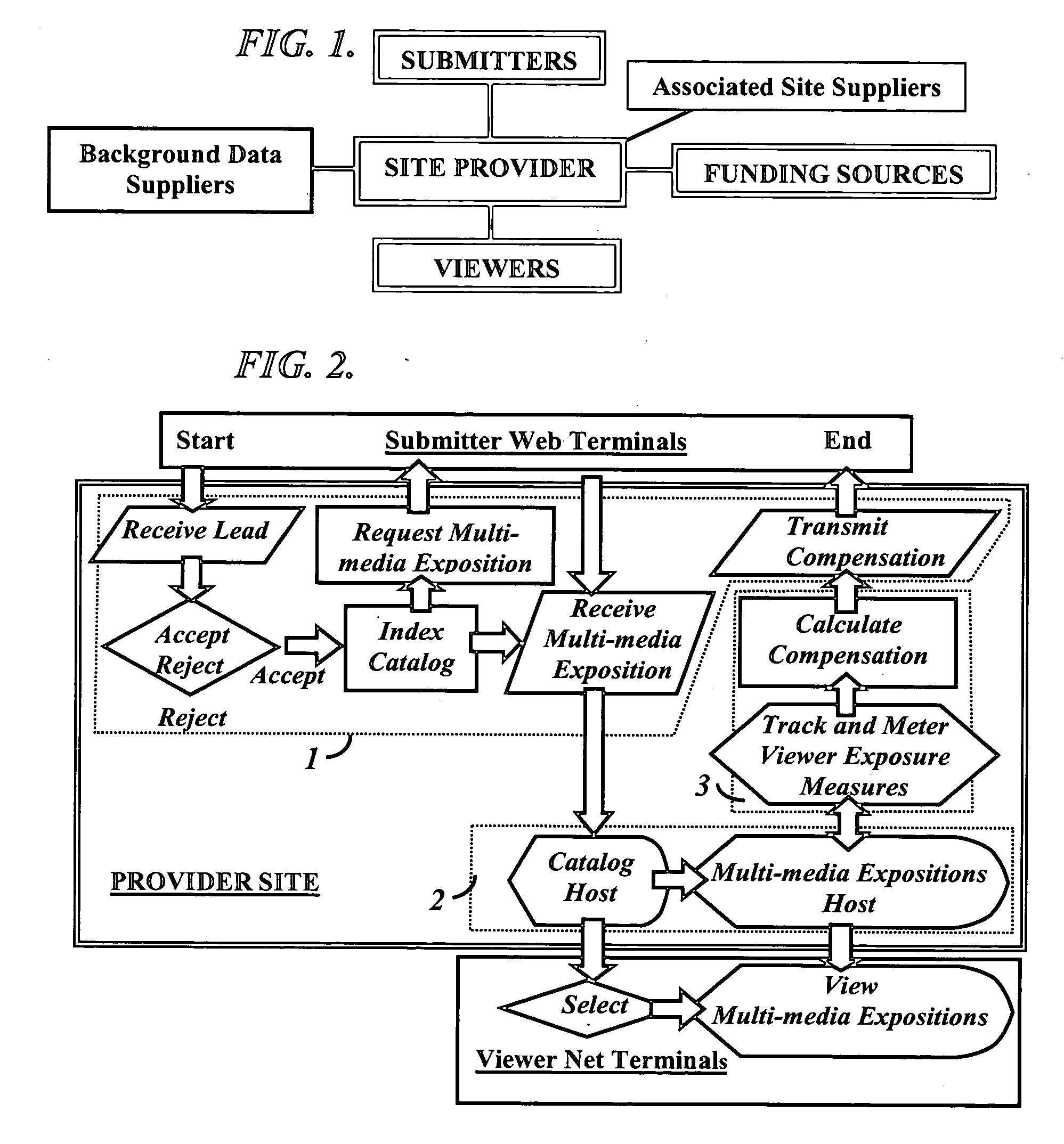

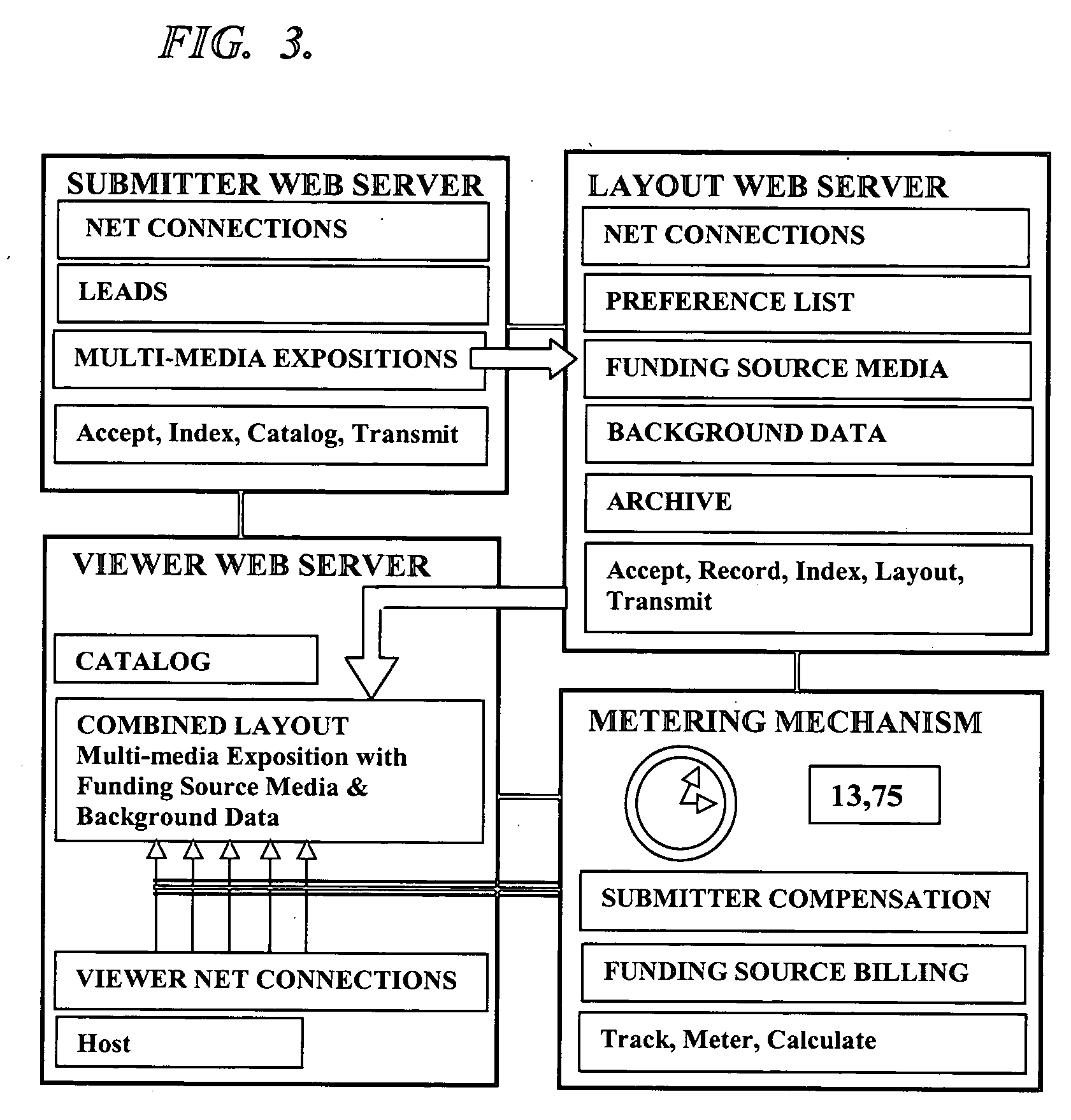

Internet news compensation system

InactiveUS20050049971A1High valueHigh chargeAdvertisementsComputer security arrangementsWeb siteCataloging

A computerized compensation system of disseminating a plurality of news and information items offered, contributed, and submitted by a plurality of independent submitters to an internet provider site. The provider site accepts, indexes, catalogs, tracks, meters, and calculates viewer exposure to each submitted news and information item chosen by a plurality of viewers. Compensation due individual submitters is transmitted in real time, as the submitter continues the submission to the provider web site. Billing of funding sources is provided.

Owner:BETTINGER DAVID S

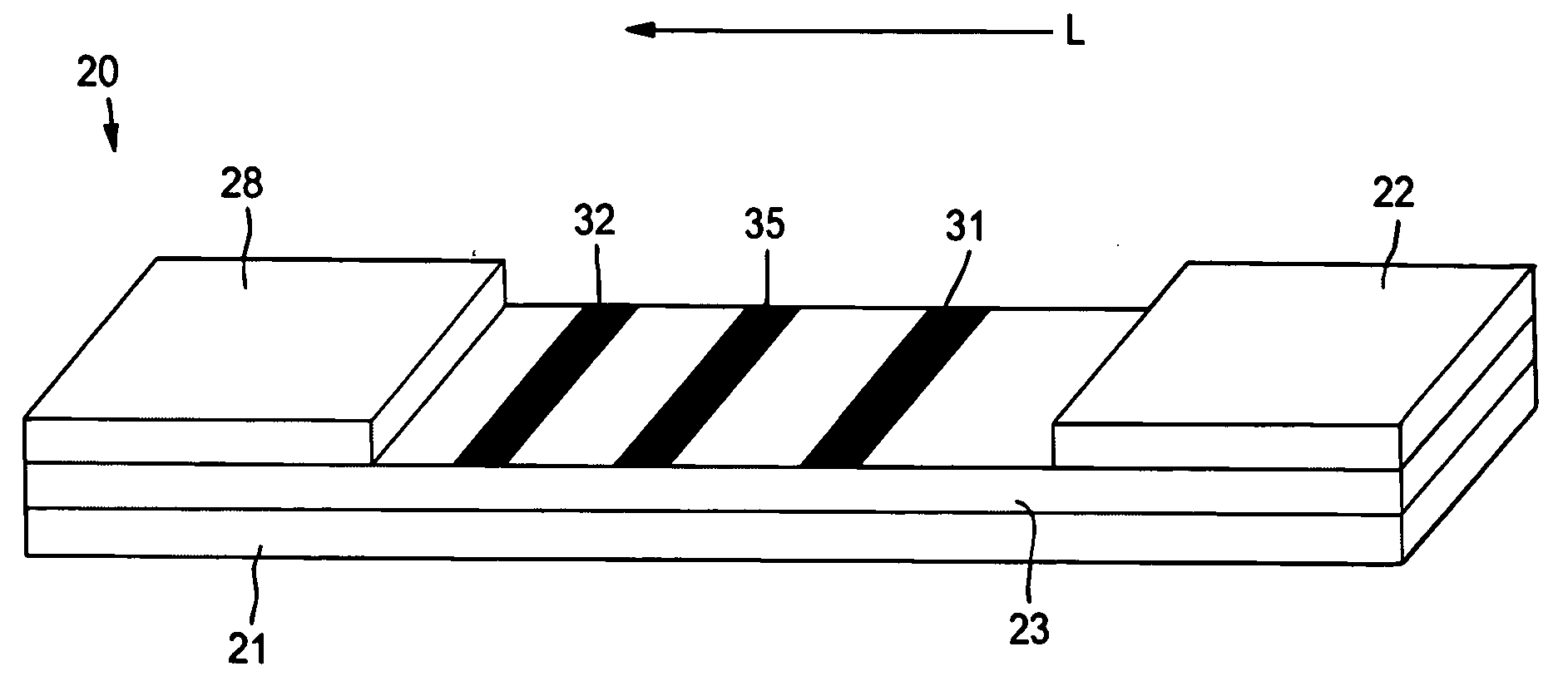

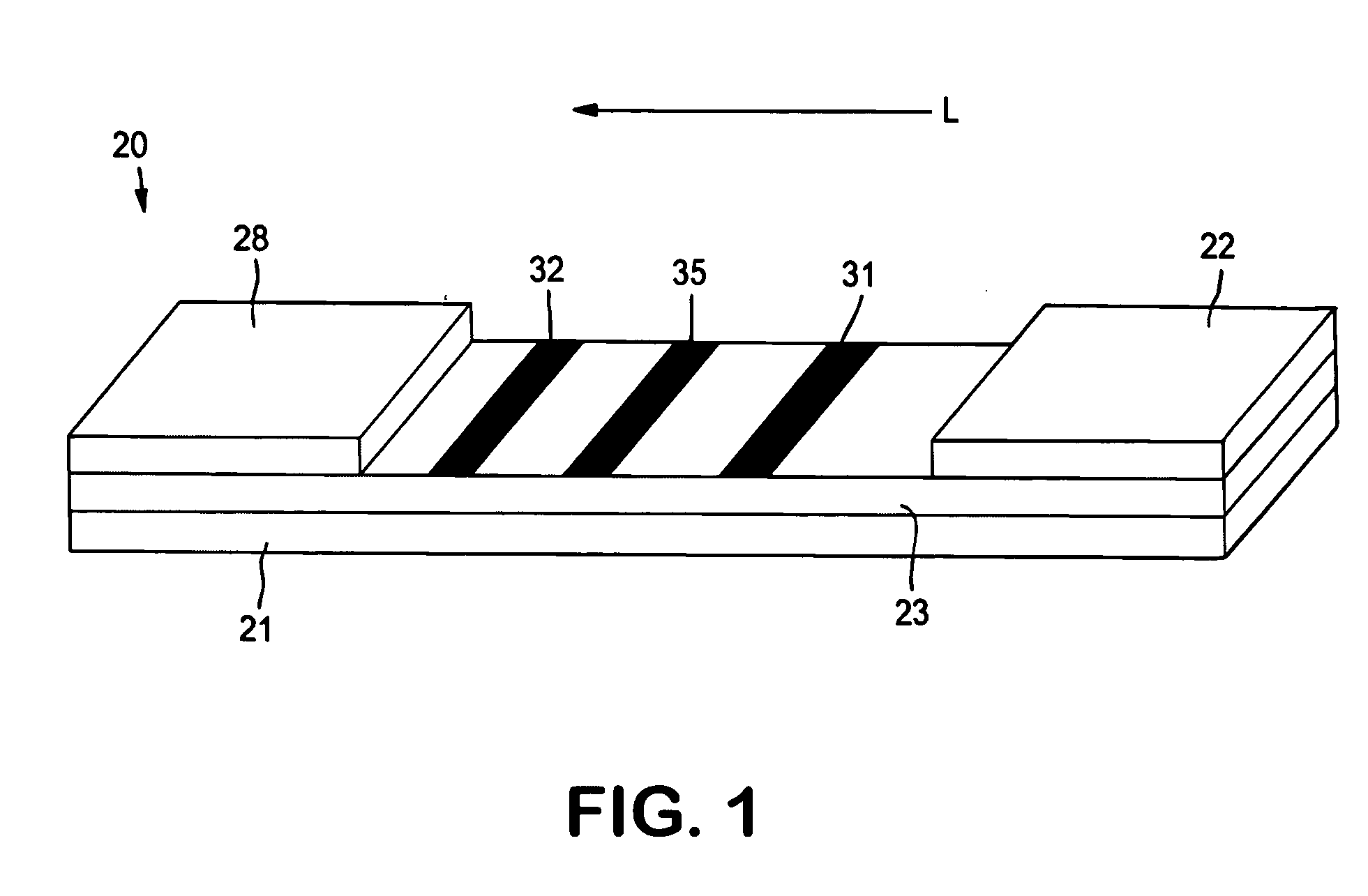

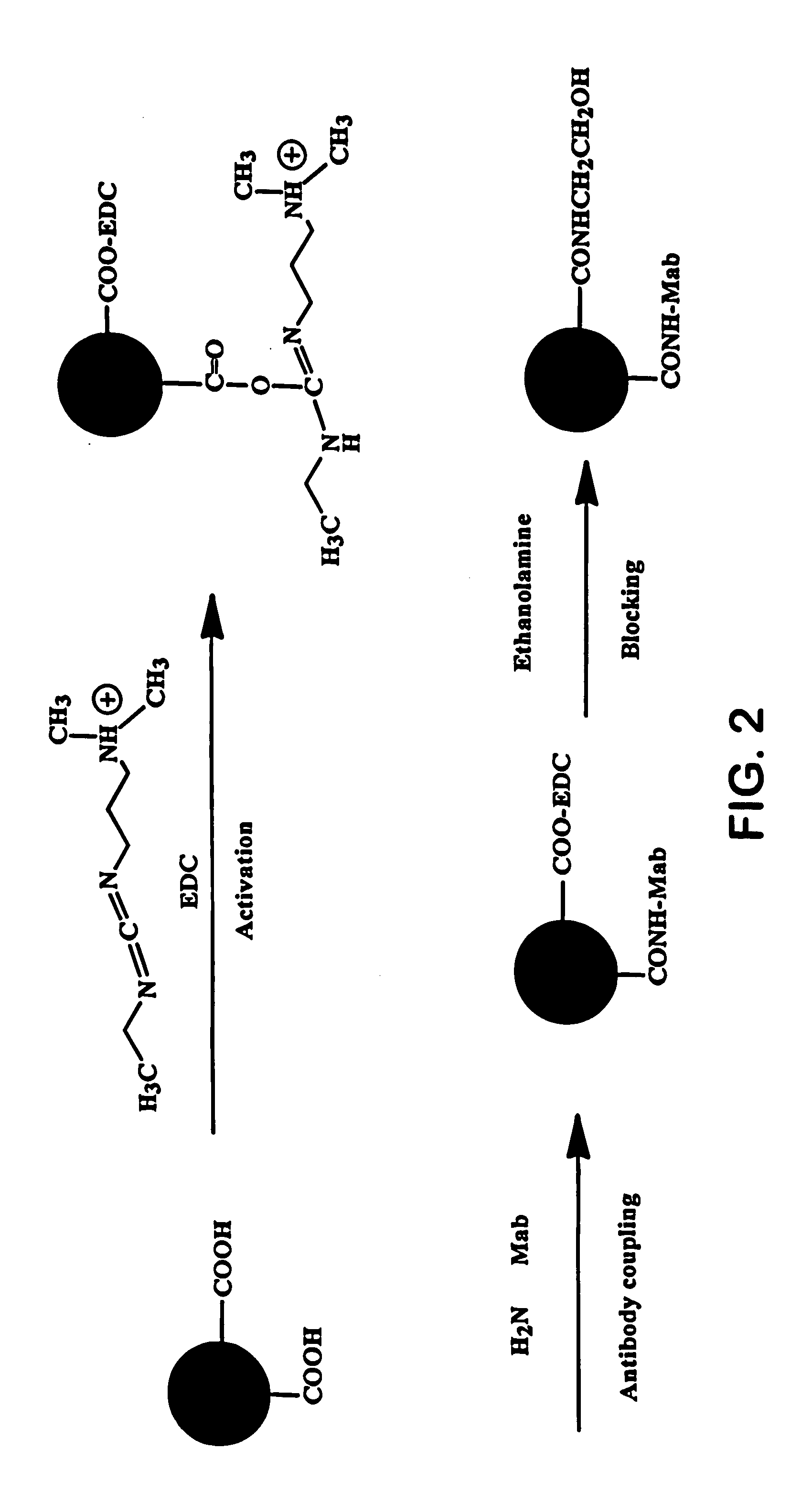

Method for extending the dynamic detection range of assay devices

InactiveUS20050112780A1Improve accuracyGood compensationBioreactor/fermenter combinationsBiological substance pretreatmentsAnalyteTest sample

A flow-through assay device for detecting the presence or quantity of an analyte residing in a test sample is provided. The device utilizes a detection zone and compensation zone within which are immobilized capture reagents. The present inventor has discovered that the presence of a compensation zone may enable the detection of an analyte over extended concentration ranges. In particular, the compensation zone facilitates the binding of probes that would otherwise bind within the interior of assay device or that would exhibit “self-quenching.”

Owner:KIMBERLY-CLARK WORLDWIDE INC

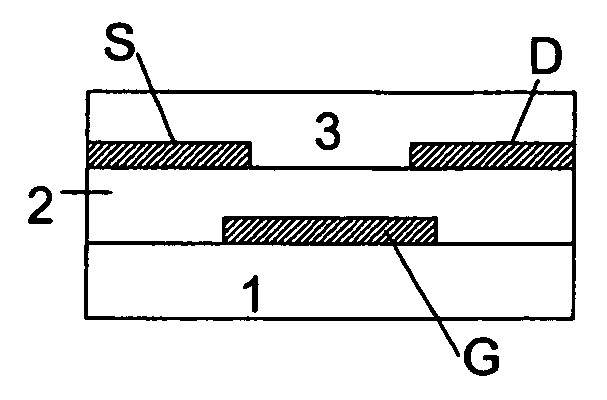

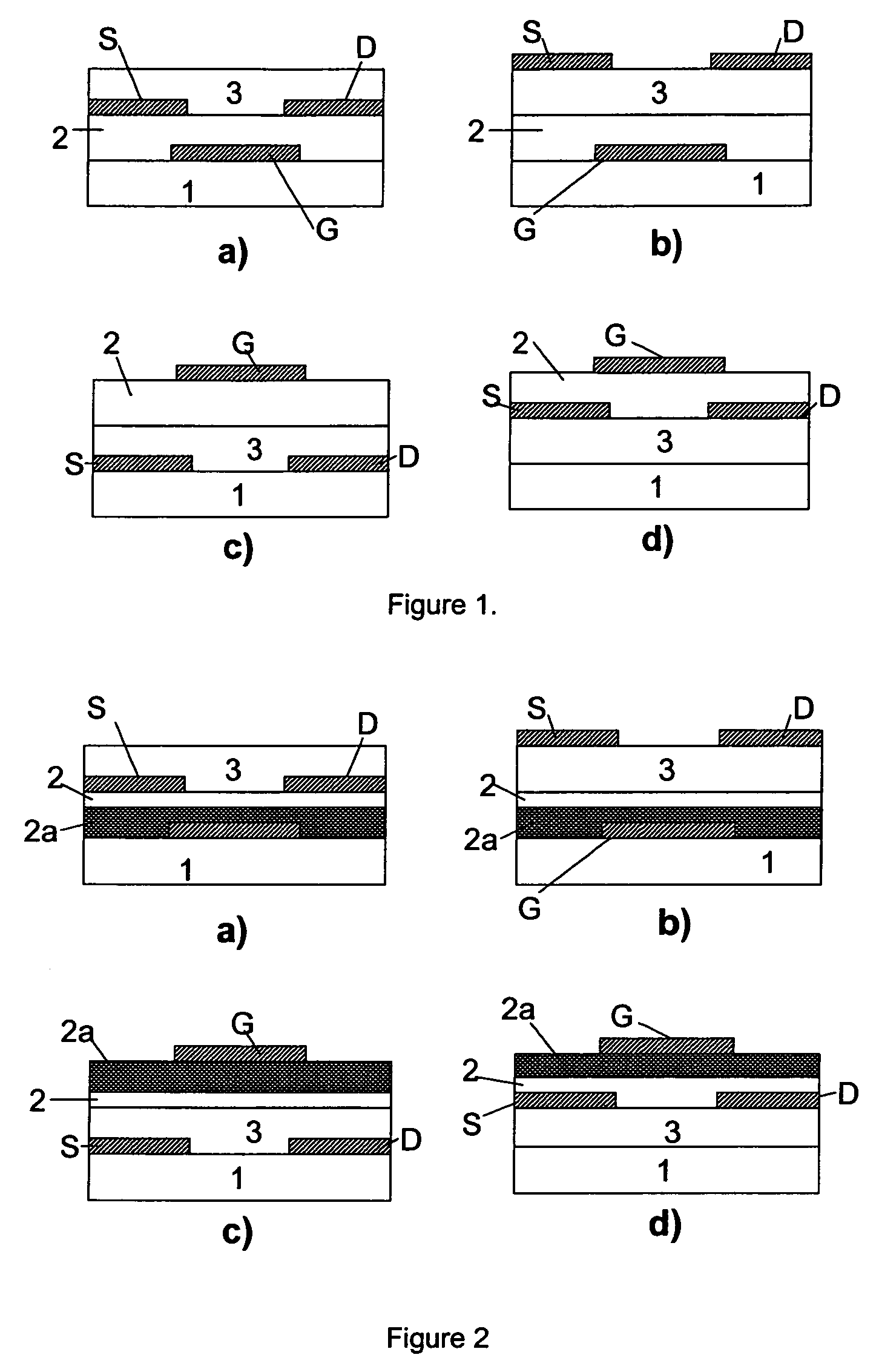

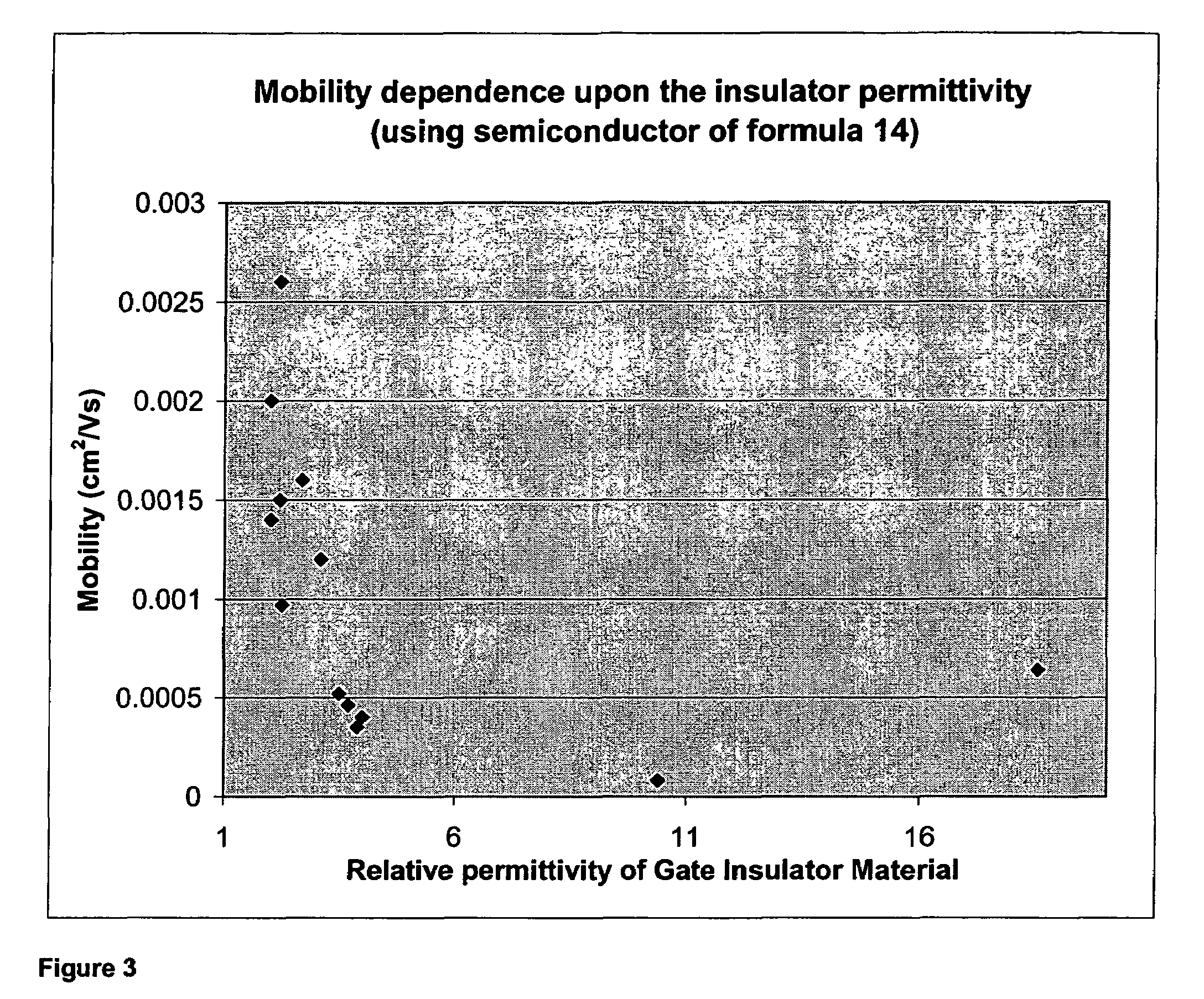

Organic field effect transistor with an organic dielectric

InactiveUS7029945B2Improve performancePreventing modulationTransistorSolid-state devicesOrganic field-effect transistorGate insulator

A process of manufacturing an organic field effect device is provided comprising the steps of (a) depositing from a solution an organic semiconductor layer; and (b) depositing from a solution a layer of low permittivity insulating material forming at least a part of a gate insulator, such that the low permittivity insulating material is in contact with the organic semiconductor layer, wherein the low permittivity insulating material is of relative permittivity from 1.1 to below 3.0. In addition, an organic field effect device manufactured by the process is provided.

Owner:MERCK PATENT GMBH

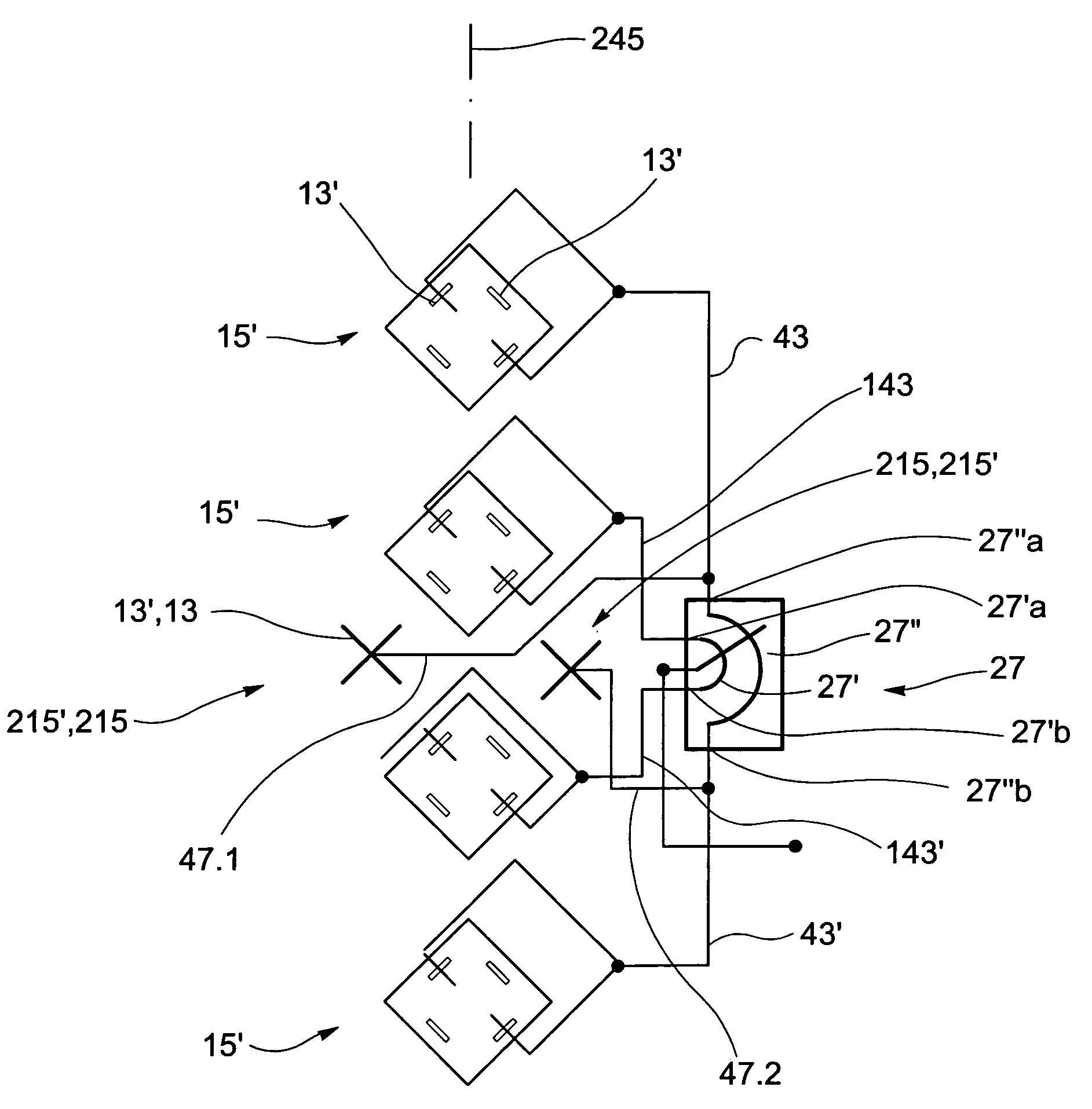

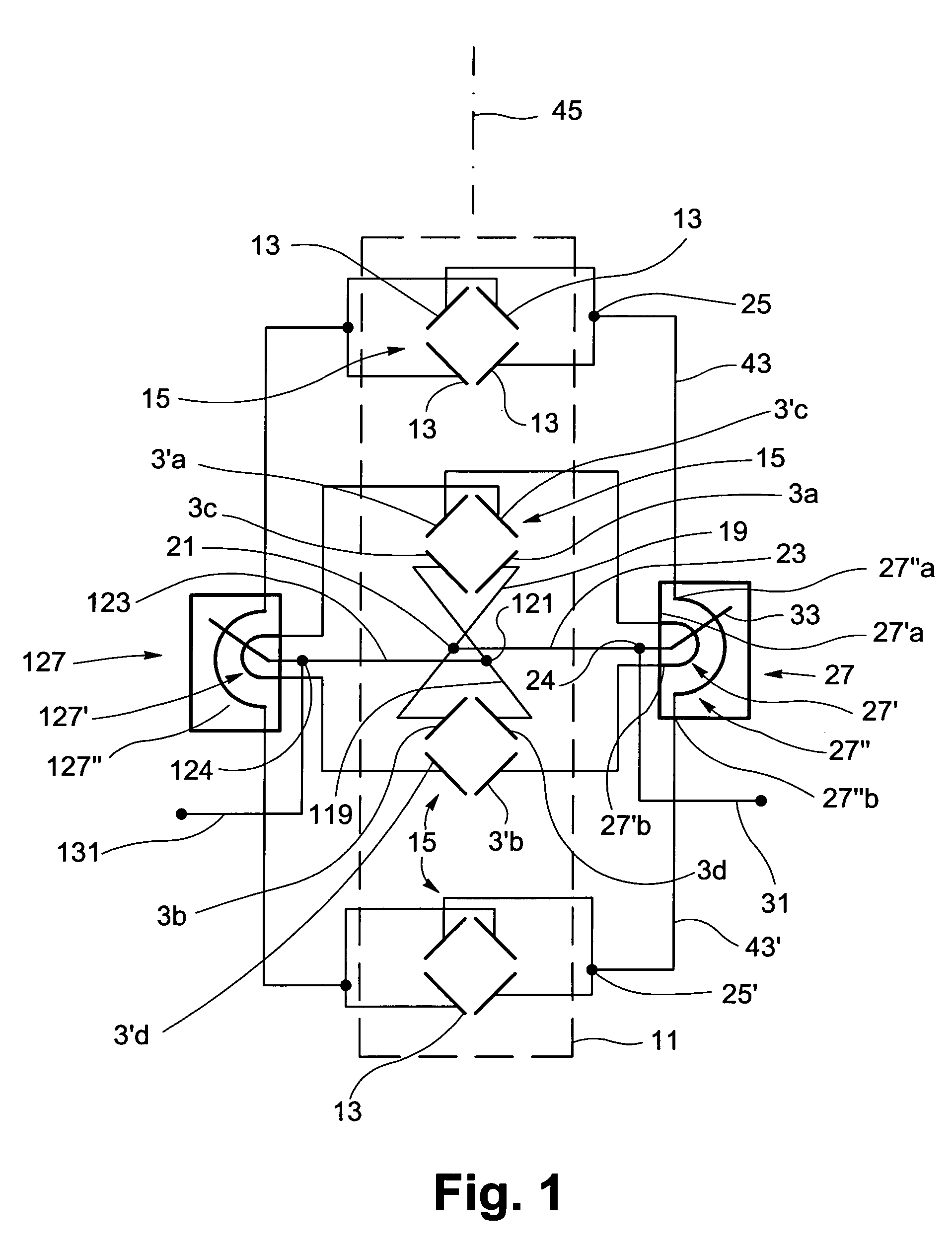

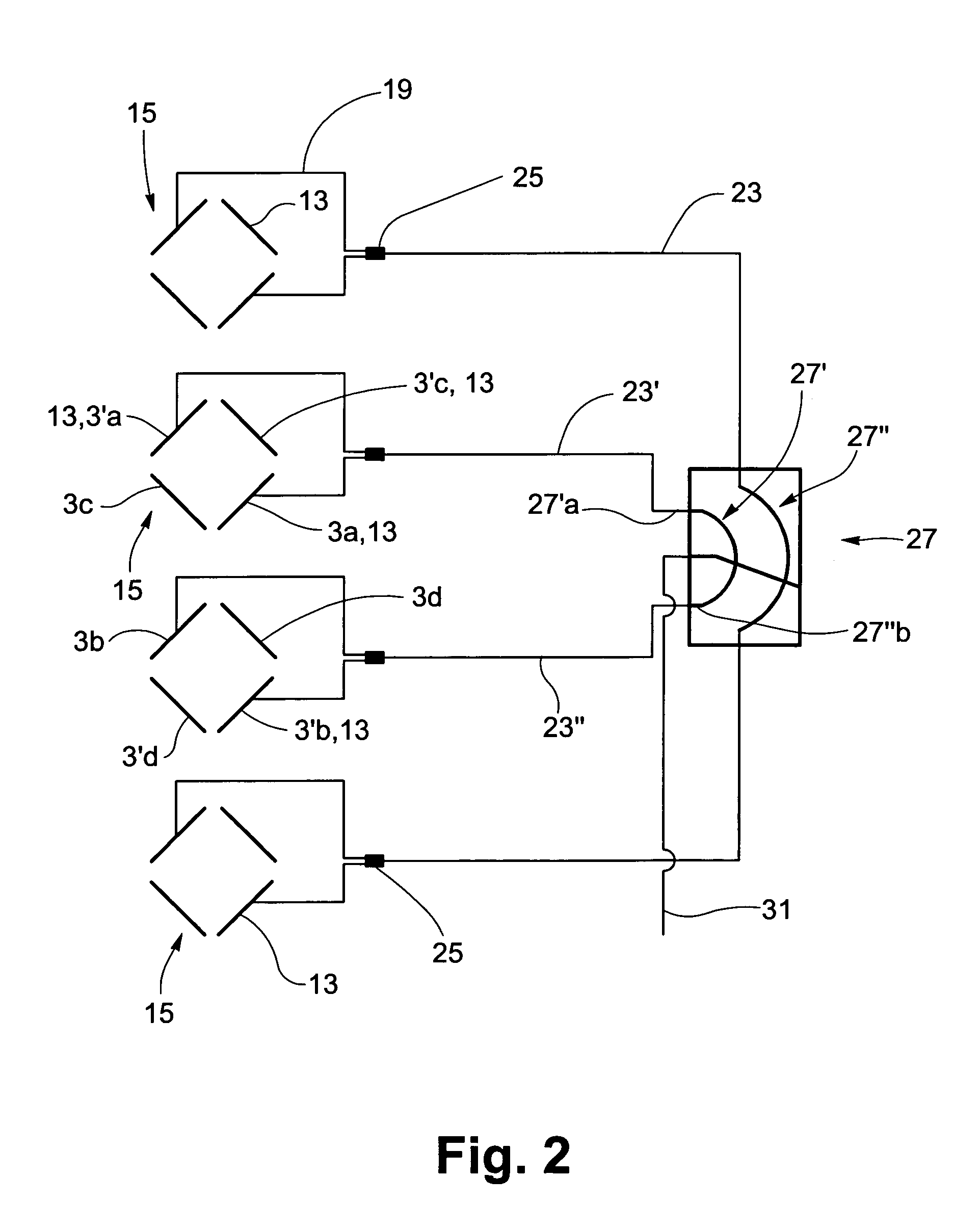

Dual-polarization antenna array

InactiveUS6985123B2Good compensationAvoid characteristicSimultaneous aerial operationsRadiating elements structural formsPhysicsPatch antenna

An improved antenna array, having at least two groups of individual antenna elements comprising a dipole square and / or patch antenna elements with a square antenna element structure. Individual antenna element arranged at least horizontally offset with respect to one another are provided for each of the two polarizations which are at right angles to one another. At least two additional antenna elements are horizontally offset with respect to one another, and / or at least two pairs of vertically aligned individual antenna elements, which are arranged with a horizontal offset with respect to one another, are provided for each of the two orthogonal polarizations. The individual antenna elements which are in each case arranged with a horizontal offset with respect to one another and are aligned parallel to one another are fed with different phase angles as a function of the depression angle.

Owner:TELEFON AB LM ERICSSON (PUBL)

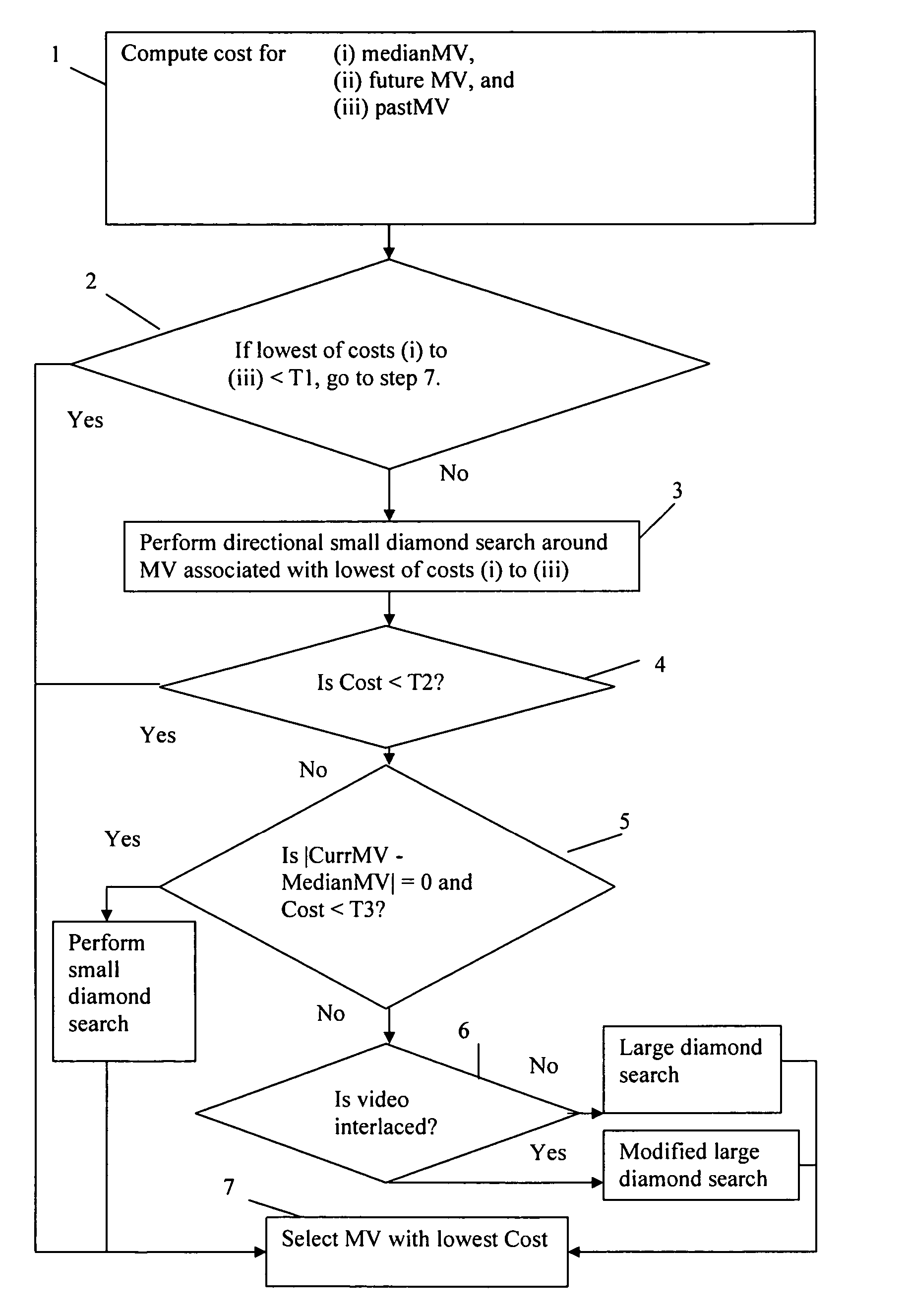

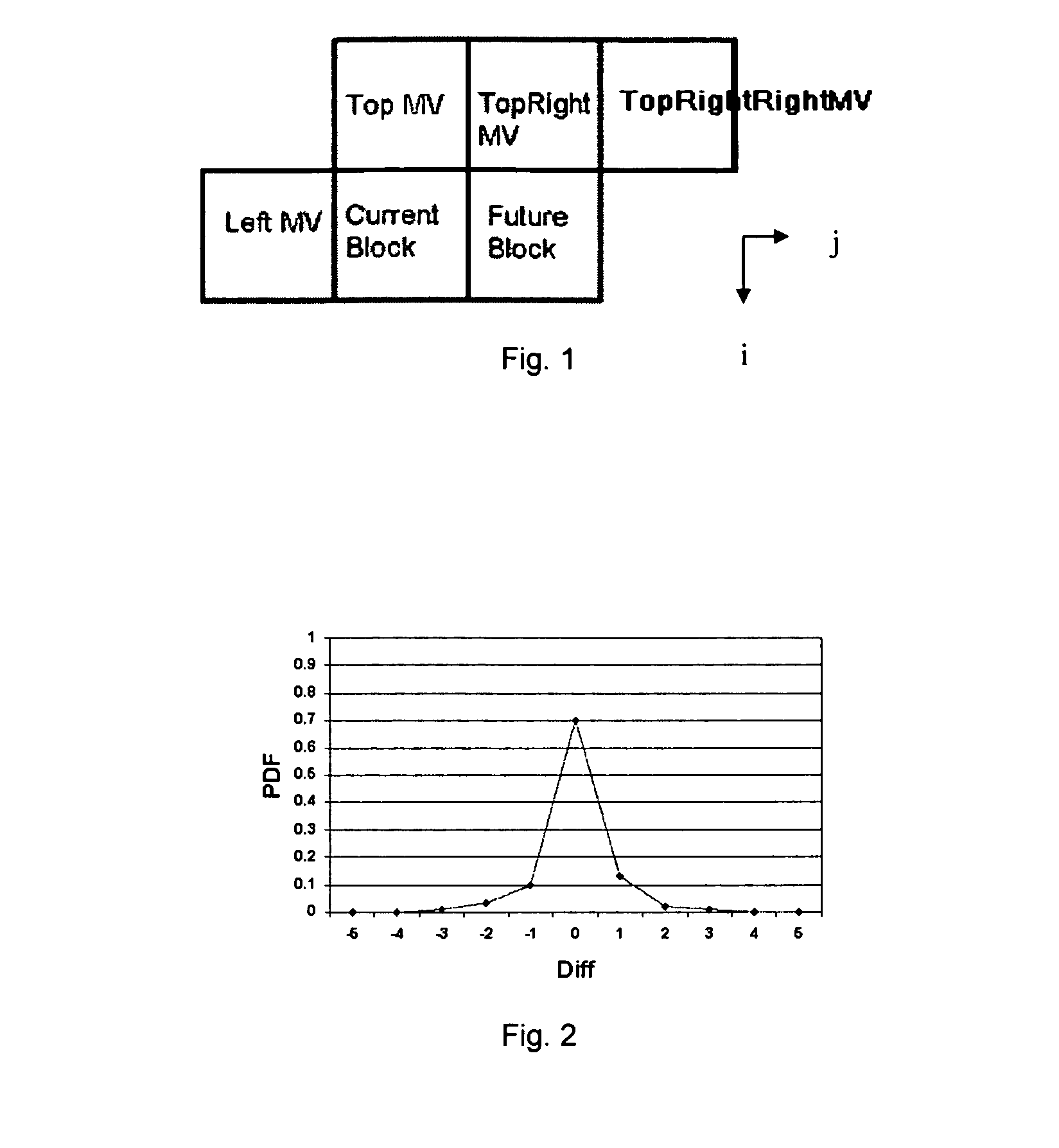

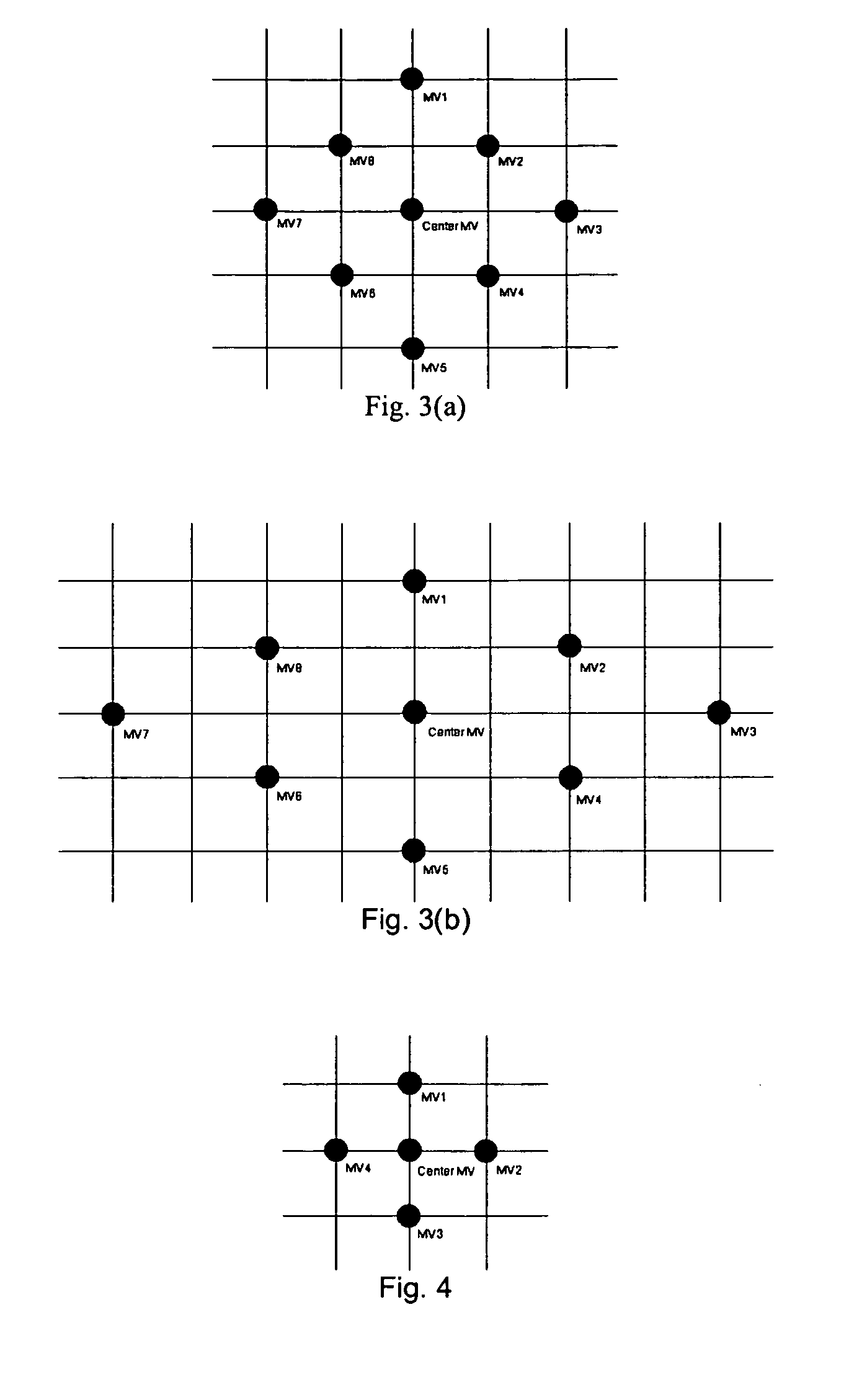

Enhanced block-based motion estimation algorithms for video compression

InactiveUS20070154103A1Improve smoothnessGood compensationCharacter and pattern recognitionDigital video signal modificationComputer graphics (images)Motion vector

Method, systems and software are proposed for obtaining for blocks of a first image similar blocks of a second image (the “reference image”). The blocks of the first image are processed sequentially, for each block trying out a number of candidate locations in the second image and evaluating a cost function for each. Each candidate location in the second image is displaced by a respective motion vector from the block of the first image. In a first aspect of the invention the cost function is a function of a predicted motion vector for future blocks of the first image (i.e. blocks of the first image which have not yet been processed). In a second aspect of the invention the motion vectors are given by location values which are not all whole pixel spacings, halves of the pixel spacing, or quarters of the pixel spacing.

Owner:THE HONG KONG UNIV OF SCI & TECH

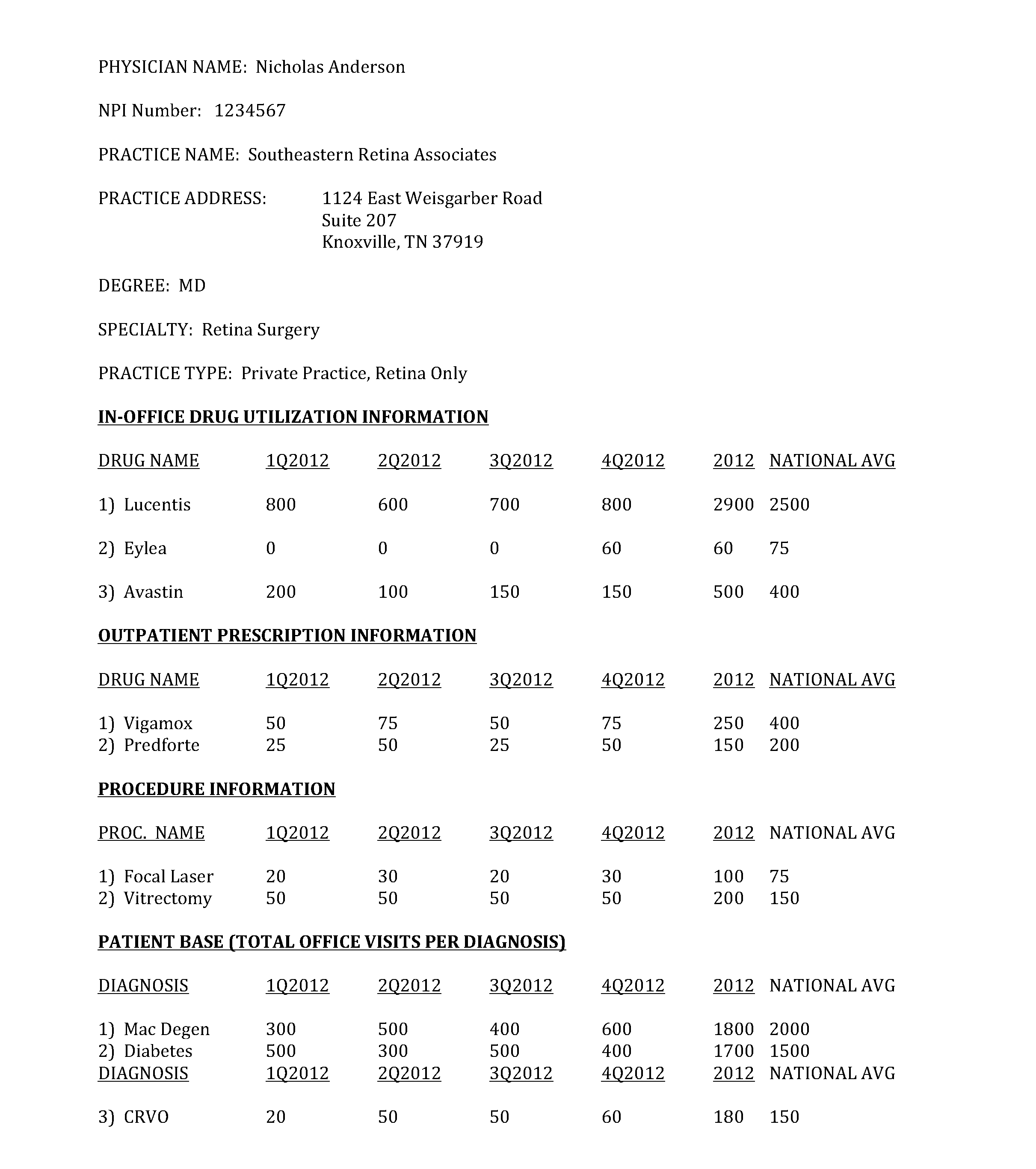

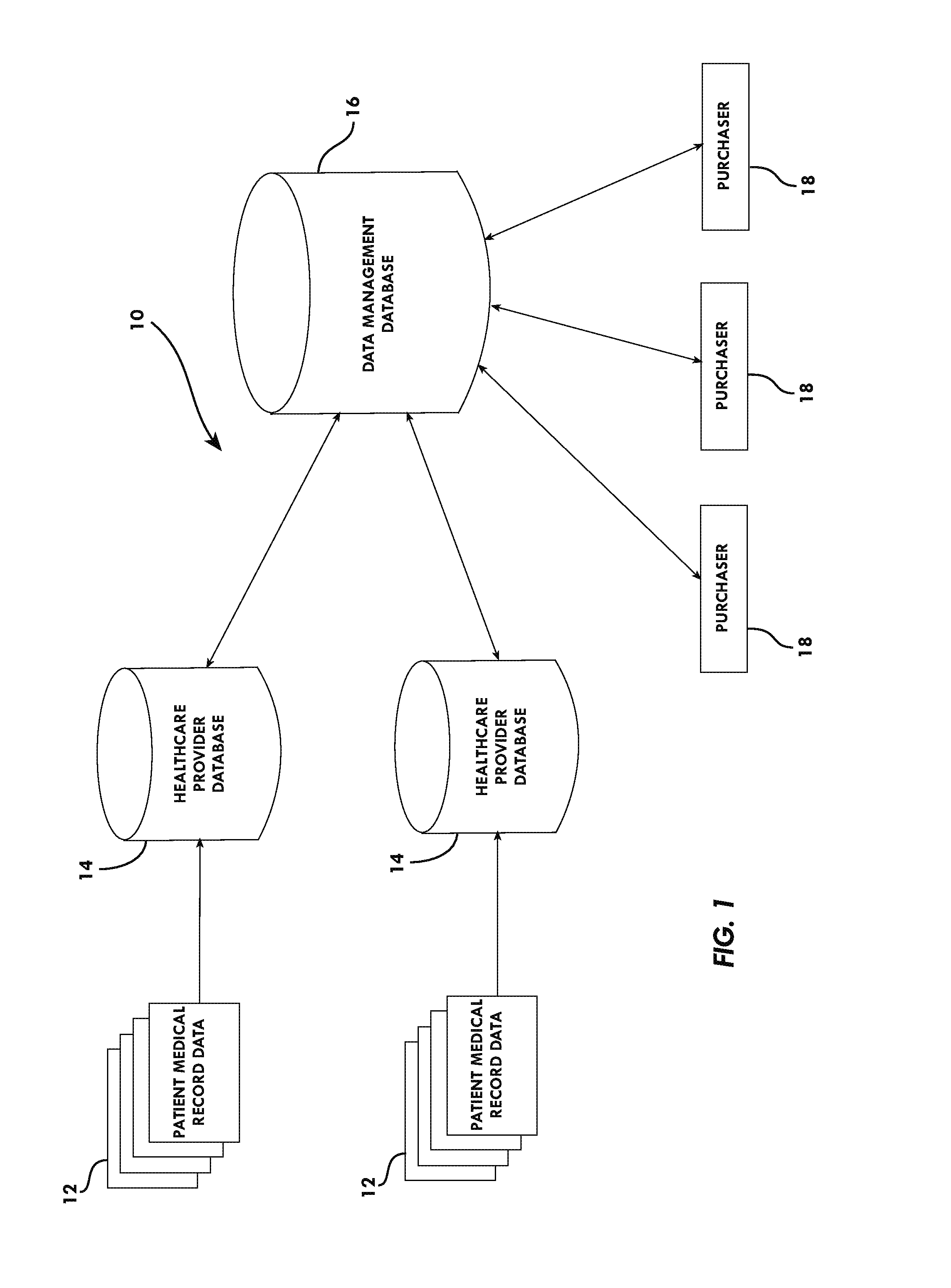

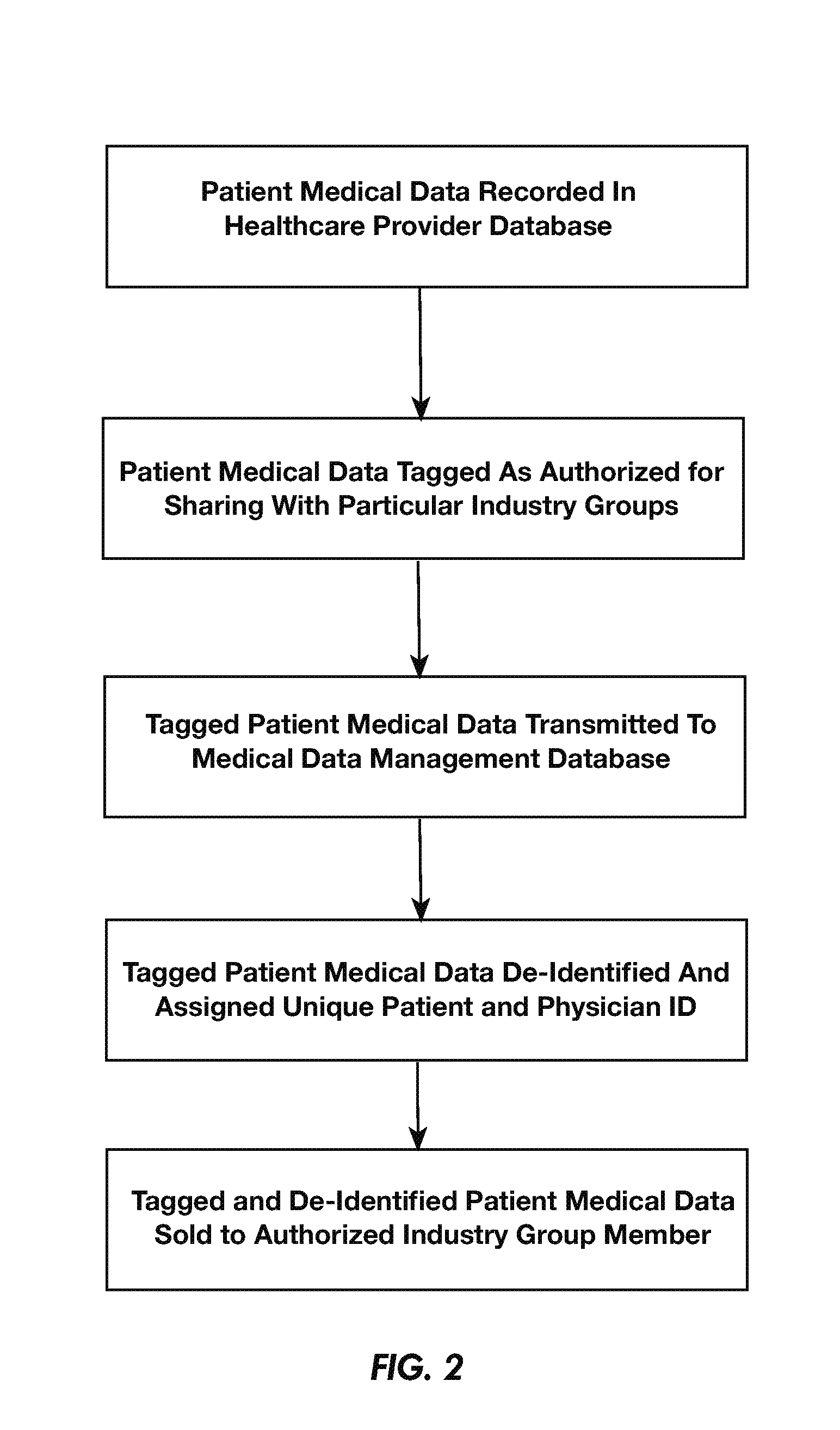

Healthcare data management system

InactiveUS20140136237A1Complete and accurate and timely and efficient distributionTimely and complete informationPatient personal data managementOffice automationMedicineData management

Owner:ANDERSON NICHOLAS G +2

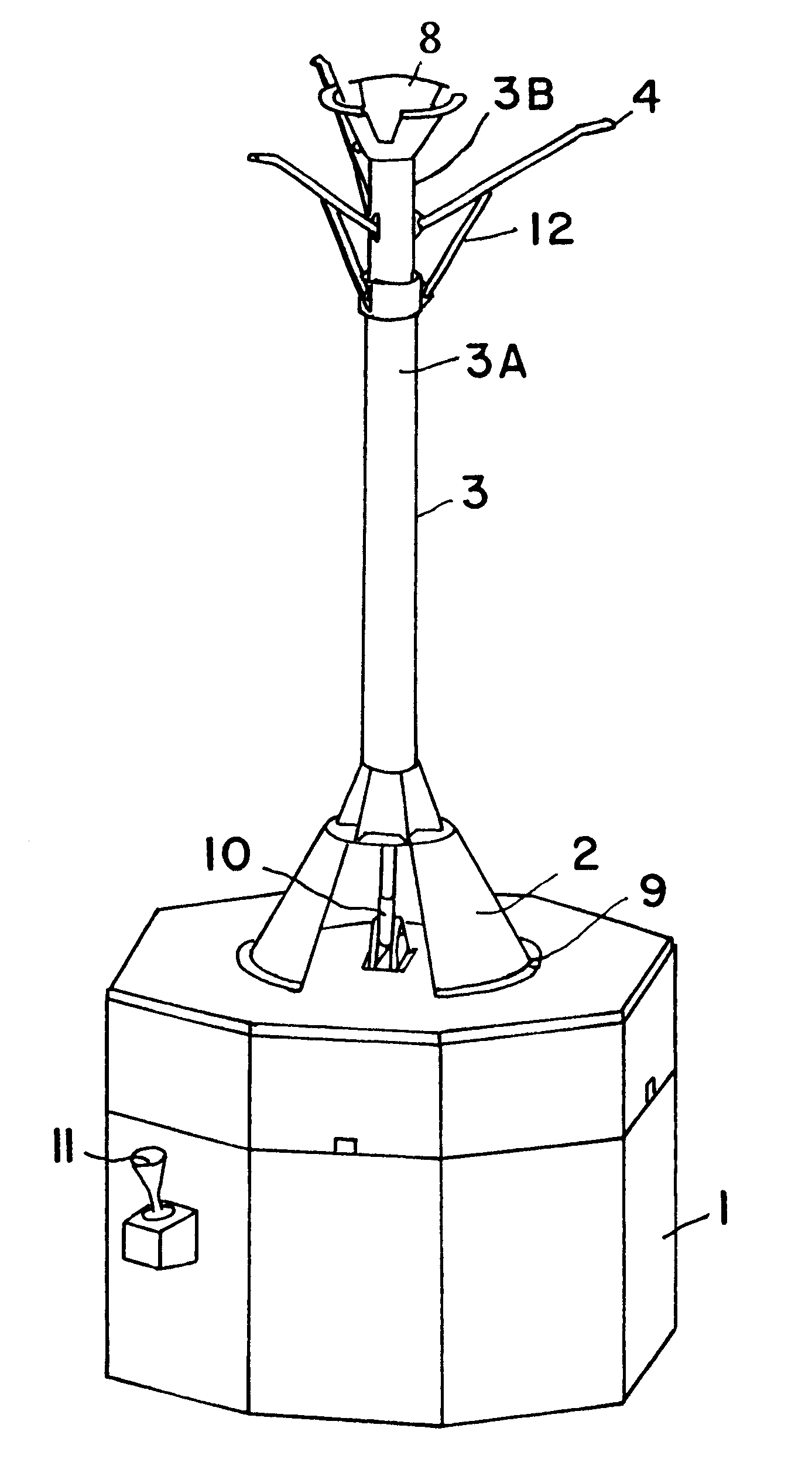

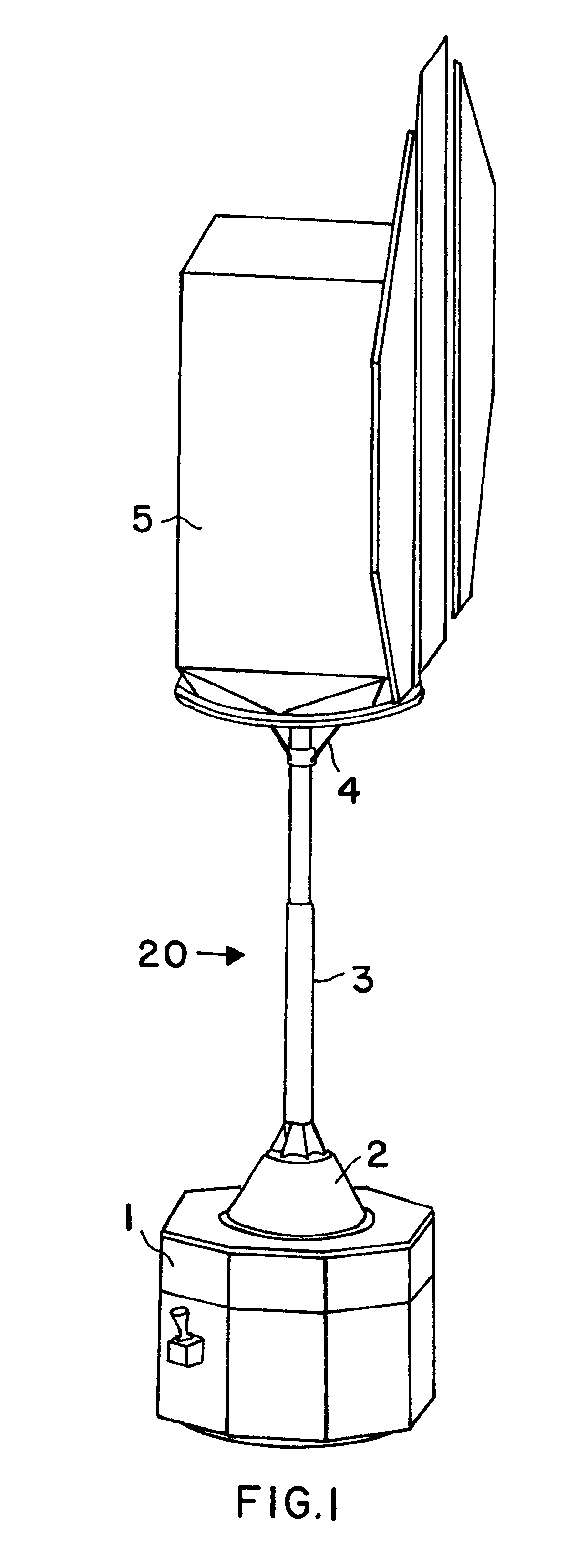

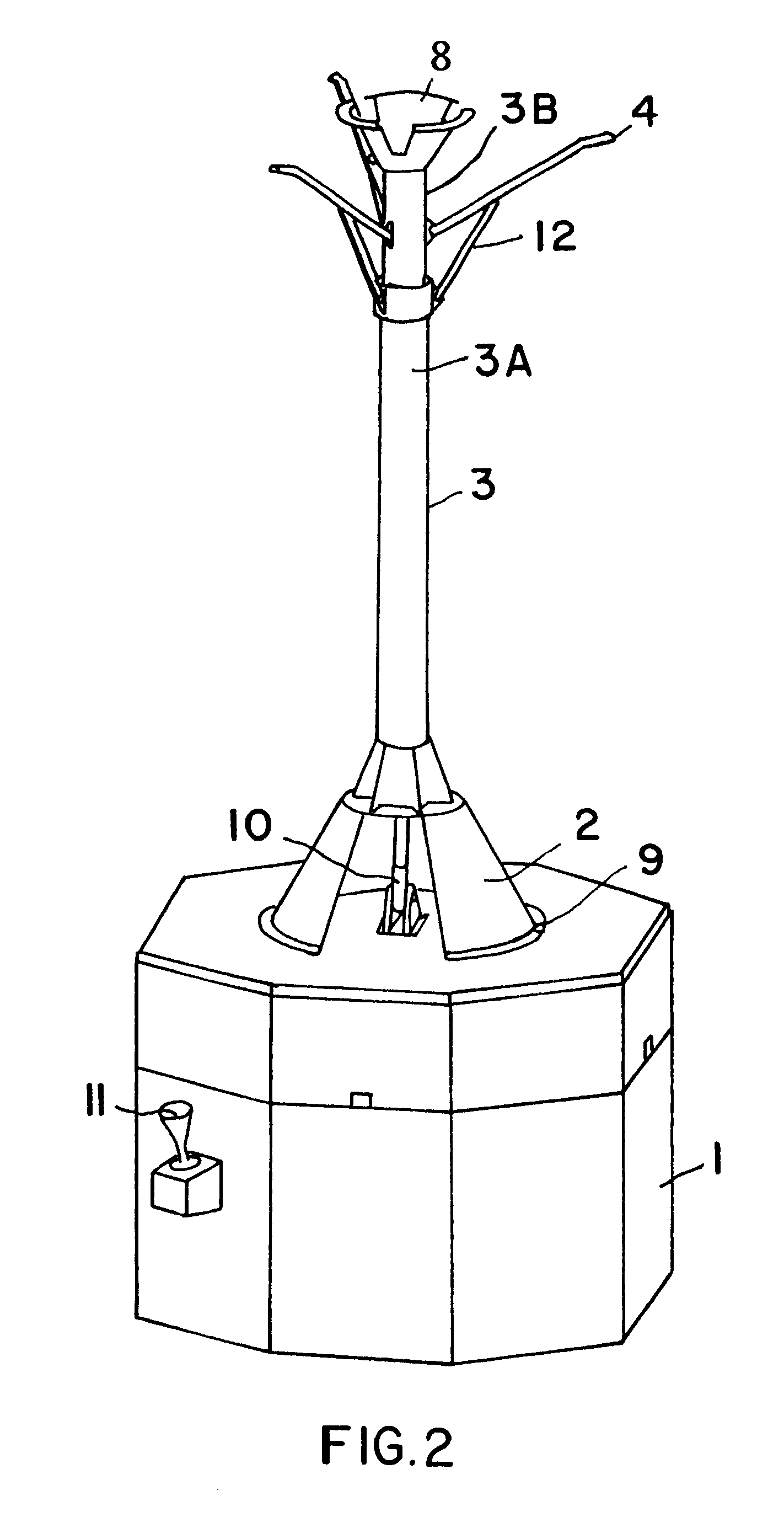

Arrangement for recovering spacecraft

A recovery craft with a coupling arrangement captures, engages, and transports a defective or expended non-maneuverable spacecraft. The coupling arrangement includes a coupling mast (e.g. a telescoping pipe), a releasable rigid mount that secures one end of the coupling mast to the recovery craft, and spreader arms that are radially spreadable from the other end of the coupling mast. The spreader arms are initially radially inwardly retracted, and are inserted into an interface ring of the spacecraft. Then the spreader arms are radially outwardly extended to engage behind a protruding rim of the interface ring. A spring braces against the spacecraft. Next, the rigid mount is released and the coupling mast remains connected to the recovery craft only by a tension-transmitting cable. Thrusters of the recovery craft are activated to tow the spacecraft to a new target position, orbit, or trajectory.

Owner:AIRBUS DEFENCE & SPACE

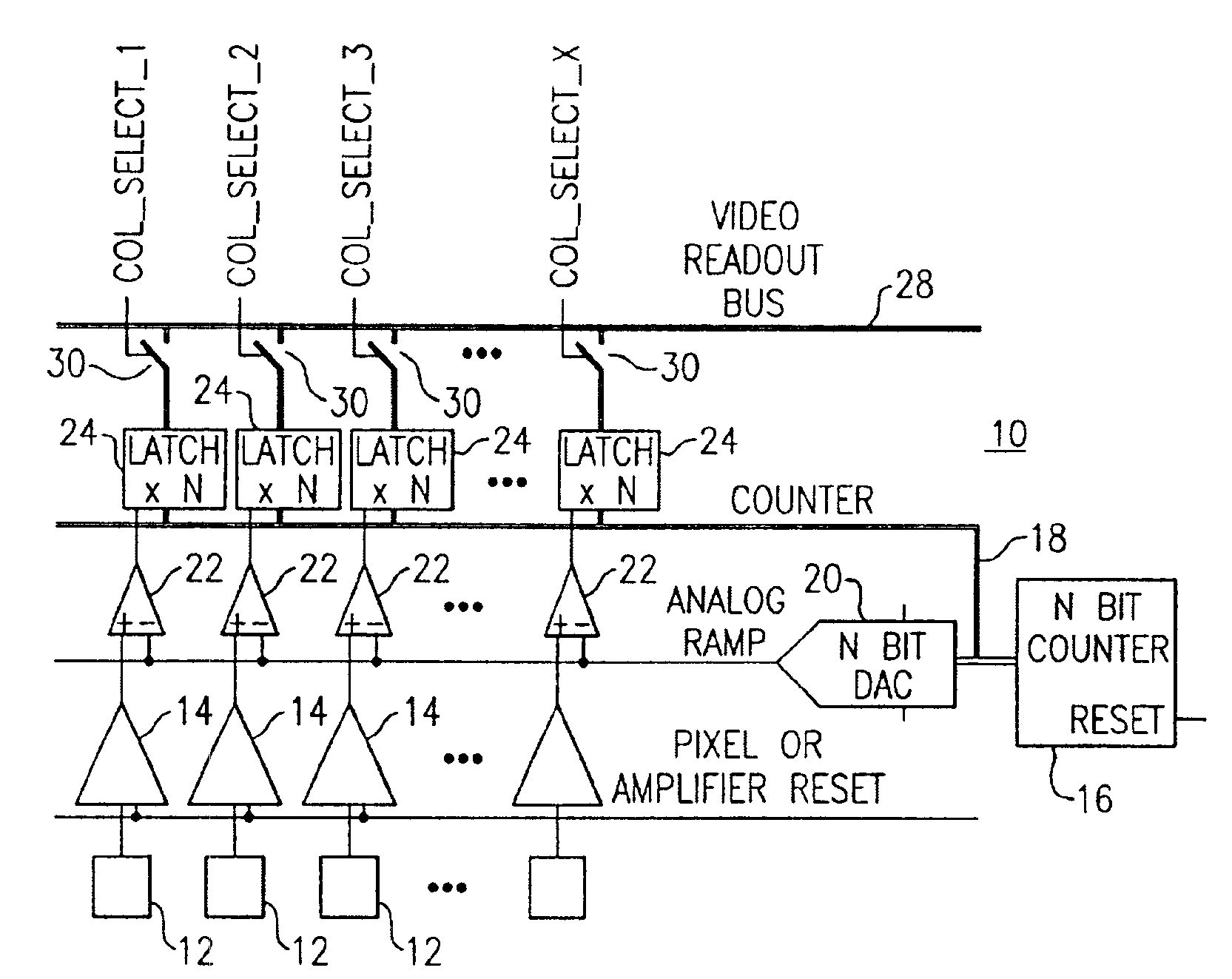

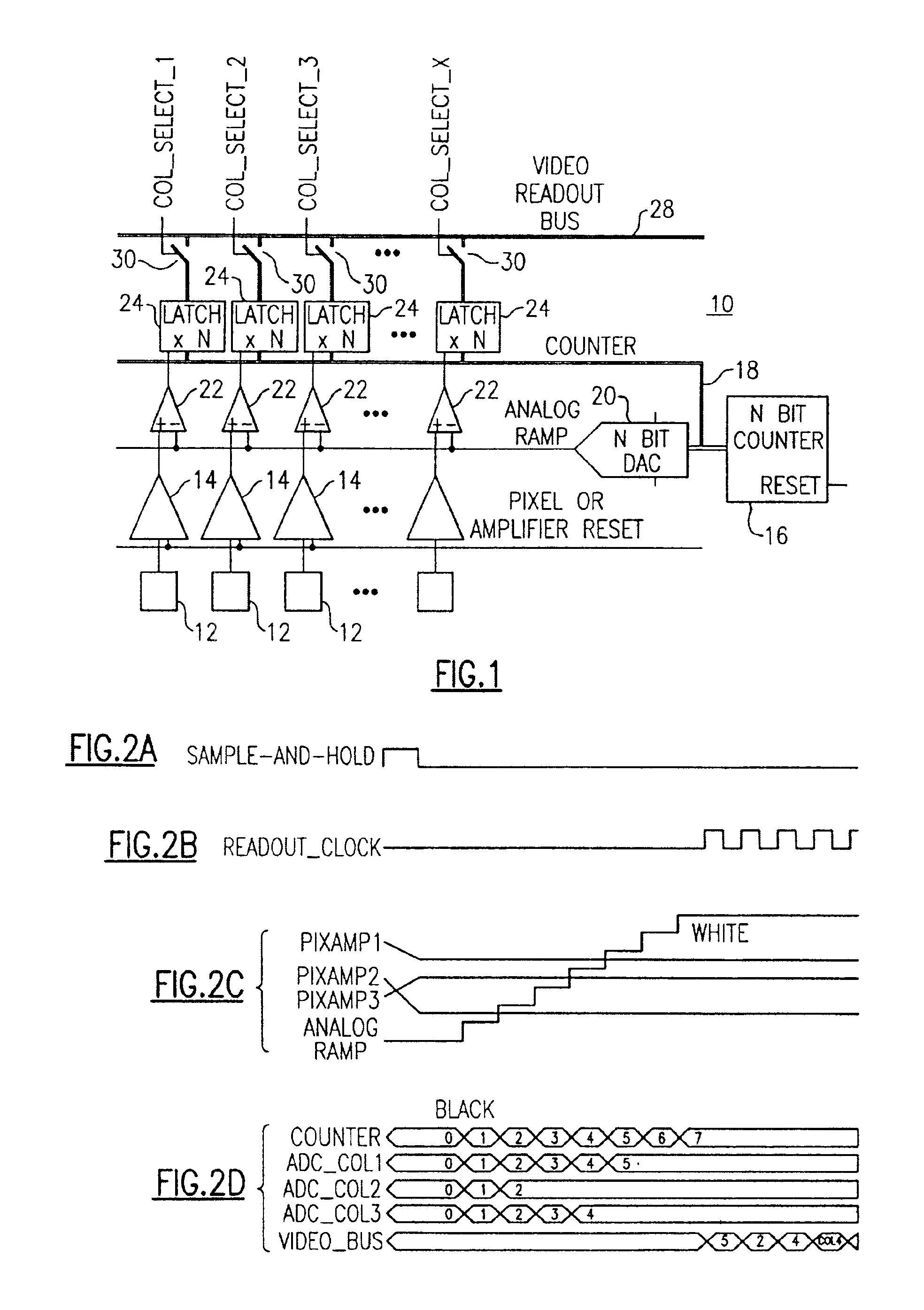

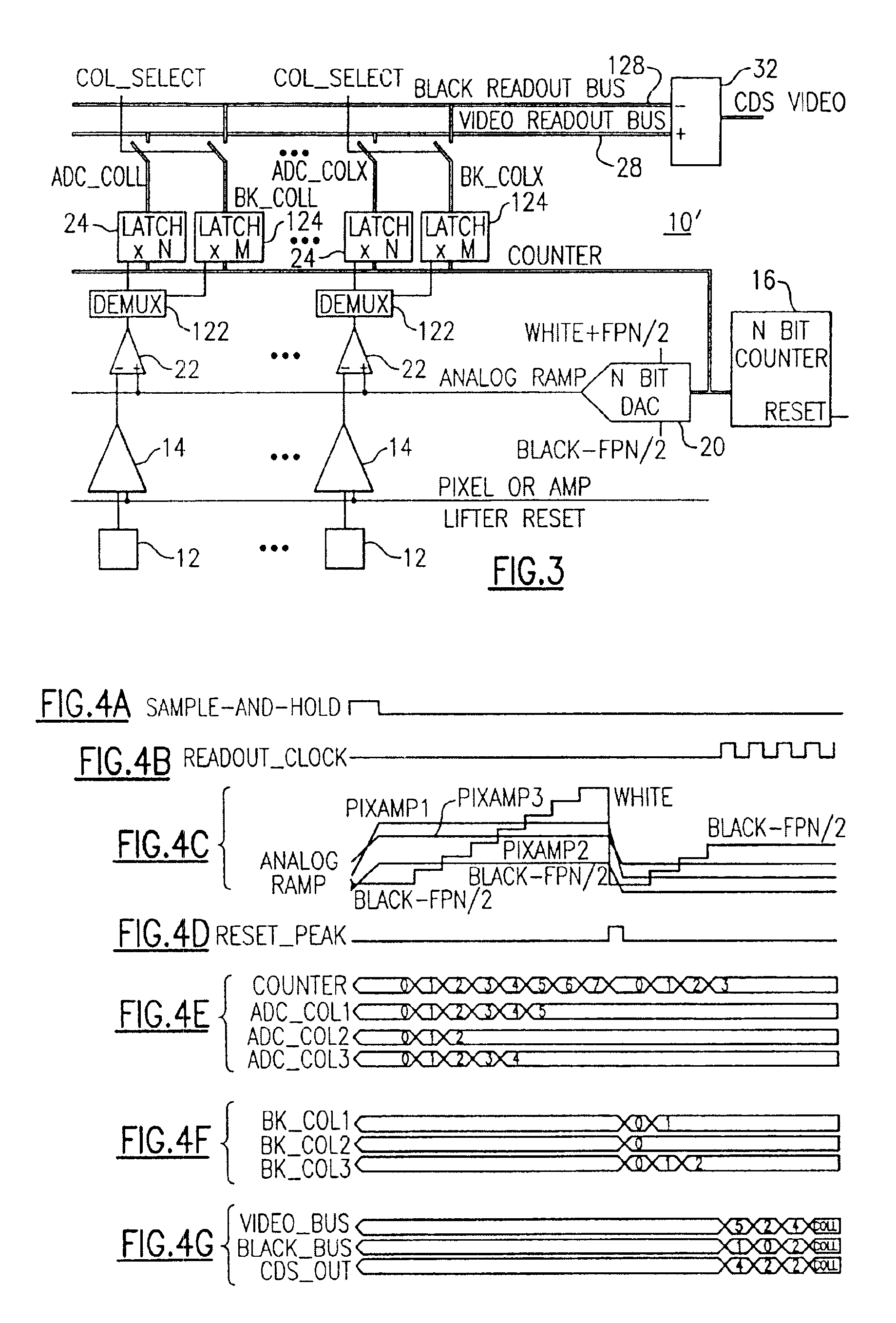

Image sensor ADC and CDS per column

ActiveUS6965407B2Available areaAvoid disadvantagesTelevision system detailsElectric signal transmission systemsDigital videoDigital storage

A solid state imager includes an arrangement for converting analog pixel values to digital form on an arrayed per-column basis. An N-bit counter supplies an N-bit DAC to produce an analog ramp output providing a ramp signal with a level that varies corresponding to the contents of the counter. Latches or equivalent digital storage elements are each associated with a respective column. A counter bus connects the counter to latch inputs of said latches, and comparators associated the columns gate the latches when the analog ramp equals the pixel value for that column. The contents of the latch elements are transferred sequentially to a video output bus to produce the digital video signal. There can be additionally black-level readout latch elements, for storing a digital value that corresponds to the dark or black video level, and a subtraction element subtracts the black level value from the pixel value to reduce fixed pattern noise. An additional array of buffer latches can be employed.

Owner:DYNAMAX IMAGING

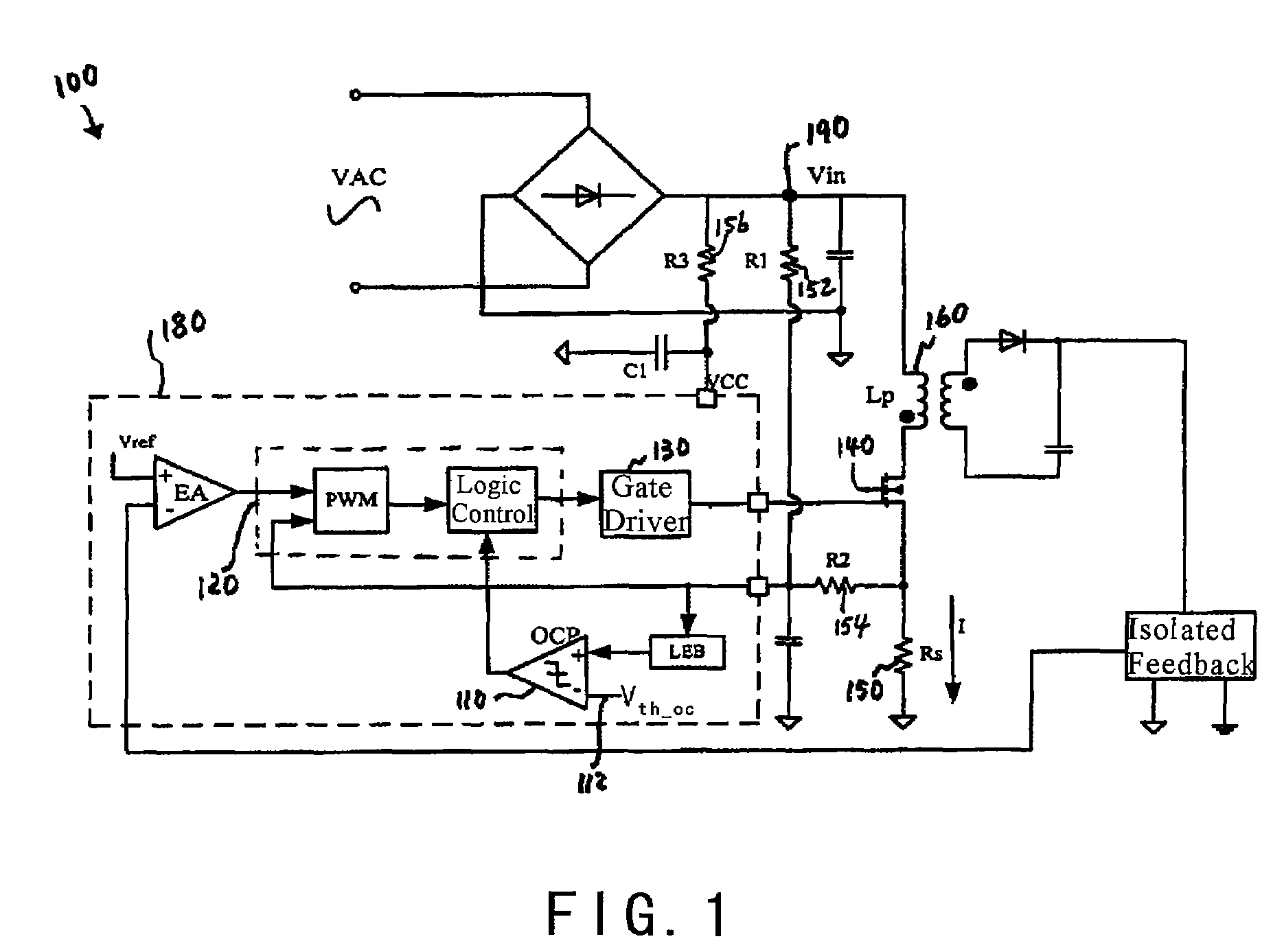

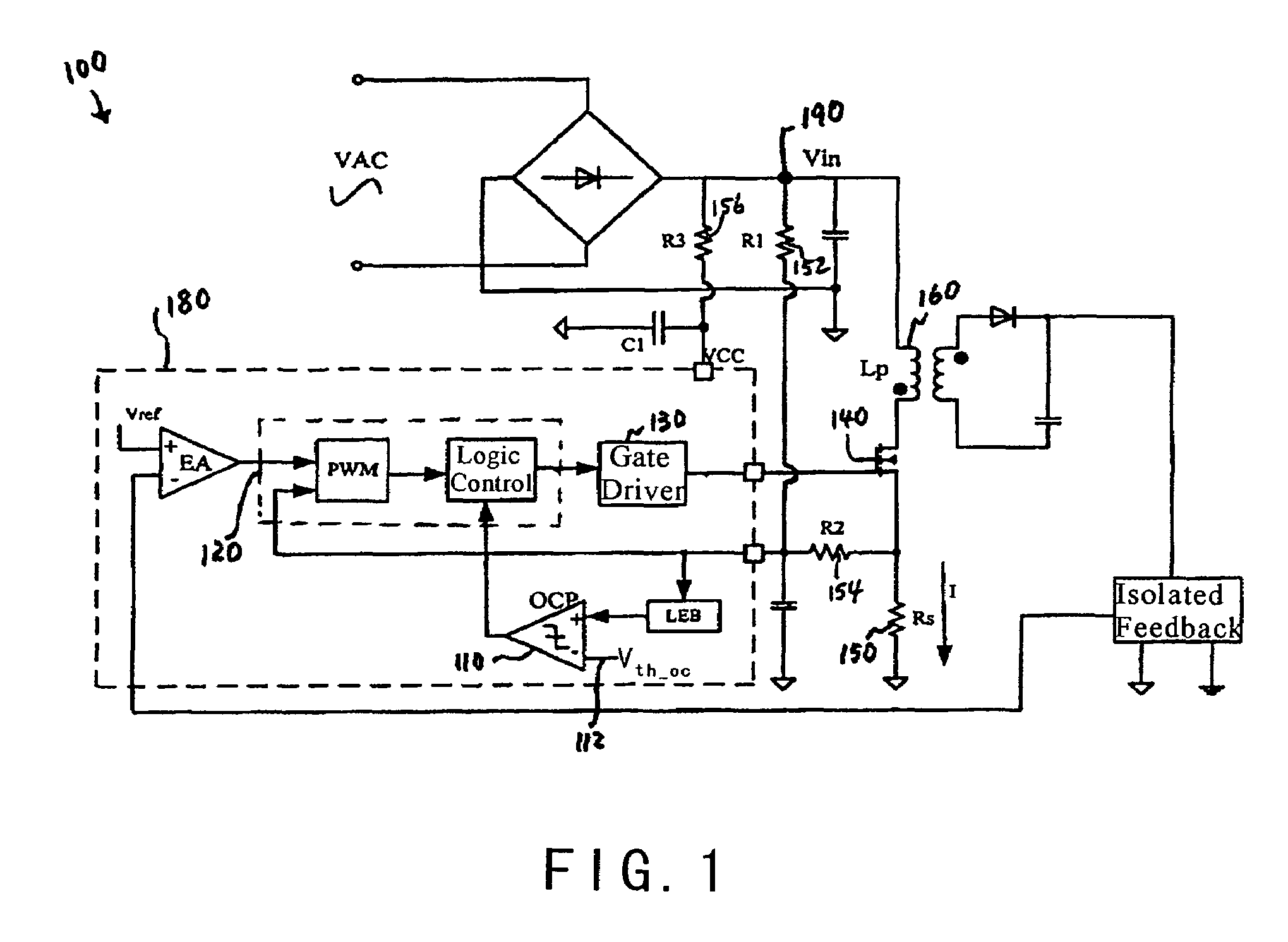

Control system and method with constant maximum current for power converter protection

InactiveUS7394634B2Good compensationEasy to adjustDc-dc conversionArrangements responsive to excess currentControl systemEngineering

System and method for protecting a power converter. The system includes a first comparator configured to receive a threshold signal and a first signal and to generate a comparison signal. The first signal is a sum of a second signal and a third signal, and the third signal is associated with an input current for a power converter. Additionally, the system includes a pulse-width-modulation generator configured to receive the comparison signal and generate a modulation signal in response to the comparison signal, and a switch configured to receive the modulation signal and control the input current for the power converter. An amplitude for the first signal becomes larger if an amplitude for the input voltage becomes larger. The second signal is generated by receiving an input voltage for the power converter, converting the received input voltage to a fourth signal, and converting the fourth signal to the second signal.

Owner:ON BRIGHT ELECTRONICS SHANGHAI

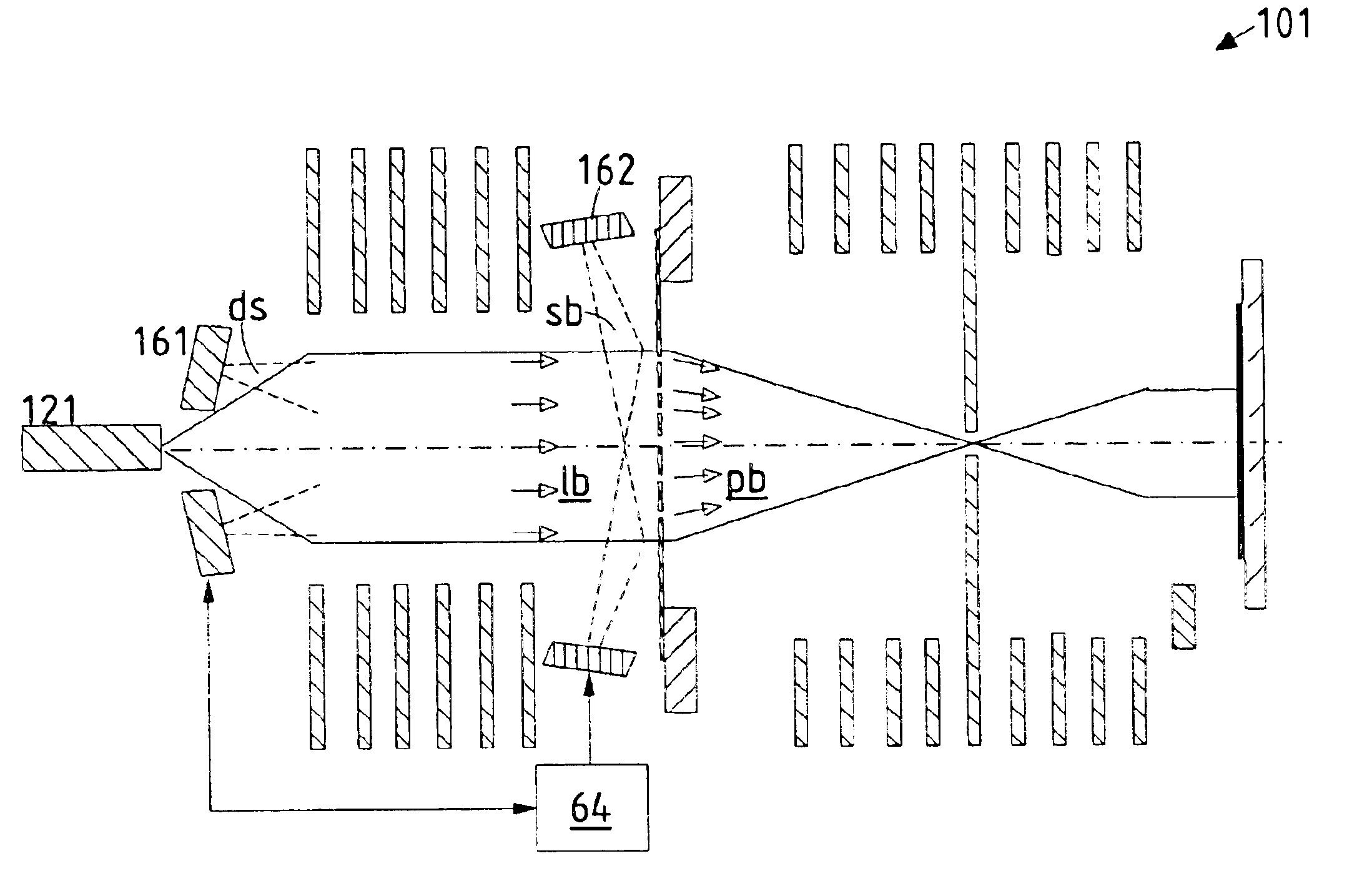

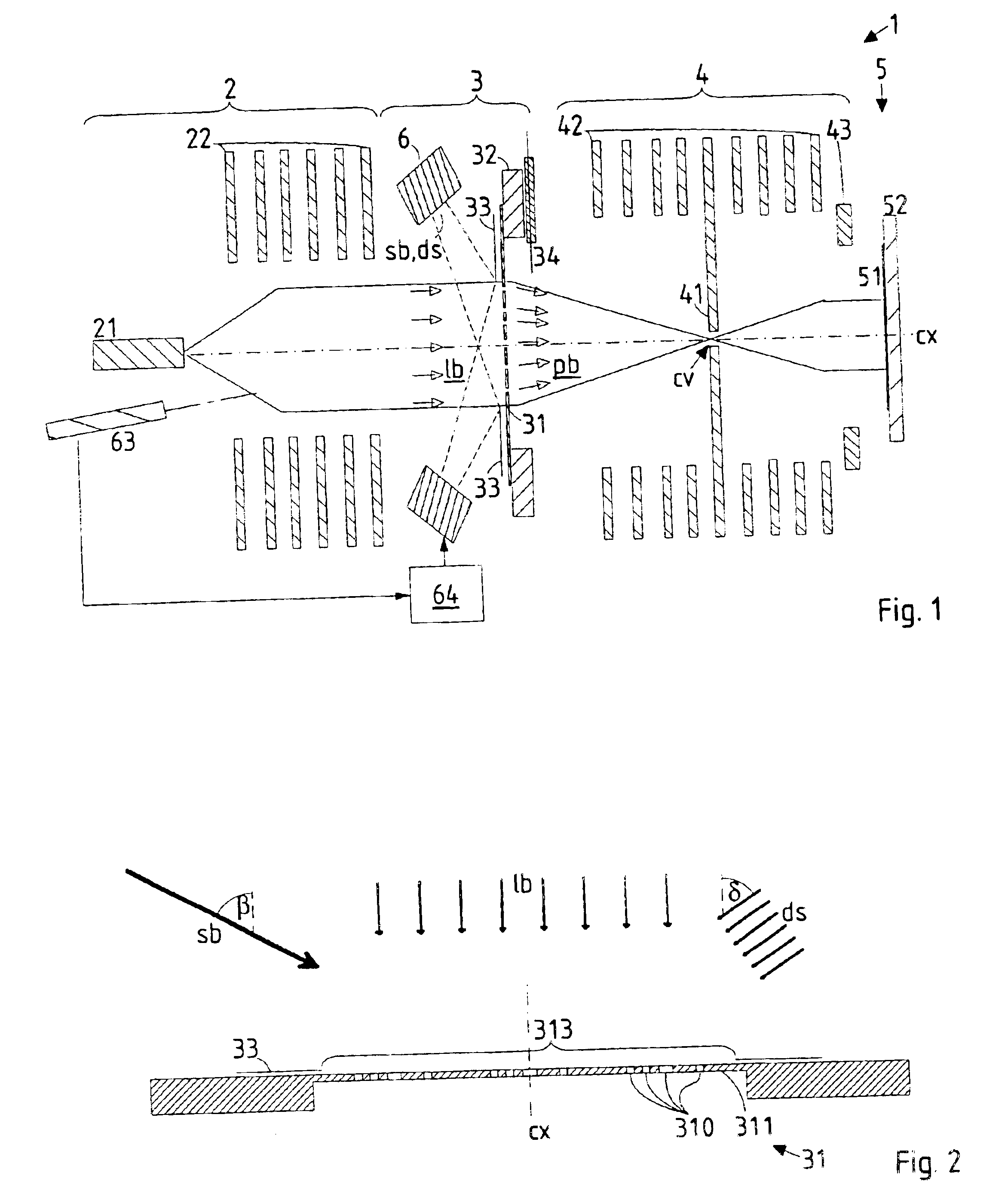

Apparatus for enhancing the lifetime of stencil masks

InactiveUS6858118B2Effective sputtering cleaningEliminate the effects ofCellsElectric discharge tubesEngineeringIon beam lithography

An apparatus for masked ion-beam lithography comprises a mask maintenance module for prolongation of the lifetime of the stencil mask. The module comprises a deposition means for depositing material to the side of the mask irradiated by the lithography beam, with at least one deposition source being positioned in front of the mask, and further comprises a sputter means in which at least one sputter source, positioned in front of the mask holder means and outside the path of the lithography beam, produces a sputter ion beam directed to the mask in order to sputter off material from said mask in a scanning procedure and compensate for inhomogeneity of deposition.

Owner:IMS NANOFABTION

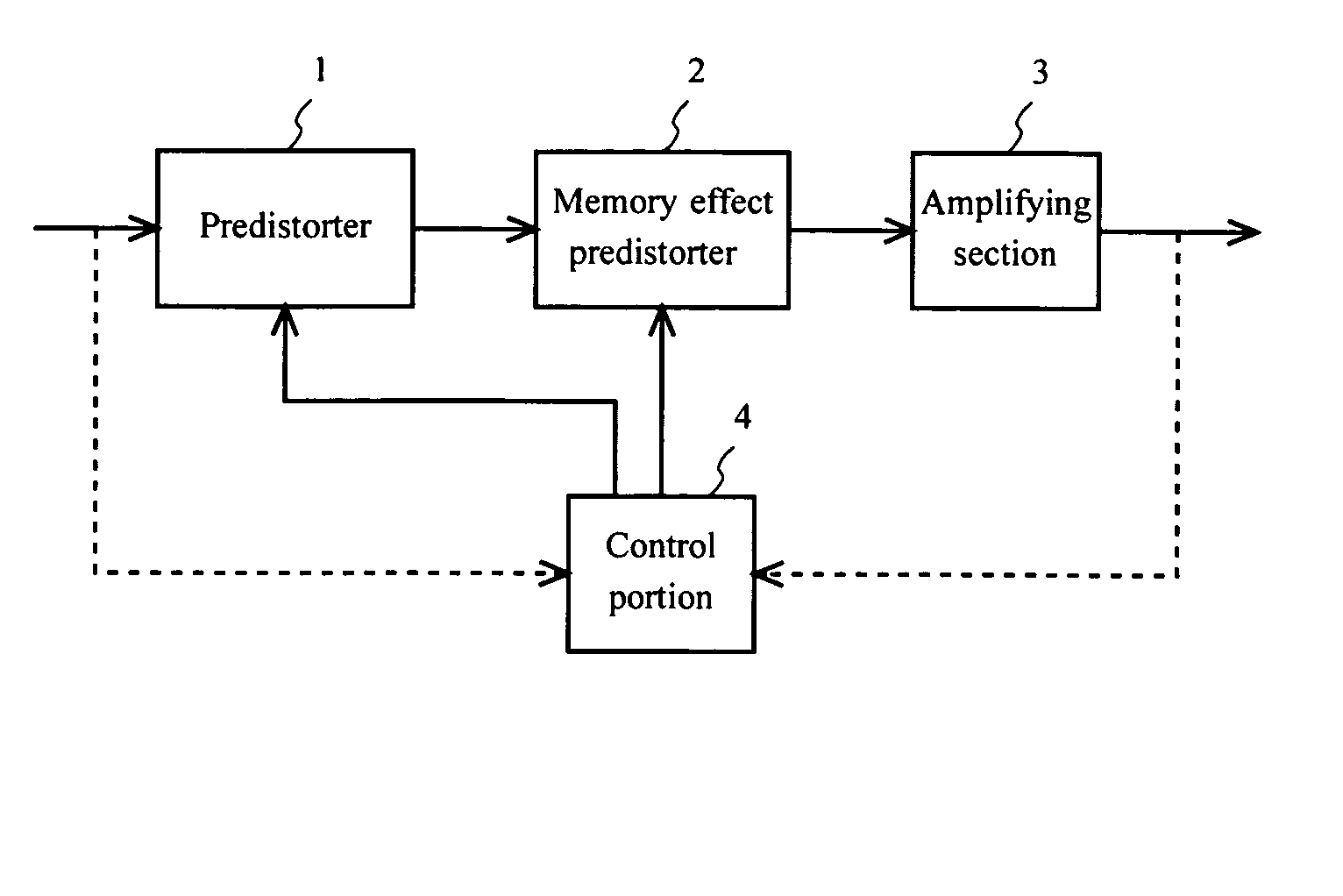

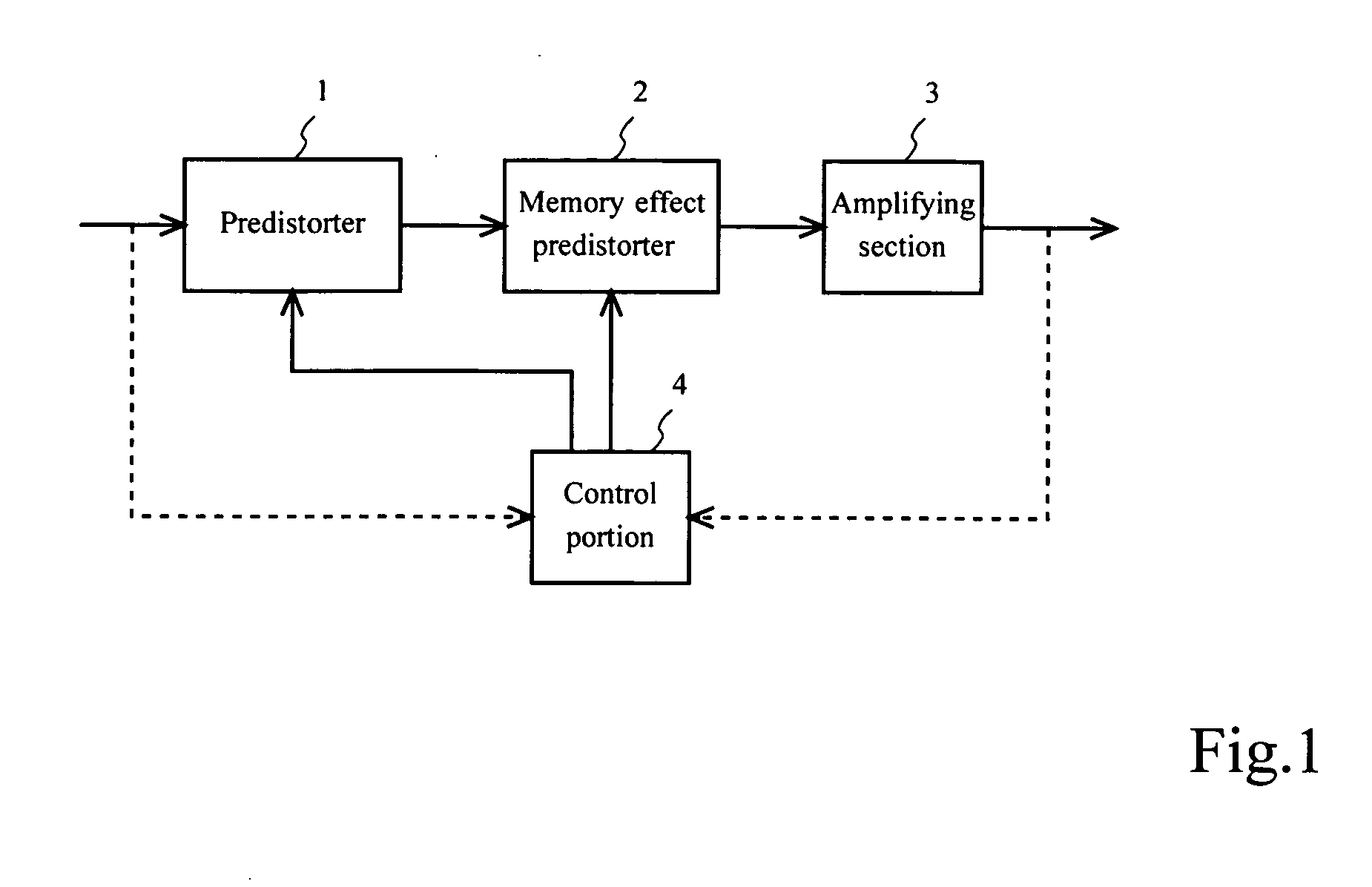

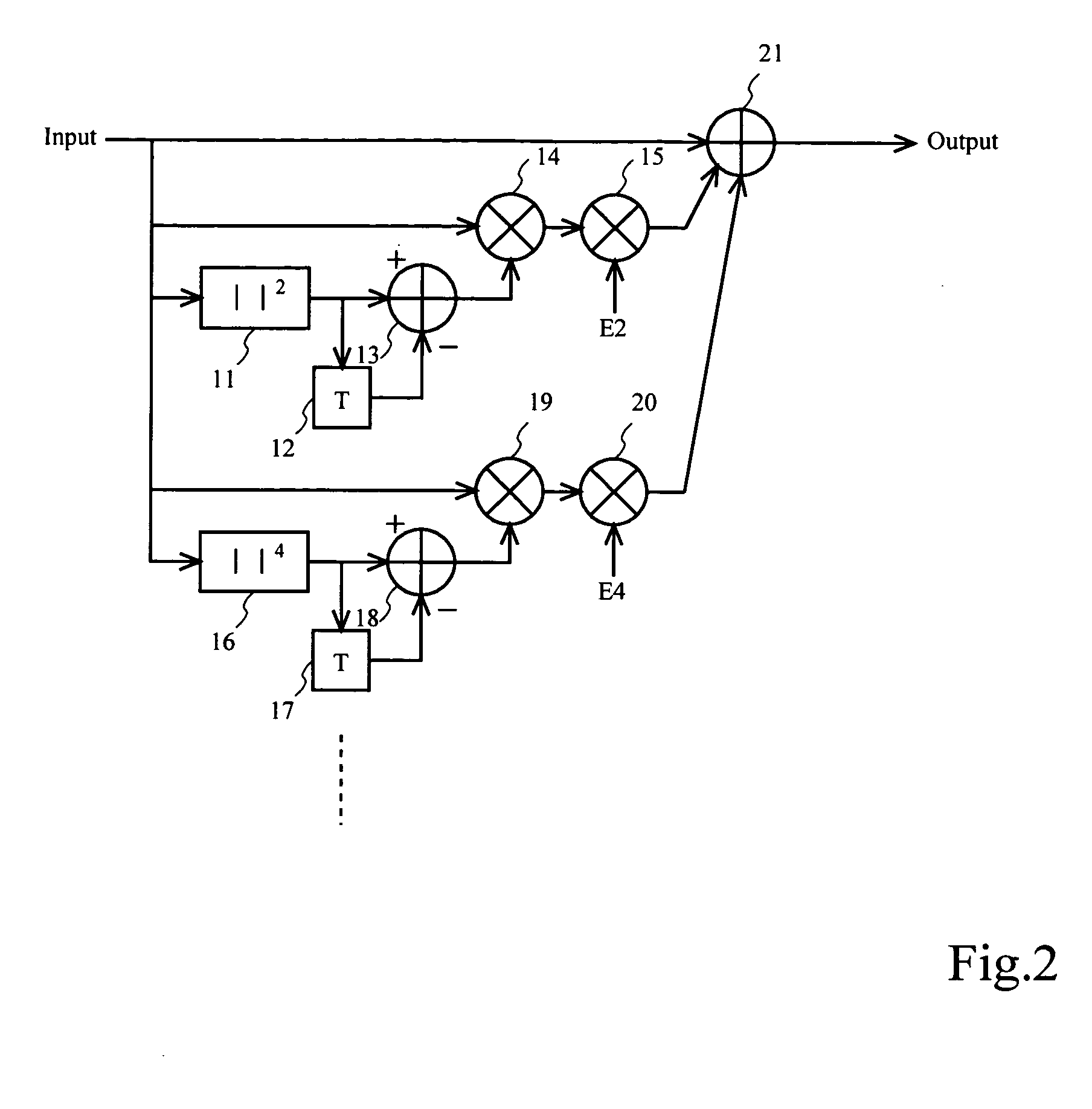

Distortion-compensated amplifier using predistortion technique

ActiveUS20050068102A1Compensation DistortionReduce the impactAmplifier modifications to reduce non-linear distortionResonant long antennasAudio power amplifierMemory effect

A memory effect distortion component compensating unit compensates for a distortion component caused by the memory effect of the amplifier by using a time difference of results from raising an input signal to even power. For example, the amplifier may include a memory effect distortion component compensating unit having an even power raising means for raising an input signal to even power, an even power raising result delaying unit for delaying a signal of a result of even power raising, an even power raising result time difference detecting unit for detecting a difference between a signal of an even power raising result and a delayed signal, an input signal multiplying unit for multiplying a signal of a detection result by an input signal, a distortion compensation coefficient multiplying unit for multiplying a signal of a multiplication result by a distortion compensation coefficient, and a distortion compensation coefficient multiplication result adding unit for adding an input signal and a signal of a multiplication result.

Owner:KOKUSA ELECTRIC CO LTD

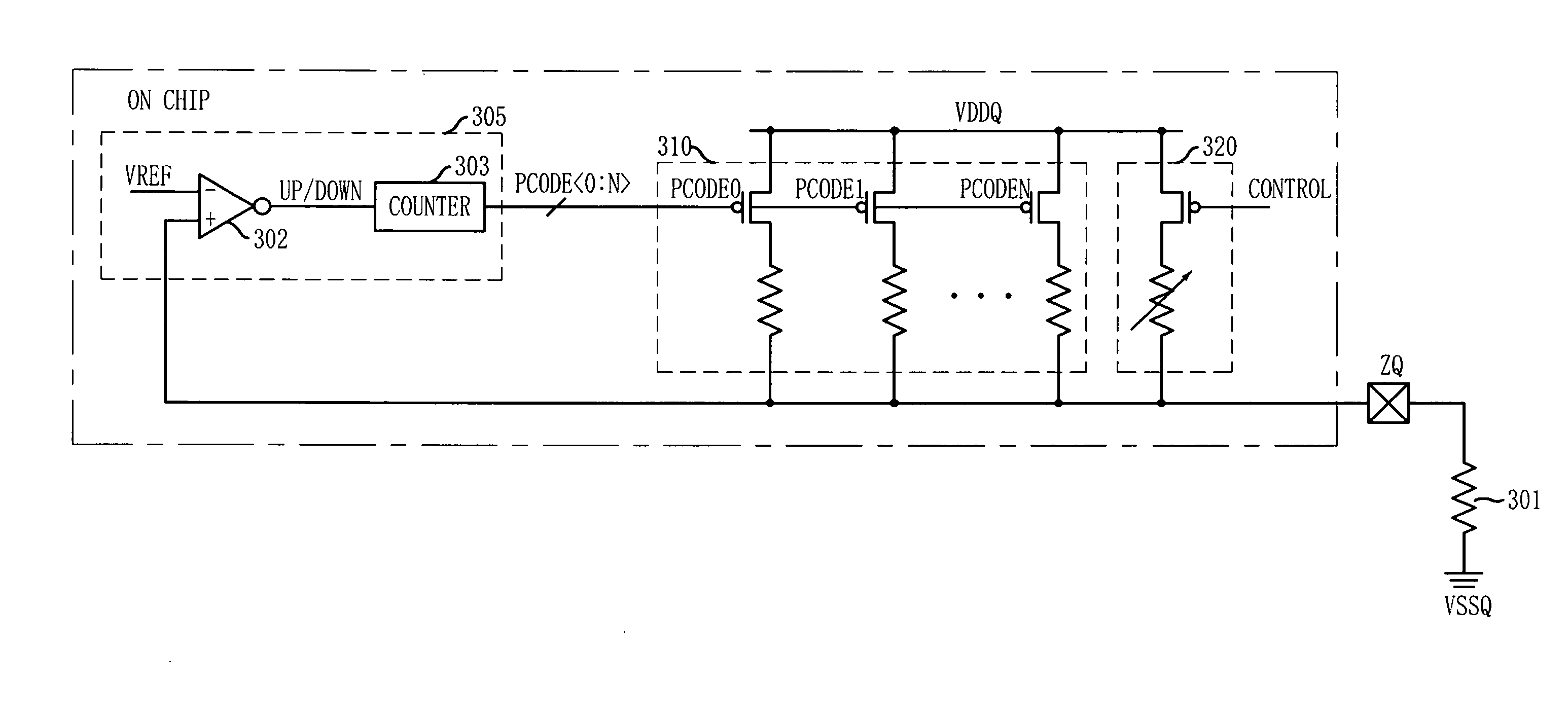

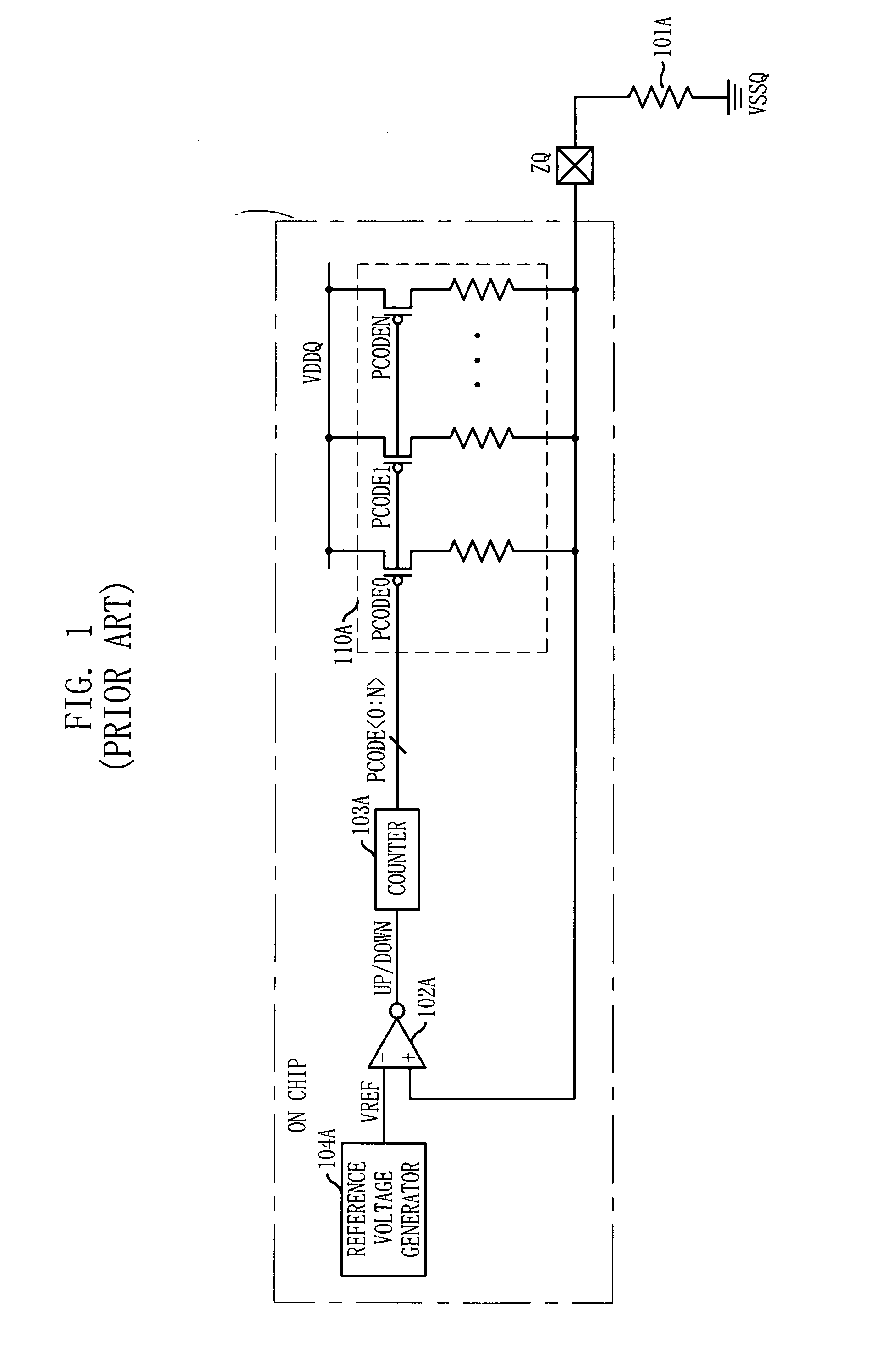

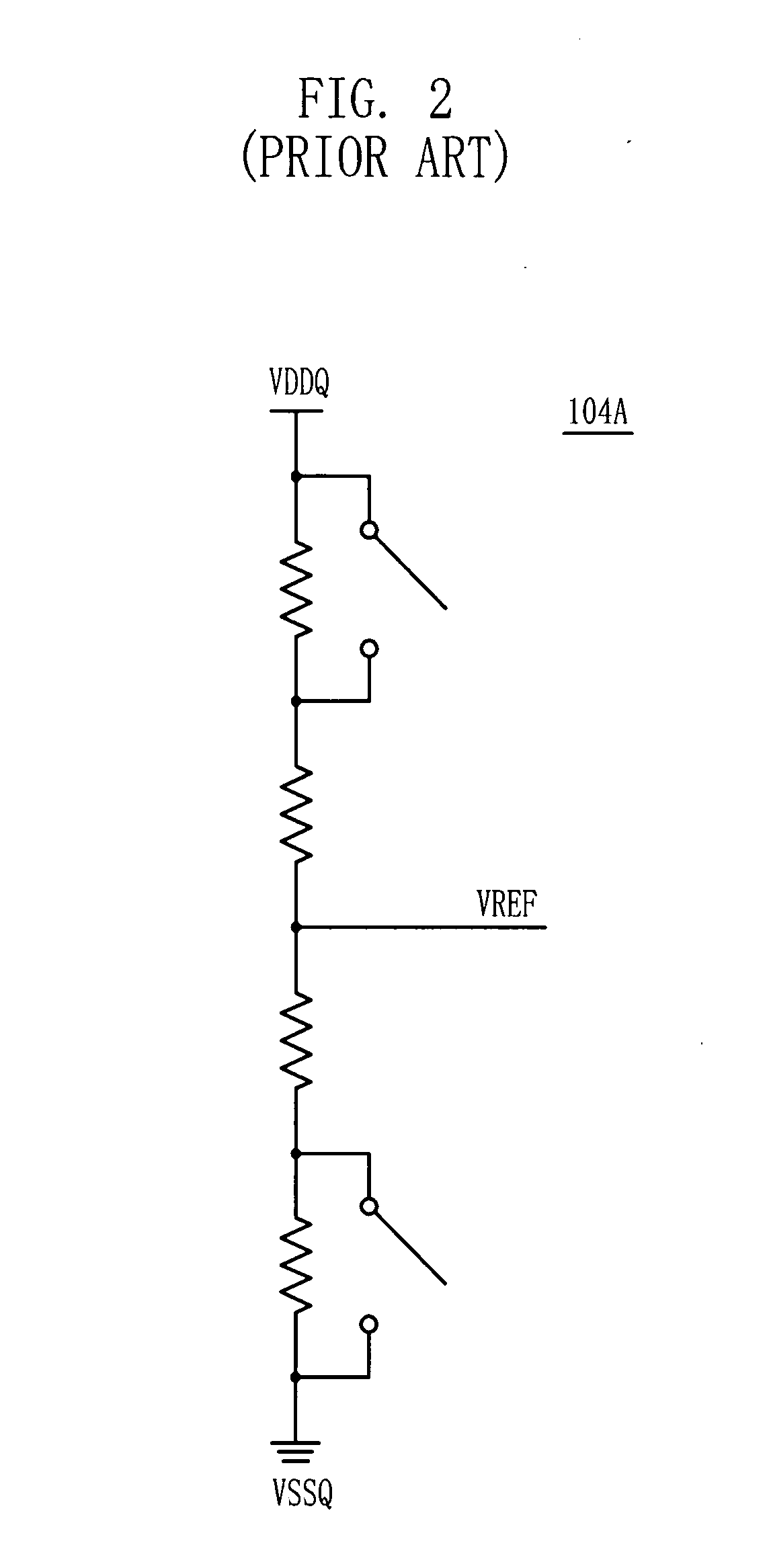

On-die termination device

ActiveUS20080048714A1Easily compensateGood compensationInput/output impedence modificationReliability increasing modificationsVoltage referenceEngineering

An one-die termination includes: a code generator configured to generate a calibration code in response to a voltage of a first node and a reference voltage; a calibration resistor unit connected to the first node, and configured to be turned on and off in response to the calibration code; and a reference resistor unit coupled to the calibration resistor unit, and configured to be turned on and off in response to a control signal.

Owner:SK HYNIX INC

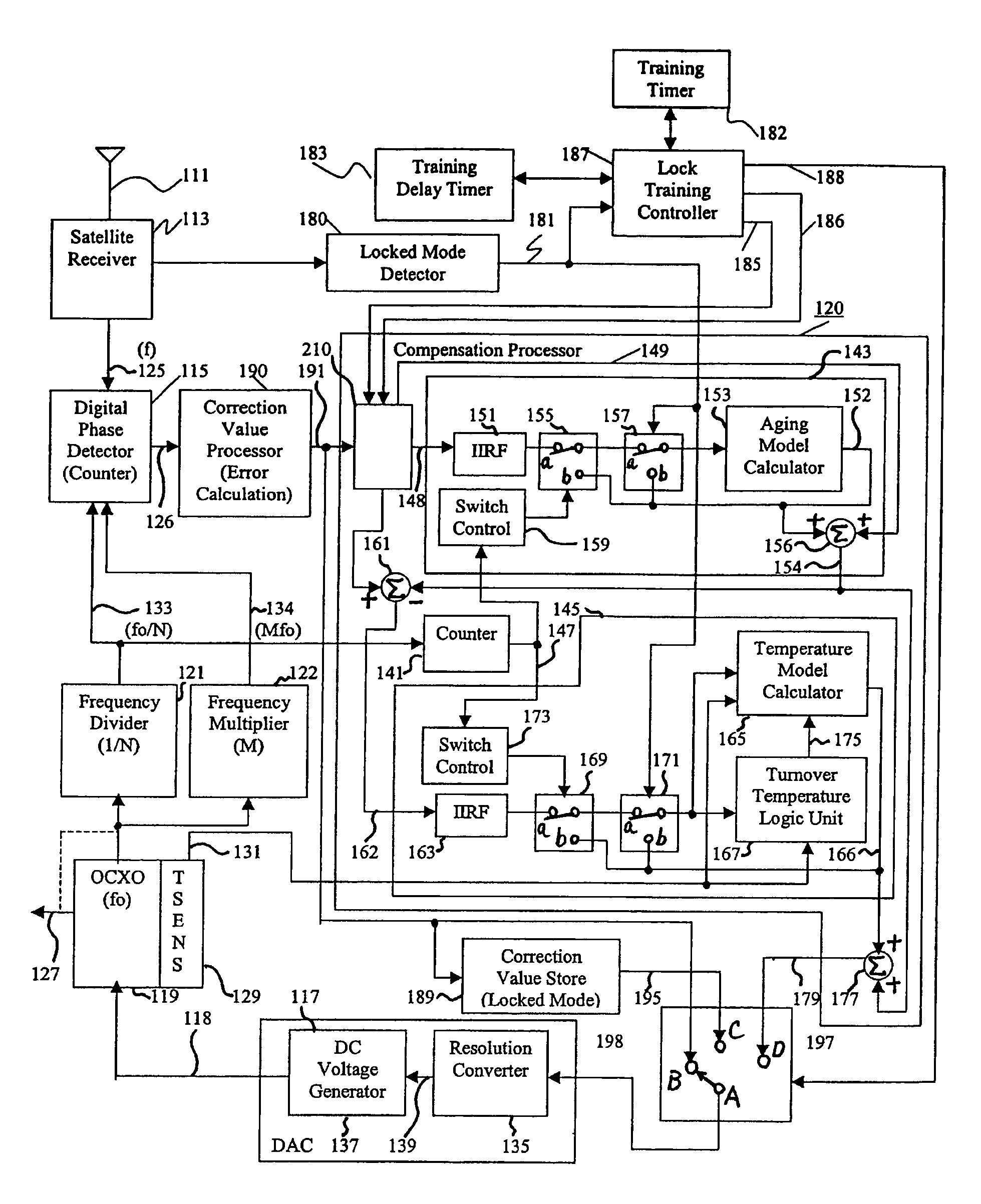

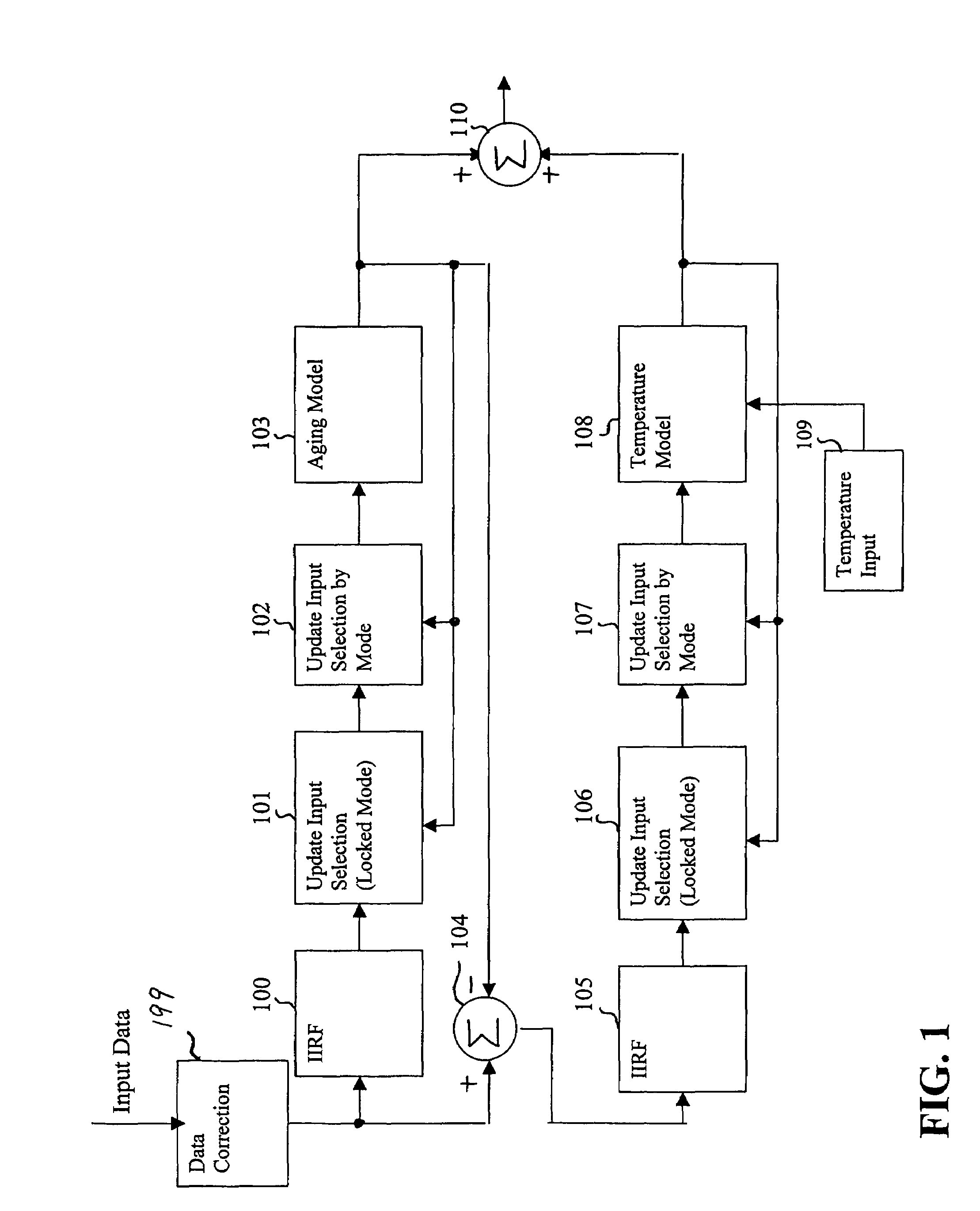

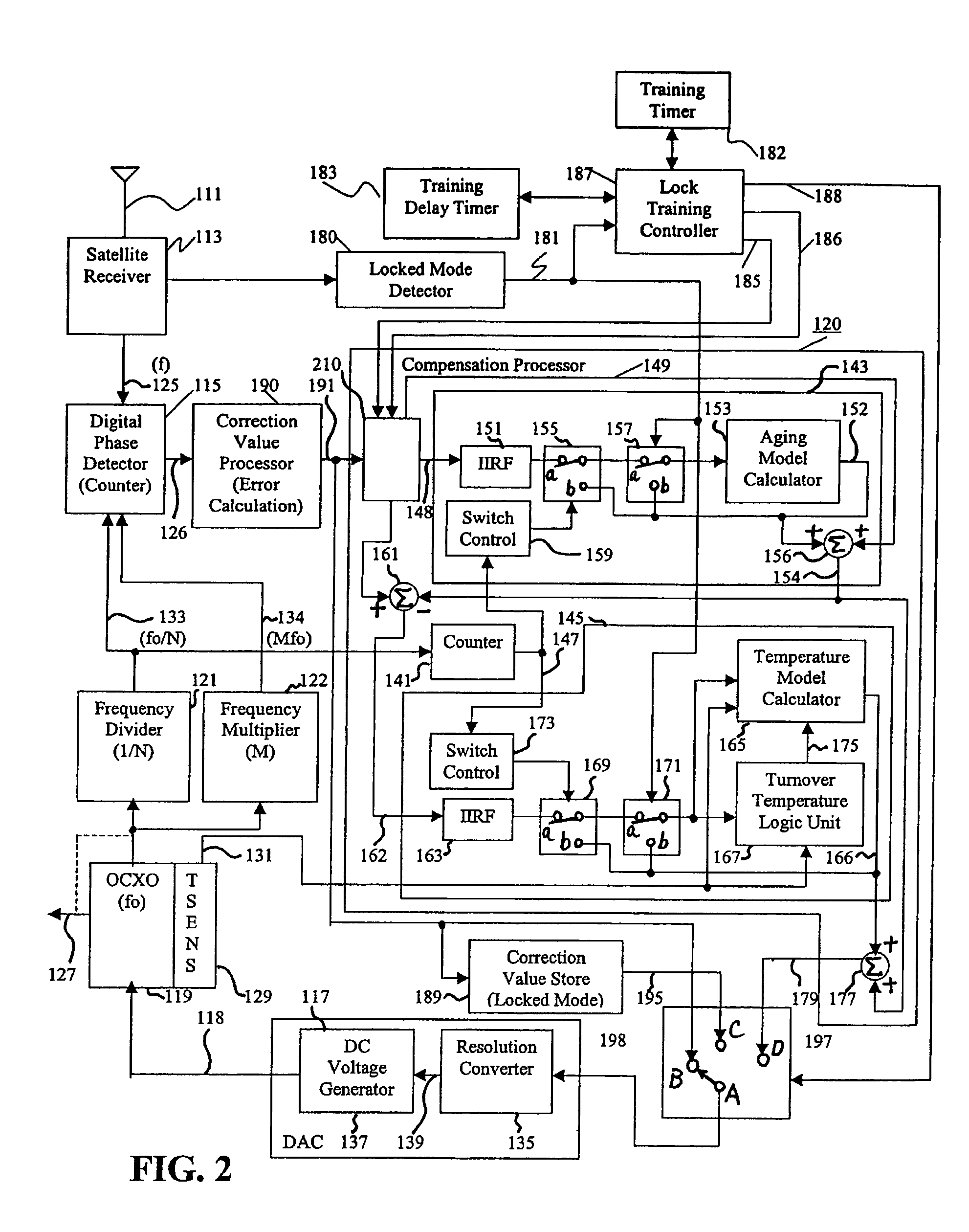

Reference timing signal apparatus and method

ActiveUS7015762B1Increase currentGood compensationRadiation pyrometryPulse automatic controlTraining periodAdaptive filter

A reference timing signal apparatus with a phase-locked loop (PLL) has a computer algorithm which adaptively models the multiple frequencies of an oscillator following a training period. The oscillator is part of a PLL and the oscillation frequency thereof is controlled in response to the phase detector output. The computer algorithm processes the control signal applied to the oscillator. The computer algorithm updates the characteristics of the model relating to the aging and temperature of the oscillator, using for example, a Kalman filter as an adaptive filter, in accordance with a cumulative phase error in the PLL calculated during a given time interval. By the algorithm, the subsequent model predicts the future frequency state of the oscillator on which it was trained. The predicted frequency of the model functions as a reference to correct the frequency of the oscillator in the event that no input reference timing signal is available. Also, the calculated phase error is stored and is used while no input reference timing signal or accurate predicted frequency value is available. With the model updating algorithm, oscillators of low stability performance may be used as cellular base station reference oscillator, which is based on satellite systems, for example, GPS, GLONASS or Galileo systems.

Owner:APPLE INC

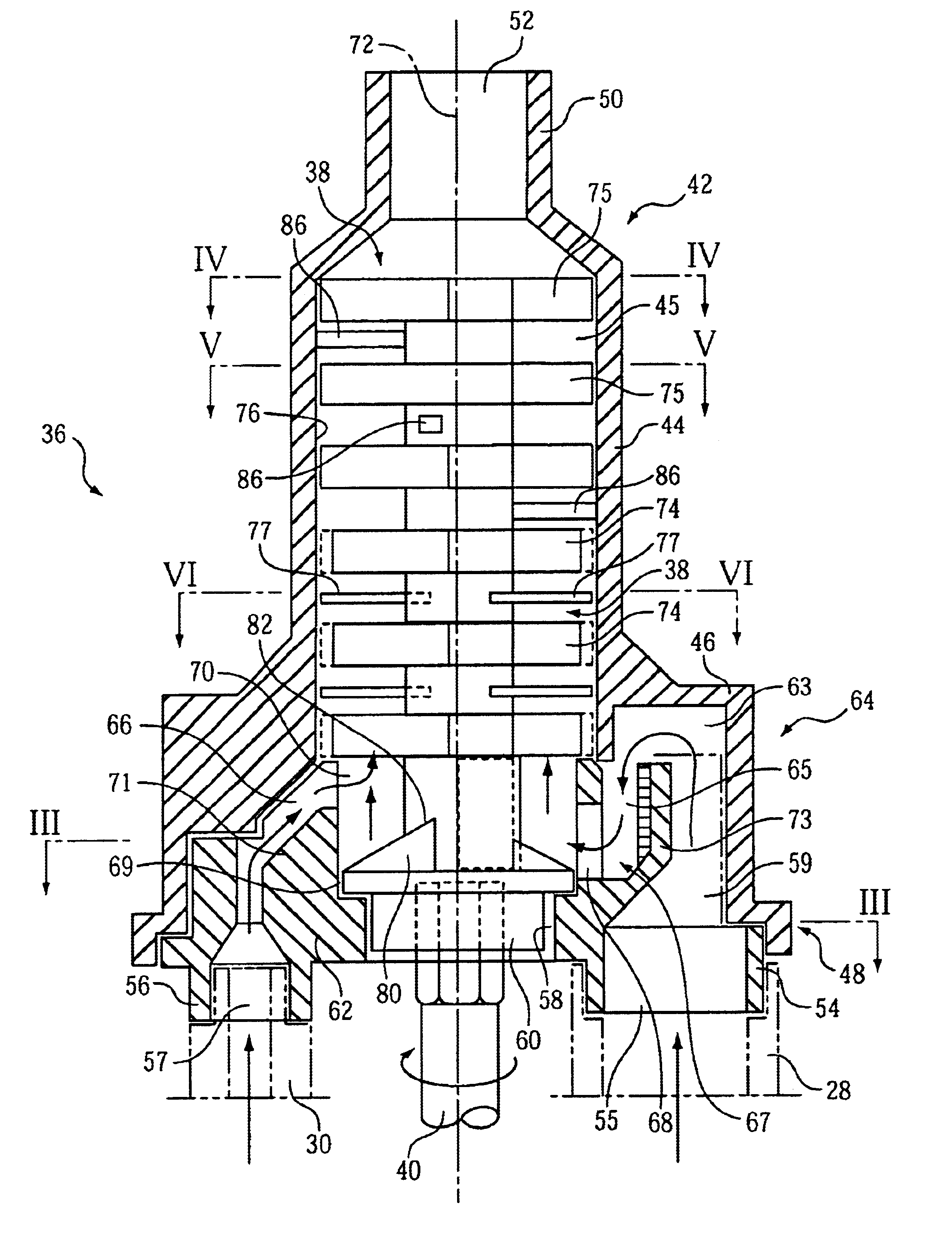

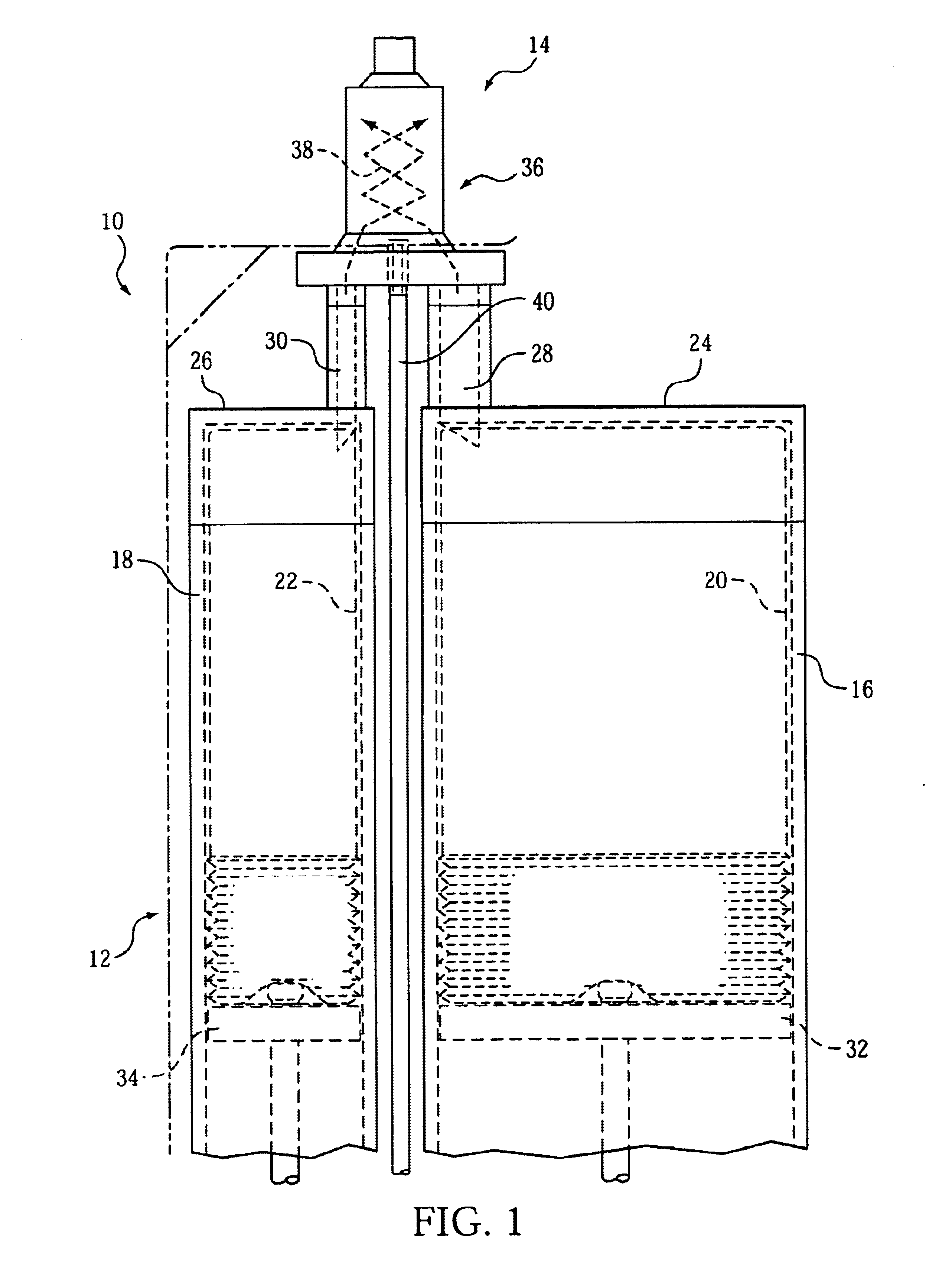

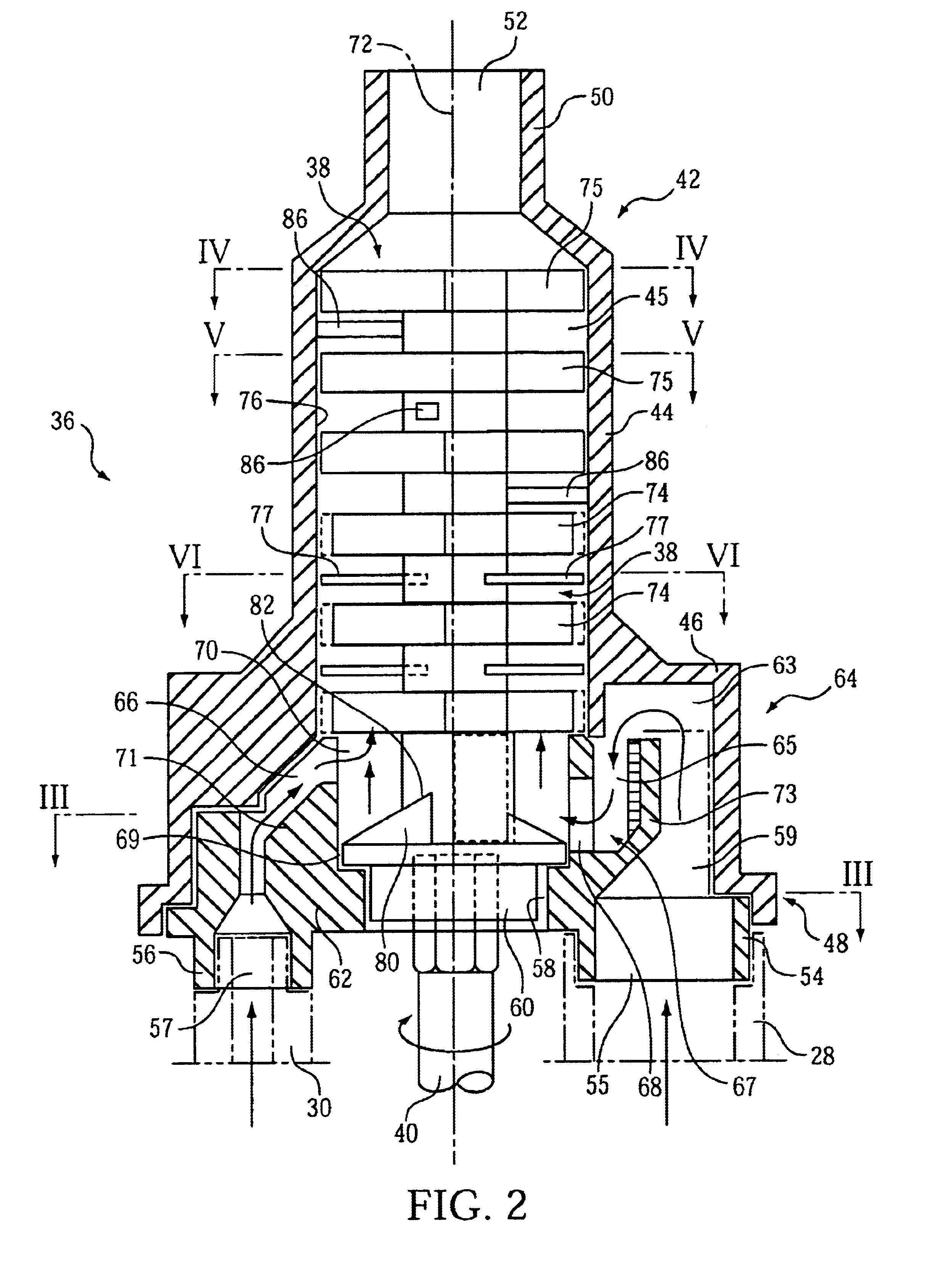

Device for mixing two paste-like compounds, in particular for mixing a dental-molding compound with a catalyzing compound

InactiveUS6837612B2Large angular rangeGood compensationLiquid surface applicatorsImpression capsEngineeringHybrid compound

A device for mixing two paste like compounds, such as a dental molding compound using a catalyst for the acceleration of polymerization. The housing has a mixing area with at least two inlet openings for the compounds and an outlet opening for the mixed compound. The device also has a mixing element that is disposed in the mixing area and propelled around a longitudinal axis. The housing has a coupling section that is situated in front of the mixing area with two coupling openings for connecting with two dispensing openings of a device for dispensing the two paste like compounds. The first and second ducts connect to the couplings via the coupling openings extending through the coupling section into the inlet openings for the mixing area. The two ducts are formed so that the first duct requires a greater time of entry of the compound into the mixing area than the time required for the second compound flowing through the second duct.

Owner:KETTENBACH GMBH & CO KG

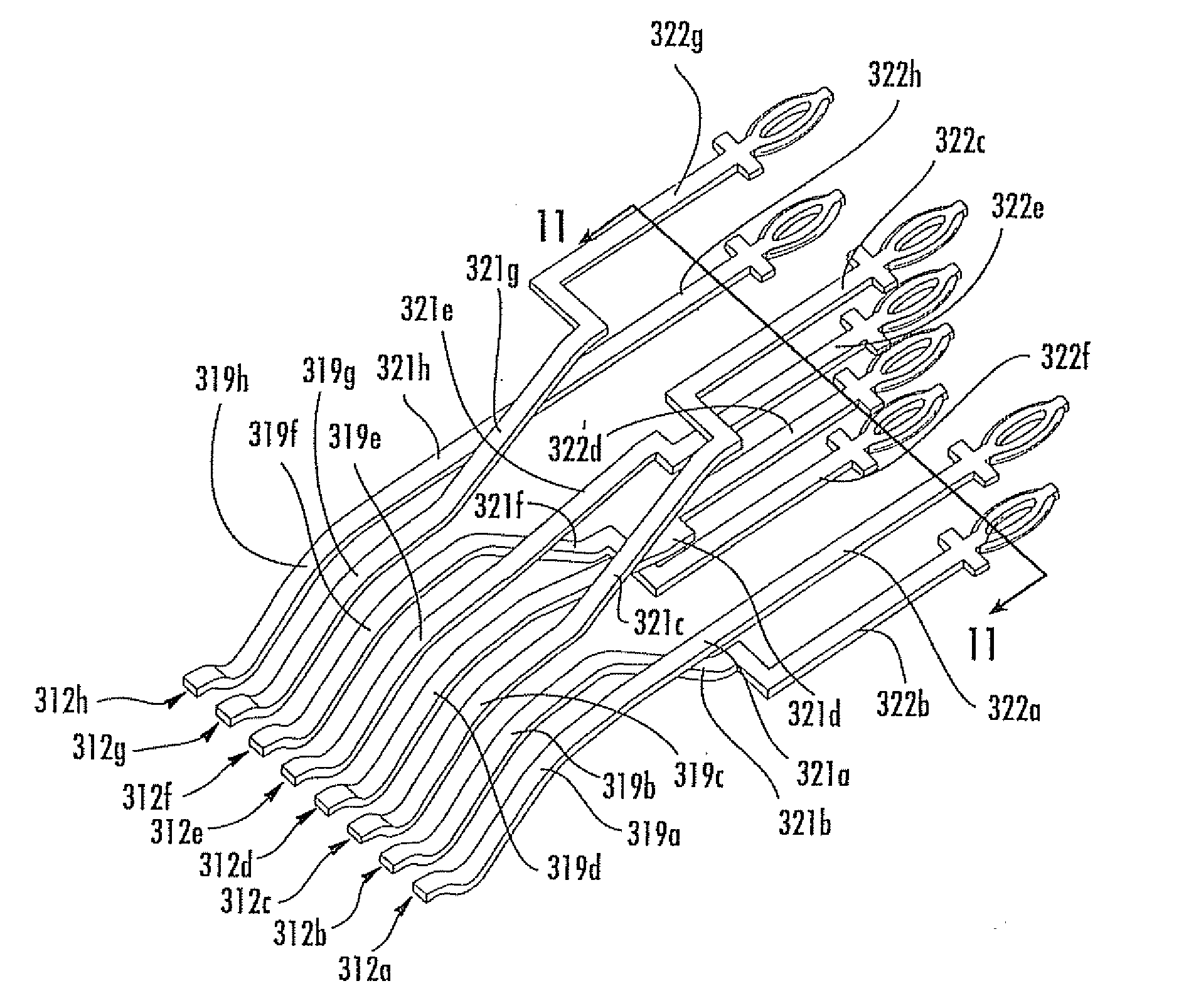

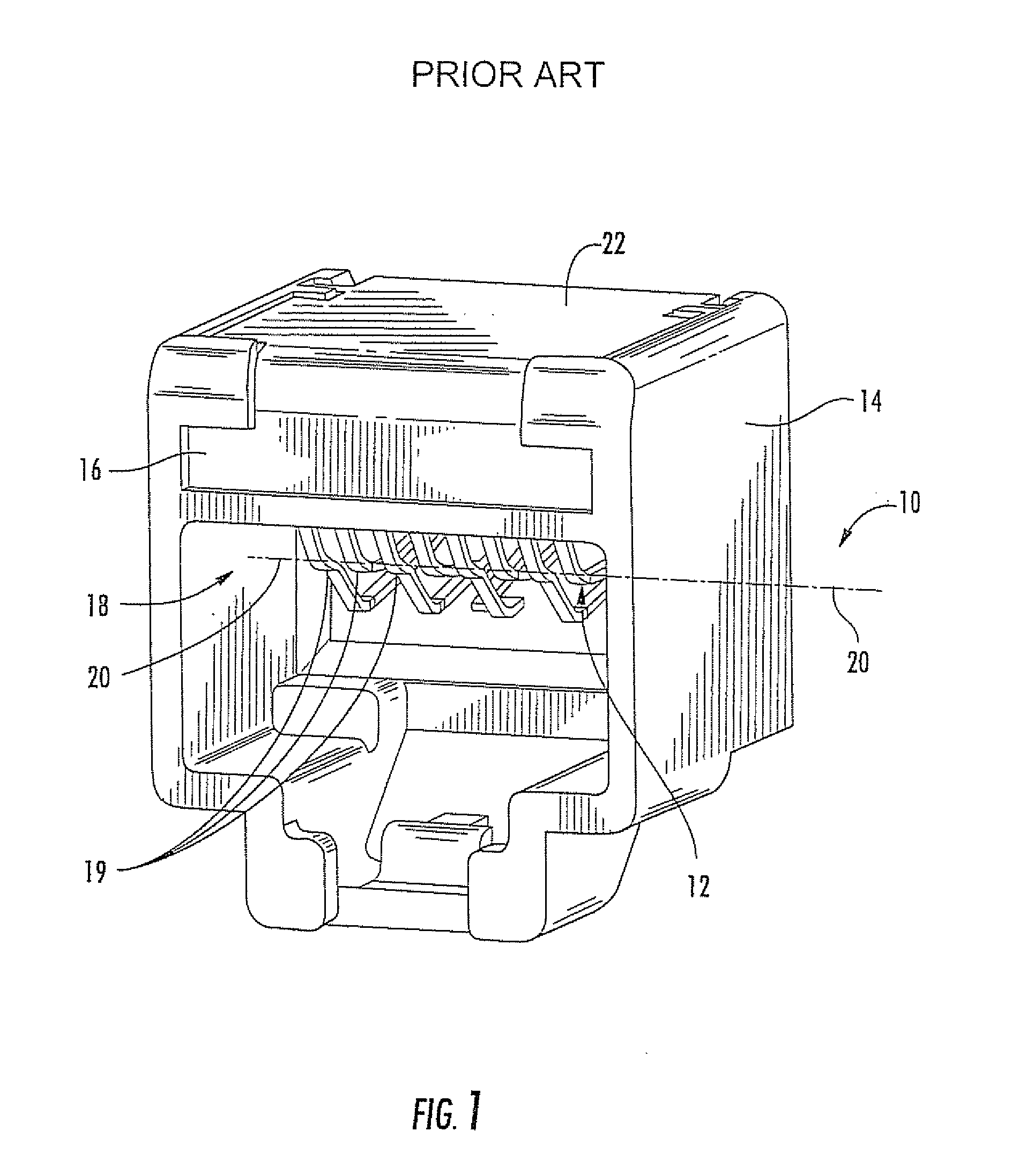

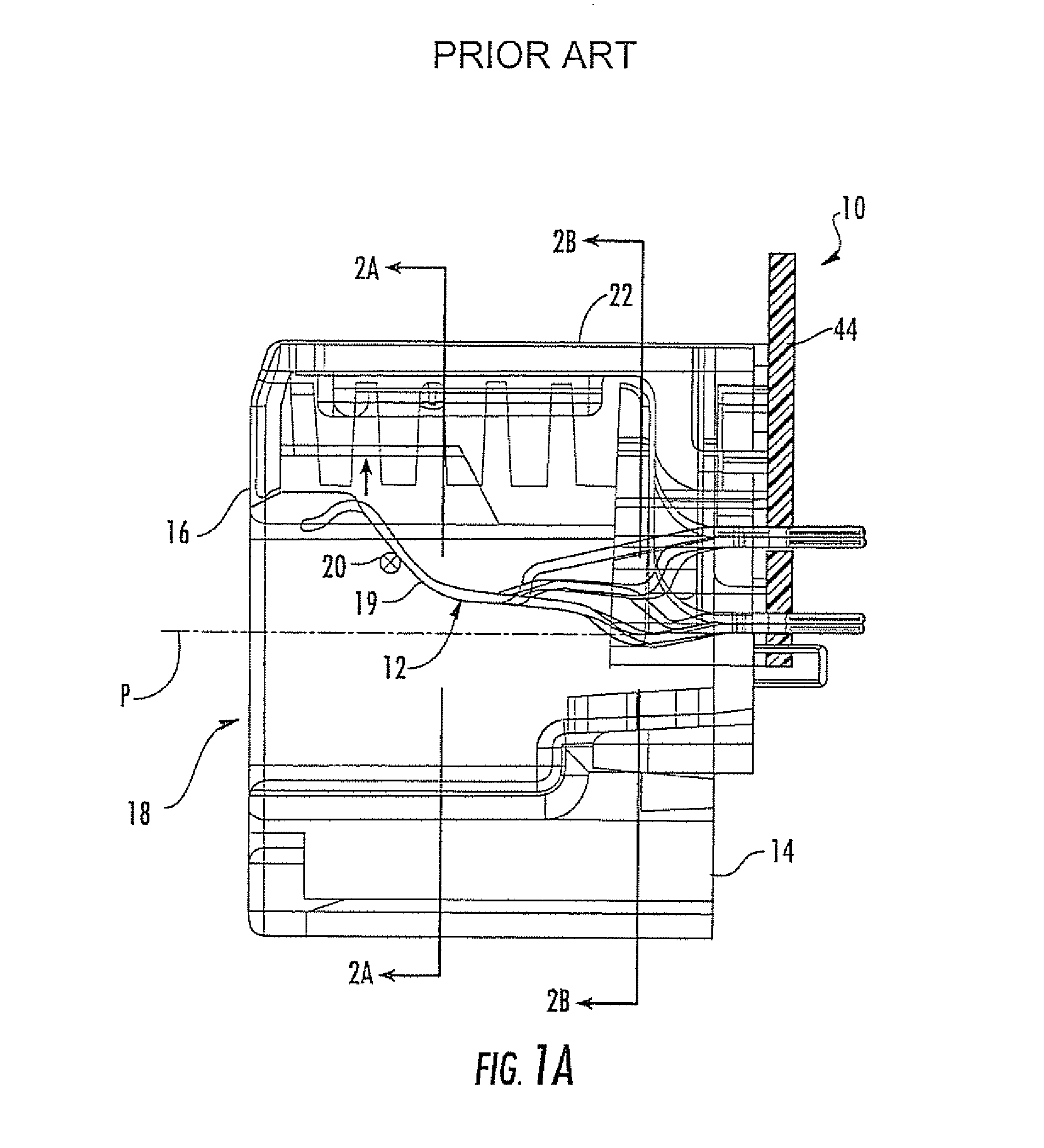

Communications connector with leadframe contact wires that compensate differential to common mode crosstalk

InactiveUS7166000B2Good compensationCoupling device detailsTwo-part coupling devicesElectrical polarityElectrical connection

A communications jack includes: a dielectric mounting substrate; and a plurality of contact wires, each of the contact wires having a contact segment, a compensating segment in electrical connection with the contact segment, and a base in electrical connection with the compensating segment and mounted in the mounting substrate. The contact segments are generally transversely aligned and parallel with each other. The contact segments are arranged in pairs, with a first pair of contact segments being immediately adjacent each other, a second pair of contact segments being immediately adjacent each other and positioned one side of the first pair, a fourth pair of contact segments being immediately adjacent each other and positioned on an opposite side of the first pair, and a third pair of contact segments sandwiching the first pair, with one of the contact segments of the third pair being disposed between the first and second pairs, and the other of the contact segments being disposed between the first and fourth pairs. The compensating segments are configured and arranged such that differential to common mode crosstalk generated between the contact segments of the second and third pairs is opposite in polarity to the differential to common mode crosstalk generated between the compensating segments of the second and third pairs.

Owner:COMMSCOPE INC

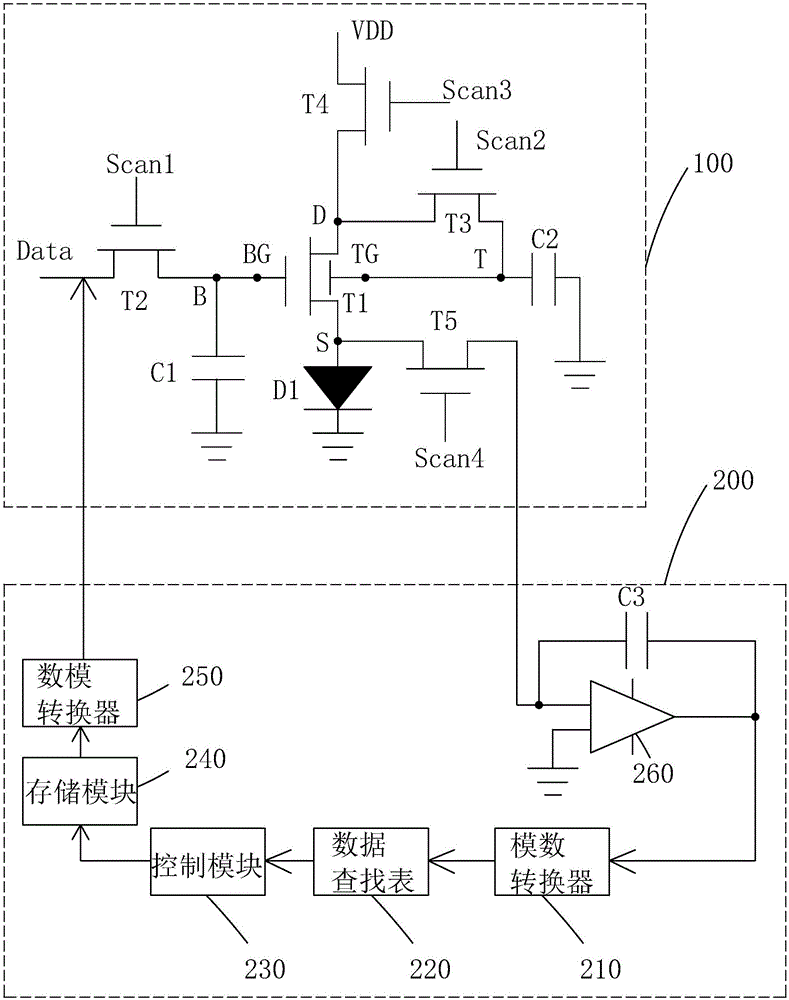

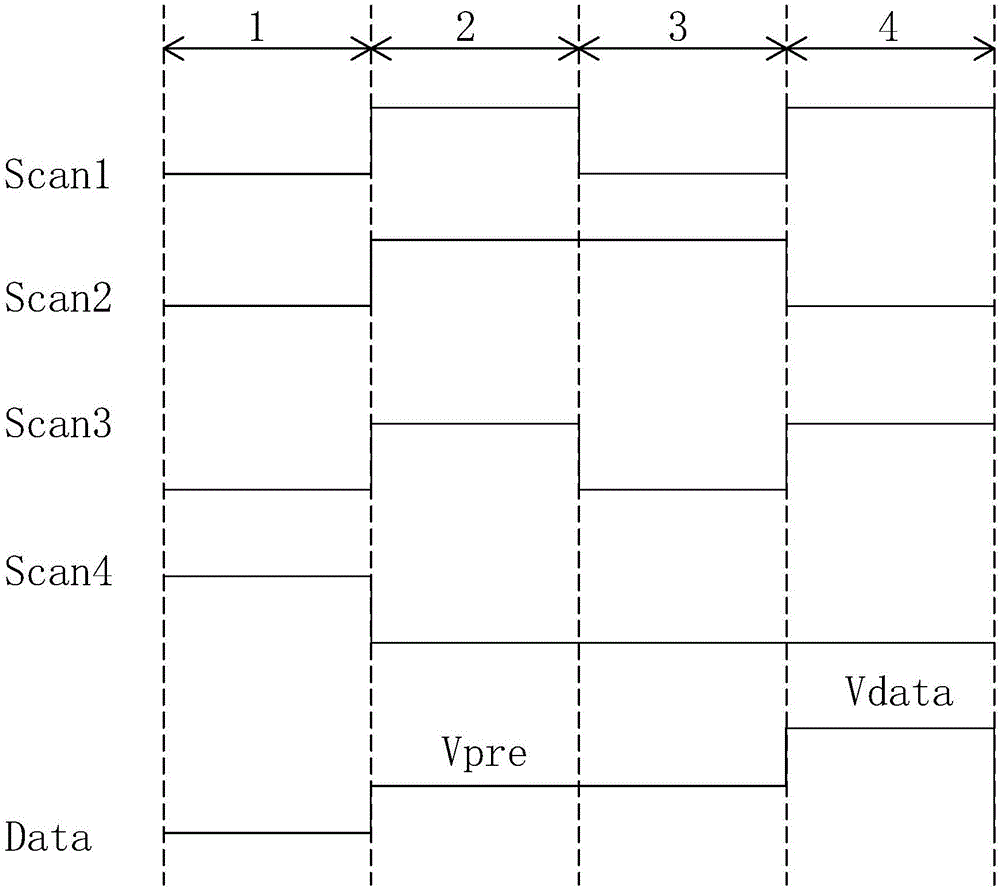

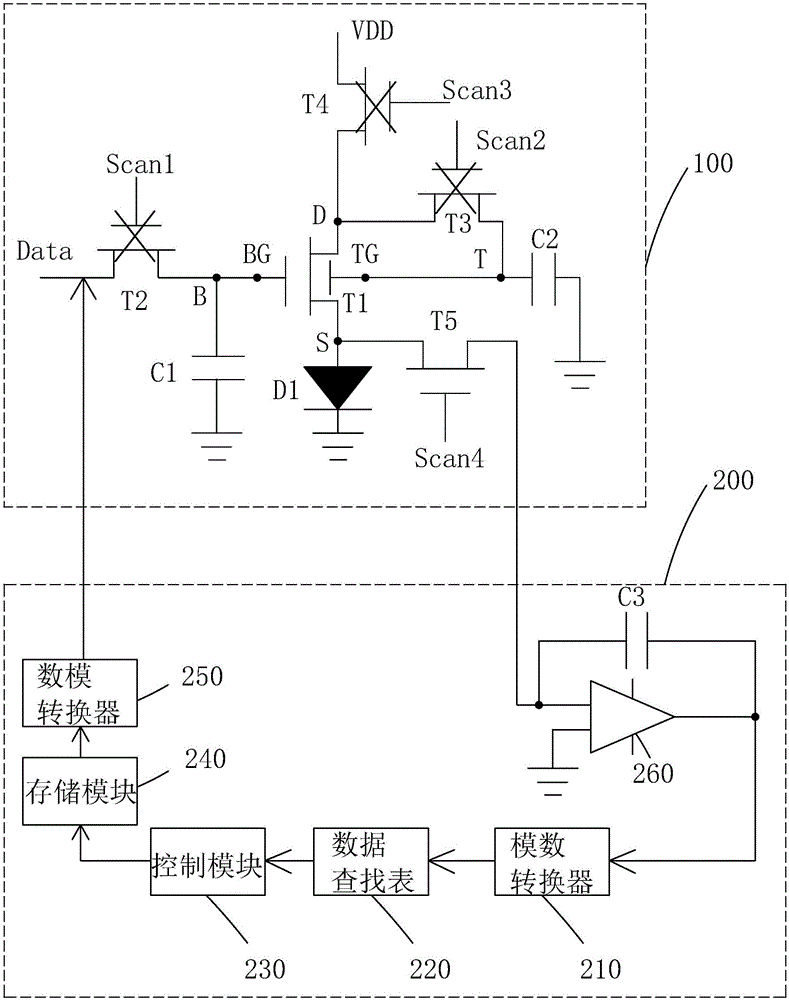

OLED pixel blending compensation circuit and blending compensation method

ActiveCN106504707AUniform luminanceGuaranteed stabilityStatic indicating devicesPower flowCompensation effect

The present invention provides an OLED pixel blending compensation circuit and a blending compensation method. A 5T2C structure is employed and a thin film transistor is driven to compensate the threshold-voltage drift for a pixel internal drive circuit (10) of a bigrid thin film transistor, and an external compensation circuit (200) is employed to compensate the non-uniform brightness of an organic light-emitting diode (D1) caused by aging and declination. Through combination of the rapid internal compensation operation speed and the big external compensation range, the OLED pixel blending compensation circuit and the blending compensation method have better compensation effects, simplify the data signals (Data) and realize the uniform brightness of the panel through the stability of the OLED current.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

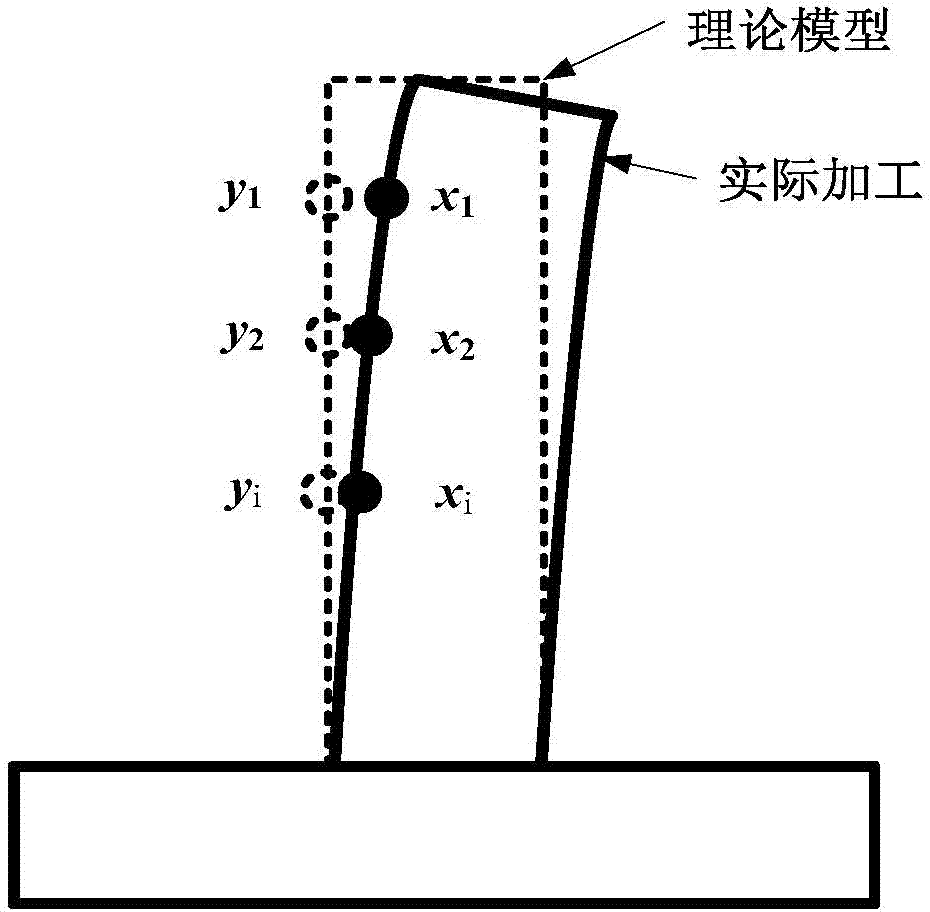

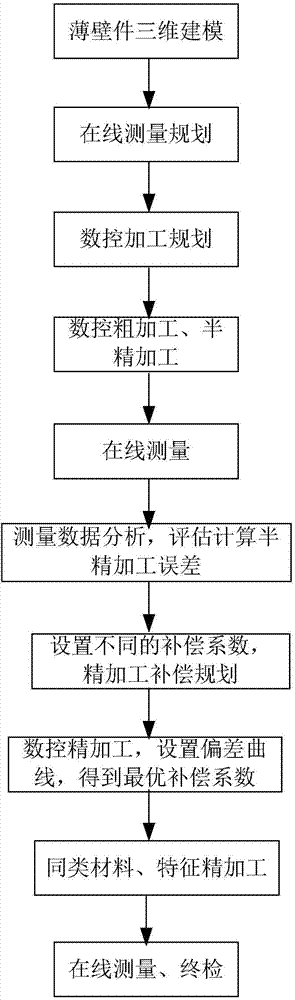

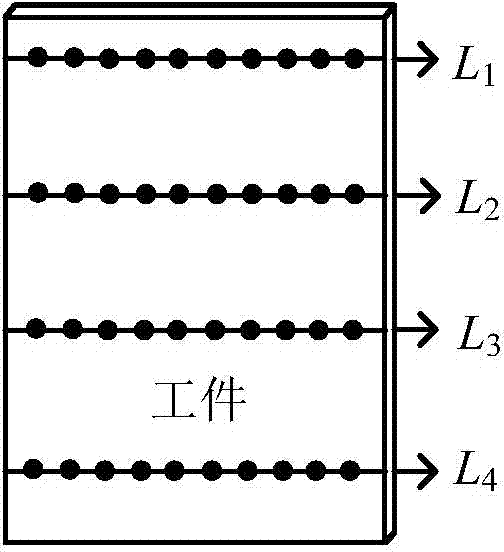

Online milling deformation measurement and complementation machining method for thin-walled part

ActiveCN104759942AAvoid insufficient boundary conditionsGood compensationGeometric CADMachine tool componentsNumerical controlMeasurement point

The invention discloses an online milling deformation measurement and complementation machining method for a thin-walled part. The online milling deformation measurement and complementation machining method for the thin-walled part comprises the steps that 1, a three-dimensional model of the thin-walled part is established, and a numerical control code is obtained; 2, measurement point locations are extracted from the three-dimensional model; 3, based on the model, a measurement path is planned; 4, rough machining and semi-precise machining are conducted on a workpiece blank; 5, online measurement is conducted, and the coordinate values of all the planed measurement point locations are obtained; 6, the obtained coordinate values of the planed measurement point locations are compared with those of the corresponding point locations on the three-dimensional model of the thin-walled part, and the difference between the coordinates of each point location of the actually machined workpiece and those of the corresponding point location on the three-dimensional model is calculated; 7, according to the machining differences, a complementation factor optimal machining path is generated according to the machining differences, precise machining is conducted according to the path, and then the final deformation deviation and the compensation values are obtained. By the adoption of the online milling deformation measurement and complementation machining method, semi-precise machining and precise machining are adopted, the identical machining parameters are adopted by the semi-precise machining and the precise machining, and the best precise machining compensation effect of the thin-walled parts which are made of the same materials and have the same characteristics can be achieved to the greatest extent through only one group of tests.

Owner:HUAZHONG UNIV OF SCI & TECH

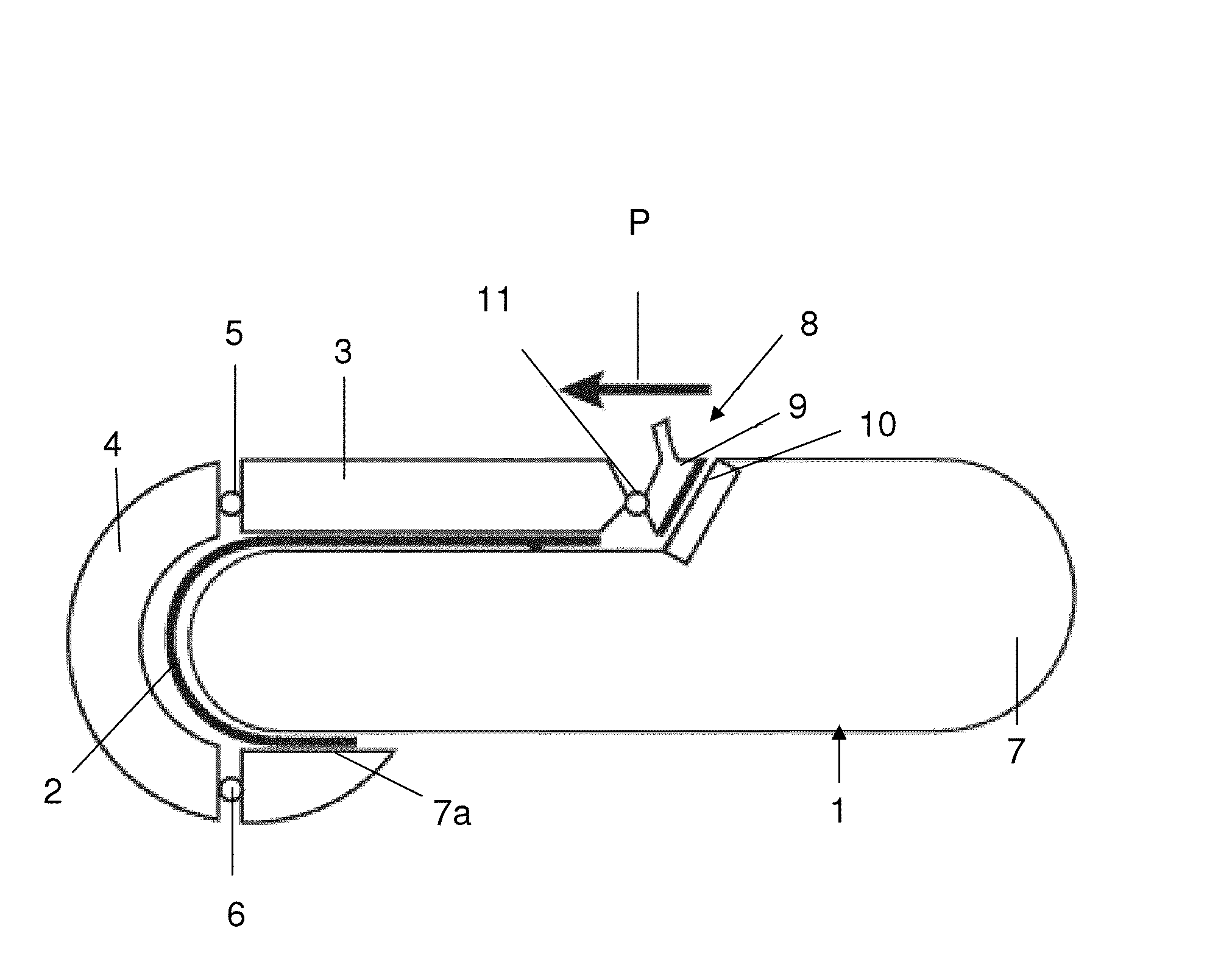

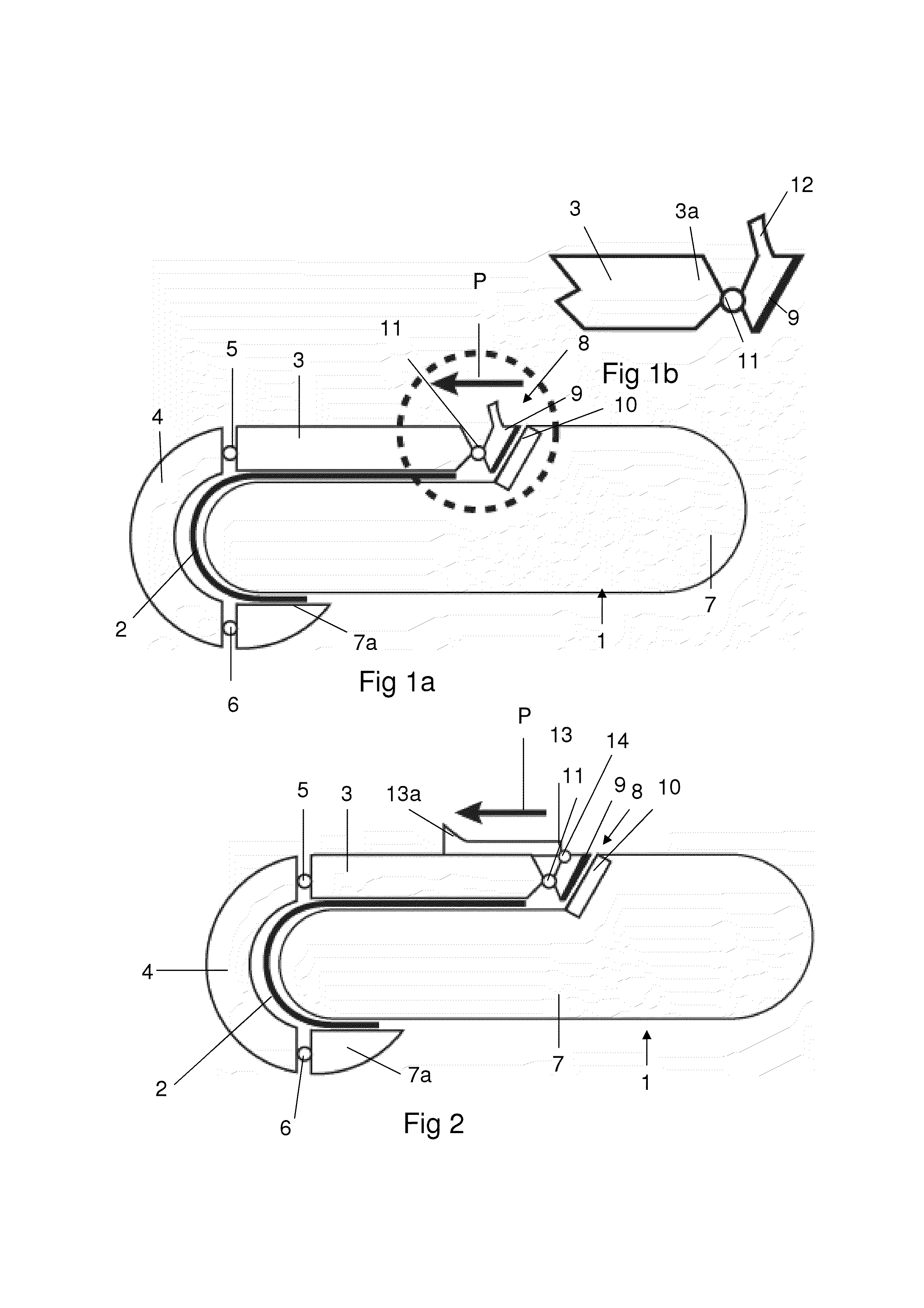

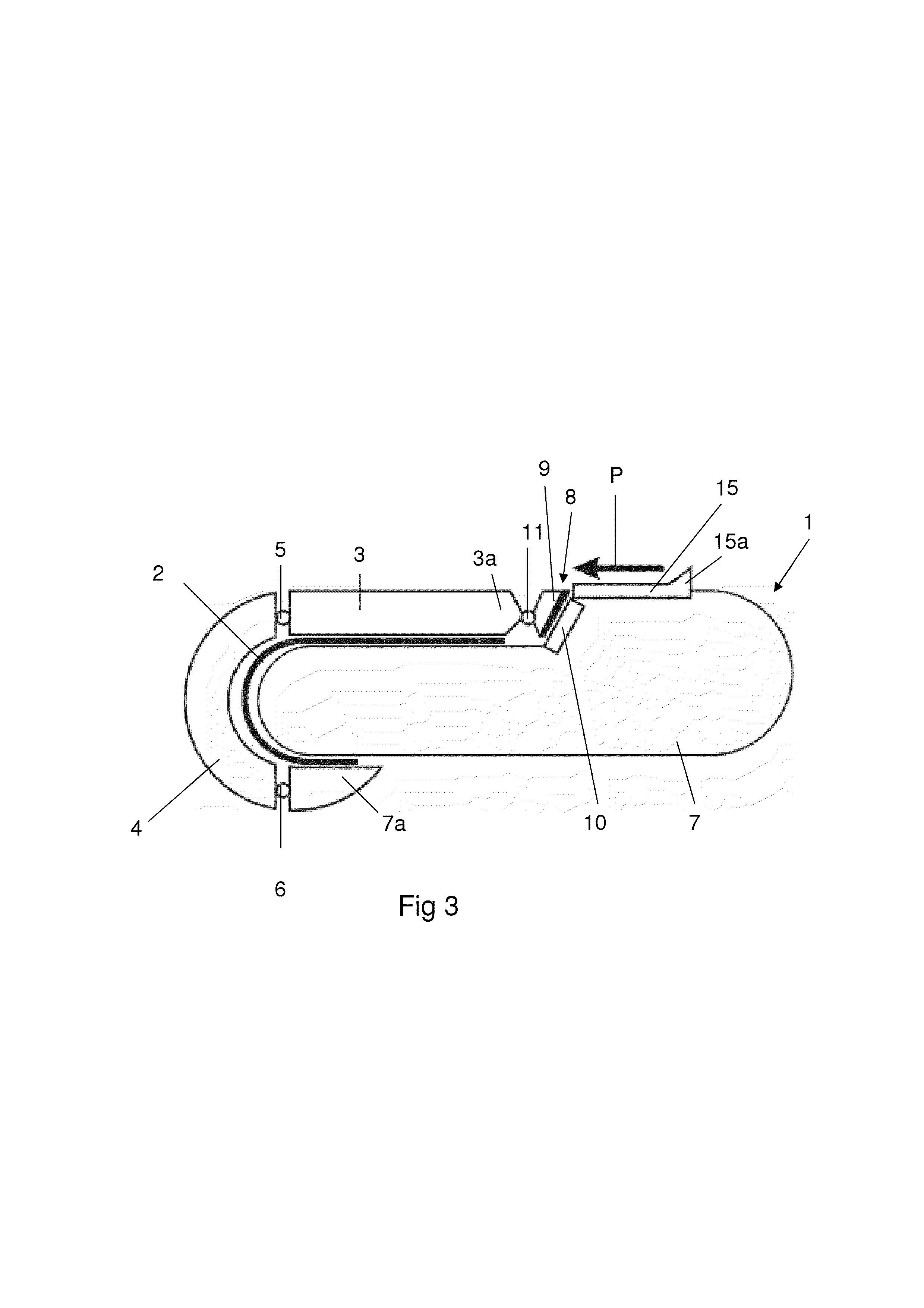

Display device with flexible display

InactiveUS20130180882A1Good compensationDigital data processing detailsRigid containersDisplay deviceEngineering

The invention relates to a display device (1) with a device body (7), a continuous flexible display (2) and an elongated support frame configured to support the flexible display, being provided with mutually movable connected frame portions (3,4) and being hingeably connected at a first end (7a) with the device body (7) between a closed configuration for fixing the flexible display in a wrapped storage position and an open configuration. The display device (1) comprises magnetic closing means (8) being provided with a first locking part (9) being movable connected with a major part of the support frame and being capable for magnetically locking of a second end (3a) of the support frame in the closed configuration to the device body (7) and being provided with at least one unlocking member (12) enabling a manual unlocking of said second end (3a) from the device body (7).

Owner:SAMSUNG ELECTRONICS CO LTD

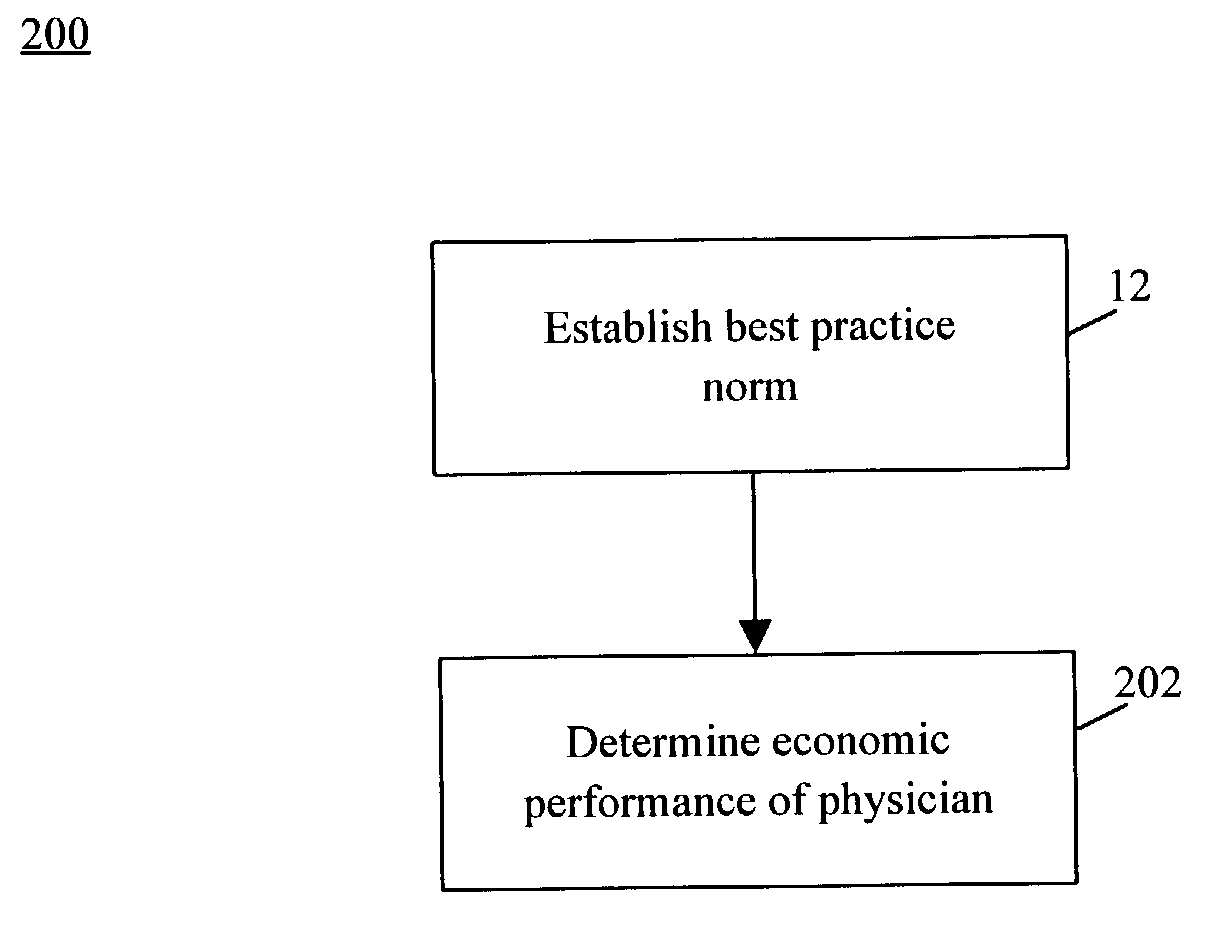

Method and system for gainsharing of physician services

ActiveUS7546245B2Impose significant, additional data collection burdens on providersEfficient and inexpensiveFinanceDigital computer detailsPaymentSeverity/Intensity

The invention relates to a method and system of physician economic performance evaluation in which the relative medical difficulty associated with patients admitted by a particular physician is determined and, given that measurement, judgments made concerning the relative amount of inpatient resources that the physician required. Also, one application of the present invention relates to a method for gainsharing of physician services using a surplus allocation methodology for rewarding physicians in relation to their performance. An incentive pool is determined from previous patient claims and payments made to physicians in advance, such as in a base year. Best practice norms are established for a plurality of classified diagnosis groups. In one embodiment of the present invention, the classified diagnosis related groups are adjusted for severity of illness to compensate for actual clinical challenges faced by individual physicians. The best practice norms can be used in the surplus allocation method for determining physician performance. The incentive is established proportional to the relationship between a physician's individual performance and the best practice norm.

Owner:AMS APPLIED MEDICAL SOFTWARE

Flexible video displays and their manufacture

ActiveUS7705826B2Simple configurationGood compensationStatic indicating devicesNon-linear opticsGamutWindow shutter

A flat panel display has a linear array of switchable light emitting diodes (“LEDs”) to emit bands of light across the display, providing a light pattern programmable at video frequencies and a two-dimensional electropolymeric shutter array to convert the light pattern into a video image. The light pattern can be varied or controlled spatially, with respect to both hue and intensity, by suitable drive signals, at points along the array determined by the location of individual LEDs, or groups of LEDs, and temporally as the shutters in the array are opened and closed to provide a pleasing full color gamut for every pixel in the display. Closed shutters, displaying a reflective appearance, can be employed for background or other effects. The shutter array can be flexibly constructed and supported on a flexible substrate to provide a flexible display.

Owner:NEW VISUAL MEDIA GROUP