Patents

Literature

61results about How to "Available area" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

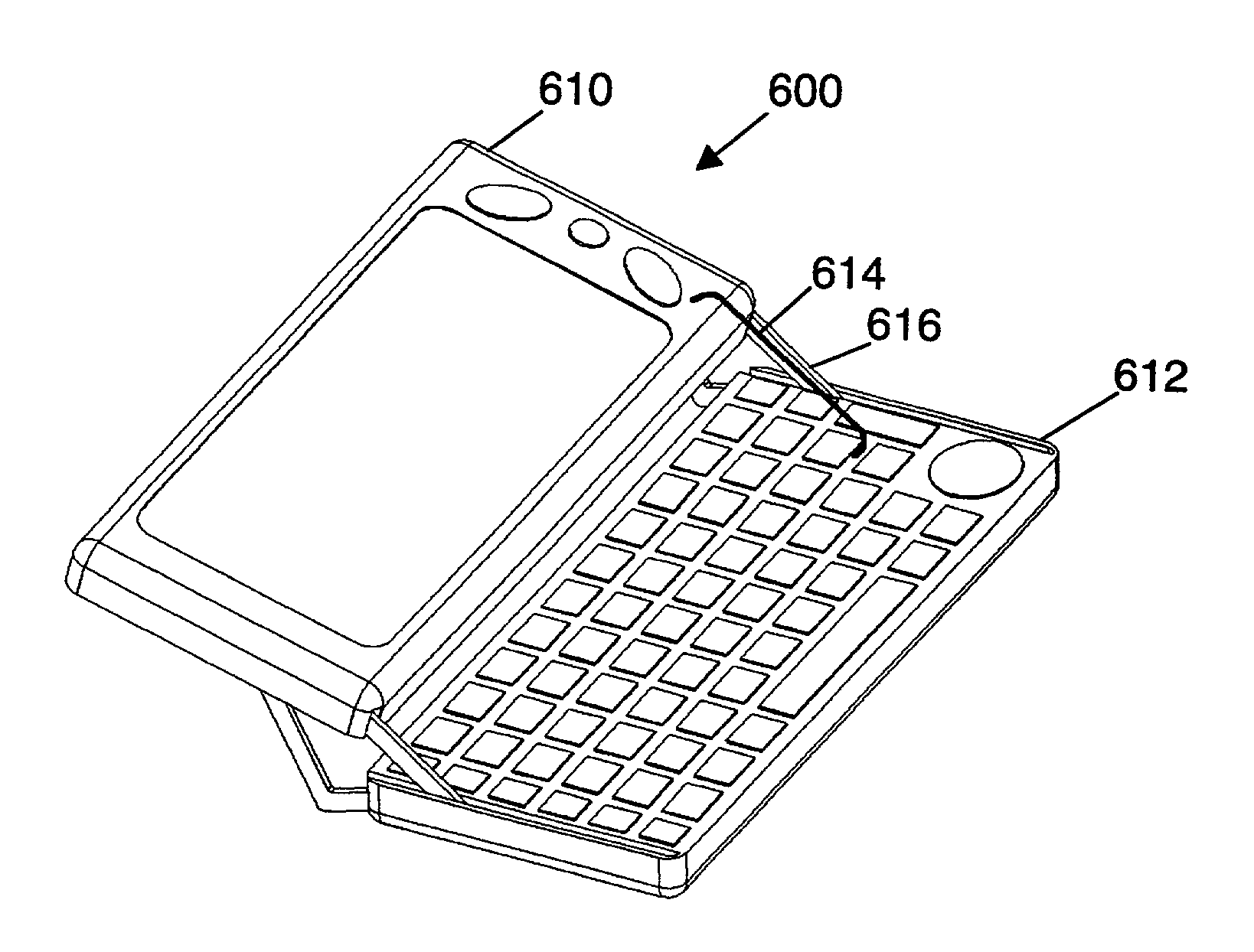

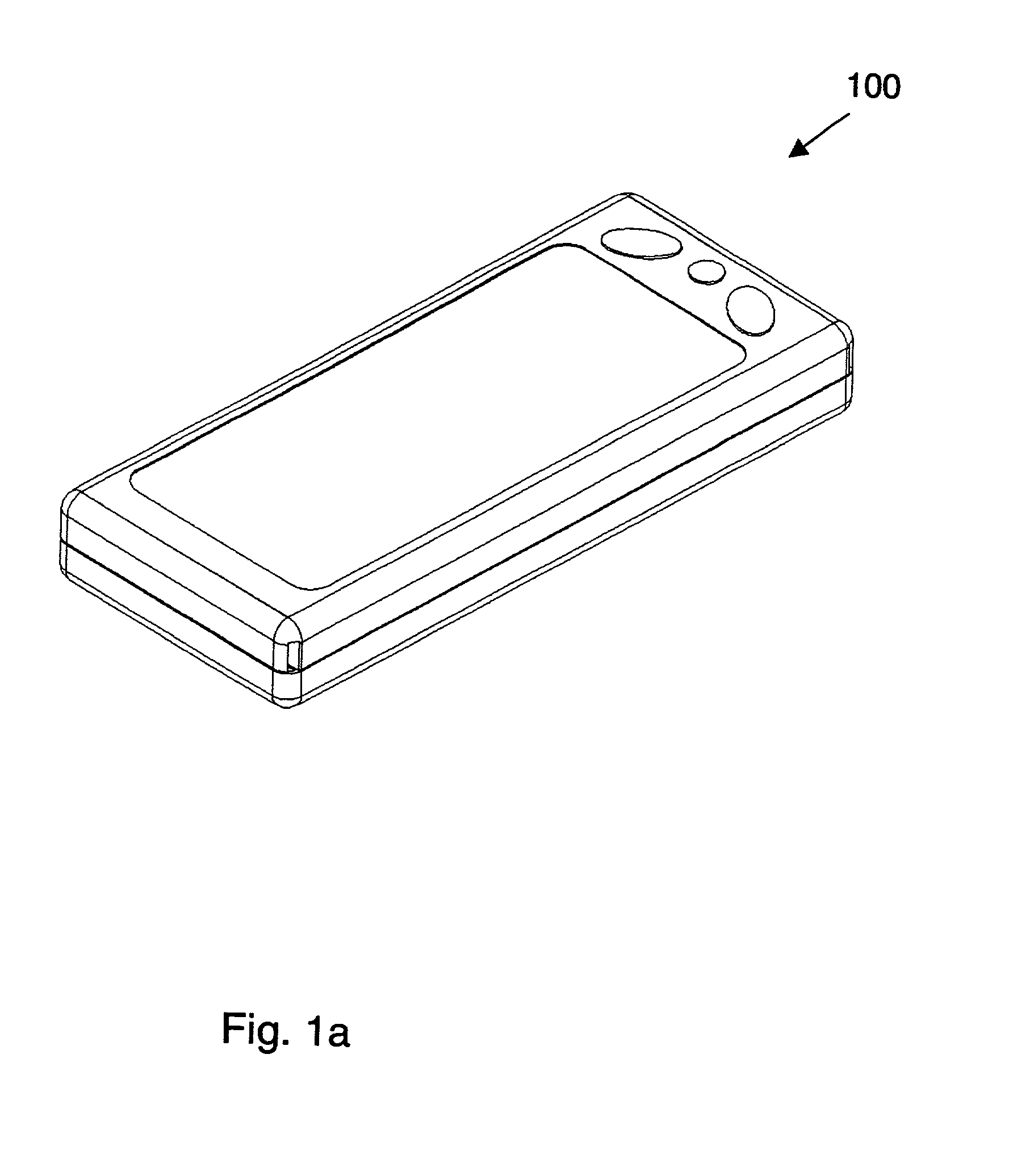

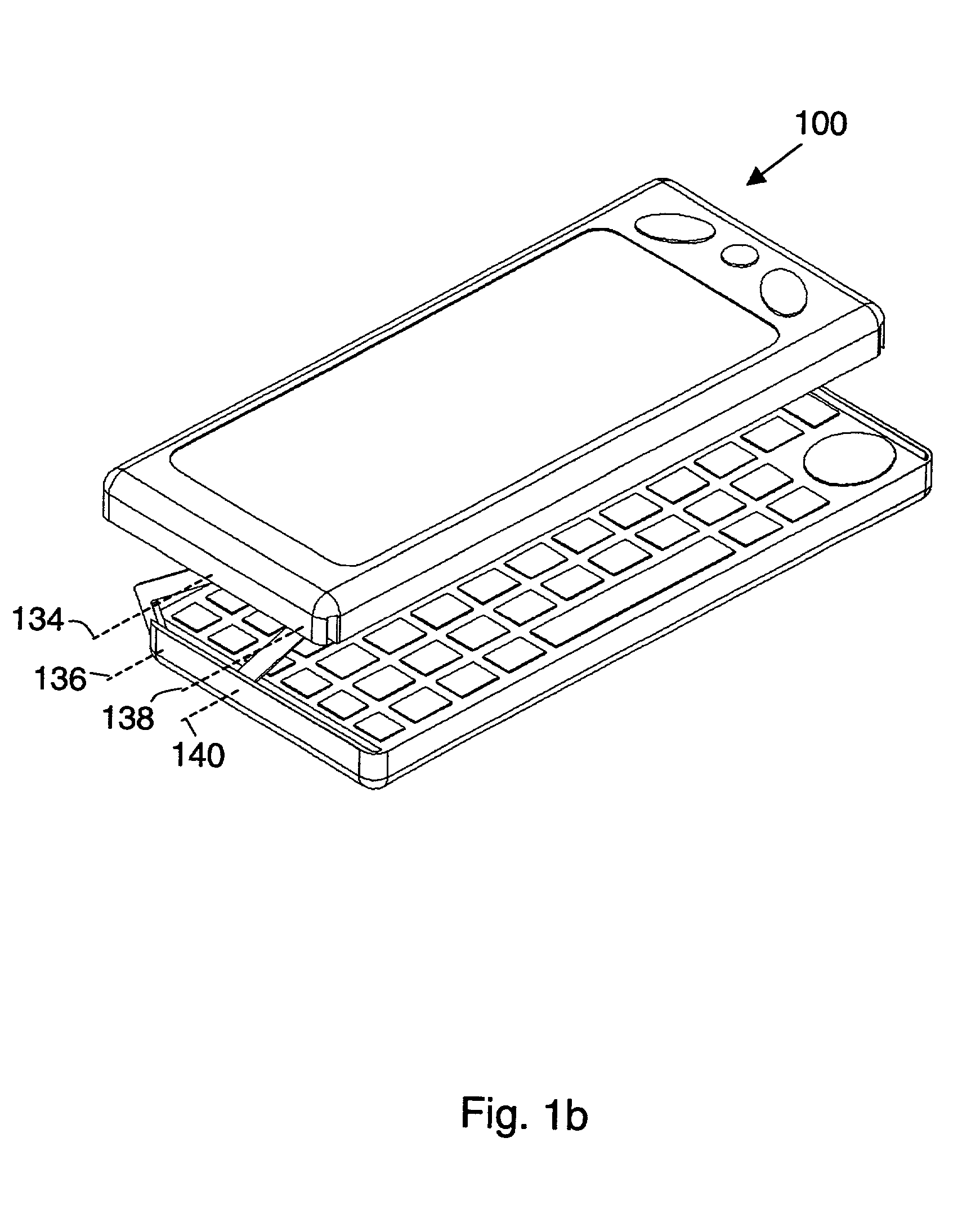

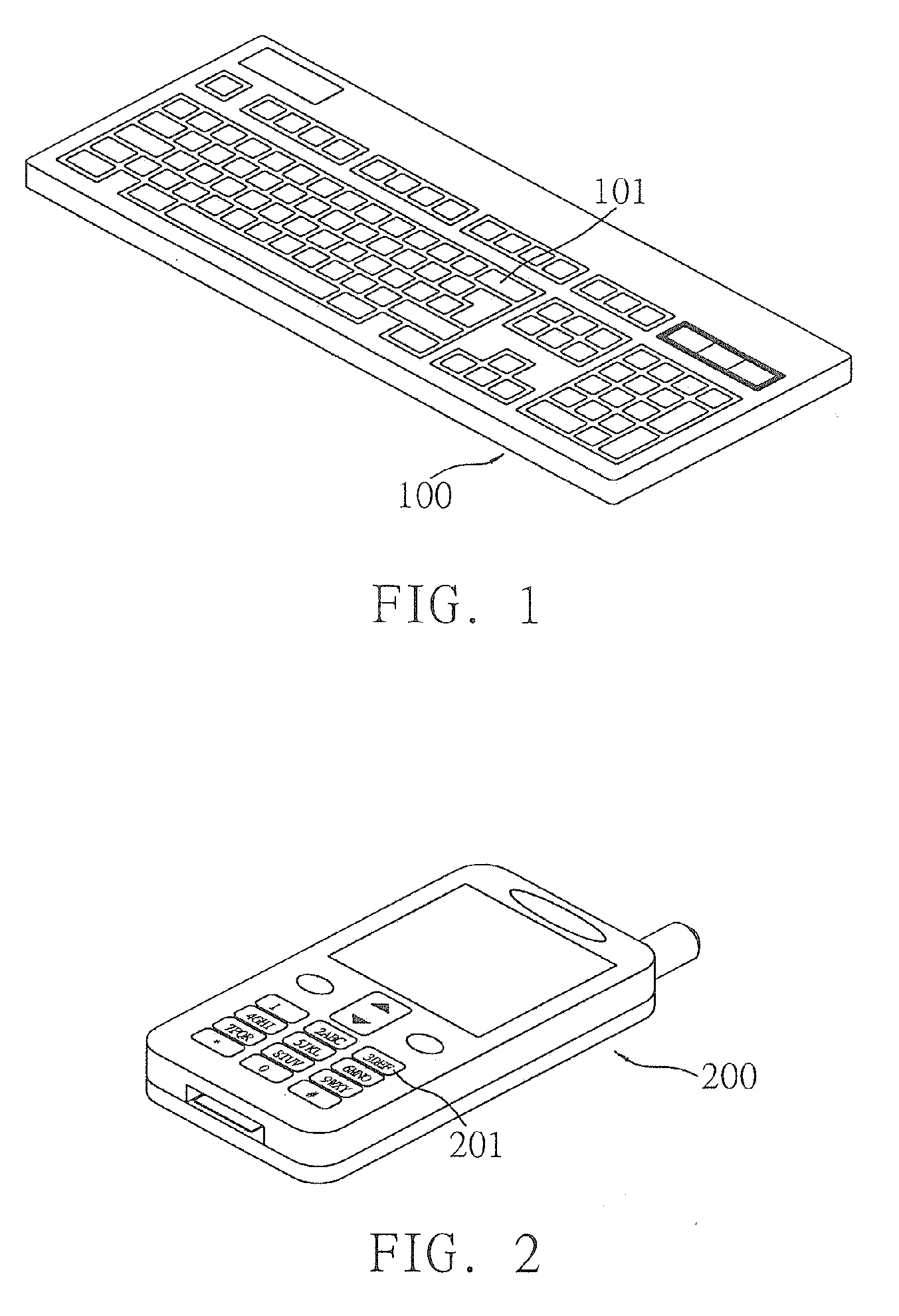

Portable electronic devices

ActiveUS7158634B2Available areaEasy to useInput/output for user-computer interactionInterconnection arrangementsDisplay deviceEngineering

Owner:NOKIA TECHNOLOGLES OY

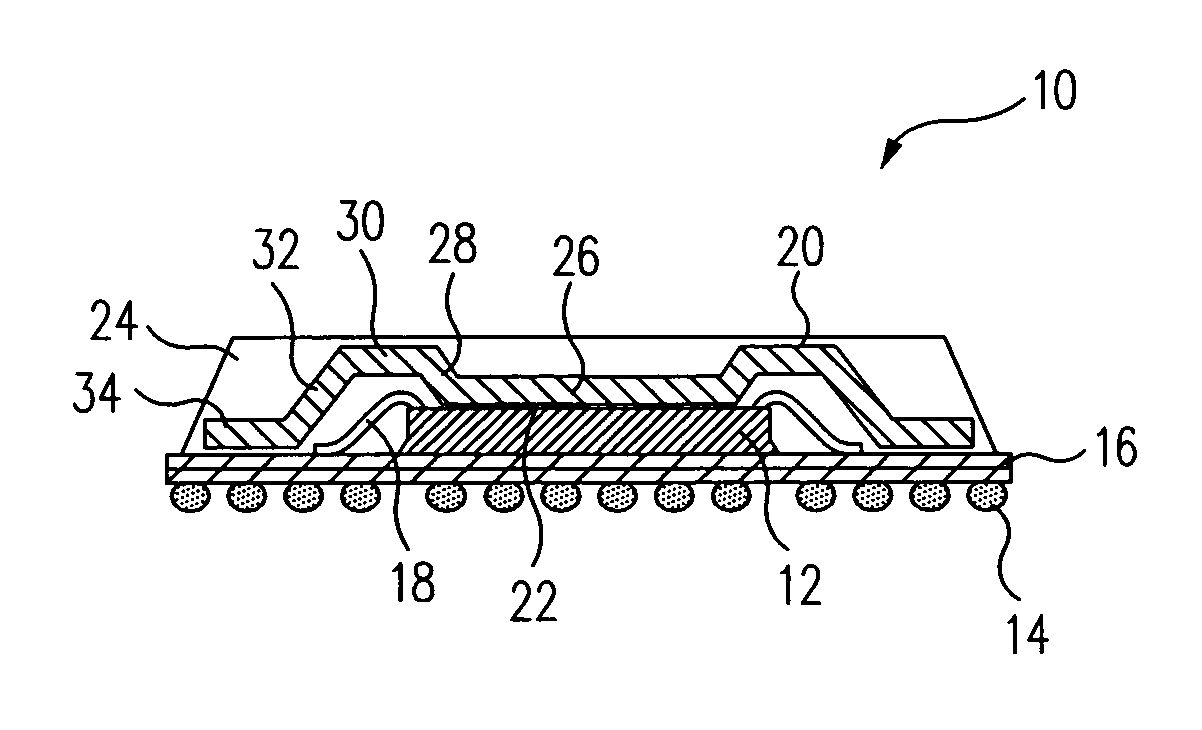

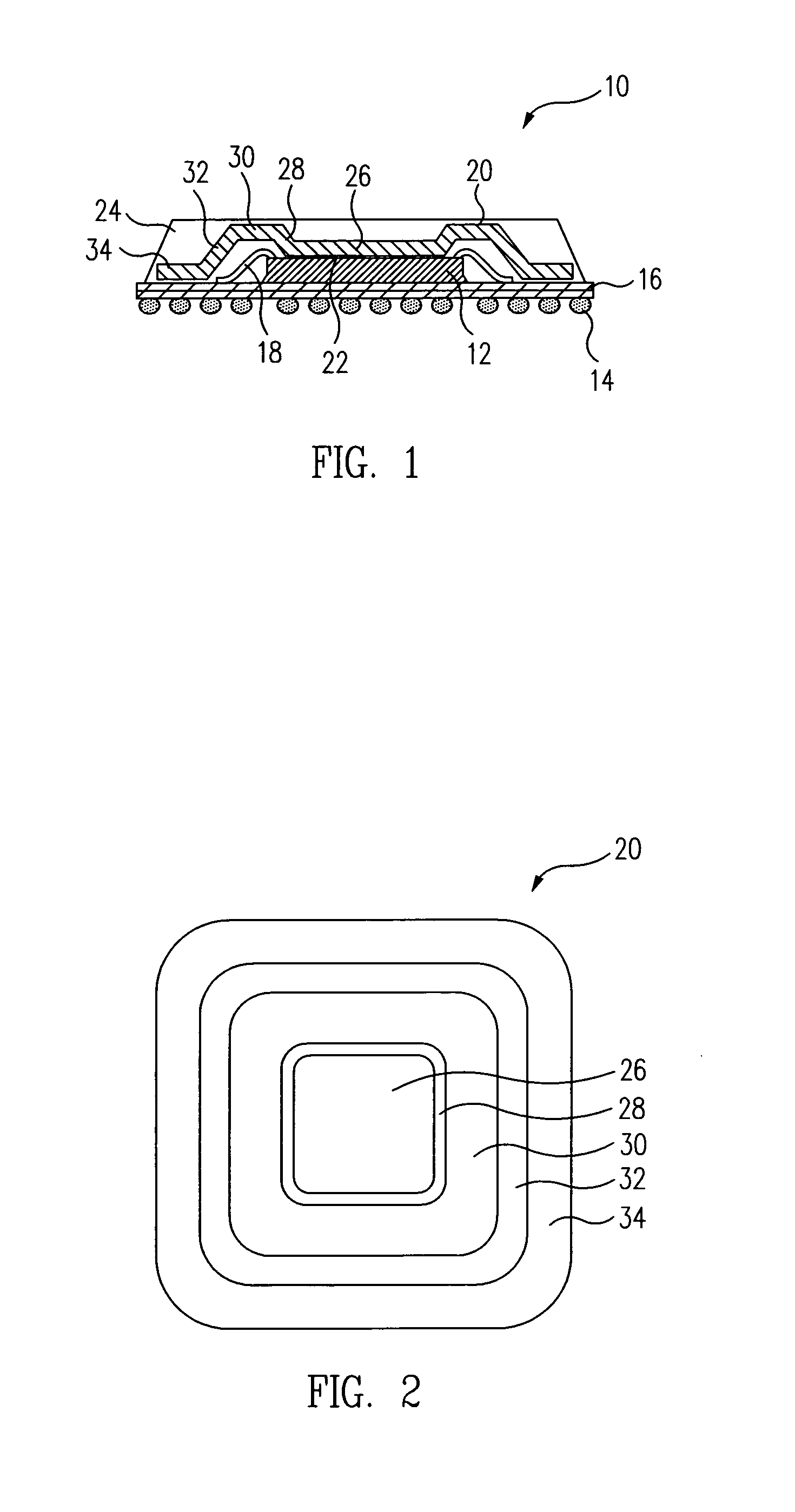

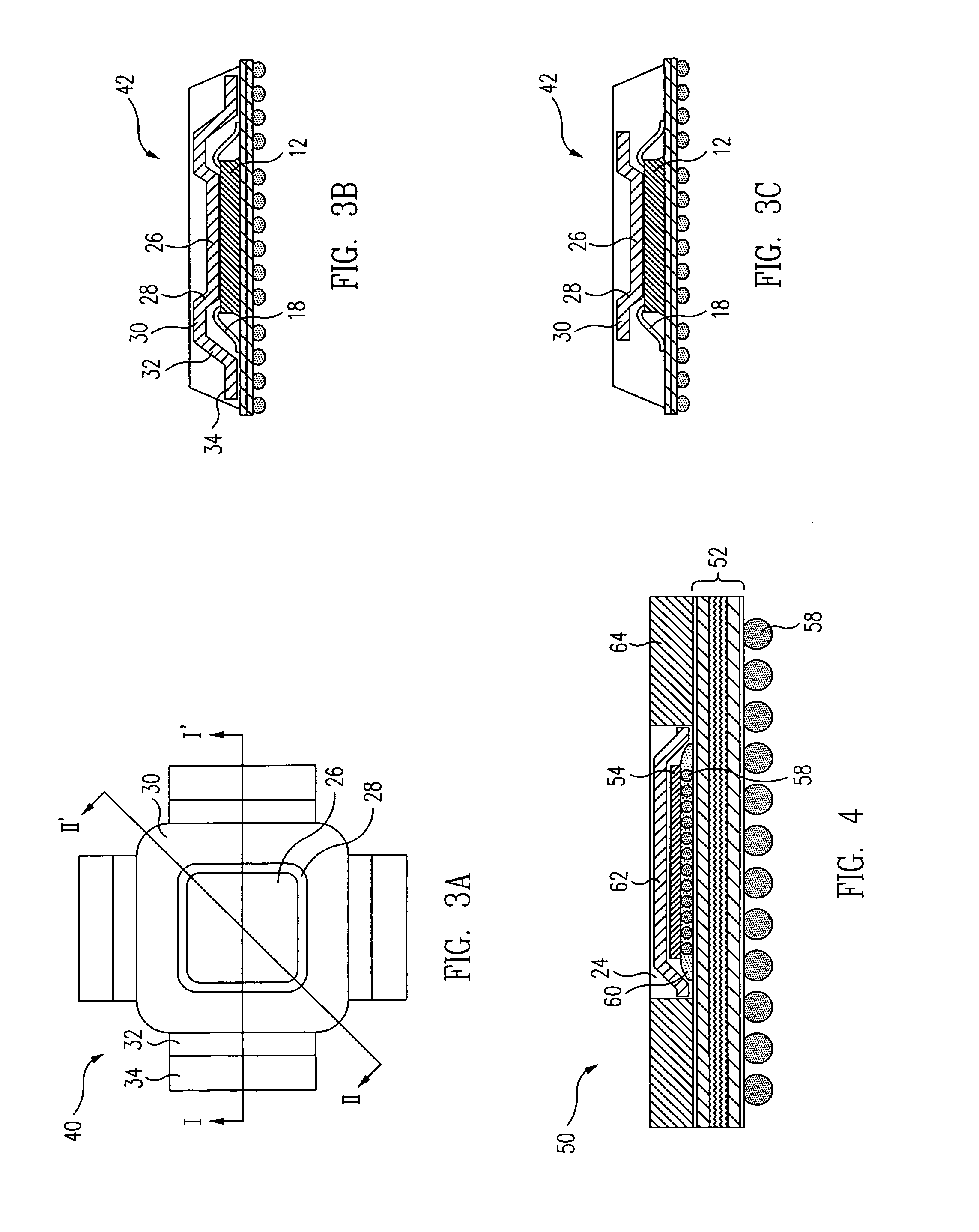

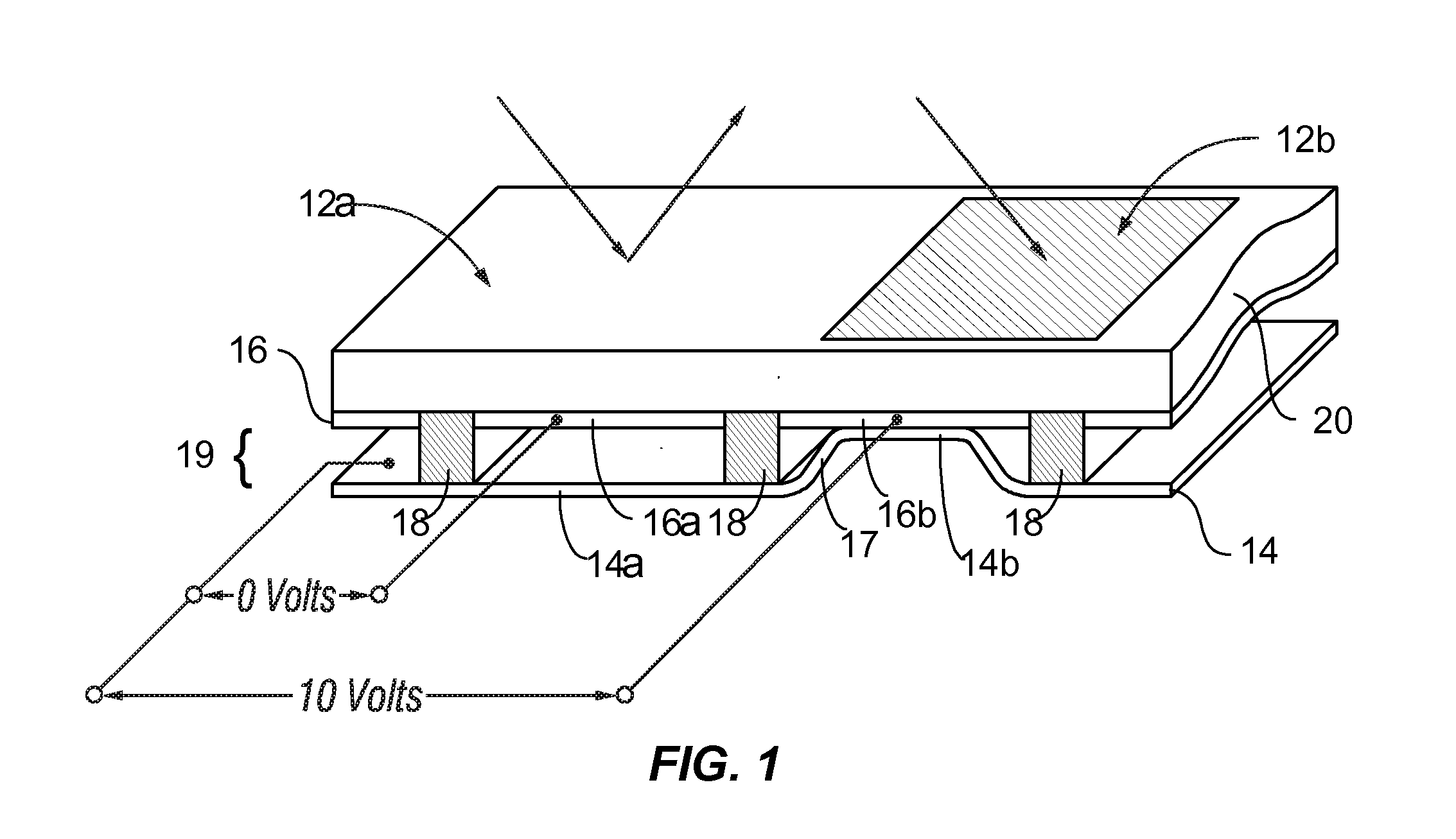

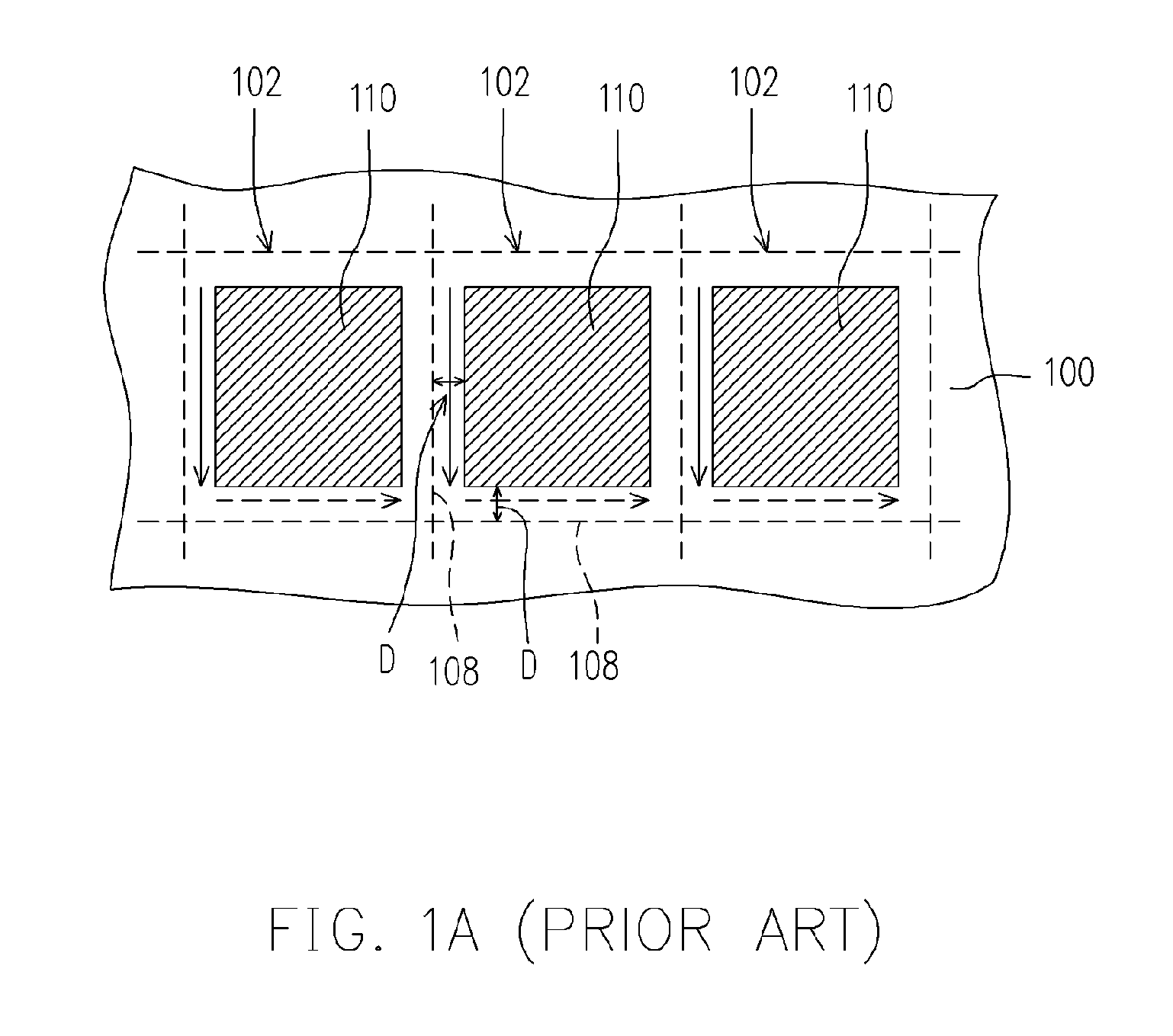

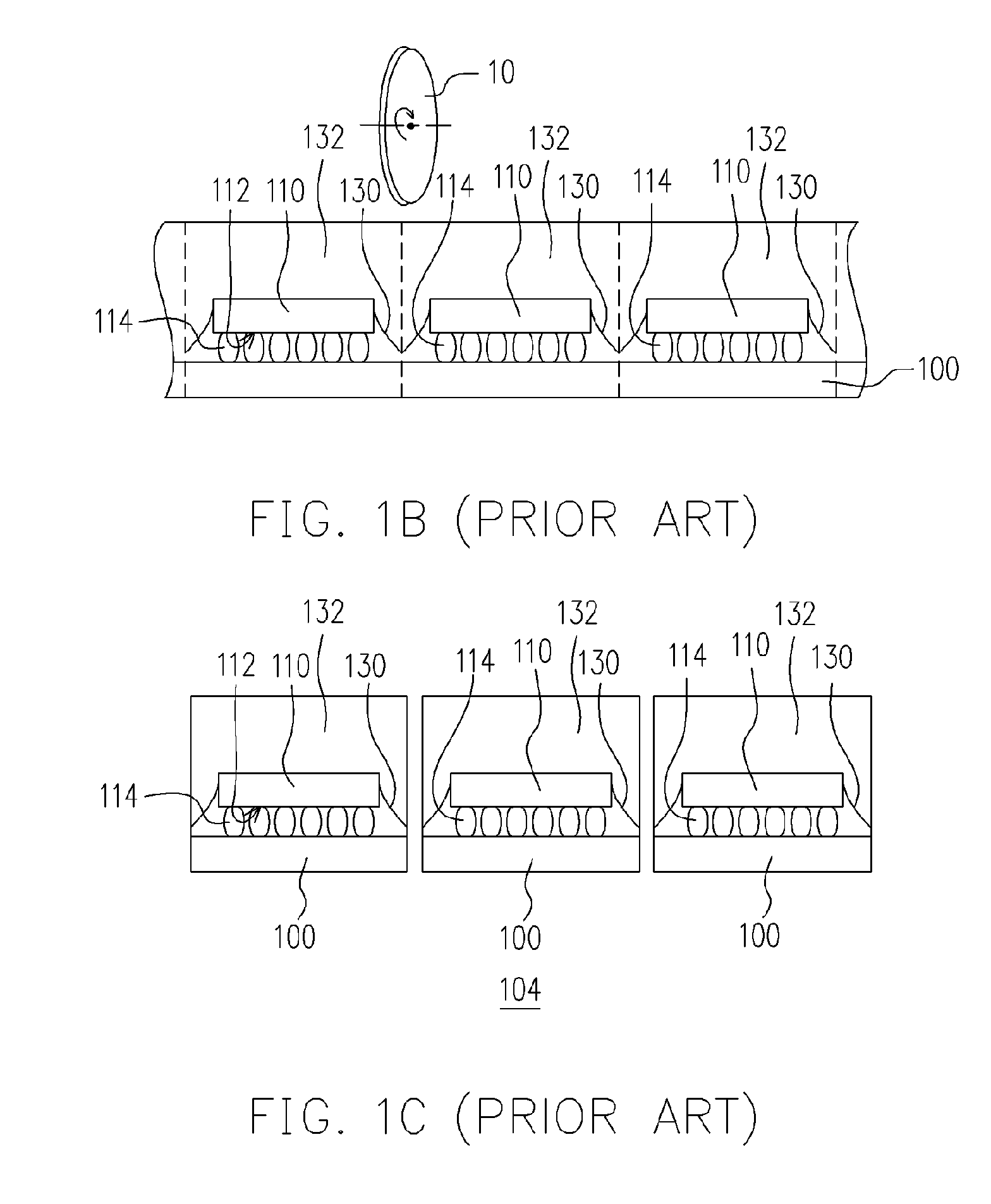

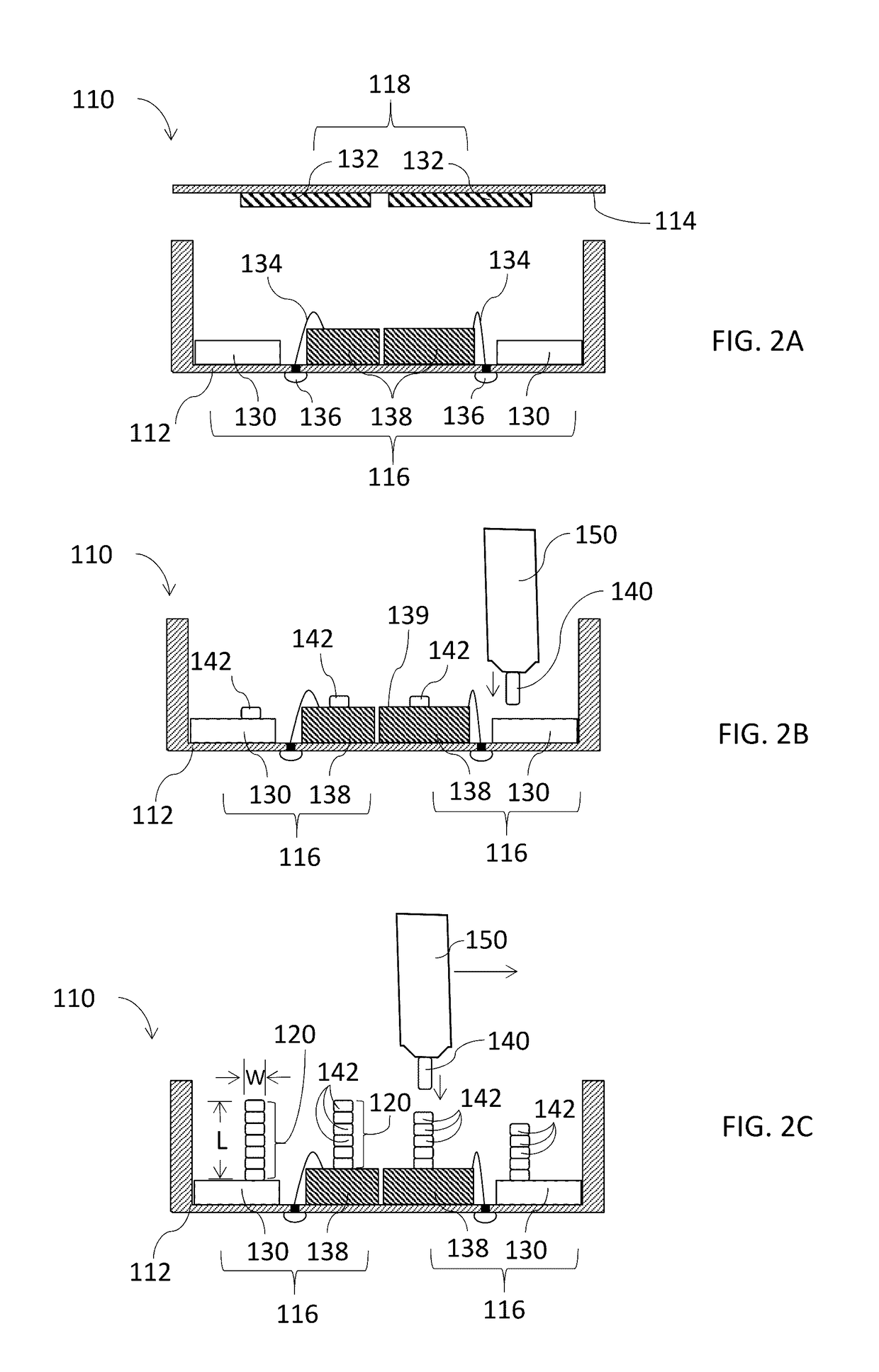

Embedded heat spreader ball grid array

InactiveUS7126218B1Reduce thermal resistanceSacrificing thermal performanceSemiconductor/solid-state device detailsSolid-state devicesInterconnectionBall grid array

A heat slug or spreader is attached directly to a surface of the die in a ball grid array (BGA) package. The heat spreader roughly conforms to the topological profile of the die, underlying substrate, and electrical interconnections between the die and the substrate, such as bond wires. The outer portion of the heat spreader substantially cover the outer portion of the substrate, or alternatively, cover only those portions extending in laterally from the sides of the chip and not the corners. An encapsulant completely covers the heat spreader and die.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

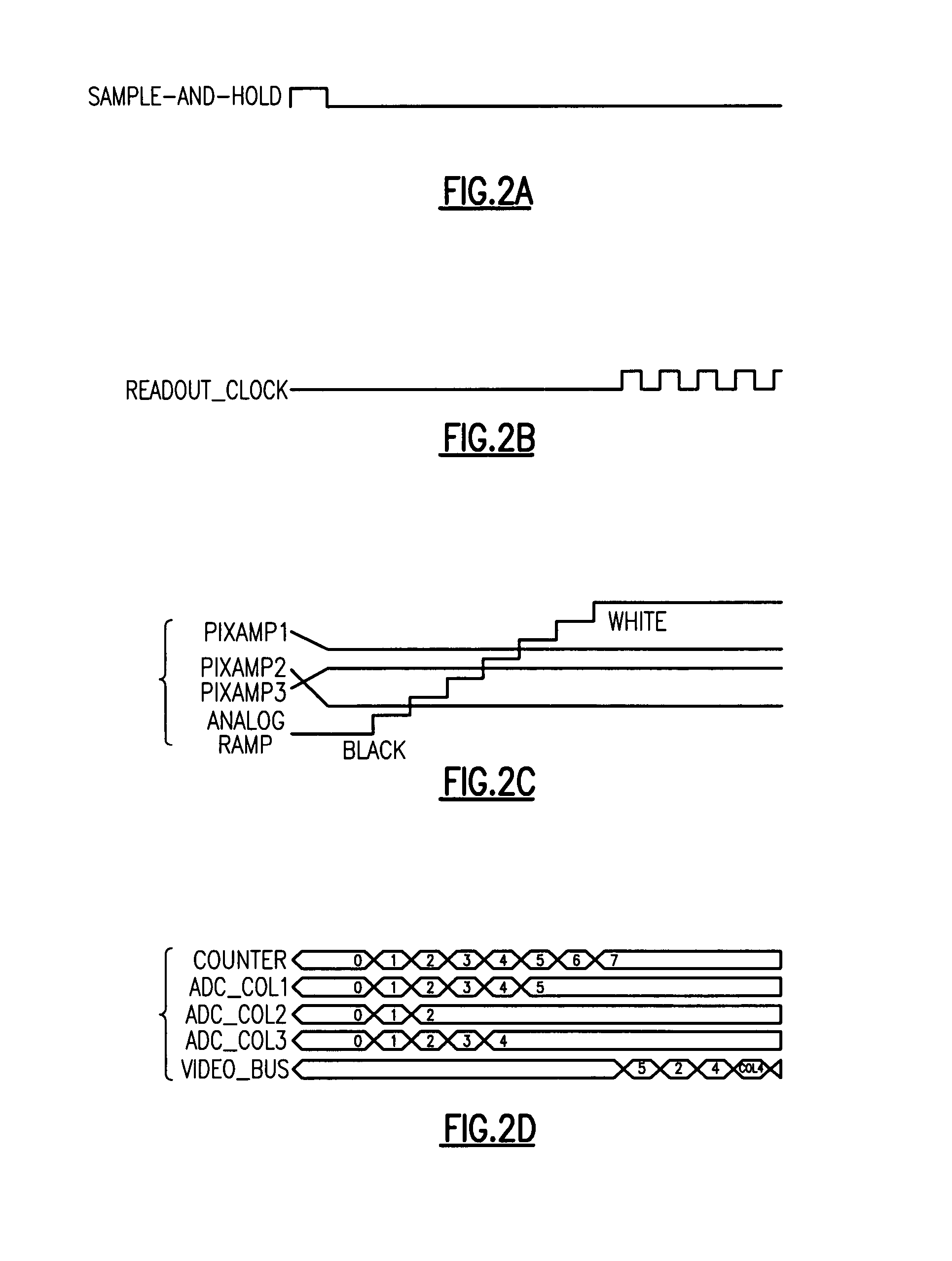

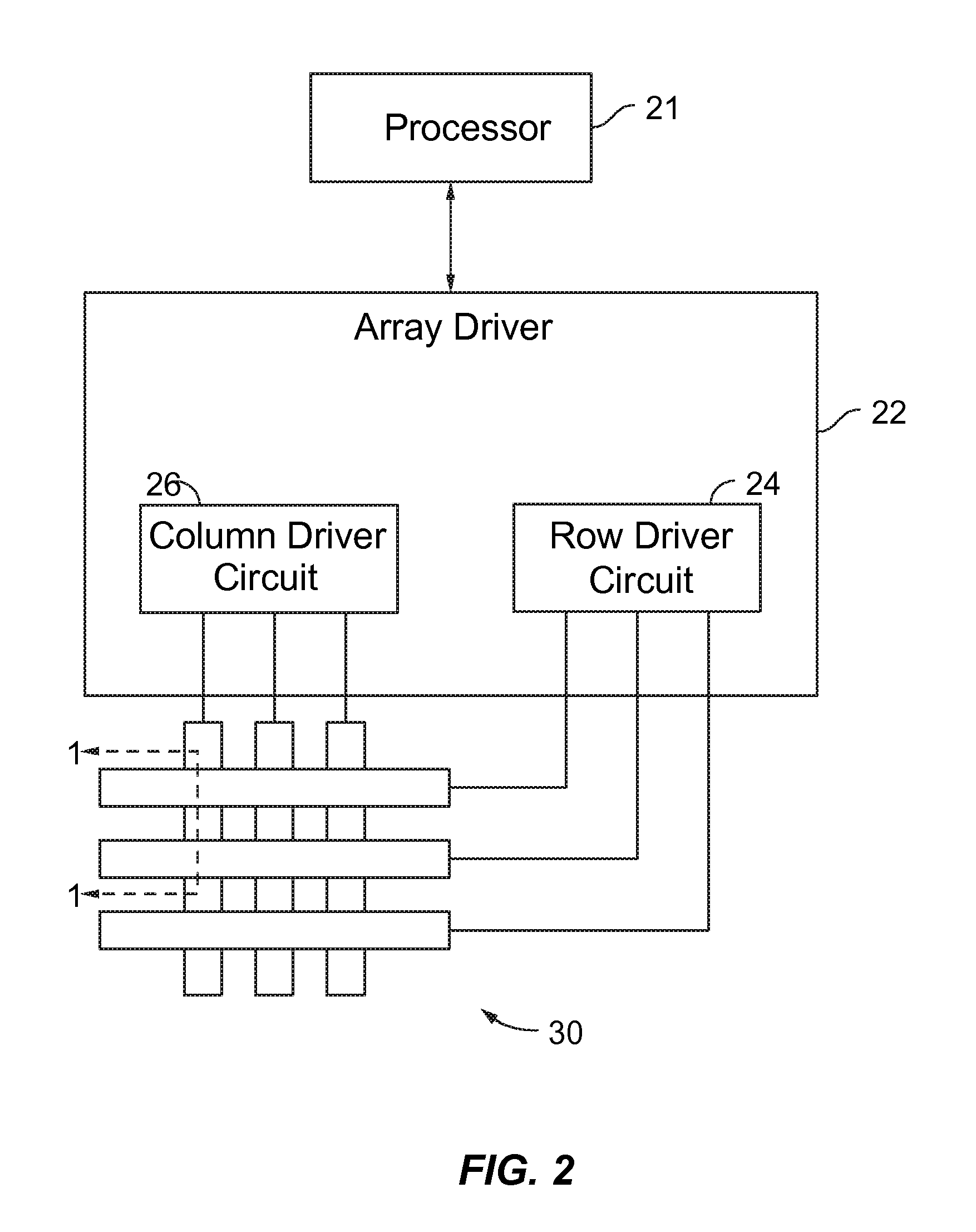

Image sensor ADC and CDS per Column with Oversampling

ActiveUS20080043128A1Available areaAvoid disadvantagesTelevision system detailsElectric signal transmission systemsDynamic rangeFixed-pattern noise

Owner:DYNAMAX IMAGING

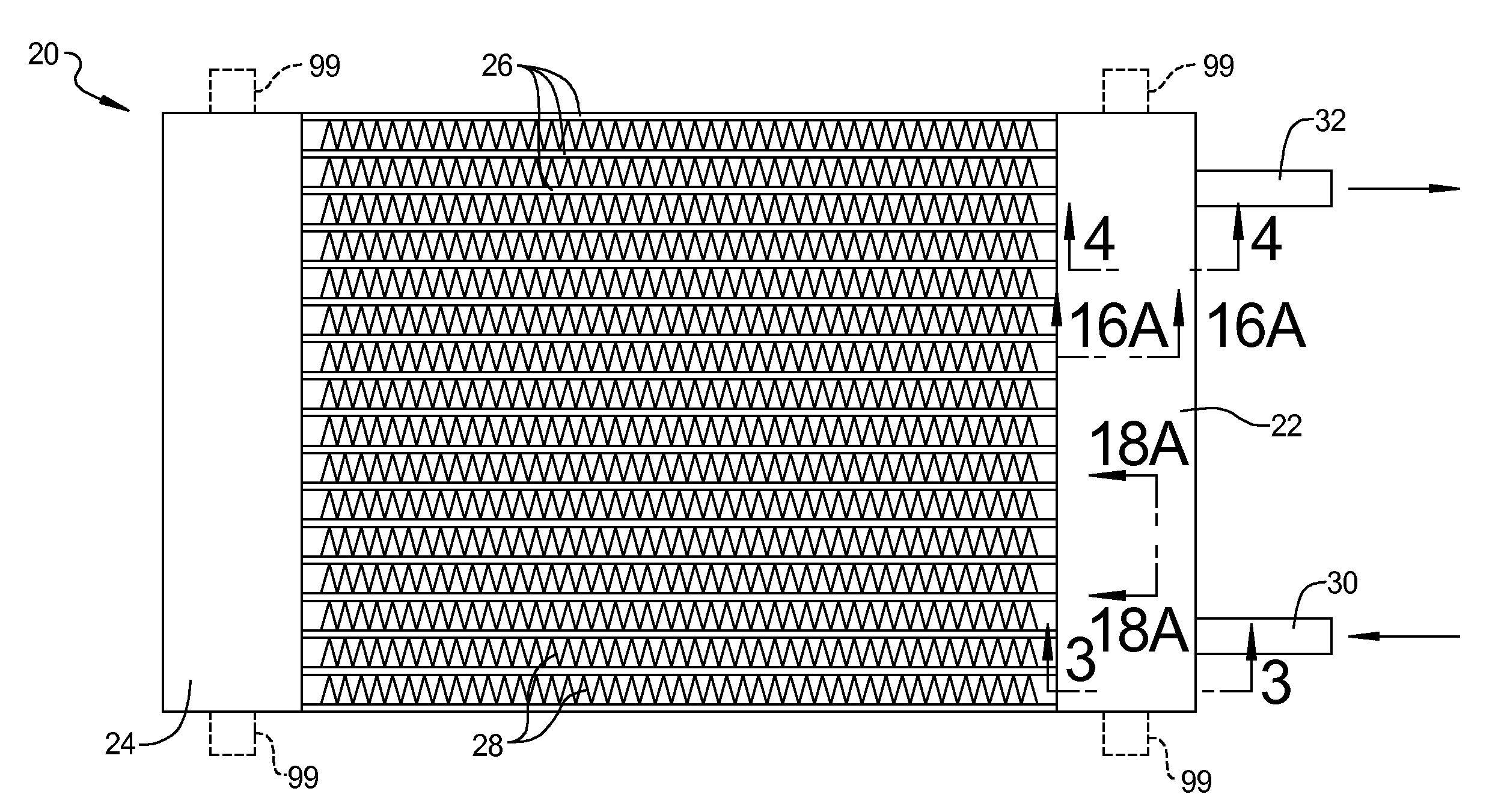

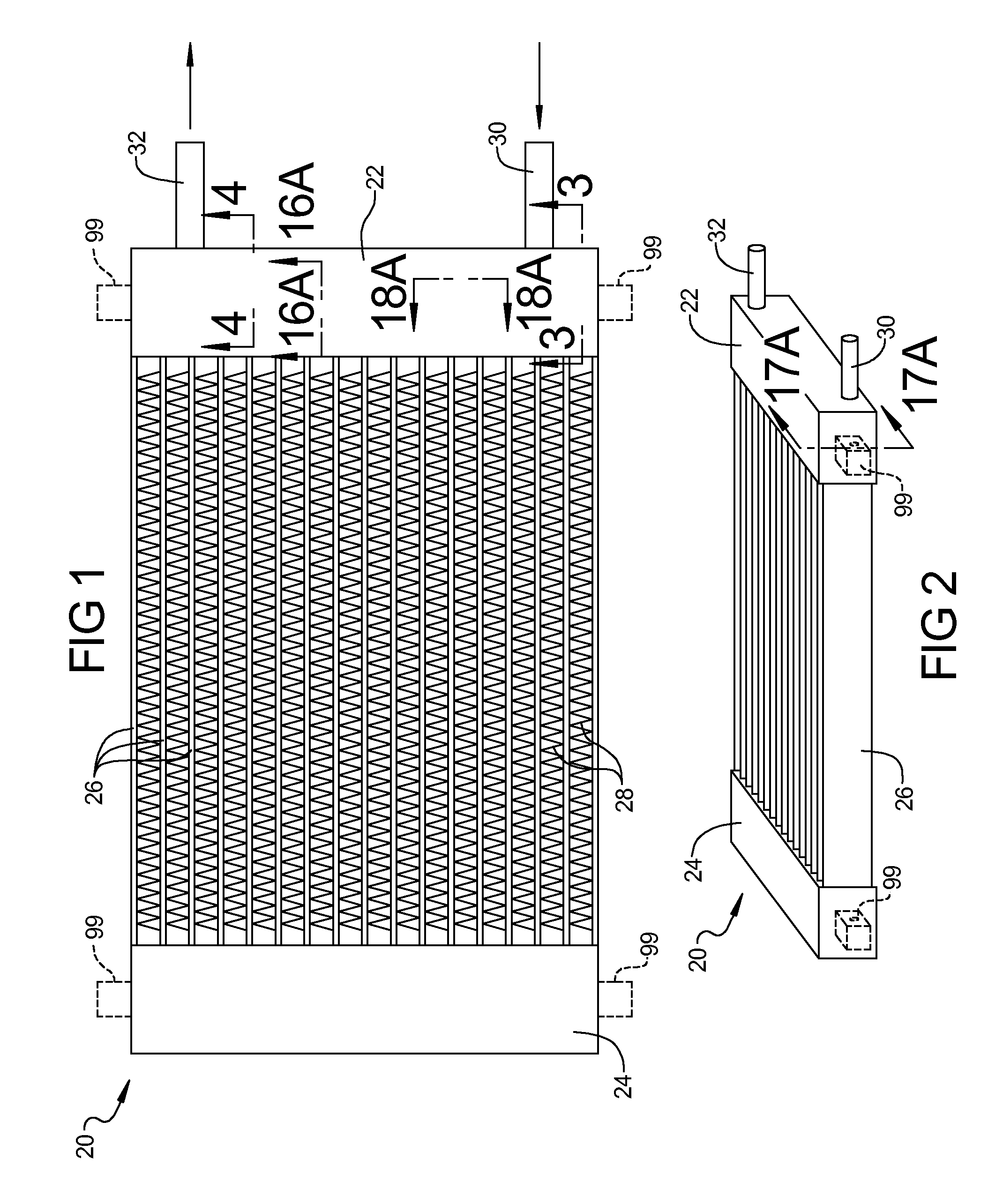

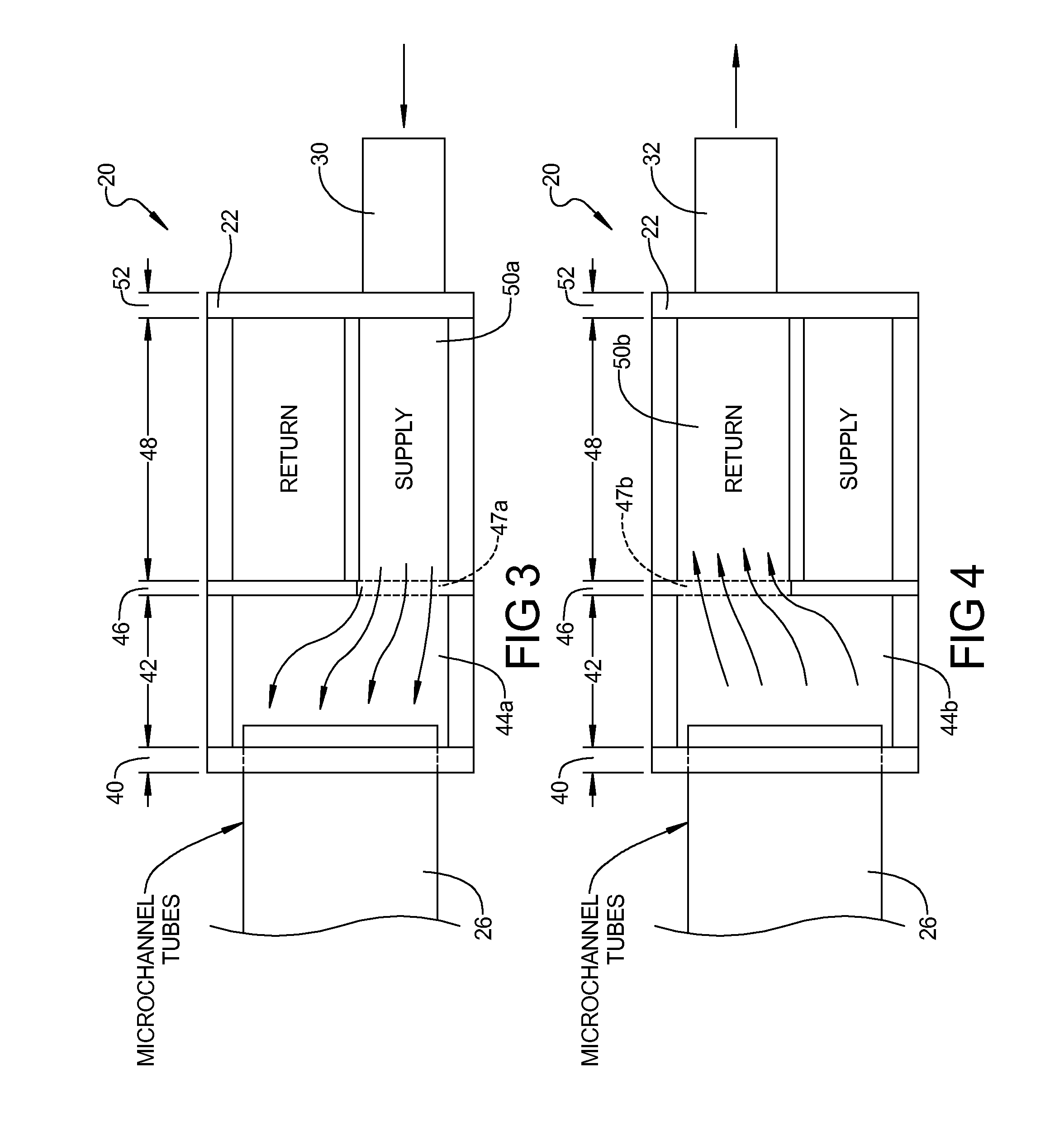

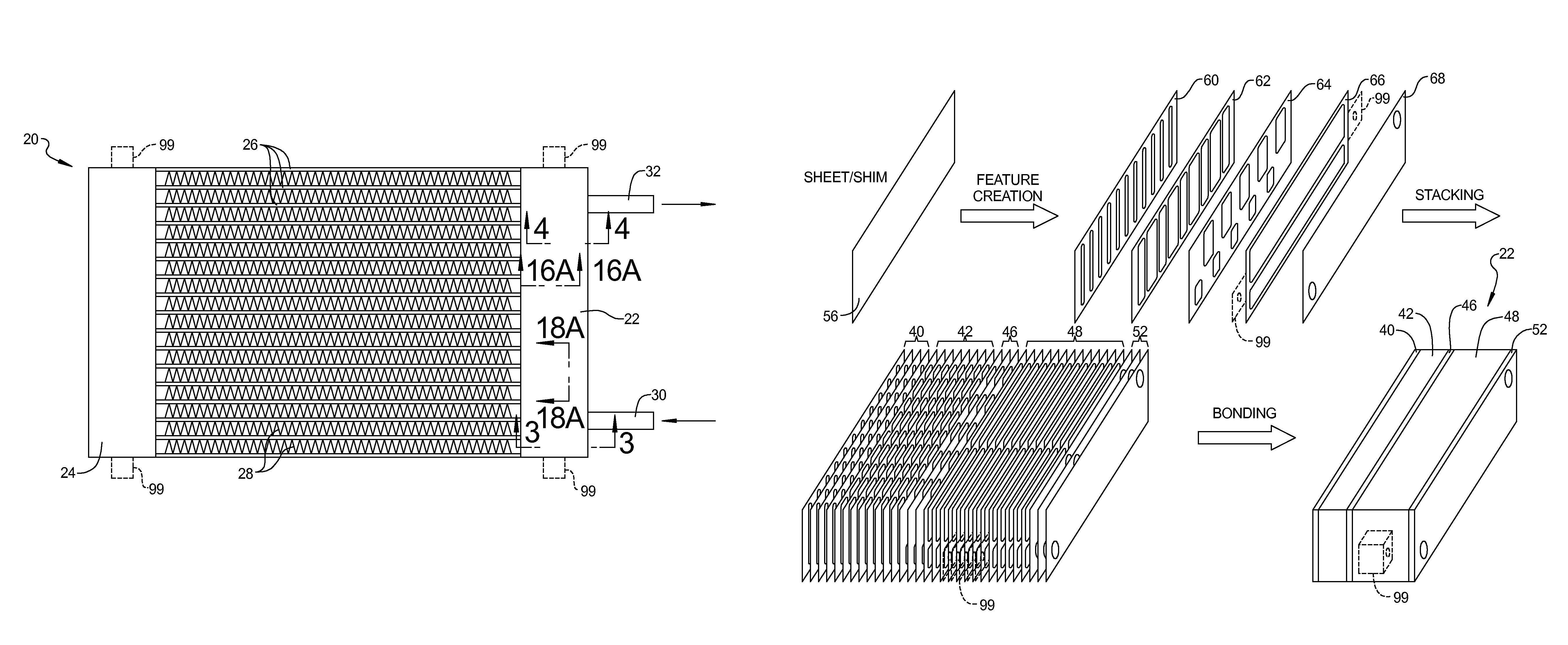

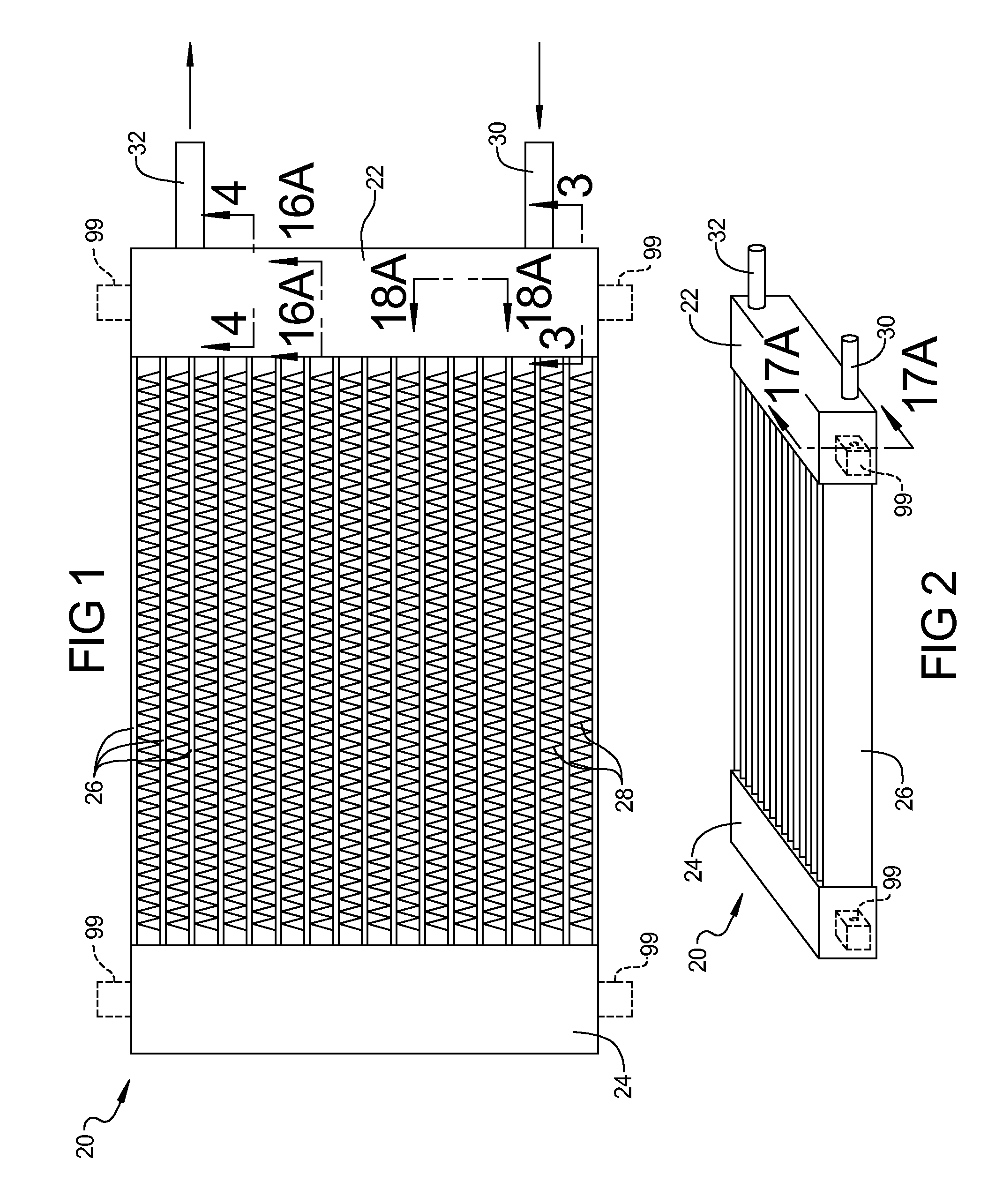

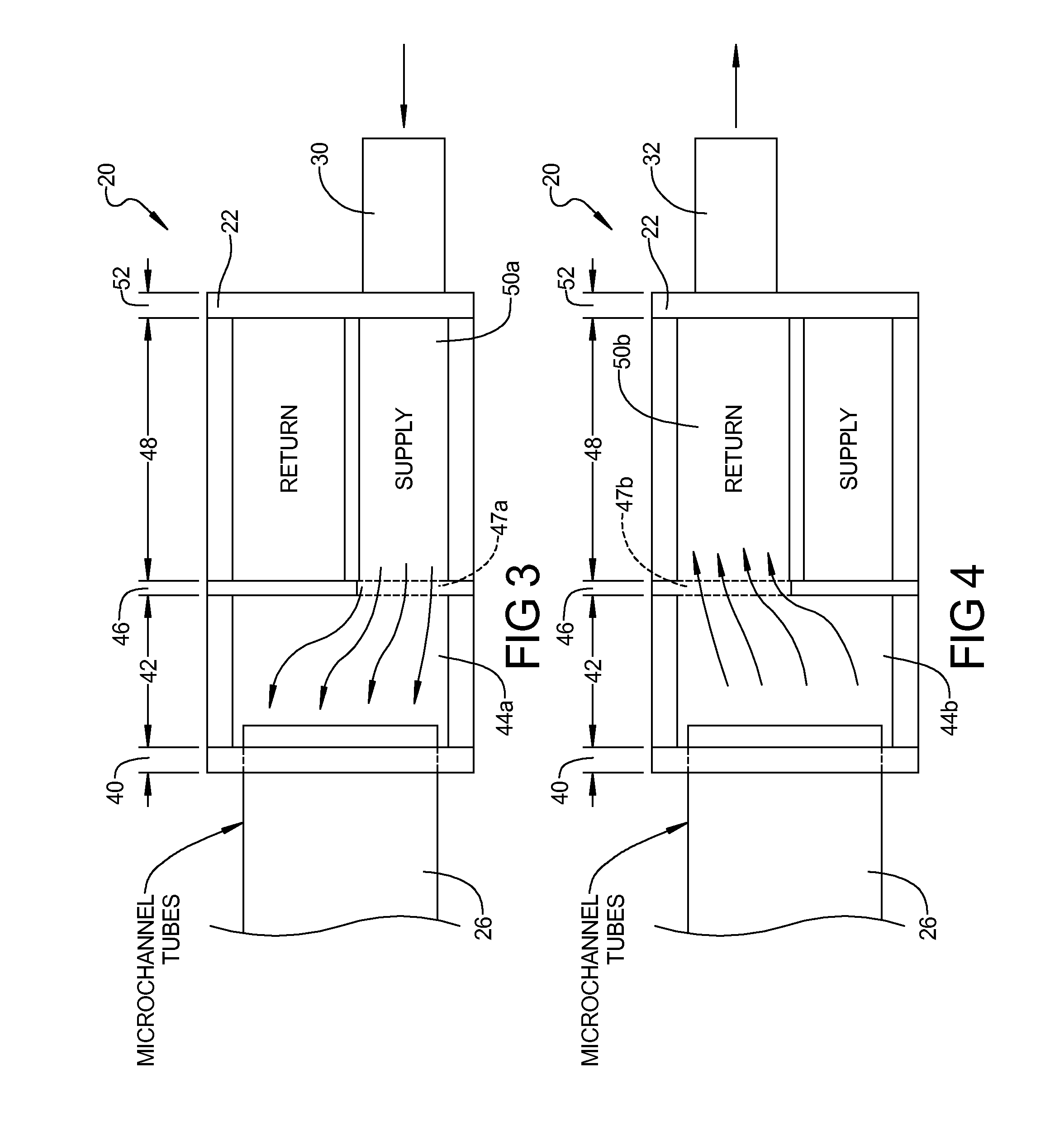

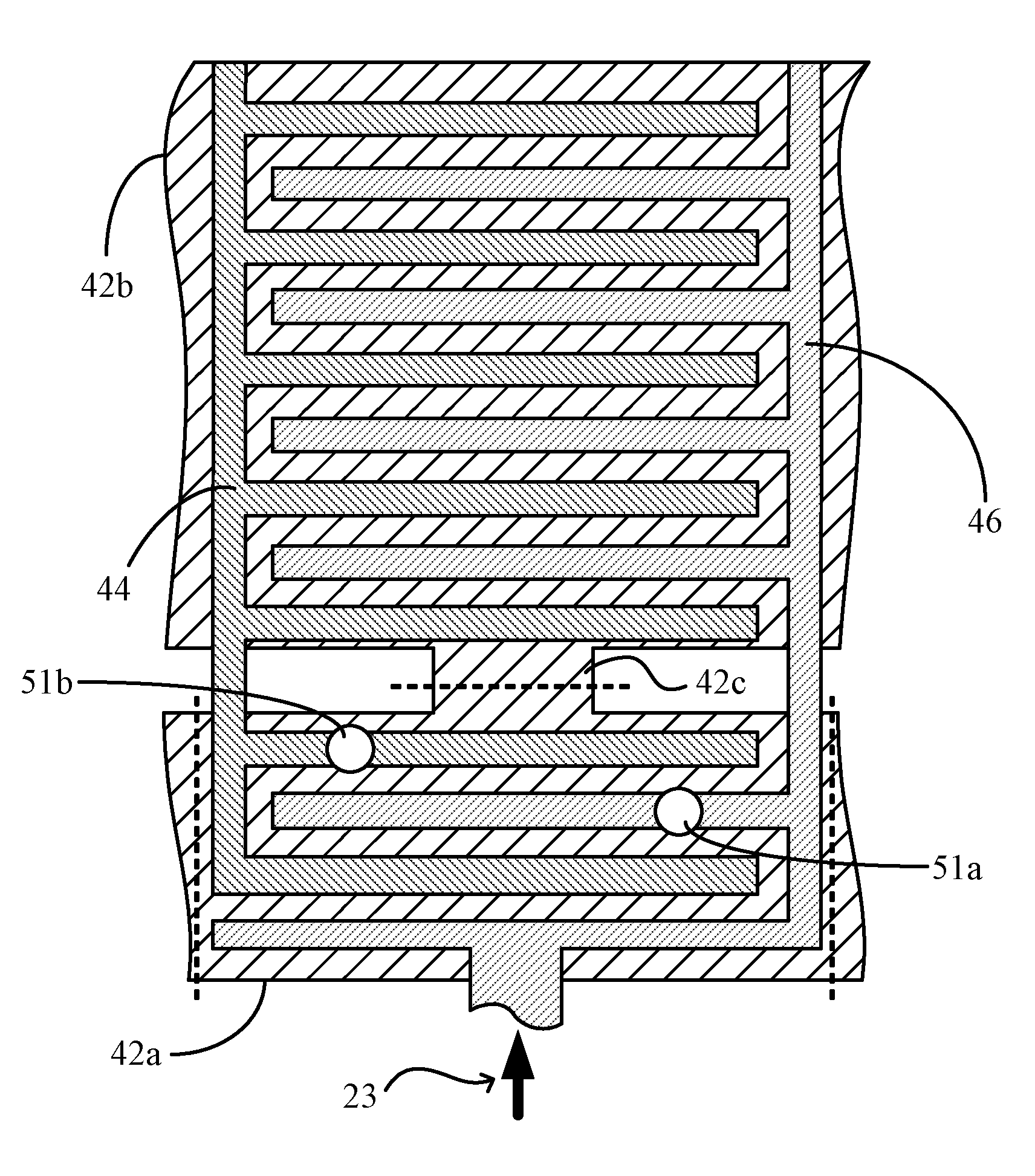

Laminated sheet manifold for microchannel heat exchanger

ActiveUS20090211743A1Easy to useLimited space availableStationary conduit assembliesHeat exchanger casingsPlate heat exchangerCoolant flow

A heat exchanger can have a manifold which includes a plurality of laminated sheets that allow a customization of the heat exchanger. The design can allow for a more optimal flow of coolant to areas of high load, thereby making the temperature distribution across the heat exchanger more uniform, or intentionally non-uniform. Furthermore, the laminated sheets can allow multiple circuits to be employed in the heat exchanger such that different coolants can be utilized therein and maintained separate from one another. The tubes can be microchannel tubes. A single set of manifolds can be used with multiple heat exchanger cores to provide a more compact heat exchanger. Mounting features can be integral with a group of the sheets.

Owner:VERTIV CORP

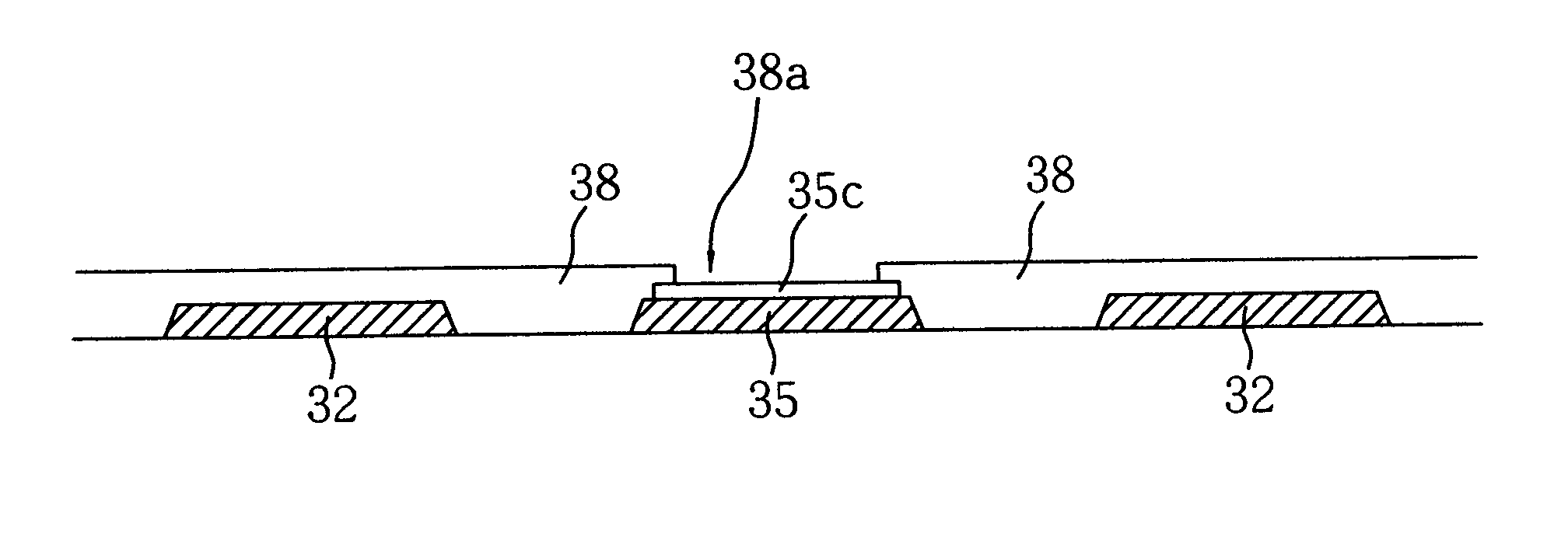

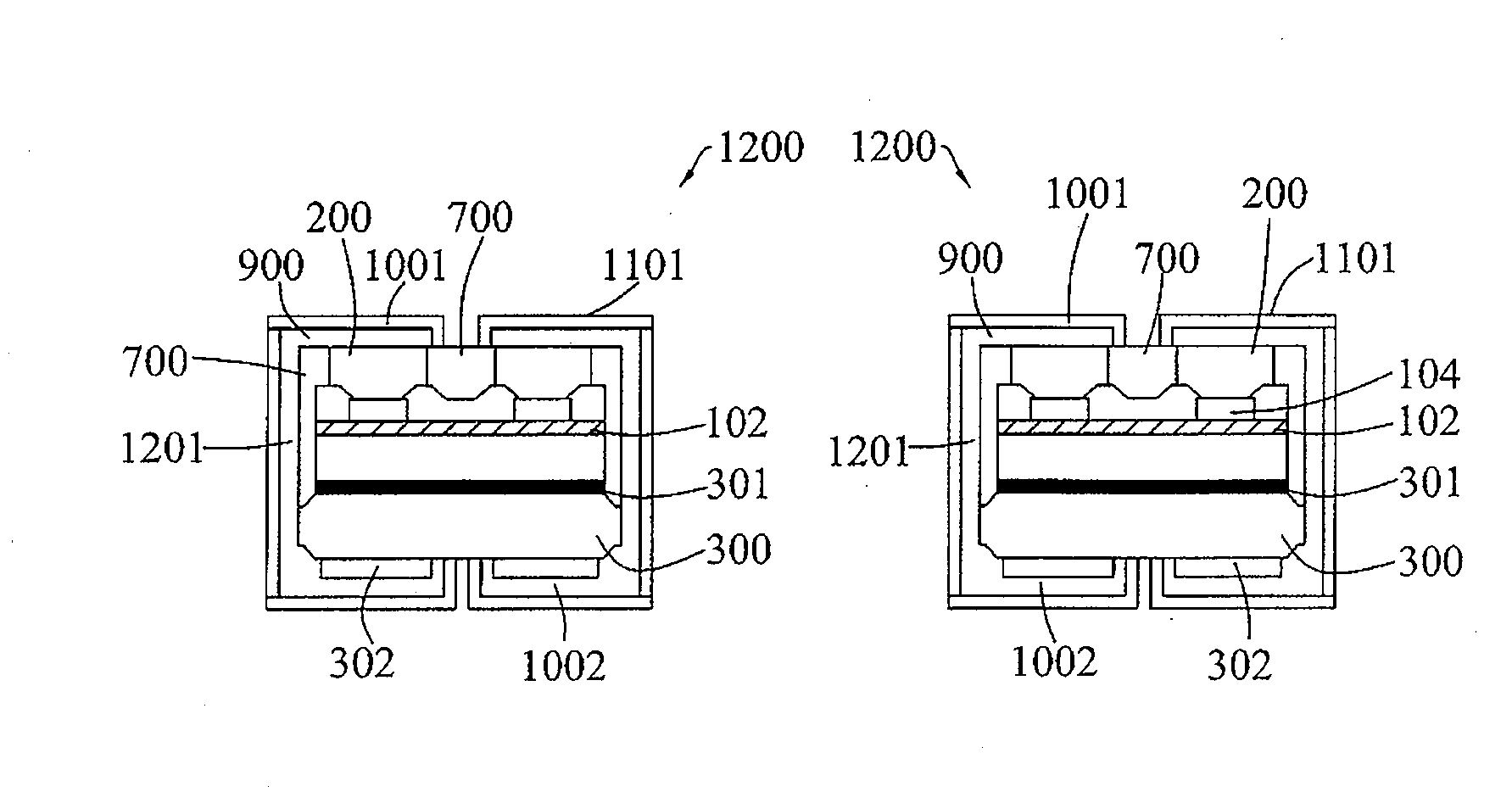

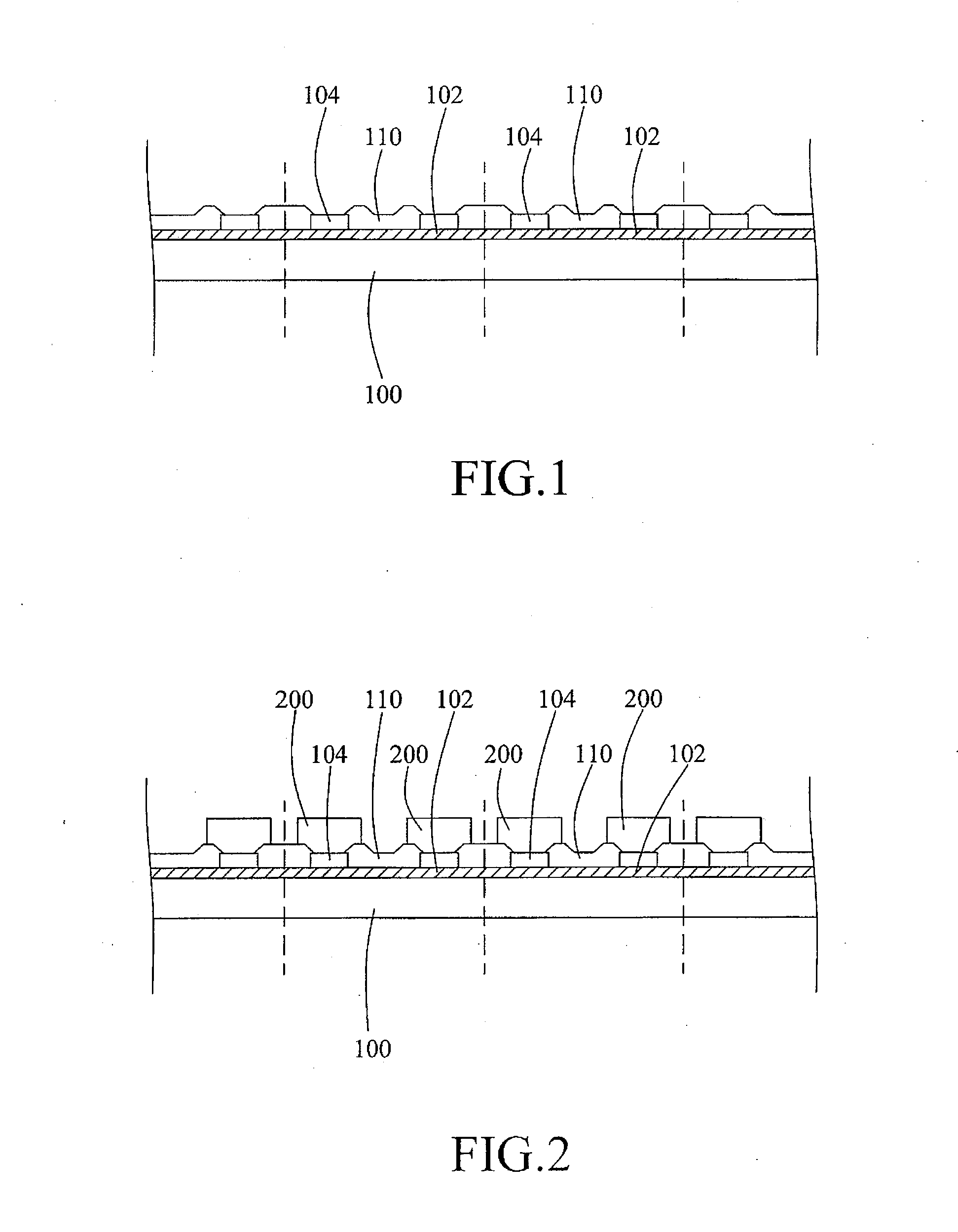

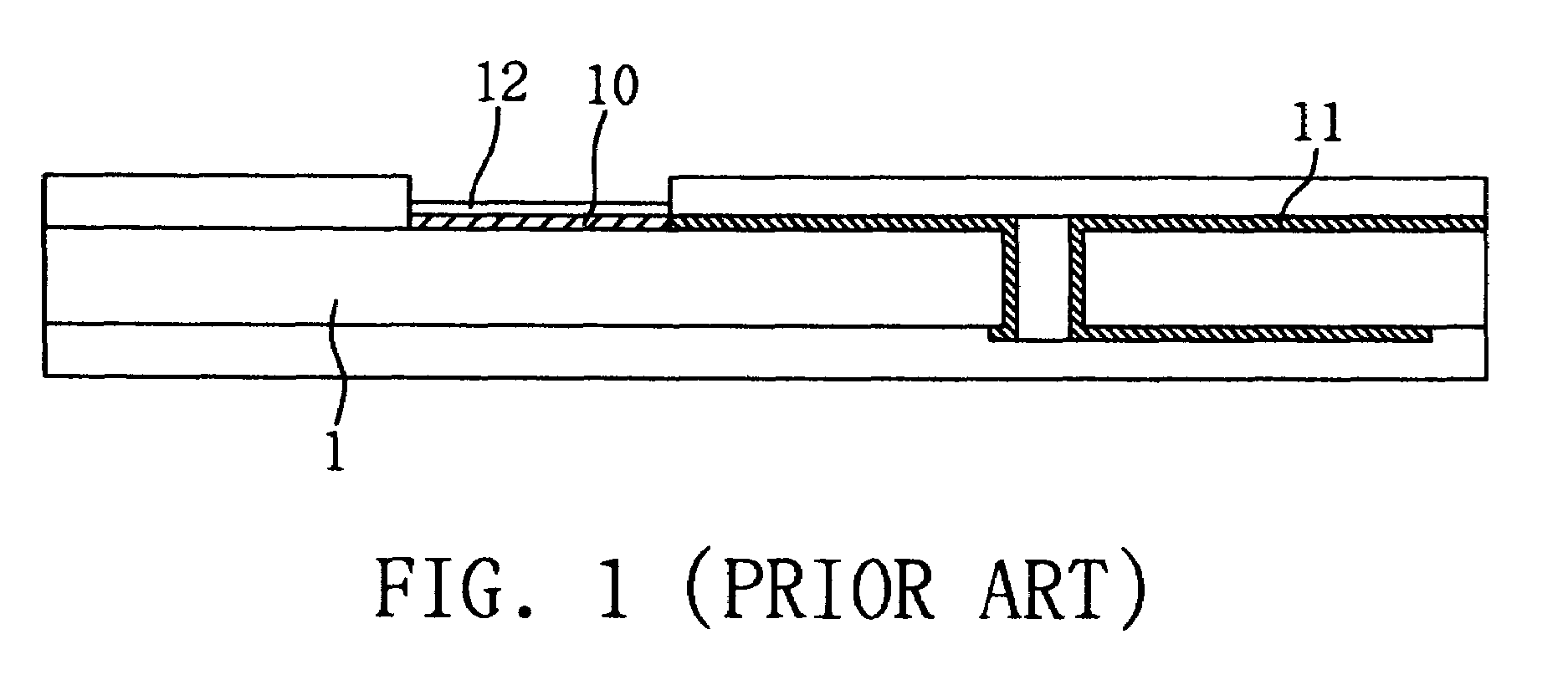

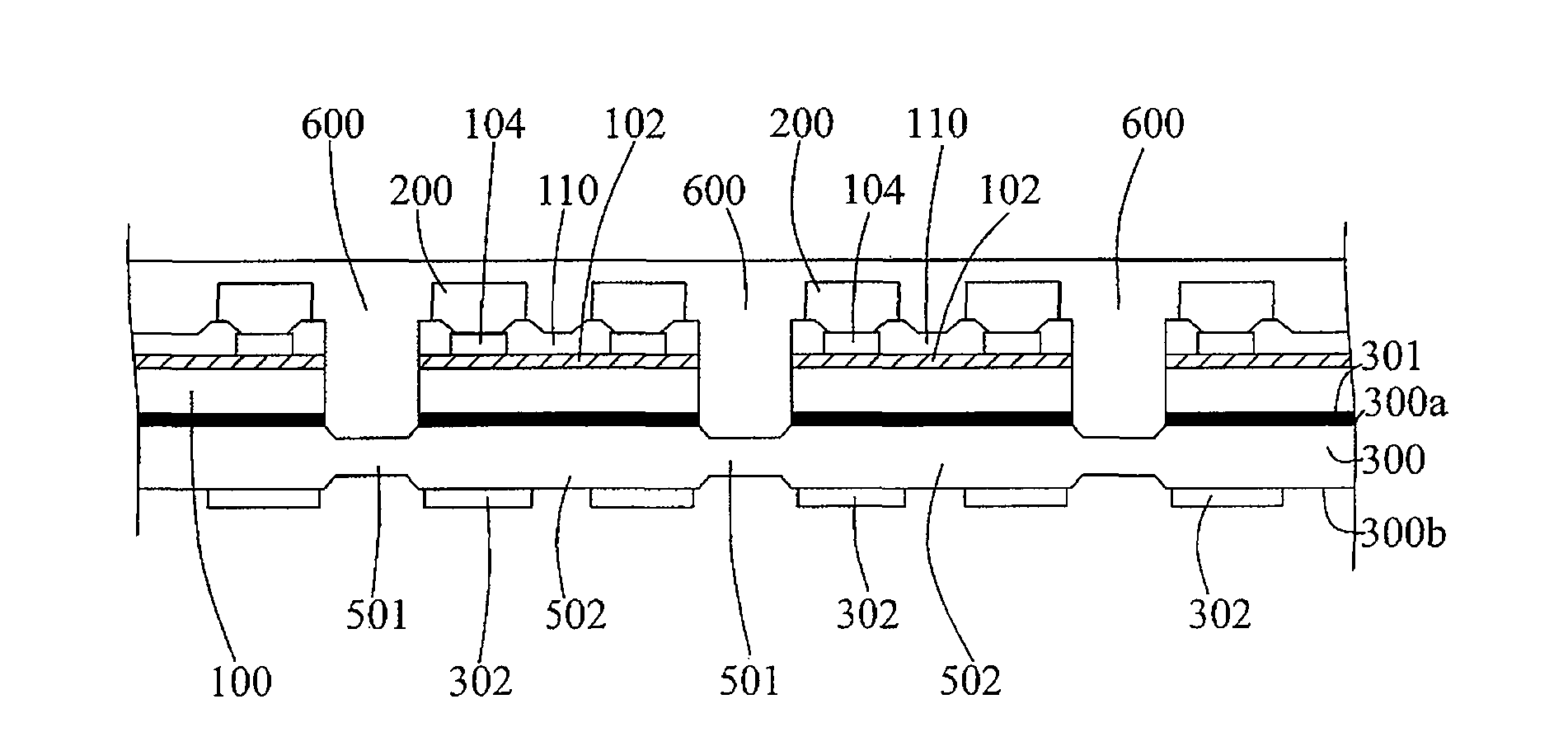

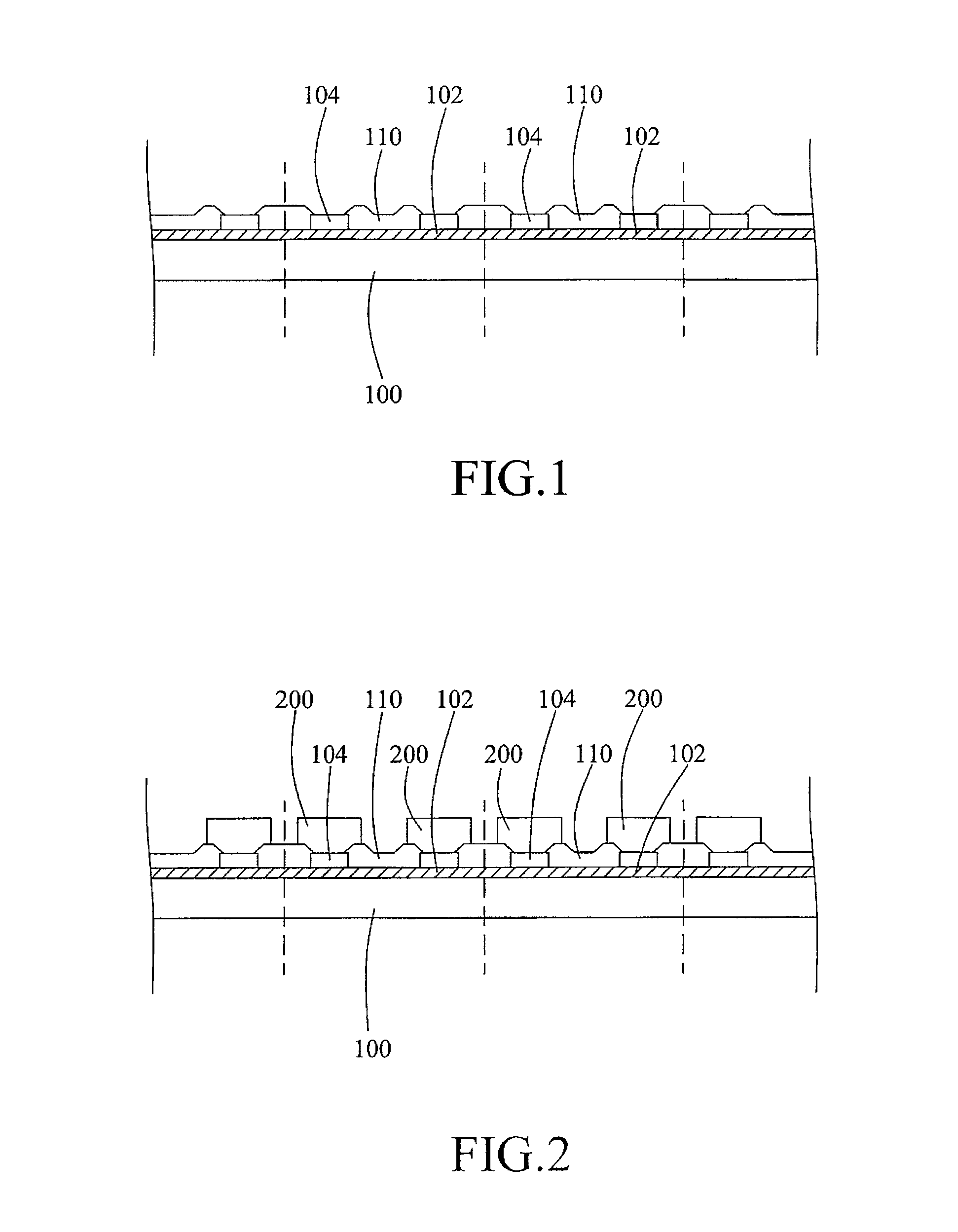

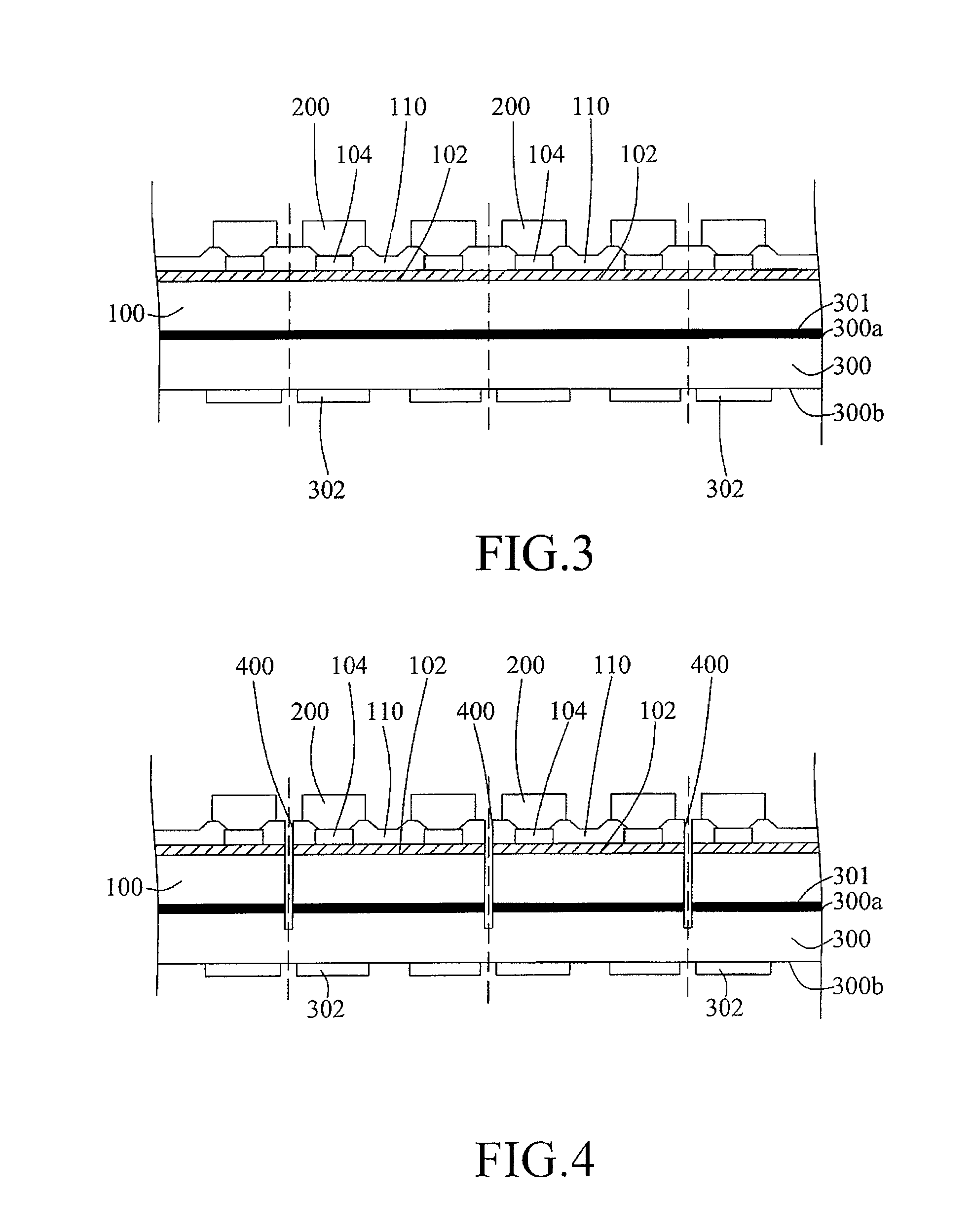

Semiconductor package substrate having bonding pads with plated layer thereon and process of manufacturing the same

InactiveUS20040099961A1Improve reliabilityAvailable areaSemiconductor/solid-state device detailsSolid-state devicesSolder maskSemiconductor package

A semiconductor package substrate is provided having a plurality of bonding pads on at least one surface thereof and covered by a conductive film. A photoresist layer formed over the conductive film has a plurality of first openings for exposing portions of the conductive film corresponding to the bonding pads. The exposed portions of the conductive film is removed to expose the bonding pads respectively via the first openings. The exposed bonding pads are plated with a metal layer respectively. Then, the photoresist layer and the remainder of the conductive film covered by the photoresist layer are removed. A solder mask having a plurality of second openings may be formed on the surface of the substrate, and allows the plated metal layer on the bonding pads respectively to be exposed via the second openings.

Owner:PHOENIX PRECISION TECH CORP

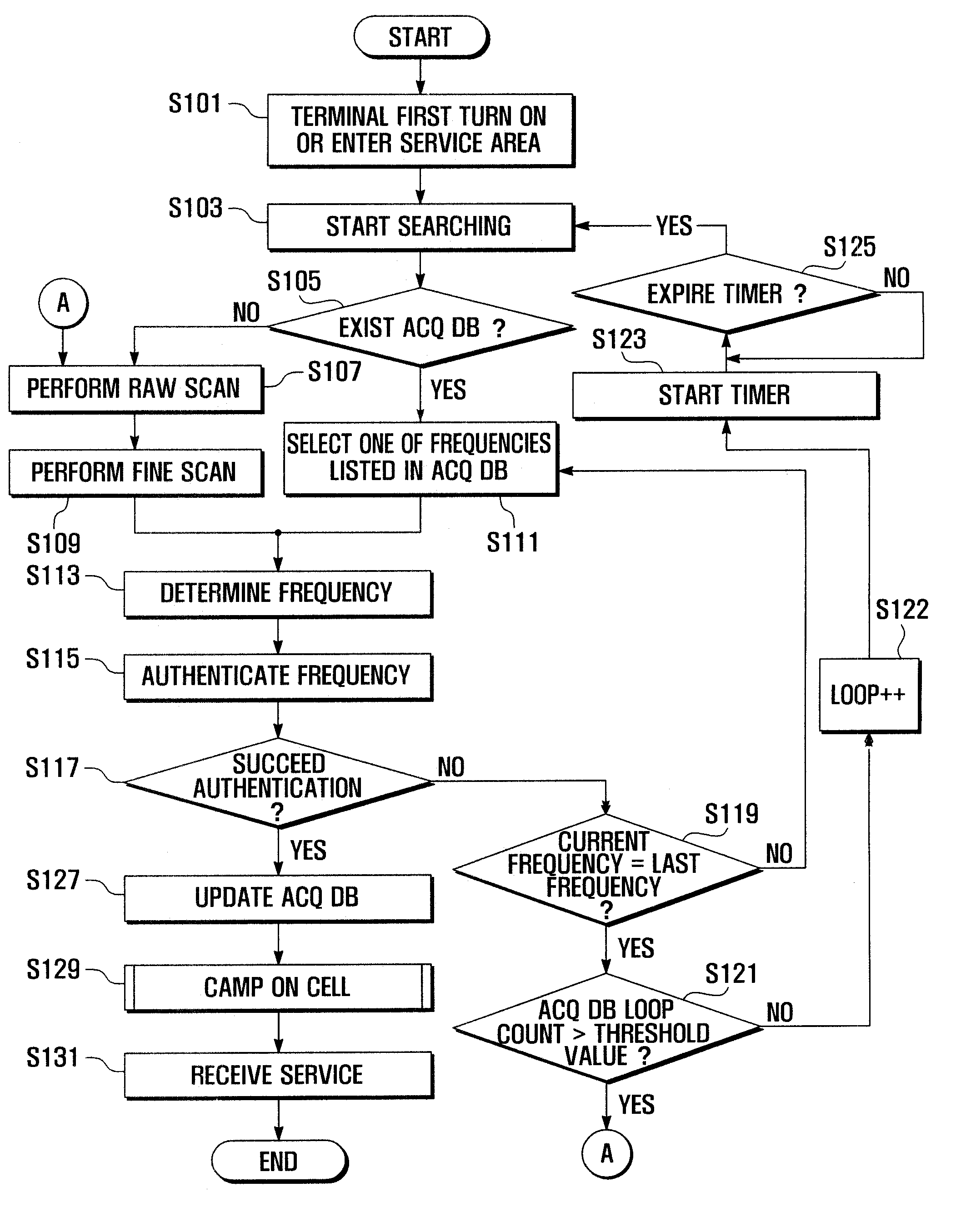

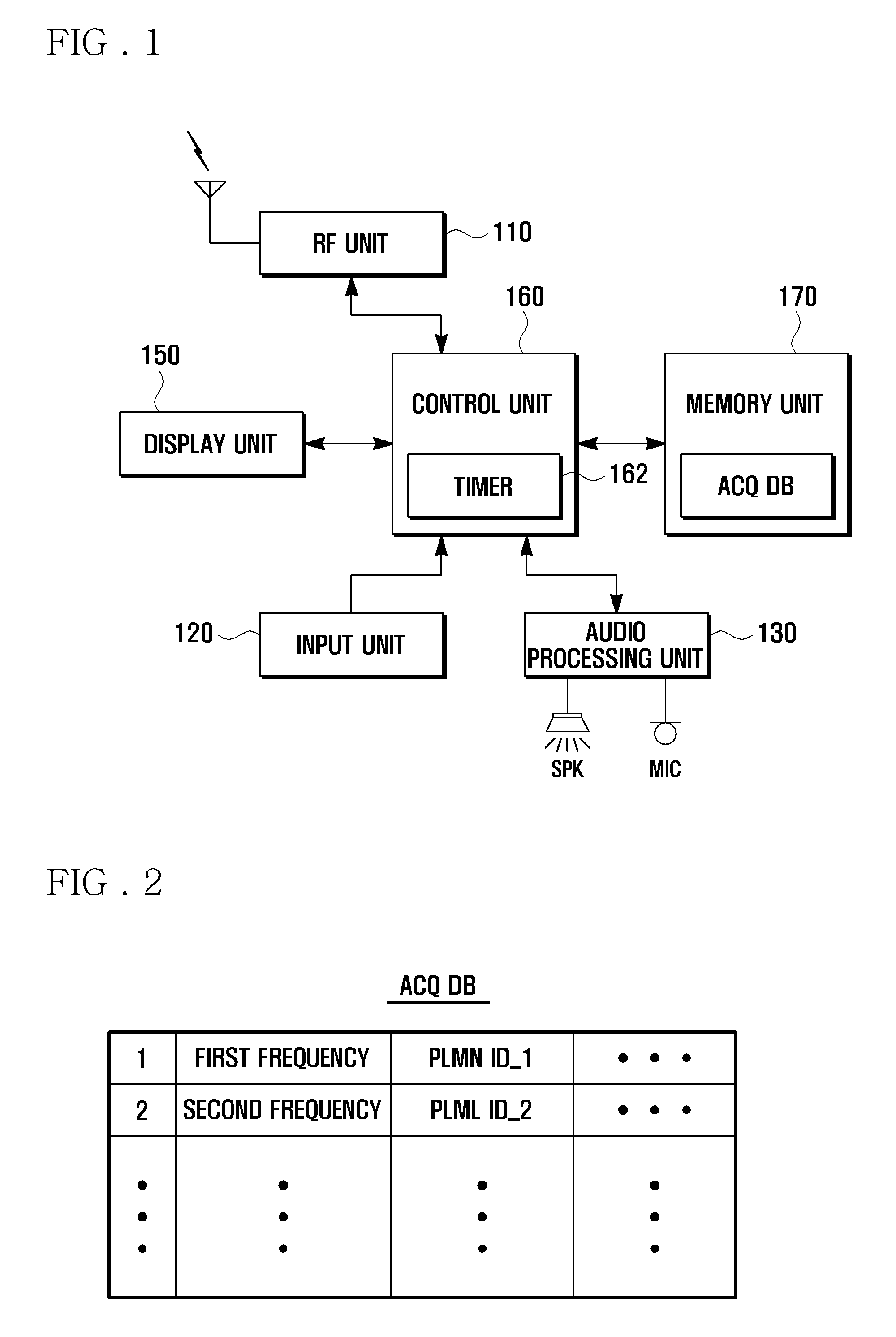

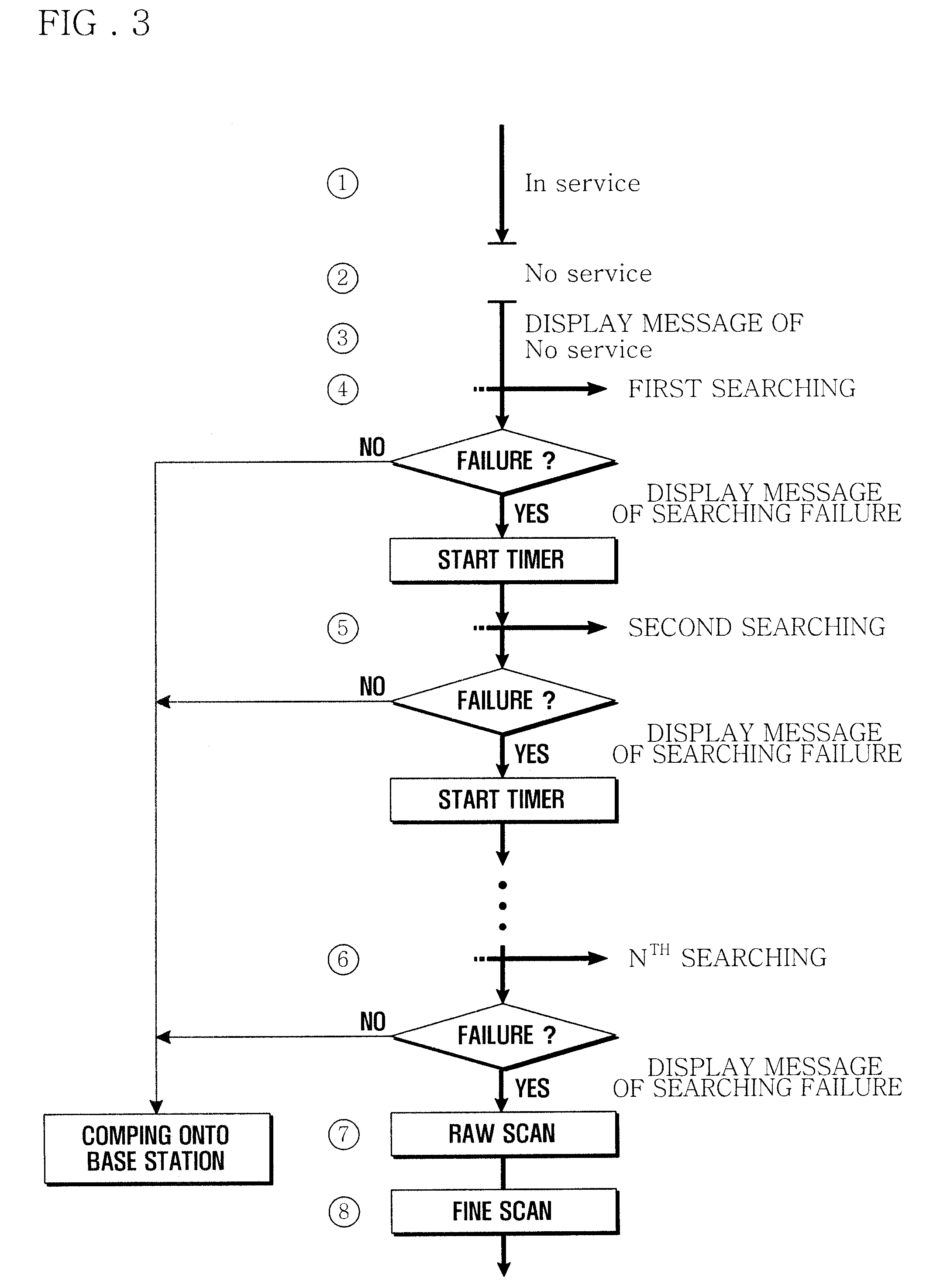

Cell searching method and mobile terminal therefor

InactiveUS20090036098A1Improve efficiencyAvailable areaUnauthorised/fraudulent call preventionEavesdropping prevention circuitsCell searchMobile communication systems

A cell searching method and mobile terminal for a mobile communication system is provided. The terminal and method facilitate cell searching by using a database that registers cell information, such as frequencies and identities. A cell searching method of a mobile terminal according to the present invention includes determining whether authentication information of at least one cell exists in a memory, selecting, when the authentication information exists, the authentication information of the at least one cell, evaluating validity of the selected authentication information and attempting to camp on the cell using the authentication information if the validity evaluation is successful.

Owner:SAMSUNG ELECTRONICS CO LTD

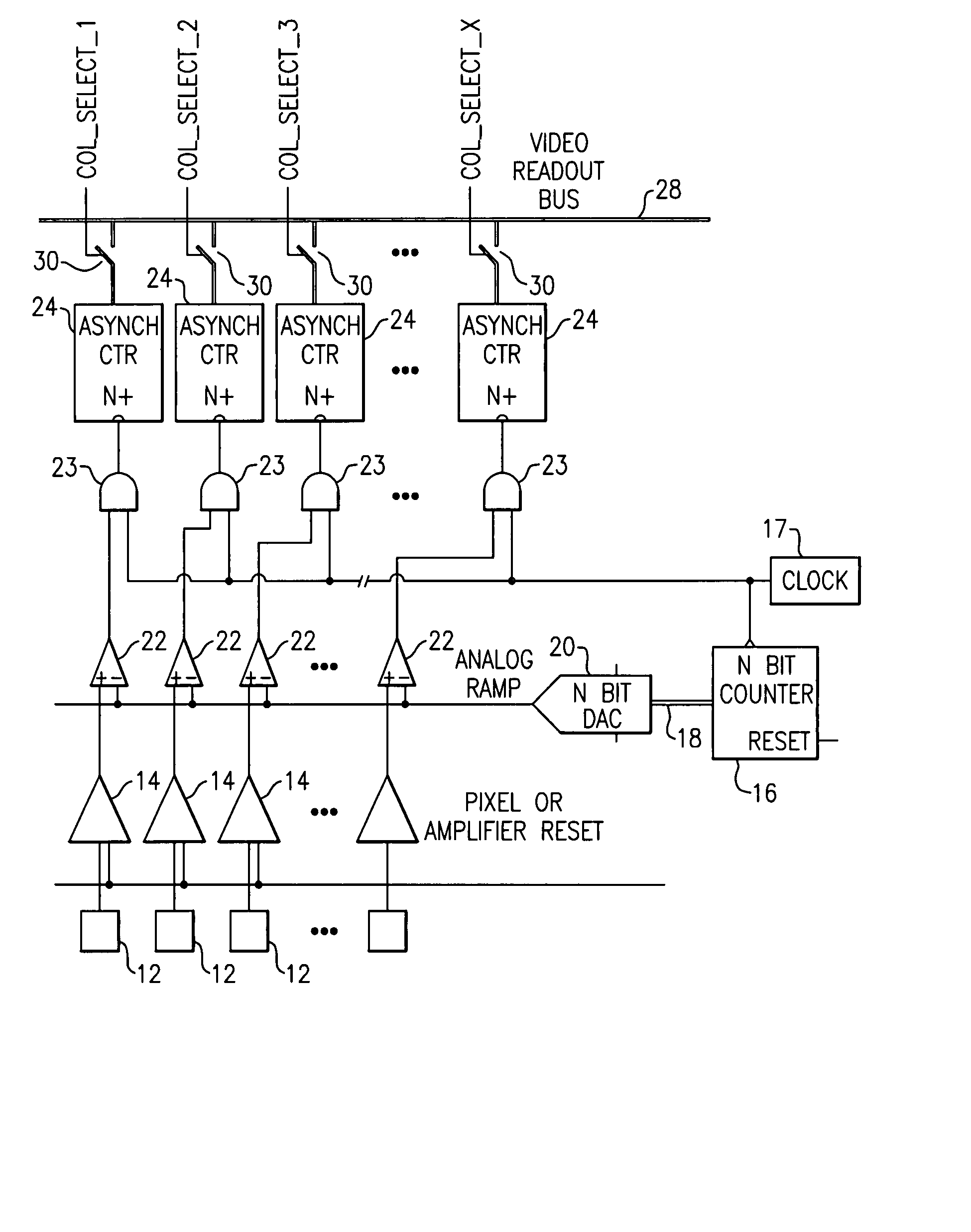

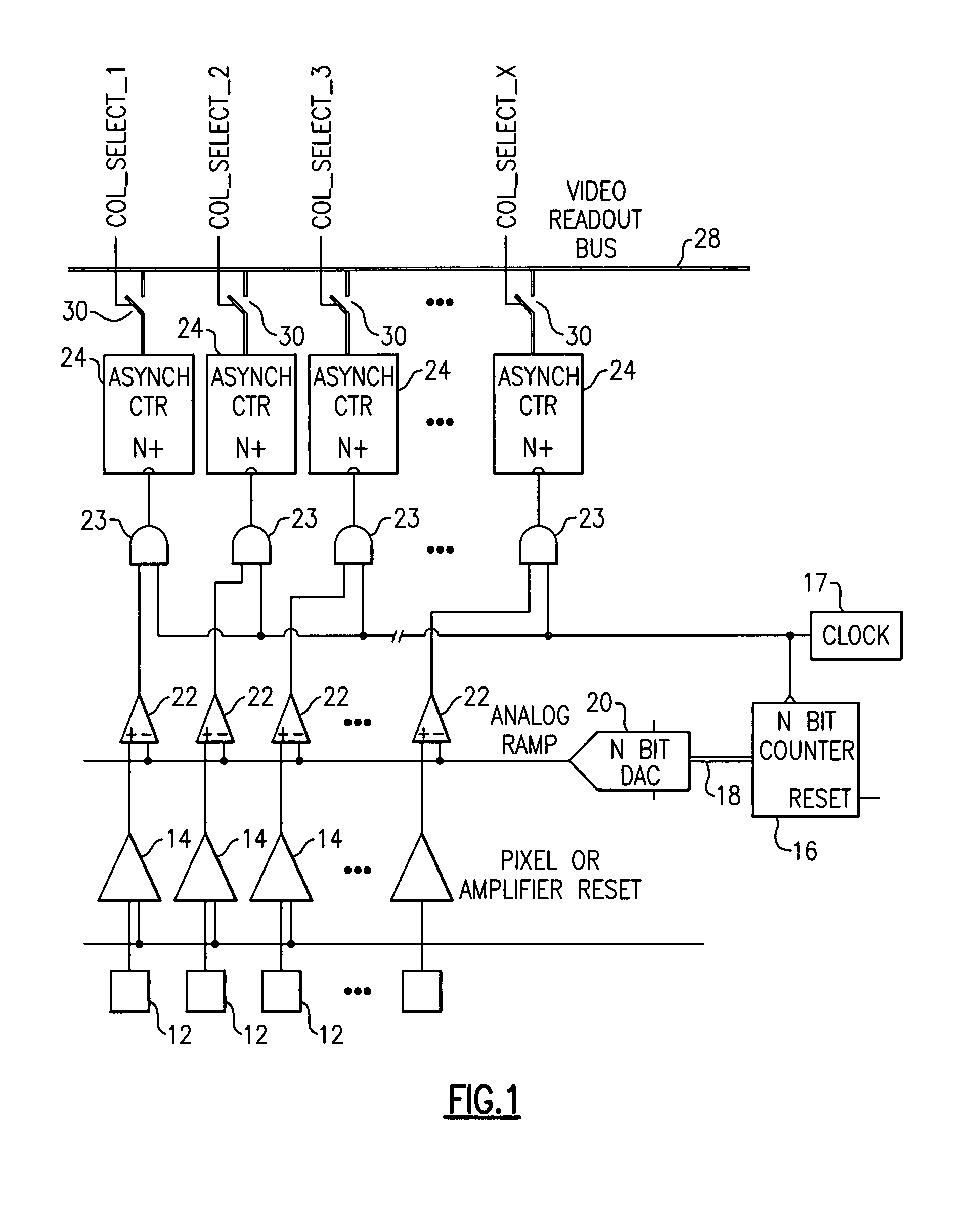

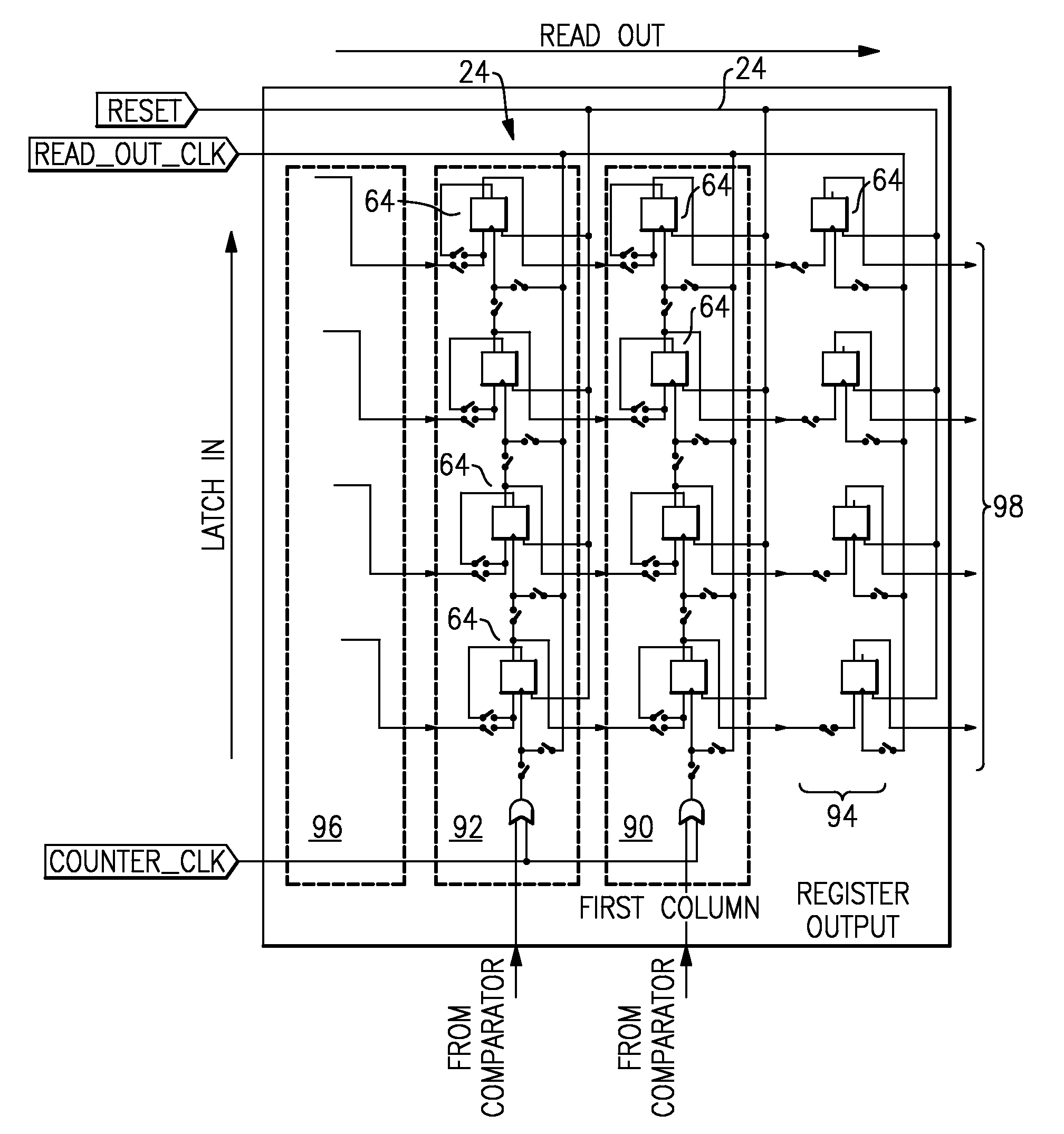

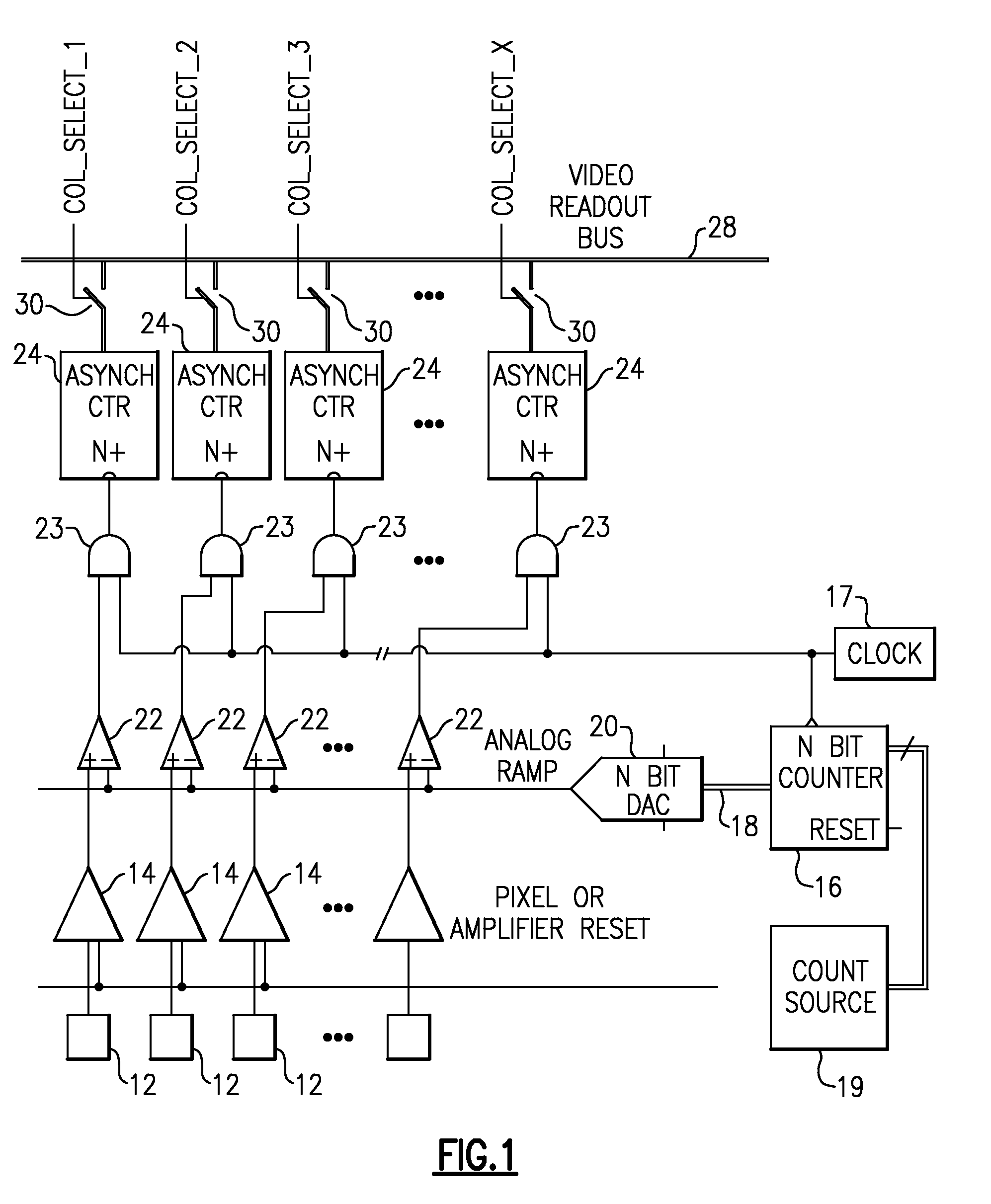

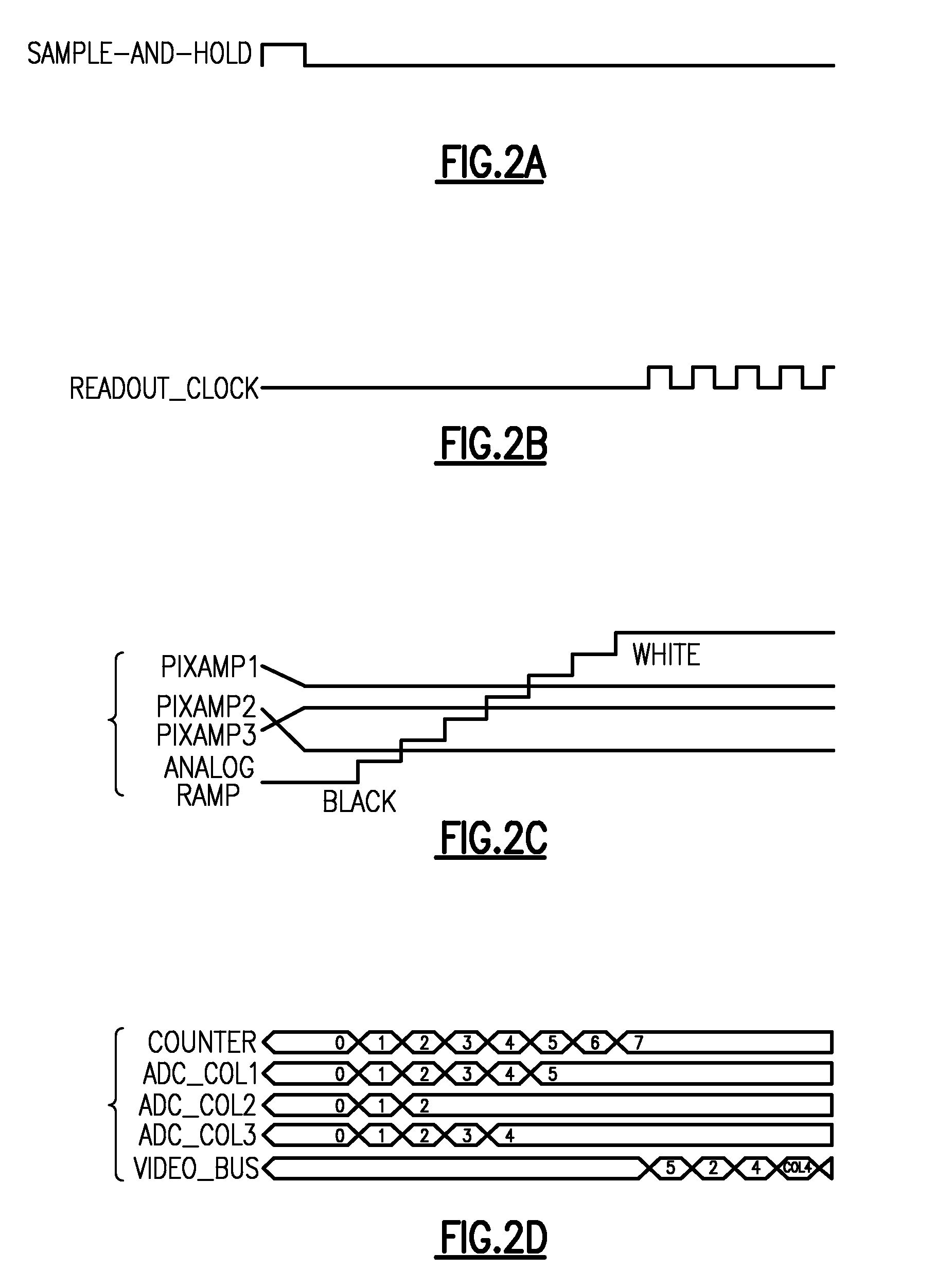

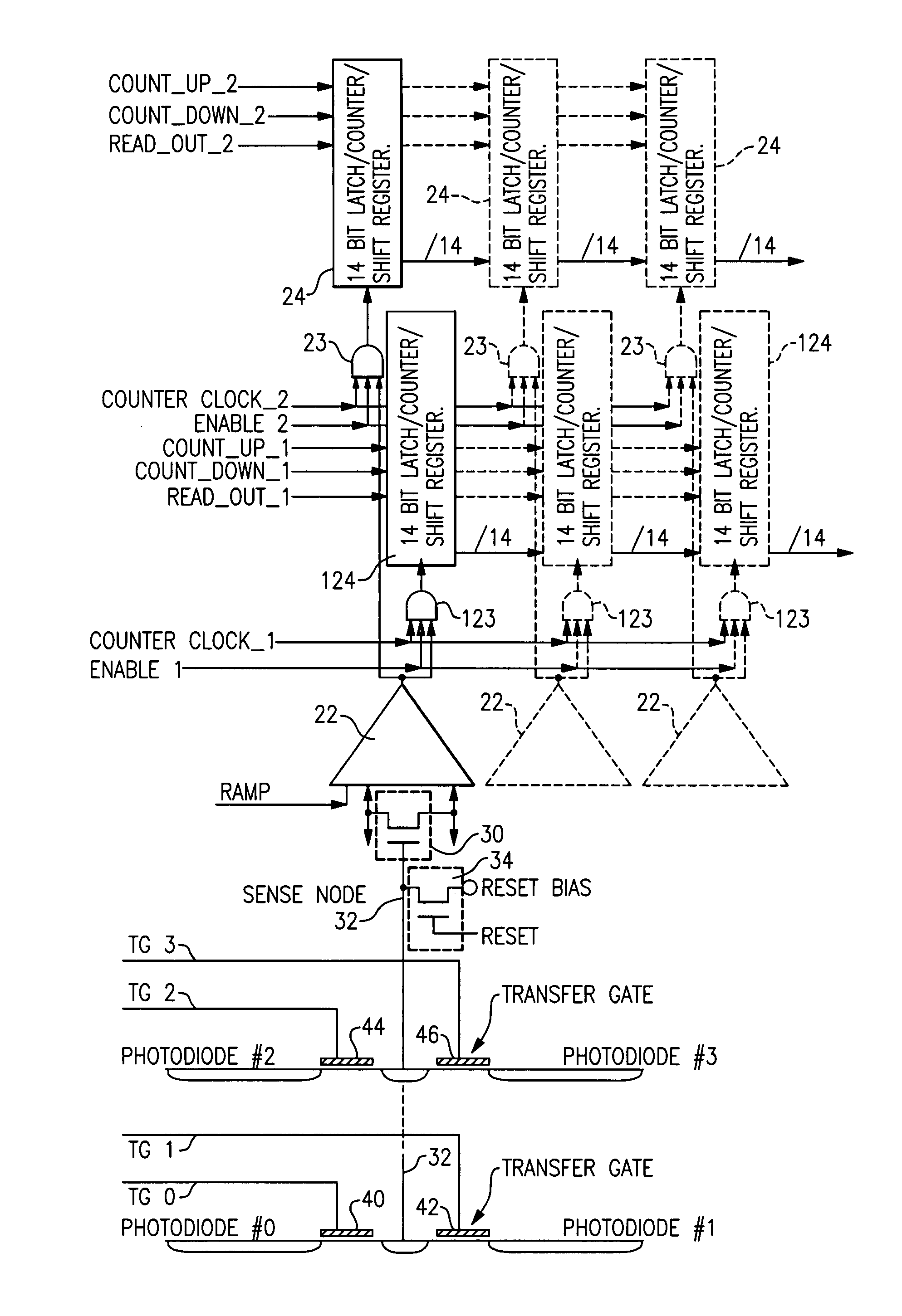

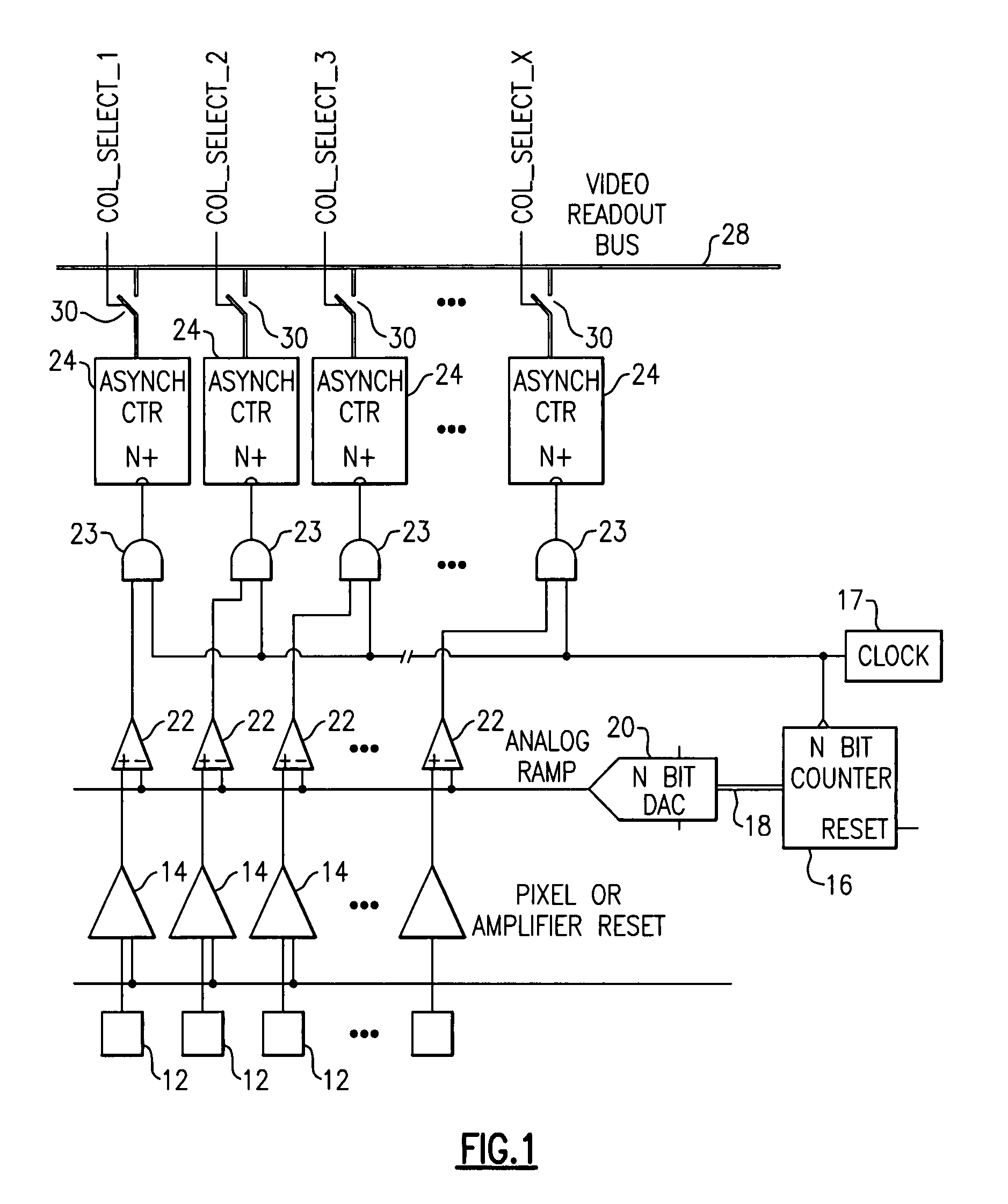

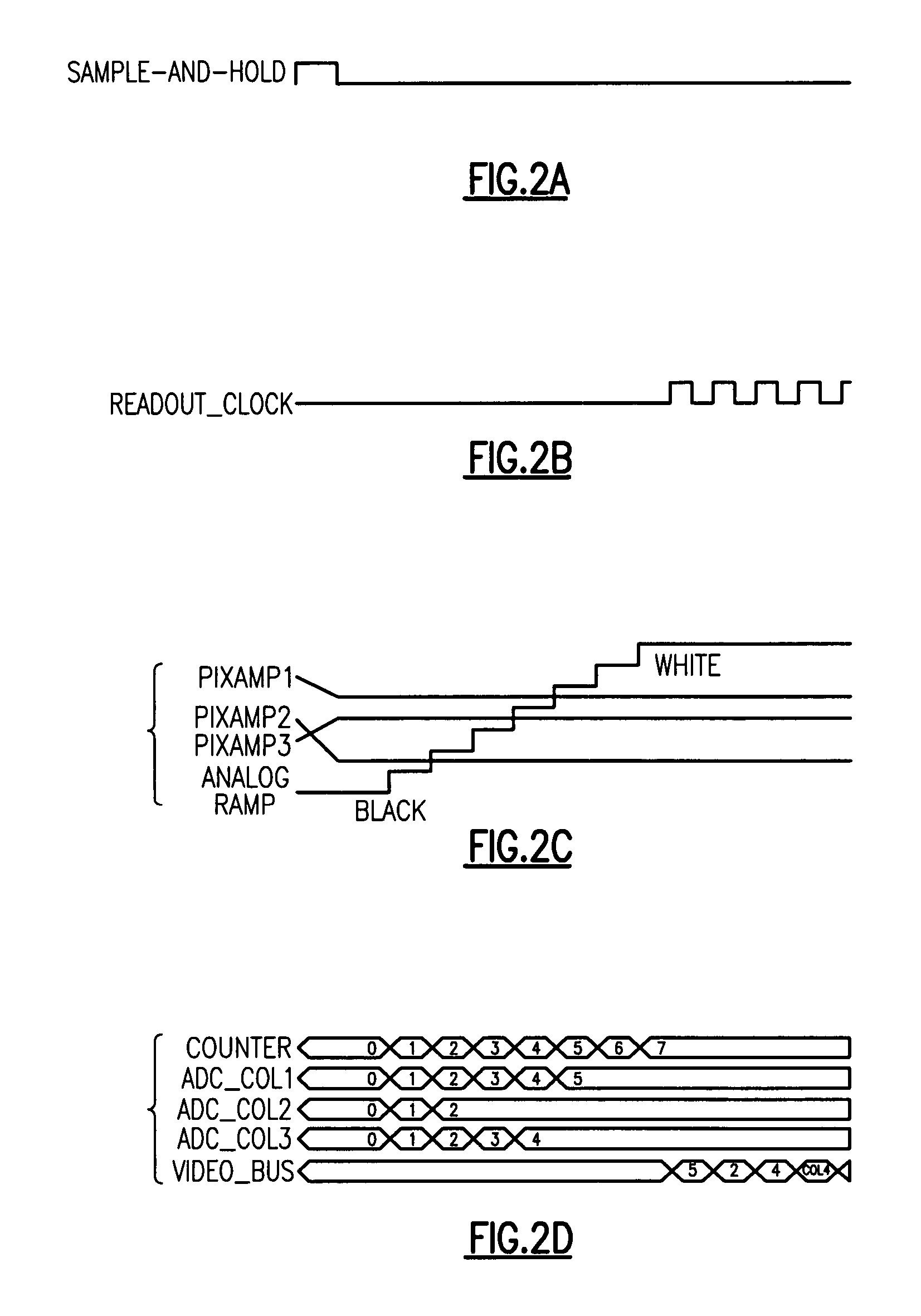

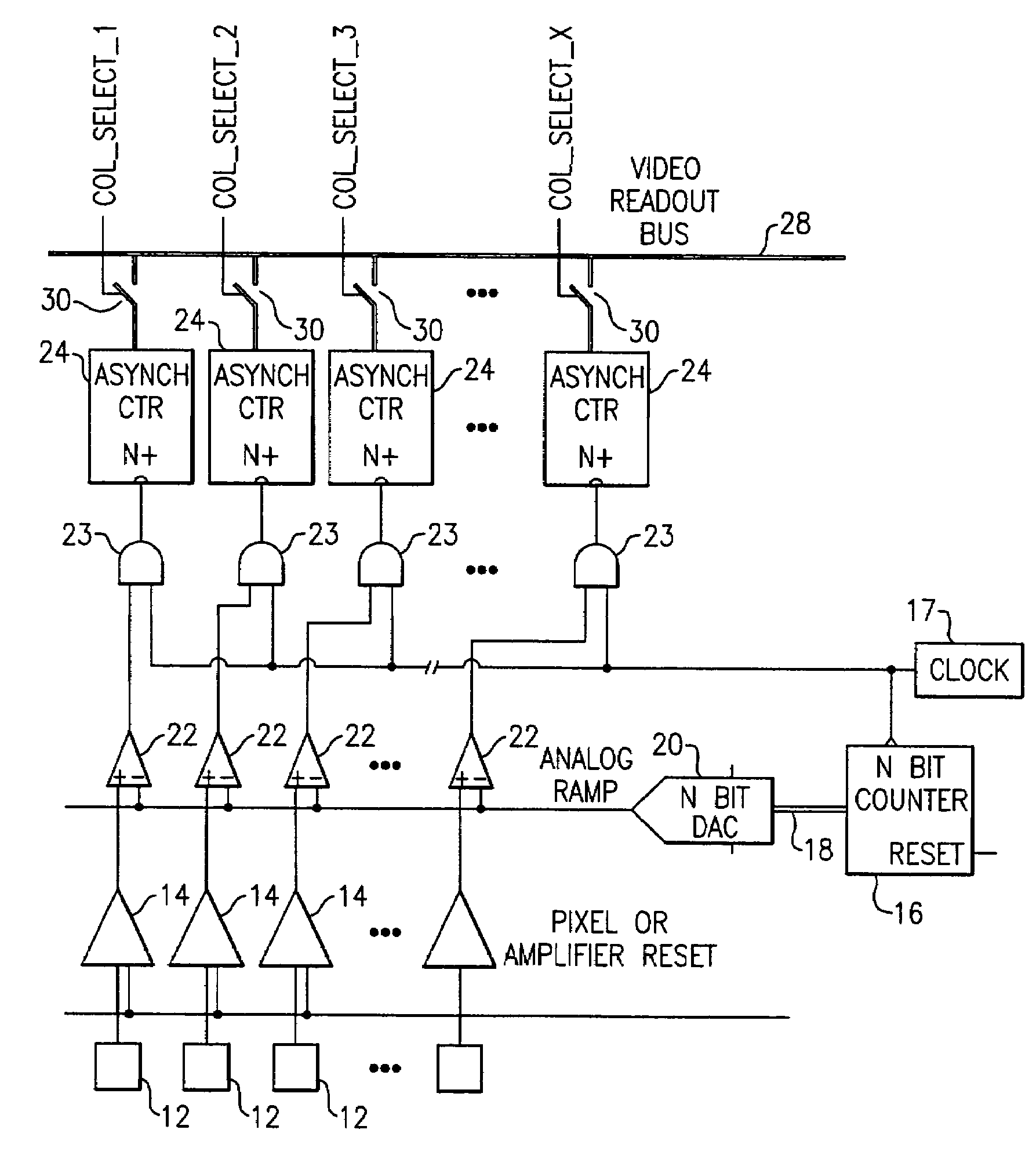

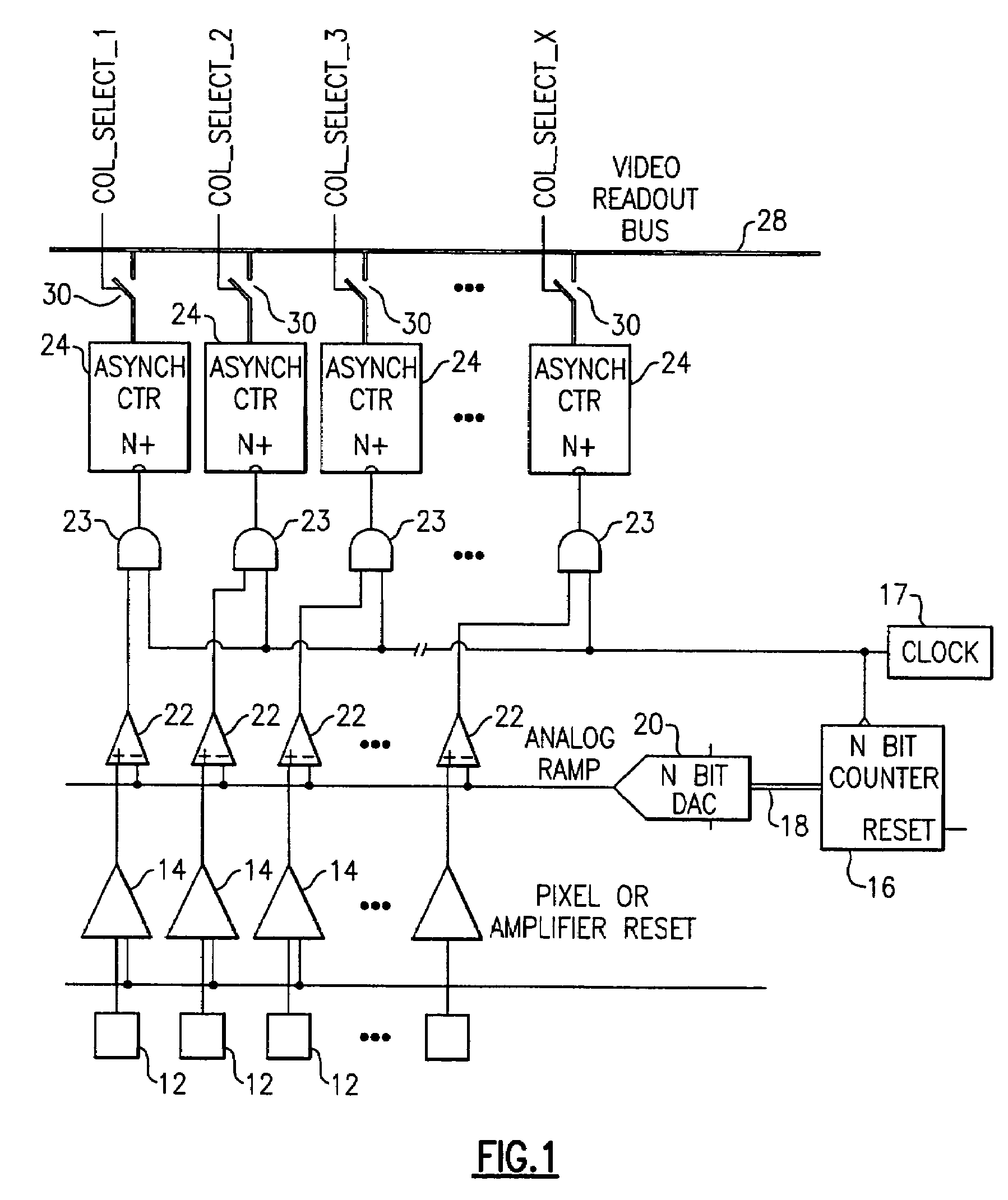

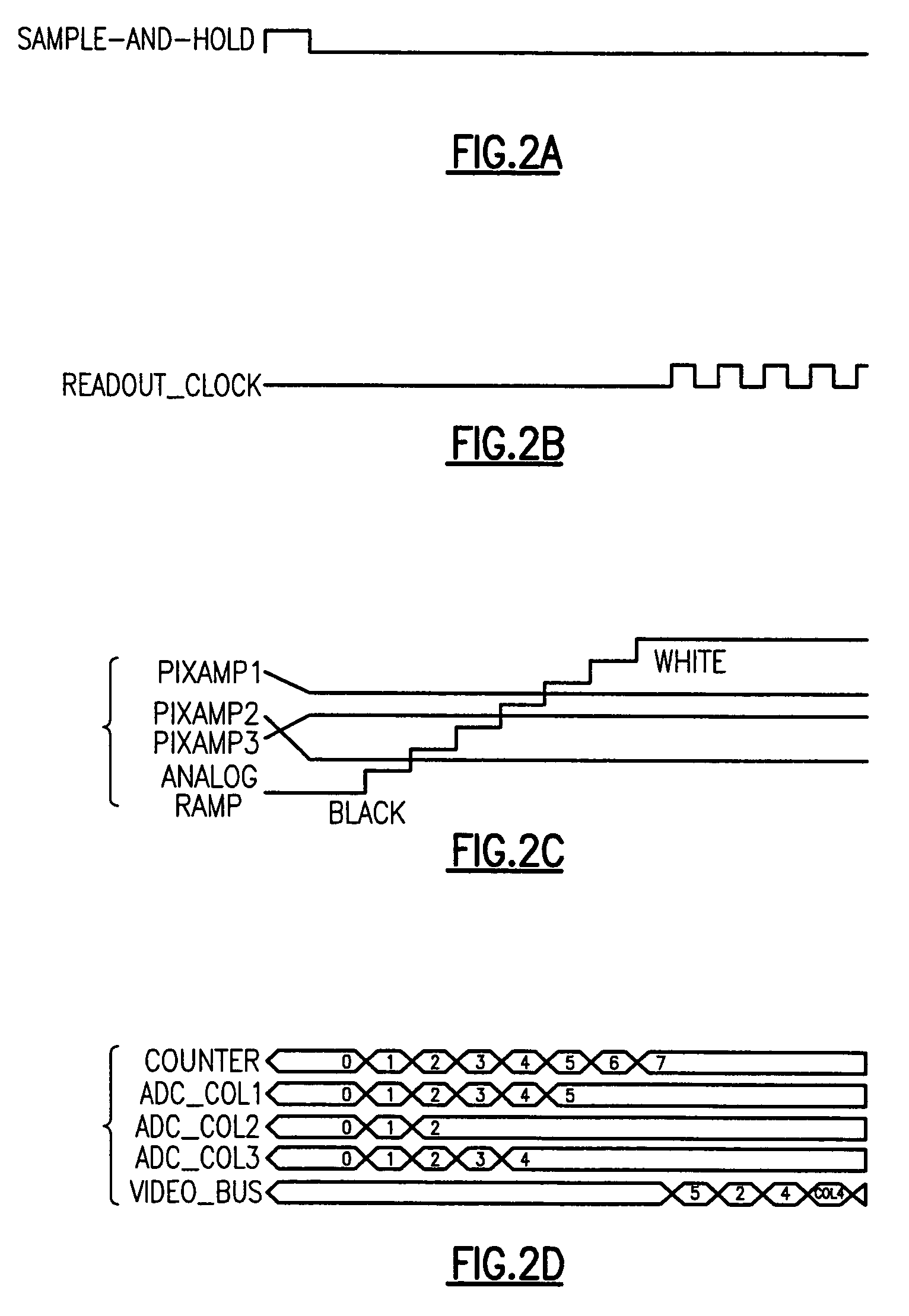

Image Sensor ADC and CDS per Column

InactiveUS20090231479A1Available areaAvoid disadvantagesAnalogue/digital conversionTelevision system detailsTwo's complementSolid-state

A solid state imager converts analog pixel values to digital form on an arrayed per-column basis. A counter is coupled to an N-bit DAC to produce an analog ramp that varies corresponding to the contents of the counter. A ripple counter is associated with each respective column. A clock or a source of counts at a predetermined sequence supplies clock signals or counts to the counter elements. Column comparators gate the counter elements when the analog ramp equals the pixel value. The counter contents feed a video output bus to produce the digital video signal. Additional black-level readout counters elements can create and store a black level digital value that is subtracted from the pixel value to reduce fixed pattern noise. The counters may employ two's complement arithmetic. An additional array of buffer counter / latches can be employed. Ripple counters can be configured as counters to capture the digital video level, and then as shift registers to clock out the video levels to an output bus. The clock pulses or counts for the DAC counter and for the ripple counters can be at the same or different rates.

Owner:DYNAMAX IMAGING

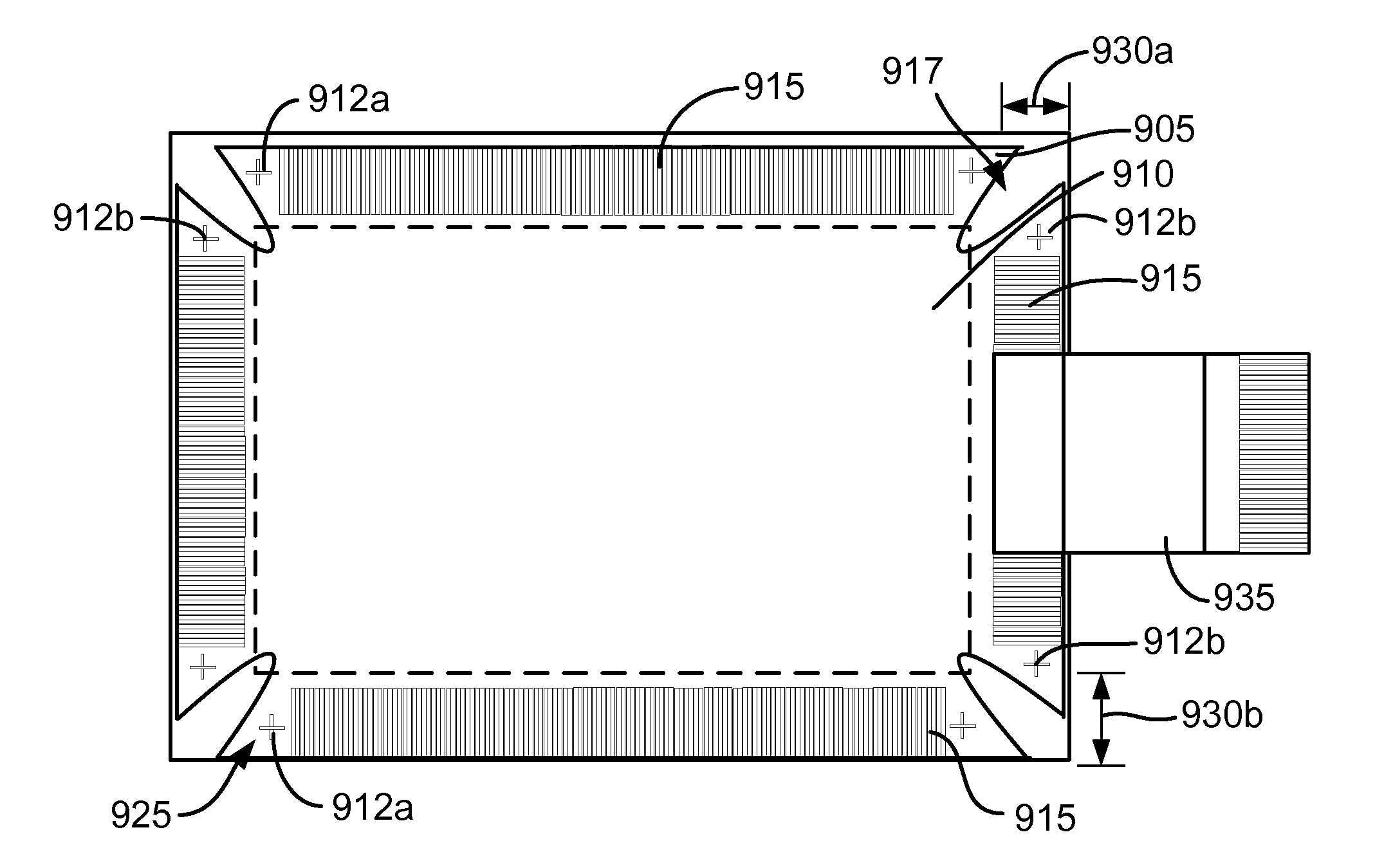

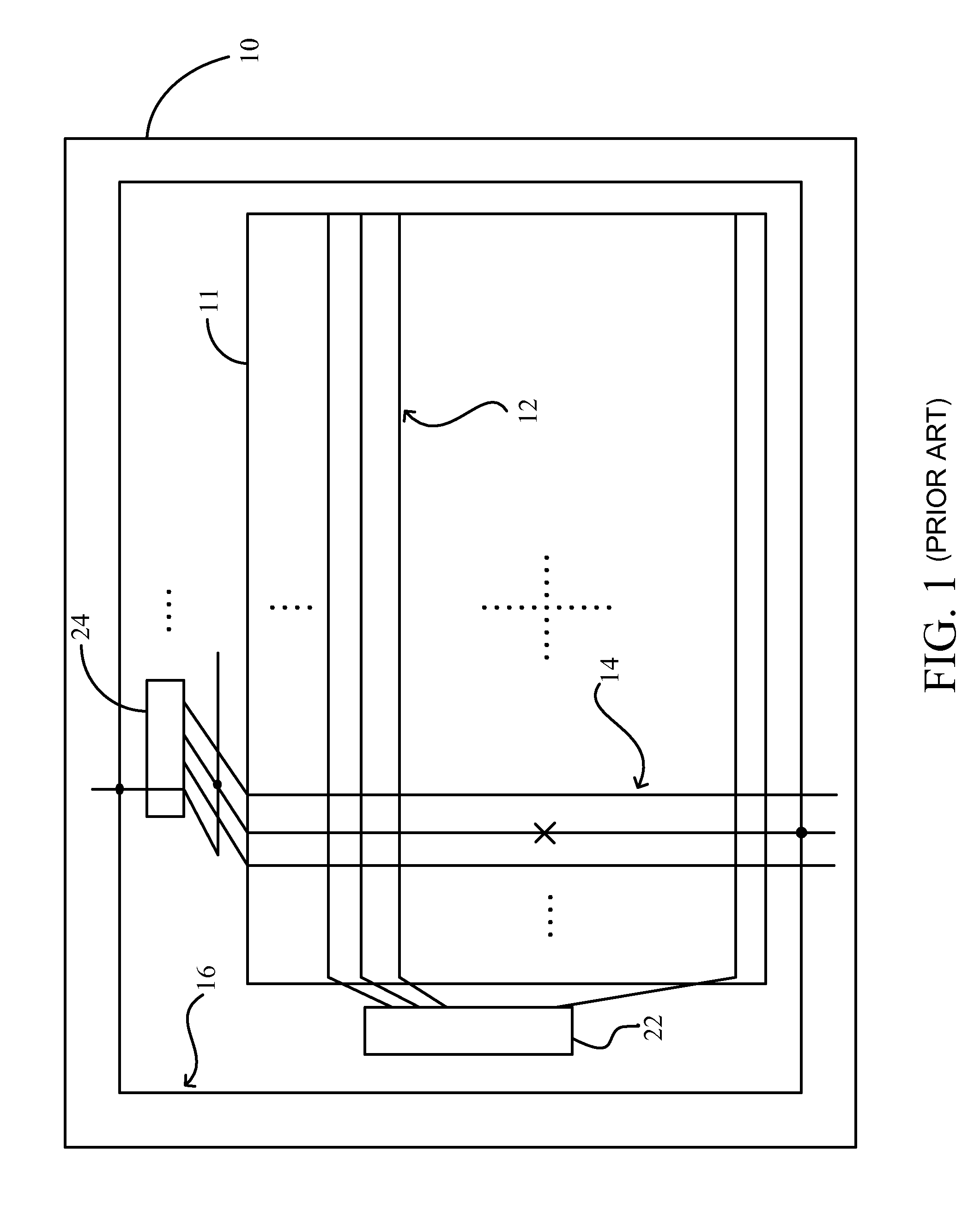

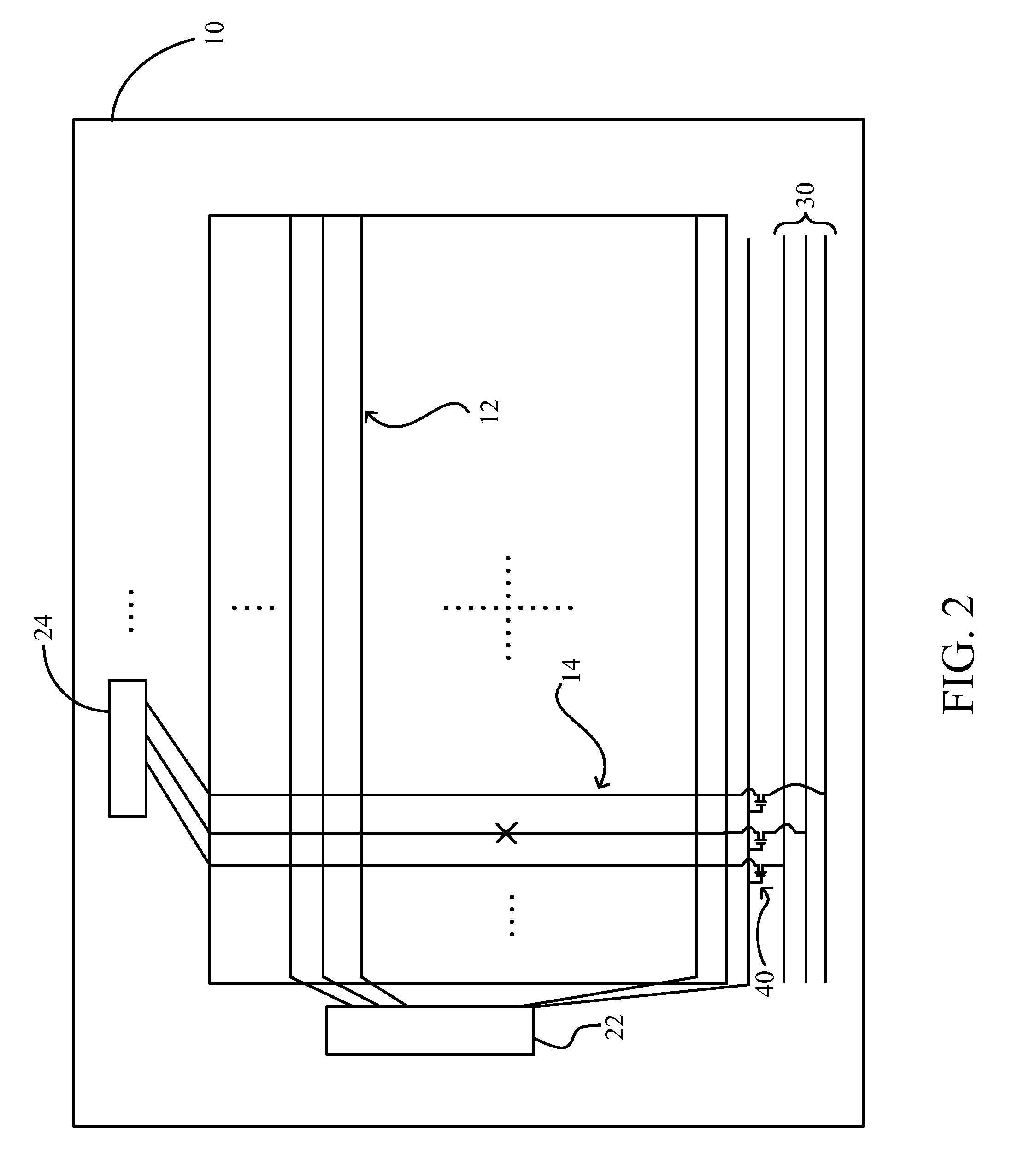

Flex Design and Attach Method for Reducing Display Panel Periphery

InactiveUS20110254758A1Available areaLength be lowTube/lamp screens manufactureStatic indicating devicesActive componentDisplay device

Owner:SNAPTRACK

Laminated sheet manifold for microchannel heat exchanger

ActiveUS8726976B2Limited space availableAvailable areaStationary conduit assembliesHeat exchanger casingsEngineeringMicro heat exchanger

A heat exchanger can have a manifold which includes a plurality of laminated sheets that allow a customization of the heat exchanger. The design can allow for a more optimal flow of coolant to areas of high load, thereby making the temperature distribution across the heat exchanger more uniform, or intentionally non-uniform. Furthermore, the laminated sheets can allow multiple circuits to be employed in the heat exchanger such that different coolants can be utilized therein and maintained separate from one another. The tubes can be microchannel tubes. A single set of manifolds can be used with multiple heat exchanger cores to provide a more compact heat exchanger. Mounting features can be integral with a group of the sheets.

Owner:VERTIV CORP

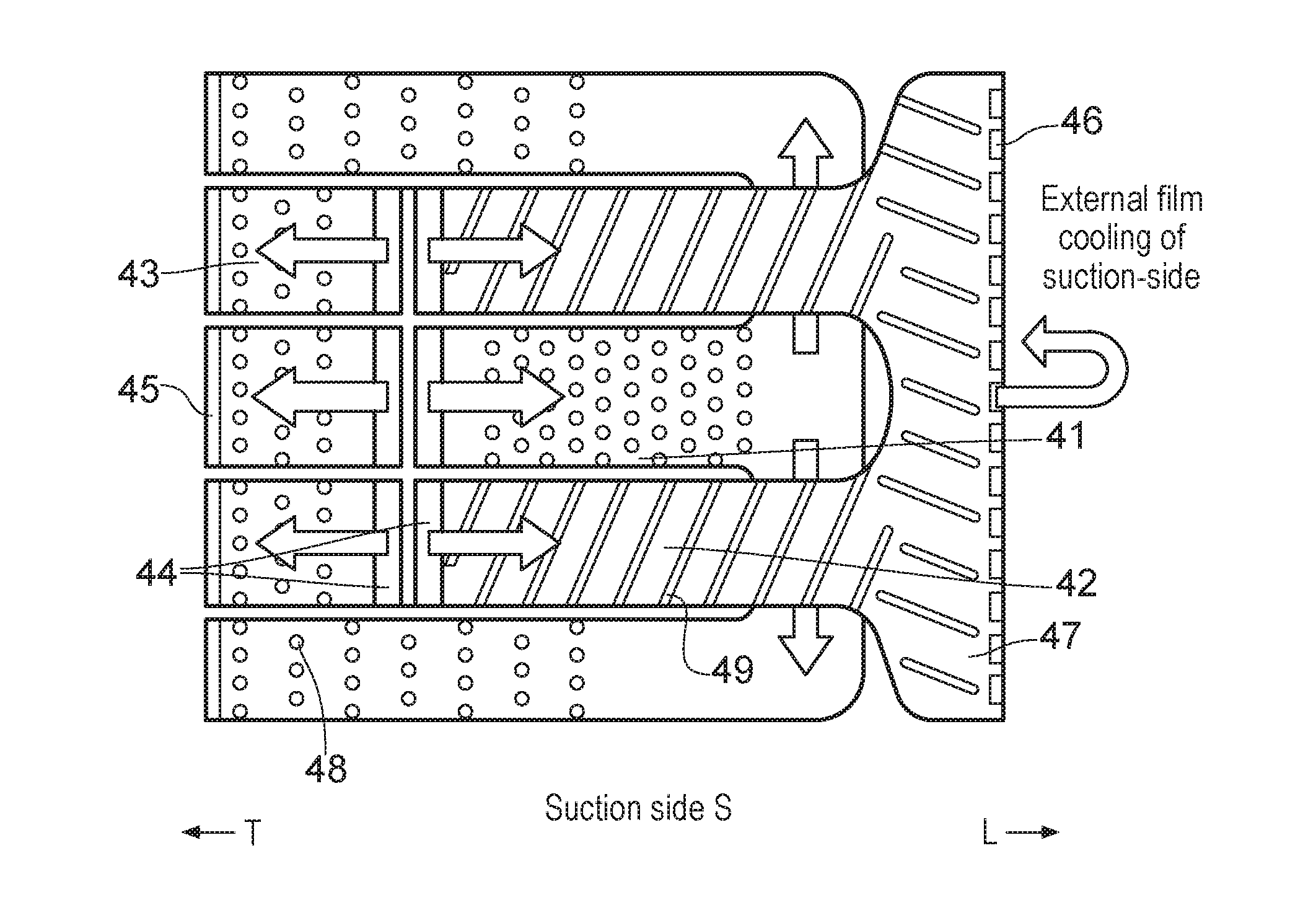

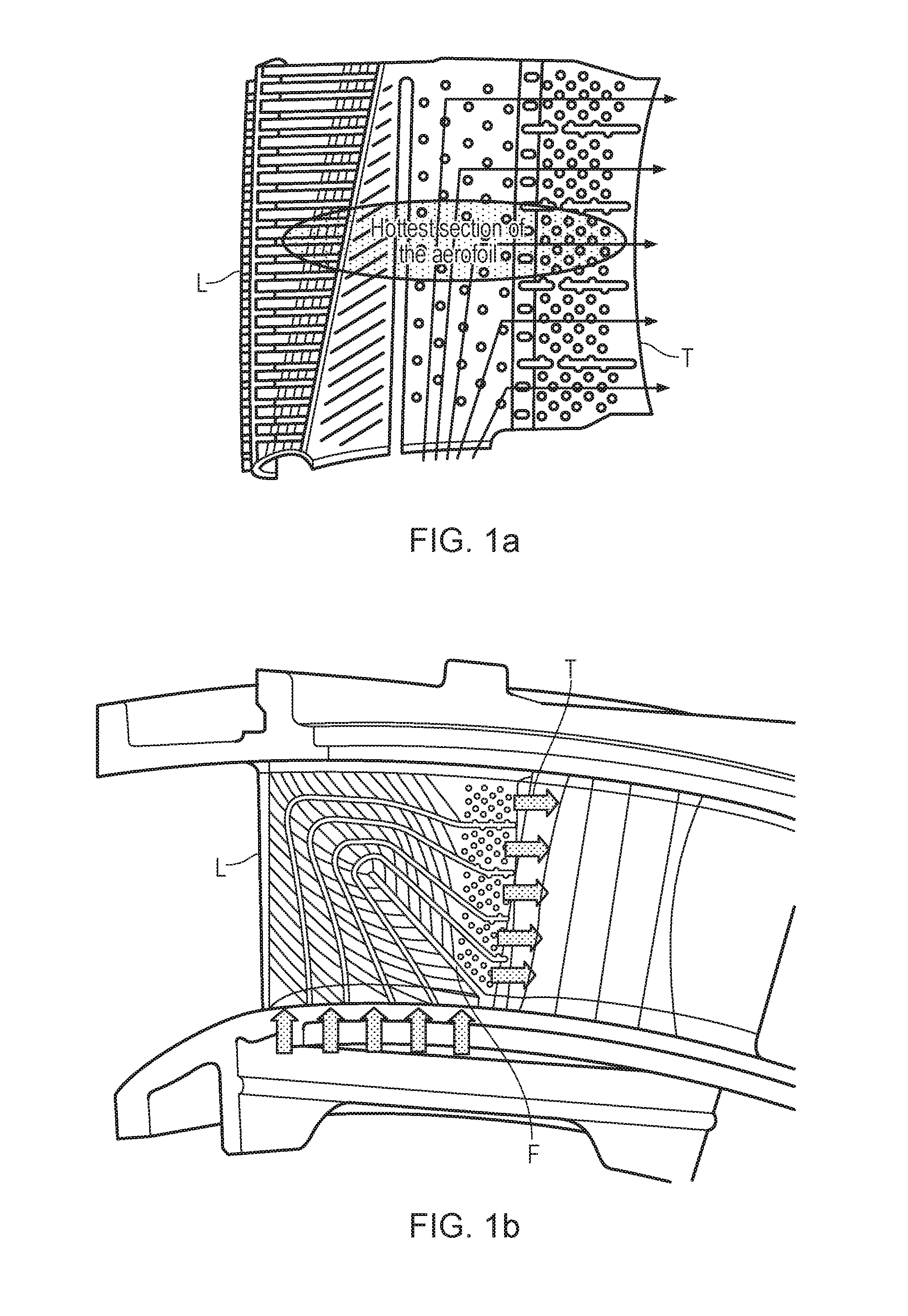

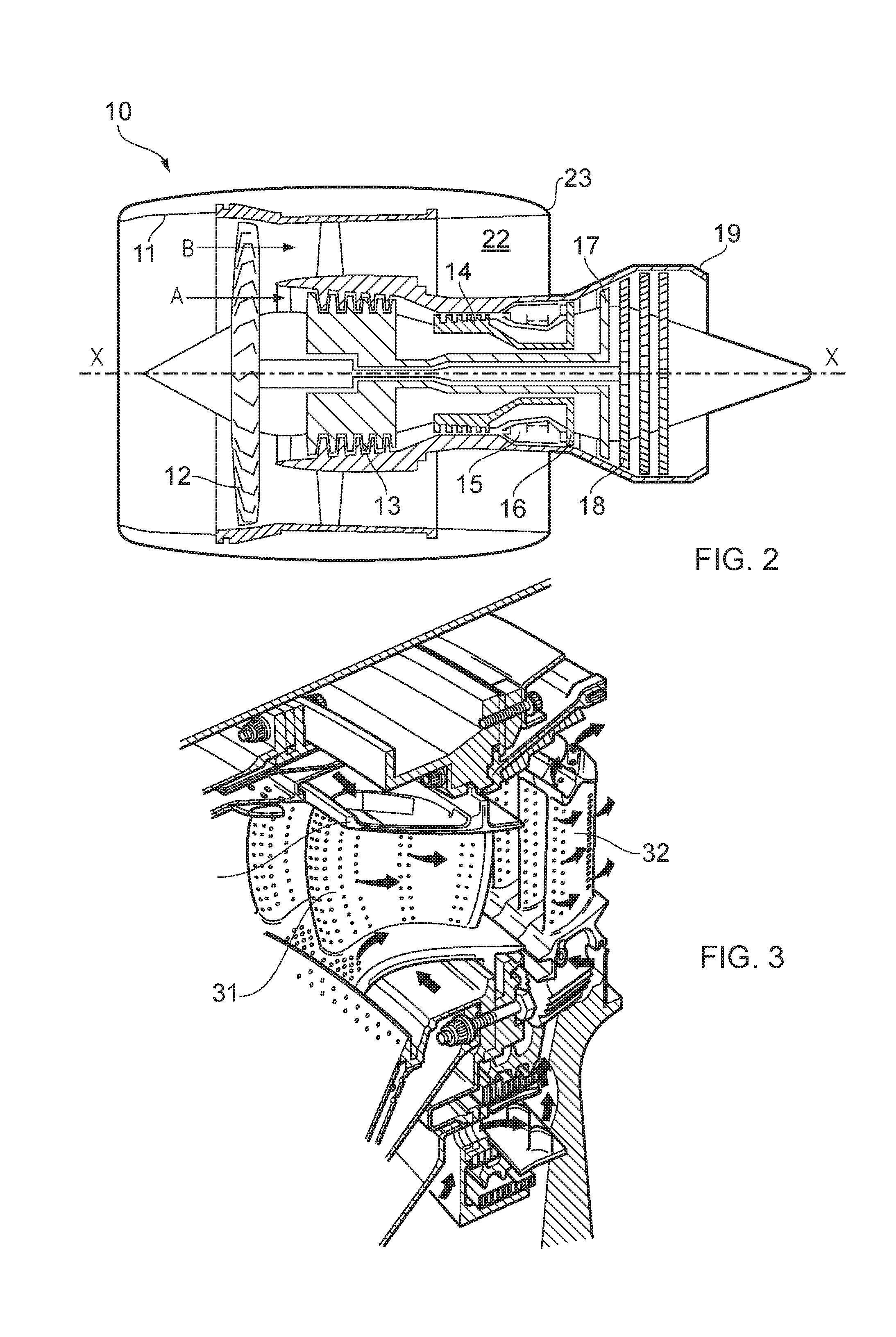

Aerofoil blade or vane

ActiveUS20160177741A1Available areaImproved profilePropellersPump componentsLeading edgeCoolant flow

An aerofoil blade or vane for the turbine of a gas turbine engine includes: an aerofoil leading edge; an aerofoil trailing edge; an aerofoil suction side; and at least one reverse-pass coolant passage, extending within the aerofoil blade or vane; wherein the at least one reverse-pass coolant passage includes a substantial reverse-pass portion in which, in use, coolant flows in a direction away from the trailing edge and towards the leading edge.

Owner:ROLLS ROYCE PLC

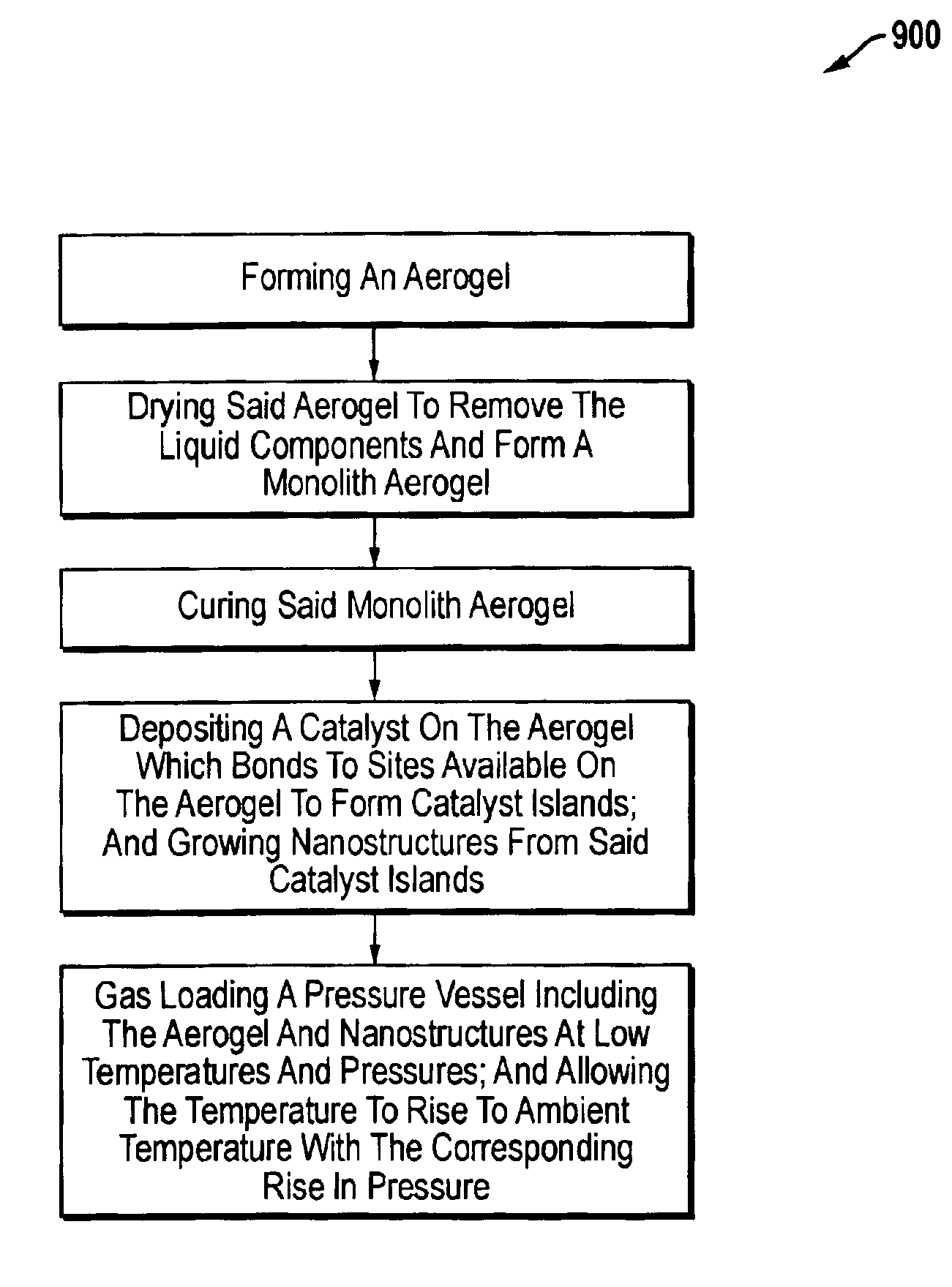

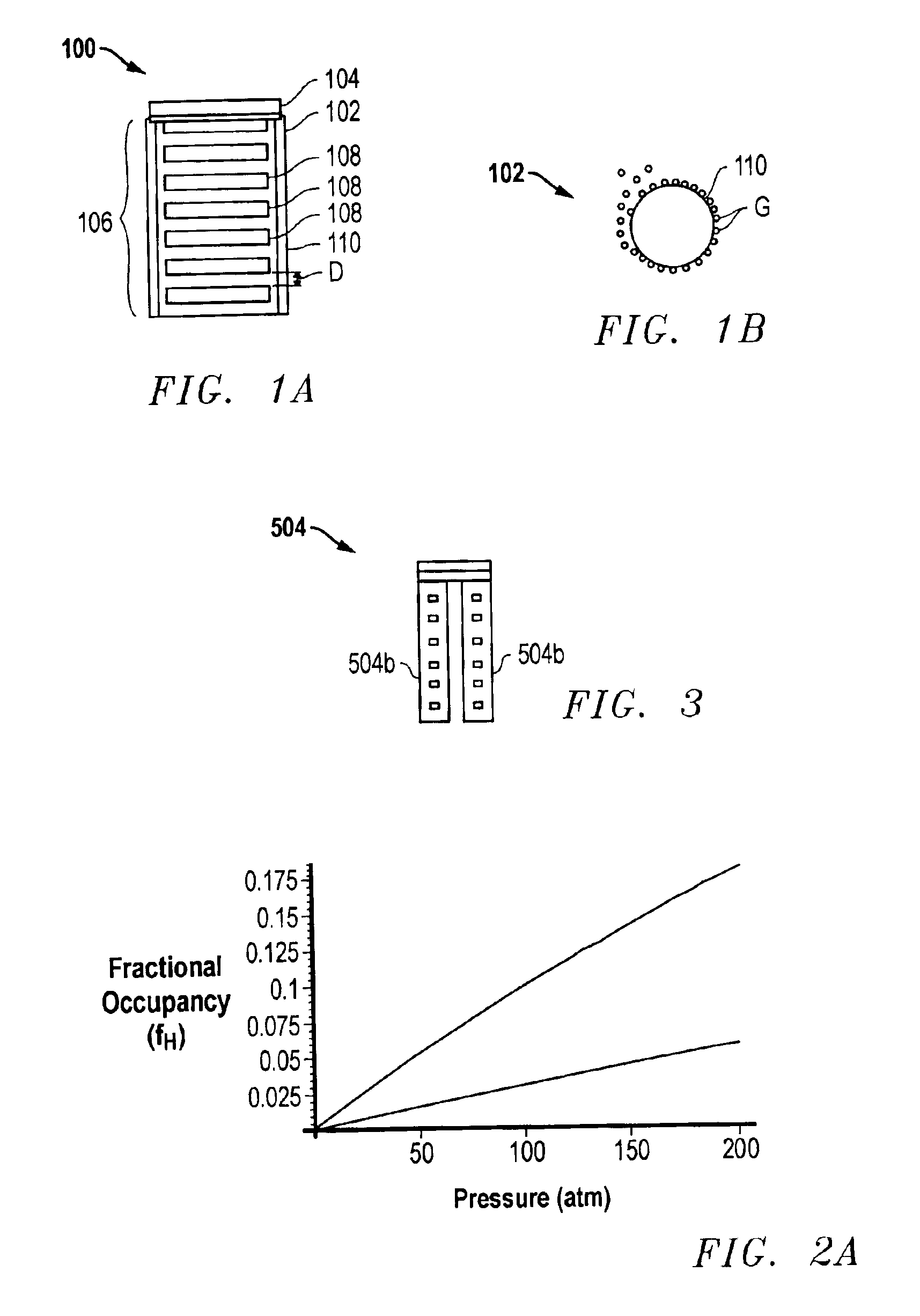

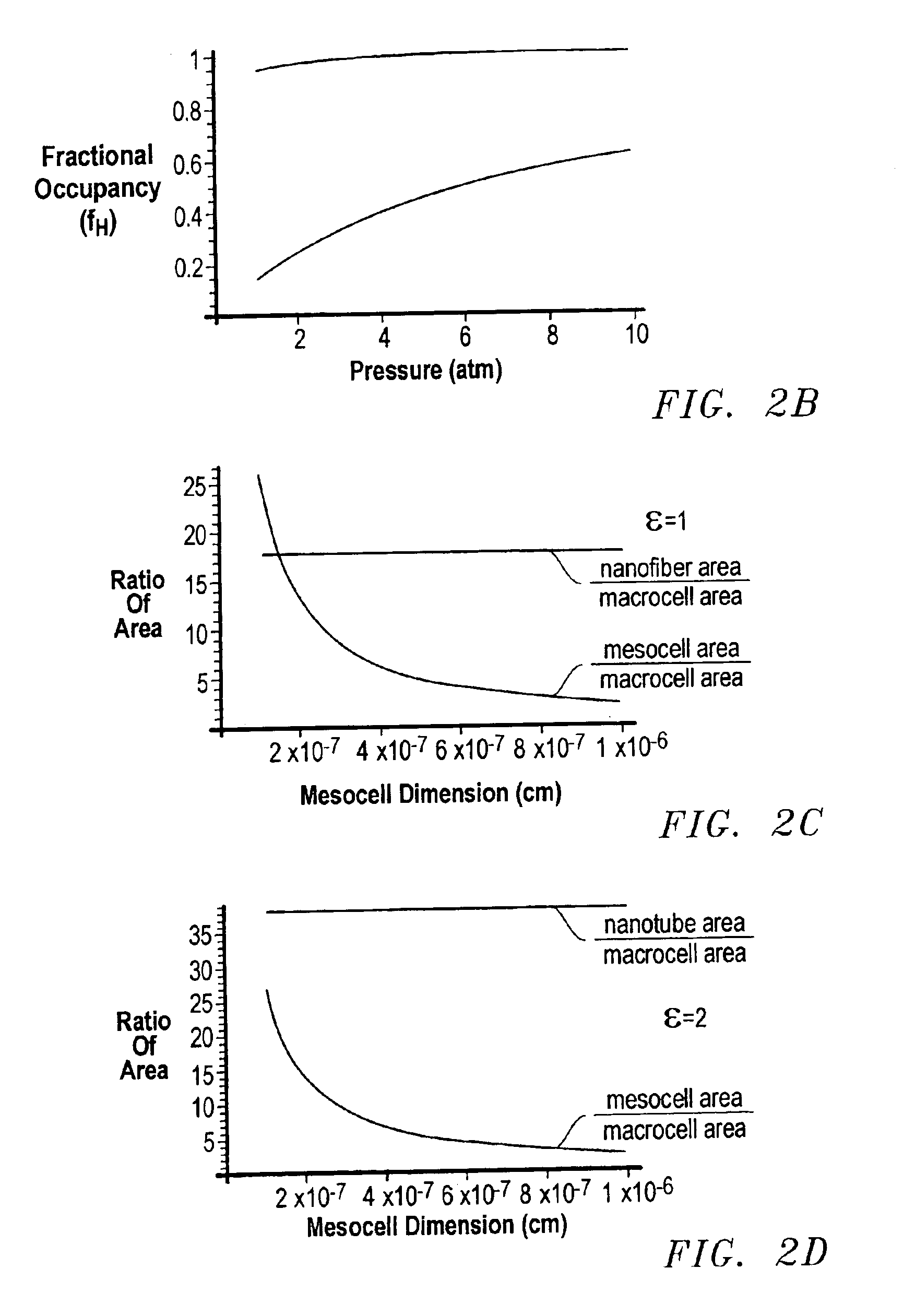

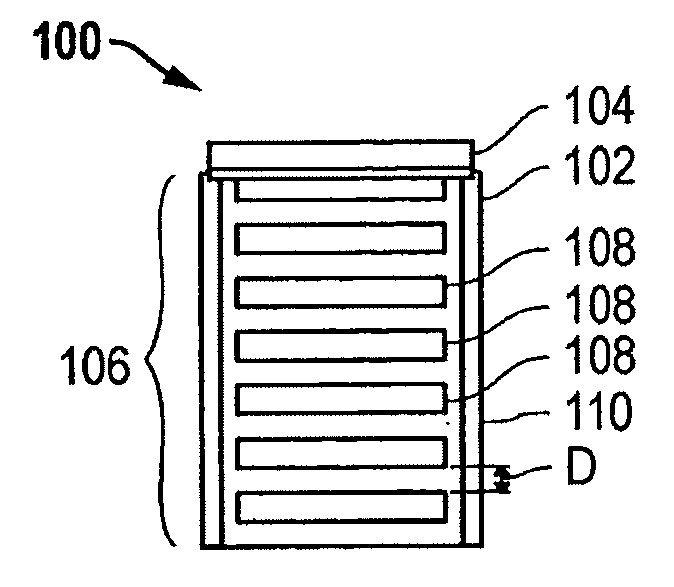

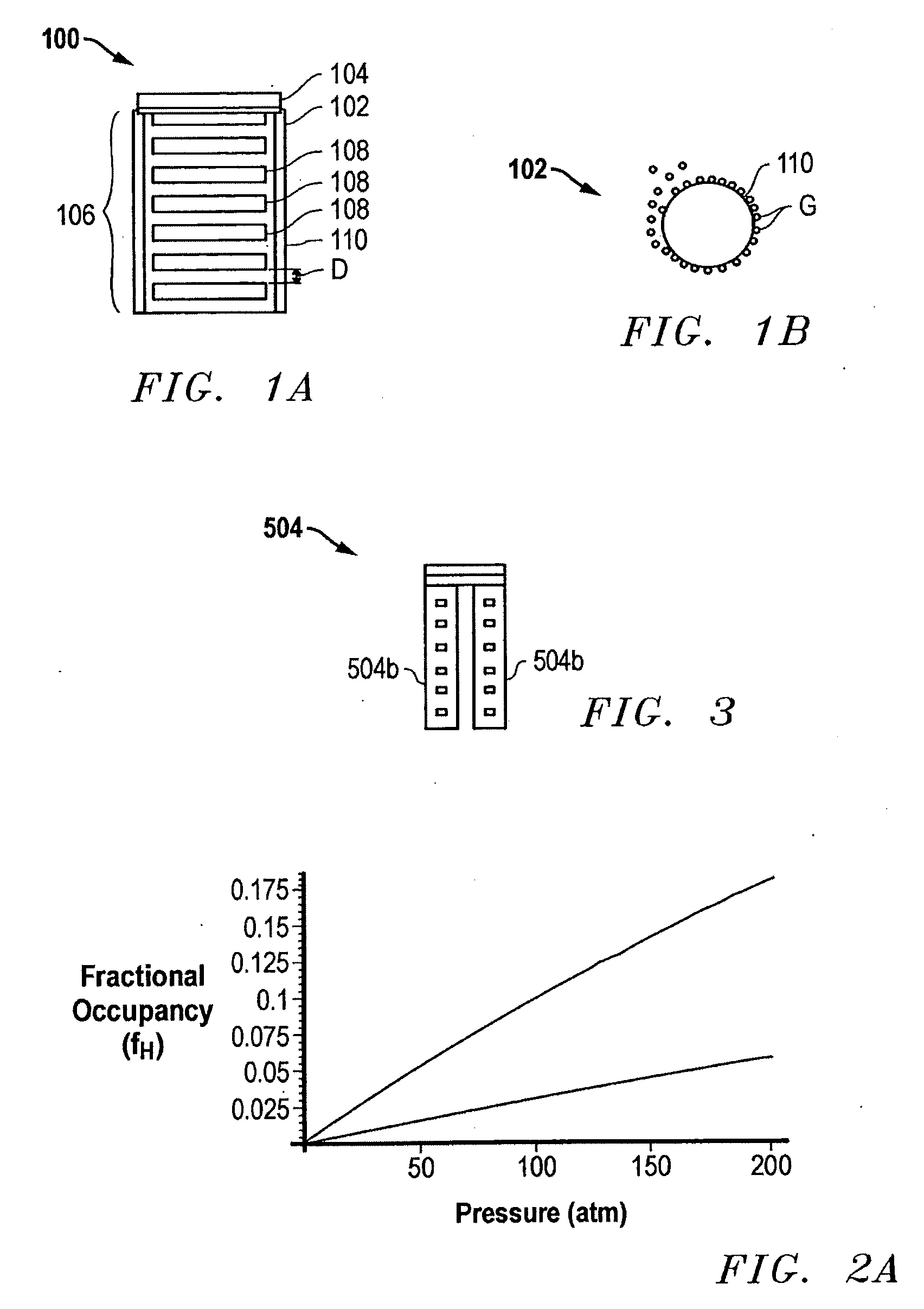

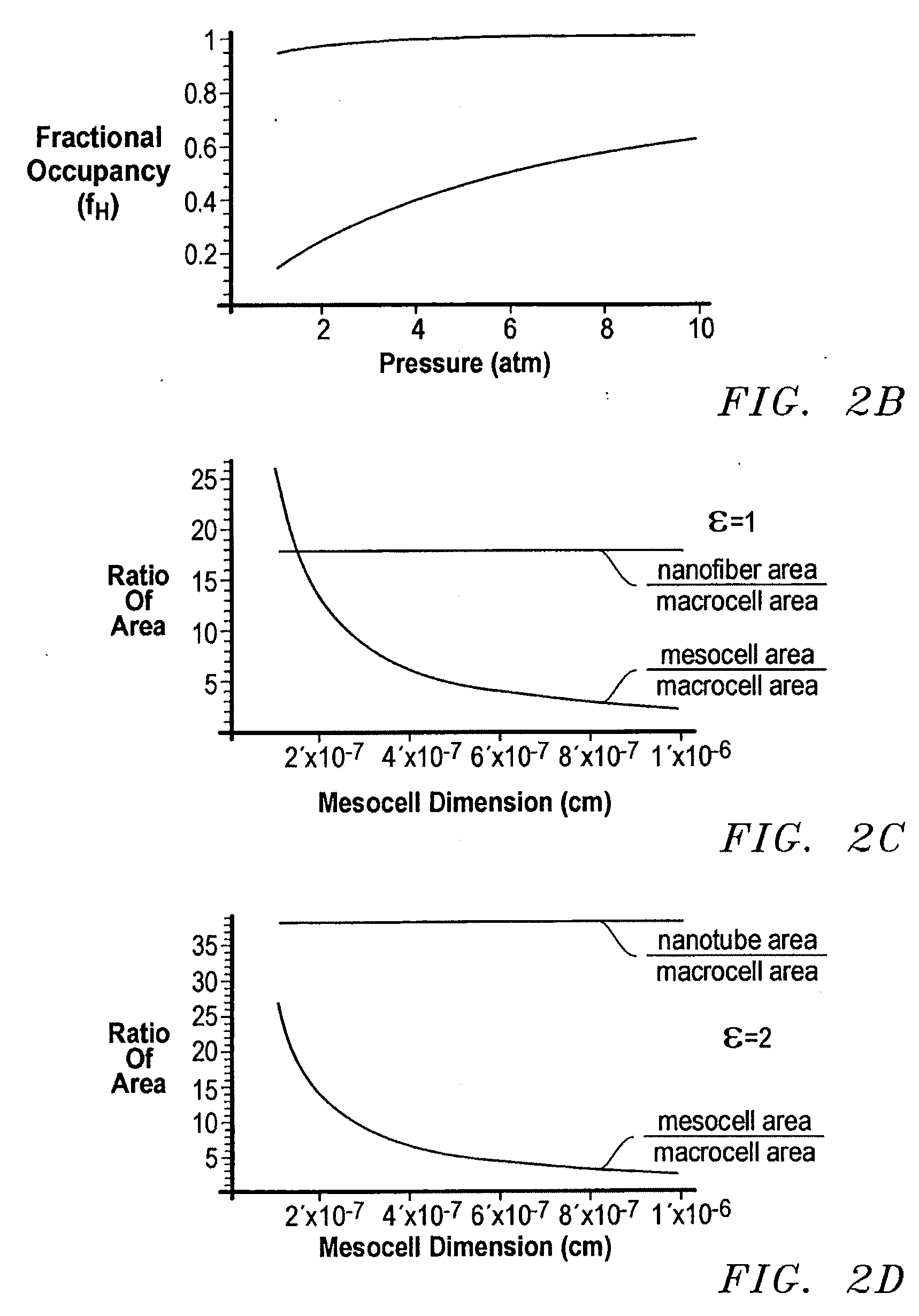

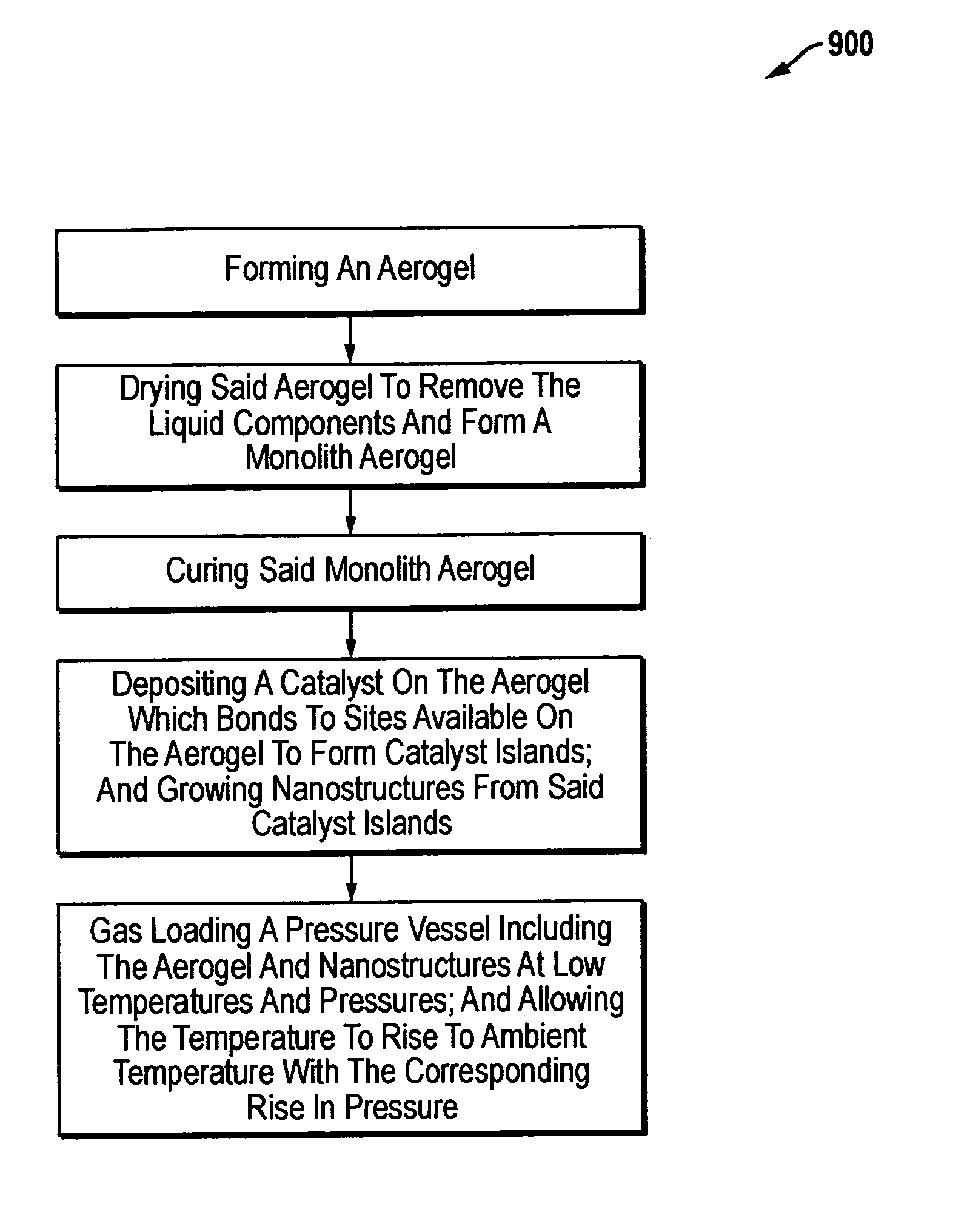

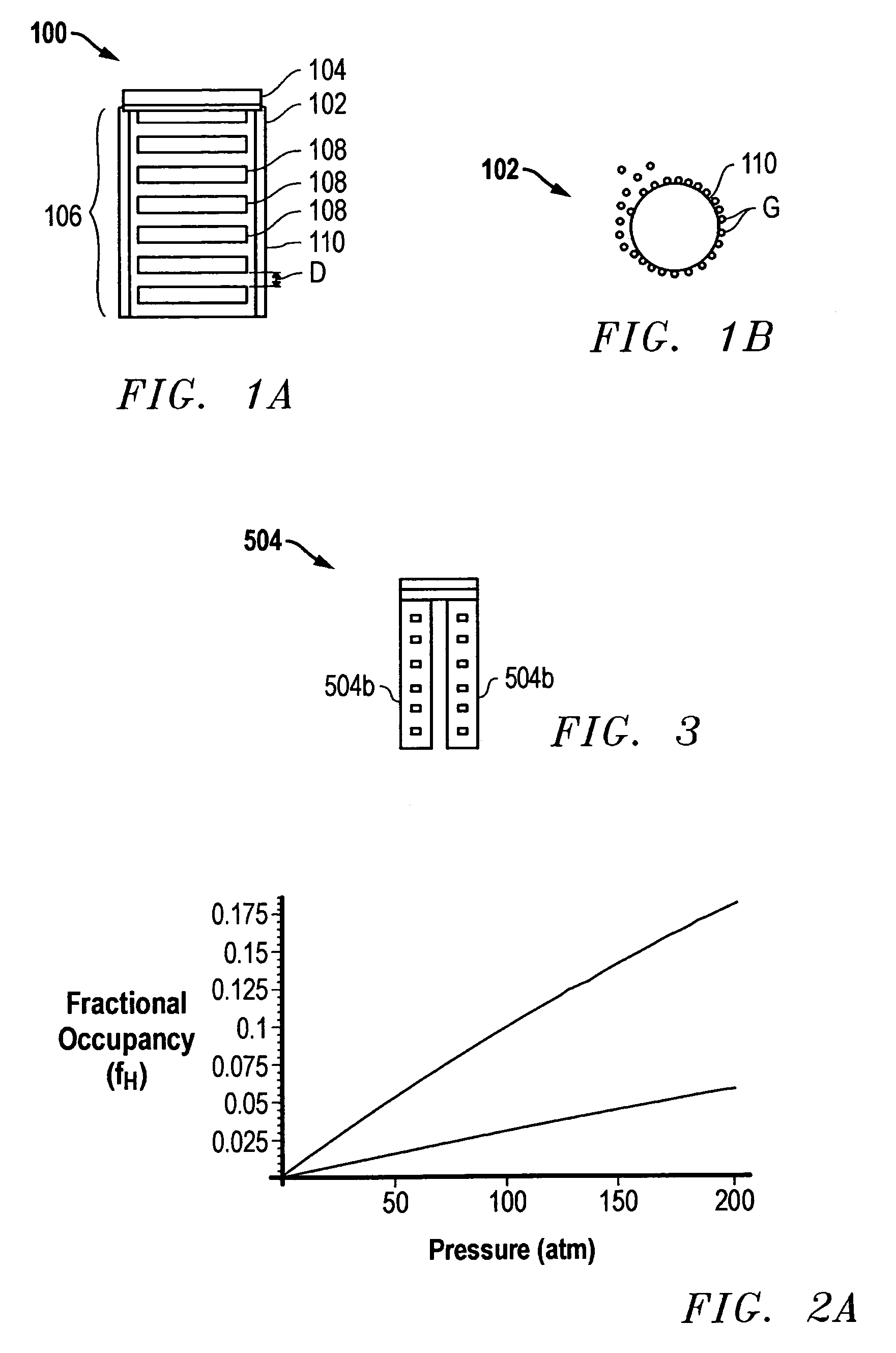

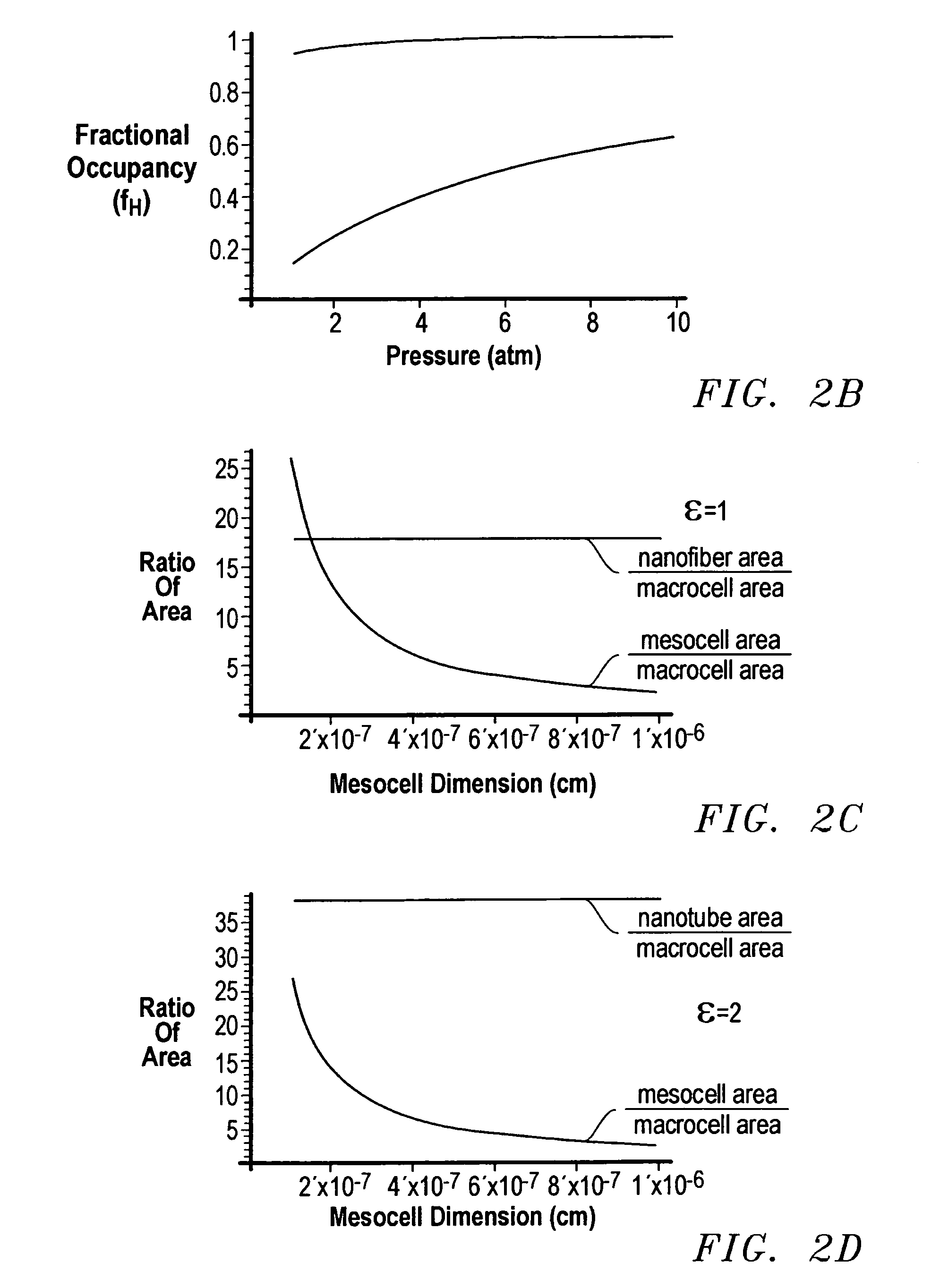

Method for sorption and desorption of molecular gas contained by storage sites of nano-filament laded reticulated aerogel

InactiveUS6906003B2Large potential surface areaIncrease depositionMaterial nanotechnologyReversible hydrogen uptakeDesorptionProduct gas

A system and method for sorption and desorption of molecular gas contained by storage sites of graphite nano-filaments randomly disposed in three-dimensional reticulated aerogel.

Owner:ENERNEXT +3

Image sensor ADC and CDS per column with oversampling

ActiveUS8169517B2Available areaAvoid disadvantagesTelevision system detailsElectric signal transmission systemsEngineeringDynamic range

A solid state imager converts analog pixel values to digital form on an arrayed per-column basis. An N-bit counter supplies an N-bit DAC to produce an analog ramp output with a level that varies corresponding to the contents of the counter. A latch / counter or equivalent is associated with each respective column. A clock supplies clock signal(s) to the counter elements. When the analog ramp equals the pixel value for that column, the latch / counter latches the value. The black level can be pre-set in the latch / counter or can be subtracted separately to reduce fixed pattern noise. The pixels can be oversampled for some number of times, e.g., n=16, to reduce the thermal noise of the sensors. Also, two or more pixels sharing a common sense node may be binned together, and two (or more) pixels having different integration times may be combined to obtain an output signal with enhanced dynamic range.

Owner:DYNAMAX IMAGING

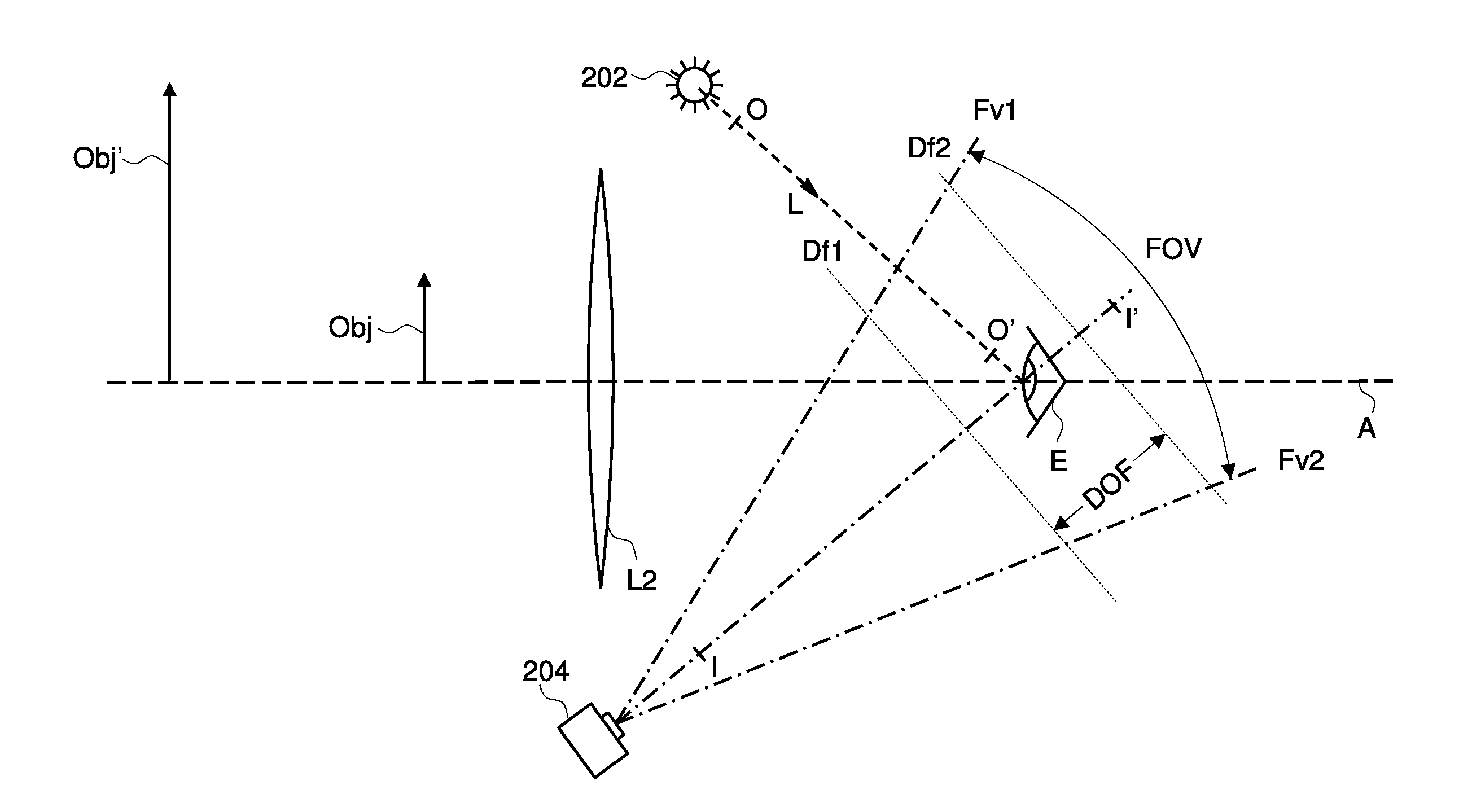

Apparatuses and methods for iris imaging

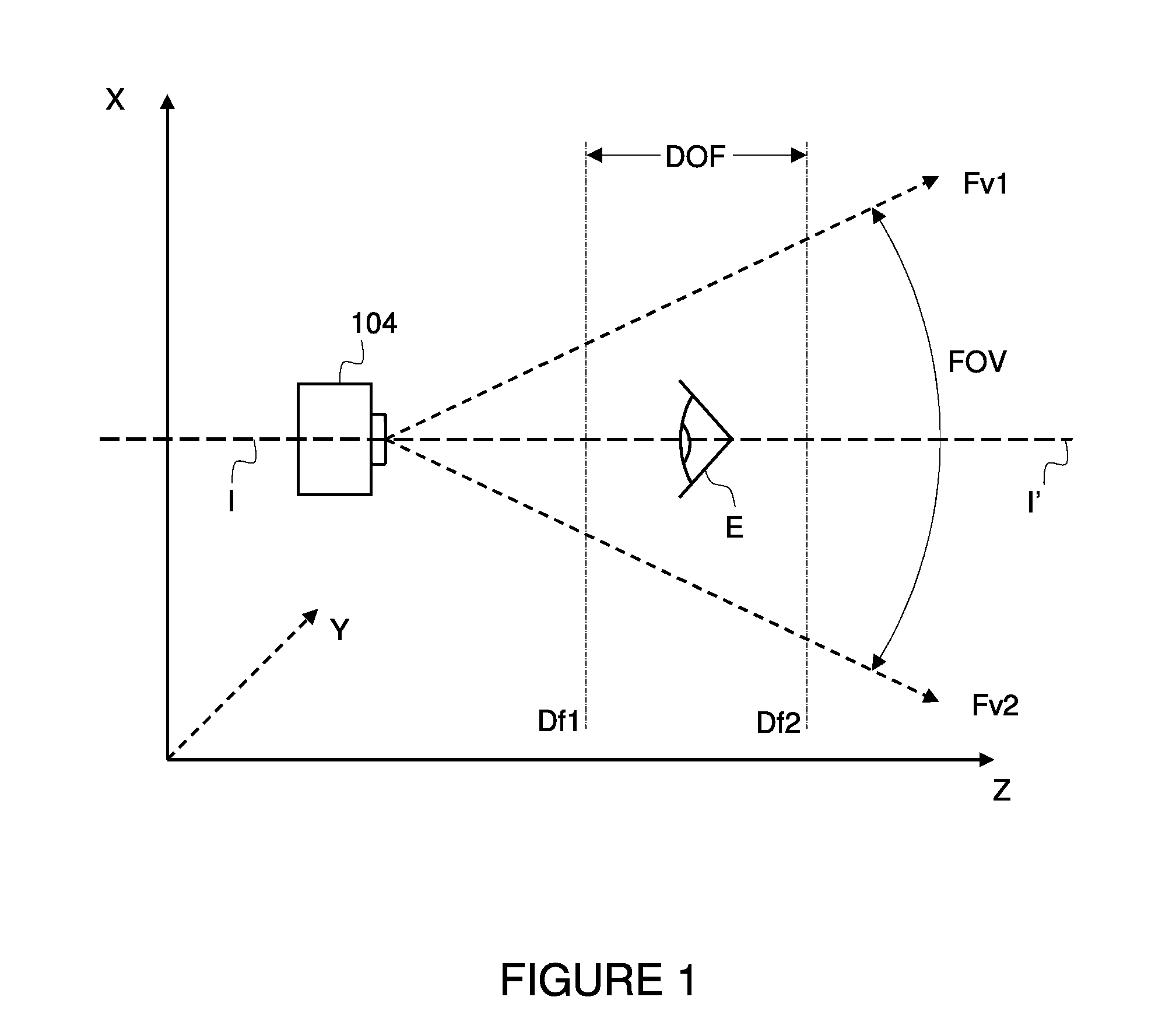

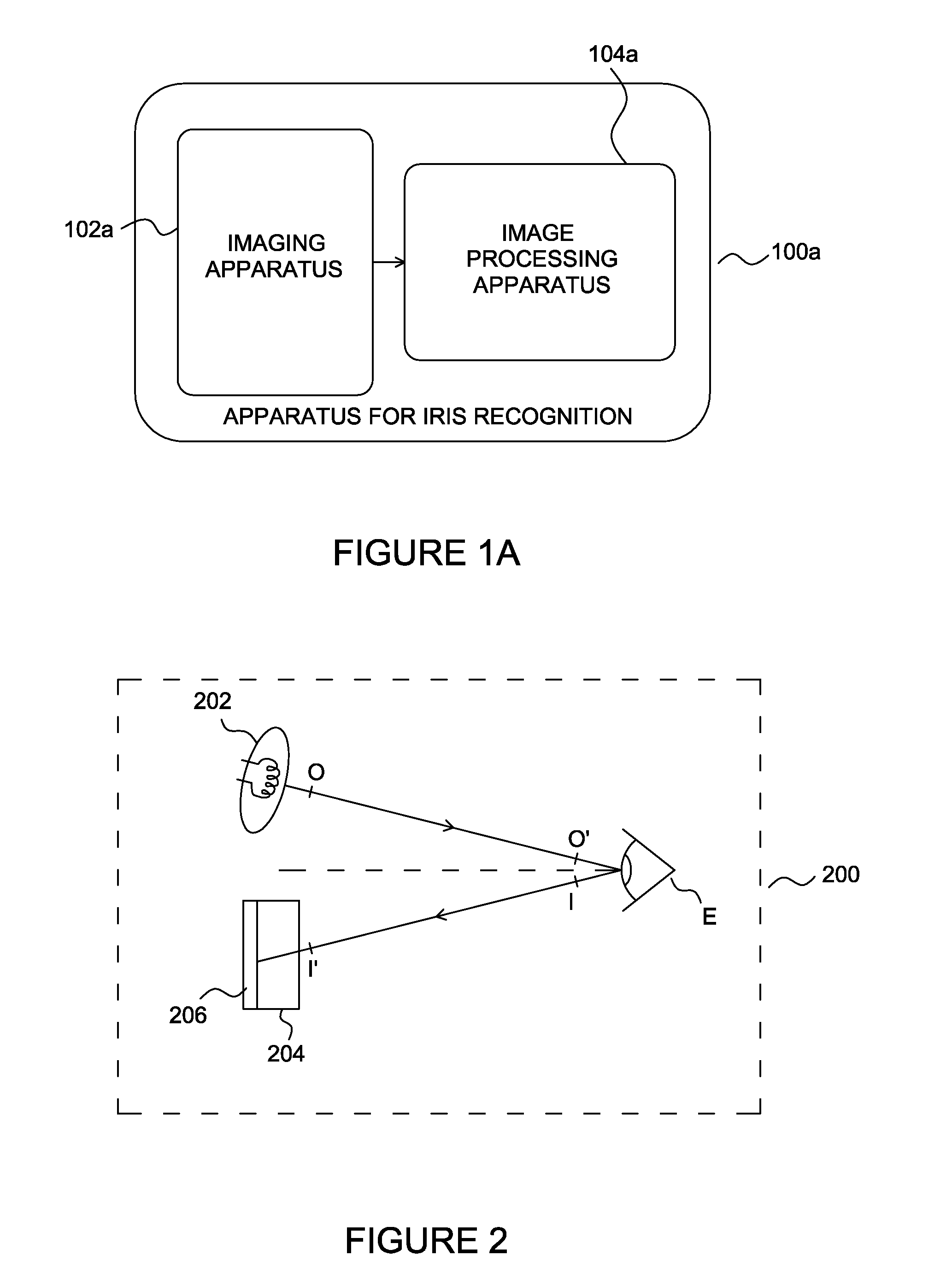

InactiveUS20140307077A1Available areaSubject's pupil to constrictAcquiring/recognising eyesColor television detailsOptical axisElectromagnetic spectrum

The invention includes a method and apparatus for acquiring an image of a subject's iris, within the near infrared region of the electromagnetic spectrum. Near infrared radiation is generated from an incandescent light source, having wavelengths spread across 700 nm to 900 nm. The iris is illuminated for imaging by directing the generated near infrared radiation along an optical path between the incandescent light source and an intersection of a field of view region and depth of field region of an iris camera. Near infrared radiation scattered by the iris and transmitted along the iris camera's optical axis is received at the iris camera. An image of the iris is then acquired at the iris camera, based on radiation scattered by the iris and received at the iris camera.

Owner:DELTA ID

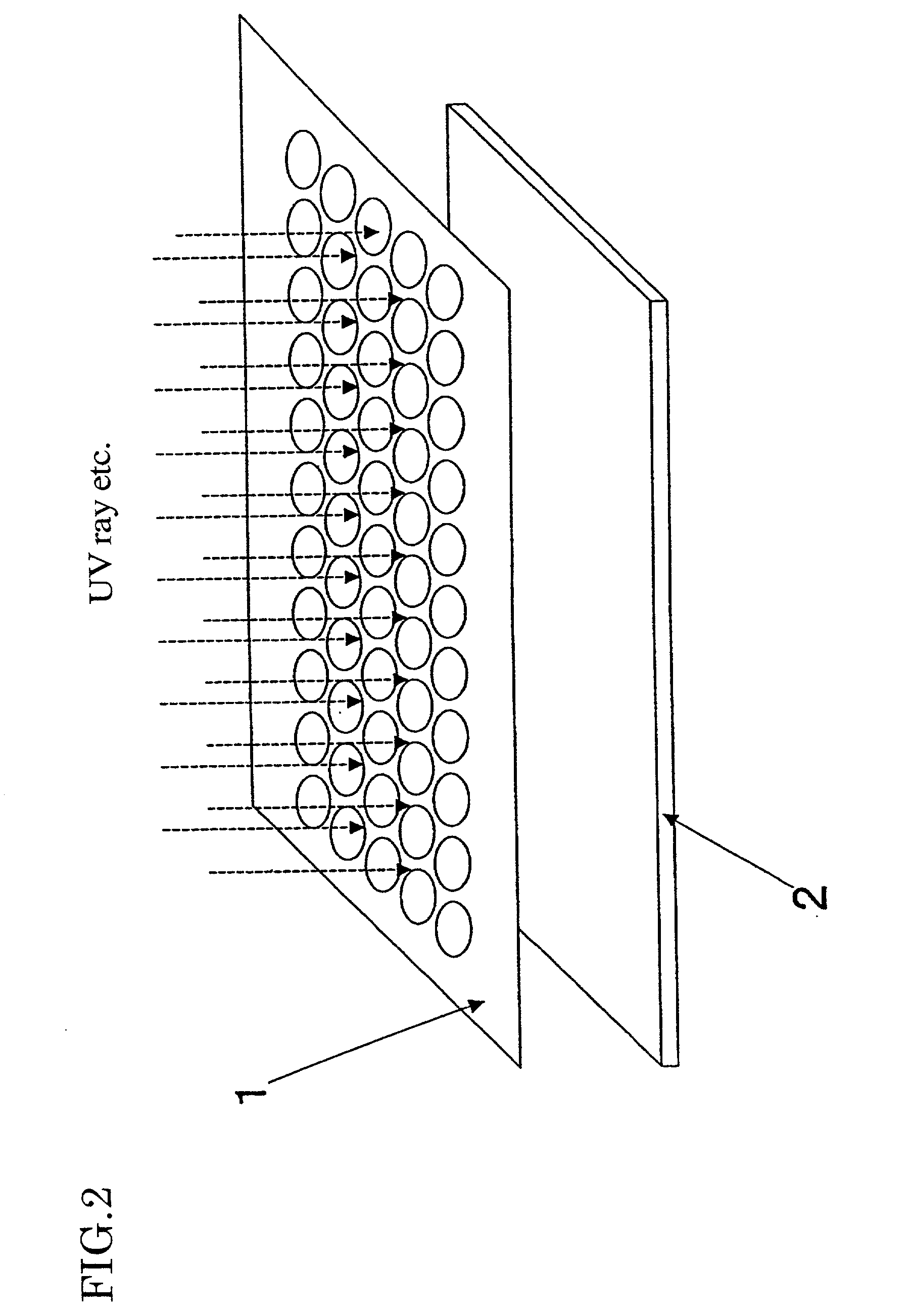

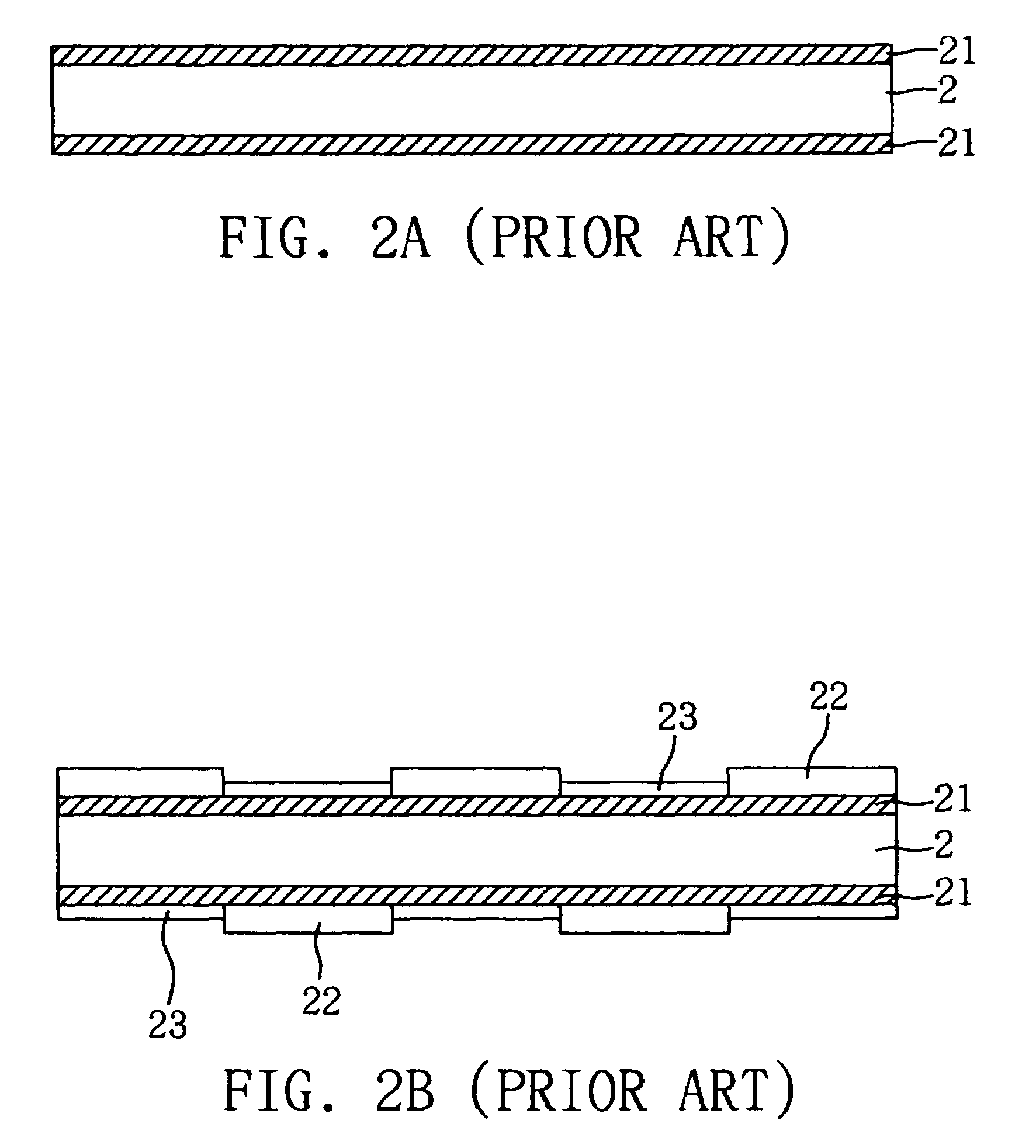

Microarray and microarray substrate

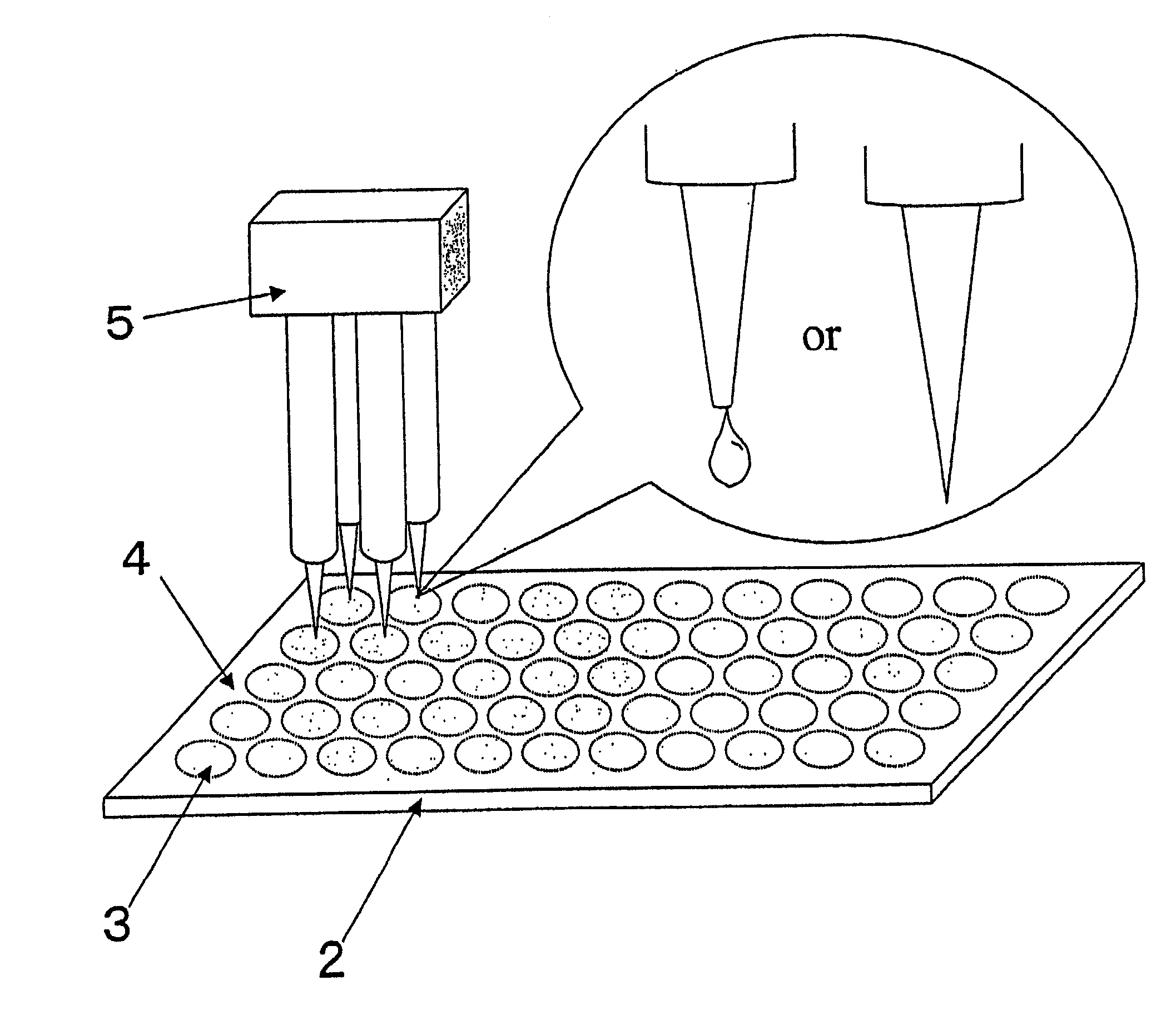

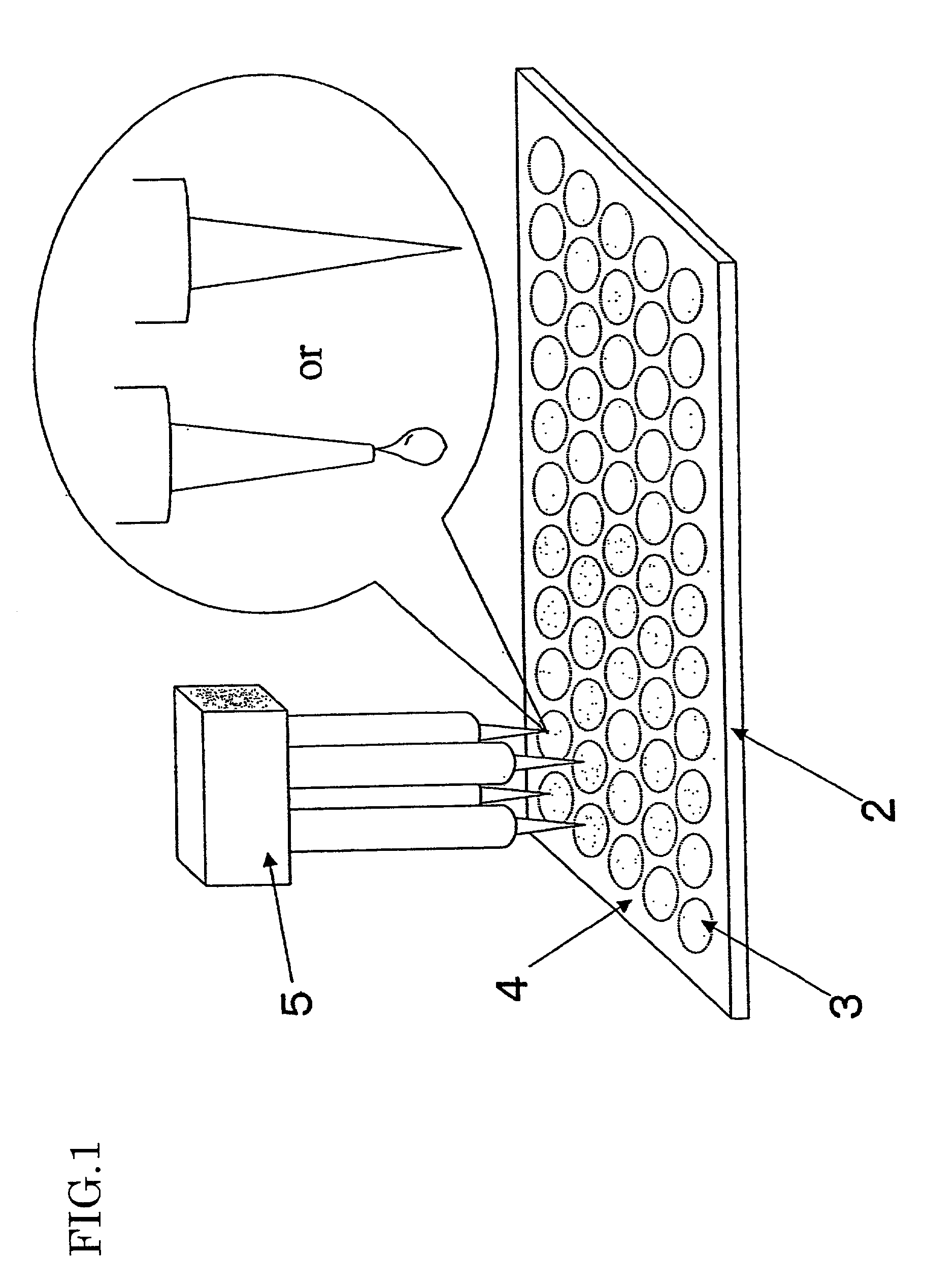

InactiveUS20020127589A1Shape stableAvailable areaBioreactor/fermenter combinationsSequential/parallel process reactionsDNAChemistry

To provide microarray capable of readily and securely making the shape of spot of probe DNA to be fixed into a desired shape. A microarray 2 of which substrate is a slide glass has a hydrophilic region 3 where the surface is hydrophilic and a probe DNA is fixed, and a hydrophobic region 4 where a probe DNA is not fixed and the surface is hydrophobic, around the hydrophilic region 3. When a solution containing the probe DNA is dropped by a spotter 5, the solution spreads in the hydrophilic region 3 while being prevented from further spreading by the hydrophobic region 4. As a result of this, it is possible to arbitrarily determine the shape of the spot, which is the hydrophilic region 3.

Owner:HITACHI SOFTWARE ENG

Image sensor ADC and CDS per column

InactiveUS7518646B2Available areaAvoid disadvantagesTelevision system detailsElectric signal transmission systemsShift registerDigital video

A solid state imager converts analog pixel values to digital form on an arrayed per-column basis. An N-bit counter supplies an N-bit DAC to produce an analog ramp output with a level that varies corresponding to the contents of the counter. A ripple counter or equivalent is associated with each respective column. A clock supplies clock signals to the counter elements. A comparator in each column gates the counter element when the analog ramp equals the pixel value for that column. The contents of the counters are transferred sequentially to a video output bus to produce the digital video signal. Additional black-level readout counter elements can create and store a digital value that corresponds to a dark or black video level. A subtraction element subtracts the black level value from the pixel value to reduce fixed pattern noise. An additional array of buffer counter / latches can be employed. The ripple counters can be configured as counters to capture the digital video level, and then as shift registers to clock out the video levels to an output bus. The clock pulses for the DAC counter and for the ripple counters can be at the same or different rates.

Owner:DYNAMAX IMAGING

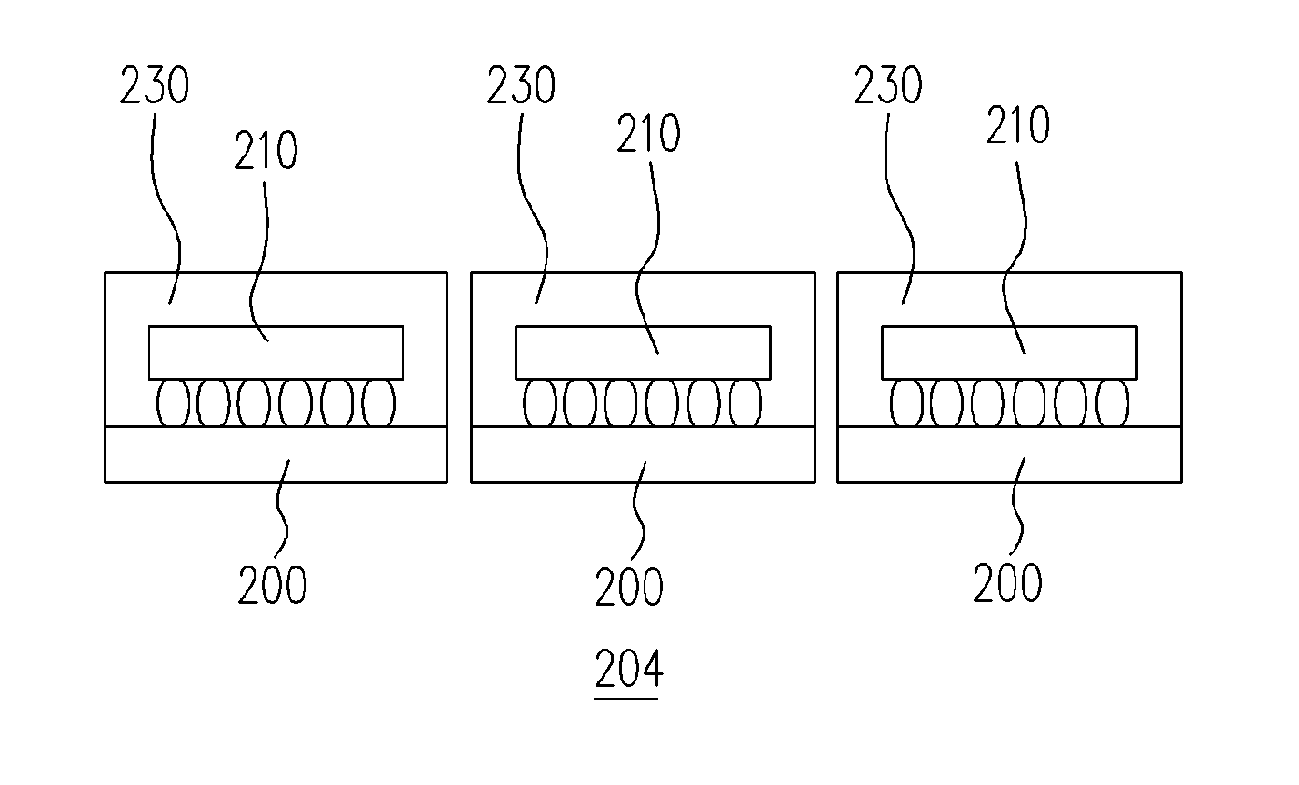

Flip chip packaging process

ActiveUS7256066B2Reduce generationIncrease the areaSemiconductor/solid-state device detailsSolid-state devicesDifferential coefficientThermal expansion

A flip chip packaging process uses an underfill as an encapsultant to reduce the possibility of delamination from occurring due to differential coefficients of thermal expansion, and thus the reliability of a flip chip package structure can be increased. Furthermore, the flooding of the encapsulant over the cutting line need not be taken into consideration for cutting the substrate. Therefore, the usage area of the substrate usage is increased, i.e., more chips can be mounted per unit area of the substrate.

Owner:ADVANCED SEMICON ENG INC

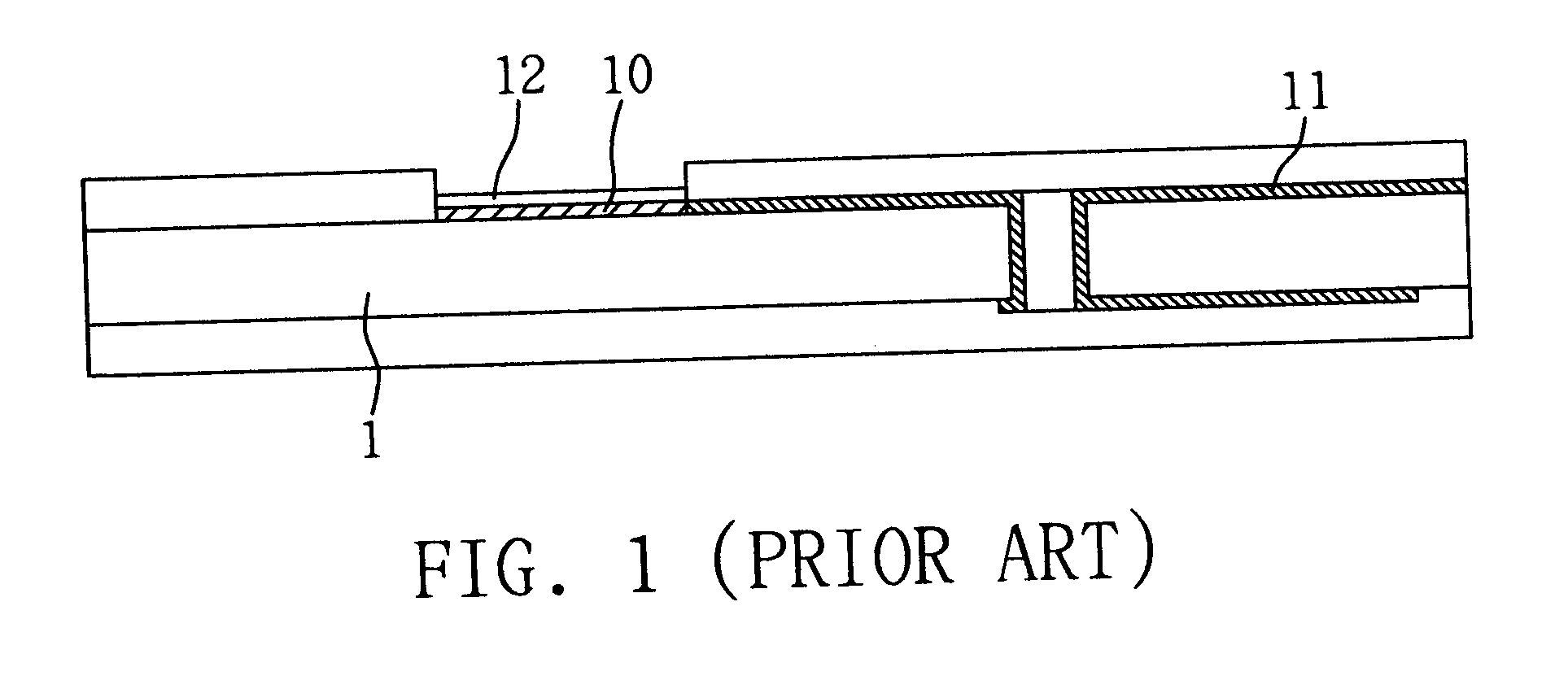

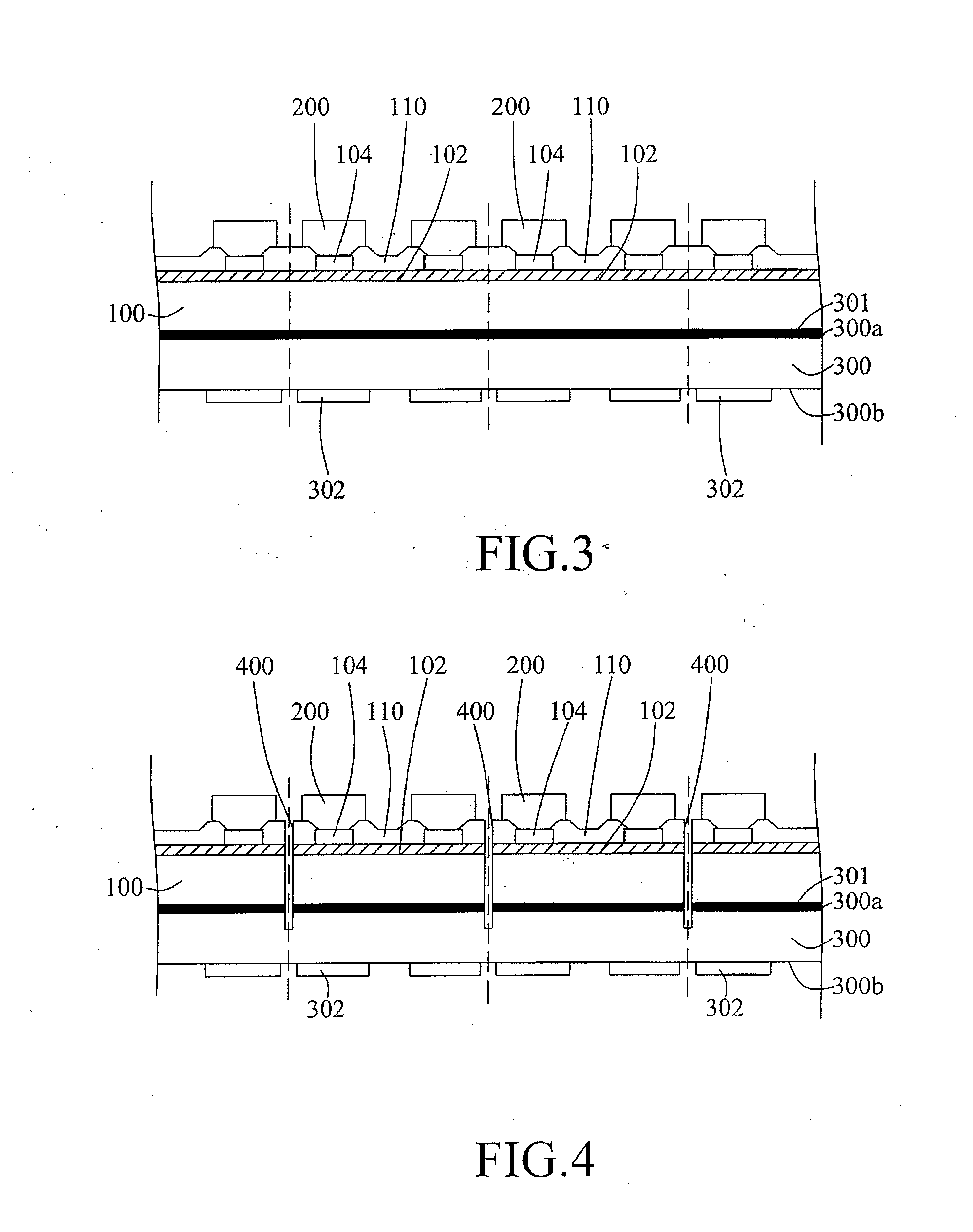

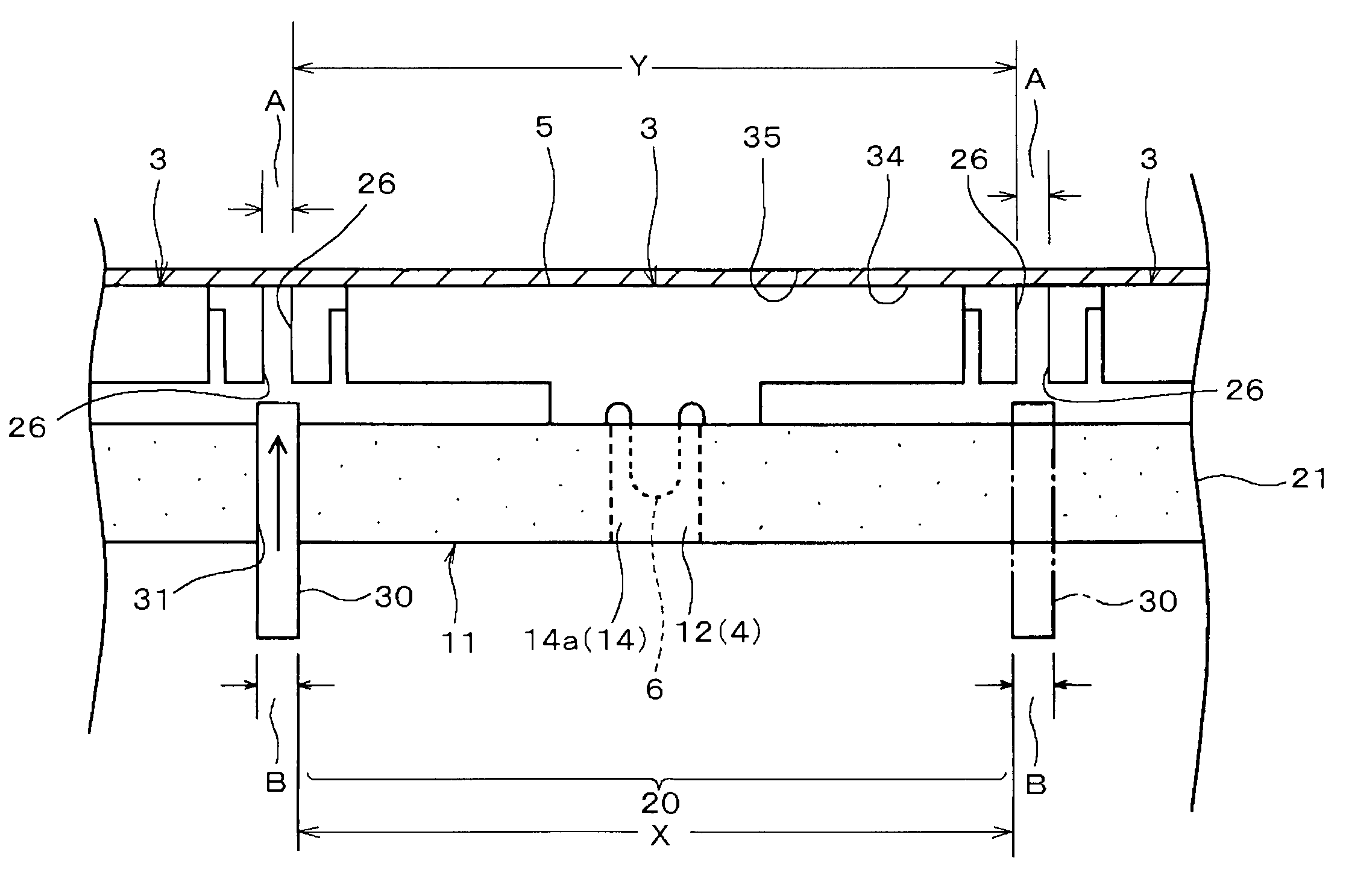

Liquid crystal display panel and method for repairing signal line thereof

ActiveUS8083561B1Reduce areaAvailable areaStatic indicating devicesNon-linear opticsLiquid-crystal displayRepair method

A display panel and a method for repairing signal lines thereof are disclosed. The display panel includes at least one shorting bar, switches, and auxiliary repair lines. The switches are electrically coupled respectively to signal lines and the at least one shorting bar. Both ends of each of the auxiliary repair lines overlap one of connections between the switches and the at least one shorting bar. When a signal line is damaged, the method for repairing includes: breaking off each of the connections between each of the switches and the at least one shorting bar by cutting; and welding both ends of one of the auxiliary repair lines which correspond to the damaged signal line with both sides of one of the connections which correspond to the damaged signal line.

Owner:CHUNGHWA PICTURE TUBES LTD

Package structure for integrated circuit device and method of the same

ActiveUS20090267230A1Small sizeAvailable areaSemiconductor/solid-state device detailsSolid-state devicesIntegrated circuit

The present invention discloses a package structure for an integrated circuit device and method for manufacturing the same. The method includes providing a wafer with multiple integrated circuit devices; providing an extendable substrate having a first surface supporting the wafer; forming multiple anti-elongation layers on a second surface of the extendable substrate, the second surface being opposite to the first surface; forming multiple recesses in the wafer for separating the integrated circuit devices from each other; elongating the extendable substrate to enlarge the multiple recesses; and forming an insulating layer to fill the recesses and cover multiple integrated circuit devices.

Owner:MUTUAL PAK TECH

Storage Device for Sorption and Desorption of Molecular gas contained by Storage Sites of Nano-filament Laded Reticulated Aerogel

InactiveUS20080011617A1Large potential surface areaIncrease depositionMaterial nanotechnologyReversible hydrogen uptakeDesorptionGraphite

Owner:STRUTHERS RALPH C +5

Semiconductor package substrate having bonding pads with plated layer thereon and process of manufacturing the same

InactiveUS7396753B2Avoid bondingReliable electrical connectionSemiconductor/solid-state device detailsSolid-state devicesSolder maskSemiconductor package

A semiconductor package substrate is provided having a plurality of bonding pads on at least one surface thereof and covered by a conductive film. A photoresist layer formed over the conductive film has a plurality of first openings for exposing portions of the conductive film corresponding to the bonding pads. The exposed portions of the conductive film is removed to expose the bonding pads respectively via the first openings. The exposed bonding pads are plated with a metal layer respectively. Then, the photoresist layer and the remainder of the conductive film covered by the photoresist layer are removed. A solder mask having a plurality of second openings may be formed on the surface of the substrate, and allows the plated metal layer on the bonding pads respectively to be exposed via the second openings.

Owner:PHOENIX PRECISION TECH CORP

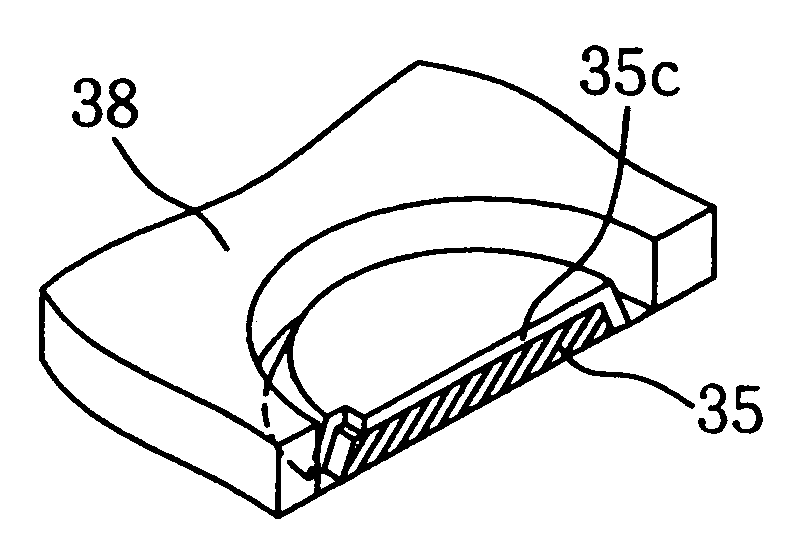

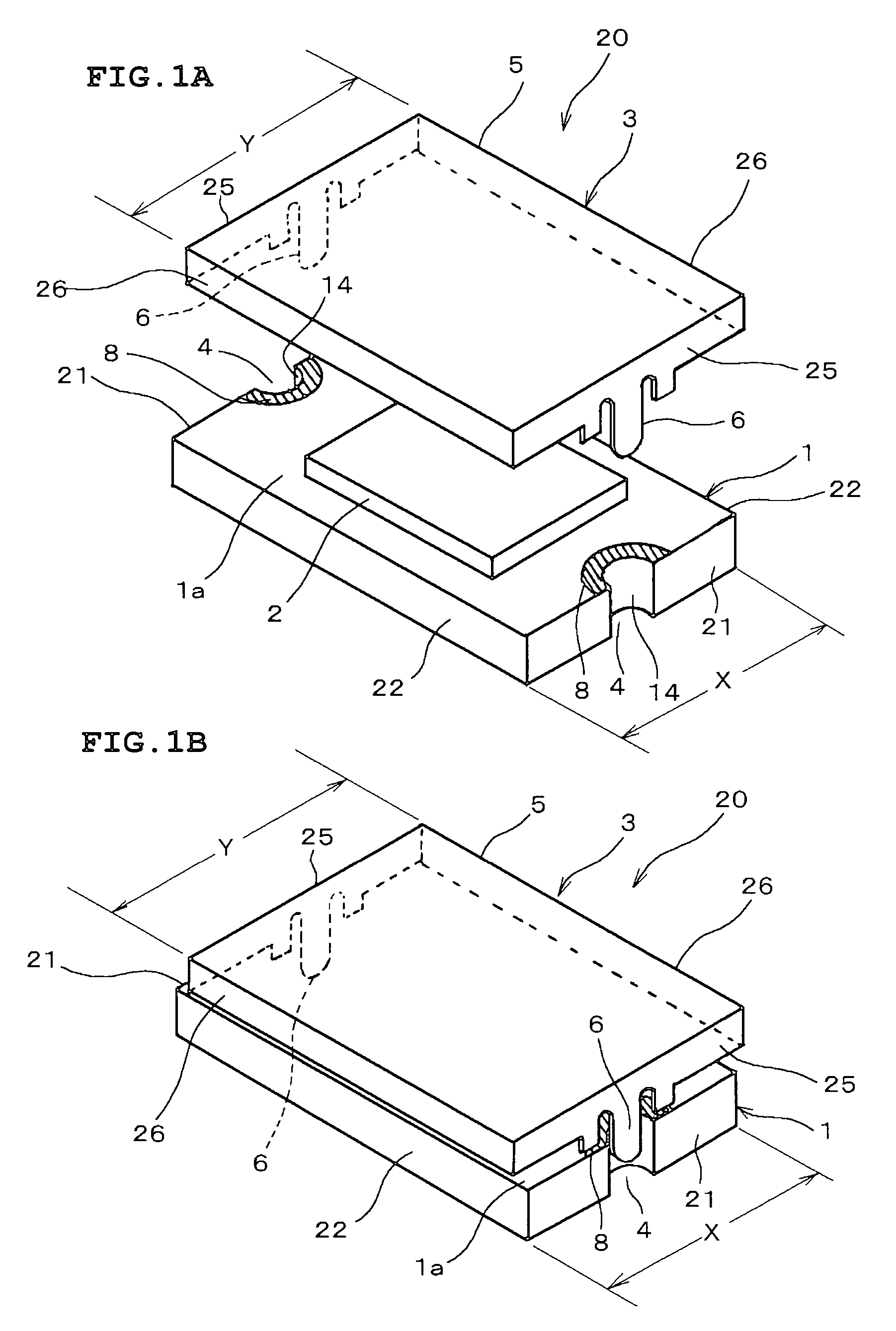

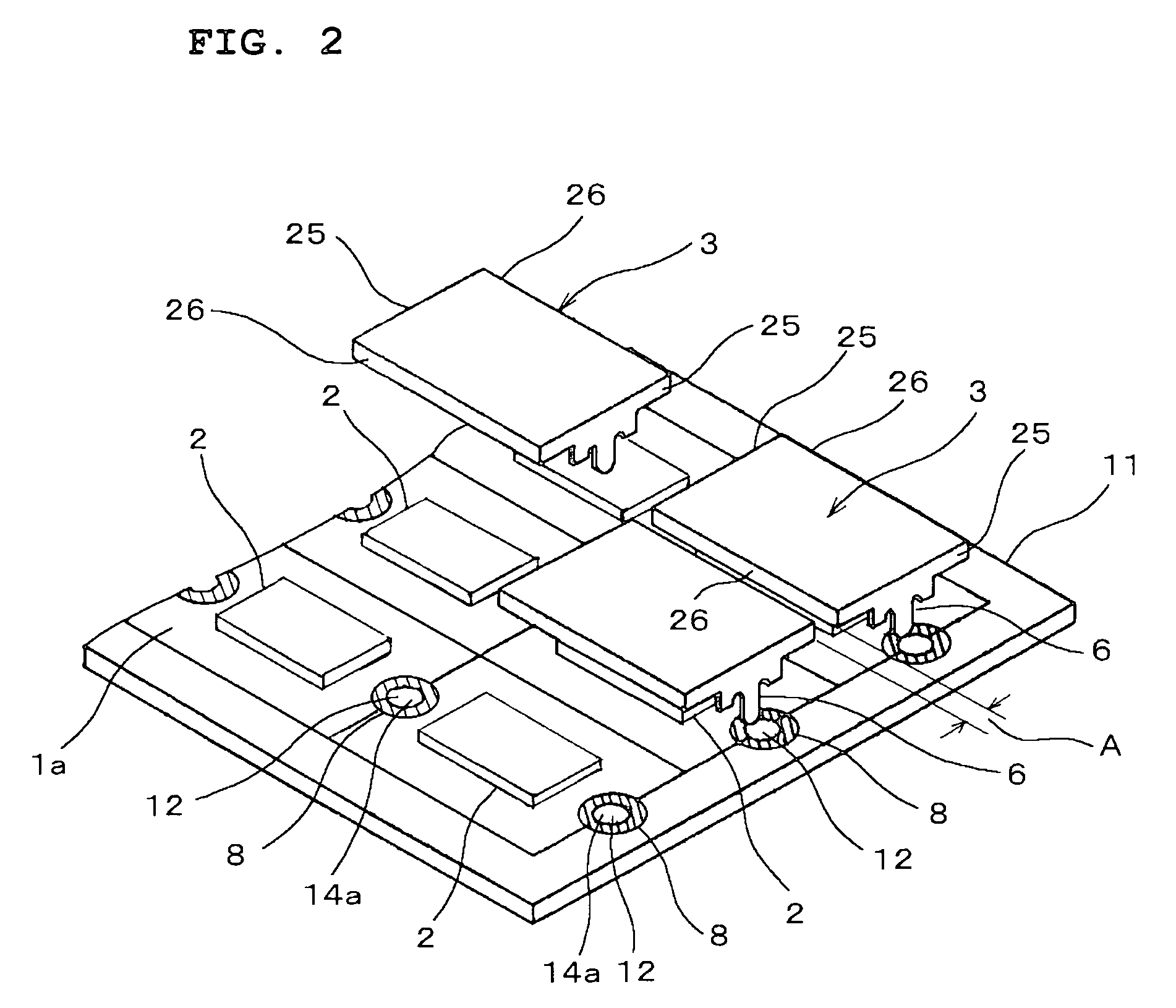

Electronic component with shielding case and method of manufacturing the same

ActiveUS7362586B2Available areaLow costPiezoelectric/electrostriction/magnetostriction machinesMagnetic/electric field screeningElectronic componentMotherboard

Shielding cases each include a pair of opposed first surfaces with catching pieces protruding therefrom and a pair of second surfaces without catching pieces. A motherboard forms substrates each including a pair of opposed first side surfaces with catching grooves and a pair of second side surfaces without catching grooves when it is divided. The shielding cases are mounted on the motherboard such that the intervals A between the second surfaces of two adjacent shielding cases are equal to or less than the widths B of cutting allowances for cutting the motherboard. The motherboard is cut from the opposite side of a surface of the motherboard on which the shielding cases are mounted at predetermined positions where the second side surfaces are formed on each substrate. In this manner, the motherboard is divided into electronic components with shielding cases.

Owner:MURATA MFG CO LTD

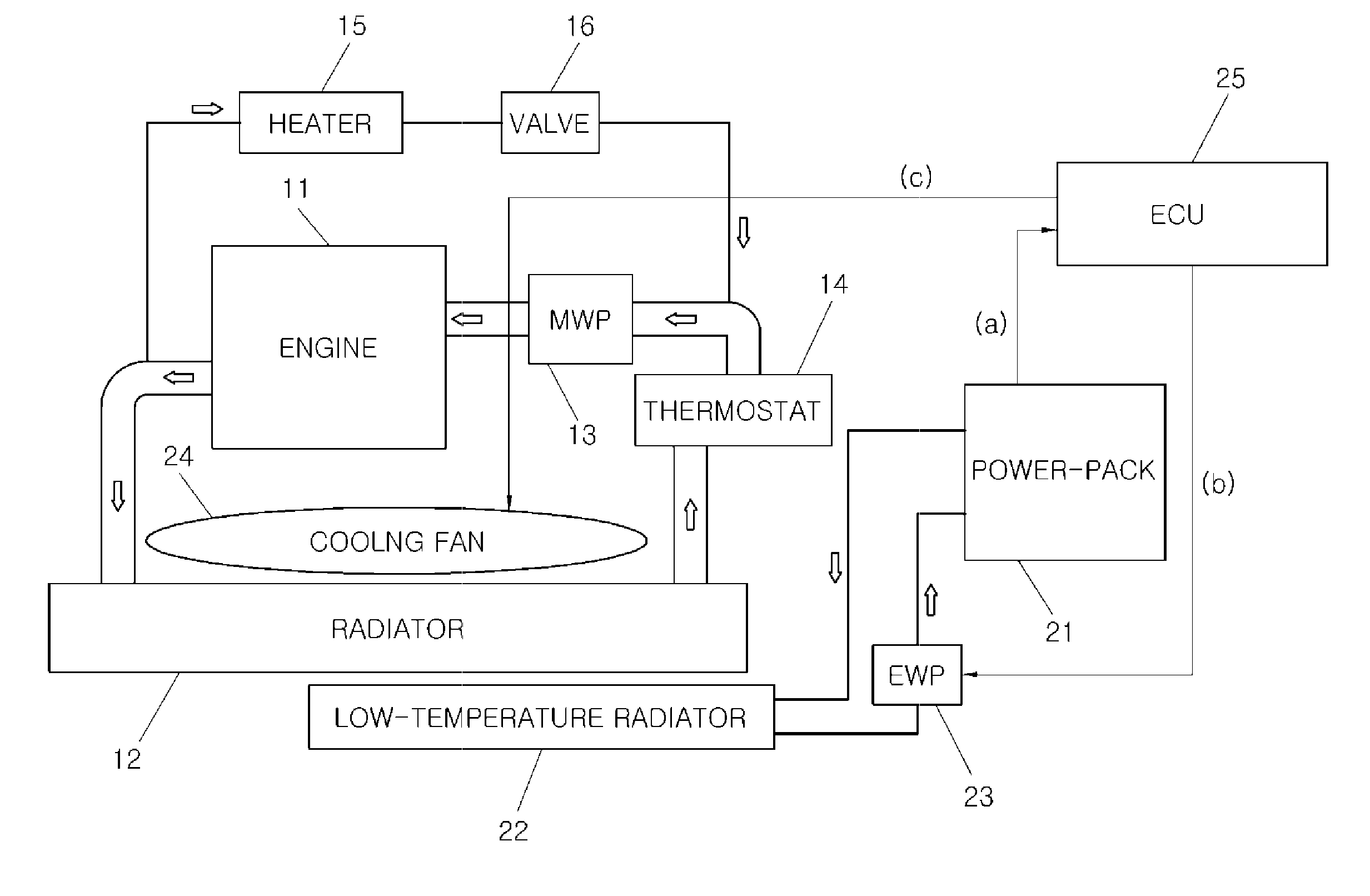

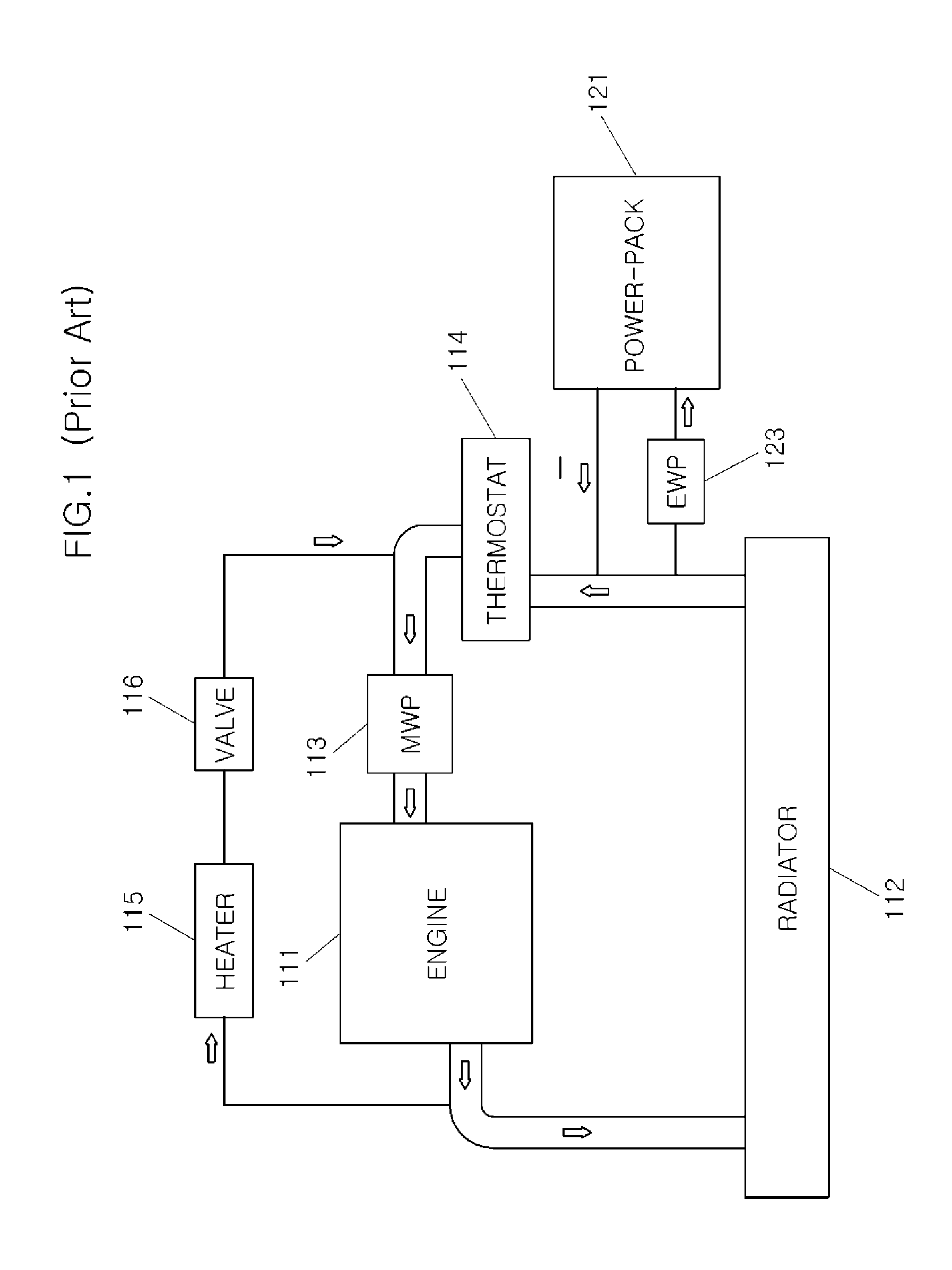

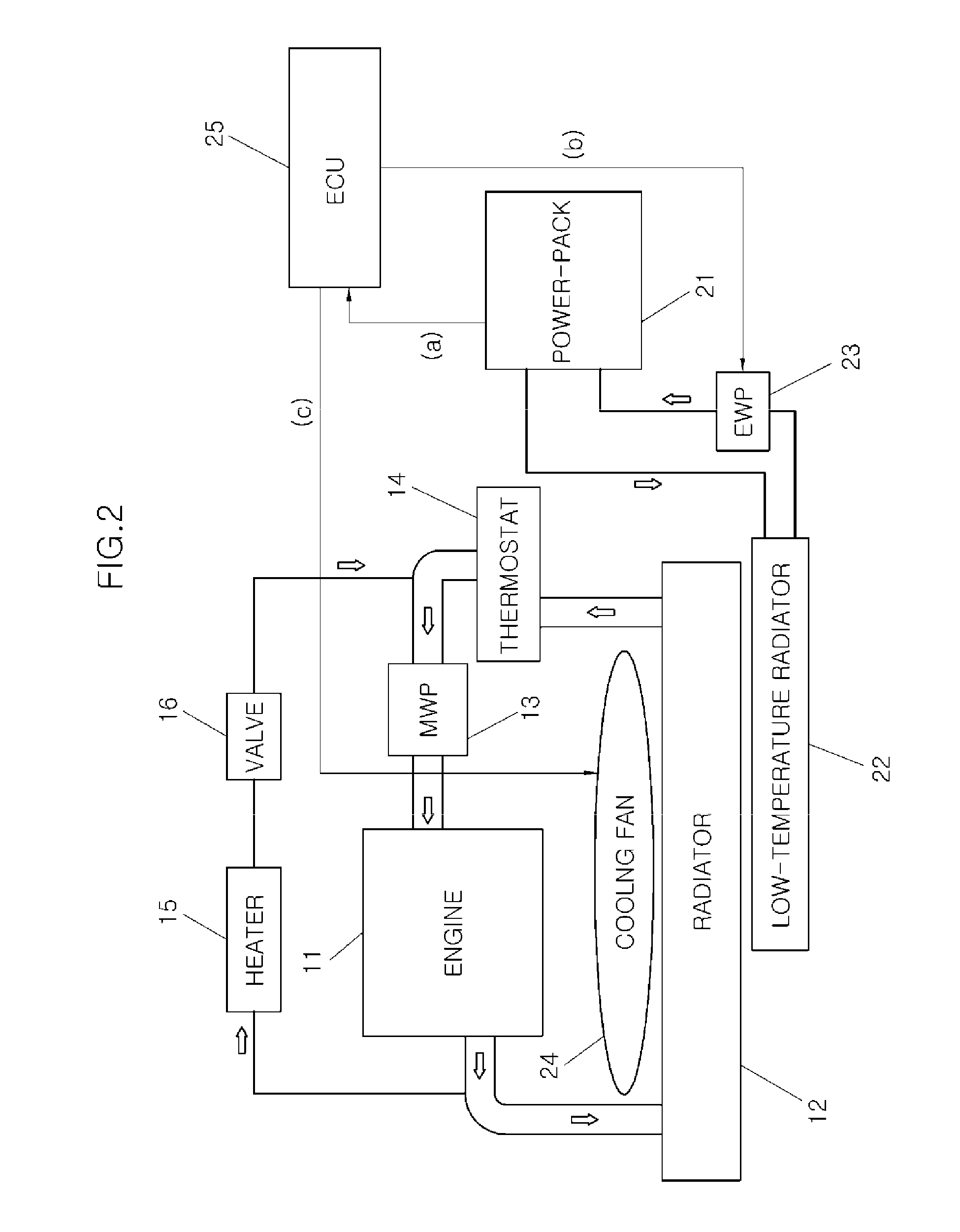

Cooling apparatus and cooling method for power-pack in hybrid vehicle

InactiveUS20130014911A1Effective controlImprove cooling effectHybrid vehiclesLiquid coolingWater dischargeWater channel

A cooling apparatus for a power-pack in a hybrid vehicle may include a power-pack that acquires traveling information of the vehicle and controls the operation of an engine and a motor, a low-temperature radiator that is connected with power-pack through a cooling water channel, dissipates heat from the cooling water discharged from power-pack, and is arranged in parallel with a radiator, and an electric water pump that is disposed in the cooling water channel and operated in response to an electric signal output from an ECU to circulate the cooling water through power-pack and low-temperature radiator. The cooling apparatus may also include a cooling fan. A cooling method of using the cooling apparatus may include determining engine operation, determining start of a water pump, and operating a water pump. The cooling method may also include starting a cooling fan, operating a cooling and examining a water pump.

Owner:HYUNDAI MOTOR CO LTD

Storage device and method for sorption and desorption of molecular gas contained by storage sites of nano-filament laded reticulated aerogel

InactiveUS7378188B2Large potential surface areaIncrease depositionMaterial nanotechnologyPigmenting treatmentDesorptionGraphite

An apparatus and method for sorption and desorption of molecular gas contained by storage sites of graphite nano-filaments randomly disposed in three-dimensional reticulated aerogel.

Owner:ENERNEXT +3

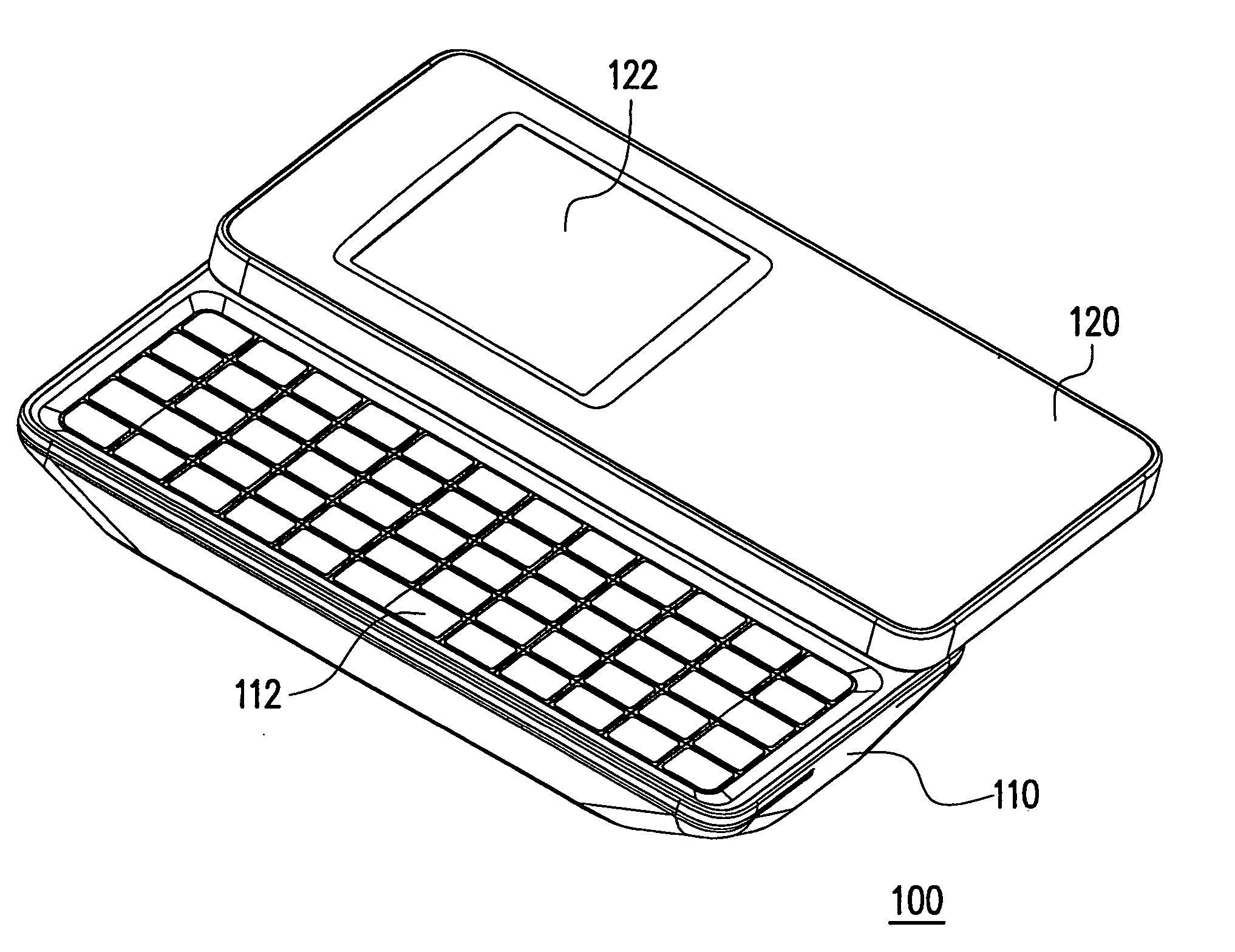

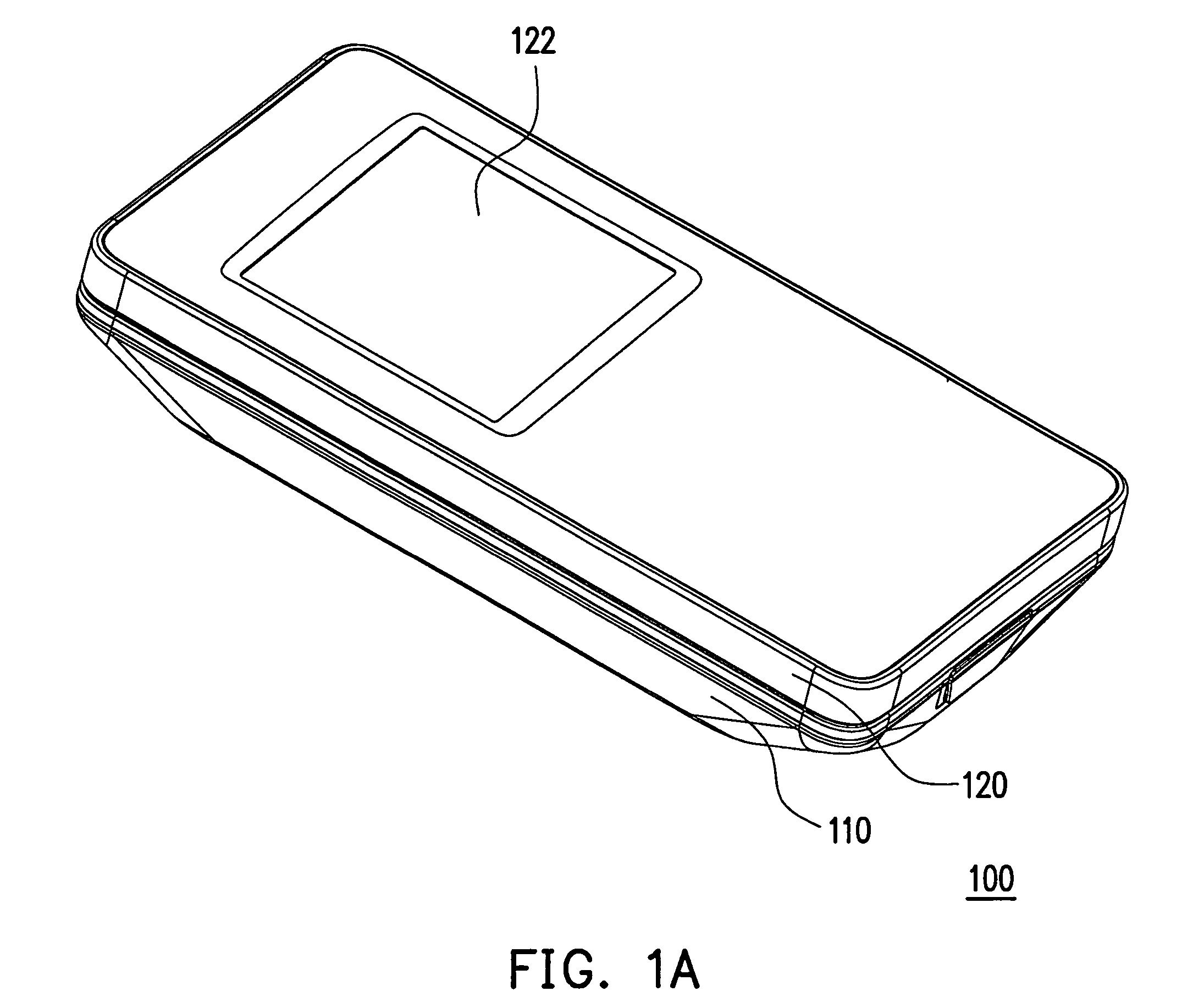

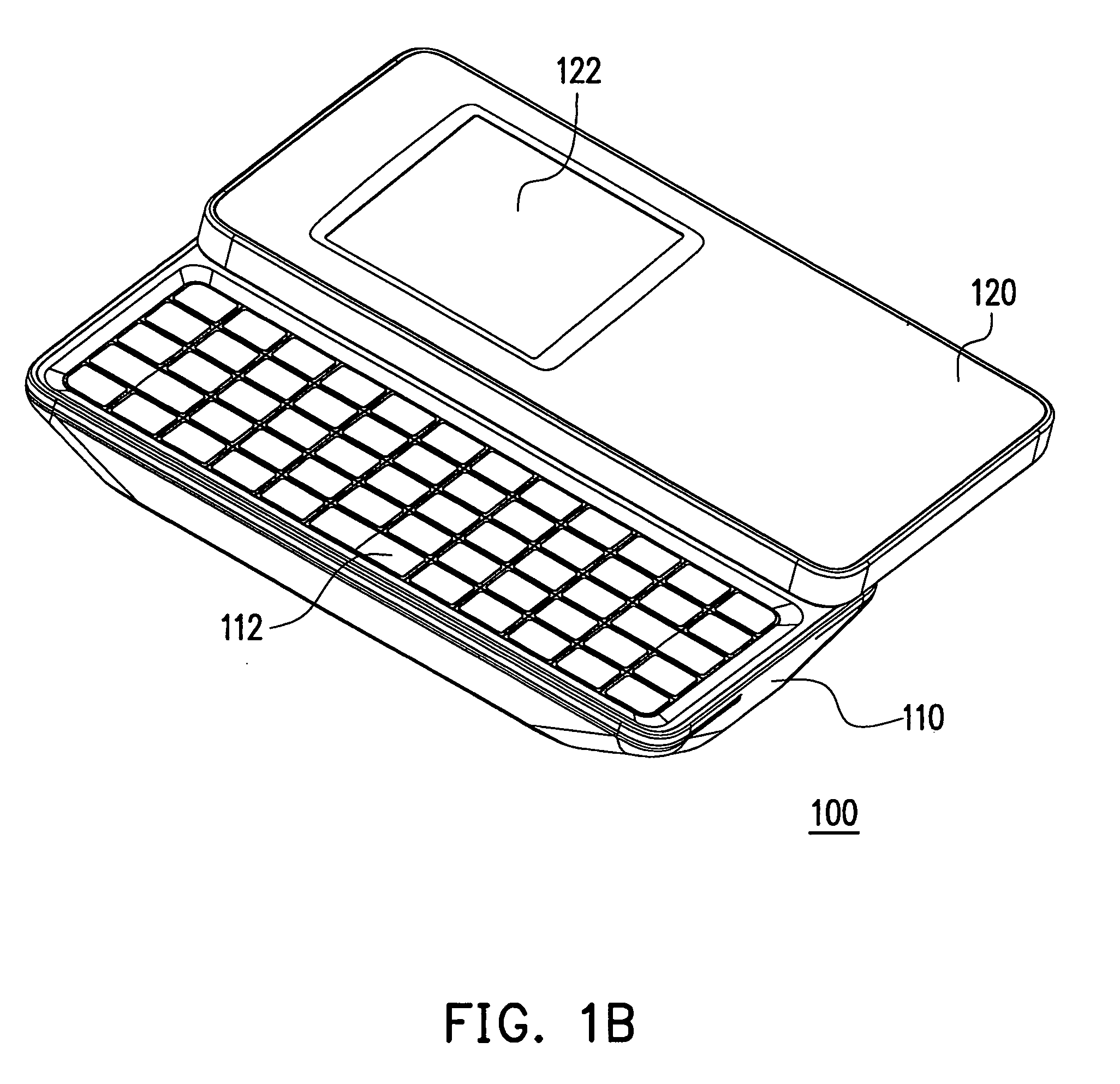

Handheld electronic device

ActiveUS20090147484A1Improve reliabilityGood lookingInterconnection arrangementsSubstation equipmentEngineeringElectrical and Electronics engineering

Owner:HTC CORP

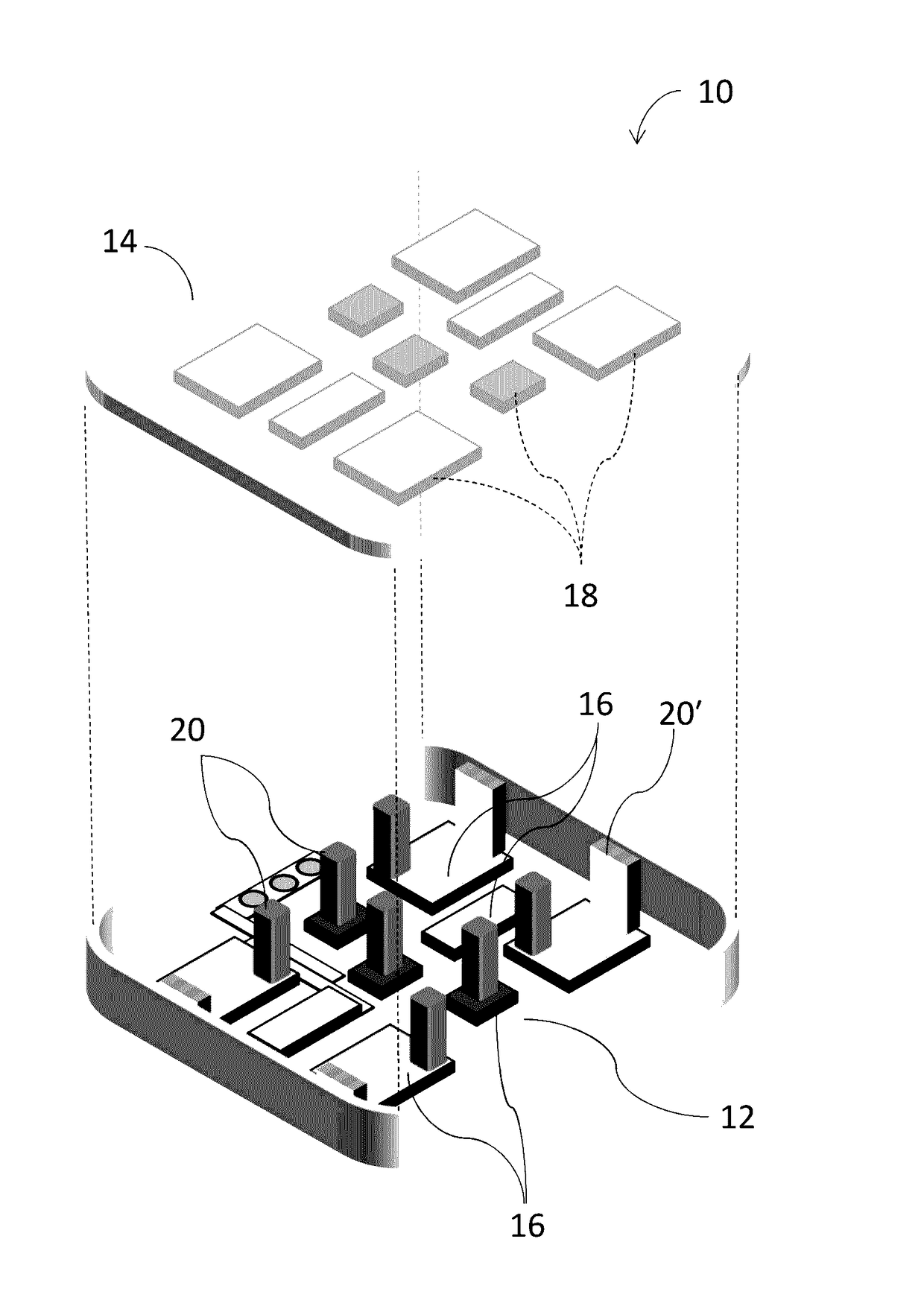

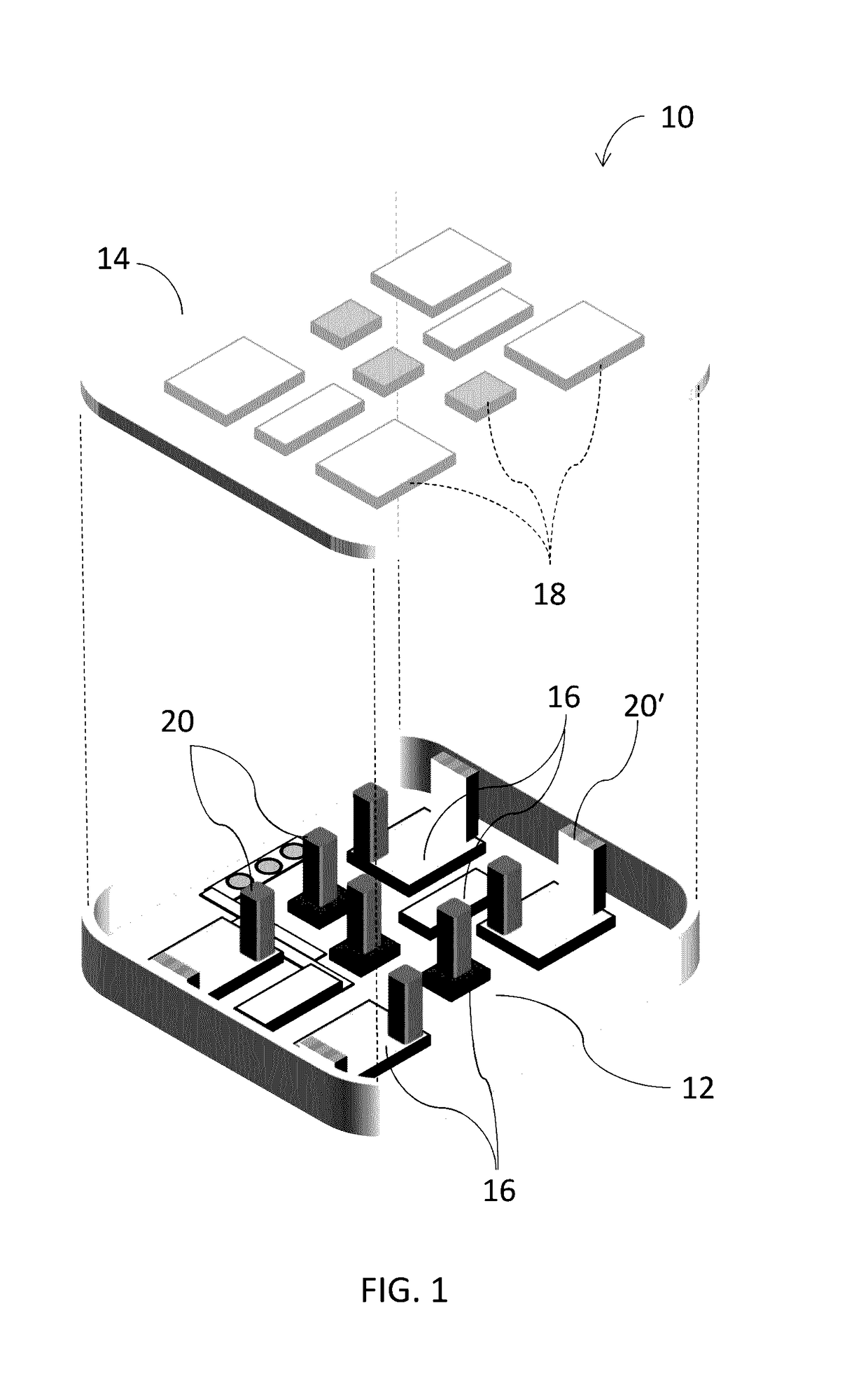

Electronic module with free-formed self-supported vertical interconnects

ActiveUS20170105311A1Improve compactnessAvailable areaSemiconductor/solid-state device detailsSolid-state devicesFree formStraight path

An electronic module, and method for making same, includes free-formed, self-supported interconnect pillars that electrically connect cover electronic components disposed on a cover substrate with base electronic components disposed on a base substrate. The free-formed, self-supported interconnect pillars may extend vertically in a straight path between the cover electronic components and the base electronic components. The free-formed, self-supported interconnect pillars may be formed from an electrically conductive filament provided by an additive manufacturing process. By free-forming the self-supported interconnect pillars directly on the electronic components, the flexibility of electronic module design may be enhanced, while reducing the complexity and cost to manufacture such electronic modules.

Owner:RAYTHEON CO

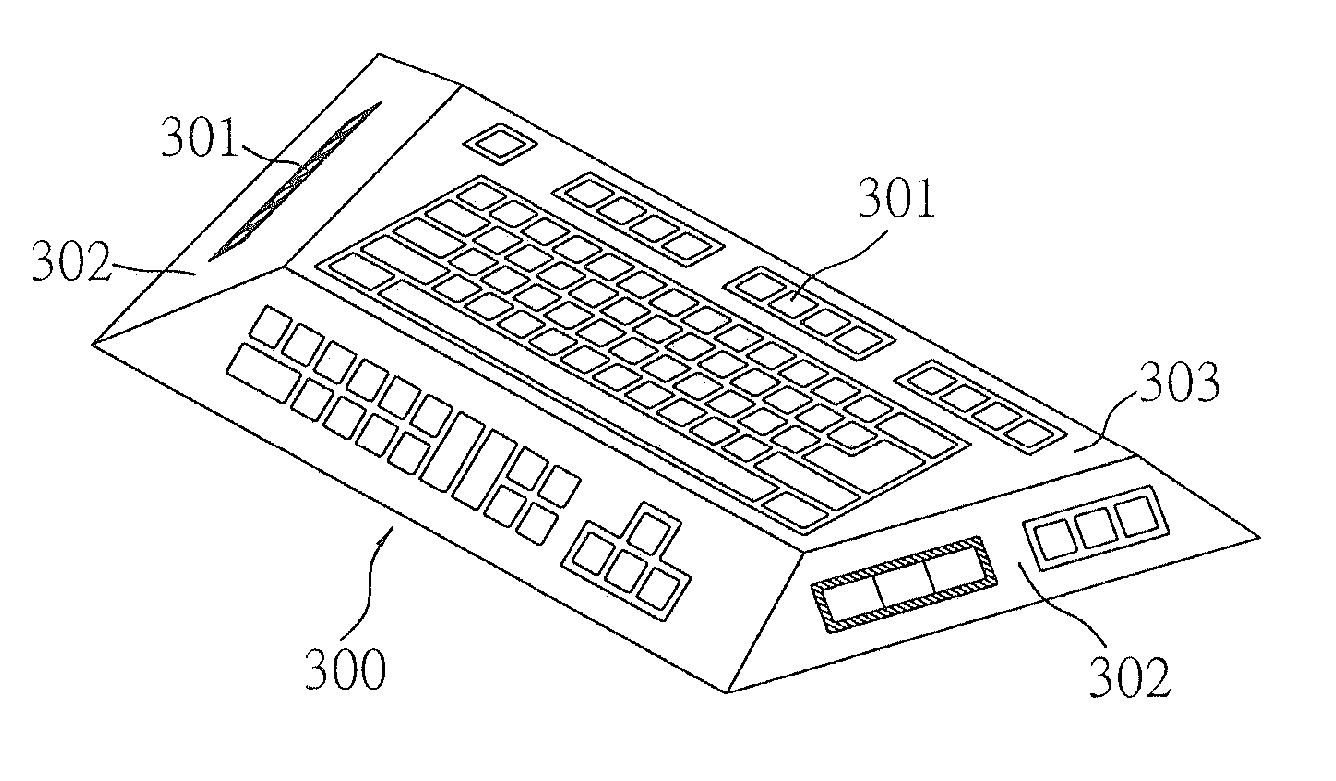

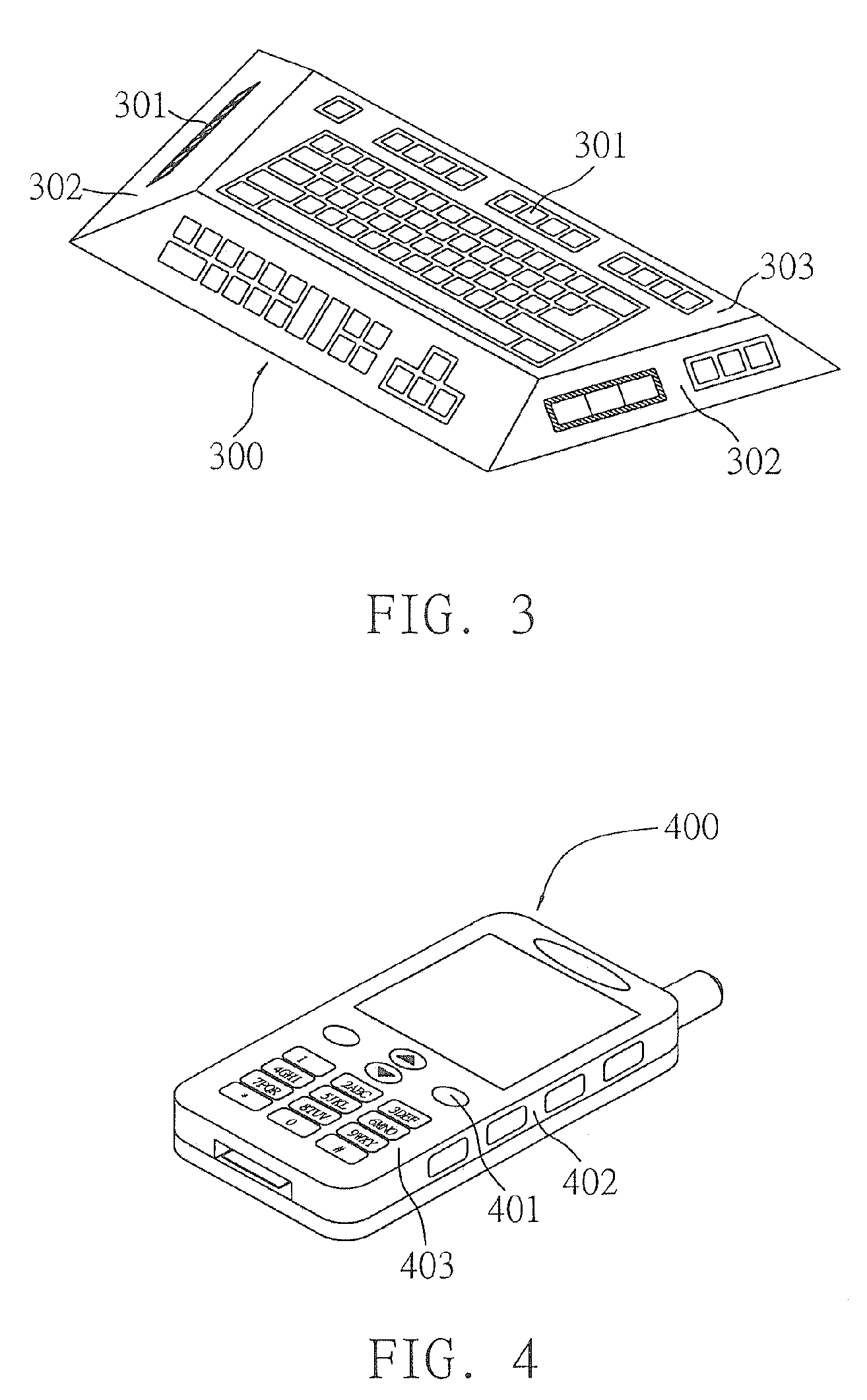

Input unit having three-dimensionally arranged keys for electronic device

InactiveUS20060077073A1Reduce probabilityAvailable areaInput/output for user-computer interactionElectronic switchingKey pressingEmbedded system

Owner:CULTURE COM TECH MACAU

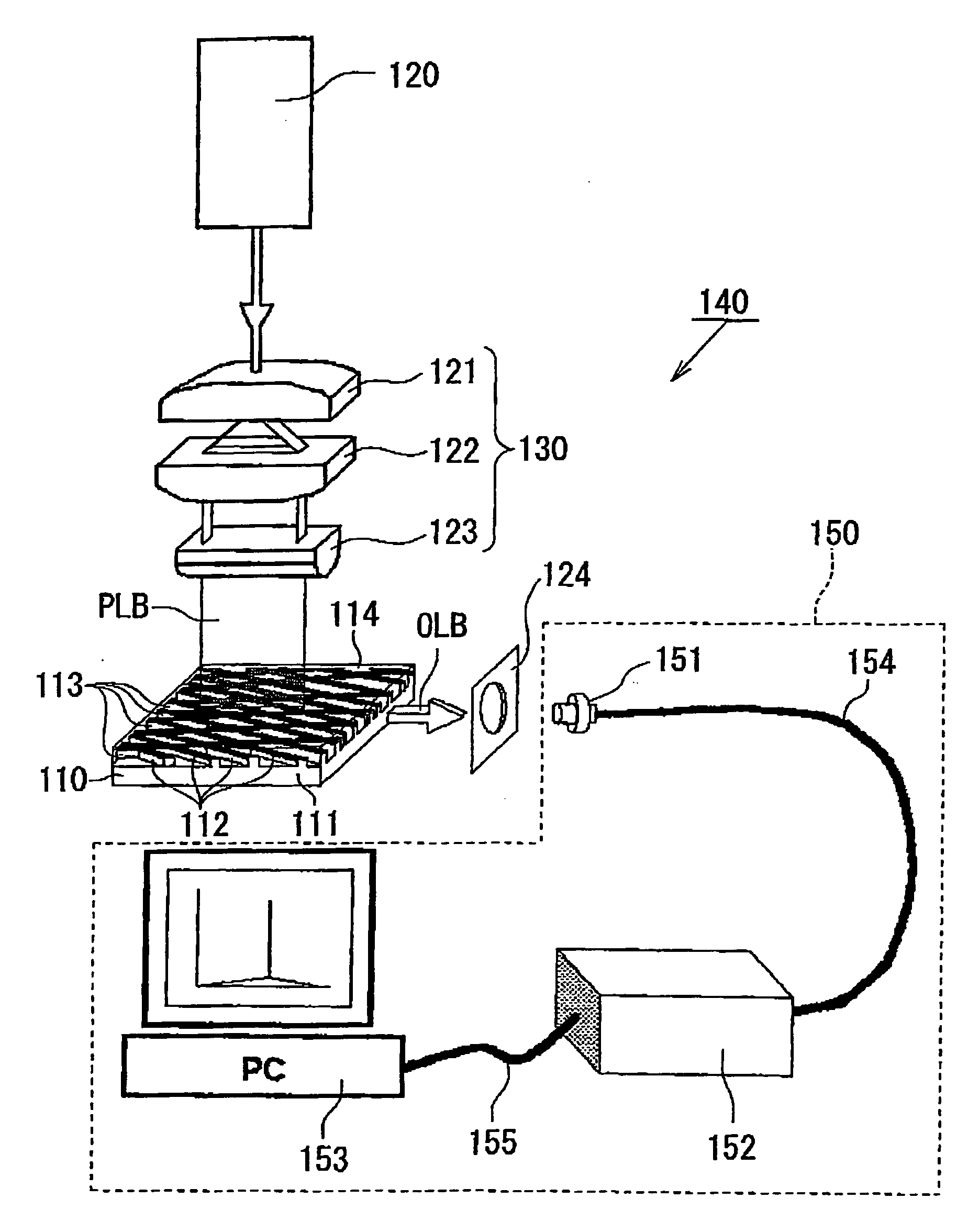

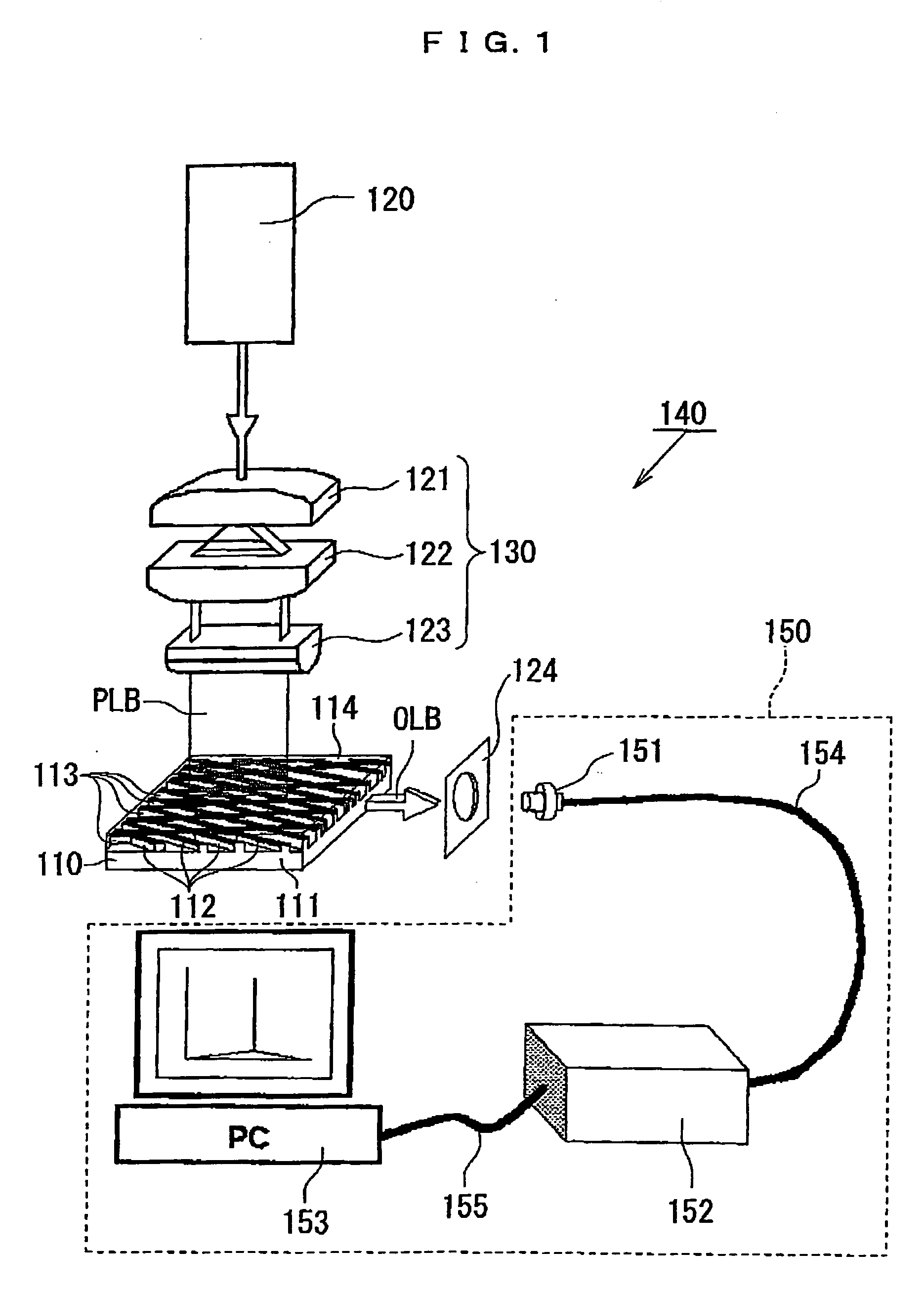

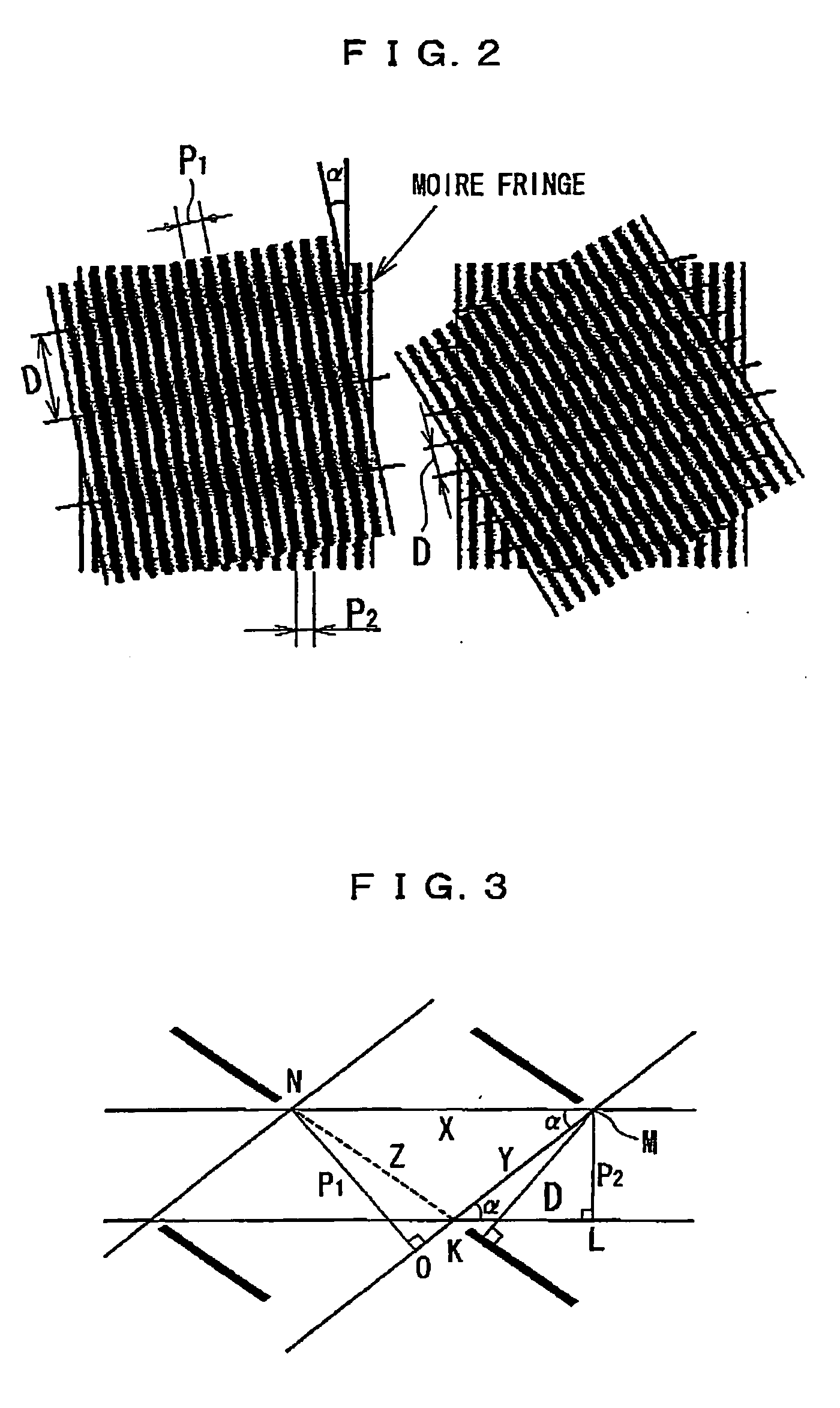

Method and apparatus for producing grating, and DFB solid-state dye laser based on the grating

InactiveUS20080165820A1Low costIncrease the areaOptical articlesActive medium materialSolid-state dye lasersGrating

To provide a DFB solid-state dye laser including a grating having Moire interference fringes. A DFB solid-state dye laser element includes: a laser medium containing an organic dye; and a distribution feedback type resonance unit having a third grating including a Moire fringe corresponding to an overlap between a first grating and a second grating formed in different directions. The third grating including a Moire fringe is formed by irradiating a photoresist with a laser for two-beam interference exposure, and then rotating a substrate by a predetermined angle and re-irradiating the substrate with the laser.

Owner:MINEBEA CO LTD

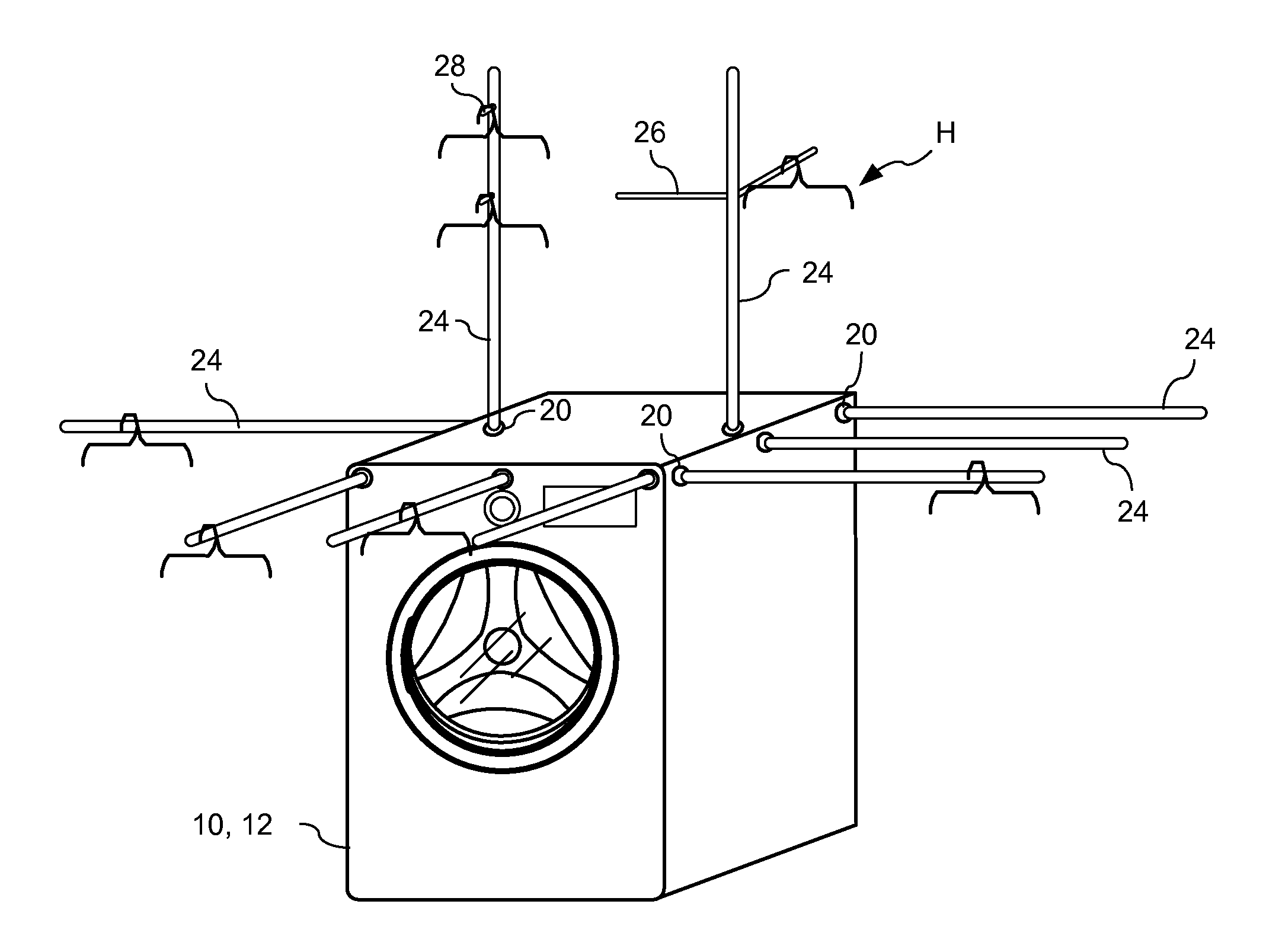

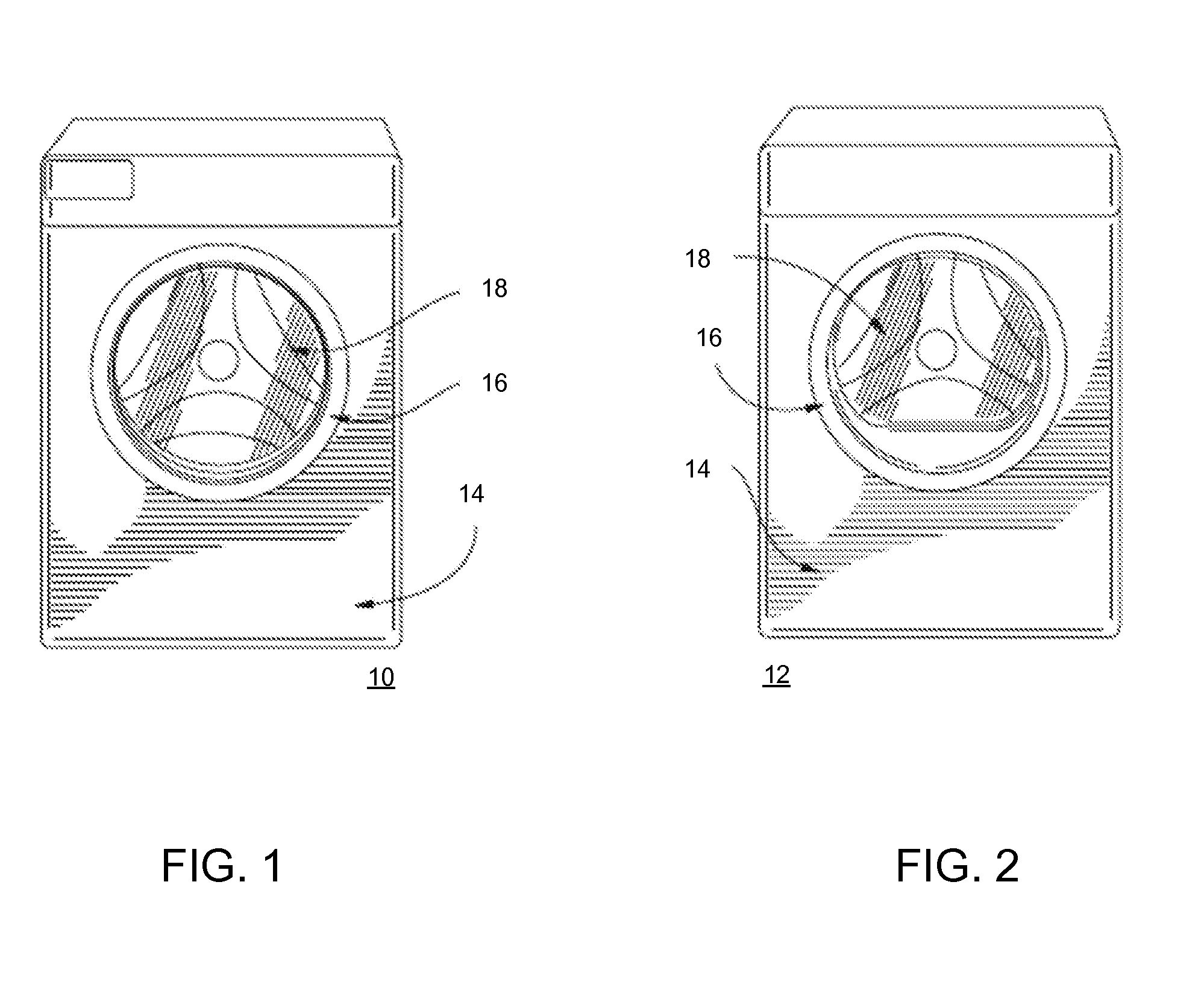

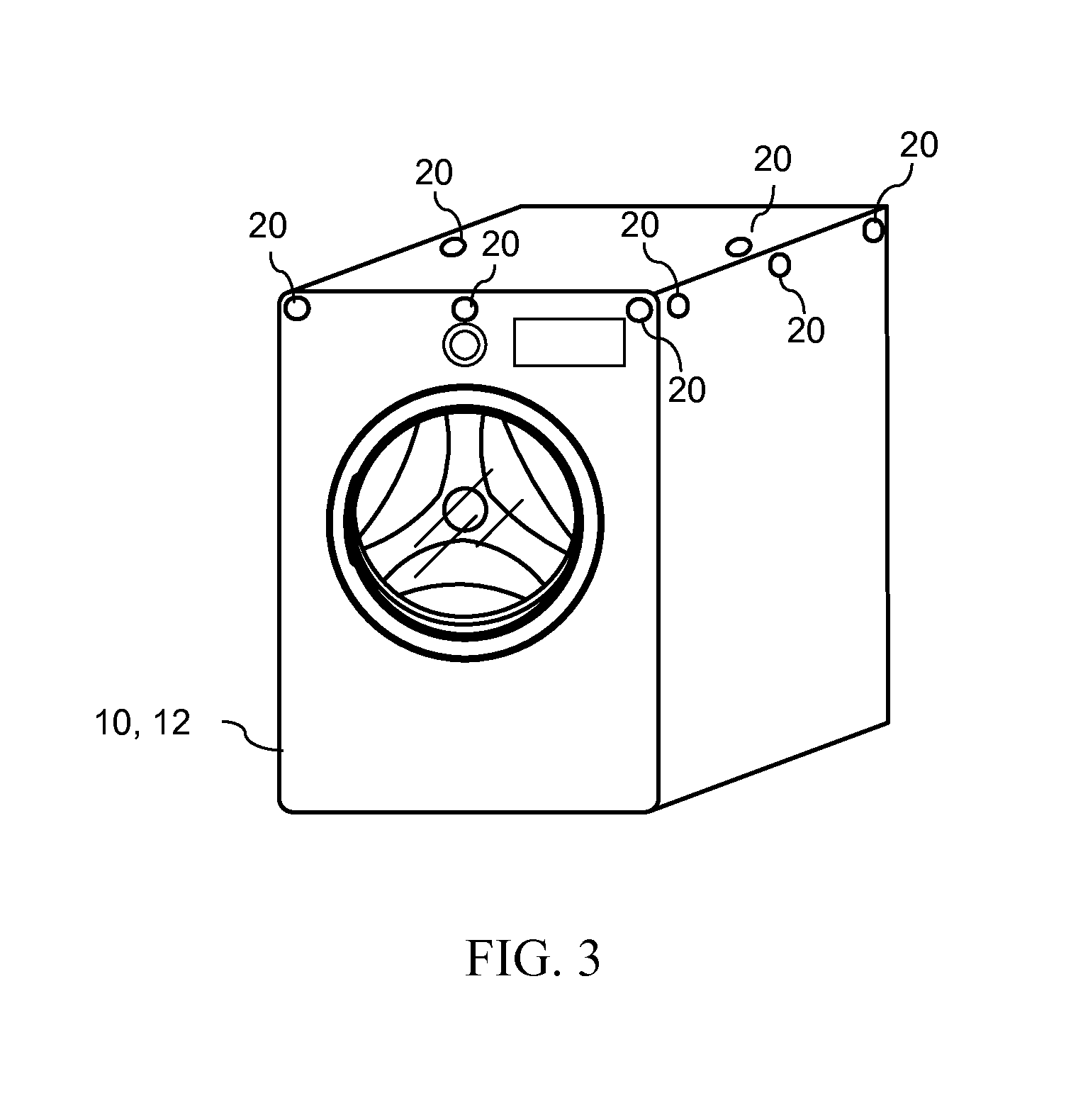

Work top and household appliance having a laundry hanging device

InactiveUS20120293052A1Reduced flexibilityDistract from aesthetic appearanceKitchenware cleanersWash-standsEngineeringHome appliance

A domestic household laundry appliance including a housing having a door for accessing an interior of the housing, and an attachment device on the housing, the attachment device for securing and supporting a laundry hanger device. The laundry hanger device is releasably secured in the attachment device.

Owner:BSH HOME APPLIANCES CORP

Package structure for integrated circuit device and method of the same

ActiveUS7943426B2Available areaSemiconductor/solid-state device detailsSolid-state devicesEngineeringIntegrated circuit

The present invention discloses a package structure for an integrated circuit device and method for manufacturing the same. The method includes providing a wafer with multiple integrated circuit devices; providing an extendable substrate having a first surface supporting the wafer; forming multiple anti-elongation layers on a second surface of the extendable substrate, the second surface being opposite to the first surface; forming multiple recesses in the wafer for separating the integrated circuit devices from each other; elongating the extendable substrate to enlarge the multiple recesses; and forming an insulating layer to fill the recesses and cover multiple integrated circuit devices.

Owner:MUTUAL PAK TECH

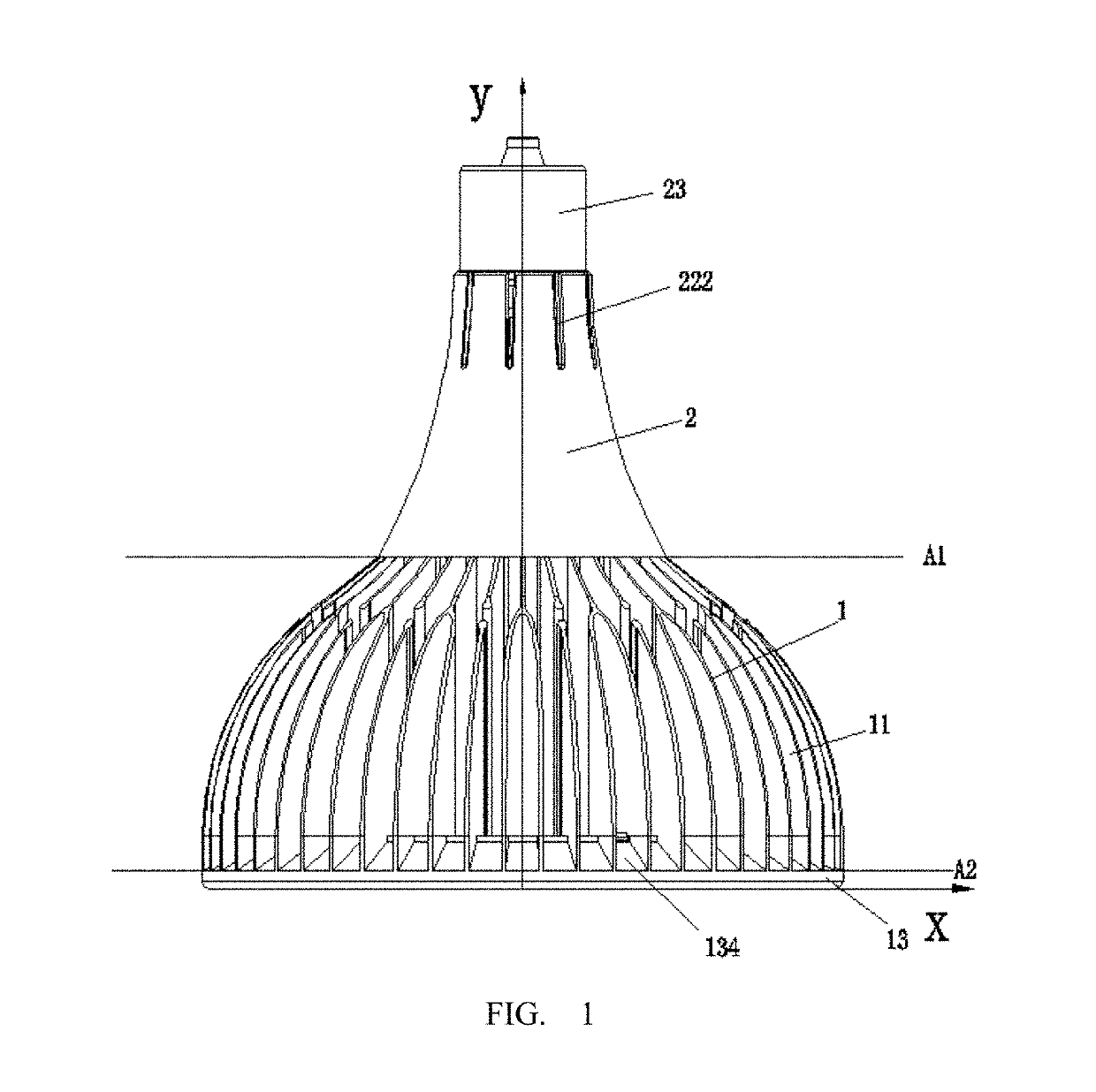

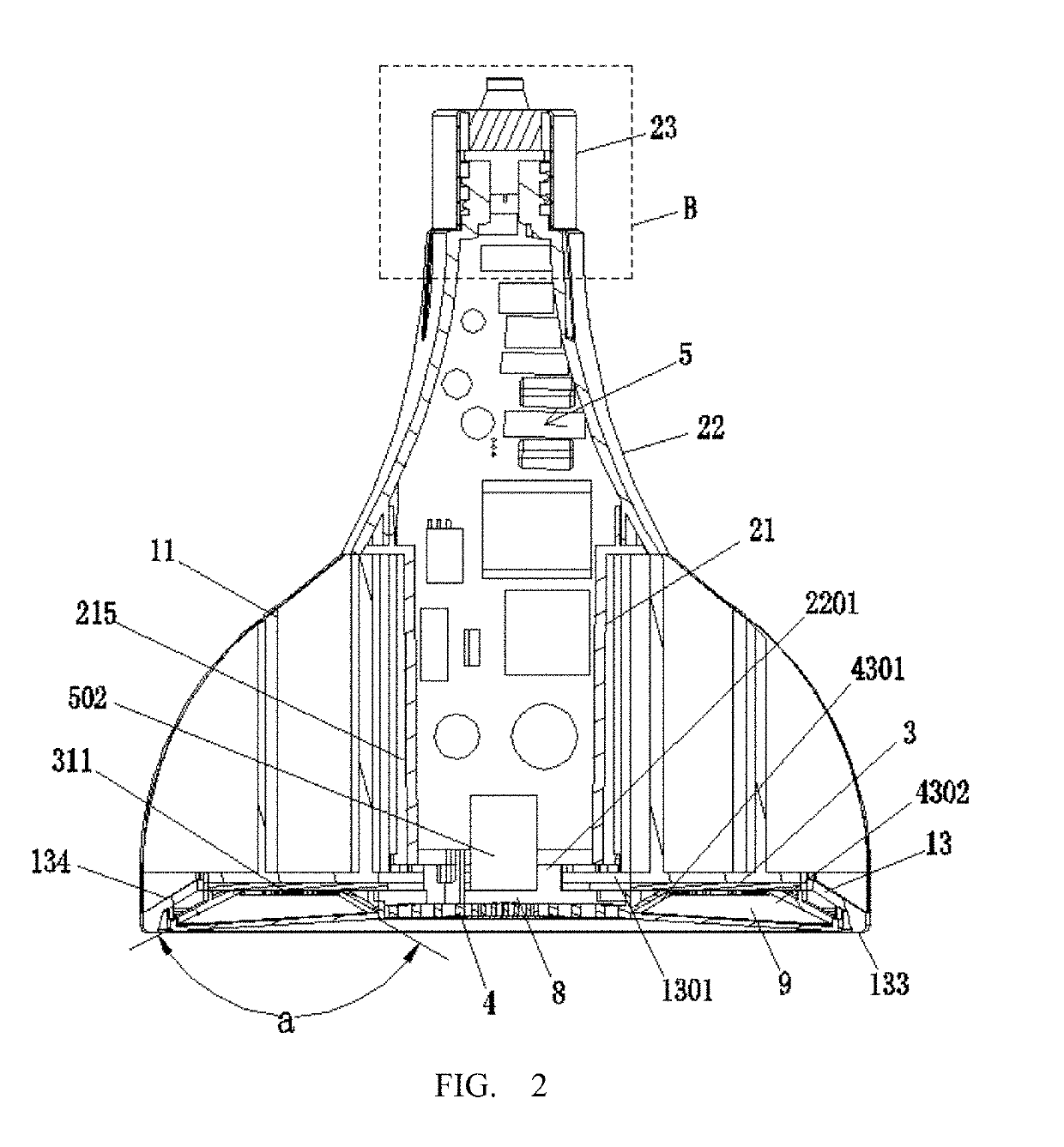

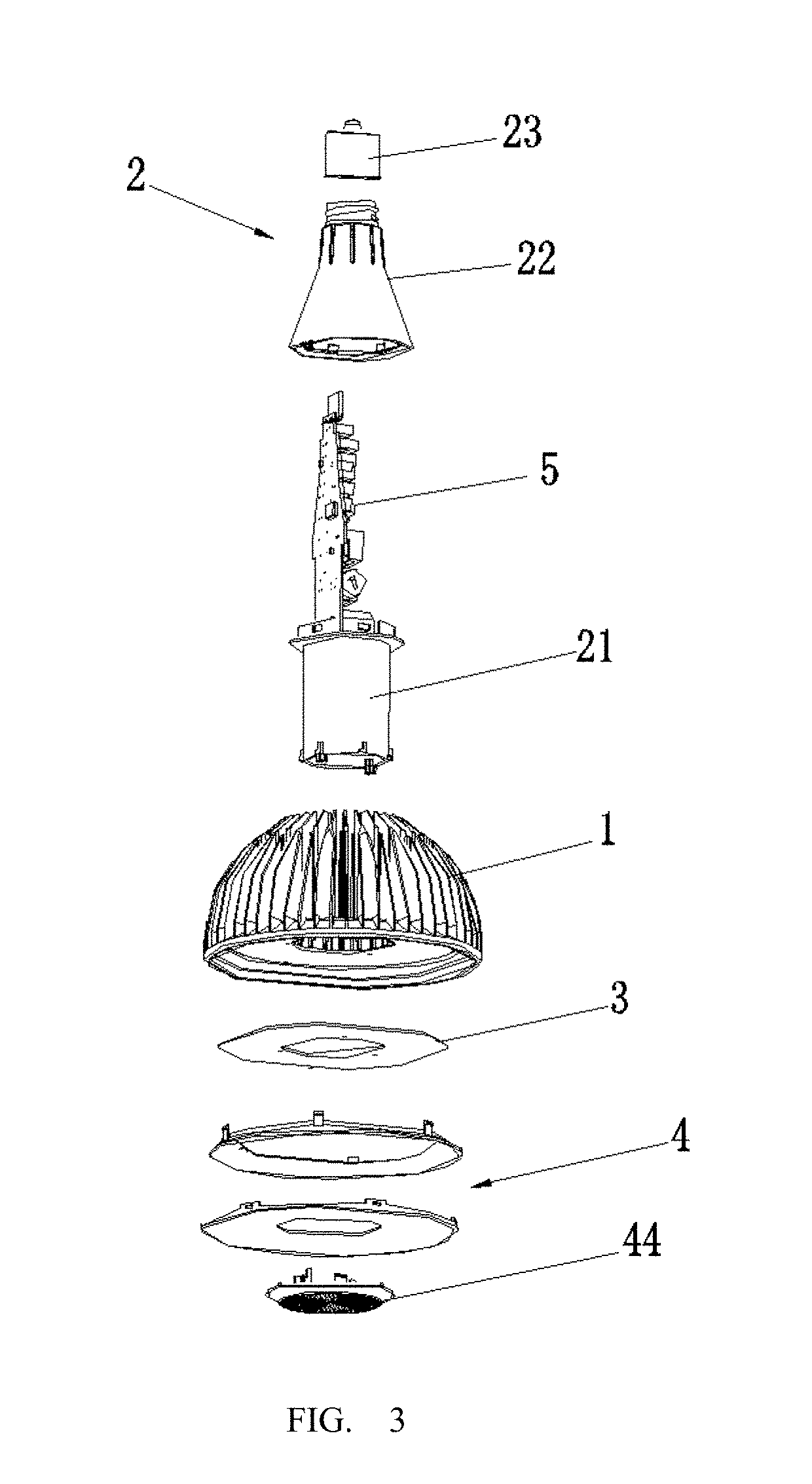

LED lamp

ActiveUS20190242569A1Enhanced convectionImprove efficiencyMultiple-port networksPlanar light sourcesEngineeringLamp shell

An LED lamp includes: a lamp shell; a passive heat dissipating element having a heat sink, and the heat sink including fins and a base and connecting to the lamp shell; a power source disposed in the lamp shell; and a light board connecting to the heat sink and including LED chips electrically connected to the power source. A chamber of the lamp shell is formed with a first heat dissipating channel. The first heat dissipating channel has a first air inlet at an end of the lamp shell. Another end of the lamp shell has a heat dissipating hole. A second heat dissipating channel is formed in the fins and base. The second heat dissipating channel has a second air inlet. Air flows into the second air inlet, passes through the second heat dissipating channel and flow out from spaces between every adjacent two of the fins.

Owner:JIAXING SUPER LIGHTING ELECTRIC APPLIANCE