Semiconductor package substrate having bonding pads with plated layer thereon and process of manufacturing the same

a technology of semiconductor package substrate and bonding pad, which is applied in the manufacture of printed circuits, conductive pattern reinforcements, basic electric elements, etc., can solve the problems of poor soldering strength, insufficient soldering strength, and large challenges faced by semiconductor package manufacturers, and achieve the effect of increasing the reliability of the semiconductor packag

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

[0033] FIG. 4A to FIG. 4H are cross-sectional views of a bonding pad electrically connecting to a semiconductor package substrate according to the invention.

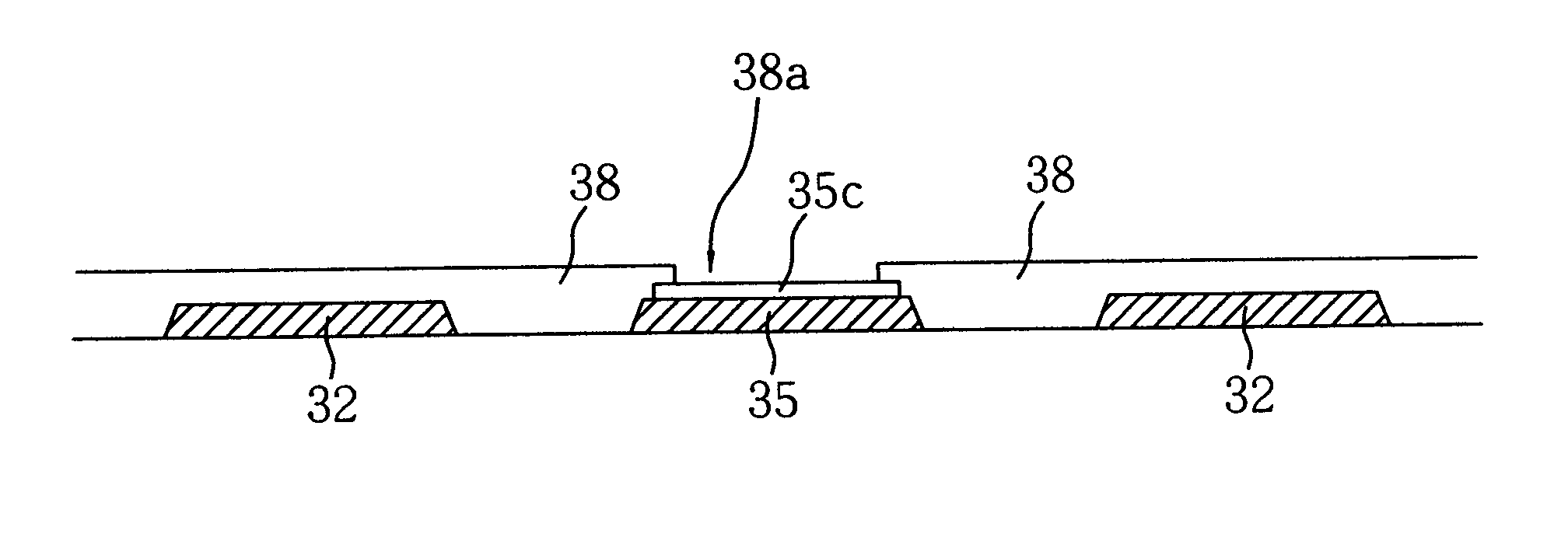

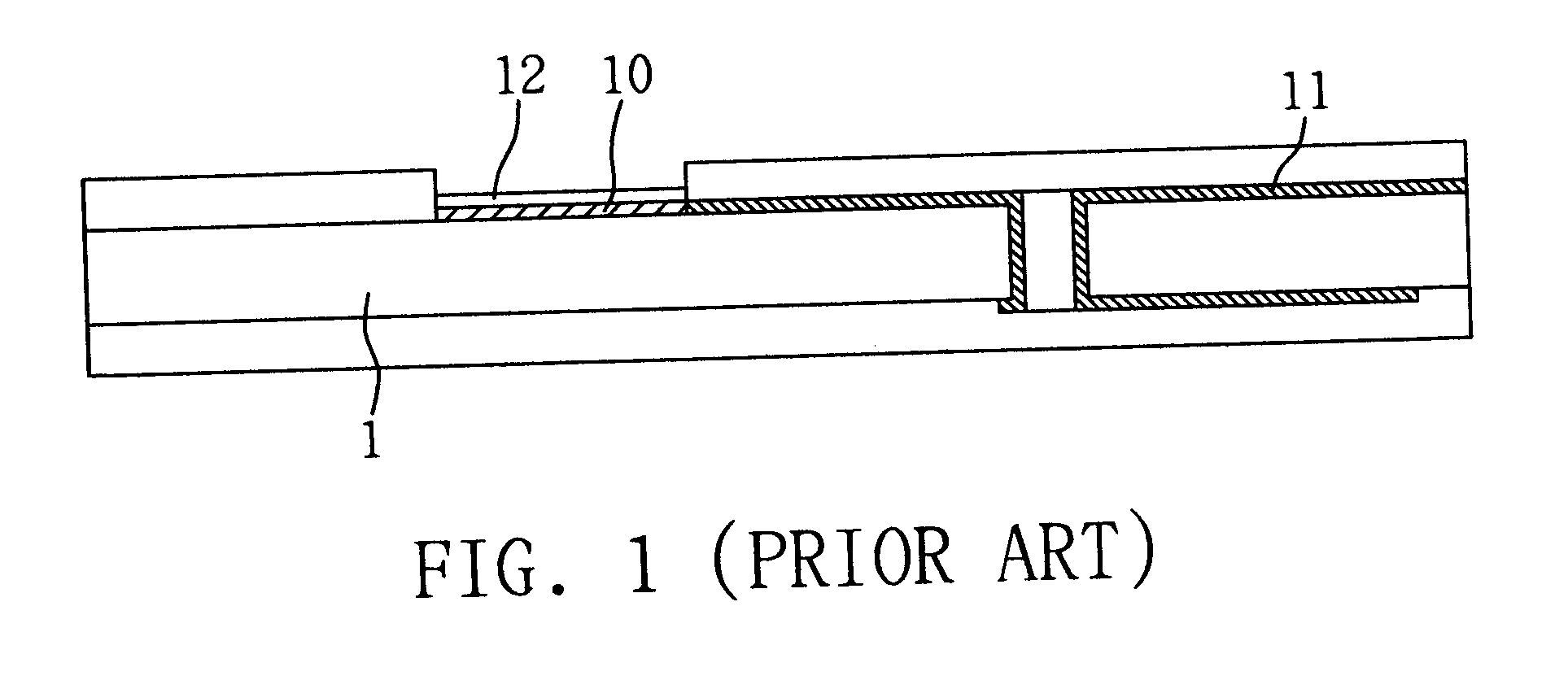

[0034] Referring to FIG. 4A, a semiconductor package substrate 3 is provided. The substrate 3 can be, for example, the flip-chip package substrate as shown in FIG. 3, or a wire-bonding package substrate. The substrate 3 has been previously subjected to a front-end process. For example, a plurality of plated through holes or blind vias have been formed through the substrate 3. The trace layers 32 have been formed on the substrate 3. The trace layers 32 further may include a plurality of bonding pads 35. The process of forming the above parts is well known in the art, and its description is omitted herein.

[0035] Referring to FIG. 4B, a conductive film 36 is formed over the substrate 3. The conductive film 36 serves as electric current paths for electroplating the metal layer 35c. The conductive film 36 is made of a metal selected ...

second embodiment

[0040] FIG. 5A to FIG. 5I are cross-sectional views of a bonding pad formed on a semiconductor package substrate according to the invention.

[0041] Referring to FIG. 5A, a package substrate 3 is provided. The substrate 3, as describe above, can be a flip-chip package substrate 3 or a wire-bonding package substrate. The substrate 3 has been subjected to a front-end process. For example, a plurality of through holes or blind holes (not shown) are formed through the substrate 3, and at least one trace layer 32 is formed on / inside the substrate 3.

[0042] Referring to FIG. 5B, a conductive film 36 as illustrated in the first embodiment of the invention is formed over the substrate 3. The conductive film 36 serves as electric current paths for the electroplating metal layer 35c.

[0043] Referring to FIG. 5C, a photoresist layer 37 is formed by printing or coating over the substrate 3 on top of the conductive film 36 thereon. The photoresist layer 37 can be, for example a dry film or a liquid ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More