Patents

Literature

153 results about "Antenna effect" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

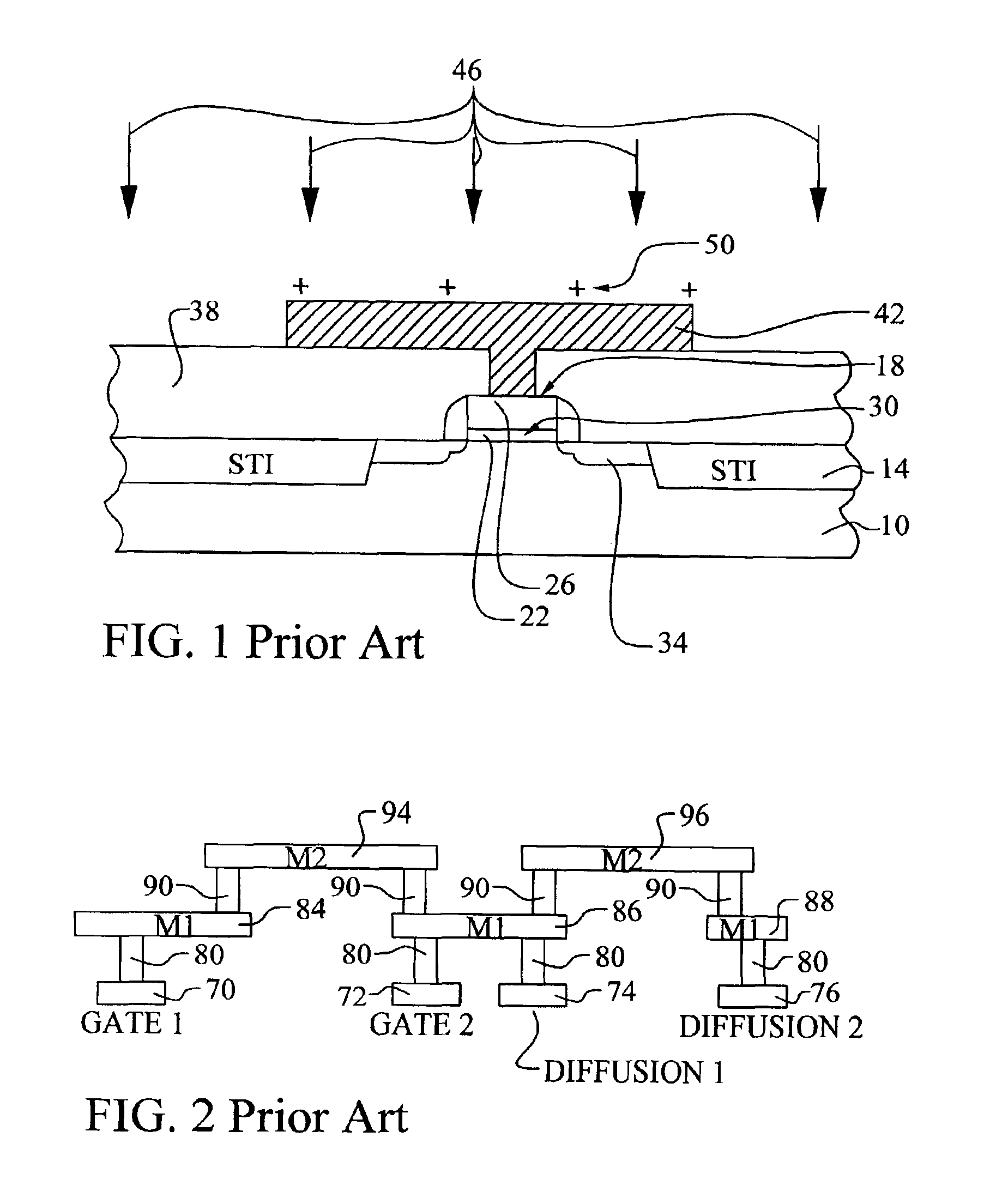

The antenna effect, more formally plasma induced gate oxide damage, is an effect that can potentially cause yield and reliability problems during the manufacture of MOS integrated circuits. Fabs normally supply antenna rules, which are rules that must be obeyed to avoid this problem. A violation of such rules is called an antenna violation. The word antenna is something of a misnomer in this context—the problem is really the collection of charge, not the normal meaning of antenna, which is a device for converting electromagnetic fields to/from electrical currents. Occasionally the phrase antenna effect is used in this context, but this is less common since there are many effects, and the phrase does not make clear which is meant.

Photomask for eliminating antenna effects in an integrated circuit and integrated circuit manufacture with same

InactiveUS6978437B1Increase antenna ratioRaise the ratioSemiconductor/solid-state device detailsSolid-state devicesAntenna effectEngineering

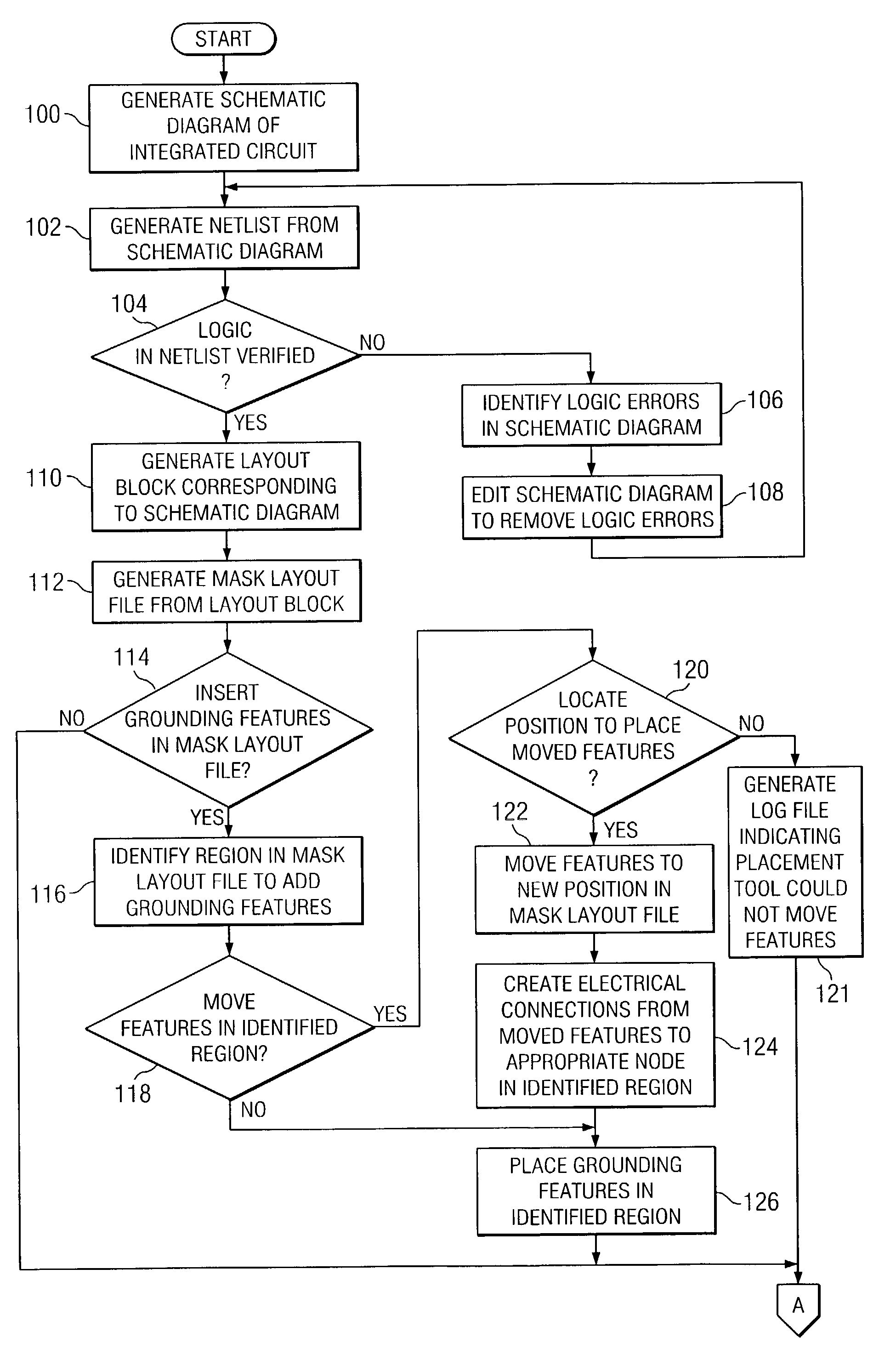

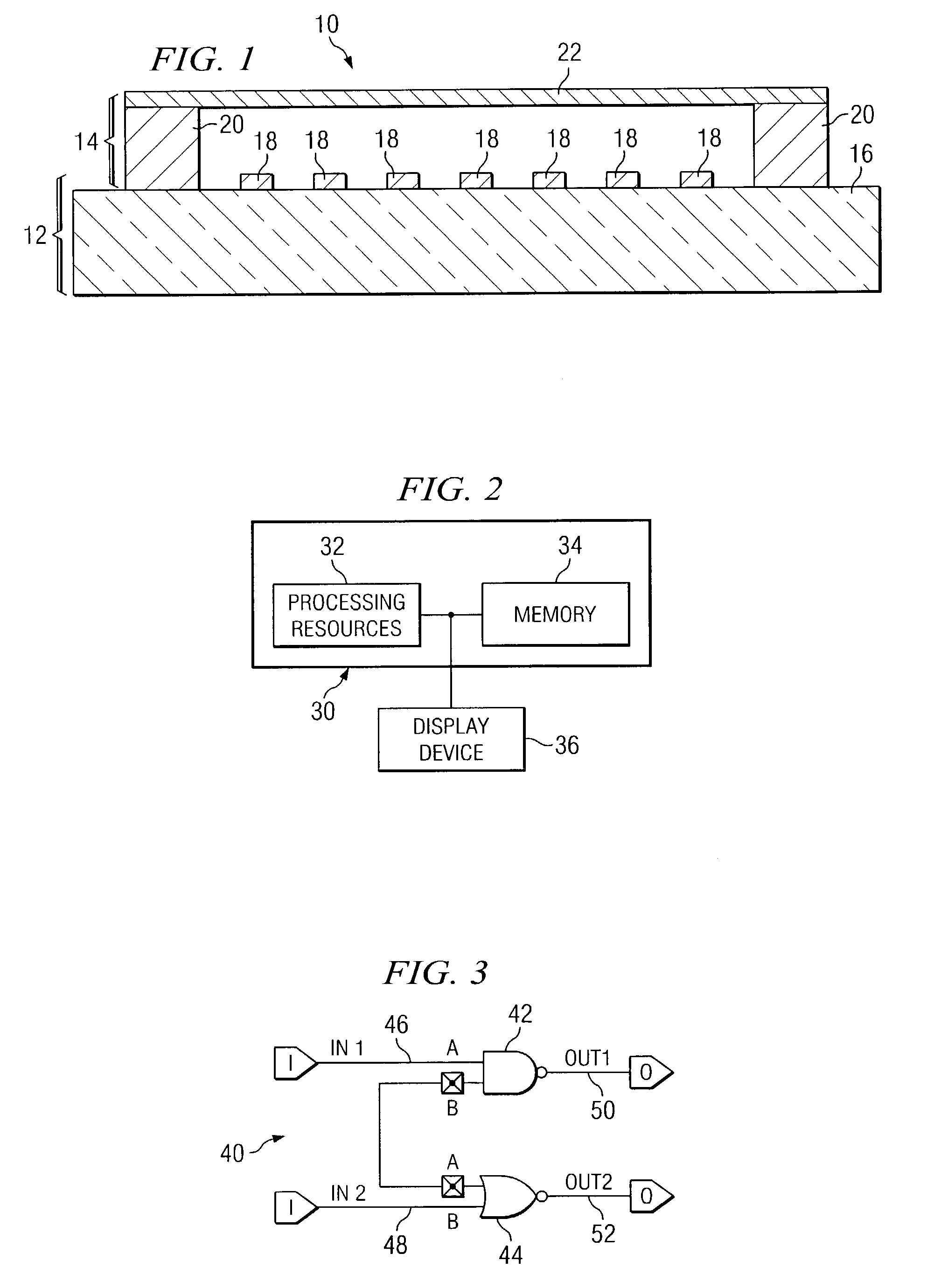

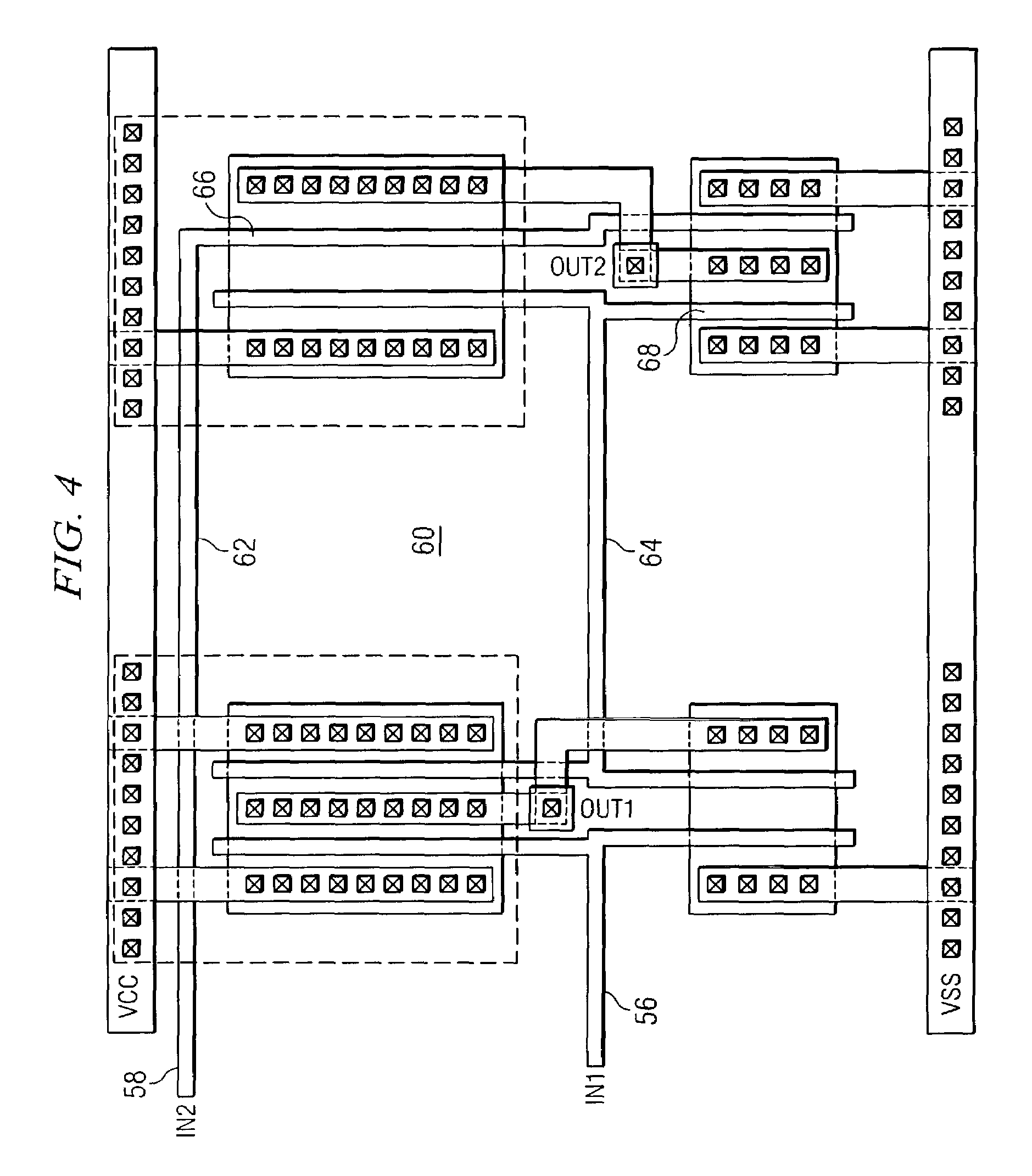

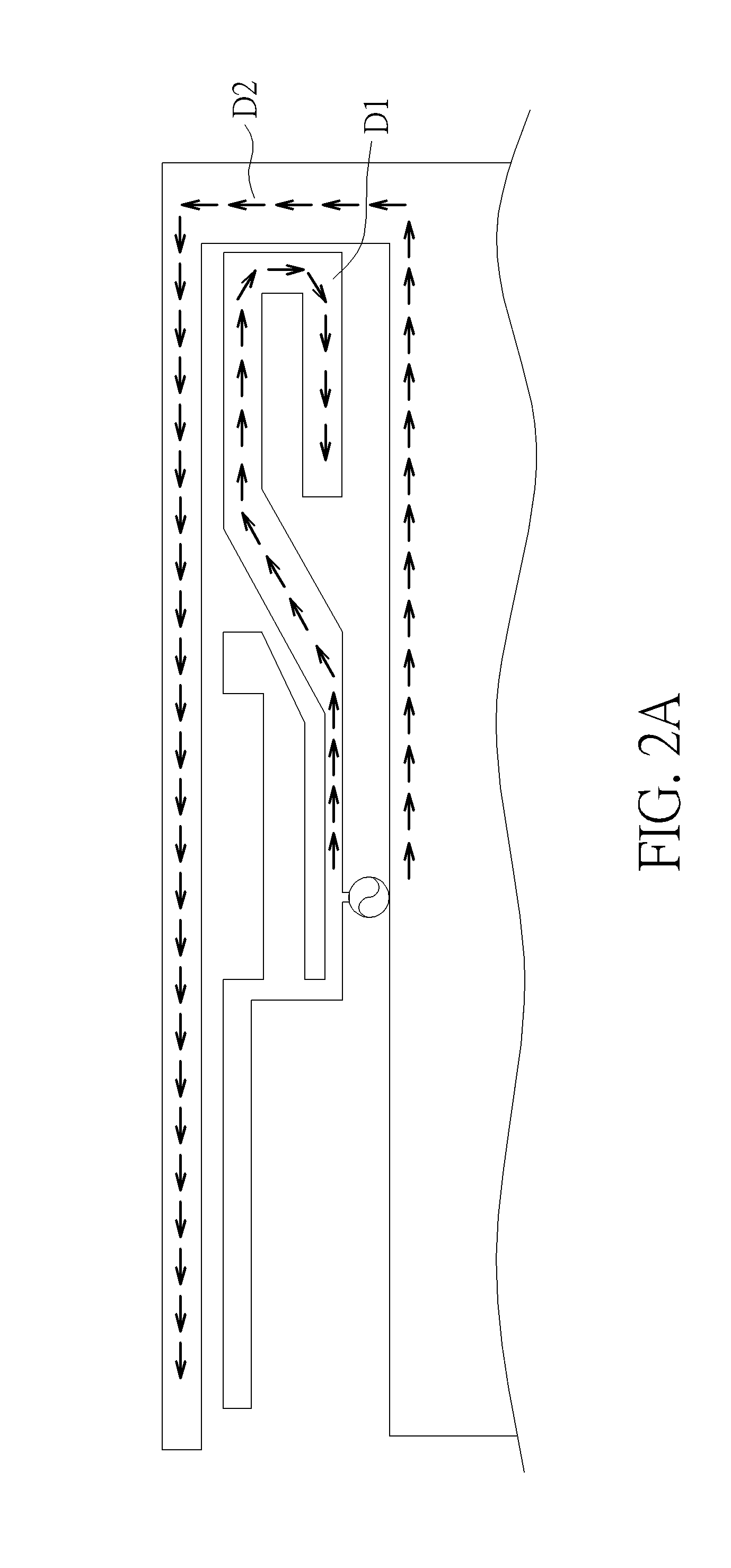

A photomask for eliminating antenna effects in an integrated circuit and integrated circuit manufactured with the photomask are disclosed. The photomask includes a substrate and a patterned layer formed on at least a portion of the substrate. The patterned layer may be formed using a mask pattern file created by analyzing a pattern in a mask layout file to identify a region including an antenna ratio less than a first design rule. A feature located in the identified region is moved based on a second design rule from a first position to a second position in the mask layout file to create a space in the identified region. A grounding feature is placed in the space and automatically connected to a gate feature in the mask layout file such that the antenna ratio is increased to greater than or approximately equal to the first design rule.

Owner:CELERICS TECH

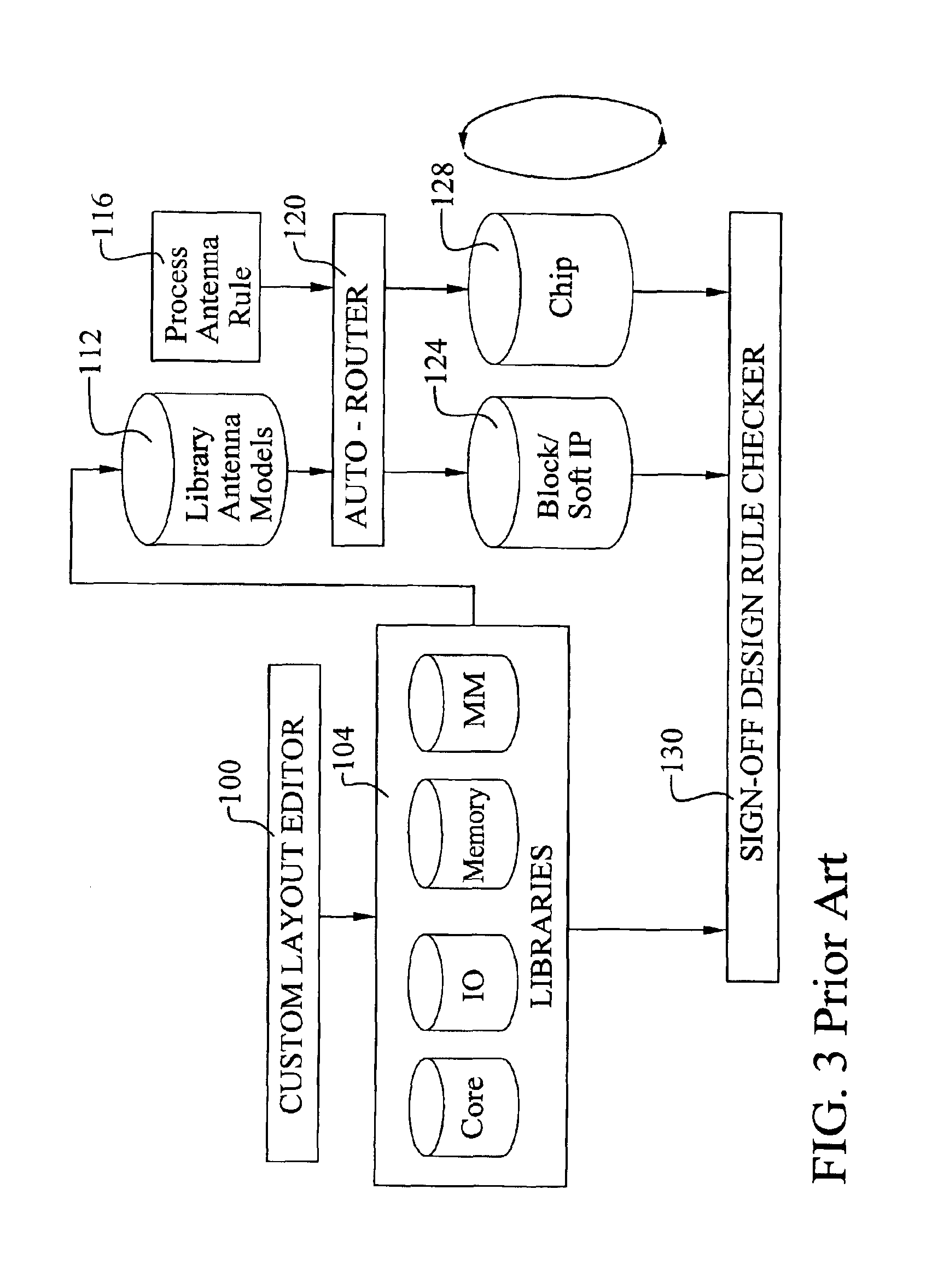

Methodology of generating antenna effect models for library/IP in VLSI physical design

InactiveUS6862723B1Efficient routingEffectiveComputer aided designSoftware simulation/interpretation/emulationAntenna effectVlsi physical design

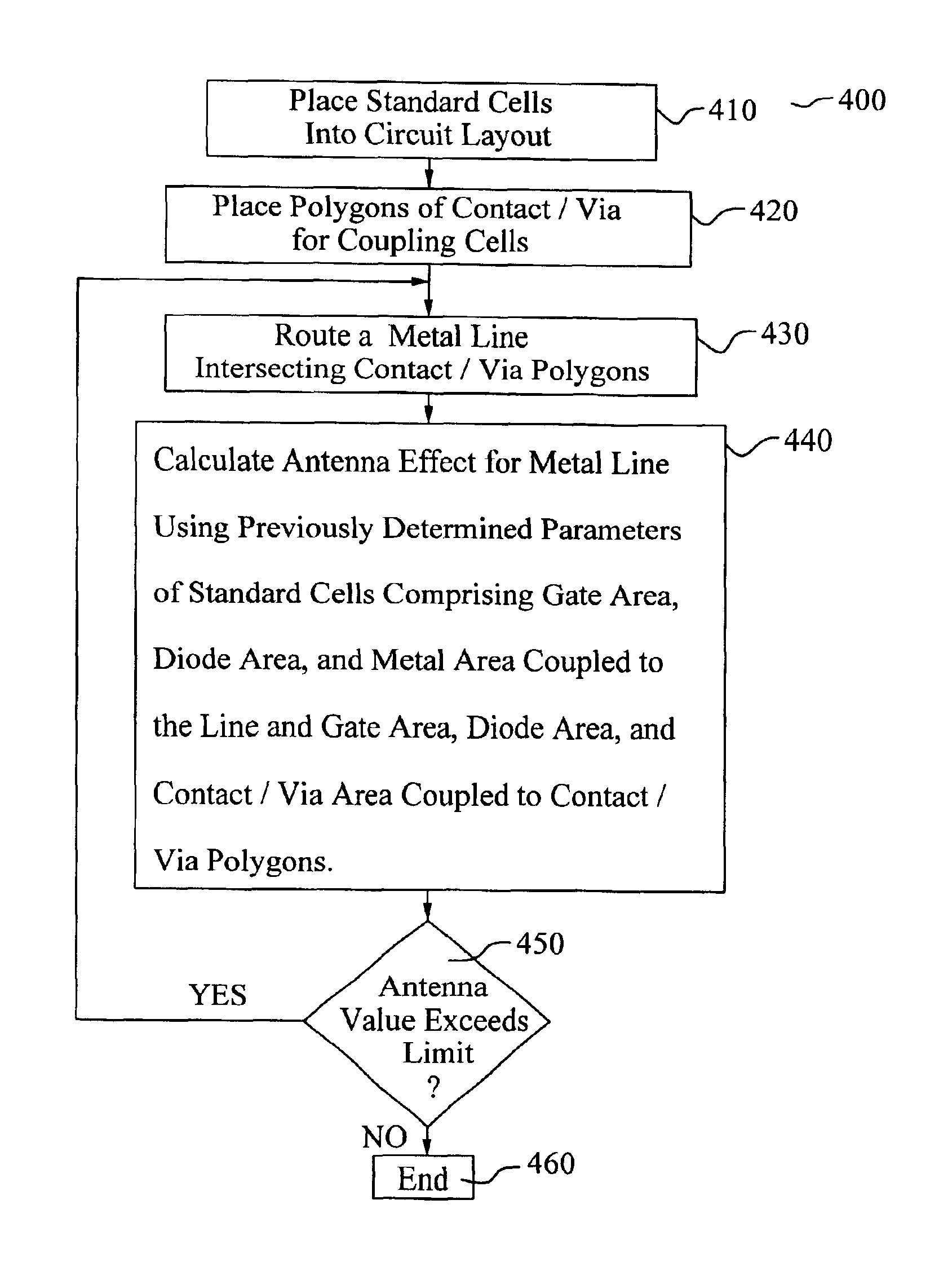

A new method to route a metal line in the layout of an integrated circuit device is achieved. The method comprises providing a layout for an integrated circuit device comprising an array of placed standard cells. Contact / via layer polygons are placed for coupling the standard cells. A line is routed in a metal layer. An antenna effect value is calculated for the line using parameters previously determined from the layout of each the standard cell. The parameters comprise gate area, diode area, metal area, and contact / via area coupled to the line. The gate area, the diode area, the metal area, and the contact / via area are segregated by metal level. The steps of routing and calculating are repeated if the antenna effect value exceeds a specified value. A method to extract parameters is disclosed.

Owner:TAIWAN SEMICON MFG CO LTD

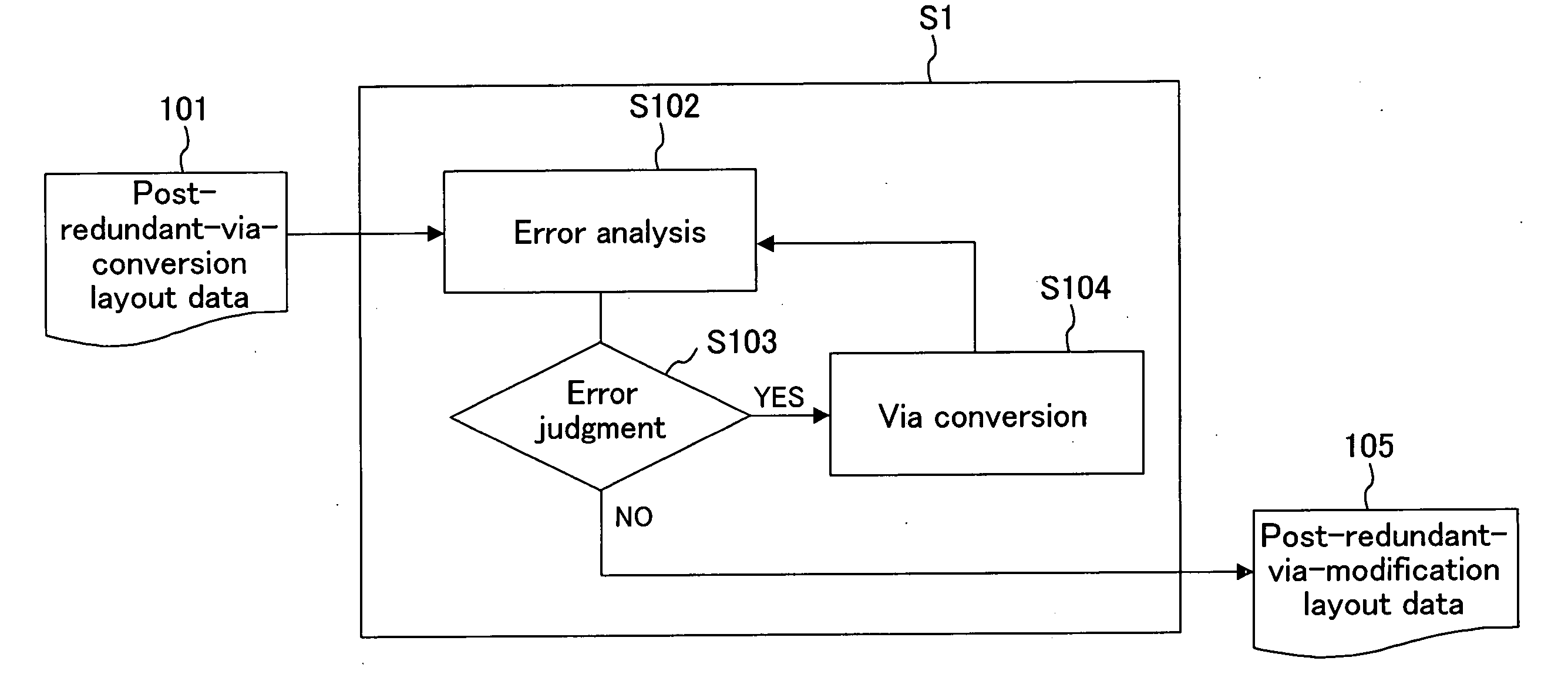

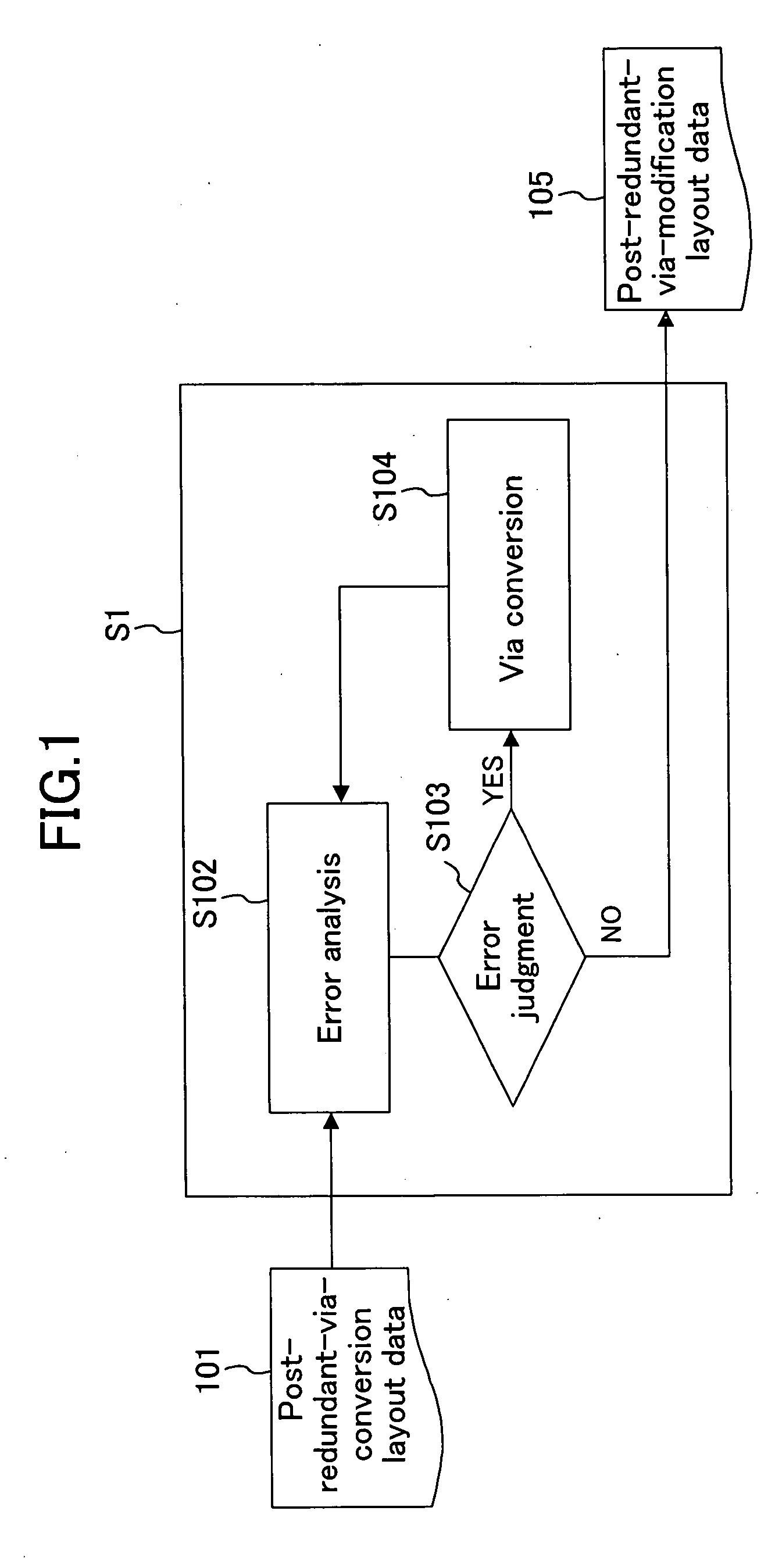

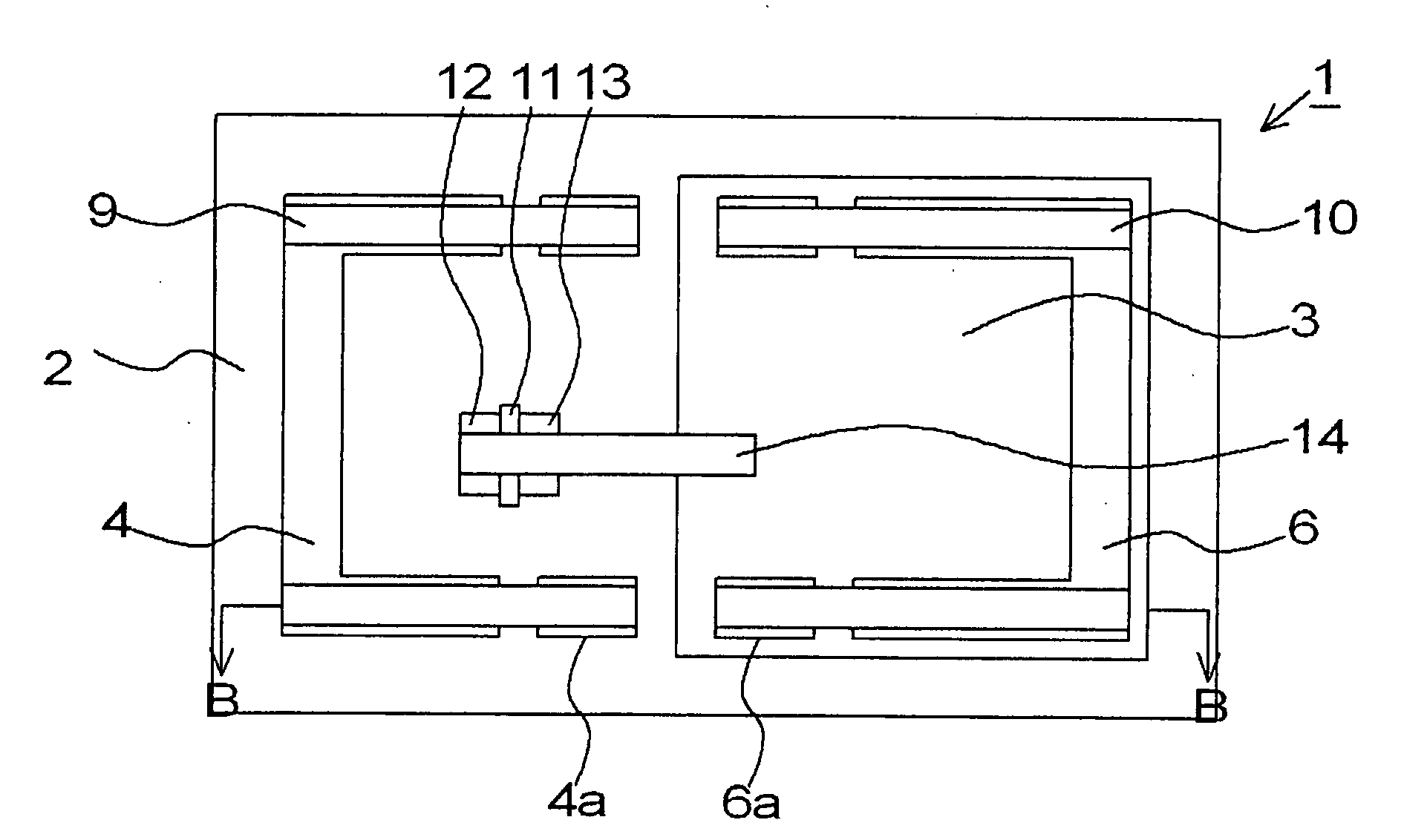

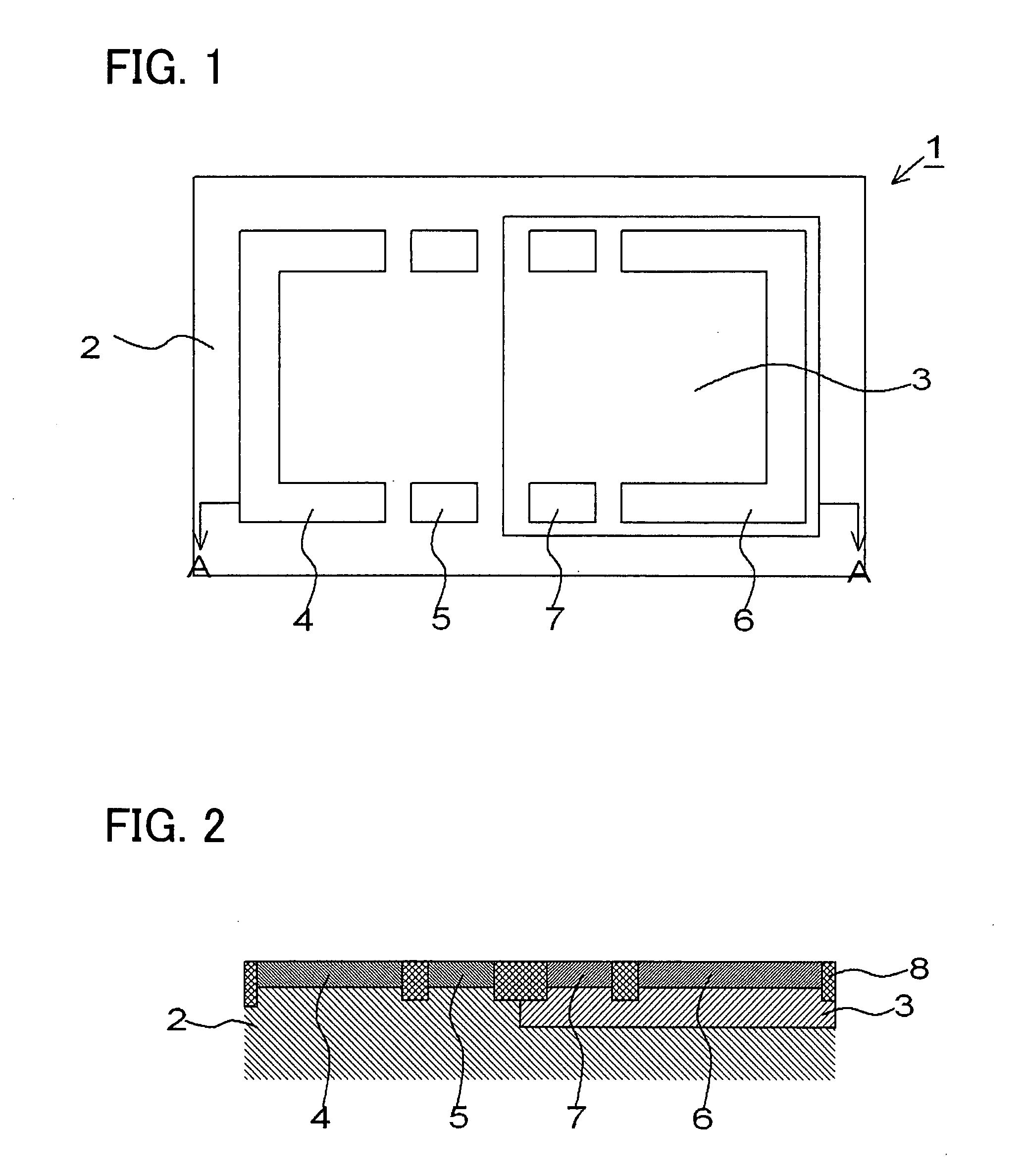

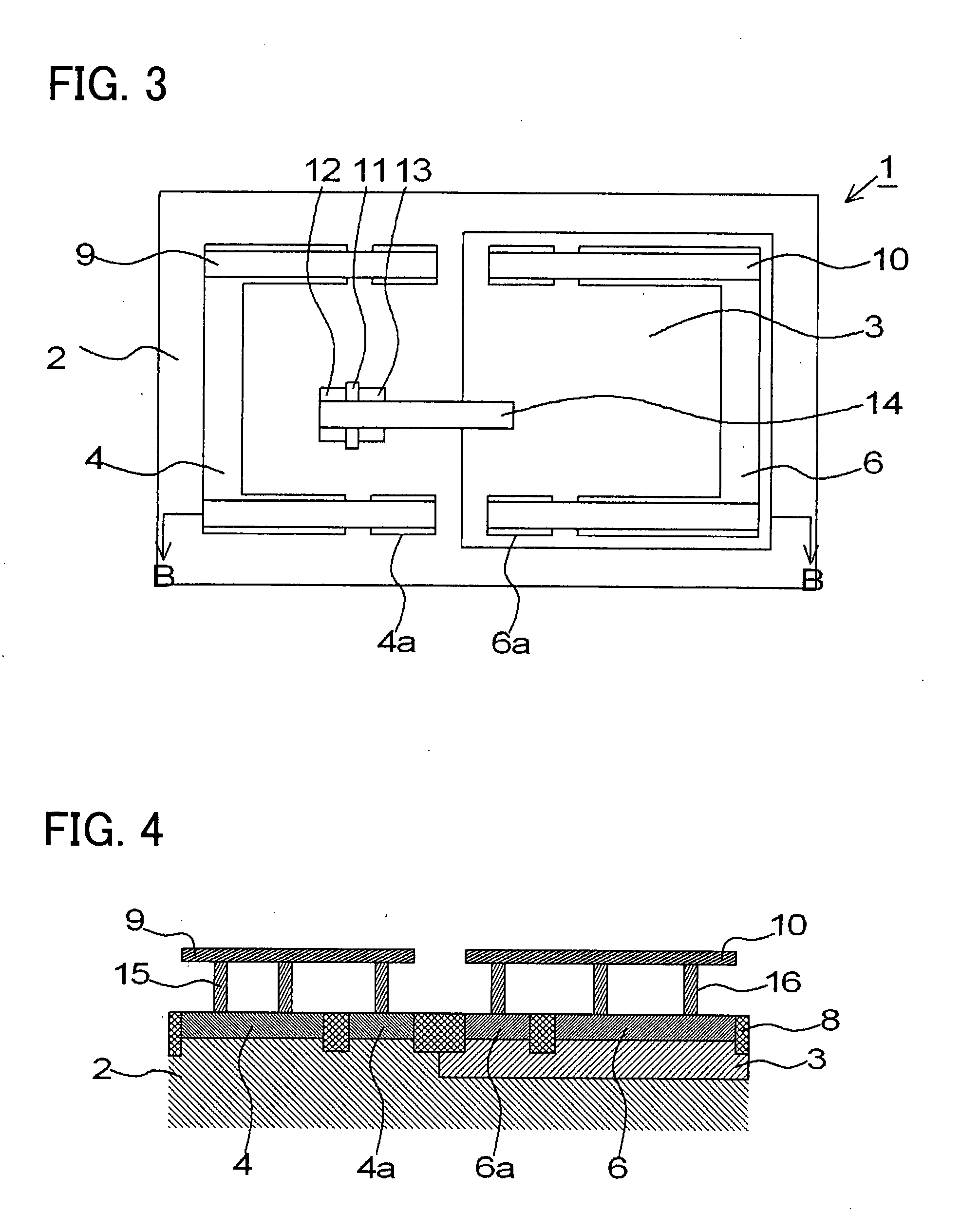

Design method of semiconductor device and semiconductor device

InactiveUS20060101367A1Improve electromigrationHigh yieldSemiconductor/solid-state device detailsSolid-state devicesAntenna effectDevice material

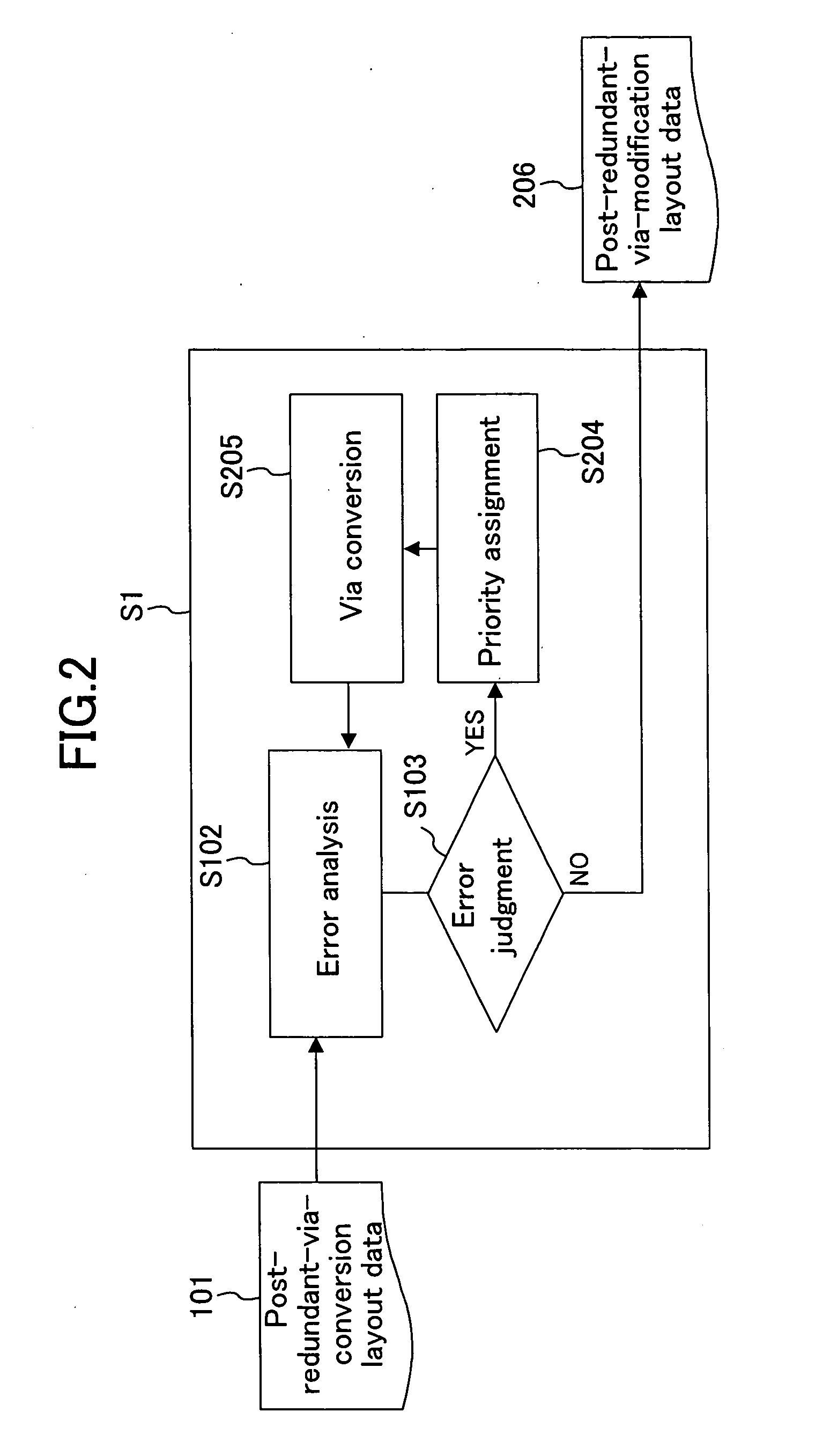

In an error analysis step, analysis of an antenna effect error, a timing constraint violation and the like is performed for layout data in which redundant via conversion has been performed. Then, whether or not an error exists is judged and, among redundant vias located on a signal line in which a design constraint violation has occurred, how many vias have to be converted to single vias, respectively, to avoid the design constraint violation is calculated. In a via conversion step, a redundant via which has caused an error is converted to a single via, based on a result of the calculation. Thus, a design constraint violation regarding an error such as an antenna effect error and a timing constraint violation caused by a redundant via obtained by converting a single via for improving yield hardly occurs.

Owner:PANASONIC CORP

Printed circuit board and electro application

ActiveUS20110026234A1Promote absorptionEfficient use ofMultiple-port networksAntenna supports/mountingsAntenna effectCost effectiveness

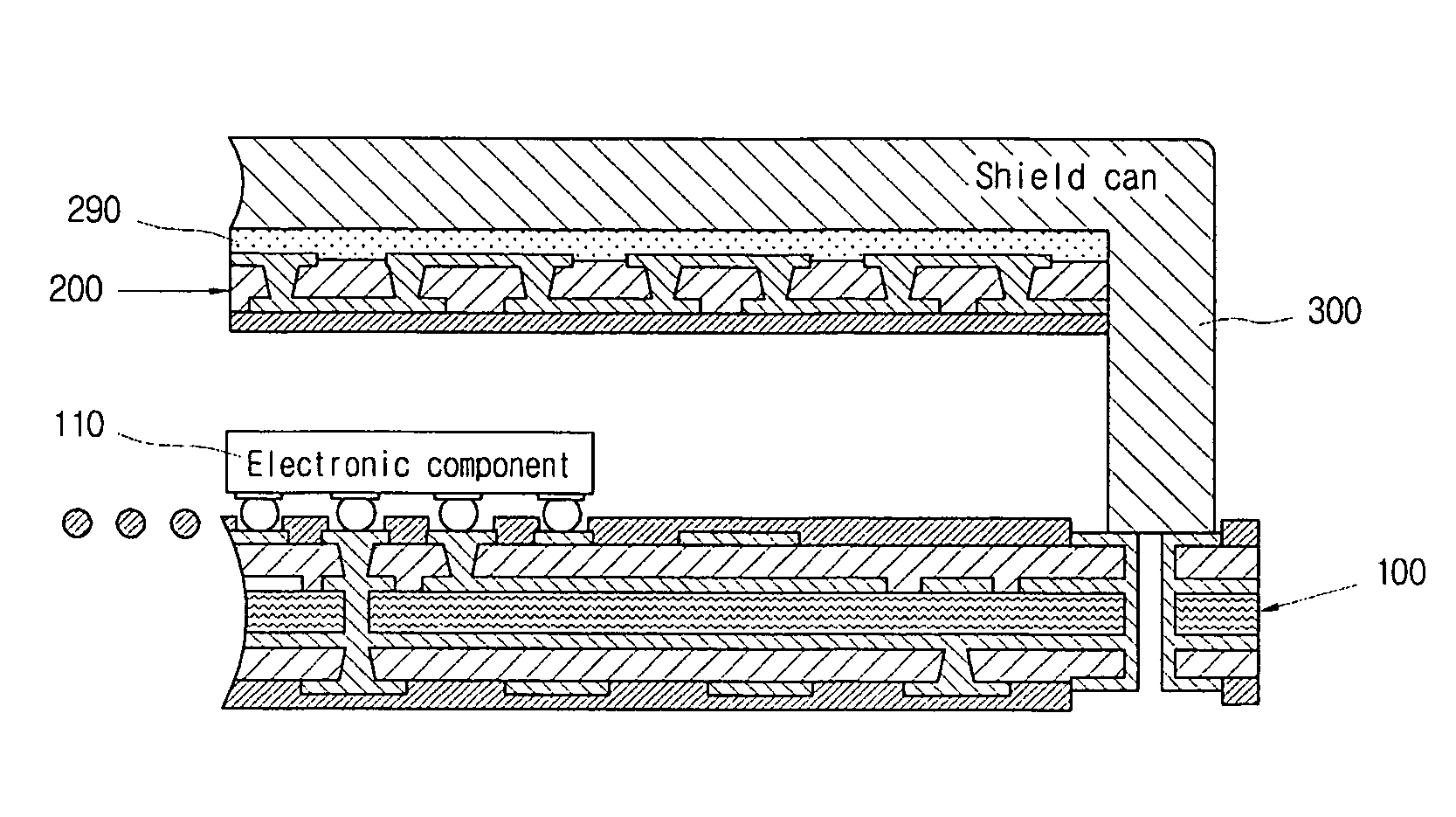

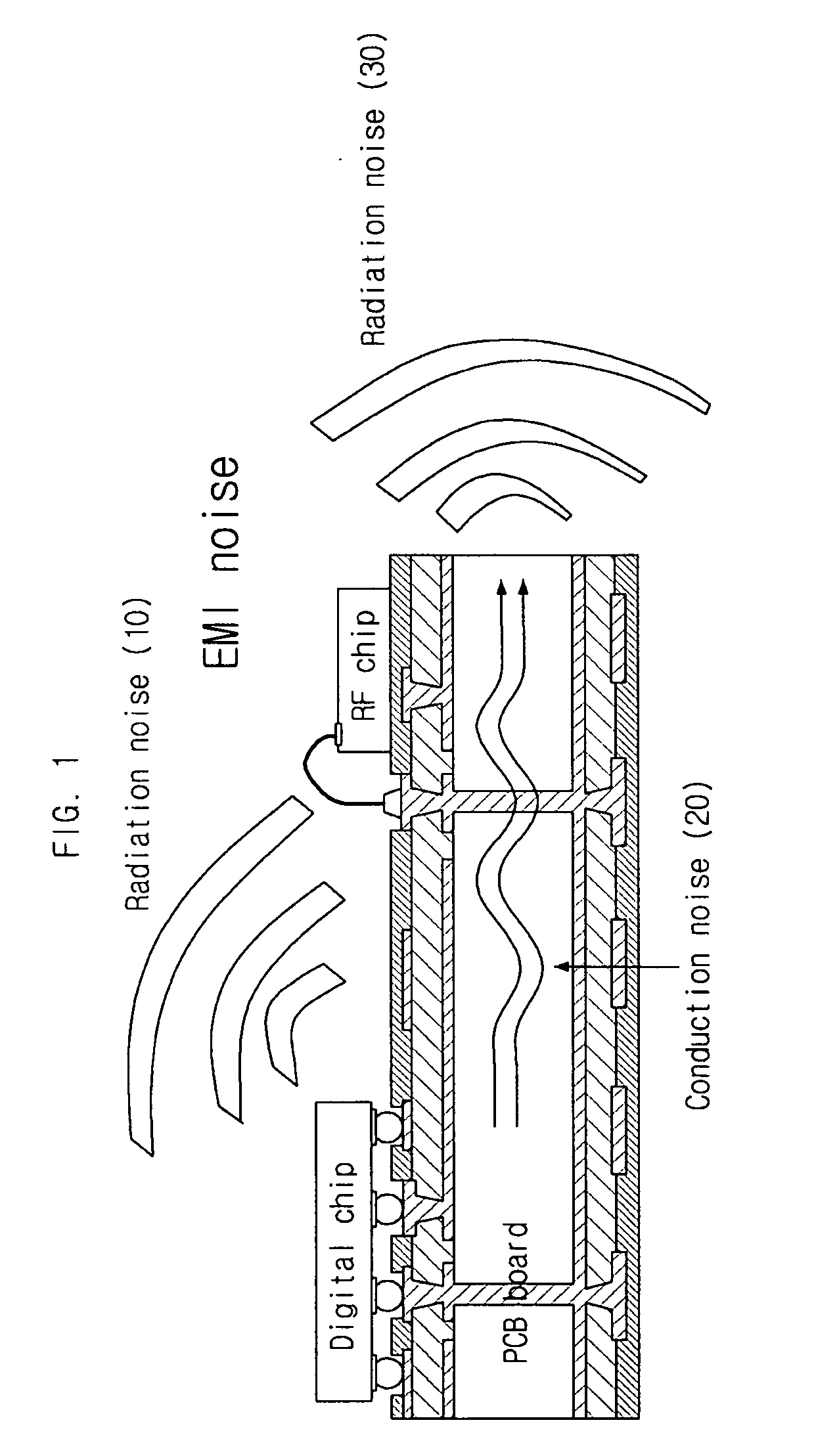

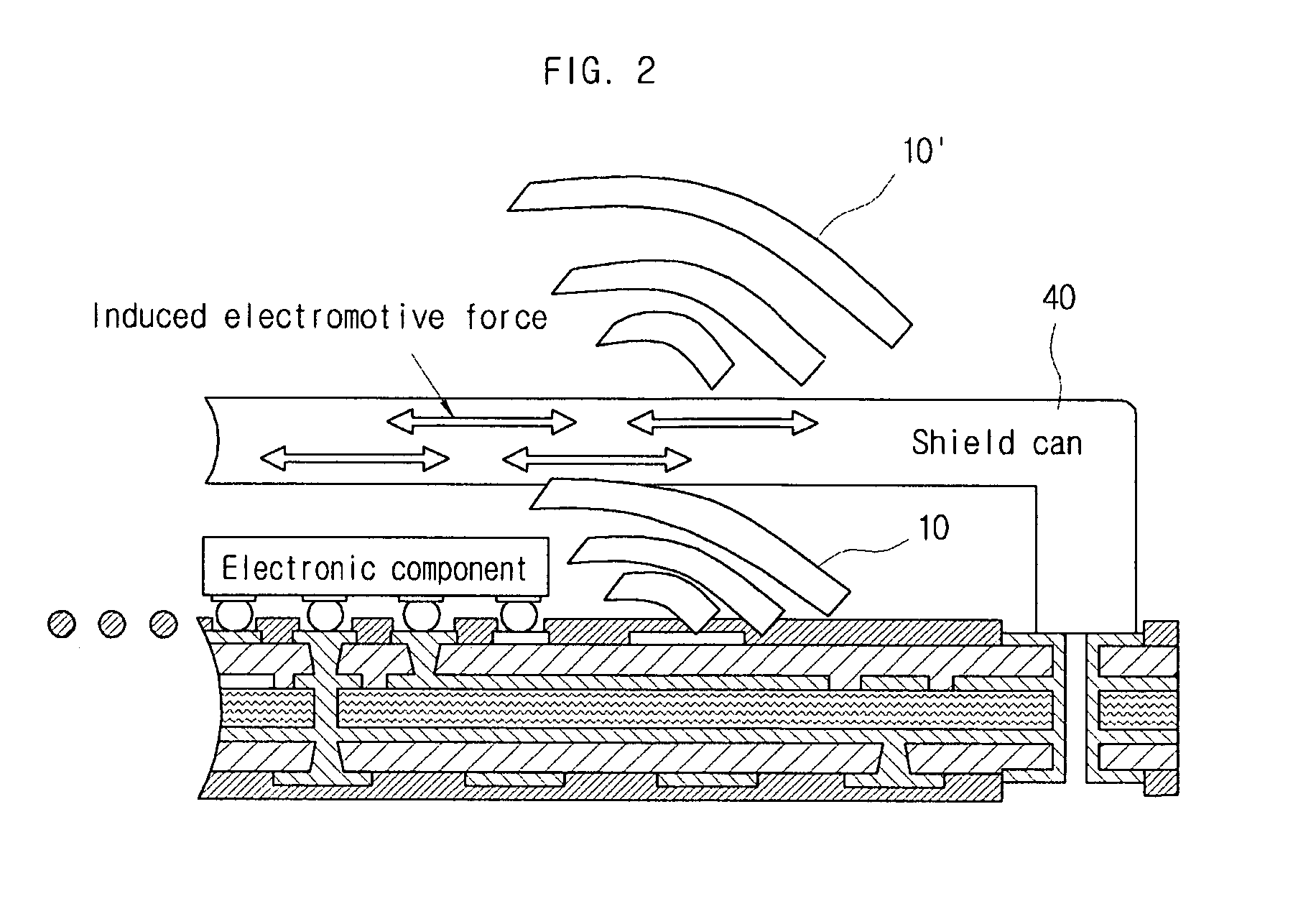

A printed circuit board and an electronic product are disclosed. In accordance with an embodiment of the present invention, the printed circuit board includes a first board, which has an electronic component mounted thereon, and a second board, which is positioned on an upper side of the first board and covers at least a portion of an upper surface of the first board and in which an EBG structure is inserted into the second board such that a noise radiating upwards from the first board is shielded. Thus, the printed circuit board can readily absorb various frequencies, be easily applied without any antenna effect and be cost-effective in manufacturing.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

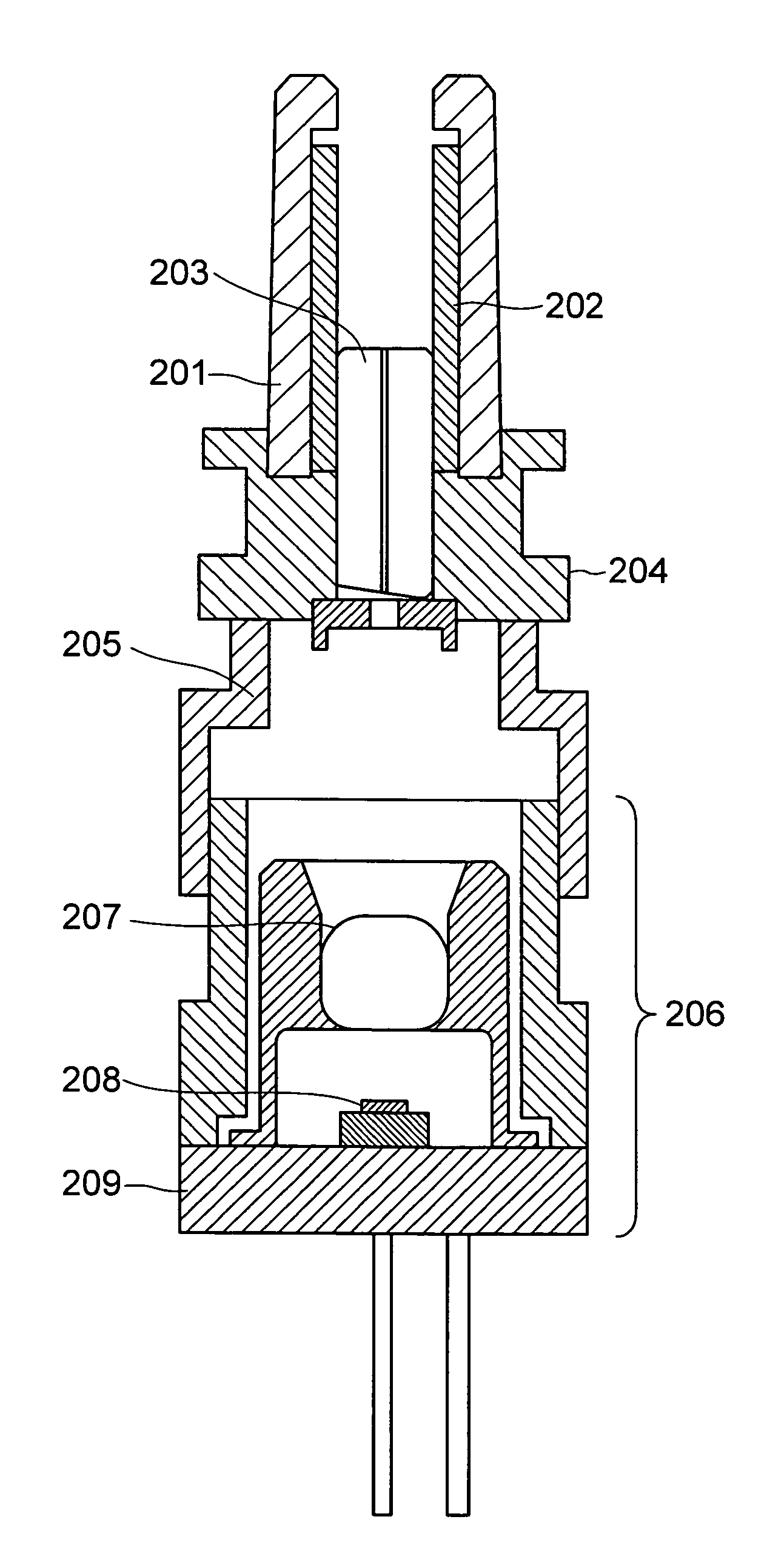

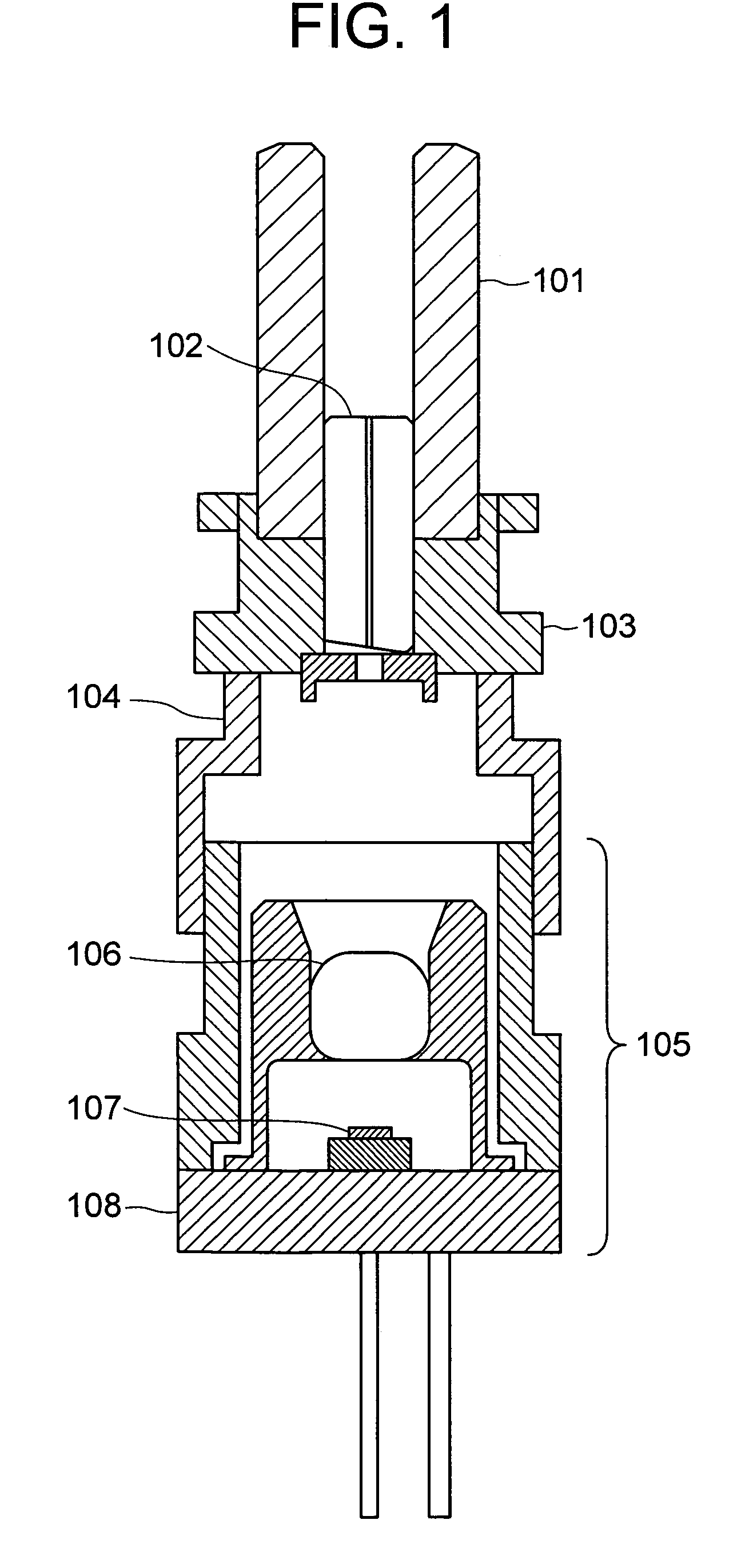

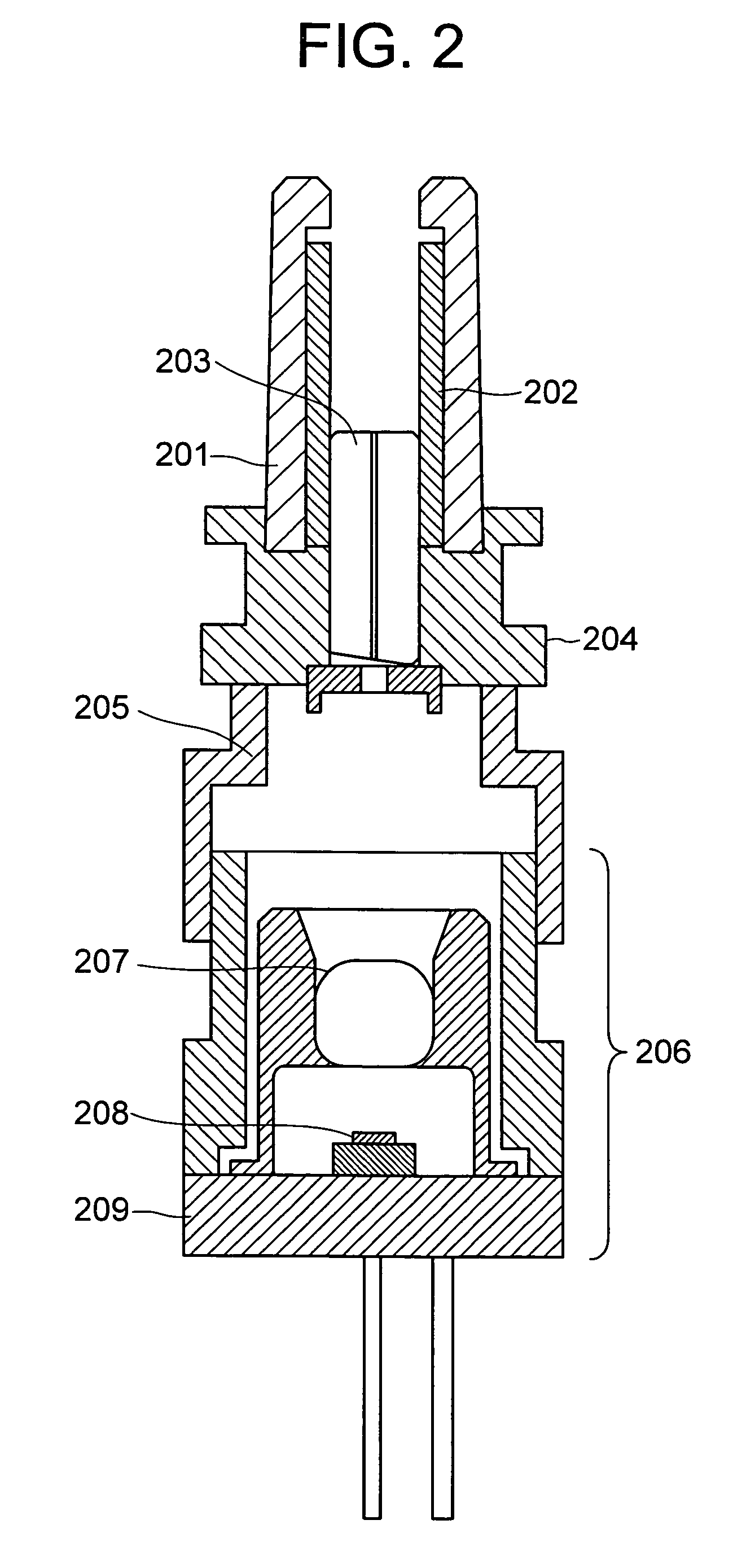

Optical device module, optical transmitter and receiver, and optical receptacle

ActiveUS7322752B2Superior in optical connection characteristicImprove the ease of assemblyLaser detailsCoupling light guidesAntenna effectOptical Module

An optical device module includes a stub ferrule for guiding a laser light to an optical fiber to be connected, a sleeve for holding an optical-connector ferrule of the optical fiber to be connected and the stub ferrule, a holder for fixing the stub ferrule and the sleeve, and an adapter for connecting the holder and an optical module, in which the sleeve is formed by a nonmetallic material, reducing the structure of metal portion and restraining the antenna effect when electromagnetic noise enters.

Owner:LUMENTUM JAPAN INC

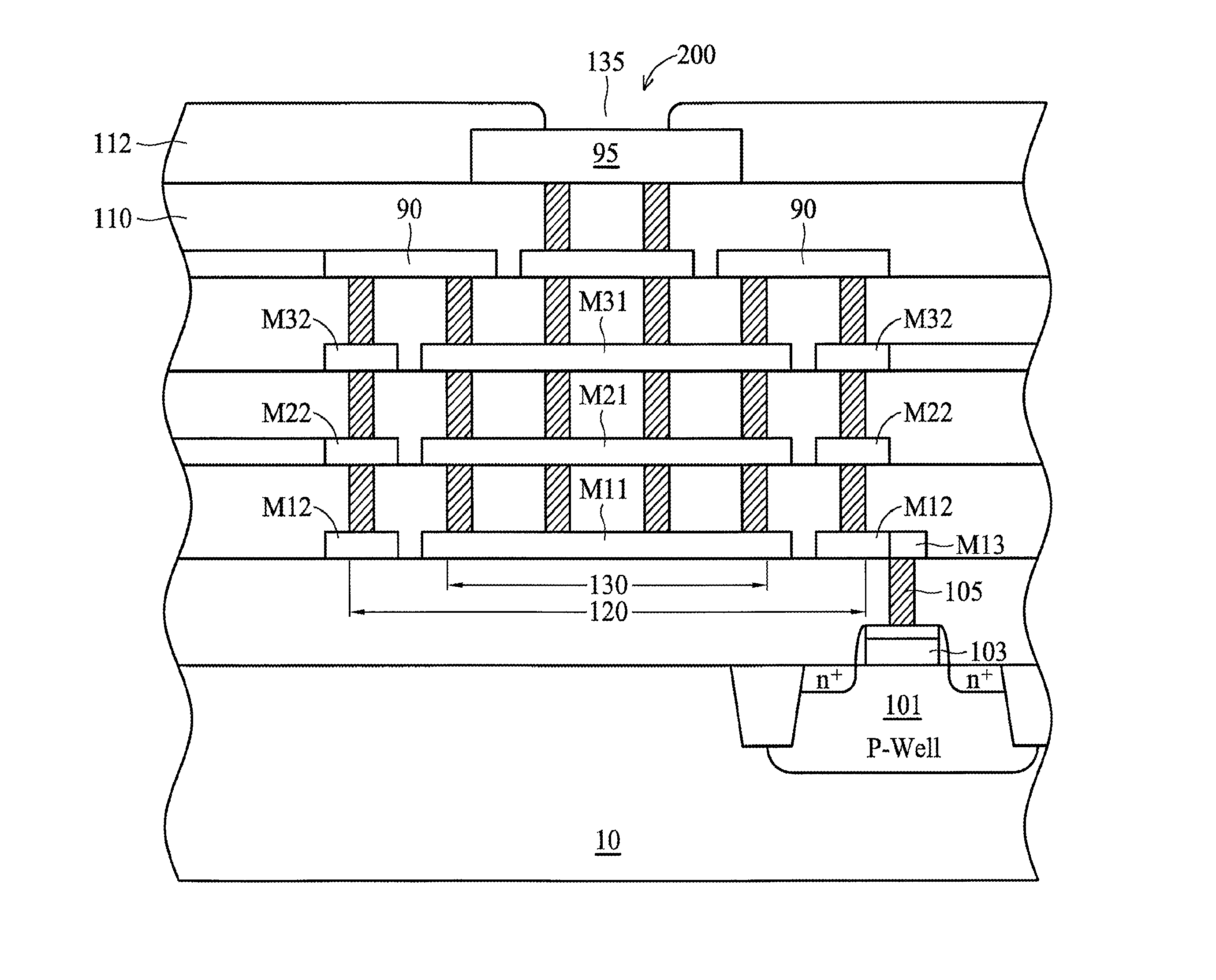

Chip Pad Resistant to Antenna Effect and Method

InactiveUS20090321871A1Resistant and immune to antenna effectSemiconductor/solid-state device detailsSolid-state devicesAntenna designAntenna effect

A chip pad structure of an integrated circuit (IC) and the method of forming are disclosed. The chip pad comprises a main pad portion and a ring pad portion. During a charging process involved in forming the chip pad structure, electrical connections from the gate electrodes of MOS transistors in the IC substrate generally are made only to the ring pad portion that has an antenna-to-gate area ratio substantially below a predetermined antenna design rule ratio, and thus is resistant or immune to antenna effect. The main pad portion and the ring pad portion are coupled together through metal bridges formed in an upper interconnect metal layer or in the top conductive pad layer. The chip pad may be used as probe pads on a parametric testline or bonding pads on an IC.

Owner:TAIWAN SEMICON MFG CO LTD

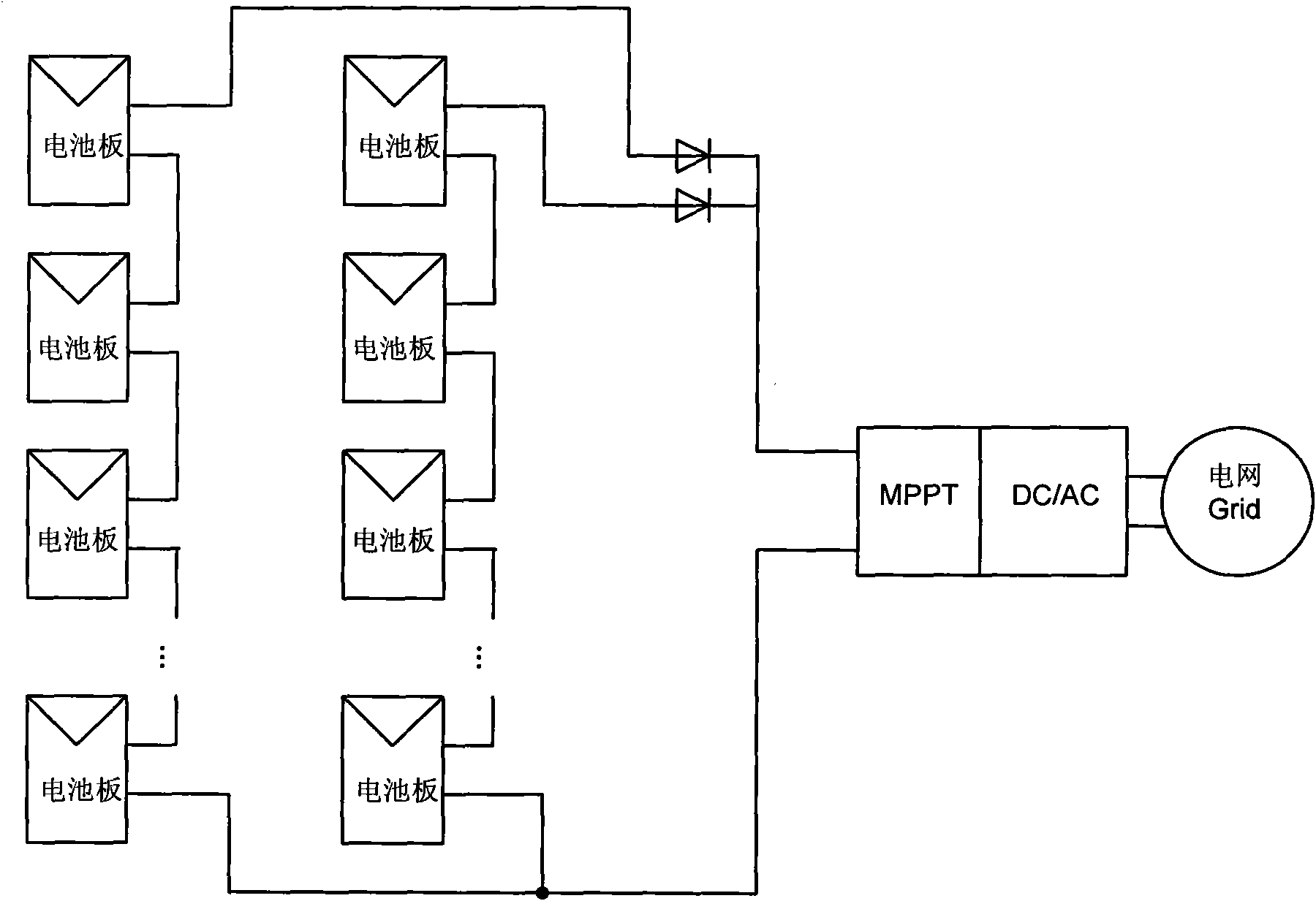

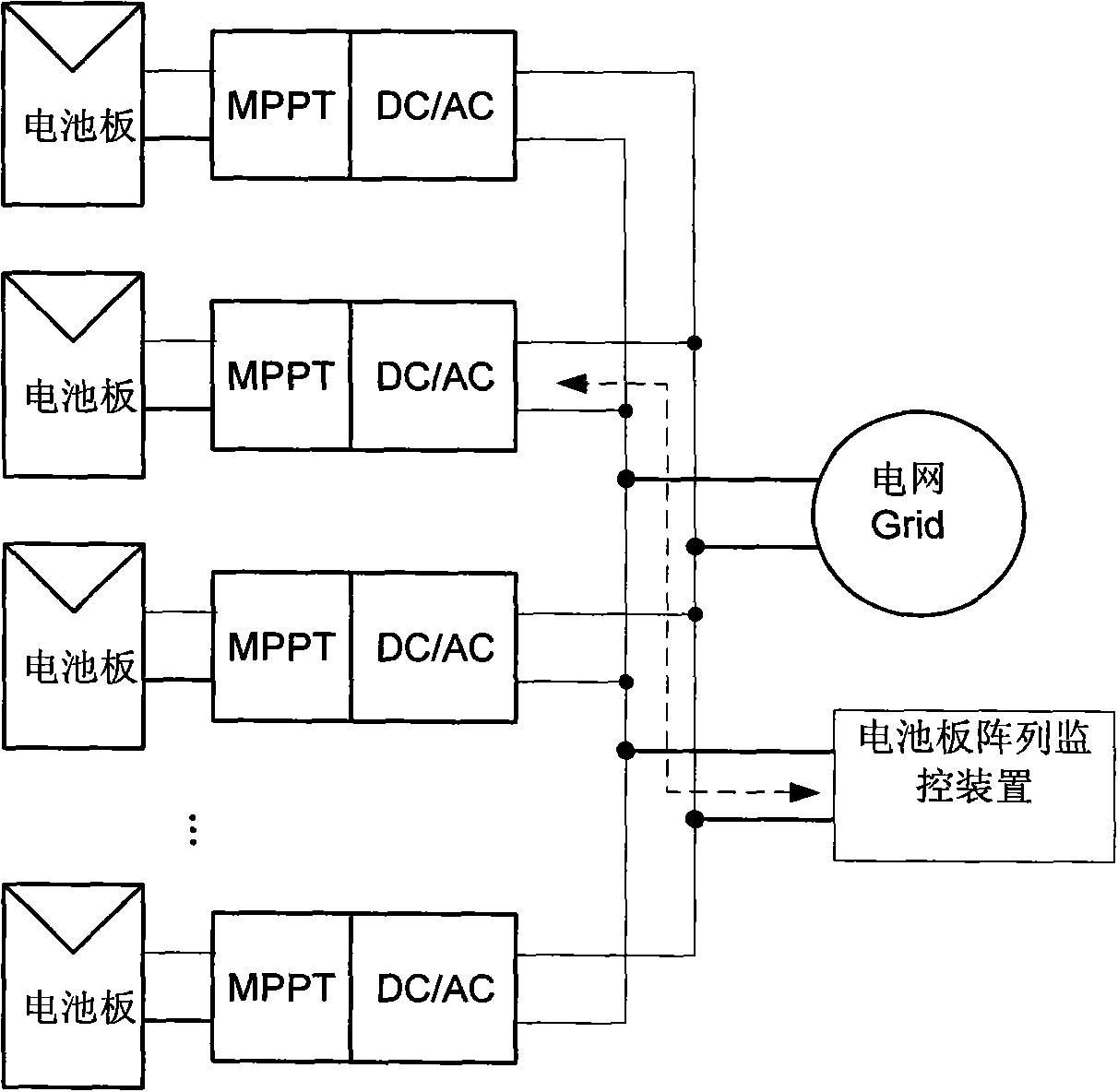

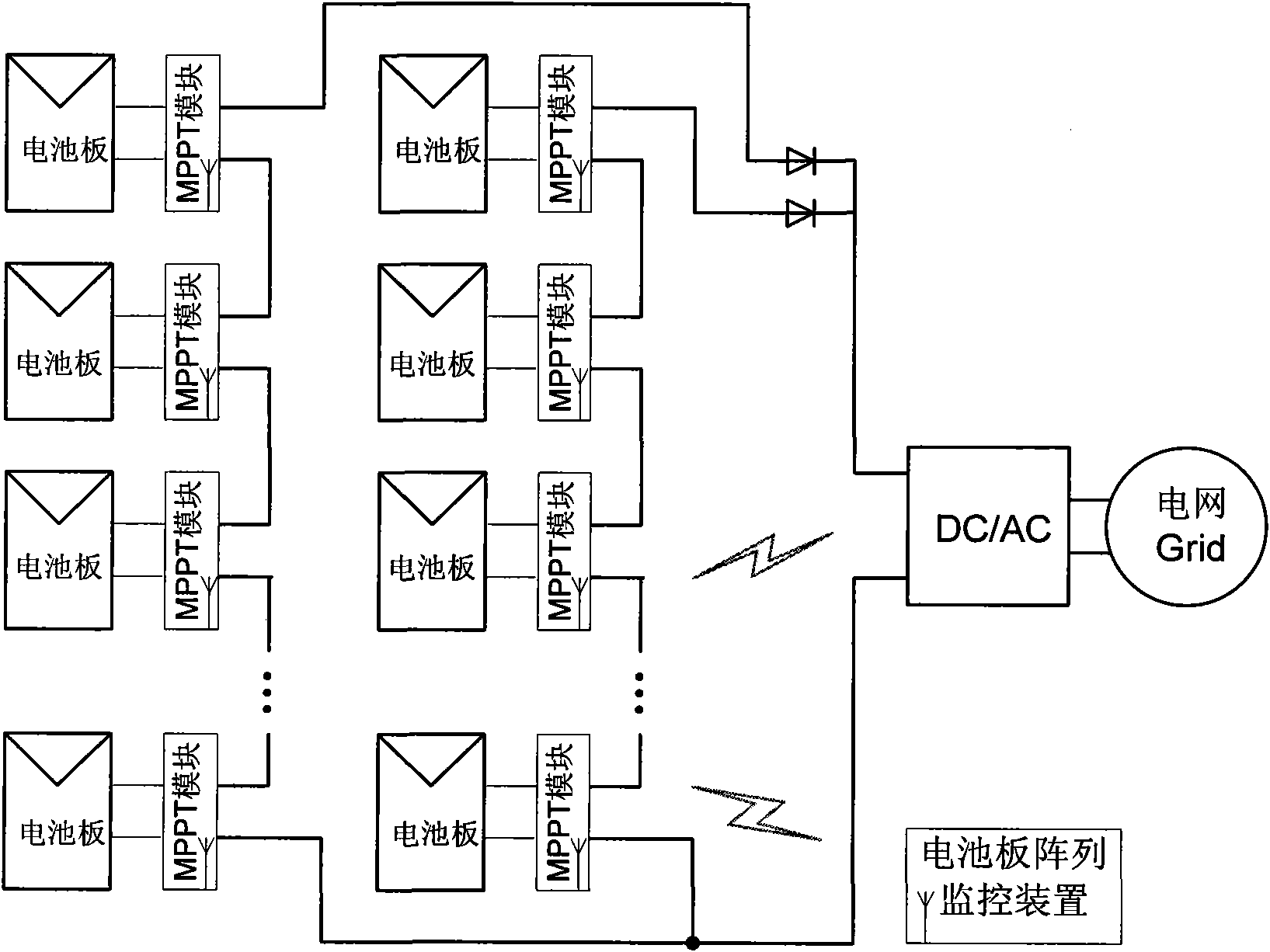

Low-cost interface structure and method for monitoring direct current side information of solar cell panel

InactiveCN101950984AAvoid noise disturbanceLow costSingle network parallel feeding arrangementsTransmissionCapacitanceAntenna effect

The invention discloses a low-cost interface structure and a method for monitoring the direct current side information of a solar cell panel. The method comprises the following steps of: constructing a low pass filter and establishing a high frequency interconnected channel at the back end of a BOOST circuit booster diode so as to perform digitized carrier communication between a monitoring device and a public direct current bus which is connected with a centralized inverter or a string inverter and performing signal coupling by using double capacitors without any communication transformer orspecial communication line; and processing a mu V level communication signal by using a low transmitting power circuit and a digital phase-locking amplifier and realizing reference signal synchronization and communication frequency switching of the digital phase-locking amplifier through a bus ripple voltage and a bus average voltage so as to reduce the problems of antenna effect and electromagnetic compatibility (EMC) caused by long-distance transportation of a high frequency signal of a direct current bus and lower the cost of a solar panel monitoring communication device. The structure andthe method have good application prospects.

Owner:WUXI MEIKAI ENERGY TECH

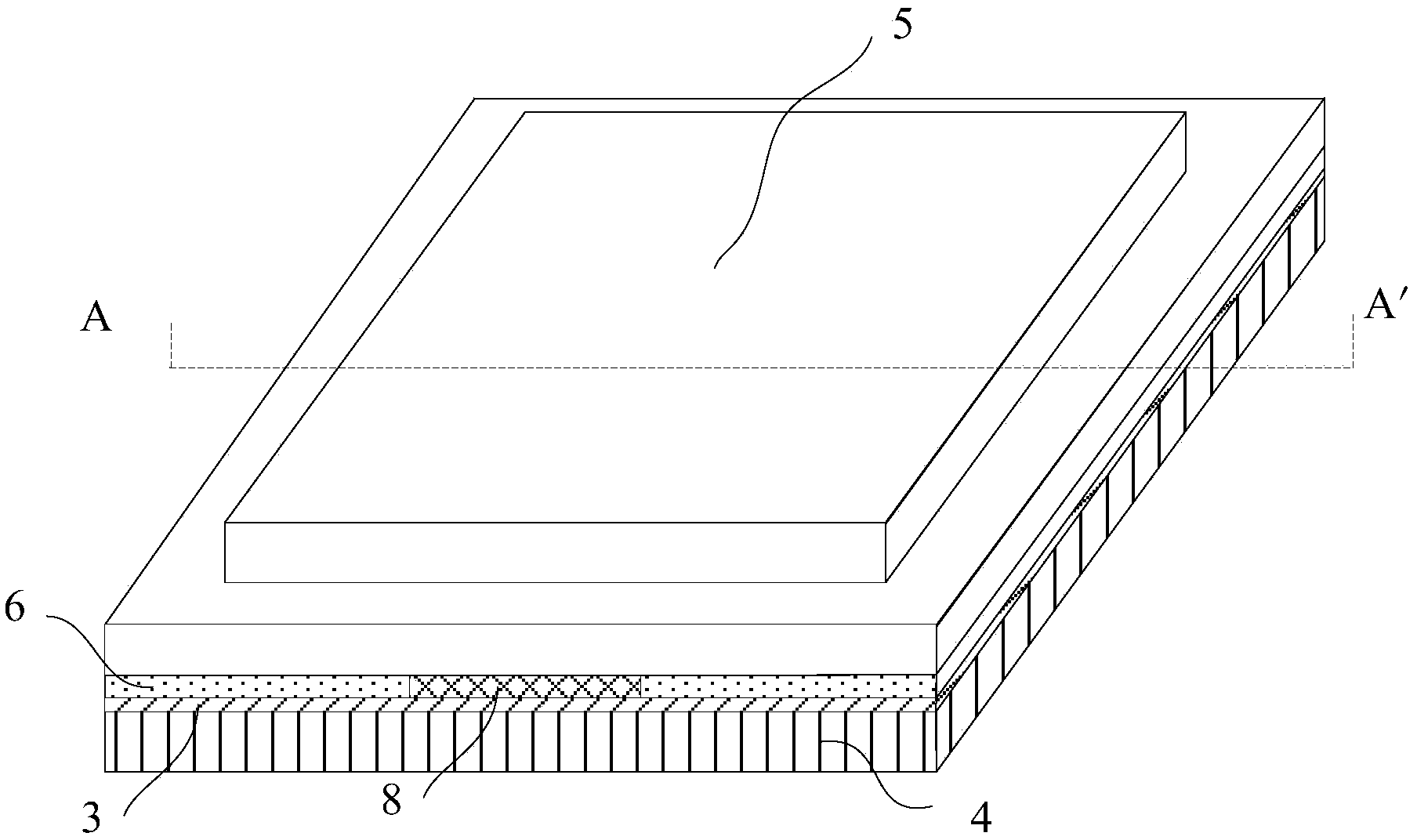

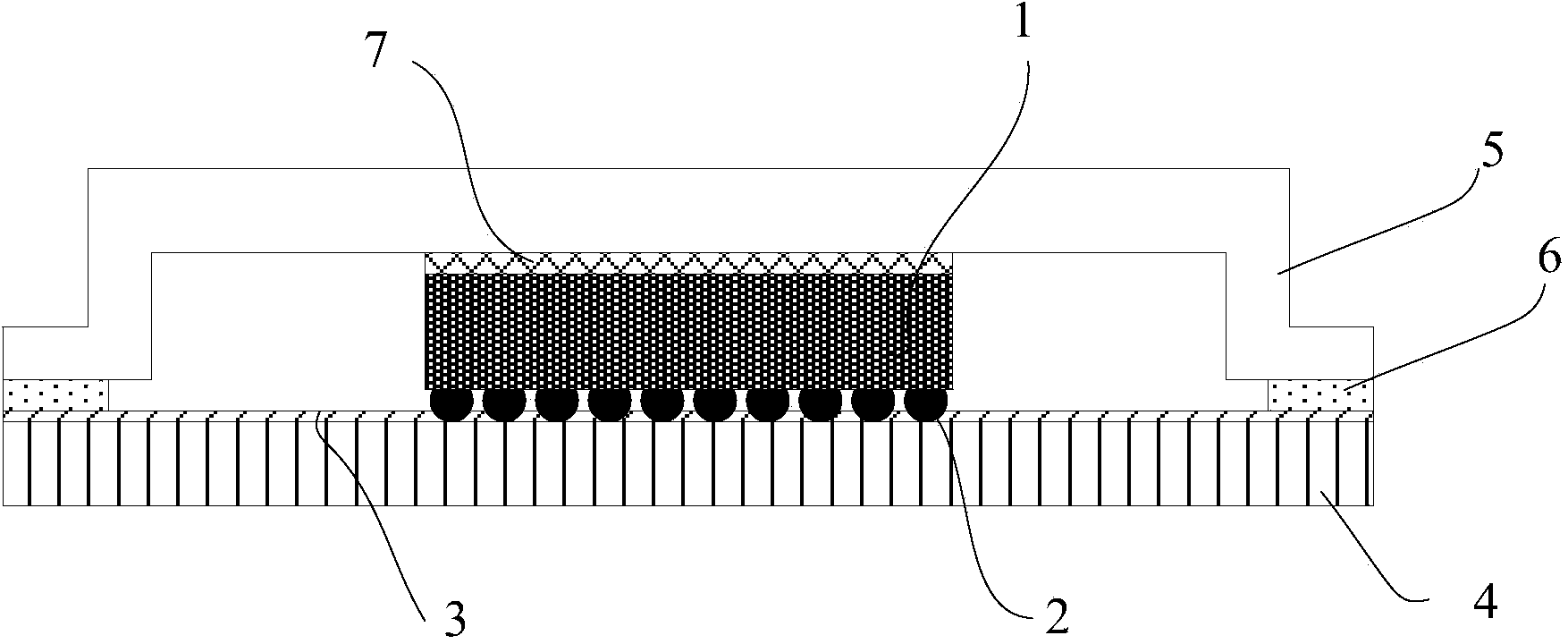

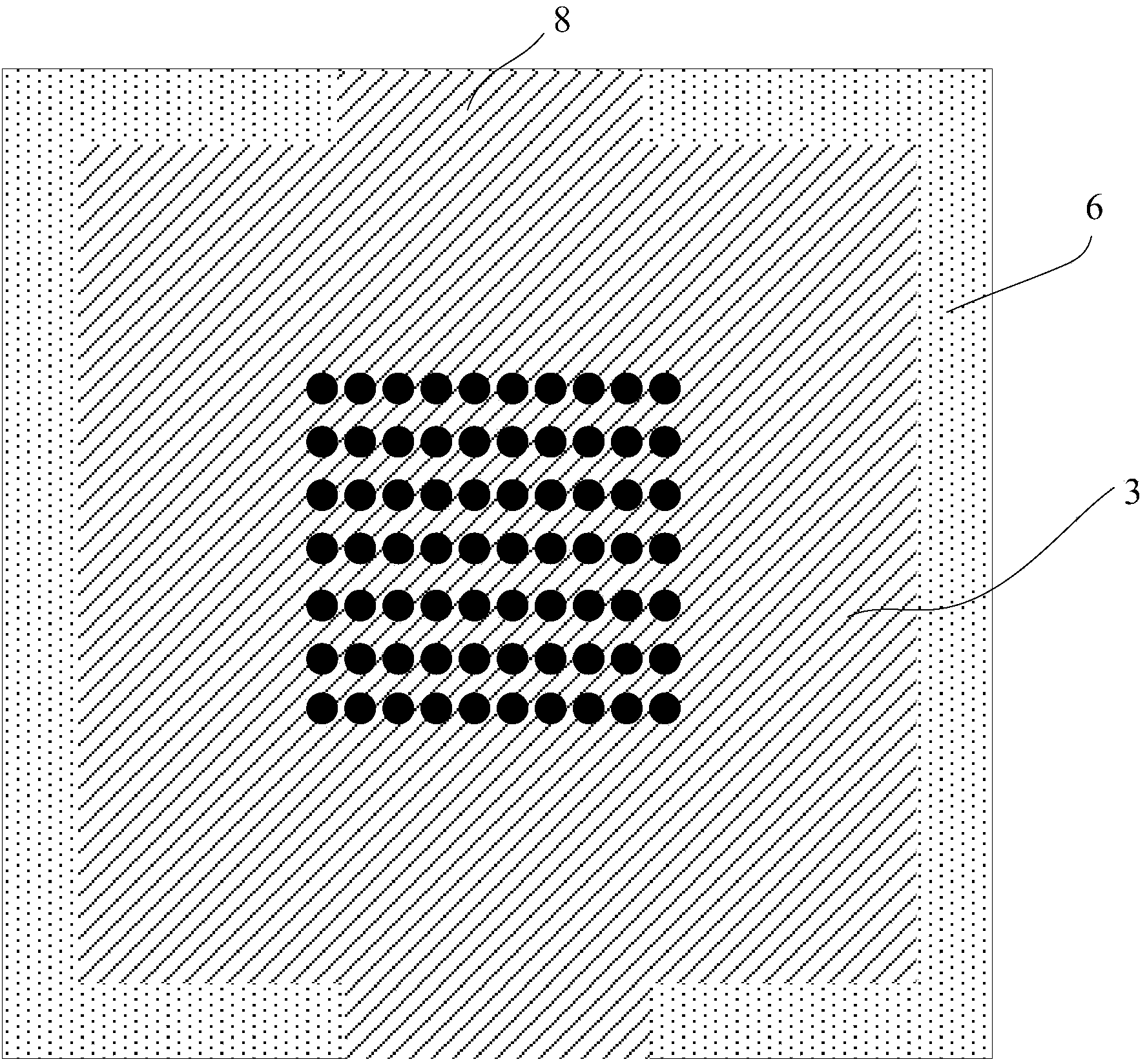

Electronic component packaging structure and electronic device

ActiveCN103943610AIncrease planar capacitance densityIncrease planar capacitanceMagnetic/electric field screeningCross-talk/noise/interference reductionCapacitanceAntenna effect

The invention discloses an electronic component packaging structure and an electronic device. The electronic component packaging structure at least comprises a substrate, a conductive housing and a non-conductive adhesive, wherein the substrate is provided with a set adhesion area, the set adhesion area is used for adhesion of an electronic component, the conductive housing is provided with a top and a side wall extending towards the substrate, a bonding end is arranged on the side, close to the substrate, of the side wall, the conductive housing is bonded to the substrate through the bonding end and the non-conductive adhesive, the adhesion area is surrounded by the conductive housing which is bonded to the substrate, a shielding space is formed above the adhesion area, the non-conductive adhesive is located between the substrate and the bonding end, the dielectric constant of the non-conductive adhesive is larger than or equal to seven, and the coating thickness of the non-conductive adhesive is smaller than or equal to 0.07 mm. By the adoption of the electronic component packaging structure and the electronic device, the planar capacitance density of a planar capacitance structure formed by the conductive housing, the non-conductive adhesive and the substrate is improved, then the planar capacitance value of the planar capacitance structure formed by the conductive housing, the non-conductive adhesive and the substrate can be increased, gap antenna effect radiation EMI at the position of the non-conductive adhesive can be effectively reduced, and the EMI shielding effect of the shielding space is improved.

Owner:HUAWEI TECH CO LTD

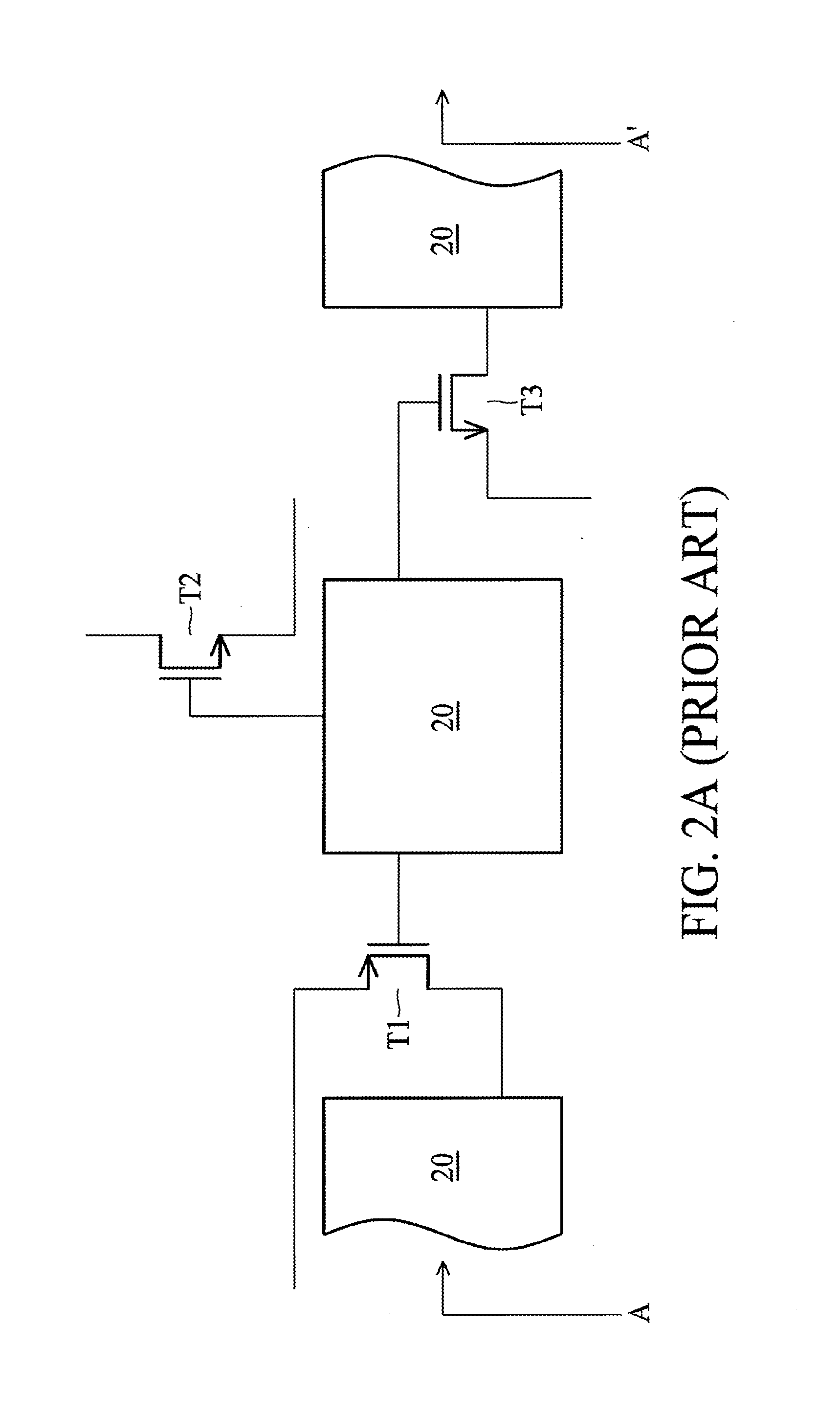

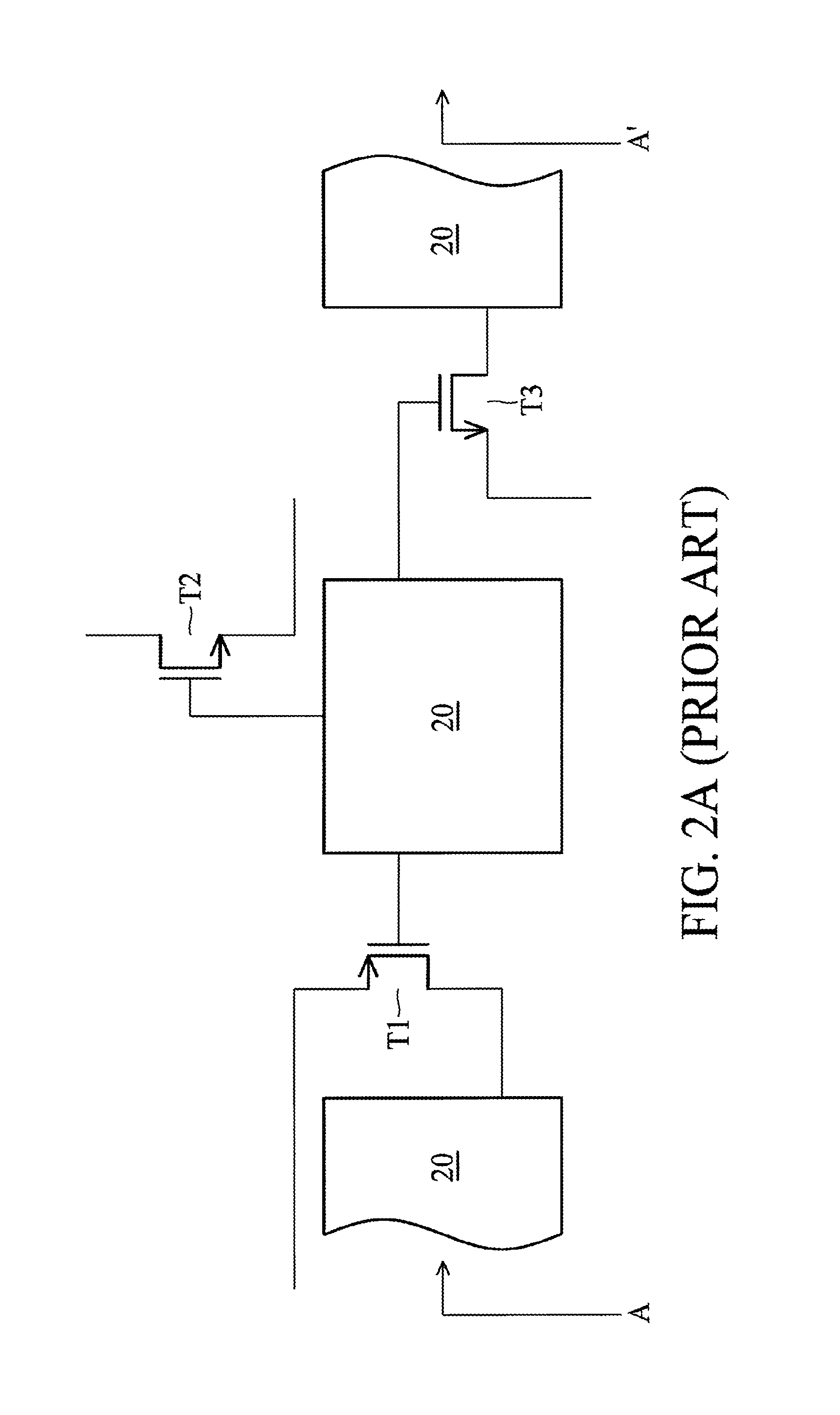

Antenna effect discharge circuit and manufacturing method

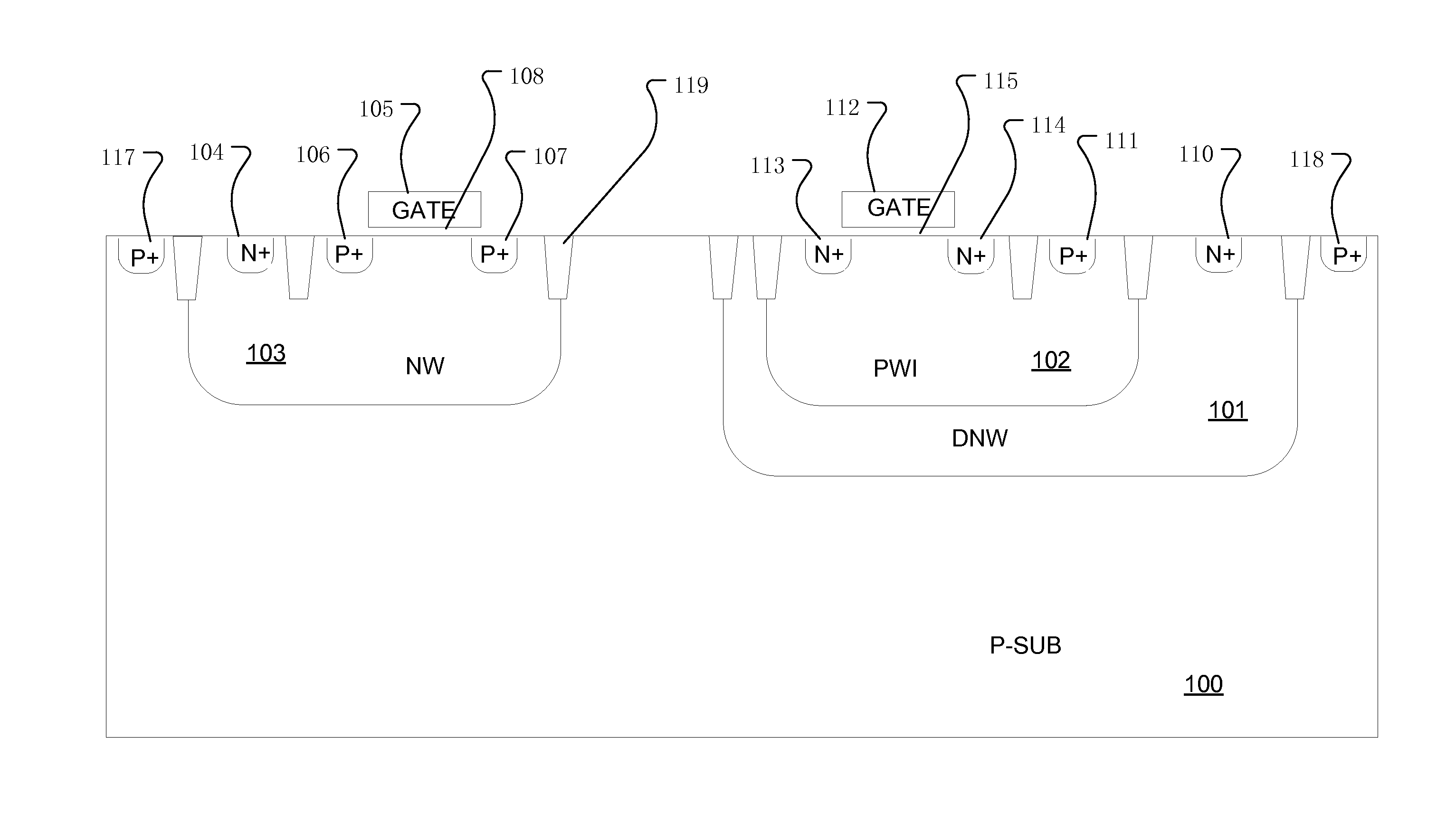

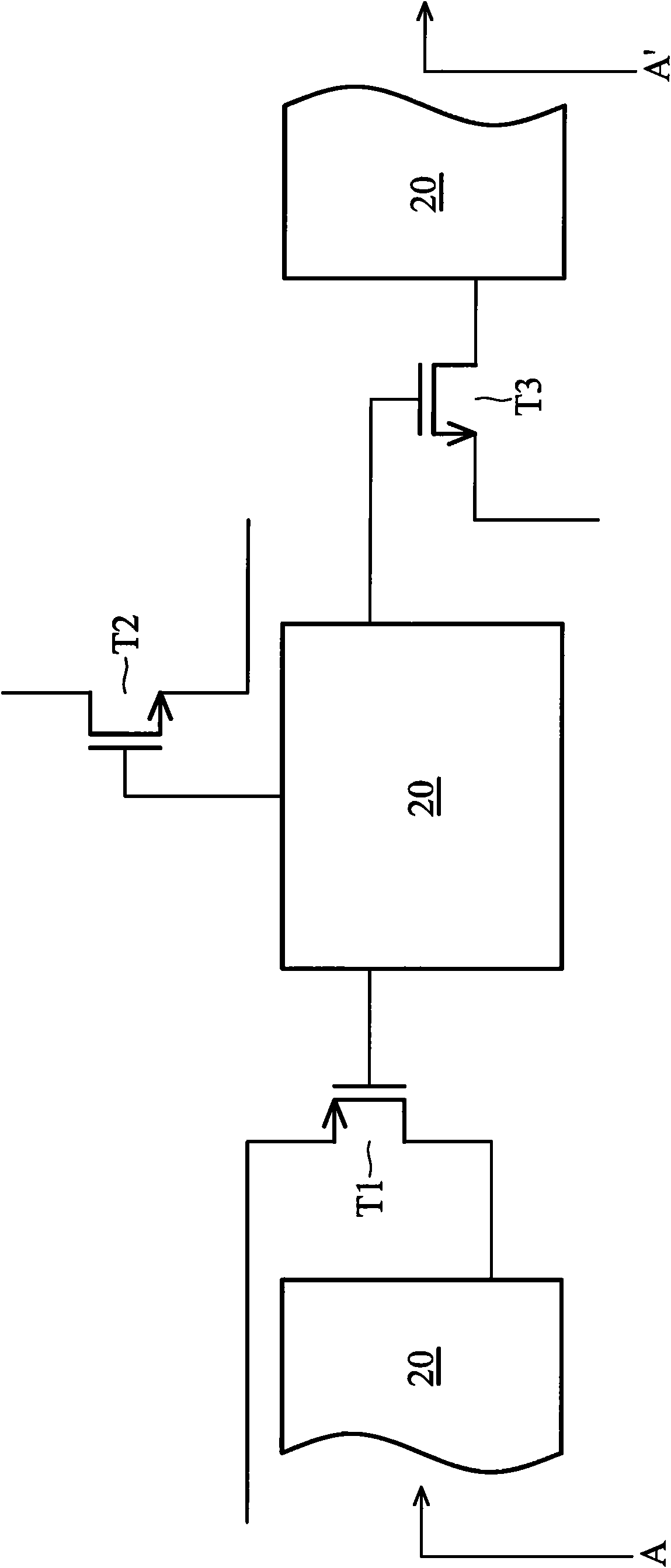

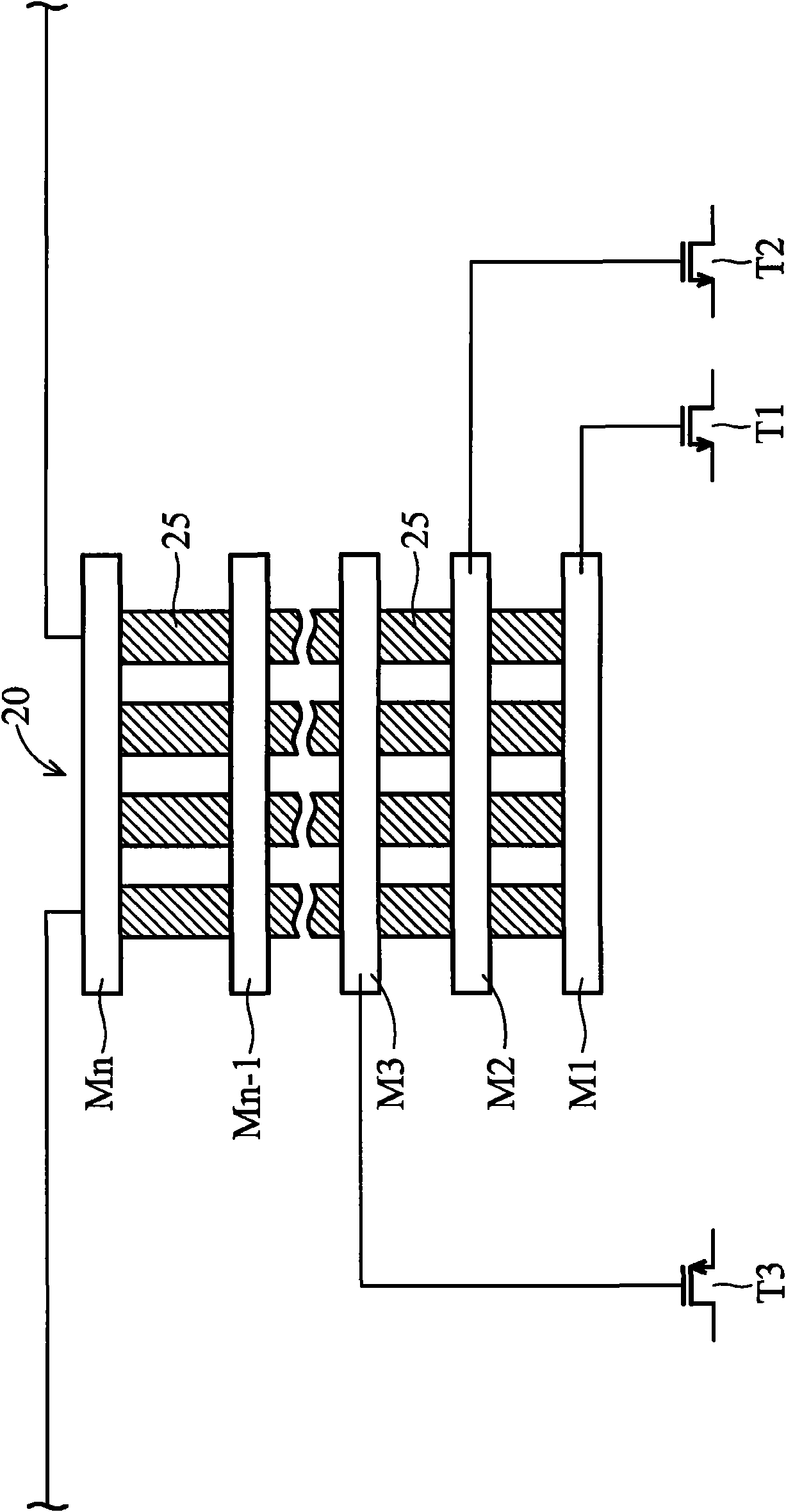

ActiveUS20150318273A1TransistorSemiconductor/solid-state device detailsAntenna effectElectrical conductor

An antenna effect discharge circuit is described for a device having patterned conductor layers, which may be exposed to charge inducing environments during a manufacturing process. The antenna effect discharge circuit has a terminal that is connected to a node on the device to be protected from charge accumulation and a gate, such as the gate of a field effect transistor in the circuit, and a terminal through which accumulated charge can be discharged to the substrate. A capacitor couples the gate in the antenna effect discharge circuit to the substrate. A voltage supply circuit is configured to provide voltage sufficient to bias the antenna effect discharge circuit in an off condition during operation of the device. A patterned conductor in the upper layer, and preferably the uppermost layer, of the device links the gate in the antenna effect discharge circuit to the voltage supply circuit.

Owner:MACRONIX INT CO LTD

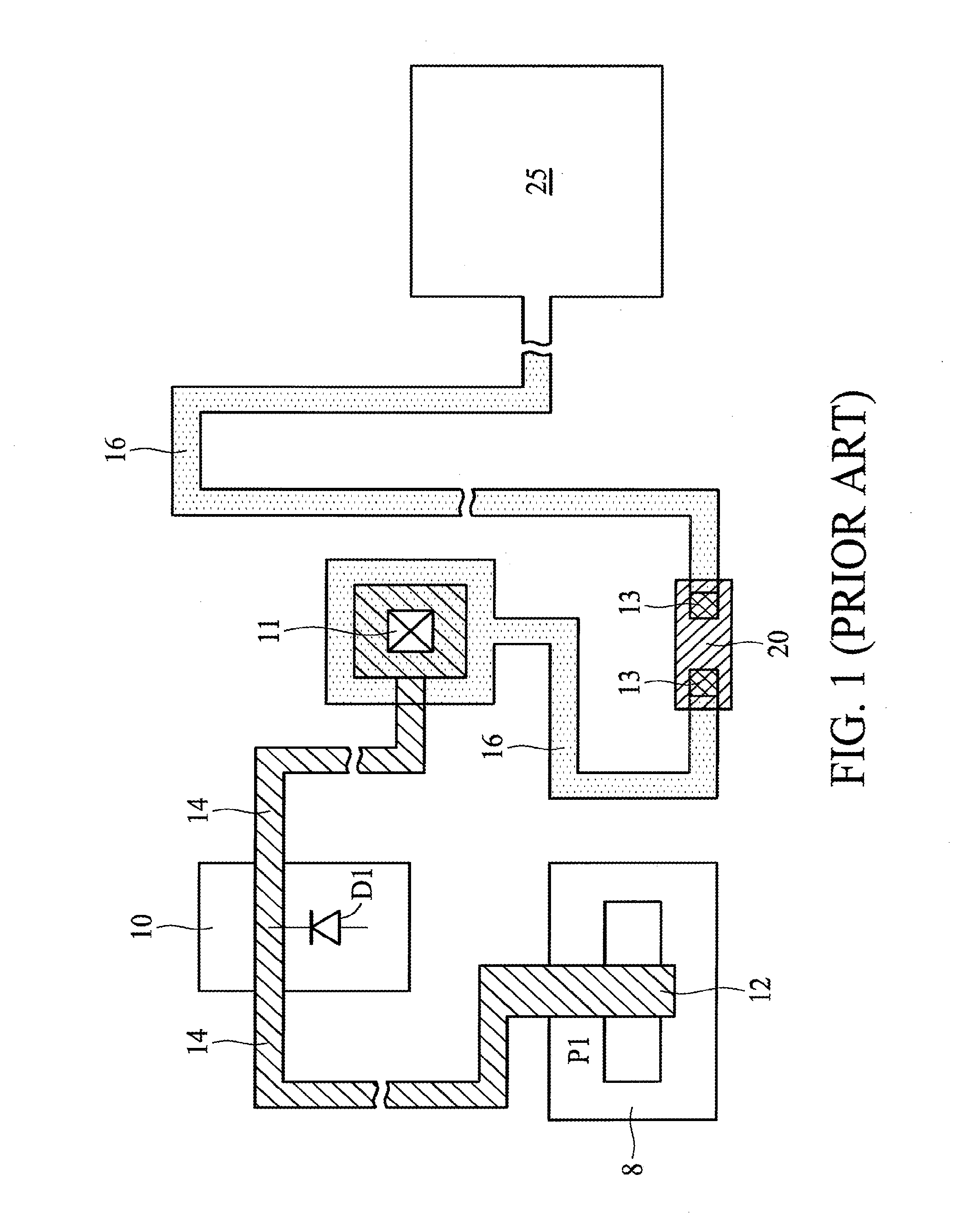

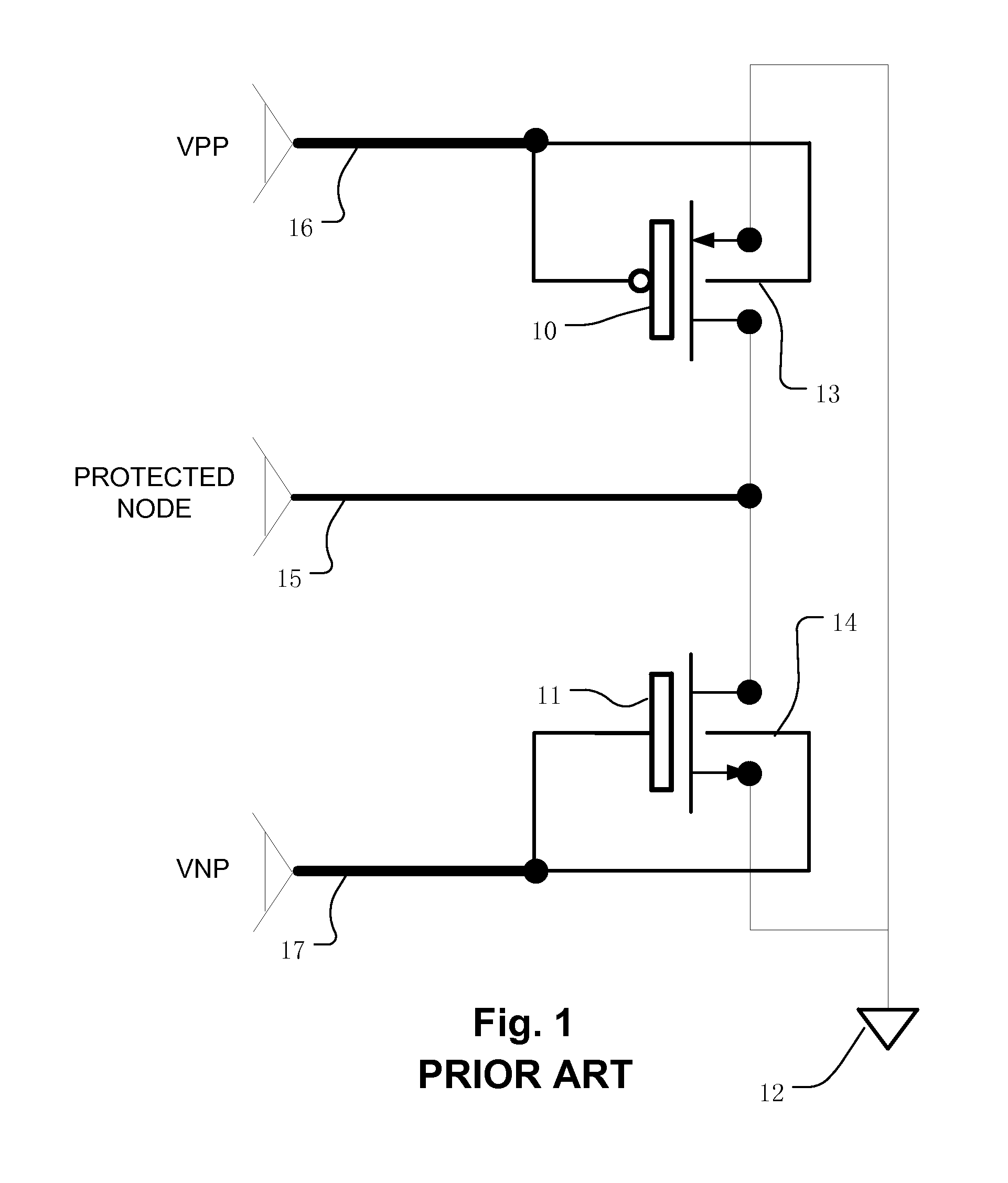

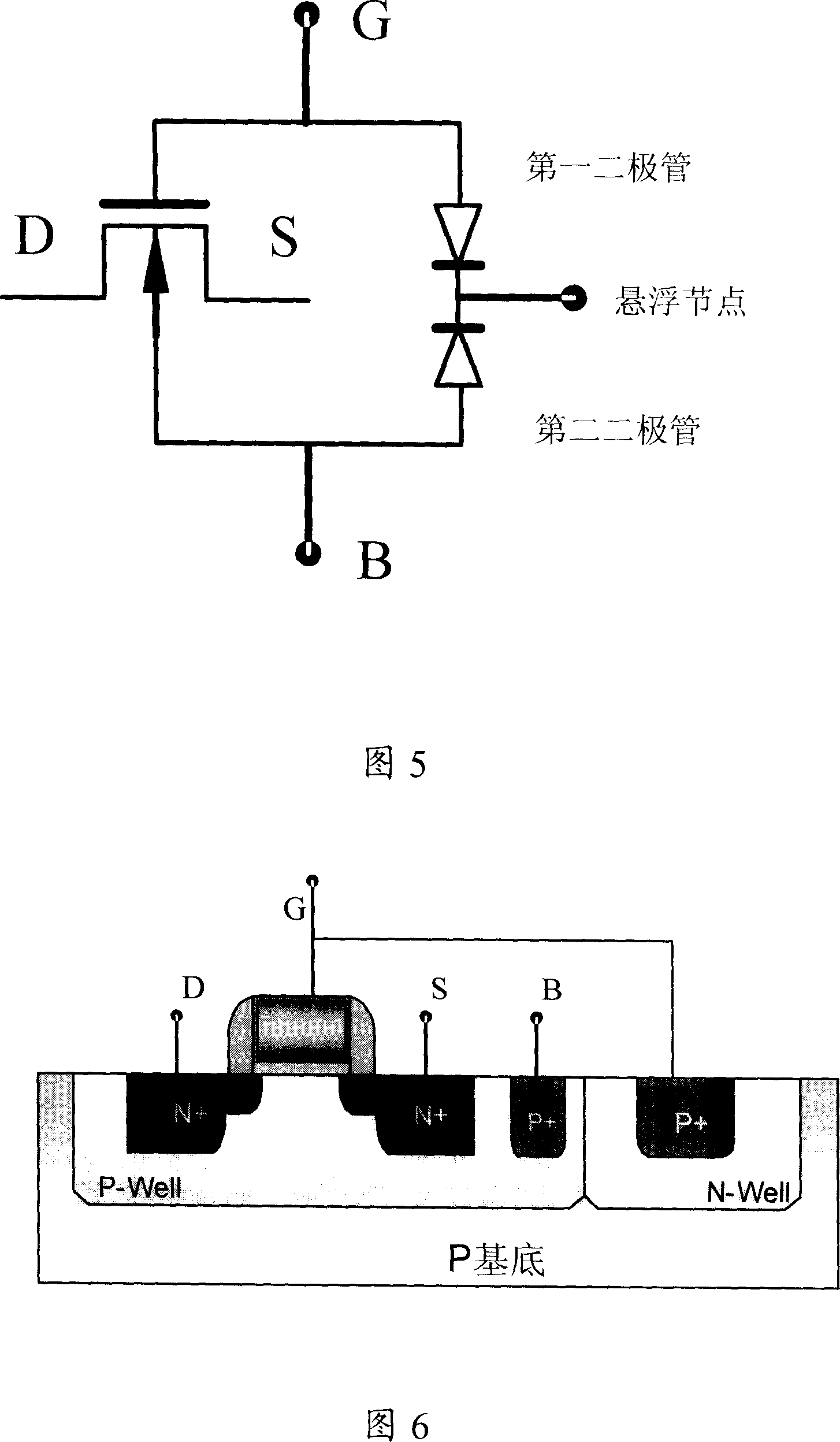

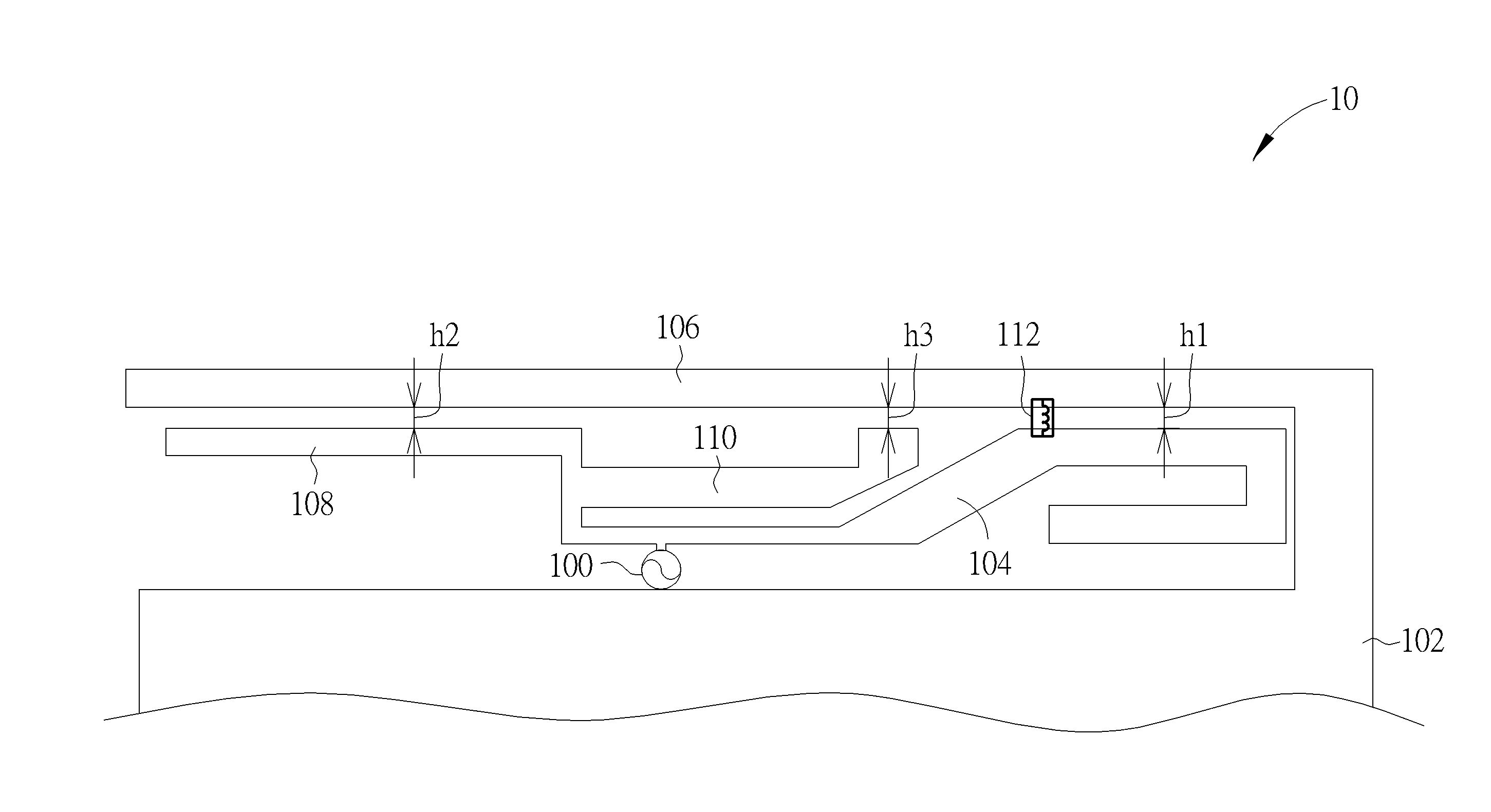

Proctive circuit of metal-oxide-semiconductor transistor and its producing method

ActiveCN101083264APrevent openingPrevents antenna effectsSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETAntenna effect

The invention is a MOS field effect transistor (MOSFET) protective circuit, comprising NMOS tube and two protective diodes, where the anodes of the two diodes are connected with grid of the NMOS tube and with a substrate, respectively, and their cathodes are interconnected with each other. And it can protect MOS from being influenced by antenna effect and besides, assure the current-voltage characteristic of MOS tube is completely measured.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Broadband Antenna

ActiveUS20150200456A1Increase antenna bandwidthReduce antenna sizeSimultaneous aerial operationsElongated active element feedElectricityAntenna effect

A broadband antenna for a wireless communication device includes a grounding unit for grounding; a first radiating element; a second radiating element electrically connected to the grounding unit; a signal feed-in element for transmitting a radio signal to the first radiating element in order to emit the radio signal via the first radiating element; and a passive component comprising an inductor, where the passive component is electrically connected between the first and the second radiating elements to work in conjunction with the first radiating element, the second radiating element and the grounding unit to form a loop antenna effect.

Owner:WISTRON NEWEB

Method for fabricating a non-volatile memory and metal interconnect process

ActiveUS6881619B1Prevent wide threshold voltage distributionReduce antenna effectSemiconductor/solid-state device manufacturingSemiconductor devicesAntenna effectMetal interconnect

A method for fabricating a non-volatile memory is provided. A stacked structure including a tunneling layer, a trapping layer, a barrier layer, and a control gate is formed on a substrate. A source region and a drain region are formed beside the stacked structure in the substrate. A silicon oxide spacer is formed on the sidewalls of the stacked structure. An ultraviolet-resistant lining layer is formed on the surfaces of the substrate and the stacked structure to prevent the ultraviolet light from penetrating into the trapping layer. A dielectric layer is formed on the ultraviolet-resistant lining layer. A contact being electrically connected to the control gate is formed in the dielectric layer. A conducting line electrically connected to the contact is formed on the dielectric layer. A lost-surface-charge lining layer is formed on the surfaces of the dielectric layer and the conducting line to reduce the antenna effect.

Owner:MACRONIX INT CO LTD

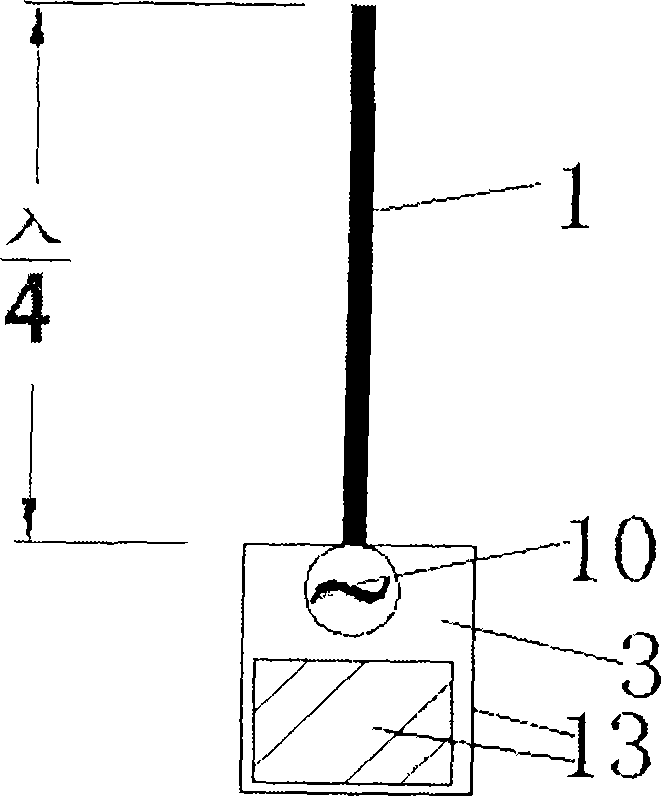

Antenna assembly construction for radio products

InactiveCN101453048AMiniaturizationSave spaceAntenna supports/mountingsElongated active element feedAntenna effectPush switch

The invention provides an antenna combination structure for a radio product, which relates to compact antenna structure technology for a portable radio product. The antenna combination structure comprises a circuit board, a button switch arranged on the circuit board, and an antenna, wherein the antenna is connected with a circuit signal end on the circuit board, and is divided into three sections, namely L1, L2 and L3, from the joint of the circuit signal end and the antenna to the tail end of the antenna in sequence; the L1 is a connecting section for connecting the circuit signal end on the circuit board and the L2; the sum of the L1, the L2 and the L3, namely the total length of the antenna is between 0.2 and 0.3 lambda; the sum of the L2 and the L3 is 0.16 lambda; the length of the L2 of the antenna is equal to that of the L3; and the L1, the L2 and the L3 are bounded at the edge of the circuit board and are arranged on the periphery of the button switch. The antenna combination structure has the advantages that space of the circuit board and space of the button on the circuit board are sufficiently utilized so as to achieve the aim of space conservation, excellent antenna effect and antenna micromation.

Owner:李伟业

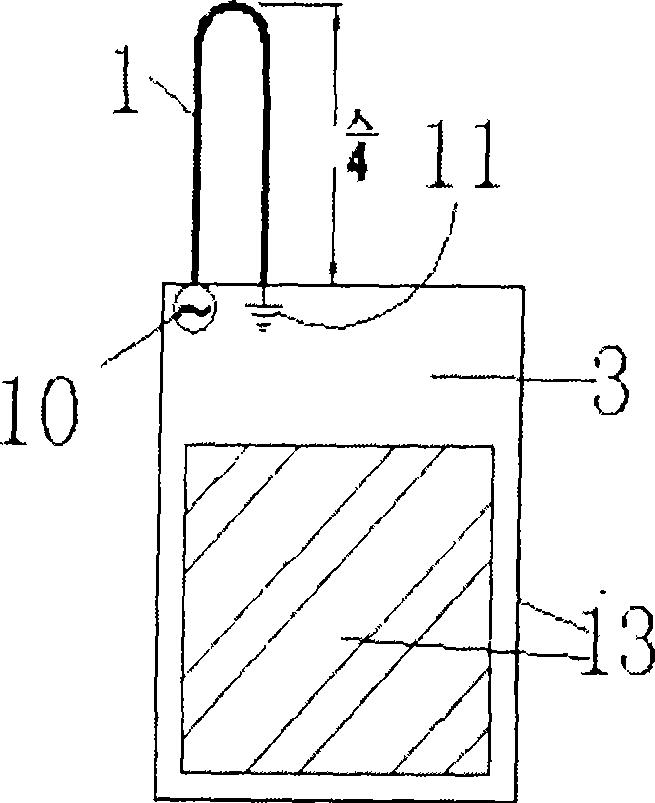

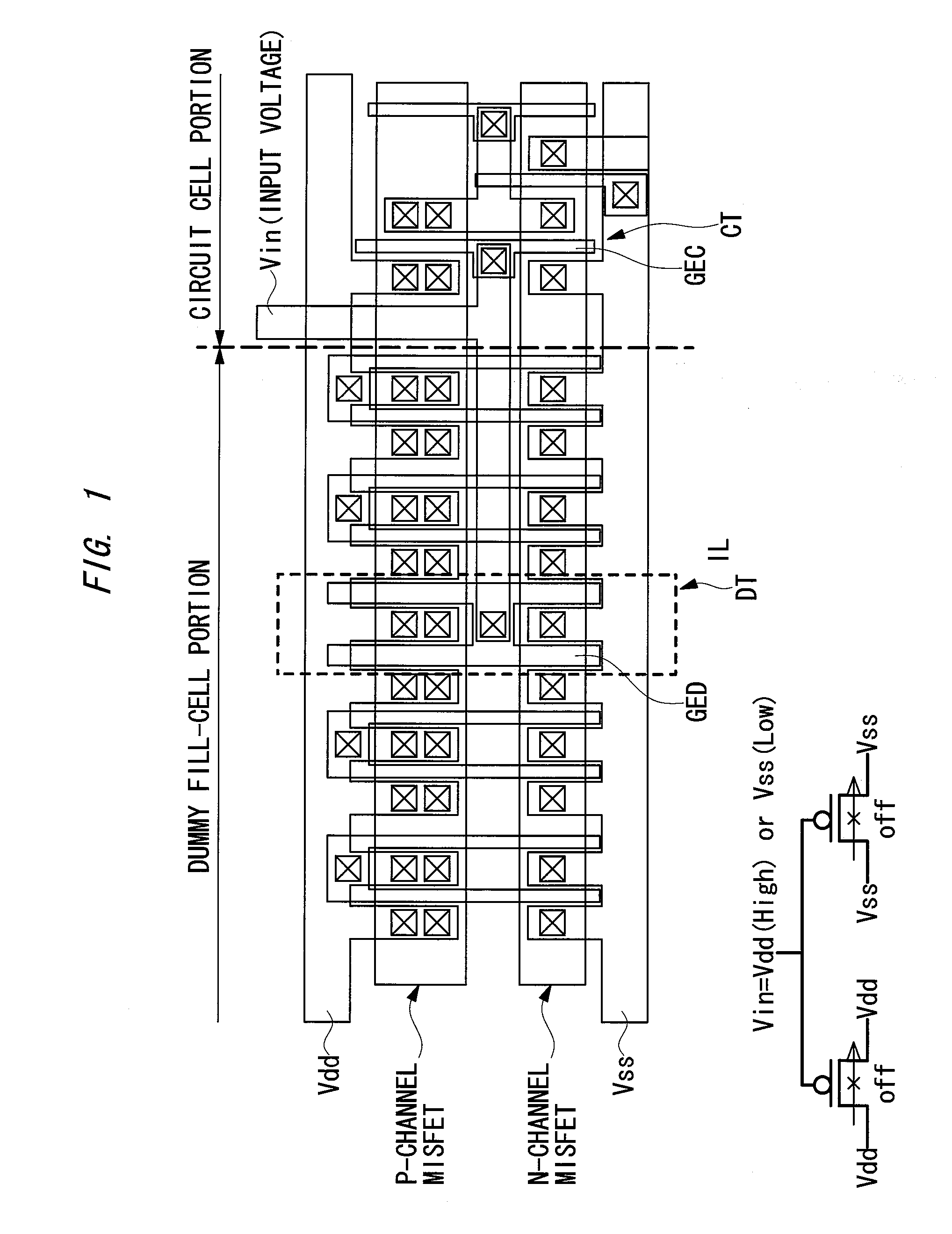

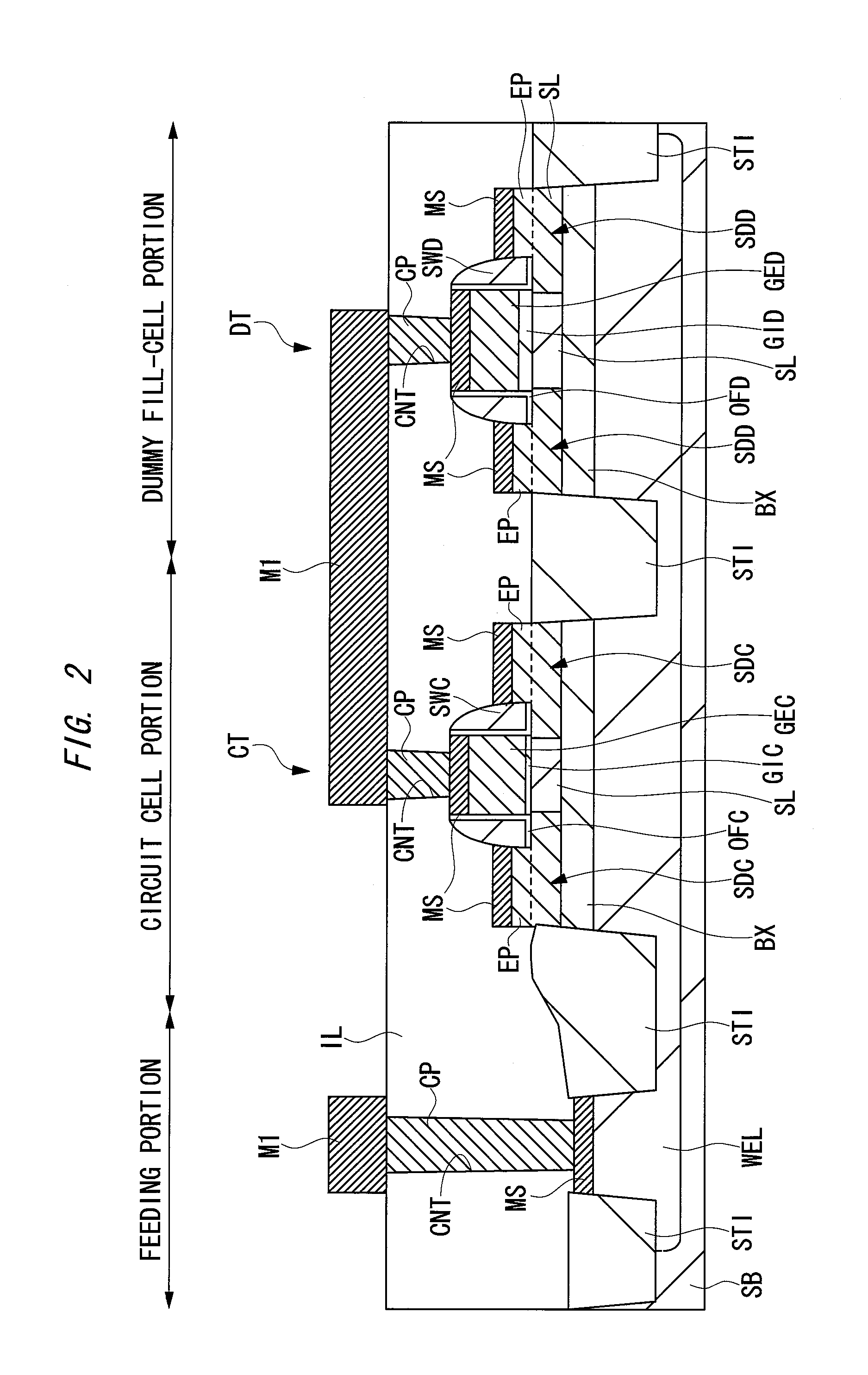

Semiconductor device and manufacturing method for the same

InactiveUS20160013207A1Reduce antenna effectEliminate the effects ofSolid-state devicesSemiconductor/solid-state device manufacturingPower semiconductor deviceCapacitance

A semiconductor device including an SOI substrate reduces a gate leak current of an anti-antenna-effect dummy fill-cell and suppresses an antenna effect. The thickness of a gate insulating film of the anti-antenna-effect dummy fill-cell is determined to be large than that of a gate insulating film of an SOI transistor. This reduces the gate leak current of the anti-antenna-effect dummy fill-cell. The gate area (gate length×gate width) of the anti-antenna-effect dummy fill-cell is determined to be large than that (gate length×gate width) of the SOI transistor. This makes the gate capacity of the anti-antenna-effect dummy fill-cell almost equal to that of SOI transistor, thereby suppressing the antenna effect.

Owner:RENESAS ELECTRONICS CORP

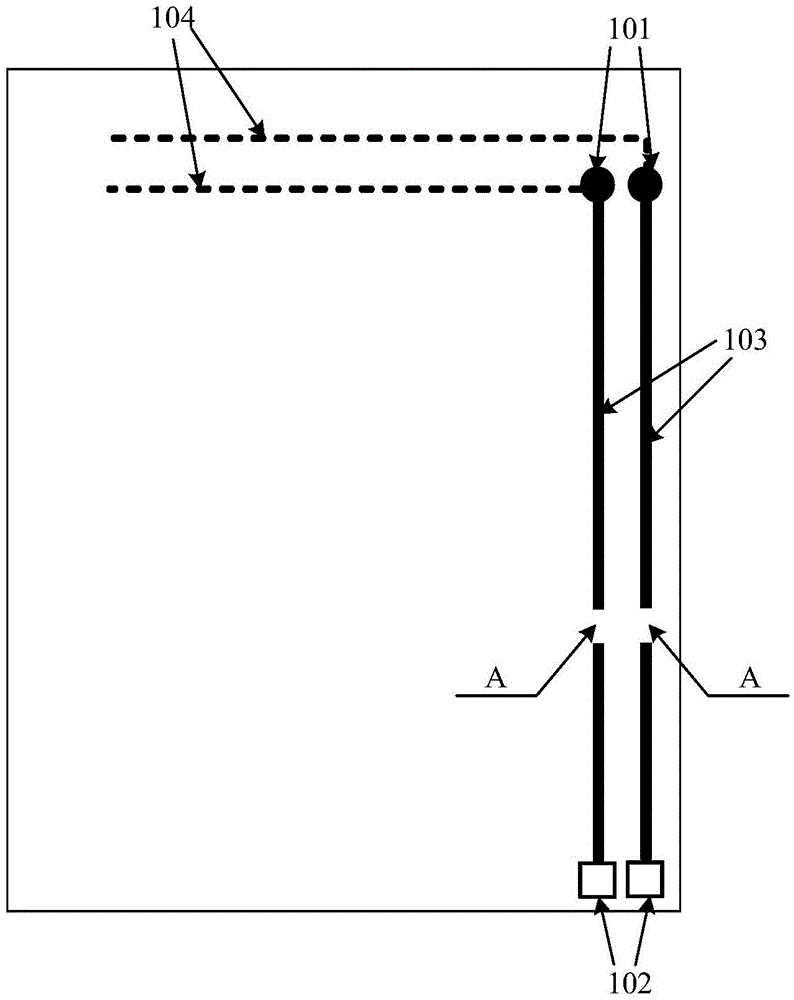

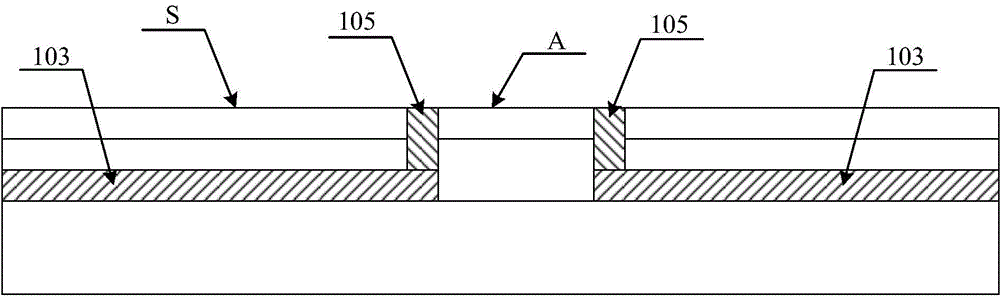

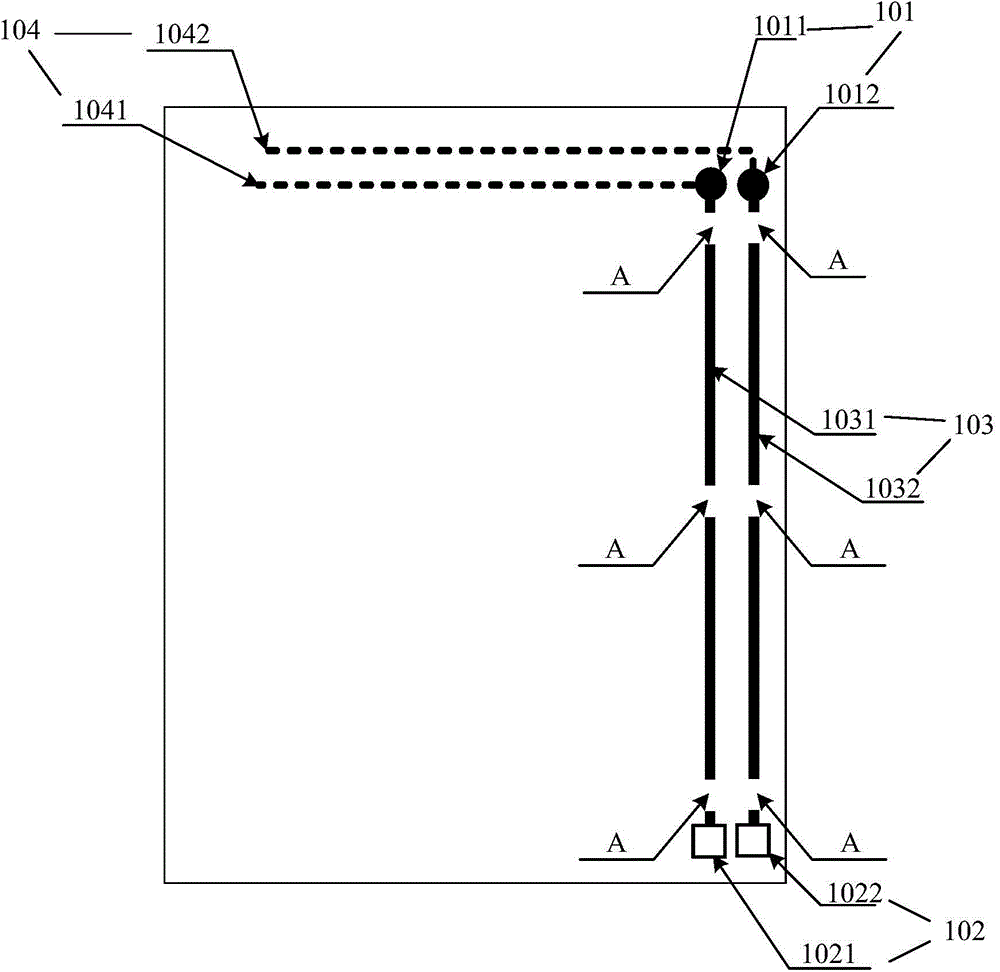

Array substrate, manufacture method for array substrate and display device

ActiveCN104701327AReduce antenna effectSolve problems that damage working circuitsSemiconductor/solid-state device testing/measurementSolid-state devicesAntenna effectDisplay device

The invention discloses an array substrate, a manufacture method for an array substrate and a display device and relates to the display technical field. The array substrate comprises a test circuit connected with a work circuit interface and a test interface; the test circuit comprises at least one cut-off point, two ends of each cut-off point on the test circuit are respectively provided with a conductive contact running through the upper surface of the array substrate; while performing the test to the work circuit, the conductive contacts at two ends of all cut-off points are switched on for having breakover for the test circuit. At least one cut-off point is formed on the test circuit during the forming process of the test circuit, and the sub test circuit cut from the cut-off point is not long, so that the antenna effect caused by longer test circuit is reduced, and the problem that the work circuit is damaged by the charge collected by the slender test circuit for the antenna effect of the related technology can be solved; the work circuit is not damaged by the test circuit due to the antenna effect.

Owner:BOE TECH GRP CO LTD +1

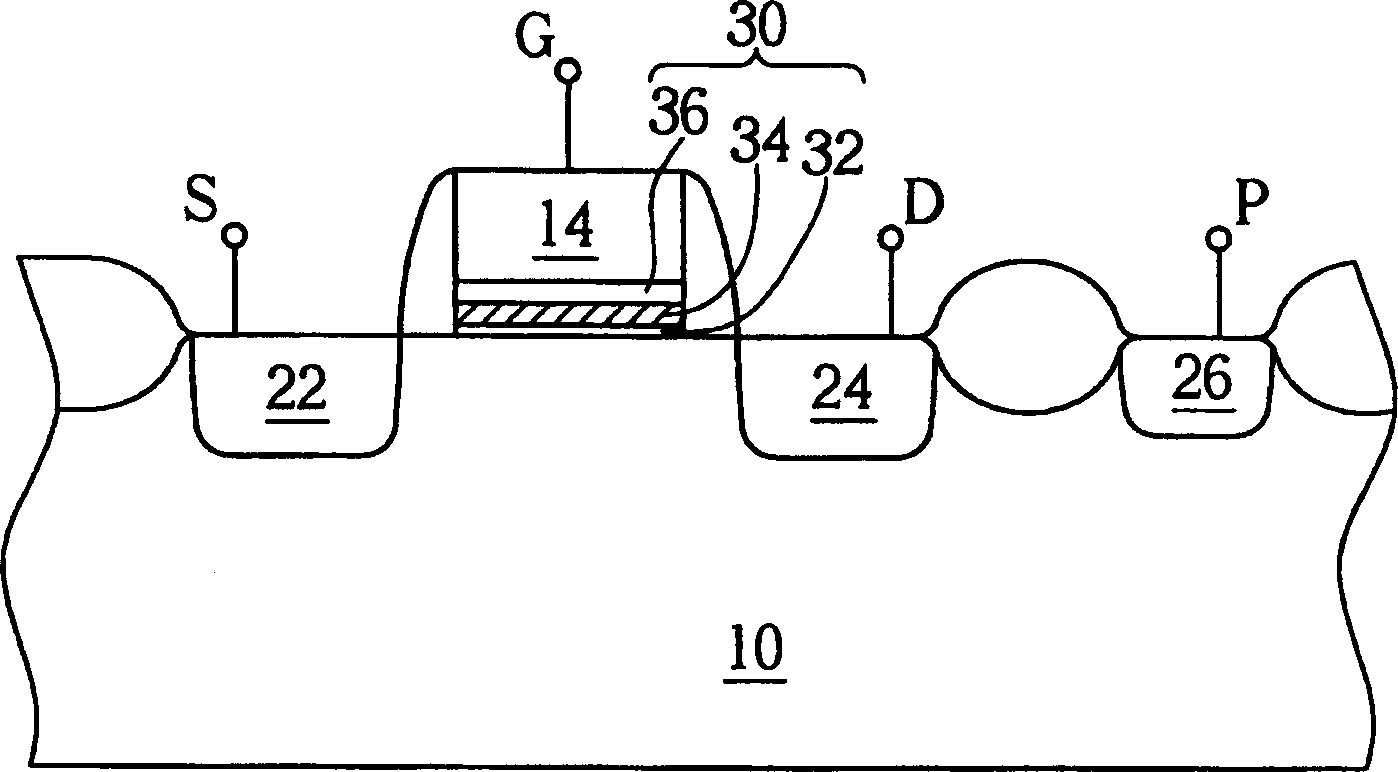

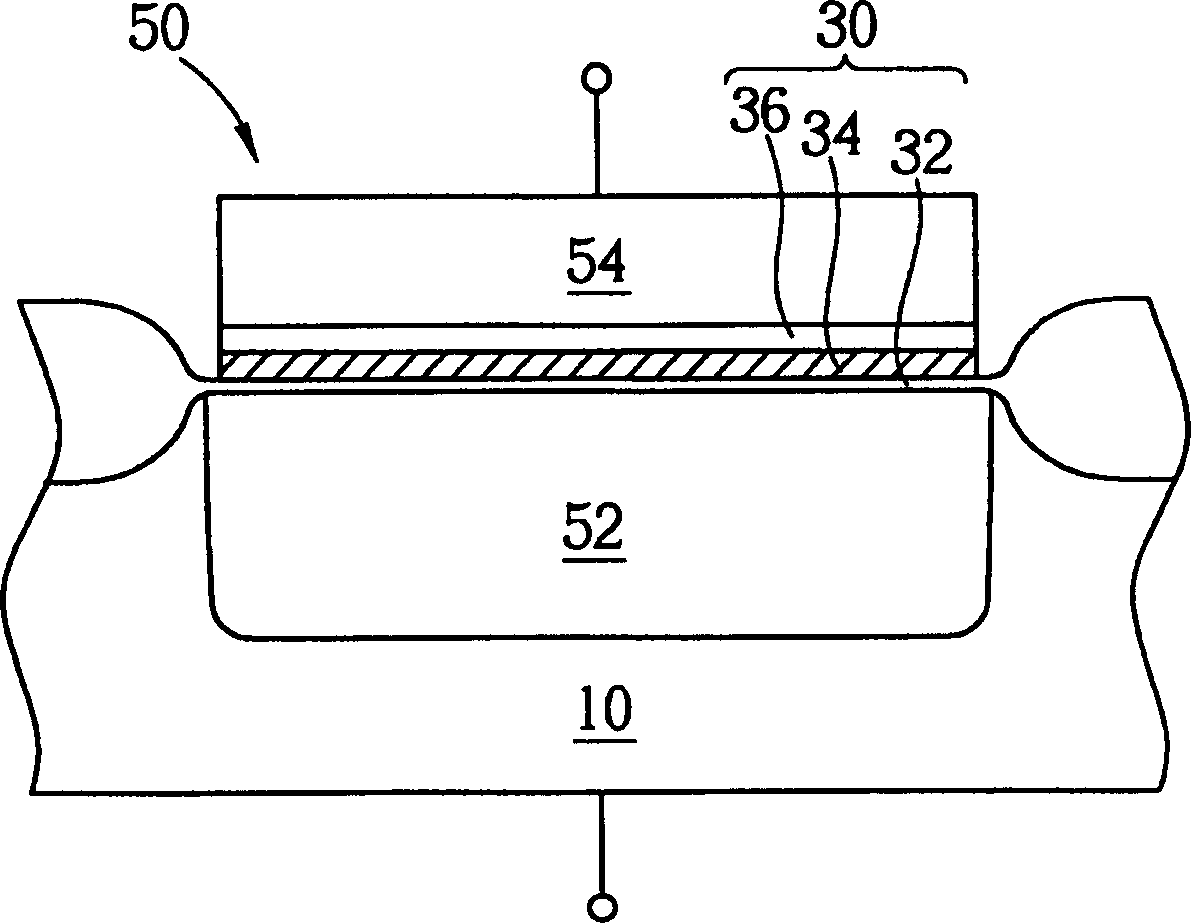

Chip pad resistant to antenna effect and method

InactiveUS8148797B2Semiconductor/solid-state device detailsSolid-state devicesAntenna effectAntenna design

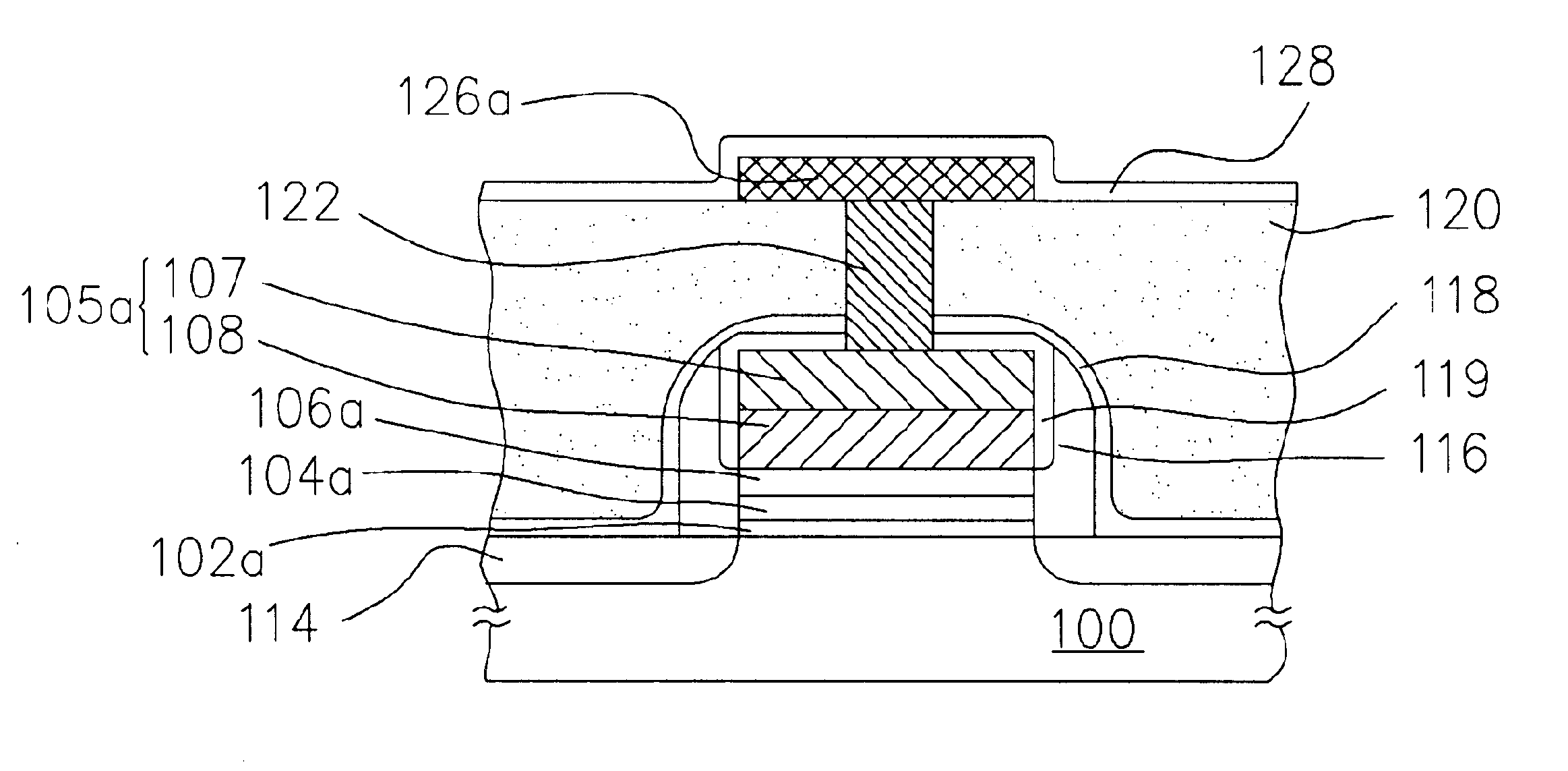

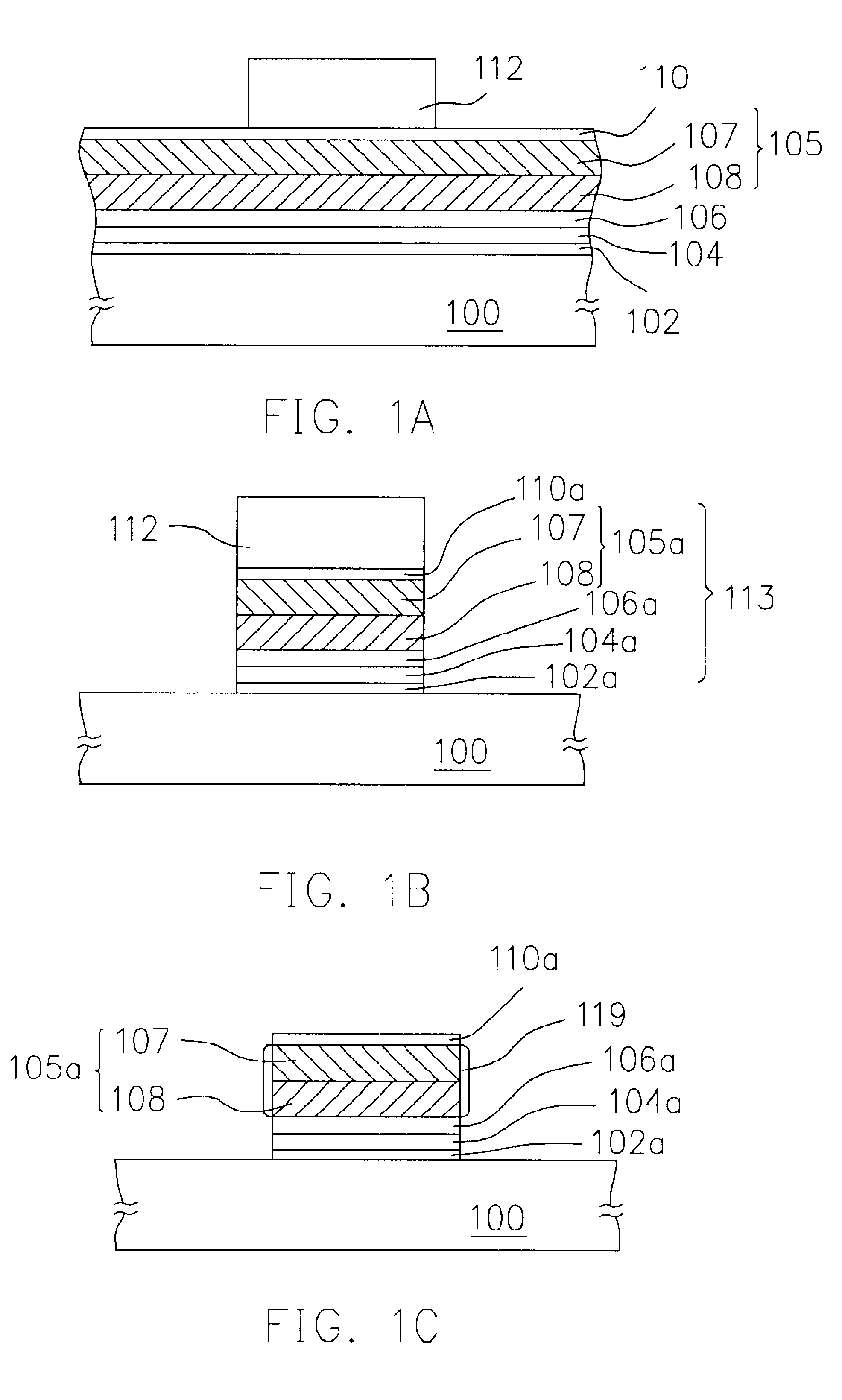

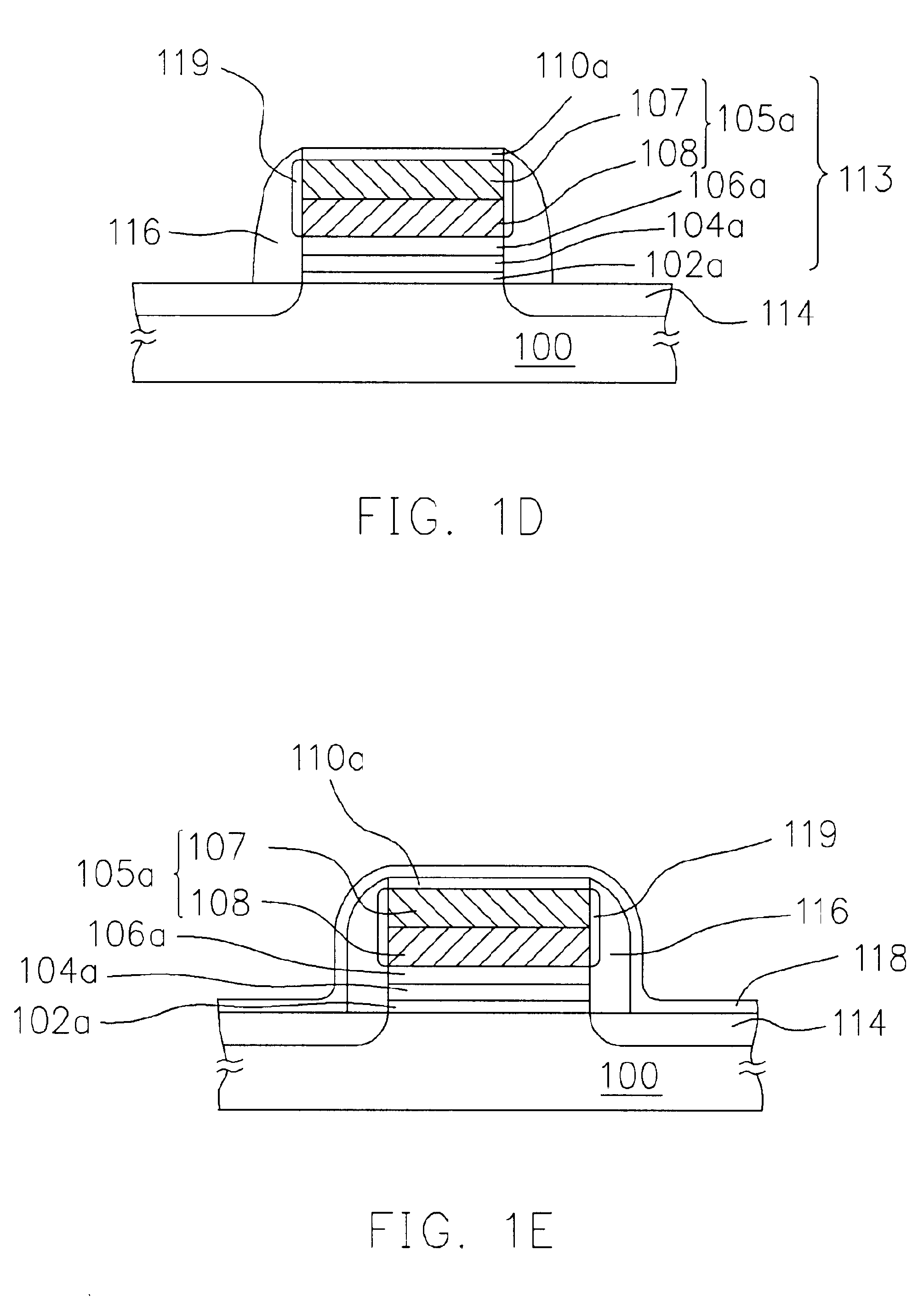

A chip pad structure of an integrated circuit (IC) and the method of forming are disclosed. The chip pad comprises a main pad portion and a ring pad portion. During a charging process involved in forming the chip pad structure, electrical connections from the gate electrodes of MOS transistors in the IC substrate generally are made only to the ring pad portion that has an antenna-to-gate area ratio substantially below a predetermined antenna design rule ratio, and thus is resistant or immune to antenna effect. The main pad portion and the ring pad portion are coupled together through metal bridges formed in an upper interconnect metal layer or in the top conductive pad layer. The chip pad may be used as probe pads on a parametric testline or bonding pads on an IC.

Owner:TAIWAN SEMICON MFG CO LTD

Semiconductor integrated circuit device

InactiveUS20070262350A1Discharge path can be readilyPromote generationSolid-state devicesSemiconductor/solid-state device manufacturingAntenna effectSemiconductor

Semiconductor integrated circuit device wherein action for averting antenna effect has been taken, and method for producing a semiconductor integrated circuit device in which action for averting the antenna effect can be taken with ease. The method for producing a semiconductor integrated circuit device includes forming step of forming a semiconductor region of first conductivity type, a first diffusion region of the first conductivity type, formed in the semiconductor region of the first conductivity type, a gate insulating film formed in the semiconductor region of the first conductivity type, gate electrode on the gate insulating film and a wiring layer electrically connected to the gate electrode. The method also includes an investigating step of investigating, following the forming step, into whether or not it is necessary to take an action for averting an antenna effect in the wiring layer. The method also includes an action-taking step of replacing the first diffusion region of the first conductivity type by a second diffusion region of a second conductivity type, in case it is verified in the investigating step that it is necessary to take an action against the antenna effect. The second diffusion region of the second conductivity type forms a pn junction with the semiconductor region of the first conductivity type. The action-taking step also electrically connects the second region of the second conductivity type to the wiring layer.

Owner:ELPIDA MEMORY INC

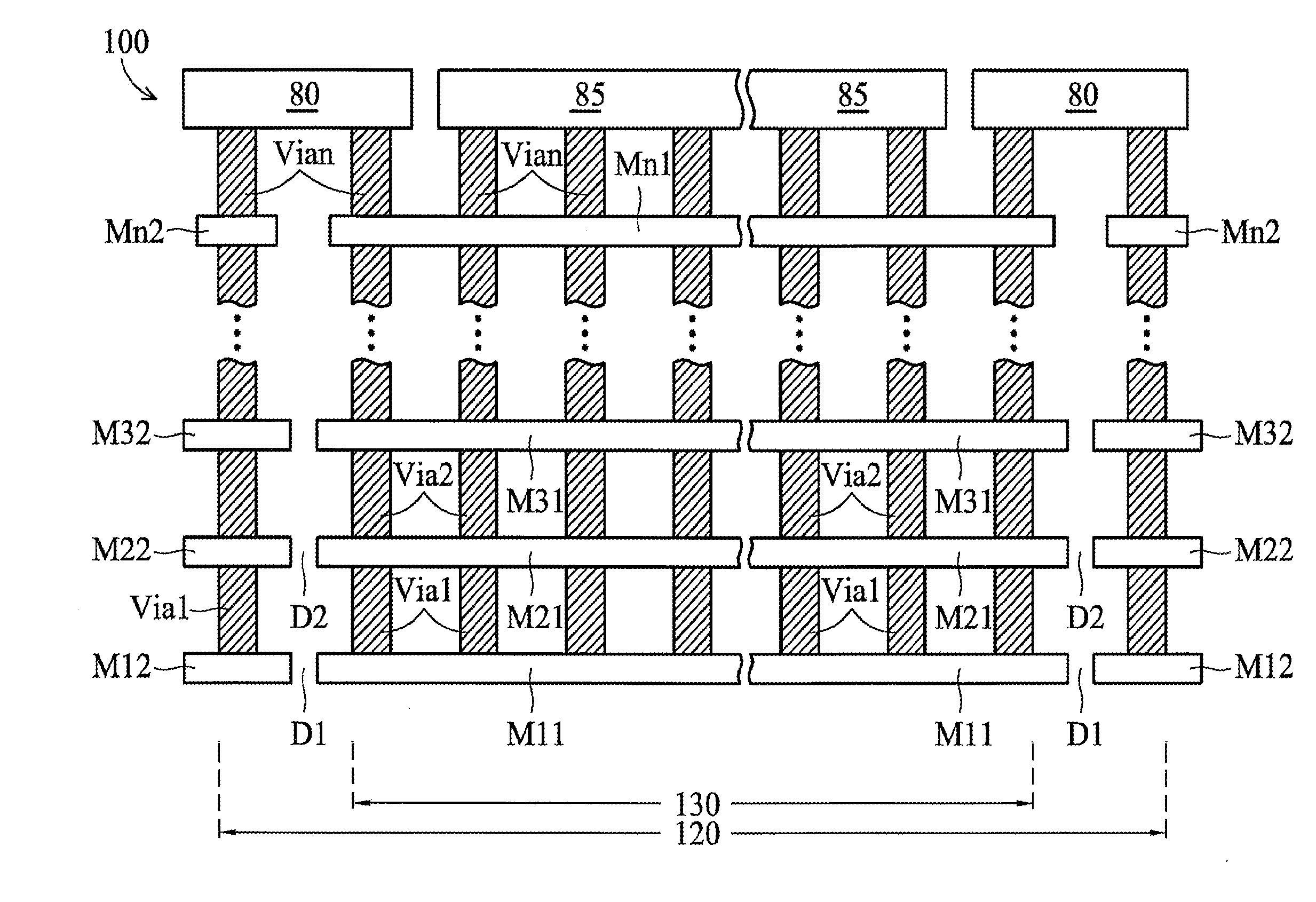

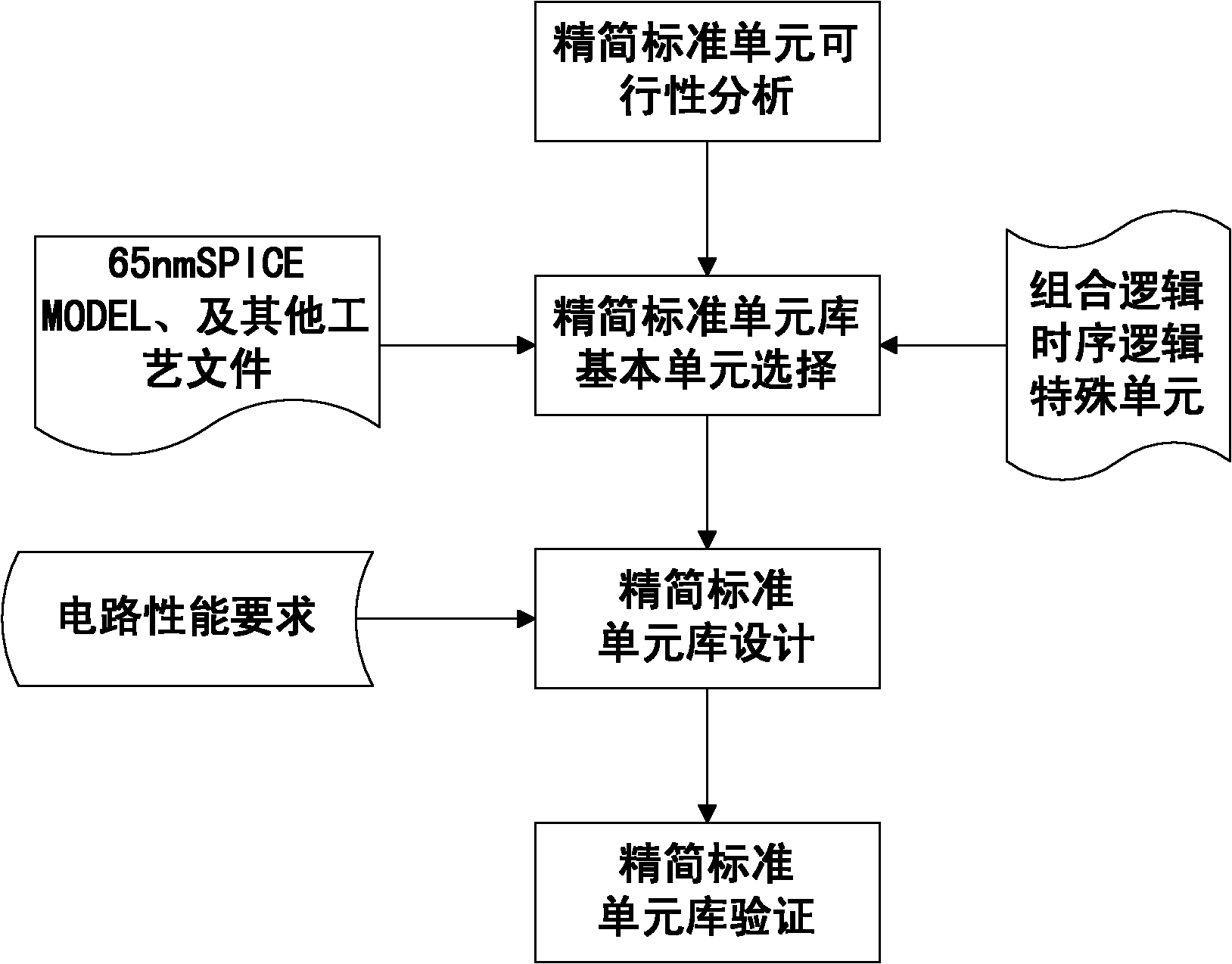

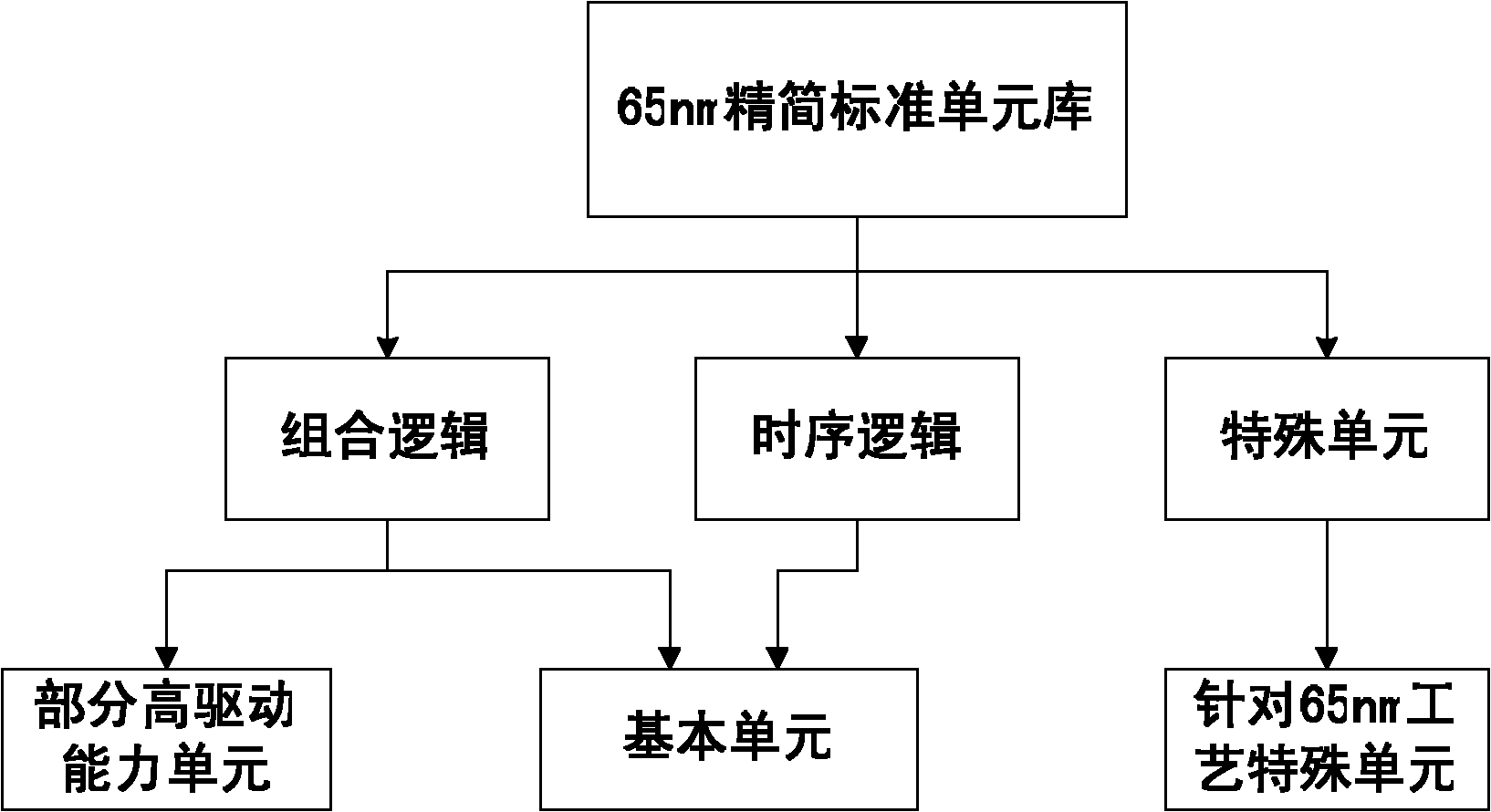

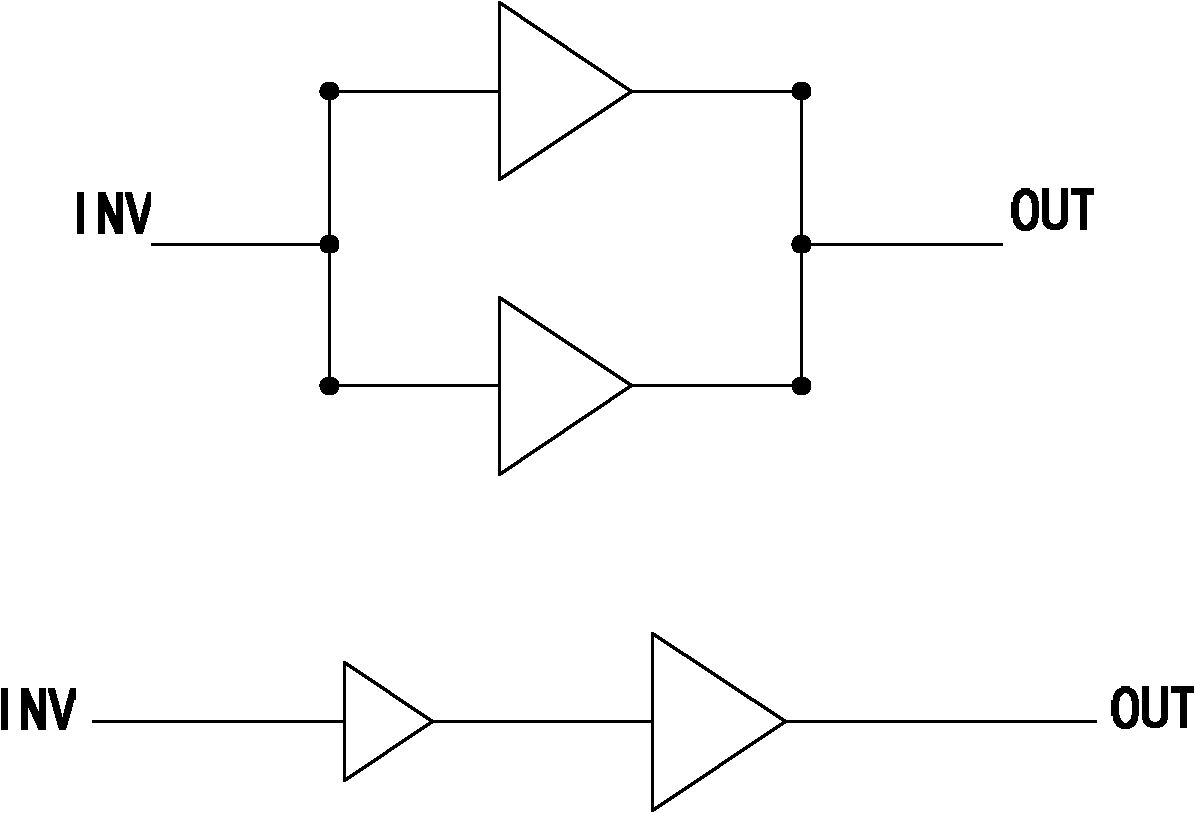

A Method for Optimizing a Compact Standard Cell Library

ActiveCN102279899AReduce the numberImprove manufacturabilitySpecial data processing applicationsAntenna effectCapacitance

The invention discloses a method for optimizing a simplified standard unit library. The method comprises the following steps of: selecting a basic unit for realizing a needed circuit function, wherein the basic unit at least comprises a phase inverter, a buffer, a basic gate unit, a mixed gate unit, an operation unit and a time sequence unit; arranging a delay unit, a pull-up / pull-down unit, a filling unit, a capacitance filling unit, a substrate link and an antenna effect restraining unit in the simplified standard unit library; selecting a multi-input logic by adopting a logical decomposition mode; and realizing a multi-driving capability by adopting a driving decomposition mode. In the method, the performance and the realizing complexity of a circuit are compromised, the quantity of domain pattern shapes is reduced, friendly photolithography is facilitated, the resolution is increased, the manufacturability and realizing efficiency of the circuit are improved, and the performance of the circuit is ensured to a certain degree.

Owner:WUXI ZHONGKE MICROELECTRONICS IND TECH RES INST

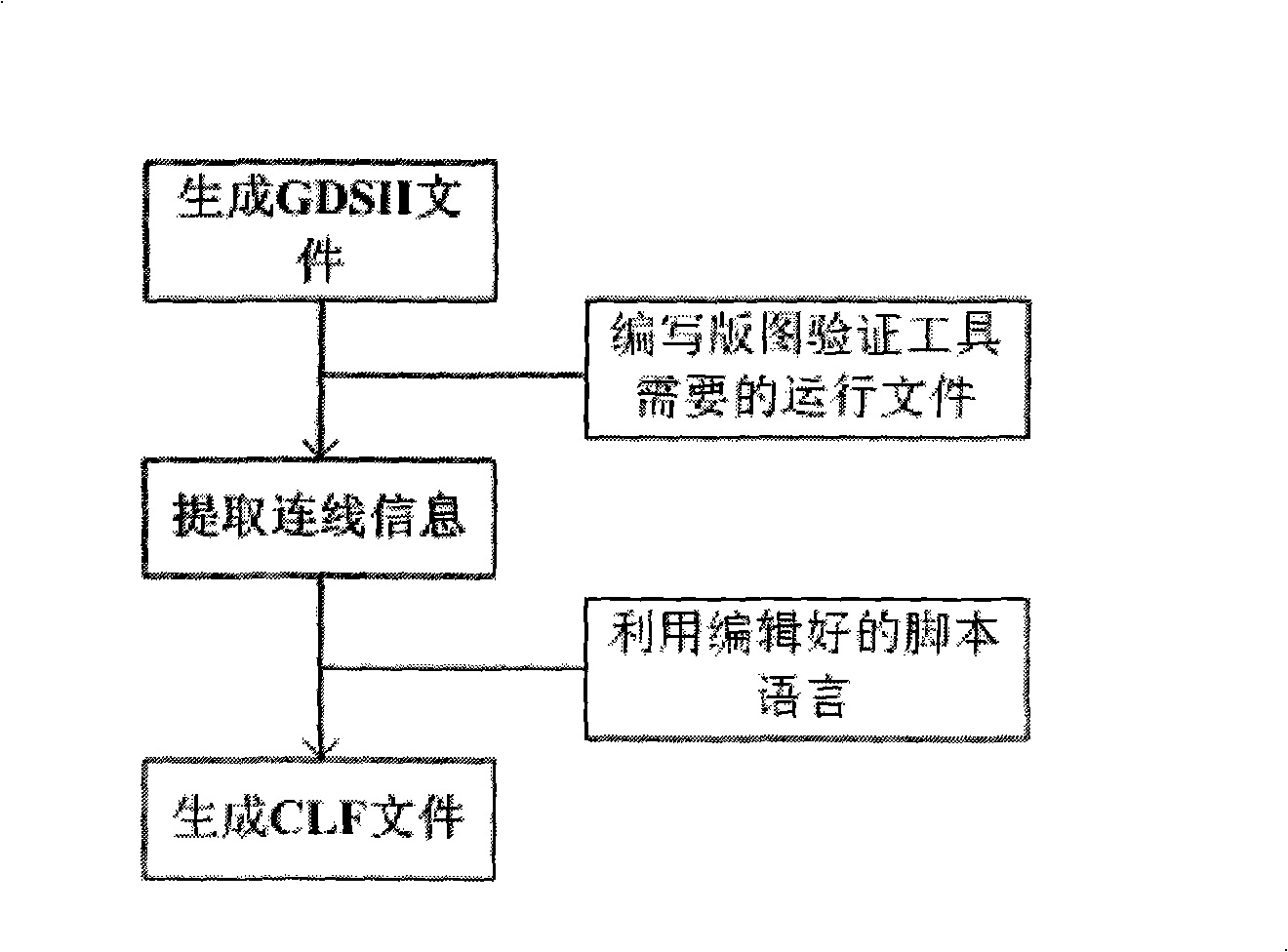

Method for creating file containing aerial effect information

InactiveCN101339578AQuick buildShorten the timeSpecial data processing applicationsScripting languageAntenna effect

The invention discloses a method for generating files containing the antenna effect information, which is characterized in that: at first, a GDSII file is generated from a layout; then the GDSII file is operated by a layout verification tool to generate files containing the information of connecting lines; at last, the information of the connecting lines in the files which contain the information of the connecting lines is written into a CLF file. By using the layout verification tool and script language, the method provided by the invention can directly extract the CLF file with a simple process of realization, thus greatly saving time of editing engineers of integrated circuit layouts and saving cost on the design of the integrated circuit layouts; the method can also generate needed CLF files rapidly with respect to varied locating and wiring tools, thus providing great convenience for entering varied locating and wiring tools needed by the same IP; for integrated circuit layouts of varied projects, an operation file and a script program file complied last time can be adopted, thus reducing time of editing engineers of integrated circuit layouts to the minimal during the process of generation of the CLF files.

Owner:IPGOAL MICROELECTRONICS (SICHUAN) CO LTD

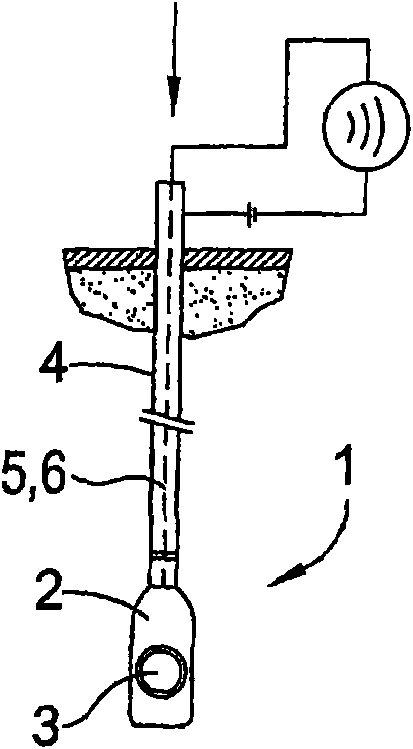

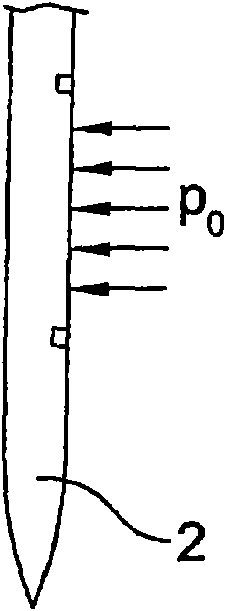

Joint probe and corresponding seismic module used for measuring static and dynamic properties of soil

The invention relates to a joint probe and a corresponding seismic module used for measuring static and dynamic properties of soil. The joint probe comprises a dilatometer probe, a gas duct, a conducting wire and the seismic module, wherein the gas duct is connected with the dilatometer probe and is used for providing a gas connection between the dilatometer probe and an external gas source; the conducting wire is positioned in the gas duct and is used for providing an electric connection between the dilatometer and an external circuit; and the seismic module is connected to a conducting wire which is positioned in the gas duct and is used for providing an electric connection between the seismic module the external circuit. The joint probe solves the problems of a plurality of conducting wires and an antenna effect.

Owner:西尔瓦诺·马尔凯蒂

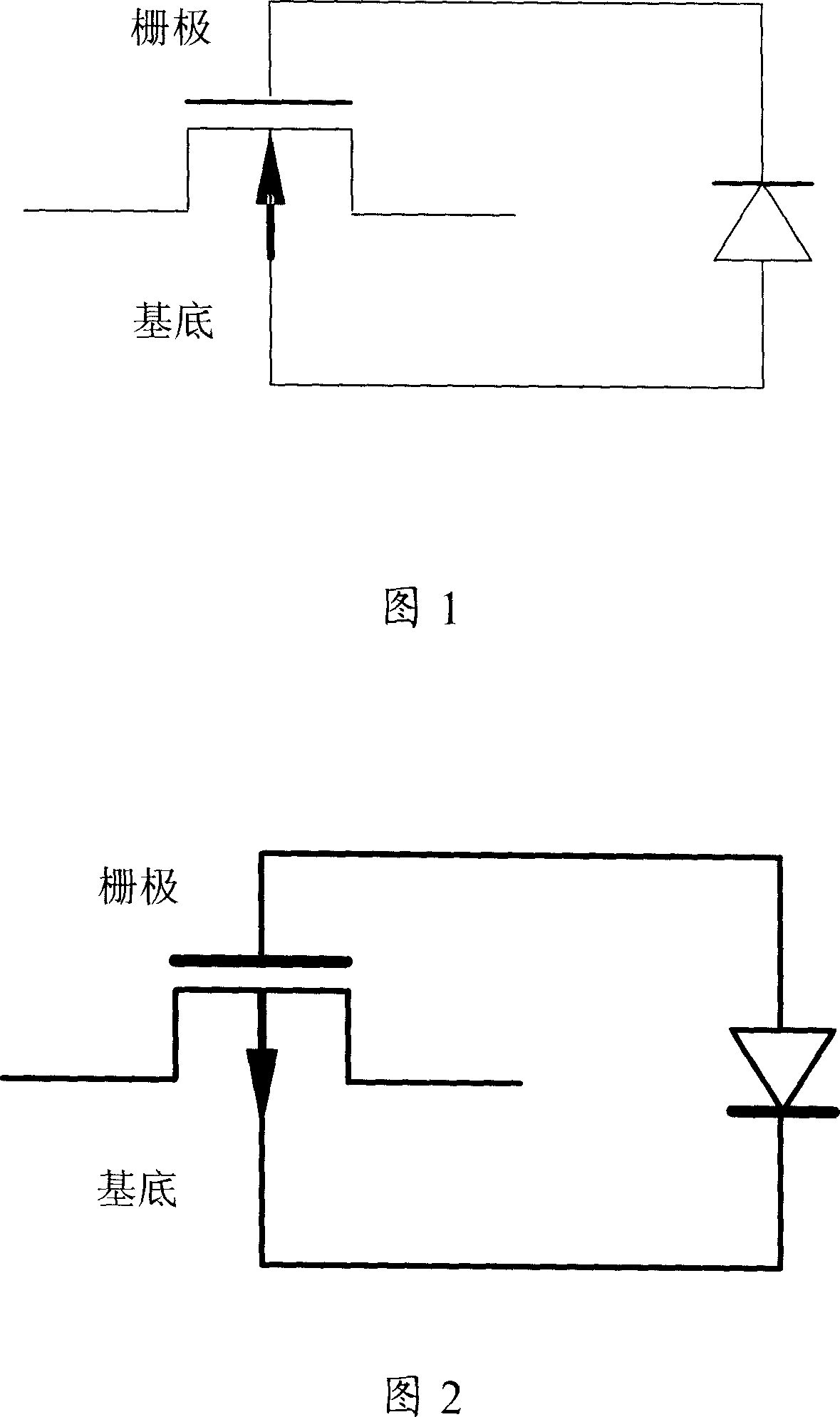

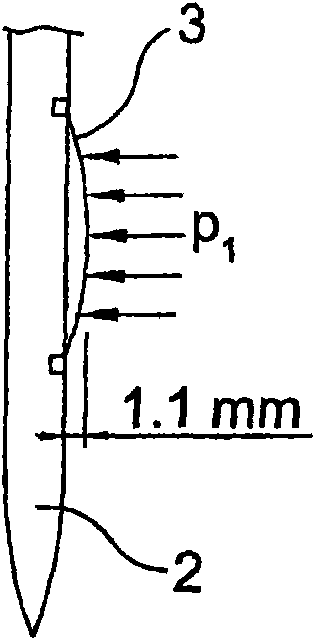

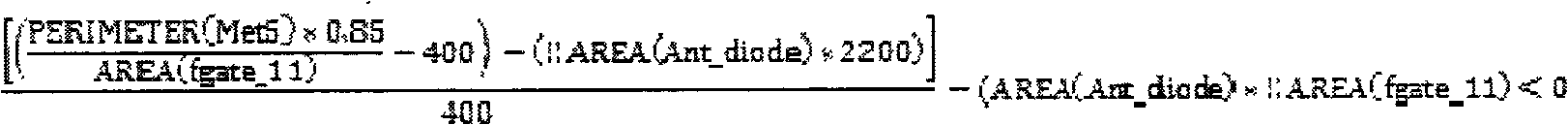

Method for solving antenna effect in chip design

InactiveCN102800667ASolve the problem of antenna effectReduce area consumptionSolid-state devicesSemiconductor devicesAntenna effectTransmission gate

The invention relates to a method and a circuit for solving the problem of antenna effect in a chip design. In some chip designs, an active shield physical protection design needs to be adopted for the purpose of preventing invasive attack to smart card chips. An active shielding layer has a defending effect on both attacks needing physical modification and those damaging partial functions of the chips. An active shielding line adopts a top layer metal and has a relatively long routing, and thus can cause severe antenna effect. When the traditional method of adding a diode is adopted, a relatively large chip area are usually occupied. The method provided by the method adopts a circuit with a transmission gate structure to solve the problem of antenna effect, and the circuit is simple in structure and easy to implement, and by using the method and the circuit, functions of the circuit are not affected.

Owner:BEIJING CEC HUADA ELECTRONIC DESIGN CO LTD

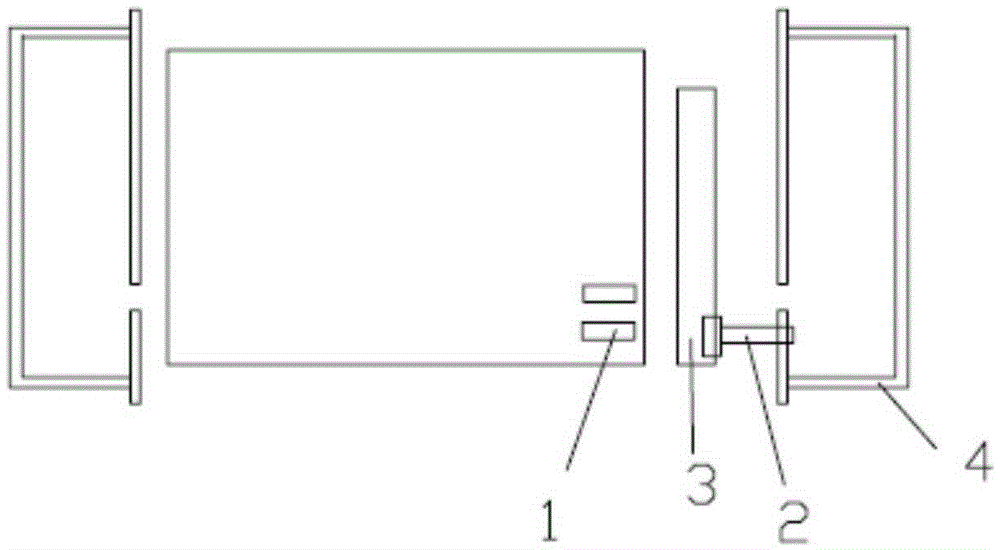

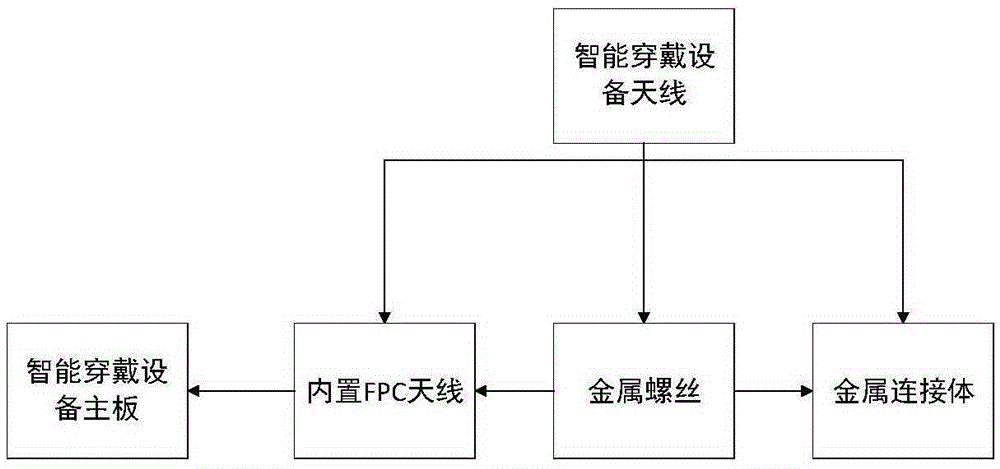

Intelligent wearable product antenna taking metal wearable product connector as main radiating body

InactiveCN105390799ABoost launchImprove reception performanceAntenna supports/mountingsAntenna adaptation in movable bodiesAntenna effectEngineering

The invention provides an intelligent wearable product antenna taking a metal wearable product connector as a main radiating body. The intelligent wearable product antenna comprises an outer shell, a FPC antenna, a metal screw and a watch buckle, wherein a main board is arranged inside the outer shell, and the main board is provided with a ground point and a feed point; the FPC antenna is assembled in the outer shell, and is connected with the feed point and services as a fine tuning part of the entire intelligent wearable product antenna; and the metal screw is connected with the FPC antenna; the watch buckle is arranged on the side edge of the outer shell, the watch buckle is provided with a metal connecting body, the metal screw is fixed in the metal connecting body, and the metal connecting body and the FPC antenna form a complete set of antenna to be connected with the main board. Therefore, the metal connecting body serves as an external antenna, increases efficiency as well as transmitting and receiving effects of the antenna, and reduces constrains and influence of the main board and environment on antenna effects.

Owner:SHENZHEN TIANDING MW TECH CO LTD

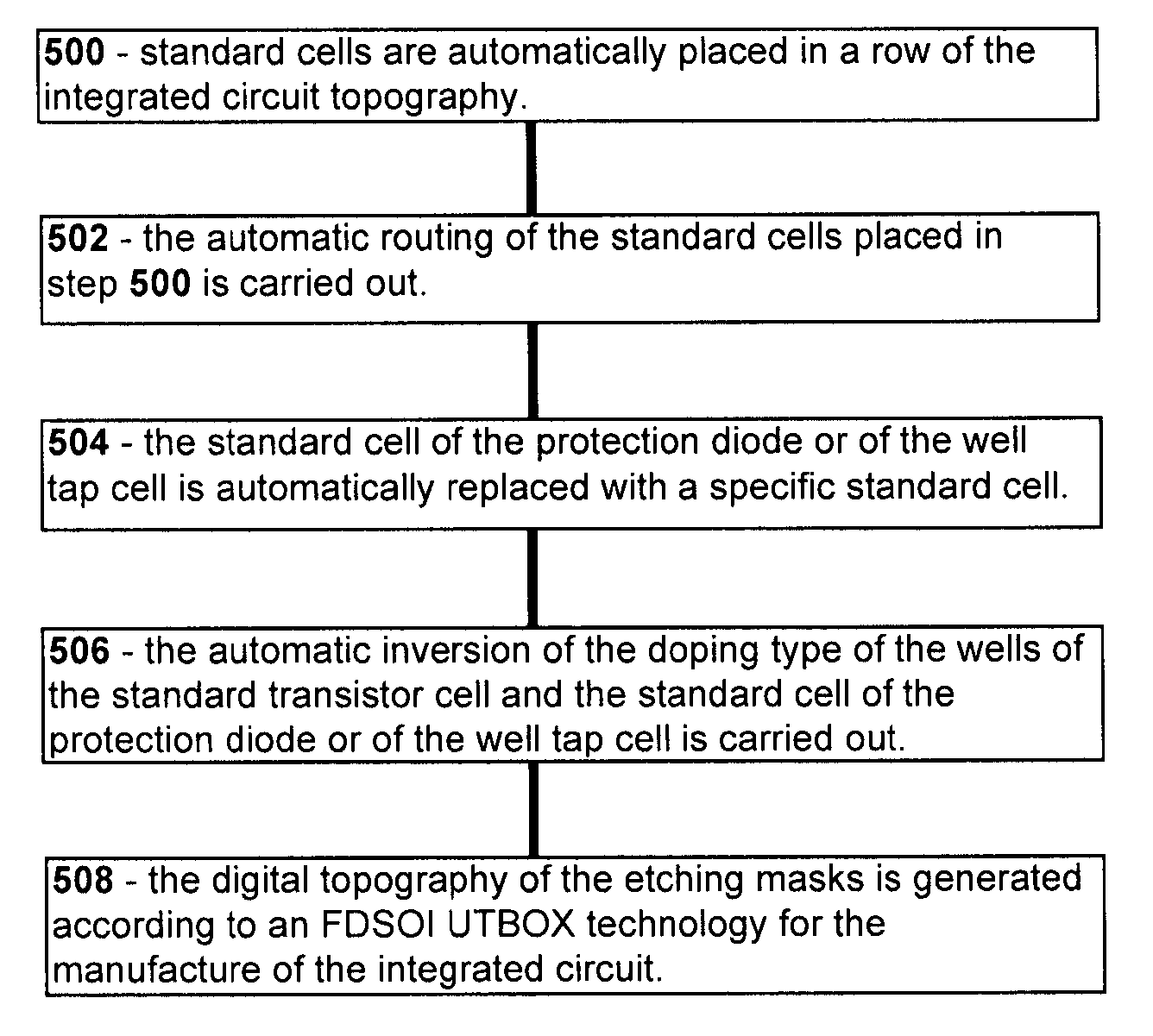

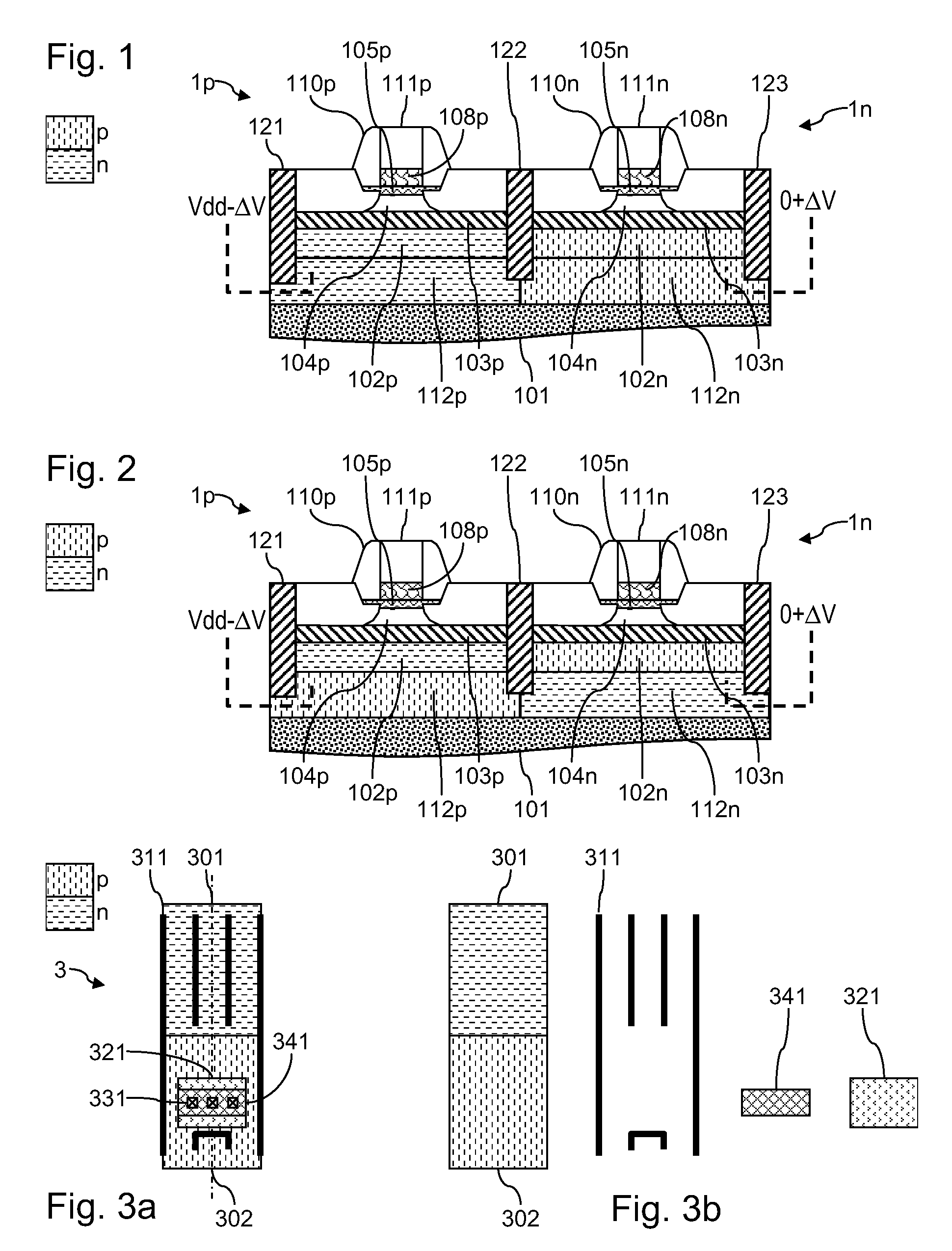

Method for generating a topography of an FDSOI integrated circuit

ActiveUS9092590B2High voltageSemiconductor/solid-state device manufacturingCAD circuit designAntenna effectGround plane

An IC including first and second FDSOI UTBOX cells arranged in a row, the first having an nMOS transistor arranged plumb with and above a ground plane and an N-type well, and a pMOS transistor arranged plumb with and above a ground plane and a P-type well, the N-type well and the P-type well being arranged on either side of a row axis, wherein the second includes a diode protecting against antenna effects or a well tap cell, the second cell comprising a P-type well arranged in the alignment of the P-type well of the pMOS transistor and comprising an N-type well arranged in the alignment of the N-type well of the nMOS transistor, the second cell comprising a metal connection coupled to its P-type well and coupled to a higher-level metal connection element arranged plumb with the N-type well, the metal connection extending on either side of the axis.

Owner:STMICROELECTRONICS SRL

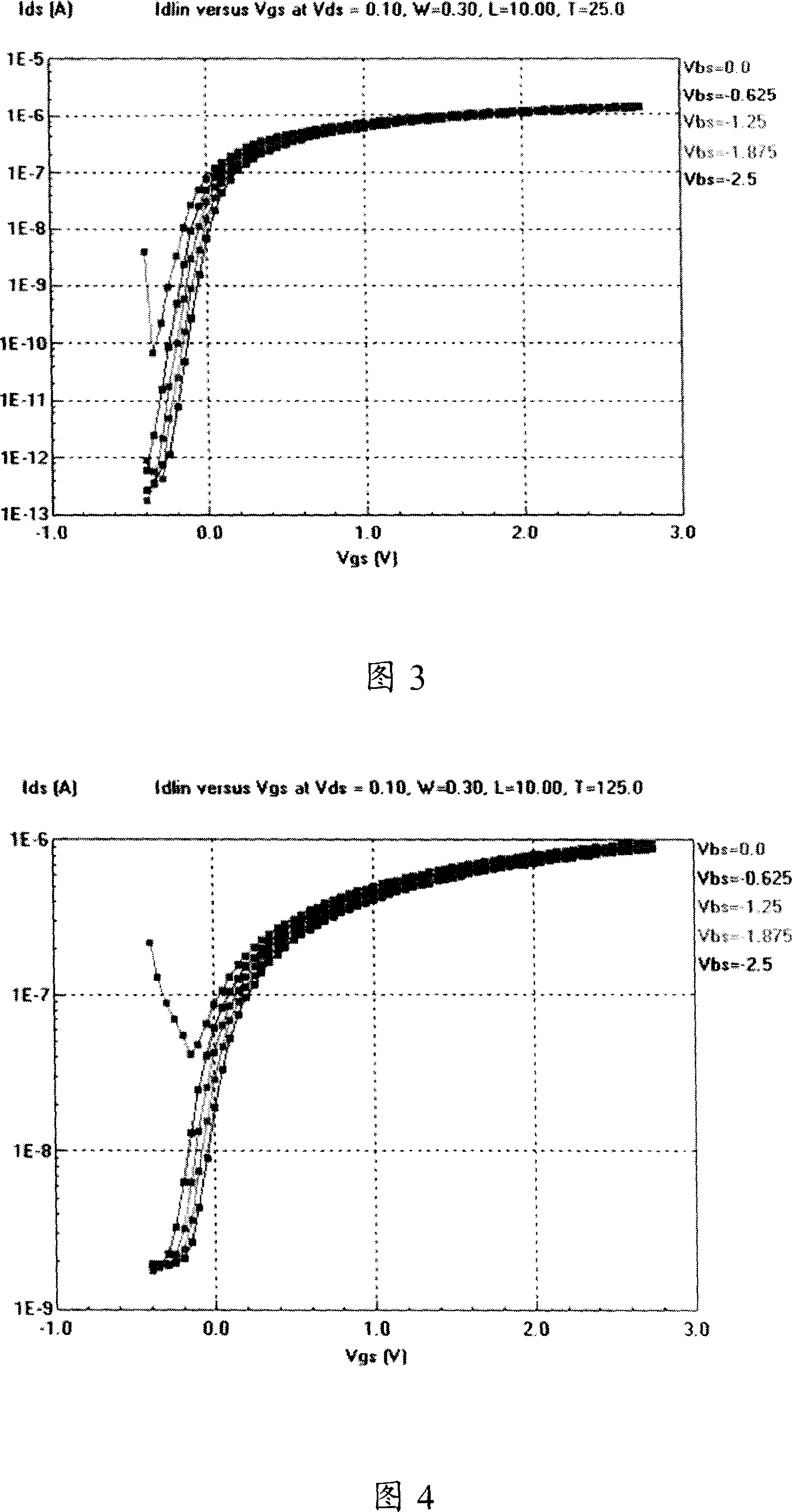

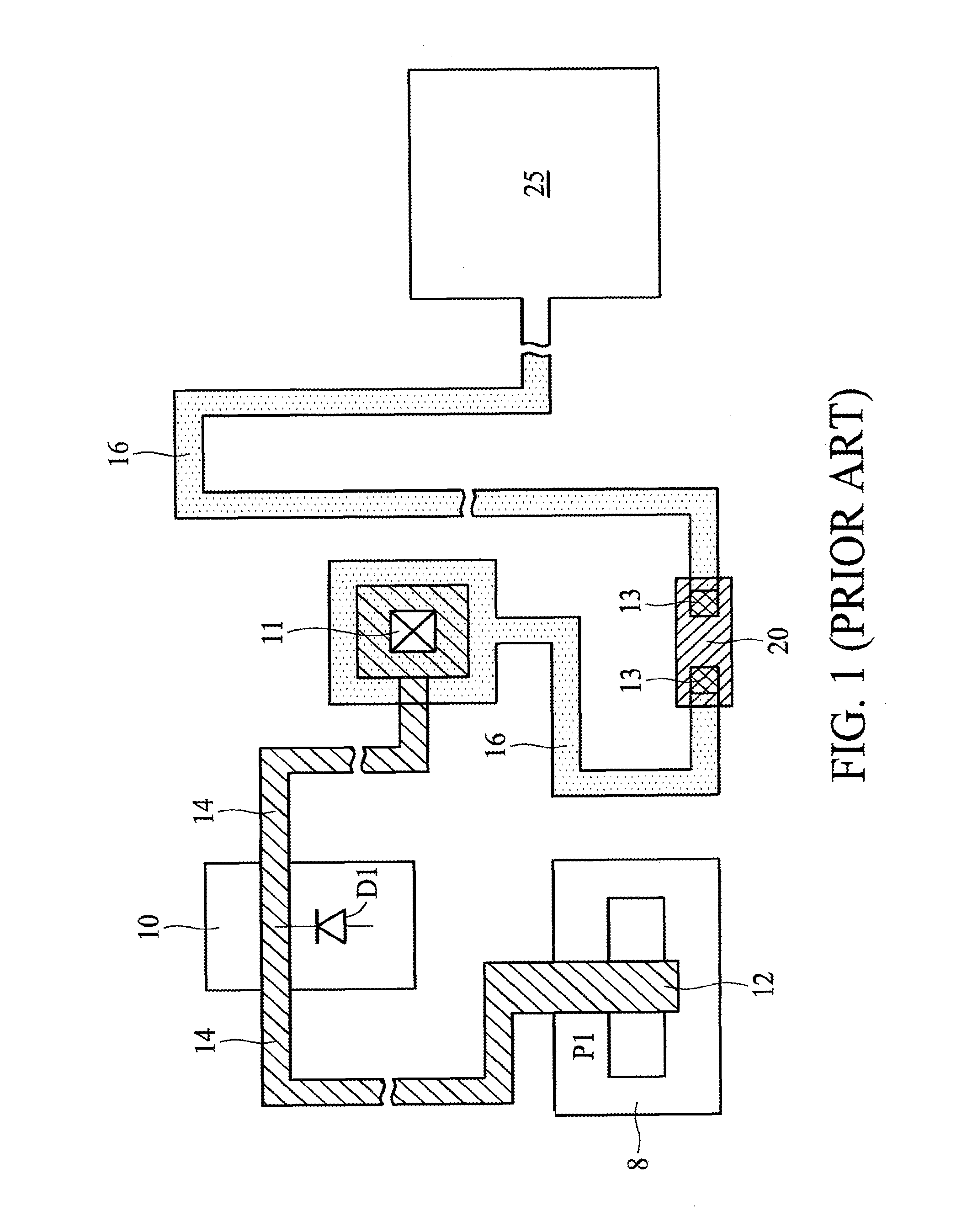

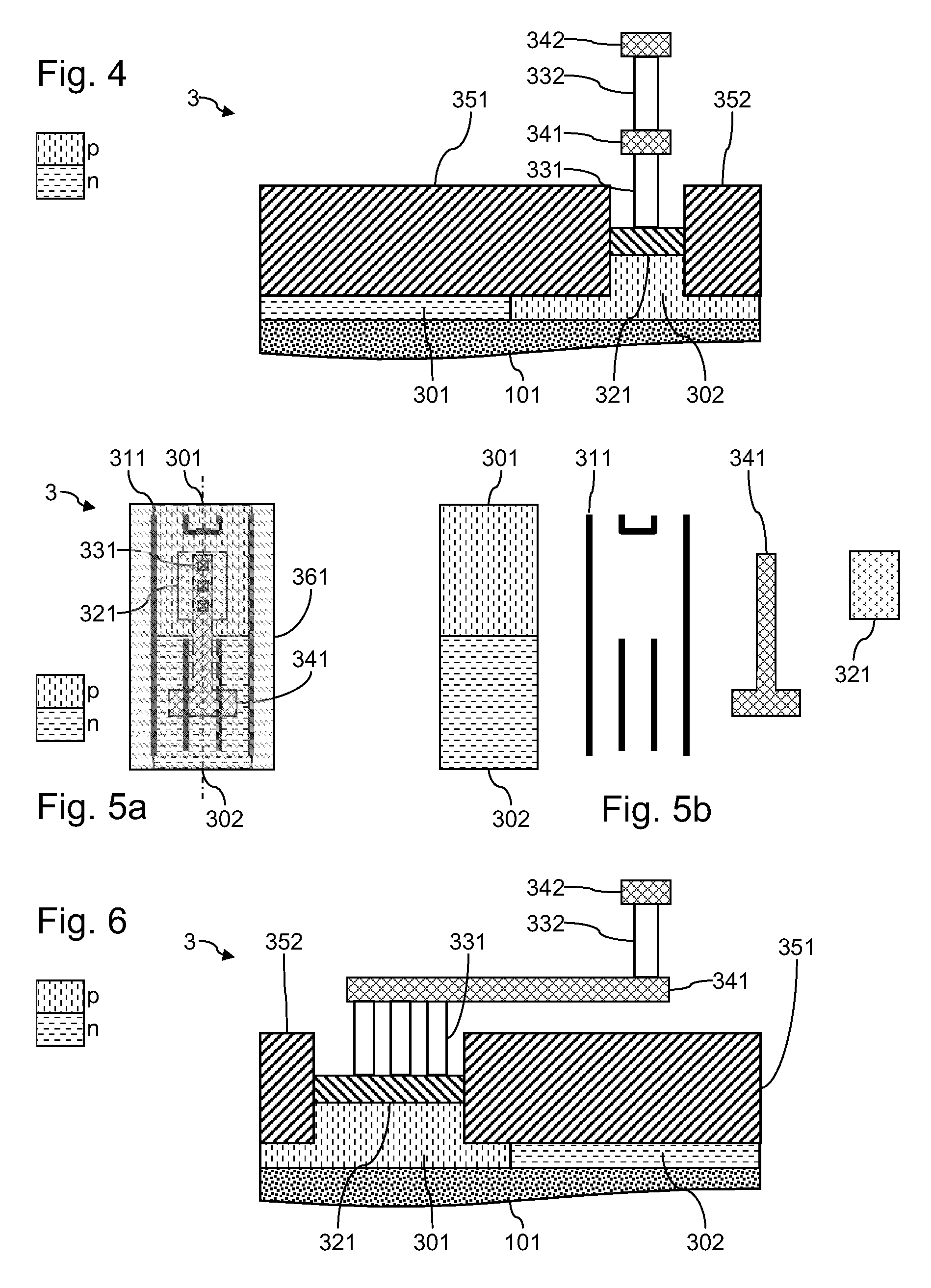

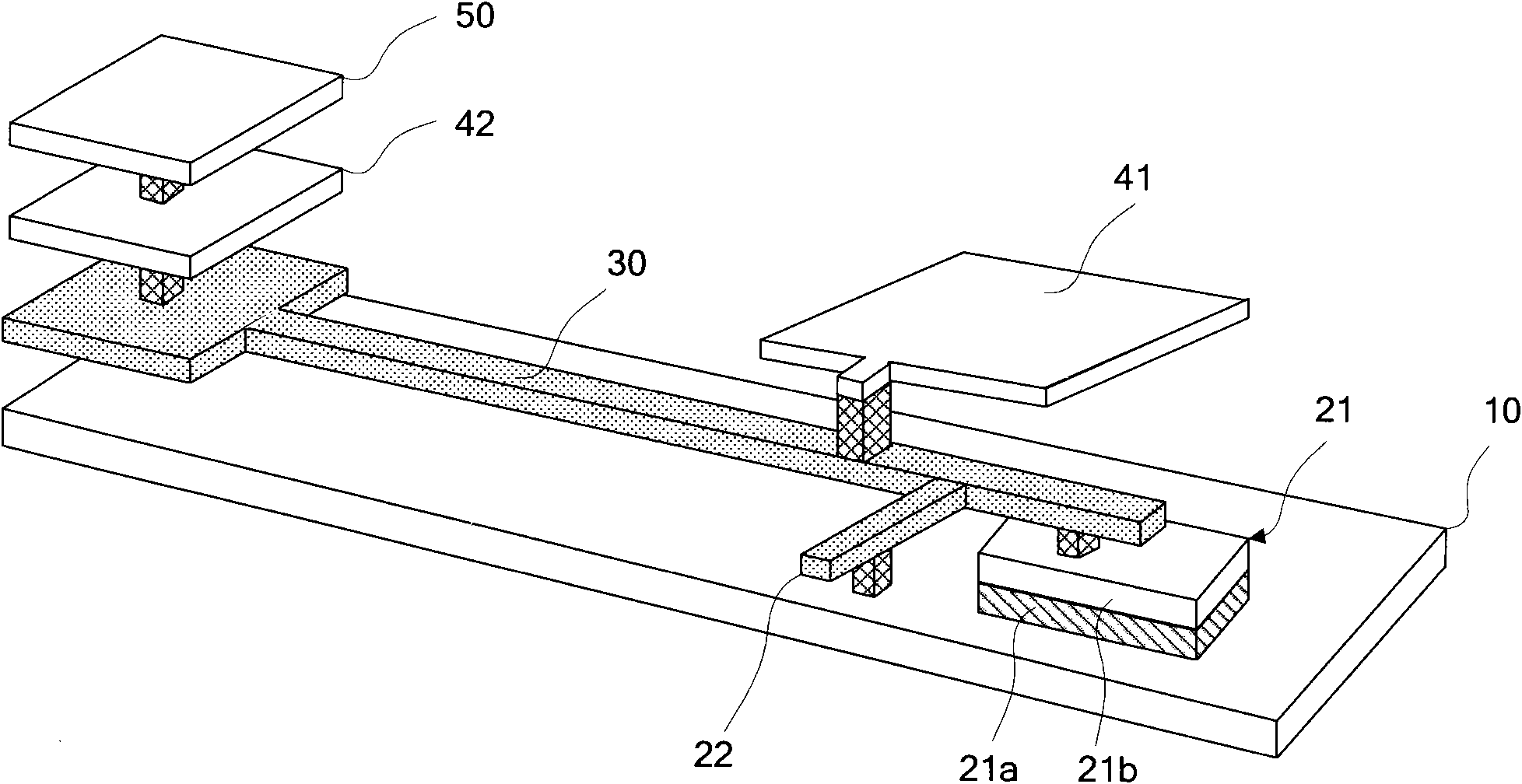

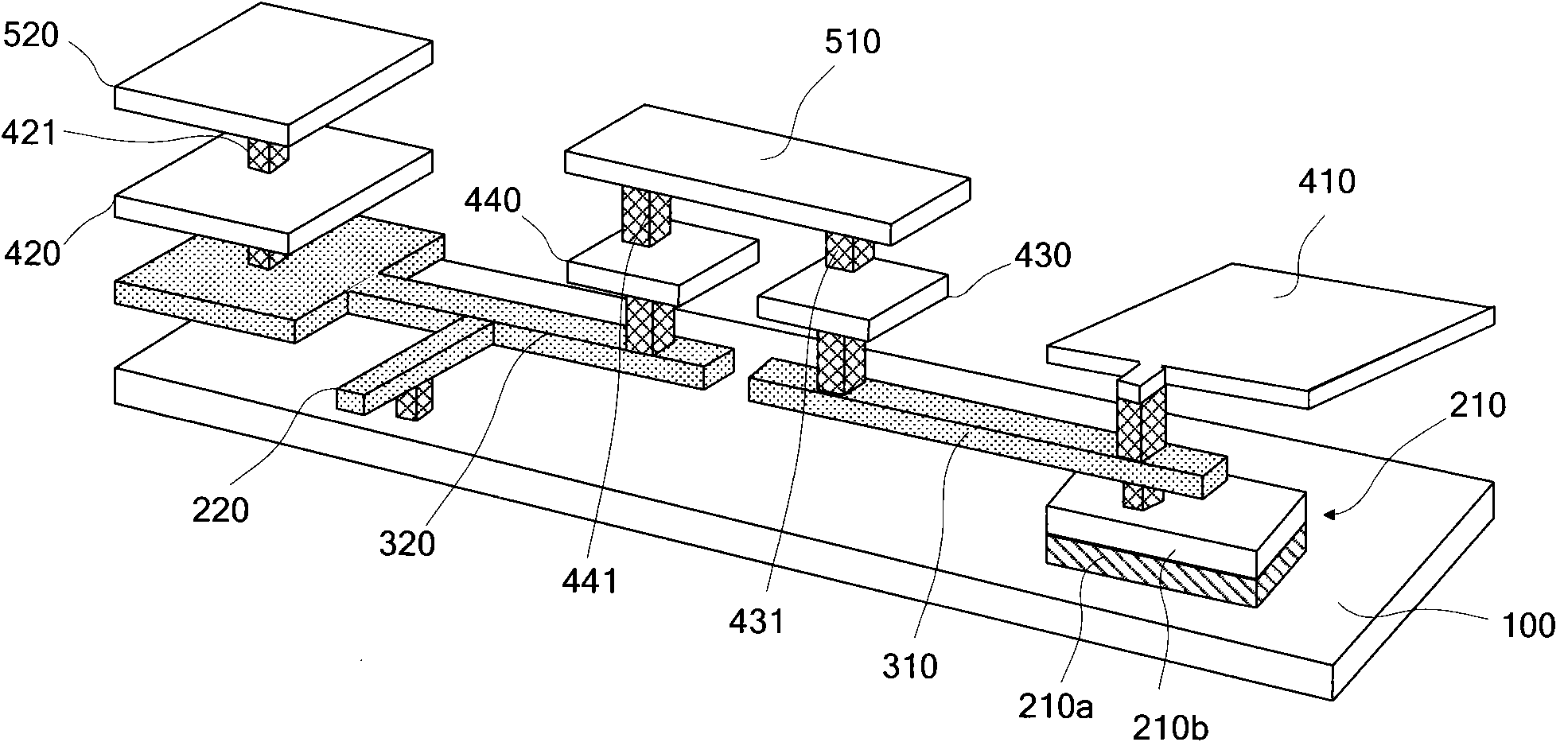

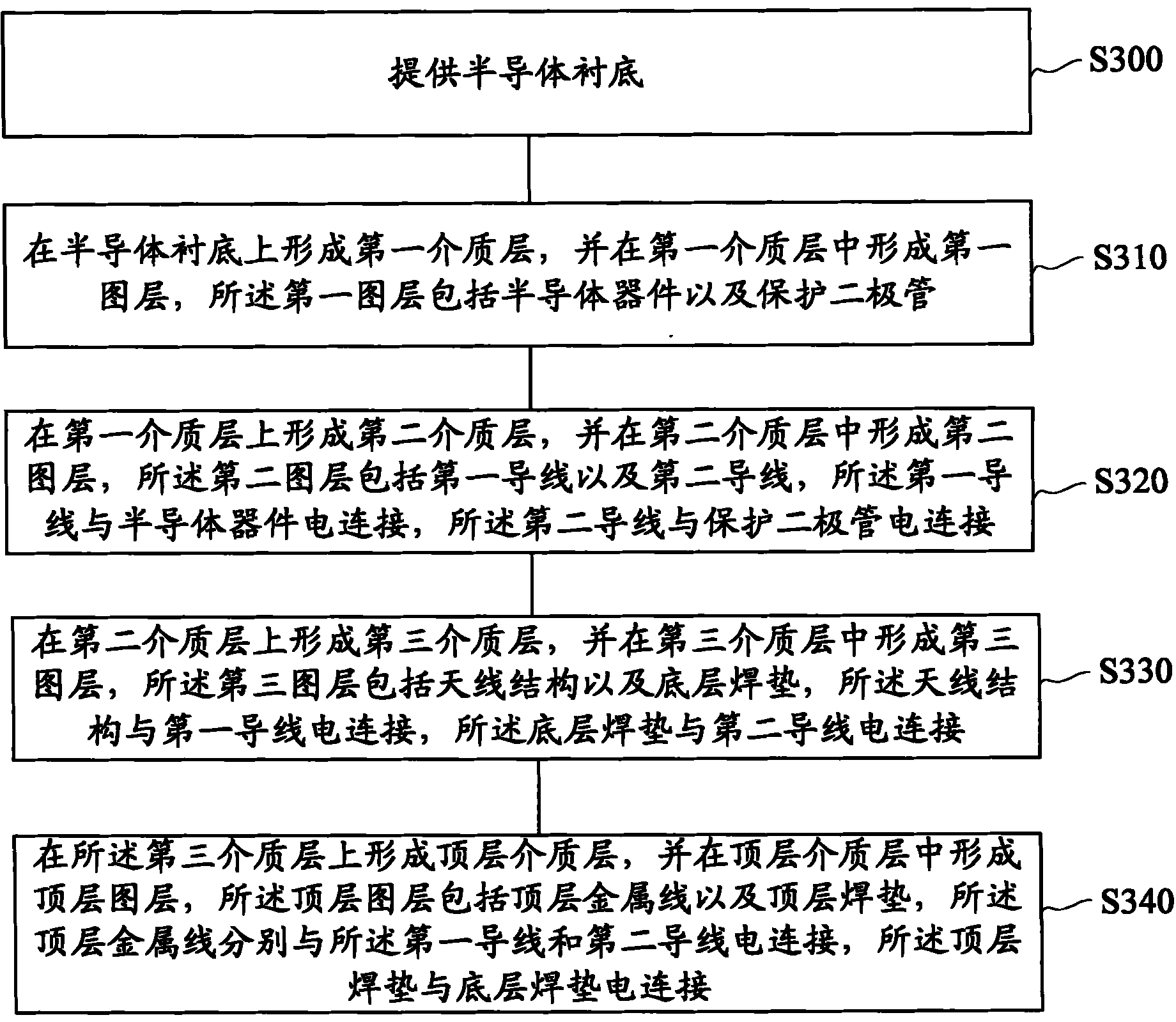

Plasma induced damage (PID) detection structure and manufacture method thereof

ActiveCN102142429AAccurate detection of sizeSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsElectricityAntenna effect

The invention discloses a plasma induced damage (PID) detection structure and a manufacture method thereof. The PID structure comprises a semiconductor substrate, a first coverage, a second coverage, a third coverage and a top coverage, wherein the first coverage is arranged in a first medium layer and comprises a semiconductor device and a protection diode formed on the semiconductor substrate; the second coverage is arranged in a second medium layer and comprises a first wire and a second wire, wherein the first wire is electrically connected with the semiconductor device, and the second wire is electrically connected with the protection diode; the third coverage is arranged in a third medium layer and comprises an antenna structure and a bottom welding pad, wherein the antenna structure is electrically connected with the first wire, and the bottom welding pad is electrically connected with the second wire; the top coverage is arranged in a top medium layer and comprises a top metalline and a top welding pad, wherein the top metal line is electrically connected with the first wire and the second wire; and the top welding pad is electrically connected with the bottom welding pad. According to the PID detection structure and the manufacture method thereof, the strength of antenna effect can be accurately detected.

Owner:SEMICON MFG INT (SHANGHAI) CORP

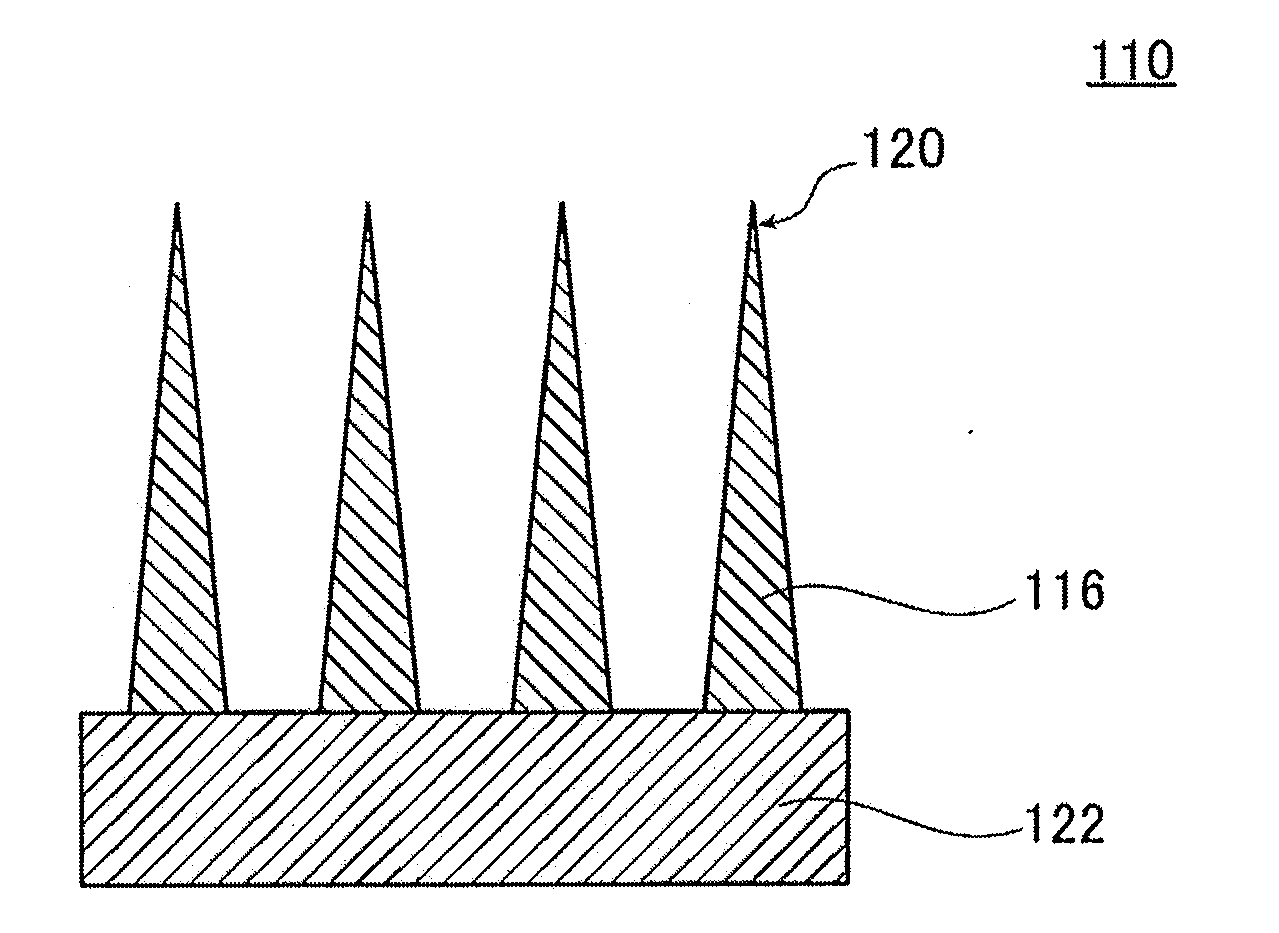

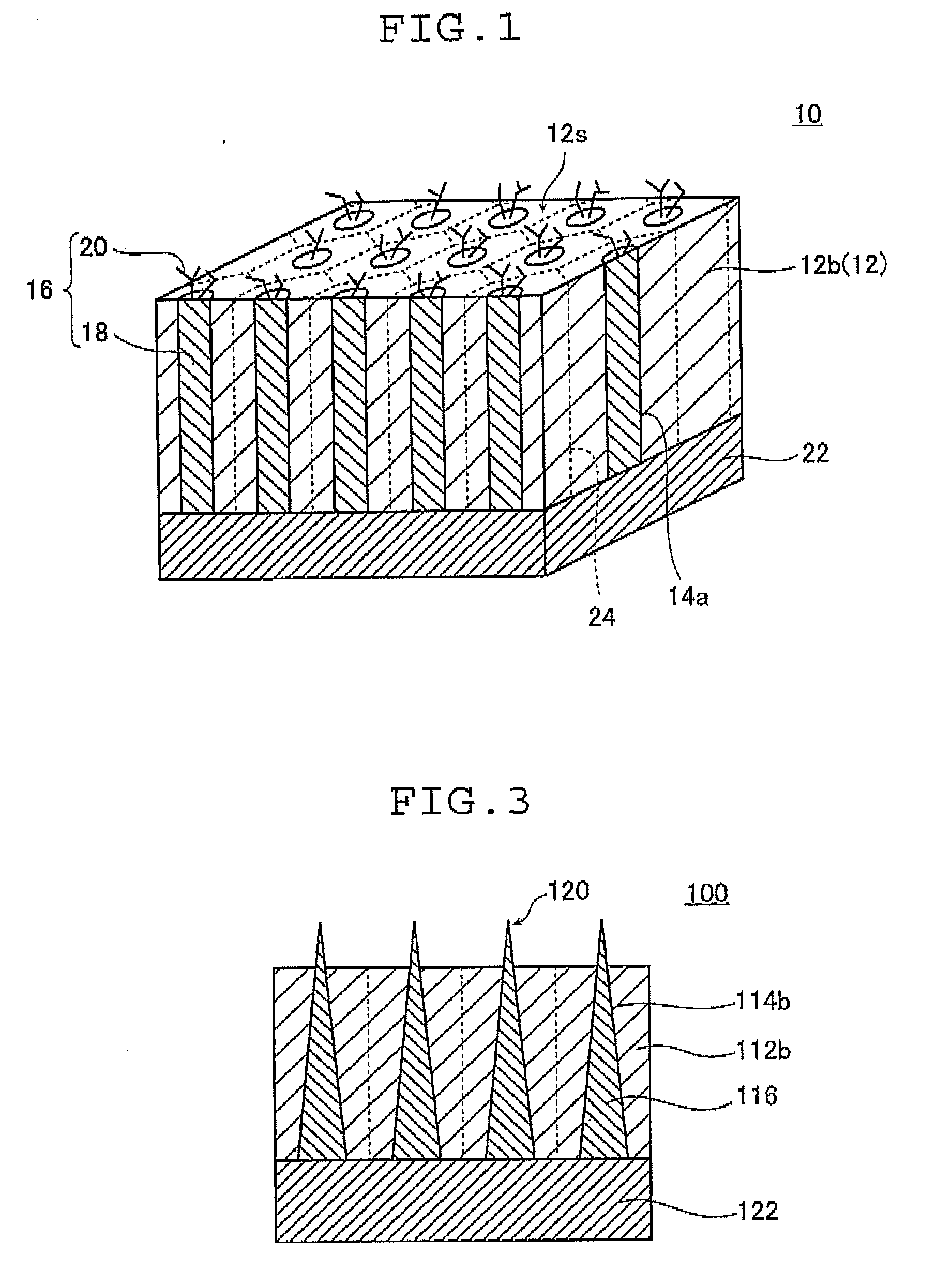

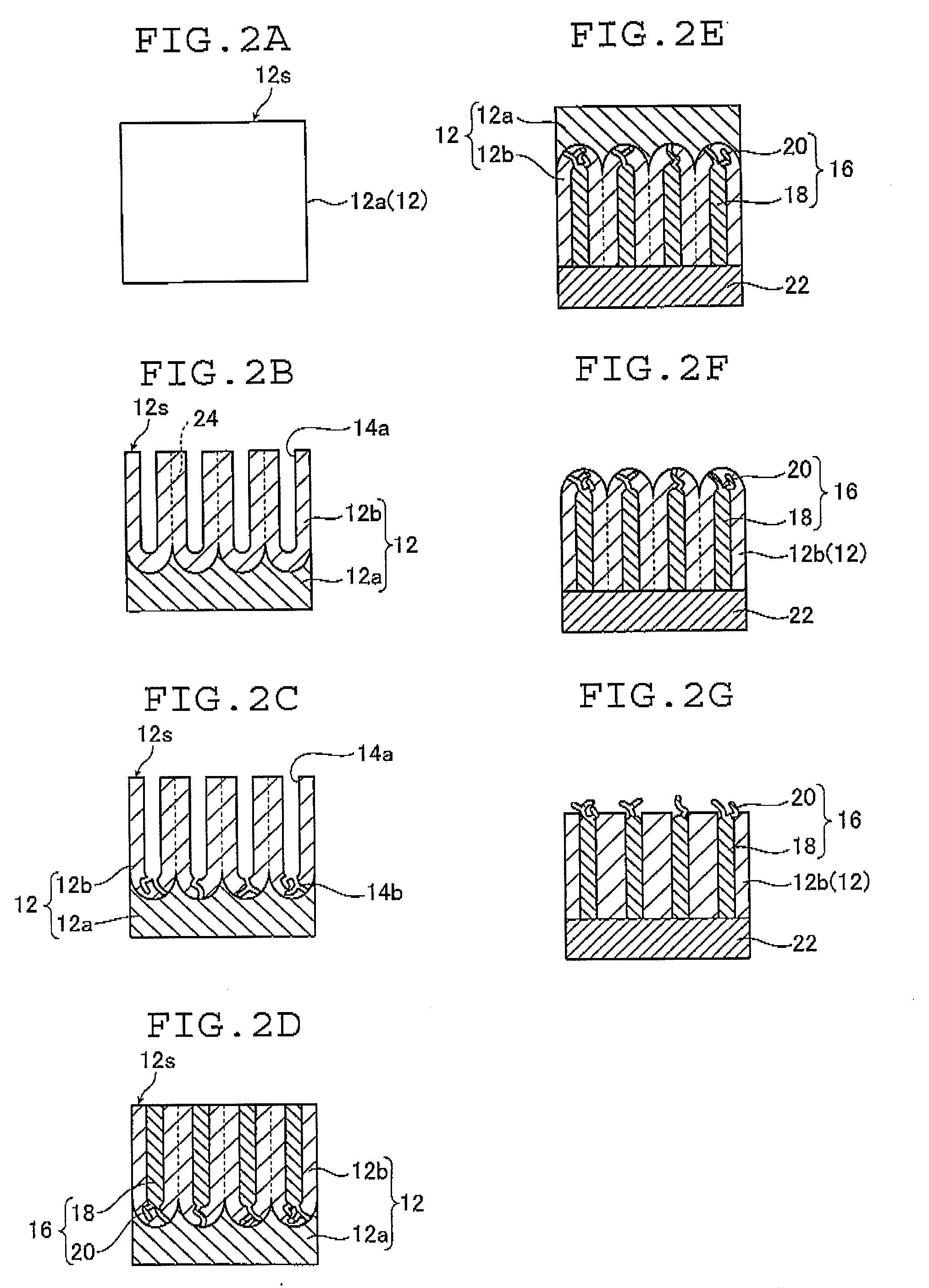

Microstructure and method of manufacturing the same

InactiveUS20090098344A1Enhanced electric fieldEasy to placeDecorative surface effectsLayered productsAntenna effectDepth direction

The method of manufacturing a microstructure having metal microbodies which generate an enhanced electric field includes forming, in a substrate, micropores each of which opens out on a surface of the substrate, has an inside diameter that varies in a depth direction, and has in a tip portion thereof a narrower, outwardly projecting recess, filling the micropores with metal to form the metal microbodies each having at a tip portion thereof a projection made of the metal filled into the outwardly projecting recess, and removing at least part of the substrate from a metal microbody tip portion side to expose at least the projection at the tip portion of each of the metal microbodies. The resulting microstructure has metallic nanostructural elements that generate an enhanced electric field by an antenna effect at their pointed tips.

Owner:FUJIFILM CORP

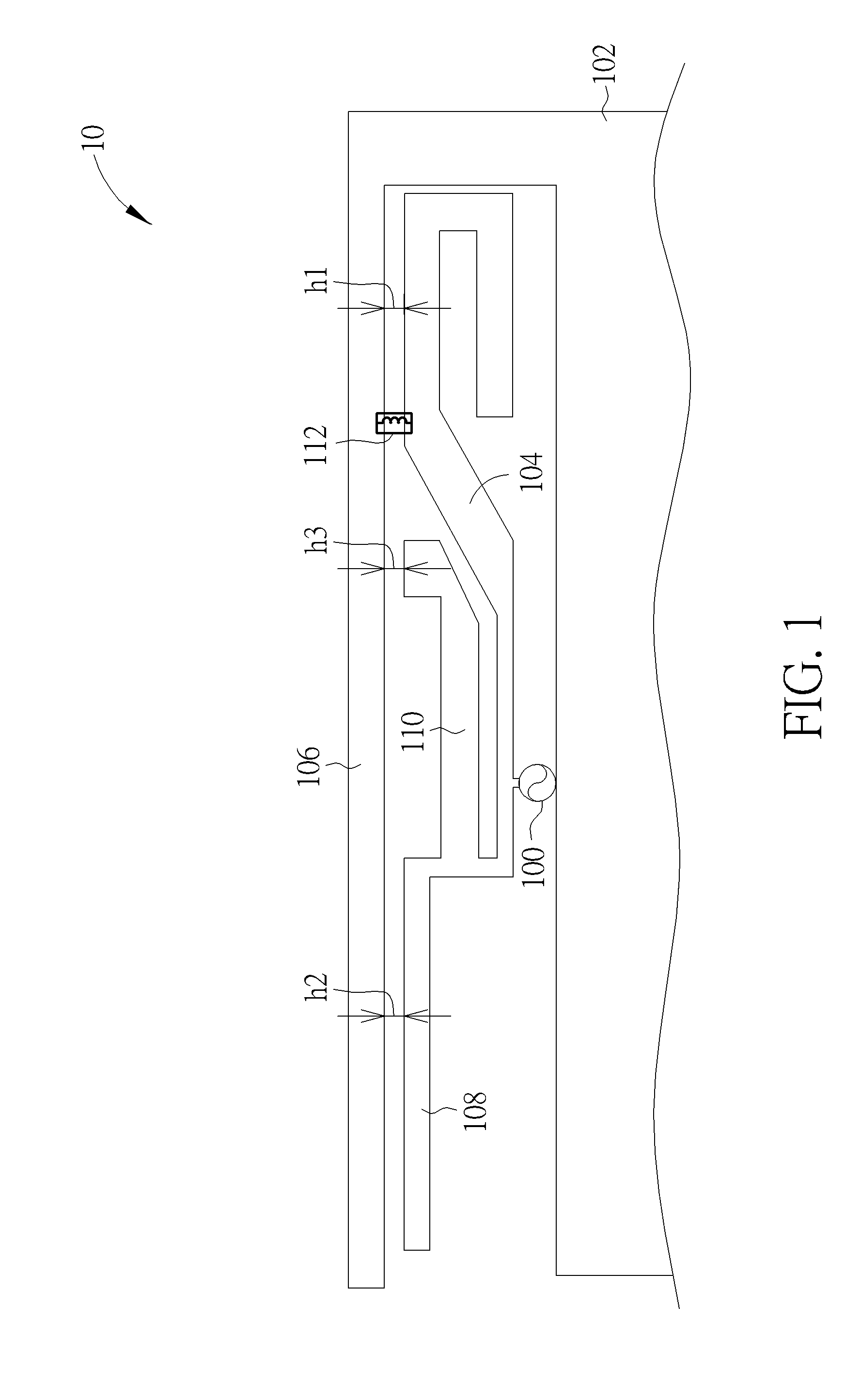

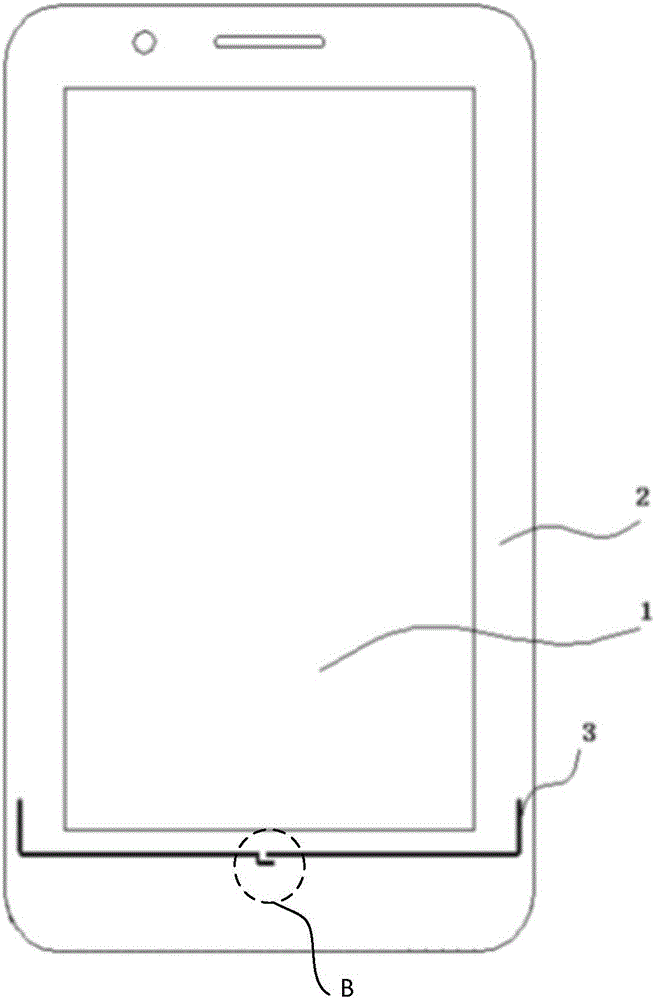

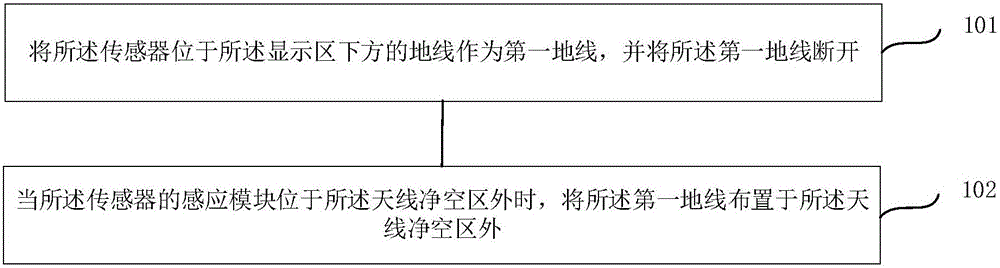

Wiring method of sensor of touch screen and sensor of touch screen

ActiveCN105930010AReduce distractionsIncreased Radiation PowerInput/output processes for data processingAntenna effectEngineering

The invention discloses a wiring method of a sensor of a touch screen and the sensor of the touch screen. The touch screen comprises a display area. The wiring method comprises the following steps of taking a ground wire of the sensor, which is arranged below the display area, as a first ground wire and disconnecting the first ground wire. The ground wire of the sensor, which is arranged below the display area, is disconnected, so that the electrostatic discharge can be prevented while the antenna effect caused by the close loop due to the ground wire of the sensor is prevented, the interference on the antenna of the equipment is reduced and the radiation power of the antenna of the equipment is promoted.

Owner:HUAQIN TECH CO LTD

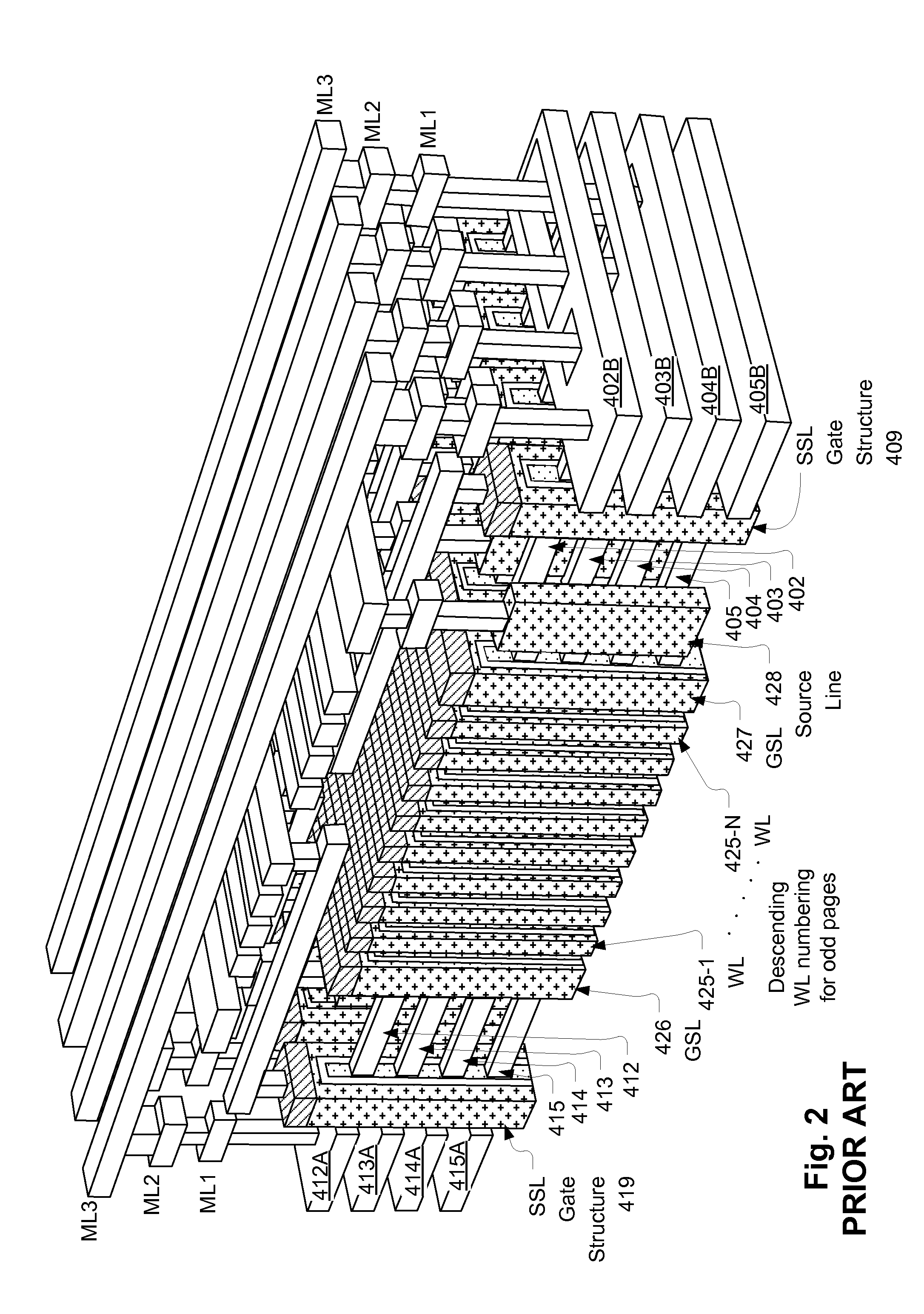

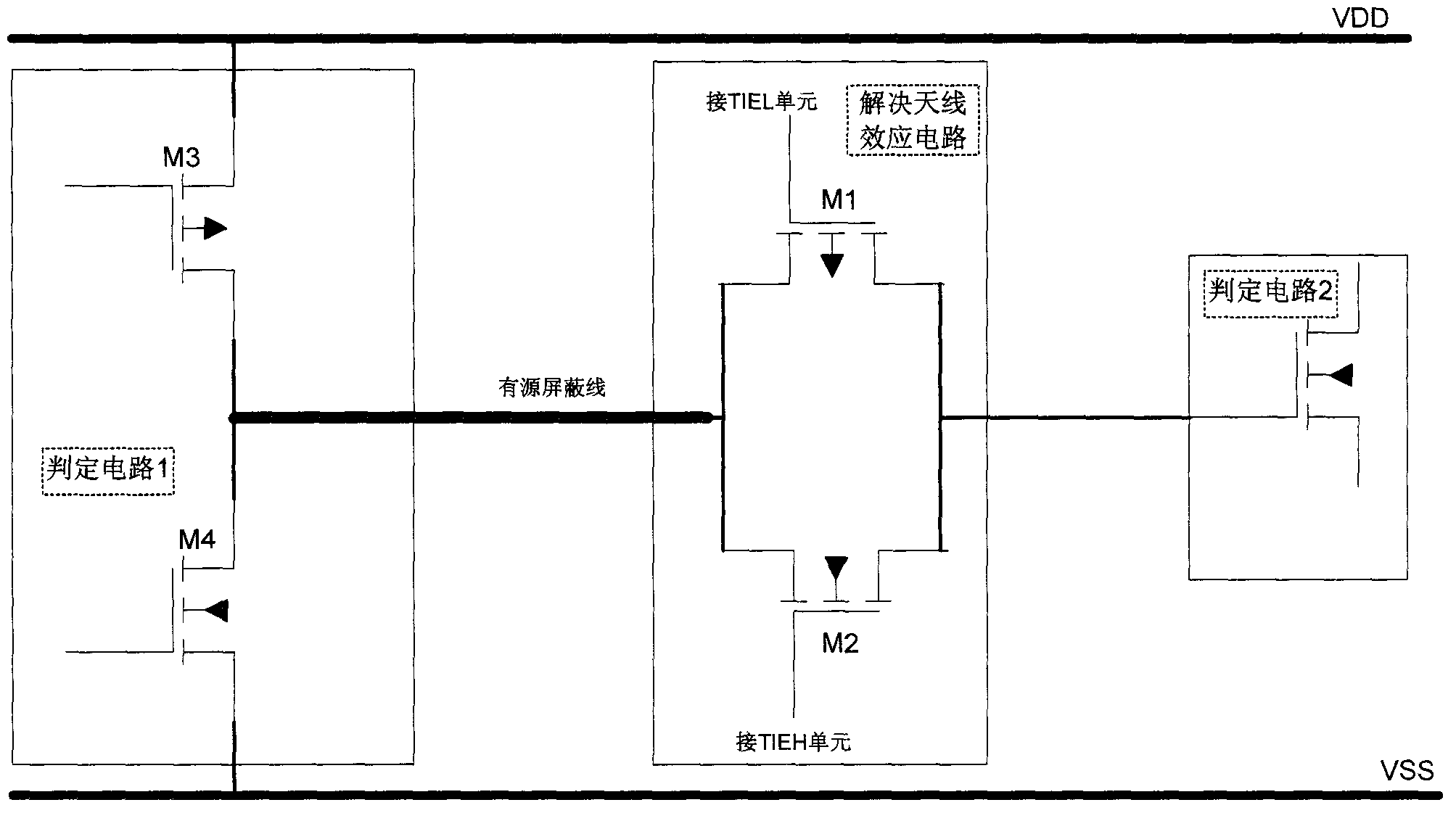

High sensitivity testing structure for evaluating plasma antenna effect

InactiveCN1452230ASemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsAntenna effectPlasma antenna

A high-sensitivity testing structure for evaluating the antenna effect of plasma is composed of a substrate, and ONO dielectric layer which consists of a lower oxide layer, a silicon nitride layer and an upper oxide layer, an electrode, and an antenna structure connected with said electrode for collecting the charges induced by plasma.

Owner:MACRONIX INT CO LTD

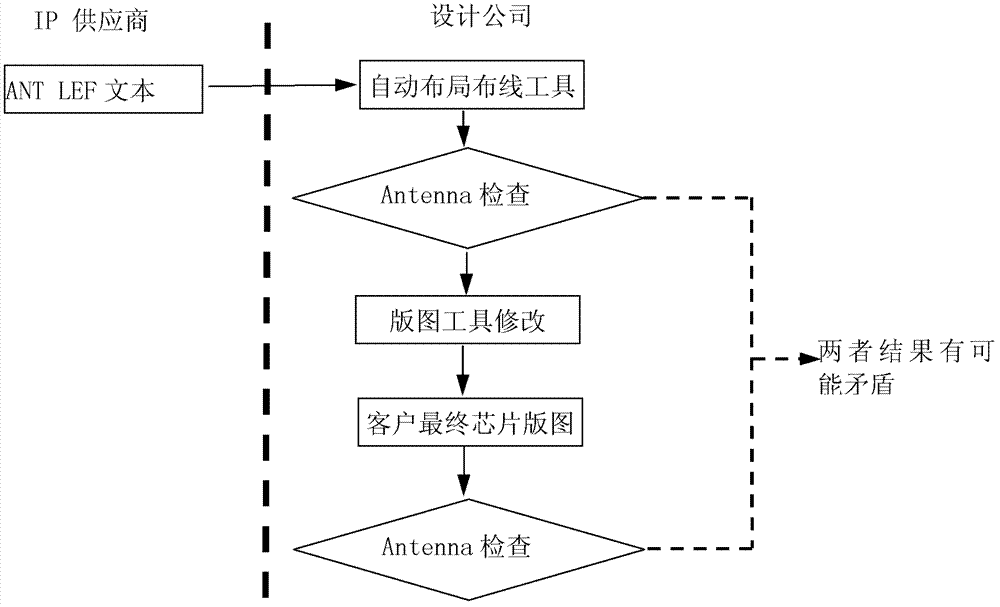

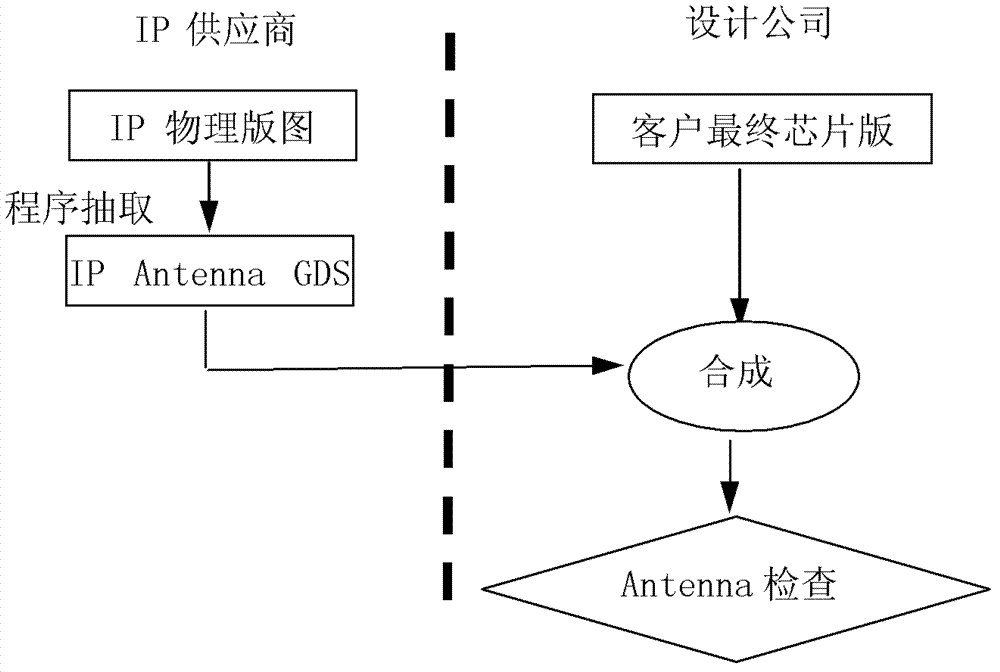

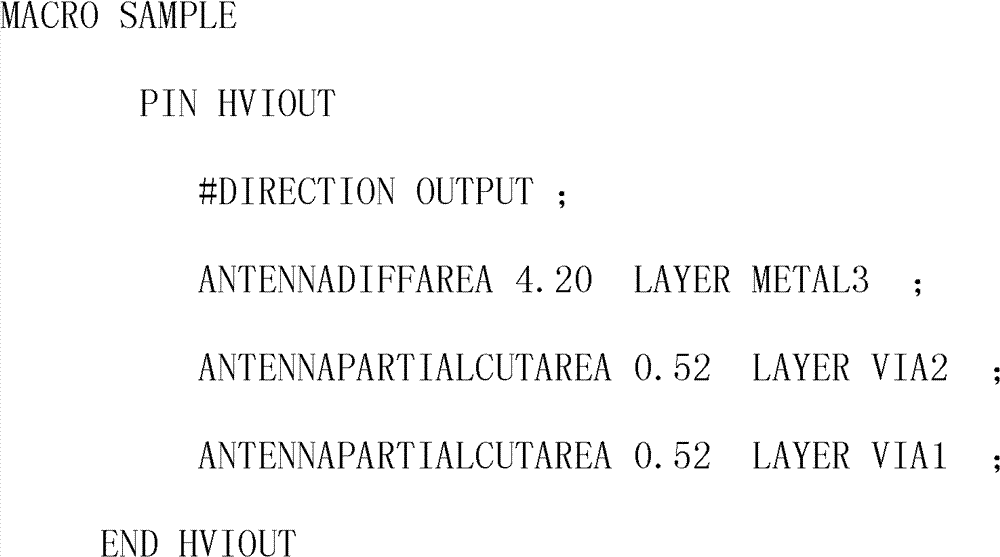

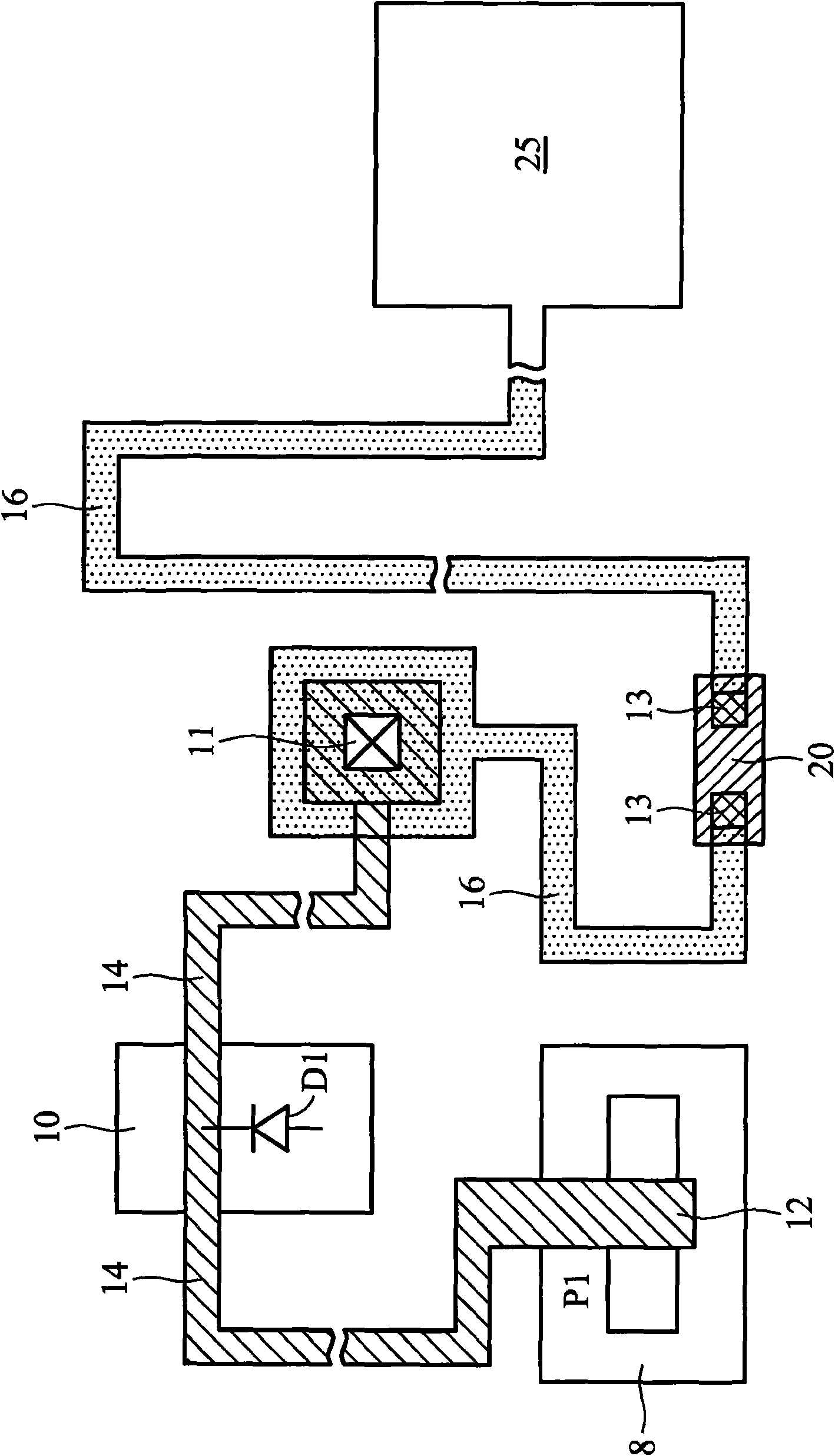

Examination method for different-party IP (internet protocol) containing client party chip antenna effect

ActiveCN102955123AAvoid repeated revisionsProtect intellectual propertyElectronic circuit testingAntenna effectAntenna design

The invention discloses an examination method for different-party IP (internet protocol) containing client party chip antenna effect. The method includes following steps: step one, identifying all input and output interfaces in an IP module layout; step two, selecting the input and output interface used for generating final data; step three, taking the input and output interface as a starting point to extract out all lines related to the antenna effect along the lines connecting every interface from top to bottom; step four, enabling the extracted lines to generate a GDSII formatted file capable of being read by a user layout tool and providing the file for a client; and step five, synthesizing the GDSII formatted file into a main chip by the client for physical layout verification of the final data. By the method, data which can be directly used for antenna design rule examination by a client party can be generated, and a design company can perform antenna effect examination close to an entity through tools before the data are given out, so that repeat data modification caused by violation of design rules by the client can be avoided.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Chip bonding pad of integrated circuit, manufacture method thereof and integrated circuit comprising bonding pad

ActiveCN101615606AReduce antenna effectSemiconductor/solid-state device detailsSolid-state devicesAntenna effectEngineering

The invention provides an integrated circuit, a chip bonding pad structure and a manufacture method. The chip bonding pad comprises a main bonding pad and a ring bonding pad. In a process of fabricating charges comprising formation of the chip bonding pad, a grid of a metal oxide semiconductor transistor in a substrate of the integrated circuit is electrically connected with the ring bonding pad,therefore area ratio from an antenna to the grid is less than a proportion of a given antenna, thus effectively reducing or avoiding antenna effect. The main bonding pad is electrically coupled with the ring bonding pad through a metal bridge formed in an upper inside cable metal layer or an uppermost conductive bonding pad layer. The chip bonding pad provided by the invention is a probe bonding pad on a parameter testing line or a bonding pad on the integrated circuit.

Owner:TSMC CHINA COMPANY

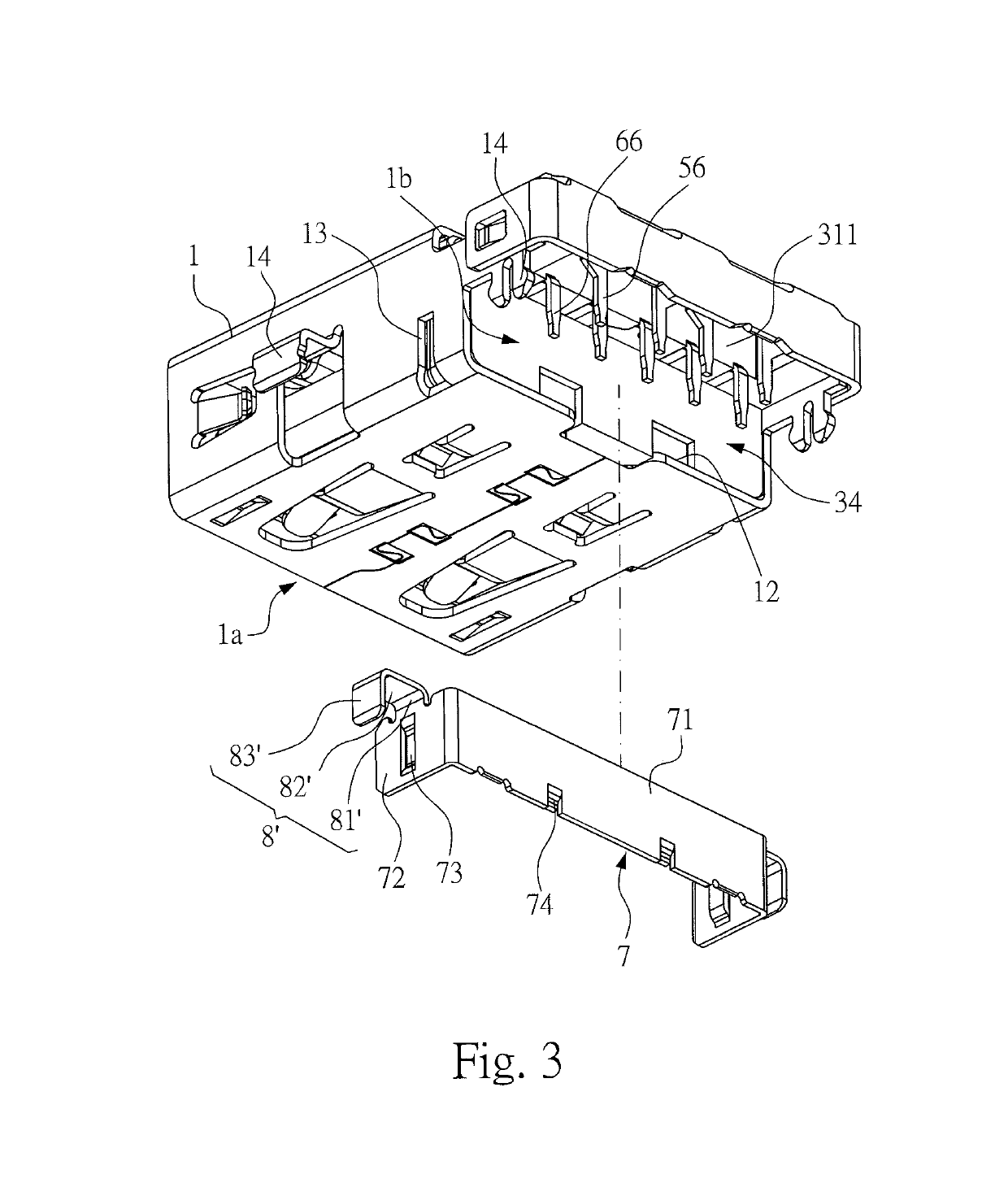

Electrical receptacle connector including a baffle plate

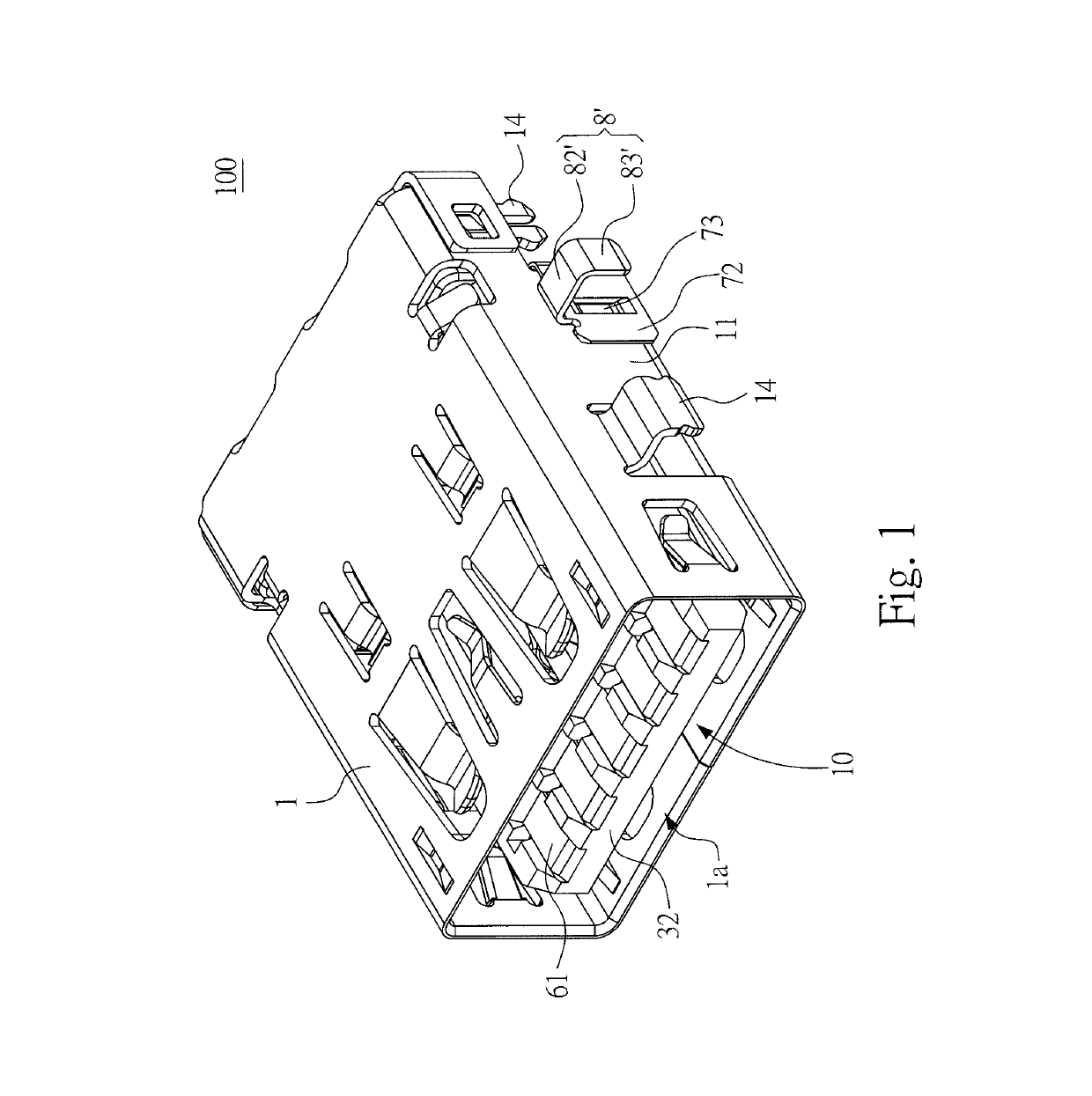

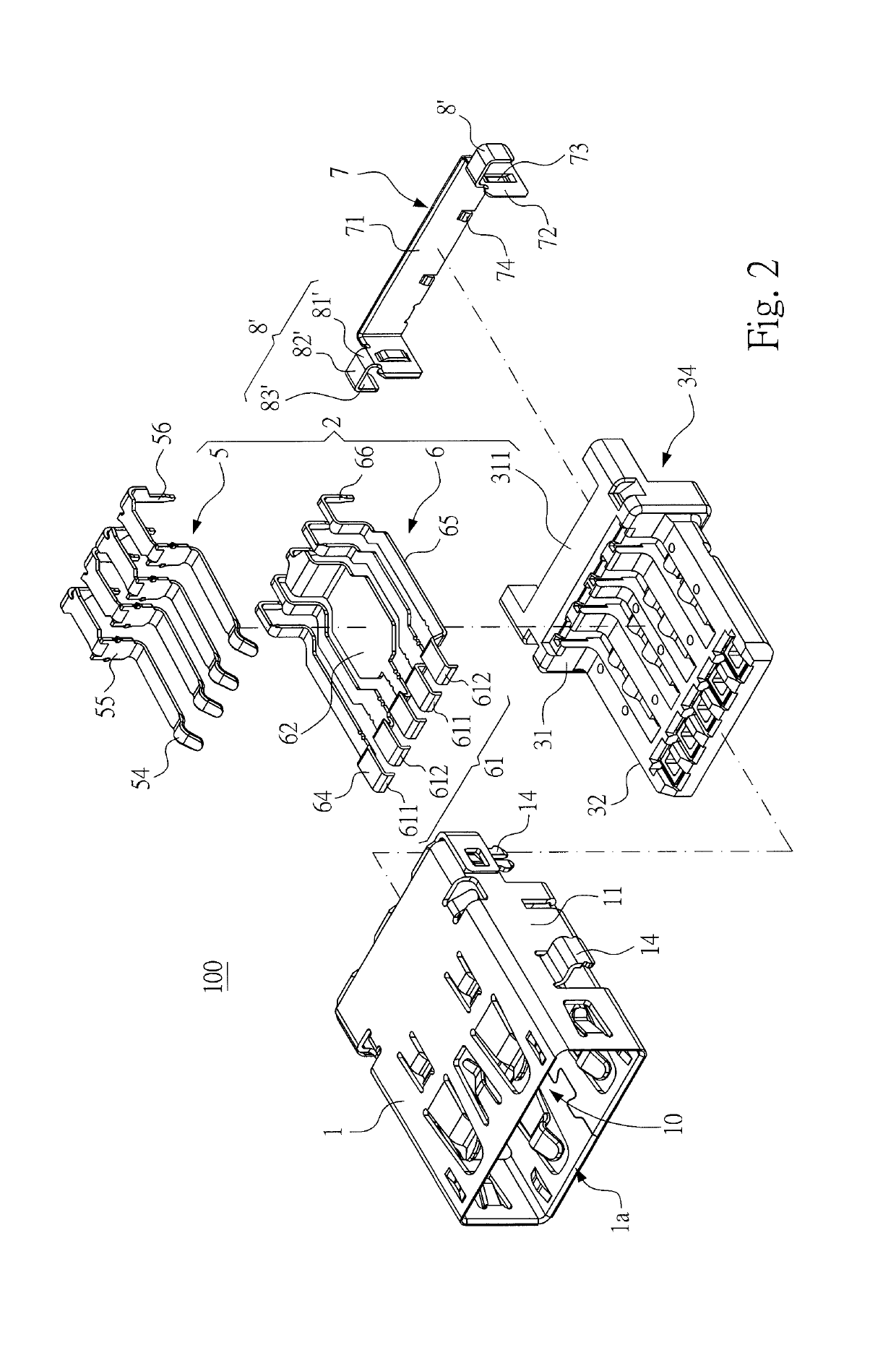

ActiveUS10305227B2Reduce noiseIntuitive effectMetal casingsTwo-part coupling devicesAntenna effectElectrical and Electronics engineering

An electrical receptacle connector includes a metallic shell, a terminal module in the metallic shell, a baffle plate at a rear portion of the metallic shell, and conductive ground legs. Accordingly, the baffle plate is at the rear portion of the metallic shell, and the conductive ground legs are at two sides of the metallic shell. Therefore, during the connector transmits data, the produced noises are shielded by the baffle plate, and the current formed by the noises is guided to a circuit board through the conductive ground legs, thus the noises are grounded and diminished. The conductive ground legs are adjacent to the baffle plate. Hence, the current flowing through the baffle plate is guided to the circuit board through the conductive ground legs, with a shorter path. Therefore, the current would not have antenna effect easily on the path, and the noise spreading can be reduced.

Owner:ADVANCED CONNECTEK INC