Method for creating file containing aerial effect information

A technology of information files and antenna effects, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve problems such as inability to extract CLF, error-prone, time-consuming, etc., achieve small time, save time, and realize the process simple effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

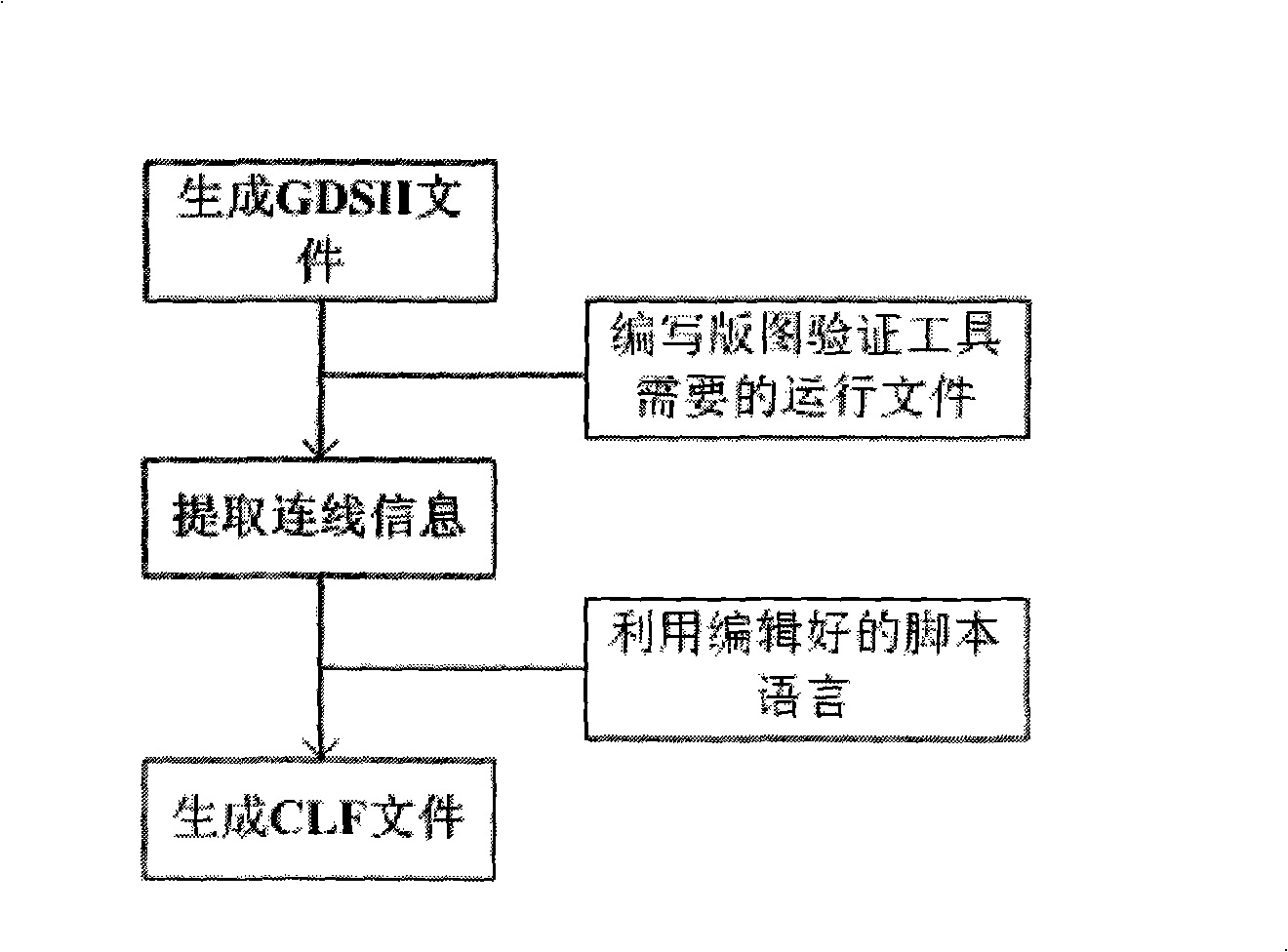

[0021] Such as figure 1 As shown, a method of generating a file containing antenna effect information, first generates a GDSII file from the edited layout, then runs the GDSII file through a layout verification tool to generate a file containing connection information, and finally converts the file containing connection information The connection information in is written to the CLF file.

[0022] The layout is a graphical representation of circuits in integrated circuit design, and is a bridge connecting integrated circuit design and integrated circuit manufacturing.

[0023] The file in the GDSII format is a graphics file of the layout of the integrated circuit, and is a file in binary form, and most layout verification tools support files in this format. In layout editing tools (such as Virtuoso, Laker, and L-edit, etc.), the GDSII file of the edited integrated circuit layout can be directly generated through the built-in functions of the layout editing tool.

[0024] In ...

Embodiment 2

[0031] In the layout editing environment of Laker (the layout editing tool of Silicon canvas company), a GDSII file is generated from the already drawn layout.

[0032] Write a file that extracts metal lines, polysilicon lines, and diffusion area information from a GDSII file. In this example, Caliber (Mentor's layout verification tool) is used to write the run file required for extraction in the syntax of Caliber, and then run Hercules to generate a file containing metal Files with information about lines, polysilicon lines, and diffusion areas.

[0033]In this example, AWK (a scripting language) is used under the LINUX system to write a script that can generate a fixed-format CLF file from the file obtained in step 2. After running the script, the required CLF file can be obtained. In this example The generated CLF file is a CLF file used in Soc Encounter (Candence's automatic placement and routing tool).

Embodiment 3

[0035] In Virtuoso (Cadence company's layout editing tool) layout editing environment, generate GDSII files from the already drawn layout.

[0036] Write a file that extracts metal lines, polysilicon lines, and diffusion area information from a GDSII file. In this example, Hercules (Synopsys' layout verification tool) is used to write the run file required for extraction in Hercules syntax, and then run Hercules to generate a file containing metal Files with information about lines, polysilicon lines, and diffusion areas.

[0037] In this example, PERL (a scripting language) is used under the LINUX system to write a script that can generate a fixed-format CLF file from the file obtained in step 2. After running the script, the required CLF file can be obtained. In this example The generated CLF file is a CLF file used in Astro (automatic placement and routing tool from Synopsys).

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More