Patents

Literature

5783results about "Cross-talk/noise/interference reduction" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

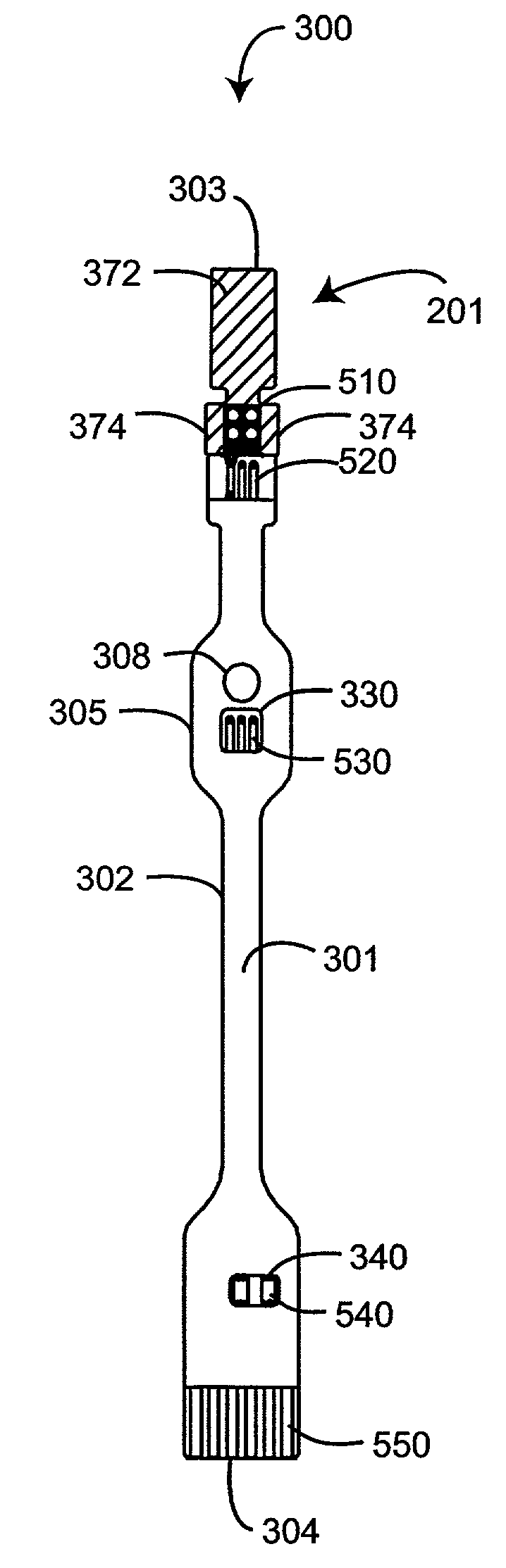

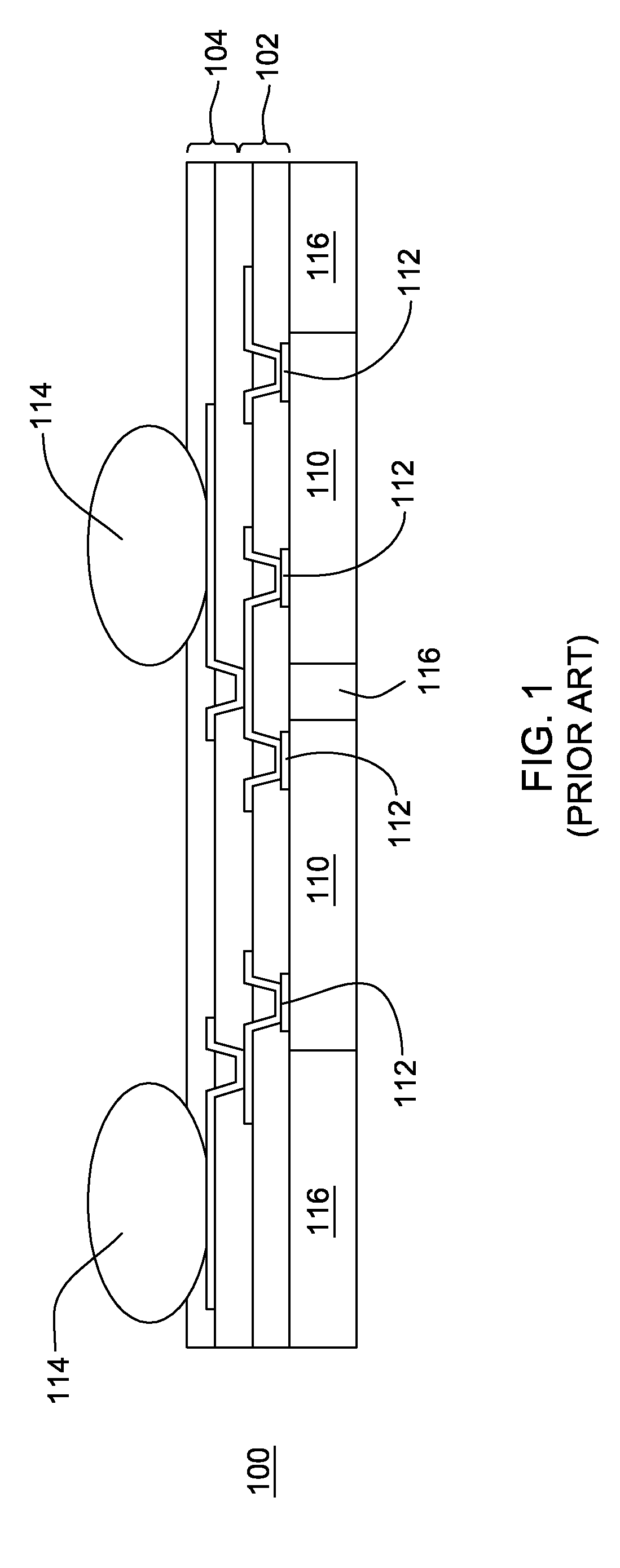

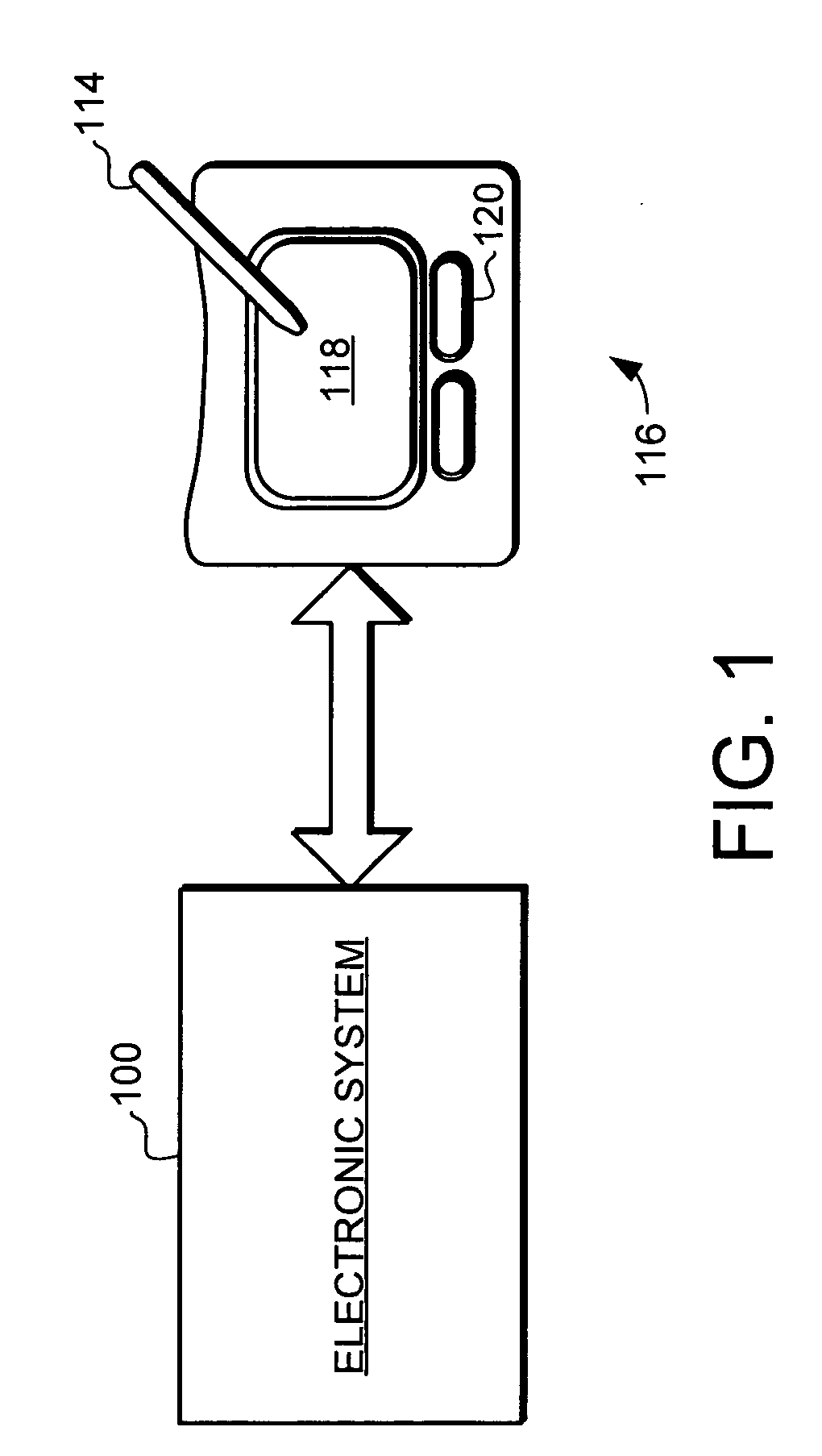

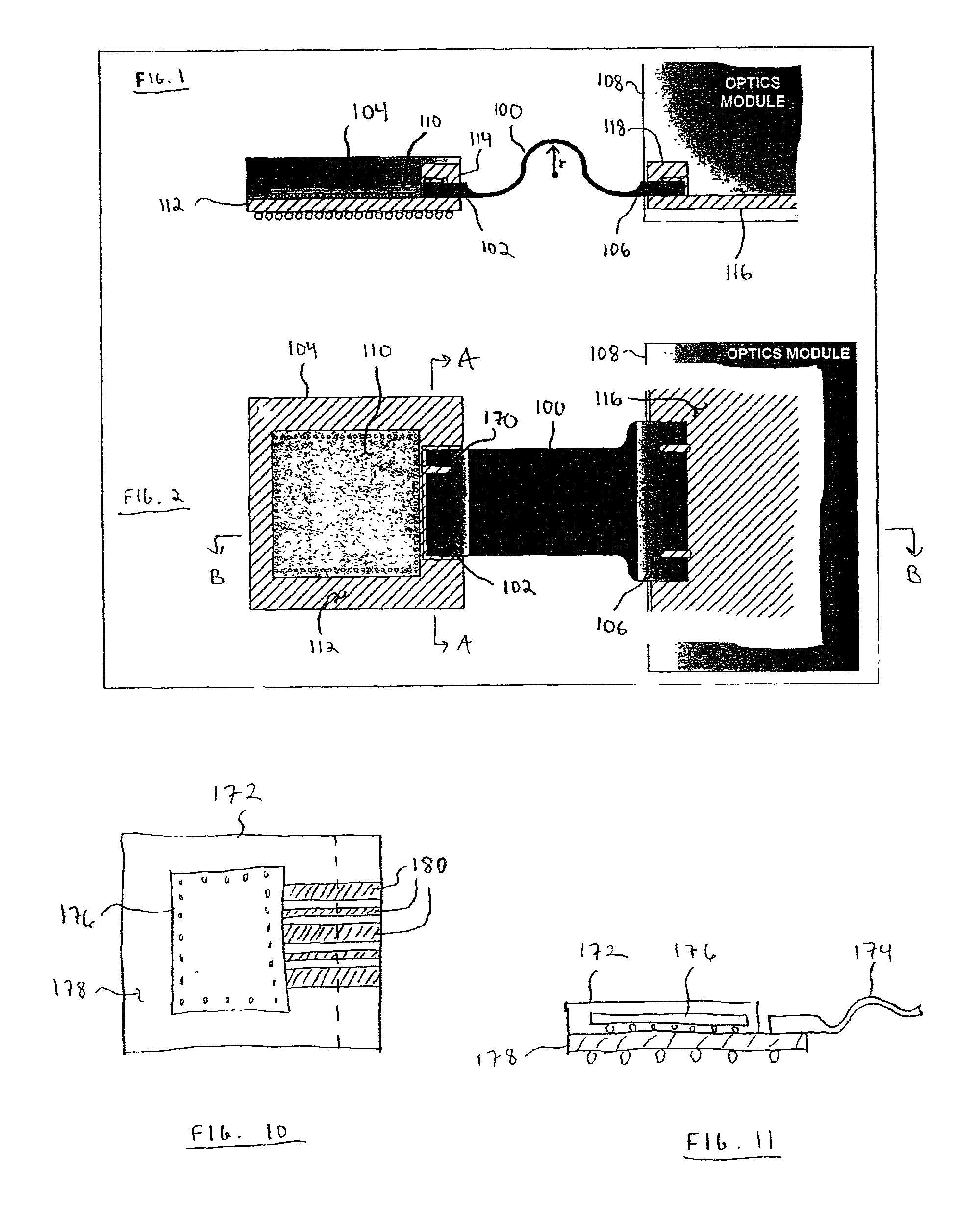

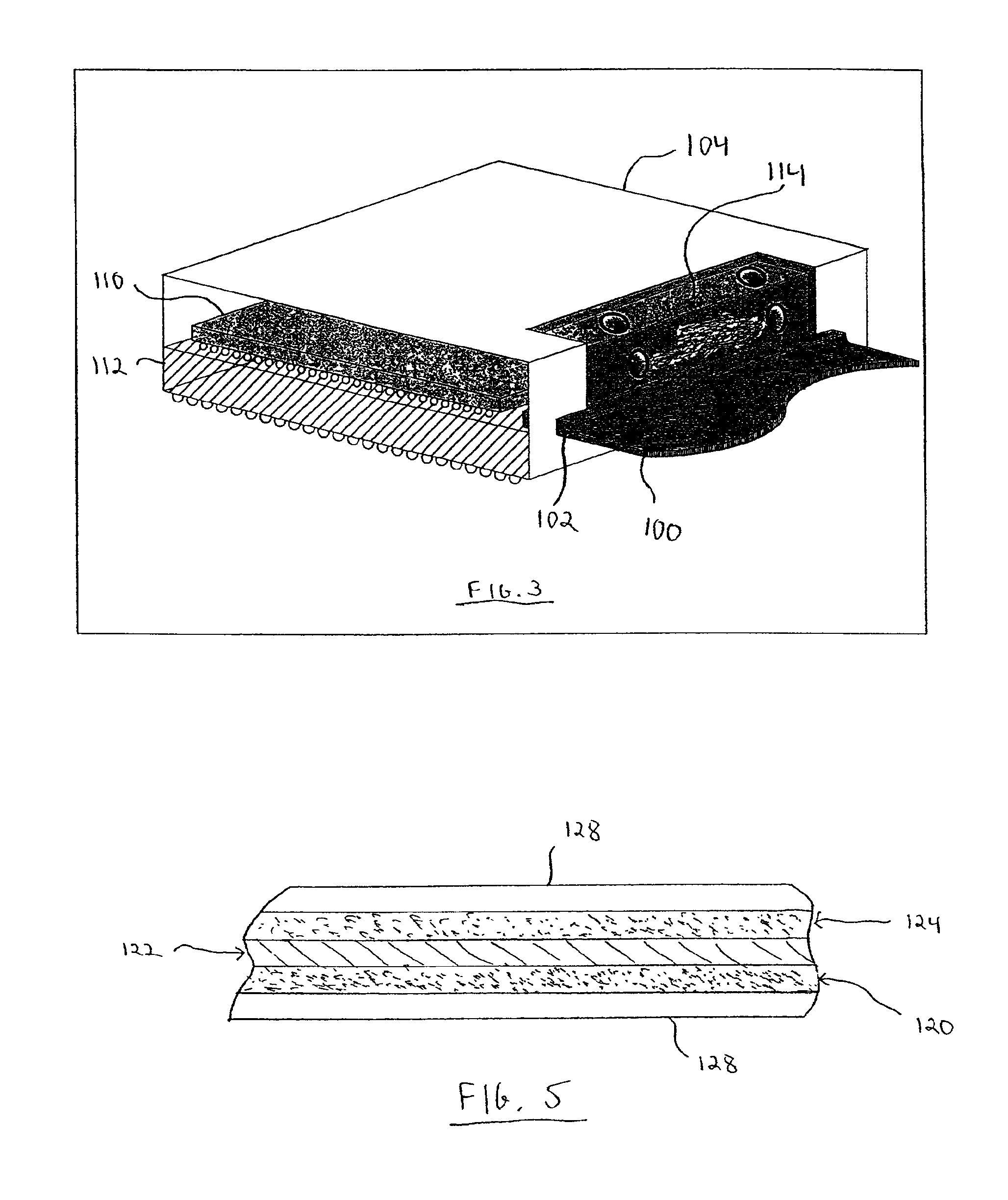

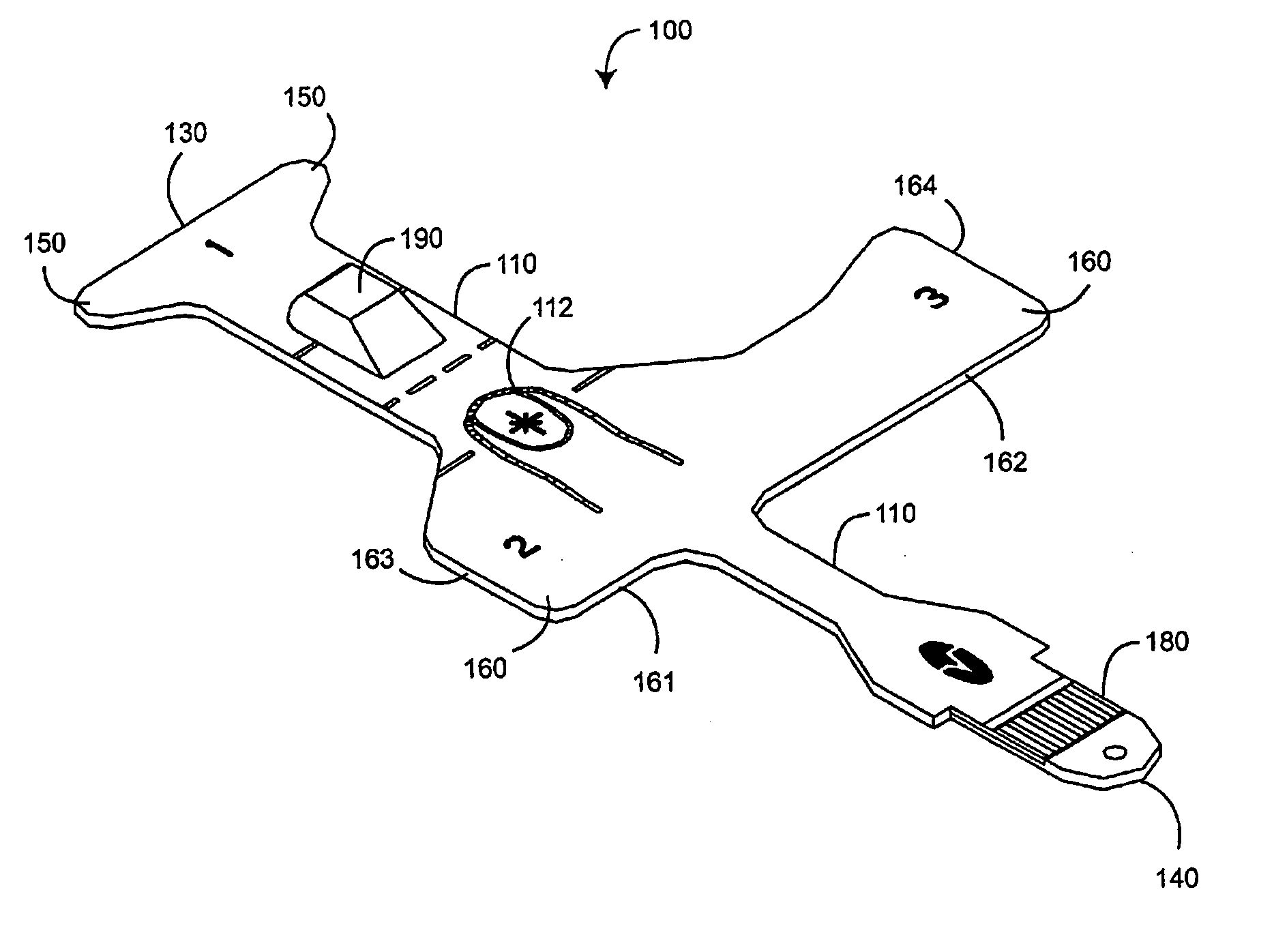

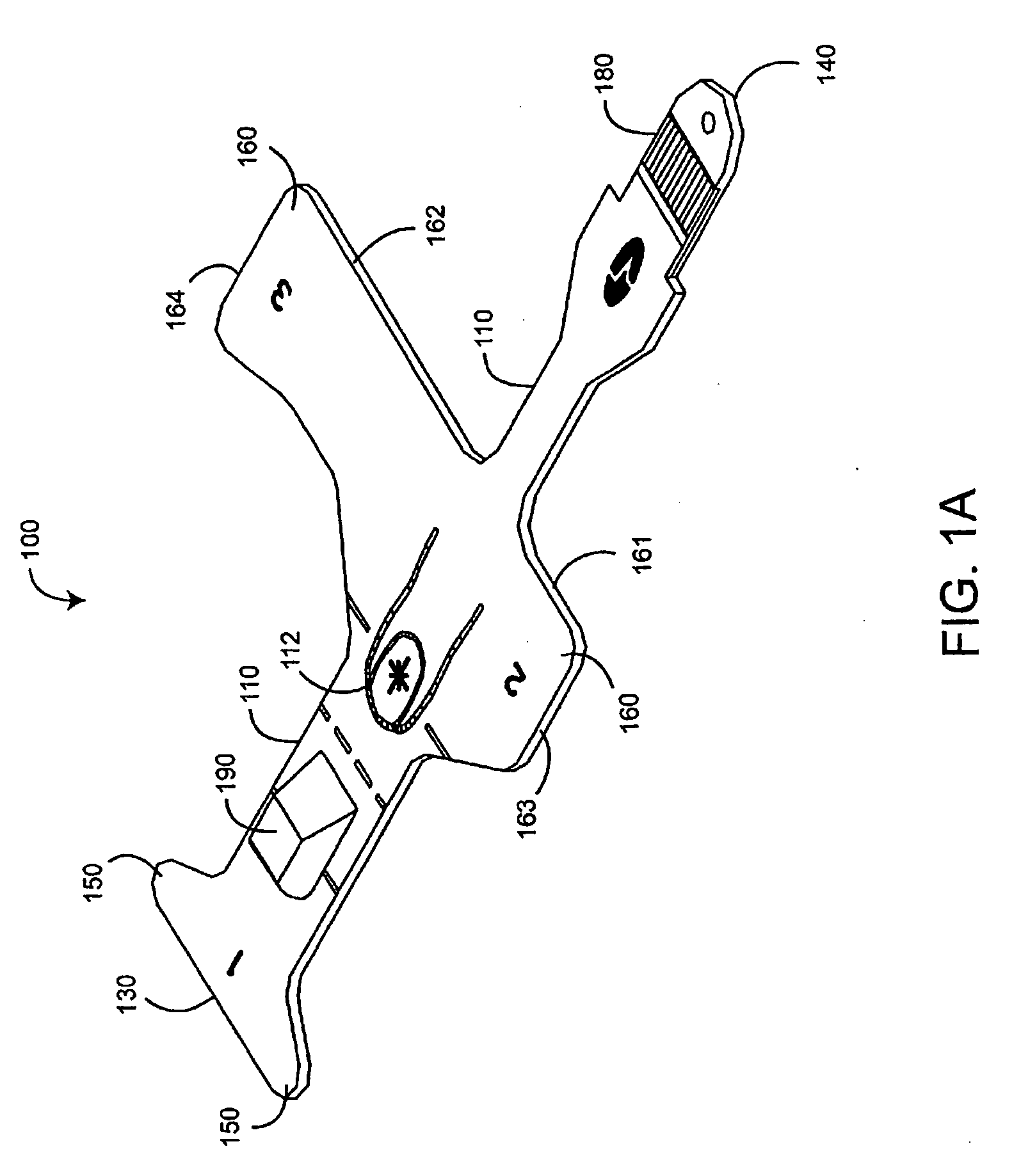

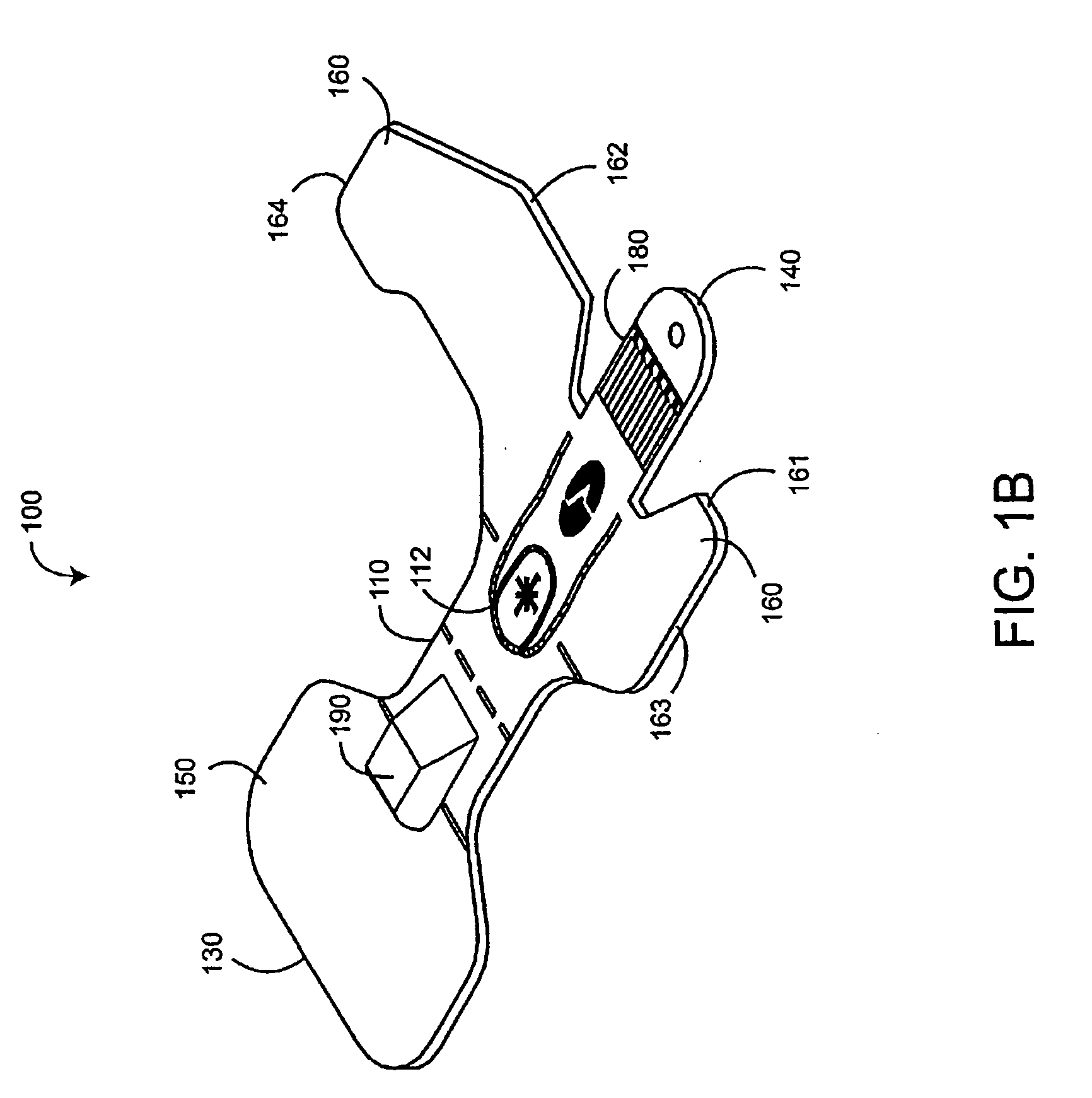

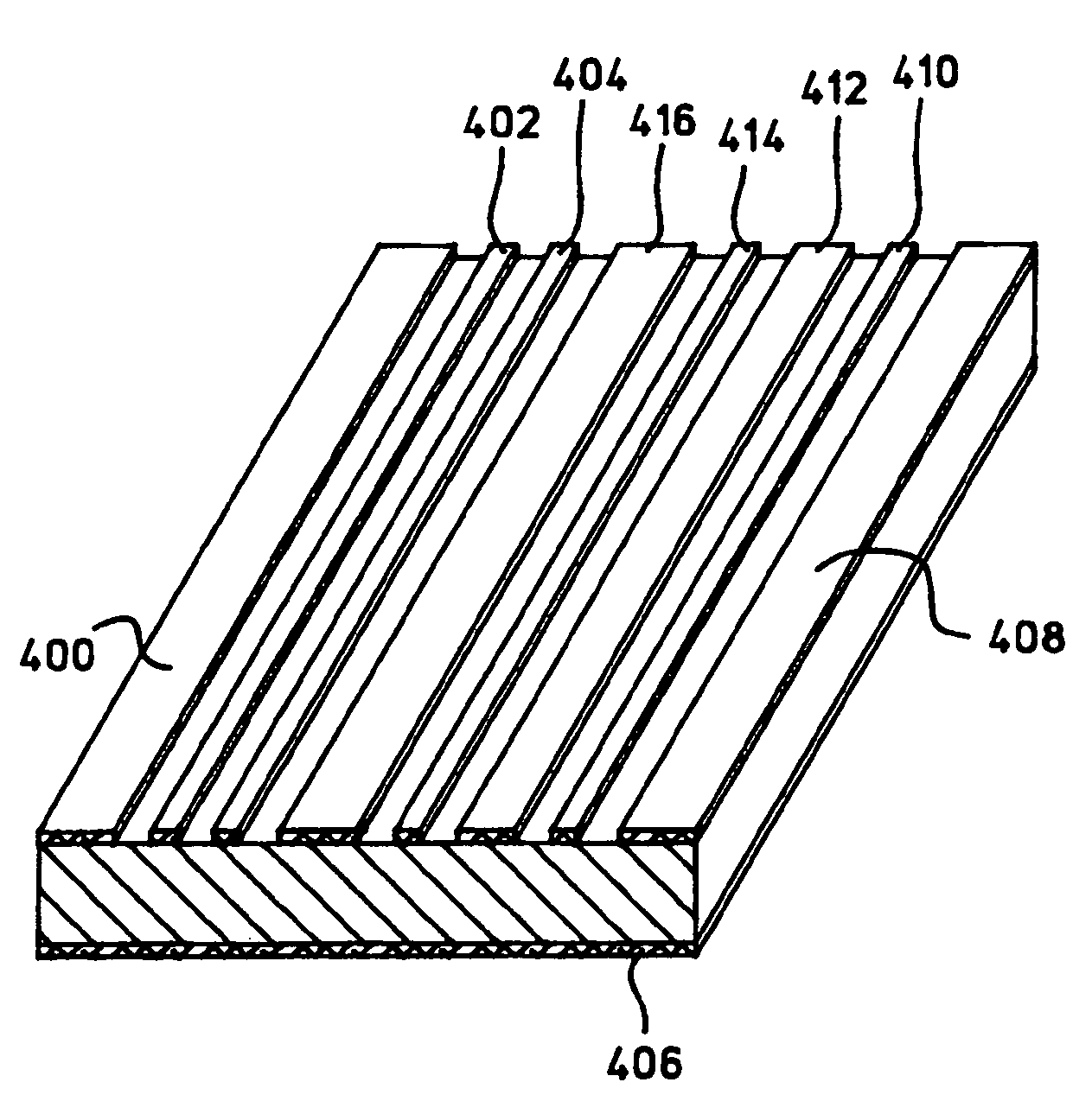

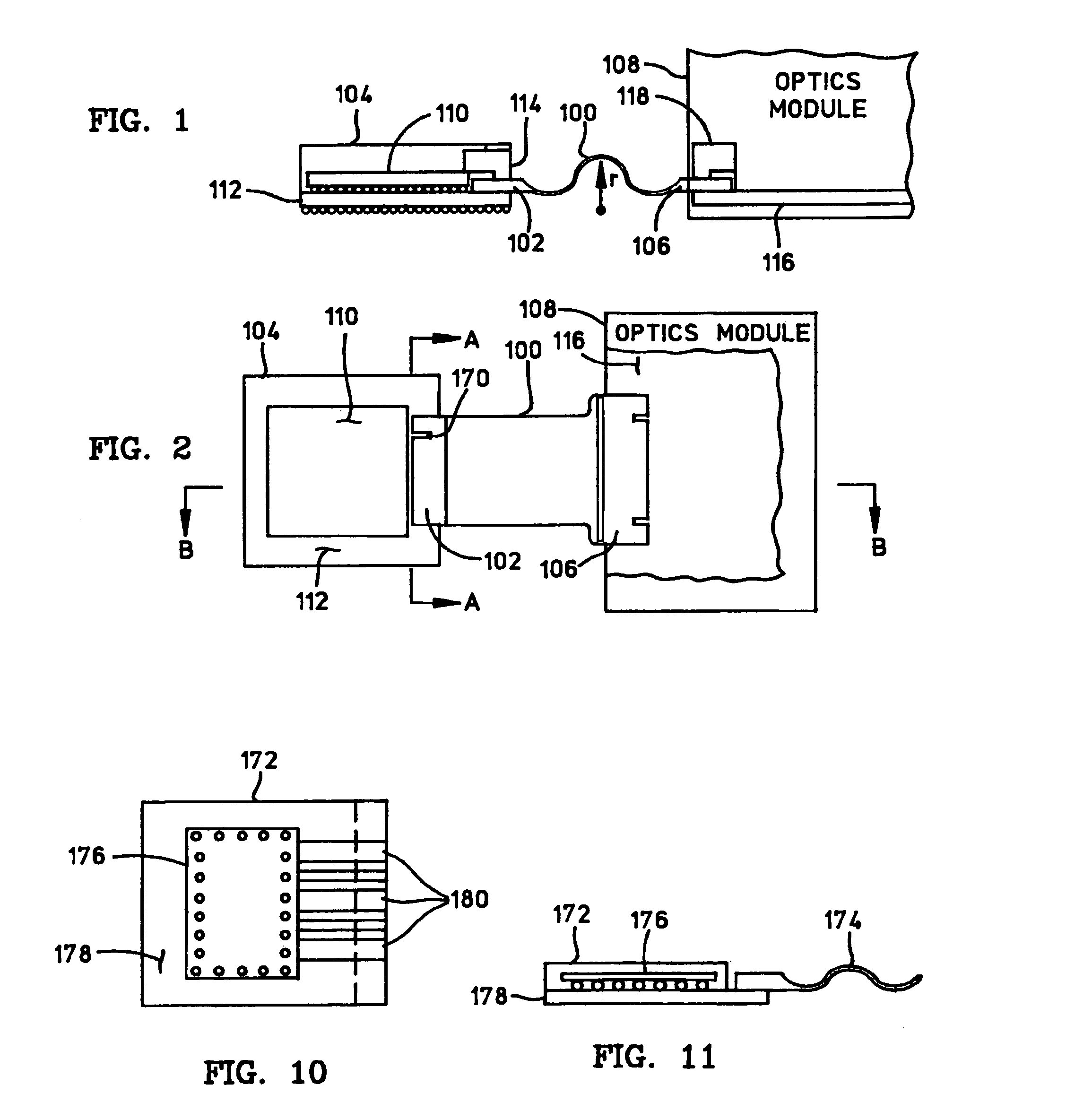

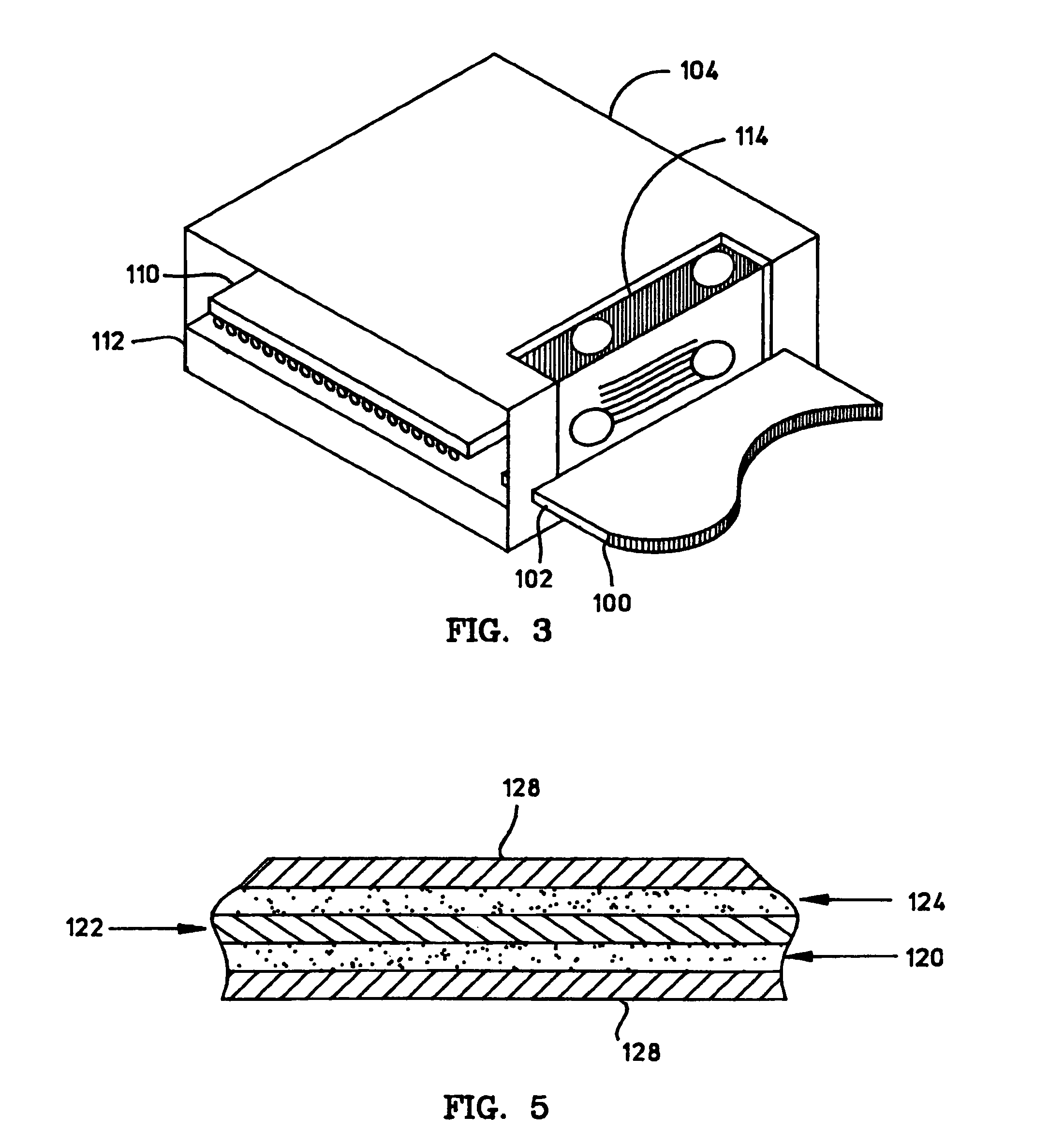

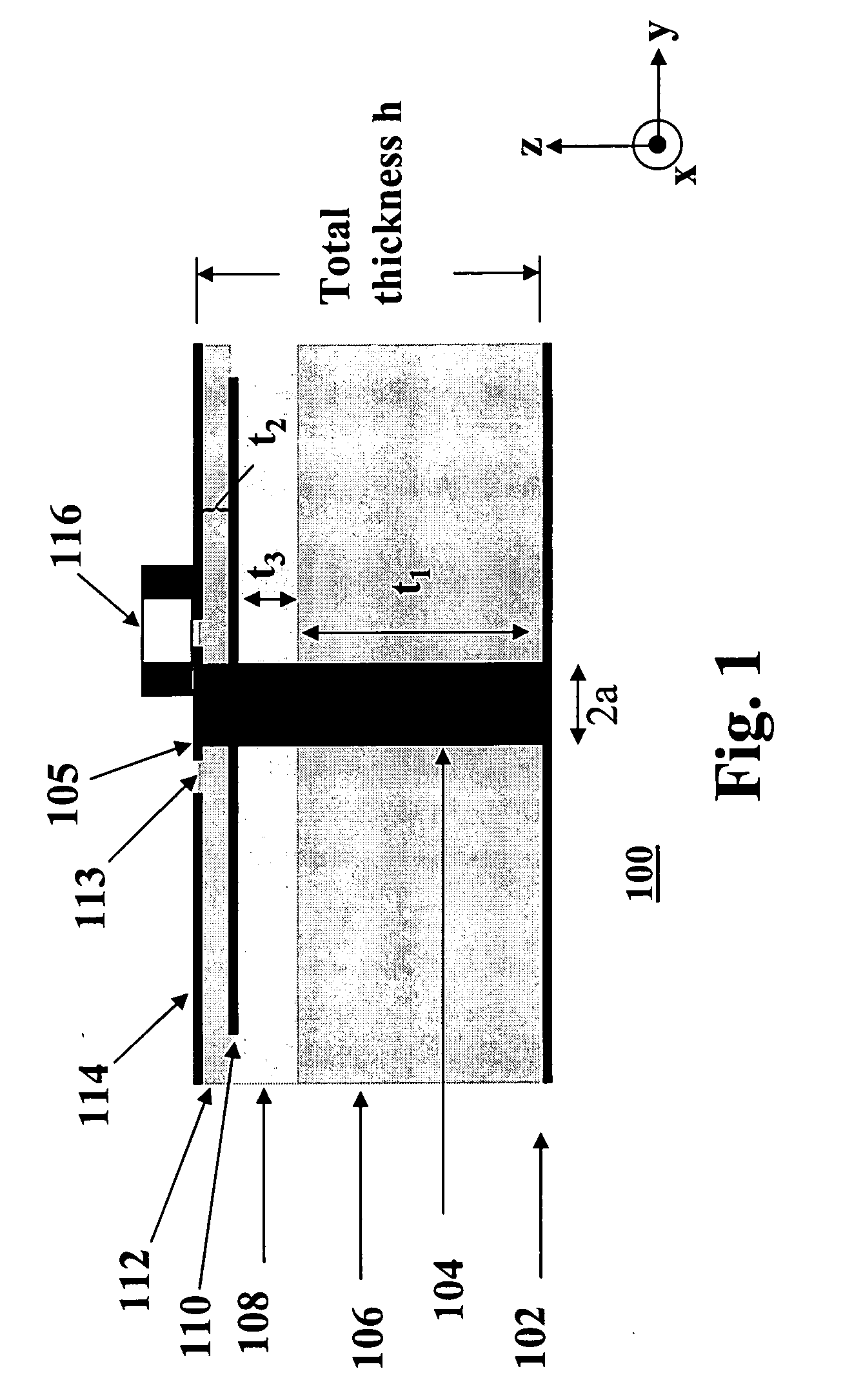

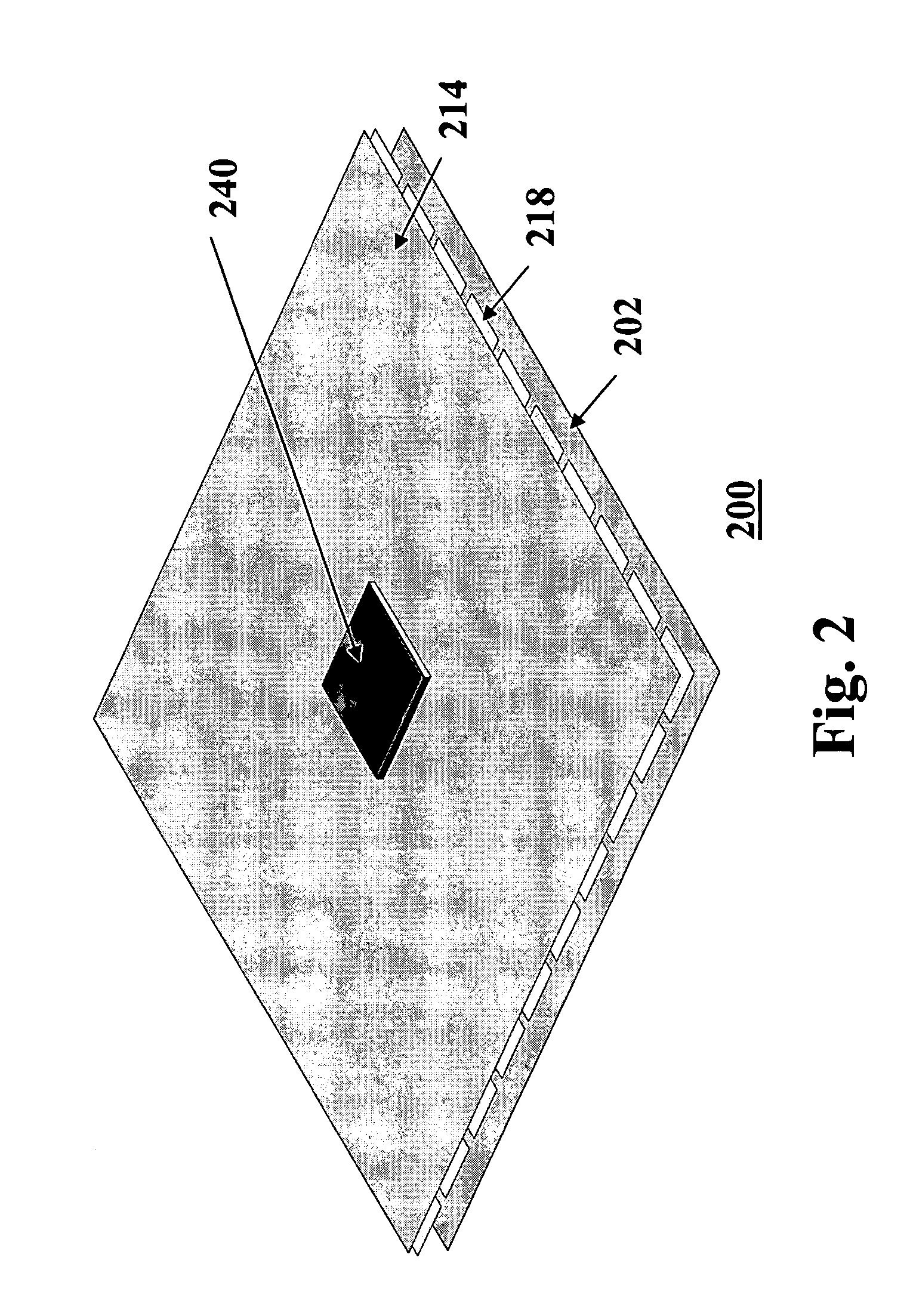

Flex circuit shielded optical sensor

InactiveUS6985764B2Cross-talk/noise/interference reductionColor/spectral properties measurementsPhotovoltaic detectorsPhotodetector

A flex circuit optical sensor has an integrated Faraday shield. A conductive trace layer disposed on a substrate is used to form a conductive grid which shields the face of a photodetector. A conductive ink layer is formed on a substrate side opposite the trace layer. The back and sides of the detector are shielded by flex circuit flaps that have the conductive ink layer but substantially exclude the trace layer so as to fold over and closely adhere to the detector body. The shielded substrate flaps advantageously eliminate a separate detector shield, which is typically fabricated with an etched copper part that must be attached to a flex circuit before mounting the detector.

Owner:JPMORGAN CHASE BANK NA

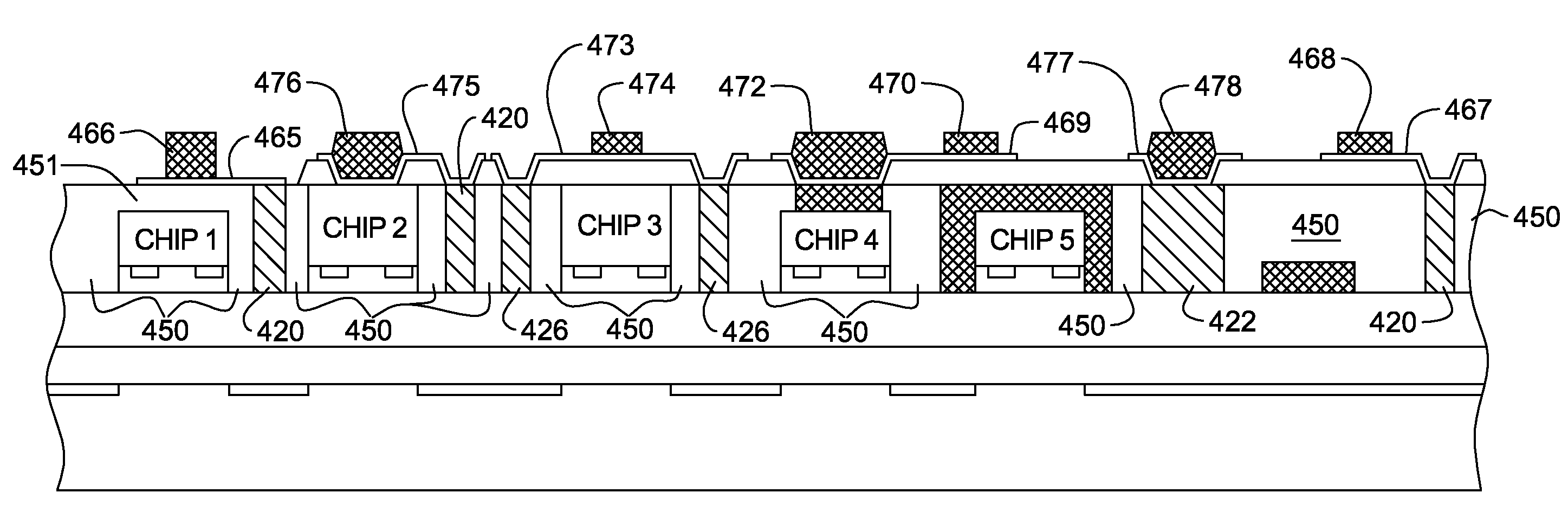

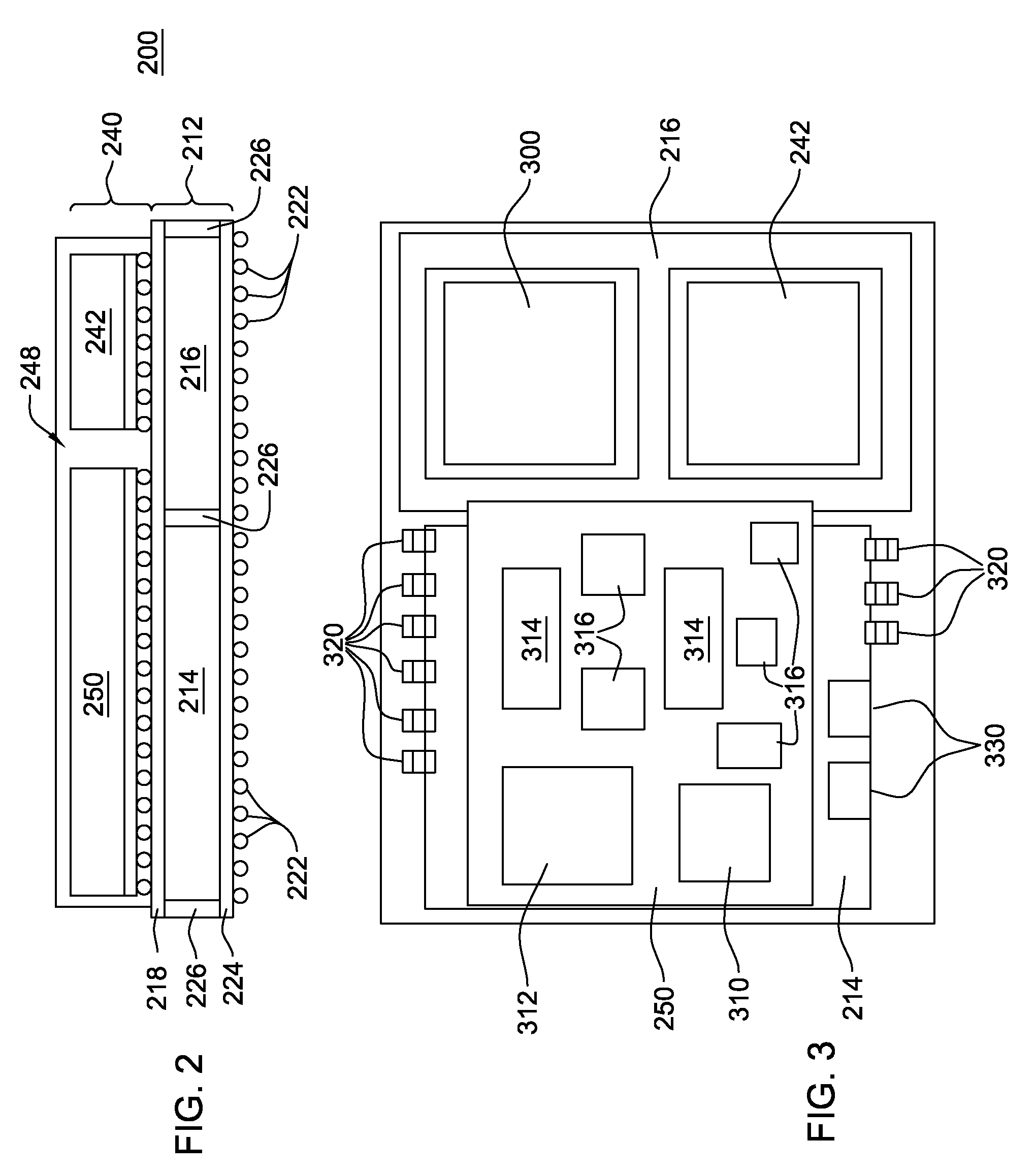

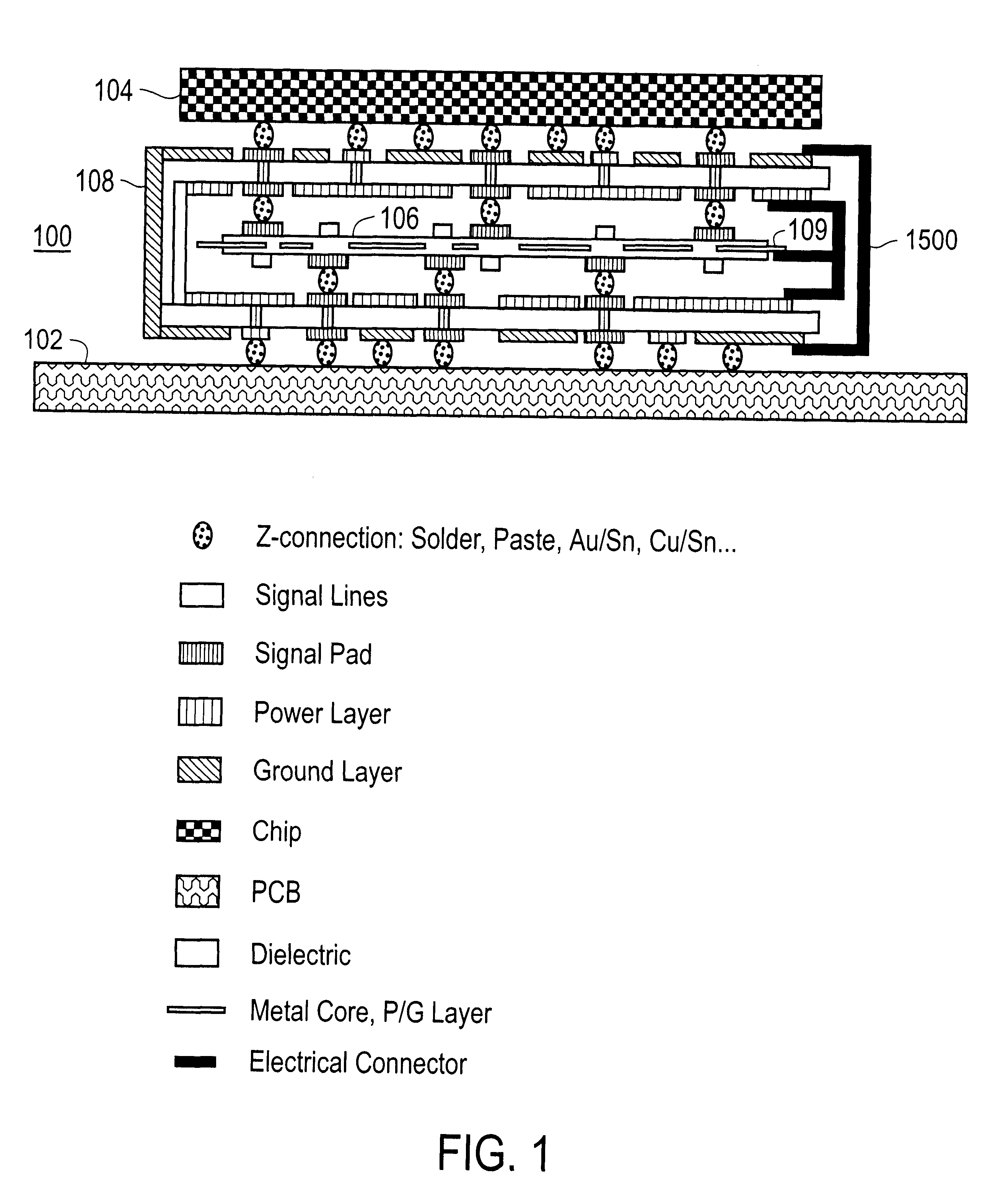

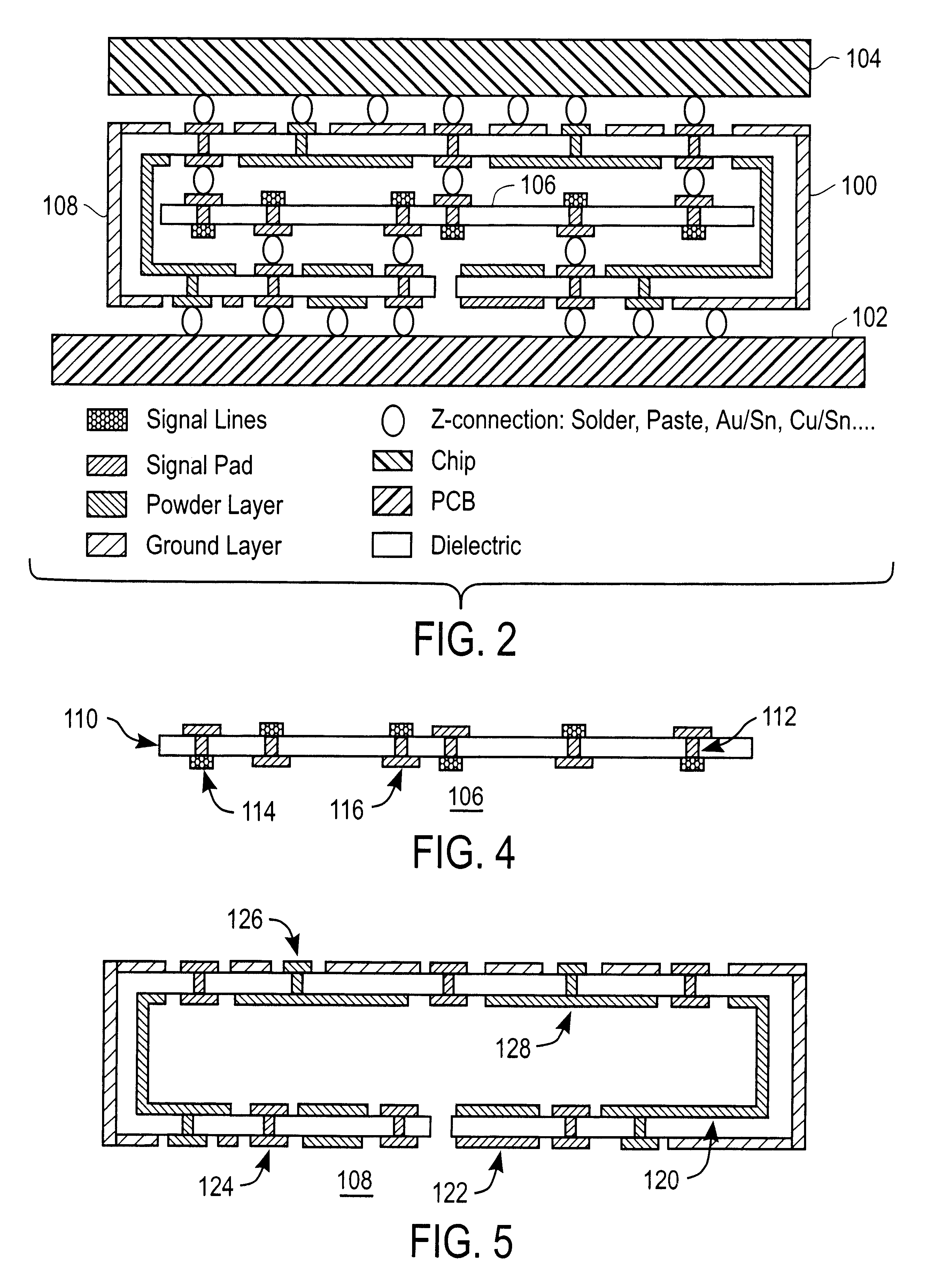

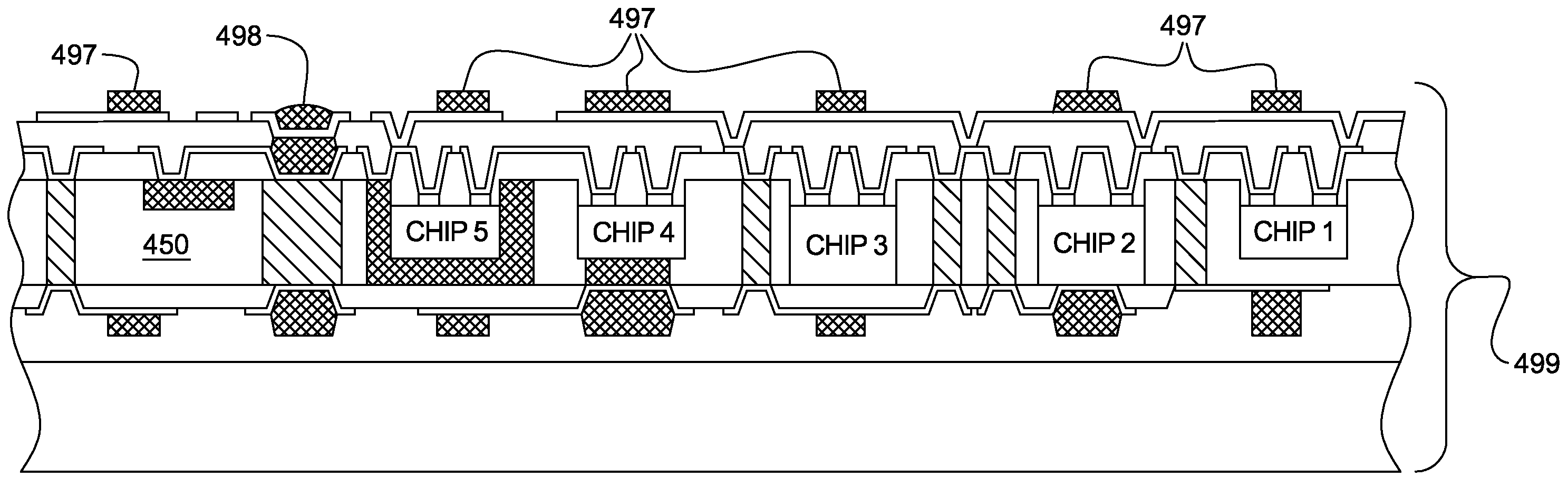

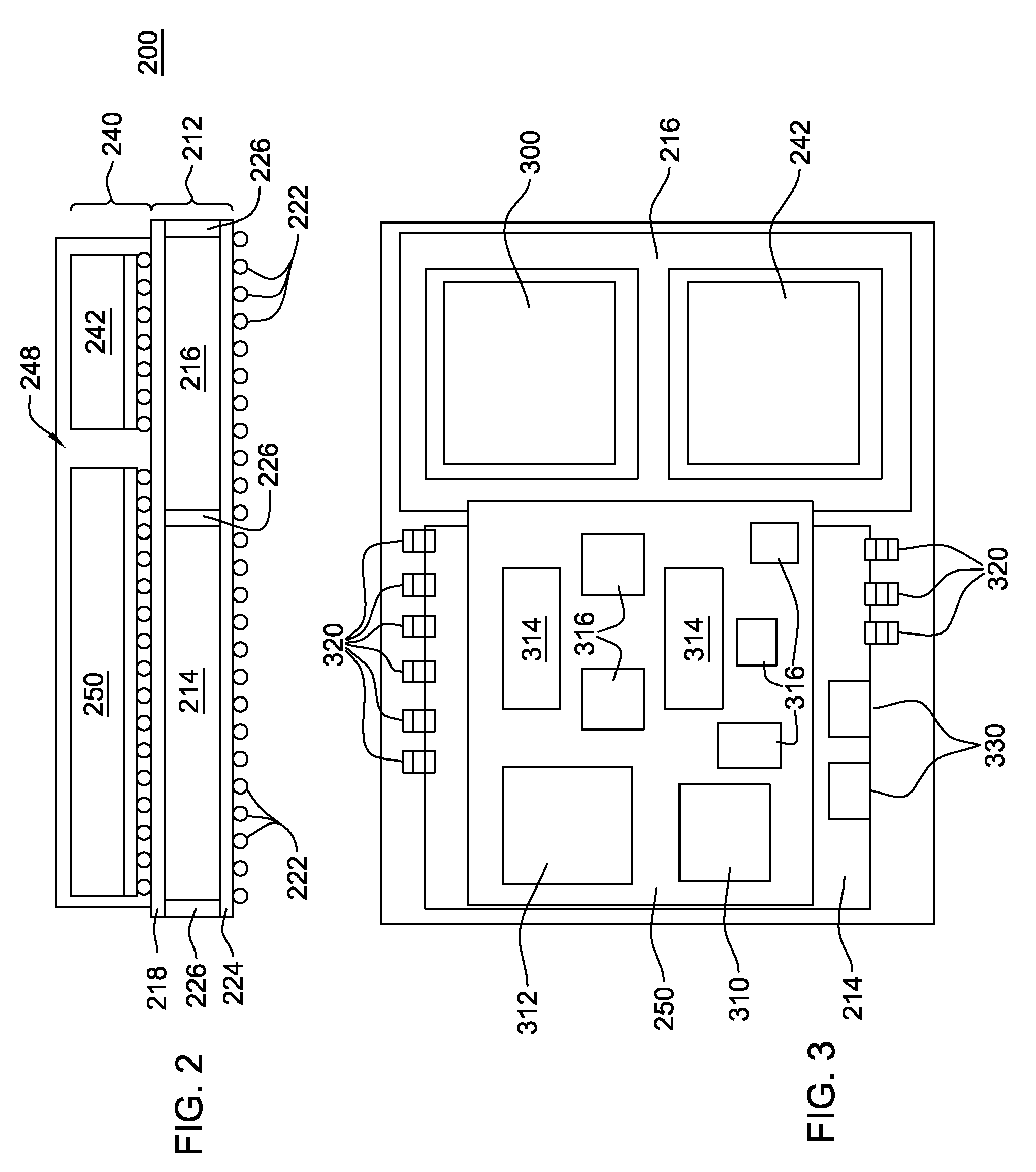

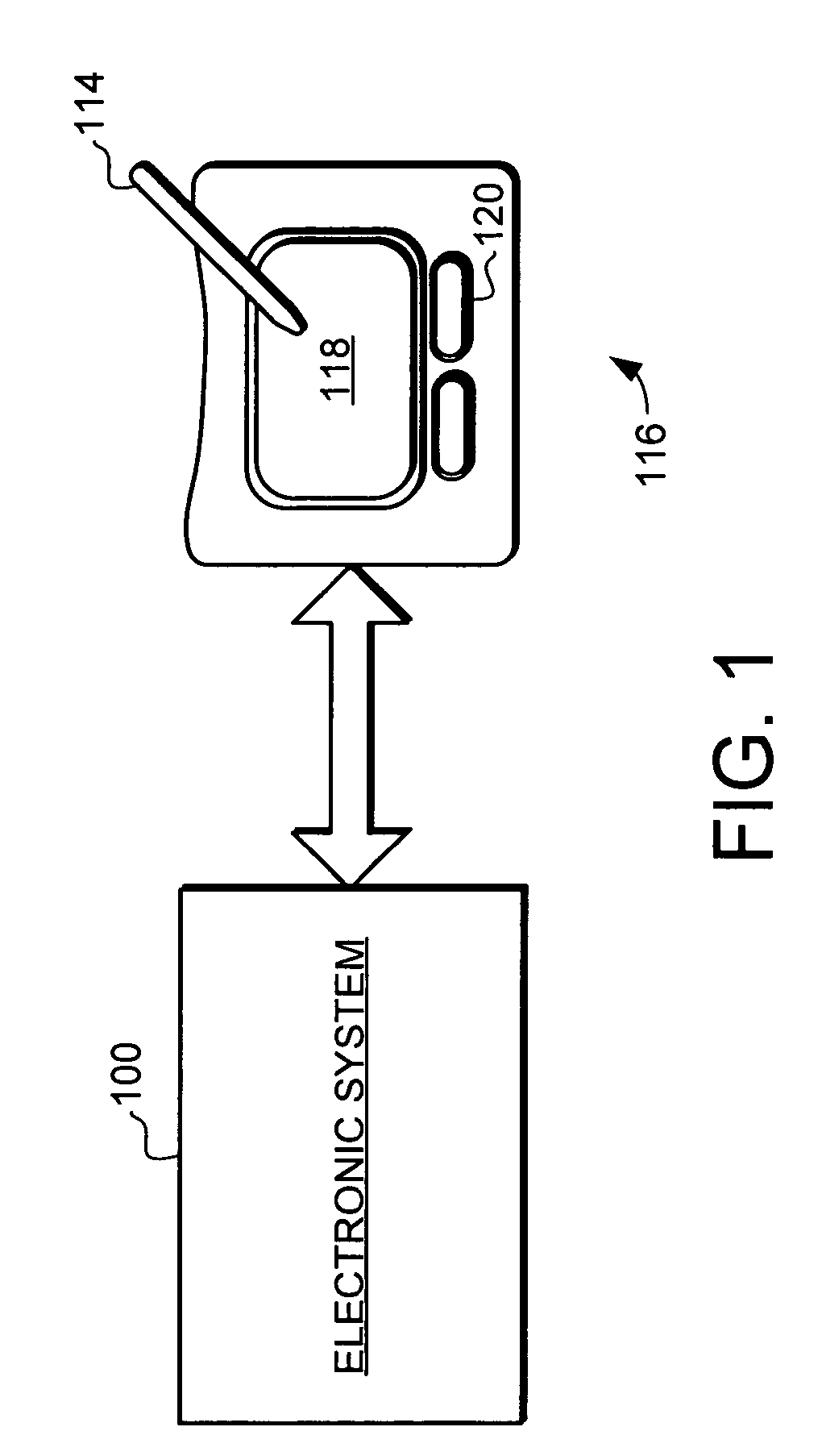

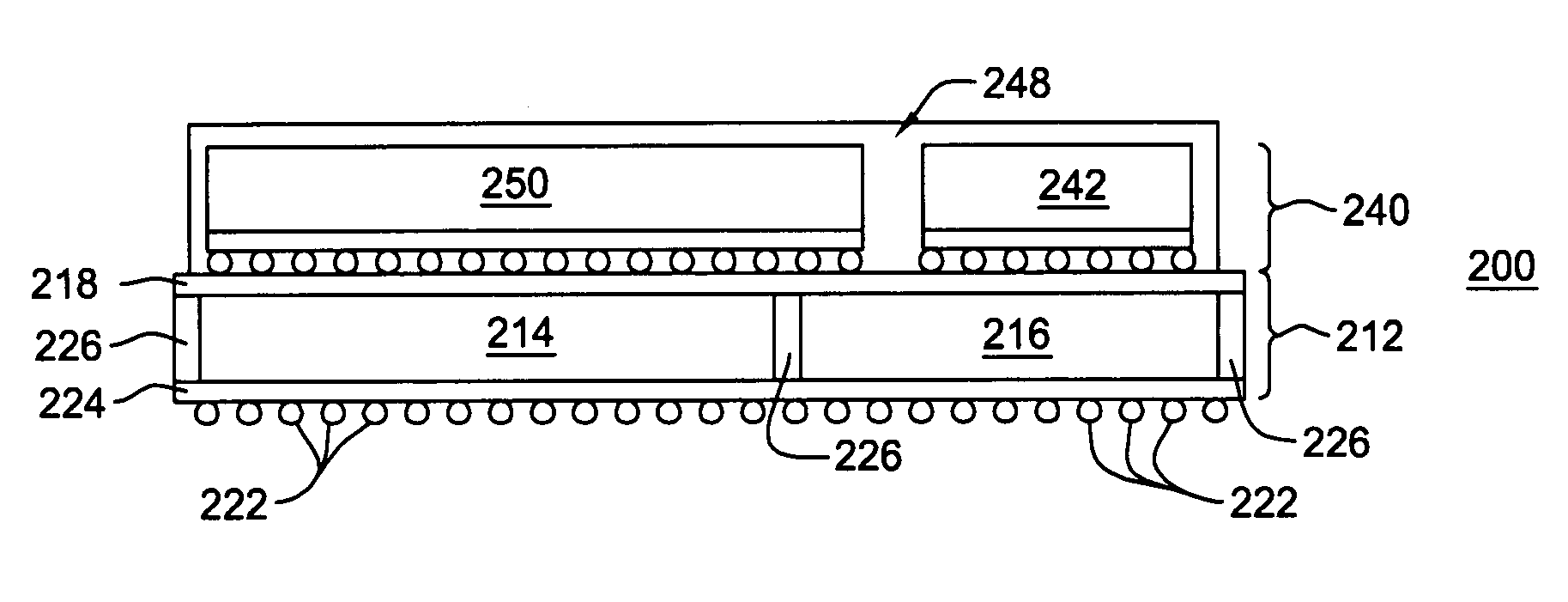

Integrated structures and fabrication methods thereof implementing a cell phone or other electronic system

ActiveUS7619901B2Semiconductor/solid-state device detailsSolid-state devicesElectronic systemsContact pad

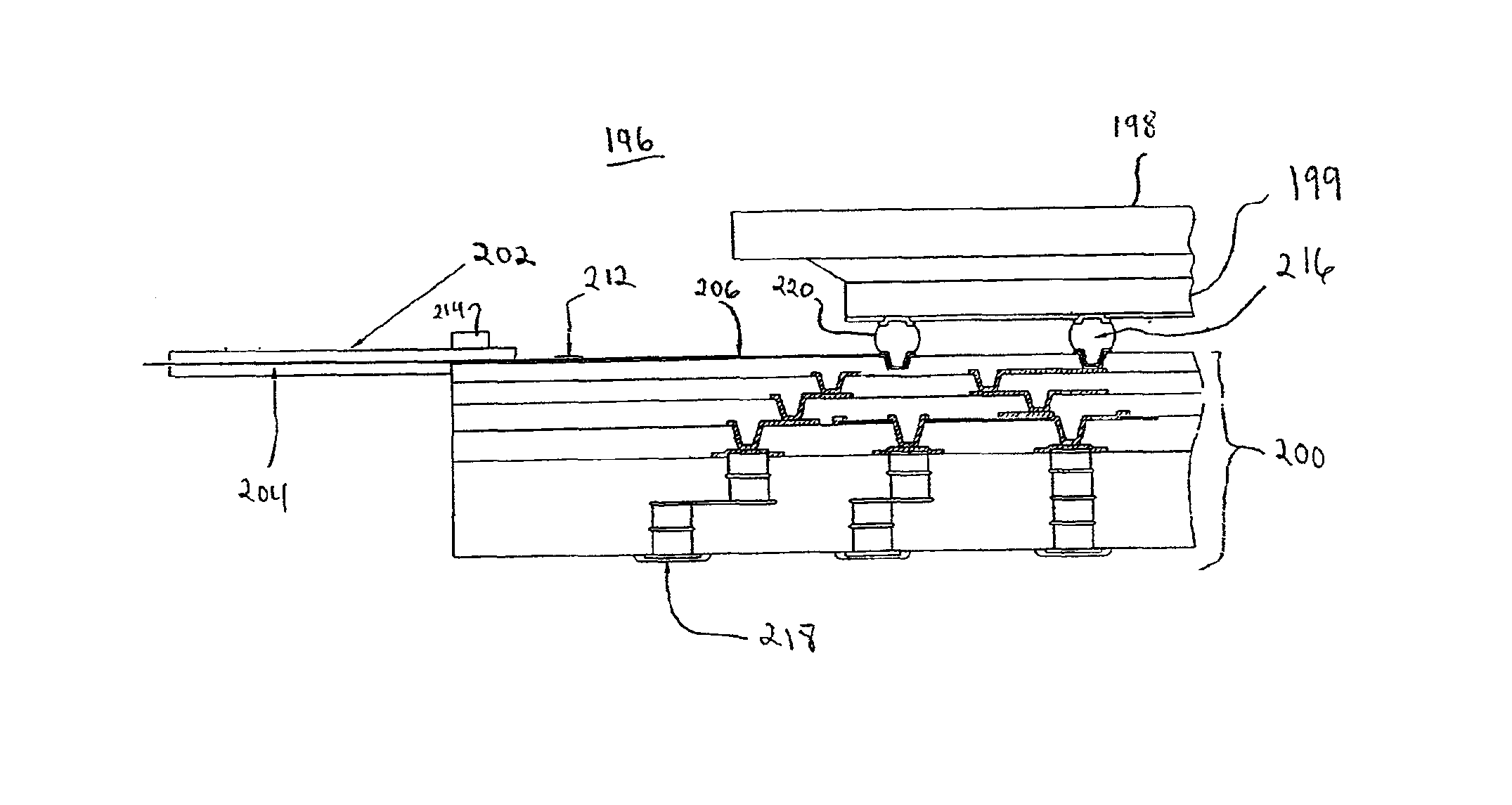

Circuit structures and methods of fabrication are provided for facilitating implementing a complete electronic system in a compact package. The circuit structure includes, in one embodiment, a chips-first multichip base layer with conductive structures extending therethrough. An interconnect layer is disposed over the front surface of the multichip layer and includes interconnect metallization electrically connected to contact pads of the chips and to conductive structures extending through the structural material. A redistribution layer, disposed over the back surface of the multichip layer, includes a redistribution metallization also electrically connected to conductive structures extending through the structural material. Input / output contacts are arrayed over the redistribution layer, including over the lower surfaces of at least some integrated circuit chips within the multichip layer, and are electrically connected through the redistribution metallization, conductive structures, and interconnect metallization to contact pads of the integrated circuit chips of the multichip layer.

Owner:EPIC TECH INC

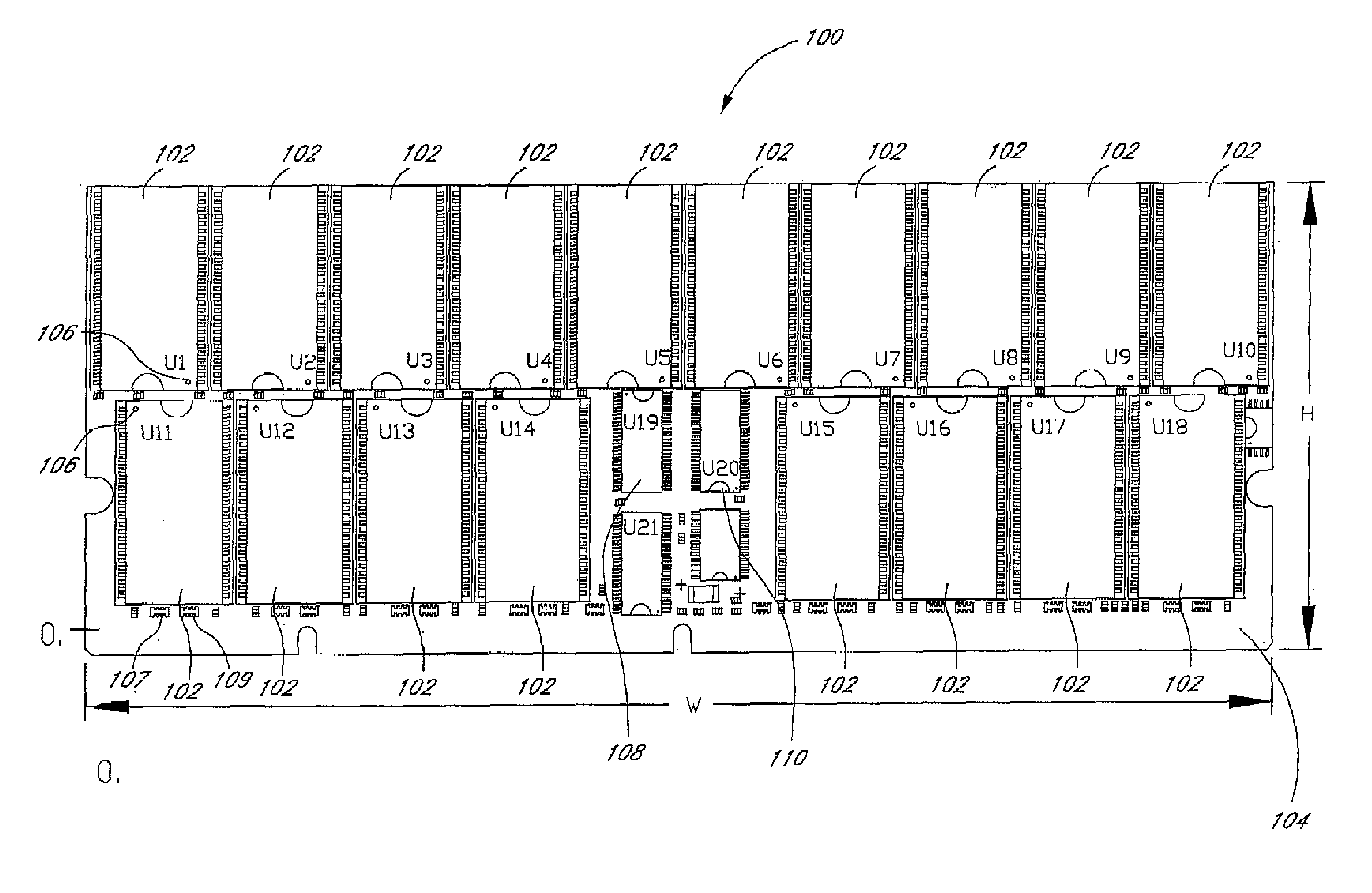

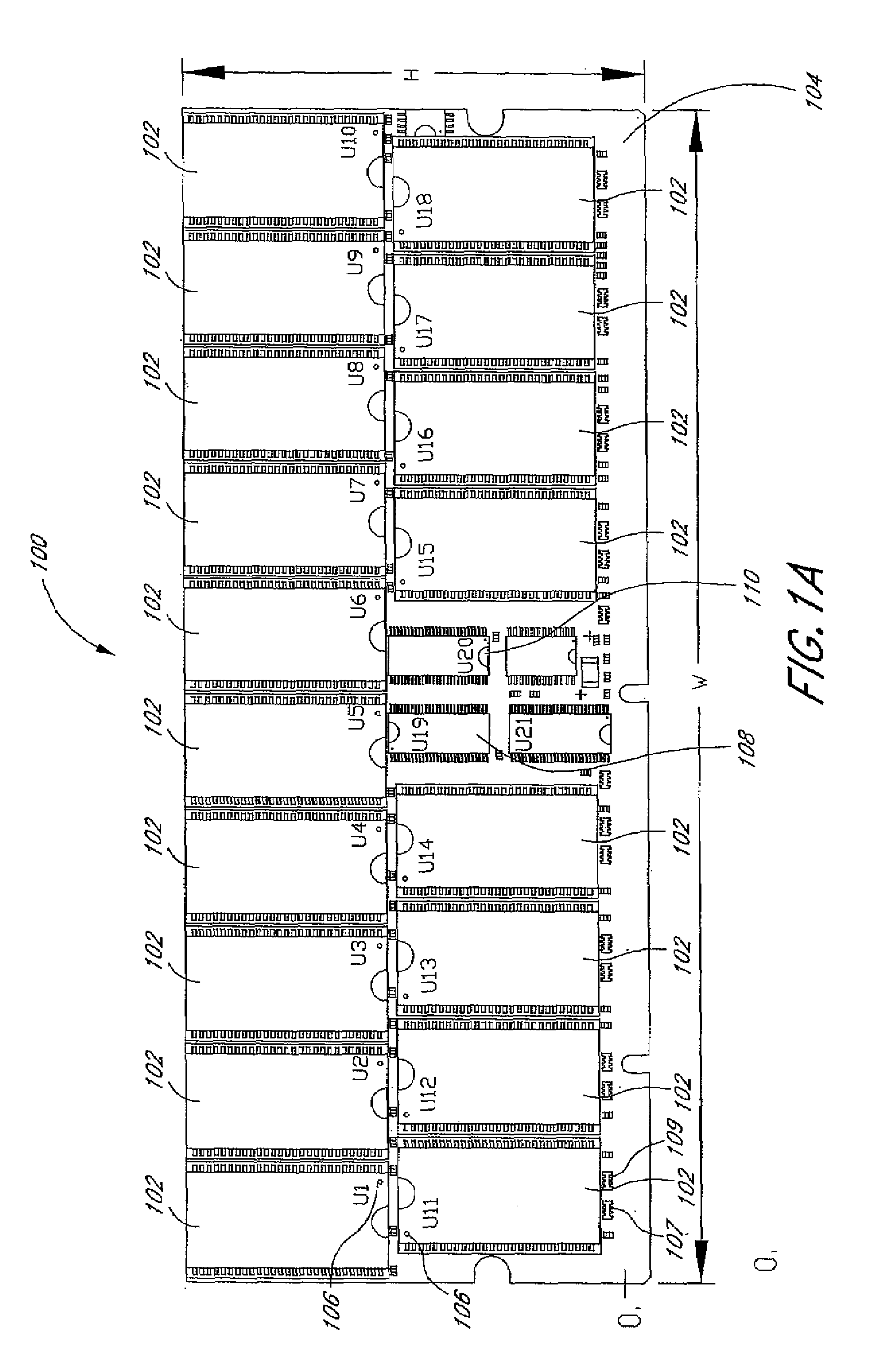

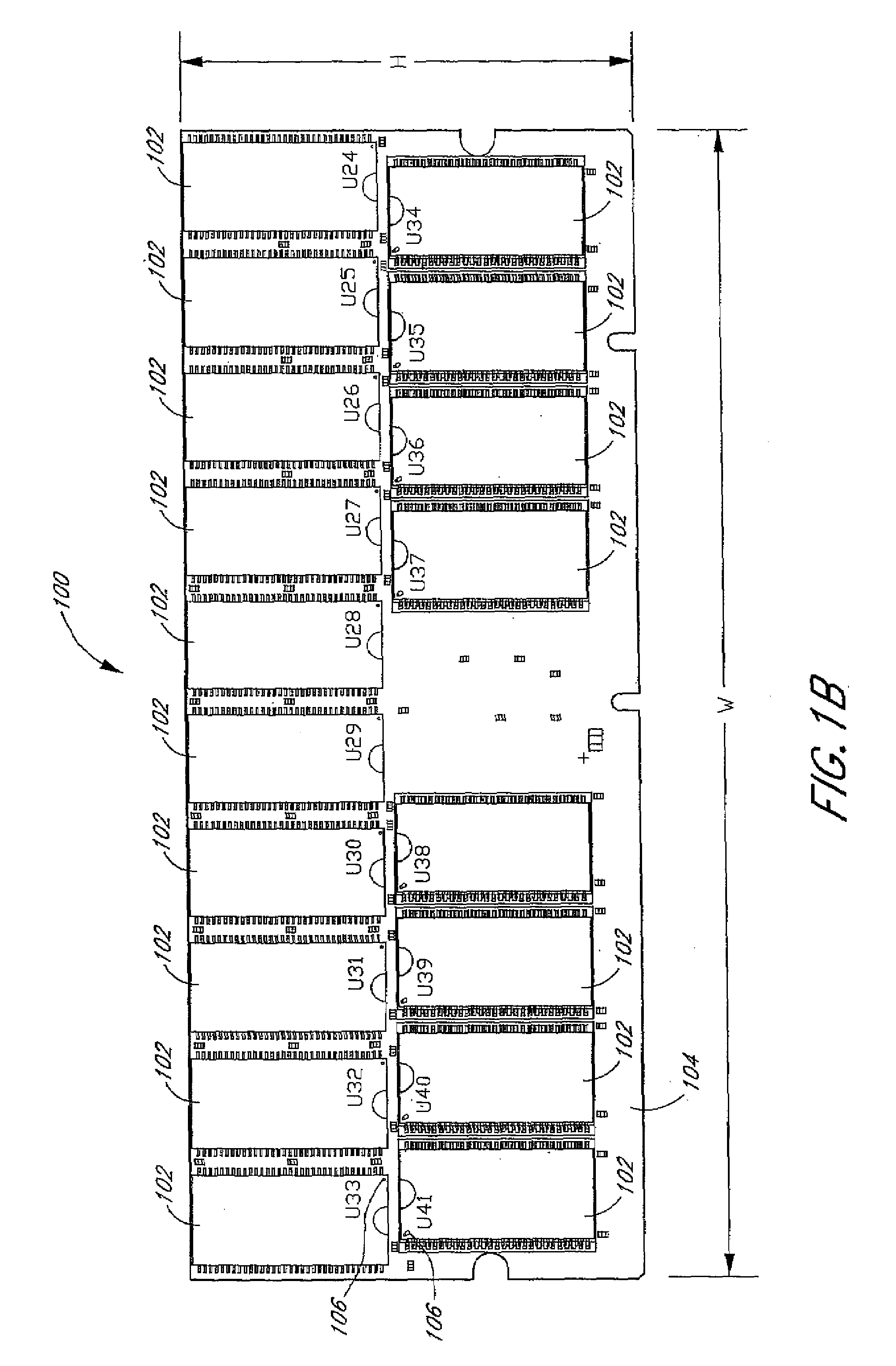

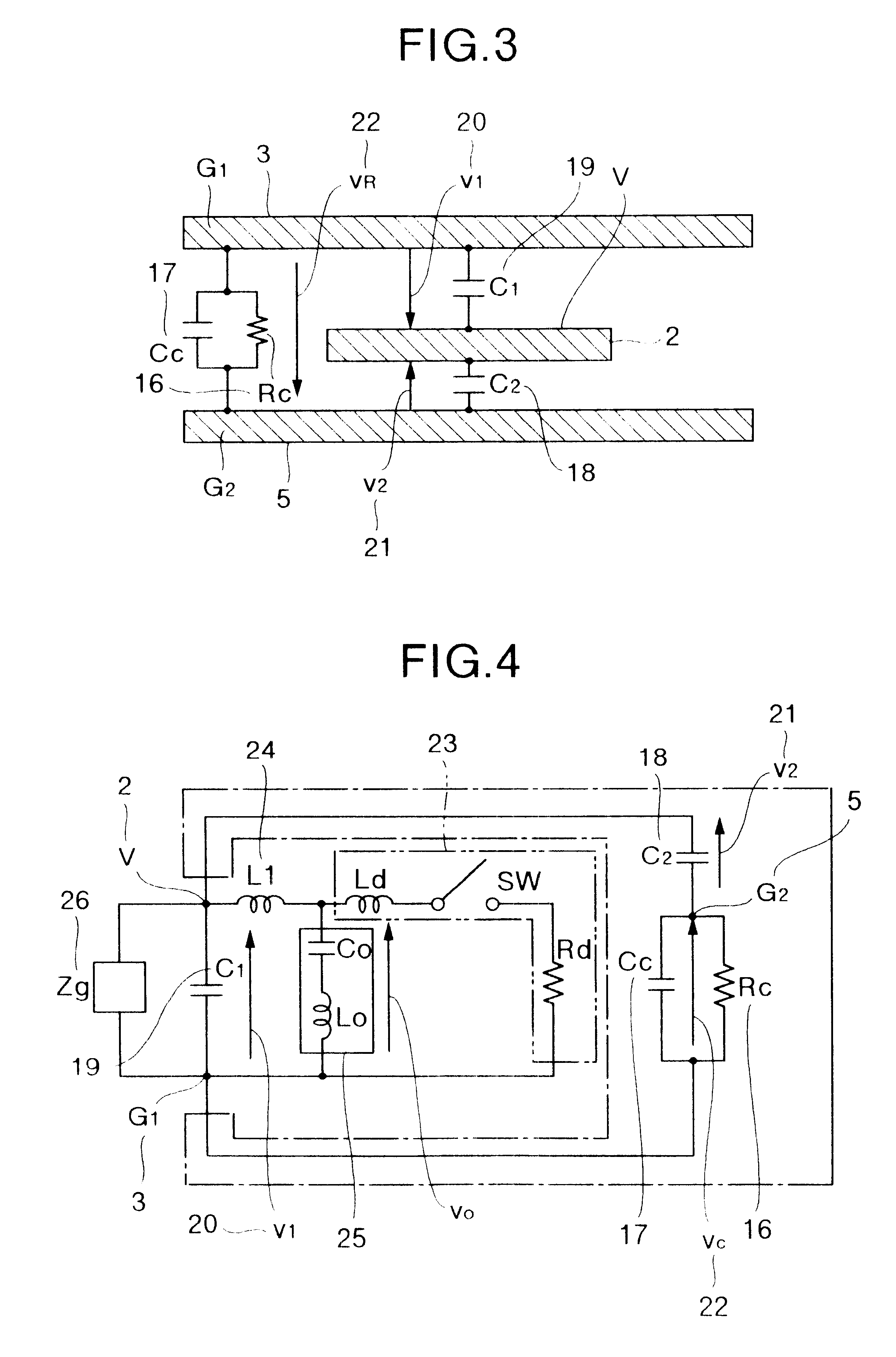

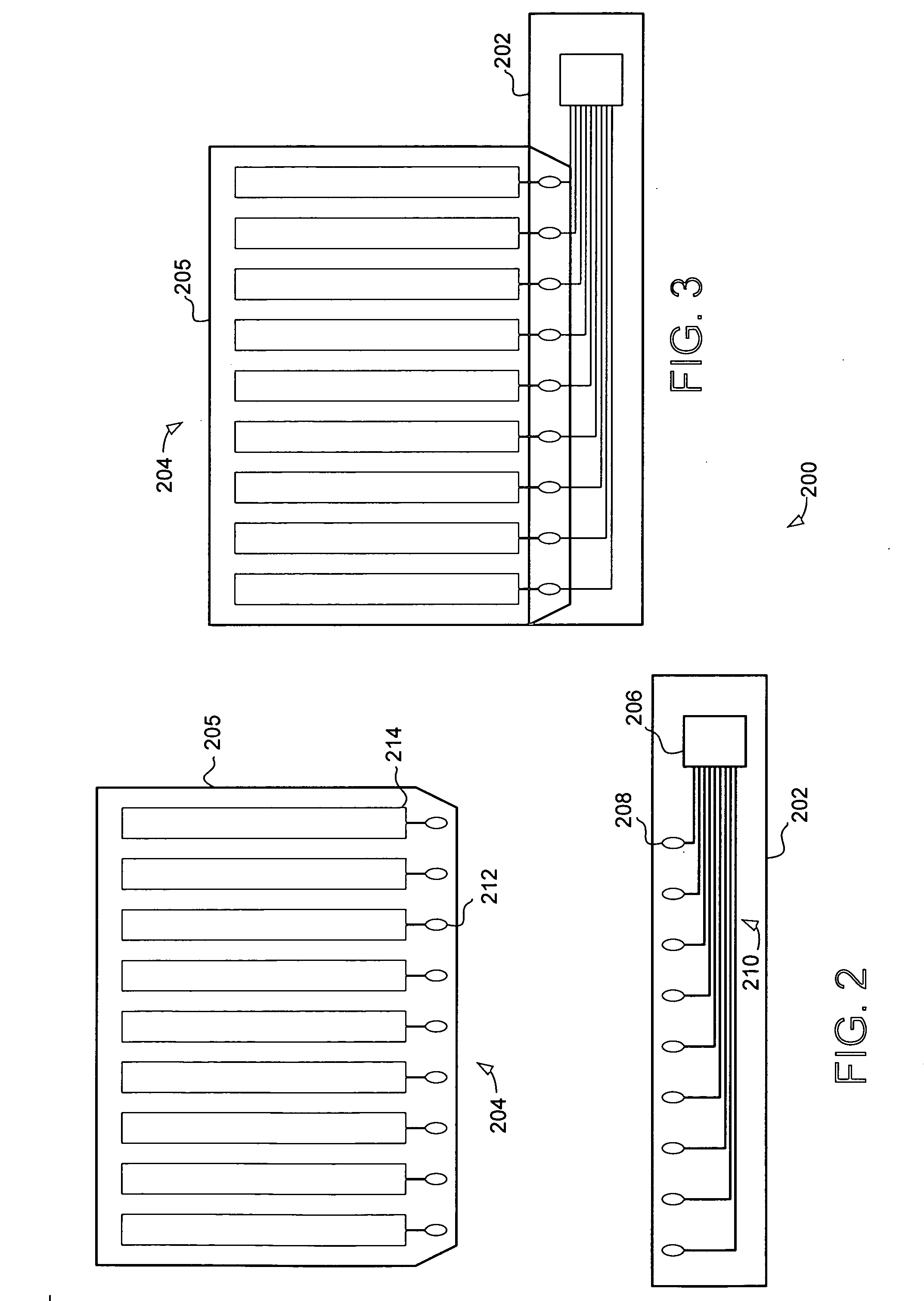

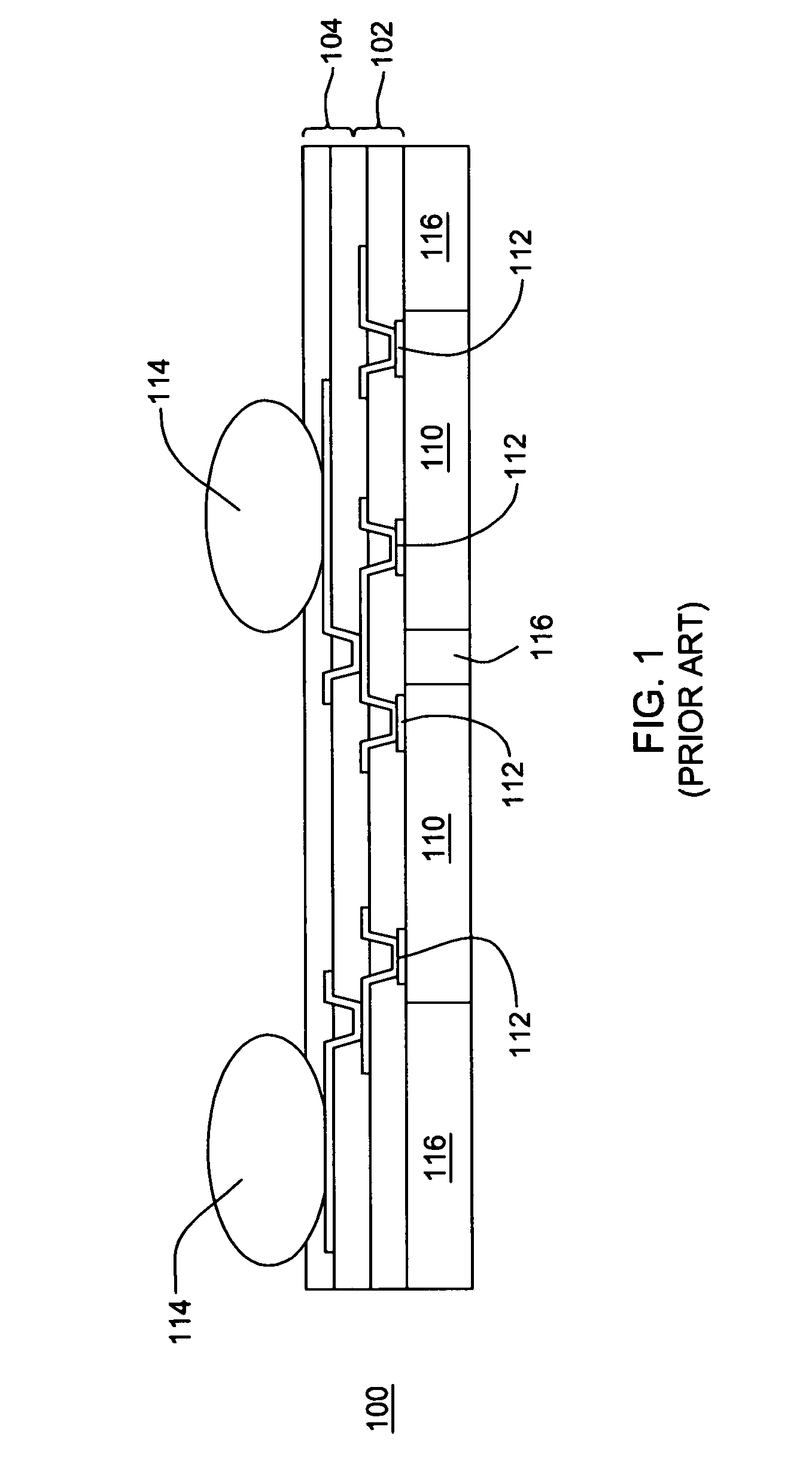

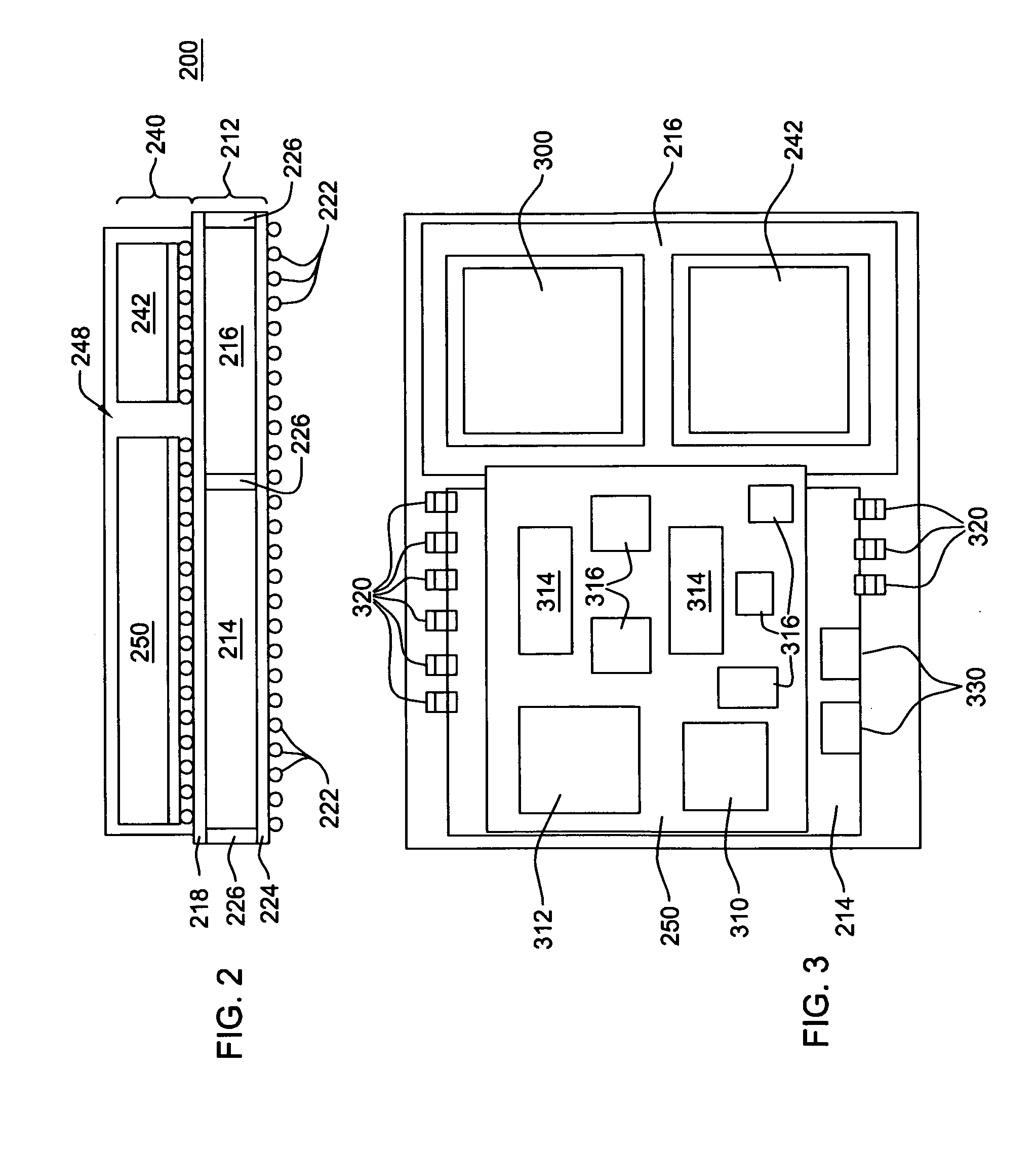

Arrangement of integrated circuits in a memory module

InactiveUS20050018495A1Final product manufactureCross-talk/noise/interference reductionGigabyteProcessor register

Abstract of the Disclosure Integrated circuits utilizing standard commercial packaging are arranged on a printed circuit board to allow the production of one-Gigabyte, two-Gigabyte, and four-Gigabyte capacity memory modules. A first row of integrated circuits is oriented in an opposite orientation to a second row of integrated circuits. The integrated circuits in the first row on a first lateral portion of the printed circuit board and in the second row on the first lateral portion are connected to a first addressing register with two register integrated circuits. The integrated circuits in the first row on the second lateral portion and in the second row on the second lateral portion are connected to a second addressing register with two register integrated circuits. Each addressing register processes a non-contiguous subset of the bits in each data word.

Owner:NETLIST INC

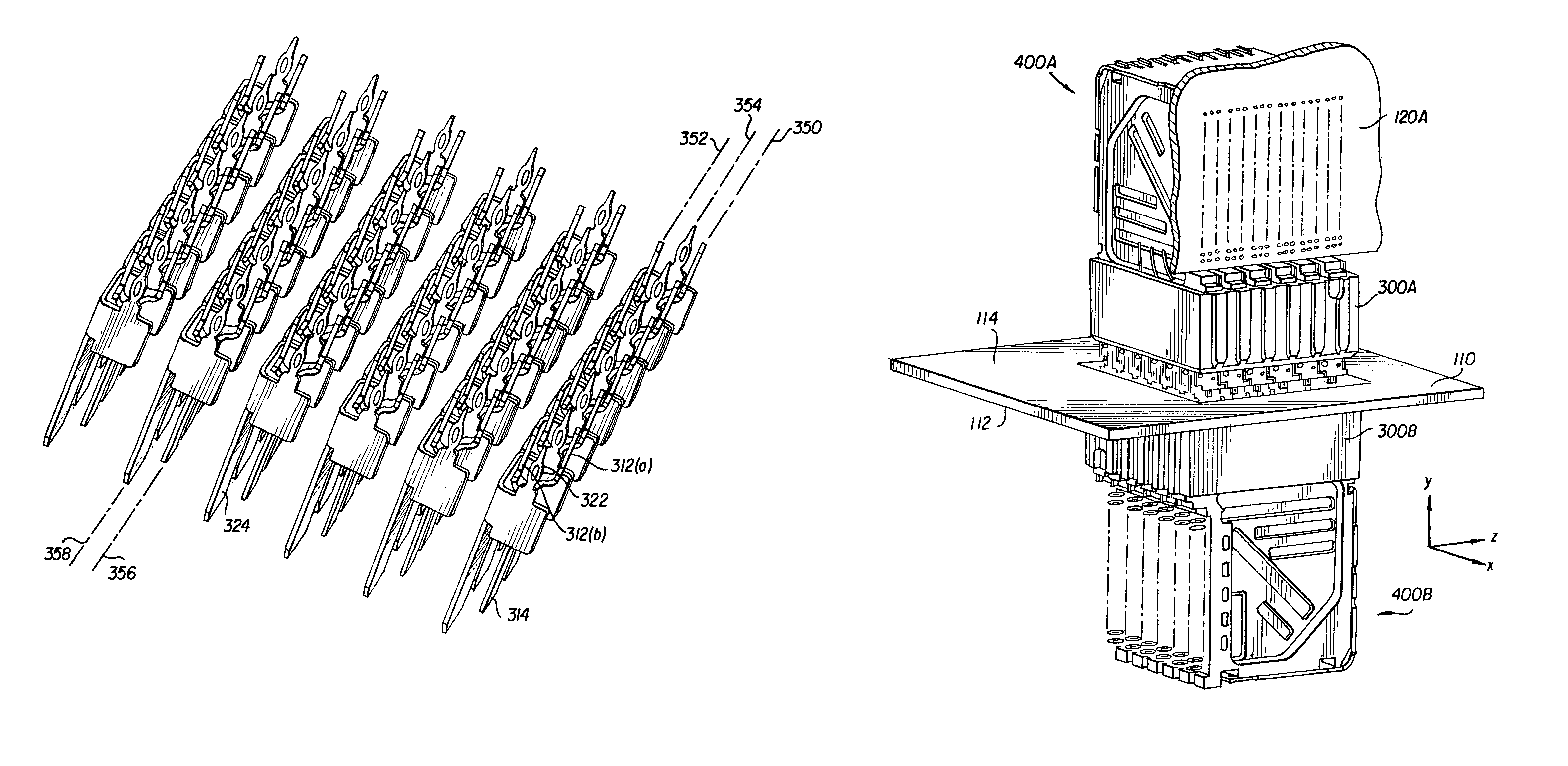

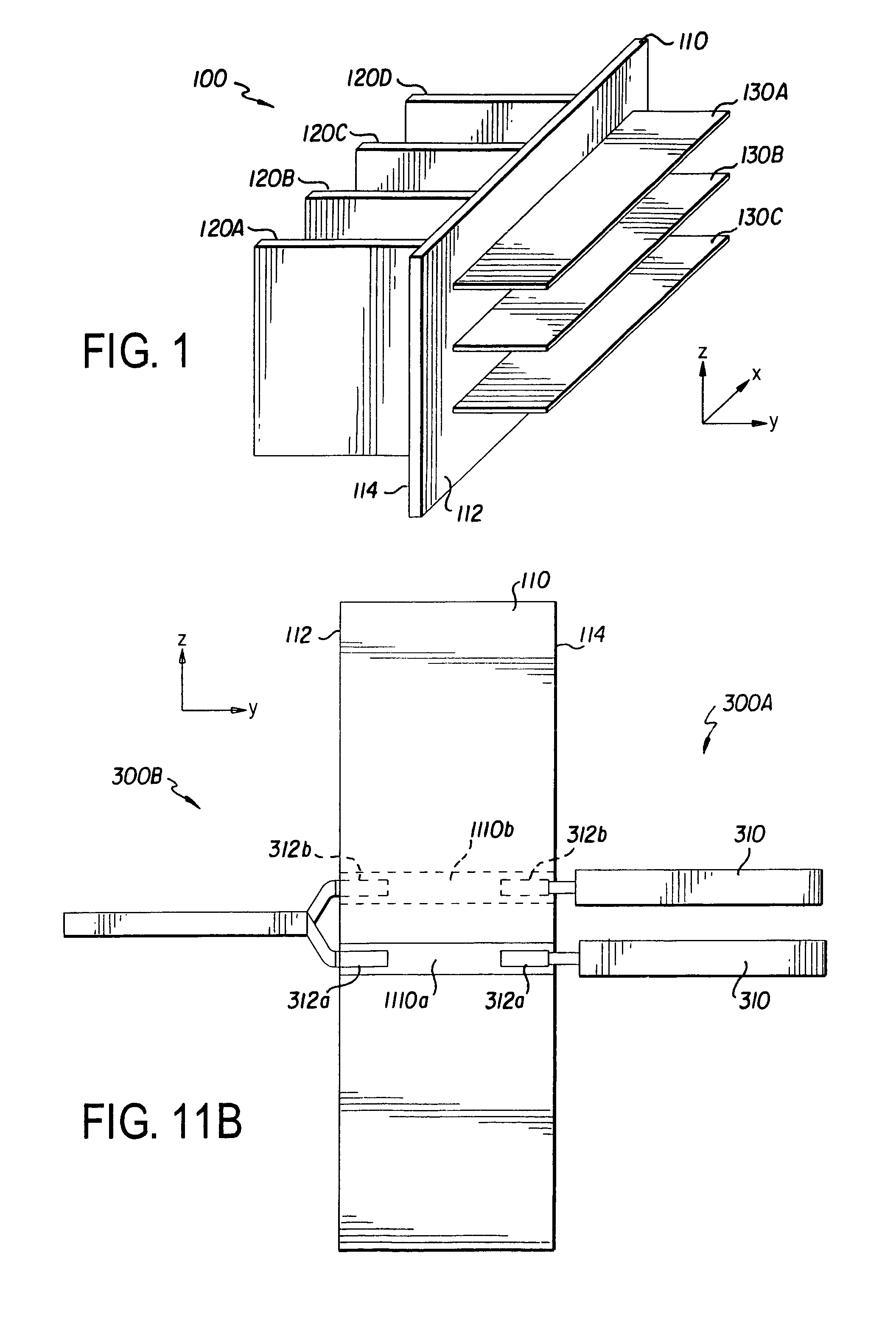

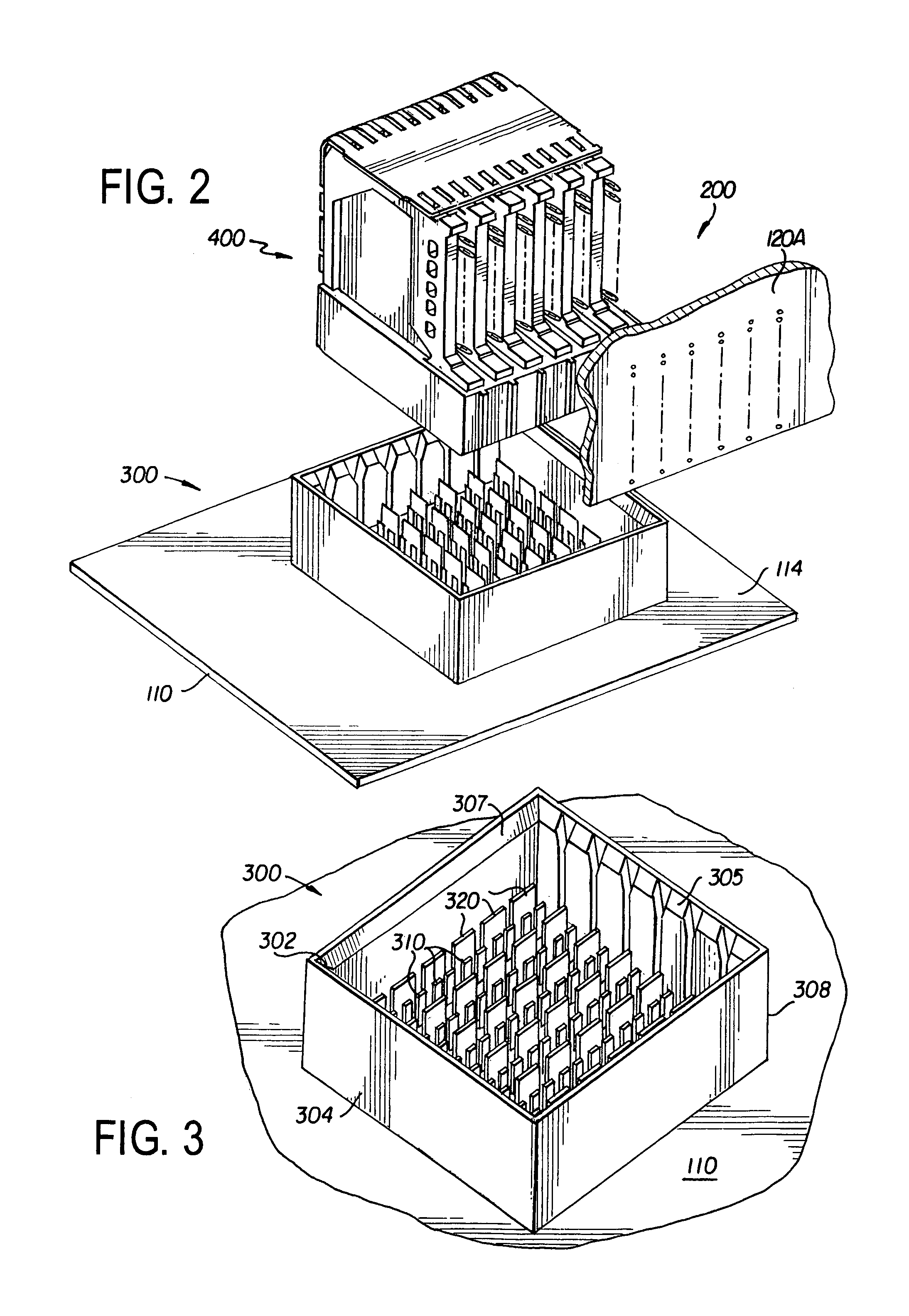

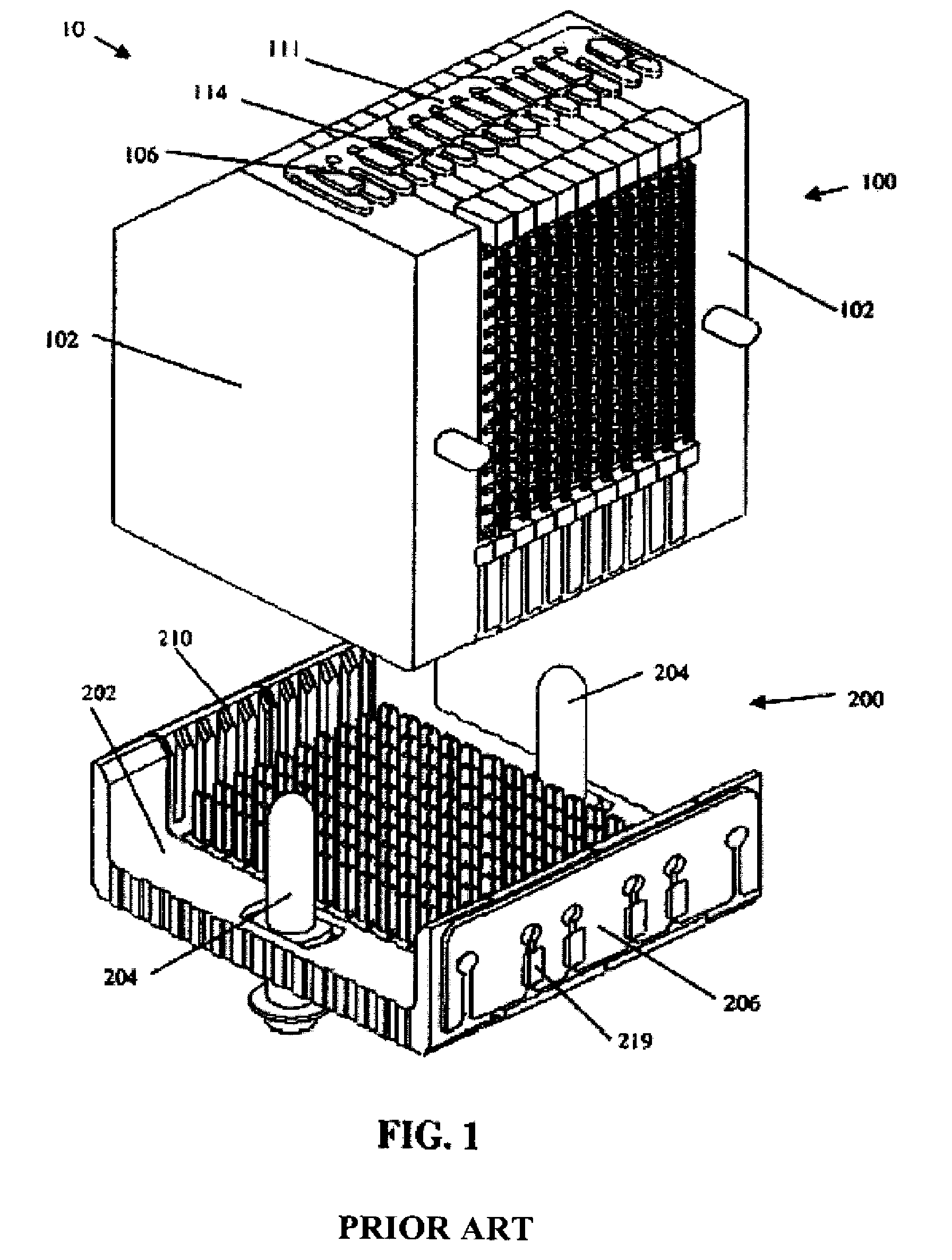

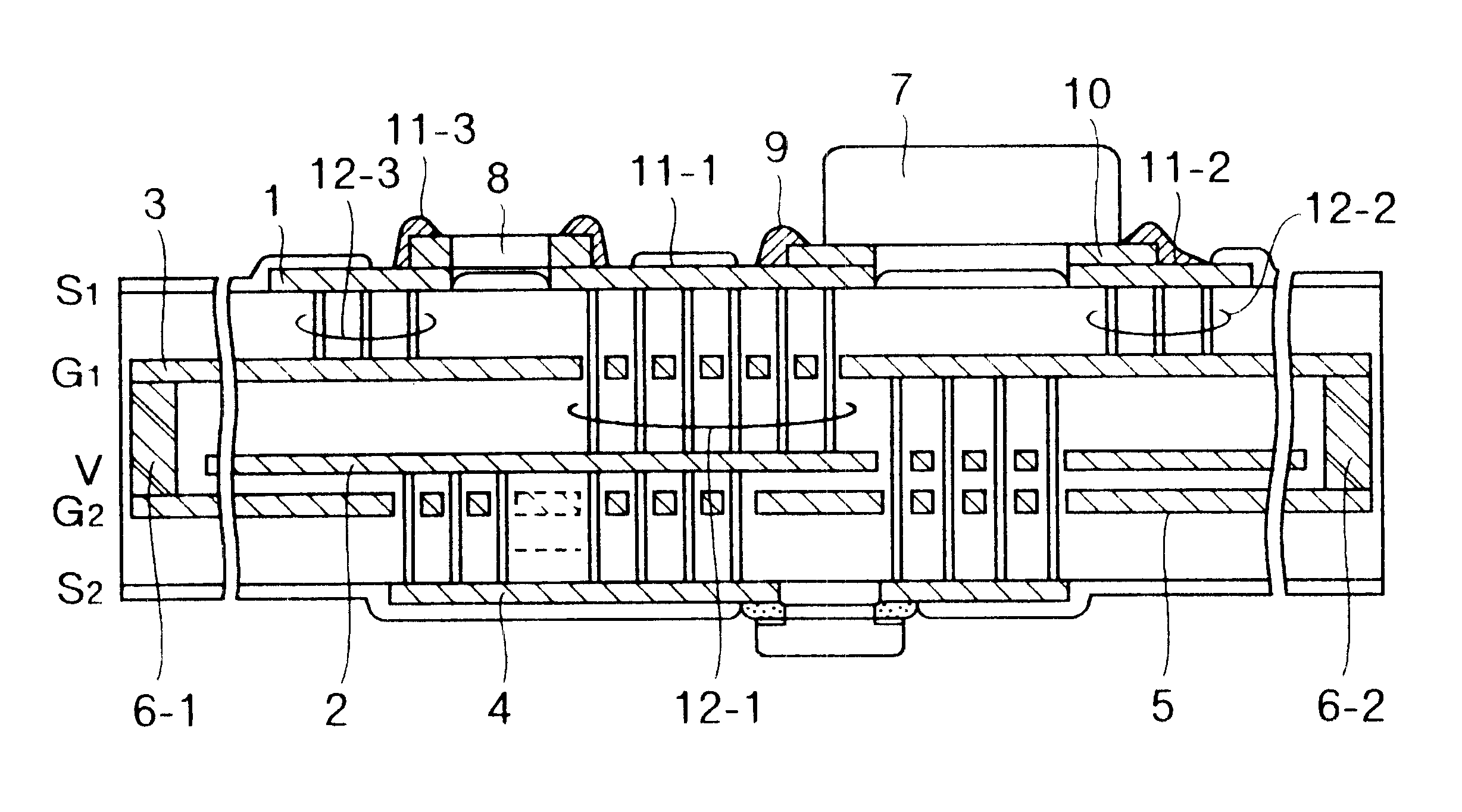

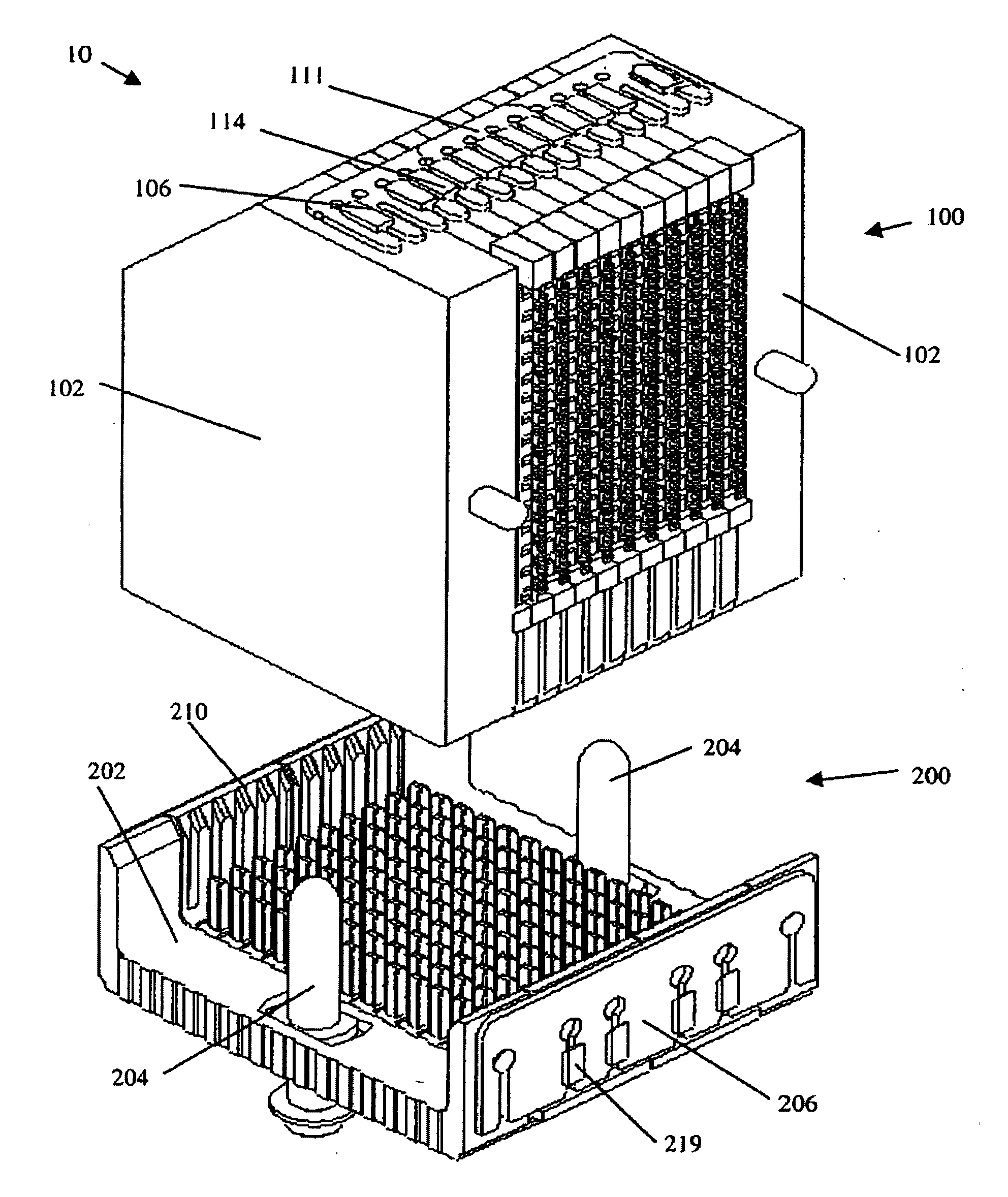

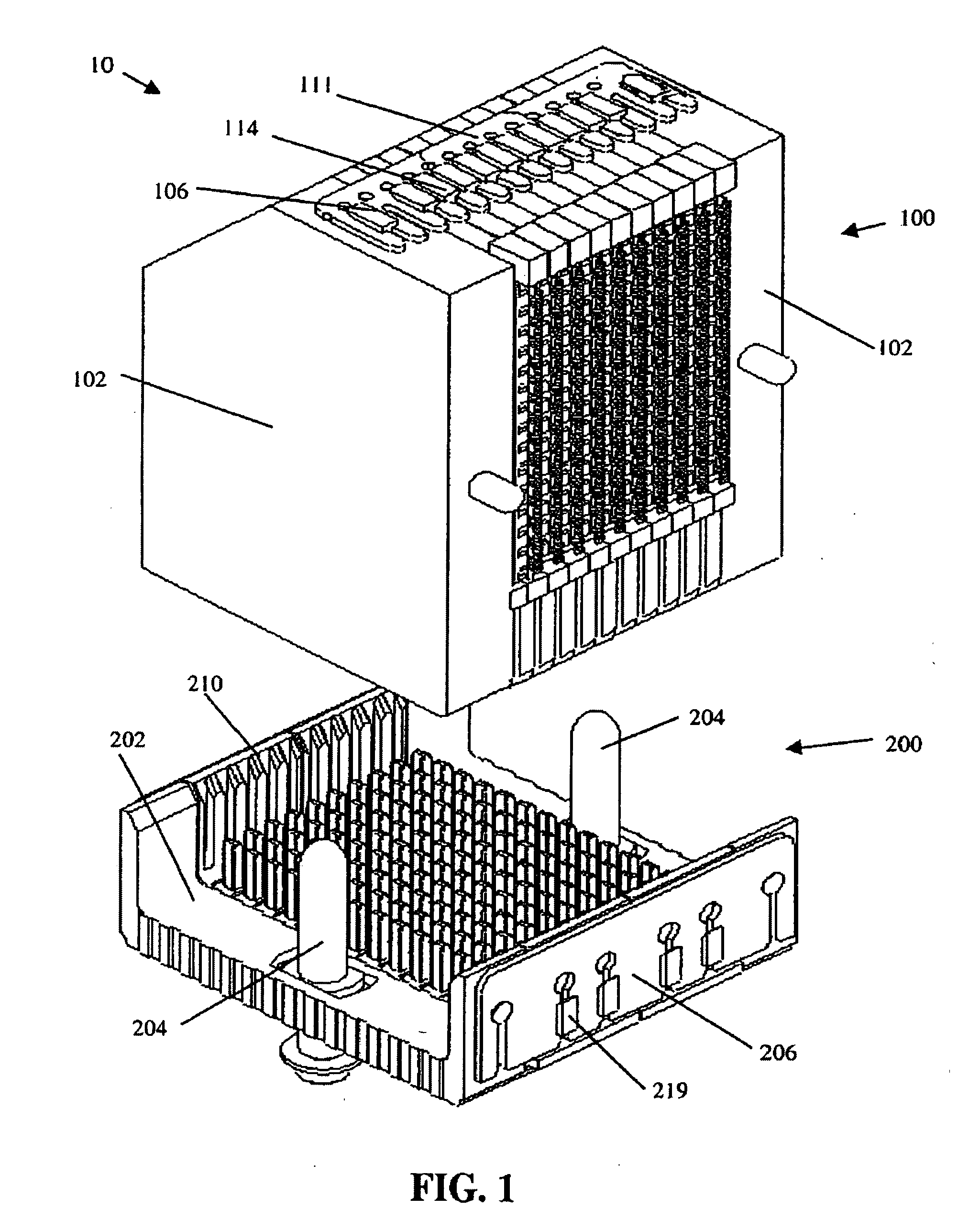

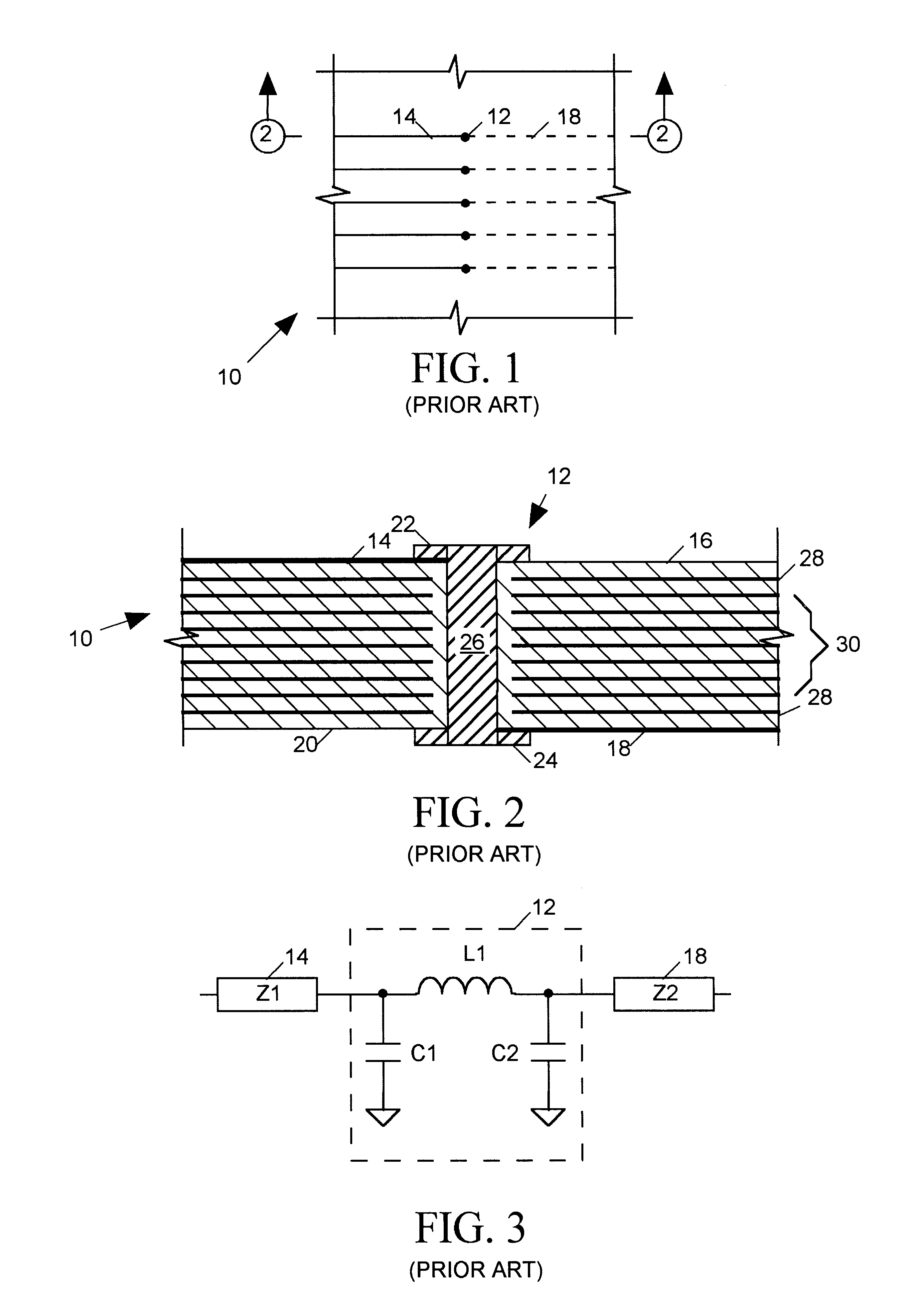

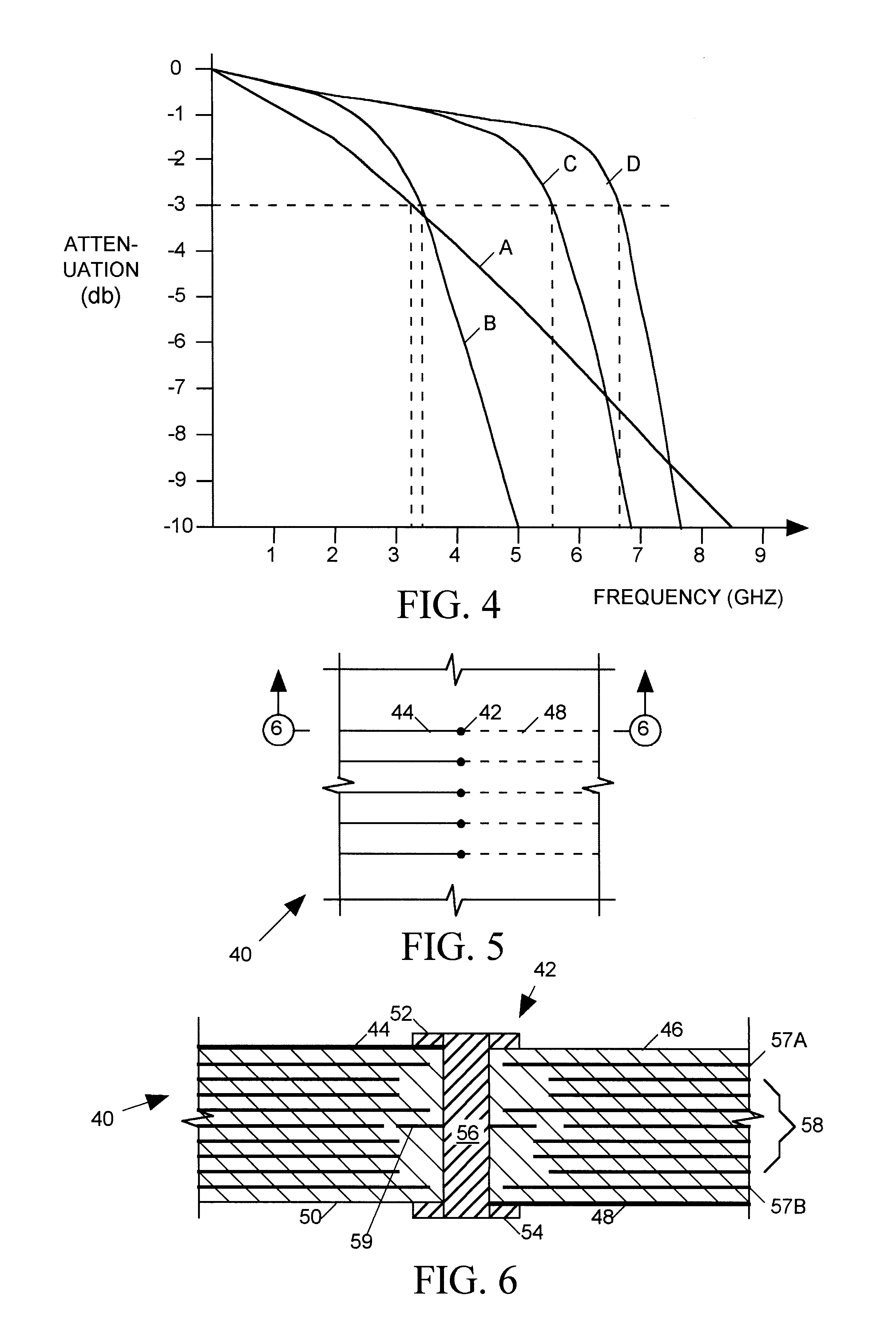

Midplane especially applicable to an orthogonal architecture electronic system

ActiveUS7108556B2Cross-talk/noise/interference reductionHigh frequency circuit adaptationsElectronic systemsEngineering

A midplane has a first side to which contact ends of a first differential connector are connected and a second side opposite the first side to which contact ends of a second differential connector are connected. The midplane includes a plurality of vias extending from the first side to the second side, with the vias providing first signal launches on the first side and second signal launches on the second side. The first signal launches are provided in a plurality of rows, with each row having first signal launches along a first line and first signal launches along a second line substantially parallel to the first line. The second signal launches are provided in a plurality of columns, with each column having second signal launches along a third line and second signal launches along a fourth line substantially parallel to the third line.

Owner:AMPHENOL CORP

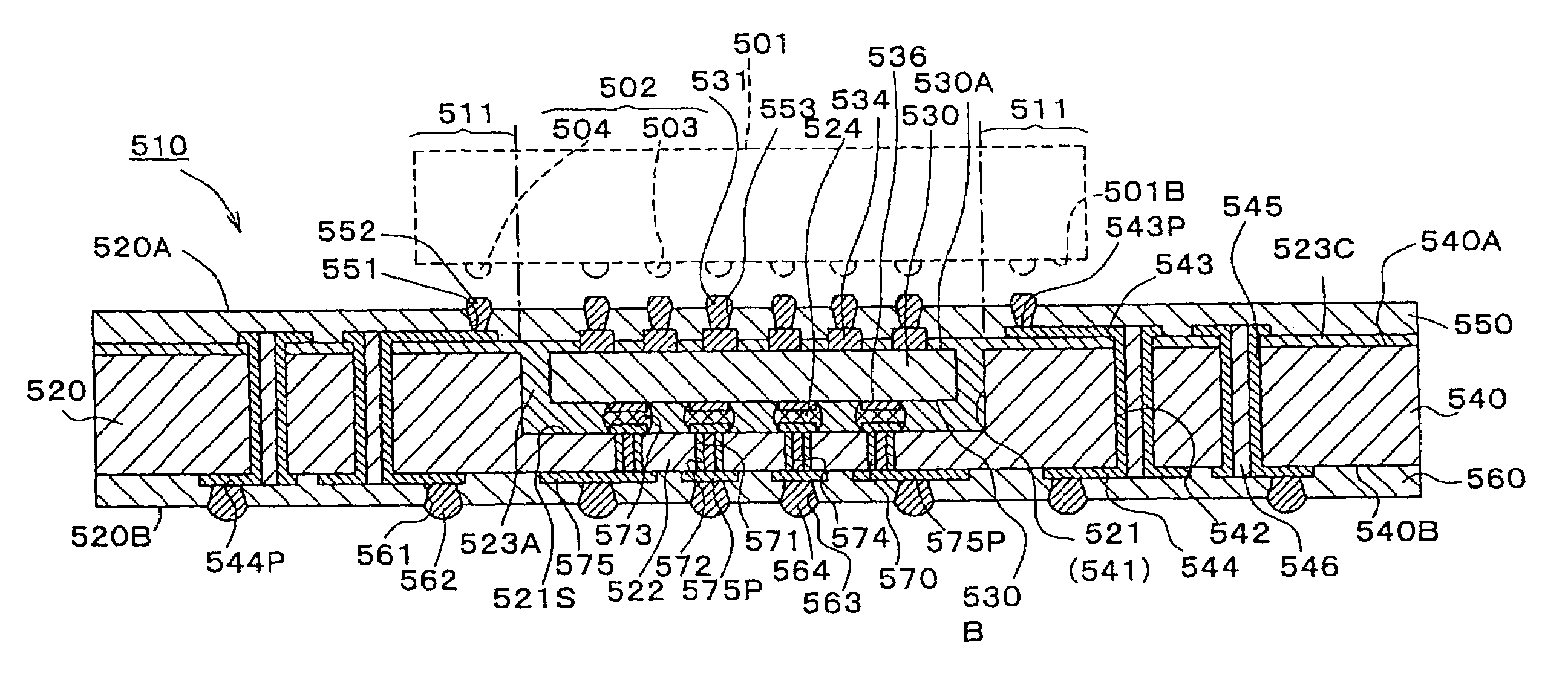

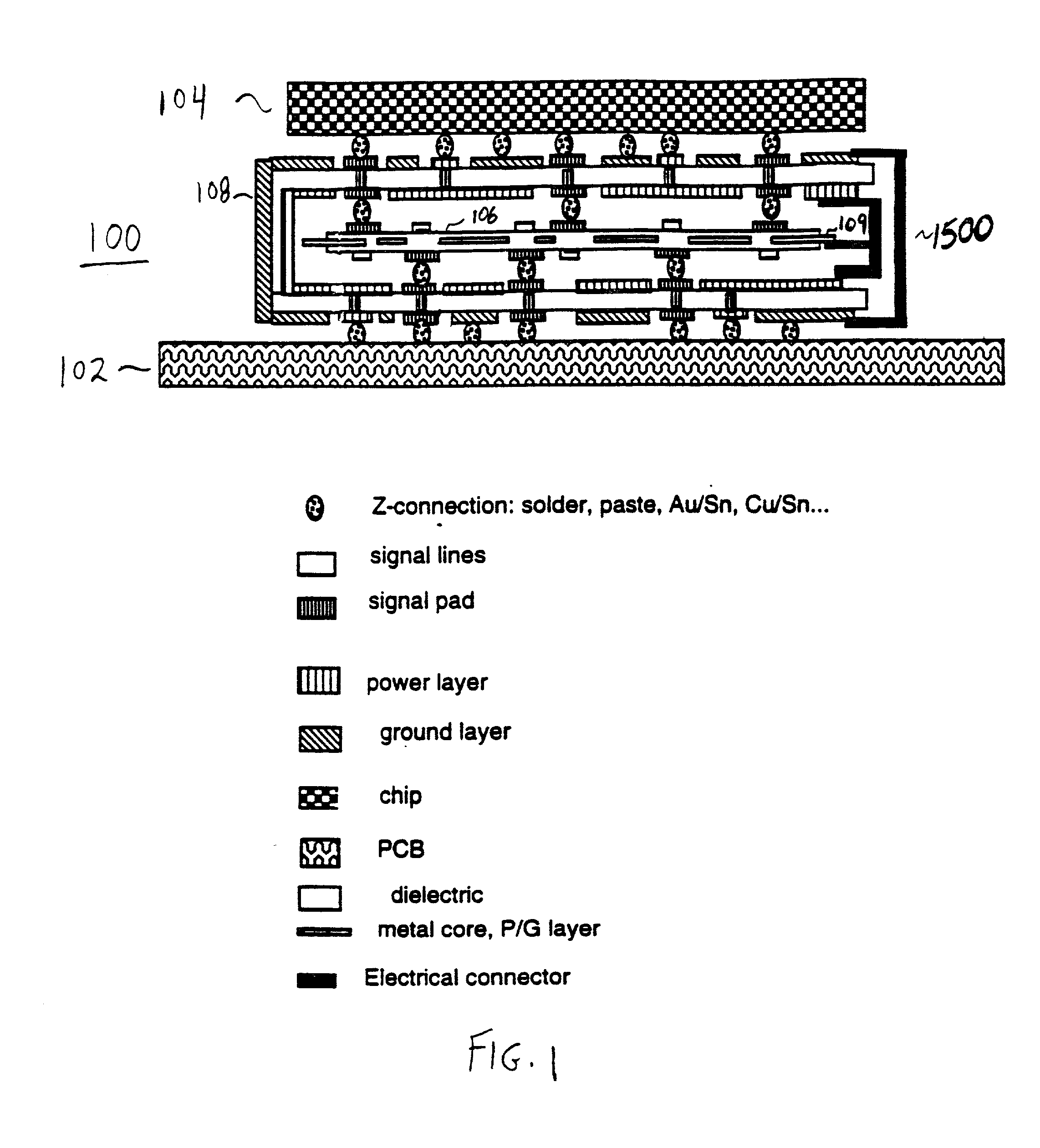

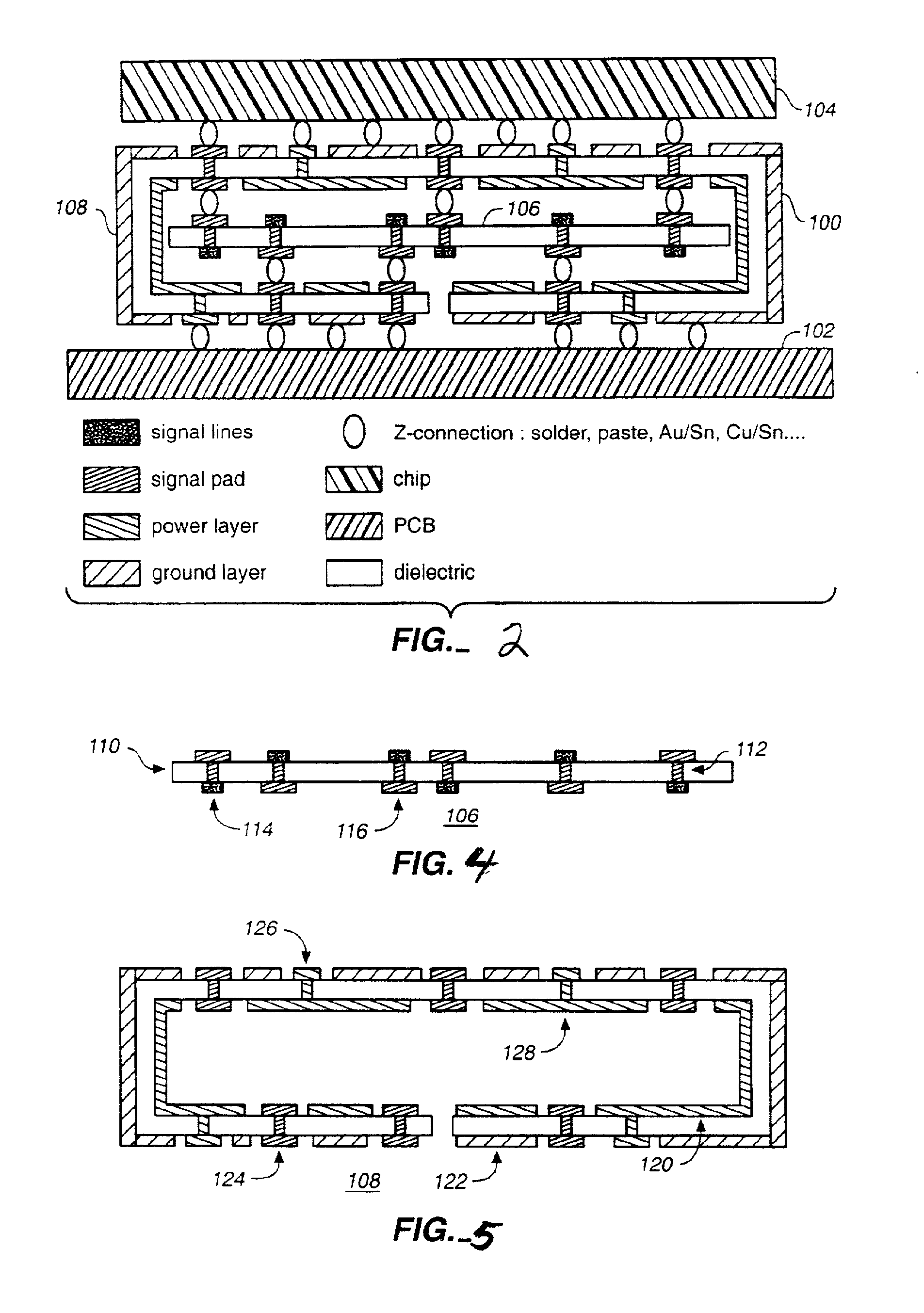

Composite interposer and method for producing a composite interposer

InactiveUS6521530B2Cross-talk/noise/interference reductionSemiconductor/solid-state device detailsEpoxyFilling materials

A composite interposer for providing power and signal connections between an integrated circuit chip or chips and a substrate. The interposer includes a signal core formed from a conductive power / ground plane positioned between two dielectric layers. A method for fabricating a composite interposer comprising disposing a silicon layer on a substrate, and selectively etching the silicon layer down to the substrate to develop silicon openings with a silicon profile, and to expose part of the substrate. Vias are formed through the exposed part of the substrate. The method additionally includes filling the vias and the silicon openings with a filler material (e.g., a high-aspect-ratio-capable photodefinable epoxy polymer) to form filled silicon openings and filled vias, forming first openings through the filled silicon openings and through the filled vias, forming second opening through filler material to expose semiconductor devices on the silicon layer, and interconnecting electrically, through the first openings and through the second openings, the exposed semiconductor devices with pads disposed against a bottom of the substrate.

Owner:FUJITSU LTD

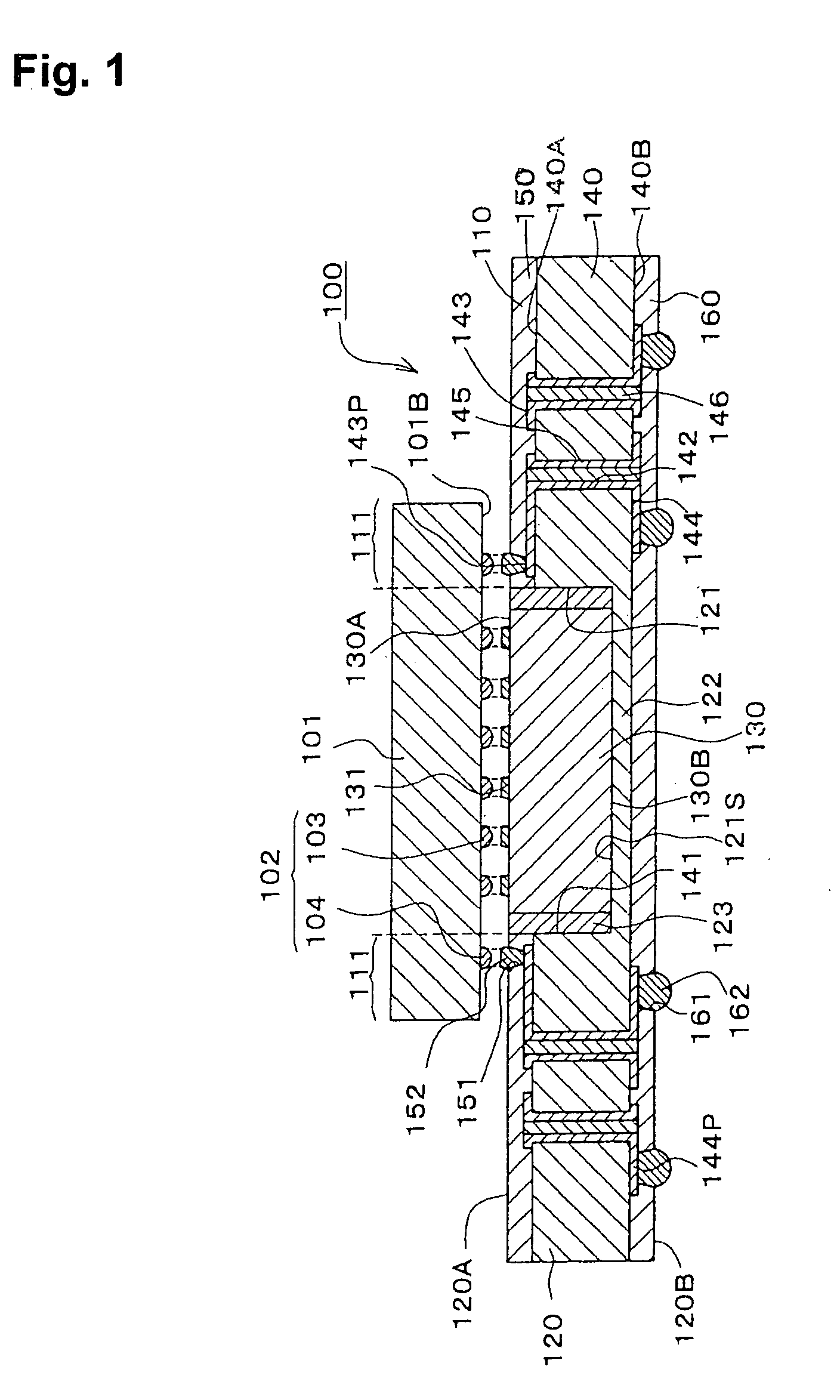

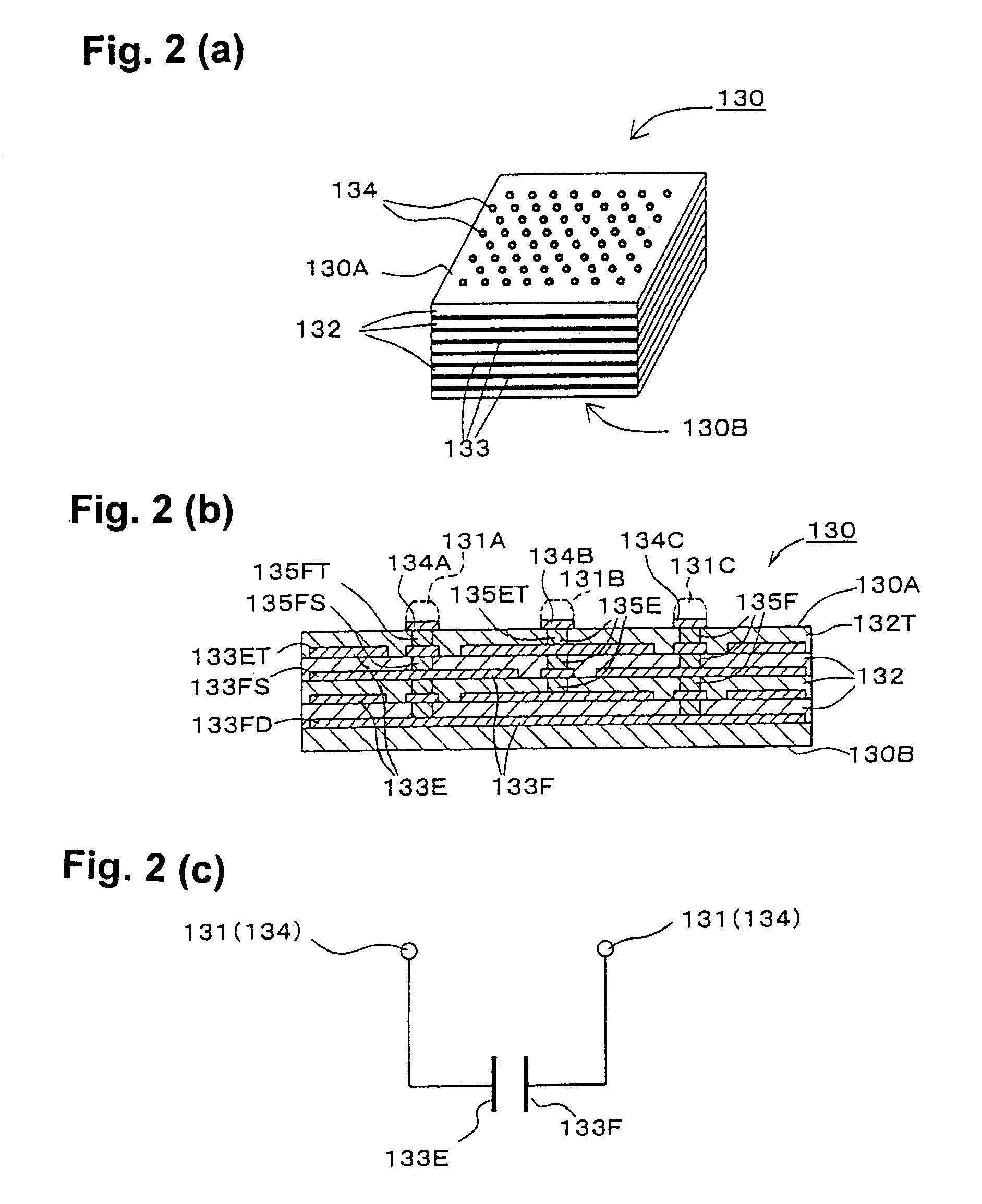

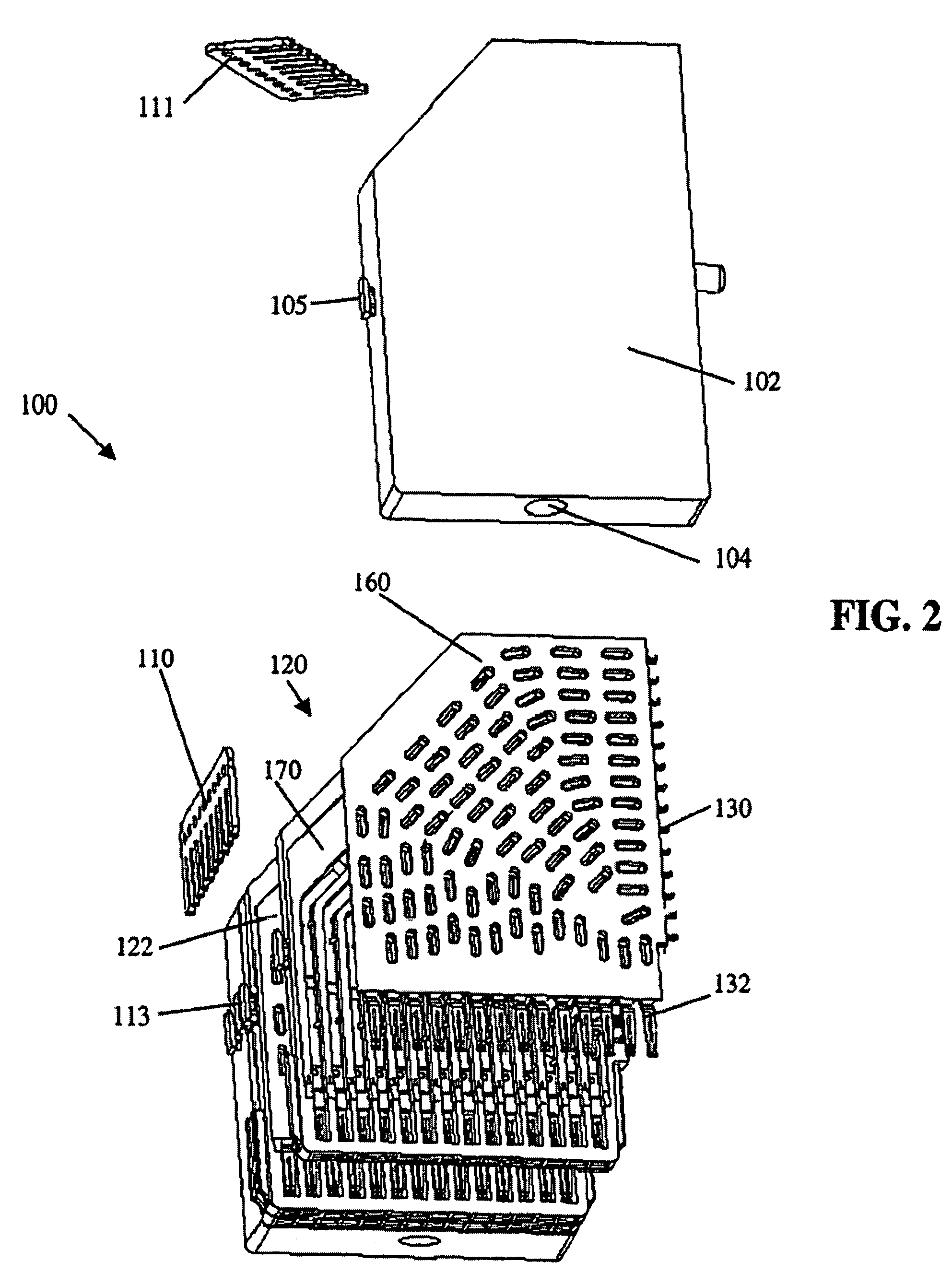

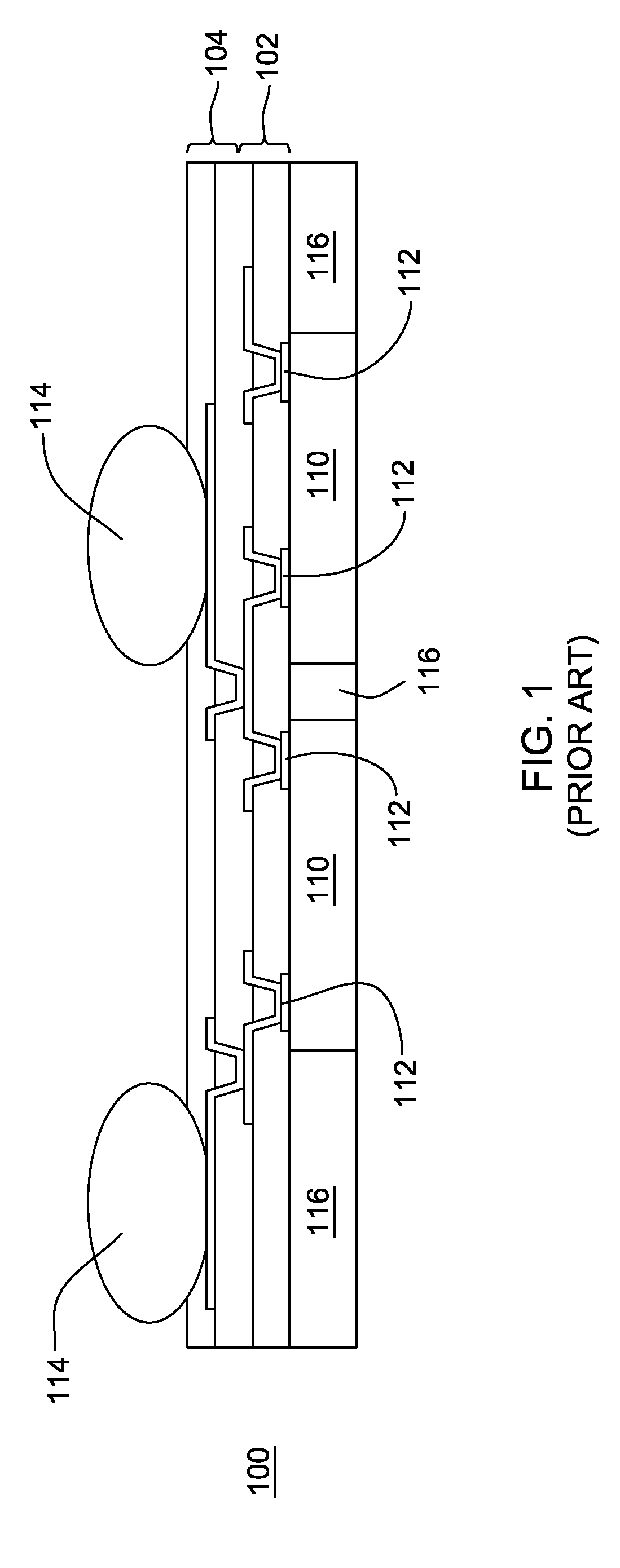

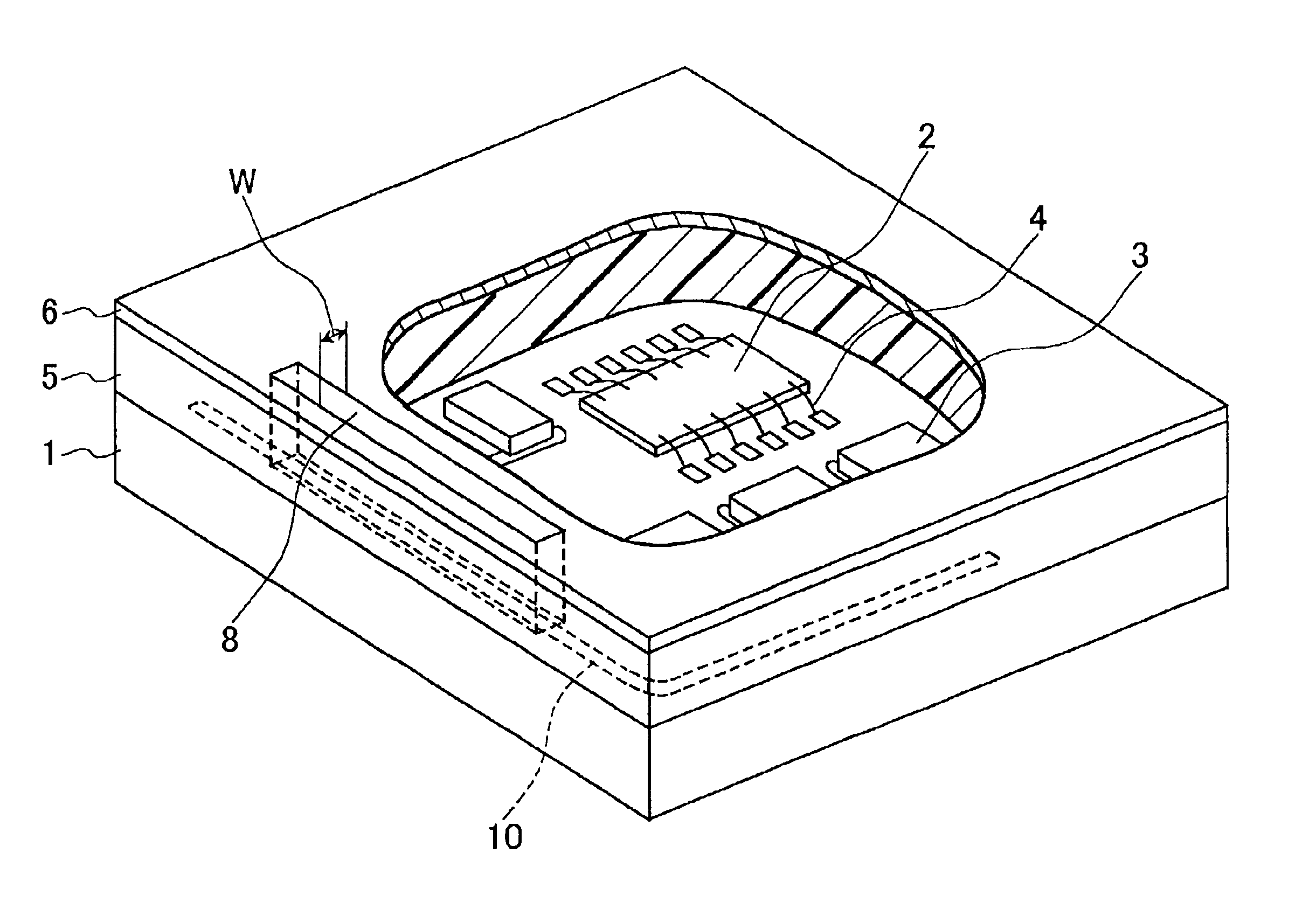

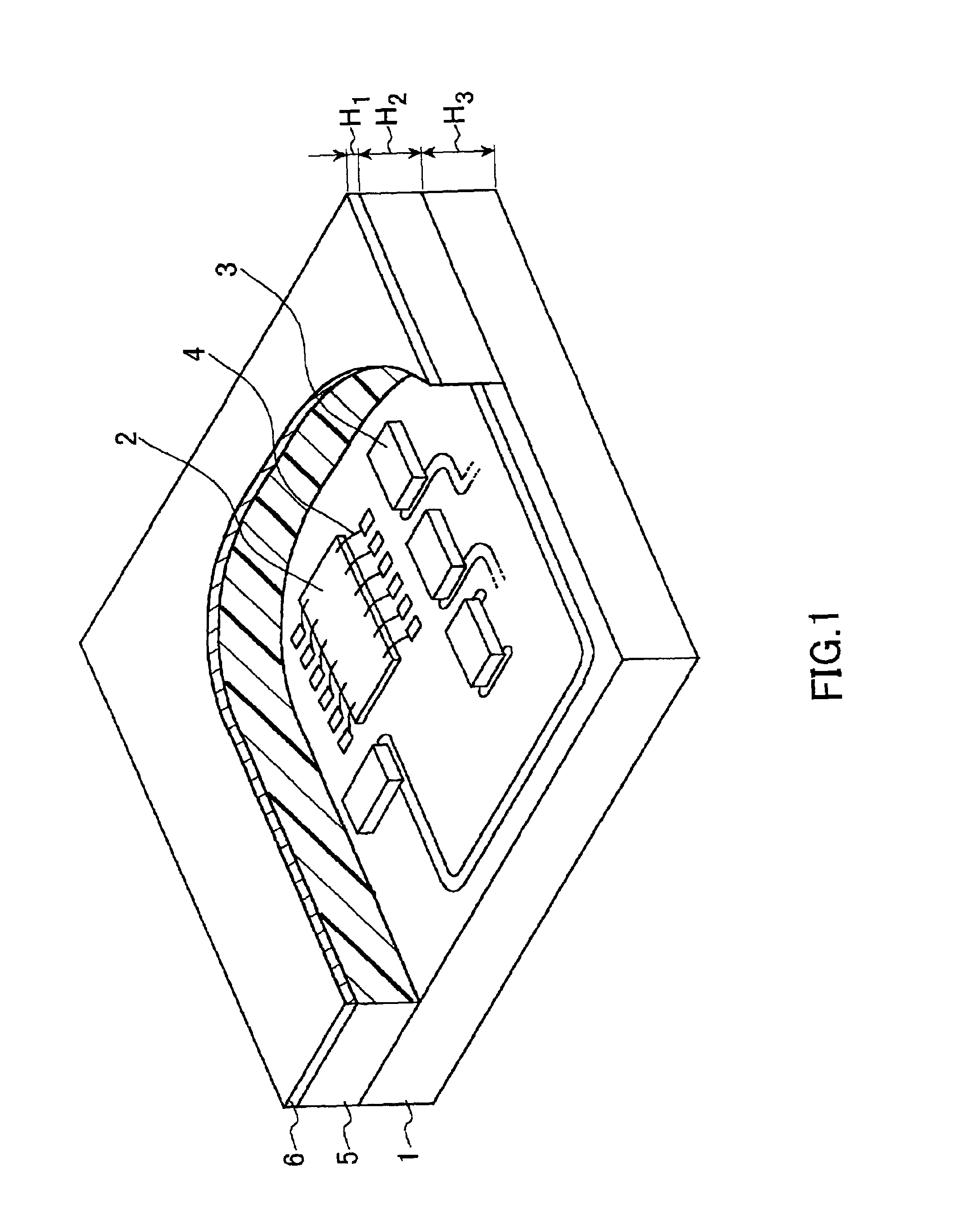

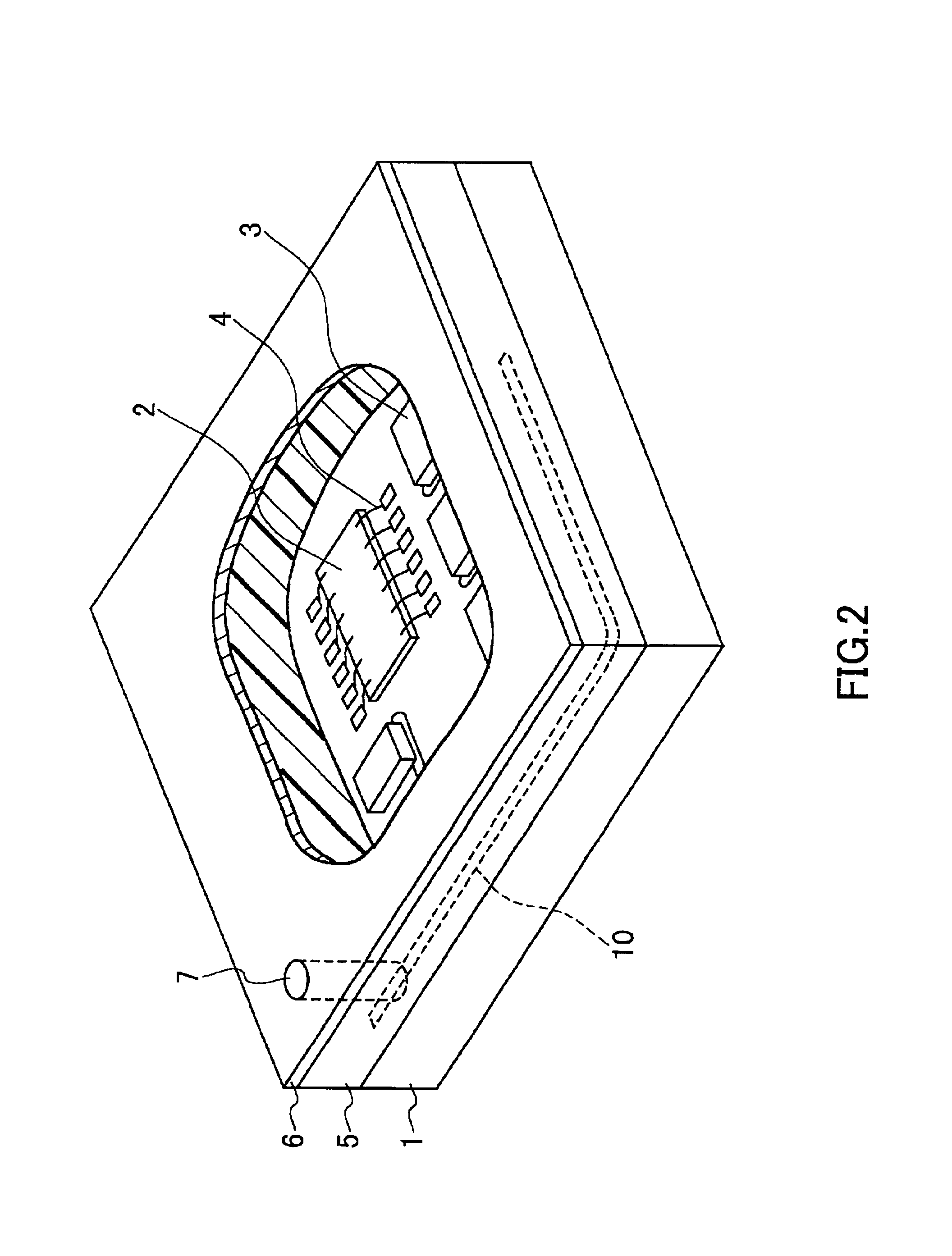

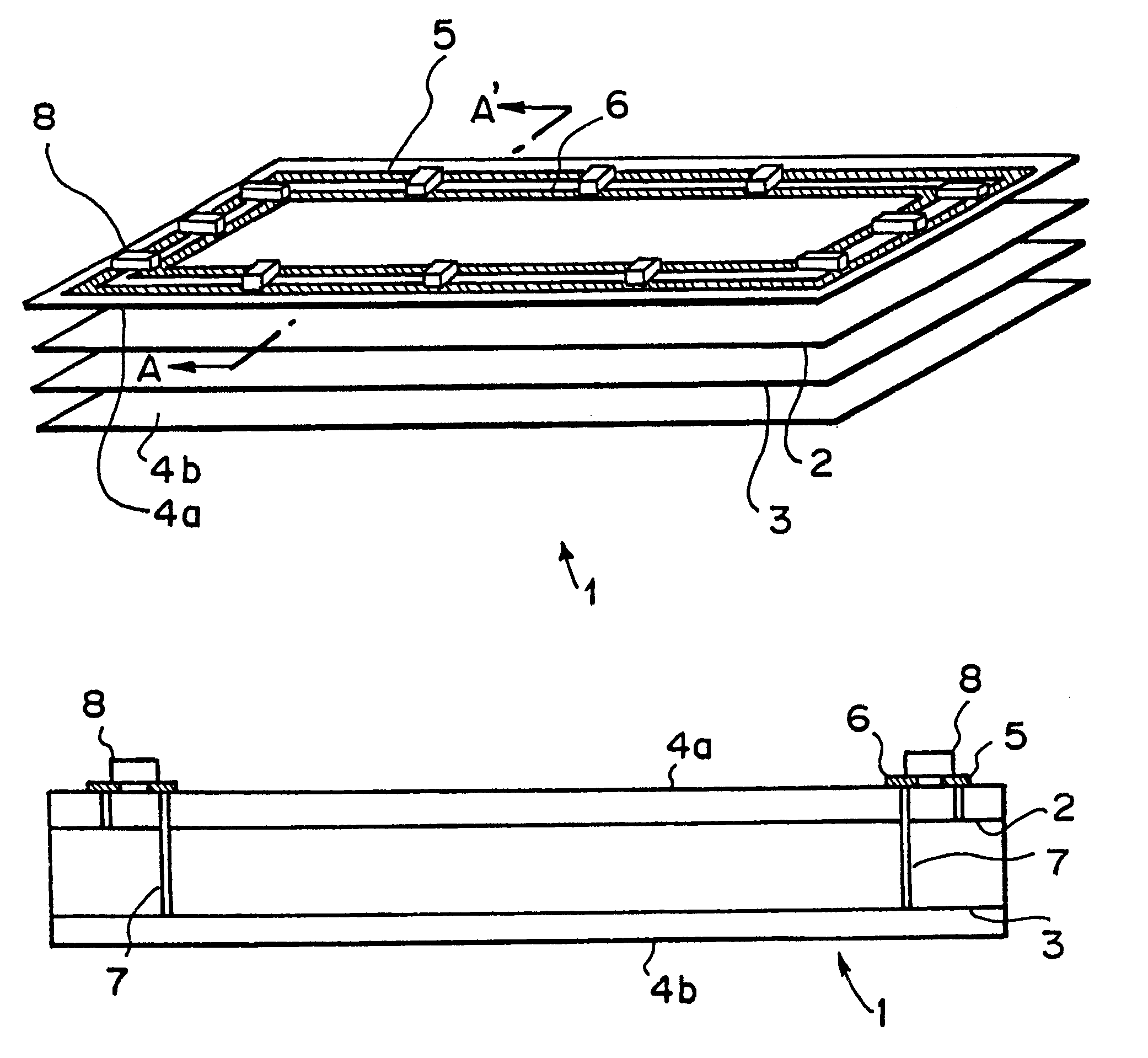

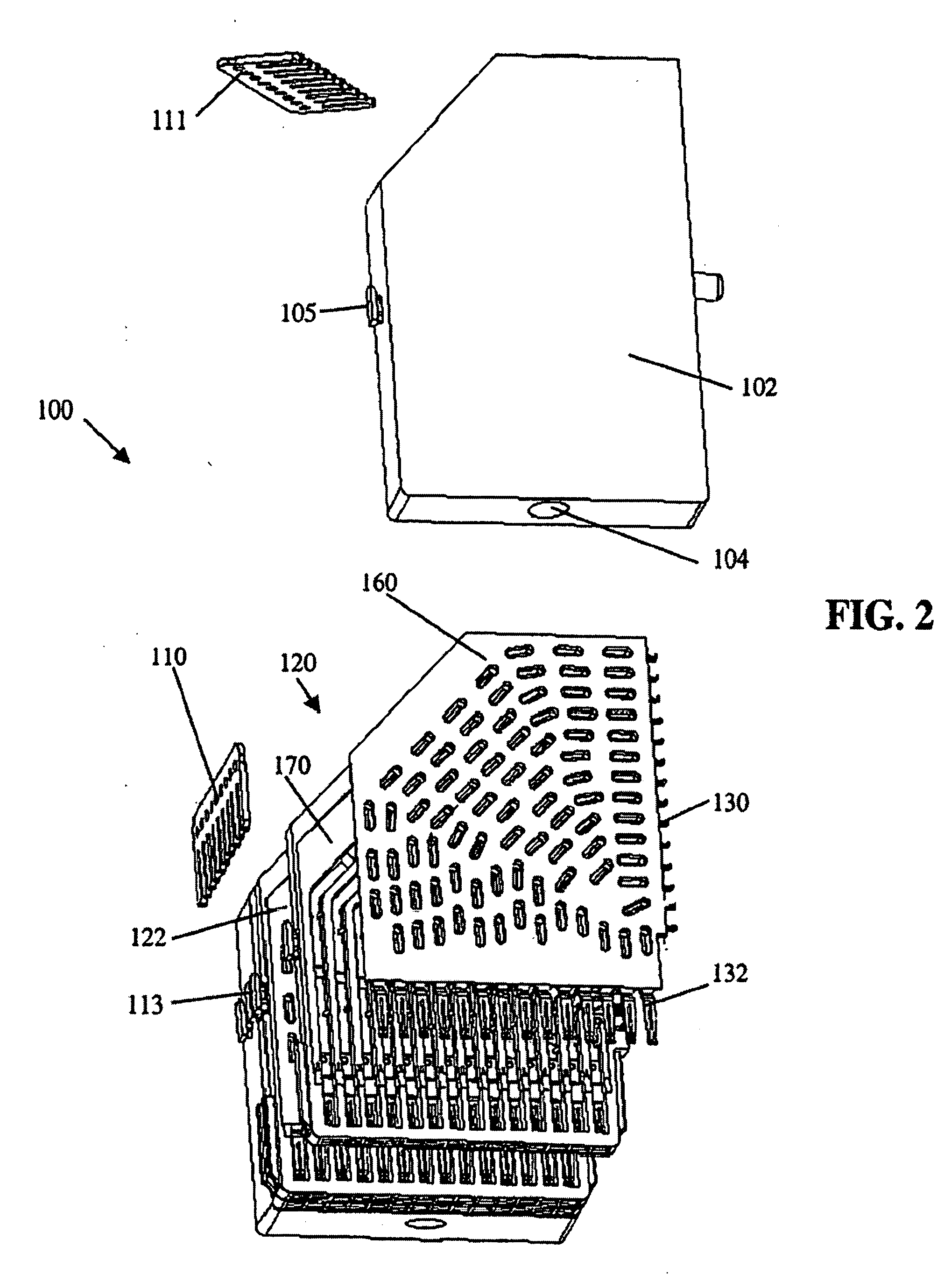

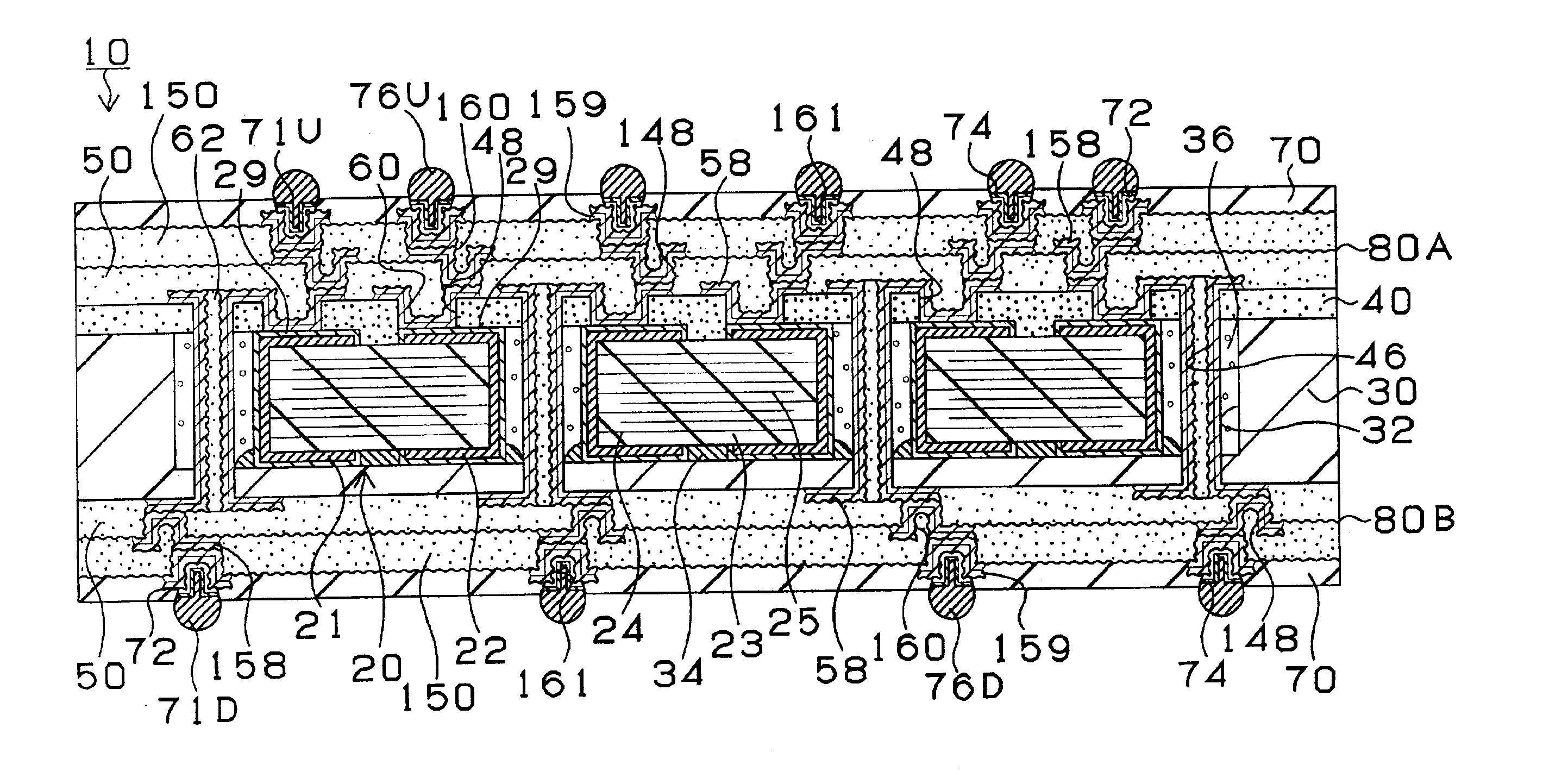

Capacitor-built-in type printed wiring substrate, printed wiring substrate, and capacitor

InactiveUS6952049B1Firmly connectedReliably eliminate noiseCross-talk/noise/interference reductionSemiconductor/solid-state device detailsLow inductanceEngineering

A capacitor-built-in-type printed wiring substrate which can reliably eliminate noise and attain extremely low resistance and low inductance in connections between an IC chip and the capacitor, and a printed wiring substrate and capacitor for use in the same. A capacitor-built-in-type printed wiring substrate 100 on which an IC chip is mounted includes a capacitor-built-in-type printed wiring substrate 110 and an IC chip 101 mounted on the capacitor-built-in-type printed wiring substrate 110. A printed wiring substrate 120 includes a number of connection-to-IC substrate bumps 152 and a closed-bottomed capacitor accommodation cavity 121 formed therein. A capacitor 130 is disposed in the cavity 121 and includes a pair of electrode groups 133E and 133F and a number of connection-to-IC capacitor bumps 131 connected to either one of the paired electrode groups 133E and 133F. The connection-to-IC capacitor bumps 131 are flip-chip-bonded to corresponding connection-to-capacitor bumps 103 on the IC chip 101. The connection-to-IC substrate bumps 152 are flip-chip-bonded to corresponding connection-to-substrate bumps 104 on the IC chip 101.

Owner:NGK SPARK PLUG CO LTD

High speed, high density electrical connector

ActiveUS7371117B2Contact member manufacturingCoupling for high frequencyHigh densityElectrical conductor

Owner:AMPHENOL CORP

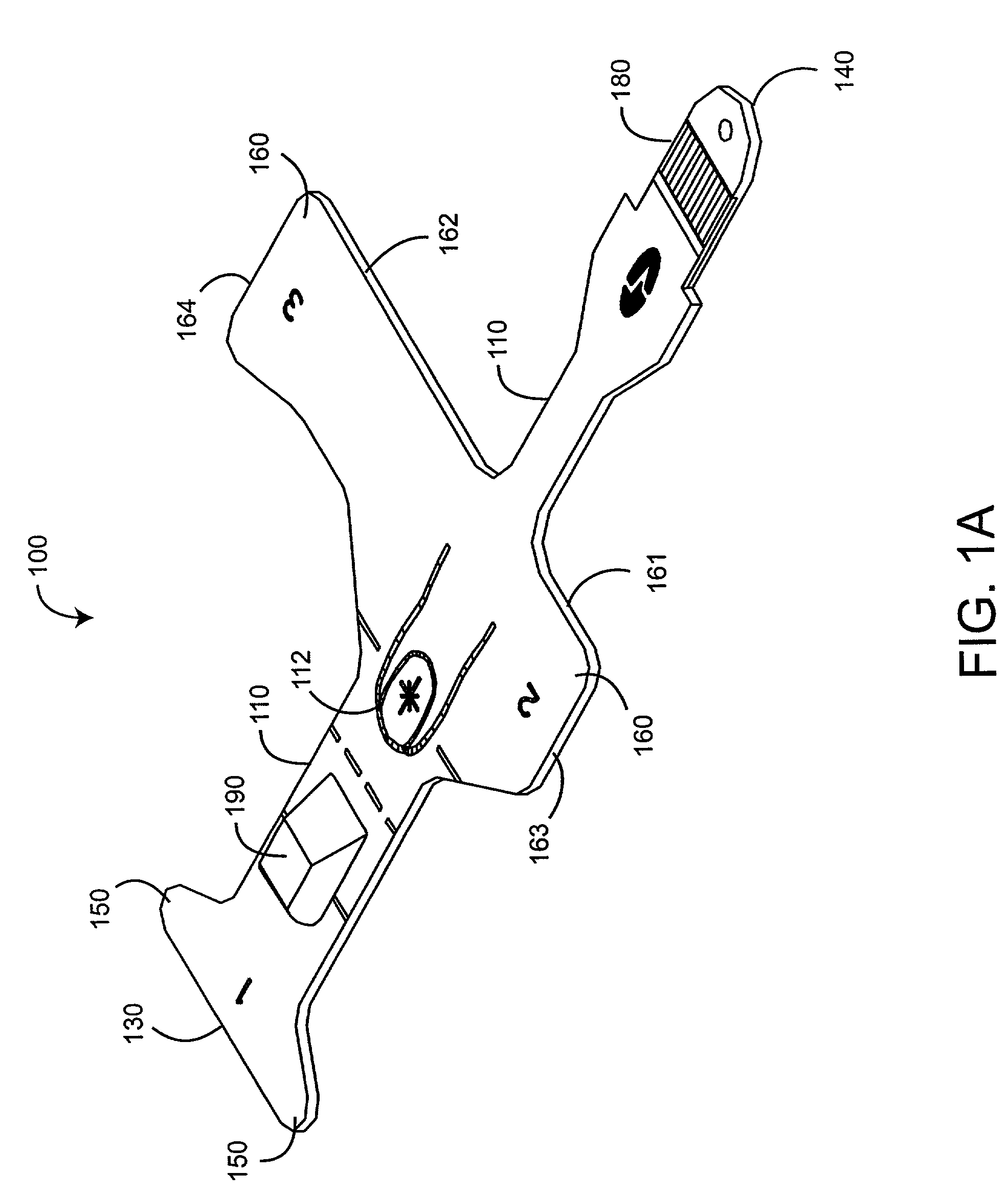

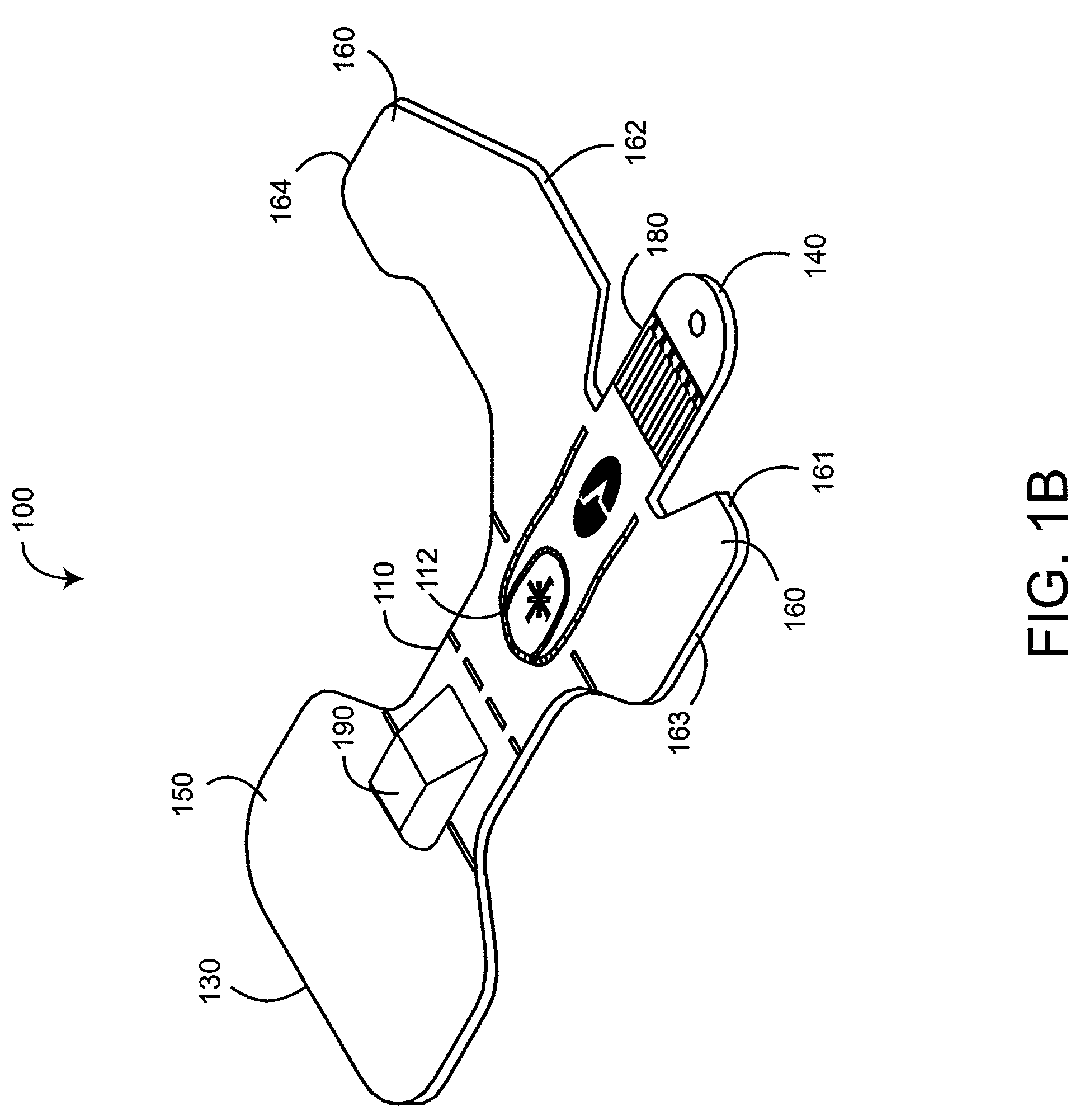

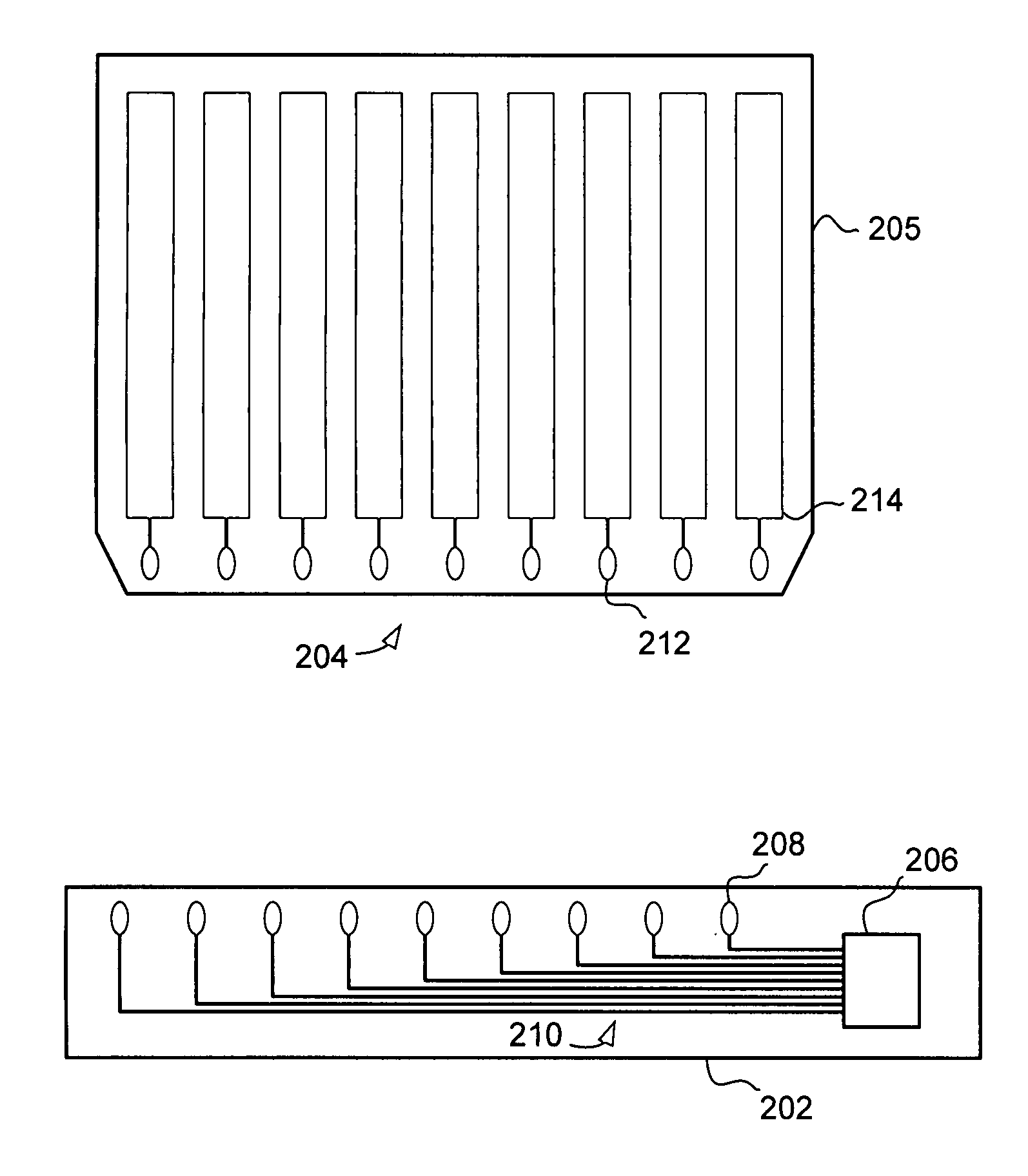

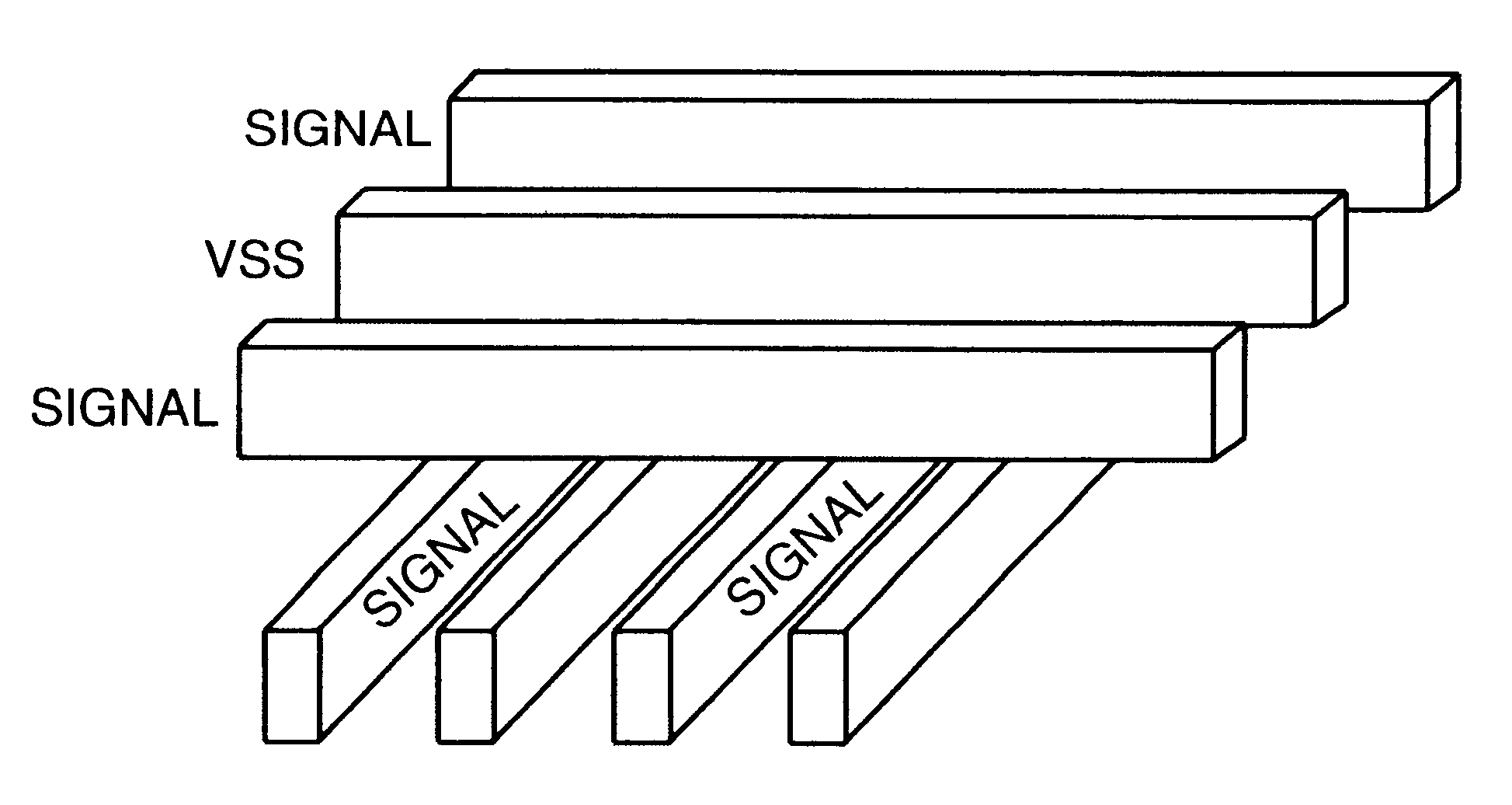

Acoustic wave touch detecting apparatus

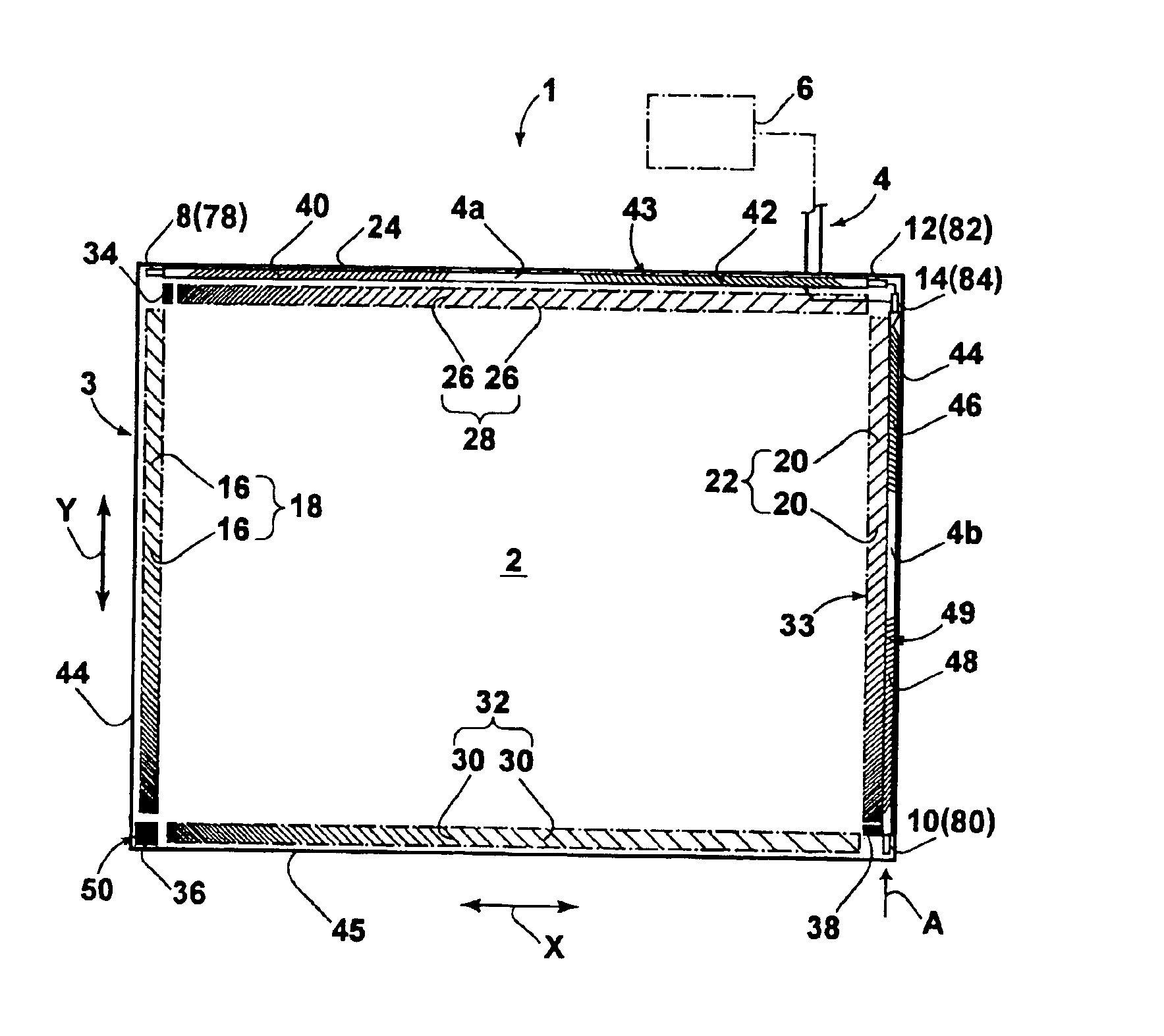

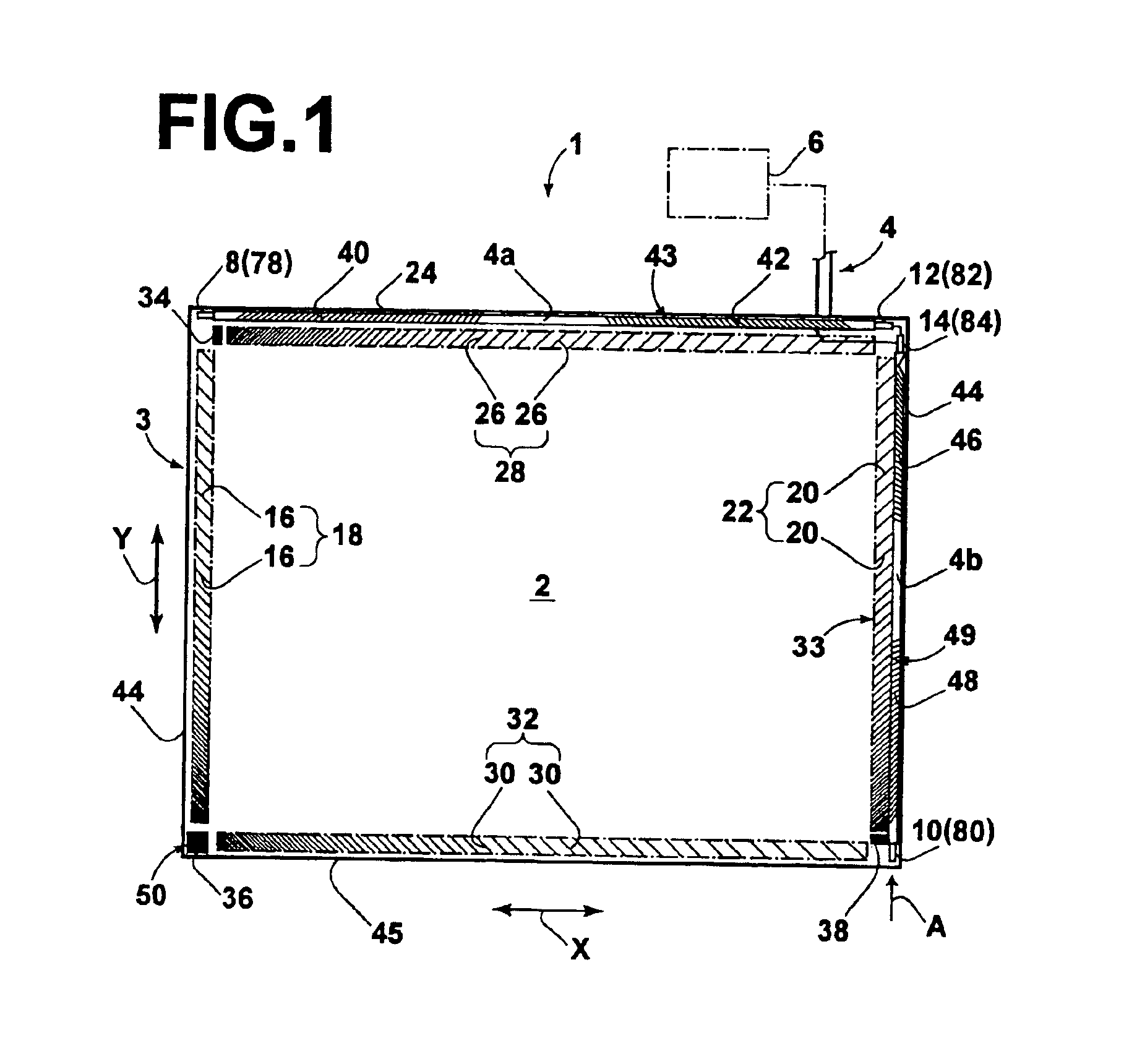

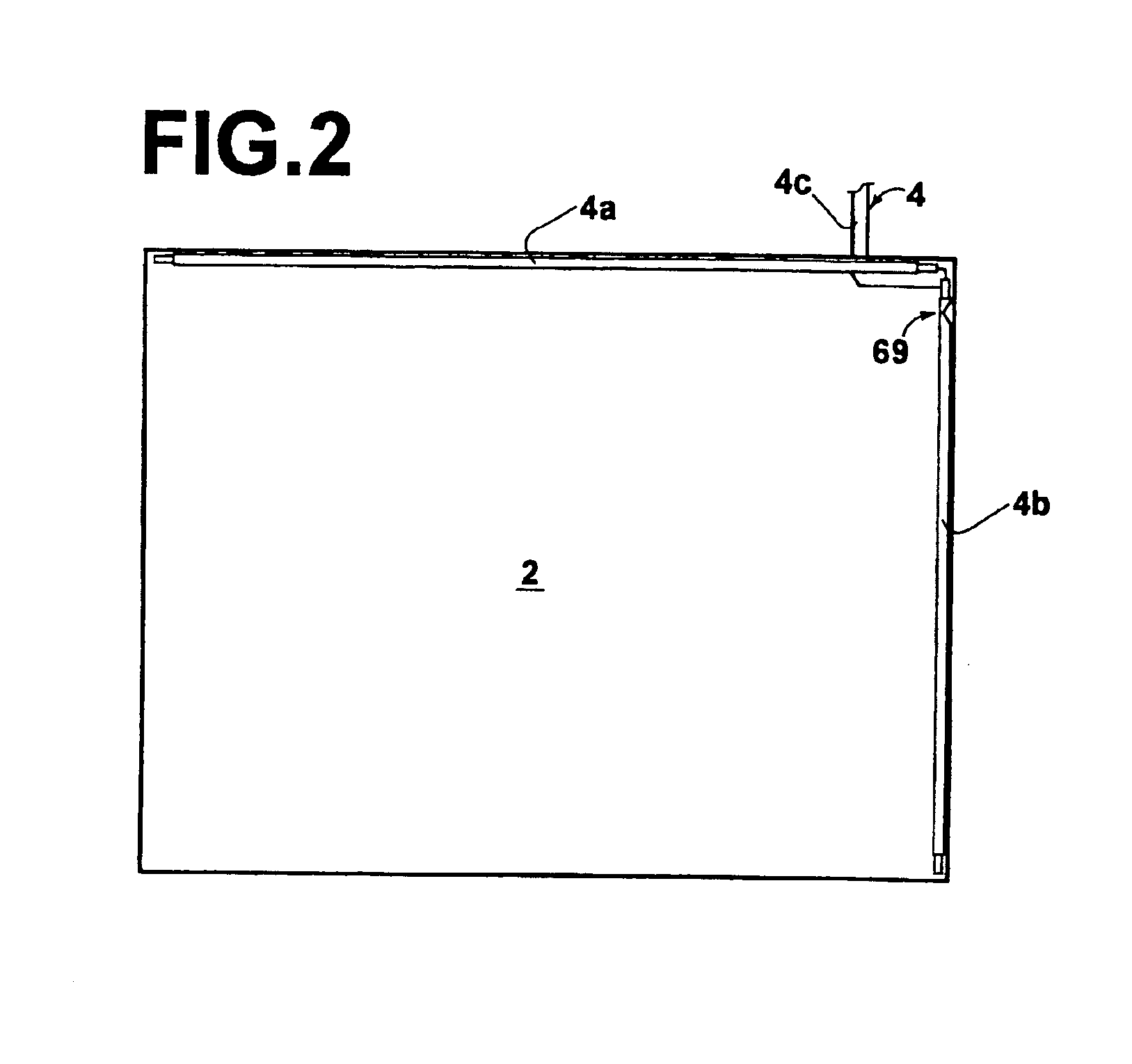

InactiveUS6948371B2Superior in anti-Electromagnetic Interference (EMI) propertiesLow costInput/output for user-computer interactionAcceleration measurement using interia forcesEngineeringAcoustic wave

An FPC is constructed of two FPC branches, and a connection line that connects to a controller. Printed wiring of the connection line includes ten printed wires. The central four printed wires are signal reception wires, which are connected to two converters (sensors). Grounding wires are provided on both sides of the four signal reception wires. Two outer signal wires are provided adjacent to the grounding wires, respectively toward the outsides thereof. Further, two more grounding wires are provided adjacent to the outer signal wires, respectively on the outsides thereof. This construction results in shielding of all of the signal wires. This relationship is maintained in the FPC branches as well.

Owner:ELO TOUCH SOLUTIONS INC

Integrated structures and fabrication methods thereof implementing a cell phone or other electronic system

ActiveUS20080316714A1Semiconductor/solid-state device detailsSolid-state devicesElectronic systemsContact pad

Circuit structures and methods of fabrication are provided for facilitating implementing a complete electronic system in a compact package. The circuit structure includes, in one embodiment, a chips-first multichip base layer with conductive structures extending therethrough. An interconnect layer is disposed over the front surface of the multichip layer and includes interconnect metallization electrically connected to contact pads of the chips and to conductive structures extending through the structural material. A redistribution layer, disposed over the back surface of the multichip layer, includes a redistribution metallization also electrically connected to conductive structures extending through the structural material. Input / output contacts are arrayed over the redistribution layer, including over the lower surfaces of at least some integrated circuit chips within the multichip layer, and are electrically connected through the redistribution metallization, conductive structures, and interconnect metallization to contact pads of the integrated circuit chips of the multichip layer.

Owner:EPIC TECH INC

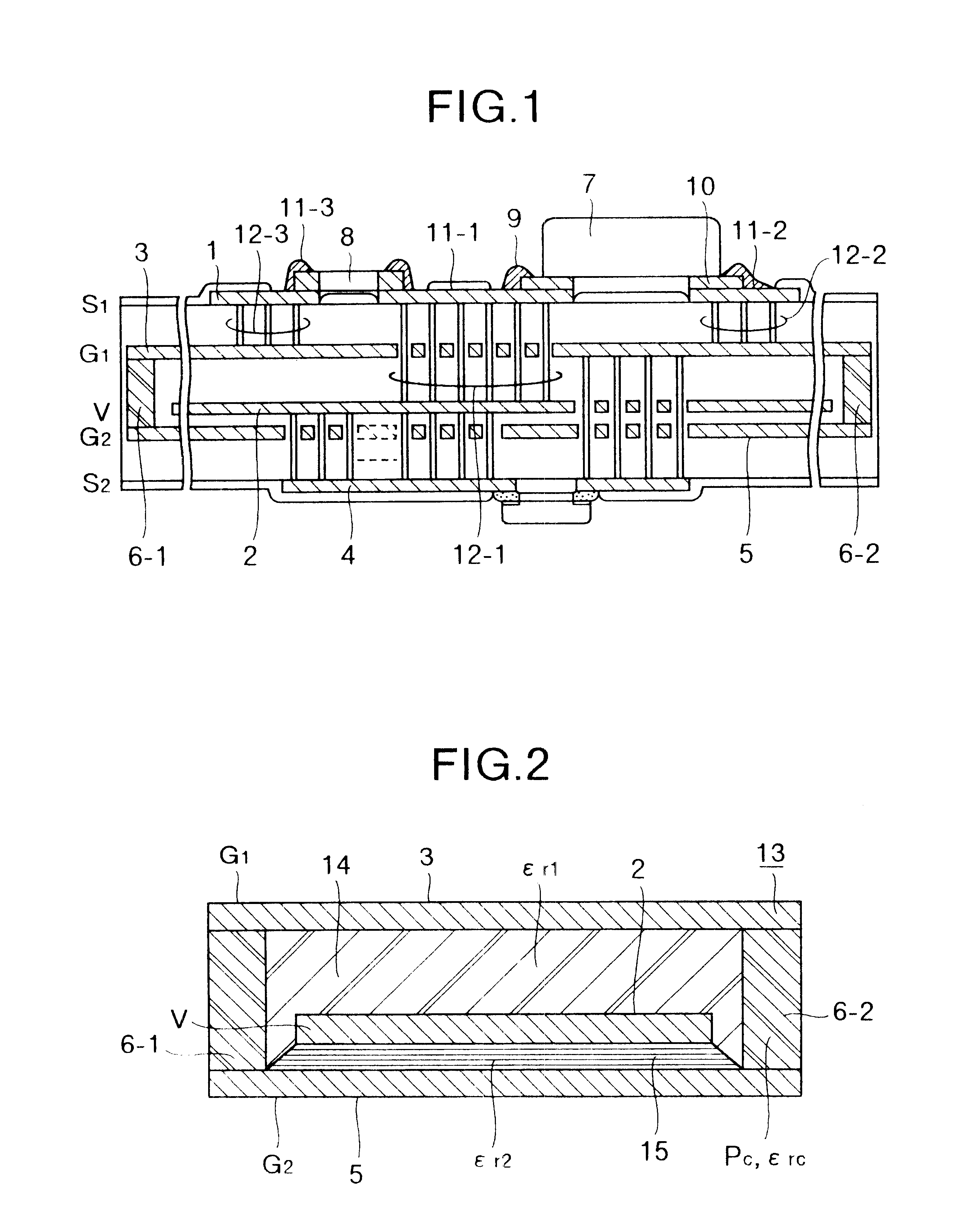

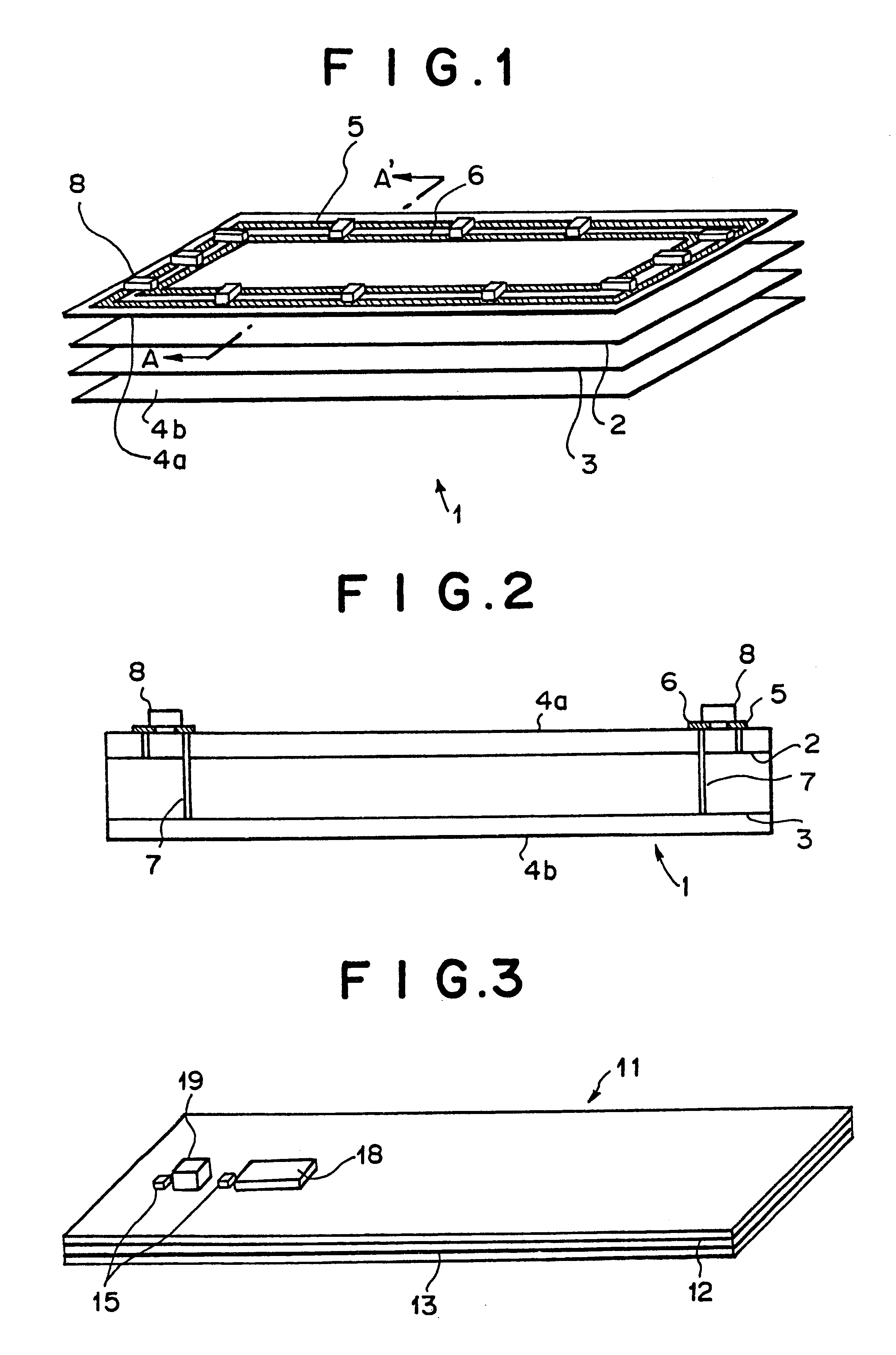

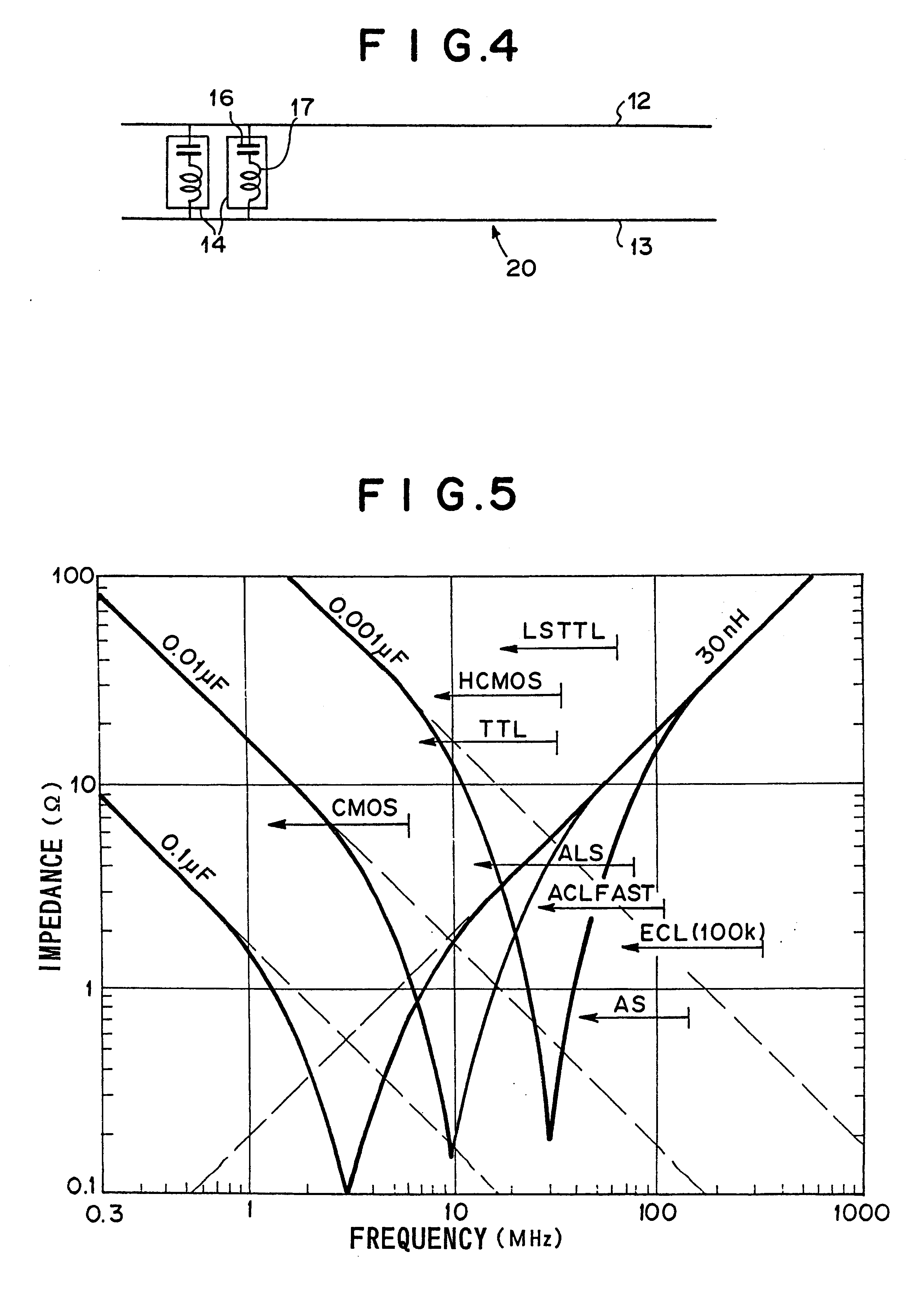

Low-EMI electronic apparatus, low-EMI circuit board, and method of manufacturing the low-EMI circuit board.

InactiveUS6353540B1Radiation suppressionHigh packageMagnetic/electric field screeningFinal product manufactureCapacitanceCountermeasure

Owner:HITACHI LTD

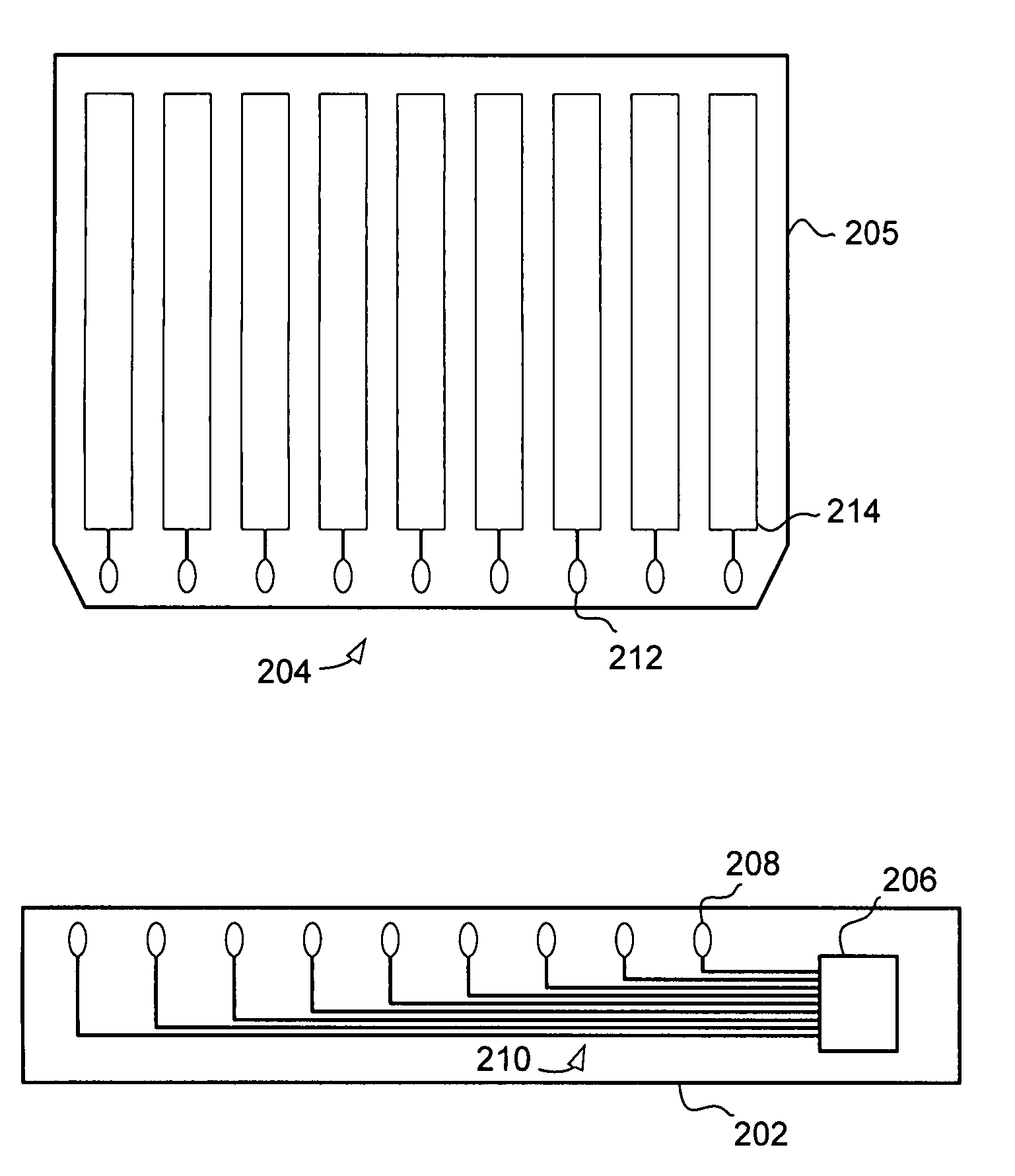

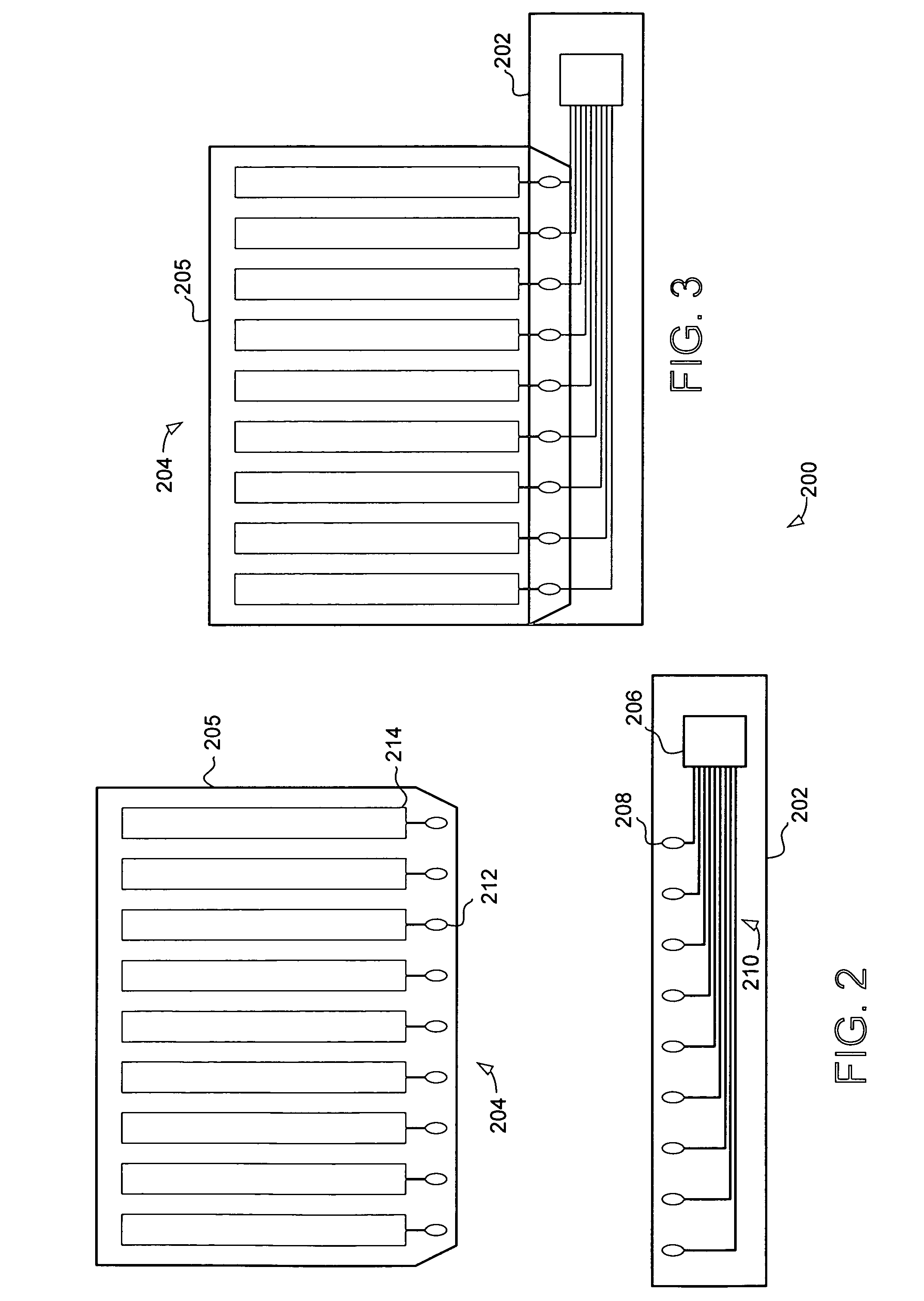

Touch pad with flexible substrate

ActiveUS20060274055A1High temperature resistanceIncrease flexibilityCircuit optical detailsCross-talk/noise/interference reductionEffective solutionFlexible circuits

A touch sensor device is provided that uses a flexible circuit substrate to provide an improved input device. Specifically, the present invention uses a touch sensor controller affixed to the flexible circuit substrate, which is coupled to a sensor component to provide a flexible, reliable and cost effective touch sensor suitable for a wide variety of applications. In one embodiment the touch sensor uses a flexible circuit substrate that provides relatively high temperature resistance. This allows the touch sensor controller to be affixed using reliable techniques, such as various types of soldering. The sensor component can comprise a relatively low-temperature-resistant substrate that can provide a cost effective solution. Taken together, this embodiment of the touch sensor provides reliability and flexibility at relatively low cost.

Owner:SYNAPTICS INC

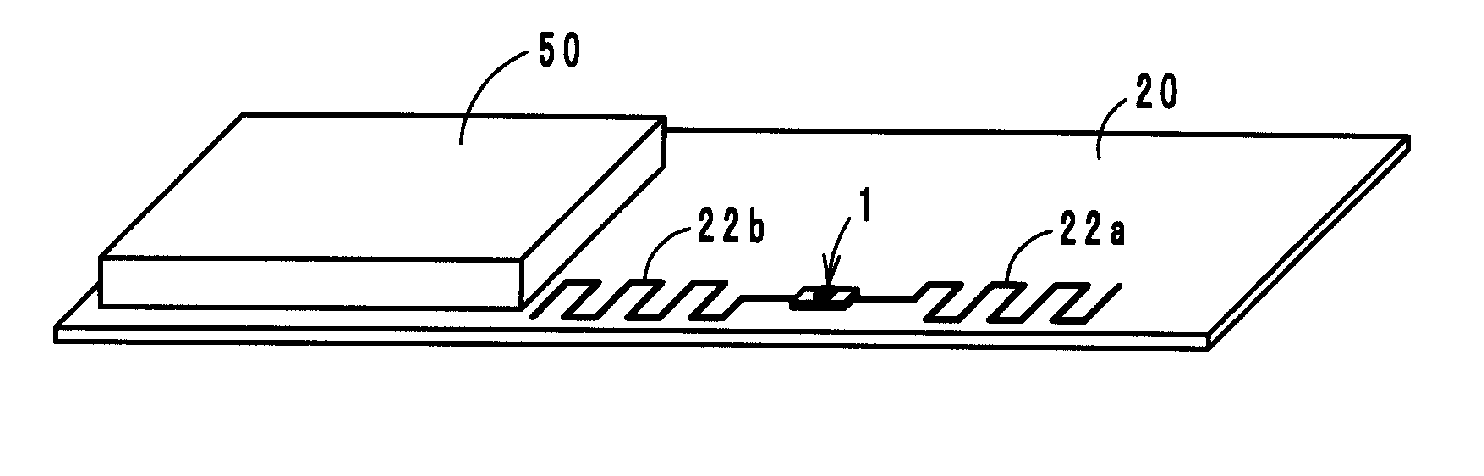

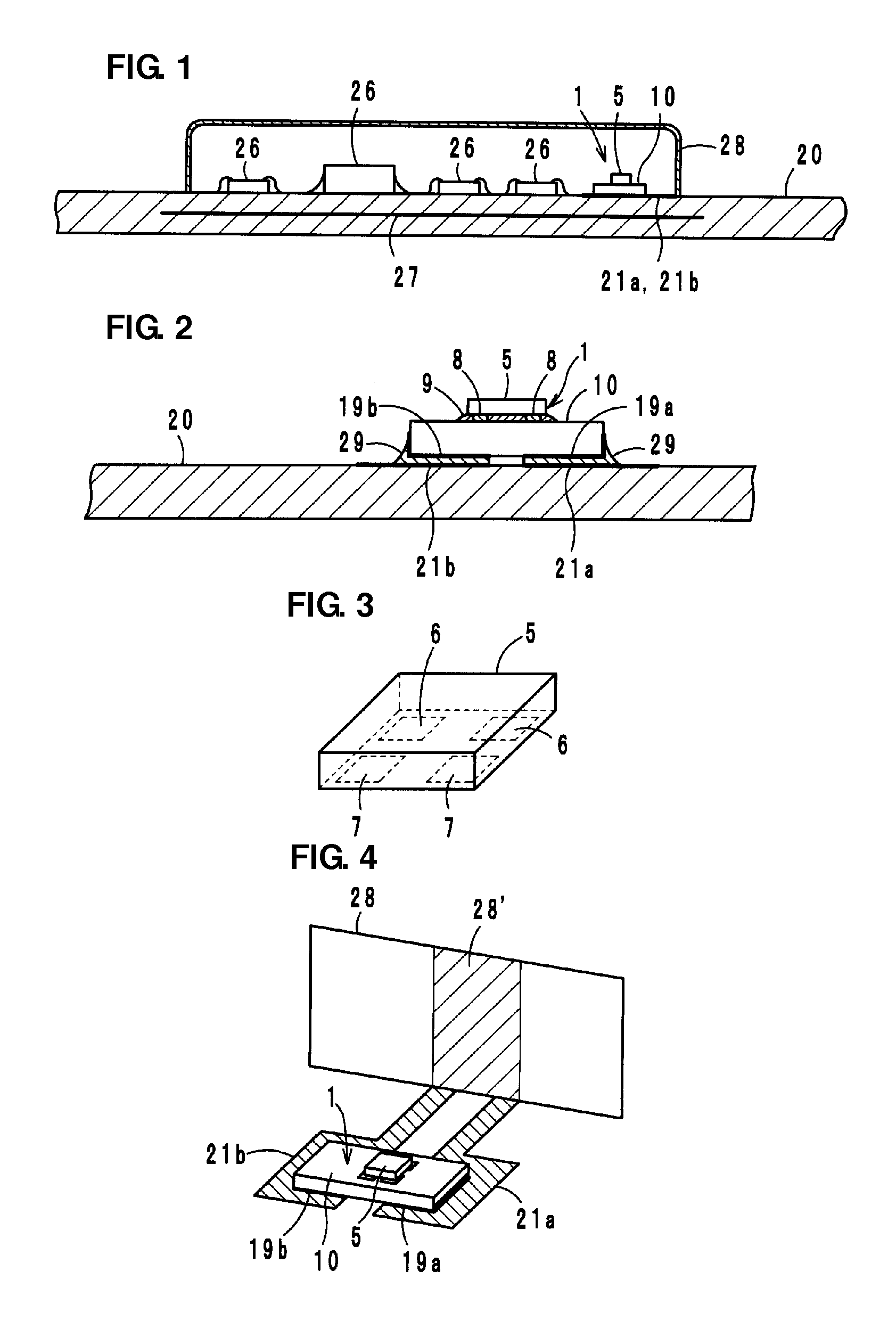

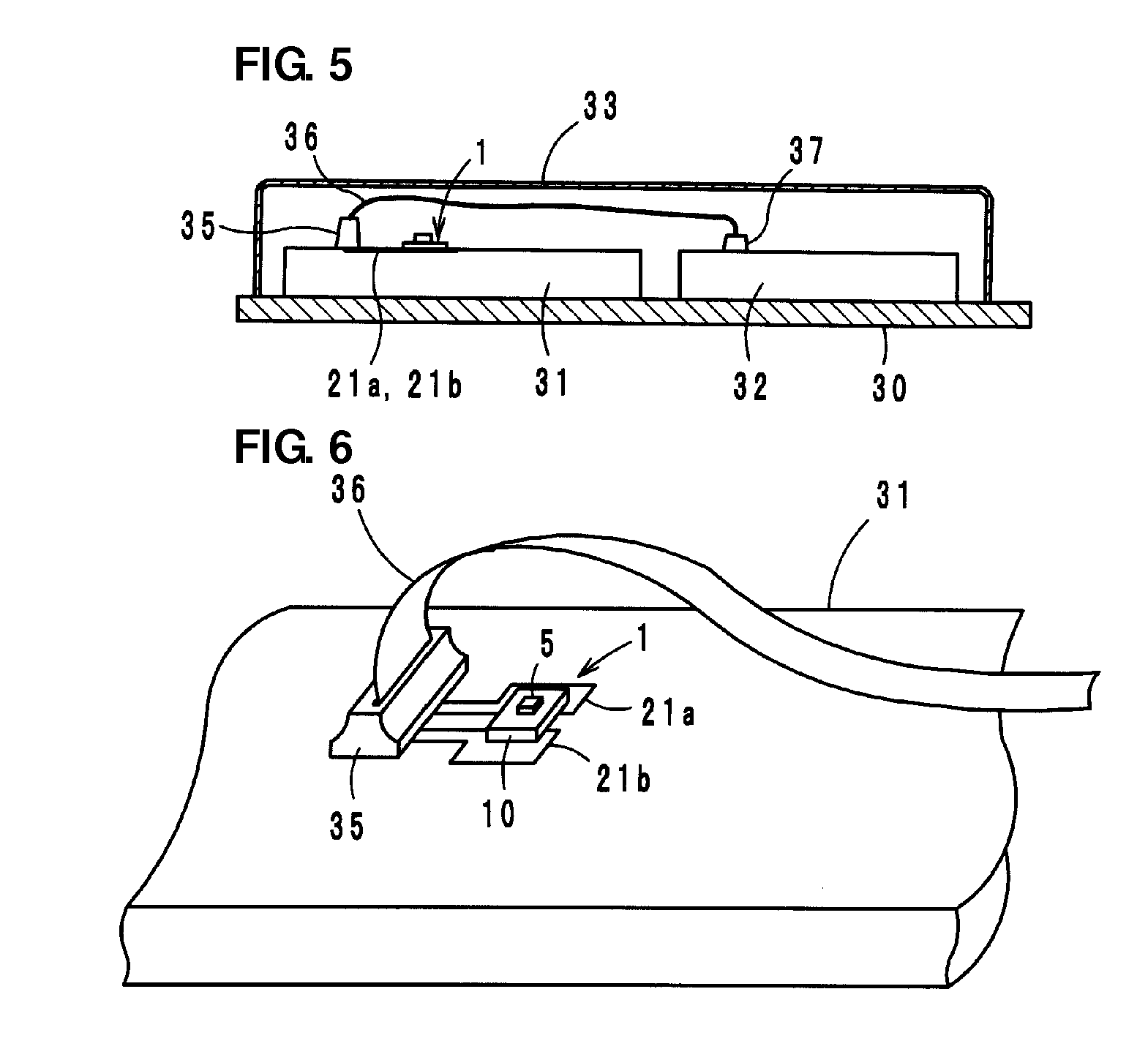

High-frequency module and method for manufacturing the same

InactiveUS7081661B2Reduce electromagnetic influencePliability problemMagnetic/electric field screeningSemiconductor/solid-state device detailsEngineeringElectronic component

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

Touch pad with flexible substrate

ActiveUS7439962B2Low costHigh temperature resistanceCircuit optical detailsTransmission systemsEffective solutionFlexible circuits

Owner:SYNAPTICS INC

Printed circuit board with capacitors connected between ground layer and power layer patterns

InactiveUS6198362B1Magnetic/electric field screeningCurrent interference reductionEngineeringGround pattern

A printed circuit board is disclosed. A top layer power supply pattern and a top layer ground pattern are formed. The top layer power supply pattern and the top layer ground pattern are connected to a power supply layer and a ground layer through a plurality of viaholes, respectively. A plurality of capacitors or a plurality of capacitor resistor series circuits are disposed at predetermined intervals between the top layer power supply pattern and the top layer ground pattern.

Owner:NEC CORP

High frequency signal transmission from the surface of a circuit substrate to a flexible interconnect cable

InactiveUS6867668B1Facilitates high speed signal transmissionLow costPrinted circuit assemblingCross-talk/noise/interference reductionElectricityCoplanar waveguide

A high speed flexible interconnect cable includes a number of conductive layers and a number of dielectric layers. Conductive signal traces, located on the conductive layers, combine with the dielectric layers to form one or more high speed electrical transmission line structures. The transmission line structure may be realized as a grounded coplanar waveguide structure, a microstrip structure, a stripline structure, or the like. The cable can be coupled to destination components using a variety of connection techniques, e.g., direct bonding to a circuit substrate, direct soldering to a flip chip, mechanical attachment to a component, or integration with a circuit substrate. The cable can also be terminated with any number of known or standardized connector packages, e.g., SMA, GPPO, or V connectors.

Owner:QUALCOMM INC

High speed, high density electrical connector

ActiveUS20060068640A1Contact member manufacturingCoupling for high frequencyHigh densityElectrical conductor

An electrical connector with electrically lossy materials bridging ground members. The lossy conductive members may be formed by filling a settable binder with conductive particles, allowing the partially conductive members to be formed through an insert molding process. Connectors assembled from wafers that contain signal conductors held within an insulative housing may incorporate lossy conductive members by having filled thermal plastic molded onto the insulatative housing. The lossy conductive members may be used in conjunction with magnetically lossy materials. The lossy conductive members reduce ground system do resonance within the connector, thereby increasing the high frequency performance of the connector.

Owner:AMPHENOL CORP

Flex circuit shielded optical sensor

InactiveUS20060084852A1Cross-talk/noise/interference reductionColor/spectral properties measurementsPhotovoltaic detectorsPhotodetector

A flex circuit optical sensor has an integrated Faraday shield. A conductive trace layer disposed on a substrate is used to form a conductive grid which shields the face of a photodetector. A conductive ink layer is formed on a substrate side opposite the trace layer. The back and sides of the detector are shielded by flex circuit flaps that have the conductive ink layer but substantially exclude the trace layer so as to fold over and closely adhere to the detector body. The shielded substrate flaps advantageously eliminate a separate detector shield, which is typically fabricated with an etched copper part that must be attached to a flex circuit before mounting the detector.

Owner:JPMORGAN CHASE BANK NA

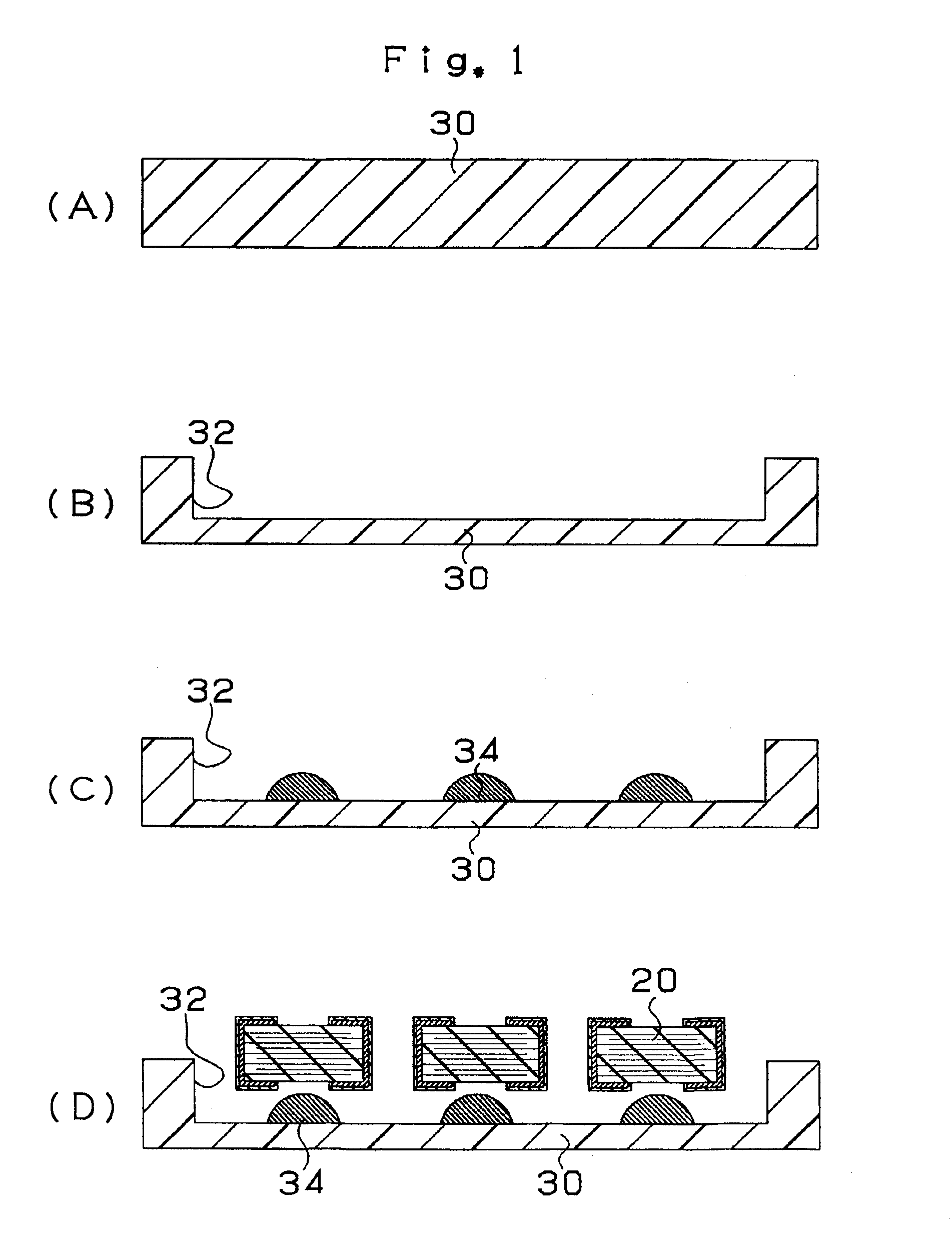

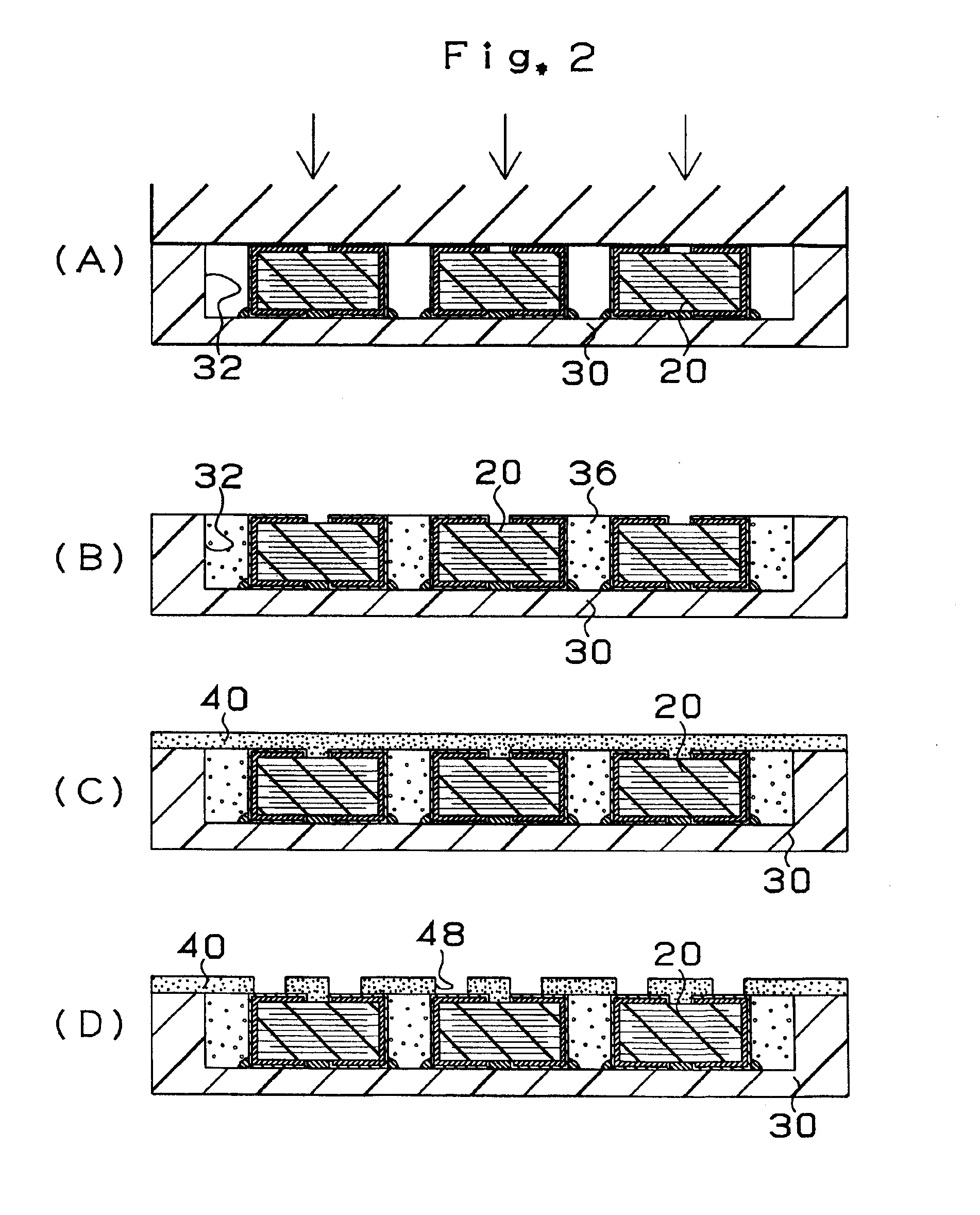

Printing wiring board and method of producing the same and capacitor to be contained in printed wiring board

InactiveUS6876554B1Improve reliabilityFlat surfaceFinal product manufactureSemiconductor/solid-state device detailsEngineeringPrinted circuit board

Chip capacitors 20 are provided in a printed circuit board 10. In this manner, the distance between an IC chip 90 and each chip capacitor 20 is shortened, and the loop inductance is reduced. In addition, the chip capacitors 20 are accommodated in a core substrate 30 having a large thickness. Therefore, the thickness of the printed circuit board does not become large.

Owner:IBIDEN CO LTD

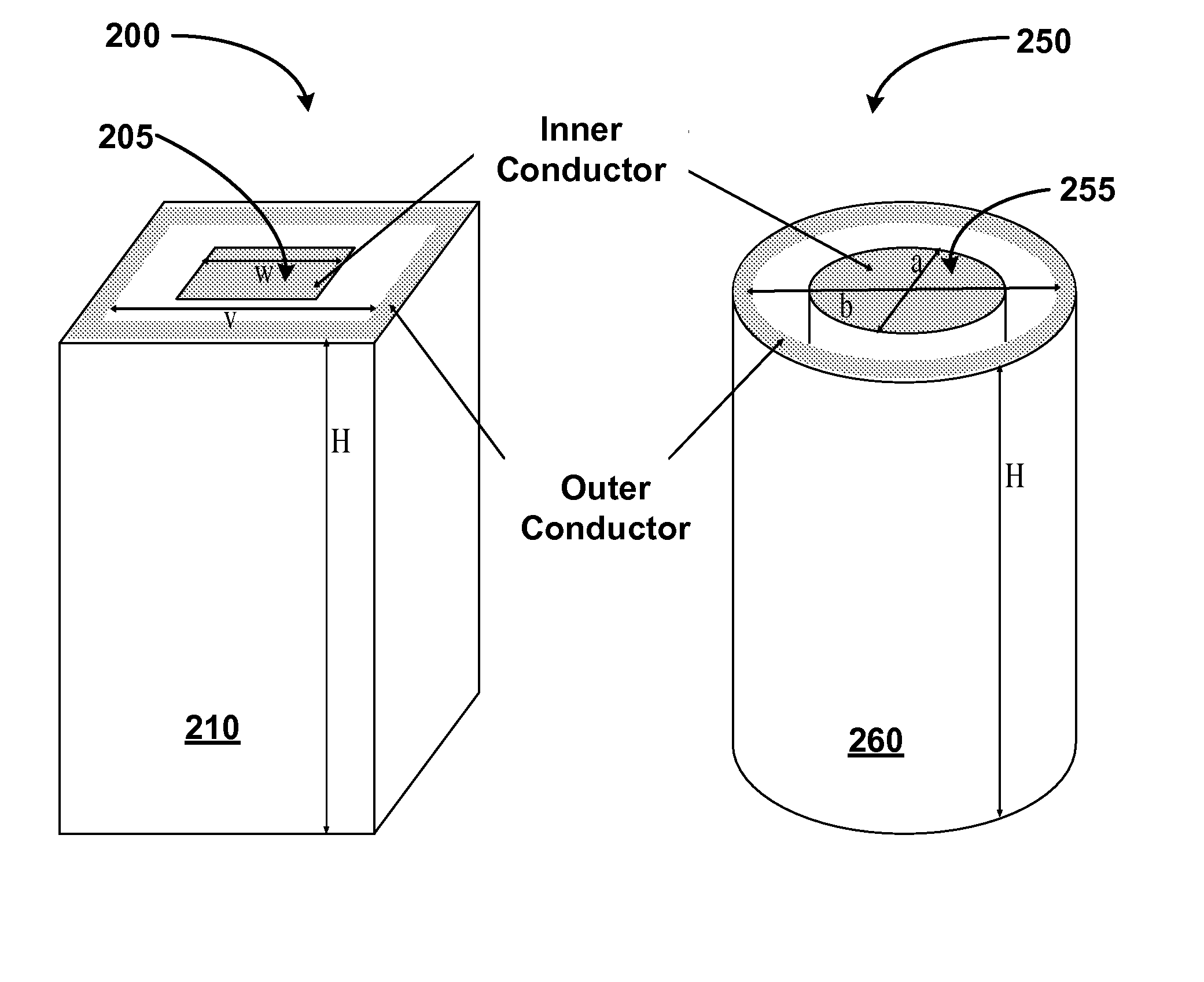

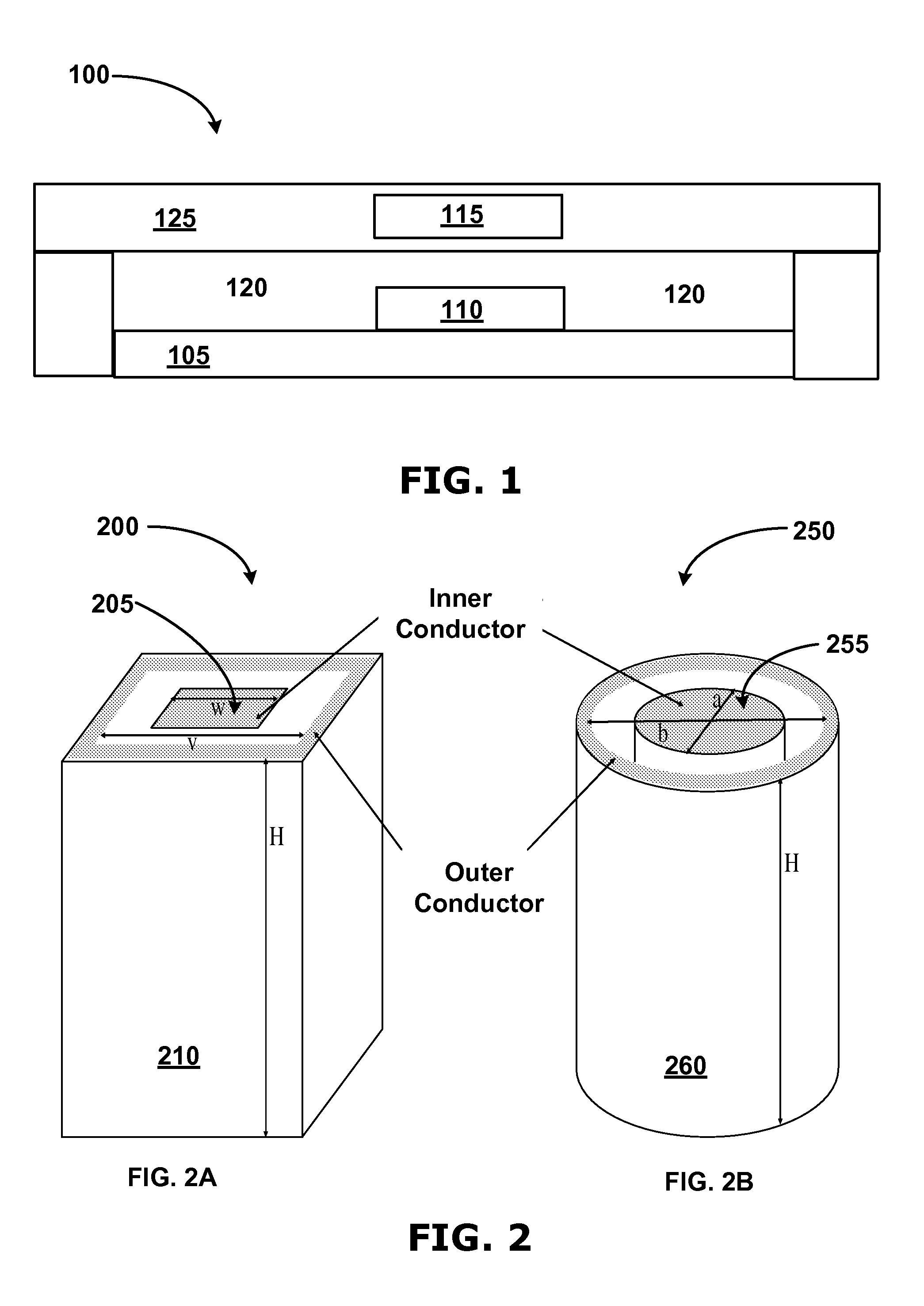

High performance interconnect devices & structures

InactiveUS20070105429A1Improve performanceCross-talk/noise/interference reductionSemiconductor/solid-state device detailsElectrical conductorEngineering

High performance interconnect devices, structures, and fabrication methods are provided herein. According to some embodiments of the present invention, an interconnect device used to connect components or route signals in an integrated circuit can comprise multiple conductors. A first conductor of the interconnect device can define a first conductor axis, and a second conductor of the interconnect device can define a second conductor axis. The second conductor can be proximate the first conduct such that first conductor axis is substantially coaxially situated relative to the second conductor axis to provide a high performance interconnect having a coaxial alignment. The first conductor and the second conductor can define a gap disposed between and separating the conductors. Other embodiments are also claimed and described.

Owner:GEORGIA TECH RES CORP

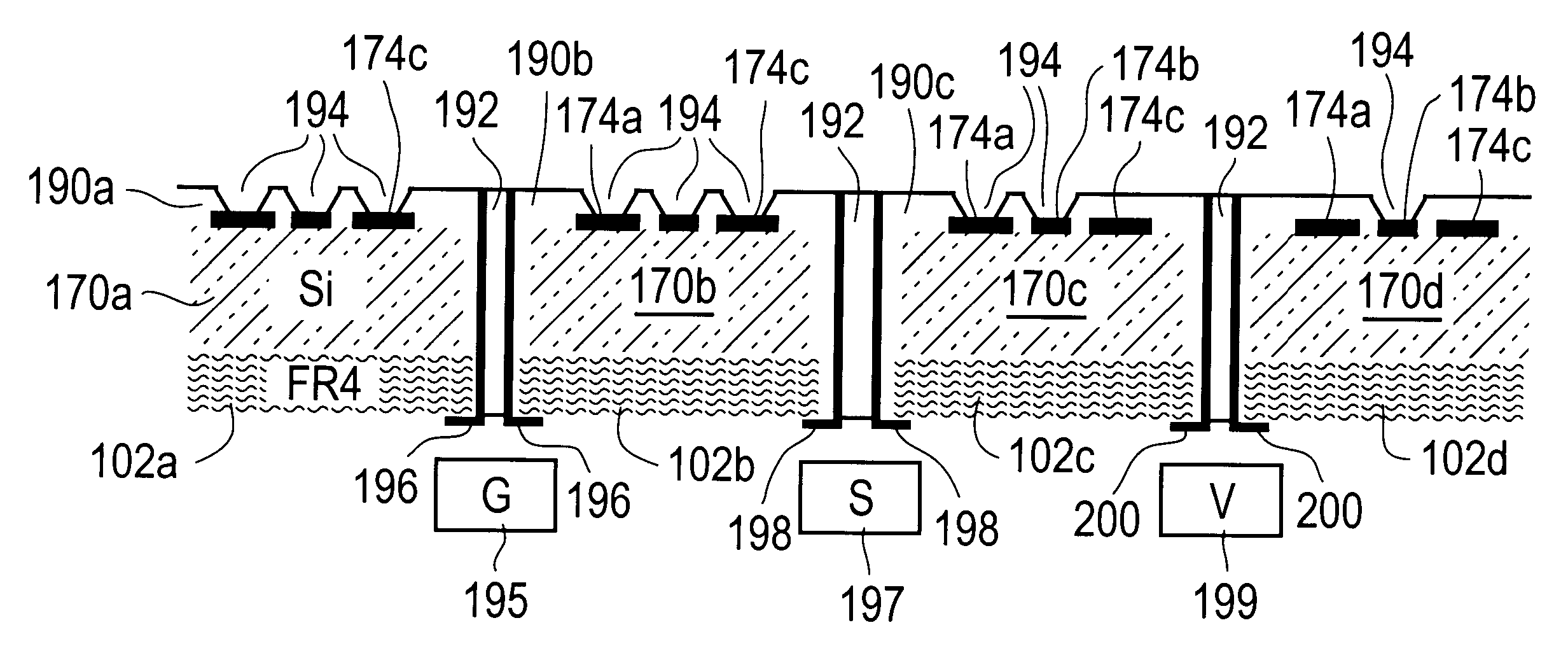

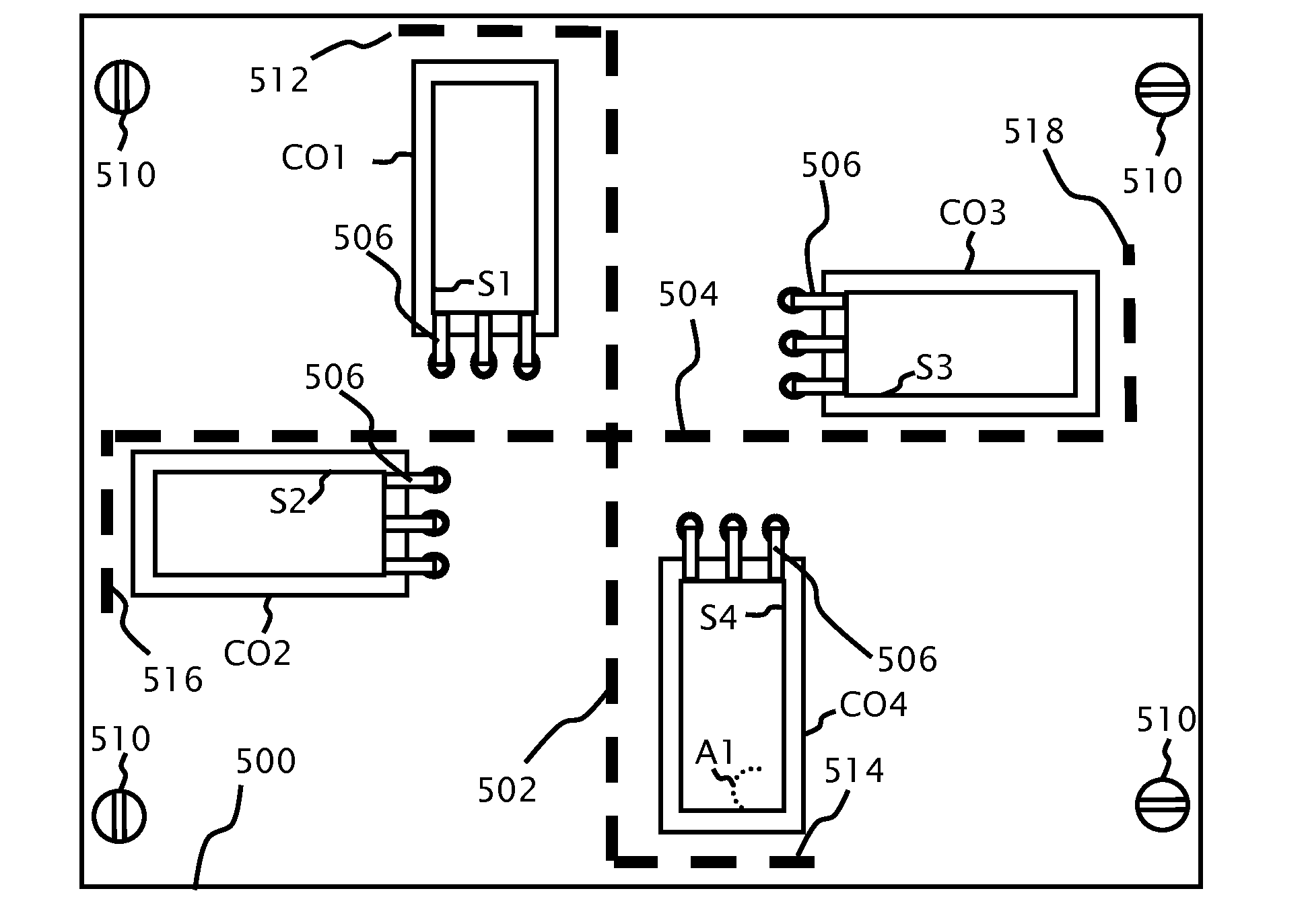

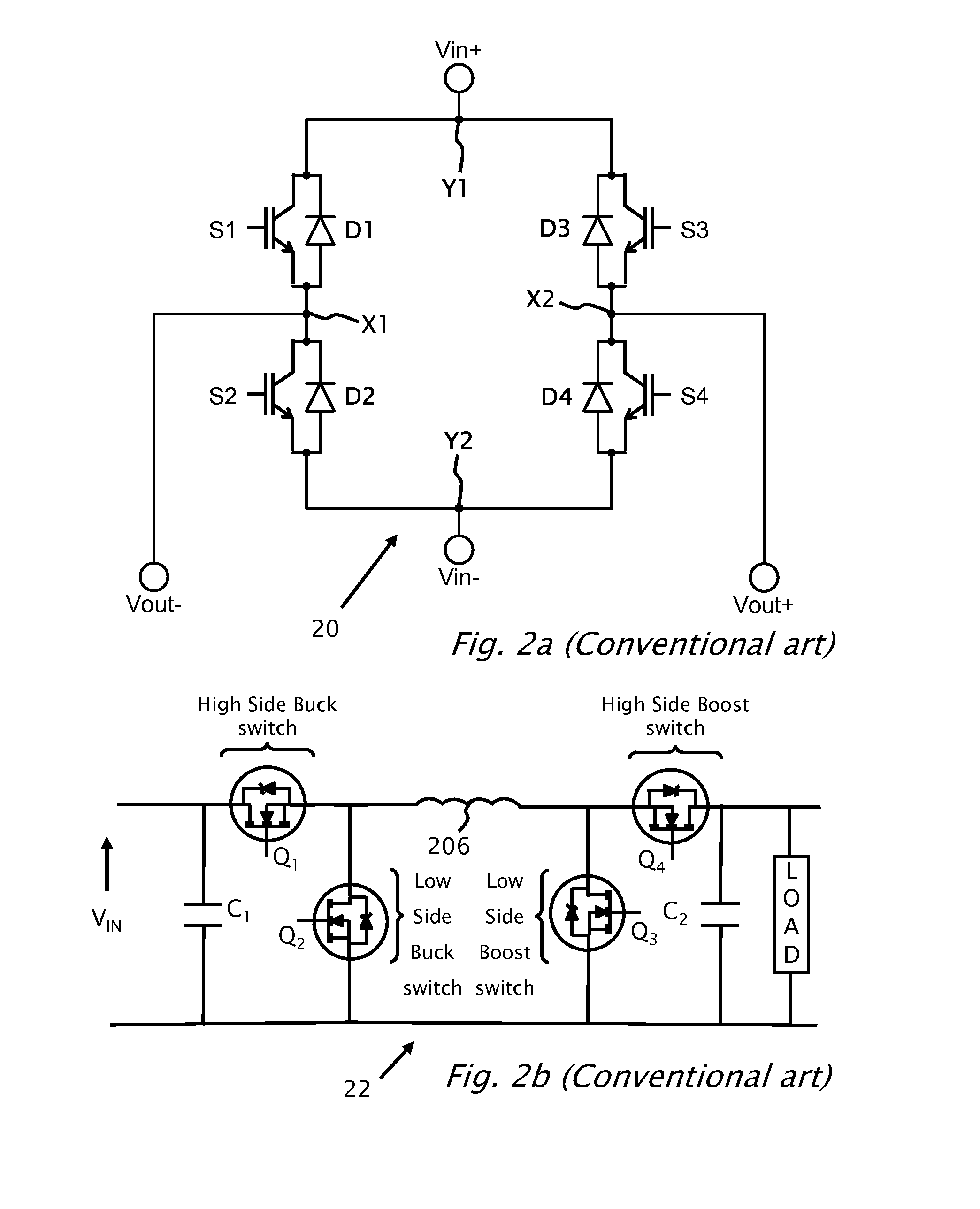

Switching Circuit Layout With Heatsink

ActiveUS20100124027A1Conversion constructional detailsCross-talk/noise/interference reductionEngineeringLine segment

A circuit board adapted for use in an switching converter for connecting a plurality of switches including a first switch, a second switch, a third switch and a fourth switch. The circuit board has a layout for connecting the switches. The layout is adapted for locating the switches substantially at or symmetrically with respect to the endpoints of a right-angle cross. The right-angle cross is formed from two line segments intersecting with a ninety degree angle. The circuit board may offsets the switches perpendicularly to the line segments at the endpoints of the line segments either in a clockwise or a counterclockwise direction.

Owner:SOLAREDGE TECH LTD

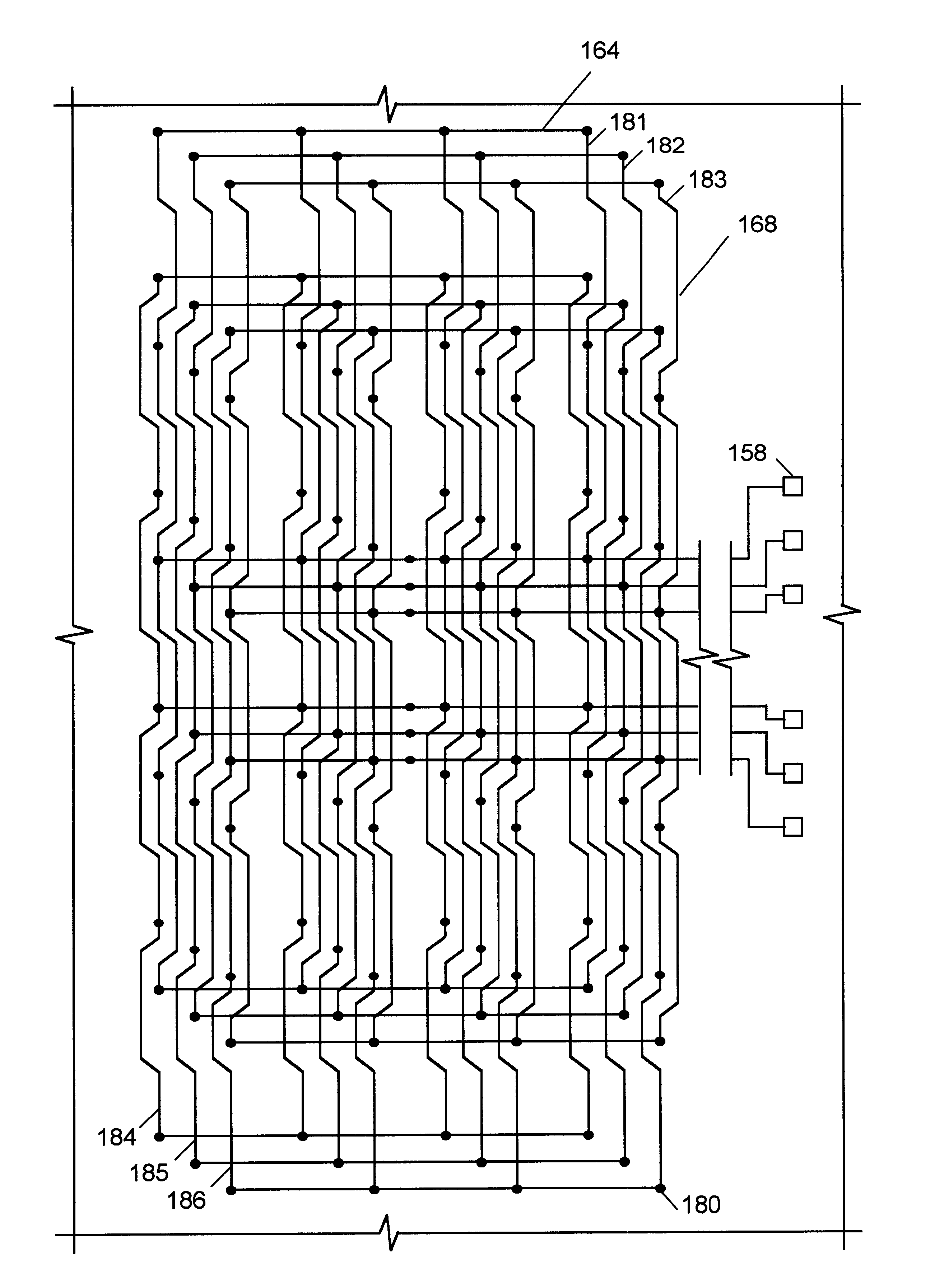

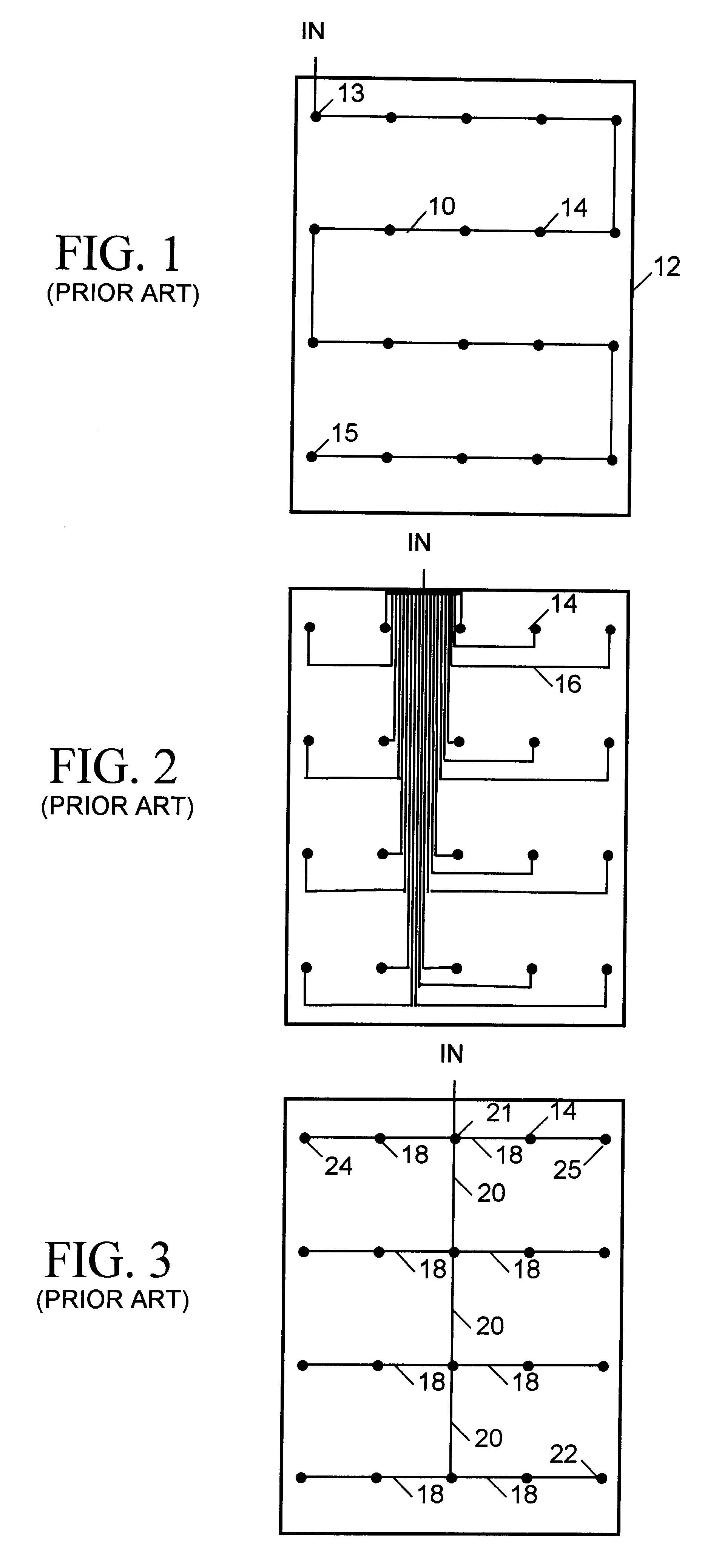

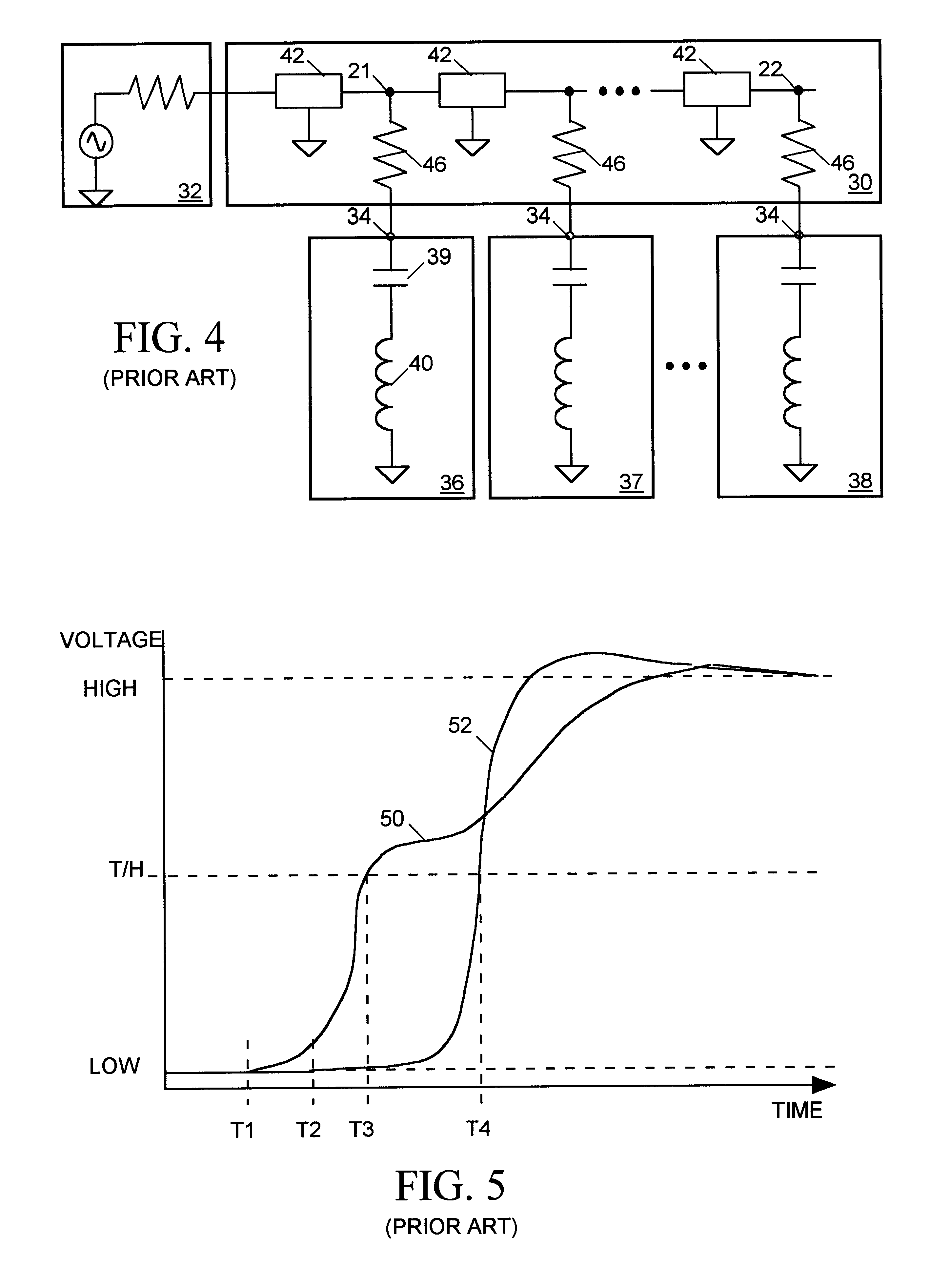

Closed-grid bus architecture for wafer interconnect structure

InactiveUS6603323B1Electrical measurement instrument detailsCross-talk/noise/interference reductionContact padSemiconductor

An interconnect structure employs a closed-grid bus to link an integrated circuit tester channel to an array of input / output (I / O) pads on a semiconductor wafer so that the tester channel can concurrently communicate with all of the I / O pads. The interconnect structure includes a circuit board implementing an array of bus nodes, each corresponding to a separate one of the I / O pads. The circuit board includes at least two layers. Traces mounted on a first layer form a set of first daisy-chain buses, each linking all bus nodes of a separate row of the bus node array. Traces mounted on a second circuit board layer form a set of second daisy-chain buses, each linking all bus nodes of a separate column of the bus node array. Vias and other circuit board interconnect ends of the first and second daisy-chain buses so that they form the closed-grid bus. Each bus node is connected though a separate isolation resistor to a separate contact pad mounted on a surface of the circuit board. A set of spring contacts or probes link each contact pad to a separate one of the I / O pads on the wafer.

Owner:FORMFACTOR INC

Composite interposer and method for producing a composite interposer

InactiveUS20020076919A1Semiconductor/solid-state device detailsCross-talk/noise/interference reductionEpoxyDevice material

A composite interposer for providing power and signal connections between an integrated circuit chip or chips and a substrate. The interposer includes a signal core formed from a conductive power / ground plane positioned between two dielectric layers. A method for fabricating a composite interposer comprising disposing a silicon layer on a substrate, and selectively etching the silicon layer down to the substrate to develop silicon openings with a silicon profile, and to expose part of the substrate. Vias are formed through the exposed part of the substrate. The method additionally includes filling the vias and the silicon openings with a filler material (e.g., a high-aspect-ratio-capable photodefinable epoxy polymer) to form filled silicon openings and filled vias, forming first openings through the filled silicon openings and through the filled vias, forming second opening through filler material to expose semiconductor devices on the silicon layer, and interconnecting electrically, through the first openings and through the second openings, the exposed semiconductor devices with pads disposed against a bottom of the substrate.

Owner:FUJITSU LTD

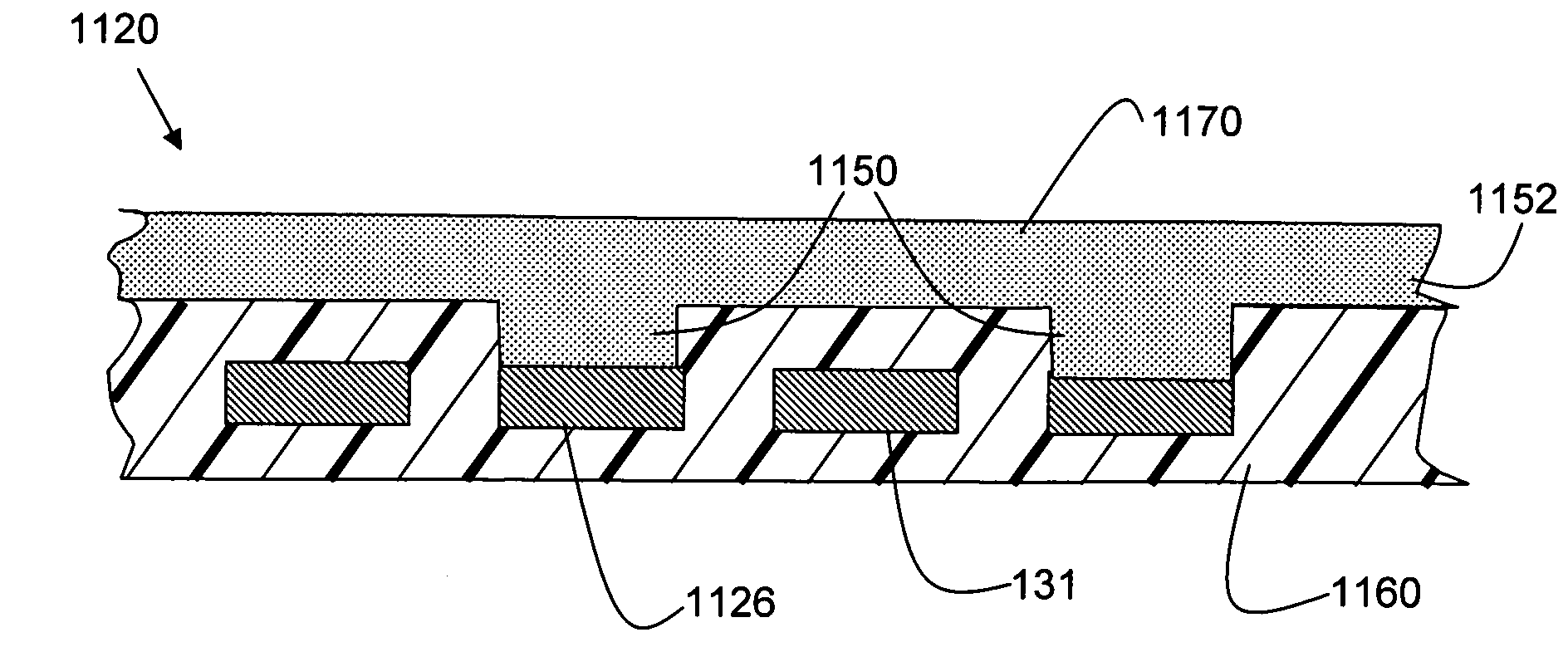

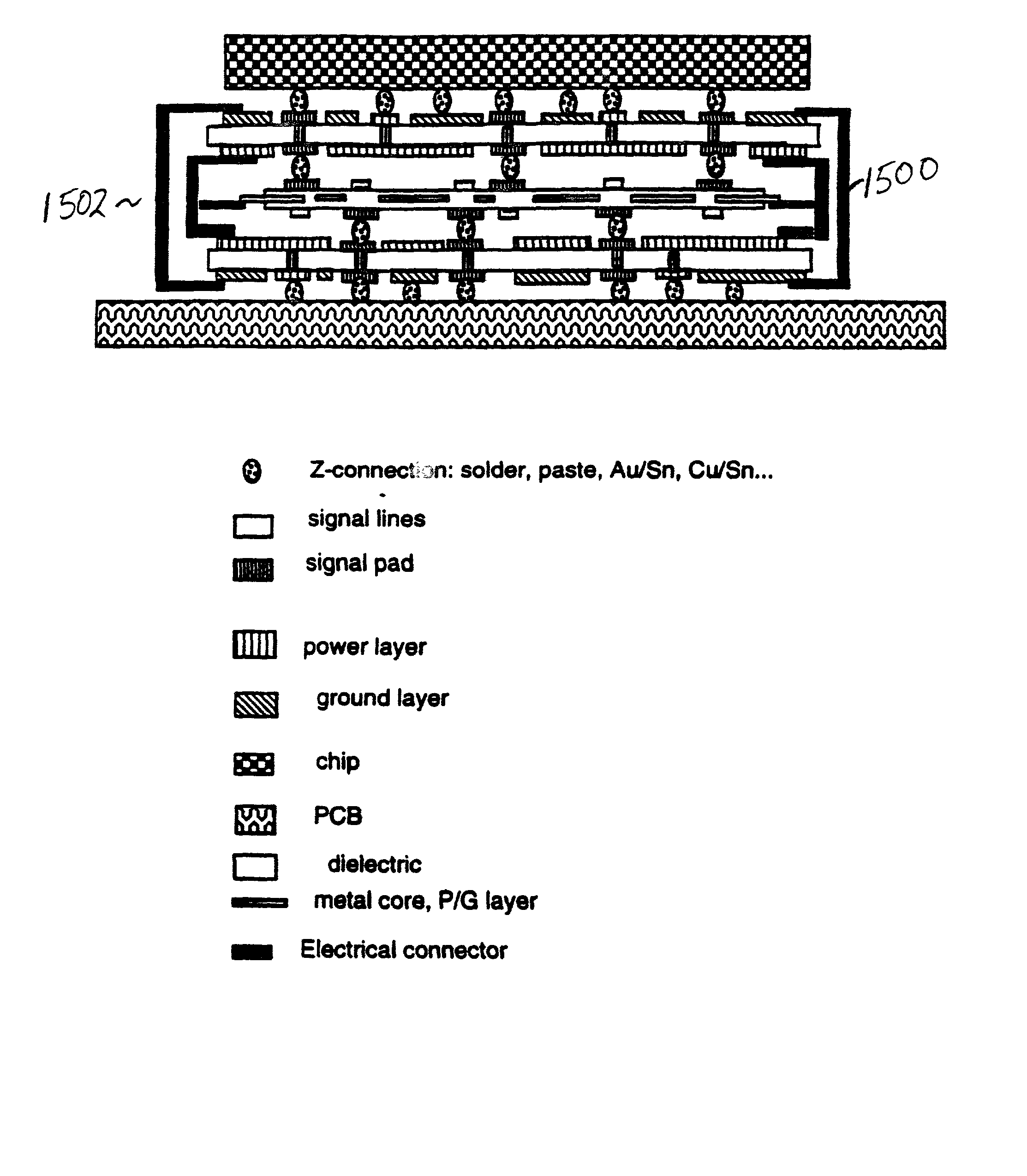

Integrated conductive structures and fabrication methods thereof facilitating implementing a cell phone or other electronic system

ActiveUS20080315375A1Printed circuit assemblingCross-talk/noise/interference reductionContact padElectronic systems

Circuit structures and methods of fabrication are provided for facilitating implementing a complete electronic system in a compact package. The circuit structure includes, in one embodiment, a chips-first multichip base layer with conductive structures extending therethrough. An interconnect layer is disposed over the front surface of the multichip layer and includes interconnect metallization electrically connected to contact pads of the chips and to conductive structures extending through the structural material. A redistribution layer, disposed over the back surface of the multichip layer, includes a redistribution metallization also electrically connected to conductive structures extending through the structural material. Input / output contacts are arrayed over the redistribution layer, including over the lower surfaces of at least some integrated circuit chips within the multichip layer, and are electrically connected through the redistribution metallization, conductive structures, and interconnect metallization to contact pads of the integrated circuit chips of the multichip layer.

Owner:EPIC TECH INC

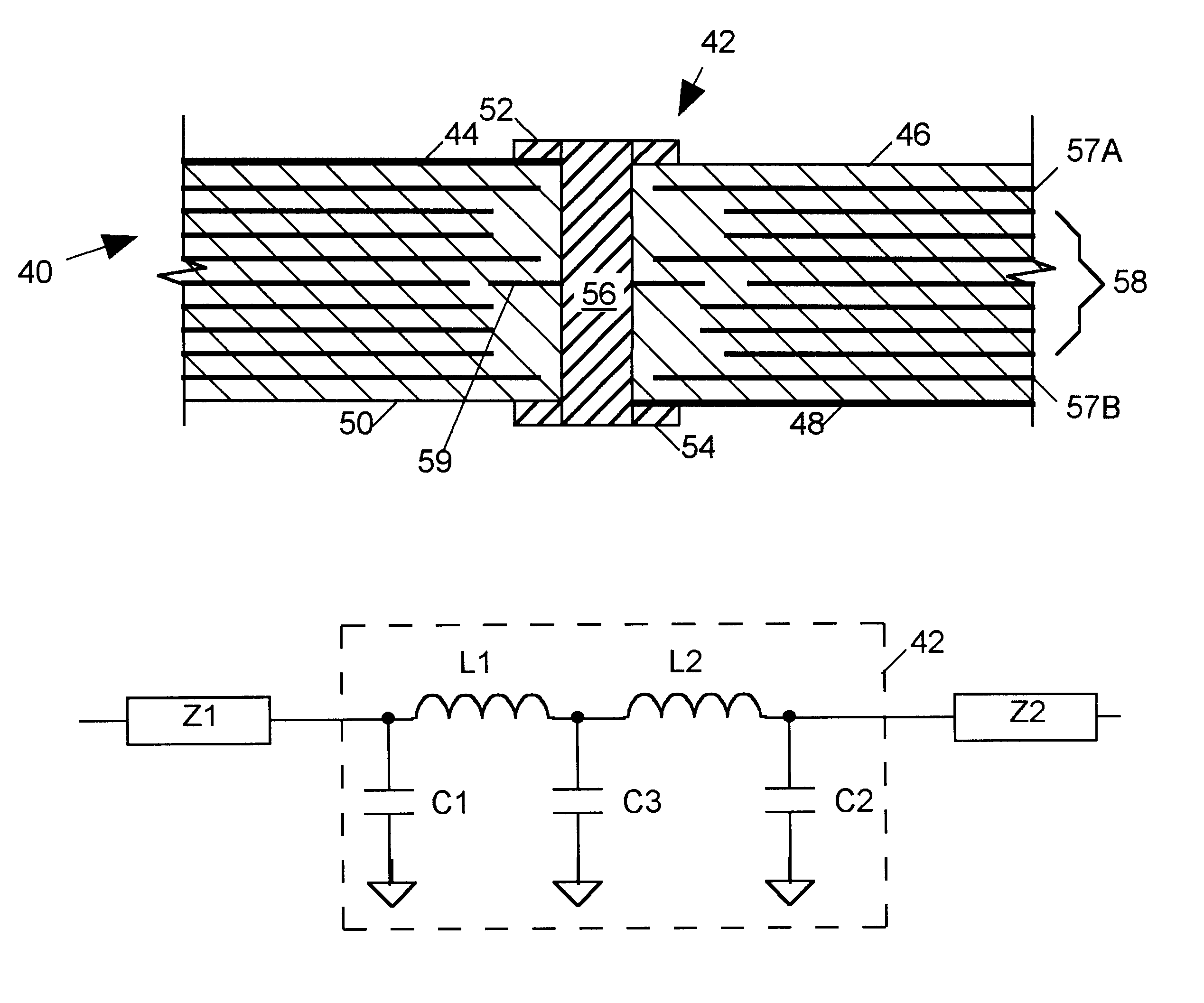

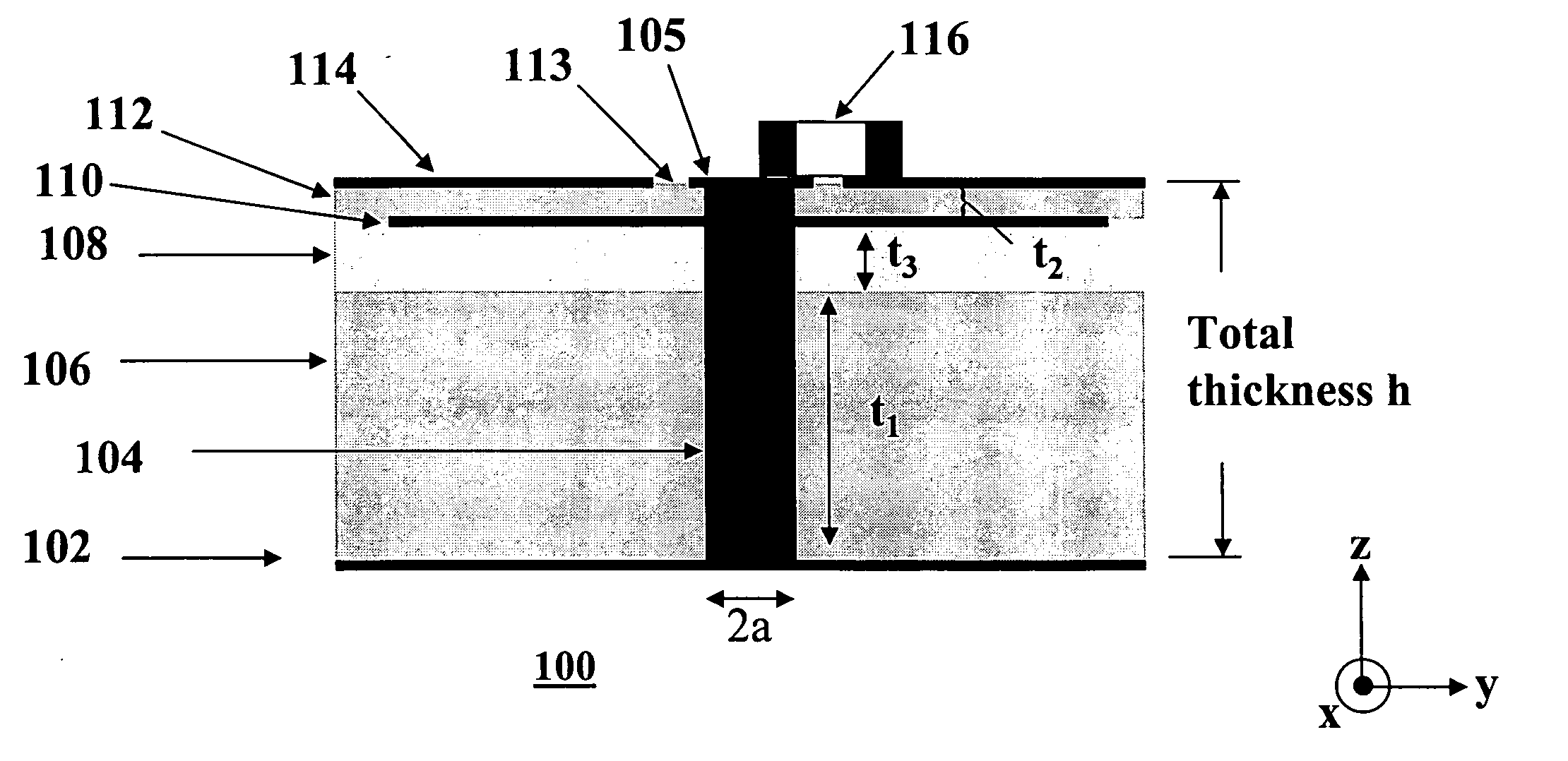

High frequency printed circuit board via

A printed circuit board (PCB) via, providing a conductor extending vertically between microstrip or stripline conductors formed on separate layers of a PCB, includes a conductive pad surrounding the conductor and embedded within the PCB between those PCB layers. The pad's shunt capacitance and the magnitudes of capacitances of other portions of the via are sized relative to the conductor's inherent inductance to optimize frequency response characteristics of the via.

Owner:FORMFACTOR INC

Flexible differential interconnect cable with isolated high frequency electrical transmission line

InactiveUS7145411B1Easy to optimizeLow costCross-talk/noise/interference reductionPrinted circuit aspectsElectricityCoplanar waveguide

A high speed flexible interconnect cable includes a number of conductive layers and a number of dielectric layers. Conductive signal traces, located on the conductive layers, combine with the dielectric layers to form one or more high speed electrical transmission line structures. The transmission line structure may be realized as a grounded coplanar waveguide structure, a microstrip structure, a stripline structure, or the like. The cable can be coupled to destination components using a variety of connection techniques, e.g., direct bonding to a circuit substrate, direct soldering to a flip chip, mechanical attachment to a component, or integration with a circuit substrate. The cable can also be terminated with any number of known or standardized connector packages, e.g., SMA, GPPO, or V connectors.

Owner:QUALCOMM INC

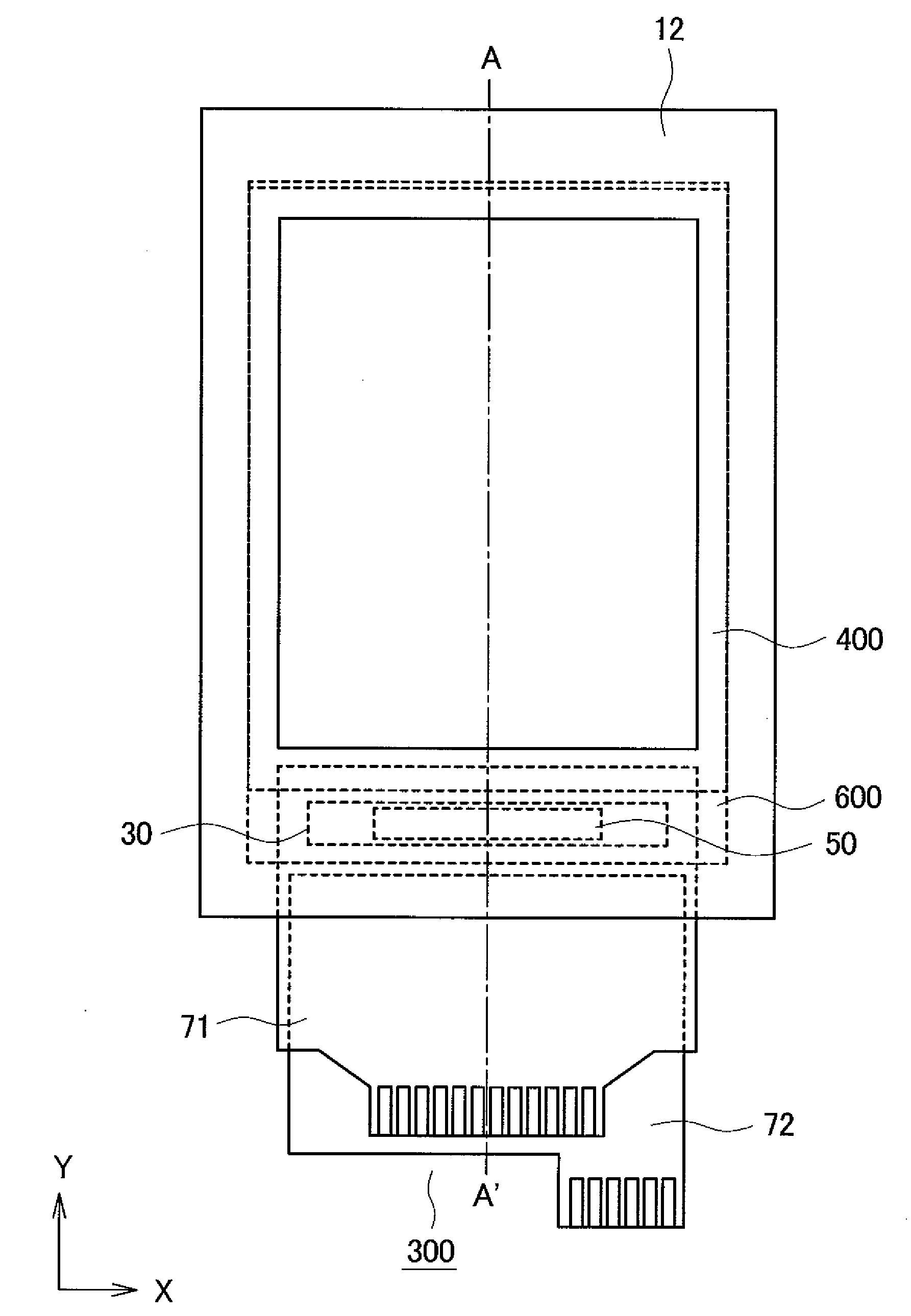

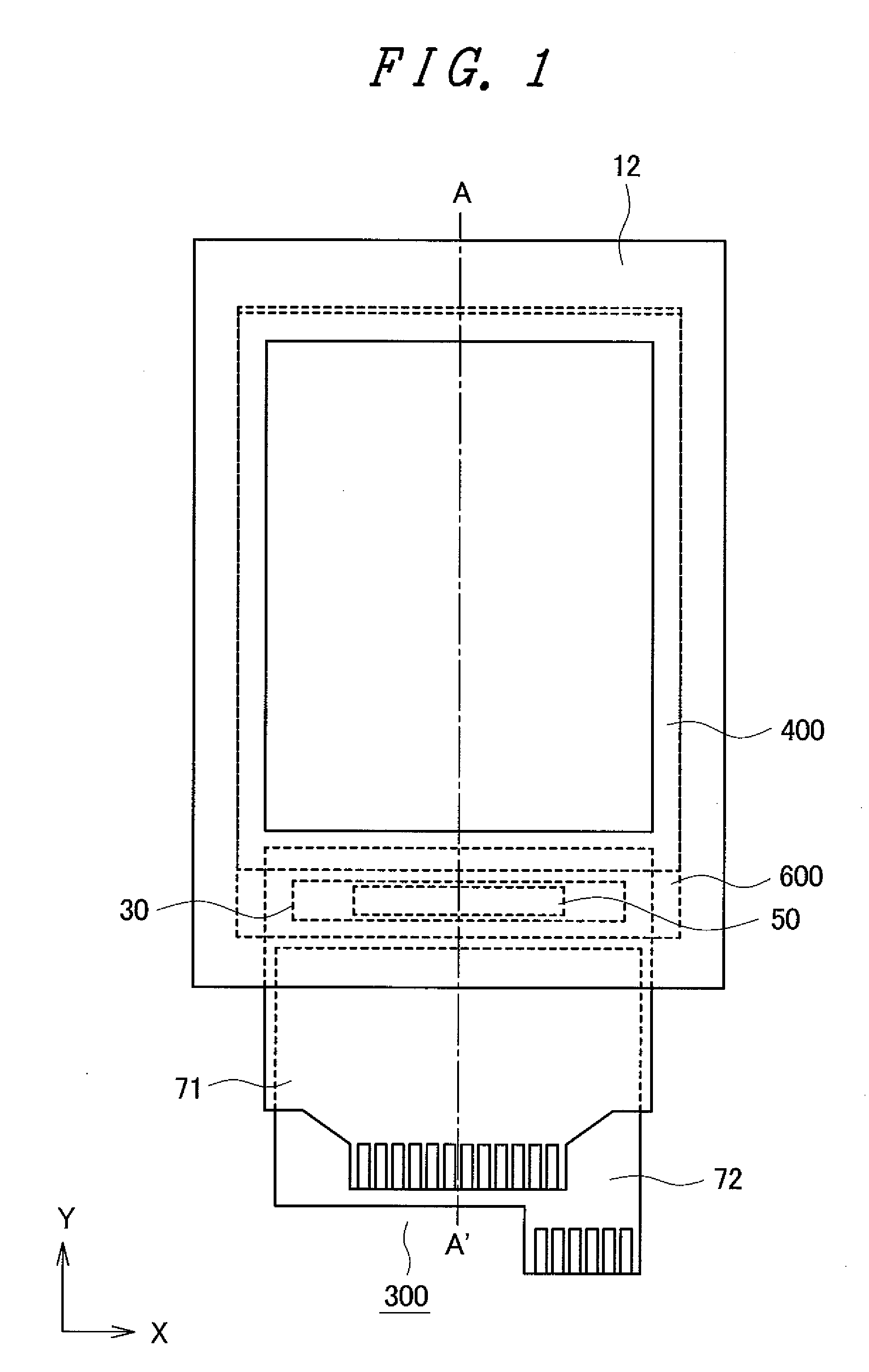

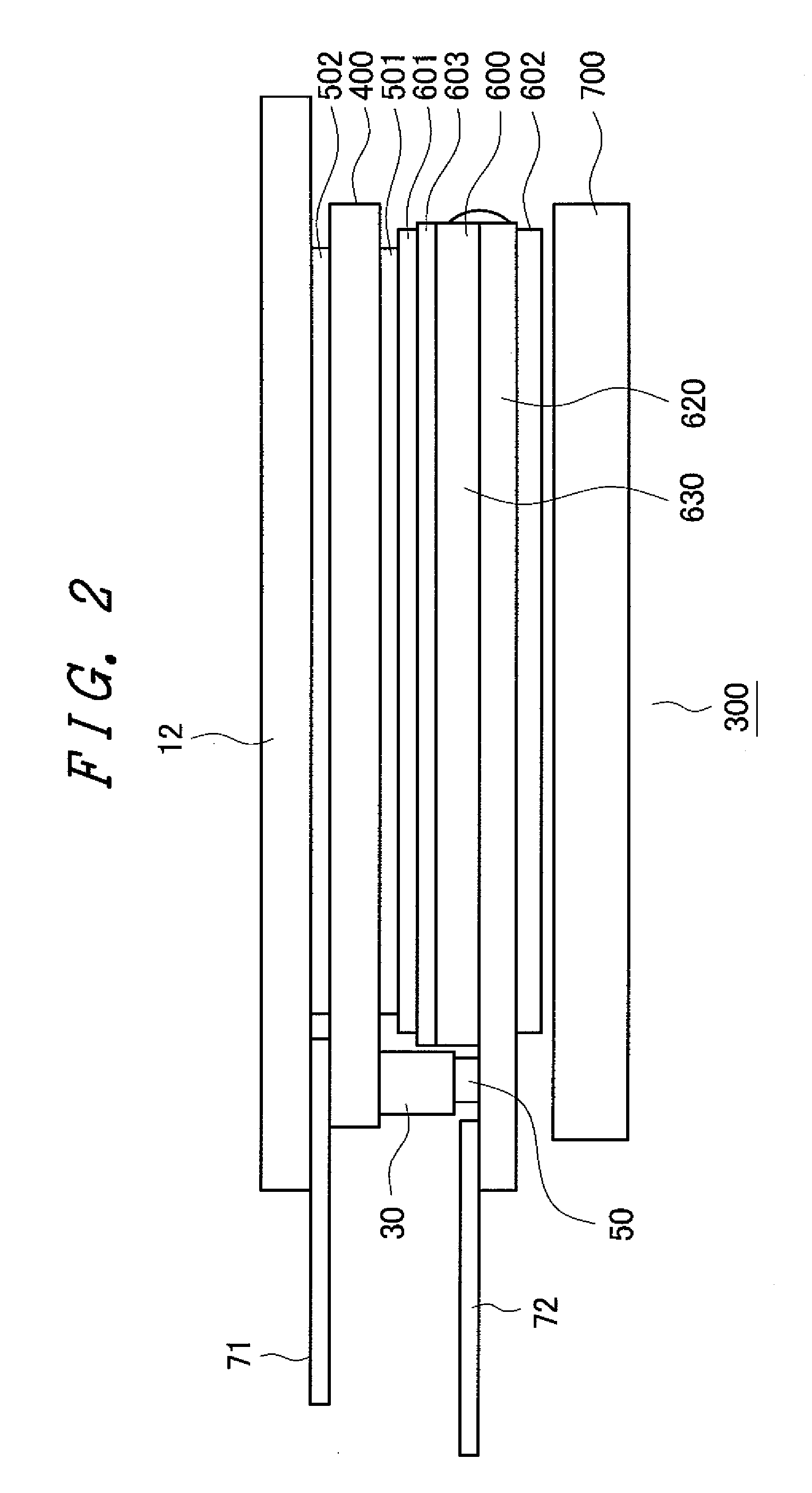

Display device

ActiveUS20100033443A1High detection sensitivityImprove reliabilityDigital data processing detailsCross-talk/noise/interference reductionCapacitanceNoise level

A display device having a highly reliable electrostatic capacitive type touch panel which allows finger touch inputting and possesses excellent detection sensitivity is provided. With respect to X electrodes and Y electrodes which are formed on an electrostatic capacitive type touch panel, either one of the X electrodes and the Y electrodes is divided corresponding to a ratio between the number of X electrodes and the number of Y electrodes, and a floating electrode is formed in gaps formed along with the reduction of area of the electrode thus adjusting the area of the electrode. Due to the contraction of the area of the individual electrode, a noise level can be lowered more compared to lowering of a signal level and hence, an S / N ratio can be increased thus enhancing the detection sensitivity. Further, a line is branched on a flexible printed circuit board, intersecting lines are formed on a back surface of the flexible printed circuit board, and the intersecting lines are arranged to orthogonally intersect with lines formed on a front surface of the flexible printed circuit board thus lowering line capacitance.

Owner:JAPAN DISPLAY INC +1

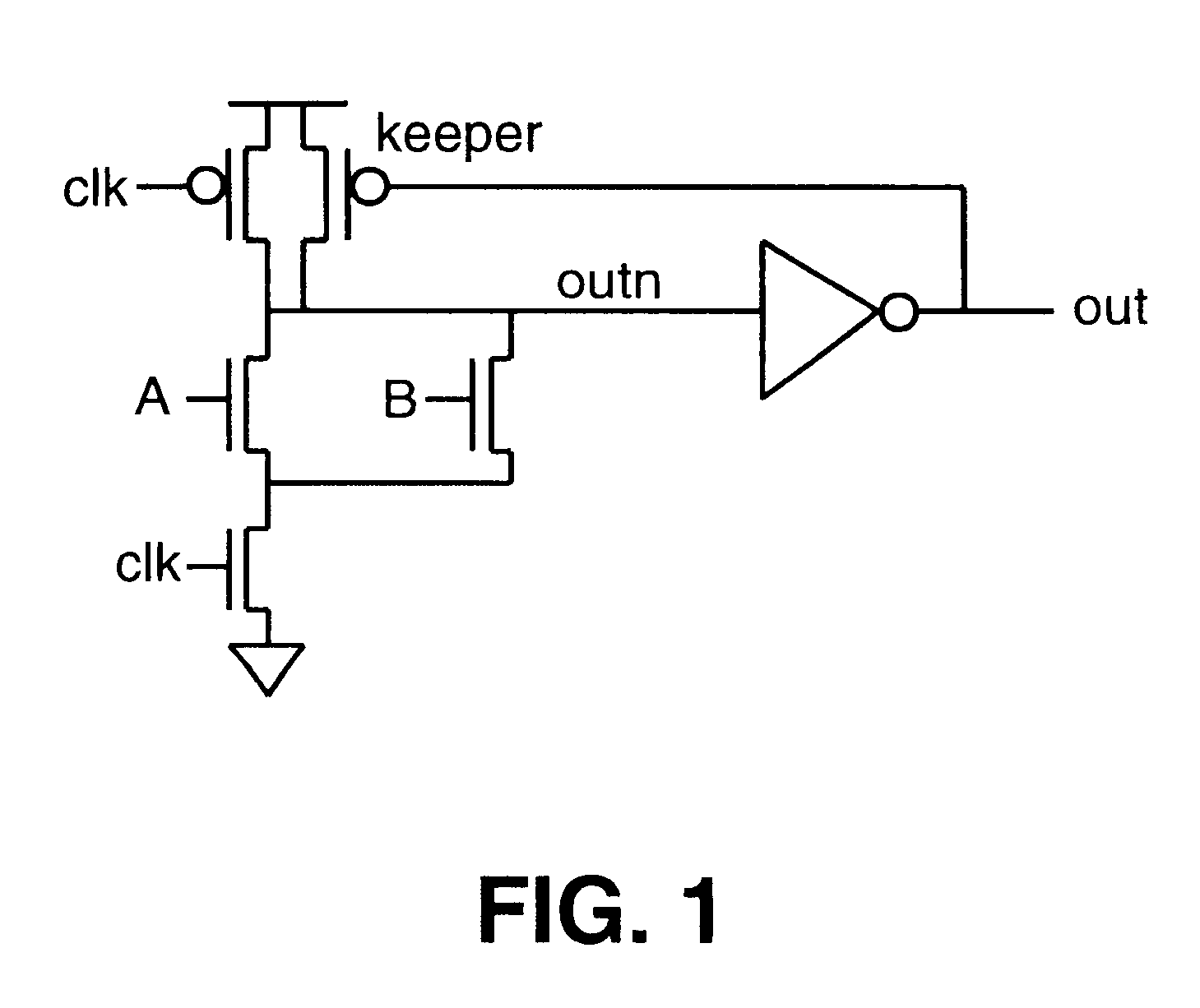

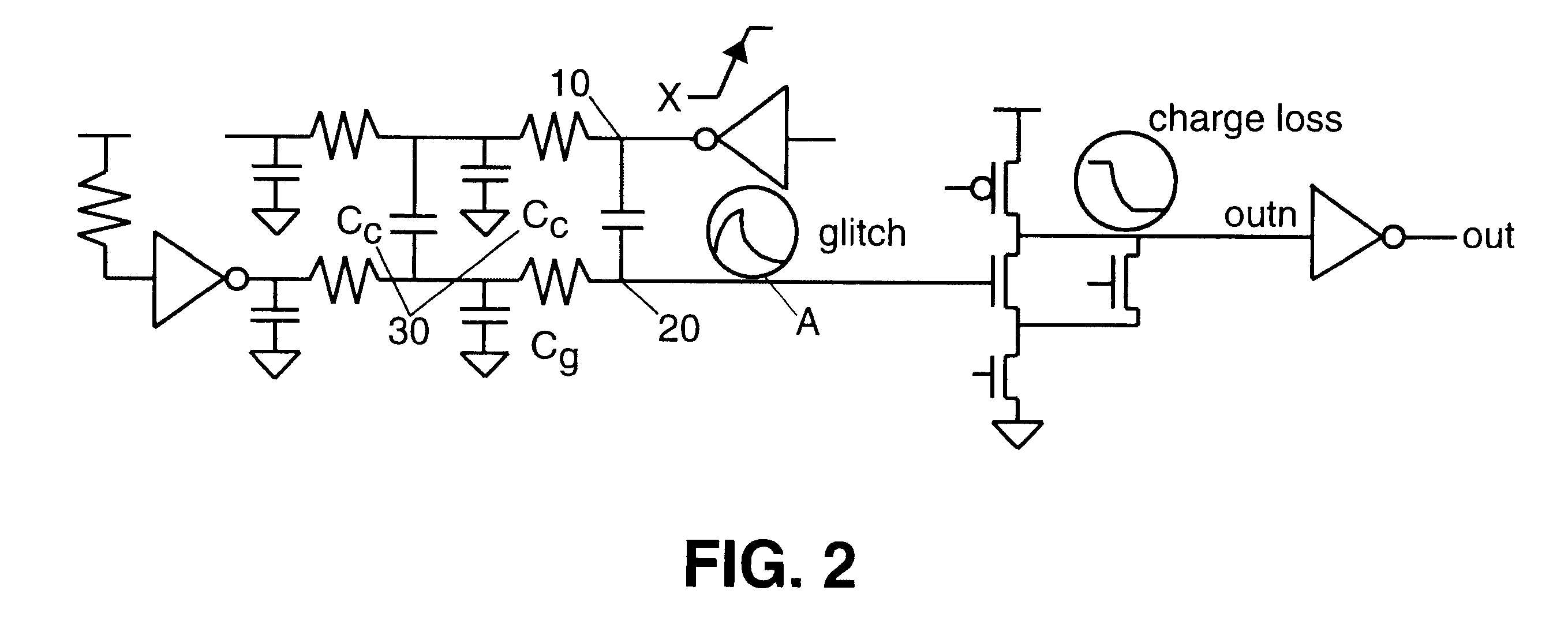

Automated shielding algorithm for dynamic circuits

InactiveUS6510545B1Semiconductor/solid-state device detailsCross-talk/noise/interference reductionIntegrated circuitCapacitance

An automated shielding tool, algorithm, and design methodology for shielding integrated circuits is disclosed herein. This is accomplished by inserting VDD and VSS wire proximate to signal wires on the same metal layer. The noise issues for dynamic circuits is described along with the benefits and costs of wire shielding. The methodology of the shield tool is a systematic approach for dealing with noise due to capacitive and inductive coupling.

Owner:ORACLE INT CORP

Radio IC device

ActiveUS20100103058A1Without reducing radiation characteristicReducing radiation characteristicAntenna supports/mountingsSemiconductor/solid-state device detailsElectromagnetic couplingEngineering

A radio IC device includes an electromagnetic coupling module includes a radio IC chip arranged to process transmitted and received signals and a feed circuit board including an inductance element. The feed circuit board includes an external electrode electromagnetically coupled to the feed circuit, and the external electrode is electrically connected to a shielding case or a wiring cable. The shielding case or the wiring cable functions as a radiation plate. The radio IC chip is operated by a signal received by the shielding case or the wiring, and the answer signal from the radio IC chip is radiated from the shielding case or the wiring cable to the outside. A metal component functions as the radiation plate, and the metal component may be a ground electrode disposed on the printed wiring board.

Owner:MURATA MFG CO LTD

Heat sink formed with conformal shield

ActiveUS20090000114A1Printed circuit assemblingWave amplification devicesEngineeringElectromagnetic shielding

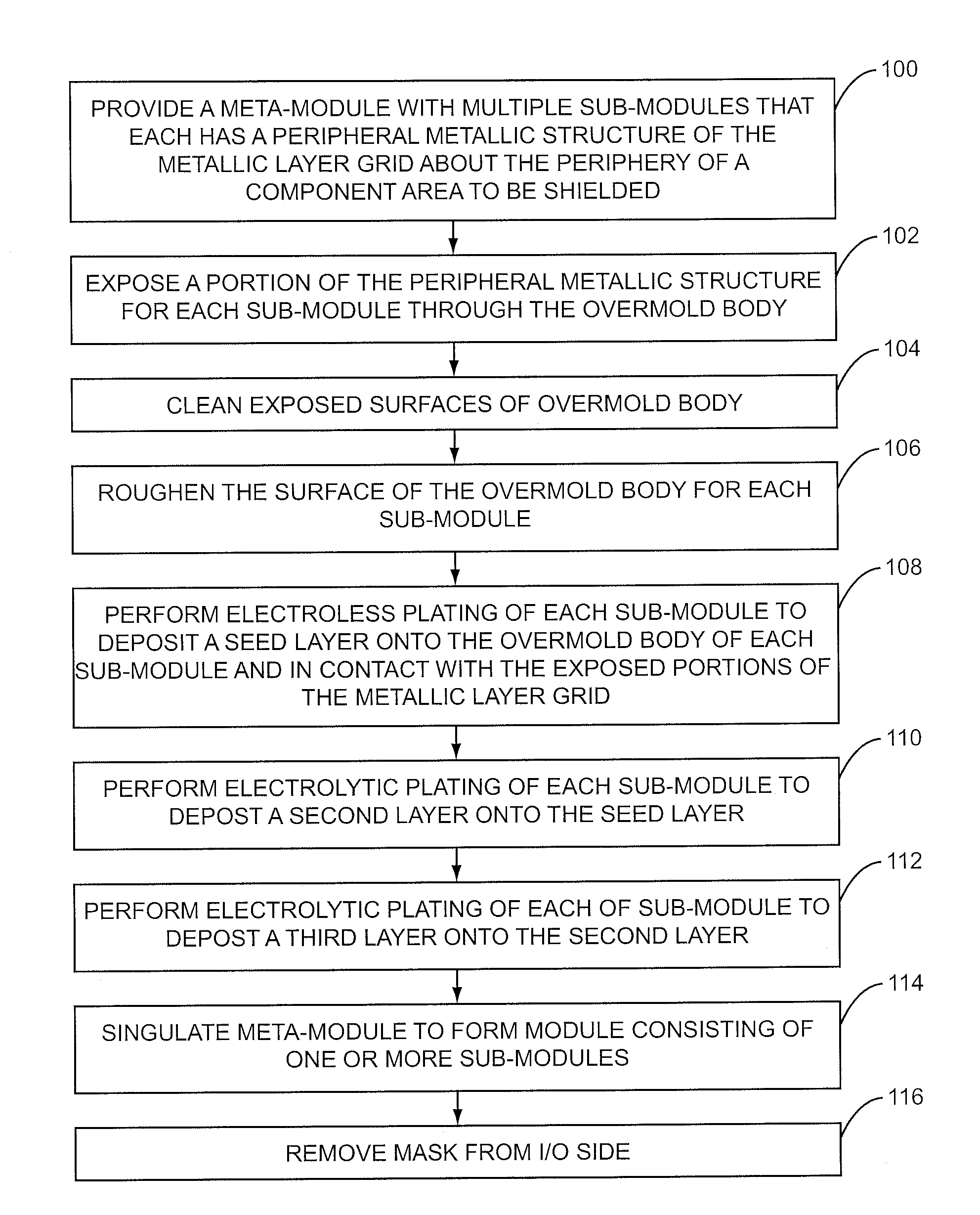

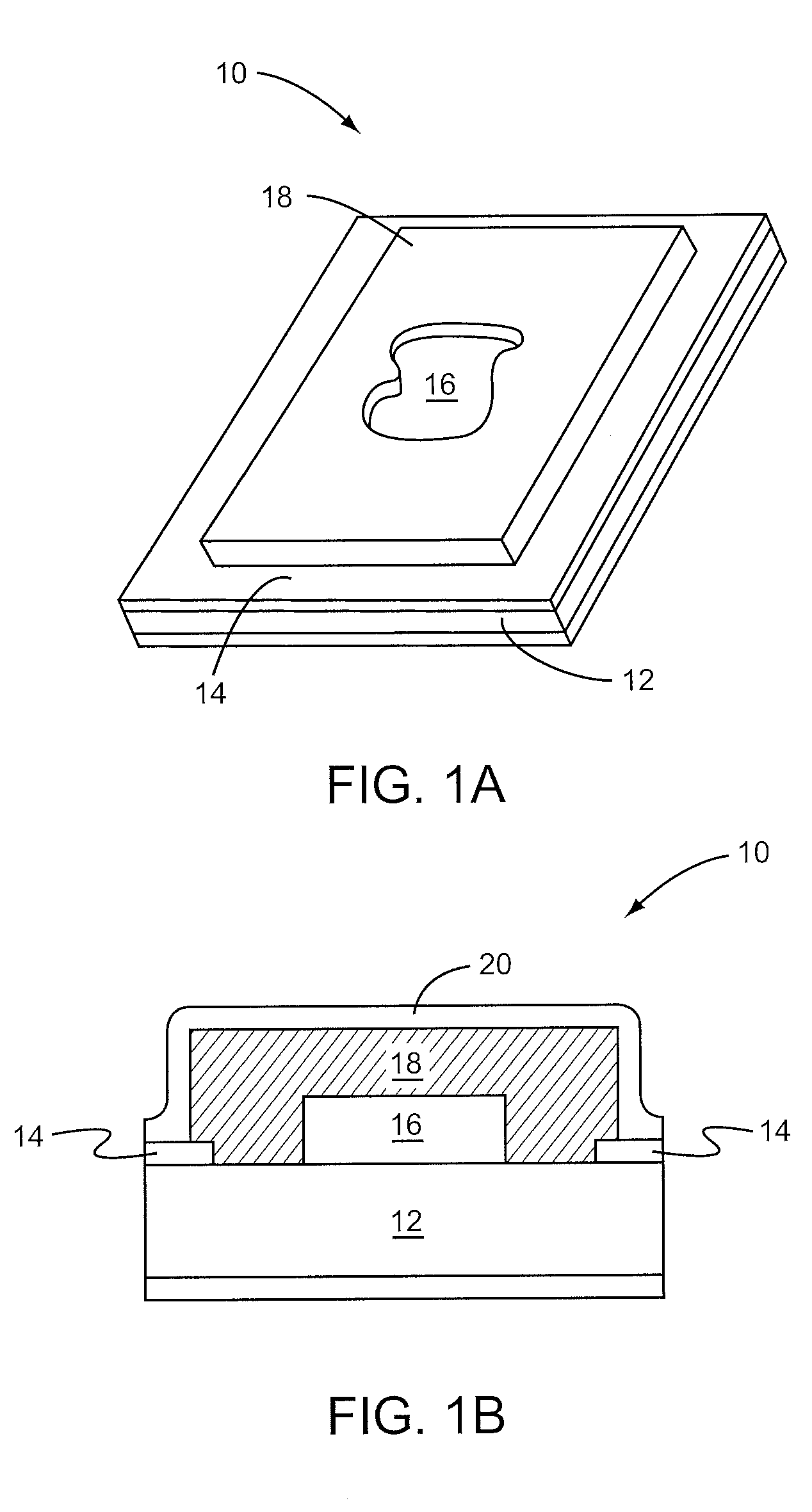

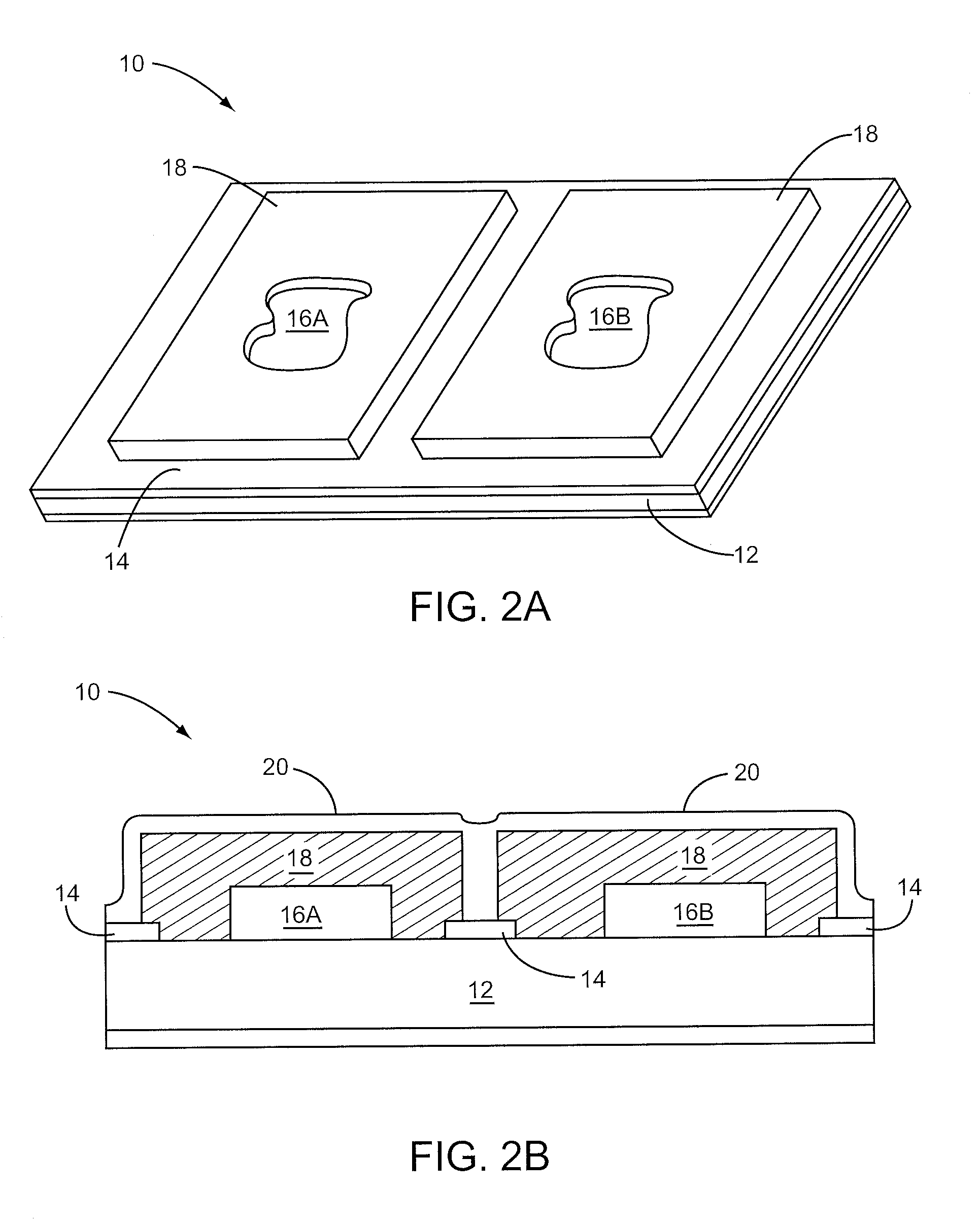

In one embodiment, a meta-module having circuitry for two or more modules is formed on a substrate, which is preferably a laminated substrate. The circuitry for the different modules is initially formed on the single meta-module. Each module will have one or more component areas in which the circuitry is formed. A metallic structure is formed on or in the substrate for each component area to be shielded. A single body, such as an overmold body, is then formed over all of the modules on the meta-module. At least a portion of the metallic structure for each component area to be shielded is then exposed through the body by a cutting, drilling, or like operation. Next, an electromagnetic shield material is applied to the exterior surface of the body of each of the component areas to be shielded and in contact with the exposed portion of the metallic structures.

Owner:QORVO US INC

Circuit and method for broadband switching noise suppression in multilayer printed circuit boards using localized lattice structures

InactiveUS20050205292A1Eliminate power plane resonanceImproved RF isolationMagnetic/electric field screeningCross-talk/noise/interference reductionBroadbandNoise suppression

An apparatus for suppressing noise in an electronic device includes a multiple layer structure in which localized arrays of chip capacitors and / or patches around sources of electromagnetic waves are used. The PCB includes multiple conductive layers at different potentials, dielectric layers separating the conductive layers, conductive rods extending between at least two of the conductive layers, and a layer of patches disposed adjacent or on one or more of the conductive layers. The conductive rods are connected to one of the conductive layers and chip capacitors connect the conductive rods to another of the conductive layers. A particular location can be effectively isolated from noise using a few unit cells of an array of patches / capacitors partially or completely surrounding the particular location.

Owner:ETENNA

Popular searches

Sensors Conductive pattern formation Measuring/recording heart/pulse rate Blood characterising devices Printed circuit non-printed electric components association Semiconductor devices Semiconductor/solid-state device manufacturing Electrical connection printed elements Electrical apparatus contructional details Printed circuits structural associations