Patents

Literature

2947 results about "Noise suppression" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

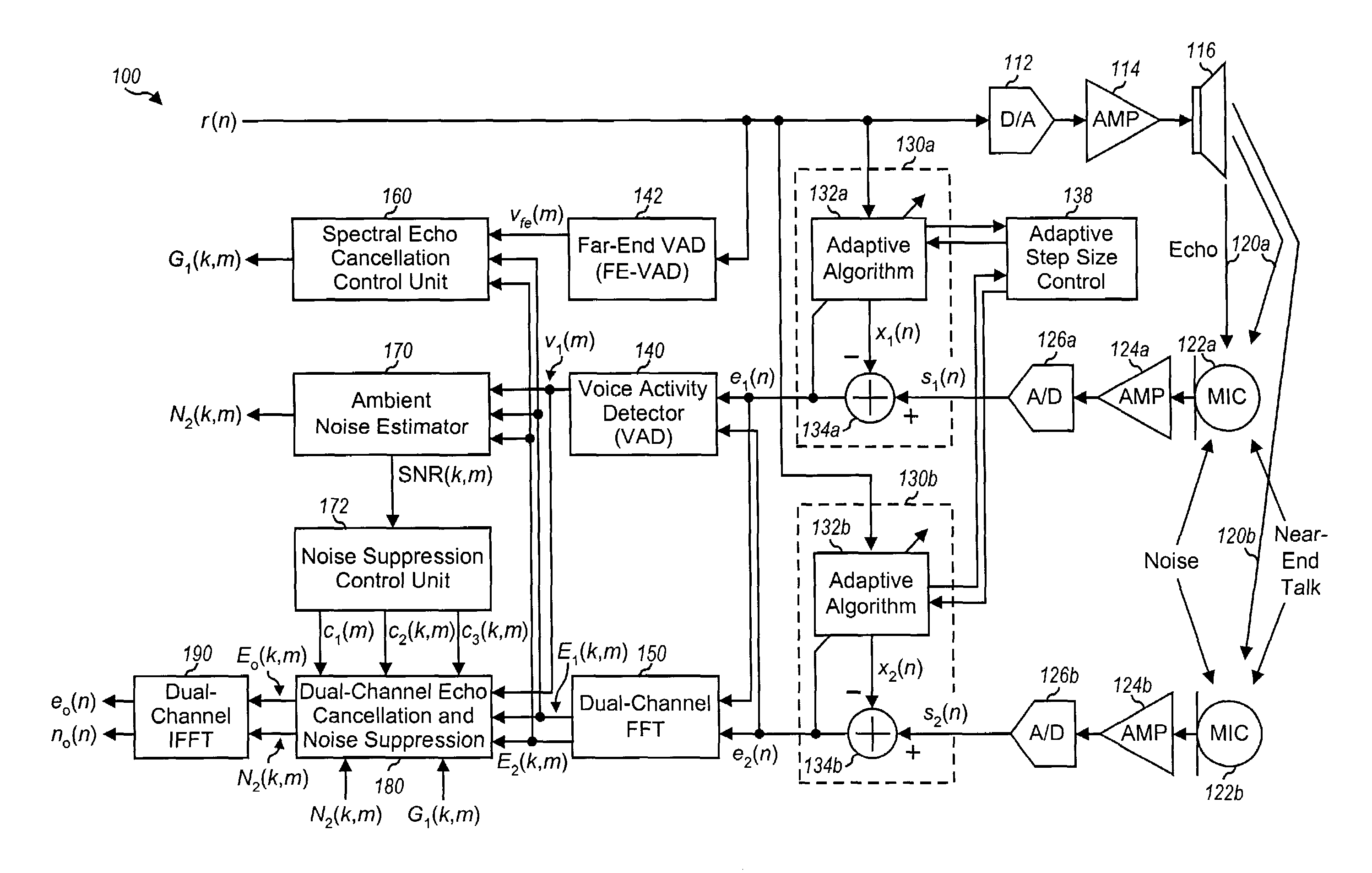

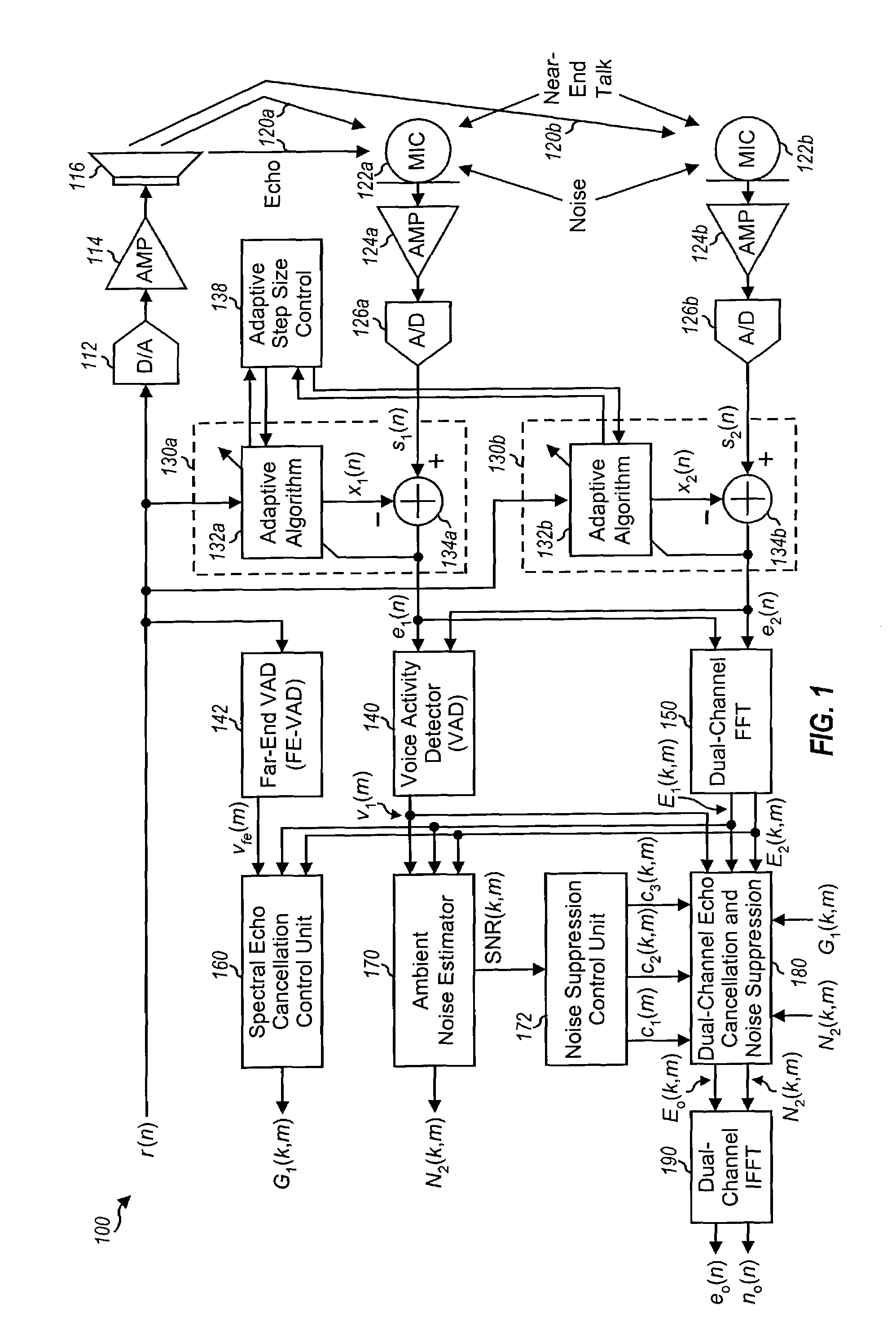

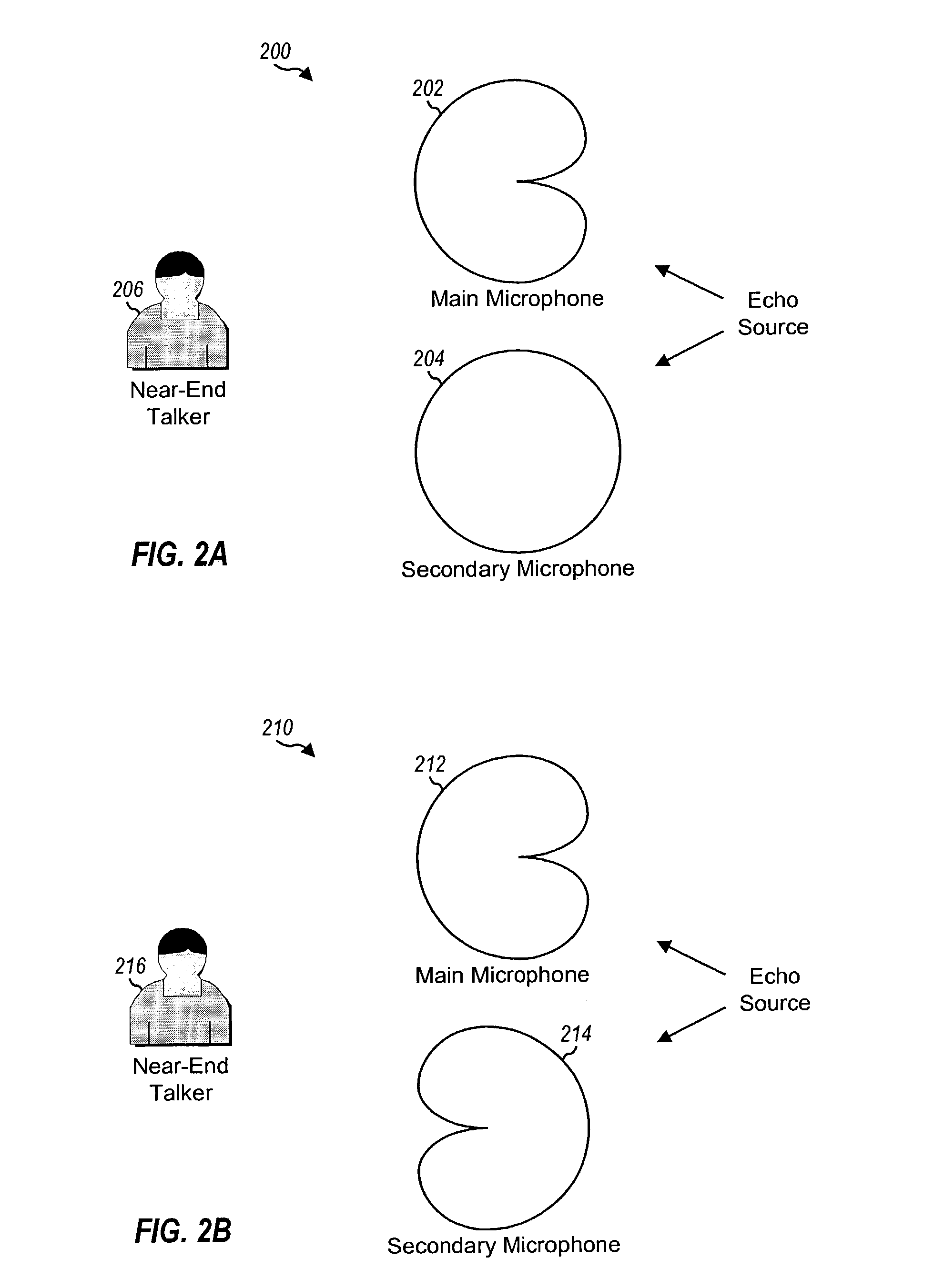

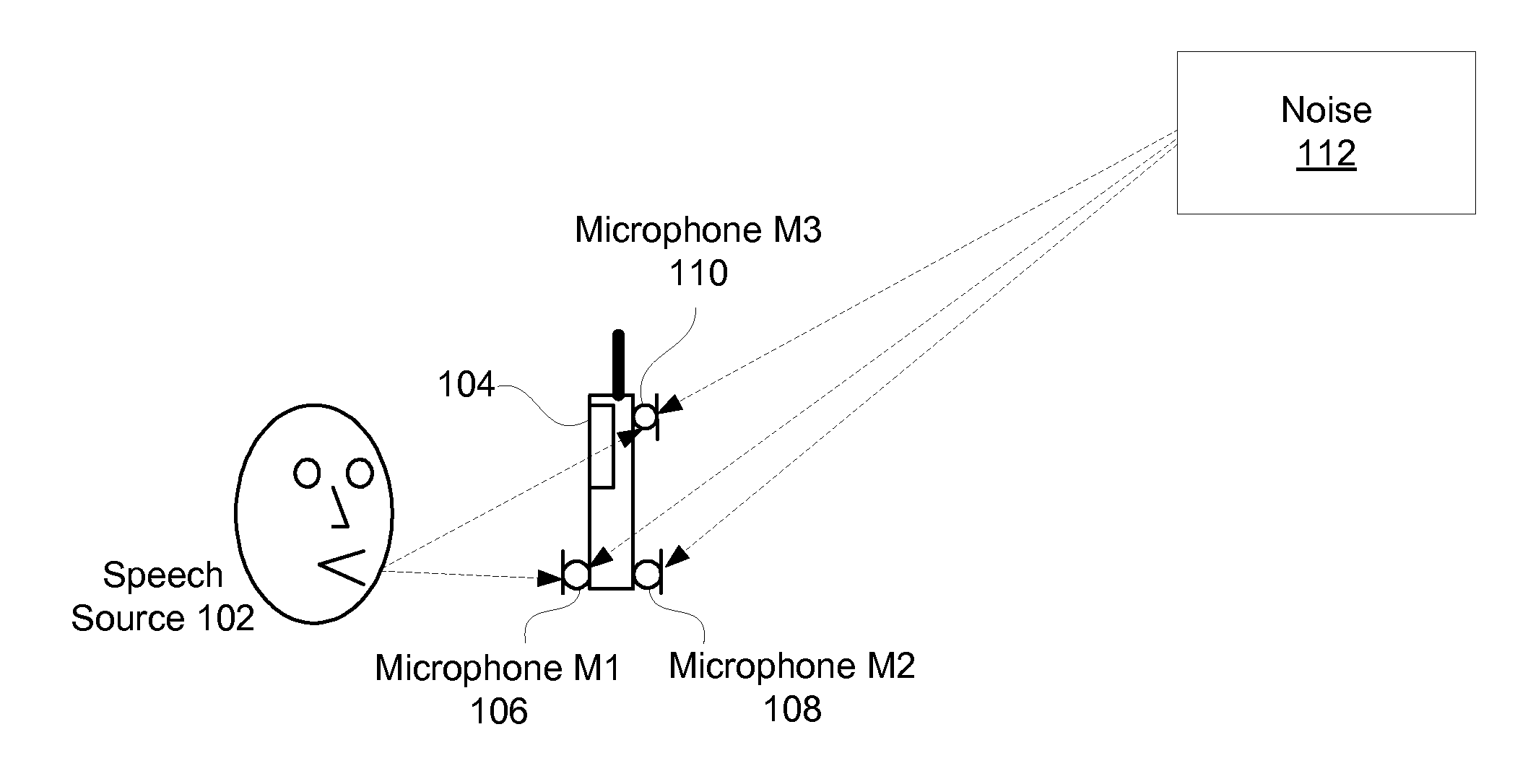

Small array microphone for acoustic echo cancellation and noise suppression

ActiveUS7003099B1Suppress noiseReducing non-stationary ambient noiseTwo-way loud-speaking telephone systemsSubstation equipmentControl signalEngineering

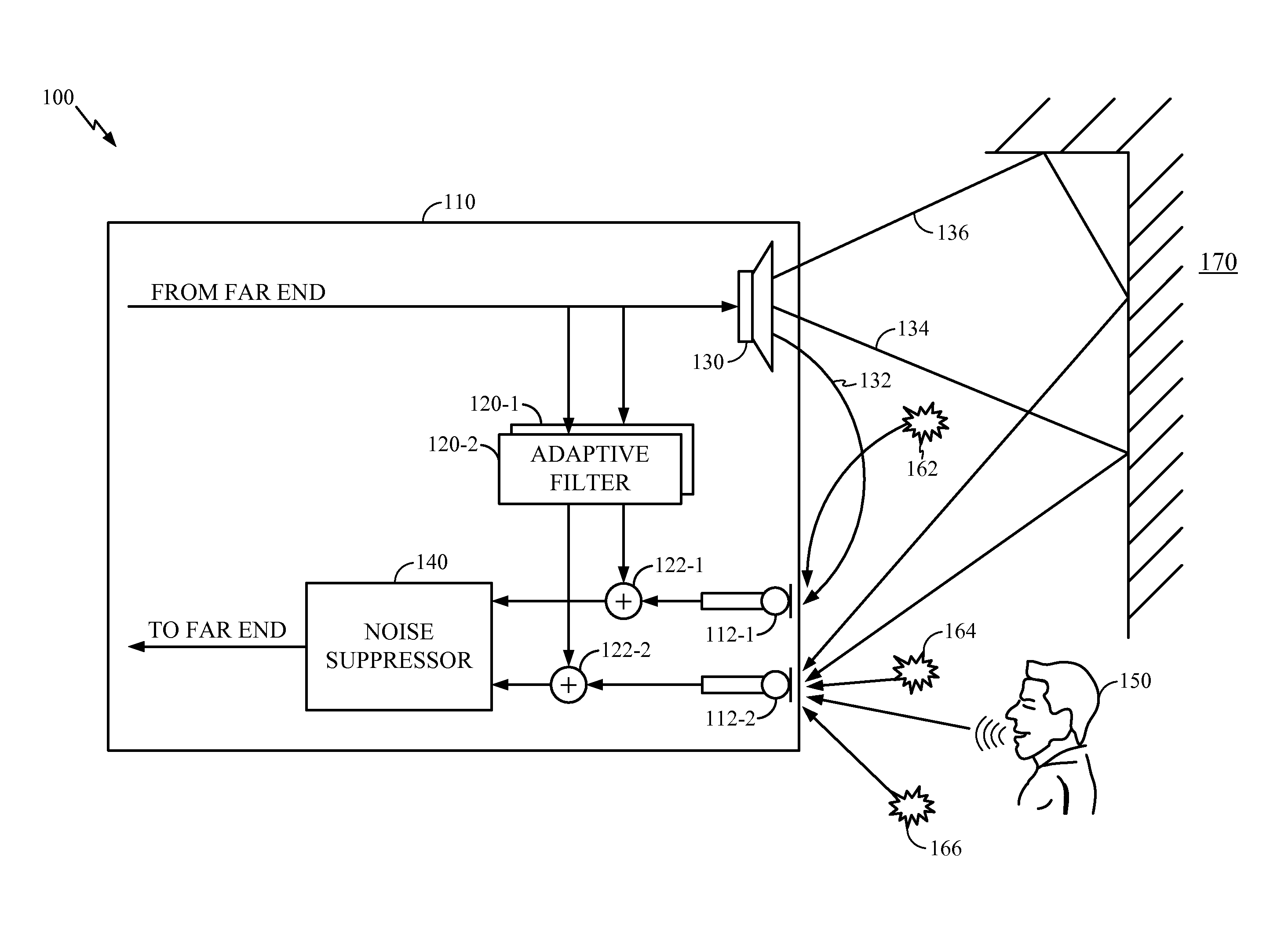

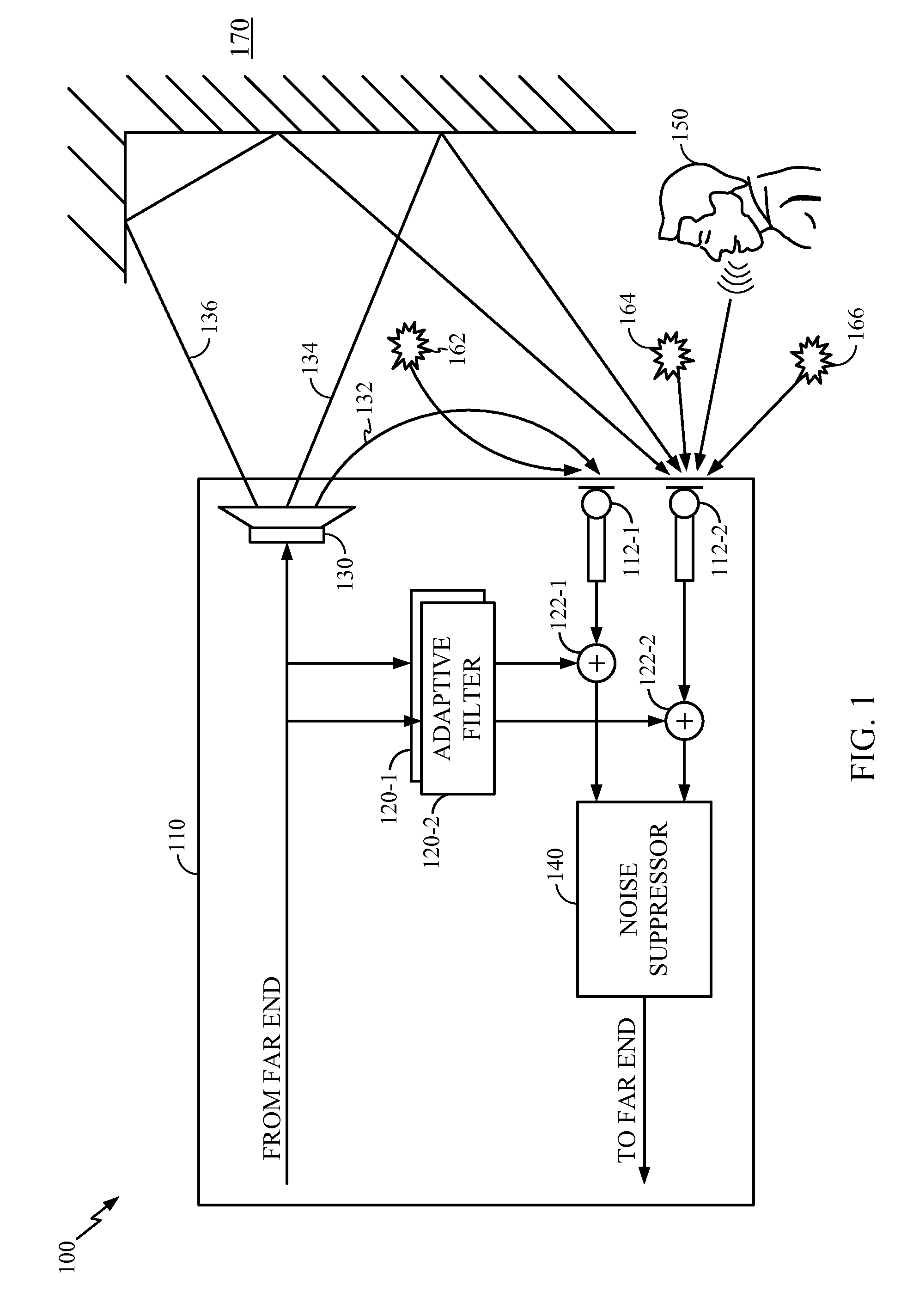

Techniques for canceling echo and suppressing noise using an array microphone and signal processing. In one system, at least two microphones form an array microphone and provide at least two microphone input signals. Each input signal may be processed by an echo canceller unit to provide a corresponding intermediate signal having some echo removed. An echo cancellation control unit receives the intermediate signals and derives a first gain used for echo cancellation. A noise suppression control unit provides at least one control signal used for noise suppression based on background noise detected in the intermediate signals. An echo cancellation and noise suppression unit derives a second gain based on the control signal(s), cancels echo in a designated intermediate signal based on the first gain, and suppresses noise in this intermediate signal based on the second gain. The signal processing may be performed in the frequency domain.

Owner:FORTEMEDIA

Individual channel phase delay scheme

ActiveUS20080157867A1Cathode-ray tube indicatorsPhase-modulated carrier systemsEngineeringNoise suppression

Embodiments of the present invention are directed to processing an incoming signal by using a demodulation signal, while controlling the phase of the demodulation signal in relation to the incoming signal. The incoming signal can be processed by being mixed with the modulation signal at a mixer. The mixing may thus cause various beneficial modifications of the incoming signal, such as noise suppression of the incoming signal, rectification of the incoming signal, demodulation of the incoming signal, etc.

Owner:APPLE INC

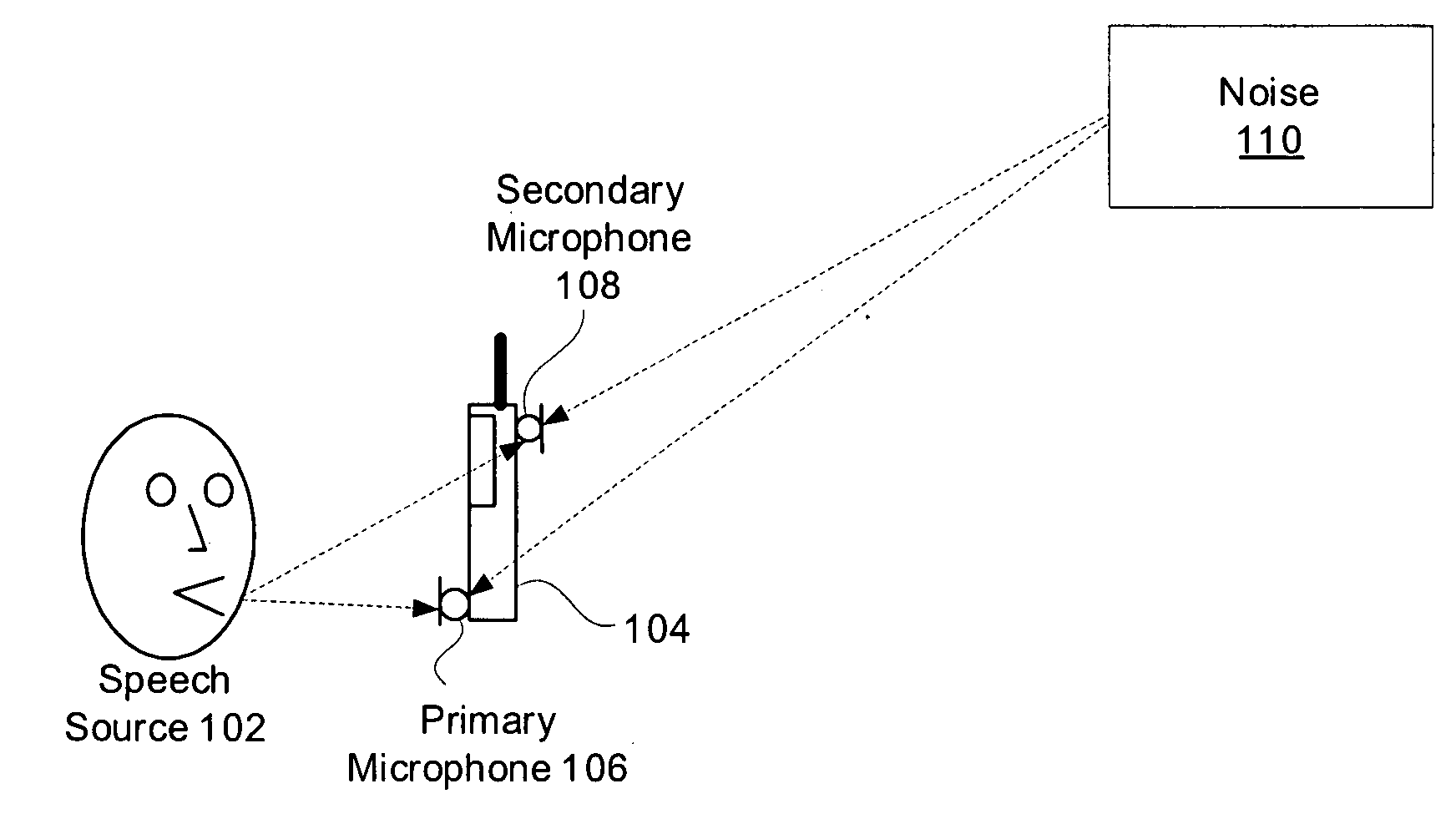

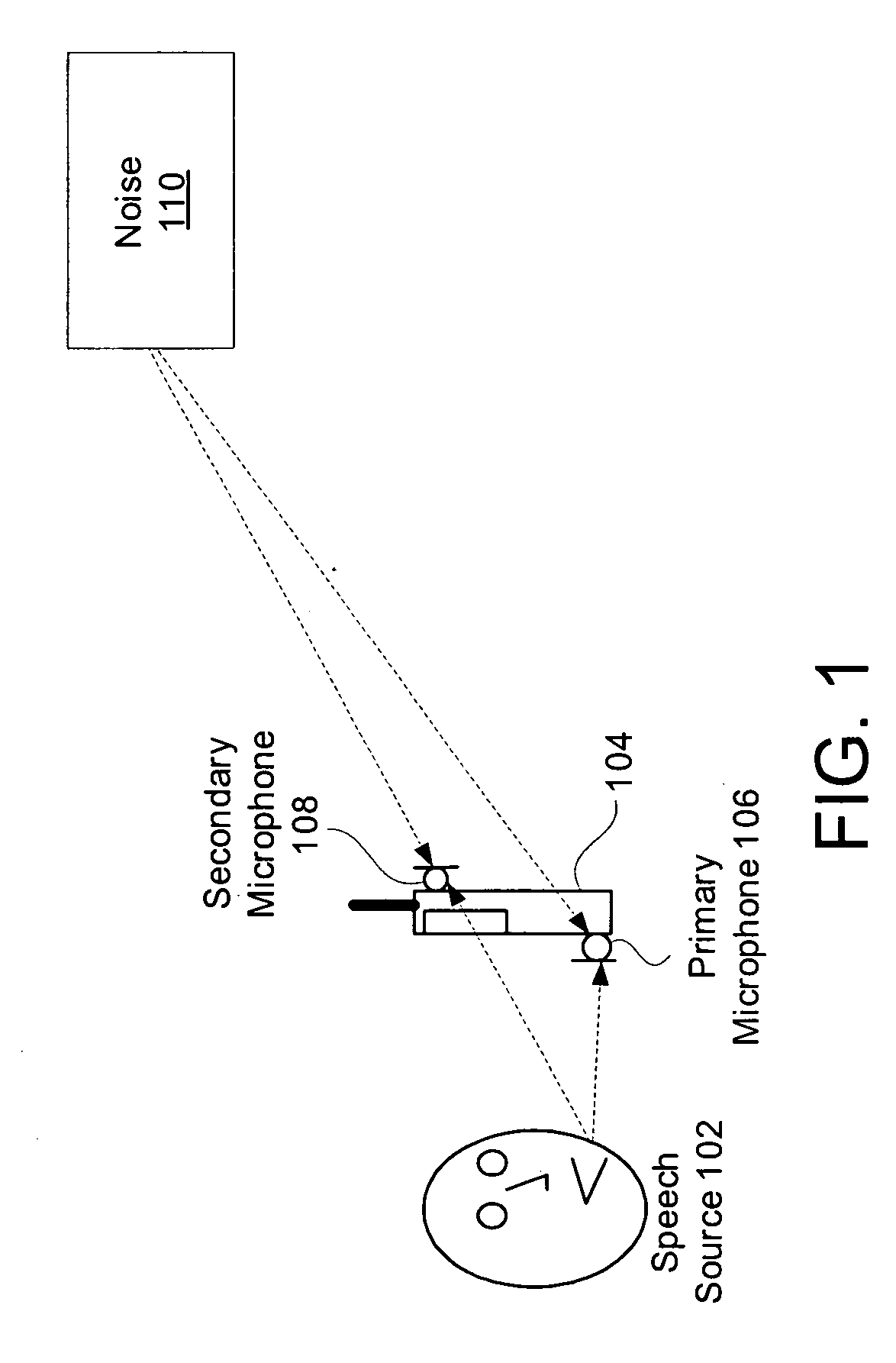

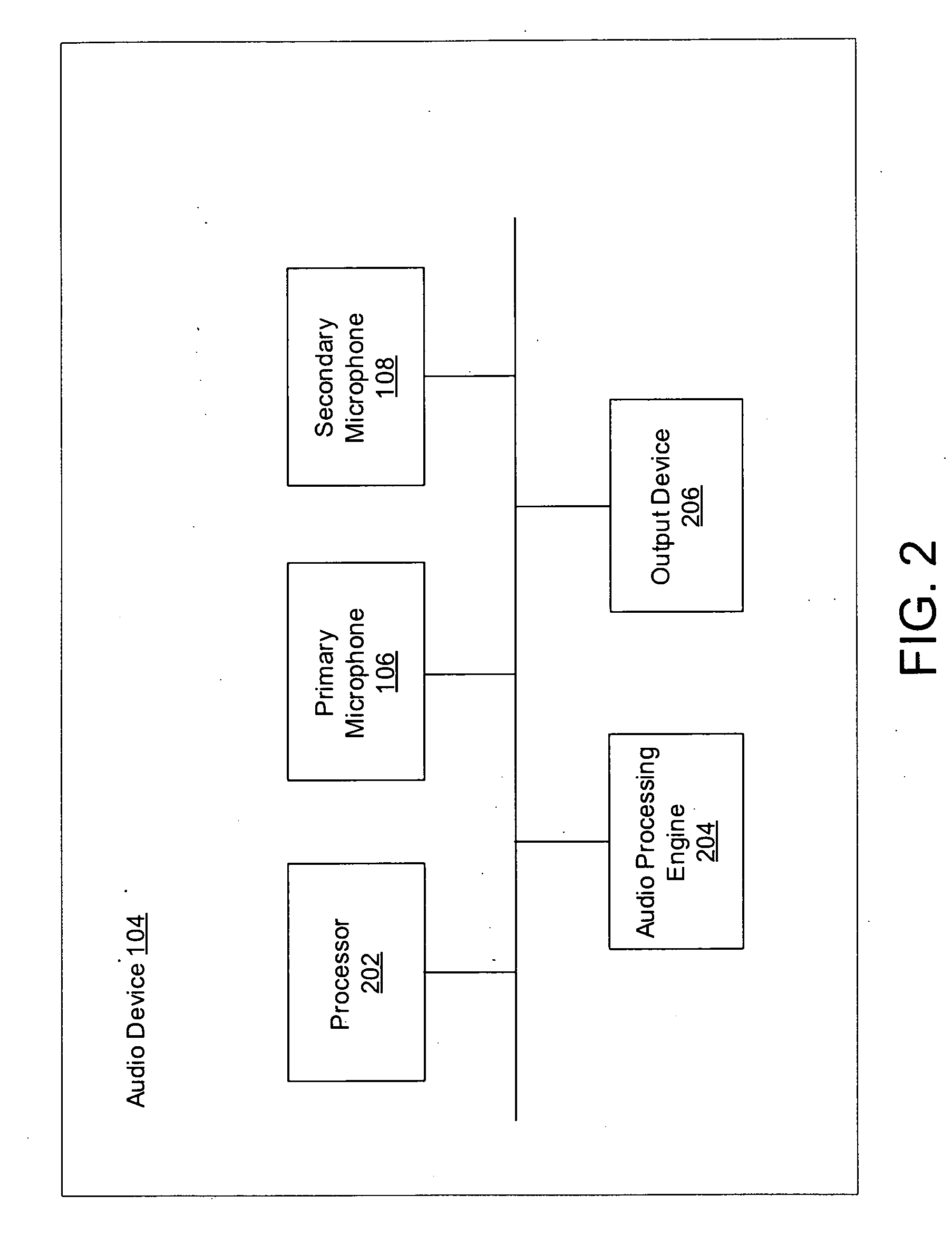

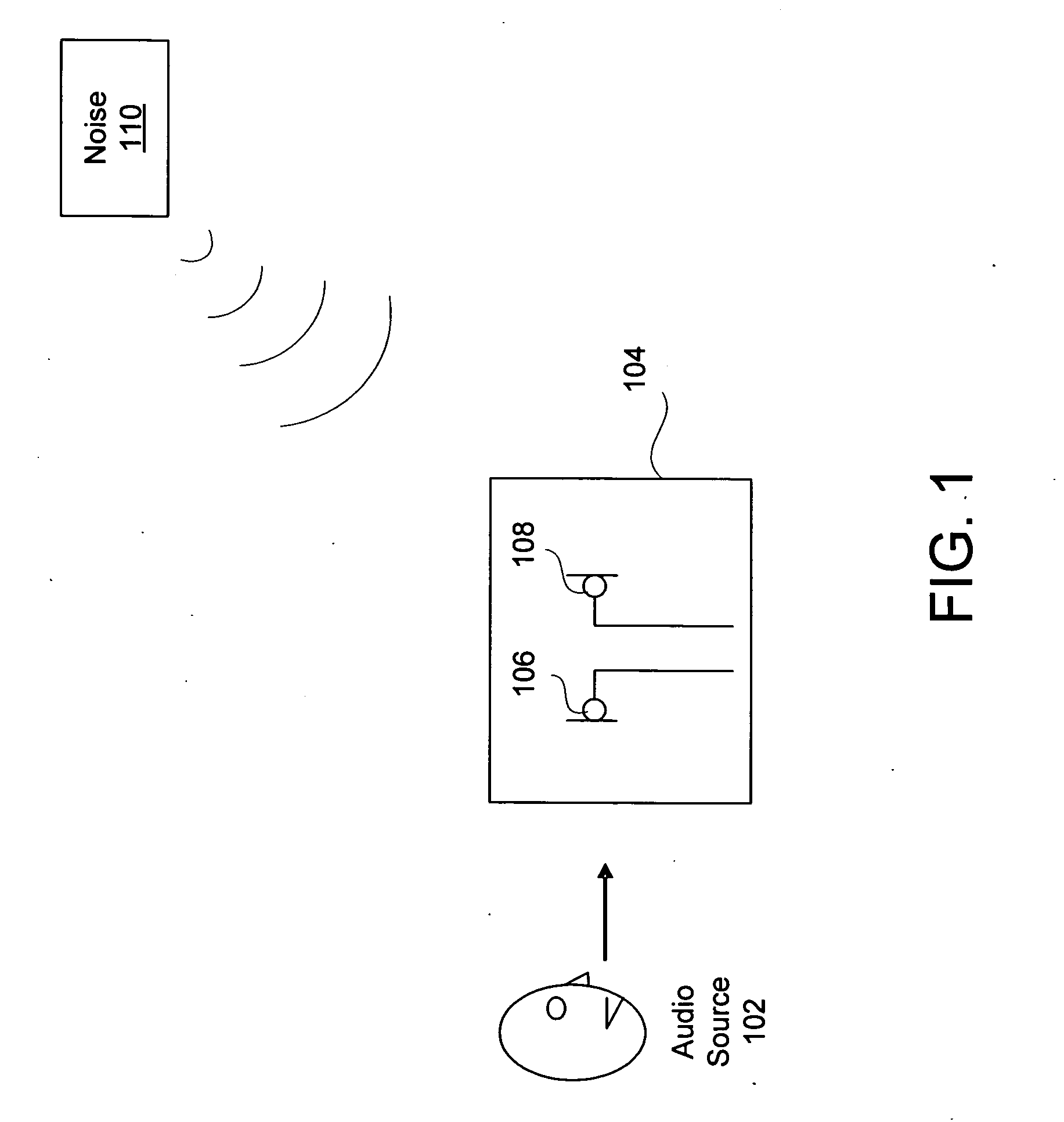

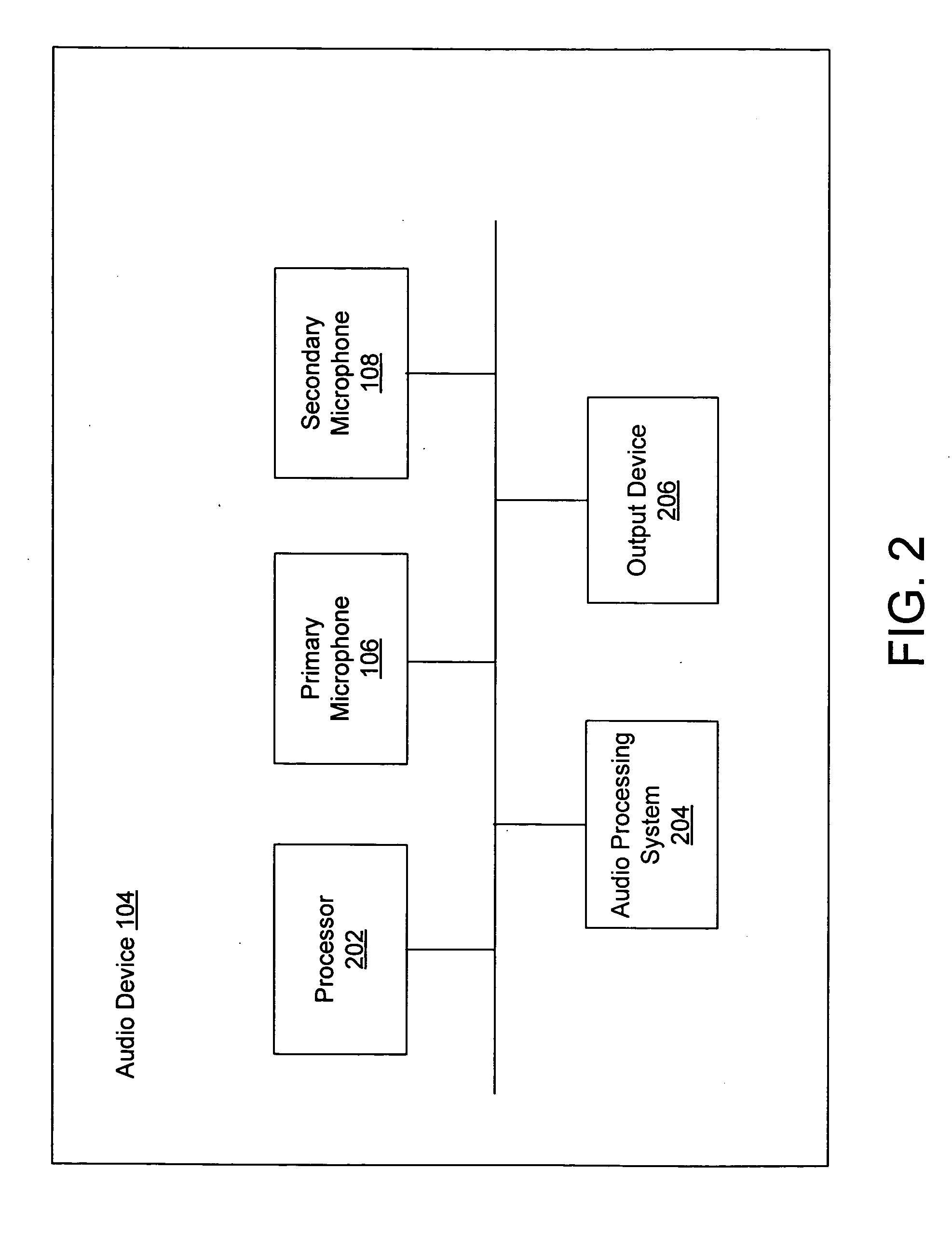

System and method for providing single microphone noise suppression fallback

Systems and methods for providing single microphone noise suppression fallback are provided. In exemplary embodiments, primary and secondary acoustic signals are received. A single microphone noise estimate may be generated based on the primary acoustic signal, while a dual microphone noise estimate may be generated based on the primary and secondary acoustic signals. A combined noise estimate based on the single and dual microphone noise estimates is then determined. Using the combined noise estimate, a gain mask may be generated and applied to the primary acoustic signal to generate a noise suppressed signal. Subsequently, the noise suppressed signal may be output.

Owner:KNOWLES ELECTRONICS INC

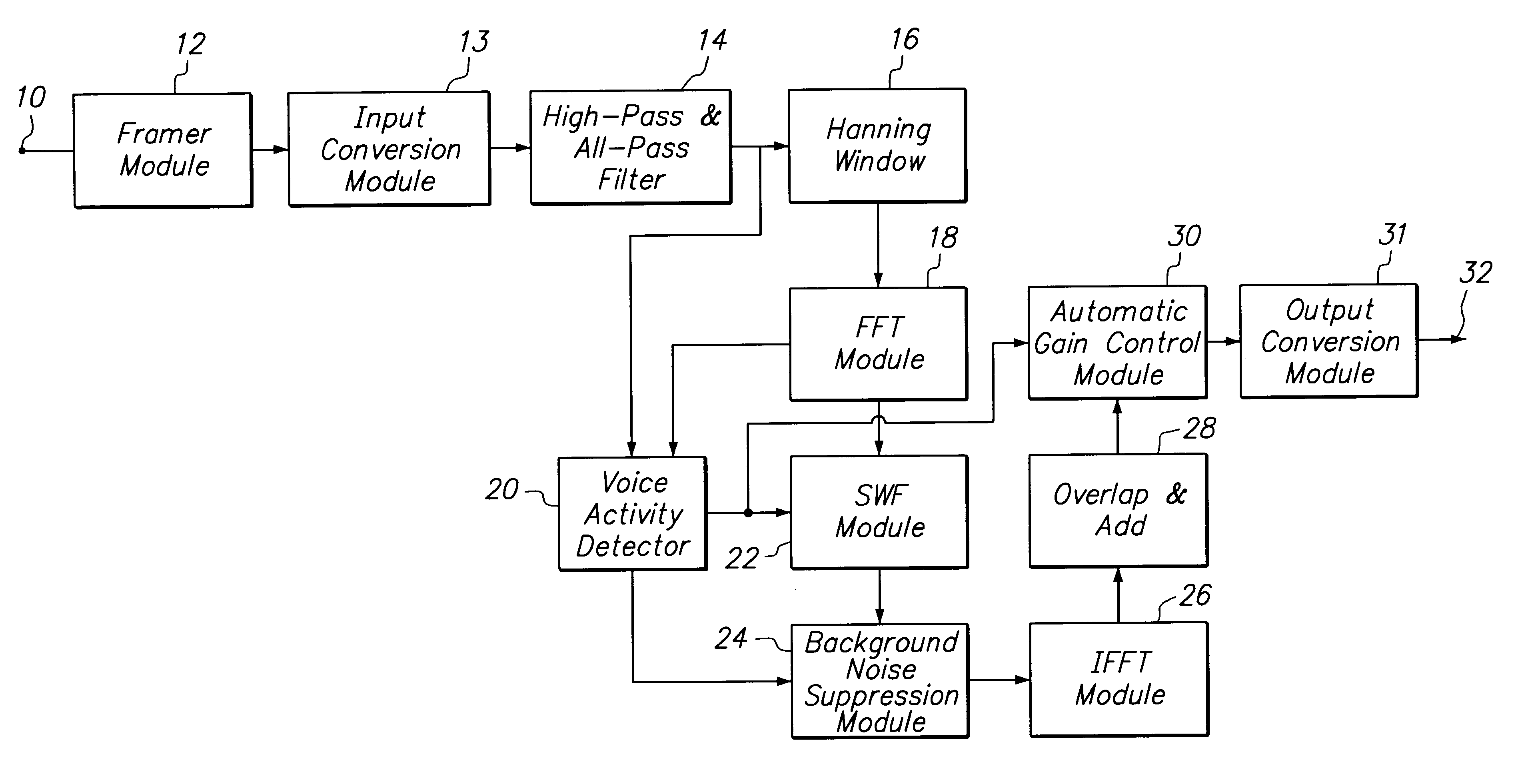

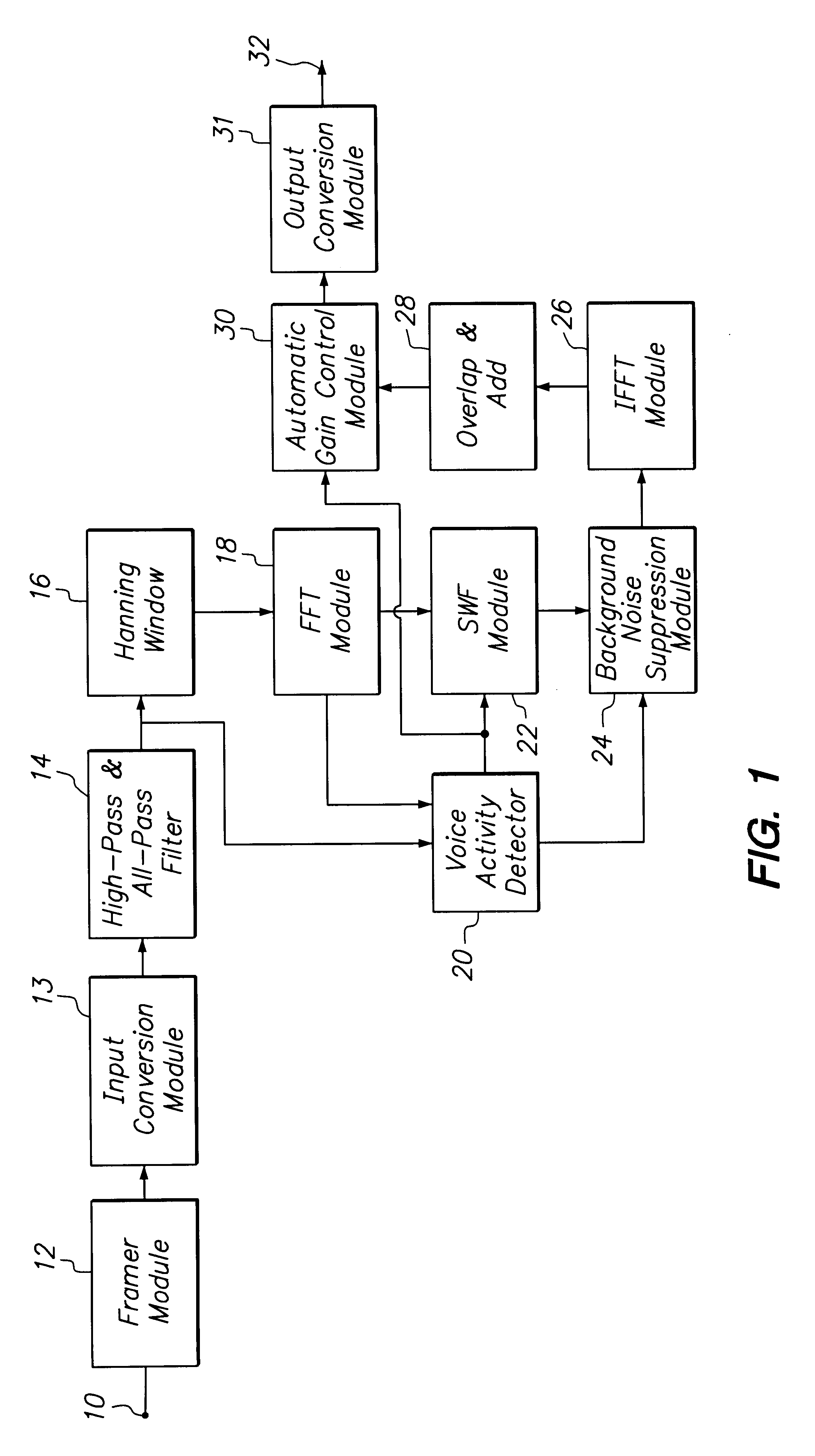

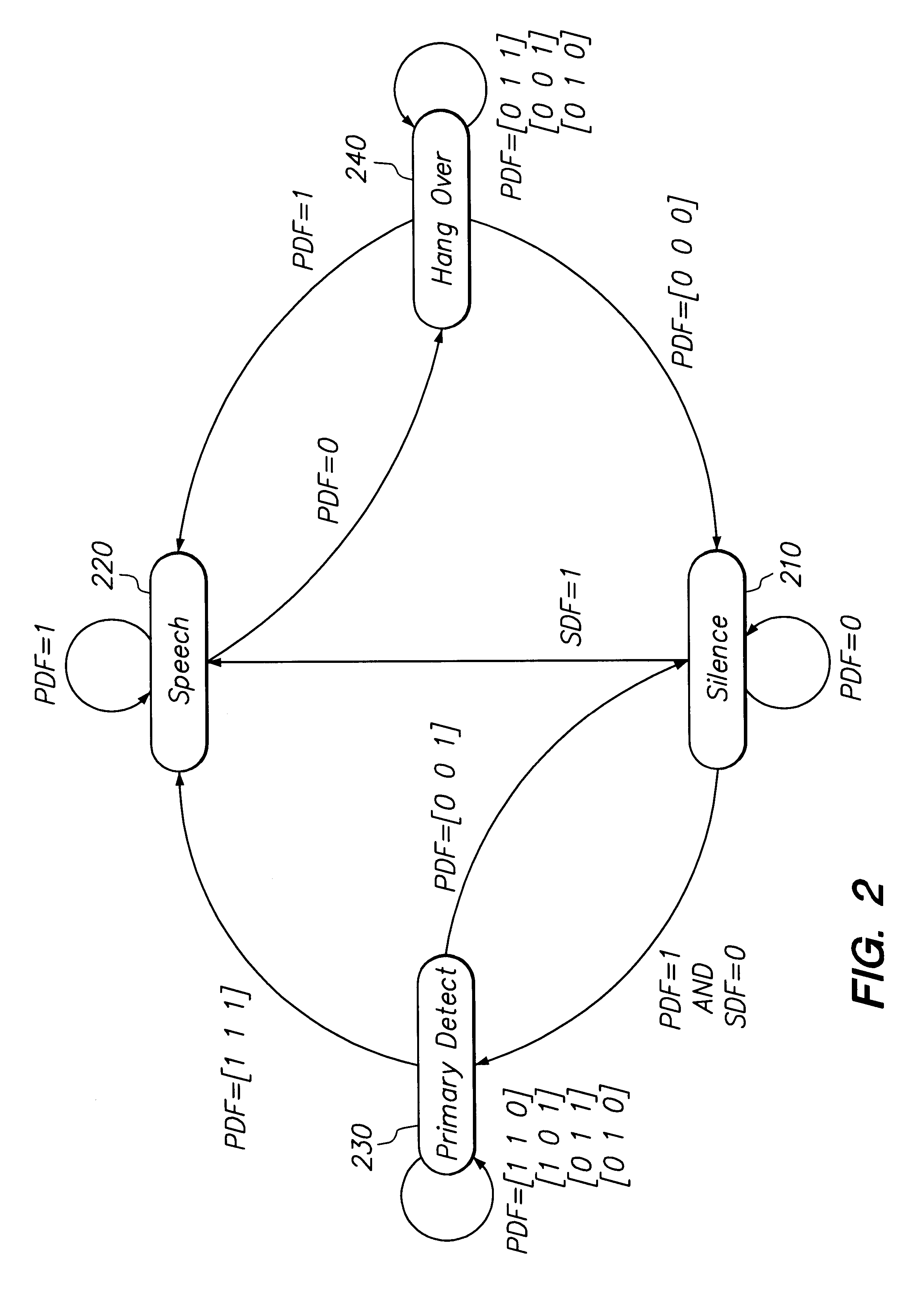

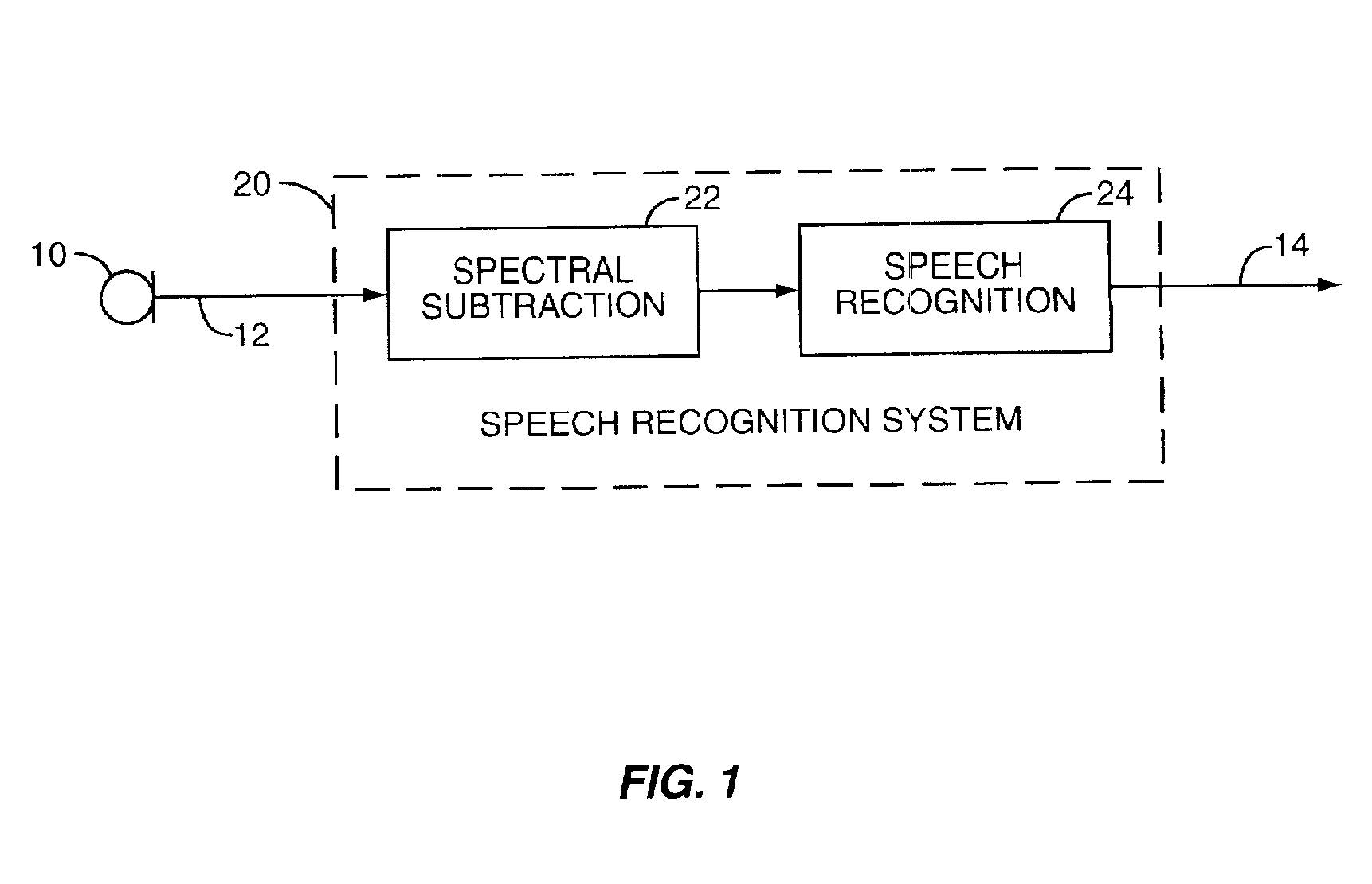

Method and apparatus for enhancing noise-corrupted speech

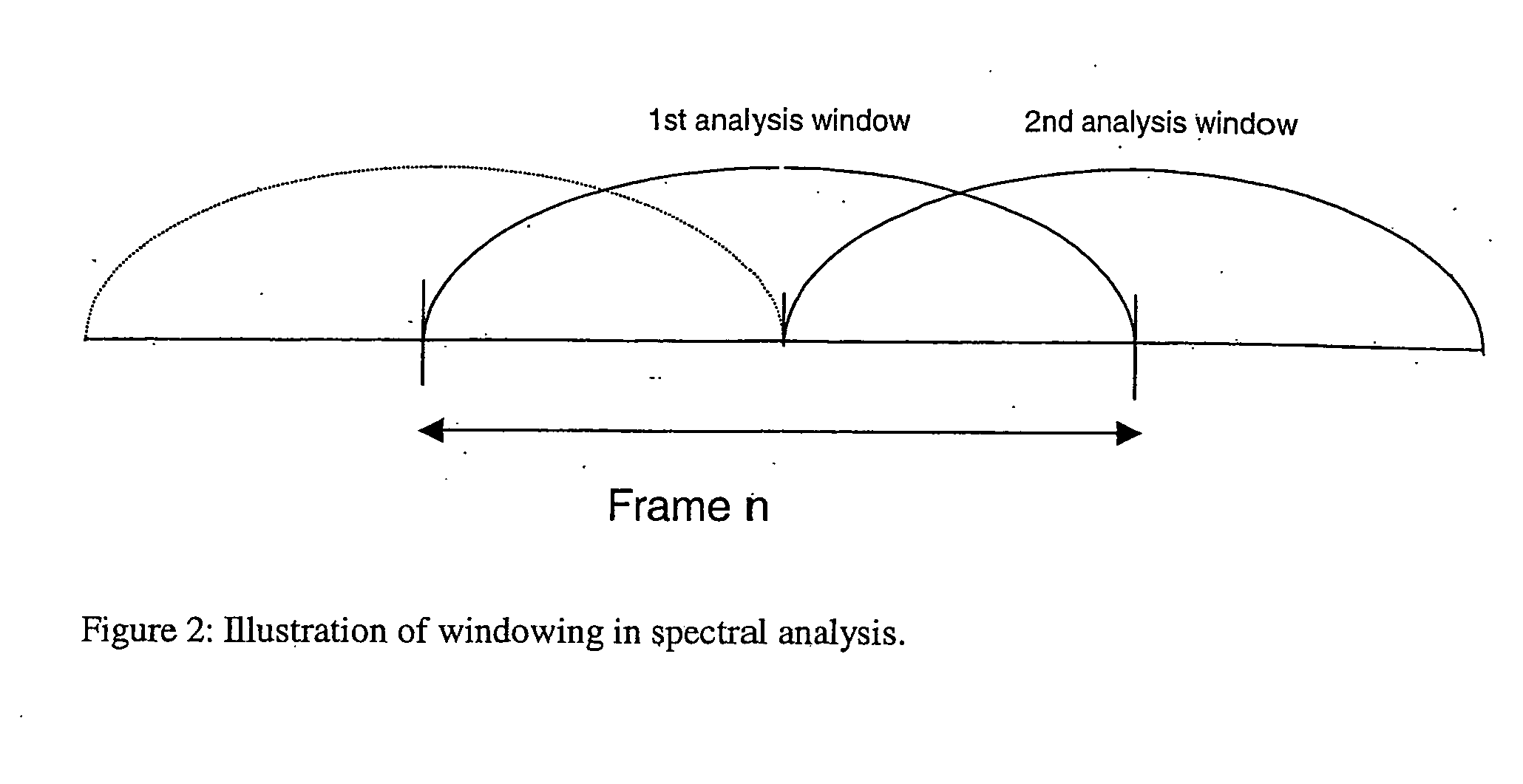

InactiveUS6415253B1Reduce peakImprove intelligibilitySpeech analysisTransmission noise suppressionTime domainFast Fourier transform

A noise suppression device receives data representative of a noise-corrupted signal which contains a speech signal and a noise signal, divides the received data into data frames, and then passes the data frames through a pre-filter to remove a dc-component and the minimum phase aspect of the noise-corrupted signal. The noise suppression device appends adjacent data frames to eliminate boundary discontinuities, and applies fast Fourier transform to the appended data frames. A voice activity detector of the noise suppression device determines if the noise-corrupted signal contains the speech signal based on components in the time domain and the frequency domain. A smoothed Wiener filter of the noise suppression device filters the data frames in the frequency domain using different sizes of a window based on the existence of the speech signal. Filter coefficients used for Wiener filter are smoothed before filtering. The noise suppression device modifies magnitude of the time domain data based on the voicing information outputted from the voice activity detector.

Owner:META C CORP

Small array microphone for beam-forming and noise suppression

ActiveUS7174022B1Suppress interferenceSuppress noiseSpeech analysisMicrophones signal combinationTime domainEngineering

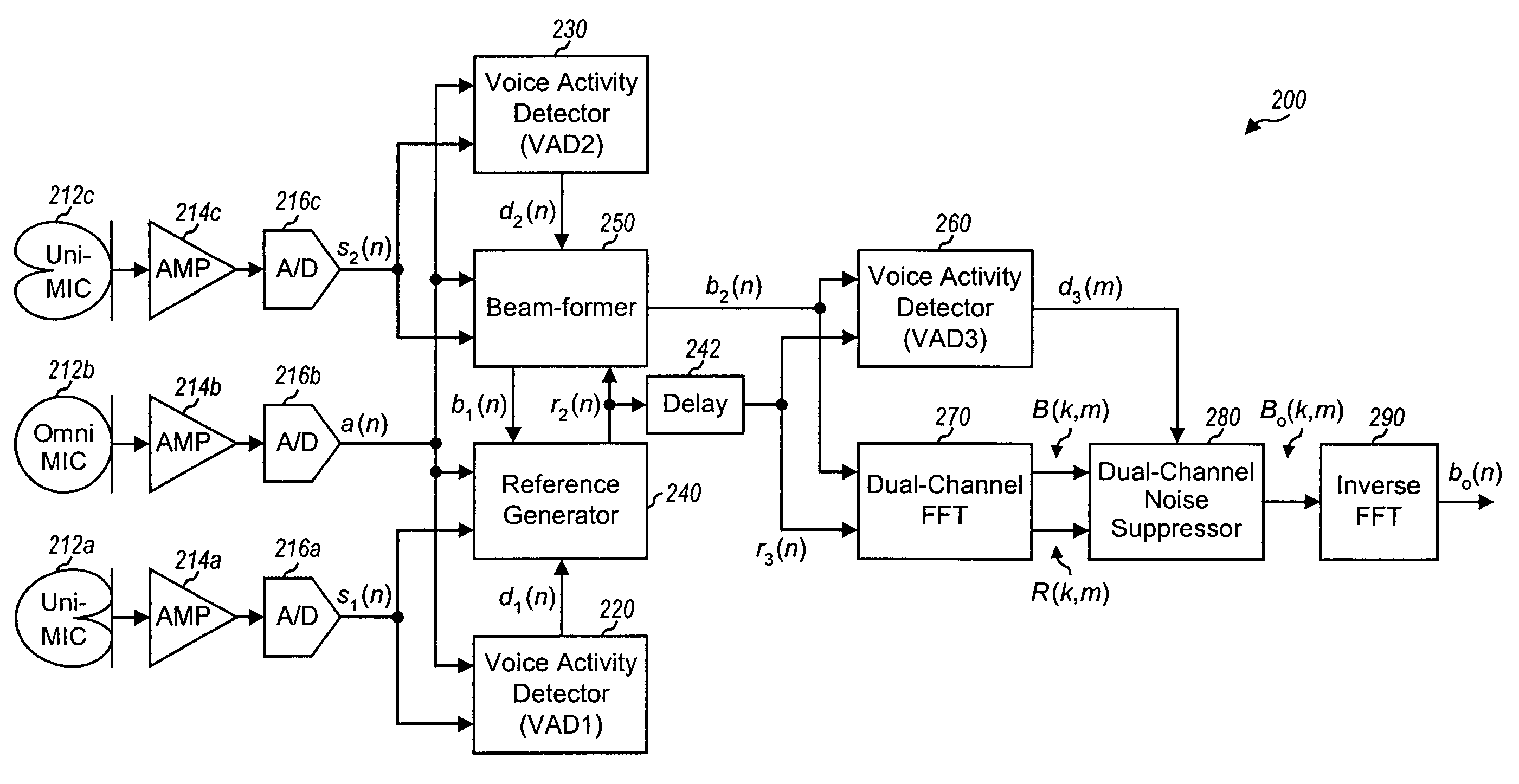

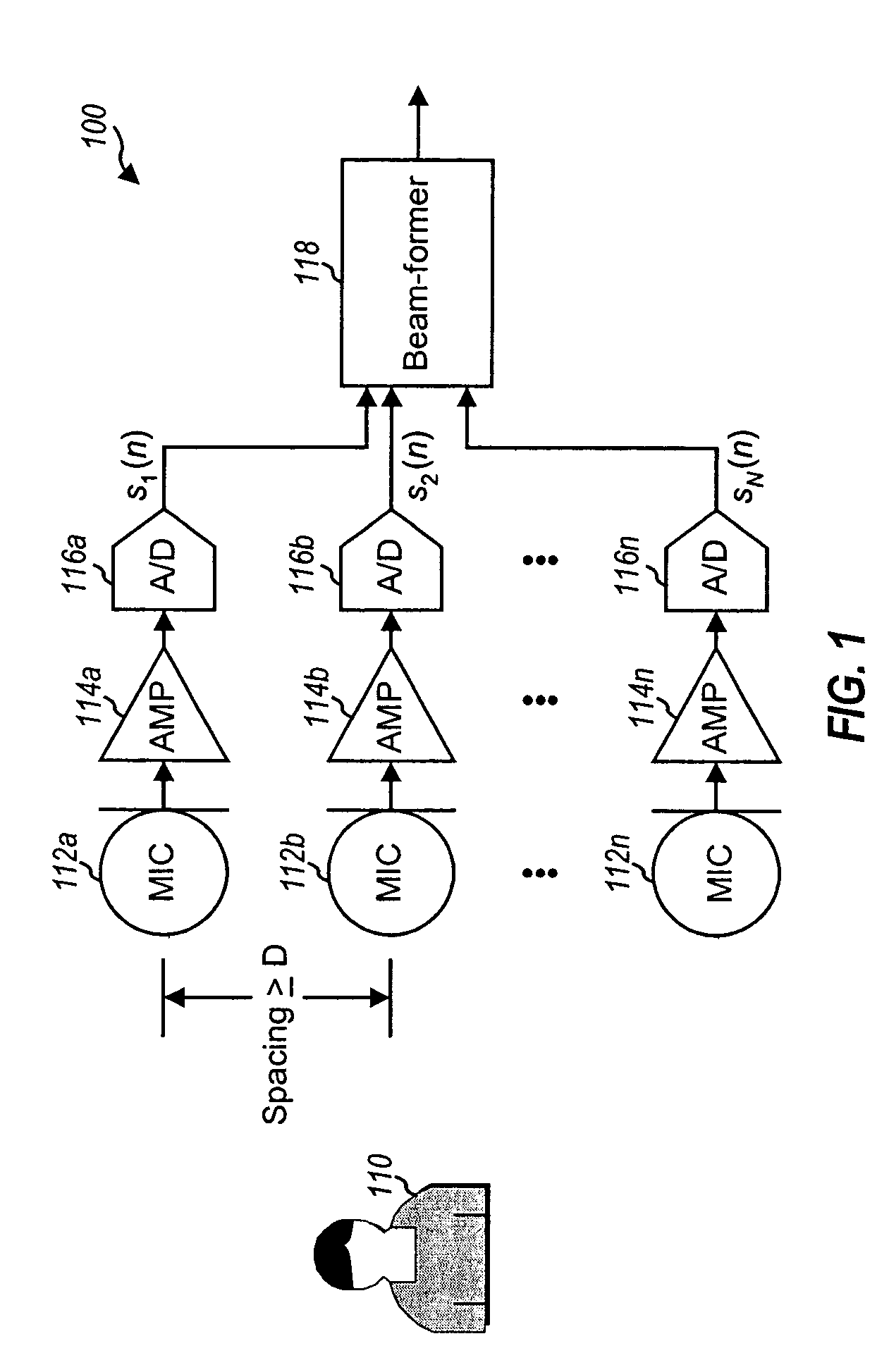

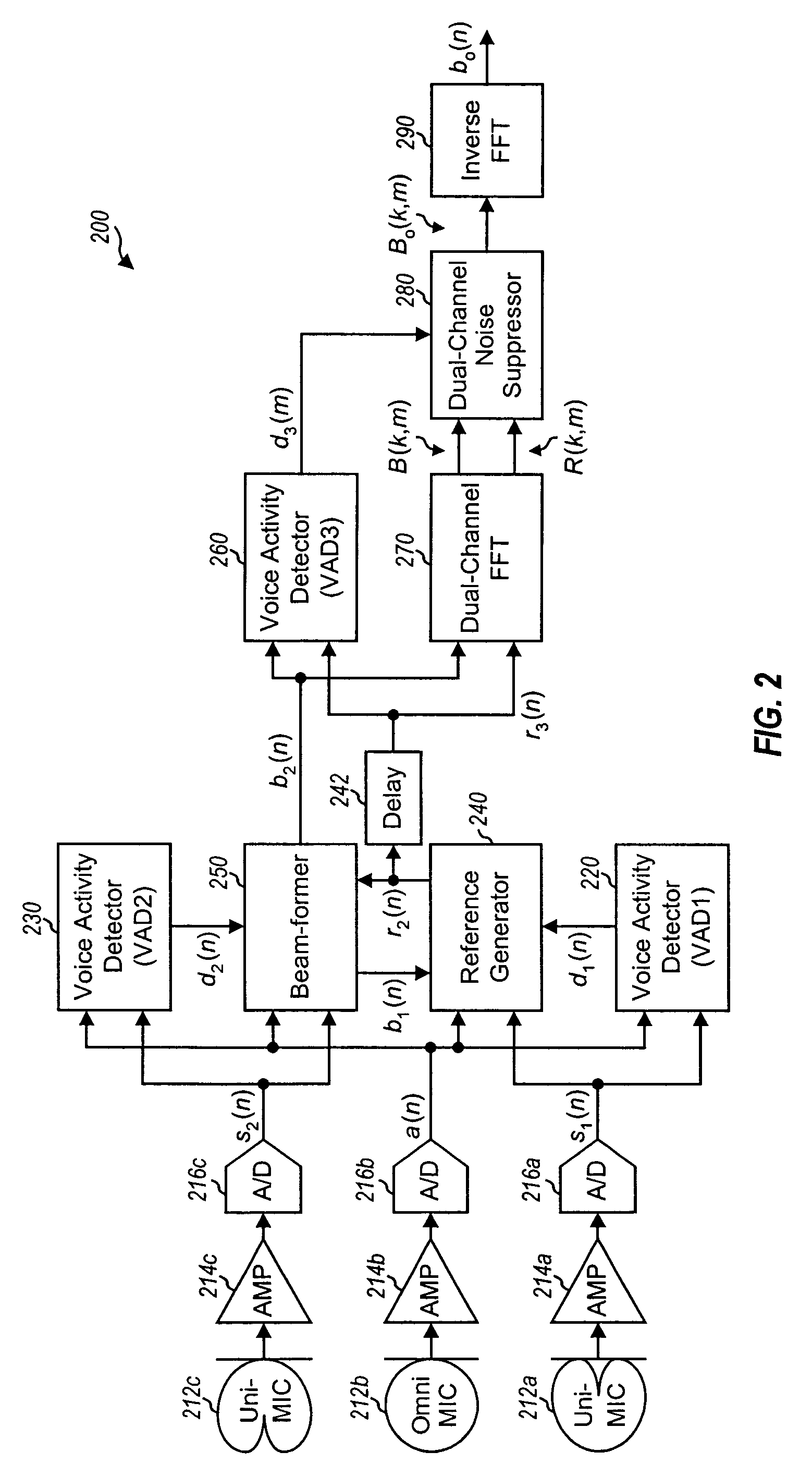

Techniques are provided to suppress noise and interference using an array microphone and a combination of time-domain and frequency-domain signal processing. In one design, a noise suppression system includes an array microphone, at least one voice activity detector (VAD), a reference generator, a beam-former, and a multi-channel noise suppressor. The array microphone includes multiple microphones—at least one omni-directional microphone and at least one uni-directional microphone. Each microphone provides a respective received signal. The VAD provides at least one voice detection signal used to control the operation of the reference generator, beam-former, and noise suppressor. The reference generator provides a reference signal based on a first set of received signals and having desired voice signal suppressed. The beam-former provides a beam-formed signal based on a second set of received signals and having noise and interference suppressed. The noise suppressor further suppresses noise and interference in the beam-formed signal.

Owner:FORTEMEDIA

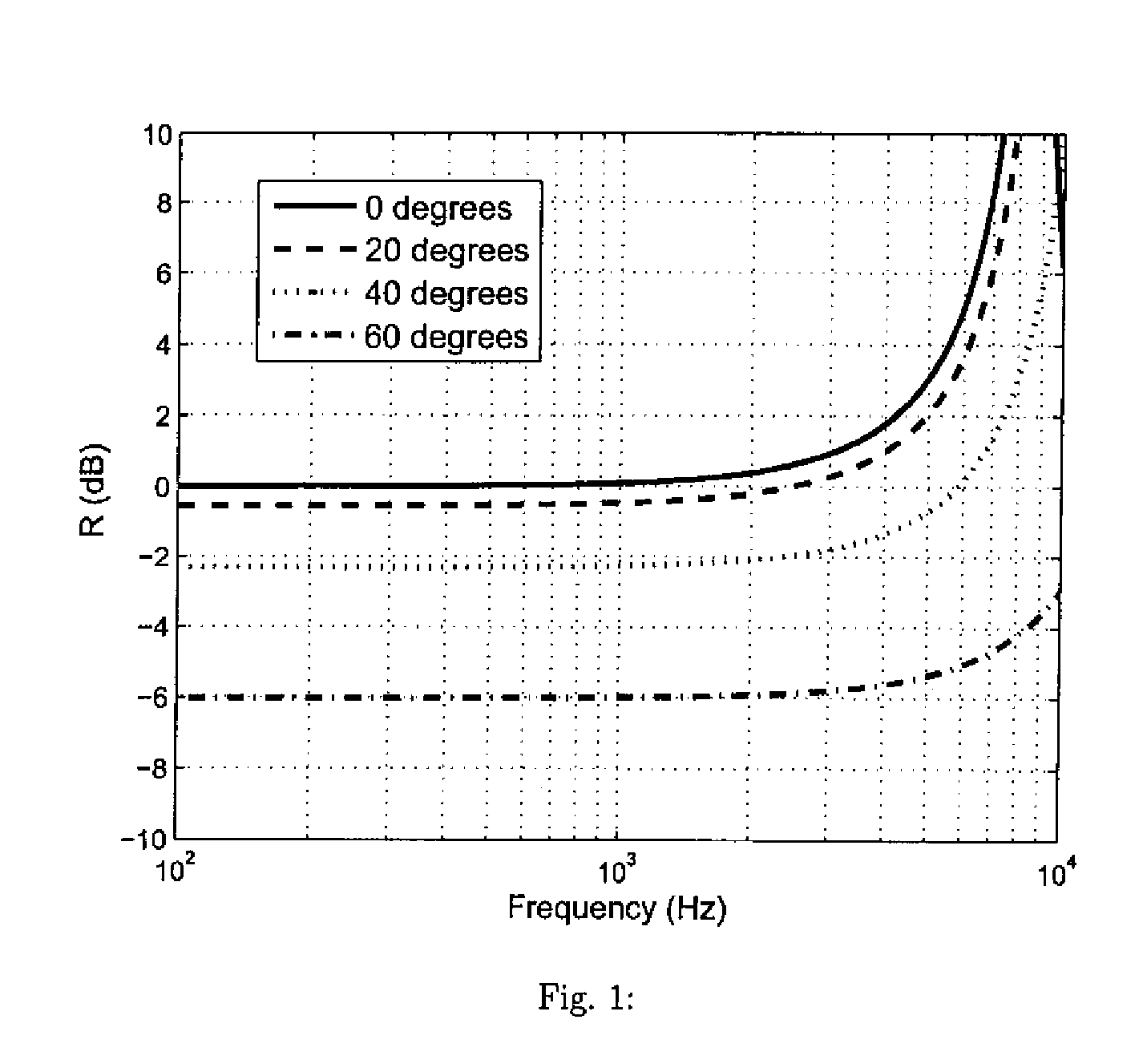

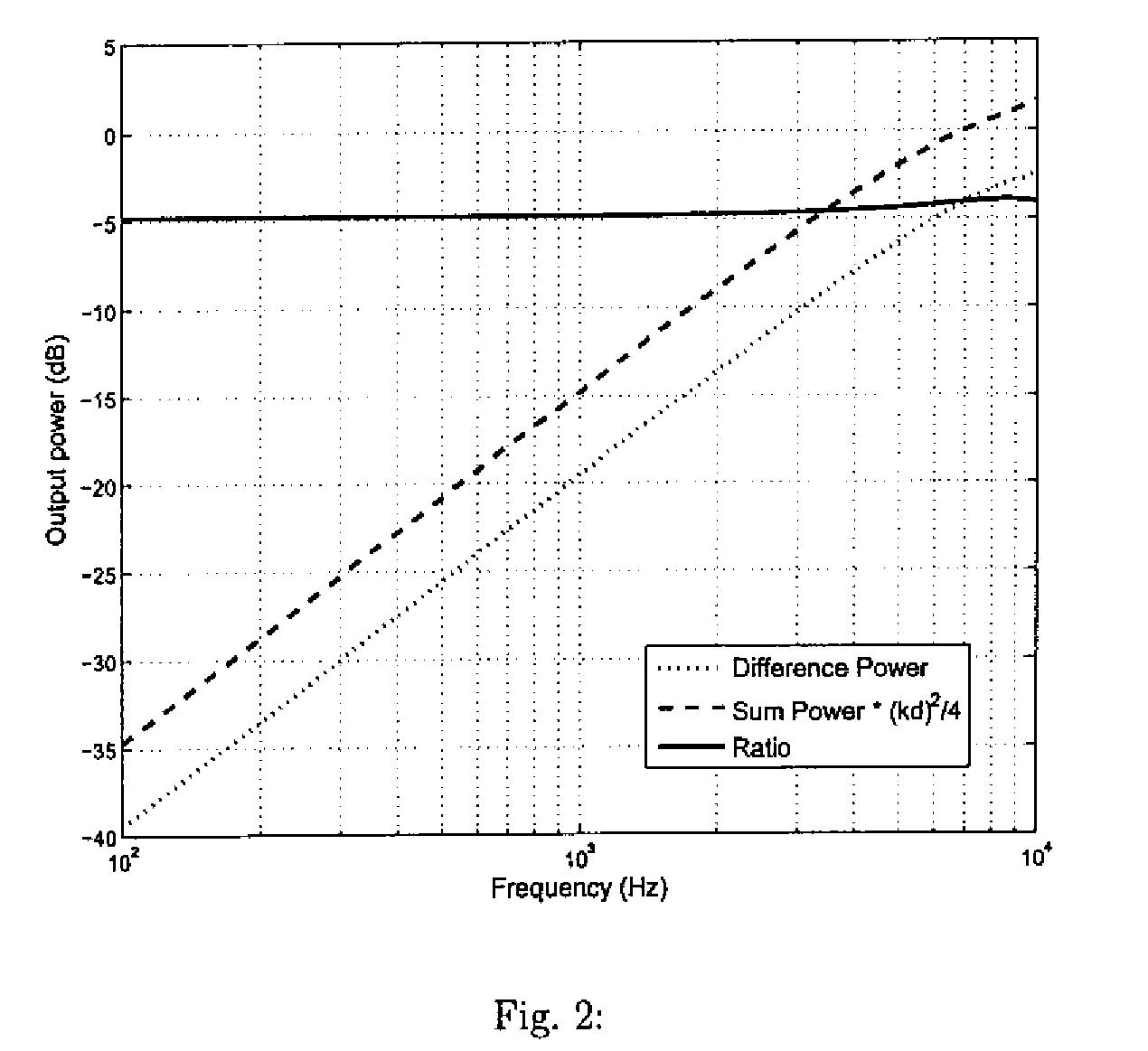

Dual-Microphone Spatial Noise Suppression

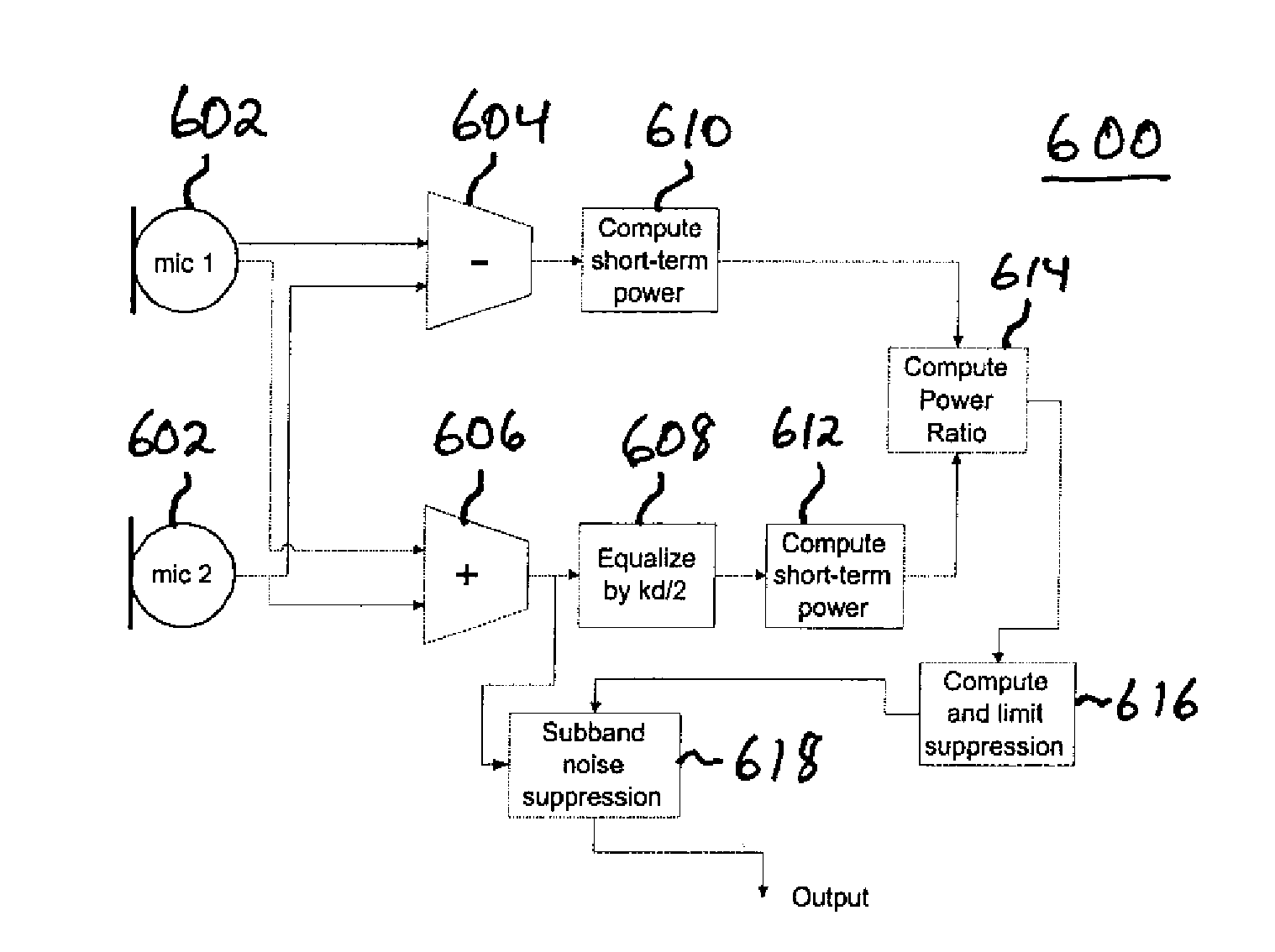

Spatial noise suppression for audio signals involves generating a ratio of powers of difference and sum signals of audio signals from two microphones and then performing noise suppression processing, e.g., on the sum signal where the suppression is limited based on the power ratio. In certain embodiments, at least one of the signal powers is filtered (e.g., the sum signal power is equalized) prior to generating the power ratio. In a subband implementation, sum and difference signal powers and corresponding the power ratio are generated for different audio signal subbands, and the noise suppression processing is performed independently for each different subband based on the corresponding subband power ratio, where the amount of suppression is derived independently for each subband from the corresponding subband power ratio. In an adaptive filtering implementation, at least one of the audio signals can be adaptively filtered to allow for array self-calibration and modal-angle variability.

Owner:MH ACOUSTICS

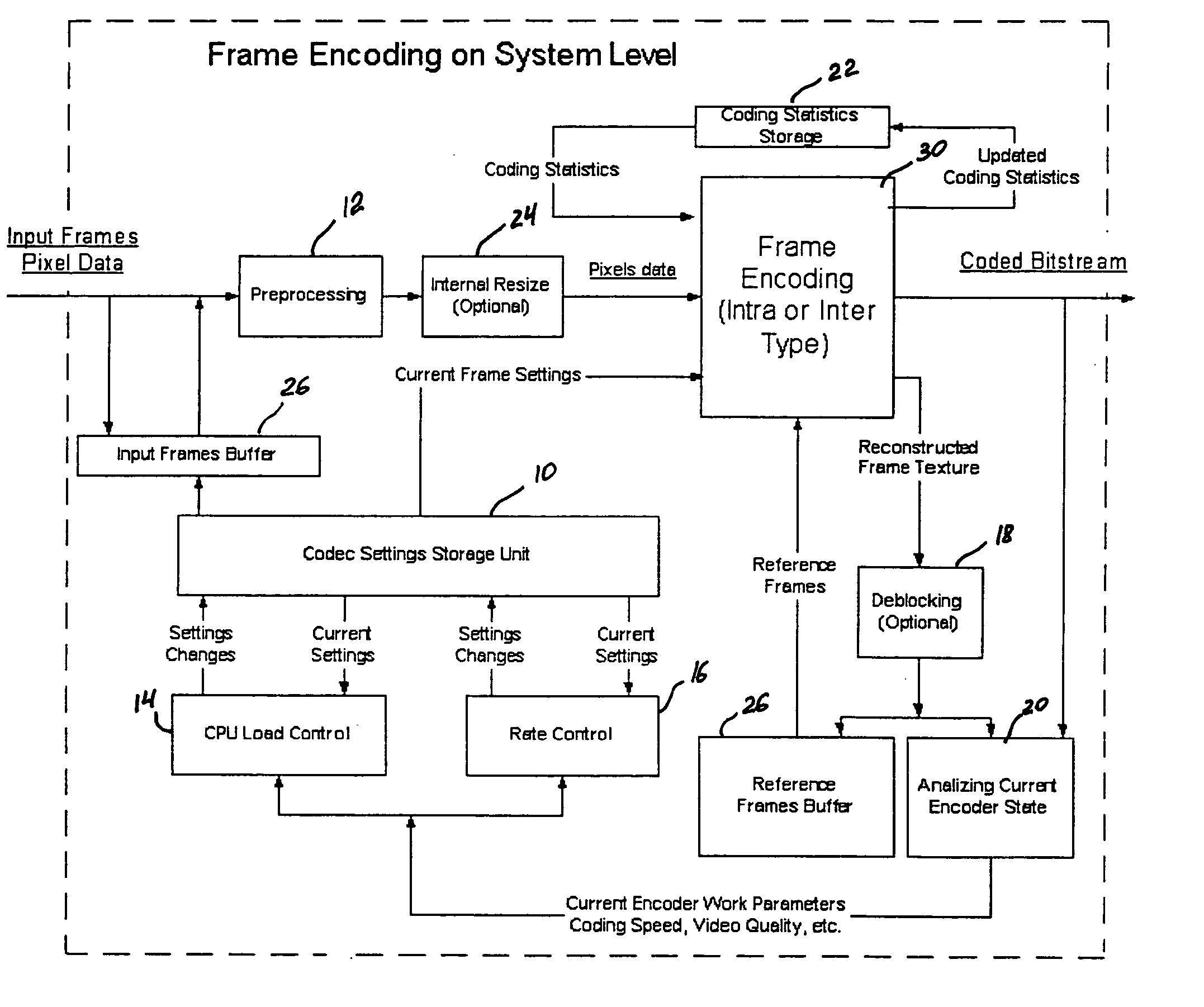

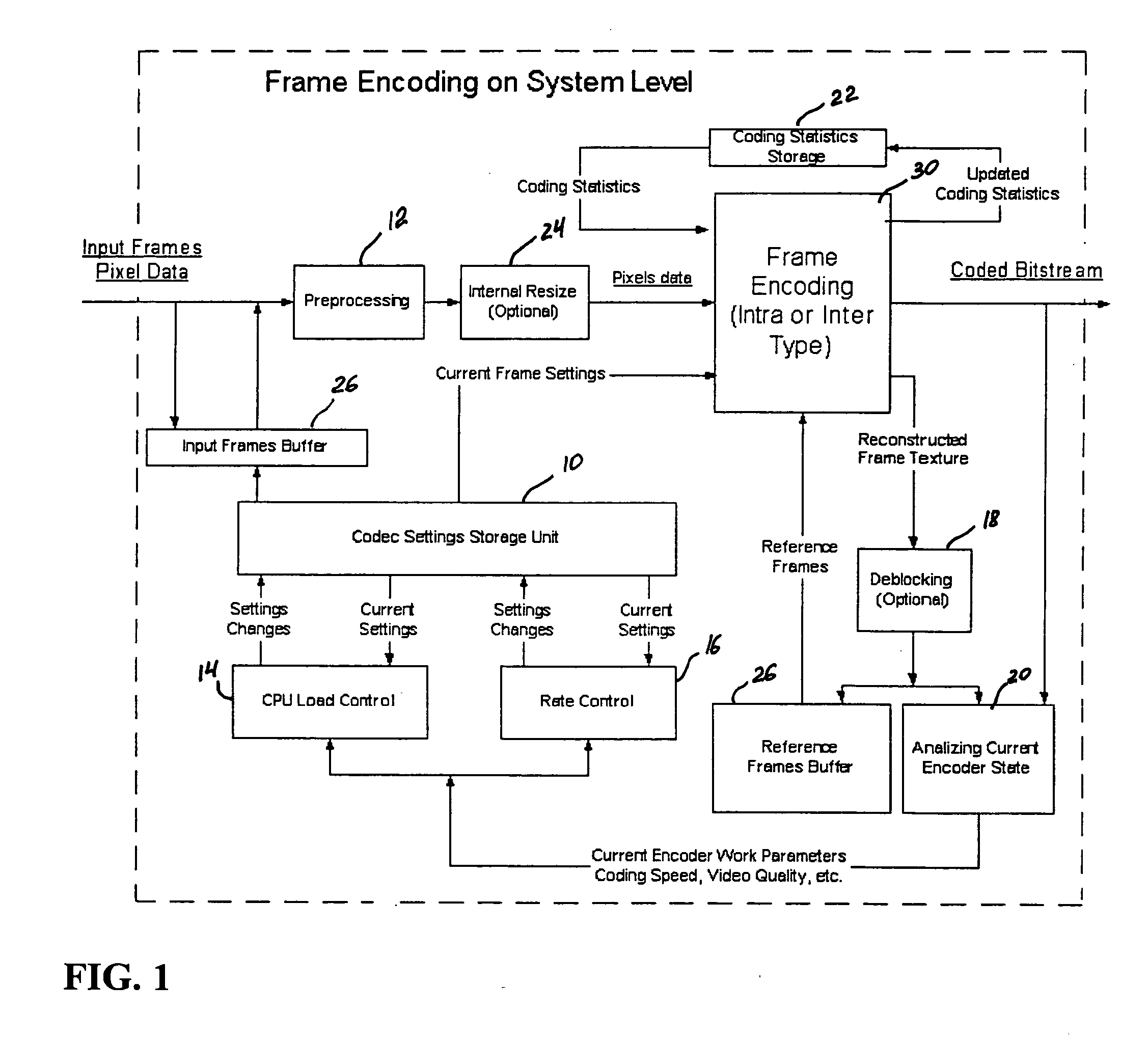

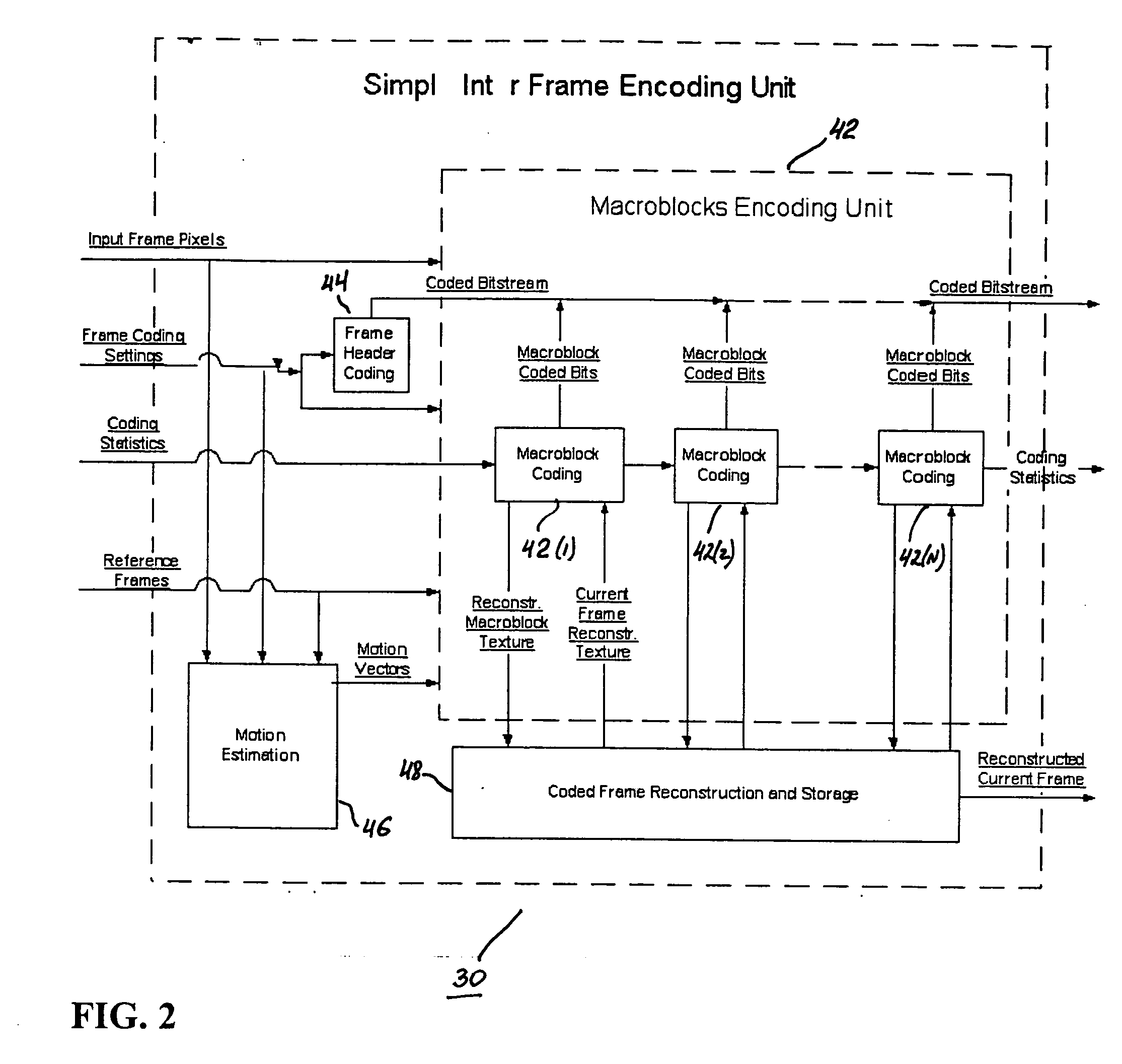

Real-time video coding/decoding

ActiveUS20050276323A1Picture reproducers using cathode ray tubesCode conversionMotion vectorDownscaling

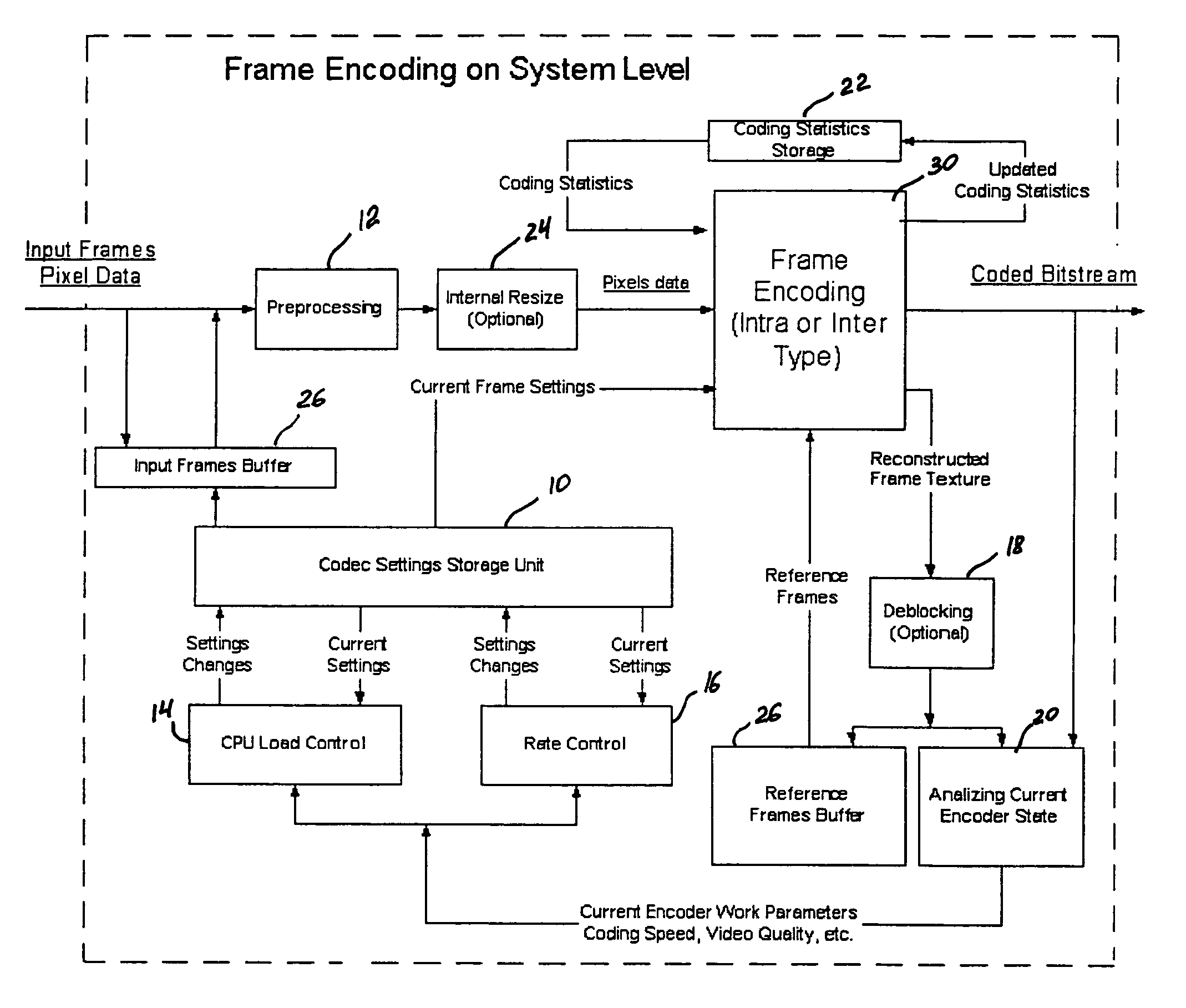

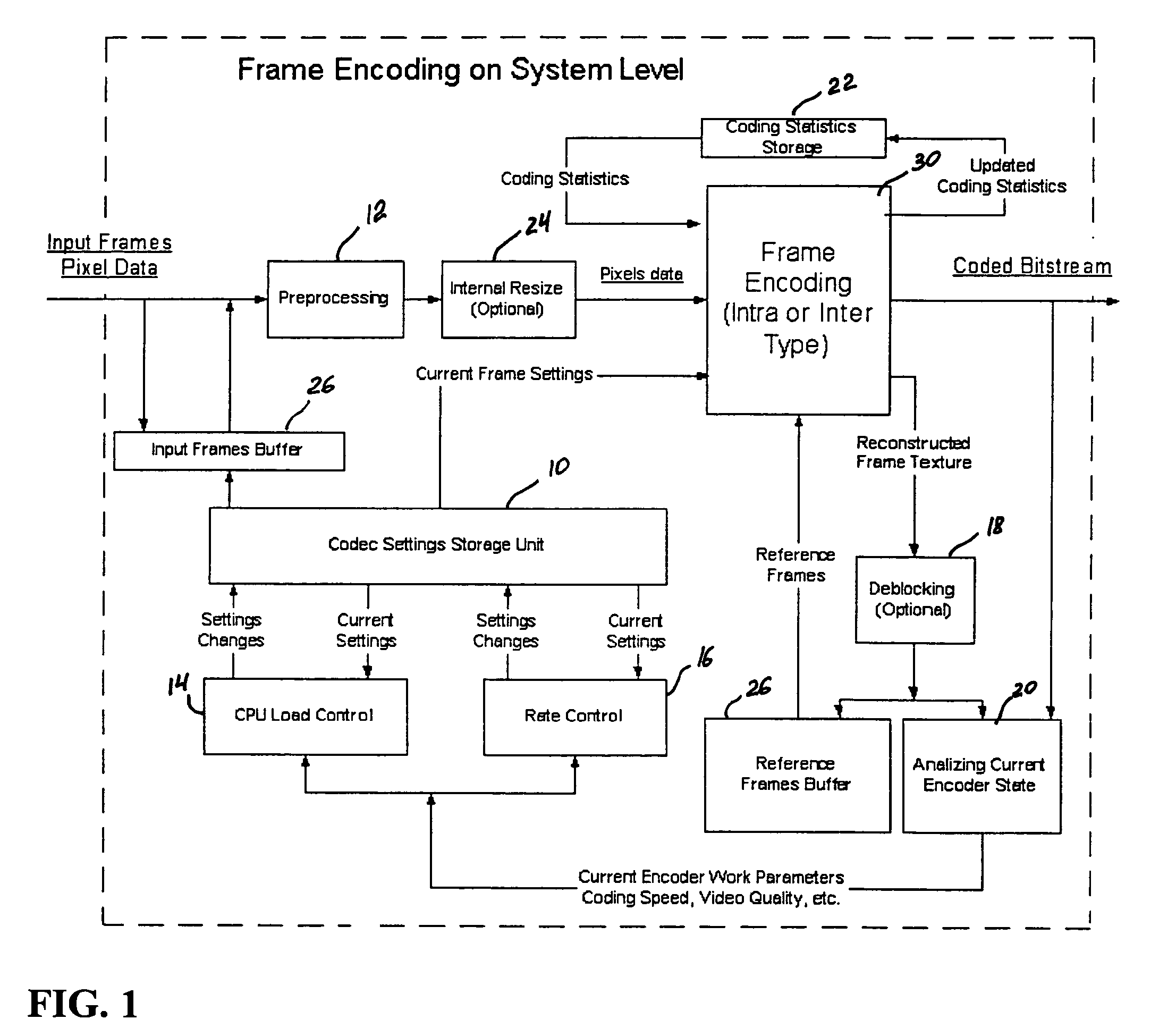

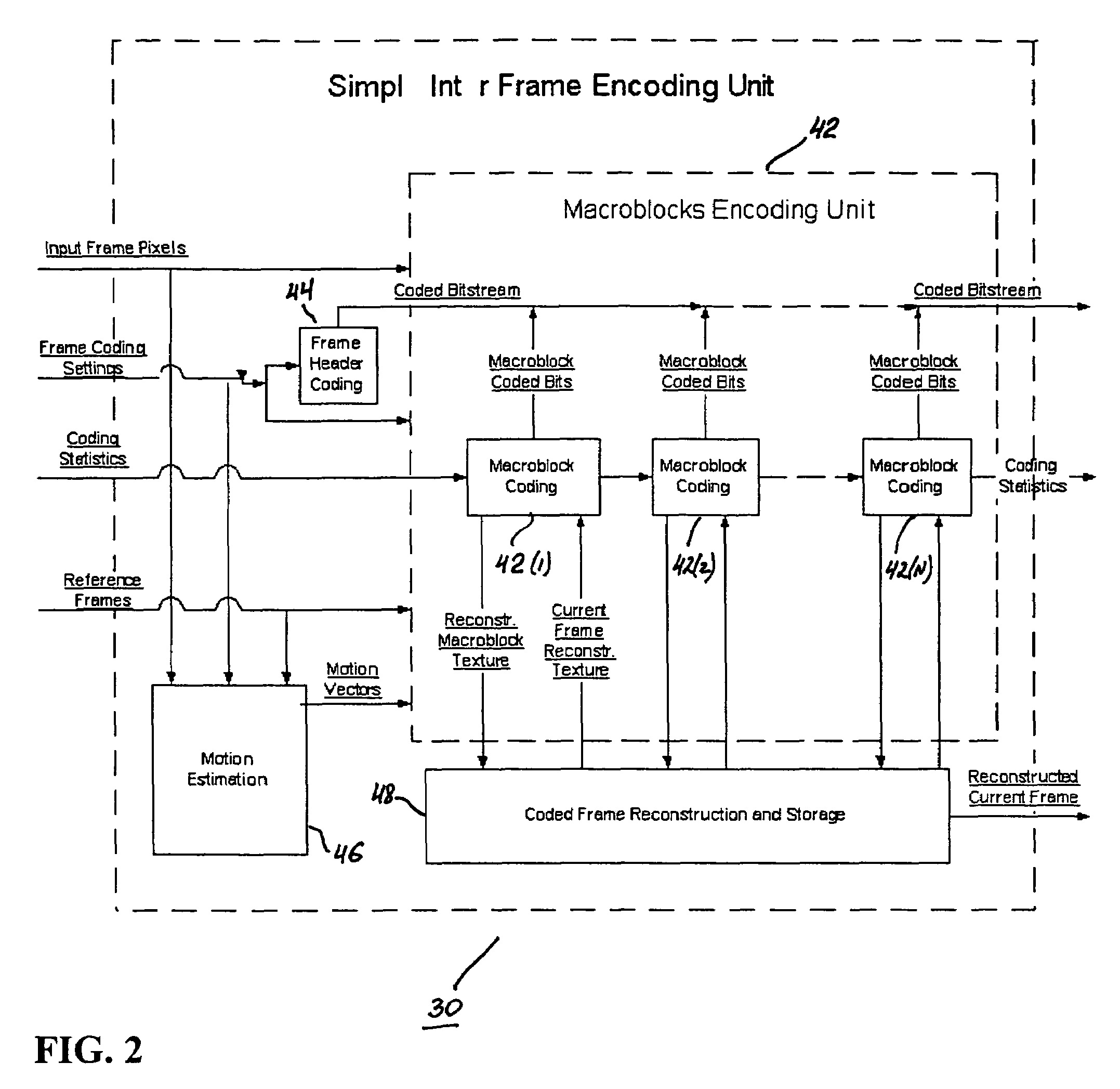

A video codec for real-time encoding / decoding of digitized video data with high compression efficiency, comprising a frame encoder receiving input frame pixels; a codec setting unit for setting and storing coding setting parameters; a CPU load controller for controlling desired frame encoding time and CPU loading; a rate controller for controlling frame size; a coding statistics memory for storing frequency tables for arithmetic coding of bitstream parameters and a reference frame buffer for storing reference frames. The frame encoder comprises a motion estimation unit, a frame head coding unit, a coded frame reconstruction and storage unit and a macroblock encoding unit. The macroblock encoding unit provides calculation of texture prediction and prediction error, transforming texture prediction error and quantization of transform coefficient, calculation of motion vector prediction and prediction error and arithmetic context modeling for motion vectors, header parameters and transform coefficients. The codec also includes a deblocking unit for processing video data to eliminate blocking effect from restored data encoded at high distortion level, which may be a part of encoder or decoder, an internal resize unit, providing matching downscaling of a frame before encoding and upscaling of decoded frame according to the coding setting parameters, and a noise suppression unit.

Owner:BEAMR IMAGING LTD

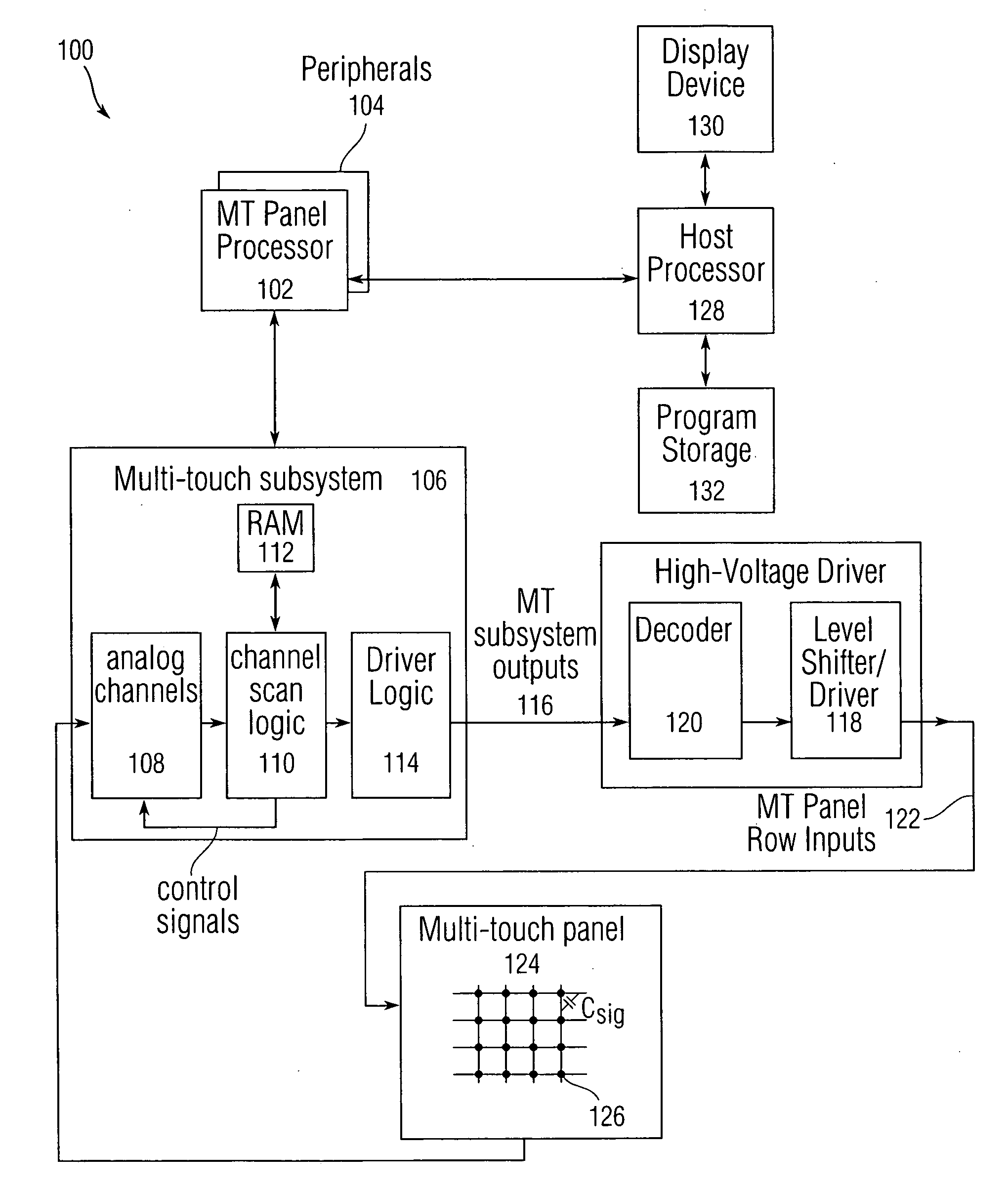

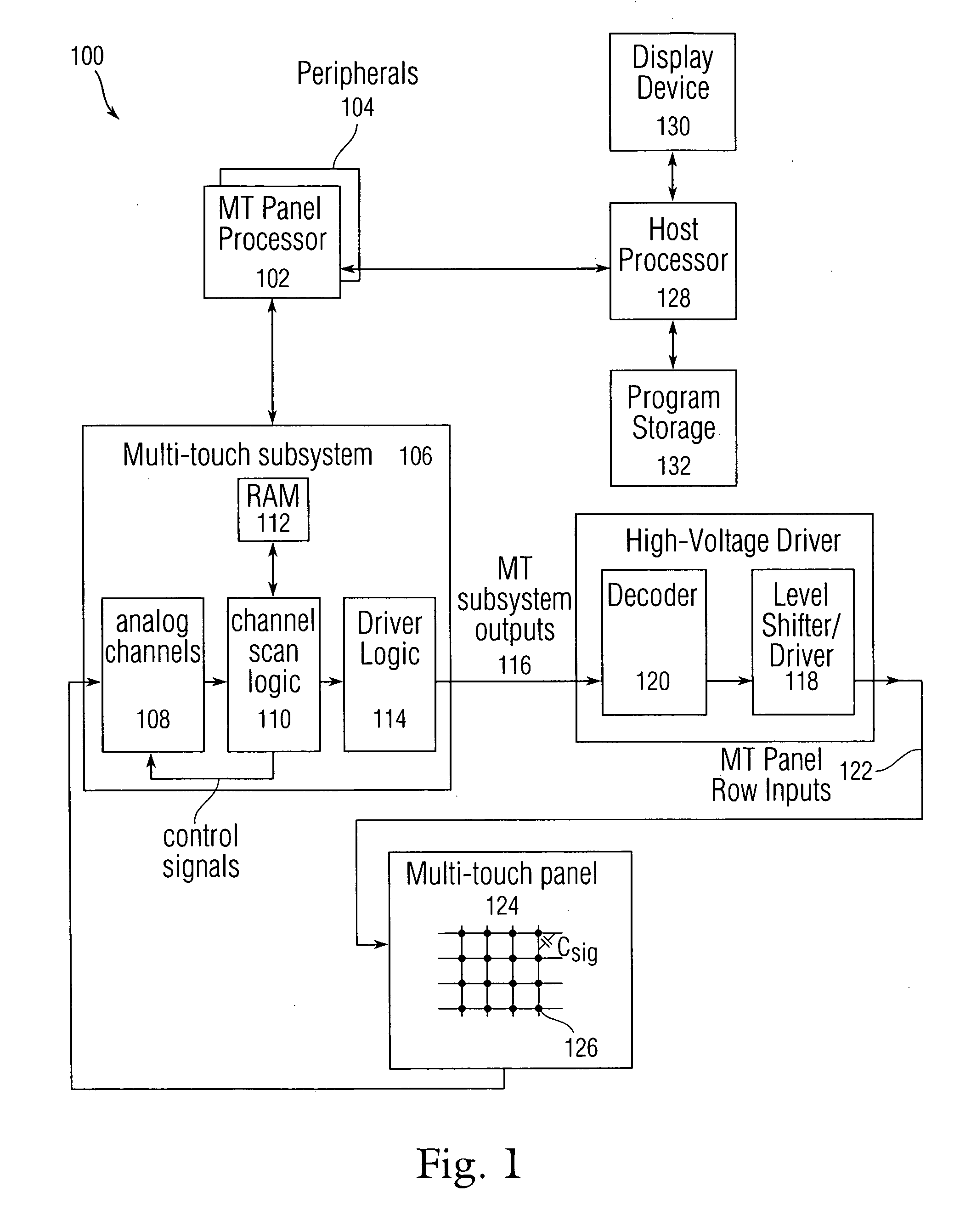

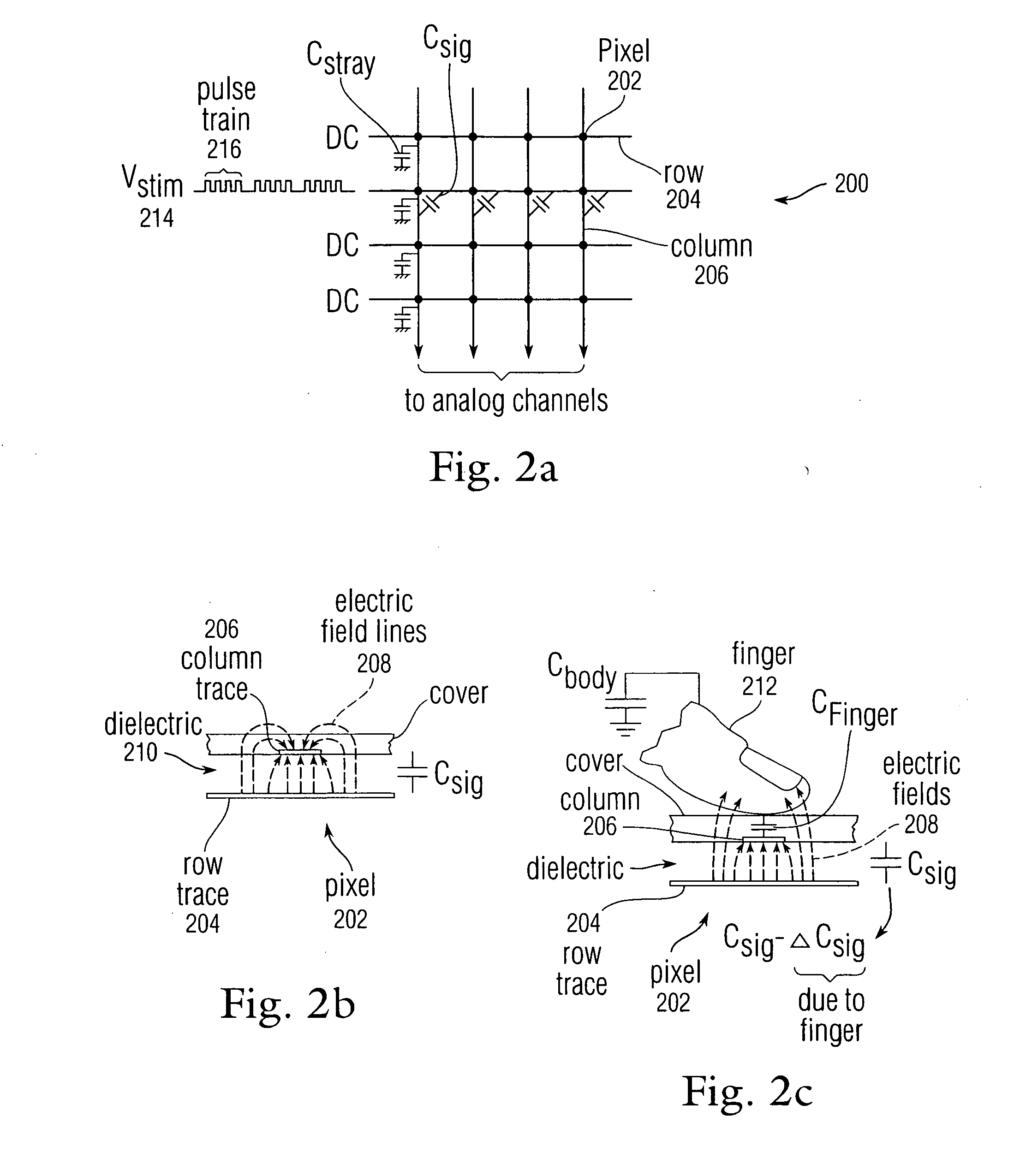

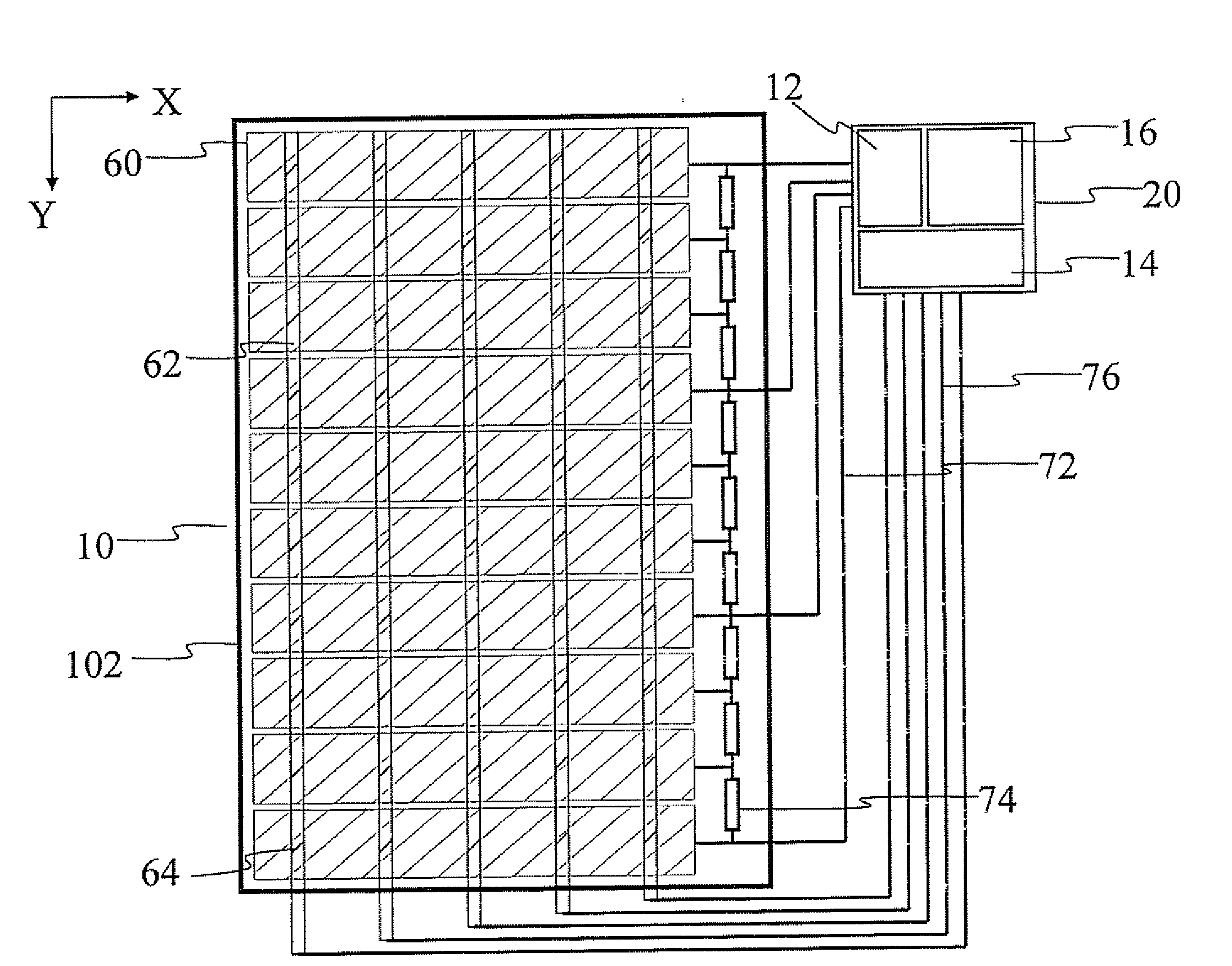

Capacitive Touch Screen with Noise Suppression

ActiveUS20100044122A1Reduce sensitivityImprove linearityTransmission systemsDigital data processing detailsDisplay deviceNoise suppression

A capacitive touch sensor wherein the touch sensitive panel has drive electrodes arranged on the lower side of a substrate and sense electrodes arranged on the upper side. The drive electrodes are shaped and dimensioned to substantially entirely cover the touch sensitive area with individual drive electrodes being separated from each other by small gaps, the gaps being so small as to be practically invisible. The near blanket coverage by the drive electrodes also serves to screen out interference from noise sources below the drive electrode layer, such as drive signals for an underlying display, thereby suppressing noise pick-up by the sense electrodes that are positioned above the drive electrodes.

Owner:NEODRON LTD +1

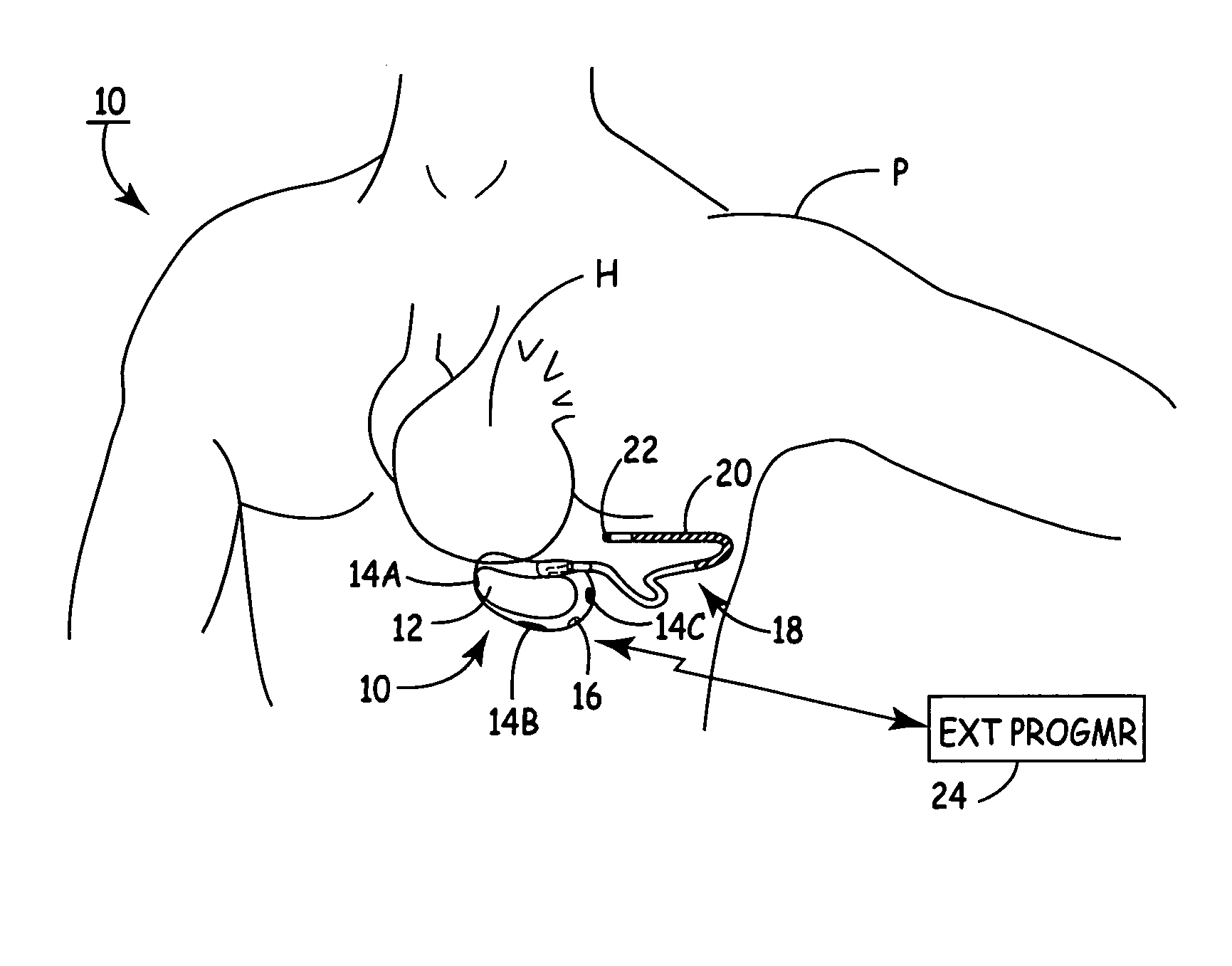

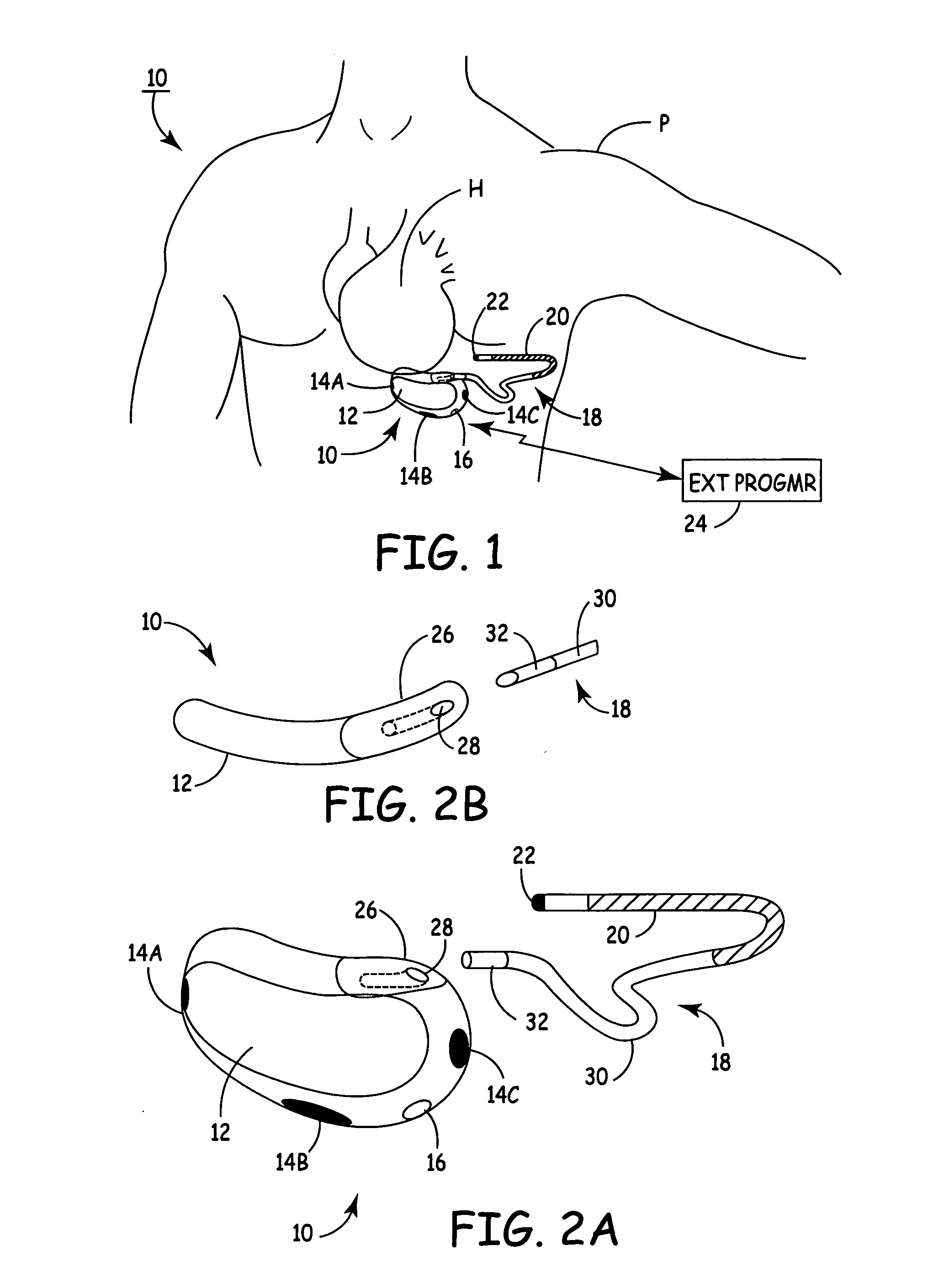

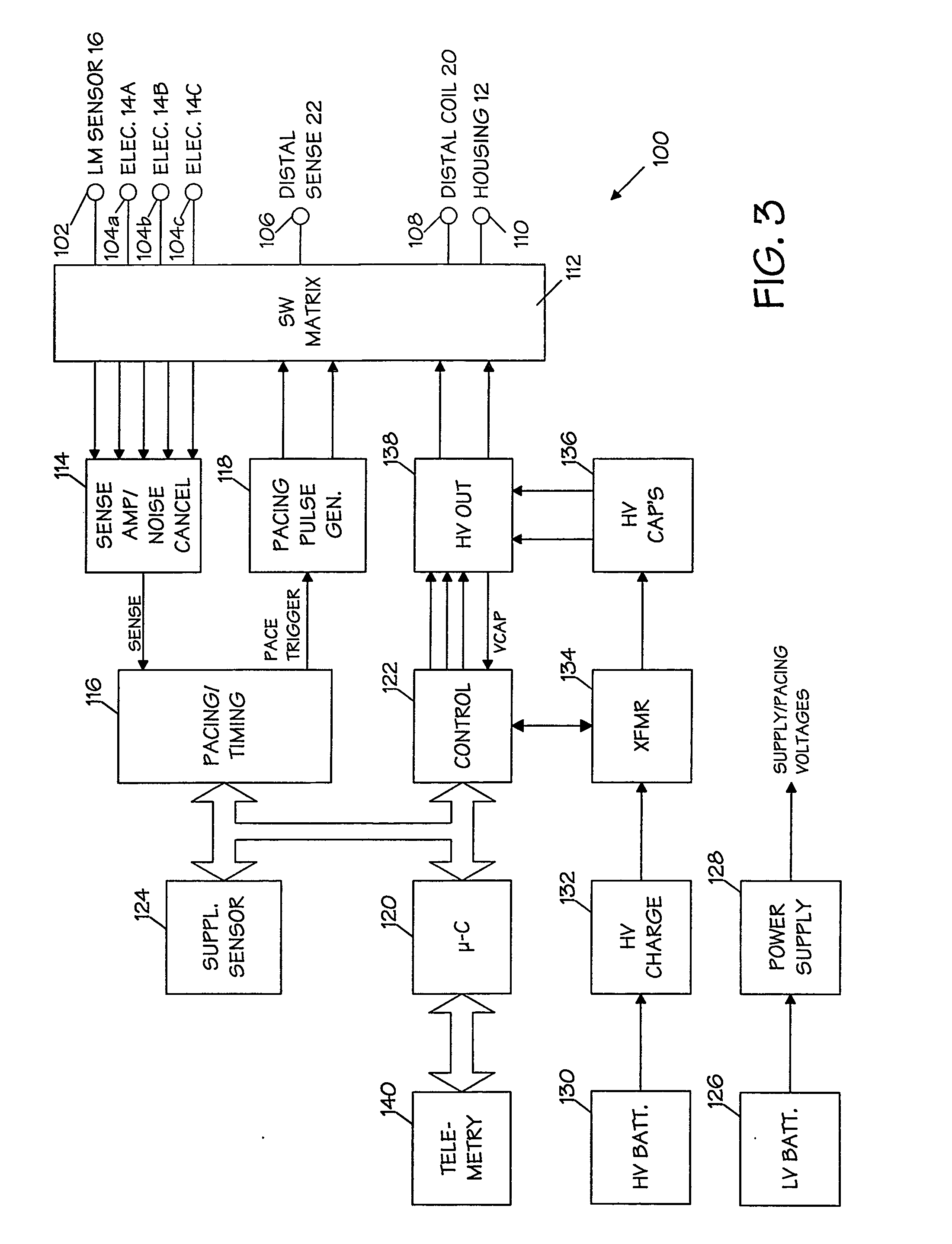

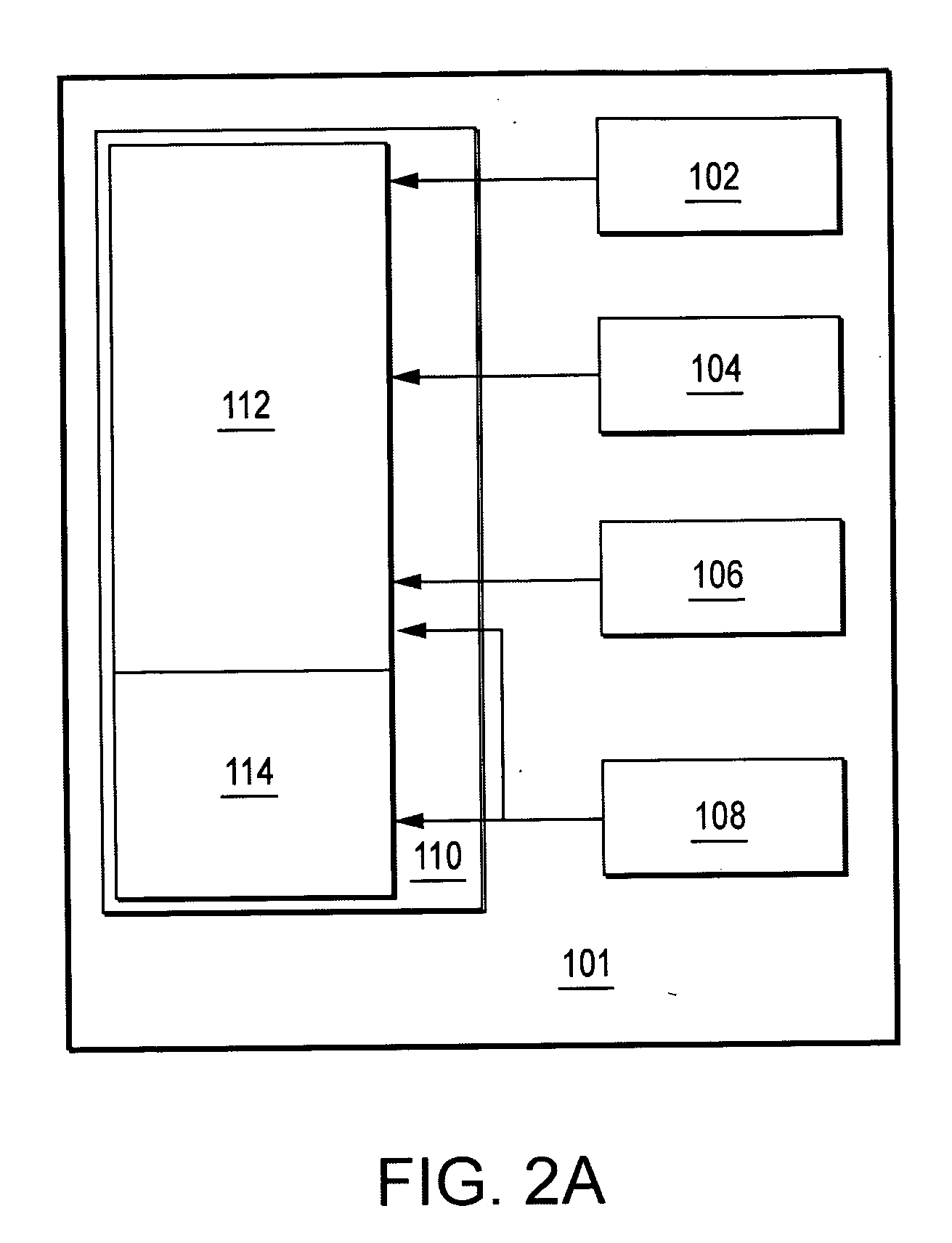

Subcutaneous ICD with motion artifact noise suppression

A subcutaneous implantable cardioverter defibrillator (SubQ ICD) includes a housing carrying electrodes for sensing ECG signals and delivering therapy. A sensor detects local motion in the area of the housing and produces a noise signal related to motion artifact noise contained in ECG signals derived from the electrode array. An adaptive noise cancellation circuit enhances ECG signals based on the local motion noise signal. A therapy delivery circuit delivers cardioversion and defibrillation pulses based upon the enhanced ECG signals.

Owner:MEDTRONIC INC

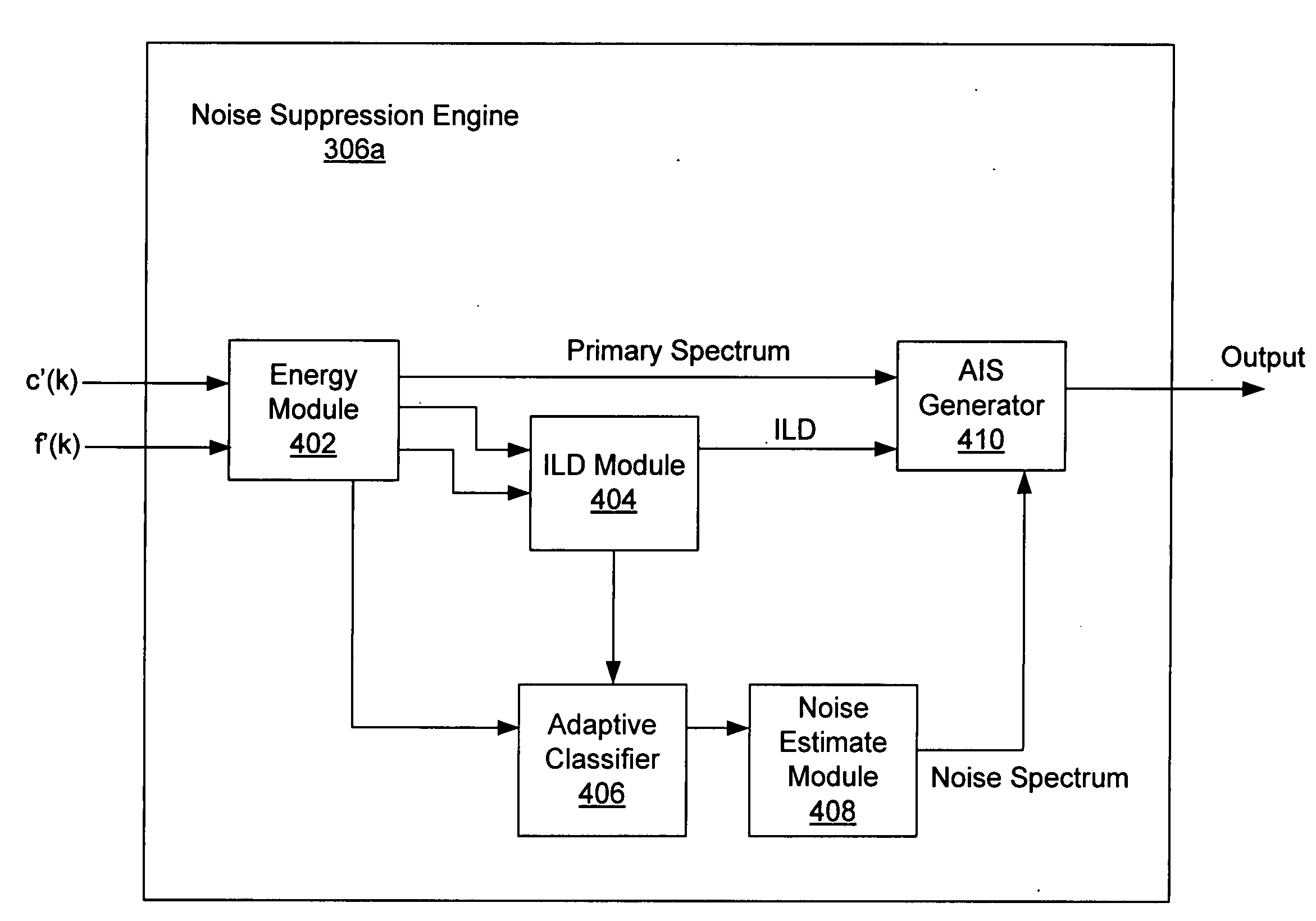

Adaptive Noise Reduction Using Level Cues

ActiveUS20110182436A1Maximize noise reduction performanceOptimizationEar treatmentSpeech analysisControl signalAdaptive denoising

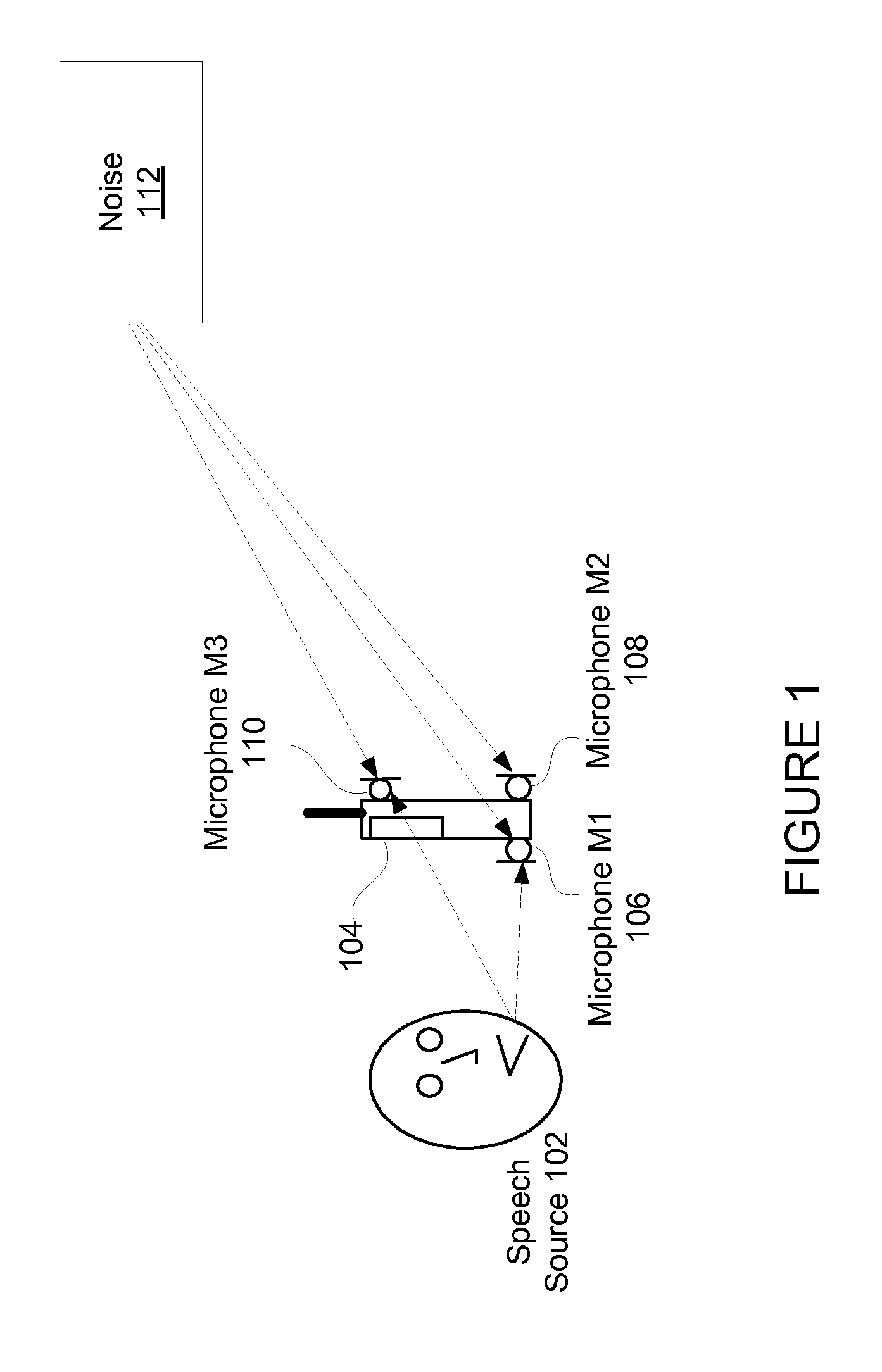

An array of microphones utilizes two sets of two microphones for noise suppression. A primary microphone and secondary microphone of the three microphones may be positioned closely spaced to each other to provide acoustic signals used to achieve noise cancellation. A tertiary microphone may be spaced with respect to either the primary microphone or the secondary microphone in a spread-microphone configuration for deriving level cues from audio signals provided by tertiary and the primary or secondary microphone. Signals from two microphones may be used rather than three microphones. The level cues are expressed via an inter-microphone level difference (ILD) which is used to determine one or more cluster tracking control signals. The ILD based cluster tracking signals are used to control the adaptation of null-processing noise cancellation modules. A noise cancelled primary acoustic signal and ILD based cluster tracking control signals are used during post filtering to adaptively generate a mask to be applied against a speech estimate signal.

Owner:KNOWLES ELECTRONICS INC

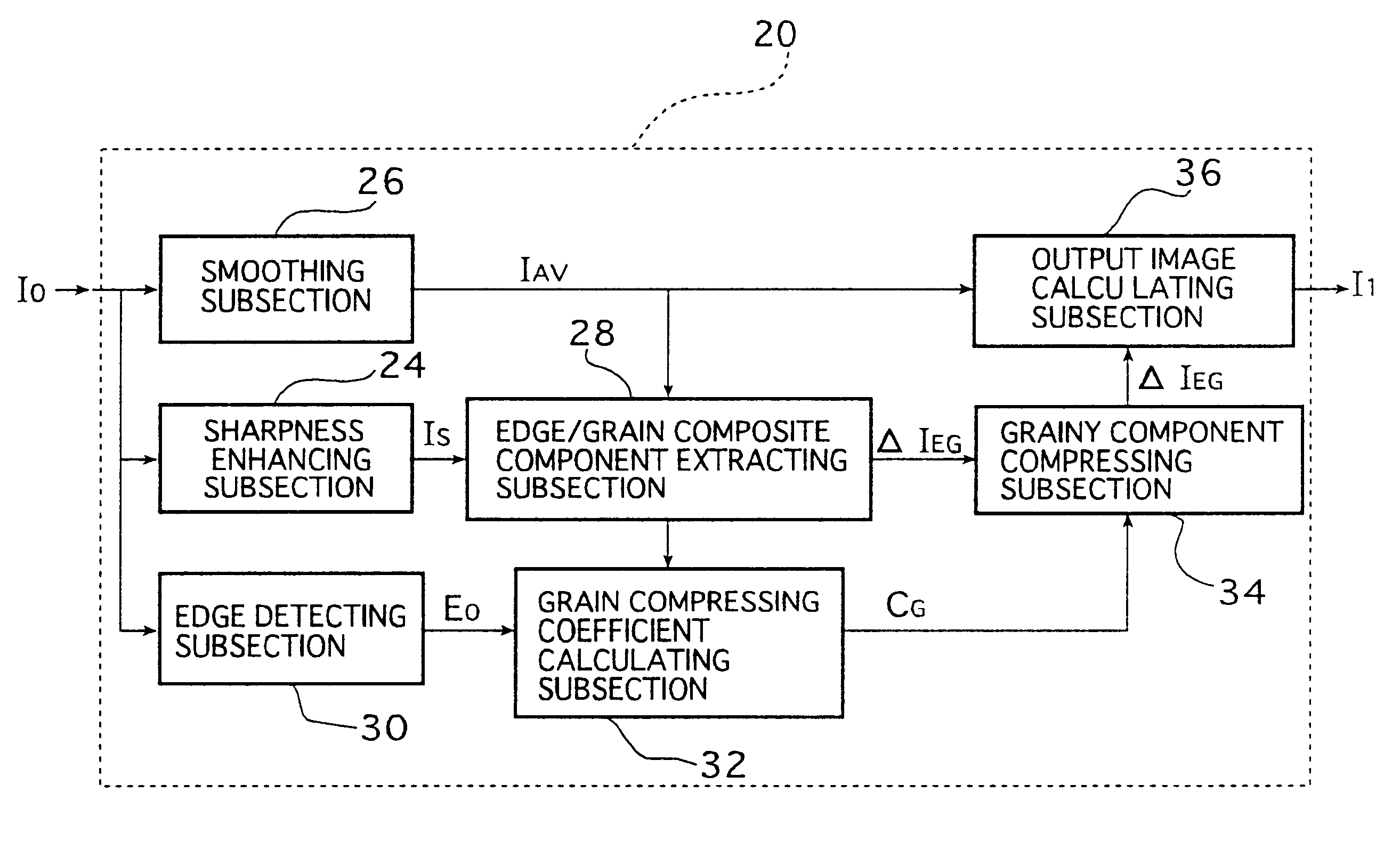

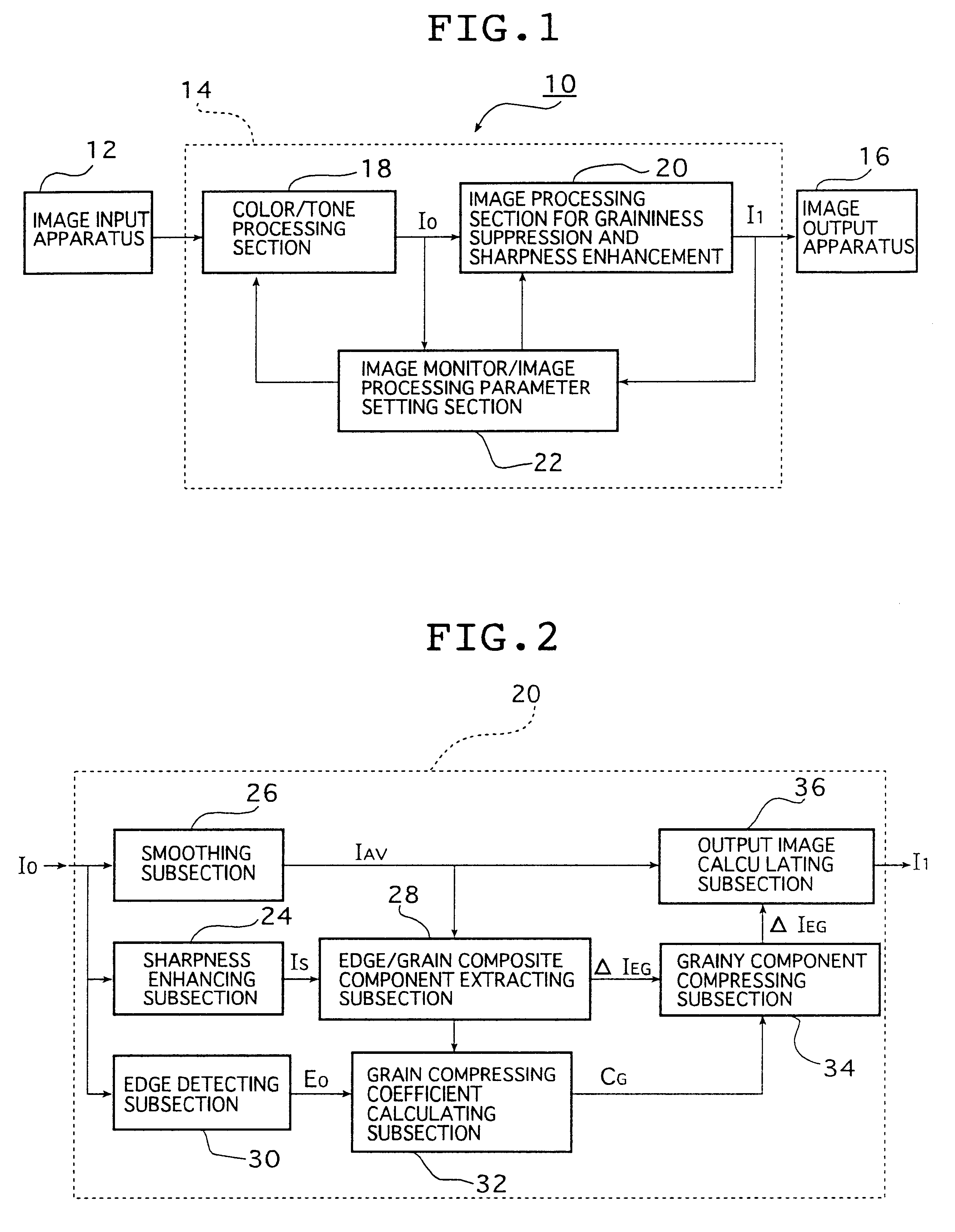

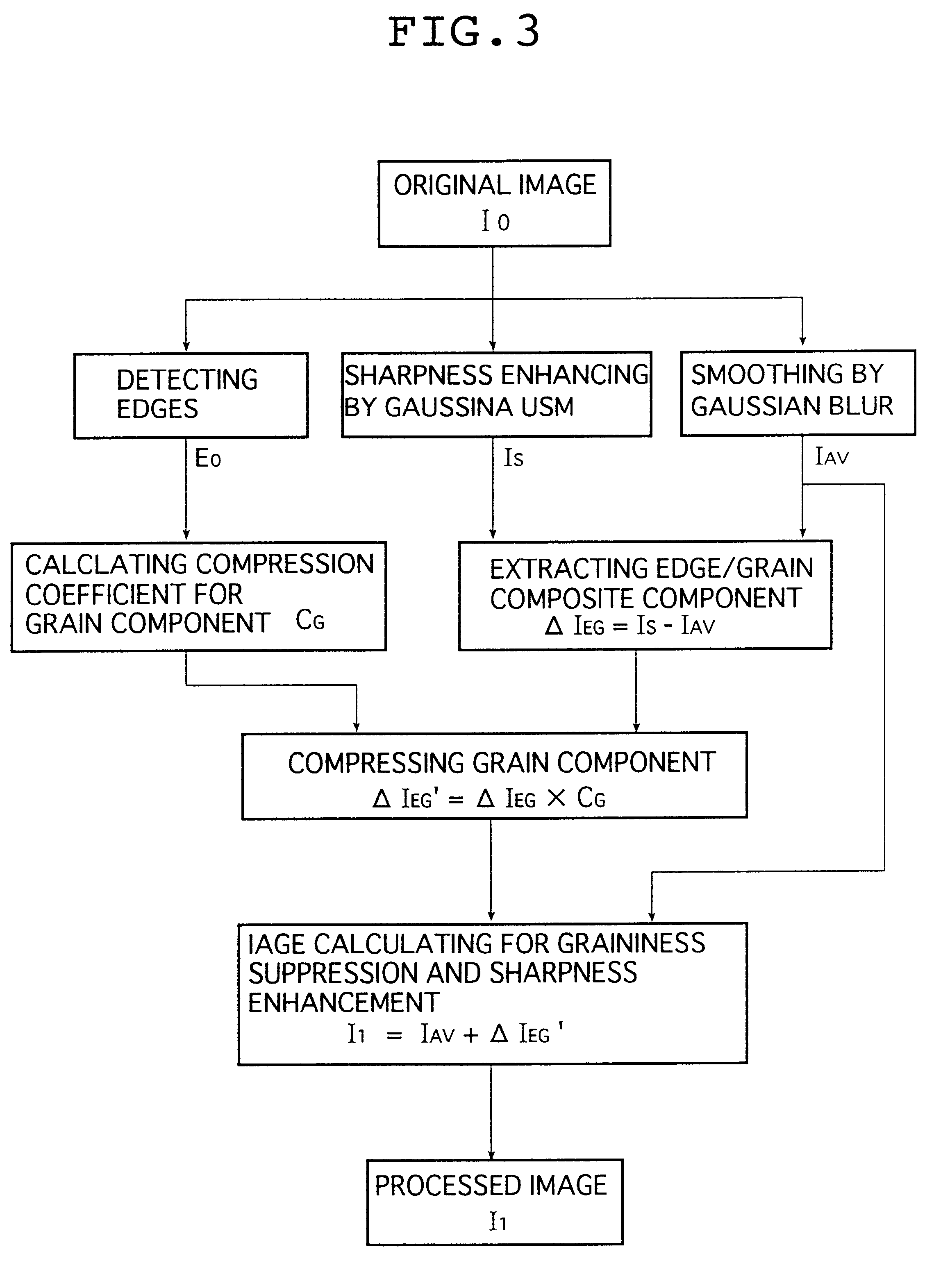

Method and apparatus for image processing

InactiveUS6373992B1Improve clarityReduce the amplitudeImage enhancementImage analysisImaging processingDigital image

There is provided a method for processing a digital image for noise suppression and sharpness enhancement, comprising the steps of performing a sharpness enhancing process on original image data to create sharpness enhanced image data; performing a smoothing process on the original image data to create smoothed image data; subtracting the smoothed image data from the sharpness enhanced image data to create first edge / grain composite image data; performing an edge detection to determine an edge intensity data; using the edge intensity data to determine grainy fluctuation compressing coefficient data for compressing amplitude of an grainy fluctuation component in the grainy region; multiplying the first edge / grain composite image data by the grainy fluctuation compressing coefficient data to compress only the grainy fluctuation component in the grainy region, and to thereby create second edge / grain composite image data; and adding the second edge / grain composite image data to the smoothed image data to thereby create an processed image. There is also provided an image processing apparatus for implementing the above method. An improvement is thus achieved in both graininess and sharpness without causing any artificiality and oddities due to "blurry graininess".

Owner:FUJIFILM CORP +1

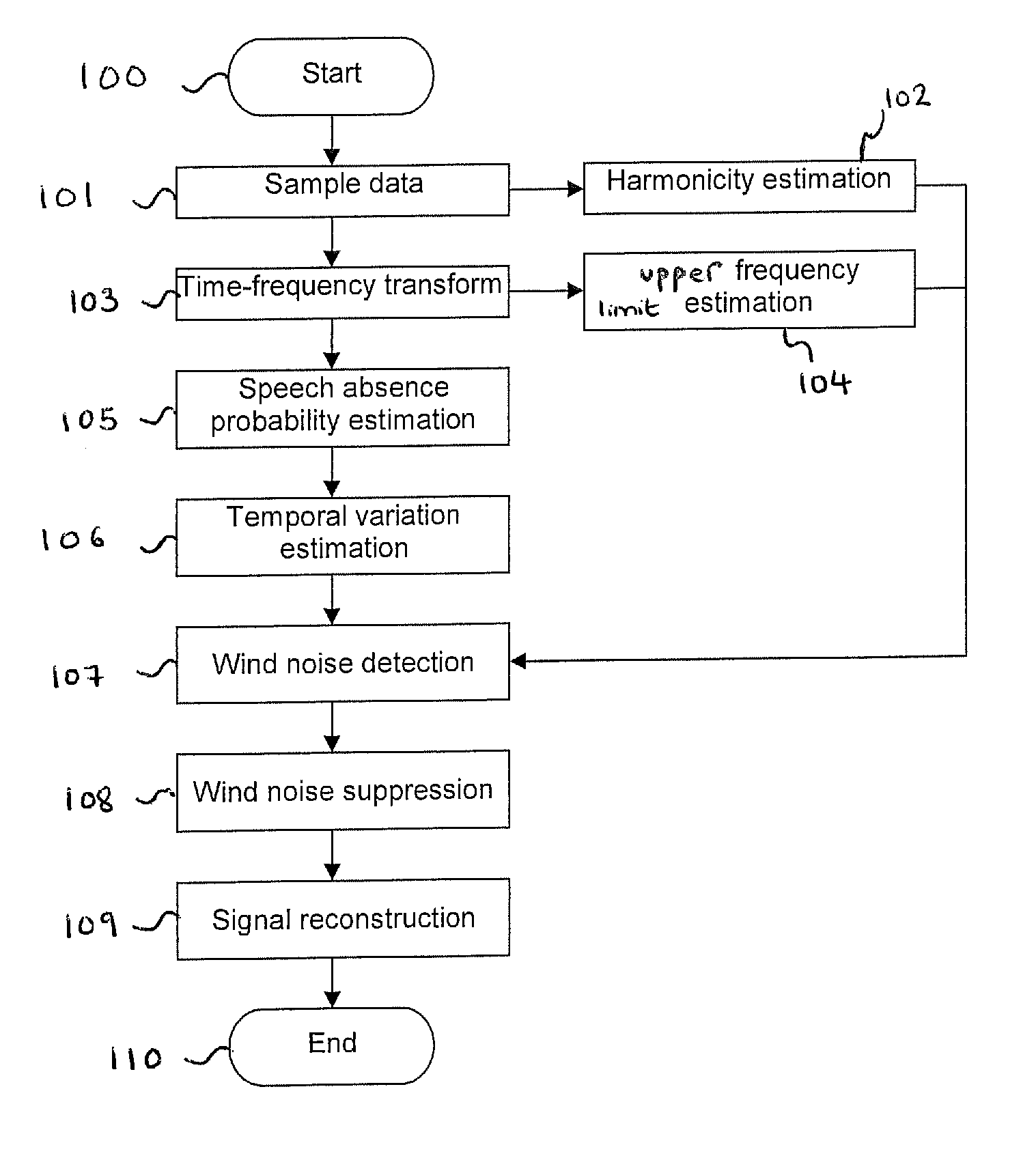

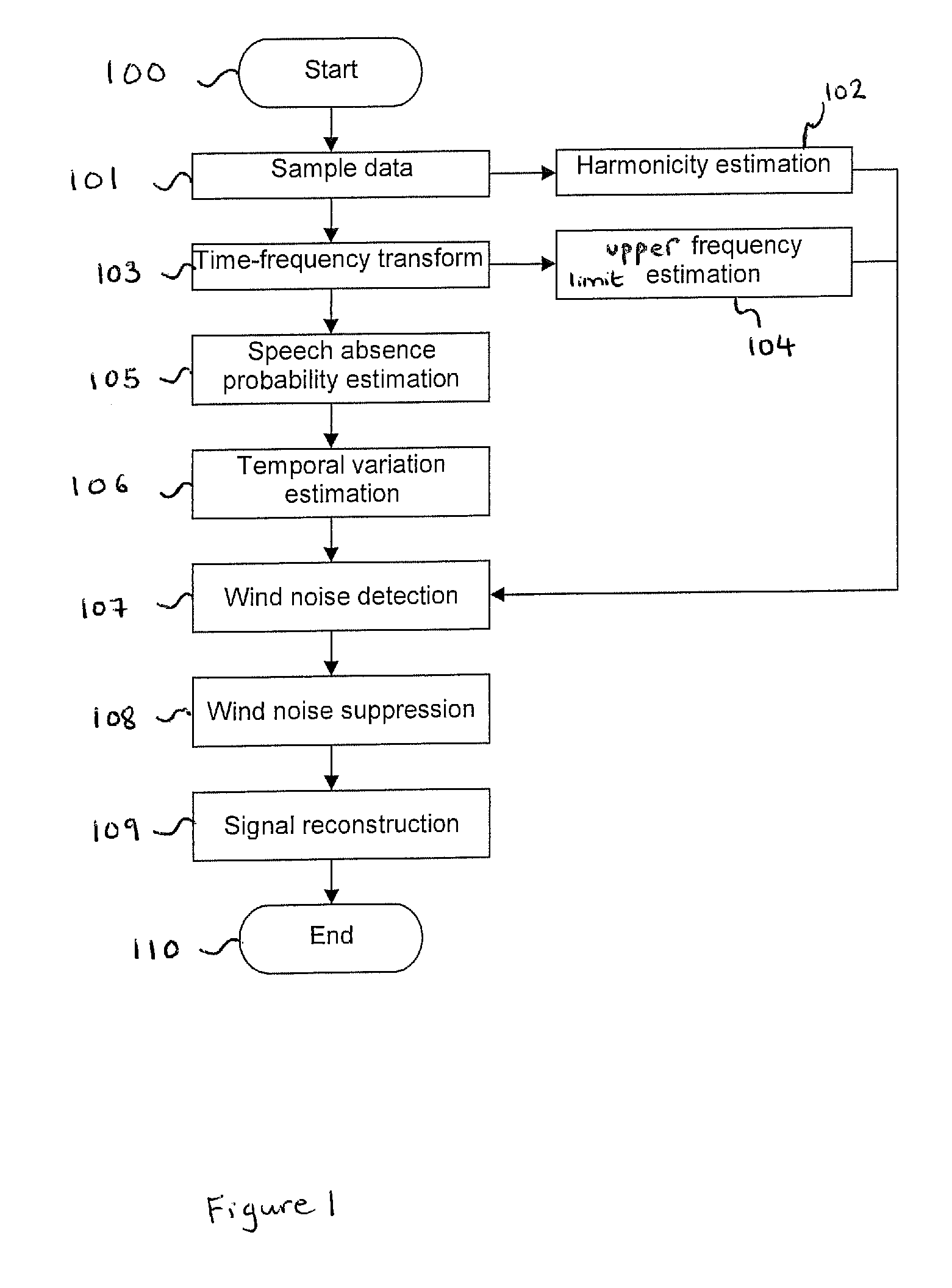

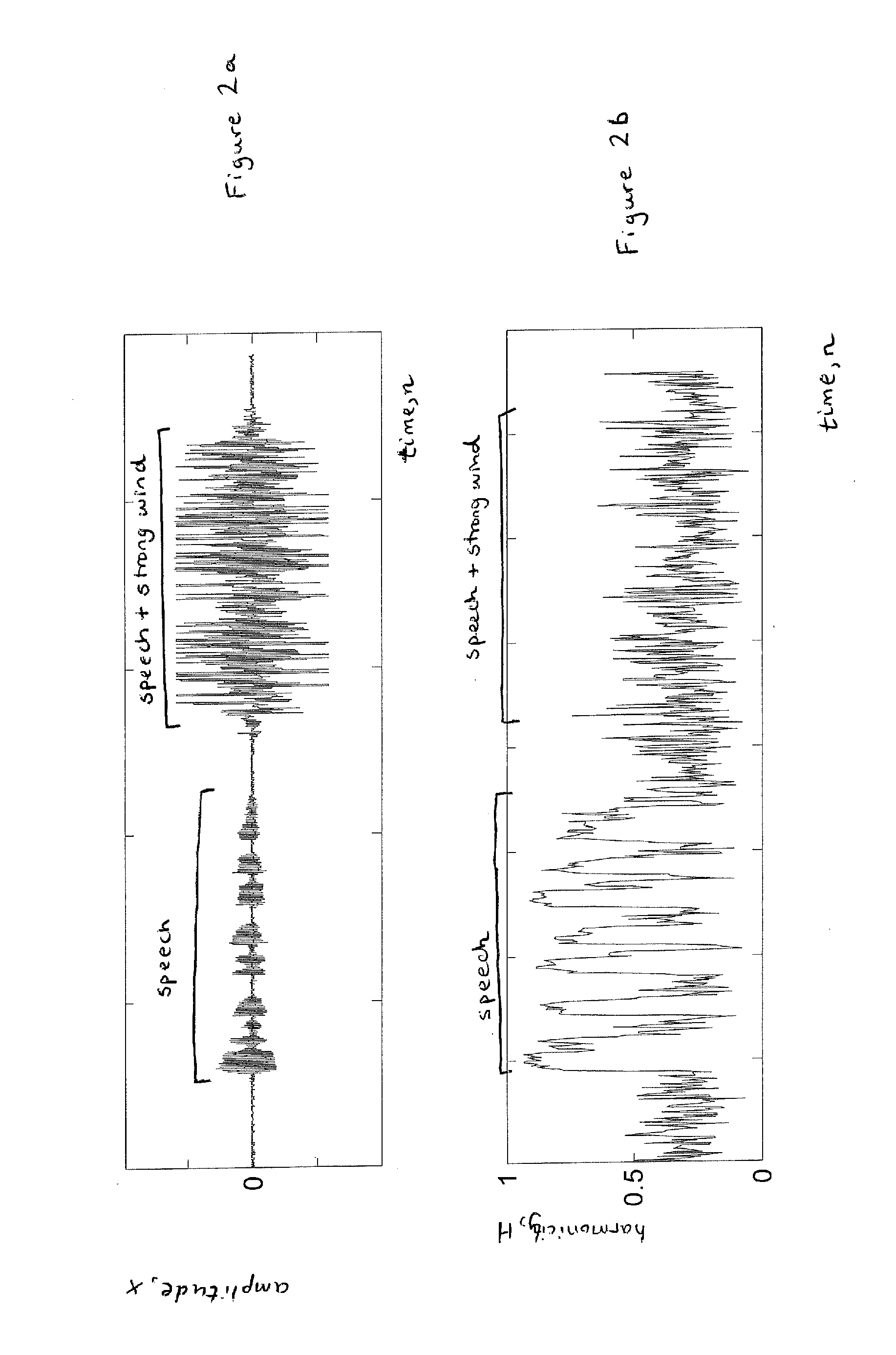

Wind Noise Suppression

InactiveUS20110103615A1Speech recognitionTransmission noise suppressionFrequency spectrumEngineering

A method of suppressing wind noise in a voice signal determines an upper frequency limit that lies within the frequency spectrum of the voice signal, and for each of a plurality of frequency bands below the upper frequency limit, compares the average power of signal components in a first portion of the signal to the average power of signal components in a second portion of the signal, where the second portion is successive to the first portion. Signal components are identified in at least one of the plurality of frequency bands as containing impulsive wind noise in dependence on the comparison, and the identified signal components are attenuated.

Owner:QUALCOMM TECH INT

Real-time video coding/decoding

Owner:BEAMR IMAGING LTD

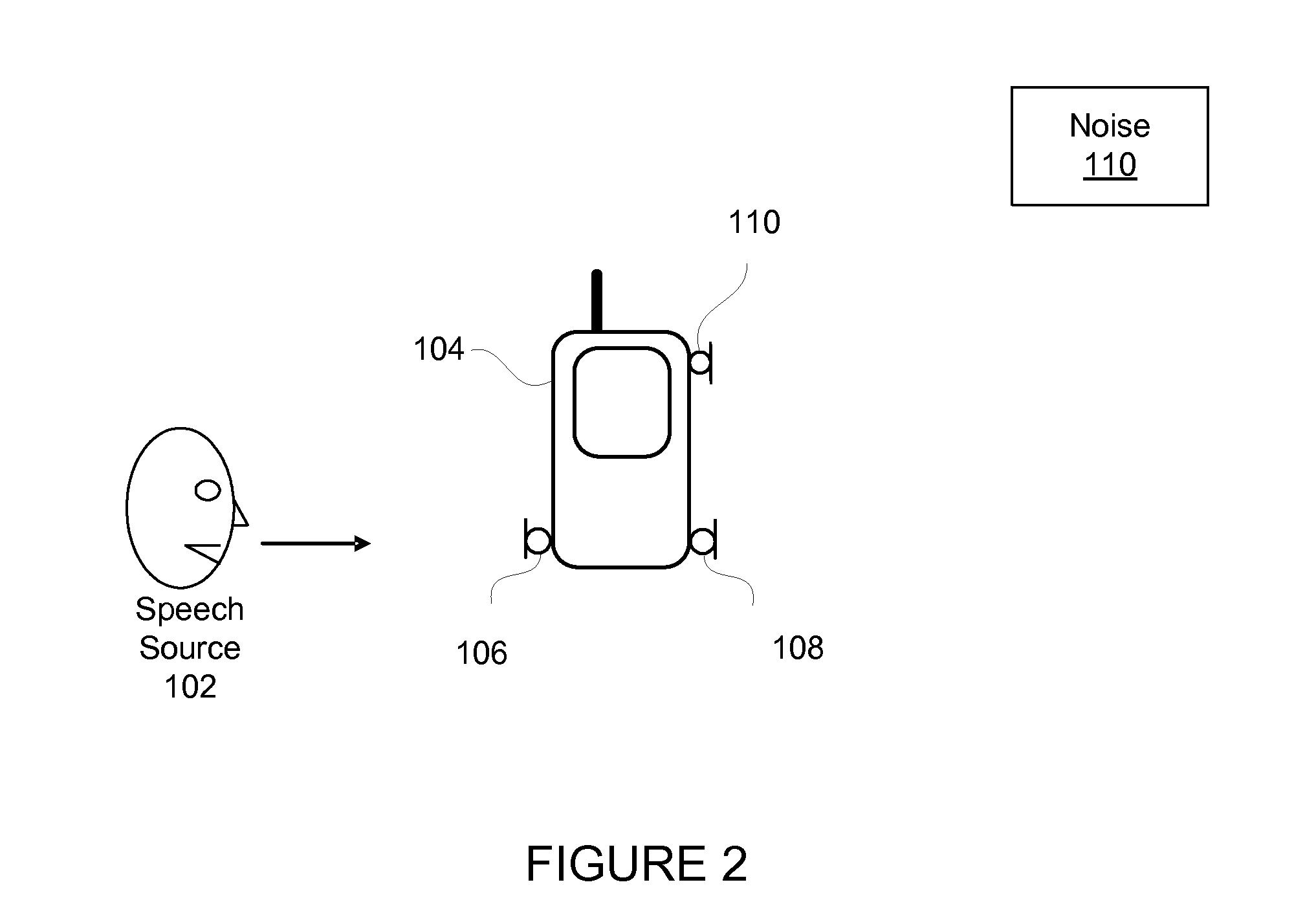

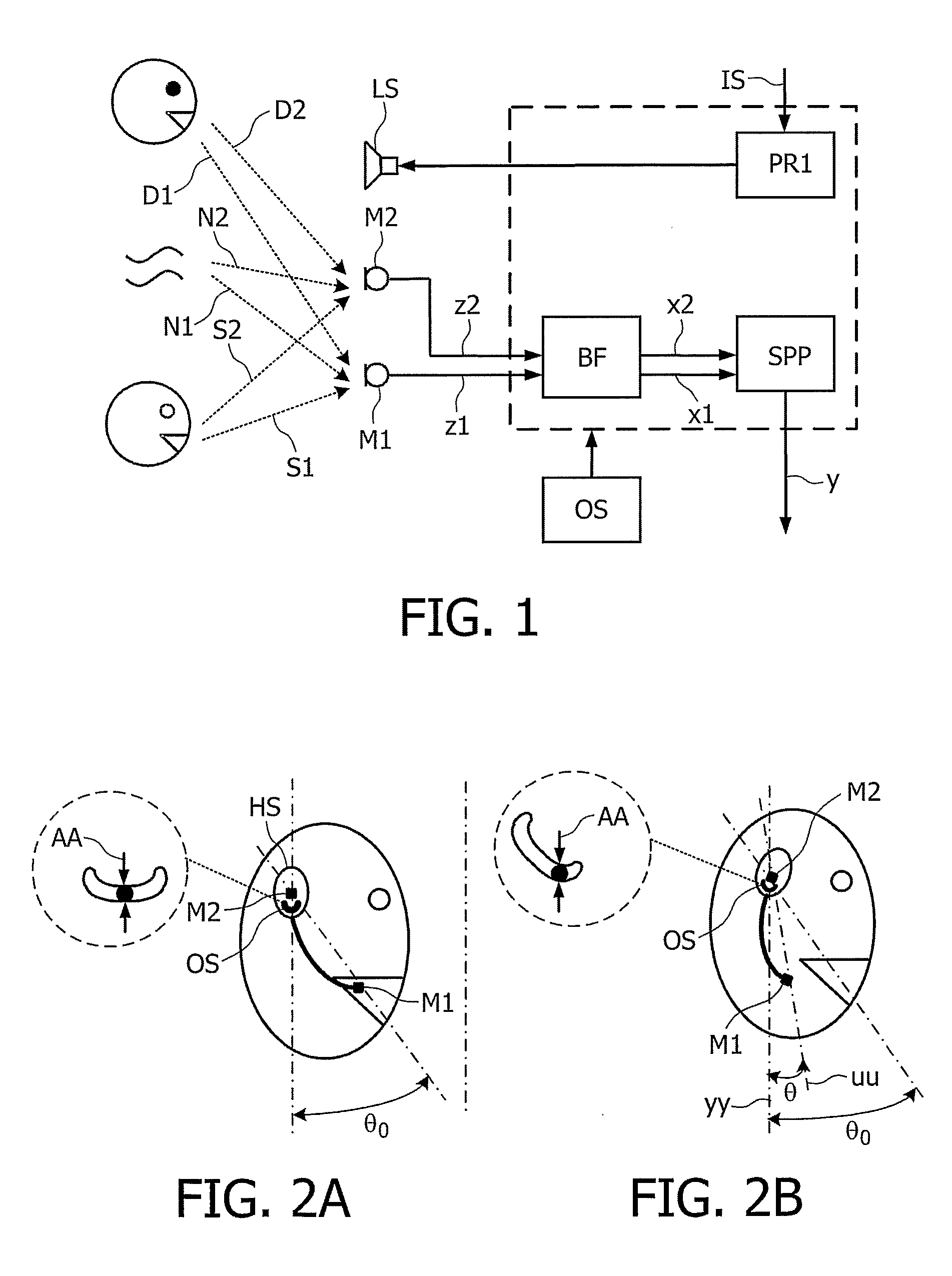

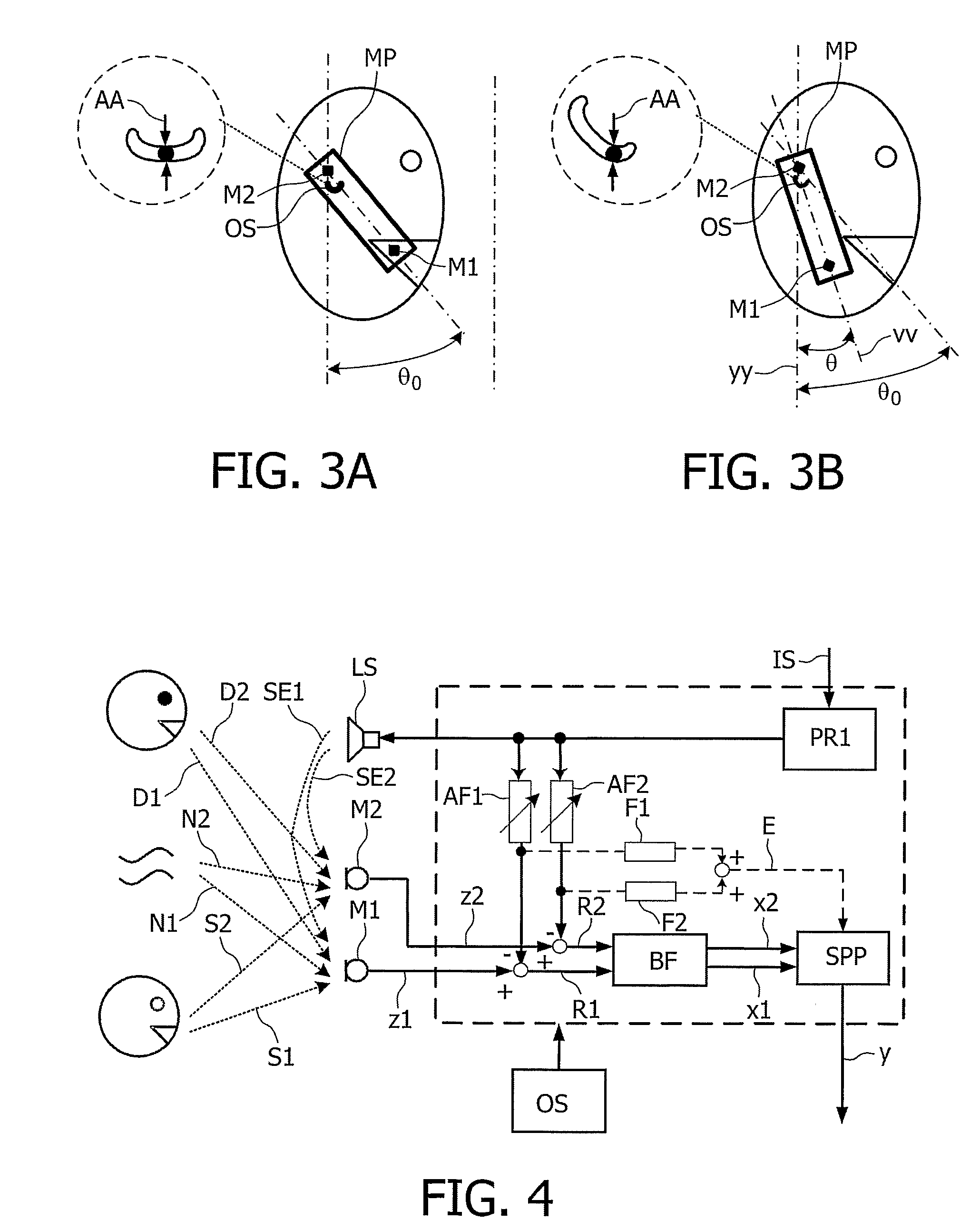

Telephony Device with Improved Noise Suppression

InactiveUS20070230712A1Unwanted noise signalMaximize qualityEar treatmentMicrophone structural associationFrequency spectrumPost processor

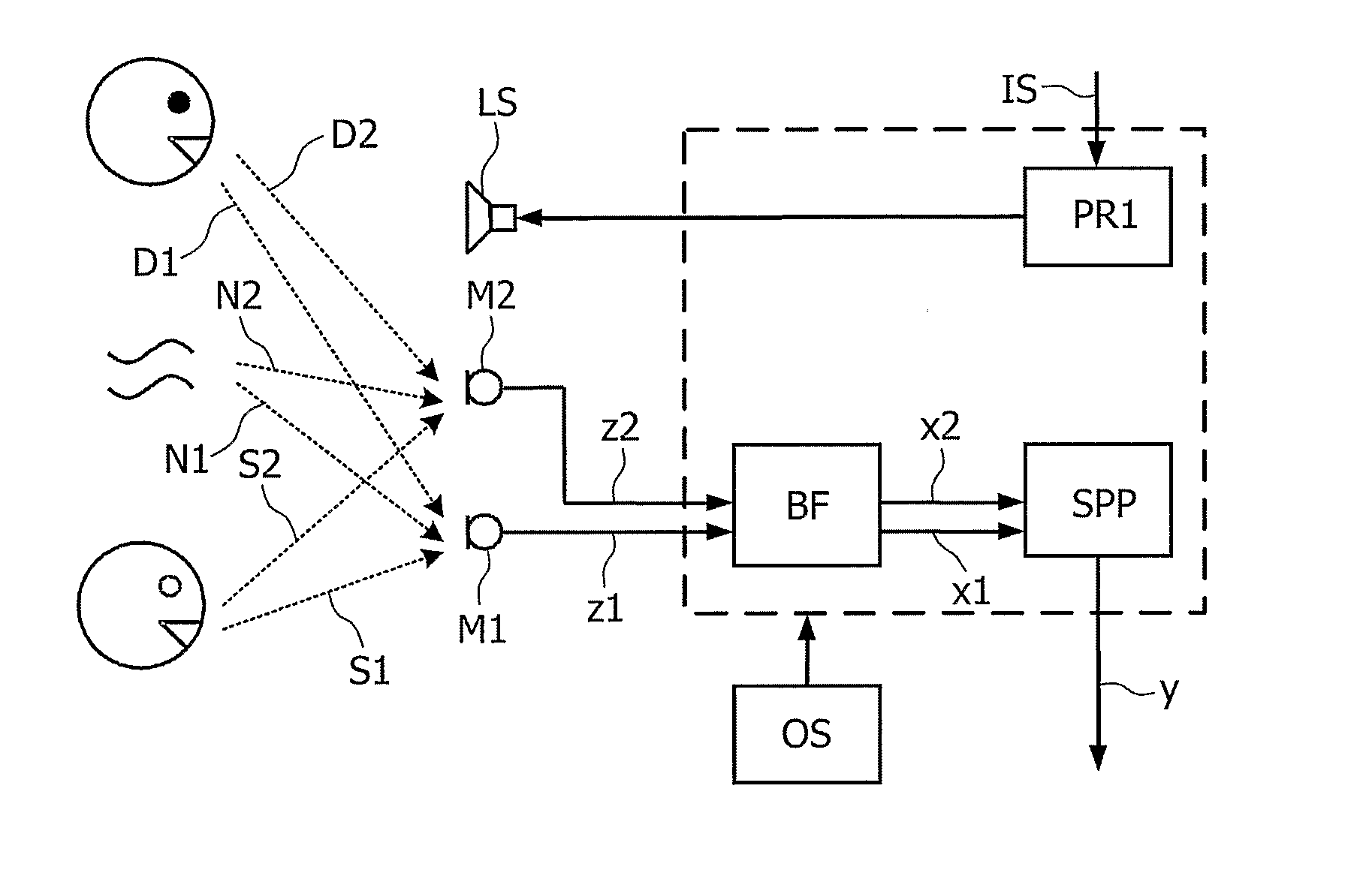

The present invention relates to a telephony device comprising a near-mouth microphone (M1) for picking up an input acoustic signal including the speaker's voice signal (S1) and an unwanted noise signal (N1,D1), a far-mouth microphone (M2) for picking up an unwanted noise signal (N2,D2) in addition to the near-end speaker's voice signal (S2), said speaker's voice signal being at a lower level than the near-mouth microphone, and an orientation sensor for measuring an orientation indication of said mobile device. The telephony device further comprises an audio processing unit comprising an adaptive beamformer (BF) coupled to the near-mouth and far-mouth microphones, including spatial filters for spatially filtering the input signals (z1,z2) delivered by the two microphones, and a spectral post-processor (SPP) for post-processing the signal delivered by the beam-former so as to separate the desired voice signal from the unwanted noise signal so as to deliver the output signal (y).

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

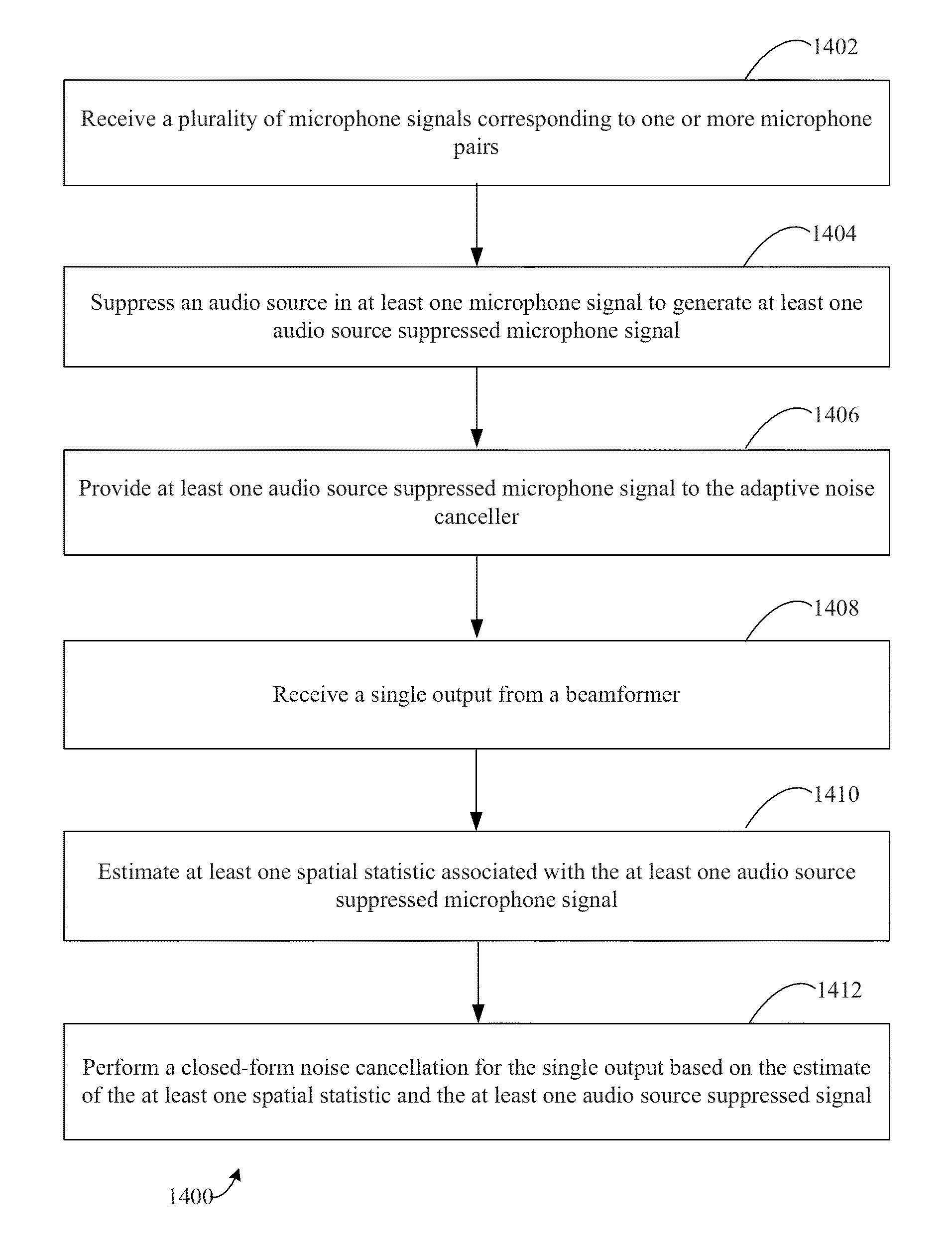

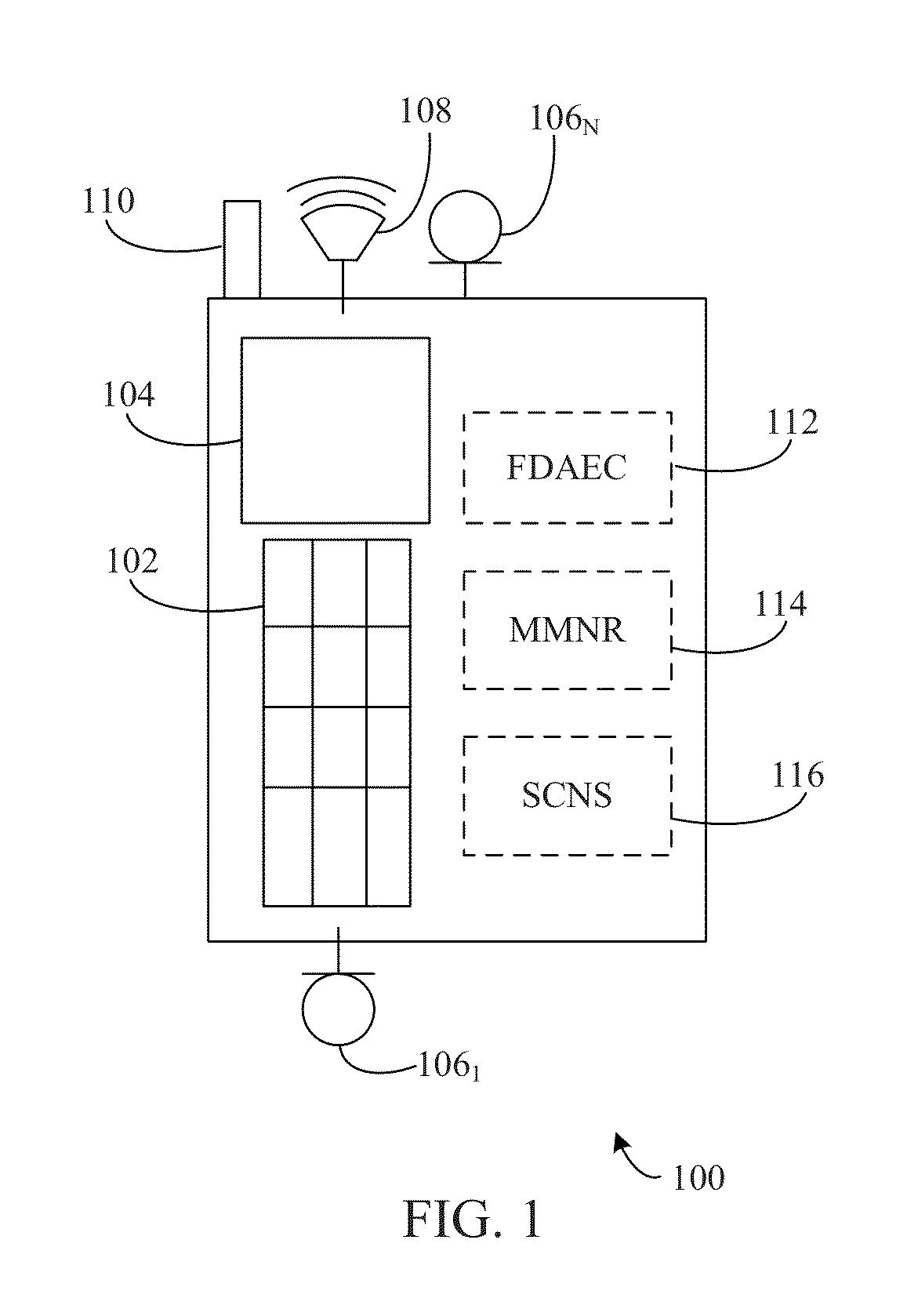

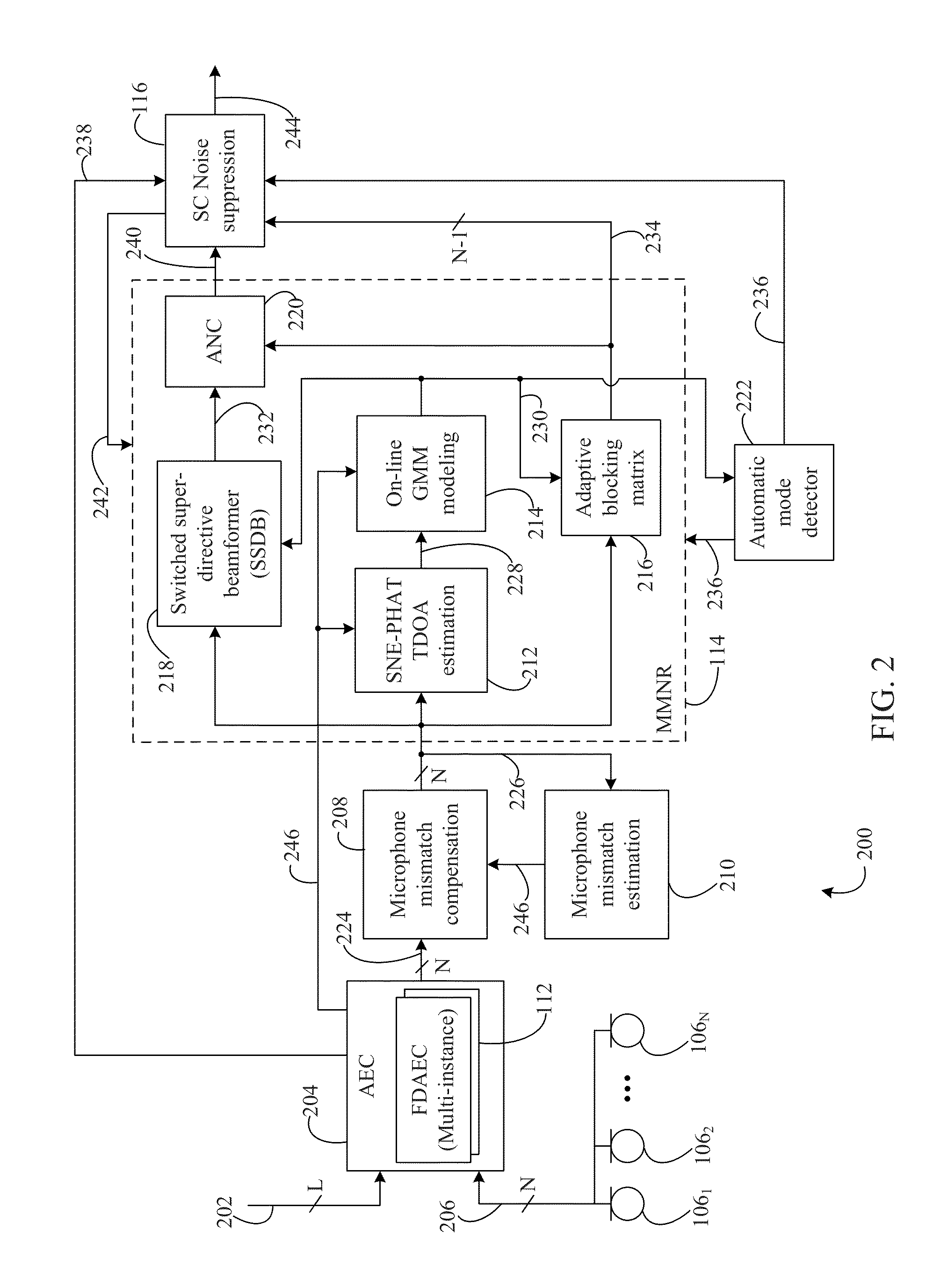

Multi-microphone source tracking and noise suppression

Methods, systems, and apparatuses are described for improved multi-microphone source tracking and noise suppression. In multi-microphone devices and systems, frequency domain acoustic echo cancellation is performed on each microphone input, and microphone levels and sensitivity are normalized. Methods, systems, and apparatuses are also described for improved acoustic scene analysis and source tracking using steered null error transforms, on-line adaptive acoustic scene modeling, and speaker-dependent information. Switched super-directive beamforming reinforces desired audio sources and closed-form blocking matrices suppress desired audio sources based on spatial information derived from microphone pairings. Underlying statistics are tracked and used to updated filters and models. Automatic detection of single-user and multi-user scenarios, and single-channel suppression using spatial information, non-spatial information, and residual echo are also described.

Owner:AVAGO TECH INT SALES PTE LTD

Method and device for speech enhancement in the presence of background noise

ActiveUS20050143989A1Suppress noiseSpeech recognitionTransmission noise suppressionFrequency spectrumNoise suppression

In one aspect thereof the invention provides a method for noise suppression of a speech signal that includes, for a speech signal having a frequency domain representation dividable into a plurality of frequency bins, determining a value of a scaling gain for at least some of said frequency bins and calculating smoothed scaling gain values. Calculating smoothed scaling gain values includes, for the at least some of the frequency bins, combining a currently determined value of the scaling gain and a previously determined value of the smoothed scaling gain. In another aspect a method partitions the plurality of frequency bins into a first set of contiguous frequency bins and a second set of contiguous frequency bins having a boundary frequency there between, where the boundary frequency differentiates between noise suppression techniques, and changes a value of the boundary frequency as a function of the spectral content of the speech signal.

Owner:NOKIA TECHNOLOGLES OY

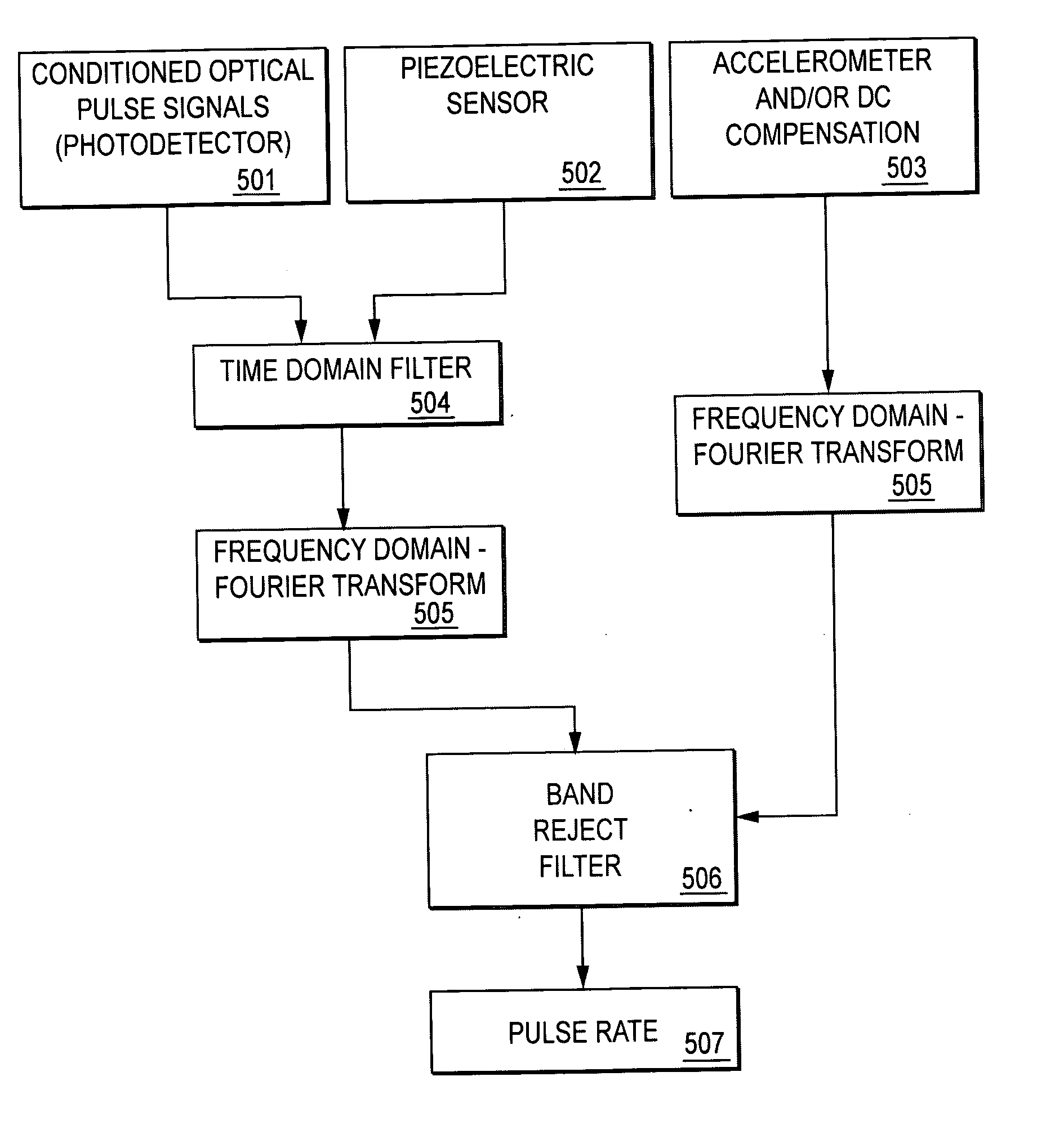

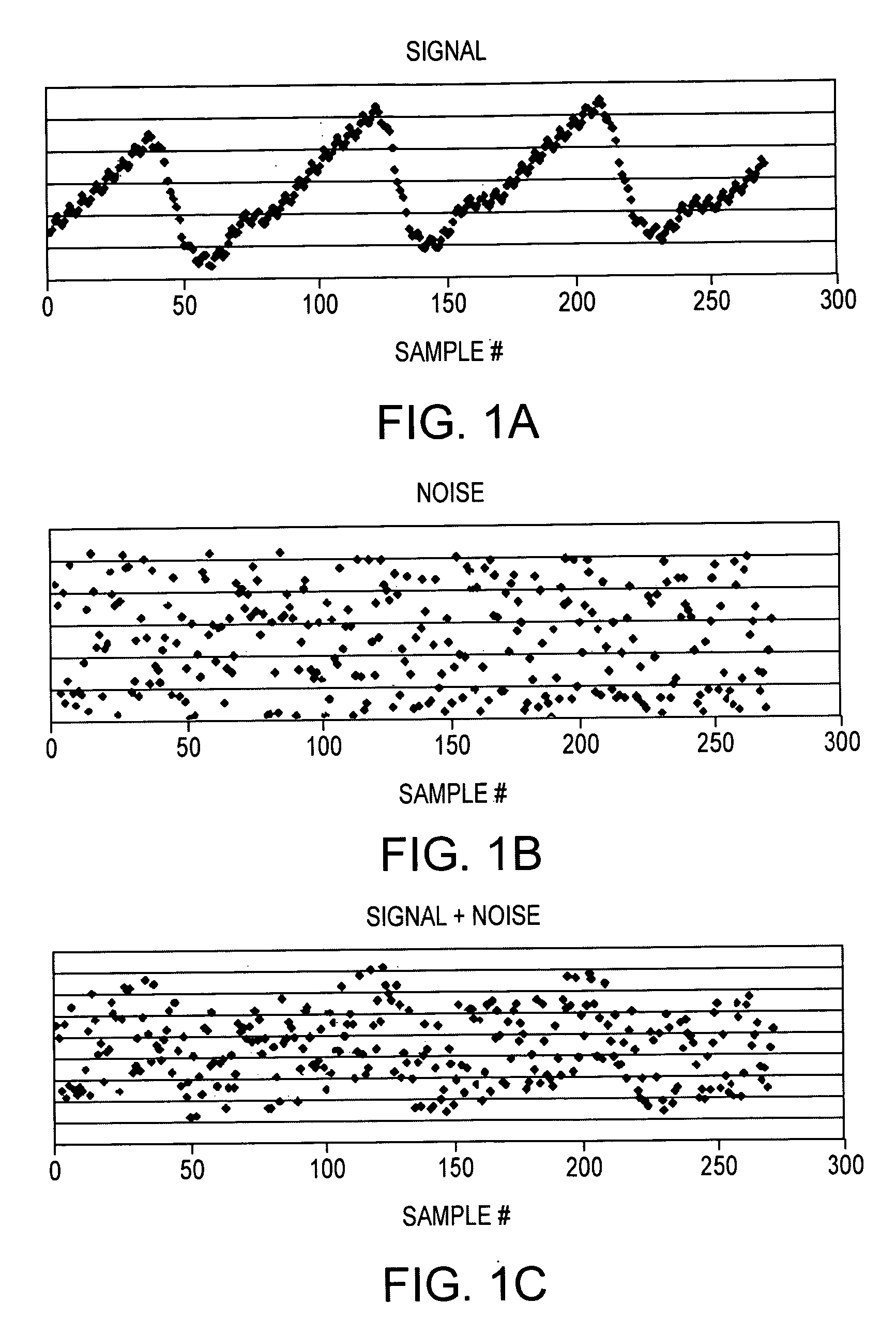

Motion cancellation of optical input signals for physiological pulse measurement

InactiveUS20060084879A1Accurate monitoringAccurately detecting pulse rateCatheterDiagnostic recording/measuringAccelerometerControl signal

A pulse rate sensor that includes an accelerometer for measuring periodic motion and a piezo sensor for detecting erratic motion is capable of more accurately determining pulse rate by accounting for these types of motion. The pulse rate sensor in accordance with the present invention diminishes pulse rate signal degradation due to erratic motion through a combination of algorithms that control signal boosting, waveform refinement and signal noise suppression.

Owner:INTEL CORP

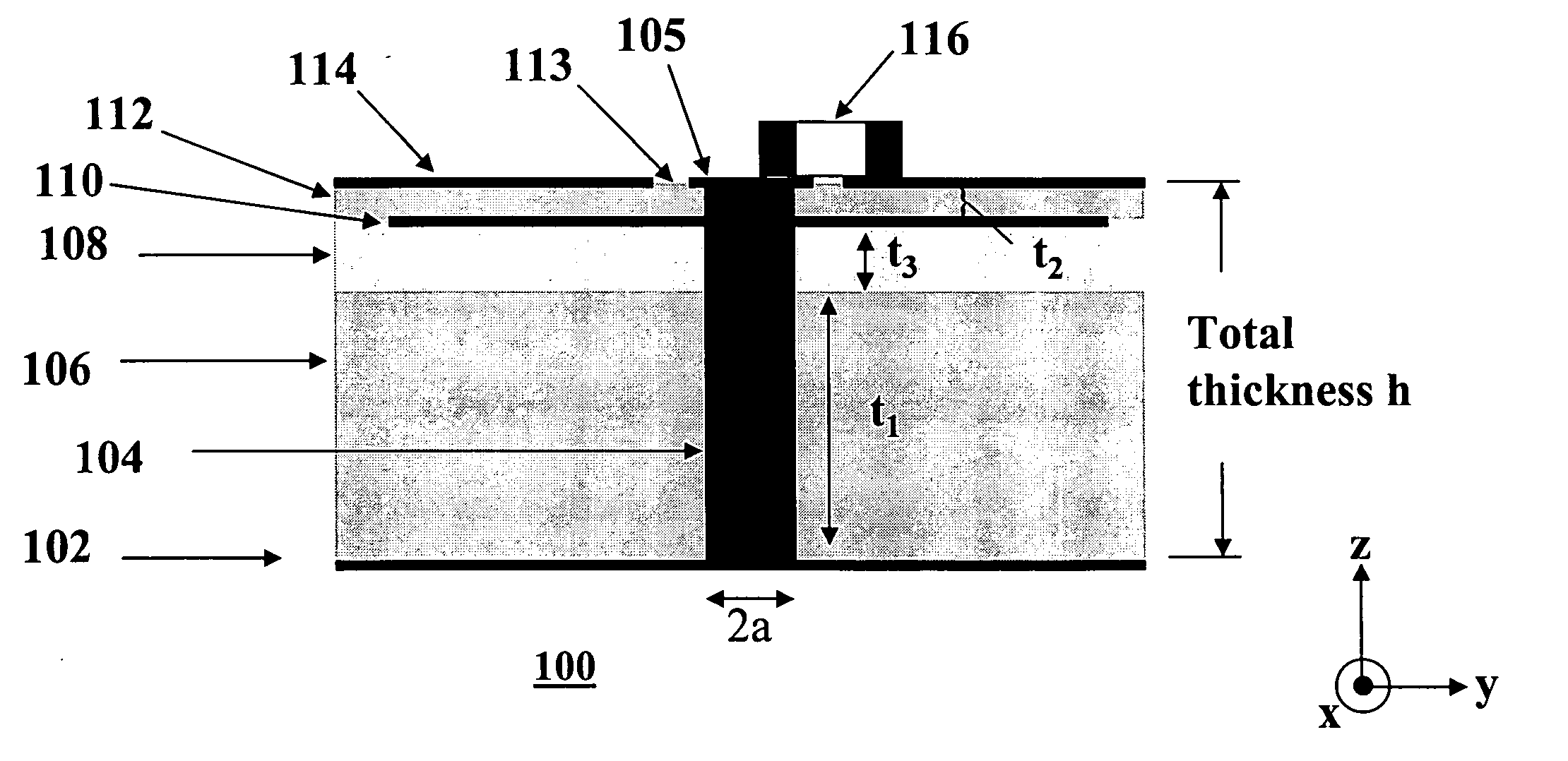

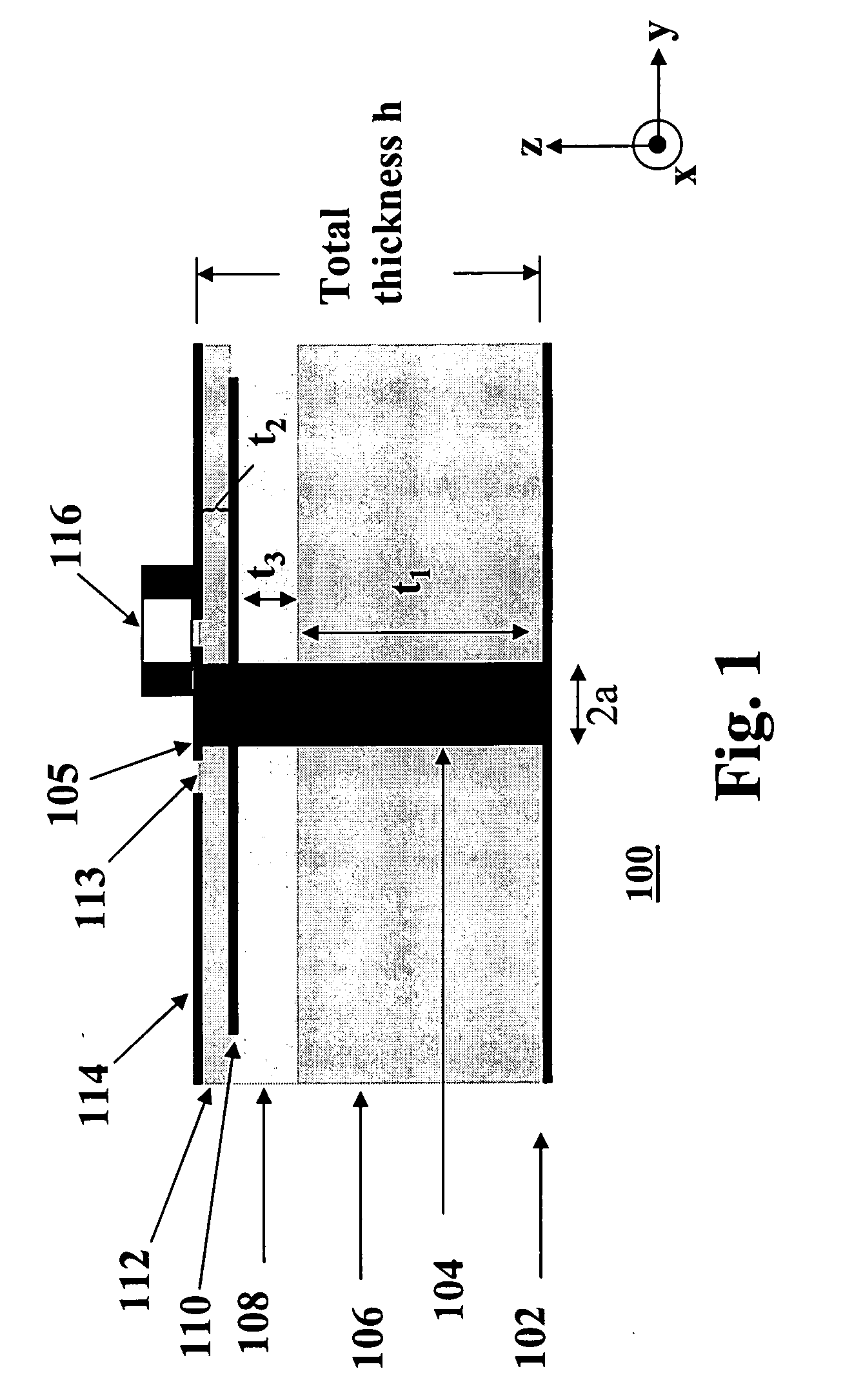

Circuit and method for broadband switching noise suppression in multilayer printed circuit boards using localized lattice structures

InactiveUS20050205292A1Eliminate power plane resonanceImproved RF isolationMagnetic/electric field screeningCross-talk/noise/interference reductionBroadbandNoise suppression

An apparatus for suppressing noise in an electronic device includes a multiple layer structure in which localized arrays of chip capacitors and / or patches around sources of electromagnetic waves are used. The PCB includes multiple conductive layers at different potentials, dielectric layers separating the conductive layers, conductive rods extending between at least two of the conductive layers, and a layer of patches disposed adjacent or on one or more of the conductive layers. The conductive rods are connected to one of the conductive layers and chip capacitors connect the conductive rods to another of the conductive layers. A particular location can be effectively isolated from noise using a few unit cells of an array of patches / capacitors partially or completely surrounding the particular location.

Owner:ETENNA

Apparatus and method of noise and echo reduction in multiple microphone audio systems

ActiveUS20090089054A1Two-way loud-speaking telephone systemsAmplifier modifications to reduce noise influenceEngineeringMicrophone signal

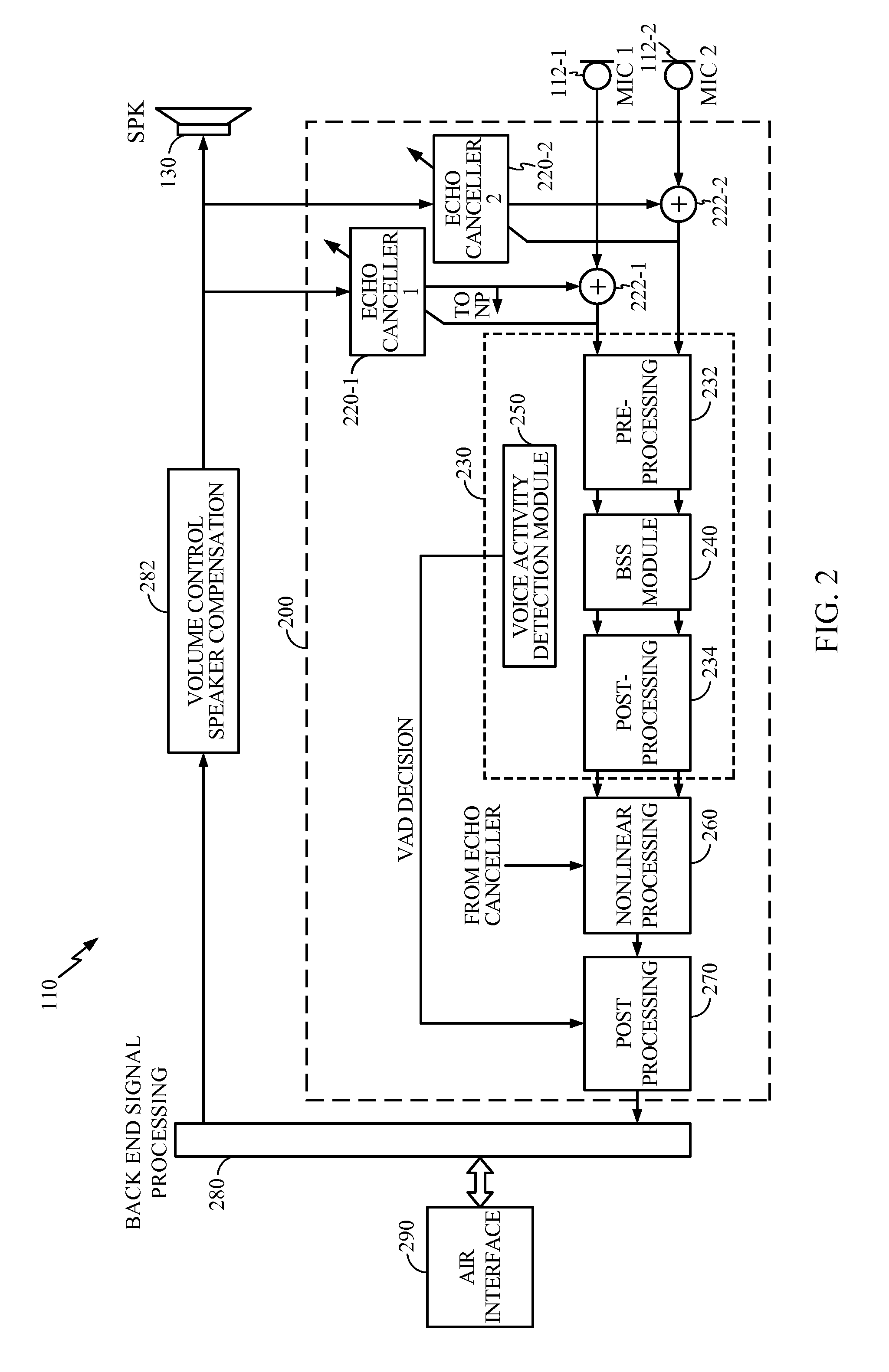

Multiple microphone noise suppression apparatus and methods are described herein. The apparatus and methods implement a variety of noise suppression techniques and apparatus that can be selectively applied to signals received using multiple microphones. The microphone signals received at each of the multiple microphones can be independently processed to cancel echo signal components that can be generated from a local audio source. The echo cancelled signals may be processed by some or all modules within a signal separator that operates to separate or otherwise isolate a speech signal from noise signals. The signal separator can include a pre-processing de-correlator followed by a blind source separator. The output of the blind source separator can be post filtered to provide post separation de-correlation. The separated speech and noise signals can be non-linearly processed for further noise reduction, and additional post processing can be implemented following the non-linear processing.

Owner:QUALCOMM INC

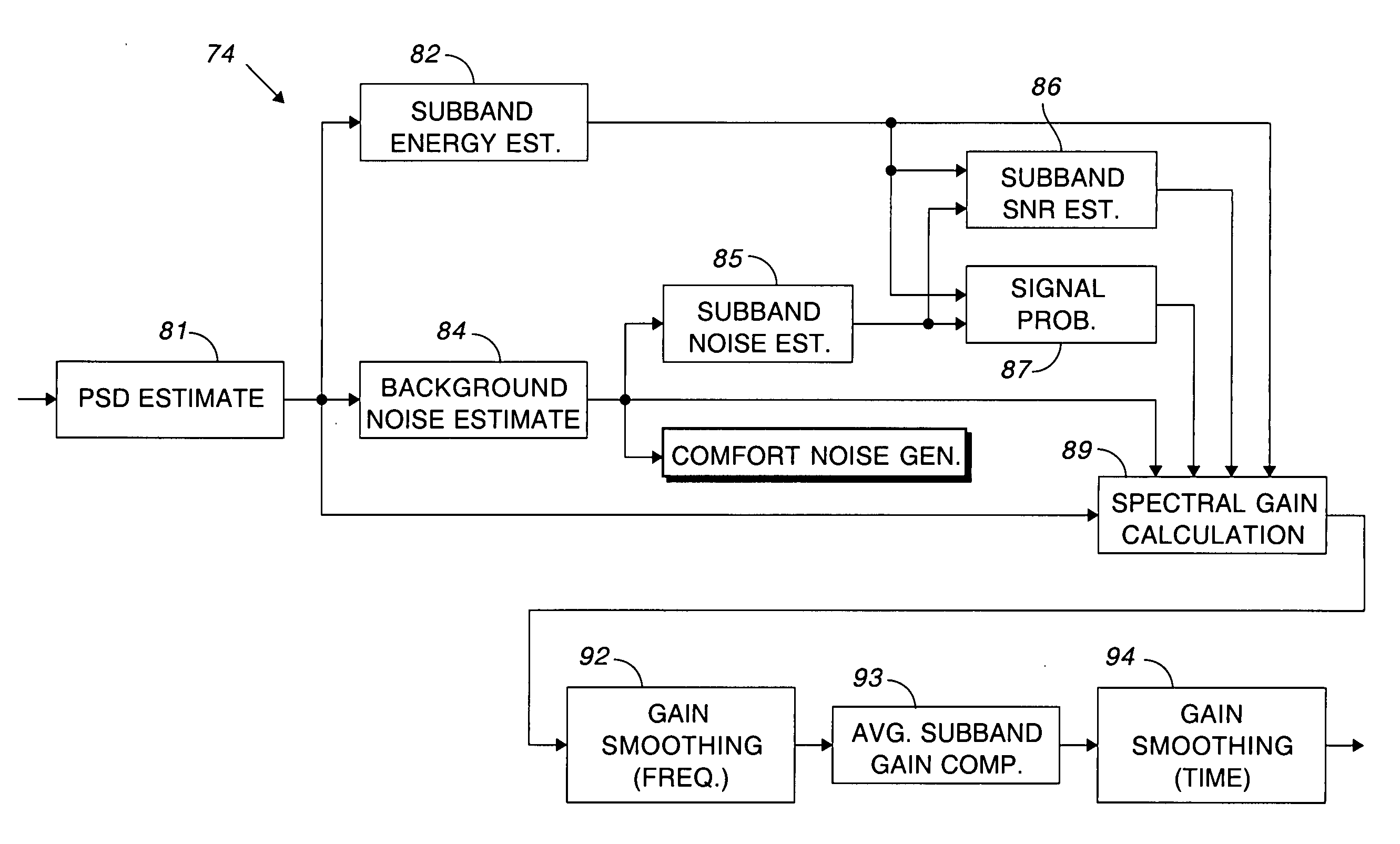

Comfort noise generator using modified doblinger noise estimate

ActiveUS20050278171A1Generate efficientlyEliminates noise pumpingSpeech analysisTime domainComfort noise

A background noise estimate based upon a modified Doblinger noise estimate is used for modulating the output of a pseudo-random phase spectrum generator to produce the comfort noise. The circuit for estimating noise includes a smoothing filter having a slower time constant for updating the noise estimate during noise than during speech. Comfort noise is smoothly inserted by basing the amount of comfort noise on the amount of noise suppression. A discrete inverse Fourier transform converts the comfort noise back to the time domain and overlapping windows eliminate artifacts that may have been produced during processing.

Owner:CIRRUS LOGIC INC

System and method for providing noise suppression utilizing null processing noise subtraction

Systems and methods for noise suppression using noise subtraction processing are provided. The noise subtraction processing comprises receiving at least a primary and a secondary acoustic signal. A desired signal component may be calculated and subtracted from the secondary acoustic signal to obtaining a noise component signal. A determination may be made of a reference energy ratio and a prediction energy ratio. A determination may be made as to whether to adjust the noise component signal based partially on the reference energy ratio and partially on the prediction energy ratio. The noise component signal may be adjusted or frozen based on the determination. The noise component signal may then be removed from the primary acoustic signal to generate a noise subtracted signal which may be outputted.

Owner:KNOWLES ELECTRONICS INC

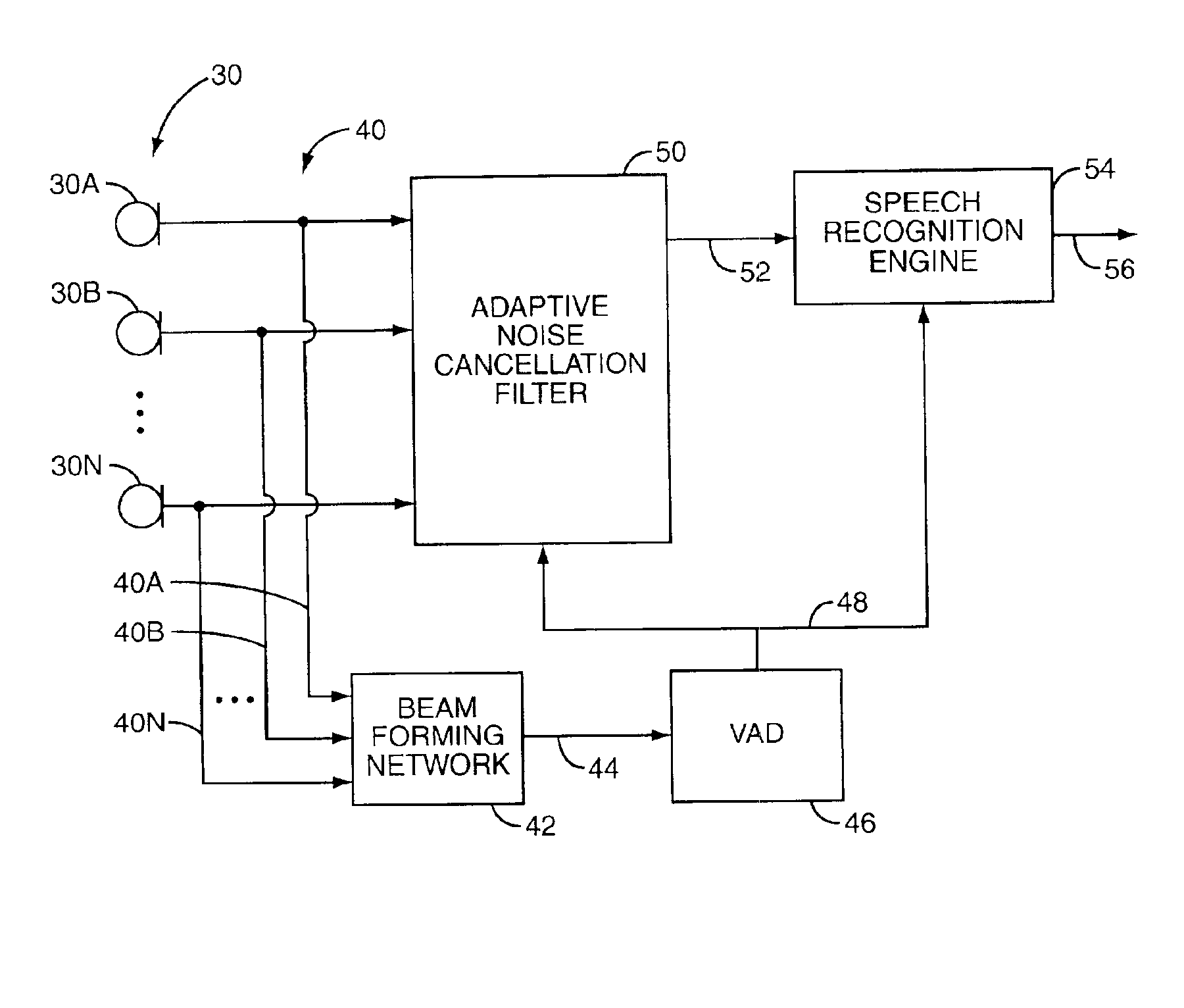

Speech recognition using microphone antenna array

A system and method of audio processing provides enhanced speech recognition. Audio input is received at a plurality of microphones. The multi-channel audio signal from the microphones may be processed by a beamforming network to generate a single-channel enhanced audio signal, on which voice activity is detected. Audio signals from the microphones are additionally processed by an adaptable noise cancellation filter having variable filter coefficients to generate a noise-suppressed audio signal. The variable filter coefficients are updated during periods of voice inactivity. A speech recognition engine may apply a speech recognition algorithm to the noise-suppressed audio signal and generate an appropriate output. The operation of the speech recognition engine and the adaptable noise cancellation filter may advantageously be controlled based on voice activity detected in the single-channel enhanced audio signal from the beamforming network.

Owner:HIGHBRIDGE PRINCIPAL STRATEGIES LLC AS COLLATERAL AGENT

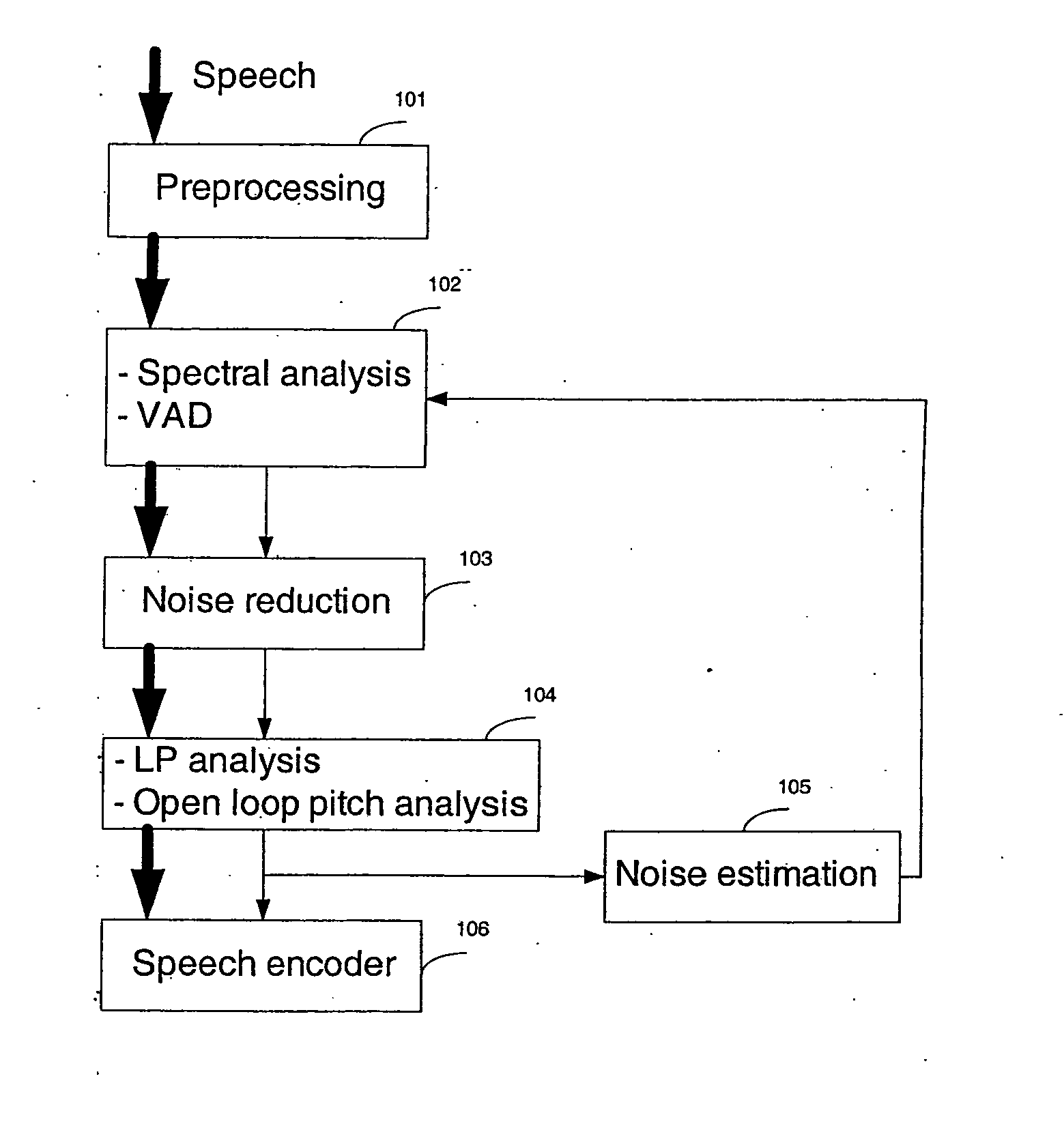

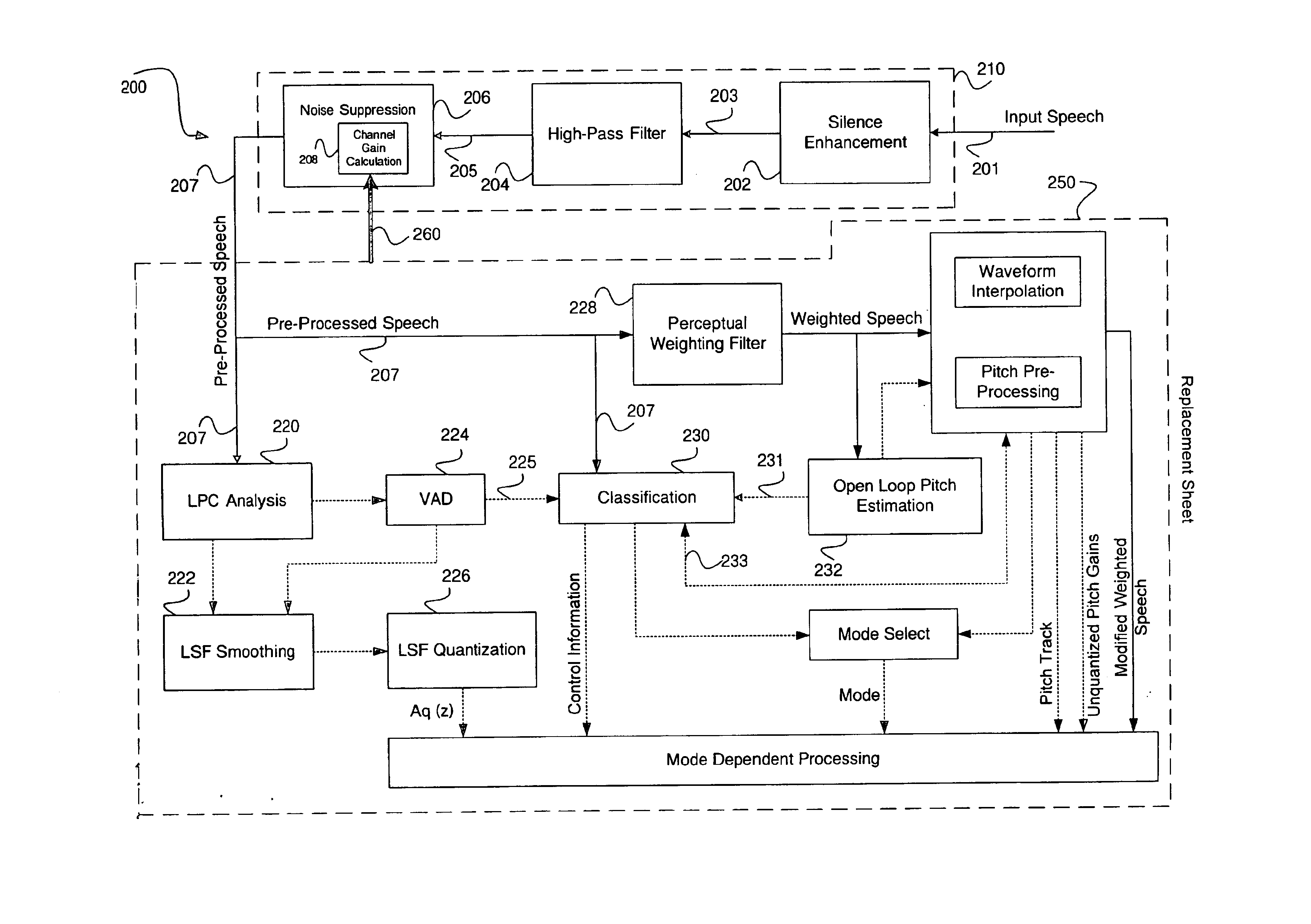

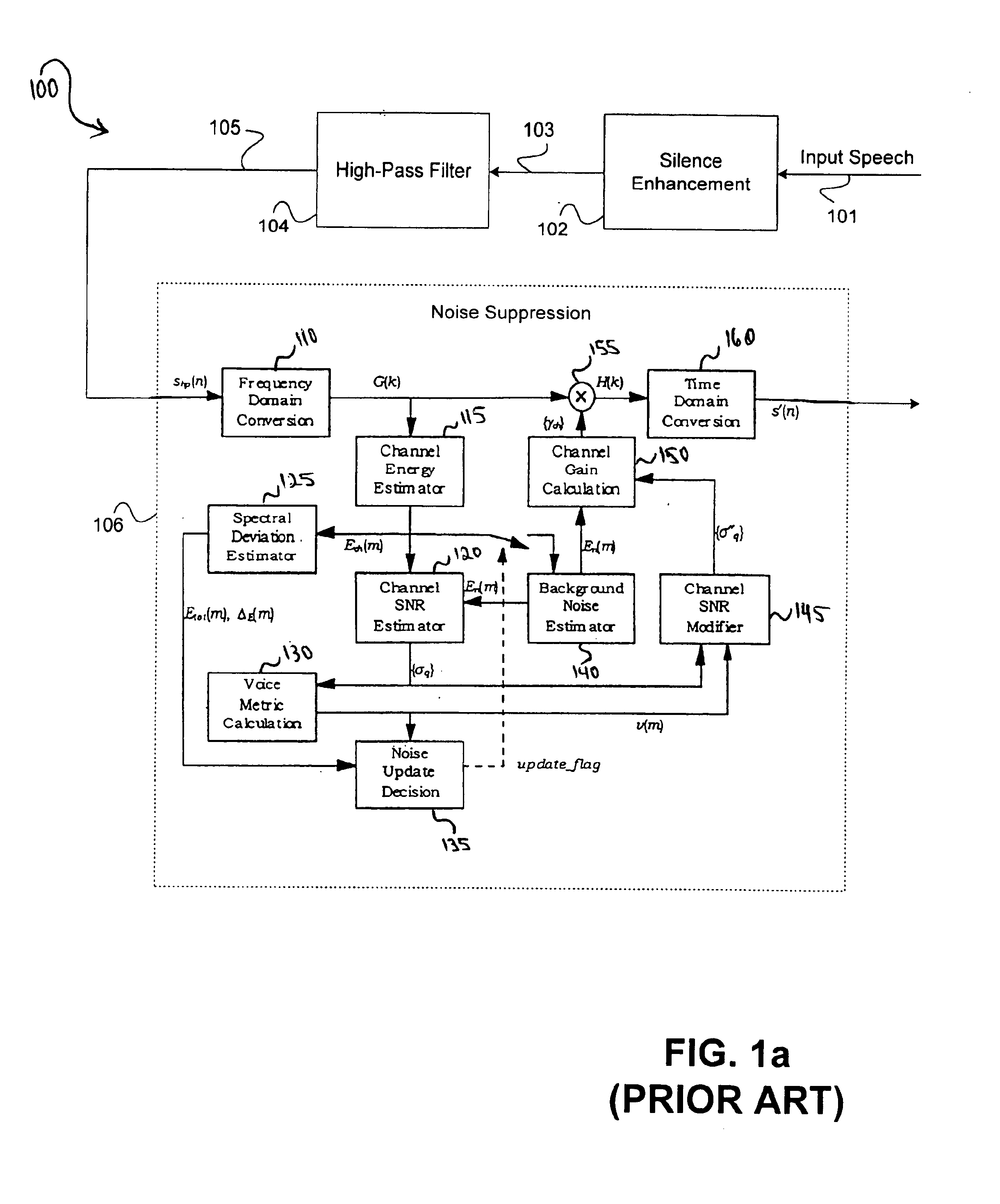

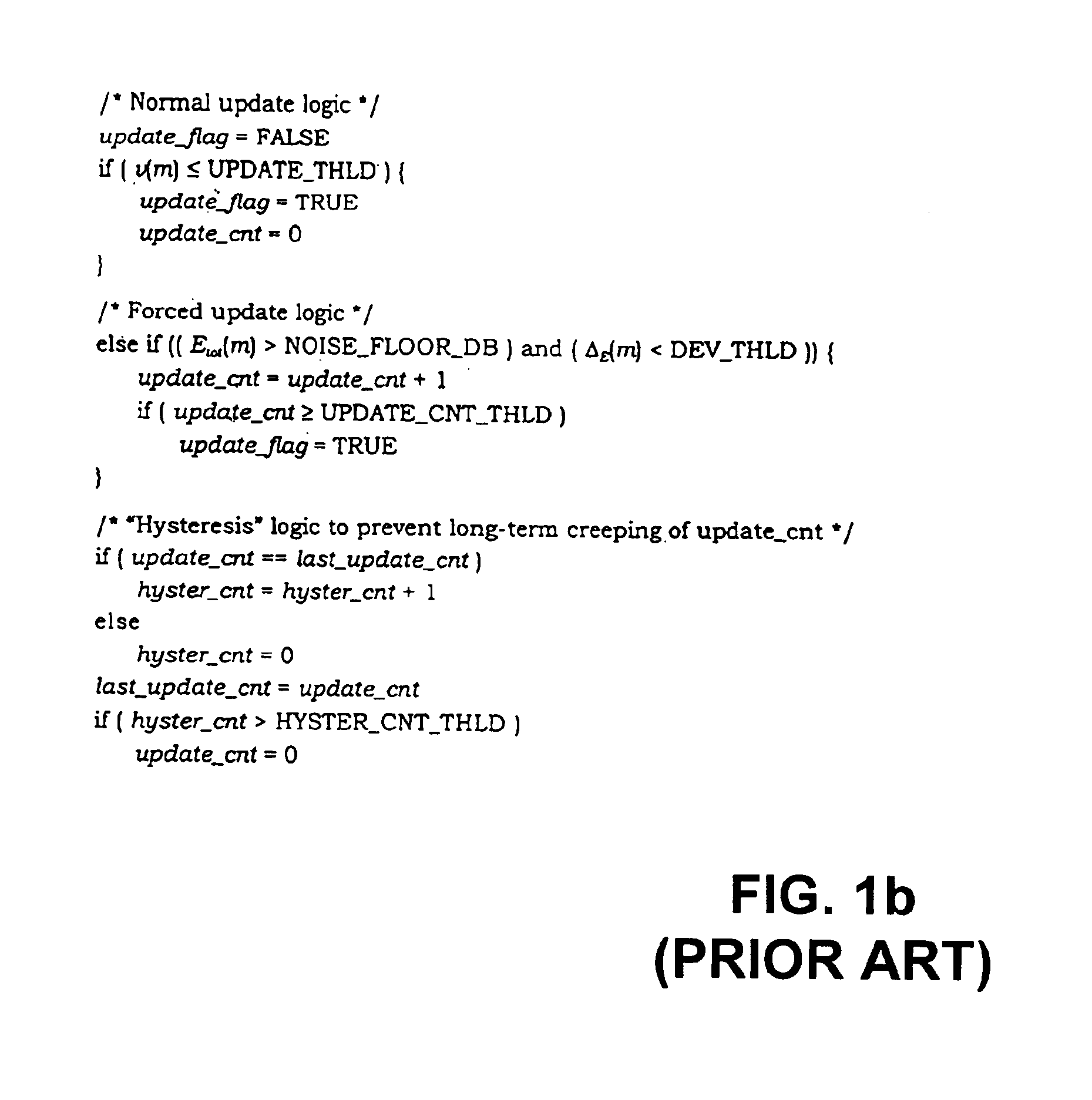

Noise suppression in the frequency domain by adjusting gain according to voicing parameters

An input signal enters a noise suppression system in a time domain and is converted to a frequency domain. The noise suppression system then estimates a signal to noise ratio of the frequency domain signal. Next, a signal gain is calculated based on the estimated signal to noise ratio and a voicing parameter. The voicing parameter may be determined based on the frequency domain signal or may be determined based on a signal ahead of the frequency domain signal with respect to time. In that event, the voicing parameter is fed back to the noise suppression system, for example, by a speech coder, to calculate the signal gain. After calculating the gain, the noise suppression system modifies the signal using the calculated gain to enhance the signal quality. The modified signal may further be converted from the frequency domain back to the time domain for speech coding.

Owner:MACOM TECH SOLUTIONS HLDG INC +1

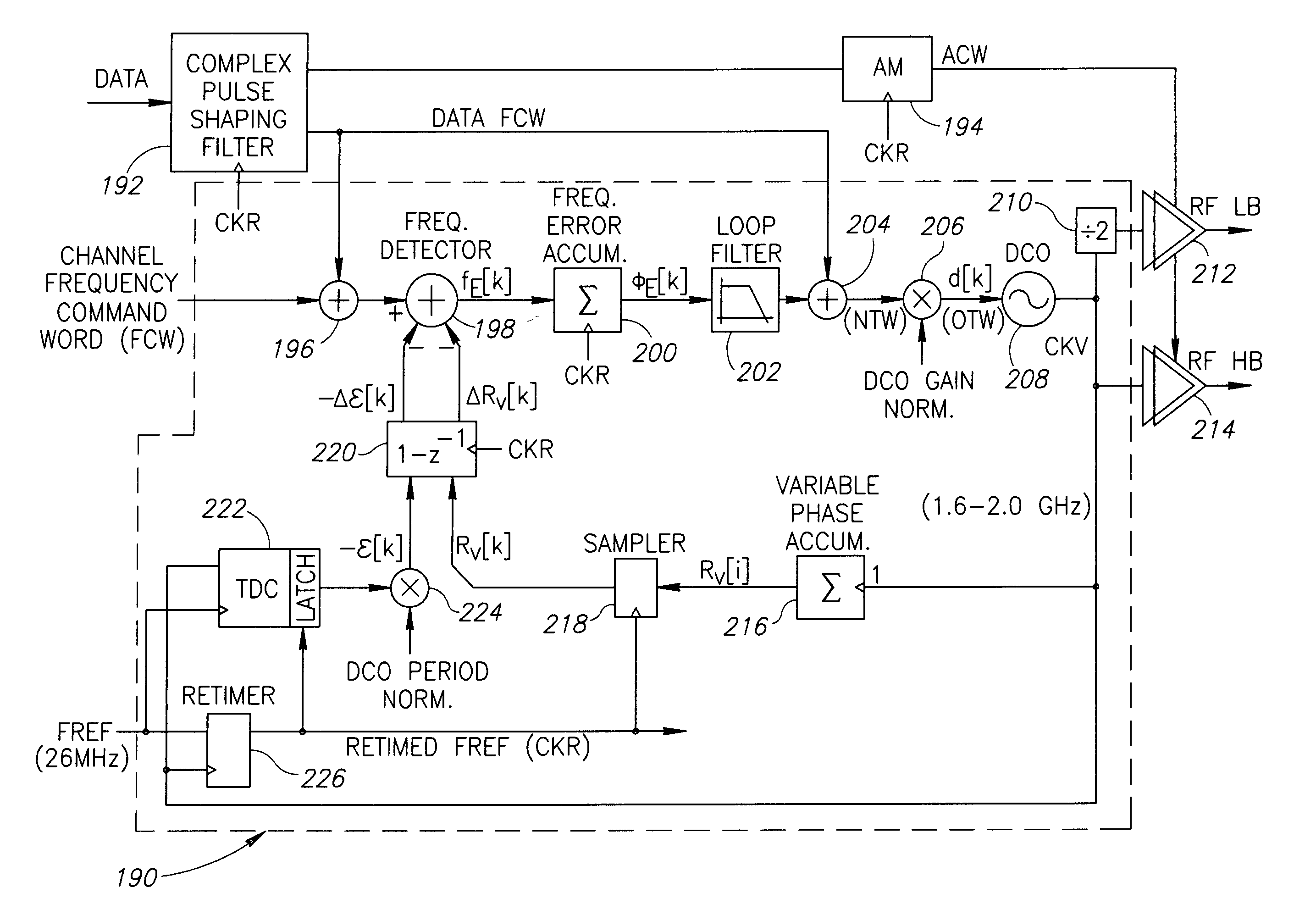

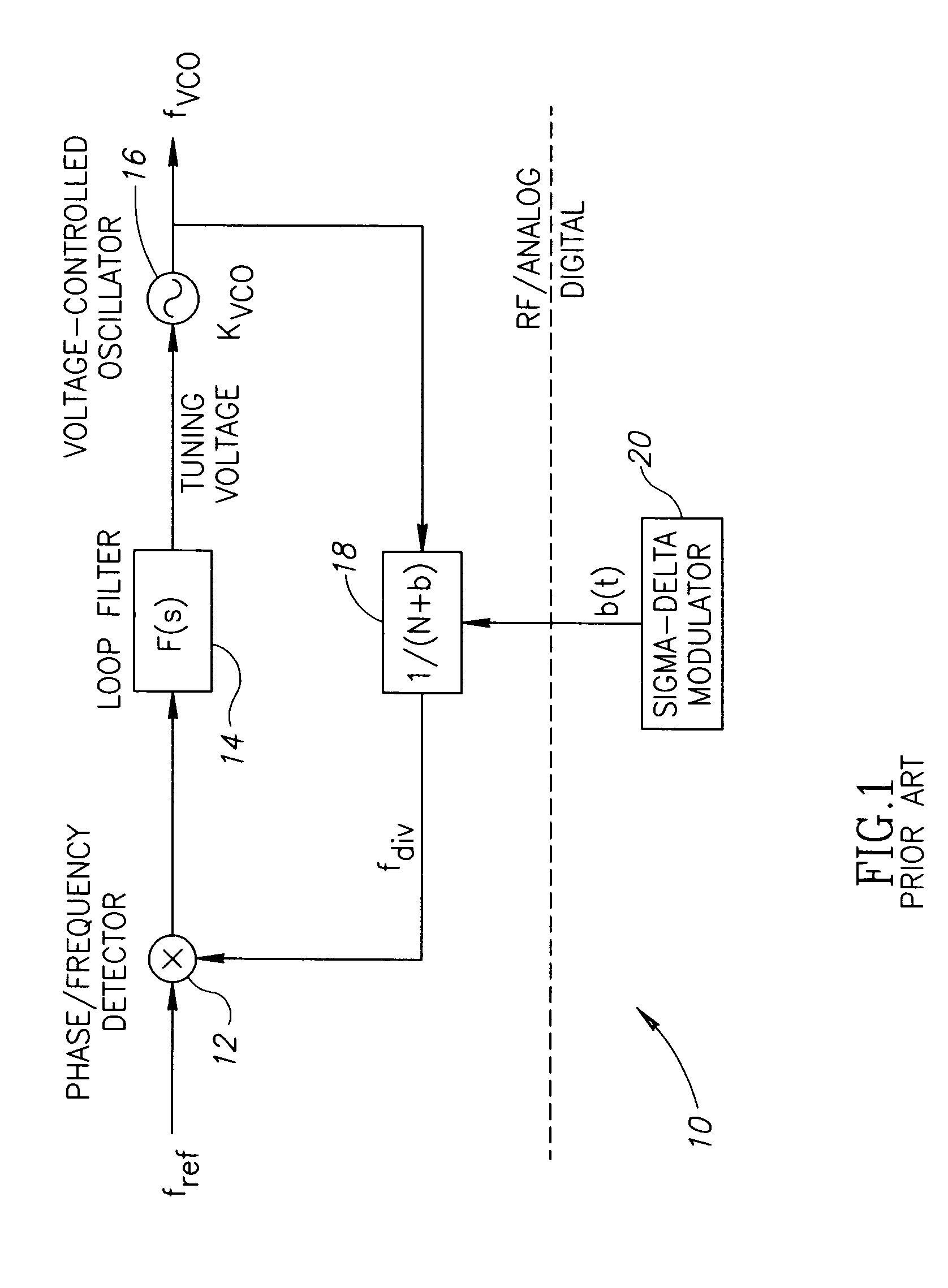

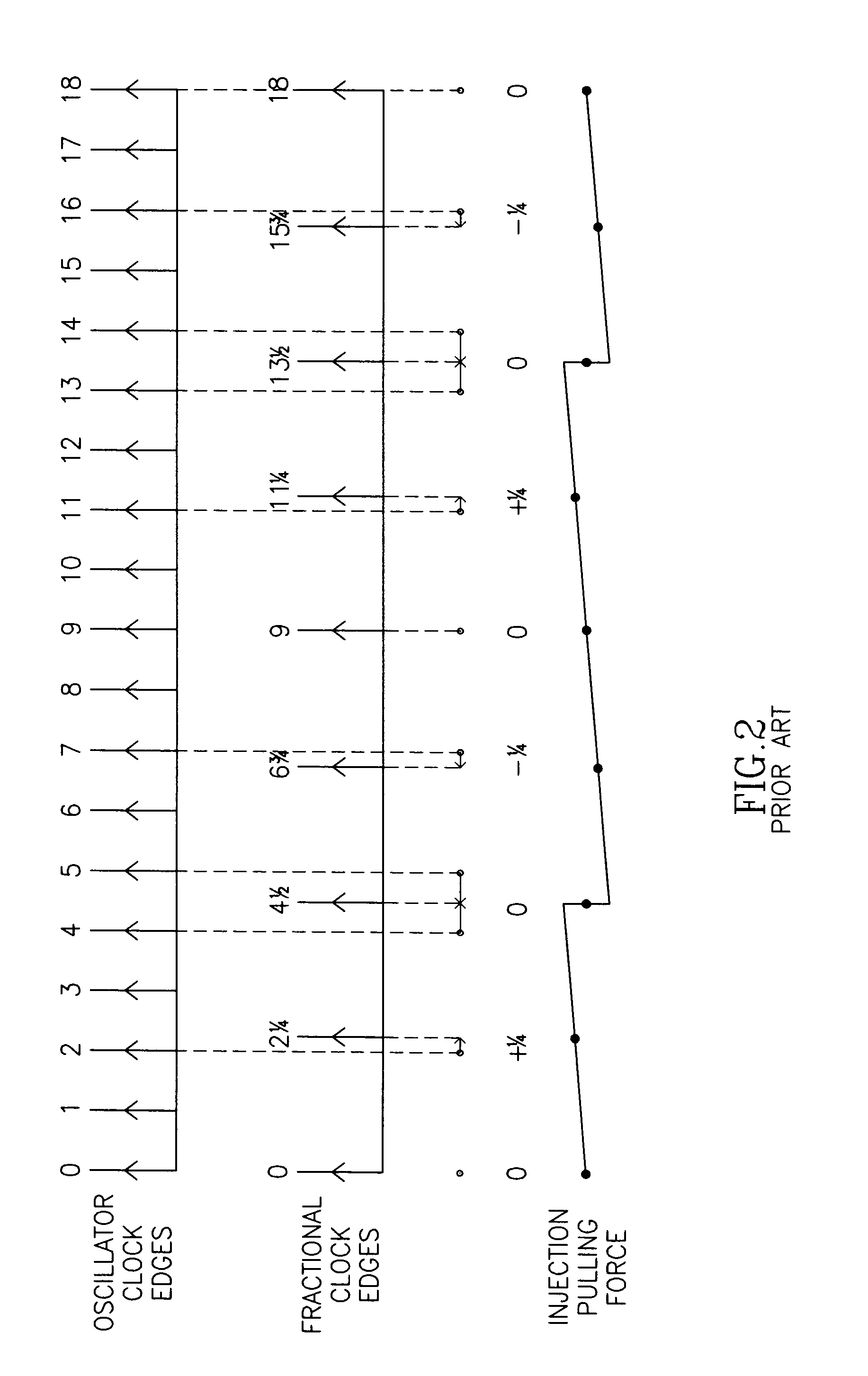

Apparatus for and method of noise suppression and dithering to improve resolution quality in a digital RF processor

InactiveUS20050186920A1Cancel noiseAvoid it happening againPulse automatic controlAngle modulationImage resolutionEngineering

A novel apparatus for and a method of noise and spurious tones suppression in a digital RF processor (DRP). The invention is well suited for use in highly integrated system on a chip (SoC) radio solutions that incorporate a very large amount of digital logic circuitry. The noise suppression scheme eliminates the noise caused by various on chip interference sources transmitted through electromagnetic, power, ground and substrate paths. The noise suppression scheme permits an all digital PLL (ADPLL) to operate in such a way to avoid generating the spurs that would normally be generated from the injection pulling effect of interfering sources on the chip. The frequency reference clock is retimed to be synchronous to the RF oscillator clock and used to drive the entire digital logic circuitry of the DRP. This ensures that the different clock edges throughout the system will not exhibit mutual drift. A method of improving the resolution quality of a time to digital converter within the ADPLL is also taught. The method dithers the reference clock by passing it through a delay circuit that is controlled by a sigma-delta modulator. The dithered reference clock reduces the affect on the phase noise at the output of the ADPLL due to ill-behaved quantization of the TDC timing estimation.

Owner:TEXAS INSTR INC

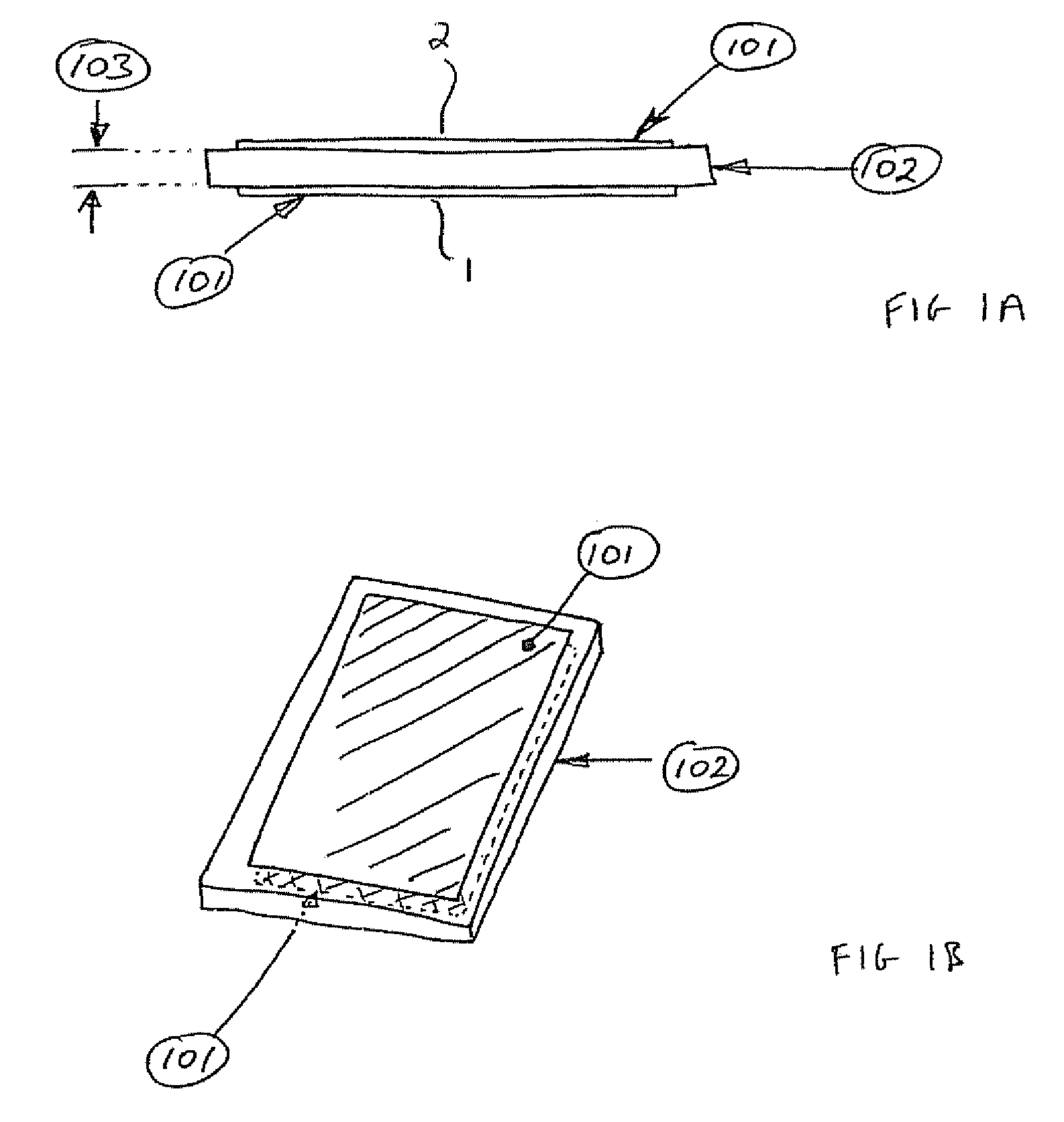

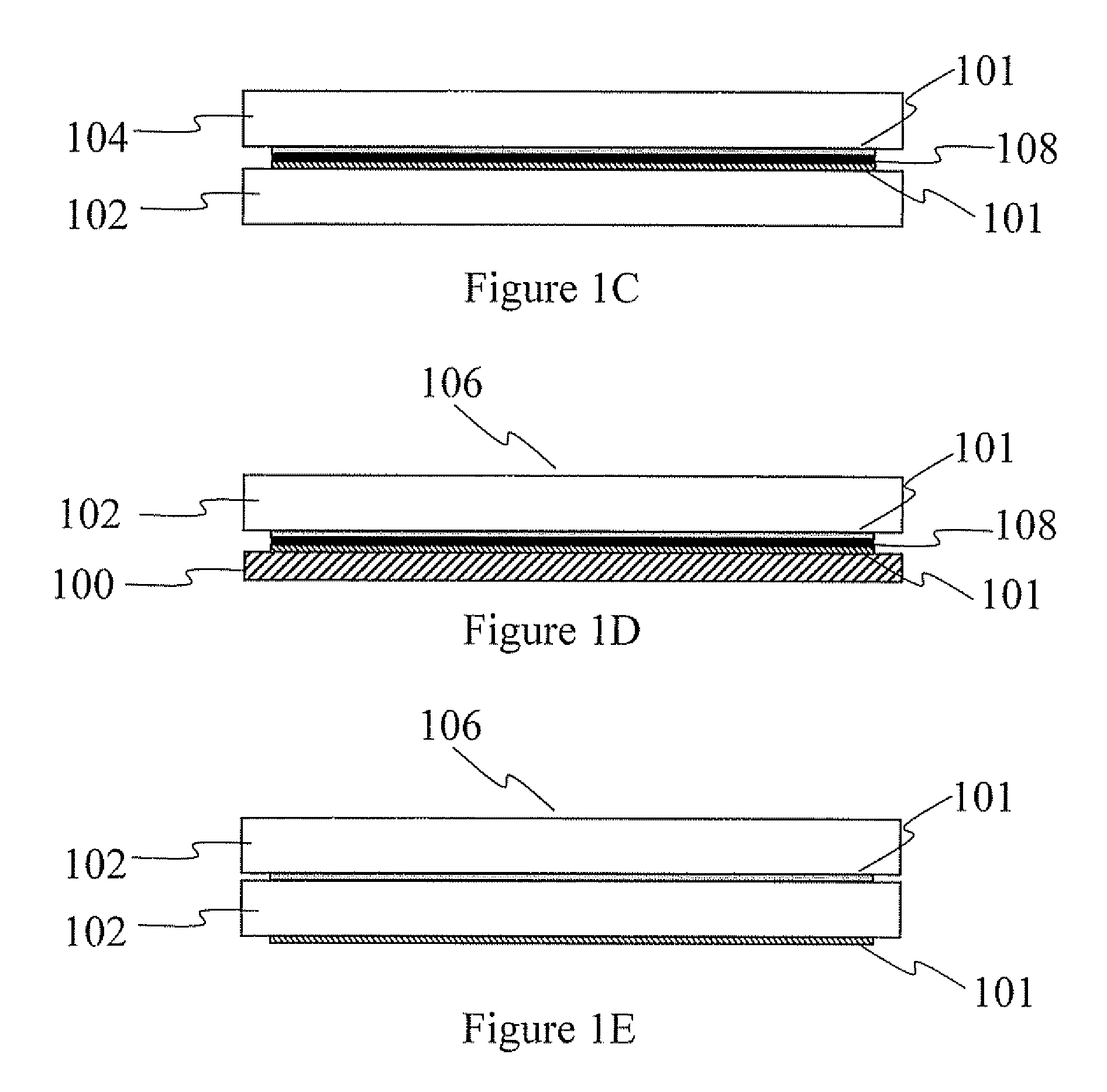

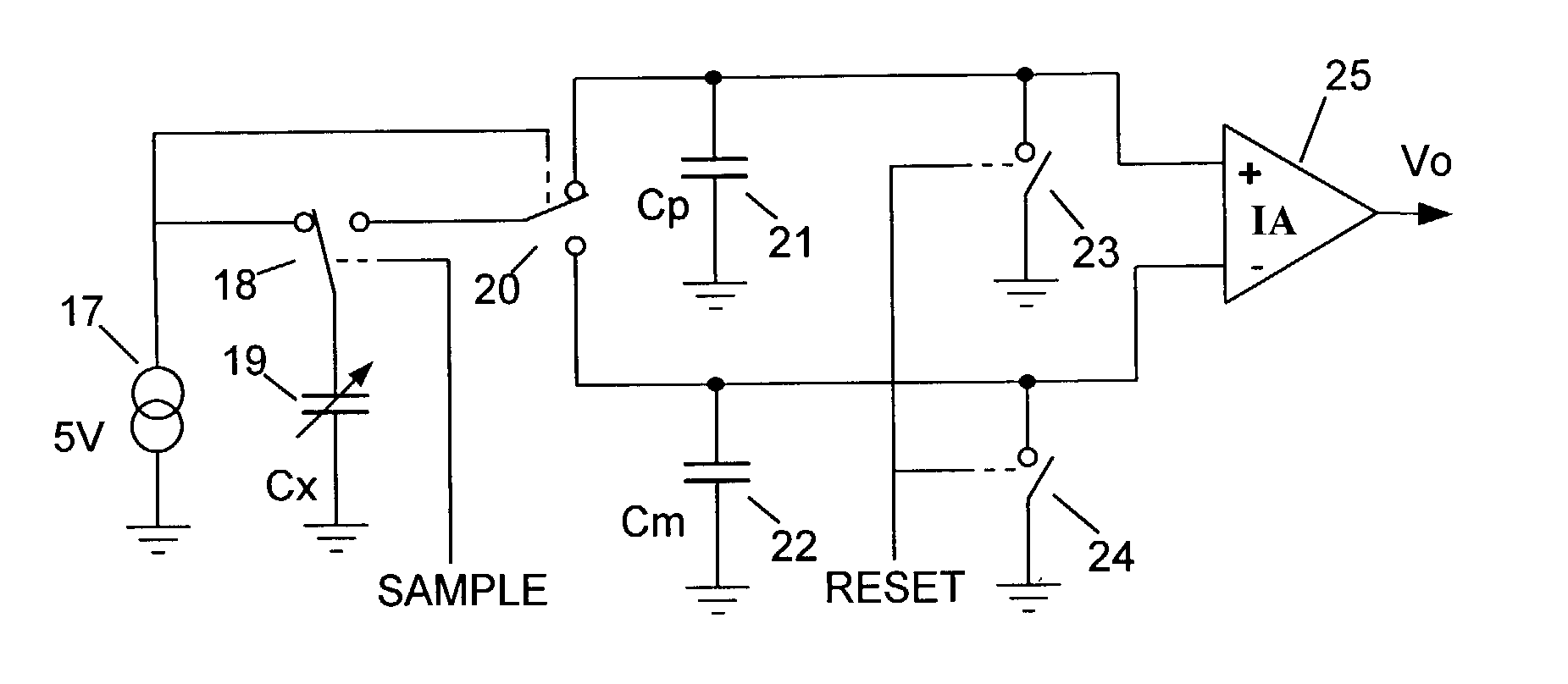

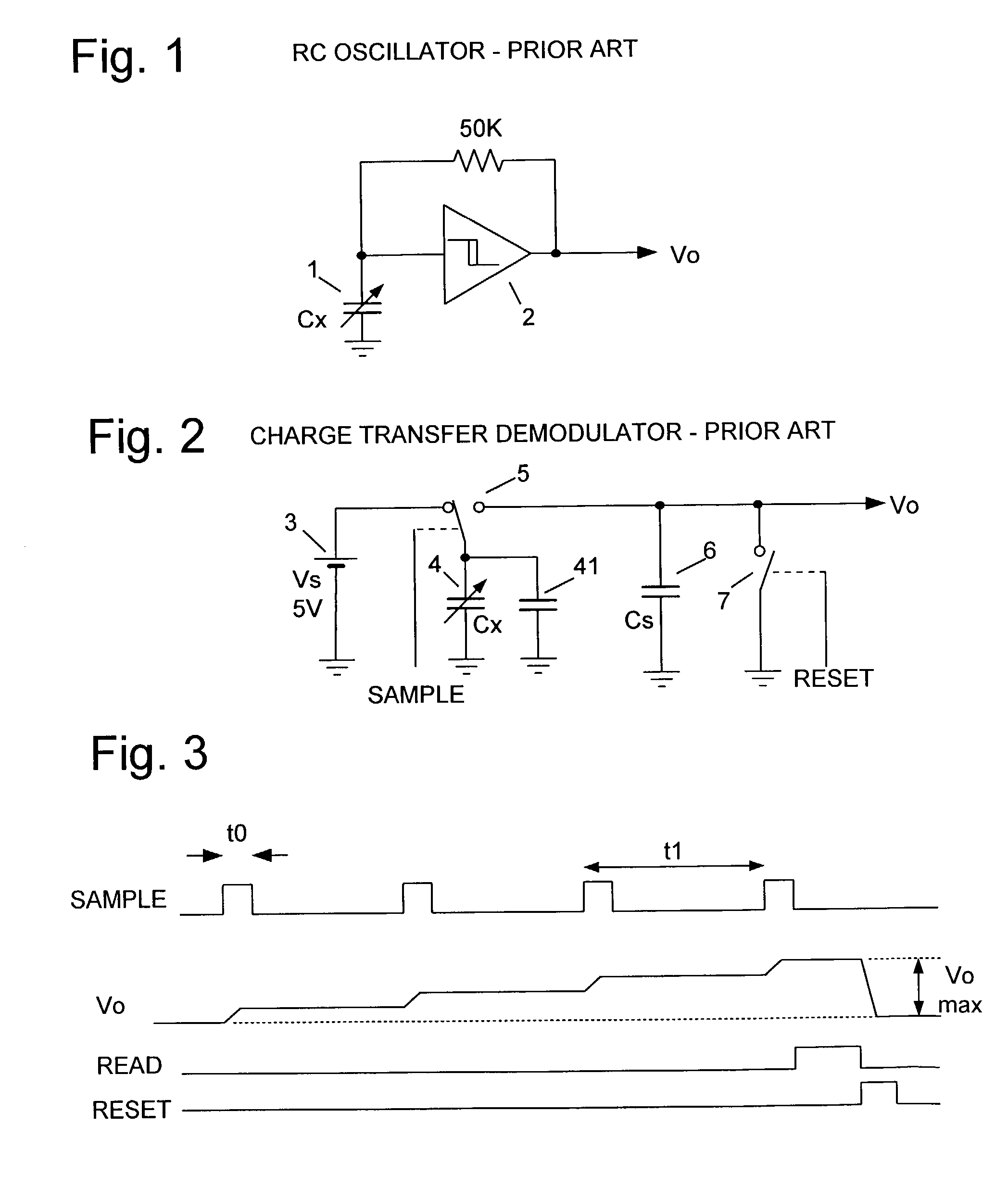

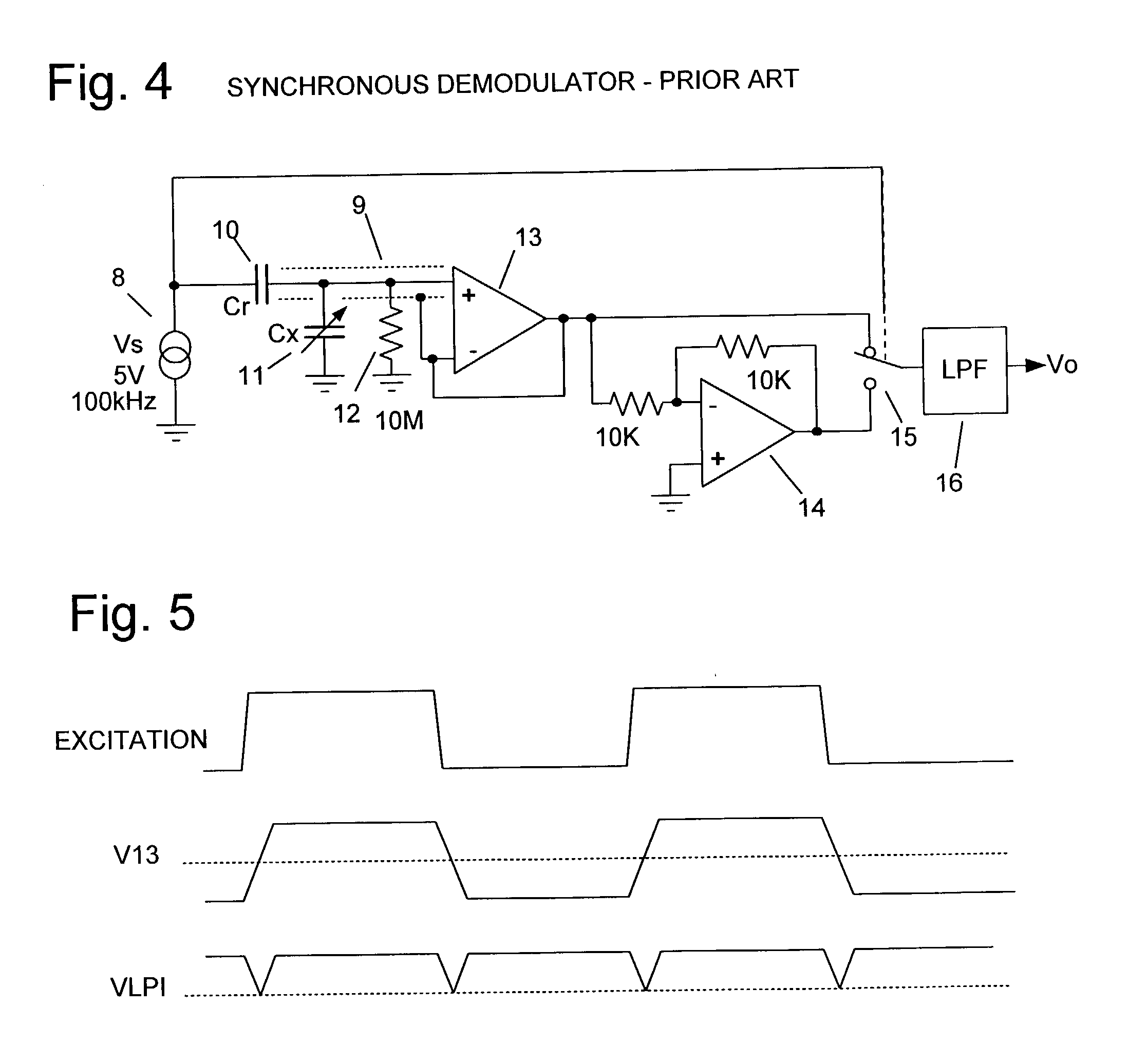

Capacitive sensor circuit with good noise rejection

InactiveUS20040004488A1Improved noise suppressionResistance/reactance/impedenceConverting sensor output electrically/magneticallyNoise suppressionImpedance sensor

This invention describes the deficiencies of current art for sensitive impedance sensors, particularly capacitive sensors, and describes several circuits that improve measurement of small value capacitances, especially in the presence of noise. It also shows various circuit architectures optimized for different capacitive sensing tasks. The circuits also describe a novel method to linearize a conventional charge-transfer capacitive sense circuit and a novel method to eliminate the effect of stray capacitance in charge-transfer capacitive sensors.

Owner:BAXTER LARRY K

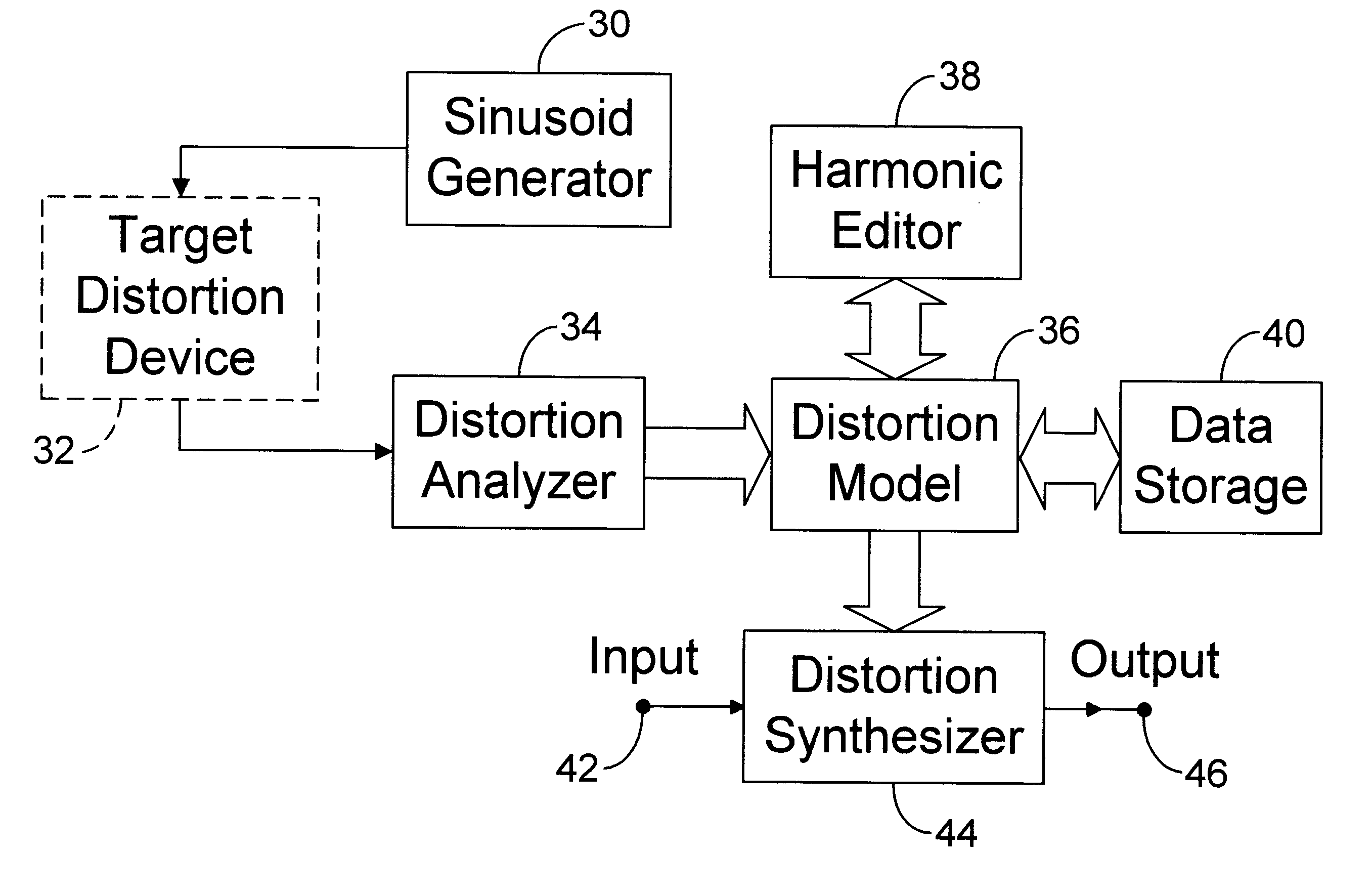

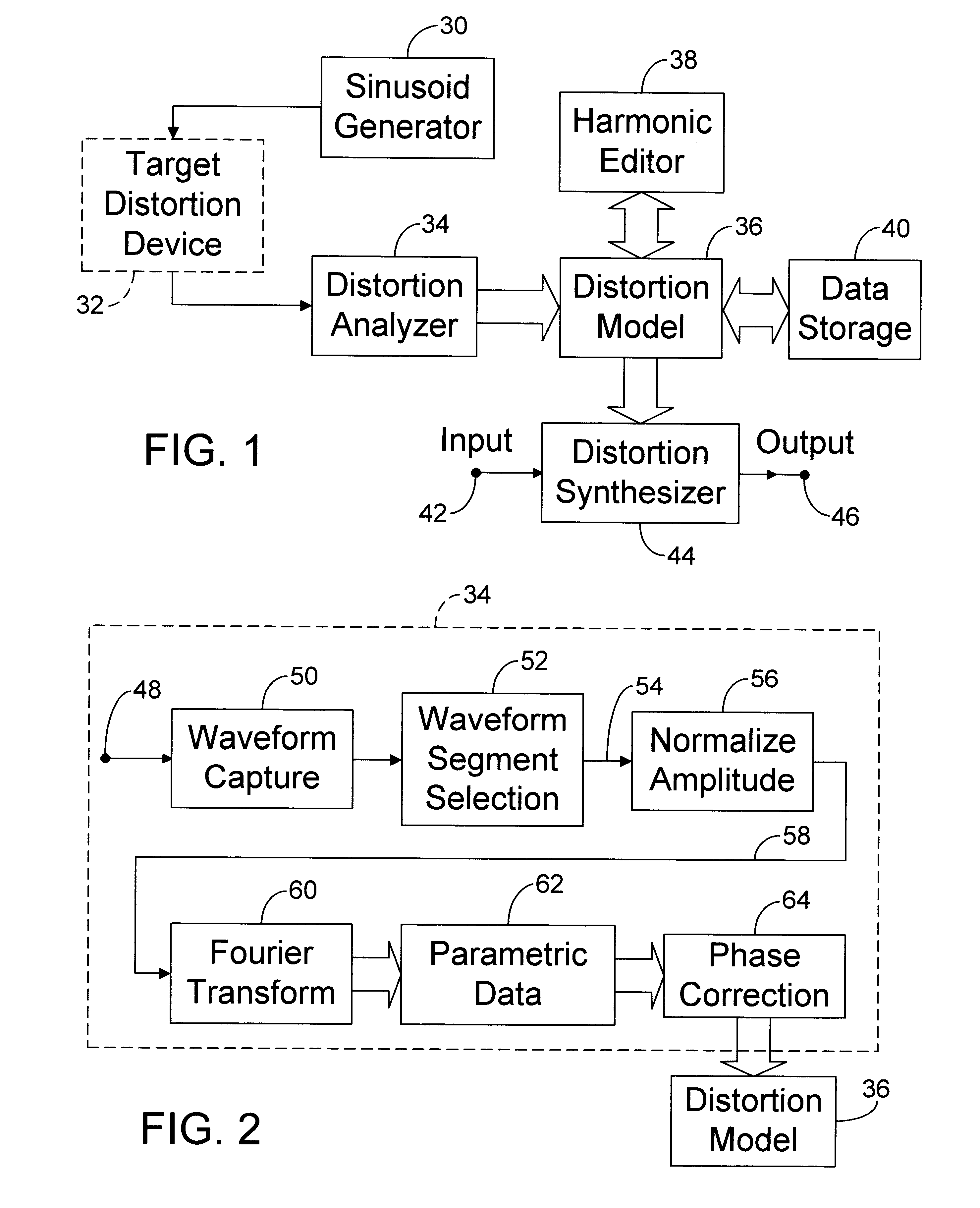

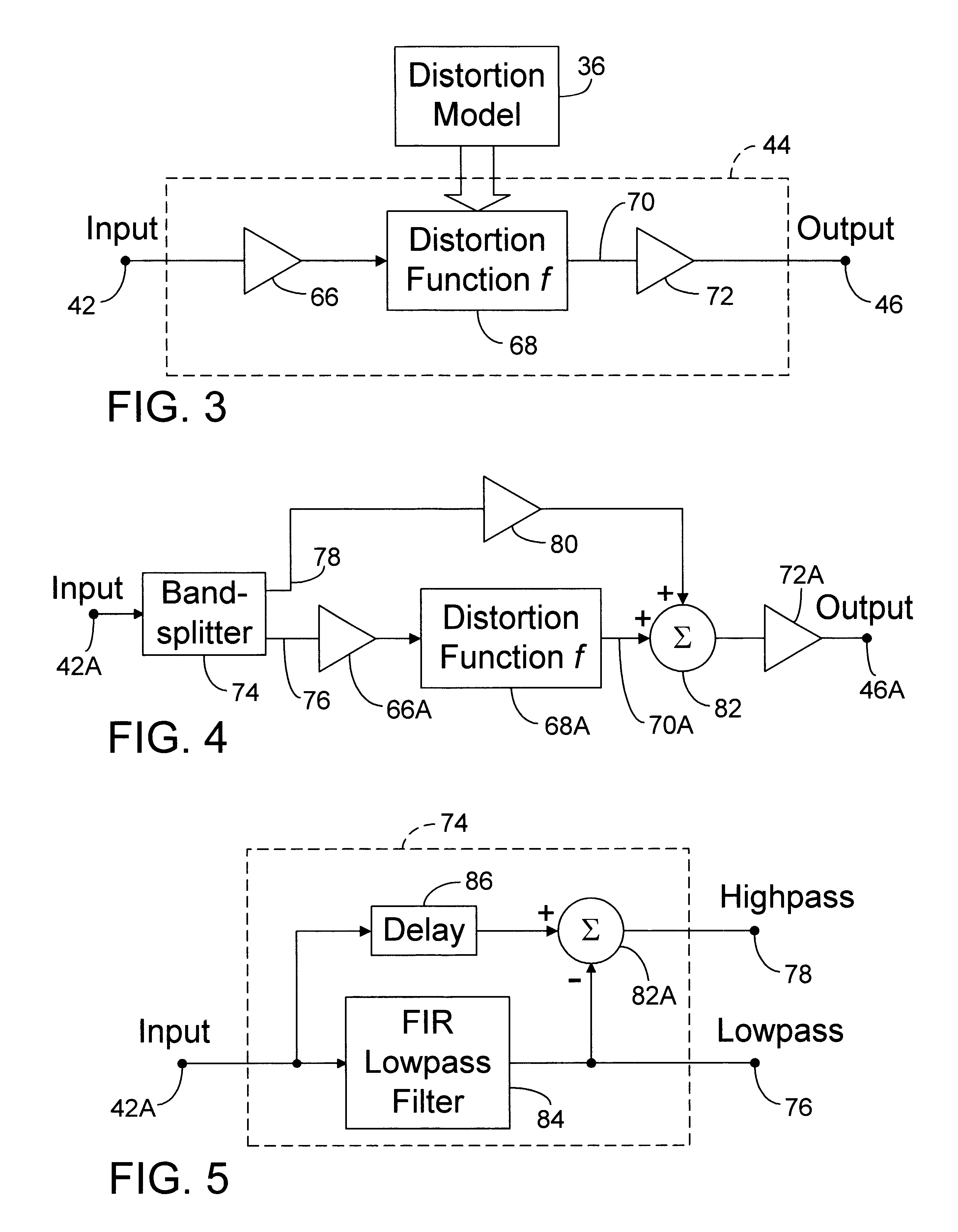

Method and apparatus for the modeling and synthesis of harmonic distortion

InactiveUS6504935B1Facilitates efficient storageImprove accuracyElectrophonic musical instrumentsGain controlFrequency spectrumTotal harmonic distortion

Distortion modeling produces distortion models for use by a distortion synthesizer to synthesize the harmonic distortion effects of audio distortion devices. A sinusoidal waveform is distorted by an audio distortion device and analyzed using a Fourier transform to produce a distortion model comprising harmonic amplitude and phase parameters. A phase correction process compensates for phase shifts induced by the audio distortion device. The distortion synthesizer uses a distortion function that distorts a digital audio signal according to the distortion model. The distortion model can be modified to alter the distortion effect and can be stored in a data-storage device for later retrieval. A frequency bandsplitter and signal mixer allow the distortion effect to be applied only to the low frequency content of the digital audio signal, thus providing spectral headroom to suppress the production of aliasing noise. Aliasing-noise suppression is provided for a full-bandwidth signal by up-converting the sampling rate of the signal before applying the distortion function and down-converting the sampling rate afterwards. A process is provided to remove the direct-current component that may be induced into the signal by the distortion function.

Owner:JACKSON DOUGLAS L

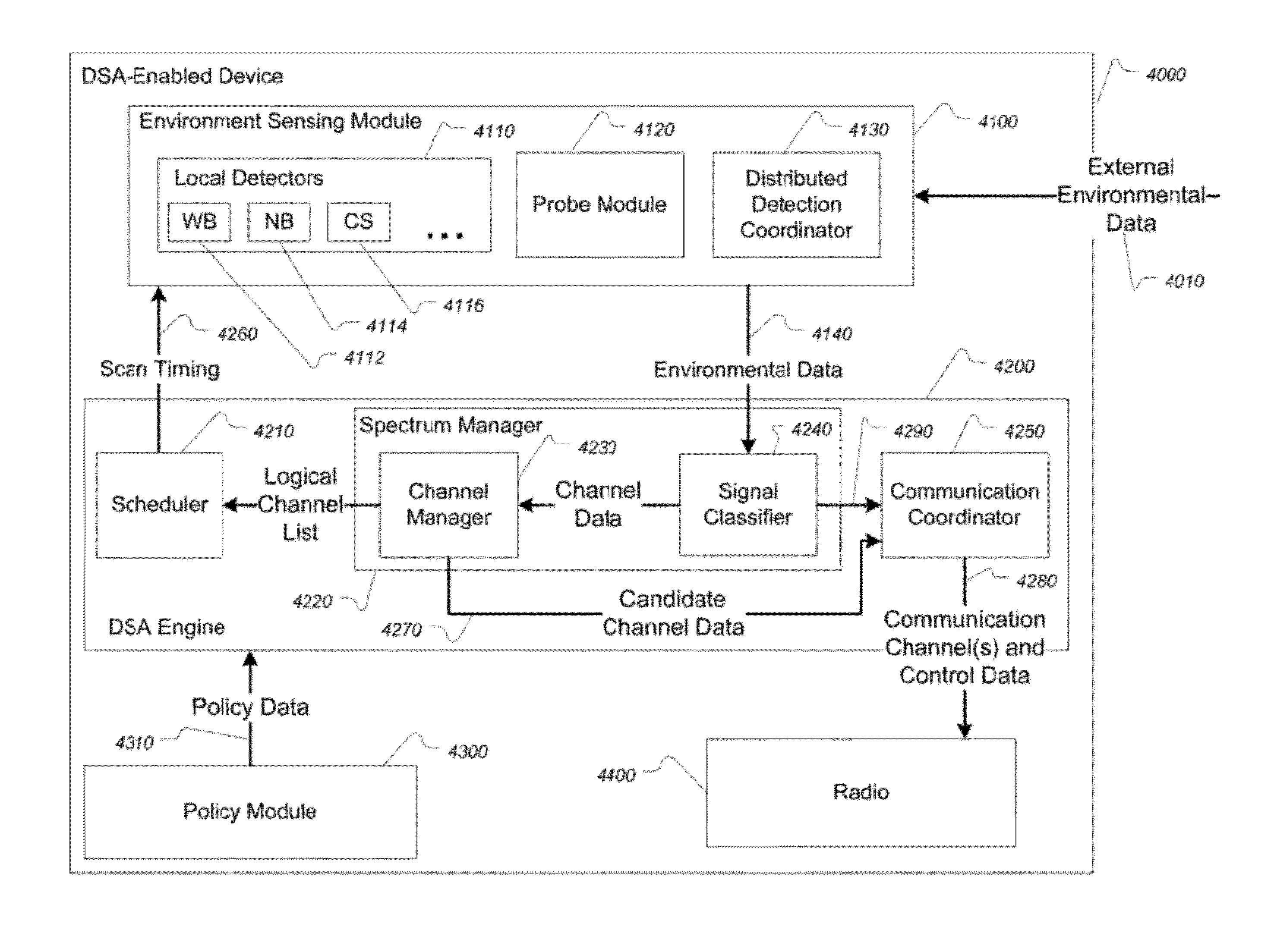

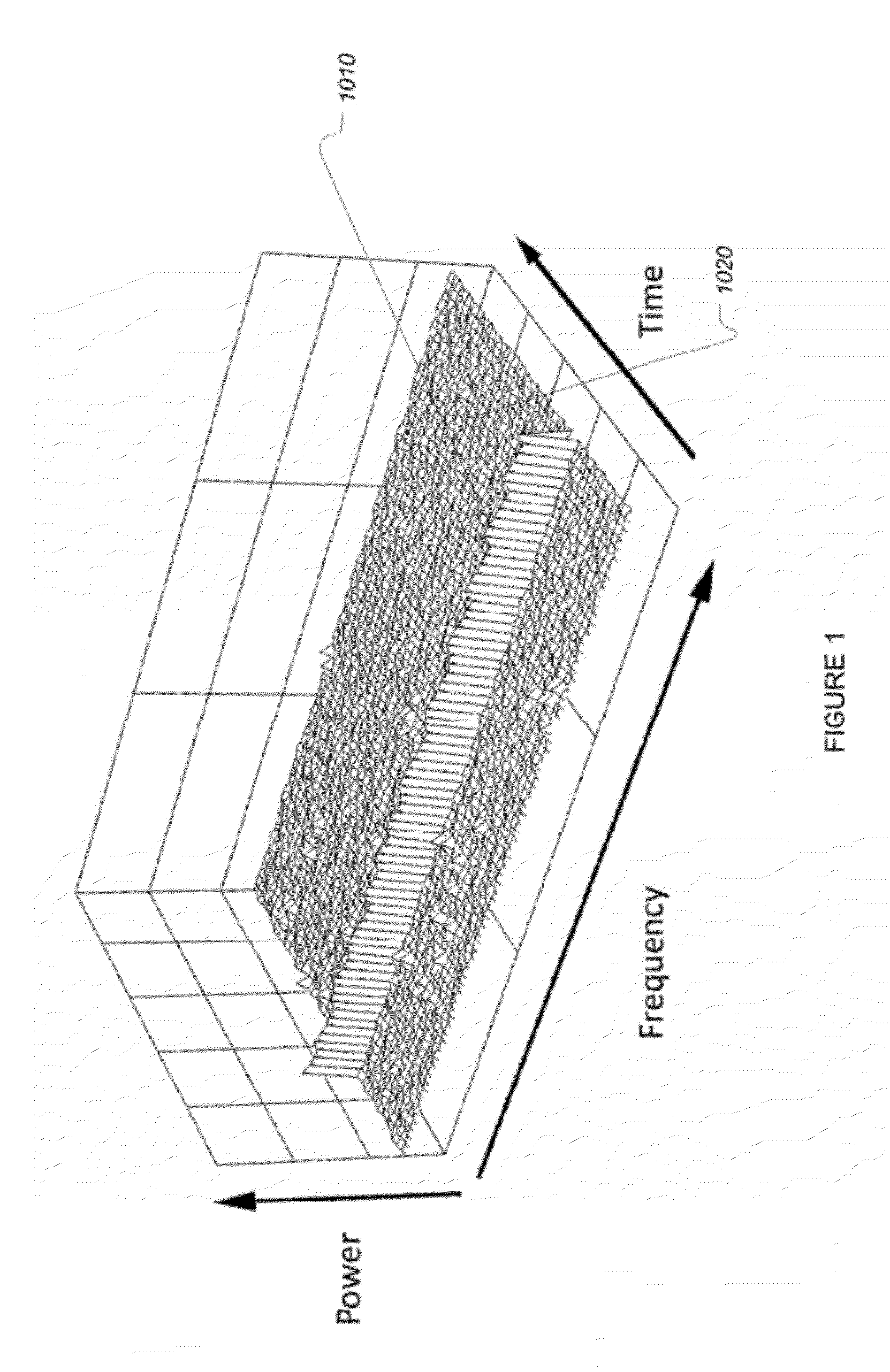

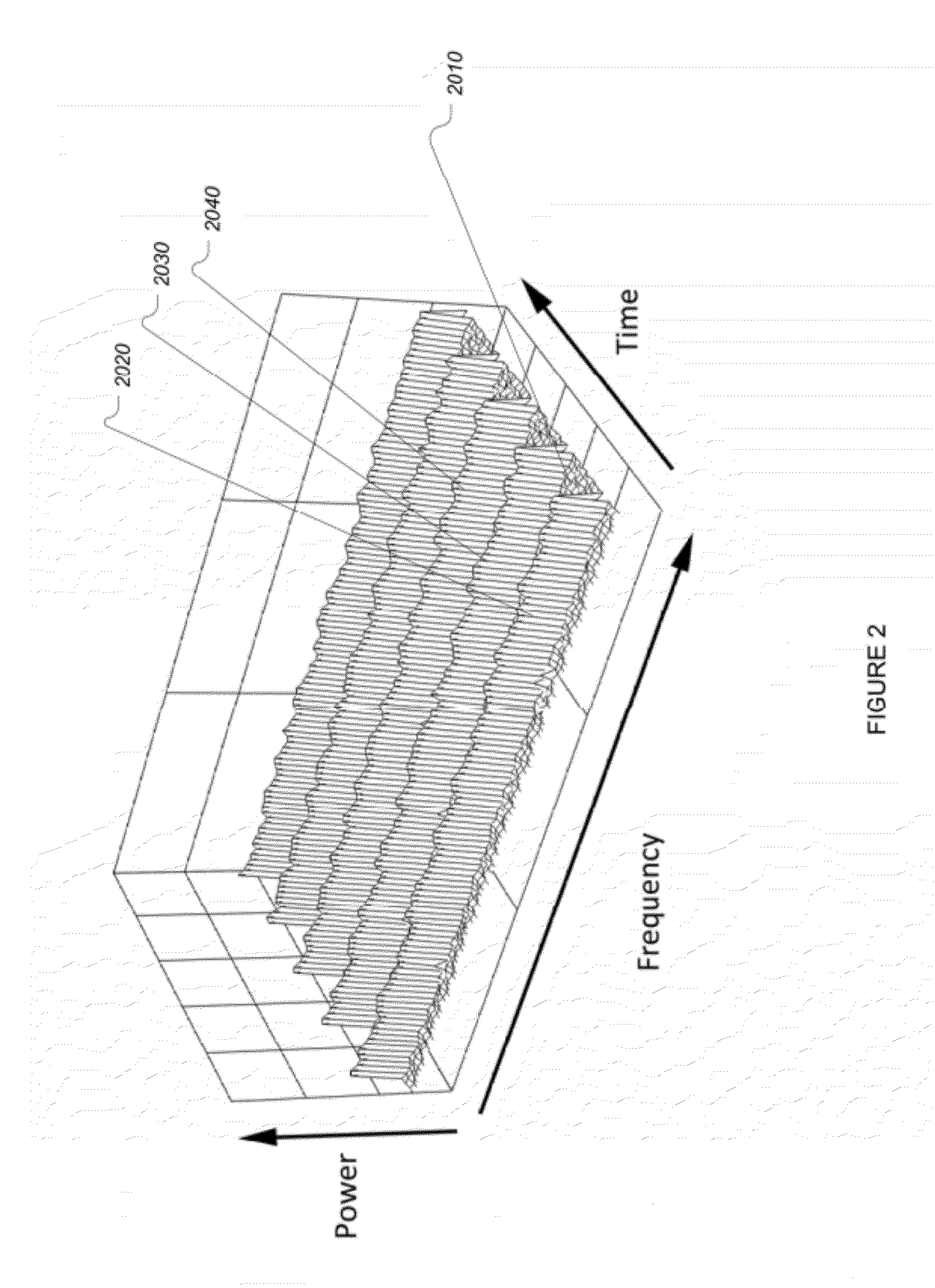

Method and system for man-made noise rejection detector

InactiveUS20120302190A1Improve performanceIncrease choiceTransmission monitoringFrequency spectrumNoise suppression

Methods and systems for dynamic spectrum access (DSA) in a wireless network are provided. A DSA-enabled device may sense spectrum use in a region and, based on the detected spectrum use, select one or more communication channels for use. The devices also may detect one or more other DSA-enabled devices with which they can form DSA networks. A DSA network may monitor spectrum use by cooperative and non-cooperative devices, to dynamically select one or more channels to use for communication while avoiding or reducing interference with other devices. A man-made noise rejection sub-system is used to permit signal detection while maintaining a low false alarm rate.

Owner:SHARED SPECTRUM

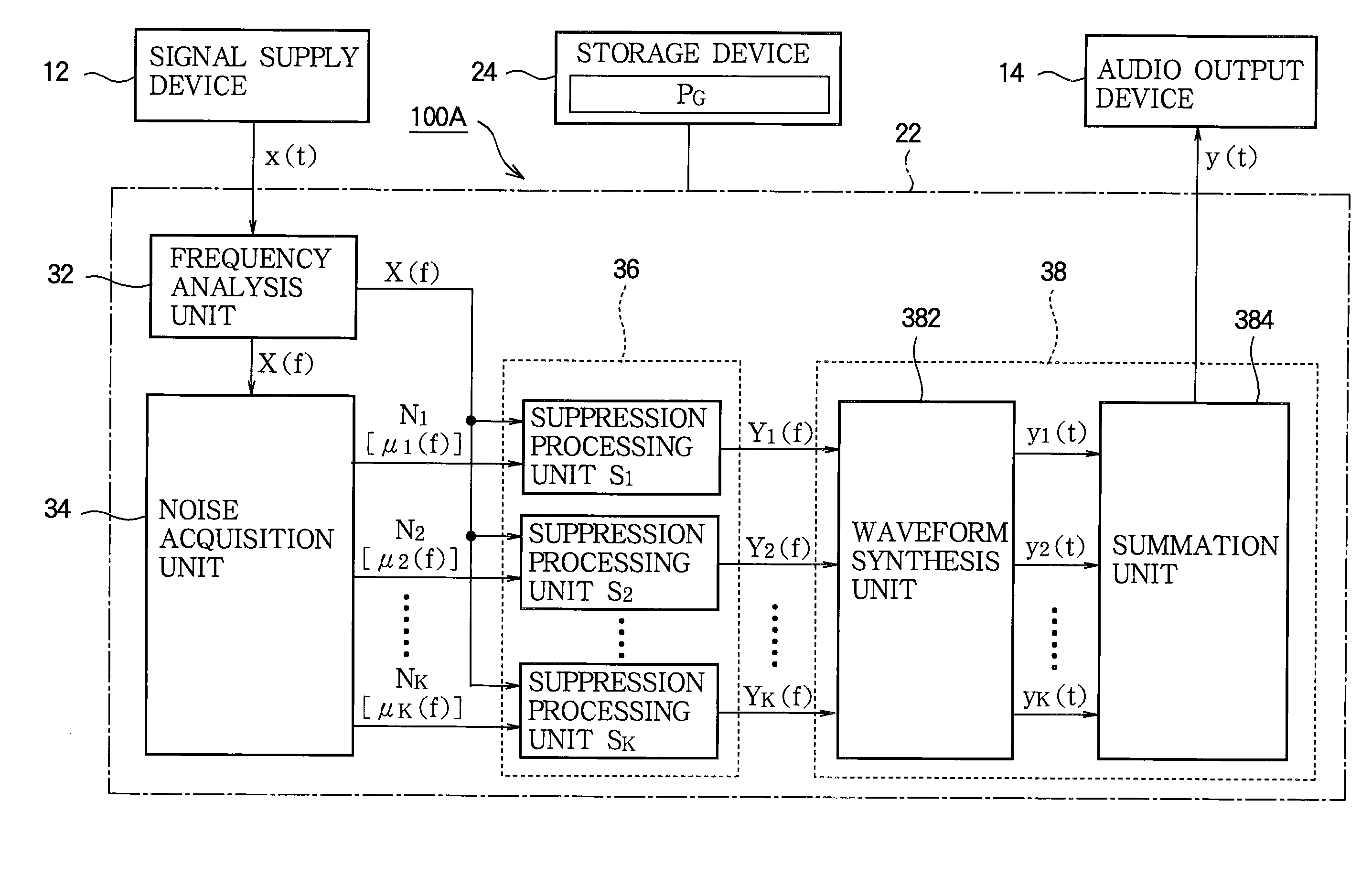

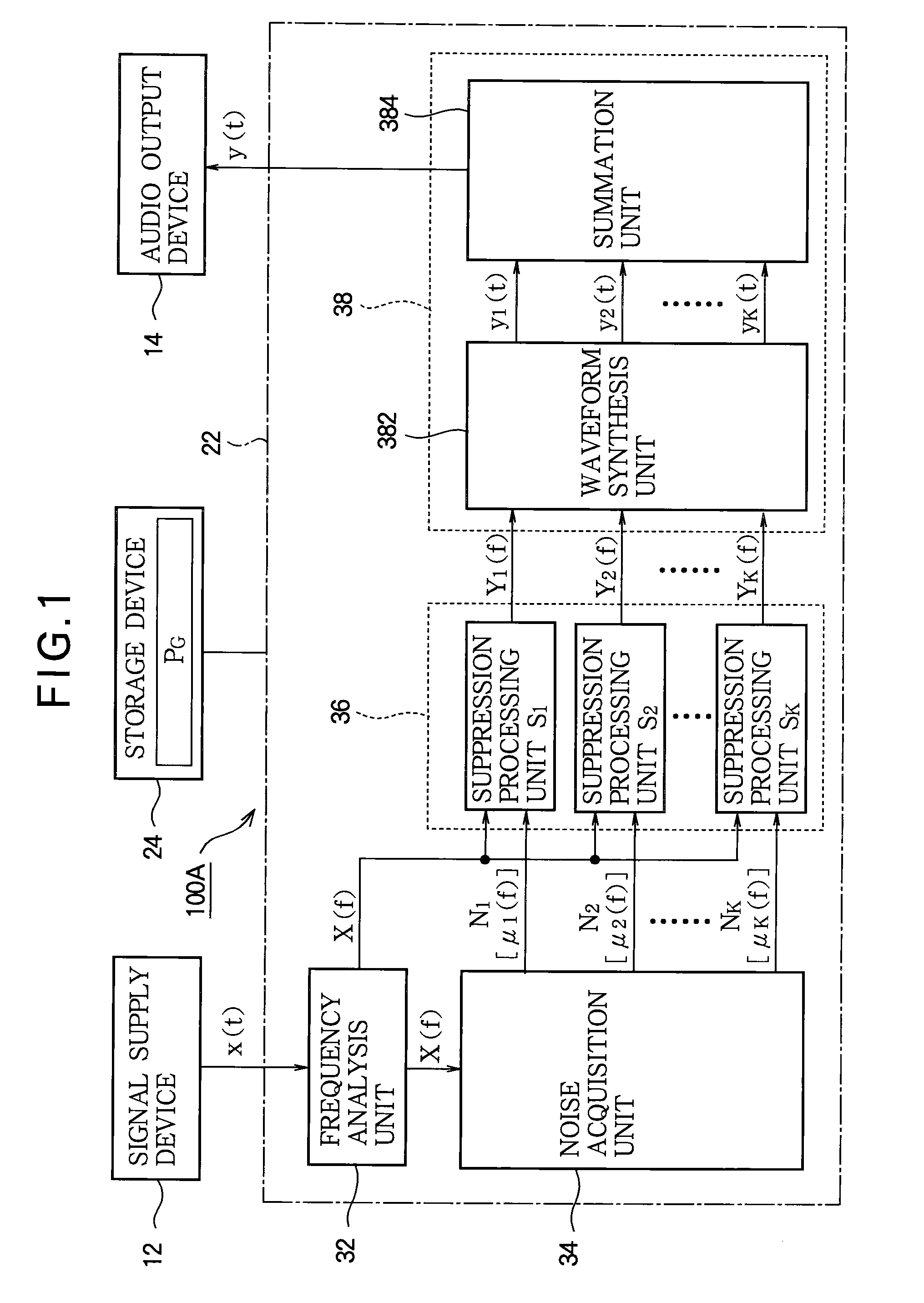

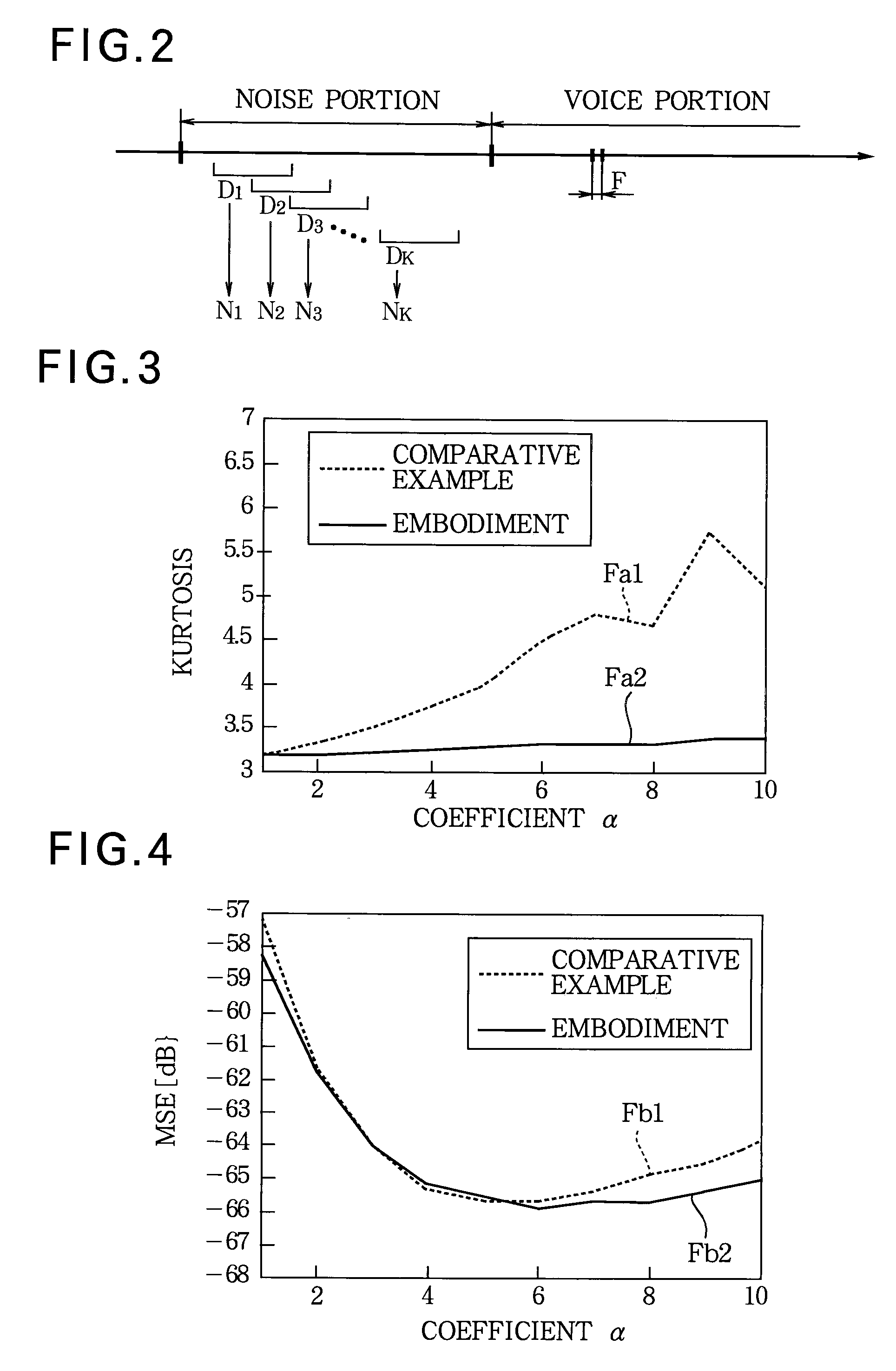

Noise suppressing device

InactiveUS20110170707A1Additional componentGood effectSpeech analysisTransmission noise suppressionEngineeringNoise suppression

A noise suppressing device is provided for suppressing noise of a first audio signal to generate a second audio signal. In the noise suppressing device, a noise acquisition unit acquires a plurality of noise components which are different from each other. A noise suppression unit generates each suppression component by suppressing each noise component from the first audio signal, thereby providing a plurality of suppression components different from each other in correspondence to the plurality of the noise components. A signal generation unit generates the second audio signal by summing the plurality of the suppression components that are provided from the noise suppression unit.

Owner:YAMAHA CORP

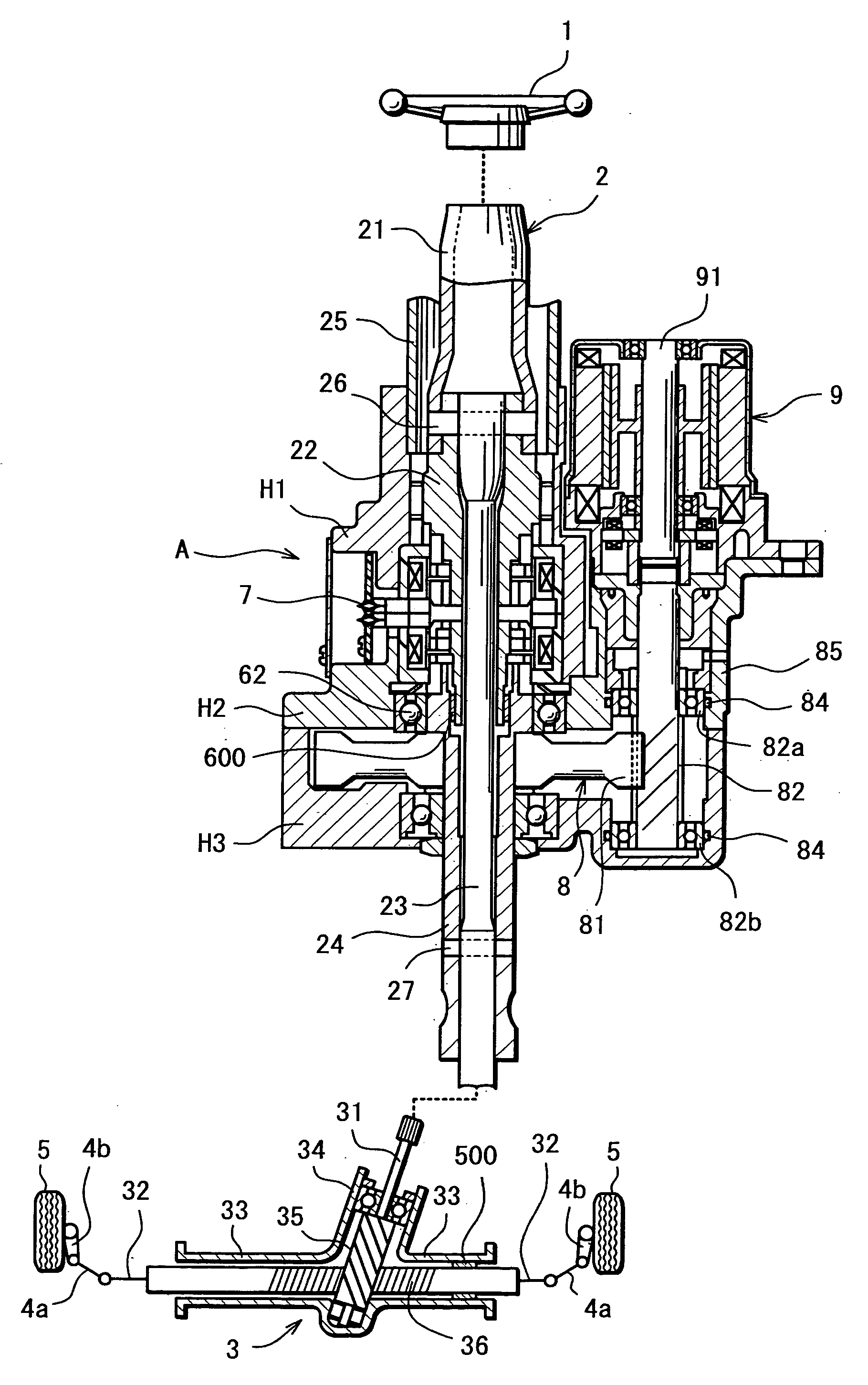

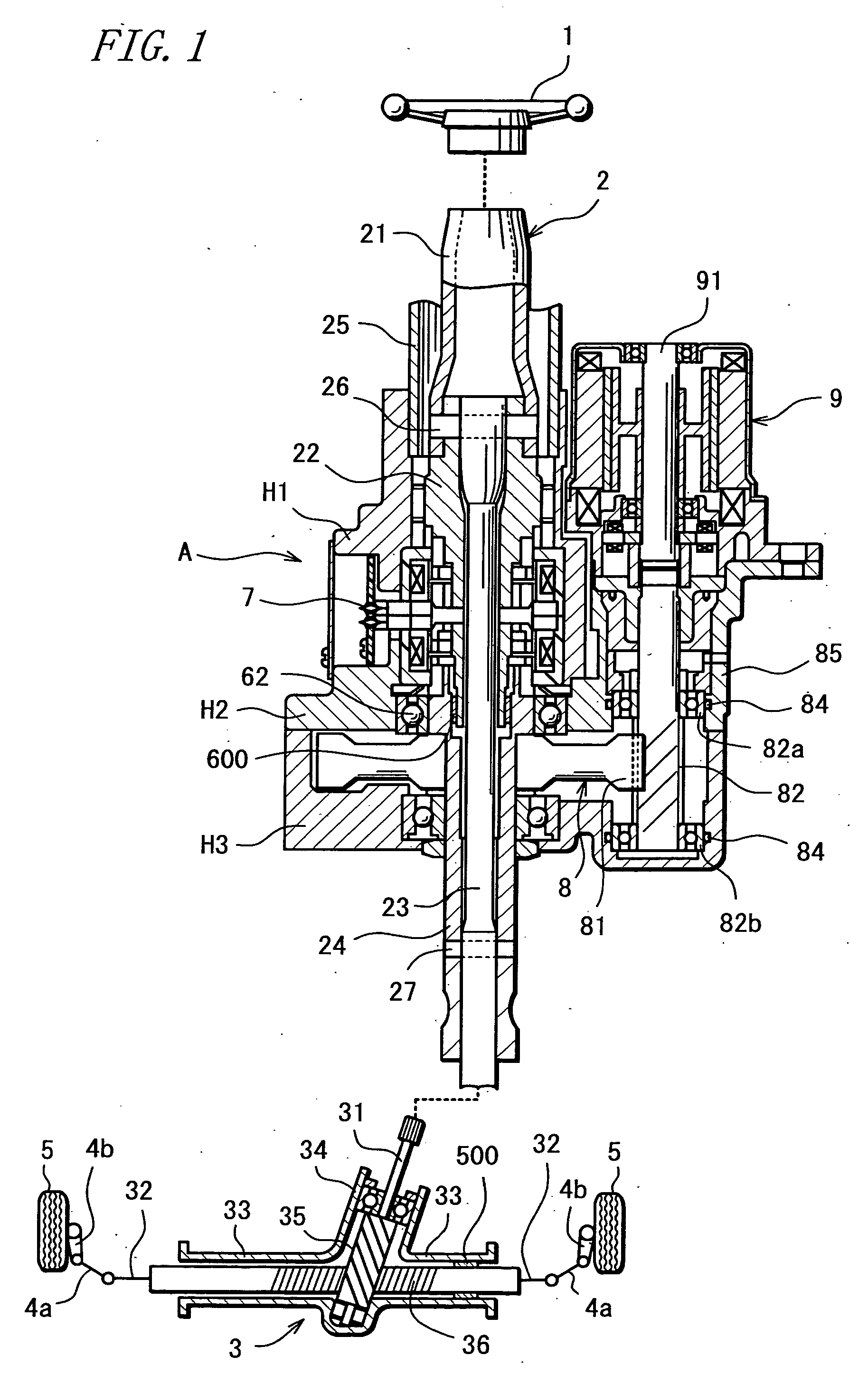

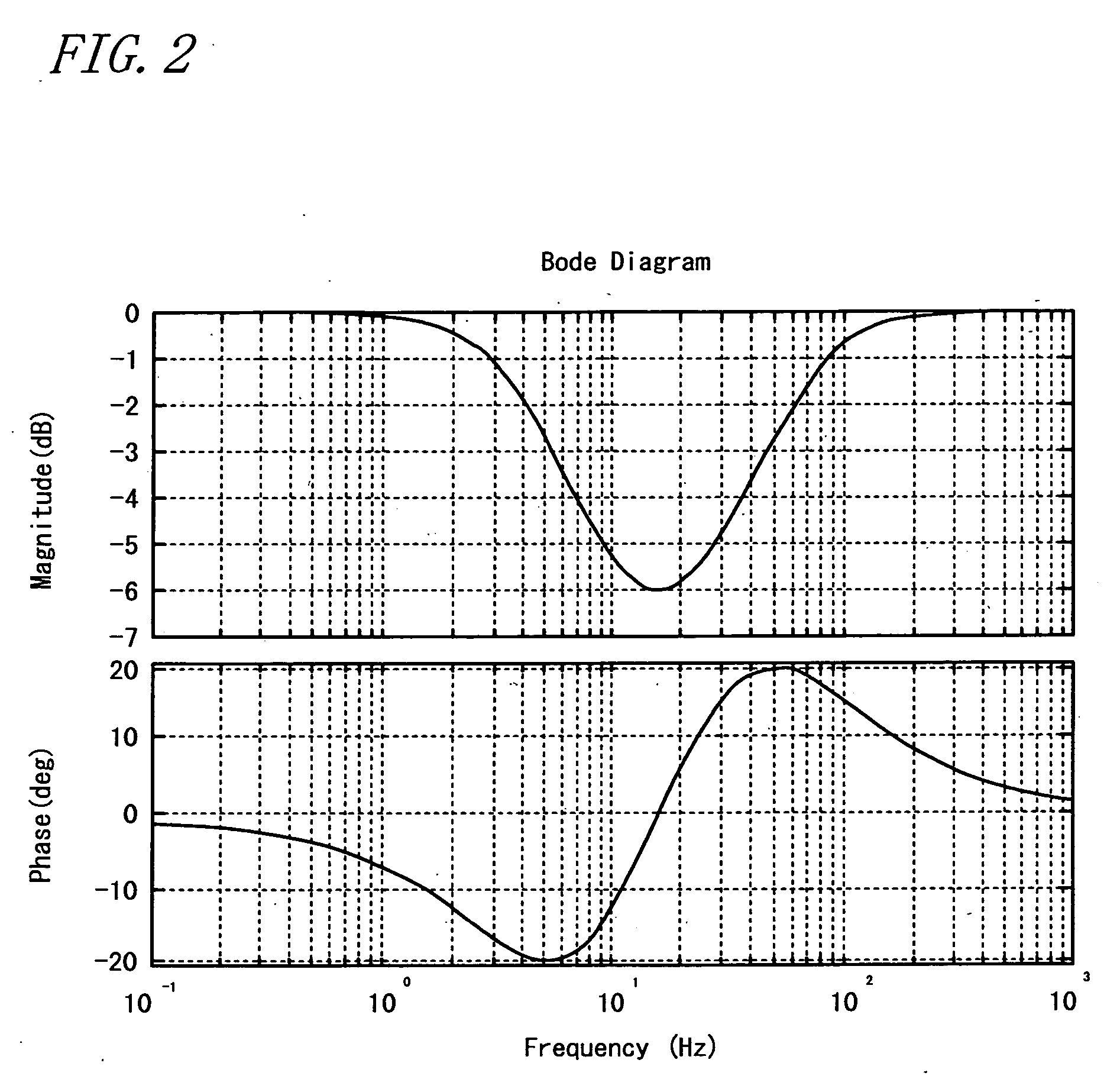

Electric Power Steering System

InactiveUS20070205041A1Favorable steering feelingLess inertia feelingSteering linkagesAutomatic steering controlElectric power steeringDamping torque

An electric power steering system is provided which is capable of providing a favorable steering feeling without using compensation logics such as of inertia compensation and friction compensation. The electric power steering system includes road-noise suppression control means (213) for controlling a steering assist motor (9) in a manner to damp torque transmission in a higher frequency region representing road noises than a frequency region representing road information. A friction value of a steering mechanism (A) is decreased enough to allow the intrinsic vibrations of the steering mechanism (A) to appear. Rotor inertia of the steering assist motor (9) is set to a value small enough to allow the frequencies of the intrinsic vibrations to be present in the frequency region where the torque transmission is damped by the road-noise suppression control means (213).

Owner:JTEKT CORP

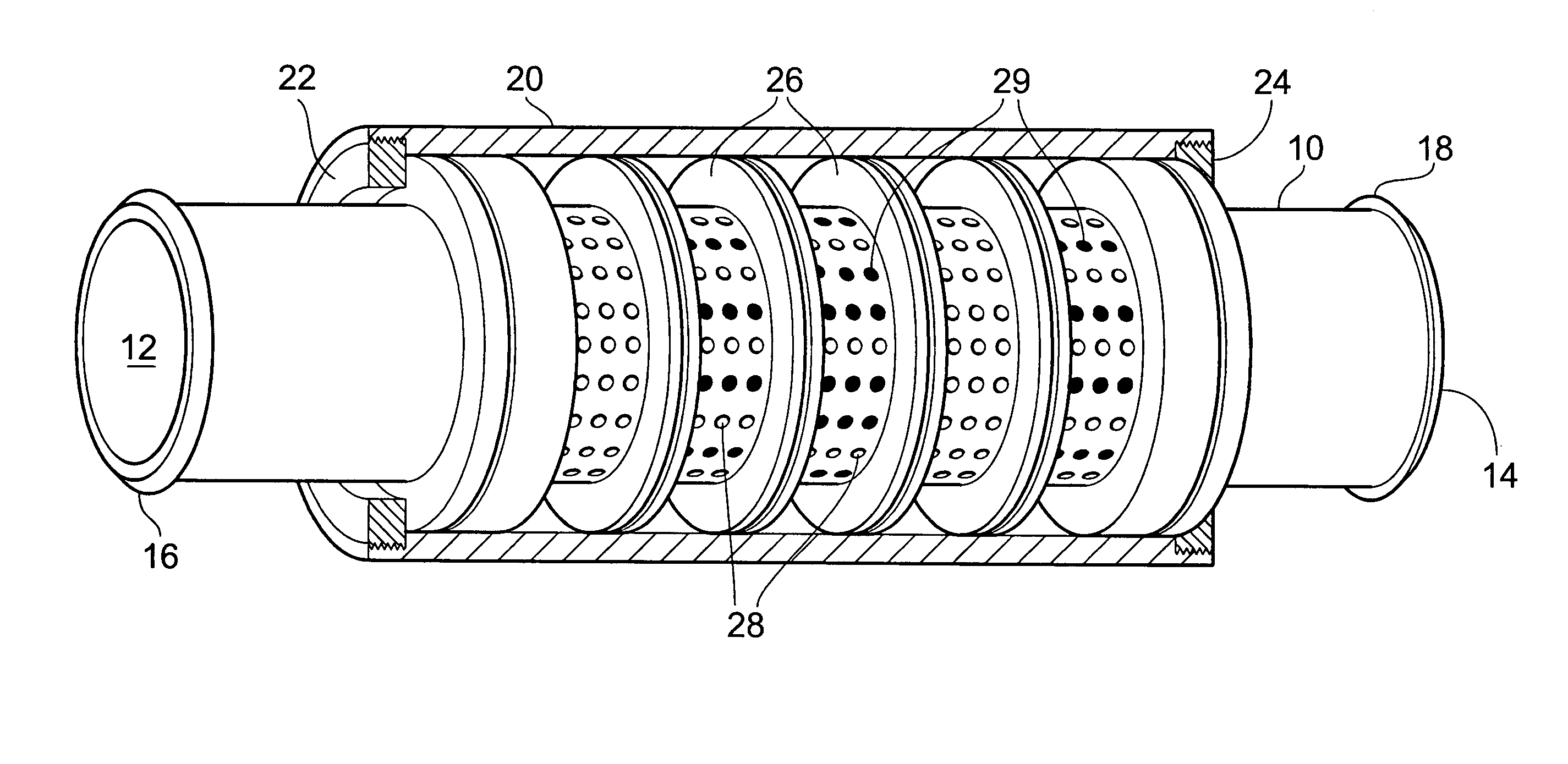

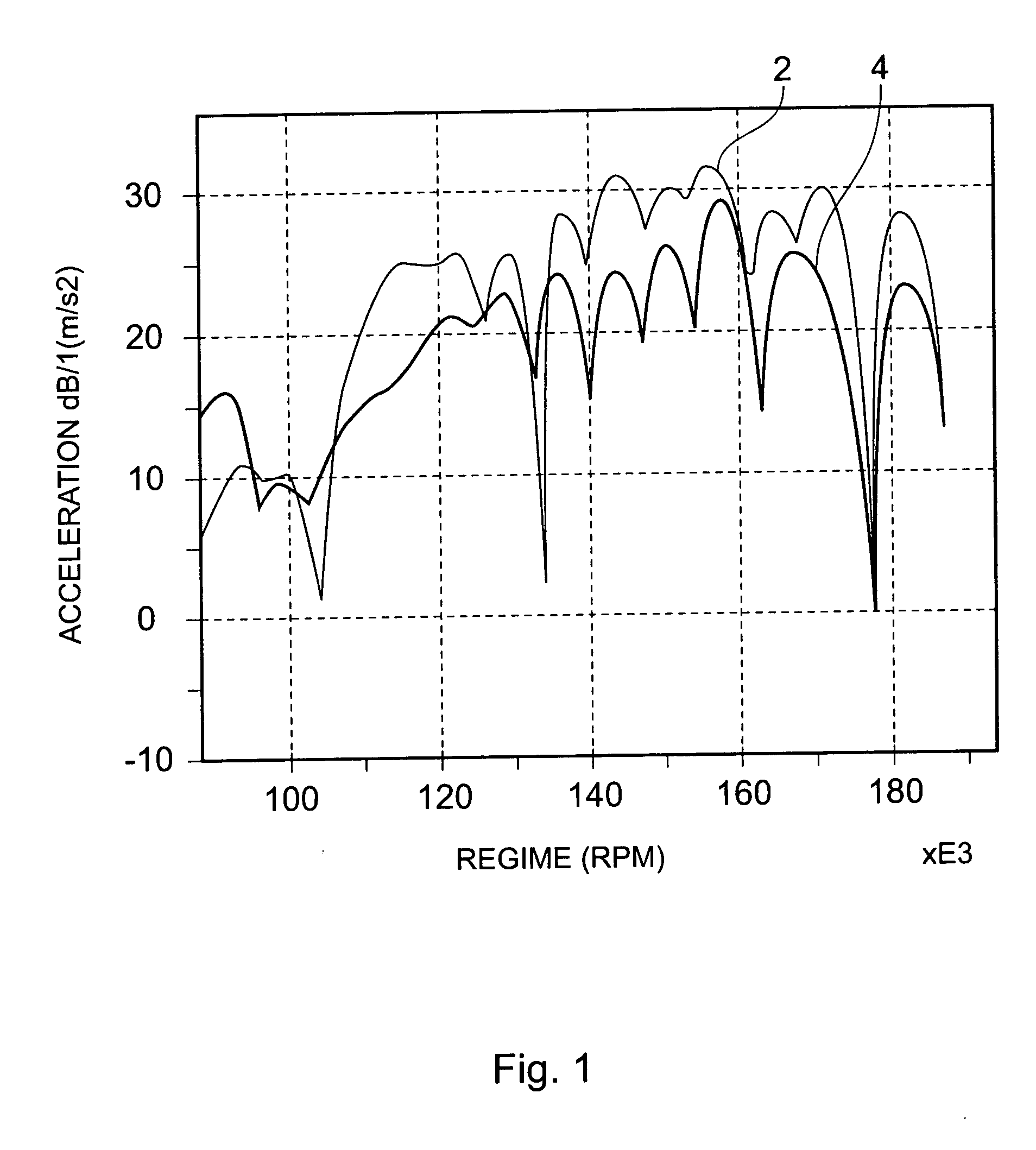

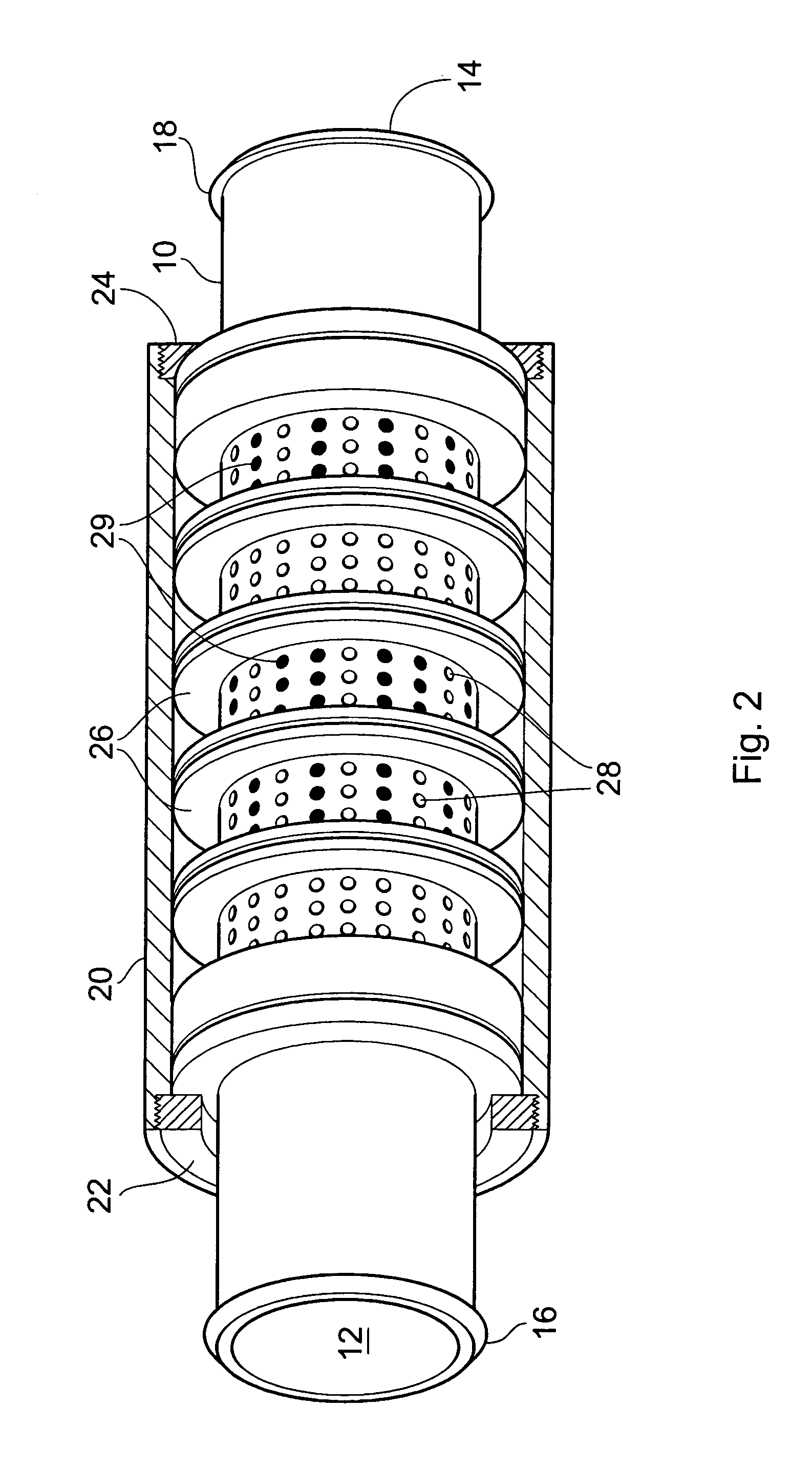

Noise and vibration suppressors

InactiveUS6983820B2Increase dampingSuppress noisePositive displacement pump componentsSilencing apparatusSuppressorModularity

In order to form a noise suppressor in a hose of e.g. a motor vehicle, modular portions are connected in series to define suppression chambers with particular noise suppression characteristics. Those characteristics are due to the volume of each chamber, to the size of the apertures from the chambers to the central duct of the suppressor, and optionally due to spacers which are inserted into at least one aperture of the chambers to alter the effective open area of that aperture. Such spacers may also be used in which the noise suppressor is not modular. Where modular portions are used, it is preferable that each chamber is bounded by parts of two modular portions. A wall of one modular portion may then close the chamber in another modular portion, making the manufacture of the modular portions easier. Also disclosed is the use of a mass acting as a damper, which may be a noise suppressor as previously discussed, within a hose. The mass is connected to the hose by resilient means, e.g. electrometric material.

Owner:CADILLAC RUBBER & PLASTICS