Patents

Literature

8387results about "Printed circuits structural associations" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

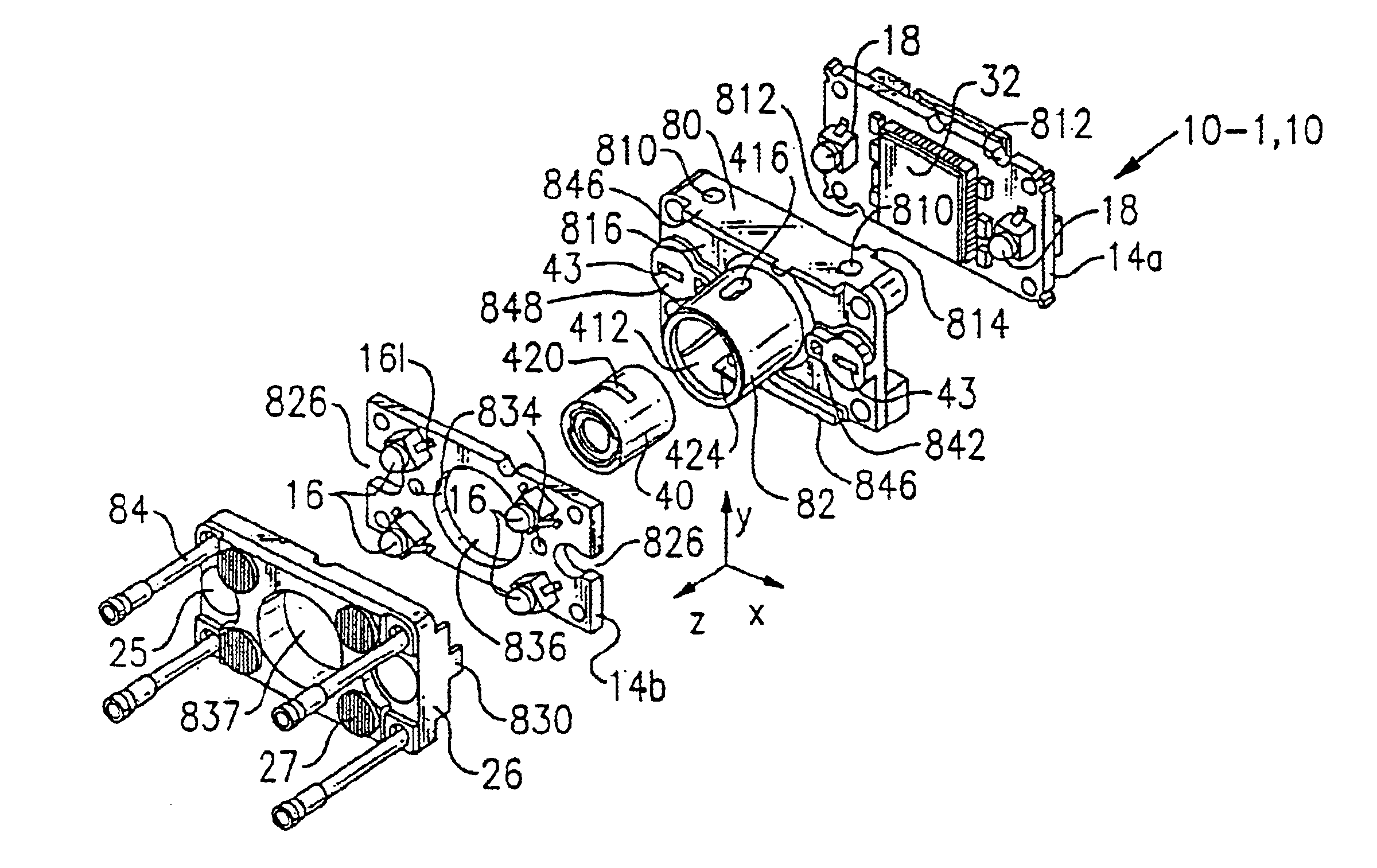

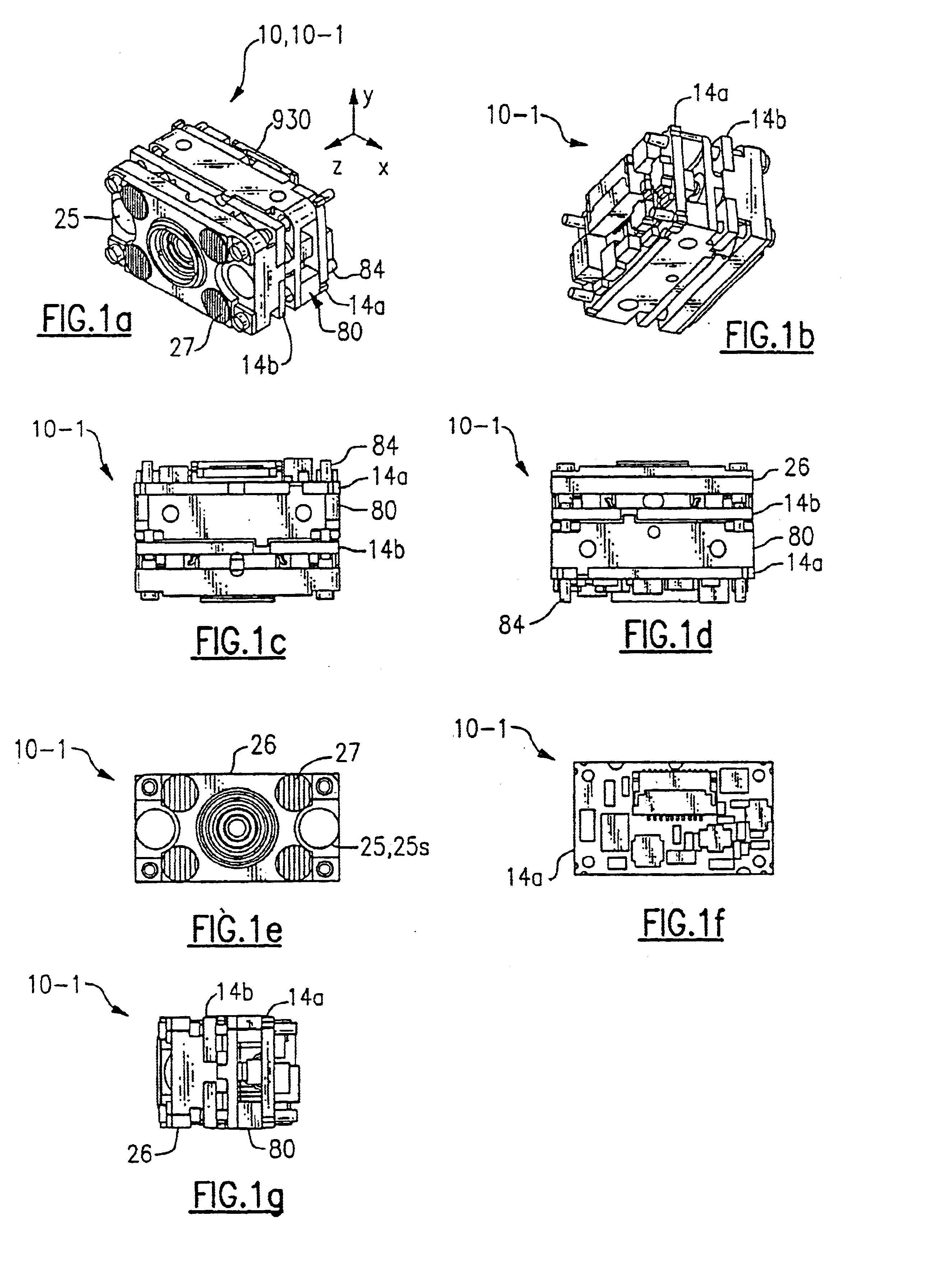

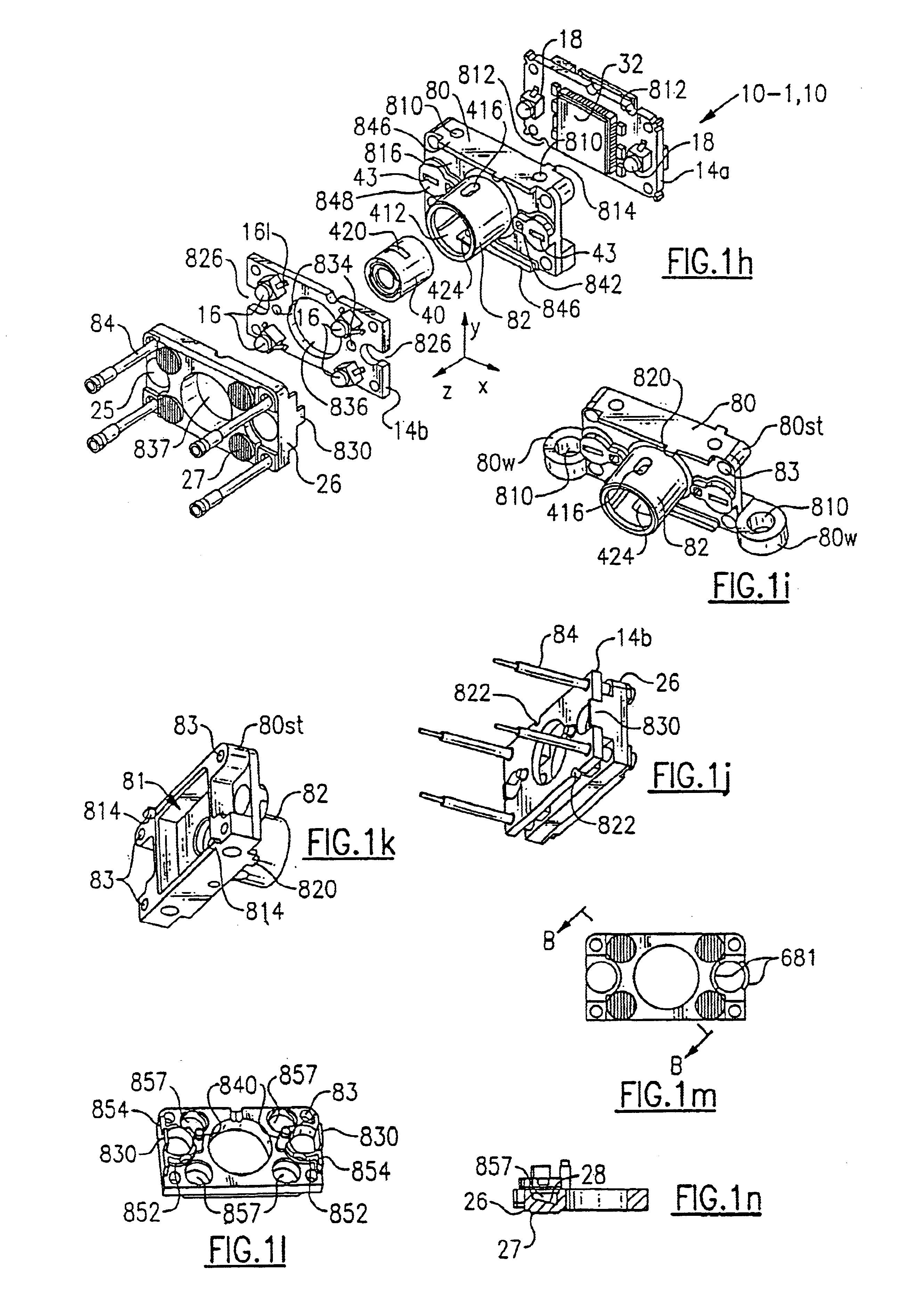

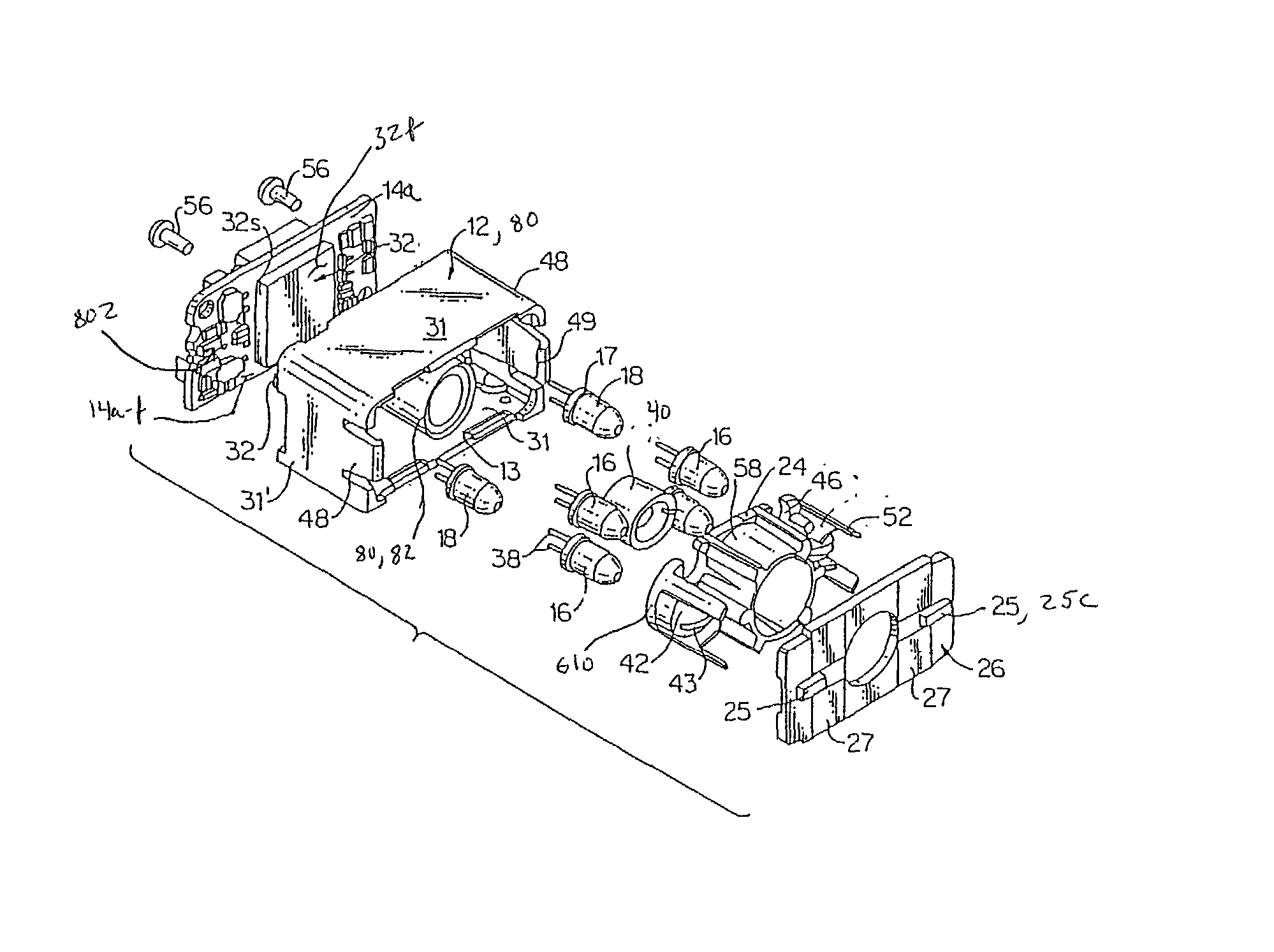

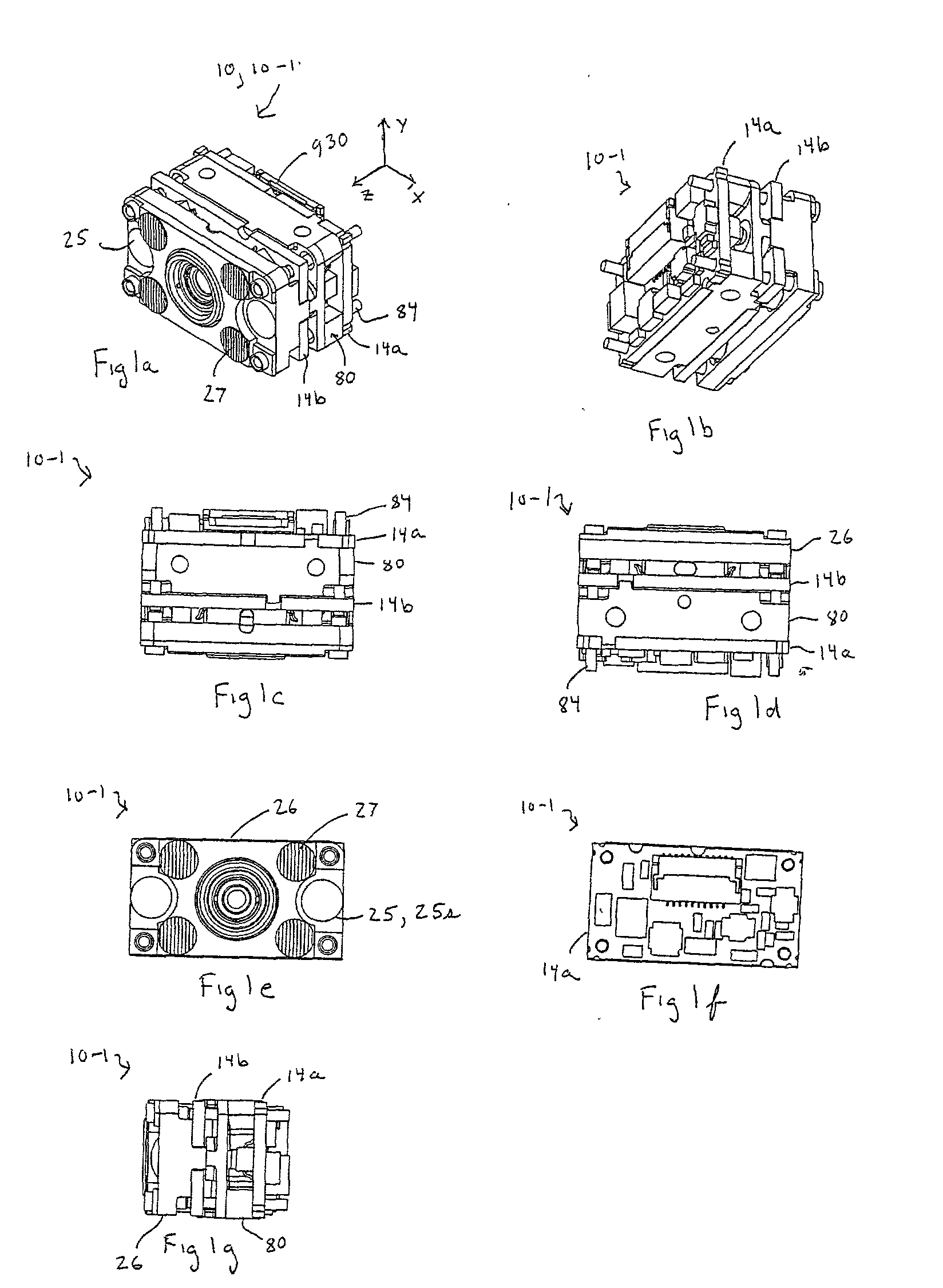

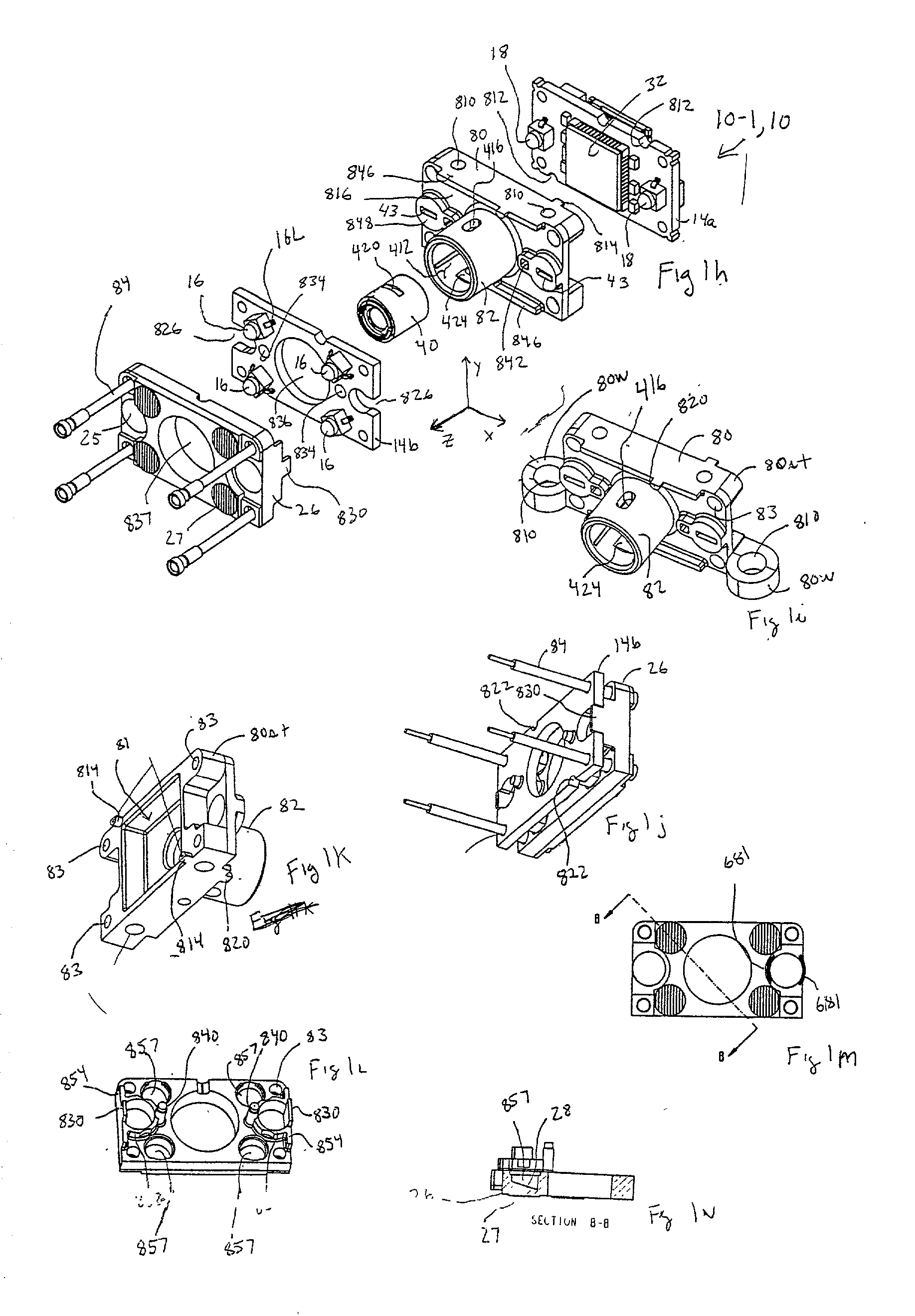

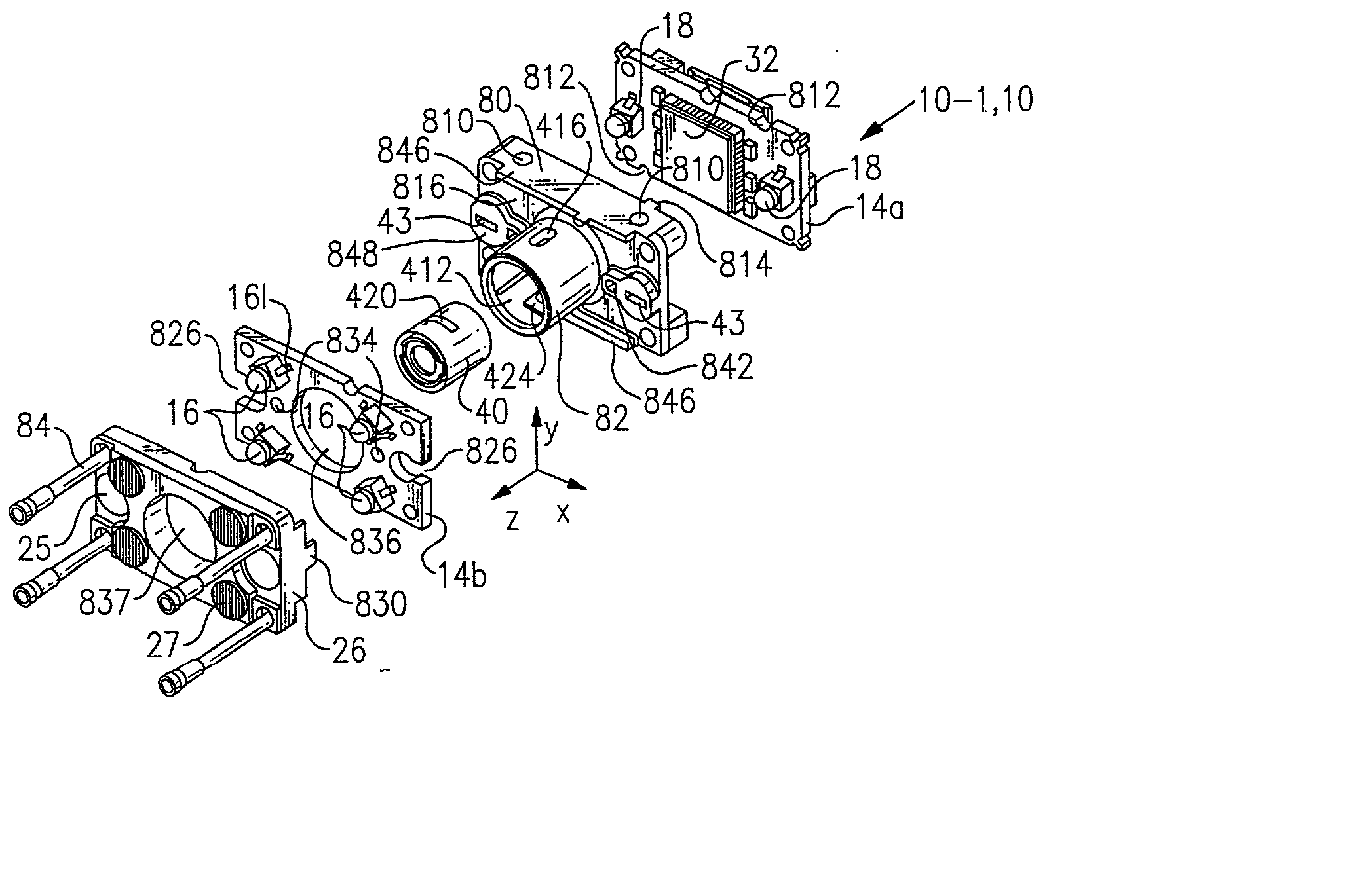

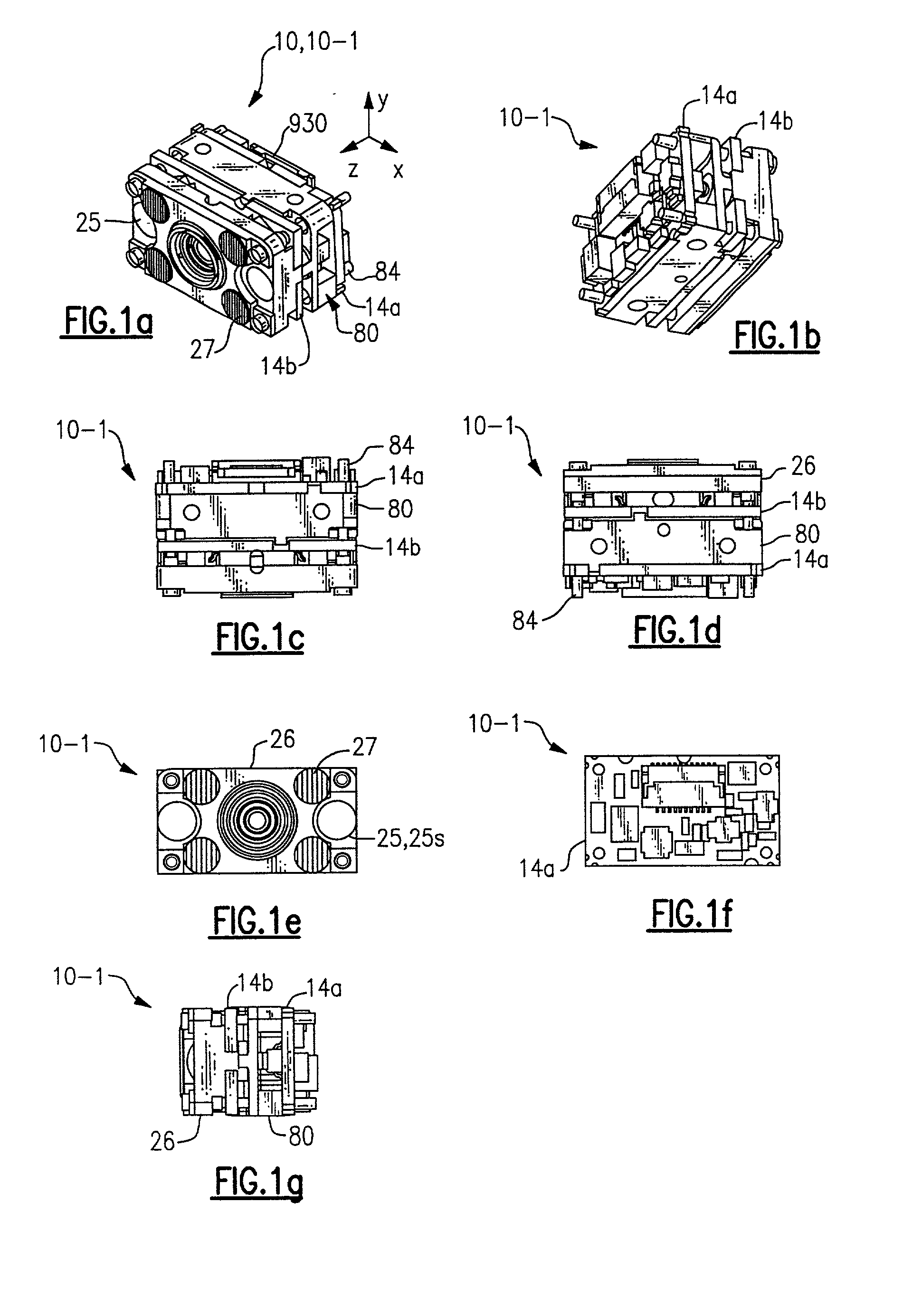

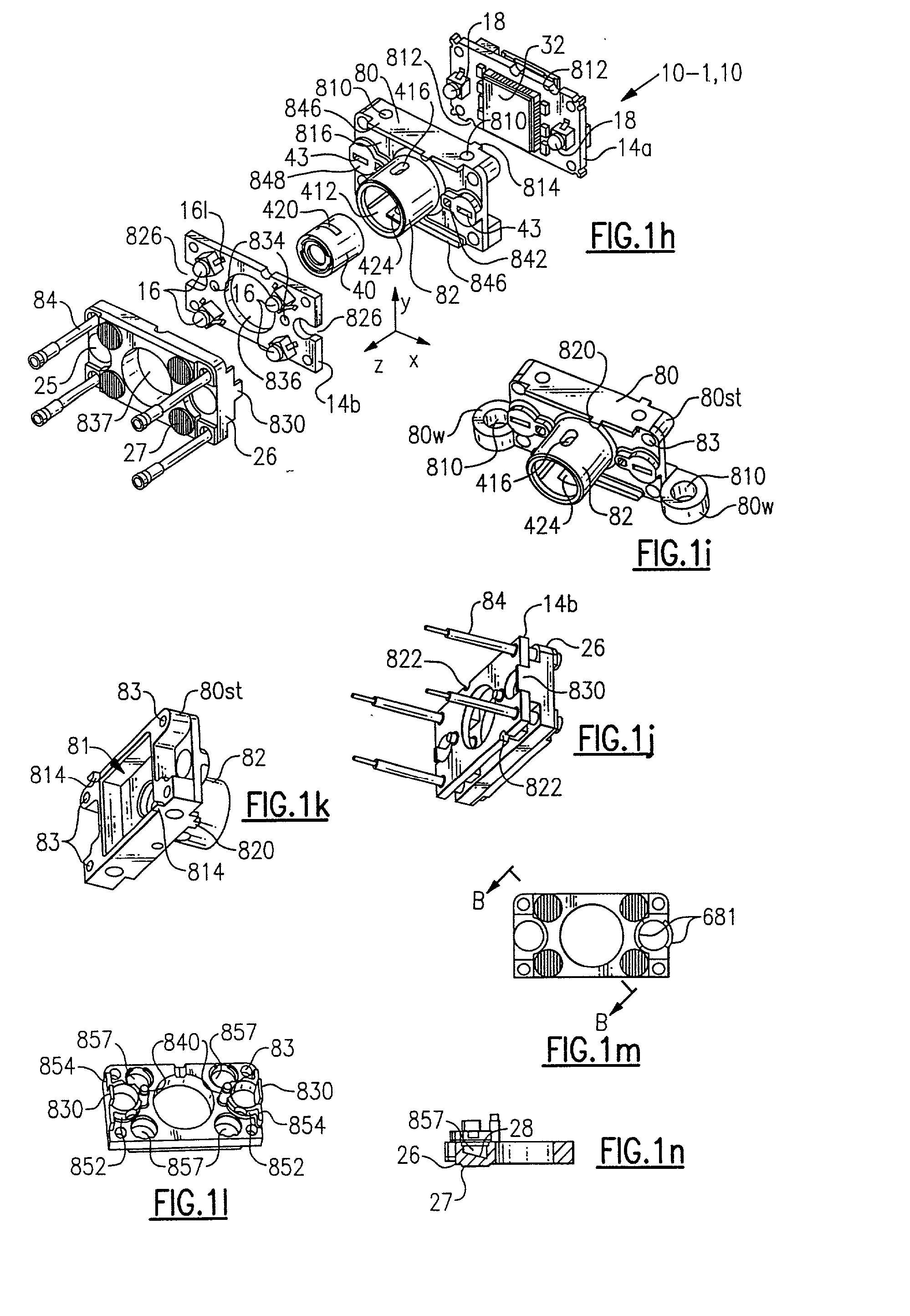

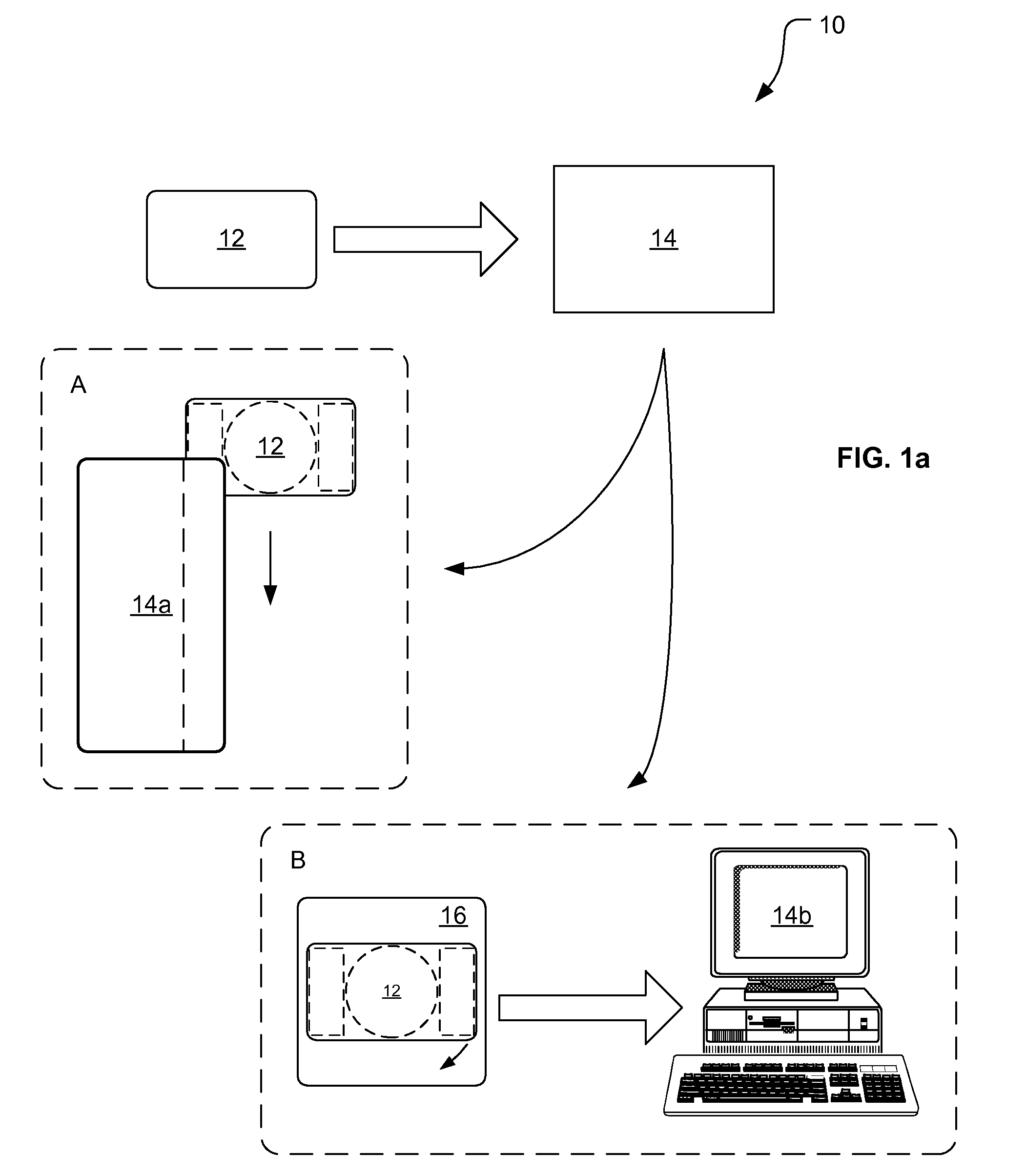

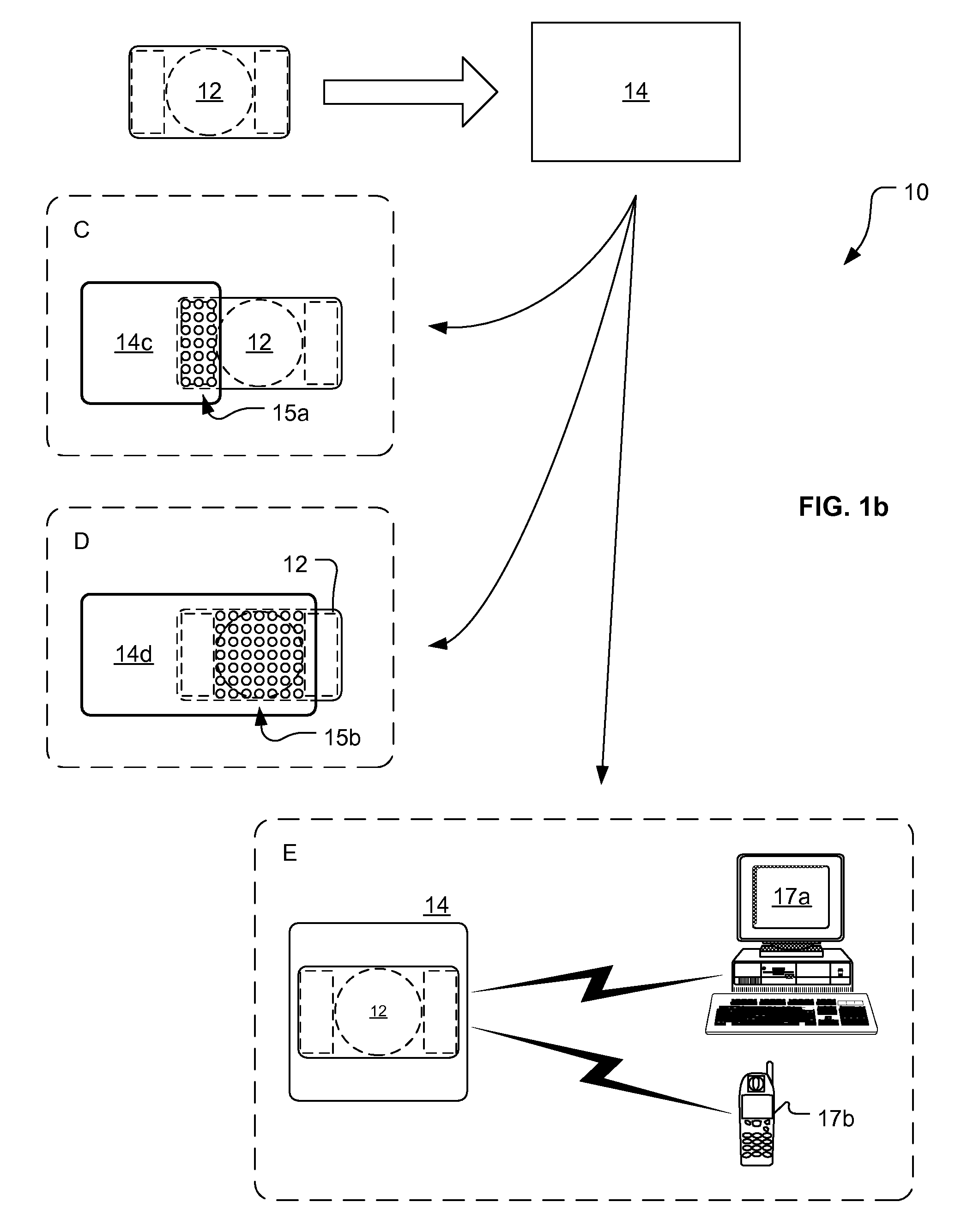

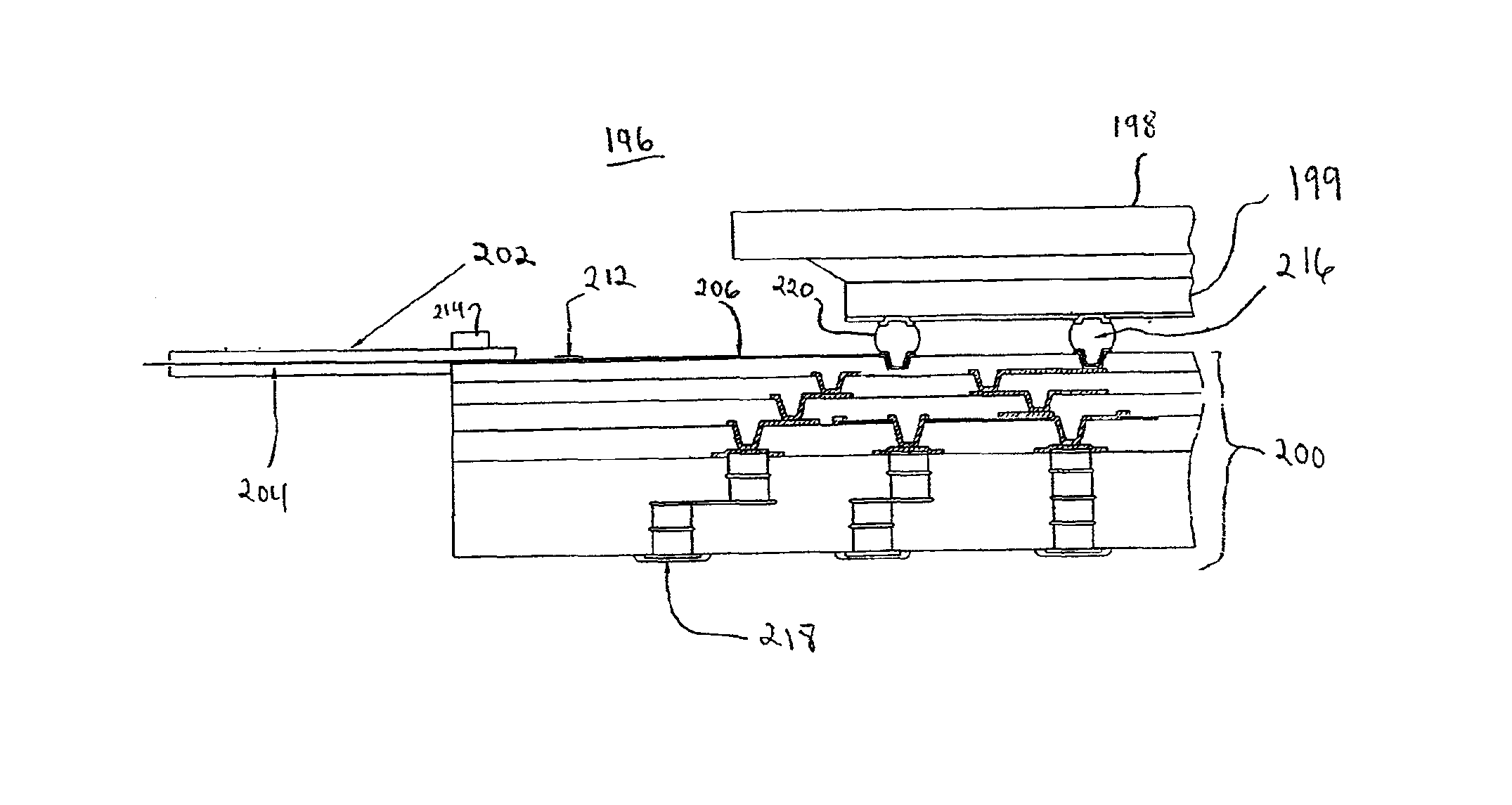

Optical reader comprising multiple color illumination

InactiveUS6832725B2Reduced dimensionOptimize architectureConveying record carriersCharacter and pattern recognitionComputer moduleLength wave

An imaging module in one embodiment includes at least one multiple color emitting light source comprising a plurality of different colored LED dies each independently driveable so that the overall color emitted by the light source can be controlled and varied. The multiple color emitting light source can be controlled so that the color emitted by the light source is optimized for imaging or reading in a present application environment of the module. Further, the module can be configured so that control of the multiple color emitting light source automatically varies depending on a sensed condition, such a color present in a field of view of the module, the distance of the module to a target, and / or a predetermined criteria being met so that feedback is provided to a user. The module in a further aspect can include illumination light sources and aiming light sources which project light in different wavelength emission bands.

Owner:HAND HELD PRODS

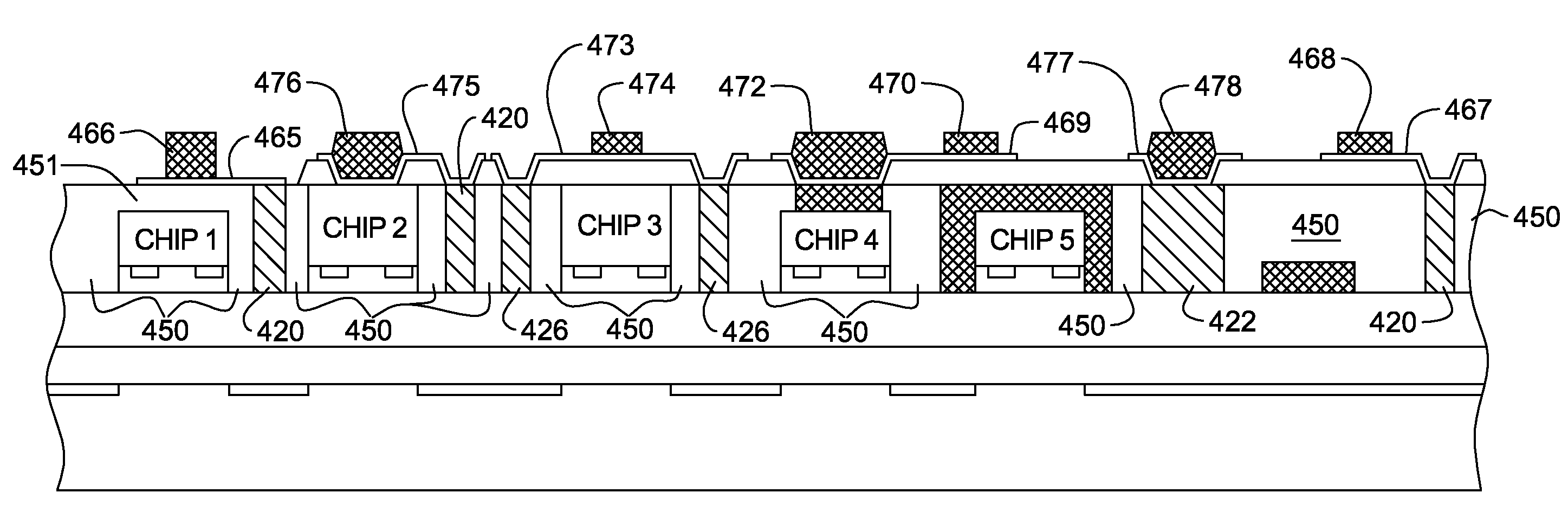

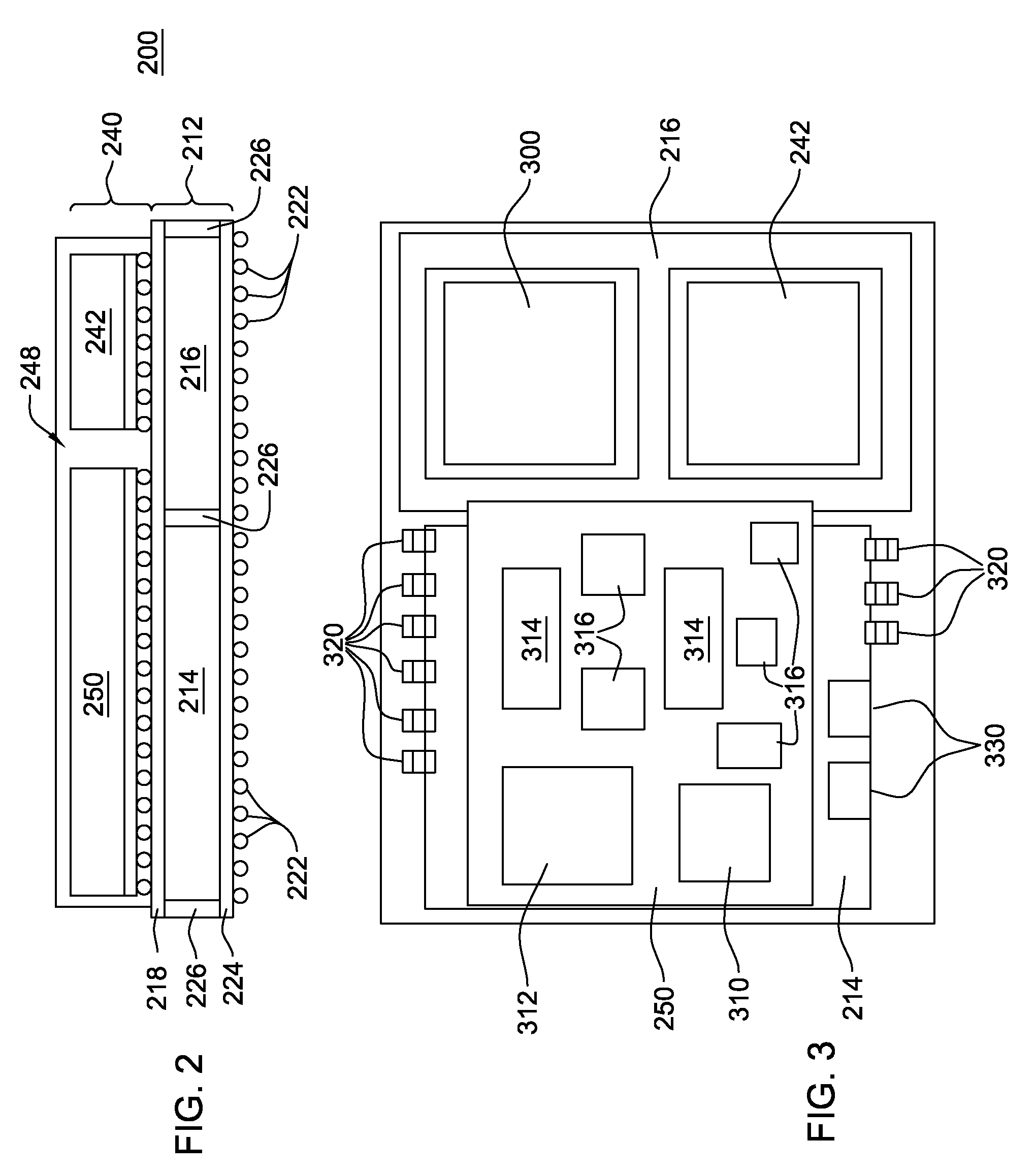

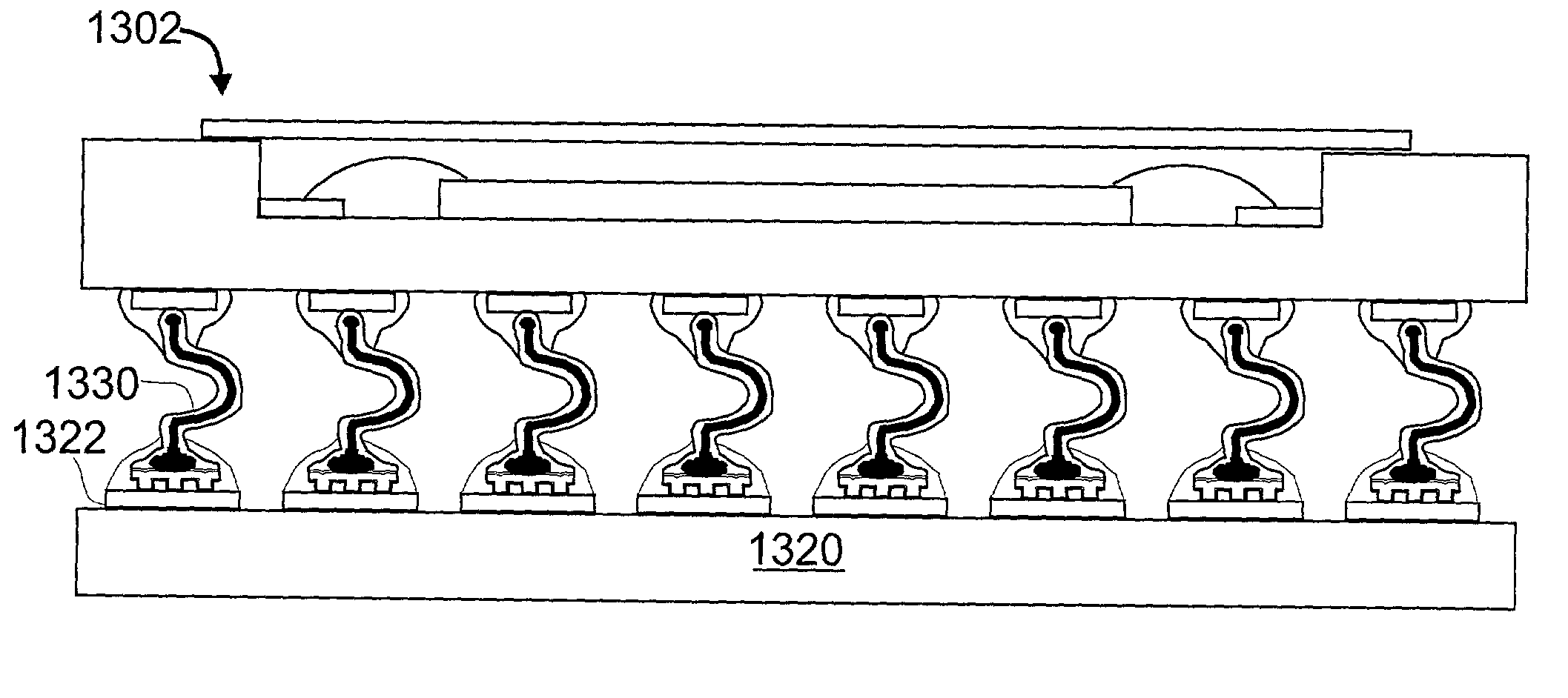

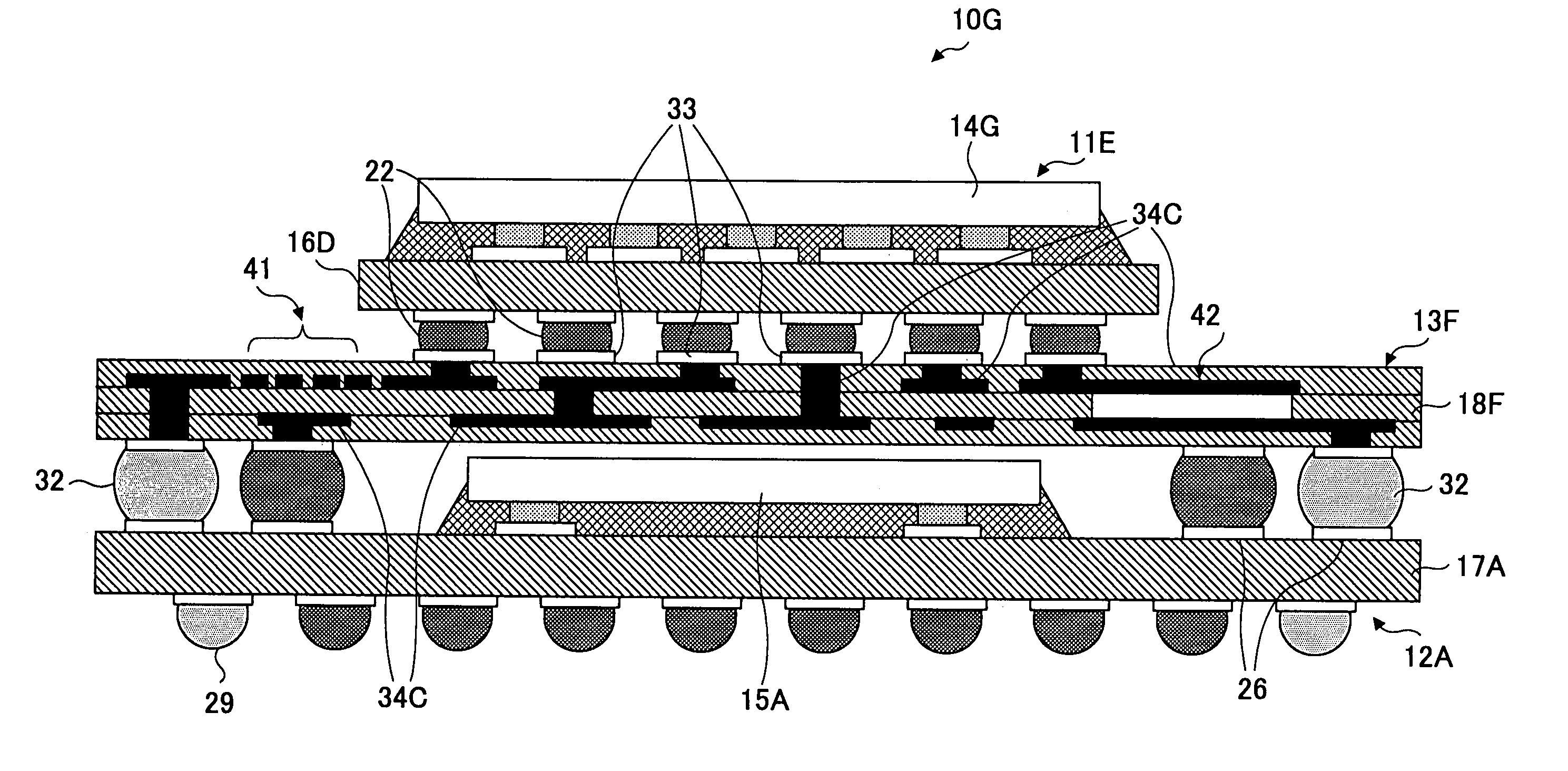

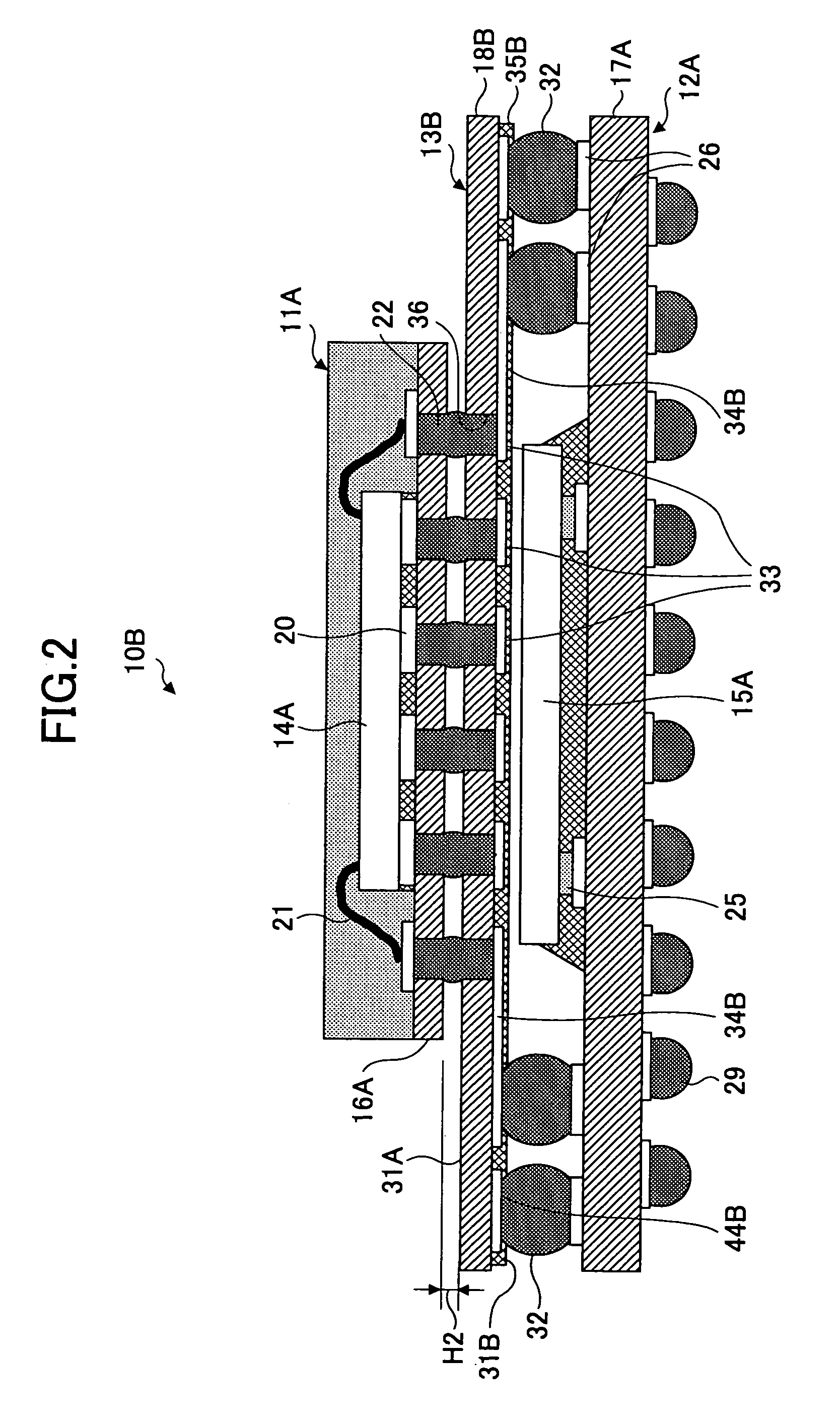

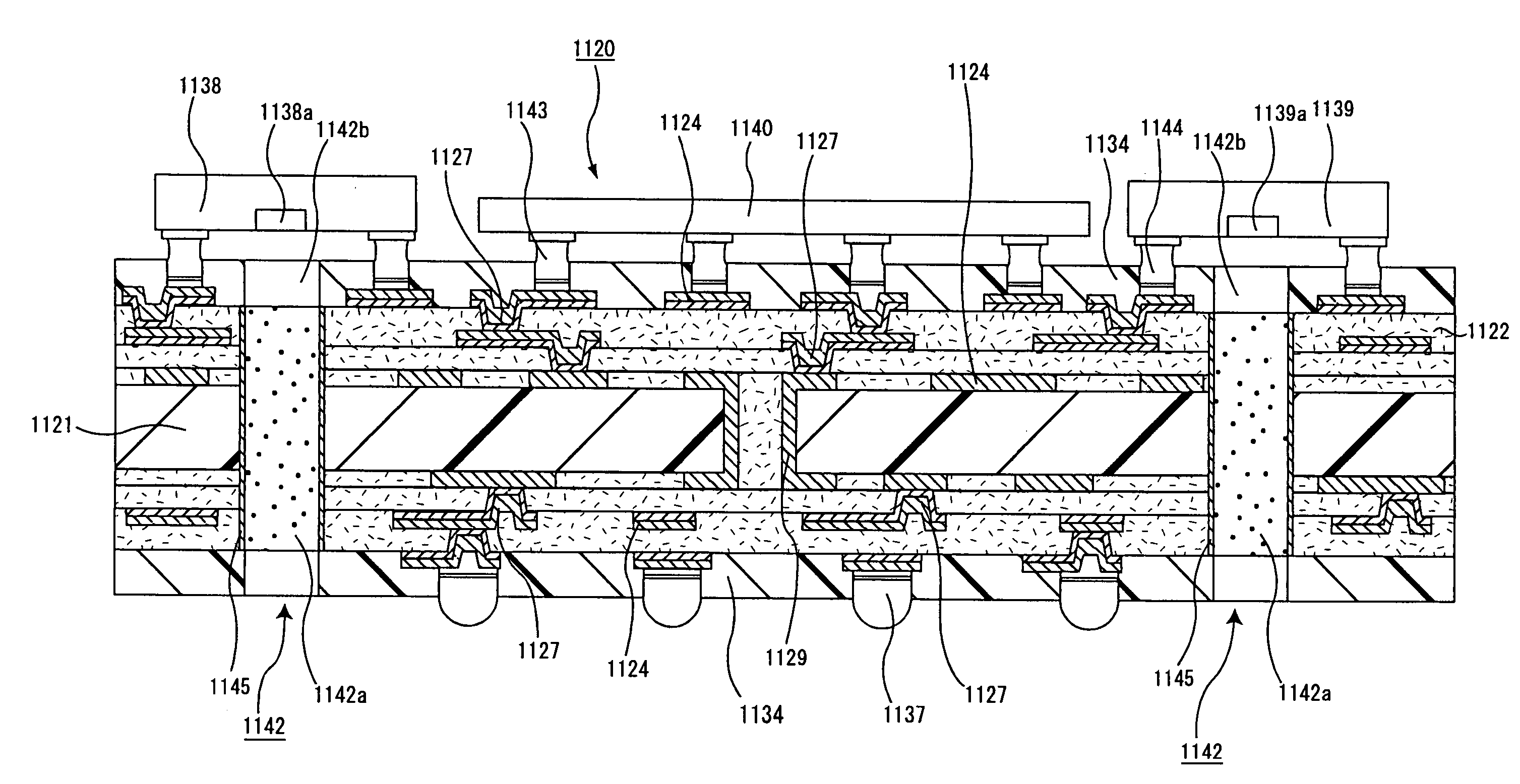

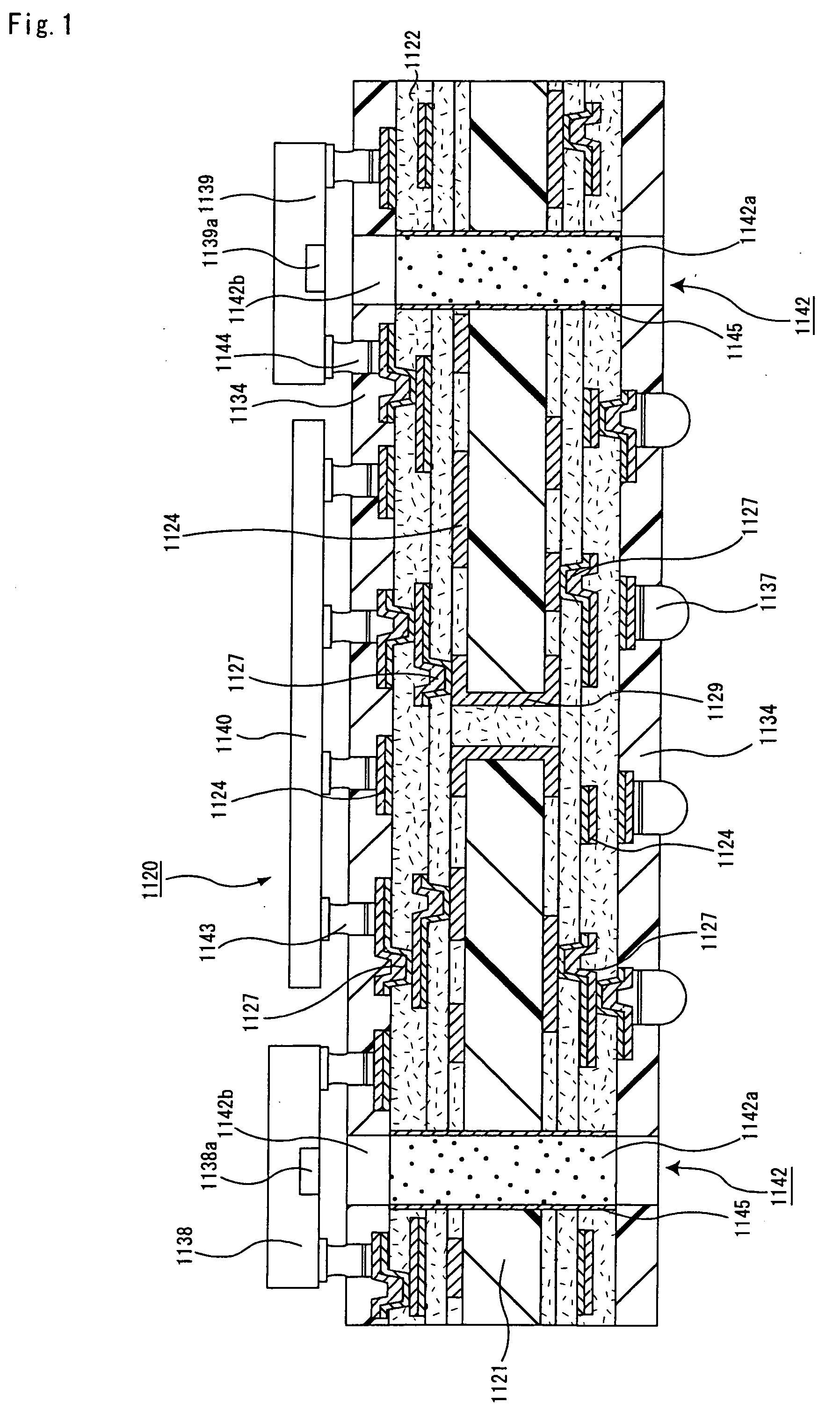

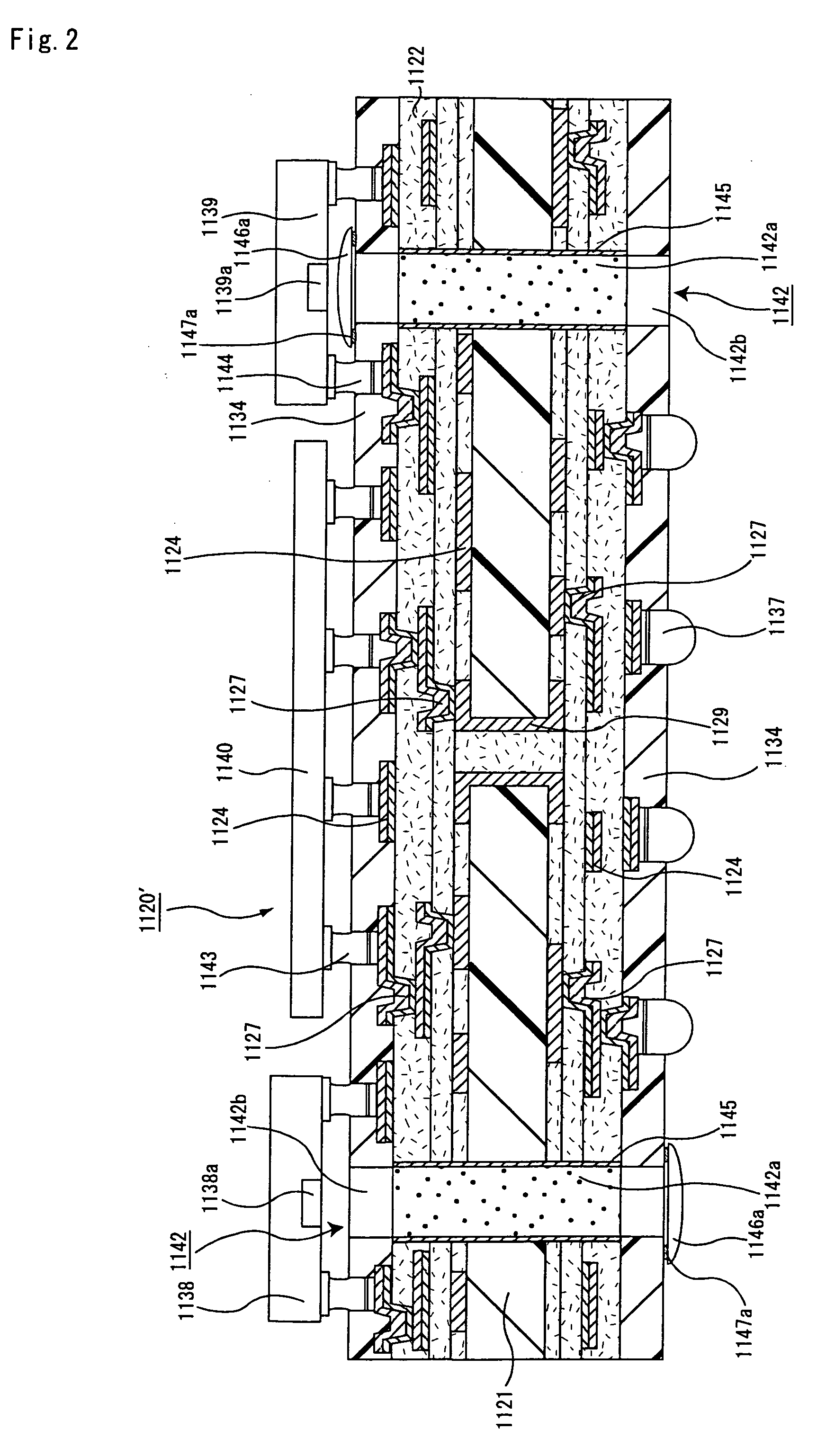

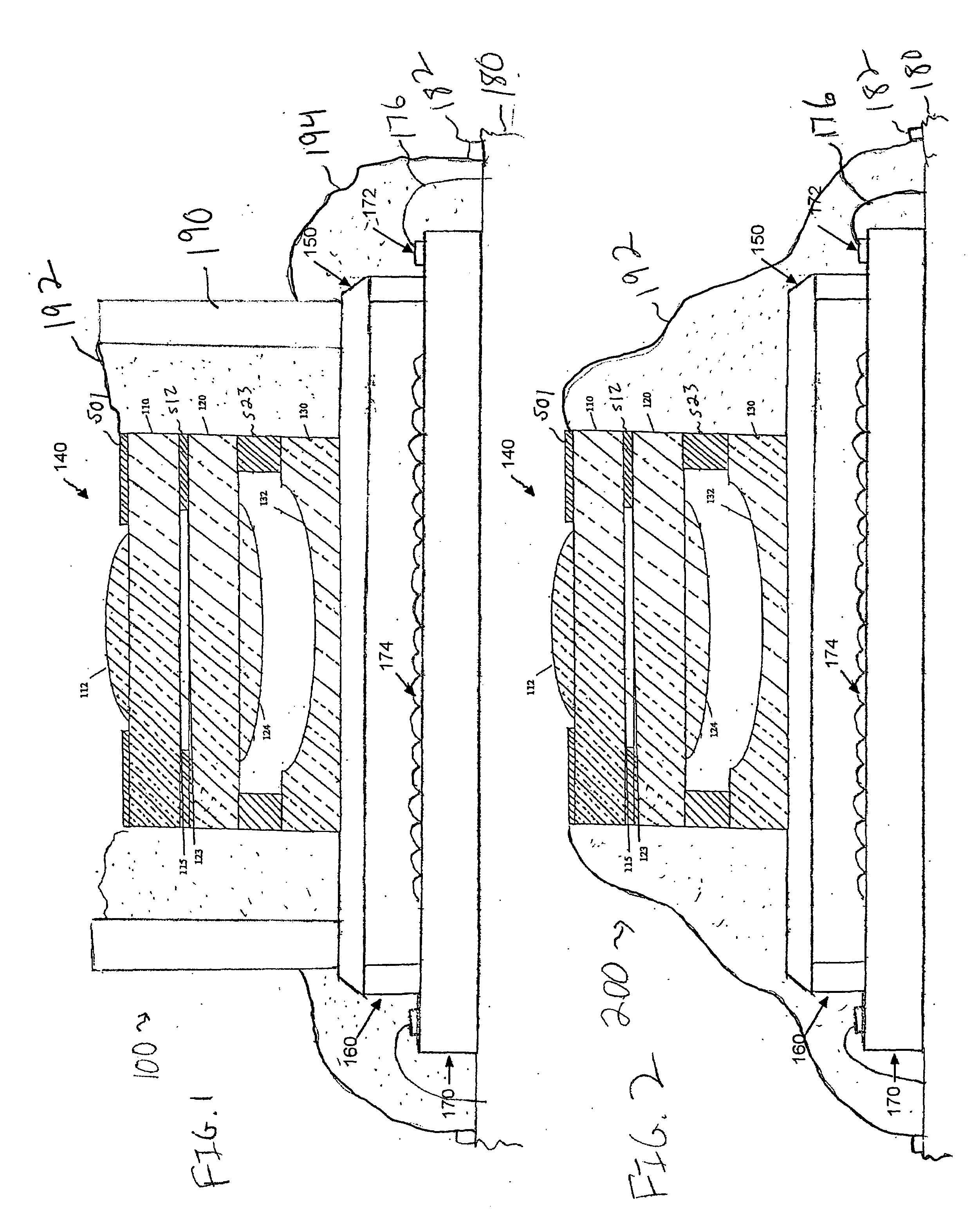

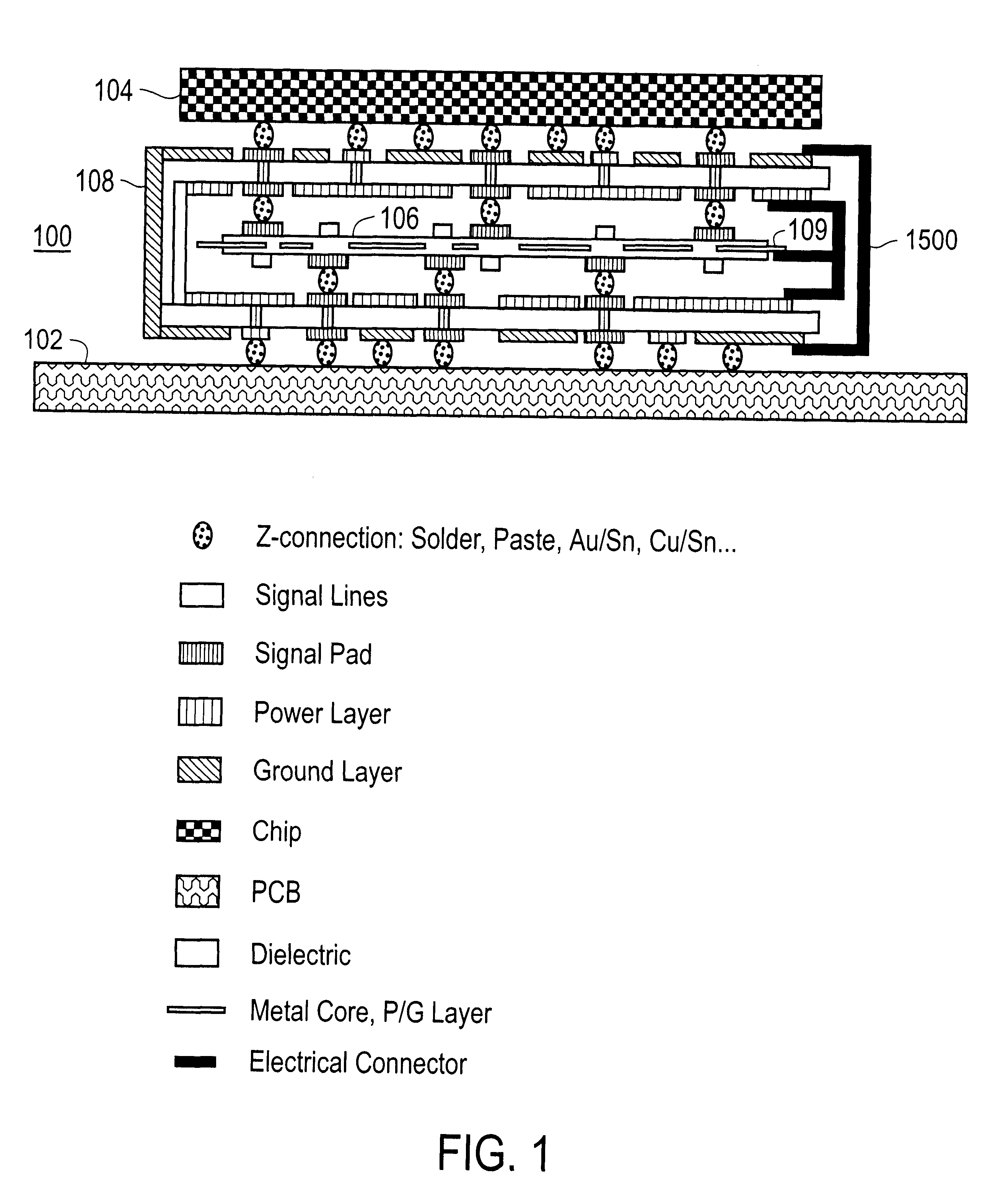

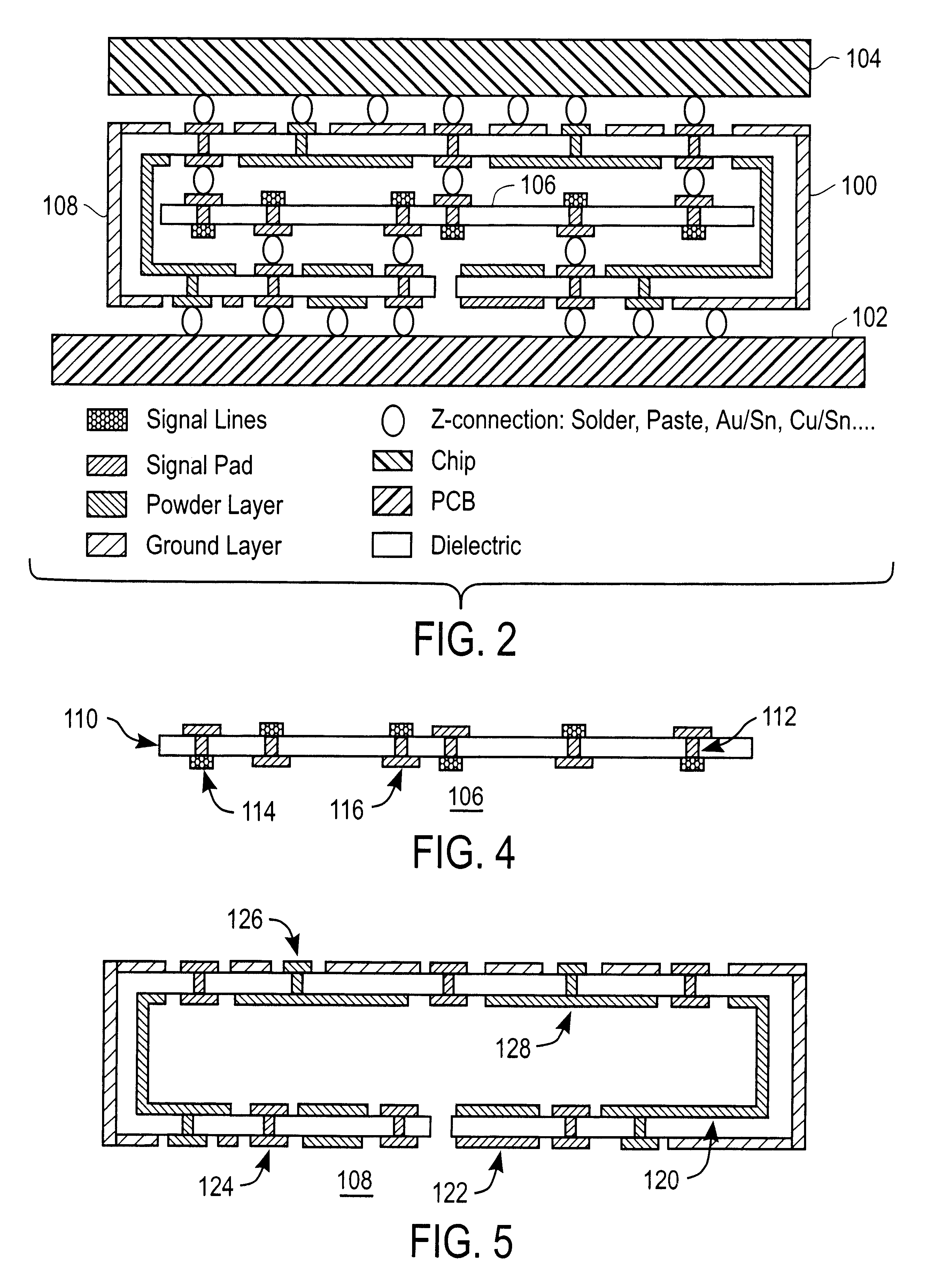

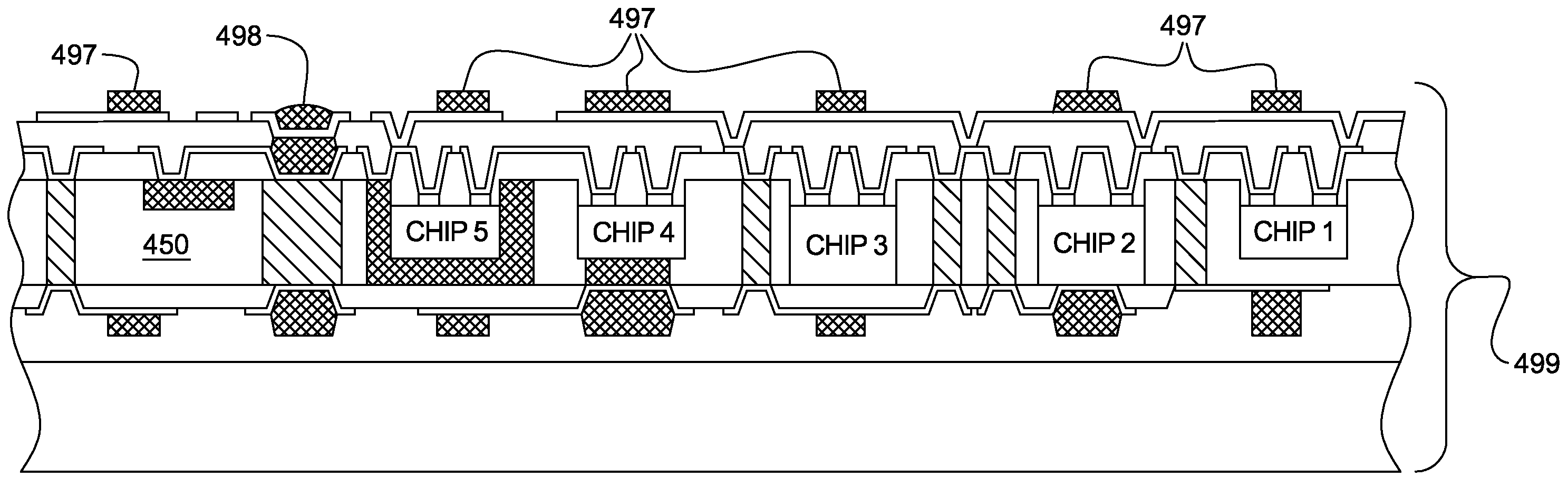

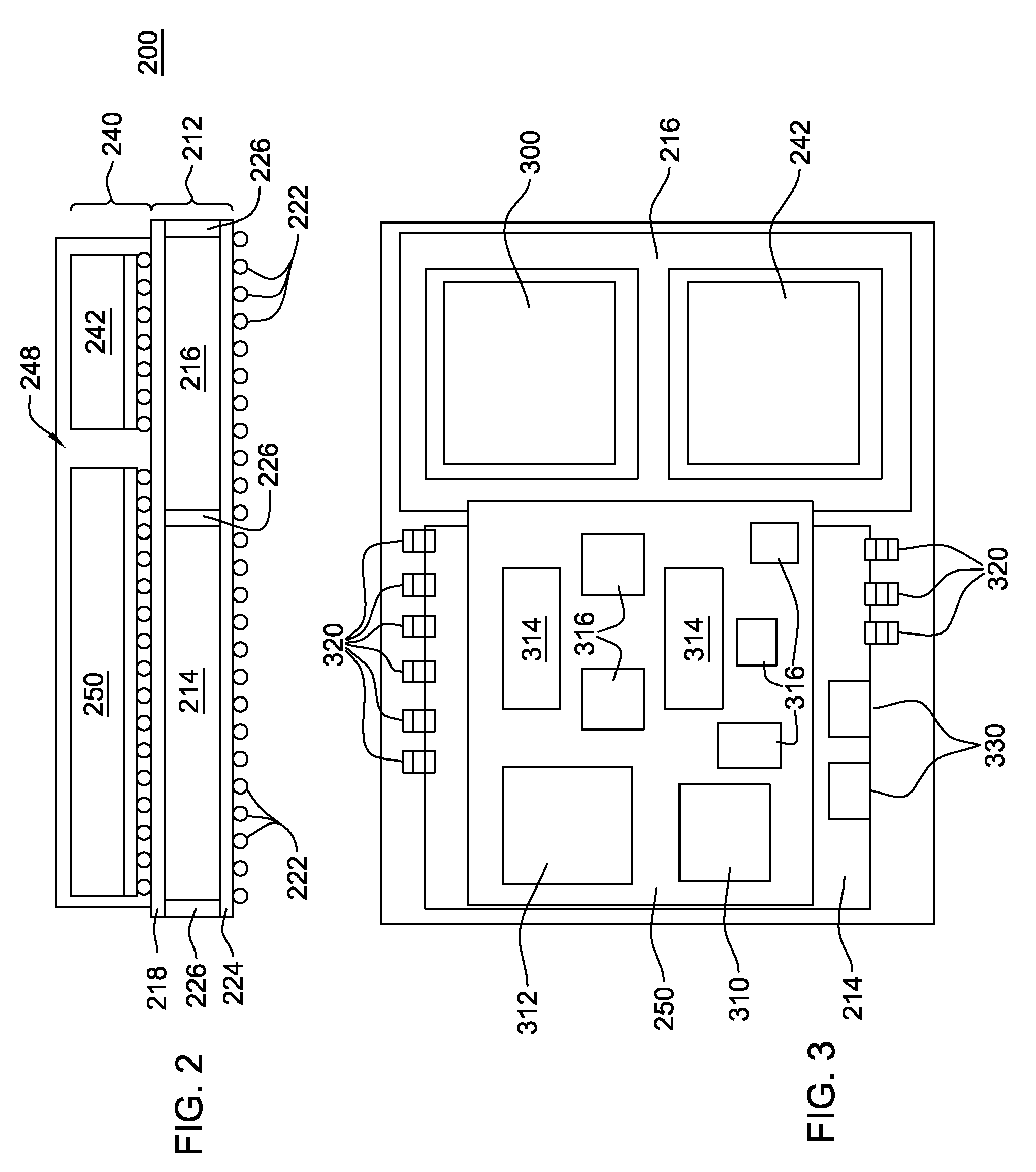

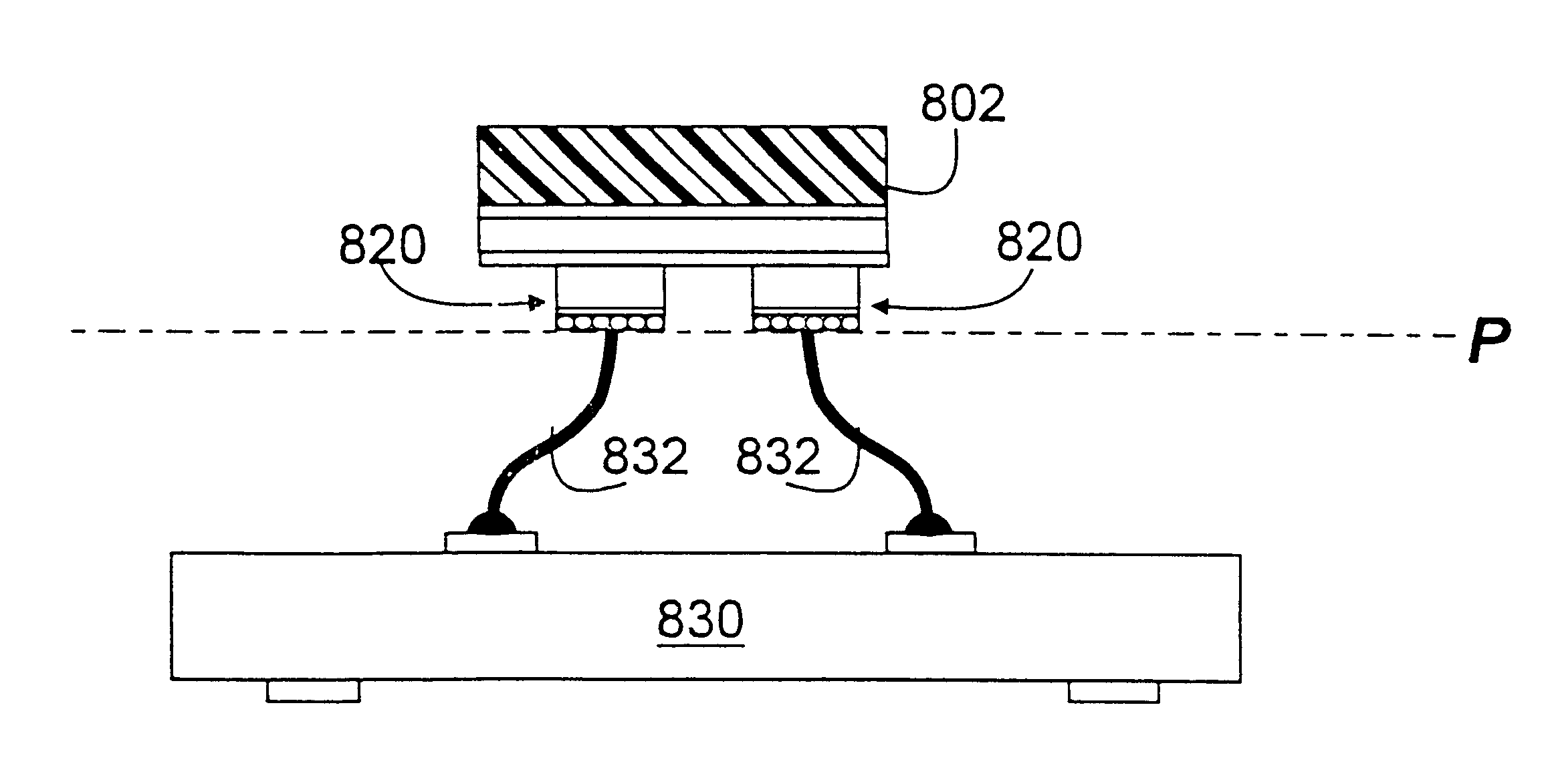

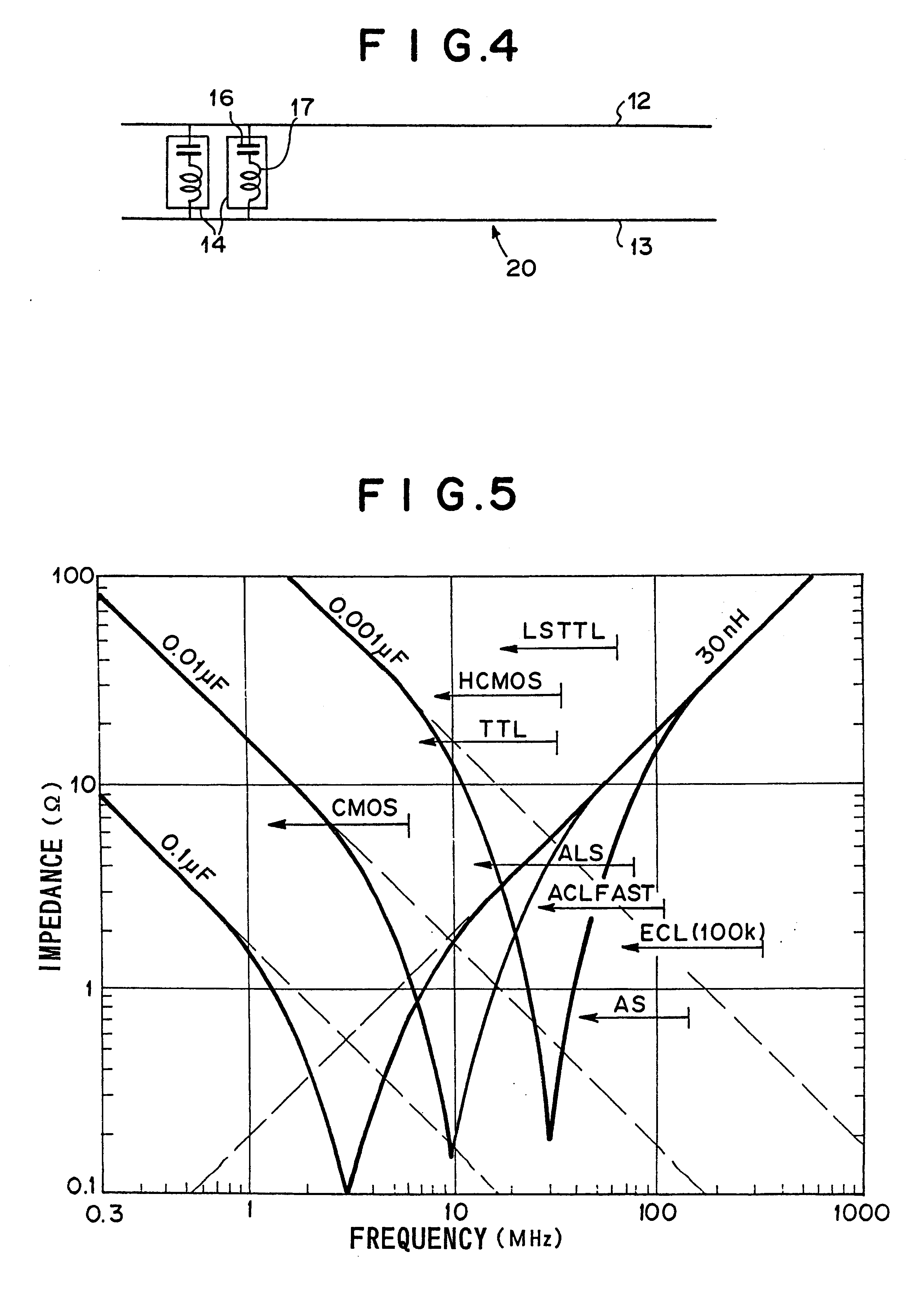

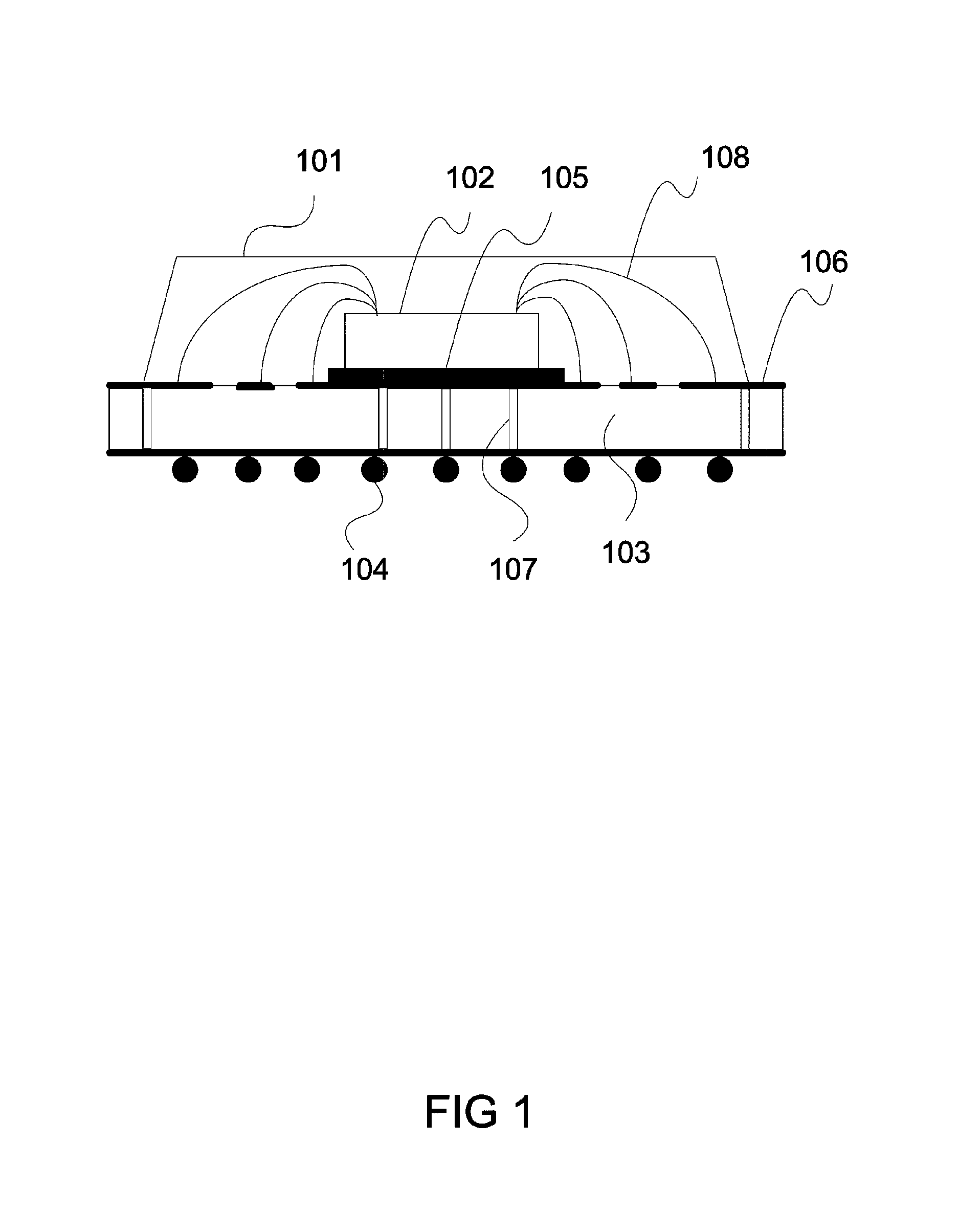

Integrated structures and fabrication methods thereof implementing a cell phone or other electronic system

ActiveUS7619901B2Semiconductor/solid-state device detailsSolid-state devicesElectronic systemsContact pad

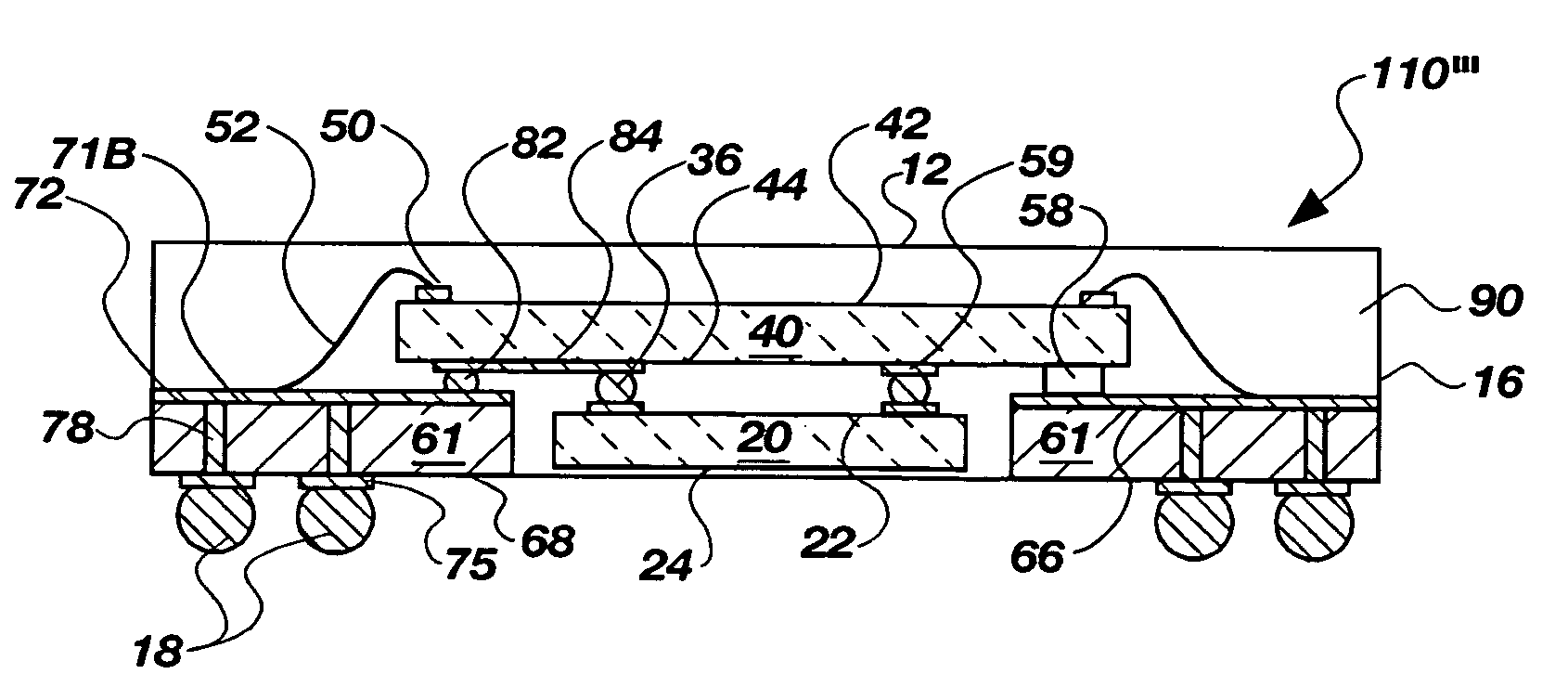

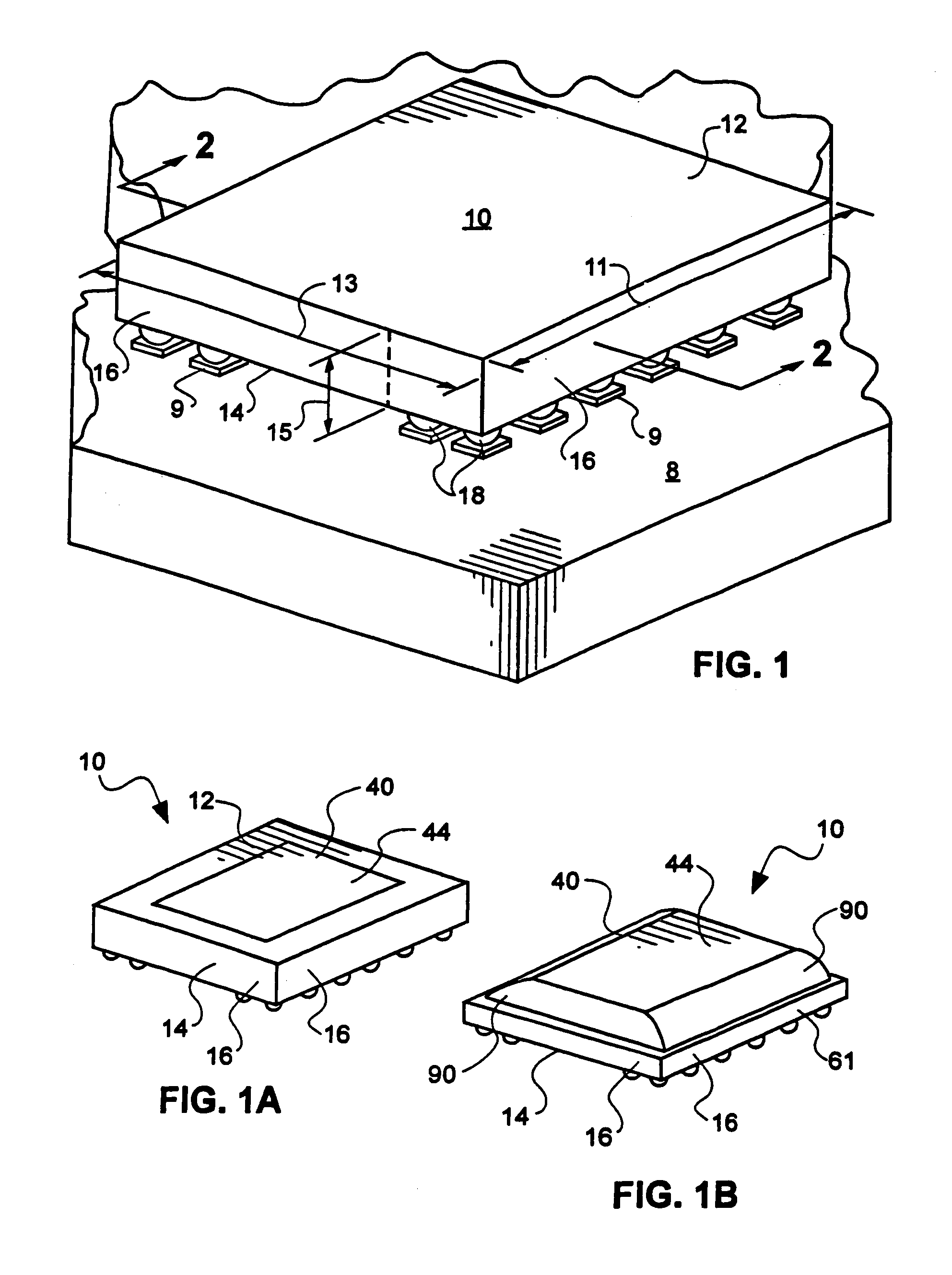

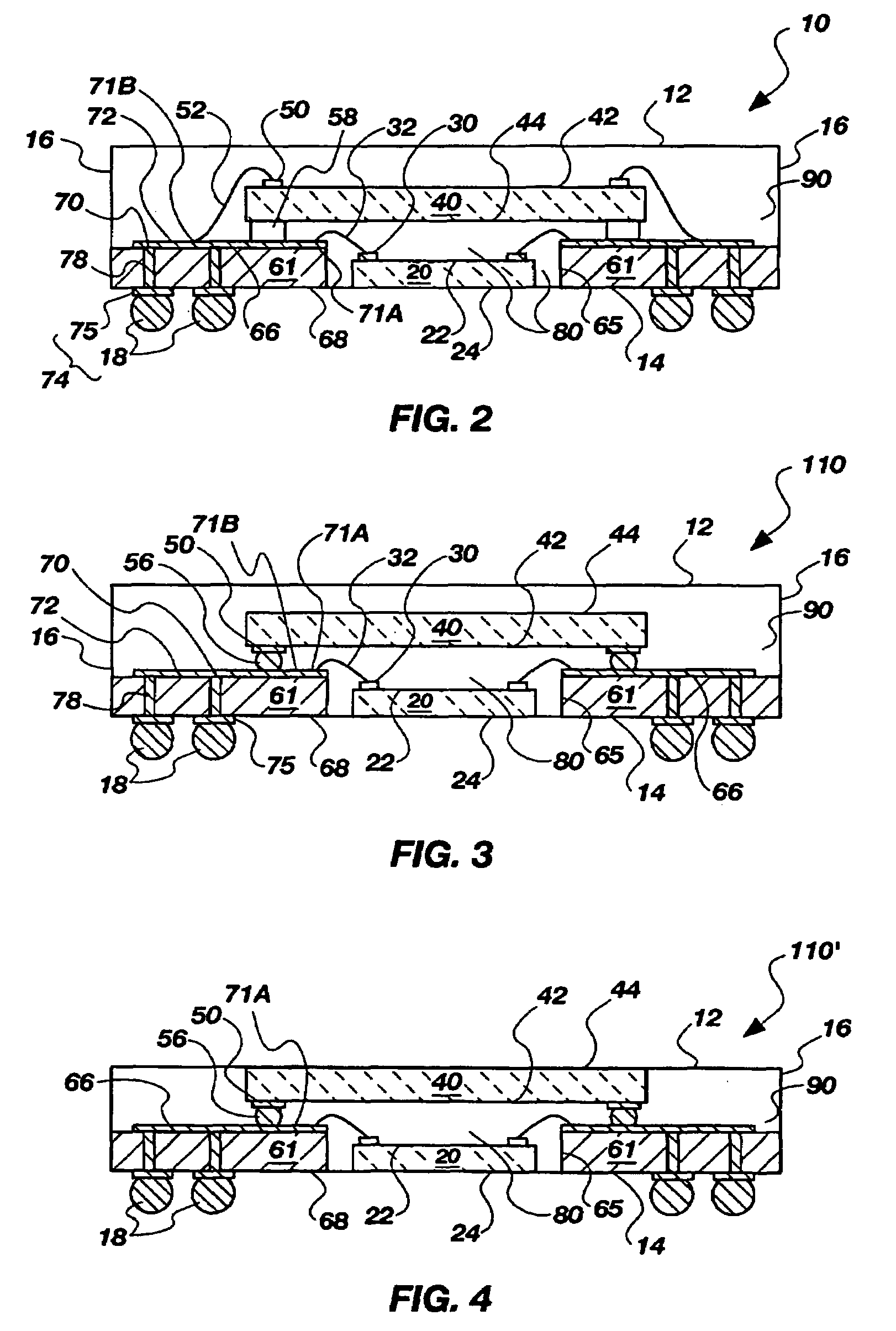

Circuit structures and methods of fabrication are provided for facilitating implementing a complete electronic system in a compact package. The circuit structure includes, in one embodiment, a chips-first multichip base layer with conductive structures extending therethrough. An interconnect layer is disposed over the front surface of the multichip layer and includes interconnect metallization electrically connected to contact pads of the chips and to conductive structures extending through the structural material. A redistribution layer, disposed over the back surface of the multichip layer, includes a redistribution metallization also electrically connected to conductive structures extending through the structural material. Input / output contacts are arrayed over the redistribution layer, including over the lower surfaces of at least some integrated circuit chips within the multichip layer, and are electrically connected through the redistribution metallization, conductive structures, and interconnect metallization to contact pads of the integrated circuit chips of the multichip layer.

Owner:EPIC TECH INC

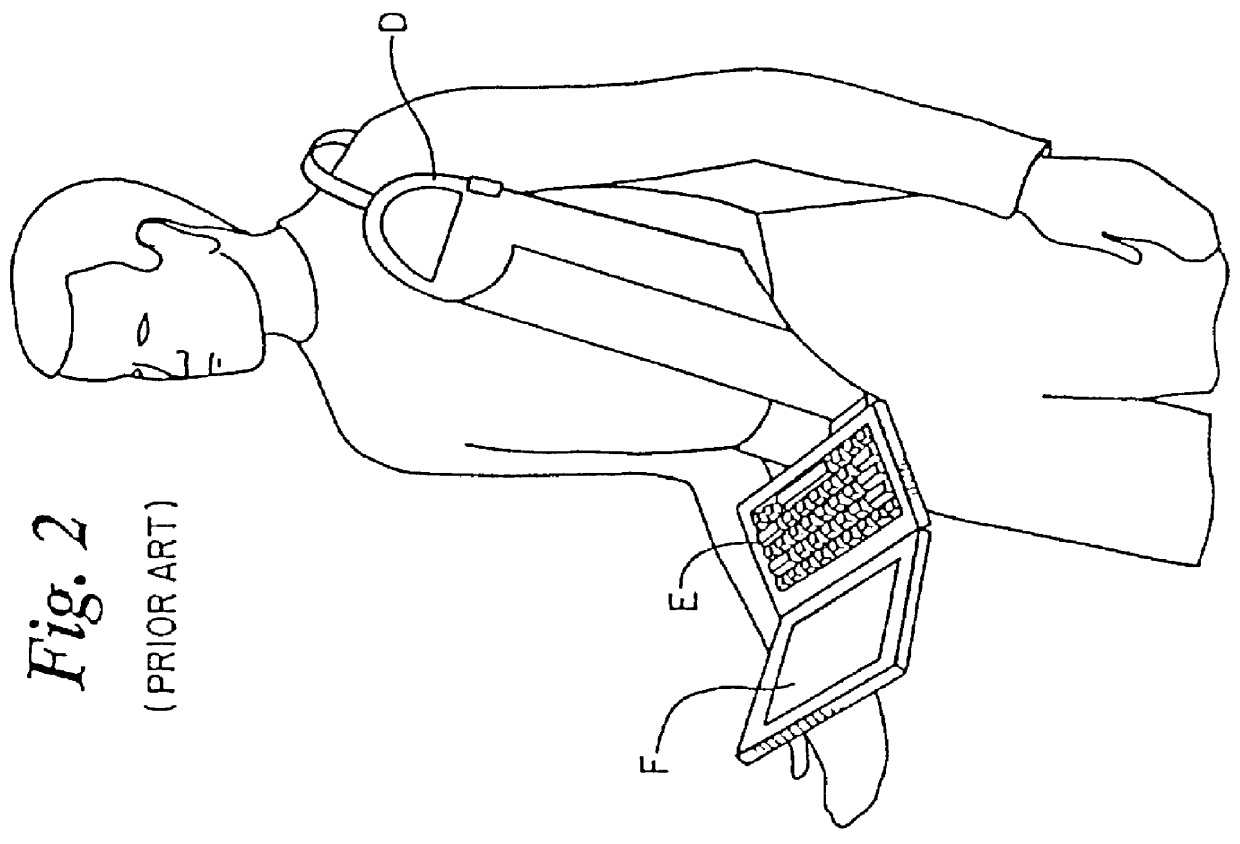

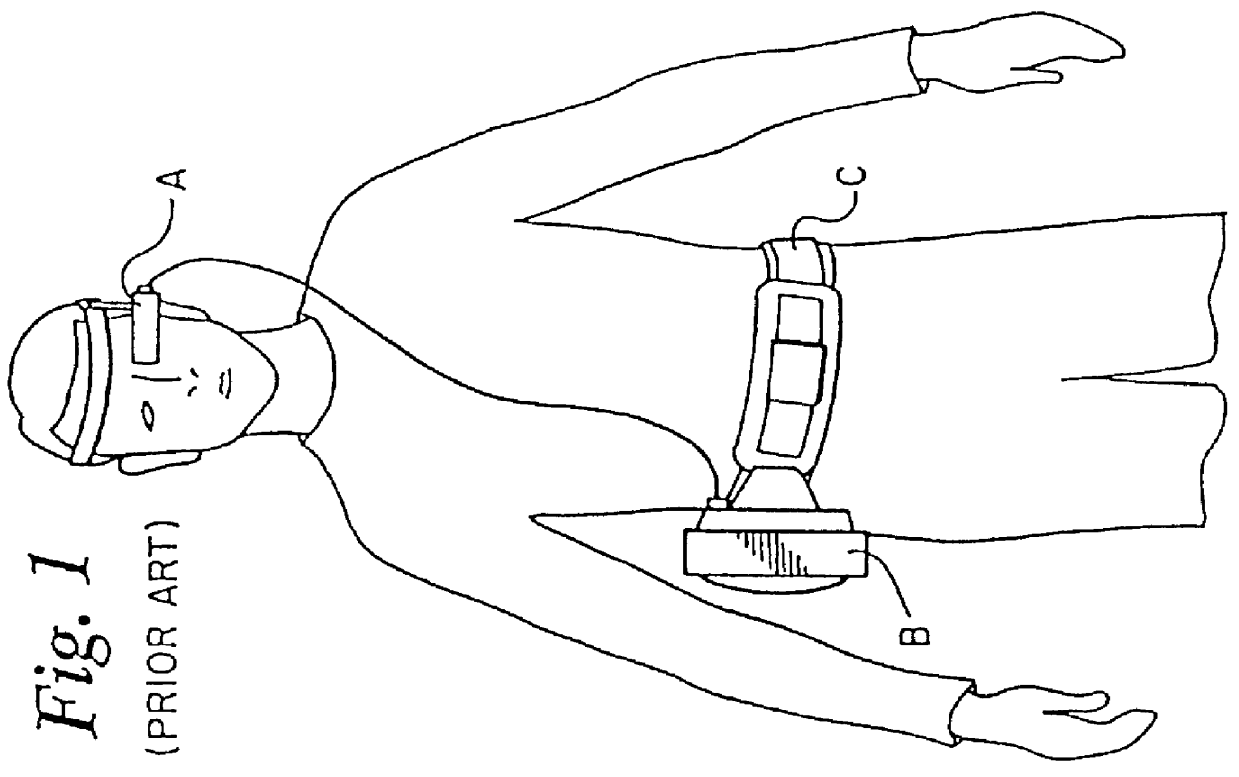

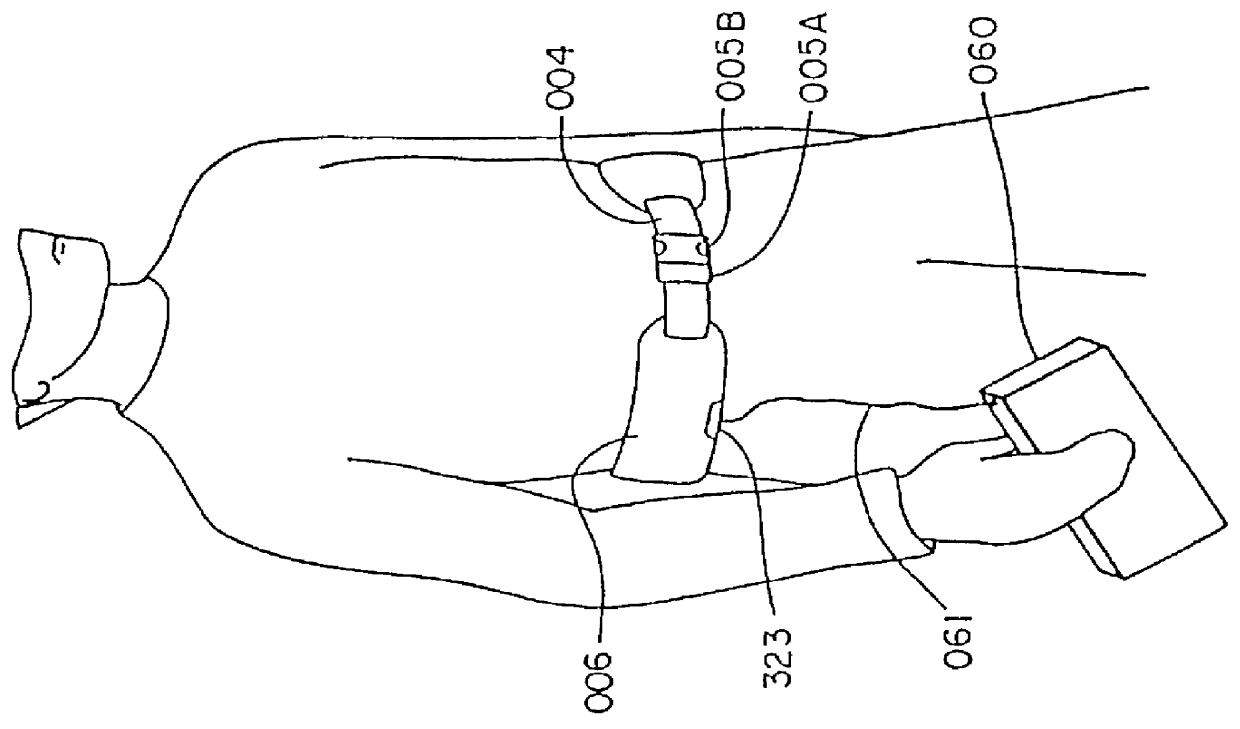

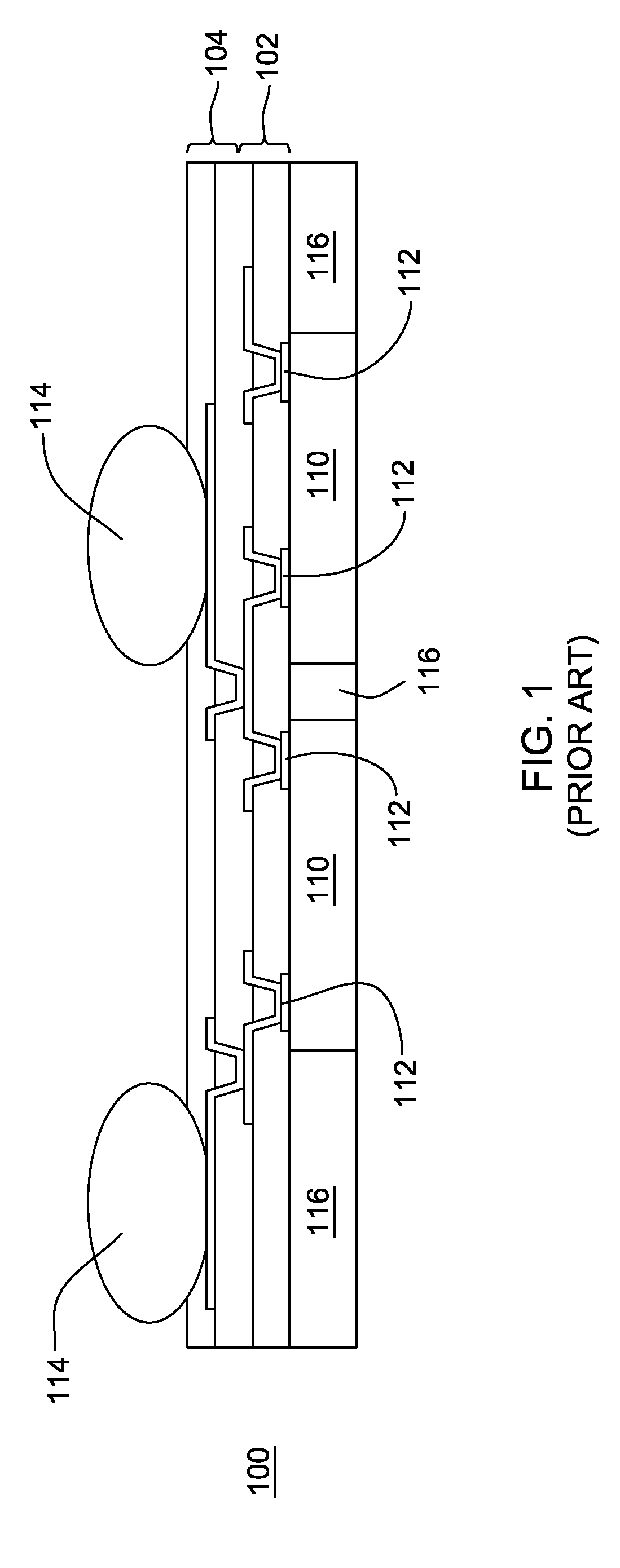

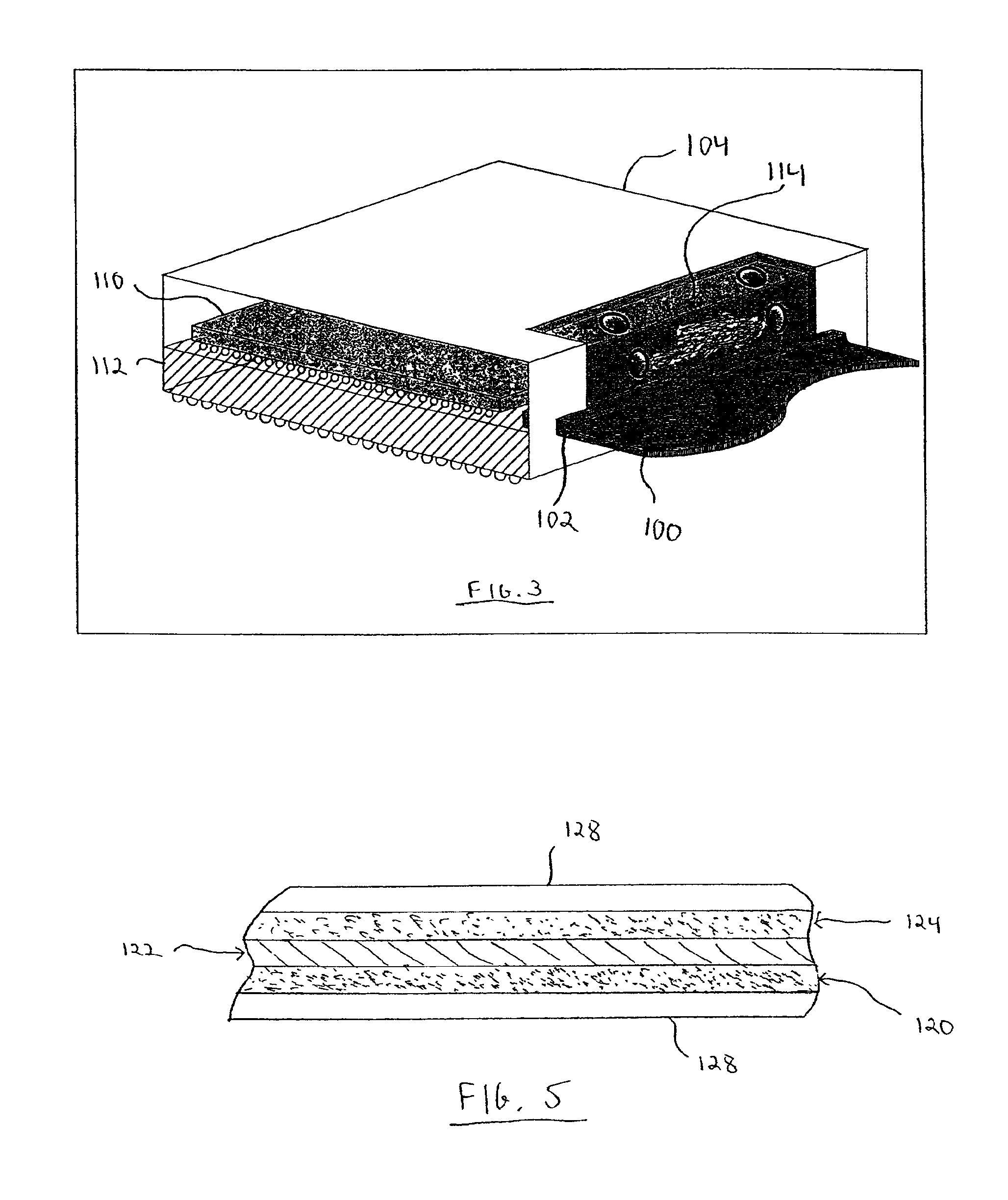

Flexible wearable computer

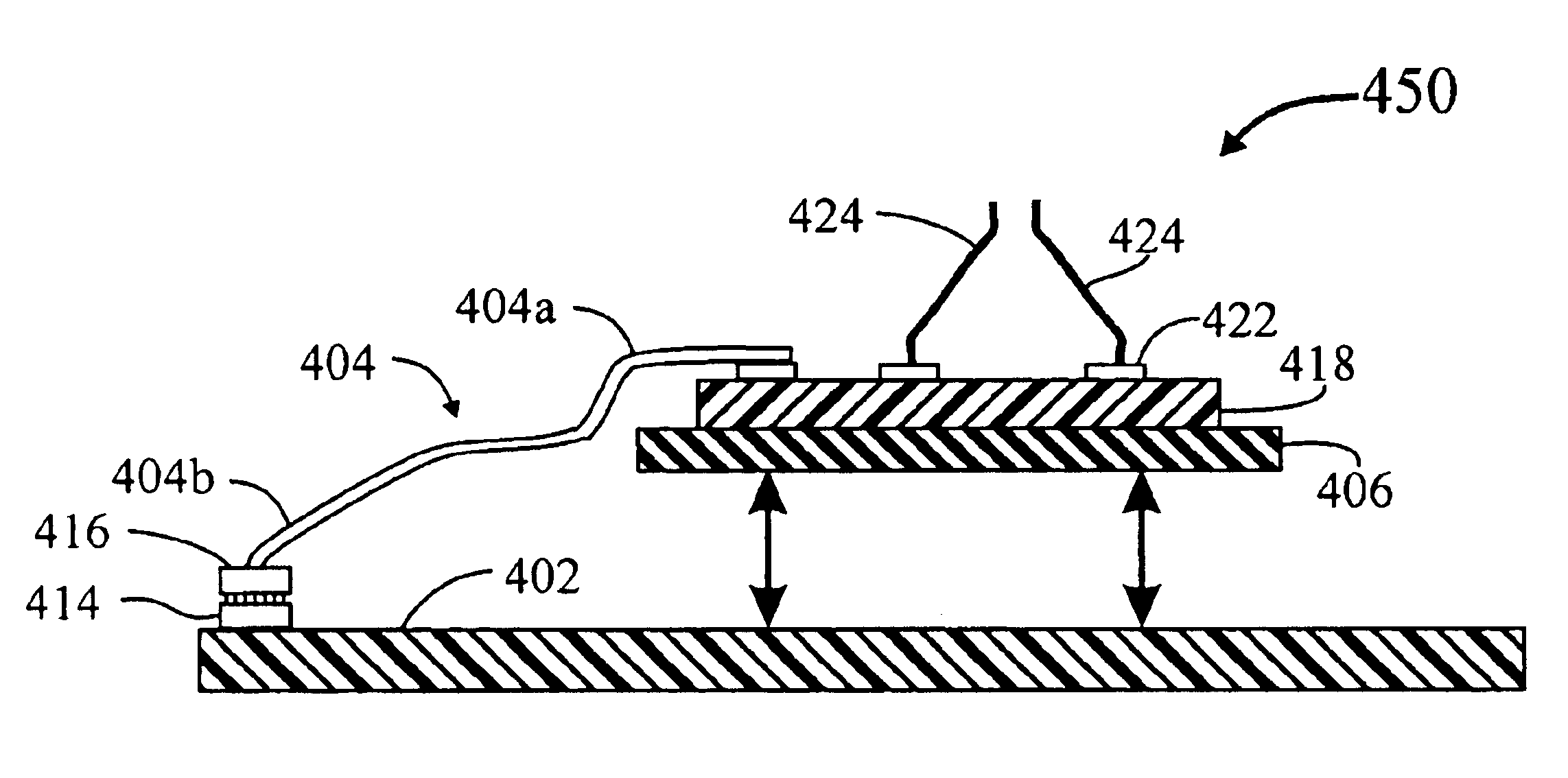

InactiveUS6108197AEasily and comfortably be expandedIncreased durabilityInput/output for user-computer interactionPrinted circuit assemblingComputer moduleRadio frequency

A wearable computing device includes computing-device component modules and flexible circuitry passing into the modules. The modules can include a top module portion and a bottom module portion, the flexible circuitry passing between the top and bottom portions. Wireless communication, e.g. by radio frequency, with a peripheral and / or a local area network is also contemplated.

Owner:EMBEDDED TECH +1

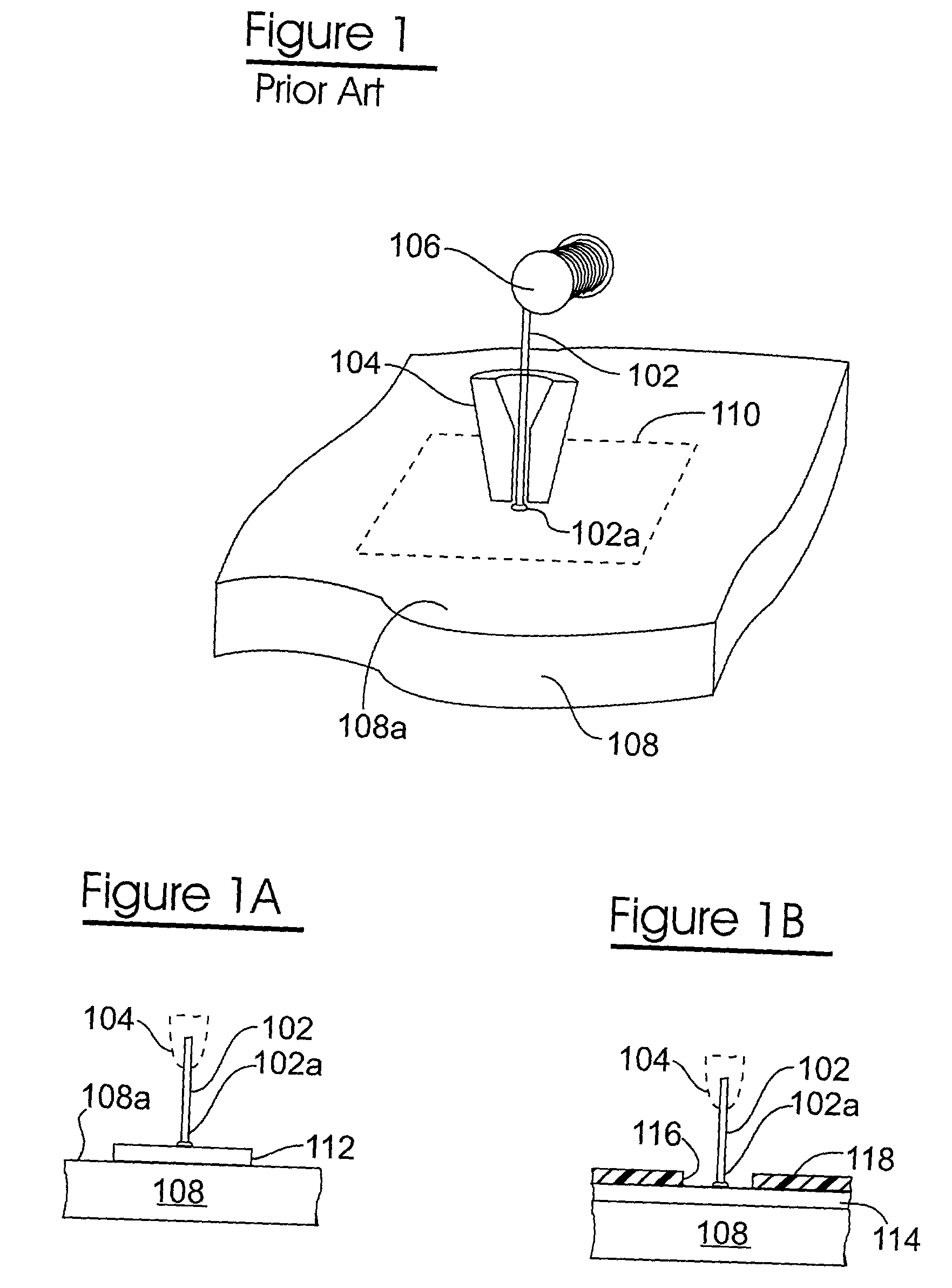

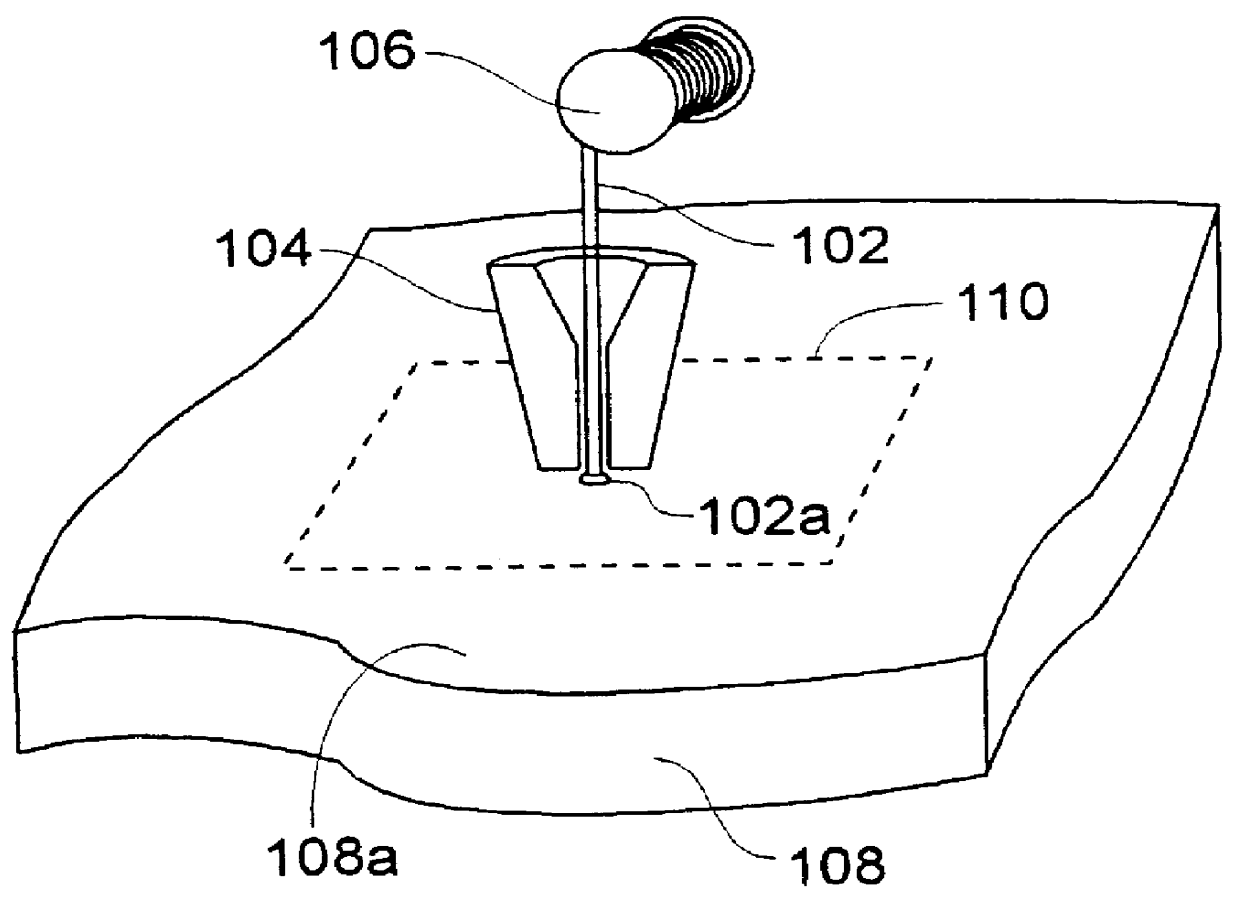

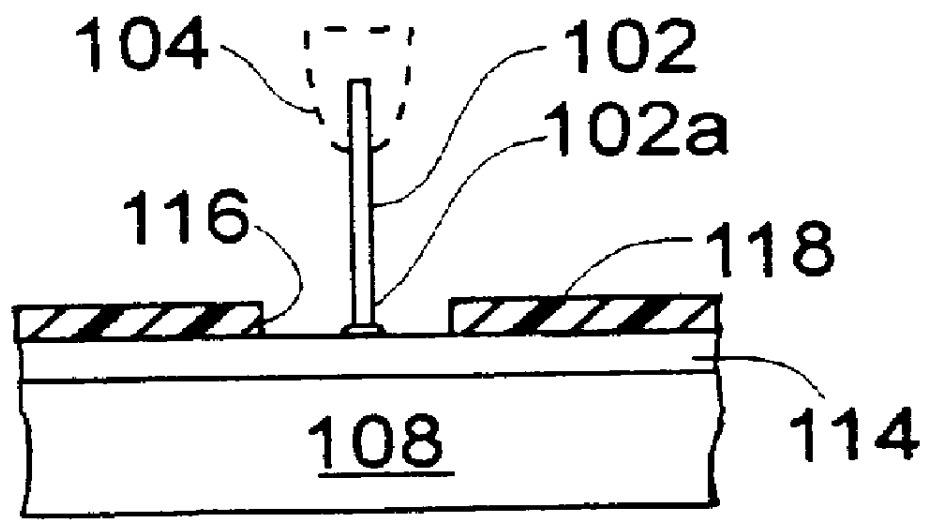

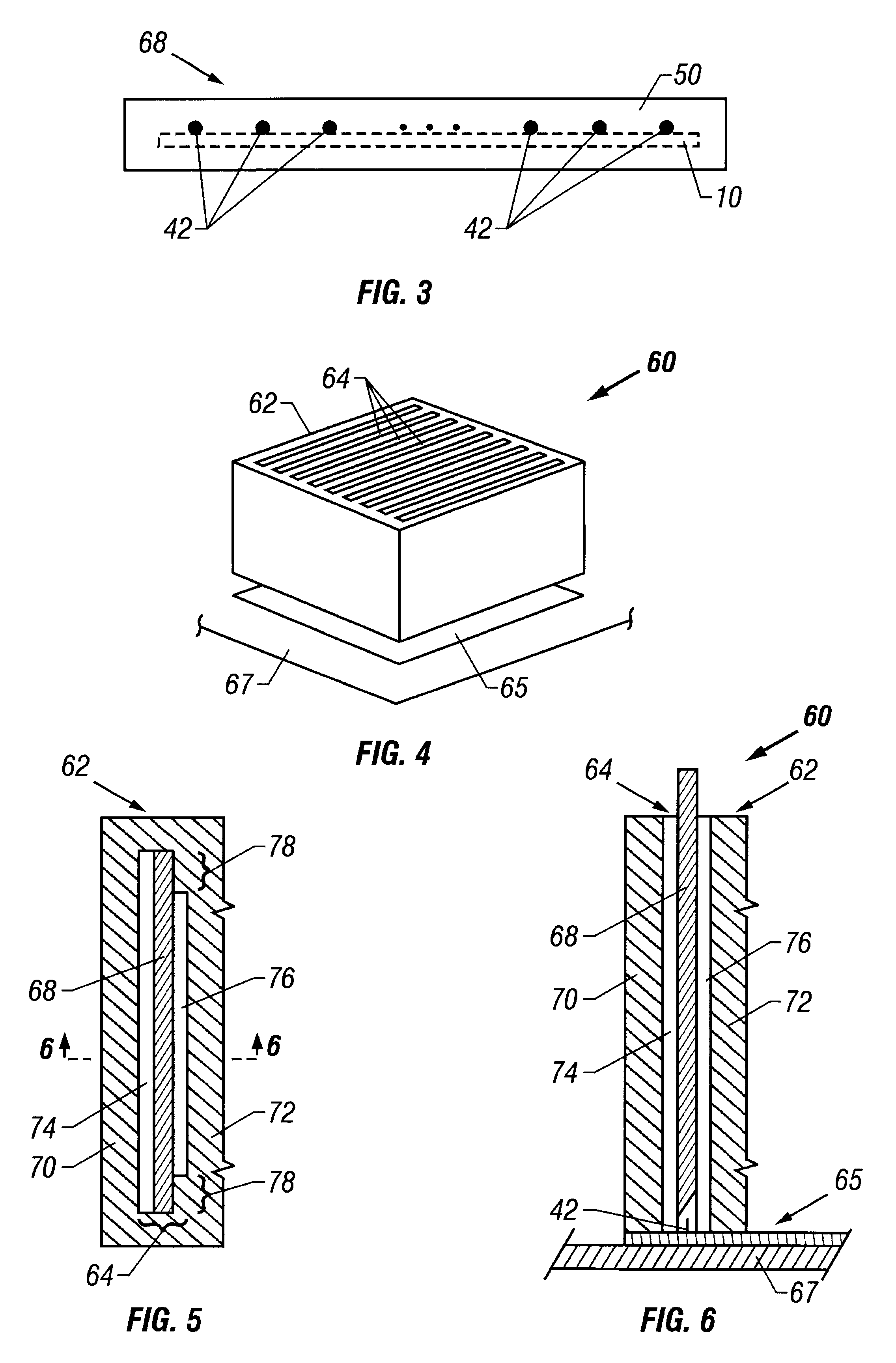

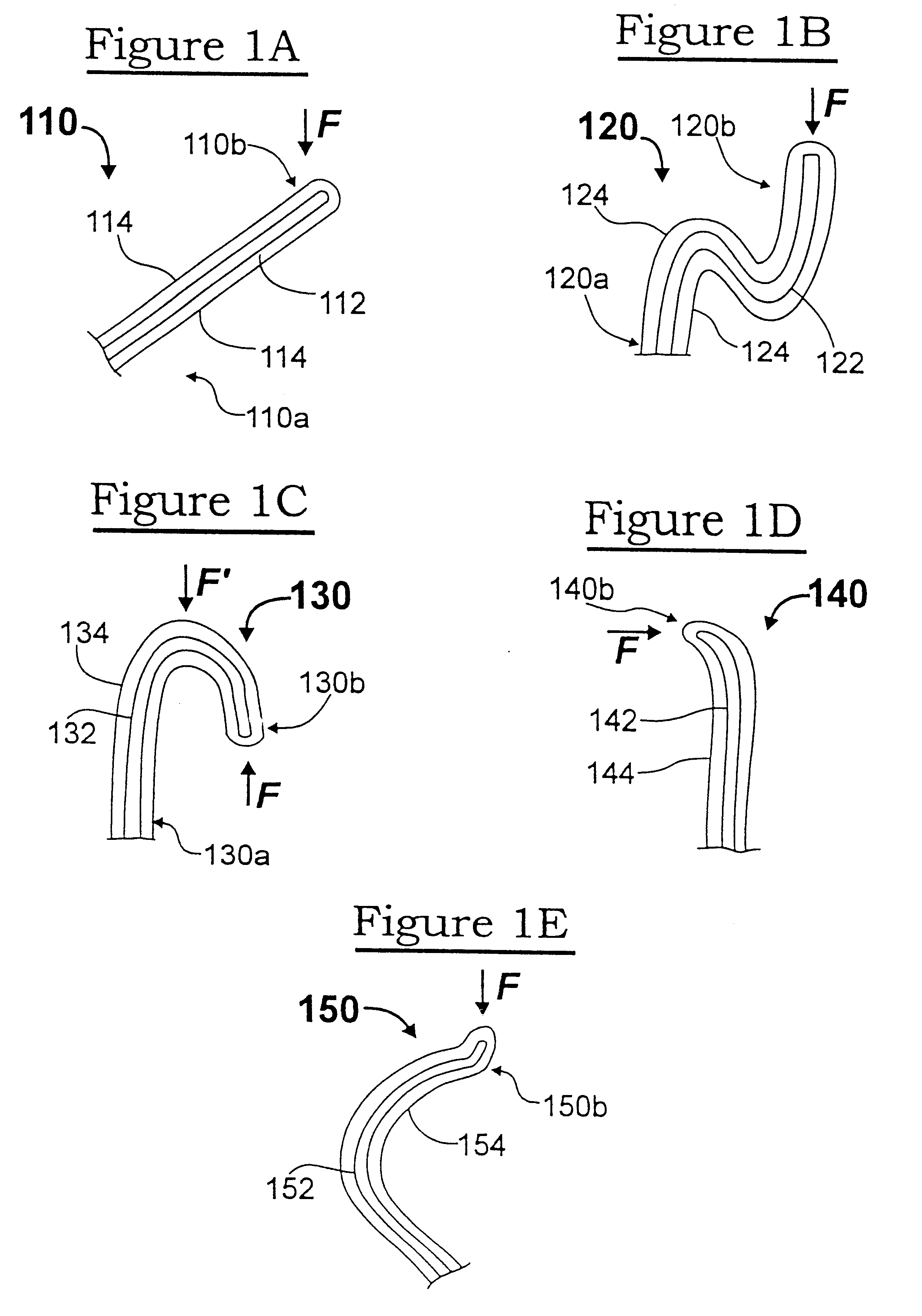

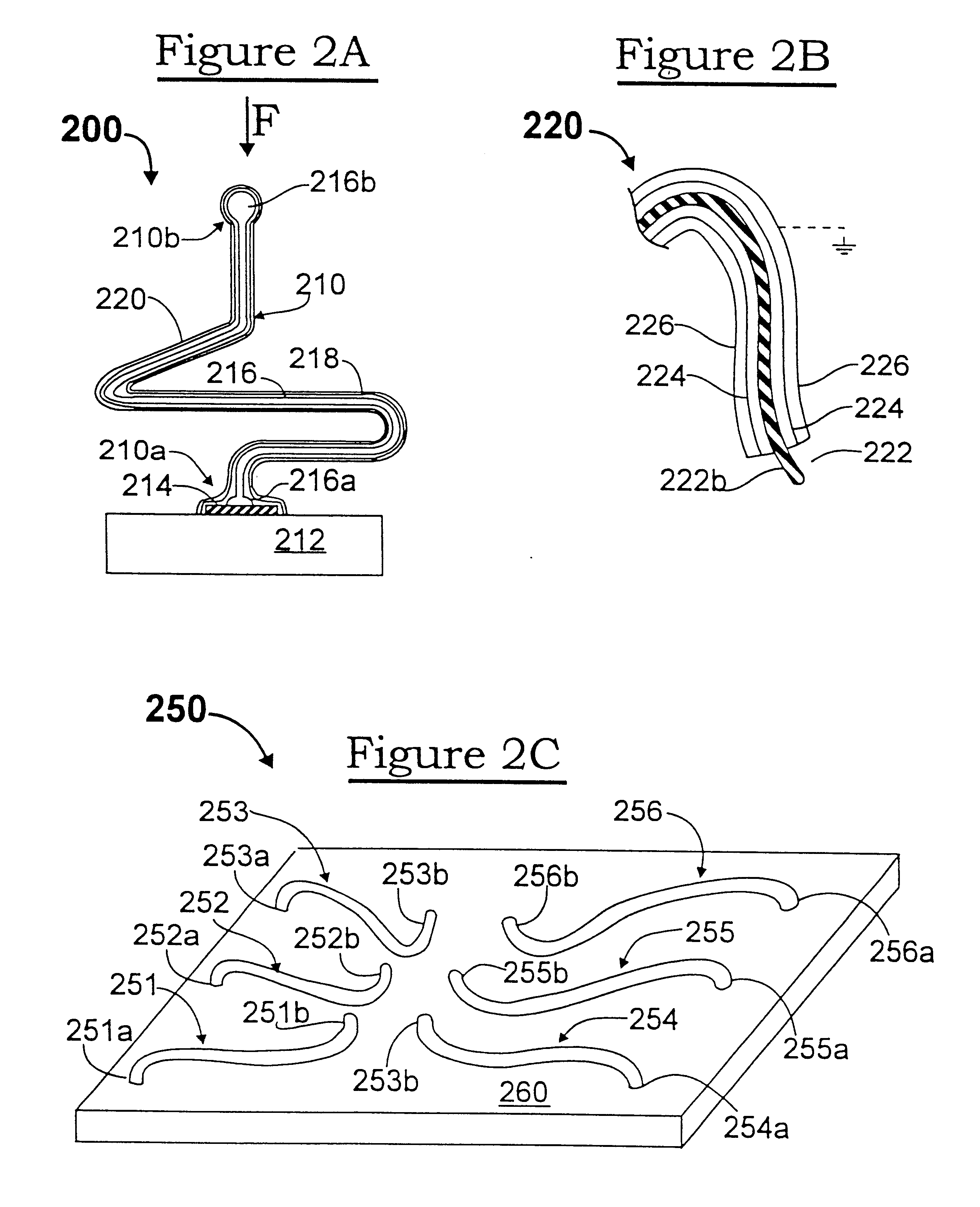

Resilient contact structures formed and then attached to a substrate

InactiveUS20020117330A1Simple technologyCoupling device connectionsSemiconductor/solid-state device testing/measurementEngineeringTopography

Owner:FORMFACTOR INC

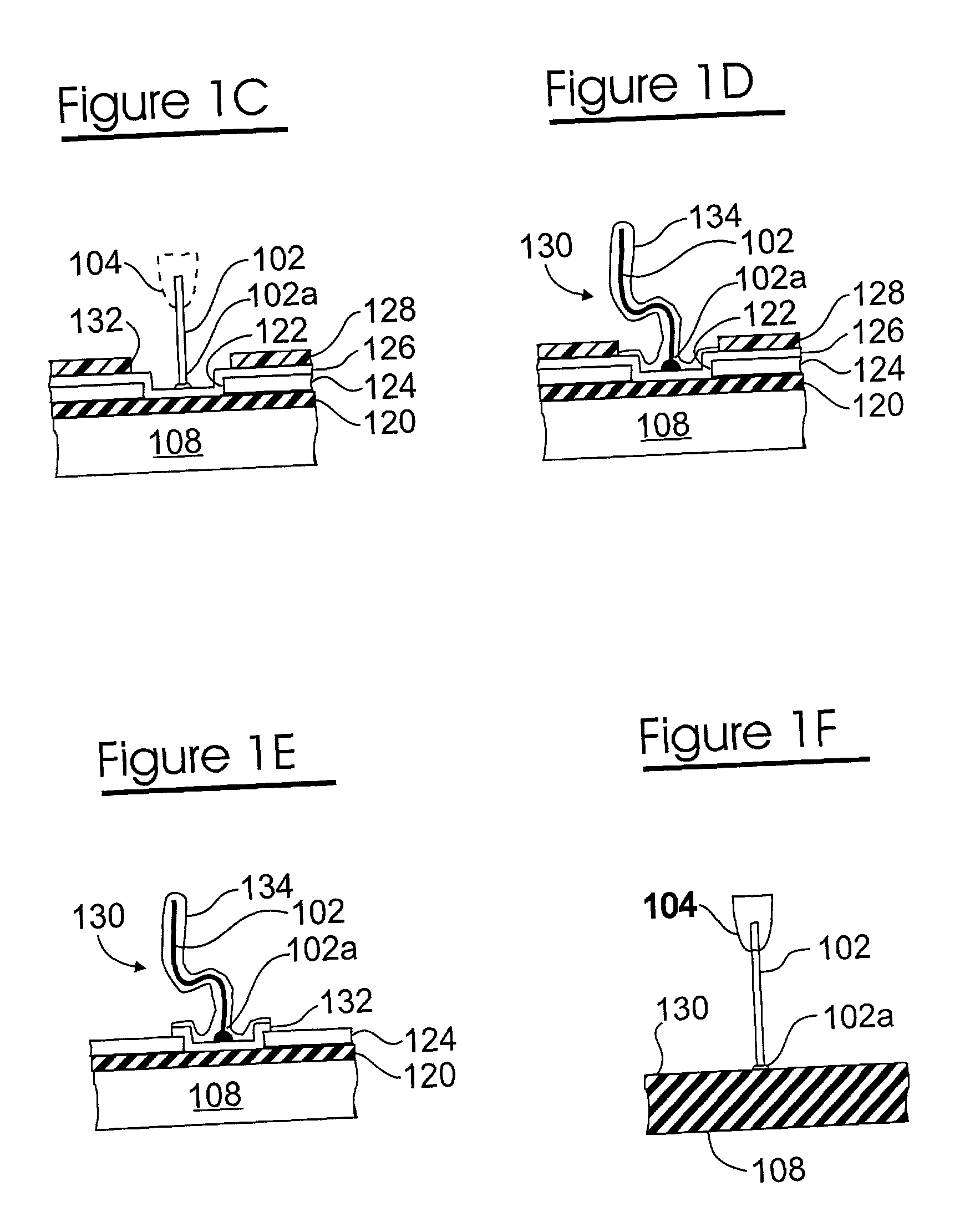

Method of modifying the thickness of a plating on a member by creating a temperature gradient on the member, applications for employing such a method, and structures resulting from such a method

InactiveUS6110823ASimple technologyTrend downSemiconductor/solid-state device testing/measurementFinal product manufactureEngineeringElectronic component

Contact structures exhibiting resilience or compliance for a variety of electronic components are formed by bonding a free end of a wire to a substrate, configuring thw wire into a wire stem having a springable shape, serving thw wire stem, and overcoating the wire stem with at least one layer of a material chosen primarily for its structural (resiliency, compliance) characteristics. A variety of techniques for configuring, serving, and overcoating the wire stem are disclosed. In an exemplary embodiment, a free end of a wire stem is bonded to a contact area on a substrate, the wire stem is configured to ahve a springable shape, the wire stem is served to be free-standing by an electrical discharge, and the free-standing wire stem is overcoating by plating.

Owner:FORMFACTOR INC

Method and apparatus for a semiconductor package for vertical surface mounting

InactiveUS6291894B1Electrically conductive connectionsDigital data processing detailsDevice materialSurface mounting

A method for packaging a semiconductor device includes connecting a plurality of wire leads to a corresponding plurality of electrical connection pads on the semiconductor device, covering at least a portion of the semiconductor device and at least a portion of each of the wire leads with an encapsulating material, and removing a portion of the encapsulating material and a portion of each of the wire leads to form a packaged semiconductor device wherein each of the wire leads has an exposed portion only at an end. The invention also includes a packaged semiconductor device having an integrated circuit device with a plurality of electrical connection pads, a plurality of wire leads coupled to the plurality of electrical connection pads, and a covering of encapsulating material covering at least a portion of the integrated circuit device and covering each of the wire leads, wherein each of the wire leads has an exposed end. The present invention contemplates wire bonding and encapsulation of individual die as well as multiple die on a single wafer.

Owner:MICRON TECH INC

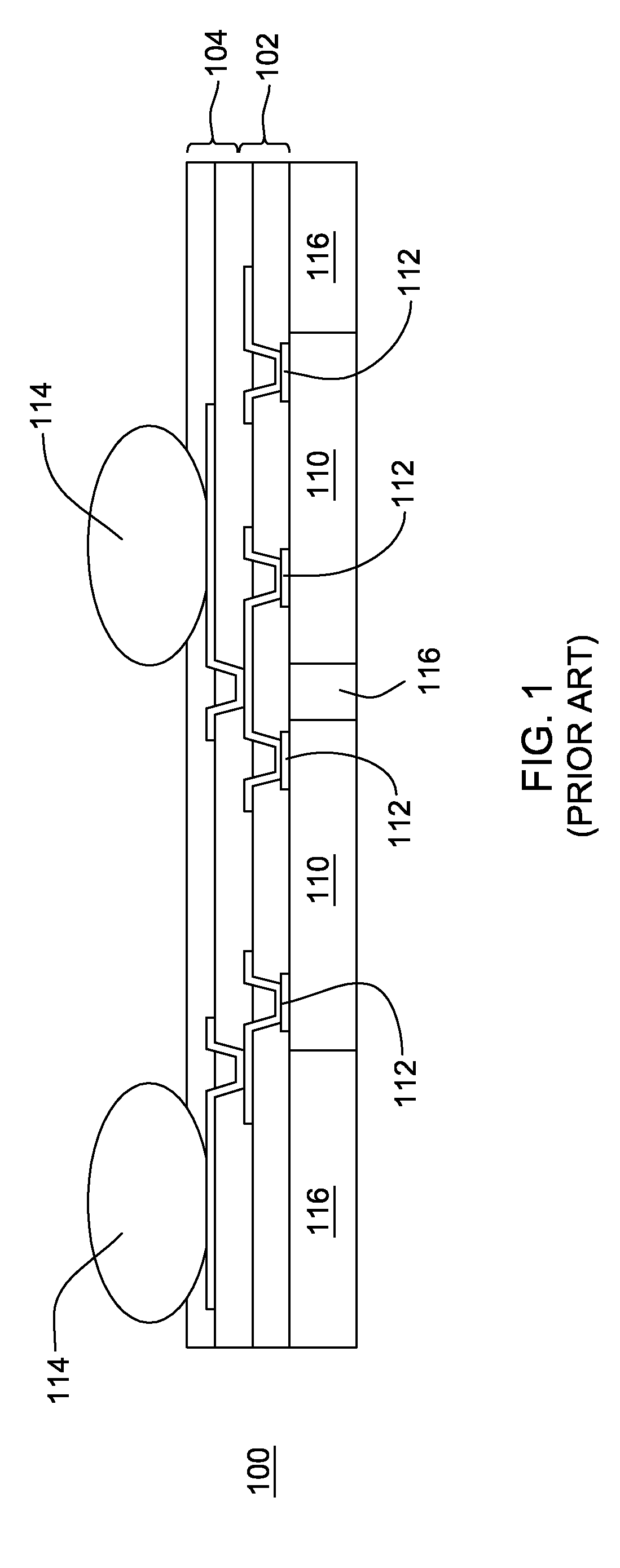

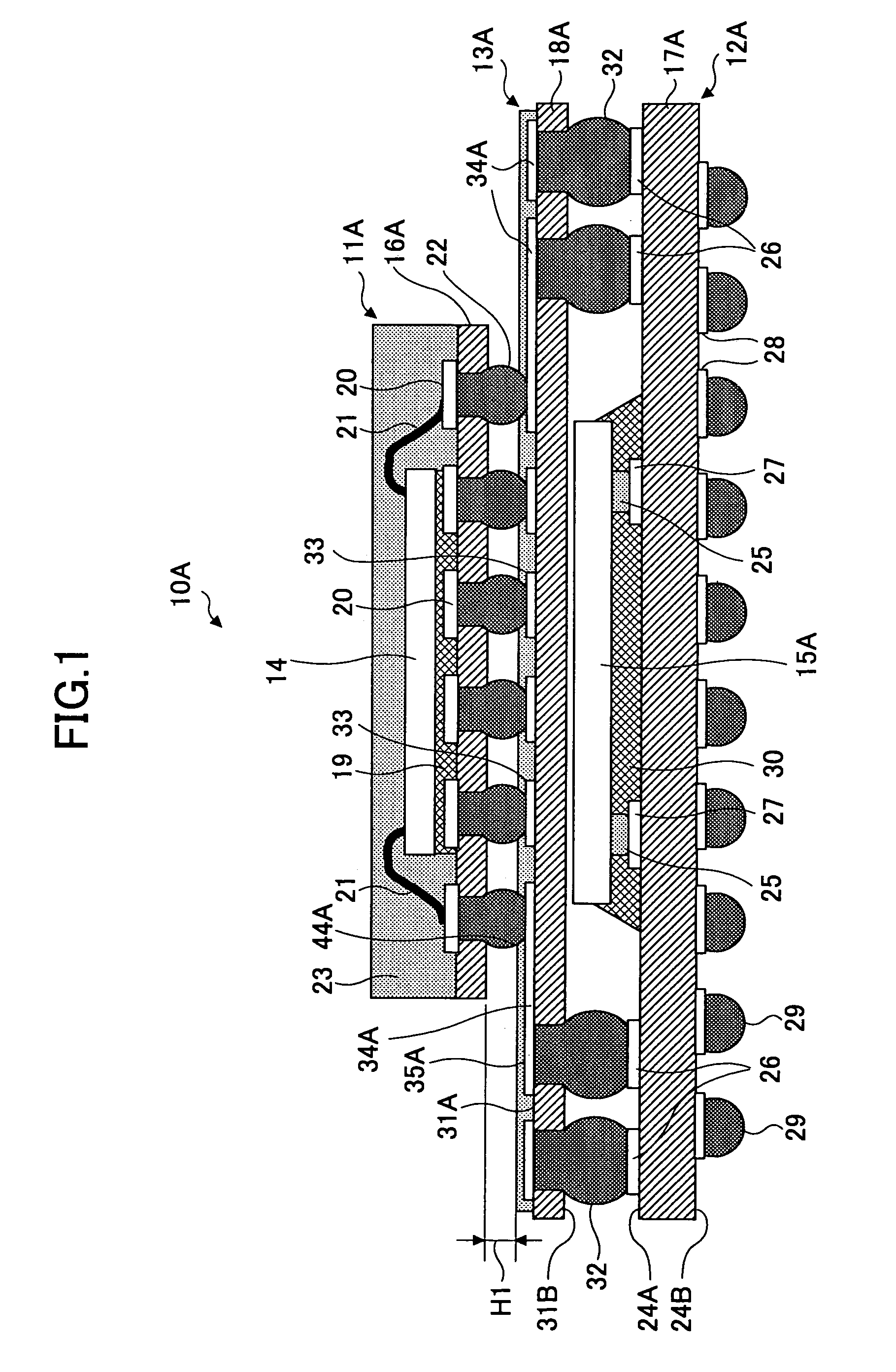

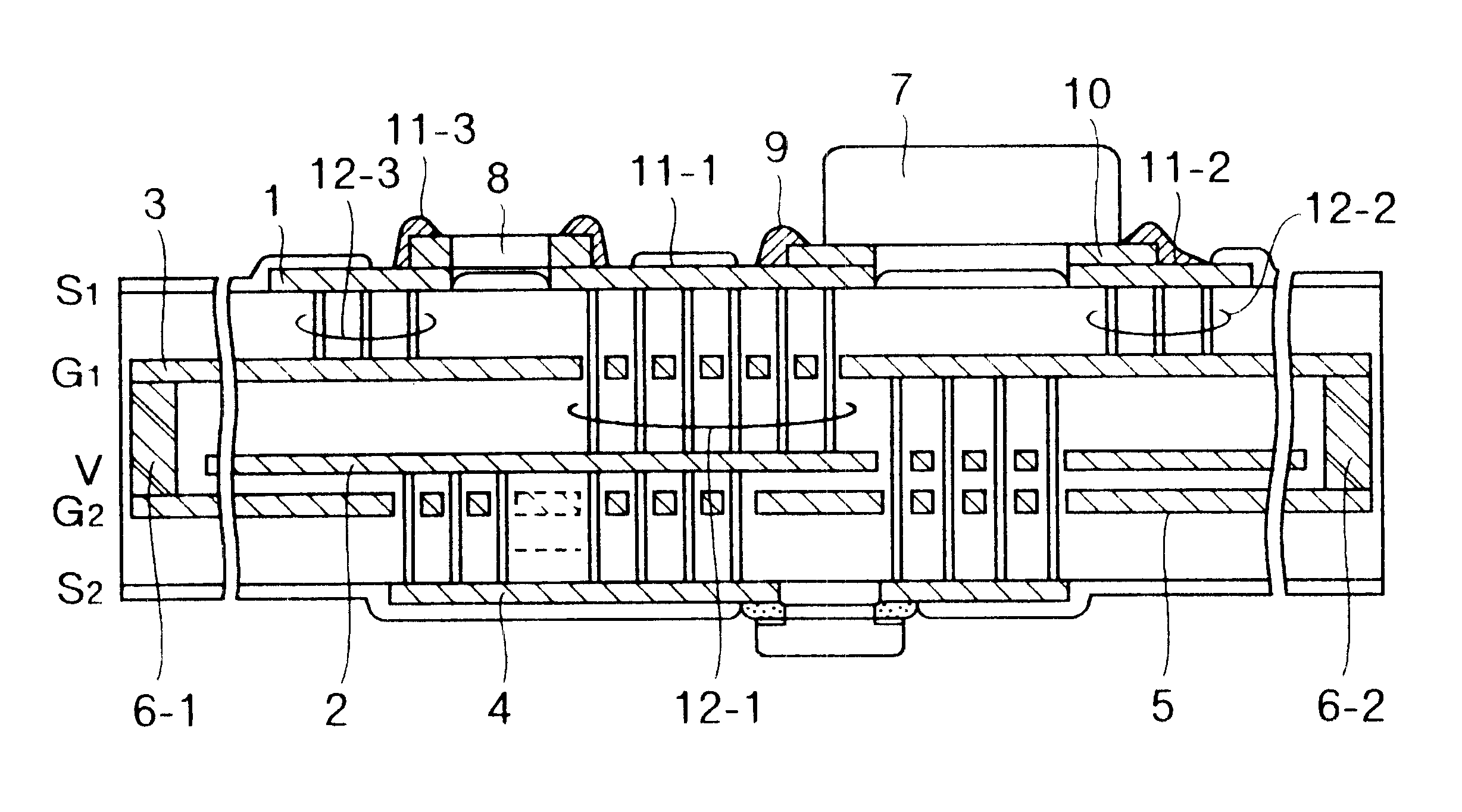

Stacked semiconductor device

ActiveUS7049692B2Eliminate the problemPrinted circuit assemblingSemiconductor/solid-state device detailsGeneral purposeEngineering

A stacked semiconductor device is disclosed that has a three-dimensional structure using general-purpose semiconductor device units (semiconductor devices) that are stacked with an interposer substrate being provided between an upper device unit and a lower device unit. The upper device unit includes a semiconductor device, a first wiring substrate, and an external connection terminal. The lower device unit includes a semiconductor device, a second wiring substrate, and a connection electrode that is prepared on the upper surface of the second wiring substrate. The interposer substrate includes a circuit board, a first conductive material connecting to the connection electrode, a second conductive material formed in a form position of the external connection terminal that is electrically connected to the second conductive material, and a third conductive material for electrically connecting the first conductive material and the second conductive material.

Owner:SOCIONEXT INC

Optical reader comprising multiple color illumination

InactiveUS20030062413A1Reduced dimensionOptimize architectureConveying record carriersCharacter and pattern recognitionLength waveComputer science

An imaging module in one embodiment includes at least one multiple color emitting light source comprising a plurality of different colored LED dies each independently driveable so that the overall color emitted by the light source can be controlled and varied. The multiple color emitting light source can be controlled so that the color emitted by the light source is optimized for imaging or reading in a present application environment of the module. Further, the module can be configured so that control of the multiple color emitting light source automatically varies depending on a sensed condition, such a color present in a field of view of the module, the distance of the module to a target, and / or a predetermined criteria being met so that feedback is provided to a user. The module in a further aspect can include illumination light sources and aiming light sources which project light in different wavelength emission bands.

Owner:HAND HELD PRODS

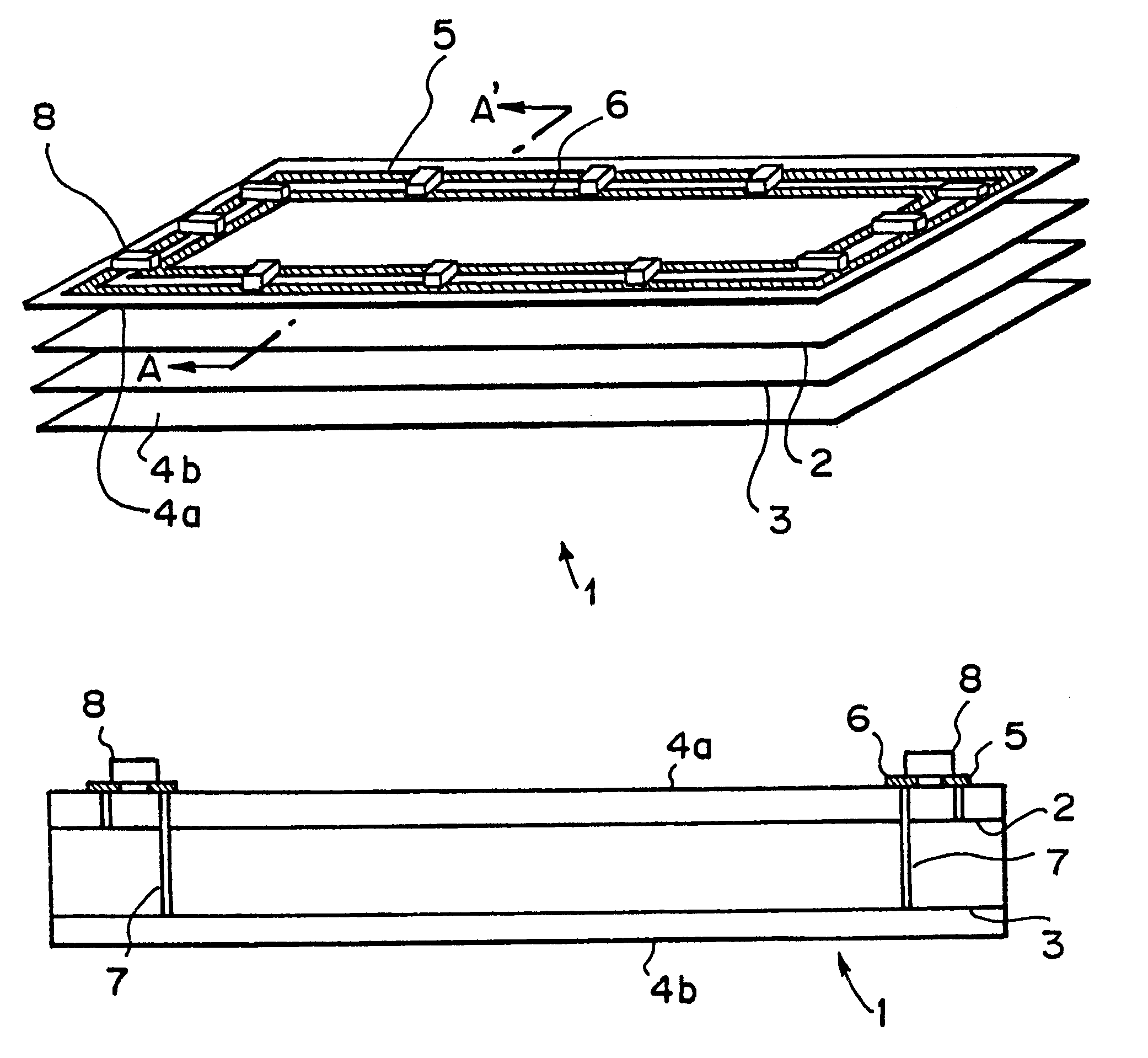

Ic chip mounting substrate, ic chip mounting substrate manufacturing method, optical communication device, and optical communication device manufacturing method

InactiveUS20060012967A1Improve connection reliabilitySmall sizeCircuit optical detailsSolid-state devicesResistElectrical conductor

An object of the present invention is to provide a substrate for mounting an IC chip which is a component for optical communication having an IC chip and an optical component integrally provided thereon, which can ensure a short distance between the IC chip and the optical component, which is excellent in electric signal transmission reliability and which can transmit optical signal through an optical path for transmitting optical signal. The substrate for mounting an IC chip of the present invention is a substrate for mounting an IC chip comprising: a substrate and, as serially built up on both faces thereof, a conductor circuit and an interlaminar insulating layer in an alternate fashion and in repetition; a solder resist layer formed as an outermost layer; and an optical element mounted thereto, wherein an optical path for transmitting optical signal, which penetrates the substrate for mounting an IC chip, is disposed.

Owner:IBIDEN CO LTD

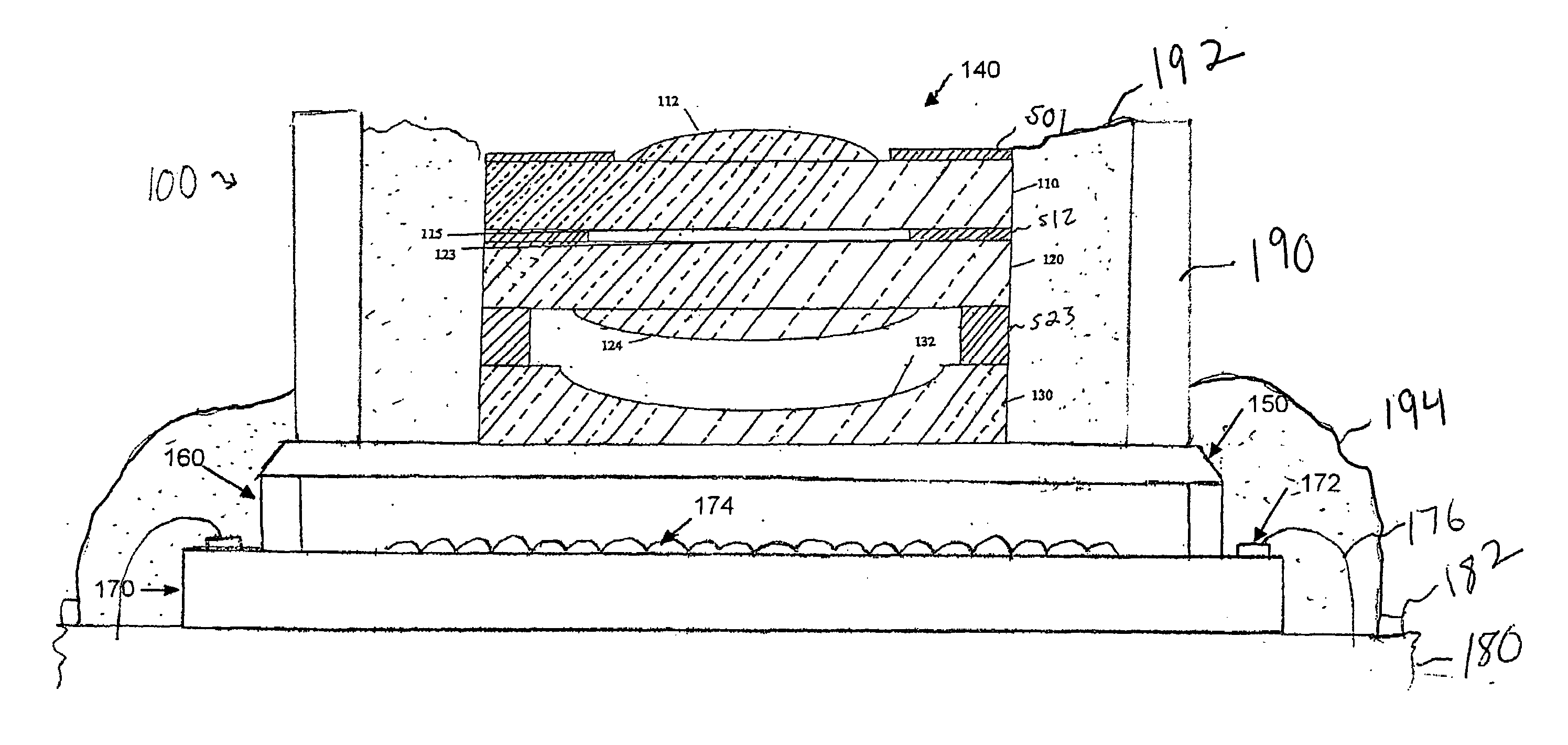

Control of stray light in camera systems employing an optics stack and associated methods

A camera system may include an optics stack including two substrates secured together in a vertical direction and an optical system on the two substrates, the two substrates having exposed sides, a detector on a detector substrate, and a stray light blocker directly on at least some sides of the optics stack.

Owner:DIGITALOPTICS CORPORATION

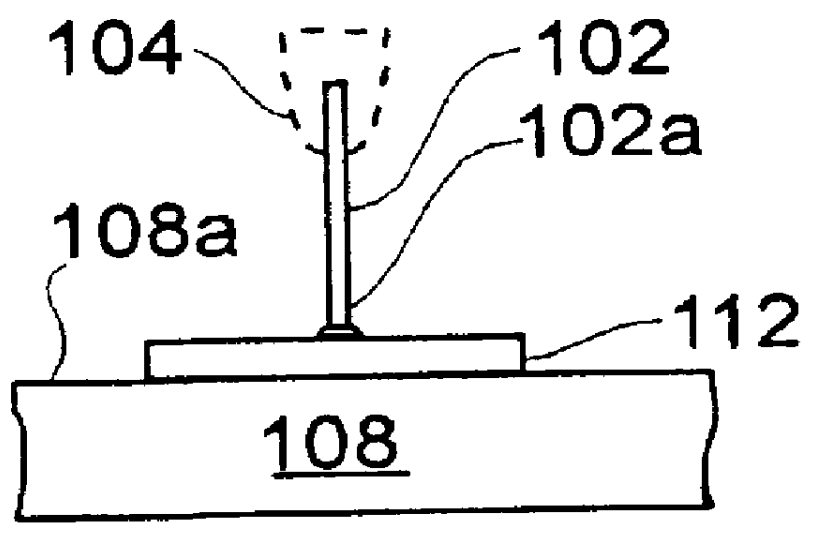

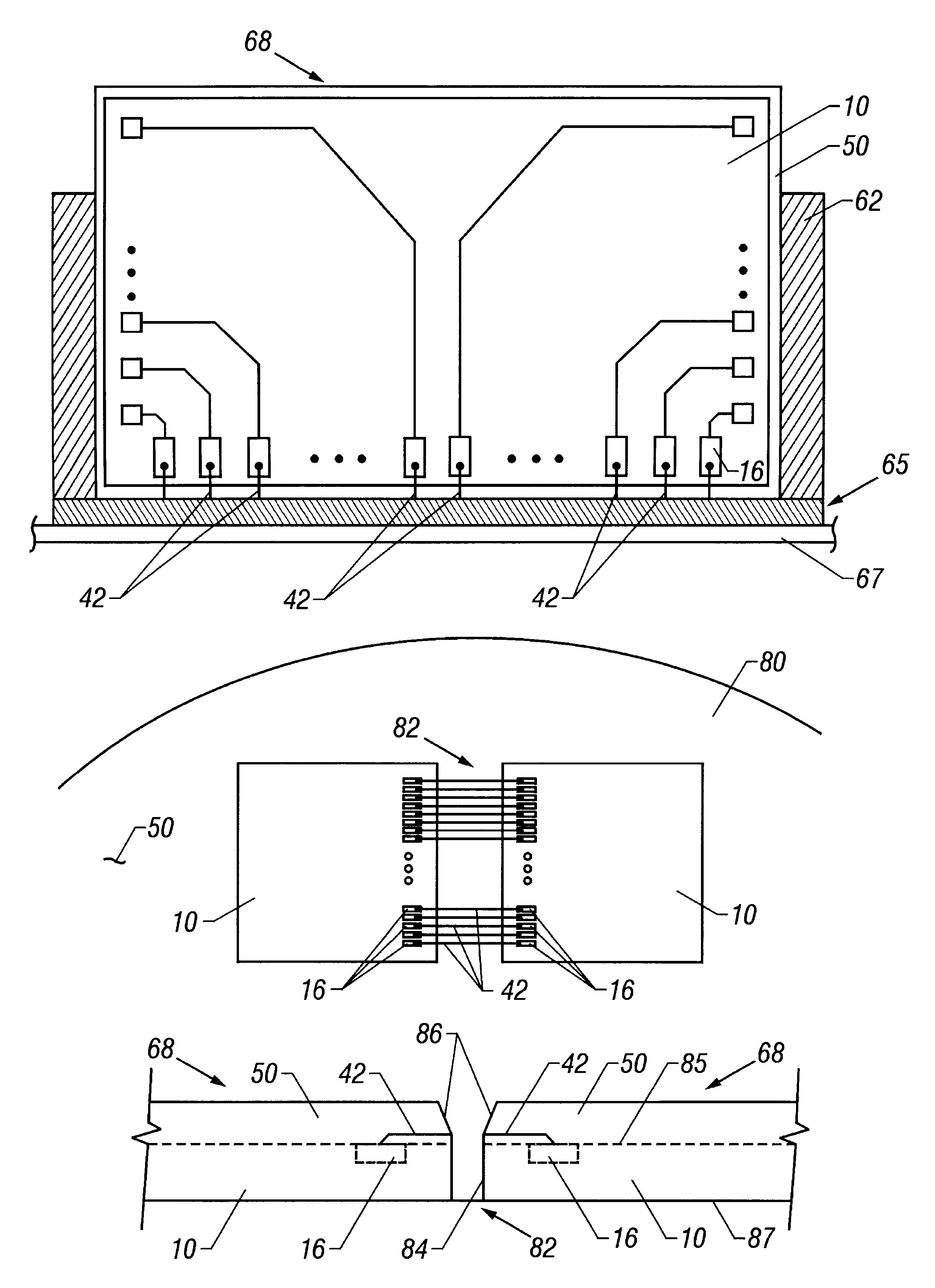

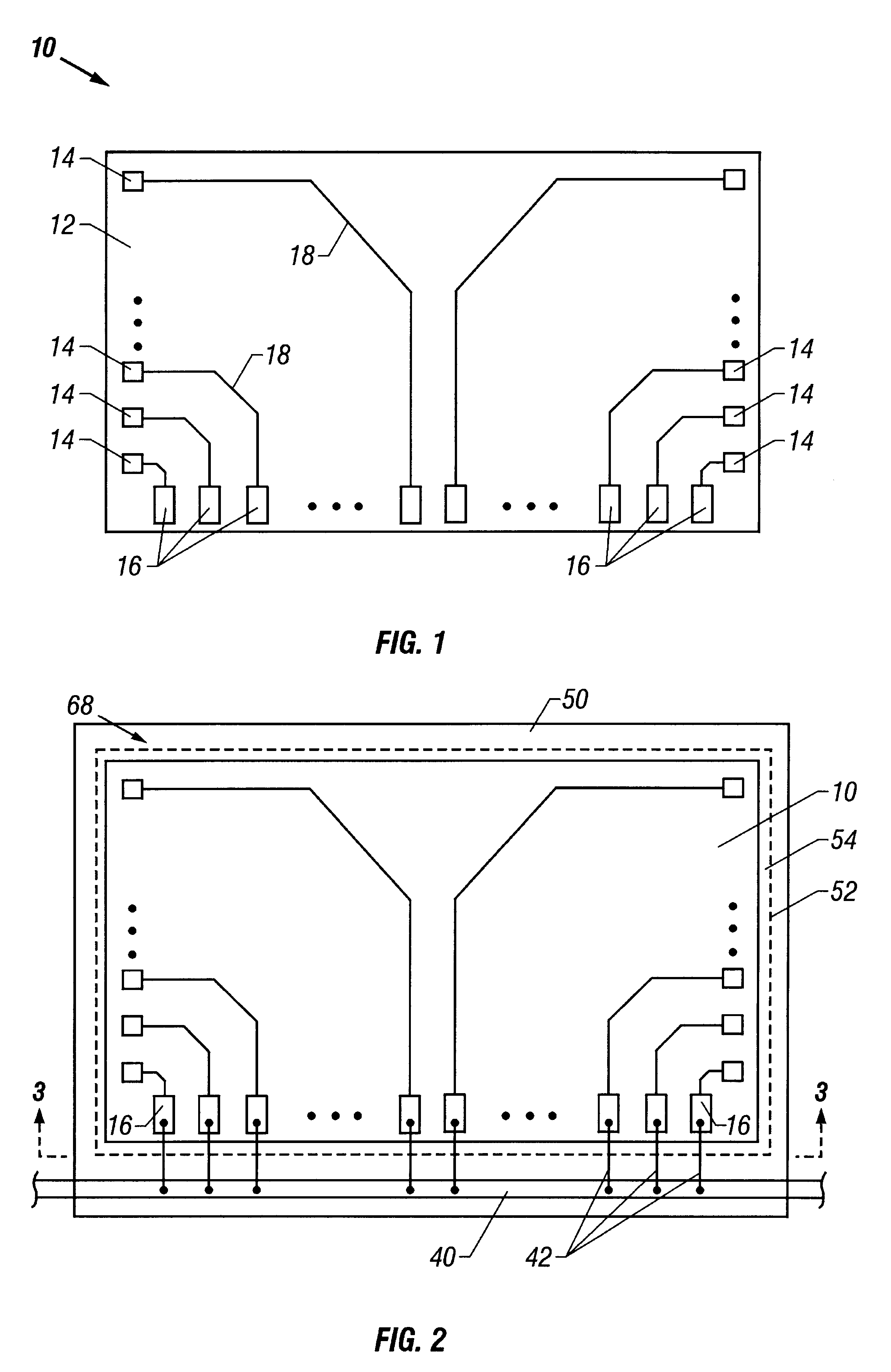

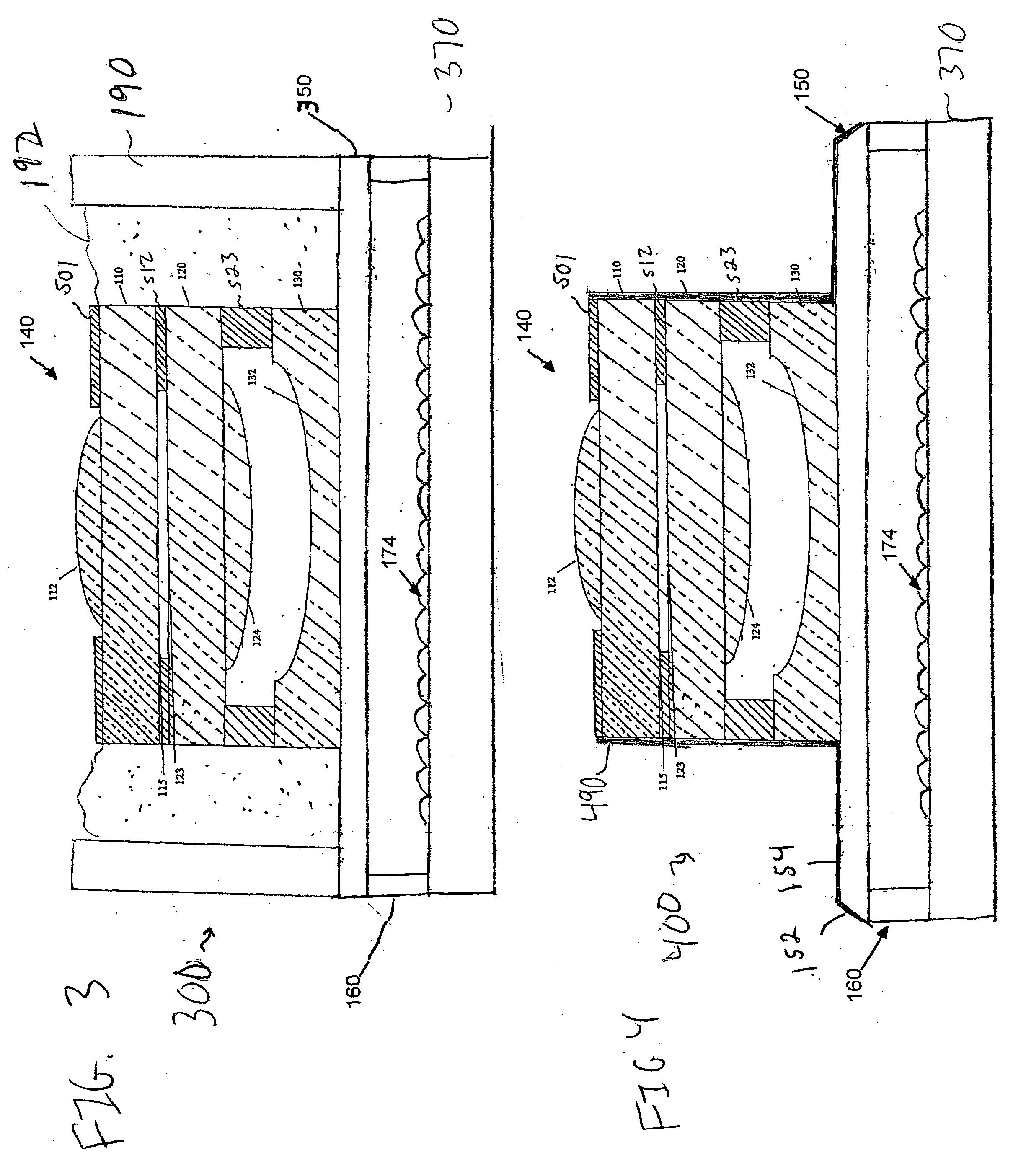

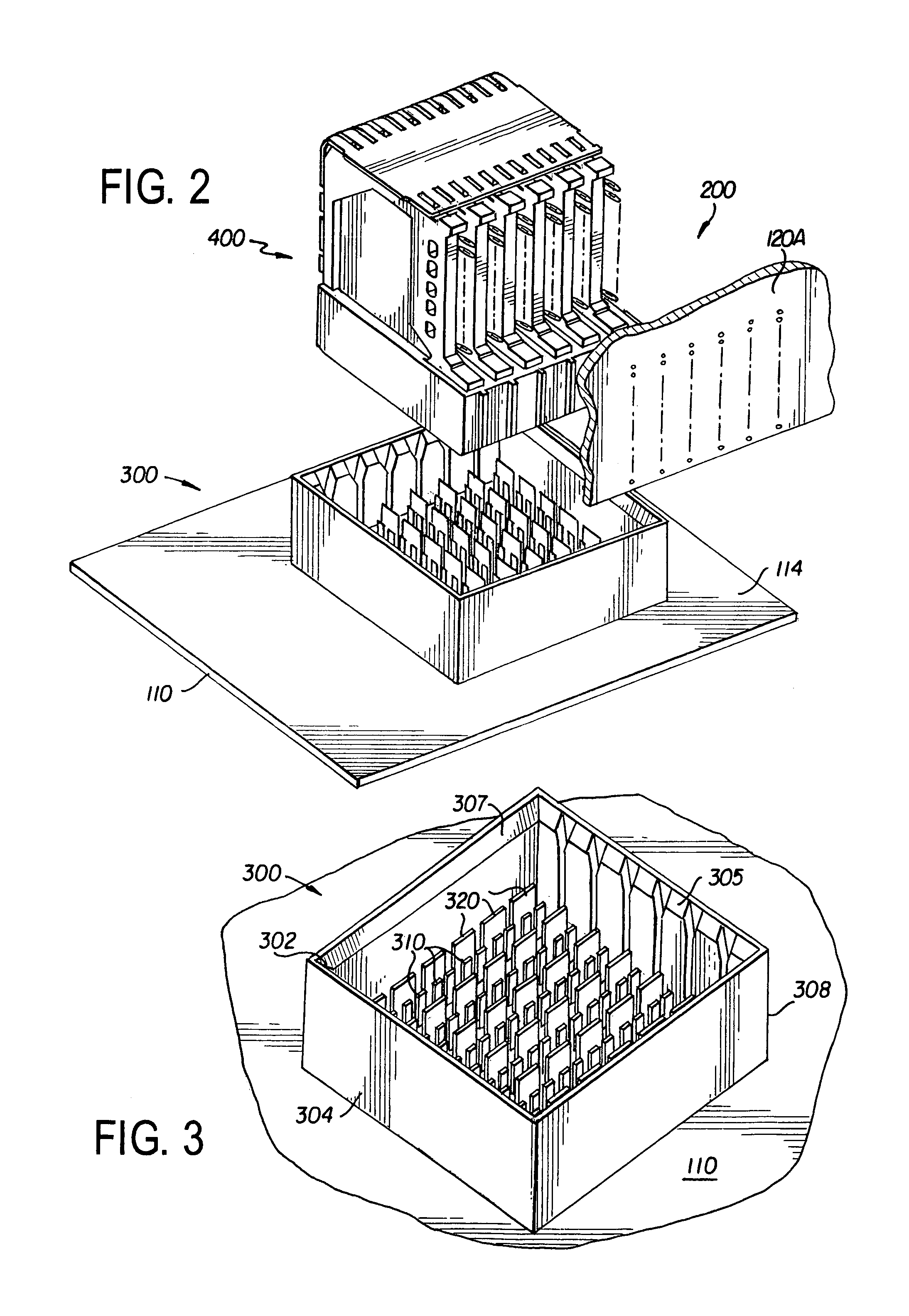

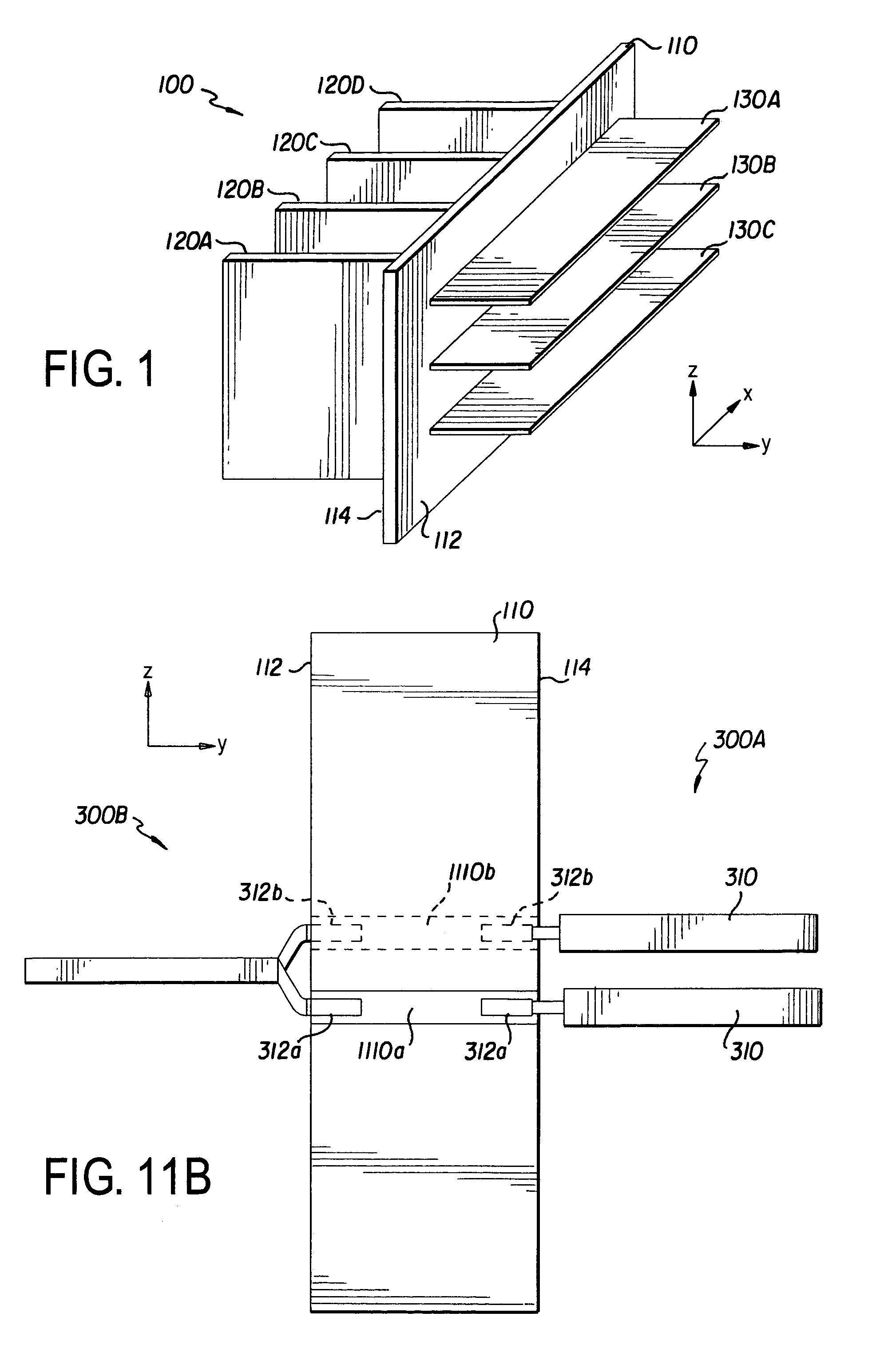

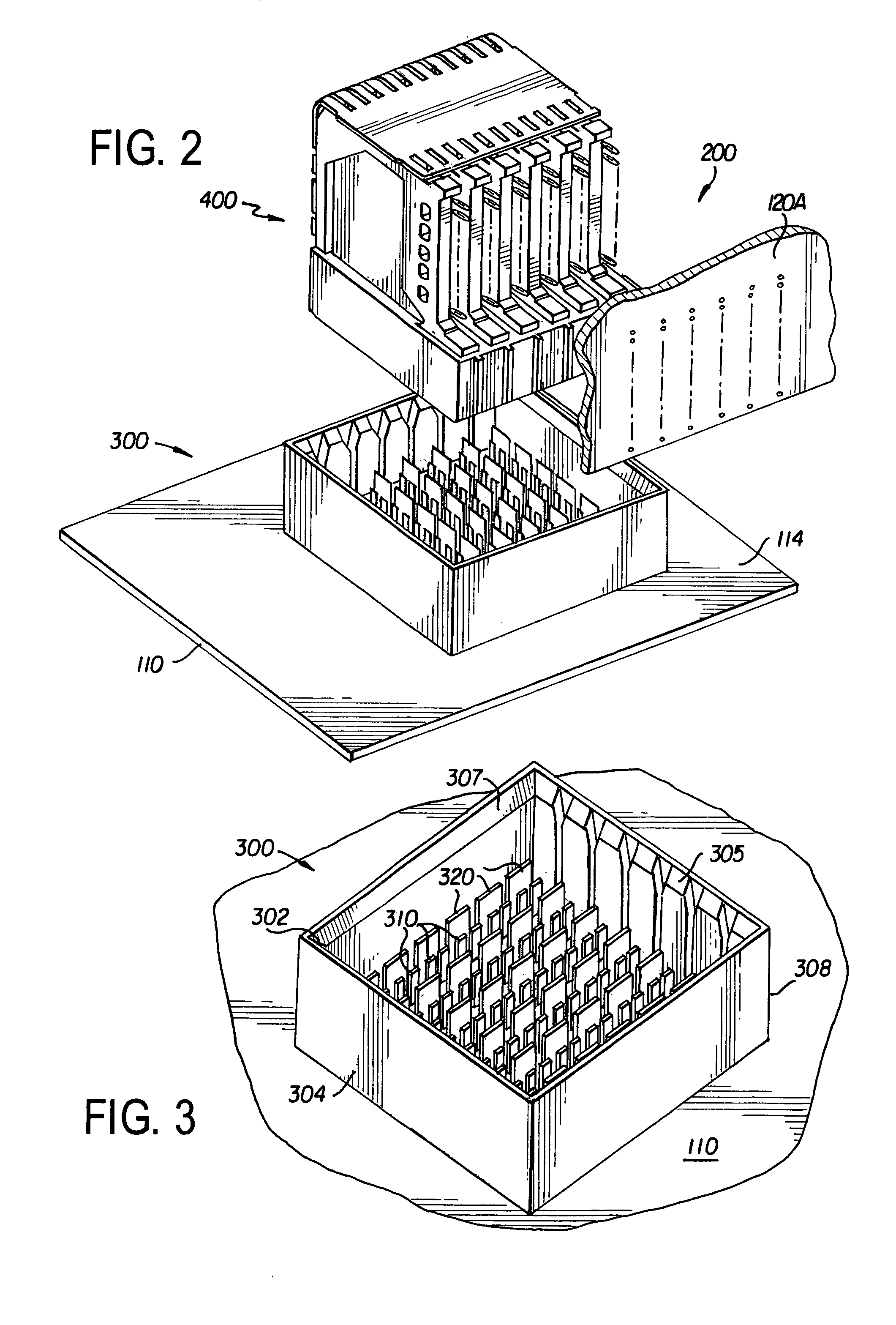

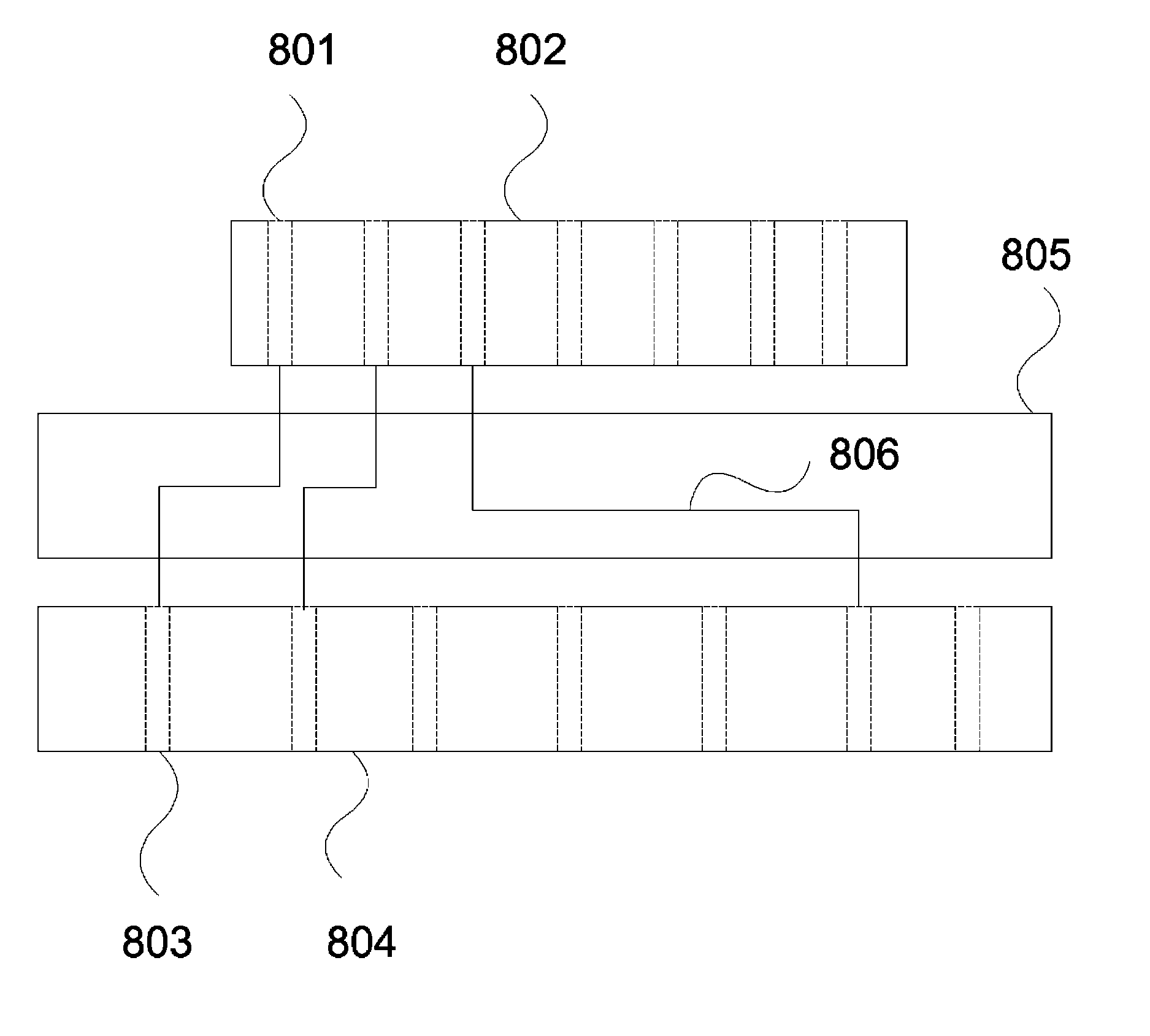

Midplane especially applicable to an orthogonal architecture electronic system

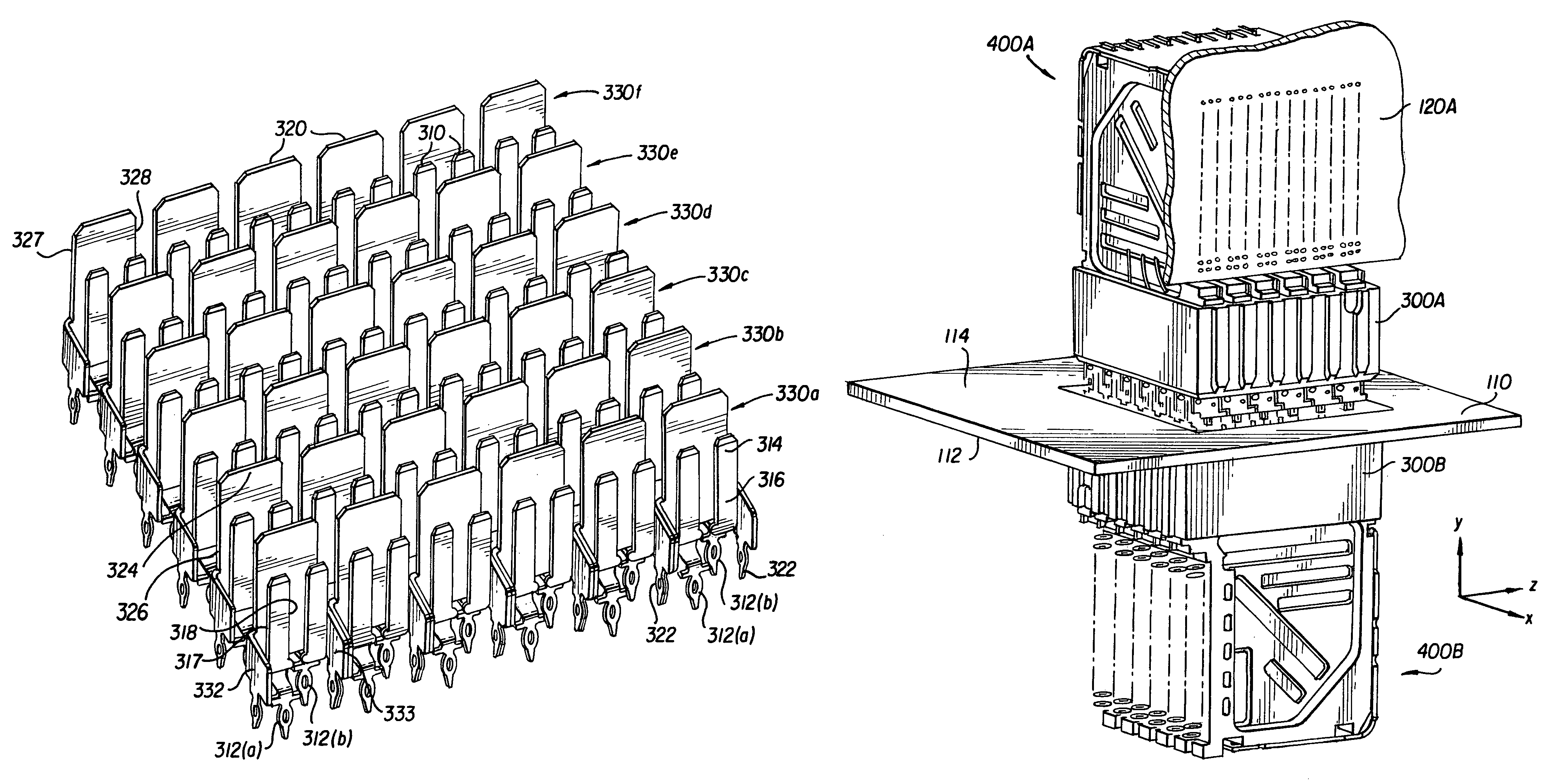

ActiveUS7108556B2Cross-talk/noise/interference reductionHigh frequency circuit adaptationsElectronic systemsEngineering

A midplane has a first side to which contact ends of a first differential connector are connected and a second side opposite the first side to which contact ends of a second differential connector are connected. The midplane includes a plurality of vias extending from the first side to the second side, with the vias providing first signal launches on the first side and second signal launches on the second side. The first signal launches are provided in a plurality of rows, with each row having first signal launches along a first line and first signal launches along a second line substantially parallel to the first line. The second signal launches are provided in a plurality of columns, with each column having second signal launches along a third line and second signal launches along a fourth line substantially parallel to the third line.

Owner:AMPHENOL CORP

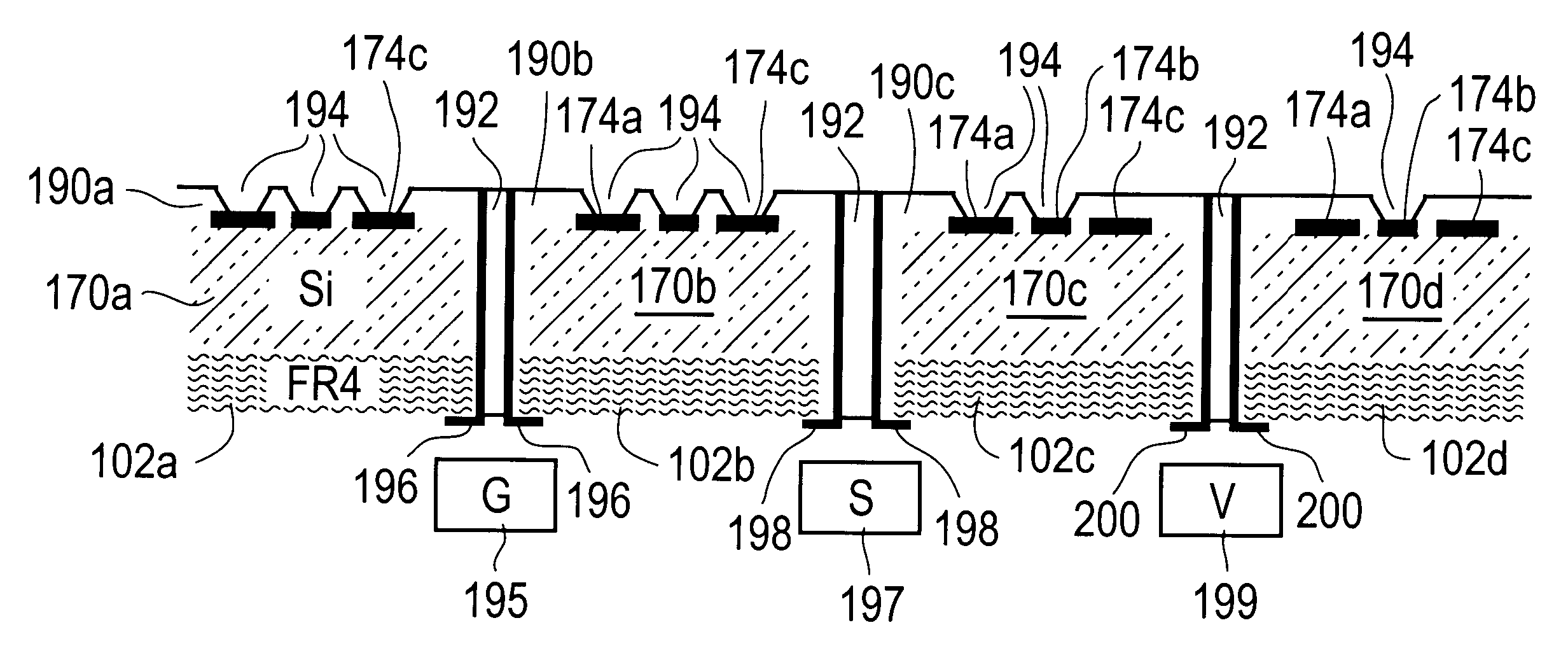

Composite interposer and method for producing a composite interposer

InactiveUS6521530B2Cross-talk/noise/interference reductionSemiconductor/solid-state device detailsEpoxyFilling materials

A composite interposer for providing power and signal connections between an integrated circuit chip or chips and a substrate. The interposer includes a signal core formed from a conductive power / ground plane positioned between two dielectric layers. A method for fabricating a composite interposer comprising disposing a silicon layer on a substrate, and selectively etching the silicon layer down to the substrate to develop silicon openings with a silicon profile, and to expose part of the substrate. Vias are formed through the exposed part of the substrate. The method additionally includes filling the vias and the silicon openings with a filler material (e.g., a high-aspect-ratio-capable photodefinable epoxy polymer) to form filled silicon openings and filled vias, forming first openings through the filled silicon openings and through the filled vias, forming second opening through filler material to expose semiconductor devices on the silicon layer, and interconnecting electrically, through the first openings and through the second openings, the exposed semiconductor devices with pads disposed against a bottom of the substrate.

Owner:FUJITSU LTD

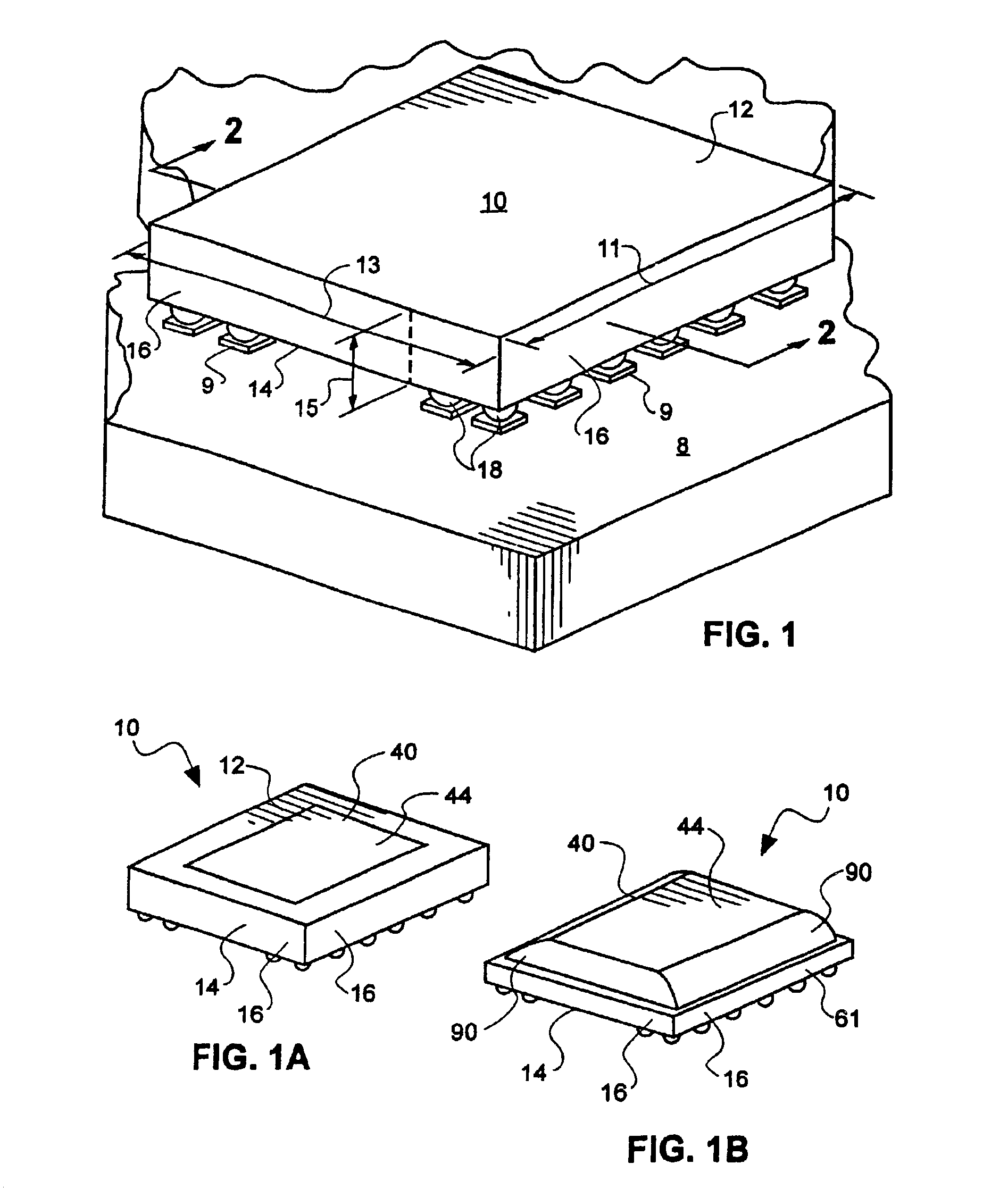

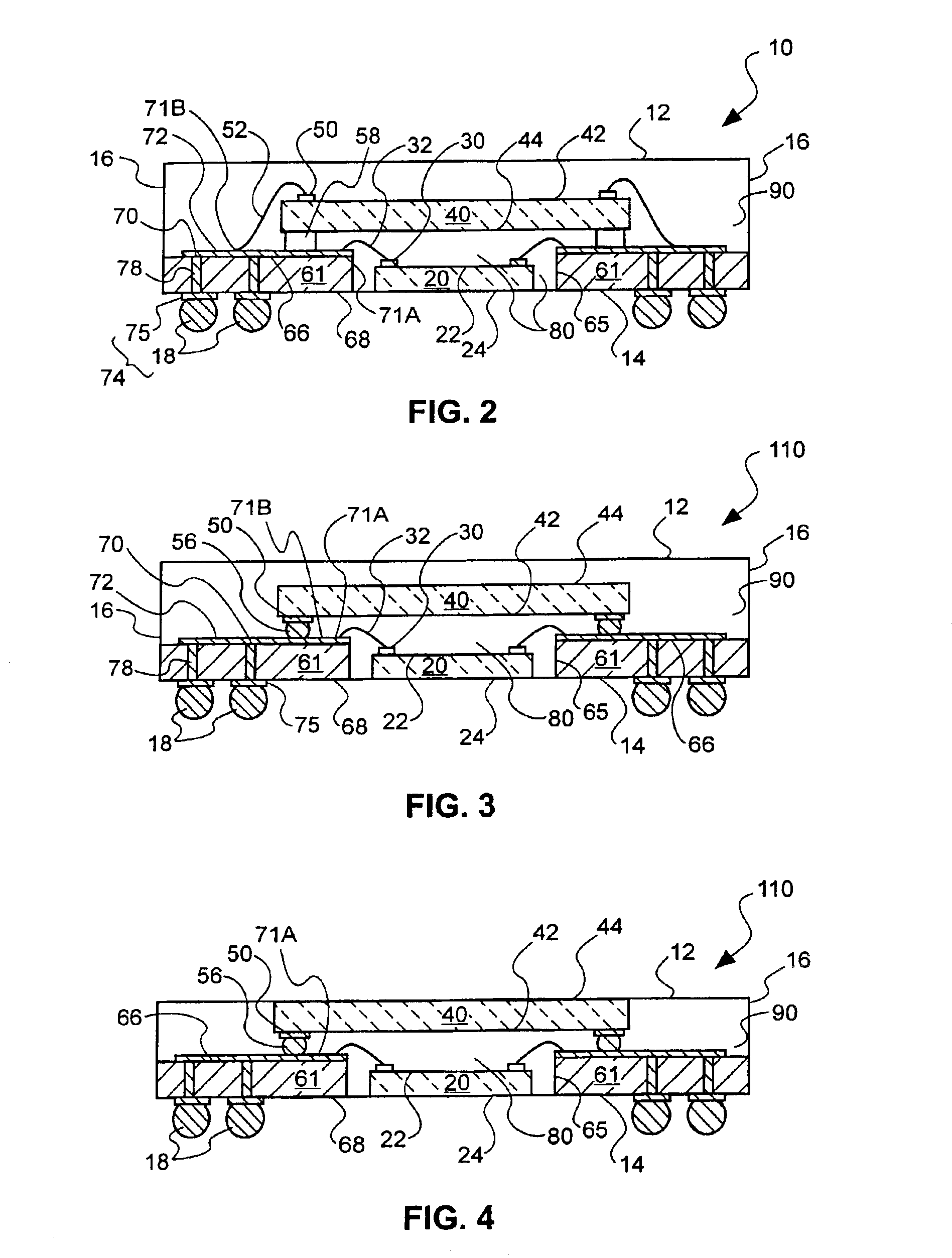

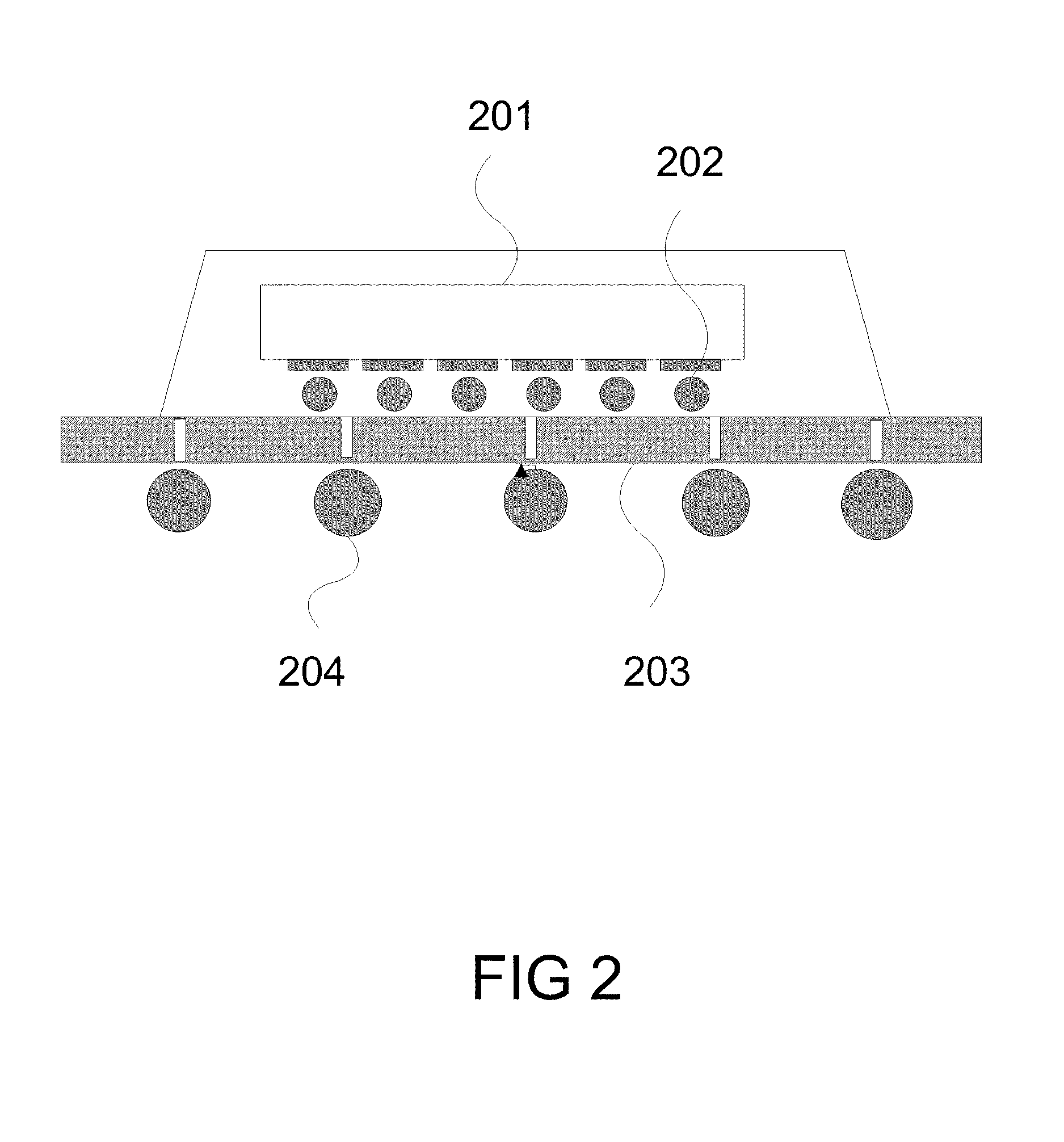

Methods for assembling multiple semiconductor devices

InactiveUS7198980B2Reduce area requirementsHelp positioningPrinted circuit assemblingSemiconductor/solid-state device detailsElectrical conductorElectrical connection

A multidie semiconductor device (MDSCD) package includes a generally planar interposer comprising a substrate with a central receptacle, upper surface conductors, and outer connectors on the lower surface of the interposer. Conductive vias connect upper surface conductors with outer connectors. One or more semiconductor devices may be mounted in the receptacle and one or more other semiconductor devices mounted above and / or below the interposer and attached thereto. The package may be configured to have a footprint not significantly larger than the footprint of the largest device and / or a thickness not significantly greater than the combined thickness of included devices. Methods for assembling and encapsulating packages from multidie wafers and multi-interposer sheets or strips are disclosed. Methods for combining a plurality of packages into a single stacked package are disclosed. The methods may include use of somewhat laterally extending intermediate conductive elements, flip-chip style electrical connection, or both within the same package.

Owner:MICRON TECH INC

Differential electrical connector assembly

ActiveUS7094102B2Orthogonal PCBs mountingPrinted circuit manufactureElectrical conductorElectrical connector

A differential connector has a plurality of rows. Each row includes a plurality of signal conductors provided as differential pairs. Each signal conductor has a first contact end connectable to a printed circuit board, a second contact end, and an intermediate portion having a first width. For each differential pair, one first contact end lies along a first line parallel to the plurality of rows and the other first contact end lies along a second line parallel to and spaced from the first line. The differential connector further includes a plurality of ground conductors, with each ground conductor corresponding to a differential pair. Each ground conductor has a first contact end connectable to the printed circuit board, a second contact end, and an intermediate portion having a second width that is at least twice the first width.

Owner:AMPHENOL CORP

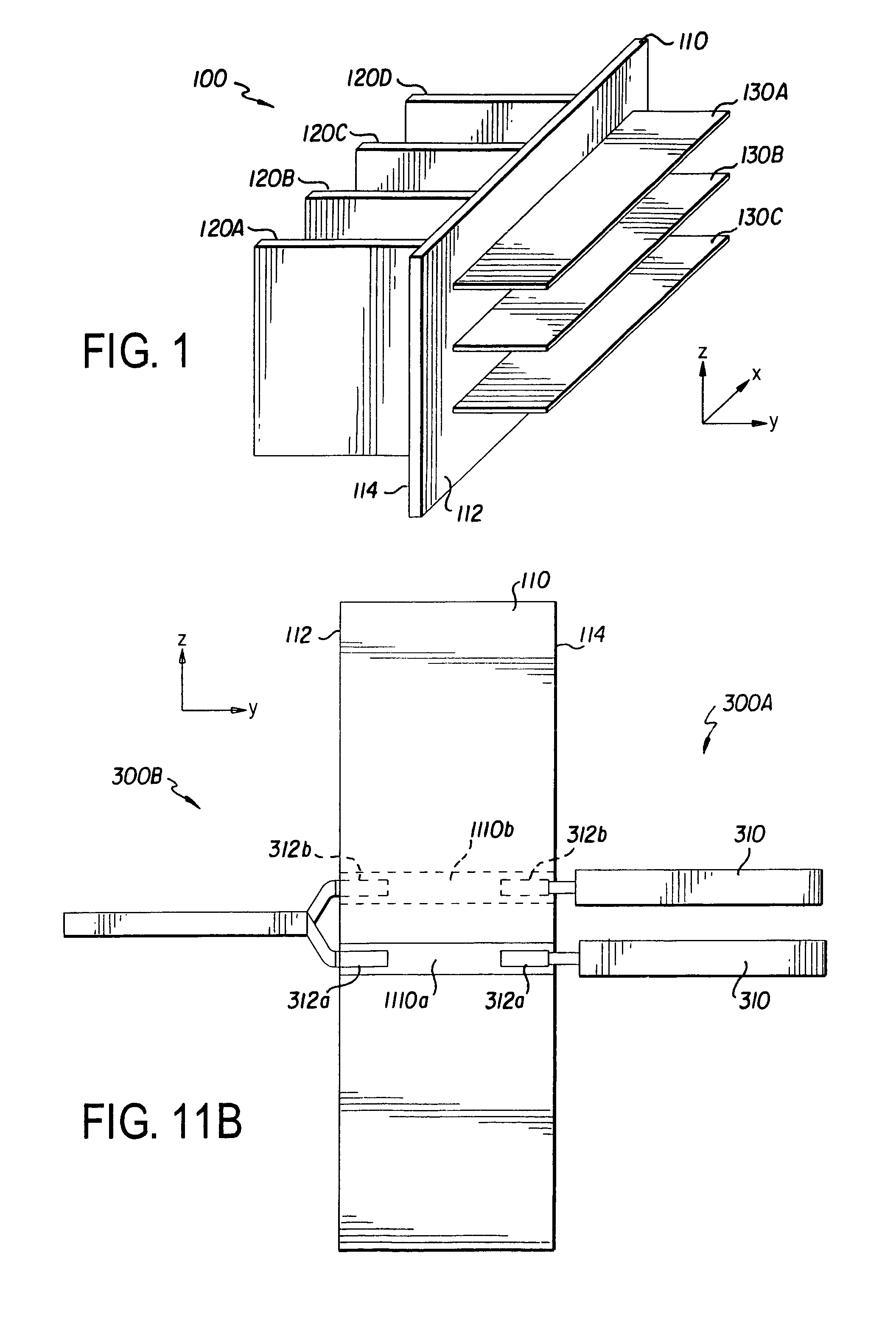

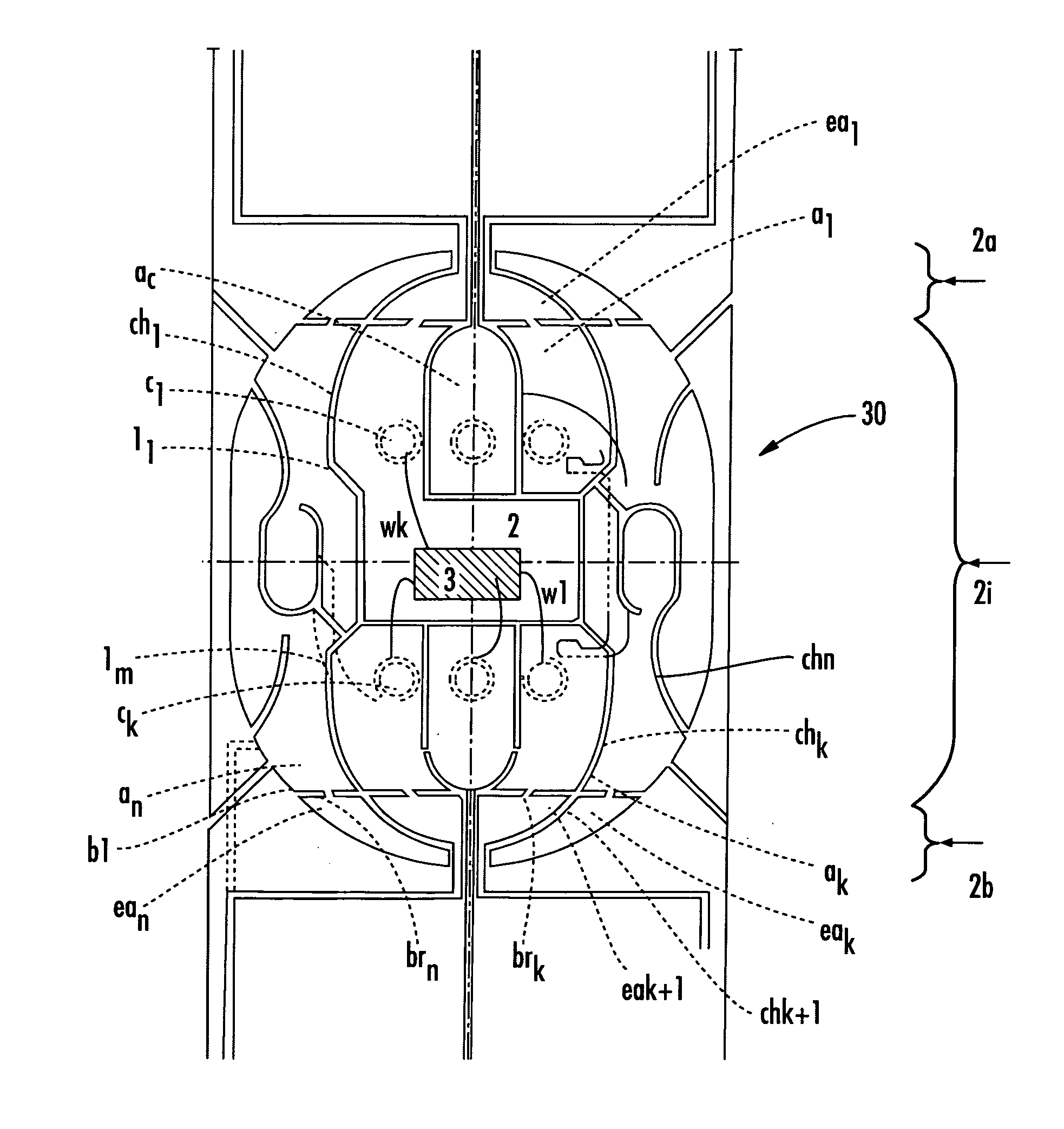

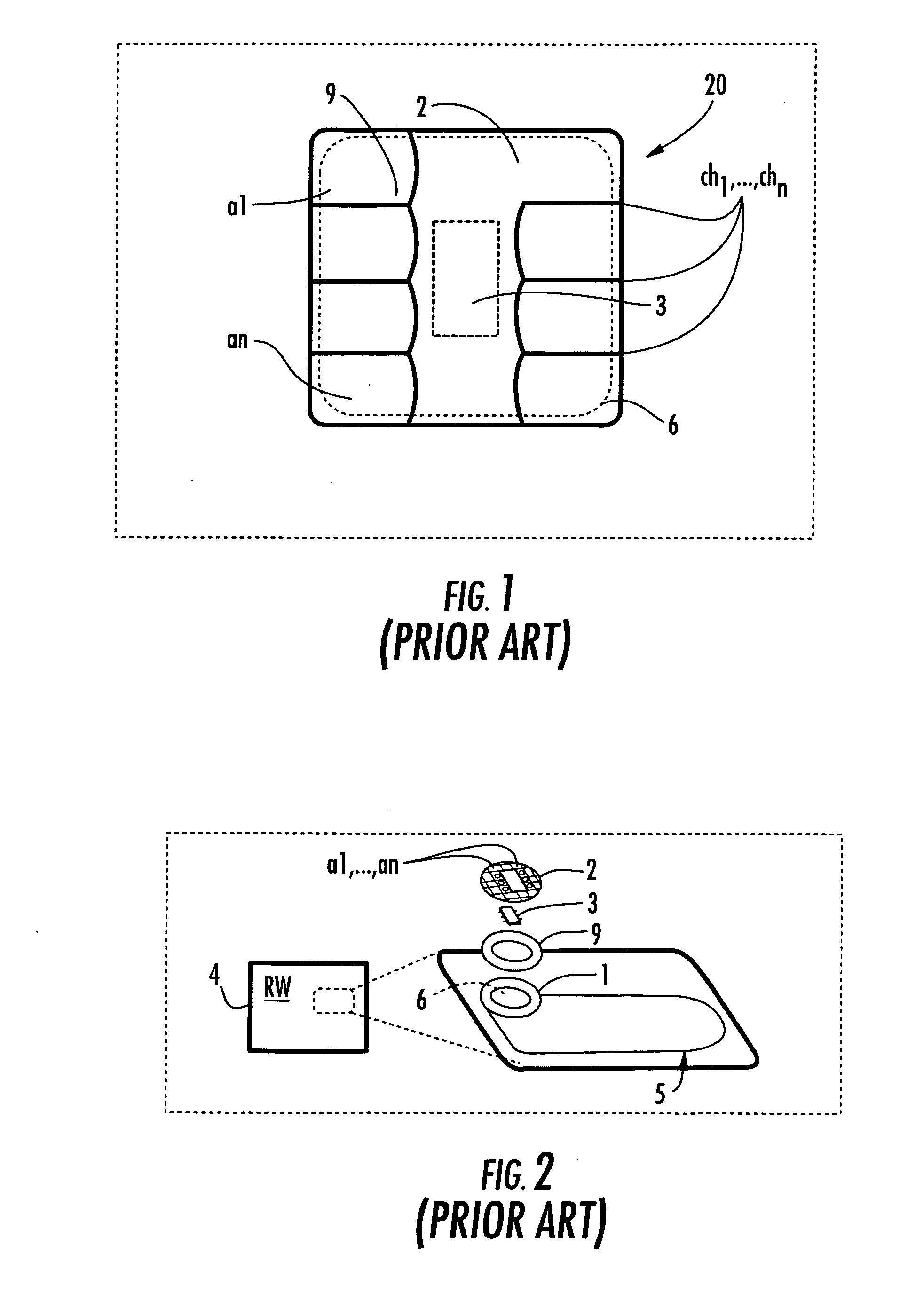

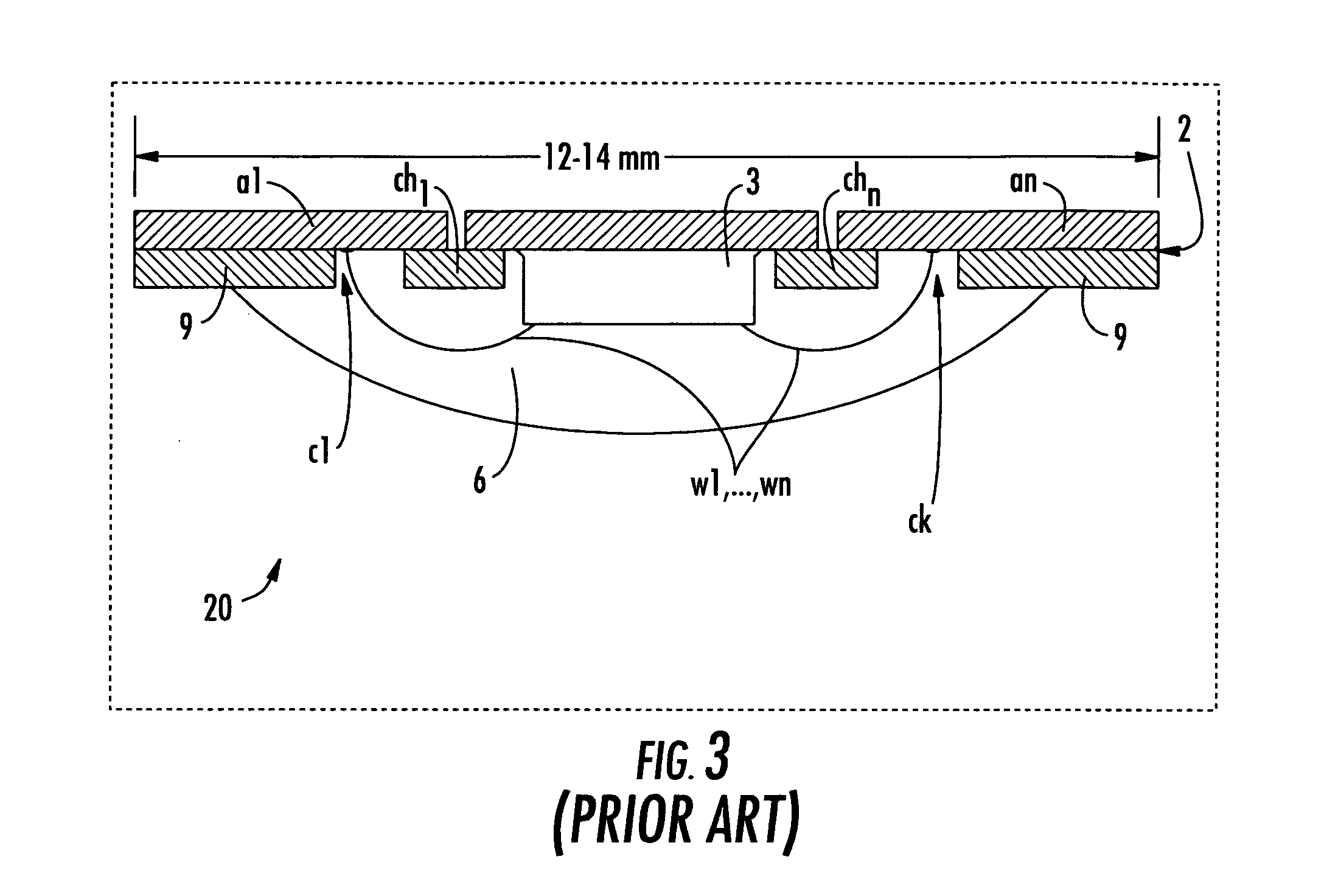

Plated module for an IC card

ActiveUS20070153487A1Reduce stressCounteracting forceSolid-state devicesElectrical apparatus contructional detailsEngineeringIntegrated circuit

A plated module is for an IC card and includes a printed circuit having a plurality of conductive areas, delimited by a network of insulating channels, for covering an integrated circuit chip intended to be hosted in a recess of a plastic support of the IC card. At least some of the conductive areas are connected to a corresponding contact points of the integrated circuit chip. At least some of the conductive areas are linked to corresponding extended areas by one or more bridges. The conductive areas are separated from the extended areas by an insulating channel crossed by the bridges. The insulating channels surround the conductive areas as a protection frame for the contact points. At least a major side of at least one of the conductive areas may be curved. Several of the advanced extended areas form a rounded border of the plated module.

Owner:STMICROELECTRONICS INT NV

Semiconductor device assemblies and packages including multiple semiconductor devices and methods

InactiveUS6906415B2Reduce area requirementsHelp positioningPrinted circuit assemblingSemiconductor/solid-state device detailsElectrical conductorElectrical connection

A multidie semiconductor device (MDSCD) package includes a generally planar interposer comprising a substrate with a central receptacle, upper surface conductors, and outer connectors on the lower surface of the interposer. Conductive vias connect upper surface conductors with outer connectors. One or more semiconductor devices may be mounted in the receptacle and one or more other semiconductor devices mounted above and / or below the interposer and attached thereto. The package may be configured to have a footprint not significantly larger than the footprint of the largest device and / or a thickness not significantly greater than the combined thickness of included devices. Methods for assembling and encapsulating packages from multidie wafers and multi-interposer sheets or strips are disclosed. Methods for combining a plurality of packages into a single stacked package are disclosed. The methods may include use of somewhat laterally extending intermediate conductive elements, flip-chip style electrical connection, or both within the same package.

Owner:MICRON TECH INC

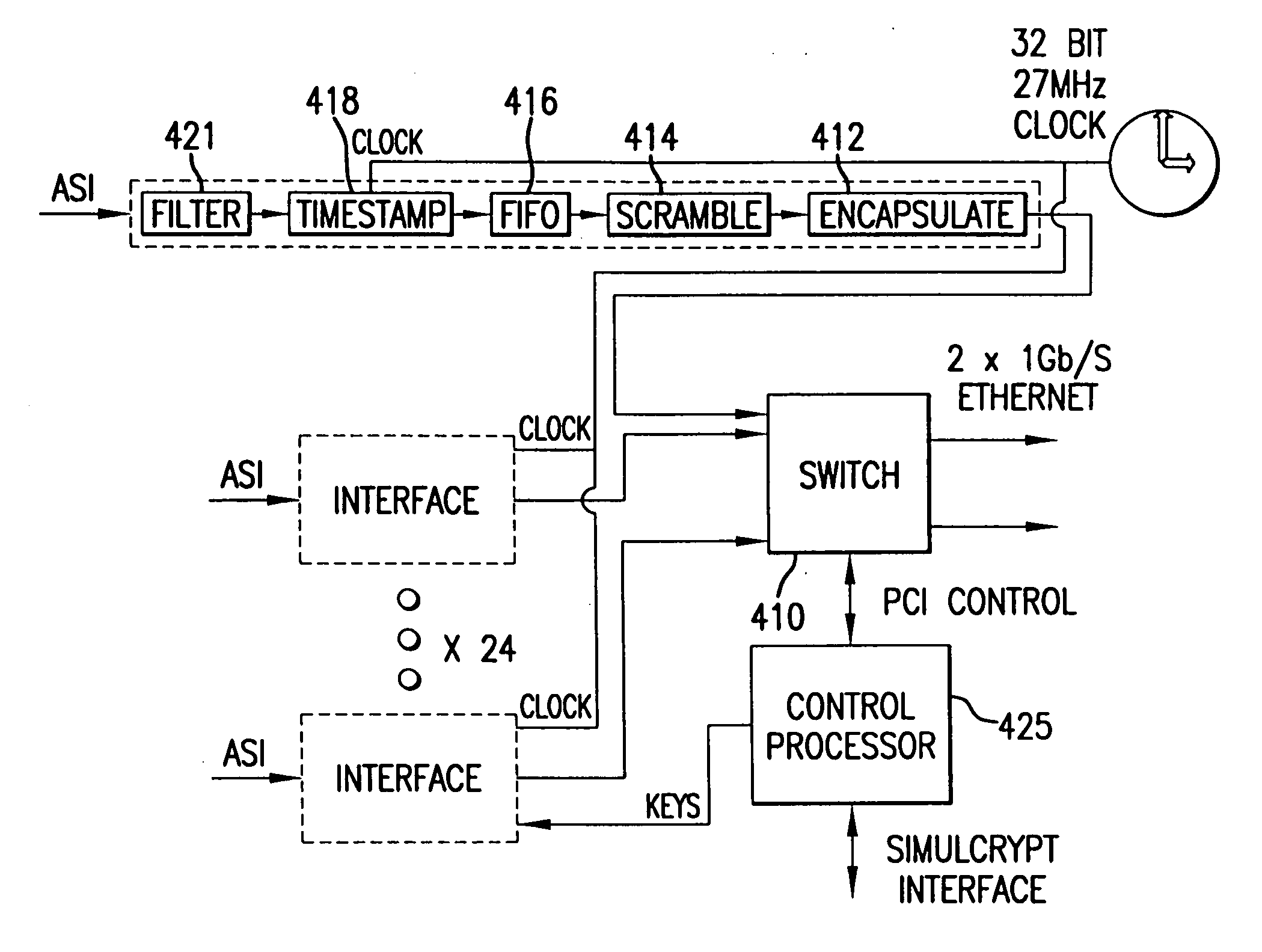

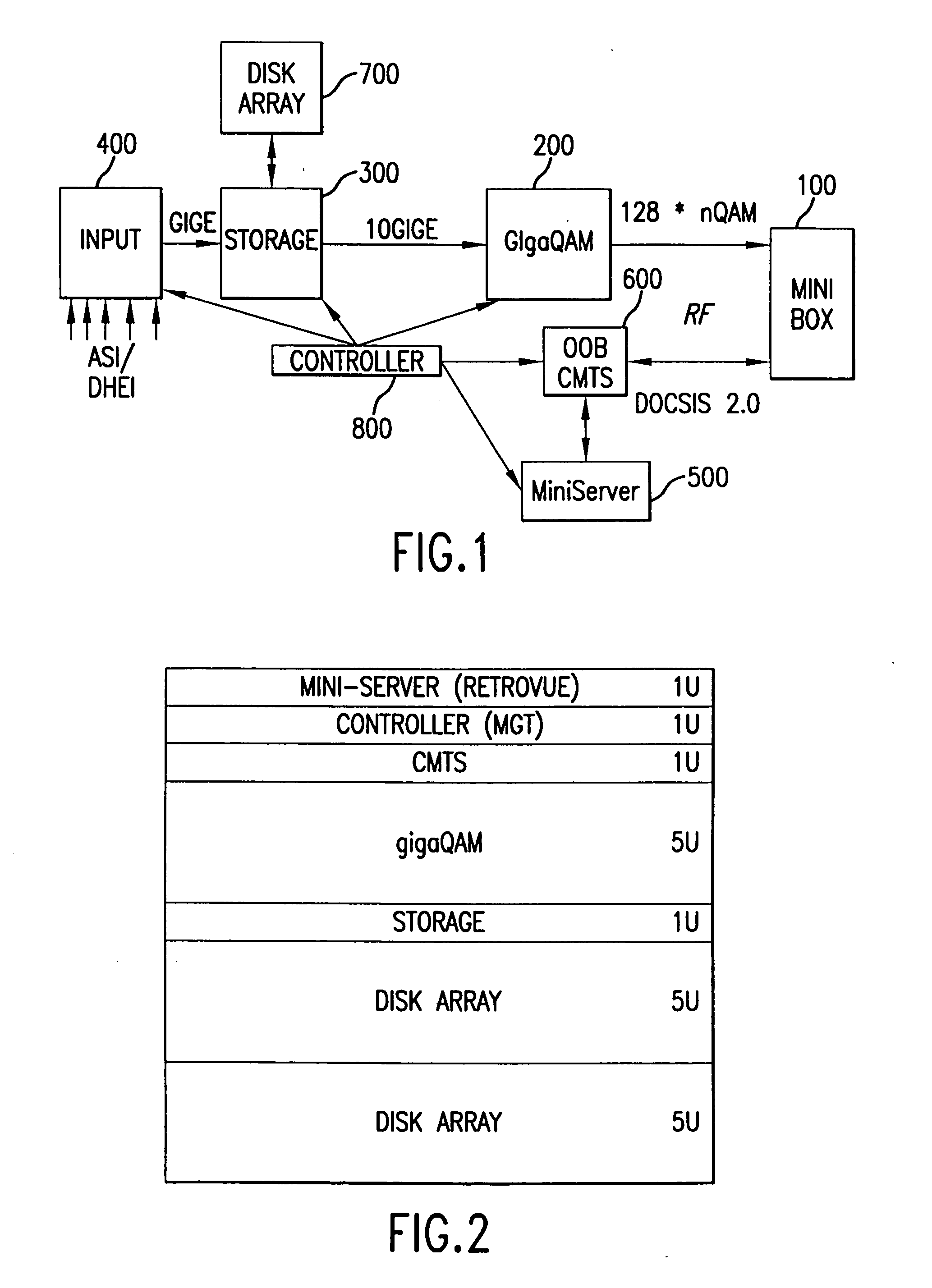

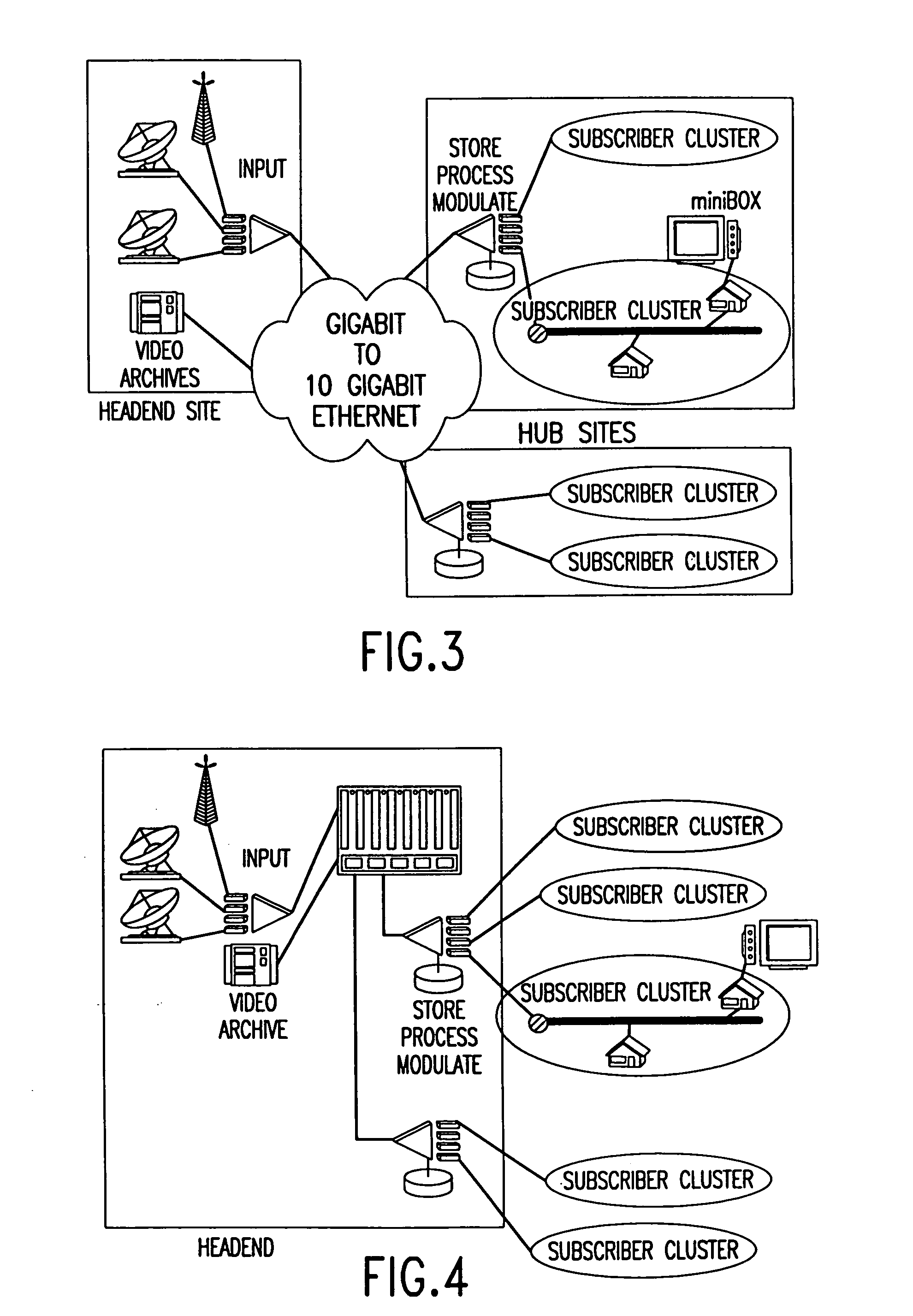

Method and apparatus for increasing video streams in a video system

InactiveUS20050108763A1Improve securityEasy to switchCircuit security detailsPrinted circuit aspectsComputer graphics (images)Ethernet

A video system for providing a large number of video streams. The video system includes a video server and dividing means. Storage means, a switch and control means are located at the video server. The video server has a plurality of central-processing units (CPUs). The dividing means divides a plurality of input video-streams entering the video system, and sends the divided plurality of input-video streams, with each divided video stream identified with a separate Ethernet address, to the video server. The storage means stores an input video-stream of the plurality of input video-streams as a stored-video stream. The switch routes an input-video stream of the plurality of input-video streams to the storage means. The control means controls the storage means to replay the stored-video stream and to control portions of the stored-video stream at an appropriate time, and controls the plurality of CPUs at the video server to work in parallel.

Owner:BARAN PAUL +3

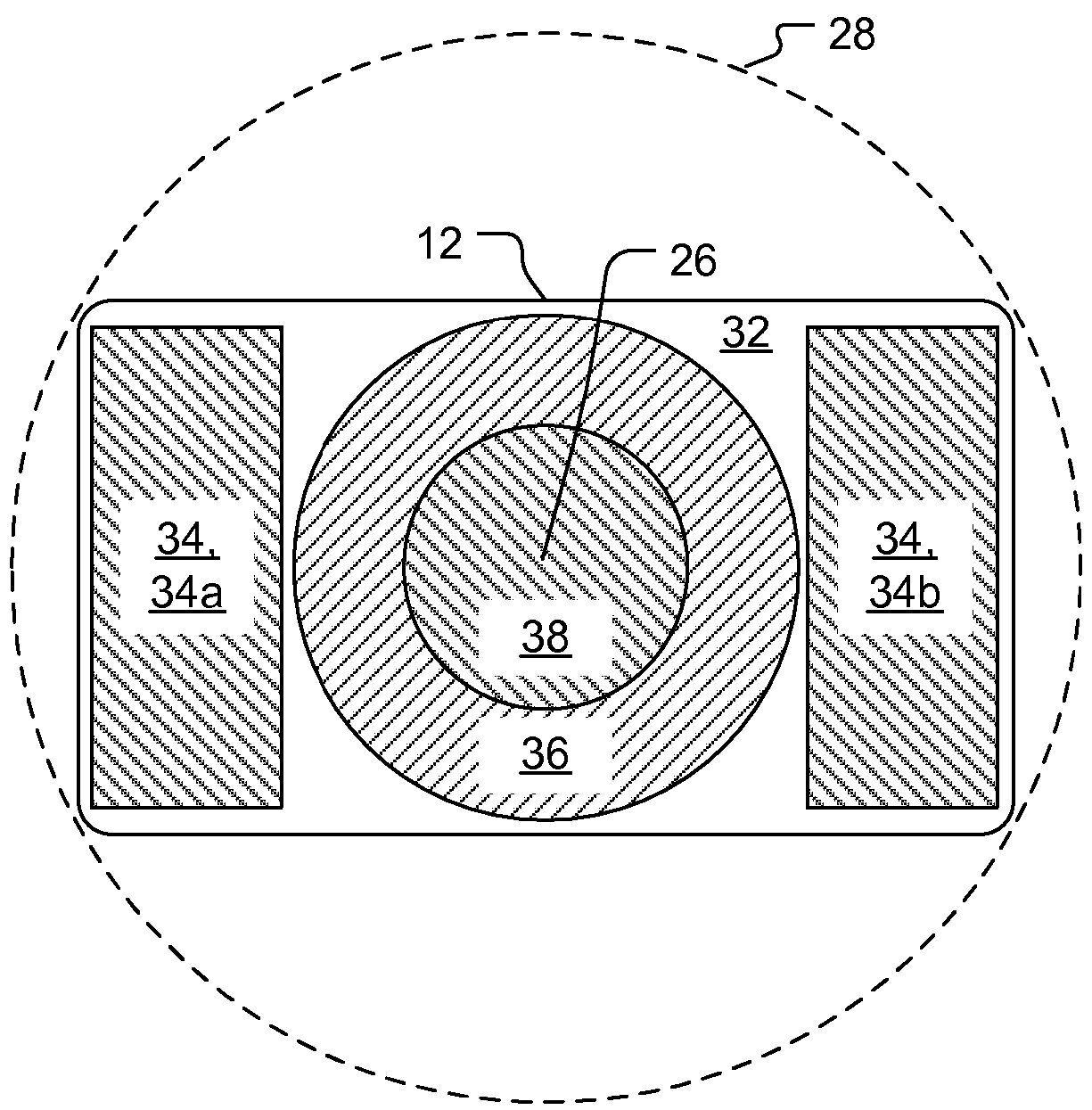

Optical reader aiming assembly comprising aperture

InactiveUS20030019934A1Reduced dimensionOptimize architectureConveying record carriersCharacter and pattern recognitionOptical readerLight source

An imaging module in one embodiment includes an aiming system having a light source, an aperture and an optical element positioned optically forward of the aperture wherein the aiming system projects a crisp and sharp aiming pattern onto a target over a wide range of distances. In one embodiment, an aiming system is configured so that a lens operates as an aperture to project a crisp sharp aiming pattern over a wide range of distances including distances at which the aiming pattern is less than optimally focused. In another embodiment an aiming system is configured so that light emanating from a thin aperture is imaged in such manner that a crisp, sharp aiming pattern is defined over a wide range of distances. The aiming pattern in one embodiment includes sharply defined lateral edges which are useful in sighting target indicia.

Owner:HAND HELD PRODS

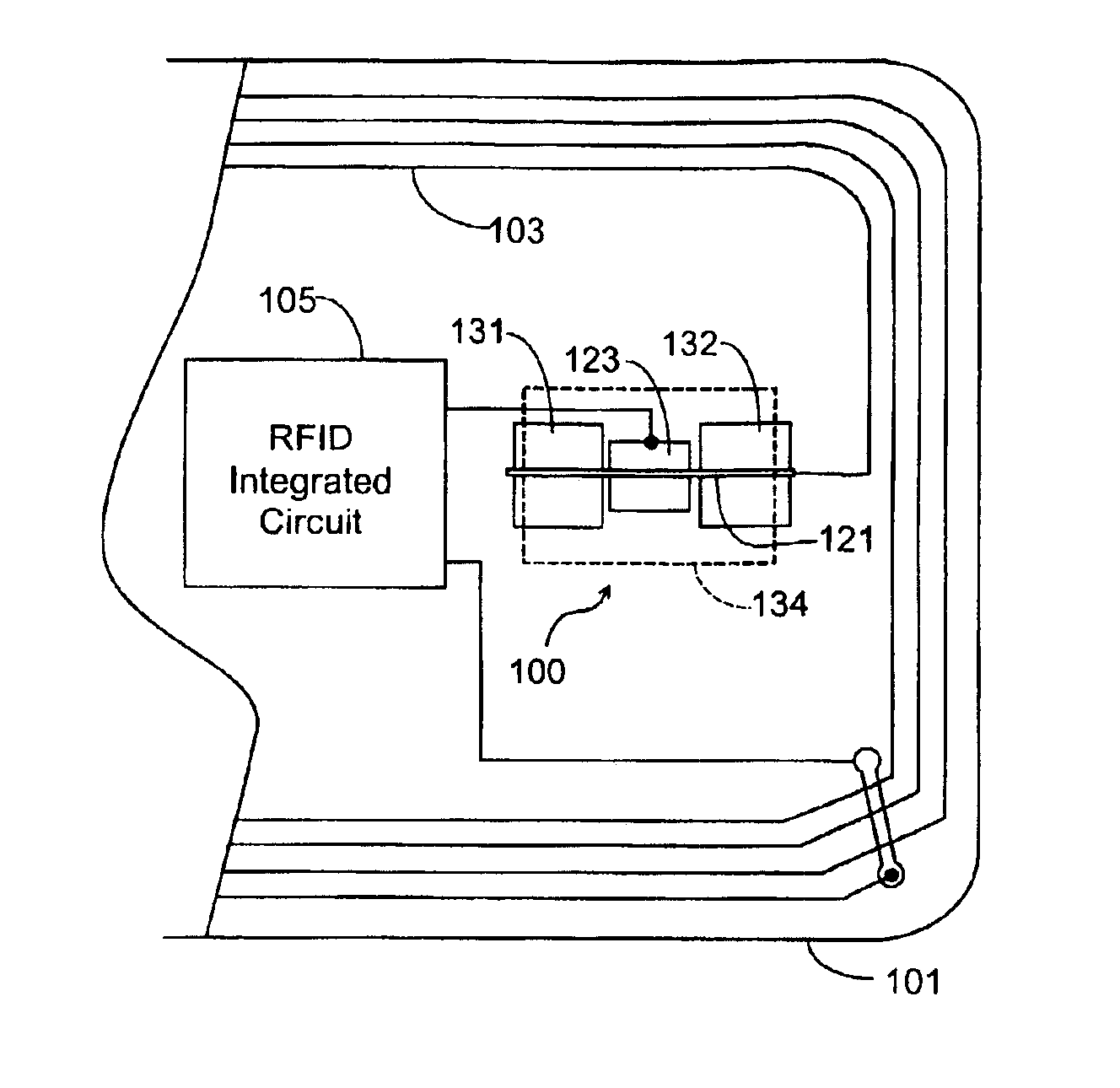

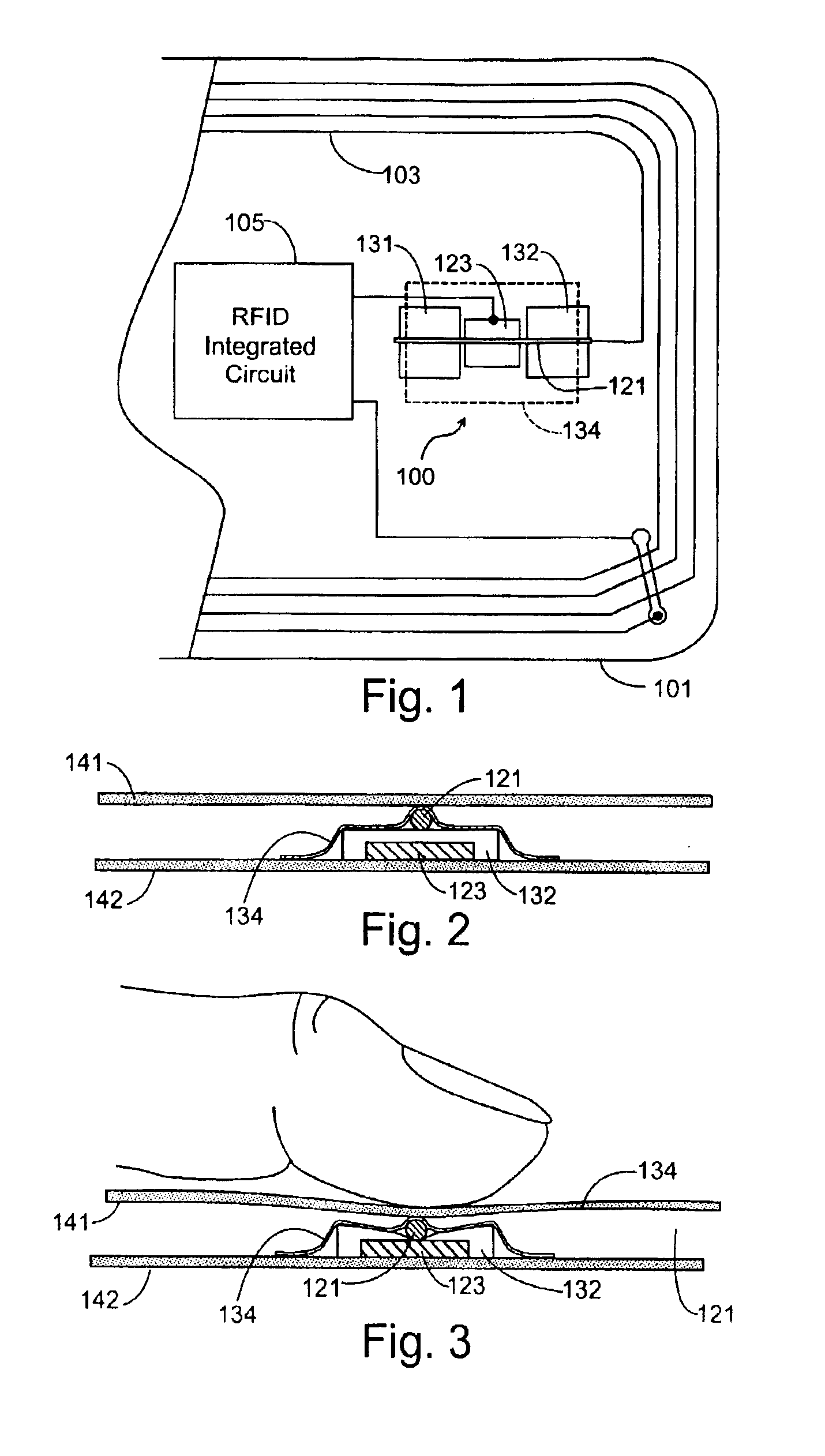

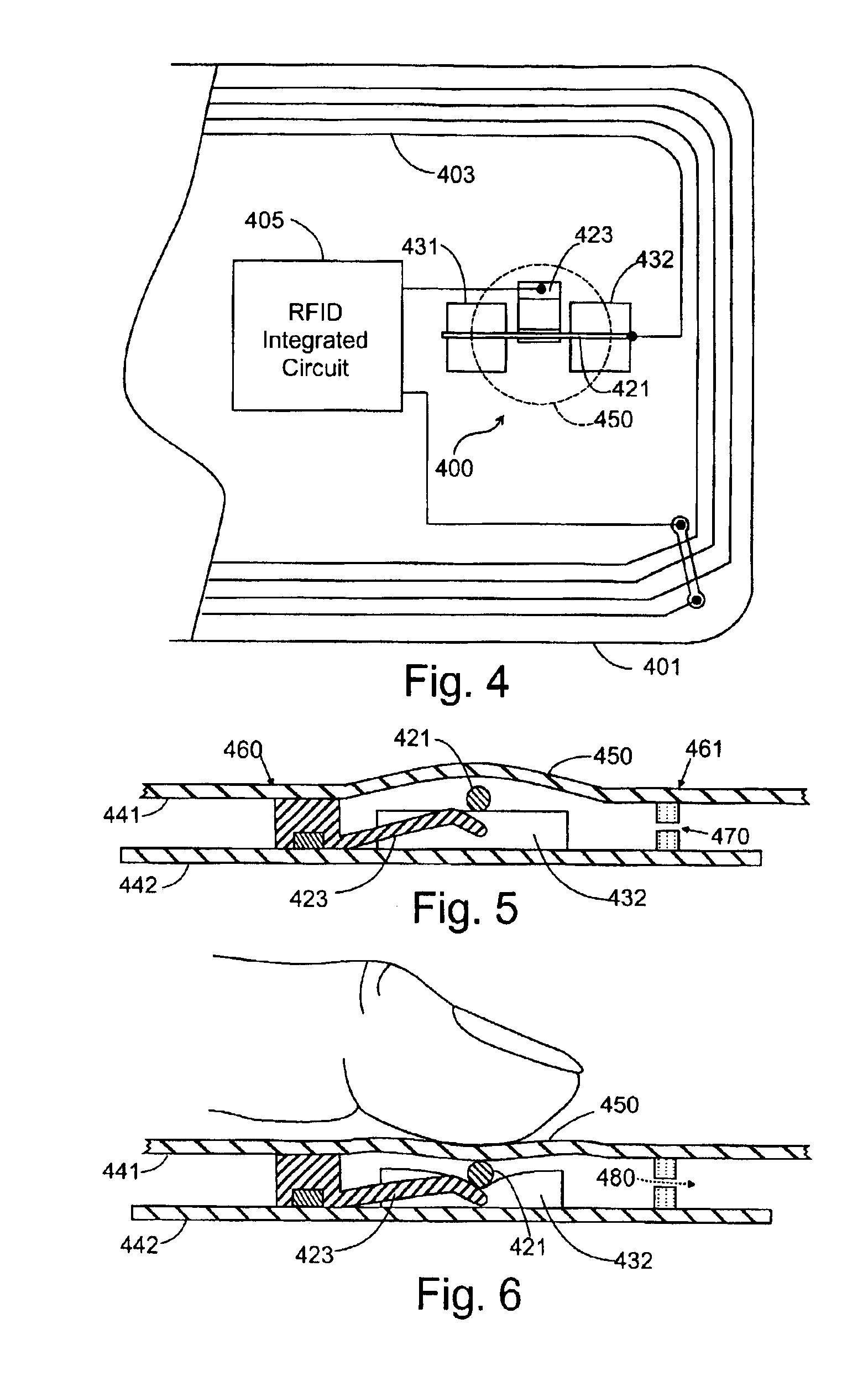

Manually operated switch for enabling and disabling an RFID card

InactiveUS6863220B2Semiconductor/solid-state device detailsSolid-state devicesTransceiverEngineering

A radio operated data card whose outer jacket forms a sealed protected housing for internal electrical components, including an RFID integrated circuit which incorporates data storage and a radio frequency transceiver, an on card antenna, and manually operated, normally open electrical switch contacts connected between the on-card electronic circuitry and the antenna. The open switch contacts normally disable the card, protecting the data on the card from being surreptitiously read until the switch contacts are intentionally closed by the cardholder to enable data transfer to occur. The cardholder may activate the card by applying external pressure to the surface of the card at a predetermined position, closing the switch contacts which open again automatically when pressure is removed. A tactile indicia on the surface of the card allows the cardholder to determine by touch where the card should be pressed to enable data transfers to occur. In an alternate embodiment, a mating key in the possession of the cardholder may be brought into proximity with the card to close the normally open switch to permit information to be read from the card.

Owner:MASSACHUSETTS INST OF TECH

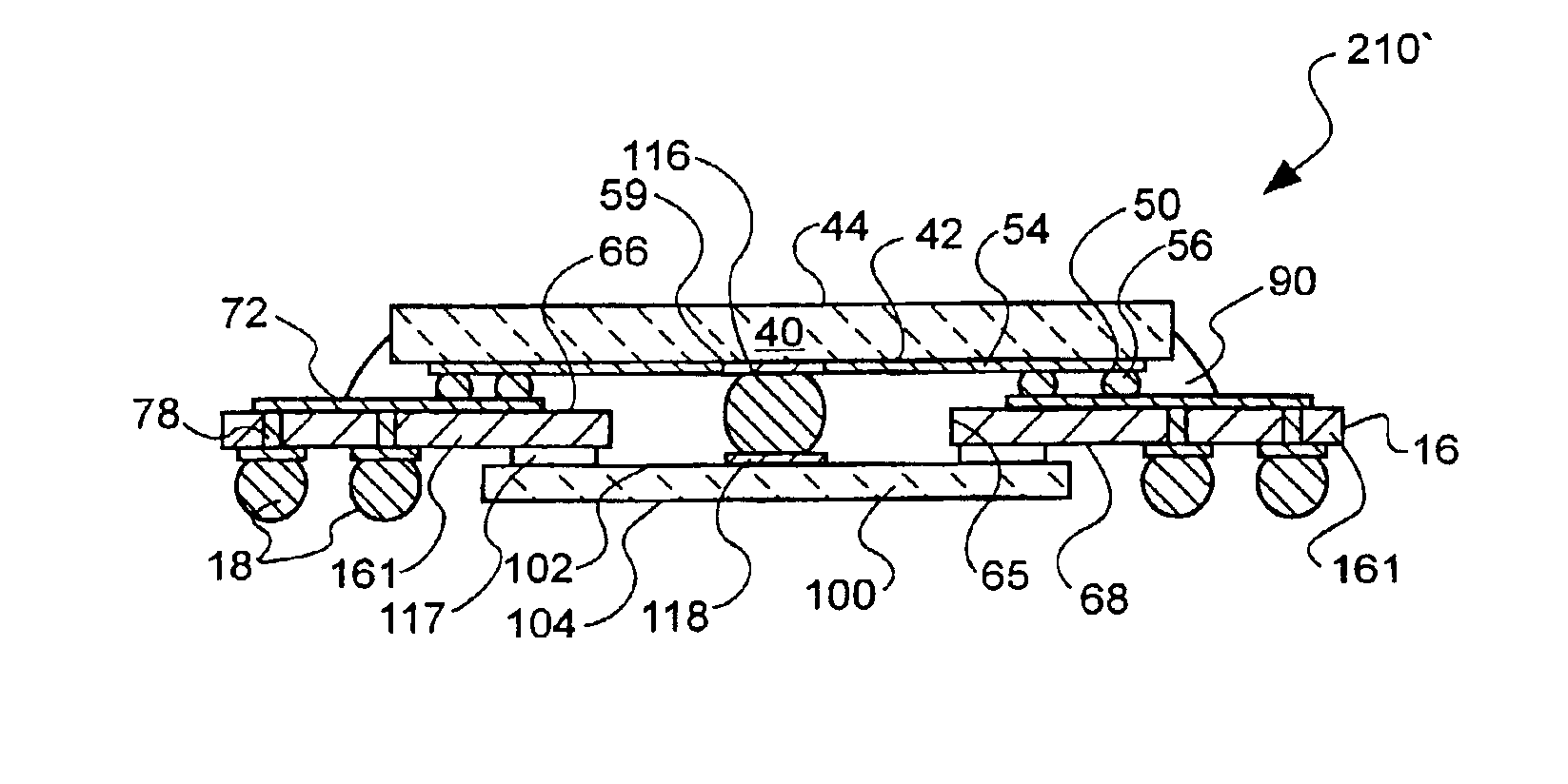

Integrated structures and fabrication methods thereof implementing a cell phone or other electronic system

ActiveUS20080316714A1Semiconductor/solid-state device detailsSolid-state devicesElectronic systemsContact pad

Circuit structures and methods of fabrication are provided for facilitating implementing a complete electronic system in a compact package. The circuit structure includes, in one embodiment, a chips-first multichip base layer with conductive structures extending therethrough. An interconnect layer is disposed over the front surface of the multichip layer and includes interconnect metallization electrically connected to contact pads of the chips and to conductive structures extending through the structural material. A redistribution layer, disposed over the back surface of the multichip layer, includes a redistribution metallization also electrically connected to conductive structures extending through the structural material. Input / output contacts are arrayed over the redistribution layer, including over the lower surfaces of at least some integrated circuit chips within the multichip layer, and are electrically connected through the redistribution metallization, conductive structures, and interconnect metallization to contact pads of the integrated circuit chips of the multichip layer.

Owner:EPIC TECH INC

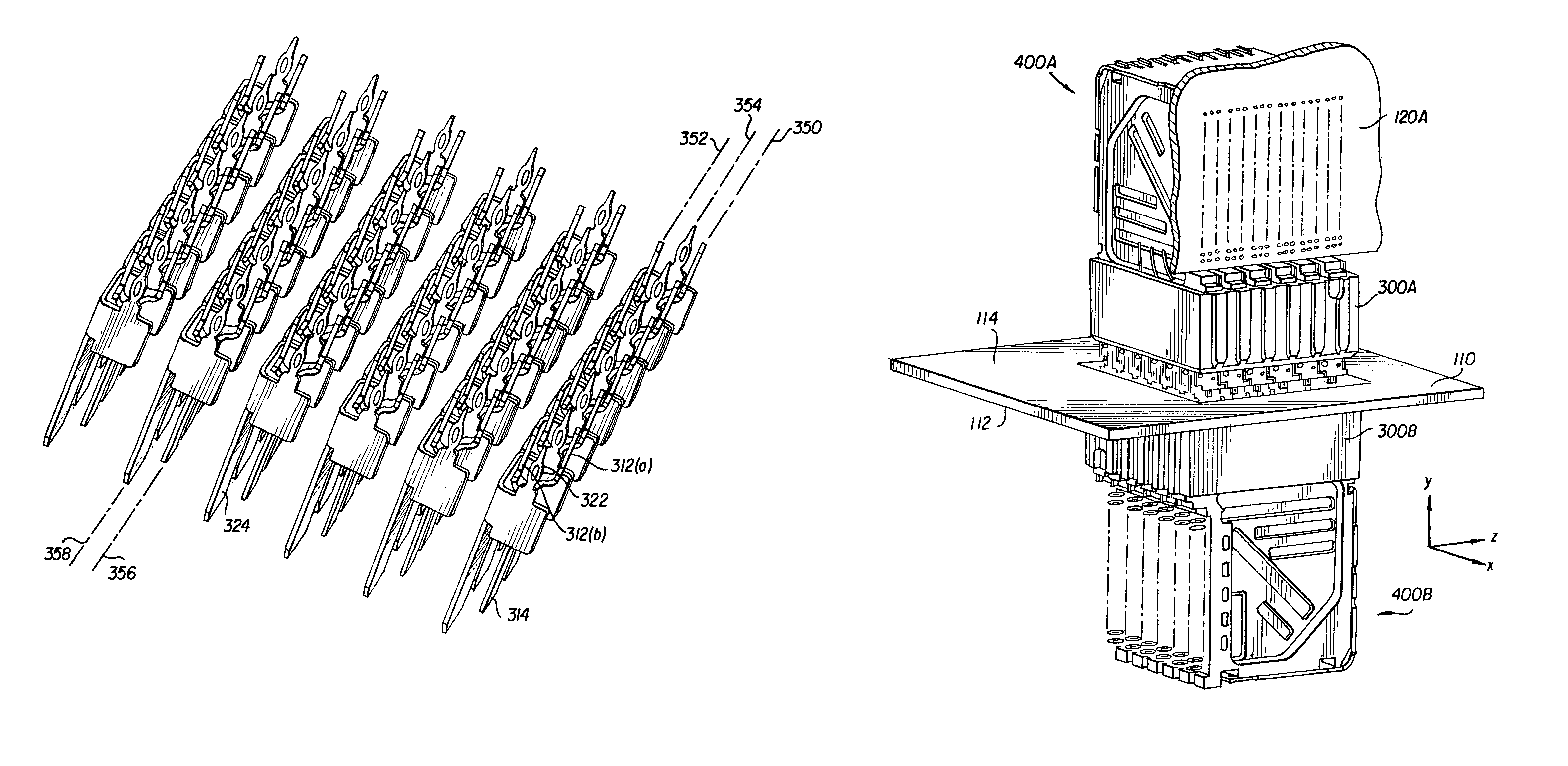

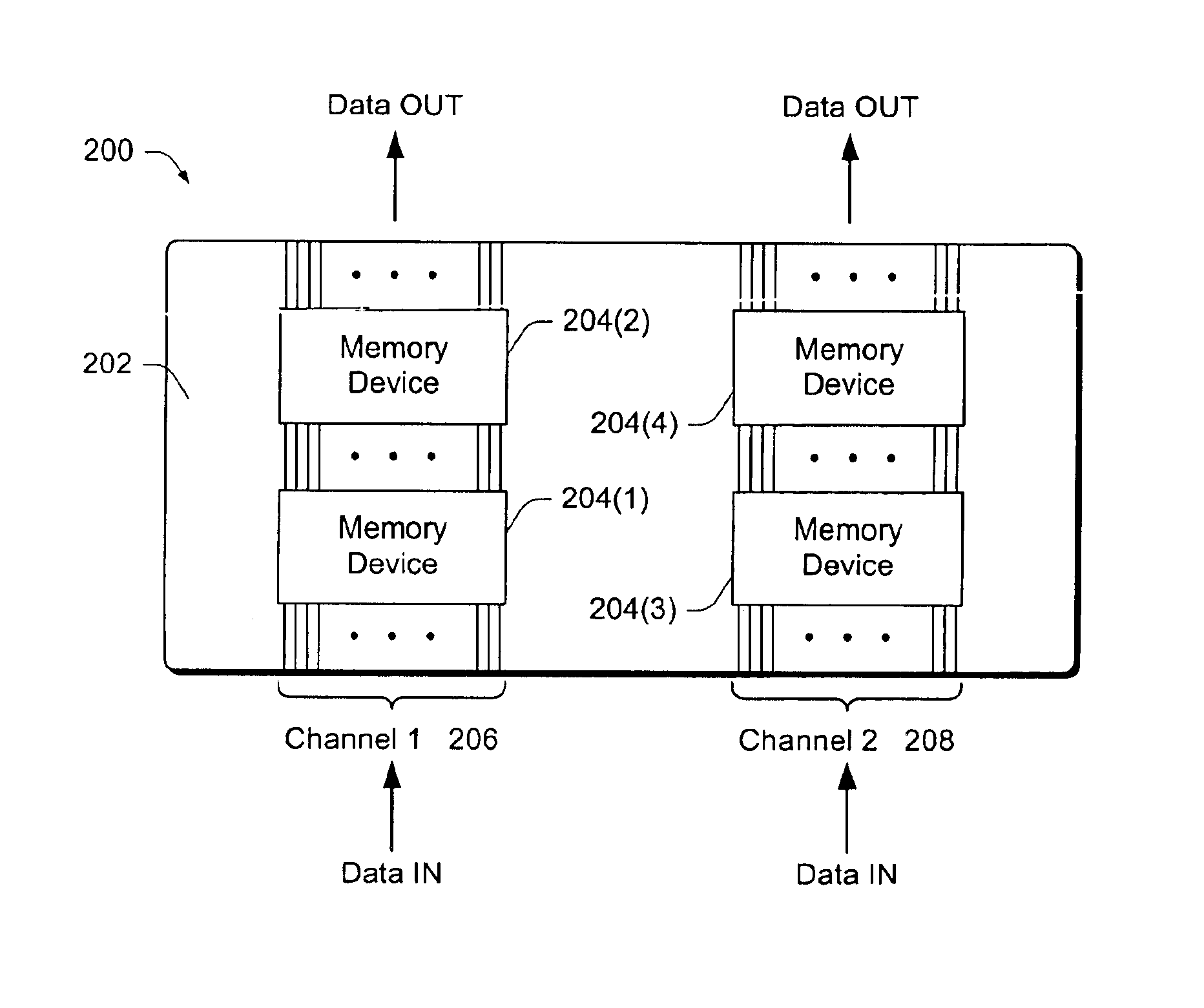

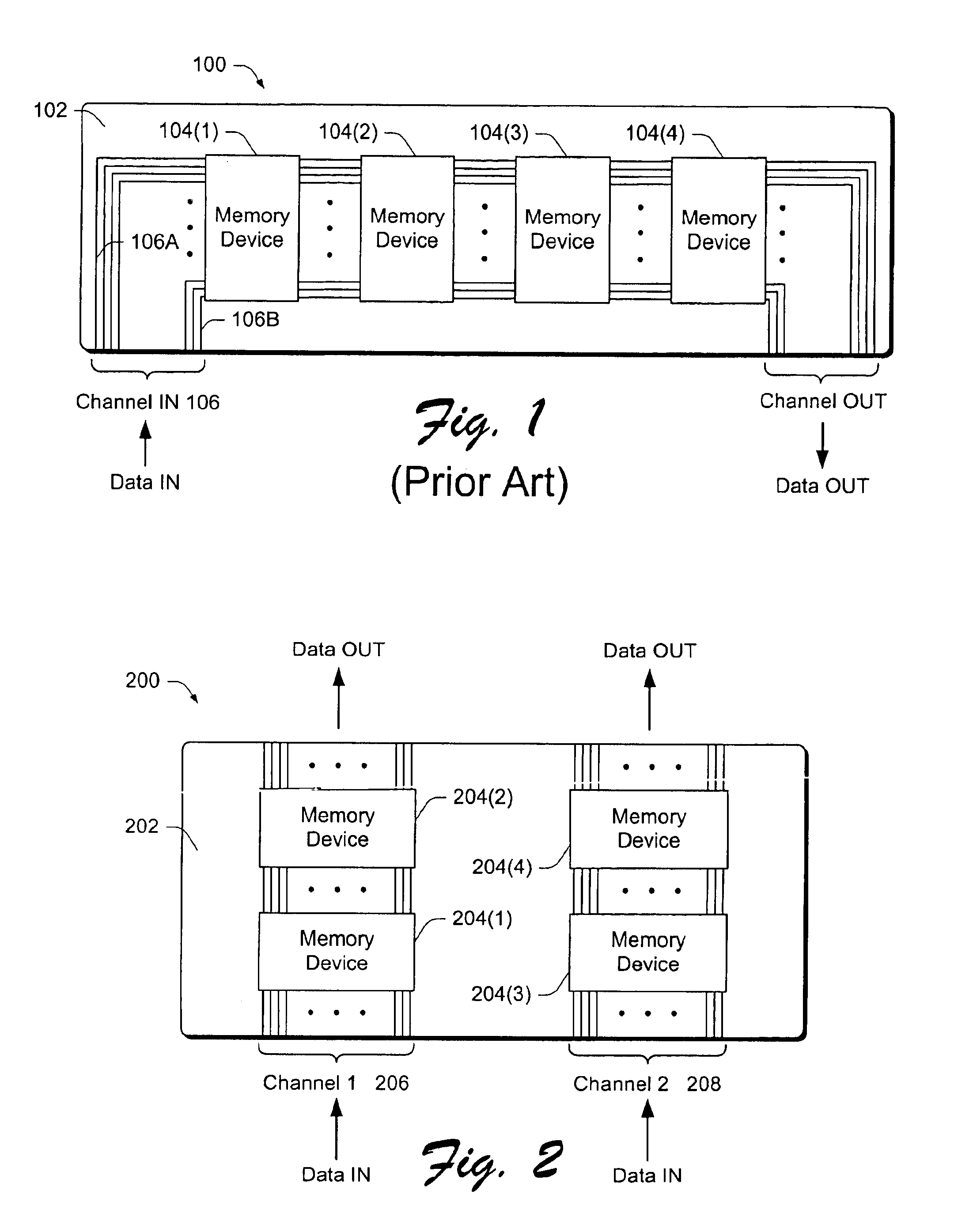

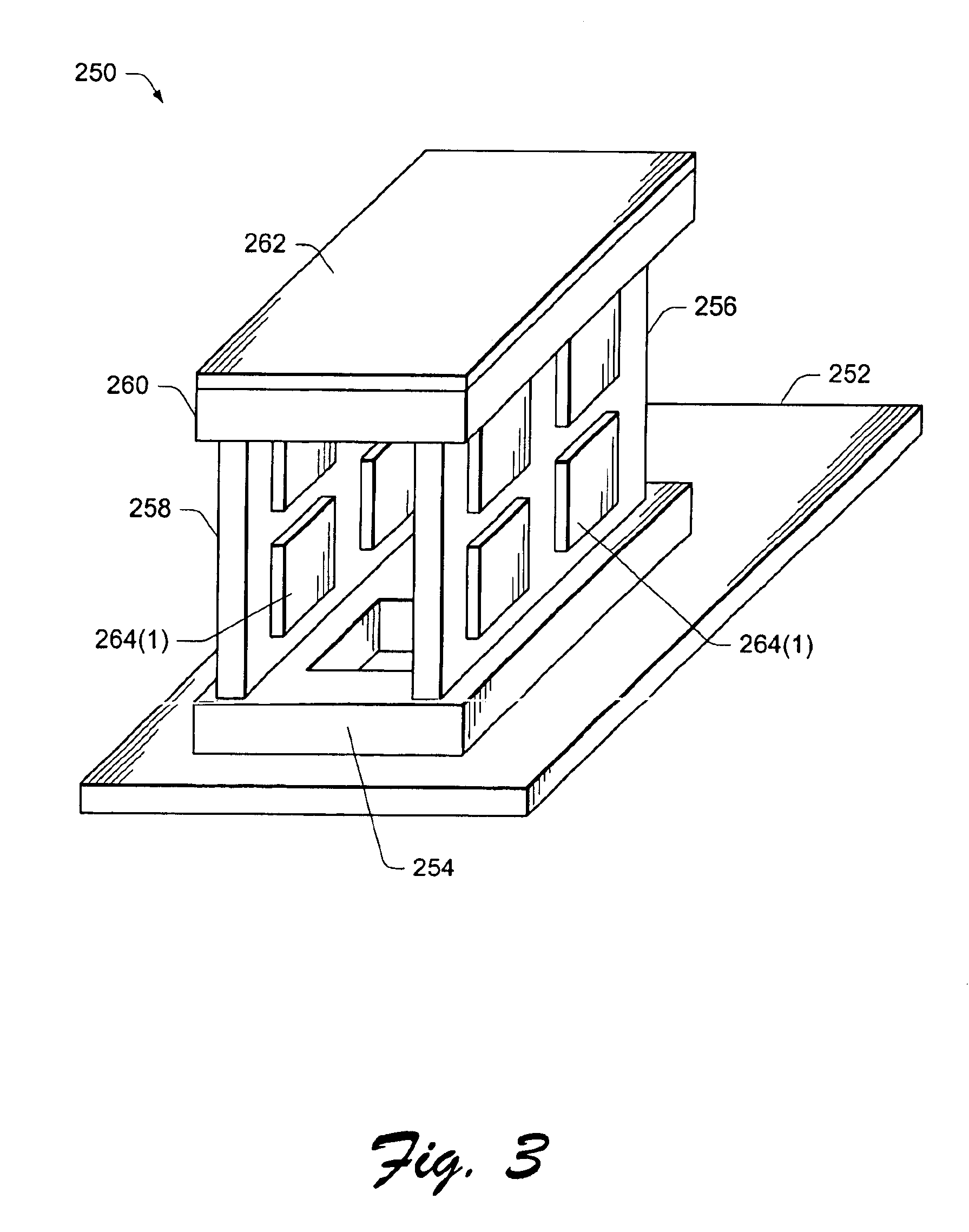

Multi-channel memory architecture

InactiveUS6853557B1Circuit arrangements on support structuresPrinted circuit aspectsElectrical conductorEngineering

A memory architecture includes a first substrate containing multiple memory devices and a first channel portion extending across the first substrate. The architecture further includes a second substrate containing multiple memory devices and a second channel portion extending across the second substrate. A connector couples the first channel portion to the second channel portion to form a single channel. The connector includes a first slot that receives an edge of the first substrate and a second slot that receives an edge of the second substrate. Another connector has a pair of slots that receive opposite edges of the first and second substrates. The channel portions extend across the substrates in a substantially linear path. Each channel portion includes multiple conductors having lengths that are approximately equal.

Owner:RAMBUS INC

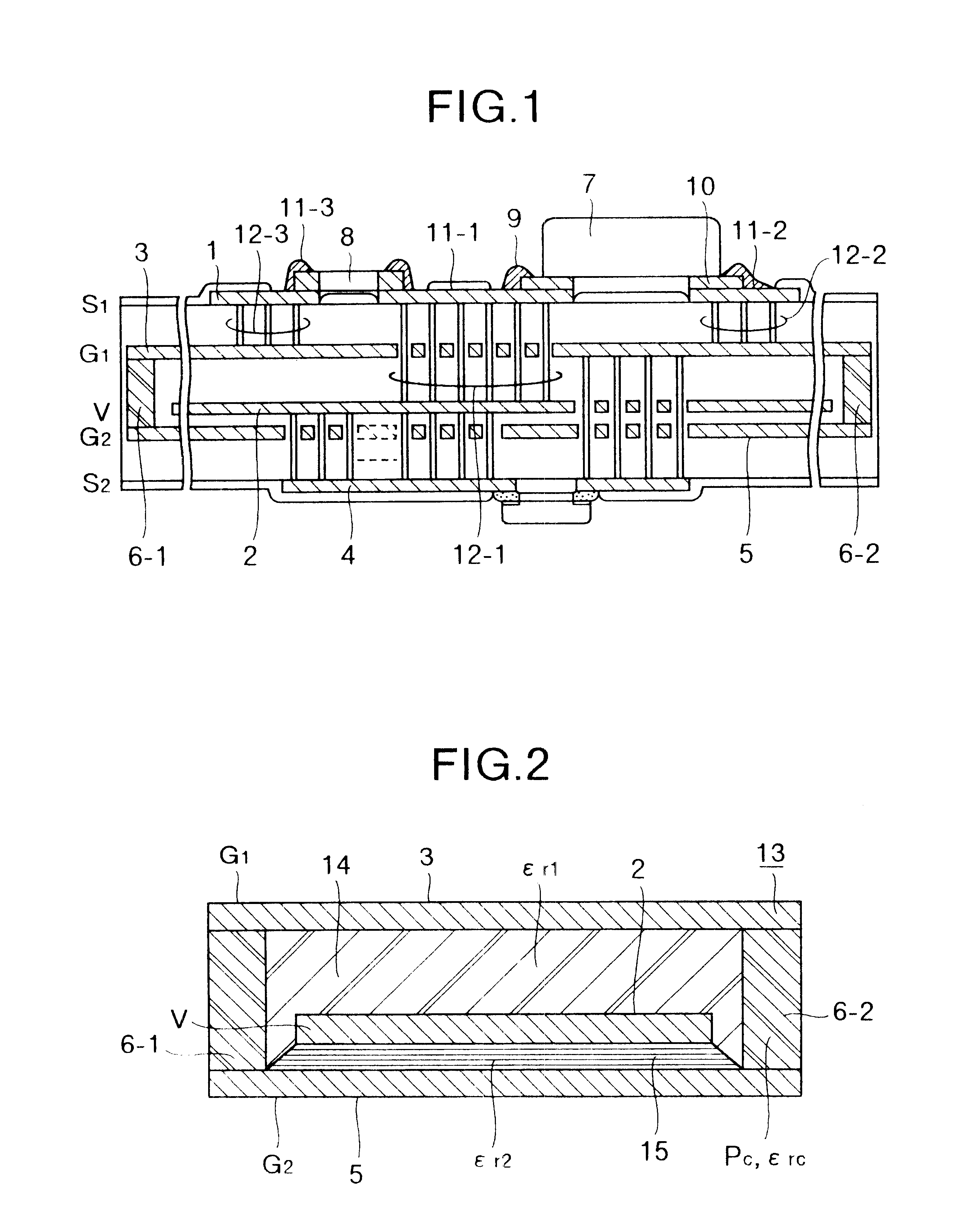

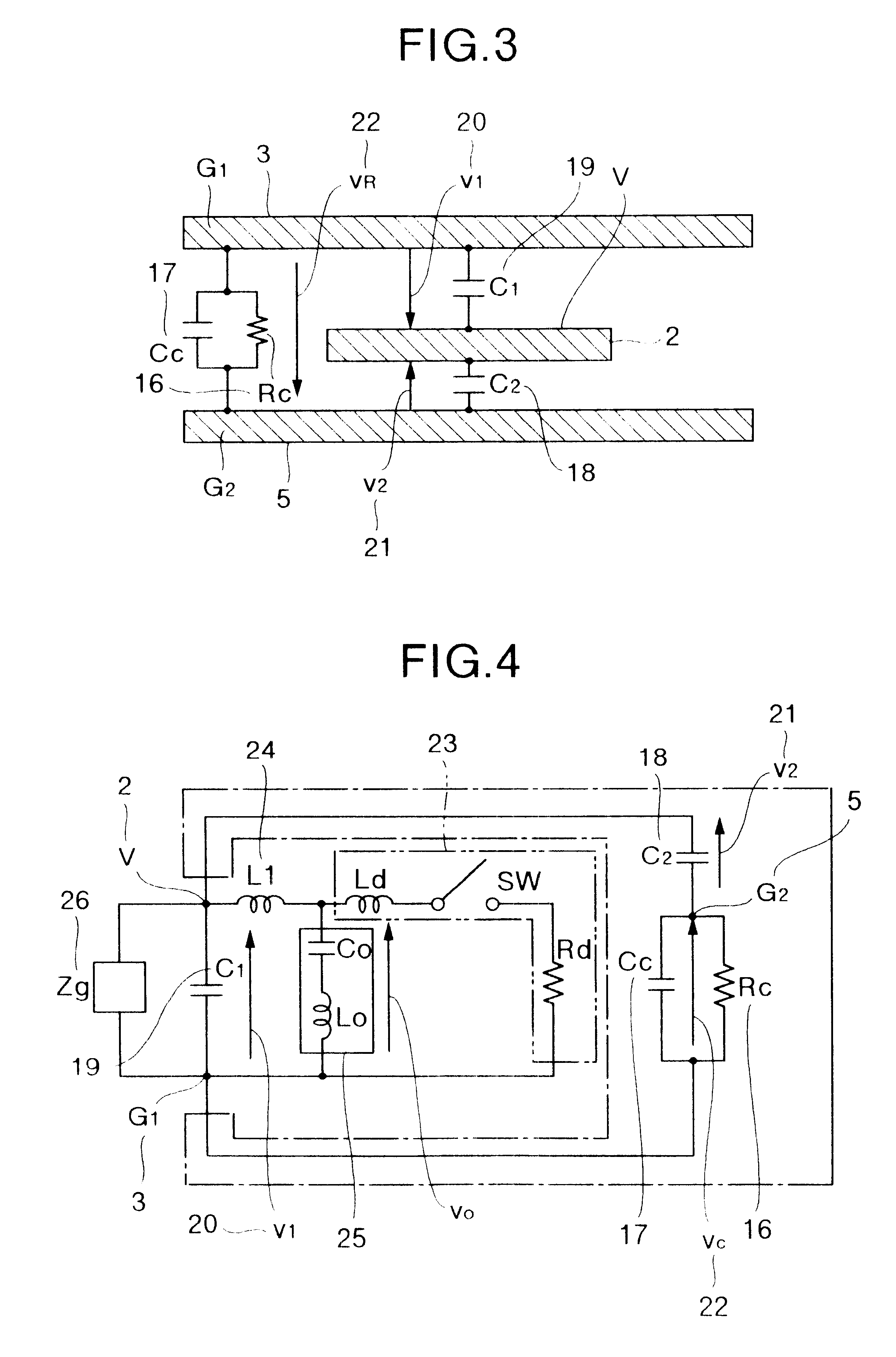

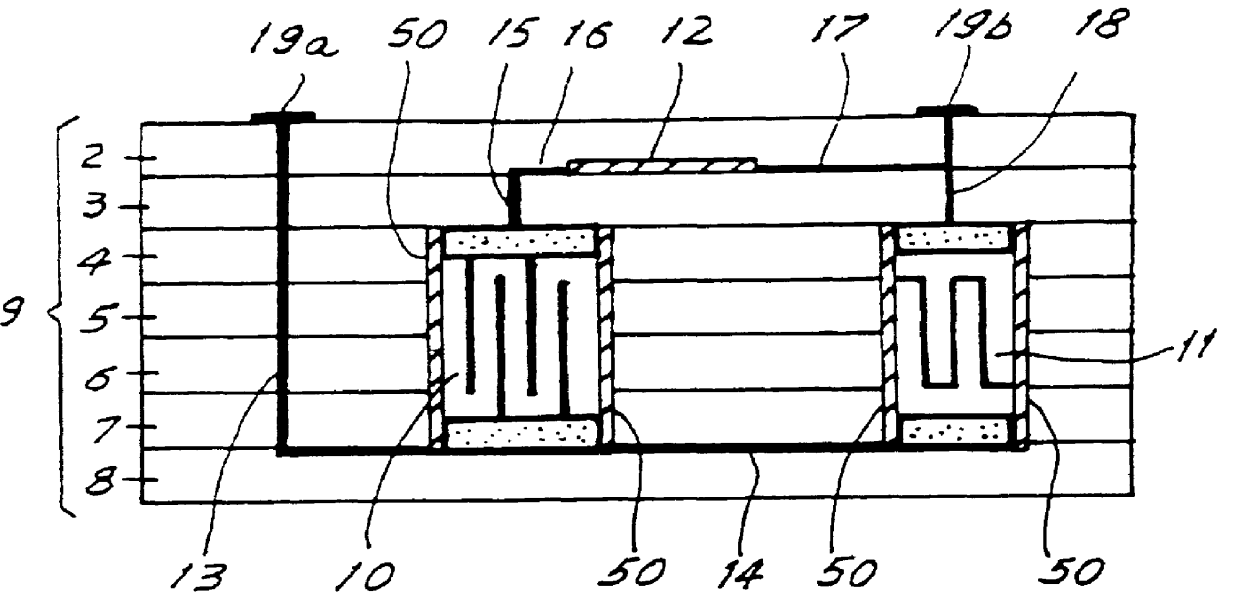

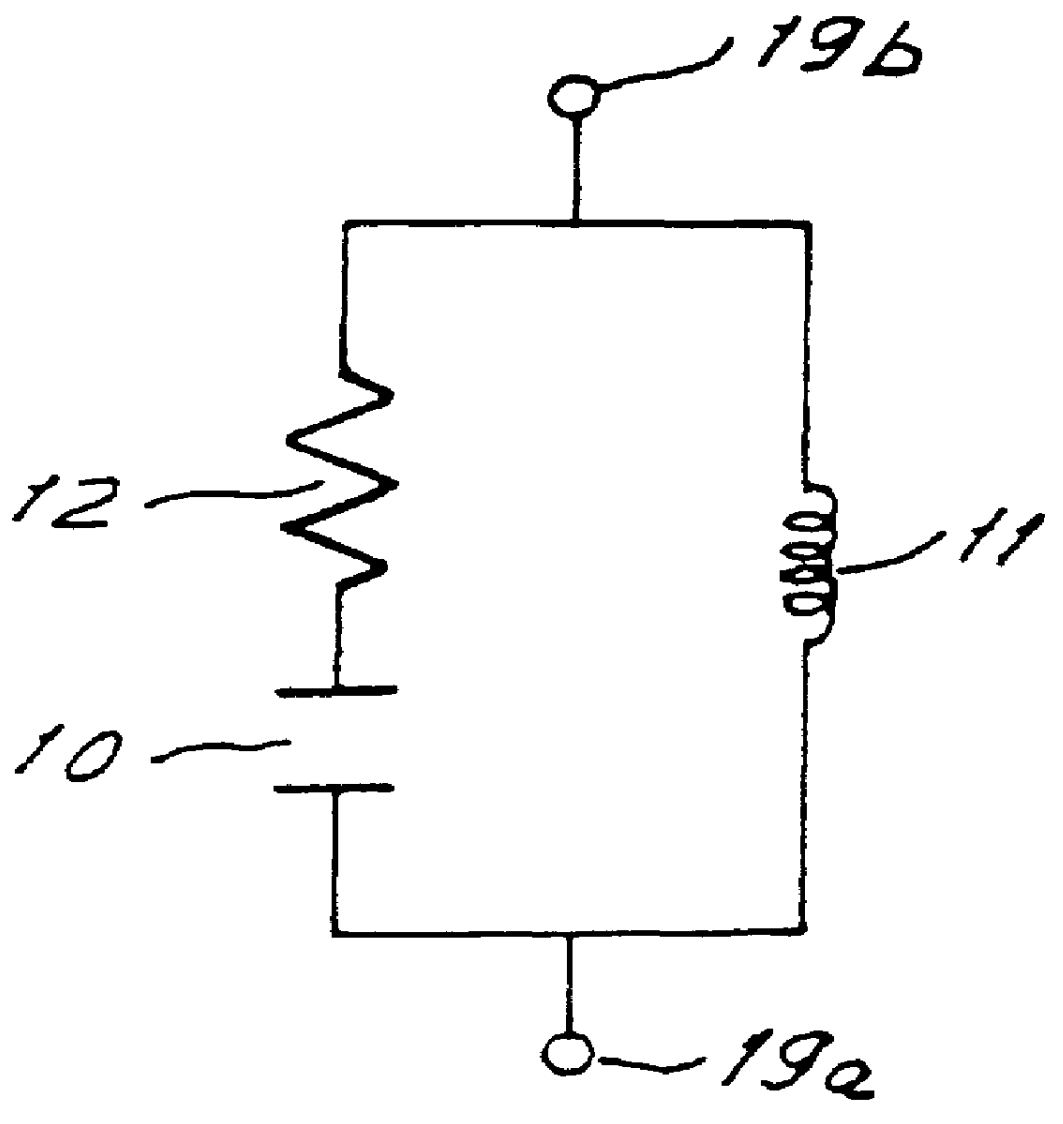

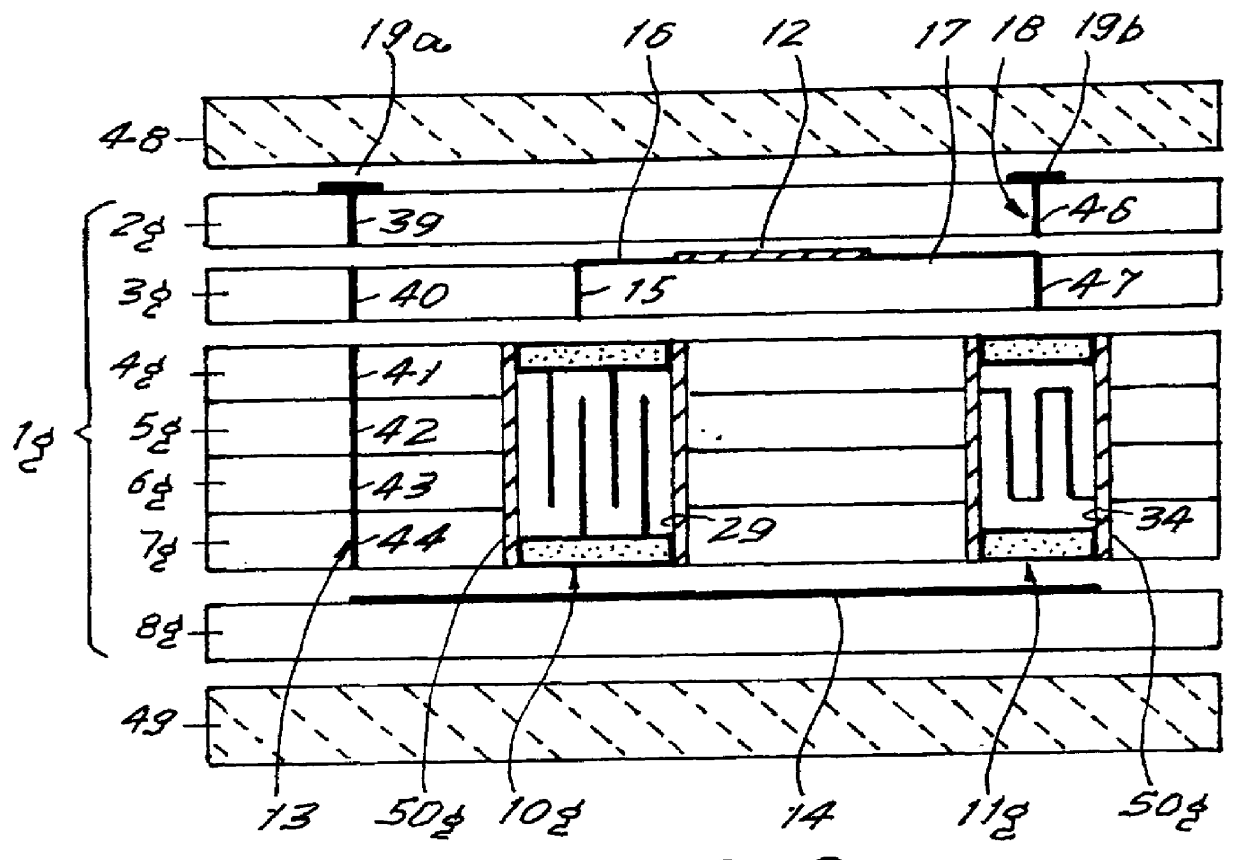

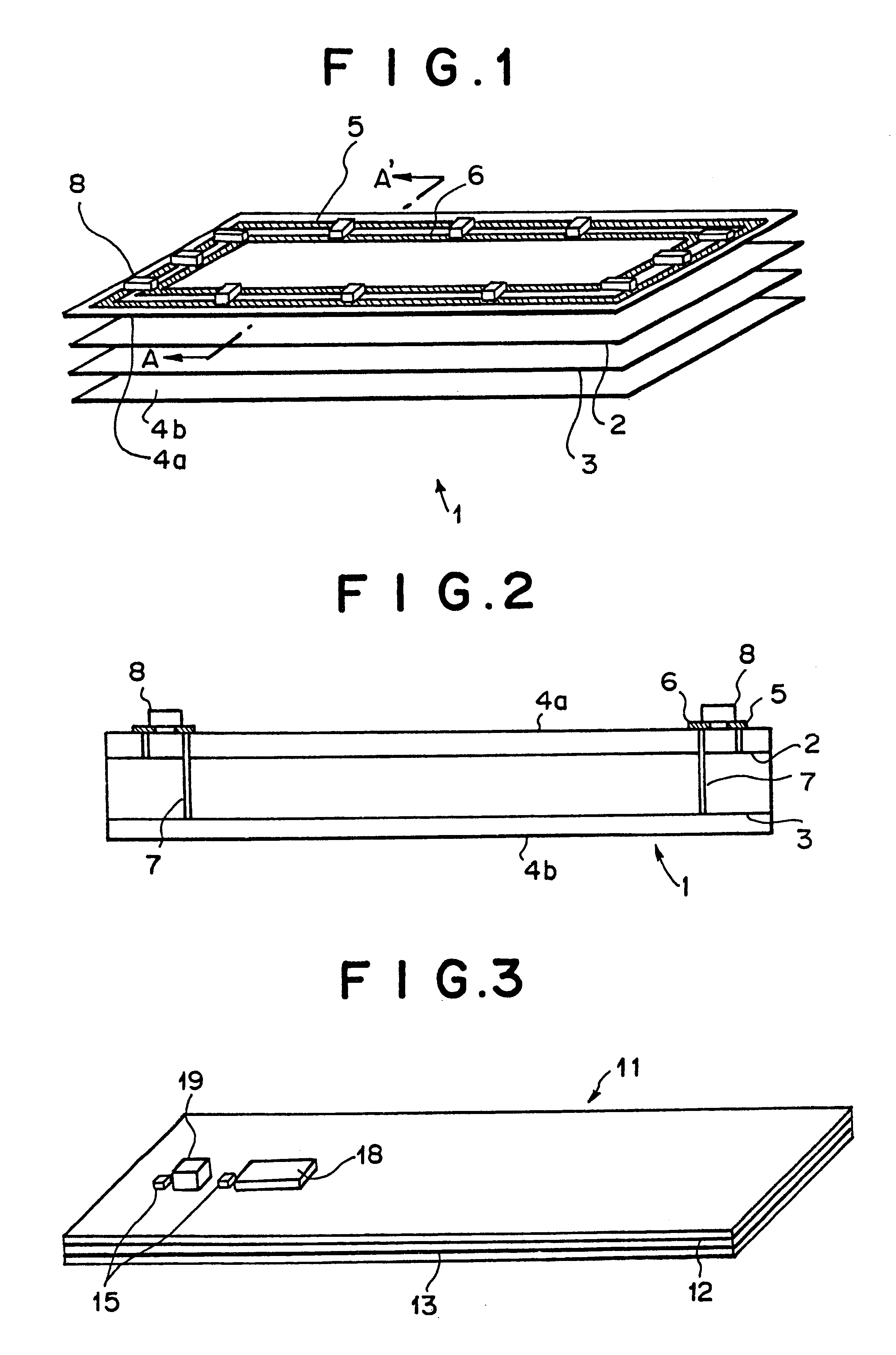

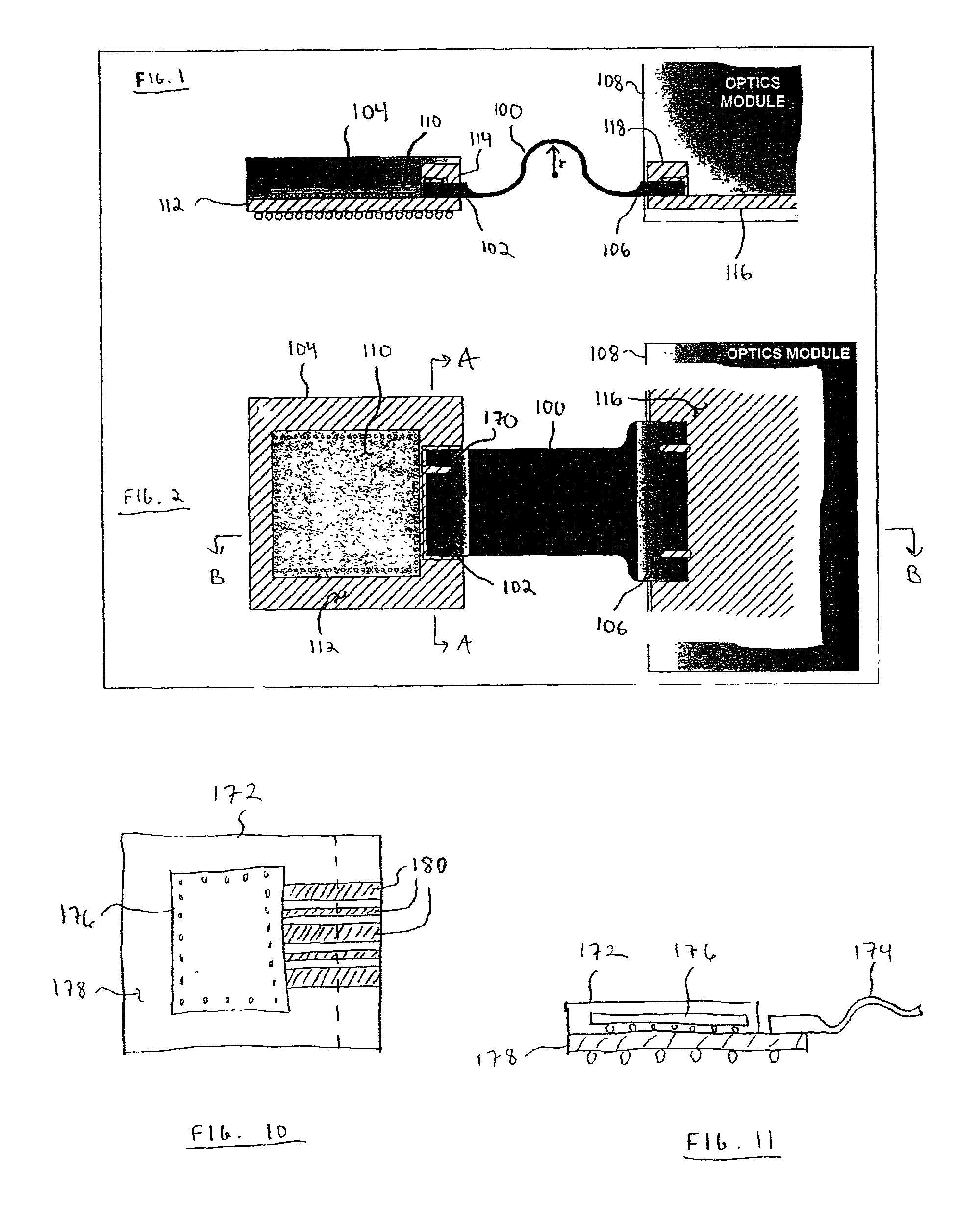

Low-EMI electronic apparatus, low-EMI circuit board, and method of manufacturing the low-EMI circuit board.

InactiveUS6353540B1Radiation suppressionHigh packageMagnetic/electric field screeningFinal product manufactureCapacitanceCountermeasure

Owner:HITACHI LTD

Probe card assembly and kit, and methods of using same

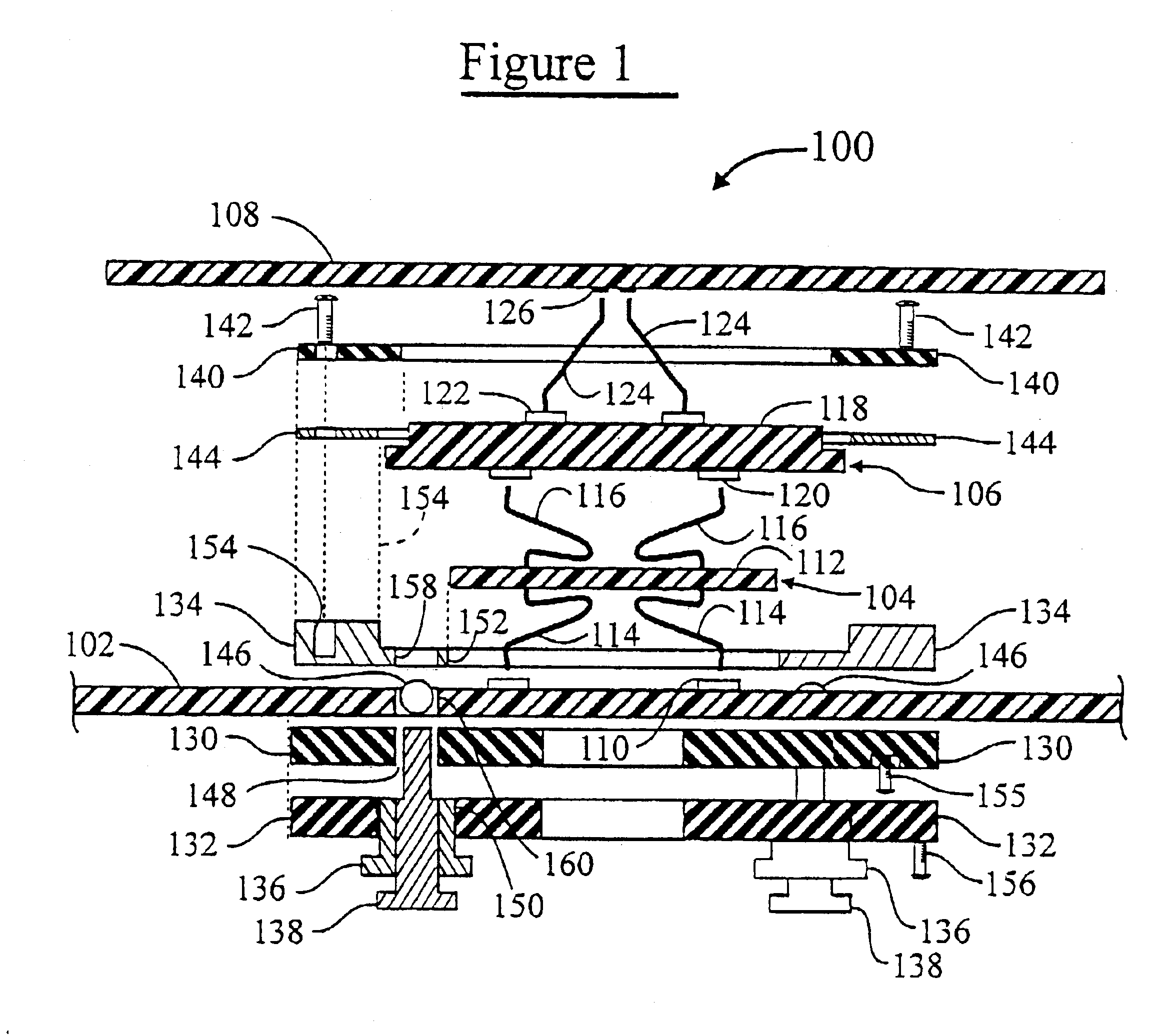

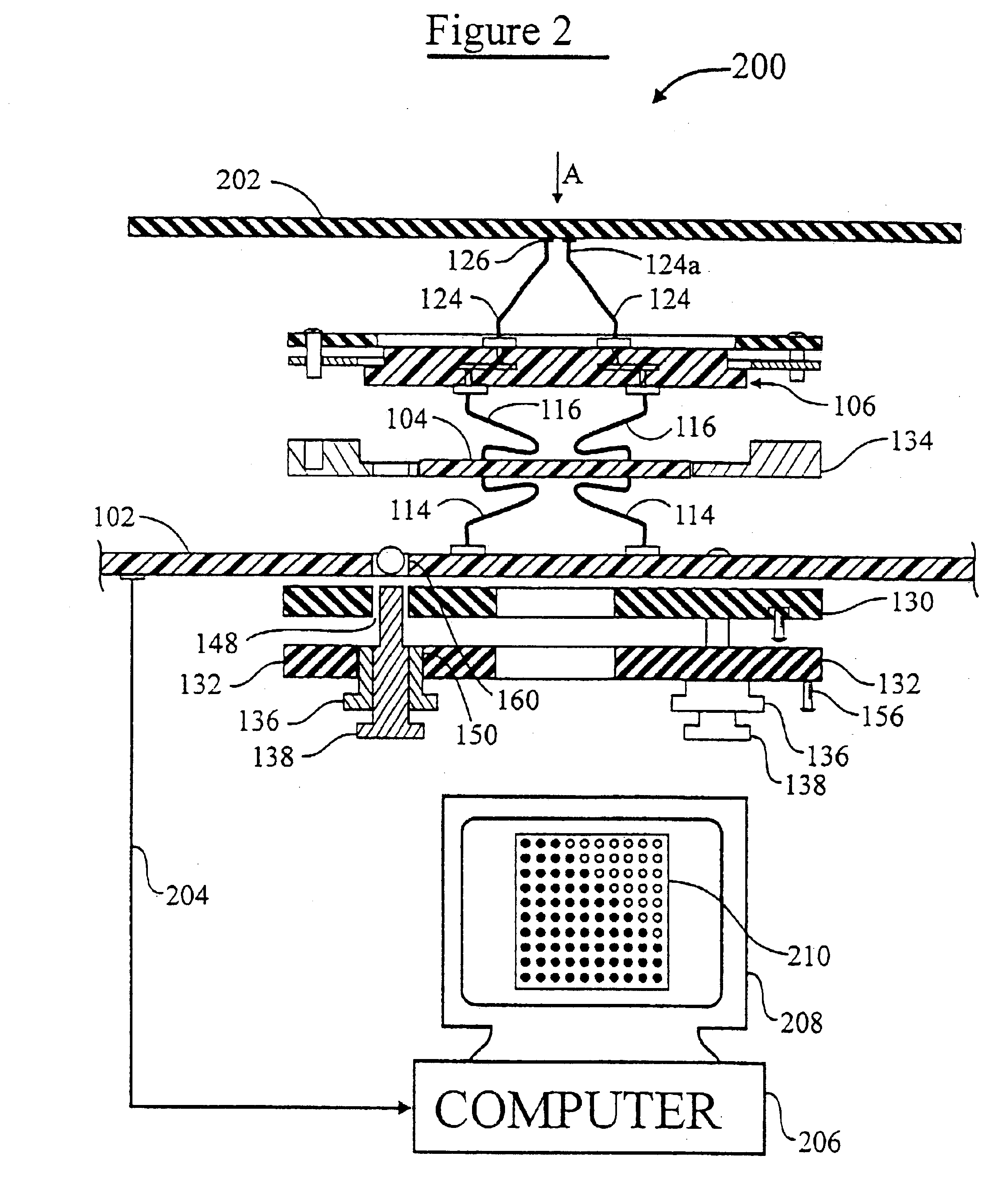

InactiveUS6246247B1Easy to disassembleEffective shieldingSemiconductor/solid-state device testing/measurementFinal product manufactureElectricityProbe card

A probe card assembly includes a probe card, a space transformer having resilient contact structures (probe elements) mounted directly thereto (i.e., without the need for additional connecting wires or the like) and extending from terminals on a surface thereof, and an interposer disposed between the space transformer and the probe card. The space transformer and interposer are "stacked up" so that the orientation of the space transformer, hence the orientation of the tips of the probe elements, can be adjusted without changing the orientation of the probe card. Suitable mechanisms for adjusting the orientation of the space transformer, and for determining what adjustments to make, are disclosed. The interposer has resilient contact structures extending from both the top and bottom surfaces thereof, and ensures that electrical connections are maintained between the space transformer and the probe card throughout the space transformer's range of adjustment, by virtue of the interposer's inherent compliance. Multiple die sites on a semiconductor wafer are readily probed using the disclosed techniques, and the probe elements can be arranged to optimize probing of an entire wafer. Composite interconnection elements having a relatively soft core overcoated by a relatively hard shell, as the resilient contact structures are described.

Owner:FORMFACTOR INC

Multi-layer ceramic substrate and method for producing the same

InactiveUS6153290AFinal product manufactureSemiconductor/solid-state device detailsHigh densityInductor

The present invention provides a method for producing a high-density multi-layer ceramic substrate with stable characteristics, the substrate incorporating therein a passive component such as a high-precision capacitor or inductor. The method comprises the steps of providing compact blocks containing a green ceramic functional material to form the passive components; providing a composite green laminate having a plurality of ceramic green sheets comprising a ceramic insulating material and in which the compact blocks are built in pre-disposed spaces and a paste containing a metal inducing, during firing, oxidation reaction accompanied by expansion is provided in space between inside walls of the spaces and the compact blocks; firing the composite green laminate in a state in which the laminate is sandwiched by the sheet-like supports formed of green ceramics that cannot be sintered at the sintering temperature, so as to prevent shrinkage of the laminate; and removing the unsintered sheet-like supports.

Owner:MURATA MFG CO LTD

Information card system

InactiveUS7290709B2Easy and inexpensive to manufactureEncouraging their ready and wide distribution and usageDifferent record carrier formsRecord information storageInformation CardDistribution system

Owner:TSAI ERICA +1

Printed circuit board with capacitors connected between ground layer and power layer patterns

InactiveUS6198362B1Magnetic/electric field screeningCurrent interference reductionEngineeringGround pattern

A printed circuit board is disclosed. A top layer power supply pattern and a top layer ground pattern are formed. The top layer power supply pattern and the top layer ground pattern are connected to a power supply layer and a ground layer through a plurality of viaholes, respectively. A plurality of capacitors or a plurality of capacitor resistor series circuits are disposed at predetermined intervals between the top layer power supply pattern and the top layer ground pattern.

Owner:NEC CORP

High frequency signal transmission from the surface of a circuit substrate to a flexible interconnect cable

InactiveUS6867668B1Facilitates high speed signal transmissionLow costPrinted circuit assemblingCross-talk/noise/interference reductionElectricityCoplanar waveguide

A high speed flexible interconnect cable includes a number of conductive layers and a number of dielectric layers. Conductive signal traces, located on the conductive layers, combine with the dielectric layers to form one or more high speed electrical transmission line structures. The transmission line structure may be realized as a grounded coplanar waveguide structure, a microstrip structure, a stripline structure, or the like. The cable can be coupled to destination components using a variety of connection techniques, e.g., direct bonding to a circuit substrate, direct soldering to a flip chip, mechanical attachment to a component, or integration with a circuit substrate. The cable can also be terminated with any number of known or standardized connector packages, e.g., SMA, GPPO, or V connectors.

Owner:QUALCOMM INC

Stacking integrated circuits containing serializer and deserializer blocks using through silicon via

ActiveUS8014166B2Efficiently routedReduce and eliminate and capacitanceSemiconductor/solid-state device detailsSolid-state devicesEngineeringThrough-silicon via

Methods and systems for stacking multiple chips with high speed serialiser / deserialiser blocks are presented. These methods make use of Through Silicon Via (TSV) to connect the dice to each other, and to the external pads. The methods enable efficient multilayer stacking that simplifies design and manufacturing, and at the same time, ensure high speed operation of serialiser / deserialiser blocks, using the TSVs.

Owner:BROADPAK CORP

Method of making a product with improved material properties by moderate heat-treatment of a metal incorporating a dilute additive

InactiveUS6150186AStable mechanical propertiesImprove conductivitySemiconductor/solid-state device testing/measurementFinal product manufactureUltimate tensile strengthMechanical property

Deposition of metal in a preferred shape, including coatings on parts, or stand-alone materials, and subsequent heat treatment to provide improved mechanical properties. In particular, the method gives products with relatively high yield strength. The products often have relatively high elastic modulus, and are thermally stable, maintaining the high yield strength at temperatures considerably above 25 DEG C. This technique involves depositing a material in the presence of a selected additive, and then subjecting the deposited material to a moderate heat treatment. This moderate heat treatment differs from other commonly employed "stress relief" heat treatments in using lower temperatures and / or shorter times, preferably just enough to reorganize the material to the new, desired form. Coating a shape and heat treating provides a shaped deposit with improved material properties. Coating a shape with a portion connected to a base and a portion detached therefrom can provide a resilient, conductive contact useful for electronic applications.

Owner:FORMFACTOR INC

Probe card assembly

InactiveUS6838893B2Easy to disassembleEffective shieldingSemiconductor/solid-state device testing/measurementFinal product manufactureProbe cardTransformer

In a probe card assembly, a series of probe elements can be arrayed on a silicon space transformer. The silicon space transformer can be fabricated with an array of primary contacts in a very tight pitch, comparable to the pitch of a semiconductor device. One preferred primary contact is a resilient spring contact. Conductive elements in the space transformer are routed to second contacts at a more relaxed pitch. In one preferred embodiment, the second contacts are suitable for directly attaching a ribbon cable, which in turn can be connected to provide selective connection to each primary contact. The silicon space transformer is mounted in a fixture that provides for resilient connection to a wafer or device to be tested. This fixture can be adjusted to planarize the primary contacts with the plane of a support probe card board.

Owner:FORMFACTOR INC

Popular searches

Exposure control Printed circuits structural associations Printed circuit non-printed electric components association Verifying markings correctness Sensing by electromagnetic radiation Semiconductor/solid-state device manufacturing Electrical connection printed elements Semiconductor devices Printed electric component incorporation Circuit thermal arrangements