Method for solving antenna effect in chip design

An antenna effect and chip design technology, applied to electrical components, electrical solid devices, circuits, etc., can solve problems such as area consumption, and achieve the effect of reducing area and consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] In order to make the purpose, technical solutions and advantages of the embodiments of the present invention clearer, the implementation of the present invention will be further described in detail below in conjunction with the accompanying drawings. Here, the exemplary embodiments and descriptions of the present invention are used to explain the present invention, but not to limit the present invention.

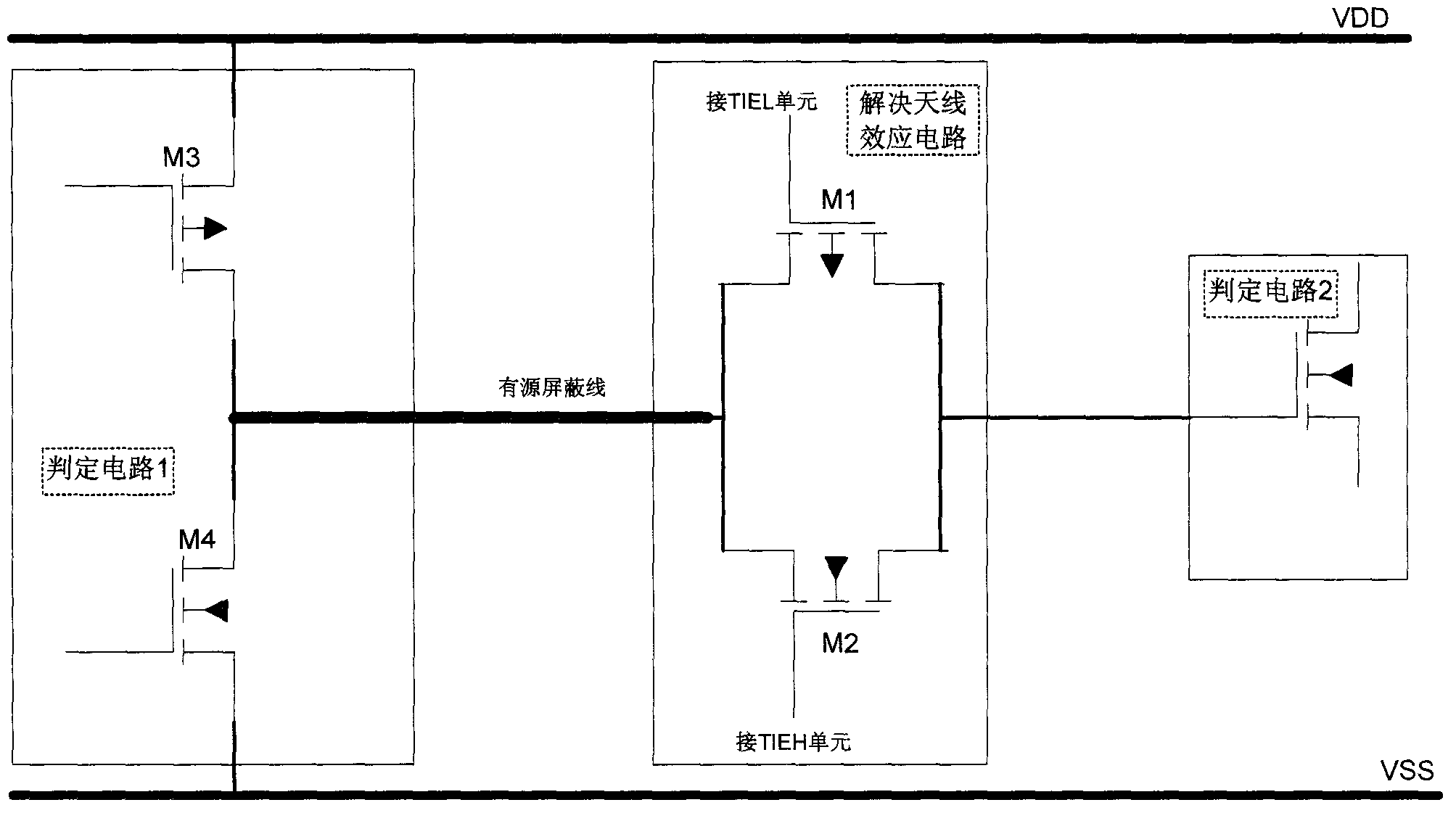

[0019] Such as figure 1 As shown, it is a frame diagram of the overall structure of the implementation method of the present invention. This embodiment includes (but not limited to) four functional modules: a judgment circuit 1, an active shielded wire, a circuit for solving antenna effects, and a judgment circuit 2.

[0020] Such as figure 1 Shown is a schematic diagram of the embodiment of the method and circuit for solving the antenna effect of the present invention, the circuit includes (but not limited to) a transmission gate circuit composed of PMOS and NMOS, a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More