Chip bonding pad of integrated circuit, manufacture method thereof and integrated circuit comprising bonding pad

A technology of an integrated circuit and a manufacturing method, which is applied in the field of anti-antenna effect chip pad structure and its manufacturing, and can solve problems such as affecting circuit performance and inappropriateness.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

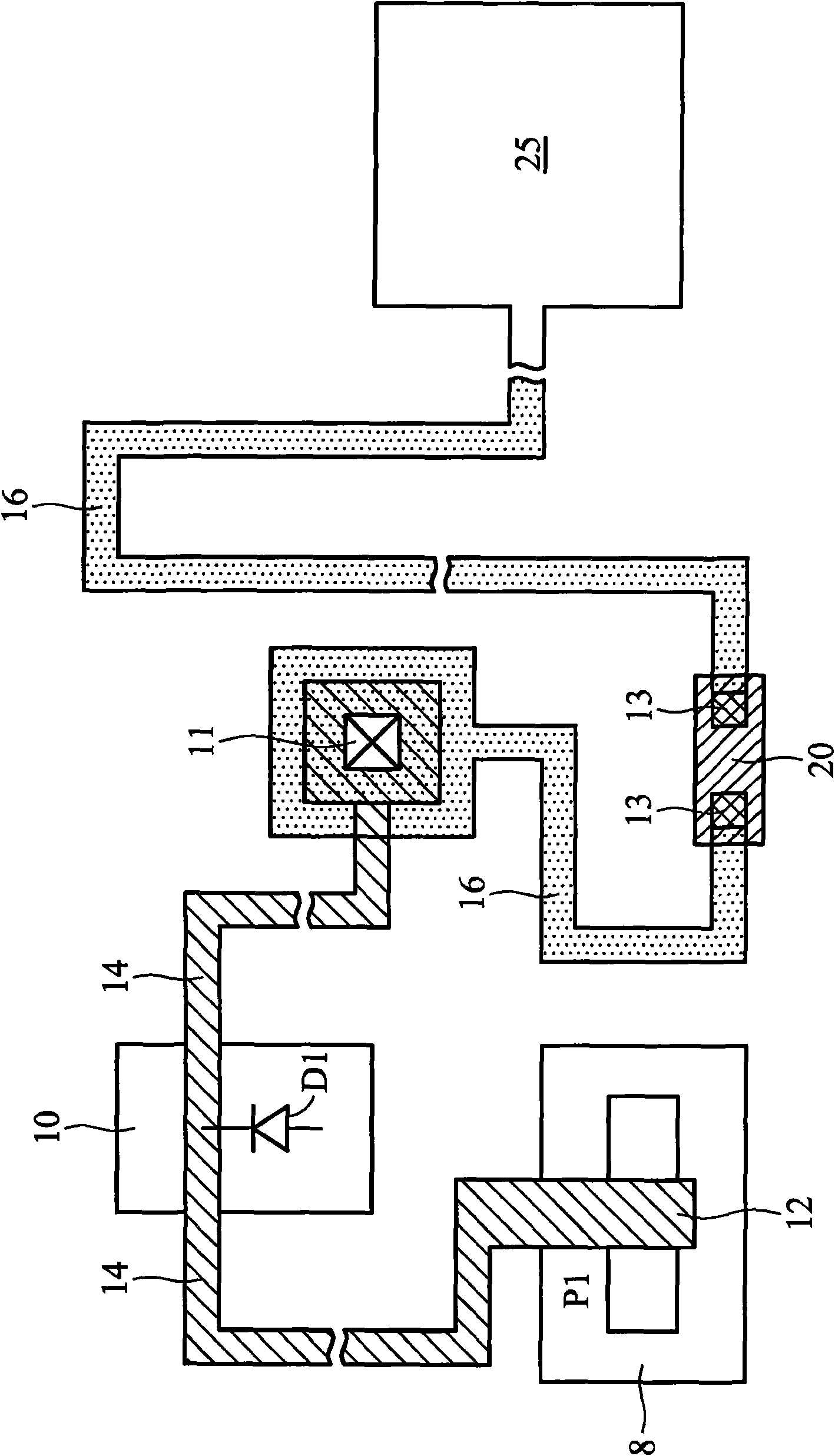

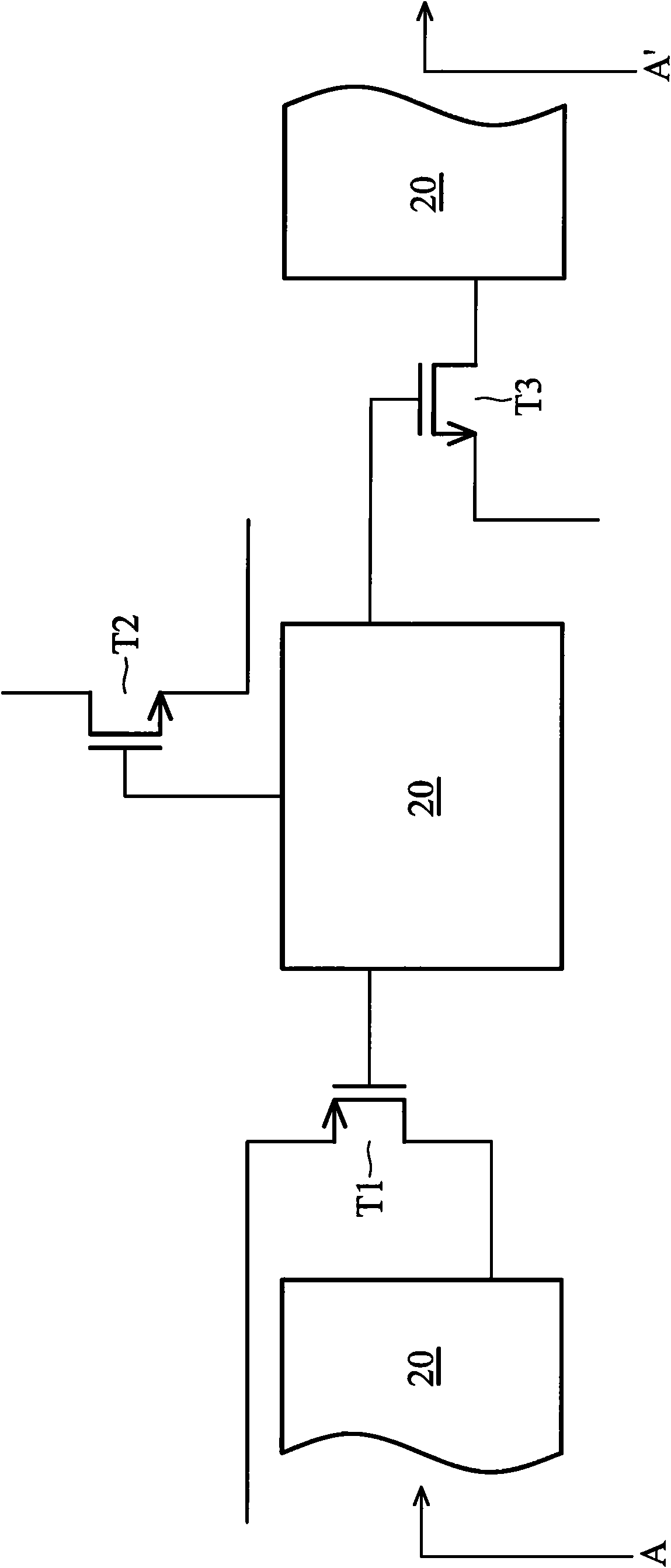

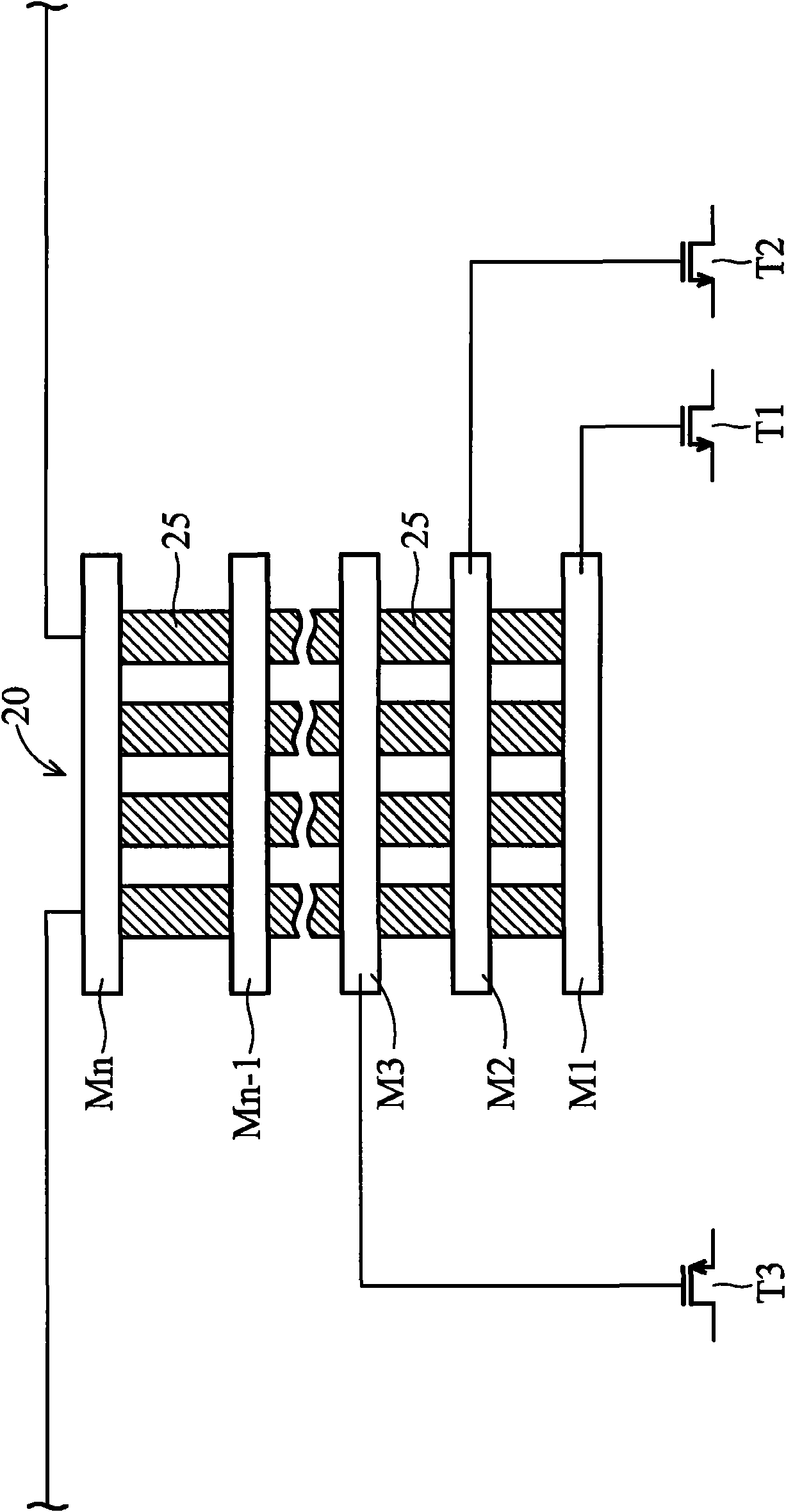

[0100] Preferred embodiments of the related content of the present invention will be described below, mainly the chip pad structure and the method of resisting the antenna effect. The preferred embodiment includes probe pads on a parametric test line, typically formed on a wafer in the area between adjacent integrated circuit dies, for measuring electrical characteristics of components formed on the integrated circuit. Preferred embodiments also include bonding pads on an integrated circuit bonded to metal wires and electrically connected to an integrated circuit package. The anti-antenna effect chip pad structure in the preferred embodiment does not include other manufacturing process steps outside the integrated circuit manufacturing flow.

[0101] Figure 2A It is a partial top view of a semiconductor integrated circuit chip, on which a plurality of chip bonding pads 20 are formed. The chip pad 20 includes a large surface layer, usually formed on the uppermost conductive ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More