Patents

Literature

555 results about "Gold layer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The Gold Layer is a secret layer that comes after Obsidian. The Gold Layer is entirely composed of Gold, and holds a higher percentage to spawning higher-value and rarer ores. A player needs a minimum of 50,000 blocks mined. The Gold Layer begins at -1602 and ends at -2101.

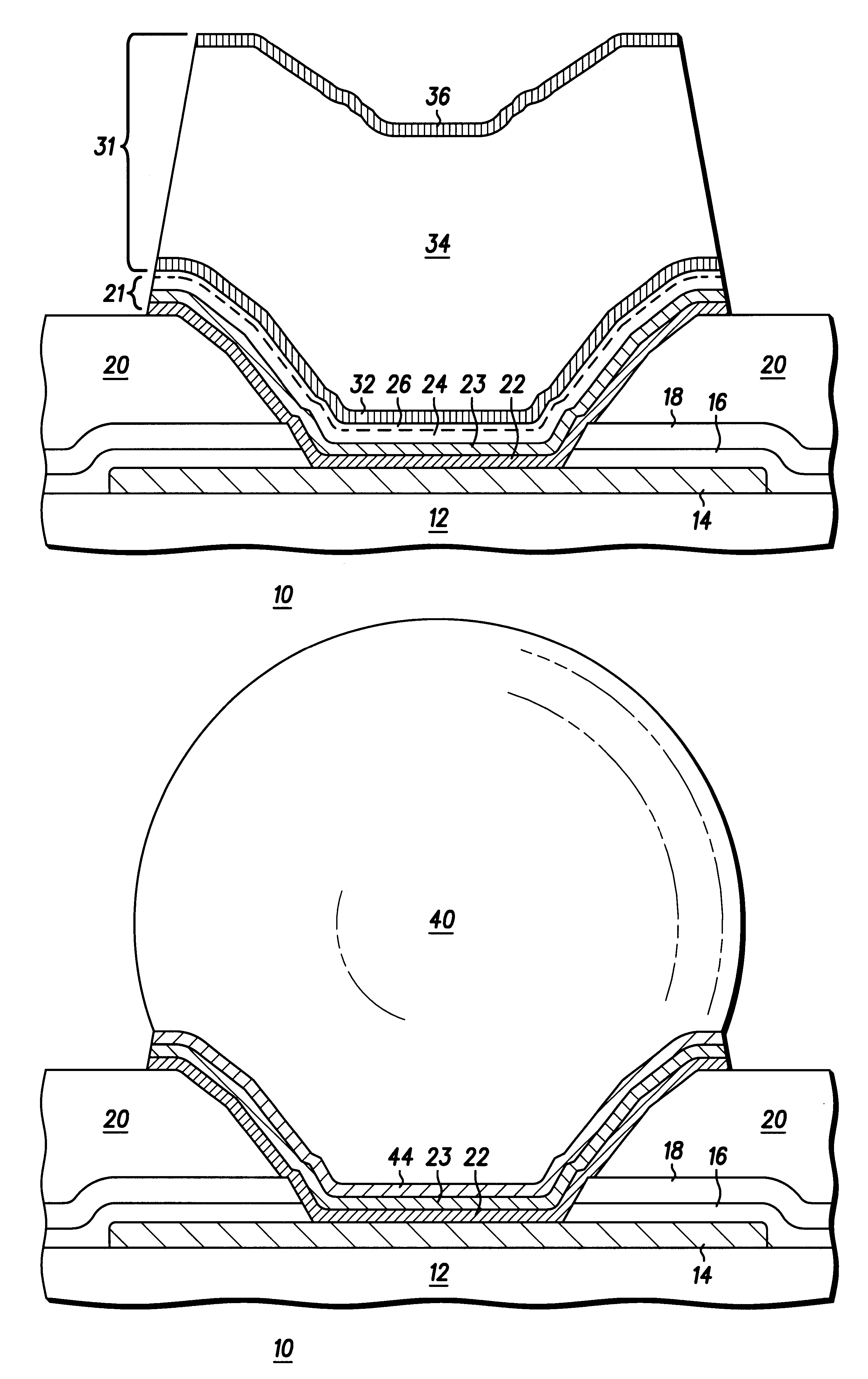

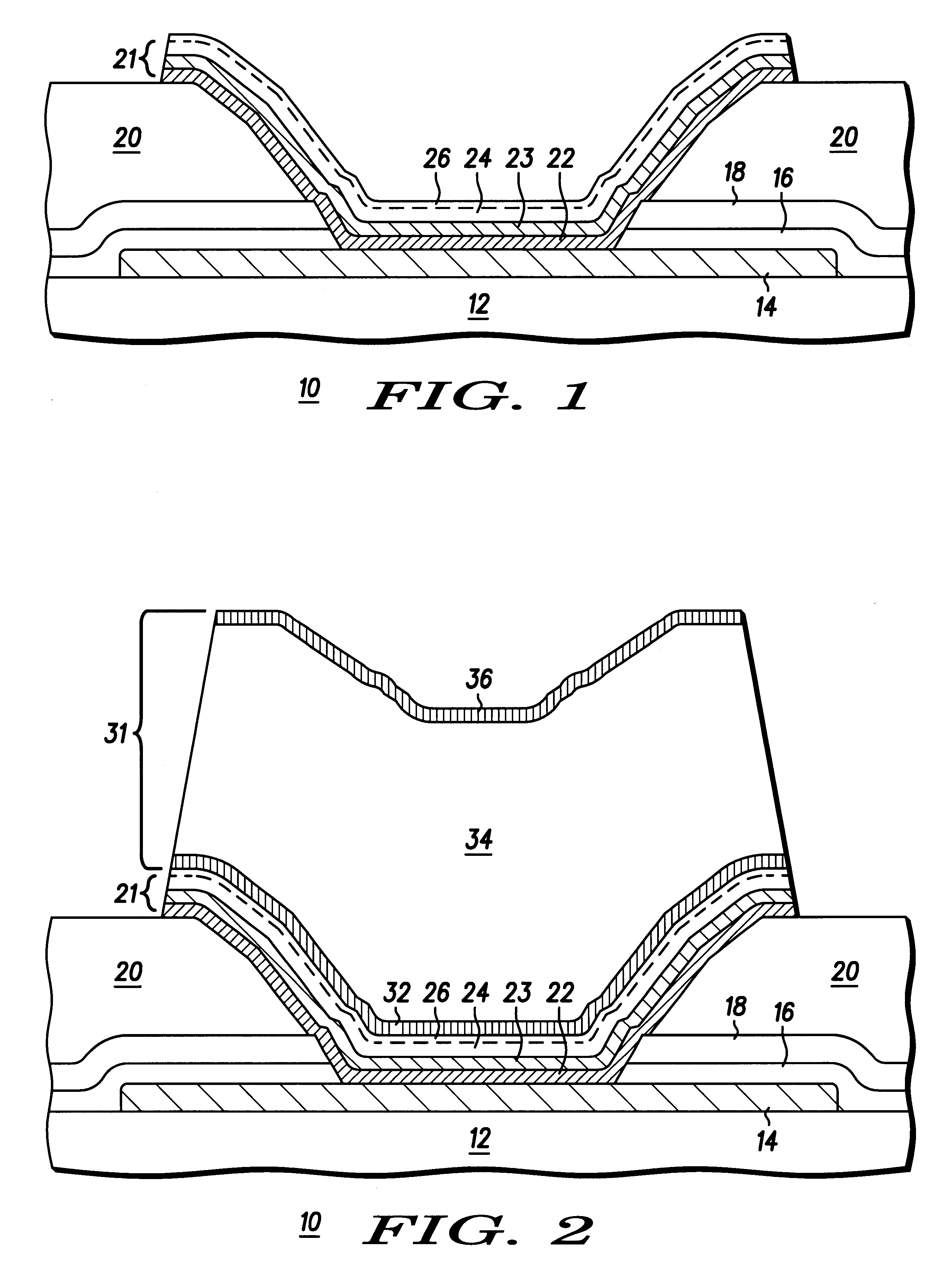

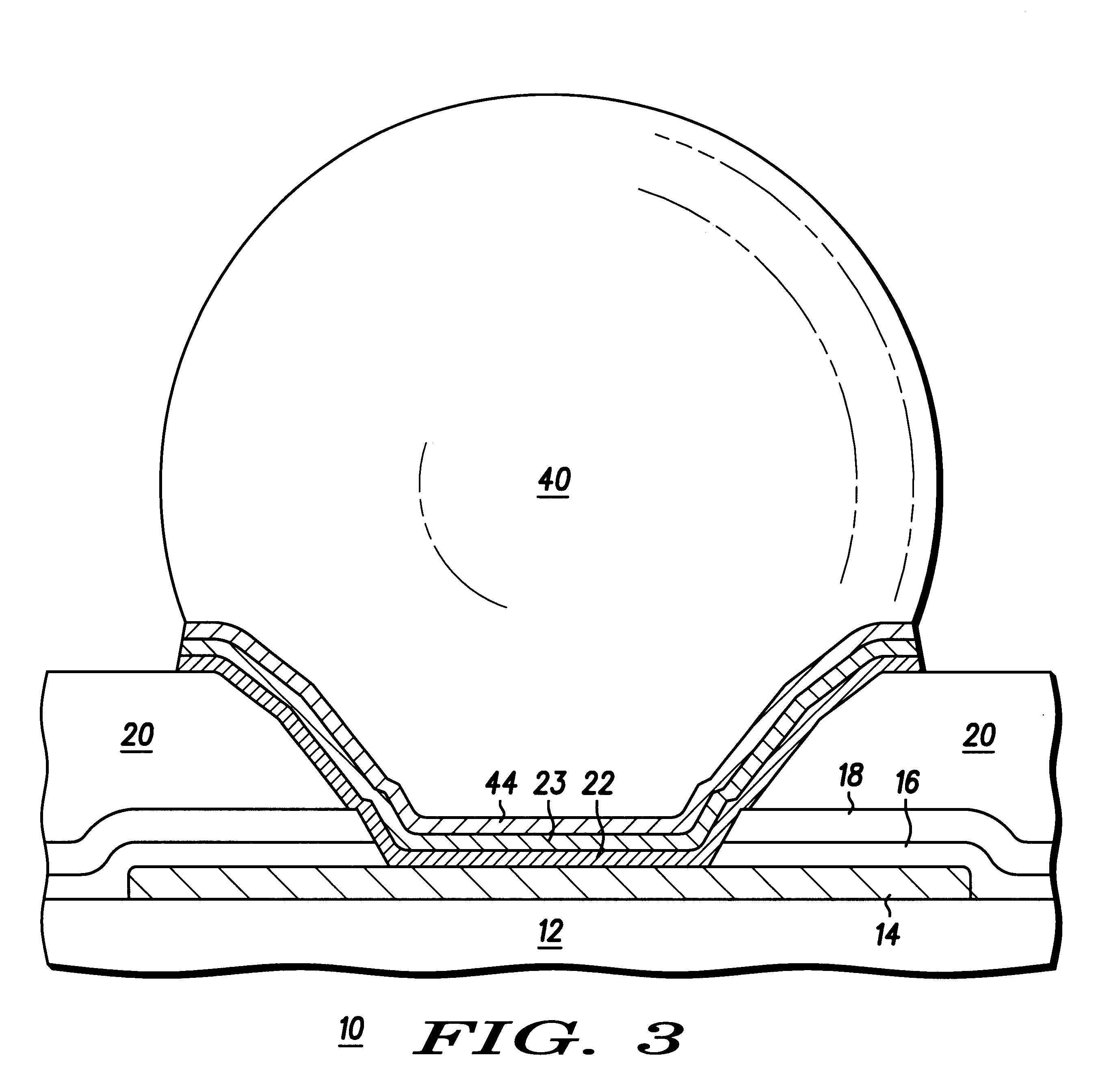

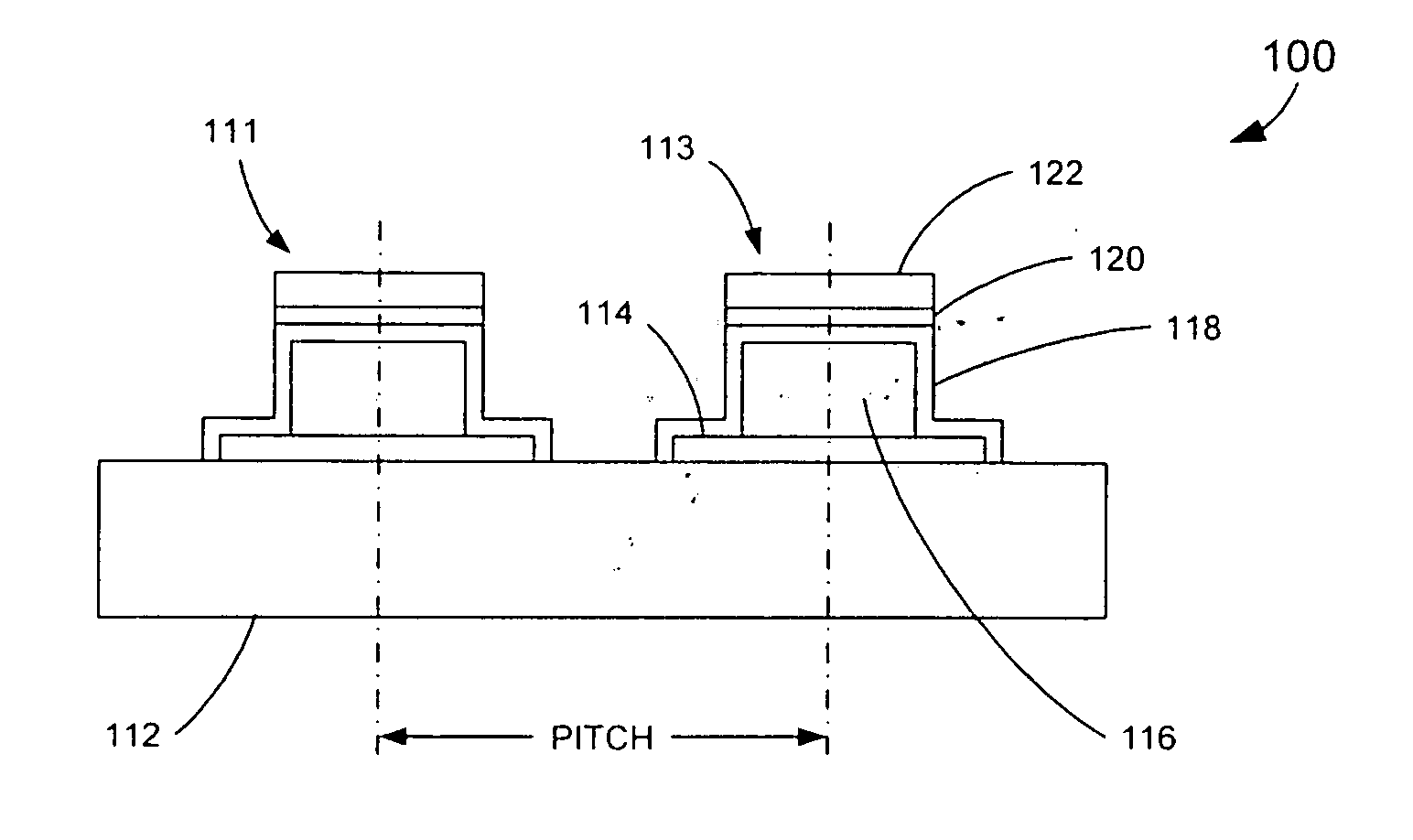

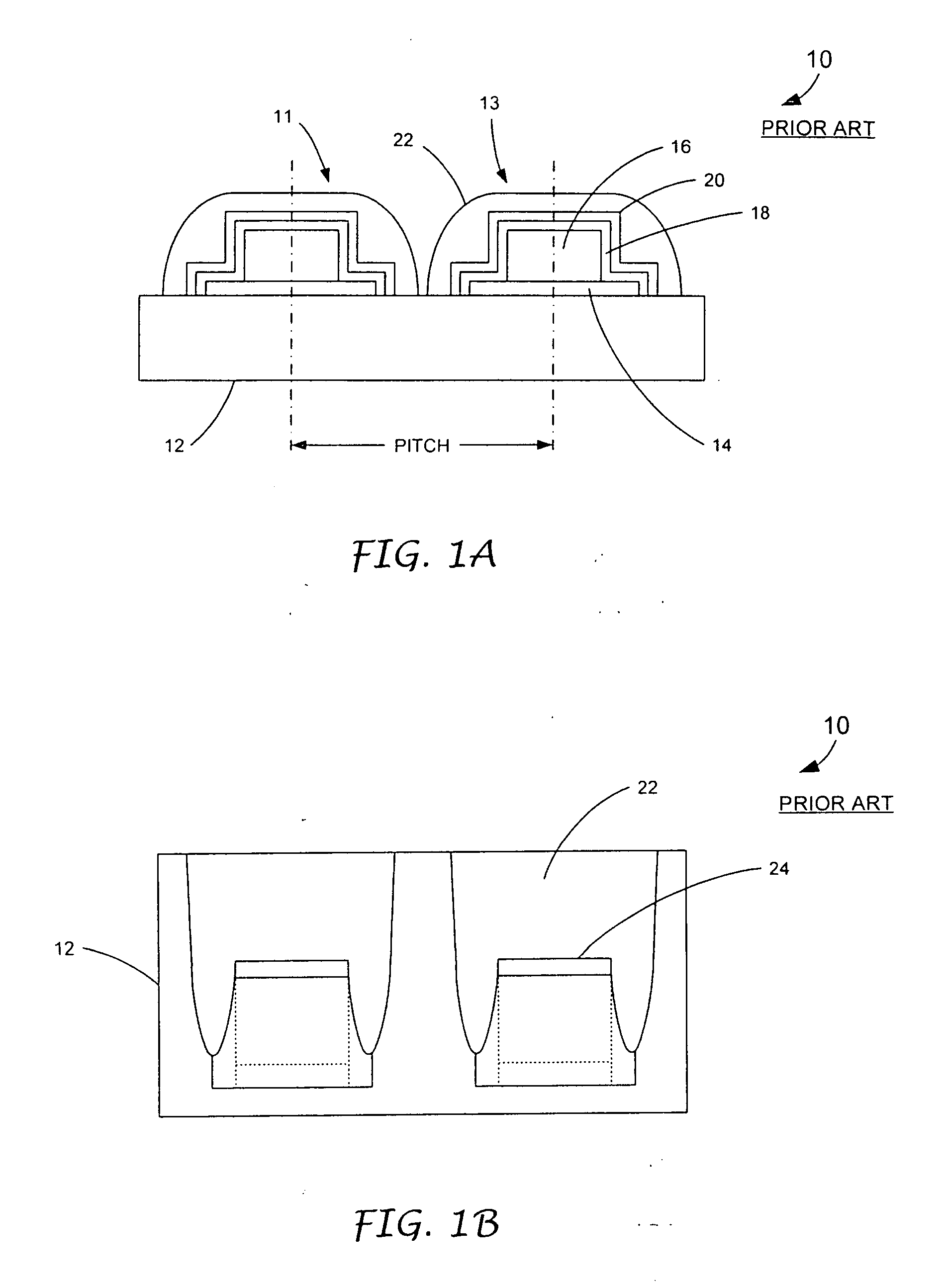

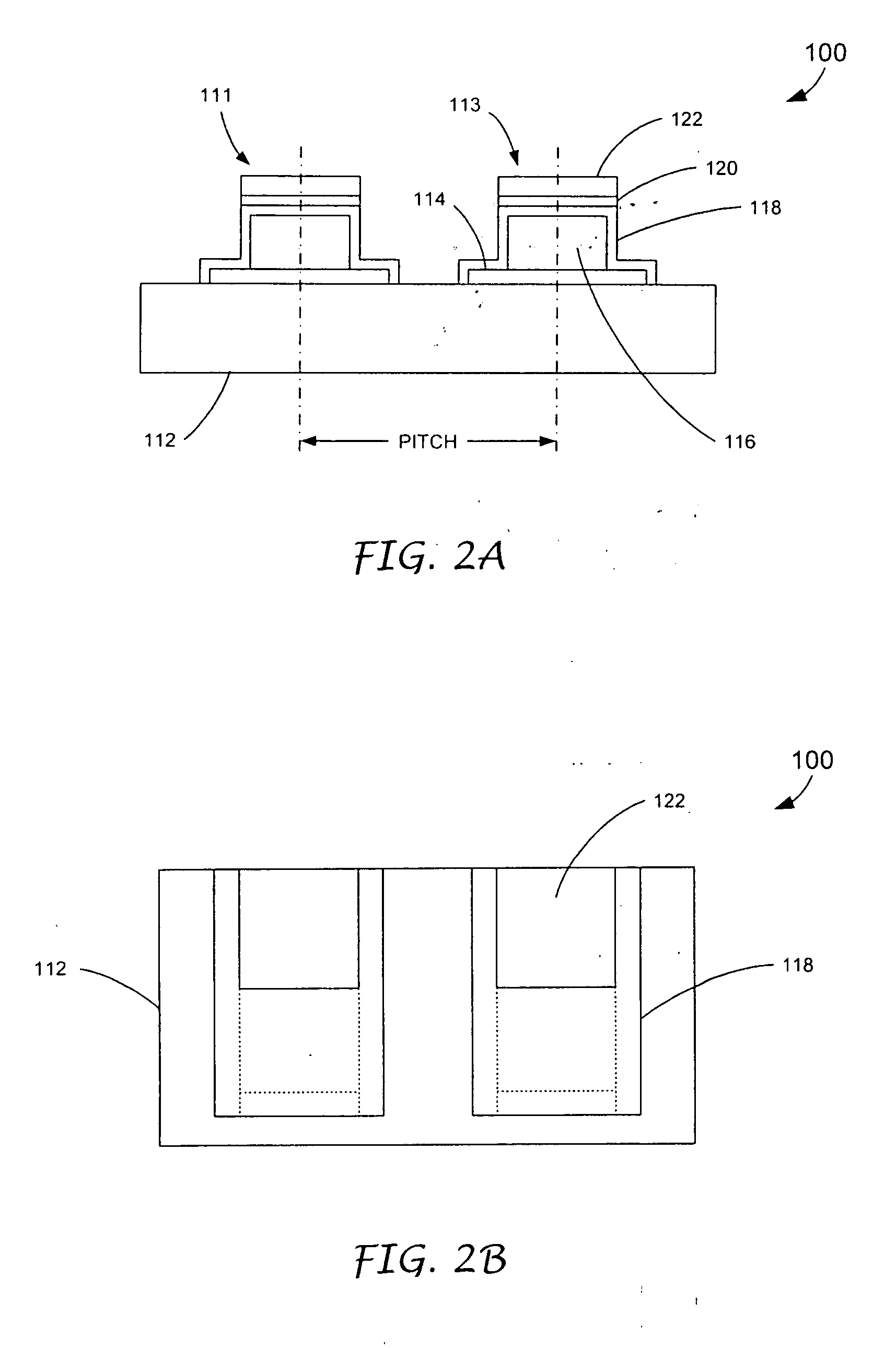

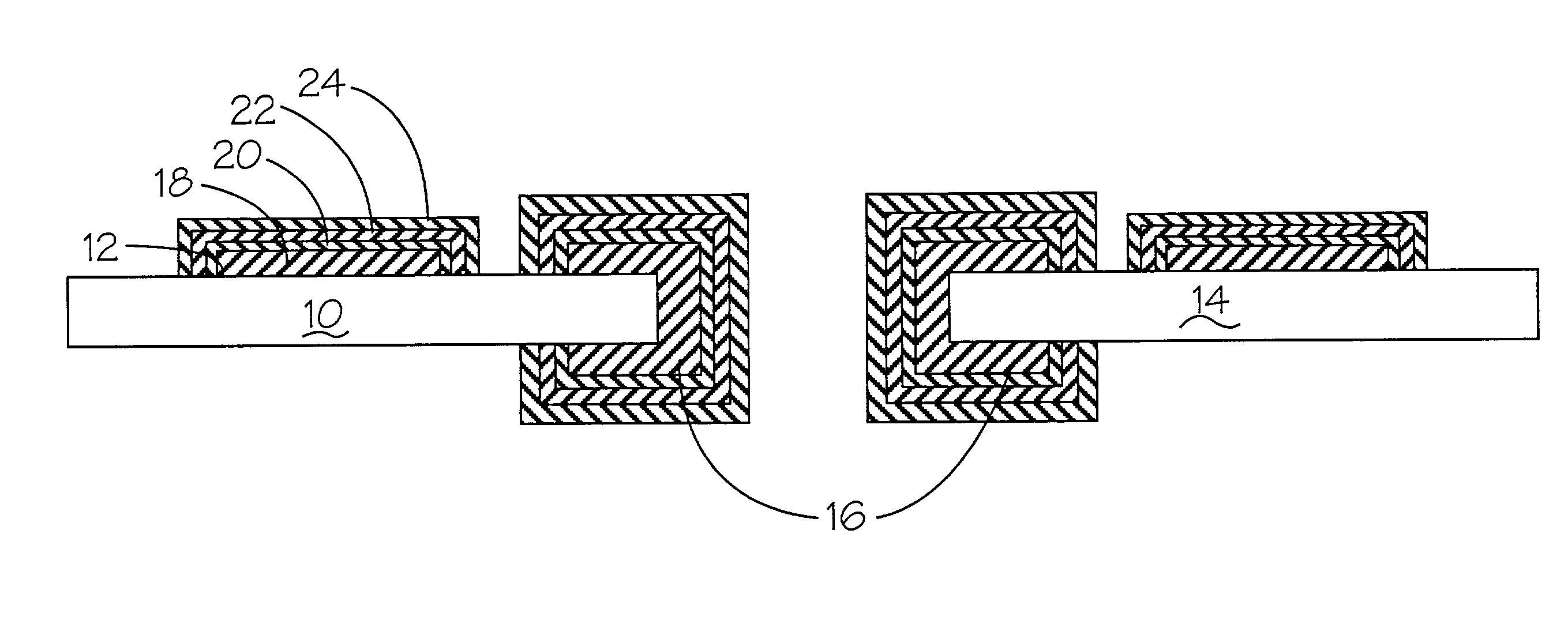

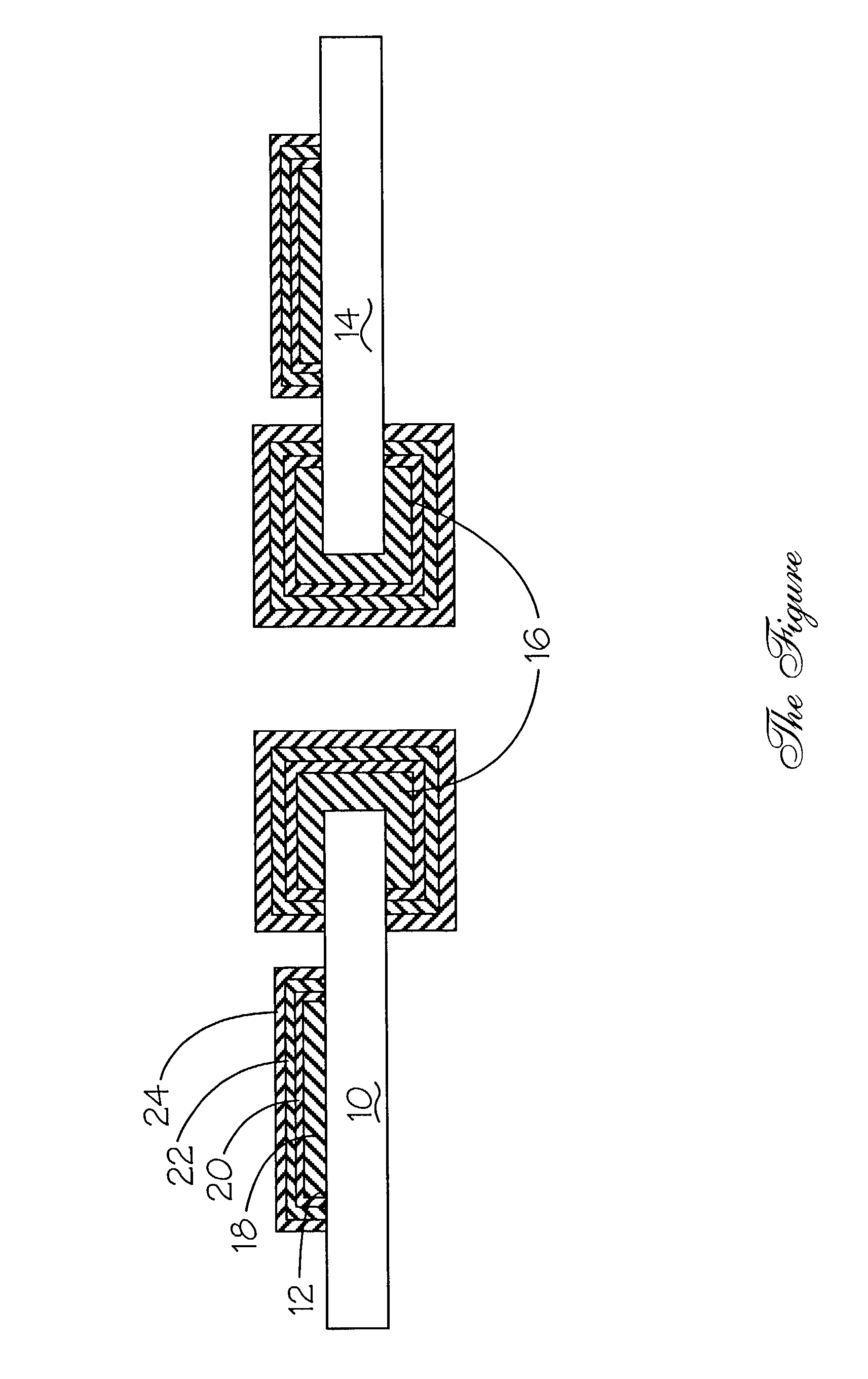

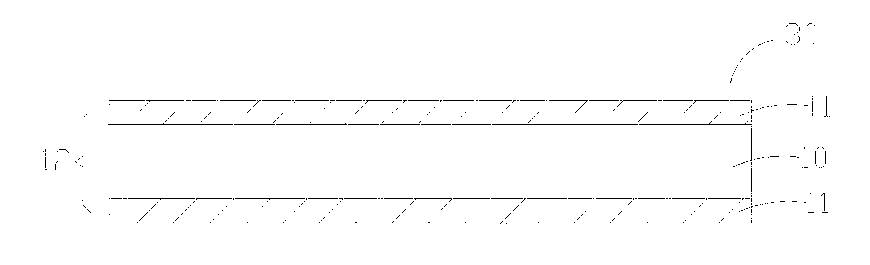

Method of forming a semiconductor device having conductive bumps without using gold

InactiveUS6489229B1Solid-state devicesSemiconductor/solid-state device manufacturingGold layerCopper

A semiconductor device (10) includes a solder bump (40) that is formed using a gold-free under-bump metallurgy (UBM) (21). In a preferred embodiment, UBM (21) includes a diffusion barrier layer (22) of chromium and a metallic layer (24) of copper. The bump layer metallurgy (31) is deposited directly on the metallic layer, without an intervening gold layer. To overcome problems associated with a native oxide layer (26) which forms on the metallic layer, especially on copper, the bump metallurgy includes a seed layer (32) of tin that is deposited prior to a bulk lead layer (34). The bump metallurgy includes a final metallic layer (36) having sufficient tin to make a bump having approximately 97% Pb and 3% tin.

Owner:NXP USA INC

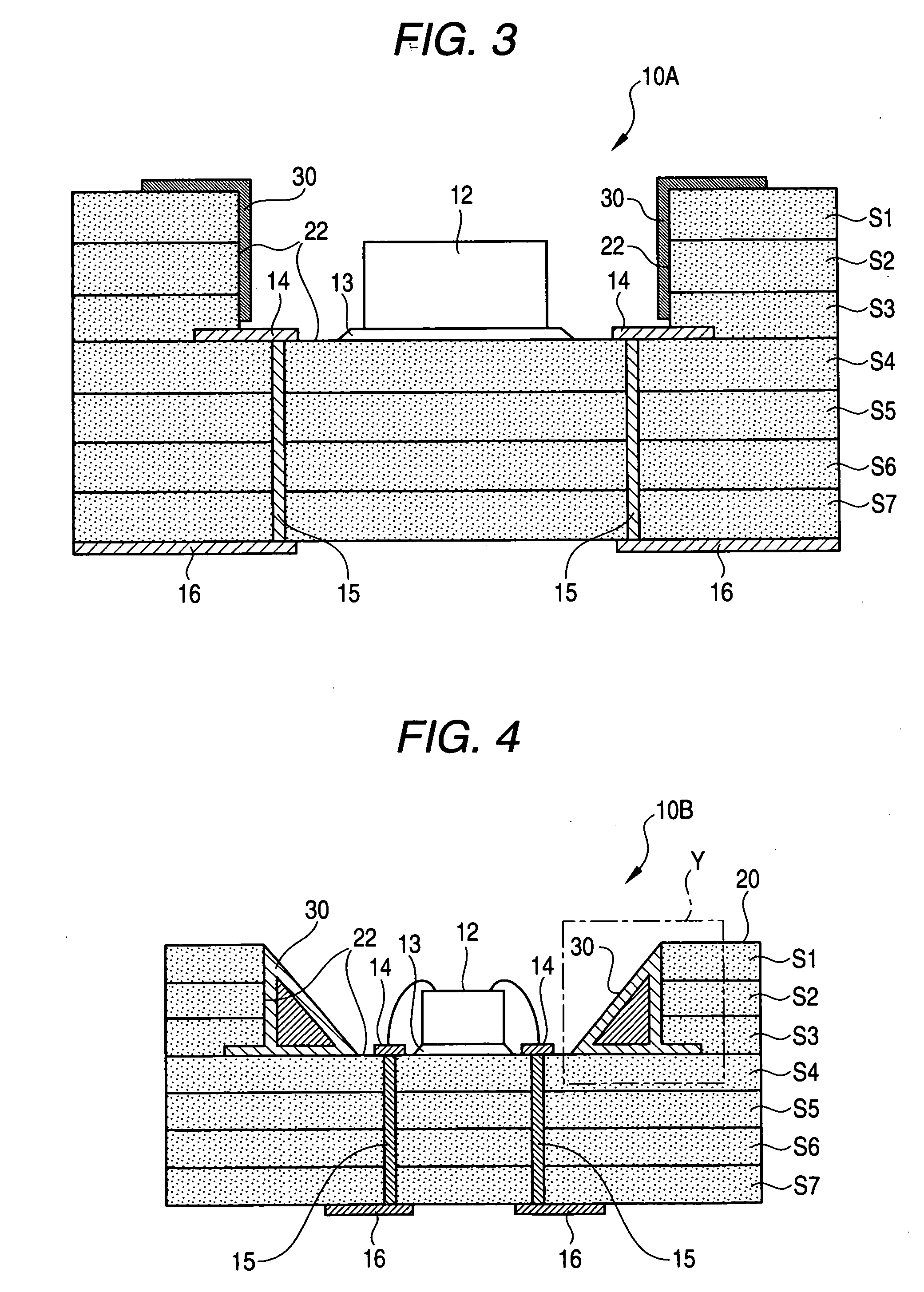

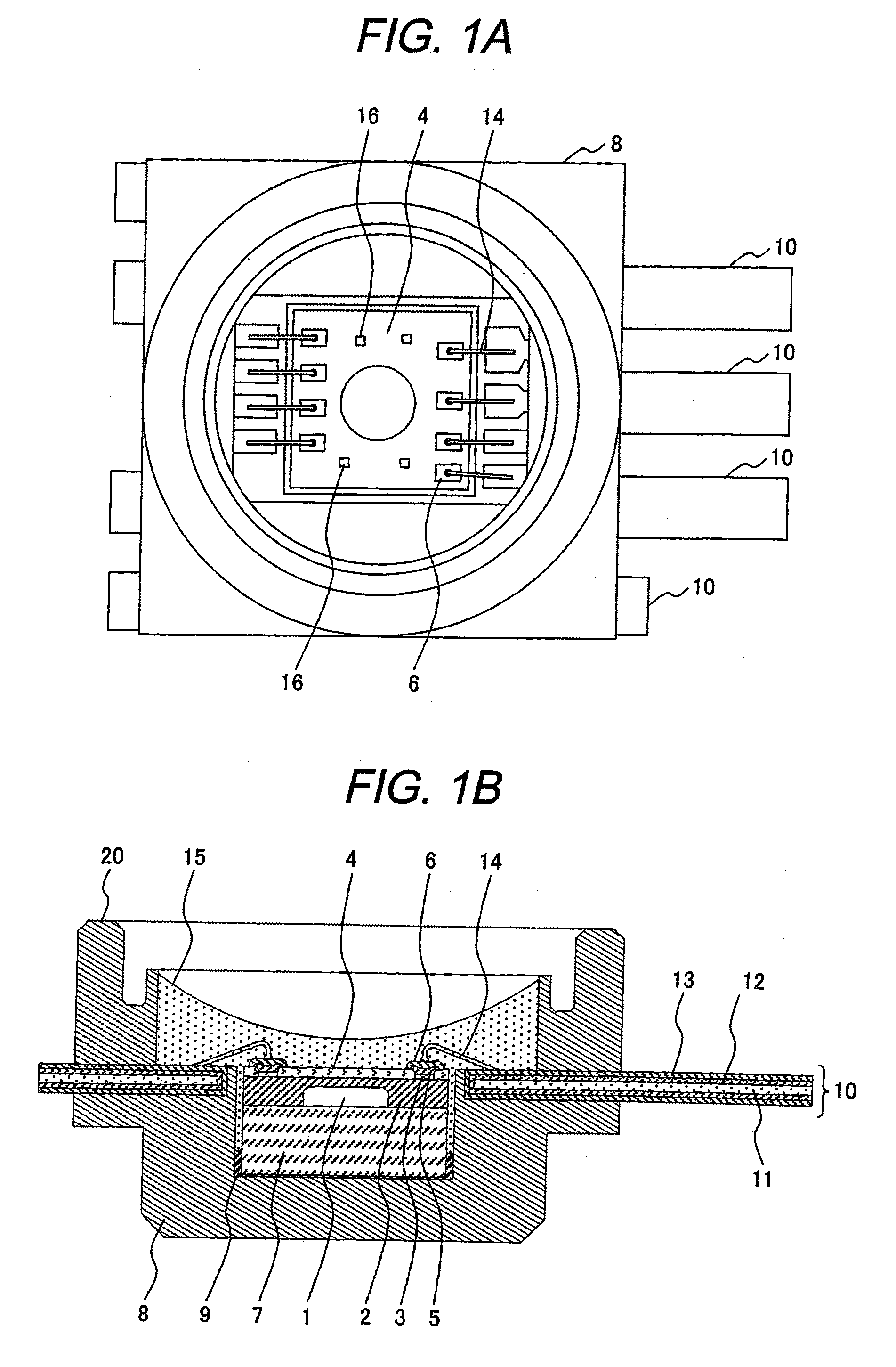

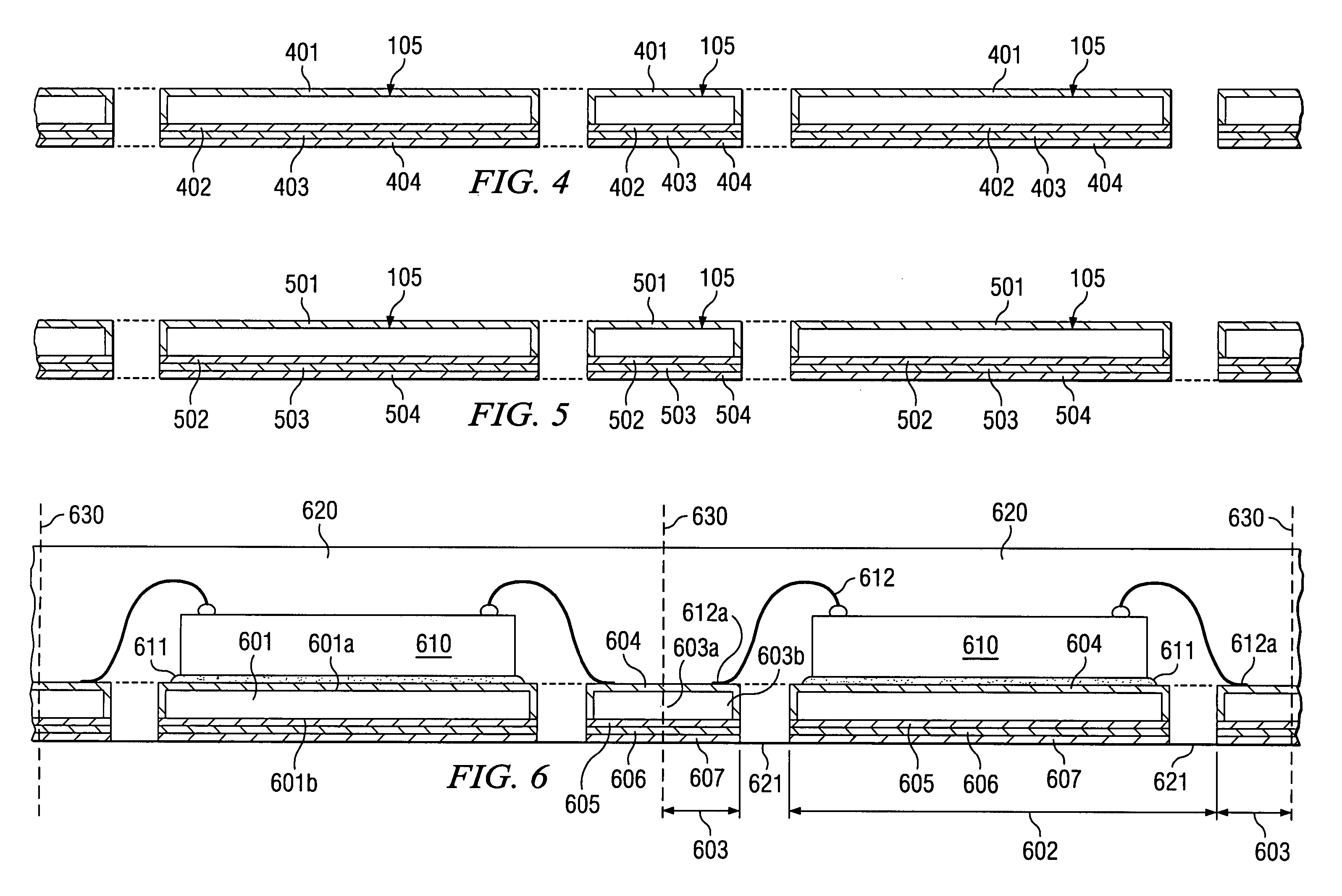

Ceramic substrate, ceramic package for housing light emitting element

InactiveUS20060147746A1Reduce smoothnessIncrease costExtrusion containersSolid-state devicesGold layerCeramic substrate

A ceramic substrate comprising a metallic layer on its surface, wherein said metallic layer includes: a silver layer containing silver; a gold layer containing gold; and a nickel layer containing nickel, in this order from an outermost layer of said metallic layer.

Owner:NGK SPARK PLUG CO LTD

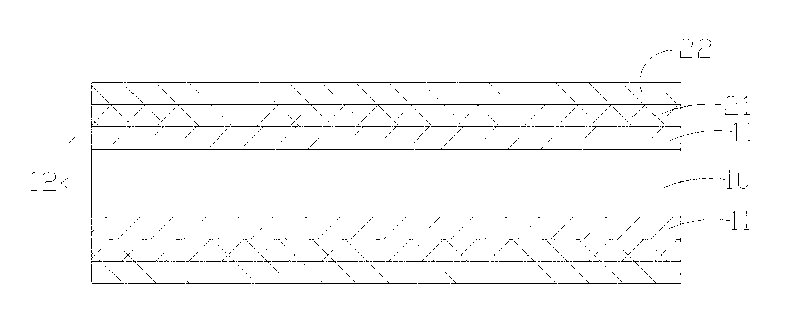

Corrosion-resistant copper bond pad and integrated device

InactiveUS20050001324A1Semiconductor/solid-state device detailsFluid pressure measurement by electric/magnetic elementsElectroless nickelAlloy

The invention provides an integrated device with corrosion-resistant capped copper bond pads. The capped copper bond pads include at least one copper bond pad on a semiconductor substrate. An activation layer comprising one of immersion palladium, electroless cobalt, or immersion ruthernium is disposed on the copper bond pad. A first intermediate layer of electroless nickel-boron alloy is disposed on the activation layer. A second intermediate layer comprising one of electroless nickel or electroless palladium is disposed on the first intermediate layer, and an immersion gold layer is disposed on the second intermediate layer. A capped copper bond pad and a method of forming the capped copper bond pads are also disclosed.

Owner:NORTH STAR INNOVATIONS

Method for fabricating chip package

InactiveUS20070275503A1Solid-state devicesSemiconductor/solid-state device manufacturingGold layerPhotoresist

The present invention provides a method for fabricating chip package comprises the following steps: forming a photoresist layer on a metal layer over a passivation layer, an opening in the photoresist layer exposing the metal layer, wherein said forming the photoresist layer comprises exposing the photoresist layer using 1X stepper with at least two of G-line, H-line and I-line; electroplating a gold layer over the metal layer exposed by the opening with an electroplating solution containing gold and sulfite ion; removing the photoresist layer and the metal layer not under the gold layer.

Owner:QUALCOMM INC

Metal pad or metal bump over pad exposed by passivation layer

ActiveUS20070026631A1Semiconductor/solid-state device detailsSolid-state devicesOptoelectronicsTitanium

A circuitry component comprising a semiconductor substrate, a pad over said semiconductor substrate, a tantalum-containing layer on a side wall and a bottom surface of said pad, a passivation layer over said semiconductor substrate, an opening in said passivation layer exposing said pad, a titanium-containing layer over said pad exposed by said opening, and a gold layer over said titanium-containing layer.

Owner:QUALCOMM INC

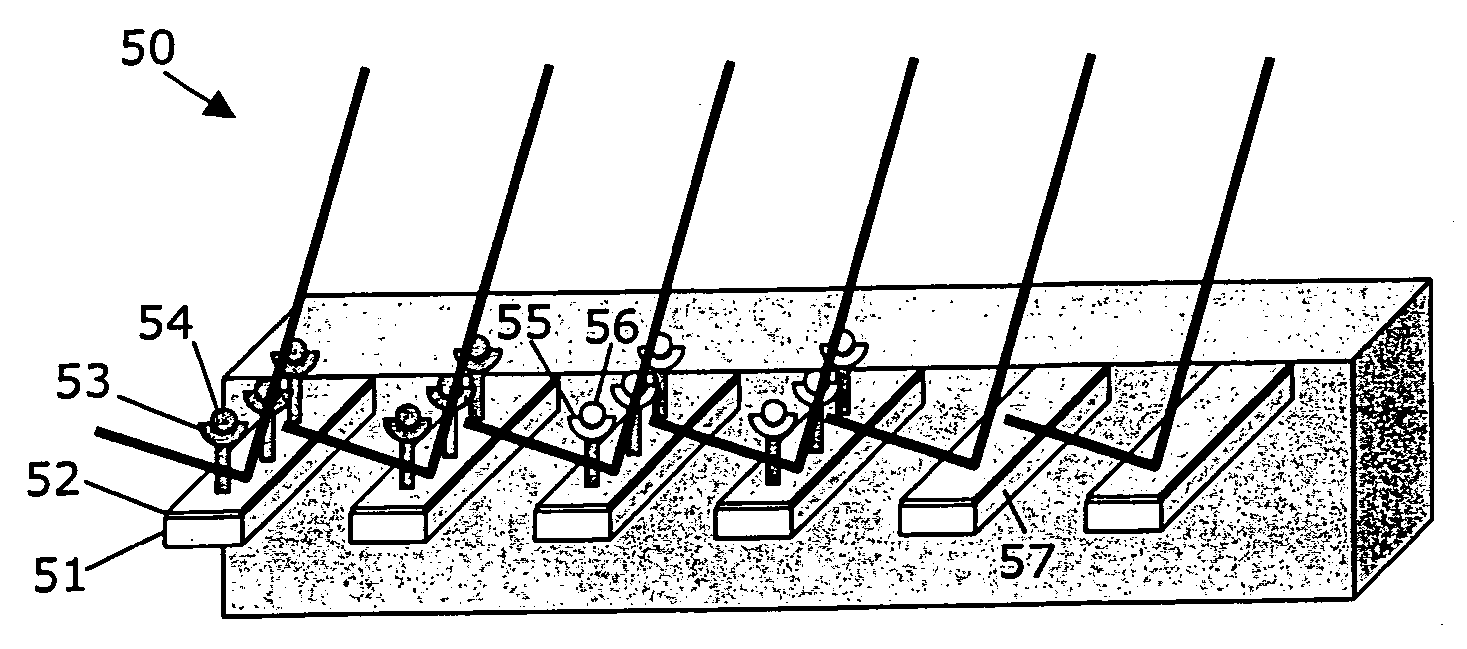

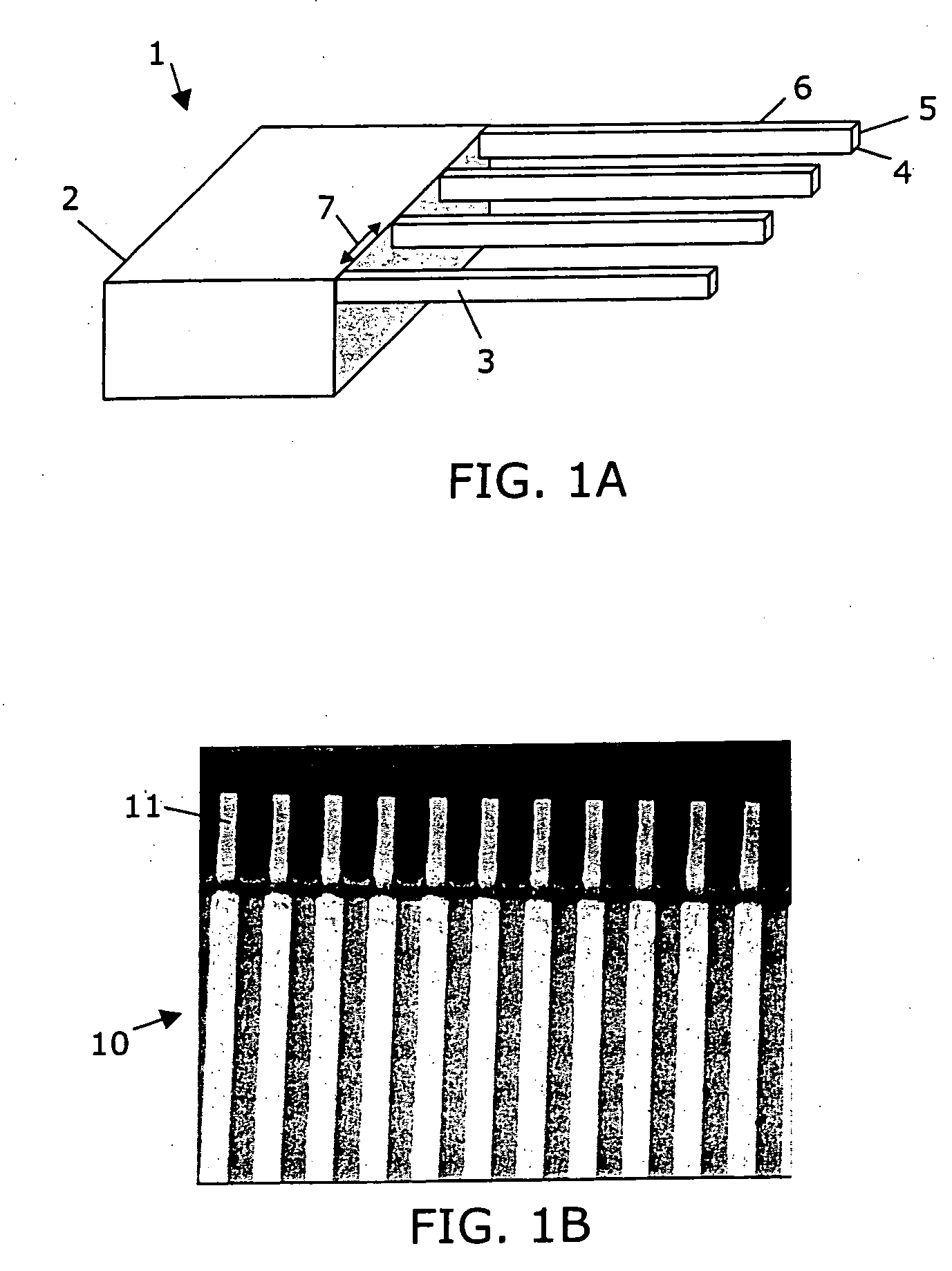

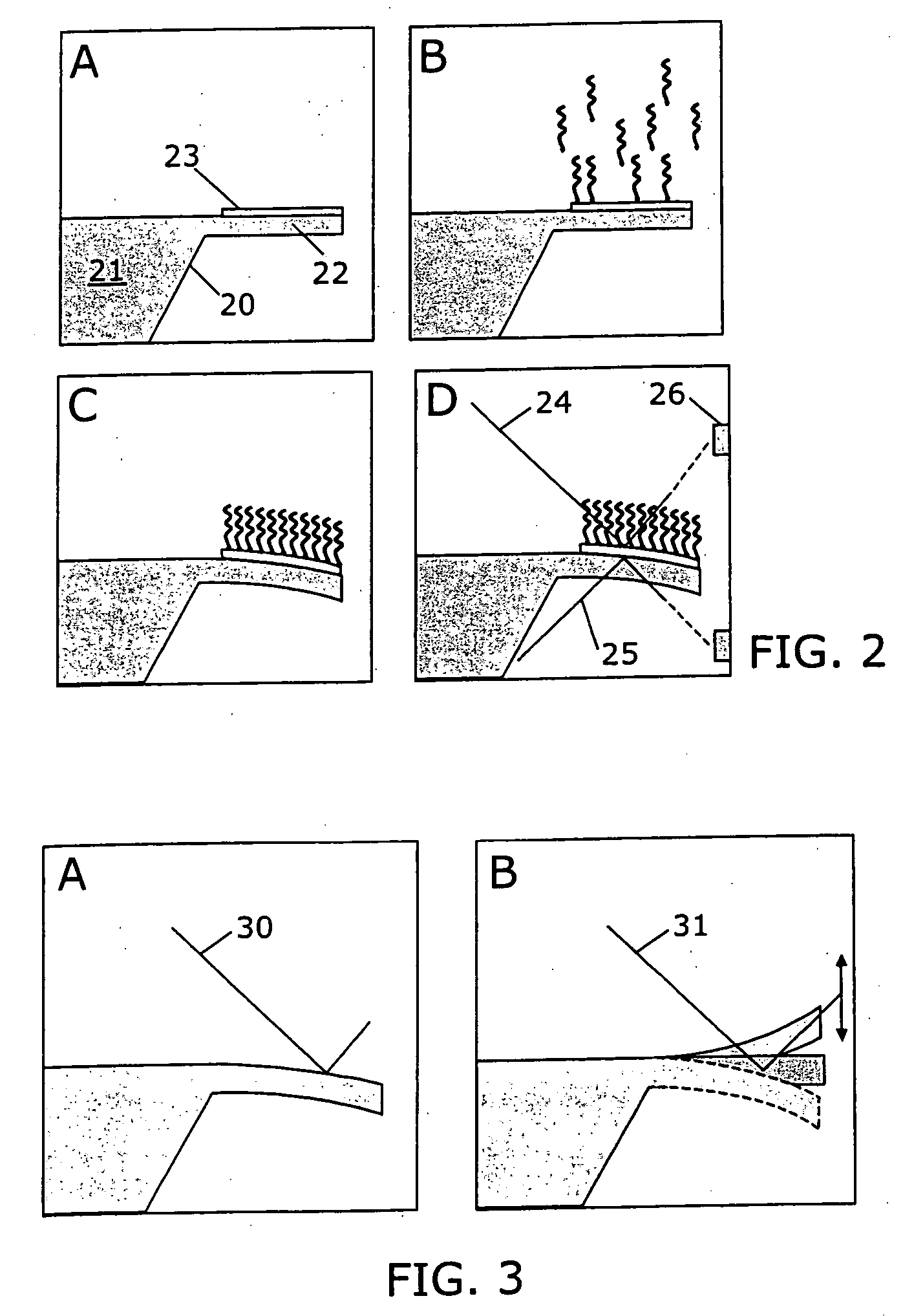

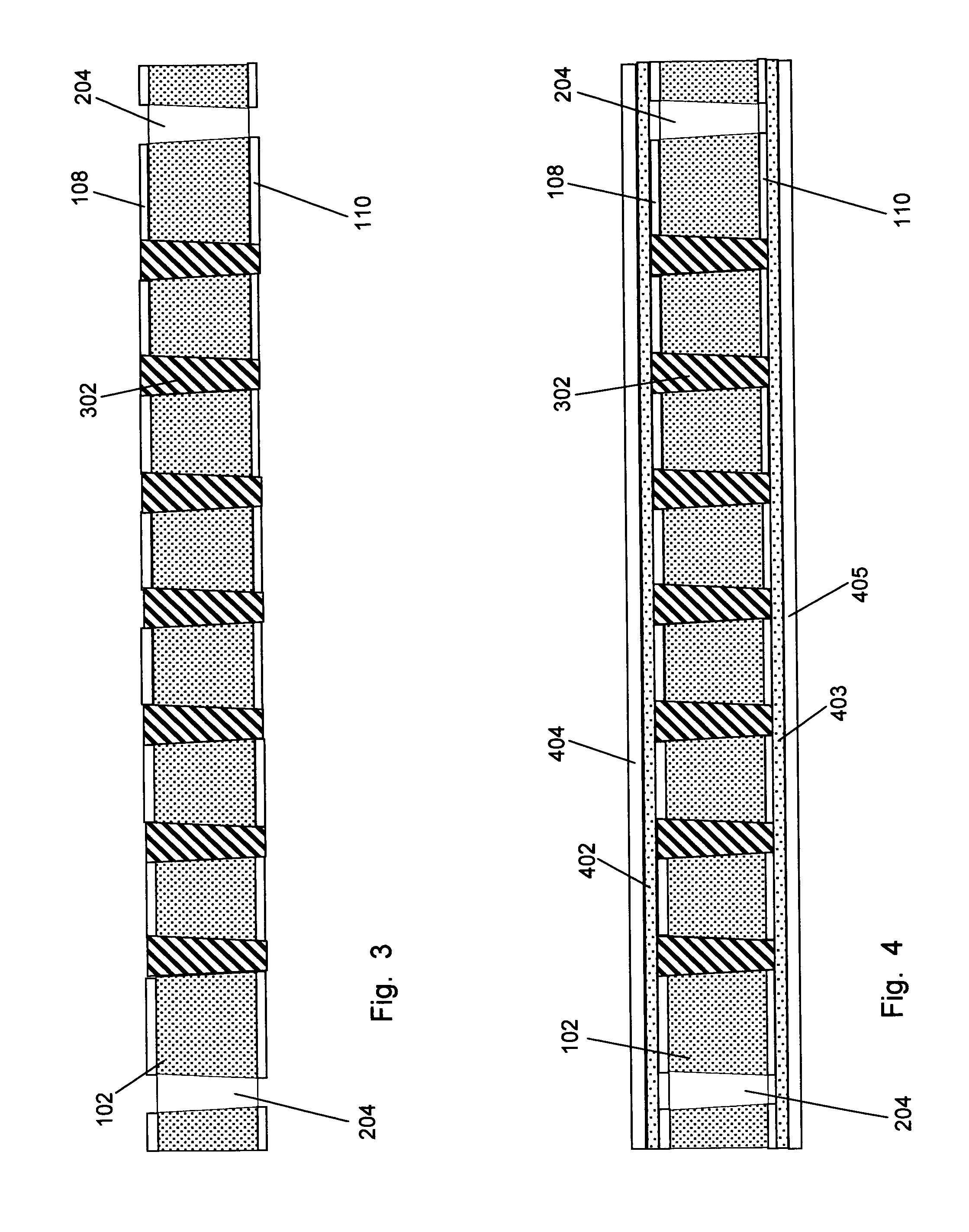

Polymer-based cantilever array with optical readout

InactiveUS20060075803A1Good chemical resistanceEasy and fast processingBioreactor/fermenter combinationsMaterial analysis using sonic/ultrasonic/infrasonic wavesGold layerOptical sensing

A cantilever array for use as a sensor, e.g. a bio / chemical sensor is disclosed. The cantilever array comprises a platform and a multitude of polymer-based cantilevers attached to the platform. Each of the cantilevers is coupled to an optical sensing means adapted to sense deformations of an individual cantilever. The cantilevers may be coated with a first and / or a second layer, the first layer being a metal layer, such as a gold layer, the second layer being a molecular layer capable of functioning as a receptor layer for molecular recognition. Further, two methods of fabricating a cantilever array are disclosed, one being based on photolithography, the other being based on micromoulding.

Owner:DANMARKS TEKNISKE UNIV

Corrosion-resistant copper bond pad and integrated device

InactiveUS7078796B2Semiconductor/solid-state device detailsFluid pressure measurement by electric/magnetic elementsElectroless nickelAlloy

The invention provides an integrated device with corrosion-resistant capped copper bond pads. The capped copper bond pads include at least one copper bond pad on a semiconductor substrate. An activation layer comprising one of immersion palladium, electroless cobalt, or immersion ruthernium is disposed on the copper bond pad. A first intermediate layer of electroless nickel-boron alloy is disposed on the activation layer. A second intermediate layer comprising one of electroless nickel or electroless palladium is disposed on the first intermediate layer, and an immersion gold layer is disposed on the second intermediate layer. A capped copper bond pad and a method of forming the capped copper bond pads are also disclosed.

Owner:NORTH STAR INNOVATIONS

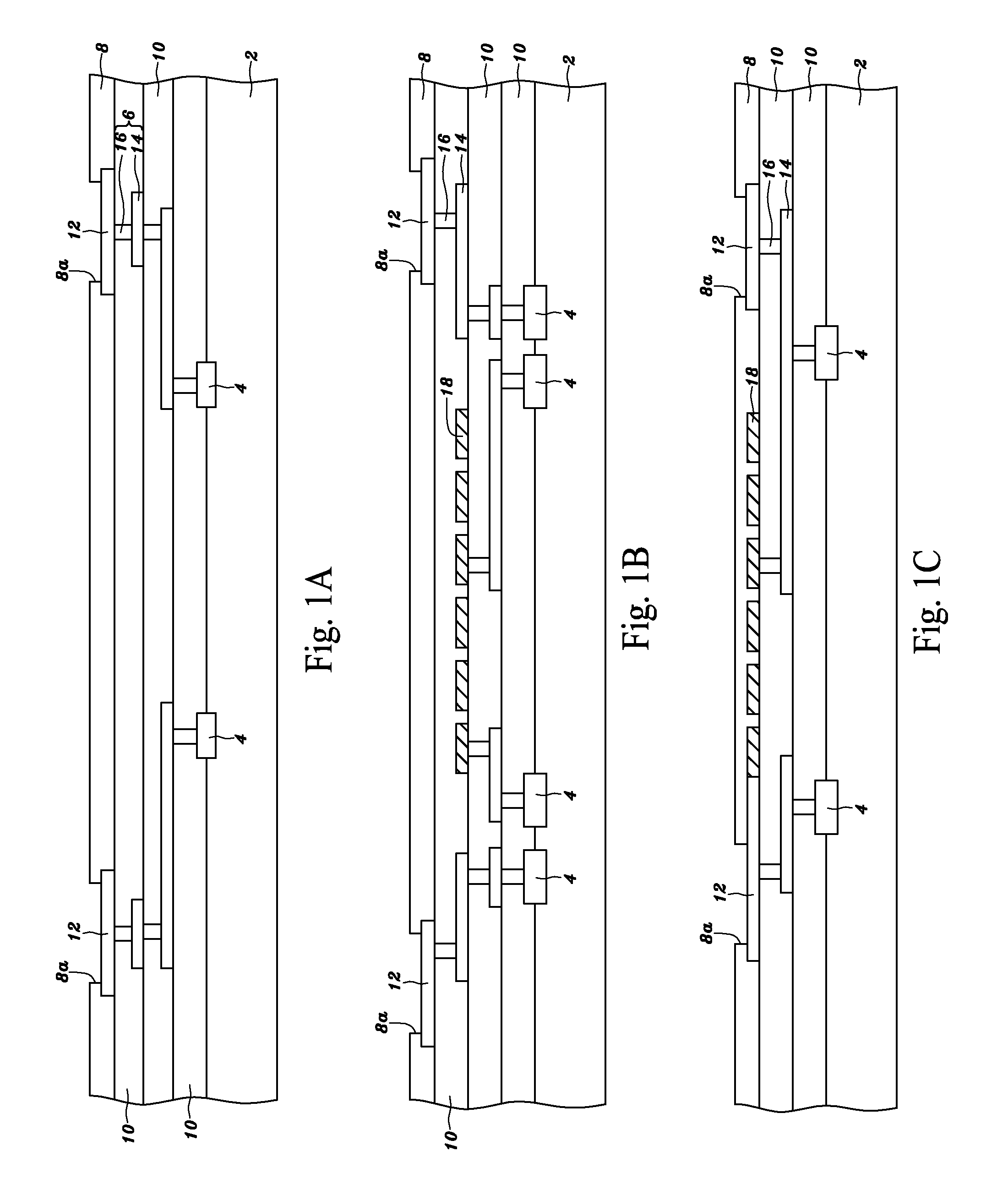

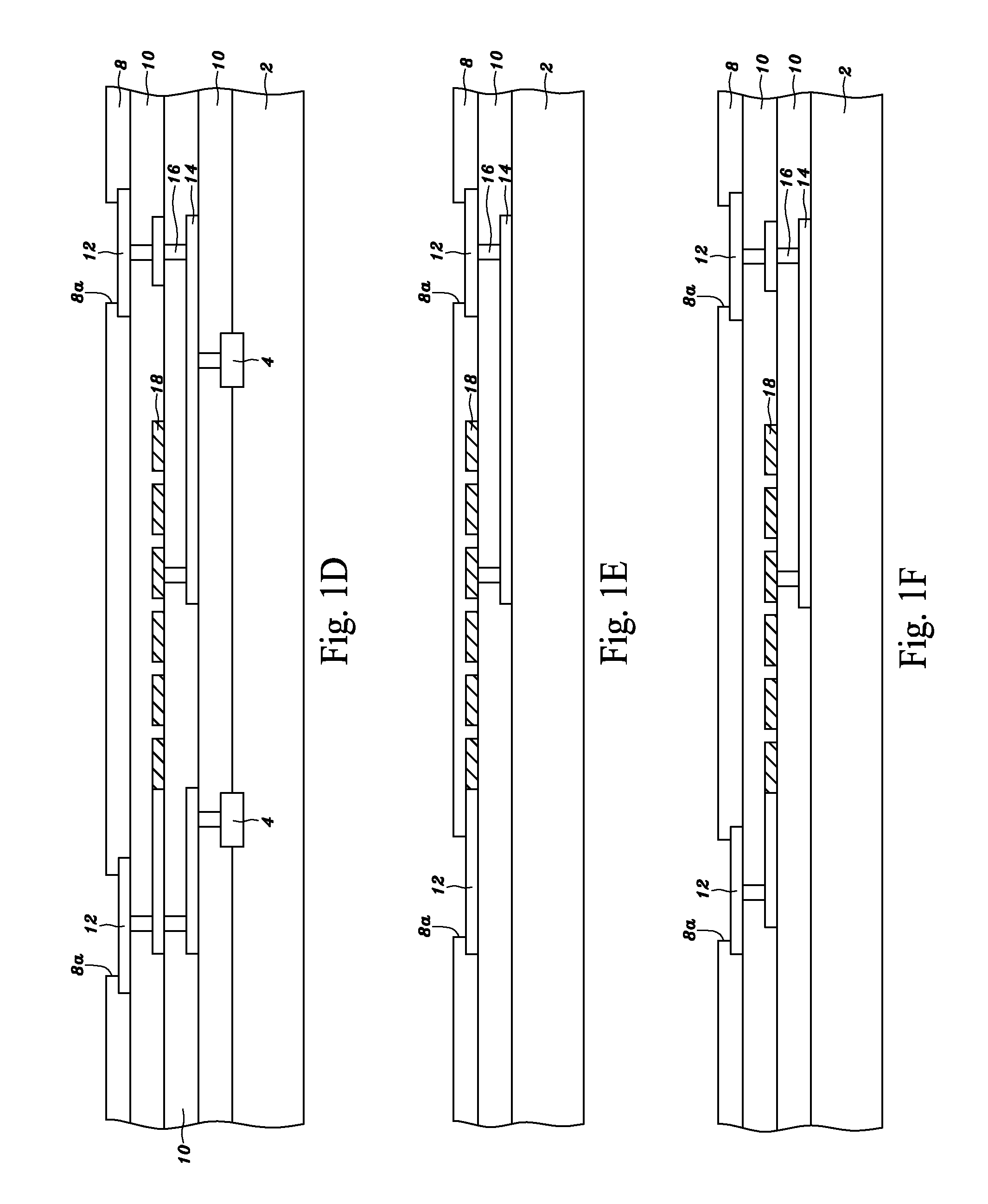

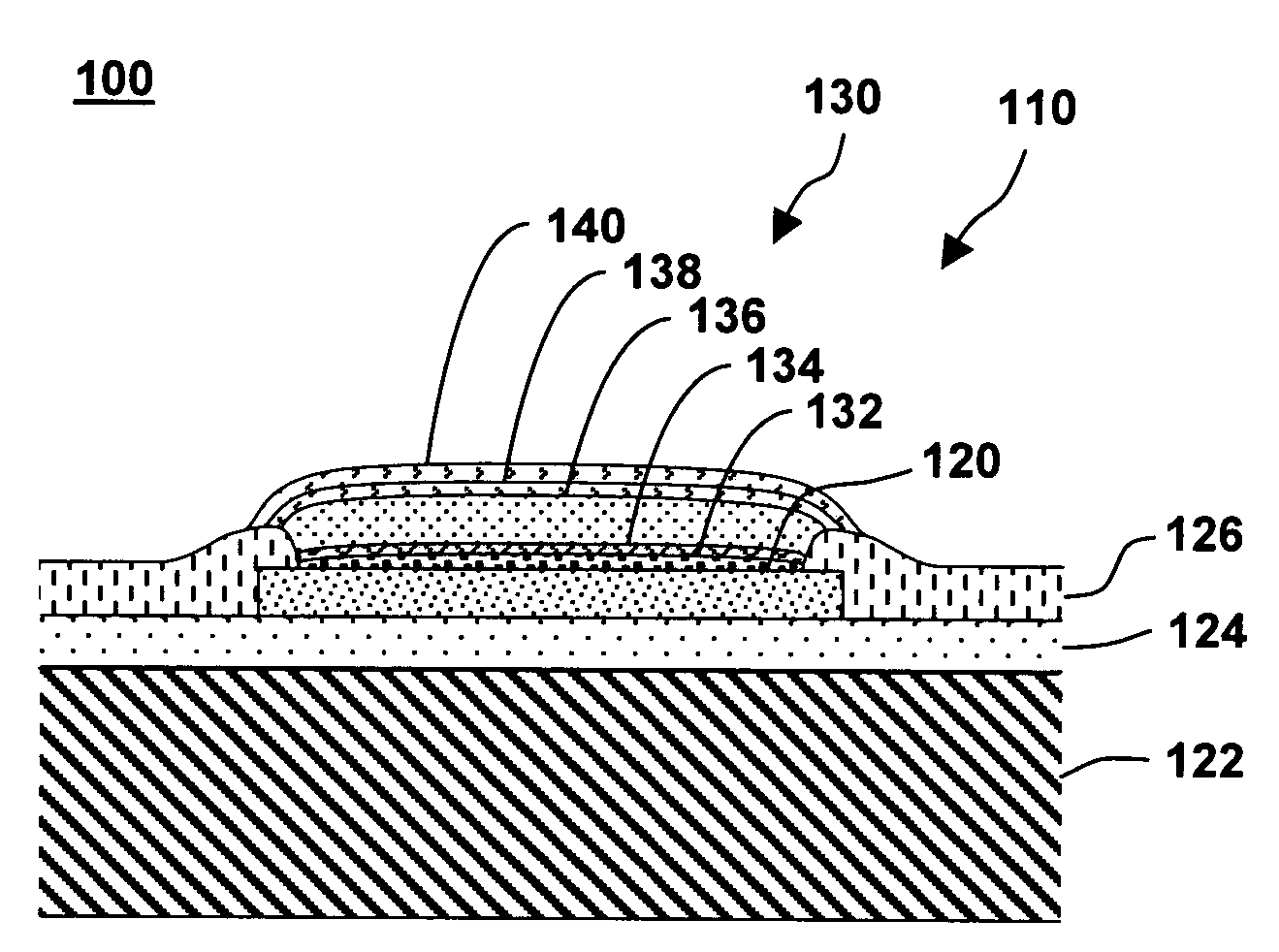

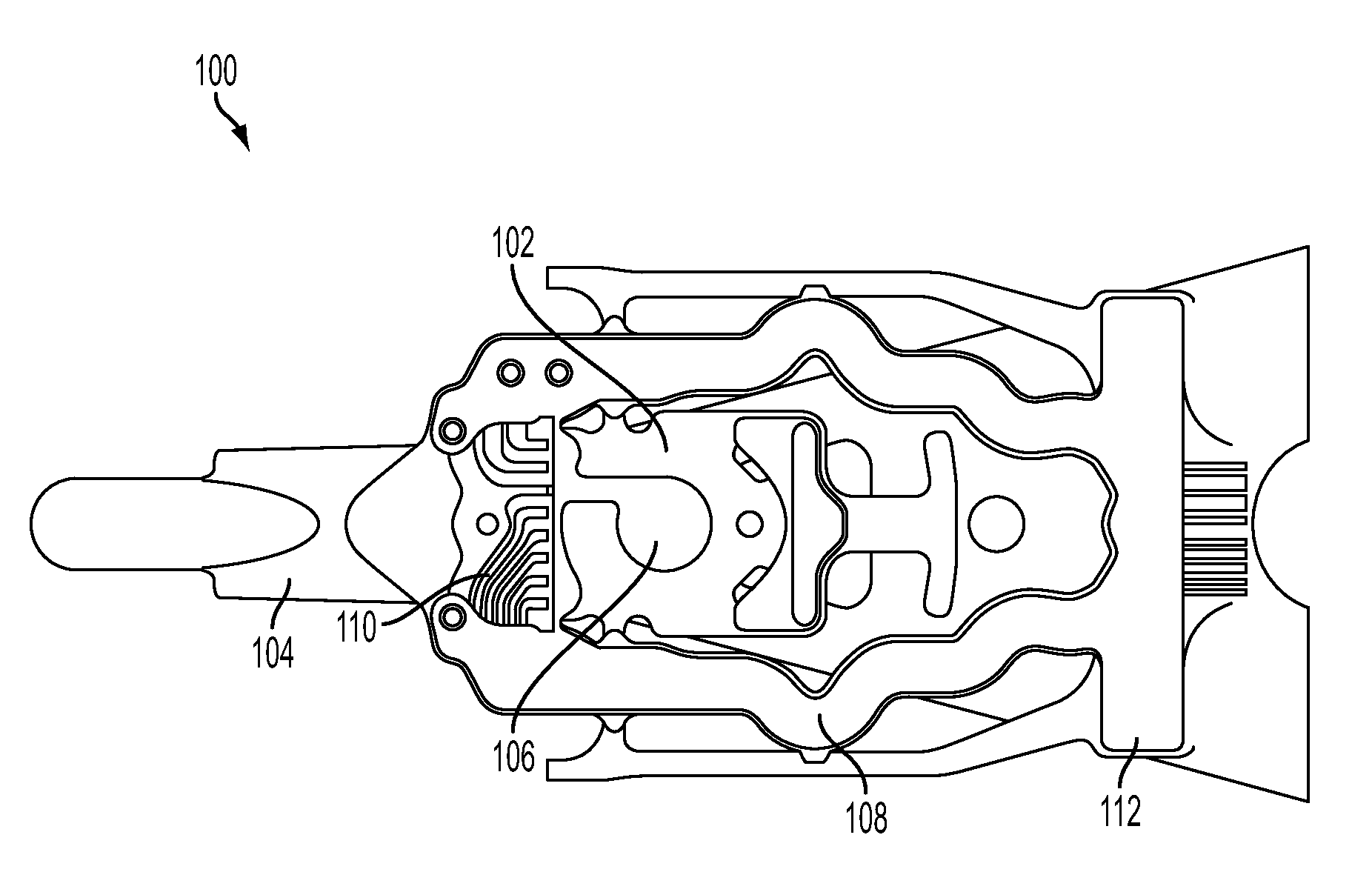

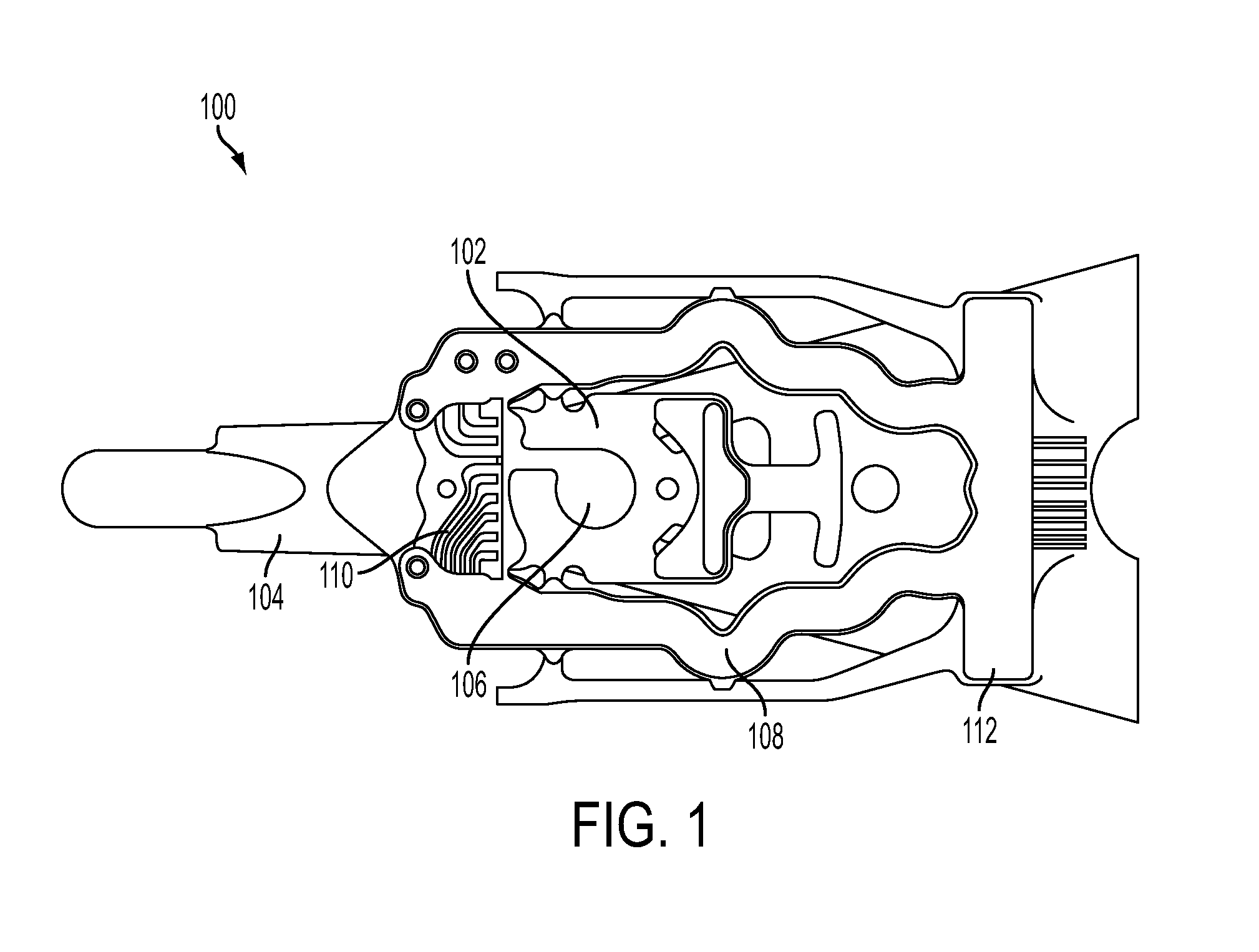

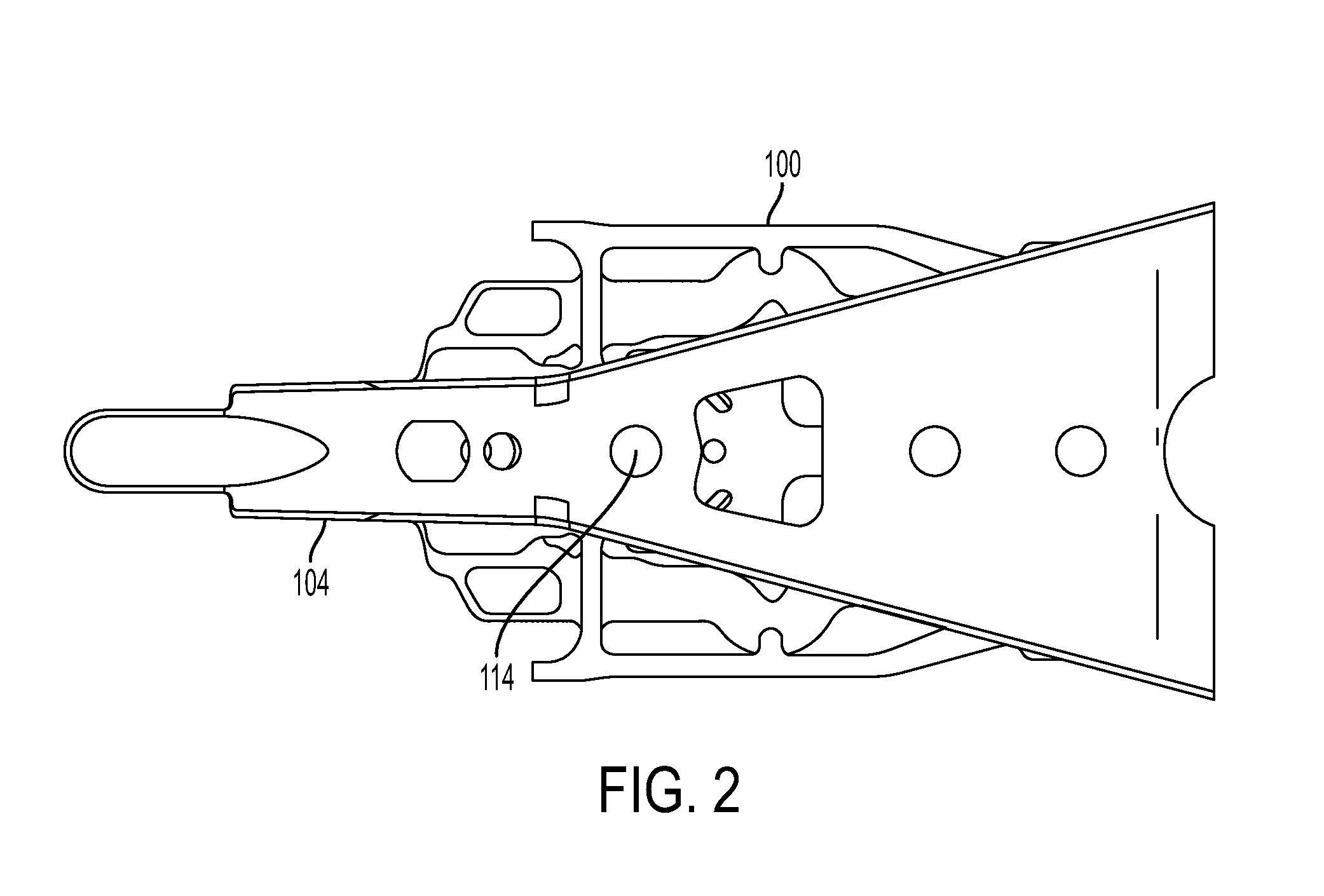

Gimbal assembly with a gold tongue/dimple interface and methods of making the same

ActiveUS20130265674A1Electrical connection between head and armRecord information storageDual stageWear particle

A gimbal assembly of a single or dual stage actuator is provided with gold at a tongue / dimple interface where a dimple of a supporting loadbeam contacts a tongue on the gimbal assembly. Using gold at the tongue / dimple interface greatly reduces the amount of wear particles formed during assembly and operation of the microactuator. The tongue may include a gold coating on the tongue at the tongue / dimple interface, or the tongue may have a hole etched in a stainless steel layer at the tongue / dimple interface to expose a gold layer disposed below the stainless steel layer. The tongue portion of the tongue / dimple interface may also be formed from a gold-coated copper pad with a polymer coating over the gold.

Owner:NHK SPRING CO LTD

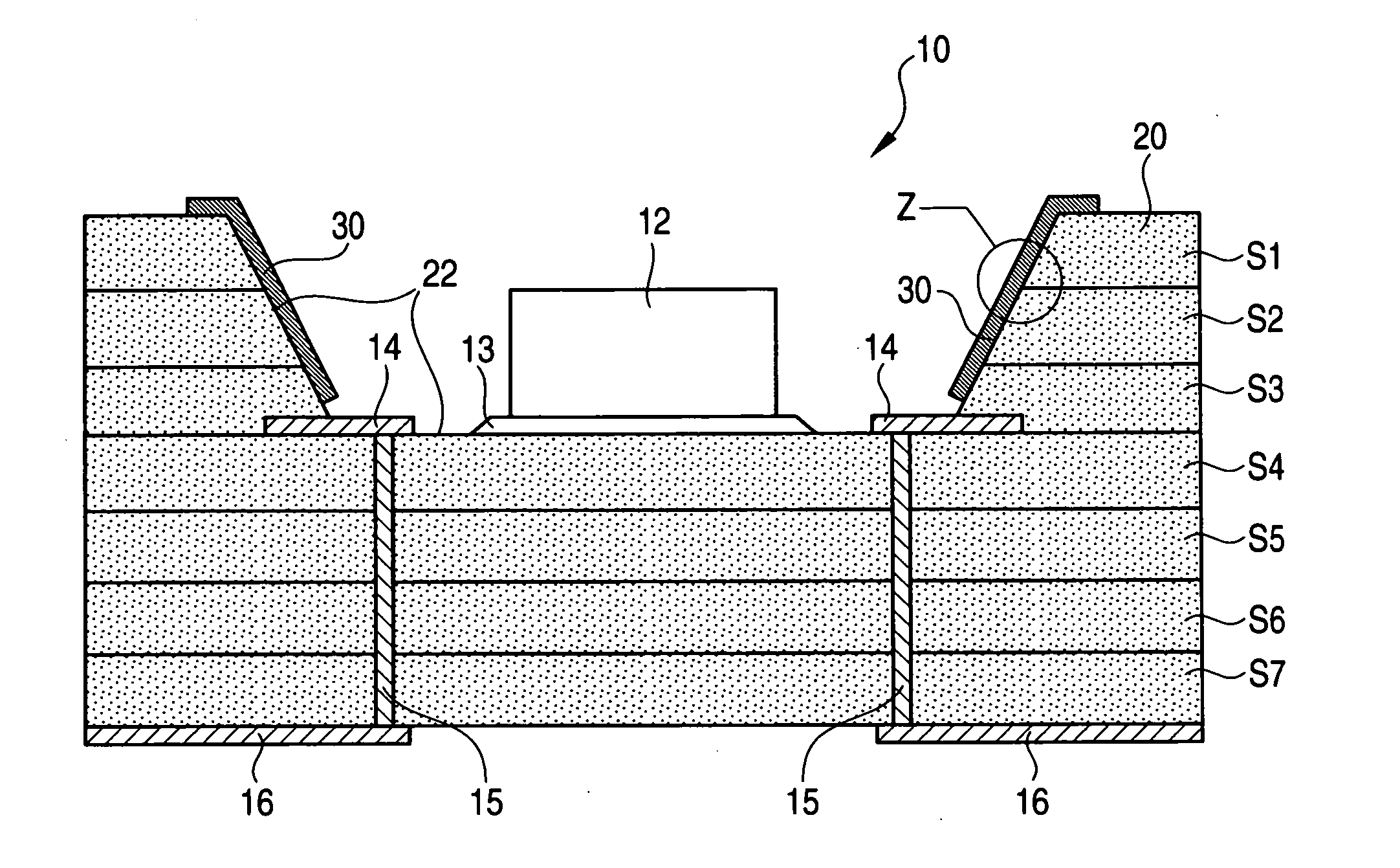

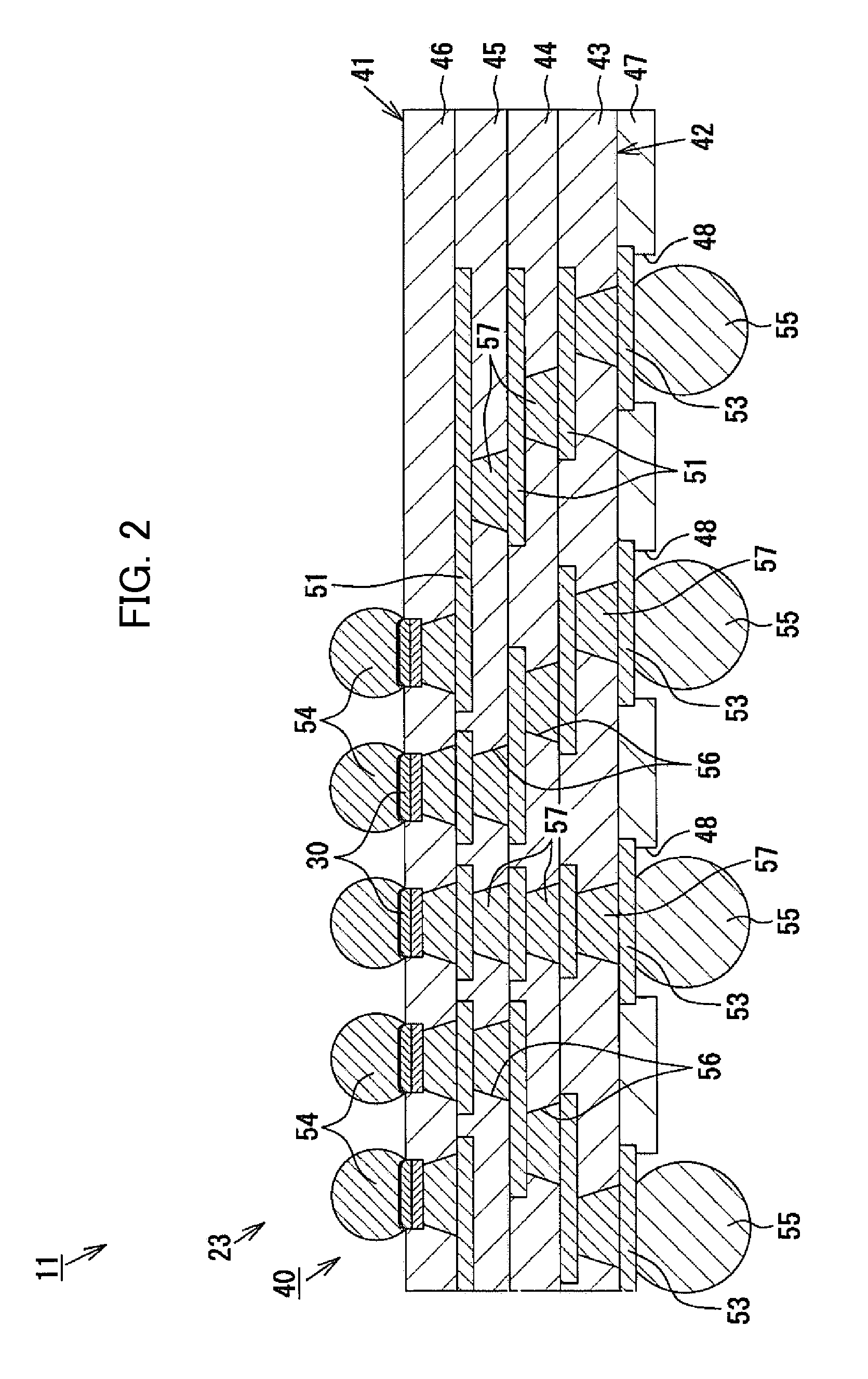

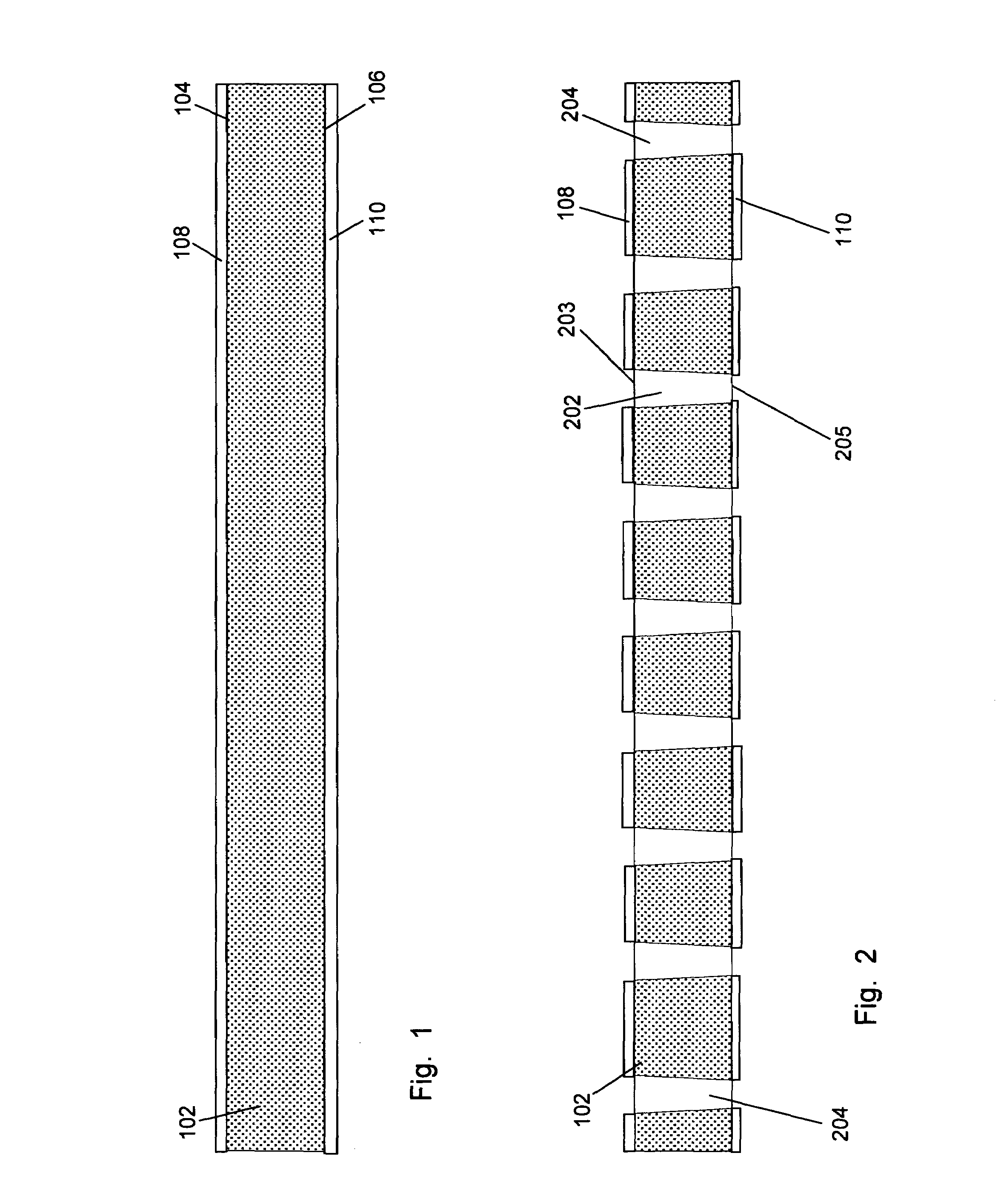

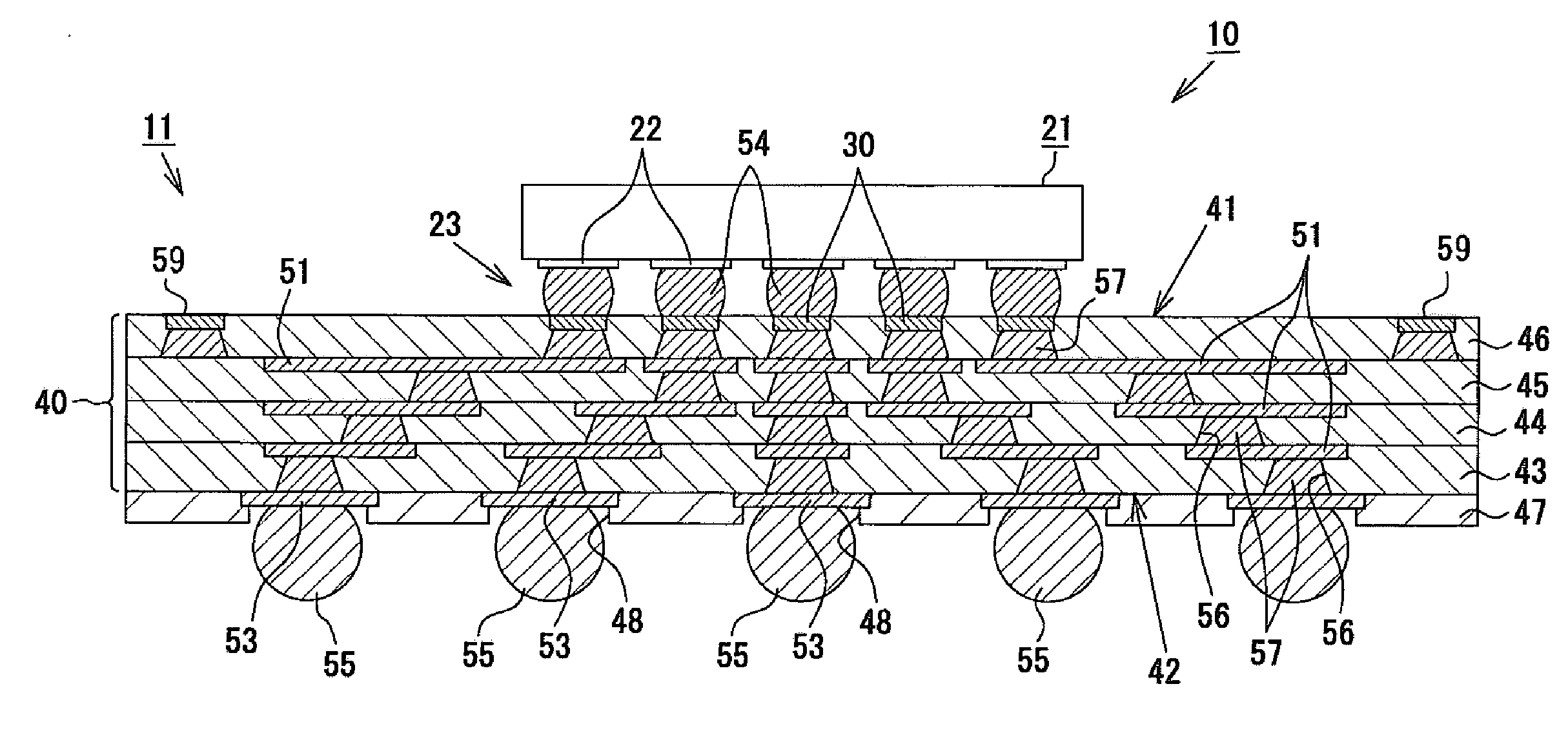

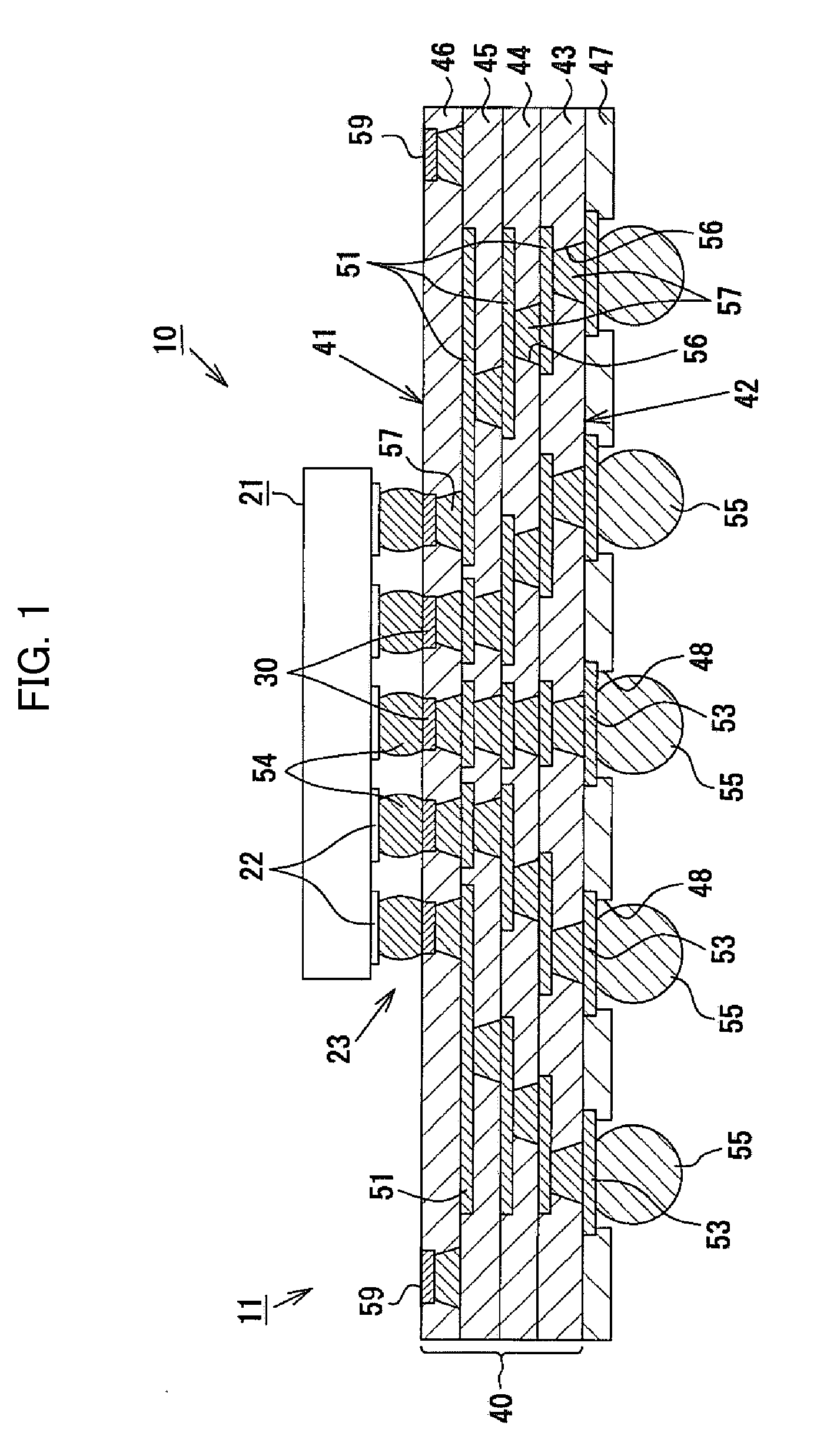

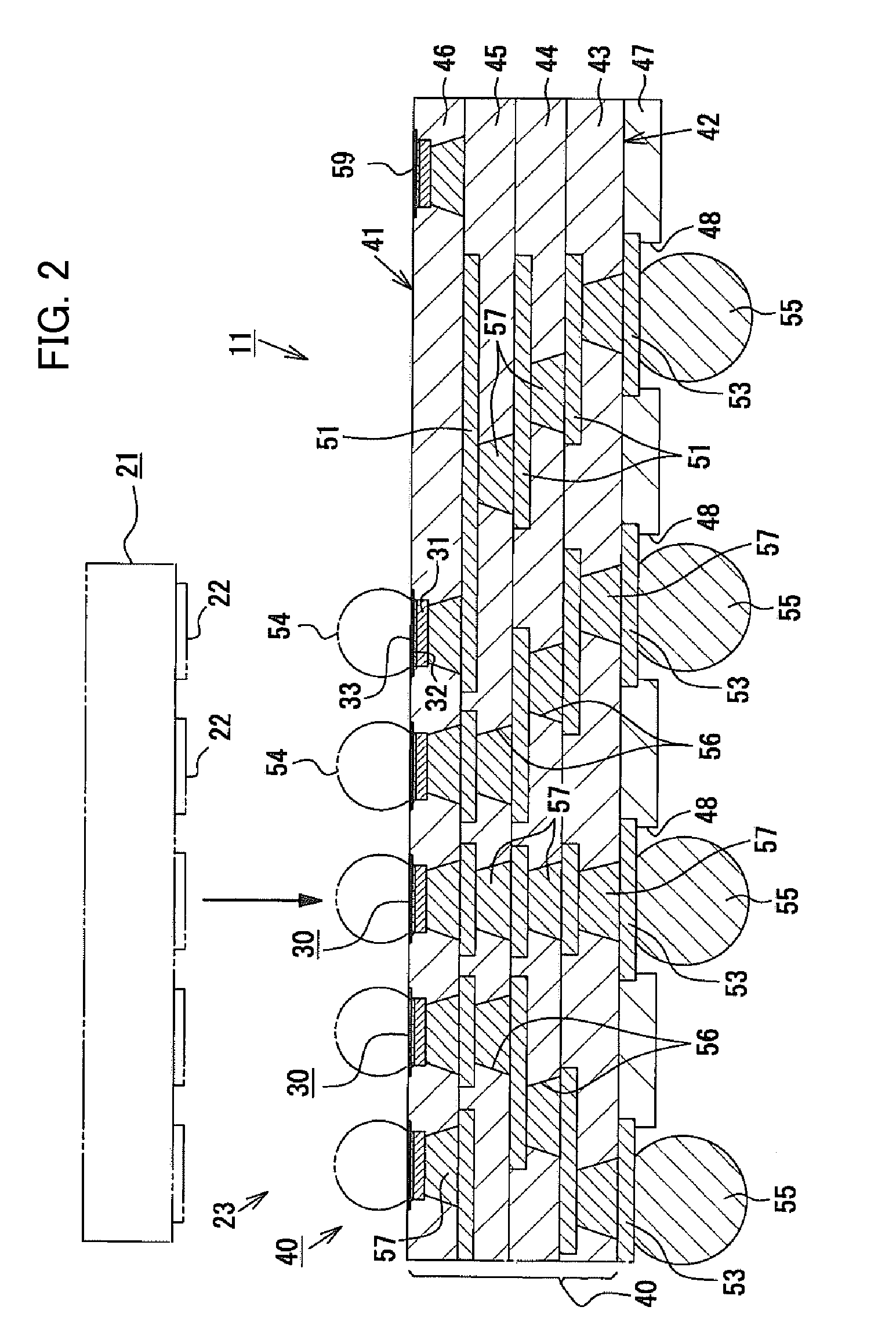

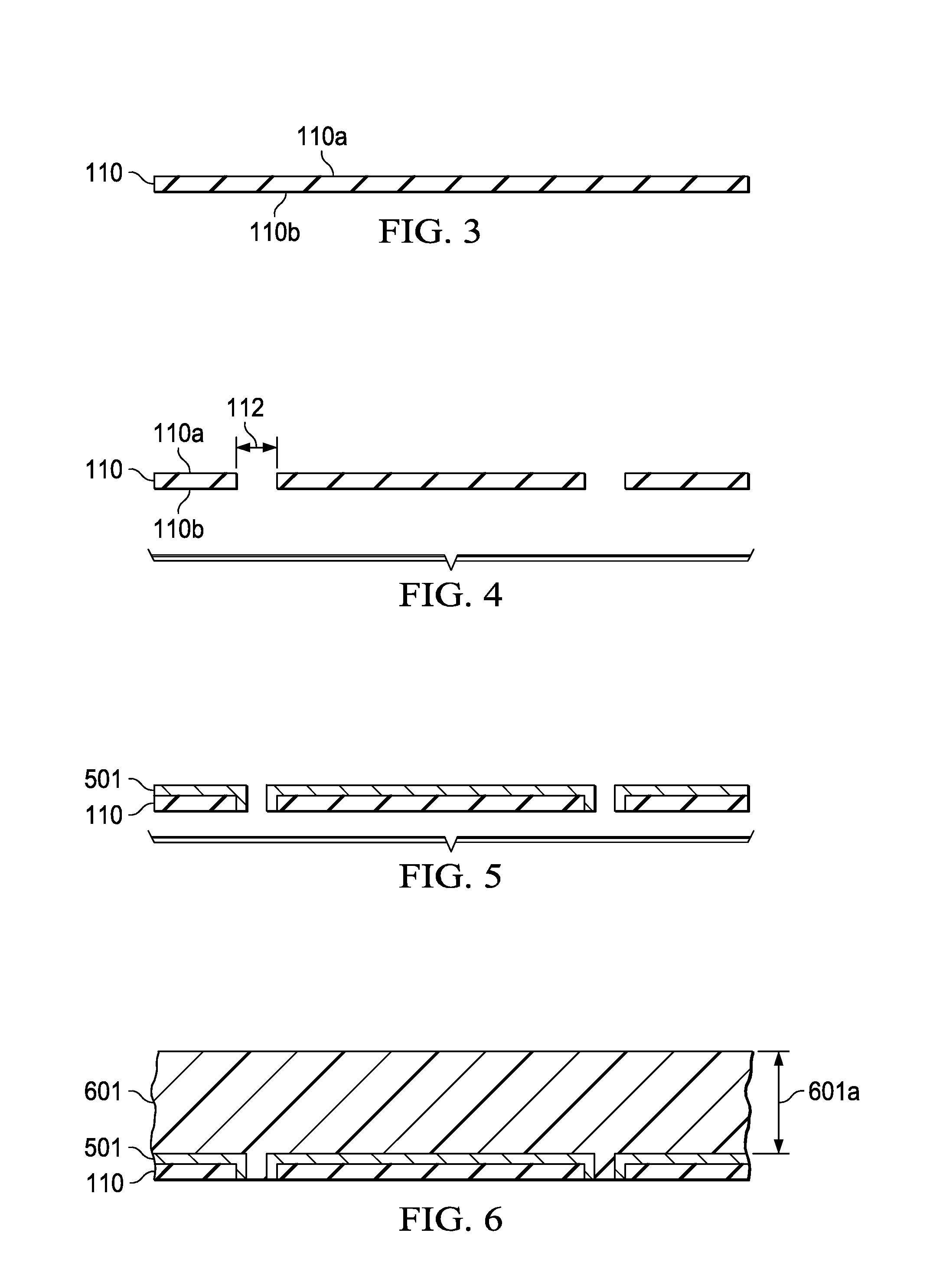

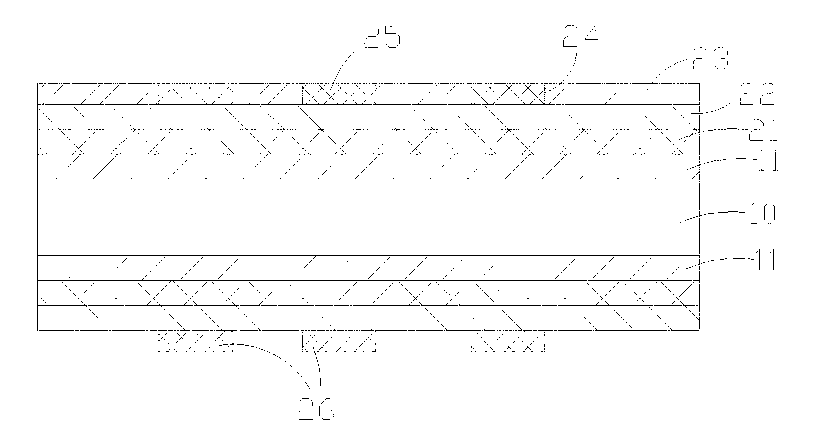

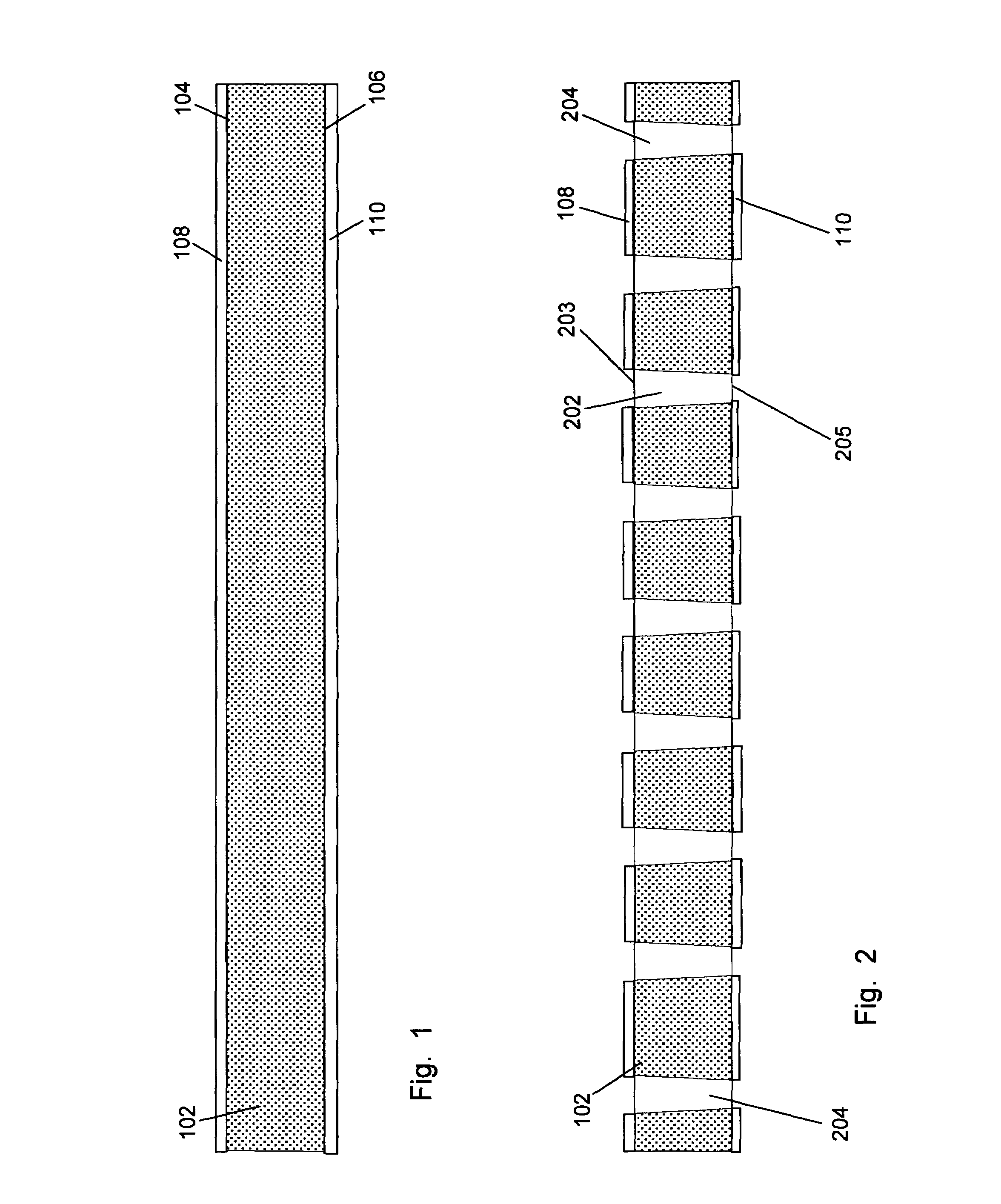

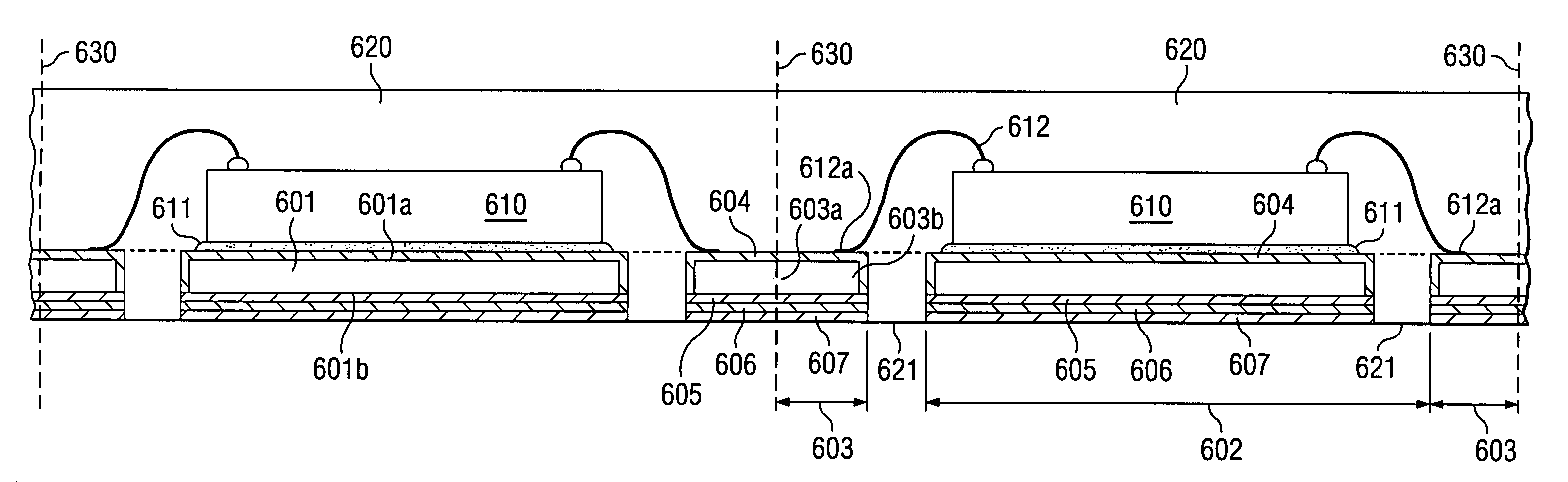

Multilayer wiring substrate and method for manufacturing the same

InactiveUS20100132997A1Improve reliabilityImprove connection reliabilitySemiconductor/solid-state device detailsPrinted circuit aspectsElectrical conductorOptoelectronics

A multilayer wiring substrate is manufactured through a recess forming step, a gold-diffusion-prevention-layer forming step, a terminal forming step, resin-insulating-layer forming step, a conductor forming step, and a metal-layer removing step. In the recess forming step, a copper foil layer is half-etched so as to form recesses. In the gold-diffusion-prevention-layer forming step, a gold diffusion prevention layer is formed in each recess. In the terminal forming step, a gold layer, a nickel layer, and a copper layer are stacked in sequence on the gold diffusion prevention layer to thereby form a surface connection terminal. In the resin-insulating-layer forming step, a resin insulating layer is formed, and, in the conductor forming step, via conductors and conductor layers are formed. In the metal-layer removing step, the copper foil layer and the gold diffusion prevention layer are removed so that the gold layer projects from the main face of the laminated structure.

Owner:NGK SPARK PLUG CO LTD

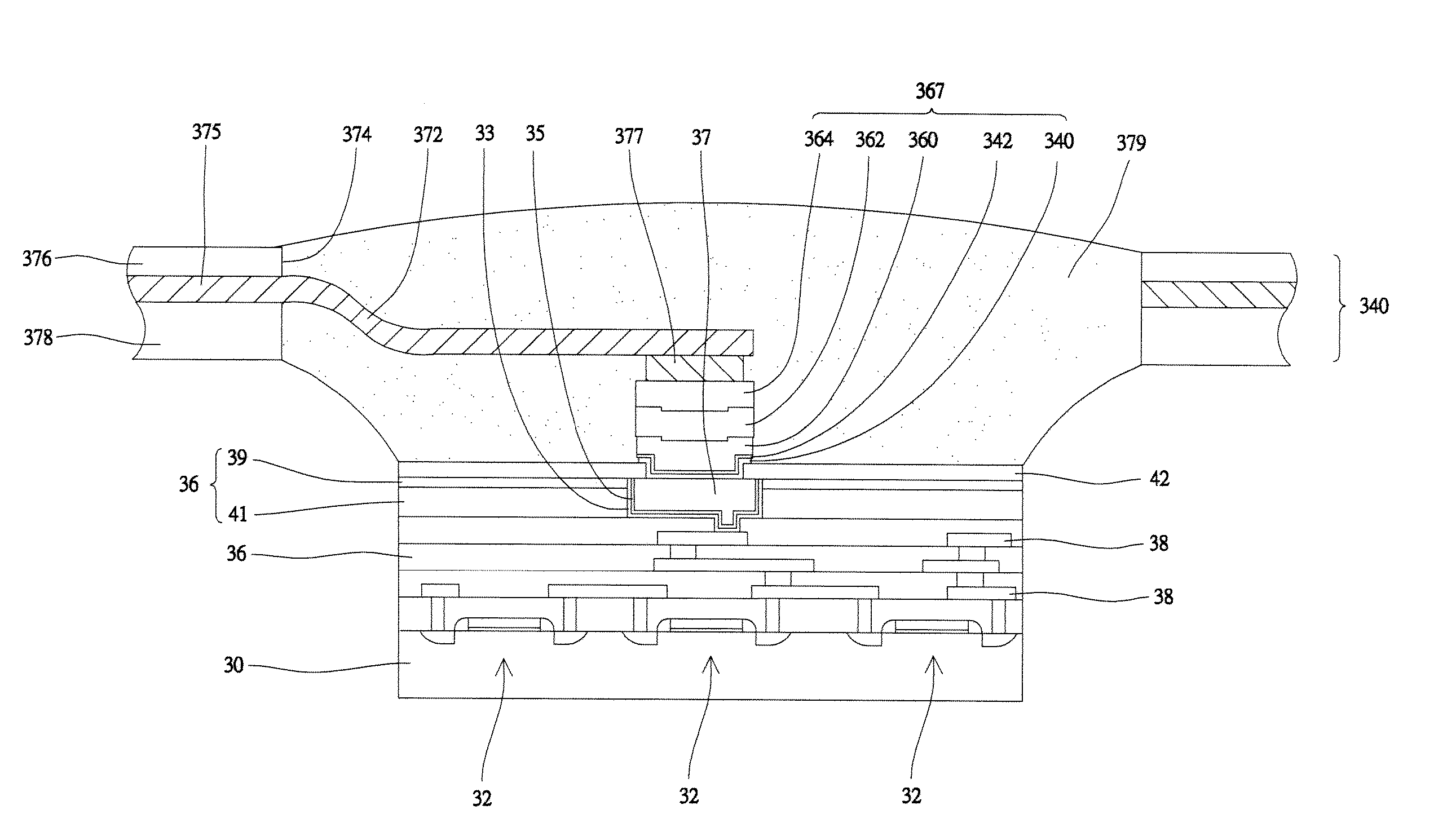

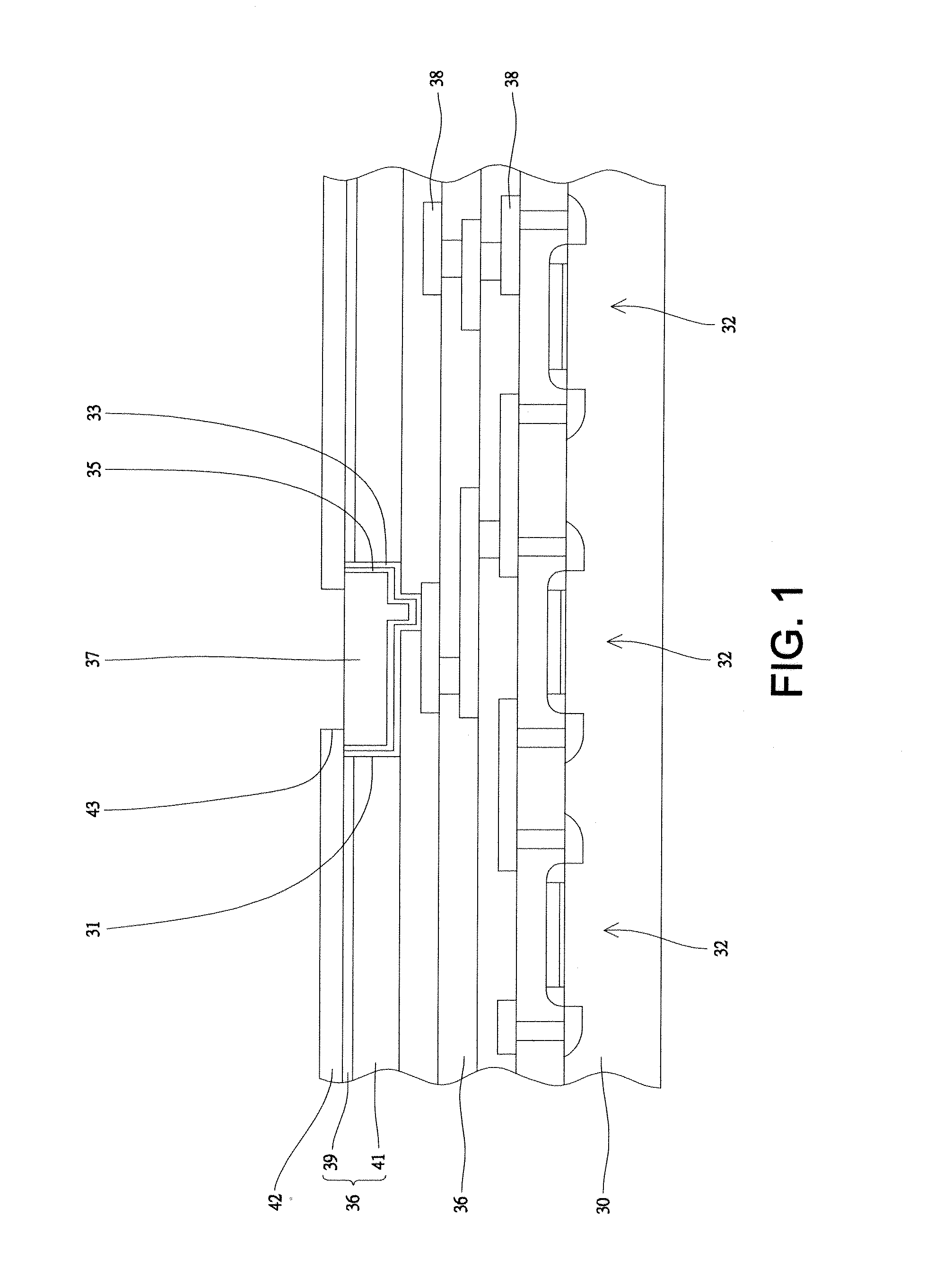

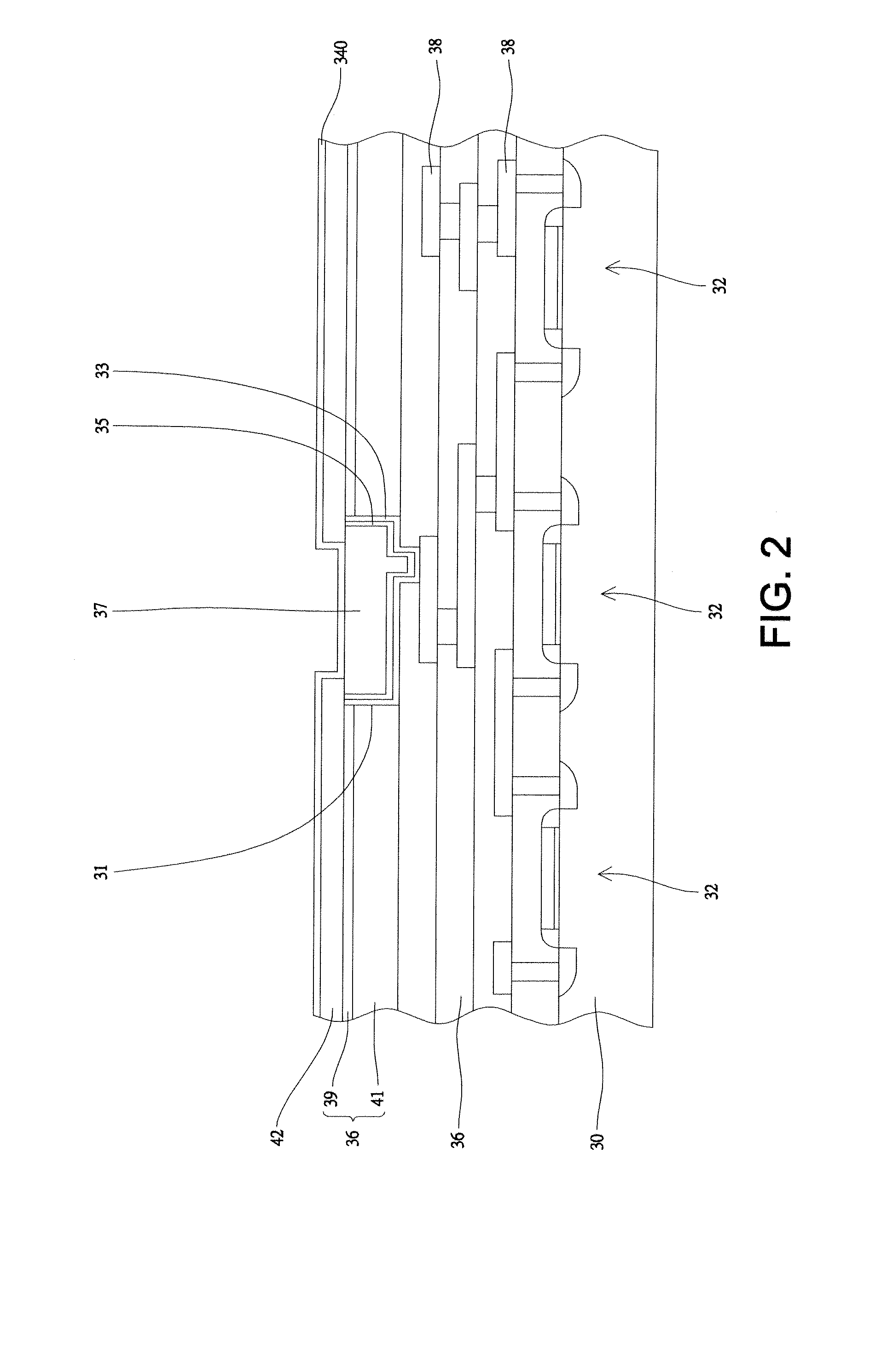

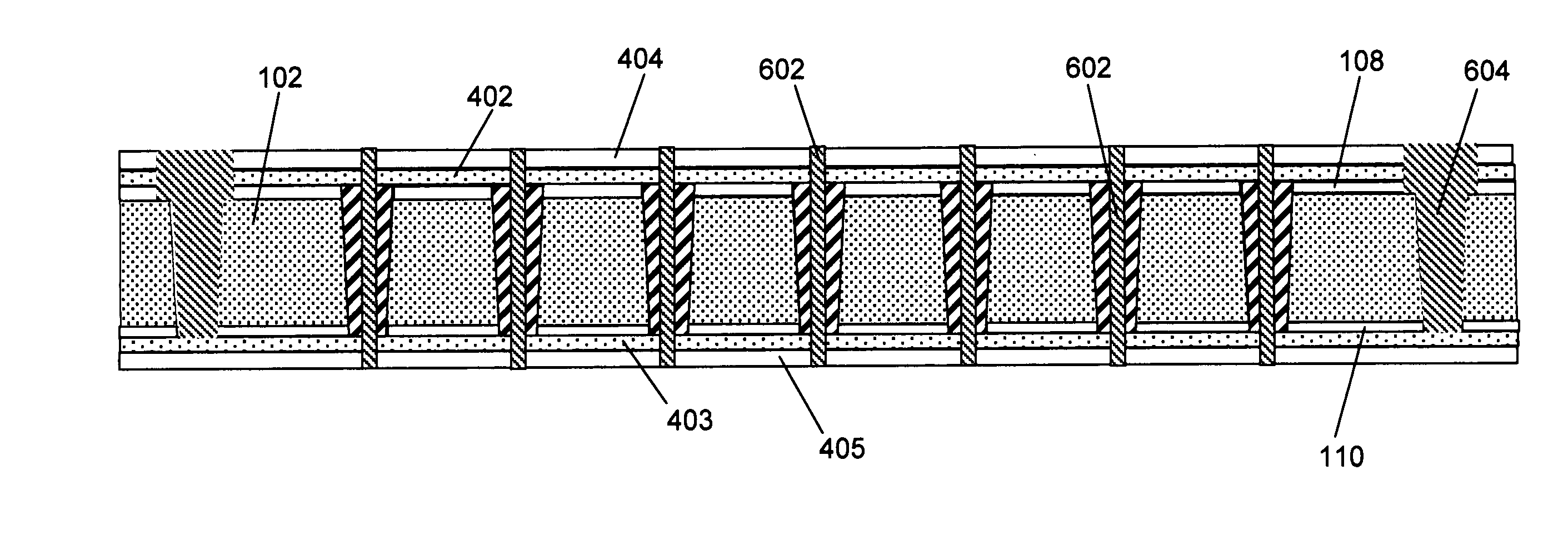

Wafer translator having a silicon core isolated from signal paths by a ground plane

ActiveUS20090224372A1Printed circuit assemblingElectrical measurement instrument detailsCopper platingCopper foil

Apparatus and methods are provided for wafer translators having a silicon core, an isolating conductive ground plane, and copper and subjacent resin layers disposed on the ground plane. A silicon substrate having at least one major surface coated with an electrically conductive layer is subjected to a number of printed circuit board manufacturing operations including, but not limited to, application of resin-coated copper foils; mechanical grinding of copper layers; mechanical drilling of via openings in a dielectric material; plating of copper, nickel, and gold layers; laser removal of metal; and chemical removal of metal; in order to produce a wafer translator having a silicon core. In further aspects of the present invention, alignment marks are formed and contact structures, such as stud bumps, are placed relative to a local set of alignment marks.

Owner:TRANSLARITY INC

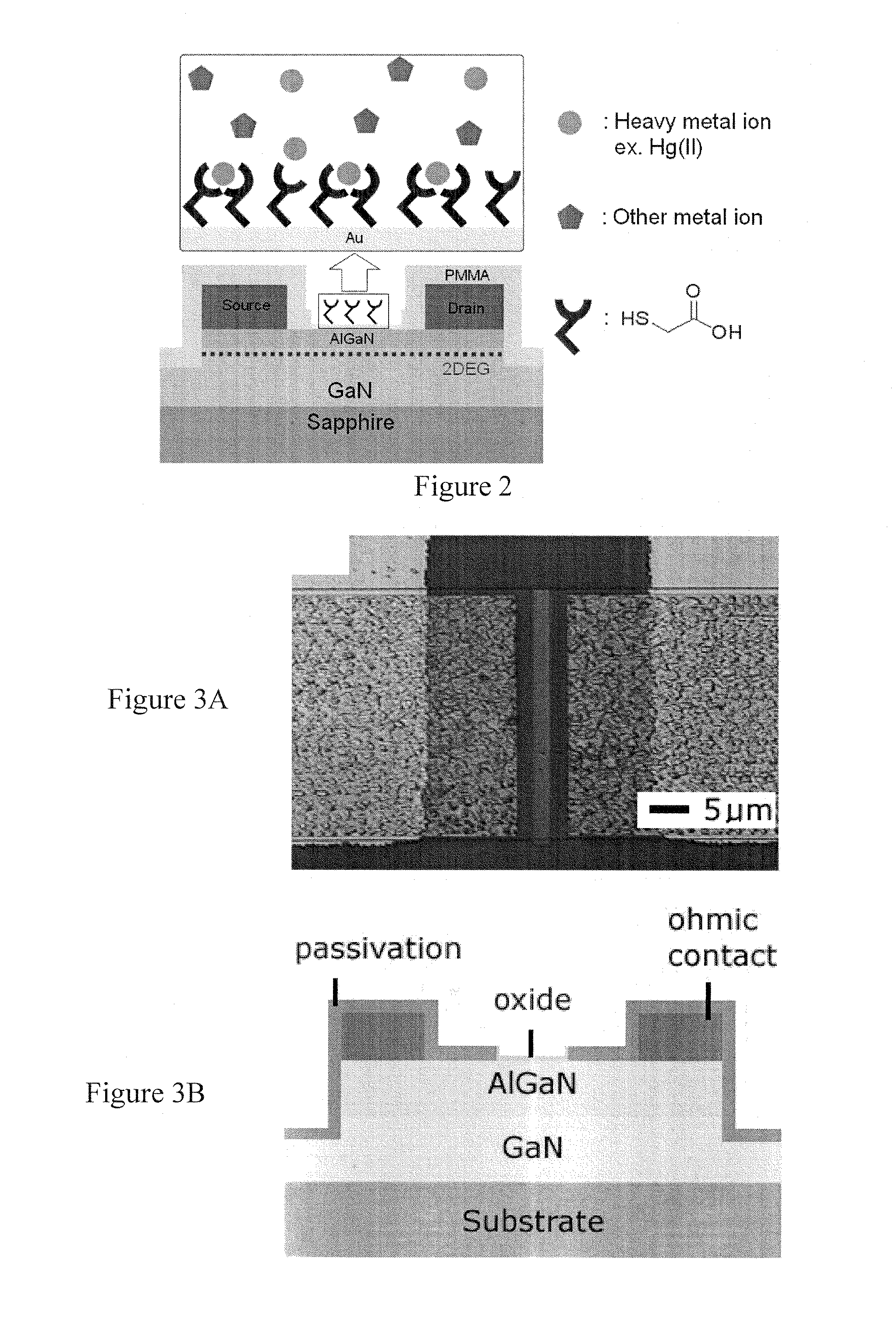

Sensors using high electron mobility transistors

InactiveUS20100188069A1Quick analysisMaterial electrochemical variablesSemiconductor devicesDielectricGate dielectric

Embodiments of the invention include sensors comprising high electron mobility transistors (HEMTs) with capture reagents on a gate region of the HEMTs. Example sensors include HEMTs with a thin gold layer on the gate region and bound antibodies; a thin gold layer on the gate region and chelating agents; a non-native gate dielectric on the gate region; and nanorods of a non-native dielectric with an immobilized enzyme on the gate region. Embodiments including antibodies or enzymes can have the antibodies or enzymes bound to the Au-gate via a binding group. Other embodiments of the invention are methods of using the sensors for detecting breast cancer, prostate cancer, kidney injury, glucose, metals or pH where a signal is generated by the HEMT when a solution is contacted with the sensor. The solution can be blood, saliva, urine, breath condensate, or any solution suspected of containing any specific analyte for the sensor.

Owner:UNIV OF FLORIDA RES FOUNDATION INC

Technique for defining a wettable solder joint area for an electronic assembly substrate

InactiveUS20060255102A1Semiconductor/solid-state device detailsPrinted circuit aspectsSolder maskGold layer

A technique for defining a wettable solder joint area for an electronic assembly reduces and / or dispenses with the use of polymer solder masks. According to the technique, a substrate is provided that includes at least one conductive trace. A nickel layer is provided on the conductive trace and gold is selectively applied on the nickel layer in a desired pattern to form a gold layer. An exposed portion of the nickel layer that does not include the gold in the desired pattern is then oxidized. Finally, a solder is applied to the gold layer, with the oxidized nickel layer providing a solder stop and defining a wettable solder joint area.

Owner:DELPHI TECH INC

Multilayer wiring substrate and method for manufacturing the same

ActiveUS20100208437A1Low connection reliabilityDeterioration of surface shapeEarth drilling toolsDrill bitsElectrical conductorEngineering

A multilayer wiring substrate of the present invention has a laminated structure composed of conductor layers and resin insulating layers stacked alternately. A plurality of surface connection terminals to which terminals of a chip component are to be surface-connected are formed on a main face of the laminated structure. A plurality of via conductors connected to the plurality of surface connection terminals are formed in the resin insulating layers. Each of the plurality of surface connection terminals has a structure in which a copper layer, a nickel layer, and a gold layer are stacked in this sequence. The gold layer is larger in diameter than at least the copper layer. The gold layer has an overhanging portion which extends radially outward from a circumference of the copper layer.

Owner:NGK SPARK PLUG CO LTD

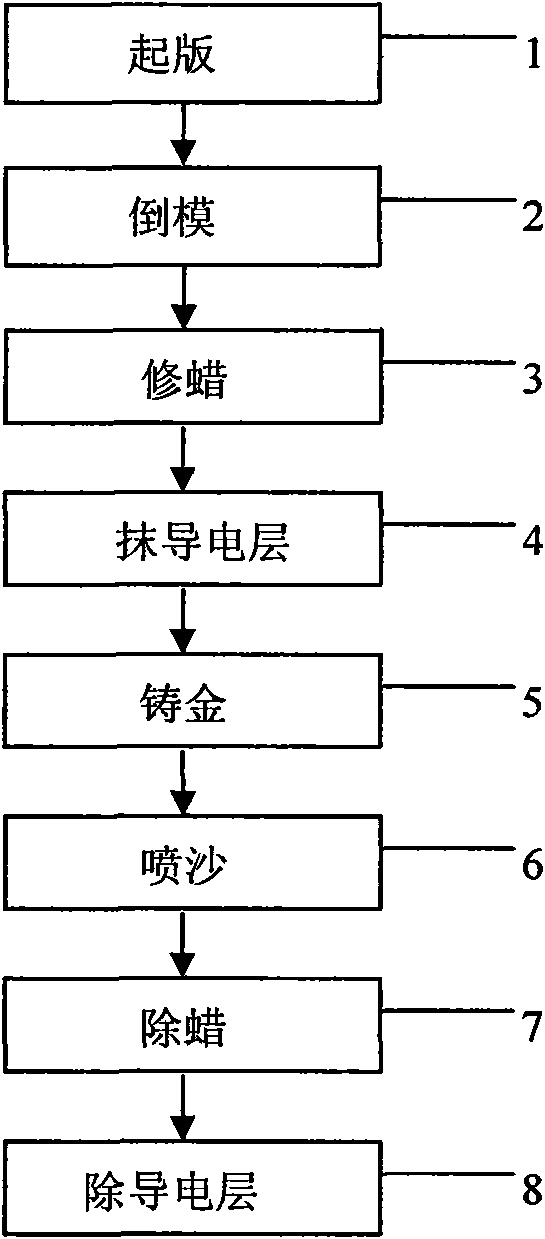

Method for electroforming hard gold product

InactiveCN101560676AIncrease in sizeHigh hardnessElectroforming processesChemical structurePotassium

The invention relates to a method for electroforming hard gold products. The method comprises the following steps: template picking, mould pouring, wax repairing and electric conducting layer coating are carried out to obtain a wax mould of a gold product to be processed, and a layer of electric conductive oil is coated on the surface of the wax mould; and a titanium net is taken as anode in the gold electroforming step, the wax mould coated with the electric conductive oil is put in an electrotyping bath as cathode, the electroforming solution is put in the electrotyping bath and includes sulfurous acid gold potassium, ammonium sulfite and potassium citrate, wherein the sulfurous acid gold potassium is combined with the ammonium sulfite, a trivalent gold ion is reduced into a univalent gold ion, the univalent gold ion generates close crystal grains, the close crystal grains are combined through the potassium citrate to form complexing gold through PH buffer solution, the gold is deposited on the wax mould to form a casting gold layer, and the half-finished product is prepared; and the wax film in the half-finished product and the electric conductive layer are removed in the wax removal step and the electric conductive layer removal step to obtain the finished product. The volume and the hardness of the gold product are changed by using the variation of the chemical structure of the gold ion, so that the hardness, the volume and the toughness of the gold product meet the standards simultaneously.

Owner:武汉金凰珠宝股份有限公司

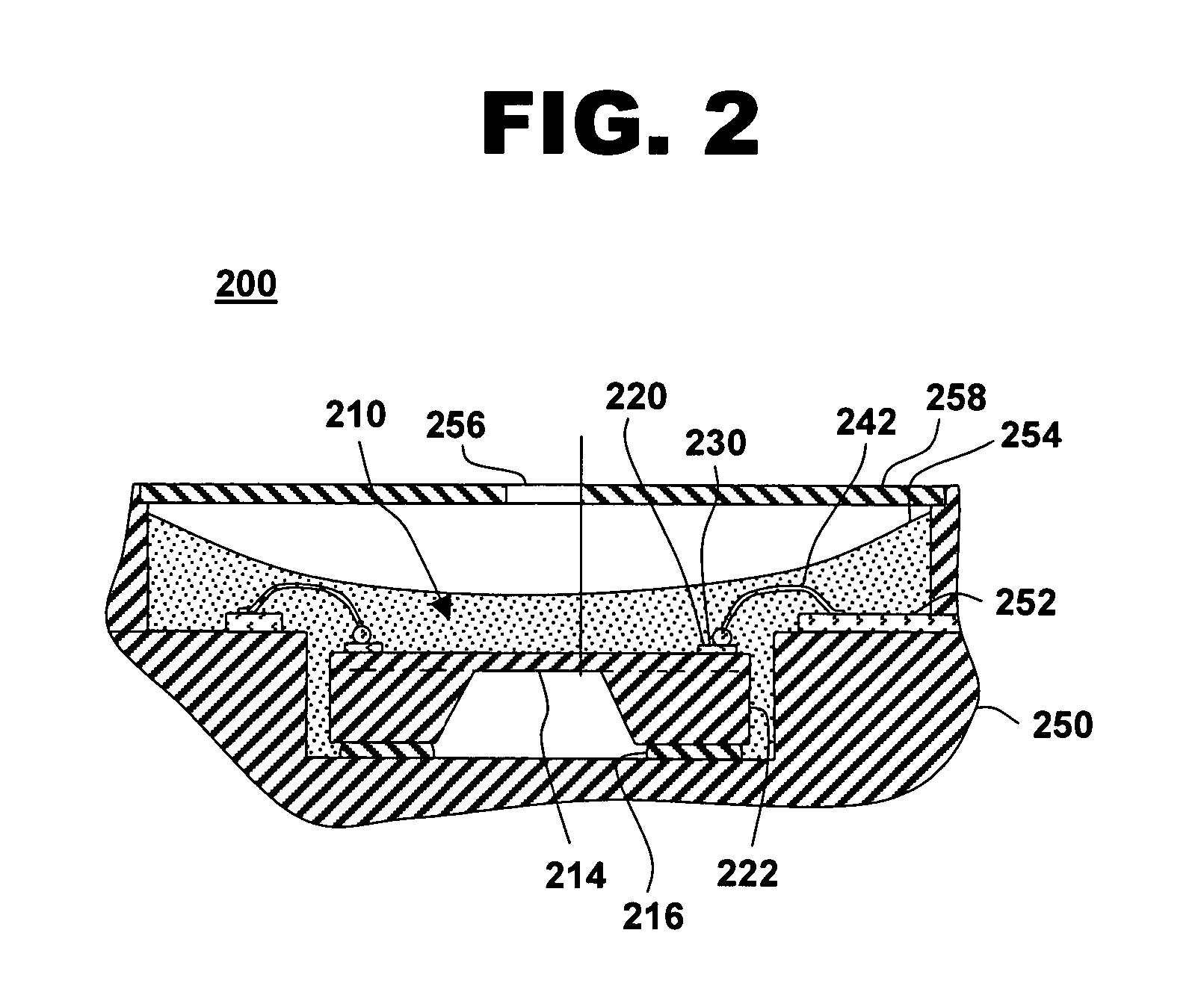

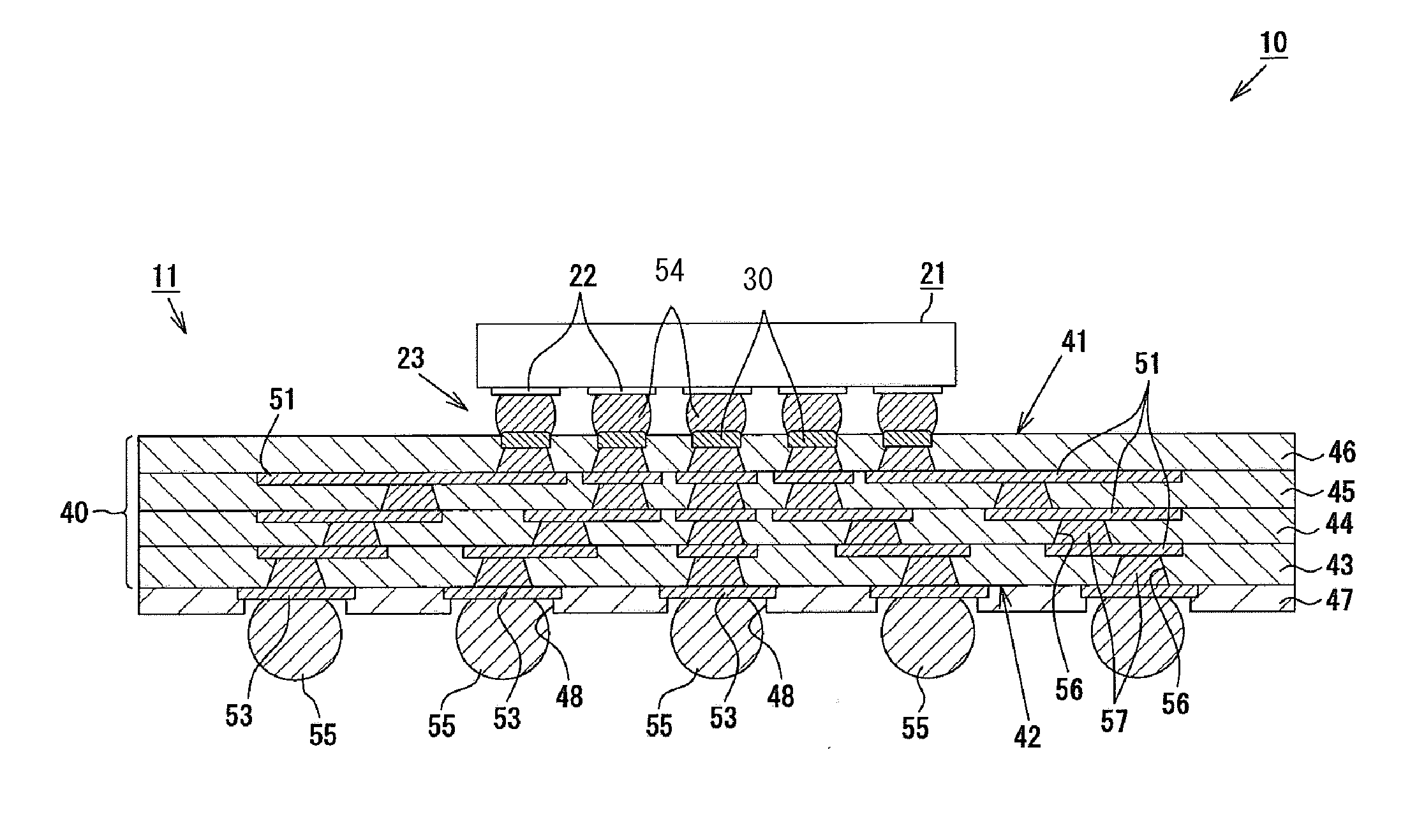

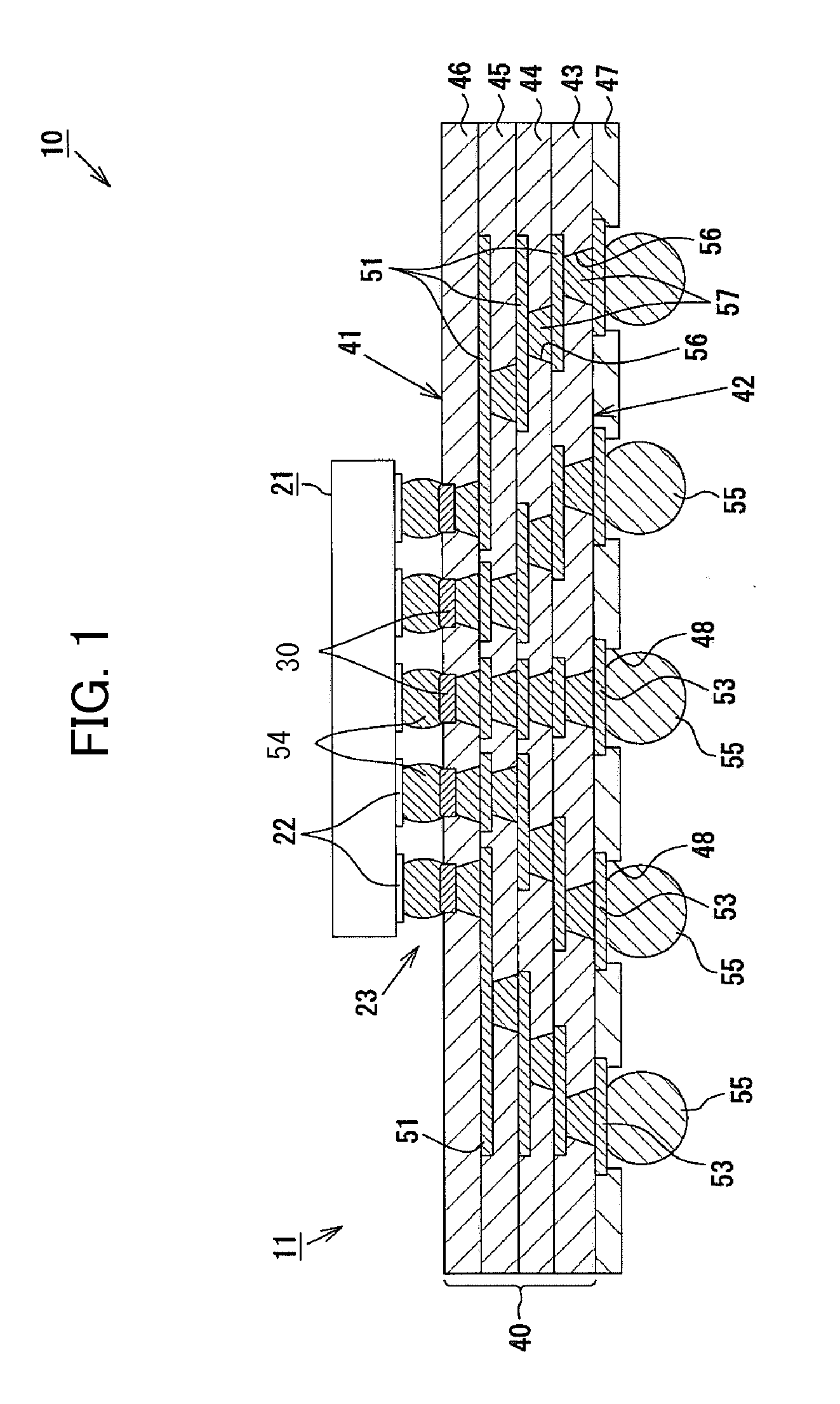

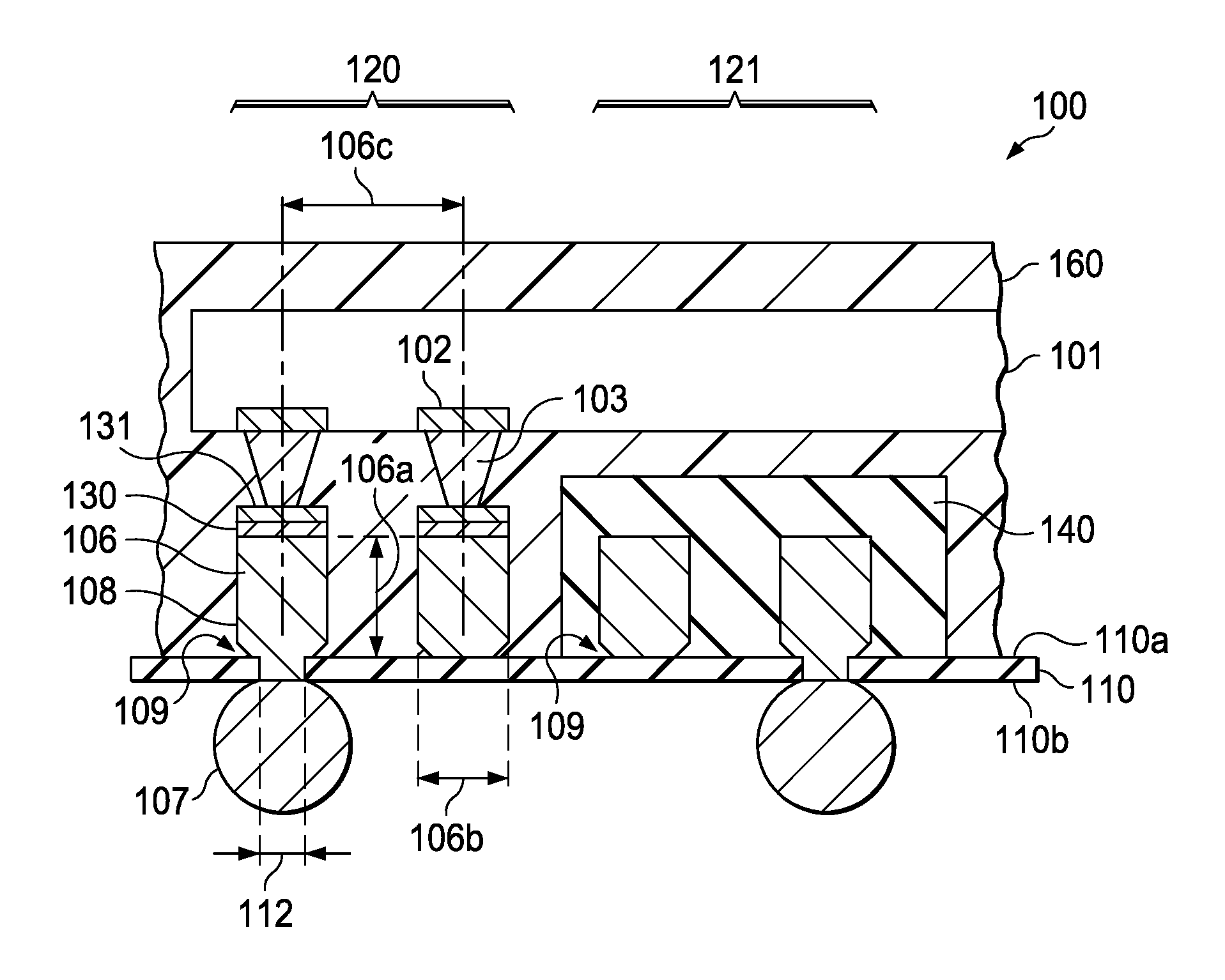

Semiconductor Package Having Buss-Less Substrate

ActiveUS20090051036A1Improve adhesionAvoid elevationSemiconductor/solid-state device detailsStacked resist layersSemiconductor chipSemiconductor package

A ball grid array device with an insulating substrate (110) having metal traces (106, for example copper, about 18 μm thick) with sidewalls (108) at right angles to the trace top. The traces are grouped in a first (120) and a second set (121). The first set traces have the top surface covered by a thin noble metal (for example a nickel layer (130) about 0.1 μm thick and an outermost gold layer (131) about 0.5 μm thick), while the sidewalls are un-covered by the noble metal. About 1.5 μm are thus gained for the trace spacing; oxidation of the trace sidewalls is enabled. The second set traces have the top surface un-covered by the noble metal; the traces are covered by an insulating soldermask. A semiconductor chip (101) with terminals (102) is attached to the substrate with the terminals connected to the noble metal of the first set traces, either by bonding wires (for example gold) or by metal studs (for example gold). The assembled chip and the first set traces are encapsulated in a polymerized compound (160), which adheres to the oxidized trace sidewalls and locks into the trace undercuts at the substrate interface.

Owner:TEXAS INSTR INC

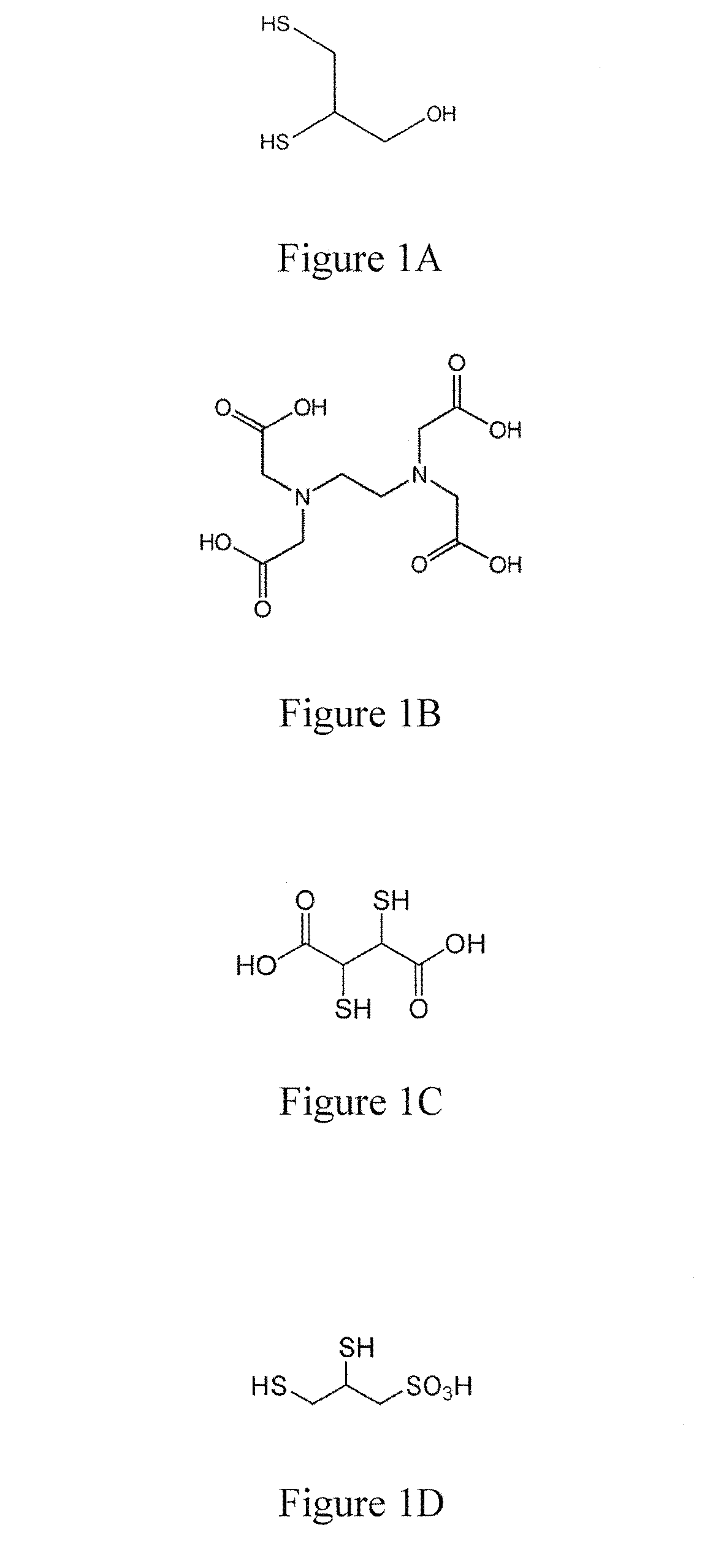

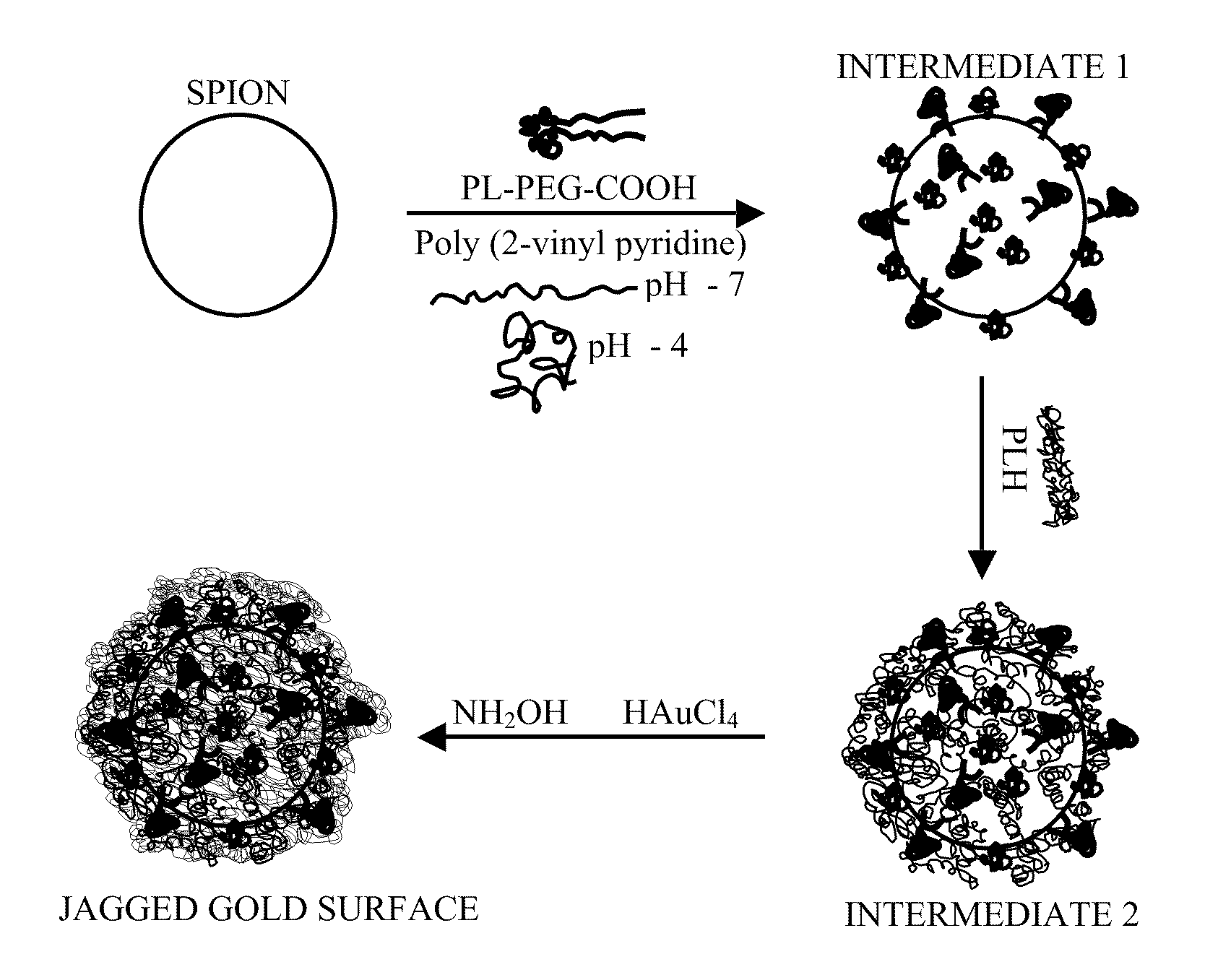

Gold coated super paramagnetic iron oxide nano-particles (spions) and a method of synthesizing the same

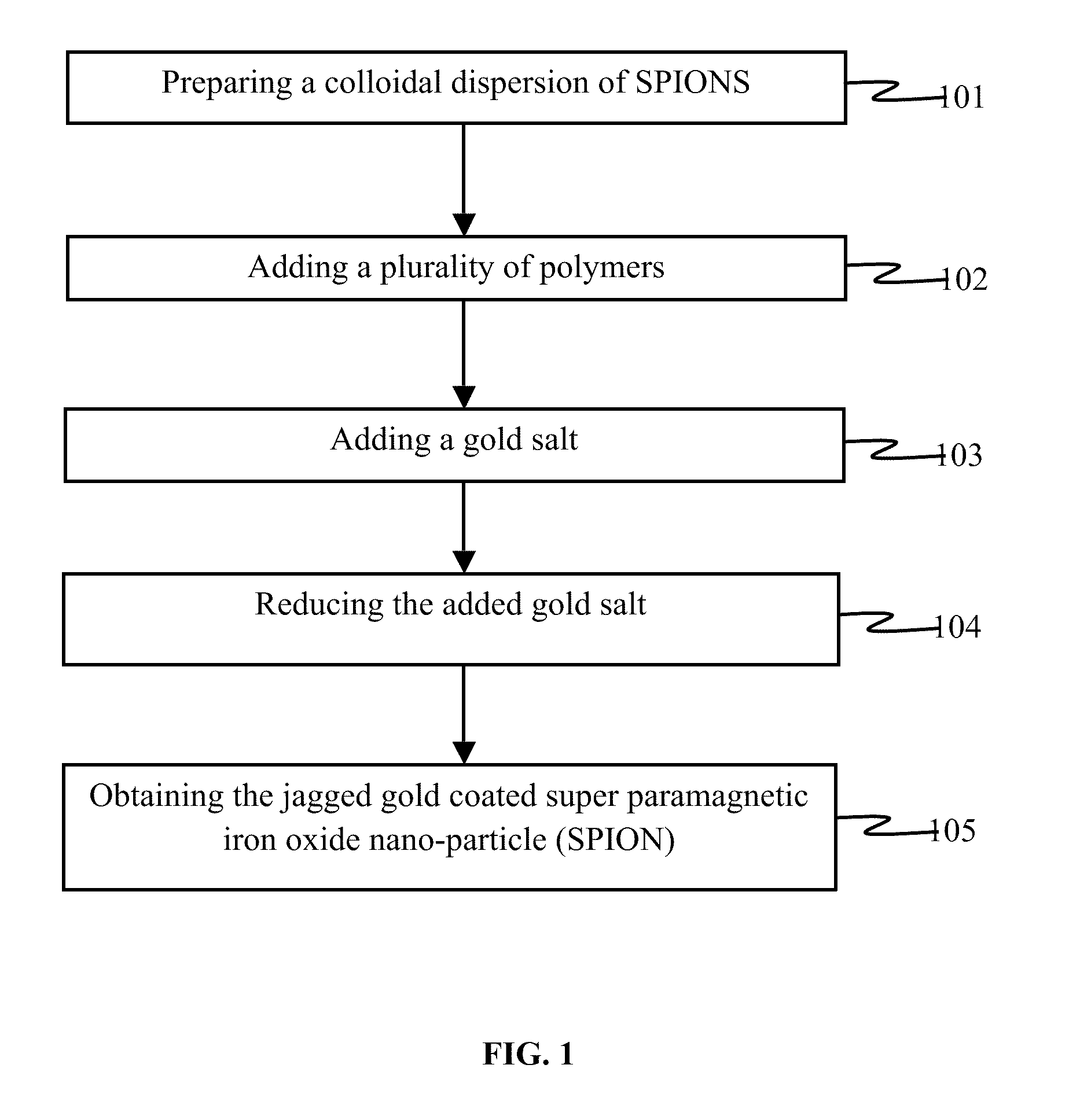

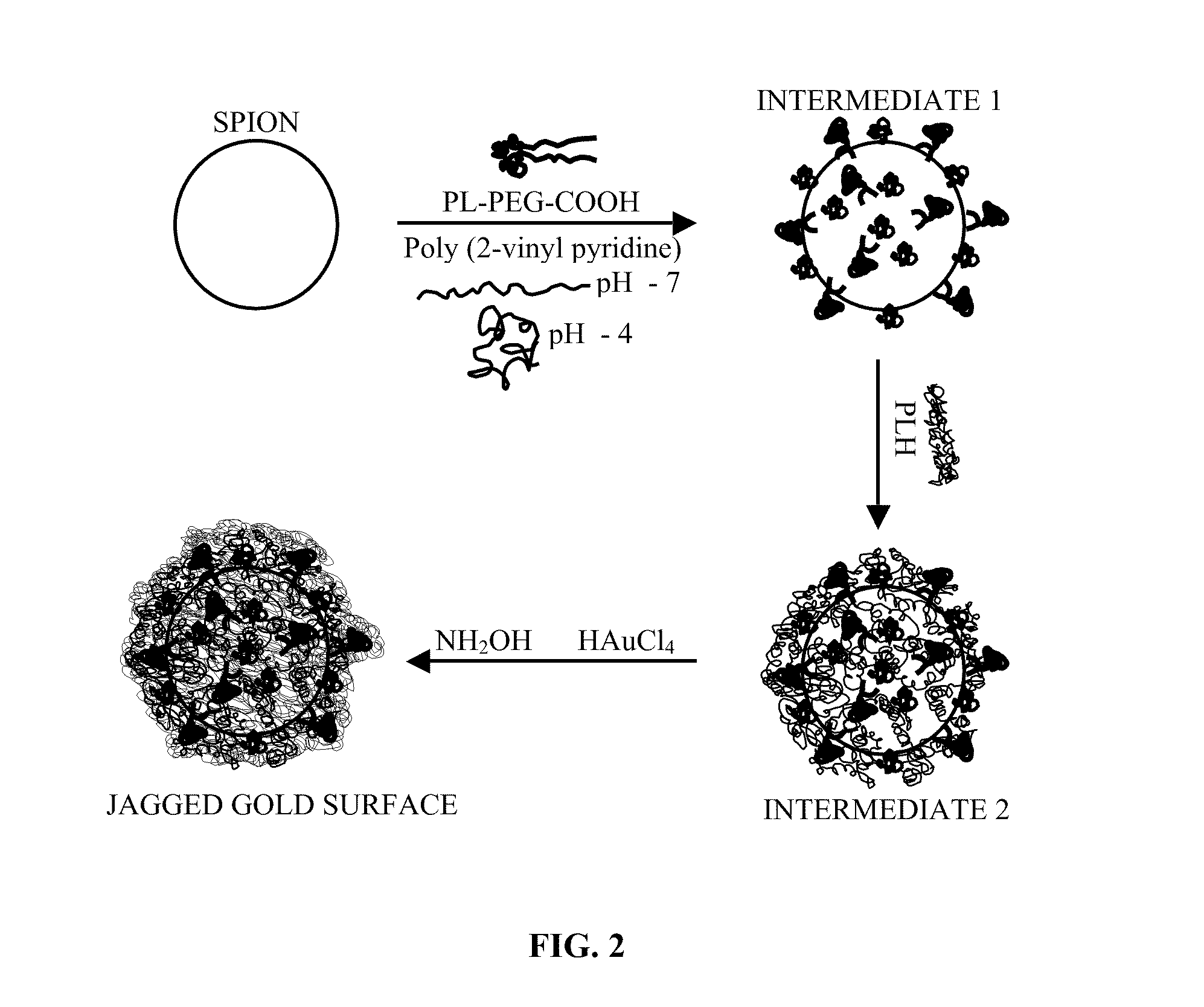

InactiveUS20110206619A1Non-uniform gapImprove abilitiesPowder deliveryMaterial nanotechnologySynthesis methodsPH-sensitive polymers

The various embodiments herein provide a gold coated SPIONs with jagged surface. The gold coated SPIONs have a core and a shell. The core is a SPION molecule and the shell is a jagged gold layer. A non-uniform polymeric gap exists between the core and the shell. The embodiments also provide a method of producing the jagged gold coated SPIONs by mixing a colloidal dispersion of SPIONs with pH sensitive polymers. Adding a gold salt to the above mixture and reducing the gold salt to form jagged gold coated SPIONs.

Owner:MAHMOUDI MORTEZA +1

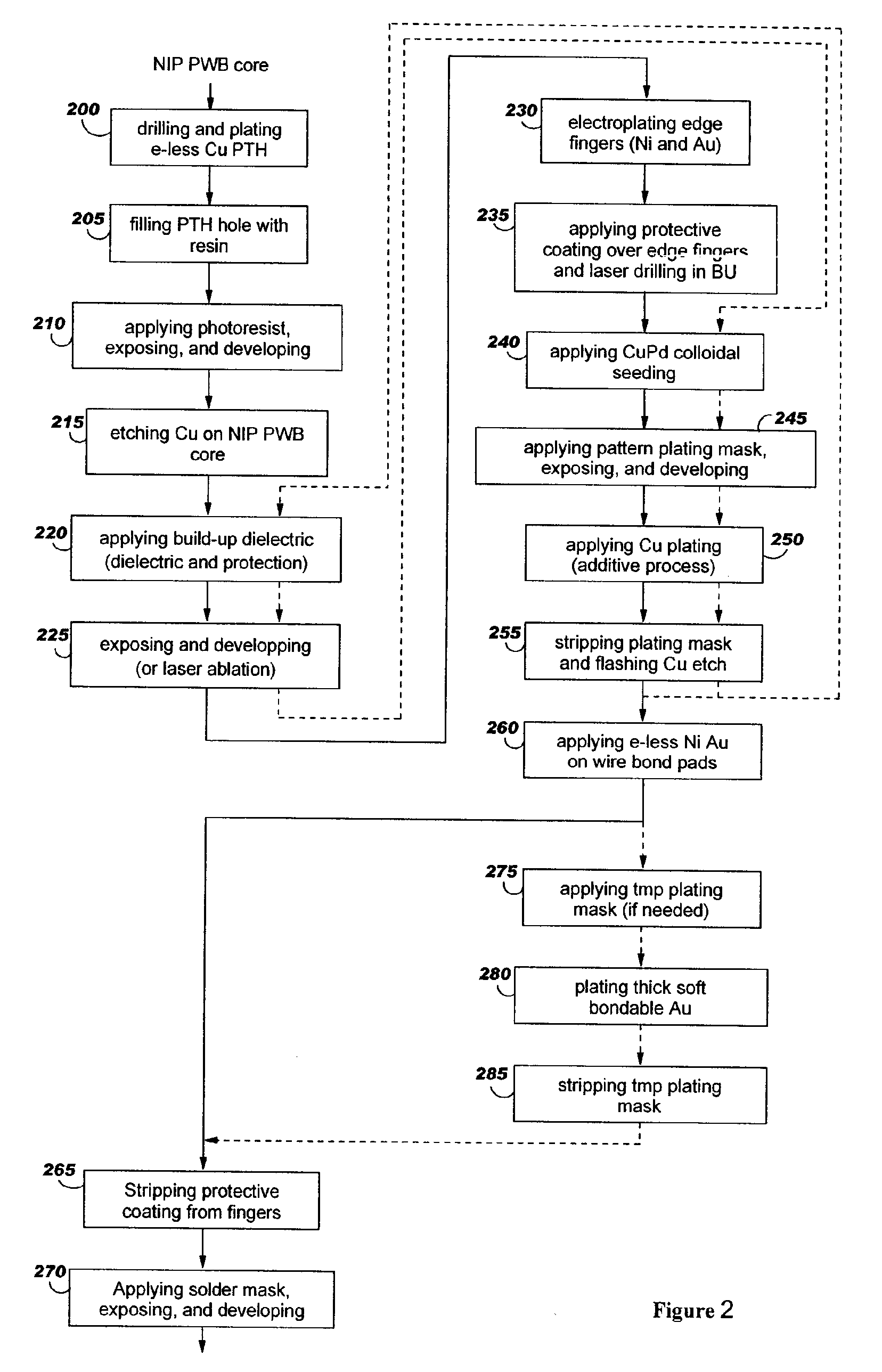

Optimized plating process for multilayer printed circuit boards having edge connectors

InactiveUS20060008970A1Printed circuit aspectsSemiconductor/solid-state device manufacturingLead bondingEngineering

A process for manufacturing printed wire boards with hard plated sliding contact tabs and soft plated wire bond pads. Sliding contact tabs are covered by a protective coating after being hard plated thus allowing the soft plating of wire bond pads without damaging the hard plated sliding contact tabs. In a preferred embodiment, the hard plating includes the step of electroplating nickel on the sliding contact tabs, followed by electroplating an alloy of gold and cobalt, using standard electroplating process. An electro-less soft plating process includes the steps of plating a nickel layer on the wire bond pads and then a gold layer after having “flash-etched” the copper seeding.

Owner:IBM CORP

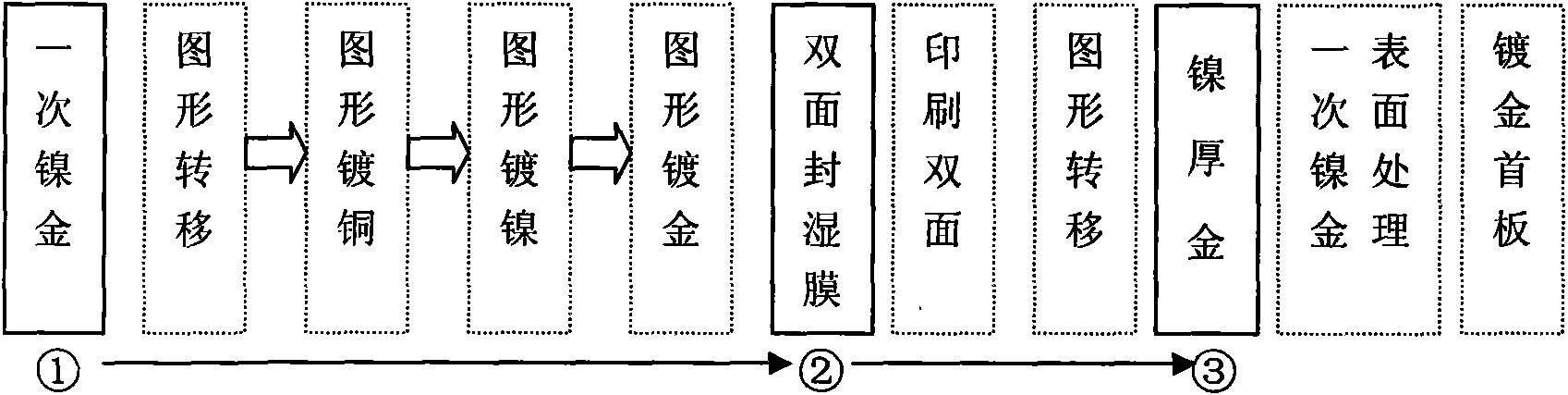

Method for plating thick gold layer in circuit board manufacturing process

InactiveCN101631427ANo pollutionImprove plating resistancePrinted circuit manufactureElectroless nickel immersion goldEtching

The invention discloses a method for plating a gold thick layer in a circuit board manufacturing process, which comprises the following steps of: A, firstly, subjecting a circuit board to pattern tin plating, circuit wire etching, solder-mask printing and chemical nickel and gold processing treatments of depositing a nickel layer and depositing a gold layer; B, carrying out the anti-oxidation post treatment of the circuit board subjected to the chemical nickel and gold processing treatments; C, covering a non-gold plated area of the circuit board; and D, after pre-treating the surface of the circuit board, plating the thick gold layer on a lead of the circuit board by a post drawing process. The invention provides a method for plating thick gold layer in the circuit board manufacturing process, which has advantages of pollution prevention, environment protection, gold salt conservation, good quality and easily controllable gold color.

Owner:深圳市九和咏精密电路有限公司

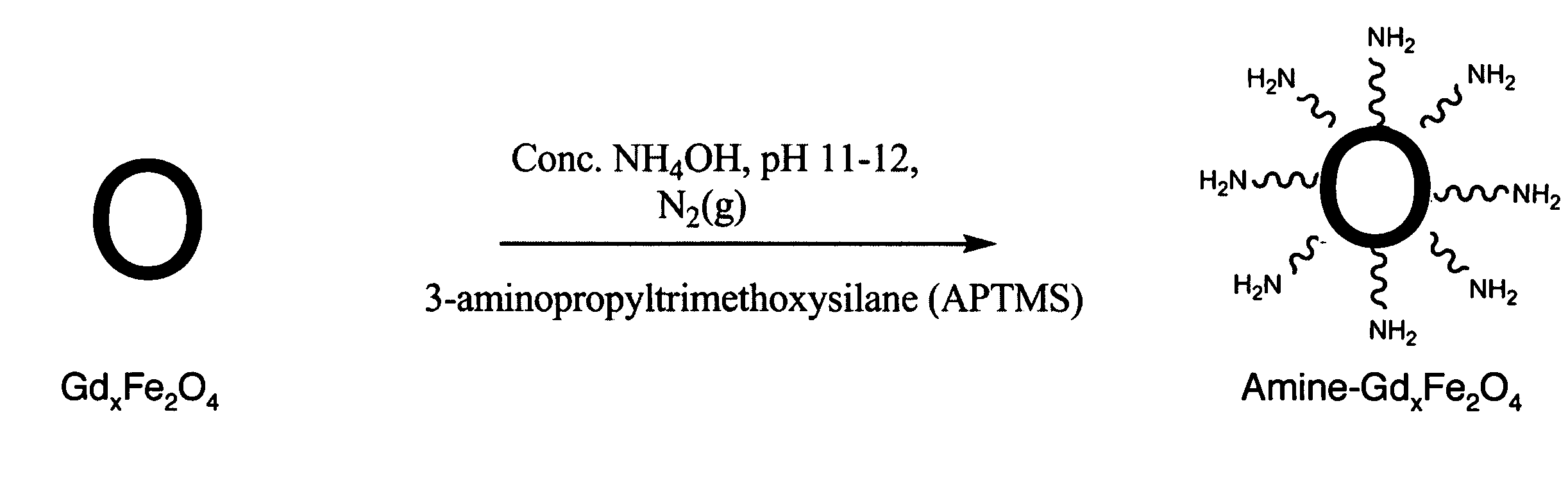

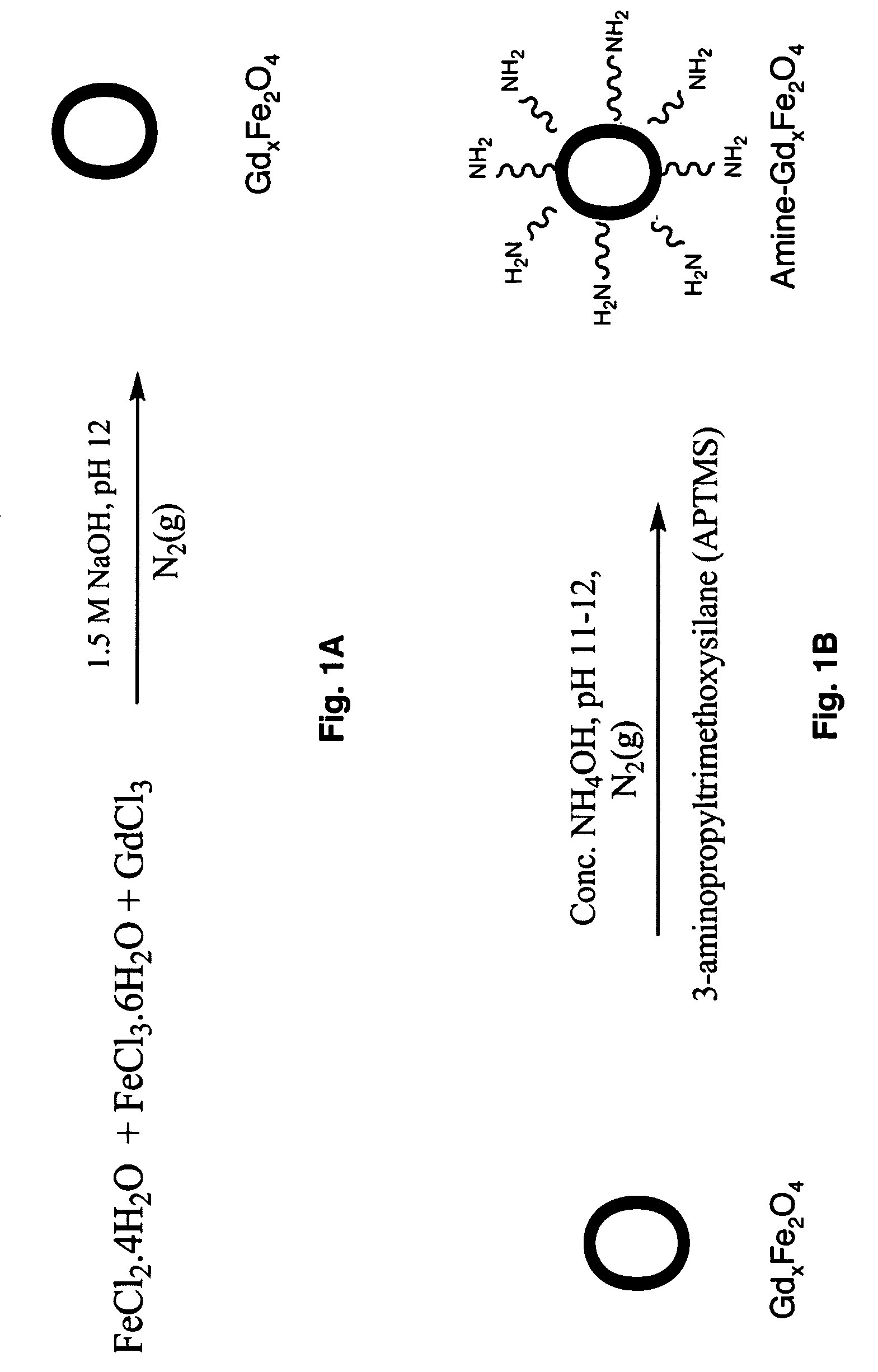

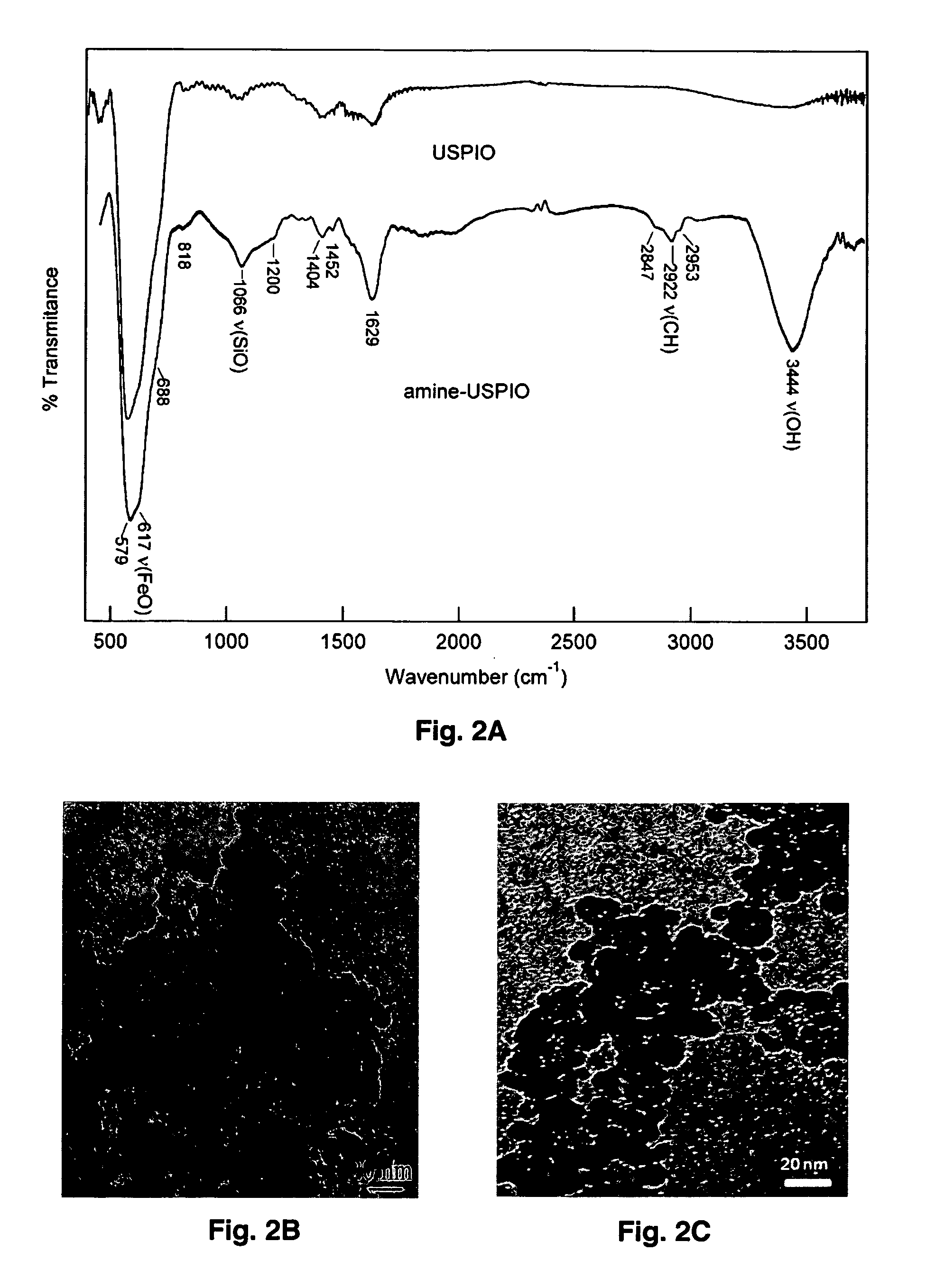

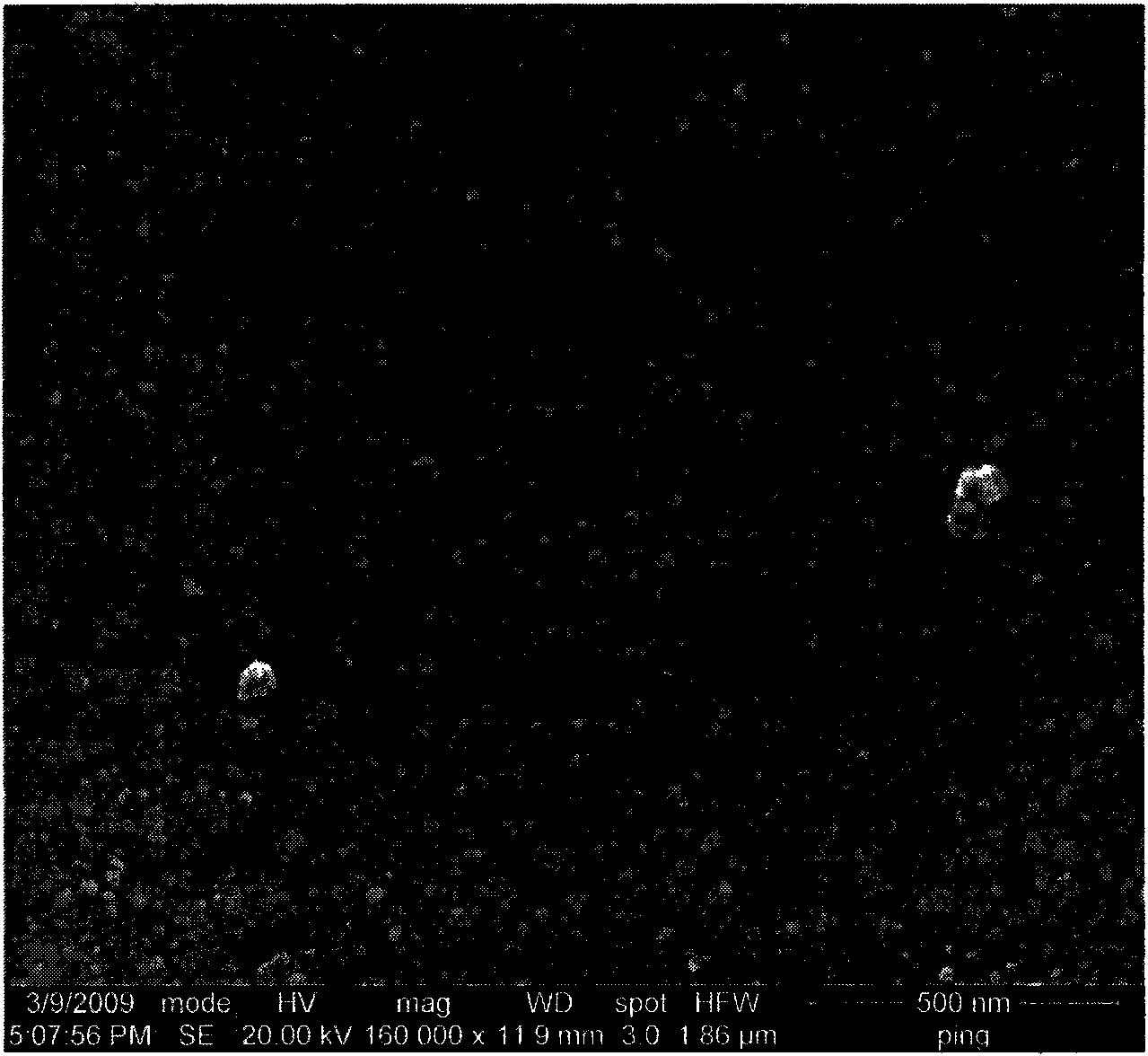

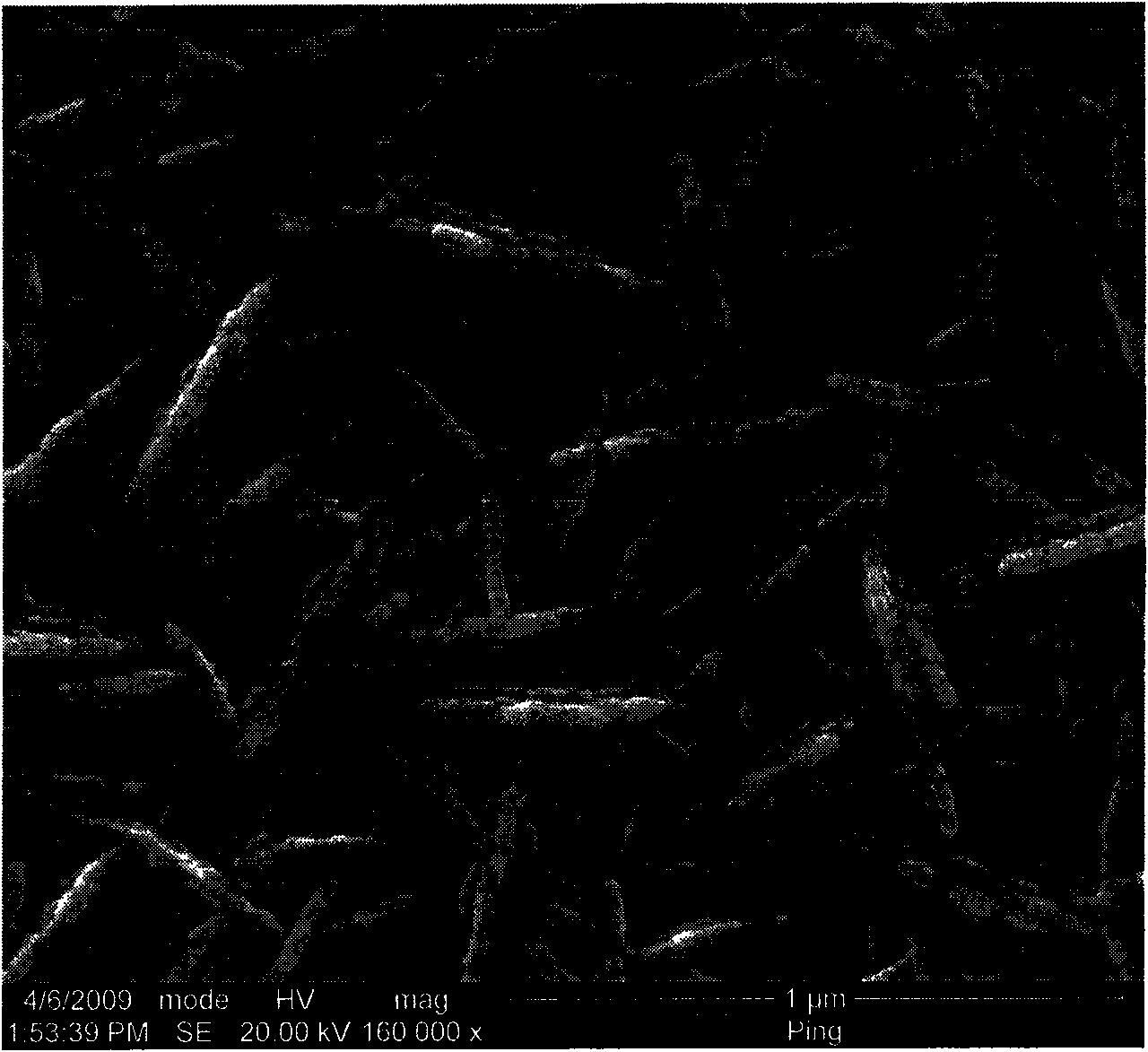

Ultrasmall superparamagnetic iron oxide nanoparticles and uses thereof

Owner:HOUSTON SYST UNIV OF

Surface enhanced raman spectroscopy substrate of continuous three dimensional structural nano silver and preparation method thereof

InactiveCN101566571ALow costStrong Raman signalNanostructure manufactureRaman scatteringSignal responseSurface-enhanced Raman spectroscopy

A surface enhanced raman spectroscopy substrate of continuous three dimensional structural nano silver and a preparation method thereof relate to a surface enhanced raman spectroscopy substrate of nano silver and a preparation method thereof. The invention solves the problems of the surface enhanced raman spectroscopy substrate of nano silver prepared by the prior art, such as poor signal uniformity, low sensitivity, complicated preparation technique and high cost. The substrate consists of a polyaniline film, a nano gold layer and a three dimensional nano silver layer sequentially from bottom to top. The preparation method of the substrate comprises the steps of: dissolving undoped polyaniline powder in N-methylpyrrolidone to form homogeneous solution, spreading the solution on a glass substrate, conducting curing to obtain the polyaniline film; later dipping the polyaniline film in gold-bearing solution to obtain the nano gold layer; and then dipping the polyaniline film coated with the nano gold layer in silver nitrate soluation for reaction to obtain the surface enhanced raman spectroscopy substrate of the continuous three dimensional structural nano silver. The substrate can be used for detection of organic molecules and biological molecules with ppm concentration and has uniform signal response, high sensitivity, simple and fast method, and low cost.

Owner:HARBIN INST OF TECH

Process for manufacturing a printed wiring board

InactiveUS7007378B2Improve conductivityEliminate needPhotomechanical apparatusSemiconductor/solid-state device manufacturingEngineeringGold layer

A process for manufacturing a land grid array connector for a printed wiring board is disclosed. The process does not require electroplating precious metal overlays. Therefore, no commoning bar is required. Another benefit of the invention includes a connector design using only a flash, soft gold application in the outer surface of the connector. Physical hardness and durability are derived from a thin palladium layer lying beneath the flash gold layer.

Owner:GLOBALFOUNDRIES INC

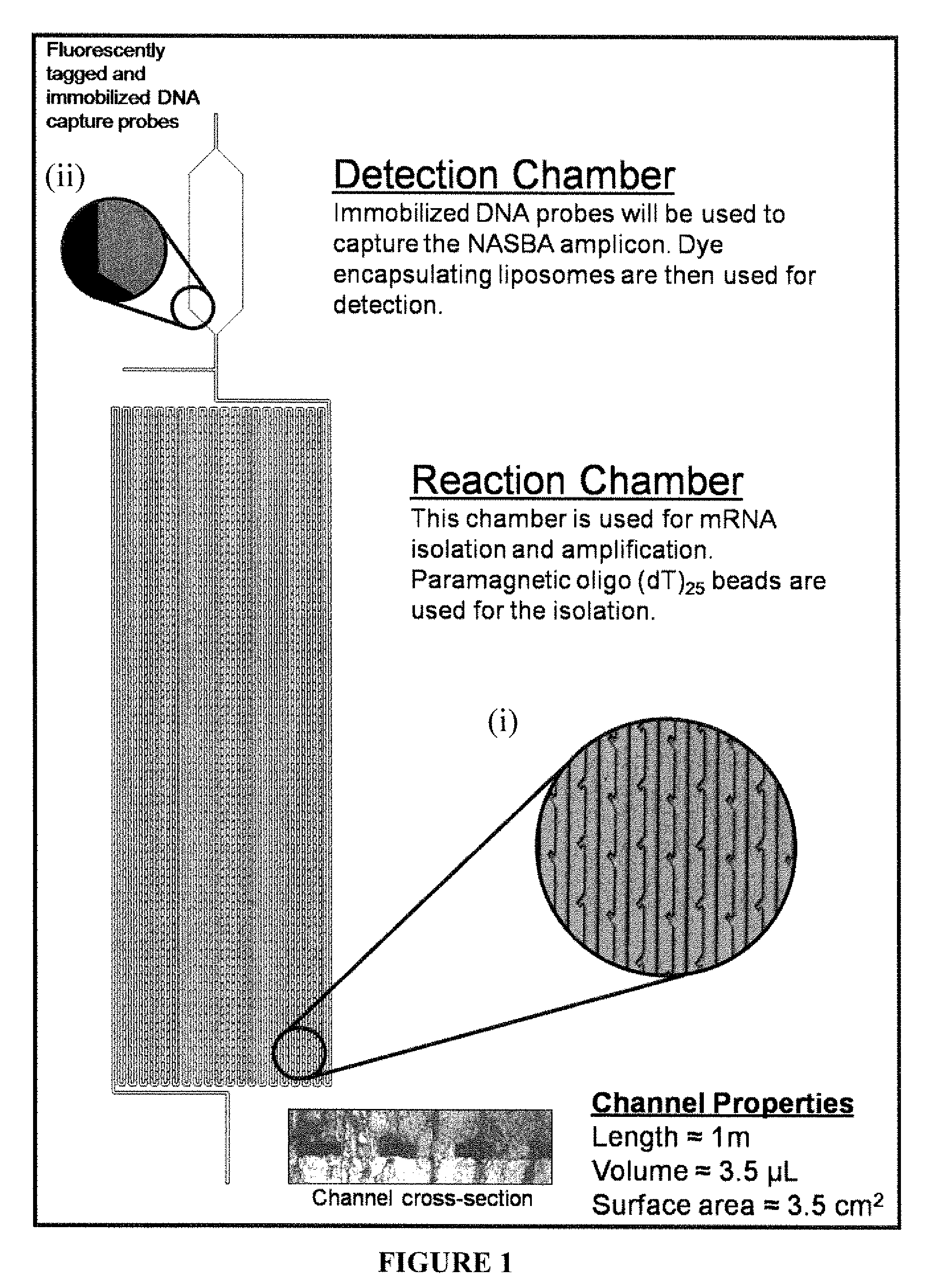

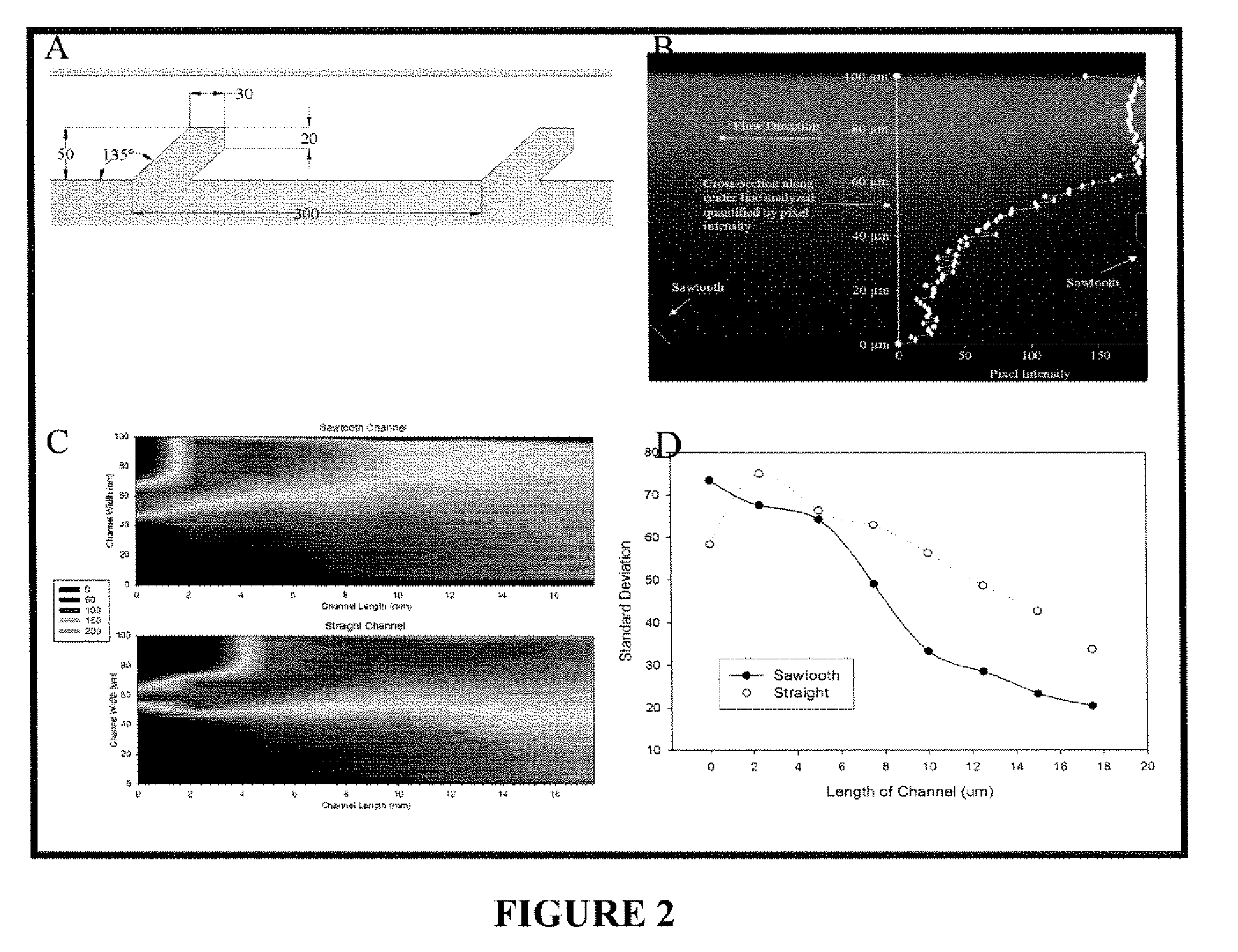

Microchannel detection device and use thereof

InactiveUS20100227323A1Shorten the timeReduce laborBioreactor/fermenter combinationsBiological substance pretreatmentsAnalyteTest sample

The present invention relates to a device and methods for detecting or quantifying an analyte in a test sample. The device includes a substrate defining one or more microchannels and having a reaction region in a first portion of the one or more microchannels, wherein the reaction region contains a first binding element selected to bind with a first portion of the analyte. The device also includes a detection region in fluid communication with the reaction region. The detection region includes a second binding element selected to immobilize the analyte within the detection region. Methods of detecting or quantifying an analyte in a test sample using the device of the present invention are also disclosed. A method for coating a polymer with a gold layer is also disclosed.

Owner:CORNELL RES FOUNDATION INC

Method for arranging metal palladium layer in conducting layer of printed circuit board and layered structure thereof

ActiveCN102802364ALow costReduce thicknessConductive pattern reinforcementMetallic pattern materialsGold layerPrinted circuit board

The invention relates to a method for arranging a metal palladium layer in a conducting layer of a printed circuit board and a layered structure thereof. The method comprises the following steps of: firstly, coating copper on an insulating substrate, and baking the substrate; then, sequentially carrying out the processes of drilling, copper precipitation, line manufacturing and insulating layer solder resisting so as to obtain a half-finished product of a board body; and finally, sequentially carrying out the processes of nickel precipitation, palladium precipitation and gold precipitation to the line part of the half-finished product of the board body. In the process of plating soft gold on the printed circuit board, a metal palladium layer is arranged between a nickel layer and a gold layer, so that the thickness of the gold layer can be greatly reduced so as to achieve the effect of lowering the material cost.

Owner:深圳和美精艺半导体科技股份有限公司

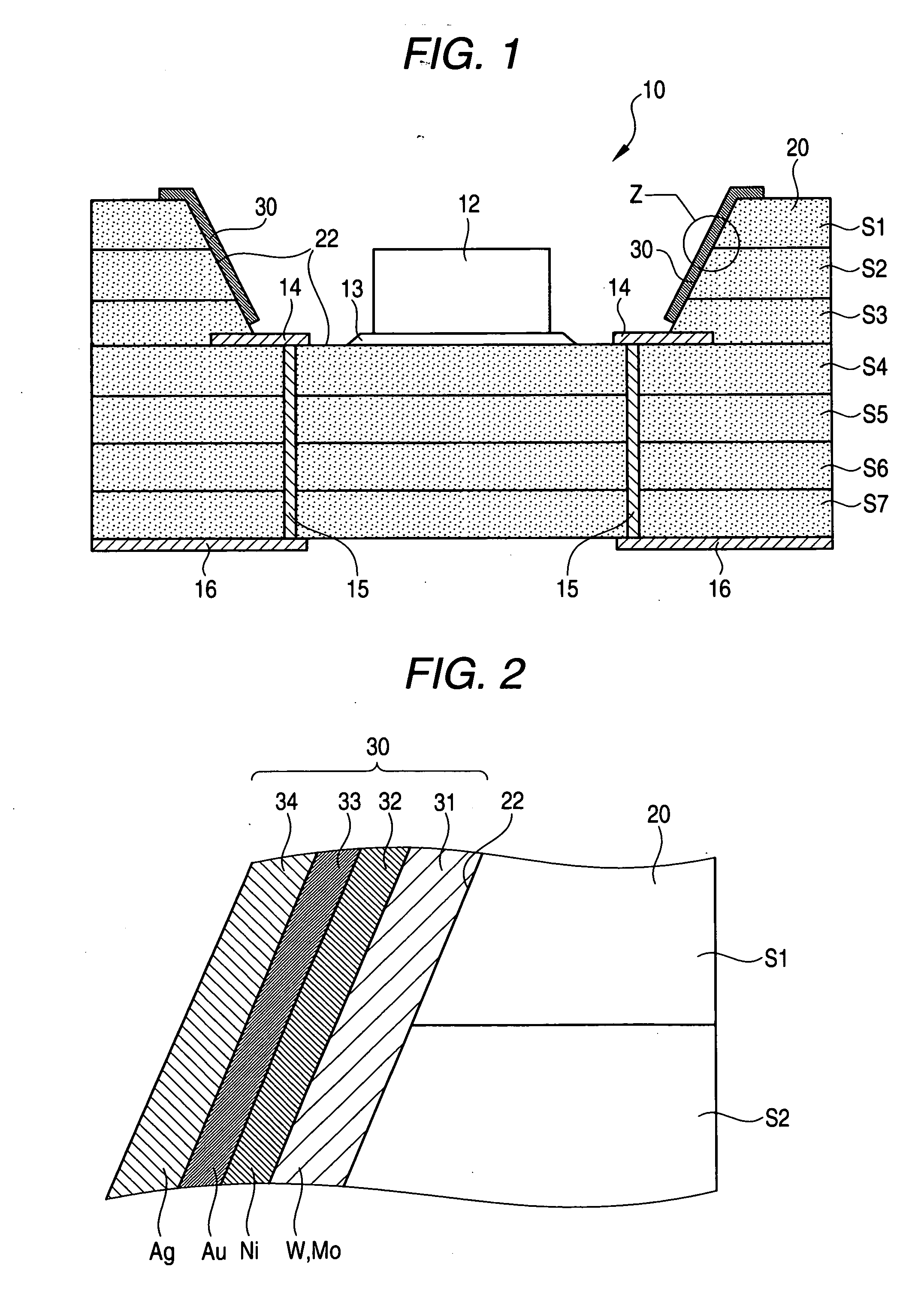

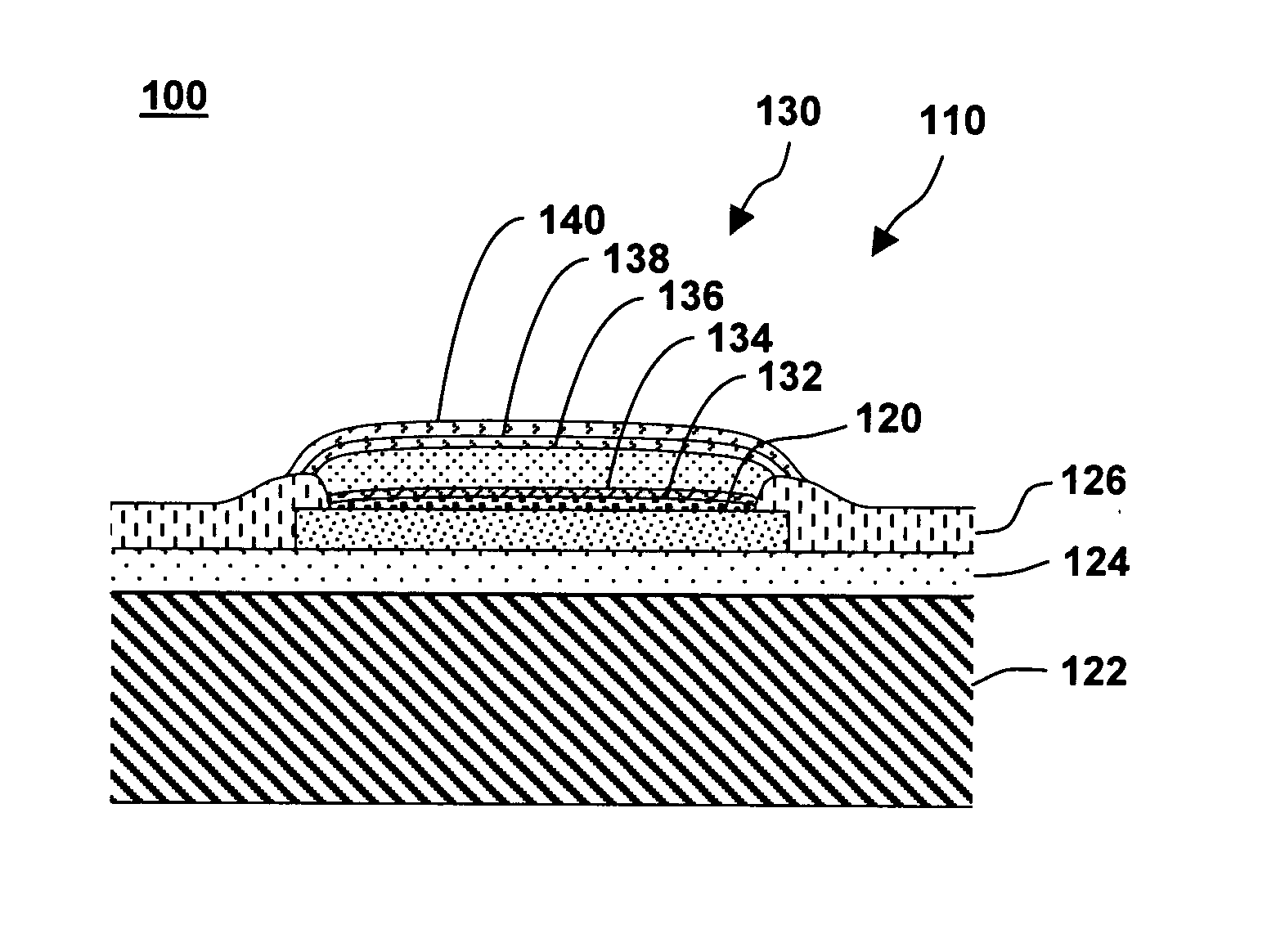

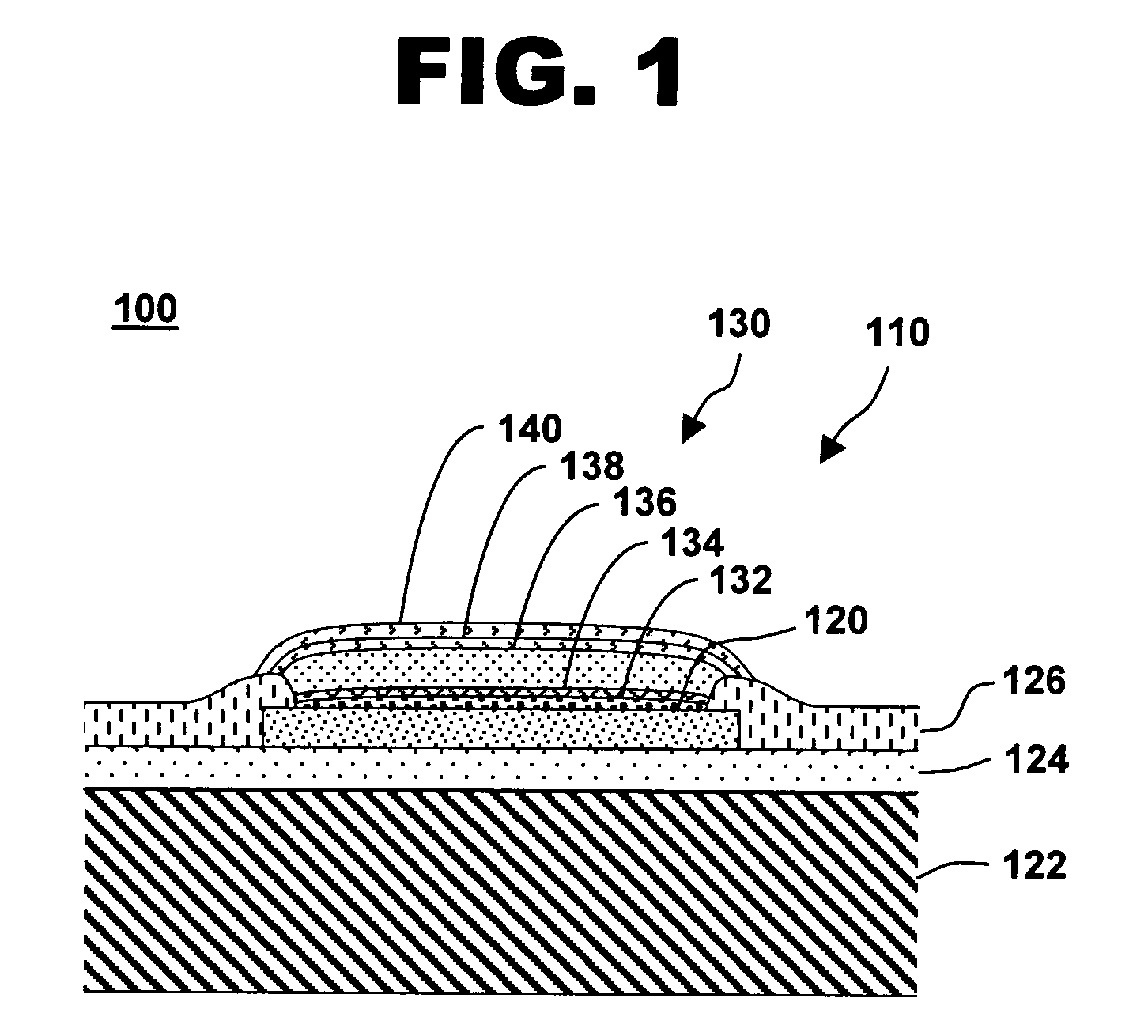

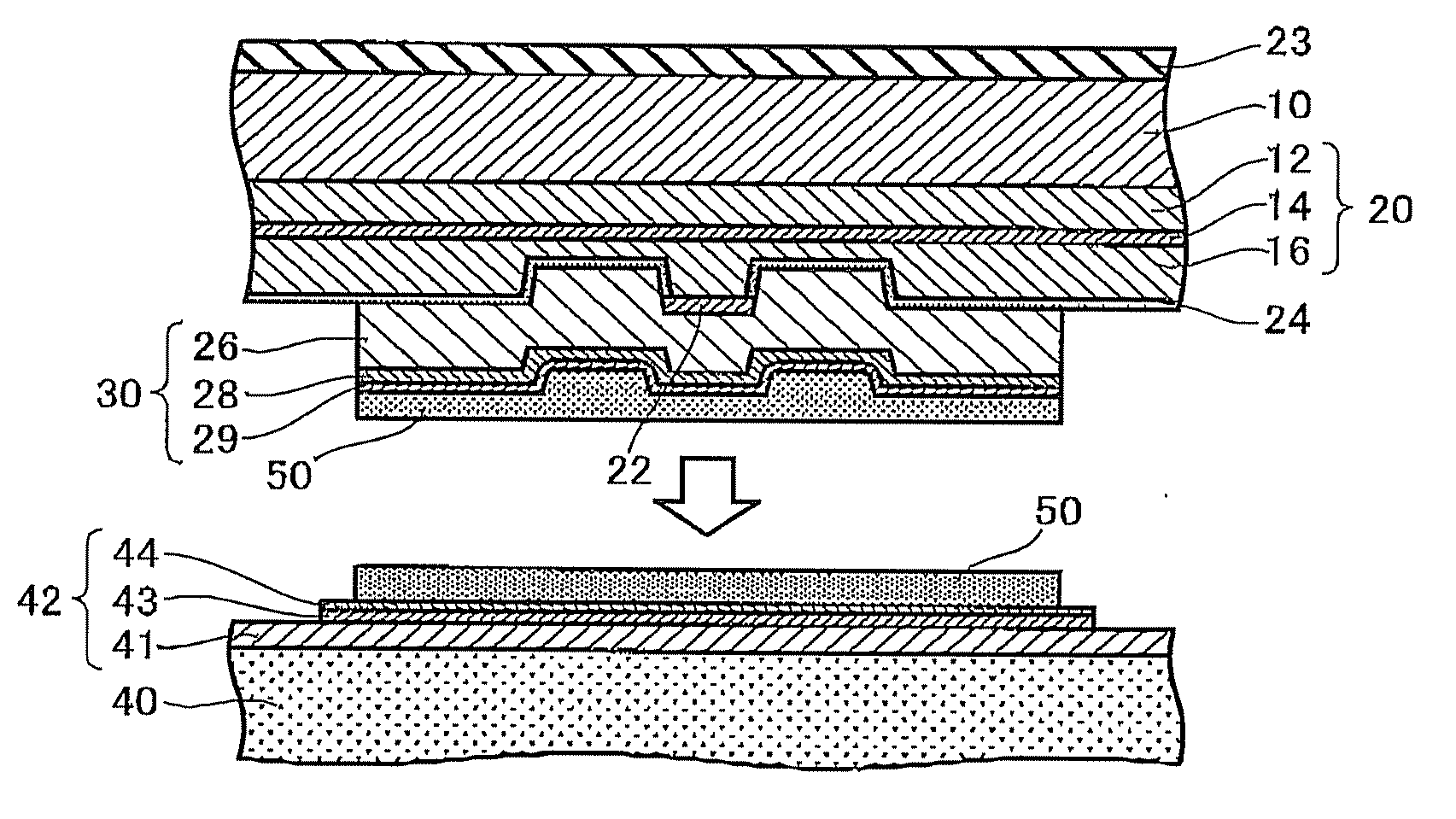

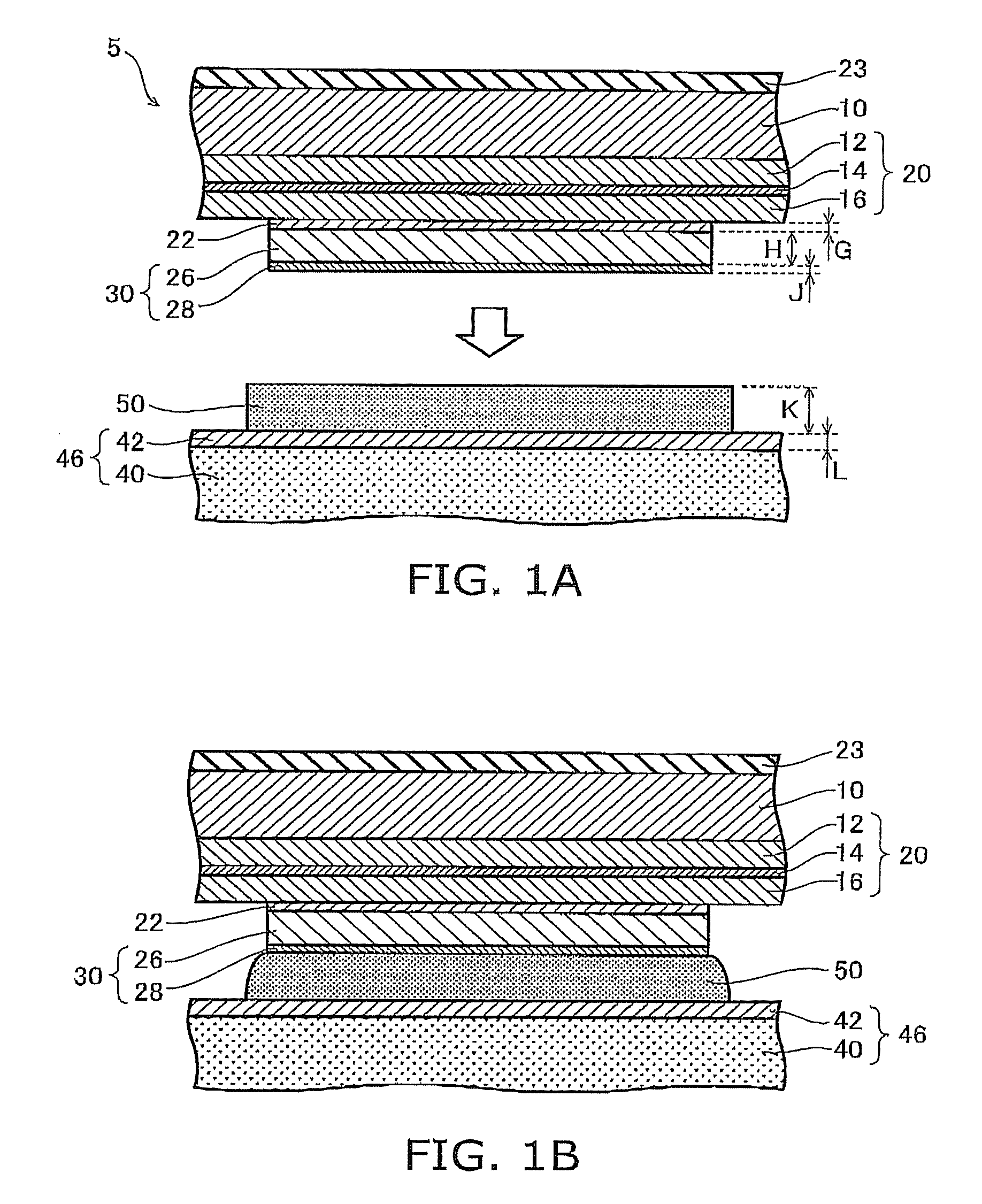

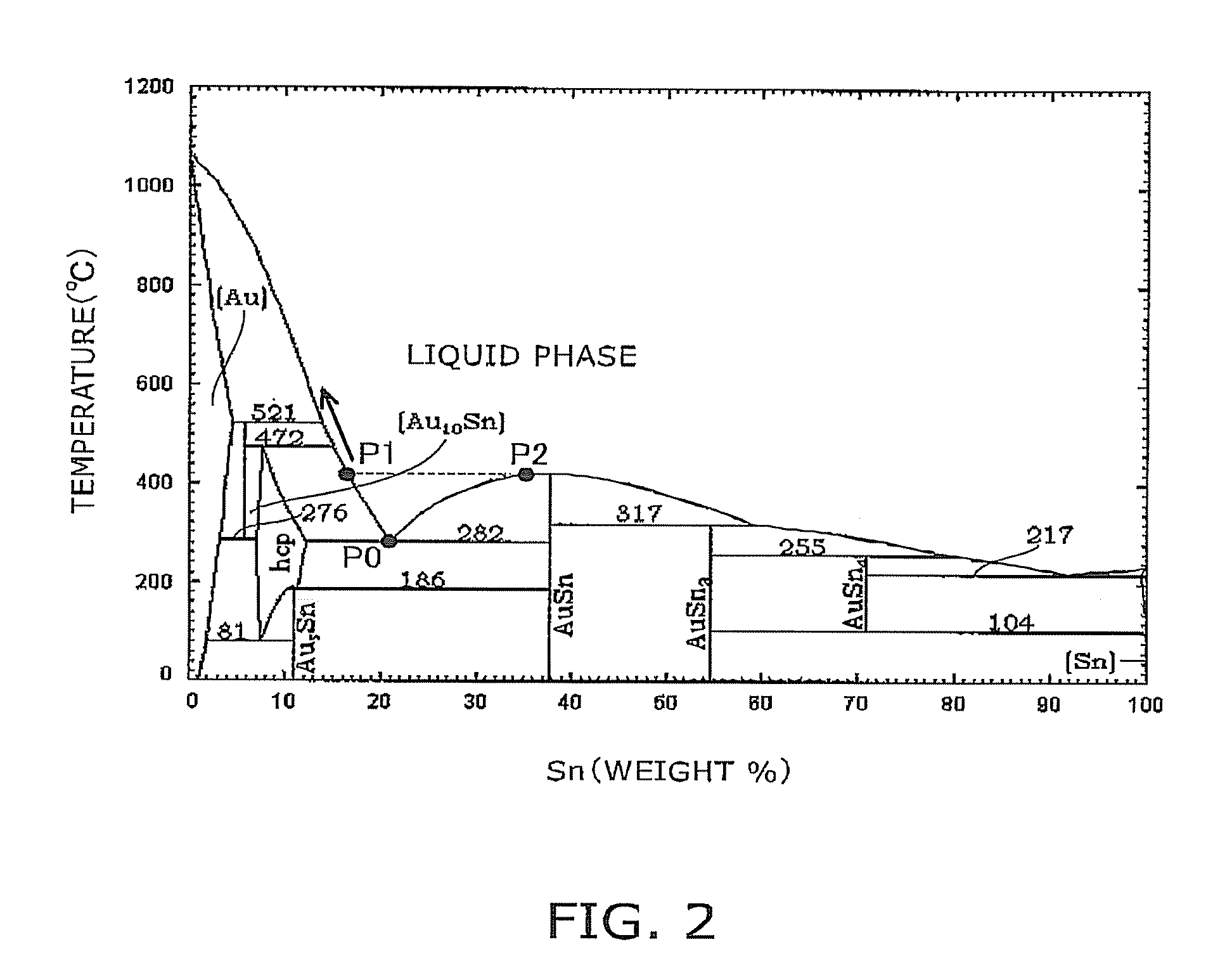

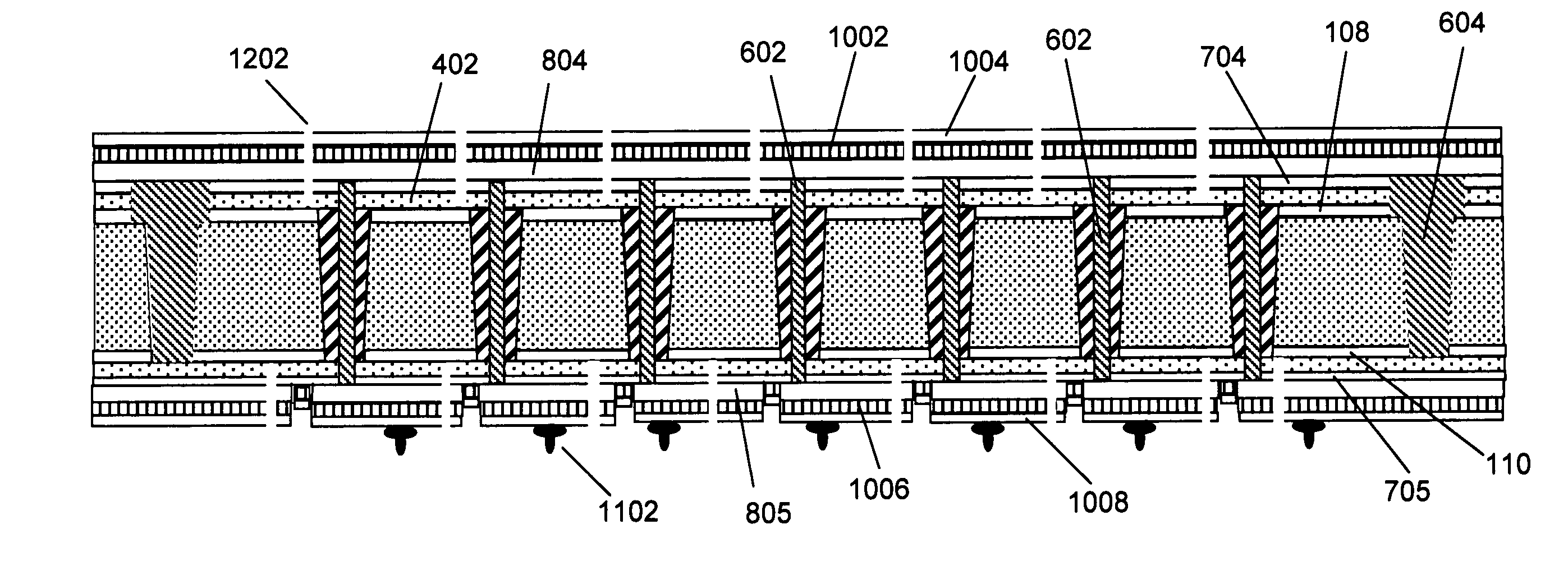

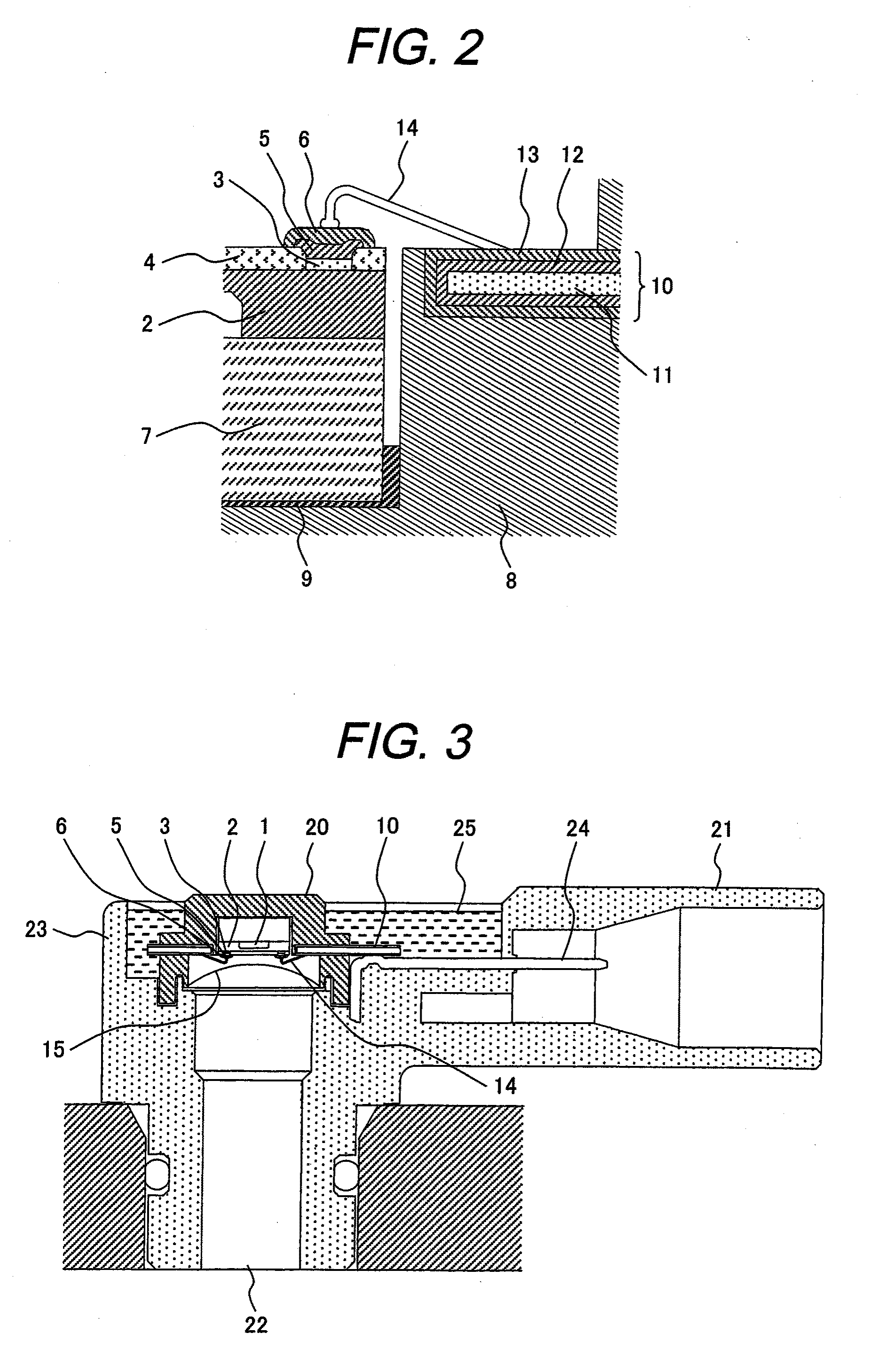

Light emitting apparatus and method for manufacturing same

A light emitting apparatus includes: a light emitting element including a laminated body, an electrode provided on the laminated body, and a pad electrode provided on the electrode, the laminated body including a semiconductor light emitting layer; a mounting member having a metal bonding layer; and an alloy solder containing gold for bonding the pad electrode to the metal bonding layer. The pad electrode has at least a first gold layer provided on the electrode and being thicker than the electrode and a first metal barrier layer provided on the first gold layer, and the melting point of the alloy solder is lower than the melting point of alloys with elements constituting the first metal barrier layer and the alloy solder.

Owner:KK TOSHIBA

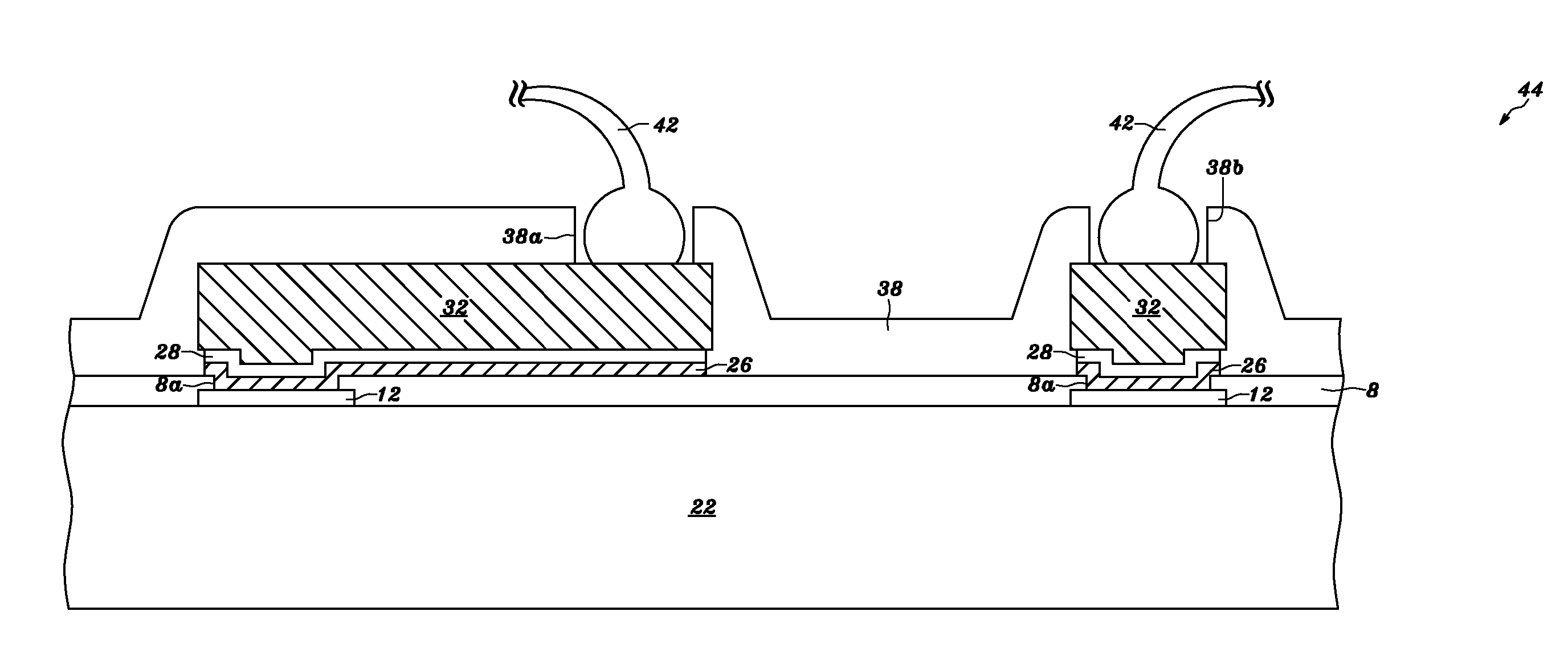

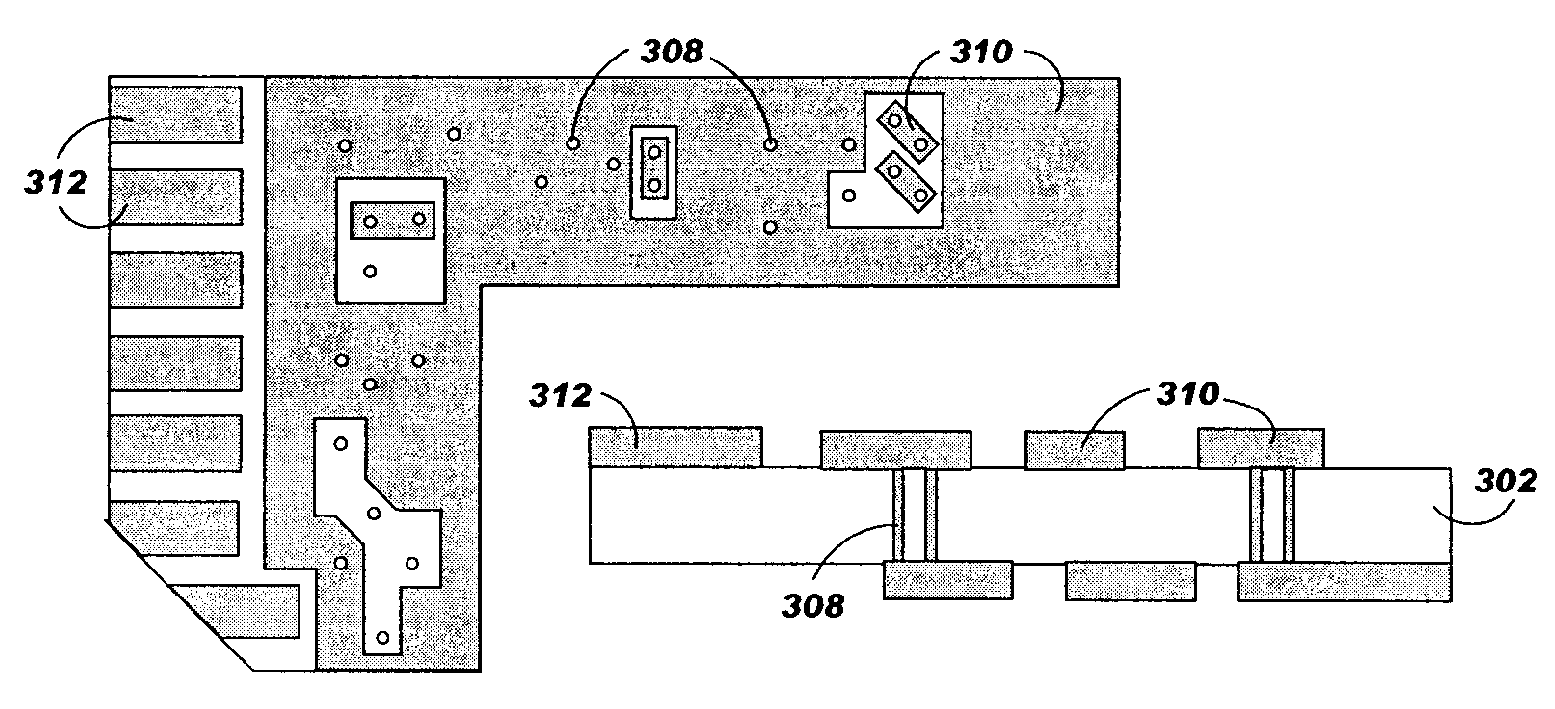

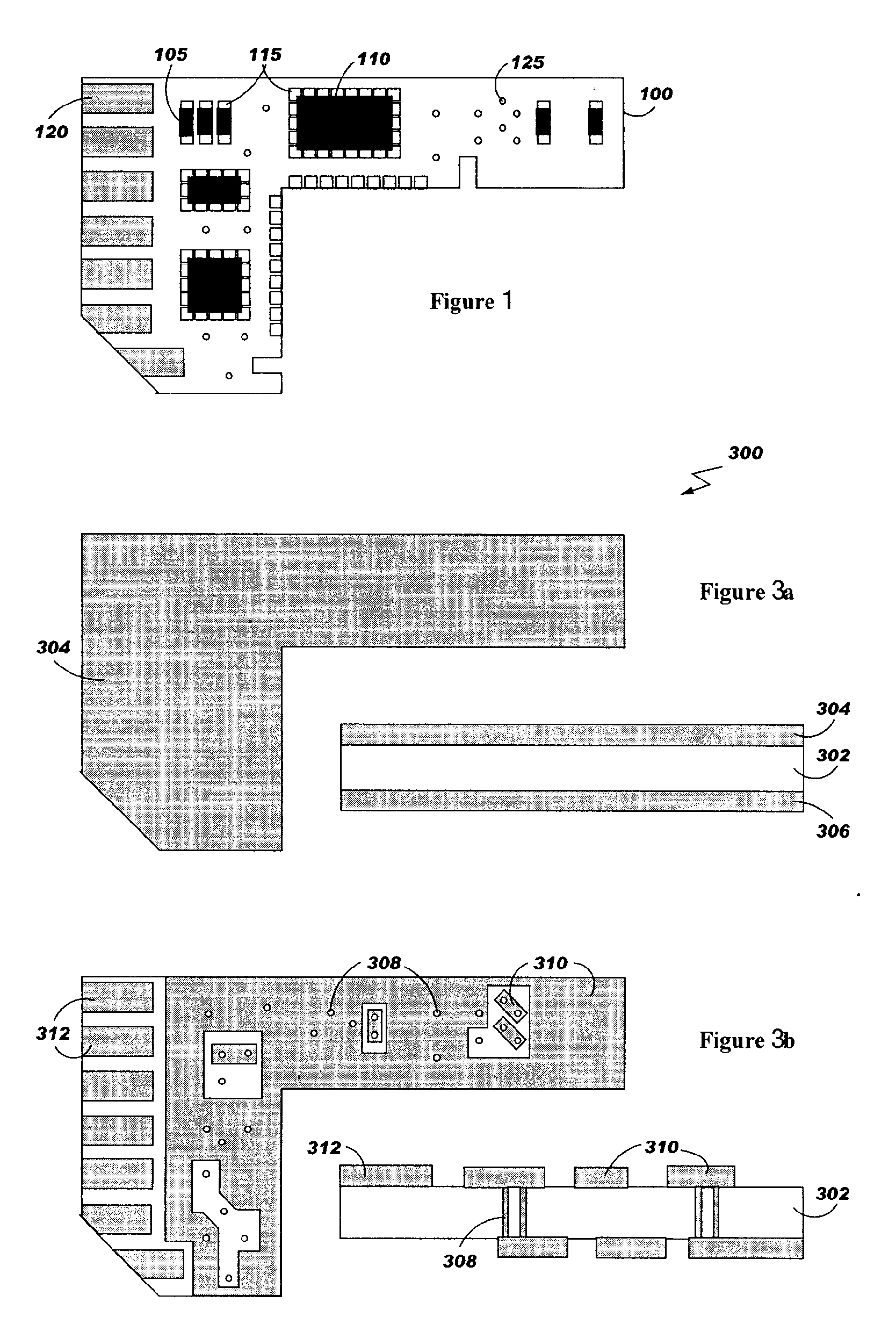

Wafer translator having a silicon core isolated from signal paths by a ground plane

ActiveUS7791174B2Printed circuit assemblingElectrical measurement instrument detailsCopper foilGold layer

Apparatus and methods are provided for wafer translators having a silicon core, an isolating conductive ground plane, and copper and subjacent resin layers disposed on the ground plane. A silicon substrate having at least one major surface coated with an electrically conductive layer is subjected to a number of printed circuit board manufacturing operations including, but not limited to, application of resin-coated copper foils; mechanical grinding of copper layers; mechanical drilling of via openings in a dielectric material; plating of copper, nickel, and gold layers; laser removal of metal; and chemical removal of metal; in order to produce a wafer translator having a silicon core. In further aspects of the present invention, alignment marks are formed and contact structures, such as stud bumps, are placed relative to a local set of alignment marks.

Owner:TRANSLARITY INC

Multilayer structure surface enhanced Raman scattering base and preparation method thereof

ActiveCN103575721ACoordination compatibilityOverall structure coordinationRaman scatteringNano structuringBiocompatibility Testing

The invention belongs to the technical field of nano-imprinting and spectra, and in particular relates to a multilayer structure surface enhanced Raman scattering base and a preparation method thereof. The surface enhanced Raman scattering base is simple in process, high in efficiency, high in enhancement factor and biocompatible. The base consists of a substrate and a periodic nano columnar structure which is positioned on the substrate, wherein the nano columnar structure is a multilayer structure; the multilayer structure consists of alternation layers and a gold layer; the alternation layers consist of silver and media; the gold layer is positioned on the topmost layer. A nano-imprinting technology is used as a core technology, and a reactive ion etching process, a metal evaporation process, a silicon dioxide plating process, a metal peeling process and the like are combined to prepare a multilayer nano structure, so that the technical problems that a silver structure base is not biocompatible and a gold structure base is low in enhancement factor are solved; on the basis of ensuring biocompatibility, the enhancement factor of the base is greatly improved, the detection is efficient and sensitive, and the base can be applied to biological detection after further treatment.

Owner:WUXI IMPRINT NANO TECH

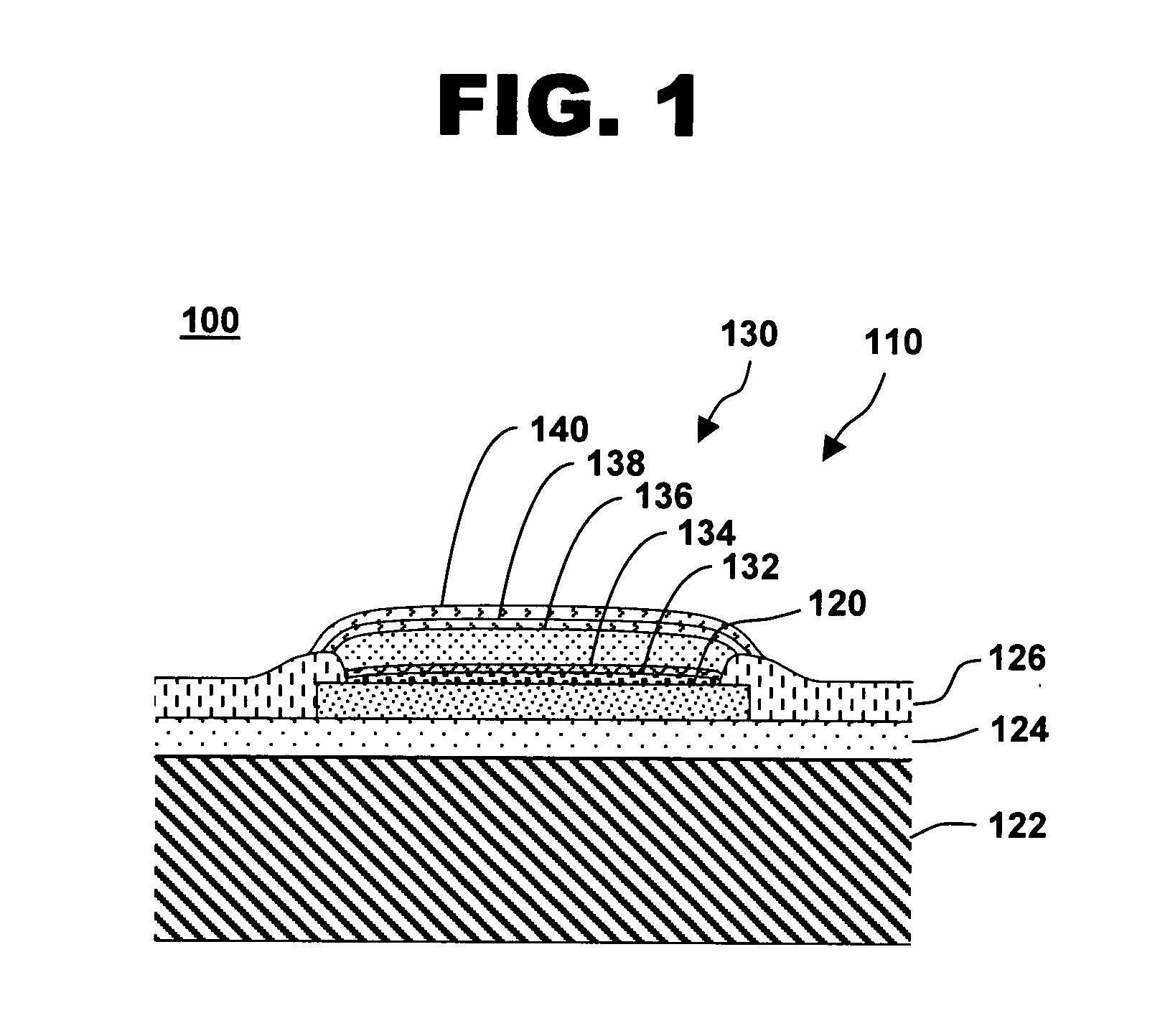

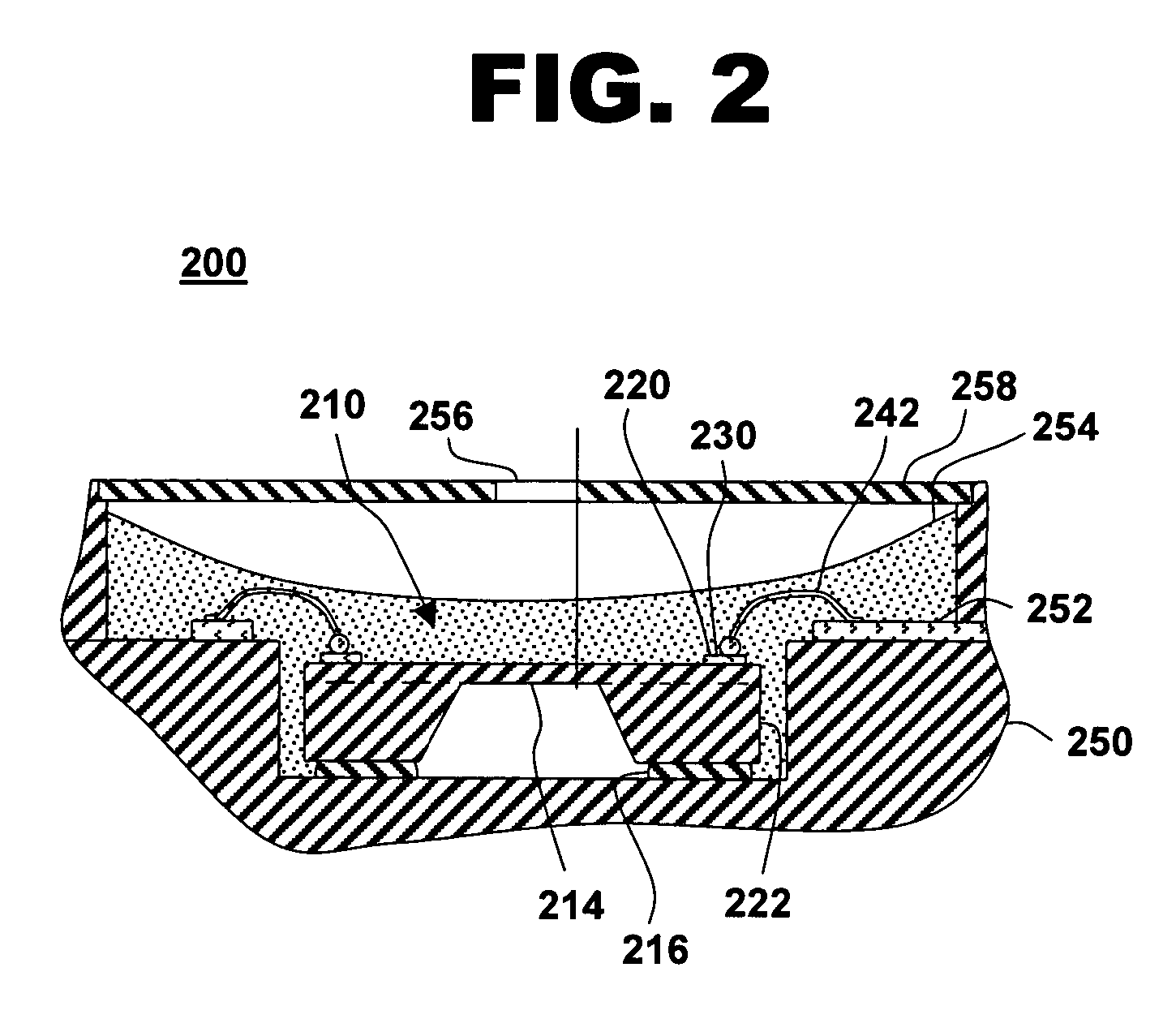

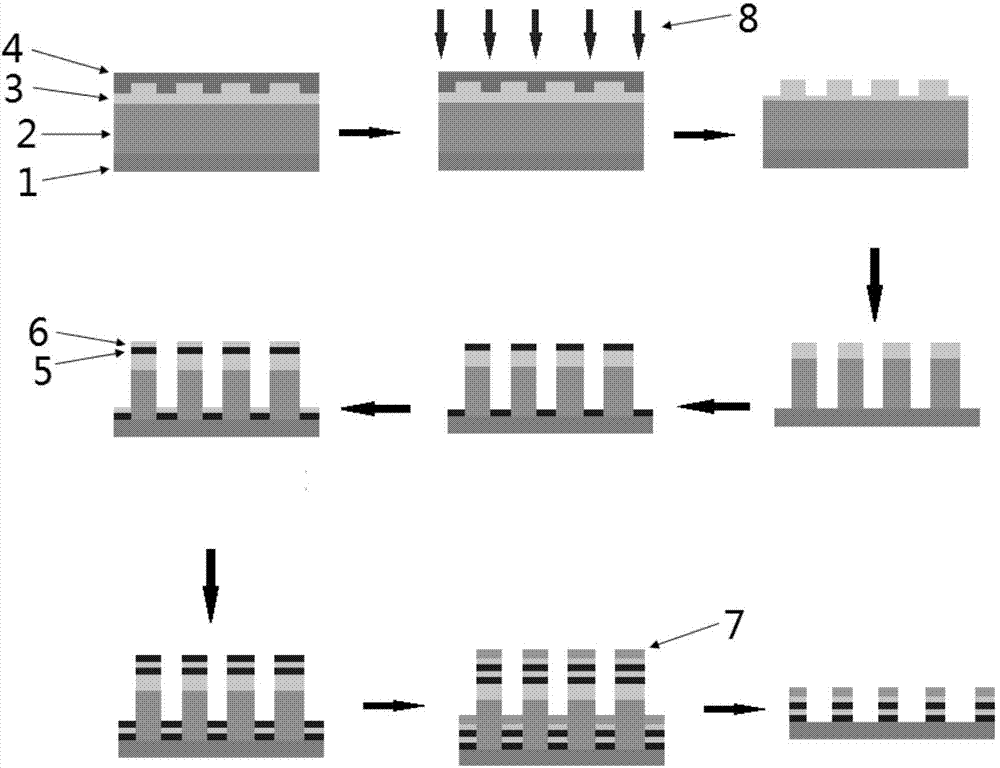

Semiconductor Pressure Sensor

ActiveUS20090218643A1Small ionization tendencyAvoid corrosionAcceleration measurement using interia forcesFluid pressure measurement by electric/magnetic elementsGold layerTitanium

An object of the present invention is to solve problems in that aluminum electrodes, aluminum wires, and I / O terminals are corroded by corrosive gasses when a pressure of a pressure medium containing corrosive matters such as exhaust gas is measured with a semiconductor sensor; and improve not only the corrosion resistance of the sensor chip but also the corrosion resistance of the portion particularly functioning as the pressure receiver.Each of the aluminum electrodes that is likely to be corroded portions is prevented from being corroded by forming a titanium-tungsten layer and gold layer on the aluminum electrode. The connecting wires are prevented from being corroded by corrosive matters by using gold wires. The I / O terminals are also prevented from being corroded by applying gold plating.

Owner:FUJI ELECTRIC CO LTD

Process for growing Ge nanoline by aluminium oxide template

InactiveCN1391237AControllable diameterEasy to control the lengthSemiconductor/solid-state device manufacturingInorganic material magnetismNanowireGas phase

Owner:ZHEJIANG UNIV

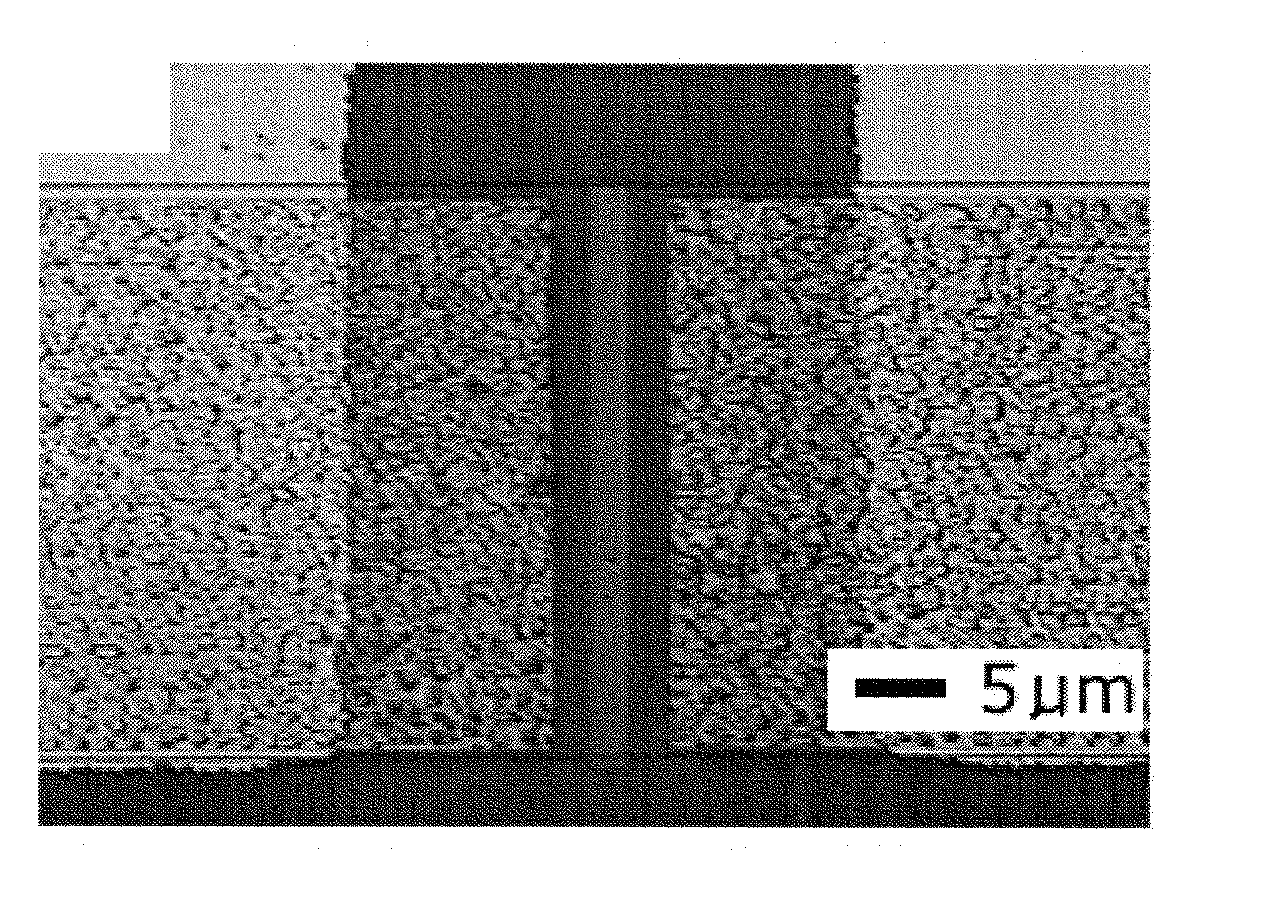

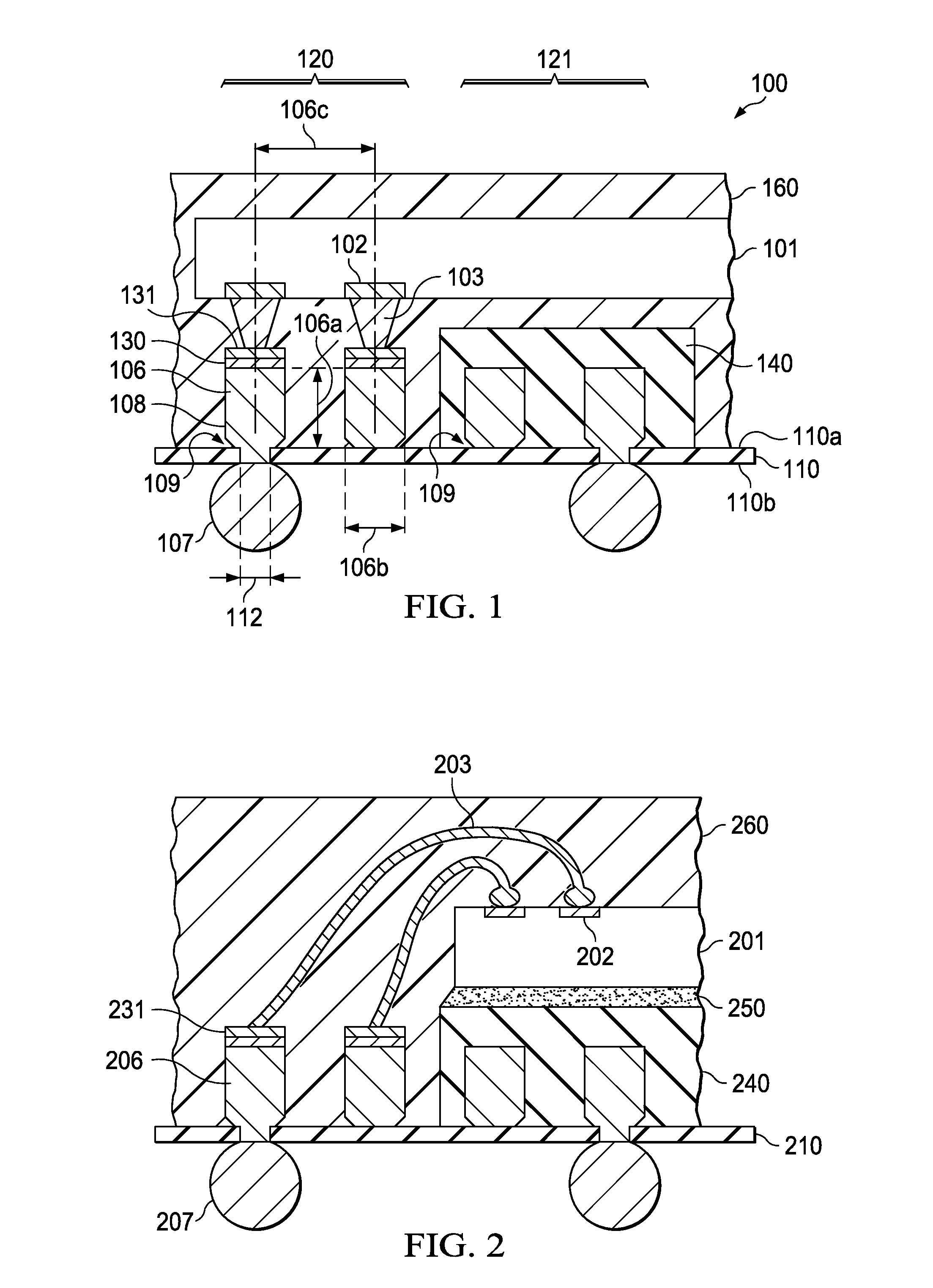

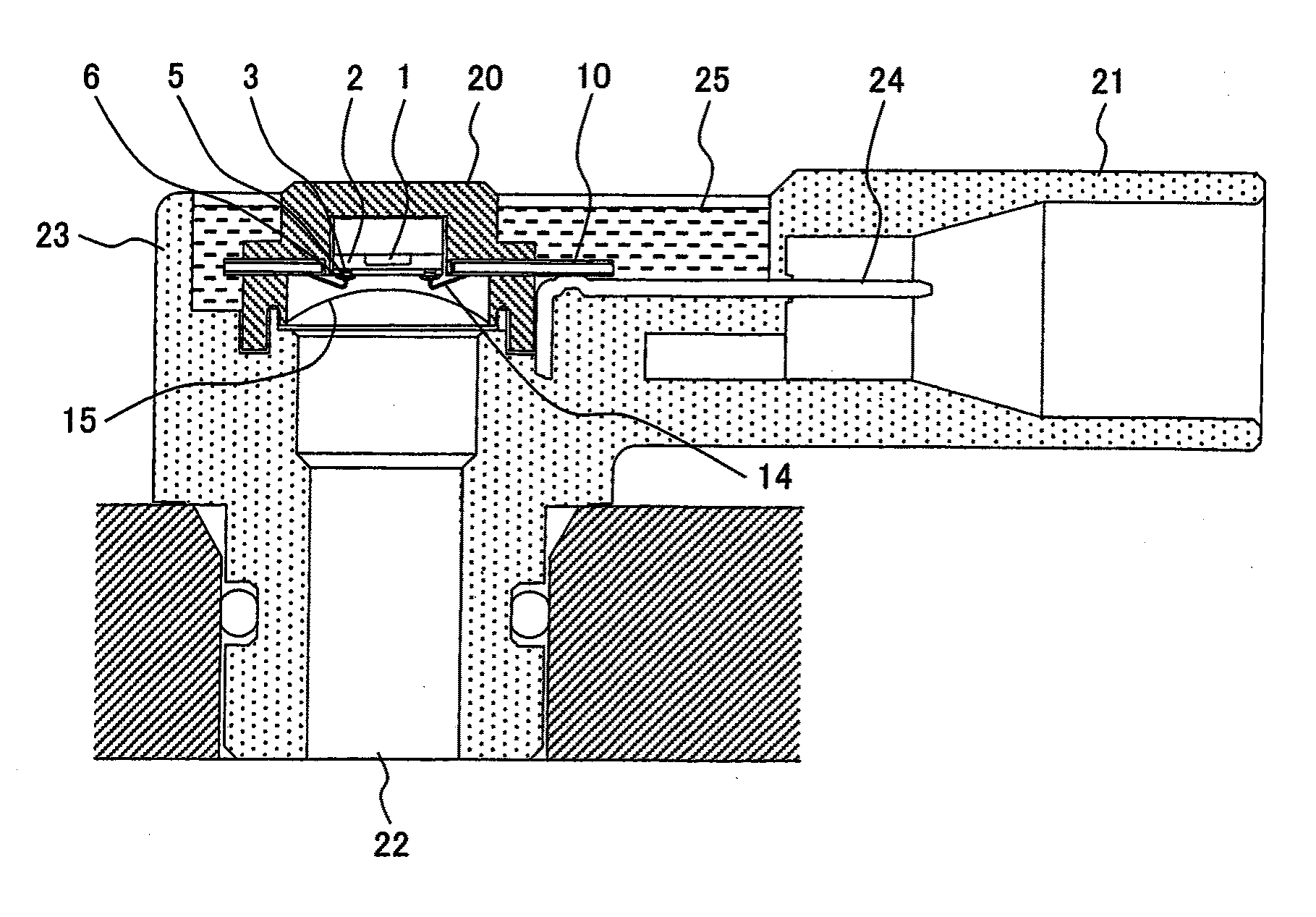

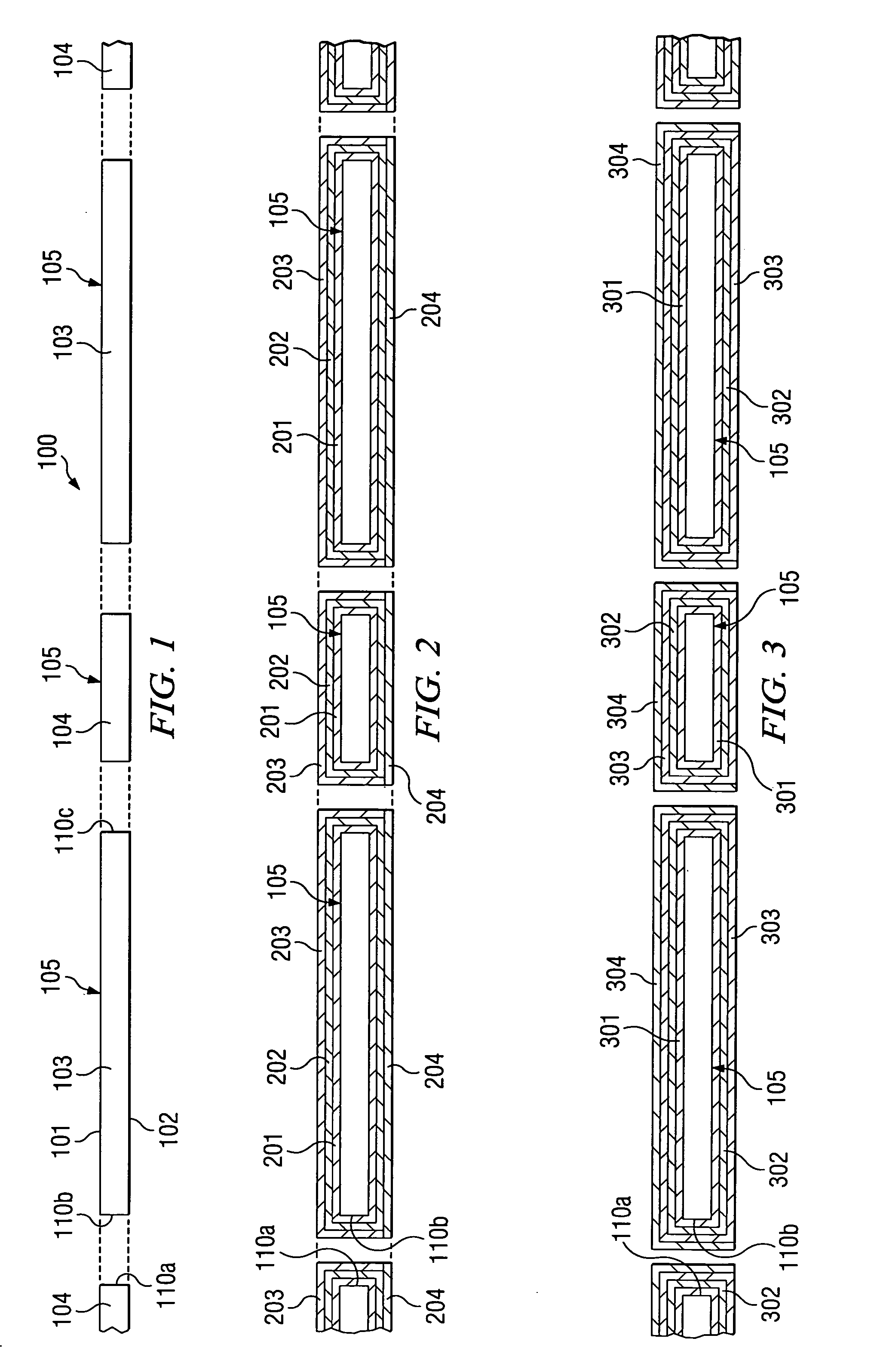

Semiconductor package having improved adhesion and solderability

InactiveUS20060125062A1Down-bonding capability is enhancedQuality improvementSemiconductor/solid-state device detailsSolid-state devicesSolderabilitySemiconductor package

A leadframe with a base metal structure (for example, copper) and first and second surfaces. A first metal layer, which is adhesive to polymeric materials such as molding compounds, is adherent to the first leadframe surface. The second leadframe surface is covered by a second metal layer for affinity to reflow metals such as tin alloy; this second metal layer has a different composition from the first metal layer. One example of the first surface is a nickel layer (201) in contact with the base metal (105), a palladium layer (202) in contact with the nickel layer, and an outermost tin layer (203) in contact with the palladium. Another example is an oxidized surface of the base metal. The second metal layer, on the second leadframe surface, comprises a nickel layer (201) in contact with the base metal (105), a palladium layer (202) in contact with the nickel layer, and an outermost gold layer (204) in contact with the palladium layer.

Owner:TEXAS INSTR INC

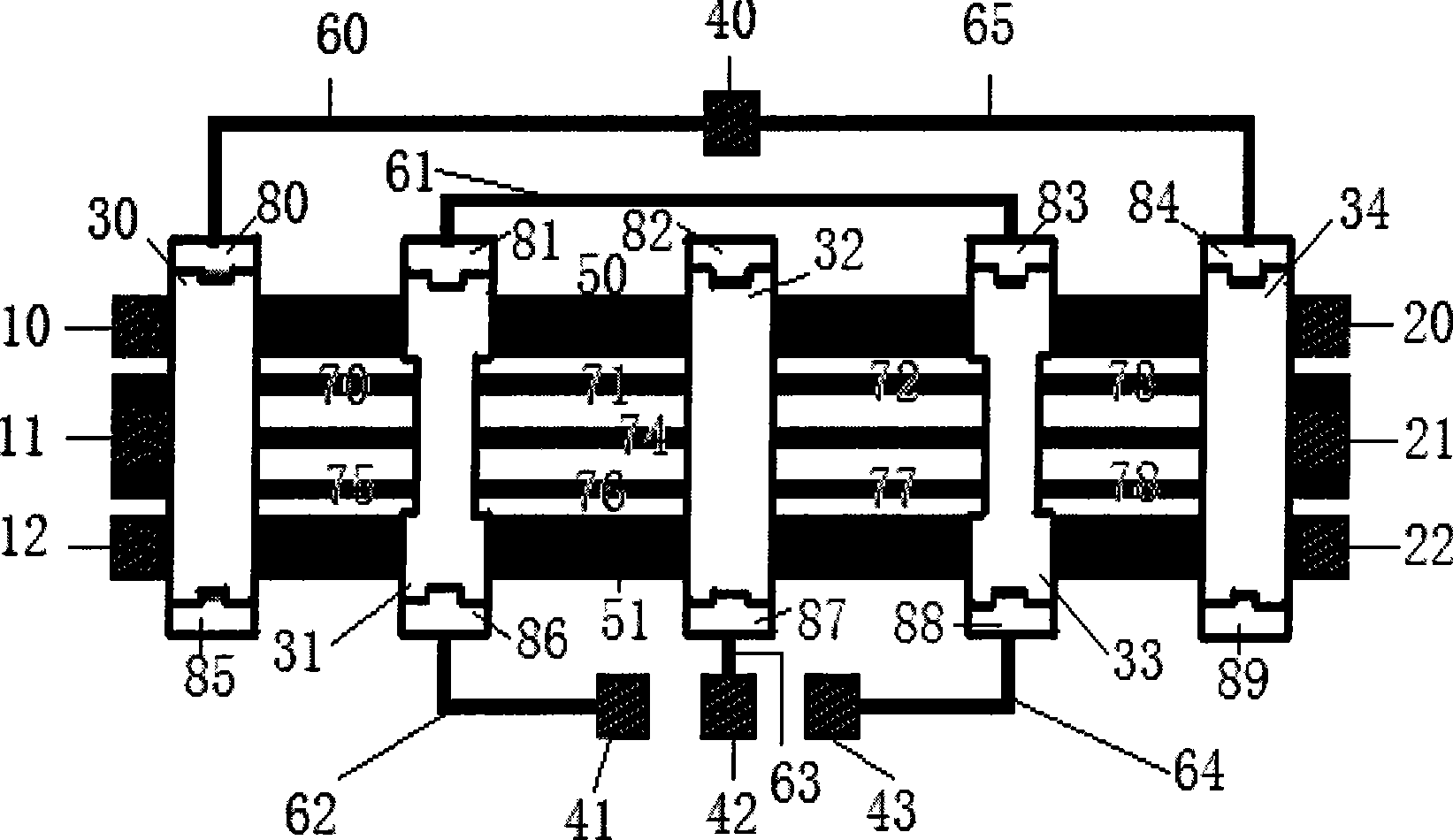

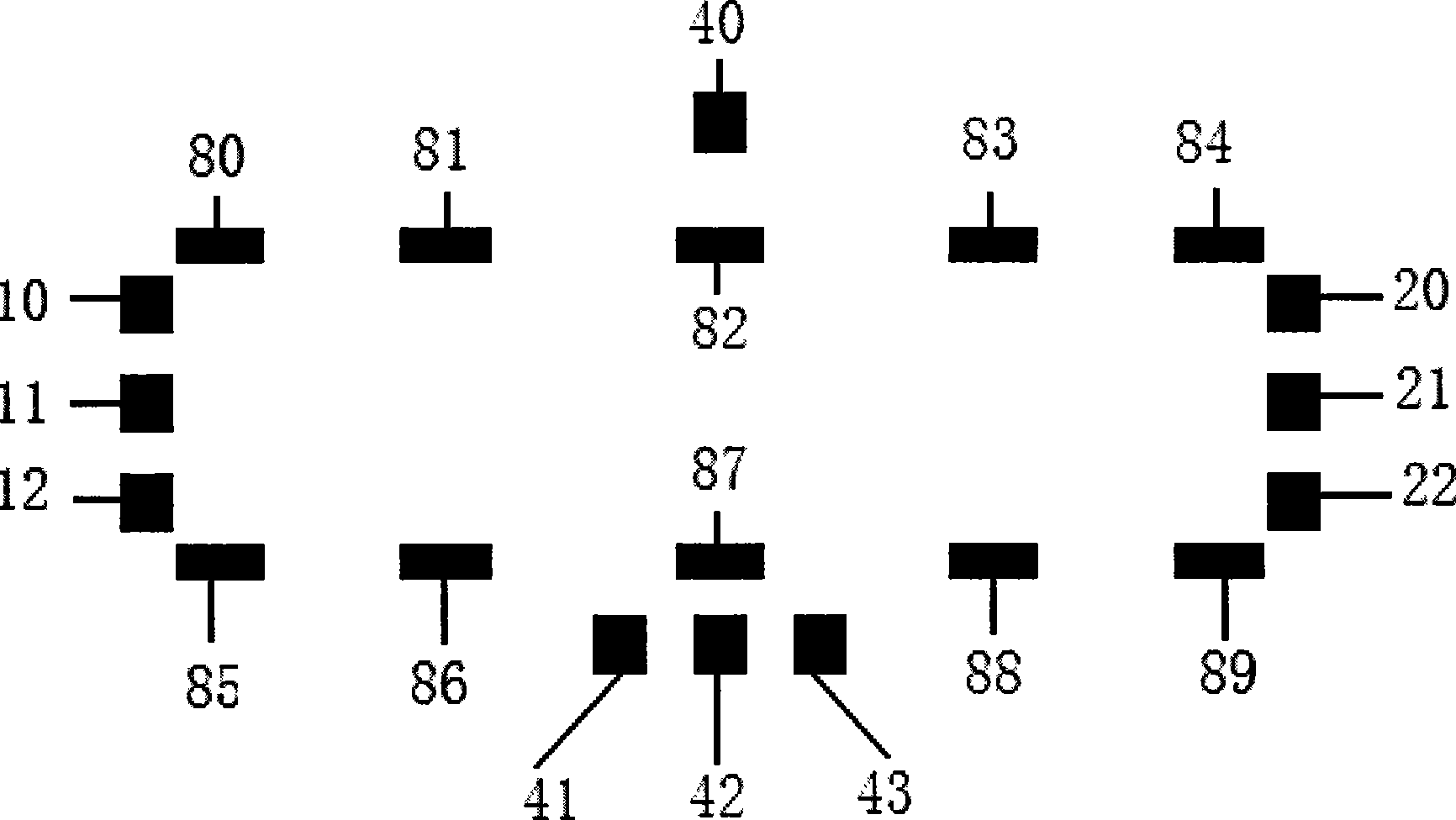

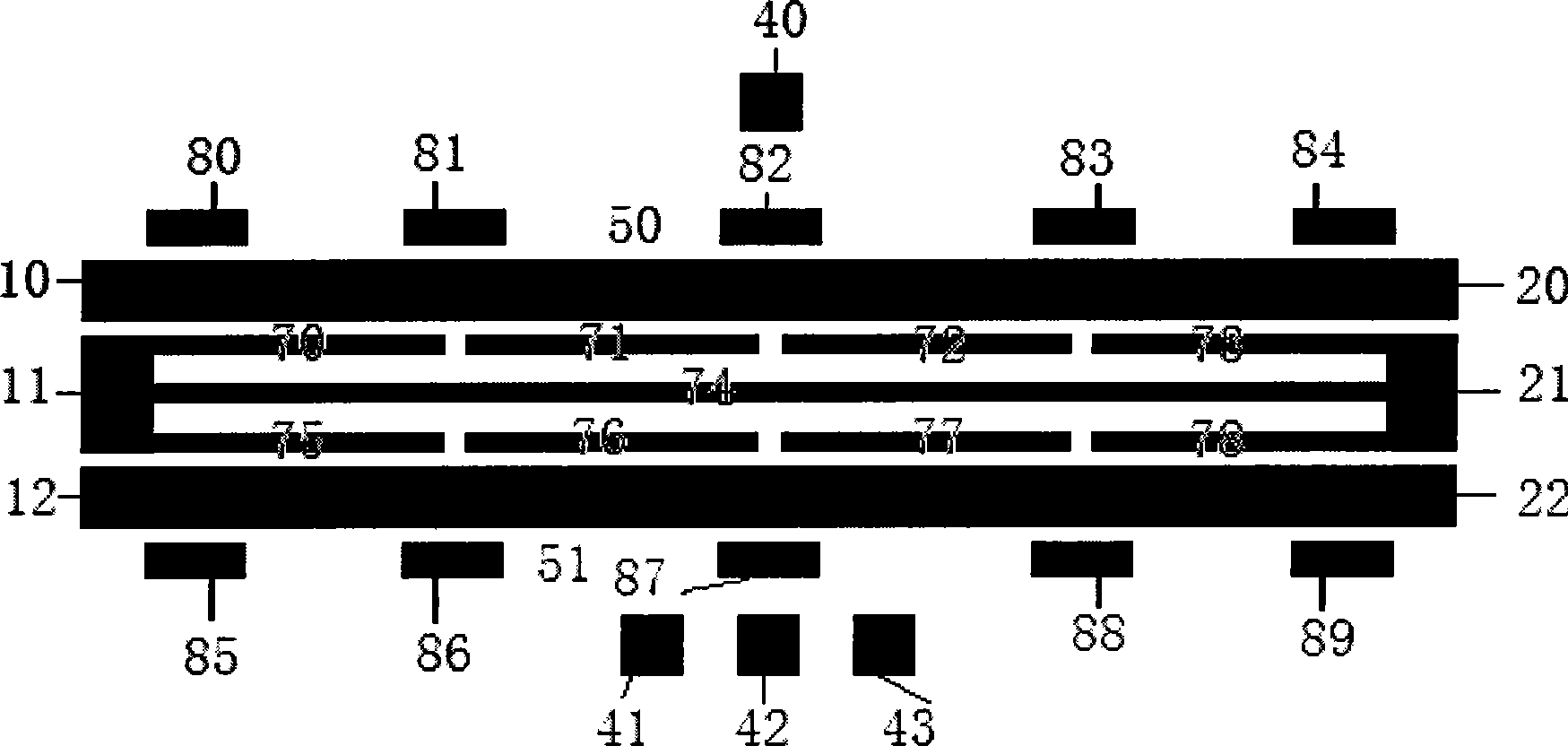

Reconfigurable microwave low-pass filter containing MEMS switch and its manufacturing method

InactiveCN101431172AReduce power consumptionCompact structureTelevision system detailsImpedence networksHigh resistanceLow-pass filter

The invention relates to a reconfigurable microwave low-pass filter containing an MEMS switch and the preparation thereof. The filter is an integrated circuit which is produced on a substrate of a high-resistance silicon wafer, an inductive reactance element is composed of a CPW ground wire and a signal wire; on one hand, the MEMS switch constitutes a capacitive reactance element, on the other hand, the MEMS switch leads the frequency of the filter to be adjustable by changing the length of the coplanar waveguide by the switching-on and off. The filter takes the high-resistance silicon wafer as the substrate, uses the process which is compatible with the IC process to evaporate a titanium layer and a gold layer by thermal oxidation, carry out the positive photoresist lithography, the electroplating and the negative photoresist lithography, corrode the gold layer and the titanium layer, remove a negative photoresist, lead a silicon nitride film to grow, remove the silicon nitride film,evaporate and deposit an aluminum-silicon alloy film, corrode the aluminum-silicon alloy film to form a bridge film, remove a sacrificial layer, and the like, for the preparation, and the filter has the advantages of compact and simple structure, small size, good isolation, low insertion loss, low power consumption of a control circuit, high working frequency, compatibility with the traditional IC process and low cost, and is applicable to mass production.

Owner:EAST CHINA NORMAL UNIVERSITY