Patents

Literature

195 results about "Under bump metallurgy" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

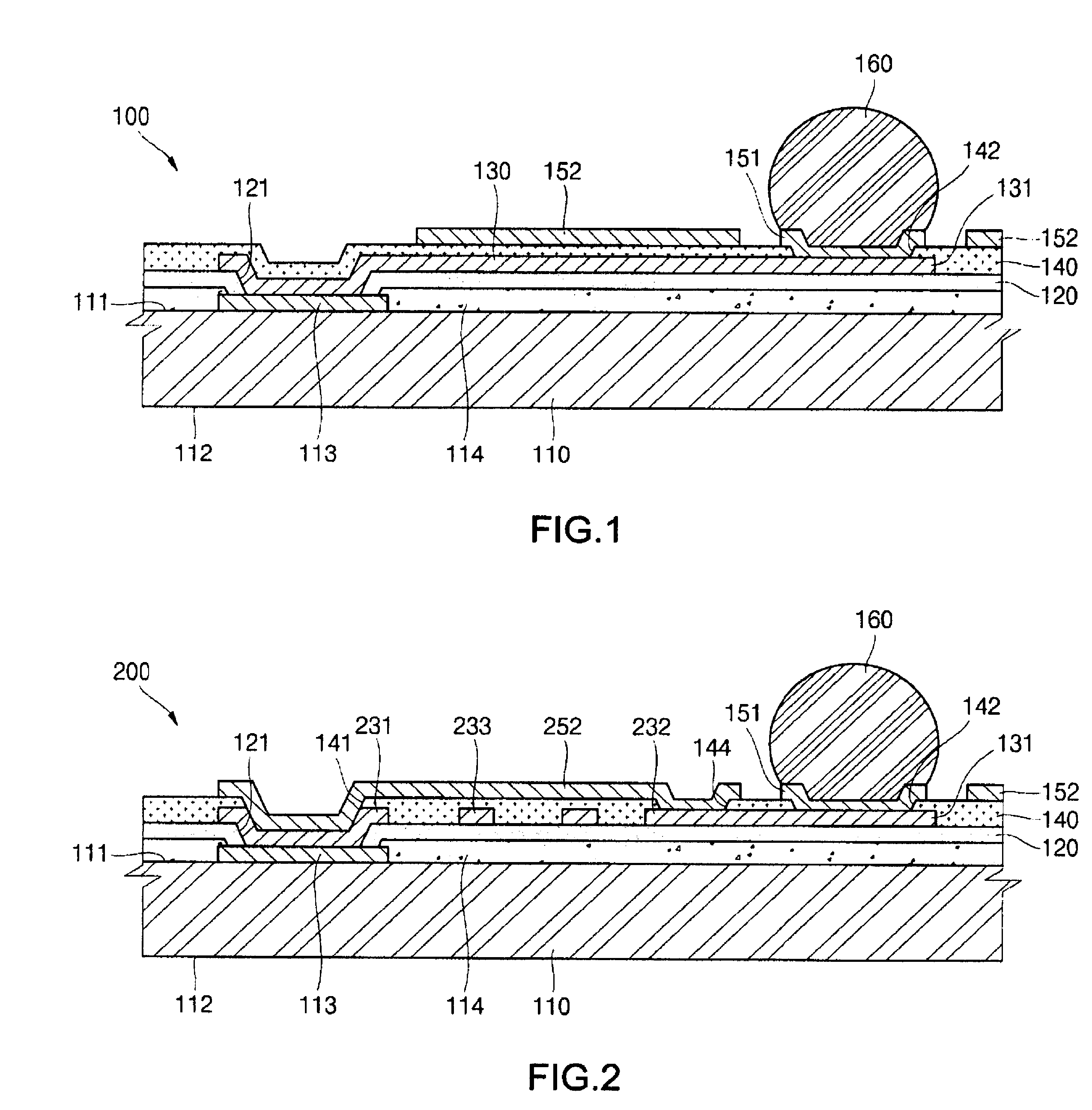

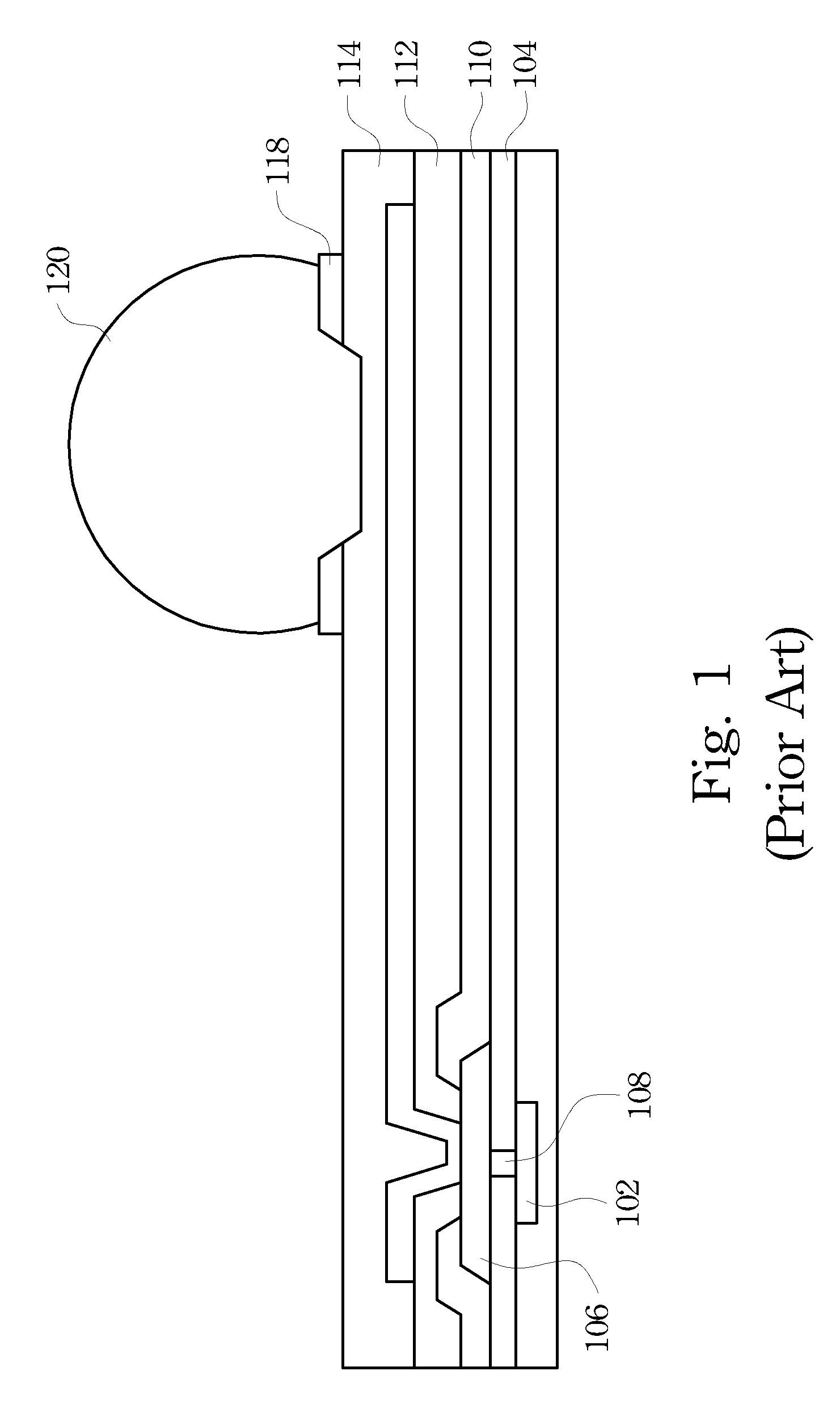

Wafer level chip size package having redistribution layers

ActiveUS7977783B1Semiconductor/solid-state device detailsSolid-state devicesRedistribution layerChip size

A wafer level chip size package (WLCSP) and a method of manufacturing the same are disclosed. Lands are formed at the ends of redistribution layers. The redistribution layers excluding the lands and a first dielectric layer are covered with a second dielectric layer. After forming a first under bump metallurgy (UBM) layer on the land, a solder ball is reflowed to the first UBM layer. A second UBM layer is widely formed on the entire second dielectric layer that is the outer circumference of the first UBM layer and is connected to the redistribution layer through a via-hole. Therefore, the second UBM layer having a large area can be used as a ground plane or a power plane. In addition, the second UBM layer can electrically connect the redistribution layers physically separated from each other. Therefore, the plurality of redistribution layers can cross each other without being electrically shorted with each other.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

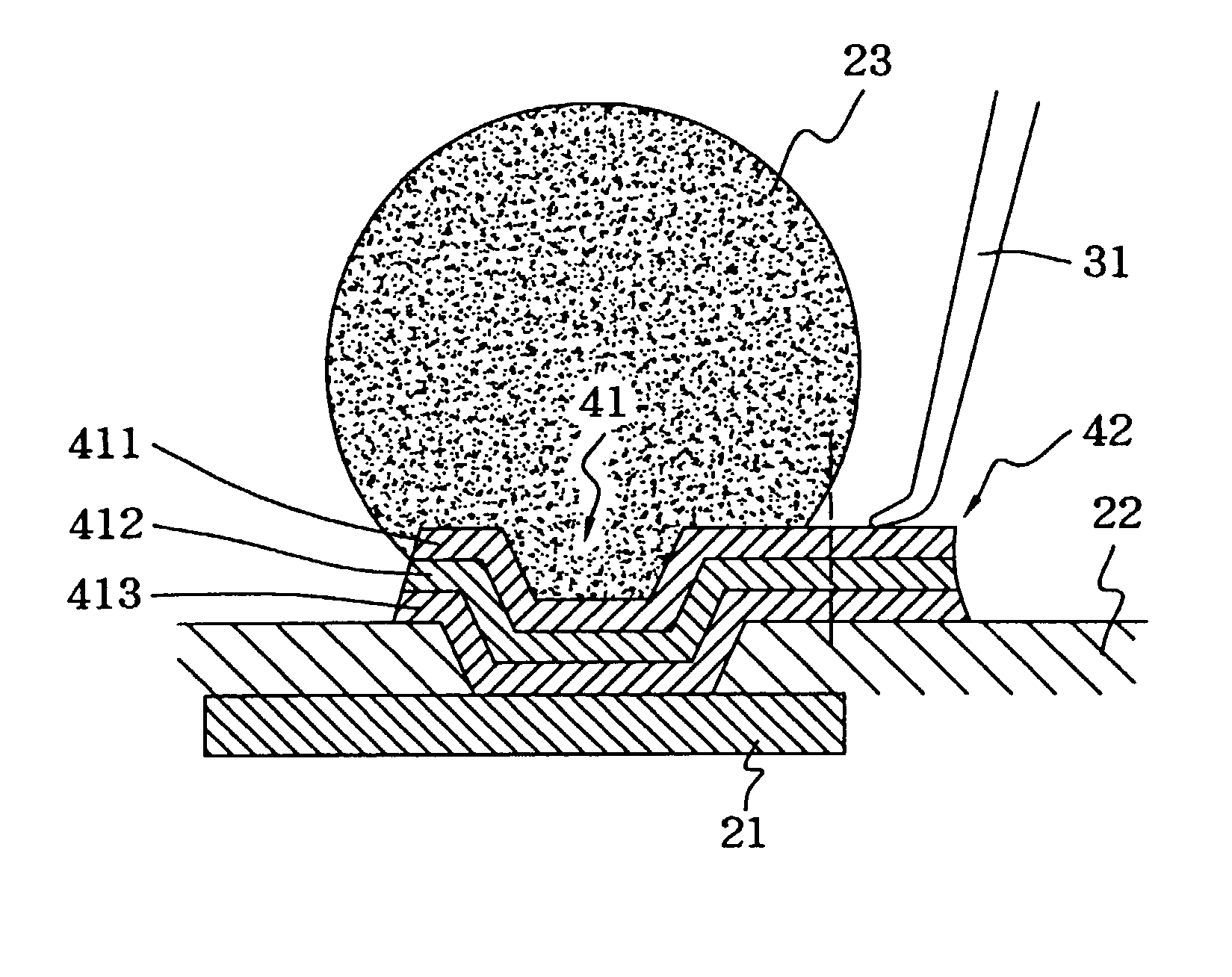

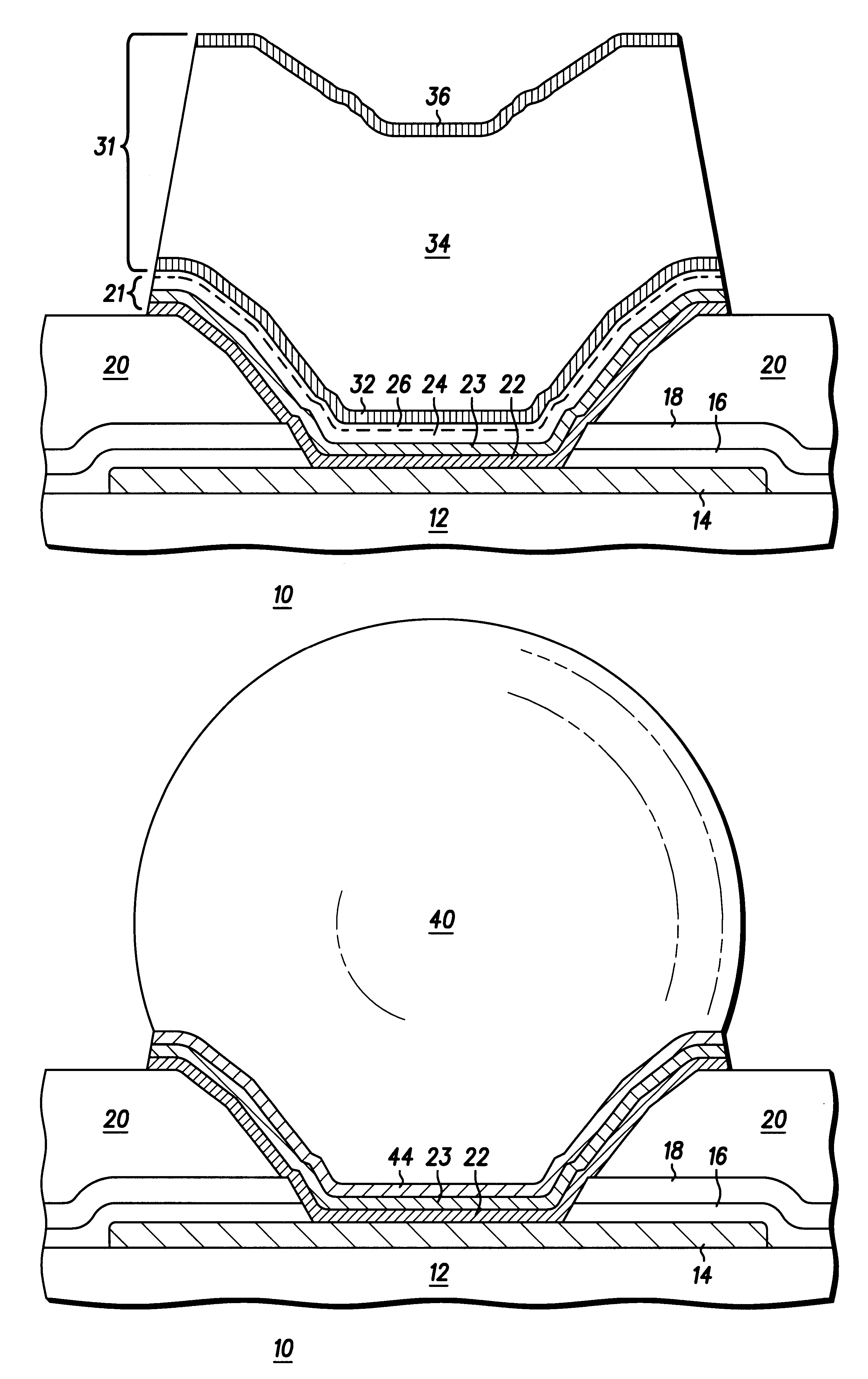

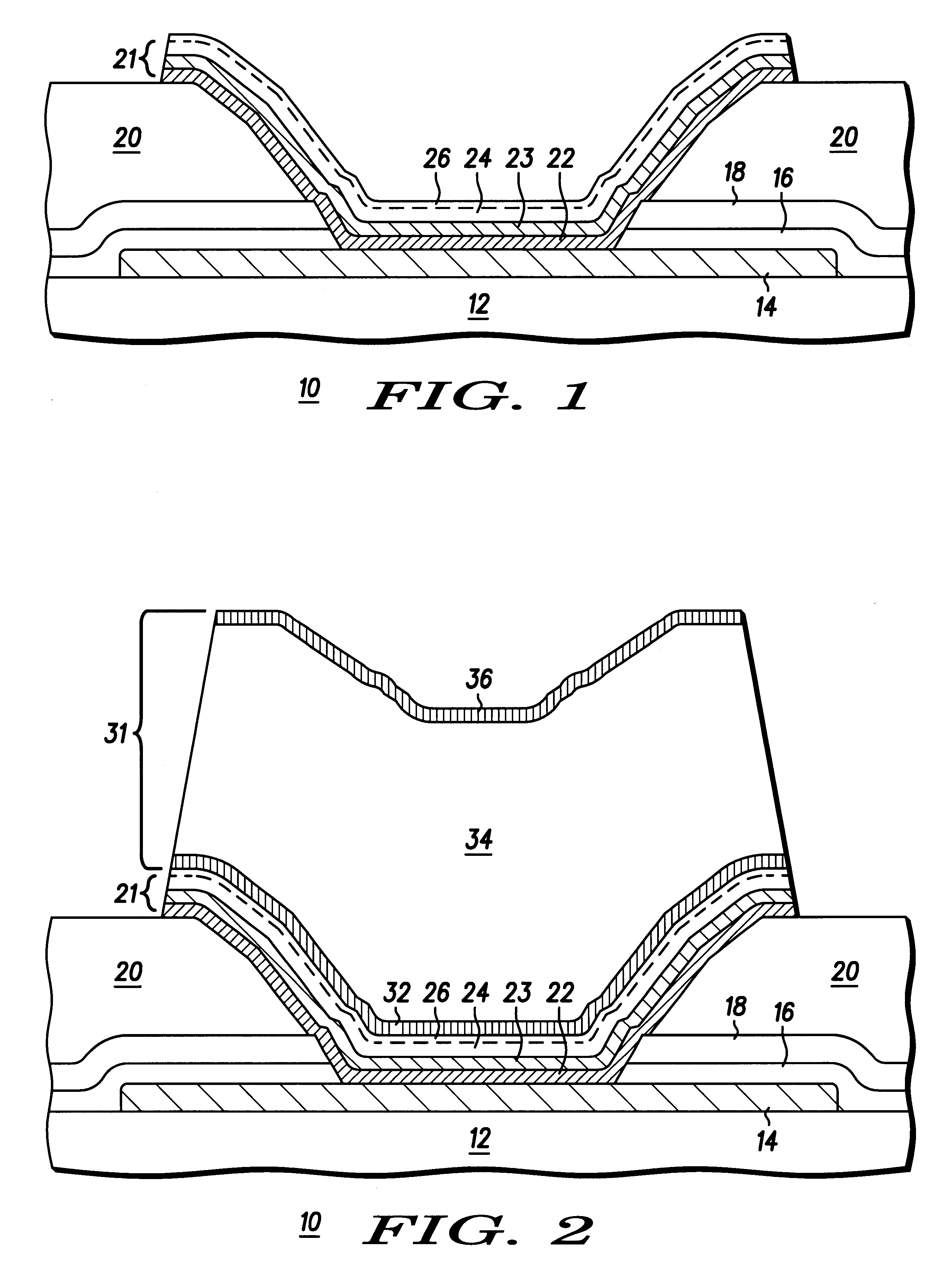

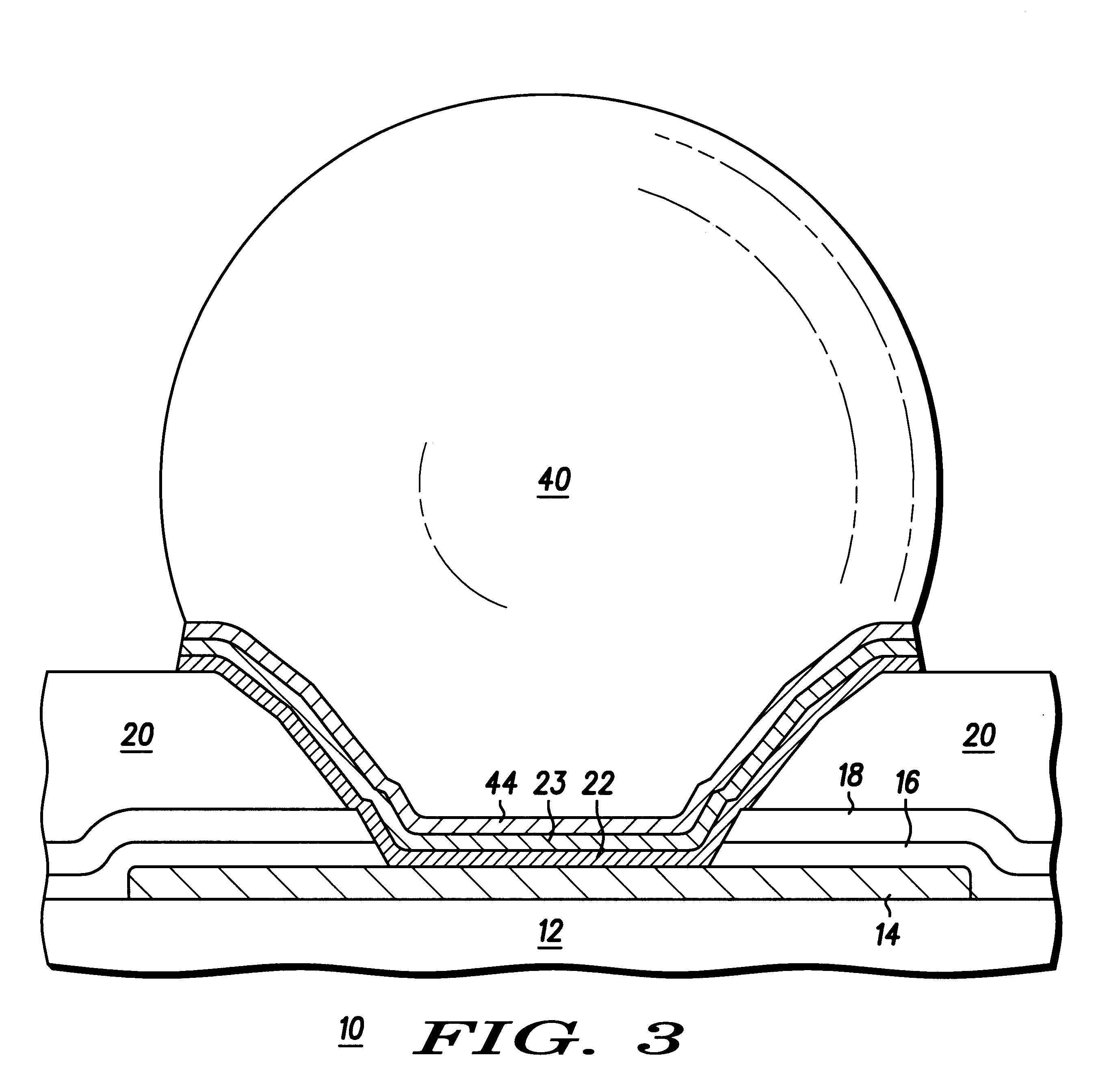

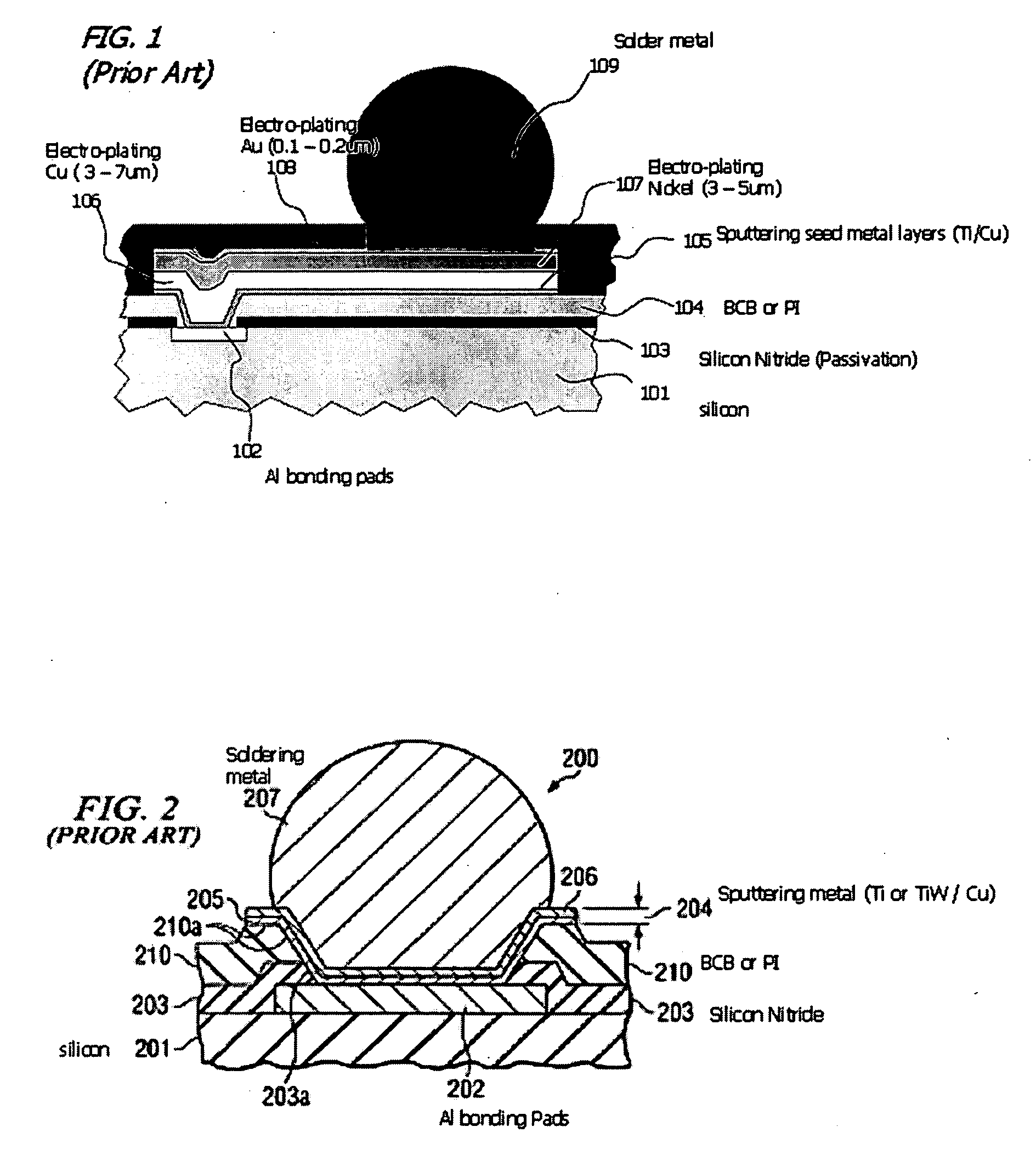

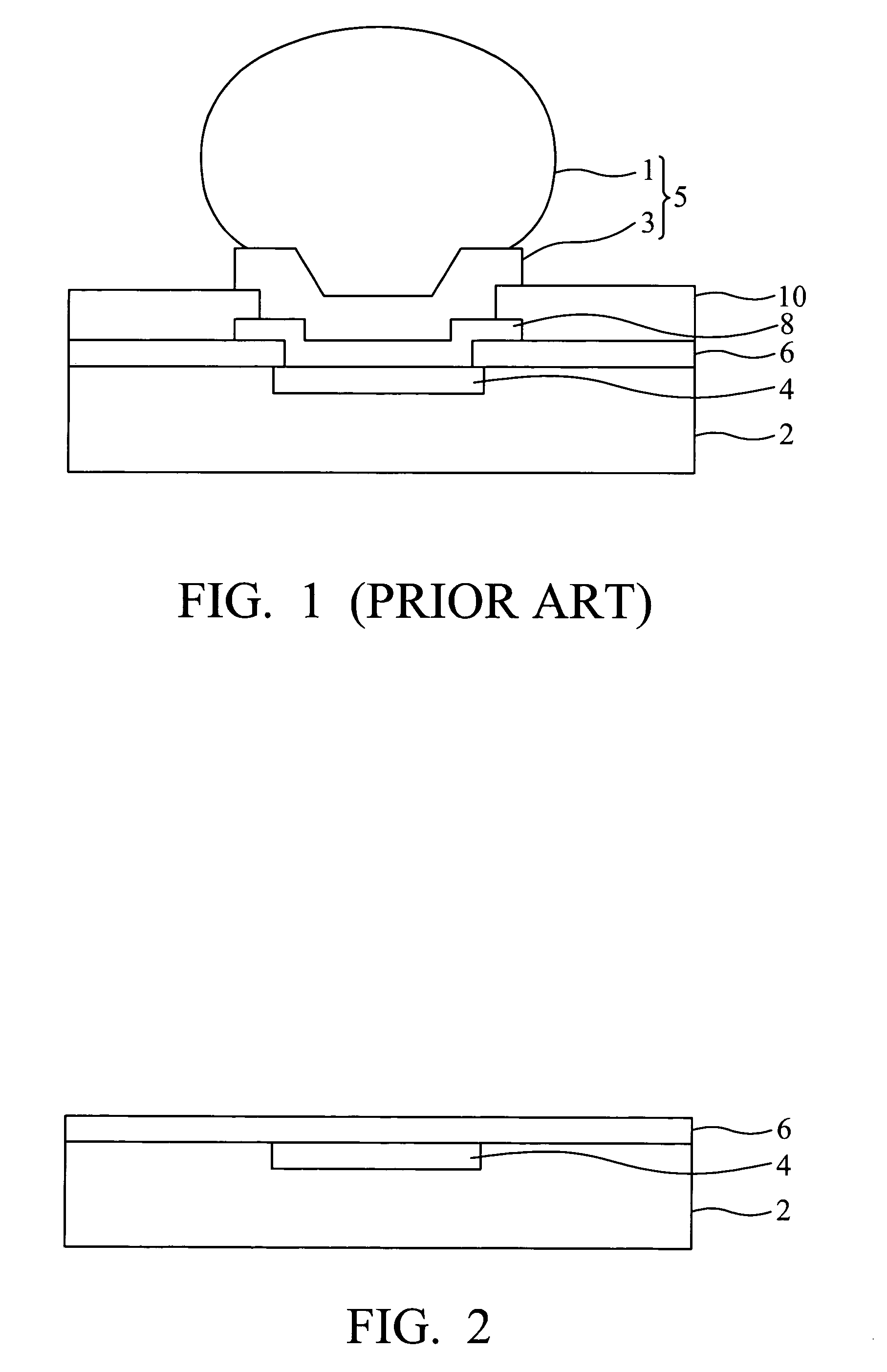

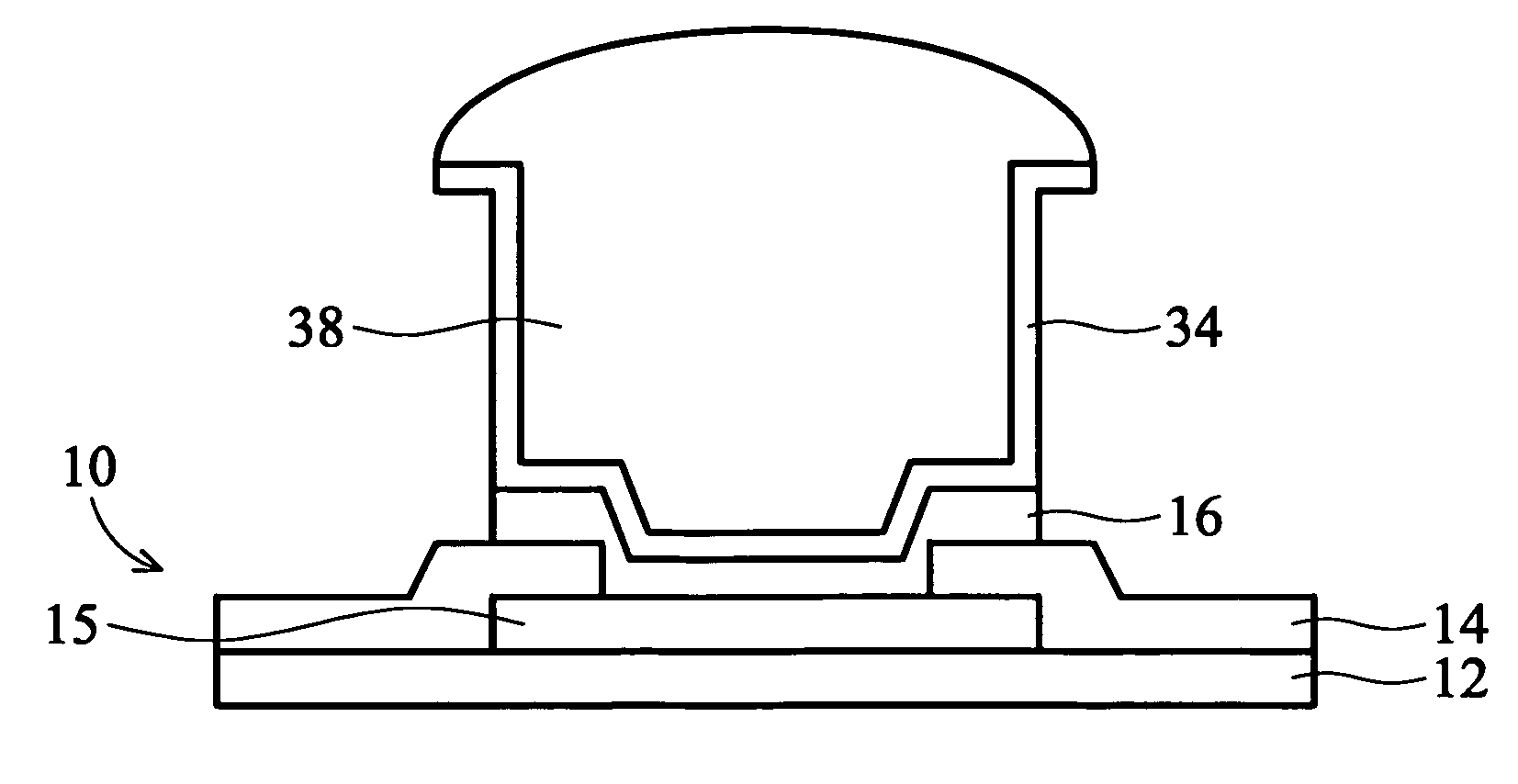

Method of forming a semiconductor device having conductive bumps without using gold

InactiveUS6489229B1Solid-state devicesSemiconductor/solid-state device manufacturingGold layerCopper

A semiconductor device (10) includes a solder bump (40) that is formed using a gold-free under-bump metallurgy (UBM) (21). In a preferred embodiment, UBM (21) includes a diffusion barrier layer (22) of chromium and a metallic layer (24) of copper. The bump layer metallurgy (31) is deposited directly on the metallic layer, without an intervening gold layer. To overcome problems associated with a native oxide layer (26) which forms on the metallic layer, especially on copper, the bump metallurgy includes a seed layer (32) of tin that is deposited prior to a bulk lead layer (34). The bump metallurgy includes a final metallic layer (36) having sufficient tin to make a bump having approximately 97% Pb and 3% tin.

Owner:NXP USA INC

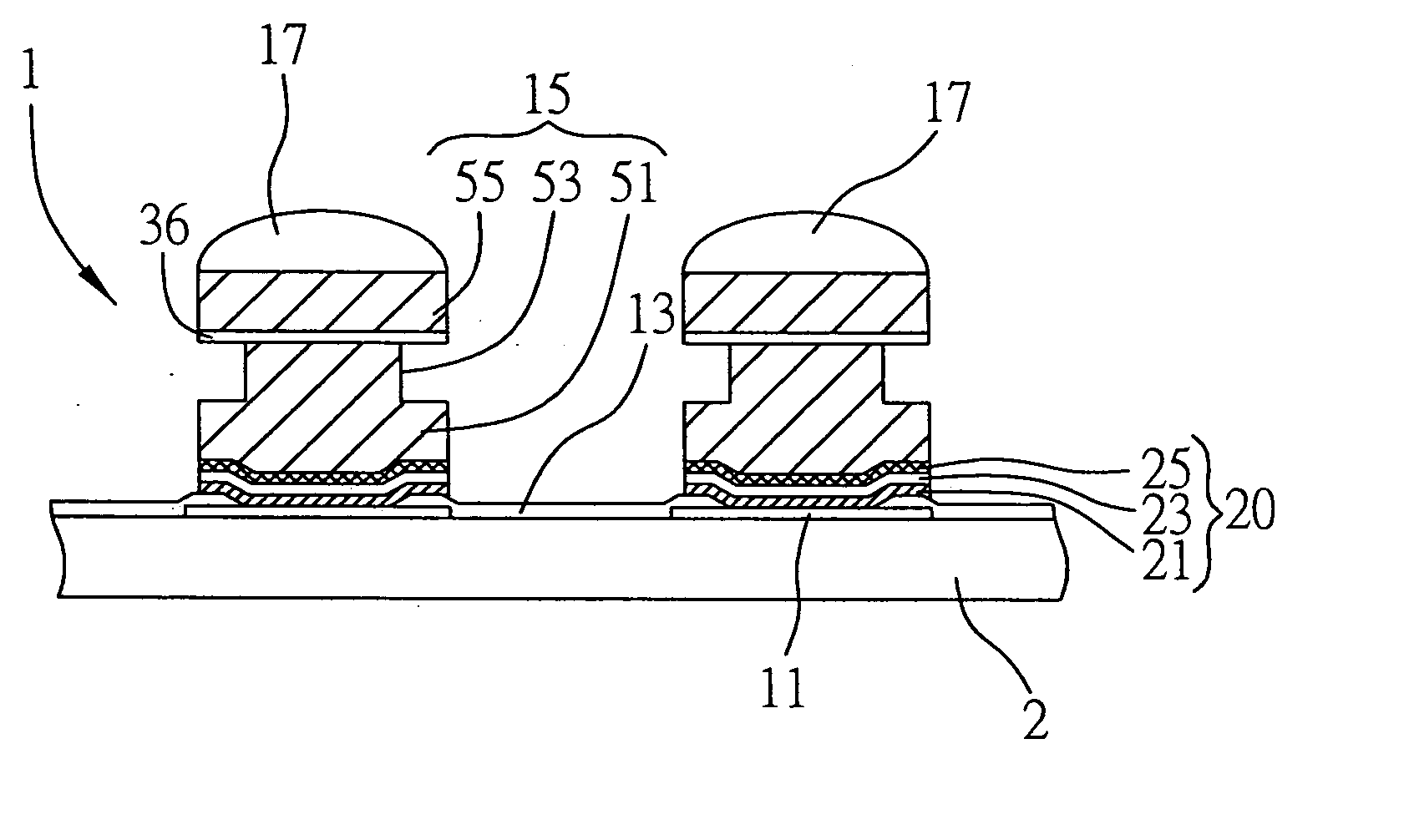

Bump structure of semiconductor package and method for fabricating the same

InactiveUS20060051954A1Increase spacingReduces the formation of voidsSemiconductor/solid-state device detailsPrinted circuit aspectsElectrical connectionSemiconductor package

A bump structure of a semiconductor package and a method for fabricating the same are provided. The bump structure is used to connect a semiconductor element to a carrier of the semiconductor package. The fabrication method primarily employs an electroplating process to form the bump structure including an under bump metallurgy (UBM) layer, at least one I-shaped conductive pillar, and a solder material. This allows fine-pitch electrical connection pads to be arranged in the semiconductor package, and also provides an enhanced support structure and a sufficient height between the semiconductor element and the carrier.

Owner:SILICONWARE PRECISION IND CO LTD

Under bump metallurgy structure of a package and method of making same

InactiveUS20080169539A1Semiconductor/solid-state device detailsSolid-state devicesRedistribution layerSolder ball

A package for a semiconductor integrated circuit die comprises a redistributed layer formed over a first barrier layer electrically connected to a bonding pad of a die. A second barrier layer is formed over the redistributed layer. A multi-metal layer is formed over the second barrier layer for coupling to a solder ball, wherein the multi-metal layer has an extending part that extends outside a second opening over the upper of the second dielectric layer to prevent tin infiltration from the solder ball to the redistribution layer.

Owner:ADVANCED CHIP ENG TECH +1

Bump structure of semiconductor package and method for fabricating the same

InactiveUS7271483B2Increase spacingReduce formationSemiconductor/solid-state device detailsPrinted circuit aspectsSemiconductor packageElectrical connection

A bump structure of a semiconductor package and a method for fabricating the same are provided. The bump structure is used to connect a semiconductor element to a carrier of the semiconductor package. The fabrication method primarily employs an electroplating process to form the bump structure including an under bump metallurgy (UBM) layer, at least one I-shaped conductive pillar, and a solder material. This allows fine-pitch electrical connection pads to be arranged in the semiconductor package, and also provides an enhanced support structure and a sufficient height between the semiconductor element and the carrier.

Owner:SILICONWARE PRECISION IND CO LTD

Back end integrated WLCSP structure without aluminum pads

ActiveUS7863742B2Reduce RC delayReduce manufacturing costSemiconductor/solid-state device detailsSolid-state devicesCopperUnder bump metallurgy

Owner:TAIWAN SEMICON MFG CO LTD

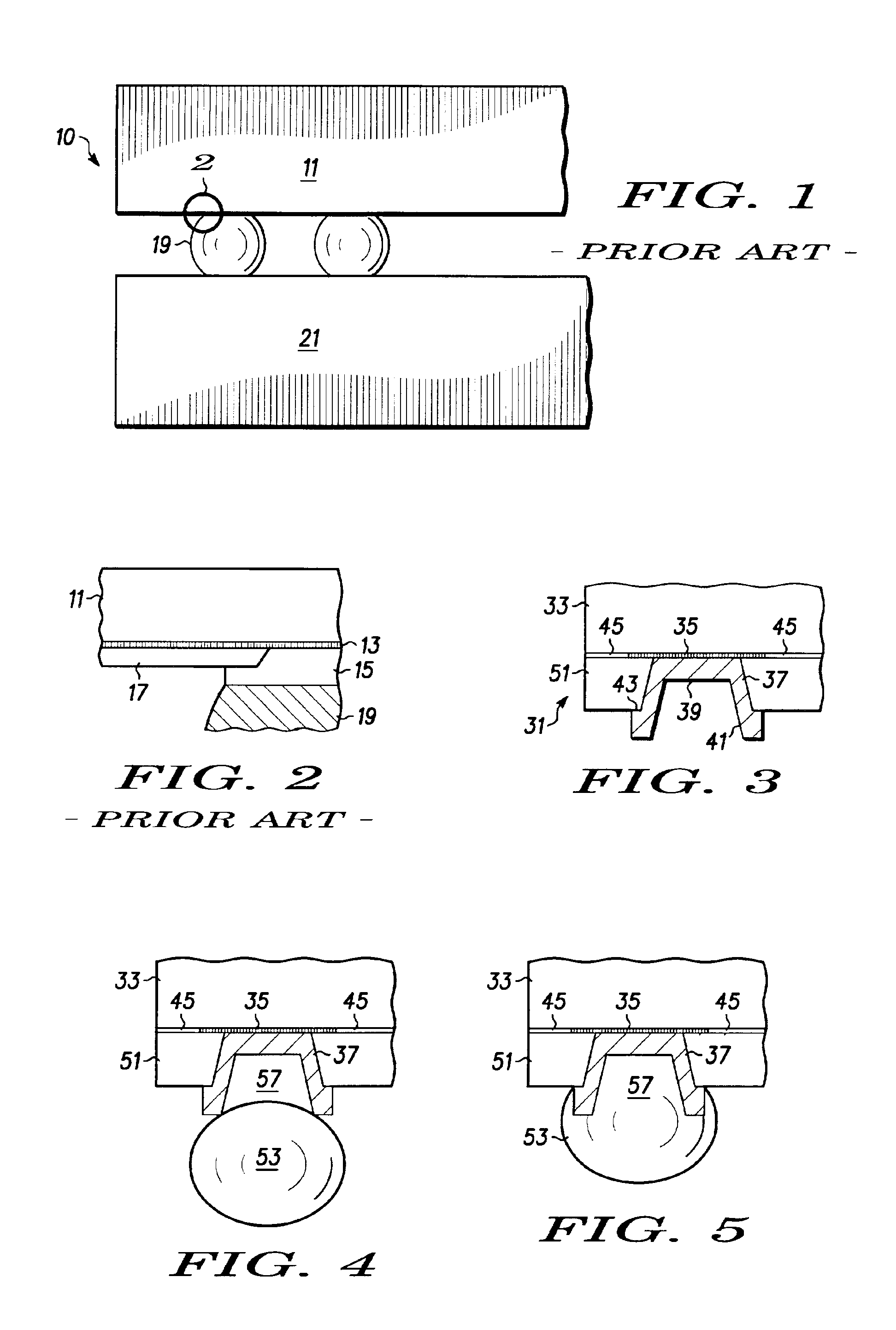

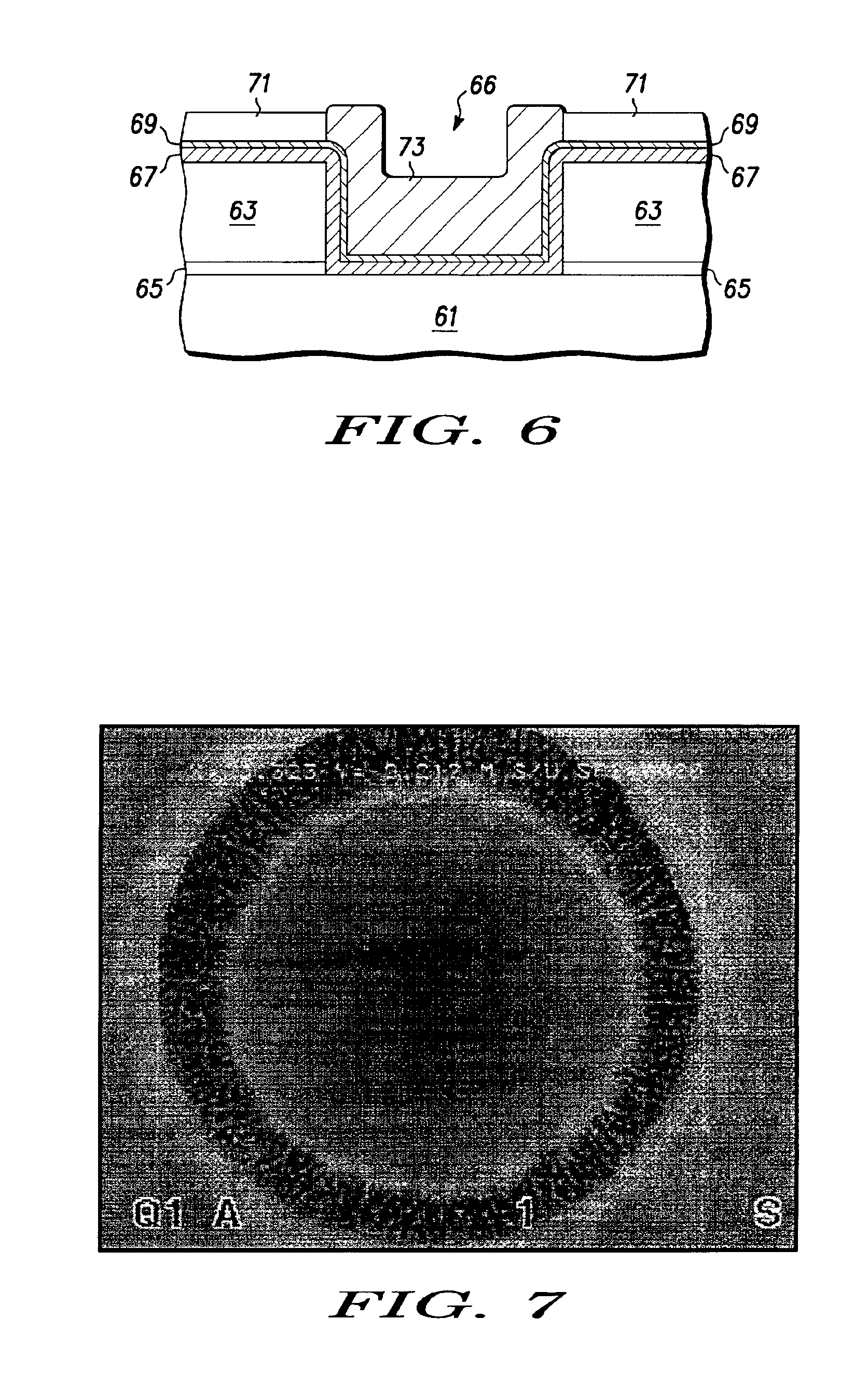

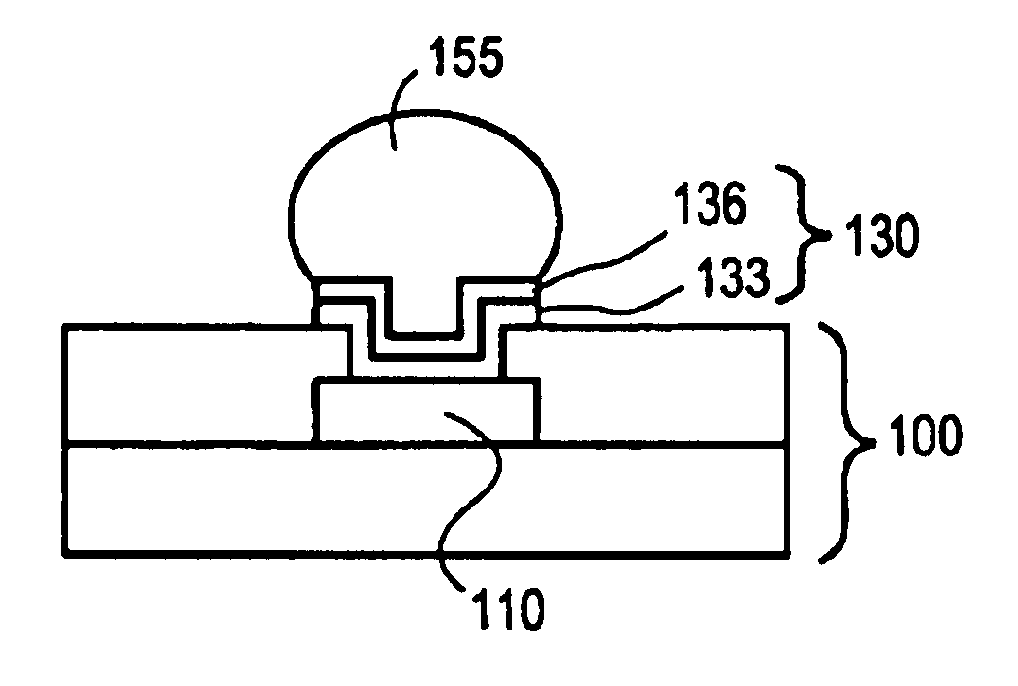

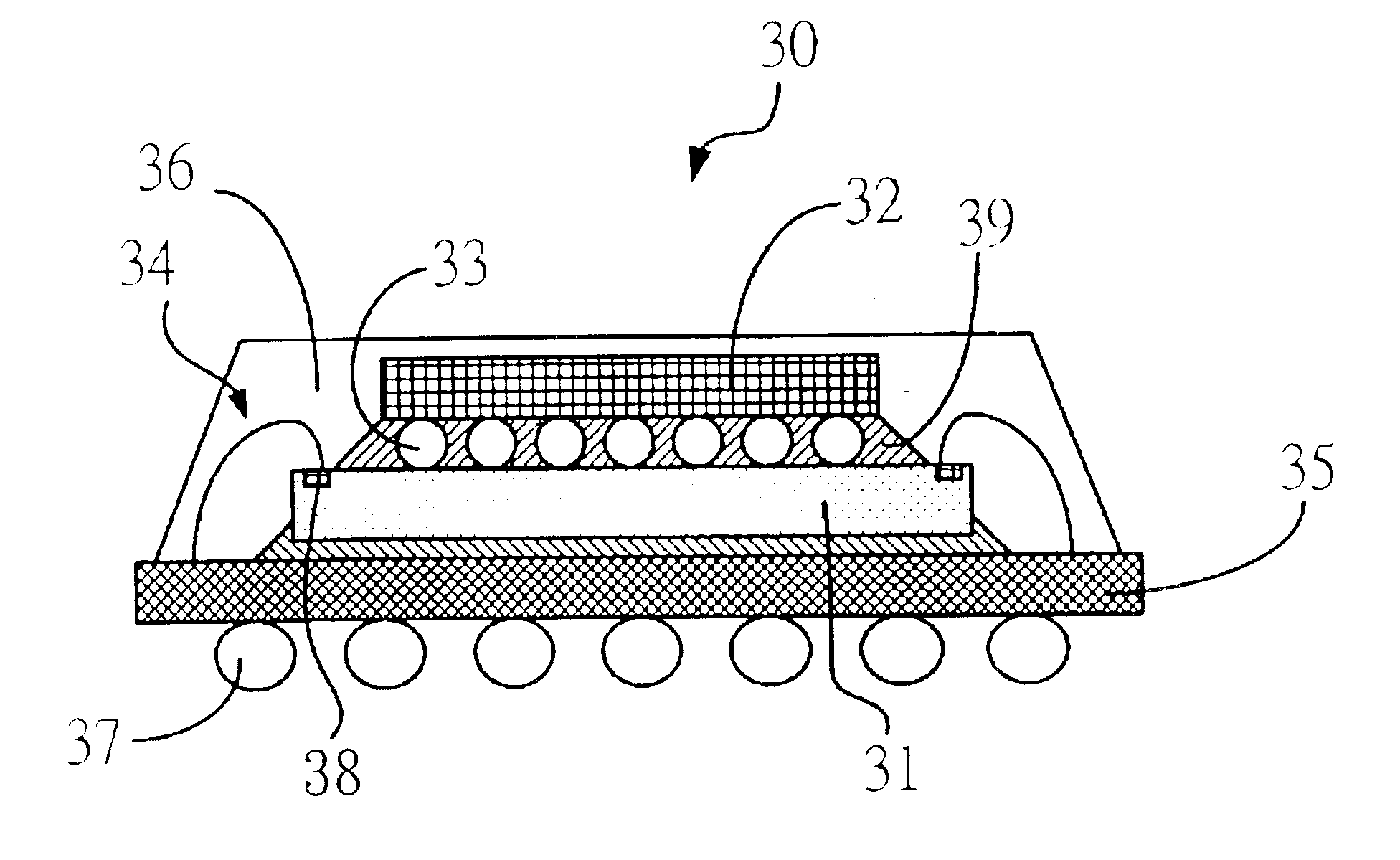

Under bump metallurgy structural design for high reliability bumped packages

InactiveUS6930032B2Effect package reliabilityImproving solder-UBM bondSemiconductor/solid-state device detailsSolid-state devicesEngineeringUnder bump metallurgy

A method for creating an under bump metallization layer (37) is provided. In accordance with the method, a die (33) is provided which has a die pad (35) disposed thereon. A photo-definable polymer (51 or 71) is deposited on the die pad, and an aperture (66) is created in the photo-definable polymer. Finally, an under bump metallization layer (37) is deposited in the aperture. A die package is also provided comprising a die having a die pad (35) disposed thereon, and having an under bump metallization layer (37) disposed on the die pad. The structure has a depression or receptacle (57) therein and has a thickness of at least about 20 microns.

Owner:NXP USA INC

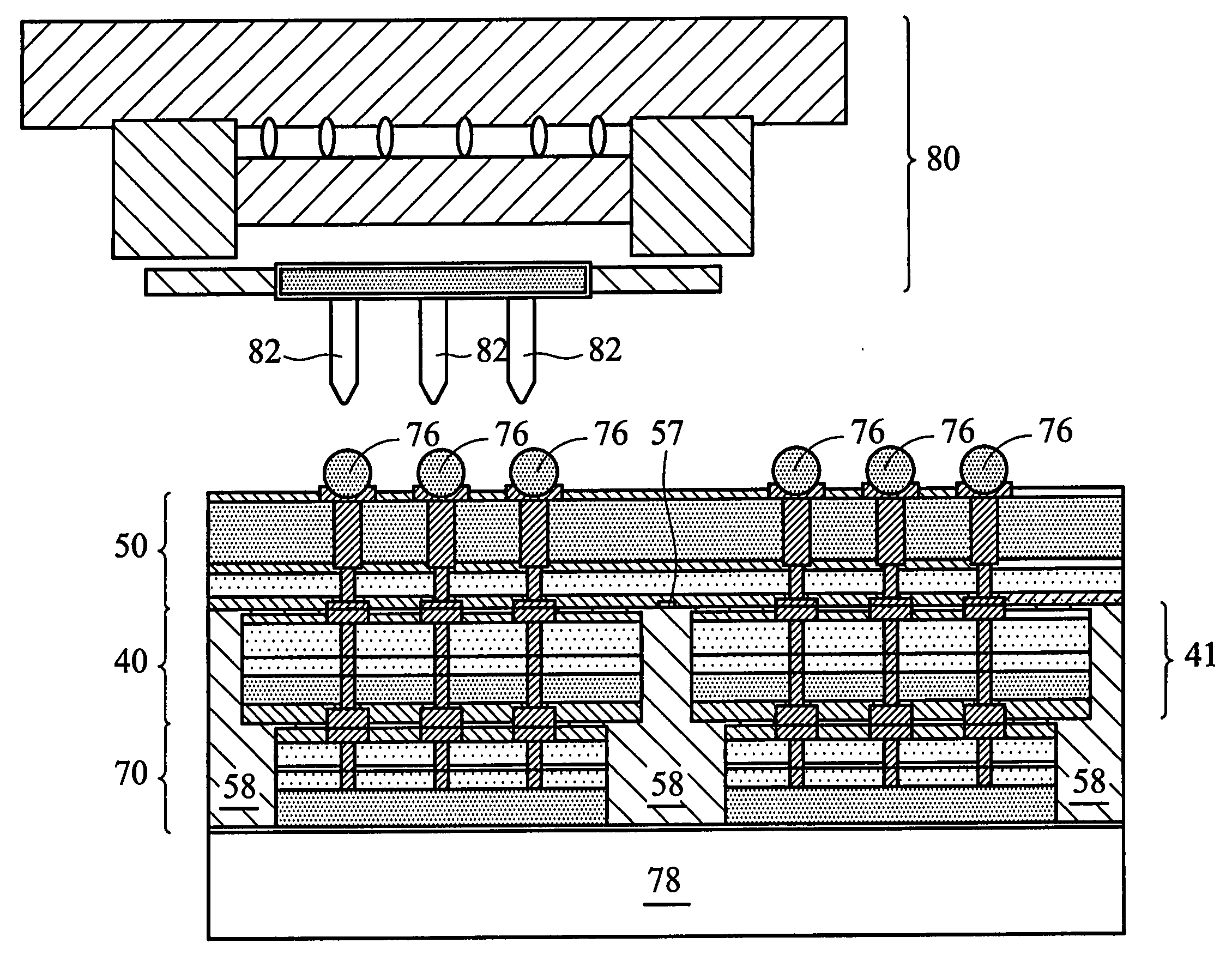

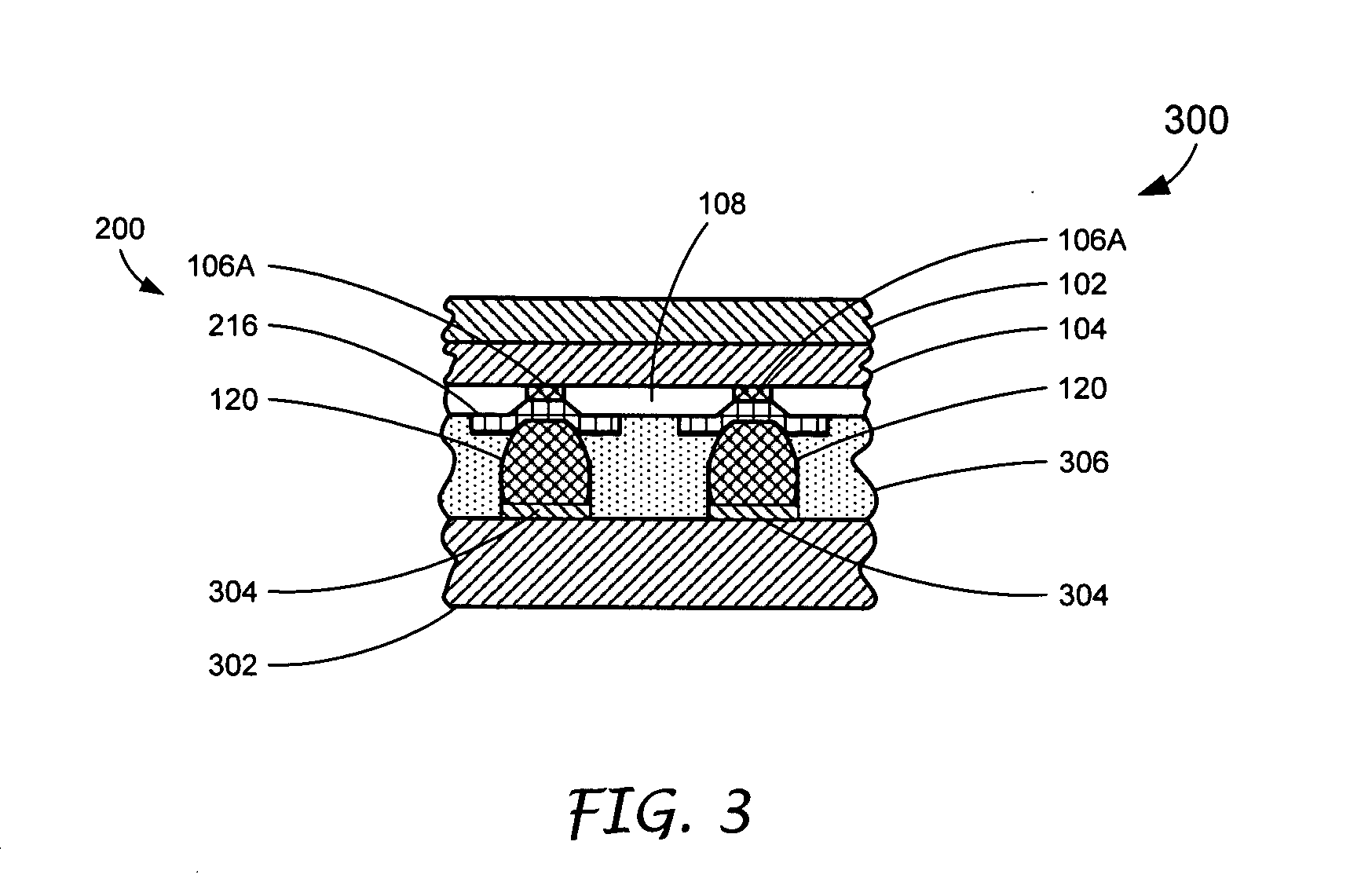

Chip-probing and bumping solutions for stacked dies having through-silicon vias

InactiveUS20080153187A1Semiconductor/solid-state device testing/measurementSolid-state devicesSemiconductor structureUnder bump metallurgy

A method of forming a semiconductor structure includes providing a stack structure having a first side and a second side opposite the first side. The stack structure includes a bottom wafer comprising a substrate; a plurality of through-silicon vias in the substrate; and a plurality of under bump metallurgies (UBMs) connected to the plurality of through-silicon vias, wherein the UBMs are on the first side of the stack structure. The method further includes attaching a handling wafer on the second side of the stack structure; performing a chip probing process; and removing the handling wafer from the stack structure.

Owner:TAIWAN SEMICON MFG CO LTD

Back End Integrated WLCSP Structure without Aluminum Pads

ActiveUS20090115058A1Reduce RC delayReduce manufacturing costSemiconductor/solid-state device detailsSolid-state devicesCopperUnder bump metallurgy

An integrated circuit structure includes a passivation layer; a via opening in the passivation layer; a copper-containing via in the via opening; a polymer layer over the passivation layer, wherein the polymer layer comprises an aperture, and wherein the copper-containing via is exposed through the aperture; a post-passivation interconnect (PPI) line over the polymer layer, wherein the PPI line extends into the aperture and physically contacts the copper-via opening; and an under-bump metallurgy (UBM) over and electrically connected to the PPI line.

Owner:TAIWAN SEMICON MFG CO LTD

Method for forming high reliability bump structure

ActiveUS7364998B2Semiconductor/solid-state device detailsSolid-state devicesContact padConductive materials

Methods for forming a bump on a semiconductor substrate, the substrate having a contact pad thereon, is provided. In one embodiment, the method comprises depositing a passivation layer over the substrate and the contact pad. The passivation layer is patterned and etched to form a plurality of openings in the passivation layer exposing portions of the contact pad. An under bump metallurgy (UBM) layer is deposited over the etched passivation layer and in the plurality of openings thereof to contact the contact pad. A photoresist layer is formed on the UBM layer and then patterned and etched to form at least one opening substantially overlying the contact pad. An electrically conductive material is deposited into the opening formed in the photoresist layer and overlying the UBM layer and aligned with the contact pad. A portion of the remaining photoresist layer is removed. The UBM layer is etched using the electrically conductive material as a mask. Thereafter, the electrically conductive material is reflowed to provide a bump on the semiconductor substrate.

Owner:TAIWAN SEMICON MFG CO LTD

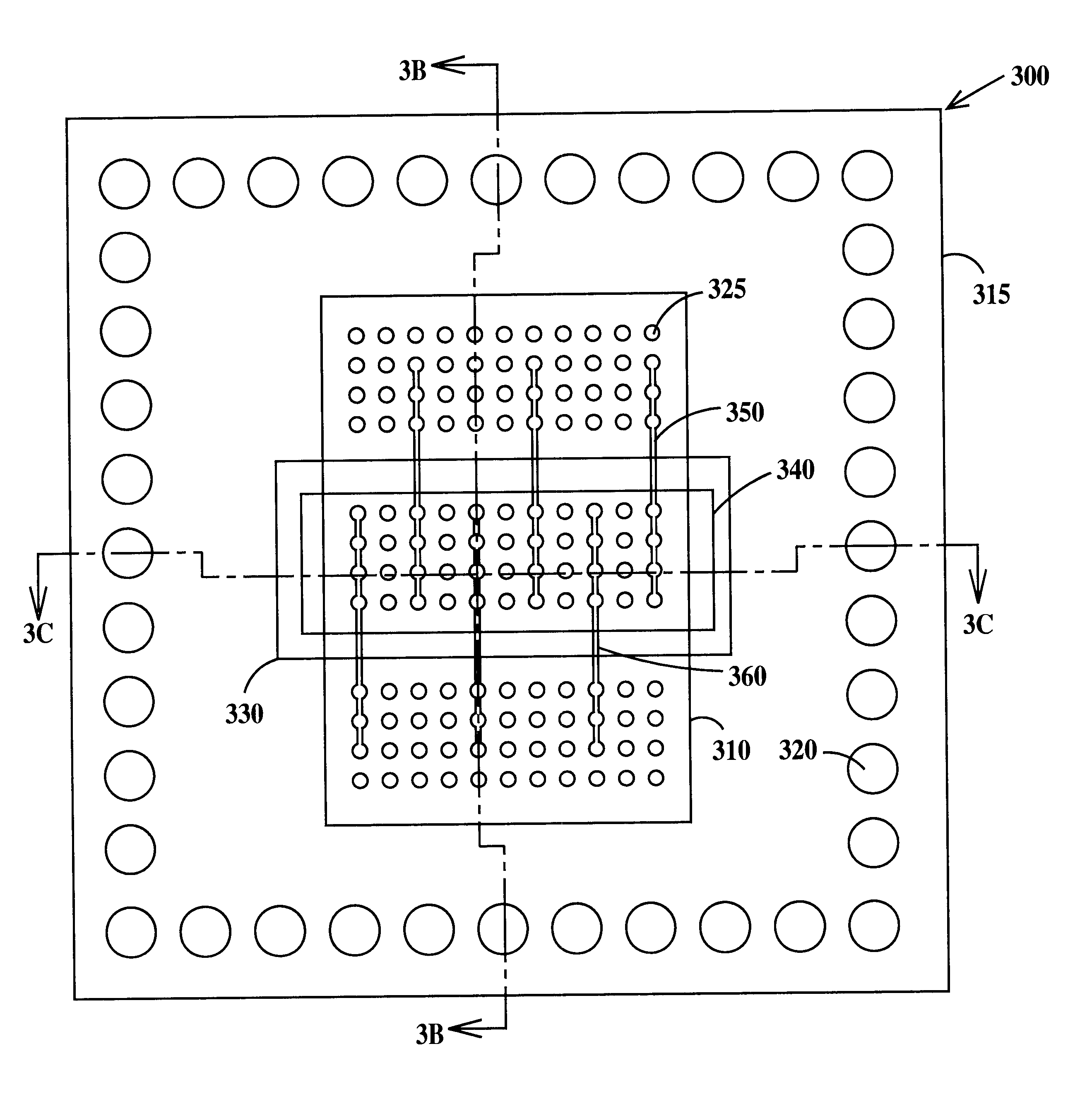

Low impedance power distribution structure for a semiconductor chip package

InactiveUS6661100B1Semiconductor/solid-state device detailsSolid-state devicesVery large scale integrated circuitsElectricity

A low impedance power distribution structure and method for substrate packaging of semiconductor chips containing very large scale integrated circuit (VLSI) circuits, such as microprocessors and associated memory, is presented. The power distribution structure incorporates under bump metallurgy (UBM) solder bump forming technology to produce not only solder bump connections that are vertically oriented, but also low impedance distribution wires that are horizontally oriented, and which provide electrical interconnection between various selected electrical contact points, such as solder bumps. These low impedance distribution wires introduce the benefits of low characteristic impedance to the substrate's power distribution structure.

Owner:GLOBALFOUNDRIES US INC

Method for forming bumps on under bump metallurgy

InactiveUS20080261390A1Avoid flowSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringCopper

A method for forming metal bumps is provided. A bonding pad is first formed on the active surface of a chip and then a passivation layer is formed on the active surface of the chip and exposes the bonding pad. An under bump metallurgy is formed on the active surface of the chip to overlay the bonding pad. A layer of patterned photoresist is formed on the under bump metallurgy and exposes the portion of the under bump metallurgy on the bonding pad. A layer of copper is plated on the exposed portion of the under bump metallurgy and then a layer of solder is printed on the copper layer. Afterward the solder is reflowed to form a spherical metal bump. Finally, the photoresist layer is removed and the exposed portion of the under bump metallurgy is etched out.

Owner:ADVANCED SEMICON ENG INC

Under bump metallurgy for lead-tin bump over copper pad

The present invention describes a method including providing a component, the component having a bond pad; forming a passivation layer over the component; forming a via in the passivation layer to uncover the bond pad; and forming an under bump metallurgy (UBM) over the passivation layer, in the via, and over the bond pad, in which the UBM includes an alloy of Aluminum and Magnesium.The present invention also describes an under bump metallurgy (UBM) that includes a lower layer, the lower layer including an alloy of Aluminum and Magnesium; and an upper layer located over the lower layer.

Owner:INTEL CORP

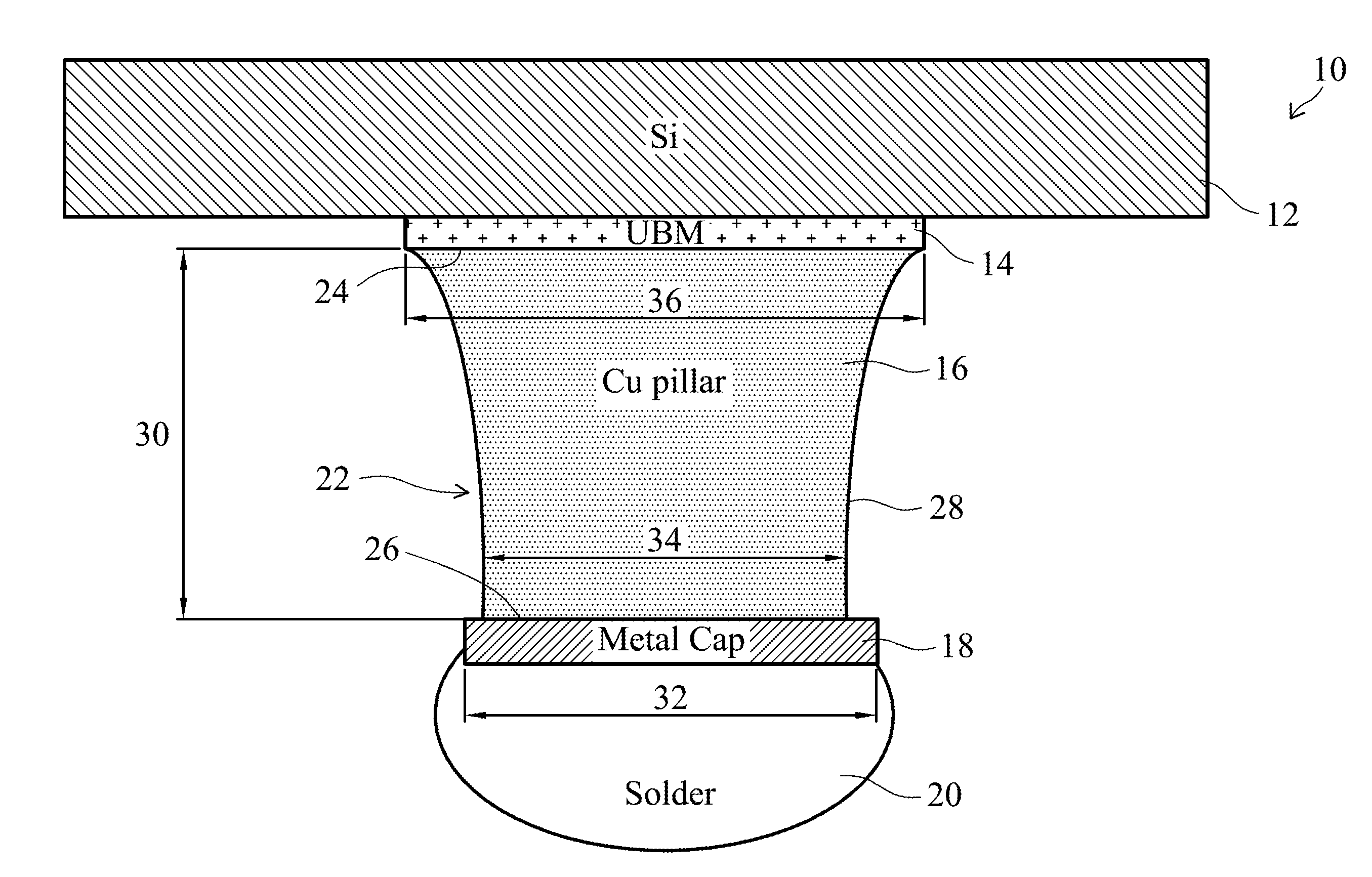

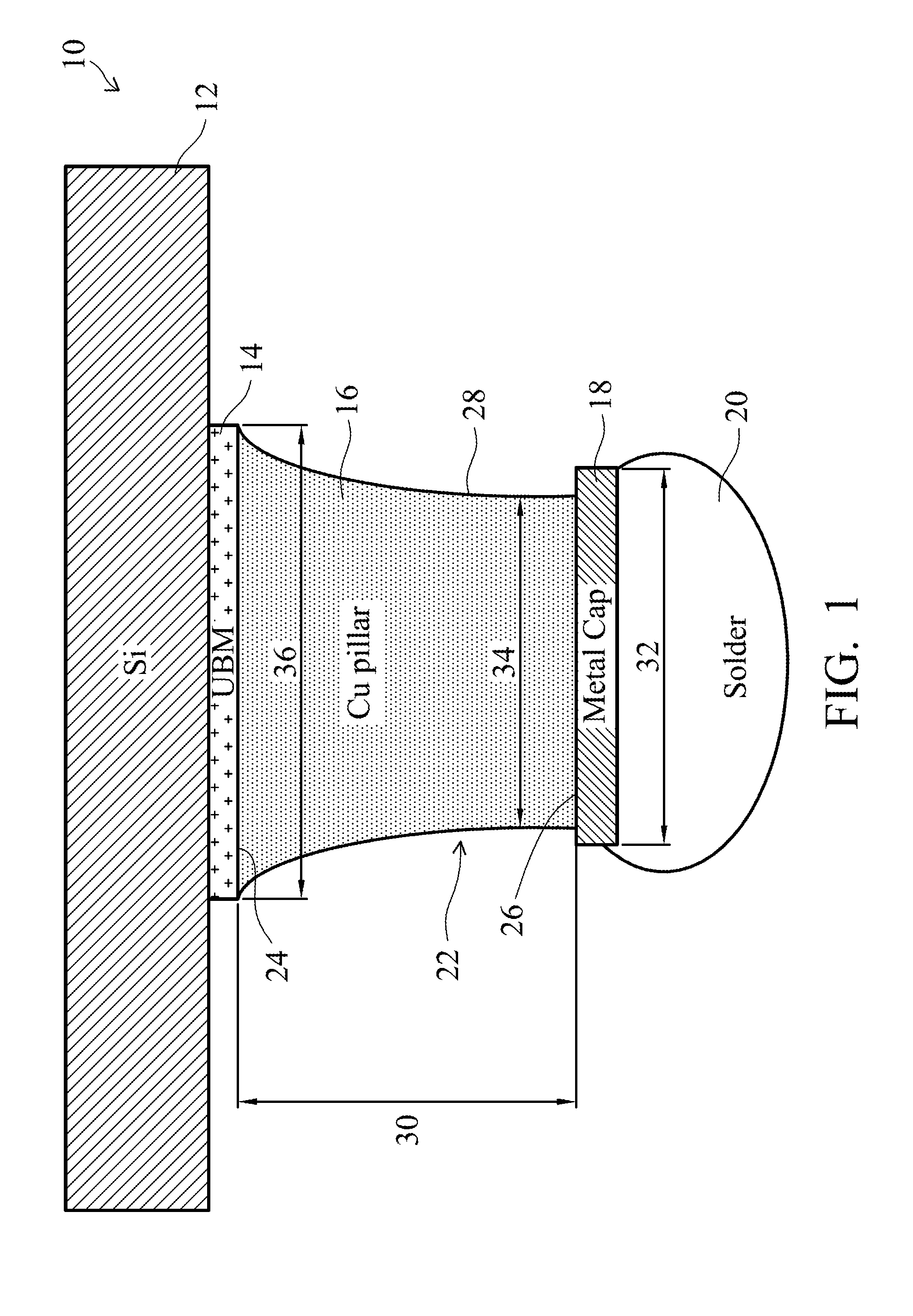

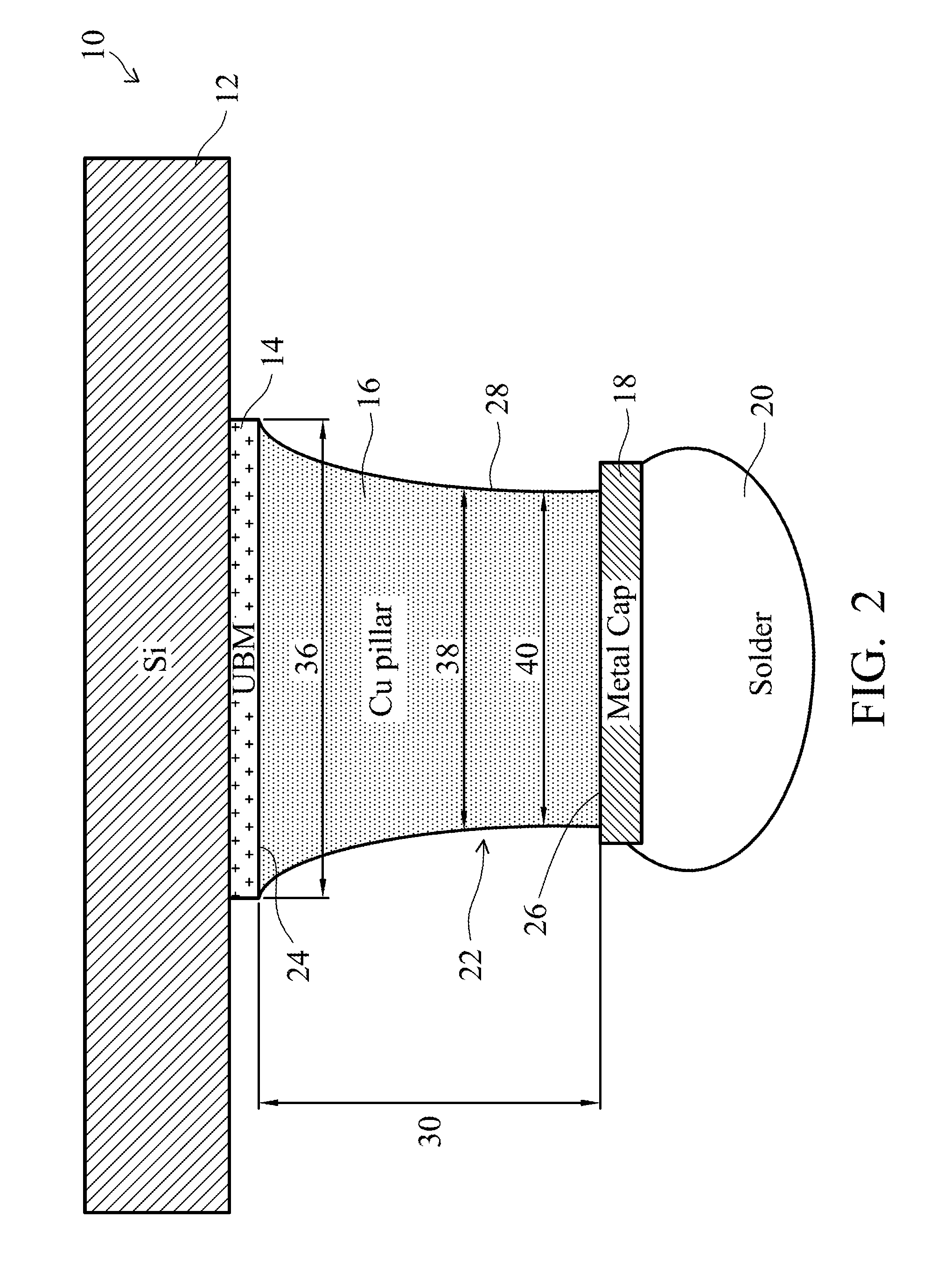

Ladder Bump Structures and Methods of Making Same

ActiveUS20140077359A1Semiconductor/solid-state device detailsSolid-state devicesUnder bump metallurgyEngineering

An embodiment ladder bump structure includes an under bump metallurgy (UBM) feature supported by a substrate, a copper pillar mounted on the UBM feature, the copper pillar having a tapering curved profile, which has a larger bottom critical dimension (CD) than a top critical dimension (CD) in an embodiment, a metal cap mounted on the copper pillar, and a solder feature mounted on the metal cap.

Owner:TAIWAN SEMICON MFG CO LTD

Semiconductor chip and manufacturing method thereof

ActiveCN102315182AReduce stressSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorSemiconductor chip

The invention discloses a semiconductor chip and a manufacturing method thereof, wherein the semiconductor chip compirses a conductive bump on a semiconductor chip. A substrate is provided. A bond pad is over the substrate. An under bump metallurgy (UBM) layer is over the bond pad. A copper pillar is over the UBM layer. The copper pillar has a top surface with a first width and sidewalls with a concave shape. A nickel layer having a top surface and a bottom surface is over the top surface of the copper pillar. The bottom surface of the nickel layer has a second width. A ratio of the second width to the first width is between about 0.93 to about 1.07. A solder material is over the top surface of the cap layer. The semiconductor chip and the manufacturing method thereof can reduce crack of the boundary between the conducting column and the soldering flux caused by stress.

Owner:TAIWAN SEMICON MFG CO LTD

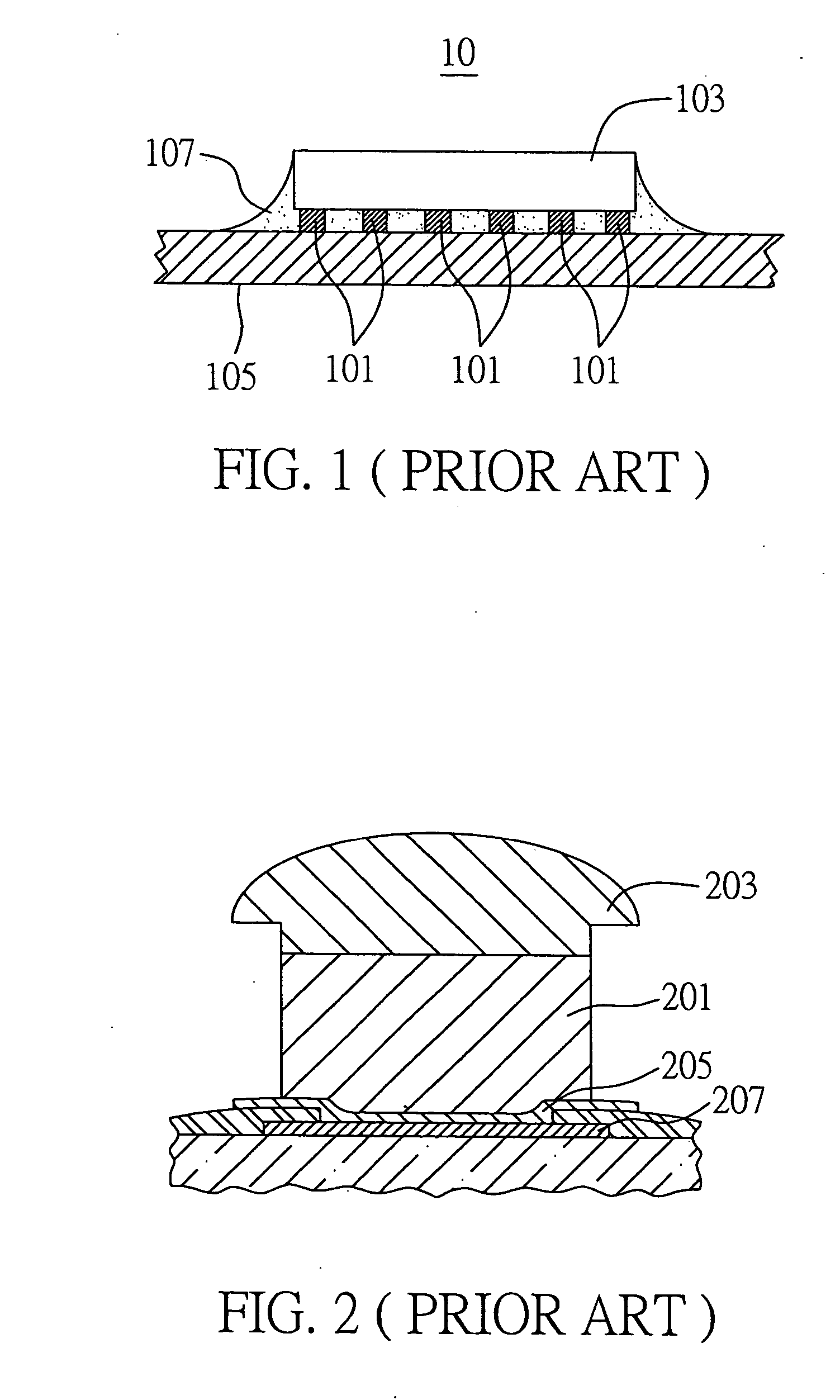

Flip chip package, semiconductor package with bumps and method for manufacturing semiconductor package with bumps

InactiveUS20050233571A1Improve electrical performanceImprove cooling effectSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageSemiconductor chip

A semiconductor chip with bumps formed therein comprises an active surface, a plurality of bonding pads, a passivation layer, a plurality of first UBMs (under bump metallurgy), a second UBM, a plurality of first bumps, and a plurality of second bumps. The bonding pads are disposed on the active surface of the semiconductor chip. The passivation layer covers the active surface of the semiconductor chip with the pads exposed out of the passivation layer. The first UMBs are individually disposed on the bonding pads. The second UMB is disposed on at least two of the bonding pads. The first bumps are disposed on the first UMBs. The second bumps are disposed on the second UBM.

Owner:ADVANCED SEMICON ENG INC

Integrated circuit package with different hardness bump pad and bump and manufacturing method therefor

InactiveUS20050242446A1Lower resistanceSmall sizeSemiconductor/solid-state device detailsSolid-state devicesContact padEngineering

A manufacturing method for an integrated circuit package is provided including forming a contact pad under a passivation layer on an integrated circuit, forming an opening in the passivation layer exposing the contact pad, and forming an under bump metallurgy over the contact pad and the passivation layer. The method further includes forming a bump pad over the under bump metallurgy of a material having a first hardness and forming a bump on and over the bump pad, the bump having a top flat surface and of a material having a second hardness softer than the first hardness.

Owner:STATS CHIPPAC LTD

Under bump metallization structure of a semiconductor wafer

ActiveUS6930389B2Slow down formationHigh bonding strengthSemiconductor/solid-state device detailsSolid-state devicesEngineeringUnder bump metallurgy

An under bump metallurgy structure is applicable to be disposed above the wafer and on the bonding pads of the wafer. The wafer comprises a passivation layer and an under bump metallurgy structure. The passivation layer exposes the wafer pads, and the under bump metallurgy structure including an adhesive layer, a first barrier layer, a wetting layer and a second barrier layer are sequentially formed on the bonding pads. Specifically, the material of the second barrier mainly includes lead.

Owner:ADVANCED SEMICON ENG INC

Method of manufacturing multi-chip stacking package

InactiveUS6820329B2Printed circuit assemblingLine/current collector detailsEngineeringUnder bump metallurgy

The present invention discloses a method of manufacturing a multi-chip stacking package. The characteristic of the invention is that after the alignment of the bumps of at least two chips, welded bumps will be generated in a high temperature welding to form a welded bump. Furthermore, one of the at least two chips may only provide bonding pad similar to the Under Bump Metallurgy and may not provide bumps, and using the bonding pad to be welded with the bump on another chip.

Owner:ADVANCED SEMICON ENG INC

Method of forming solder bump with reduced surface defects

InactiveUS20050164483A1Quality improvementReduce yieldSemiconductor/solid-state device detailsSolid-state devicesEngineeringUnder bump metallurgy

A method of forming a solder bump may involve forming a first photoresist pattern on a wafer having a pad. The first photoresist pattern may have an opening that exposes a portion of the pad. A first under bump metallurgy (UBM) layer may be formed on the pad, and a second UBM layer may be formed on the first photoresist pattern. A second photoresist pattern may be formed that exposes the first UBM layer and covers the second UBM layer. A solder bump may be formed in the opening. The second photoresist pattern and the first photoresist pattern may be removed using a stripper, thereby removing the second UBM layer by a lift-off method.

Owner:SAMSUNG ELECTRONICS CO LTD

Integrated circuit with low-stress under-bump metallurgy

InactiveUS20070029669A1Semiconductor/solid-state device detailsSolid-state devicesContact padSemiconductor materials

An integrated circuit (IC) includes a semiconductor material, electronic circuitry formed on the semiconductor material, a contact layer formed on the electronic circuitry, a final passivation layer formed on the contact layer and an under-bump metallurgy (UBM) formed on at least a portion of the final passivation layer. The contact layer includes a plurality of contacts pads for providing external access to the electronic circuitry. The final passivation layer includes a plurality of windows that extend through the final passivation layer to the contact pads. The UBM includes an aluminum layer having a thickness of about 800 angstroms to about 1200 angstroms, a nickel / vanadium (Ni / V) layer having a thickness of about 800 angstroms to about 1200 angstroms and a copper (Cu) layer having a thickness of about 800 angstroms to about 1200 angstroms.

Owner:DELPHI TECH INC

Method to increase bump height and achieve robust bump structure

InactiveUS7112522B1Semiconductor/solid-state device detailsSolid-state devicesContact padEngineering

Methods for forming solder bumps on a semiconductor device are provided. In one embodiment, a substrate is provided having at least one contact pad formed thereon. A passivation layer is formed overlying the substrate, the passivation layer having at least one opening therein exposing a portion of the contact pad. A UBM (Under Bump Metallurgy) layer is formed overlying the passivation layer and the contact pad. A patterned and etched light sensitive layer is provided overlying the UBM layer, the light sensitive layer defining at least one opening therein. A sidewall bump layer is formed over the exposed surfaces of the light sensitive layer and the UBM layer. A portion of the sidewall bump layer above the light sensitive layer is removed. A solder material is deposited in the opening bordered by the etched sidewall bump layer to form a solder column. The solder column is then reflown to create a solder bump.

Owner:TAIWAN SEMICON MFG CO LTD

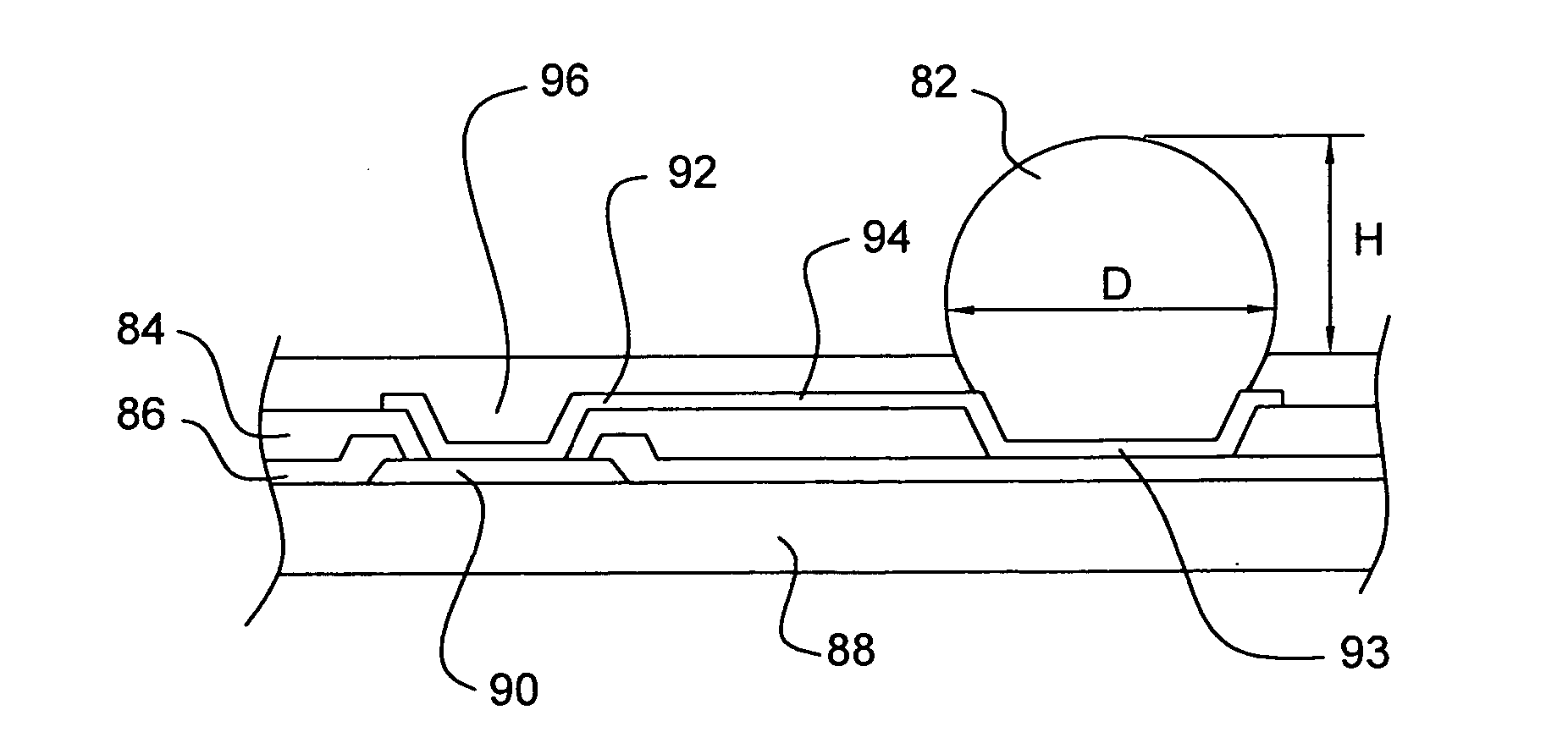

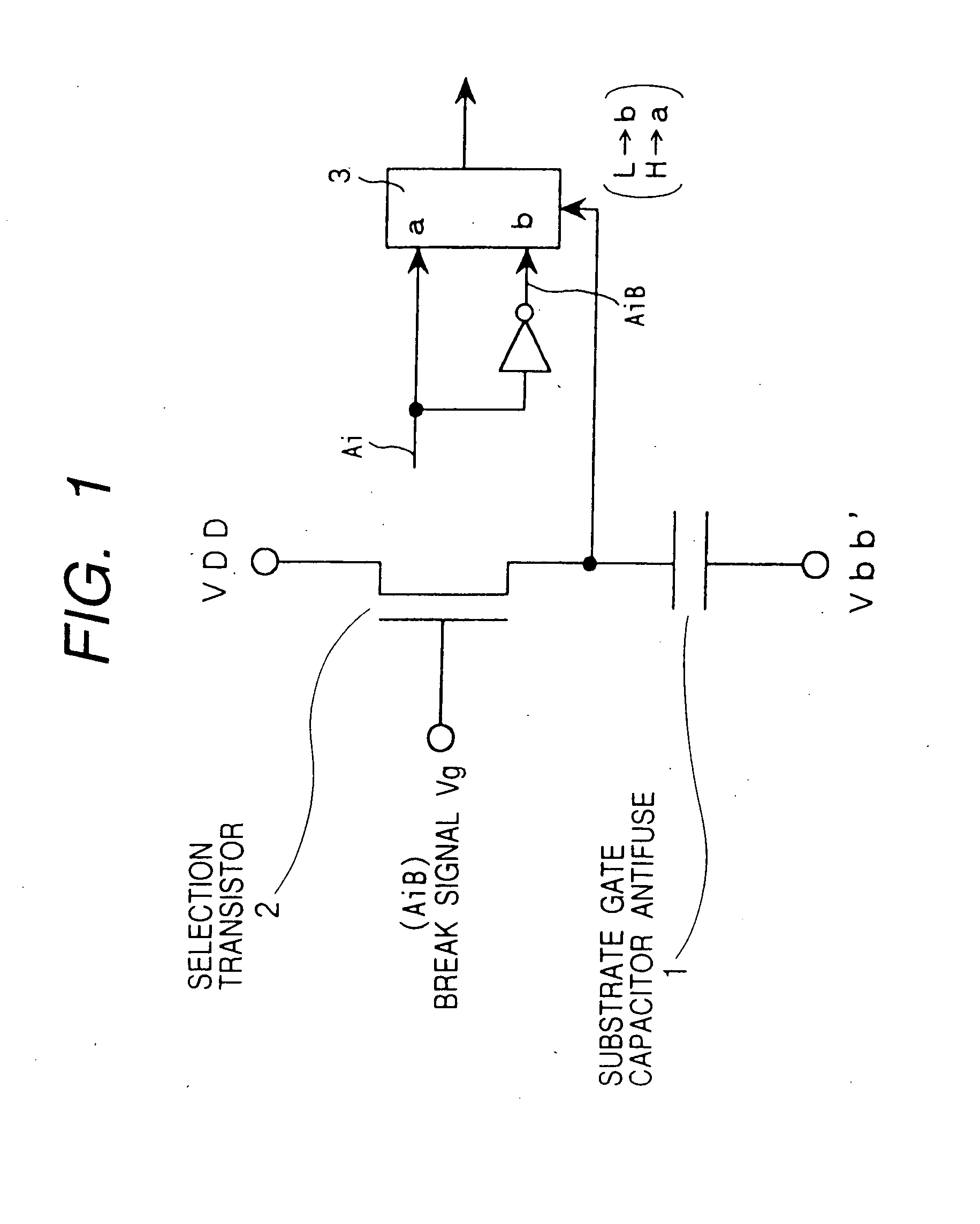

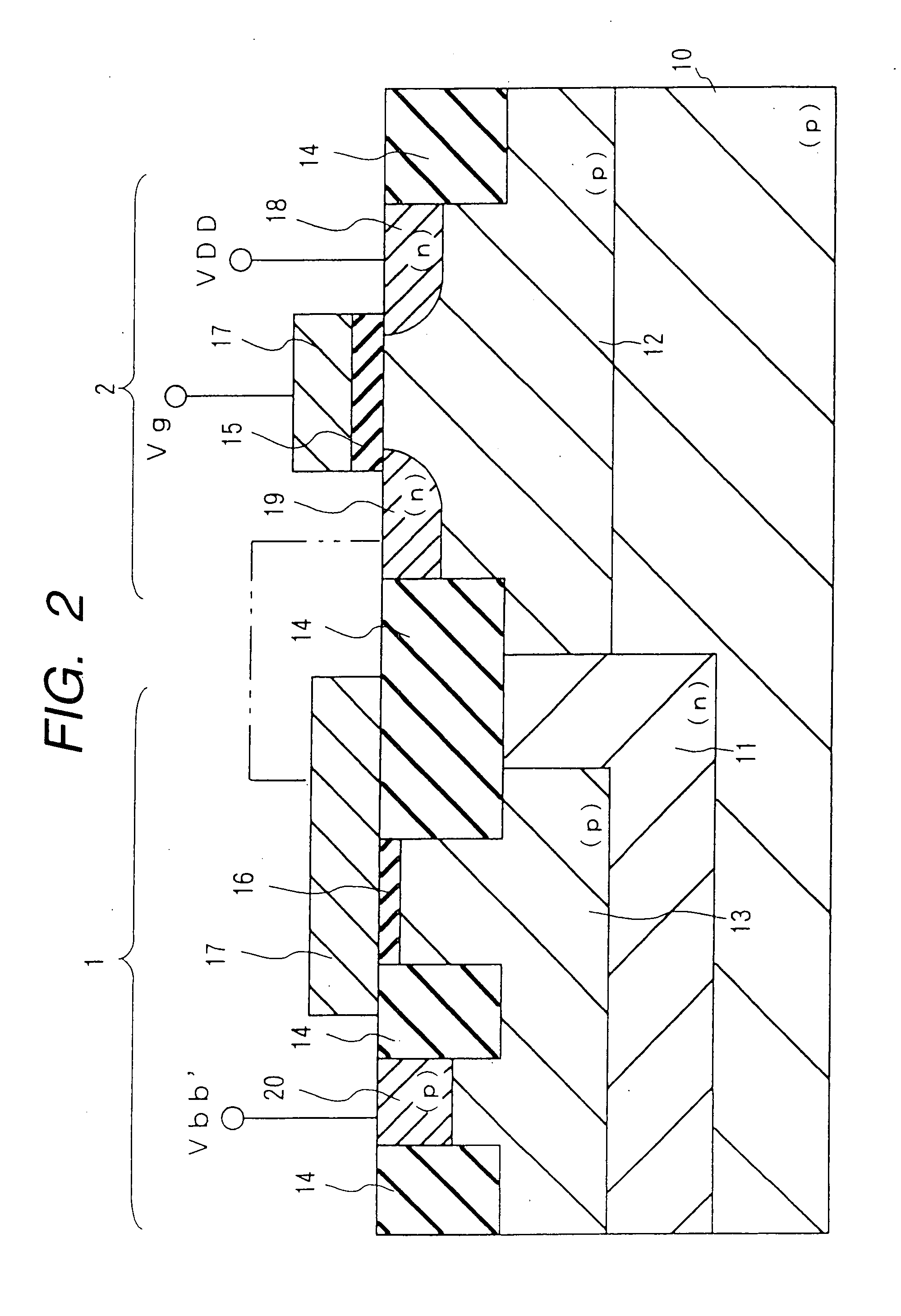

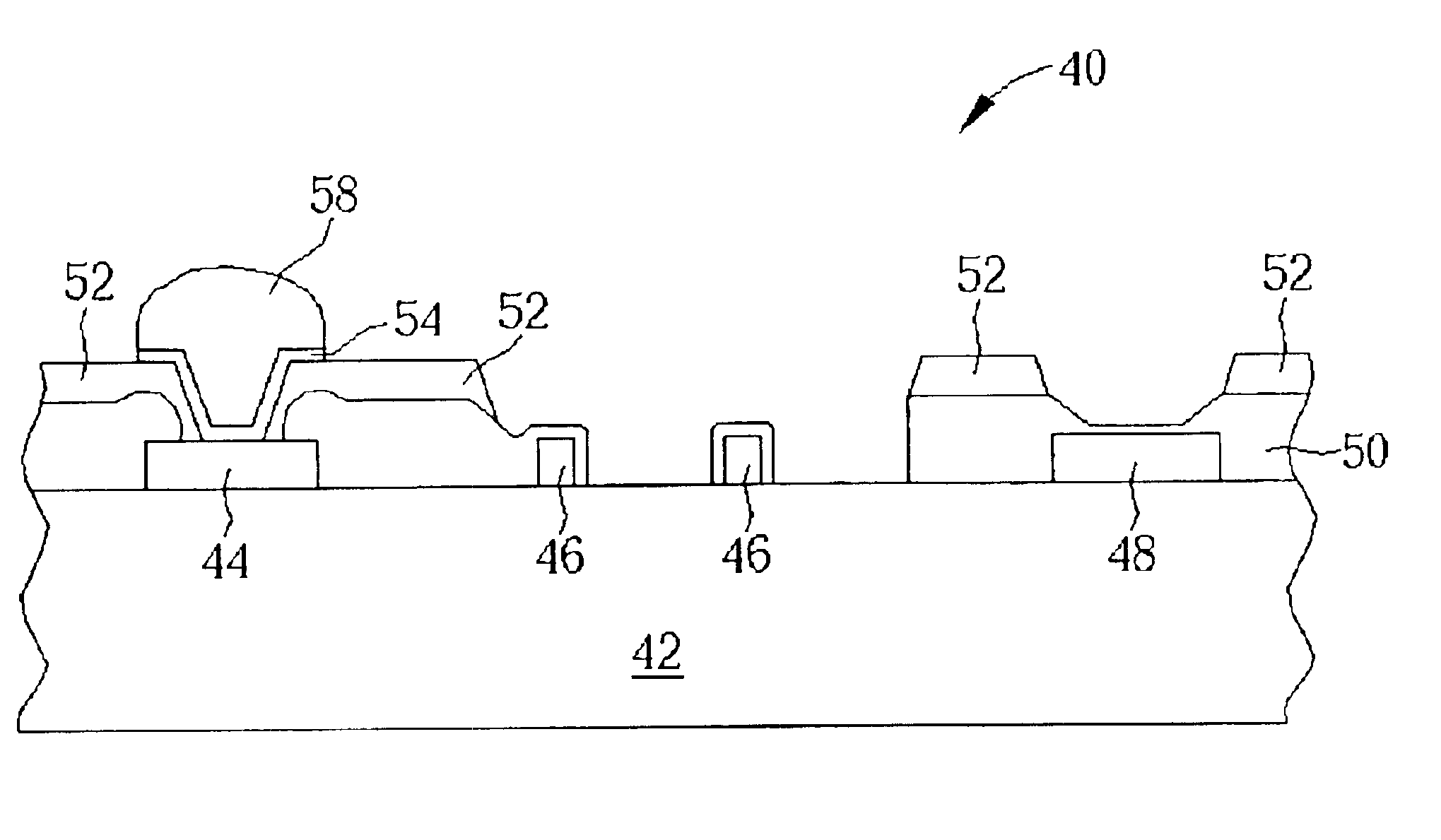

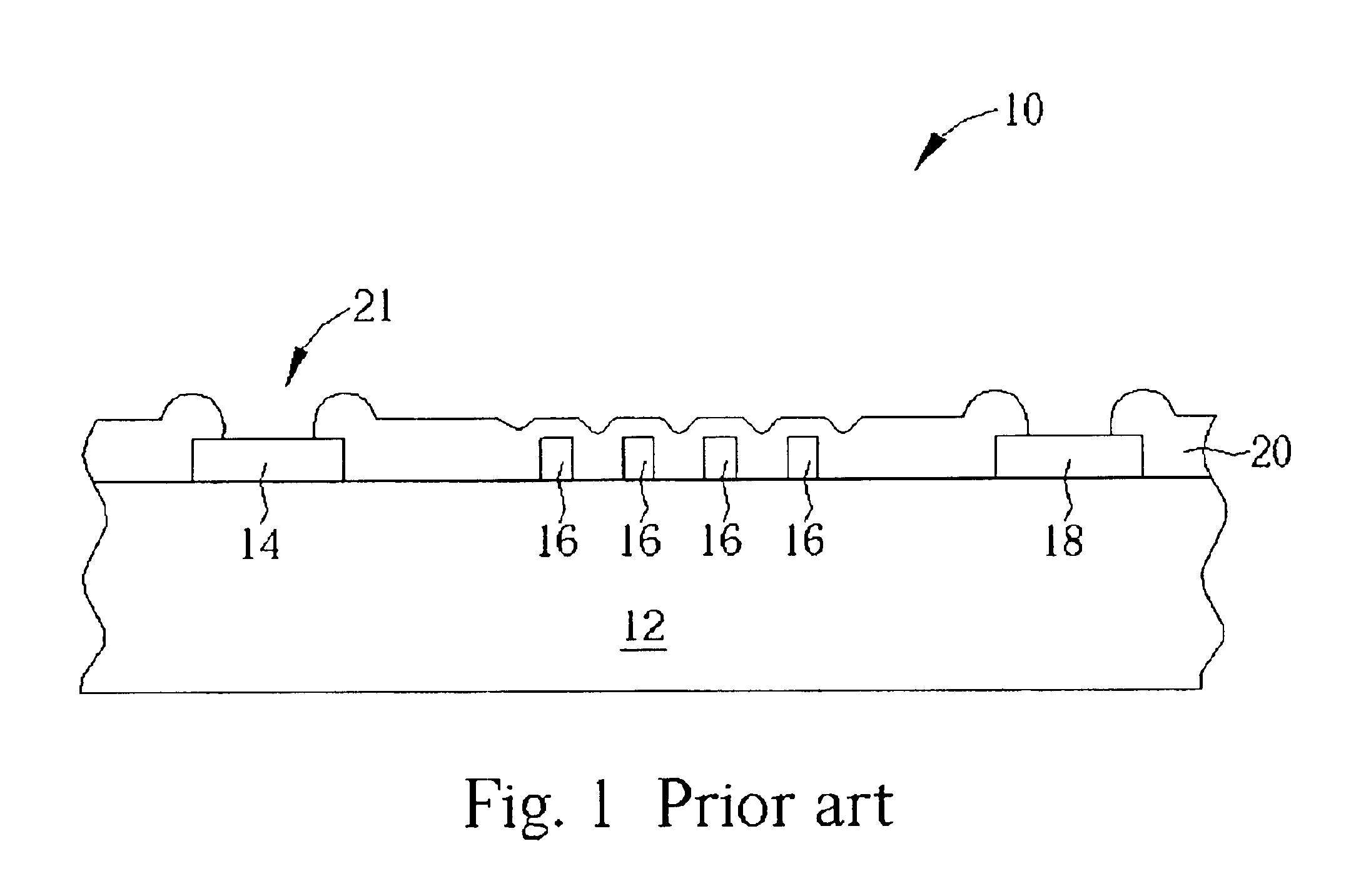

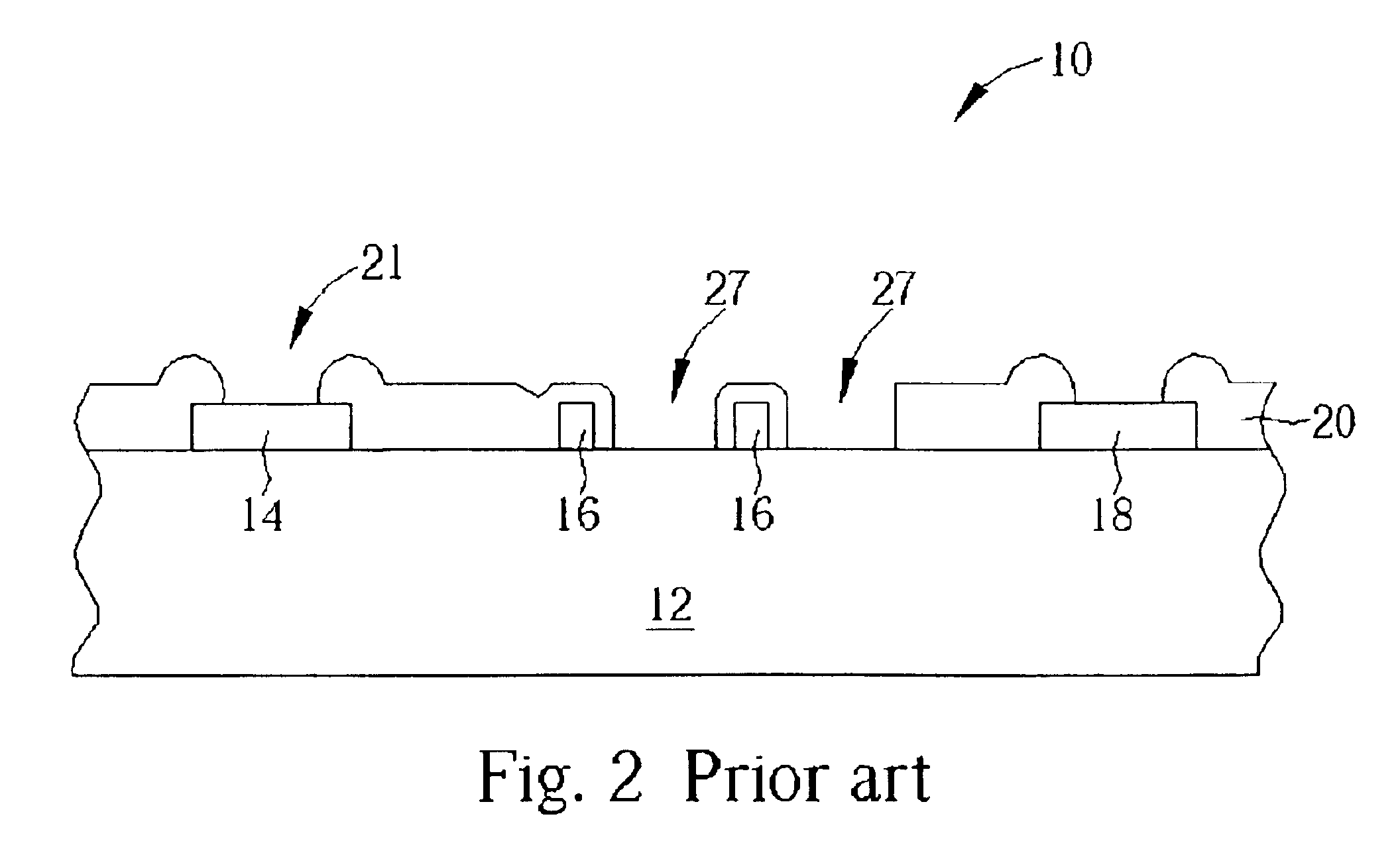

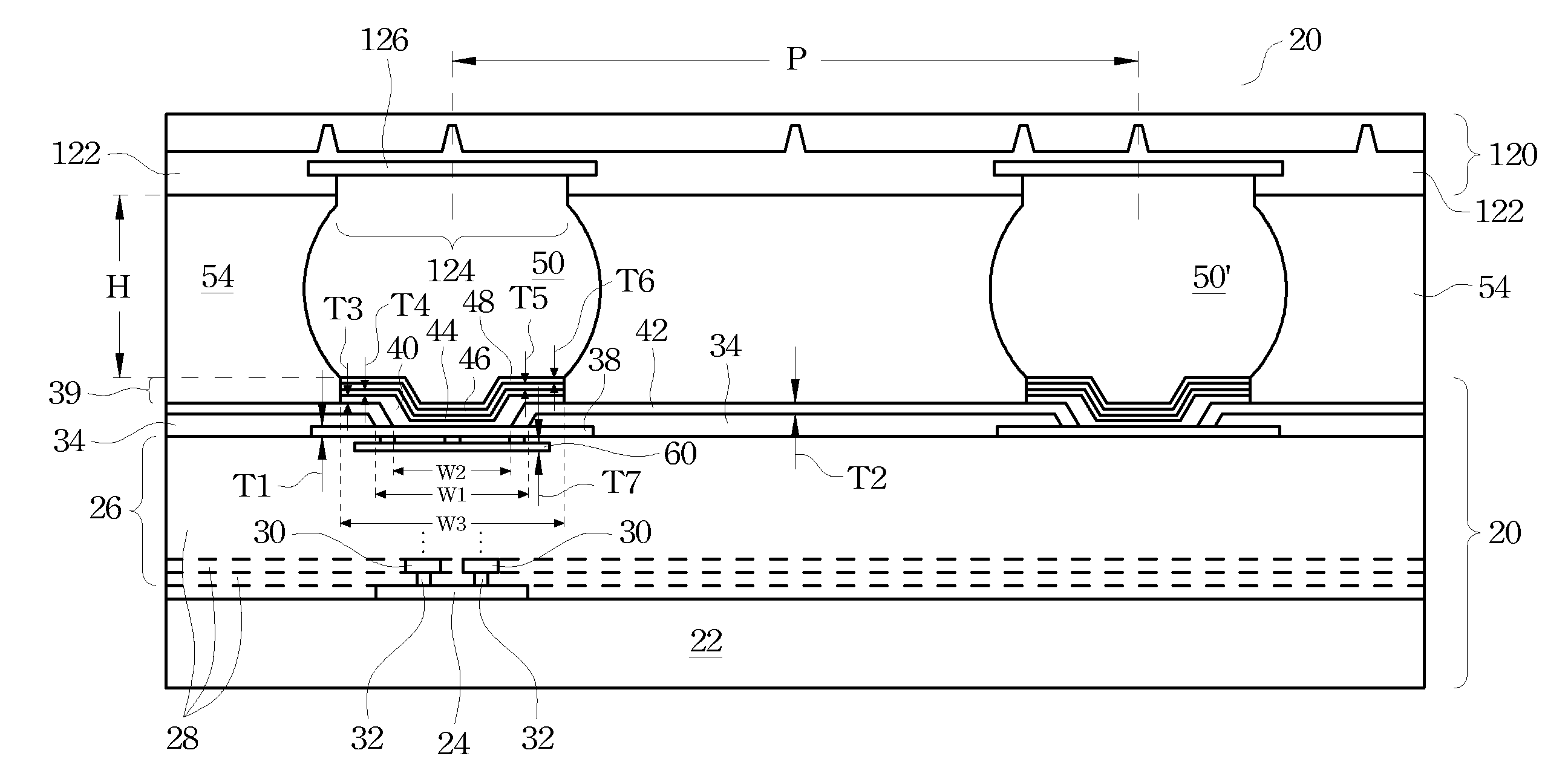

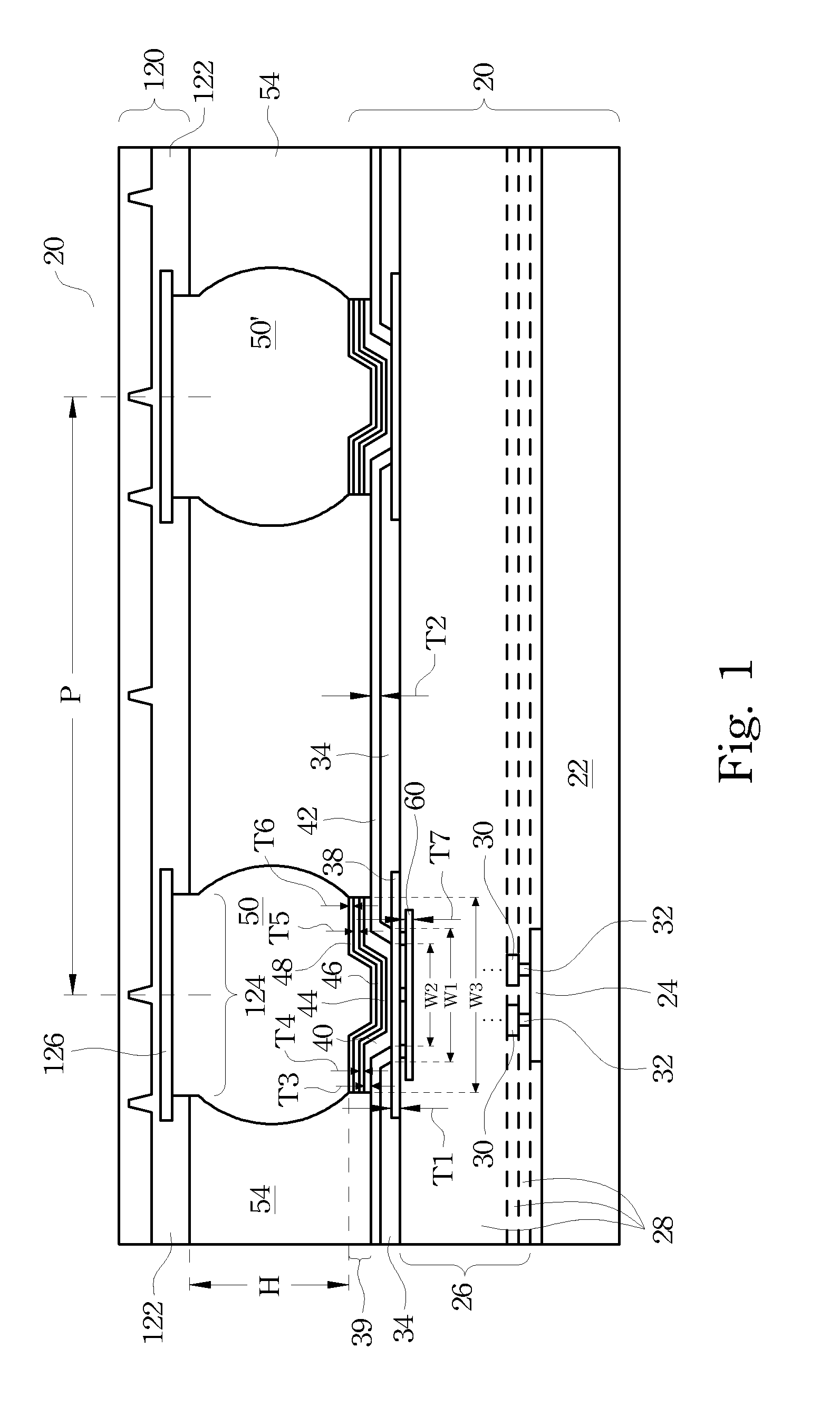

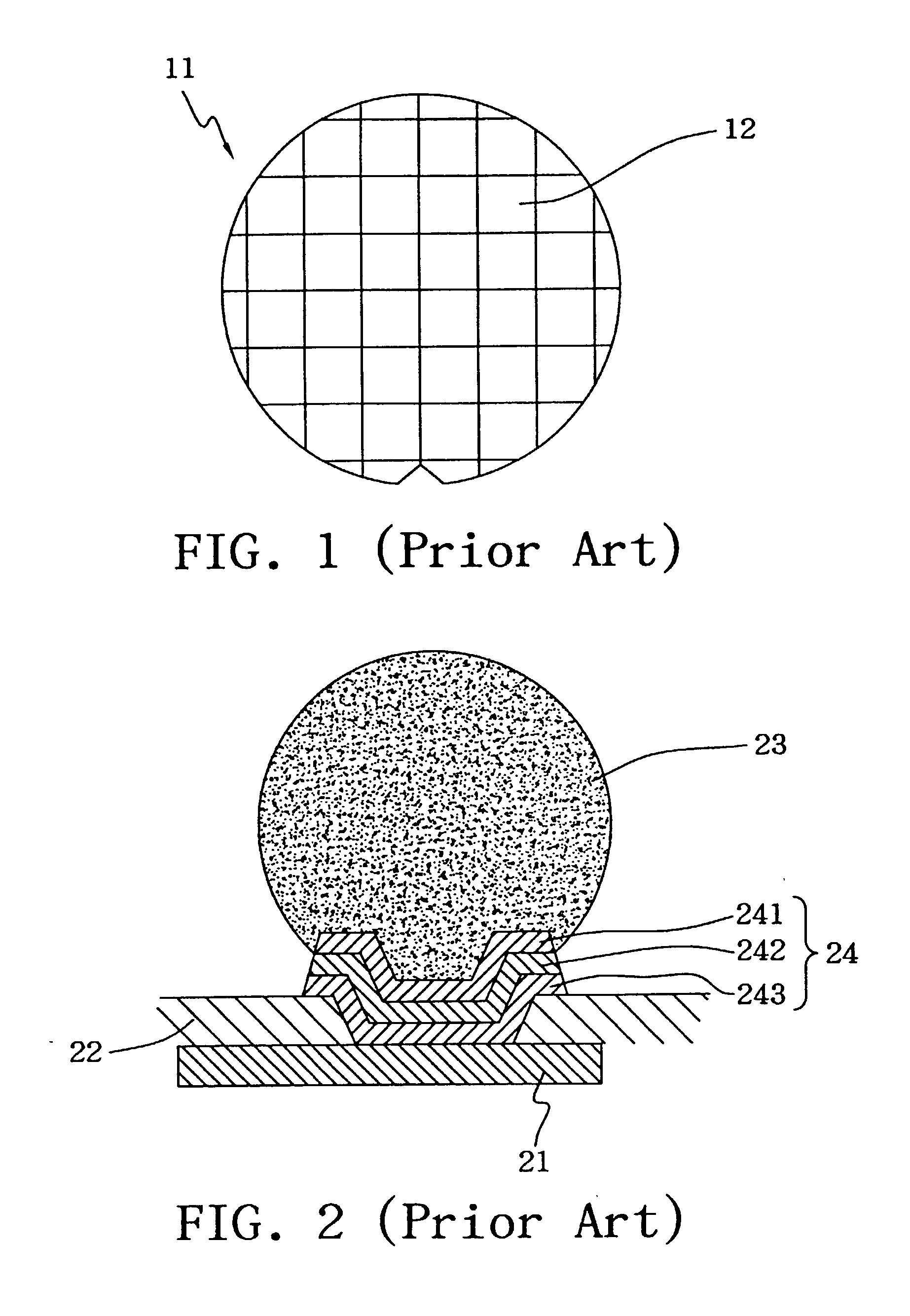

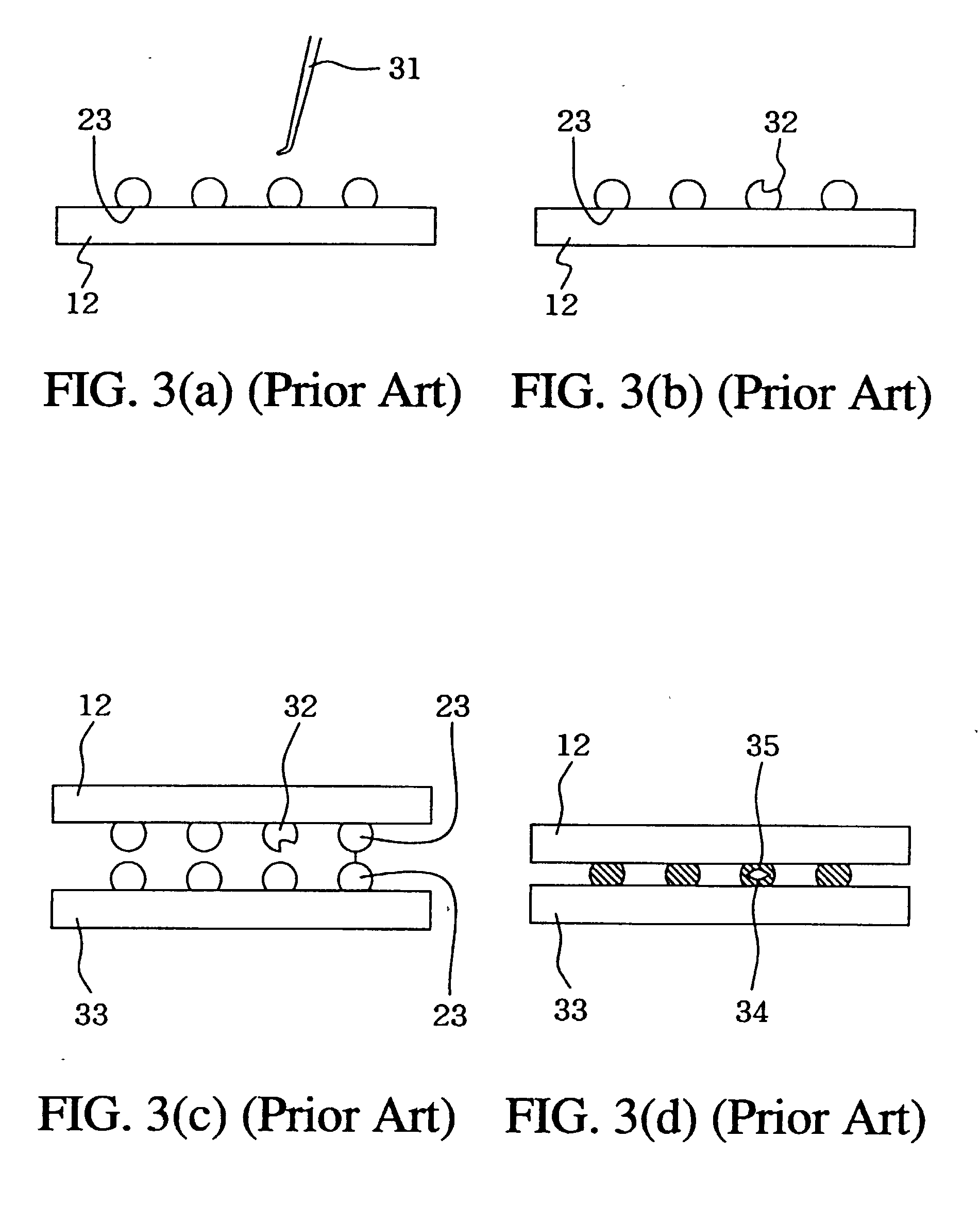

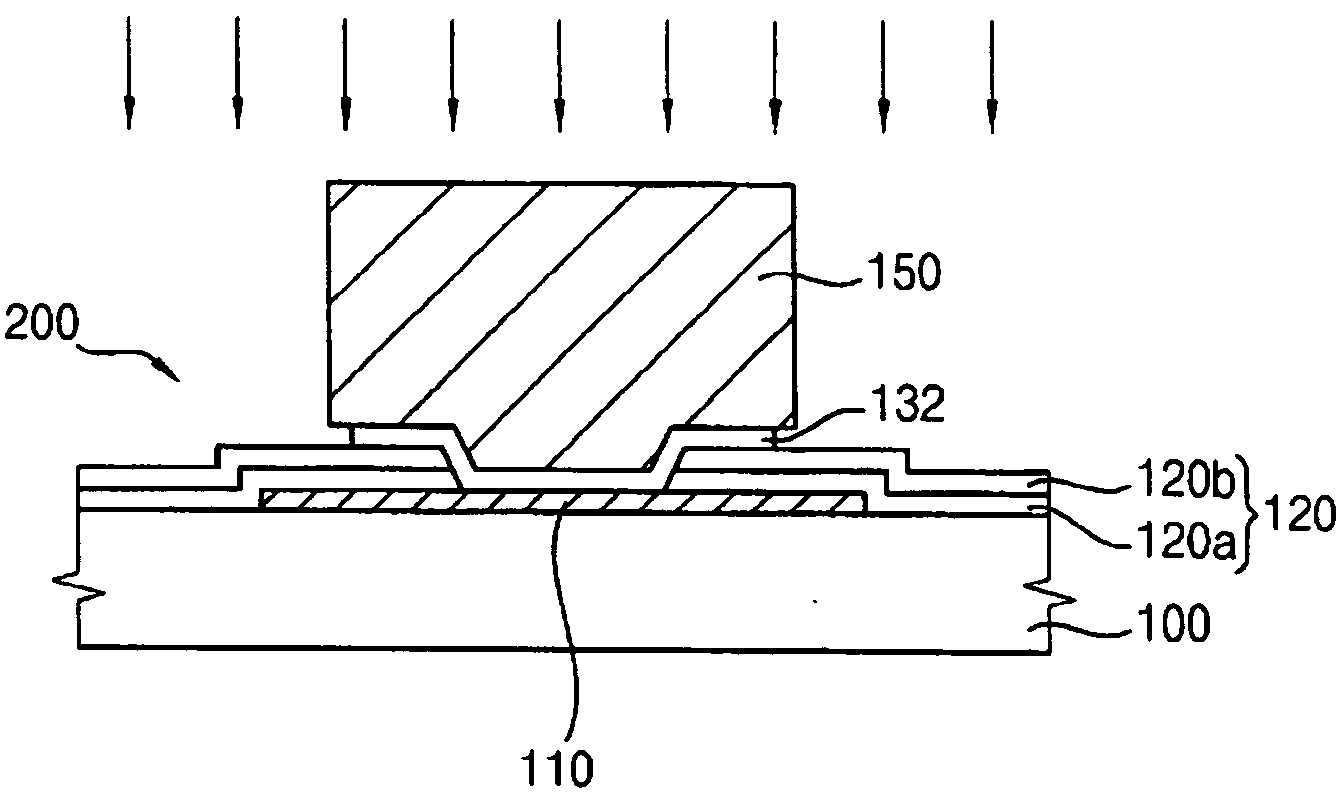

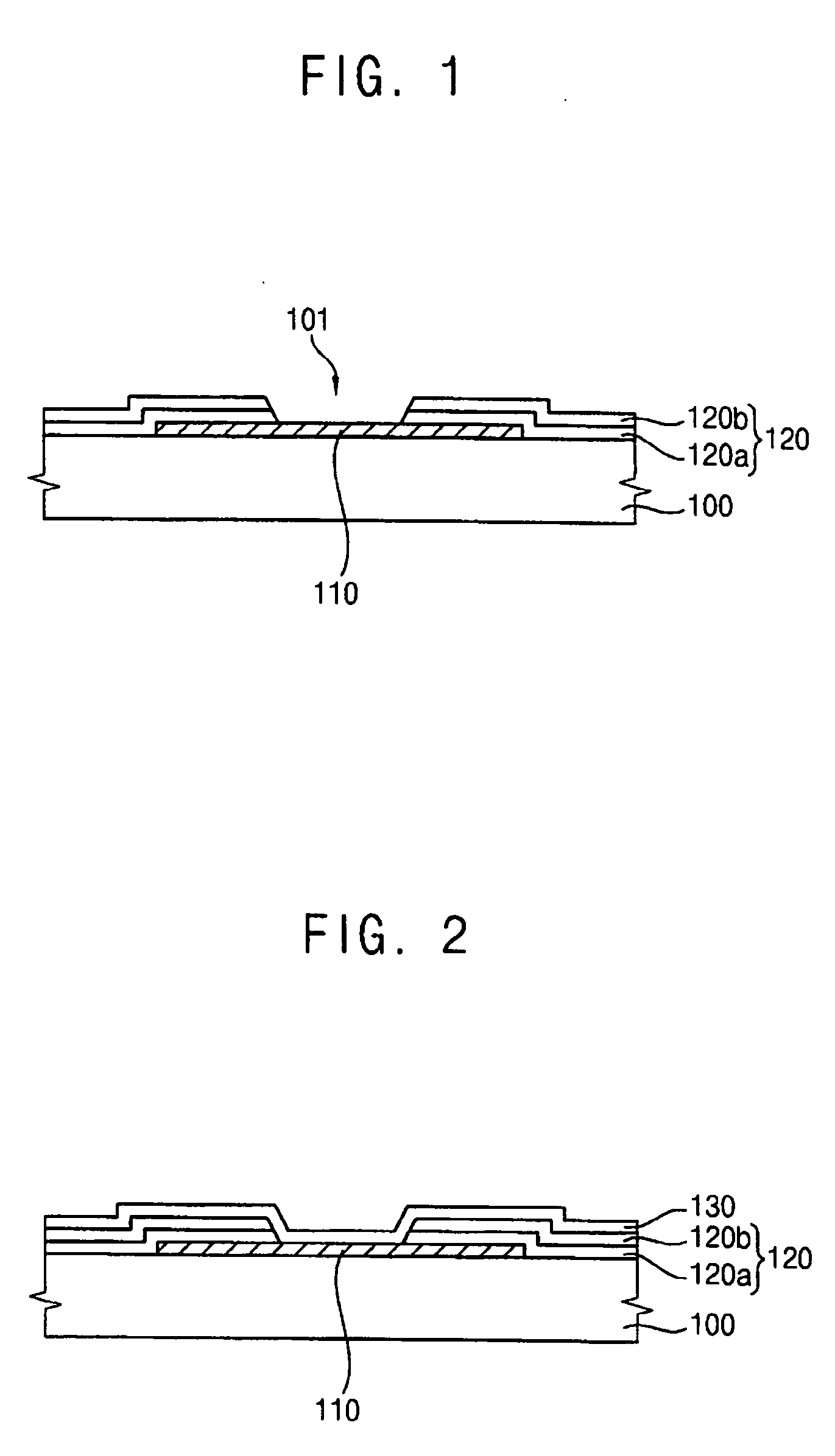

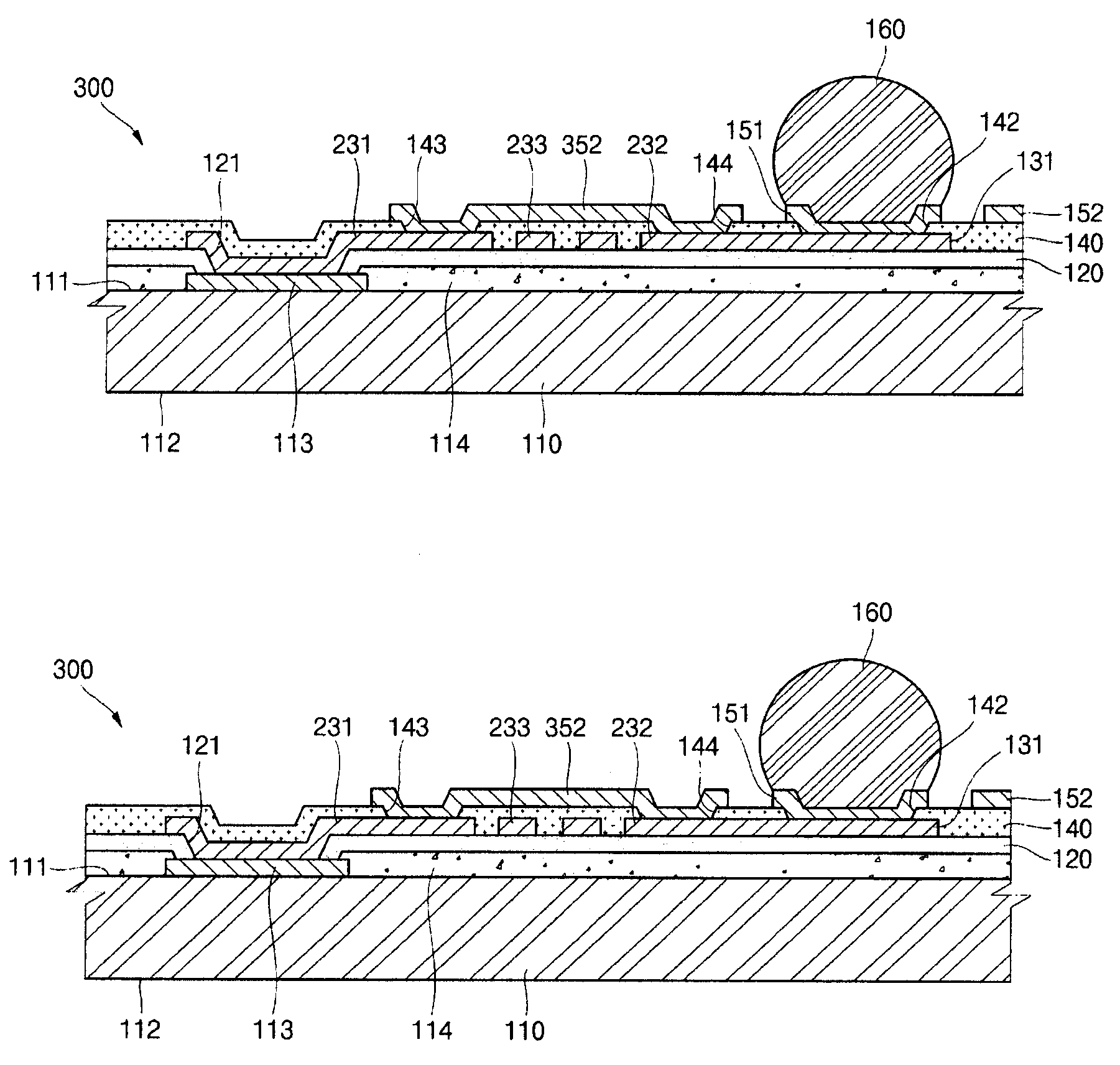

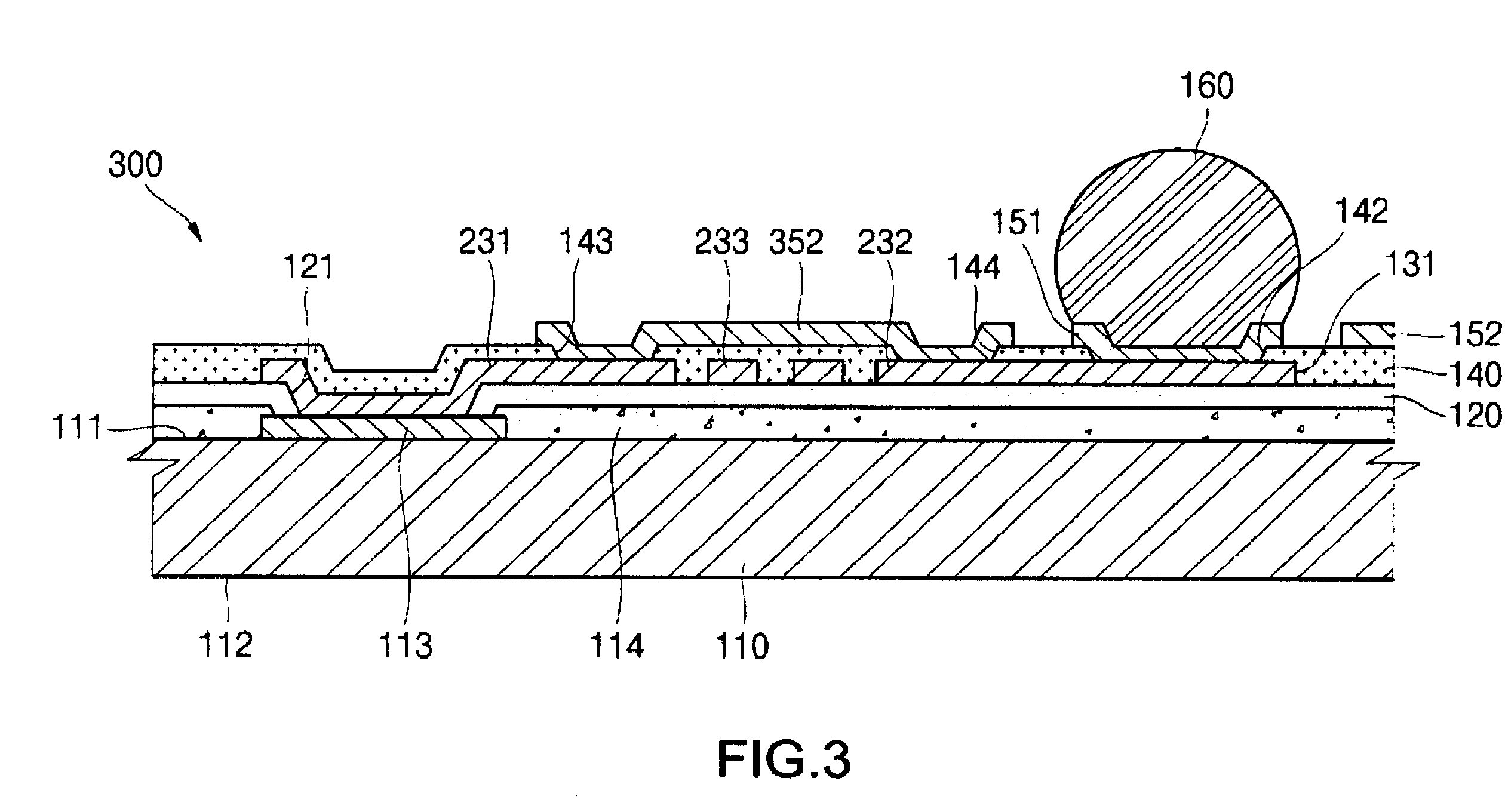

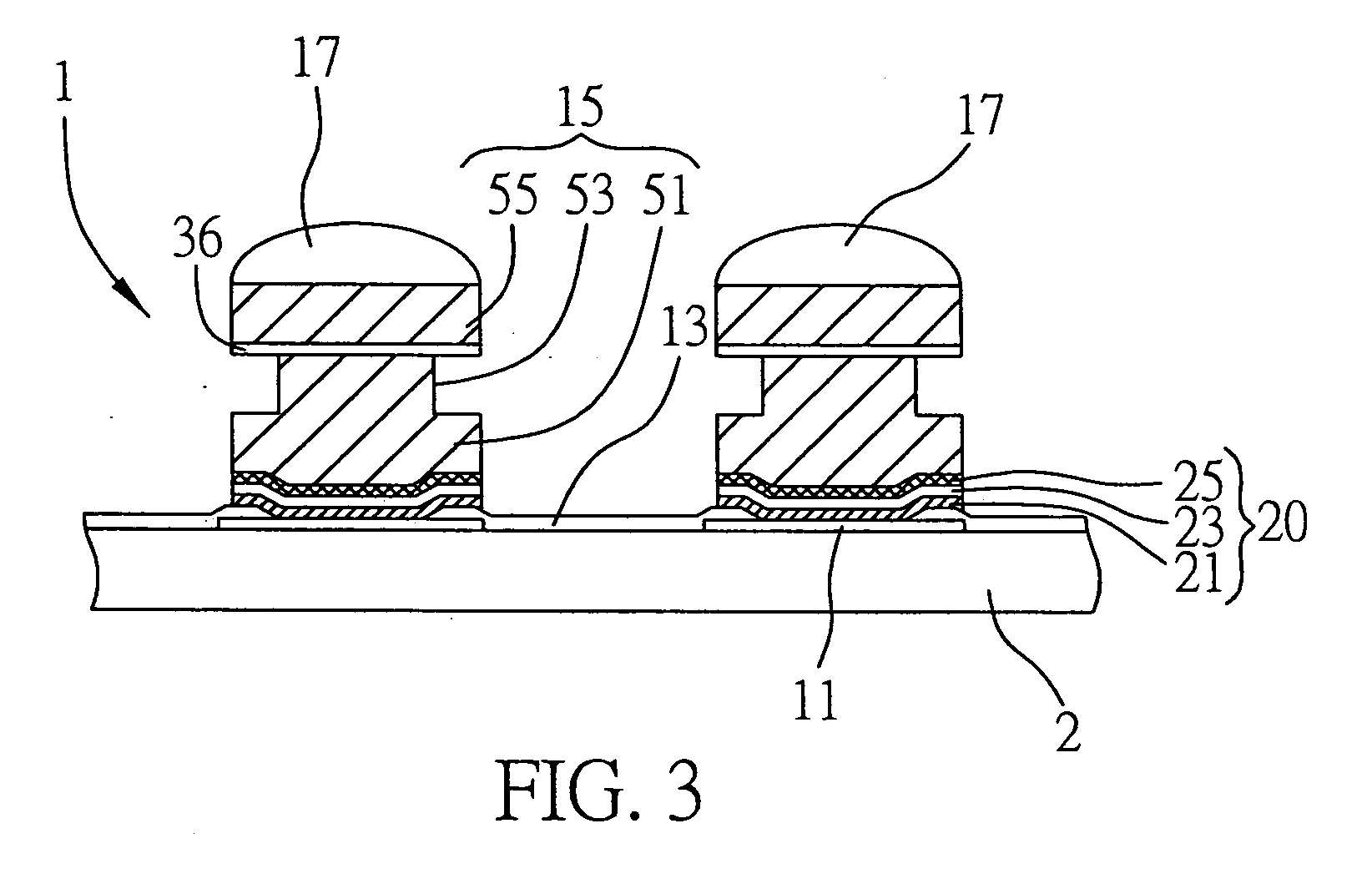

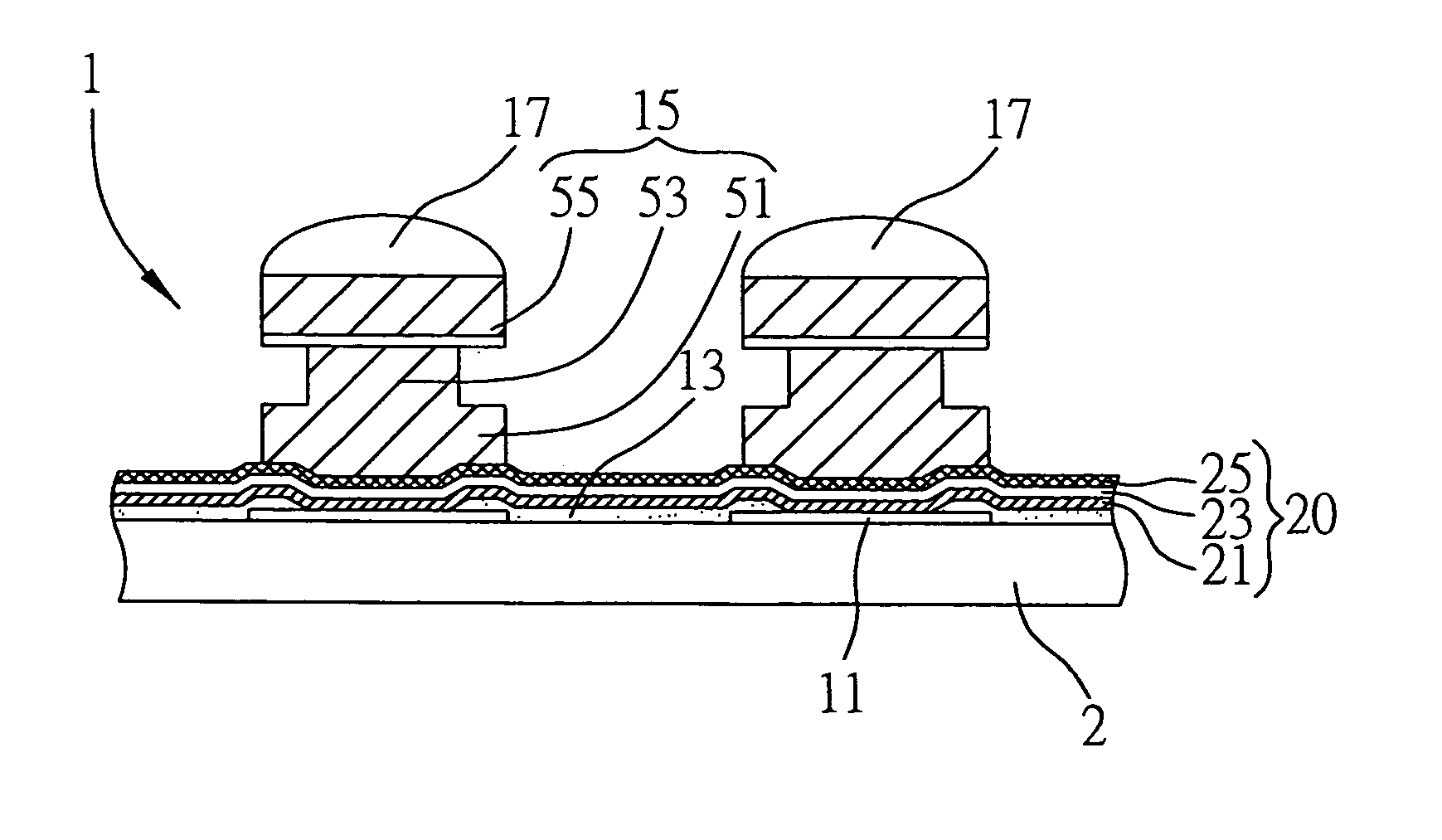

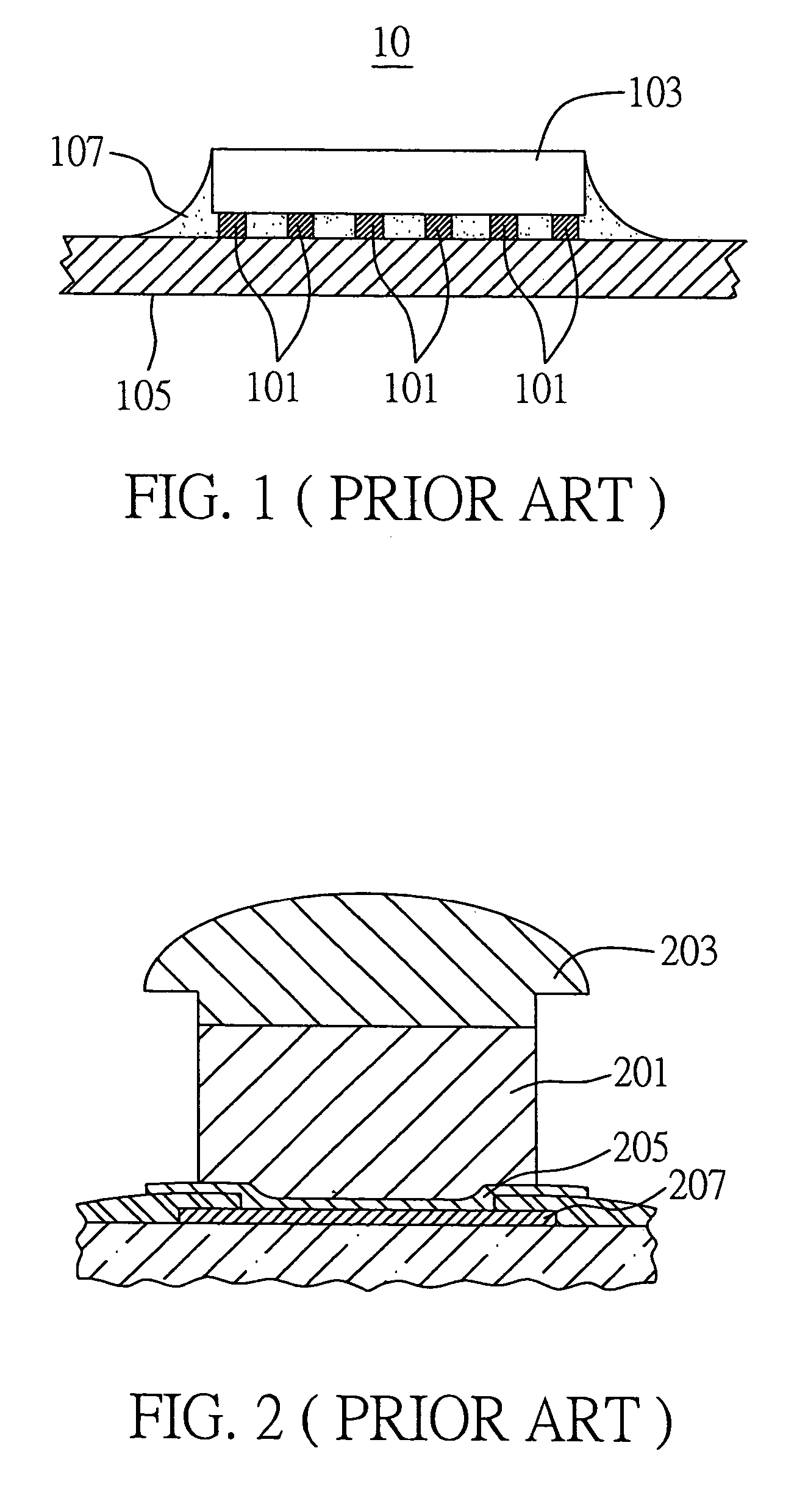

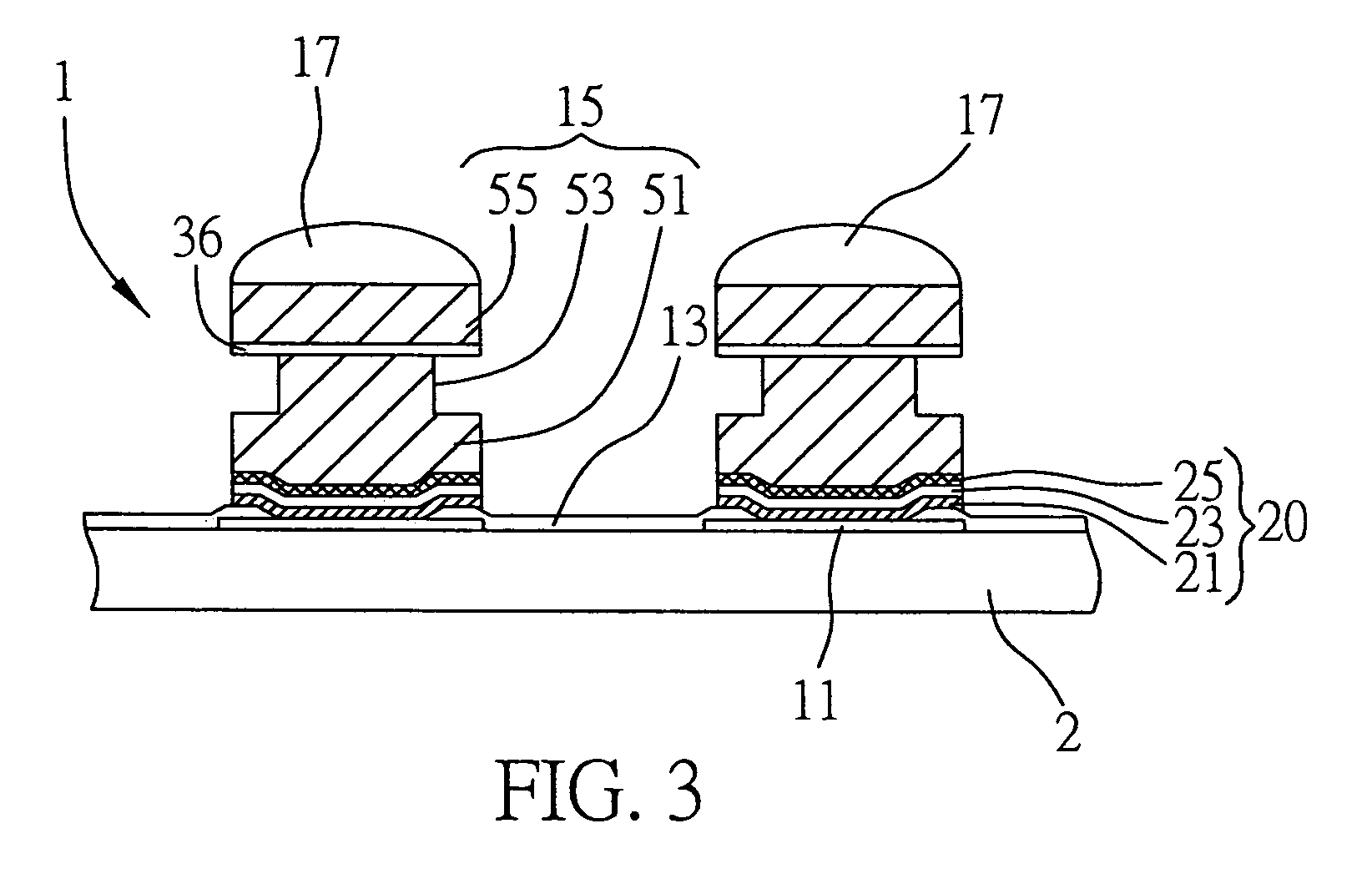

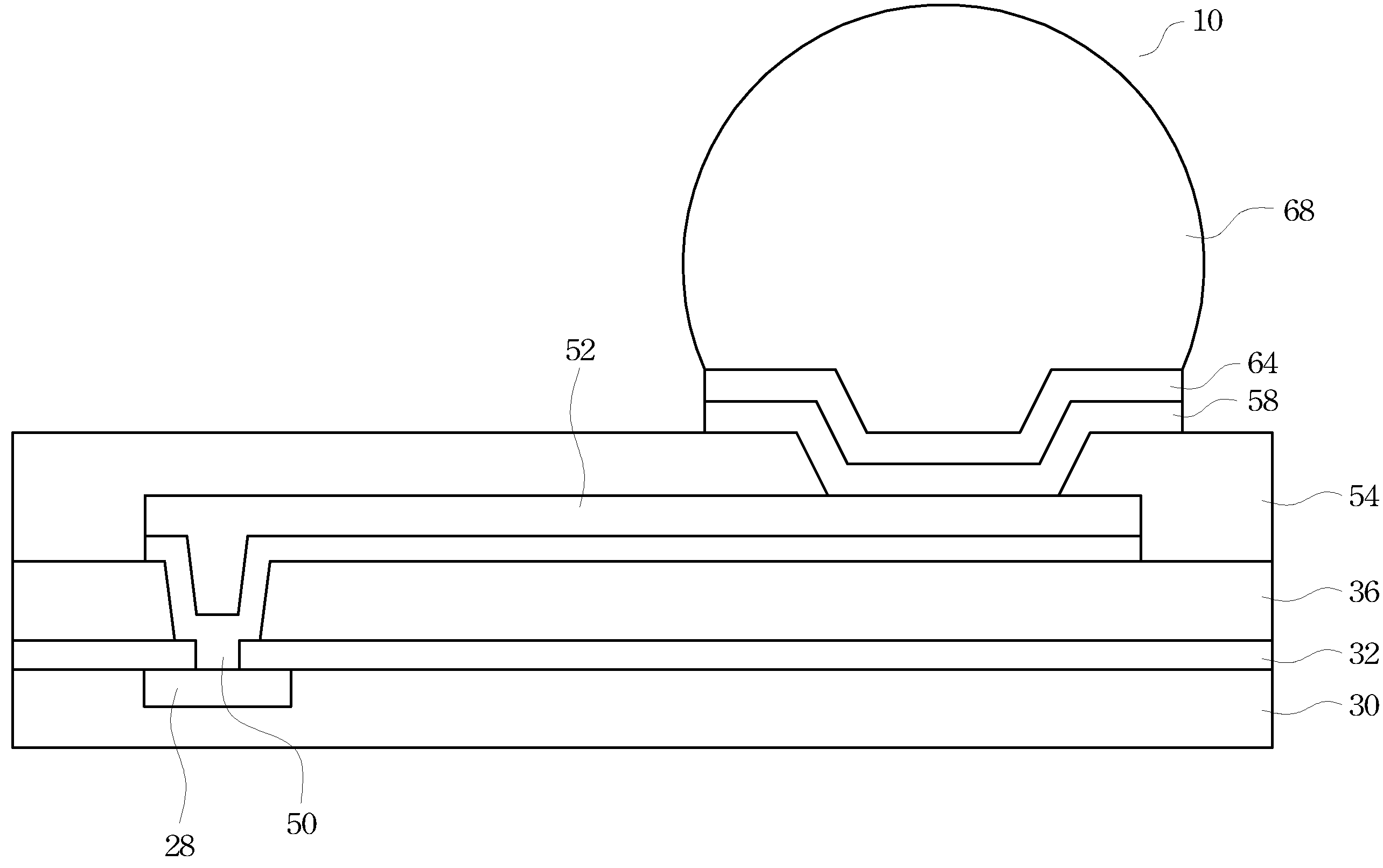

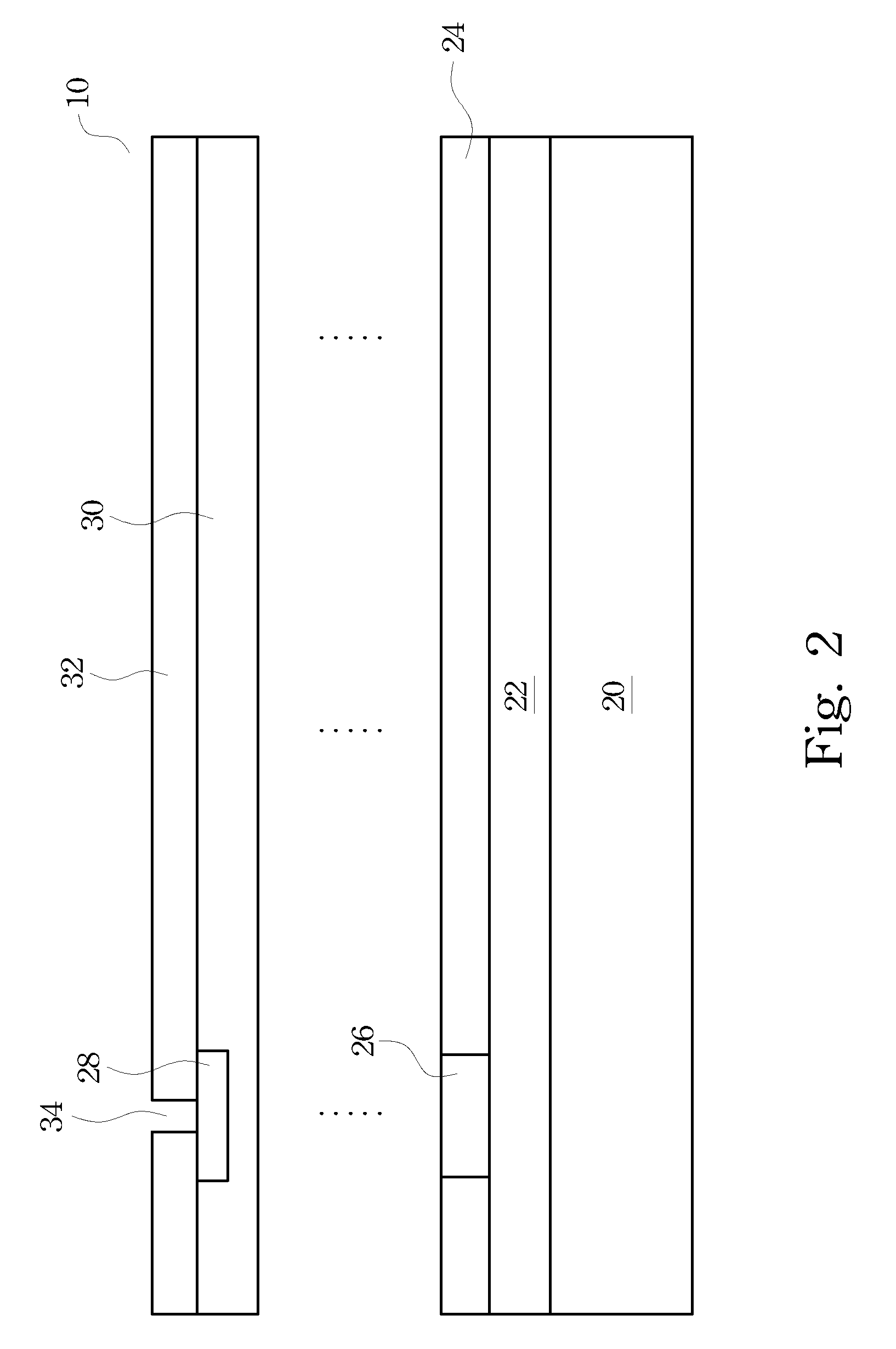

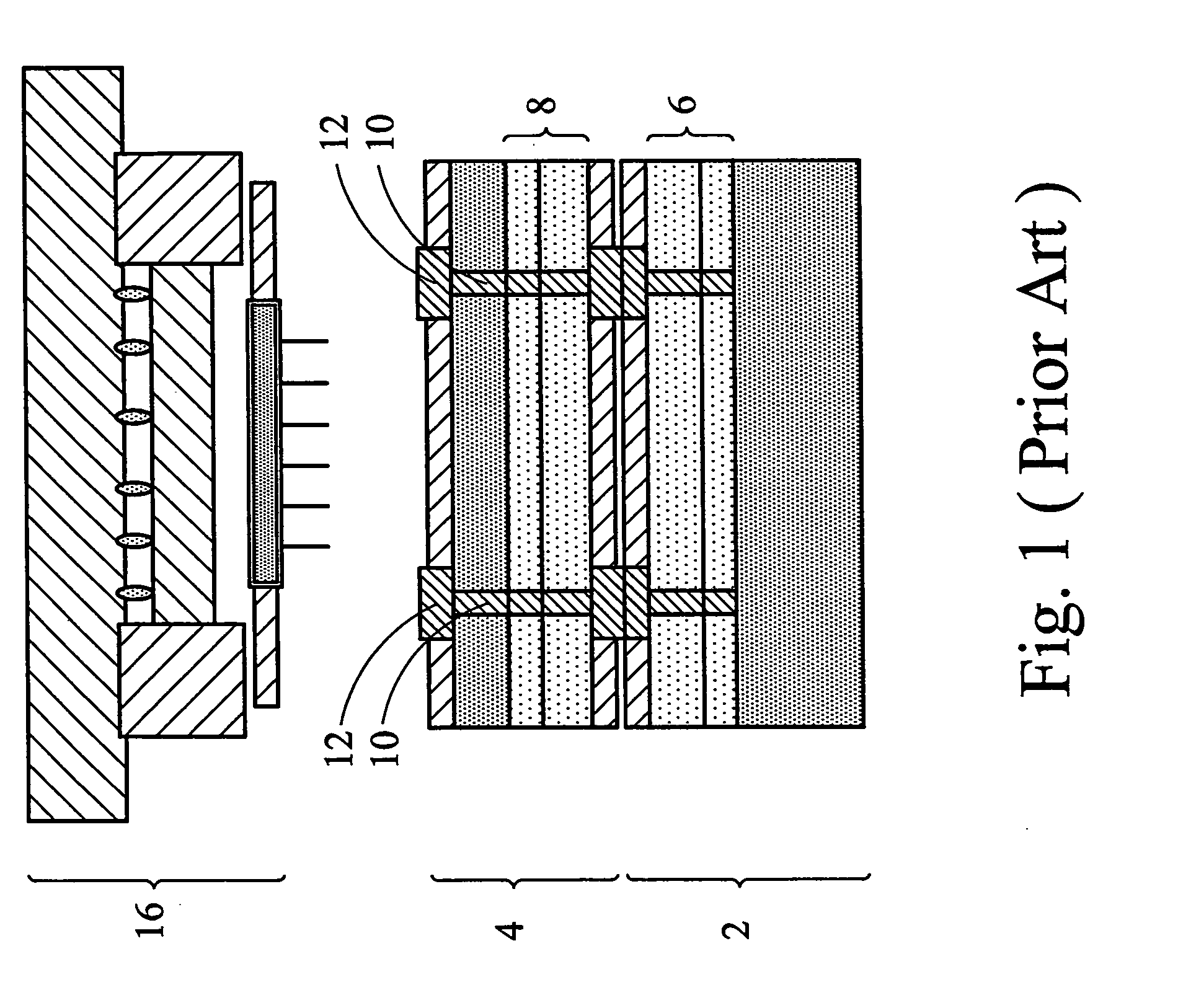

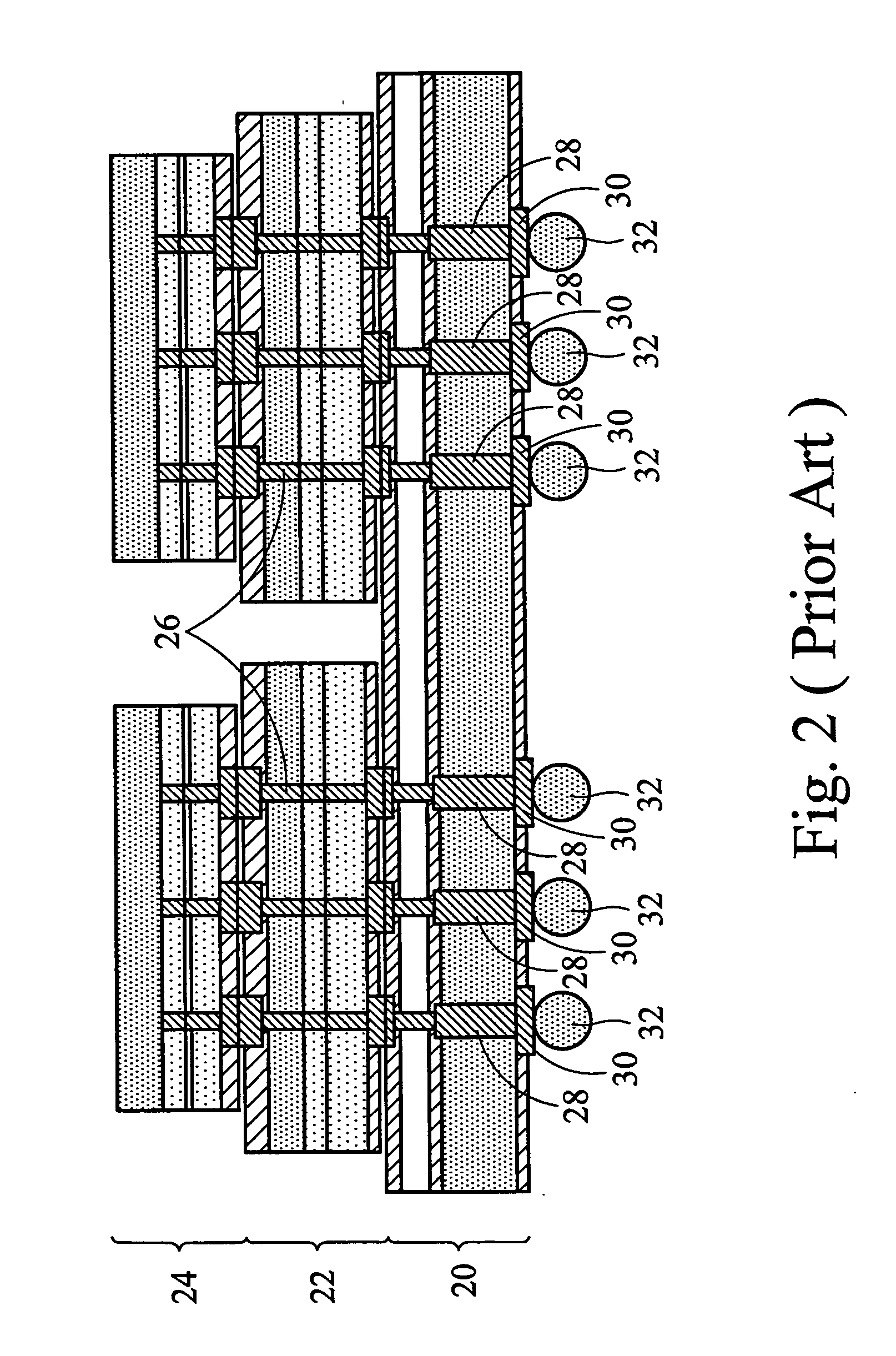

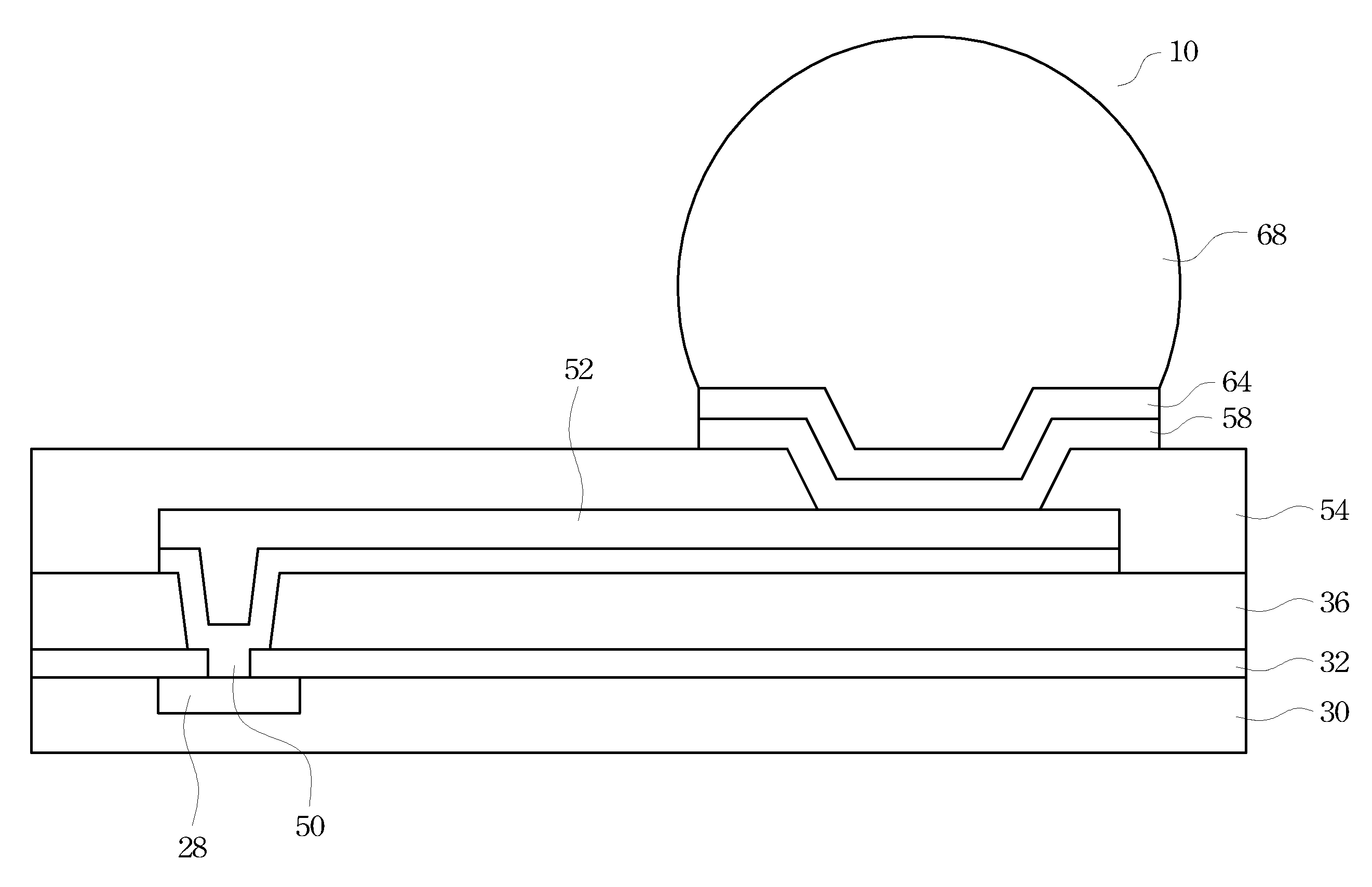

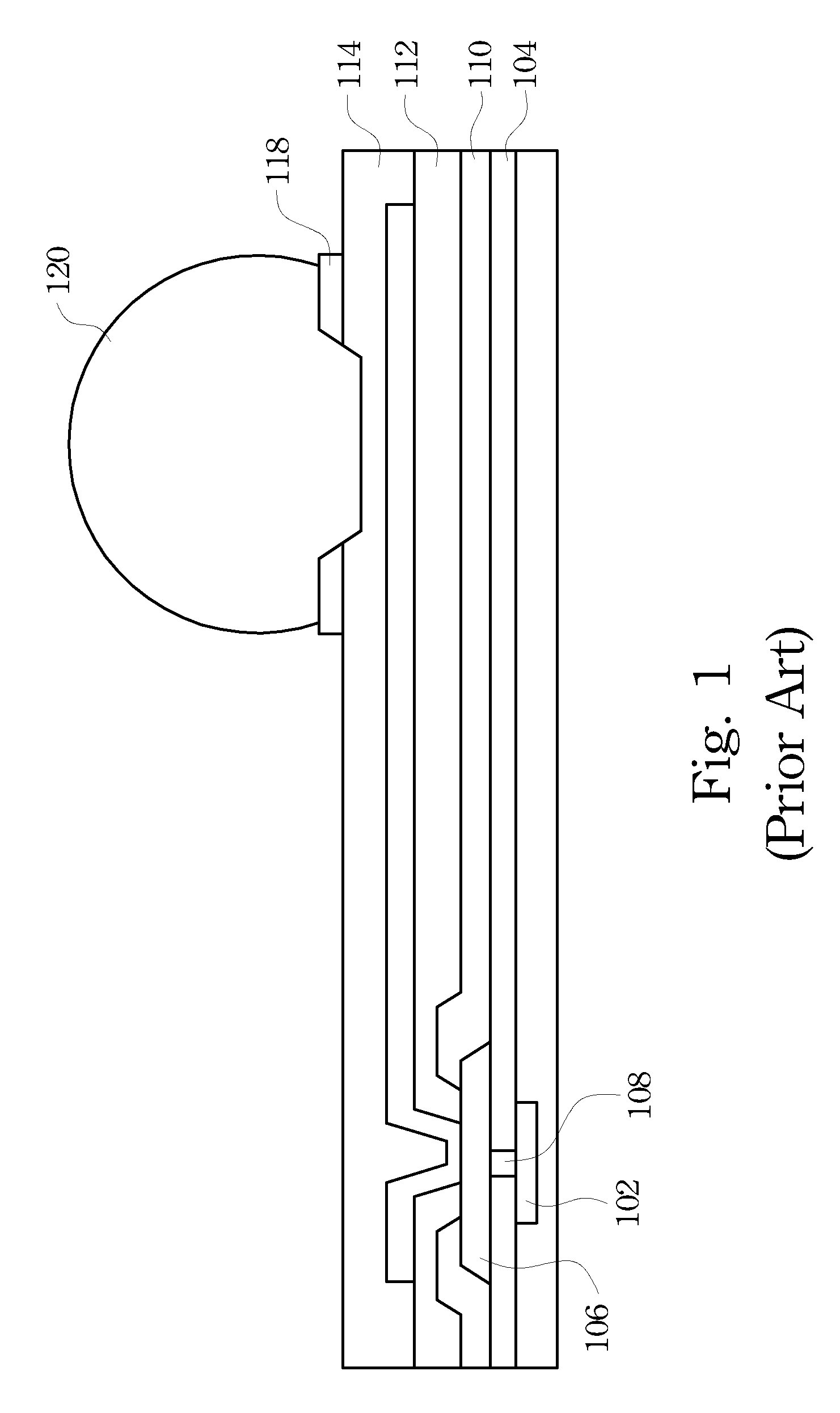

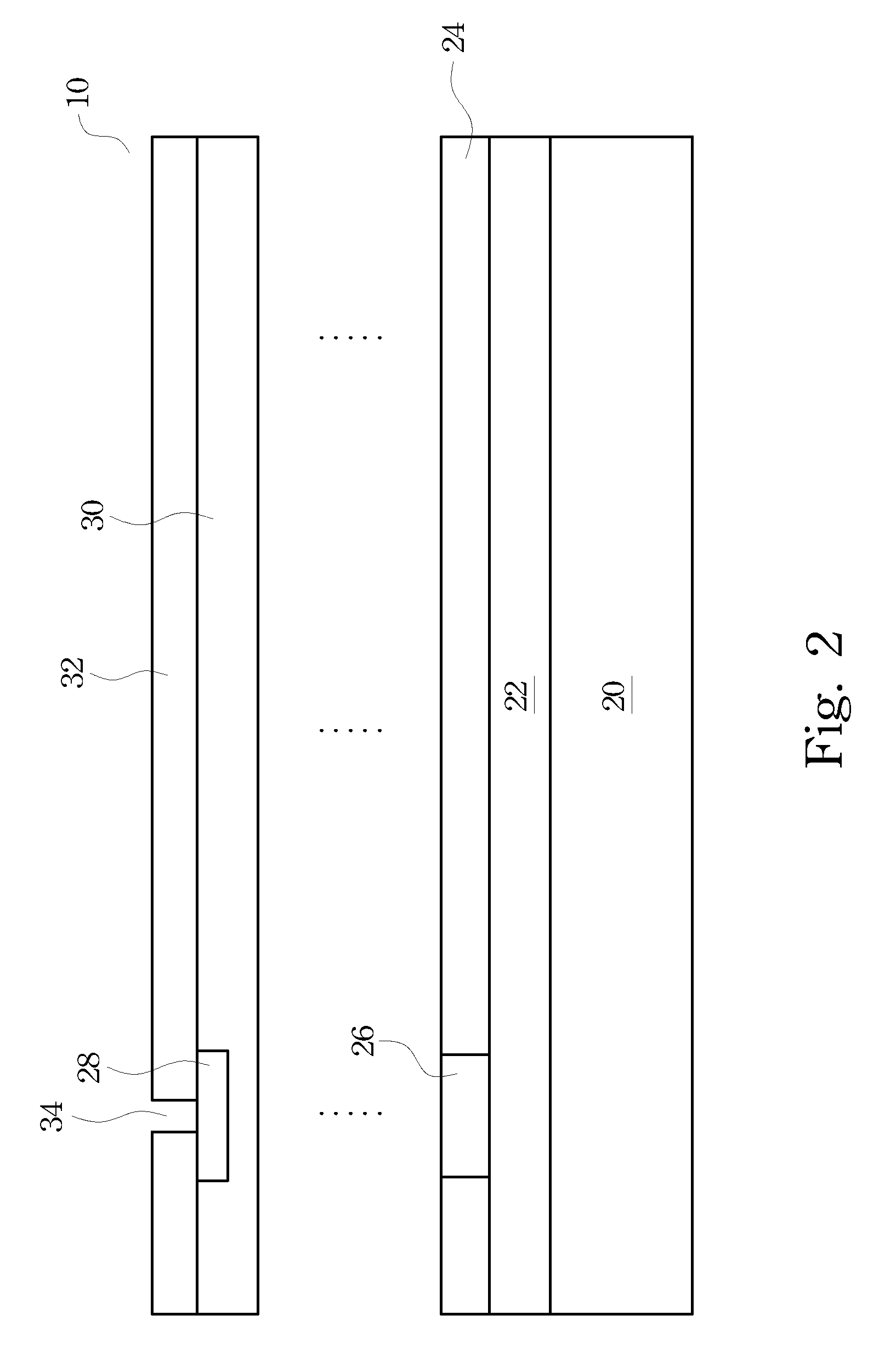

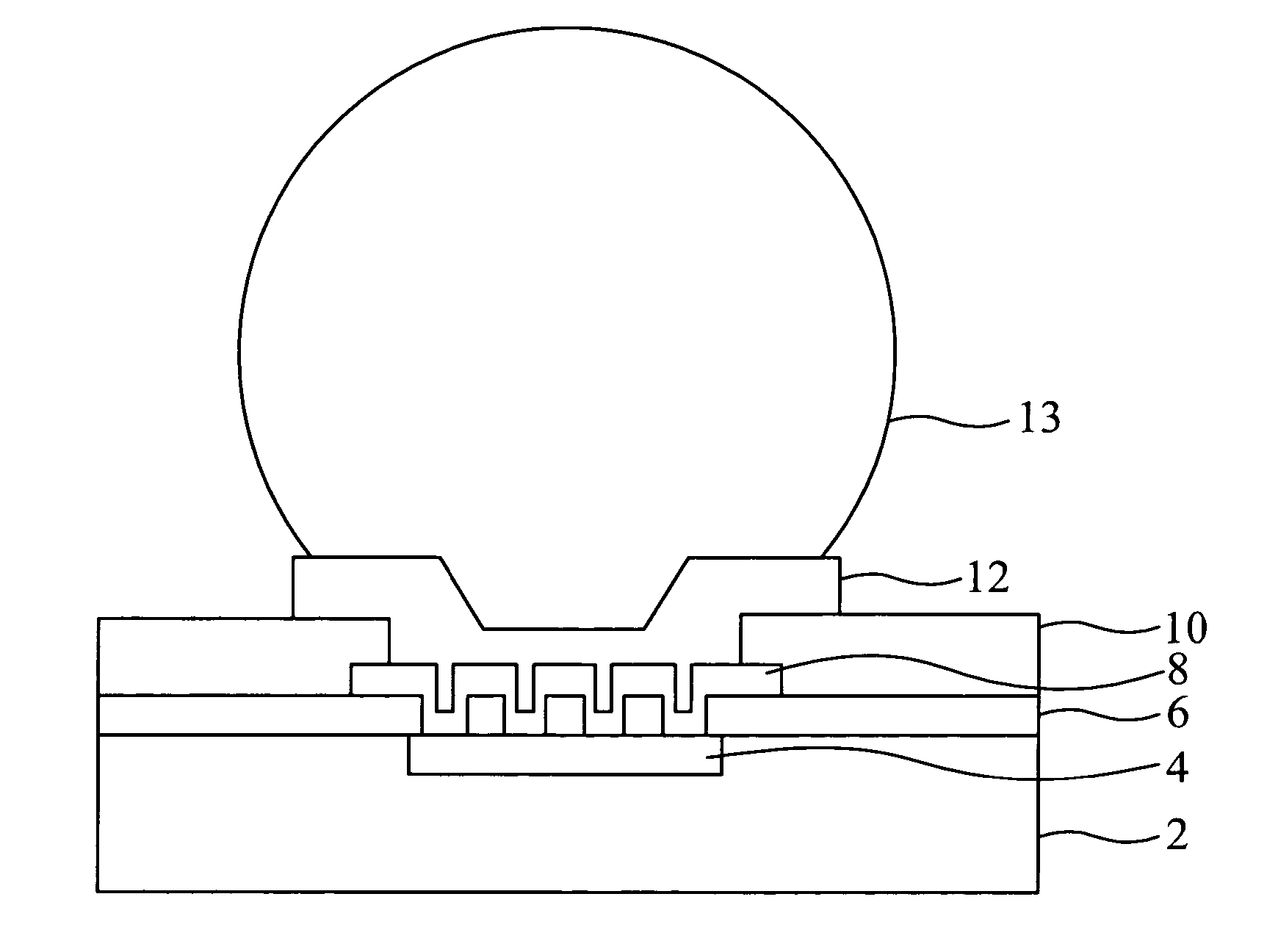

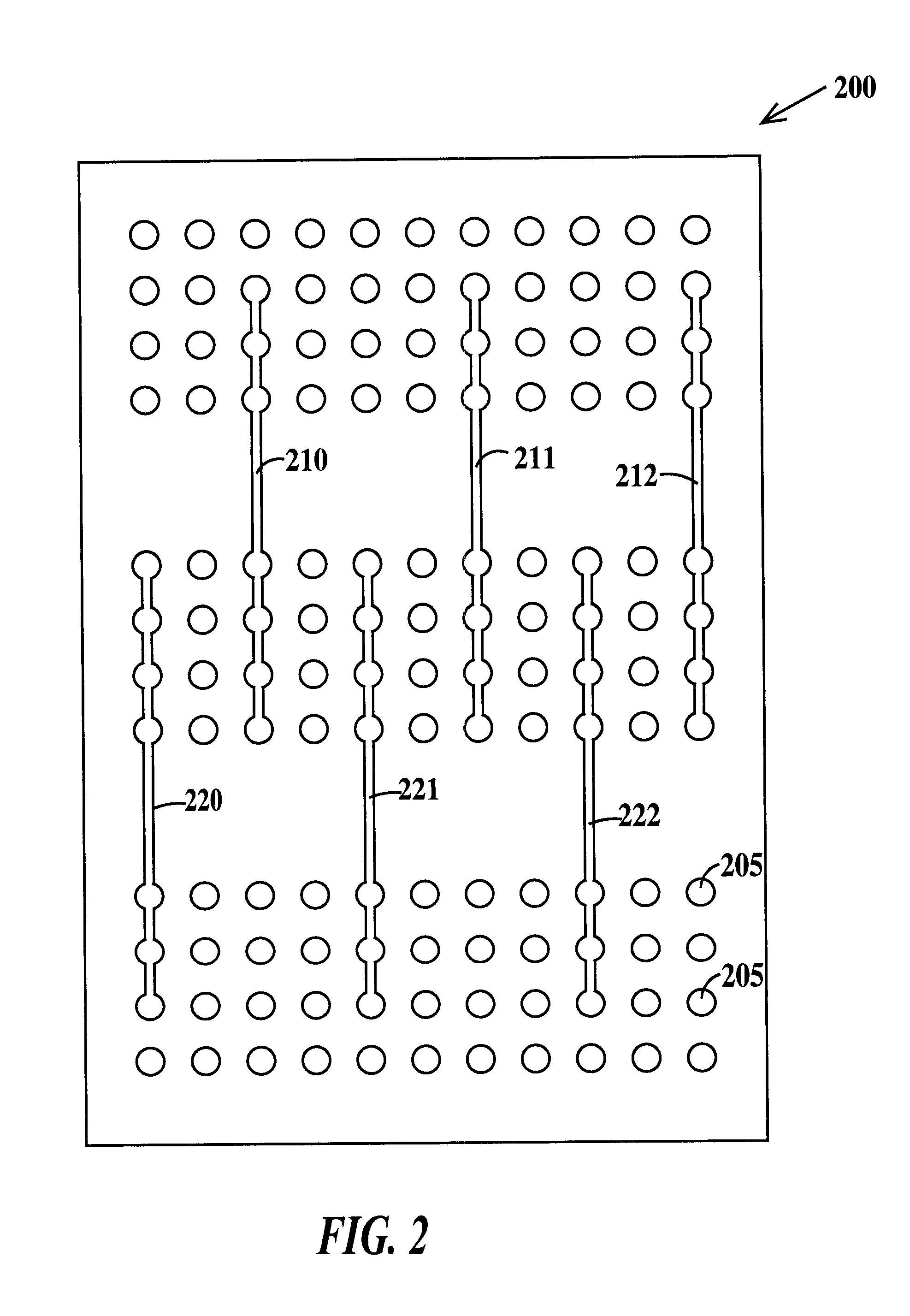

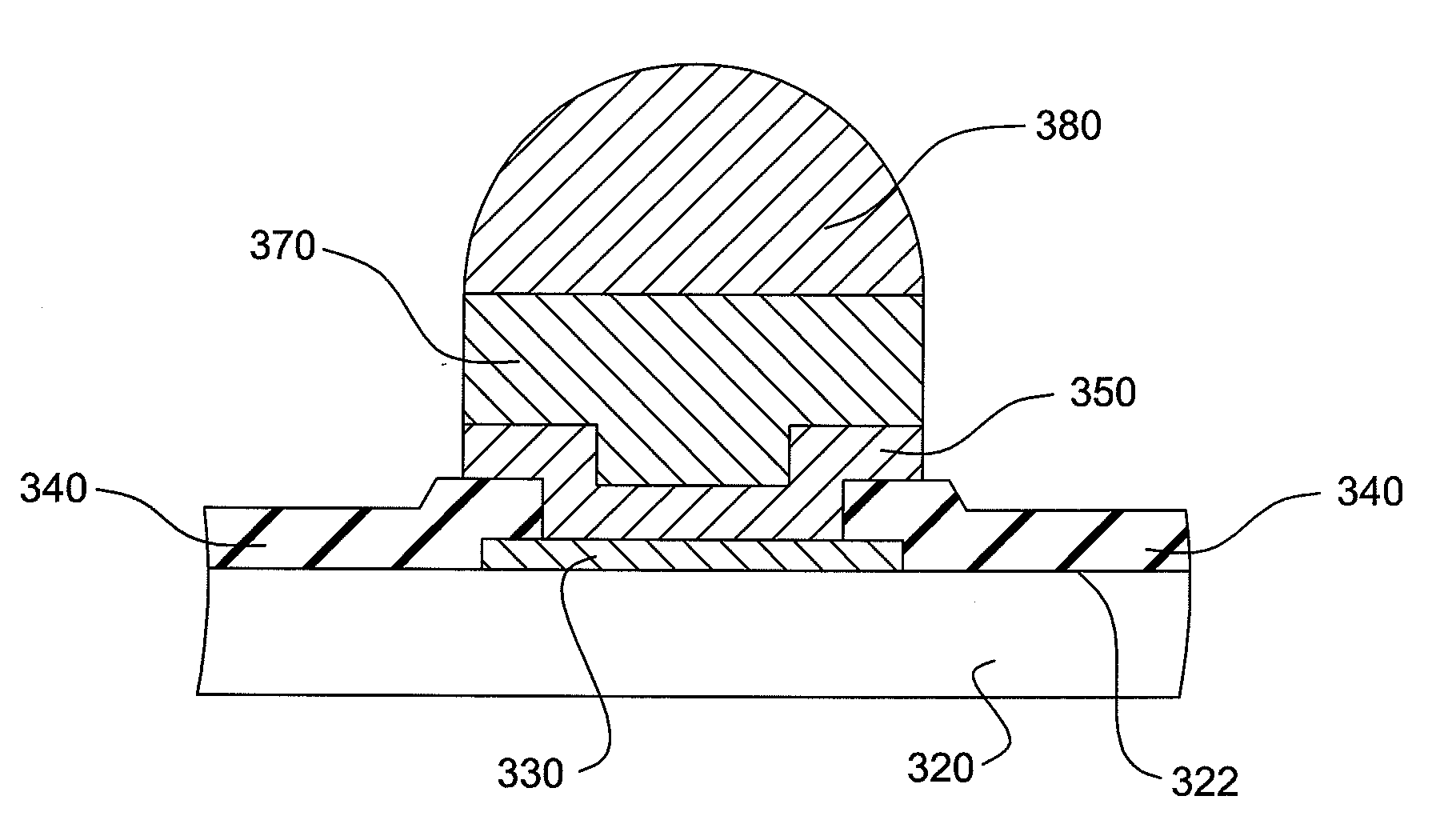

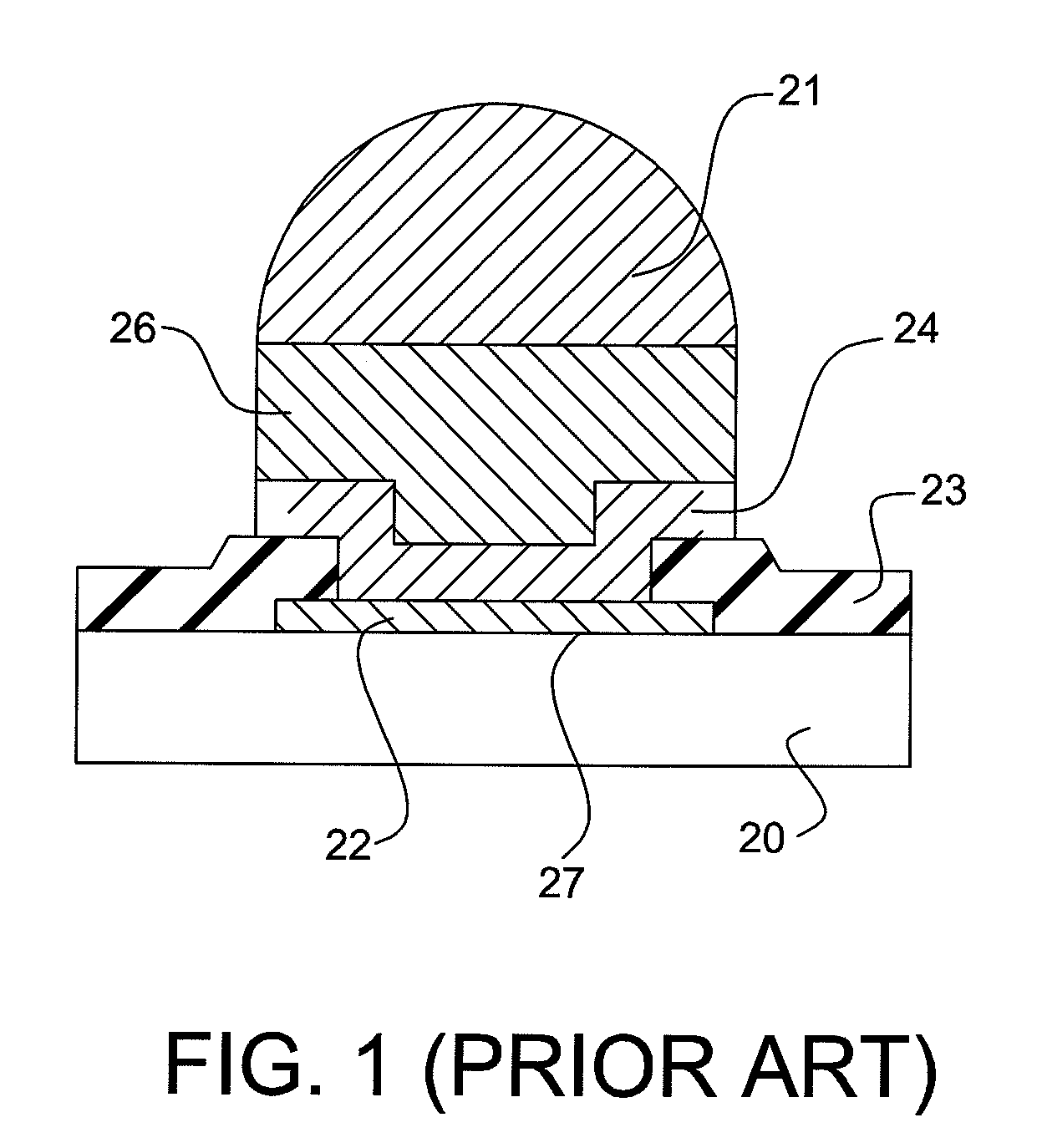

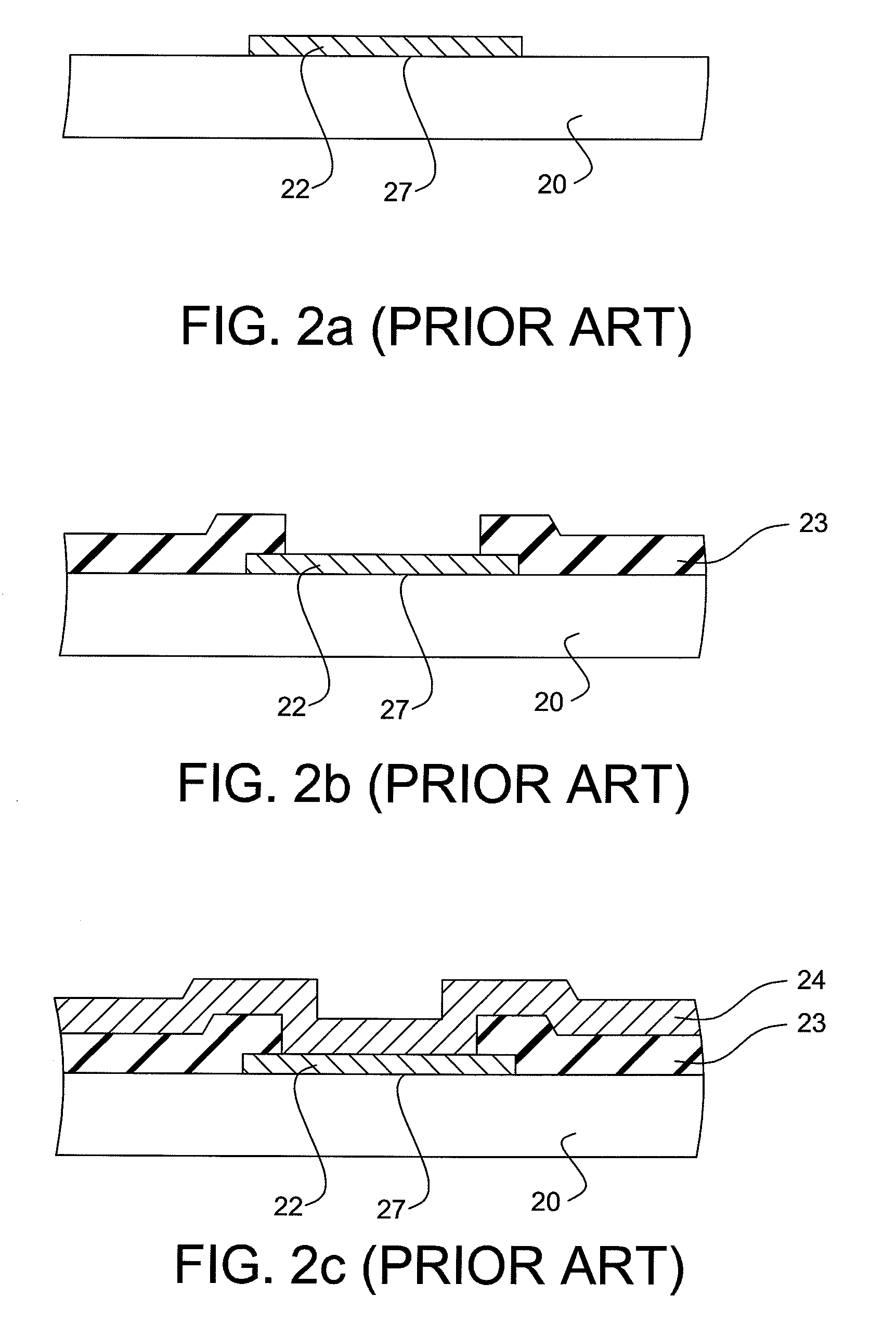

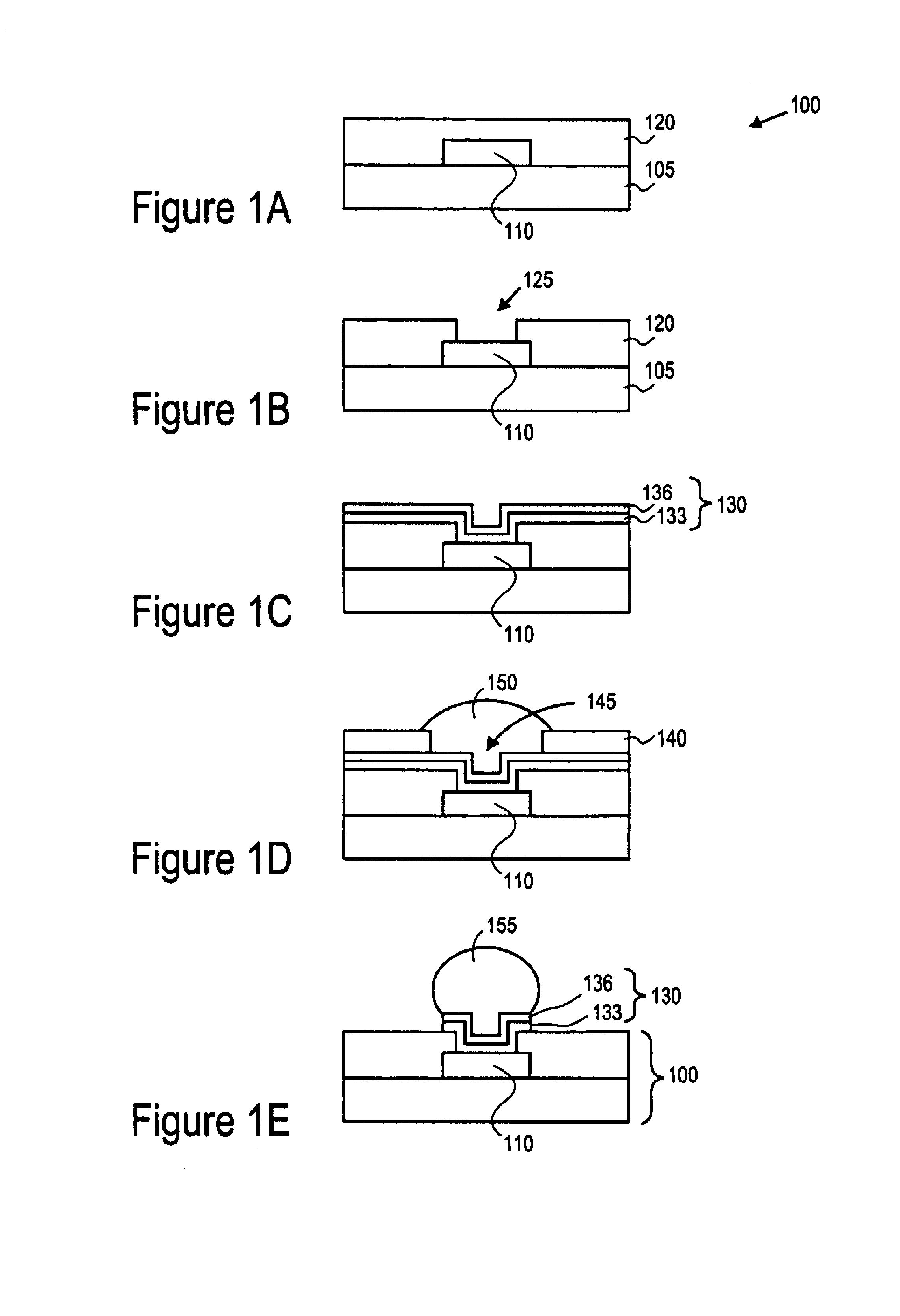

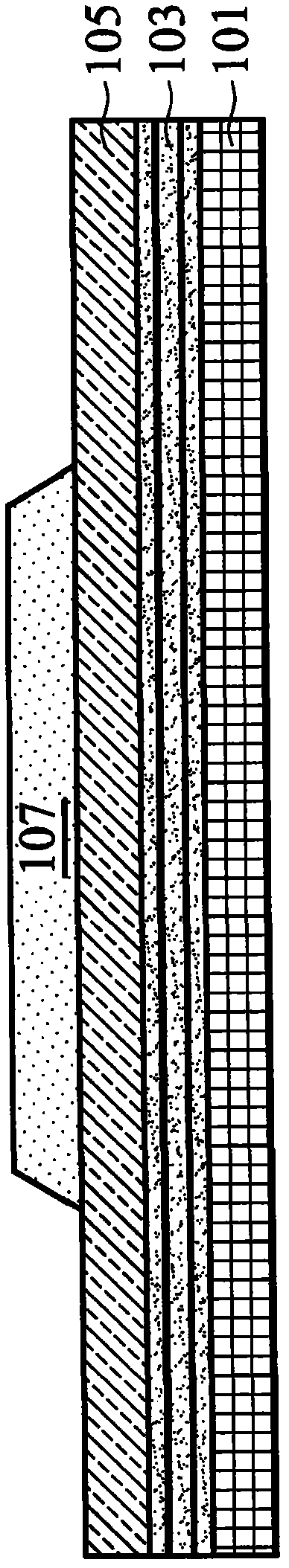

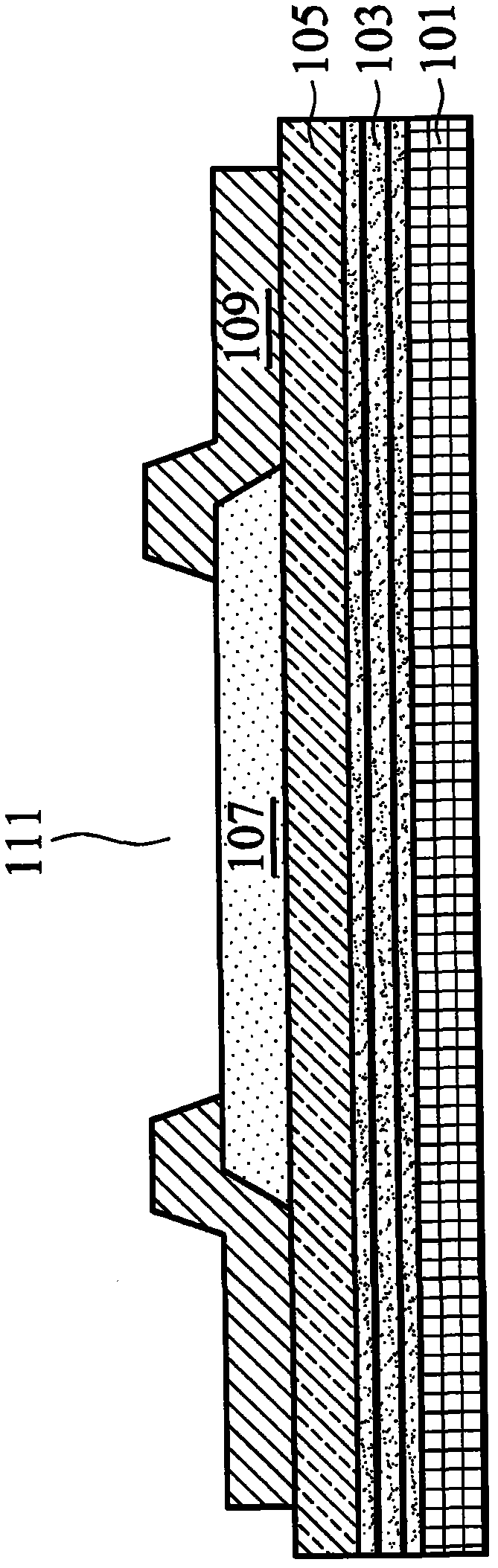

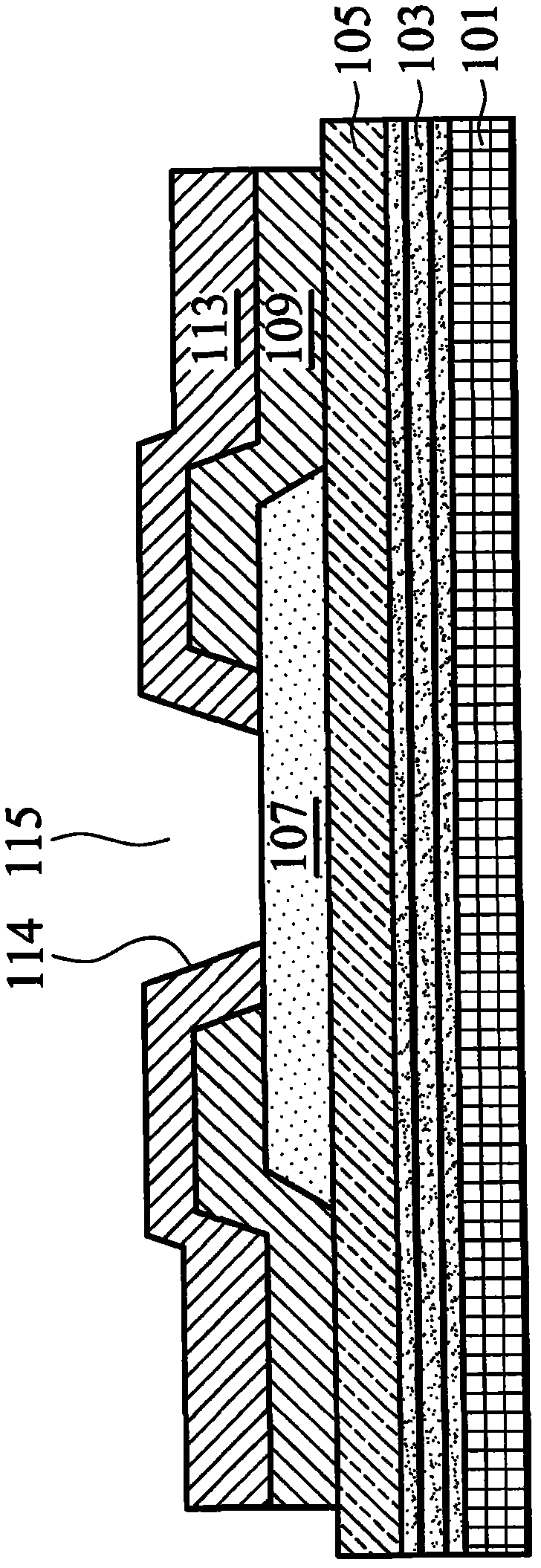

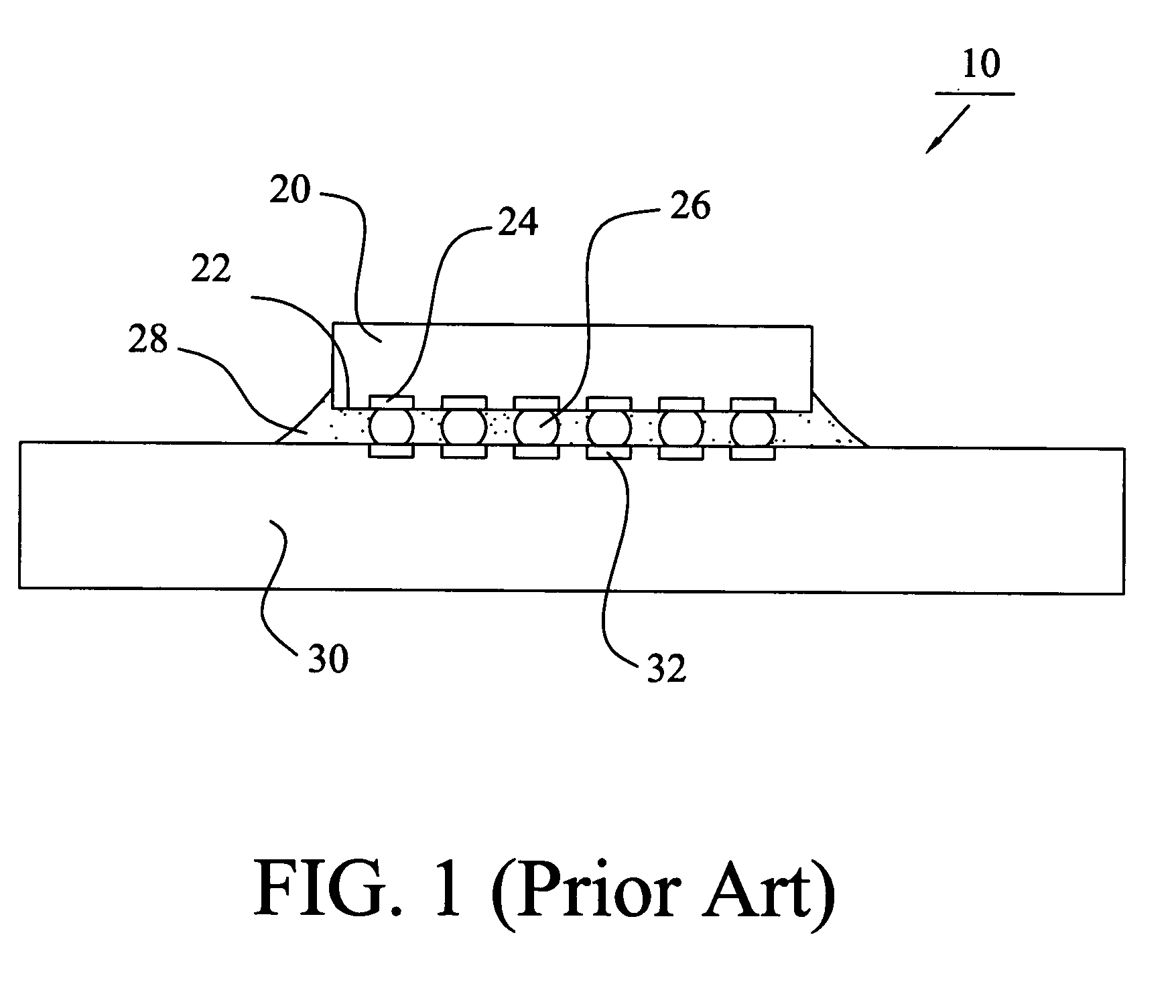

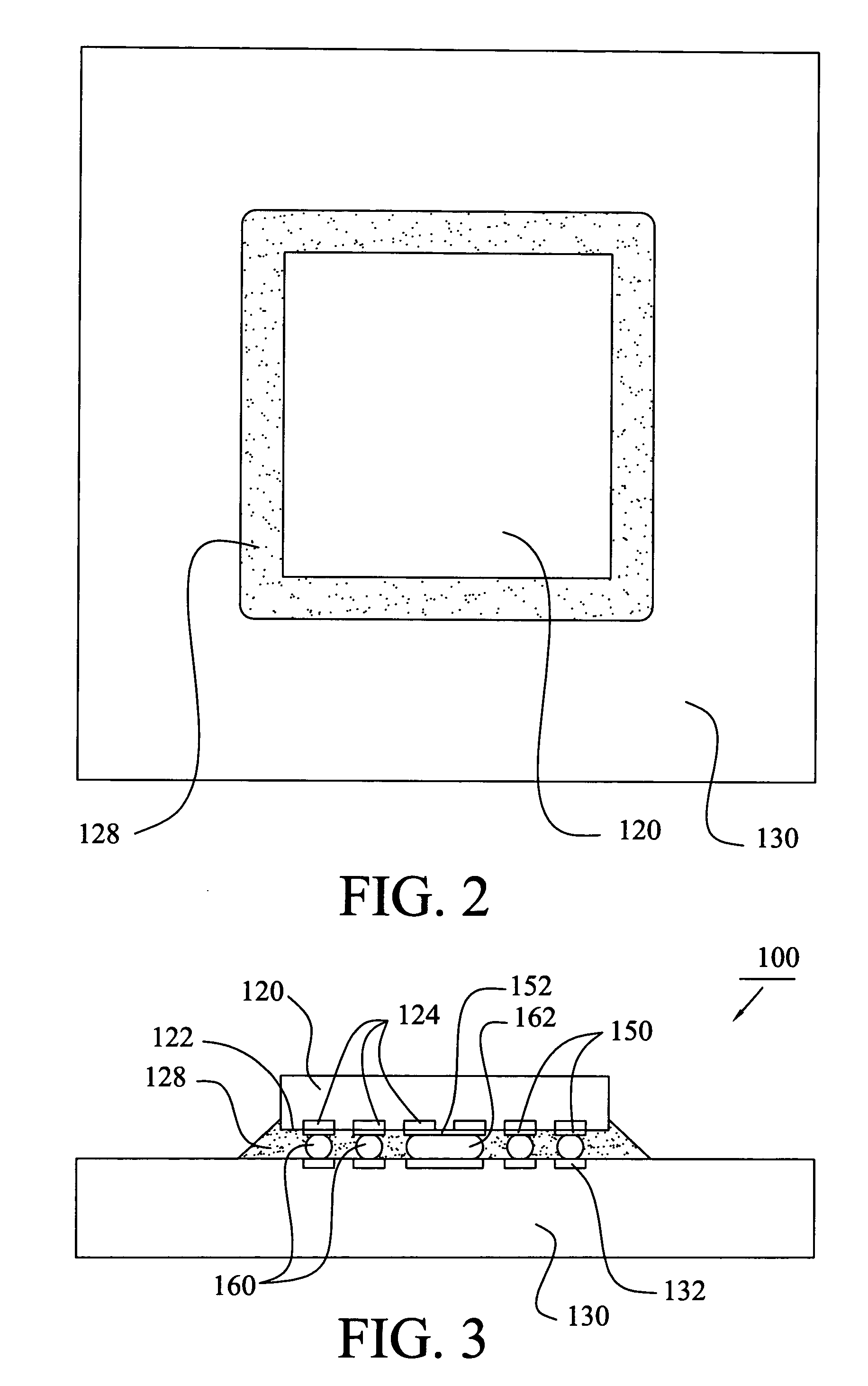

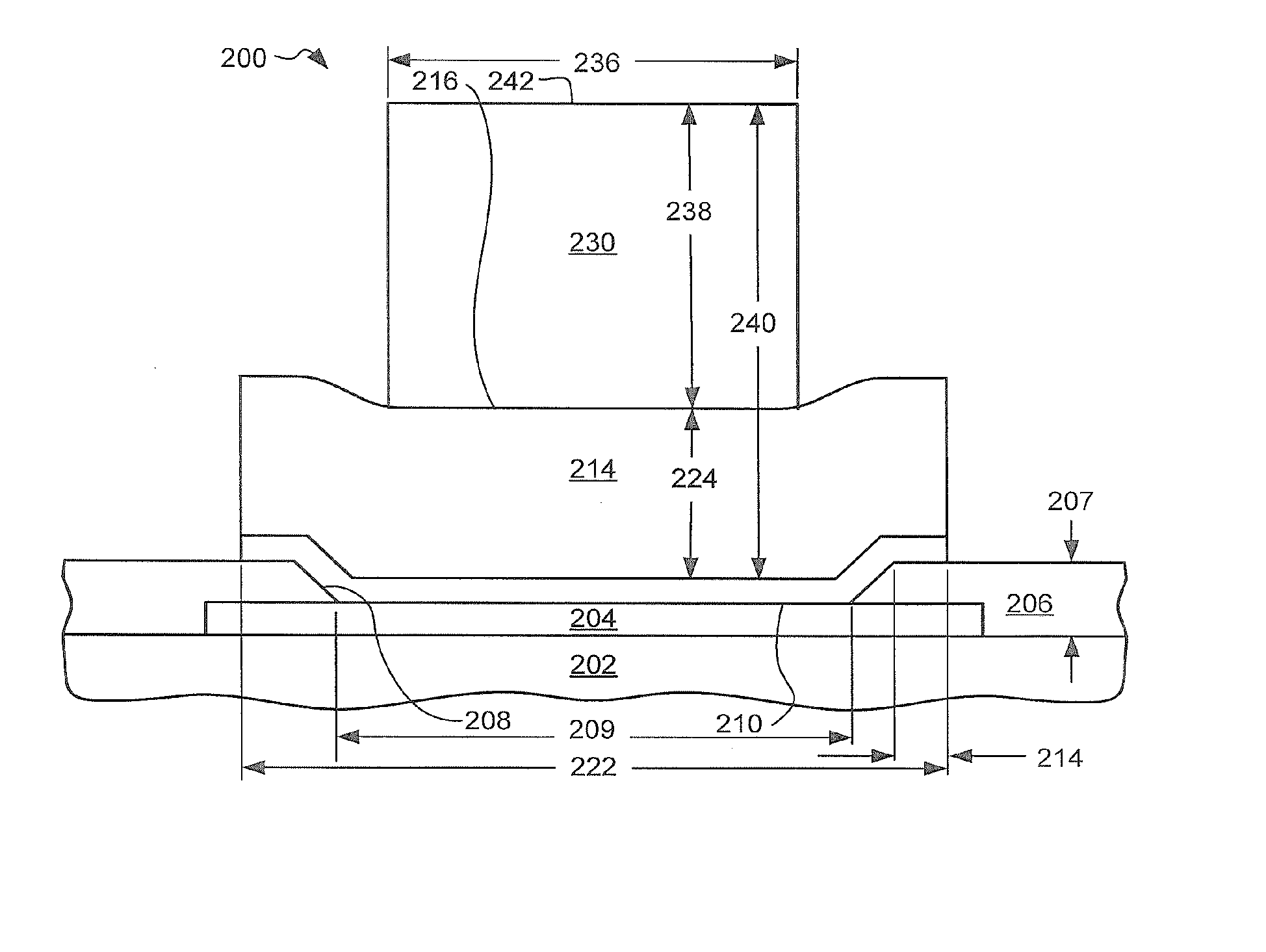

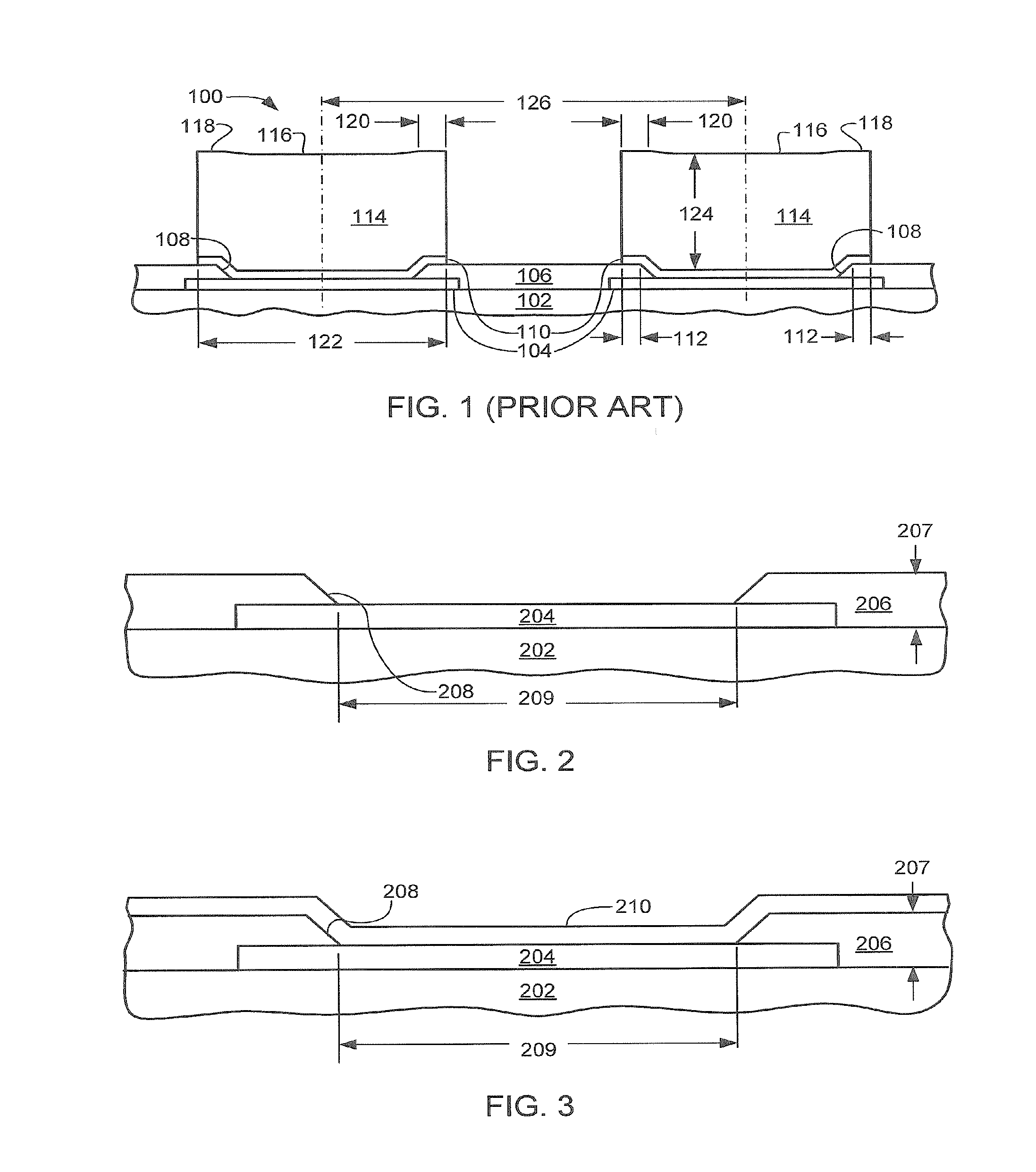

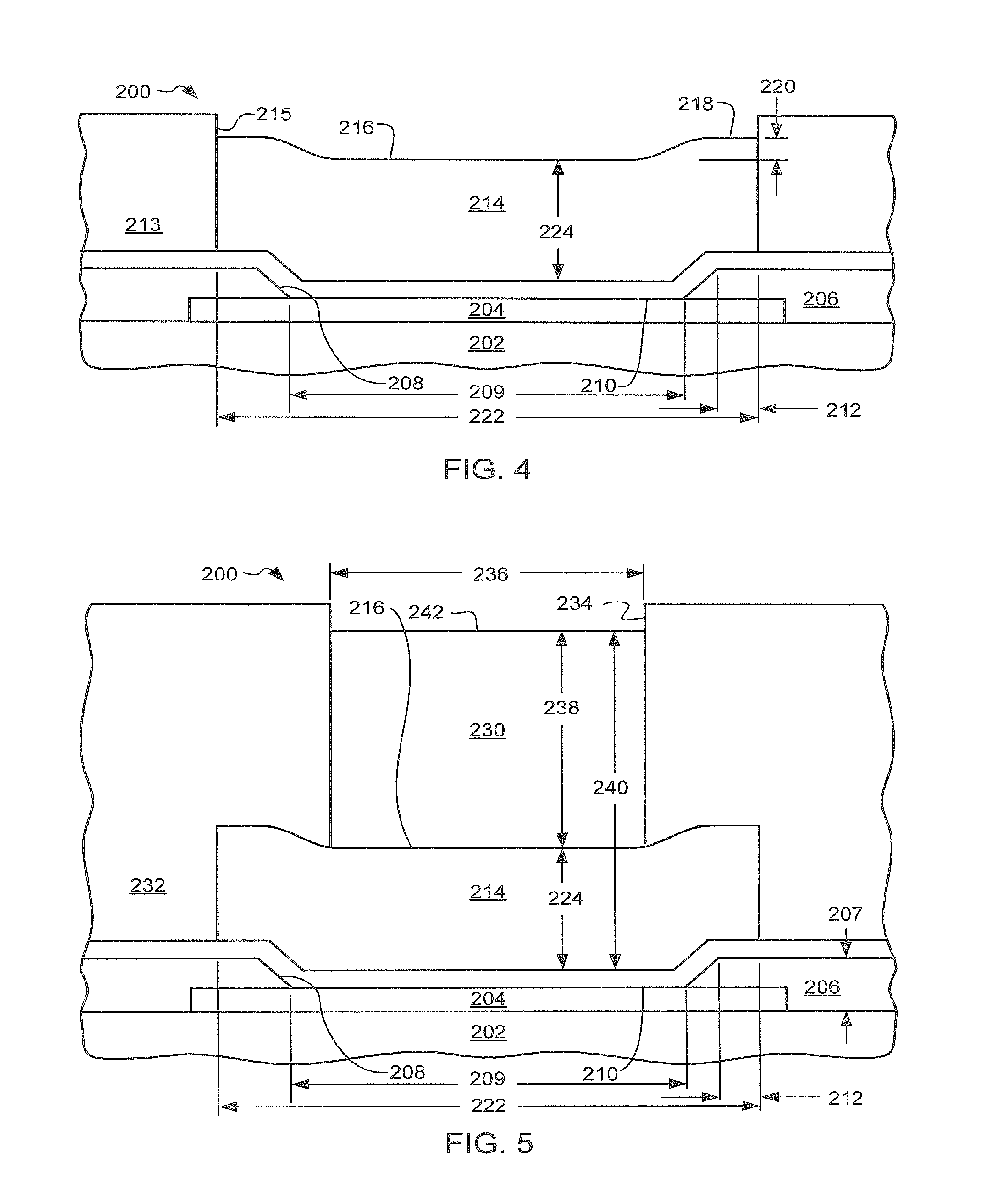

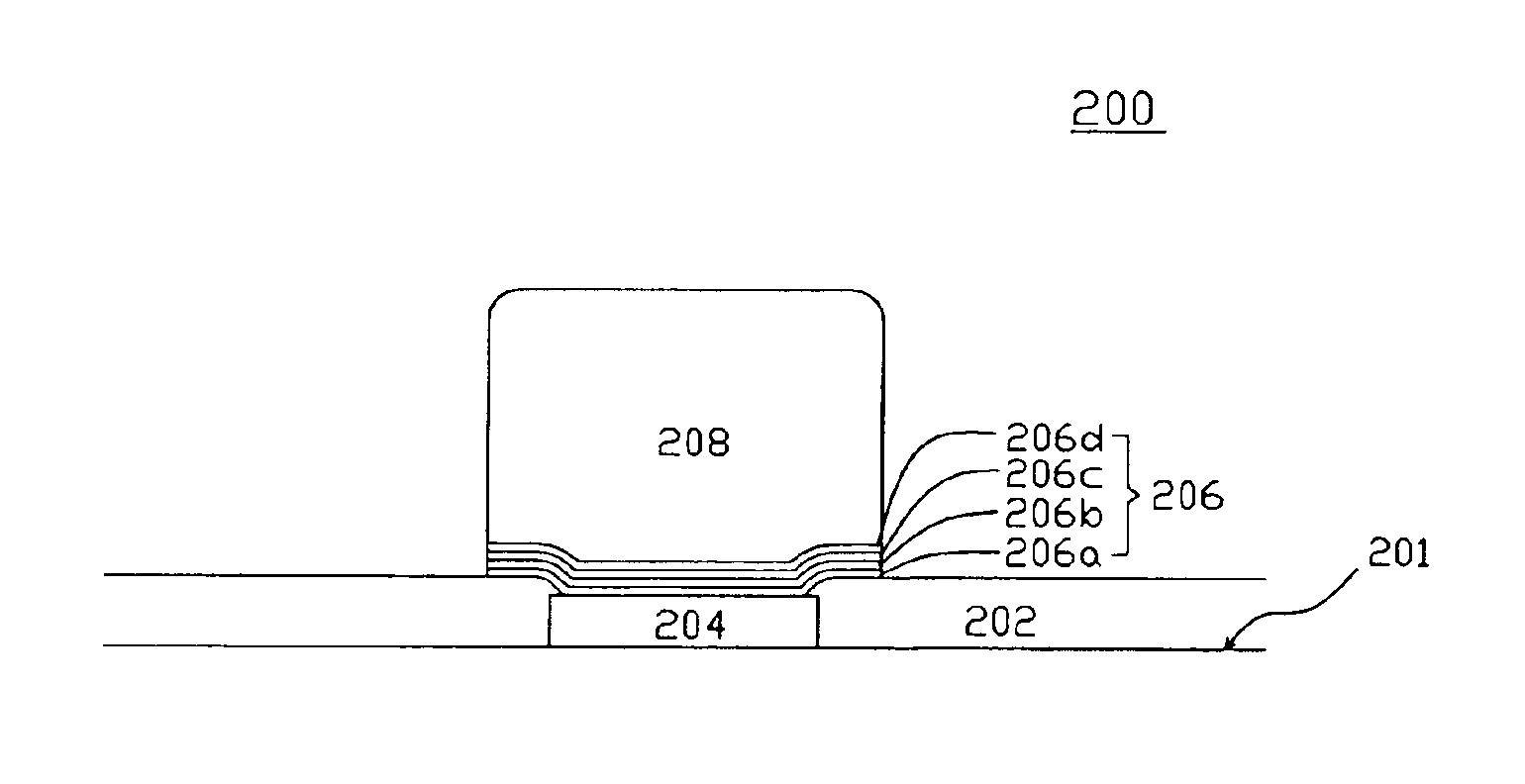

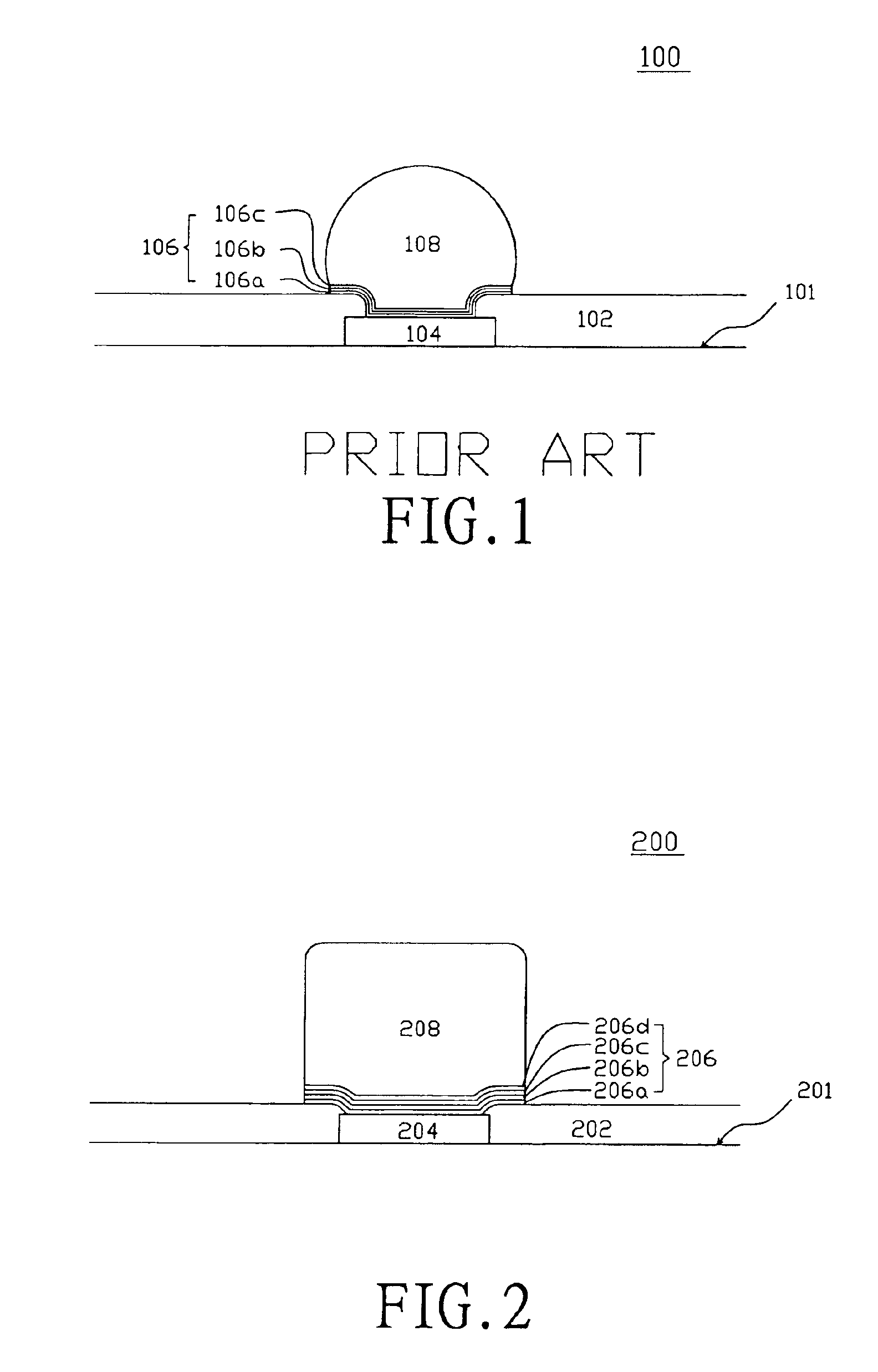

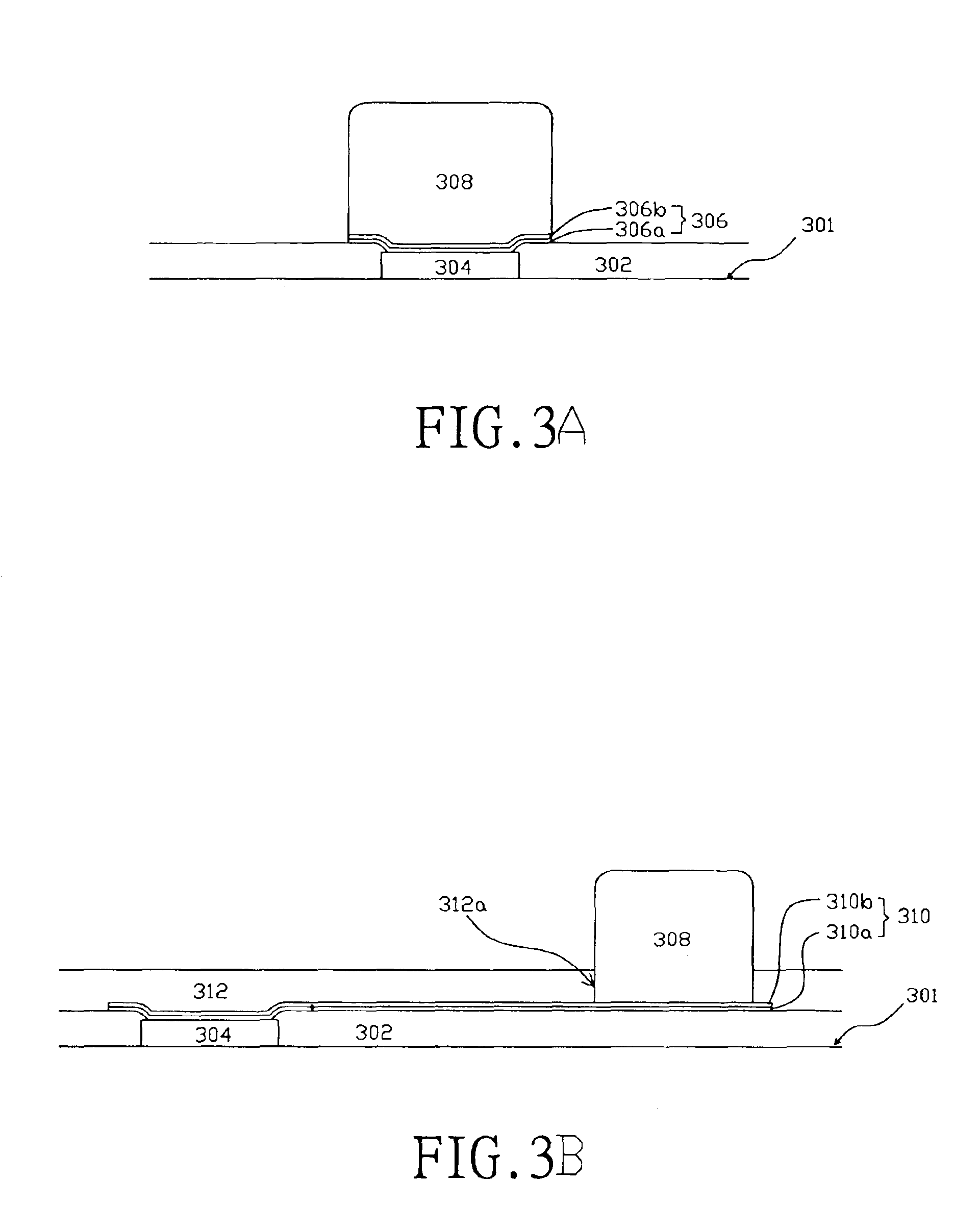

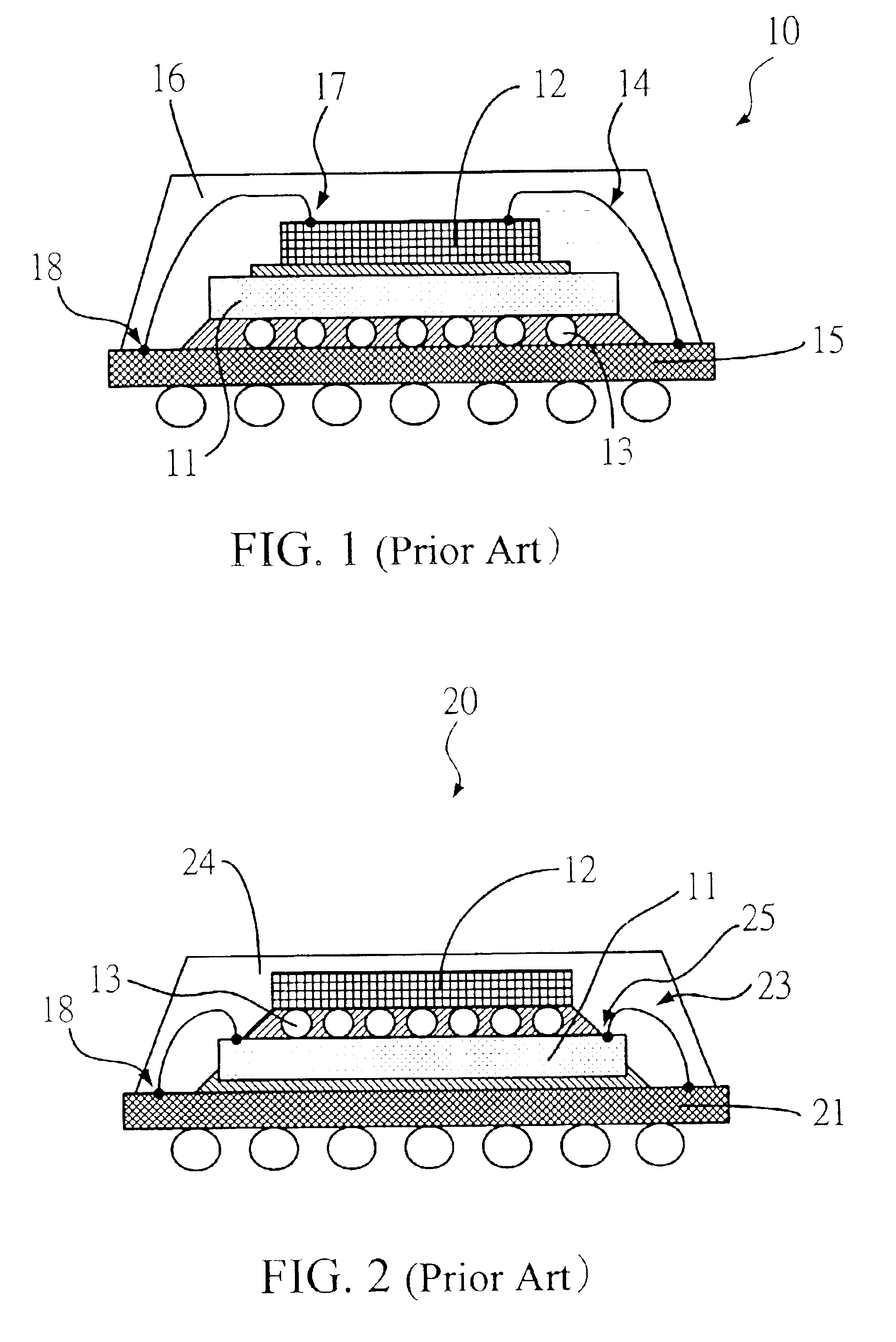

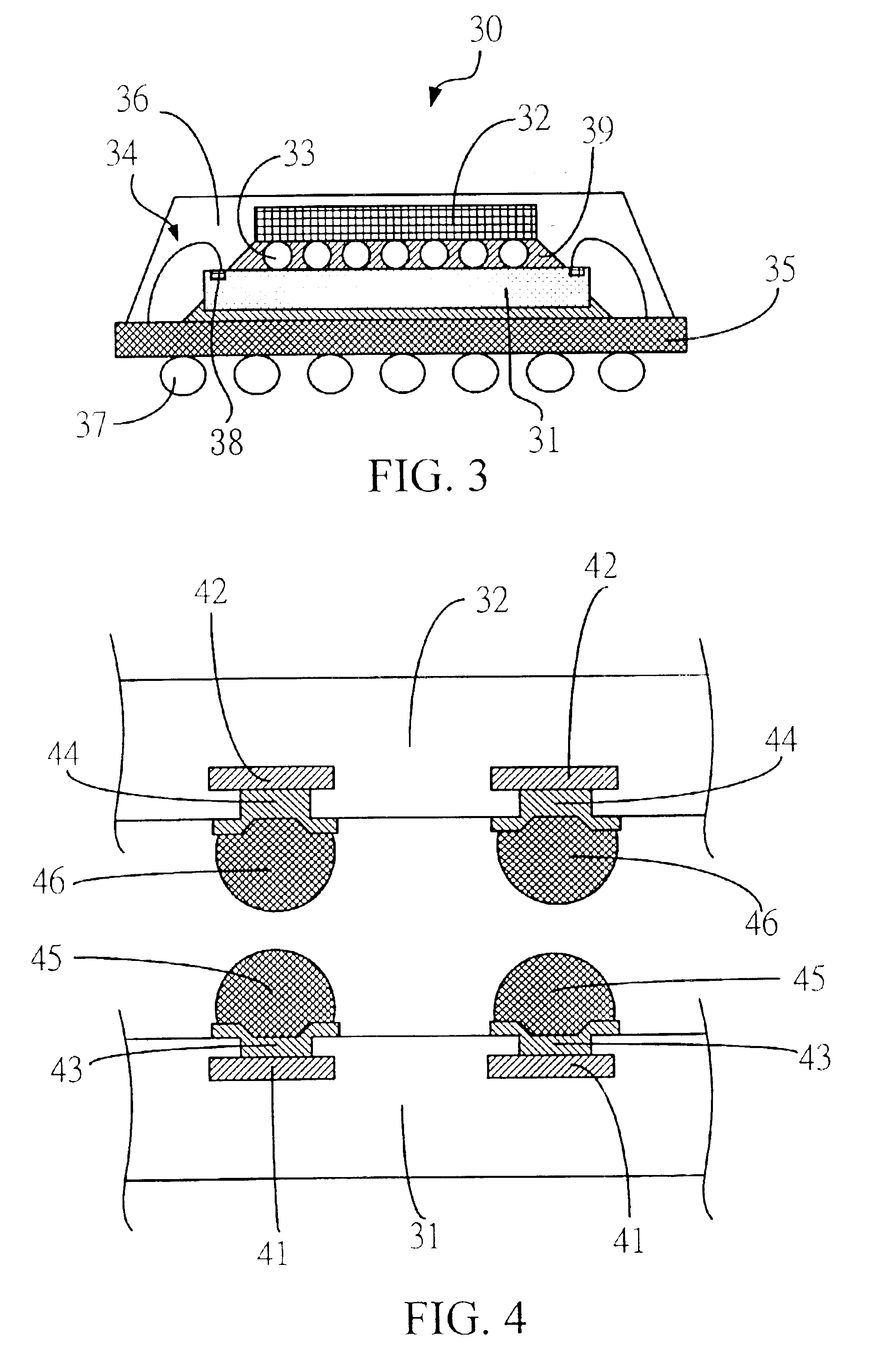

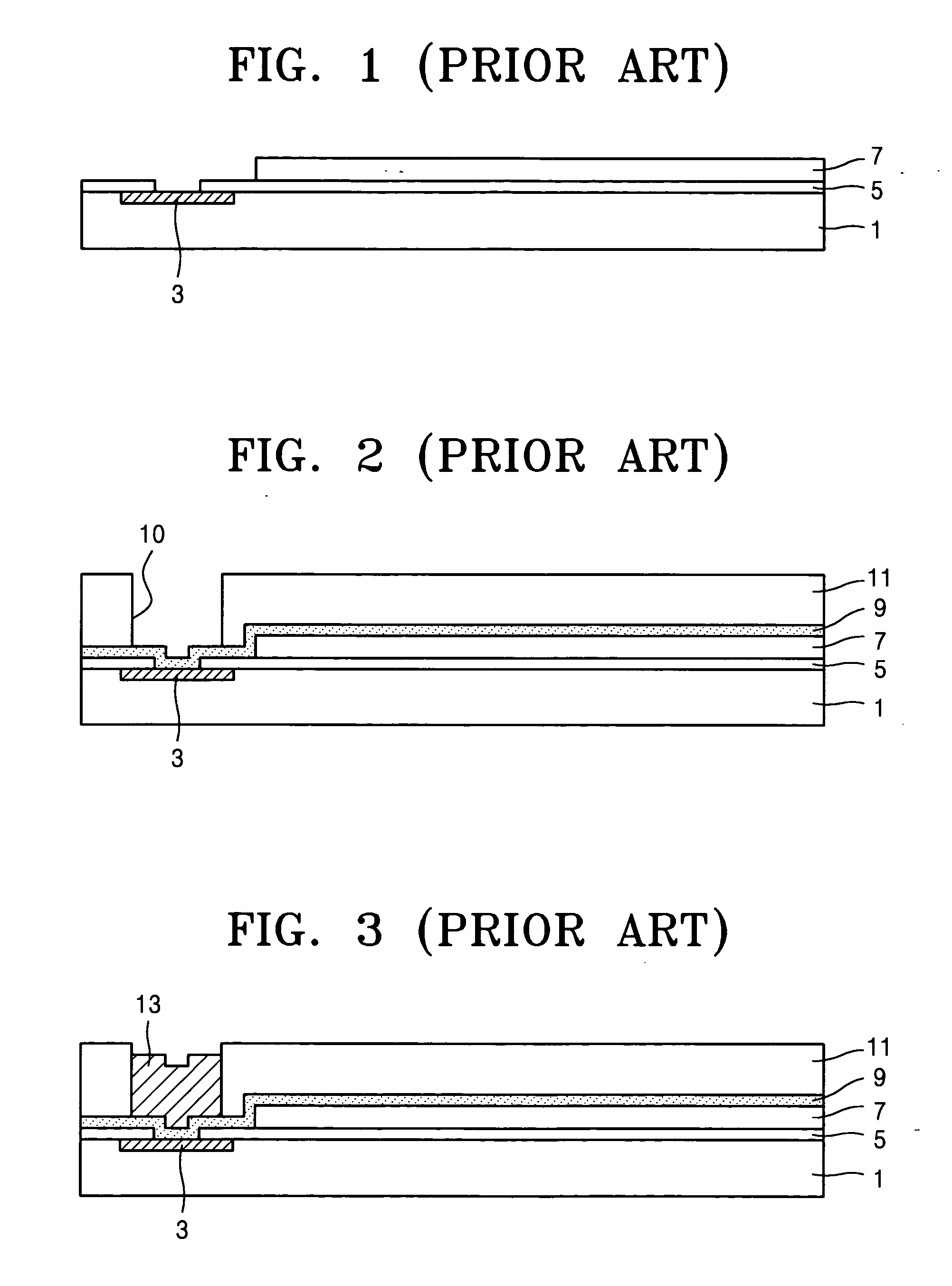

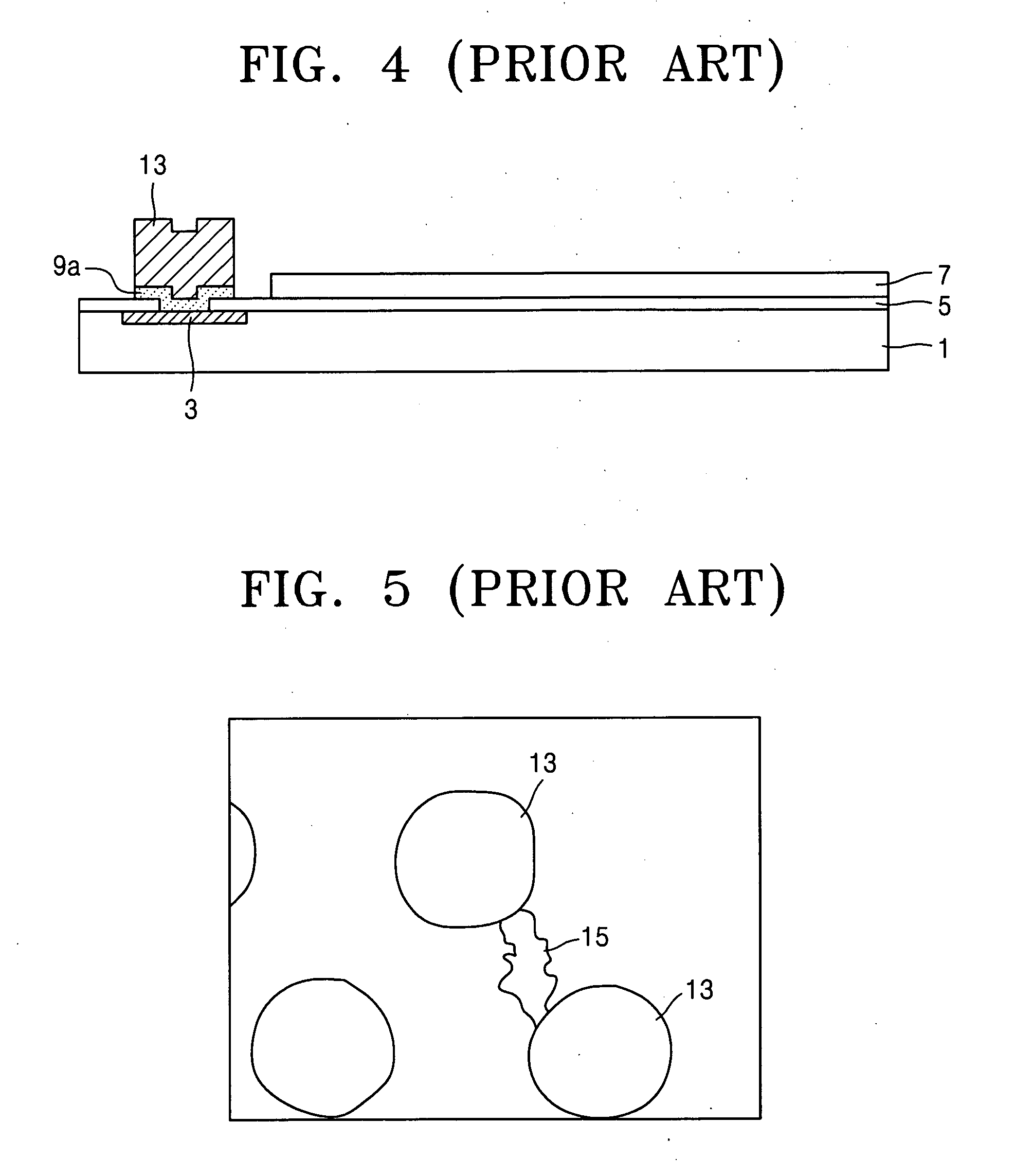

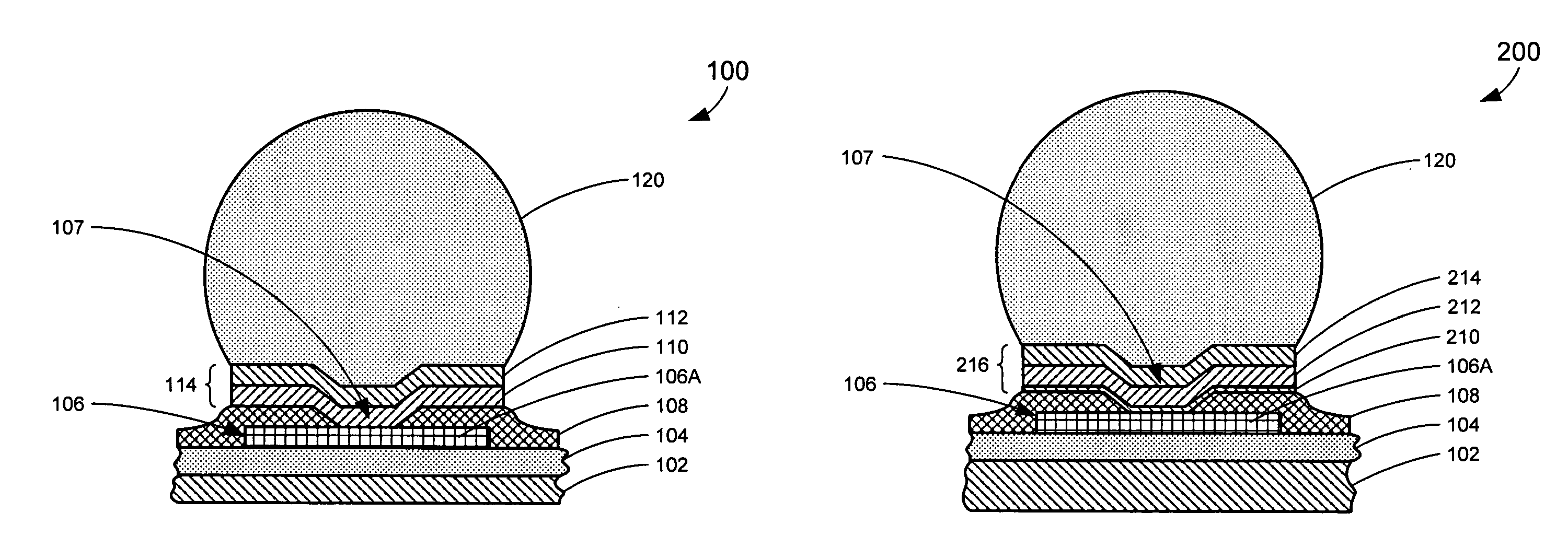

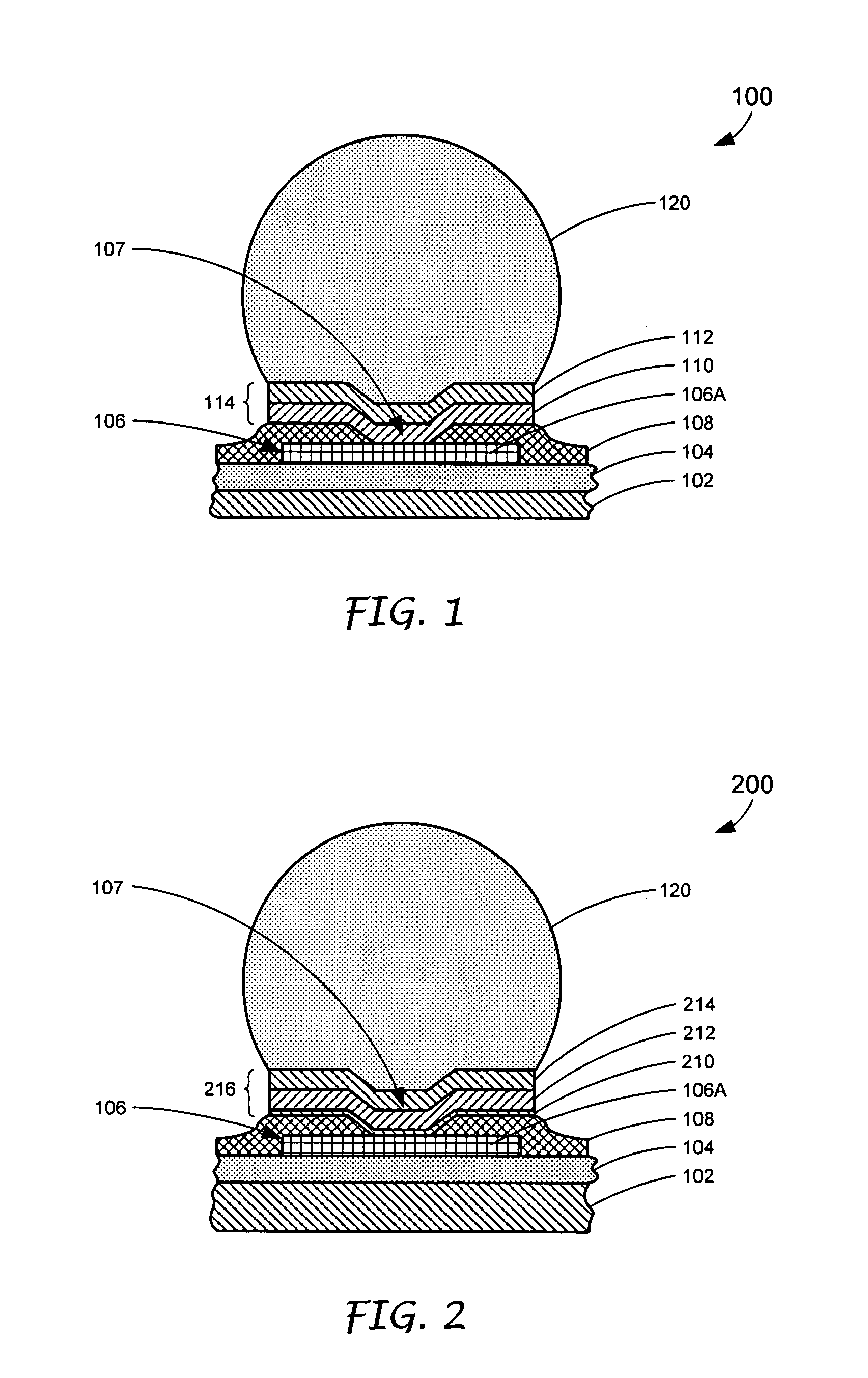

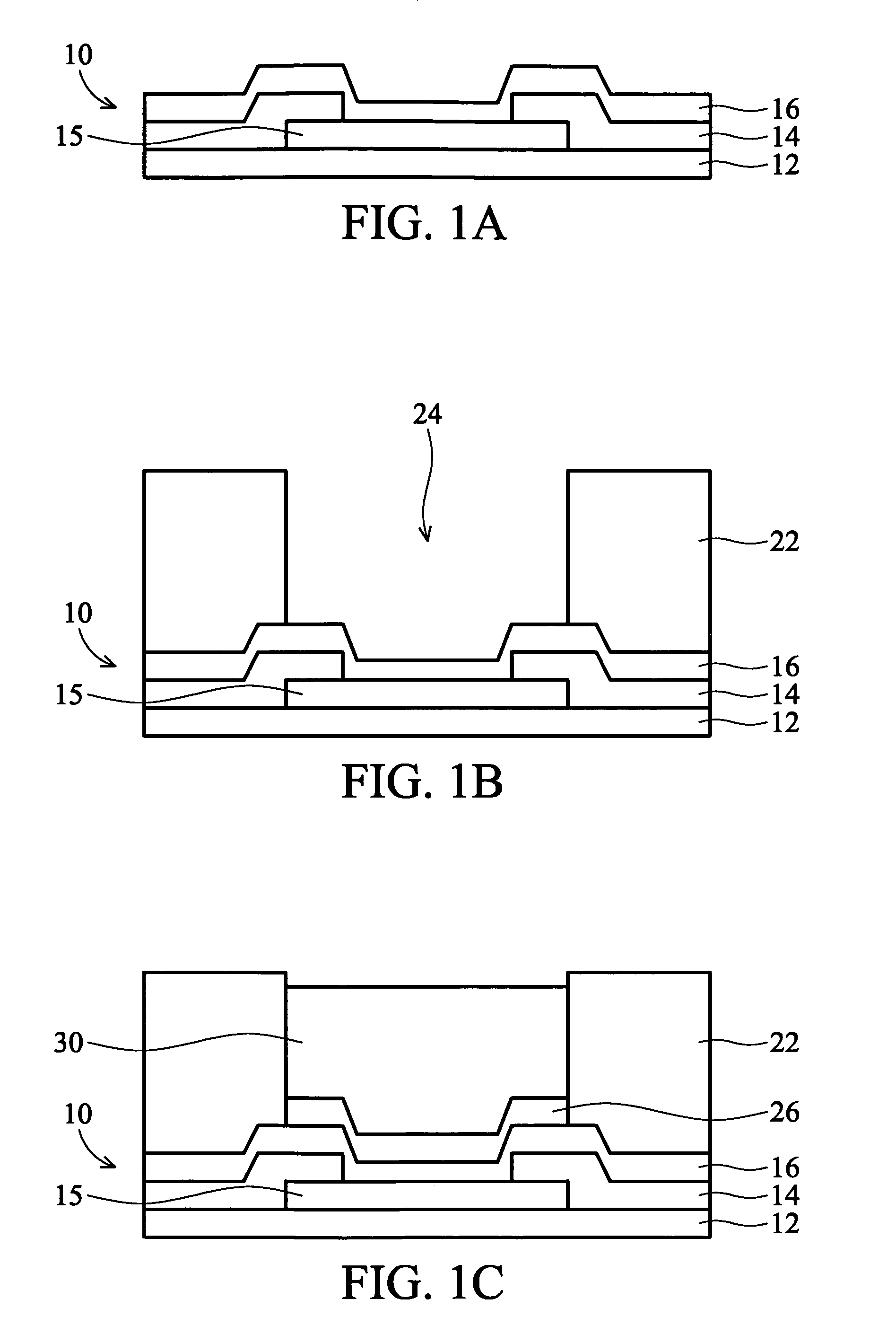

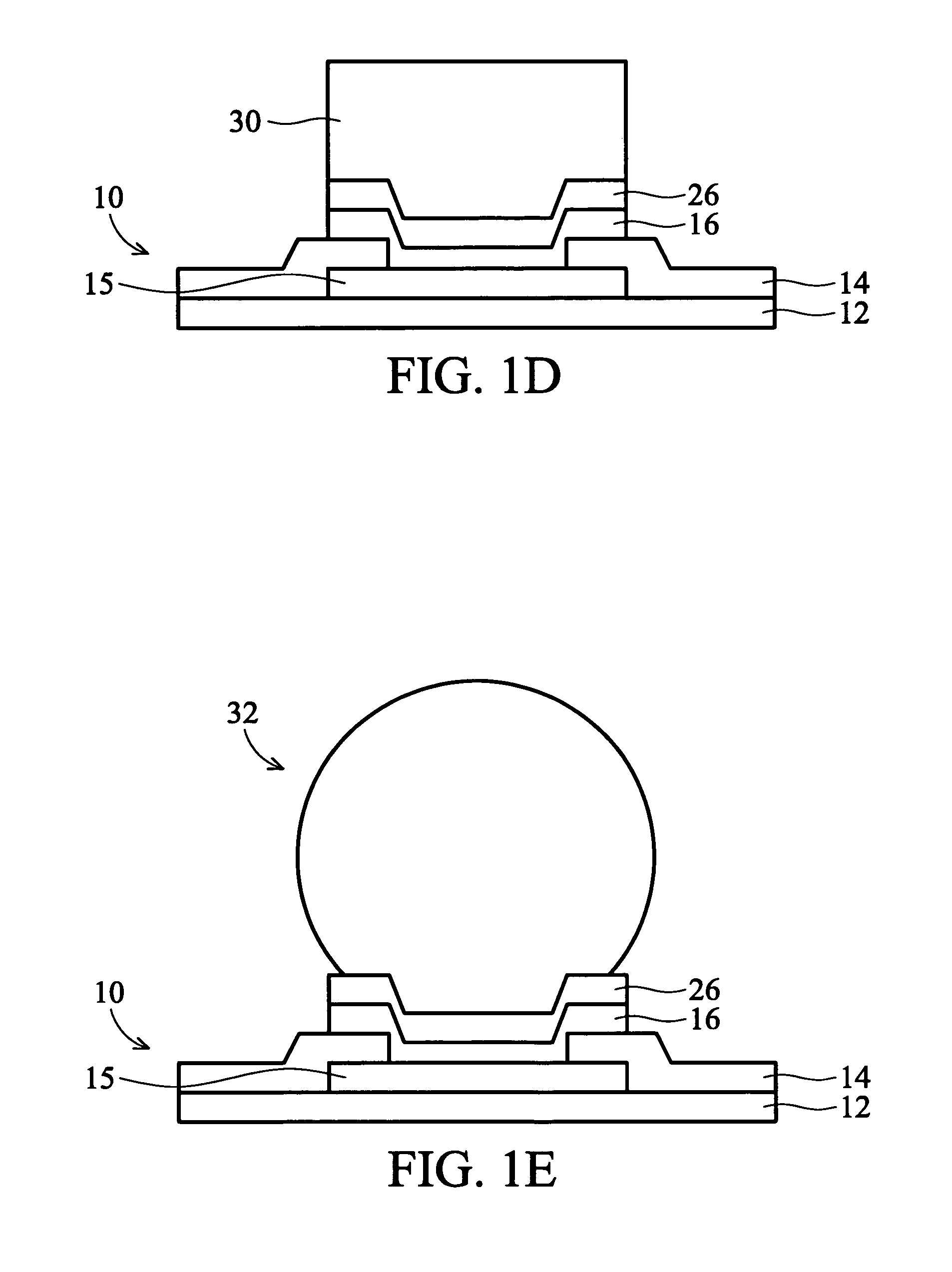

[a wafer bumping process]

ActiveUS20040185649A1Increase distanceReduce shear stressSemiconductor/solid-state device detailsSolid-state devicesEngineeringUnder bump metallurgy

A wafer bumping process is disclosed. A wafer having a plurality of bonding pads formed thereon is provided. A first under bump metallurgy layer is formed to cover the bonding pads. A first patterned photoresist layer having a plurality of first openings is formed on the first under bump metallurgy layer, wherein a portion of the first under bump metallurgy layer is exposed within the first openings. A second under bump metallurgy layer is formed within the first openings, wherein the second under bump metallurgy layer is much thicker than the first under bump metallurgy layer. A second patterned photoresist layer having a plurality of second openings is formed on the first patterned photoresist layer, wherein the second openings being larger than the first openings. After filling the second openings with a solder material, a reflowing process is performed to form a plurality of solder bumps, wherein the material of the second under bump metallurgy layer has a melting point higher than that of the solder material.

Owner:ADVANCED SEMICON ENG INC

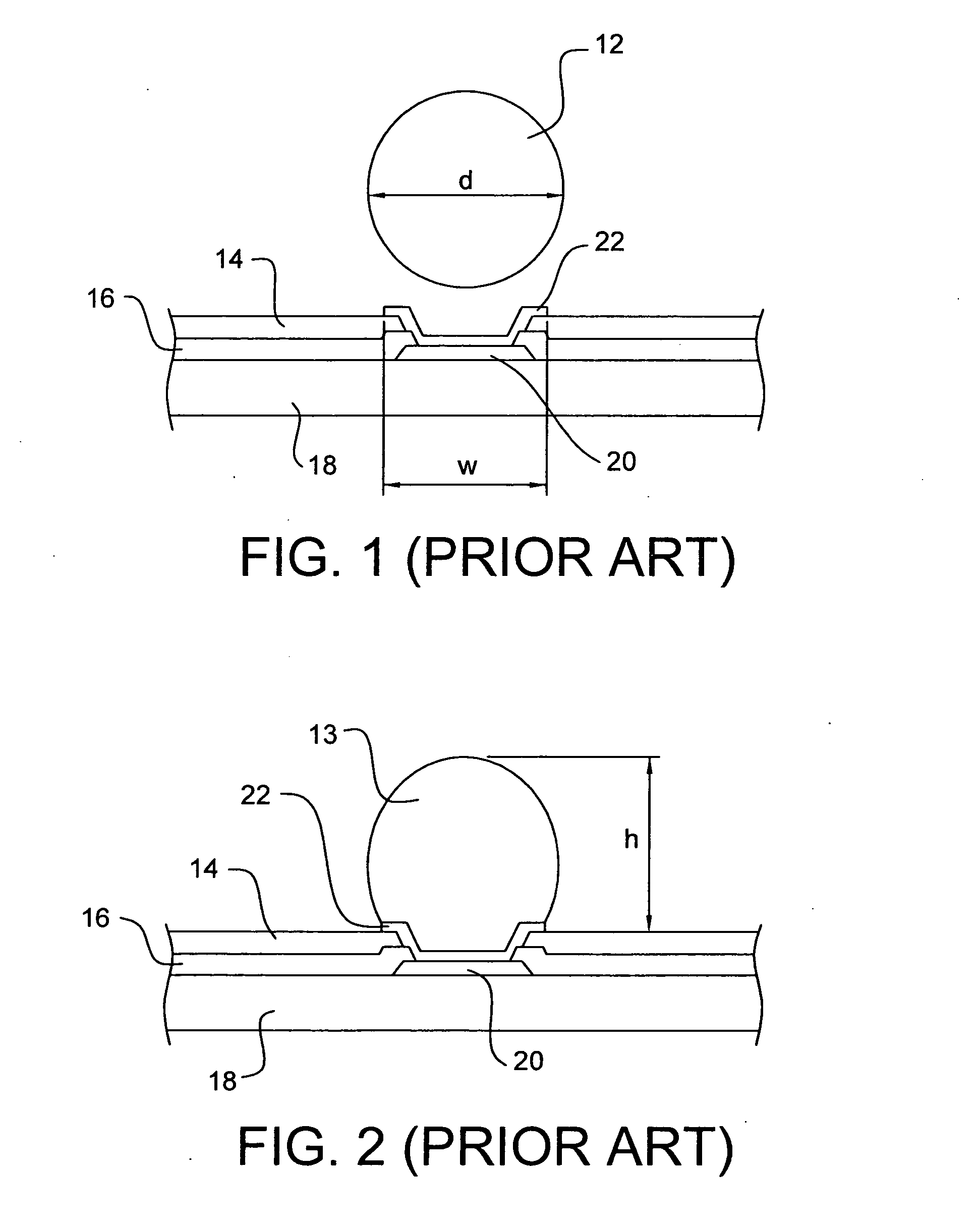

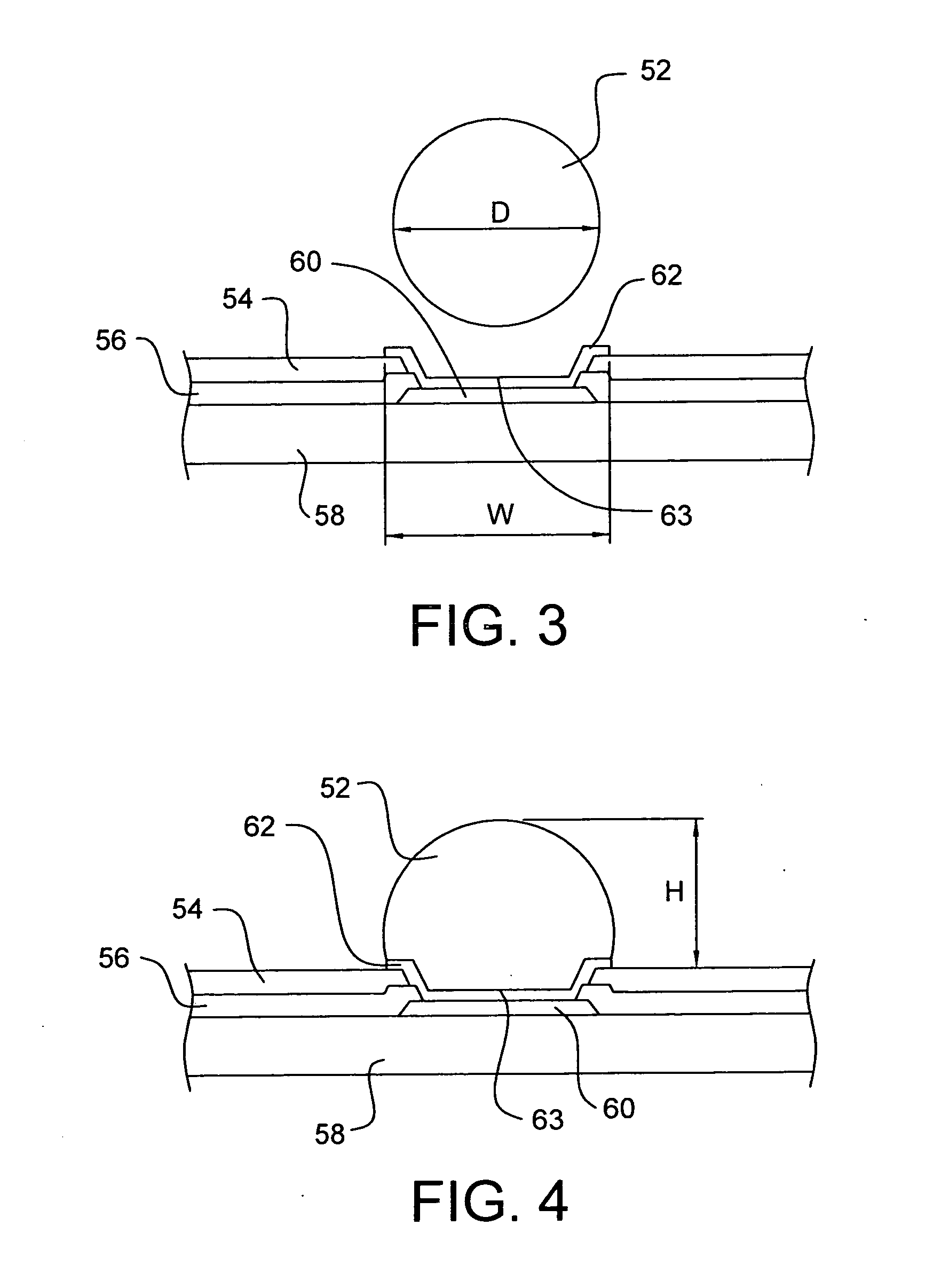

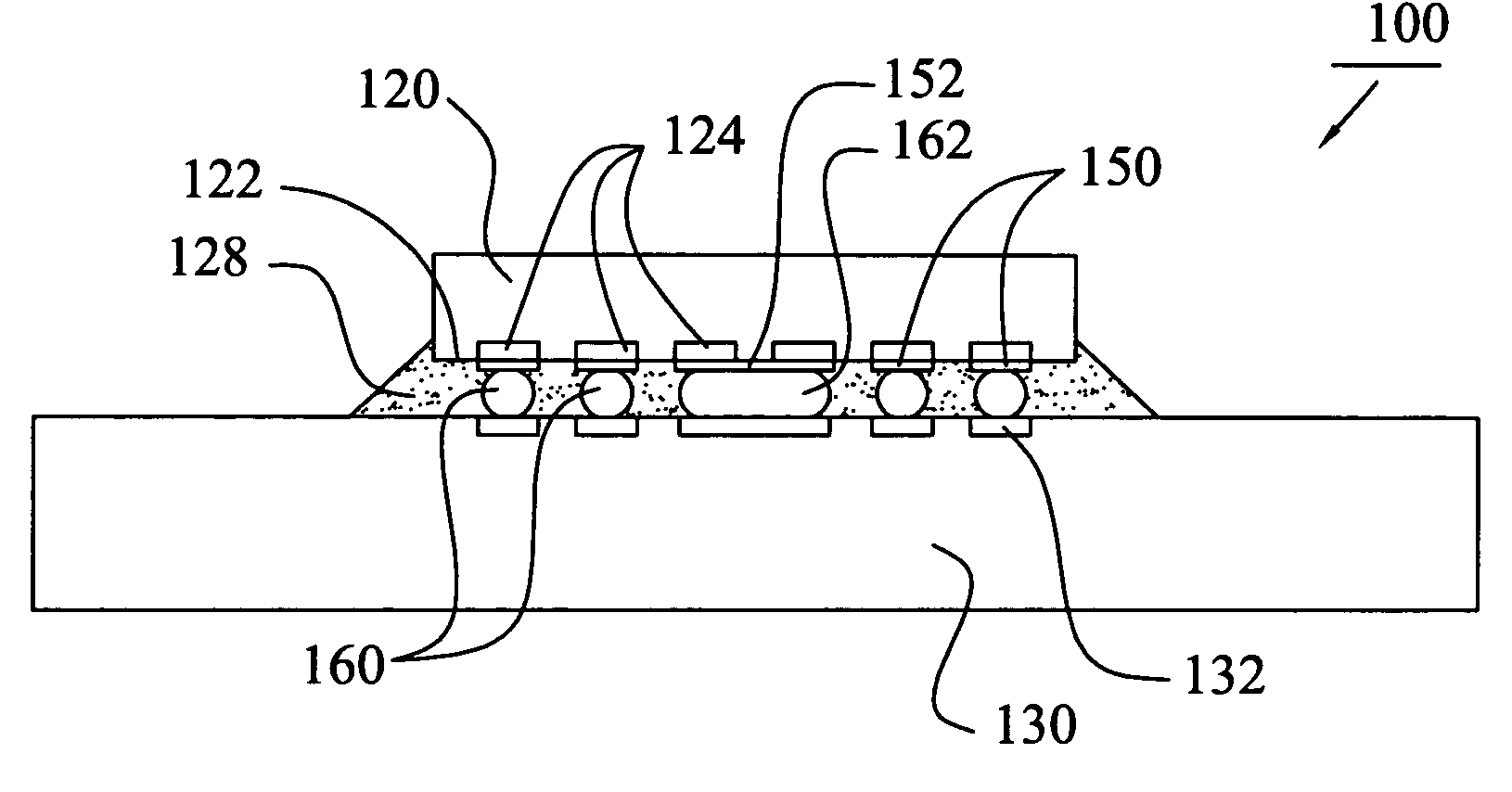

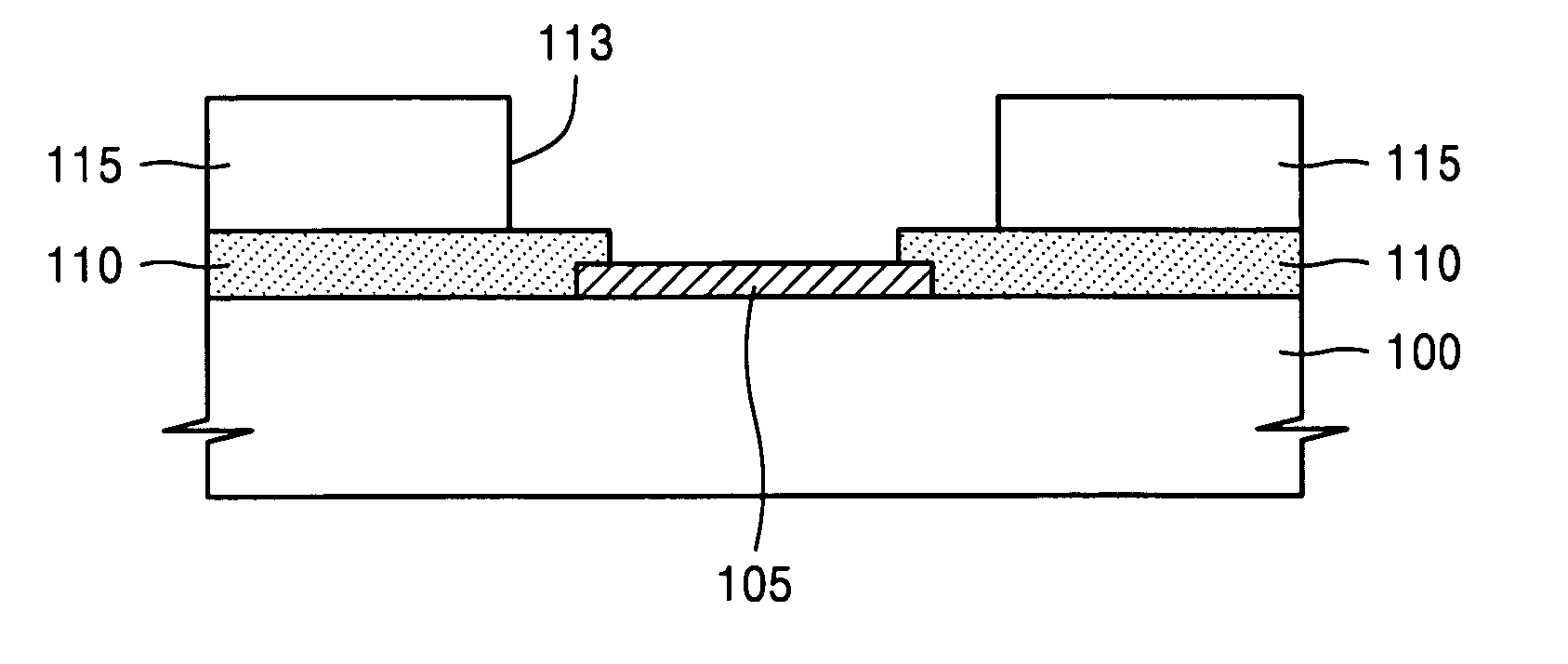

Semiconductor chip with bumps and method for manufacturing the same

ActiveUS20050035451A1Reduce the overall heightWithout increasing cost and difficultySemiconductor/solid-state device detailsSolid-state devicesSolder ballSemiconductor chip

A method for manufacturing a semiconductor chip with bumps comprises providing a semiconductor chip, which defines an active surface and a back surface and has a plurality of pads disposed on the active surface, and a plurality of preformed solder balls. A passivation is disposed on the active surface of the semiconductor chip with the pads exposed. A plurality of UBMs (Under Bump Metallurgy) are disposed on the pads and define a plurality of bump pads. The diameter of the bump pads is about 100% to about 130% of the diameter of the preformed solder balls. The preformed solder balls are placed on the bump pads and then reflowed to form a plurality of bumps on the semiconductor chip.

Owner:ADVANCED SEMICON ENG INC

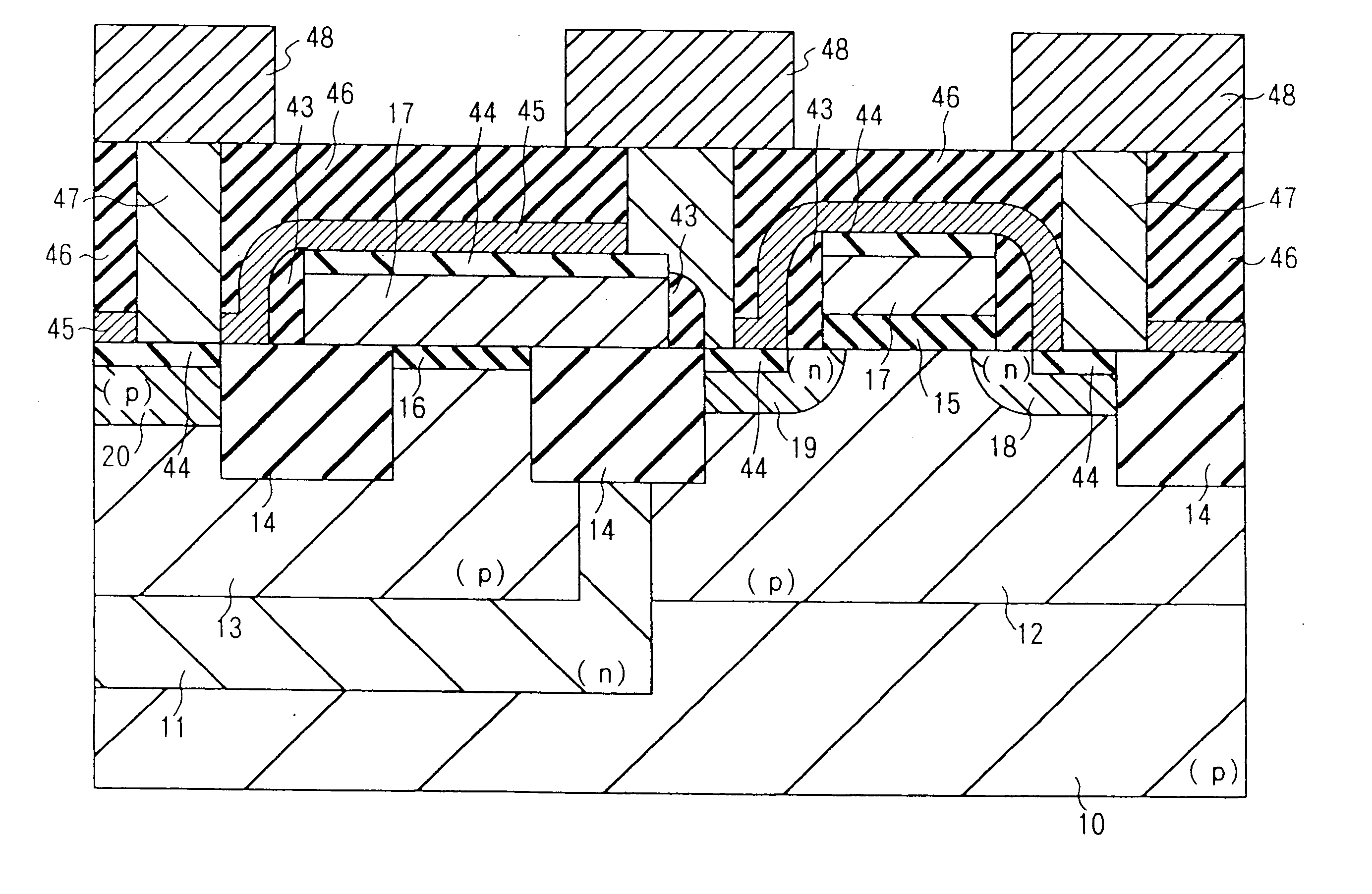

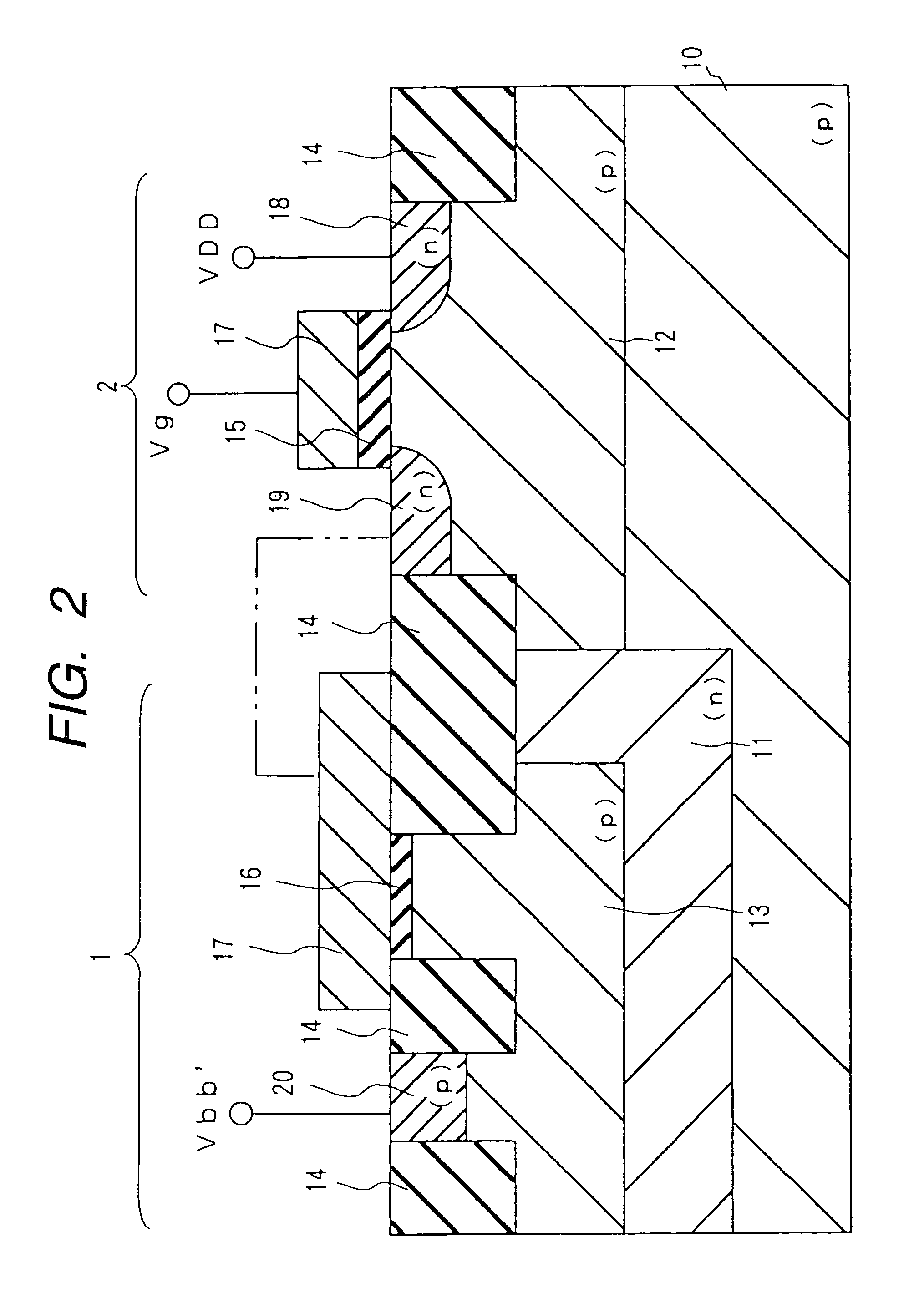

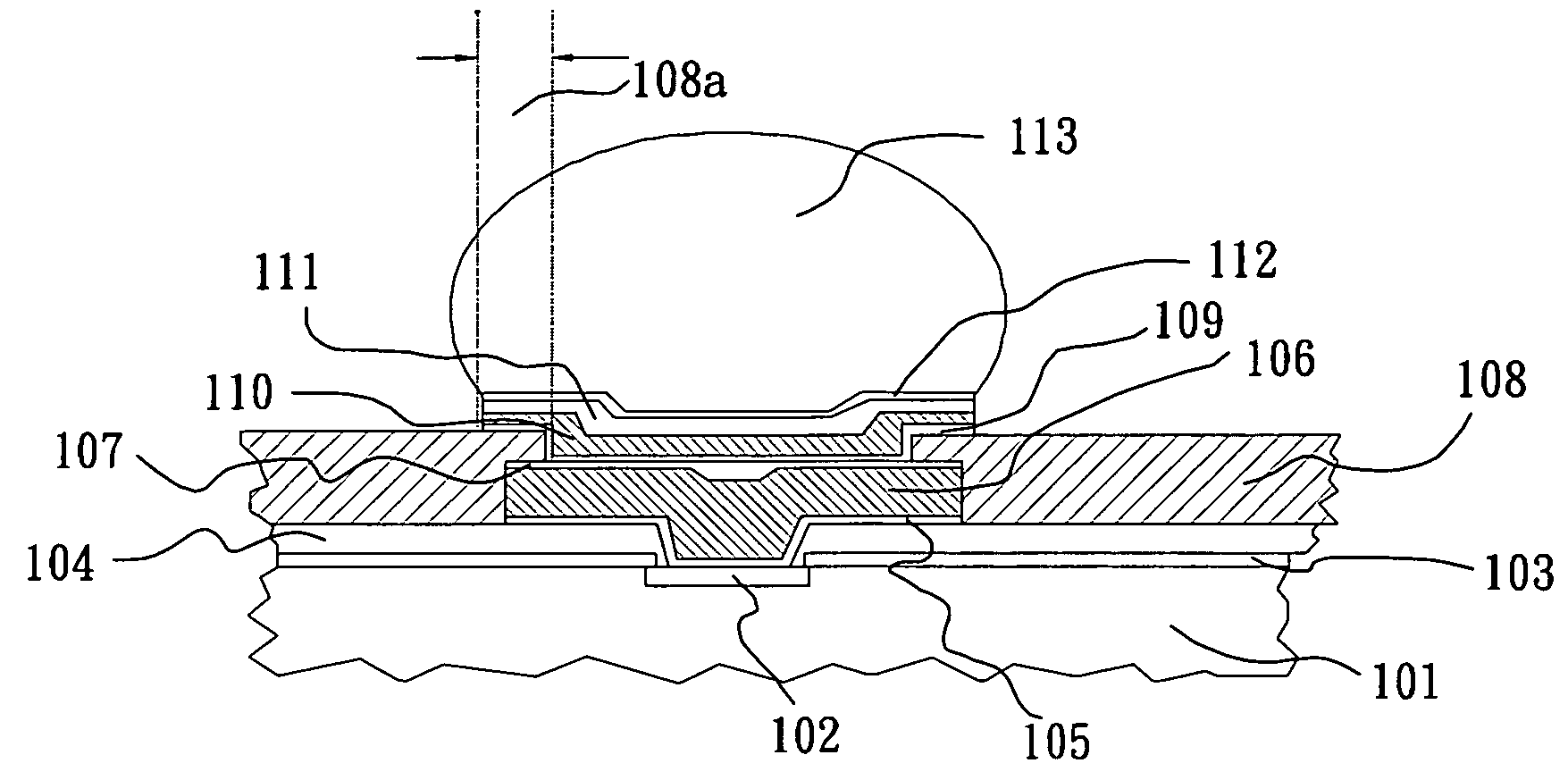

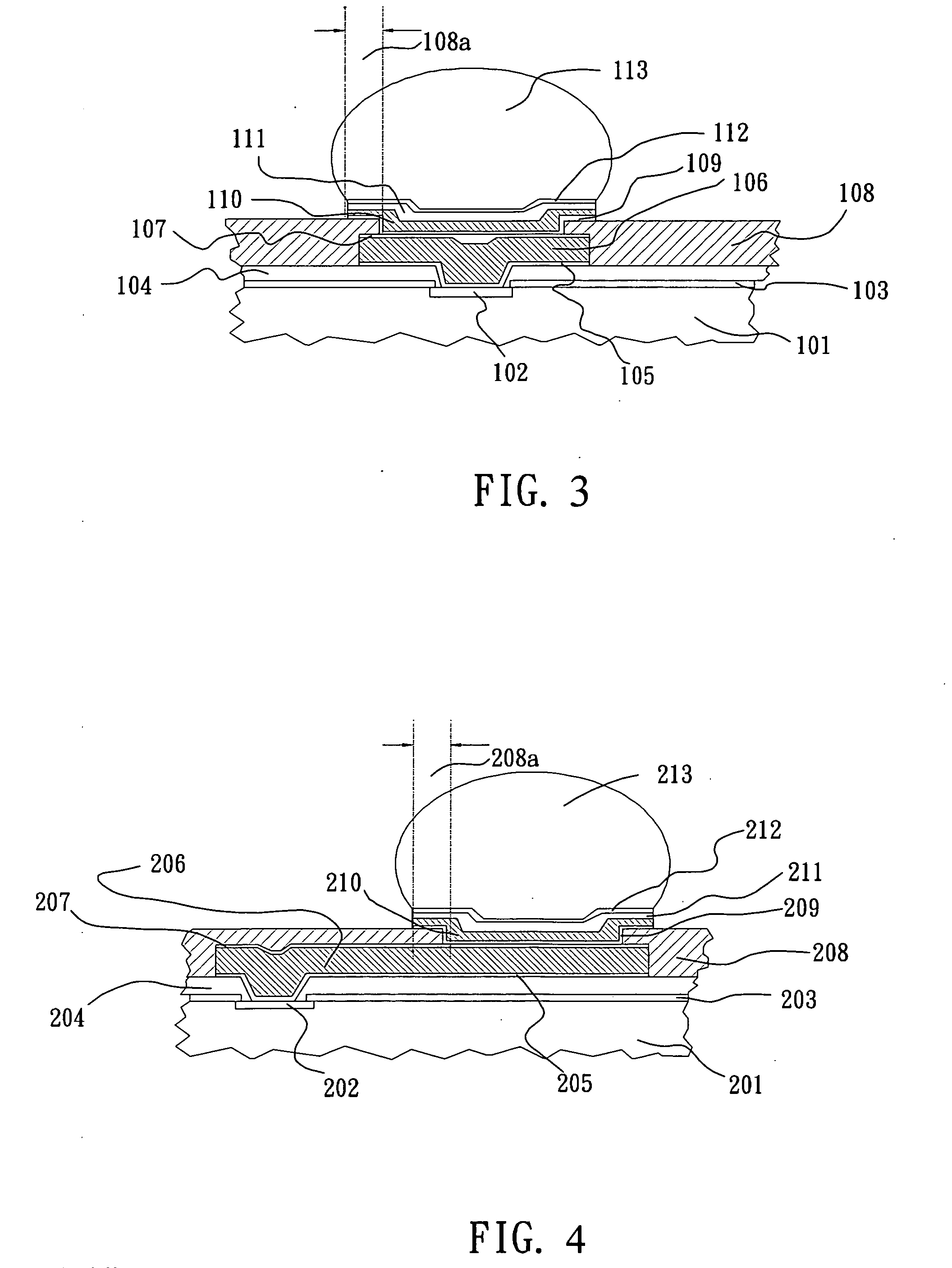

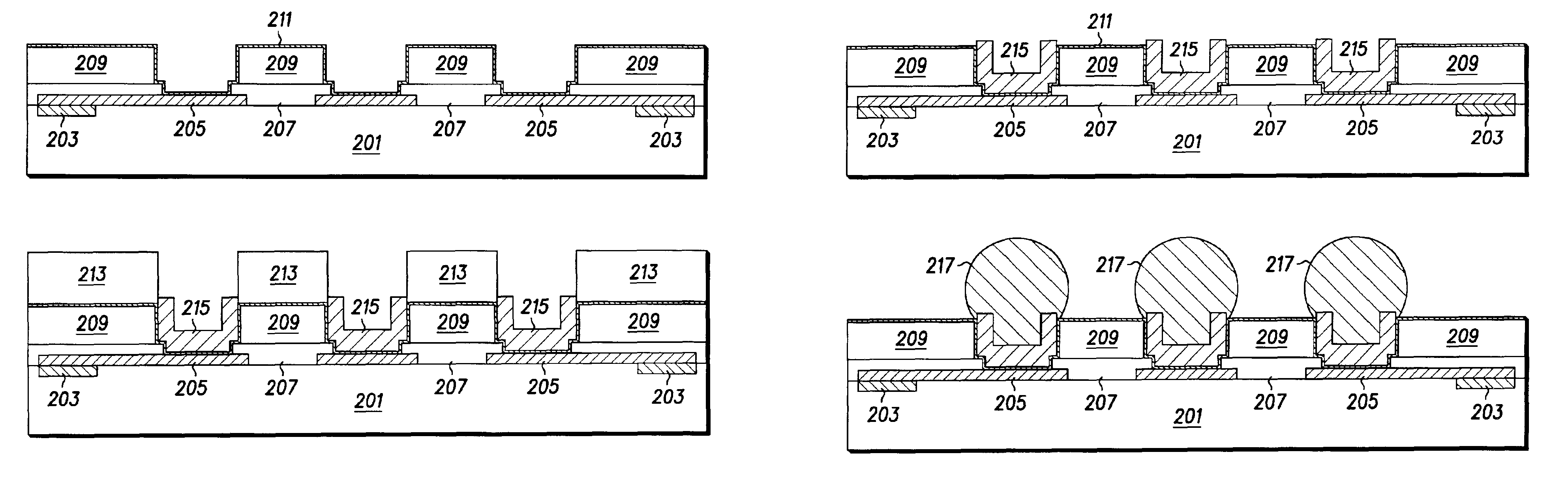

Semiconductor integrated circuit device and manufacture thereof

InactiveUS20070241330A1Easy to transformIncreasing the thicknessSemiconductor/solid-state device testing/measurementElectronic circuit testingMetallic materialsCombined use

In a semiconductor integrated circuit device, testing pads (209b) using a conductive layer, such as relocation wiring layers (205) are provided just above or in the neighborhood of terminals like bonding pads (202b) used only for probe inspection at which bump electrodes (208) are not provided. Similar testing pads may be provided even with respect to terminals like bonding pads provided with bump electrodes. A probe test is executed by using these testing pads or under the combined use of under bump metallurgies antecedent to the formation of the bump electrodes together with the testing pads. According to the above, bump electrodes for pads dedicated for probe testing may not be added owing to the use of the testing pads. Further, the use of testing pads provided in the neighborhood of the terminals like the bonding pads and smaller in size than the under bump metallurgies enables a probe test to be executed after a relocation wiring process.

Owner:TESSERA ADVANCED TECH

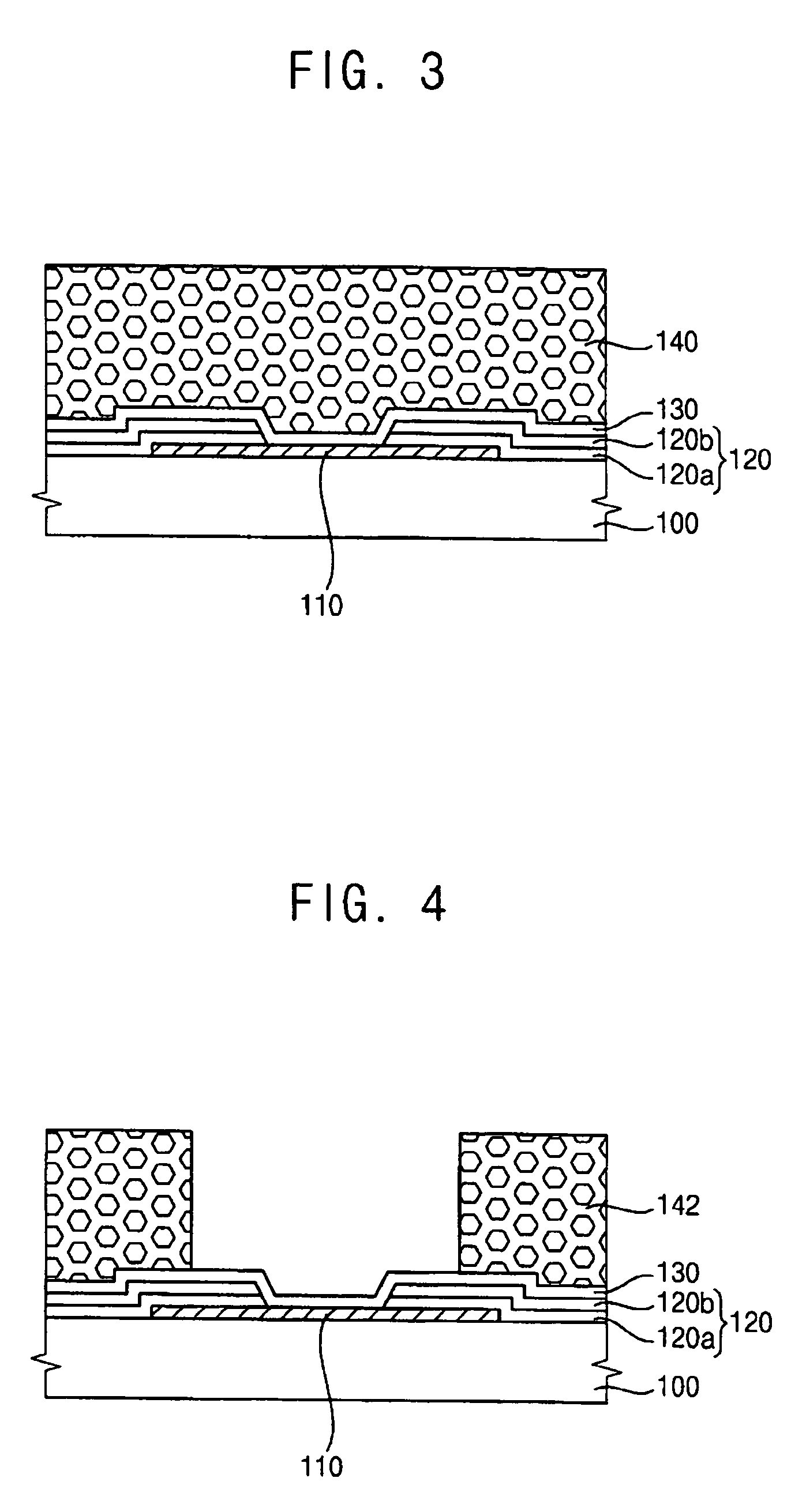

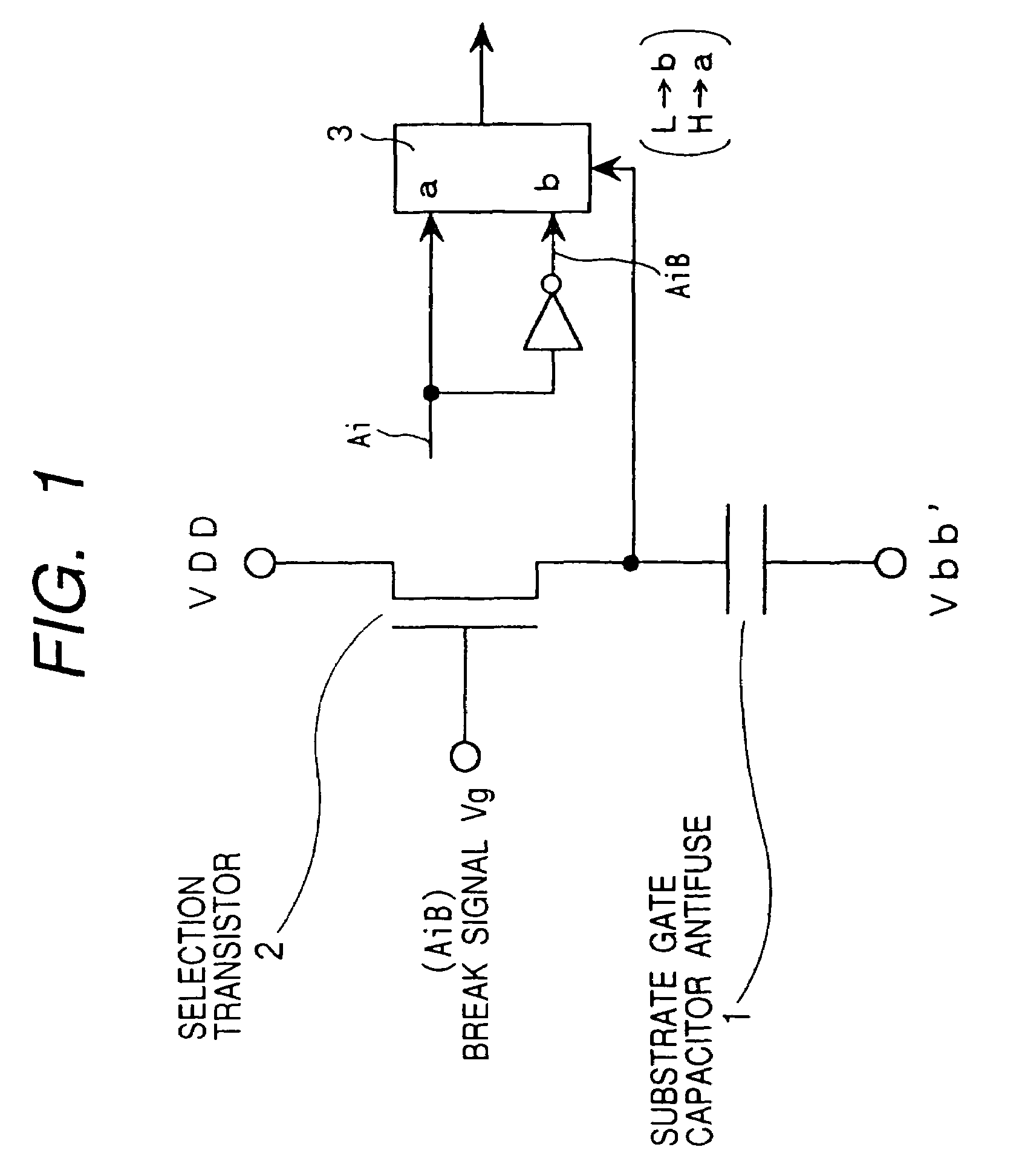

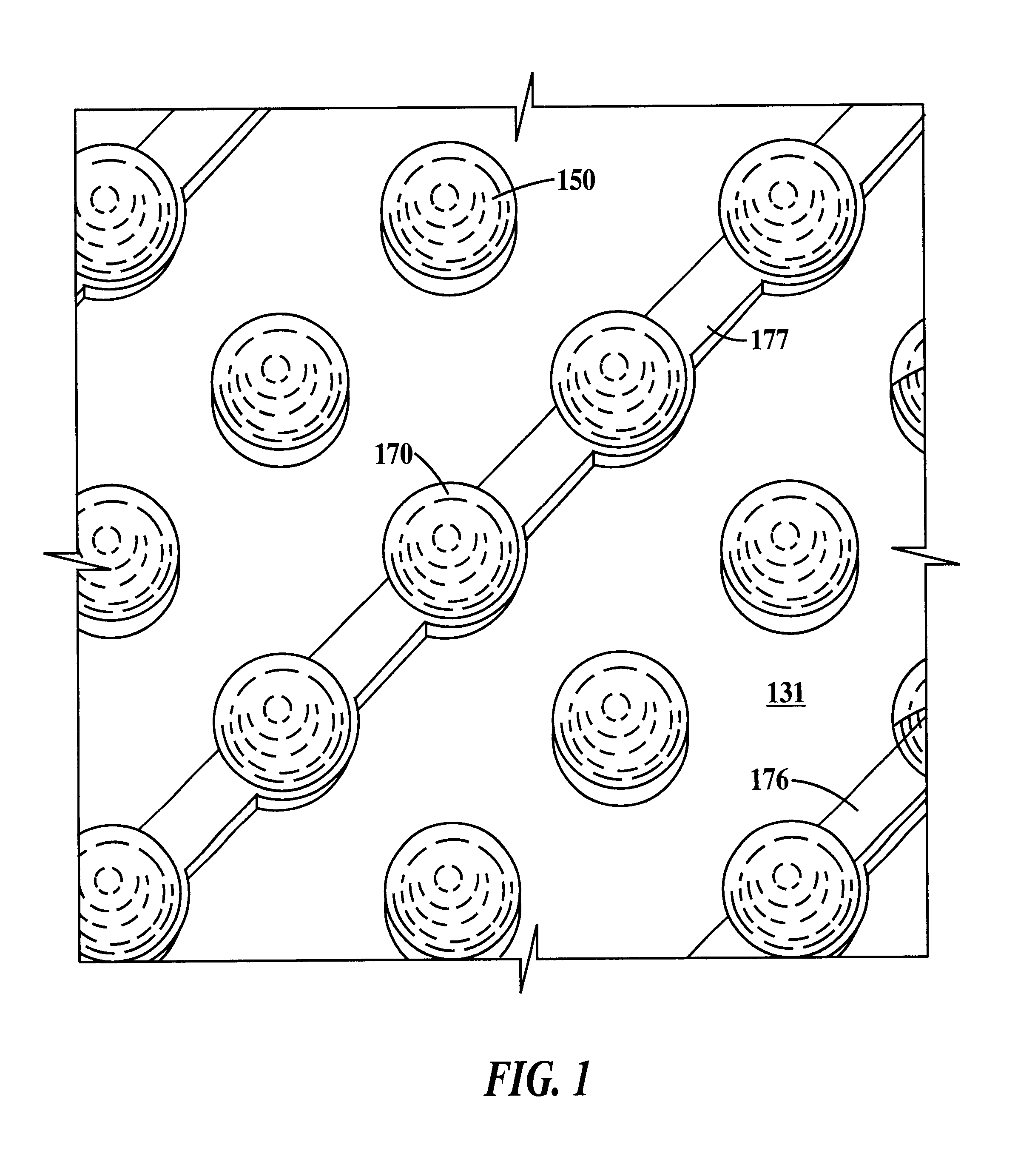

Solder bump structure and laser repair process for memory device

InactiveUS6881654B2Inhibition formationAffect reliabilityLight-sensitive devicesSemiconductor/solid-state device detailsEngineeringUnder bump metallurgy

A solder bump structure and laser repair process for memory device include forming a first dielectric layer on a bump pad of a semiconductor wafer. After that, the first dielectric layer is etched to form a contact hole and to expose portions of the bump pad. A second dielectric layer is then formed on a surface of the semiconductor wafer outside of the contact hole. An under bump metallurgy (UBM) process is performed to form a metal layer on a surface of the contact hole, and a solder bump is formed on the metal layer. Finally, the laser repair process for memory device is completed.

Owner:UNITED MICROELECTRONICS CORP

Interconnect Structures Having Lead-Free Solder Bumps

ActiveUS20100314756A1Improve reliabilityImprove production yieldSemiconductor/solid-state device detailsSolid-state devicesMetallurgyUnder bump metallurgy

An integrated circuit structure includes a semiconductor substrate, and a polyimide layer over the semiconductor substrate. An under-bump-metallurgy (UBM) has a first portion over the polyimide layer, and a second portion level with the polyimide layer. A first solder bump and a second solder bump are formed over the polyimide layer, with a pitch between the first solder bump and the second solder bump being no more than 150 μm. A width of the UBM equals one-half of the pitch plus a value greater than 5 μm.

Owner:TAIWAN SEMICON MFG CO LTD

Device for testing electrical characteristics of chips

InactiveUS20030094963A1Semiconductor/solid-state device testing/measurementElectronic circuit testingElectricityUnder bump metallurgy

The present invention discloses a device for testing electrical characteristics of a chip, which is capable of verifying whether each chip can meet the requirement of the electrical specifications, and sort out the chips under the specifications. The invention utilizes a probe to contact the extension area of the under bump metallurgy to detect if the electrical characteristics of the chip can meet the requirement of the specifications. As the bumps on the chip do not actually contact the probe, the intact profile for the bumps on the chips can be assuredly kept so that the problem of voids existing in the melted bumps during reflow process can be avoided.

Owner:ADVANCED SEMICON ENG INC

Etching composition for an under-bump metallurgy layer and method of forming a bump structure using the same

ActiveUS20090176363A1Improve reliabilityReducing and preventing impuritySolid-state devicesSemiconductor/solid-state device manufacturingEthylenediamineAlcohol

In an etching composition for an under-bump metallurgy (UBM) layer and a method of forming a bump structure, the etching composition includes about 40% by weight to about 90% by weight of hydrogen peroxide (H2O2), about 1% by weight to about 20% by weight of an aqueous basic solution including ammonium hydroxide (NH4OH) or tetraalkylammonium hydroxide, about 0.01% by weight to about 10% by weight of an alcohol compound, and about 2% by weight to 30% by weight of an ethylenediamine-based chelating agent. The etching composition may effectively etch the UBM layer including titanium or titanium tungsten and remove impurities. A method of forming a bump structure may employ such an etching composition.

Owner:SAMSUNG ELECTRONICS CO LTD

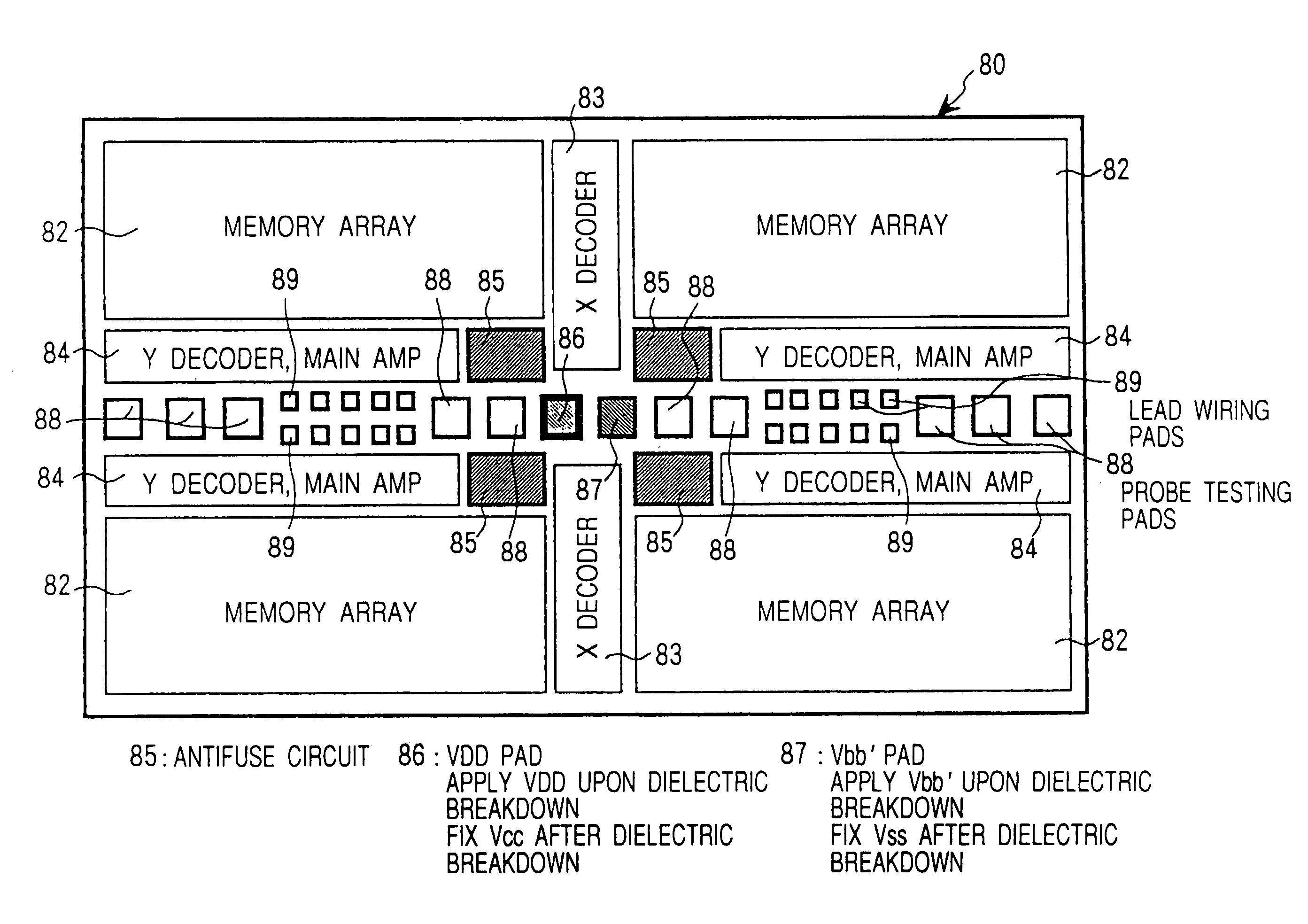

Semiconductor integrated circuit device having particular testing pad arrangement

InactiveUS7247879B2Improve reliabilityIncrease productionSemiconductor/solid-state device testing/measurementElectronic circuit testingCombined useUnder bump metallurgy

In a semiconductor integrated circuit device, testing pads (209b) using a conductive layer, such as relocation wiring layers (205) are provided just above or in the neighborhood of terminals like bonding pads (202b) used only for probe inspection at which bump electrodes (208) are not provided. Similar testing pads may be provided even with respect to terminals like bonding pads provided with bump electrodes. A probe test is executed by using these testing pads or under the combined use of under bump metallurgies antecedent to the formation of the bump electrodes together with the testing pads. According to the above, bump electrodes for pads dedicated for probe testing may not be added owing to the use of the testing pads. Further, the use of testing pads provided in the neighborhood of the terminals like the bonding pads and smaller in size than the under bump metallurgies enables a probe test to be executed after a relocation wiring process.

Owner:TESSERA ADVANCED TECH

![[a wafer bumping process] [a wafer bumping process]](https://images-eureka.patsnap.com/patent_img/392c92d6-558c-491c-a774-c592a49583b9/US20040185649A1-20040923-D00000.png)

![[a wafer bumping process] [a wafer bumping process]](https://images-eureka.patsnap.com/patent_img/392c92d6-558c-491c-a774-c592a49583b9/US20040185649A1-20040923-D00001.png)

![[a wafer bumping process] [a wafer bumping process]](https://images-eureka.patsnap.com/patent_img/392c92d6-558c-491c-a774-c592a49583b9/US20040185649A1-20040923-D00002.png)