Semiconductor chip and manufacturing method thereof

A manufacturing method, semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve problems such as stress generation, reliability impact, high leakage current, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The fabrication and discussion of various embodiments of the present invention are discussed in detail below. However, it should be noted that these embodiments provided in the present invention only provide the inventive concept of the present invention, which can be applied in a broad form to various specific cases. The embodiments discussed herein are for illustration only, and do not limit the present invention in various forms.

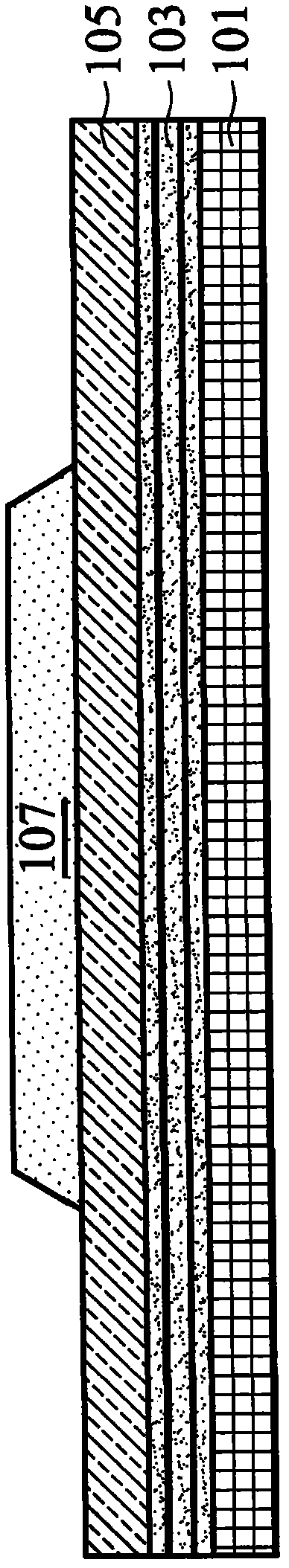

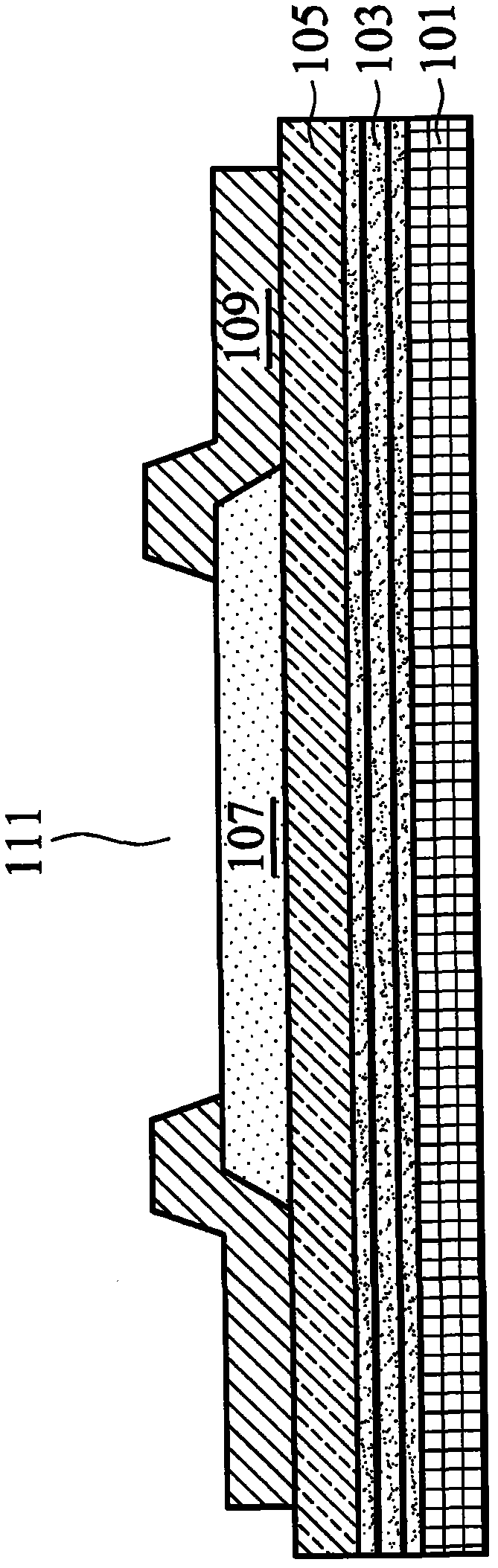

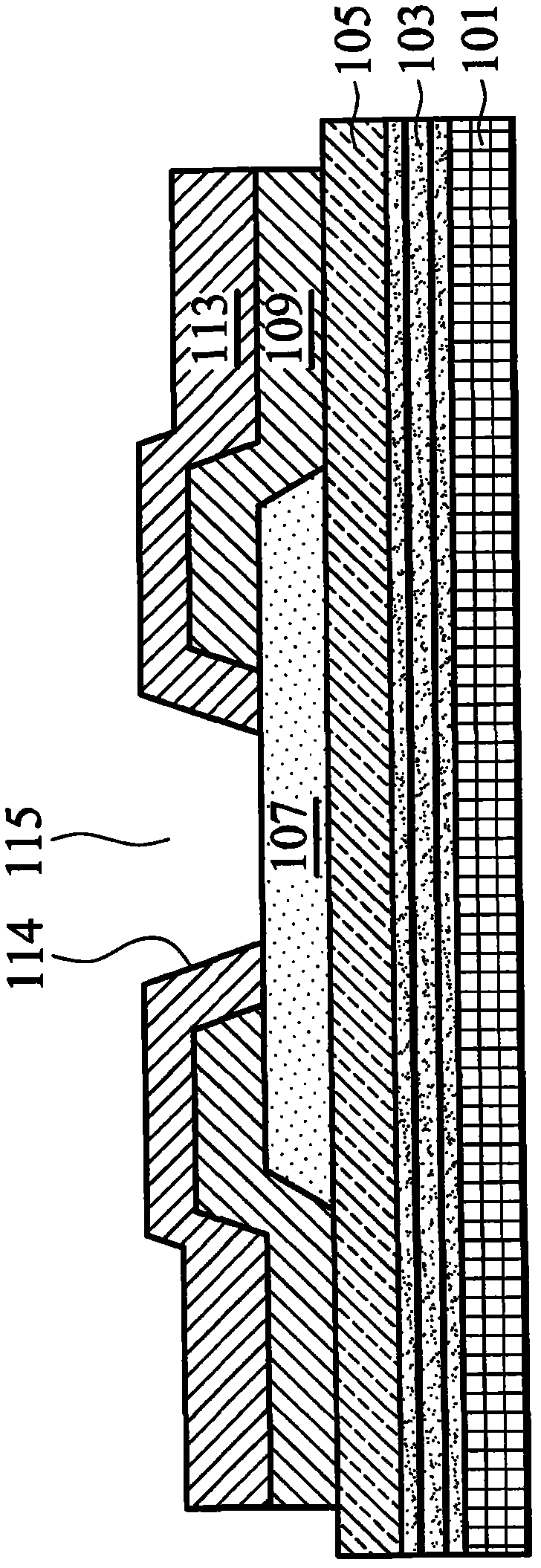

[0029] Figure 1 to Figure 14 Cross-sectional views of structures at various stages of fabrication are shown in accordance with one or more embodiments of the invention. The term "substrate" as used herein refers to a semiconductor substrate on which various film layers and integrated circuit elements are formed. The substrate may comprise silicon or a compound semiconductor such as gallium arsenide, indium phosphide, silicon / germanium or silicon carbide. In some embodiments, layers may include dielectric layers, doped layers, metal lay...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More