Patents

Literature

386 results about "Power planes" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Power plane is a plane that carrys the voltage of the system. Usually its 5V,12V ir even 3.3V or 1.8V these days. The advantages of running a power plane instead of tracks is better decoupling, Improved EMI considerations and higher current carrying capacity.

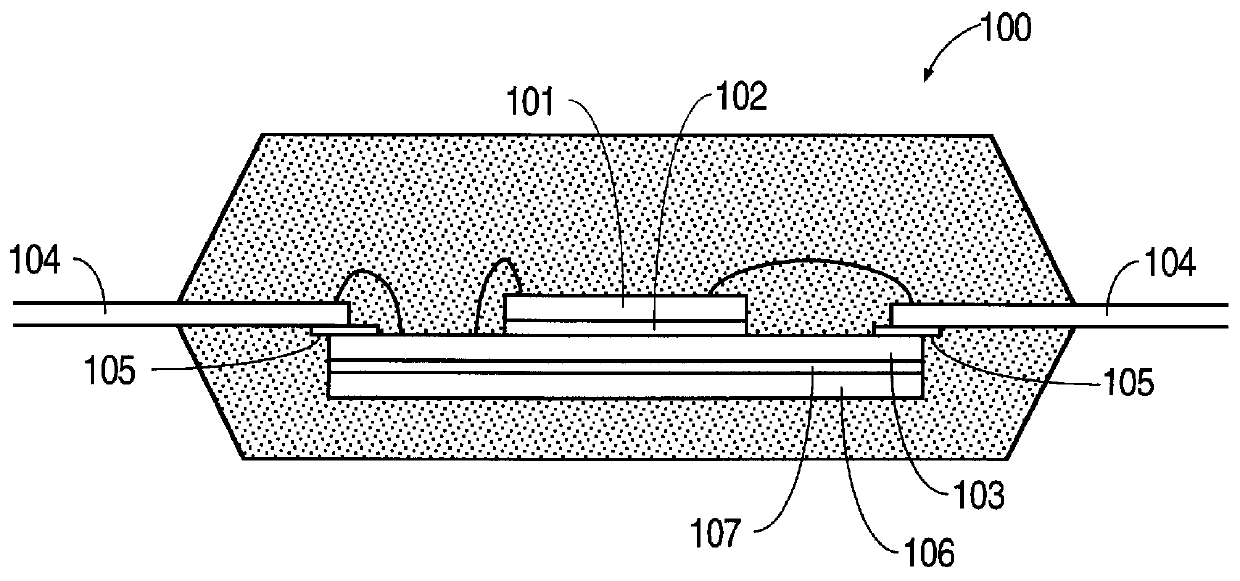

Integrated circuit substrate having laser-embedded conductive patterns and method therefor

InactiveUS6930256B1Printed electric component incorporationSemiconductor/solid-state device detailsScreen printingHigh density

An integrated circuit substrate having laser-embedded conductive patterns provides a high-density mounting and interconnect structure for integrated circuits. Conductive patterns within channels on the substrate provide interconnects that are isolated by the channel sides. A dielectric material is injection-molded or laminated over a metal layer that is punched or etched. The metal layer can provide one or more power planes within the substrate. A laser is used to ablate channels on the surfaces of the outer dielectric layer for the conductive patterns. The conductive patterns are electroplated or paste screen-printed and an etchant-resistive material is applied. Finally, a plating material can be added to exposed surfaces of the conductive patterns. An integrated circuit die and external terminals can then be attached to the substrate, providing an integrated circuit having a high-density interconnect.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

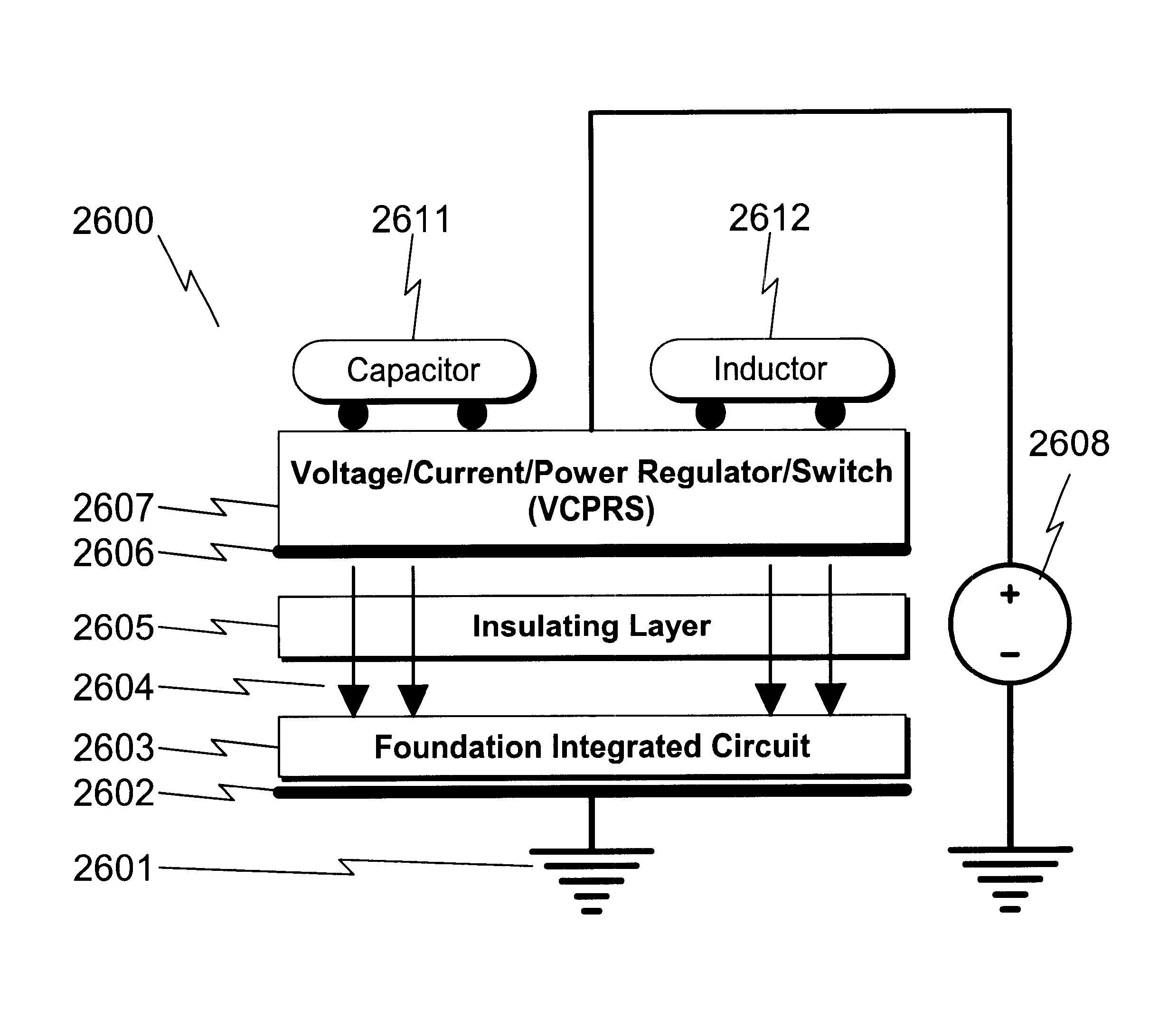

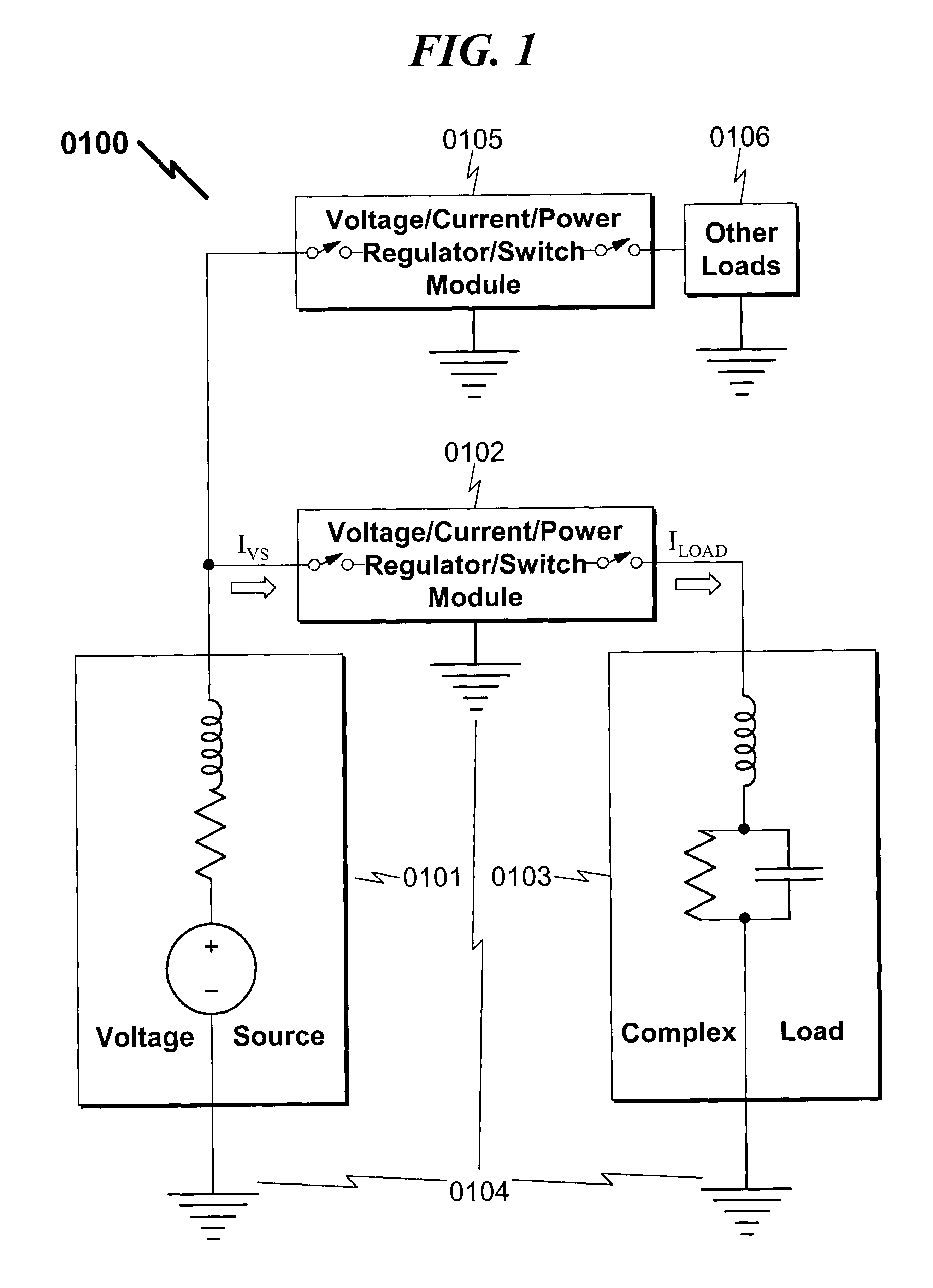

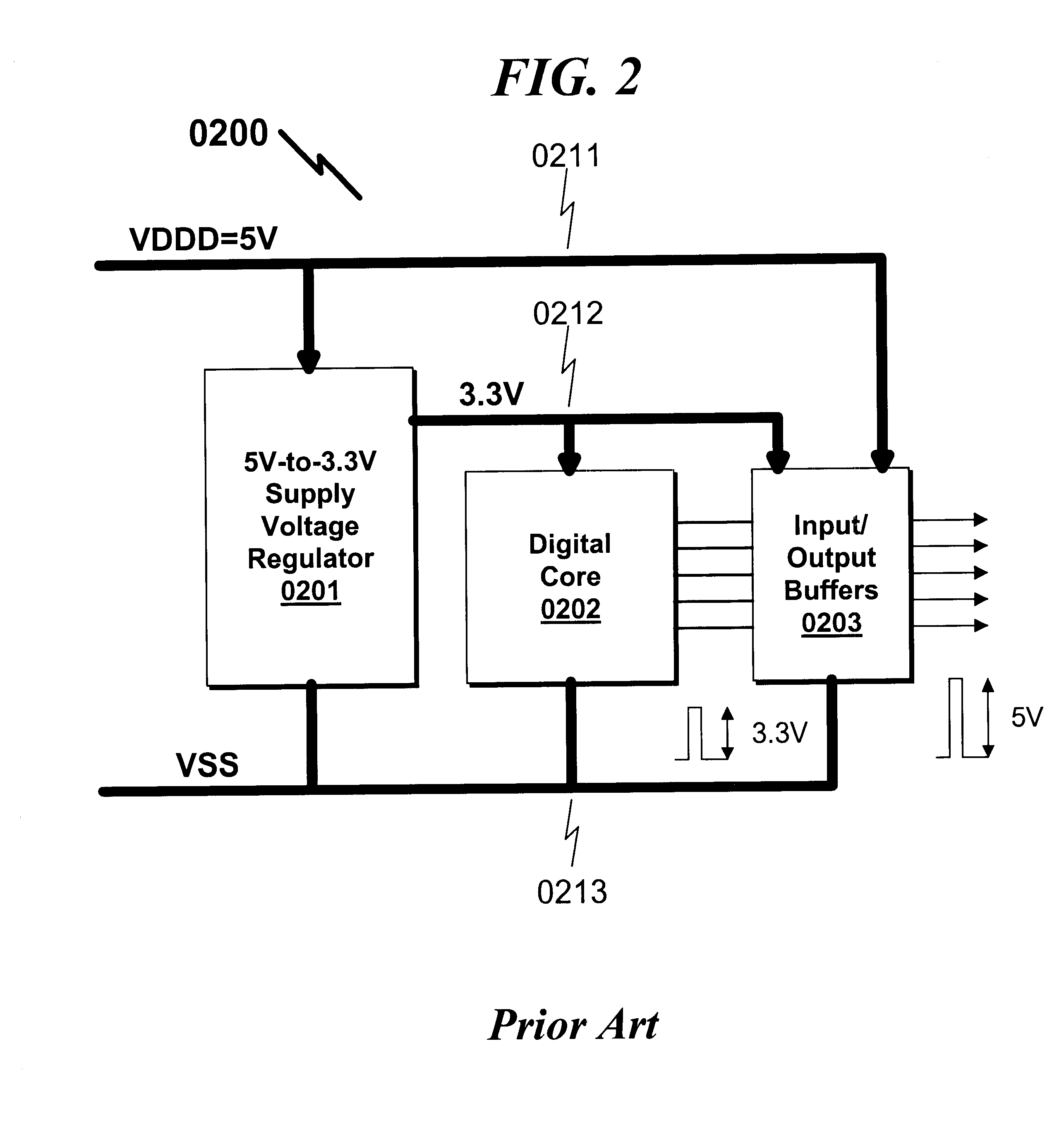

Integrated voltage/current/power regulator/switch system and method

InactiveUS6396137B1Minimal noiseGood PSRRSemiconductor/solid-state device detailsDc-dc conversionPower applicationPower capability

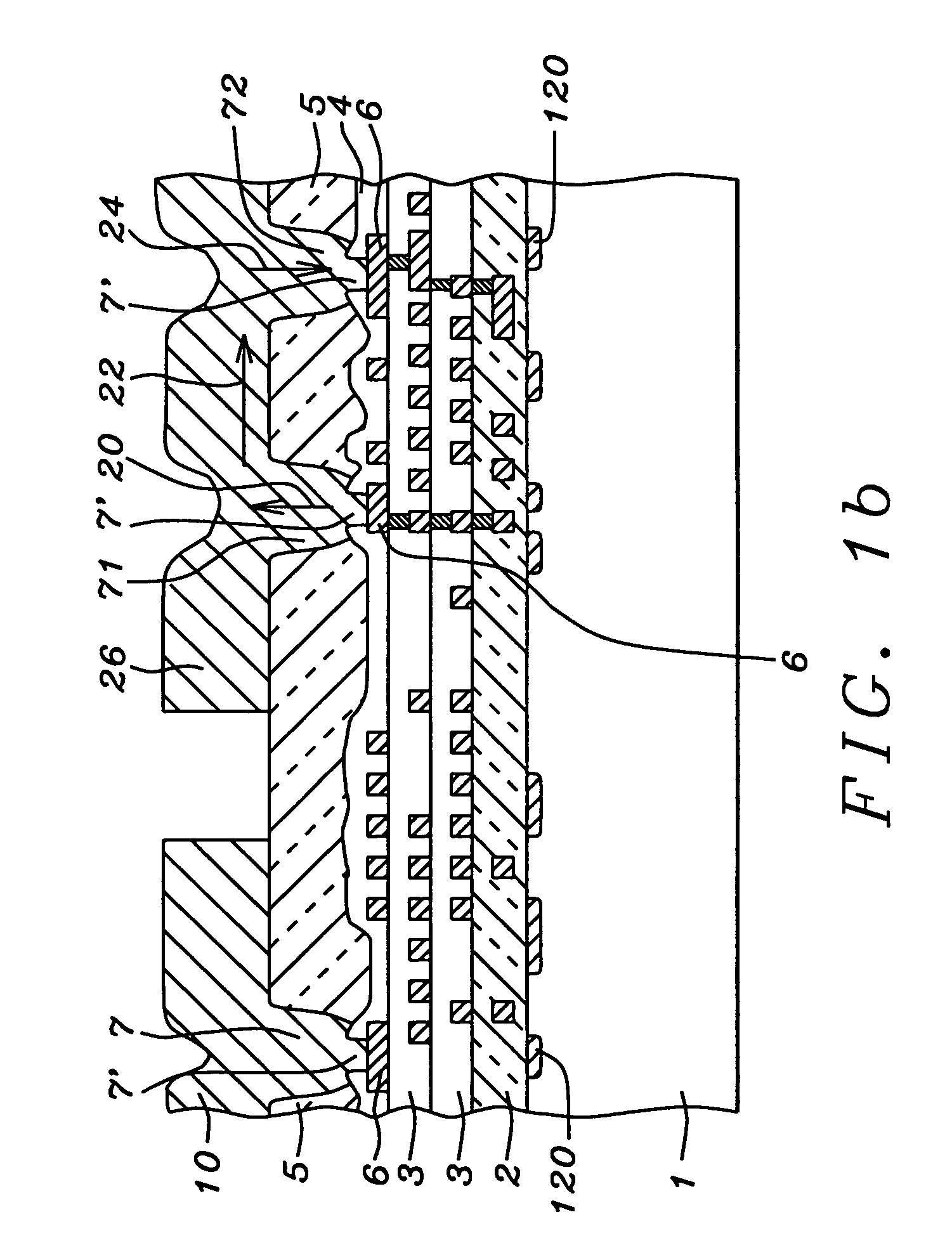

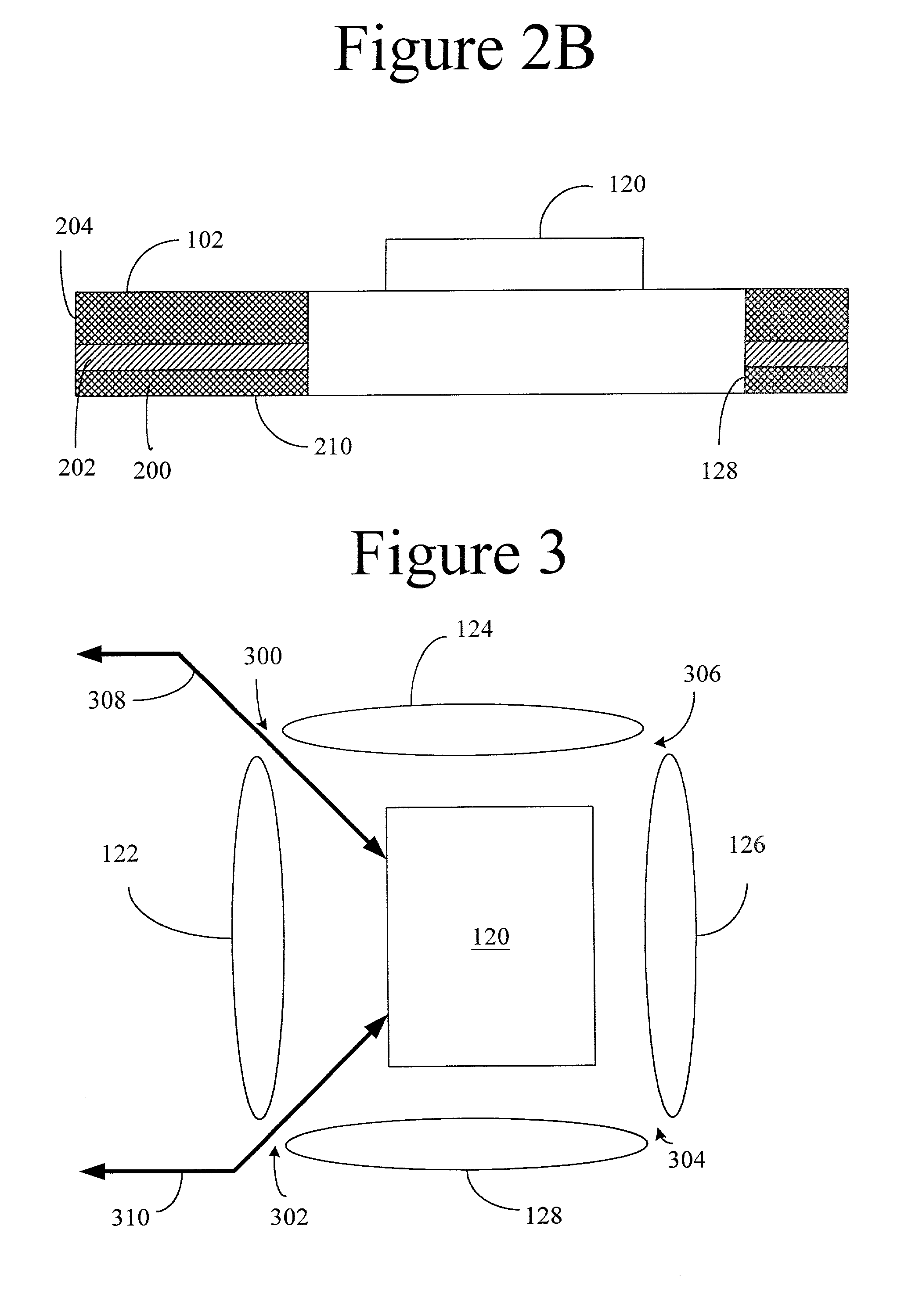

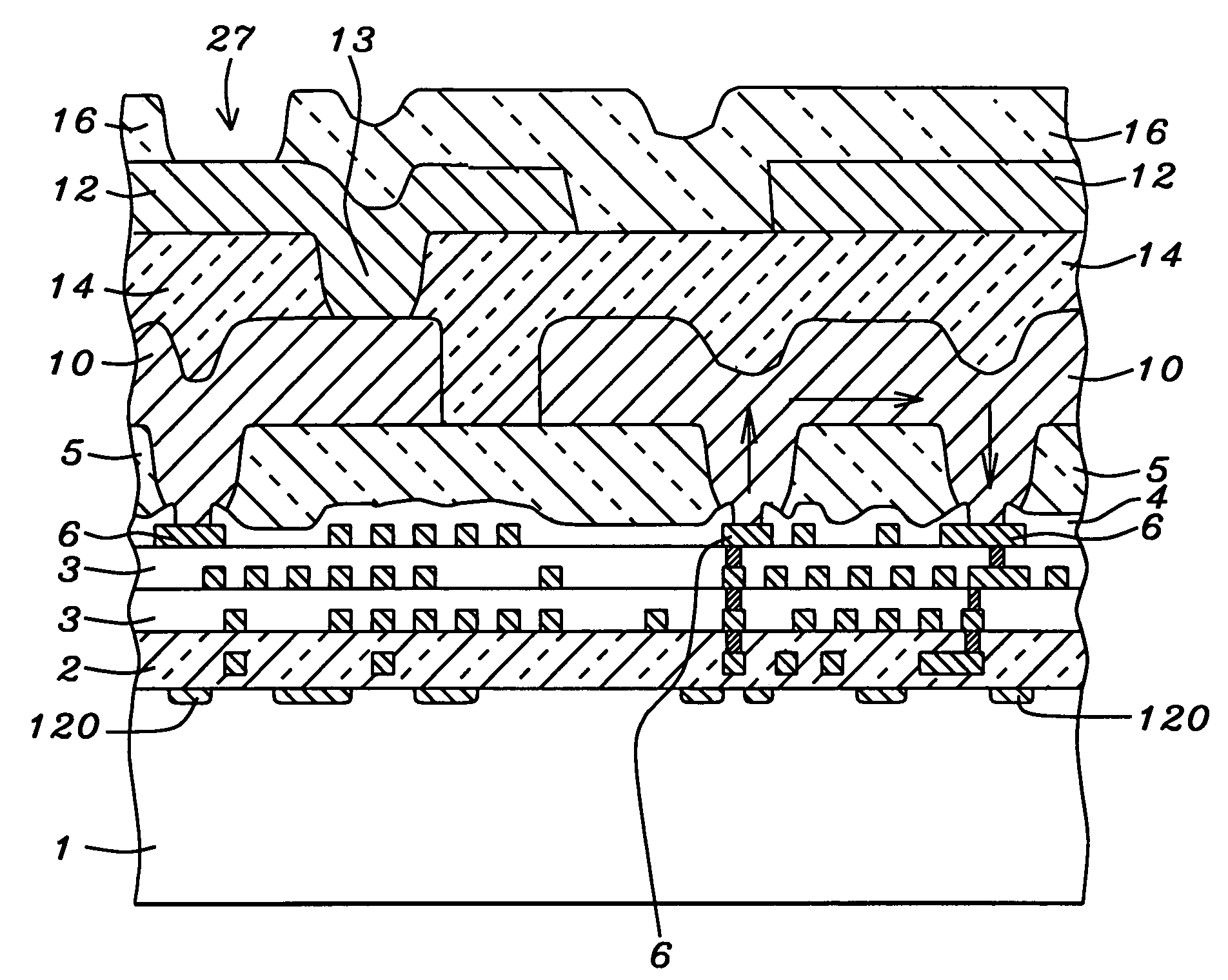

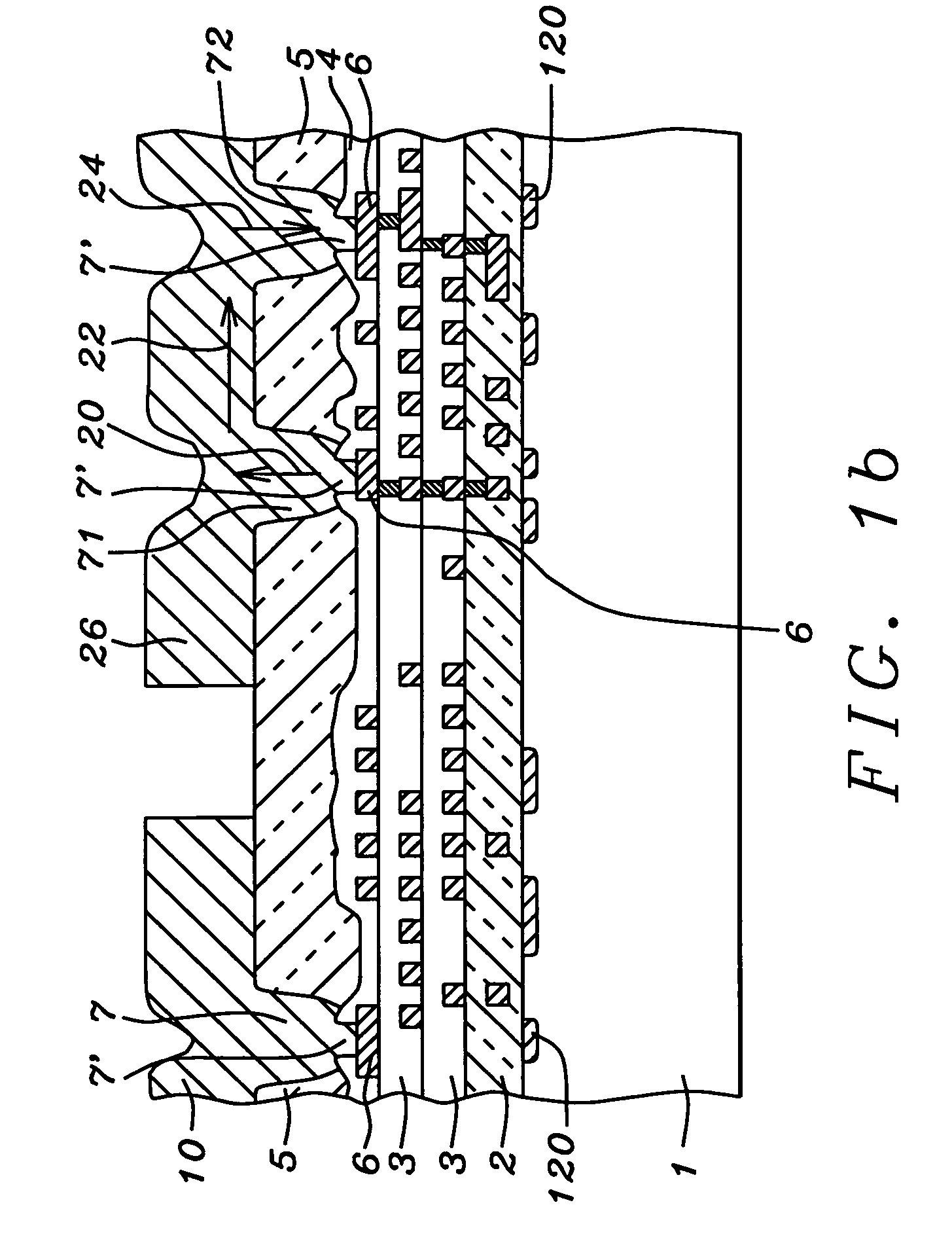

An integrated voltage / current / power regulator / switch (VCPRS) system and method are disclosed in which regulator / switch circuitry is vertically integrated on top of an existing integrated circuit. The present invention does not require additional integrated circuit chip area for the regulator pass device as is required in the prior art, and by virtue of its construction provides a significantly reduced on-resistance as compared to all prior art implementations. The present invention both stabilizes the power supply for large area integrated circuits and permits individual areas of the integrated circuit to have switched power capability, a highly desirable feature in low power and battery power applications. The present invention permits an increase in the power supply rejection ratio (PSRR) for digital, analog, and especially mixed-signal integrated circuit designs by permitting various circuit blocks to have localized power regulation that is obtained from a common power supply plane within the integrated circuit framework. Finally, the present invention appears to be the only economically practical method of addressing the power supply regulation requirements of modern and future integrated microprocessor designs.

Owner:KLUGHART KEVIN MARK

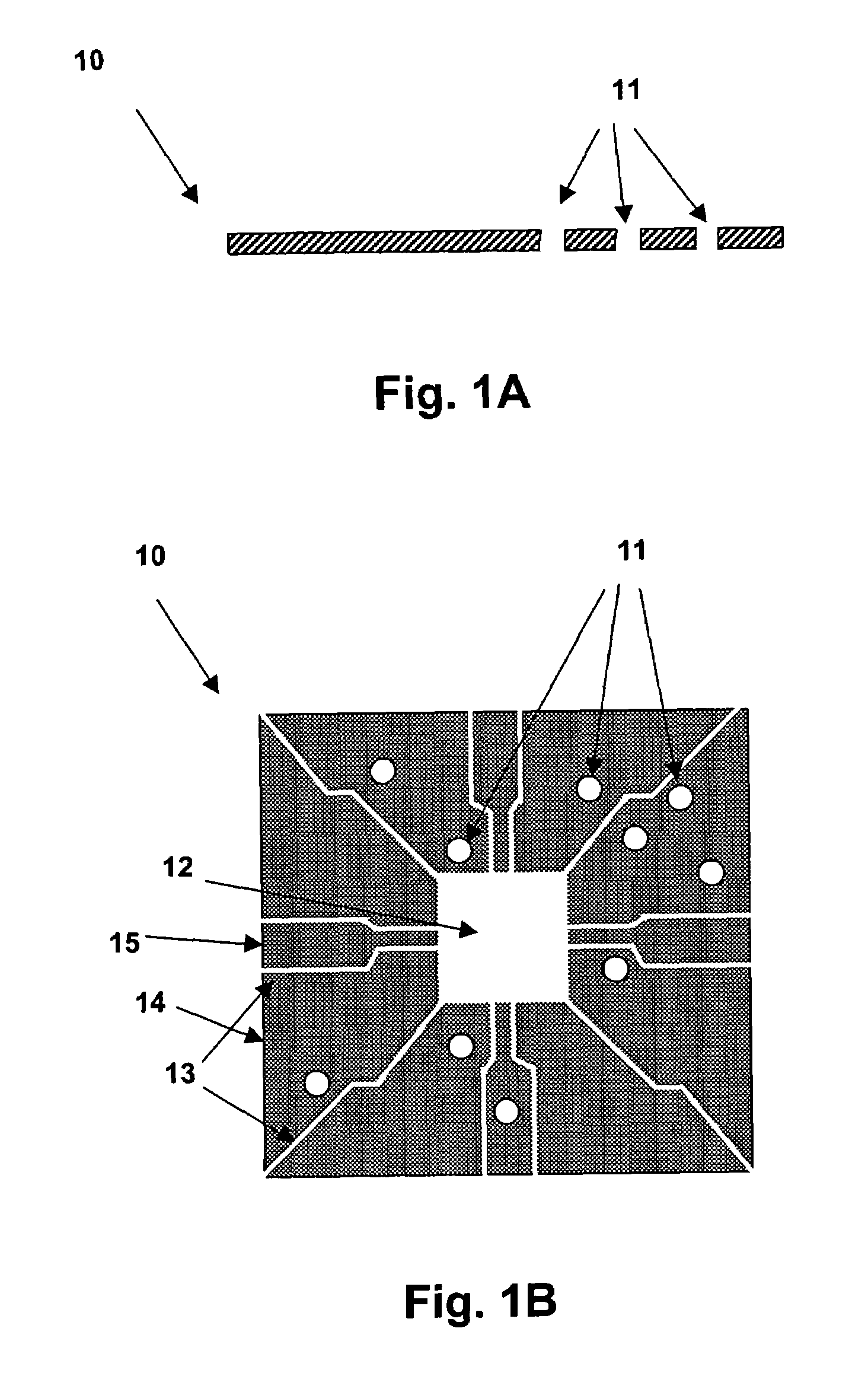

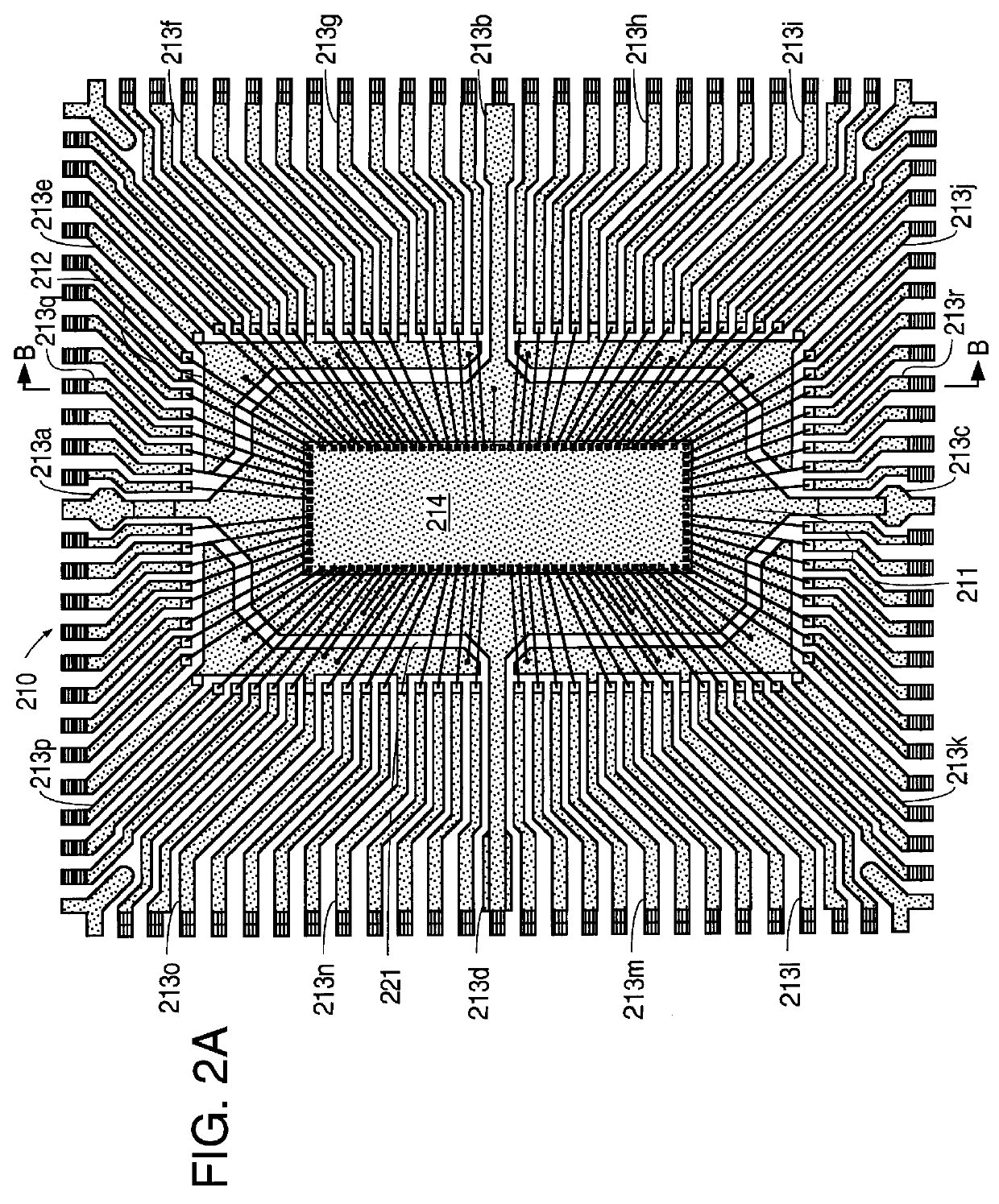

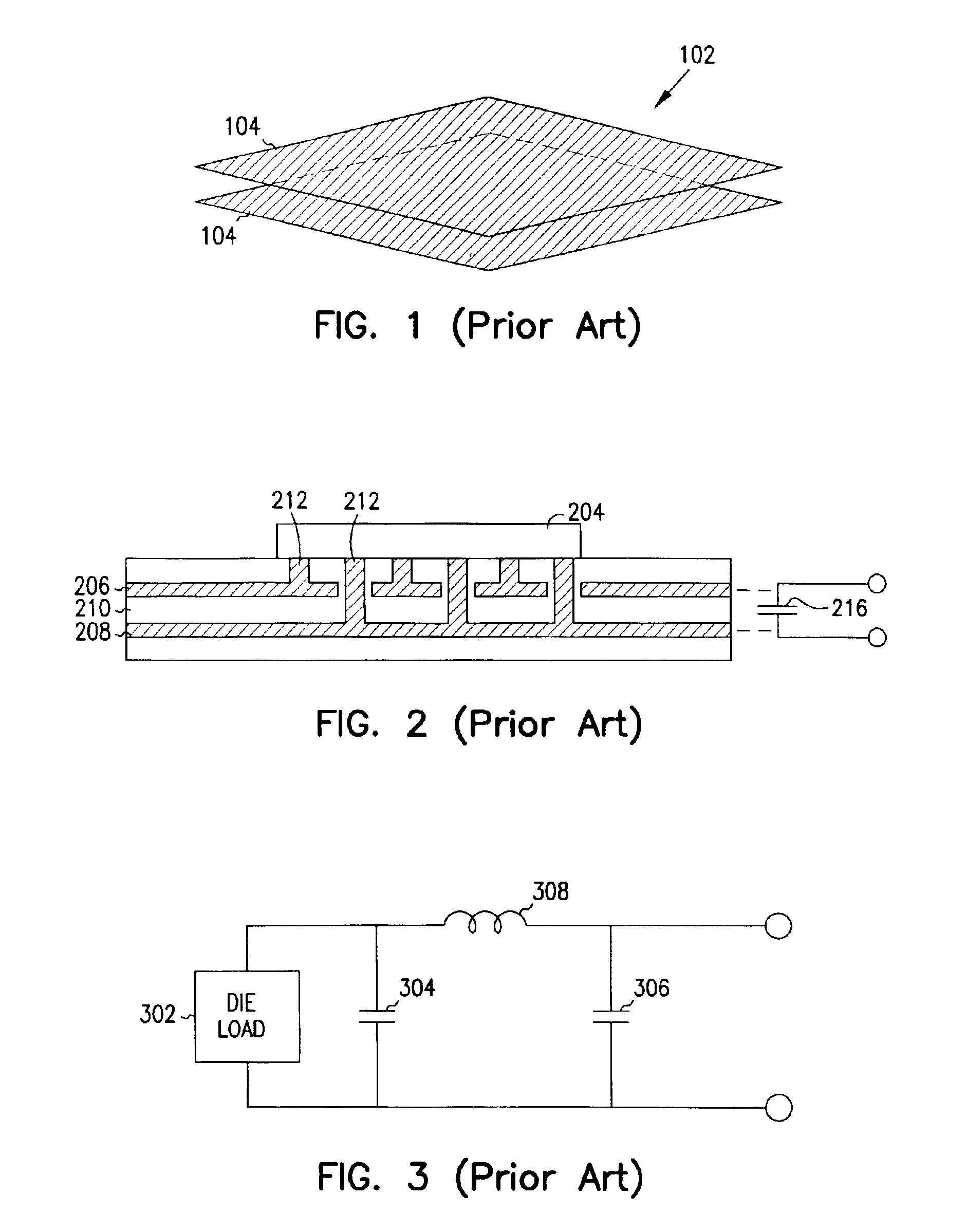

Leadframe with power and ground planes

InactiveUSRE36907E1Reduced effective inductanceReduce crosstalkSemiconductor/solid-state device detailsSolid-state devicesVoltage sourceLead frame

A leadframe for use in an integrated circuit package is described. The leadframe comprises a plurality of electrically conductive leads, a die attach pad, and an electrically conductive ring or rings formed generally around the circumference of the die attach pad and between the die attach pad and leads. In one embodiment, at least one of the leads is formed integrally with each ring. The die attach pad may also be formed integrally with one or more leads. In another embodiment, the ring or rings are formed so that they are electrically isolated from the die attach pad, and the die attach pad, leads, and ring or rings are all formed in substantially the same plane. In some embodiments, the ring or rings are broken into electrically isolated sections. Each of the ring sections (and die attach pad, if appropriate) may be electrically connected to a voltage source outside the integrated circuit package (e.g., a power supply or ground). The leadframe is formed from a single sheet of material by, for instance, stamping or etching. The leadframe may be used in either ceramic or plastic packages. The leadframe reduces switching noise and crosstalk, allows more flexibility in placement of power and / or ground bond pads on the die, and allows provision of ground and power planes in an integrated circuit package that is thinner than previous integrated circuit packages containing both ground and power planes.

Owner:INTEGRATED DEVICE TECH INC

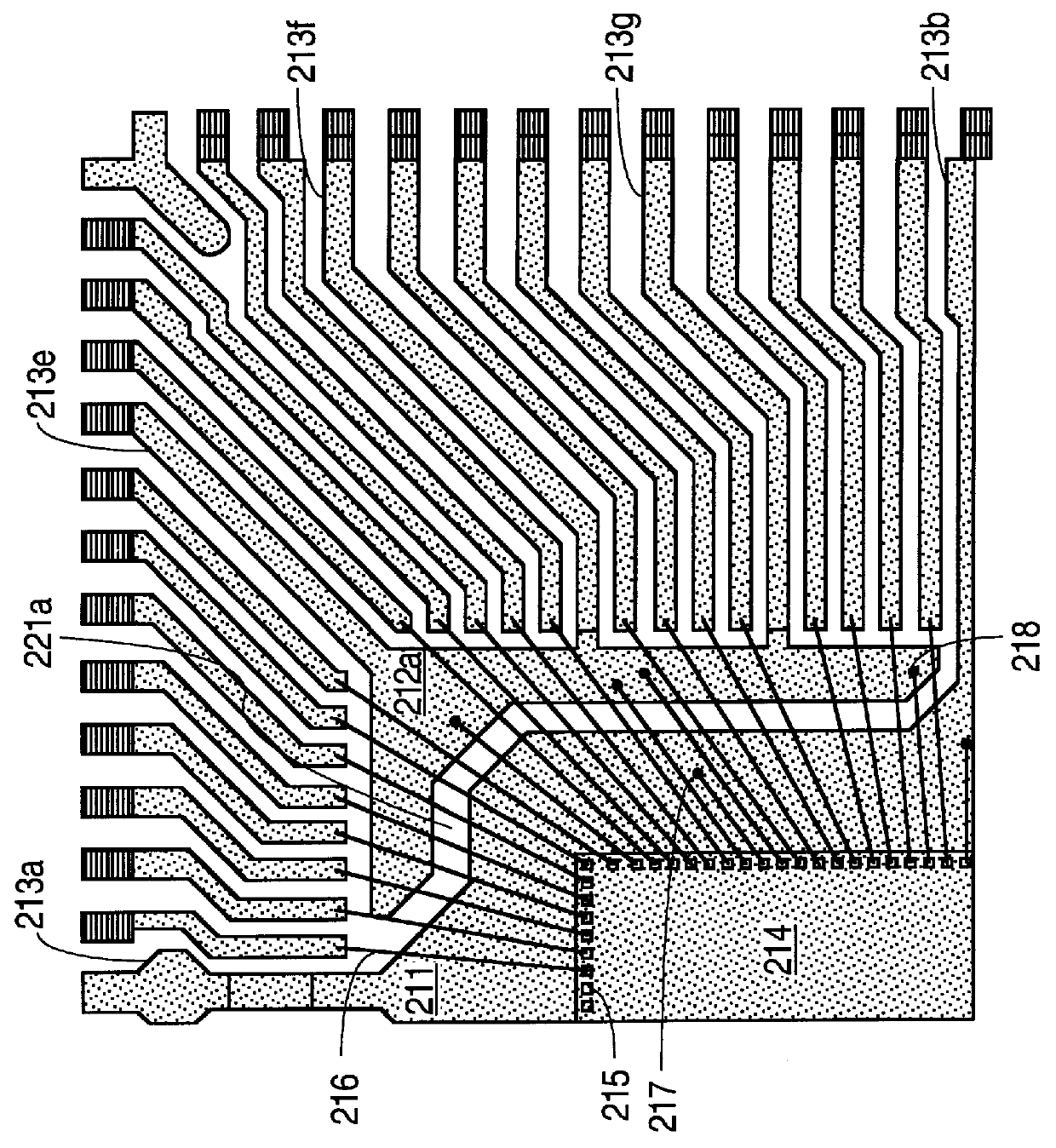

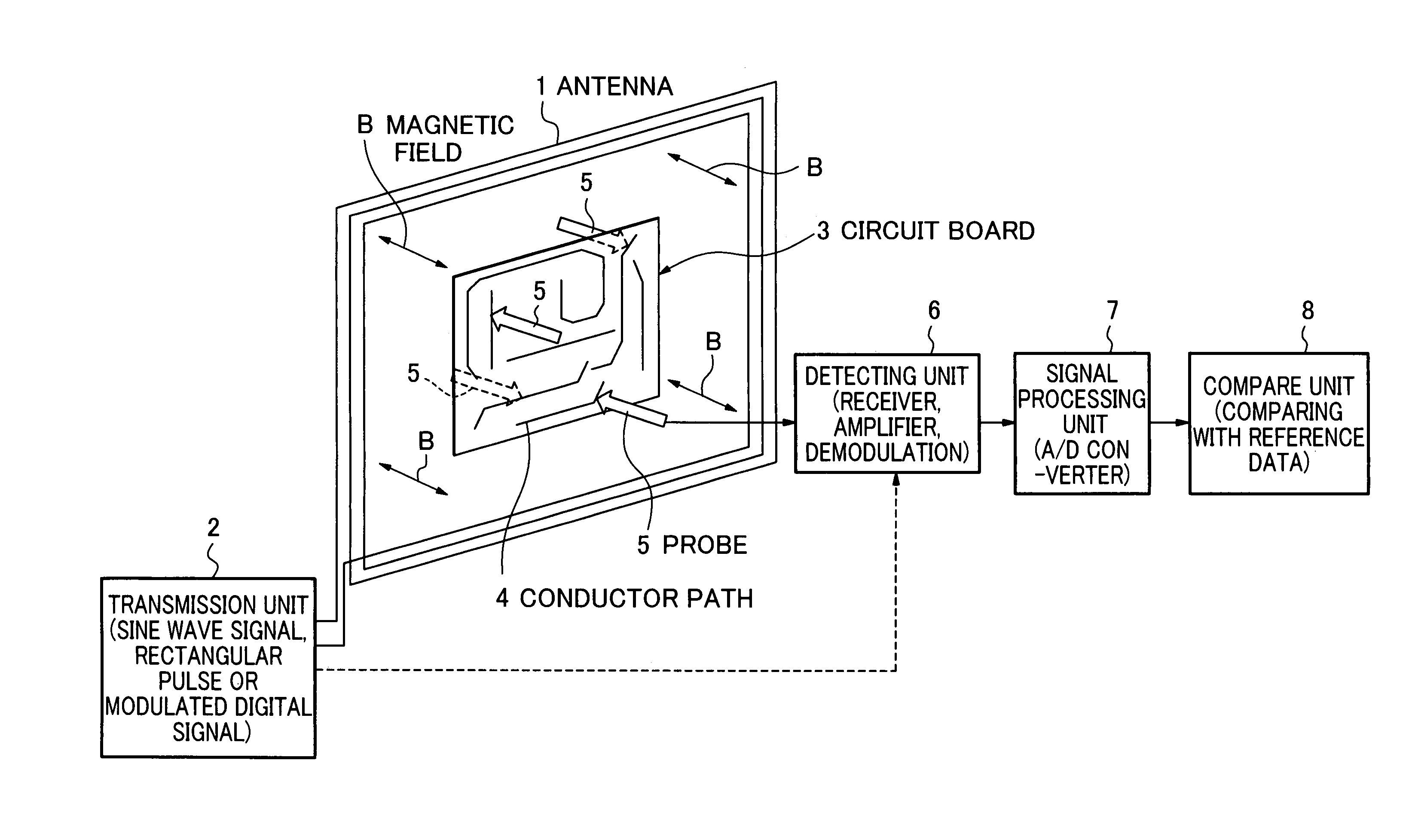

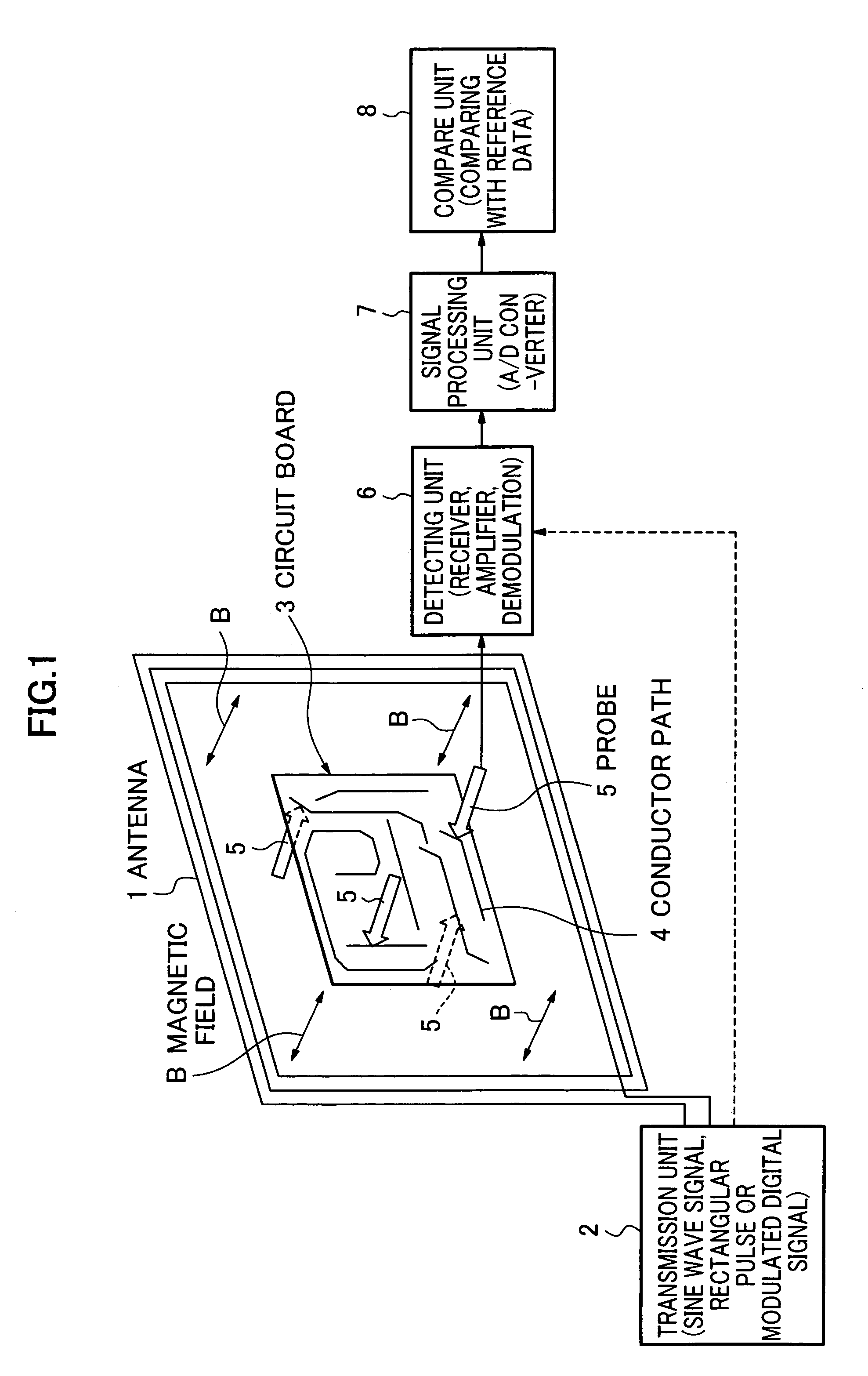

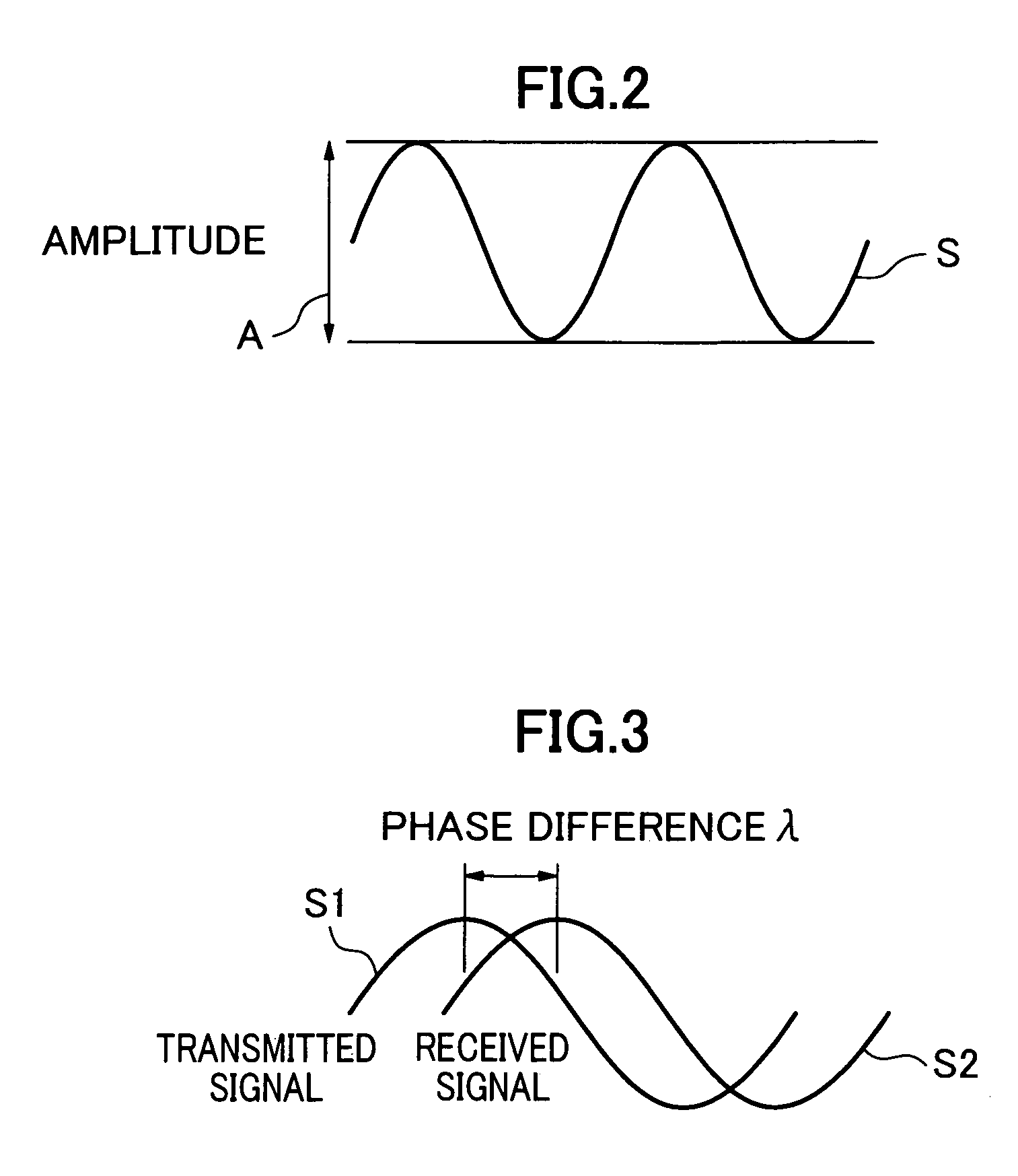

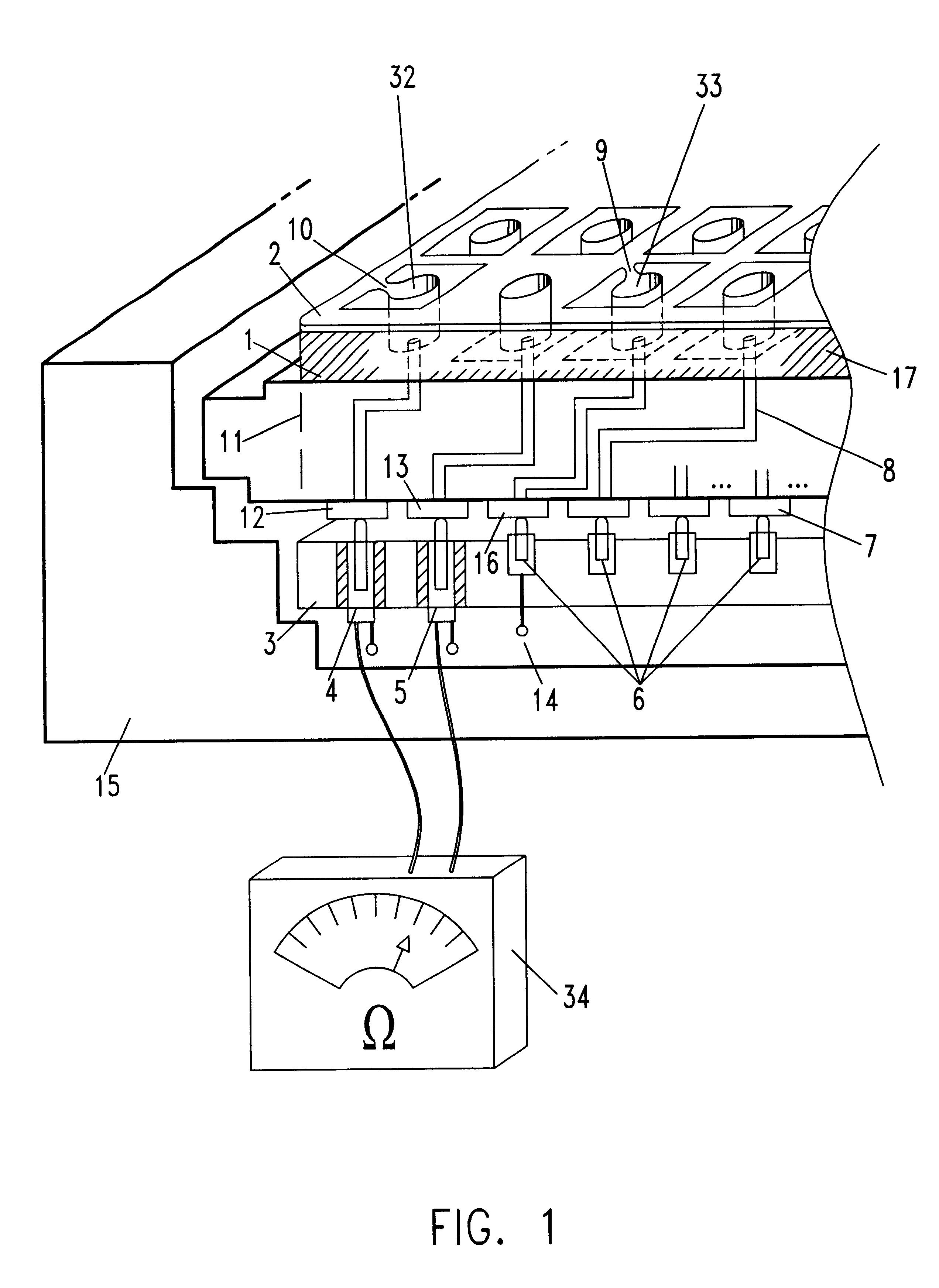

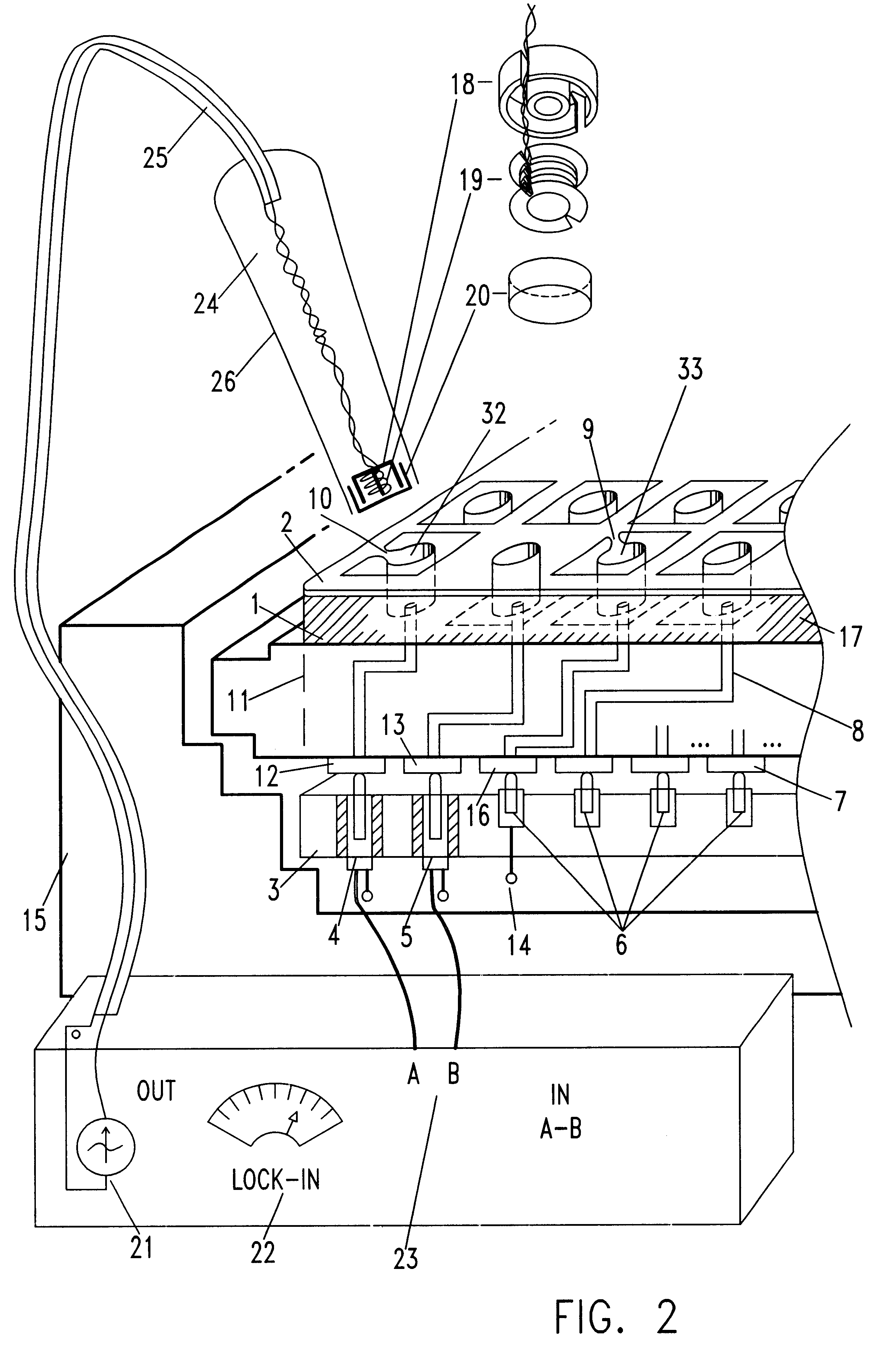

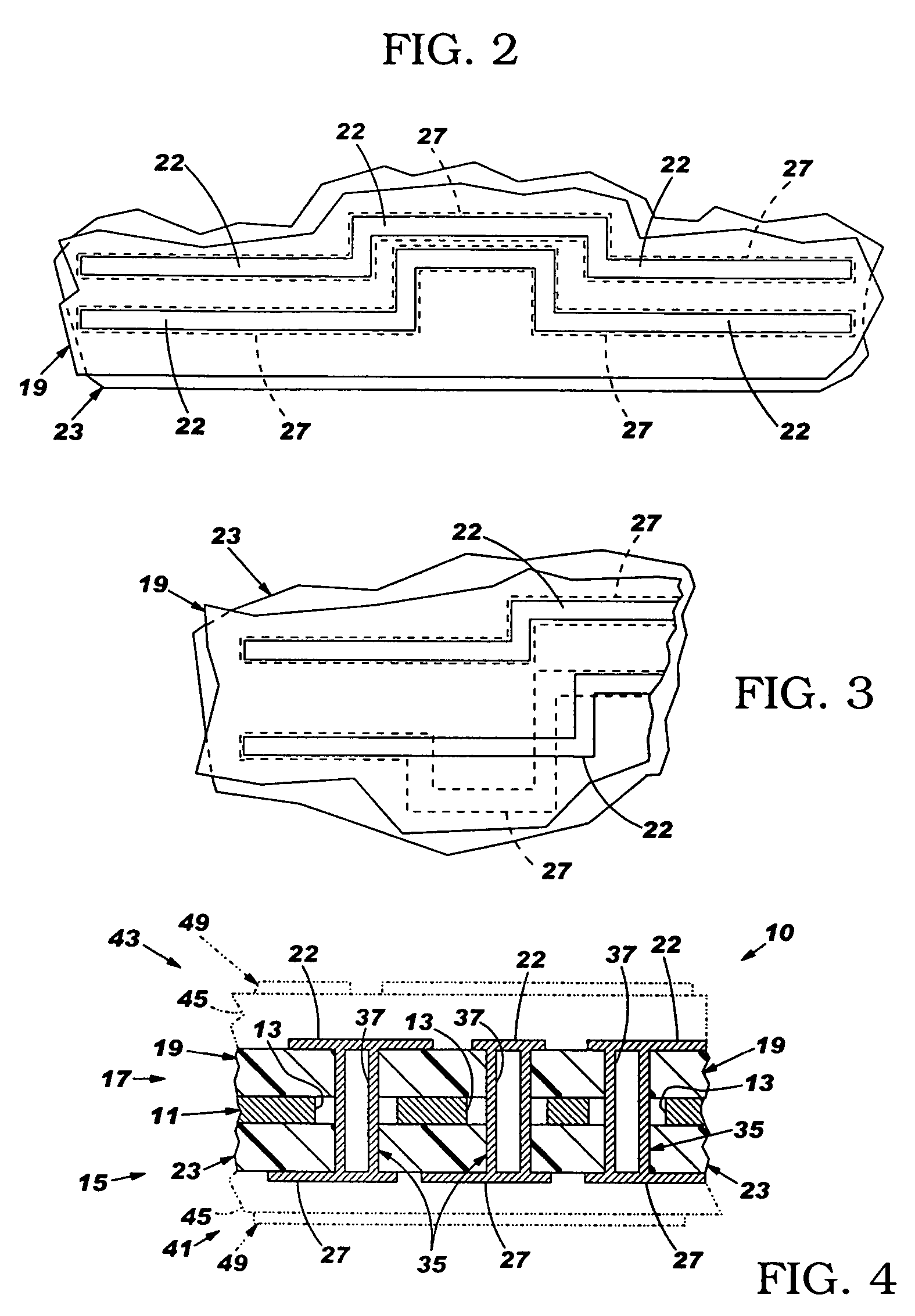

Method and apparatus for testing circuit boards

ActiveUS7188037B2Shorten the timeHigh-precision detectionResistance/reactance/impedenceError detection/correctionElectrical conductorPath network

The invention provides a method of apparatus for testing circuit boards which does not require any inner wide power plane so as to detect an open circuit defect and / or a short circuit defect in a conductor path network formed in the circuit board quickly and accurately. An apparatus for testing a circuit board according to the present invention includes a transmission unit (2) for transmitting electromagnetic (radio) wave signal by way of an antenna (1) to a circuit board (3) to be tested, a detecting unit (3) for detecting signal received by a conductor path (4) of the circuit board (3) by using the conductor path (4) as a receiving antenna, and compare unit (8) for determining whether or not there is an open circuit defect or a short circuit defect in the conductor path (4) by comparing the detected signal with reference data of corresponding to a conductor path not including any defect.

Owner:MICROCRAFT

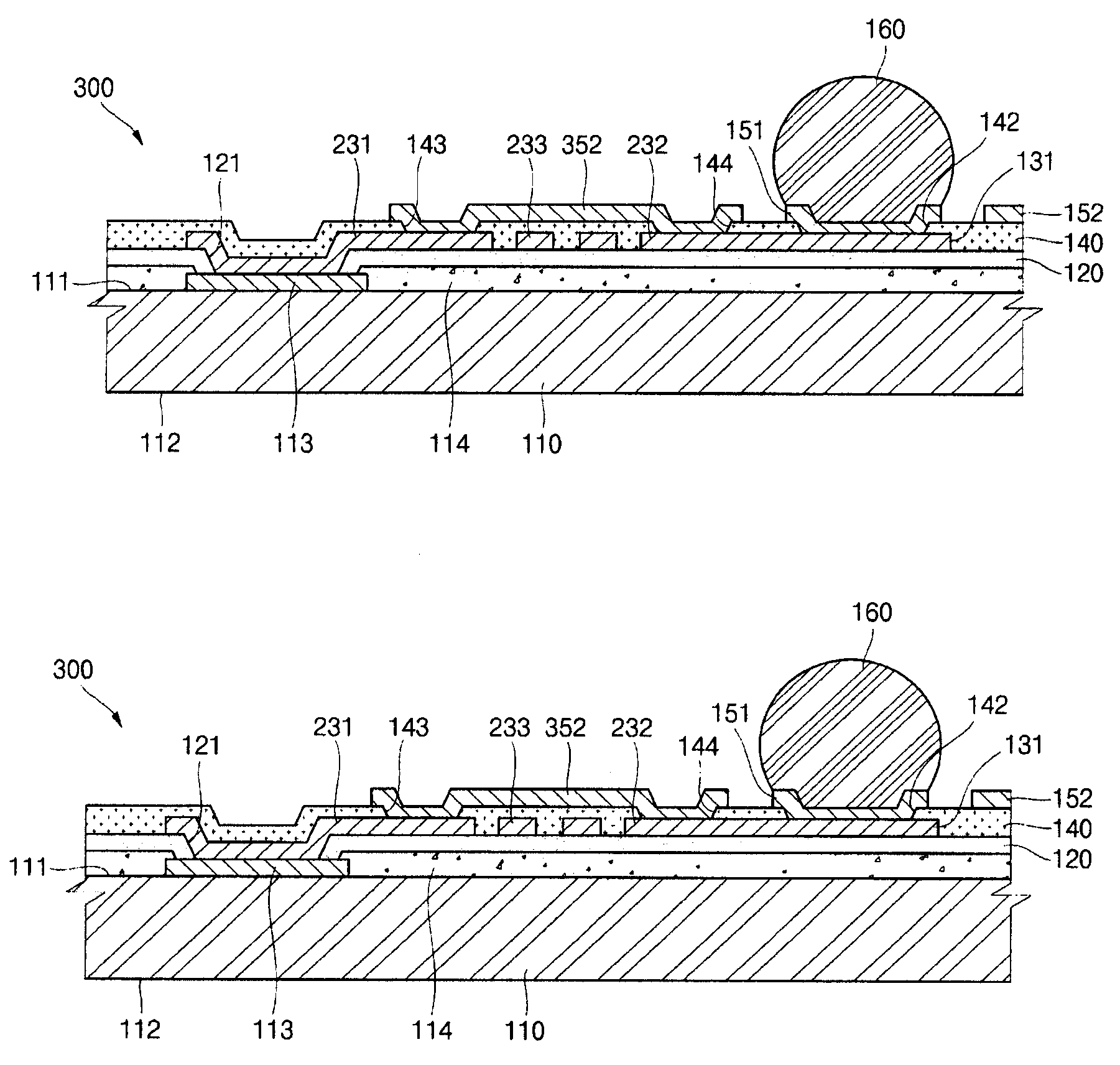

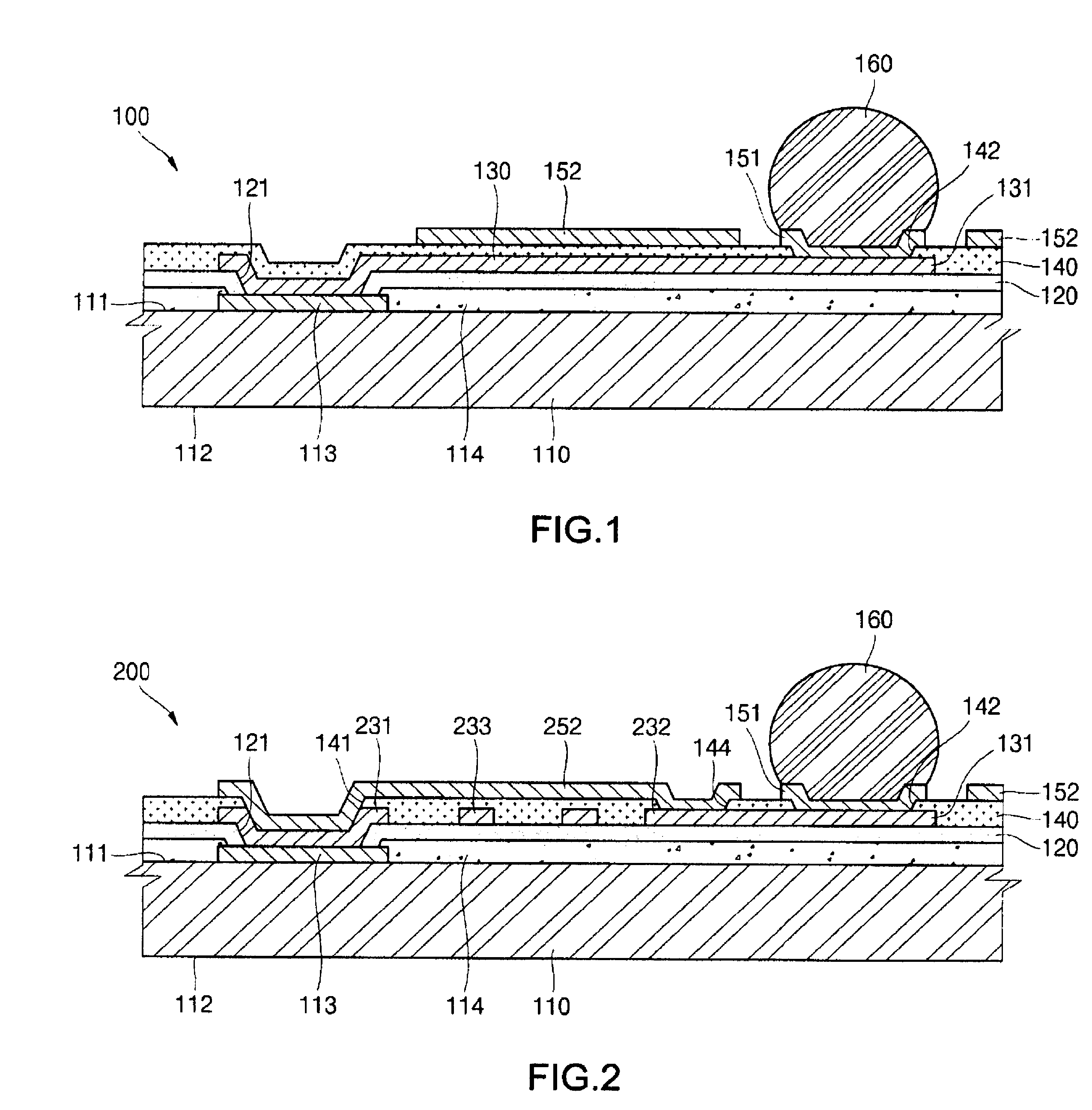

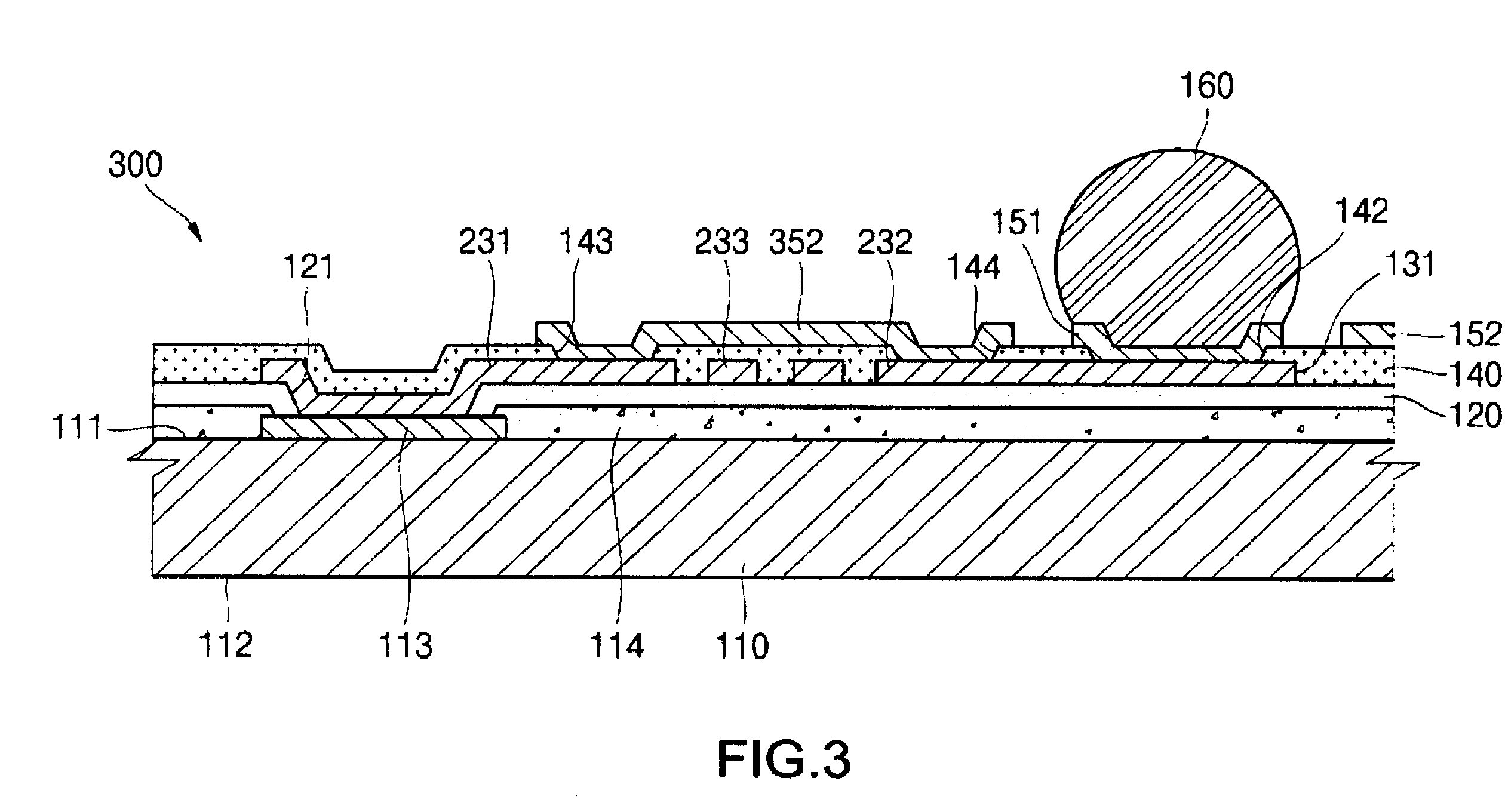

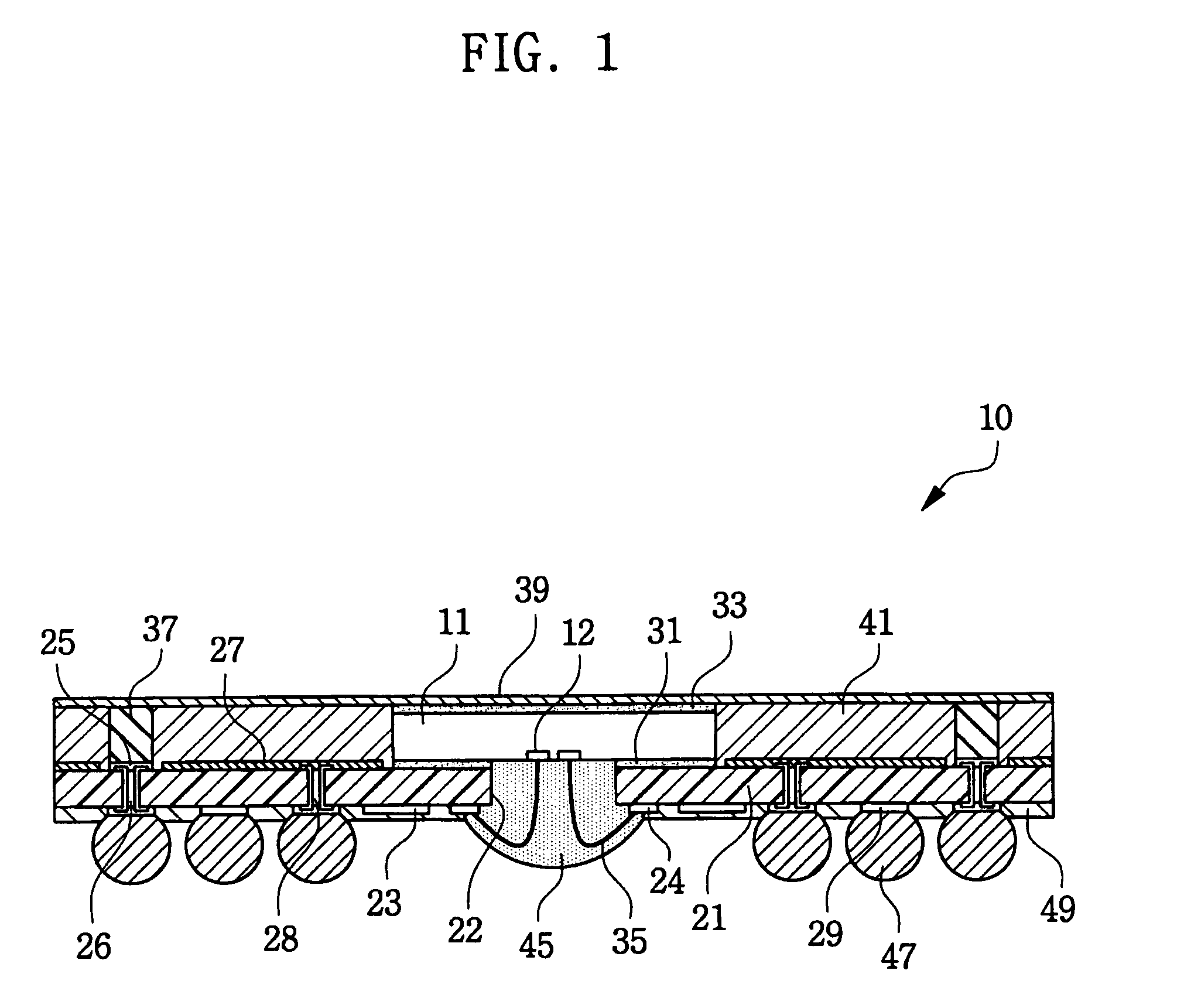

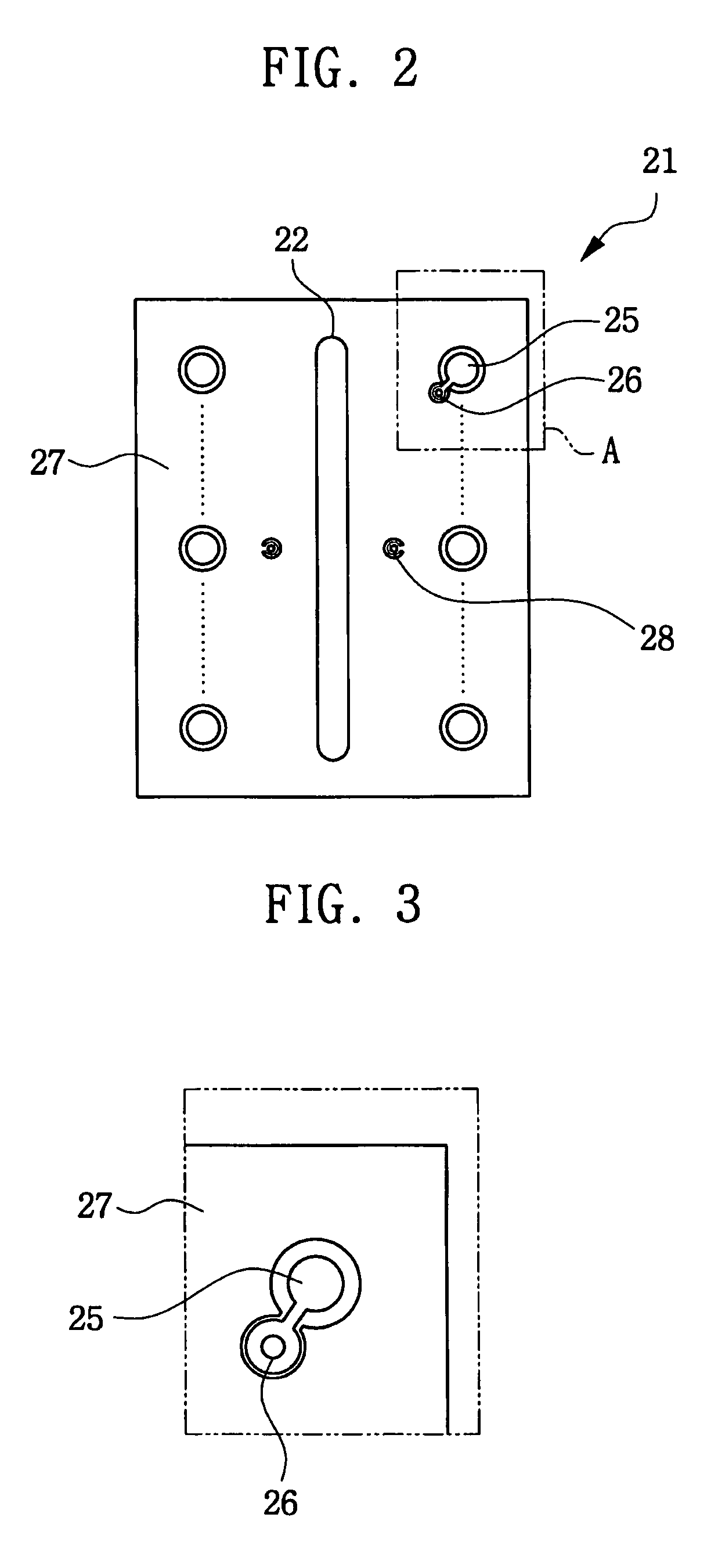

Wafer level chip size package having redistribution layers

ActiveUS7977783B1Semiconductor/solid-state device detailsSolid-state devicesRedistribution layerChip size

A wafer level chip size package (WLCSP) and a method of manufacturing the same are disclosed. Lands are formed at the ends of redistribution layers. The redistribution layers excluding the lands and a first dielectric layer are covered with a second dielectric layer. After forming a first under bump metallurgy (UBM) layer on the land, a solder ball is reflowed to the first UBM layer. A second UBM layer is widely formed on the entire second dielectric layer that is the outer circumference of the first UBM layer and is connected to the redistribution layer through a via-hole. Therefore, the second UBM layer having a large area can be used as a ground plane or a power plane. In addition, the second UBM layer can electrically connect the redistribution layers physically separated from each other. Therefore, the plurality of redistribution layers can cross each other without being electrically shorted with each other.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

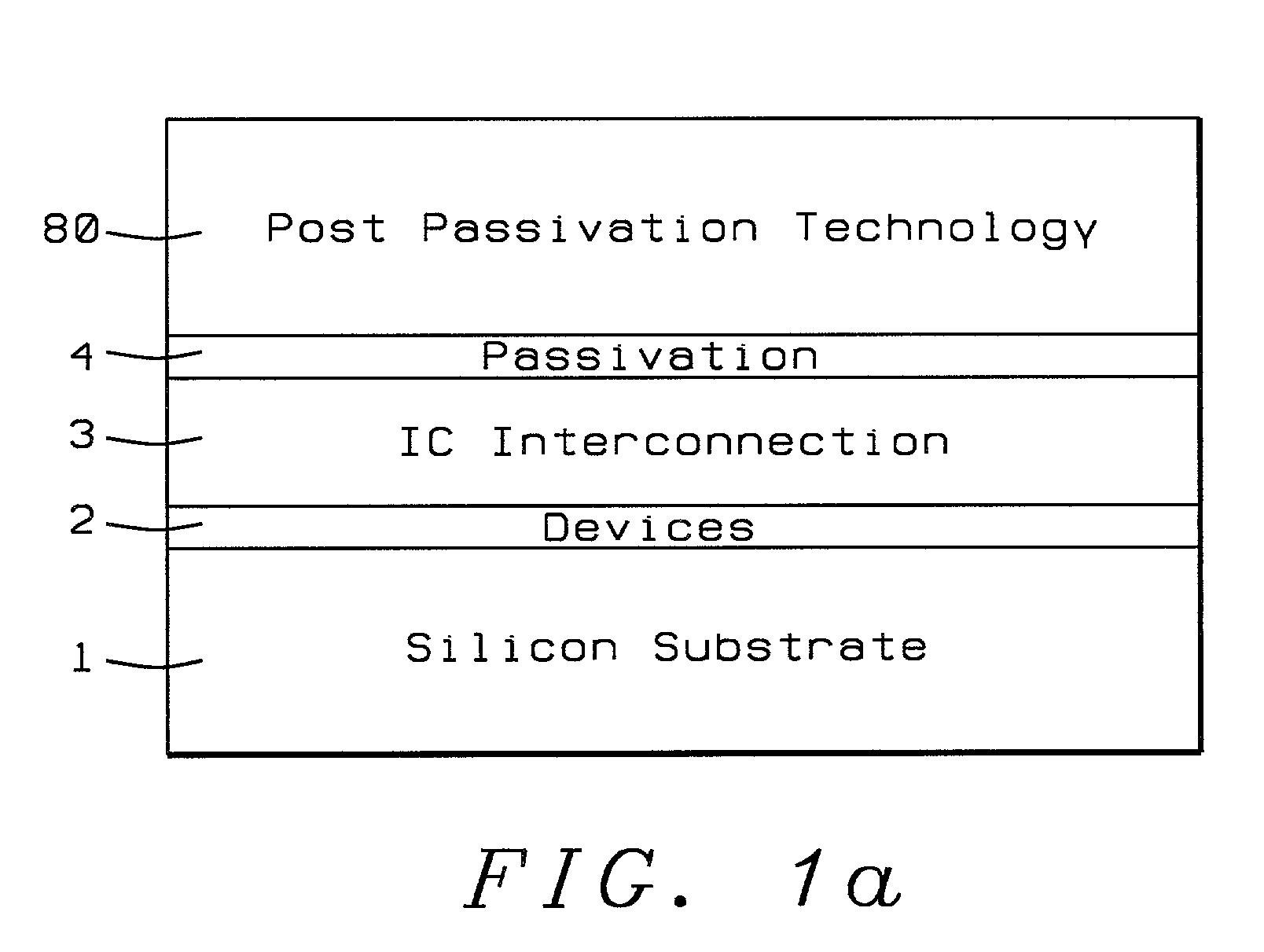

Top layers of metal for integrated circuits

ActiveUS20060063378A1Improve performanceReduce resistive voltage dropSemiconductor/solid-state device detailsSolid-state devicesCritical signalSemiconductor

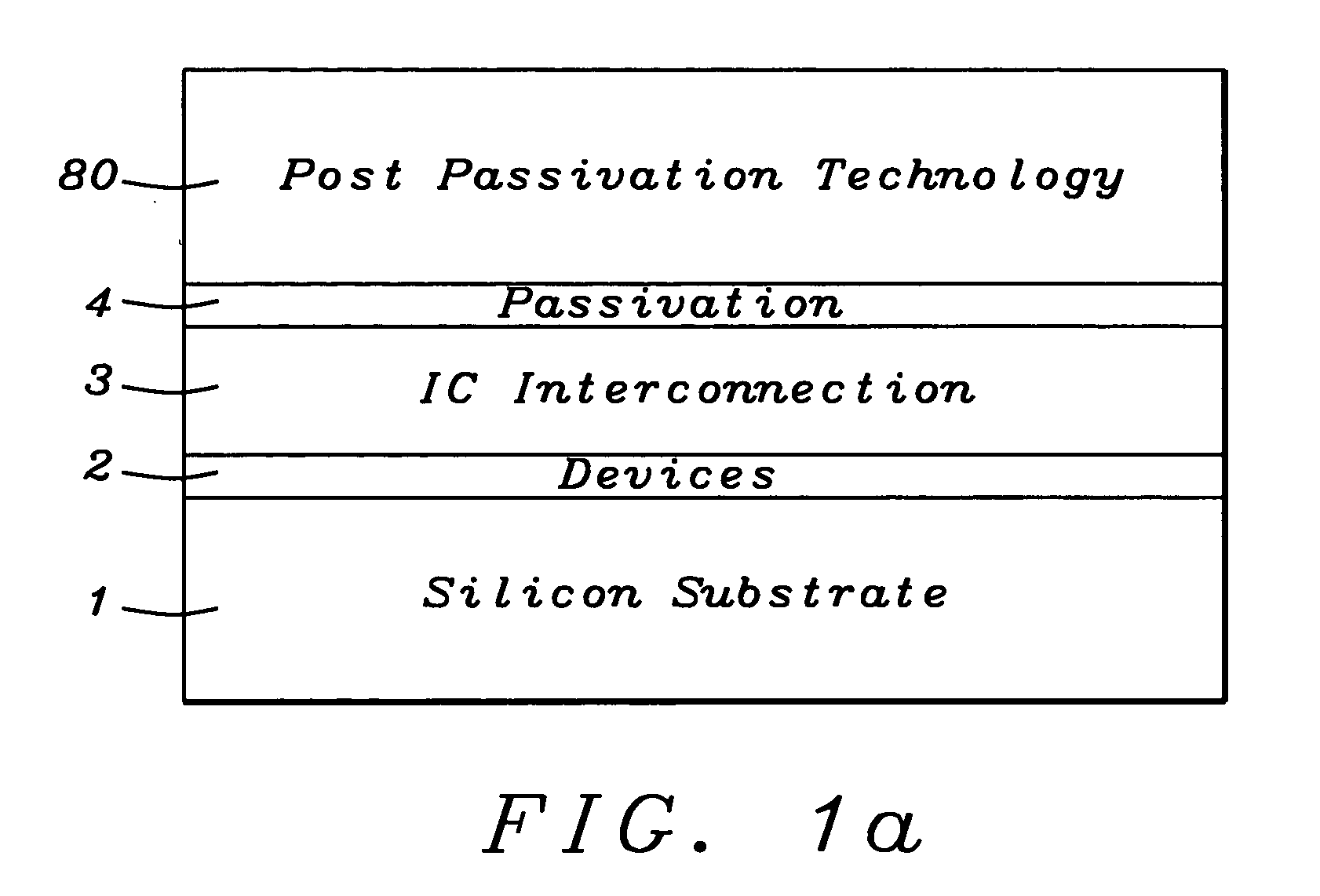

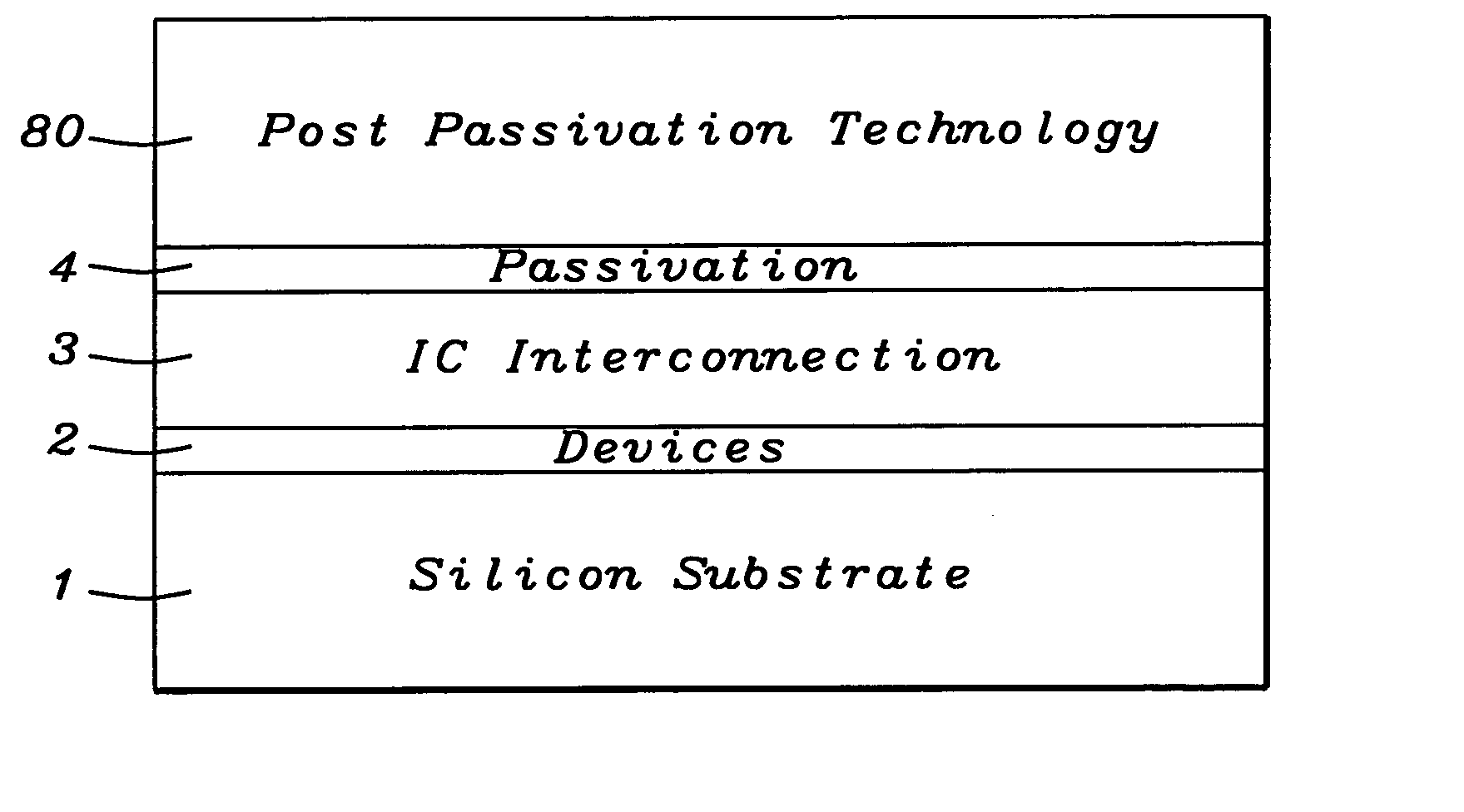

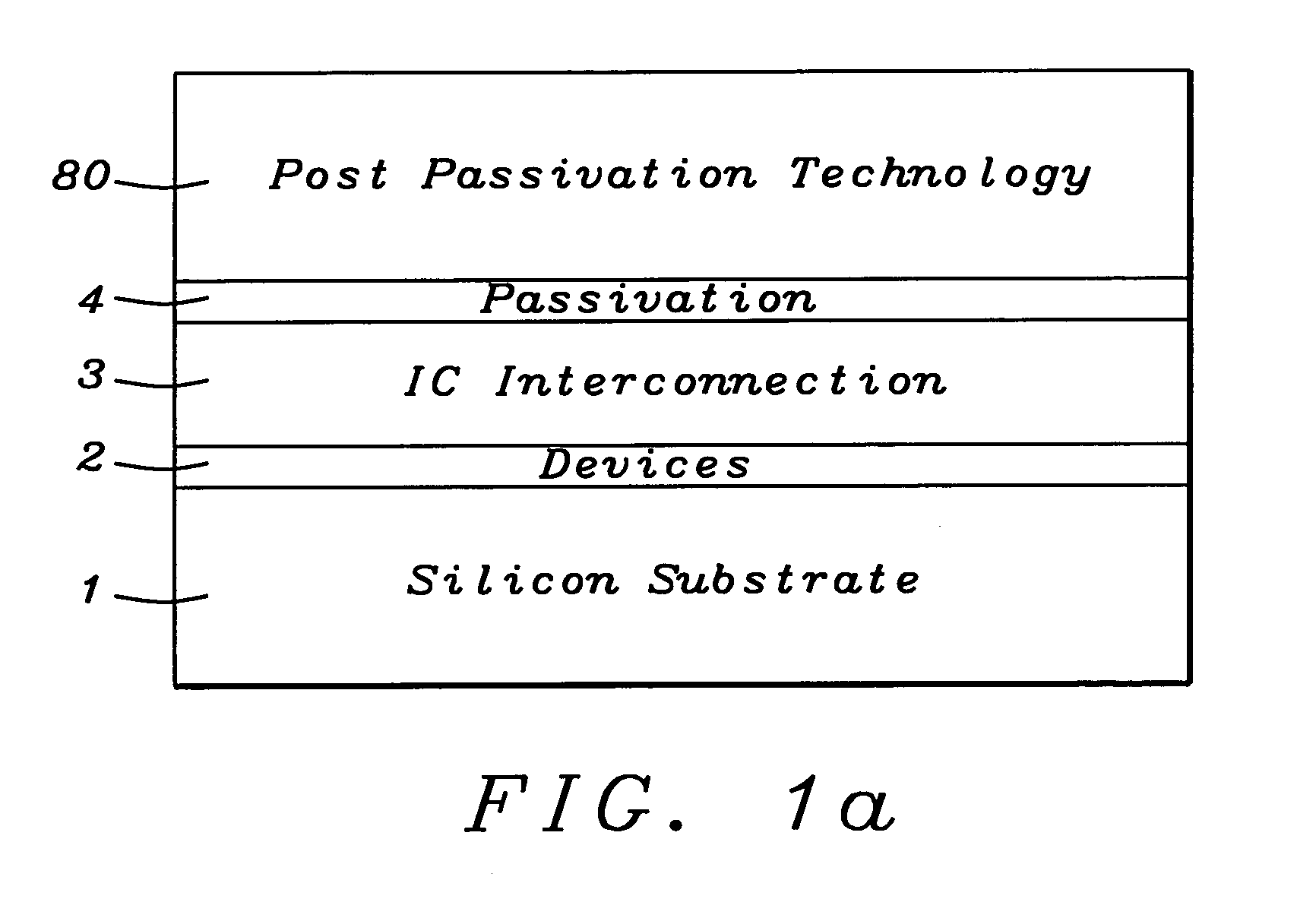

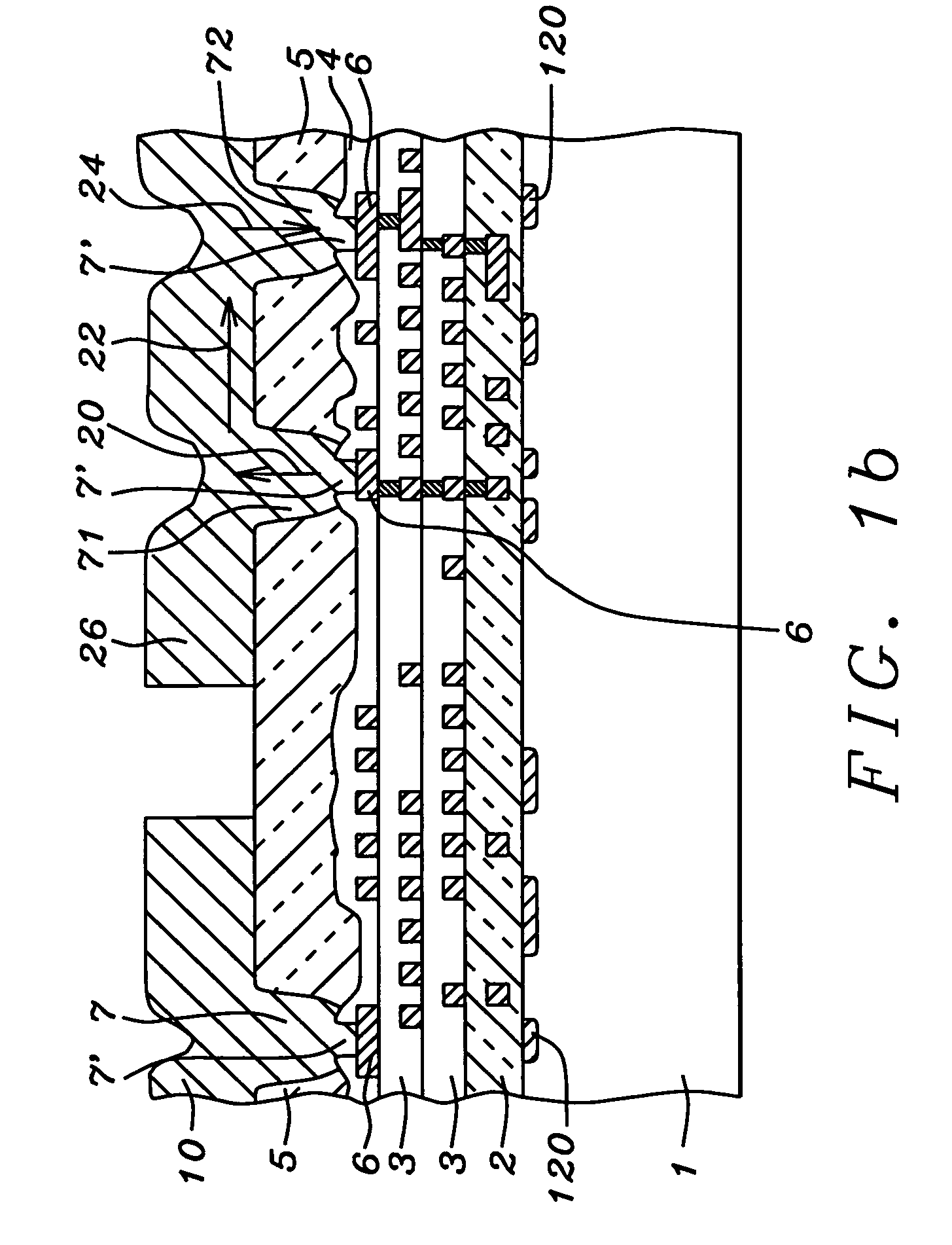

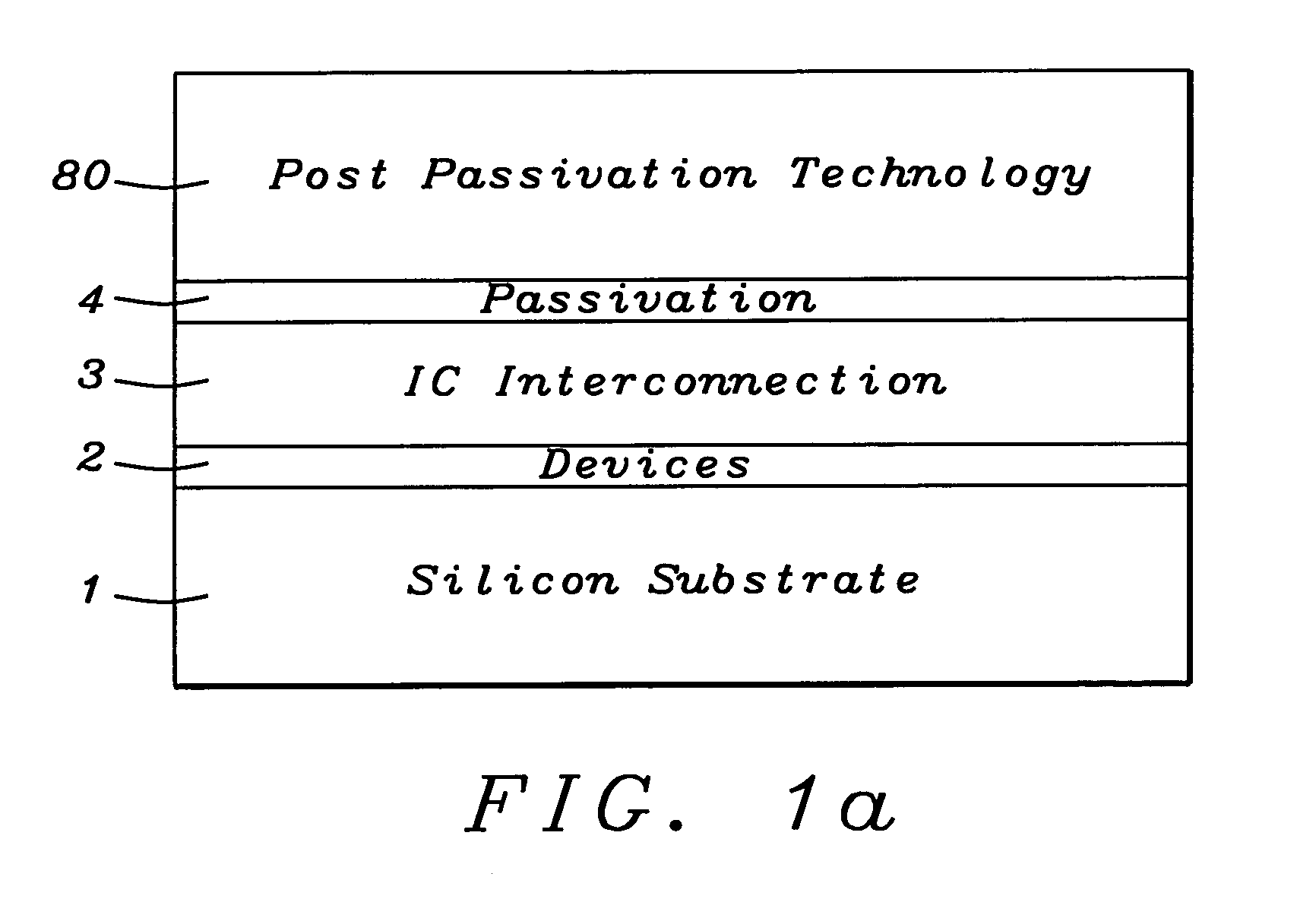

The present invention adds one or more thick layers of polymer dielectric and one or more layers of thick, wide metal lines on top of a finished semiconductor wafer, post-passivation. The thick, wide metal lines may be used for long signal paths and can also be used for power buses or power planes, clock distribution networks, critical signal, and re-distribution of I / O pads.

Owner:QUALCOMM INC

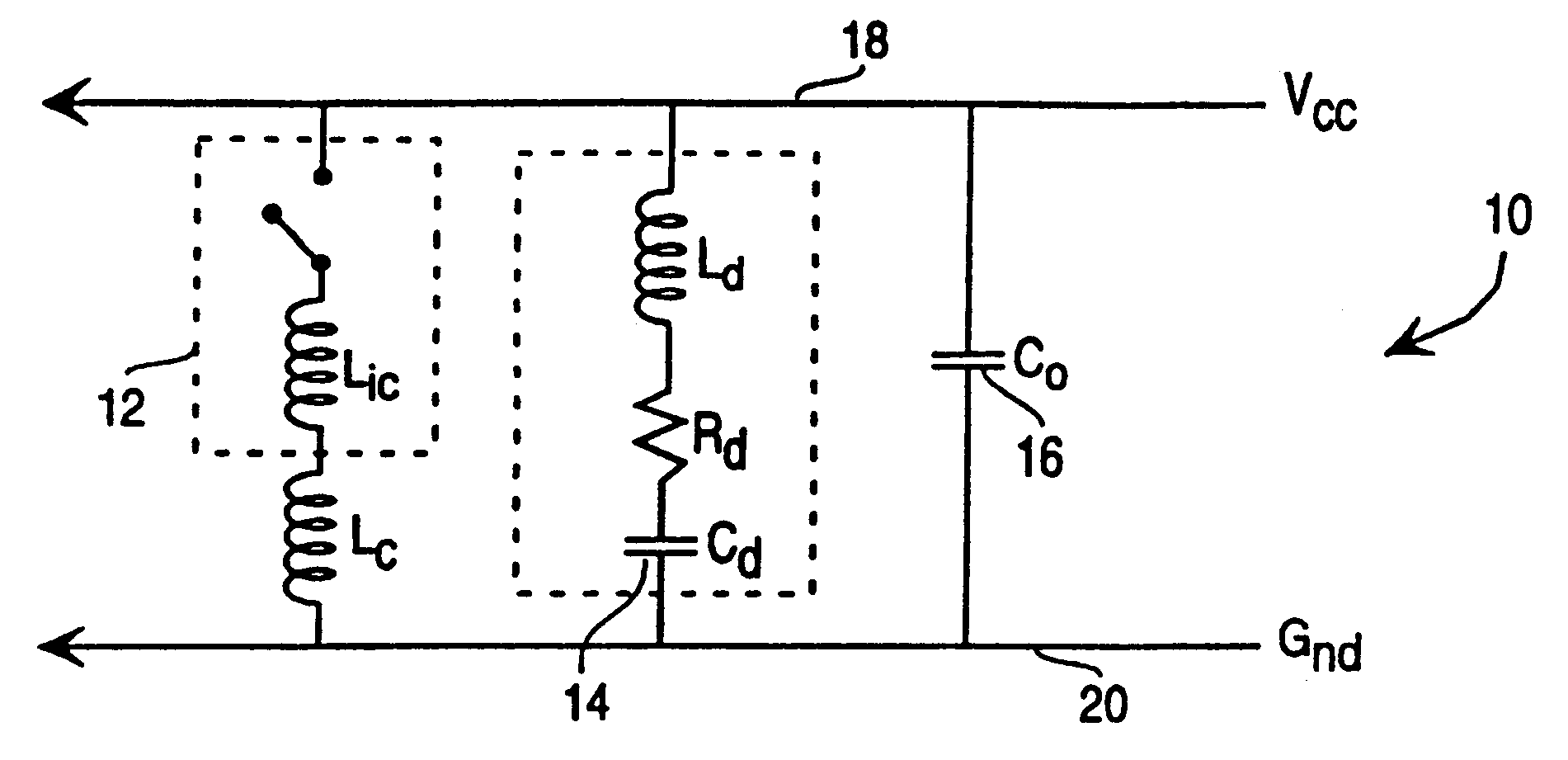

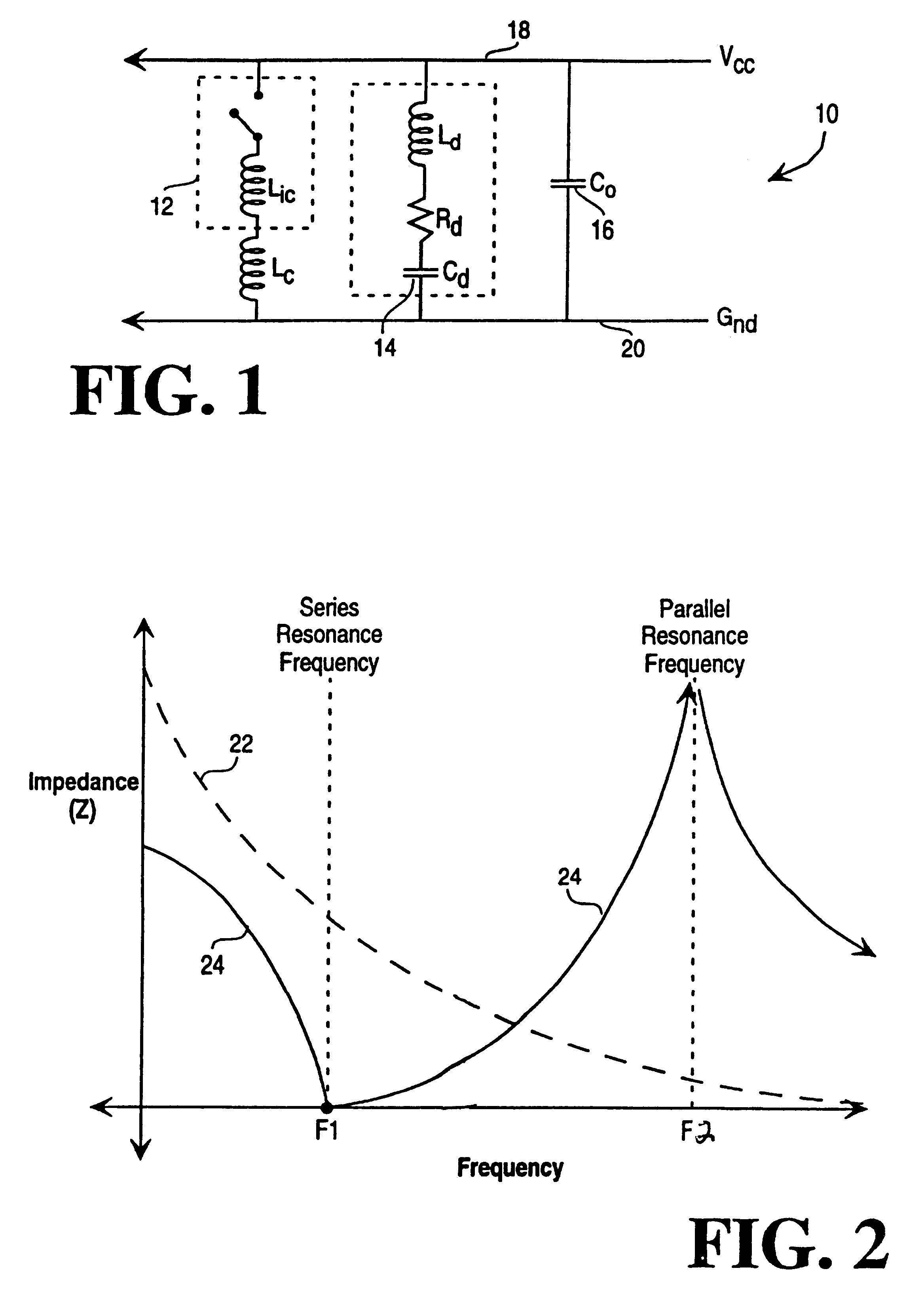

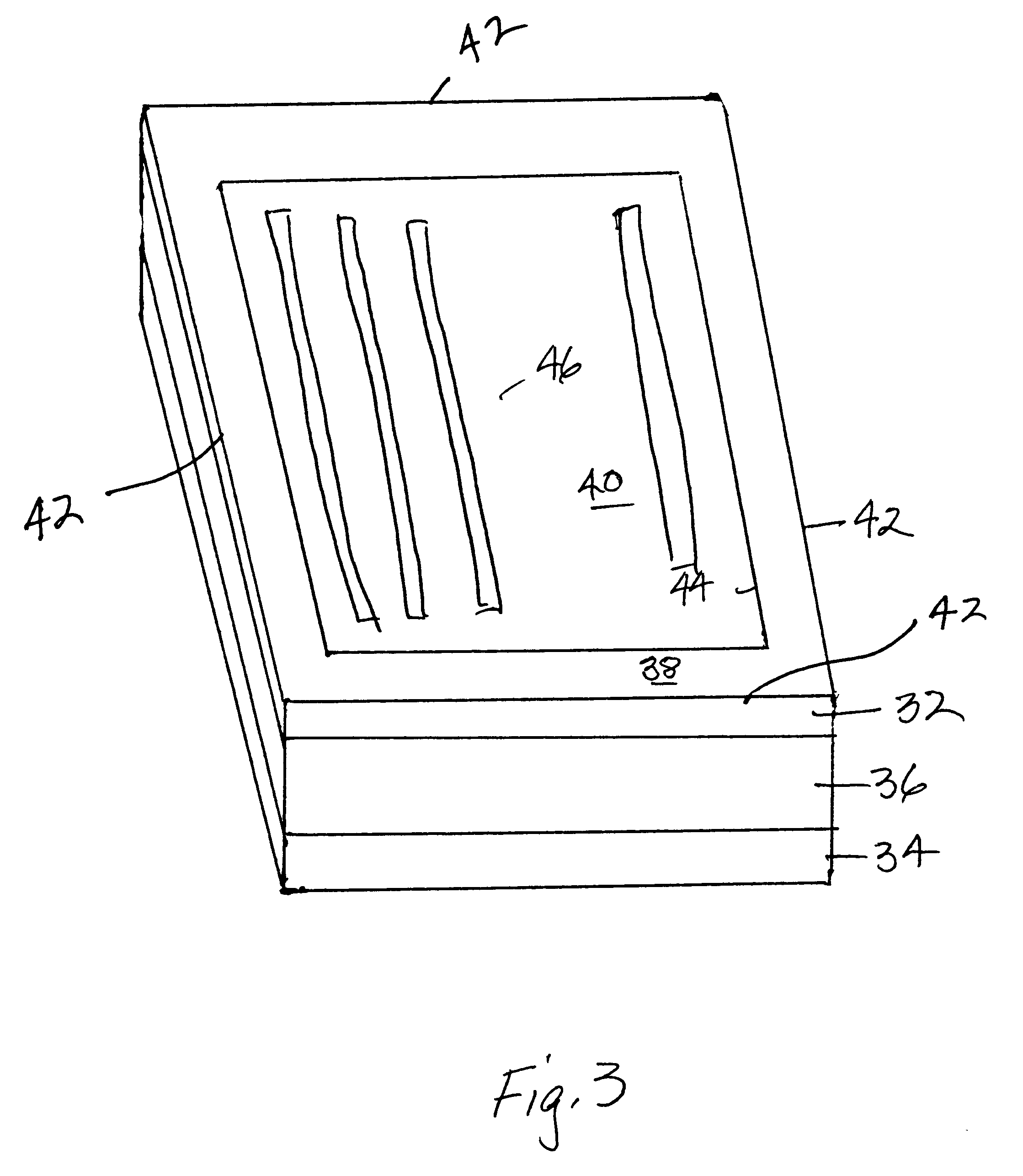

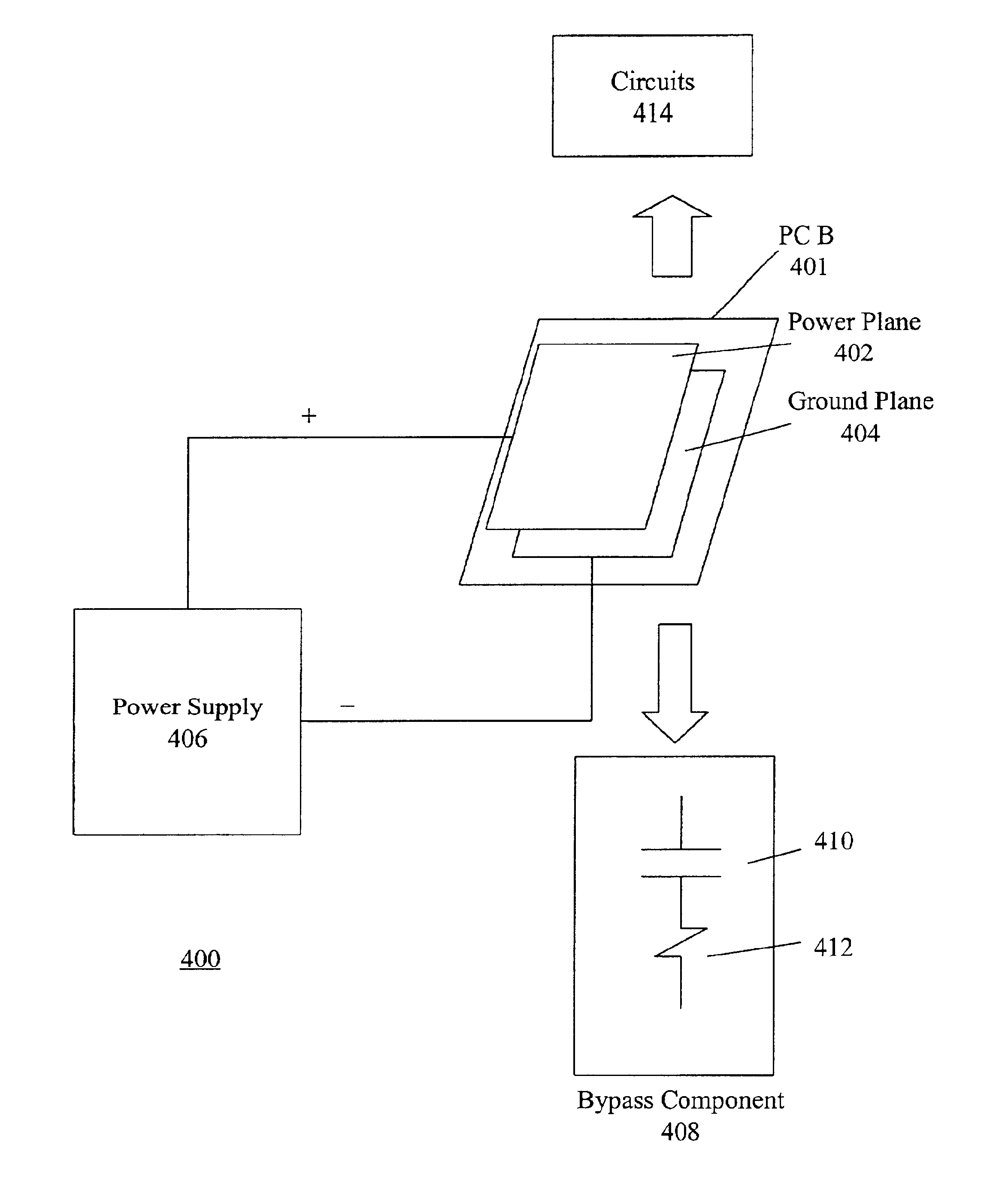

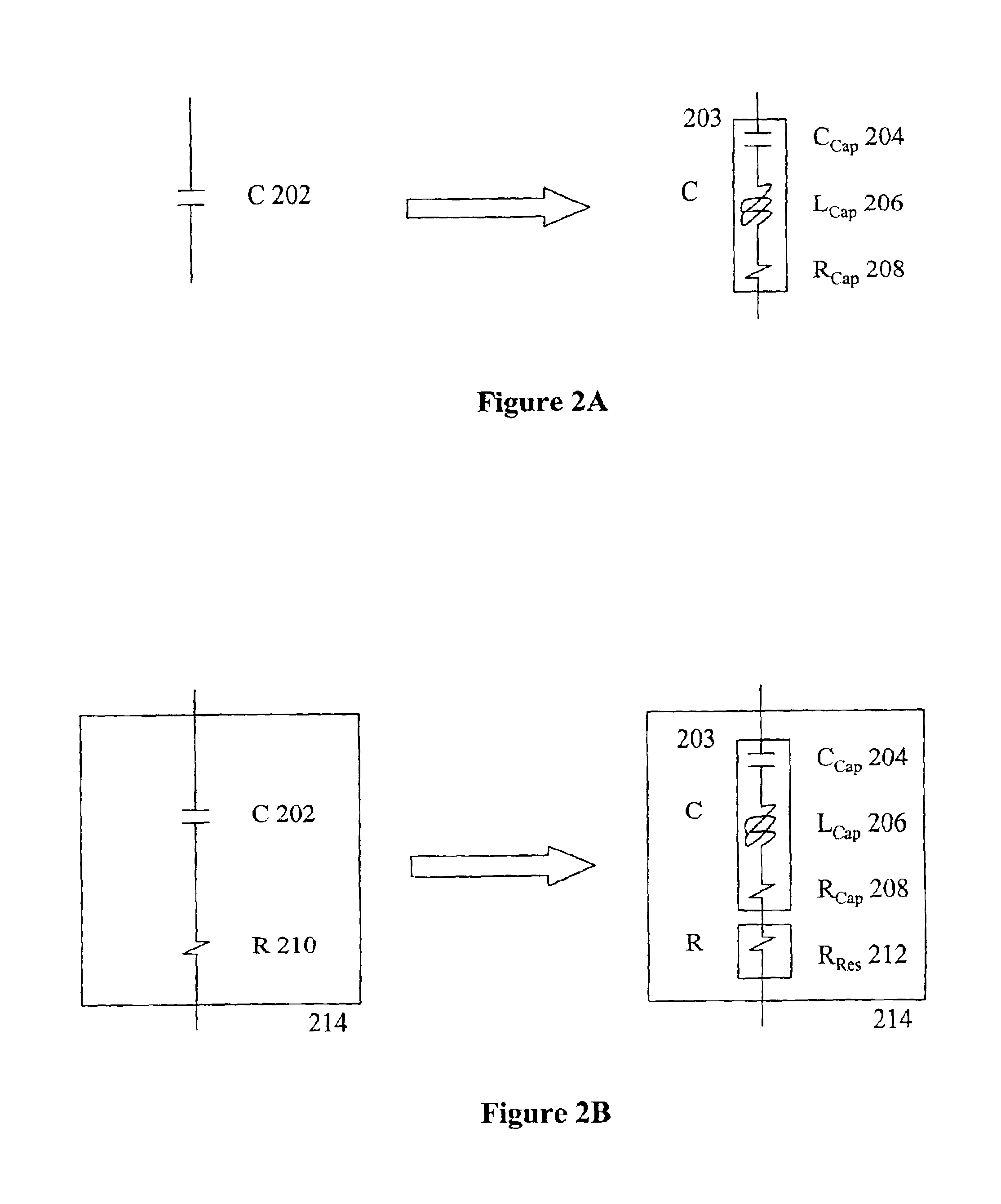

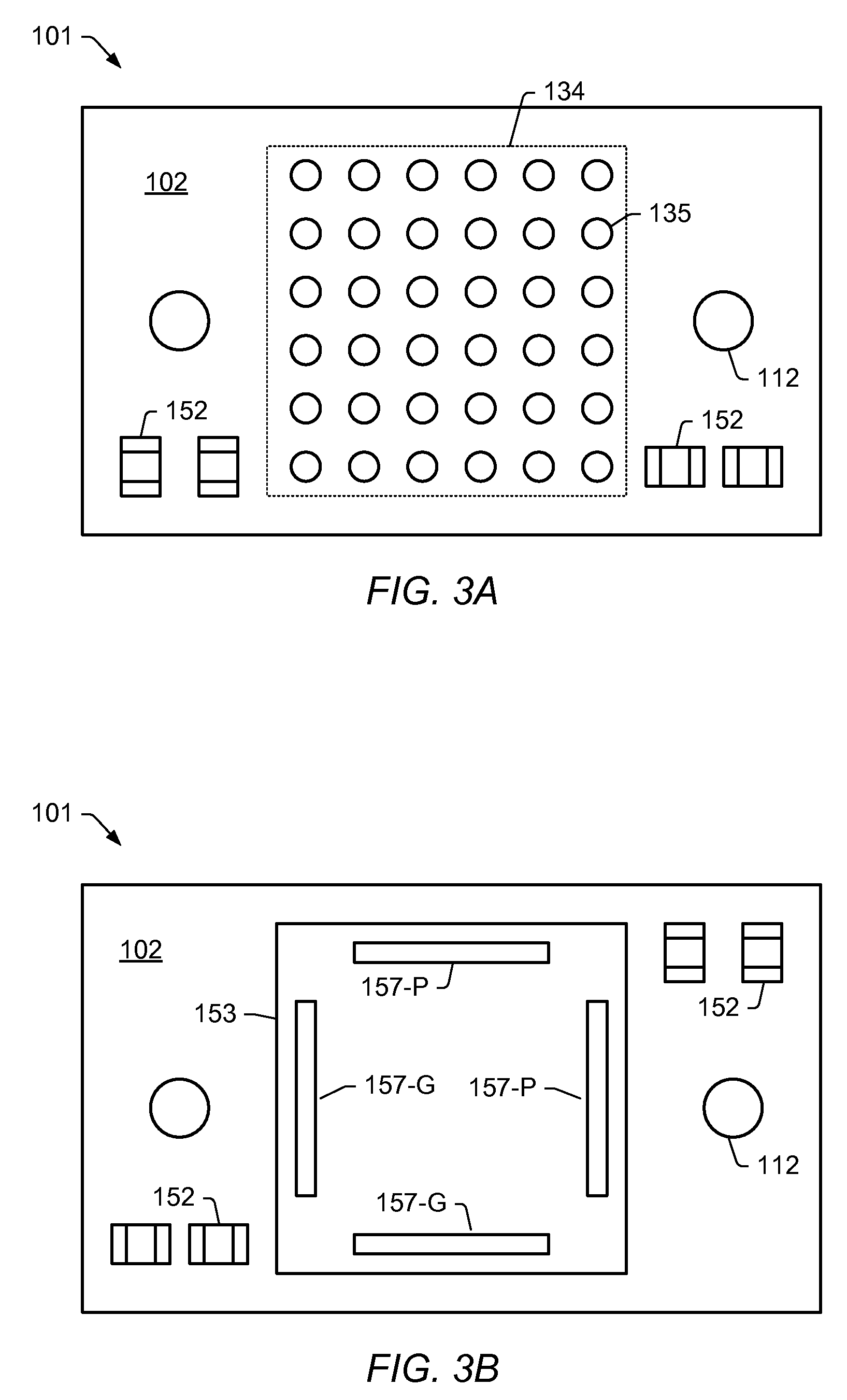

Method and means for decoupling a printed circuit board

InactiveUS6418031B1Cross-talk/noise/interference reductionPrinted circuit aspectsImproved methodPower planes

An improved method and means for decoupling a printed circuit board are disclosed. A power plane is included having a peripheral edge. The power plane includes a first region and a second region which is separate from and contiguous to the first region. The first region is located from the peripheral edge to a middle portion of the power plane. The first region includes a peripheral portion of the power plane. The second region includes only the middle portion of the power plane. A ground plane is coupled in parallel to the power plane. The ground plane has a peripheral edge. The ground plane includes a first region, and a second region which is separate from and contiguous to the first region. The first region includes the peripheral edge and includes a peripheral portion of the ground plane. The second region includes a middle portion of the ground plane. A first plurality of decoupling elements are connected to the first region of the power plane and to the first region of the ground plane. A second plurality of decoupling elements are connected to the second region of the power plane and to the second region of the ground plane. The first and second plurality of decoupling elements are utilized to decouple the power plane and ground plane pair.

Owner:TWITTER INC

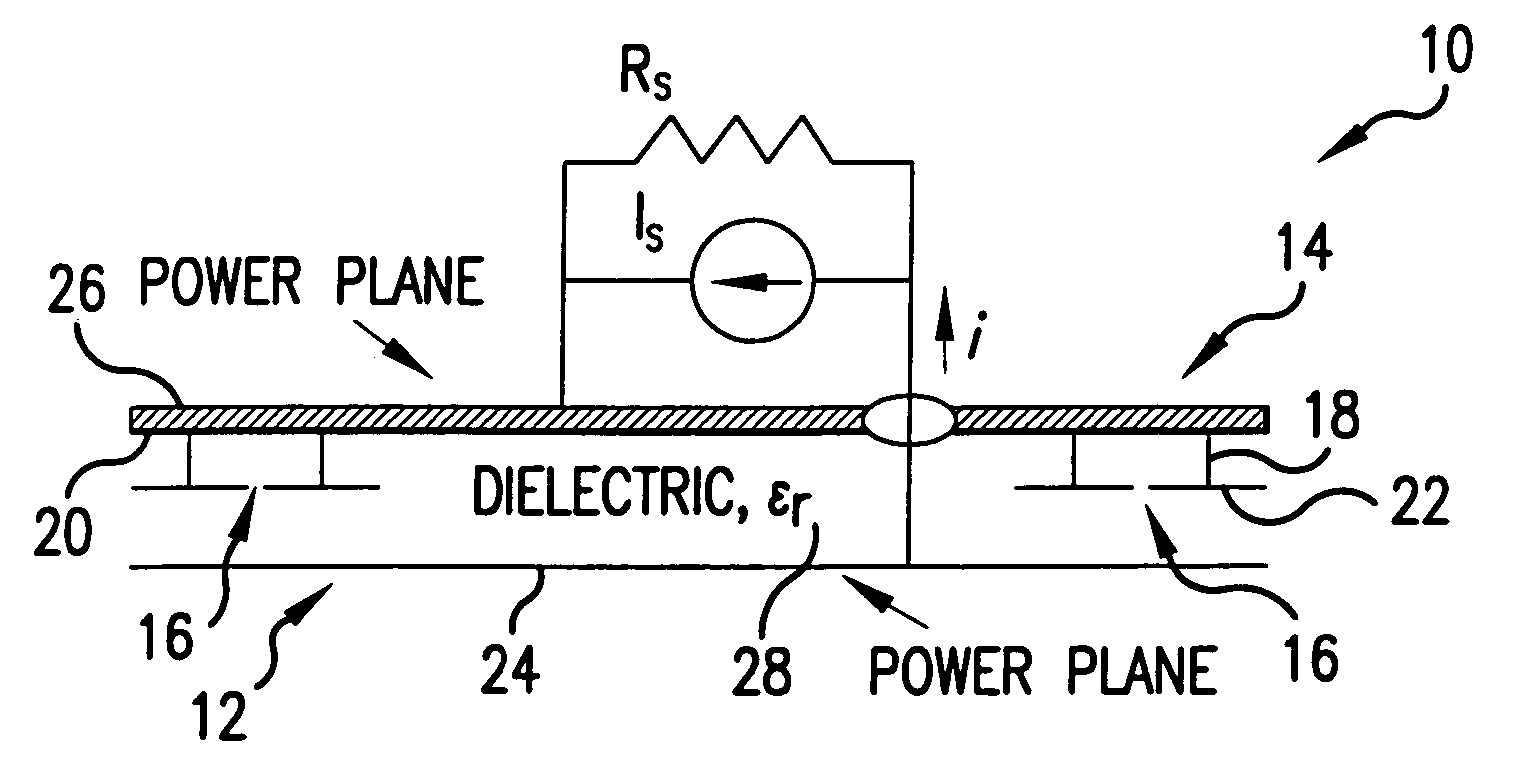

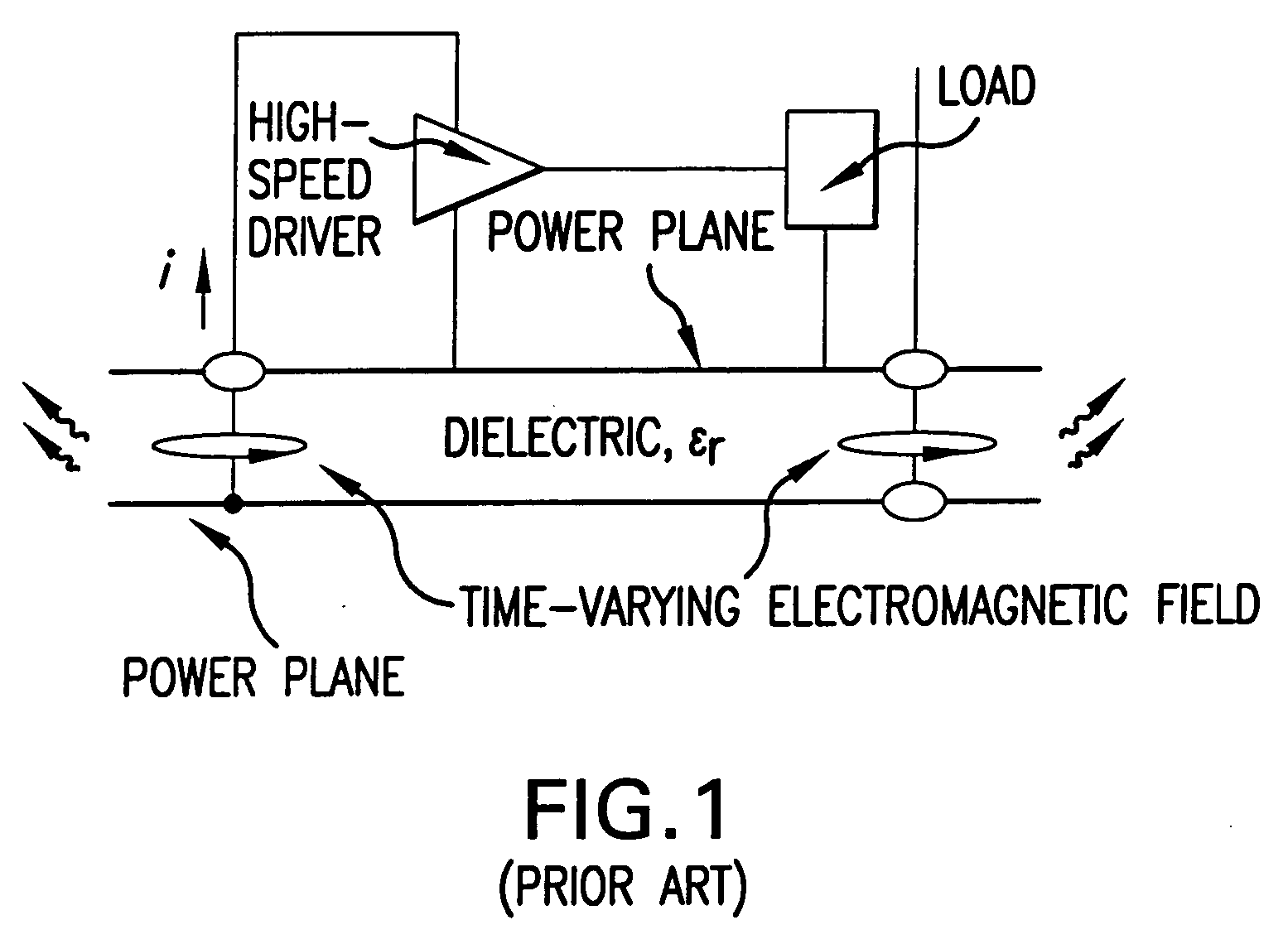

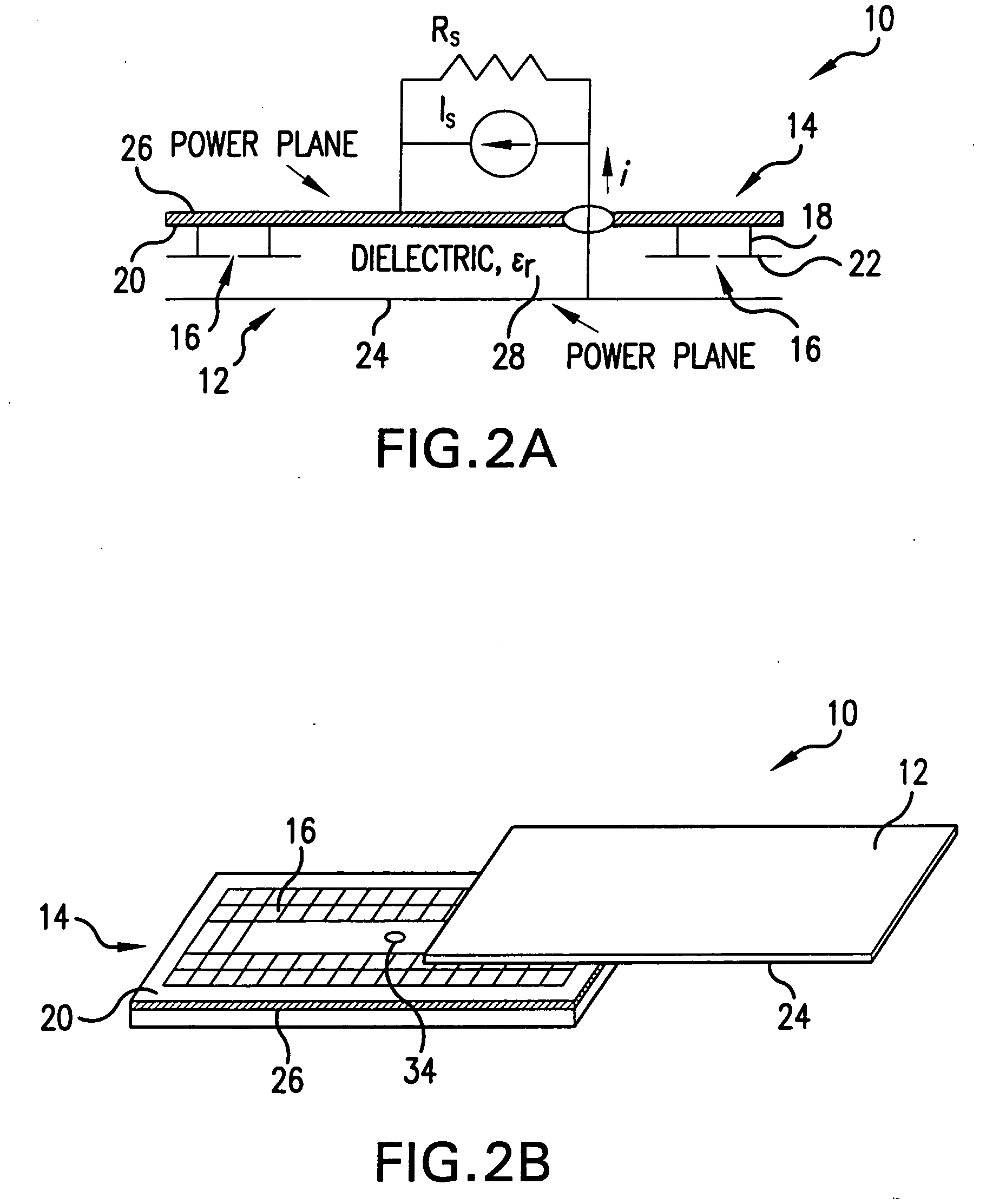

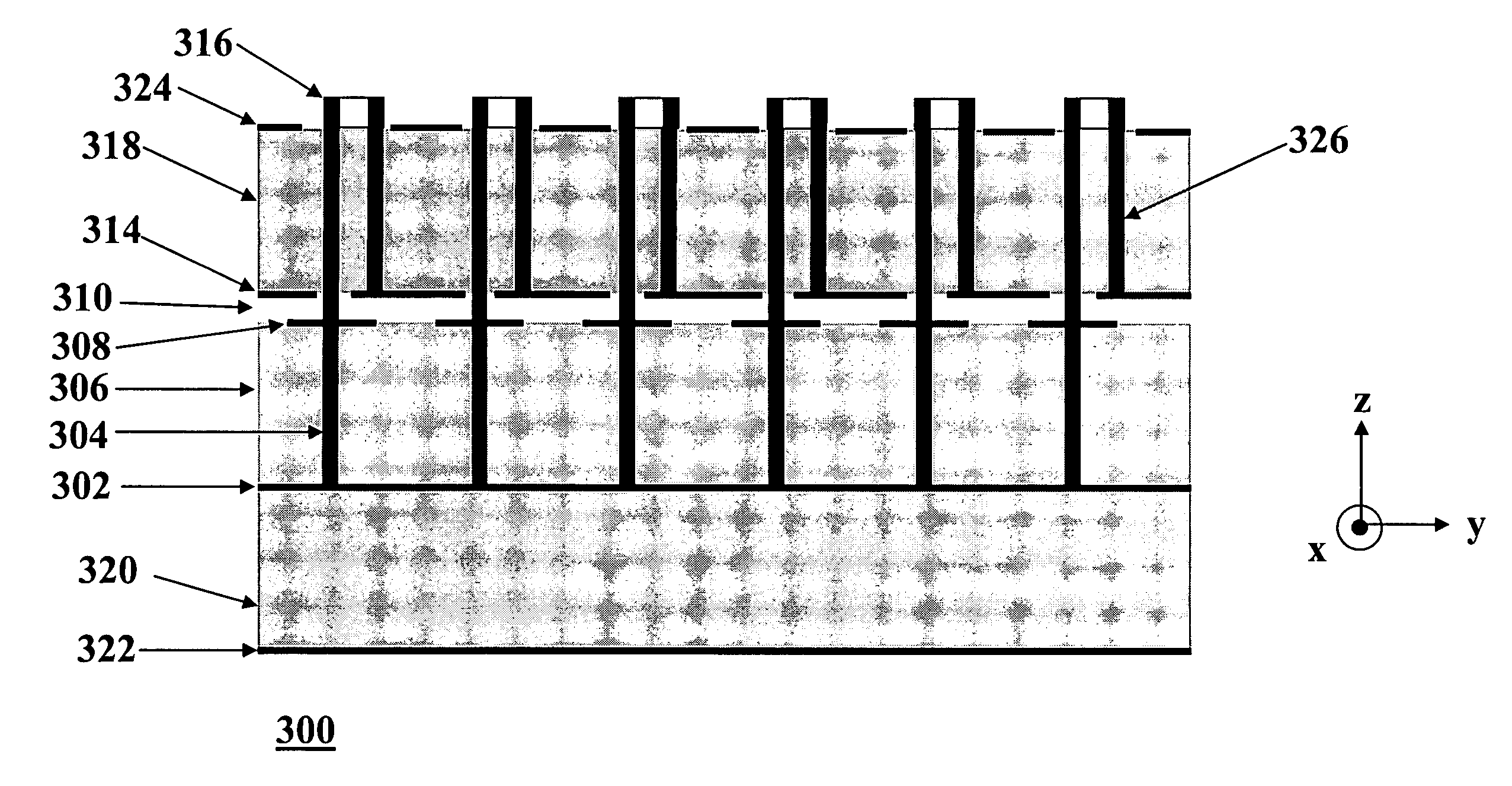

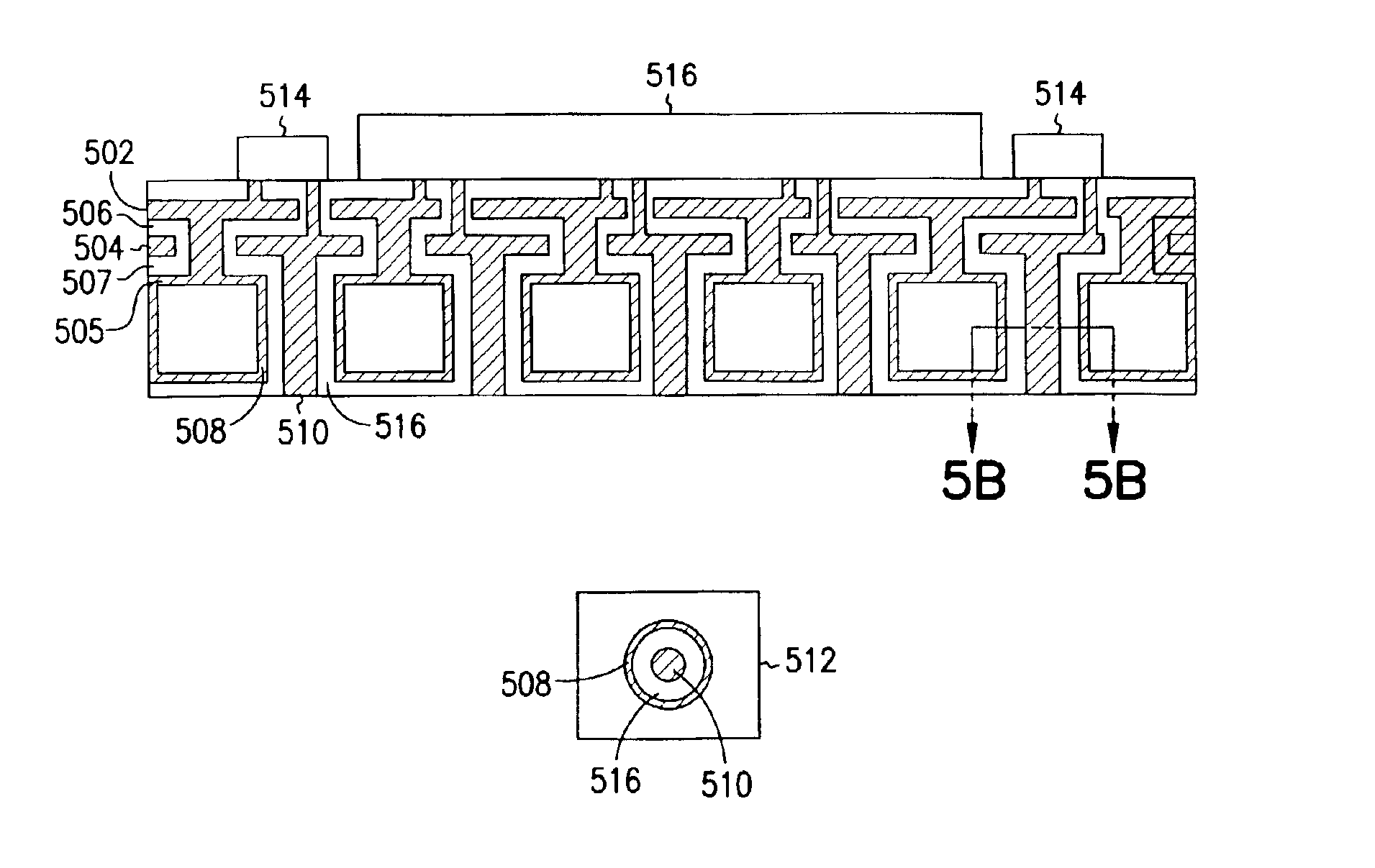

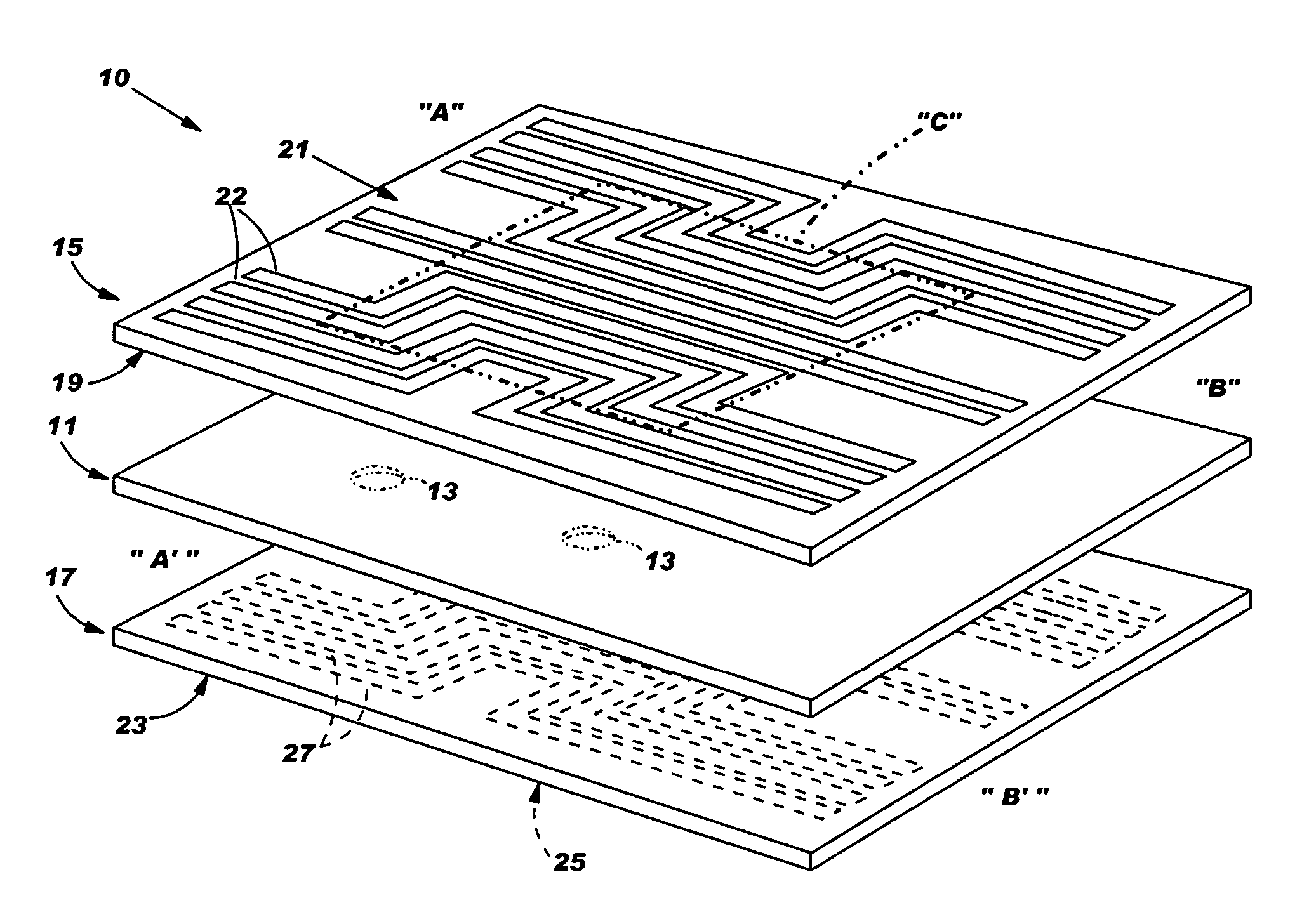

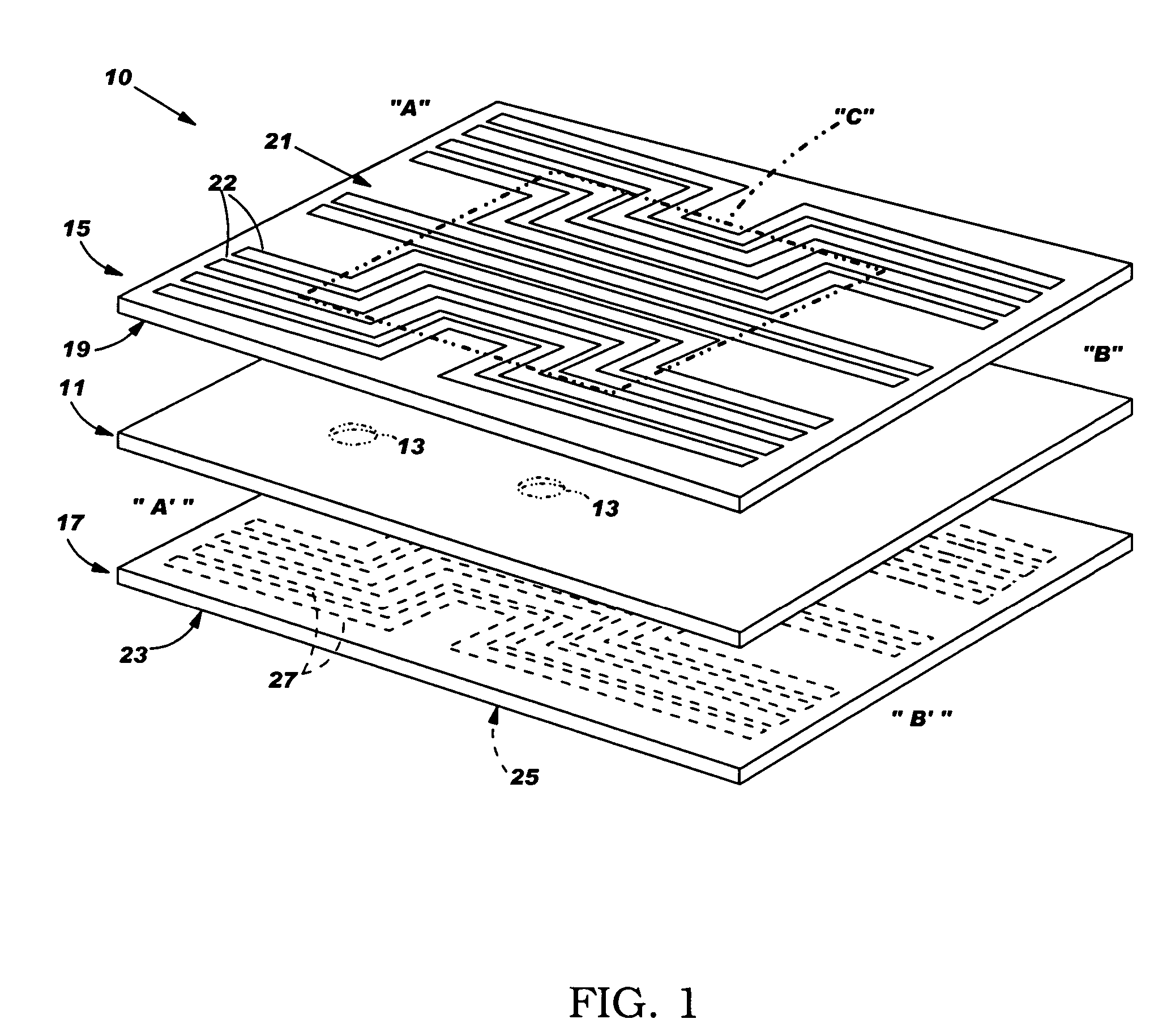

System and method for noise mitigation in high speed printed circuit boards using electromagnetic bandgap structures

InactiveUS20050104678A1Improved performance characteristicsReduce radiationCurrent interference reductionCross-talk/noise/interference reductionEngineeringElectromagnetic radiation

Electromagnetic Bandgap (EBG) structures are embedded between adjacent power planes in a multi-layer PCB to decrease the emanation of Electromagnetic radiation induced by power buses, signal layers, as well as to suppress the switching noise. EBG stages with different stop bands are cascaded to create rejection over a wider frequency region. The cascading can be performed in series, or may be formed in a variety of arrangements such as a checkerboard design or concentric ribbons positioned along the perimeter of the PCB. Each EBG stage is composed of conductive patches and via posts extending from each patch, which are positioned at a predetermined distance from each other. By surrounding the source of the noise with EBG stages, a sufficient suppression of electromagnetic noise over specific frequency bands of interest is achieved.

Owner:UNIV OF MARYLAND

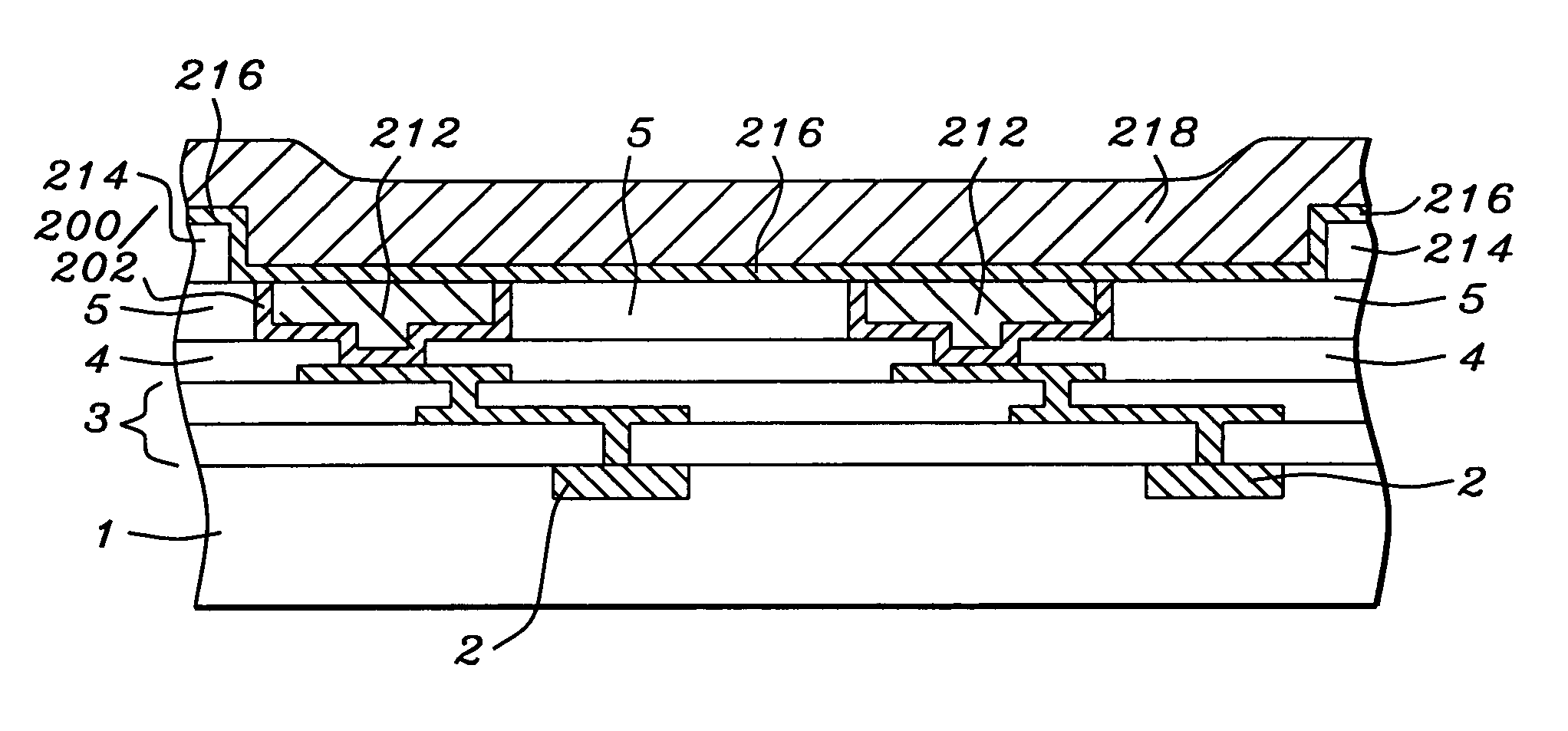

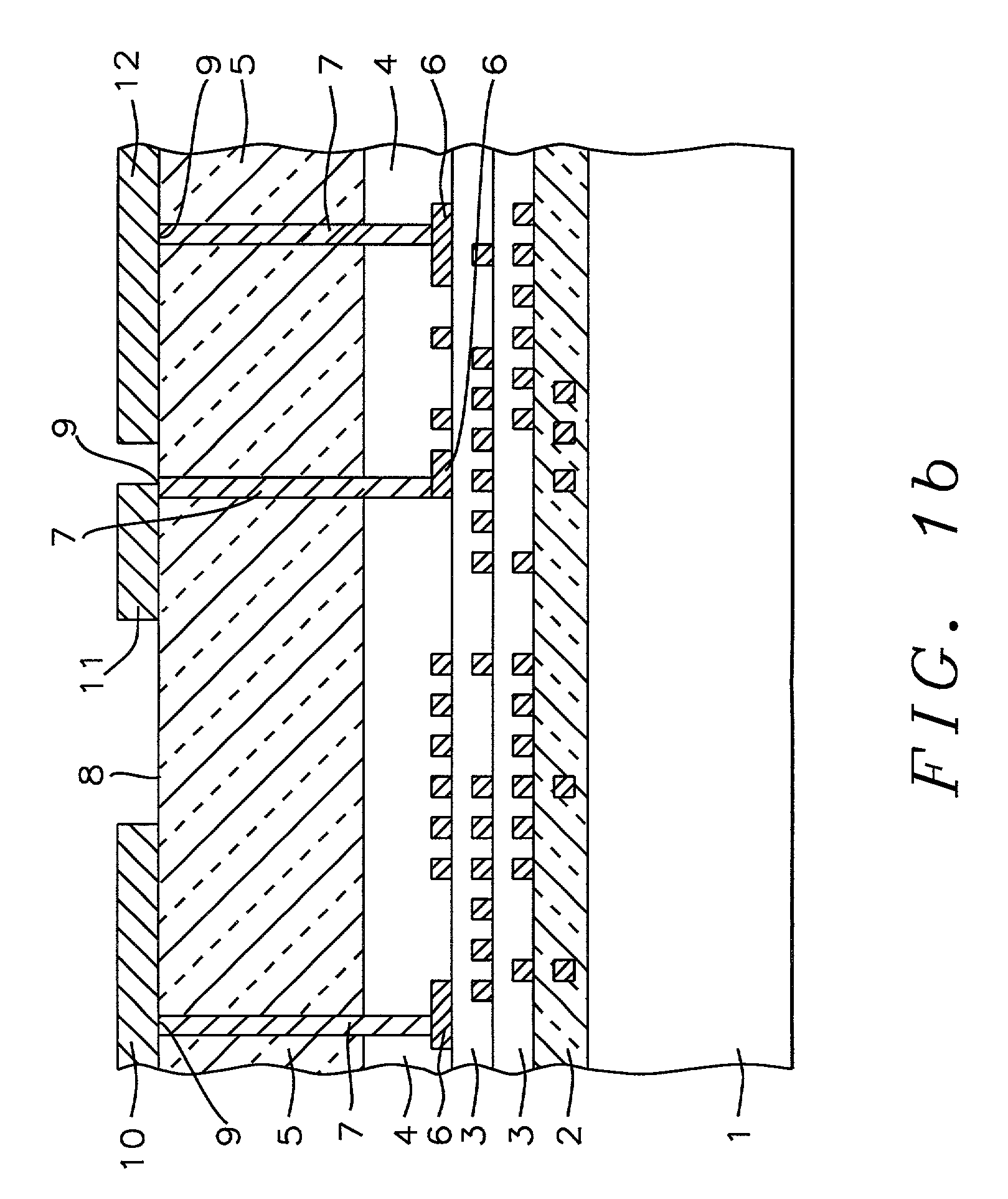

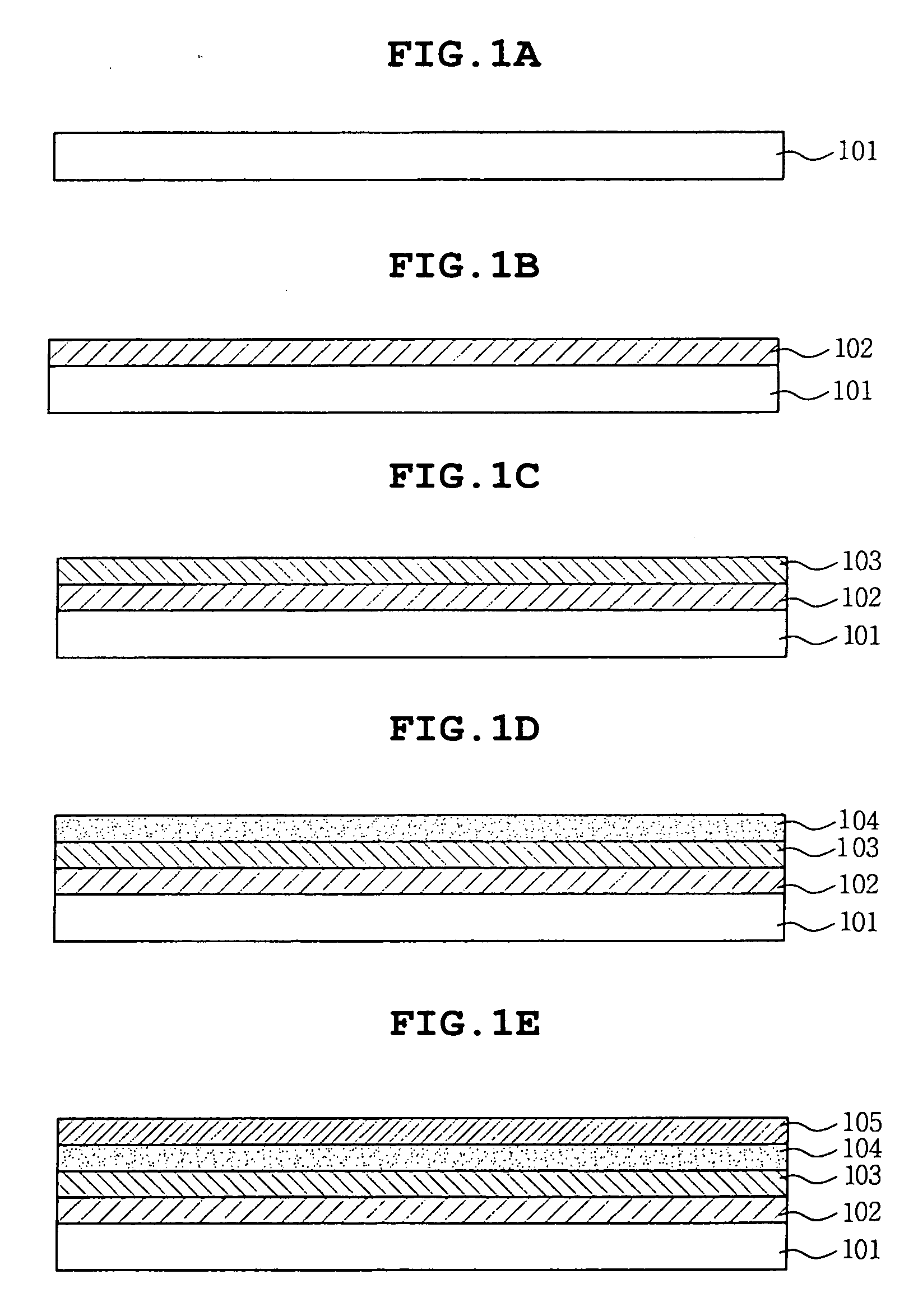

Post passivation method for semiconductor chip or wafer

InactiveUS7405149B1Improve performanceReduce resistive voltage dropSemiconductor/solid-state device detailsSolid-state devicesPolymer dielectricsSemiconductor chip

The present invention adds one or more thick layers of polymer dielectric and one or more layers of thick, wide metal lines on top of a finished semiconductor wafer, post-passivation. The thick, wide metal lines may be used for long signal paths and can also be used for power buses or power planes, clock distribution networks, critical signal, and re-distribution of I / O pads for flip chip applications. Photoresist defined electroplating, sputter / etch, or dual and triple damascene techniques are used for forming the metal lines and via fill.

Owner:QUALCOMM INC

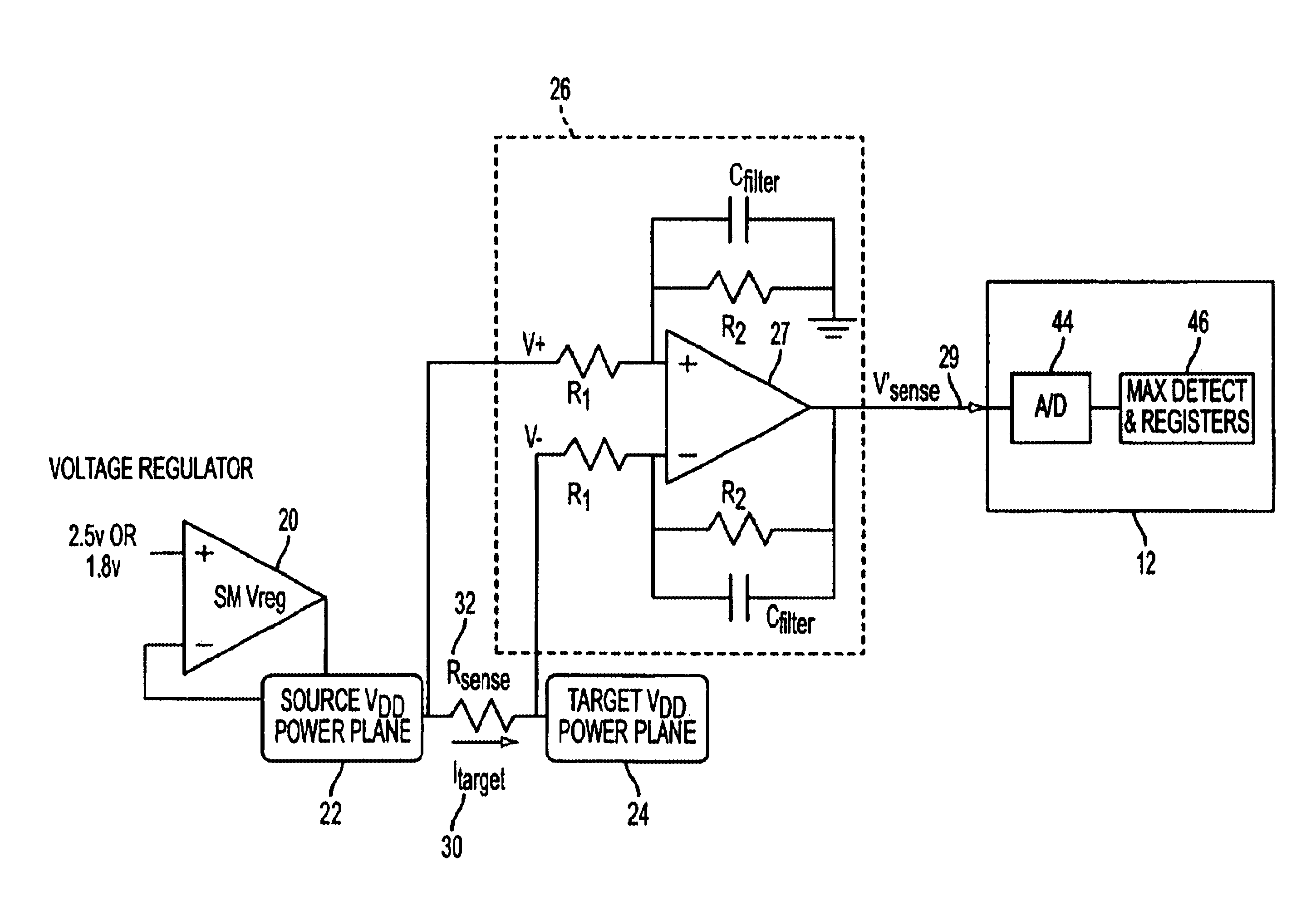

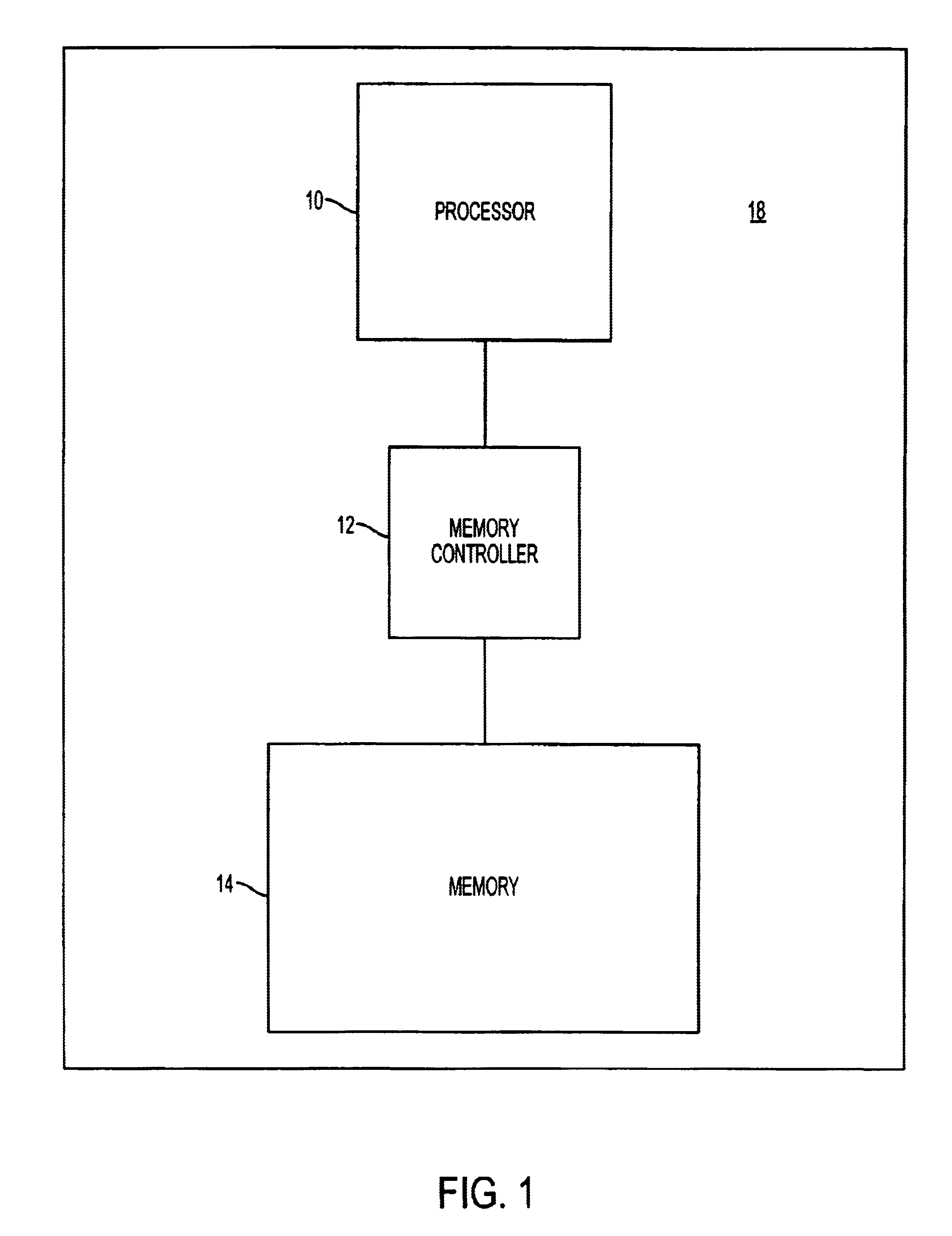

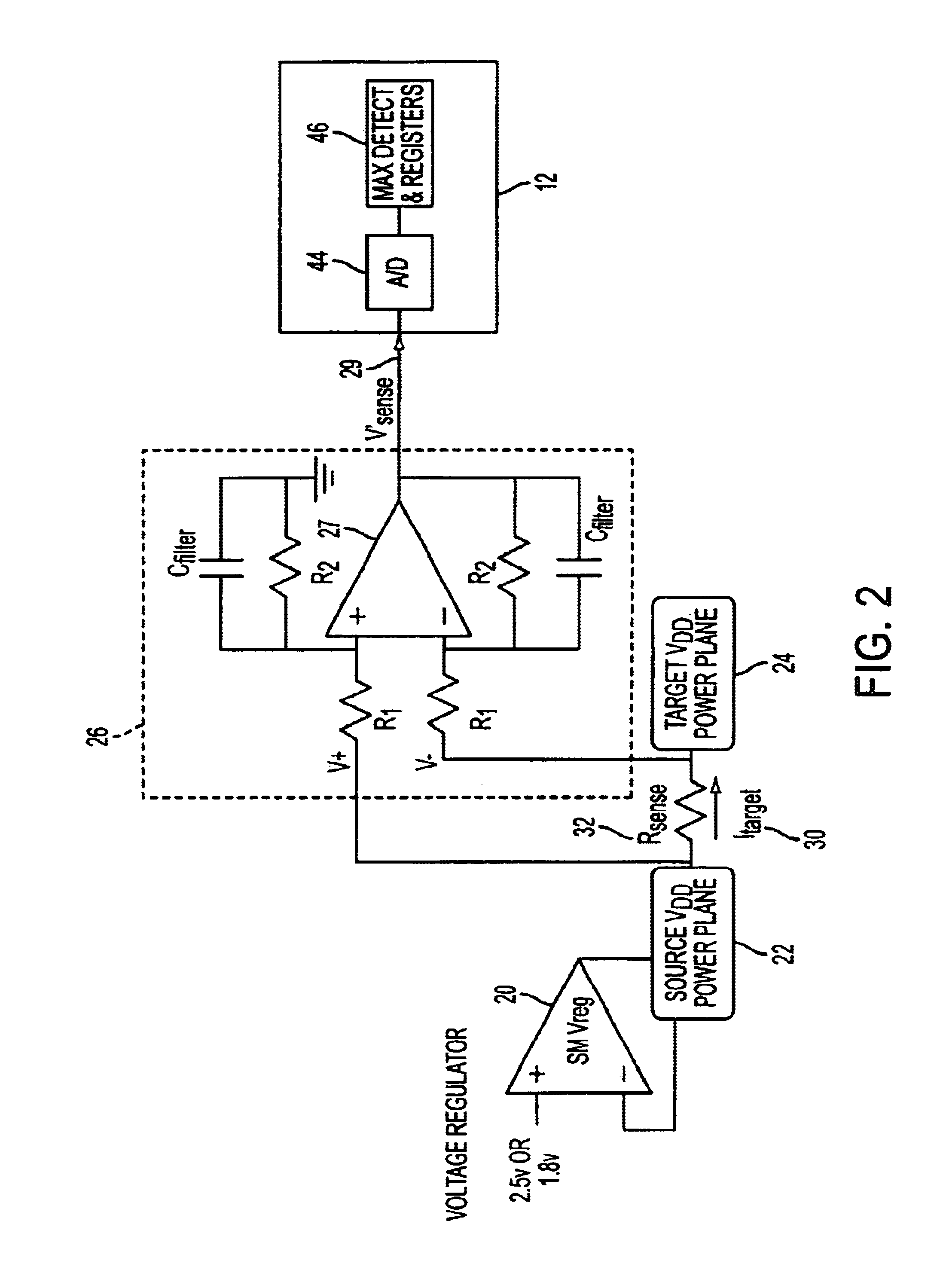

Memory system that measures power consumption

InactiveUS6944084B2Memory adressing/allocation/relocationDigital storageComputer moduleMemory controller

A memory system includes a memory controller and a plurality of memory devices located on a power plane and coupled to the memory controller. The memory system further includes a sense resistor coupled to the power plane and a power source coupled to the sense resistor. The memory system further includes a measurement module that is coupled to the memory controller and that measures a power consumption of the power plane.

Owner:INTEL CORP

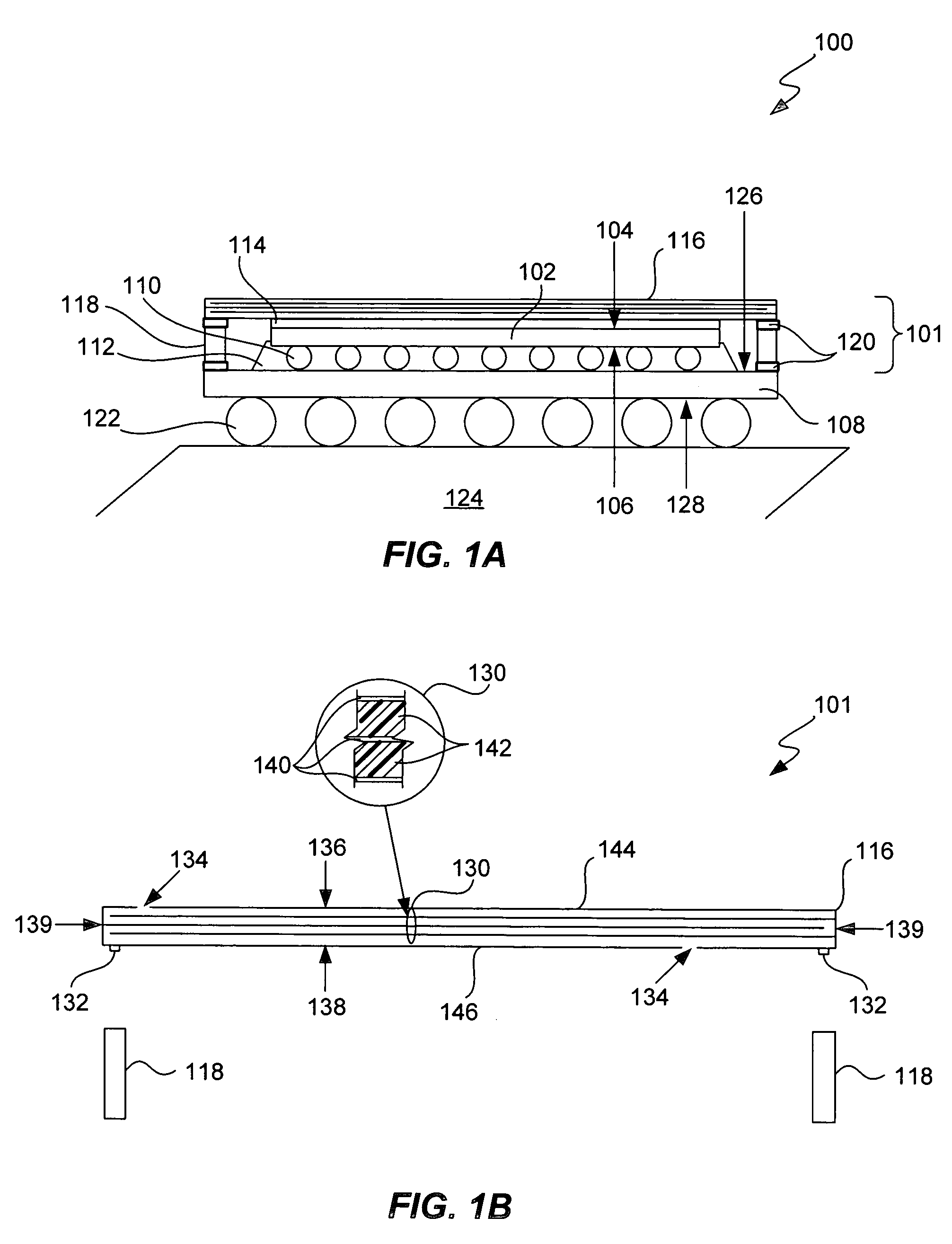

Bypass capacitor embedded flip chip package lid and stiffener

InactiveUS7115988B1Minimize SSNInstant powerElectrolytic capacitorsSemiconductor/solid-state device detailsCapacitanceSemiconductor

The present invention provides a heat spreader with a bypass capacitor to provide substantially instant power and / or to control simultaneous switching noise (SSN). The present invention also provides a semiconductor device package incorporating this heat spreader. In addition, fabrication methods for such heat spreaders and packages are provided. Generally, the heat spreaders and packages of the present invention include an embedded bypass capacitor that can provide decoupling capacitance in order to deliver near instant power to the die and / or minimize SSN. In a preferred embodiment, the embedded bypass capacitor is connected to terminals integrated with the heat spreader (e.g., lid; stiffener) and / or to a package plane (e.g., power plane or ground plane) in the package substrate for connection via the flip chip package's power delivery system to a power source and / or component.

Owner:ALTERA CORP

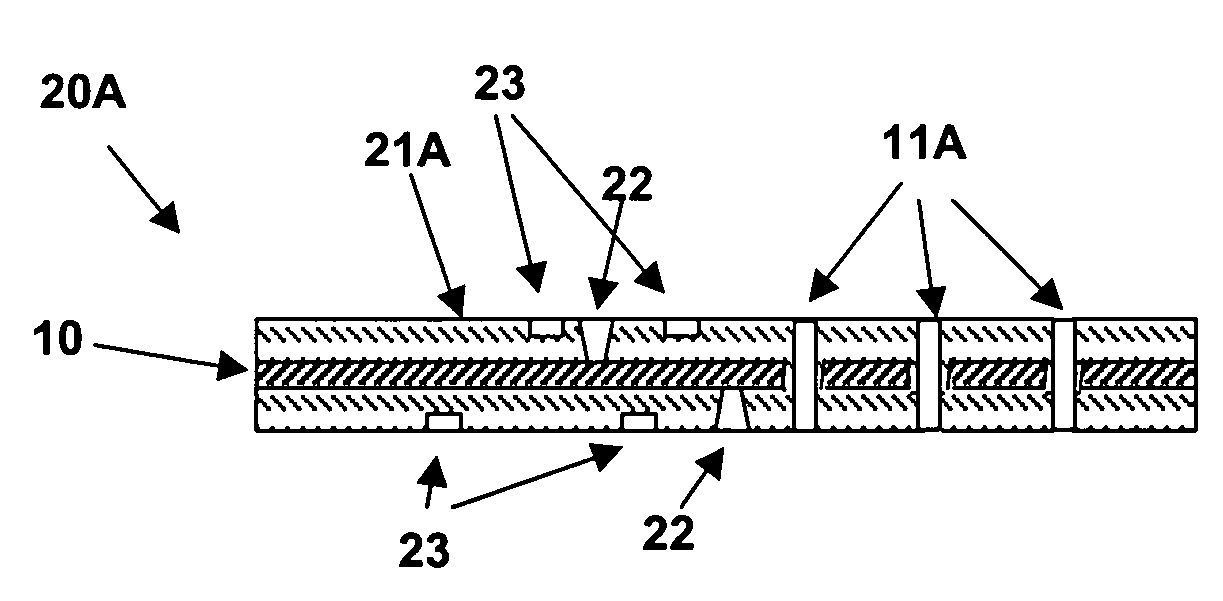

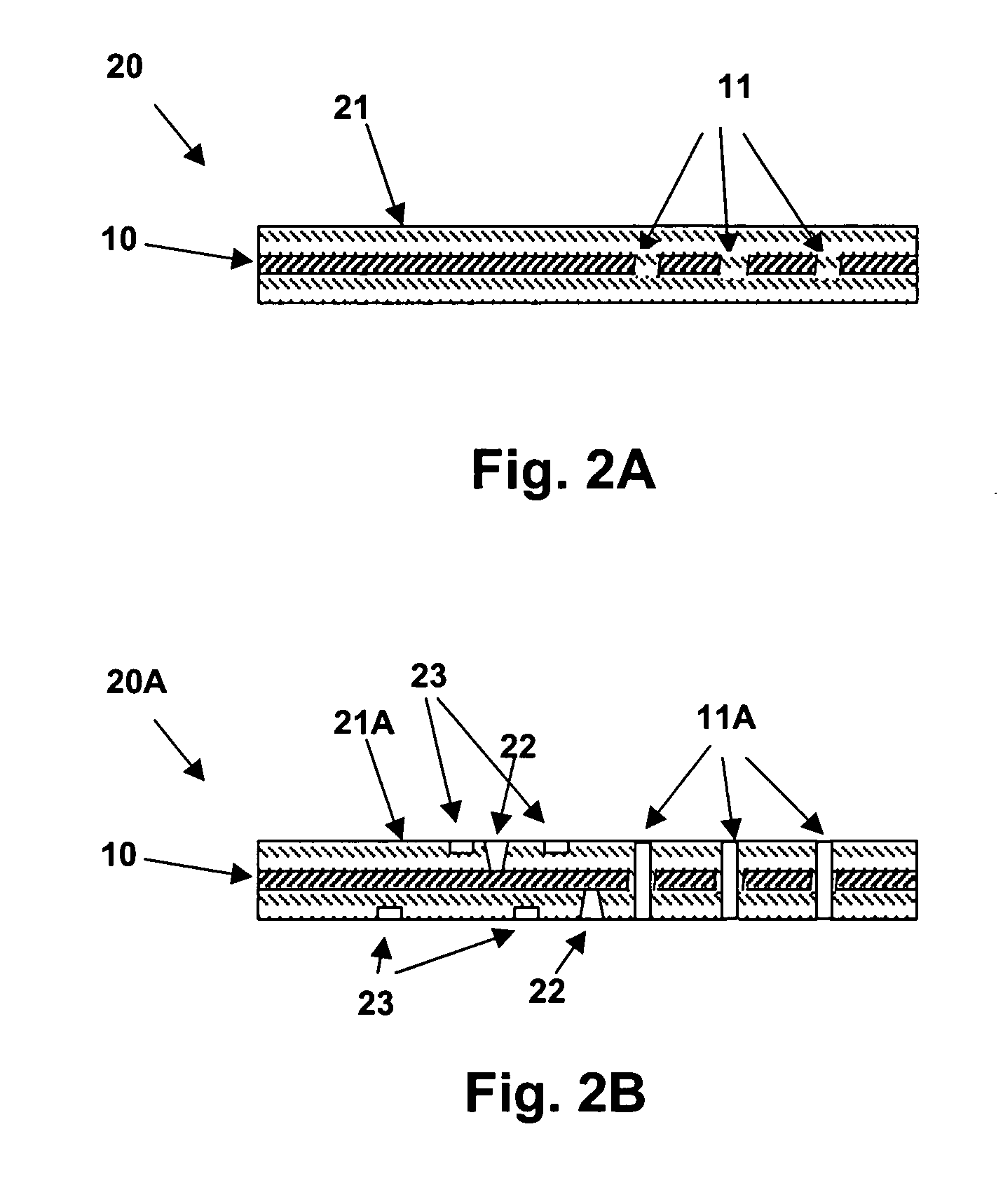

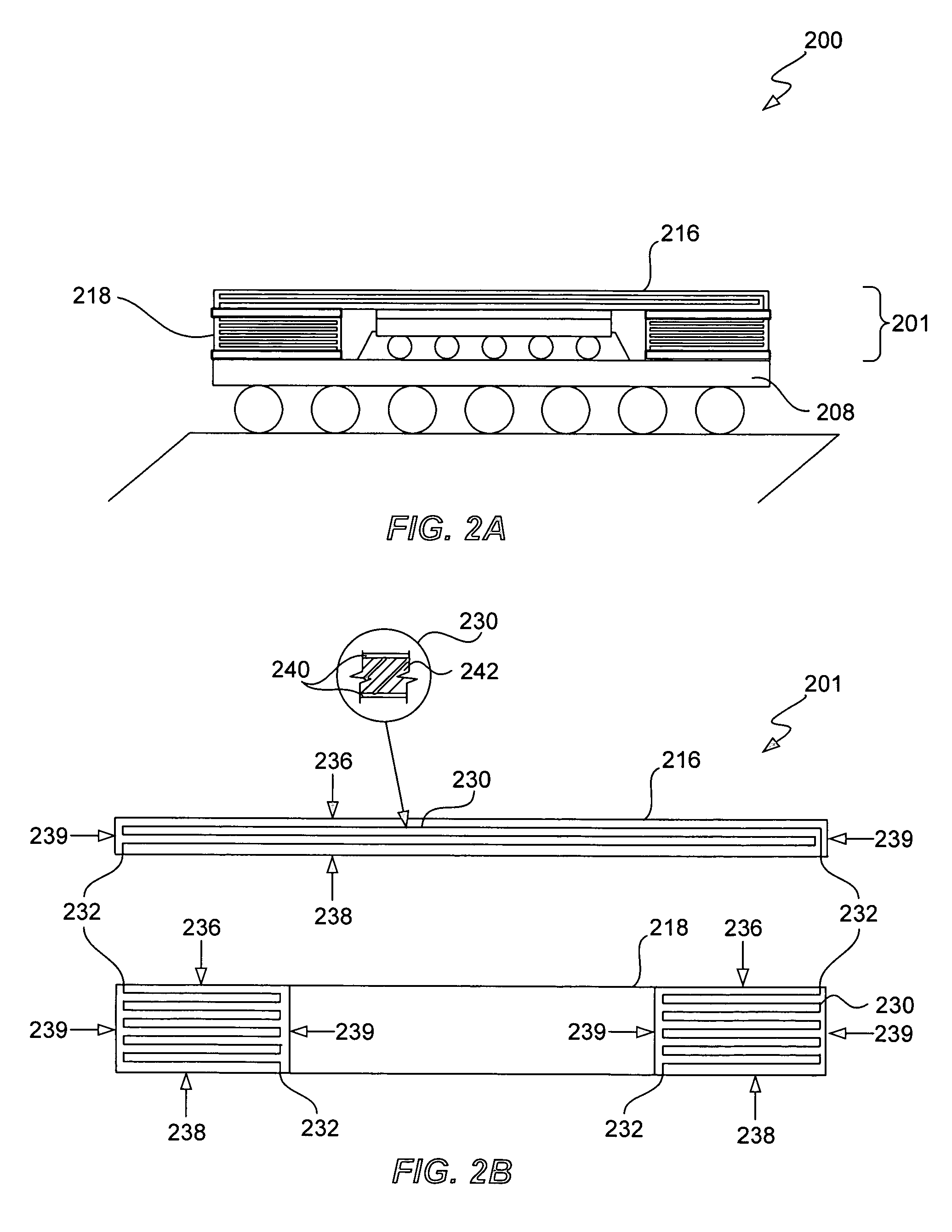

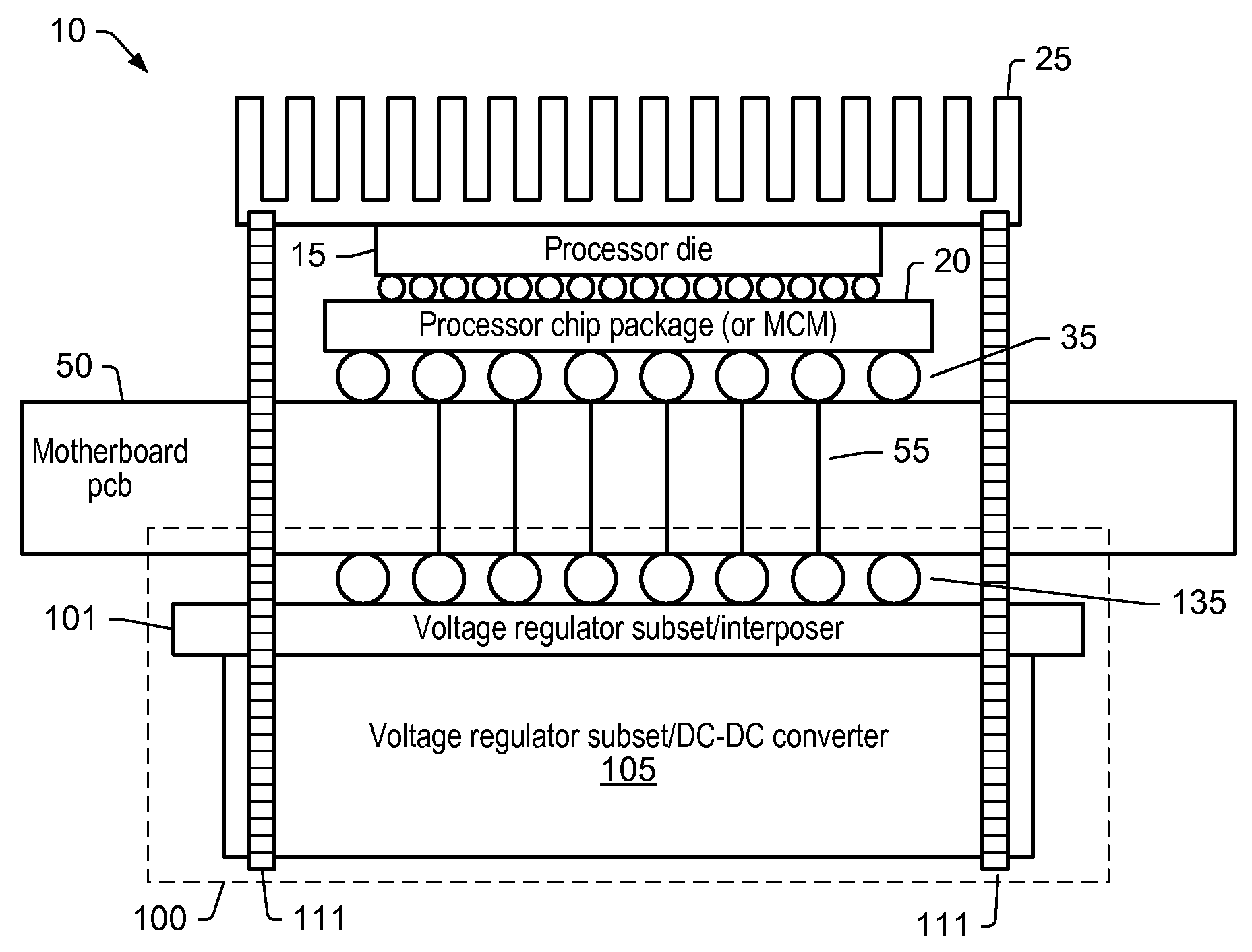

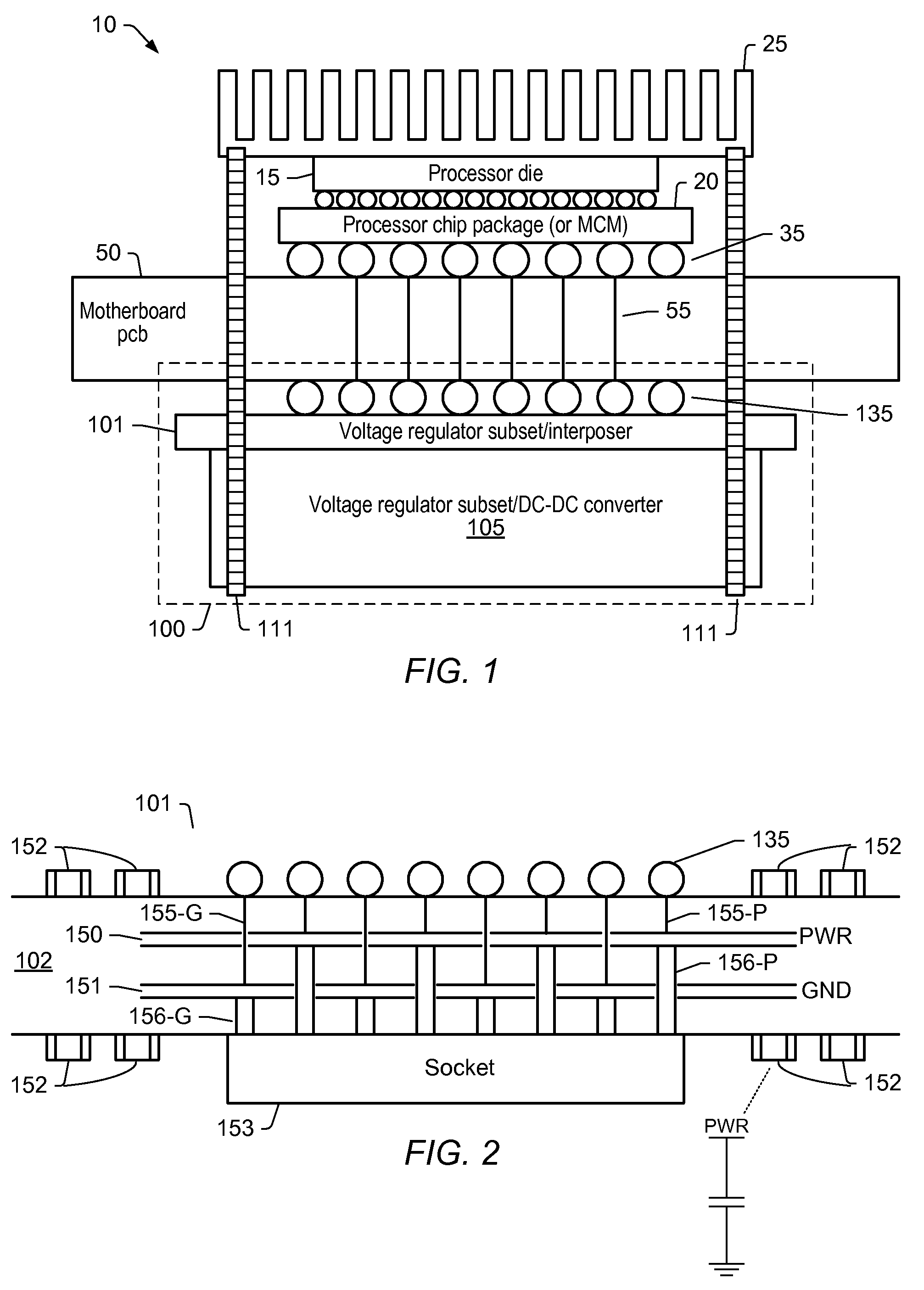

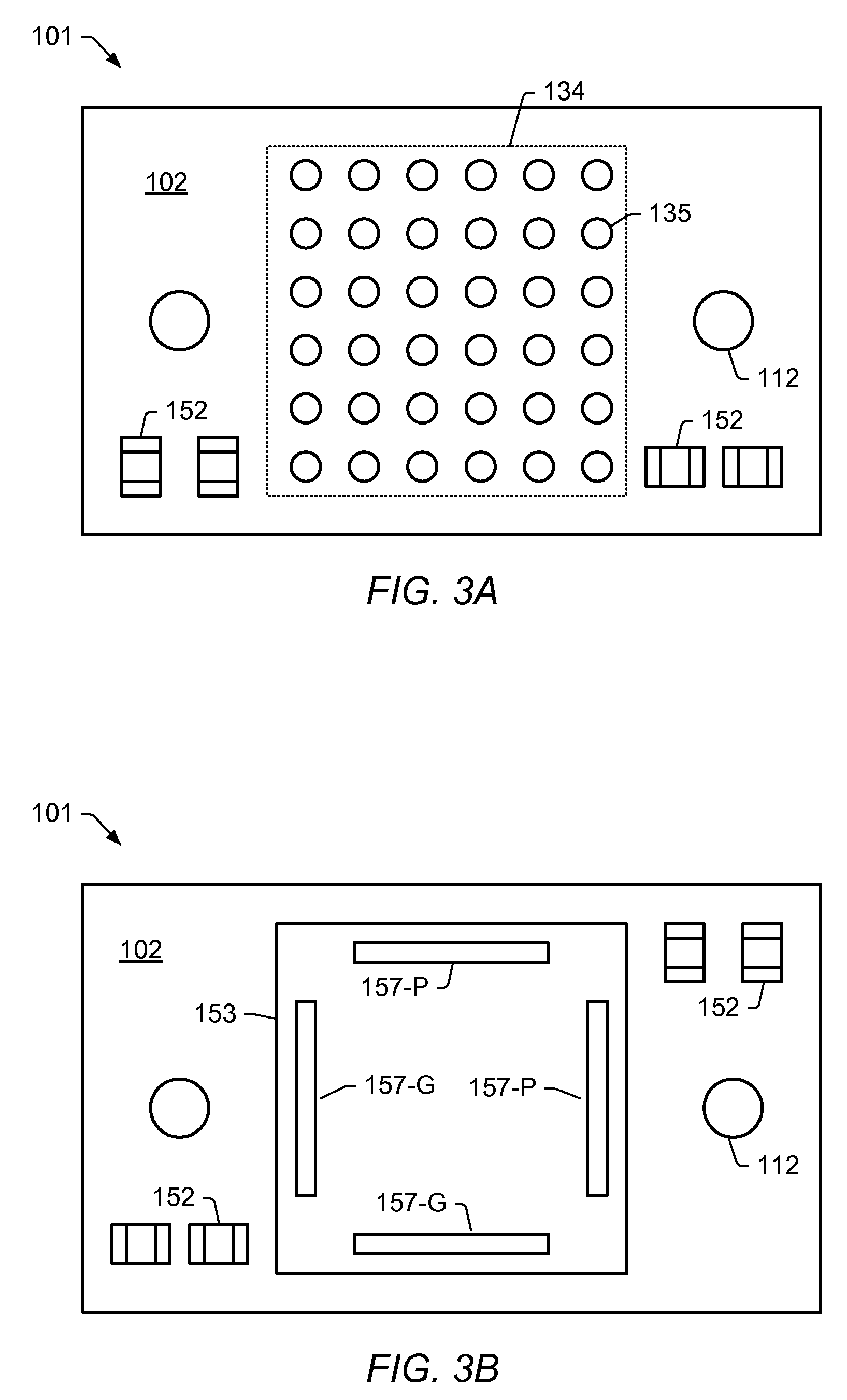

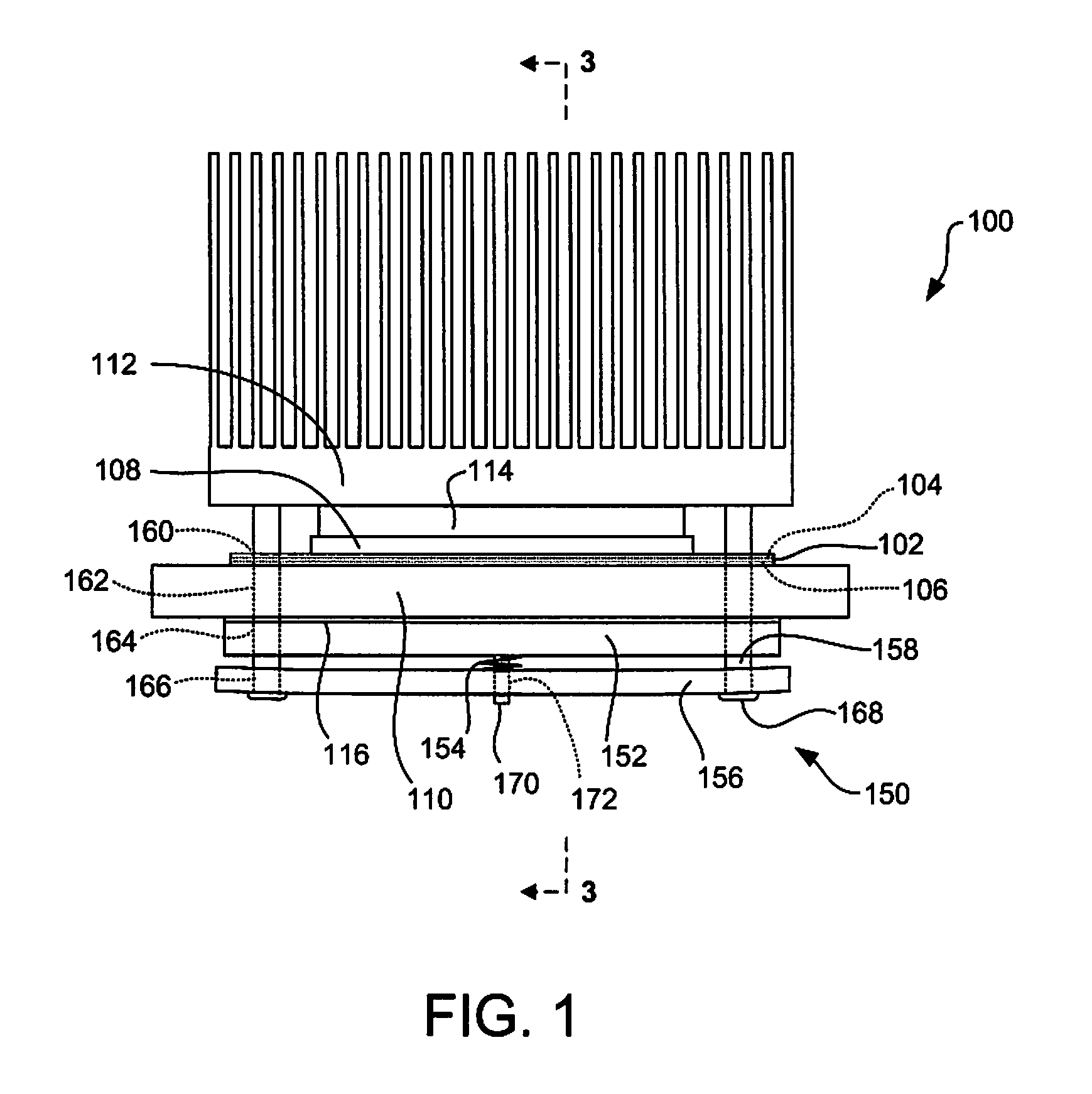

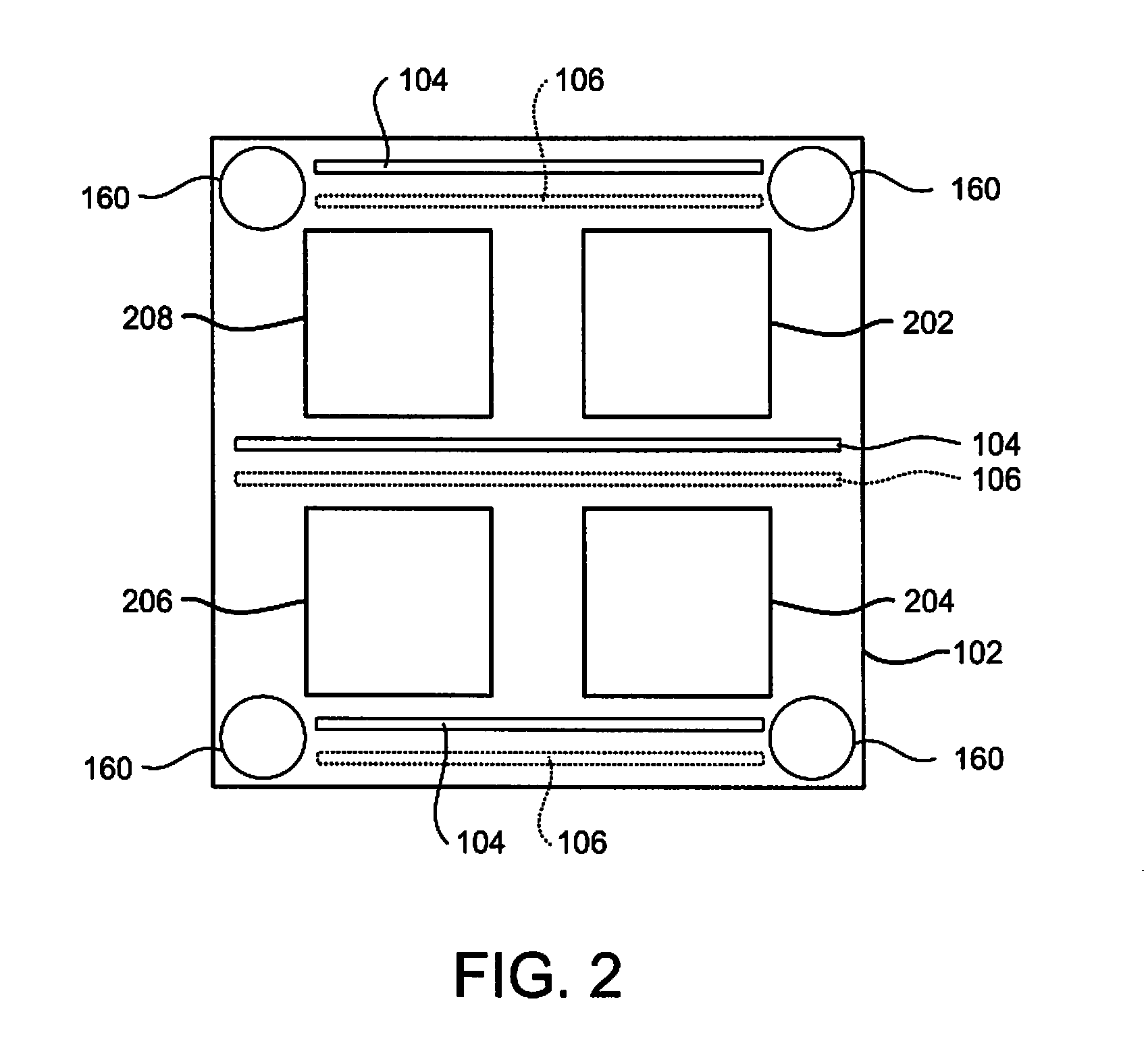

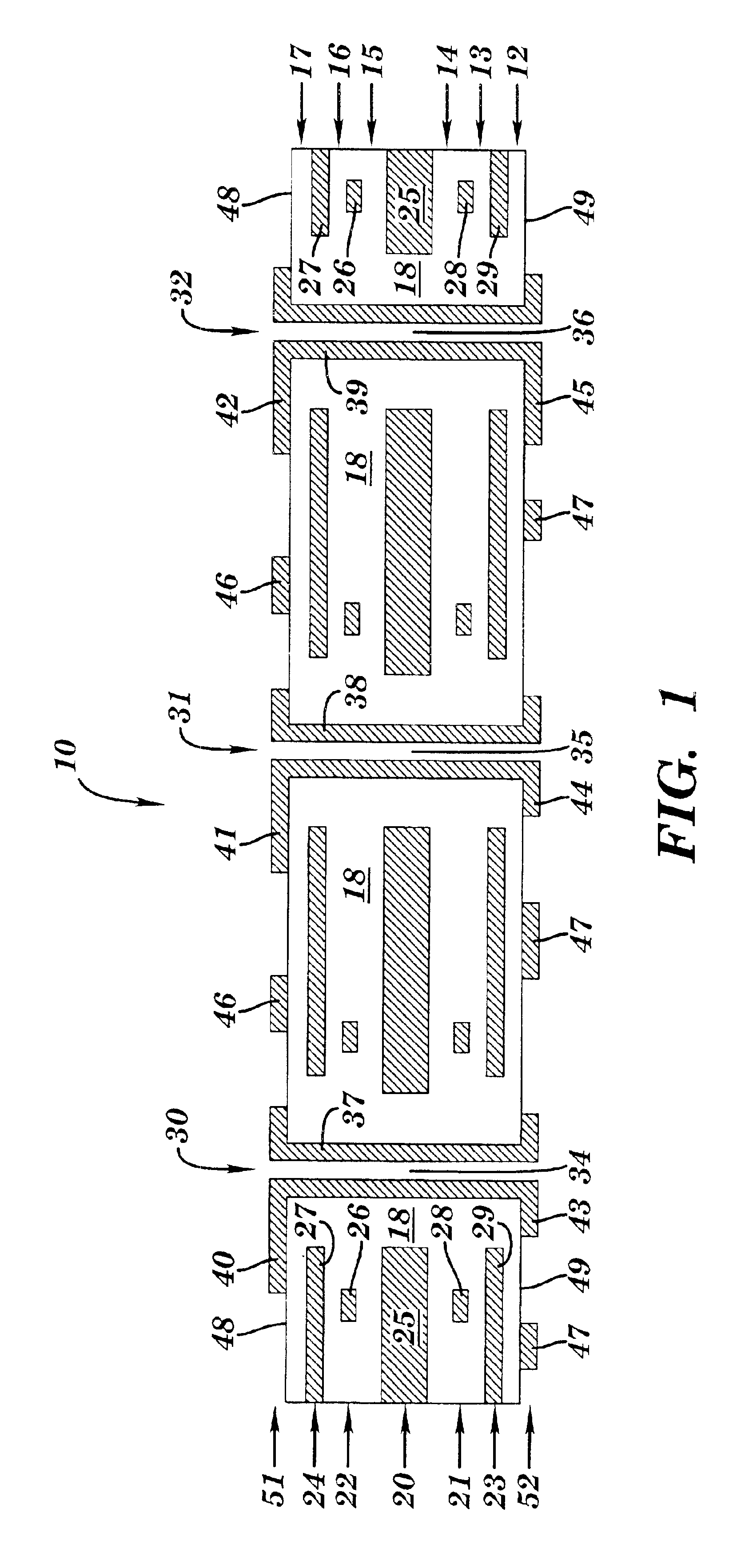

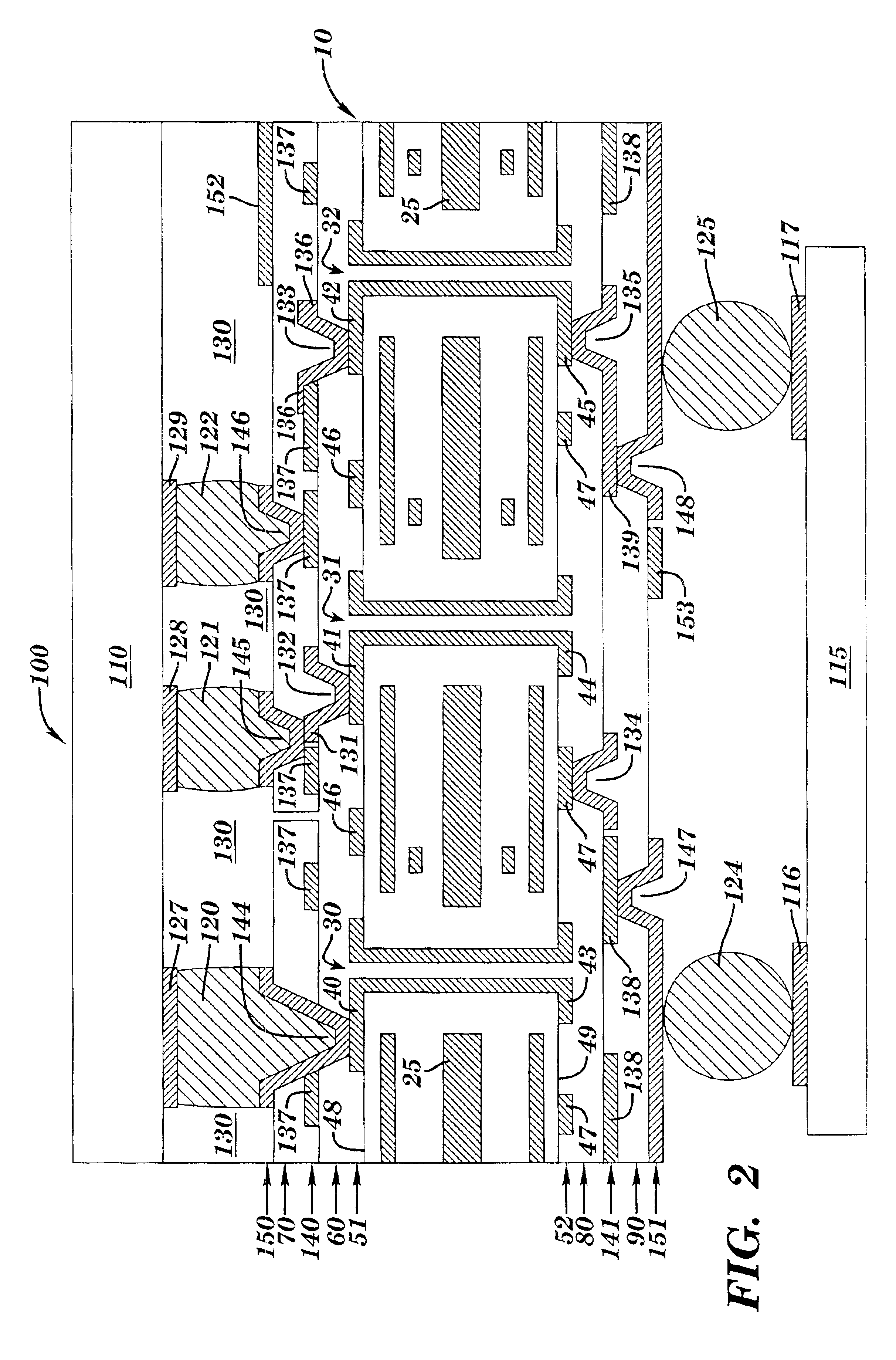

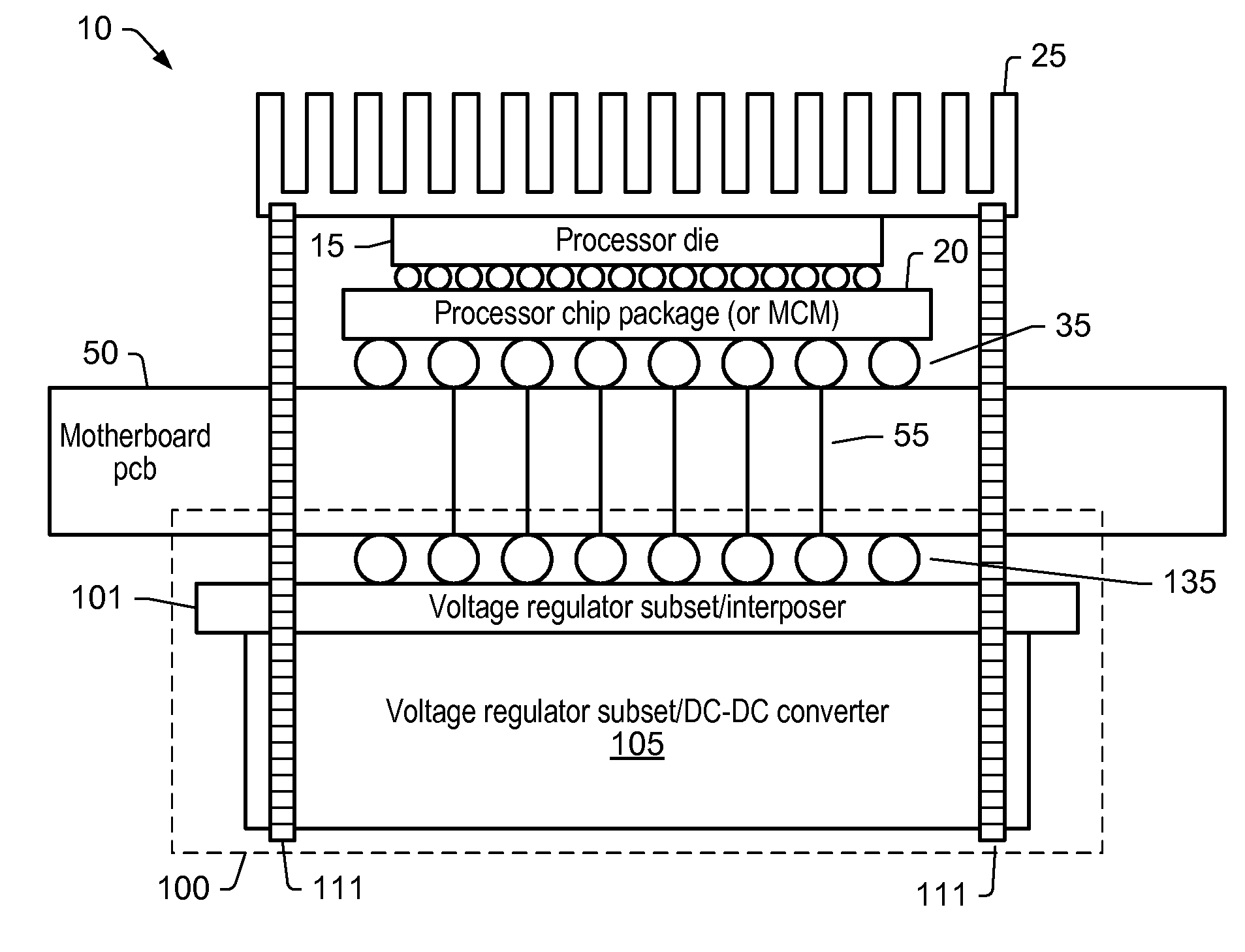

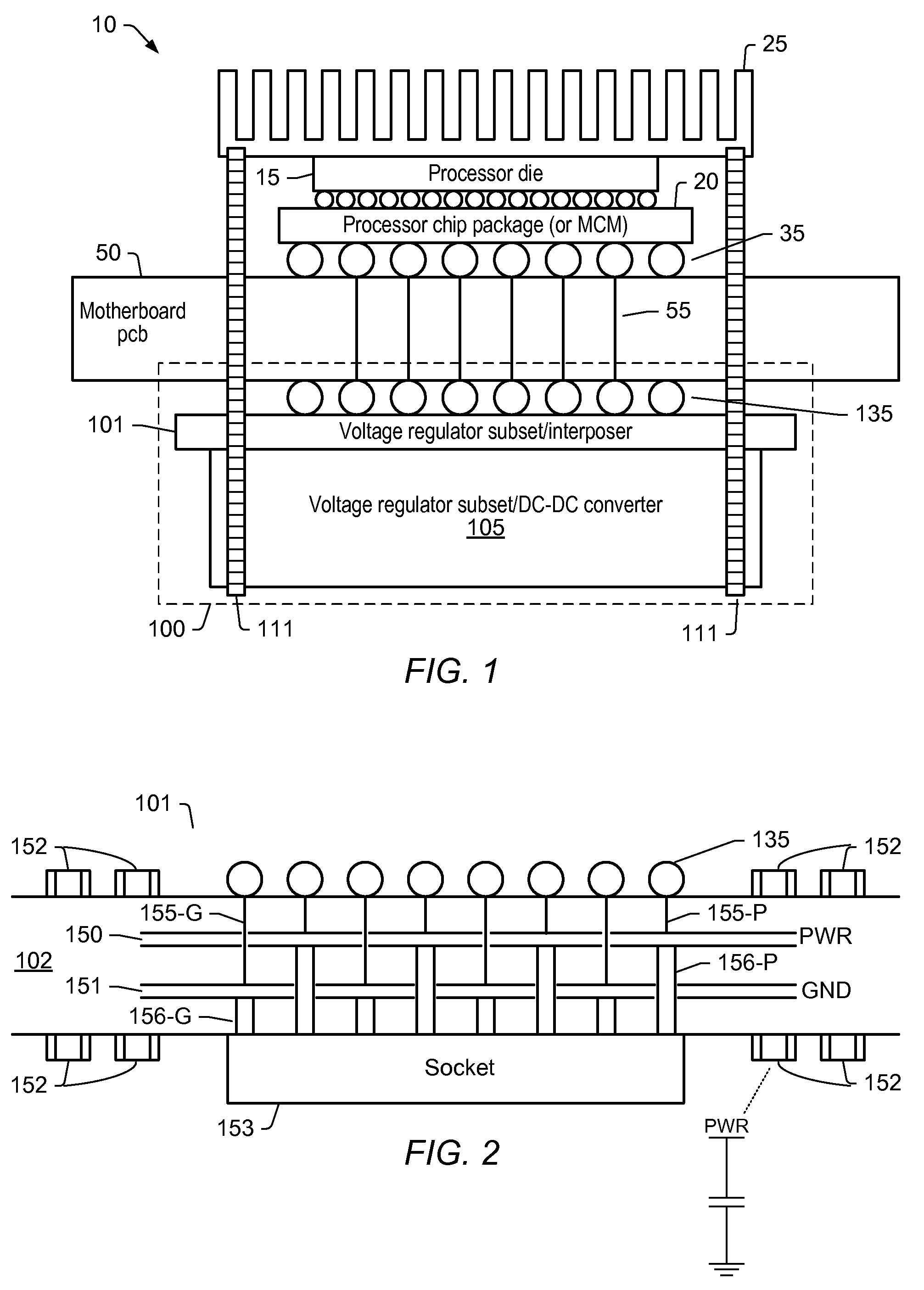

Voltage regulator attach for high current chip applications

ActiveUS20090296360A1Small thermal massGreat massDigital data processing detailsSemiconductor/solid-state device detailsElectricityDc dc converter

A voltage regulator. The voltage regulator includes an interposer having, on a first side, a plurality of electrical connections suitable for coupling to a printed circuit board (PCB). The interposer also includes at least one power plane and at least one ground plane, wherein each of the power and ground planes is coupled to one or more of the electrical connections. The voltage regulator further includes a DC-DC converter that is electro-mechanically attachable to and detachable from the interposer. The interposer includes a socket, on a second side, that is suitable to receive two or more electro-mechanical connecting members of the DC-DC converter. When the DC-DC converter is attached to the interposer, at least one of the electromechanical connecting members is electrically coupled to a power plane of the interposer, while at least one other one of the electromechanical connecting members is electrically coupled to the ground plane.

Owner:ORACLE INT CORP

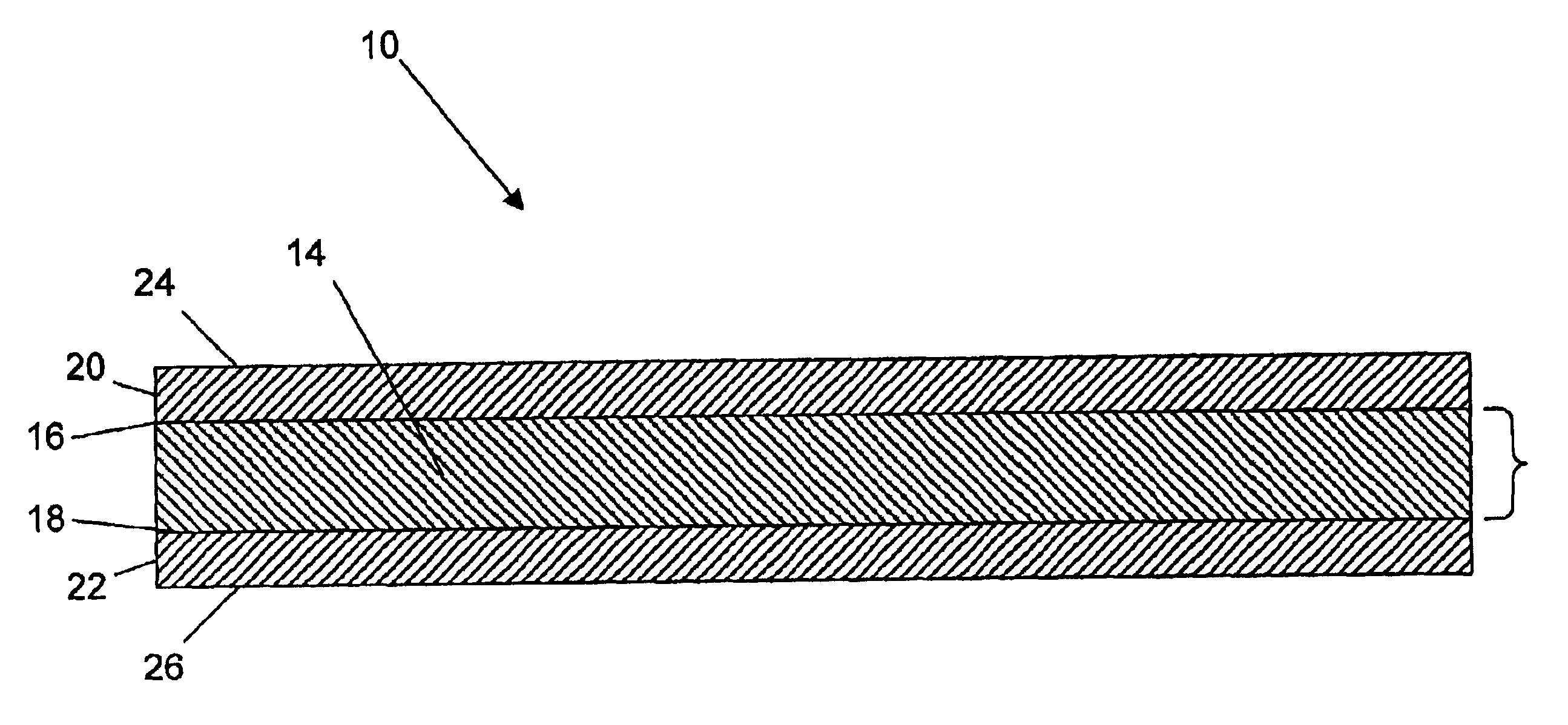

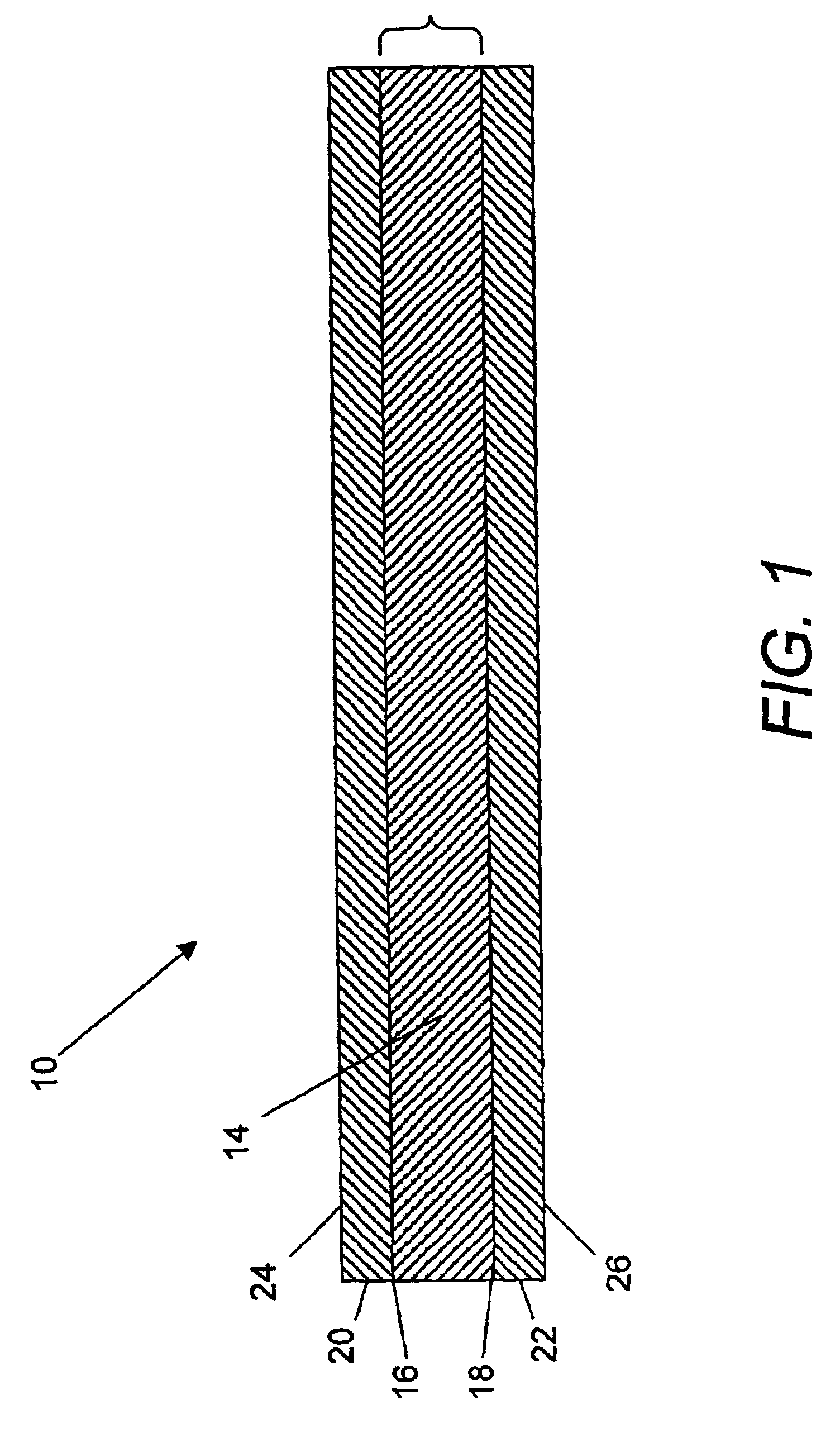

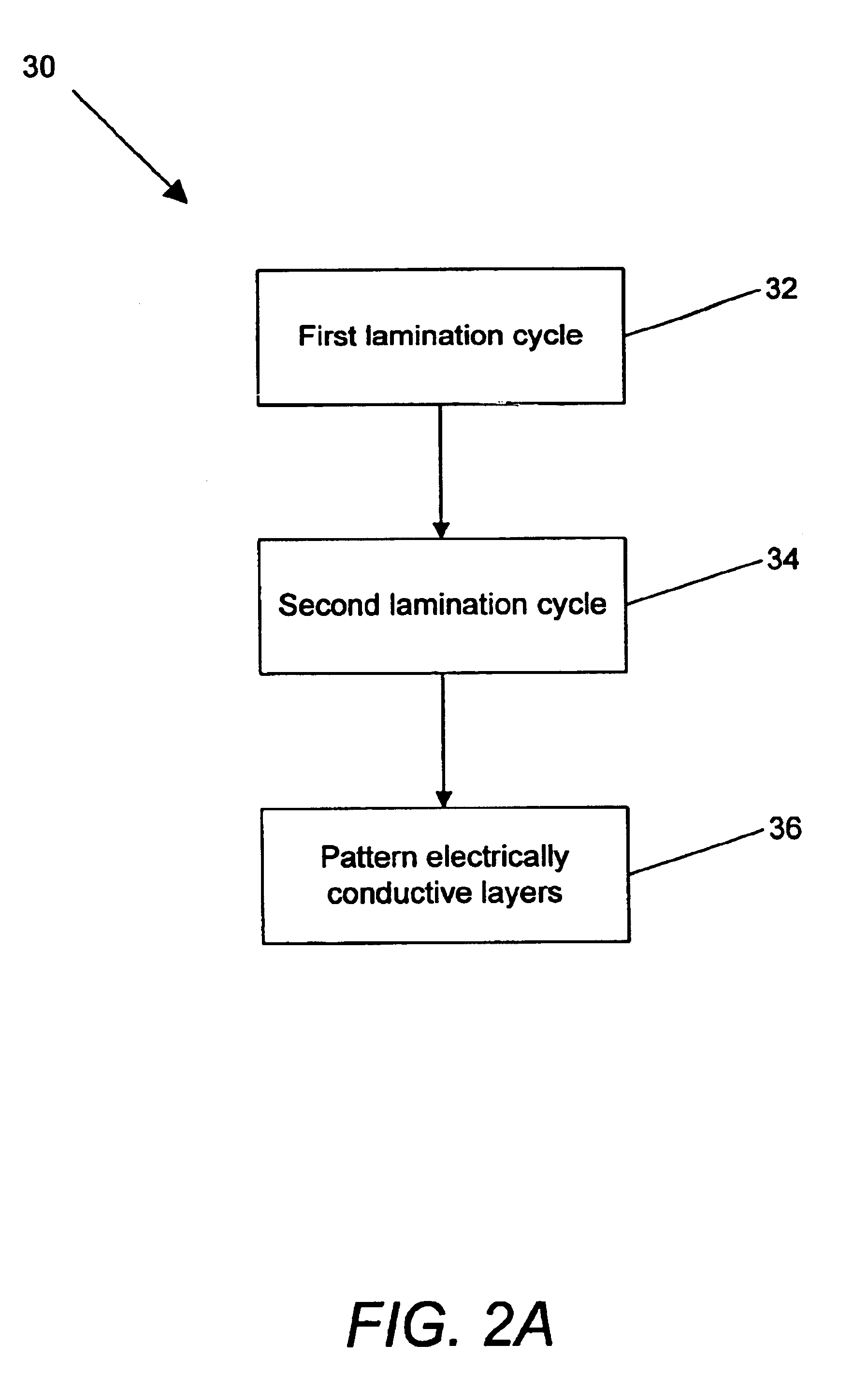

Lightweight circuit board with conductive constraining cores

InactiveUS6869664B2Improve performanceCeramic layered productsElectrical connection printed elementsBoard structureElectrical and Electronics engineering

Prepregs, laminates, printed wiring board structures and processes for constructing materials and printed wiring boards that enable the construction of printed wiring boards with improved thermal properties. In one embodiment, the prepregs include substrates impregnated with electrically and thermally conductive resins. In other embodiments, the prepregs have substrate materials that include carbon. In other embodiments, the prepregs include substrates impregnated with thermally conductive resins. In other embodiments, the printed wiring board structures include electrically and thermally conductive laminates that can act as ground and / or power planes.

Owner:STABLCOR TECH

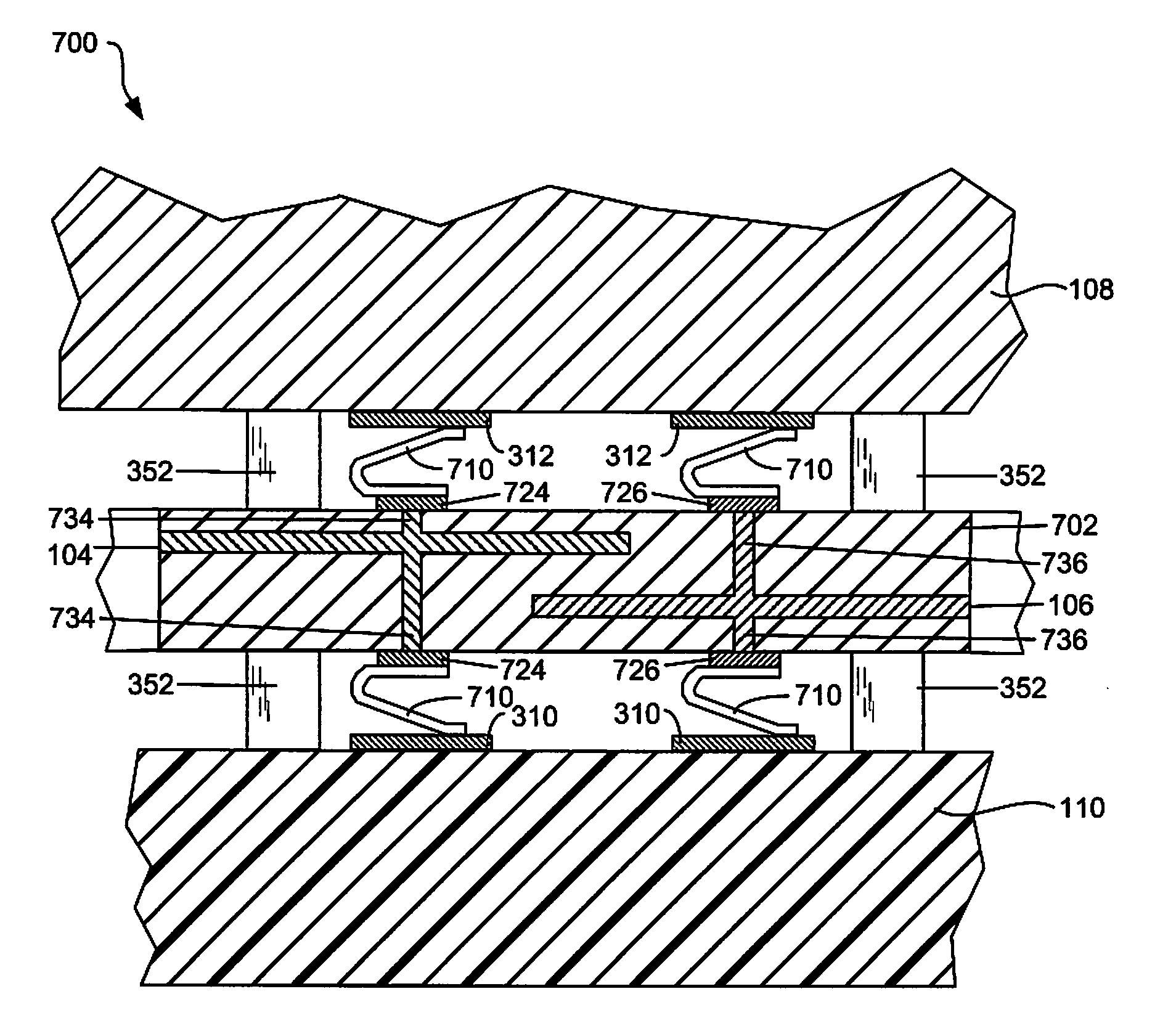

Method and Apparatus for Electrically Connecting Two Substrates Using a Land Grid Array Connector Provided with a Frame Structure Having Power Distribution Elements

InactiveUS20080239683A1Line/current collector detailsElectrically conductive connectionsPower cableInterposer

A method and apparatus for electrically connecting two substrates using a land grid array (LGA) connector provided with a frame structure having power distribution elements. In an embodiment, the frame structure includes a frame having one or more conductive layers sandwiched between non-conductive layers. The frame may, for example, be a printed wire board (PWB) having power planes that distribute power from a first substrate (e.g., a system PWB) and / or a power cable to a second substrate (e.g., an electronic module). The frame includes one or more apertures configured to receive an LGA interposer for electrically connecting the two substrates. Preferably, the frame includes four apertures arranged in quadrants that each receive an interposer, and at least one power plane extends between two quadrants and / or adjacent to a peripheral edge of one or more quadrants in the form of stacked and / or parallel bus bars each defining a power domain.

Owner:IBM CORP

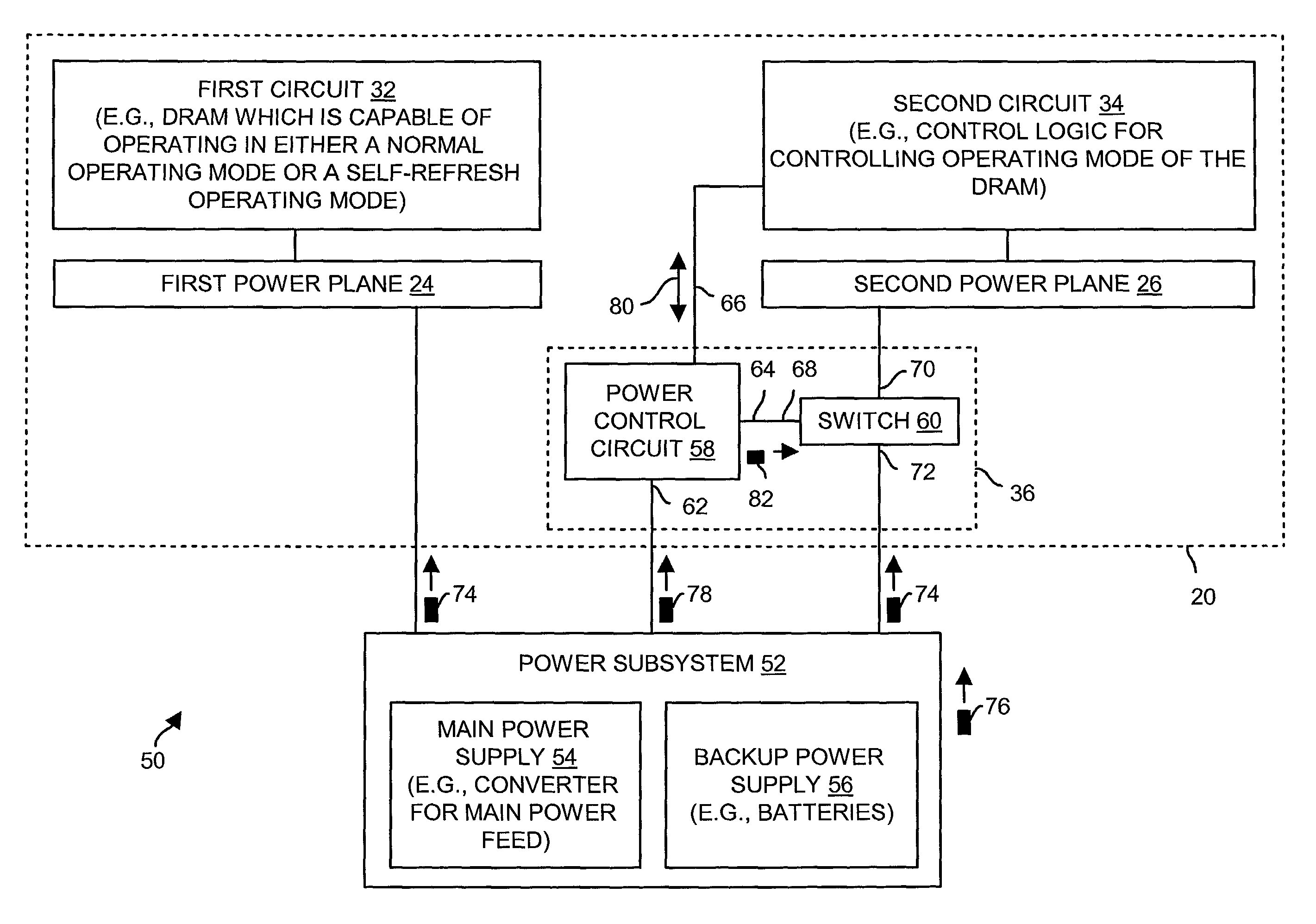

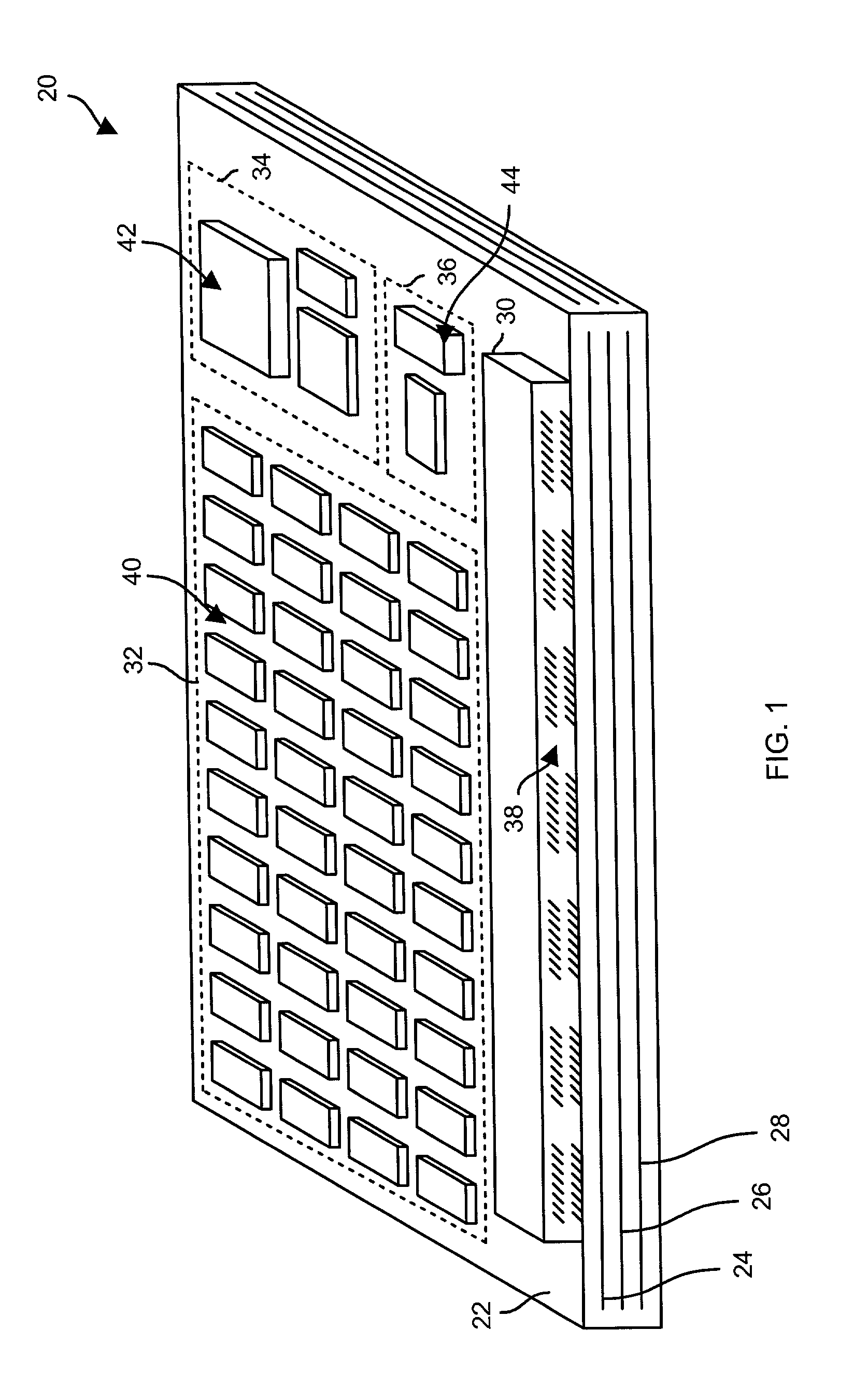

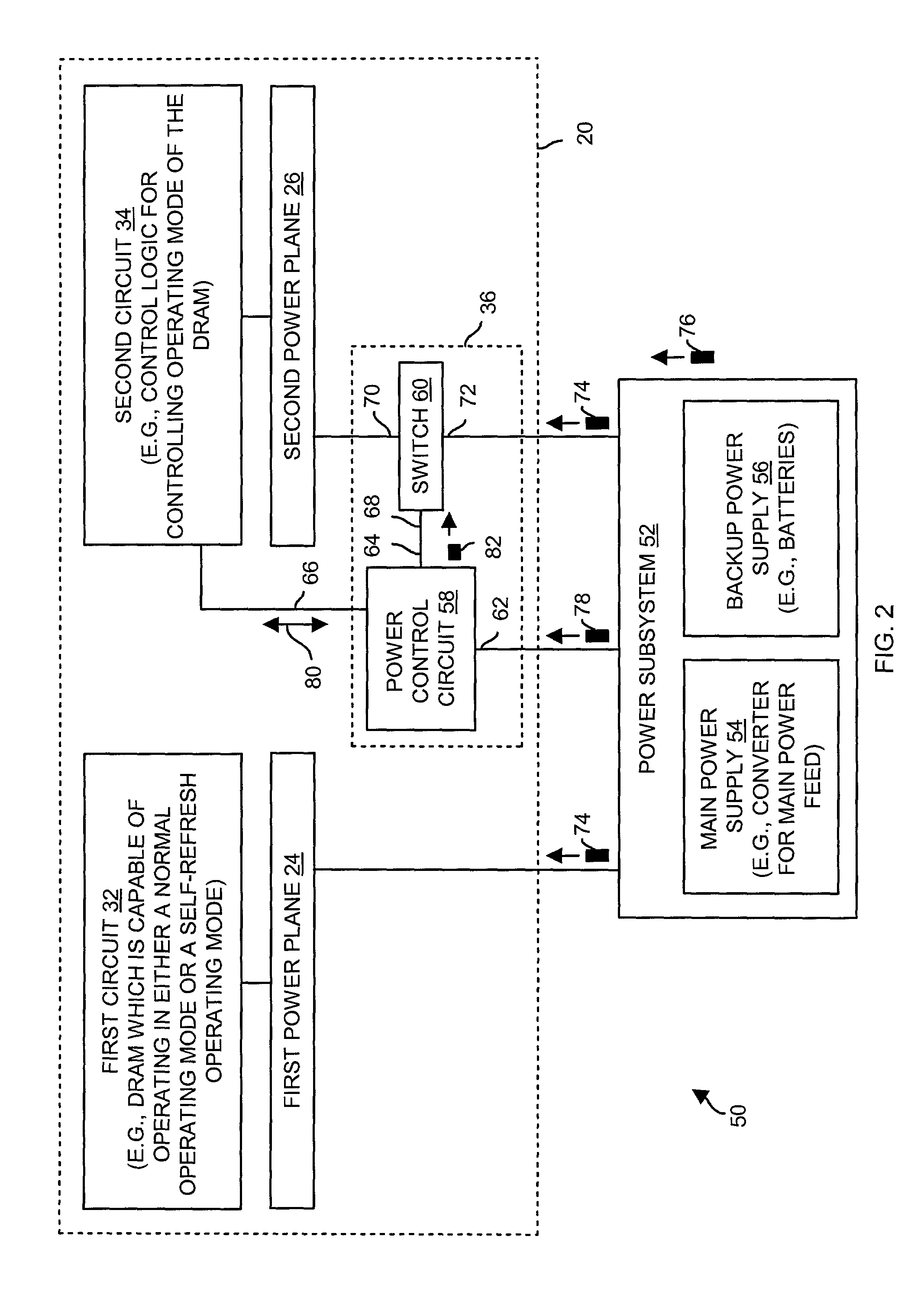

System, method and apparatus for controlling supply of backup power to first and second power planes in the event of a power failure of a main power supply

ActiveUS7058835B1Reduce probabilityReduce power consumptionVolume/mass flow measurementHardware monitoringStandby powerHemt circuits

A circuit board includes a first circuit connected to a first power plane, a second circuit connected to a second power plane, and a power controller connected to the second power plane. The power controller connects the second power plane to a power subsystem such that the second circuit receives a main power signal through the second power plane while the power subsystem provides the main power signal to the first circuit through the first power plane. The power controller (i) detects a power failure event in which the power subsystem provides a backup power signal in place of the main power signal and, in response to the power failure event, (ii) disconnects the second power plane from the power subsystem such that the second circuit does not receive the backup power signal thus reducing backup power consumption.

Owner:EMC IP HLDG CO LLC

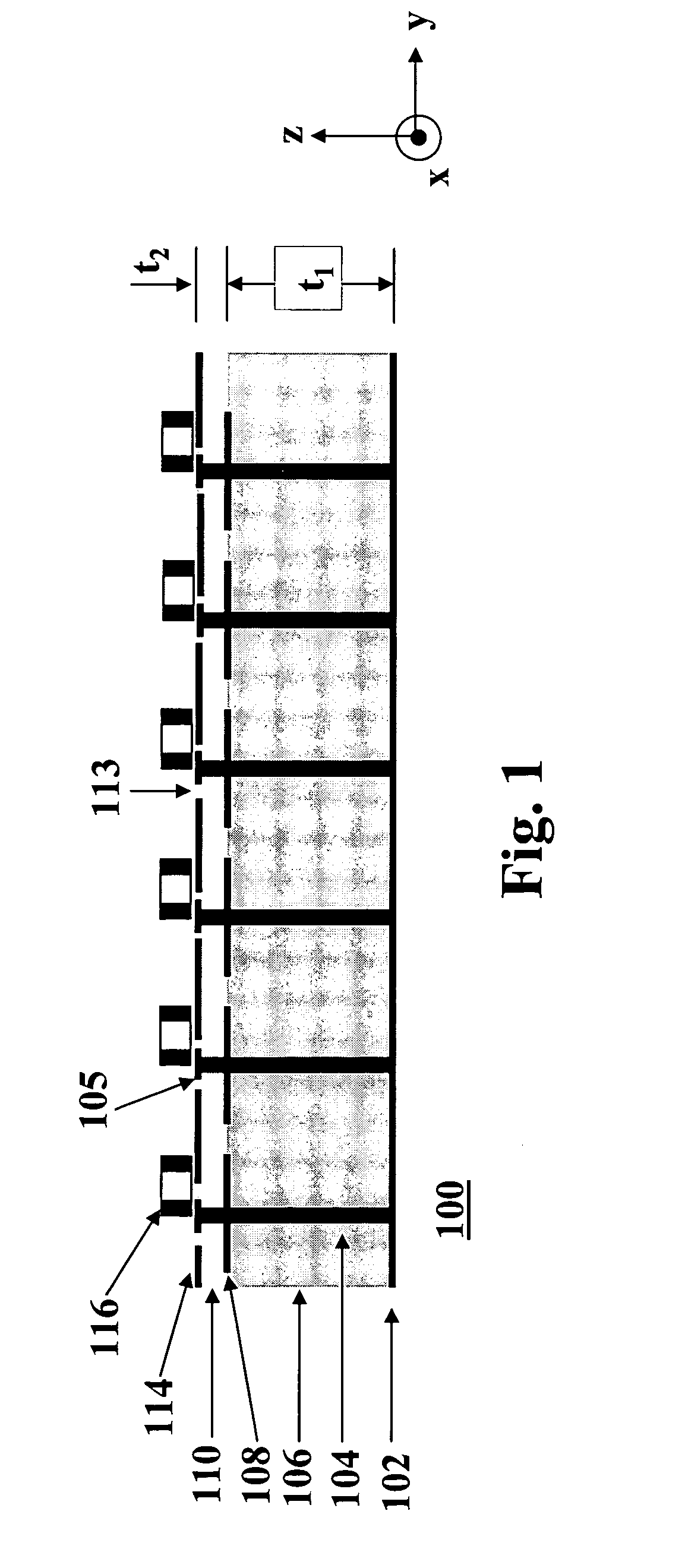

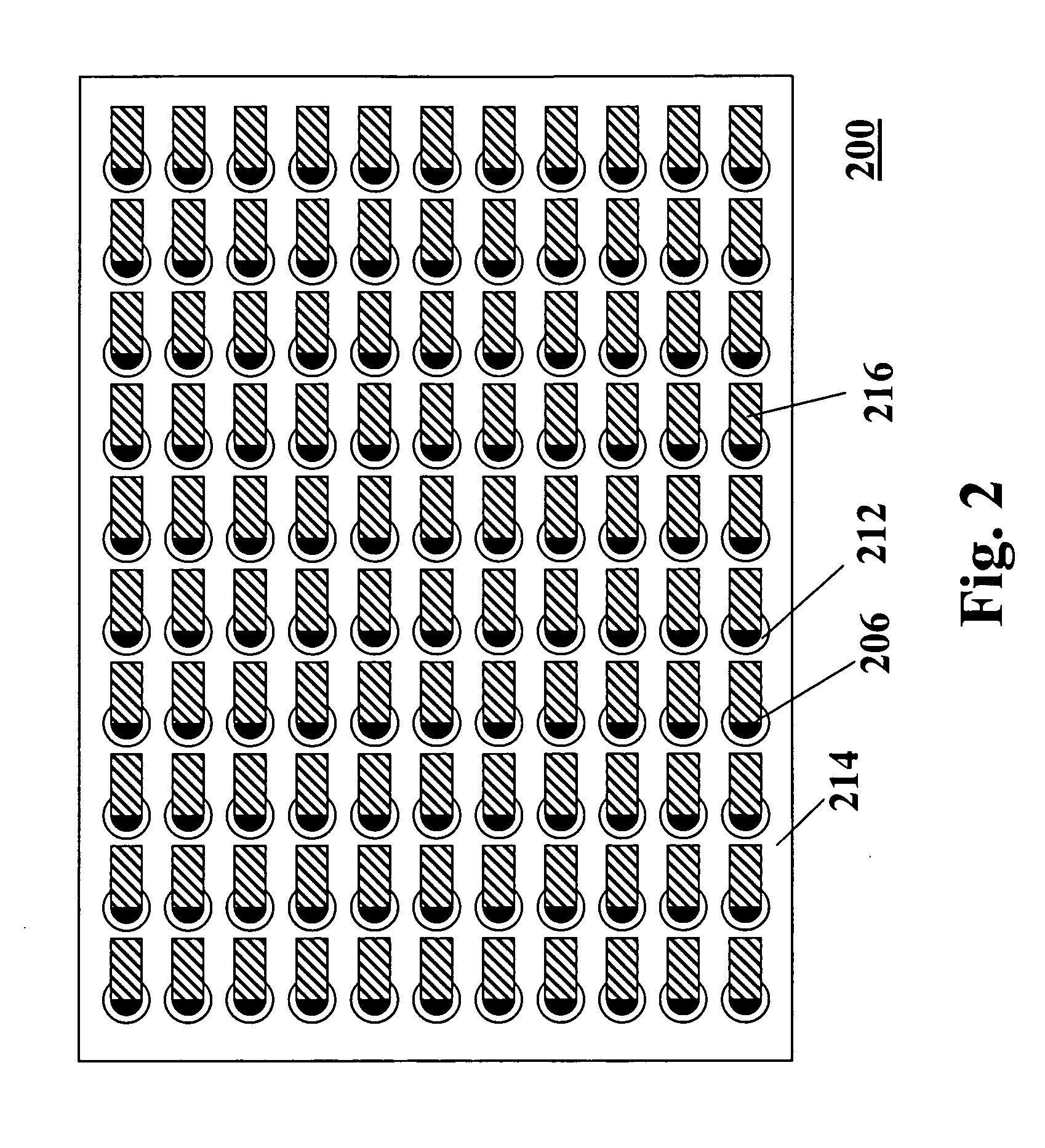

Circuit and method for enhanced low frequency switching noise suppression in multilayer printed circuit boards using a chip capacitor lattice

InactiveUS20050224912A1Suppress powerRemoval of powerCross-talk/noise/interference reductionSemiconductor/solid-state device detailsSignal routingEngineering

A printed circuit board (PCB) uses arrays of chip capacitors over the entire surface of the PCB. The PCB includes an upper conductive surface routing signals to components of the PCB, a lower conductive surface, vias between the upper and lower surfaces, and a layer of patches disposed between the upper and lower surfaces to which the vias and chip capacitors are connected. The chip capacitors connect the vias to the upper conductive surface. The use of chip capacitors in a periodic lattice extends the frequency range for suppressing noise in power planes of isolated capacitors from several hundred MHz or less to 4 GHz. Combining the capacitors along with the buried patches extends the low frequency cutoff of high frequency reference noise suppression circuits to 50 MHz or less.

Owner:WEMTEC

Semiconductor device having electrical contact from opposite sides

InactiveUS20050042867A1TransistorSemiconductor/solid-state device detailsMetal interconnectDevice material

Owner:NORTH STAR INNOVATIONS

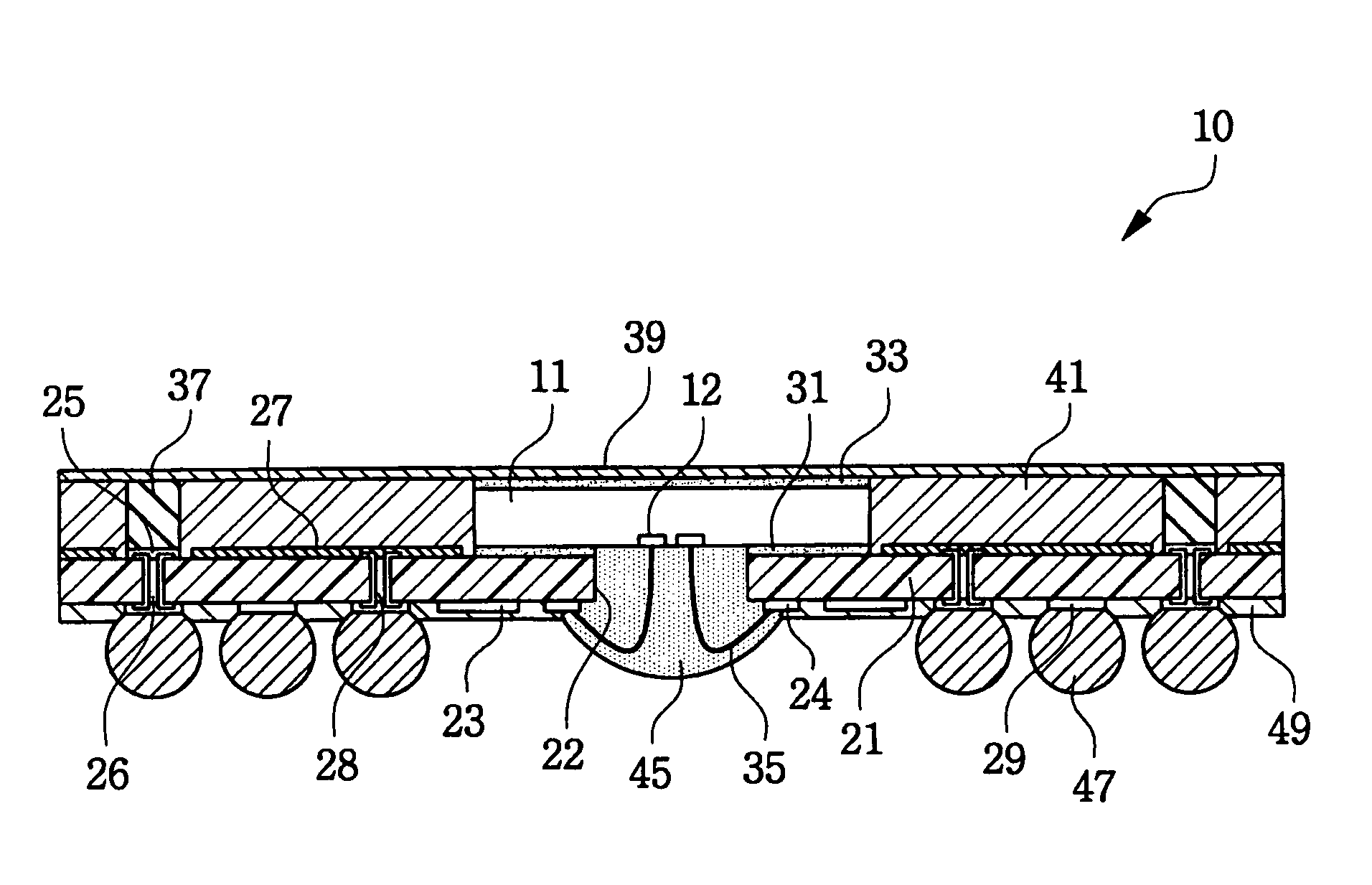

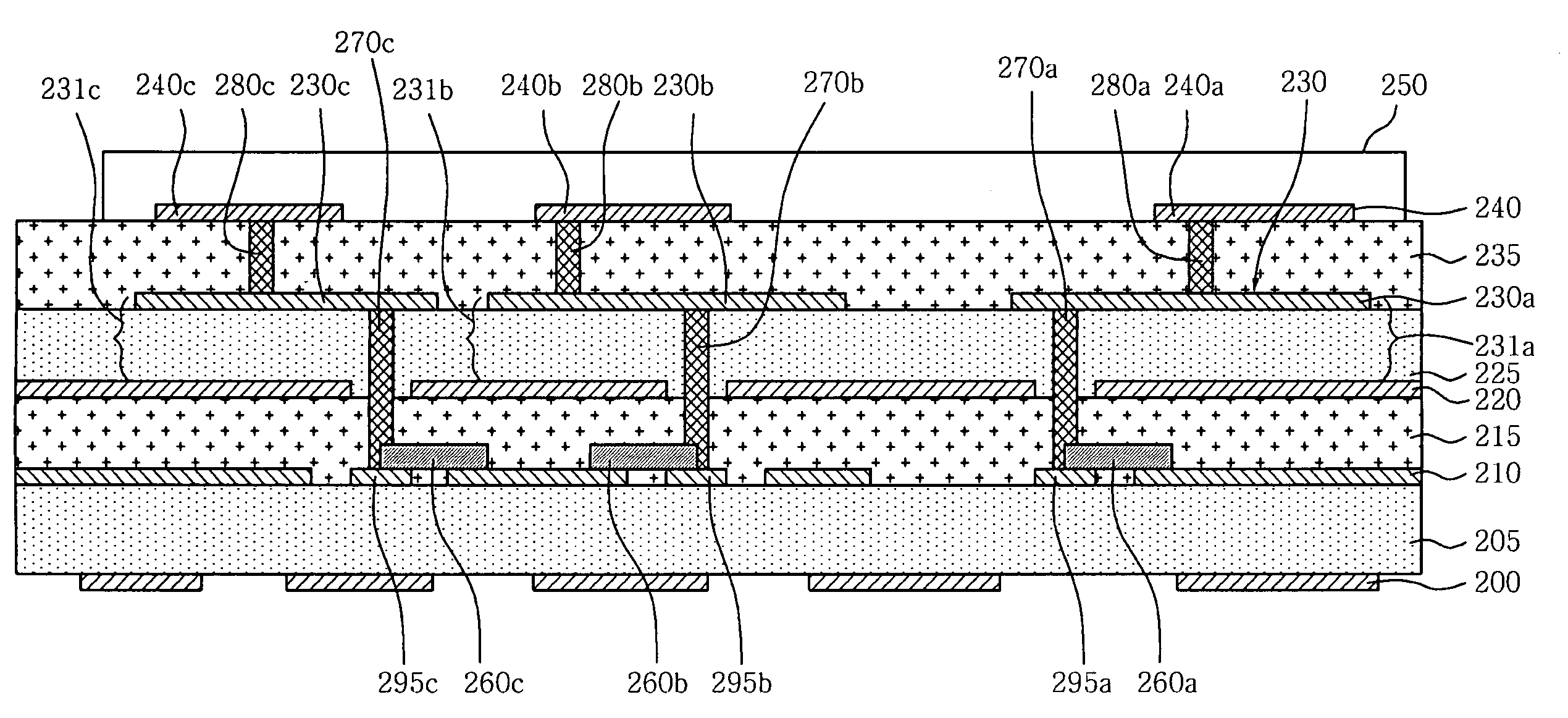

Semiconductor chip package having decoupling capacitor and manufacturing method thereof

ActiveUS7129571B2Short pathImproved decoupling capacitorSemiconductor/solid-state device detailsSolid-state devicesSolder ballSemiconductor chip

A semiconductor chip package has a substrate that includes circuit lines provided on first and / or second surfaces, a power plane provided on the second surface, bump lands provided on the second surface and coupled to the circuit lines, and ball lands provided on the first surface. The package further has a semiconductor chip attached to the second surface of the substrate and electrically coupled to the circuit lines, and a dielectric layer provided on the second surface of the substrate. The dielectric layer surrounds laterally the chip, covers the power plane, and exposes the bump lands. The package further has a ground plane provided on both the chip and the dielectric layer, vertical connection bumps provided within the dielectric layer and on the bump lands and electrically coupled to the ground plane, and solder balls provided on the ball lands.

Owner:SAMSUNG ELECTRONICS CO LTD

Method and apparatus for isolating an ambient air temperature sensor

A method and apparatus for thermally isolating a temperature sensor mounted on a printed circuit board from a heat generating component mounted on the printed circuit board is provided. Generally, a thermal isolation region, which may be comprised of a plurality of openings in the printed circuit board, is disposed about the temperature sensor to interrupt conductive transfer of heat from the heat generating component to the temperature sensor. The openings extend sufficiently far into the printed circuit board to remove at least a portion of a conductive layer, such as a power plane from the region surrounding the temperature sensor. Electrical power and signals may be provided to the temperature sensor through regions intermediate the openings.

Owner:ORACLE INT CORP

Top layers of metal for integrated circuits

InactiveUS20060063371A1Improve performanceReduce resistive voltage dropSemiconductor/solid-state device detailsSolid-state devicesEngineeringCritical signal

The present invention adds one or more thick layers of polymer dielectric and one or more layers of thick, wide metal lines on top of a finished semiconductor wafer, post-passivation. The thick, wide metal lines may be used for long signal paths and can also be used for power buses or power planes, clock distribution networks, critical signal, and re-distribution of I / O pads.

Owner:QUALCOMM INC

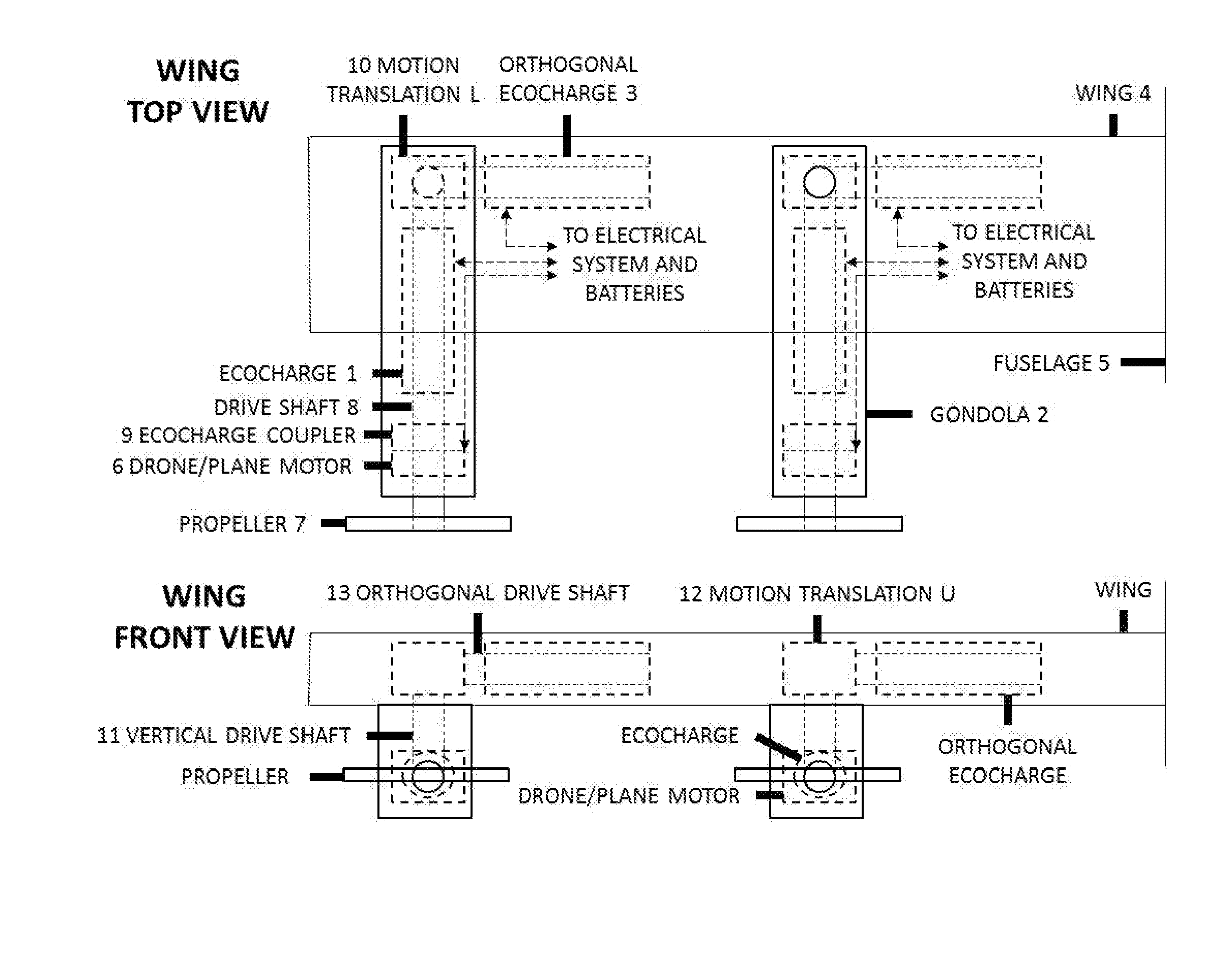

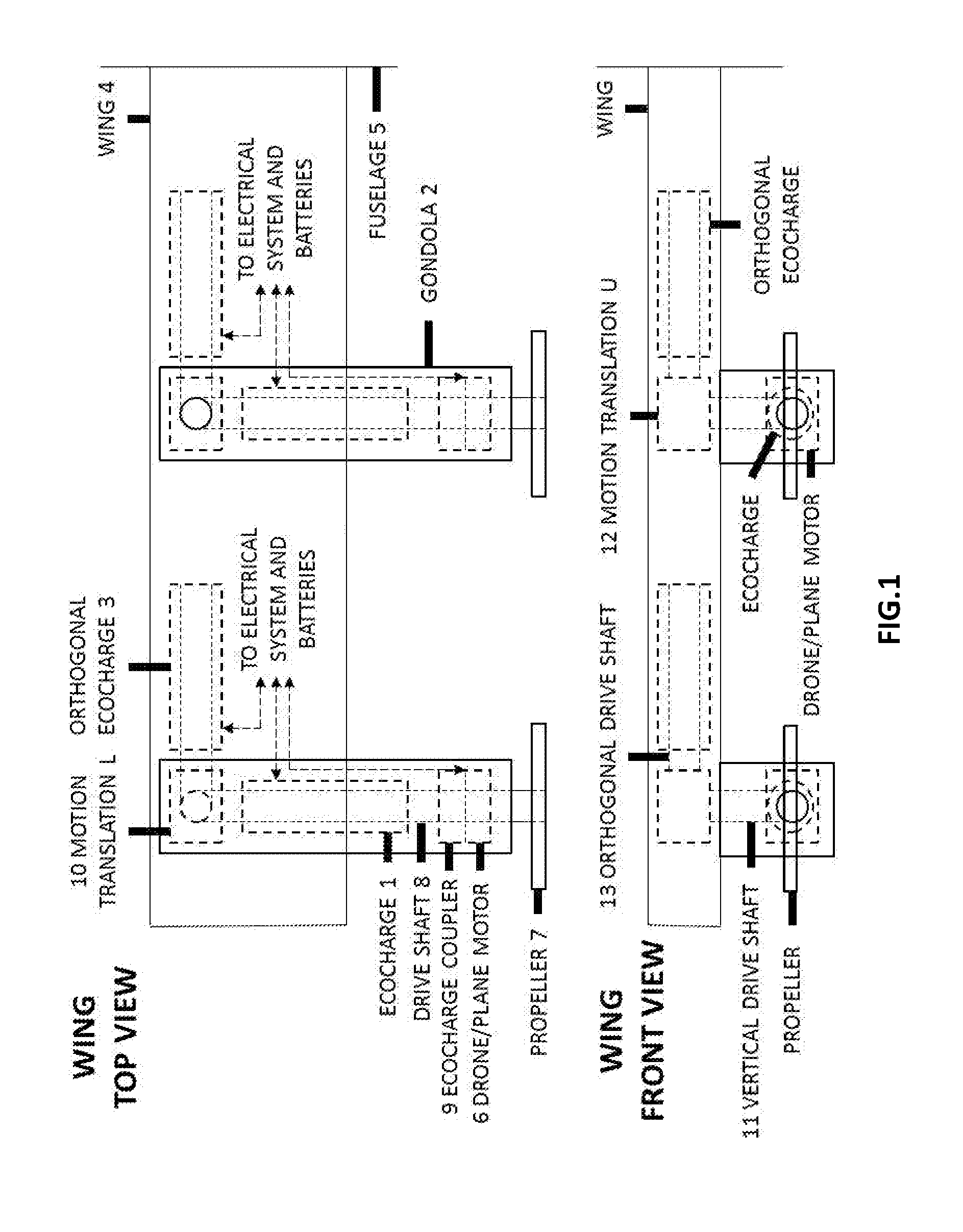

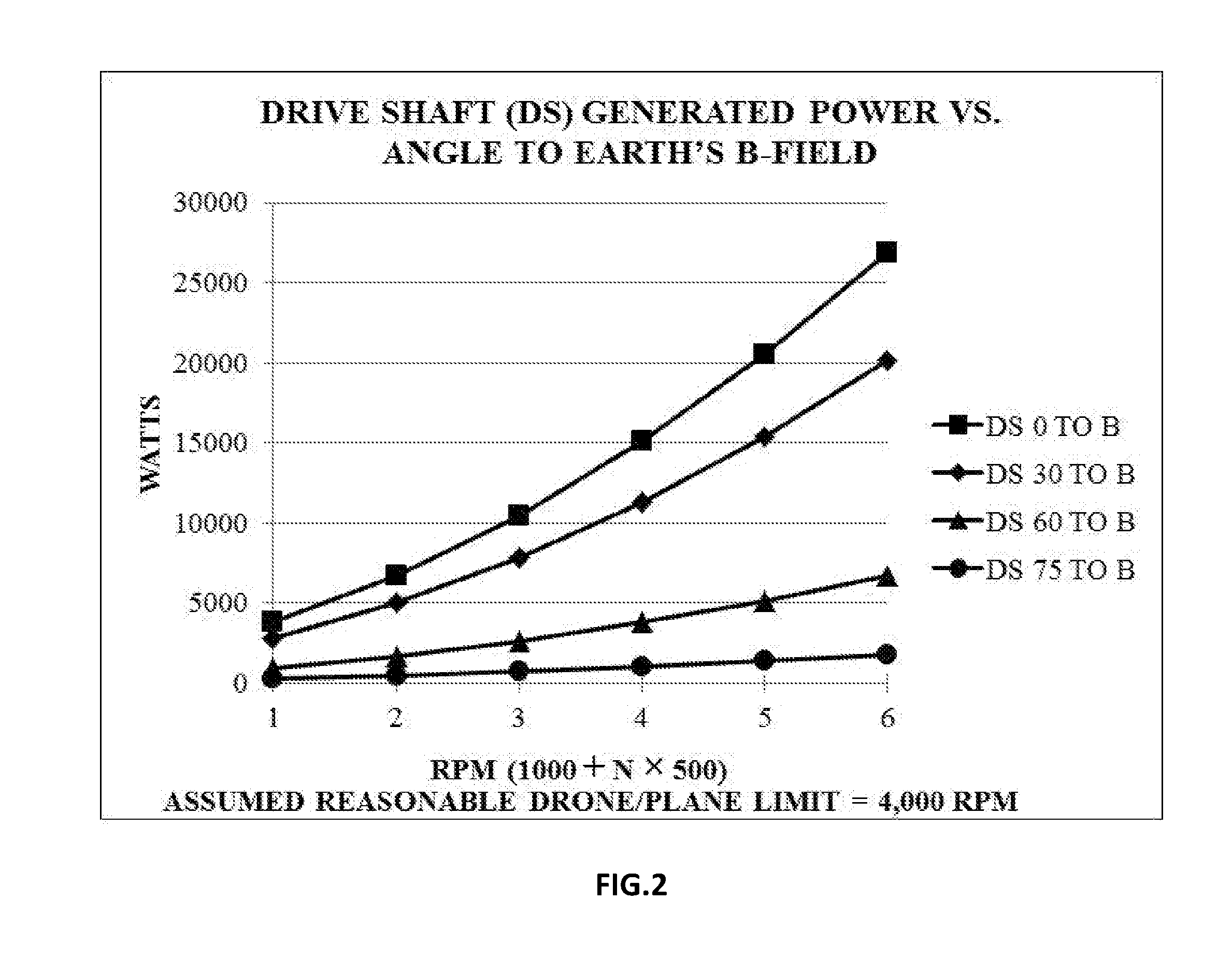

EcoCharge Powered Planes and Drones

ActiveUS20160280075A1Maximizing conversionMaximum conversionElectric power distributionUnmanned aerial vehiclesDisruptive technologyGraphene

The earth's magnetic field has not been mined as a source of energy. With average field strength of 0.5×10−4 Tesla around the world it is easy to understand why. A disruptive technology is needed to mine the earth's magnetic field. Such a technology, graphene, is now at an early stage of development with excellent properties in the form of high conductivity, low resistivity, durable, light weight, low cost sheets. Multiple sheets of graphene provide a significant multiplier to earth's magnetic field yielding a feasible source of ecologically clean power. Graphene based EcoCharge units can be driven by electric motors putting graphene in motion to mine the earth's magnetic field. Estimates show that for a Solar Impulse 2 like electric plane, eight EcoCharge units weighing 64 lbs generate 60 kW RMS continuously replacing 3,000 lbs of photovoltaic cells generating 50 kW RMS during the day only.

Owner:MCCRADY DENNIS DRAKE

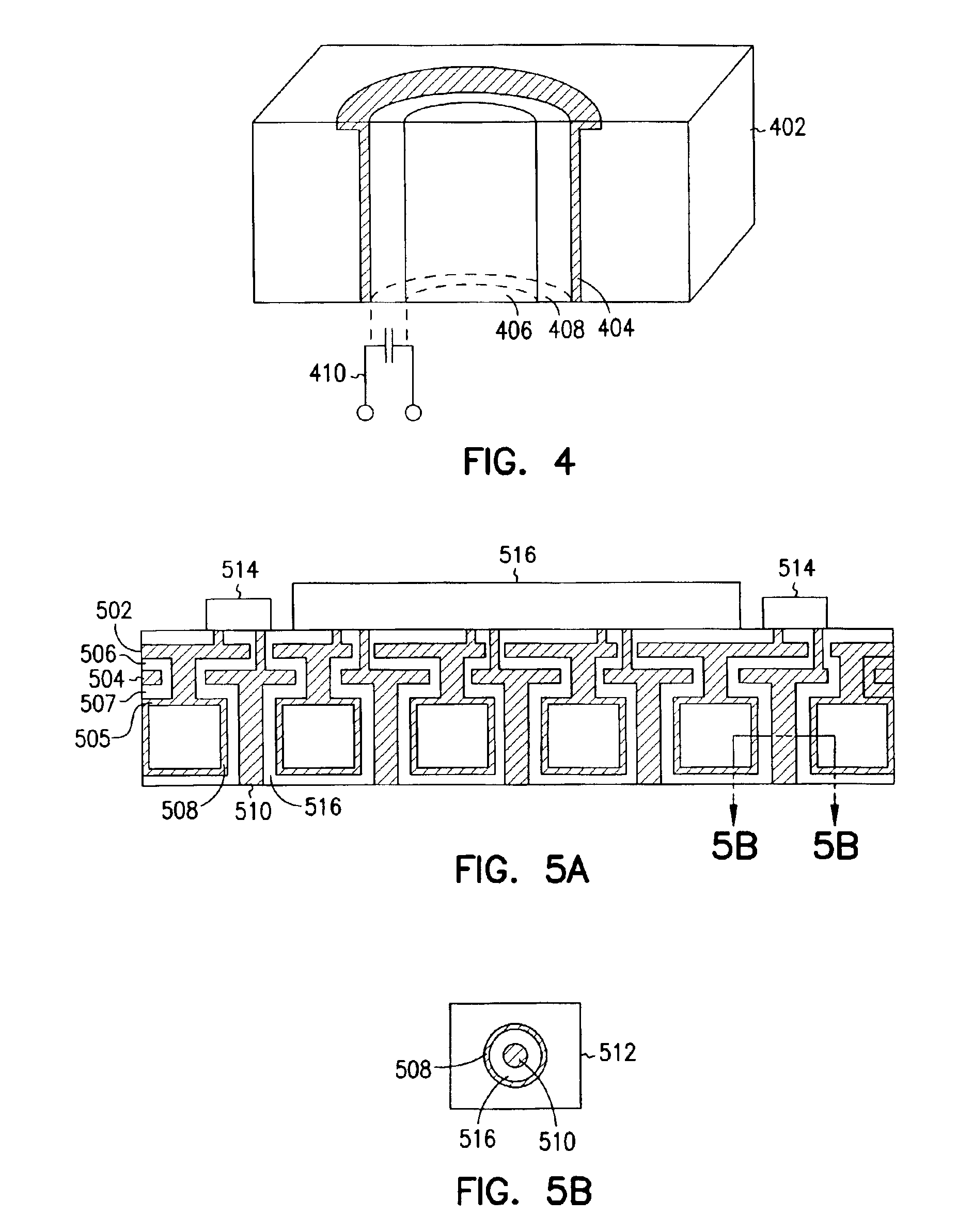

Hybrid capacitor, circuit, and system

InactiveUS6920051B2Multiple fixed capacitorsSemiconductor/solid-state device detailsCapacitanceElectrical conductor

A hybrid capacitor associated with an integrated circuit package provides multiple levels of excess, off-chip capacitance to die loads. The hybrid capacitor includes a low inductance, parallel plate capacitor embedded within the package, and electrically connected to a second source of off-chip capacitance. The parallel plate capacitor is disposed underneath a die, and includes a top conductive layer, a bottom conductive layer, and a thin dielectric layer that electrically isolates the top and bottom layers. The second source of off-chip capacitance is a set of self-aligned via capacitors, and / or one or more discrete capacitors, and / or an additional parallel plate capacitor. Each of the self-aligned via capacitors is embedded within the package, and has an inner conductor and an outer conductor. The inner conductor is electrically connected to either the top or bottom conductive layer, and the outer conductor is electrically connected to the other conductive layer. The discrete capacitors are electrically connected to contacts from the conductive layers to the surface of the package. During operation, one of the conductive layers of the low inductance parallel plate capacitor provides a ground plane, while the other conductive layer provides a power plane.

Owner:INTEL CORP

DC power plane structure

InactiveUS20080158840A1Increase manufacturing costReduce usageCross-talk/noise/interference reductionPrinted circuit aspectsElectricityEngineering

A DC power plane structure applied in multi-layer circuit board is provided. The DC power plane structure includes a first circuit area for receiving a DC power, a noise filter with one end electrically connected to a DC power output end of the first circuit area, and a second circuit area which is electrically isolated from the first circuit area. The second circuit area has a band gap structure, and the DC power input end of the band gap structure is electrically connected to the other end of the noise filter for inhibiting high-frequency noise generated between layers of the multi-layer circuit board.

Owner:INVENTEC CORP

Top layers of metal for integrated circuits

InactiveUS7416971B2Improve performanceReduce resistive voltage dropSemiconductor/solid-state device detailsSolid-state devicesEngineeringCritical signal

Owner:QUALCOMM INC

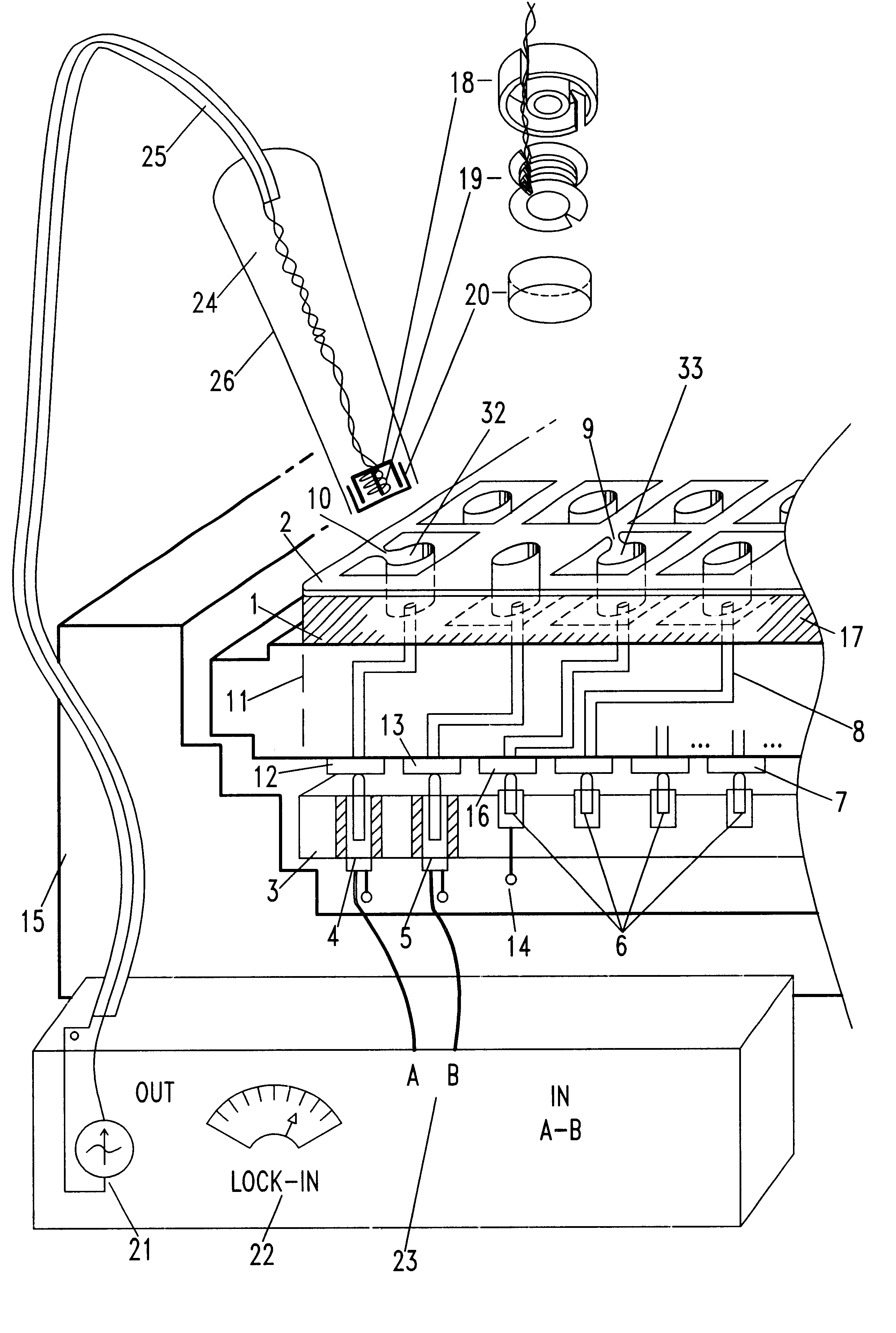

Method for detecting power plane-to-power plane shorts and I/O net-to power plane shorts in modules and printed circuit boards

InactiveUS6242923B1The testing process is simpleLow costElectrical measurement instrument detailsShort-circuit testingHigh resistanceCapacitance

A method of locating in a non-destructive and non-invasive manner power plane-to-power plane shorts or I / O net-to-power plane shorts found in a printed circuit board or a multi-chip-module by way of a magnetic field generating probe is described. Thousands of nets can be simultaneously tested to detect not only the presence of a short but also to accurately pinpoint its position. For high resistance shorts, the probe is provided with a pot core housed inductor located at its tip, and is used at low frequencies to minimize the effect of the capacitive impedance between the power planes. For low resistance shorts, the probe is used at high frequencies, delivering equal but opposite current to each of two matched inductors at the tip of the probe to maximize mutual inductive coupling while minimizing electrostatic capacitive coupling with the board or module. In both cases, the highest current stress is on the probe rather than on the expensive and fragile package under inspection. This allows the test to be both more sensitive to high resistance shorts at low frequencies and is less destructive, thereby being less likely to blow filamentary shorts due to high current stresses through the board or module.

Owner:IBM CORP

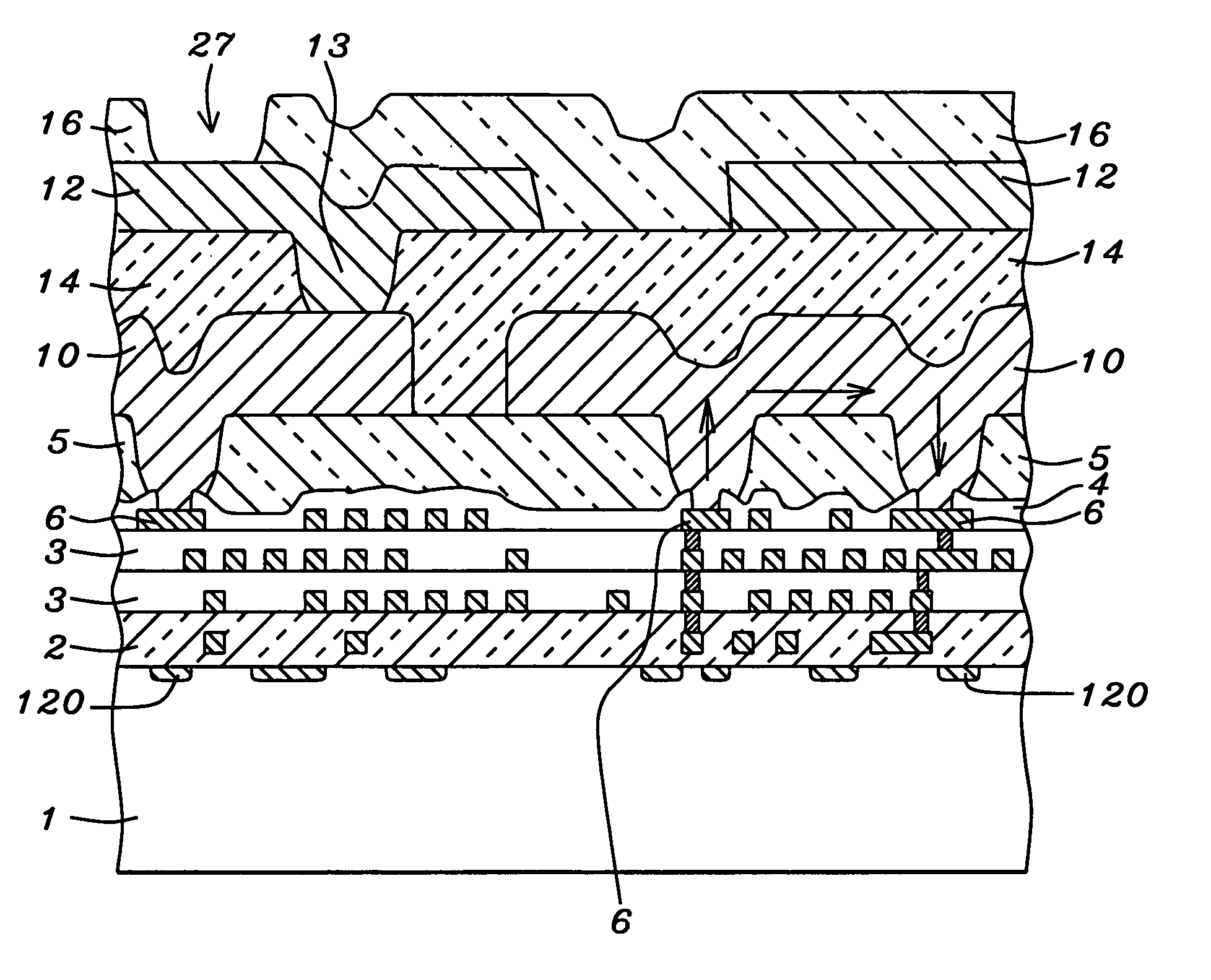

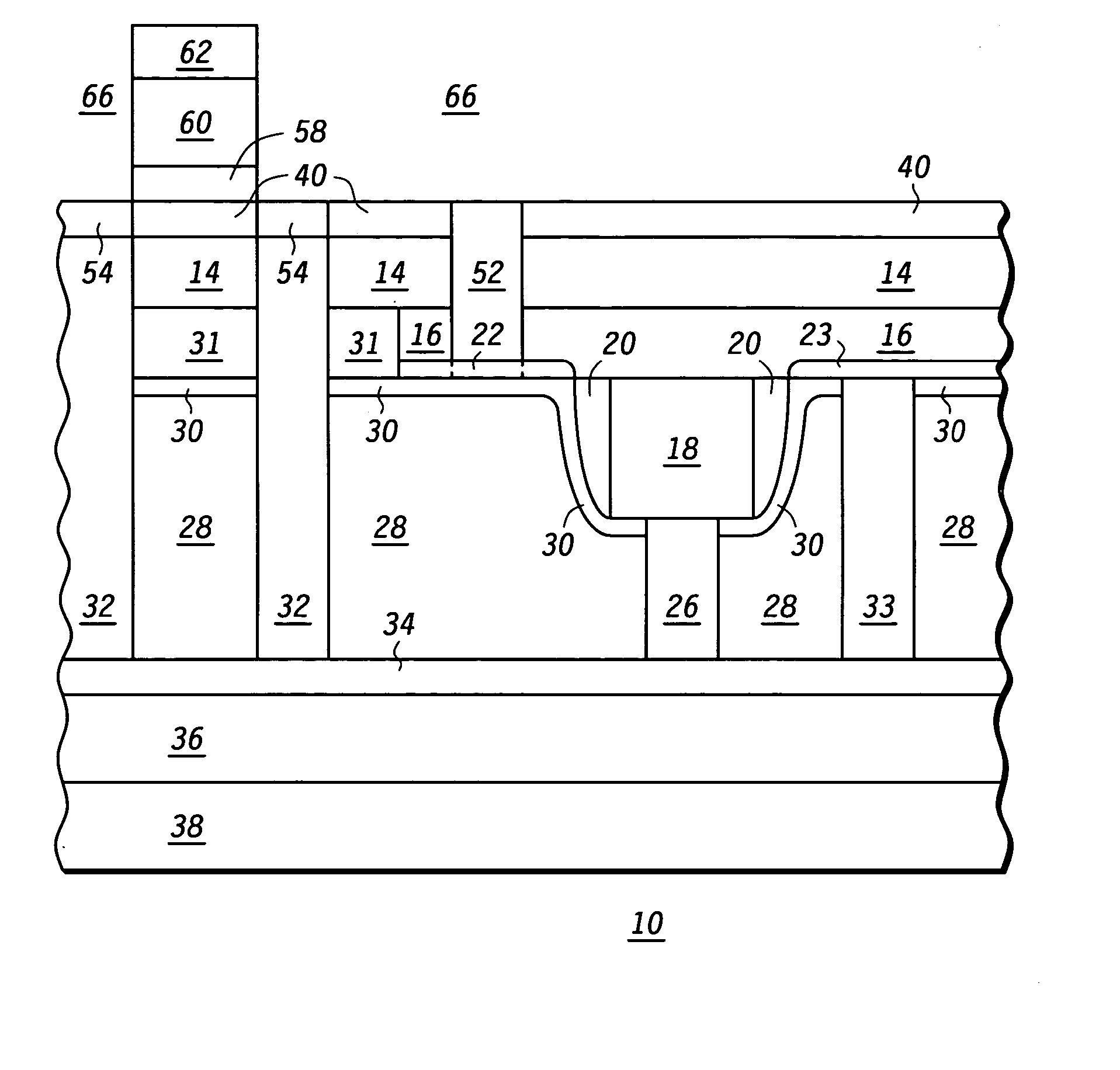

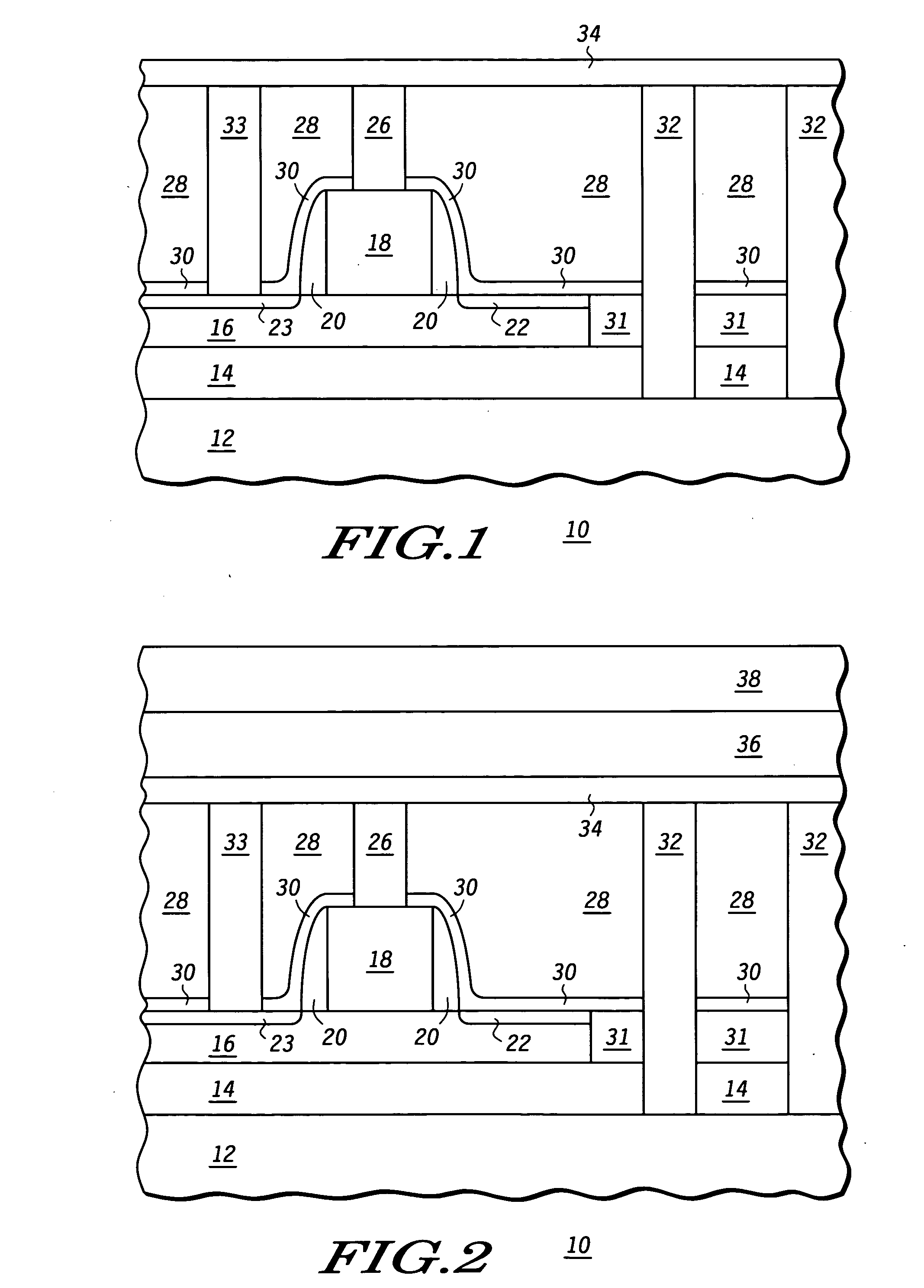

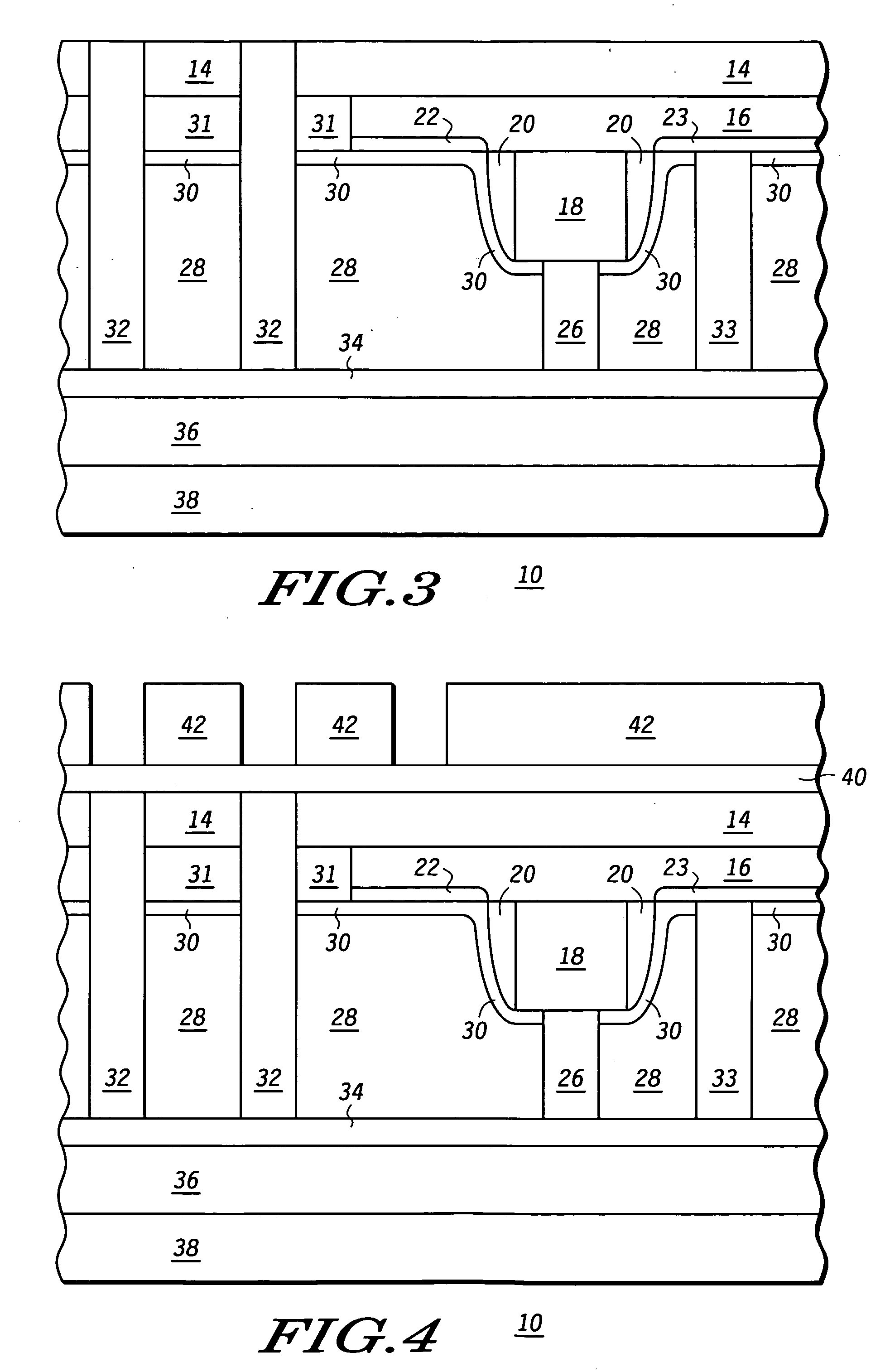

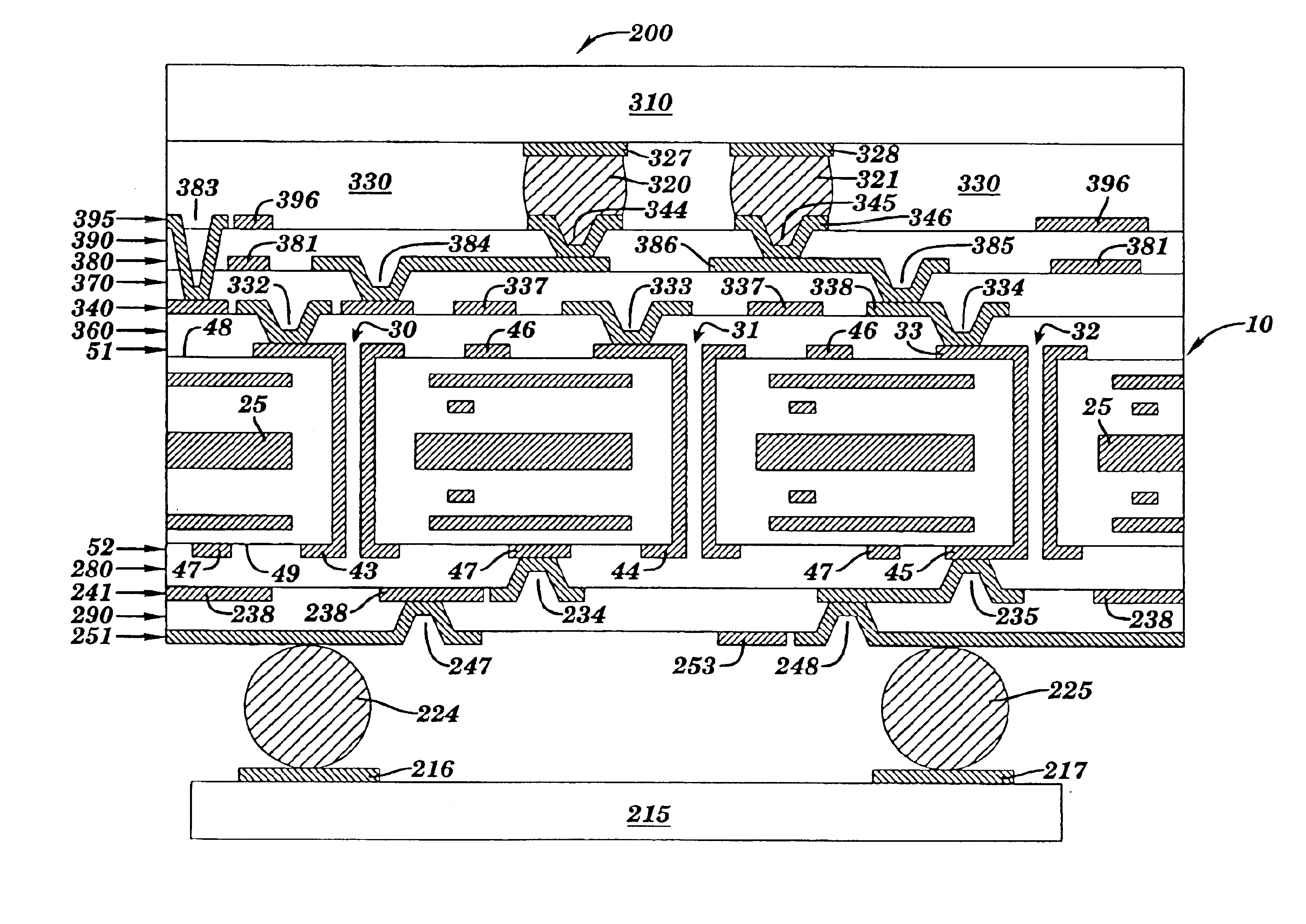

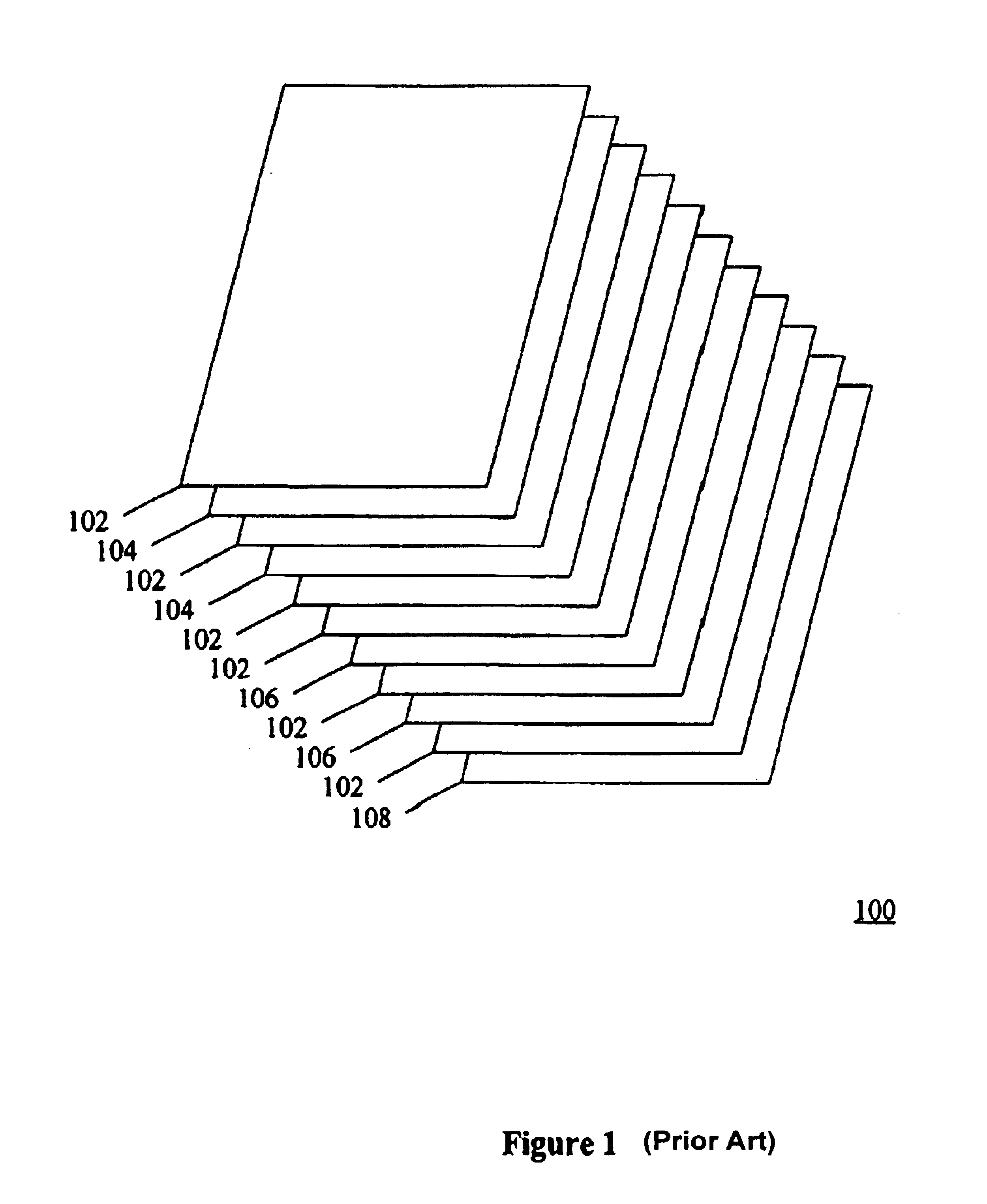

Hyperbga buildup laminate

InactiveUS6879492B2Semiconductor/solid-state device detailsSolid-state devicesElectronic structureDielectric layer

A method and structure for forming an electronic structure that comprises a redistribution structure on a circuitized substrate. The redistribution structure includes N dielectric layers (N ≧2) and N metal planes formed in the following sequence: dielectric layer 1 on a metallic plane that exists on a surface of the substrate, metal plane 1 on dielectric layer 1, dielectric layer 2 on dielectric layer 1 and metal plane 1, metal plane 2 on the dielectric layer 2, . . . , dielectric layer N on dielectric layer N-1 and metal plane N-1, and metal plane N on the dielectric layer N. Metal planes or metallic planes may include signal planes, power planes, ground planes, etc. A microvia structure, which is formed through the N dielectric layers and electrically couples metal plane N to the metallic plane, includes a microvia or a portion of a microvia through each dielectric layer.

Owner:IBM CORP

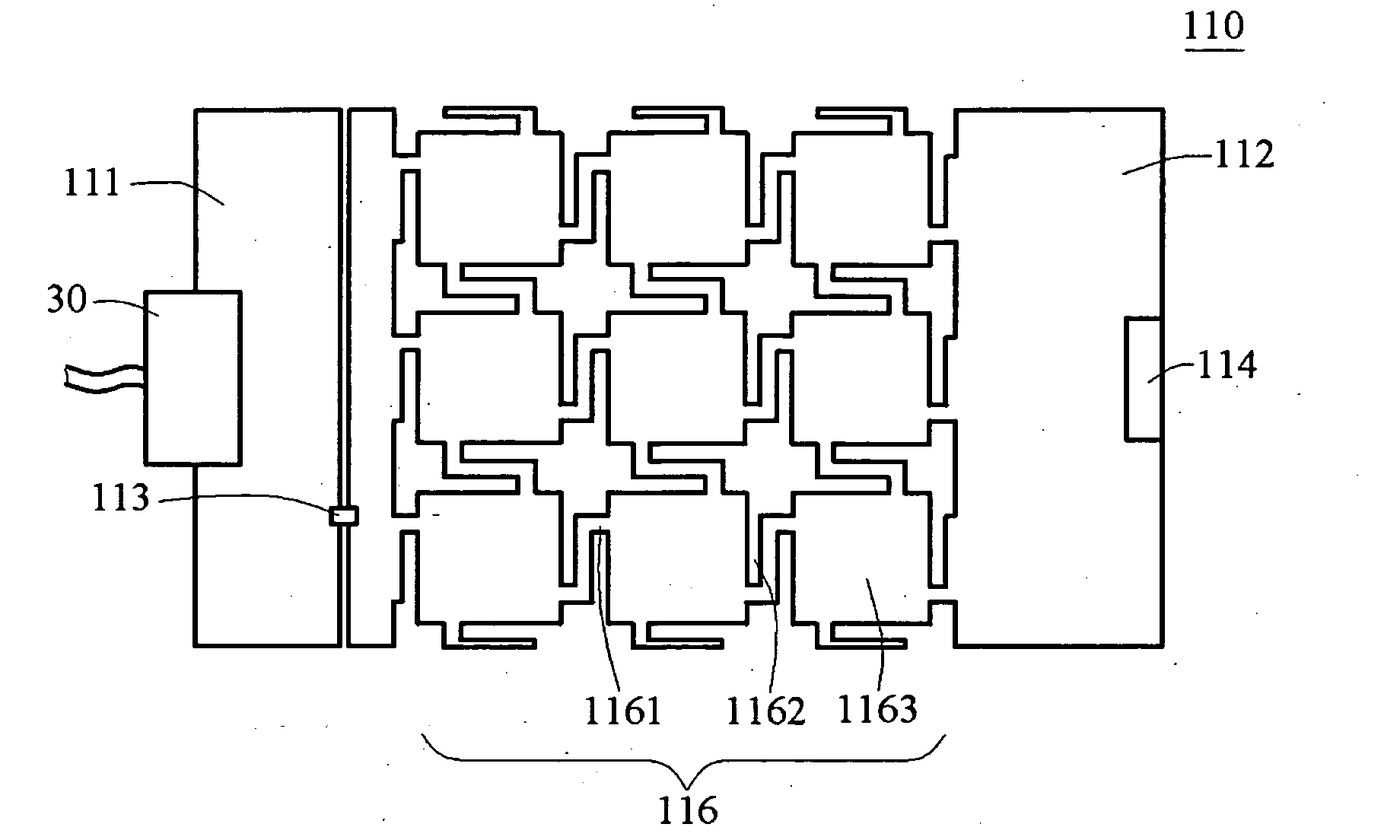

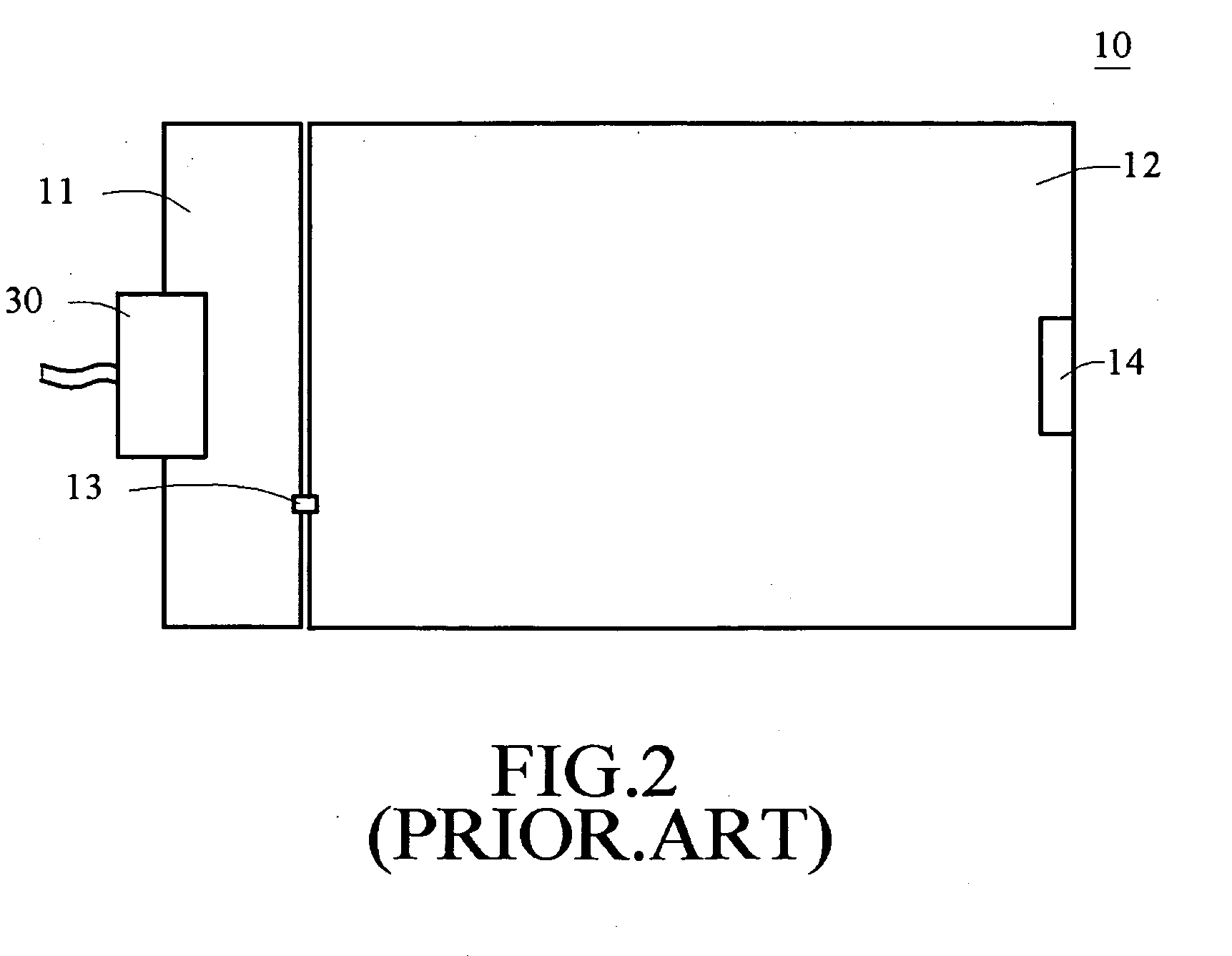

Printed circuit board having embedded RF module power stage circuit

InactiveUS20060291177A1Improve performanceEasy to integrateCross-talk/noise/interference reductionPrinted circuit aspectsEngineeringInductor

Disclosed herein is a printed circuit board having an RF module power stage circuit embedded therein. Specifically, this invention relates to a printed circuit board having an RF module power stage circuit embedded therein, in which a terminal pad for a resistor, a bead, or an inductor is defined or formed on a power supply plane of a multilayered wired board to connect the resistor, the bead, or the inductor to the power supply plane, and the resistor, the bead, or the inductor is connected in parallel with a decoupling capacitor by using a via hole or by embedding the resistor, the bead or the inductor perpendicular to the power supply plane, thus decreasing the size of the RF module and improving the performance thereof.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

Method and apparatus to attenuate power plane noise on a printed circuit board using high ESR capacitors

InactiveUS6870436B2Reduce and minimize noiseMultiple-port networksMagnetic/electric field screeningElectrical resistance and conductanceNegative power

In a method of the present invention, performance characteristics of a printed circuit board are analyzed. The printed circuit board, bypass components and an applied stimulus are modeled. Each of the bypass components includes a capacitor and a resistor in series with each other. Alternatively, a second capacitor is coupled in parallel to the above capacitor and resistor. A simulation of the circuit model is then performed. In this embodiment of the invention, the simulation is responsive to the stimulus as is performed over a range of bypass resistor values. In another embodiment of the invention, a printed circuit board is described with components and characteristics that reduce noise. Such a printed circuit board includes a power plane and a plurality of bypass components. Moreover, the plurality of bypass components include bypass capacitors and bypass resistors coupled in series between the positive power plane and the negative power plane.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP +1

Printed circuit board with low cross-talk noise

InactiveUS7176383B2Minimal crosstalkHigh density wiring patternCross-talk/noise/interference reductionPrinted circuit aspectsEngineeringDielectric layer

Owner:WACHOVIA CAPITAL FINANCE NEW ENGLAND AS AGENT +1

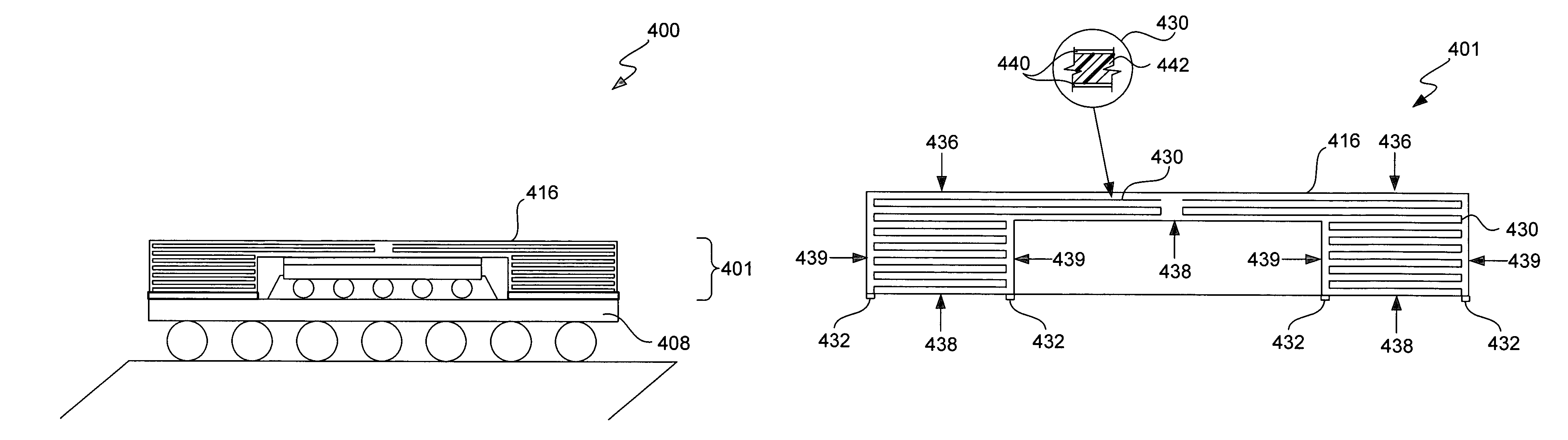

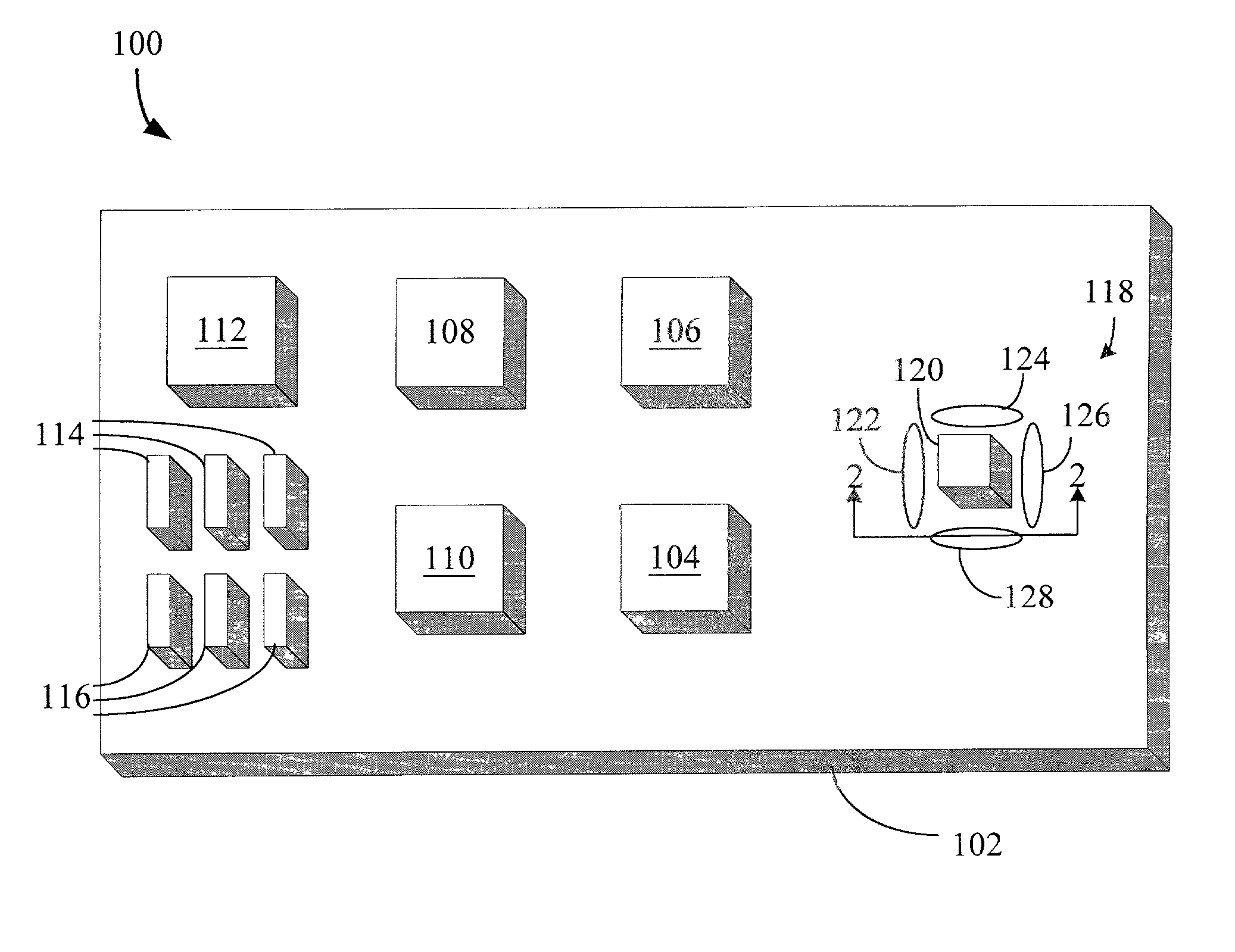

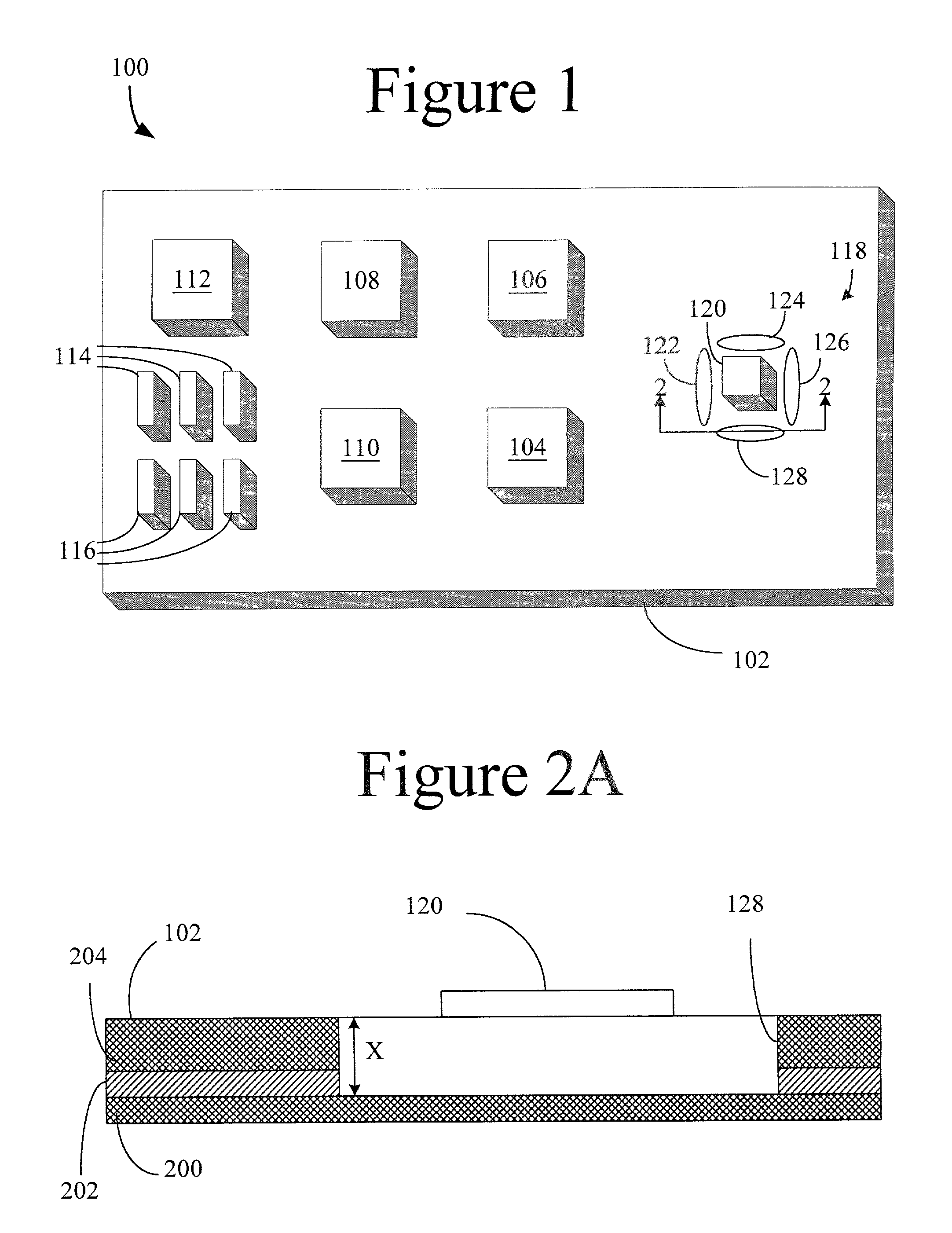

Voltage regulator attach for high current chip applications

ActiveUS8018738B2Digital data processing detailsSemiconductor/solid-state device detailsElectricityDc dc converter

A voltage regulator. The voltage regulator includes an interposer having, on a first side, a plurality of electrical connections suitable for coupling to a printed circuit board (PCB). The interposer also includes at least one power plane and at least one ground plane, wherein each of the power and ground planes is coupled to one or more of the electrical connections. The voltage regulator further includes a DC-DC converter that is electro-mechanically attachable to and detachable from the interposer. The interposer includes a socket, on a second side, that is suitable to receive two or more electro-mechanical connecting members of the DC-DC converter. When the DC-DC converter is attached to the interposer, at least one of the electromechanical connecting members is electrically coupled to a power plane of the interposer, while at least one other one of the electromechanical connecting members is electrically coupled to the ground plane.

Owner:ORACLE INT CORP