Patents

Literature

149 results about "Critical signal" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

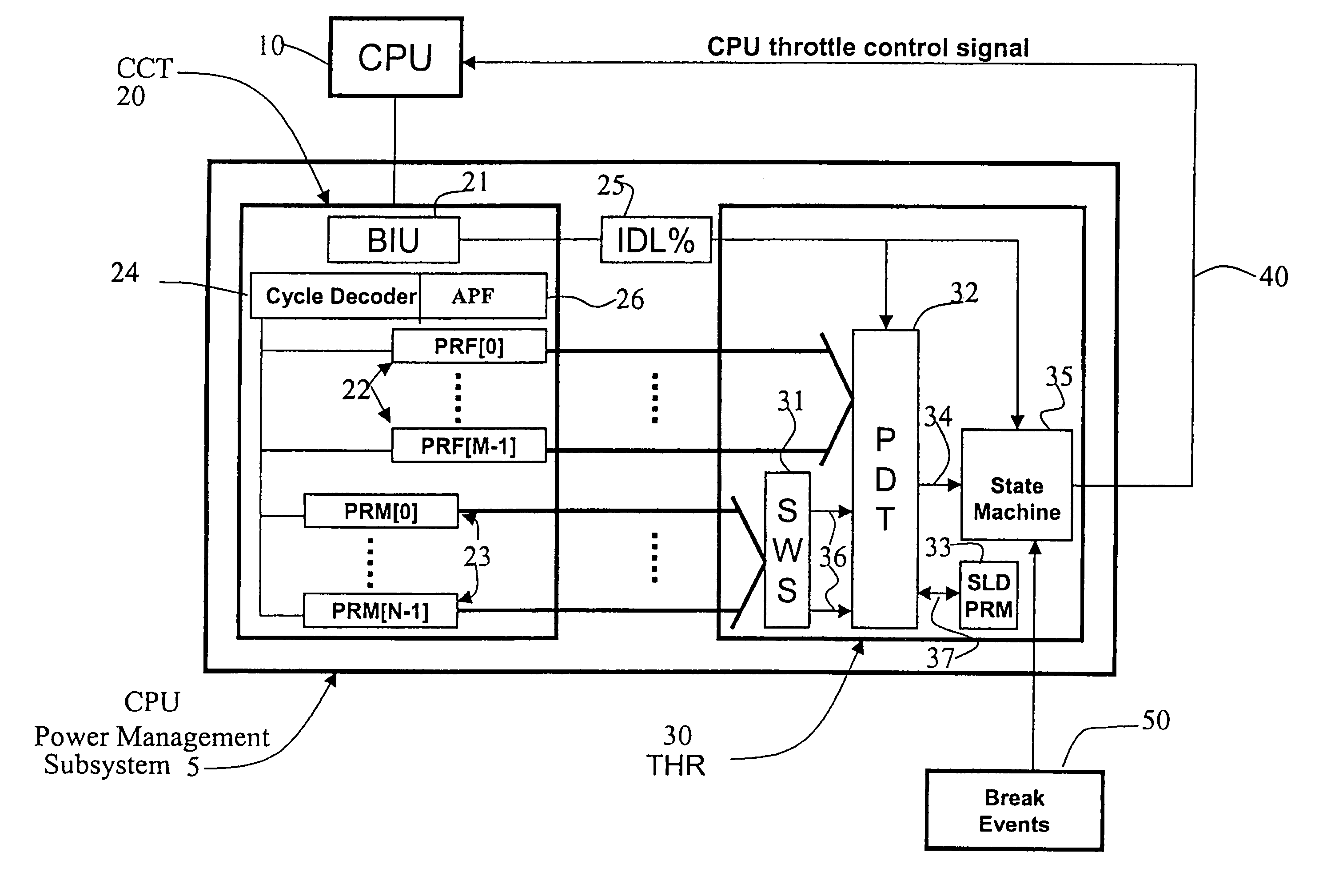

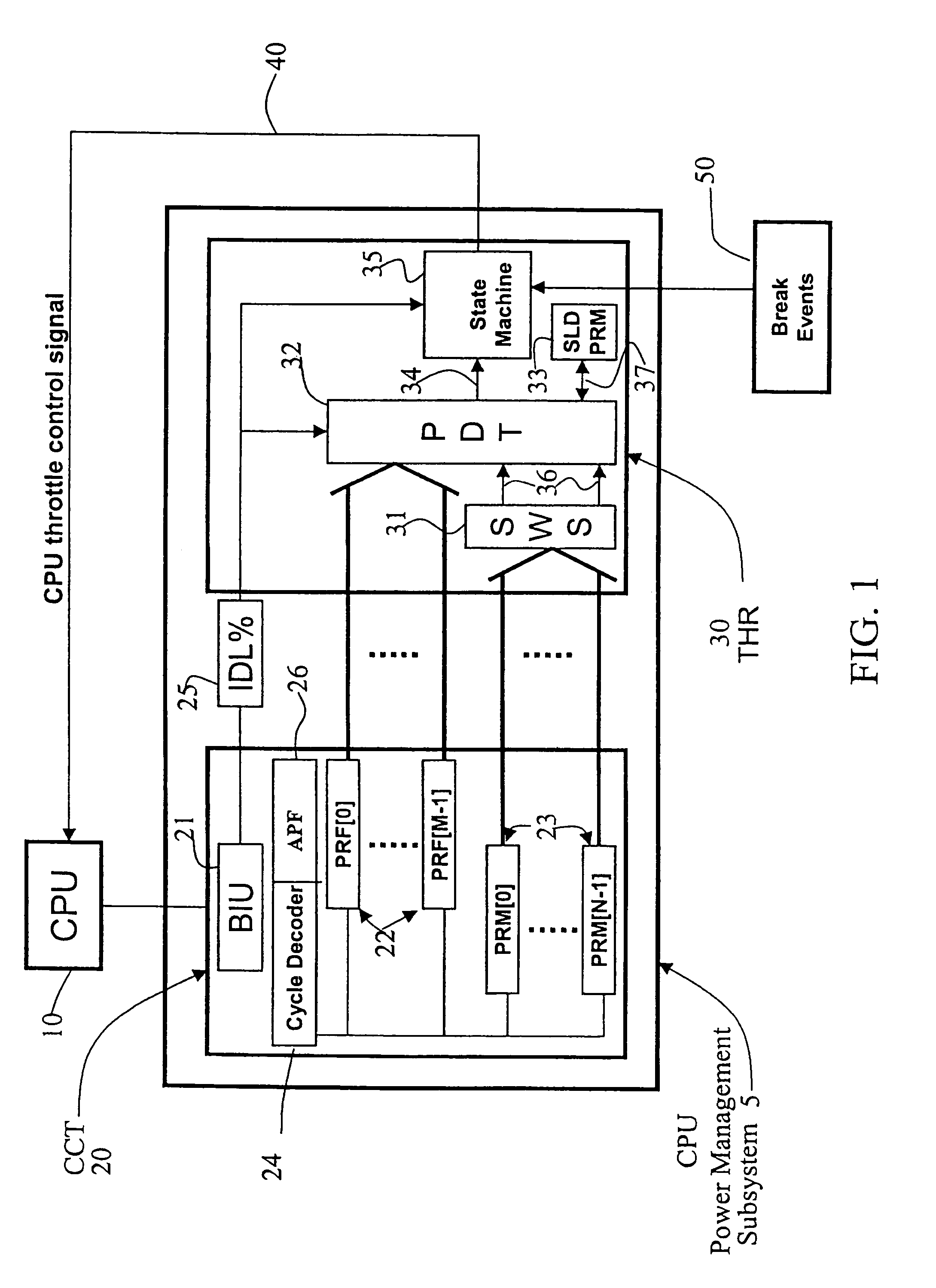

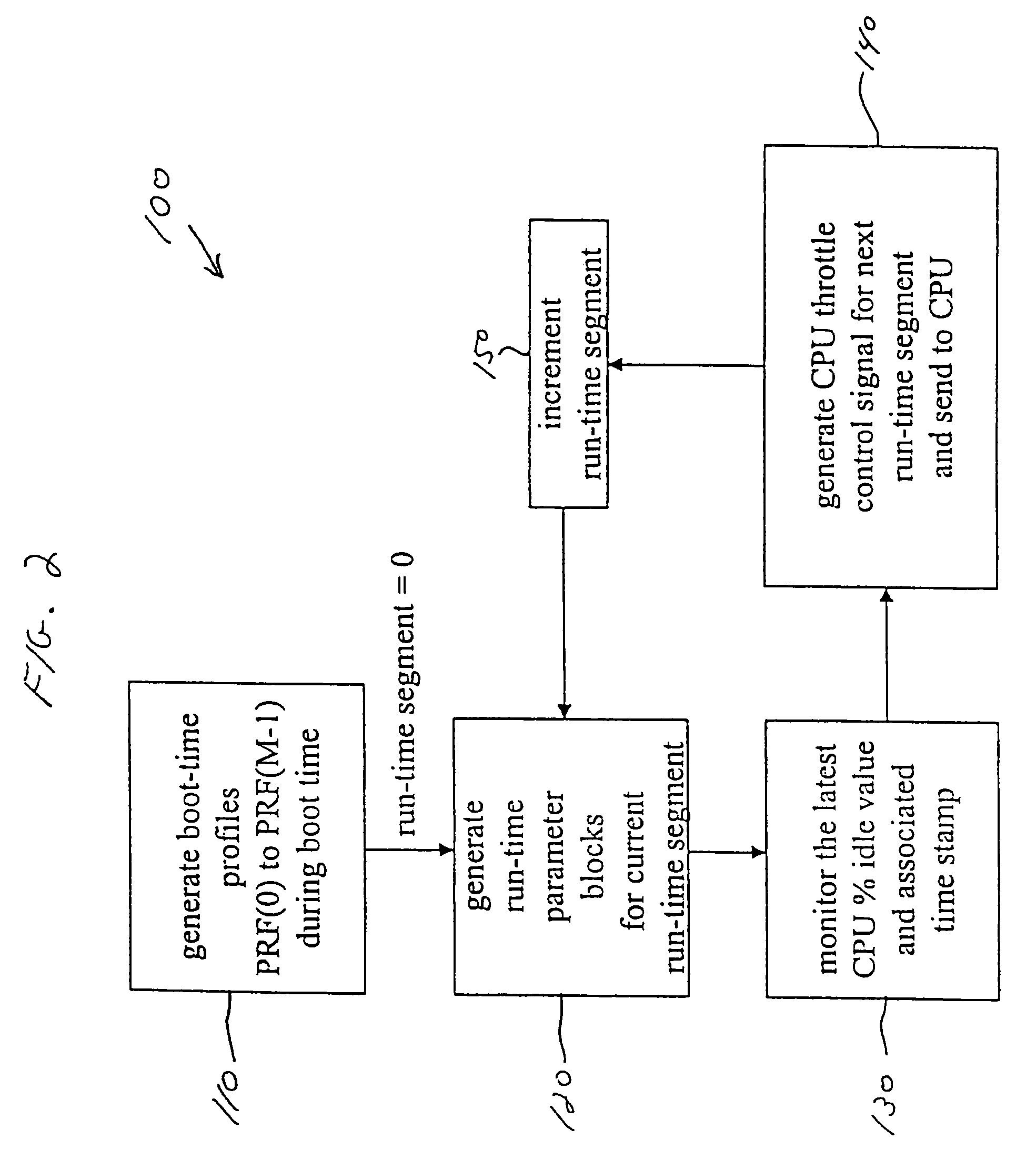

Method and apparatus for adaptive CPU power management

A method and apparatus are disclosed for performing adaptive run-time power management in a system employing a CPU and an operating system. A CPU cycle tracker (CCT) module monitors critical CPU signals and generates CPU performance data based on the critical CPU signals. An adaptive CPU throttler (THR) module uses the CPU performance data, along with a CPU percent idle value fed back from the operating system, to generate a CPU throttle control signal during predefined run-time segments of the CPU run time. The CPU throttle control signal links back to the CPU and adaptively adjusts CPU throttling and, therefore, power usage of the CPU during each of the run-time segments.

Owner:AVAGO TECH INT SALES PTE LTD

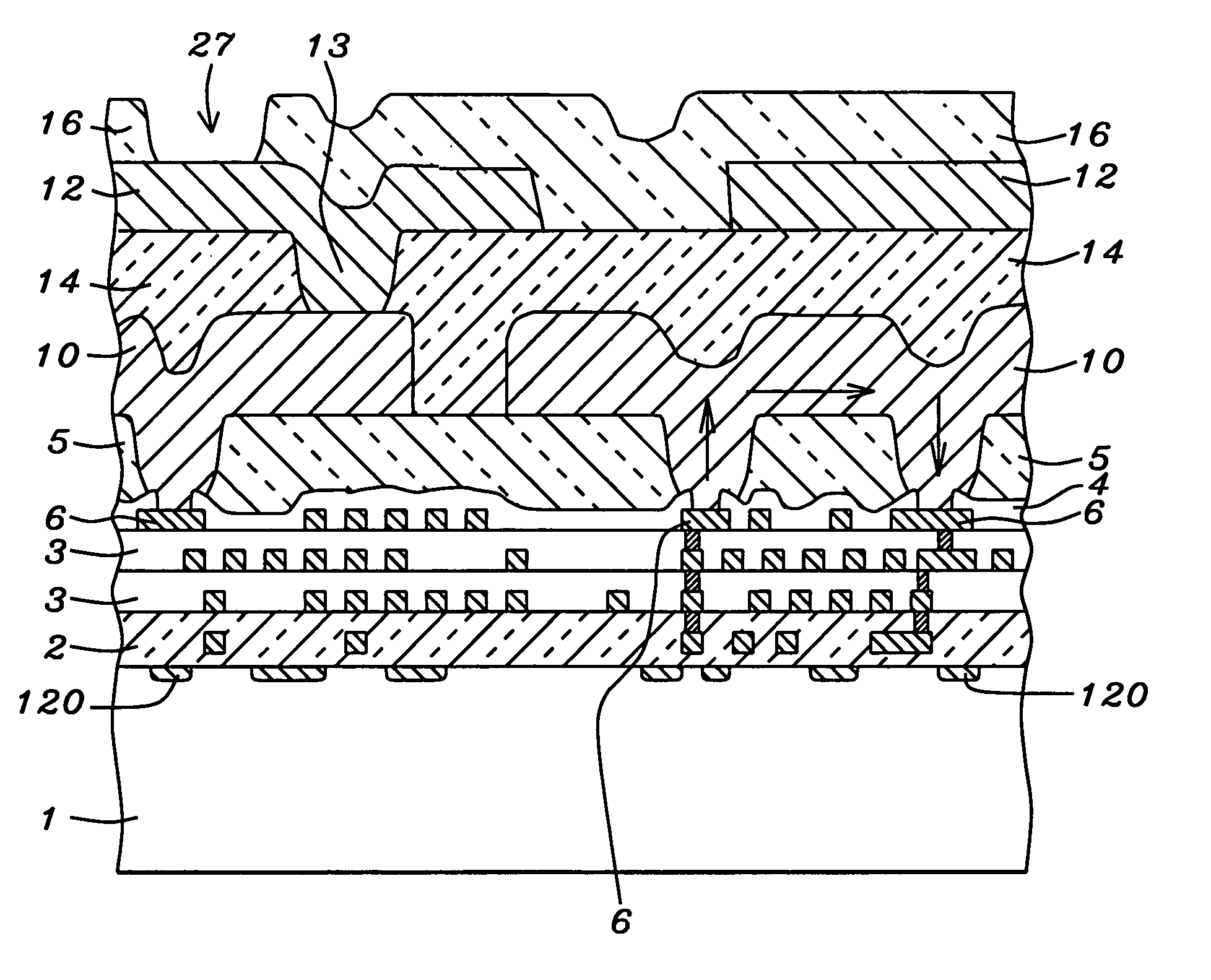

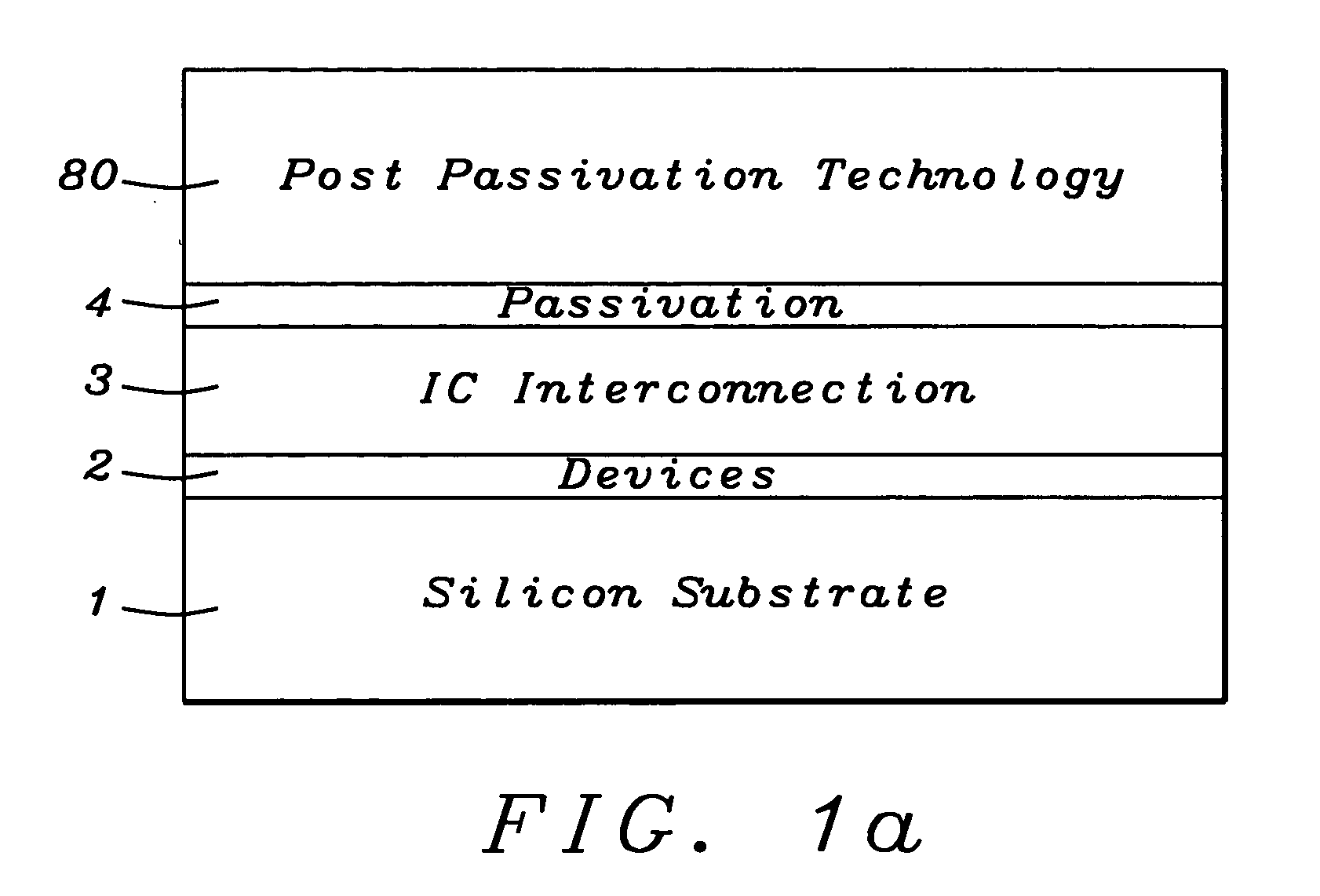

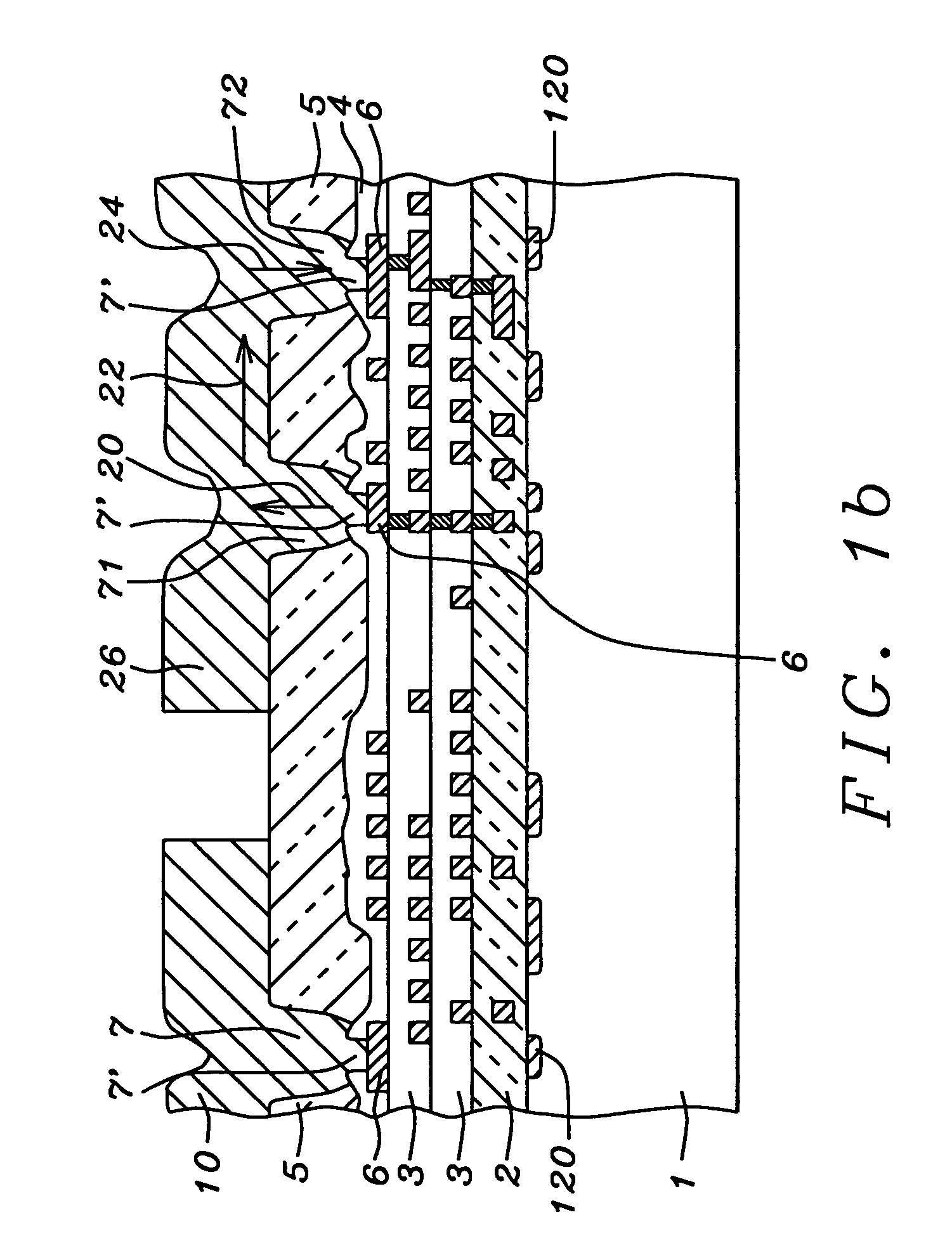

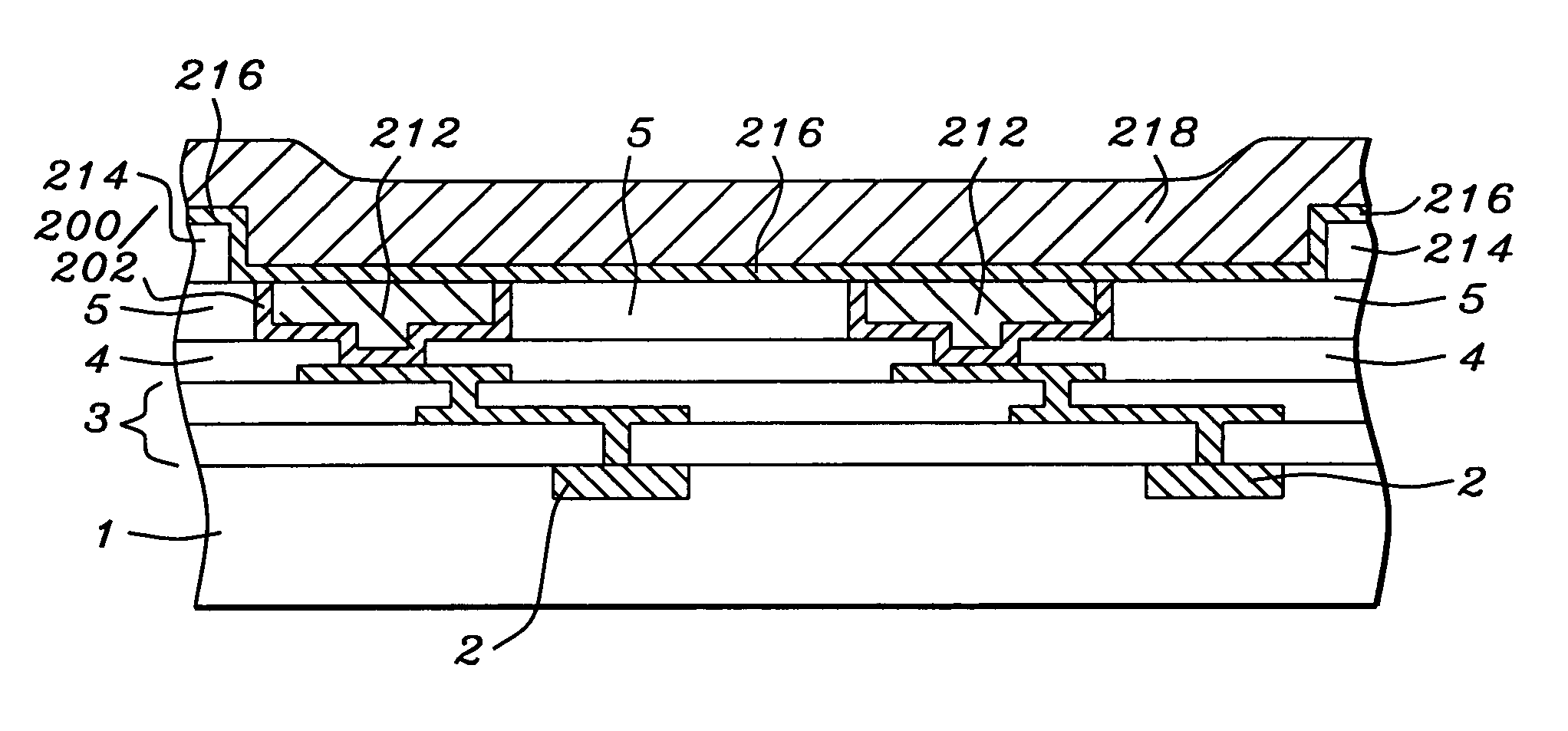

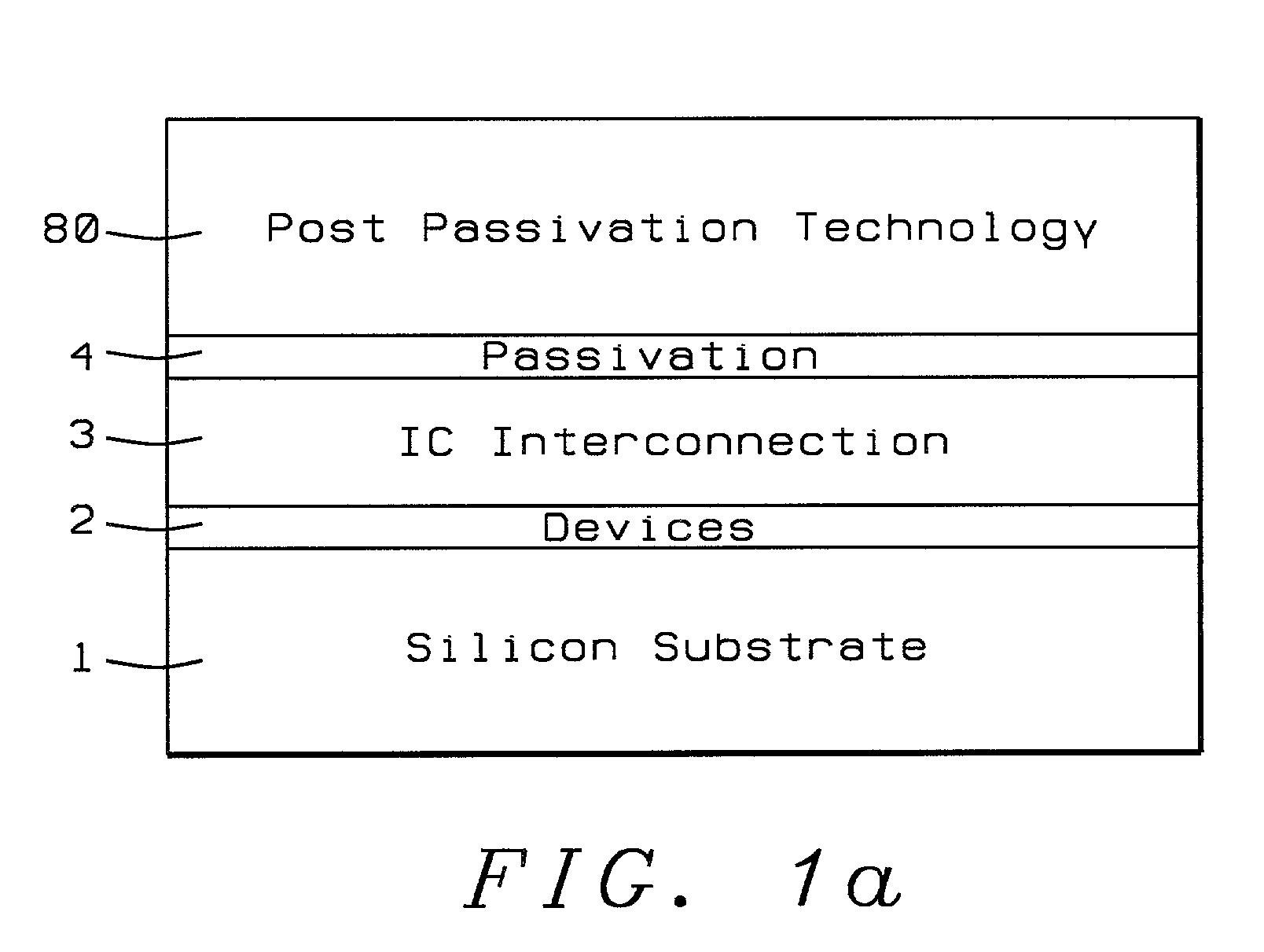

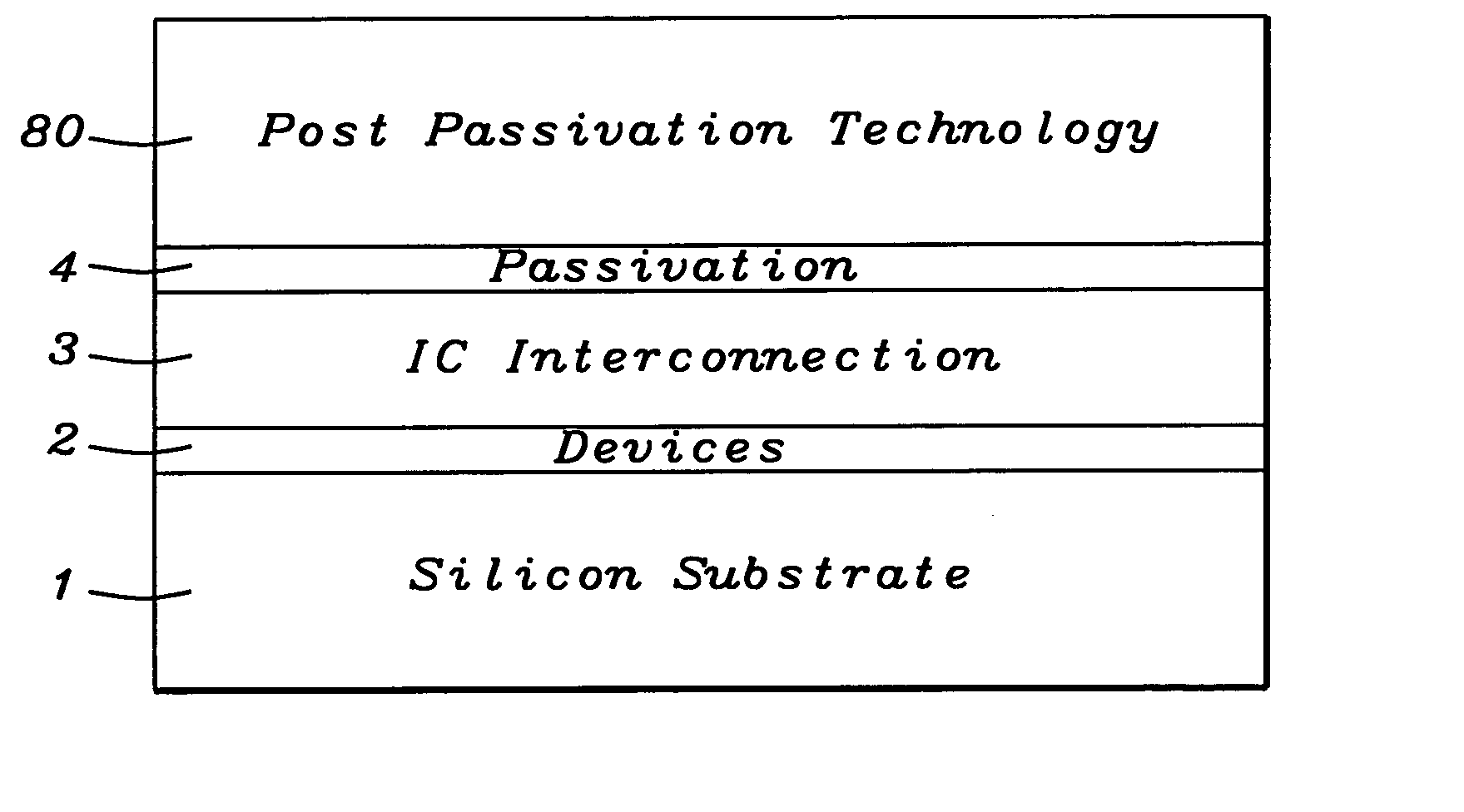

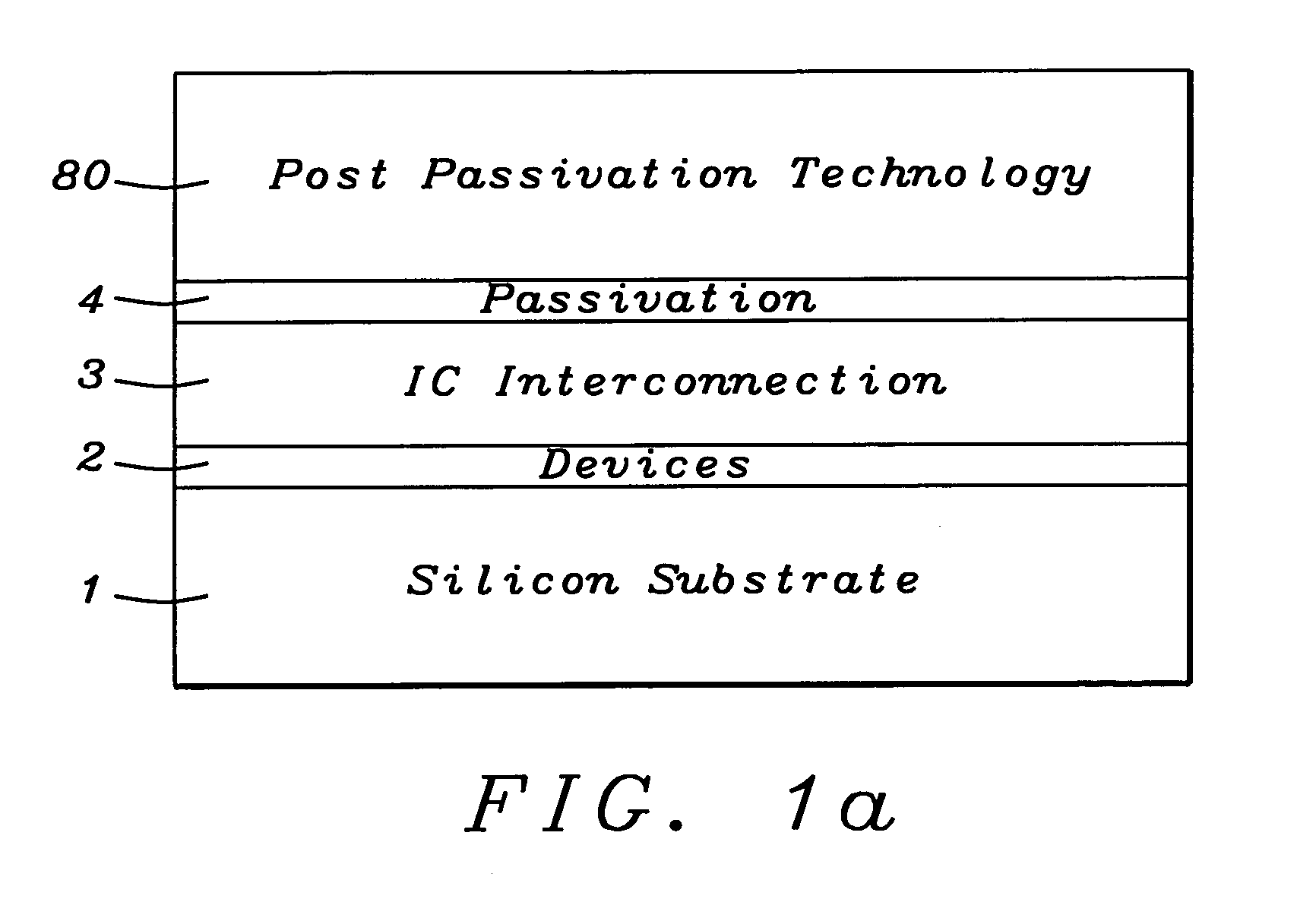

Top layers of metal for integrated circuits

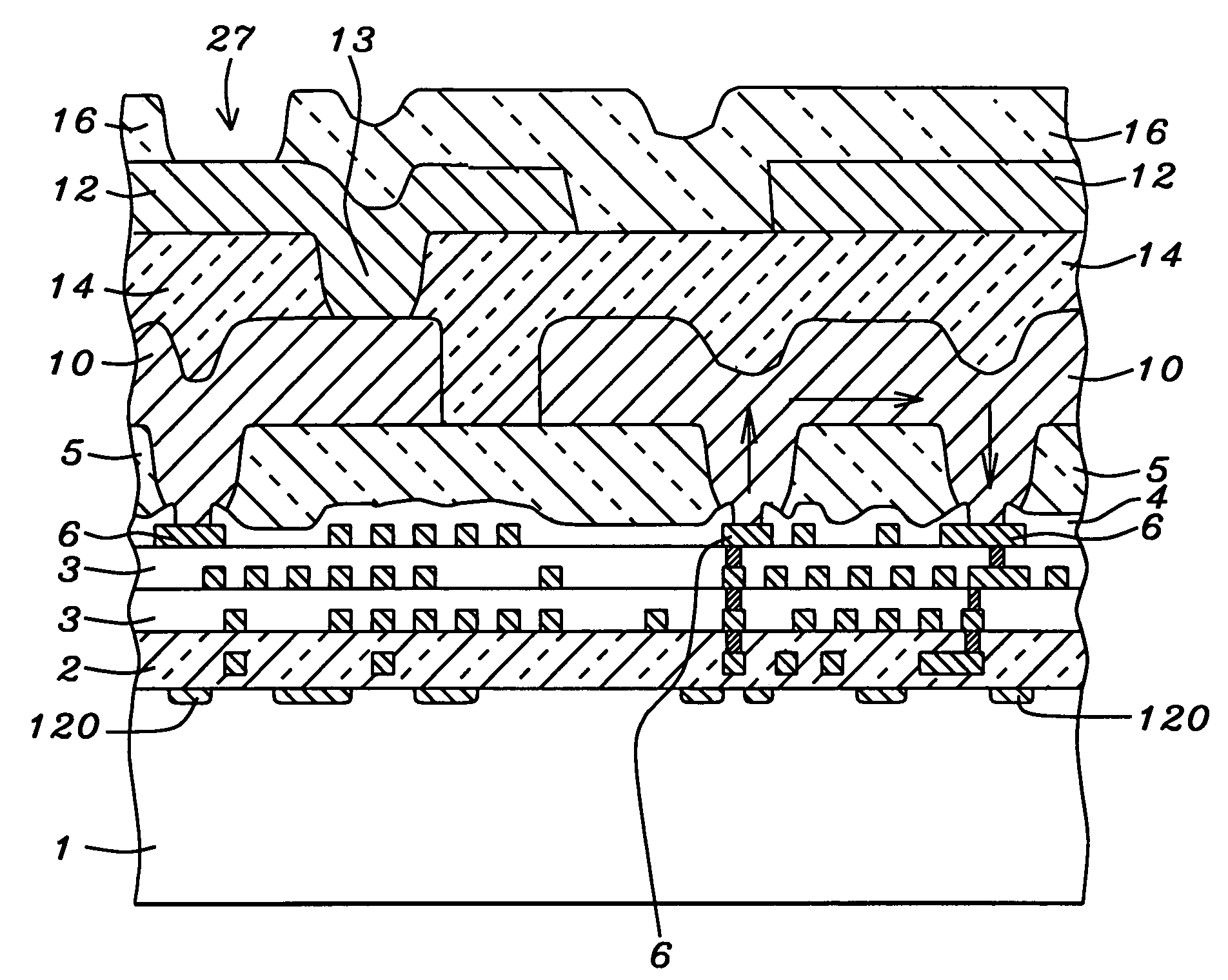

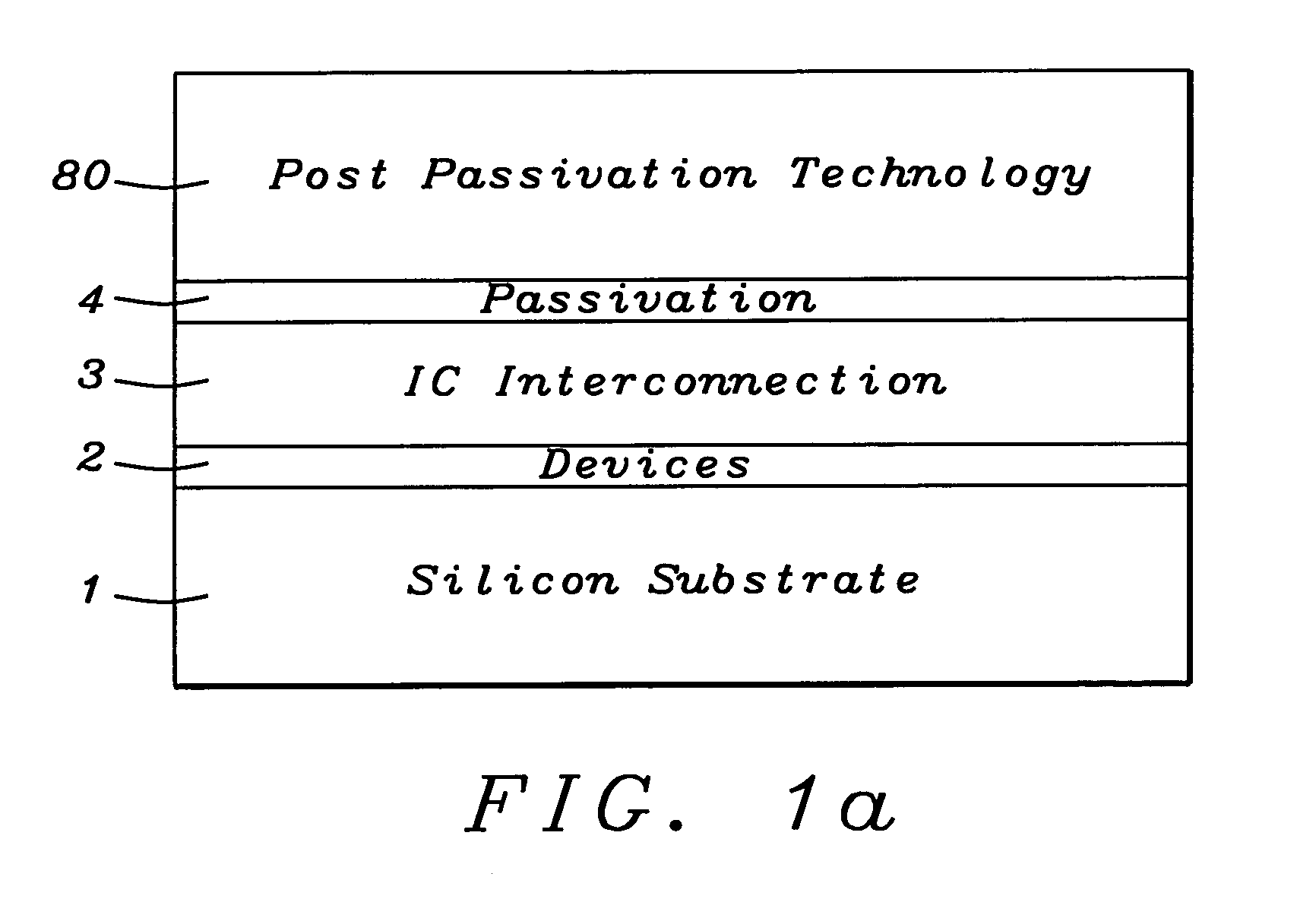

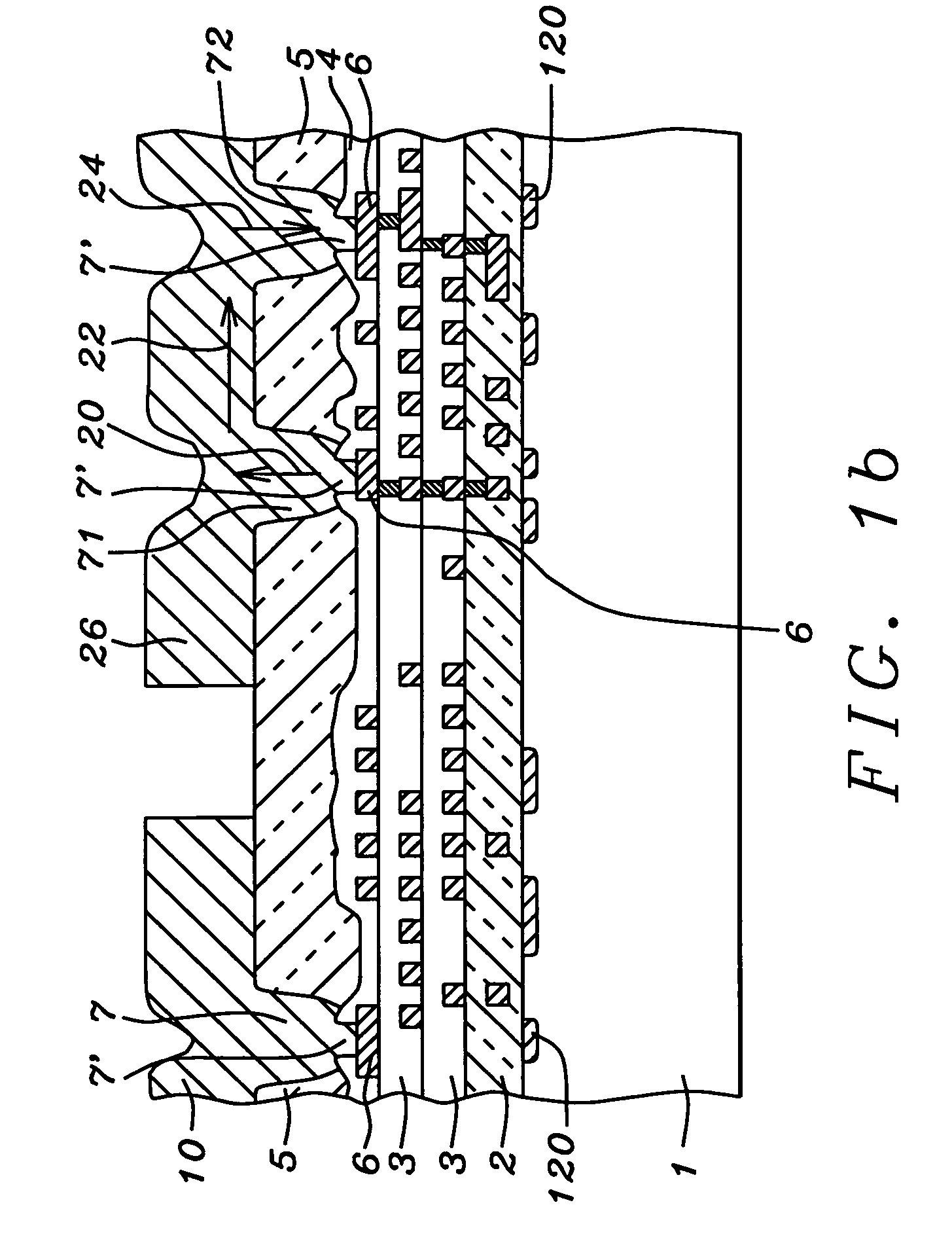

ActiveUS20060063378A1Improve performanceReduce resistive voltage dropSemiconductor/solid-state device detailsSolid-state devicesCritical signalSemiconductor

The present invention adds one or more thick layers of polymer dielectric and one or more layers of thick, wide metal lines on top of a finished semiconductor wafer, post-passivation. The thick, wide metal lines may be used for long signal paths and can also be used for power buses or power planes, clock distribution networks, critical signal, and re-distribution of I / O pads.

Owner:QUALCOMM INC

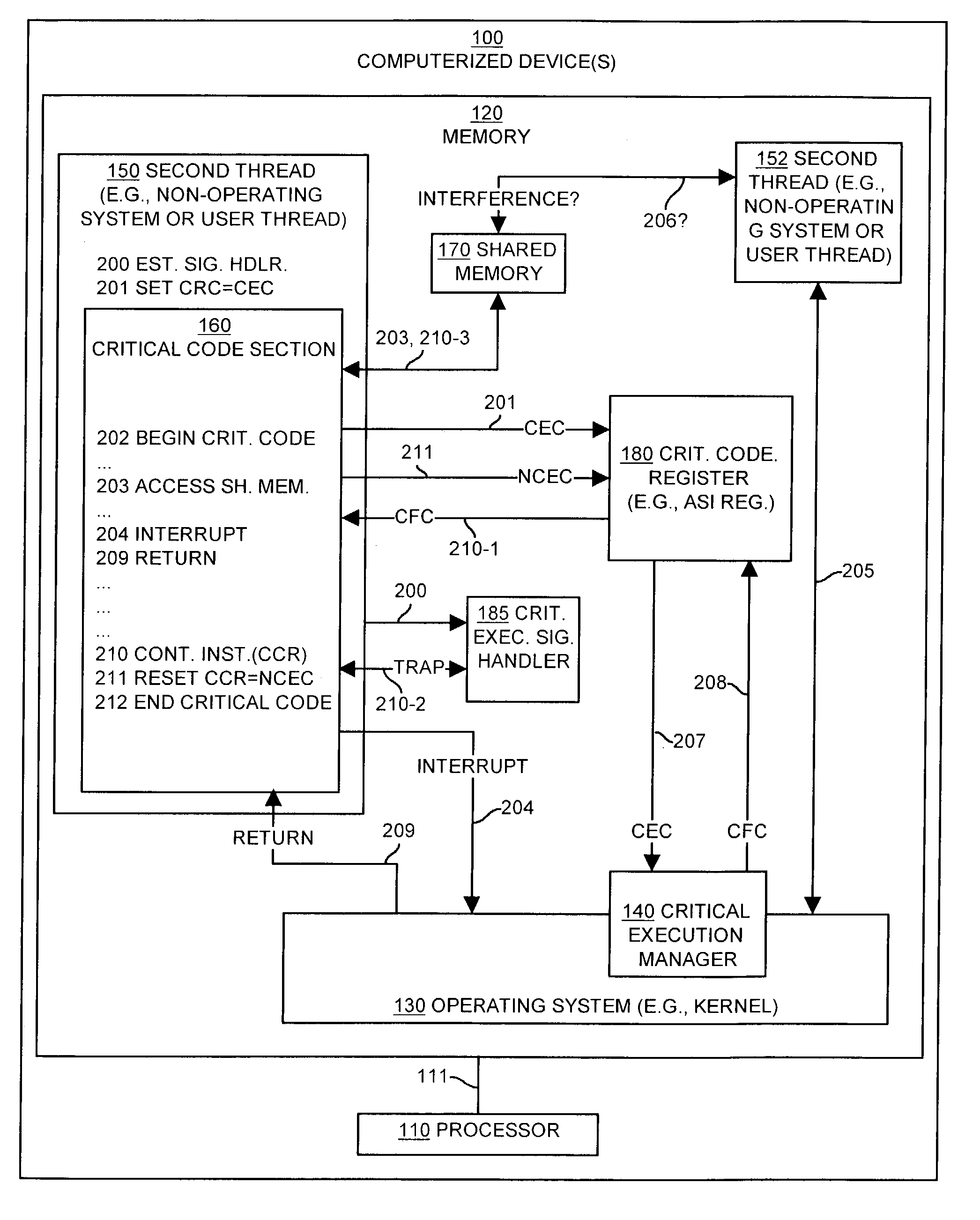

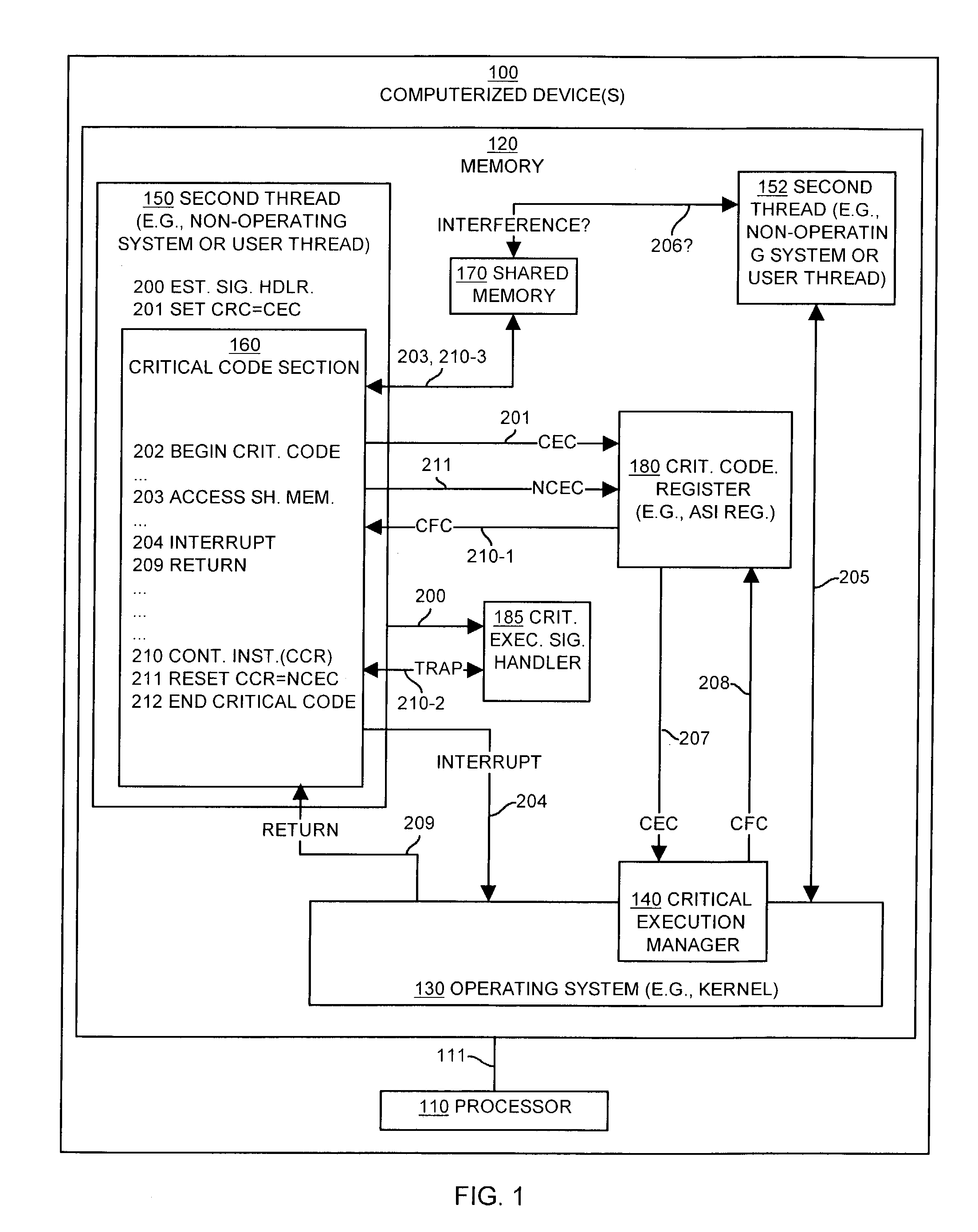

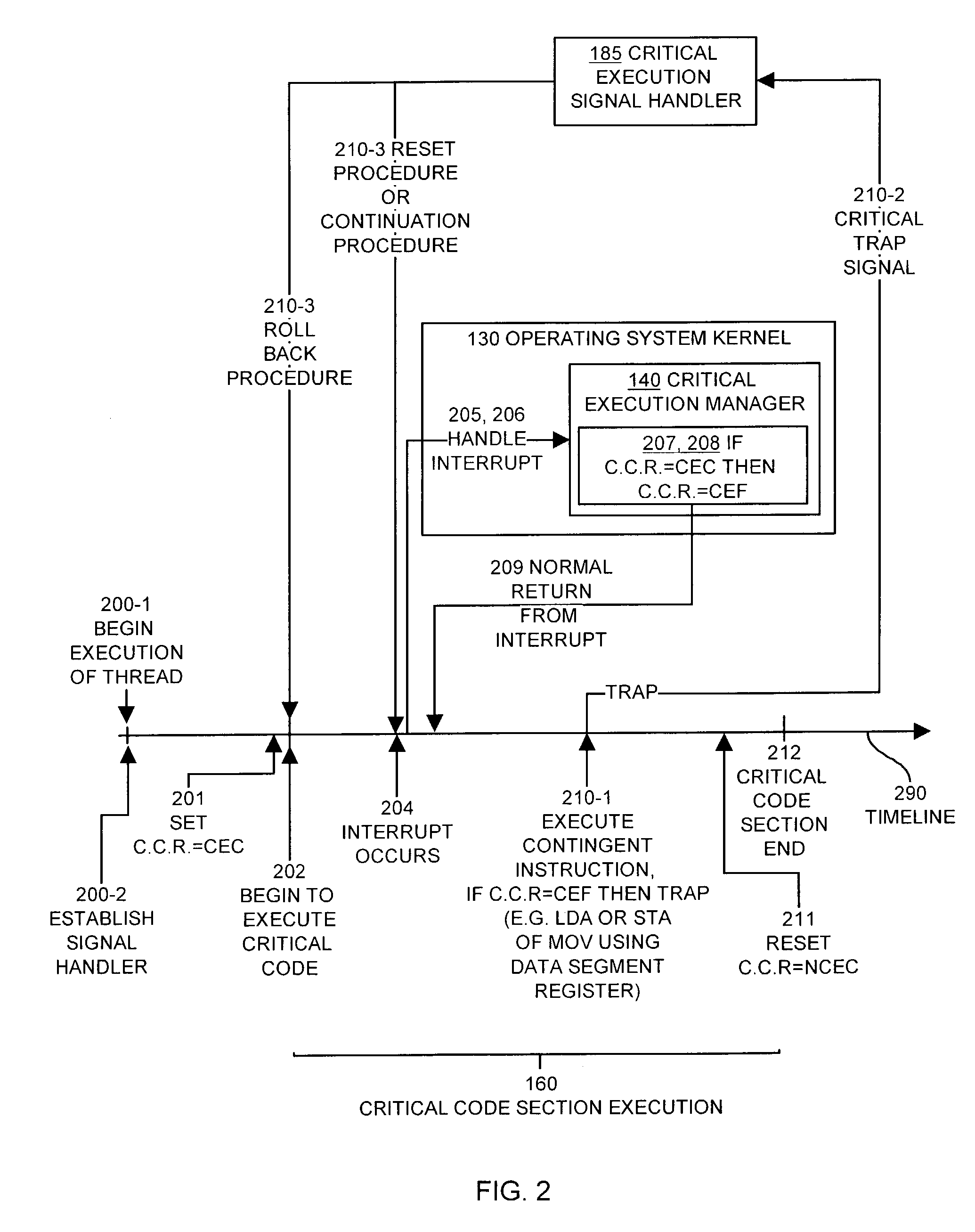

Methods and apparatus for executing code while avoiding interference

ActiveUS7178062B1Inhibition effectAvoid interferenceError detection/correctionDigital computer detailsOperational systemProcessor register

Mechanisms and techniques operate in a scalable or non-scalable processing architecture computerized device to execute critical code while overcoming interference from interruptions. A critical signal handler is registered and a non-operating system thread sets a value of a critical code register to indicate a critical execution condition. The non-operating system thread then executes a critical code section until an interruption occurs. In response to the interruption to the critical code section, an operating system thread detects if the critical code register is equivalent to a critical execution condition and if so, sets the value of the critical code register to indicate a critical execution failure. Upon returning to execution of the critical code section, the critical code section attempts to execute a contingent instruction in the critical code section that is contingent upon the value of the critical code register. The attempted execution of the contingent instruction triggers a critical trap signal when the critical code register is set to a value that indicates the critical execution failure. The critical execution signal handler processes the critical trap signal to avoid any interference that may have been caused by the interruption.

Owner:ORACLE INT CORP

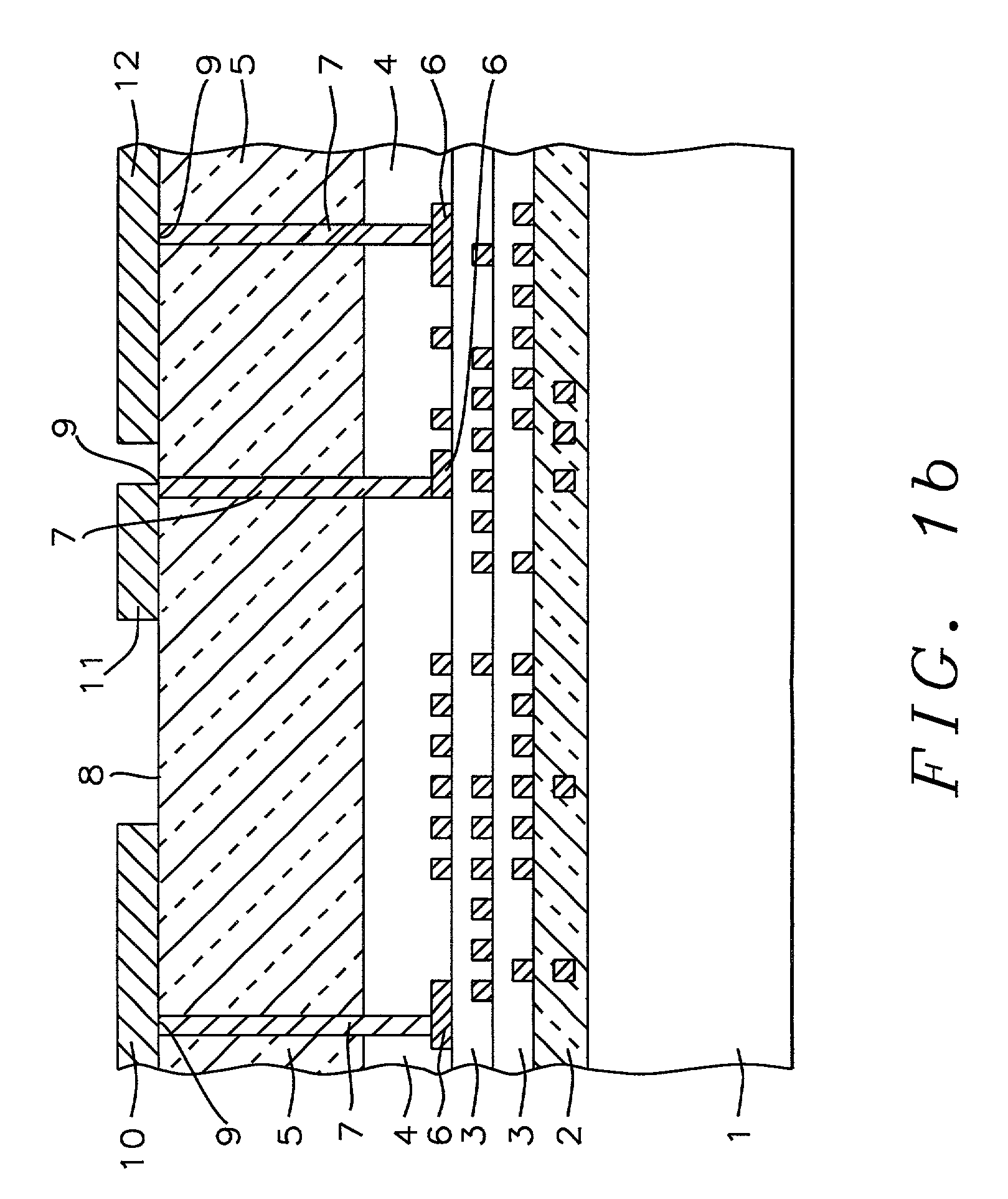

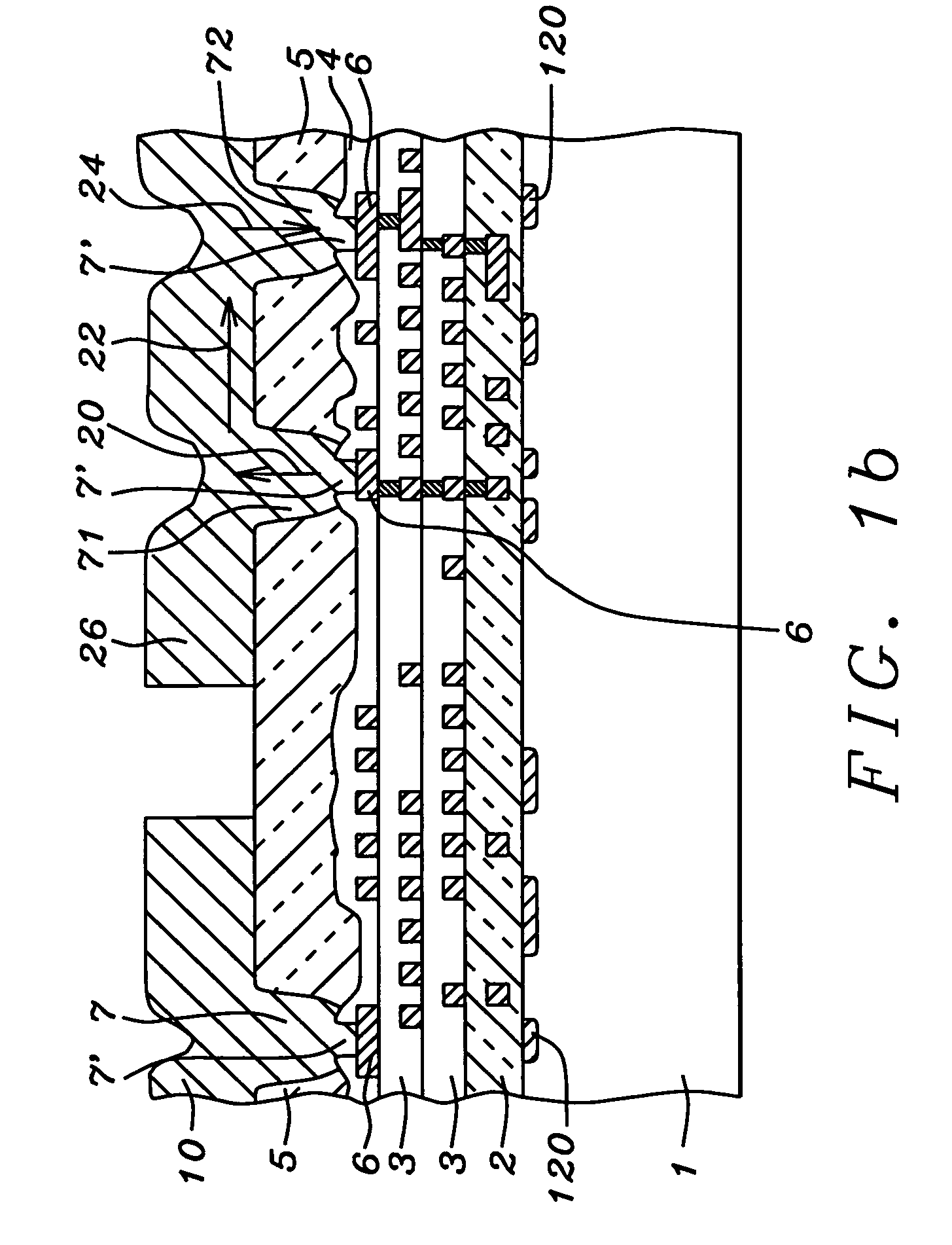

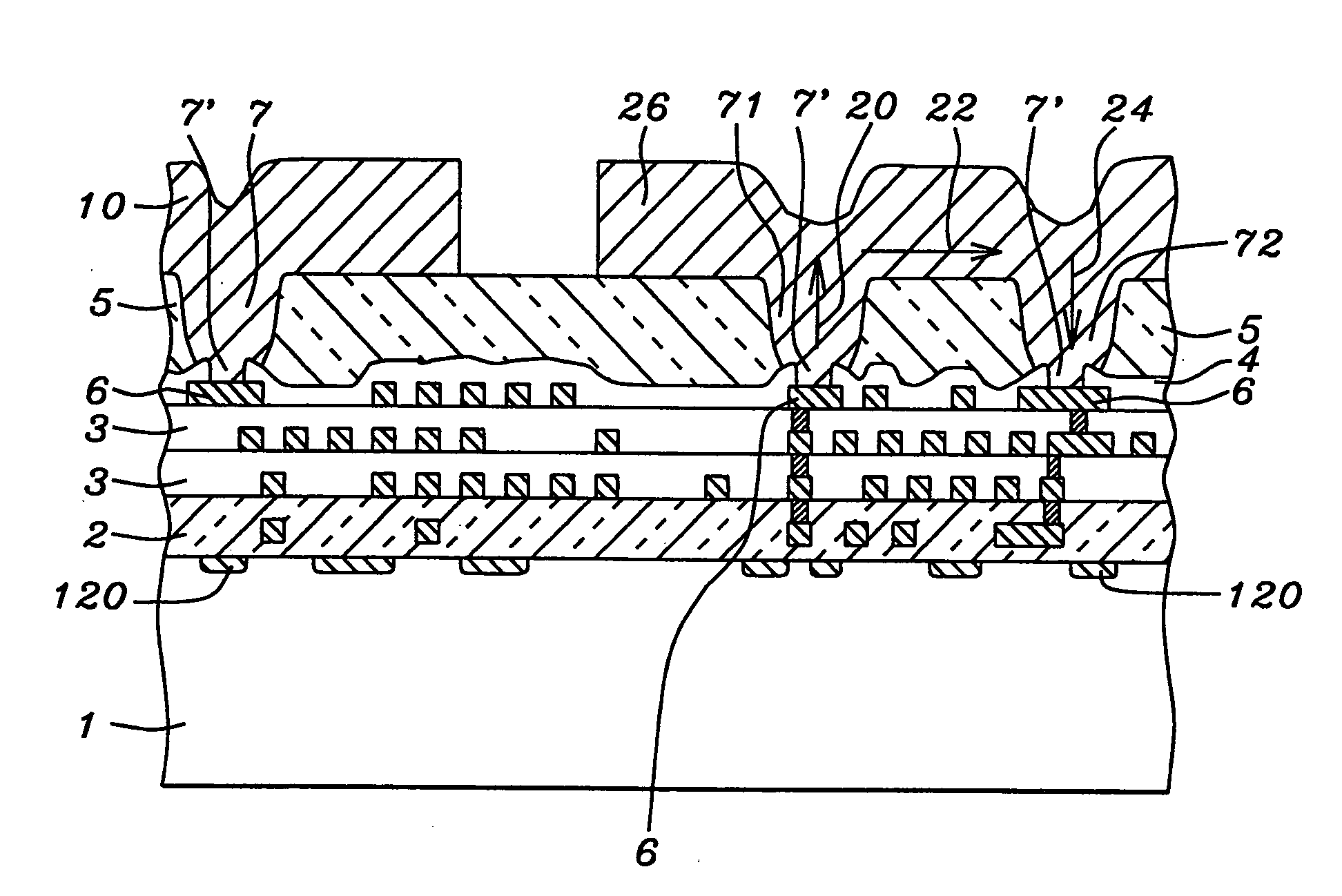

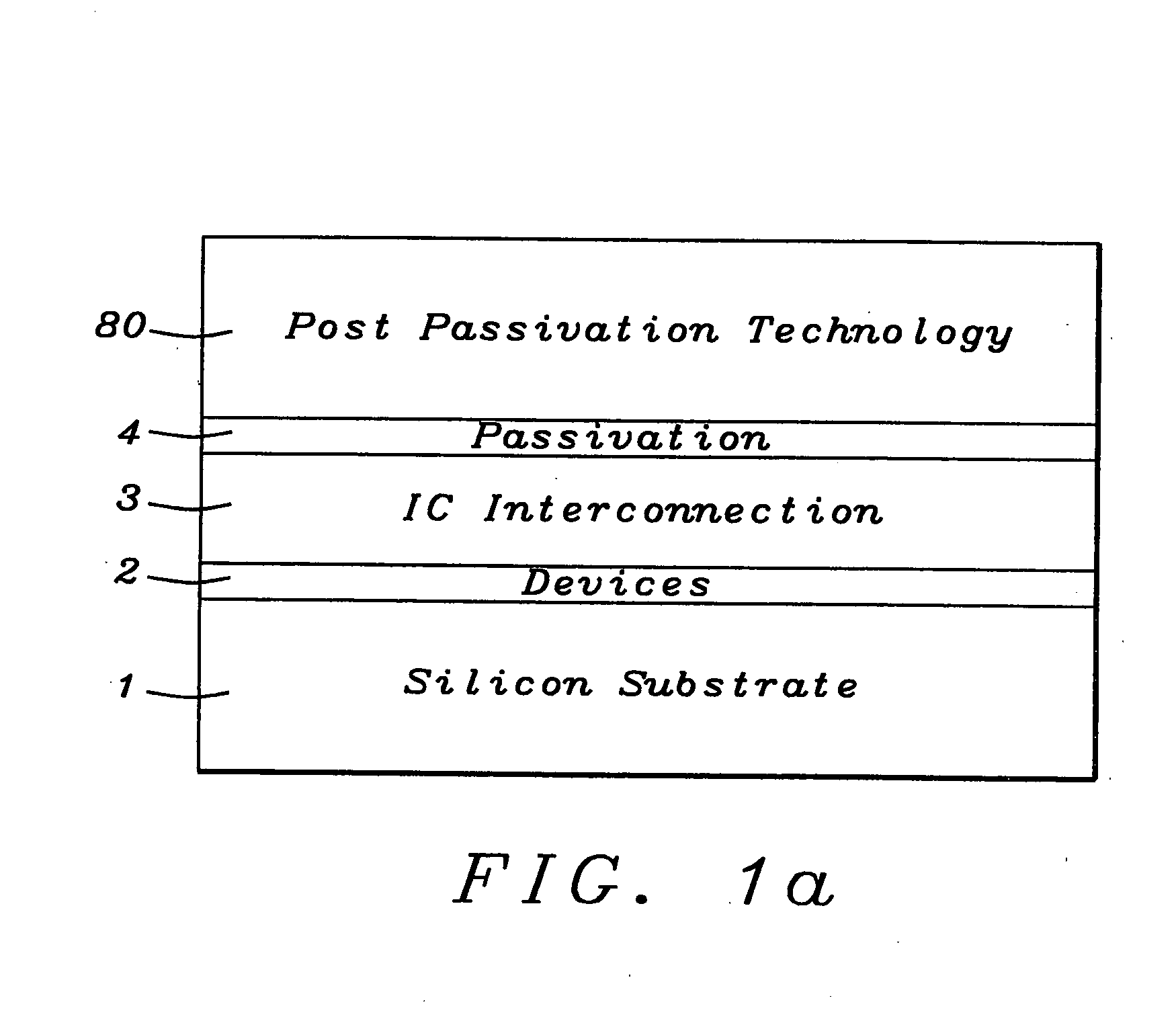

Post passivation method for semiconductor chip or wafer

InactiveUS7405149B1Improve performanceReduce resistive voltage dropSemiconductor/solid-state device detailsSolid-state devicesPolymer dielectricsSemiconductor chip

The present invention adds one or more thick layers of polymer dielectric and one or more layers of thick, wide metal lines on top of a finished semiconductor wafer, post-passivation. The thick, wide metal lines may be used for long signal paths and can also be used for power buses or power planes, clock distribution networks, critical signal, and re-distribution of I / O pads for flip chip applications. Photoresist defined electroplating, sputter / etch, or dual and triple damascene techniques are used for forming the metal lines and via fill.

Owner:QUALCOMM INC

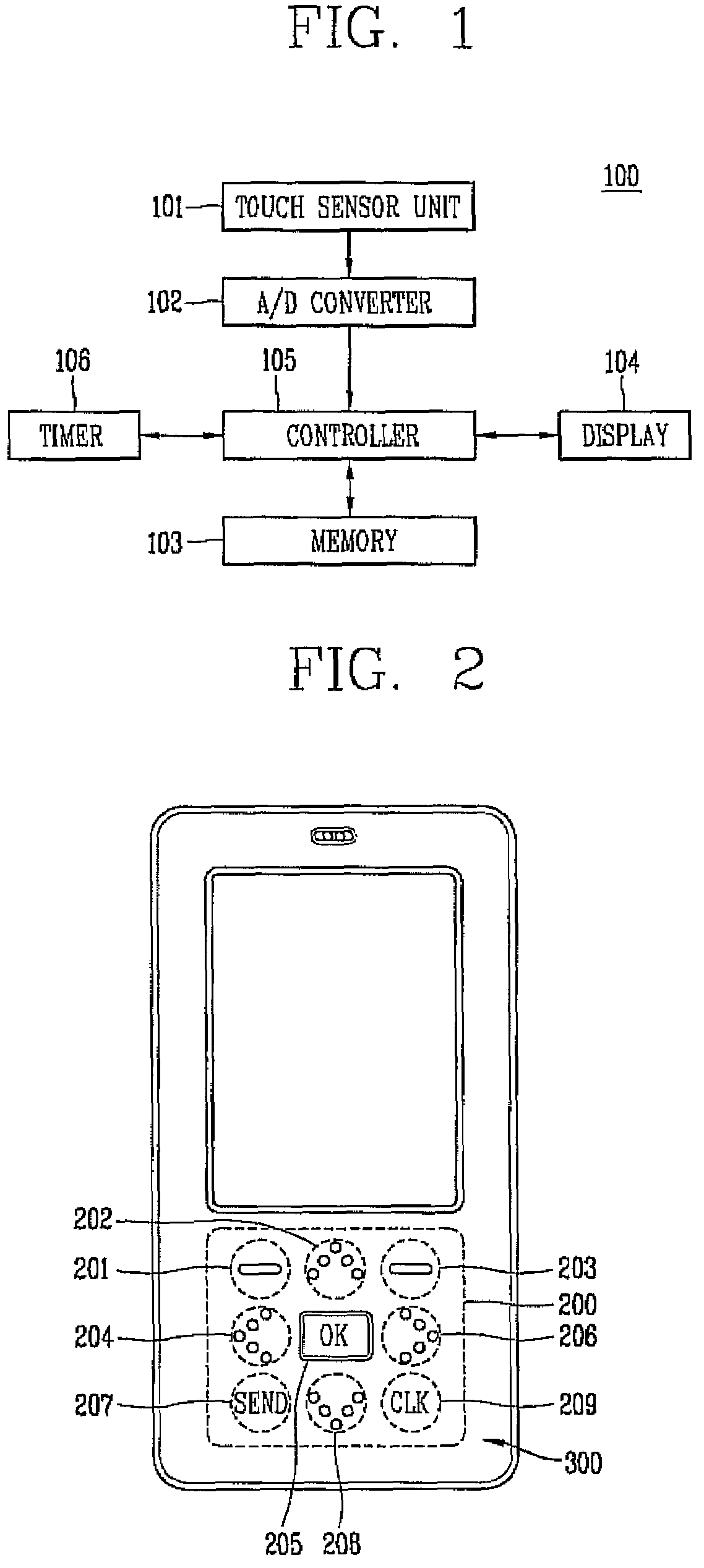

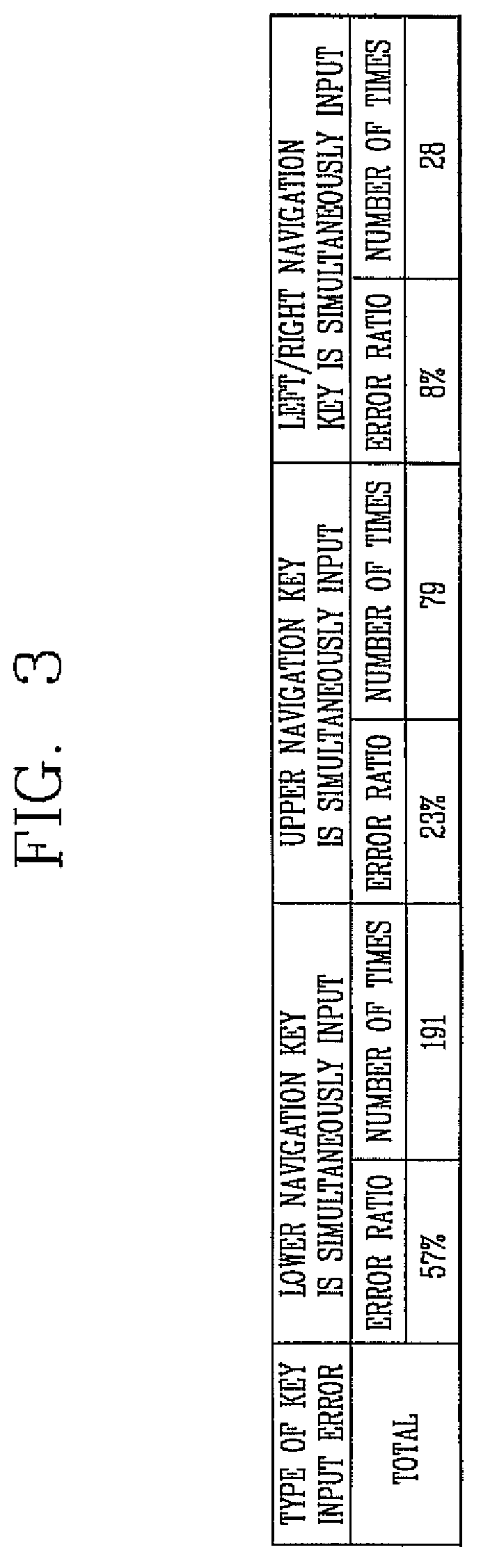

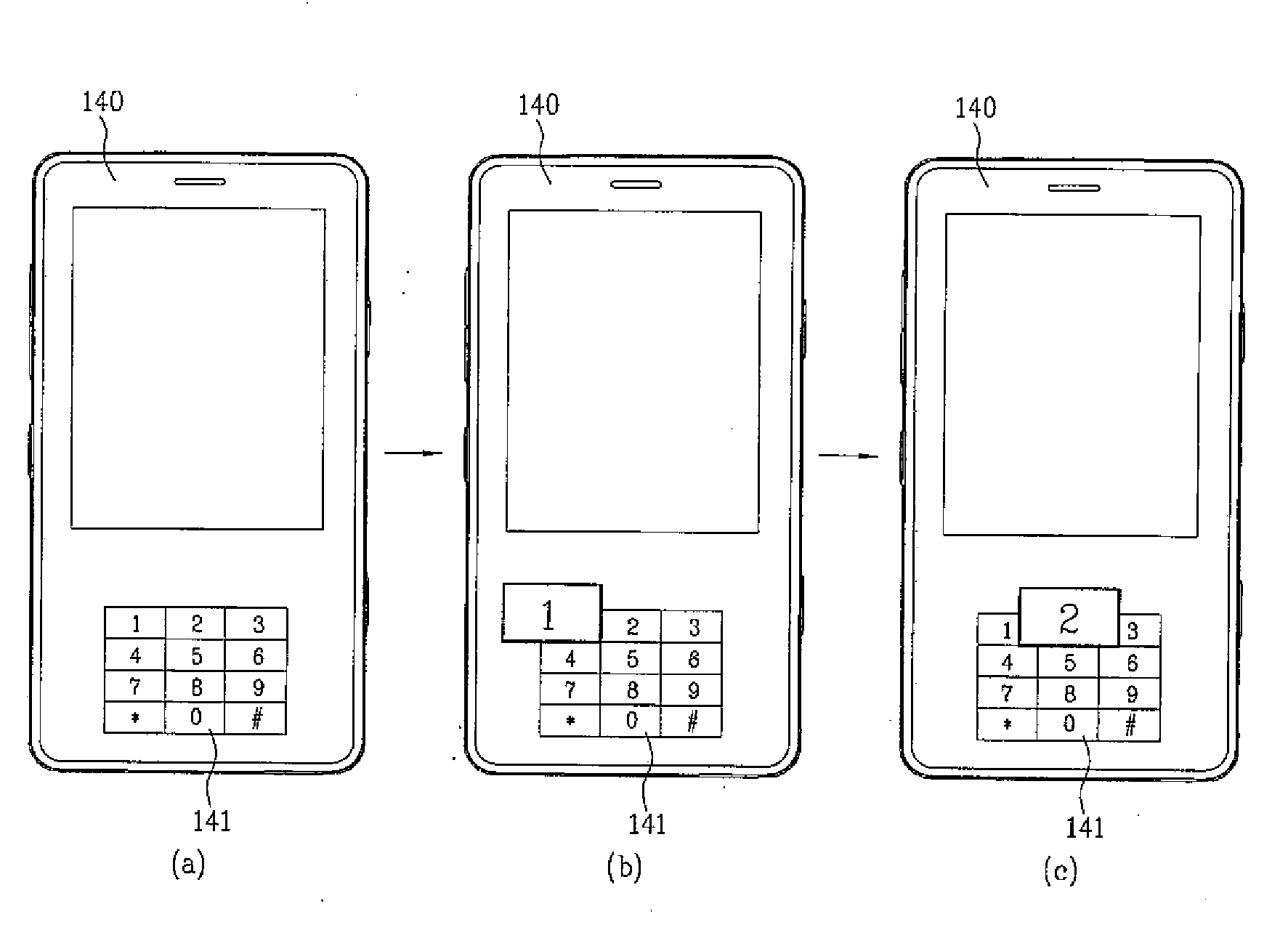

Mobile communications terminal having key input error prevention function and method thereof

ActiveUS20090215500A1Inhibit inputInput/output for user-computer interactionCathode-ray tube indicatorsComputer terminalError prevention

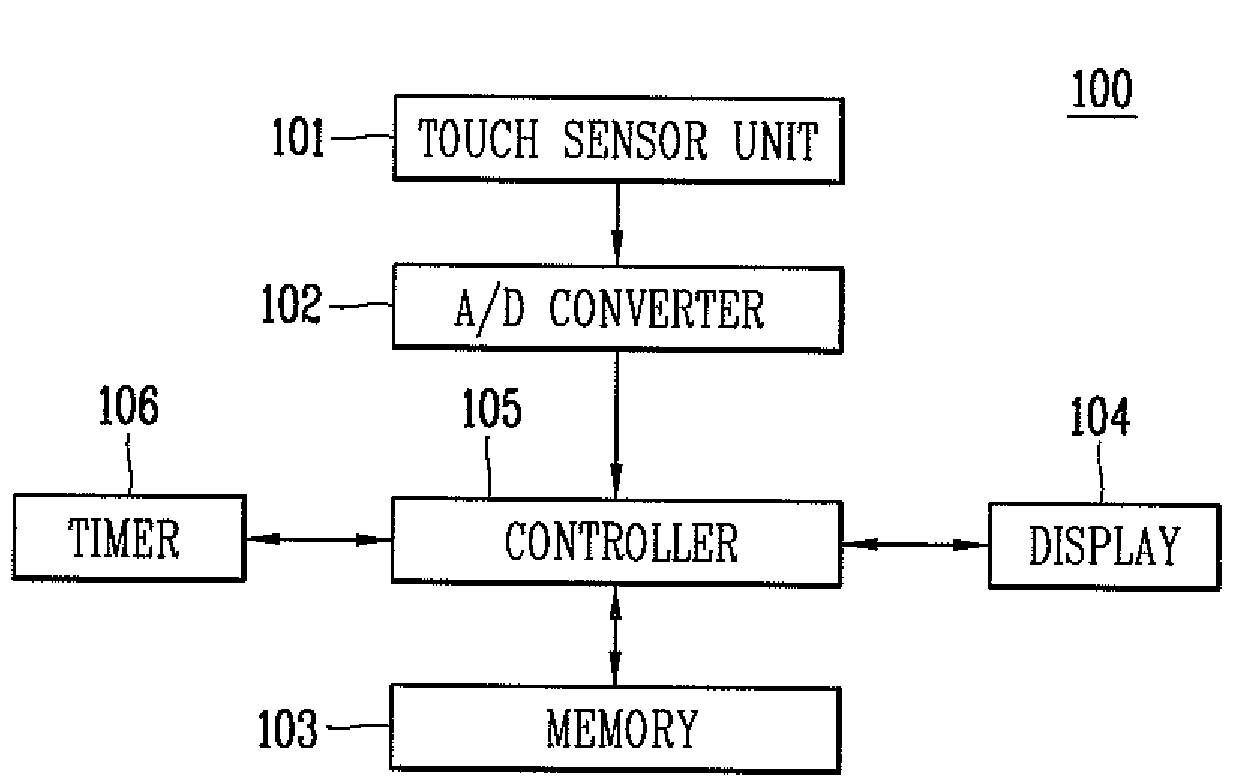

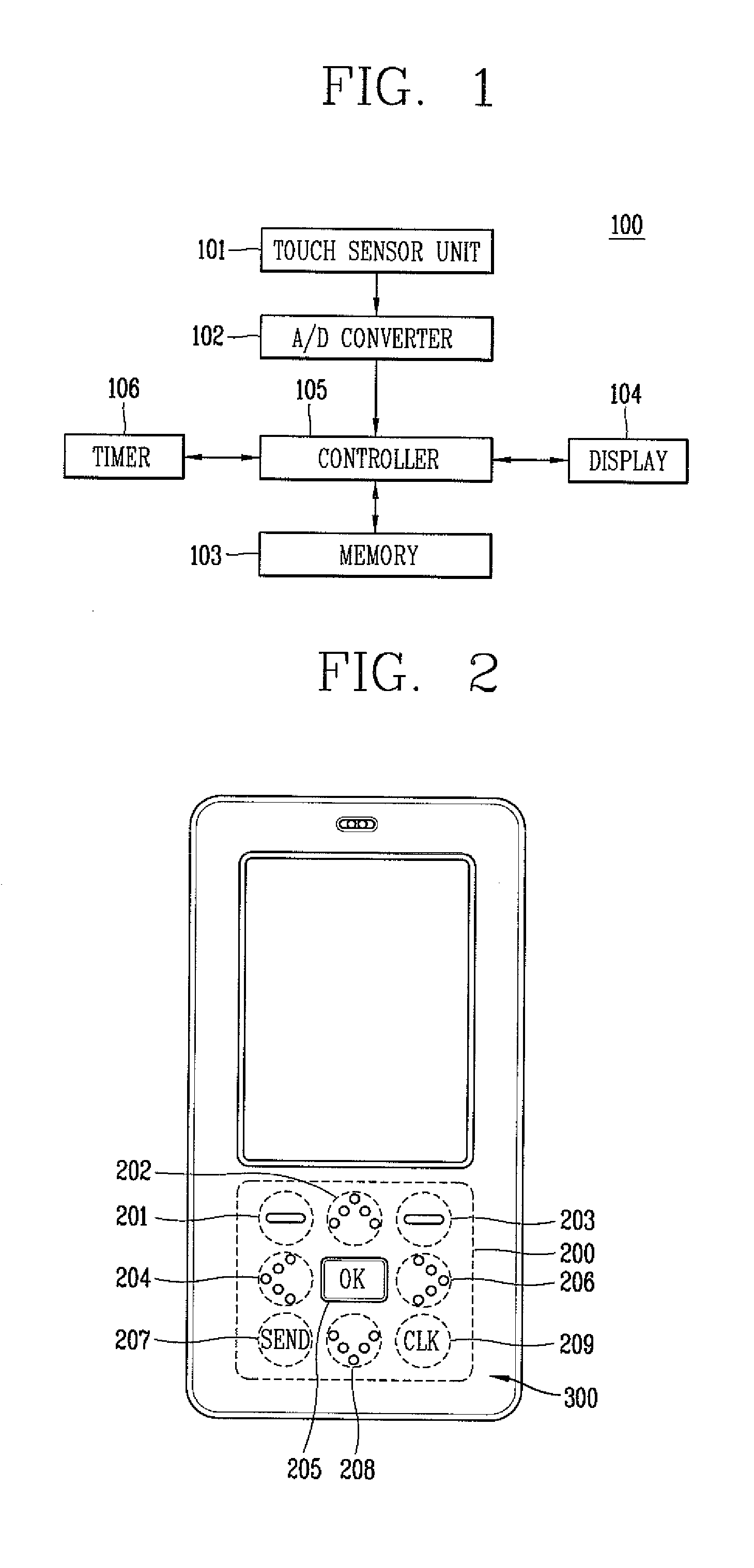

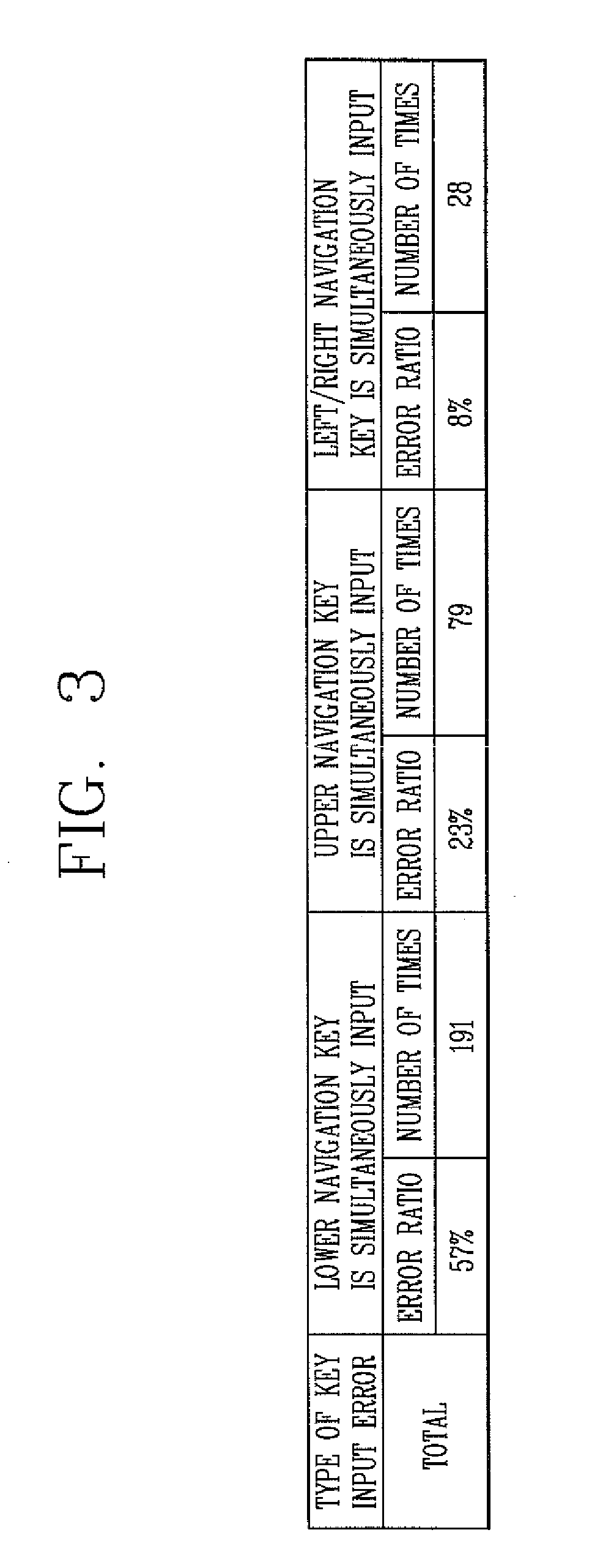

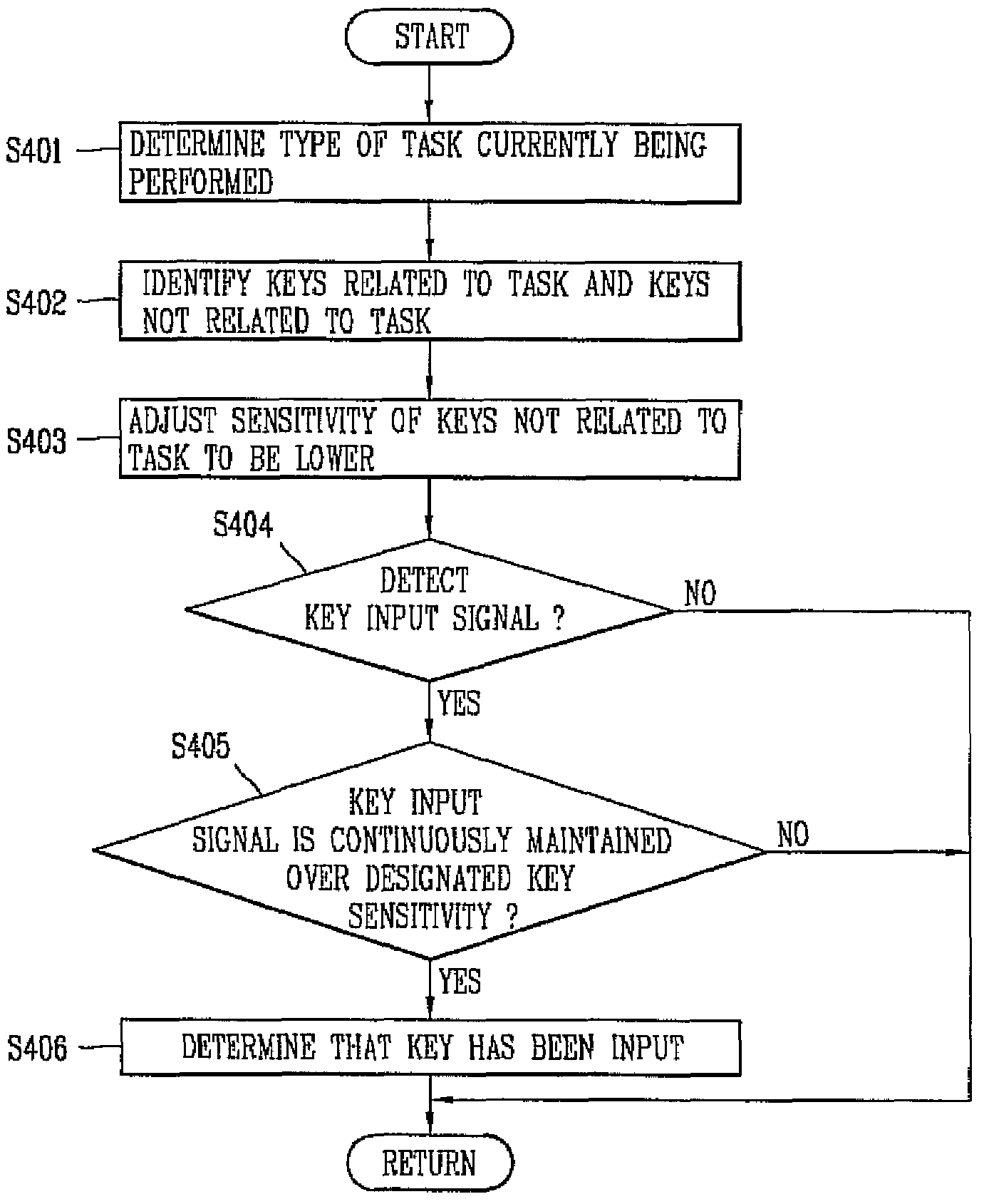

A mobile communications terminal and a method for preventing an input error of a key input unit are provided. The mobile communications terminal includes a touch sensor unit for sensing a key that is input by touching a keypad region in order to output a key input signal corresponding to the key and a controller adapted to determine a key input according to either a priority between multiple keys from which key signals are received or whether a received key signal was generated inadvertently.

Owner:TELEFON AB LM ERICSSON (PUBL)

Mobile communications terminal having key input error prevention function and method thereof

ActiveUS7535459B2Inhibit inputInput/output for user-computer interactionElectronic switchingError preventionComputer terminal

A mobile communications terminal and a method for preventing an input error of a key input unit are provided. The mobile communications terminal includes a touch sensor unit for sensing a key that is input by touching a keypad region in order to output a key input signal corresponding to the key and a controller adapted to determine a key input according to either a priority between multiple keys from which key signals are received or whether a received key signal was generated inadvertently.

Owner:TELEFON AB LM ERICSSON (PUBL)

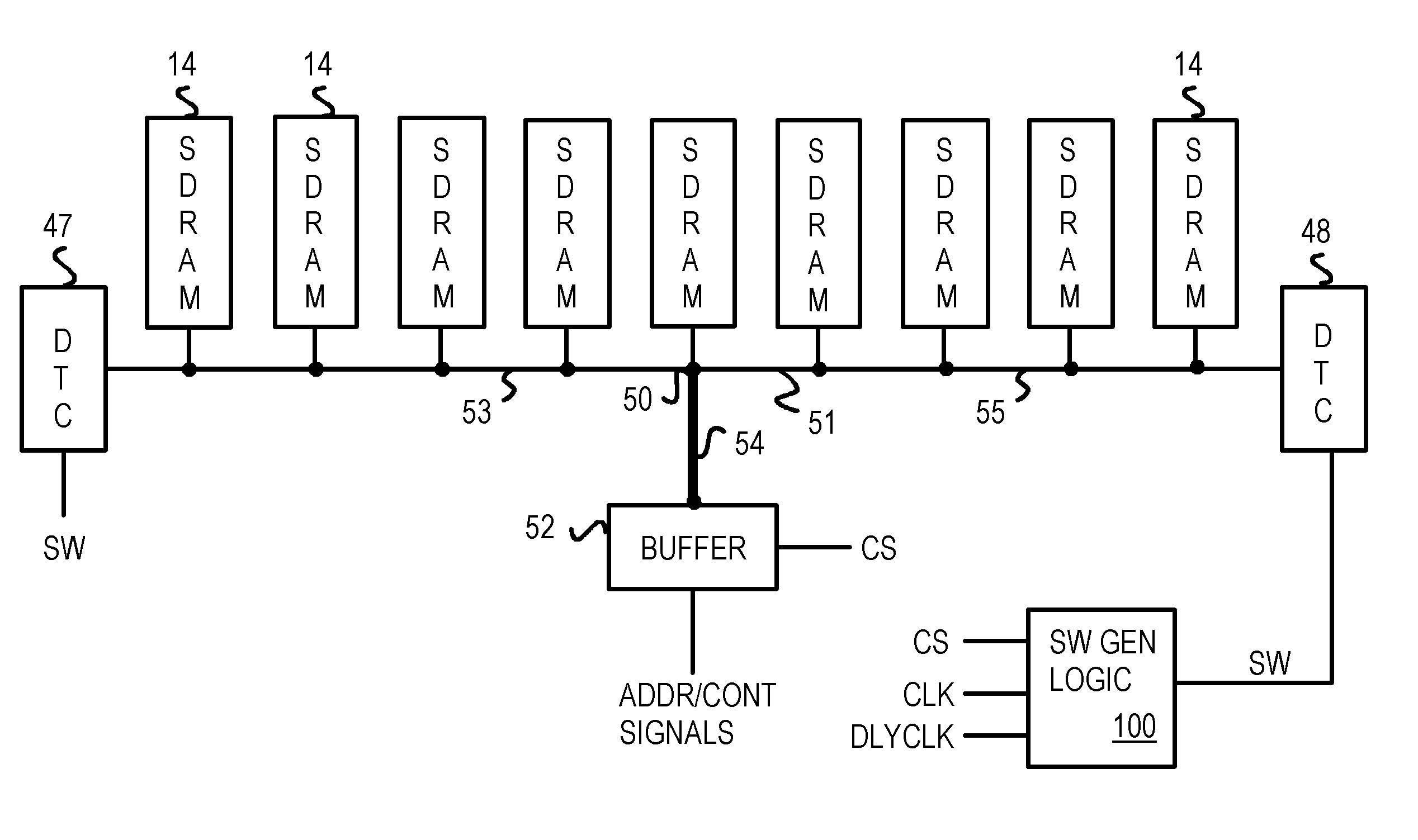

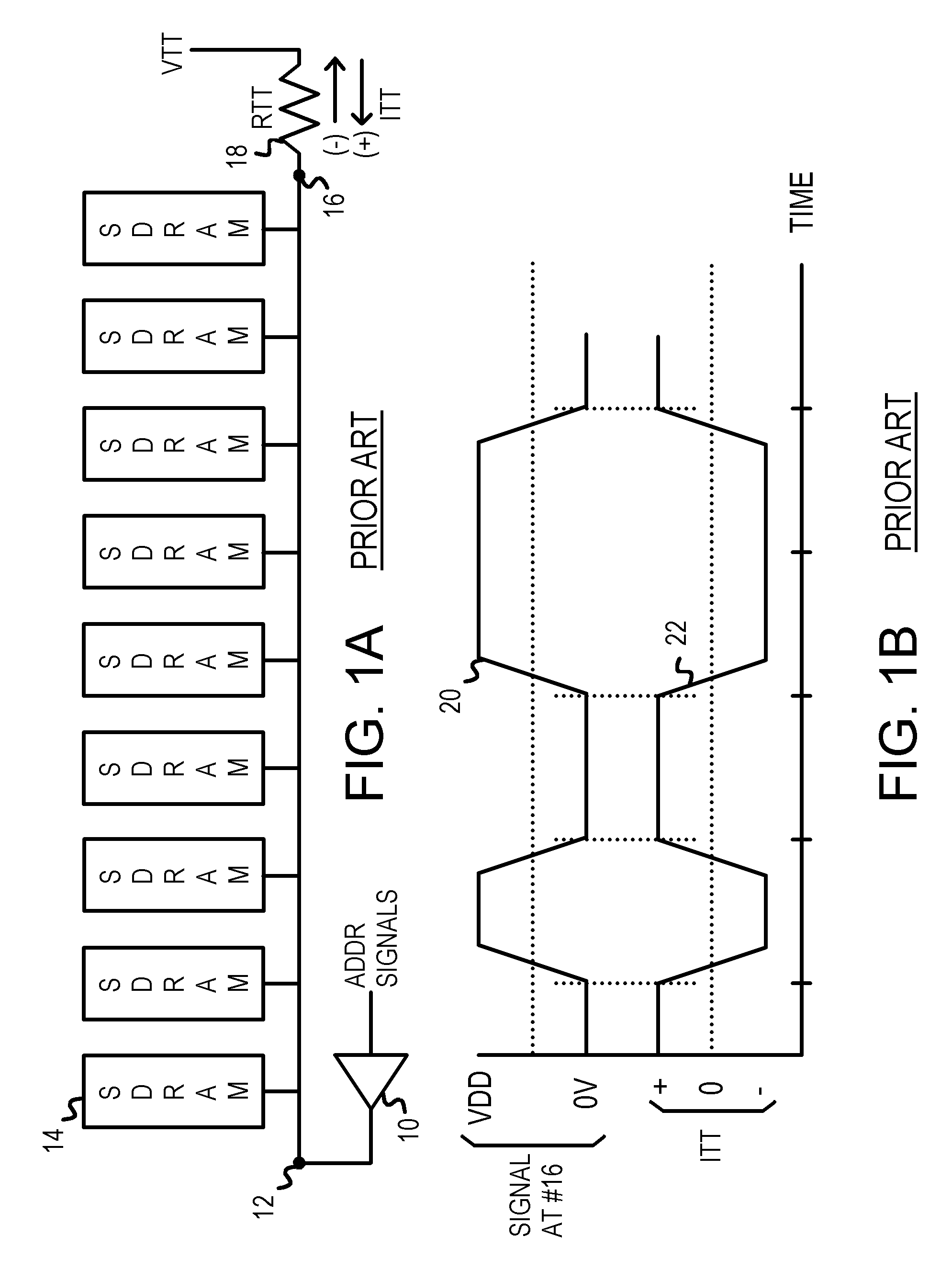

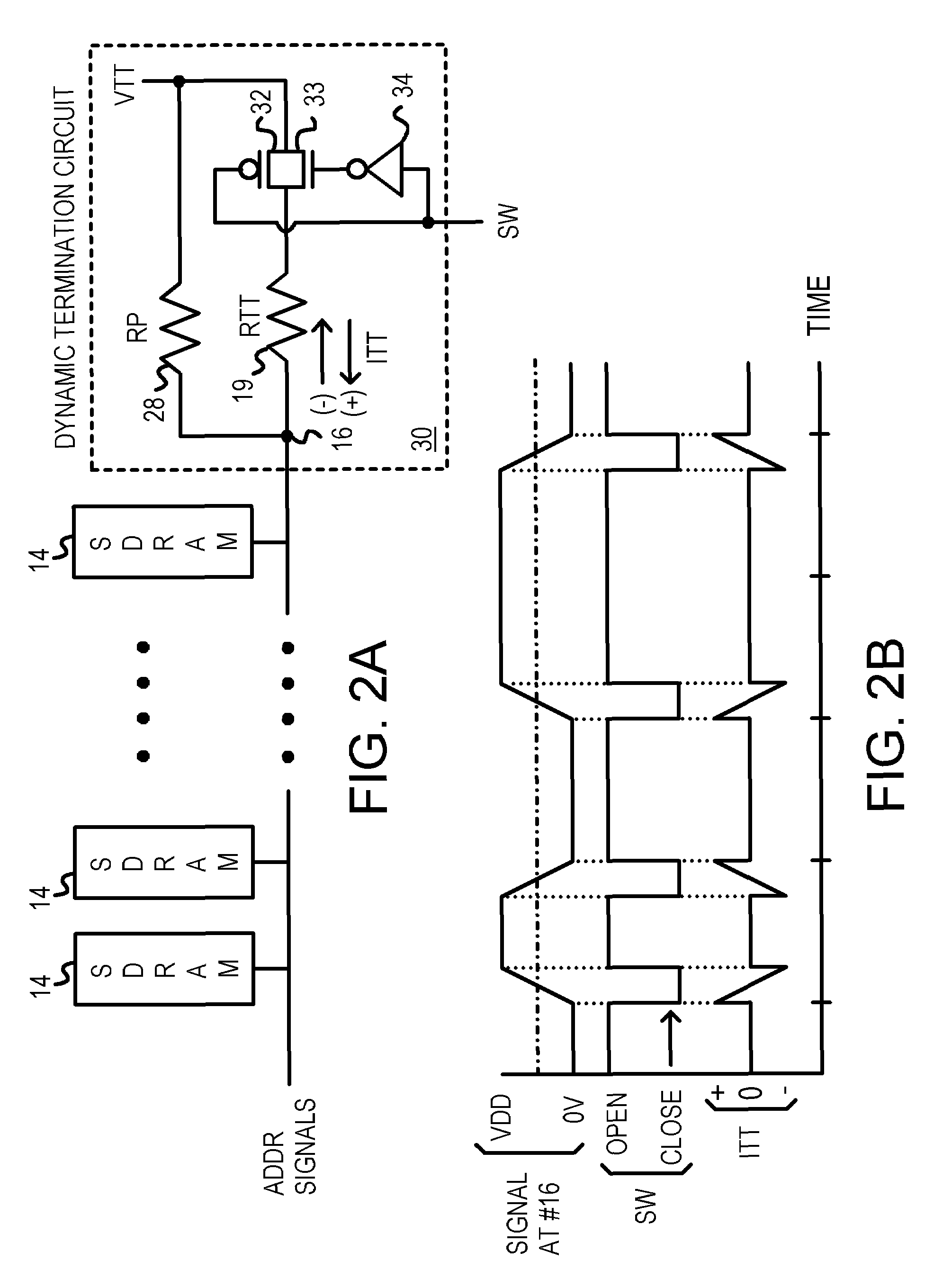

Memory module with dynamic termination using bus switches timed by memory clock and chip select

InactiveUS7068064B1Energy efficient ICTReliability increasing modificationsTransmission gateChip select

A low-power memory module has an active termination circuit at each end of critical signal traces. The dynamic termination circuit has a low-value resistor that is connected to a termination voltage by a transmission gate that is turned on by a switch signal. The switch signal is activated when the memory module is selected by a chip-select signal, and when a time window is open. The time window is generated from the clock to synchronous DRAMs on the memory module. The time window can be one-quarter of the clock period by ANDing the clock and a delayed clock that is delayed by one-quarter of a cycle. A static terminating resistor in parallel with the low-value resistor provides a much smaller terminating current that is not switched on and off. Traces can be impedance-matched at junctions to branches that each has a dynamic termination circuit at the far end.

Owner:DIODES INC

Top layers of metal for integrated circuits

InactiveUS20060063371A1Improve performanceReduce resistive voltage dropSemiconductor/solid-state device detailsSolid-state devicesEngineeringCritical signal

The present invention adds one or more thick layers of polymer dielectric and one or more layers of thick, wide metal lines on top of a finished semiconductor wafer, post-passivation. The thick, wide metal lines may be used for long signal paths and can also be used for power buses or power planes, clock distribution networks, critical signal, and re-distribution of I / O pads.

Owner:QUALCOMM INC

Top layers of metal for integrated circuits

InactiveUS7416971B2Improve performanceReduce resistive voltage dropSemiconductor/solid-state device detailsSolid-state devicesEngineeringCritical signal

Owner:QUALCOMM INC

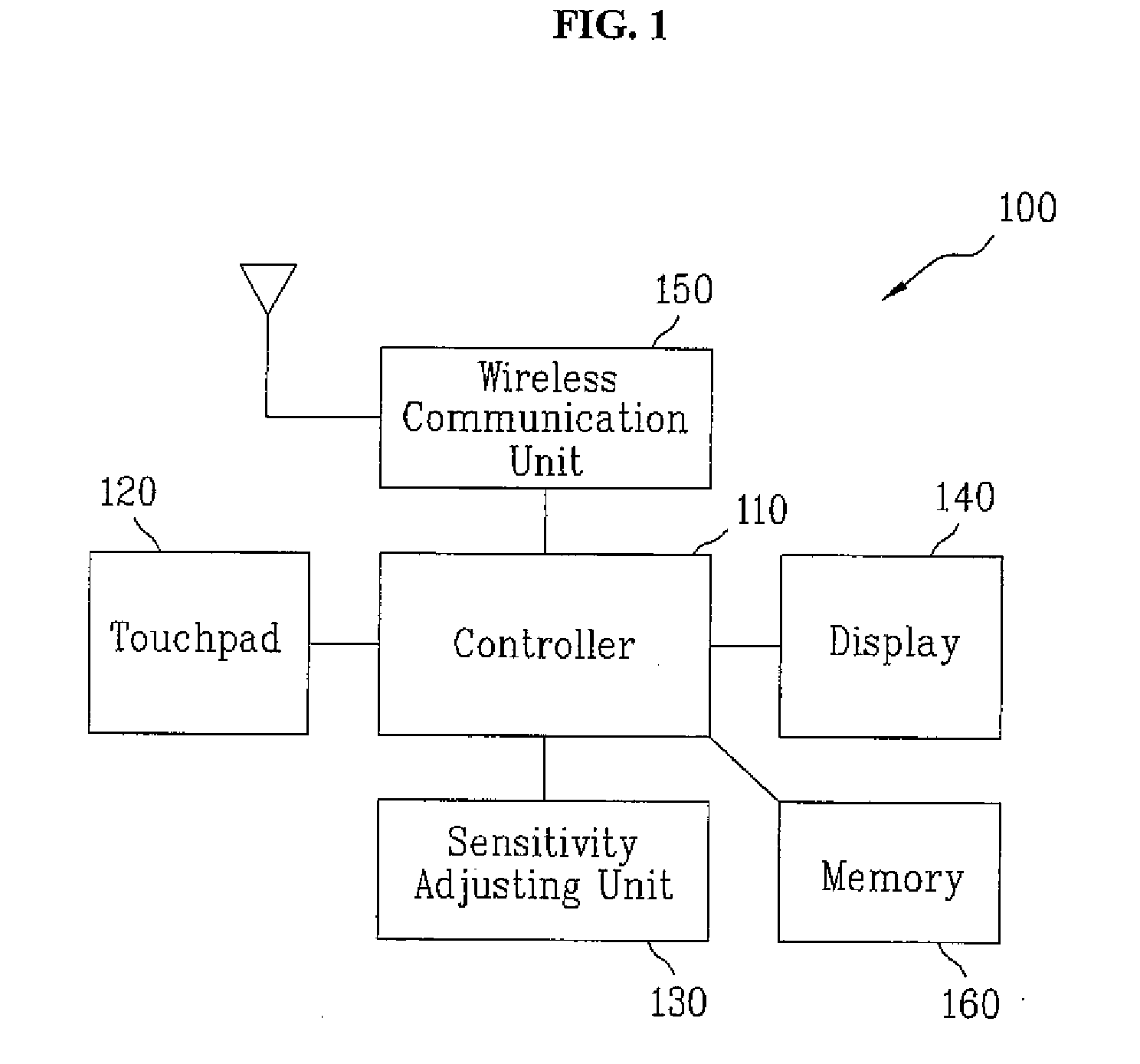

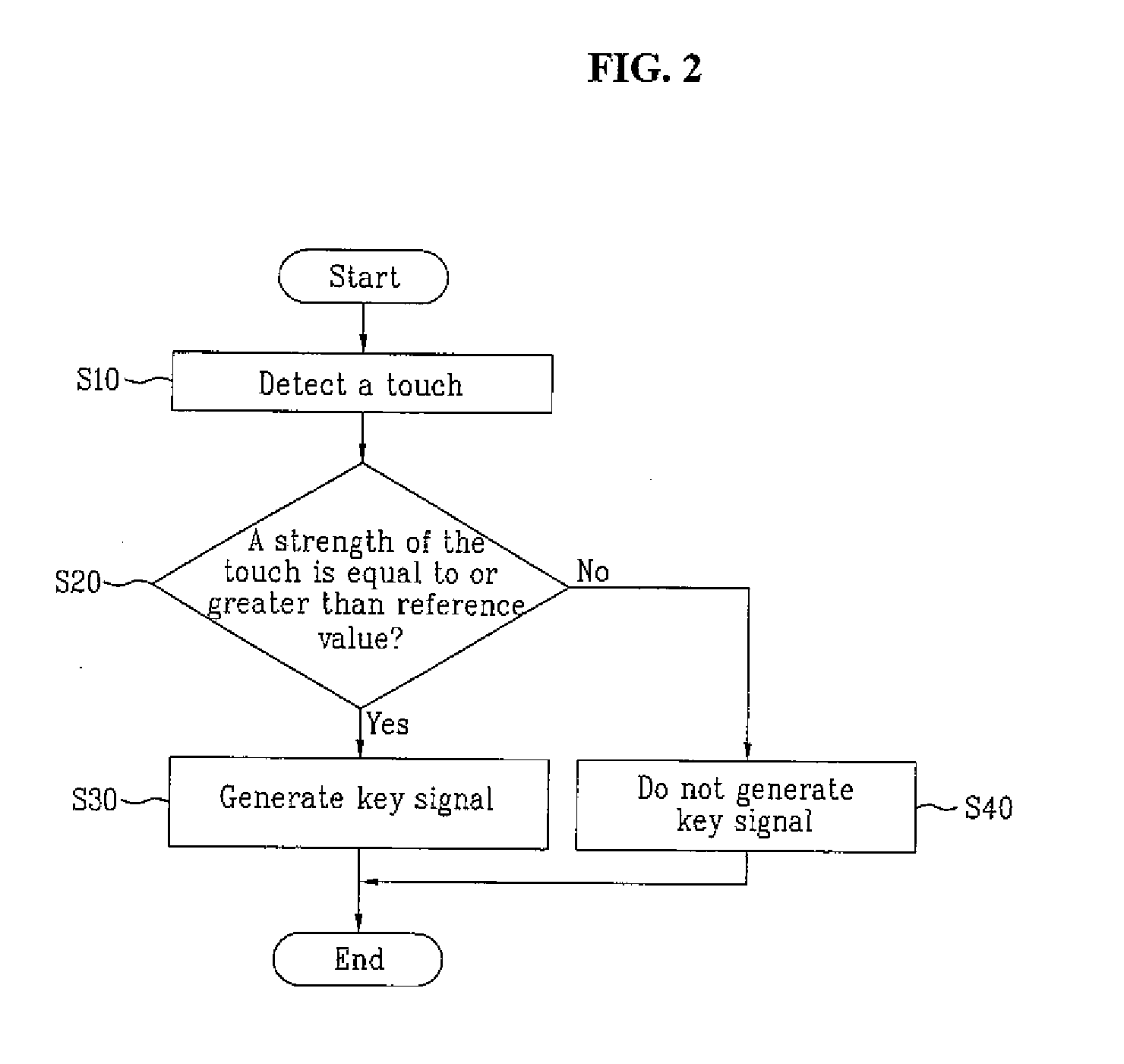

Mobile terminal and method of generating key signal therein

A mobile terminal and method of generating a key signal therein are disclosed, by which the key signal can be generated in a manner of adjusting touch sensitivity. The present invention includes a touchpad for a key signal input, a controller generating a key signal corresponding to a touched position if the touchpad is touched by a user and a strength of the touch is equal to or greater than a reference value, and a sensitivity adjusting unit adjusting the reference value.

Owner:LG ELECTRONICS INC

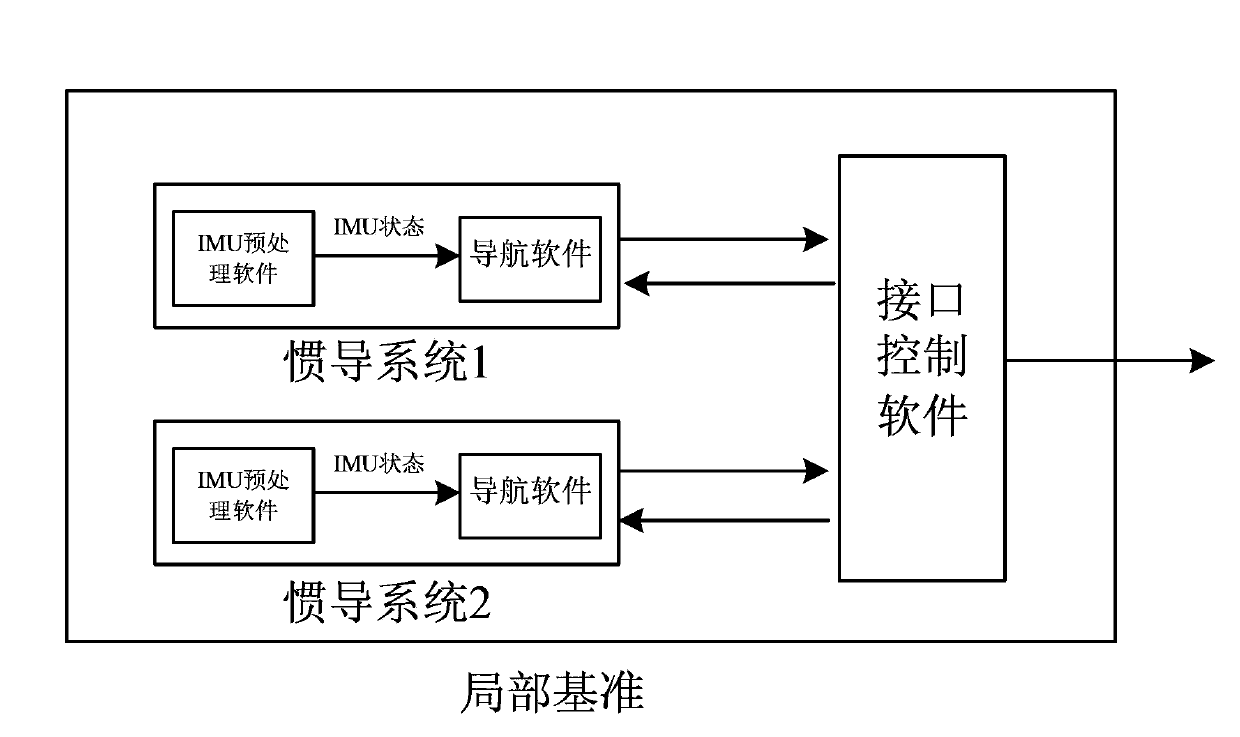

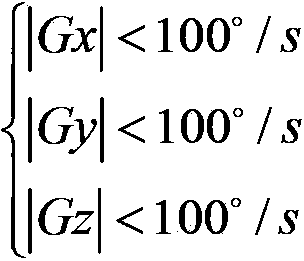

Method for quickly detecting failure of dual-redundancy inertial navigation system

ActiveCN103471615AImprove detection efficiencyPrecise positioningMeasurement devicesCritical signalSystem failure

The invention belongs to the field of inertia navigation techniques, and particularly relates to a method for quickly detecting a failure of a dual-redundancy inertial navigation system. The method disclosed by the invention comprises the following steps of detecting a bottom layer inertia navigation failure; detecting a failure in navigation software; and detecting a failure in interface control software. According to the method provided by the invention, the technical problems of low detection efficiency and difficulty in location of a specific fault device in the method for quickly detecting the failure of the dual redundancy inertial navigation system in the prior art are solved, inertia elements and key signals of two sets of inertial navigation systems in a local datum can be detected in real time, the detection efficiency is high, the fault elements can be accurately located, and the guarantee is provided for normal work of the local datum.

Owner:BEIJING AUTOMATION CONTROL EQUIP INST

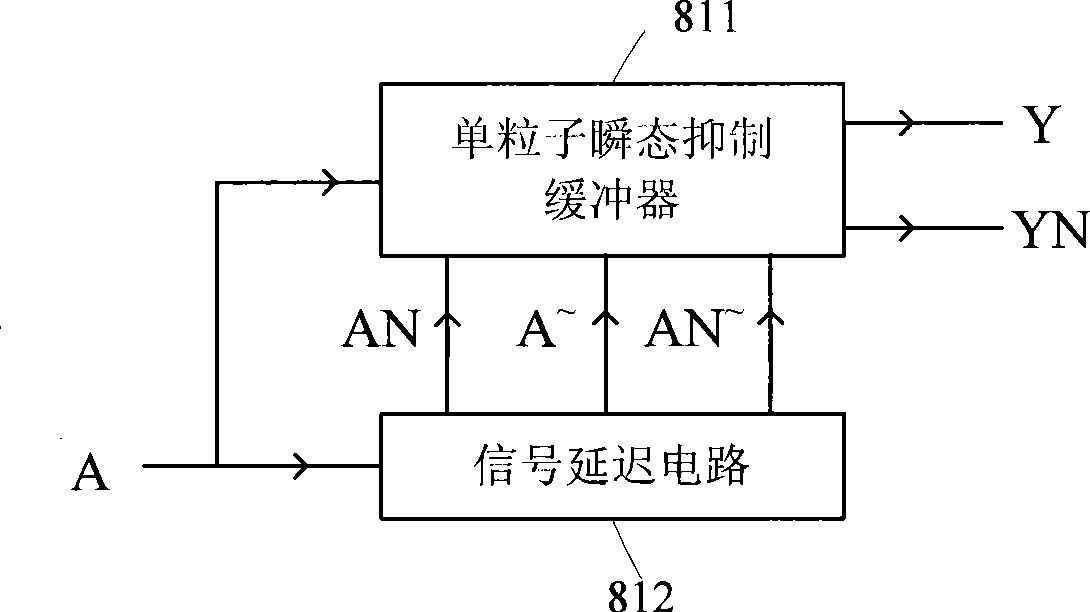

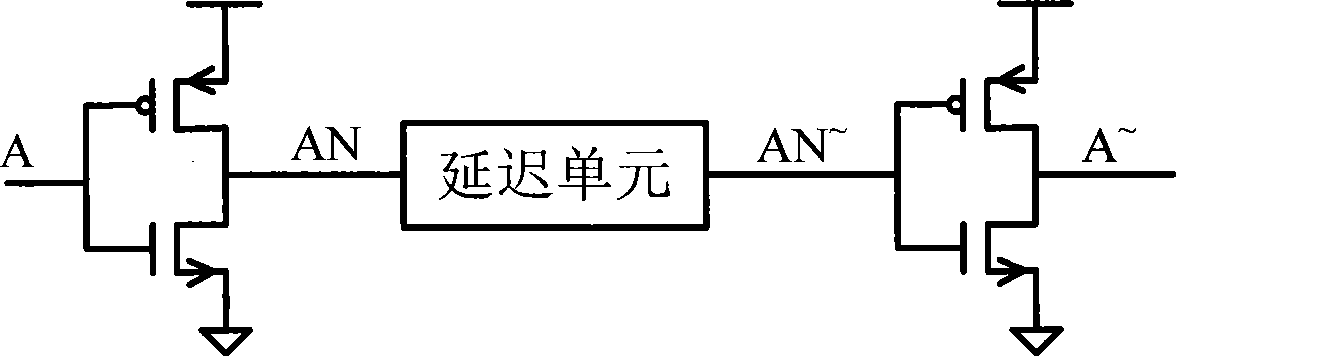

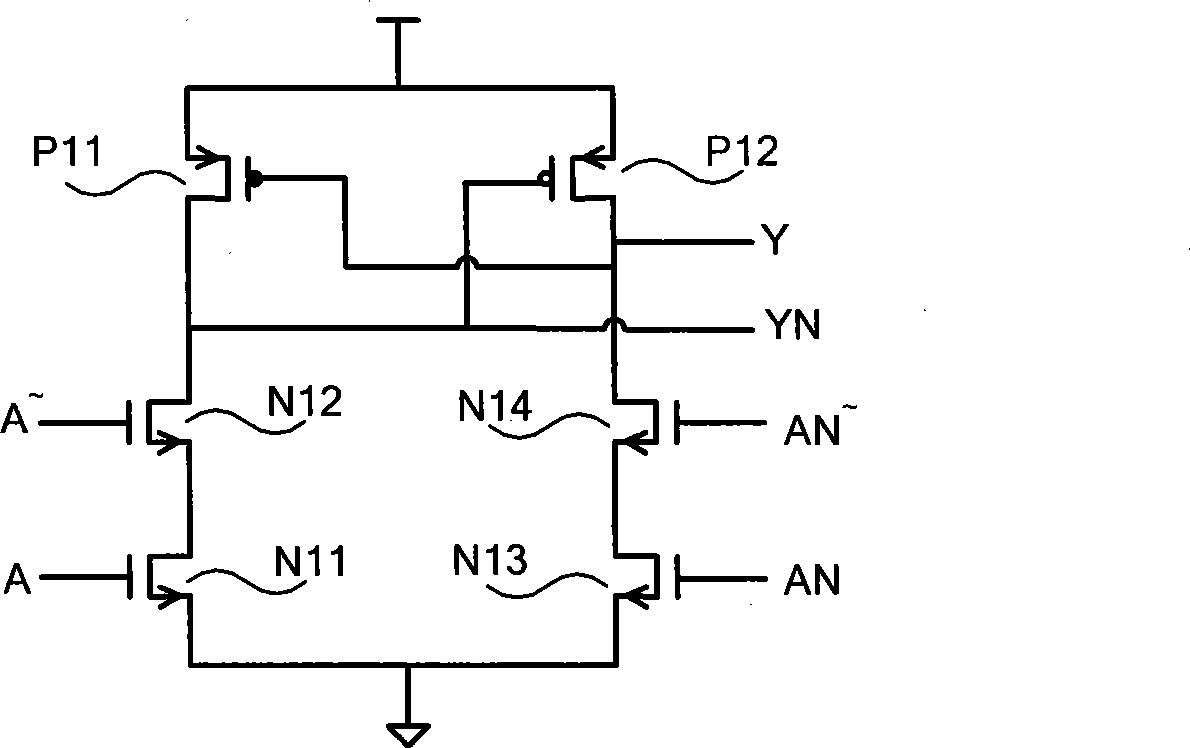

Buffer cell circuit for resisting single-particle transient state

InactiveCN101447786AAbility to suppress transient pulsesEliminate the effects ofLogic circuits coupling/interface using field-effect transistorsTransient stateDelayed time

The invention relates to a buffer cell circuit for resisting the single-particle transient state which mainly consists of a single-particle transient-suppression buffer circuit and a signal-delay circuit, wherein, the signal-delay circuit consists of an inverter and a delay unit, the single-particle transient-suppression buffer circuit is an N-shaped single-particle transient-suppression buffer circuit or a P-shaped single-particle transient-suppression buffer circuit. With the adoption of the buffer circuit of the invention, the single-particle transient pulse which is generated on an input signal and provided with a pulse width smaller than the delay time internally set in a buffer, is eliminated, and key signals such as a clock, a reset, data, and the like, are effectively protected. At the same time, the buffer also possesses the strong ability for resisting single-particle transient state. In addition, The design for a circuit resisting single-particle is reinforced by adopting the buffer cell circuit for resisting the single-particle transient state, so that the area caused by the reinforcement of single-particle resistance and the power consumption are remarkably reduced compared with the common reinforcing methods, such as the triple modular redundancy, and the like.

Owner:BEIJING MXTRONICS CORP +1

Multiprotocol computer bus interface adapter and method

Owner:AVAGO TECH INT SALES PTE LTD

Top layers of metal for integrated circuits

InactiveUS20080121943A1Improve performanceReduce resistive voltage dropSemiconductor/solid-state device detailsSolid-state devicesEngineeringIntegrated circuit layout

The present invention adds one or more thick layers of polymer dielectric and one or more layers of thick, wide metal lines on top of a finished semiconductor wafer, post-passivation. The thick, wide metal lines may be used for long signal paths and can also be used for power buses or power planes, clock distribution networks, critical signal, and re-distribution of I / O pads.

Owner:QUALCOMM INC

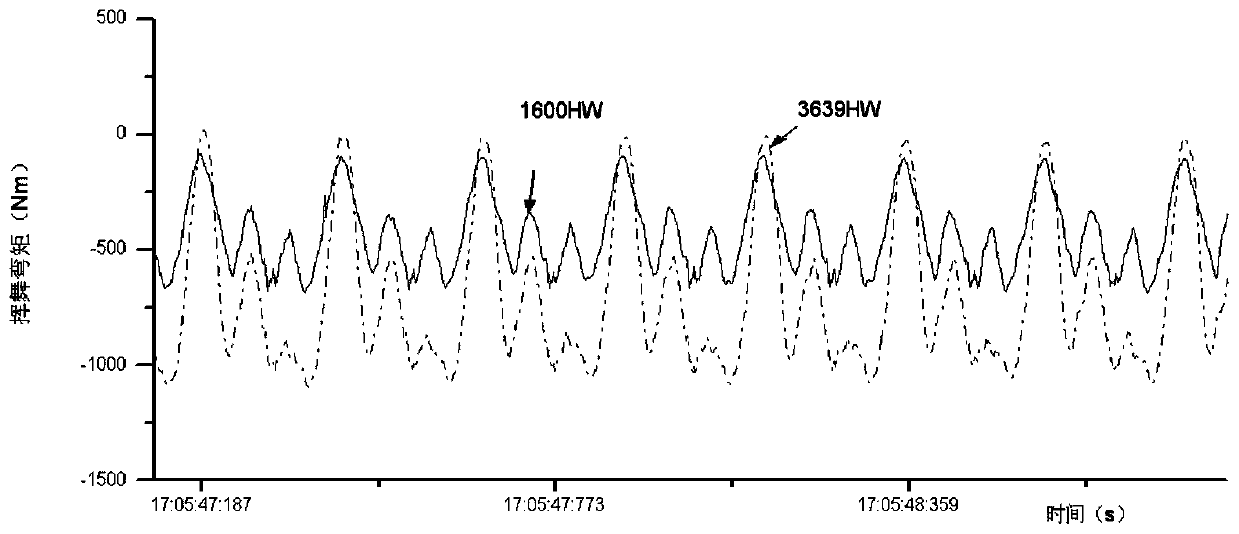

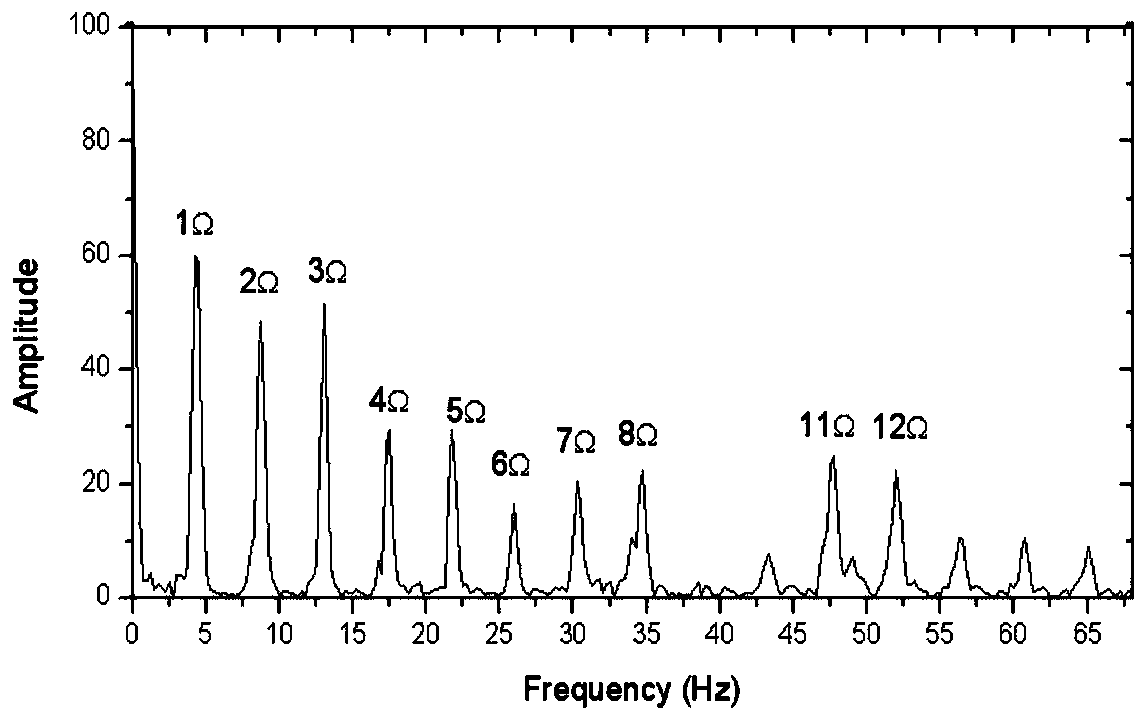

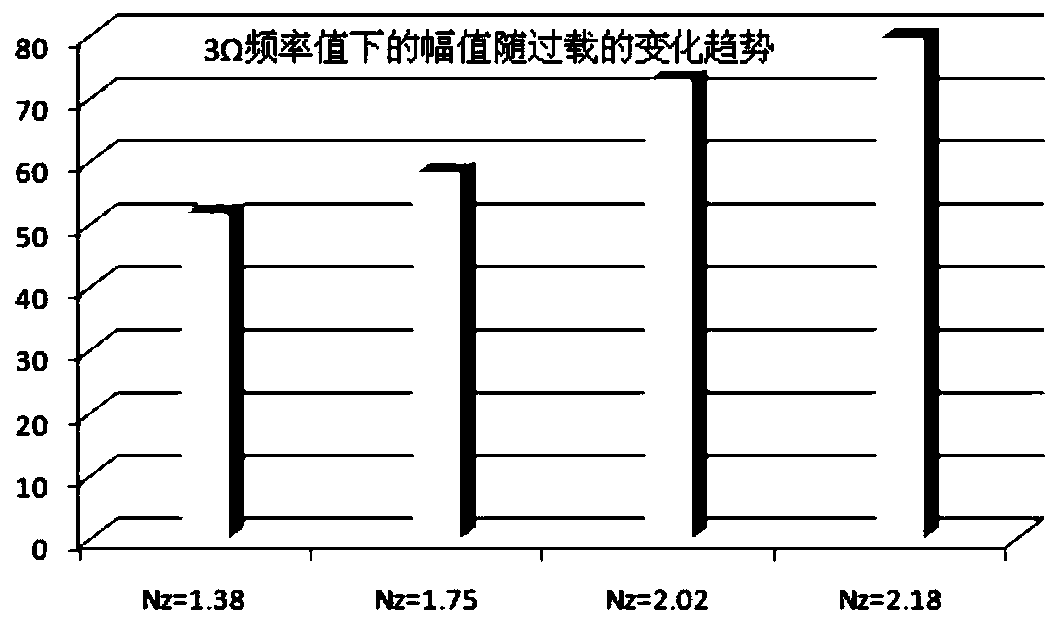

Rotor pneumatic load analysis method based on actually measured structural load

ActiveCN109977448AReliable dynamic analysis rulesGeometric CADSustainable transportationStatistical analysisEngineering

The invention discloses a rotor pneumatic load analysis method based on actually measured structural load, and belongs to the technical field of flight tests. The invention discloses a helicopter rotor working method. Measurement of the key structure load of the helicopter rotor is determined. The method comprises the following steps of carrying out resistance strain gauge installation and groundload calibration test on the strain gauge; testing and adding a key signal of rotor wing rotation; through flight tests in different states, carrying out statistical analysis on the actually measuredrotor structure load in the time domain and the frequency domain without focus on a plurality of assumptions in the helicopter theoretical model simulation process, Meanwhile, different from the aerodynamic environment simulation conditions such as pneumatic test and rotor tower test processes, the aerodynamic condition of the helicopter rotor can be reflected more truly, and a more reliable helicopter rotor aerodynamic analysis rule is obtained.

Owner:CHINESE FLIGHT TEST ESTAB

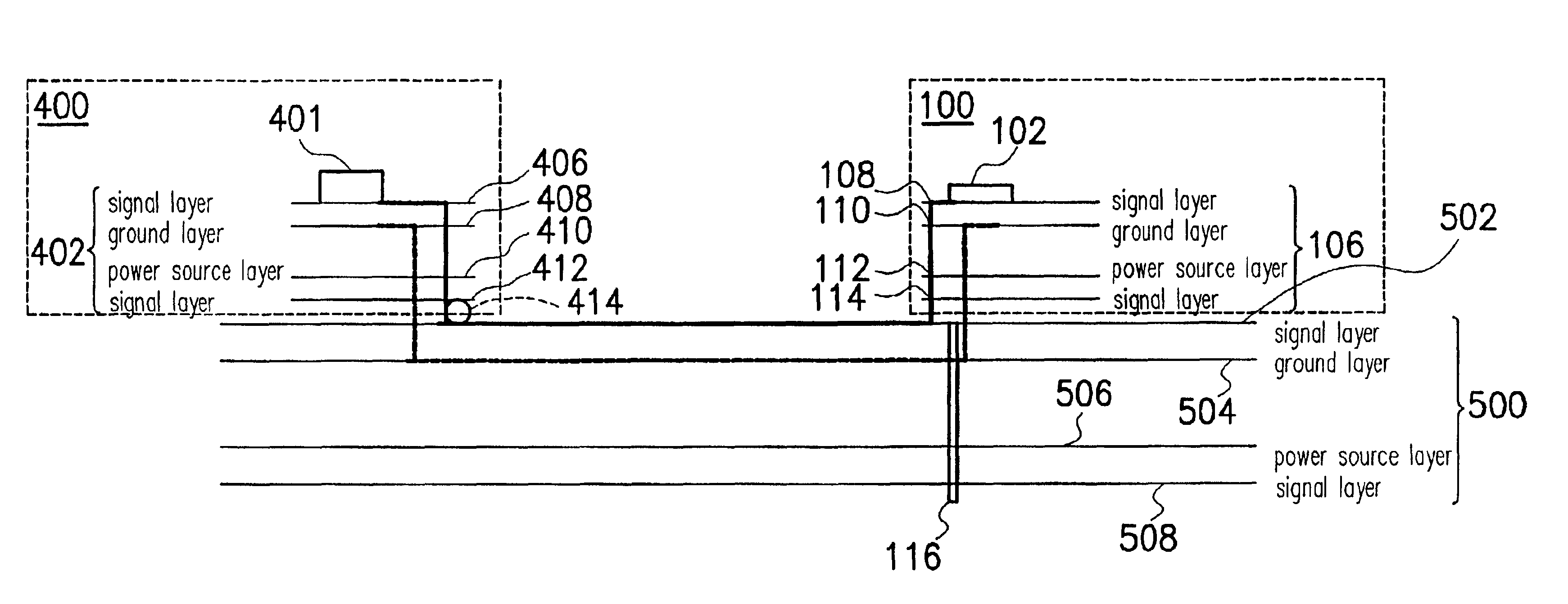

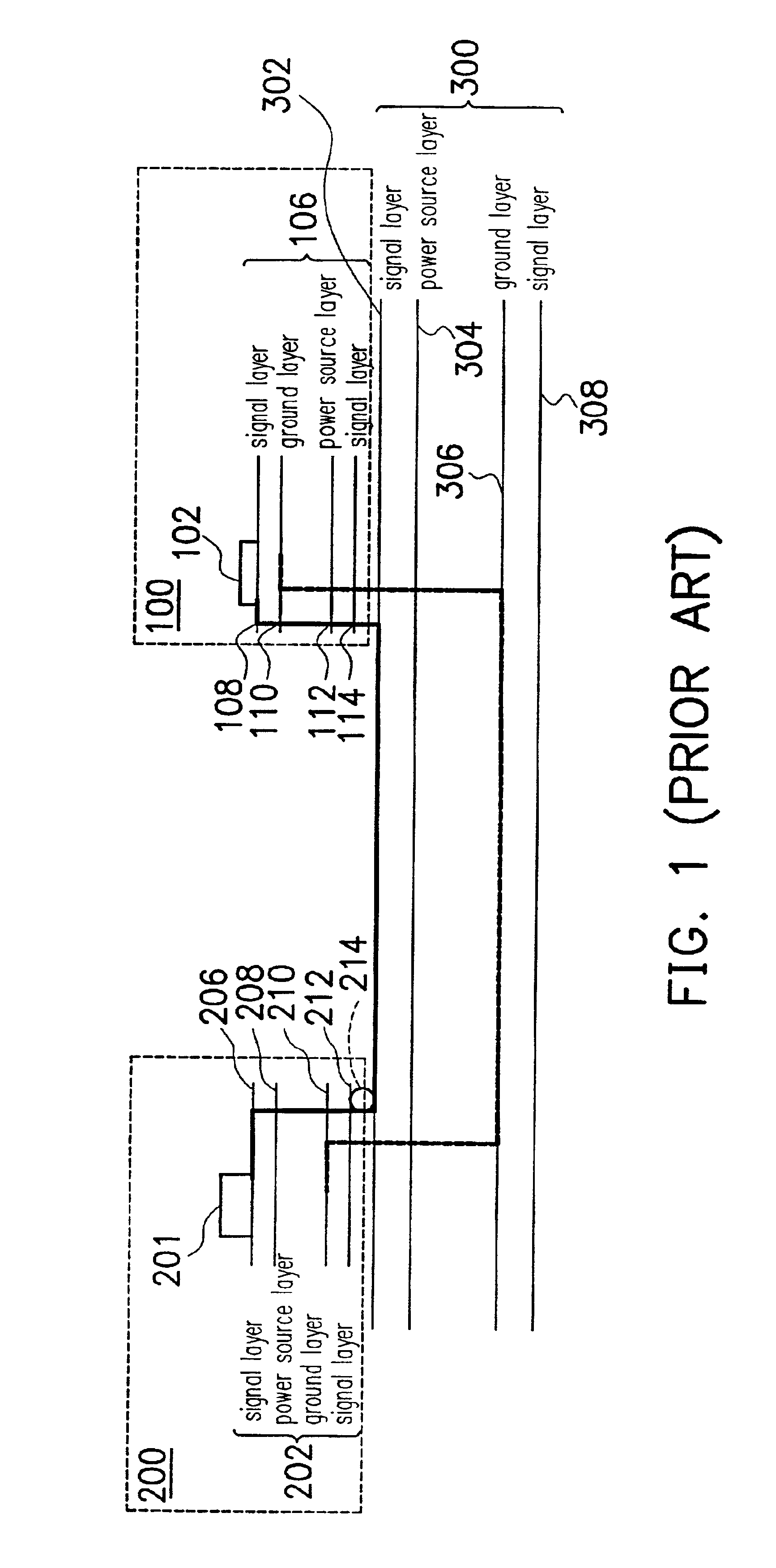

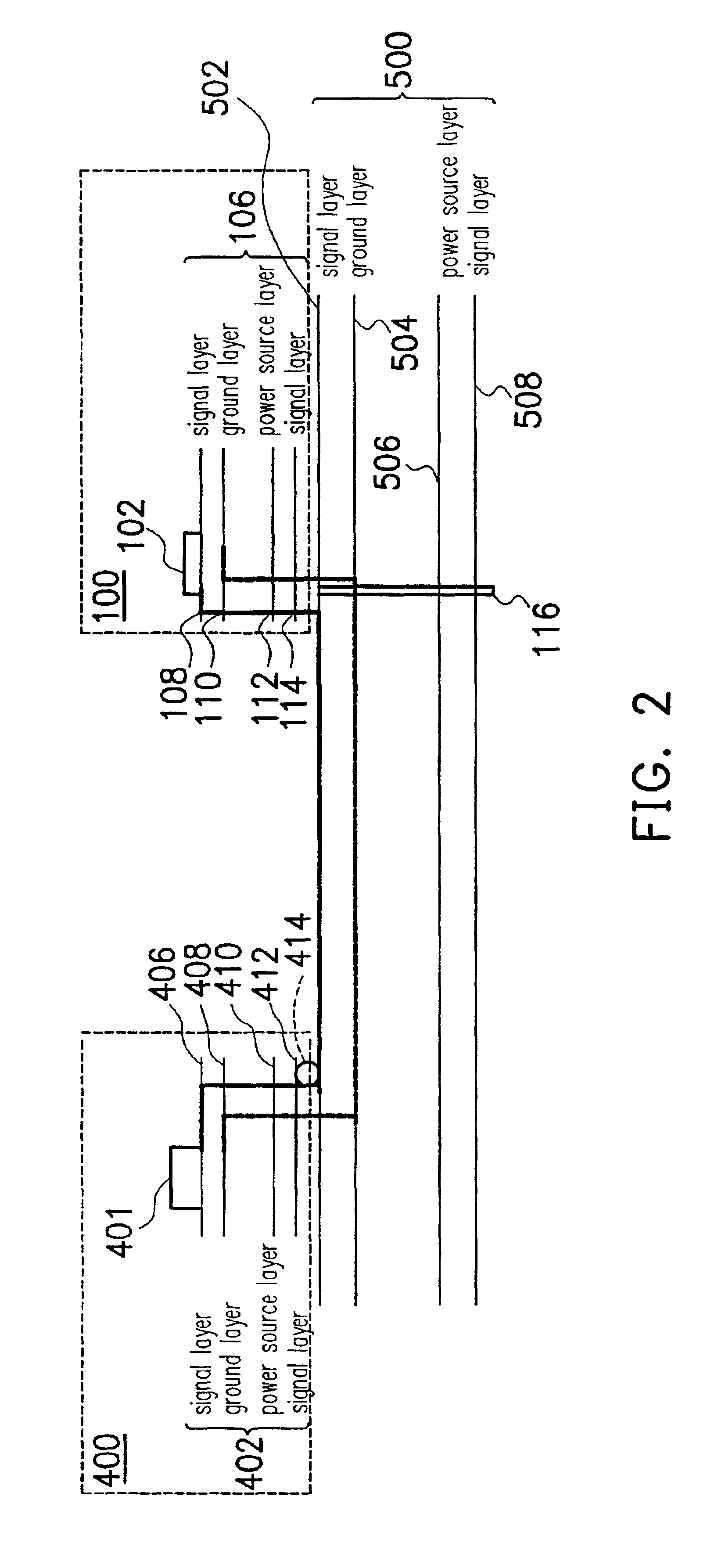

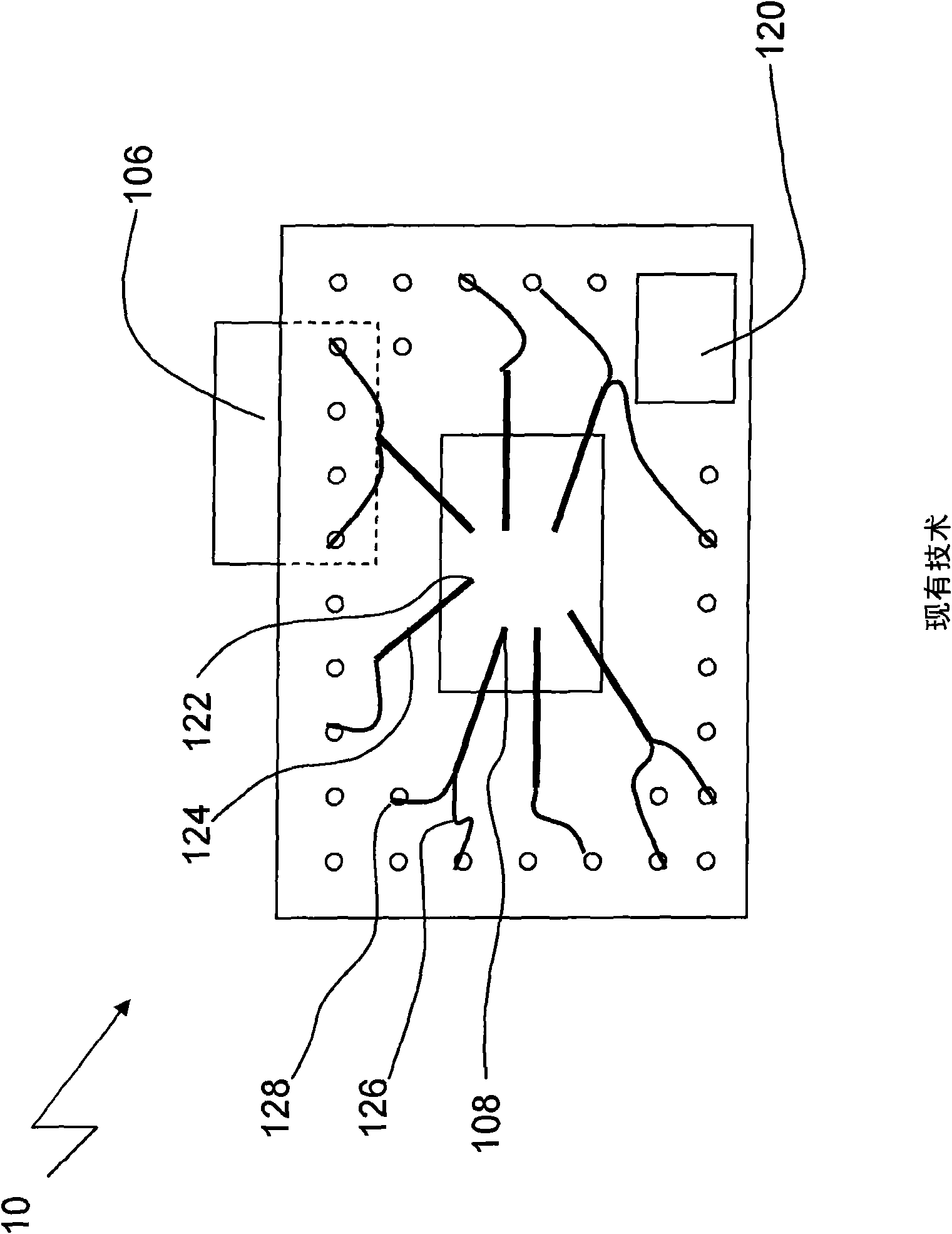

Data processing system and associated control chip and printed circuit board

InactiveUS6842347B2Low production costSemiconductor/solid-state device detailsSolid-state devicesData processing systemCritical signal

A data processing system including a control chip, a central processing unit and a printed circuit board is provided. In the data processing system, the printed circuit board not only supports the control chip and the central processing unit, but also serves as an interface for transferring signals between the control chip and the central processing unit. Critical signals can be transmitted from the central processing unit to the control chip via the printed circuit with a better return path.

Owner:VIA TECH INC

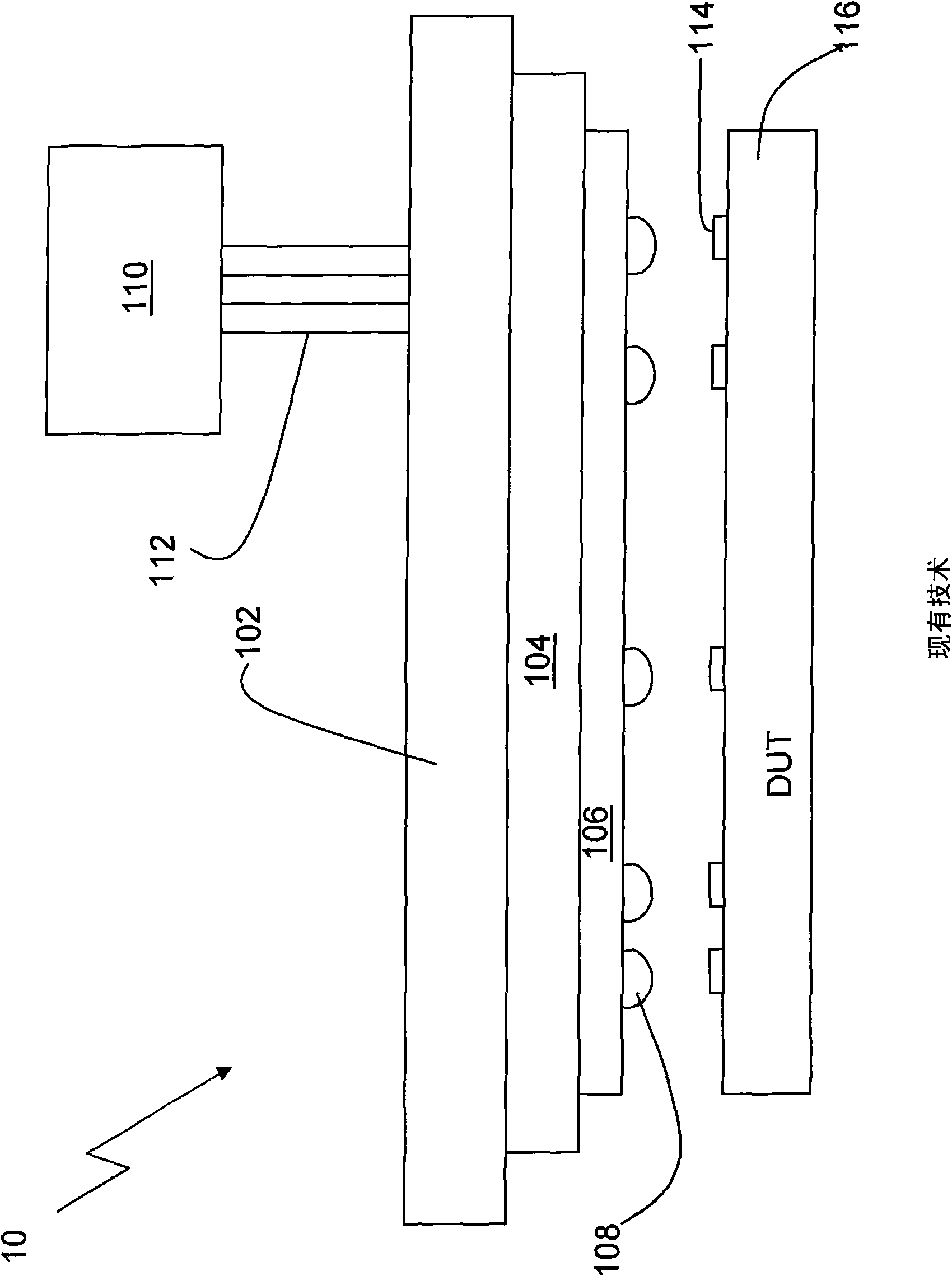

Testing of electronic circuits using an active probe integrated circuit

InactiveCN101680914AReduce or remove deteriorationReduce or eliminate lossesElectronic circuit testingMeasurement leads/probesProbe cardAutomatic test equipment

A method and apparatus are provided for transmission / reception of signals between automatic test equipment (ATE) and a device under test (DUT). A probe card has a plurality of associated proximate active probe integrated circuits (APIC) connected to a plurality of probes. Each APIC interfaces with one or more test interface points on the DUT through probes. Each APIC receives and processes signalscommunicated between the ATE and the DUT. Low information content signals transmitted from the ATE are processed into high information content signals for transmission to the probe immediately adjacent the APIC, and high information content or time critical signals received by the APIC from the DUT are transmitted as low information content signals to the ATE. Because the APIC is immediately adjacent the probe there is minimum loss or distortion of the information in the signal from the DUT.

Owner:SCANIMETRICS

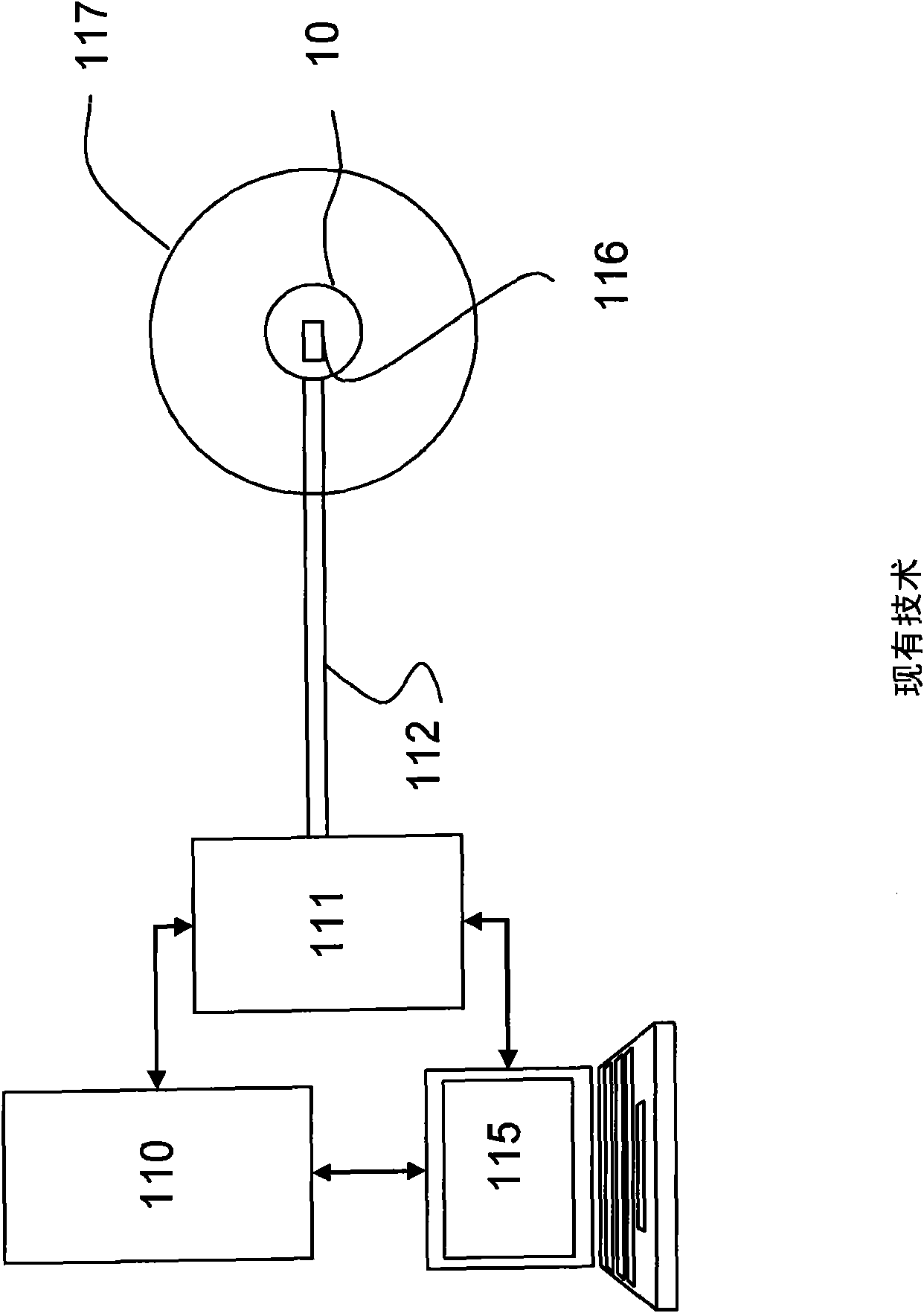

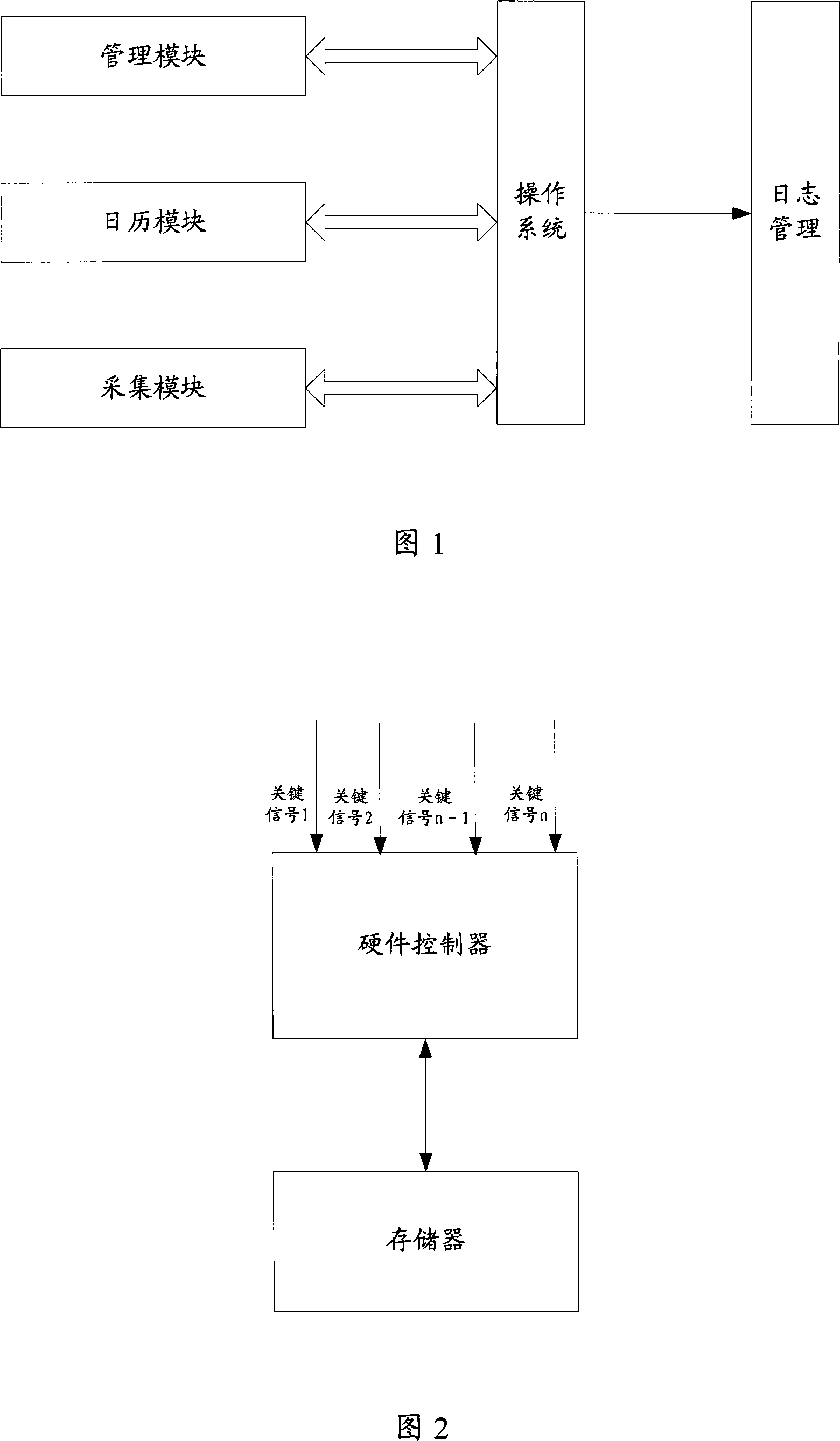

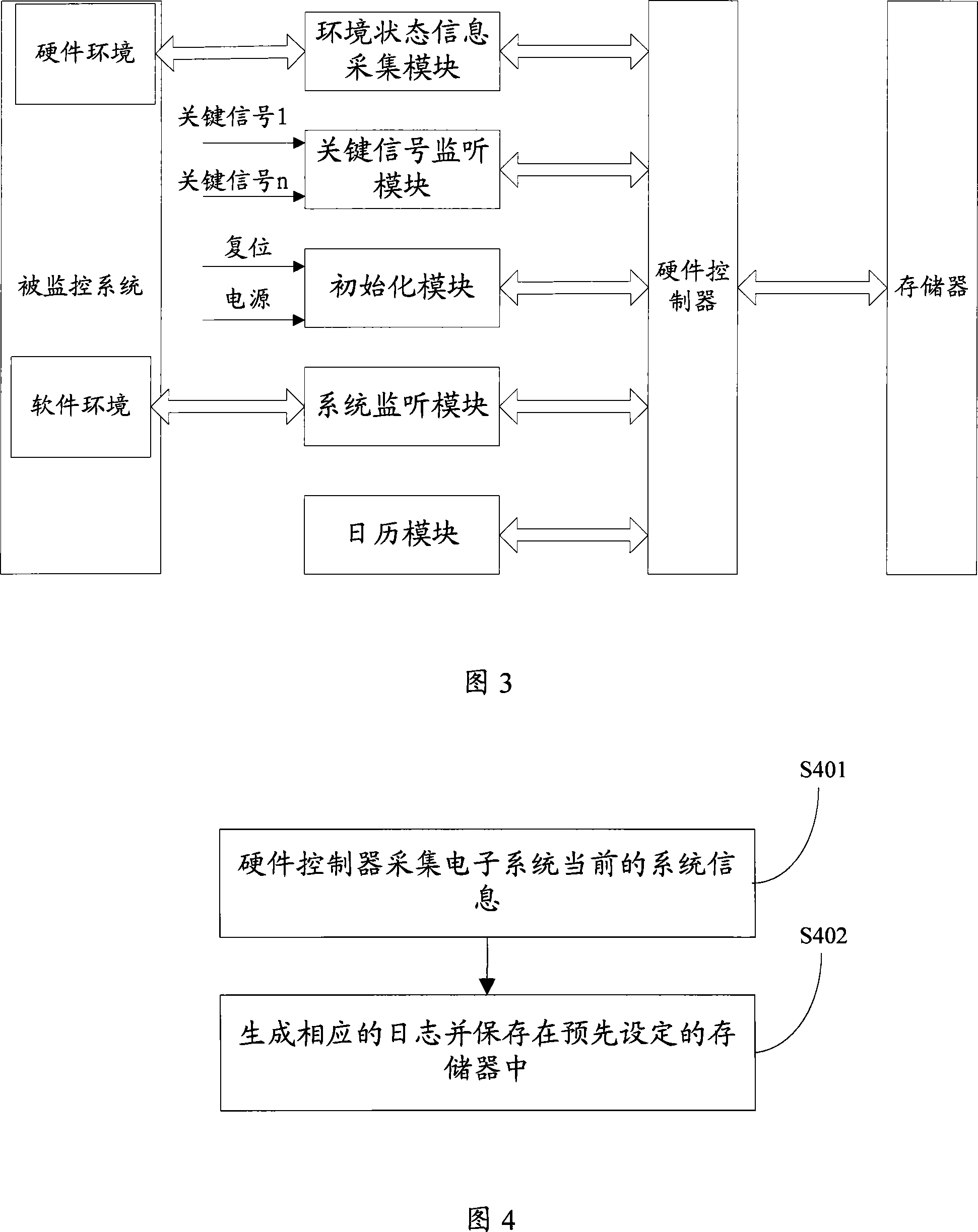

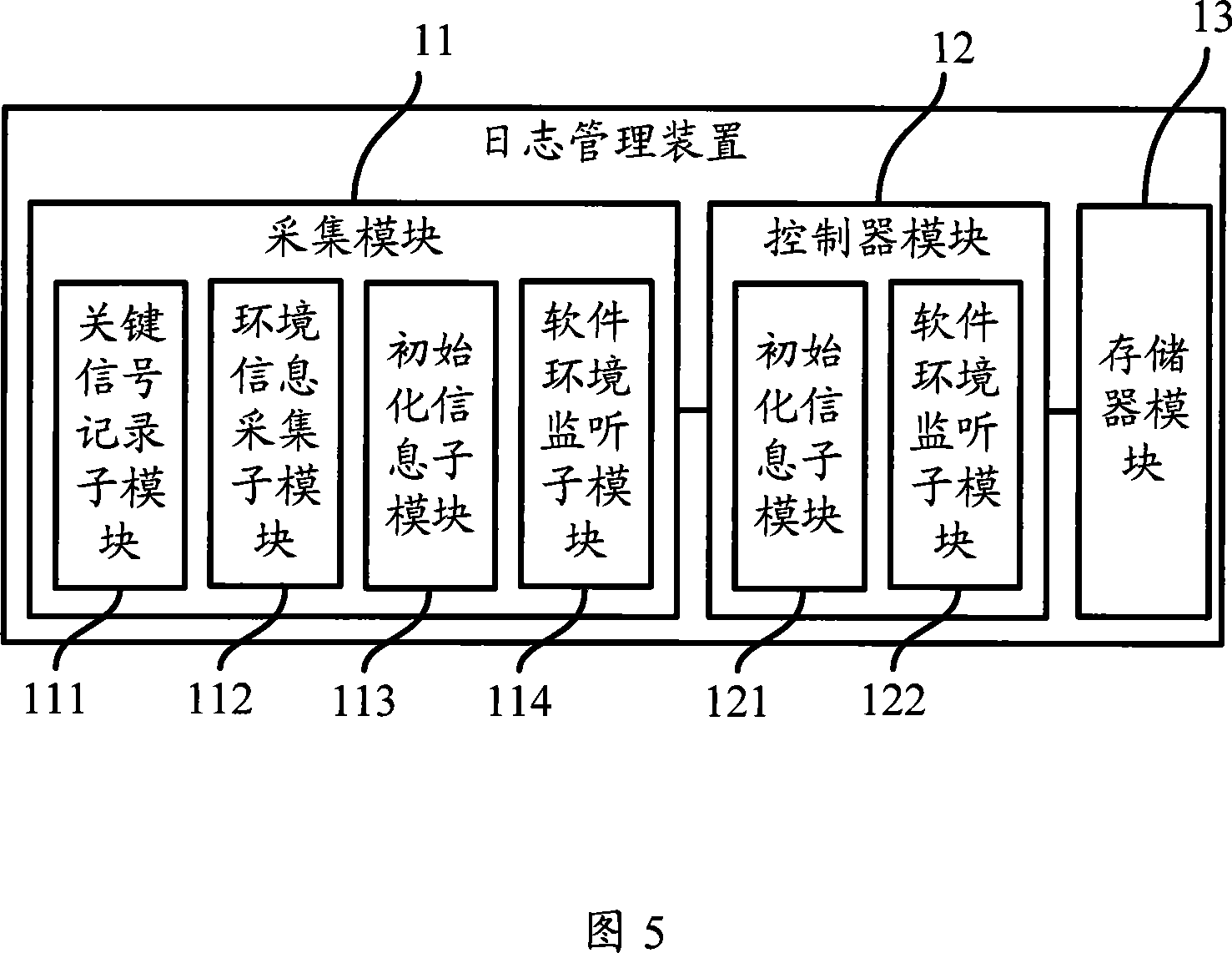

Diary management techniques and device

The invention discloses a log management method, which records the log of the electronic system in a manner independent of the operating system, including: collecting the key signal of the key hardware by directly connecting with the key hardware of the electronic system, and not being affected by the electronic system during the collection process. The operating system control directly introduces key signals into the hardware controller; the hardware controller generates and saves logs according to the collected key signals. The state information of the system is collected and stored through the set hardware controller to generate logs, and there is no need to generate corresponding logs only through the current operating system of the system as in the prior art. In this way, when the system fails, such as crash, power failure, etc., it can also record the current status information of the system in time, generate and save the log, prevent the loss of key information, and improve the reliability and maintainability of the system.

Owner:NEW H3C TECH CO LTD

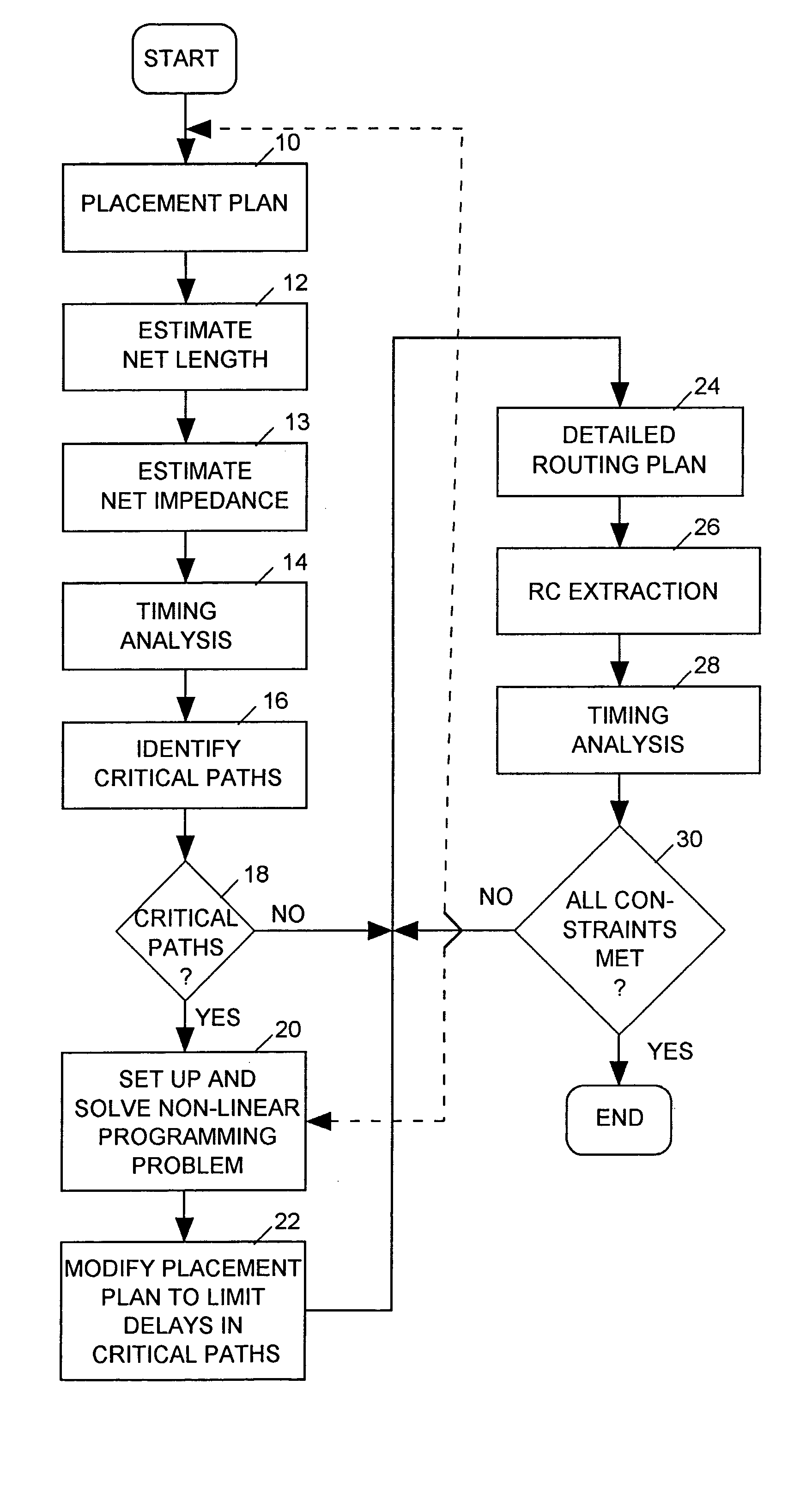

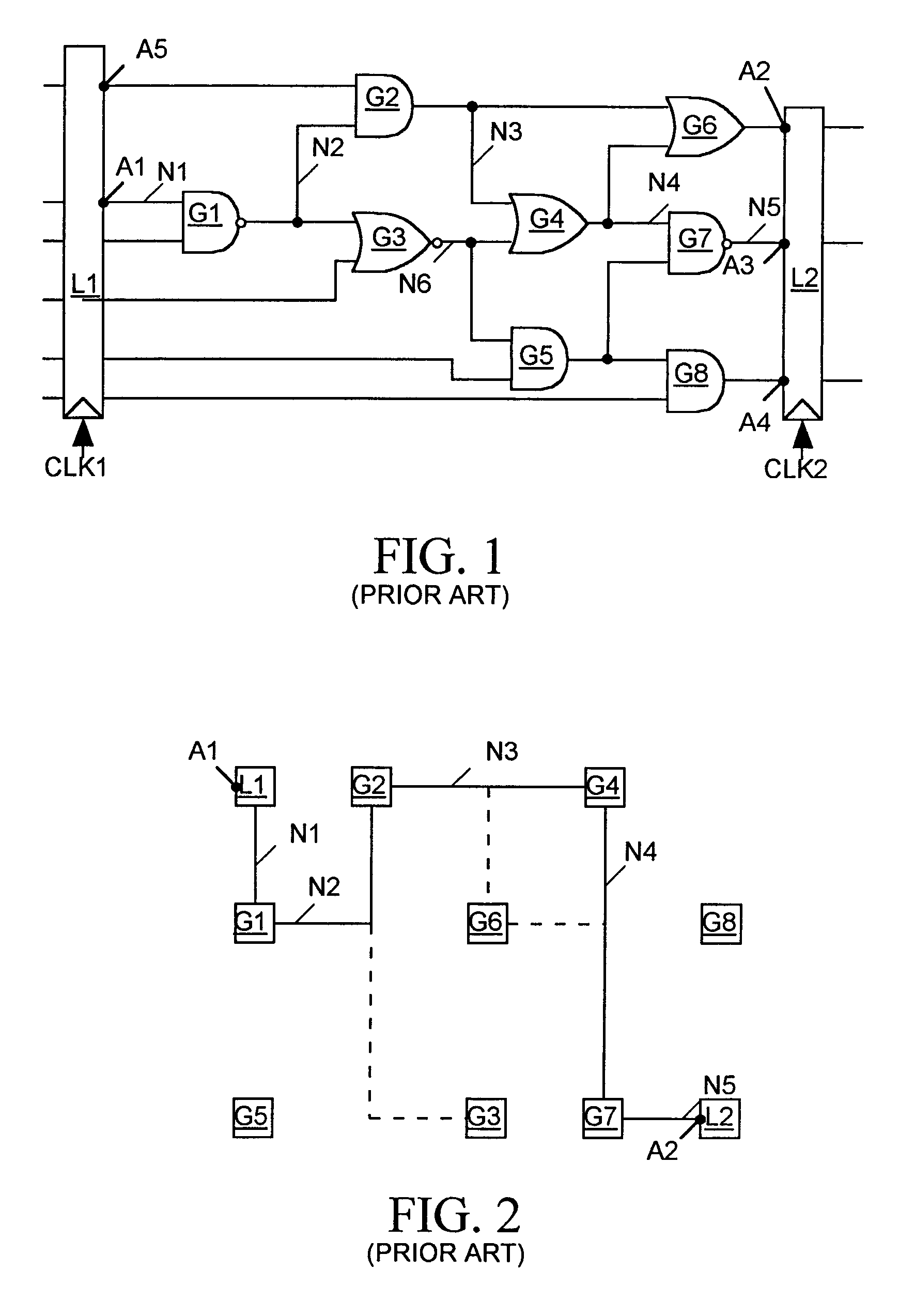

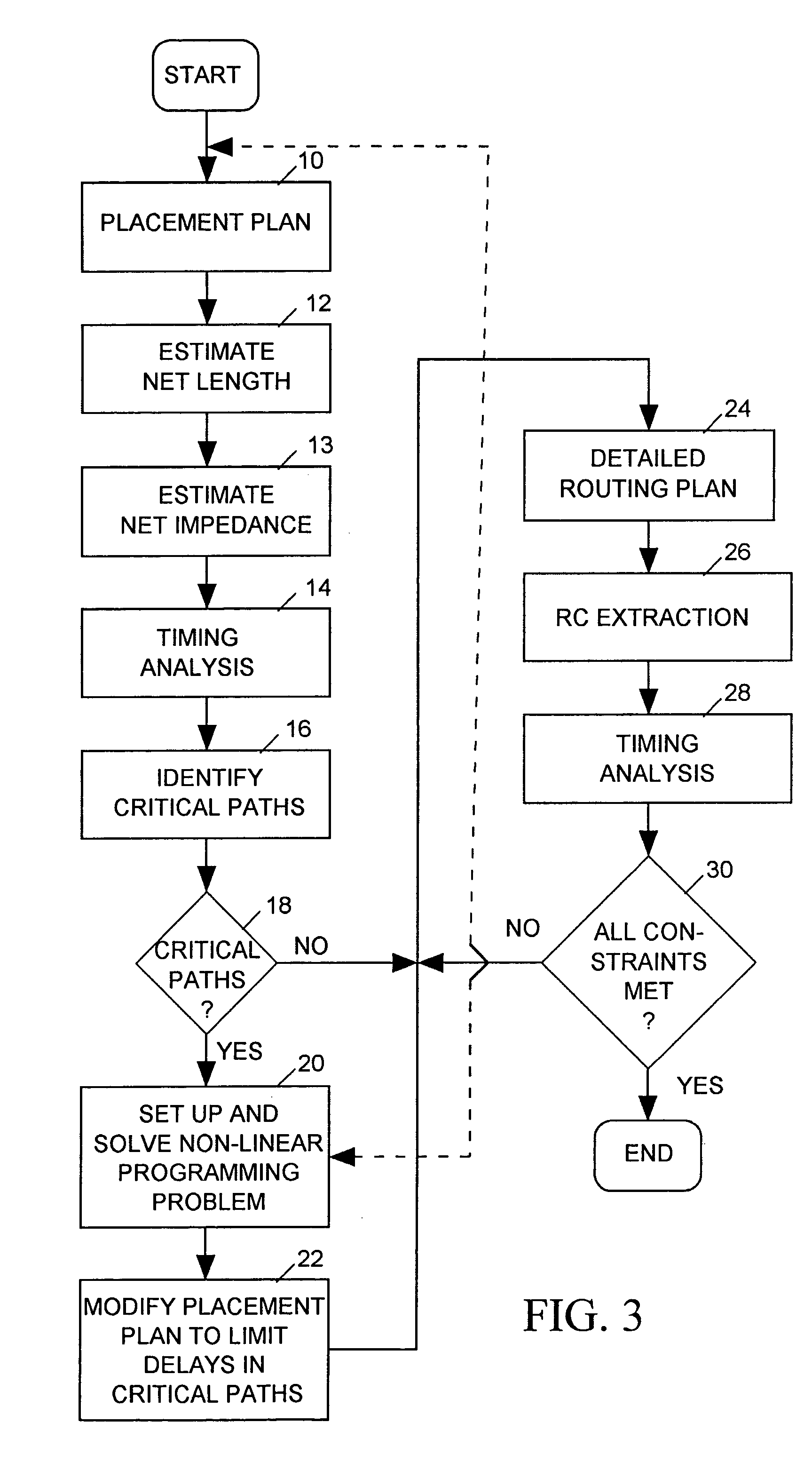

Post-placement timing optimization of IC layout

InactiveUS7137093B2Computer aided designSoftware simulation/interpretation/emulationElectrical resistance and conductanceCapacitance

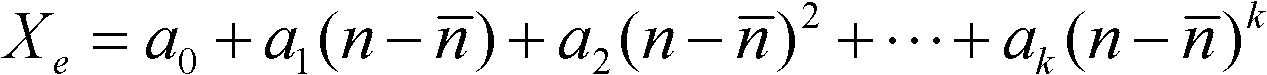

When an IC layout is to include time-constrained signal paths, a placement plan defining positions of cells forming the IC is analyzed to estimate lengths of nets needed to interconnect the cells based on the positions of cells included in those signal paths. A capacitance and resistance of each net is then estimated based on its estimated length. The delay through each time-constrained signal path is then estimated based on the estimated capacitance and resistance of each net to be included in the time-constrained signal path and on the terminal impedances, switching speeds and driving strengths of the cells included in the signal path. The estimated path delay for each signal path is then compared to its timing constraint to determine whether that signal path is a “critical signal path” likely to fail to meet its timing constraint following development of a detailed routing plan. A non-linear programming technique is then employed to determine how, with minimal disturbance to the placement plan, to reposition cells forming the critical paths so that when the nets are routed between the cells, all critical paths will be more likely to satisfy their timing constraints.

Owner:CADENCE DESIGN SYST INC

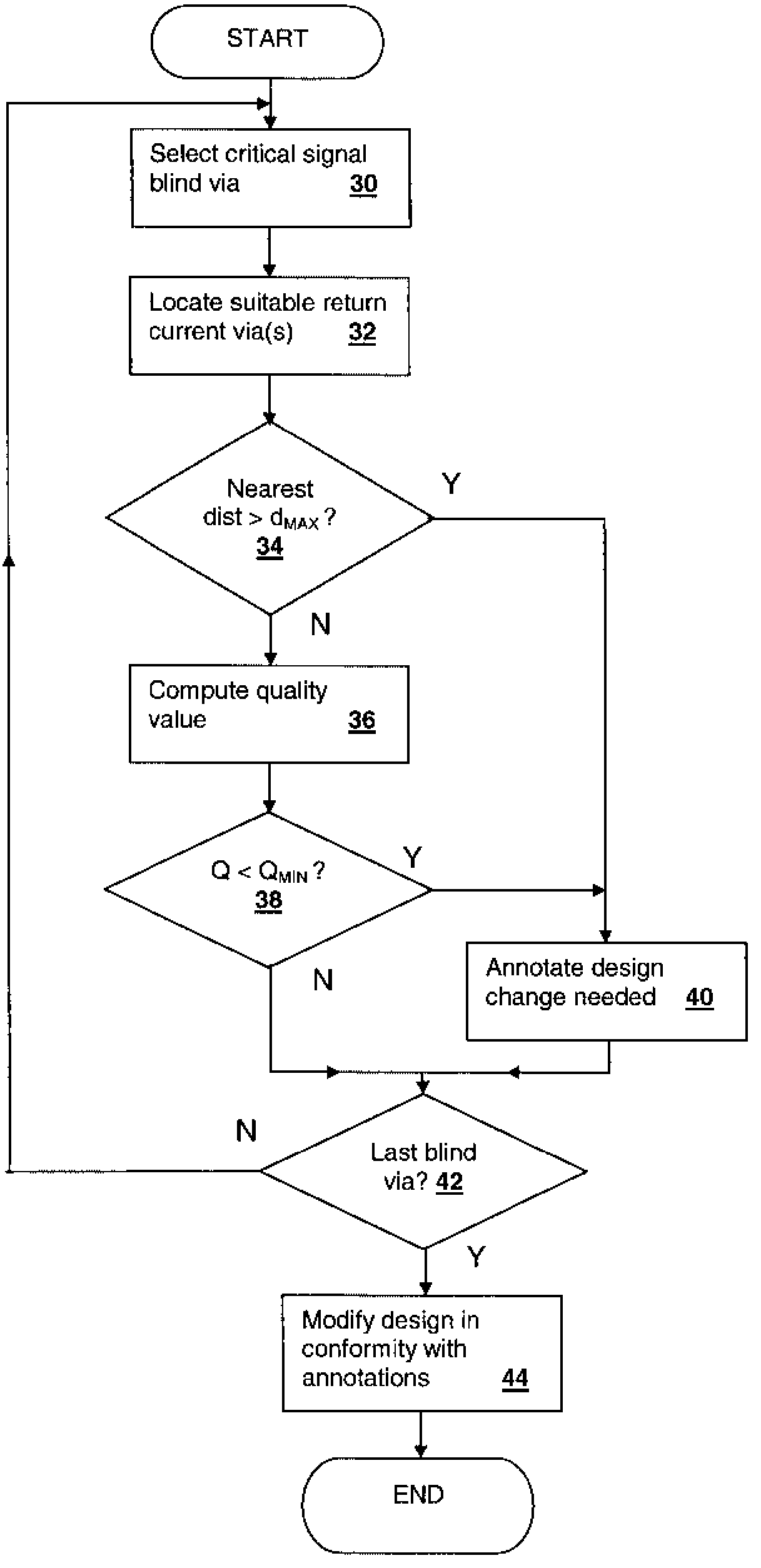

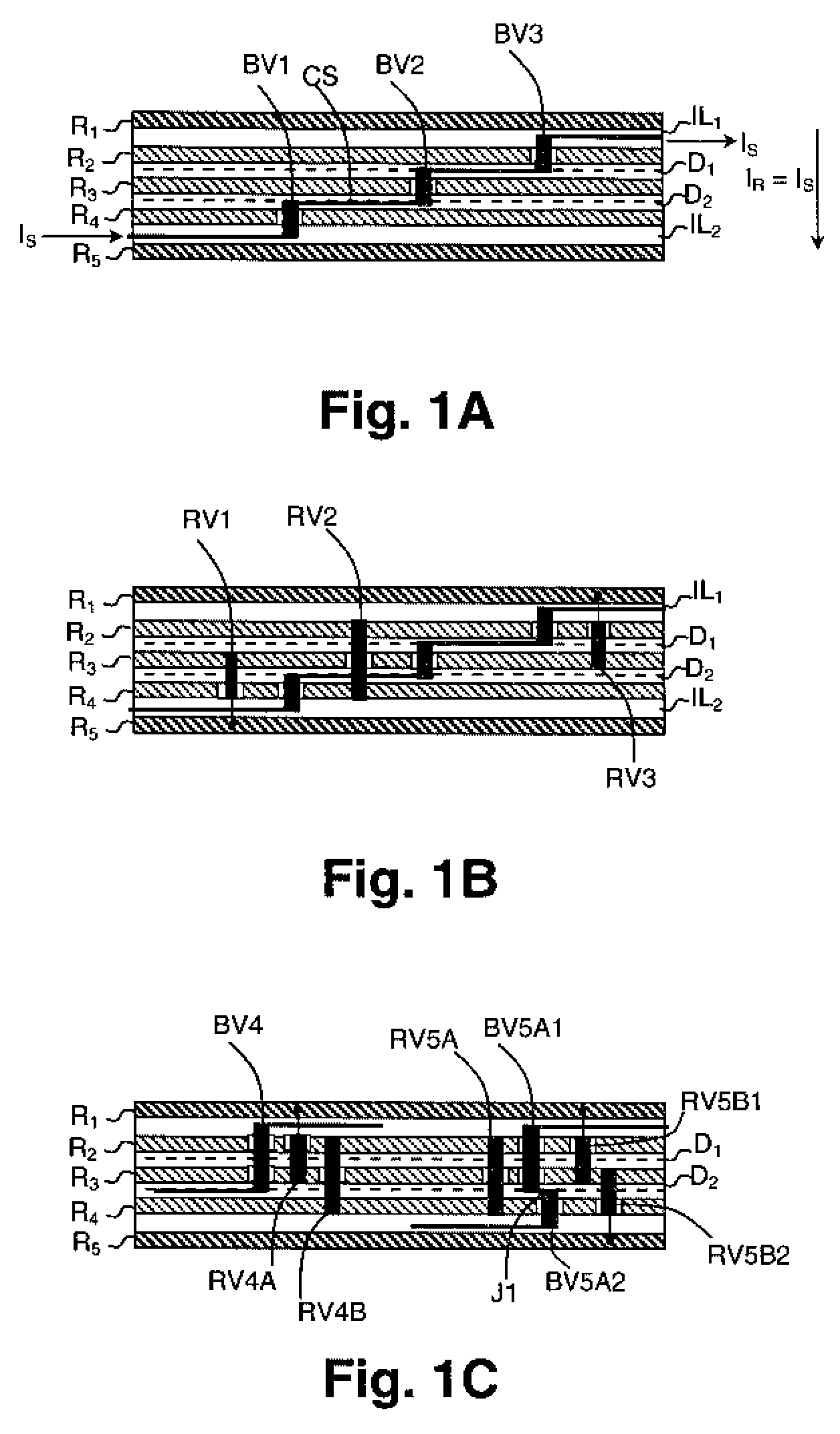

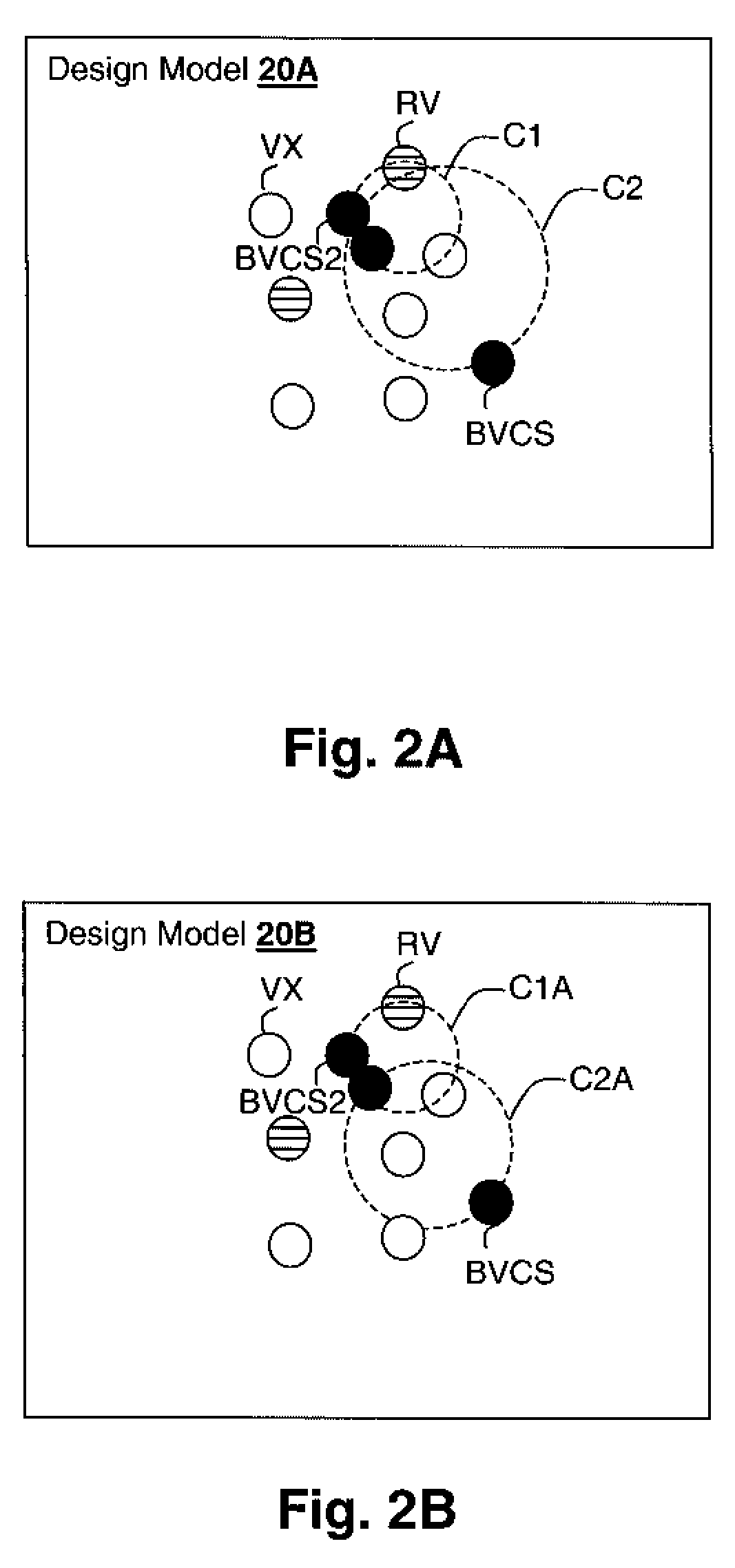

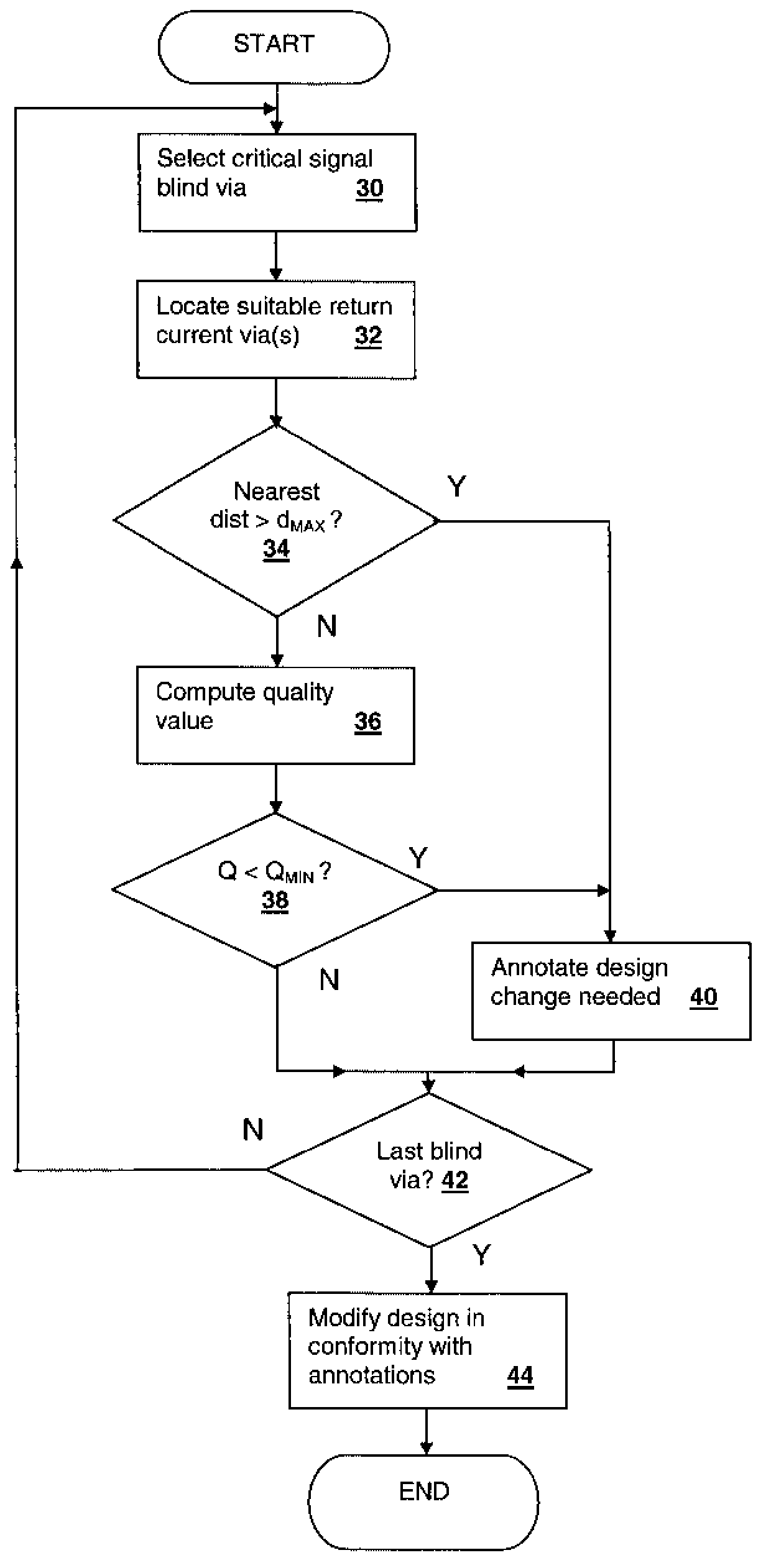

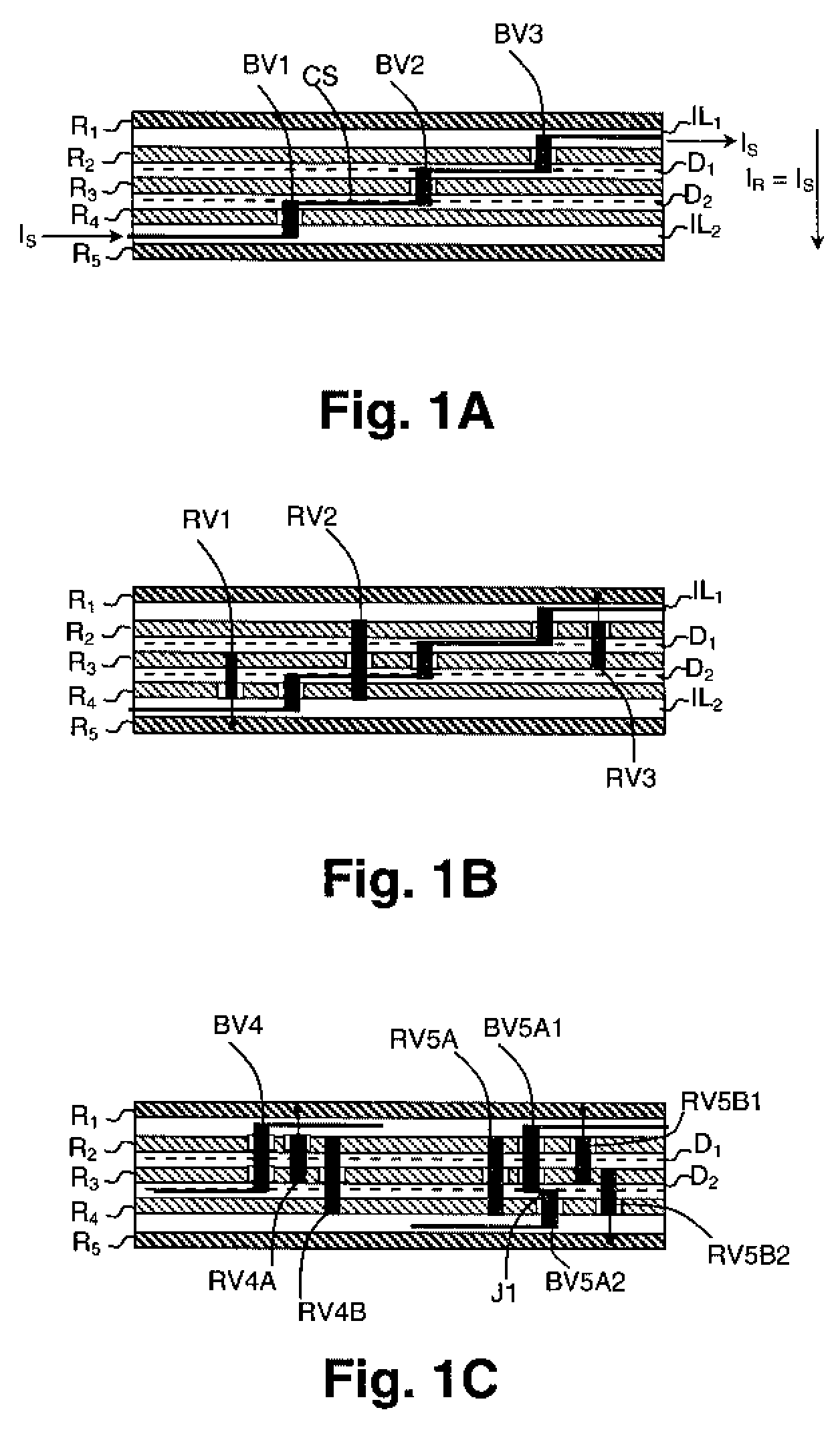

Design method and system for minimizing blind via current loops

ActiveUS7765504B2Cross-talk/noise/interference reductionPrinted circuit aspectsElectricityReturn current

A design method and system for minimizing blind via current loops provides for improvement of electrical interconnect structure design without requiring extensive electromagnetic analysis. Other vias in the vicinity of a blind via carrying a critical signal are checked for suitability to conduct return current corresponding to the critical signal that is disrupted by the transition from a layer between two metal planes to another layer. The distance to the return current via(s) is checked and the design is adjusted to reduce the distance if the distance is greater than a specified threshold. If the blind via transition is to an external layer, suitable vias connect the reference plane at the internal end of the blind via to an external terminal. If the transition is between internal layers, suitable vias are vias that connect the two reference planes surrounding the reference plane traversed by the blind via.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

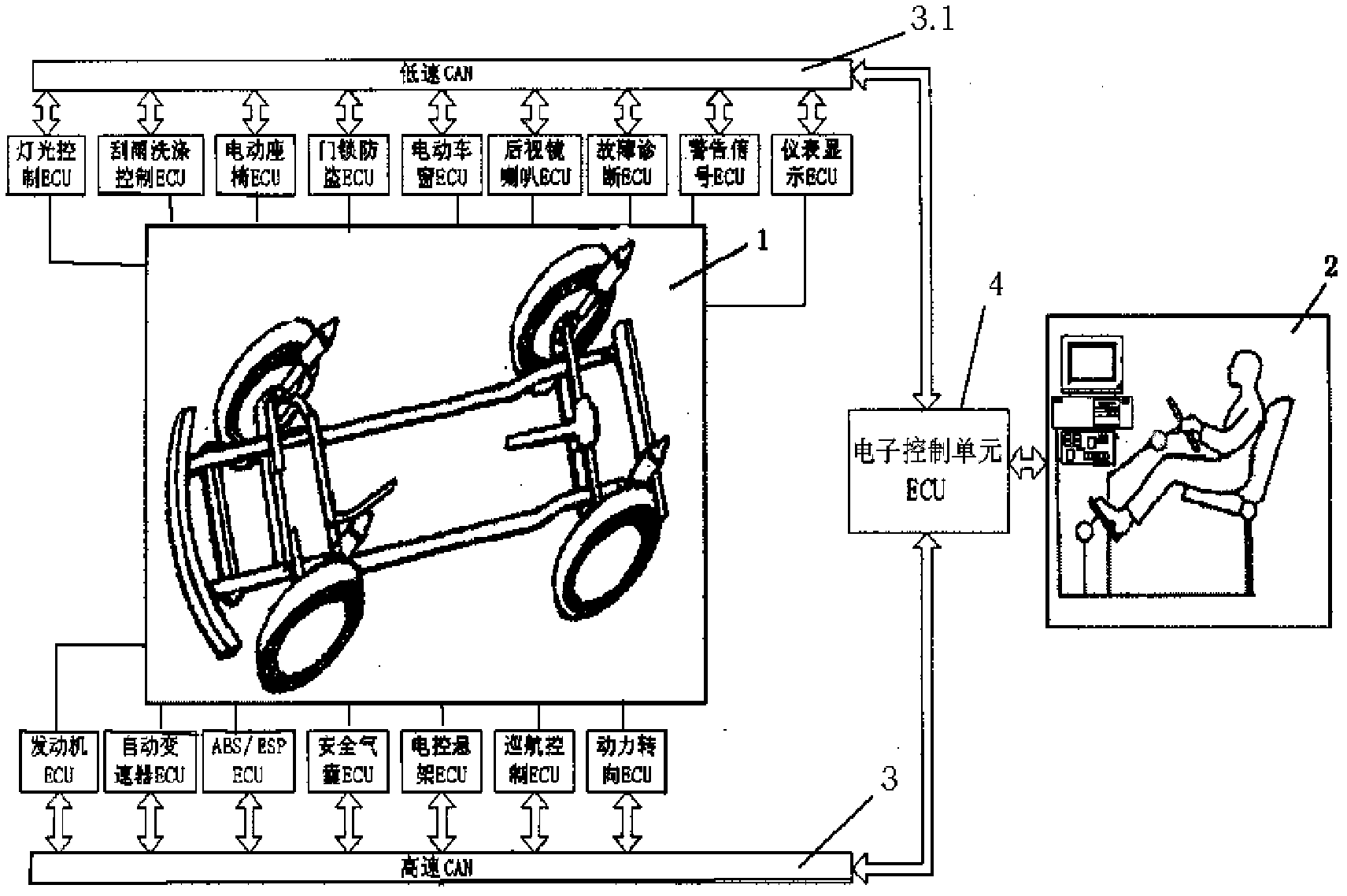

Automobile semi-physical simulation experimental system combining controller area network (CAN) bus and electronic control unit

InactiveCN102306022AOvercoming dangerOvercome inconvenienceTotal factory controlProgramme total factory controlVehicle frameArea network

The invention discloses an automobile semi-physical simulation experimental system combining a controller area network (CAN) bus and an electronic control unit, and belongs to the technical field of automobile design and development. The automobile semi-physical simulation system mainly comprises two parts: an entity part and a virtual simulation part, wherein the entity part is connected with the CAN bus through all systems including wheels, a frame, a power system and sensors of all control systems on an automobile chassis; the CAN bus is connected with the virtual simulation part through the electronic control unit; the virtual simulation part comprises a road view and a mathematical model; physical hardware is embedded into the simulation system; a software and hardware technique and an electronic technique are combined together; a computer is used for establishing a virtual model for reflecting an objective law; the virtual model is used for performing experiments; and certain acquired key signals are sent out by real hardware. The automobile semi-physical simulation system saves the cost compared with pure hardware, and has higher reliability compared with pure software.

Owner:CHINA AGRI UNIV

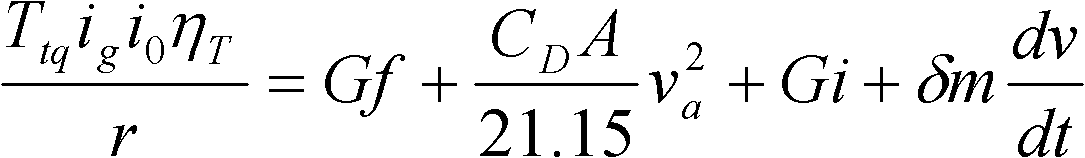

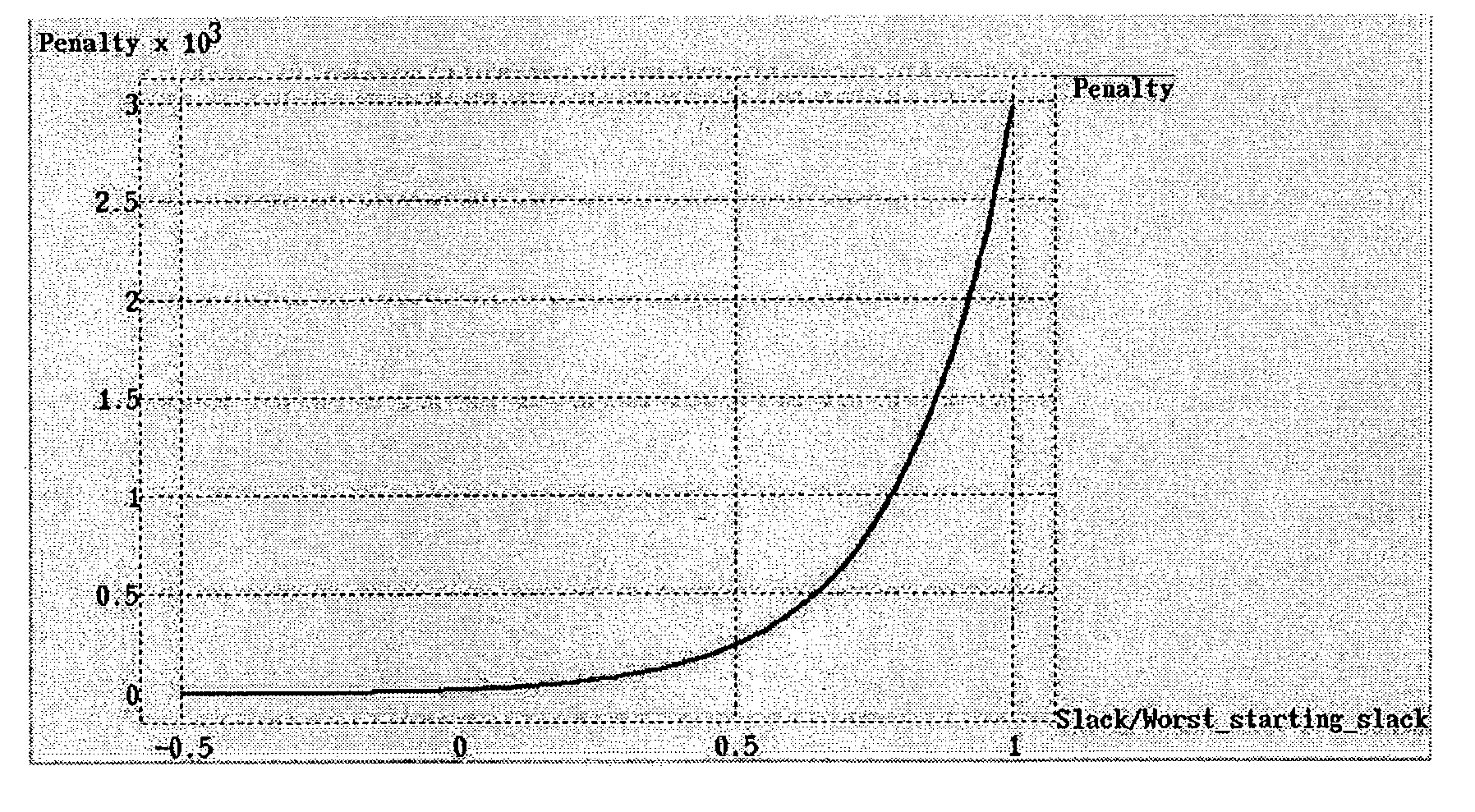

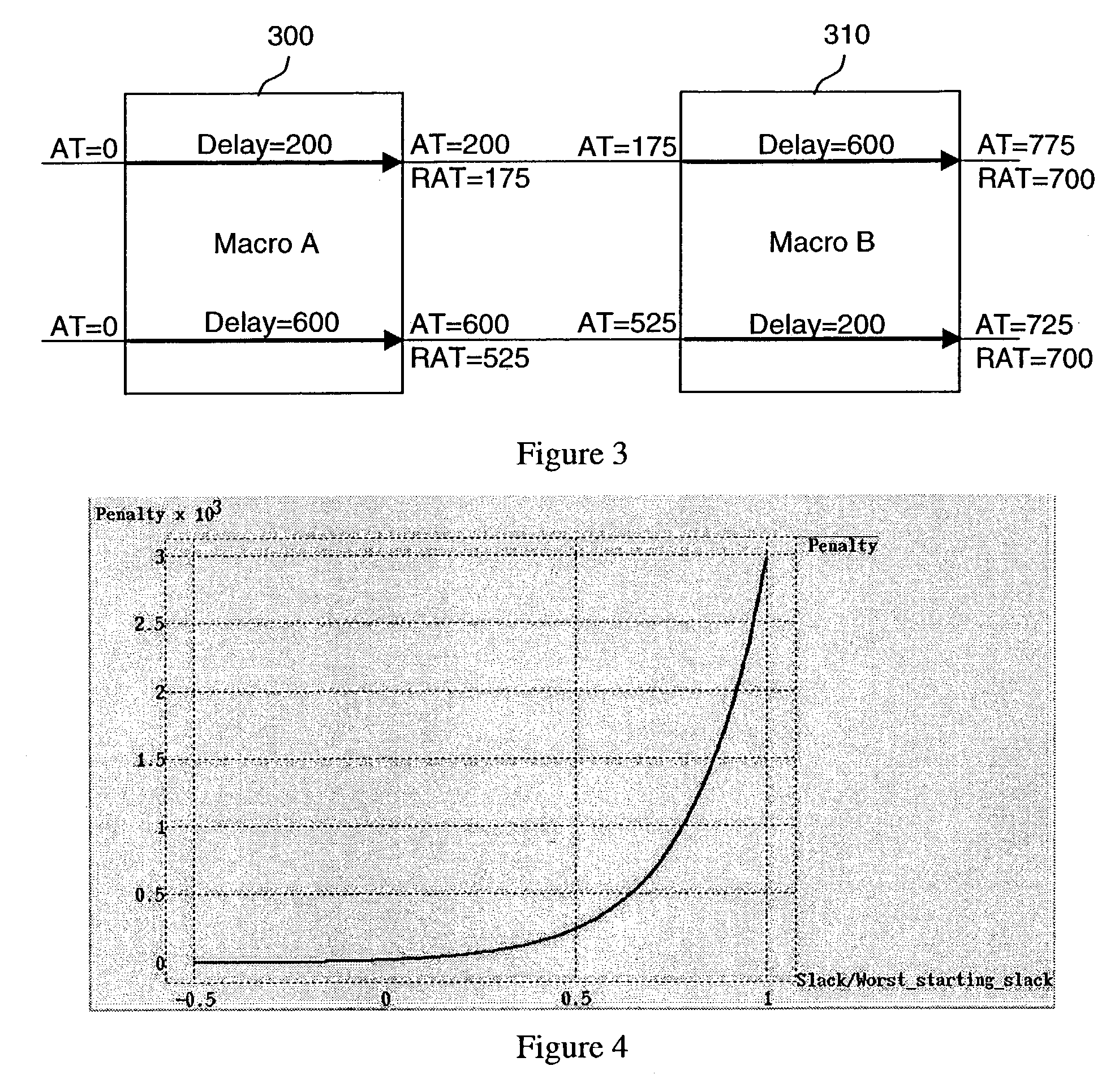

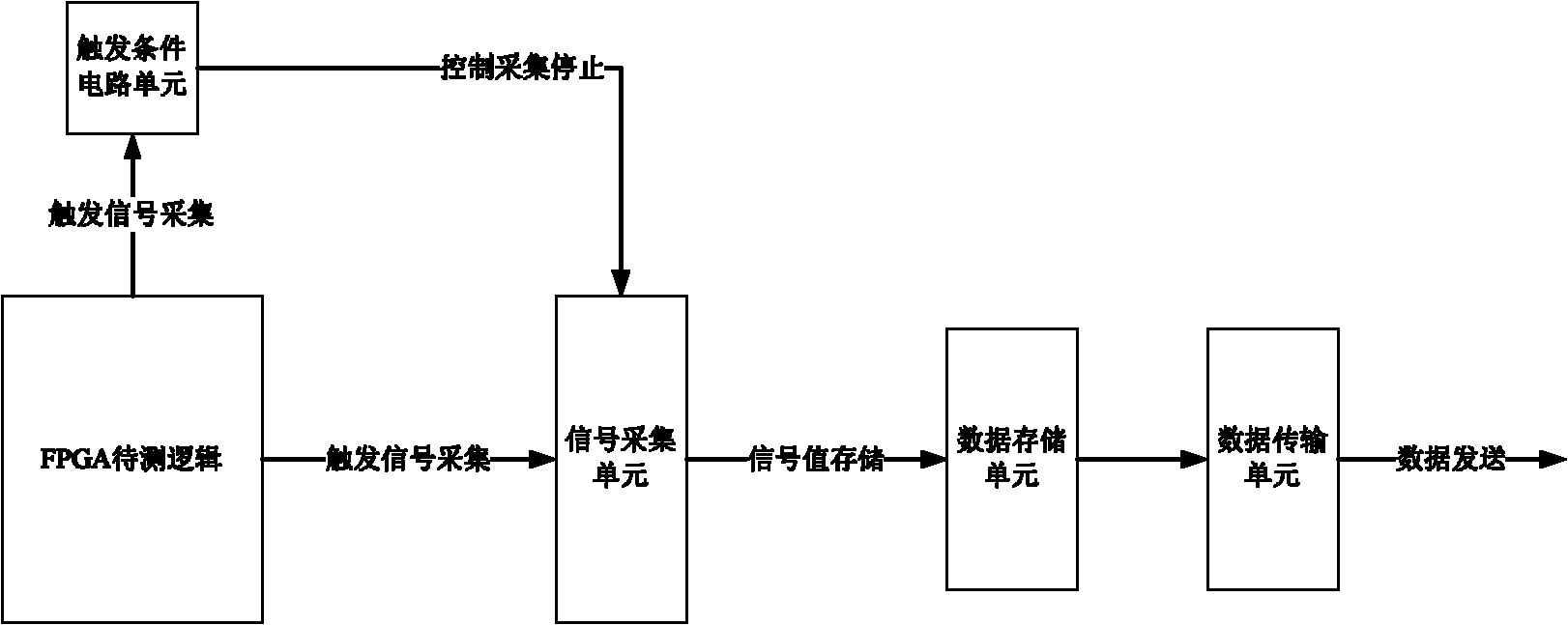

Method of achieving timing closure in digital integrated circuits by optimizing individual macros

InactiveUS7003747B2Computer aided designSoftware simulation/interpretation/emulationEngineeringTiming closure

Disclosed is a method for enhanced efficiency and effectiveness in achieving timing closure of large, complex, high-performance digital integrated circuits. Circuit macros are re-optimized and re-tuned in the timing closure loop by means of a reformulated objective function that allows the optimizer to improve the slack of all signals rather than just the most critical one(s). The incentive to improve the timing of a sub-critical signal is a diminishing function of the criticality of the signal. Thus all signals are improved during the optimization, with the highest incentive to improve on the most critical signals, leading to faster and more effective overall timing closure.

Owner:GLOBALFOUNDRIES INC

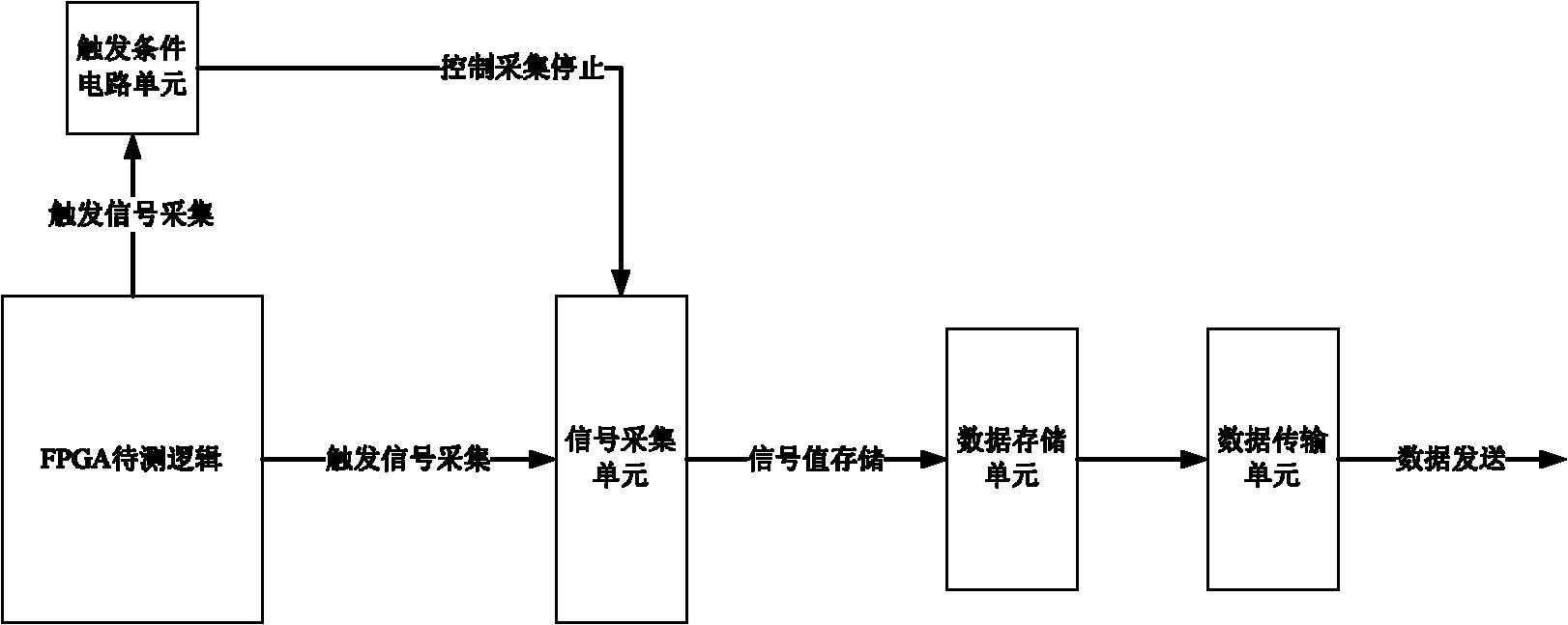

System and method for debugging FPGA (field programmable gate array)

The invention provides a system and a method for debugging an FPGA (field programmable gate array). The system comprises an FPGA logic module to be tested, a signal acquisition unit module, a trigger condition circuit unit module and a data transmission unit module, wherein the signal acquisition unit module acquires trigger signals transmitted from the FPGA logic module to be tested, and the trigger condition circuit unit module controls stopping of signal acquisition of the signal acquisition unit. The method adds a trigger condition circuit unit for debugging and a signal acquisition unit for acquiring key signals. The system and the method for debugging the FPGA have the advantages that external cables in debugging are omitted, the system is convenient to use, external high-capacity storage resources of the FPGA can be used, analyzable data volume after condition trigger is increased, and rapider positioning is benefited.

Owner:DAWNING INFORMATION IND BEIJING +1

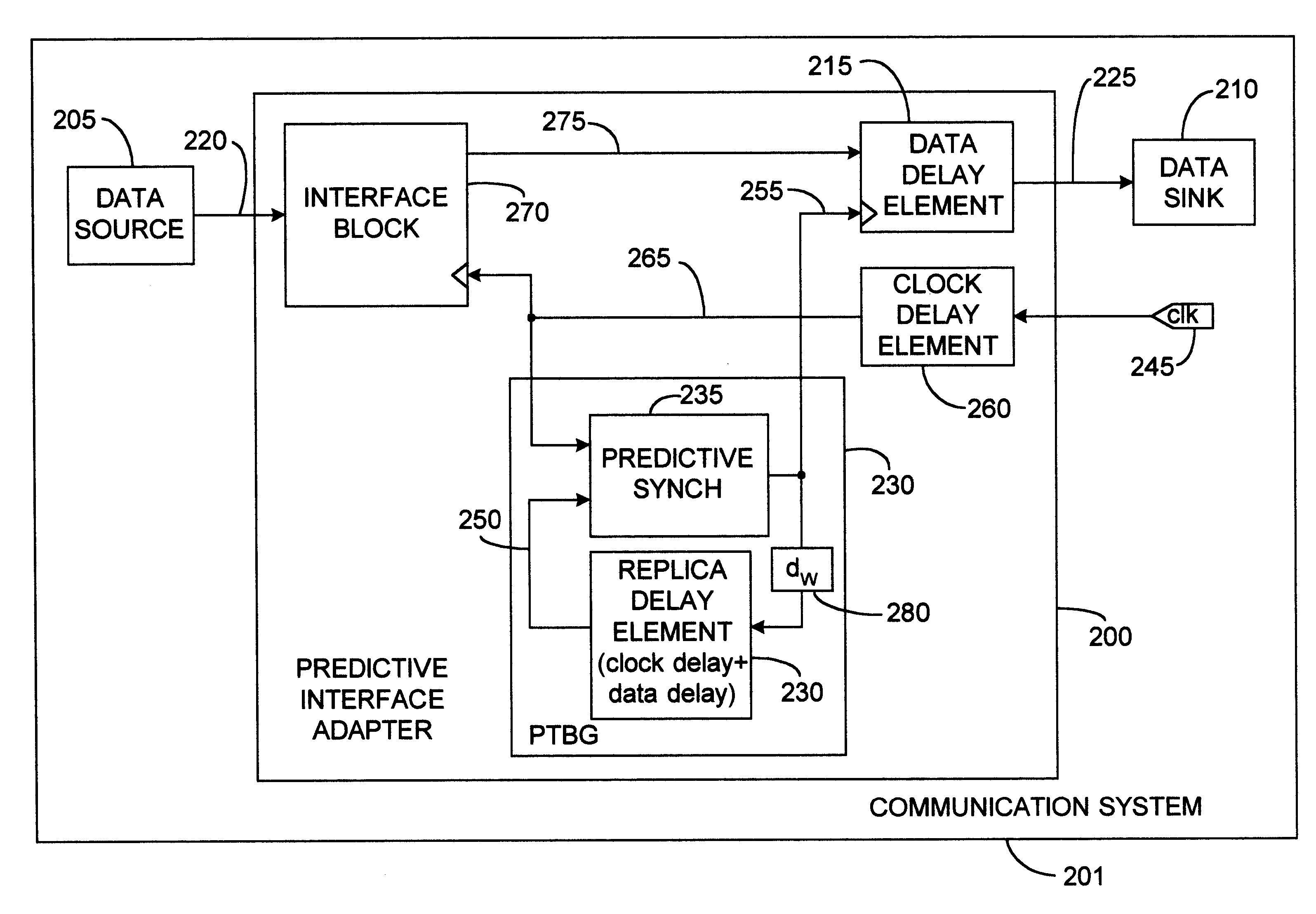

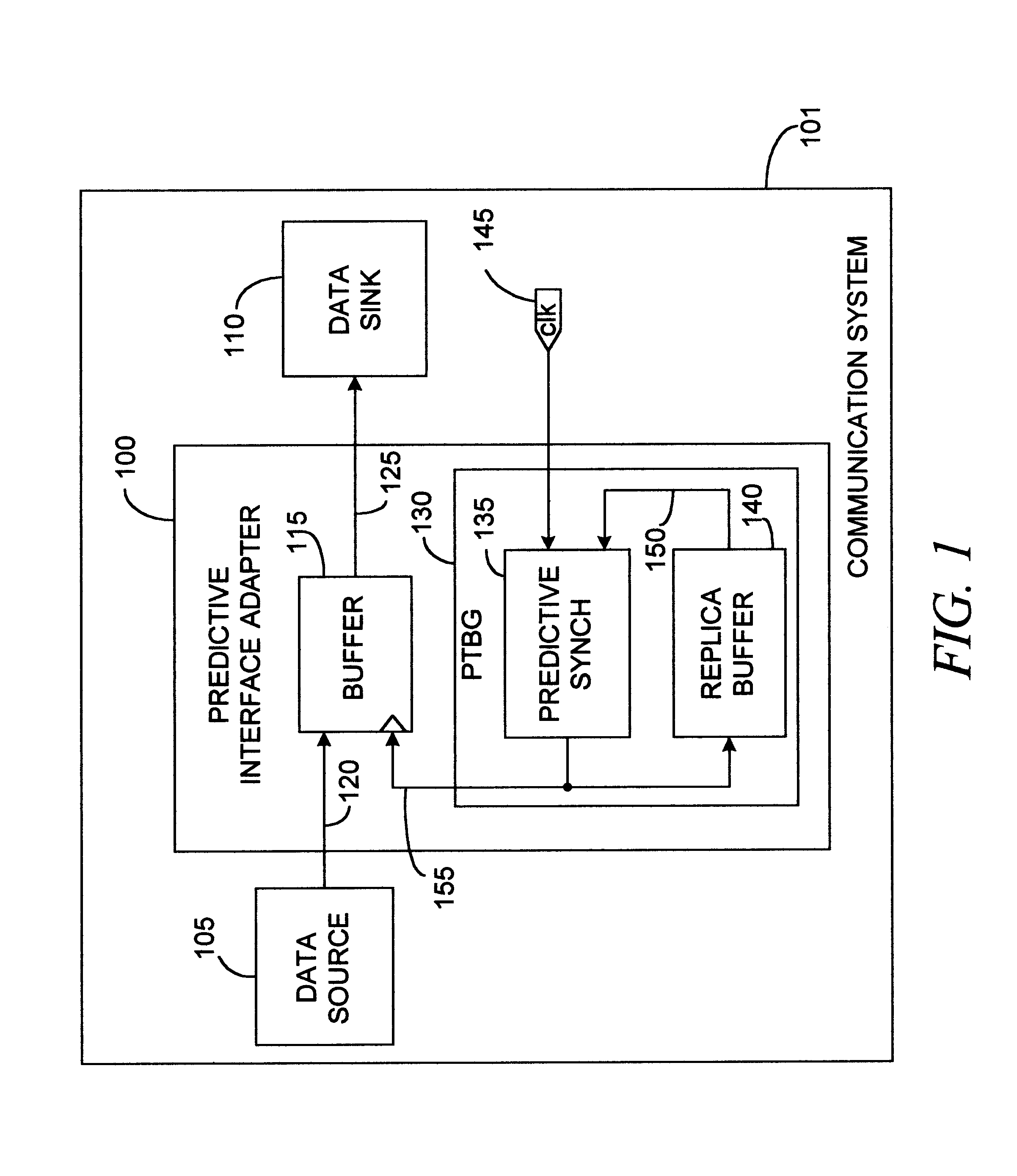

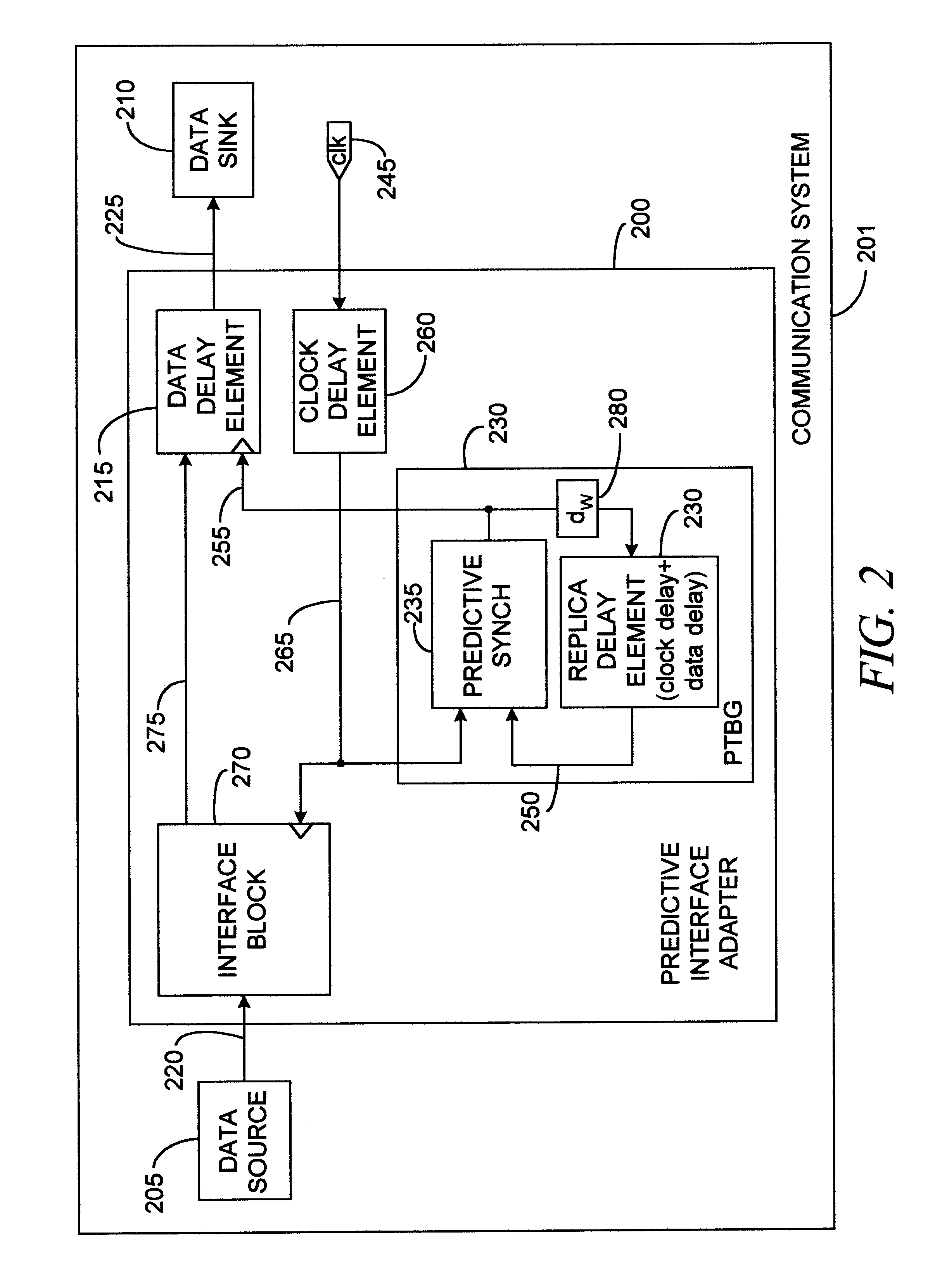

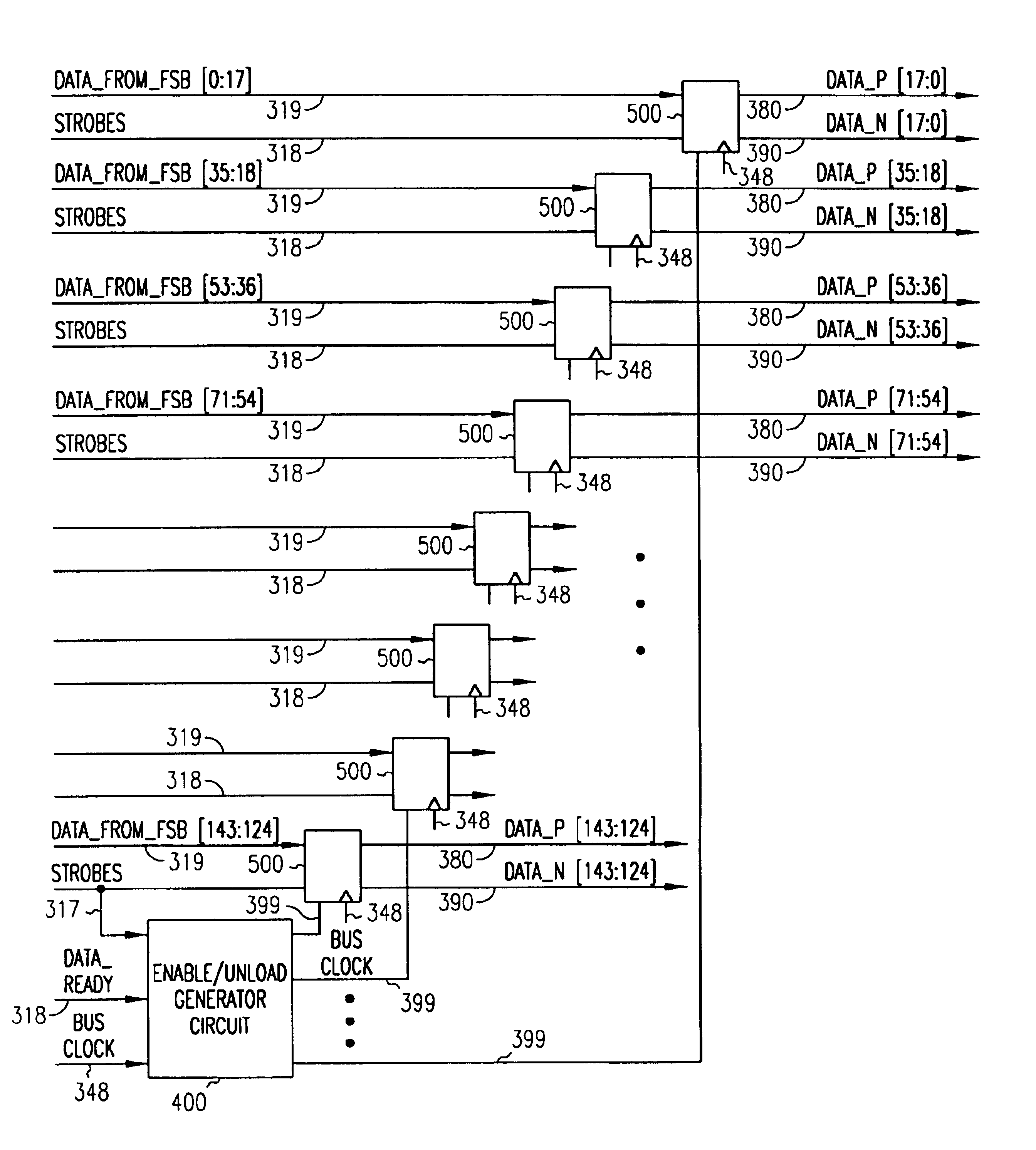

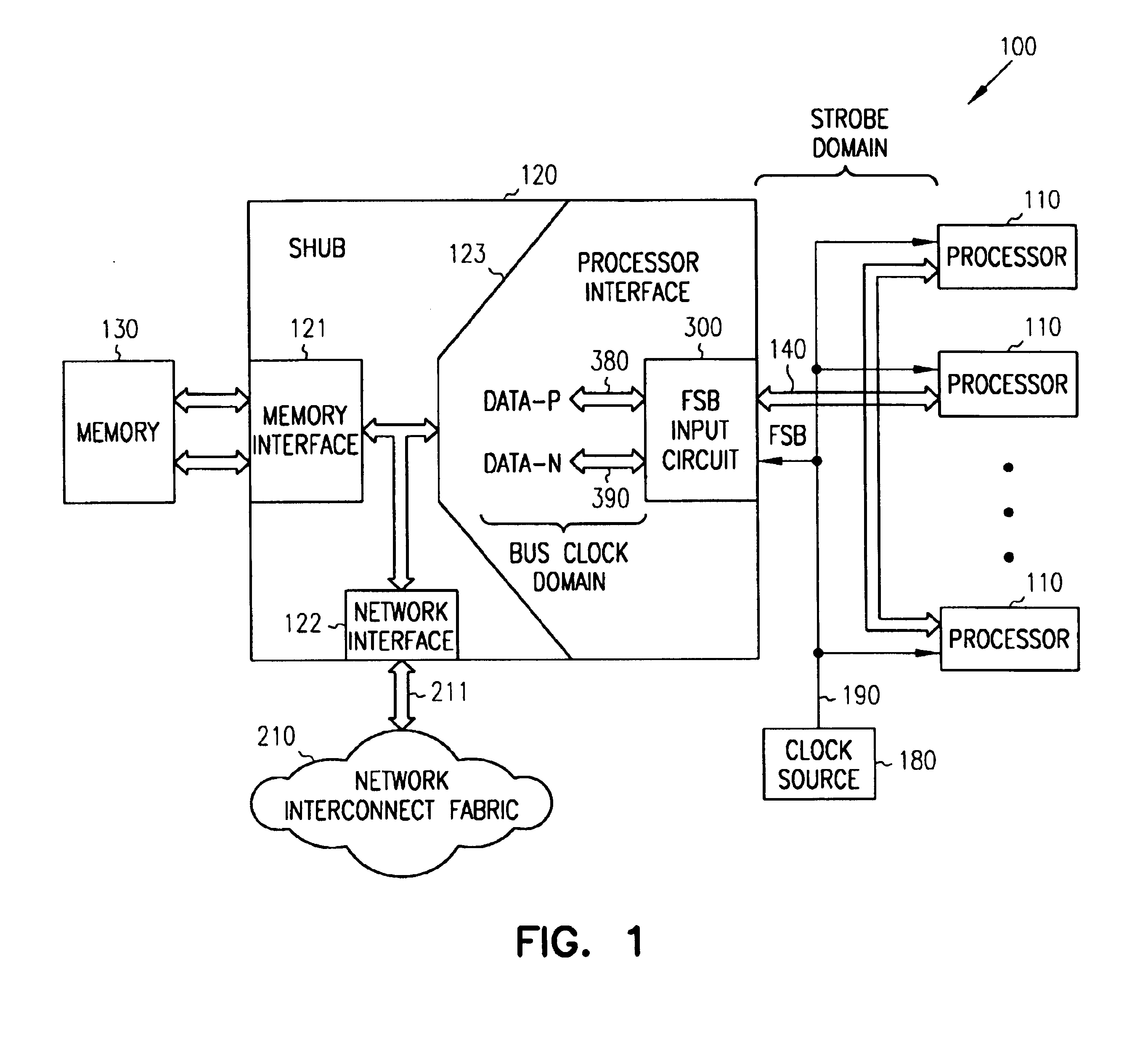

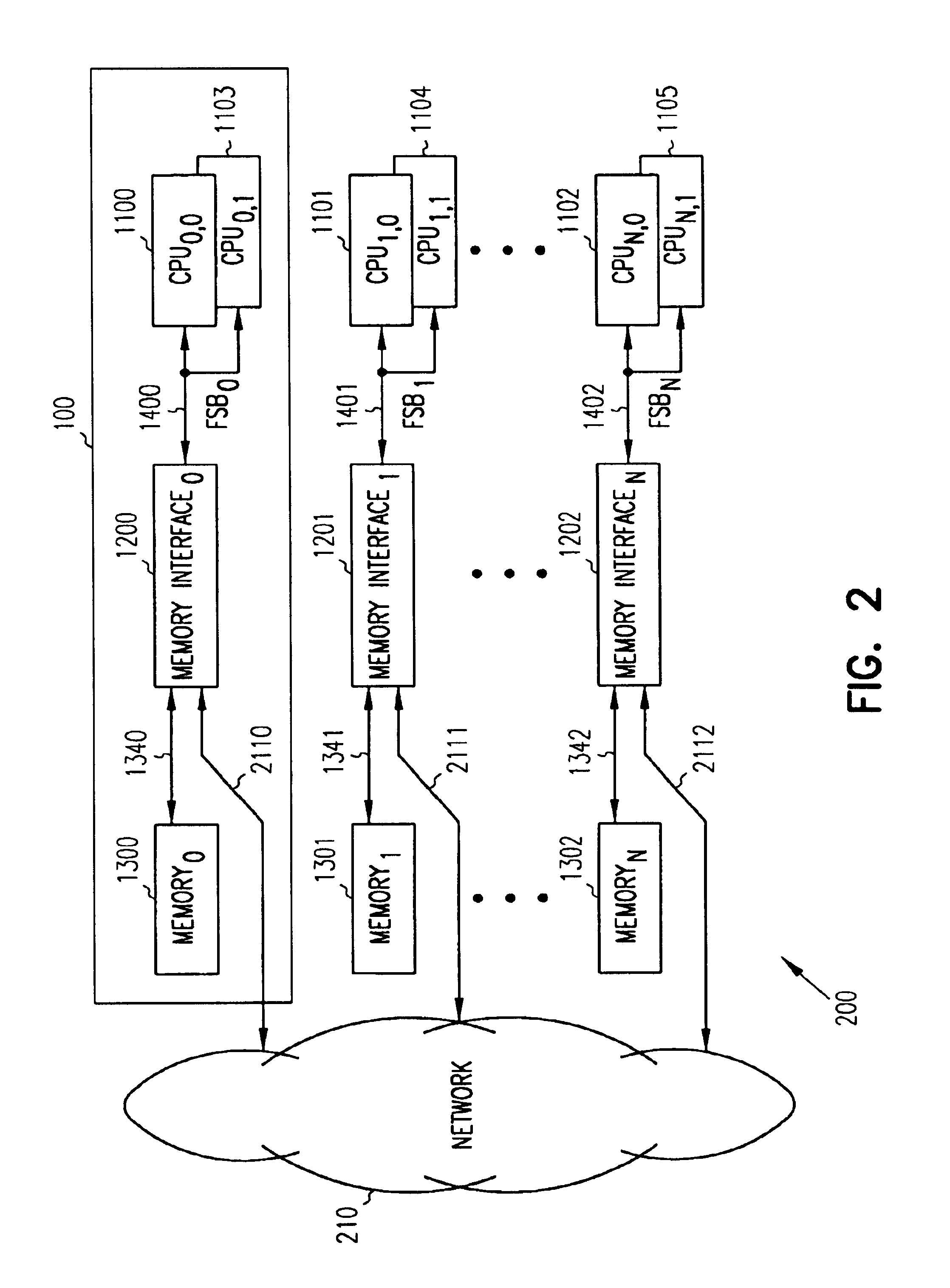

Method and circuit for reliable data capture in the presence of bus-master changeovers

InactiveUS6839856B1Data collection is reliableTo overcome the large delayDigital storageGenerating/distributing signalsData synchronizationData stream

A bus interface circuit and method for reliable data capture in the presence of bus-master changeovers and / or for synchronizing received data to an internal clock signal, wherein the received data includes a strobe. Since the strobe may have a delay that is unknown (due to varying distances from the driver, clock jitter, and / or other causes), it is important to re-synchronize to the internal clock, and to do so with the smallest delay possible. This synchronization is provided in a way that also eliminates potential problems due to bus-master changeover, and in a way that minimizes time-critical signal generation. One aspect provides a method and / or apparatus for reliable data capture. The method includes: providing an N-stage latch including a first stage latch and a second stage latch, wherein N is two or larger; loading every Nth word of a data stream into the first stage latch using a first signal based on a strobe passed in the data stream; loading every N+1st word of the data stream into the second stage latch using a second signal based on the strobe passed in the data stream; unloading every Nth word from the first stage latch using a third signal based on an internal bus clock; and unloading every N+1st word from the second stage latch using a fourth signal based on the internal bus clock. In some embodiments, the first signal and the second signal are further based on a first stage selector and on a data_ready signal passed in the data stream.

Owner:MORGAN STANLEY

Design Method and System for Minimizing Blind Via Current Loops

ActiveUS20090031270A1Cross-talk/noise/interference reductionPrinted circuit aspectsElectricityReturn current

A design method and system for minimizing blind via current loops provides for improvement of electrical interconnect structure design without requiring extensive electromagnetic analysis. Other vias in the vicinity of a blind via carrying a critical signal are checked for suitability to conduct return current corresponding to the critical signal that is disrupted by the transition from a layer between two metal planes to another layer. The distance to the return current via(s) is checked and the design is adjusted to reduce the distance if the distance is greater than a specified threshold. If the blind via transition is to an external layer, suitable vias connect the reference plane at the internal end of the blind via to an external terminal. If the transition is between internal layers, suitable vias are vias that connect the two reference planes surrounding the reference plane traversed by the blind via.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

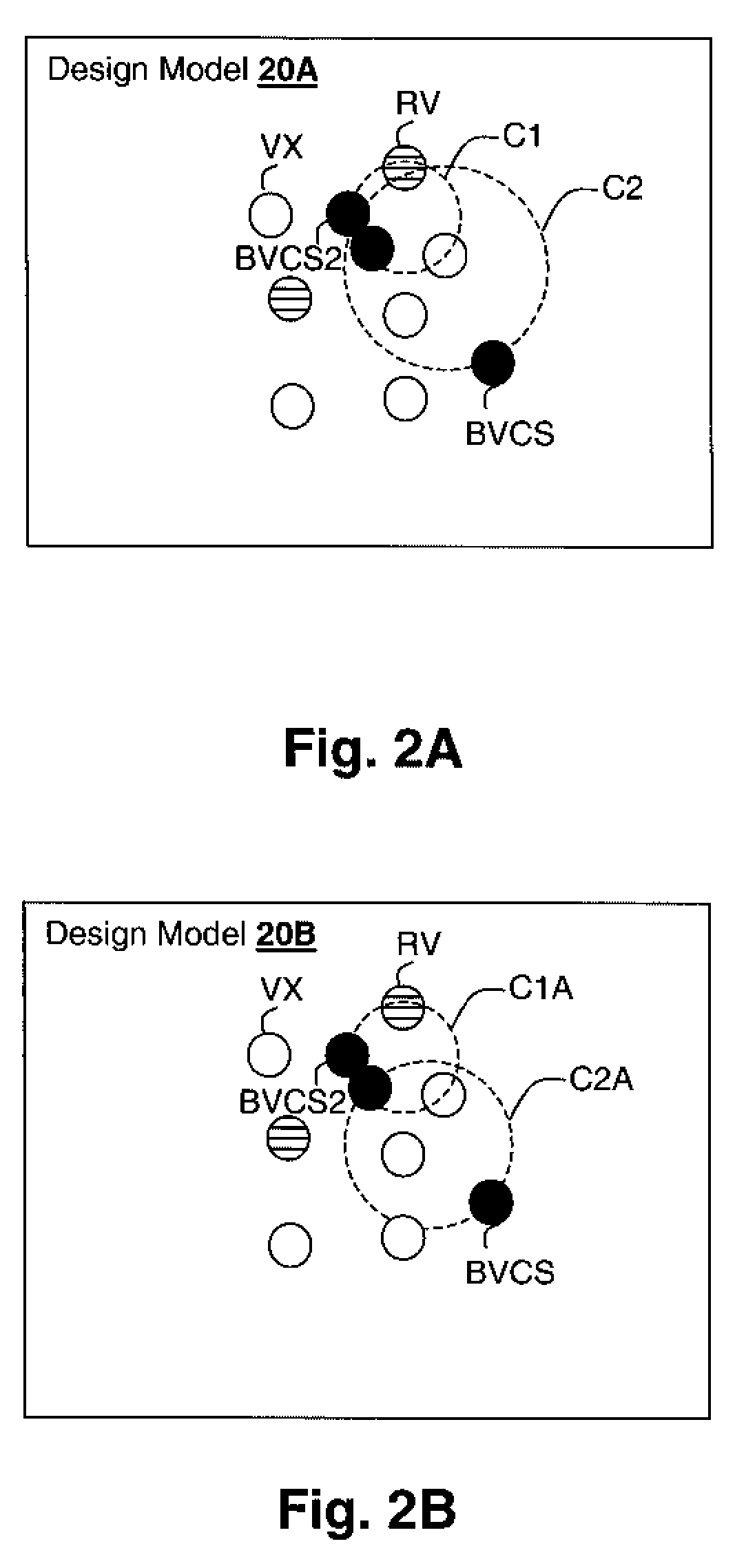

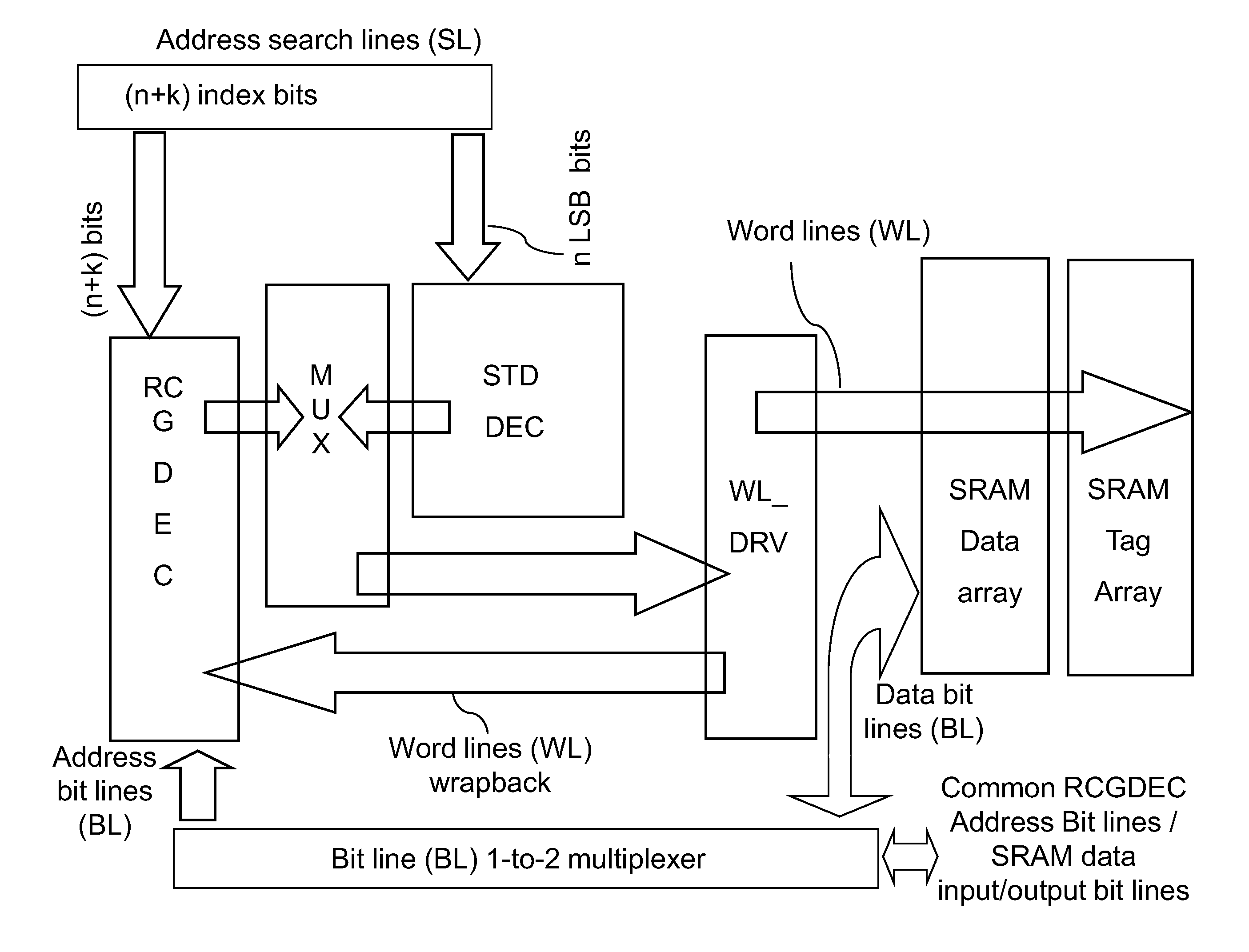

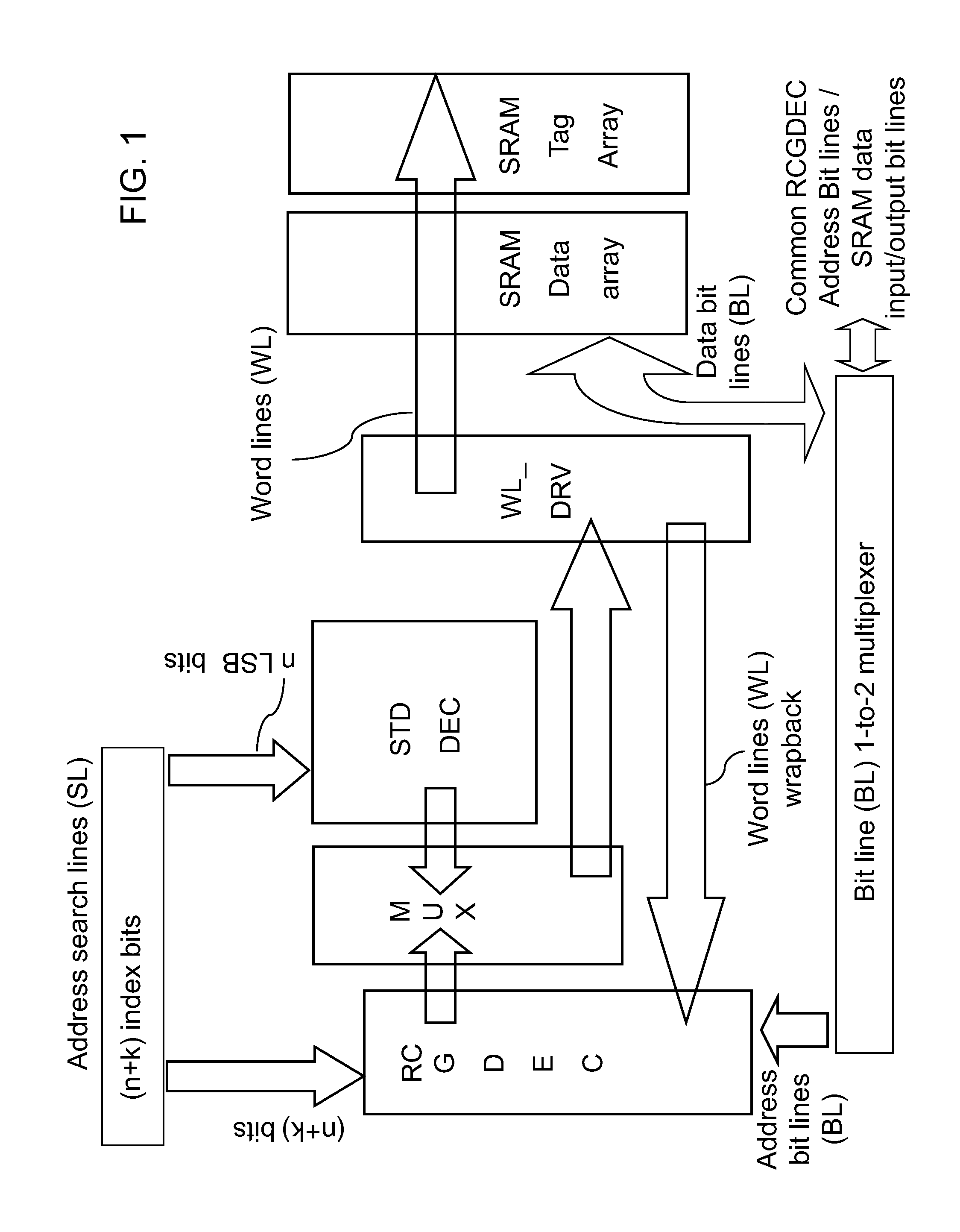

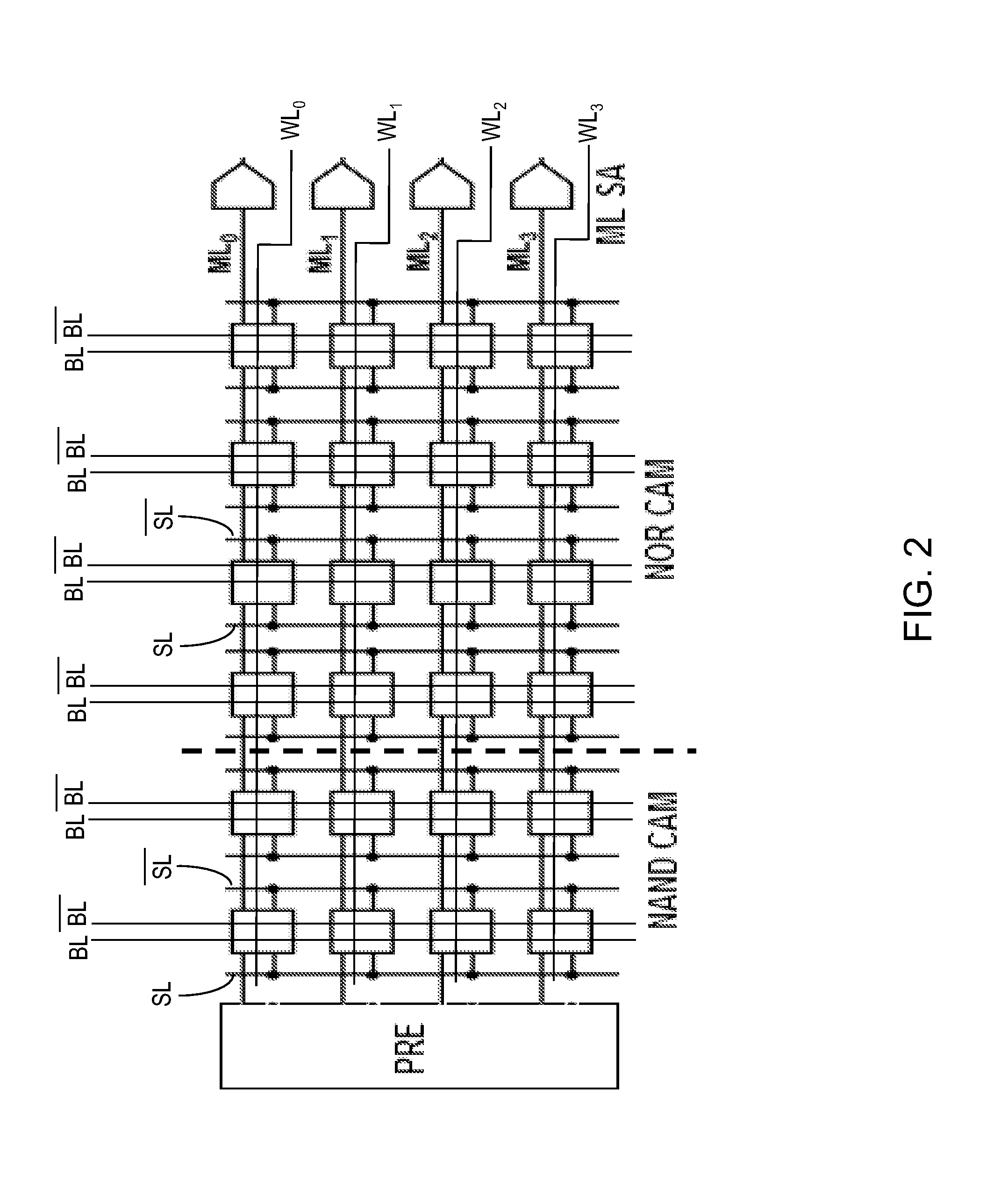

Self-reconfigurable address decoder for associative index extended caches

InactiveUS20140025881A1Low area overheadLevel of associativityMemory architecture accessing/allocationMemory adressing/allocation/relocationAddress decoderOperation mode

Associative index extended (AIX) caches can be functionally implemented through a reconfigurable decoder that employs programmable line decoding. The reconfigurable decoder features scalability in the number of lines, the number of index extension bits, and the number of banks. The reconfigurable decoder can switch between pure direct mapped (DM) mode and direct mapped-associative index extended (DM-AIX) mode of operation. For banked configurations, the reconfigurable decoder provides the ability to run some banks in DM mode and some other banks in DM-AIX mode. A cache employing this reconfigurable decoder can provide a comparable level of latency as a DM cache with minimal modifications to a DM cache circuitry of an additional logic circuit on a critical signal path, while providing low power operation at low area overhead with SA cache-like miss rates. Address masking and most-recently-used-save replacement policy can be employed with a single bit overhead per line.

Owner:GLOBALFOUNDRIES INC

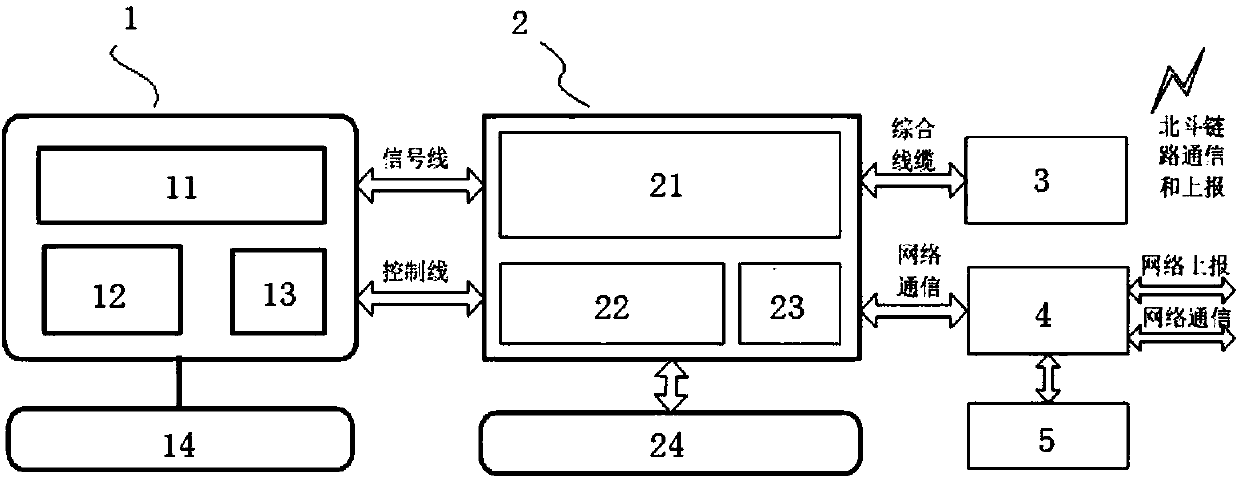

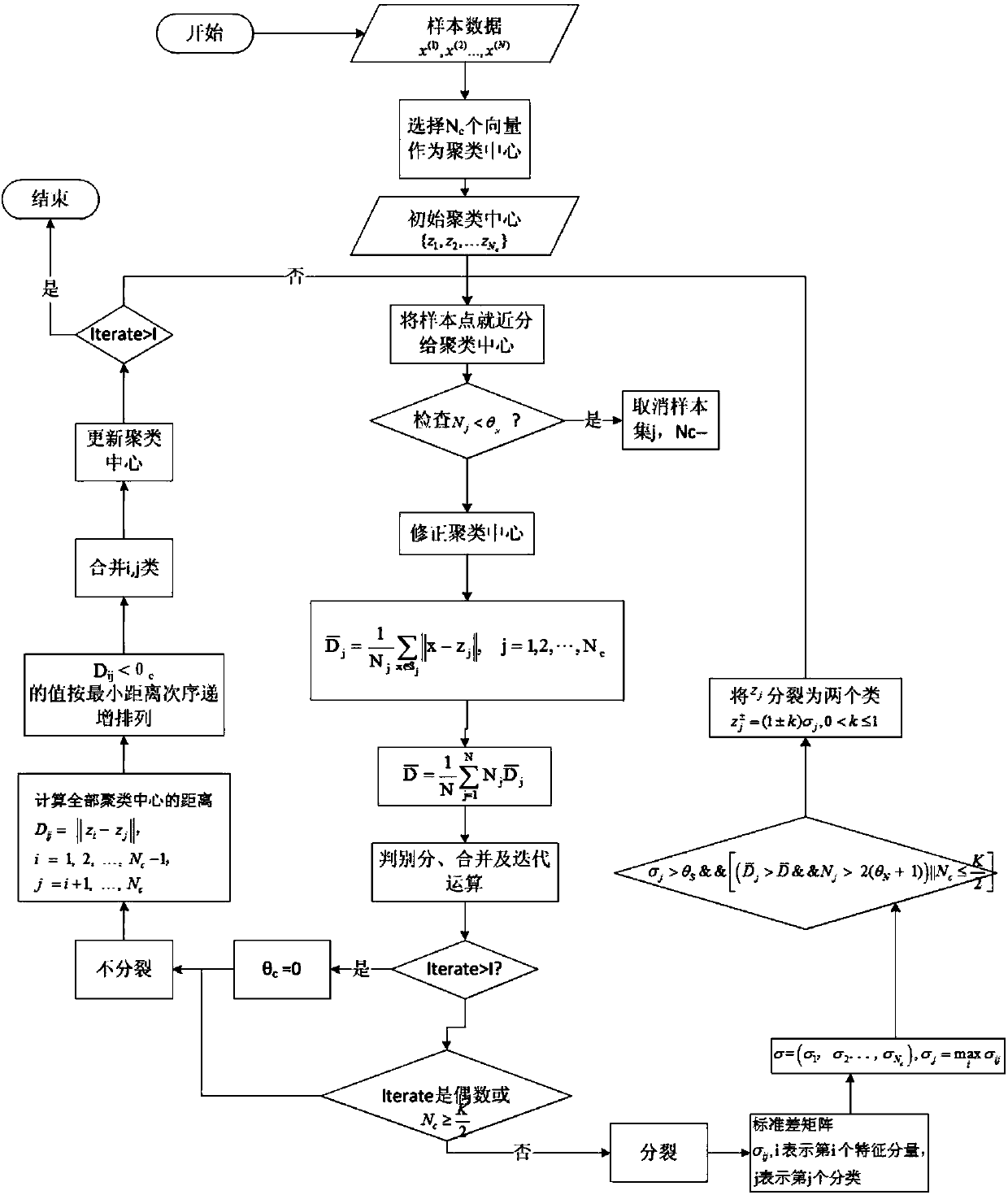

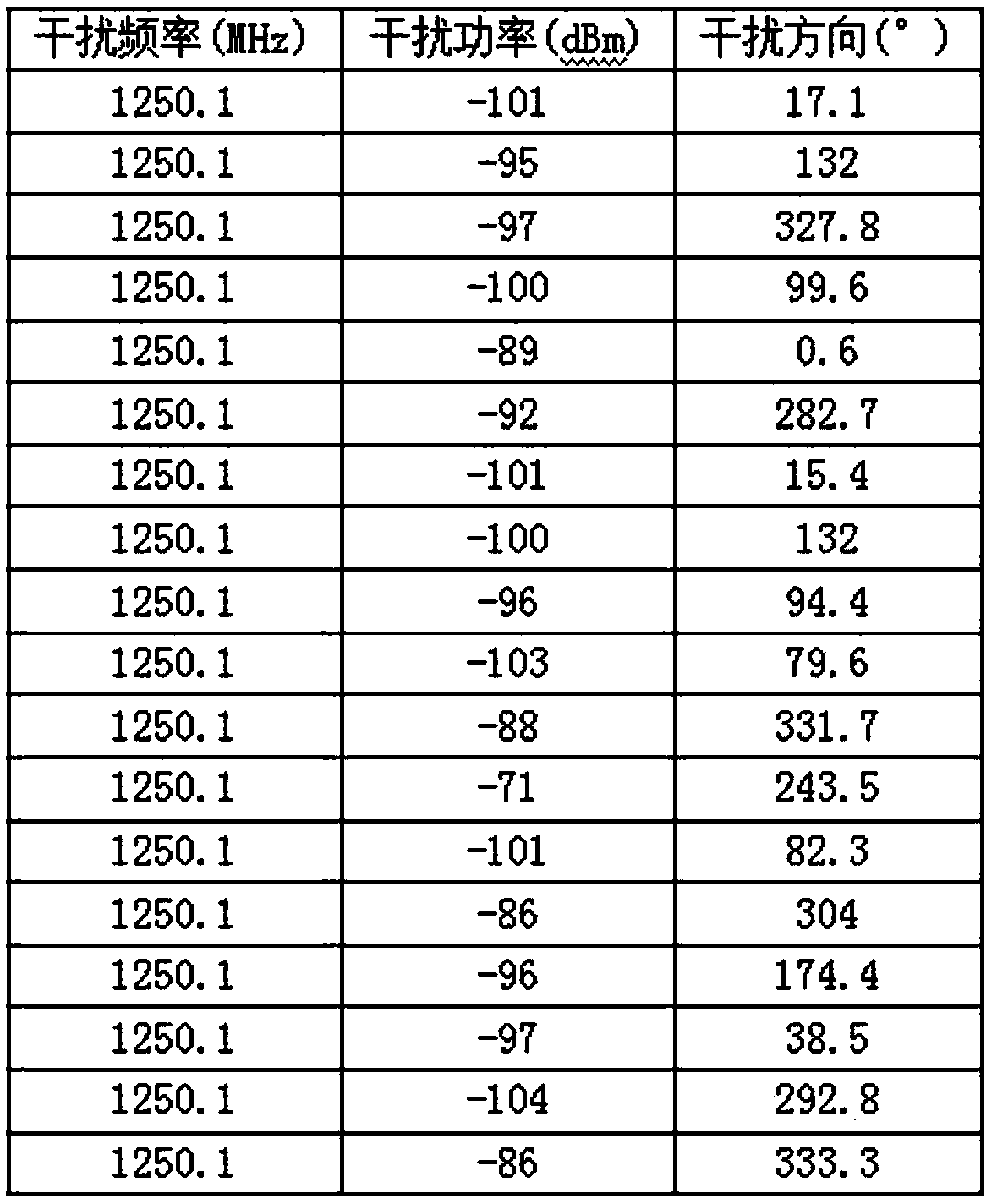

ISODATA-based interference source classification and identification algorithm and device

ActiveCN107729916ASimplicity concernsGeneral concernCharacter and pattern recognitionDirection findersIdentification deviceElectronic information

The invention relates to an ISODATA-based interference source classification and identification algorithm and an ISODATA-based interference source classification and identification device, which belong to the field of electronic information, and perform classification and identification on unknown interference sources in space. The ISODATA-based interference source classification and identification algorithm comprises the steps of: acquiring PDW of signals in a region by using an interference source monitoring and positioning device, subjecting each class of eigenvalue output by the interference source monitoring and positioning device to one-dimensional ISODATA resolving, extracting an original eigenvalue within a time period from a queue to be retrived in an eigenvalue database, performing clustering analysis on the original eigenvalue by adopting multi-dimensional ISODATA, outputting a number of clustering and a feature clustering center value to a user in real time, and regarding the number of clustering and the feature clustering center value as effective features of a most possible interference signal. The ISODATA-based interference source classification and identification algorithm and the ISODATA-based interference source classification and identification device perform quasi-real-time unsupervised clustering analysis on an original monitoring result of the interferencesource monitoring and positioning device so as to present feature parameters of key signals in the monitoring result to the user, have higher flexibility, and are more reasonable.

Owner:CHENGDU ZHONGSEN COMM TECH CO LTD

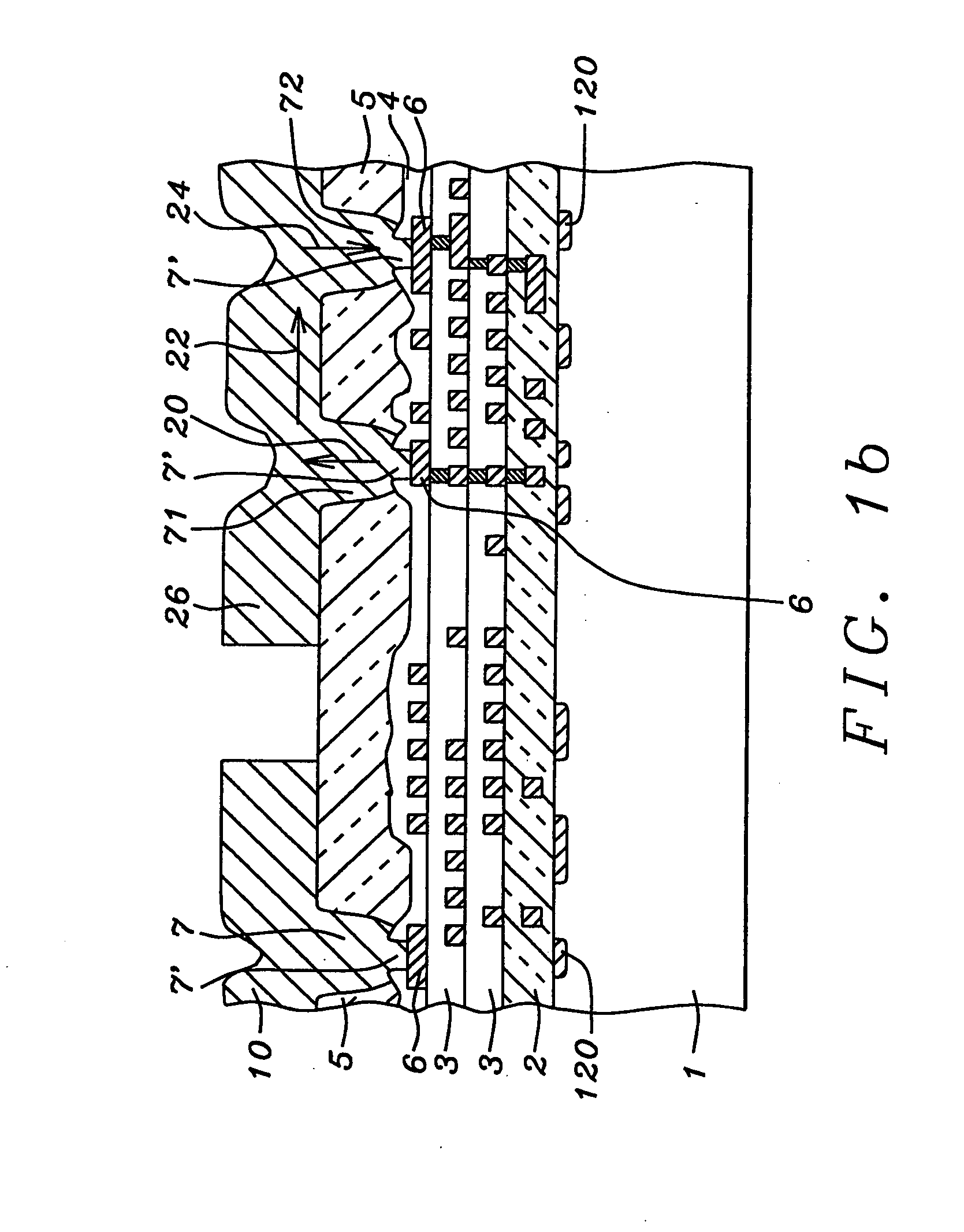

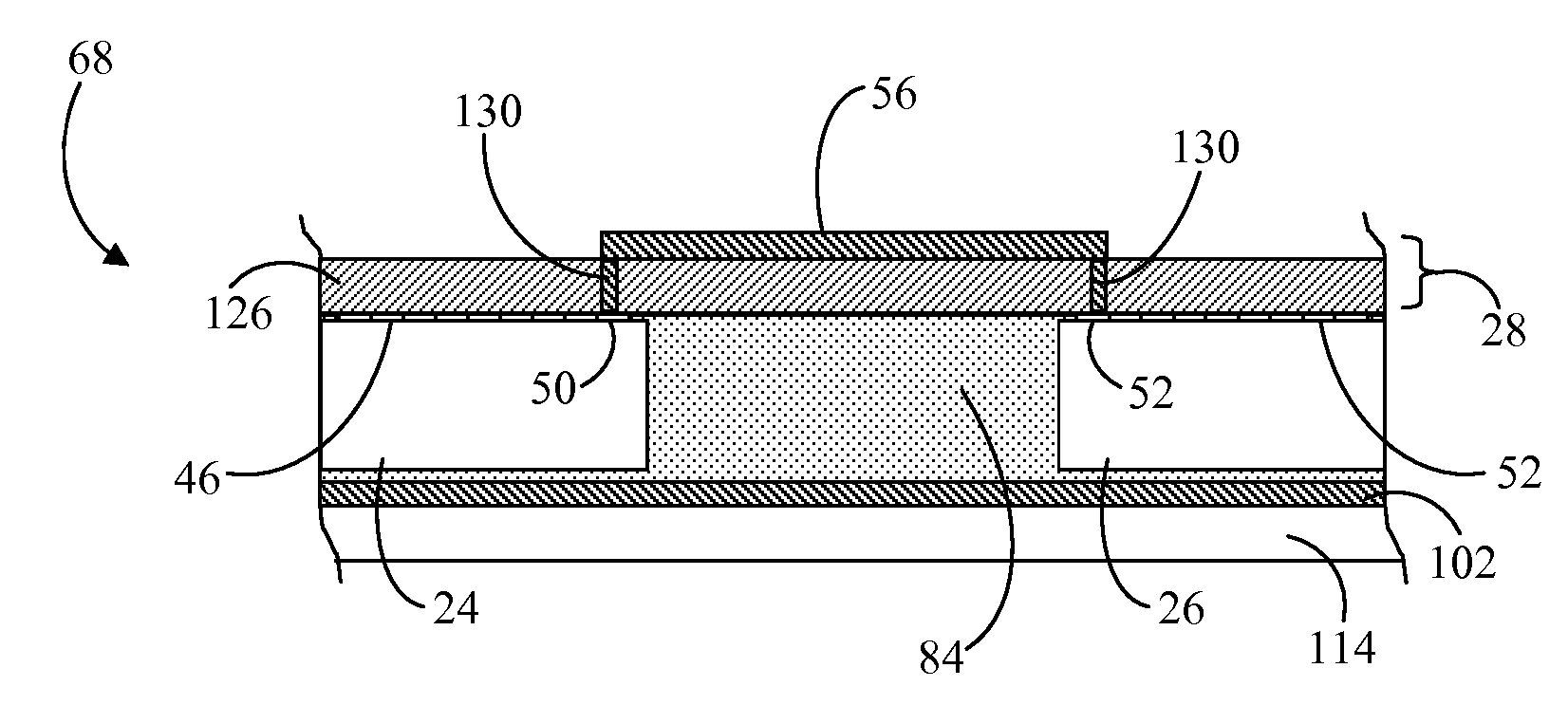

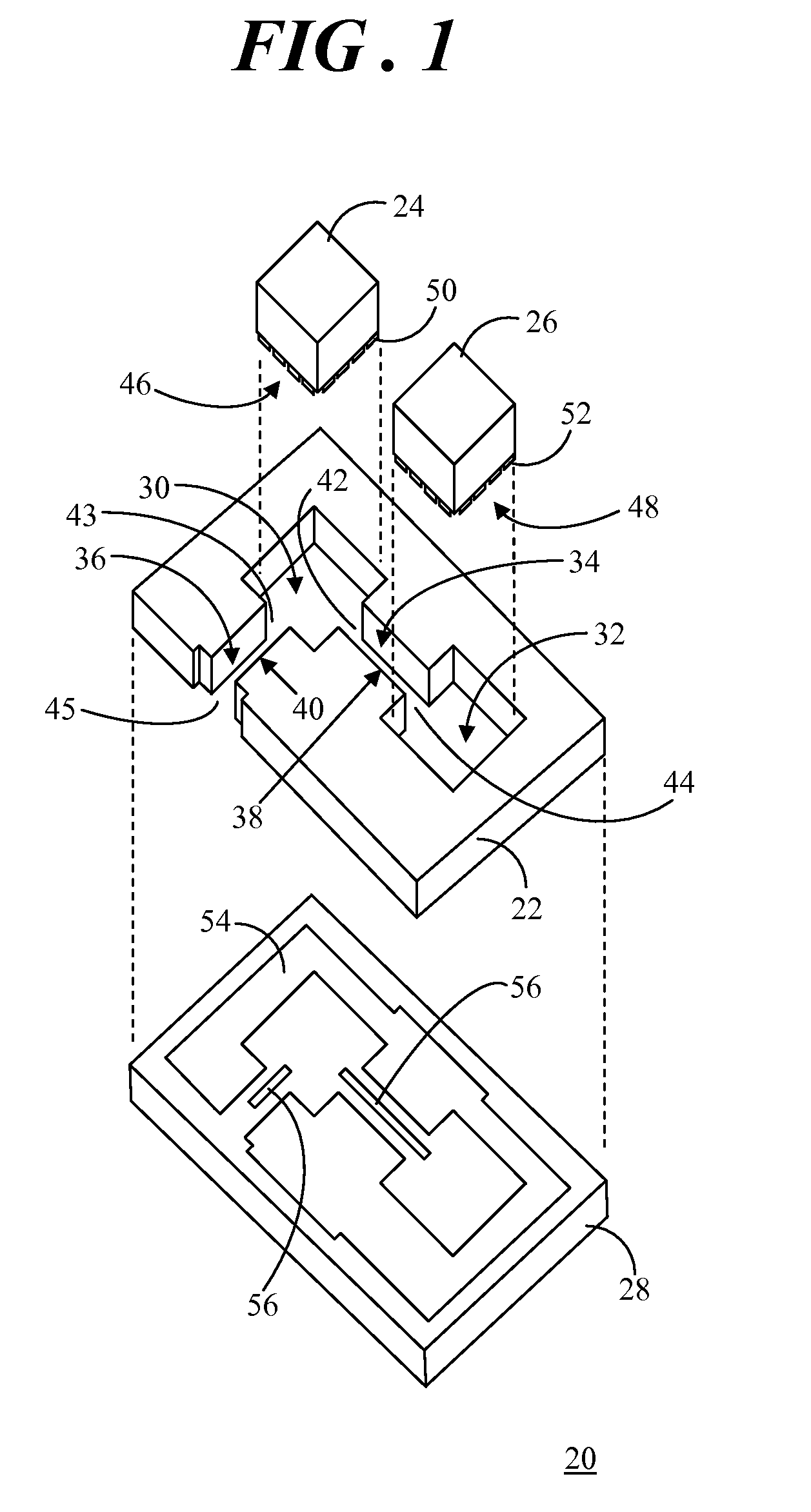

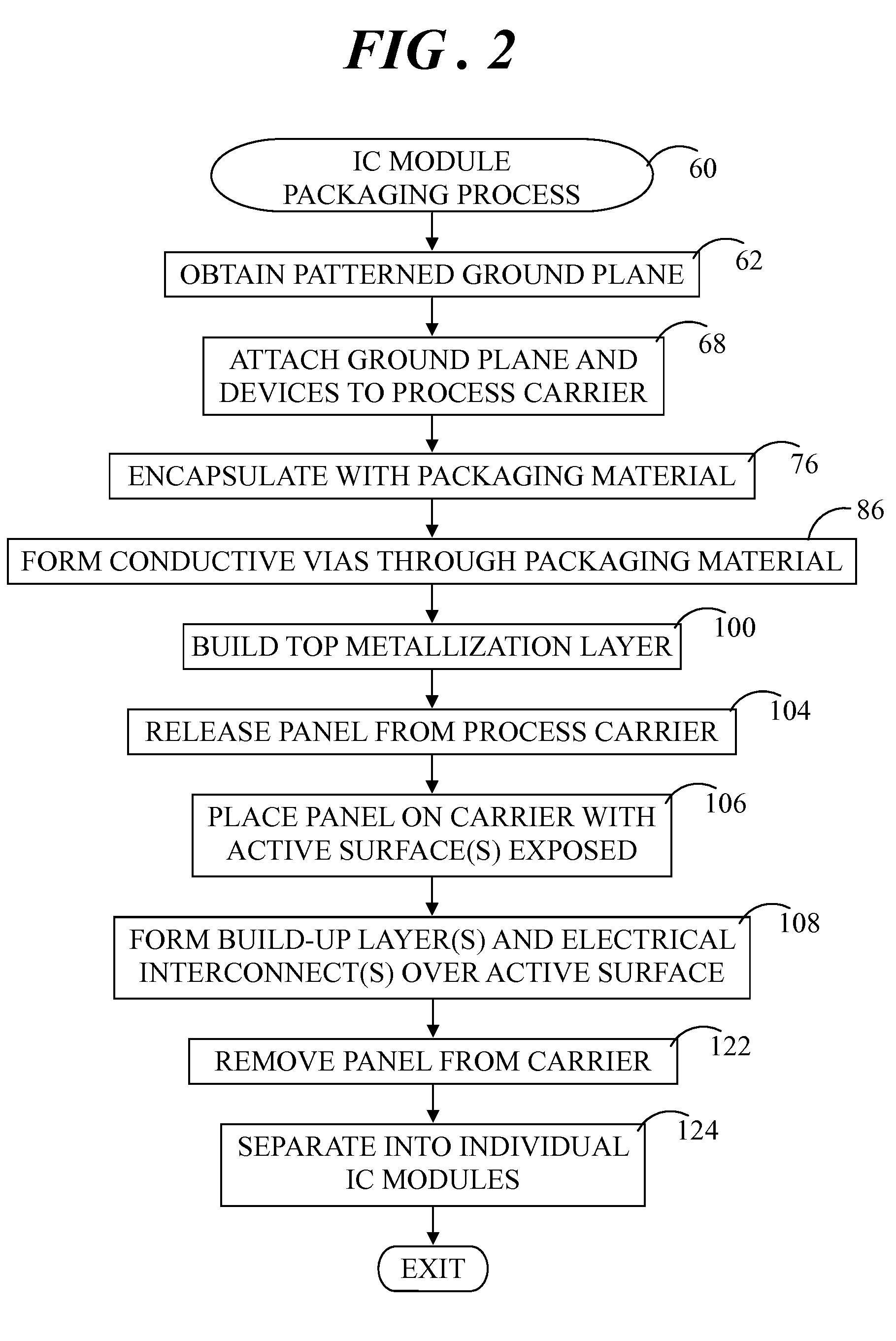

Integrated circuit module and method of packaging same

ActiveUS20100127396A1Semiconductor/solid-state device detailsSolid-state devicesSignal onElectromagnetic interference

An integrated circuit (IC) module (20) includes a ground plane (22) having adjoining cutouts (30, 32). The cutout (32) defines a critical signal pathway (38). A device (24) is positioned in the cutout (30) and a device (26) is positioned outside of the cutout (30) adjacent to the cutout (32). An electrical interconnect (56) positioned in the critical signal pathway (38) interconnects the device (24) with the device (26). A method (60) of packaging the IC module (20) entails encapsulating the ground plane (22) and devices (24, 26) in a packaging material, and forming conductive vias (92) in the packaging material (84) that extend between the ground plane (22) and an exterior surface (94) of the packaging material (84). The conductive vias (92) surround the device (24) and cutout (32) to protect again electromagnetic interference and to provide guided signal pathways for high frequency signals on electrical interconnect (56).

Owner:NXP USA INC

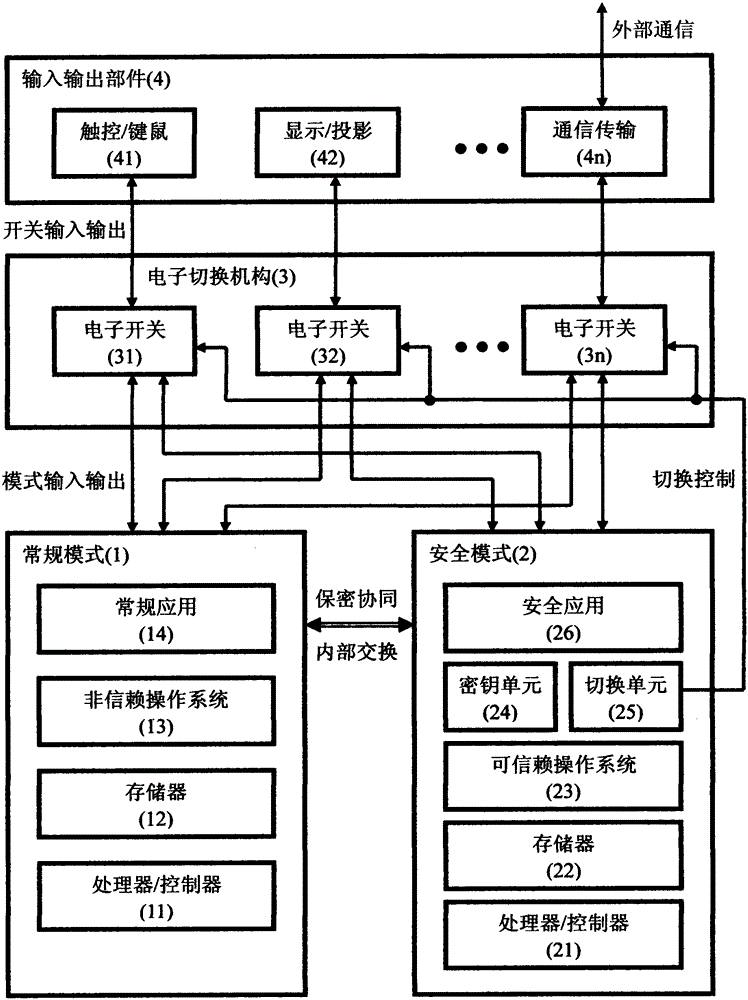

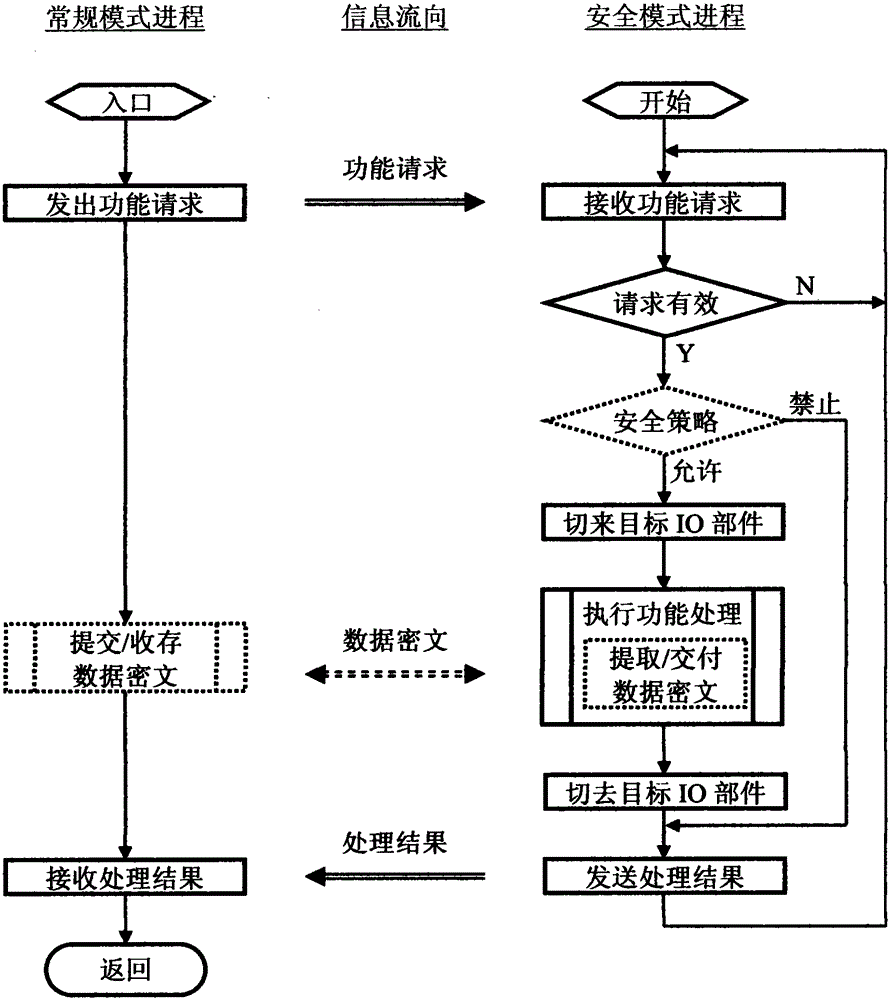

Information security electronic equipment and application architecture

InactiveCN105243341APromote the advancement of information security technologyProtect interestsInternal/peripheral component protectionPlatform integrity maintainanceConfidentialityCritical signal

The invention discloses information security electronic equipment and application architecture, and relates to the technical field of electron, communication, software and information security. Typical equipment, including a computer, a communication terminal and intelligent wearing equipment, comprises a conventional mode and a secure mode, wherein the conventional mode and the secure mode operate in parallel, are independently provided with an independent processor which operates in an independent address space, and share input / output components; an electronic switching mechanism controlled under the secure mode is arranged in the equipment; circuit selection is synchronously implemented on a key signal wire group to control to switch a target input / output component to be in exclusive communication with one of the conventional mode and the secure mode; and the conventional mode and the secure mode are subjected to linkage cooperation, confidentiality synergy and transparent switching. The application architecture comprises a conventional module and a secure module, wherein the conventional module and the secure module are independently installed and operated on the two models to be subjected to the linkage cooperation, a confidentiality synergy frame is constructed, and the electronic switching mechanism is controlled to transparently switch the target input / output component. The embodiment provides secure computer and mobile equipment as well as file, electronic bank and WeChat architecture. Therefore, the sharing and the switching of the equipment architecture can be controlled, the bottleneck of the information security of computers and mobile phones is expected to break through, and equipment suppliers can favorably intervene in derivative value-added services to make profits

Owner:深圳金澜汉源科技有限公司 +1

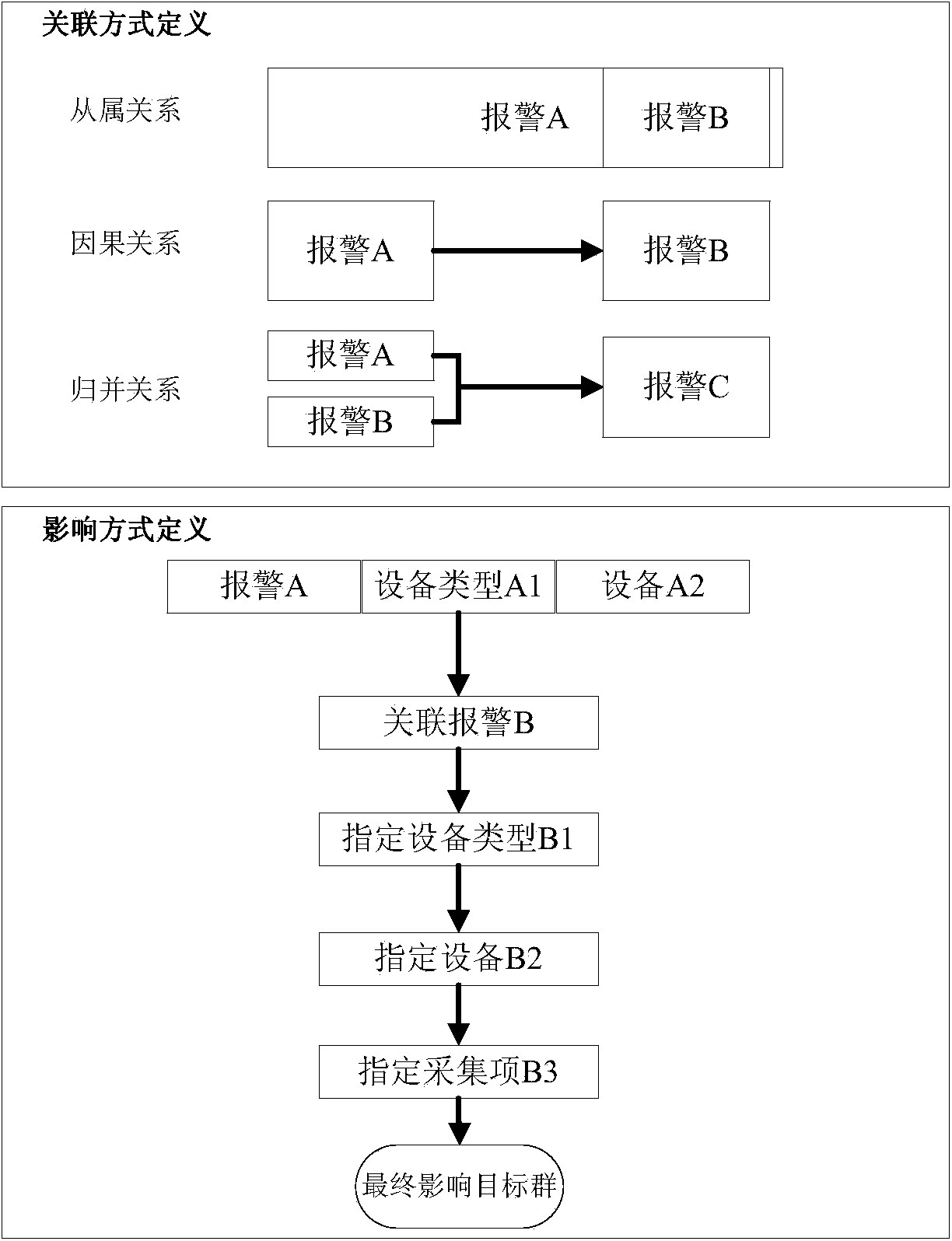

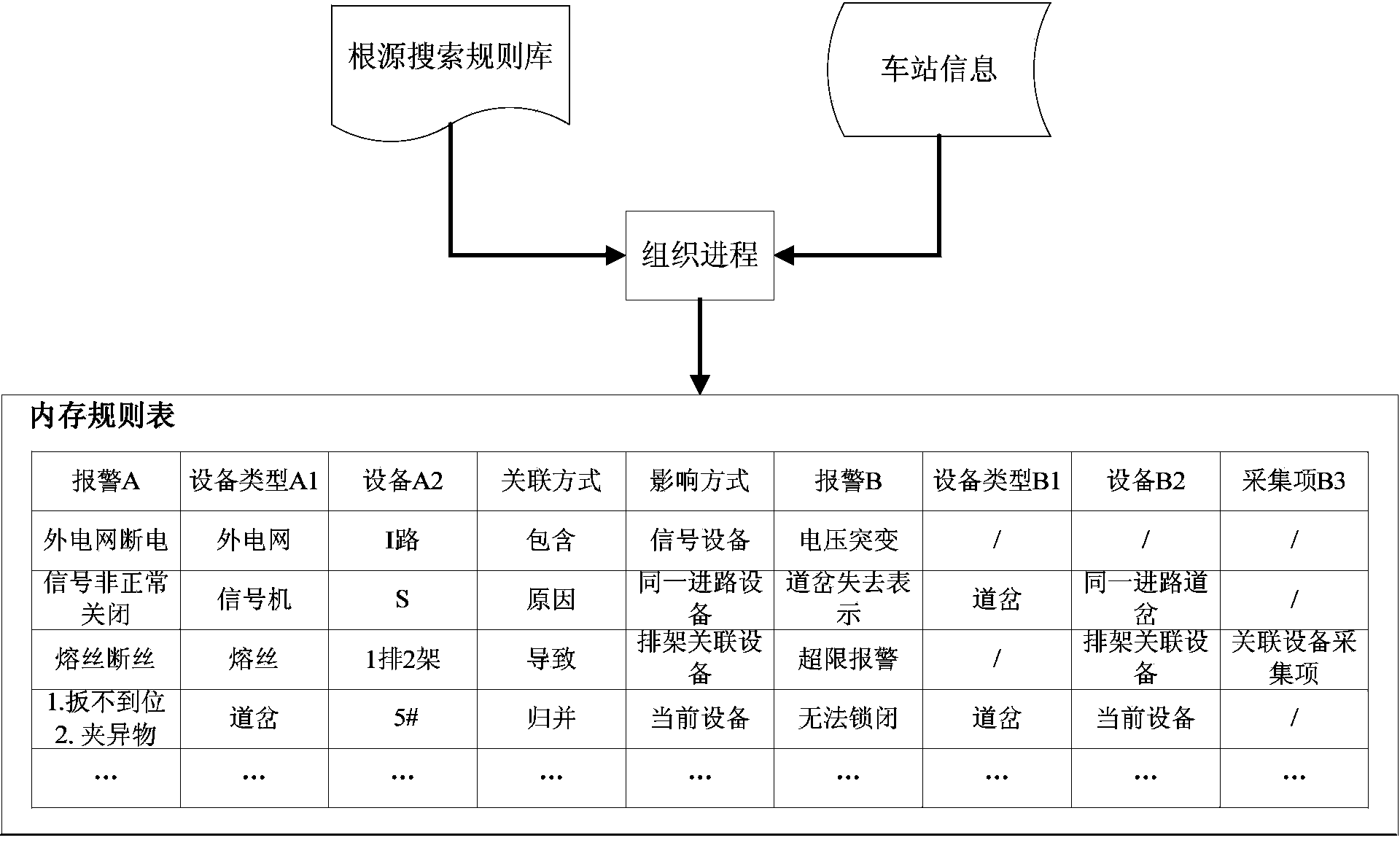

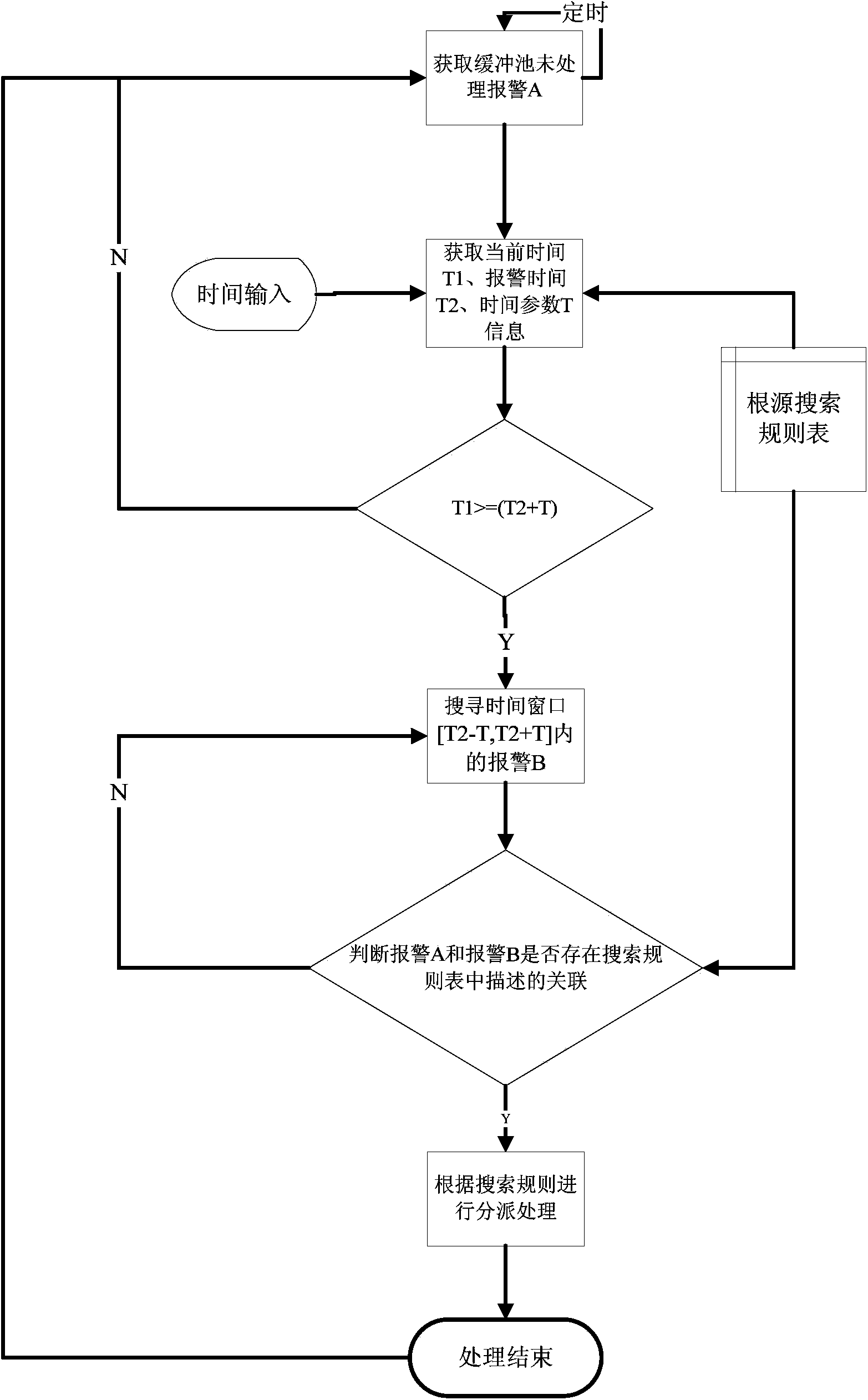

Signal appliance fault source searching method for signal central monitoring system

ActiveCN103713976AImprove maintenance management levelReduce work intensityDetecting faulty computer hardwareSpecial data processing applicationsMonitoring systemFailure analysis

The invention relates to a signal appliance fault source searching method for a signal central monitoring system. The signal appliance fault source searching method comprises the following steps that firstly, a key signal appliance fault source searching knowledge base is established; secondly, a fault source searching method is defined, the signal appliance warning information can be divided into three classes according to the linkage mode and can be divided into four classes according to the influence ways, and a source searching analyzing result is comprehensively controlled according to time parameters; thirdly, a fault source searching rule is converted, namely, a logical fault source searching rule is converted into a fault source searching information rule list; fourthly, the dynamic detecting judgment of a fault warning buffer pool is carried out, namely, a warning storage buffer pool is established, the dynamical warning source analysis is achieved through the fault source searching information rule list, and a warning result with the relation expression capability is finally formed through a plurality of related warning basis relevance modes; fifthly, the source warning is shown, and the fault analyzing method is refined. Compared with the prior art, the signal appliance fault source searching method has the advantage that the warning quality and the effectiveness are improved.

Owner:CASCO SIGNAL