System and method for debugging FPGA (field programmable gate array)

A debugging system and signal acquisition technology, which is applied in the field of FPGA debugging system, can solve problems such as information flooding, real-time data storage problems, invalidity, etc., and achieve the effect of increasing data volume and quickly locating problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

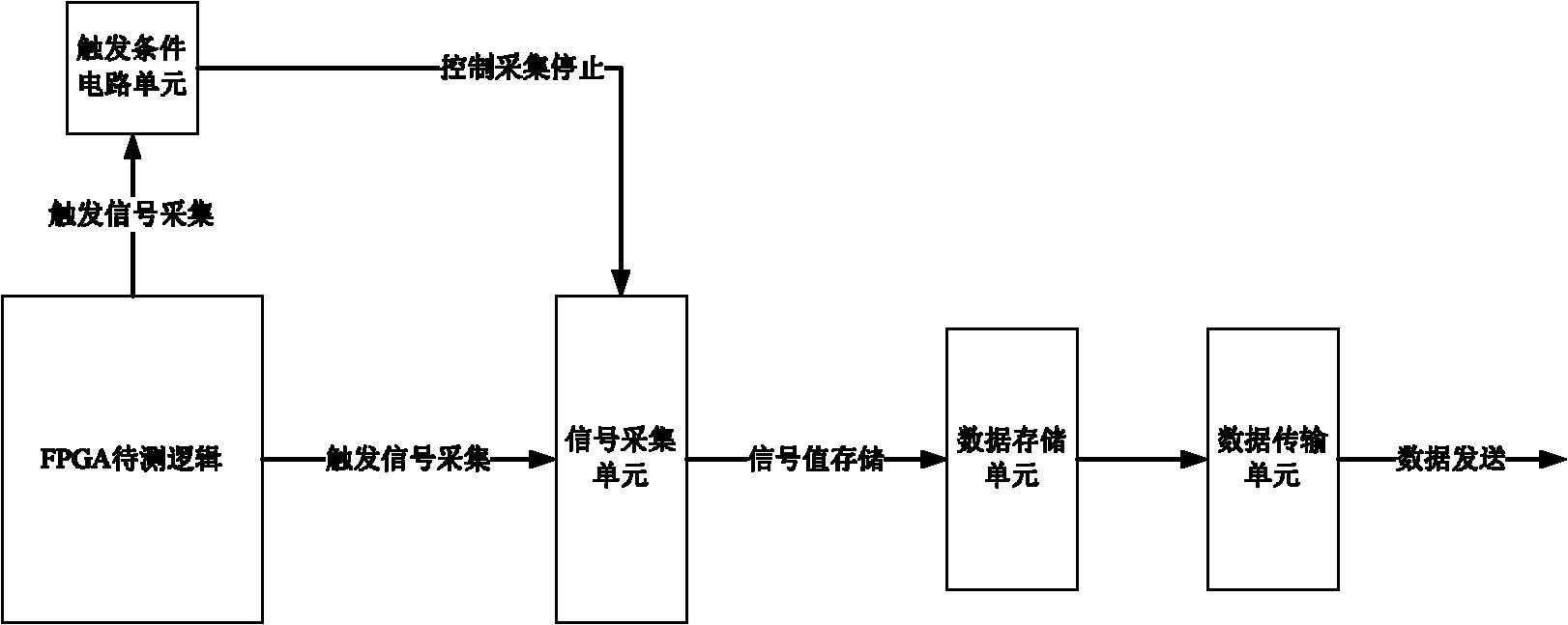

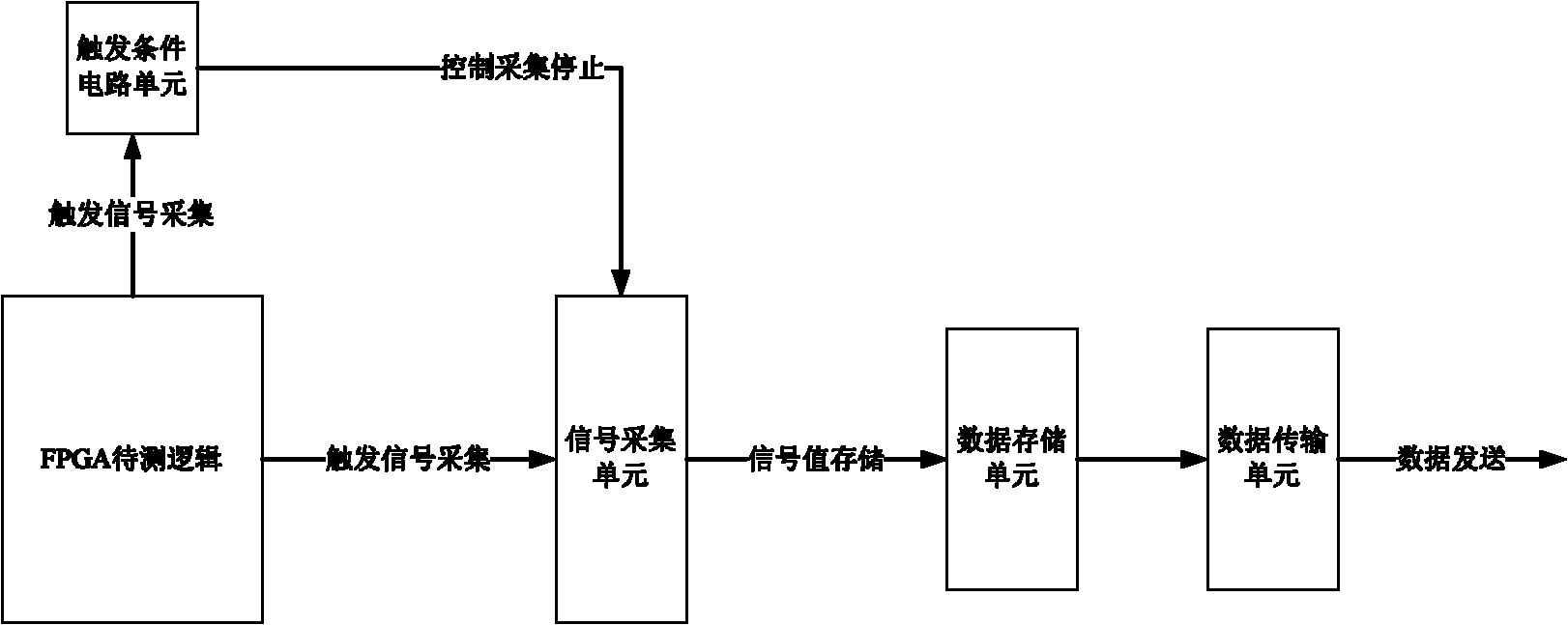

[0025] The present invention proposes a kind of FPGA debugging method, specifically as follows:

[0026] 1) Add a trigger condition circuit unit for debugging and a signal acquisition unit for collecting key signals in the FPGA logic.

[0027] 2) Allocate signal acquisition resources, that is, data storage units, according to the usage of FPGA storage resources (on-chip RAM, off-chip DDR SDRAM or SRAM, etc.), and then set the signal acquisition depth n according to the number of acquisition signals, that is, acquisition and storage number of cycles.

[0028] 3) The collected data is stored in the data storage unit in a first-in-first-out manner. When the storage resources of the data storage unit are used up, the data collected later squeezes out the data collected earlier.

[0029] 4) When n / 2 cycles after the trigger condition is satisfied, the trigger condition circuit unit controls the signal acquisition unit to stop acquisition.

[0030] 5) The data transmission unit tr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More