Patents

Literature

9206results about "Differential amplifiers" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

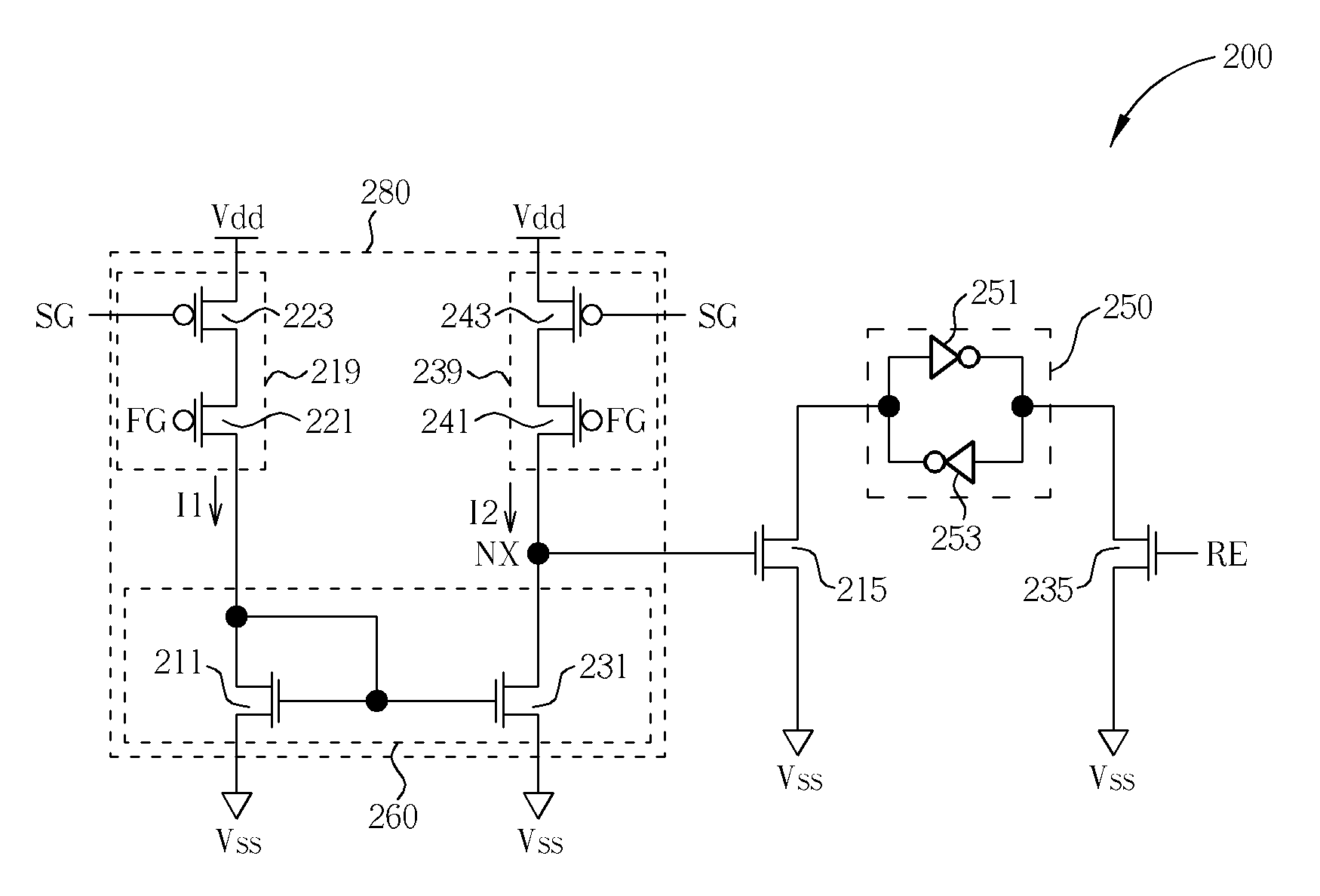

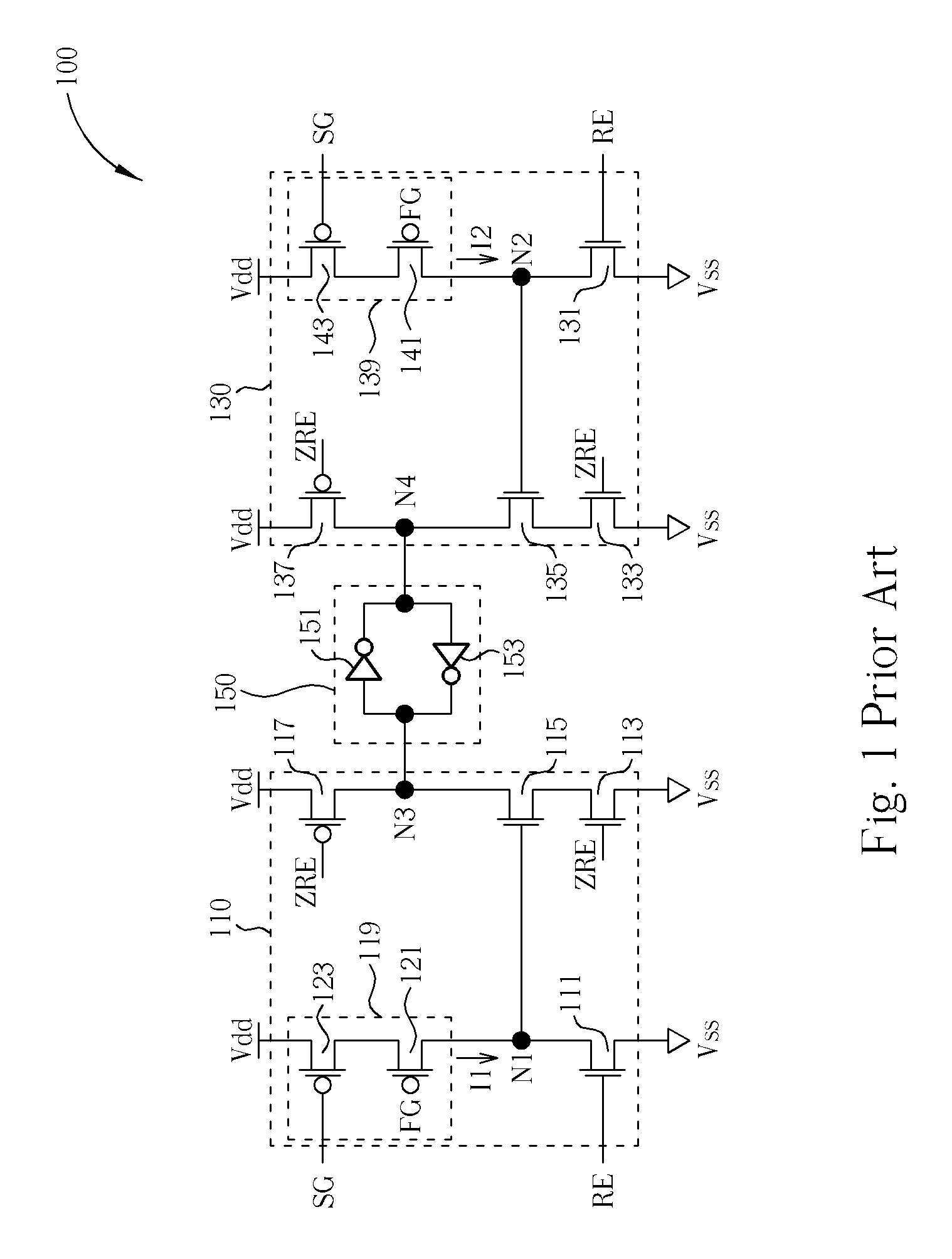

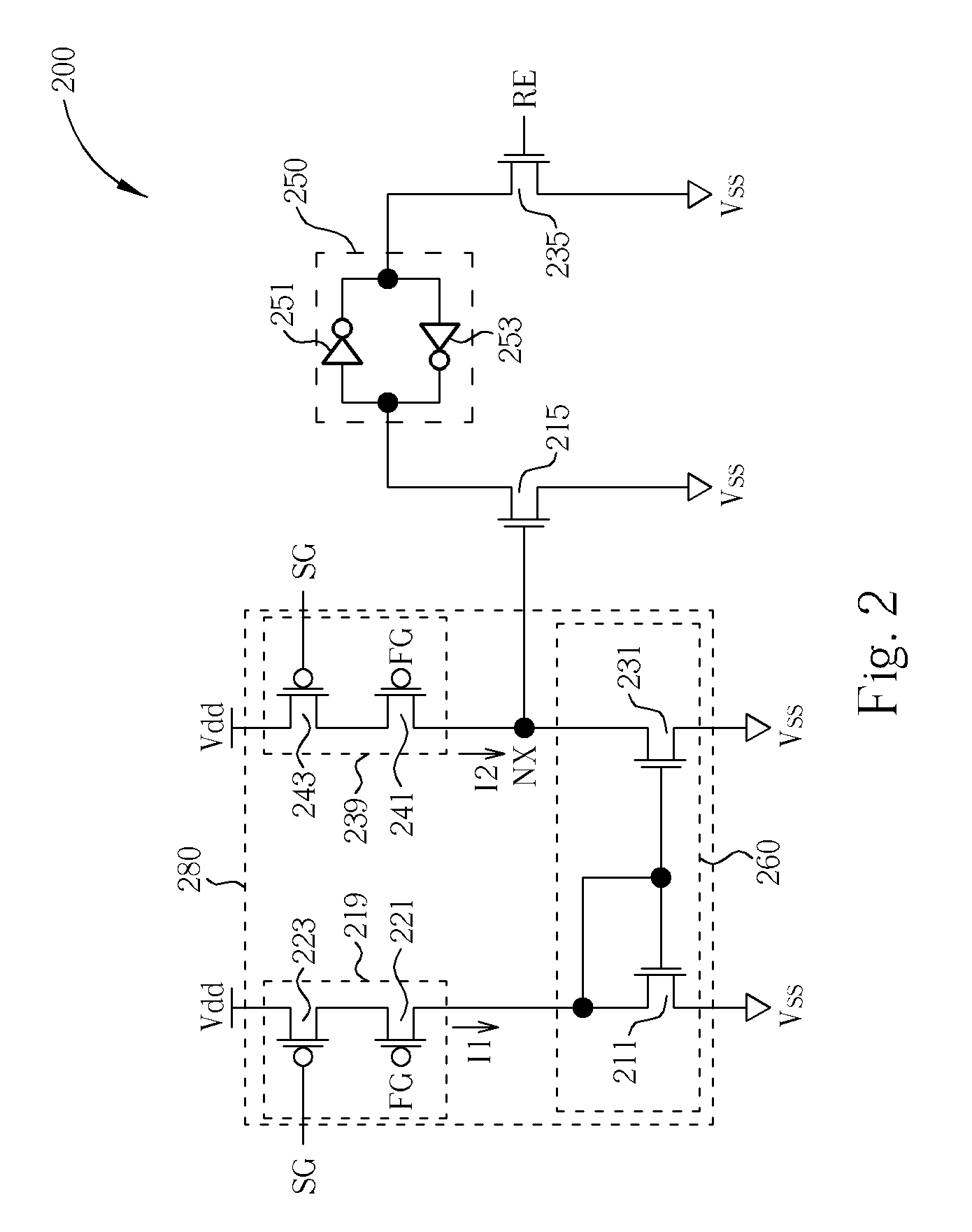

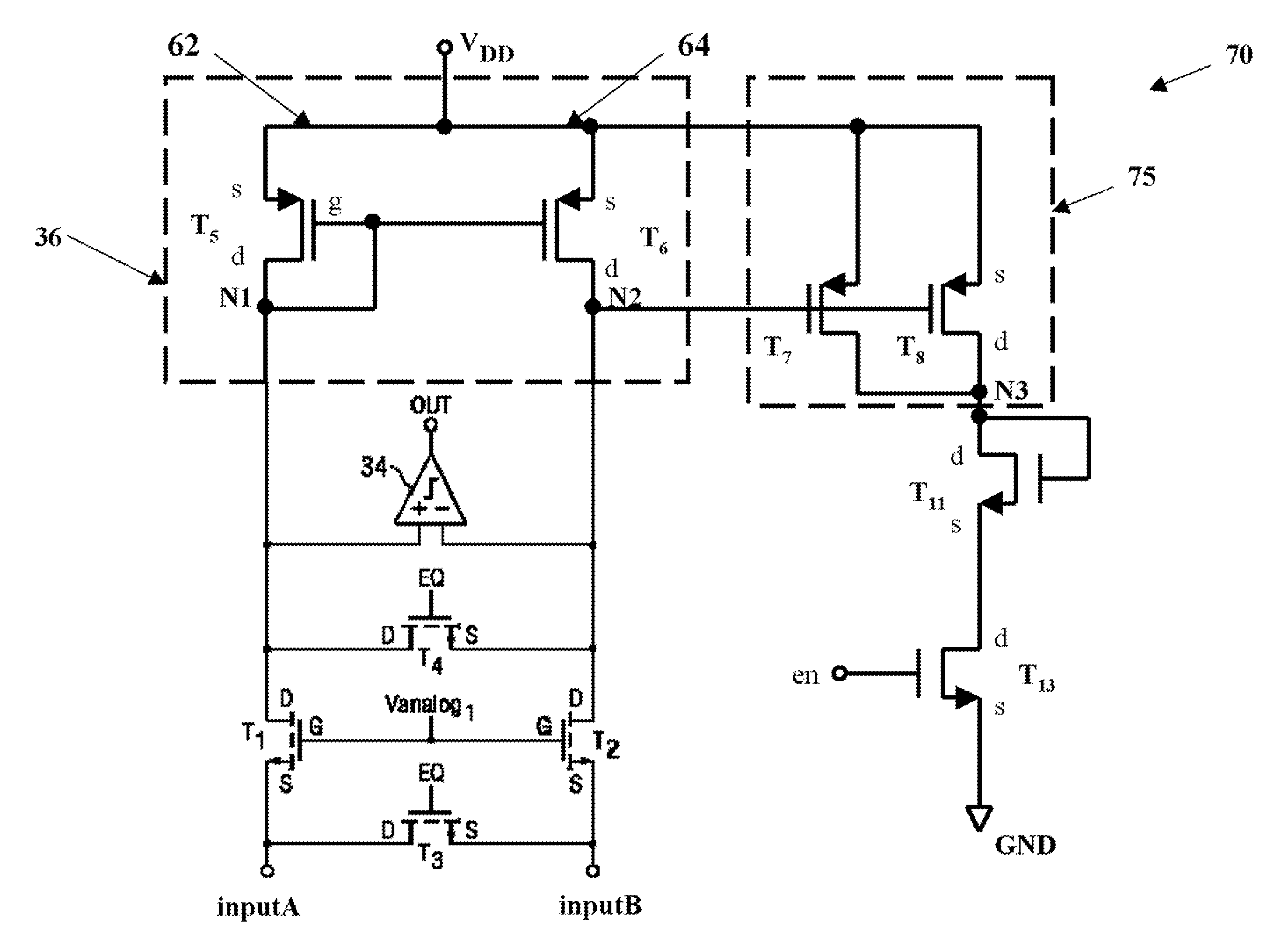

Sense amplifier circuit having current mirror architecture

A sense amplifier circuit for use in a semiconductor memory device has complemented logic states at opposite sides of the latch circuit in the sense amplifier circuit determinate all the time in operation. The sense amplifier circuit takes advantage of a current mirror circuit for ascending or descending a voltage level at the gate of a transistor by charge accumulation or charge dissipation, which turns on or off the transistor so as to control the logic states at opposite sides of the latch circuit in the sense amplifier circuit.

Owner:EMEMORY TECH INC

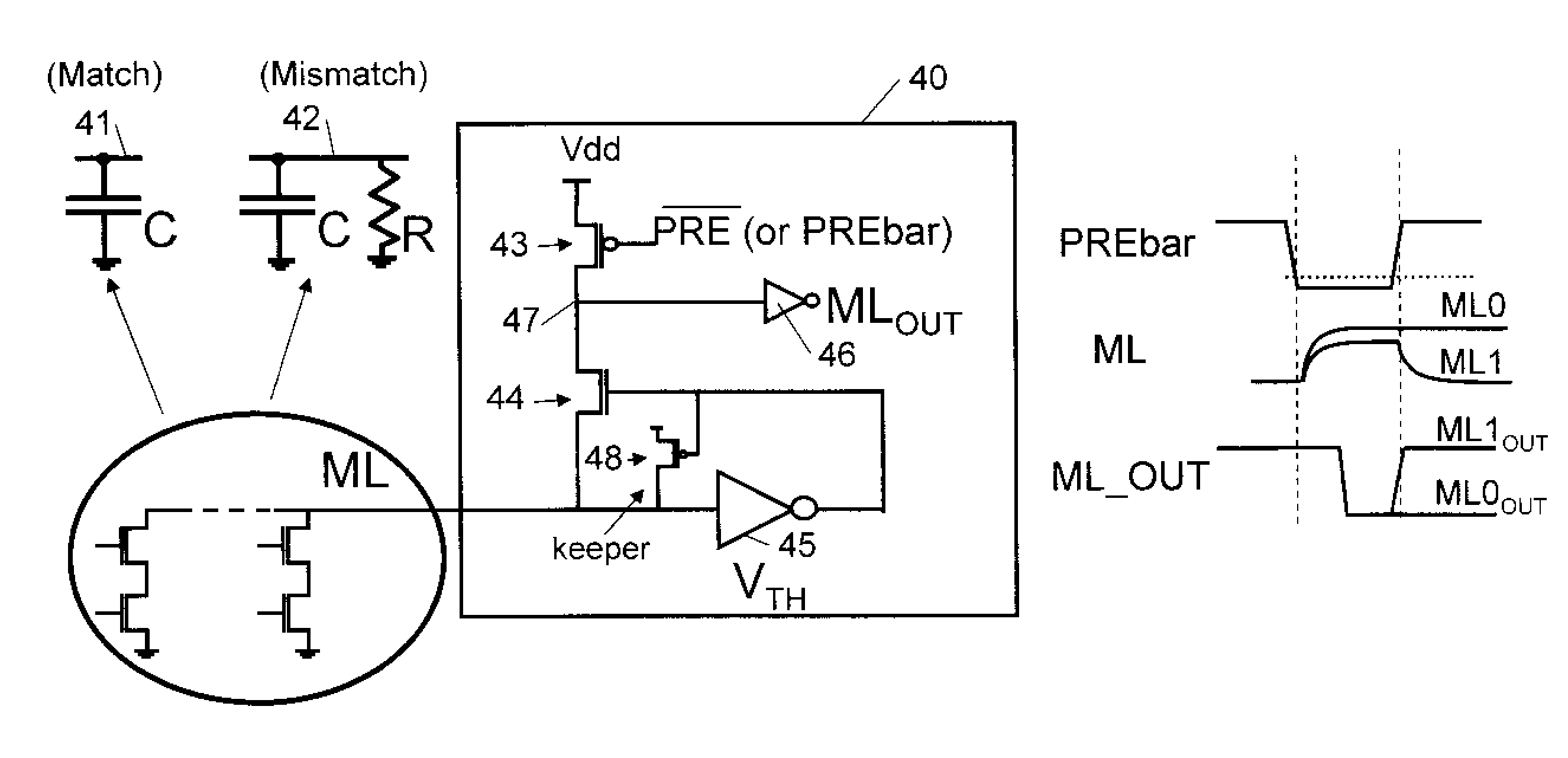

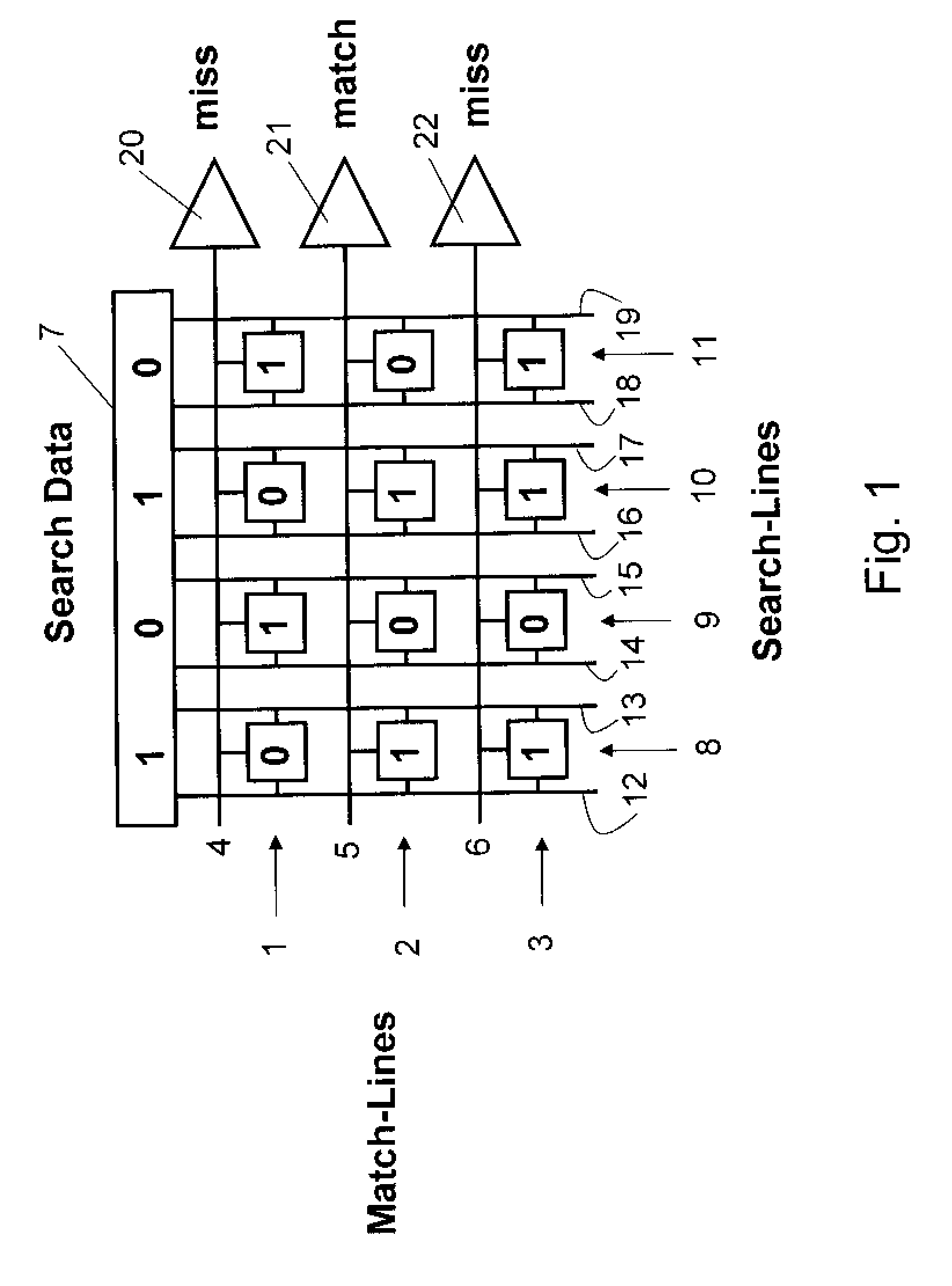

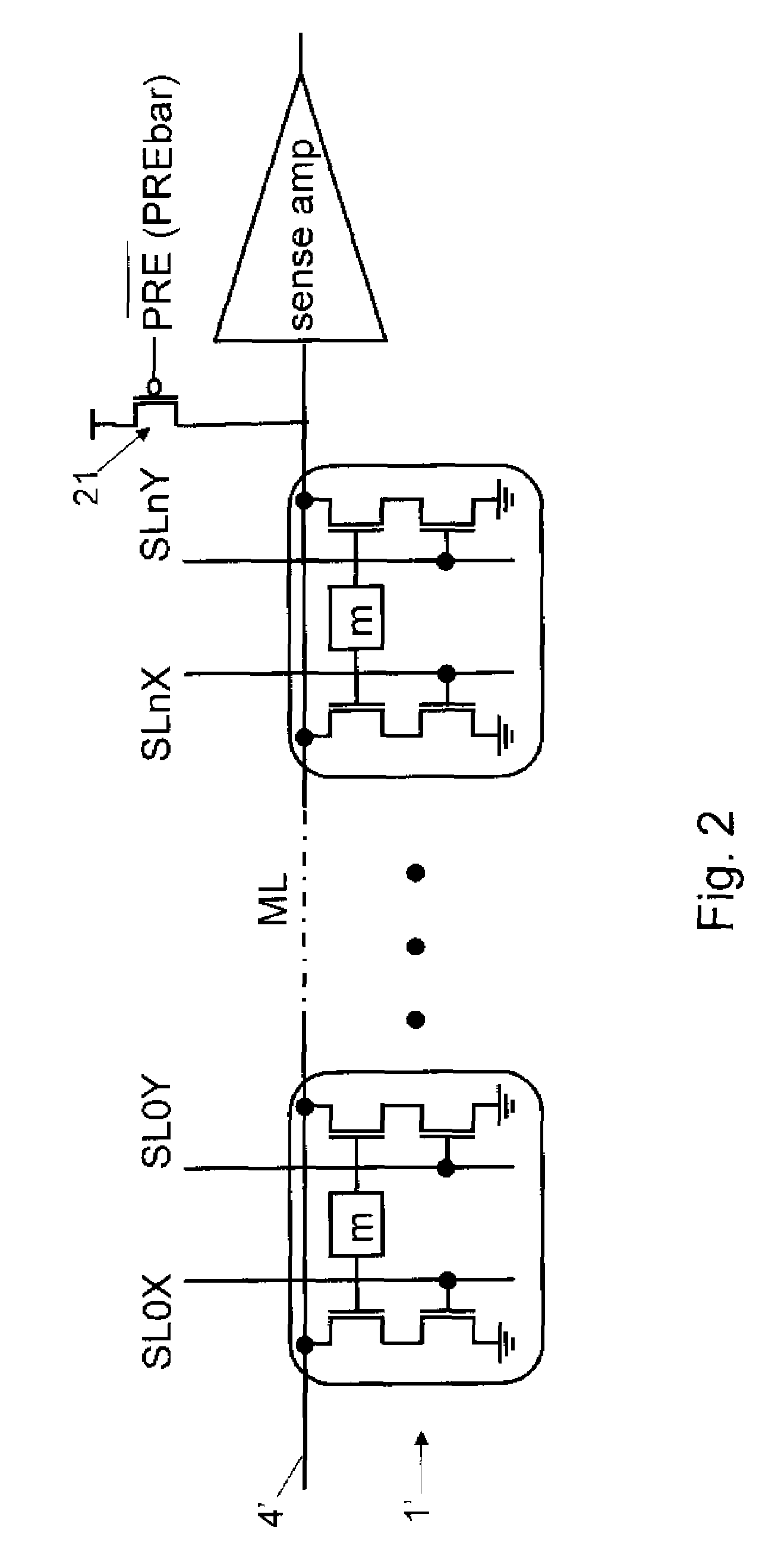

Self-Referenced Match-Line Sense Amplifier For Content Addressable Memories

ActiveUS20080025073A1Reduce the impactReduce impactCurrent/voltage measurementDigital storageAudio power amplifierComputer science

A content addressable memory (CAM) device and process for searching a CAM. The CAM device includes a plurality of CAM cells, match-lines (MLs), search lines, and ML sense amplifiers. The ML sense amplifiers are capable of self-calibration to their respective thresholds to reduce effects of random device variation between adjacent sense amplifiers.

Owner:MARVELL ASIA PTE LTD

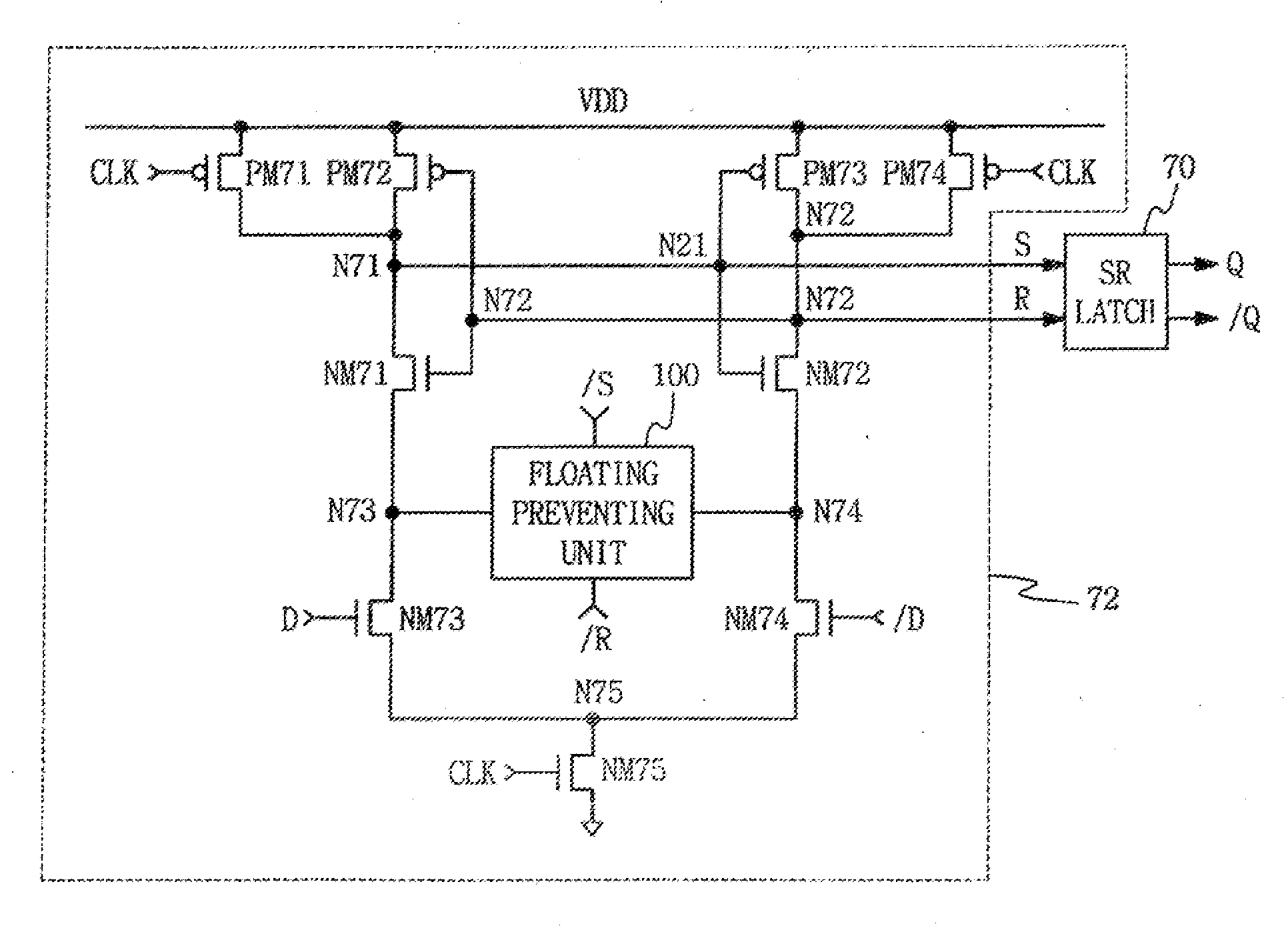

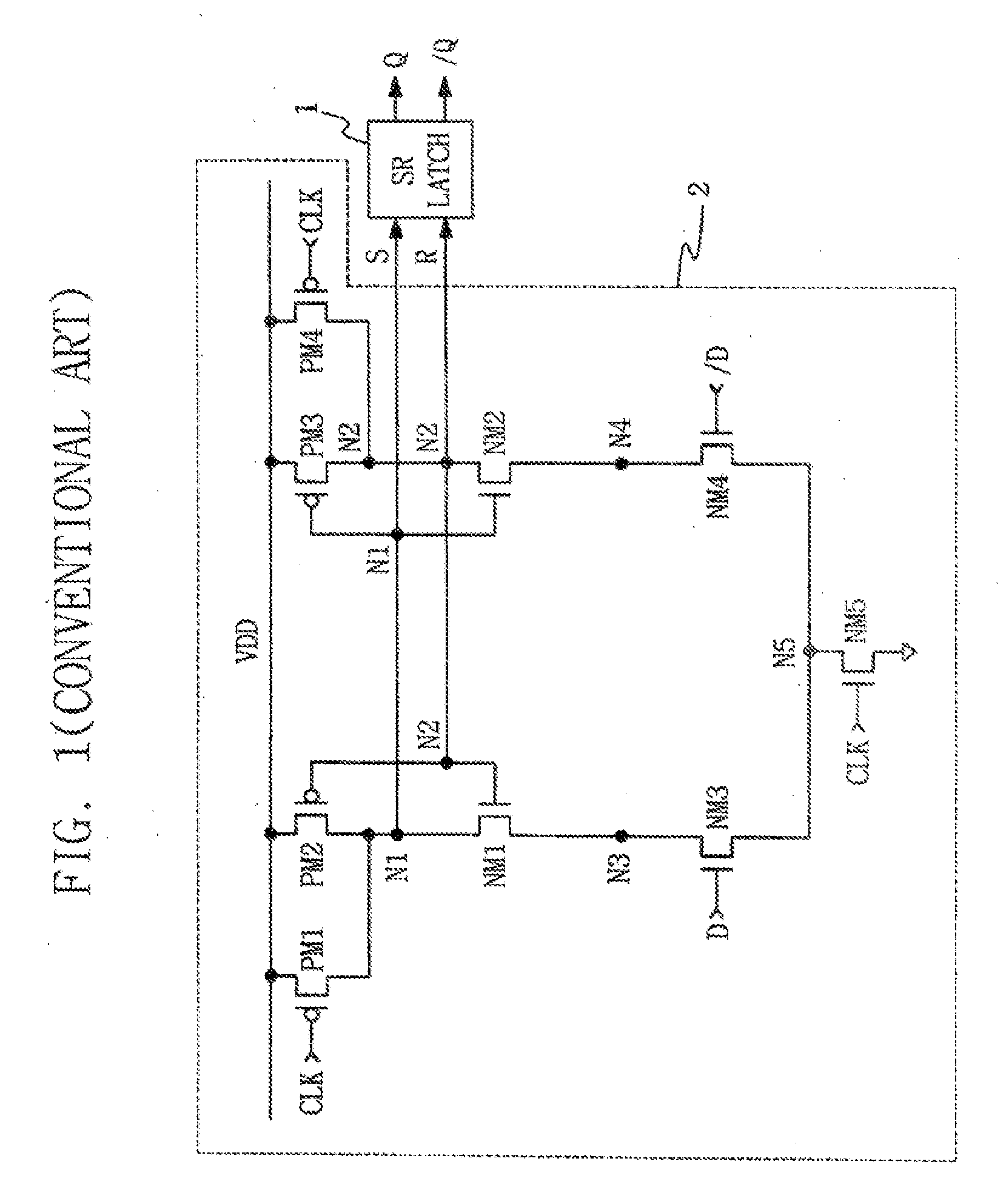

Sense amplifier circuit and sense amplifier-based flip-flop having the same

ActiveUS20070285131A1Reducing signal delay timePrevent degradation of outputCurrent/voltage measurementDigital storageAudio power amplifierControl delay

A sense amplifier-based flip-flop includes a first latch, a second latch, a floating reduction unit, an input signal applying unit, a ground switch and a delay reduction unit. The first latch outputs a signal to a first output terminal pair, and outputs an evaluation signal pair corresponding to an input single pair to the first output terminal pair. The second latch latches the evaluation signal pair and outputs the evaluation signal pair to a second output terminal pair. The floating reduction unit is controlled by signals of the first output terminal pair and is operationally connected between current passing nodes of the first latch to prevent the first output terminal pair from floating. The input signal applying unit is disposed between the current passing nodes and a ground terminal, and receives the input signal pair. The ground switch is disposed between the input signal applying unit and the ground terminal, and is controlled by the clock signal. The delay reduction unit is disposed between the input signal applying unit and the ground switch, and reduces a signal delay from when the clock signal to when the evaluation signal pair is output from the second output terminal pair.

Owner:SAMSUNG ELECTRONICS CO LTD

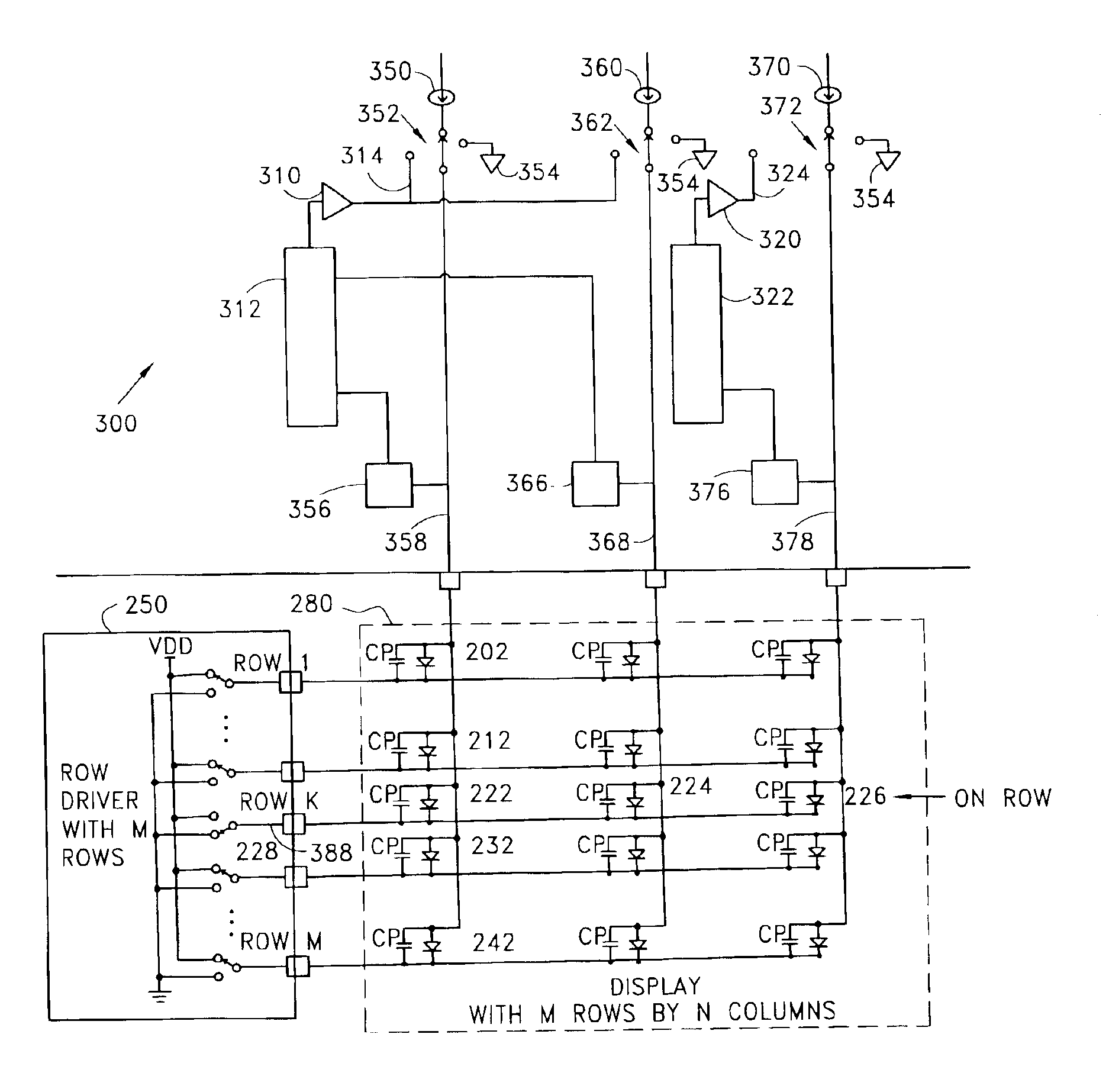

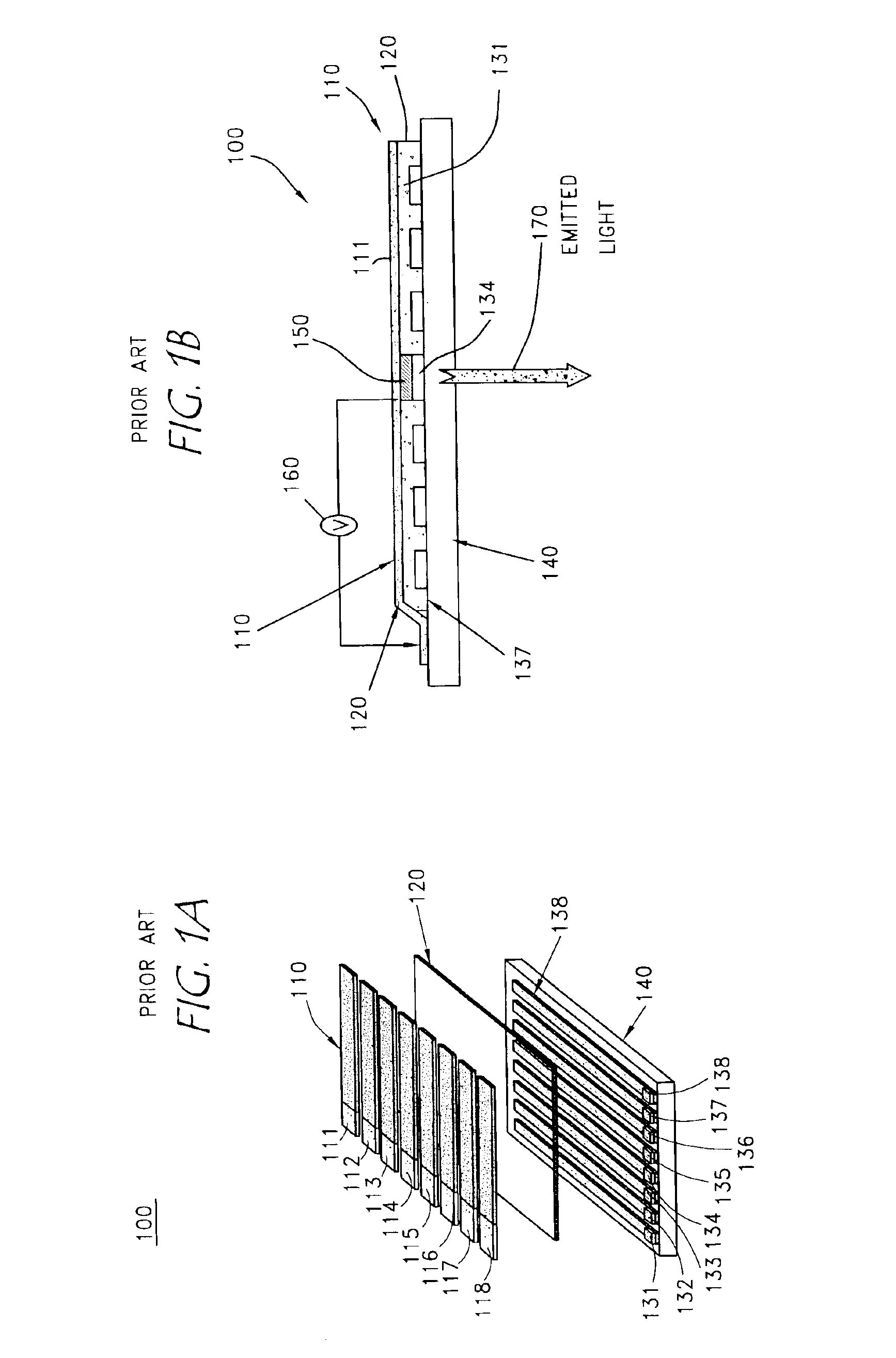

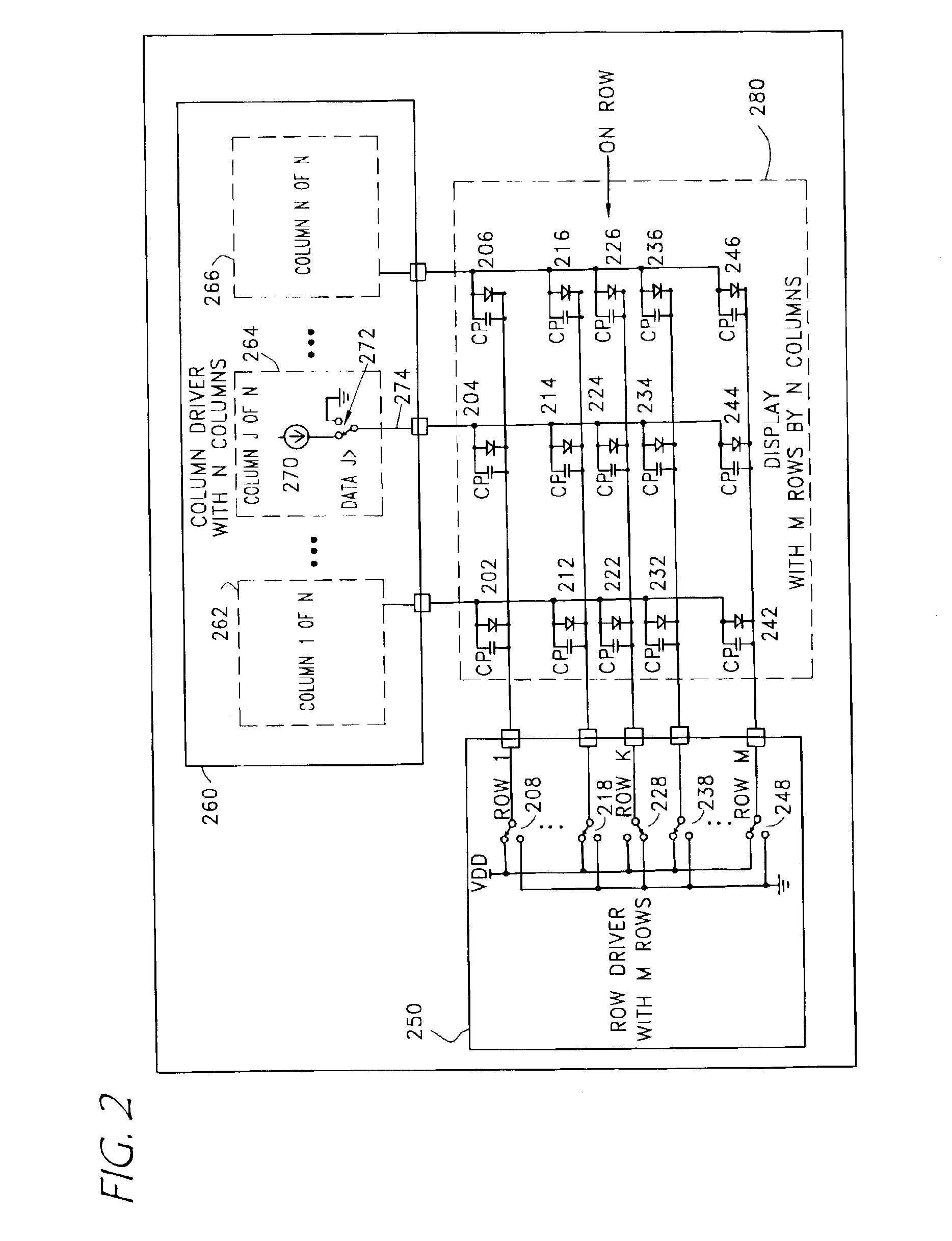

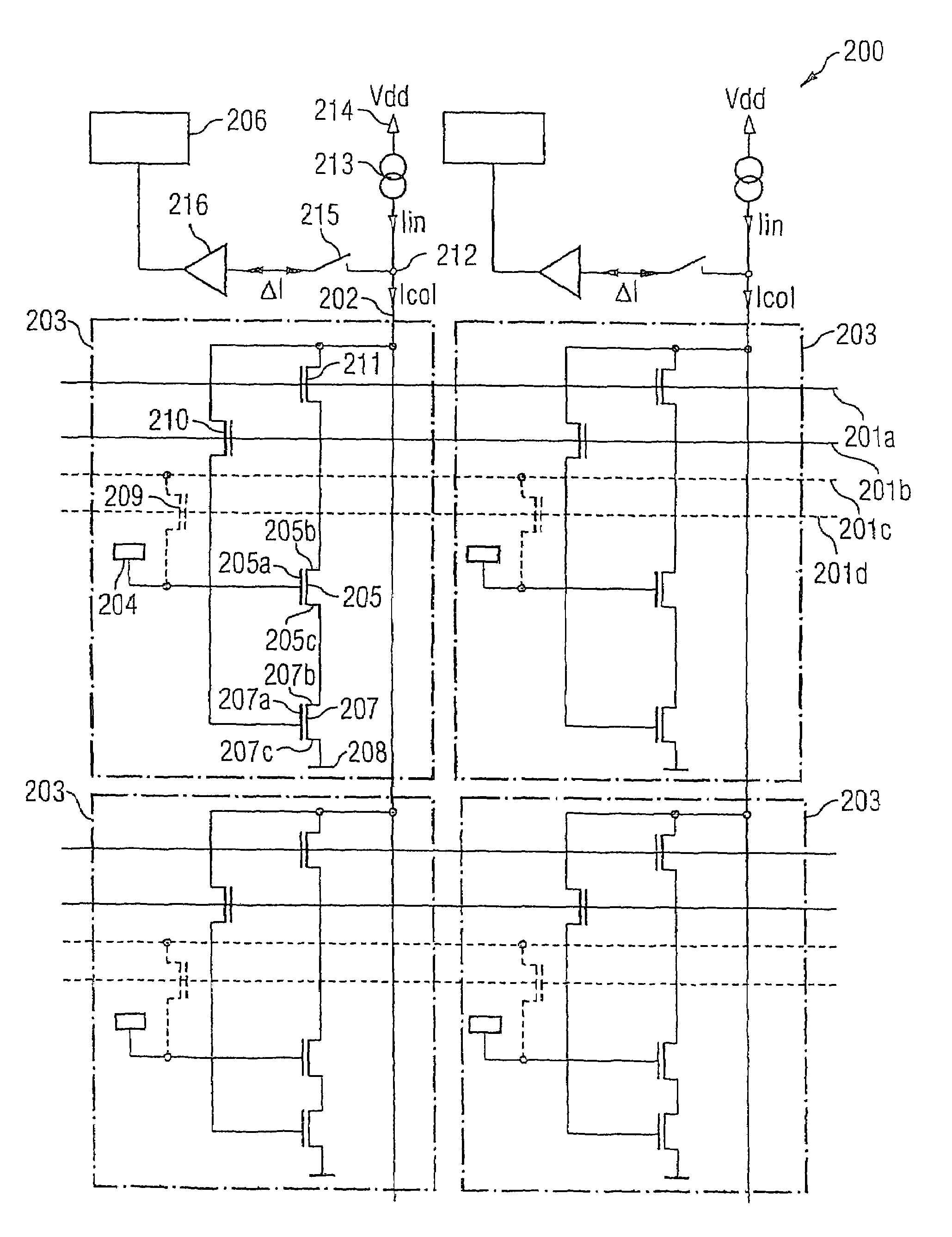

Matrix element precharge voltage adjusting apparatus and method

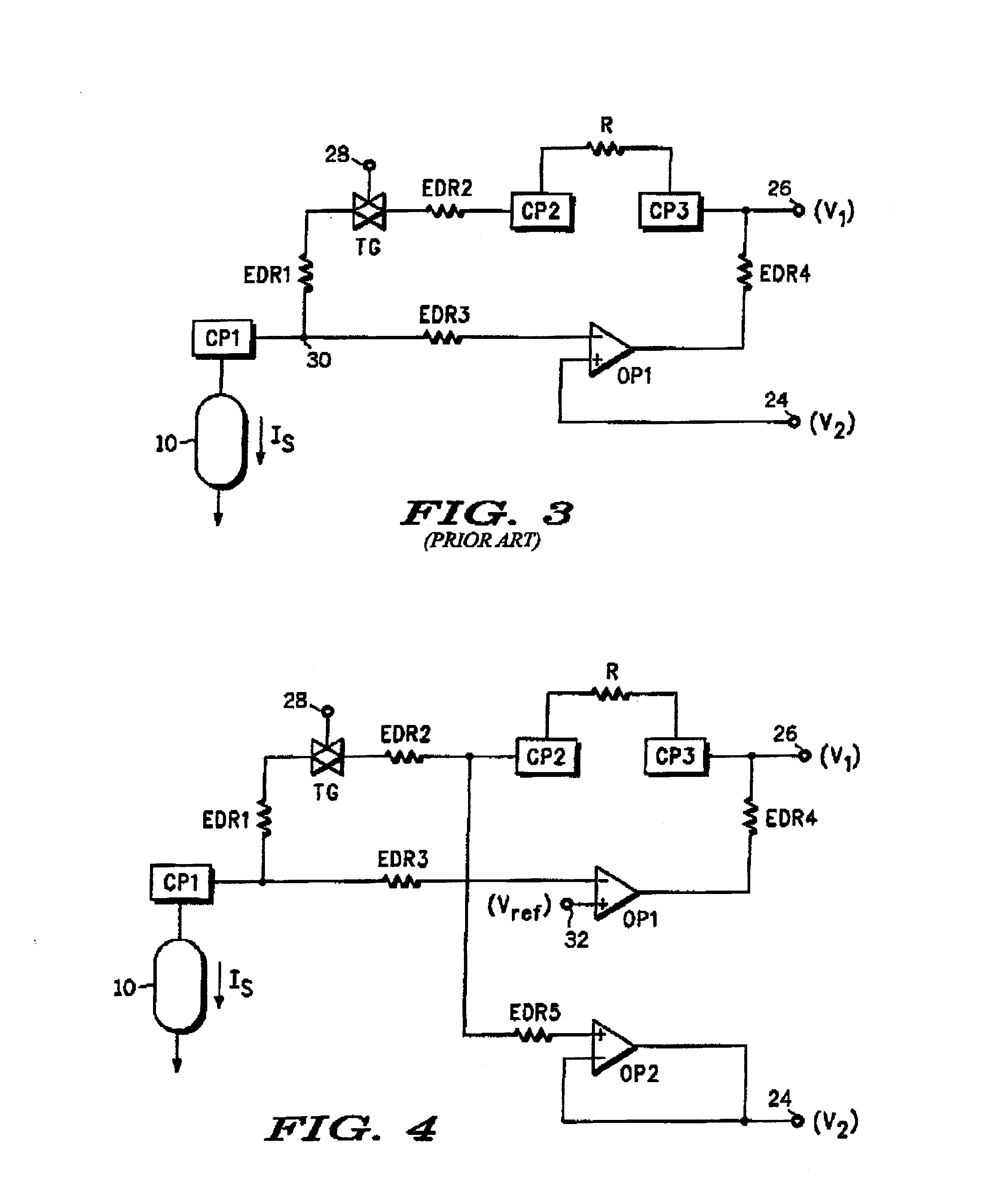

An apparatus for establishing and applying a voltage to precharge current-driven elements in a matrix. During ordinary scan cycles, a conduction voltage is sensed while the elements conduct a selected current. One or more such sensed conduction voltages are combined to provide a basis for a precharge voltage. Conduction and transient errors are determined, and are compensated for by offsetting the final precharge voltage from the conduction voltage basis. The final precharge voltage is provided to one or more columns during a precharge period of the scan cycle.

Owner:CLARE MICRONIX INTEGRATED SYST

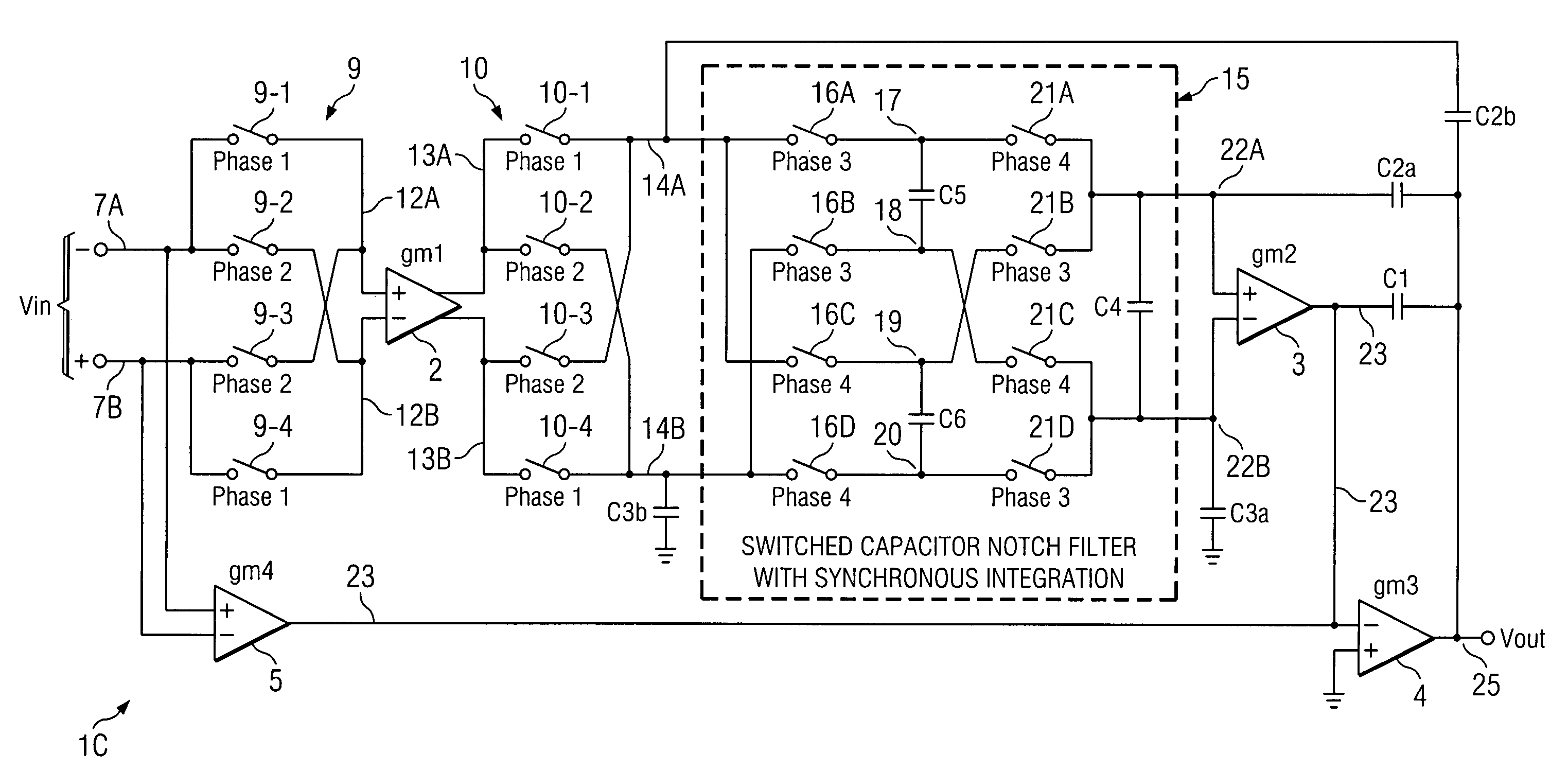

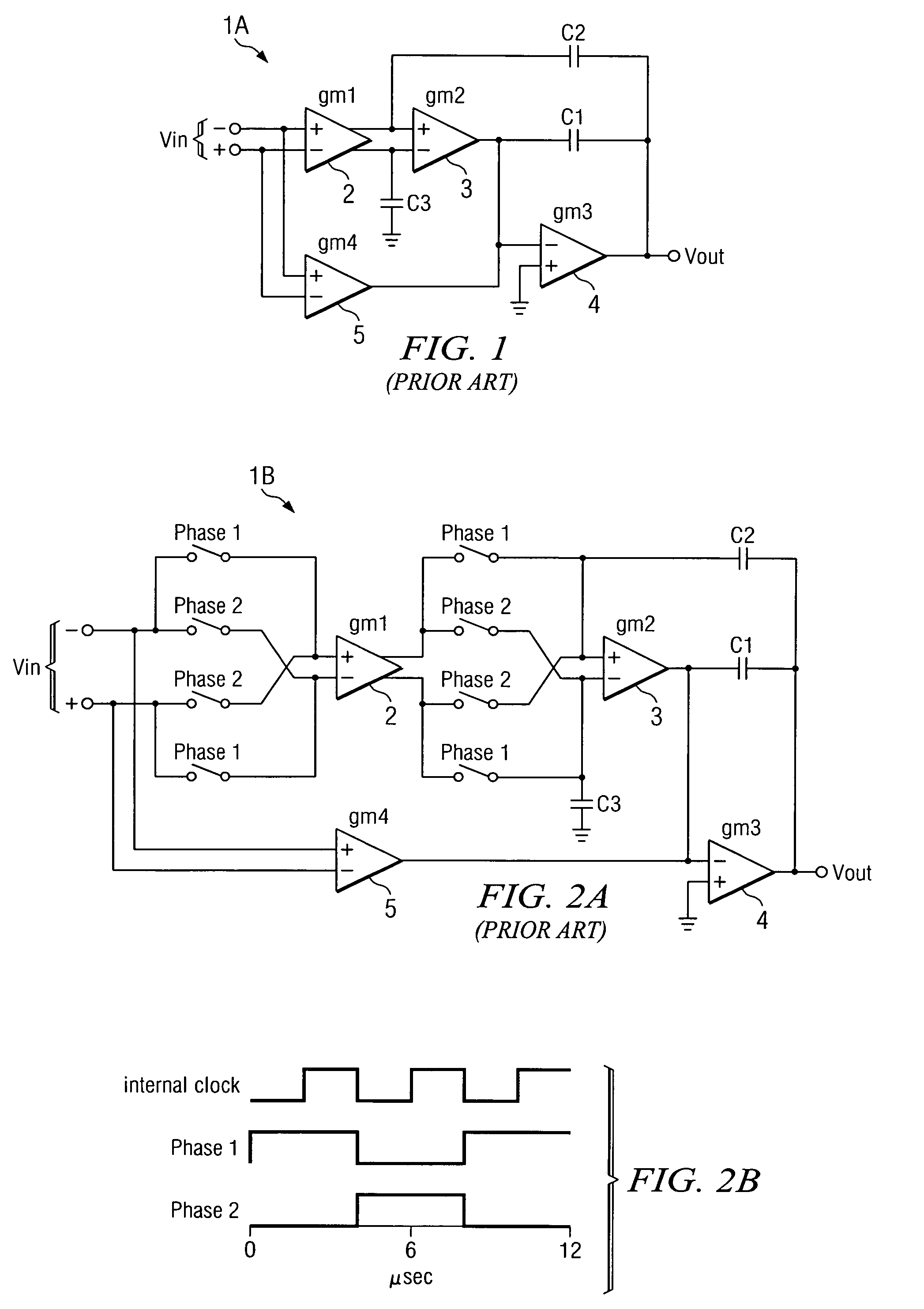

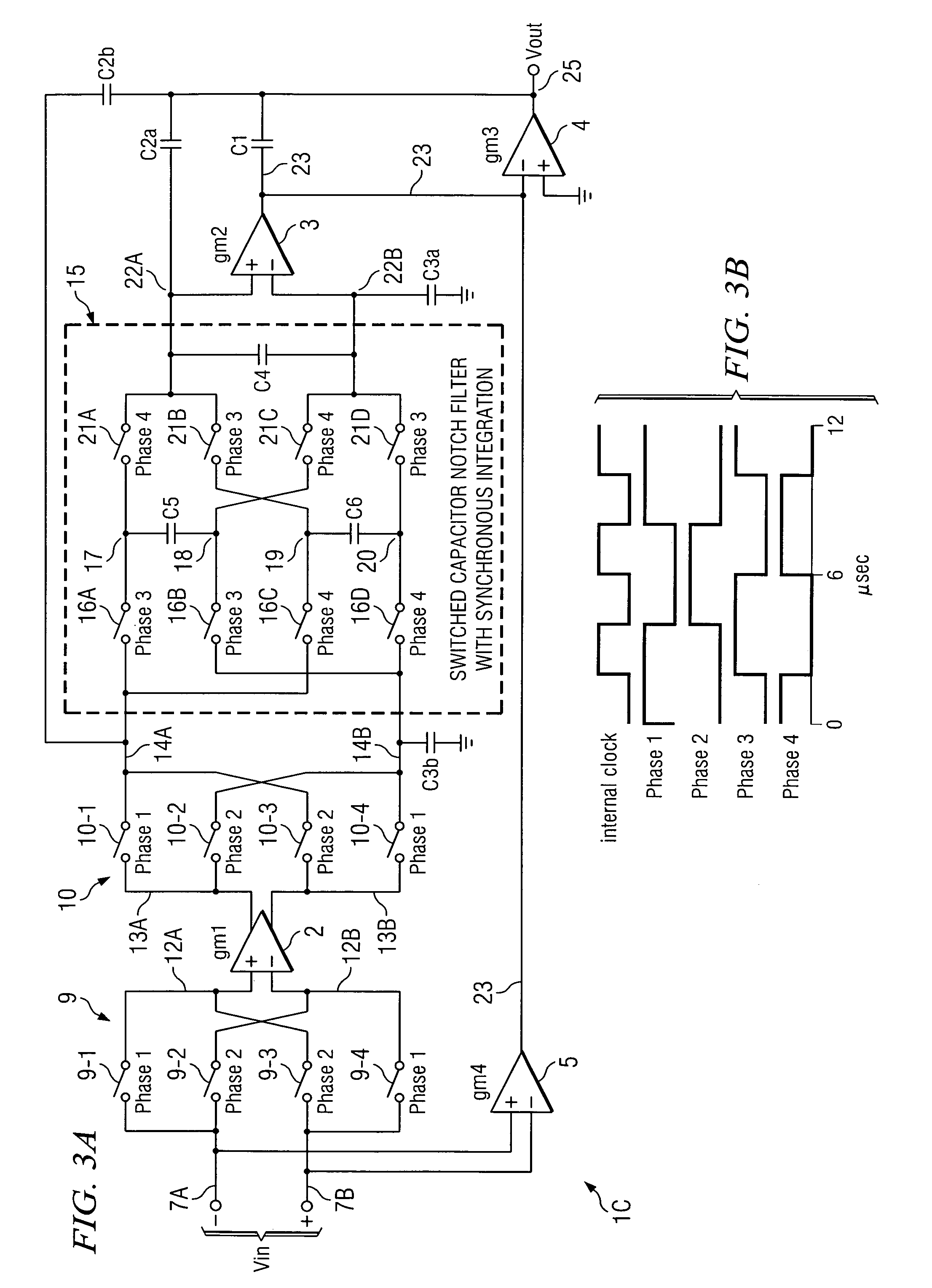

Notch filter for ripple reduction in chopper stabilized amplifiers

ActiveUS7292095B2Reduce ripple noiseFast signalAmplifier modifications to reduce noise influenceAmplifier modifications to raise efficiencyAudio power amplifierEngineering

A chopper-stabilized amplifier receiving an input signal includes a first operational transconductance amplifier having an input chopper and an output chopper for chopping an output signal produced by the first operational transconductance amplifier. A switched capacitor notch filter filters the chopped output signal by operating synchronously with the chopping frequency of output chopper to filter ripple voltages that otherwise would be produced by the output chopper. In one embodiment, a second operational transconductance amplifier amplifies the notch filter output. The input signal is fed forward, summed with the output of the second operational transconductance amplifier, and applied to the input of a fourth operational transconductance amplifier. Ripple noise and offset are substantially reduced.

Owner:TEXAS INSTR INC

Current-controlled CMOS wideband data amplifier circuits

InactiveUS6624699B2Maximum bandwidth expansionReduced Miller CapacitanceAmplifier combinationsAmplifier modifications to reduce detrimental impedenceCapacitanceCMOS

Expansion of the bandwidth of a wideband CMOS data amplifier is accomplished using various combinations of shunt peaking, series peaking, and miller capacitance cancellation. These various combinations are employed in any of the amplifier input stage, in intermediate stages, or in the last stage.

Owner:AVAGO TECH INT SALES PTE LTD

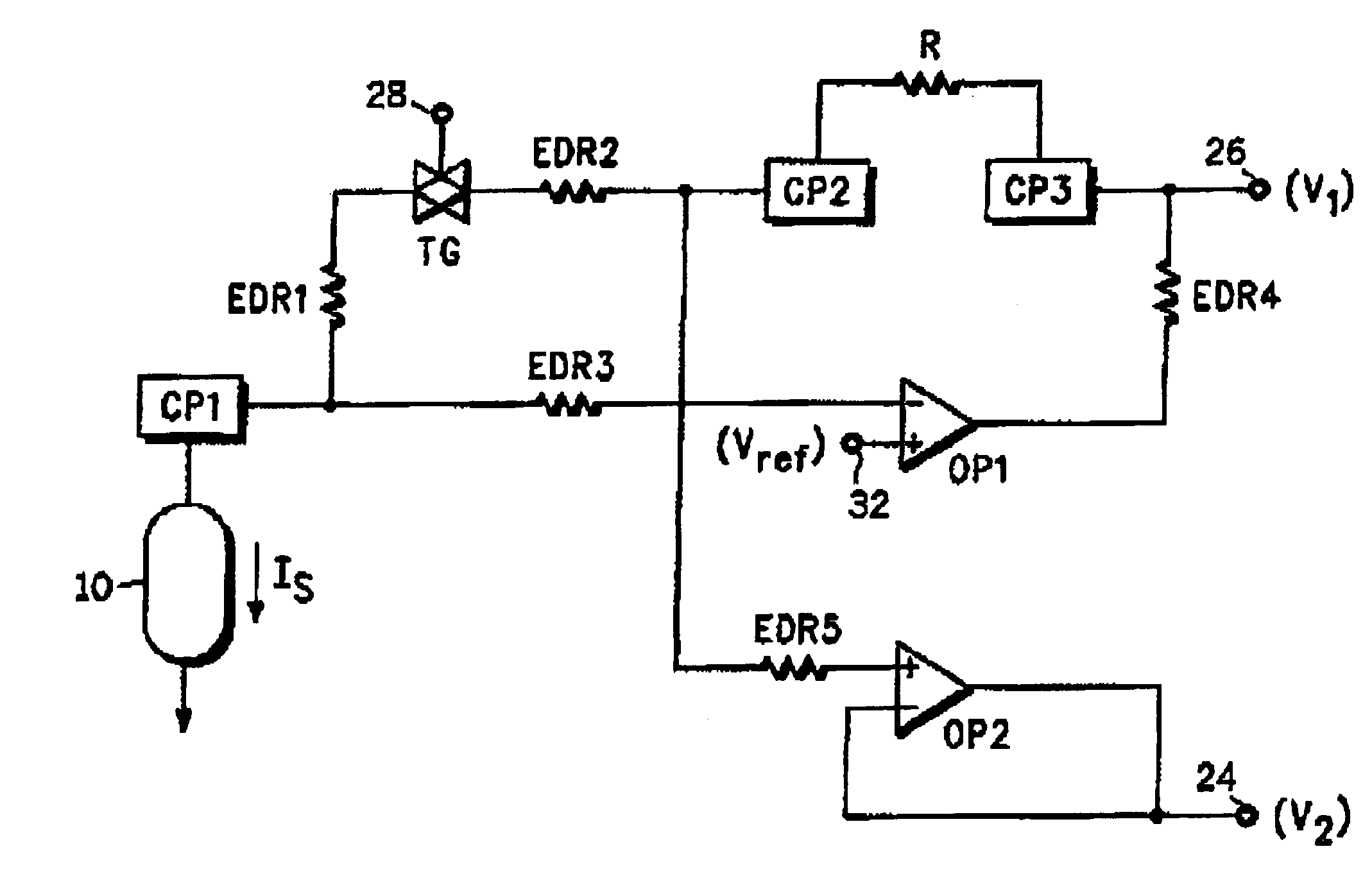

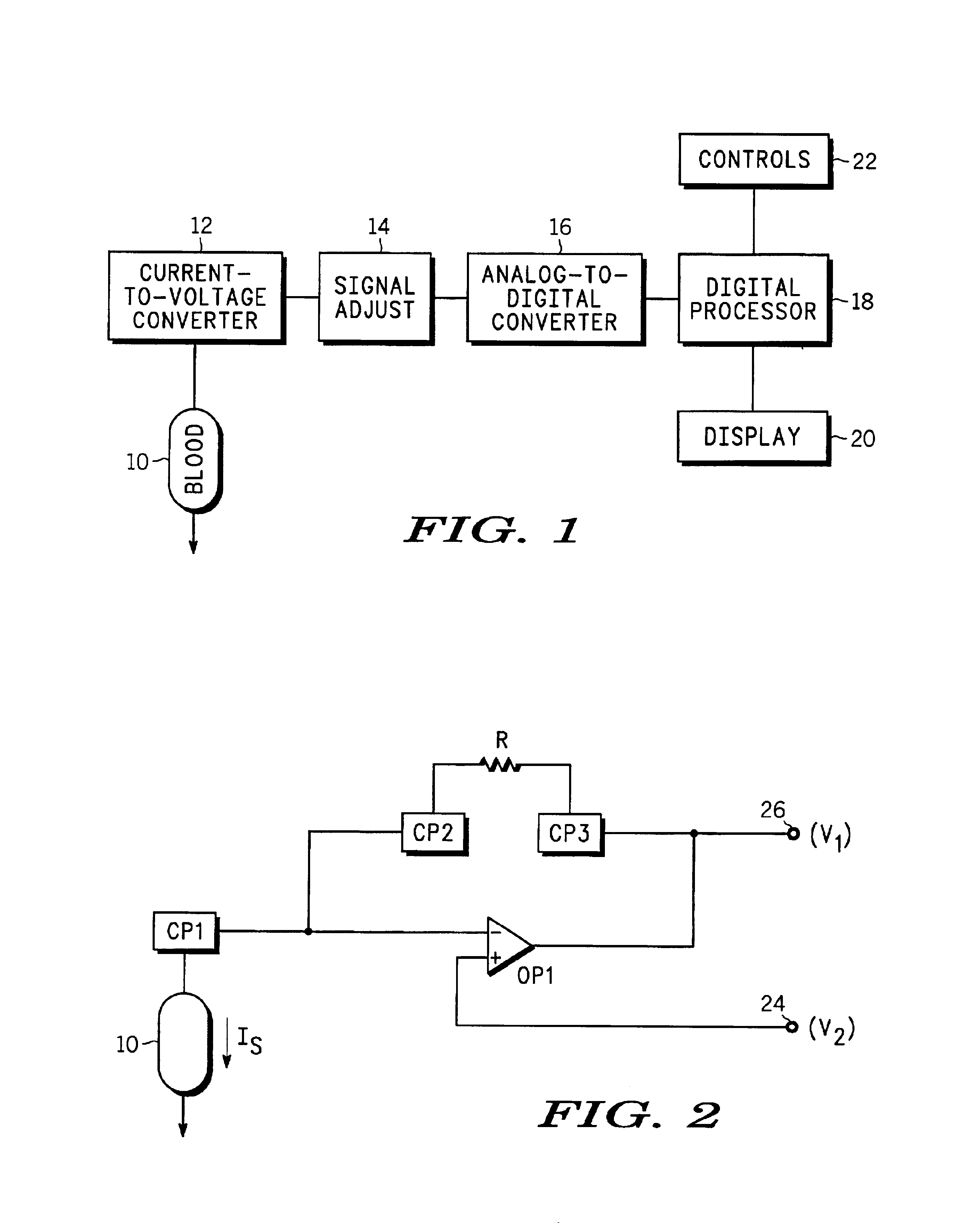

Current-to-voltage-converter for a biosensor

InactiveUS6908535B2Immobilised enzymesBioreactor/fermenter combinationsVoltage converterAudio power amplifier

An integrated current-to-voltage conversion circuit converts a first current to an output voltage representative of the first current. The circuit includes a first contact pad and second and third contact pads capable of being coupled across a first resistor. A first operational amplifier has a first input coupled to the first contact pad for producing a first voltage thereat, a second input for receiving a reference voltage, and a first output coupled to the third contact pad. A second voltage appears at the third contact pad. A second operational amplifier has a second output at which a third voltage appears, a first input coupled to the second output, and a second input coupled to the second contact pad. The output voltage is substantially equal to the difference between the second and third voltages.

Owner:MEDTRONIC INC

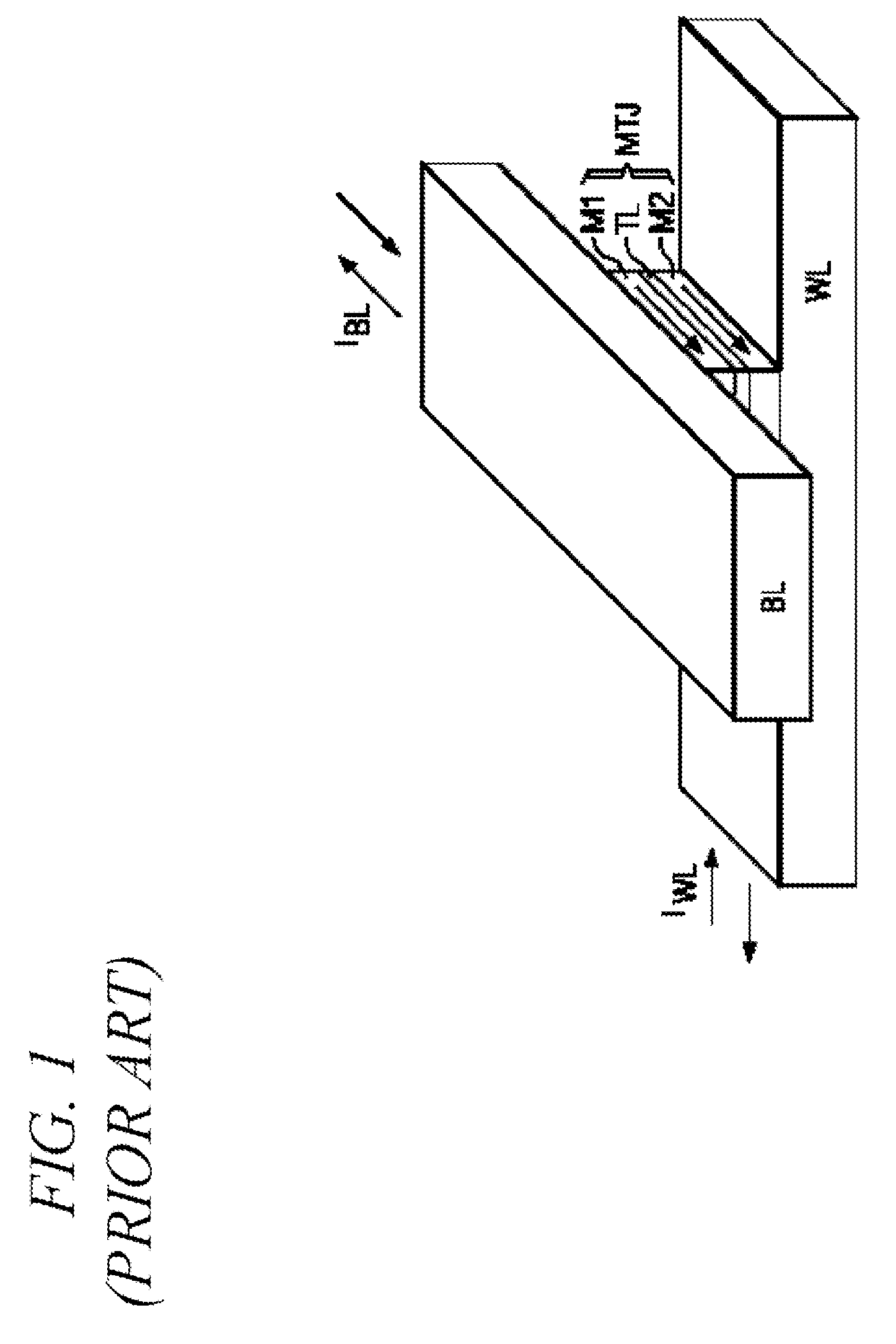

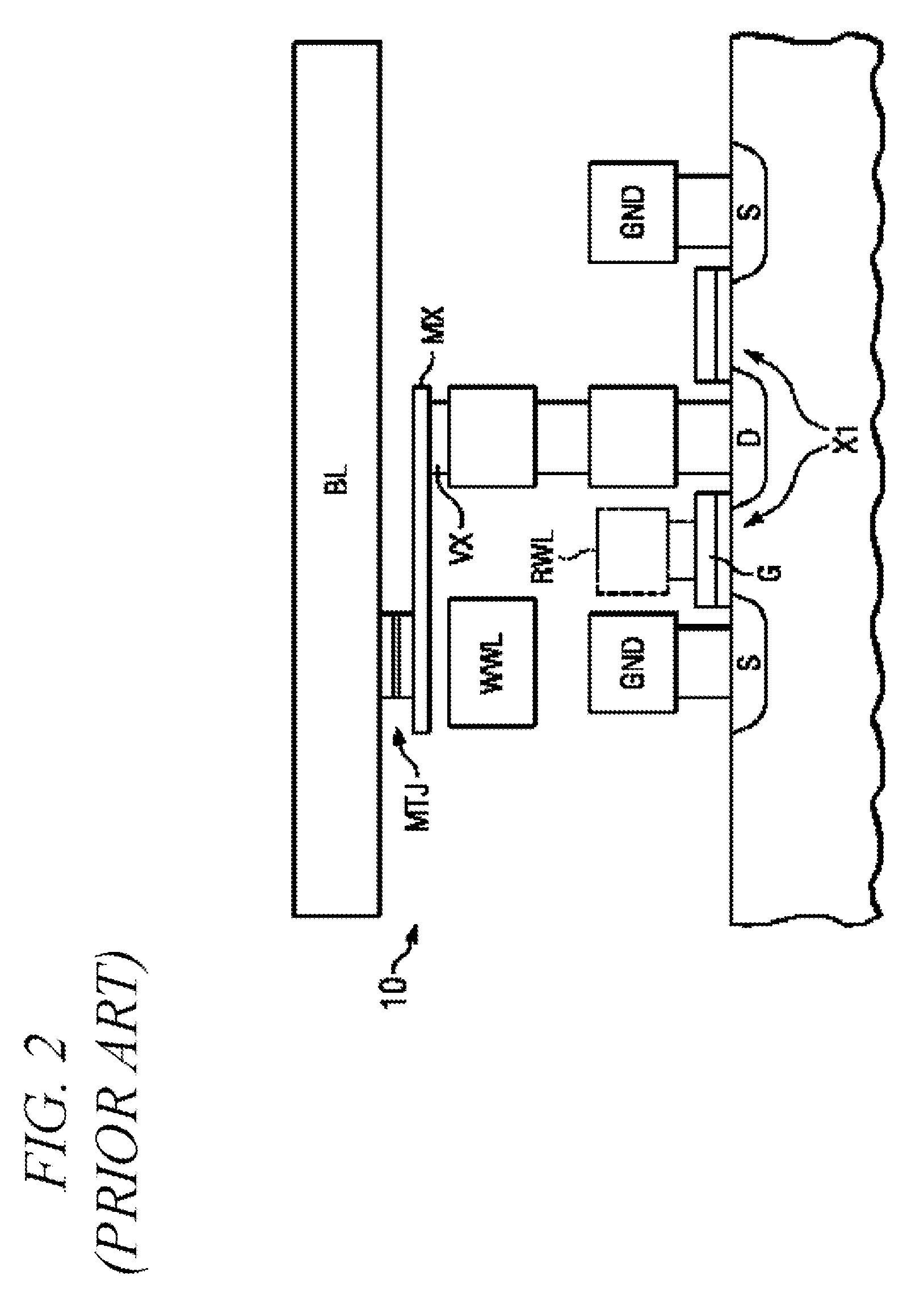

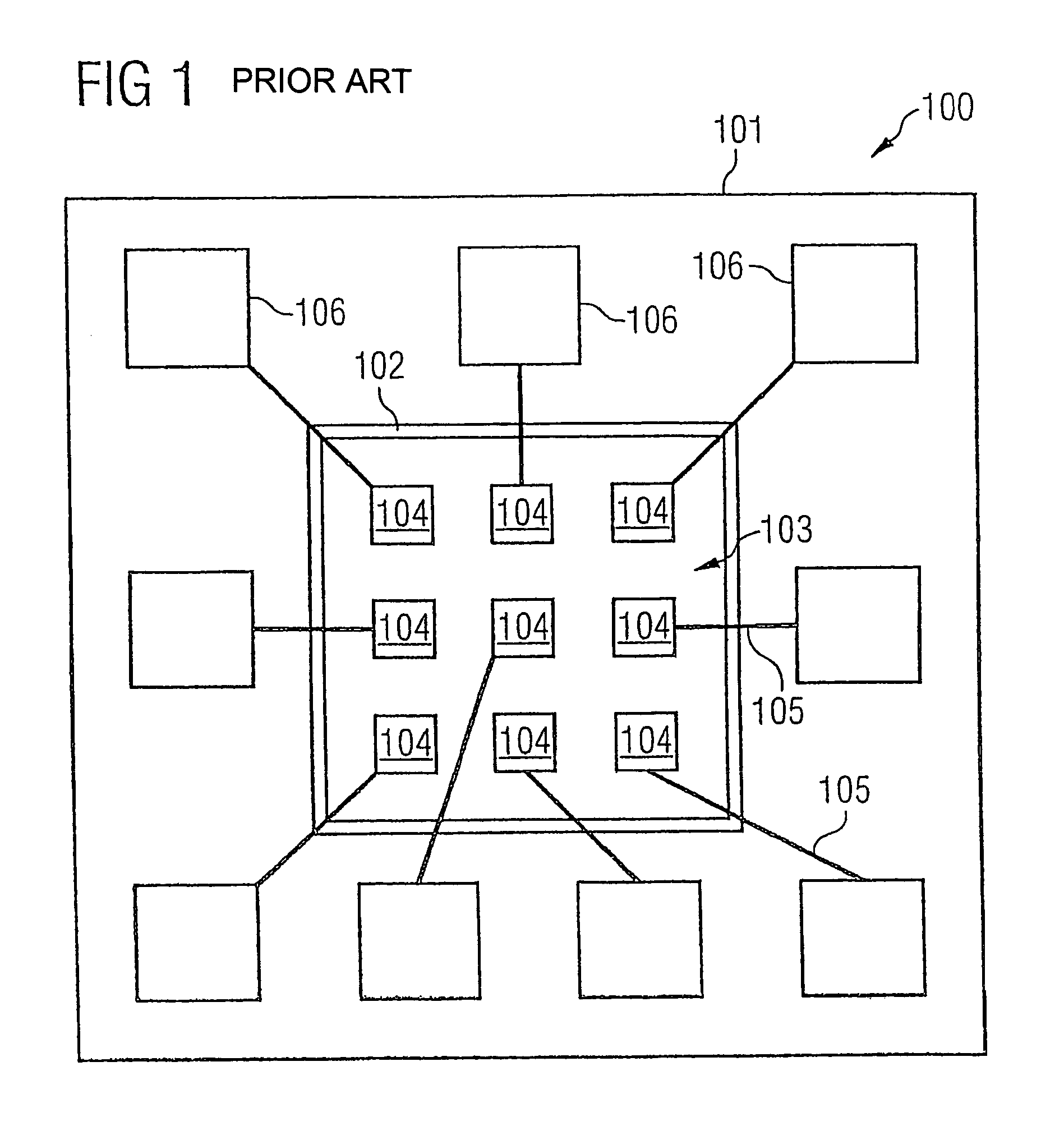

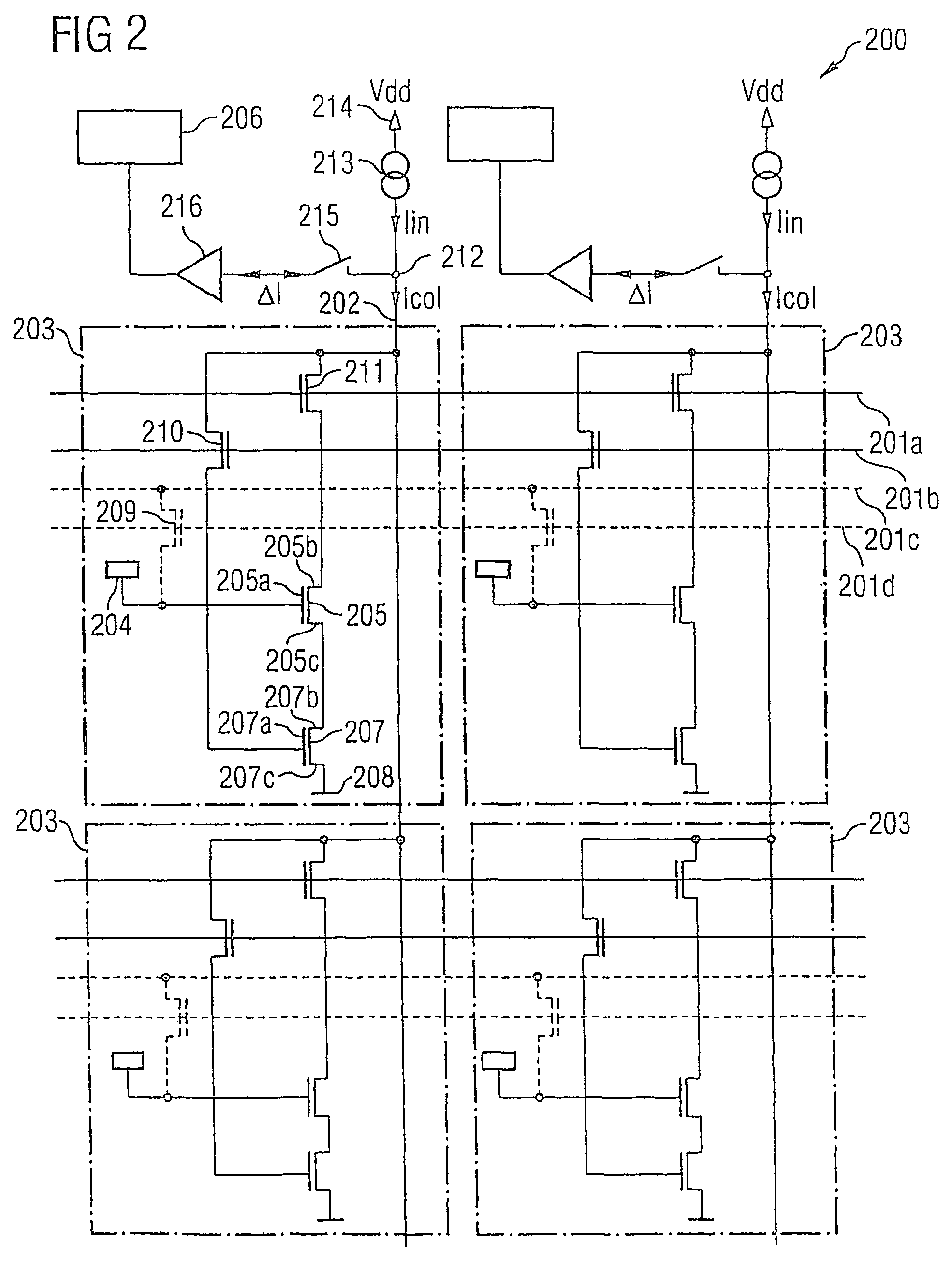

Integrated Circuit, Method of Operating an Integrated Circuit, Method of Manufacturing an Integrated Circuit, Memory Module, Stackable Memory Module

InactiveUS20080002481A1Improve performanceIncrease speedCurrent/voltage measurementDigital storageCapacitanceAudio power amplifier

An integrated circuit has a current sense amplifier that includes a voltage comparator having a first input, a second input and an output; a first clamping device coupled between the first input of the voltage comparator and a first input signal node, a second clamping device coupled between the second input of the voltage comparator and a second input signal node, a current mirror having a first side and a second side, the current mirror first side including a first transistor coupled between a voltage source and the first clamping device and the current mirror second side including a second transistor coupled between the voltage source and the second clamping device, and a sensing scheme including an actively balanced capacitance coupled to the source and drain of the second transistor.

Owner:POLARIS INNOVATIONS

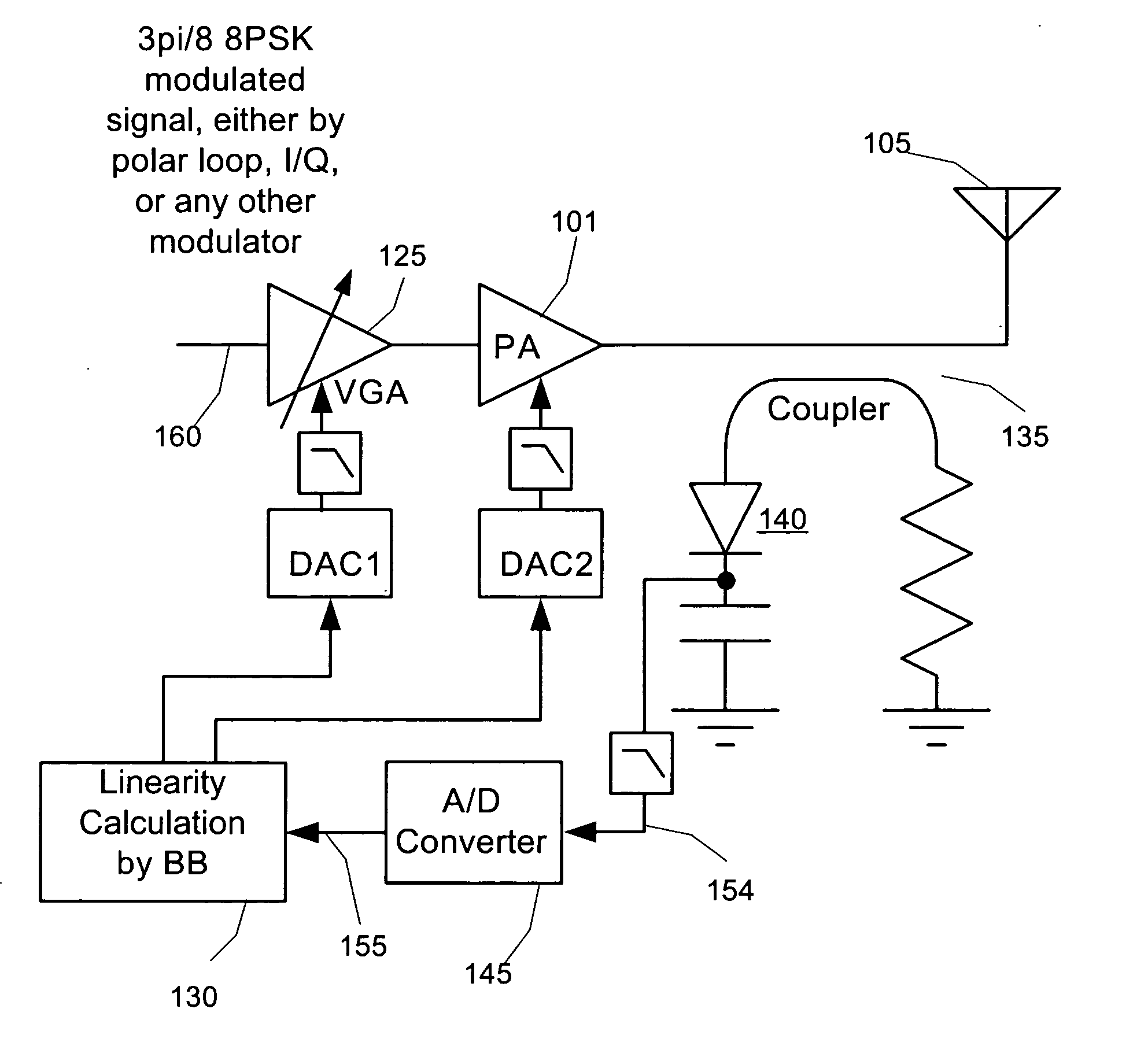

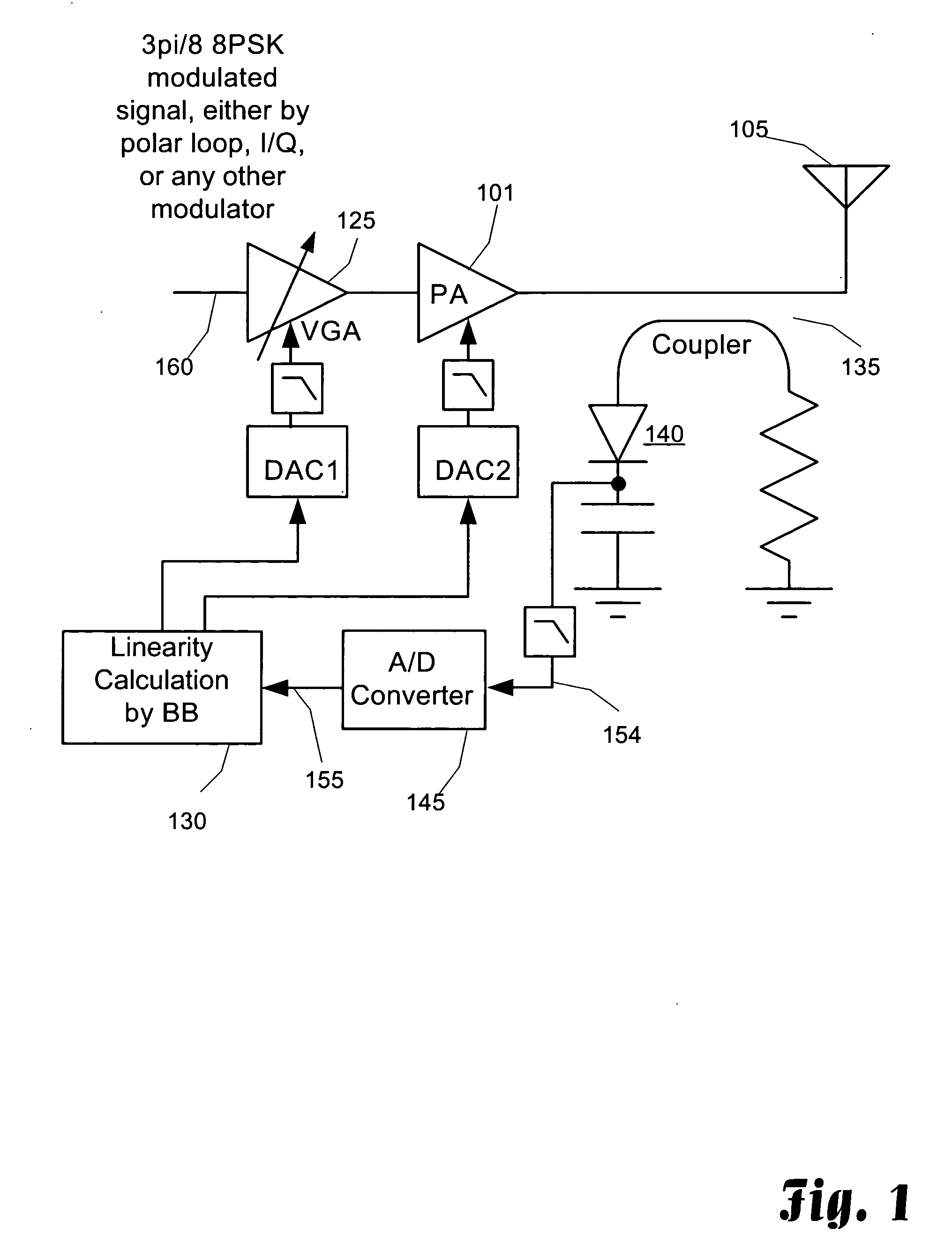

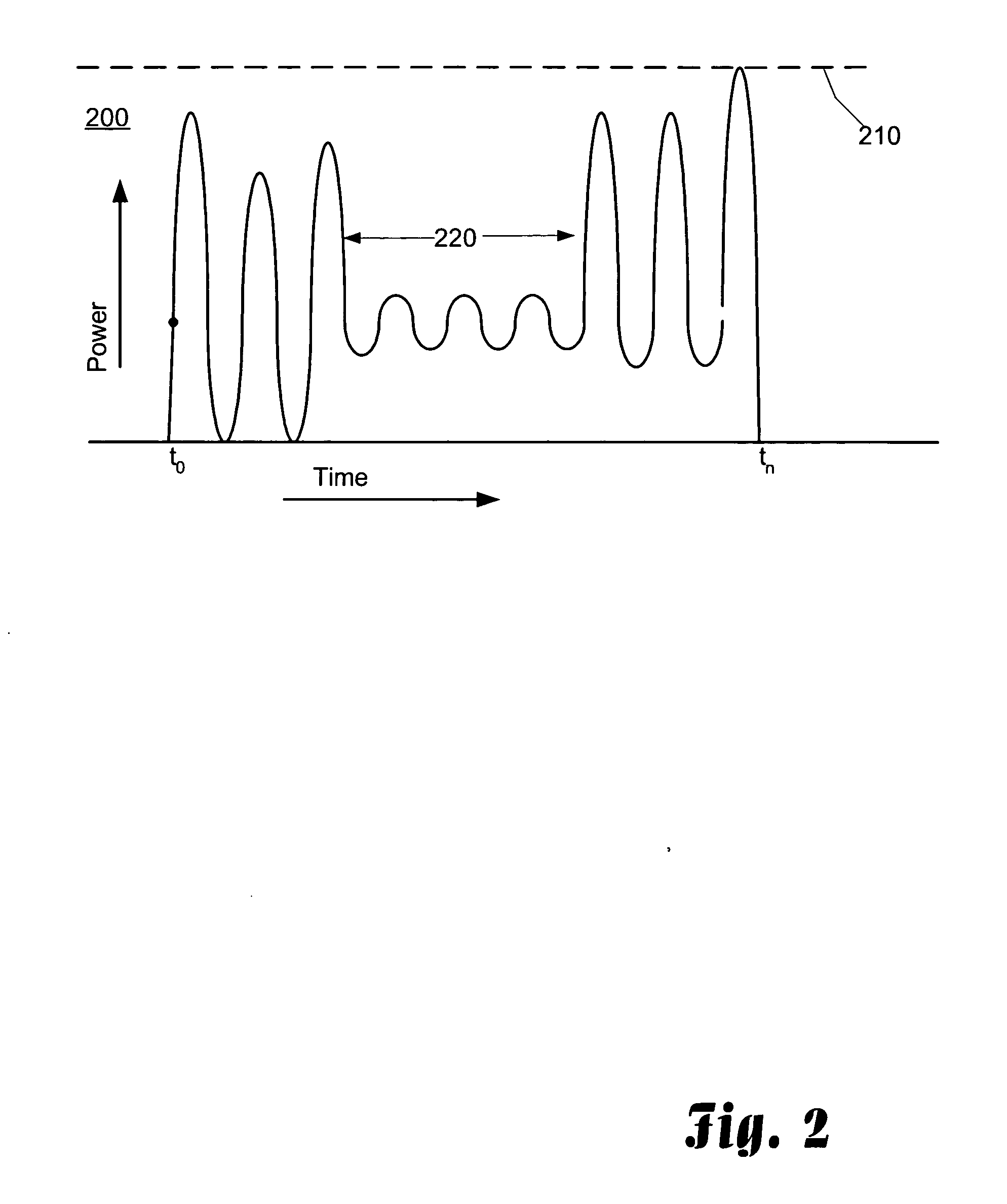

Detecting and maintaining linearity in a power amplifier system through comparing peak and RMS power levels

InactiveUS20050227646A1Raise the ratioRestore linearityResonant long antennasSupply voltage varying controlAudio power amplifierLinear region

Small portable communication devices that support multiple modulation techniques cannot gain the benefits of using an isolator at the output of a power amplifier to provide stability in the load impedance. However, for communication devices that include amplitude modulation schemes, maintaining linear operation of the power amplifier is still required. In the presence of unstable load impedance, this can be a difficult task. As a solution, the linearity of the power amplifier is detected by determining the peak power of the output signal and the average or root-mean-square of a portion of the output signal, such as a mid-amble). The ratio of the peak power and the average power of the output signal are used to determine if the power amplifier is operating in the linear region. If the ratio is too high, then the power amplifier may be operating in the linear region. By adjusting the power level of the input signal to the power amplifier when the ratio increases, linearity of the power amplifier is maintained.

Owner:PANASONIC CORP

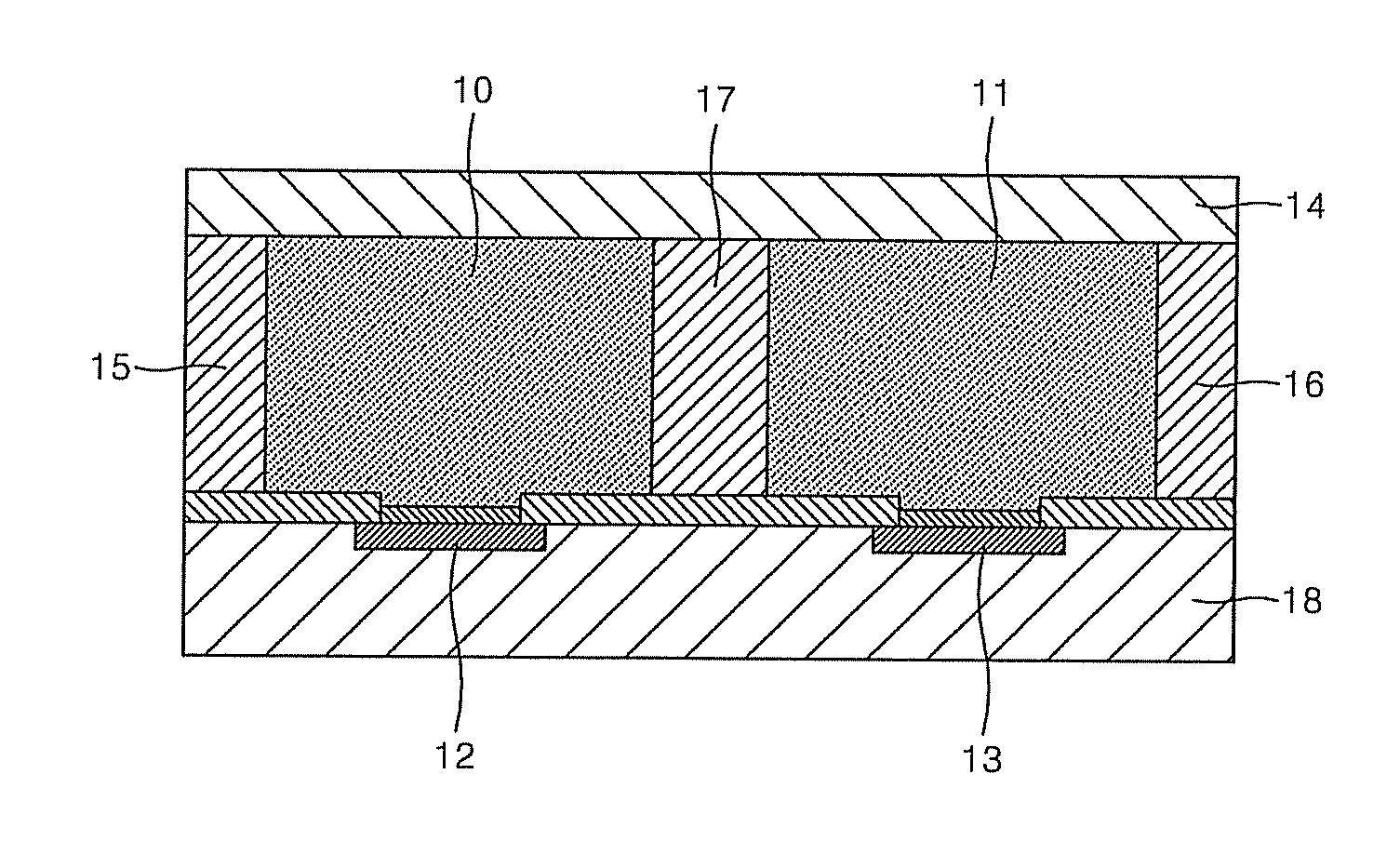

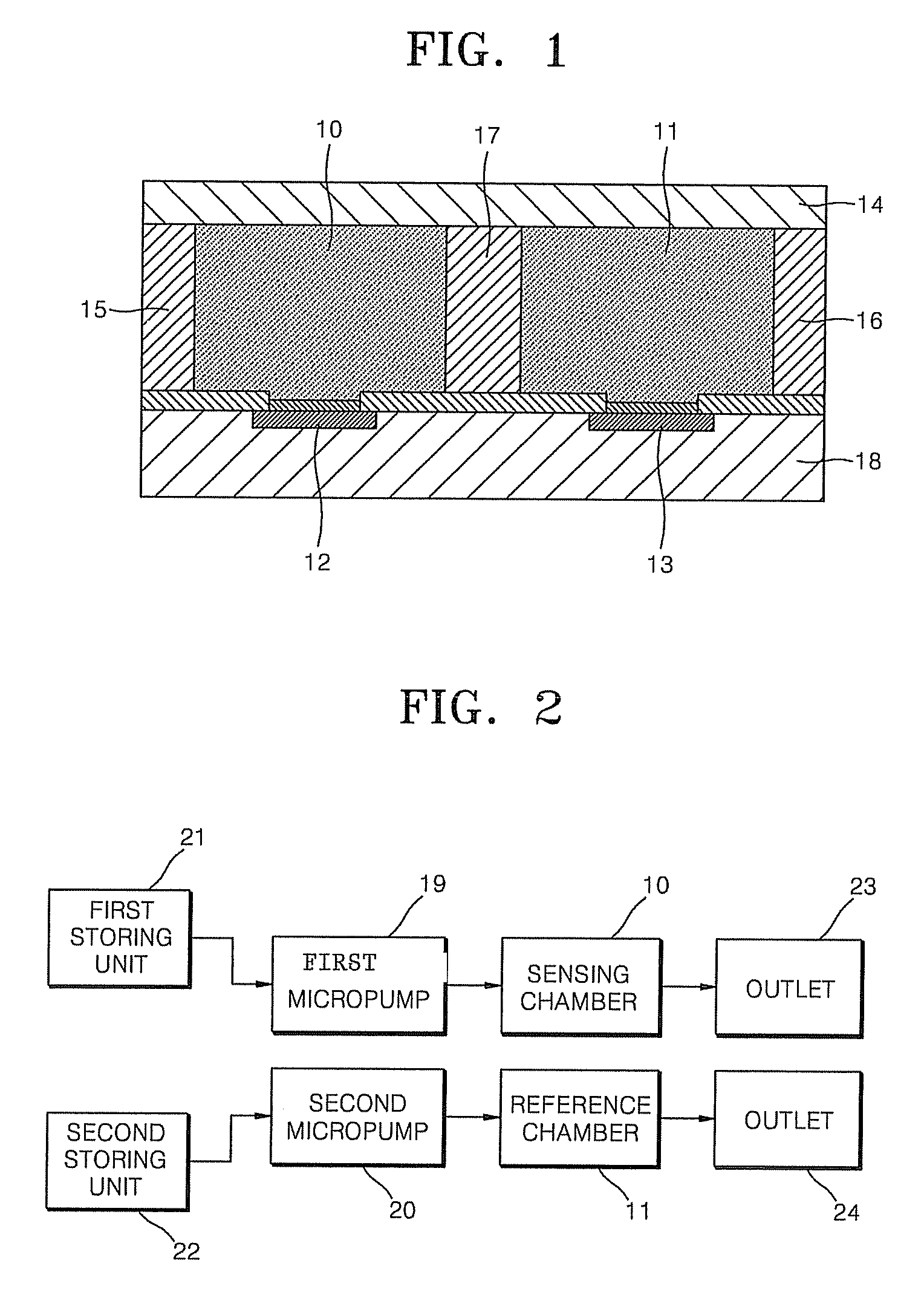

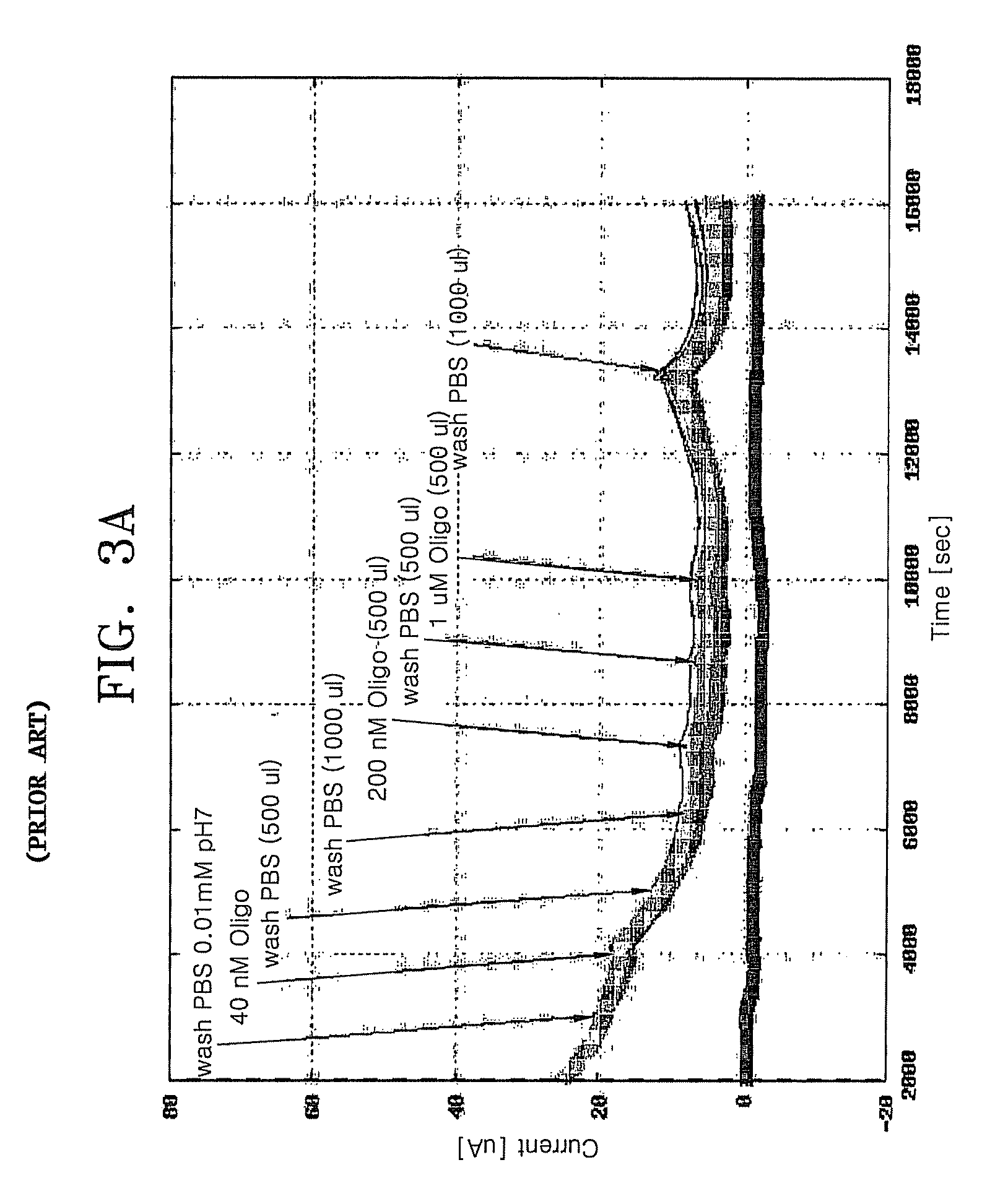

FET-based sensor for detecting ionic material, ionic material detecting device using the FET-based sensor, and method of detecting ionic material using the FET-based sensor

ActiveUS7859029B2Reduce concentrationHigh sensitivityDrying solid materials without heatSolid-state devicesEngineeringElectric current

Provided are a FET-based sensor for detecting an ionic material, an ionic material detecting device including the FET-based sensor, and a method of detecting an ionic material using the FET-based sensor. The FET-based sensor includes: a sensing chamber including a reference electrode and a plurality of sensing FETs; and a reference chamber including a reference electrode and a plurality of reference FETs. The method includes: flowing a first solution into and out of the sensing chamber and the reference chamber of the FET-based sensor; flowing a second solution expected to contain an ionic material into and out of the sensing chamber while continuously flowing the first solution into and out of the reference chamber; measuring a current in a channel region between the source and drain of each of the sensing and reference FETs; and correcting the current of the sensing FETs.

Owner:SAMSUNG ELECTRONICS CO LTD

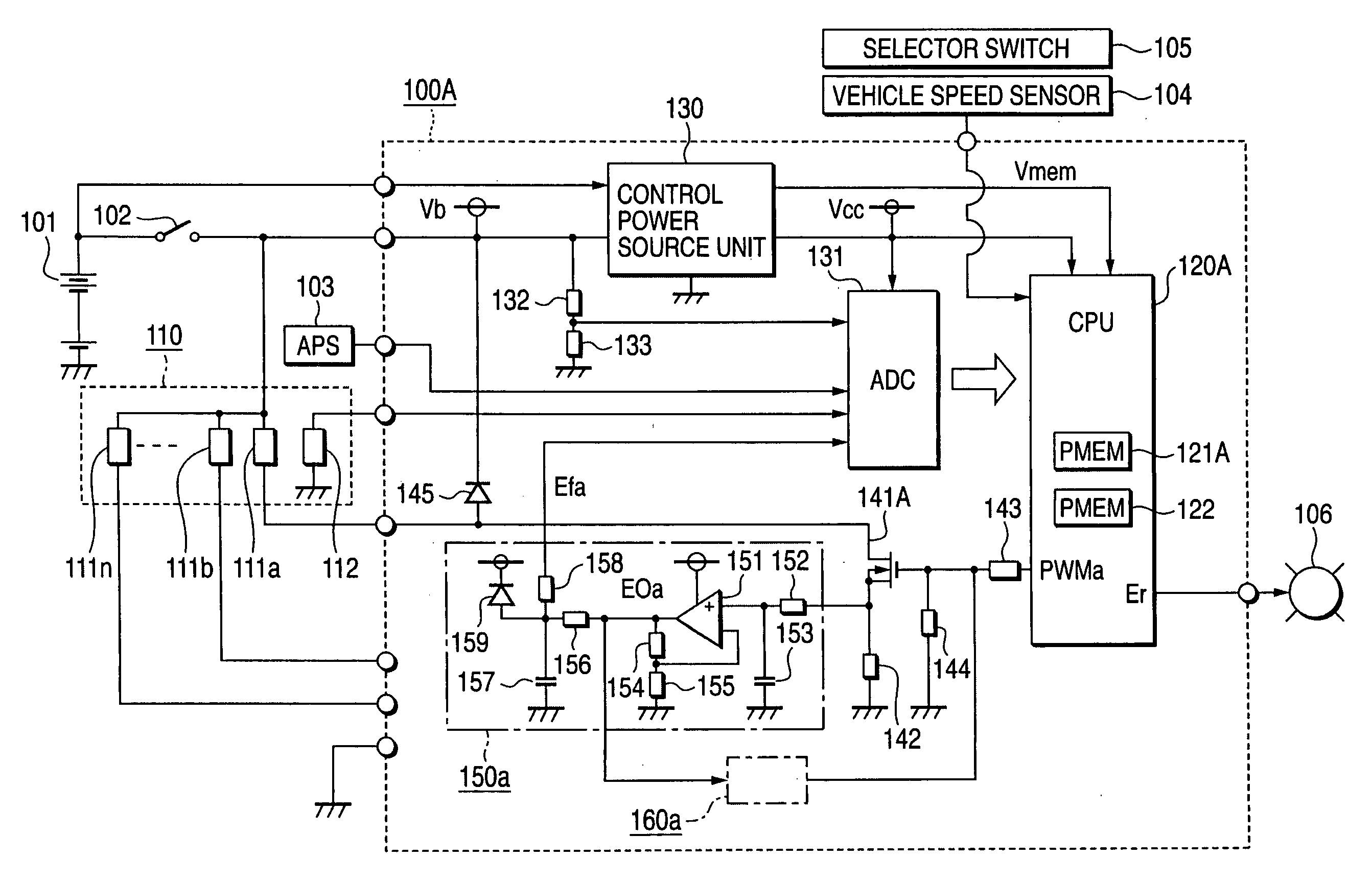

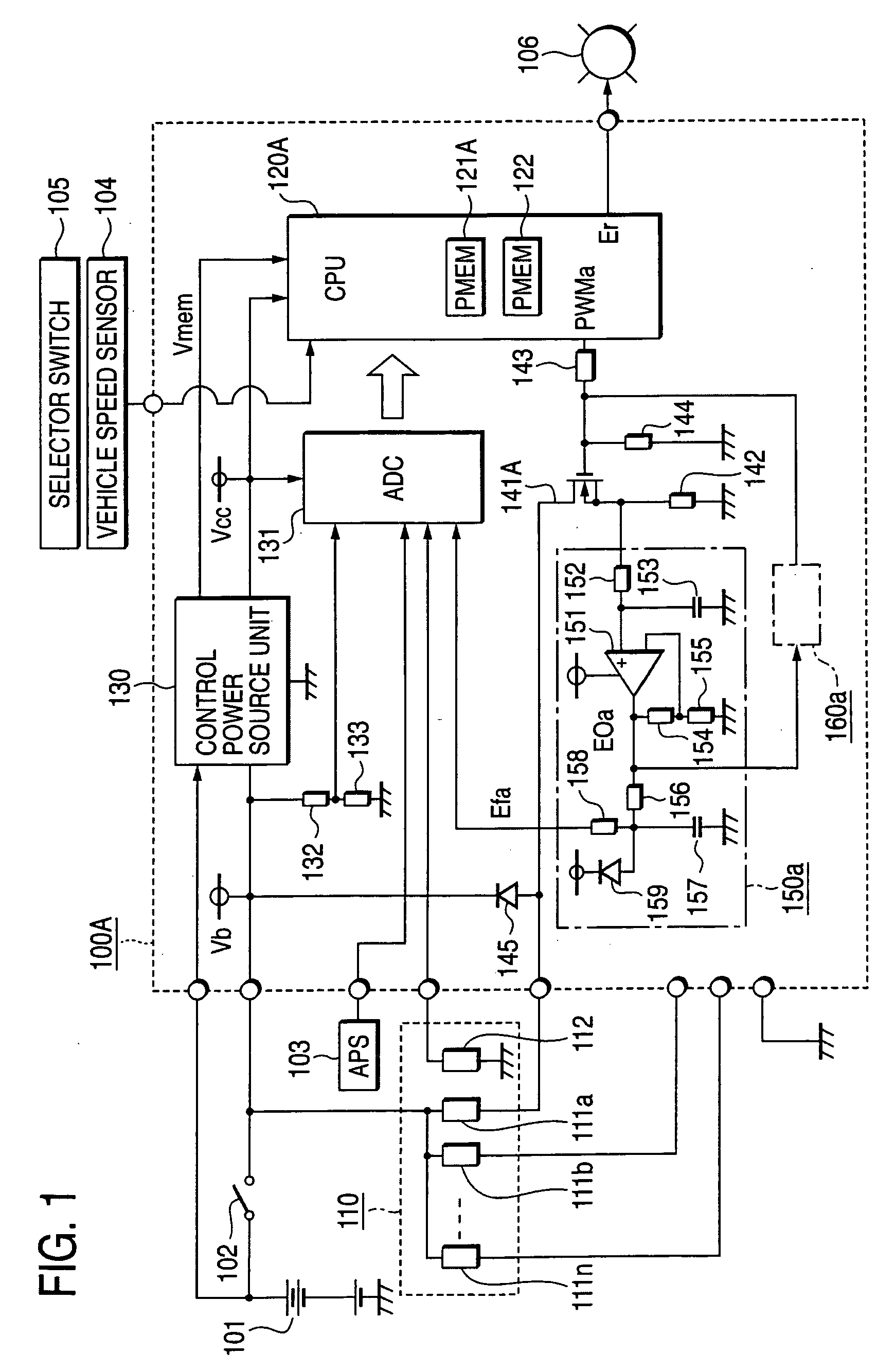

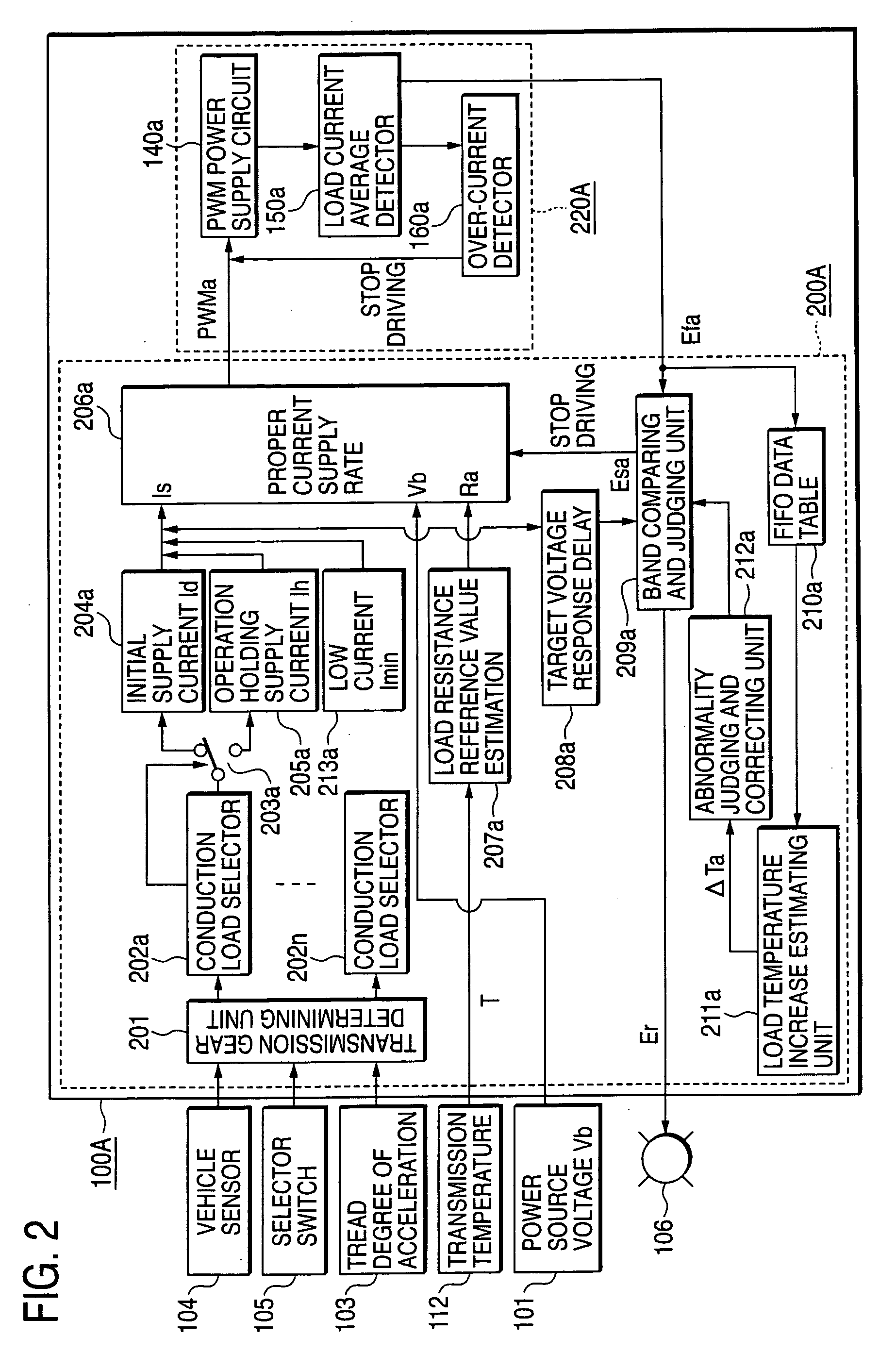

Non-feedback type load current controller

InactiveUS20070030068A1Improve securityThermometer detailsDigital computer detailsLoop controlSwitched current

An electrical load is supplied with power from a driving power source, and a microprocessor (CPU) controls the opening / closing current supply rate (duty factor) of an opening / closing element in accordance with target current and driving power source voltage so that open loop control is carried out to achieve predetermined target current. The voltage between both the ends of a current detecting resistor connected to the ground side of the opening / closing element is input as a monitoring voltage from a current detecting amplifying circuit portion through a multichannel AD converter to CPU. When the error between the comparison target voltage corresponding to the target current and the monitoring voltage is above a first permissible error, CPU judges that there is an abnormality sign, and if the error is above a larger second permissible error, CPU judges that there is appearing abnormality. Accordingly, an abnormality sign of a semi-wire-breaking / semi-short-circuit state of the electrical load can be sensed, and abnormality notification can be carried out.

Owner:MITSUBISHI ELECTRIC CORP

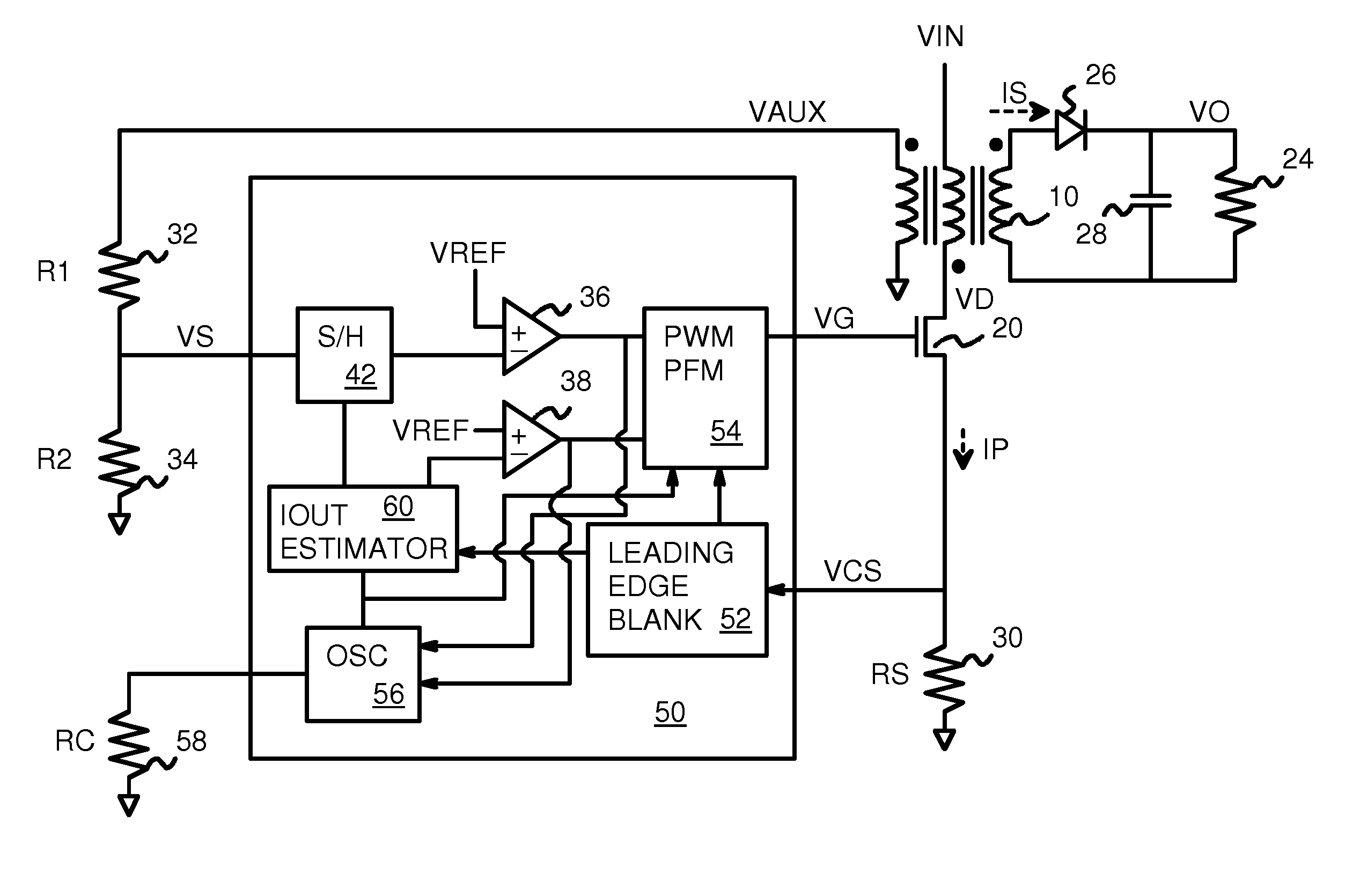

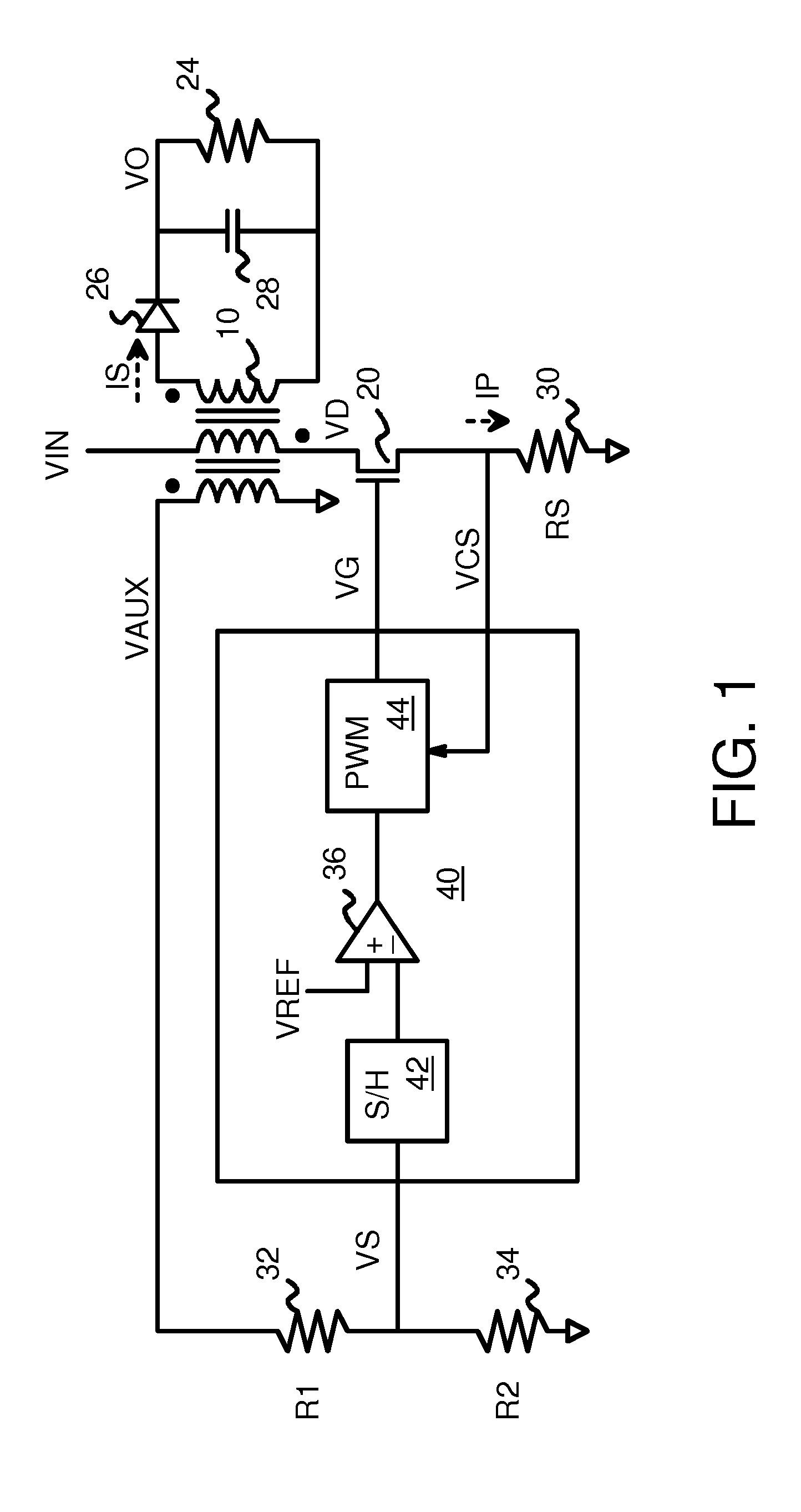

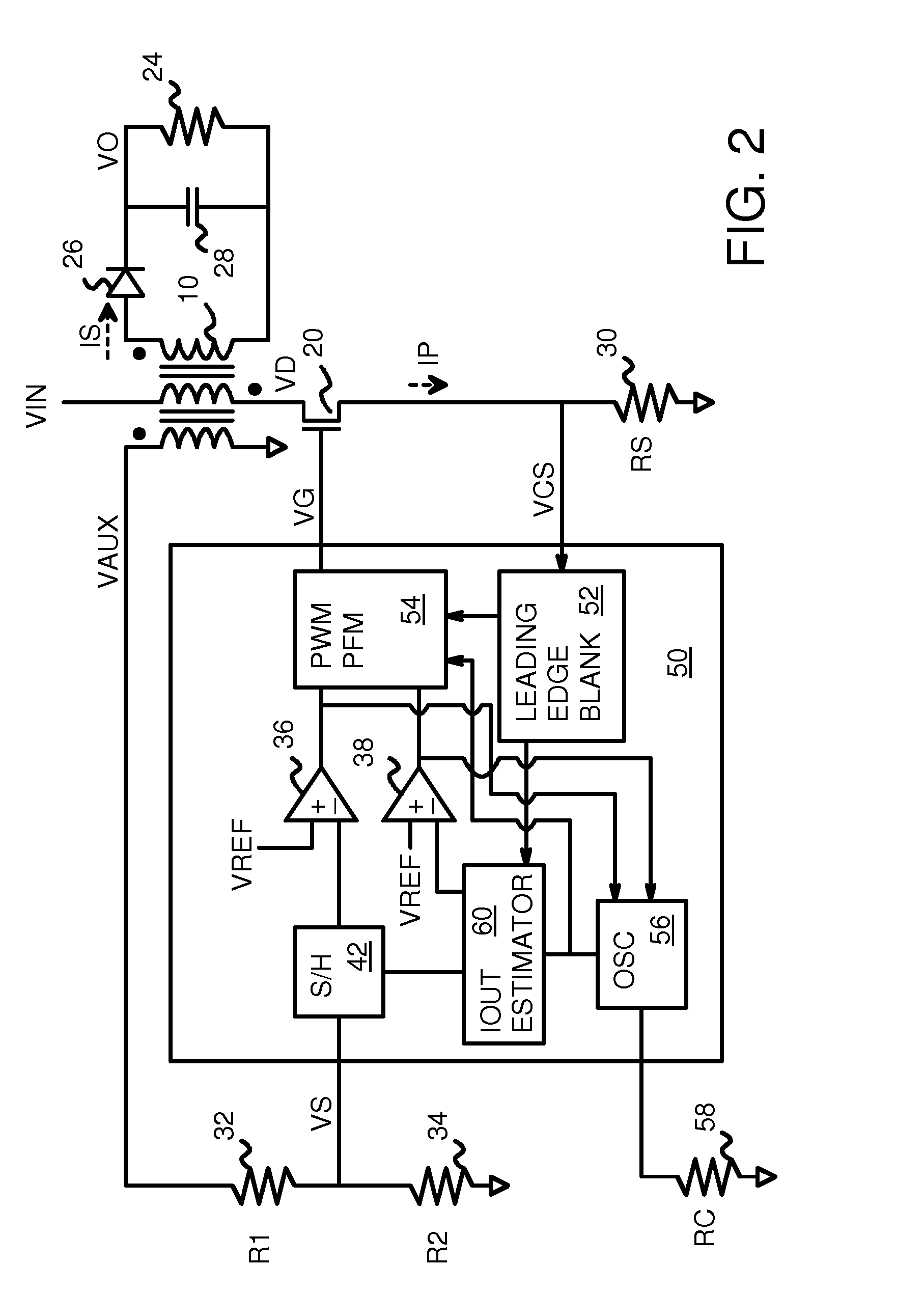

Output Current Estimation for an Isolated Flyback Converter With Variable Switching Frequency Control and Duty Cycle Adjustment for Both PWM and PFM Modes

InactiveUS20130294118A1Dc-dc conversionDifferential amplifiersTransformerSwitching frequency control

A fly-back power converter has a current-estimating control loop that senses the primary output current in a transformer to control the secondary output. A primary-side control circuit switches primary current through the transformer on and off. A discharge time when a secondary current through an auxiliary winding of the transformer is flowing is generated by sampling a voltage divider on an auxiliary loop for a knee-point. A normalized duty cycle is calculated by multiplying the discharge time by a current that is proportional to the switching frequency and comparing to a sawtooth signal having the switching frequency. The peak of a primary-side voltage is sensed from the primary current loop and converted to a current and multiplied by the normalized duty cycle to generate an estimated current. An error amp compares the estimated current to a reference to adjust the oscillator frequency and peak current to control primary switching.

Owner:HONG KONG APPLIED SCI & TECH RES INST

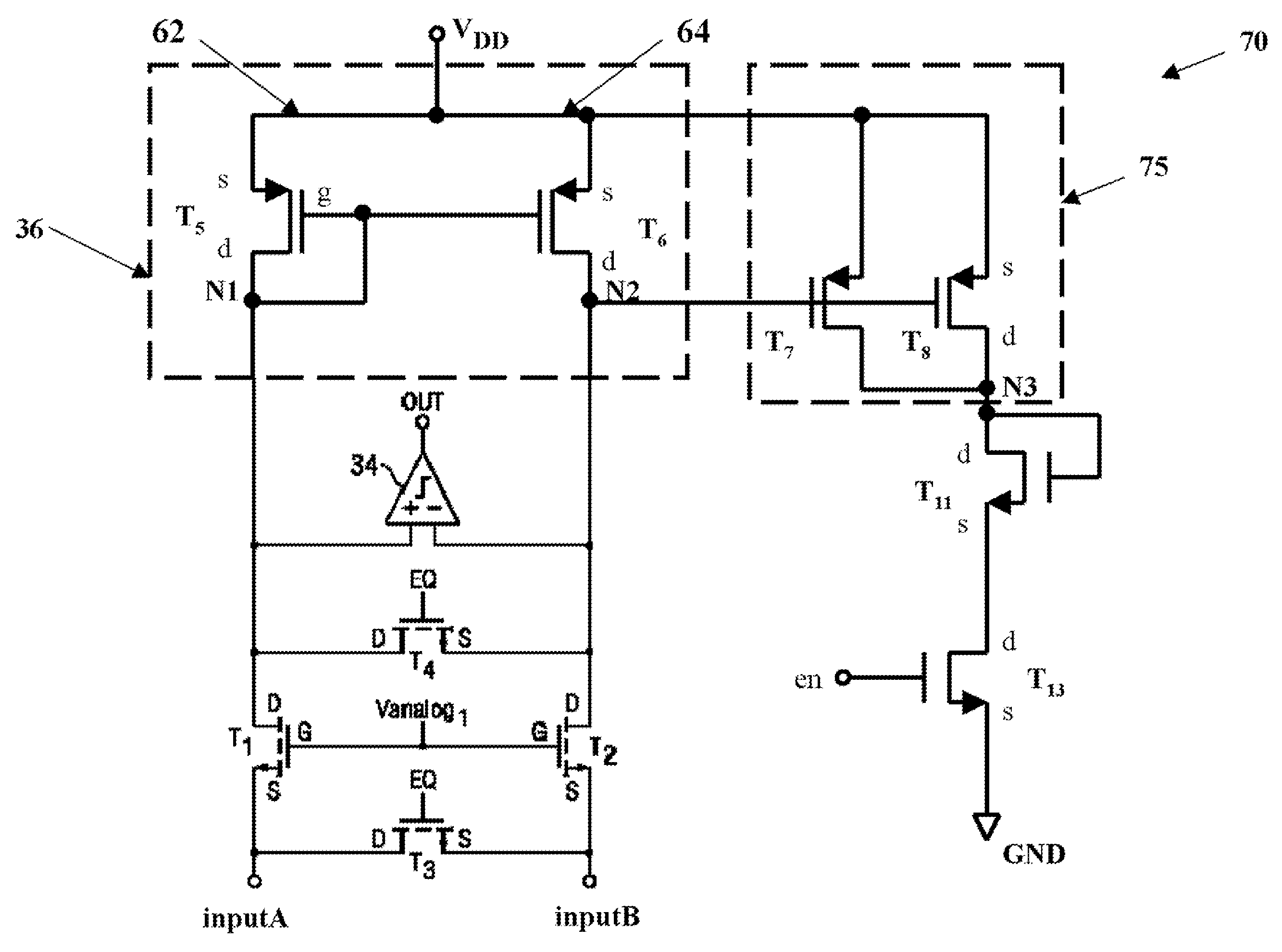

Integrated circuit, method of operating an integrated circuit, method of manufacturing an integrated circuit, memory module, stackable memory module

InactiveUS7433253B2Design and efficient manufactureAccurate balanceCurrent/voltage measurementDigital storageCapacitanceEngineering

An integrated circuit has a current sense amplifier that includes a voltage comparator having a first input, a second input and an output; a first clamping device coupled between the first input of the voltage comparator and a first input signal node, a second clamping device coupled between the second input of the voltage comparator and a second input signal node, a current mirror having a first side and a second side, the current mirror first side including a first transistor coupled between a voltage source and the first clamping device and the current mirror second side including a second transistor coupled between the voltage source and the second clamping device, and a sensing scheme including an actively balanced capacitance coupled to the source and drain of the second transistor.

Owner:POLARIS INNOVATIONS LTD

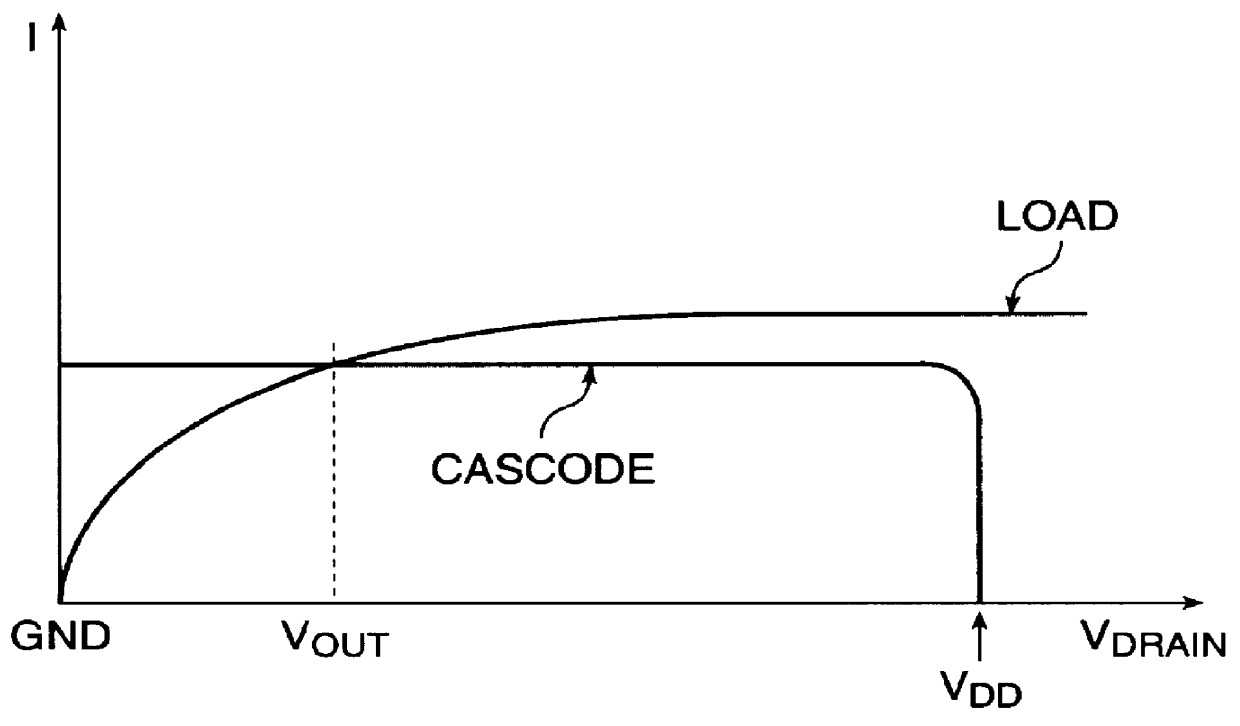

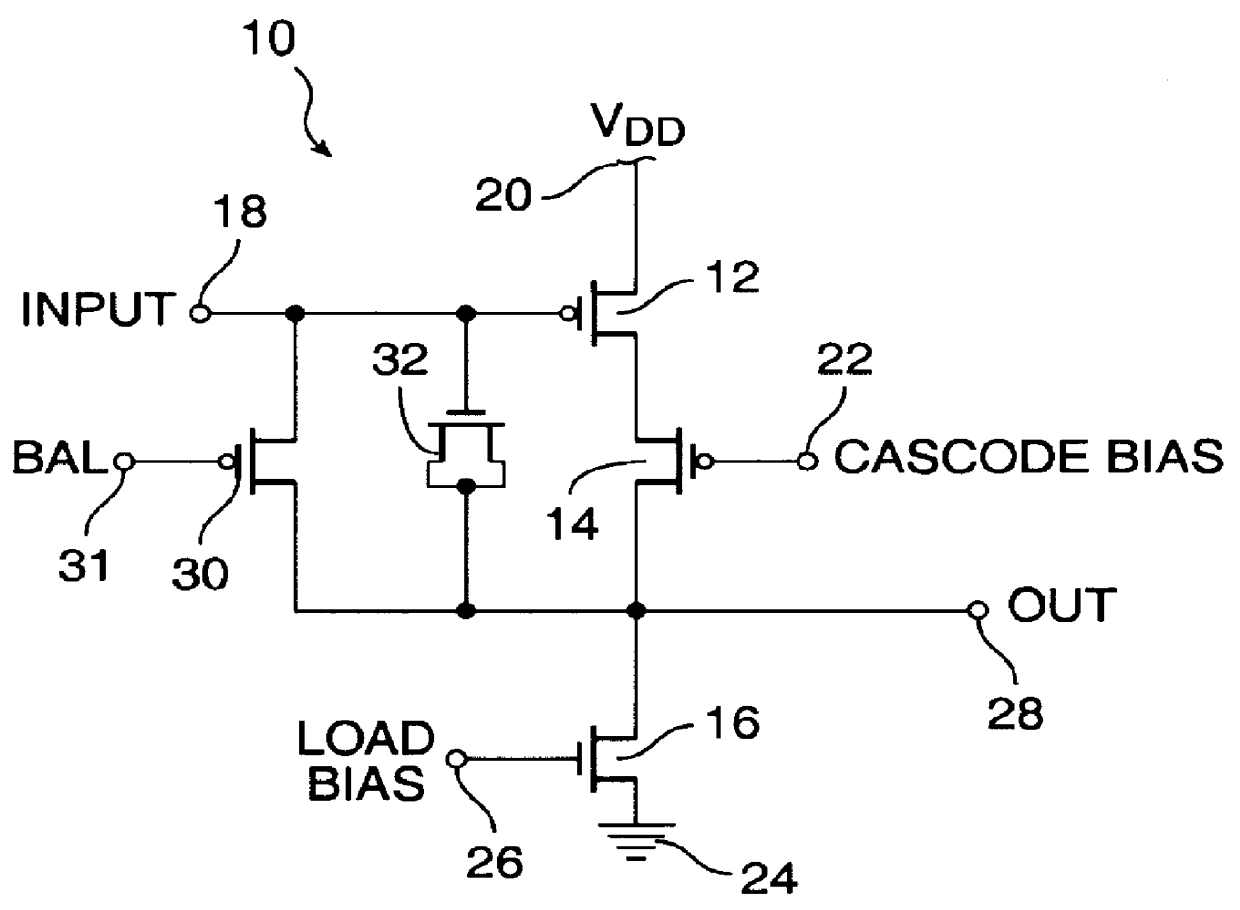

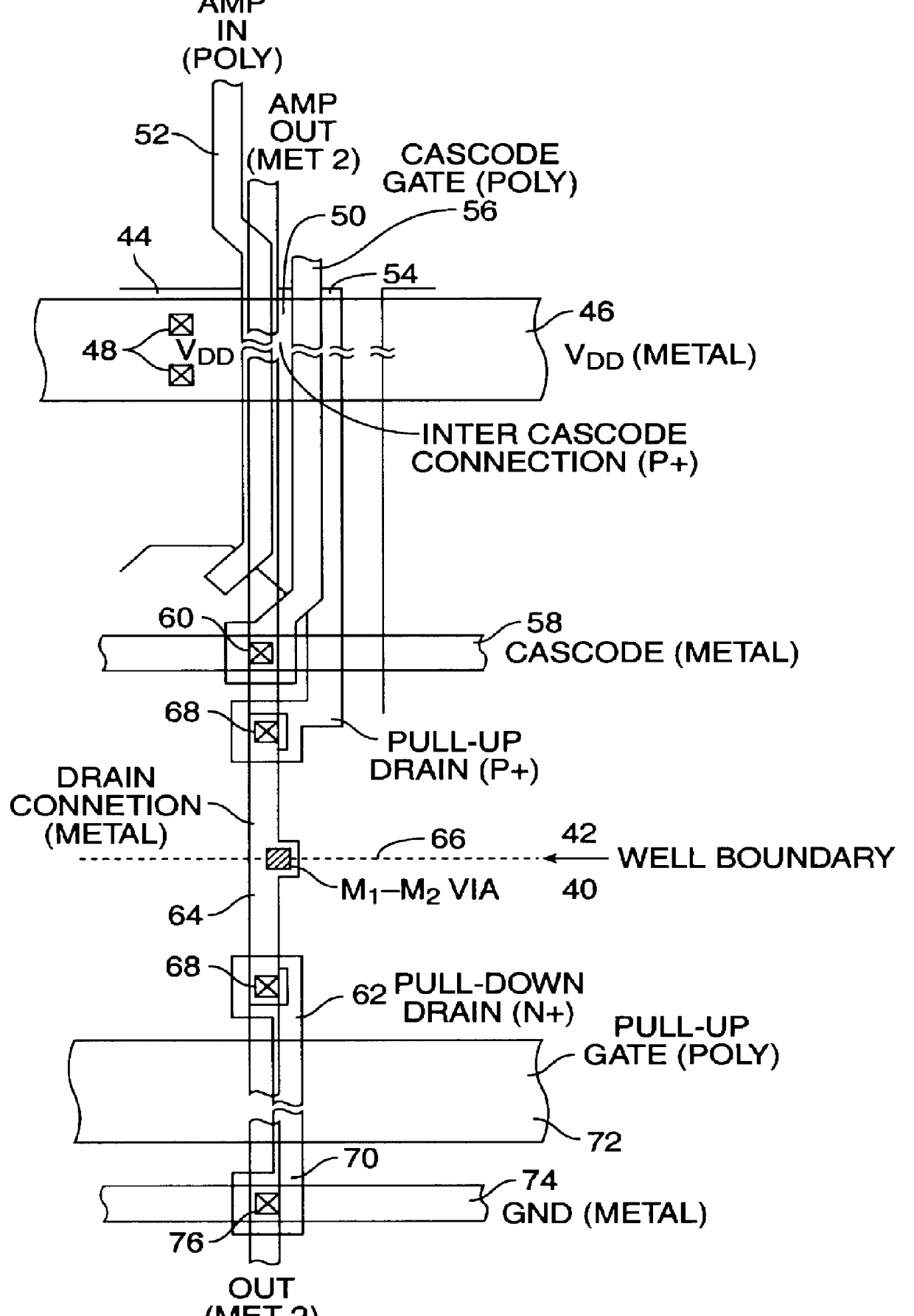

Sense amplifier for high-density imaging array

InactiveUS6097432ATelevision system detailsTelevision system scanning detailsHigh densityAudio power amplifier

A sense amplifier comprises an input node and an output node. An input transistor has a gate connected to the input node, a source connected to a first supply voltage rail, and a drain. A cascode transistor has a gate connected to a cascode node, a source connected to the drain of the input transistor, and a drain connected to the output node. A load transistor has a gate connected to a bias node, a drain connected to the output node, and a source connected to a second supply voltage rail. The gates of the cascode transistor and the load transistor are biased such that the input transistor and the cascode transistor are operated near their threshold and the load transistor is operated above threshold. In a presently preferred embodiment of the present invention, the input transistor and the cascode transistor of the sense amplifier are wide and short, such that they operate in below threshold, whereas the load transistor is made long and relatively narrow, so that it operates above threshold.

Owner:FOVEON

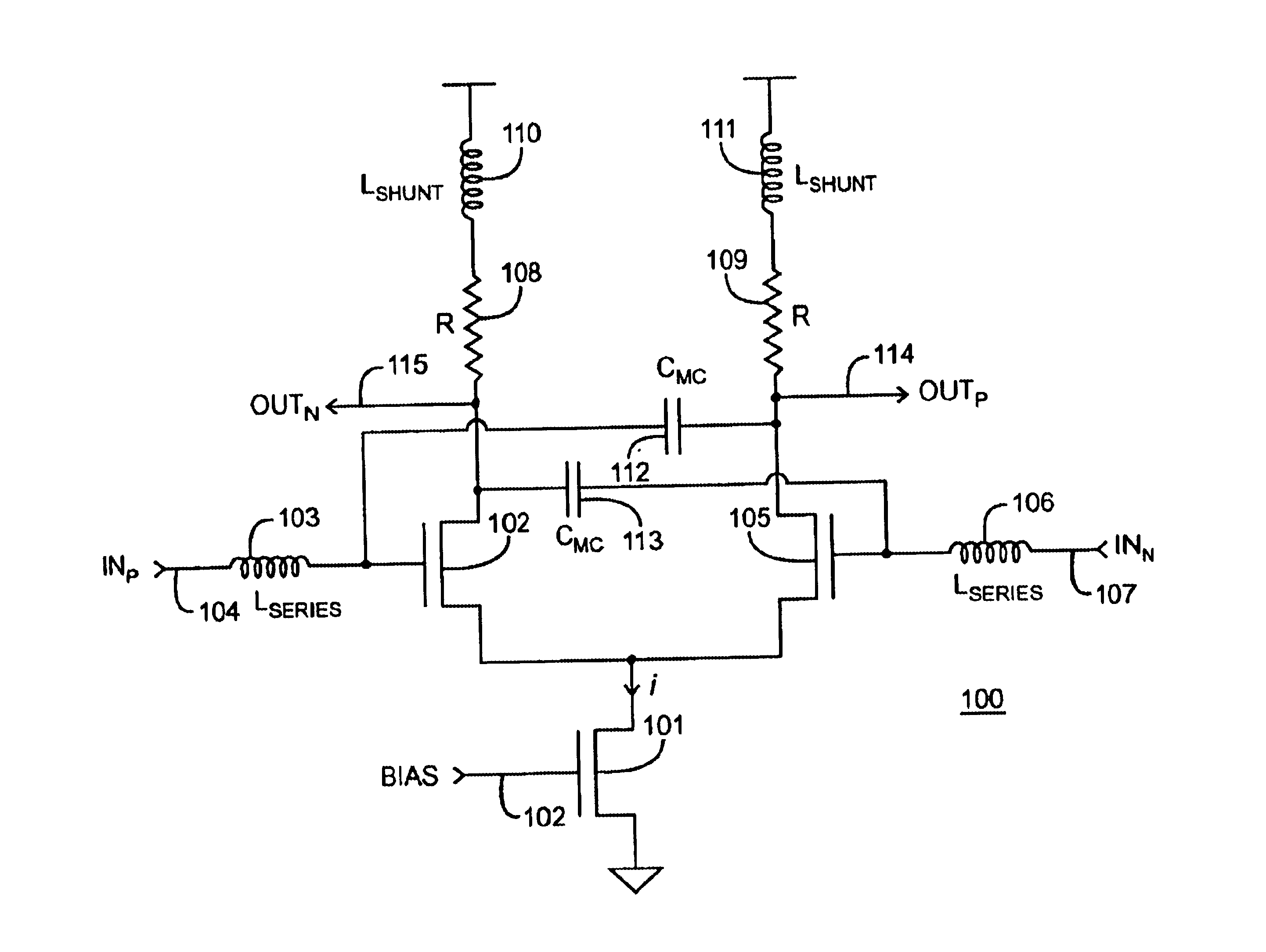

Gain boosting RF gain stage with cross-coupled capacitors

ActiveUS7697915B2Tighter current flow controlHigh gainHigh frequency amplifiersRadio transmissionCapacitanceGain stage

A RF differential gain stage has cross-coupled capacitors between input and output nodes of the amplifier stage to boost gain. The gain boost allows cancellation of the series resistance of an inductive load of the amplifier stage.

Owner:QUALCOMM INC

Biosensor circuit and sensor array consisting of a plurality of said biosensor circuits and biosensor array

InactiveUS7019305B2Highly integratedHigh degree of miniaturizationMaterial analysis by electric/magnetic meansMaterial analysis by optical meansSensor arrayDevice form

Biosensor circuit arrangement including a substrate, a sensor element formed in or on a surface region of the substrate with a physical parameter, which is coupled to a substance to be examined, the type of coupling having a resistive component, the sensor element having an electrically conductive sensor electrode that is coupled to the substance to be examined, the sensor element having a measuring transistor the gate terminal of which is coupled to the electrically conductive sensor electrode, and the physical parameter being the threshold voltage of the measuring transistor, and a calibration device formed in or on the substrate, the calibration device being set up such that it is used to at least partly compensate for an alteration of the value of the physical parameter of the sensor element.

Owner:INFINEON TECH AG

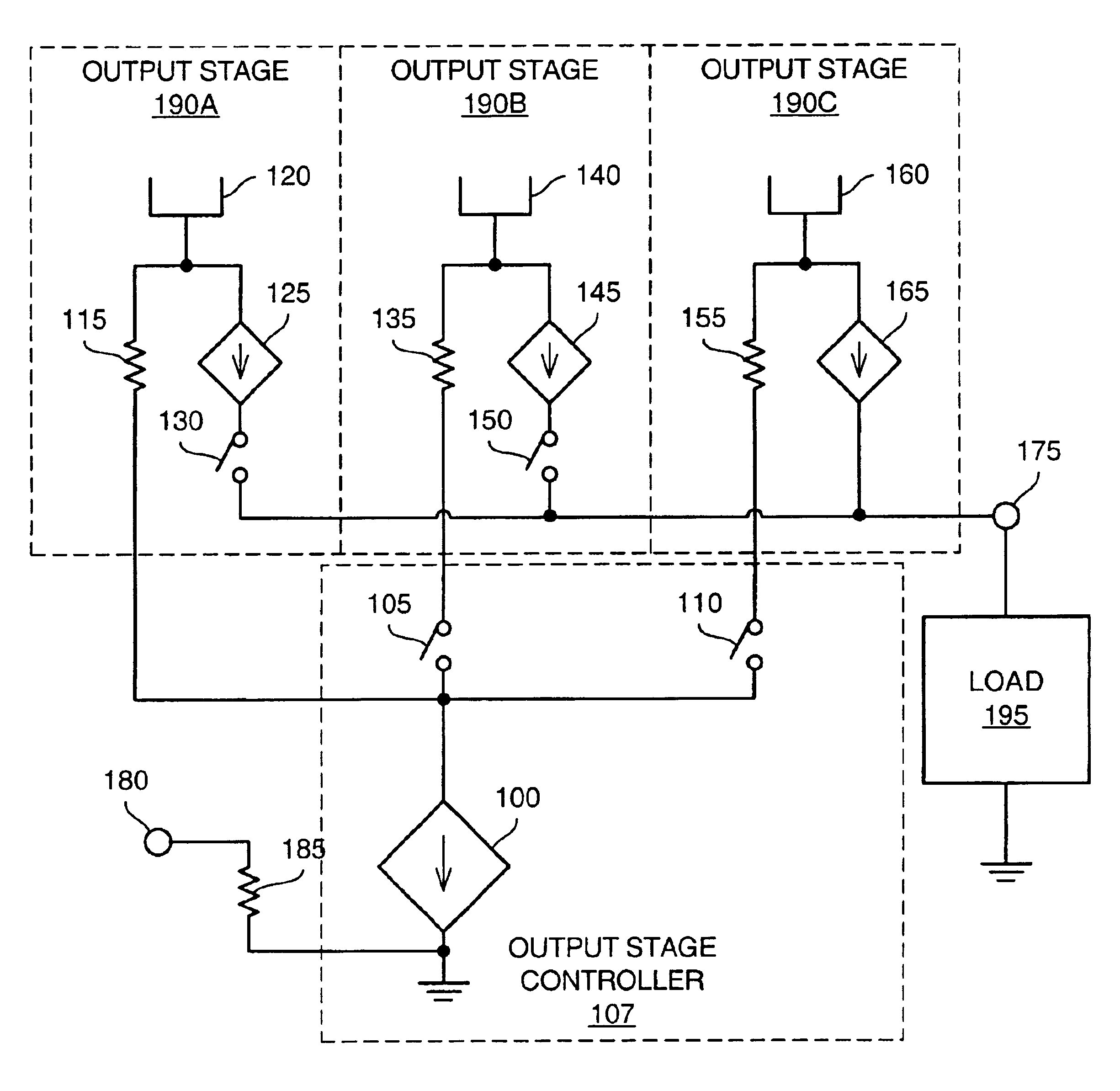

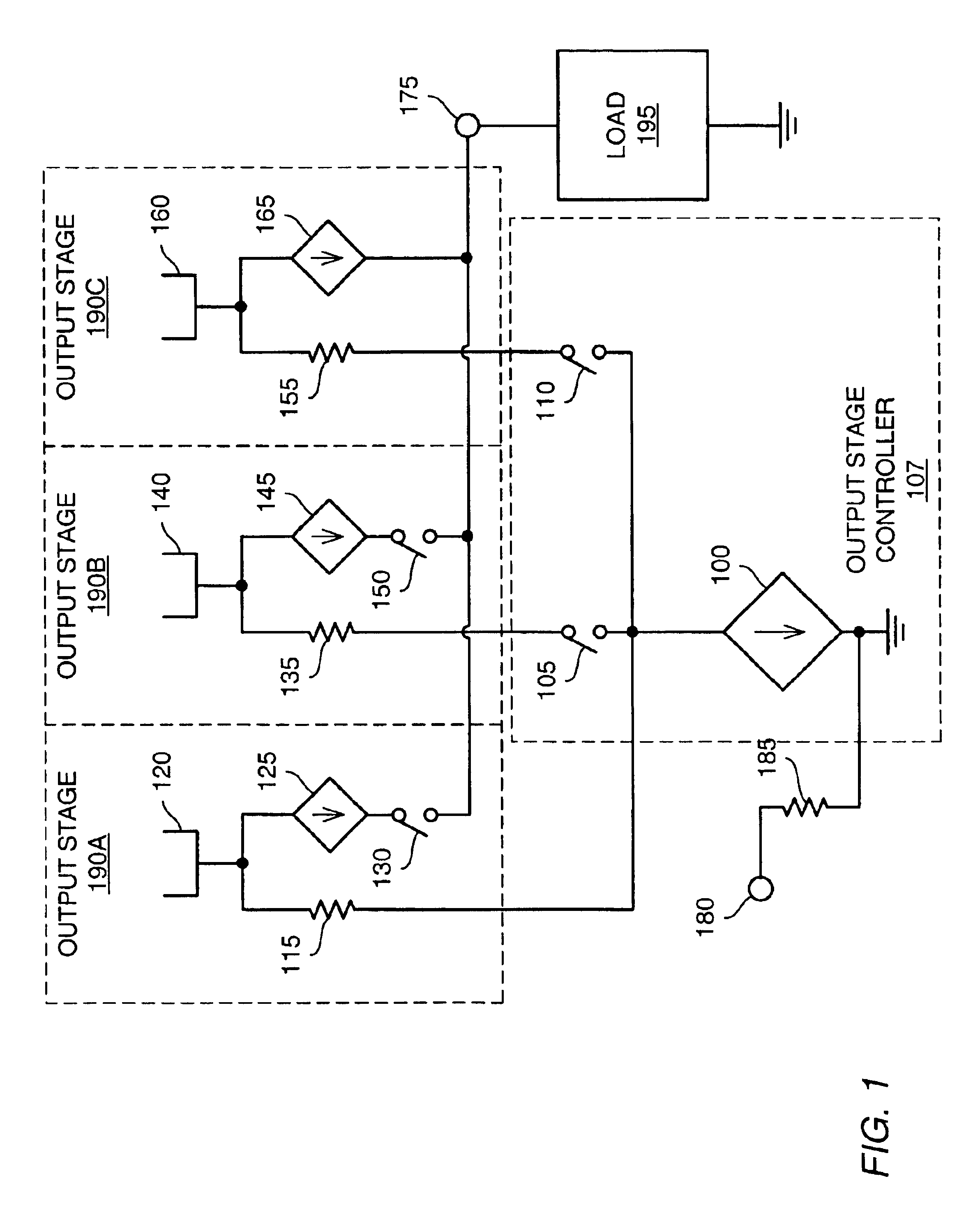

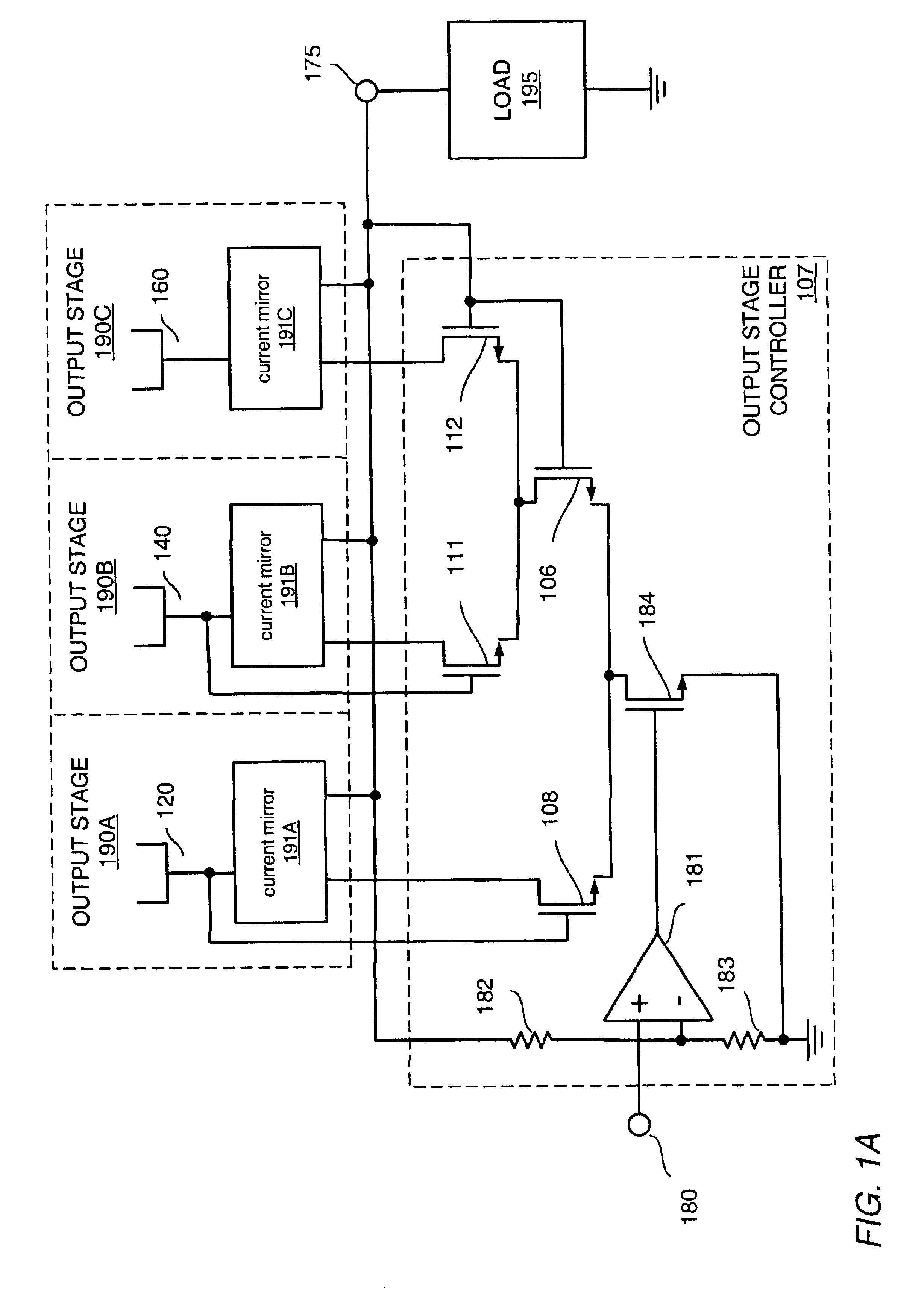

Efficient class-G amplifier with wide output voltage swing

InactiveUS6838942B1Reduce noiseImprove efficiencyGated amplifiersPower amplifiersCMOSAudio power amplifier

Various embodiments of methods and apparatus for an amplifier with wide output voltage swing are disclosed. The amplifier may include multiple output stages, each associated with a distinct supply voltage. Each output stage may contribute current to the output of the amplifier over a range of amplifier output voltages and these ranges may overlap. Each output stage may contribute current until the amplifier output voltage reaches the supply voltage associated with that output stage. The amplifier output may be as great as the largest supply voltage minus a drop equal to Rdson for an output transistor multiplied by the output current. In a CMOS implementation, this voltage drop may be approximately 0.15V. When the amplifier output voltage is close to the supply voltage associated with an output stage, both that output stage and the output stage associated with the next highest supply voltage may contribute to the amplifier output.

Owner:MICROCHIP TECH INC

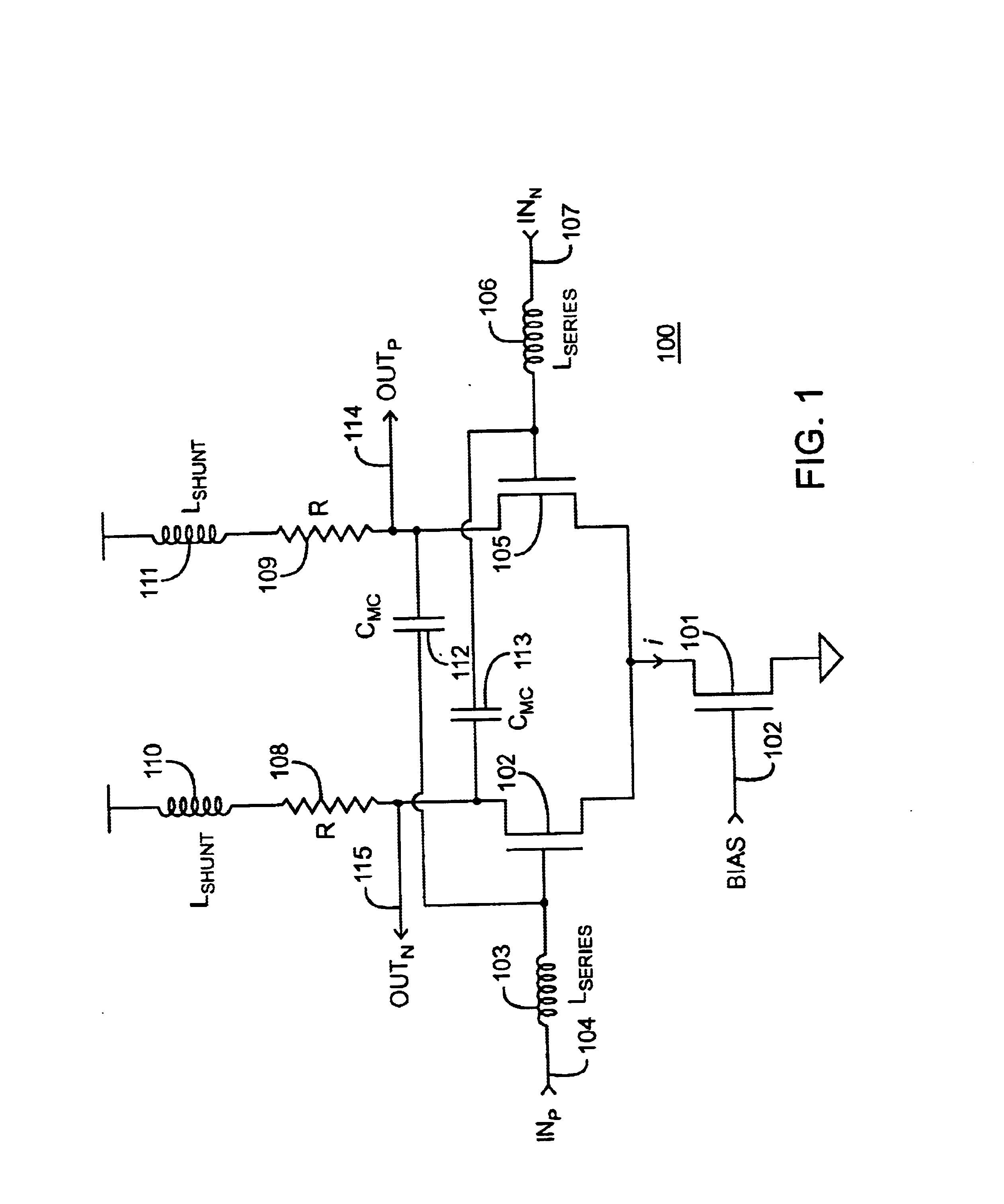

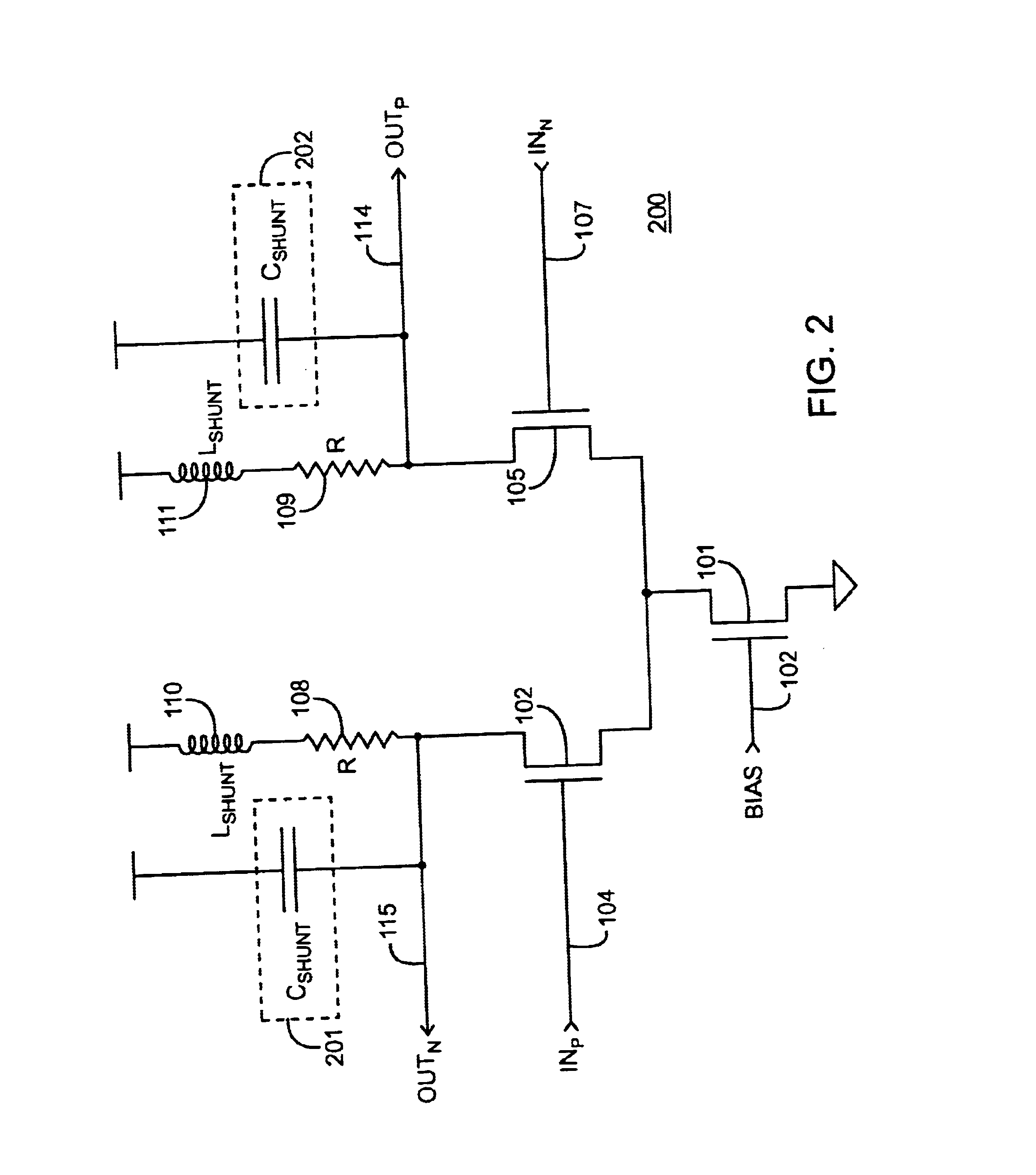

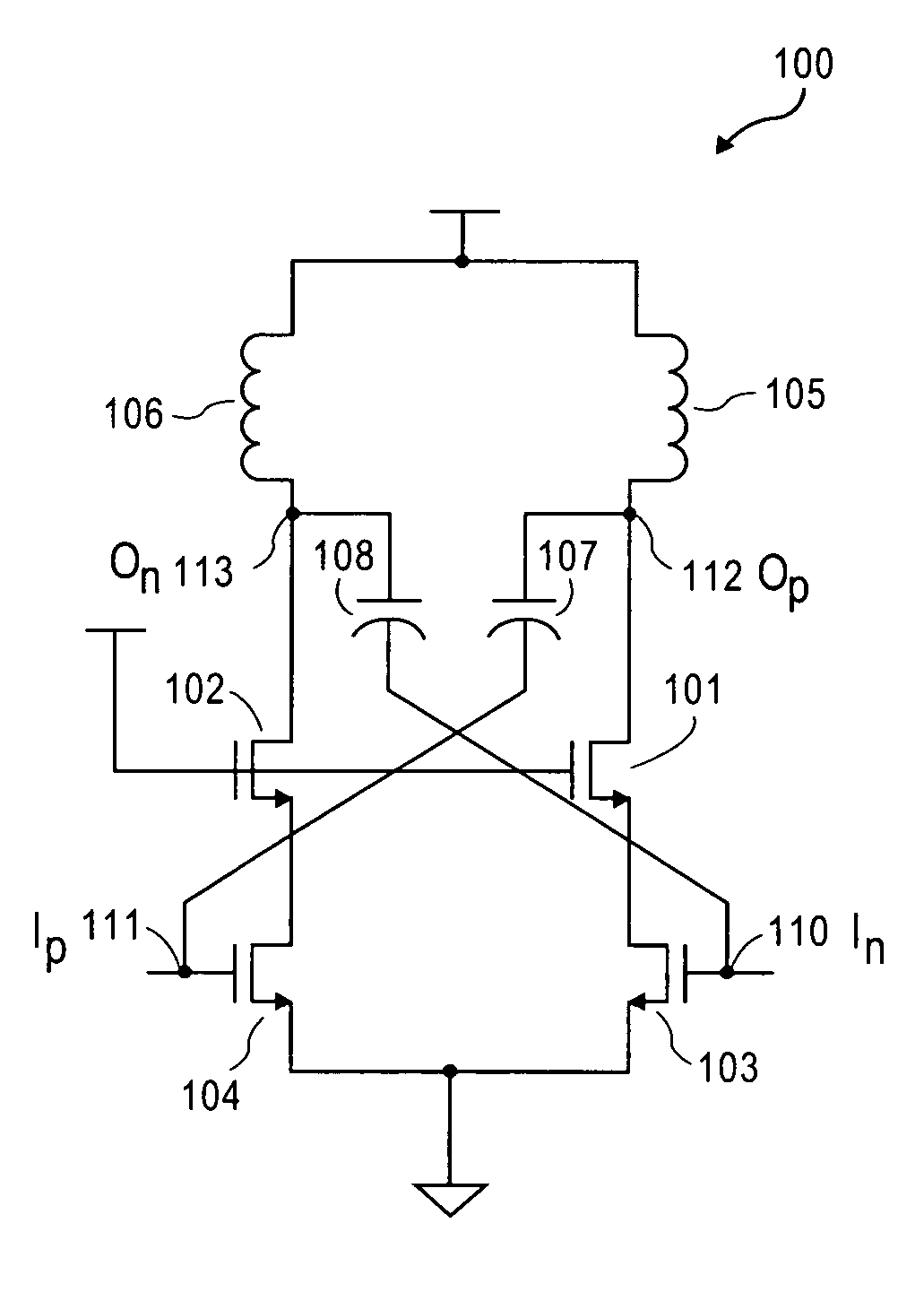

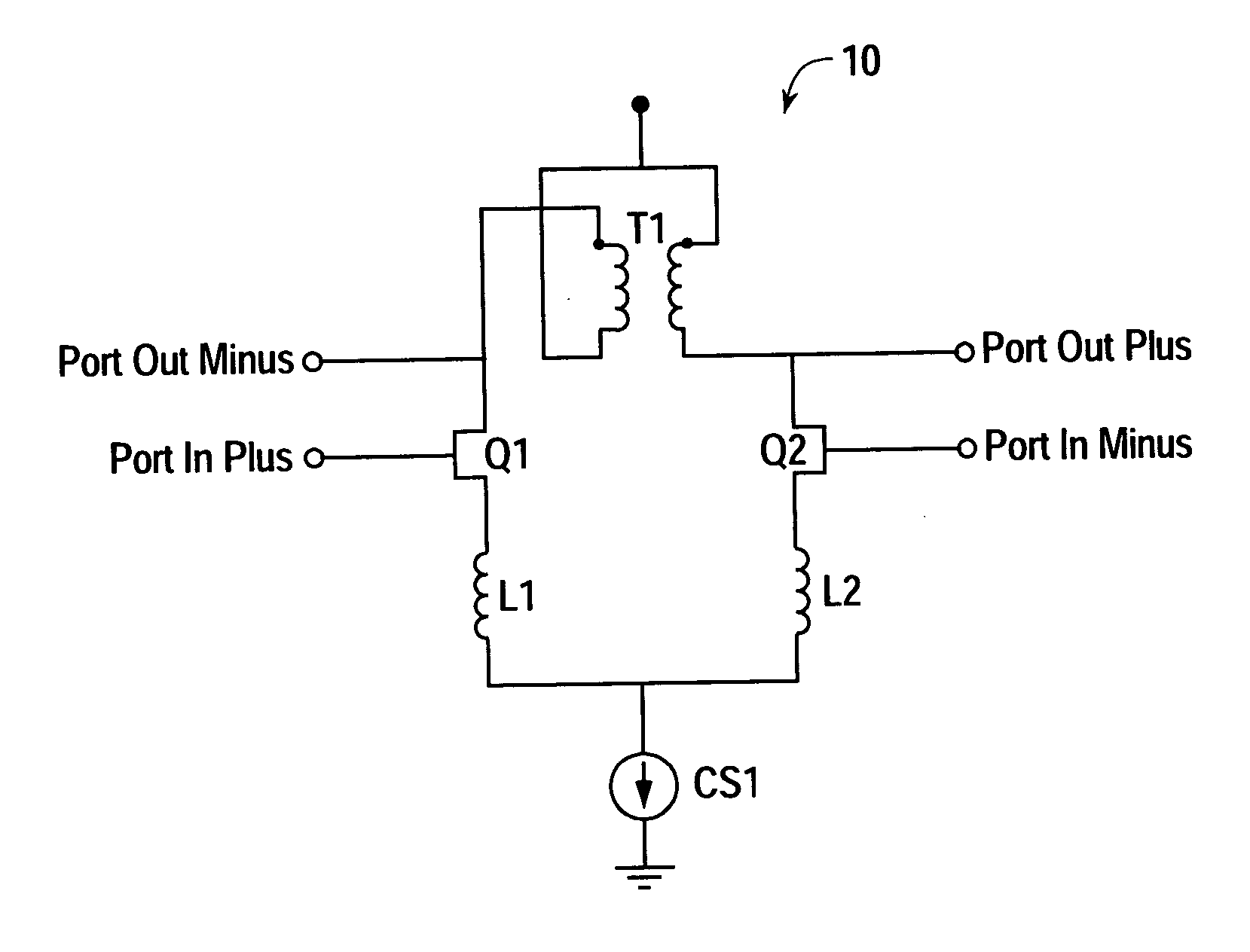

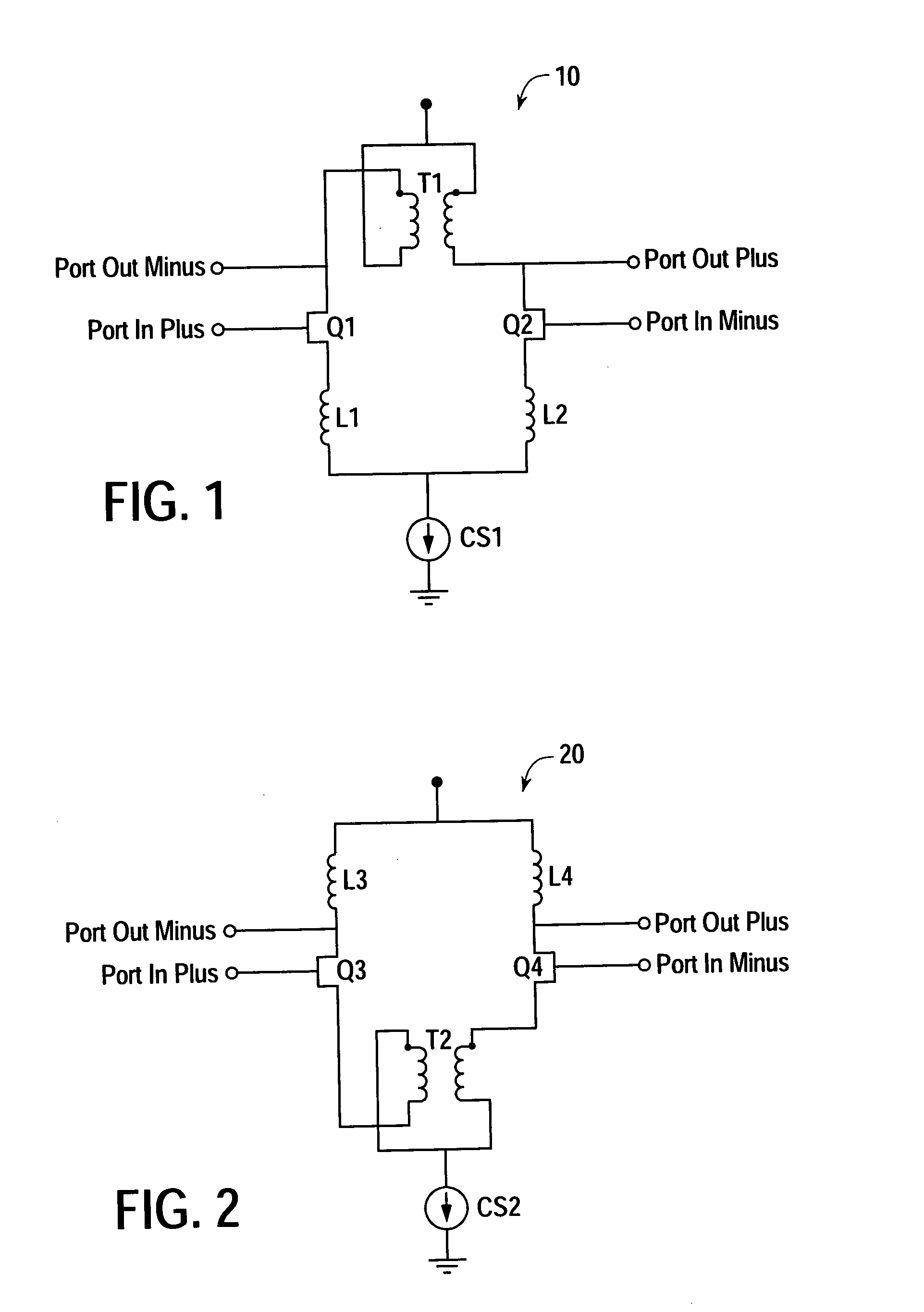

Coupled-inductance differential amplifier

ActiveUS20050062533A1Amplifier modifications to reduce noise influenceDifferential amplifiersSmall form factorEngineering

A differential amplifier that employs mutually coupled inductors to provide desired levels of inductance in a substantially smaller form factor in comparison to individual inductor components. Mutually coupled inductors according to the present teachings may also be used to increase common mode rejection in a differential amplifier.

Owner:AVAGO TECH INT SALES PTE LTD

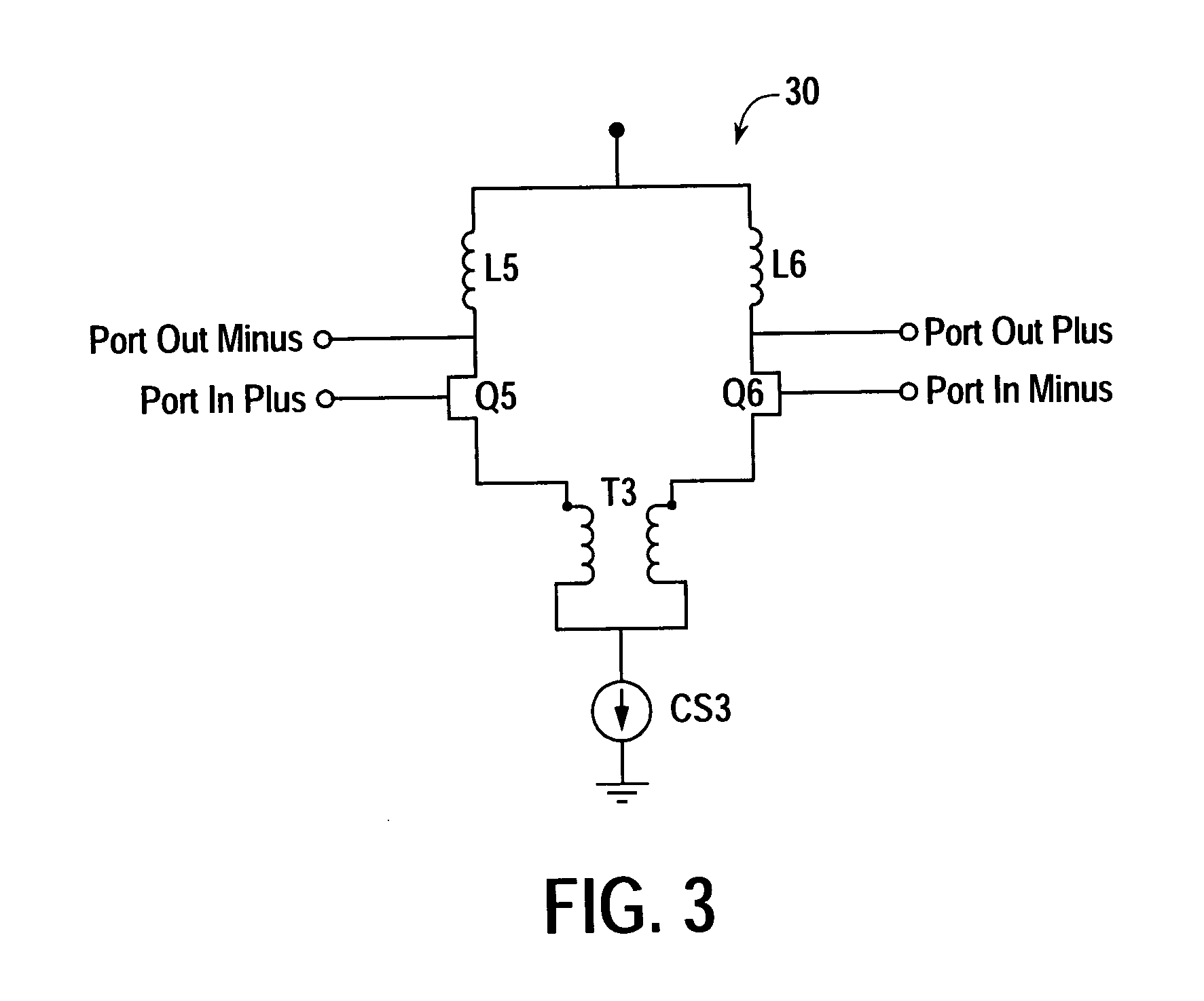

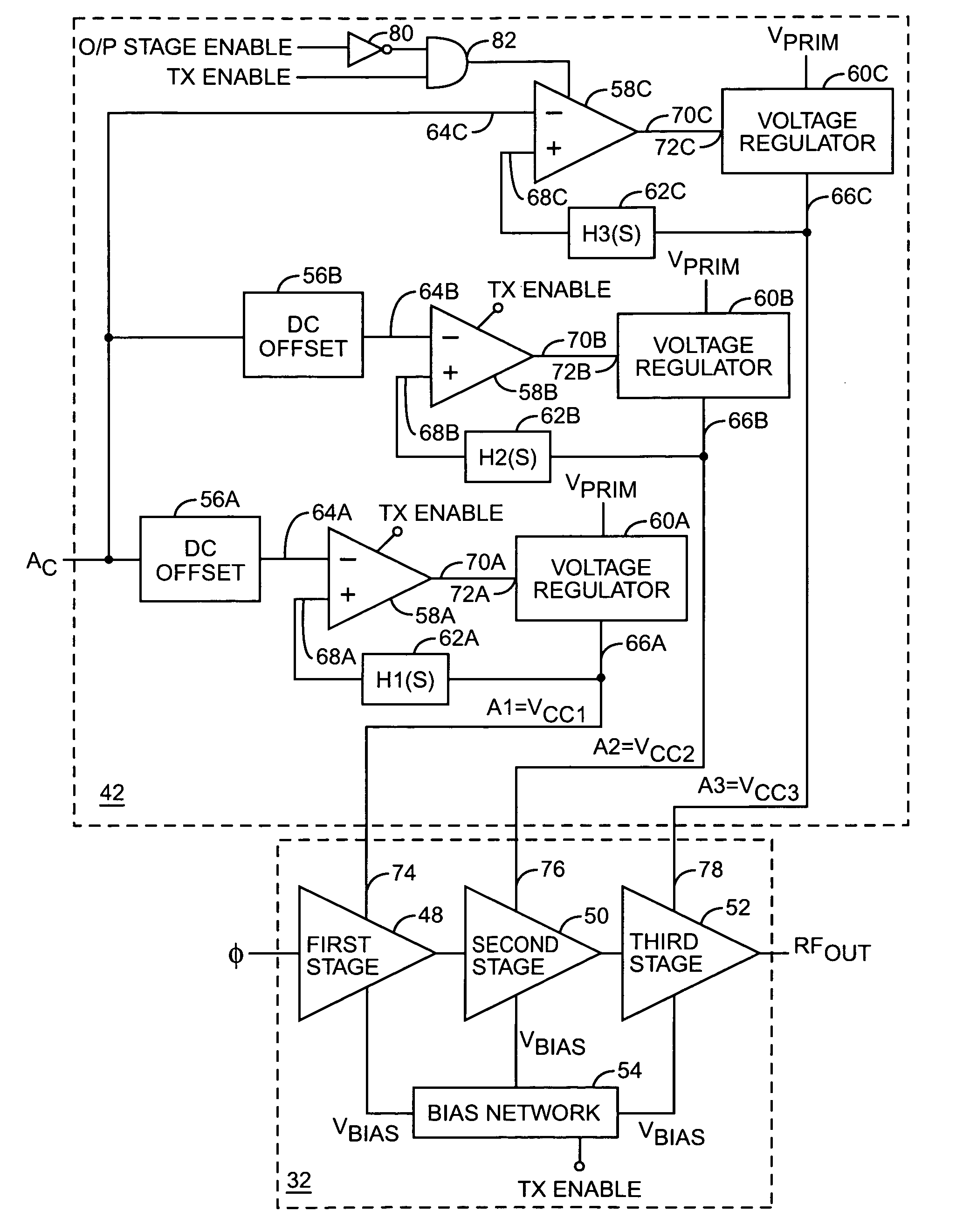

Tailored collector voltage to minimize variation in AM to PM distortion in a power amplifier

ActiveUS7109791B1Reduce variationAmplifier modifications to reduce non-linear distortionPulse automatic controlAudio power amplifierControl signal

A system is provided for substantially reducing variation in AM to PM distortion of a power amplifier caused by variations in RF drive power and temperature. The system includes power control circuitry and power amplifier circuitry. The power amplifier circuitry includes an input amplifier stage and at least one additional amplifier stage coupled in series with the input amplifier stage. The power control circuitry provides a first supply voltage to the input amplifier stage based on a control signal such that the first supply voltage has a predetermined DC offset with respect to the control signal. The first supply voltage is provided such that the predetermined DC offset substantially reduces variations in the AM to PM distortion of the power amplifier due to variations in radio frequency (RF) drive power.

Owner:QORVO US INC

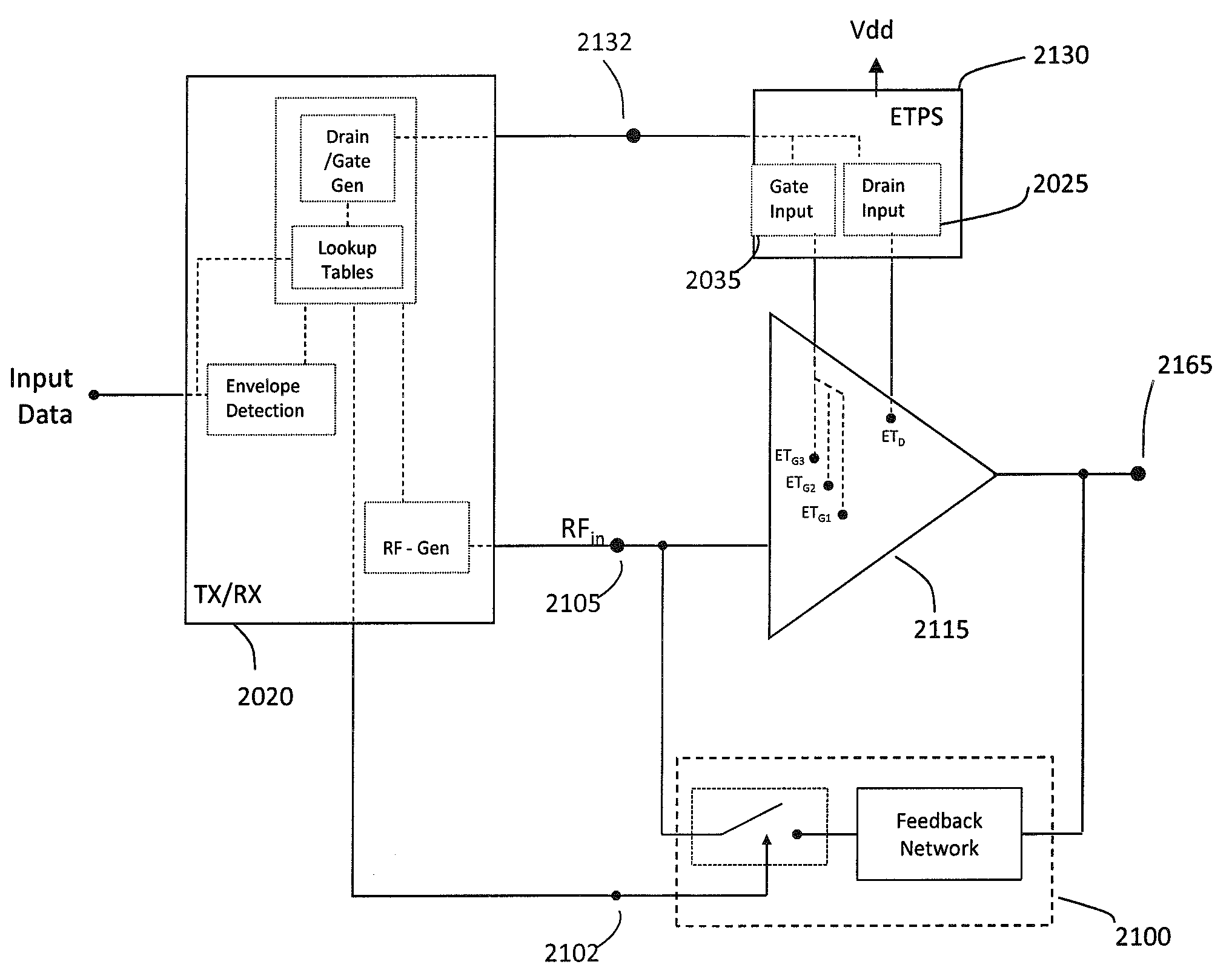

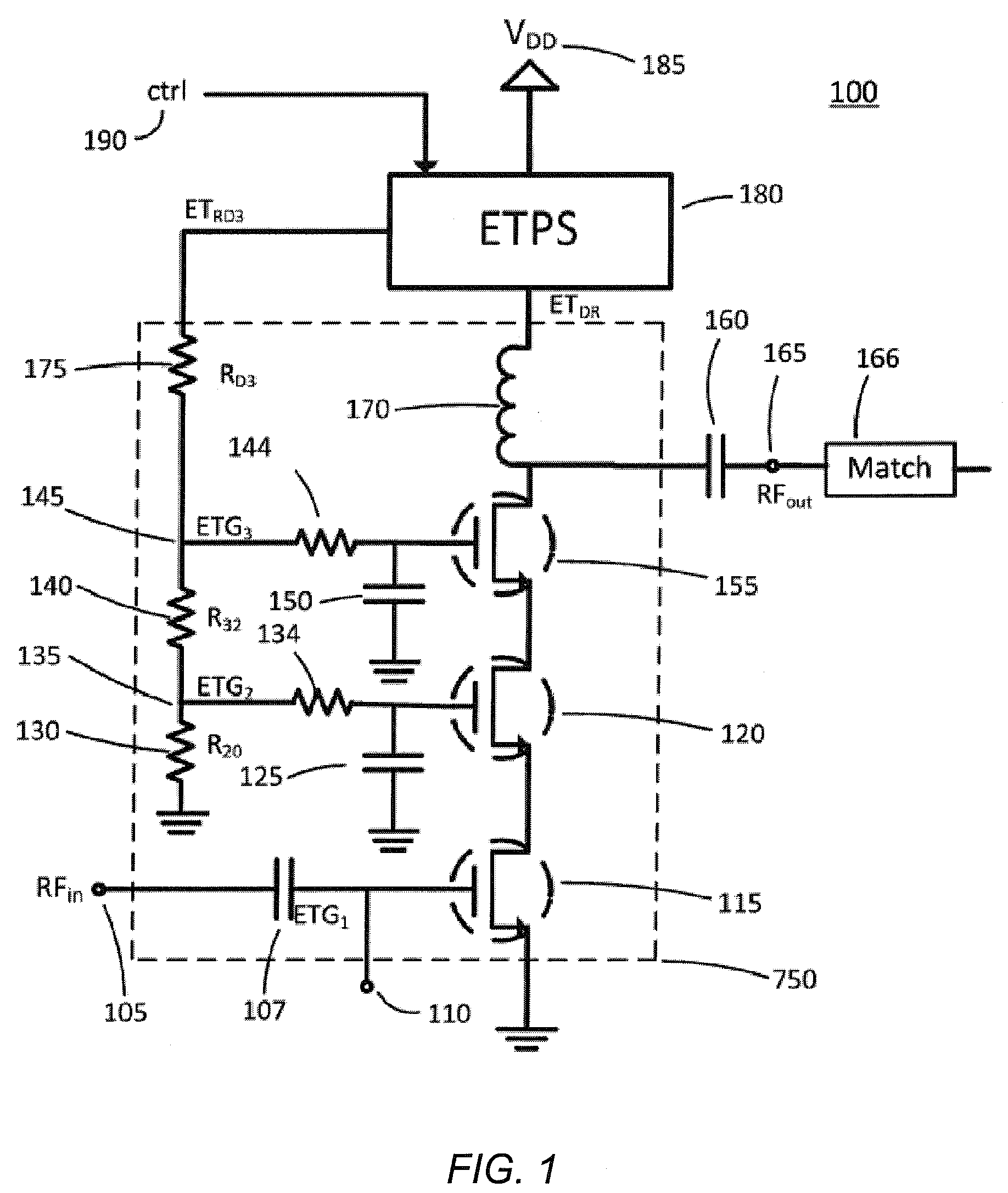

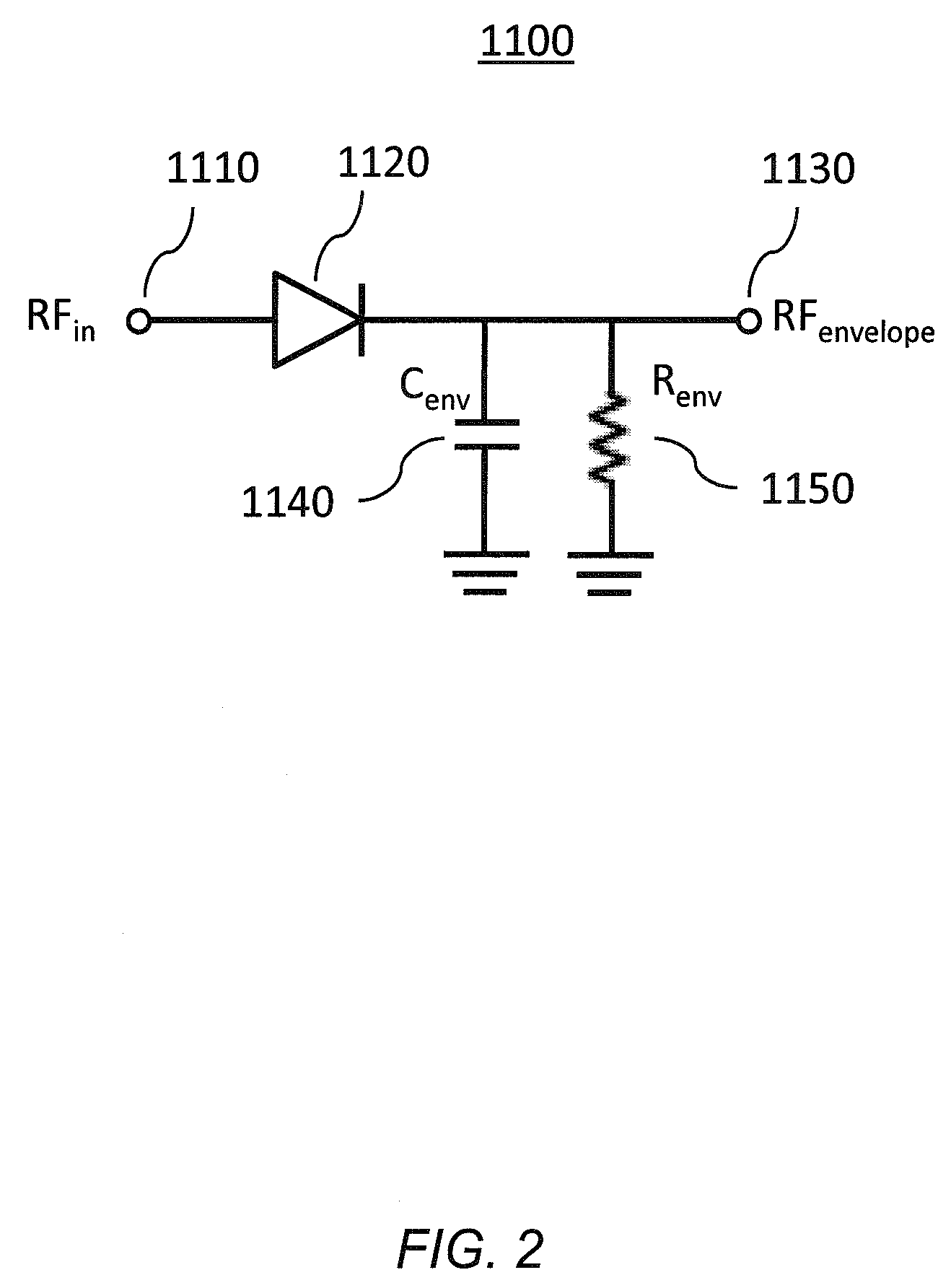

Optimization methods for amplifier with variable supply power

ActiveUS9219445B2Amplifier modifications to reduce non-linear distortionGain controlLinear regionAudio power amplifier

Owner:PSEMI CORP

Method for dynamic insertion loss control for 10/100/1000 mhz ethernet signaling

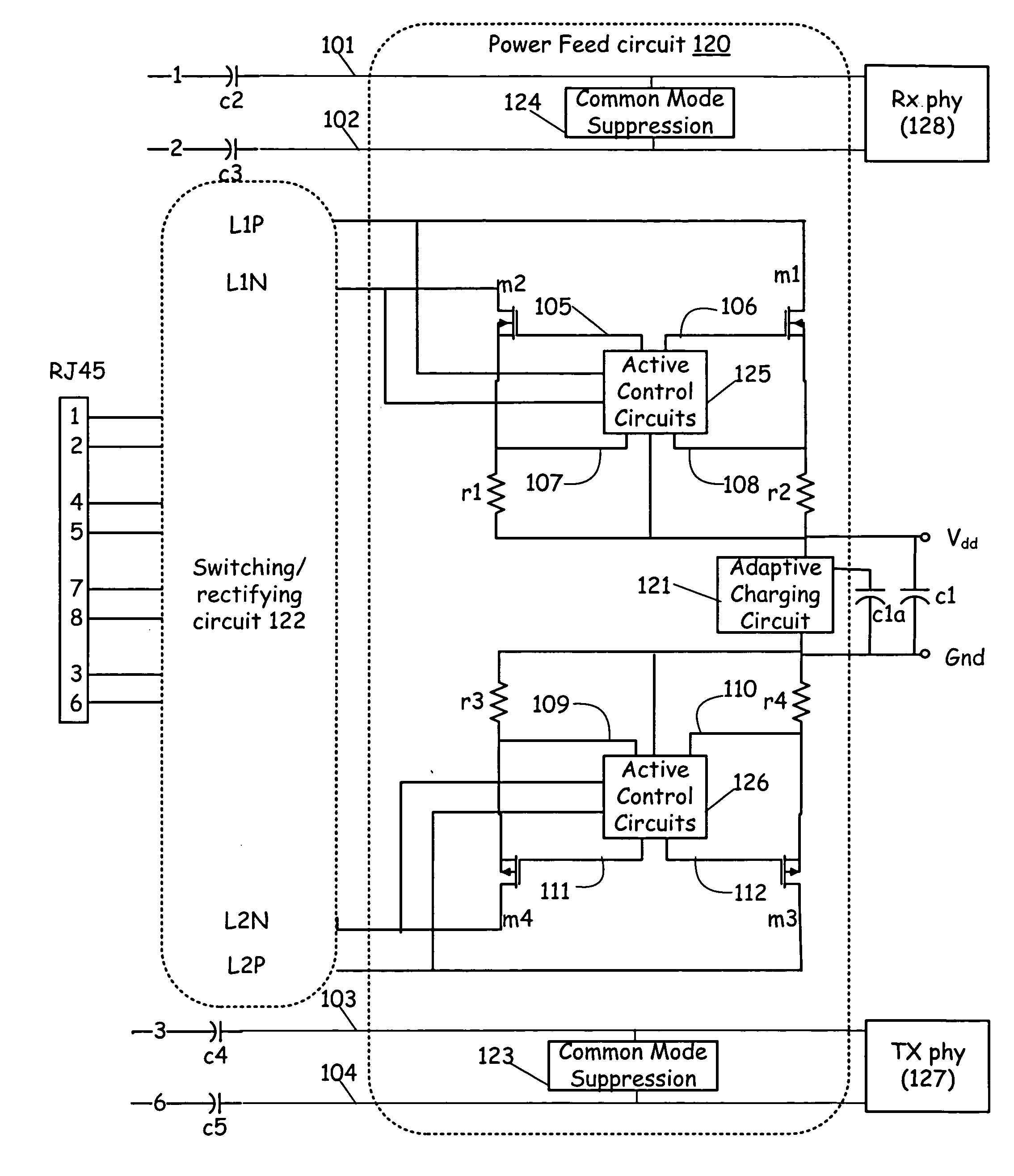

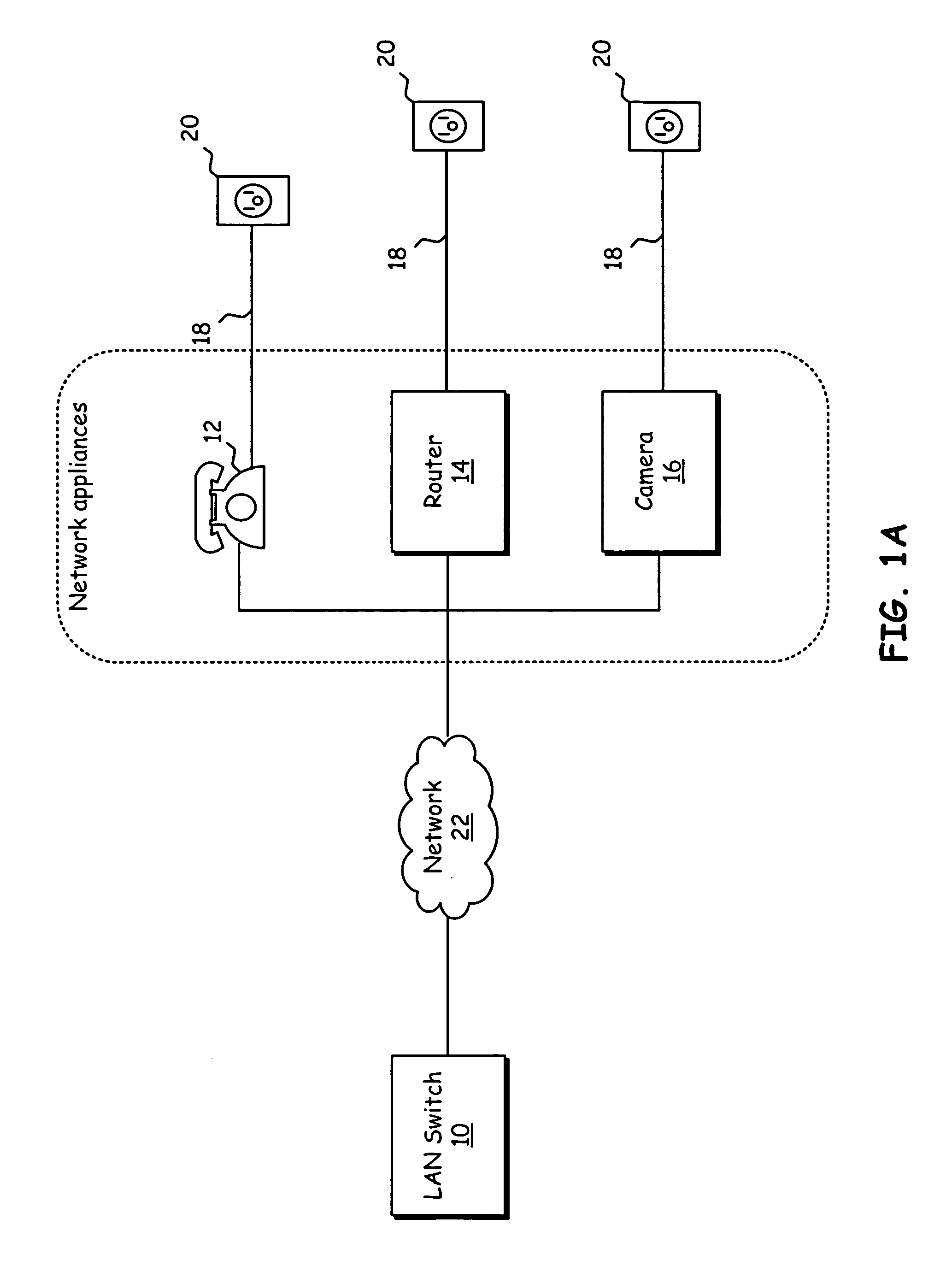

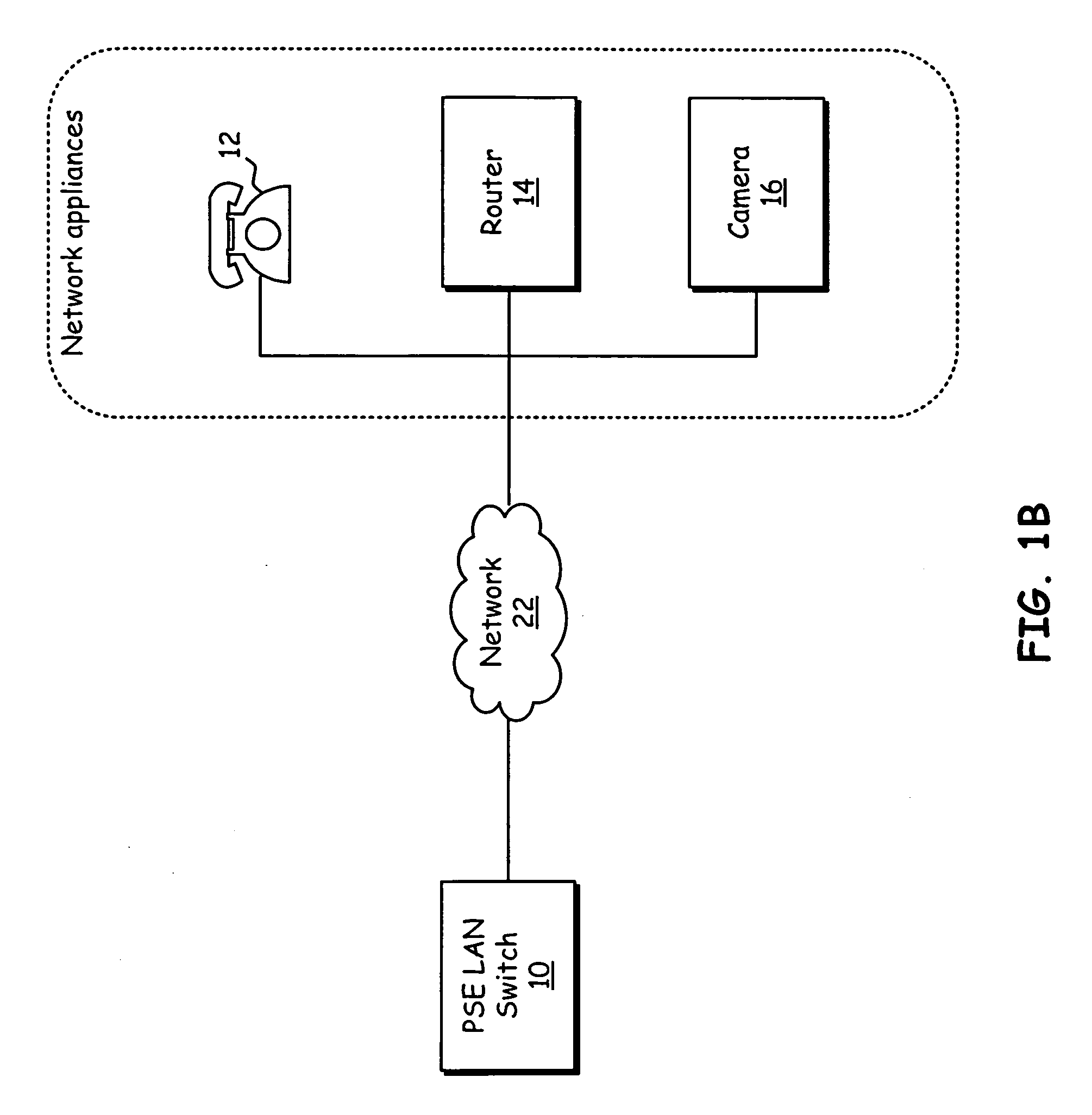

ActiveUS20060238250A1Suppression of insertion lossReduced insertion lossResistance/reactance/impedenceDigital data processing detailsNetworking protocolNetwork connection

The present invention provides for dynamic insertion loss control for a 10 / 100 / 1000 megahertz Ethernet power on differential cable pairs. A power feed circuit supplies power to a network attached device (PD). An insertion loss control circuit limits power loss in a coupled power feed circuit. The insertion loss control circuit determines an insertion loss limit and senses an average power of the power signals to produce a common mode feedback signal to the power feed circuit. The insertion loss limit is determined for the received signals based on a differential RMS of the received Ethernet power signals as seen by a differential transistor pair. Alternatively, the insertion loss limit may be determined logically by the higher layers of the network protocol based on the AC differential portion of the network power signal. When the insertion loss limit is determined based on the differential RMS, the insertion loss control circuit is operable to automatically reduce the insertion loss based upon transmission losses experienced over the network connection between the power sending equipment and network-attached device.

Owner:KINETIC TECH INT HLDG LP

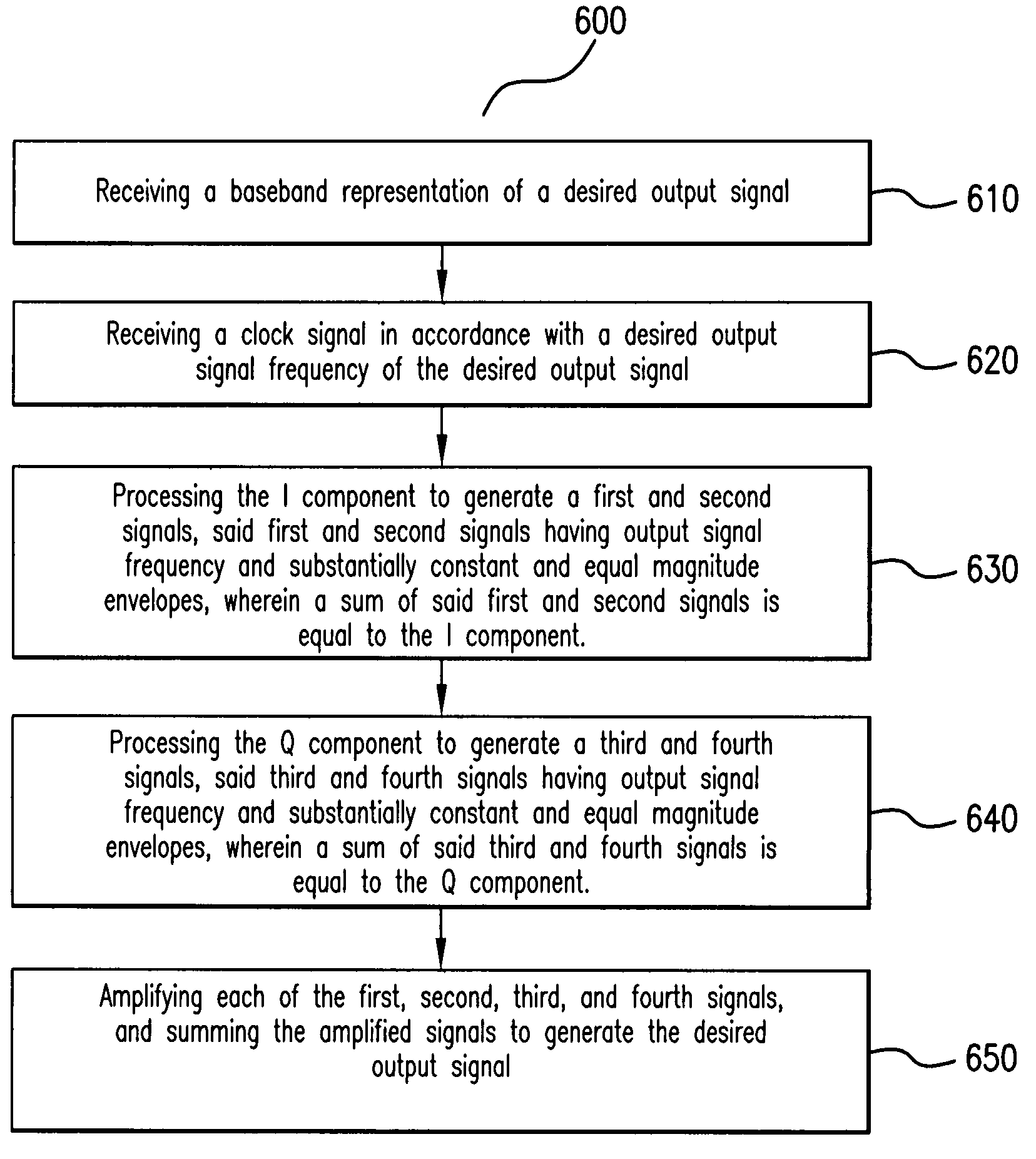

Systems and methods of RF power transmission, modulation, and amplification, including architectural embodiments of same

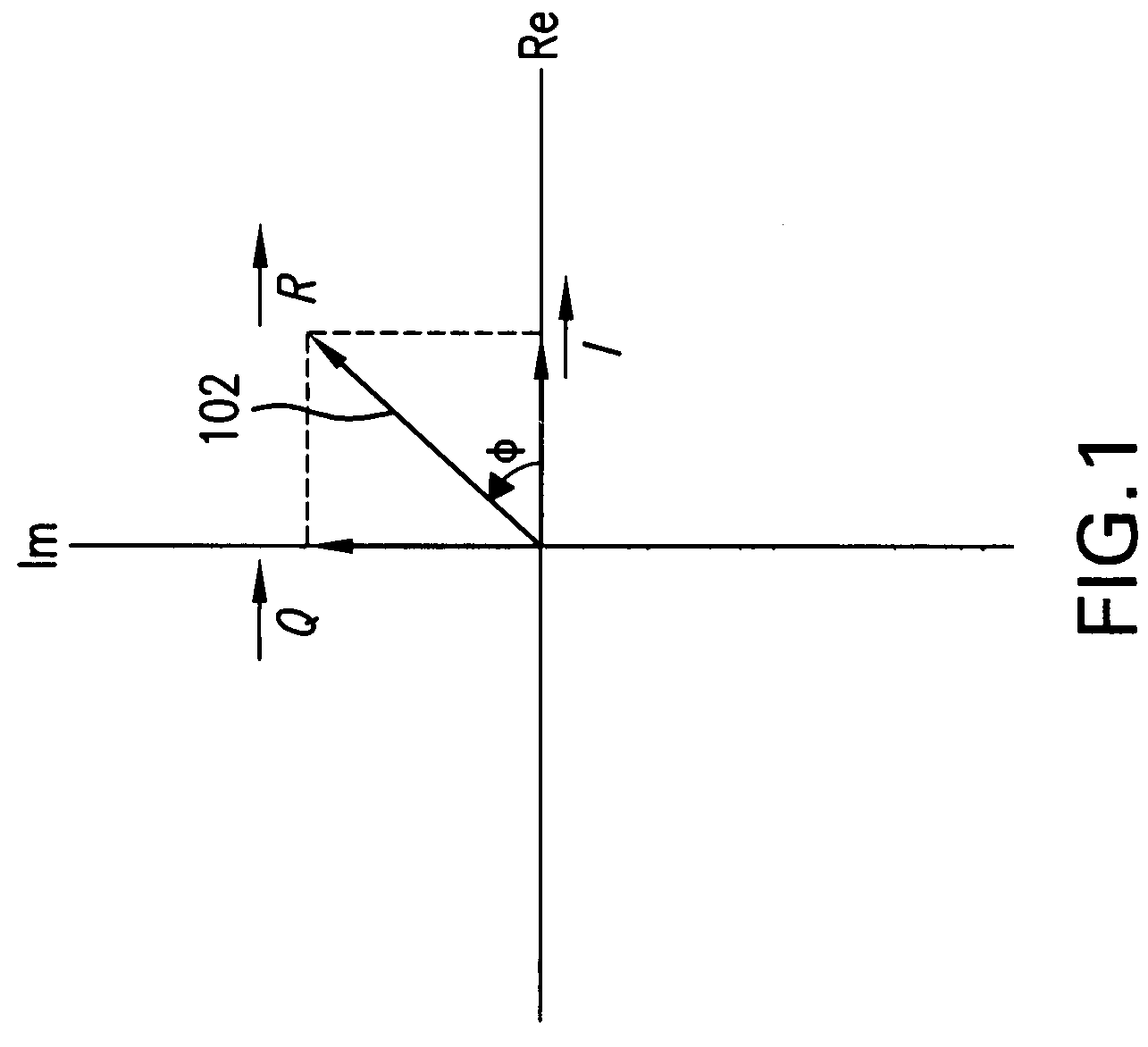

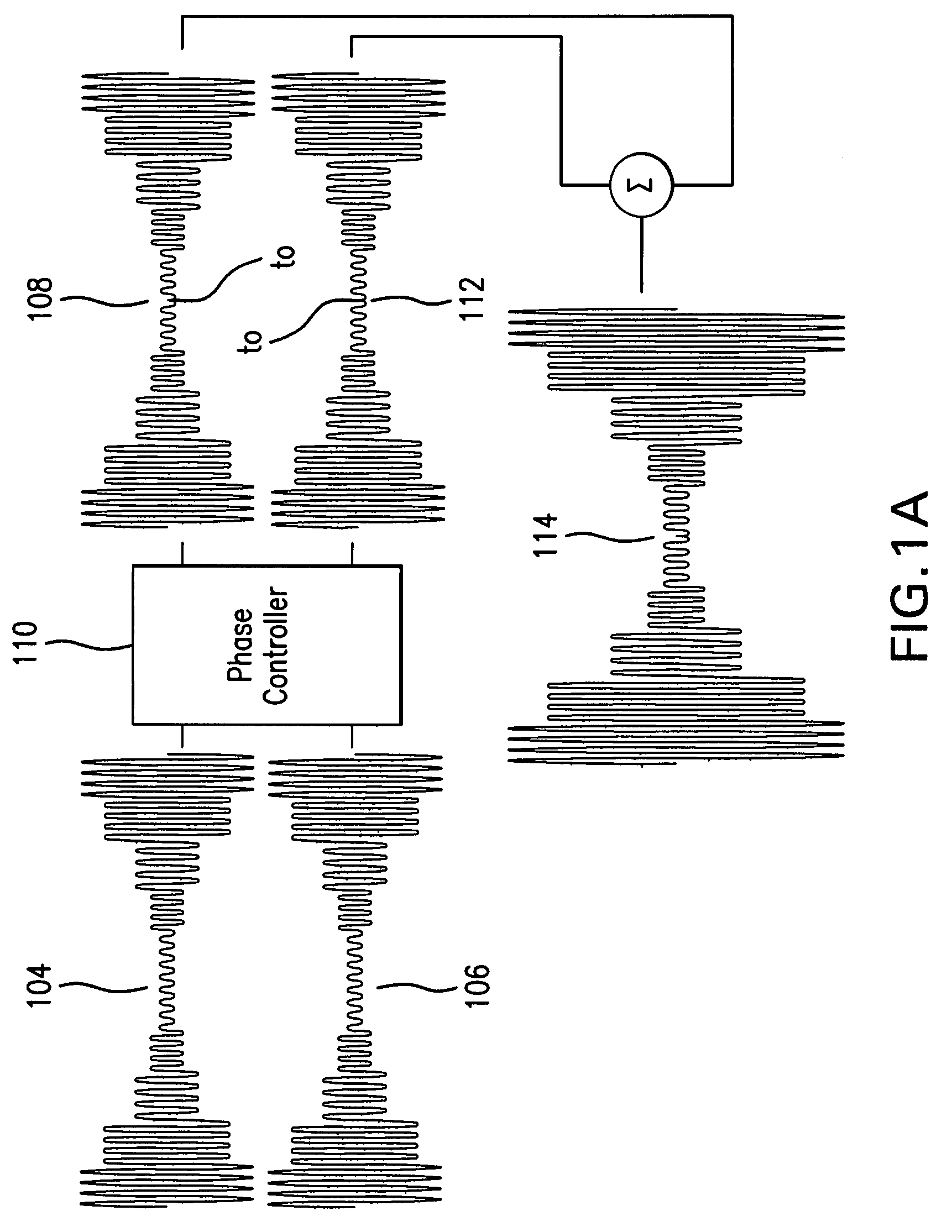

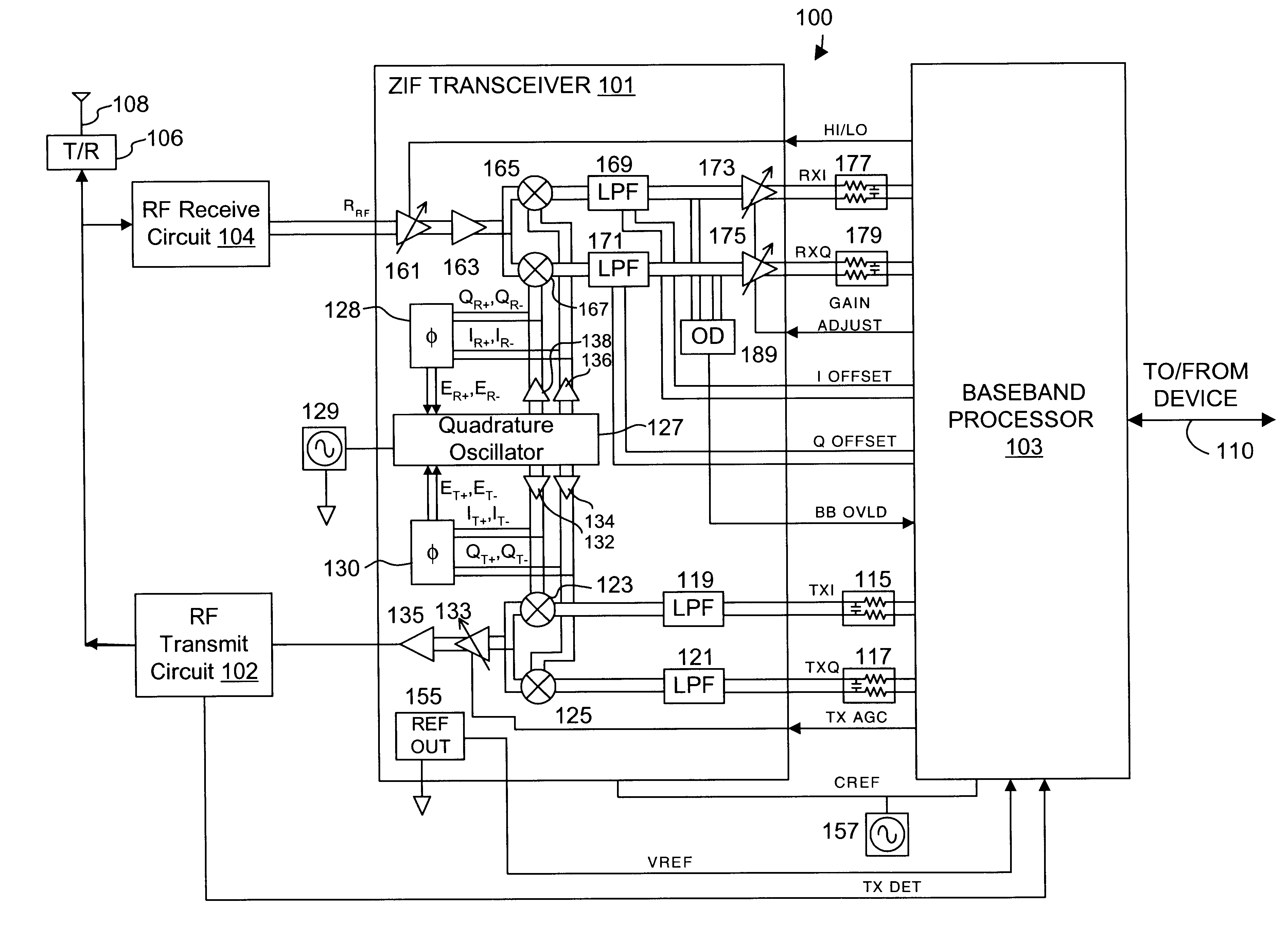

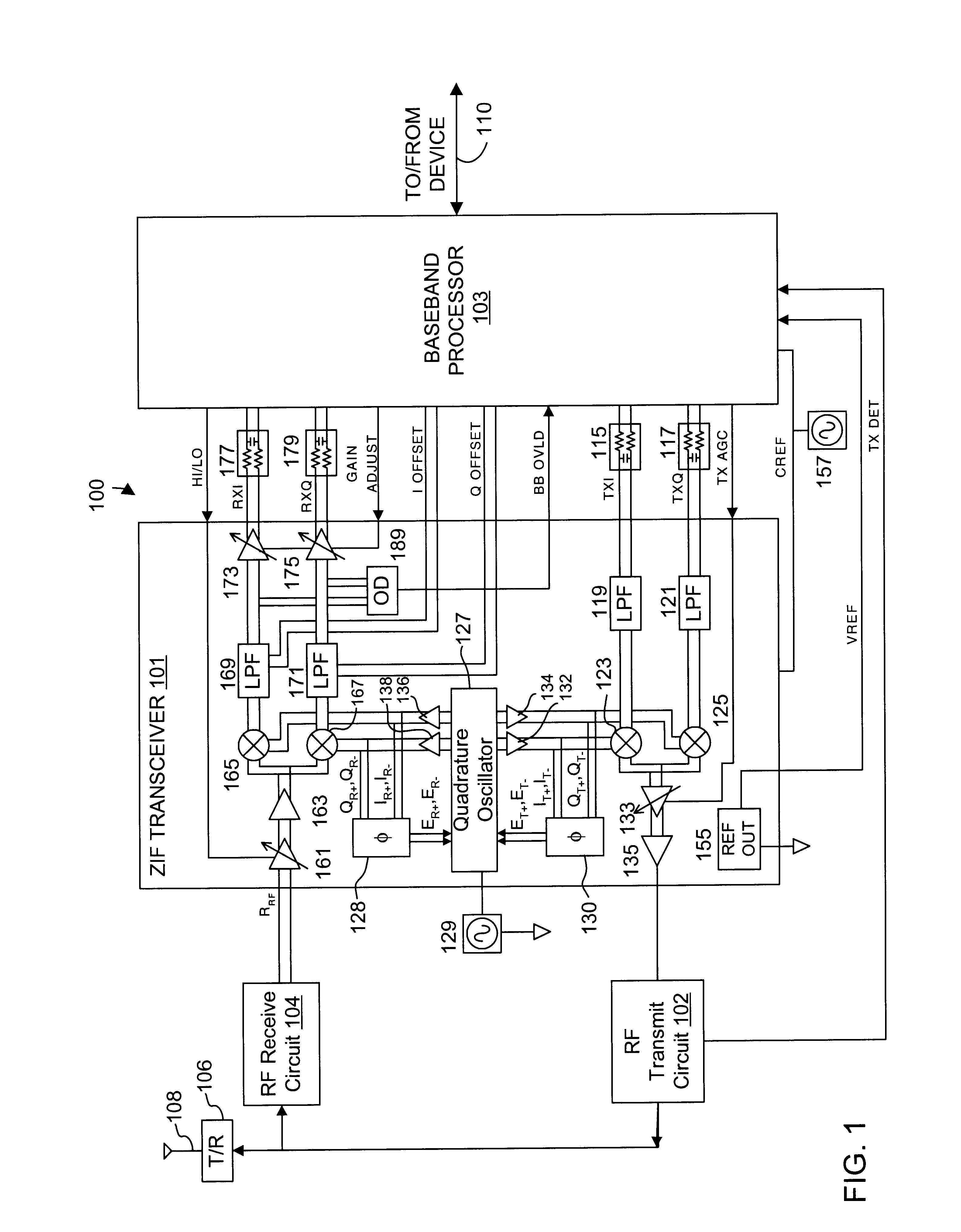

InactiveUS7885682B2Multiple-port networksResonant long antennasElectric power transmissionUp conversion

Methods and systems for vector combining power amplification are disclosed herein. In one embodiment, a plurality of signals are individually amplified, then summed to form a desired time-varying complex envelope signal. Phase and / or frequency characteristics of one or more of the signals are controlled to provide the desired phase, frequency, and / or amplitude characteristics of the desired time-varying complex envelope signal. In another embodiment, a time-varying complex envelope signal is decomposed into a plurality of constant envelope constituent signals. The constituent signals are amplified equally or substantially equally, and then summed to construct an amplified version of the original time-varying envelope signal. Embodiments also perform frequency up-conversion.

Owner:PARKER VISION INC

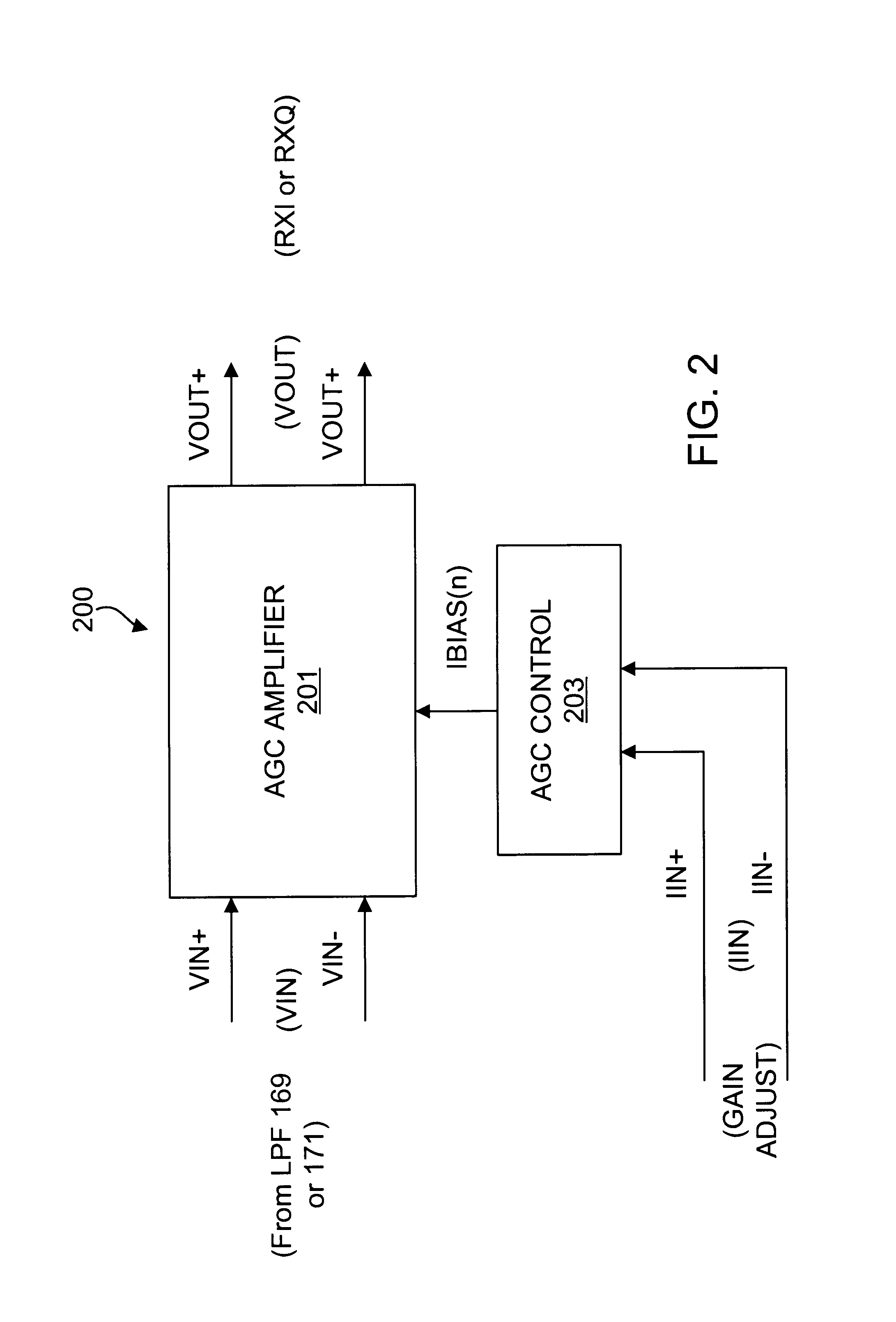

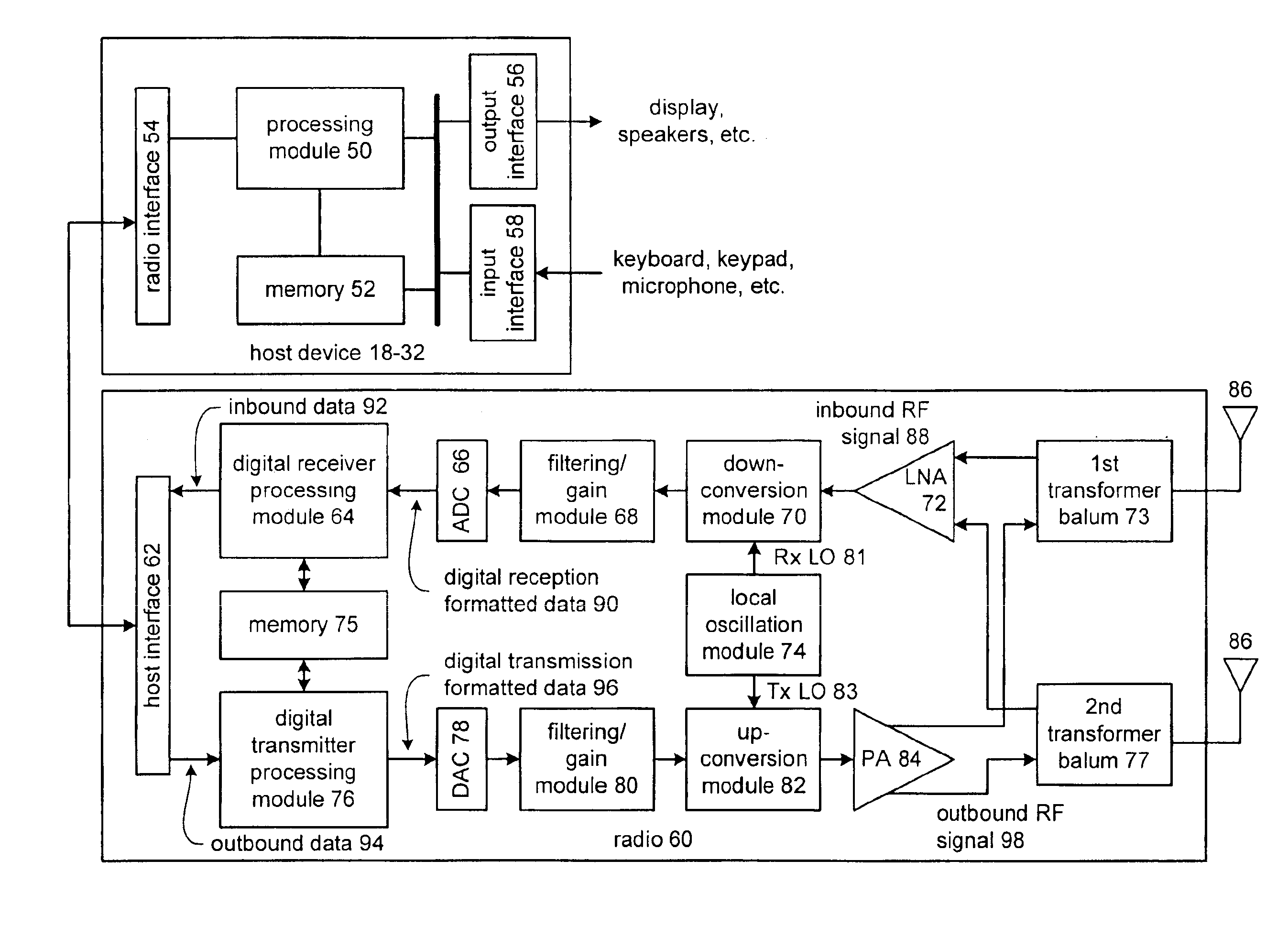

Precision automatic gain control circuit

InactiveUS6763228B2Low absolute gain toleranceImprove matchResonant long antennasVolume compression/expansion having semiconductor devicesAudio power amplifierClosed loop

An automatic gain control (AGC) amplifier including a high gain transimpedance amplifier, a resistive feedback network and multiple transconductance stages coupled in the feedback path of the AGC amplifier. The feedback network receives an input signal and is coupled to the output of the high gain amplifier and has multiple intermediate nodes. Each transconductance stage has an input coupled to an intermediate node of the feedback network and an output coupled to the input of the high gain amplifier. Each transconductance stage is independently controllable to position a virtual ground within the feedback network to control closed loop gain. Each transconductance stage may have a bias current input coupled to a bias current control circuit. The control circuit controls each bias current to vary the gain of the AGC amplifier. The bias currents may be linearly controlled employing a ramp function to achieve a linear in dB gain response.

Owner:M RED INC

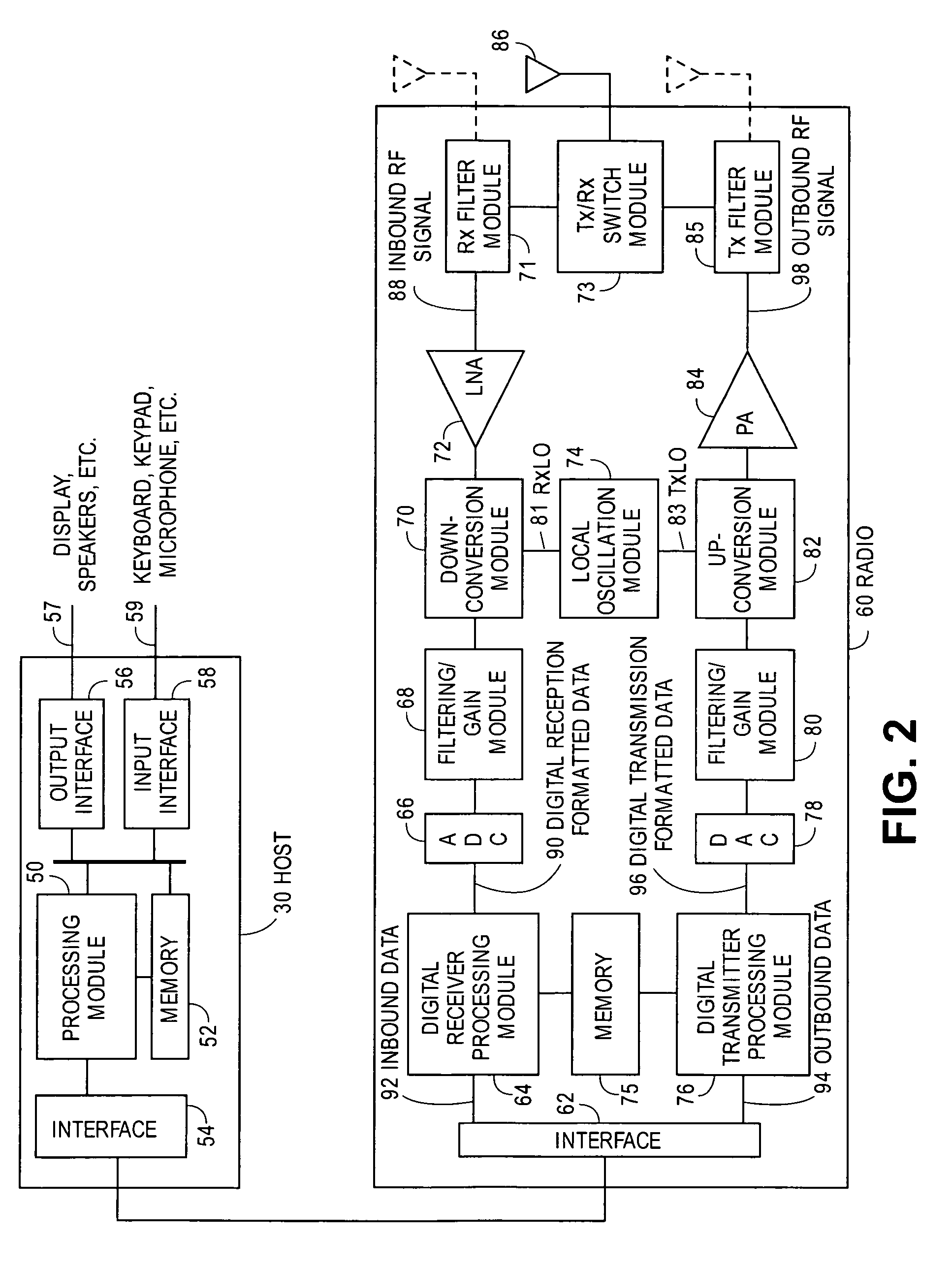

Radio frequency integrated circuit having an antenna diversity structure

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

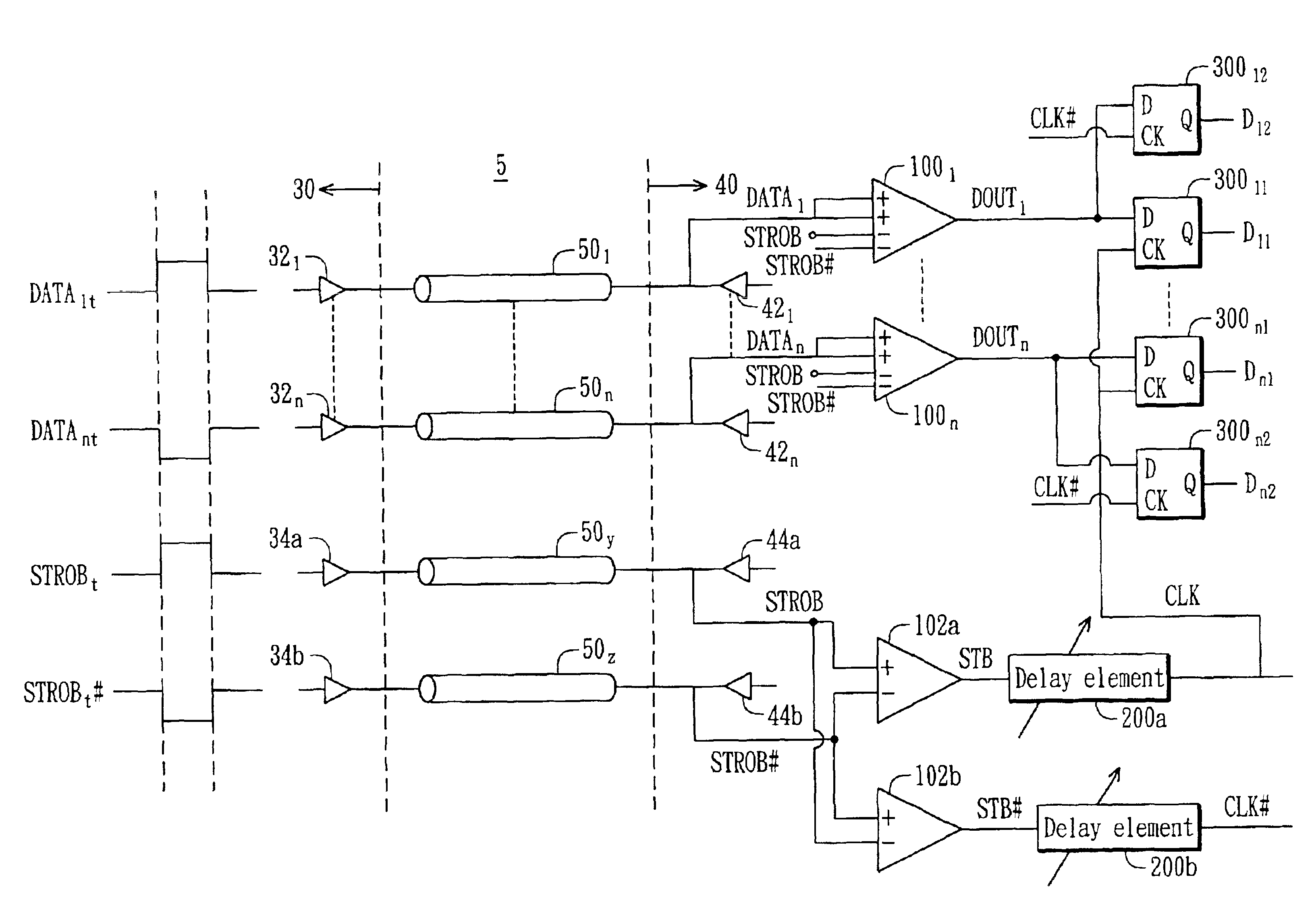

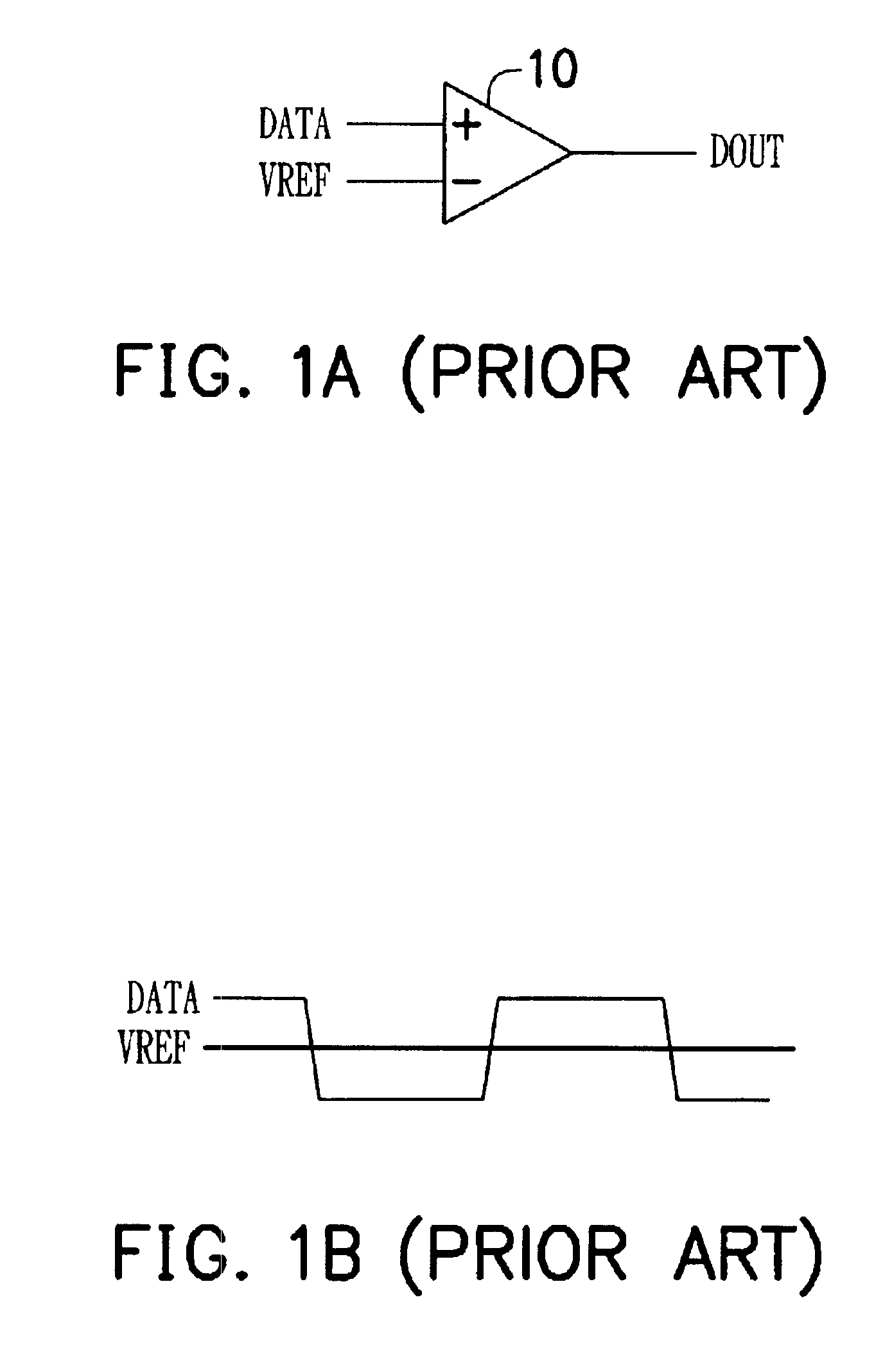

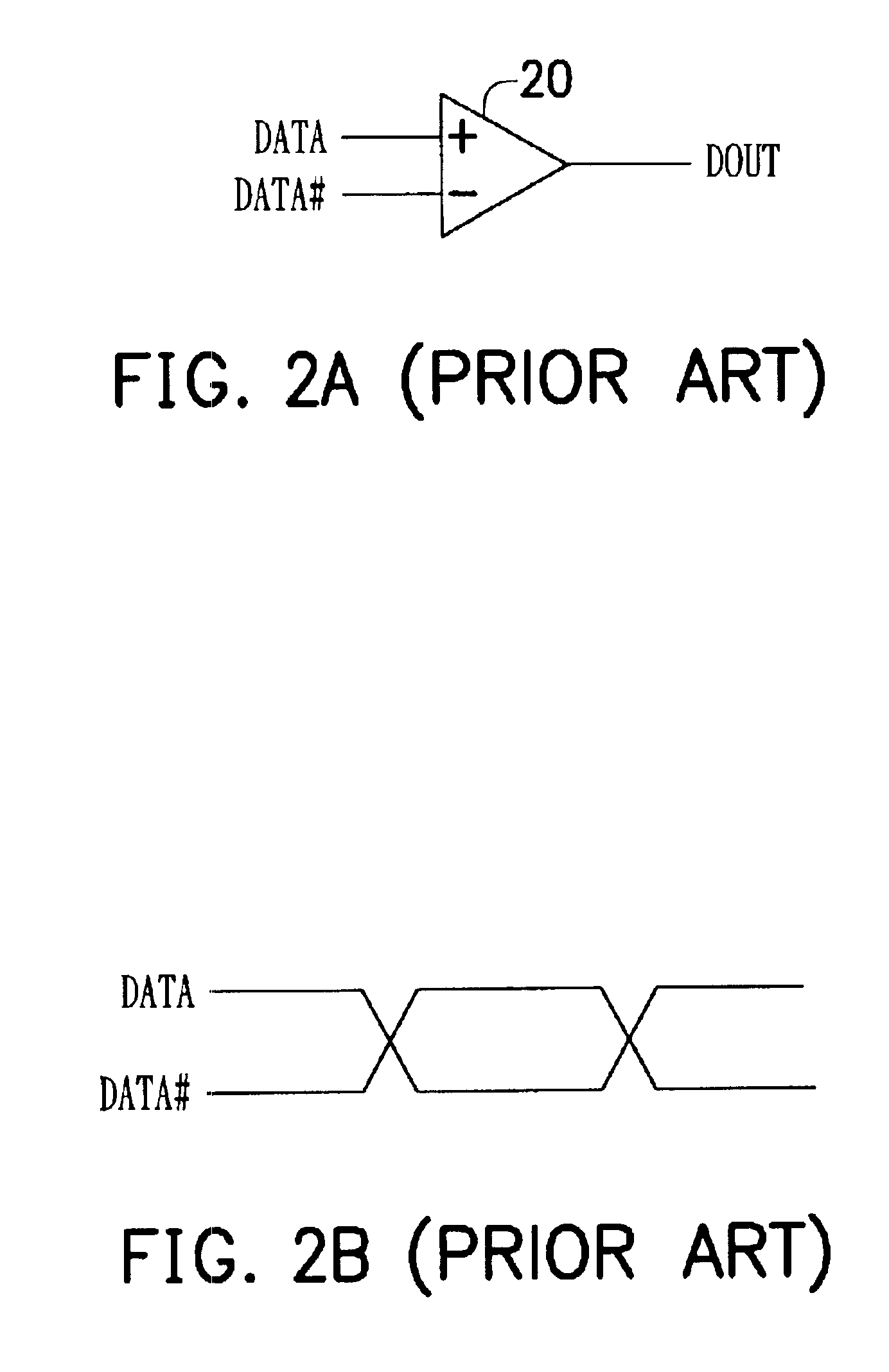

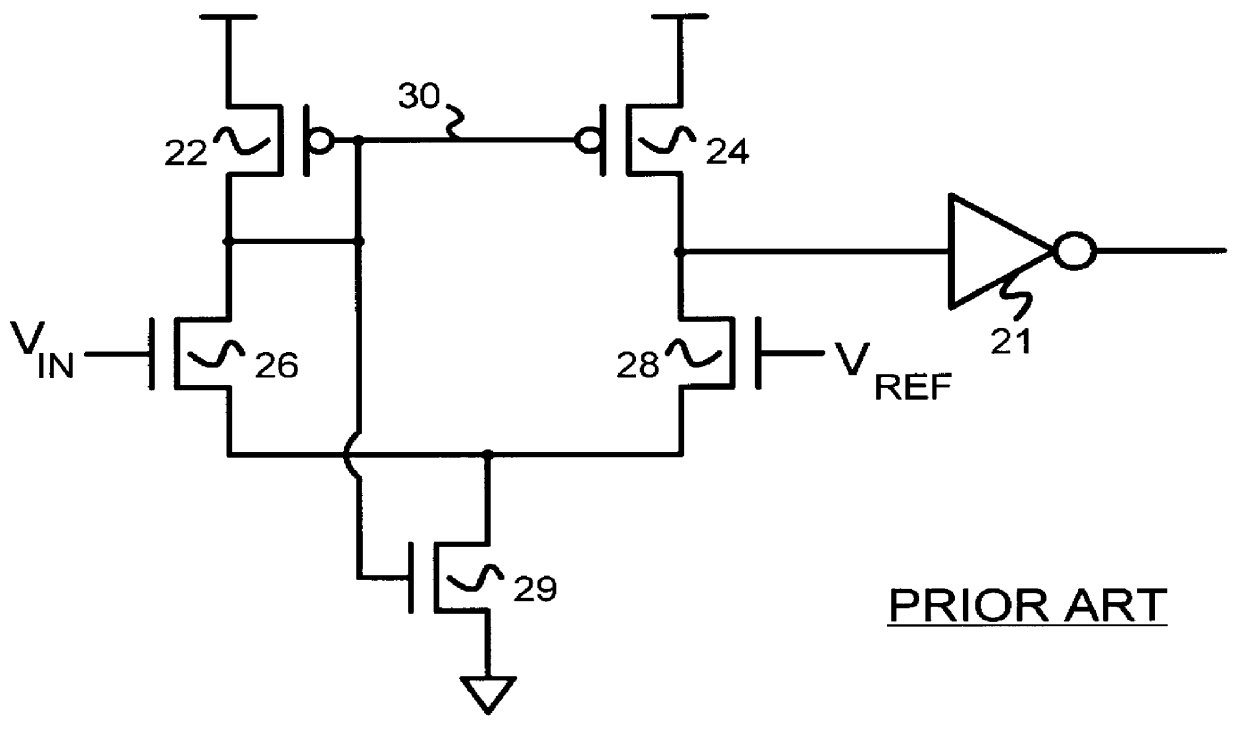

System for latching an output signal generated by comparing complimentary strobe signals and a data signal in response to a comparison of the complimentary strobe signals

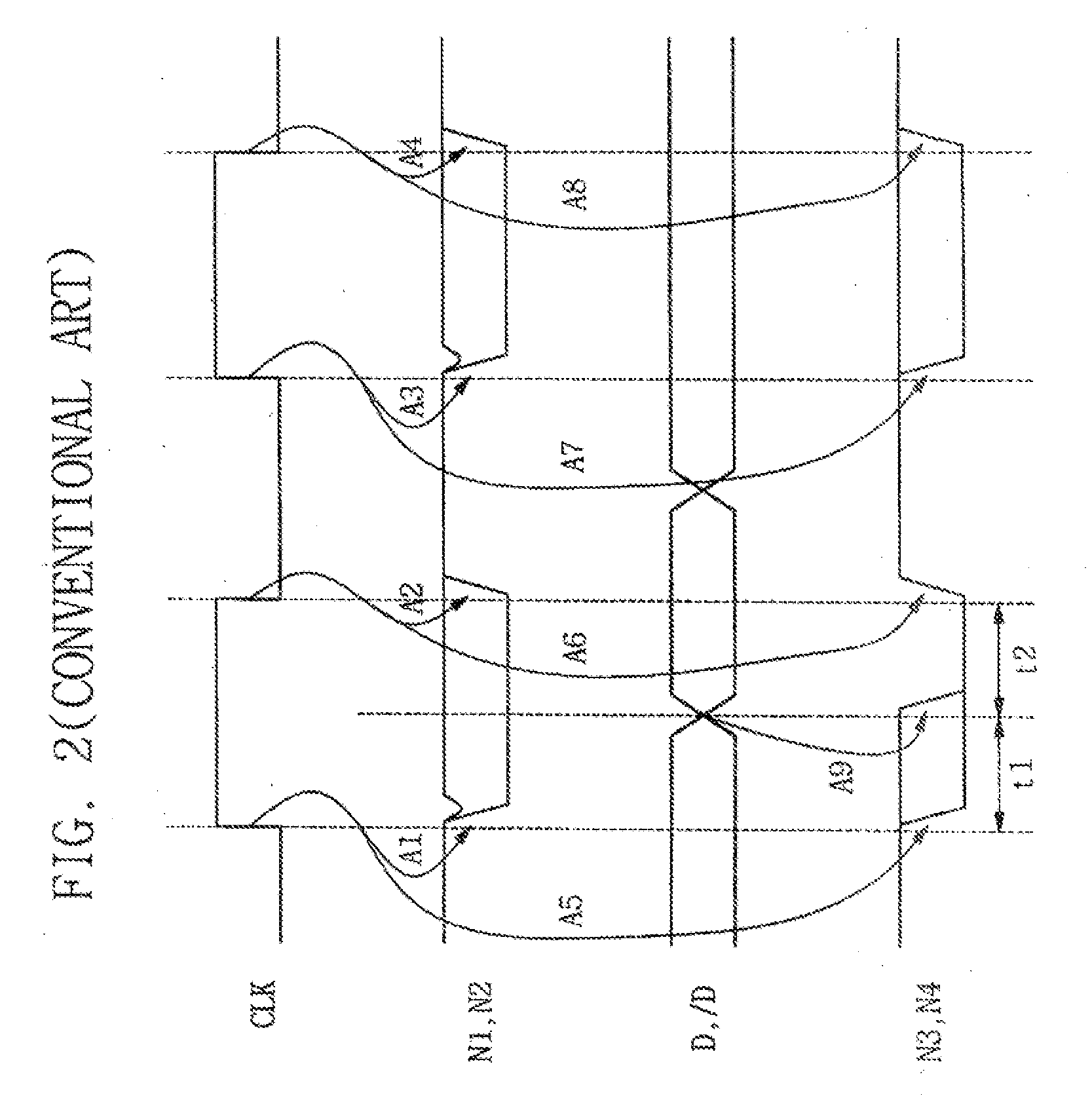

ActiveUS6898724B2Prevent erroneous samplingOvercomes drawbackSynchronisation information channelsTime-division multiplexData signalOutput device

A data transmission system using a pair of complement signals (STROB / STROB#) as an edge-aligned strobe signal and input / output buffers therein. Several data signals and a pair of STROB / STROB# signals are transmitted from a data output device to a data input device therein. These data signals and the STROB / STROB# signals are edge-aligned and transmitted through the same transmission architecture. The data input device includes several data comparators for generating output signals from the received data signals using the received STROB / STROB# signals as a dynamic reference voltage. In addition, the data input device further includes several comparators and delay elements for generating a pair of non-inverting / inverting latch clock signals from the STROB / STROB# signals. Each of the output signals is sent to two data latch circuits for outputting two latched data based on the latch clock signals.

Owner:VIA TECH INC

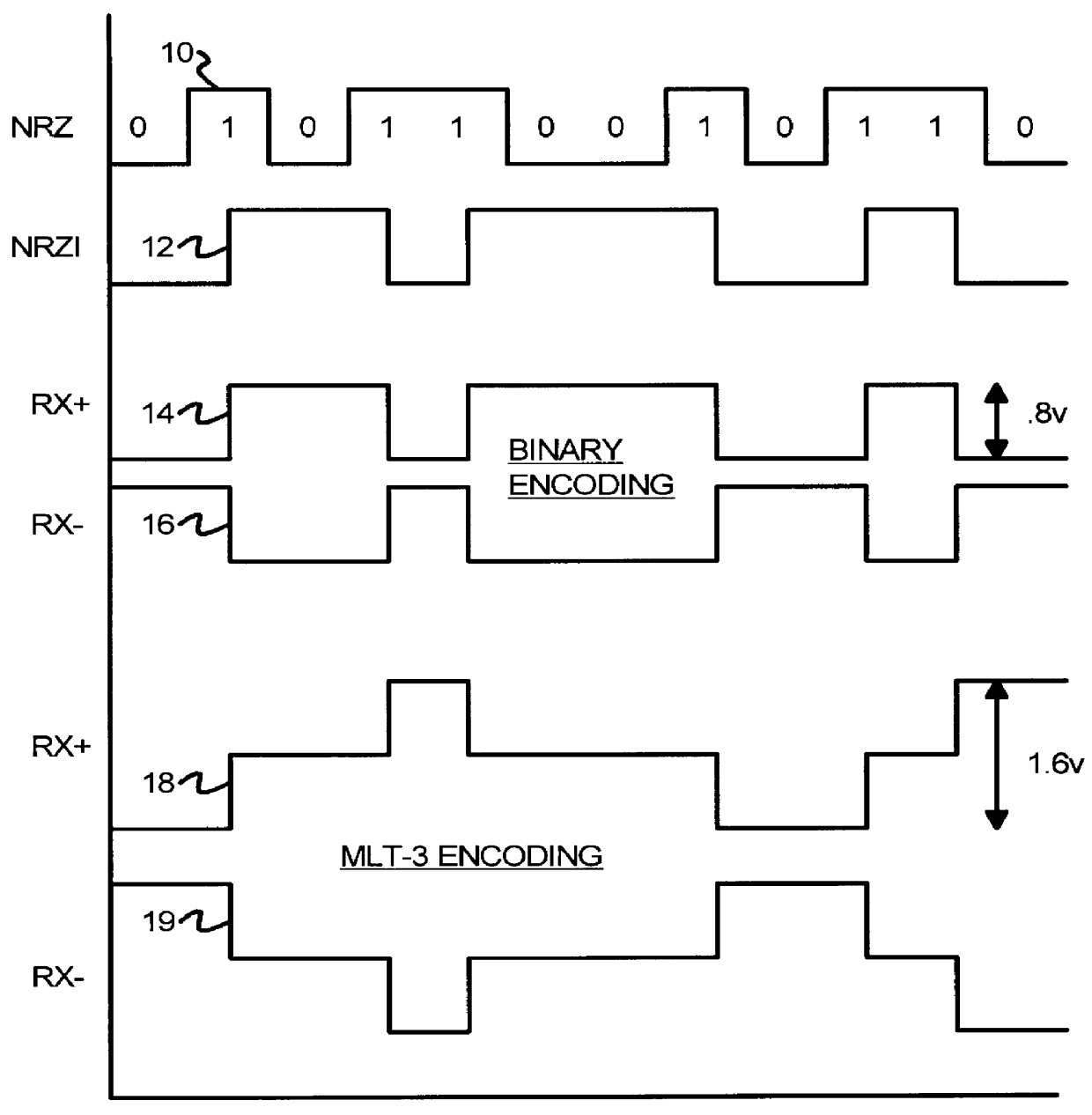

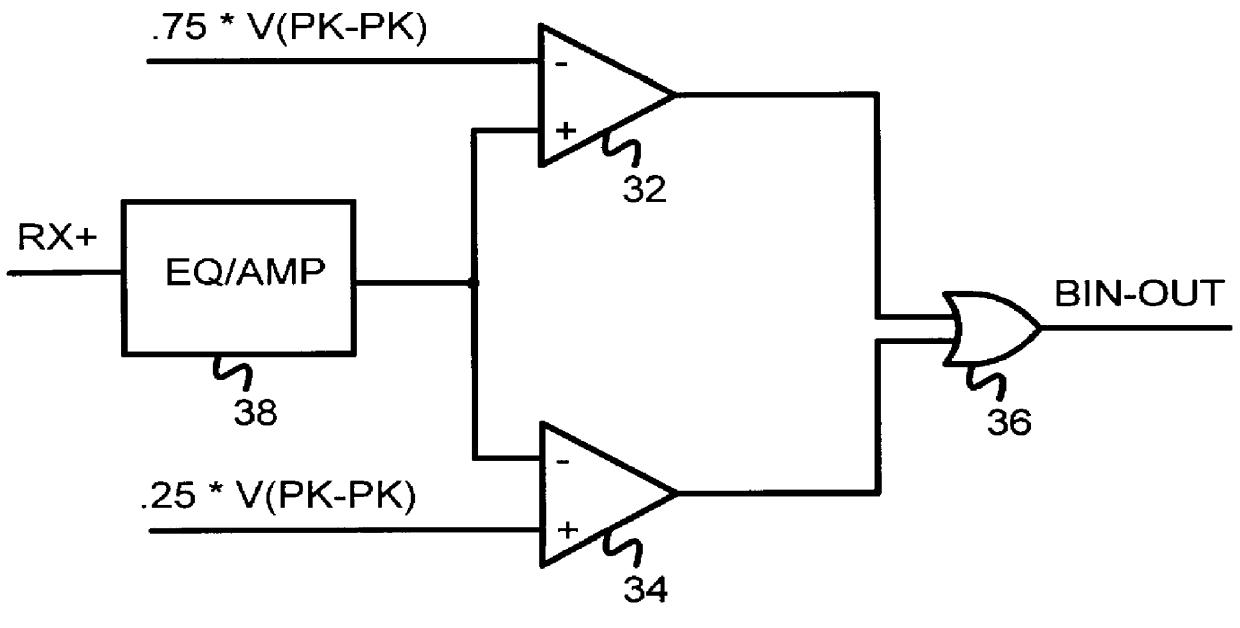

Self-biasing CMOS PECL receiver with wide common-mode range and multi-level-transmit to binary decoder

InactiveUS6049229AReduced Power RequirementsSimplify interconnect routingLogic circuits characterised by logic functionLogic circuits coupling/interface using field-effect transistorsThree levelEmitter-coupled logic

A pseudo-emitter-coupled-logic (PECL) receiver has a wide common-mode range. Two current-mirror CMOS differential amplifiers are used. One amplifier has n-channel differential transistors and a p-channel current mirror, while the second amplifier has p-channel differential transistors and an n-channel current mirror. When the input voltages approach power or ground, one type of differential transistor continues to operate even when the other type shuts off. The outputs of the two amplifiers are connected together and each amplifier receives the same differential input signals. The tail-current transistor is self-biased using the current-mirror's gate-bias. This self biasing of each amplifier eliminates the need for an additional voltage reference and allows each amplifier to adjust its biasing over a wide input-voltage range. Thus the common-mode input range is extended using self biasing and complementary amplifiers. The complementary self-biased comparators can be used for receiving binary or multi-level-transition (MLT) inputs by selecting different voltage references for threshold comparison. Using the same reference on both differential inputs eliminates a second reference for multi-level inputs having three levels. Thus binary and MLT inputs can be detected and decoded by the same decoder.

Owner:DIODES INC

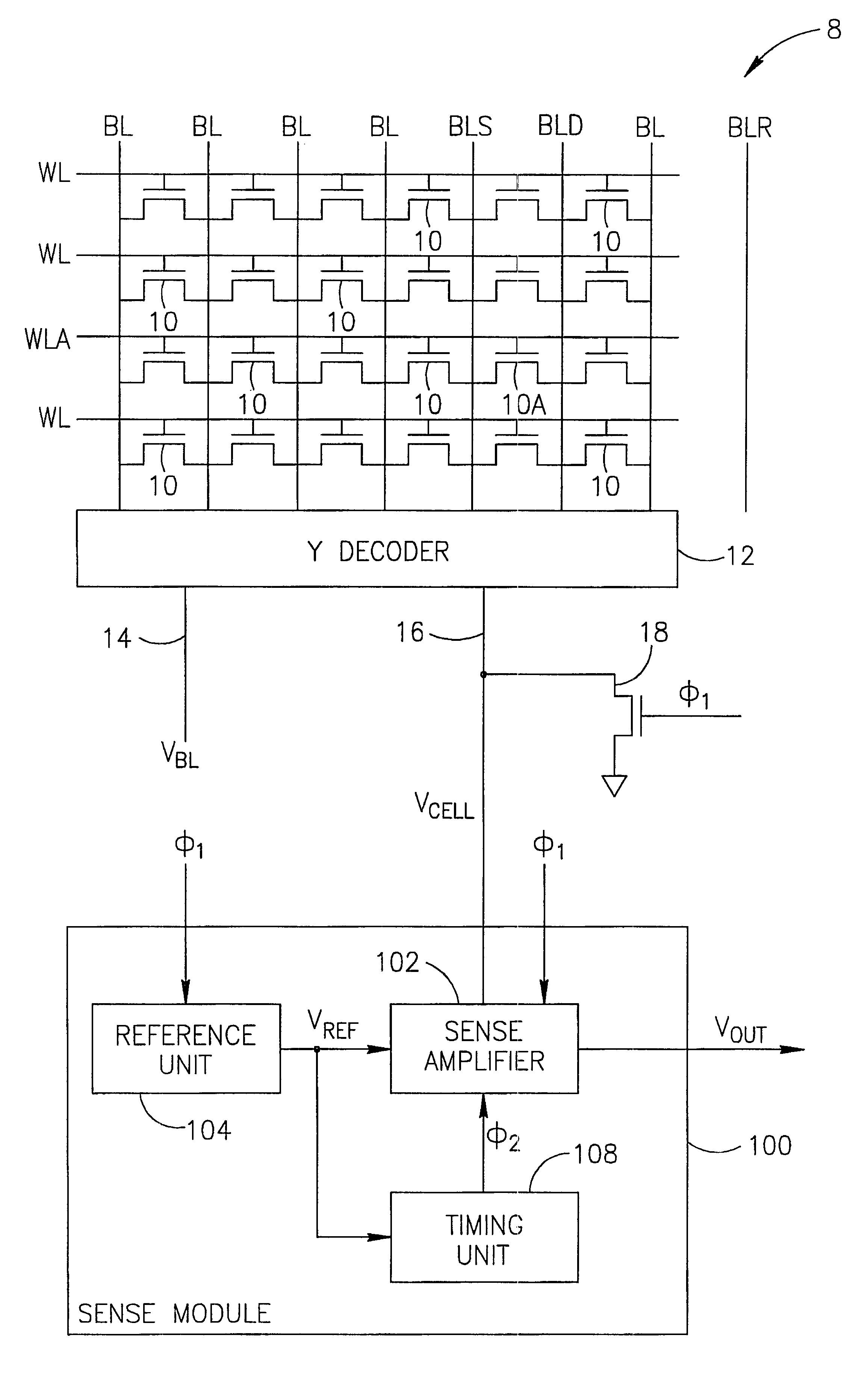

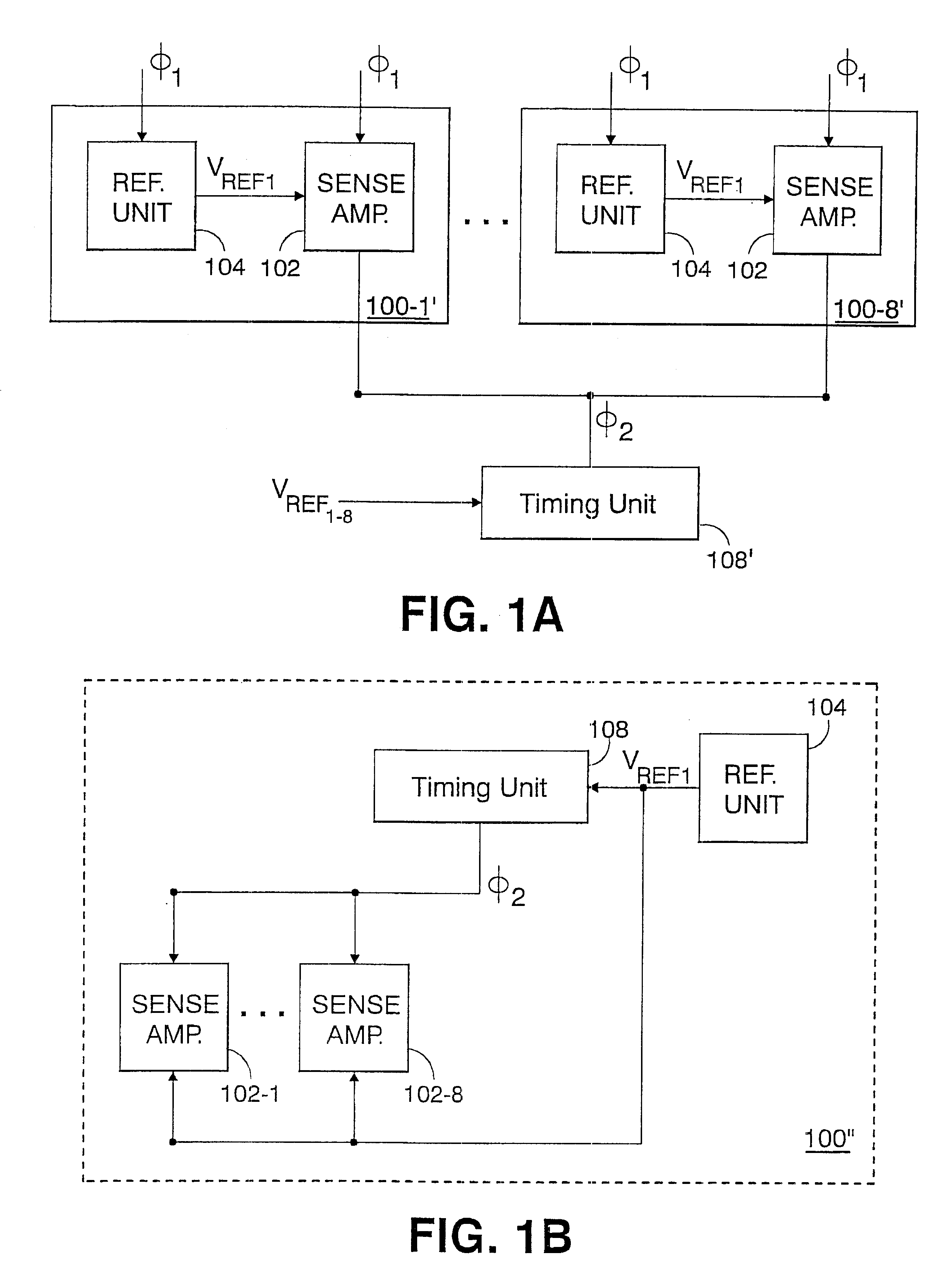

Architecture and scheme for a non-strobed read sequence

An architecture and method for implementing a non-strobed operation on an array cell within a memory array in which a reference unit is provided for emulating the response of an array cell during a desired operation, for example, a read, program verify, erase verify or other types of read operations. The reference unit includes a reference cell which is driven by a non-strobed gate voltage. The architecture and method permit relatively noise-free array cell interrogations at close to ground voltage levels.

Owner:SPANSION ISRAEL

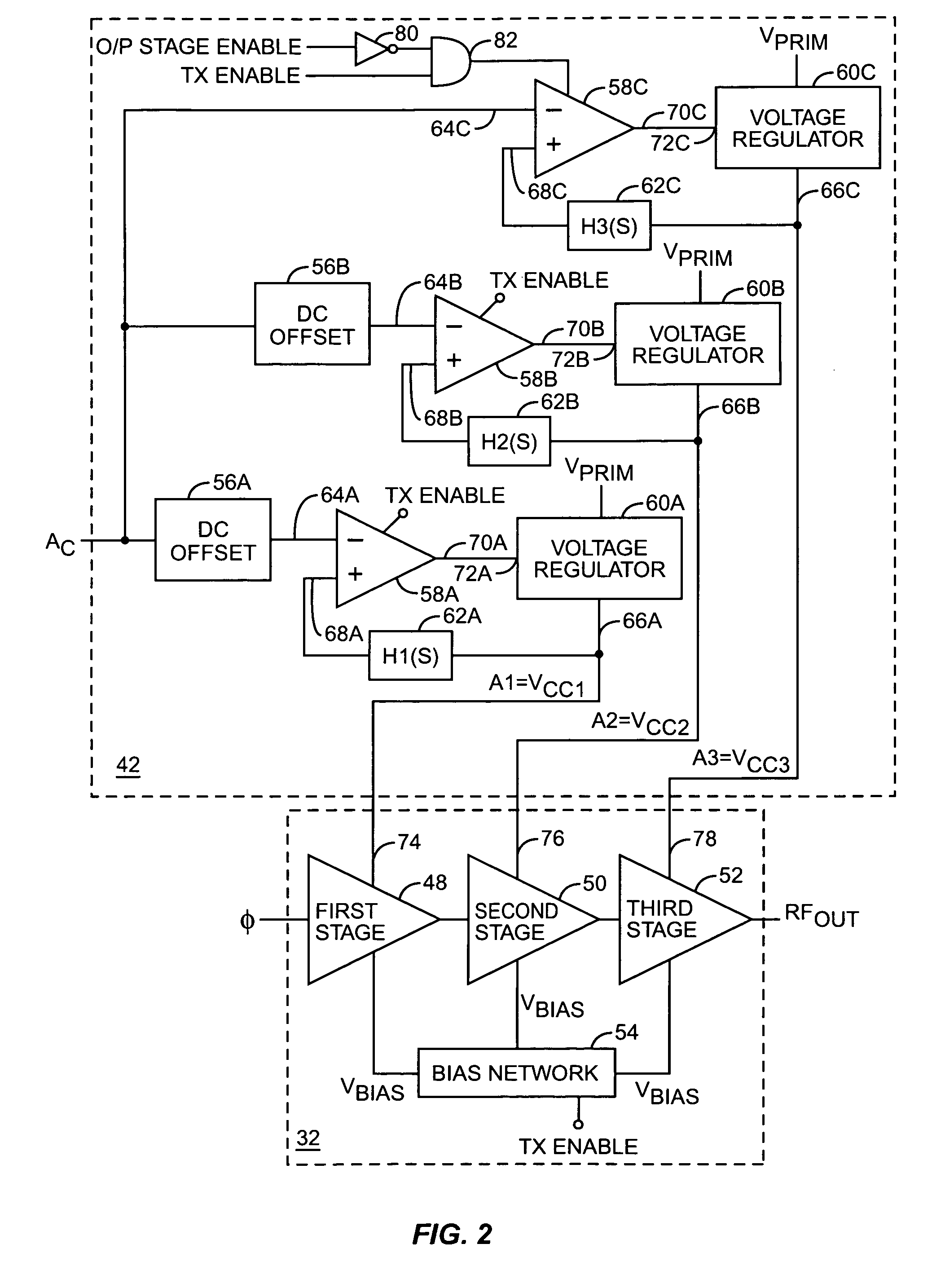

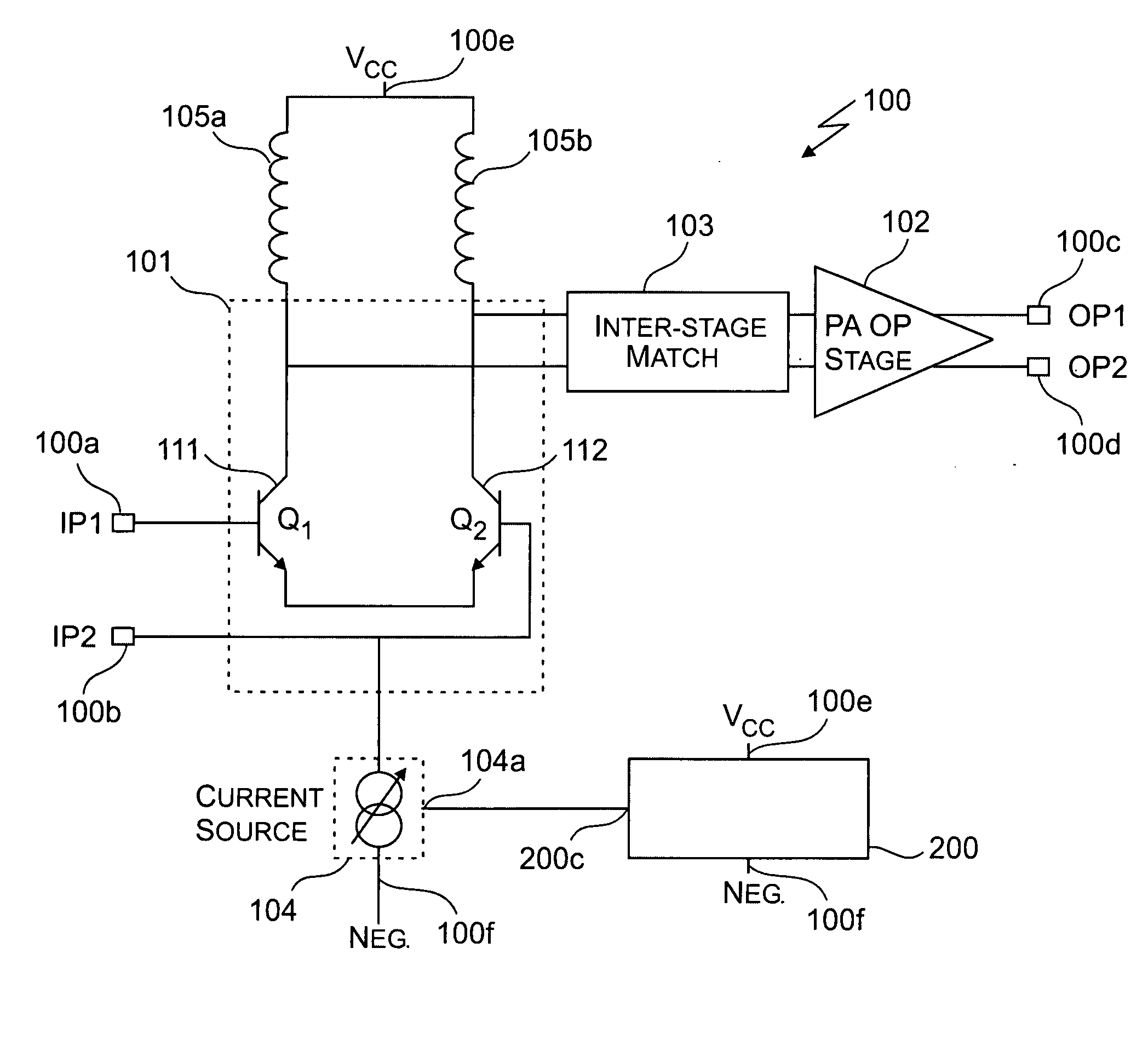

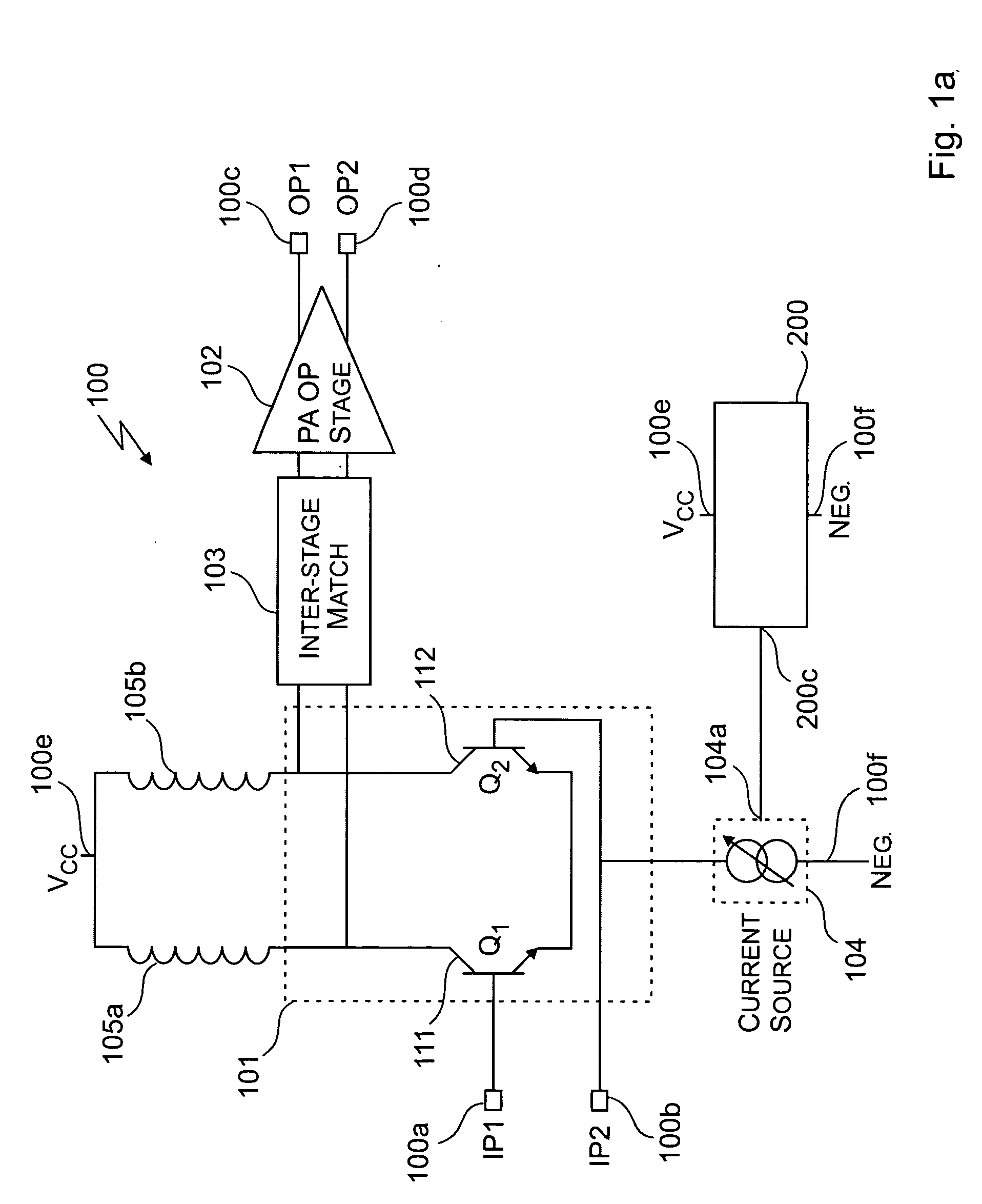

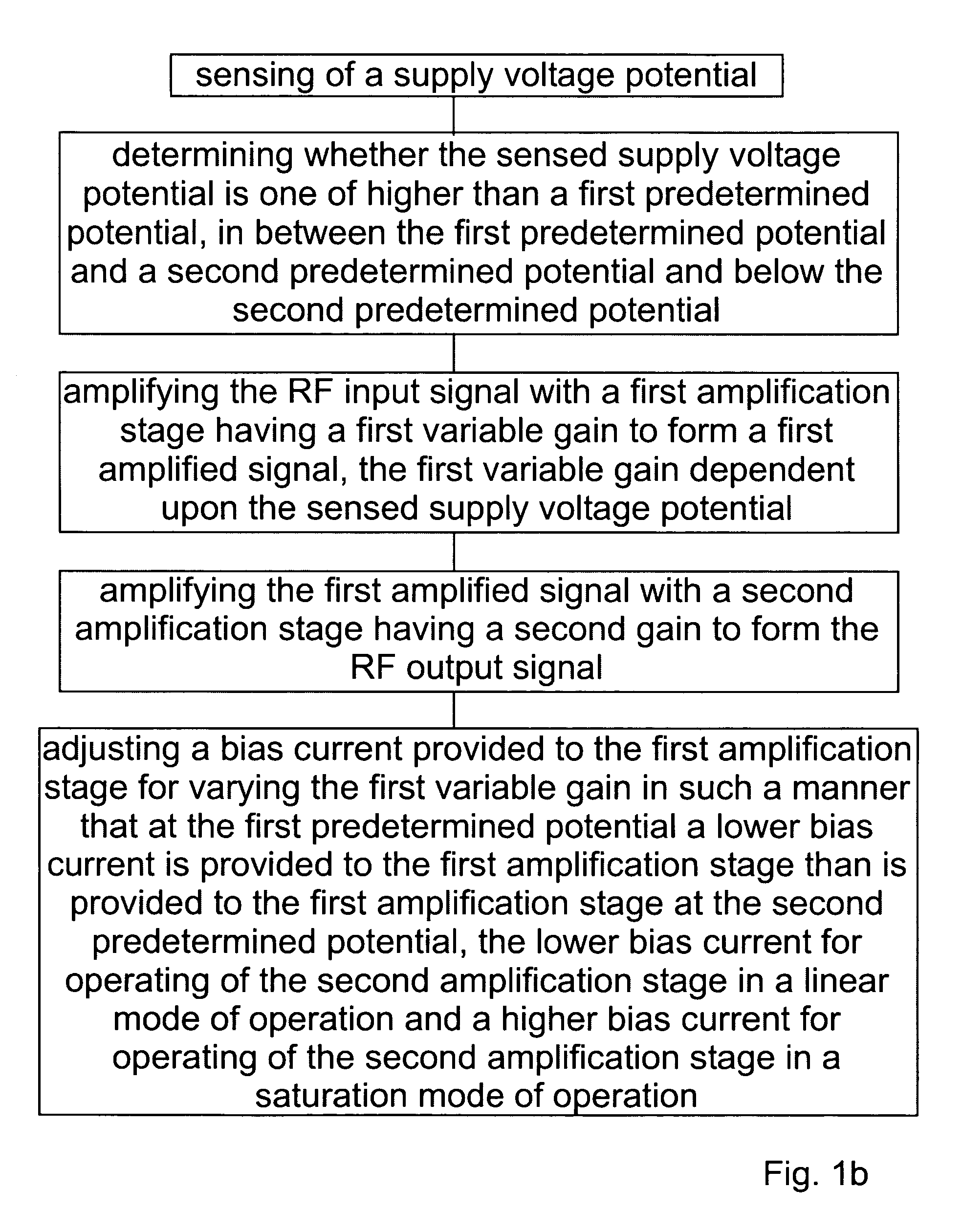

Power level controlling of first amplification stage for an integrated RF power amplifier

A power amplifier circuit is disclosed having a first amplification stage and a second amplification stage. The first amplification stage is biased using a controllable current source that provides a variable bias current thereto. A control circuit is provided for controlling the variable bias current in dependence upon the supply voltage and temperature of the power amplifier circuit. The control signal varies the variable bias current in dependence upon the supply voltage varying between first and second potential, where each potential supplies sufficient potential for operation of the power amplifier circuit.

Owner:SIGE SEMICON

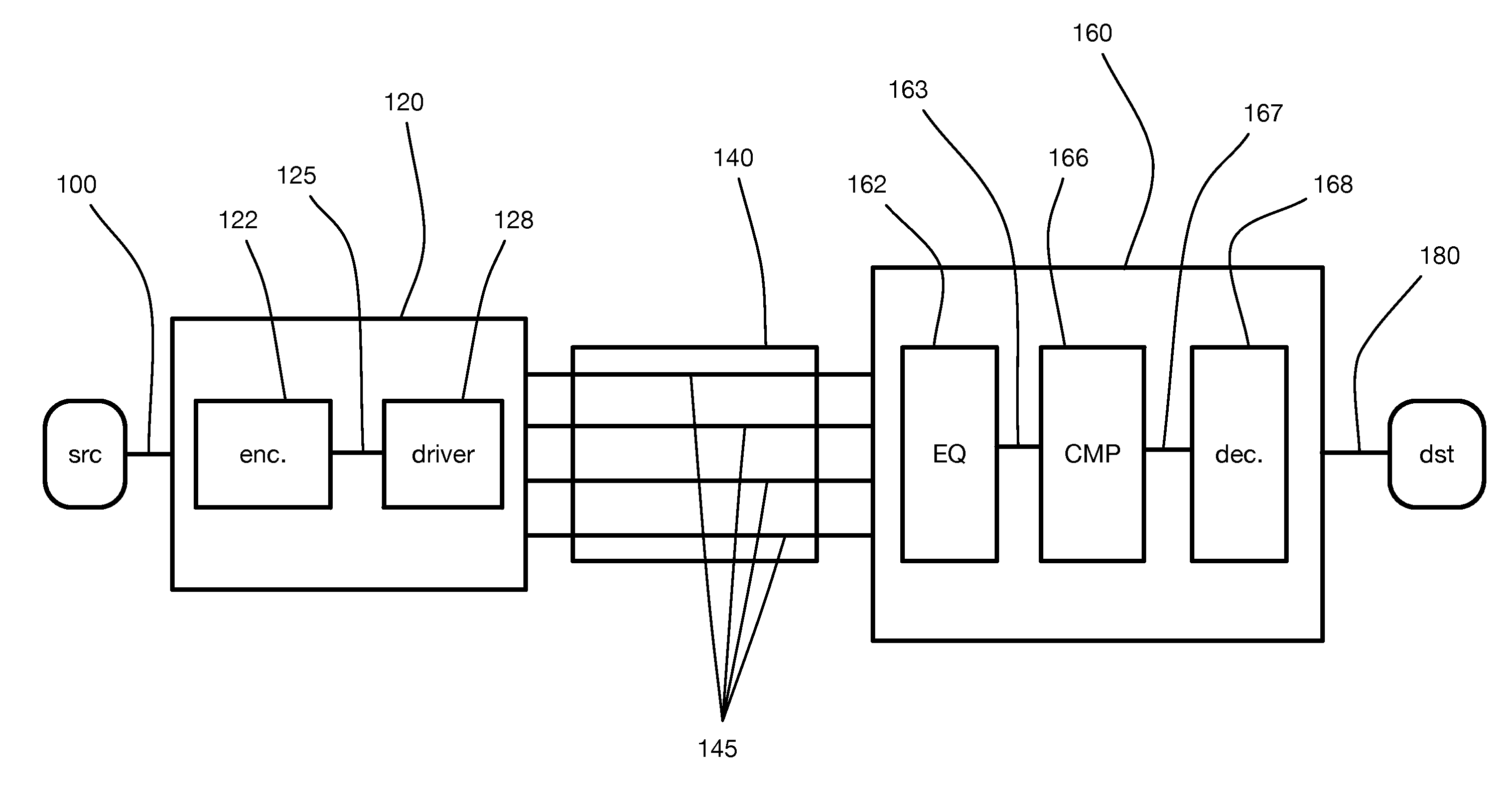

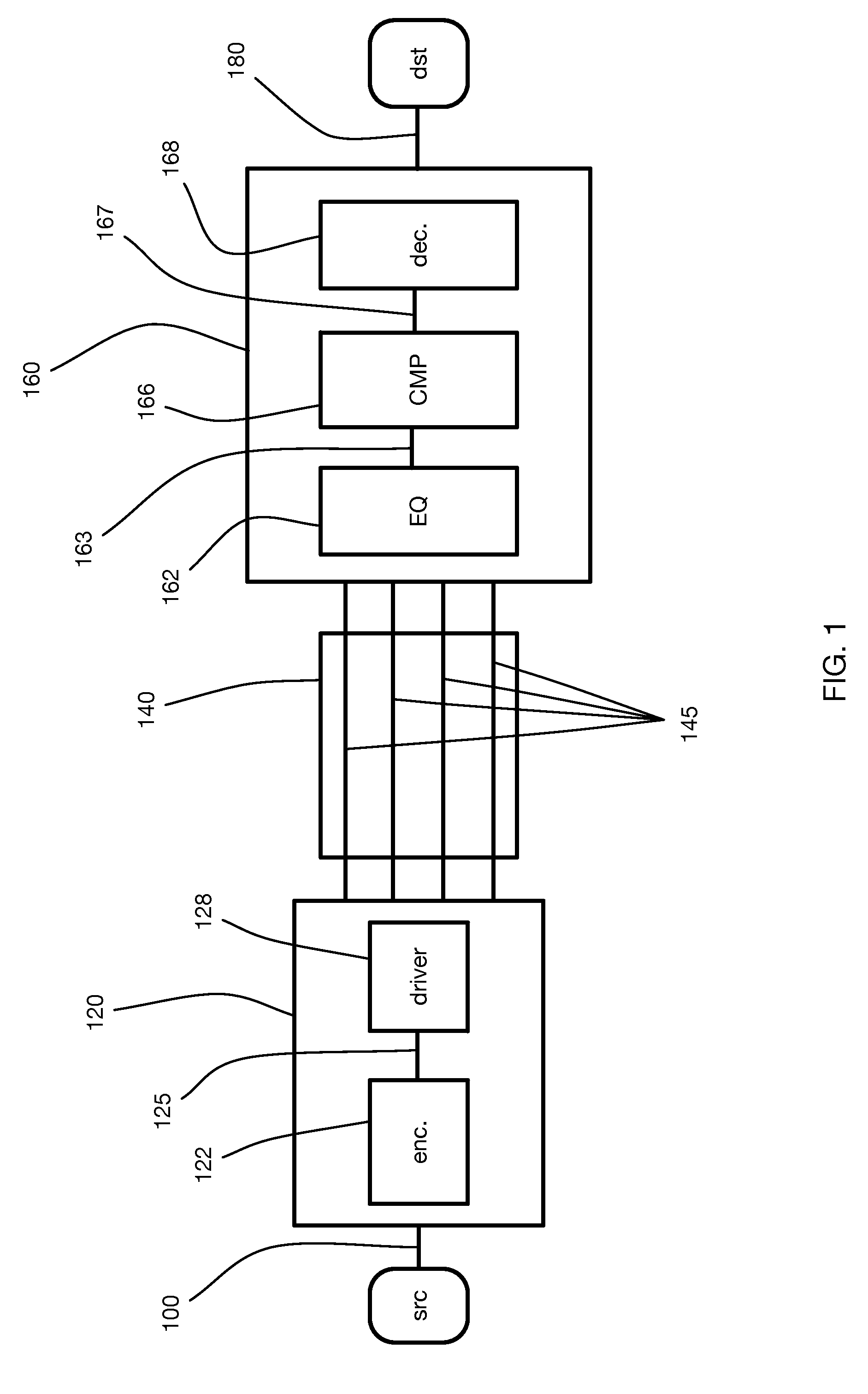

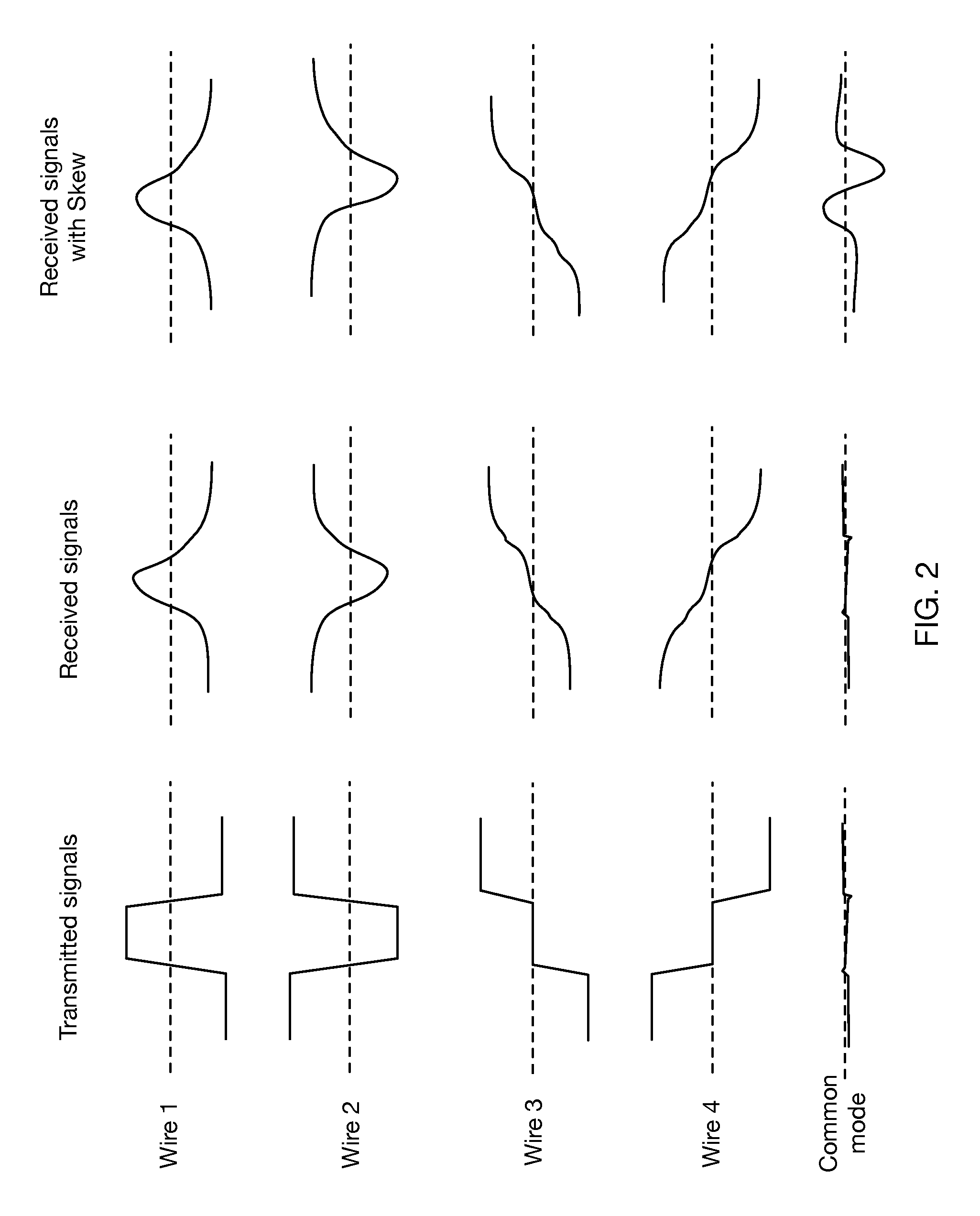

Multiwire linear equalizer for vector signaling code receiver

ActiveUS9106465B2Improve efficiencyReduce power consumptionMultiple-port networksHigh frequency amplifiersSignal onEqualization

Continuous-time linear equalization of received signals on multiple wire channels while maintaining accurate common mode signal values. Multiwire group signaling using vector signaling codes simultaneously transmits encoded values on multiple wires, requiring multiple receive signals to be sampled simultaneously to retrieve the full transmitted code word. By misaligning transitions on multiple wires, skew introduces a transient common mode signal component that is preserved by using frequency-selective common mode feedback at the receiver to obtain accurate sampling results.

Owner:KANDOU LABS

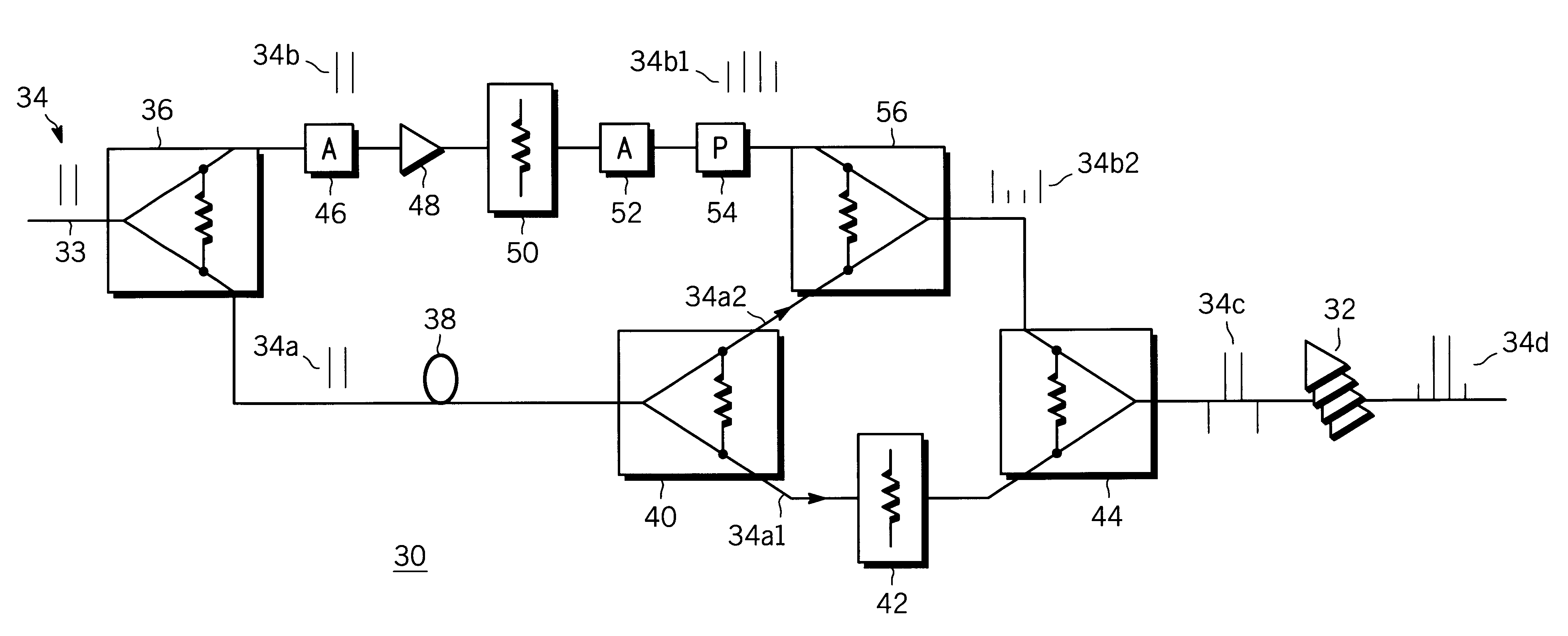

Power amplifier array with same type predistortion amplifier

InactiveUS6646505B2Amplifier modifications to reduce non-linear distortionAmplifier modifications to reduce noise influenceAudio power amplifierCarrier signal

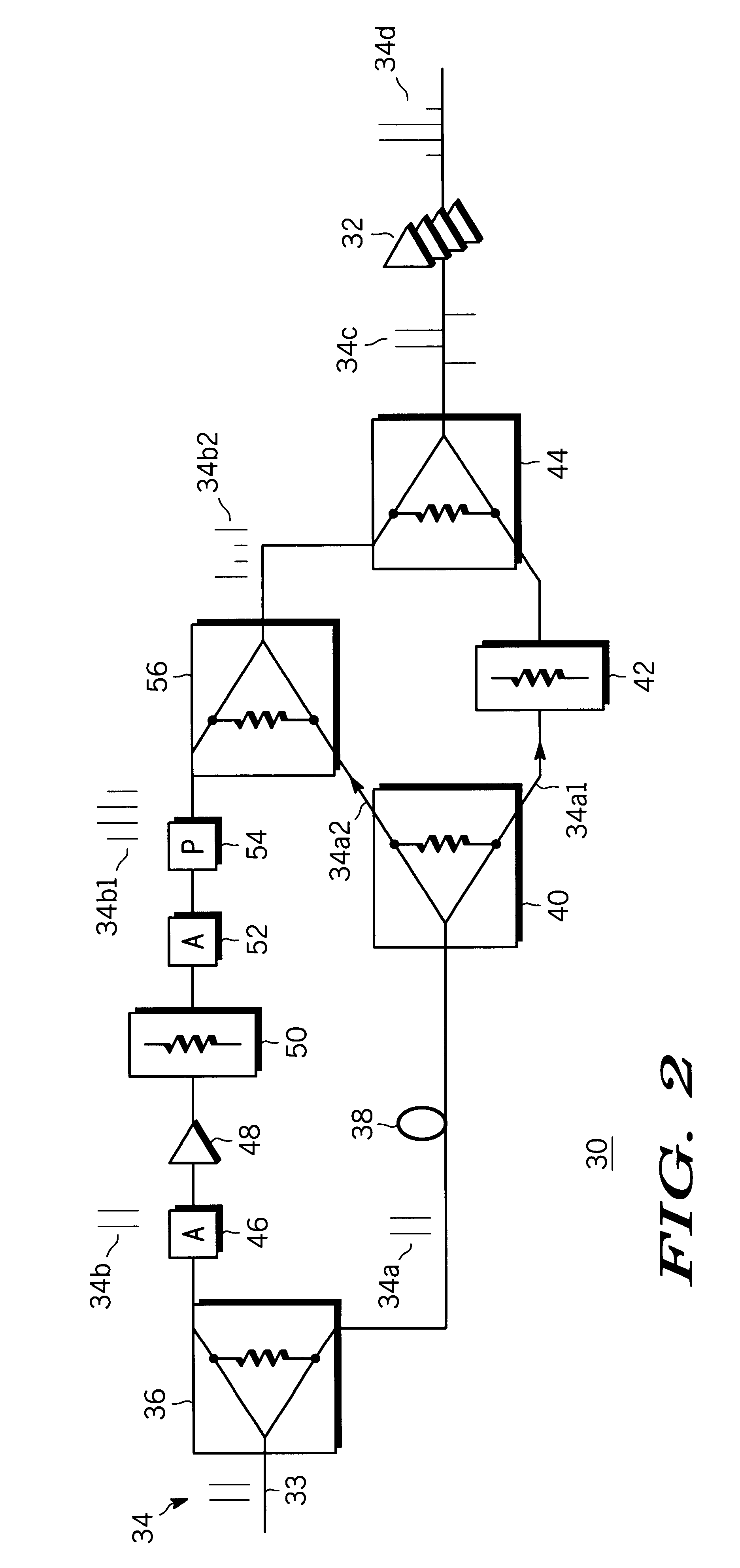

A power amplifier circuit (30, 60) improves the linearity of an amplified output signal. The power amplifier circuit (30, 60) includes an input (33, 63) for receiving a carrier signal (34, 64) and an array of combined amplifiers (32, 62) of a predetermined type for amplifying the carrier signal (34, 64). At least one amplifier (48, 78) of the predetermined type is located between the input (33, 63) and the array of combined amplifiers (32, 62) for amplifying the carrier signal (34, 64) to produce a predistorted carrier signal (34b1, 64b1) with a carrier signal component and a distortion component to condition the carrier signal (34, 64) for input into the array of combined amplifiers (32, 62), and specifically to compensate for nonlinearities produced by the array of combined amplifiers (32, 62).

Owner:GOOGLE TECH HLDG LLC

Popular searches

Dc-amplifiers with dc-coupled stages Electric pulse generator Logic circuits Apparatus without intermediate ac conversion Cathode-ray tube indicators Electric variable regulation Switched capacitor networks Active element network Amplifiers using switched capacitors Amplifier modifications to extend bandwidth