Patents

Literature

422results about "Amplifiers using switched capacitors" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

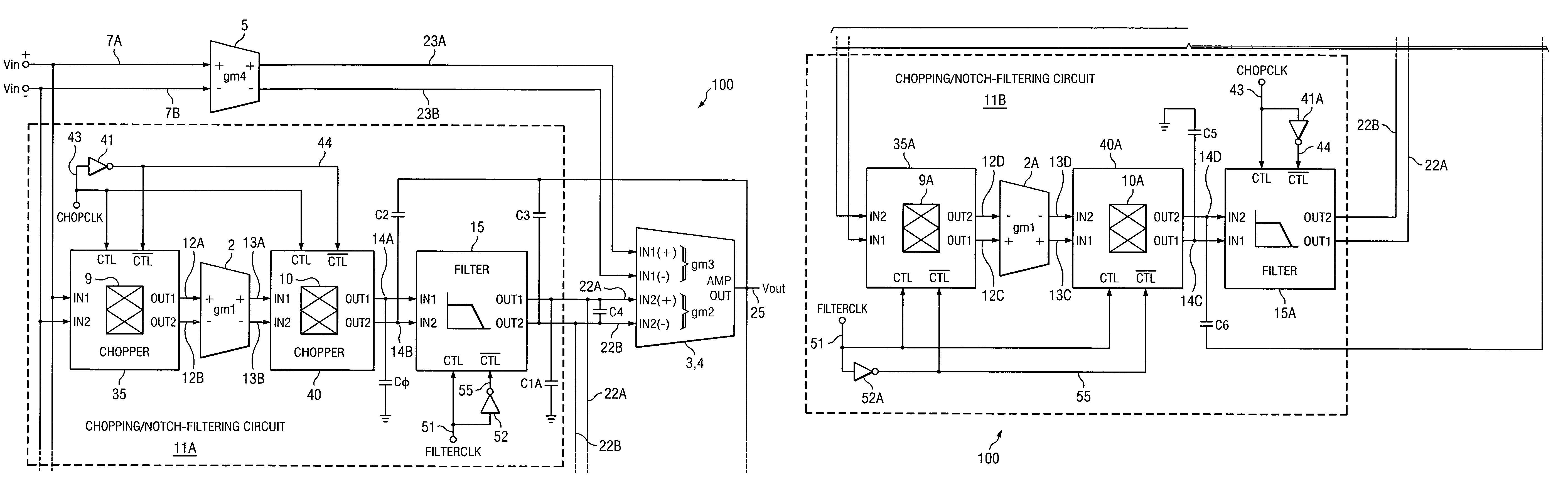

Notch filter for ripple reduction in chopper stabilized amplifiers

ActiveUS7292095B2Reduce ripple noiseFast signalAmplifier modifications to reduce noise influenceAmplifier modifications to raise efficiencyAudio power amplifierEngineering

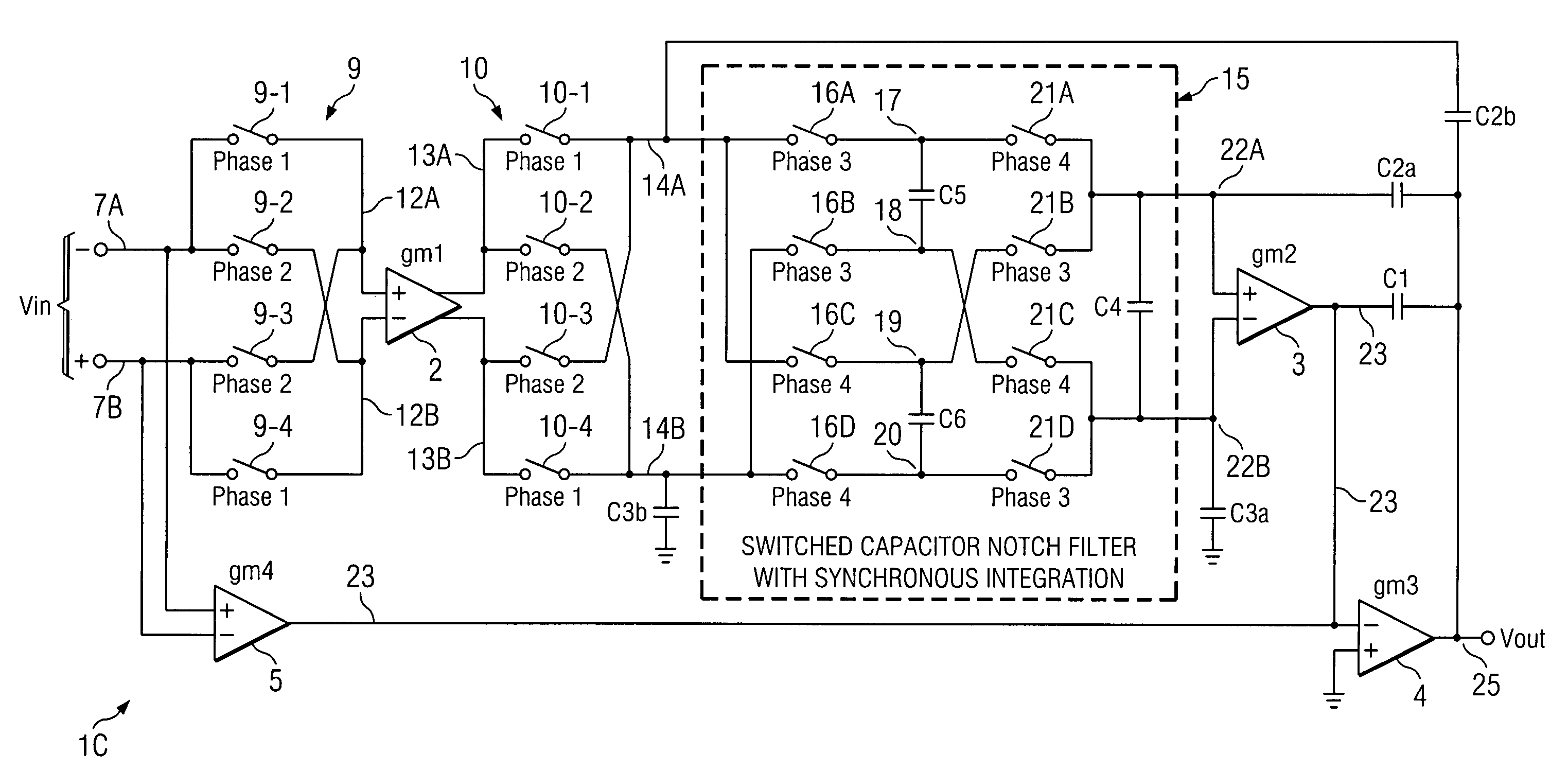

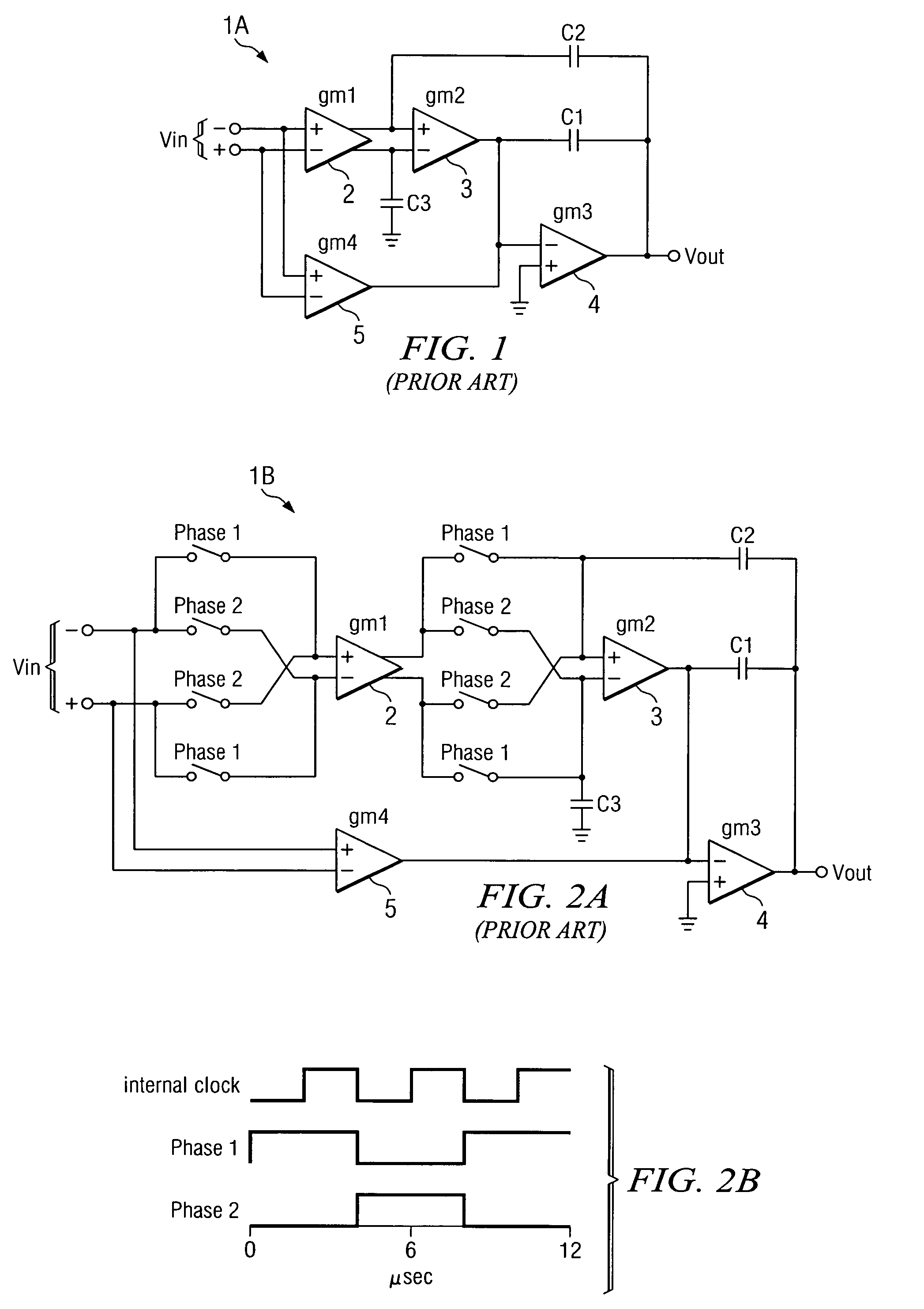

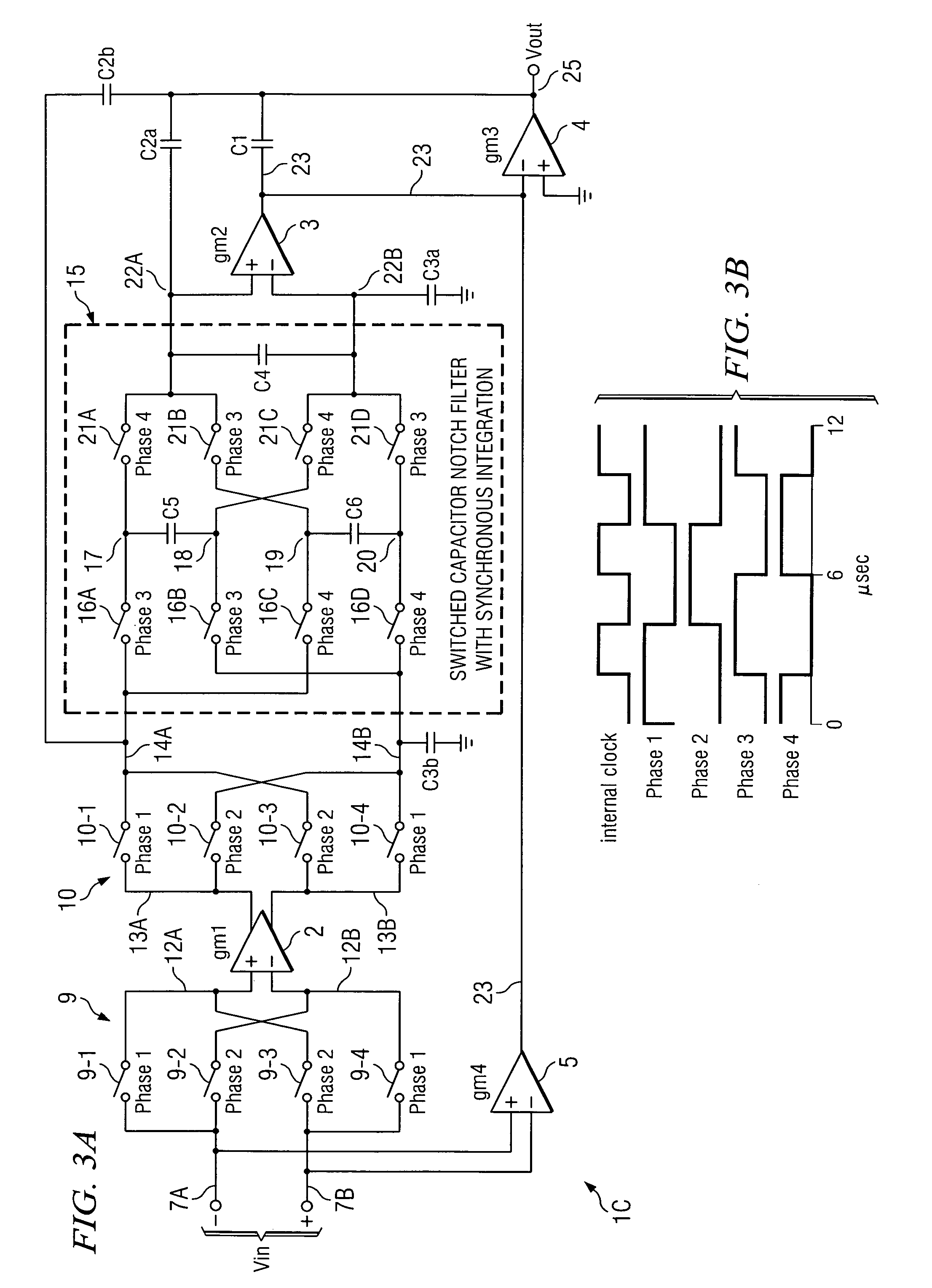

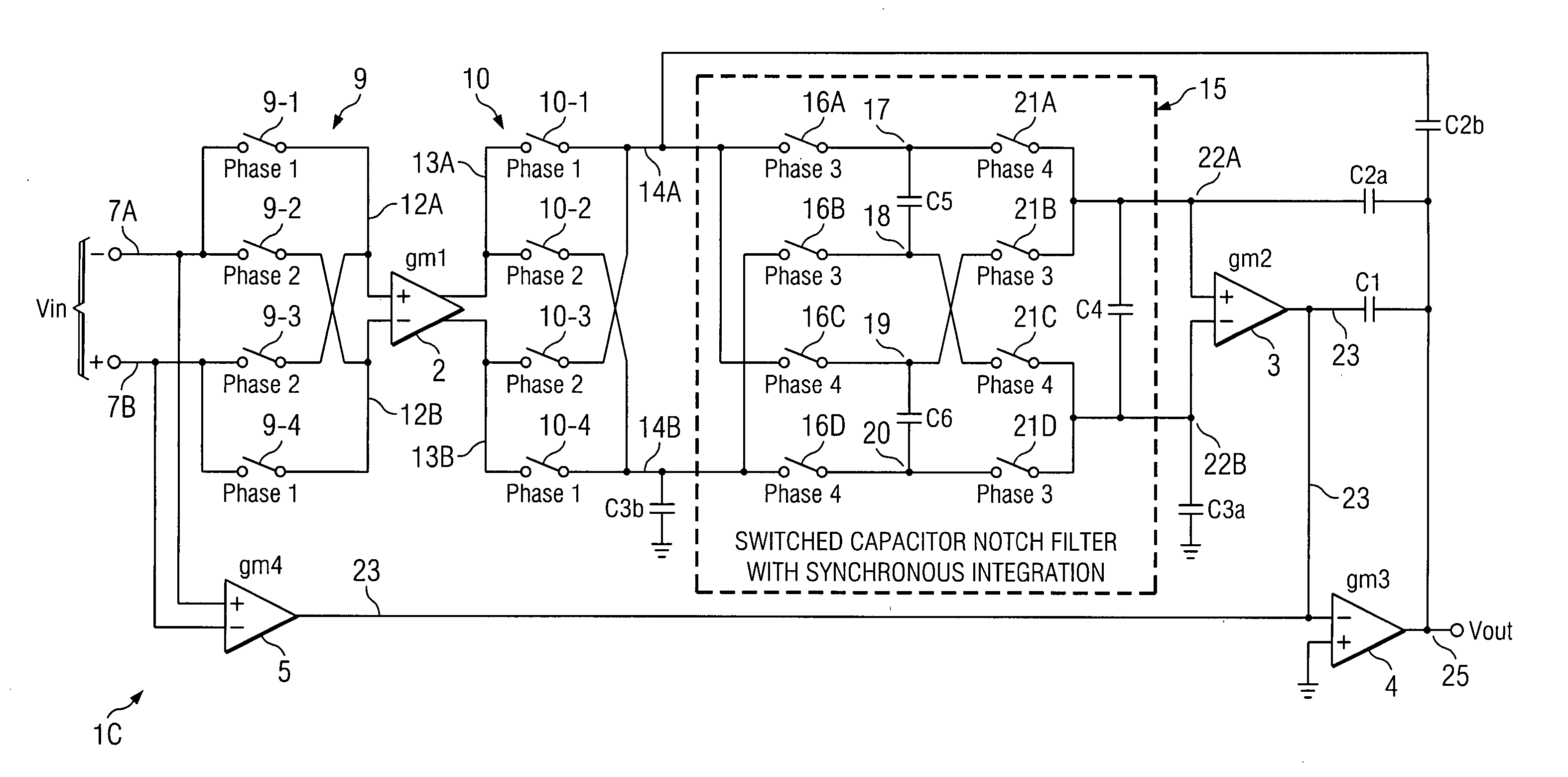

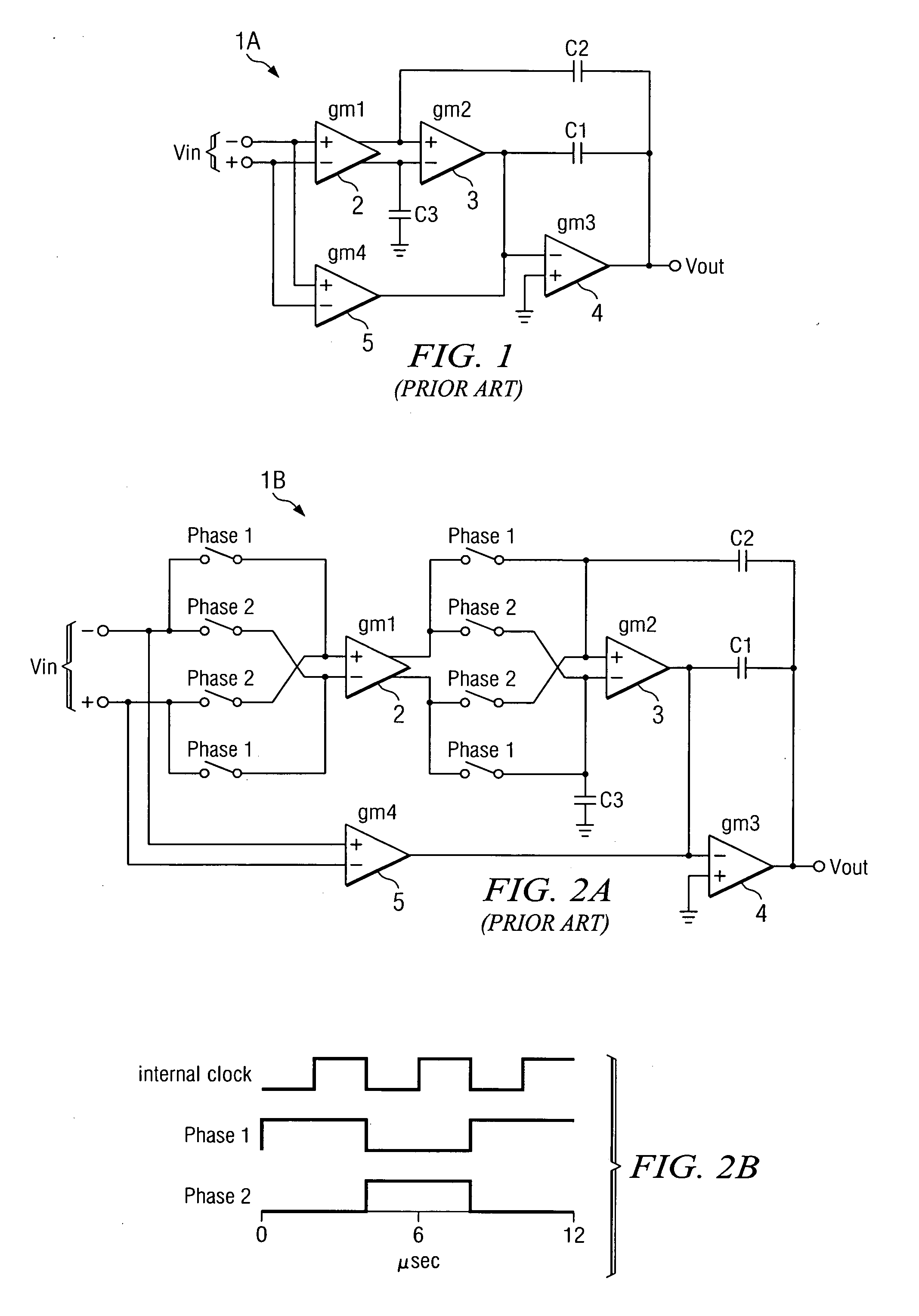

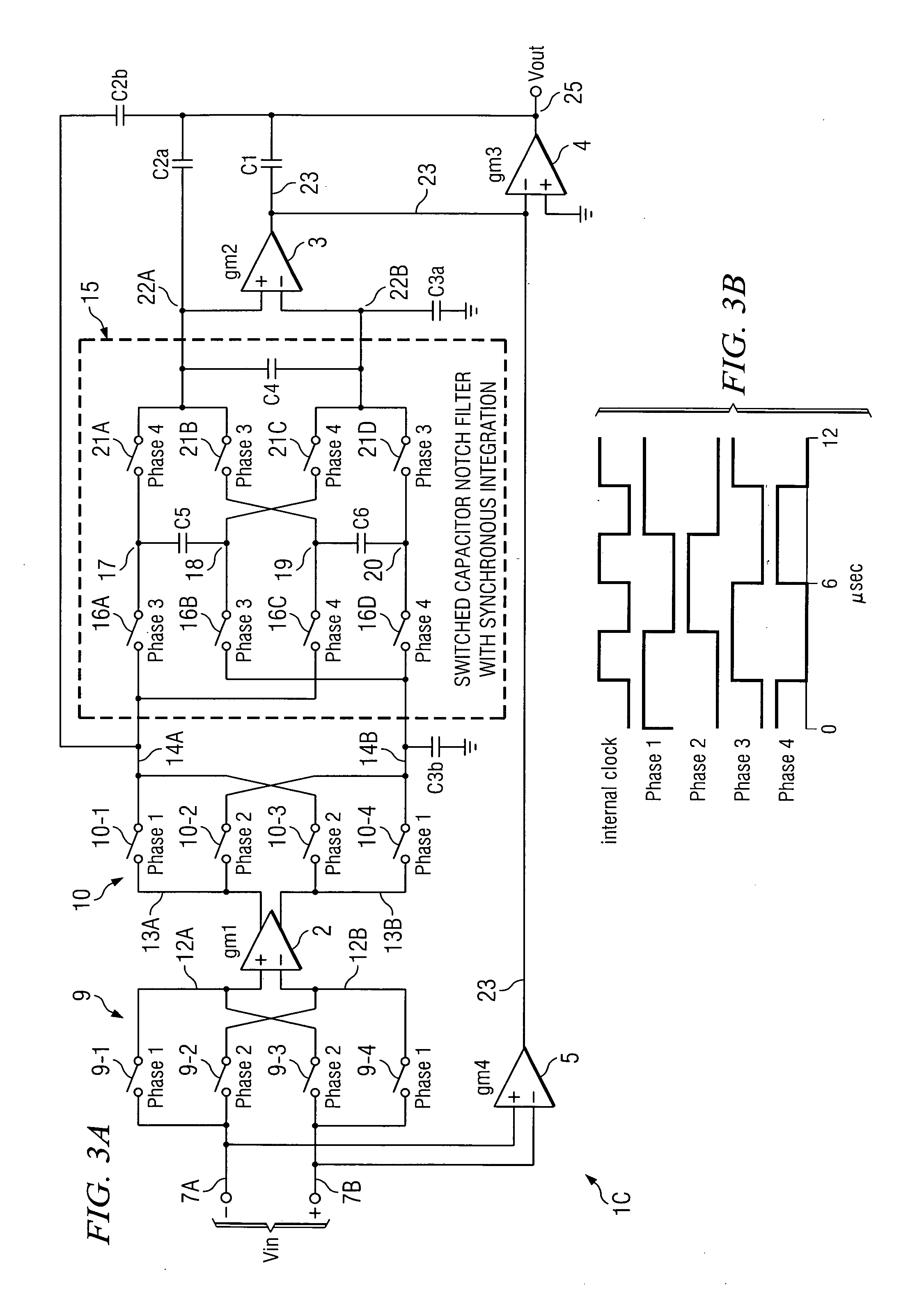

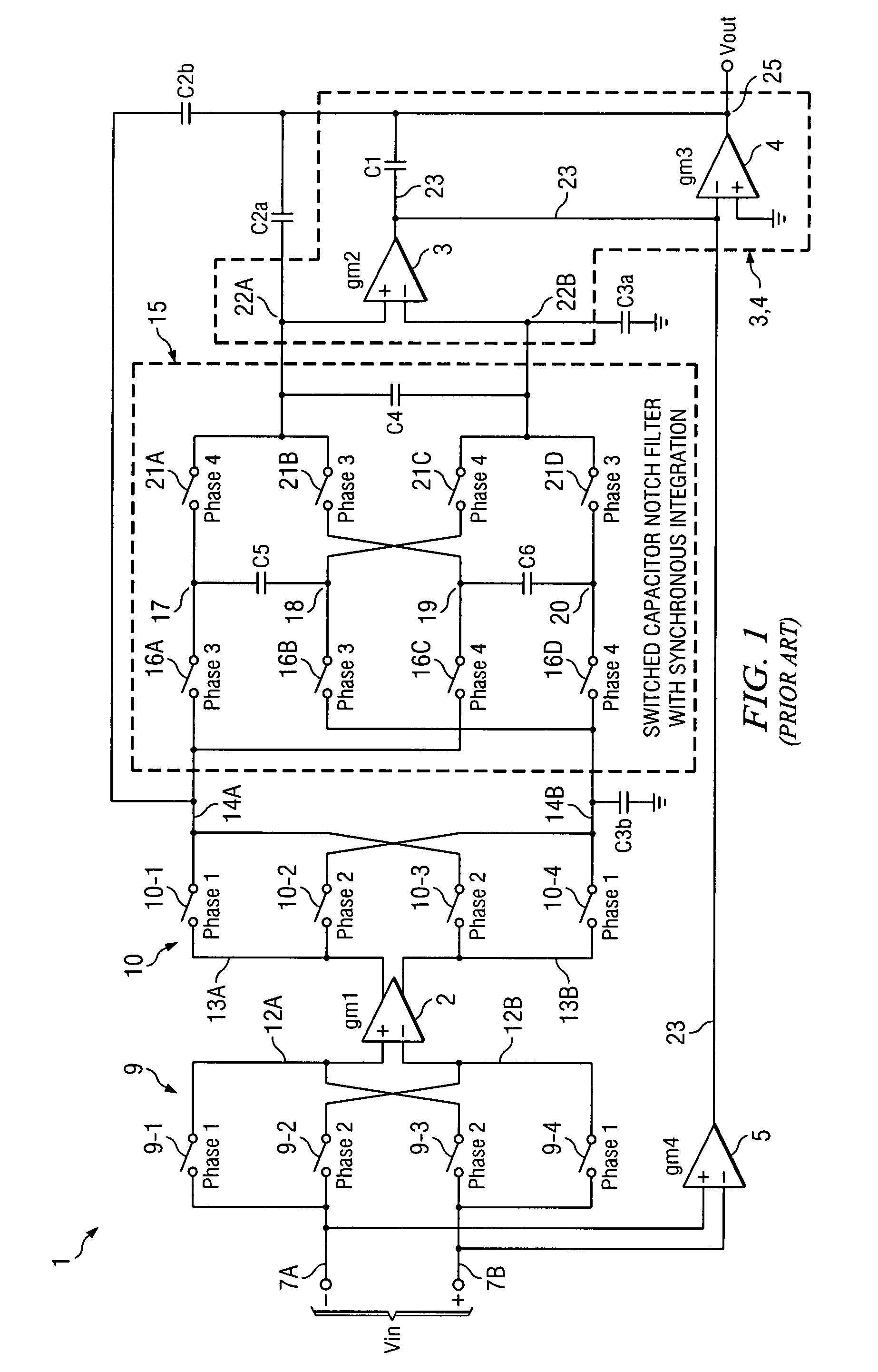

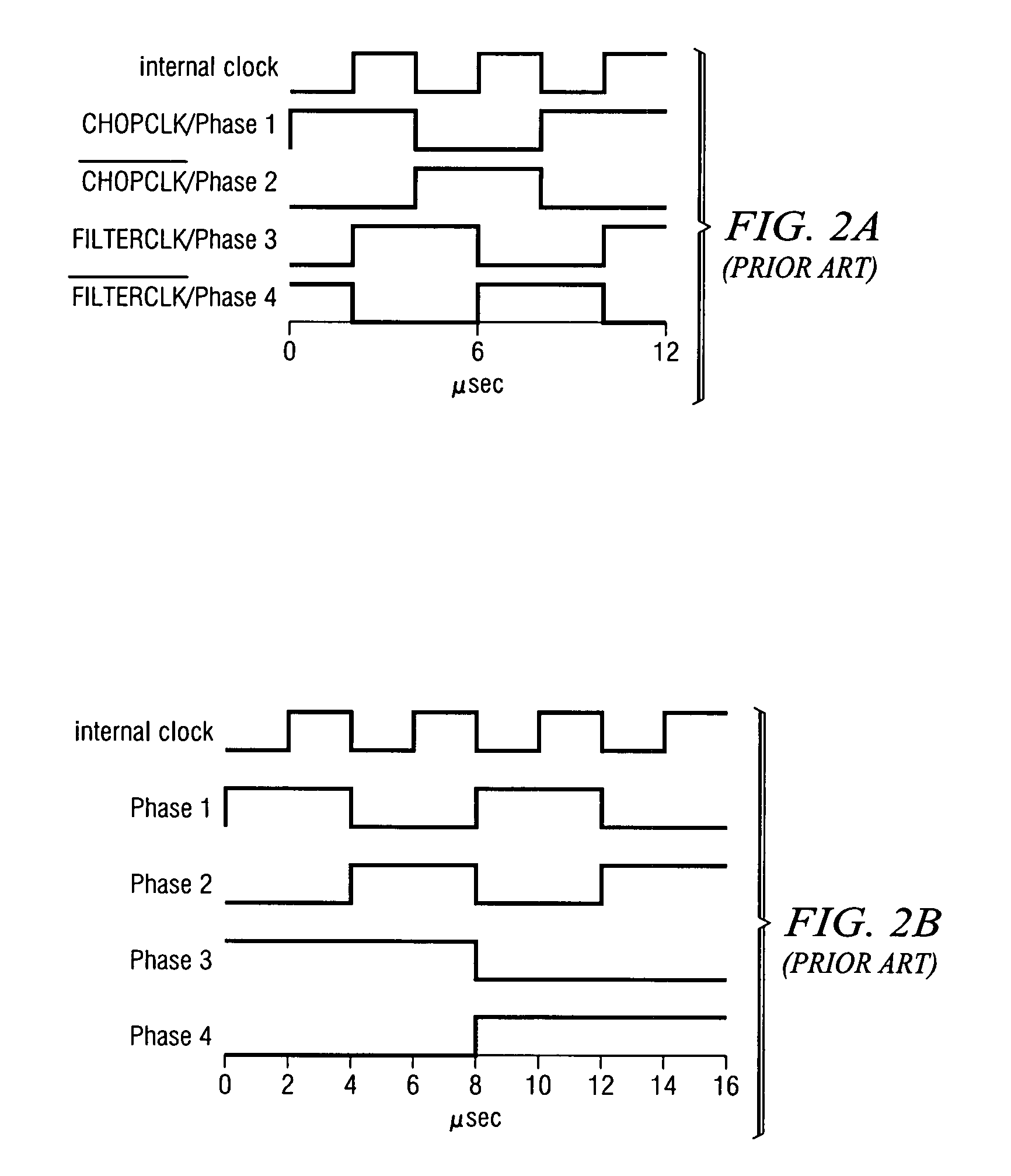

A chopper-stabilized amplifier receiving an input signal includes a first operational transconductance amplifier having an input chopper and an output chopper for chopping an output signal produced by the first operational transconductance amplifier. A switched capacitor notch filter filters the chopped output signal by operating synchronously with the chopping frequency of output chopper to filter ripple voltages that otherwise would be produced by the output chopper. In one embodiment, a second operational transconductance amplifier amplifies the notch filter output. The input signal is fed forward, summed with the output of the second operational transconductance amplifier, and applied to the input of a fourth operational transconductance amplifier. Ripple noise and offset are substantially reduced.

Owner:TEXAS INSTR INC

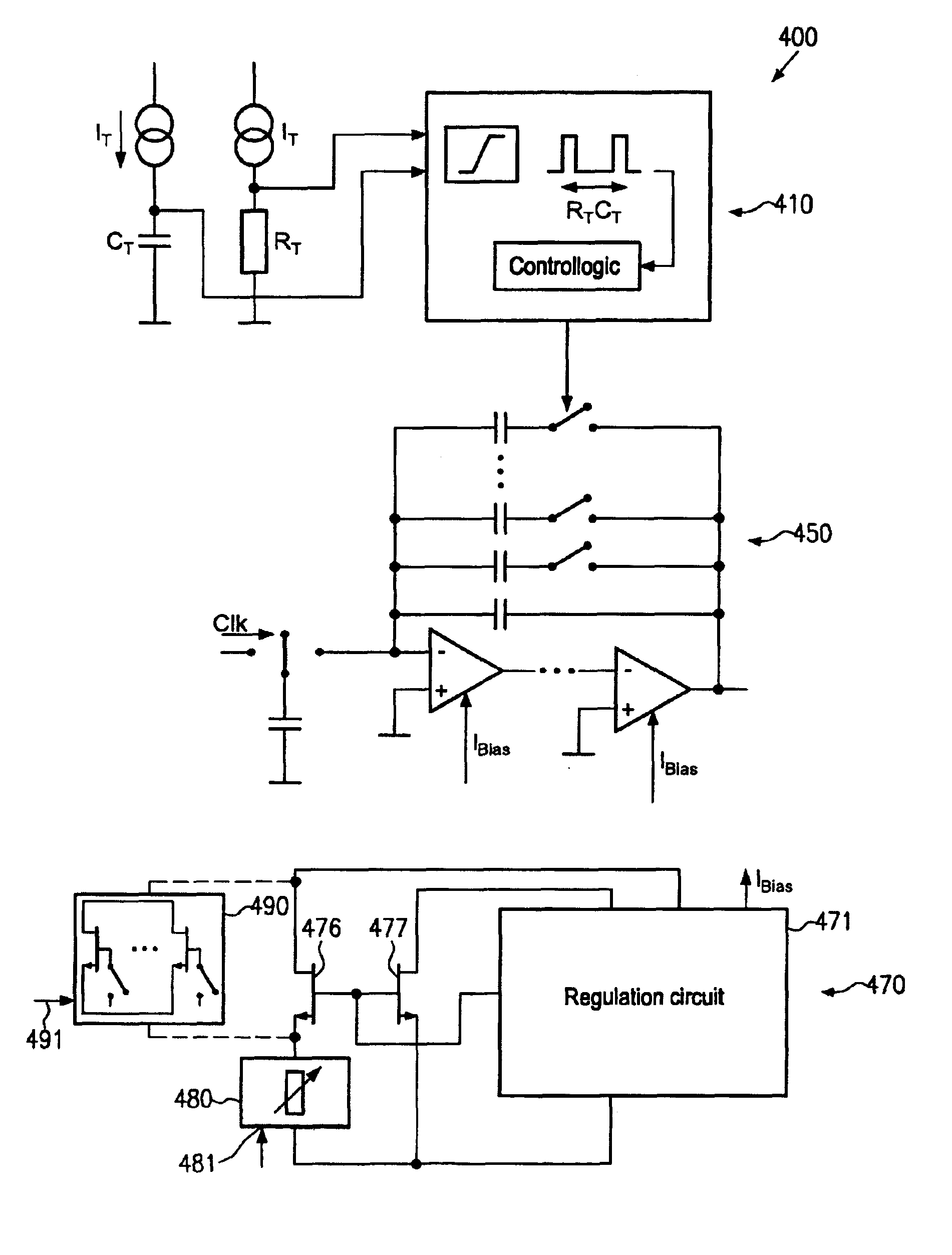

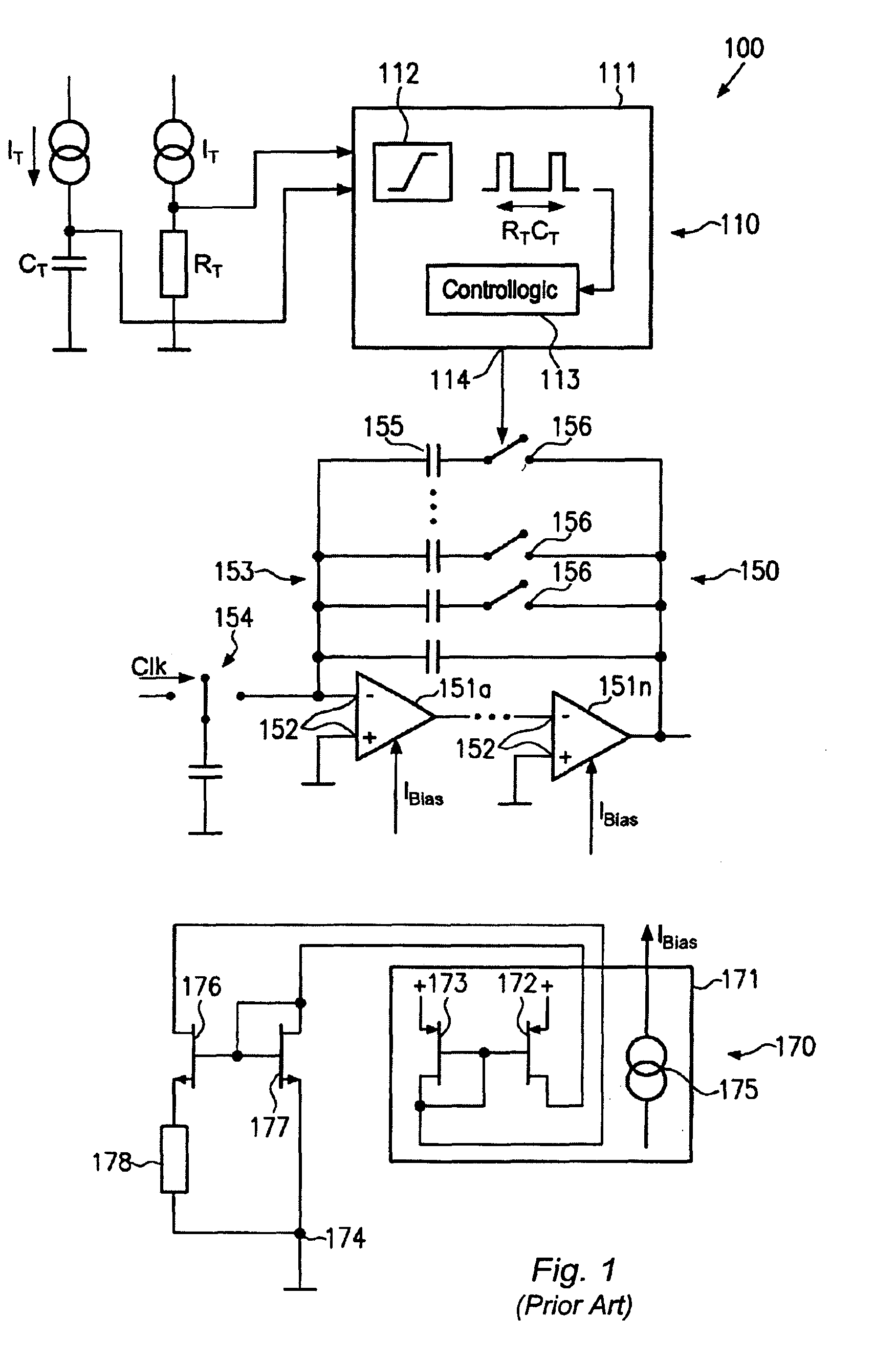

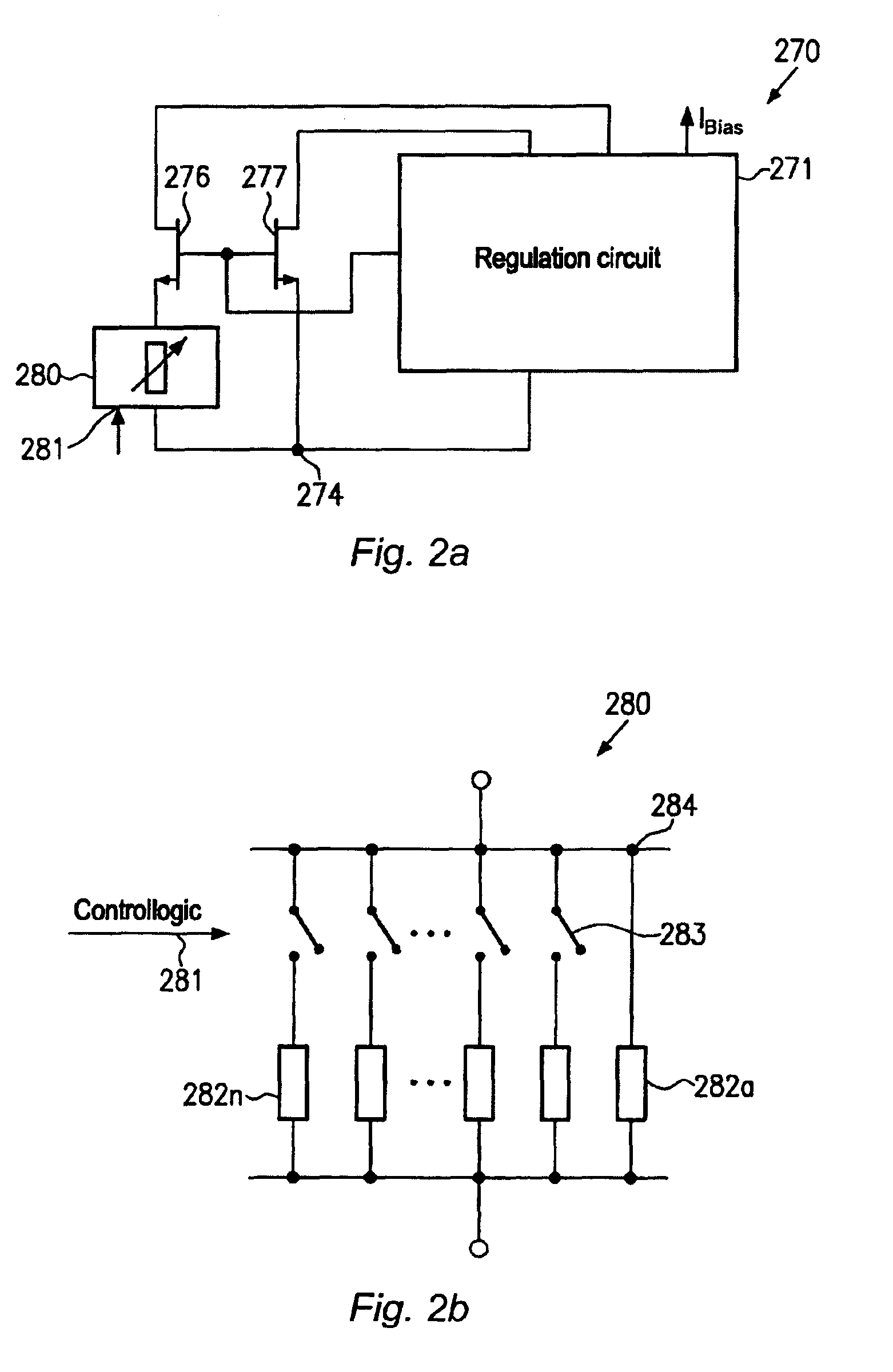

Circuit and a method for controlling the bias current in a switched capacitor circuit

InactiveUS6891439B2Effective compensationAmplifier modifications to reduce temperature/voltage variationAmplifier modifications to raise efficiencyElectrical resistance and conductanceAudio power amplifier

A tunable constant GM circuit allows to compensate for temperature and process variations with high precision by correspondingly adjusting a resistance value and / or the ratio of transistor widths. Thus, in switched capacitor circuits the frequency behaviour, such as the settling time, may be controlled by providing a compensated bias to the transconductance amplifiers typically used in these circuits.

Owner:ADVANCED MICRO DEVICES INC

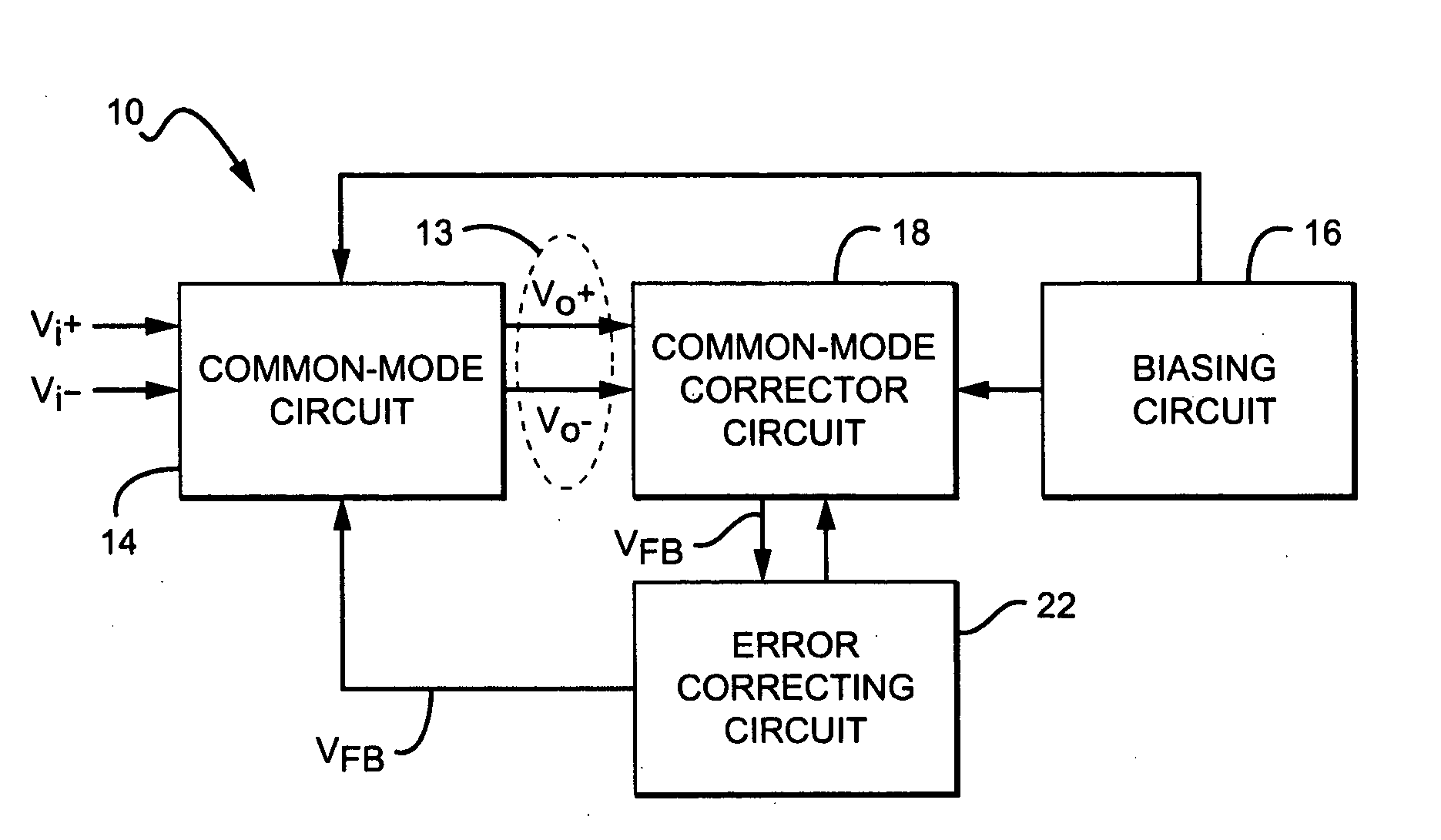

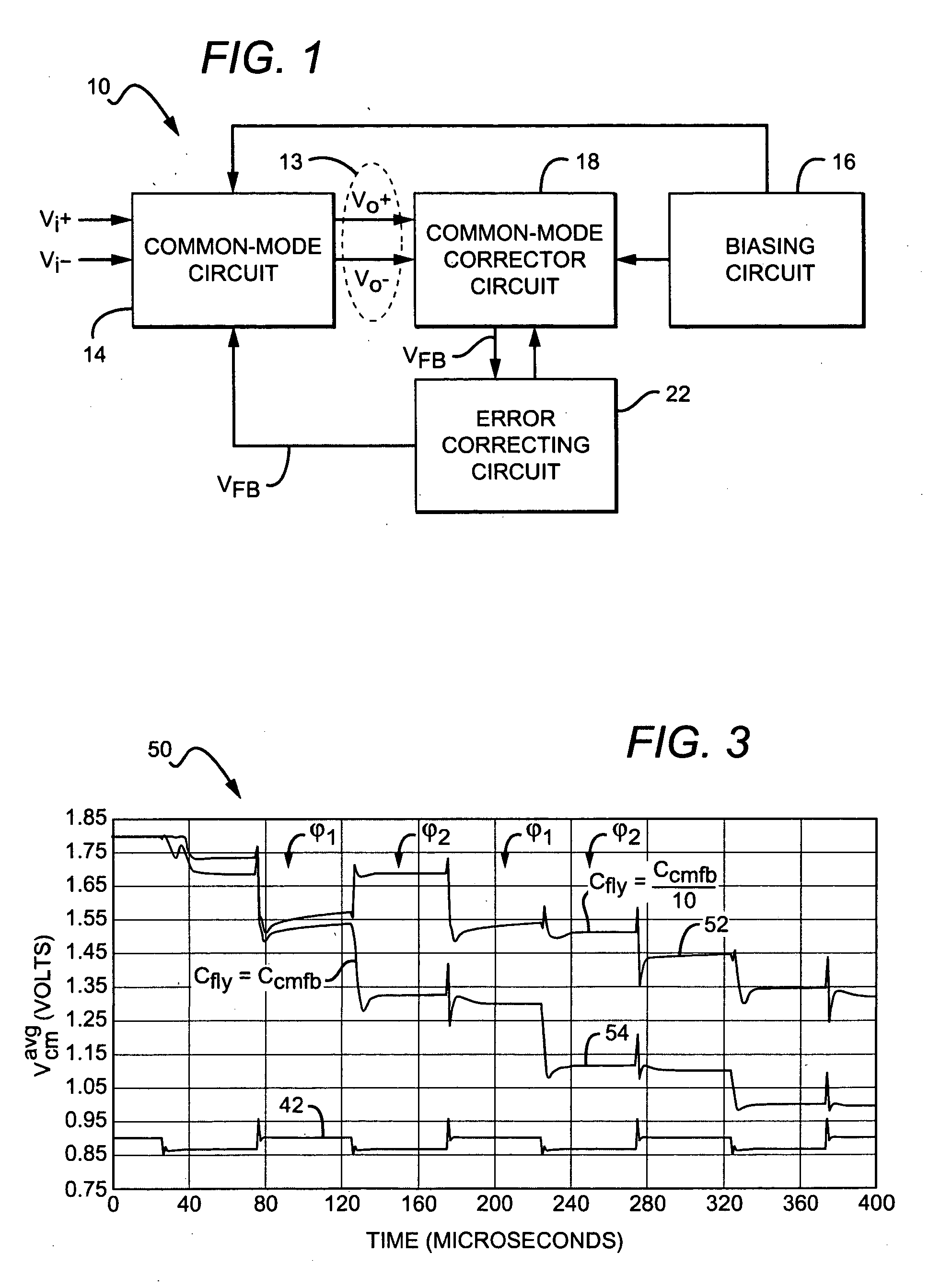

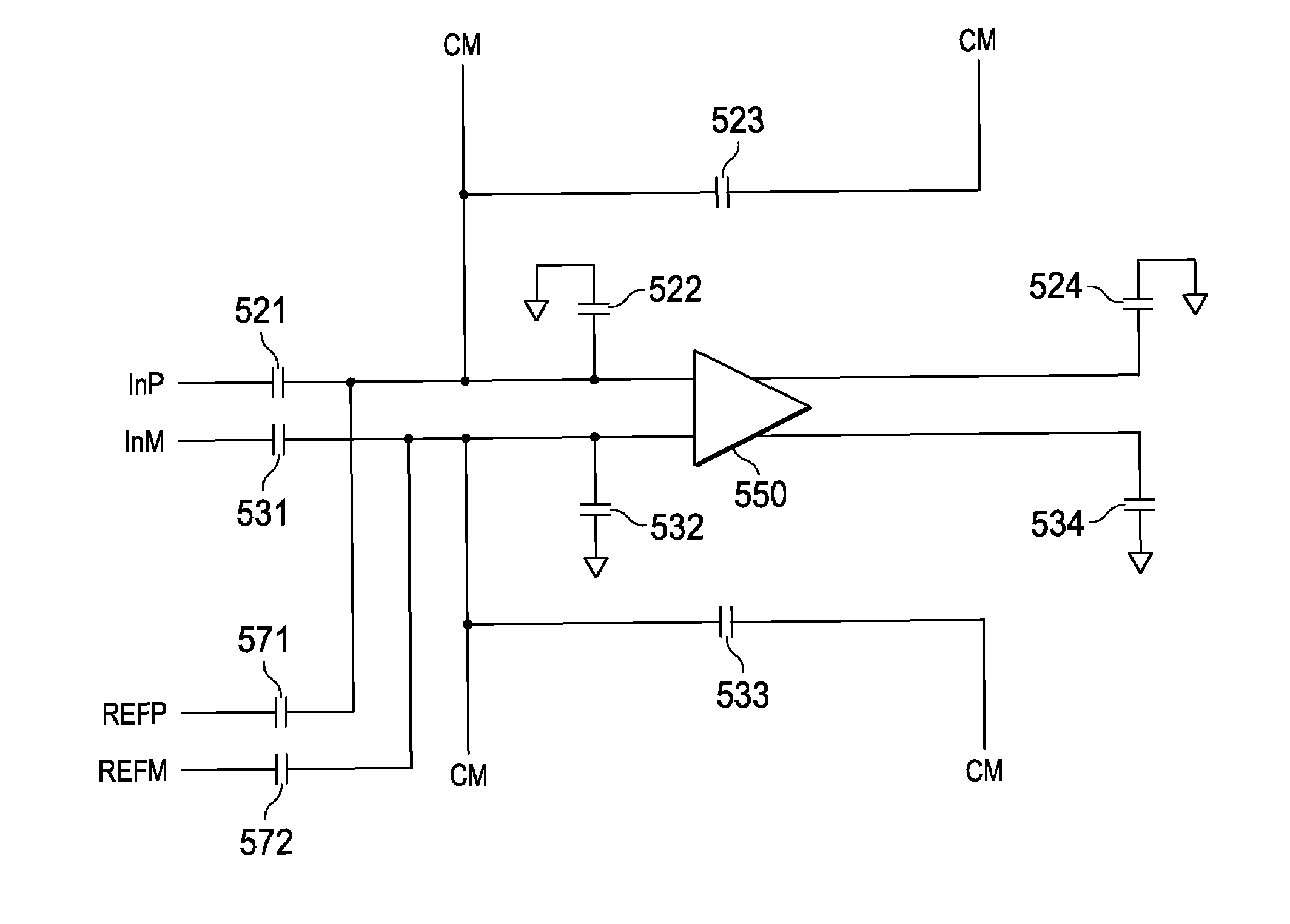

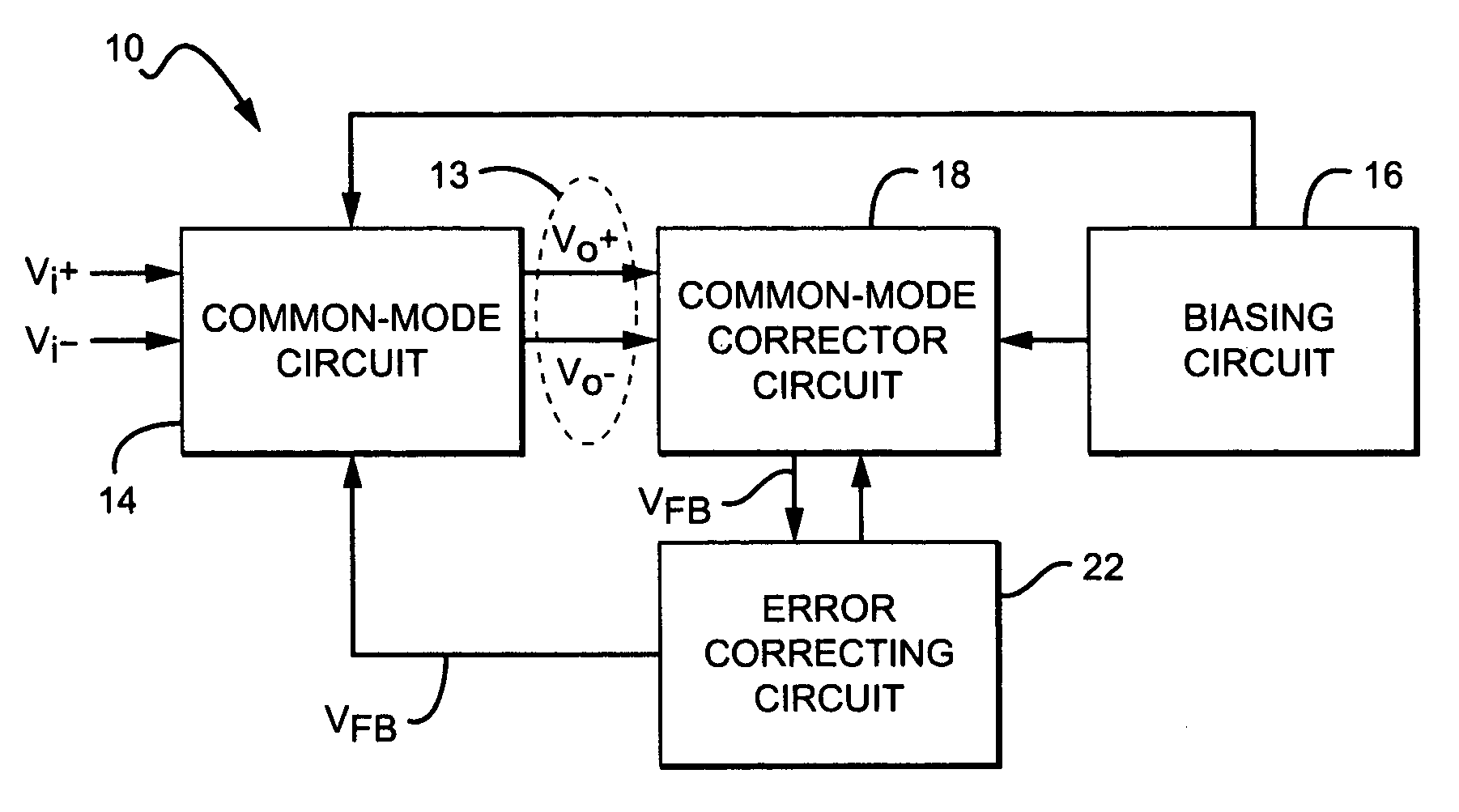

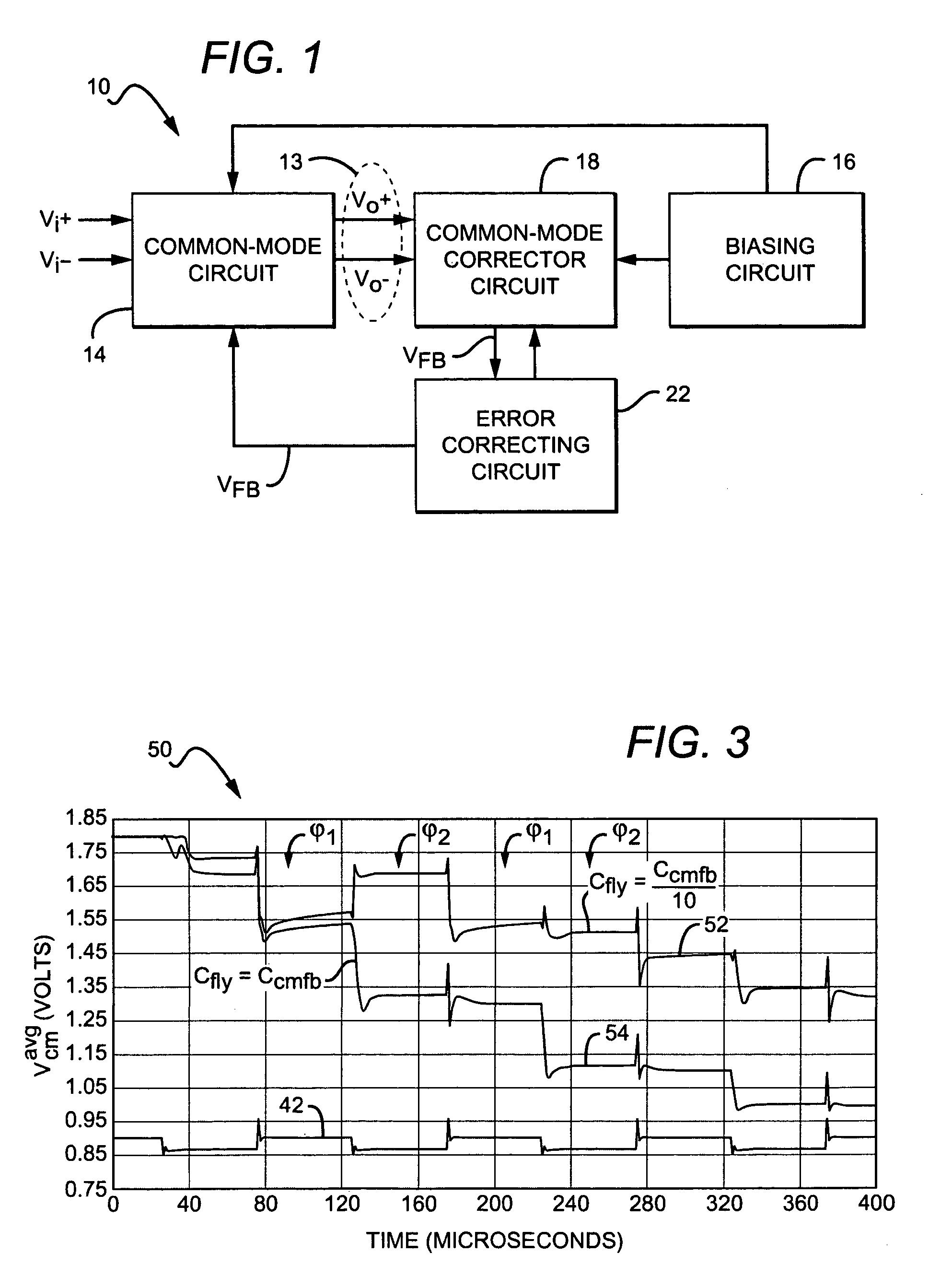

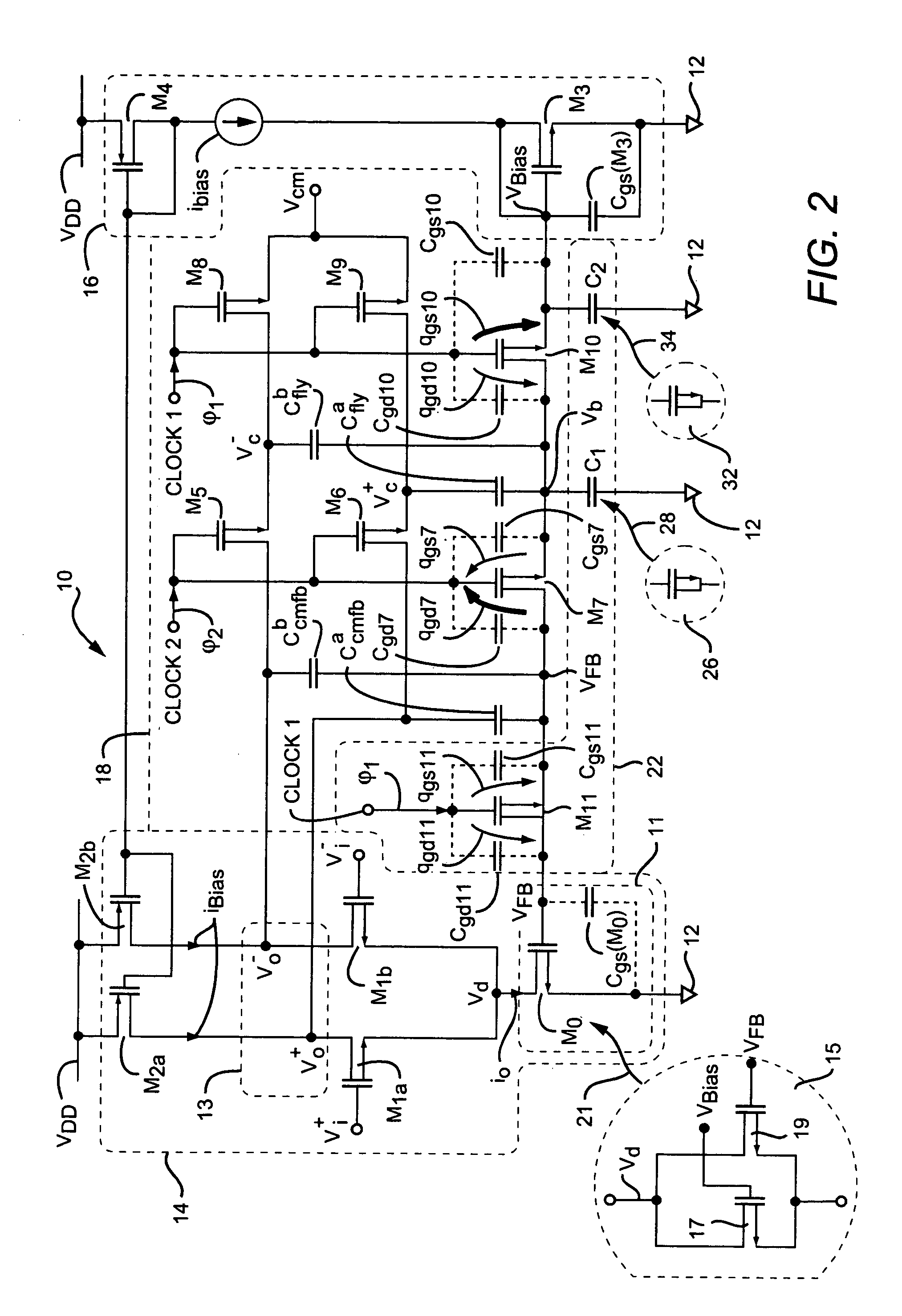

Switched capacitor circuit with reduced common-mode variations

ActiveUS20050134380A1Amplifier modifications to raise efficiencyDifferential amplifiersEngineeringImpedance matching

A circuit with a common-mode dual output includes a feedback circuit connected to alternate the states of the dual output between an average output level and a desired common-mode level. The difference between the average and desired levels is proportional to a signal offset level. An impedance matching circuit is connected to the feedback circuit to adjust the signal offset level.

Owner:ANALOG DEVICES INC

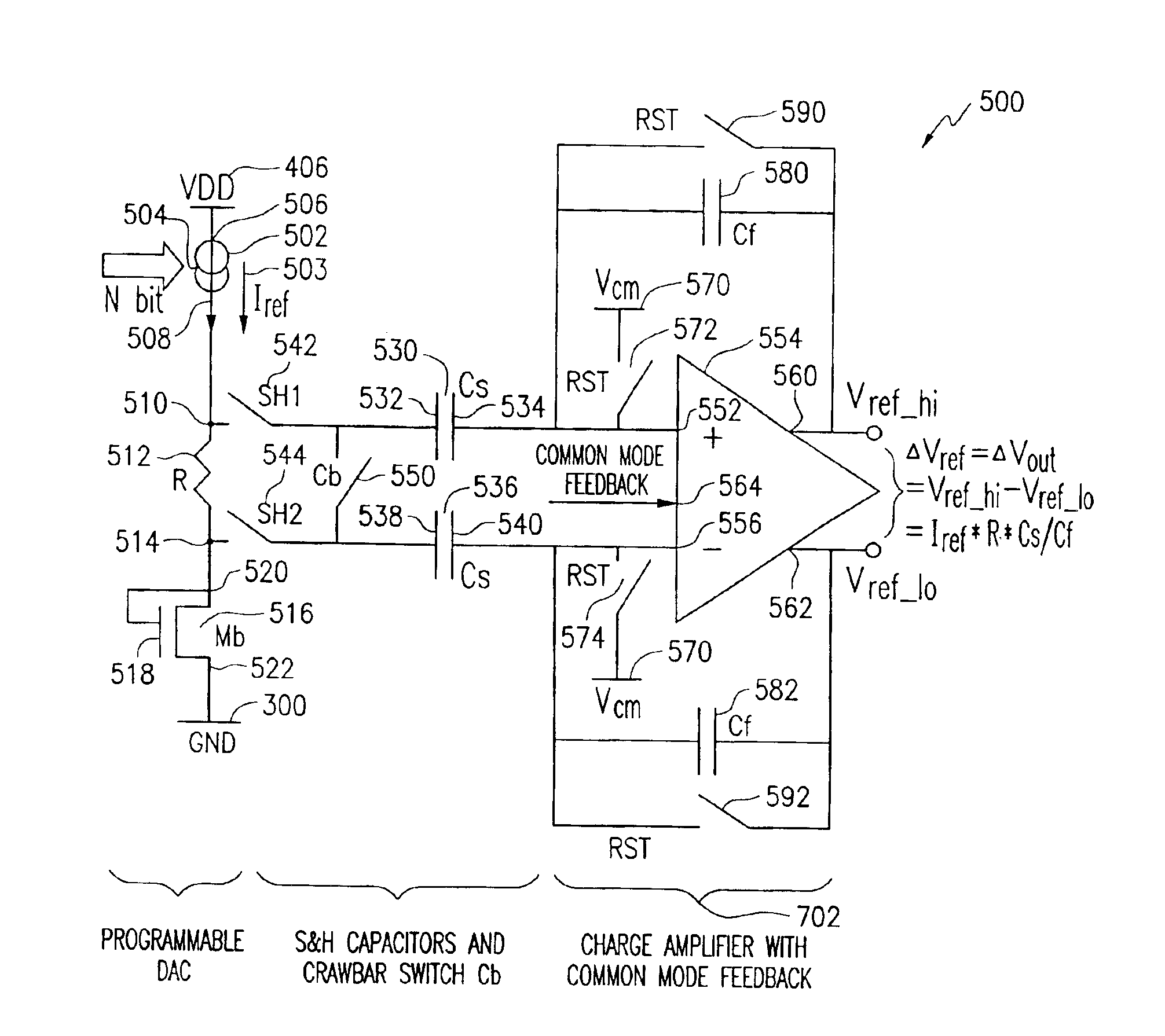

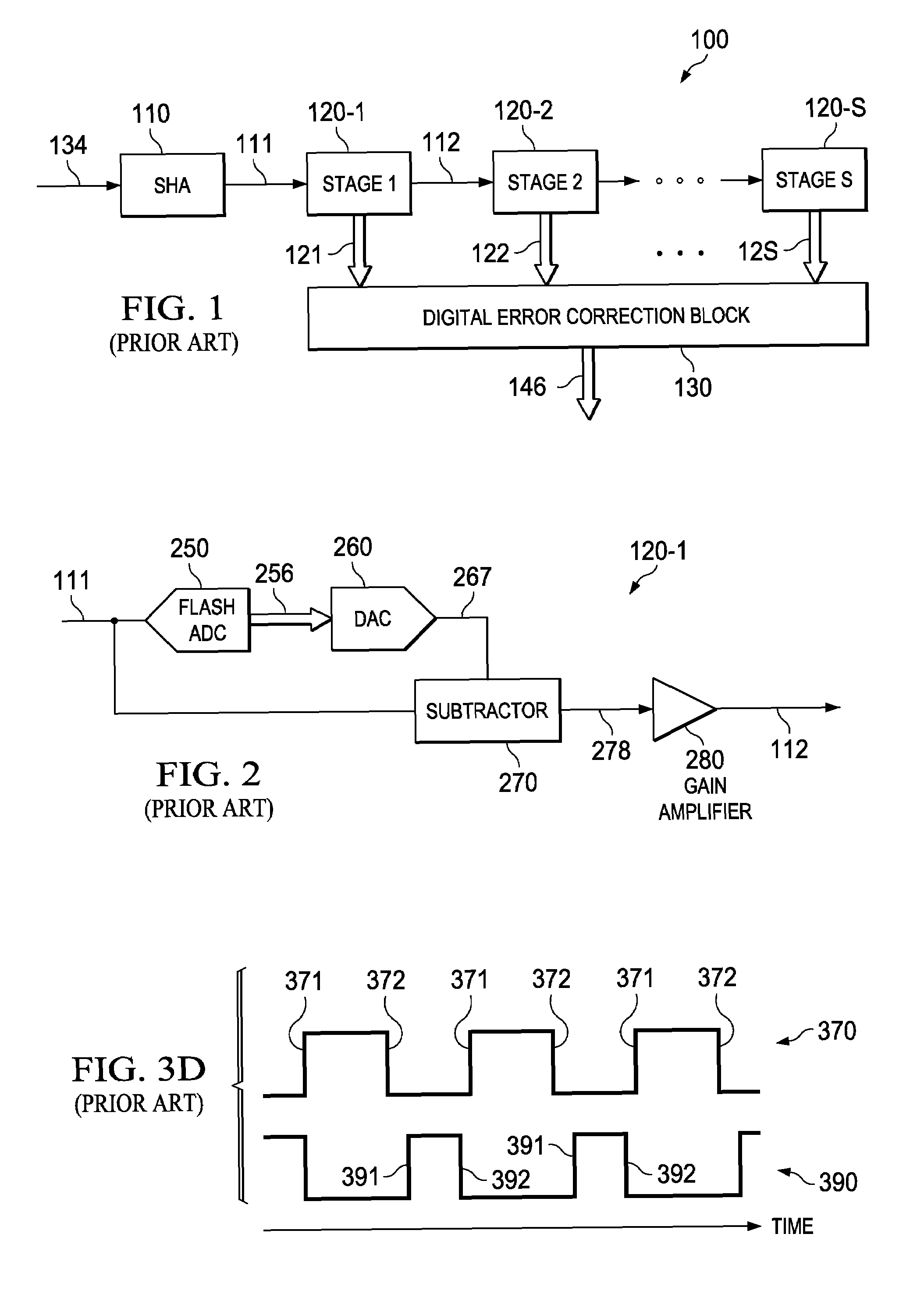

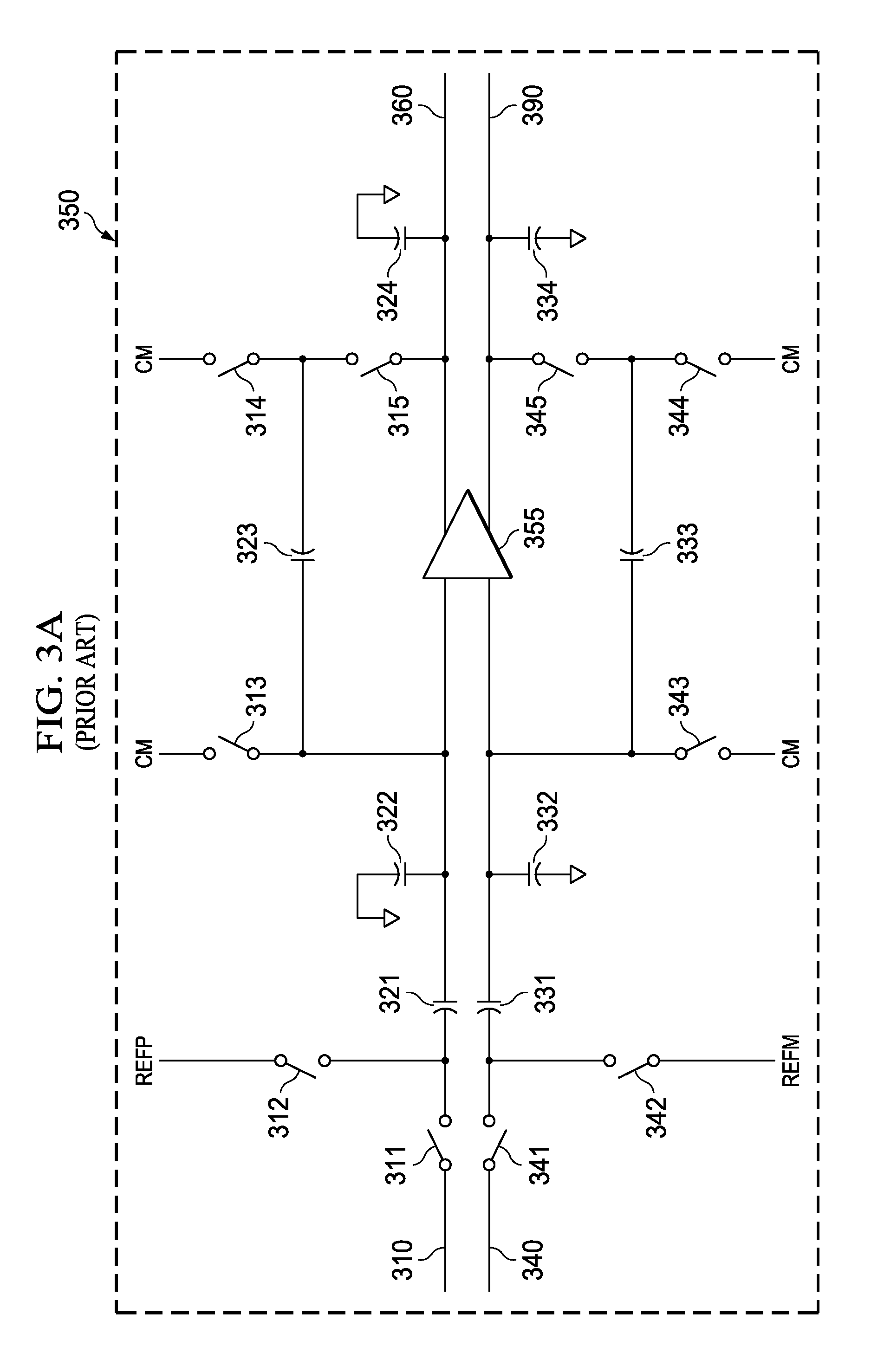

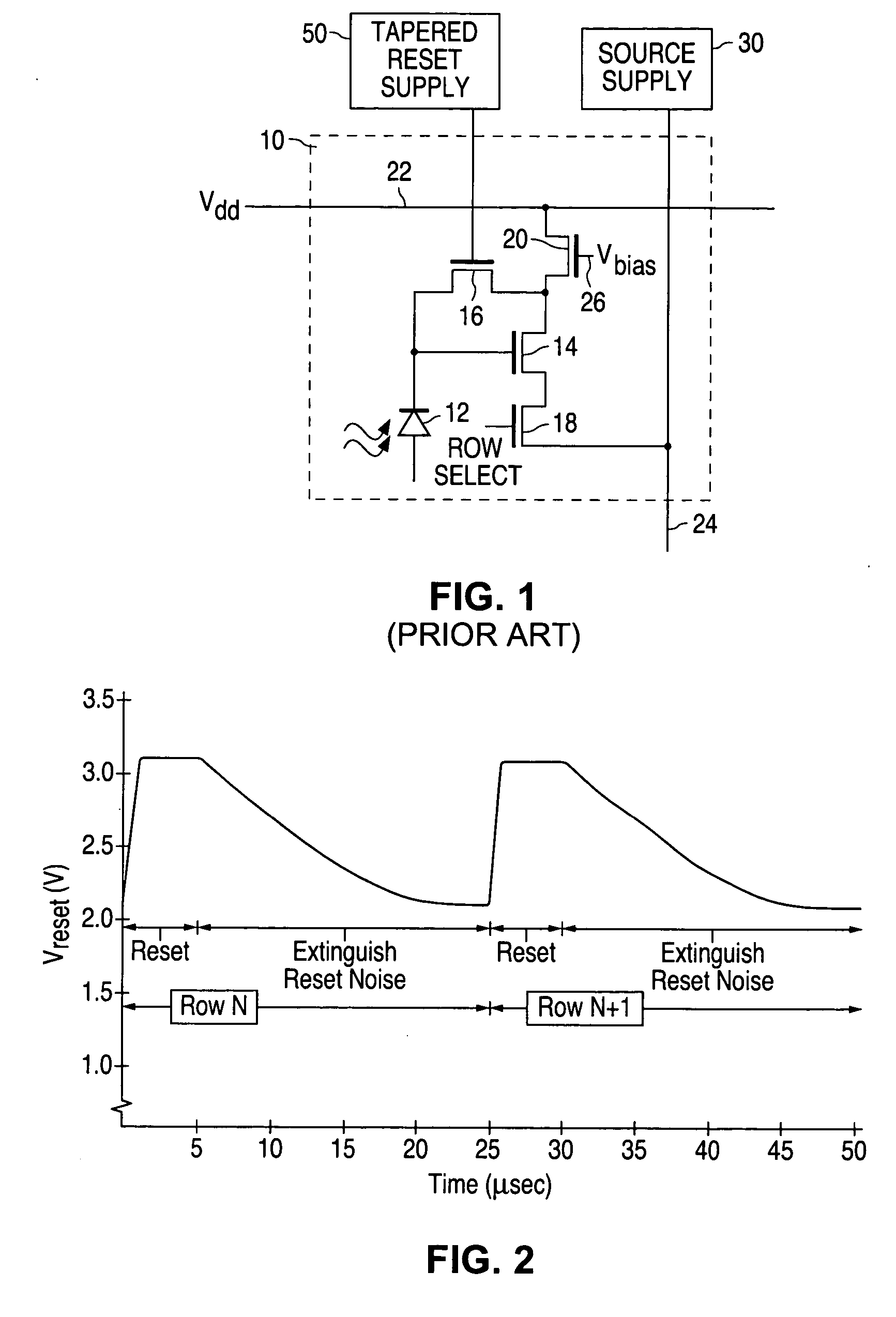

Fully differential reference driver for pipeline analog to digital converter

InactiveUS6909391B2Electric signal transmission systemsAnalogue-digital convertersCapacitanceVoltage reference

An analog to digital conversion (ADC) circuit is disclosed including a fully differential reference voltage source. The reference voltage source includes a programmable current supply adapted to drive a programmed current through a resistor so as to establish an initial reference voltage. The initial reference voltage is sampled onto a capacitive network during a first sampling time interval. The capacitive network is coupled to a differential input of a fully differential amplifier, and maintained at a differential output of the differential amplifier during a second output time interval. An output coupling between the differential output and differential input of the differential amplifier acts to maintain stability of the output voltage during the output time interval.

Owner:APTINA IMAGING CORP

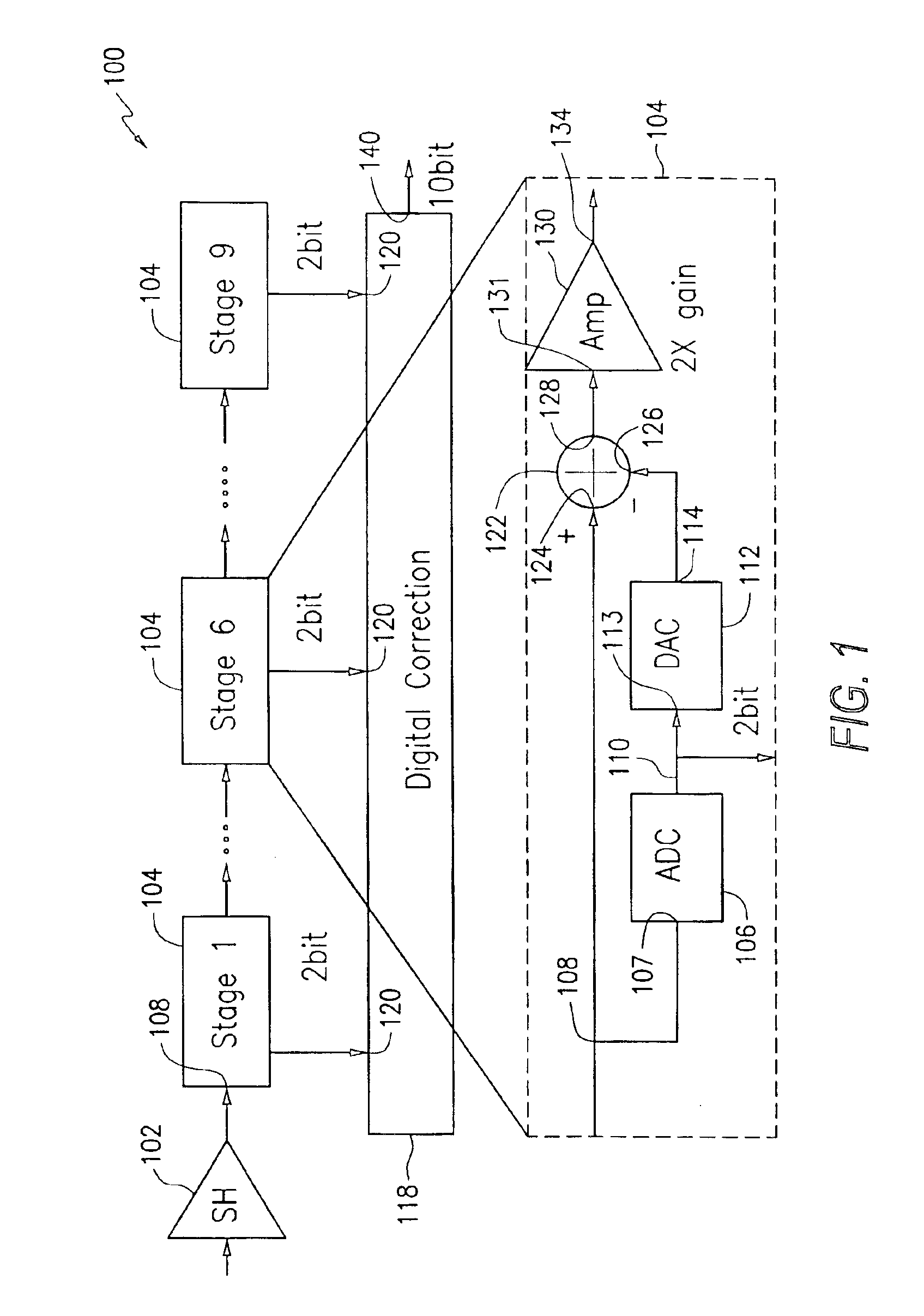

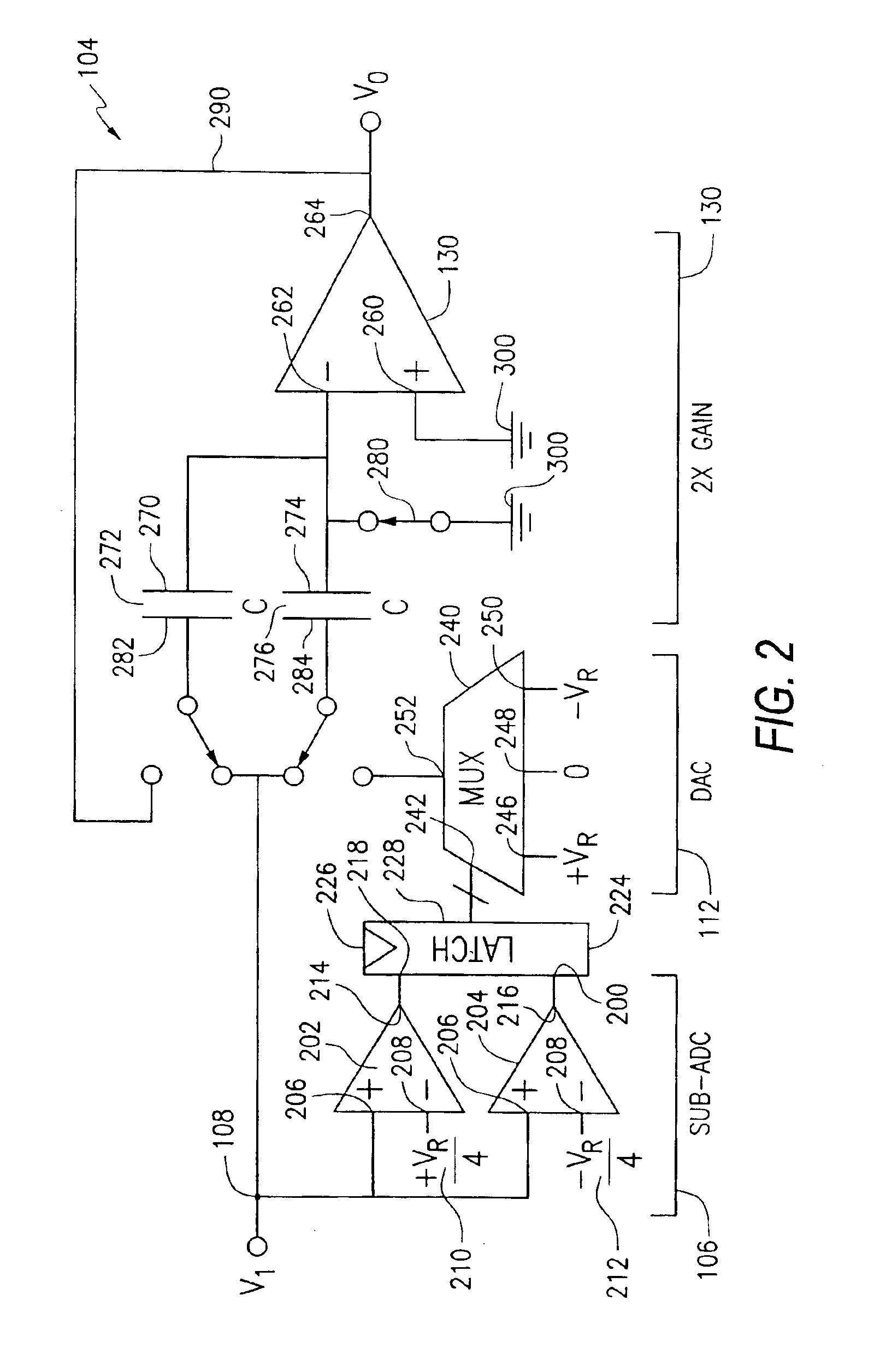

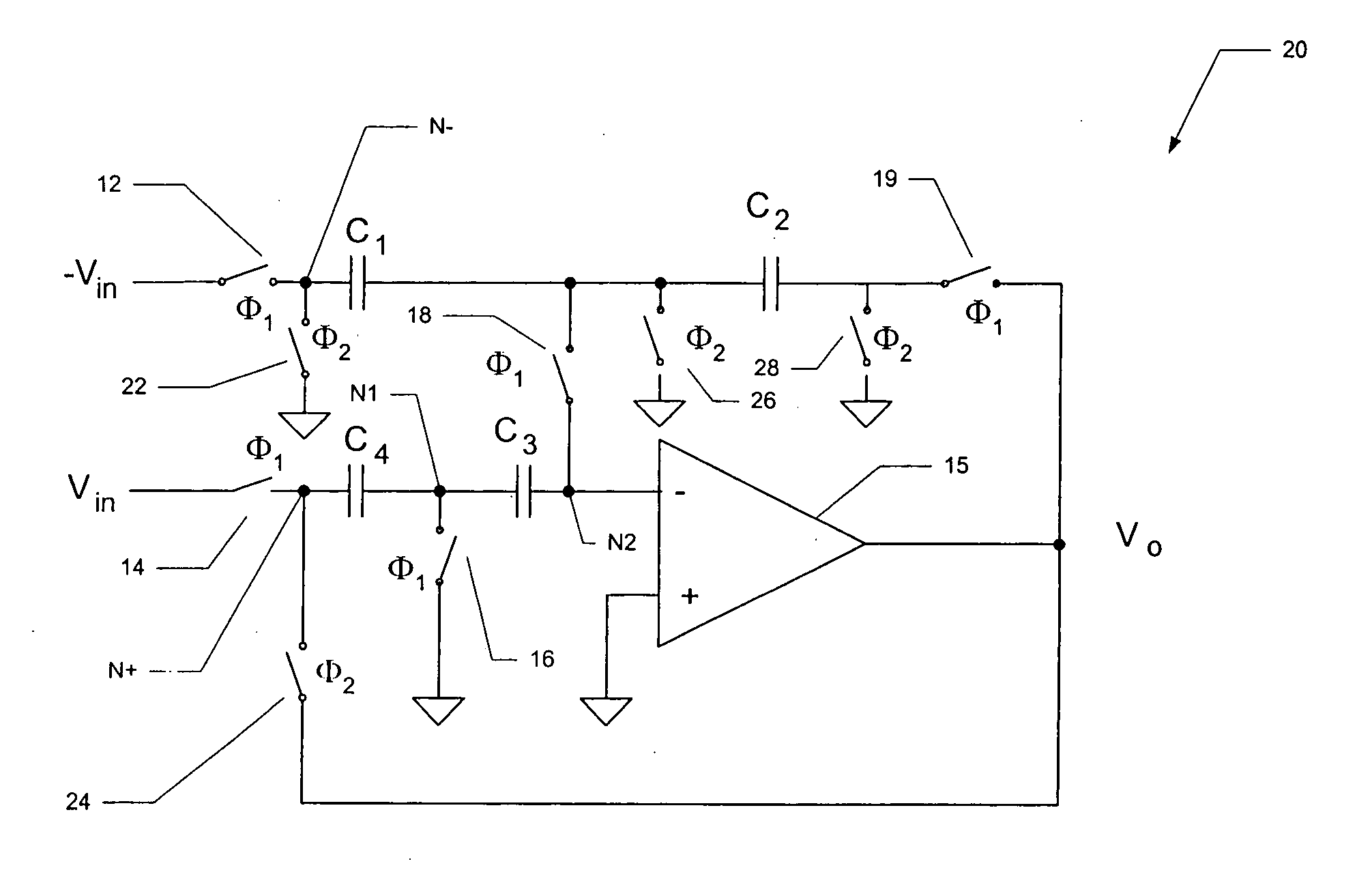

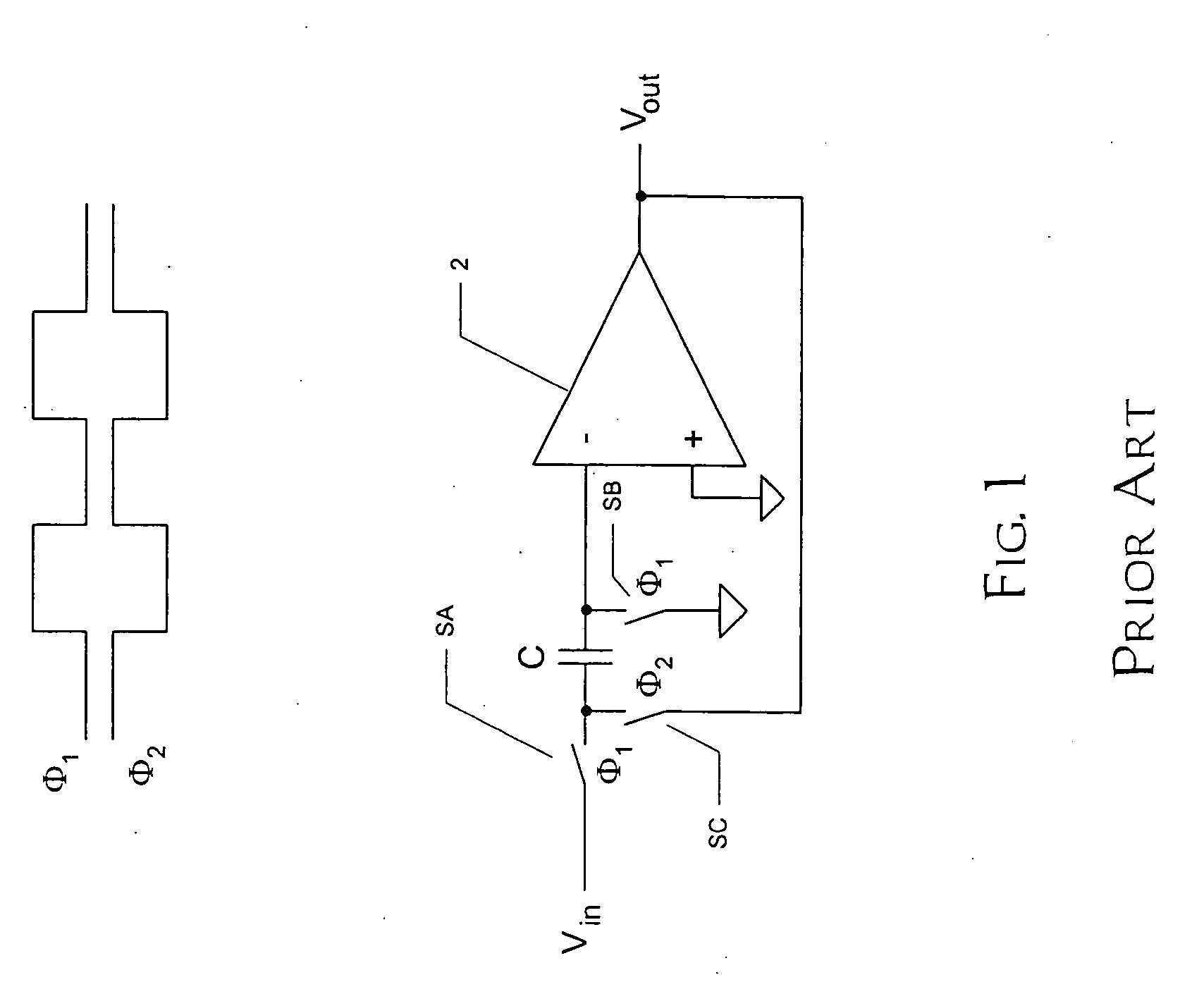

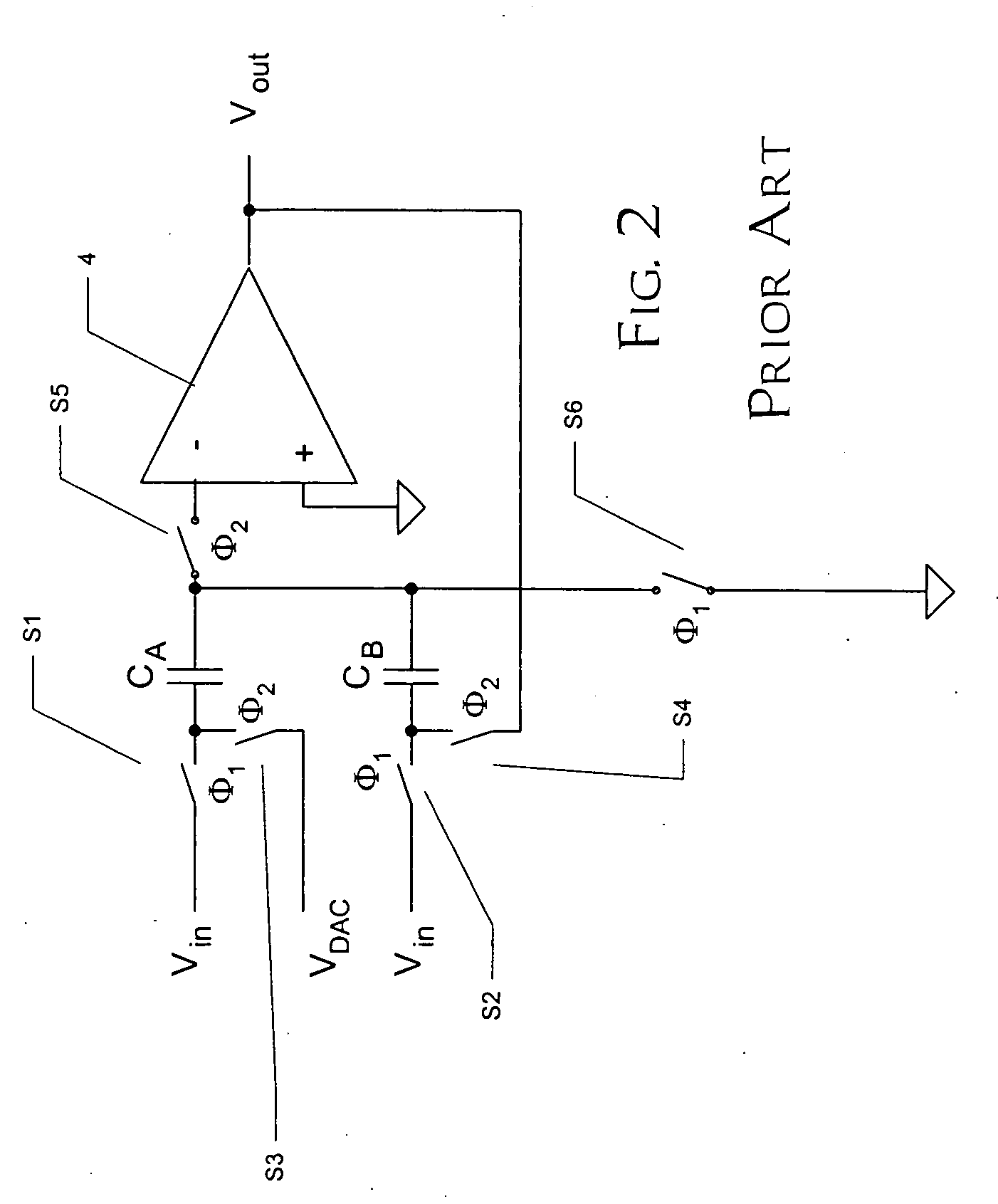

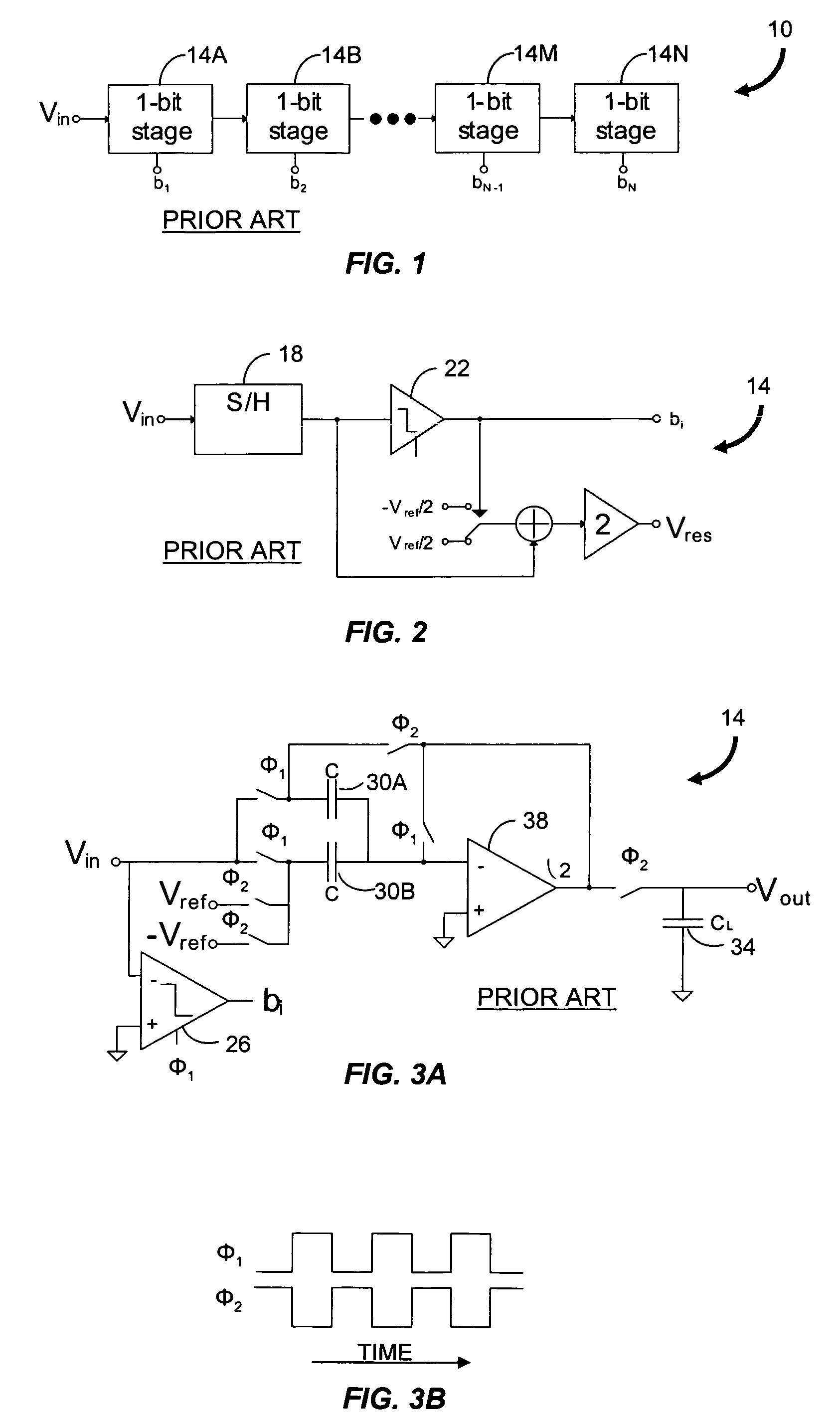

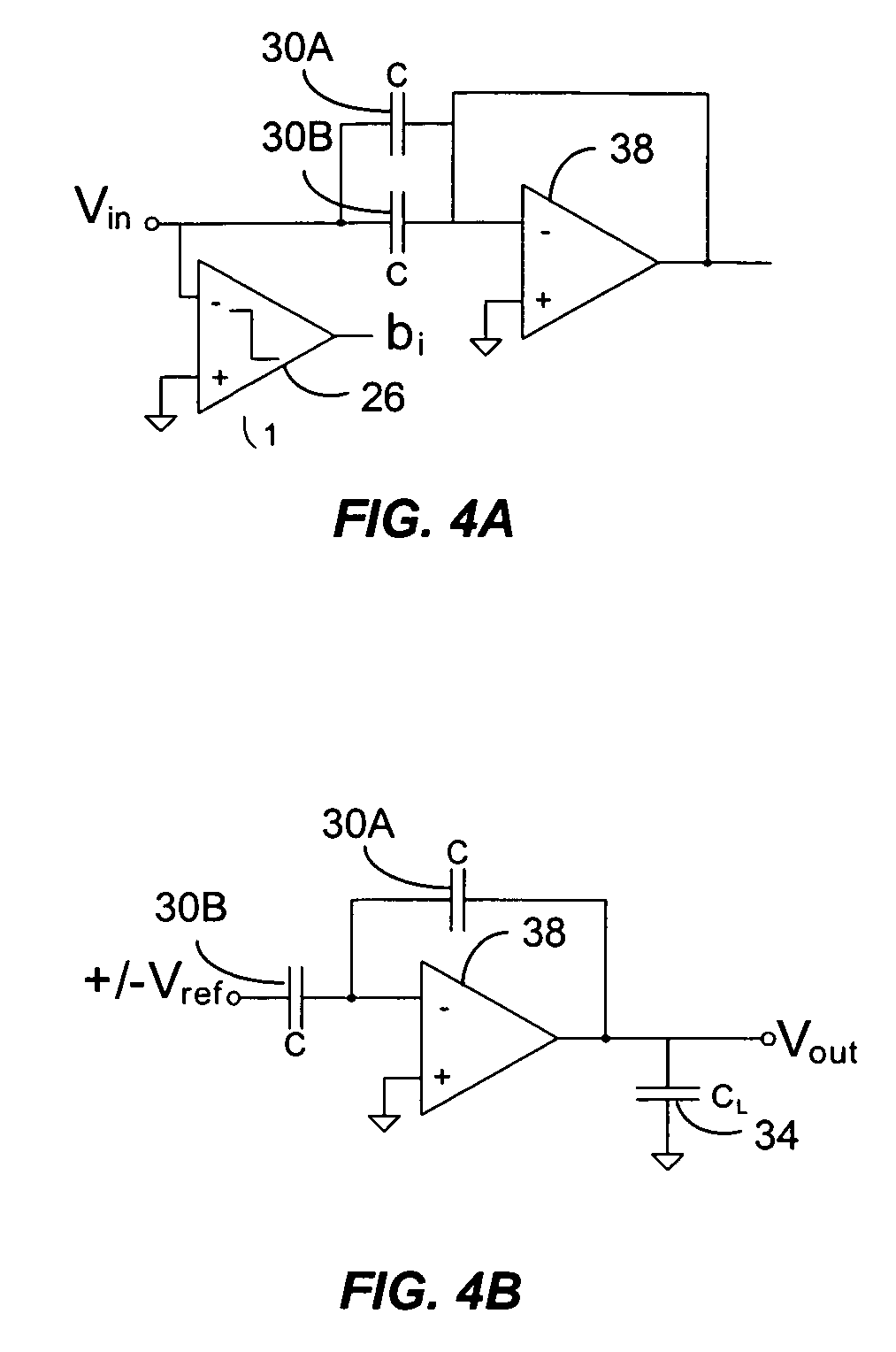

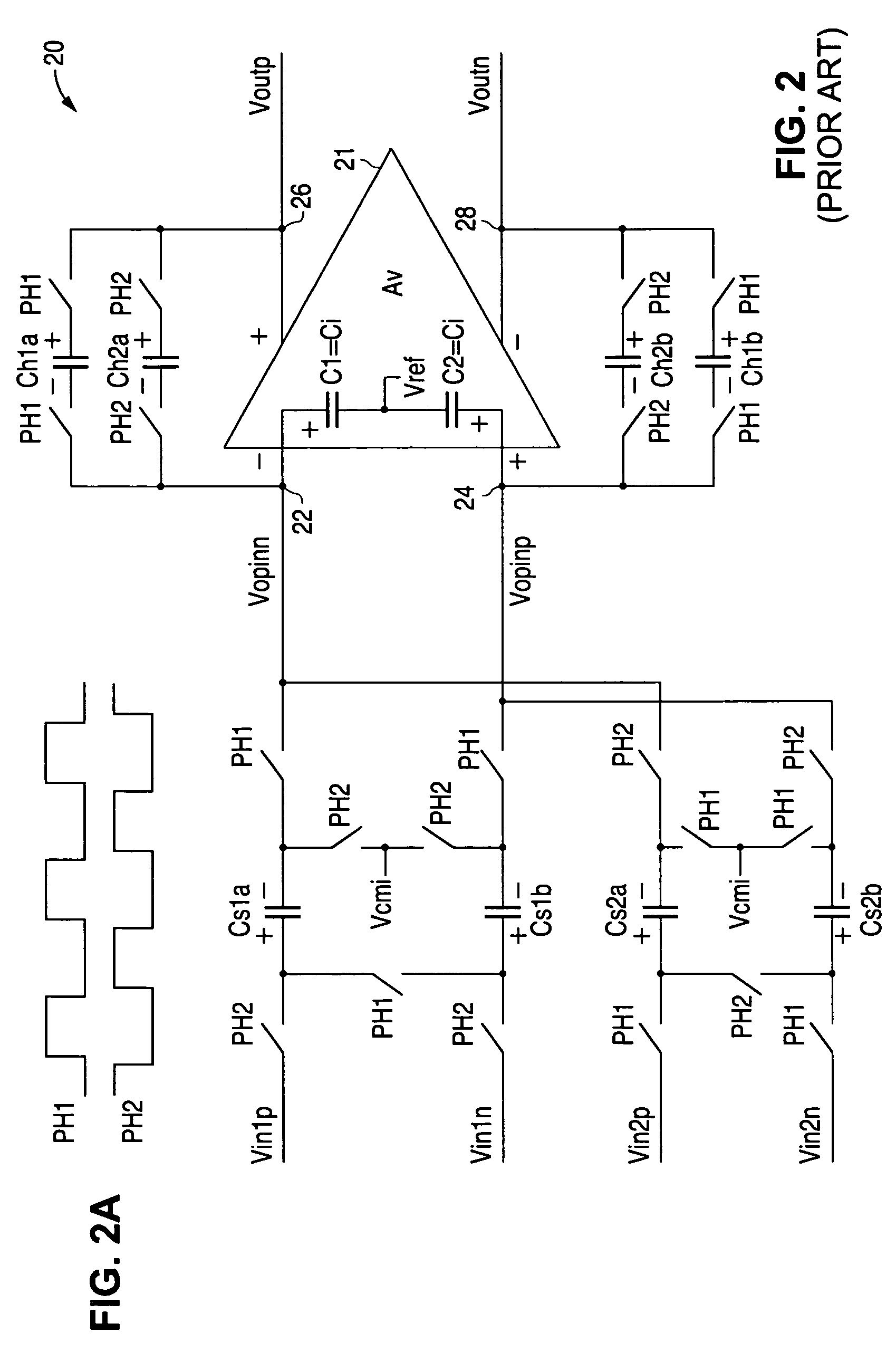

Switched-capacitor circuits with reduced finite-gain effect

ActiveUS20060071709A1Minimize impactGood effectAmplifier modifications to raise efficiencyDifferential amplifiersCapacitanceAudio power amplifier

Operational amplifier circuits (20, 30) including error capacitors (C3, C13) for storing finite gain effect error voltages for correction of output voltages of the circuits (20, 30), are disclosed. The circuits (20, 30) are operated in a sample clock phase to produce an approximation of the output voltage, using negative polarity versions of the input voltages to the circuit. The approximate output voltage is used to produce and store an error voltage, corresponding to the differential voltage at the input of the operational amplifier (15, 25), relative to virtual ground. This error voltage is then subtracted from the input voltage applied in the operate clock phase, to correct for the finite gain effect. A pipelined analog-to-digital converter (50) using the disclosed operational amplifier circuits (20, 30) is also disclosed.

Owner:TEXAS INSTR INC

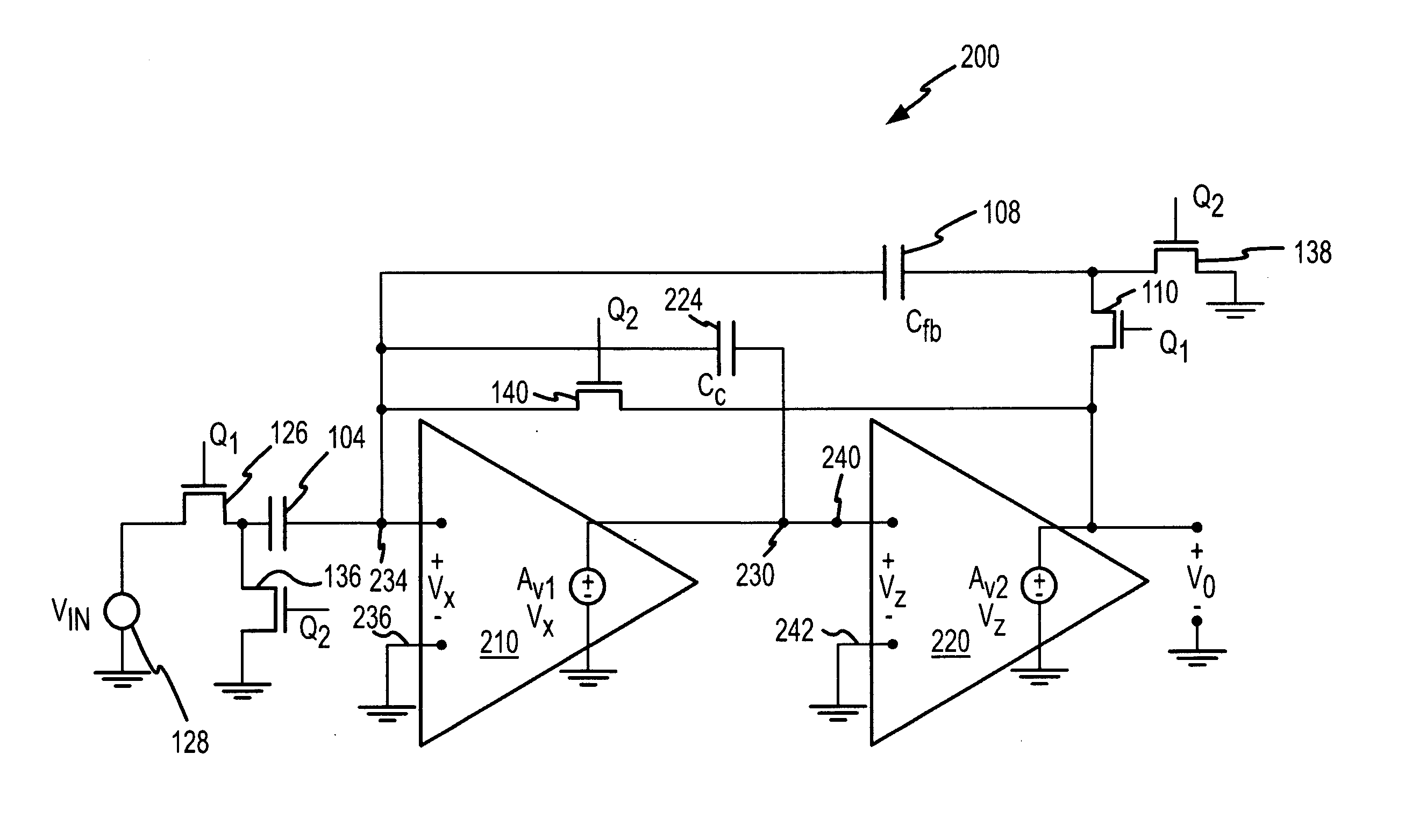

Switched capacitor amplifier with higher gain and improved closed-loop gain accuracy

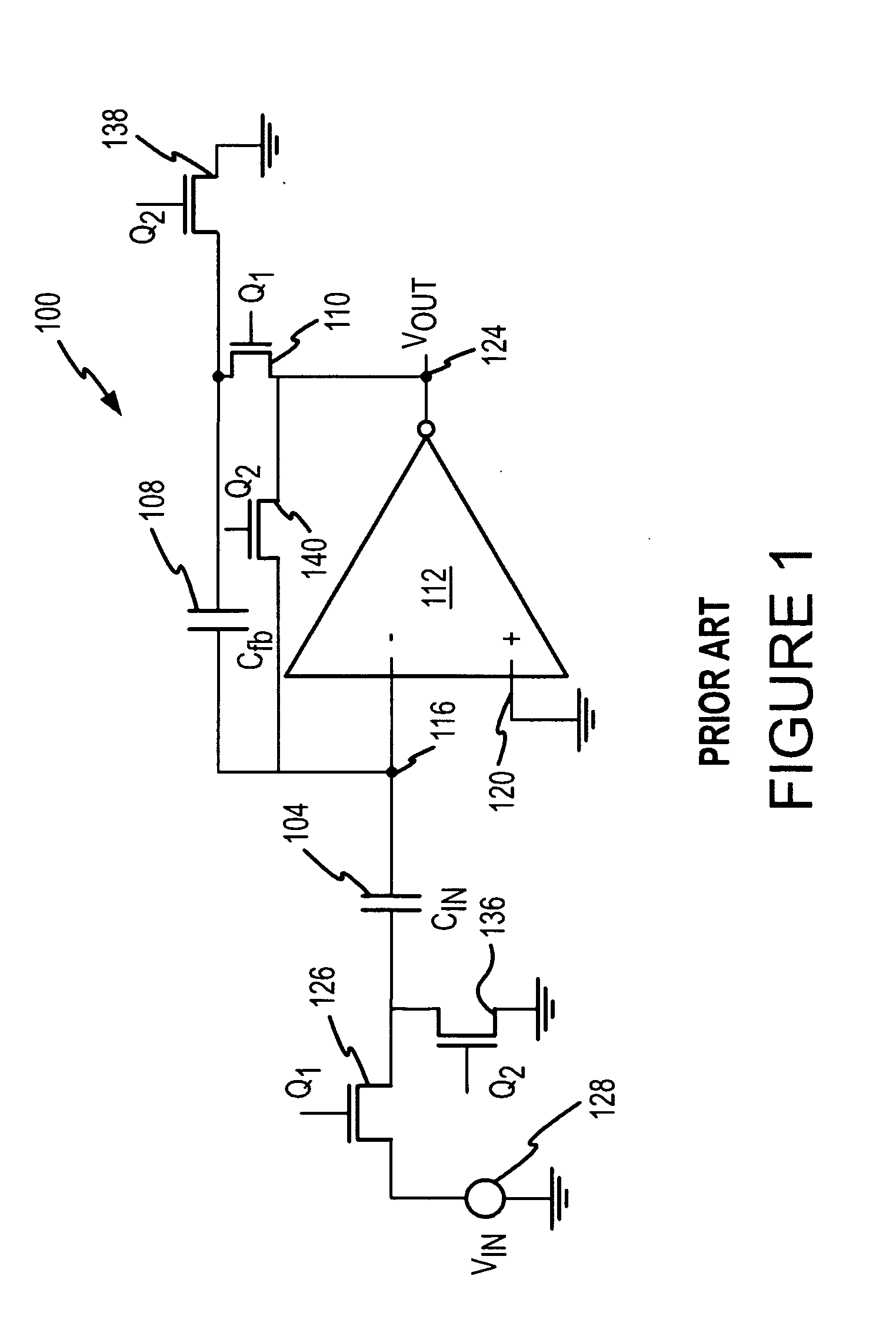

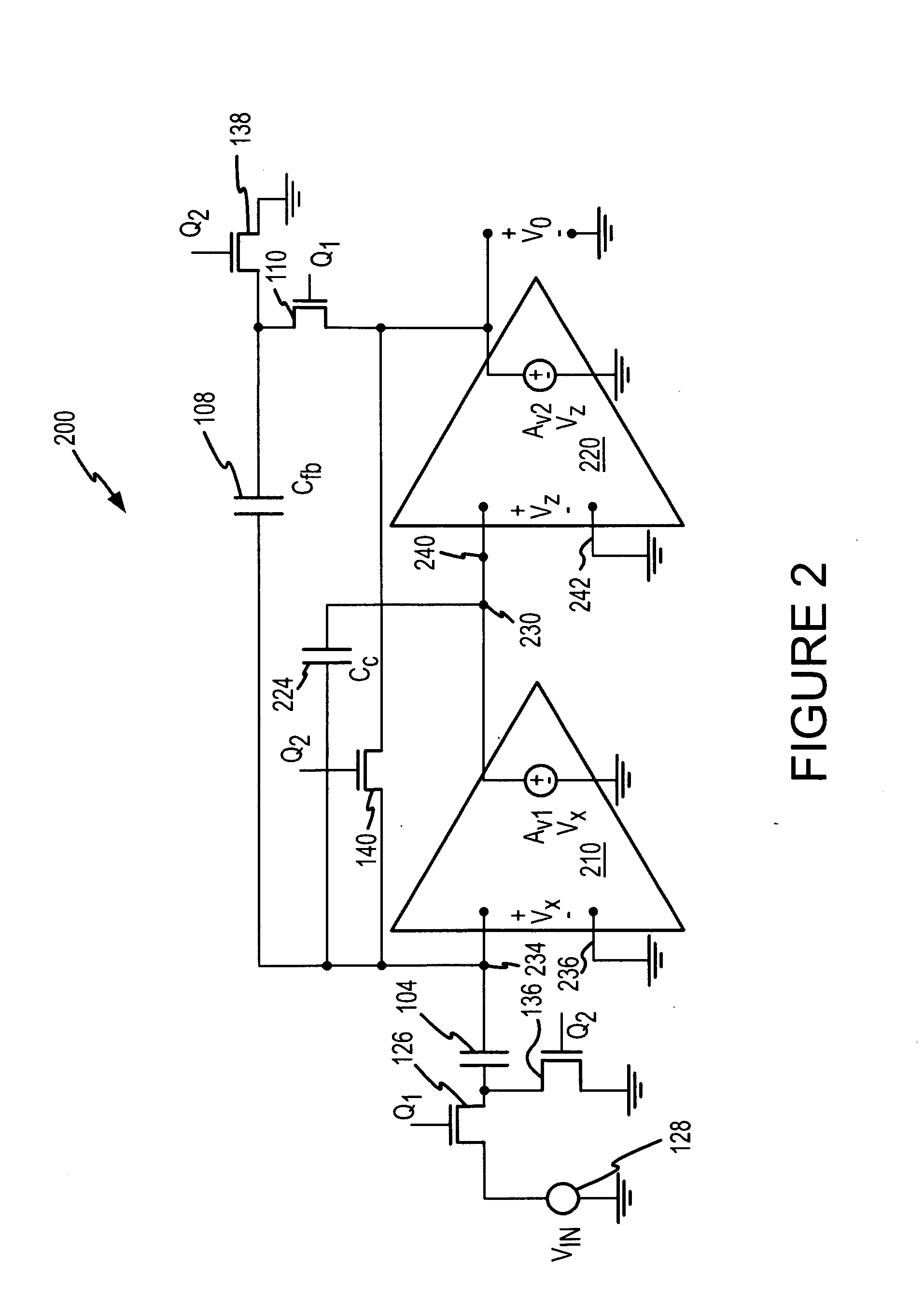

ActiveUS20080186093A1Negative-feedback-circuit arrangementsAmplifier combinationsCapacitanceAudio power amplifier

A switched capacitor CMOS amplifier uses a first stage non-inverting CMOS amplifier driving a second stage inverting CMOS amplifier. The first stage amplifier is provided with positive feedback to substantially increase the gain of the first stage amplifier. In the described examples, the positive feedback is provided either by connecting a capacitor from the output to the input of the first stage amplifier or by connecting a shunt transistor in parallel with an input transistor and driving the transistor from the output of the first stage amplifier. The substantially increased gain resulting from the positive feedback allows the gain of the switched capacitor amplifier to be set by the ratio of the capacitance of an input capacitor to the capacitance of a feedback capacitor. The amplifier also includes switching transistors for periodically discharging the input capacitor and the feedback capacitor.

Owner:MICRON TECH INC

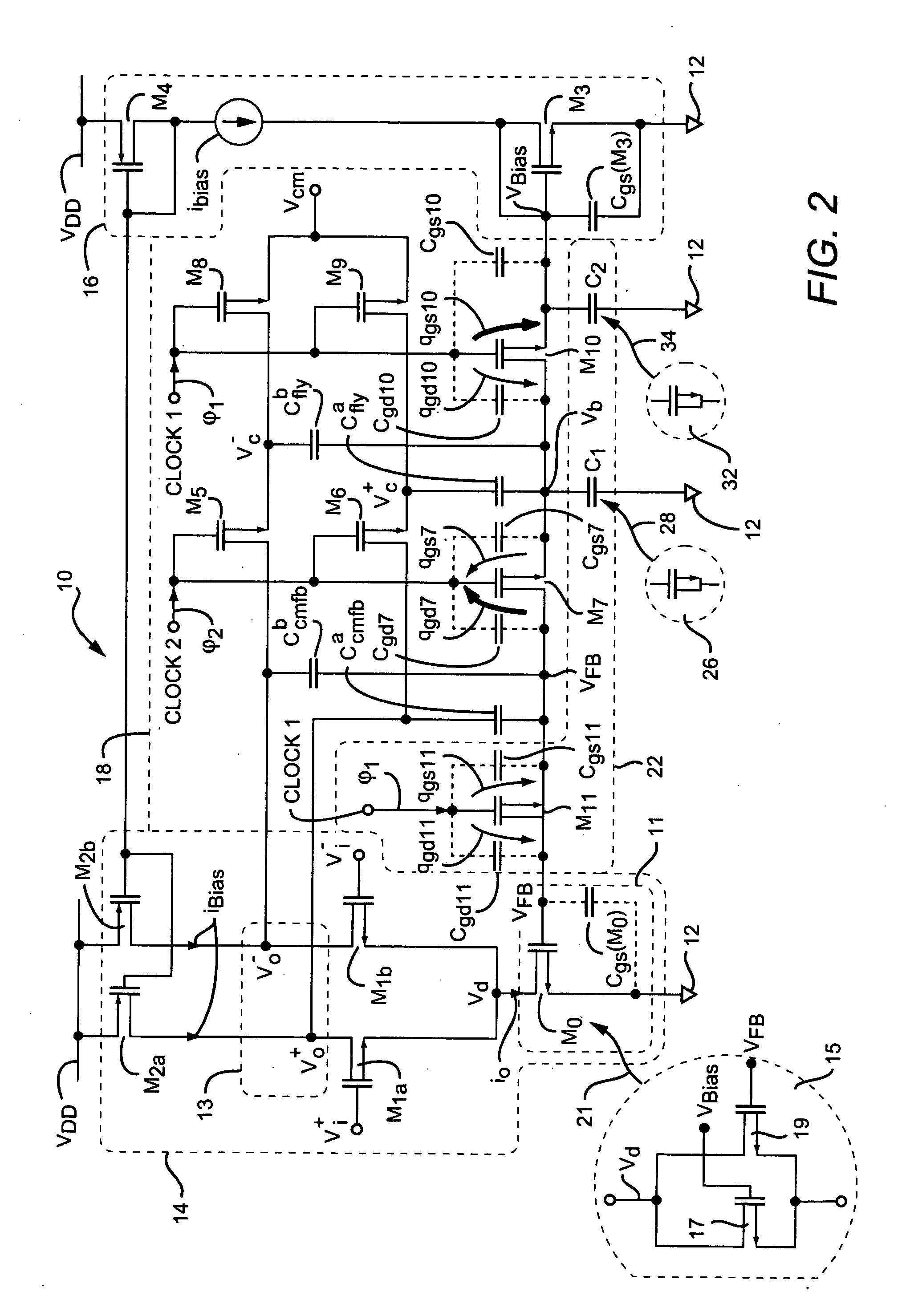

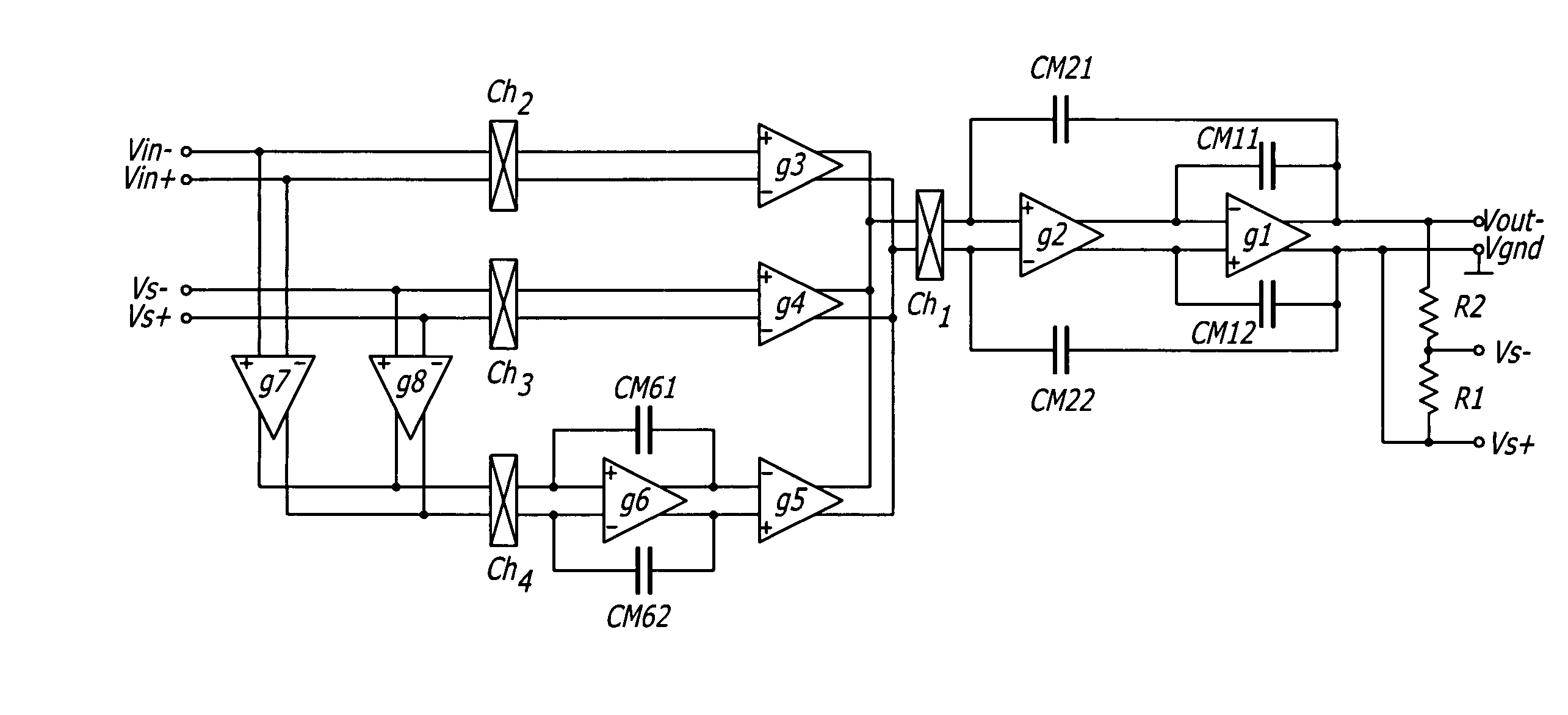

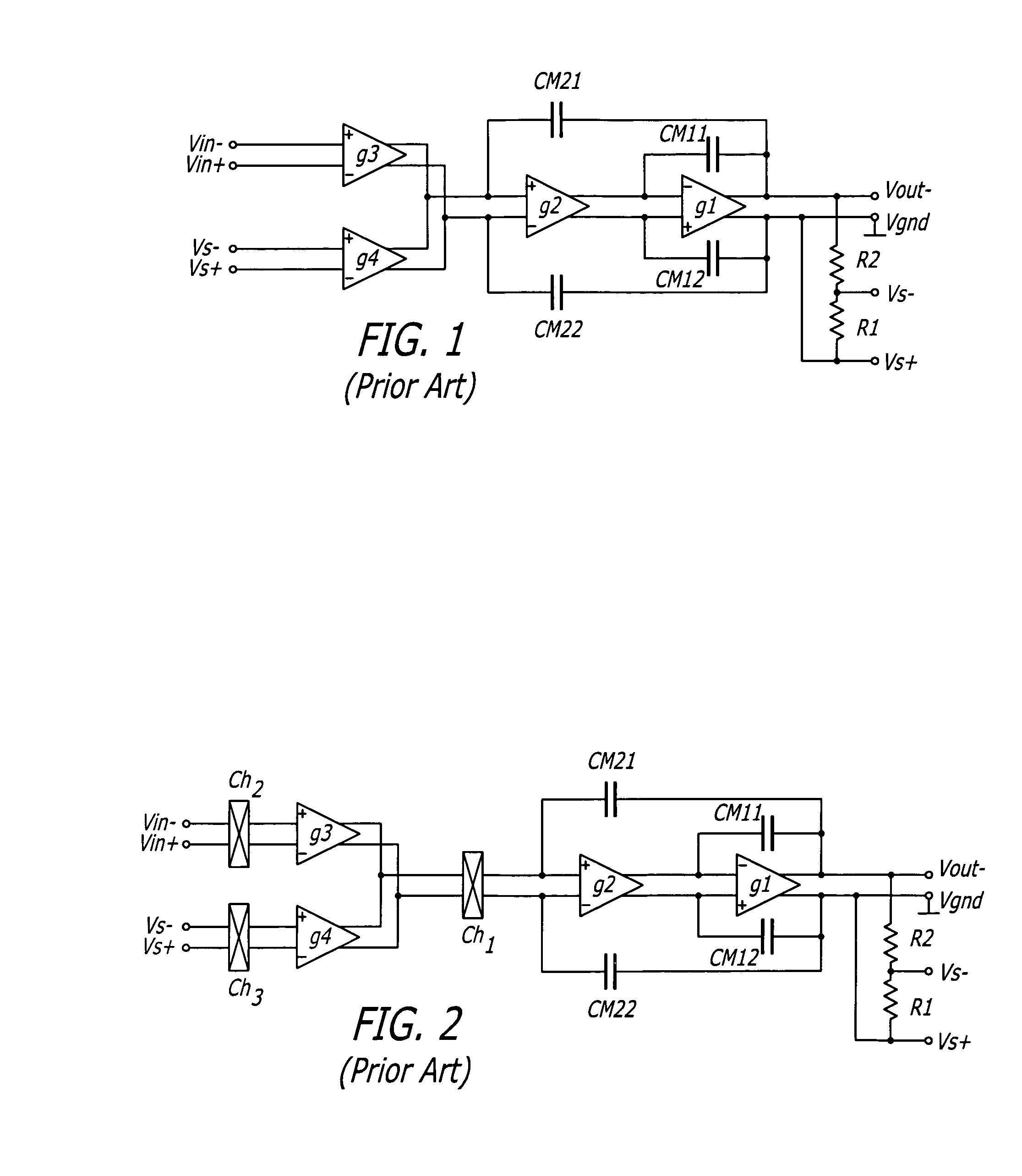

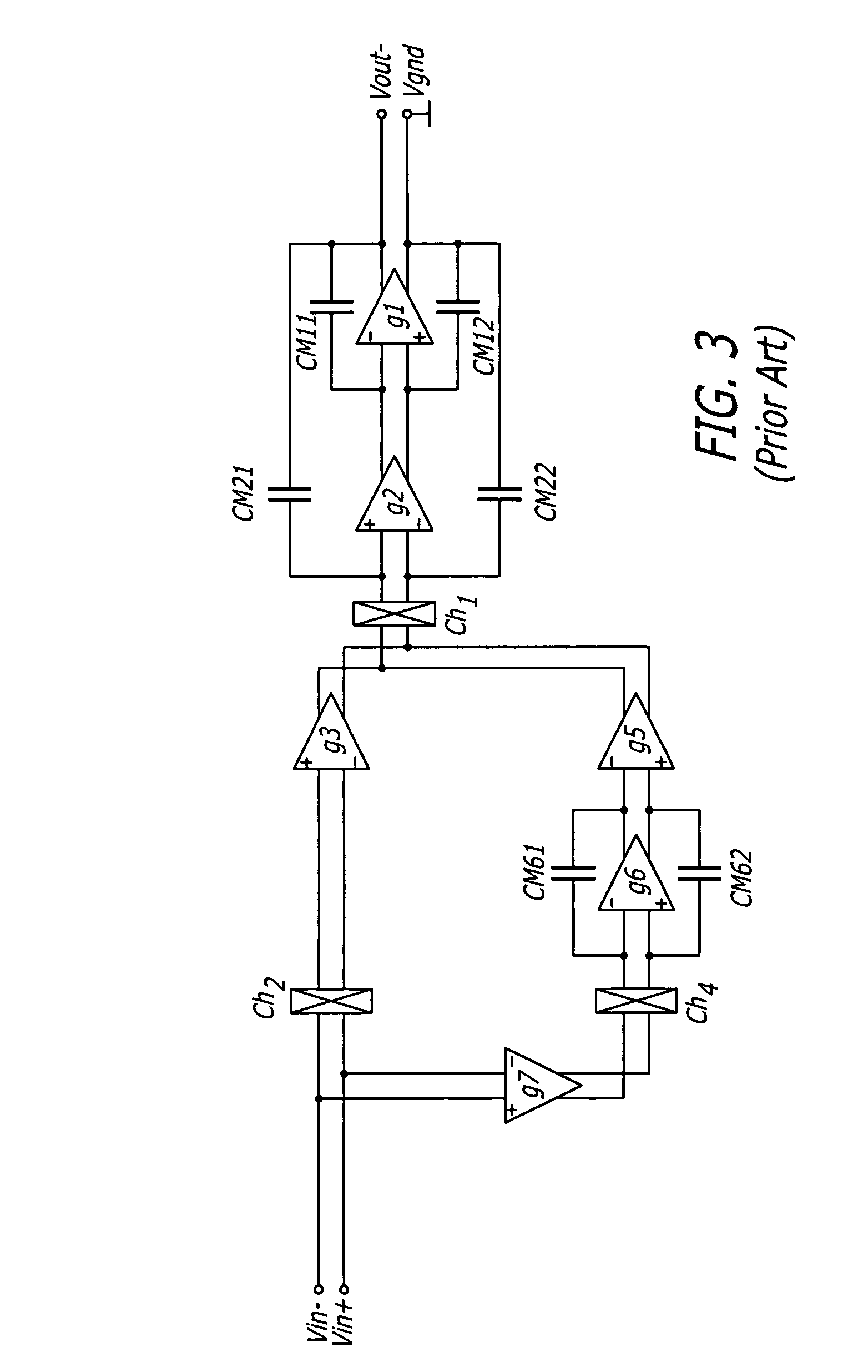

Chopper chopper-stabilized instrumentation and operational amplifiers

ActiveUS7132883B2Amplifier modifications to raise efficiencyElectronic switchingAudio power amplifierInstrumentation amplifier

Chopper chopper-stabilized instrumentation and operational amplifiers having ultra low offset. The instrumentation amplifiers use current-feedback, and include, in addition to a main chopper amplifier chain, a chopper stabilized loop for correcting for the offset of the input amplifiers for the input signal and for receiving the feedback of the output voltage sense signal. Additional loops, which may include offset compensation and autozeroing loops, may be added to compensate for offsets in the chopper stabilized loop for correcting for the offset of the input amplifiers. Similar compensation is disclosed for decreasing the offset in operational amplifiers.

Owner:MAXIM INTEGRATED PROD INC

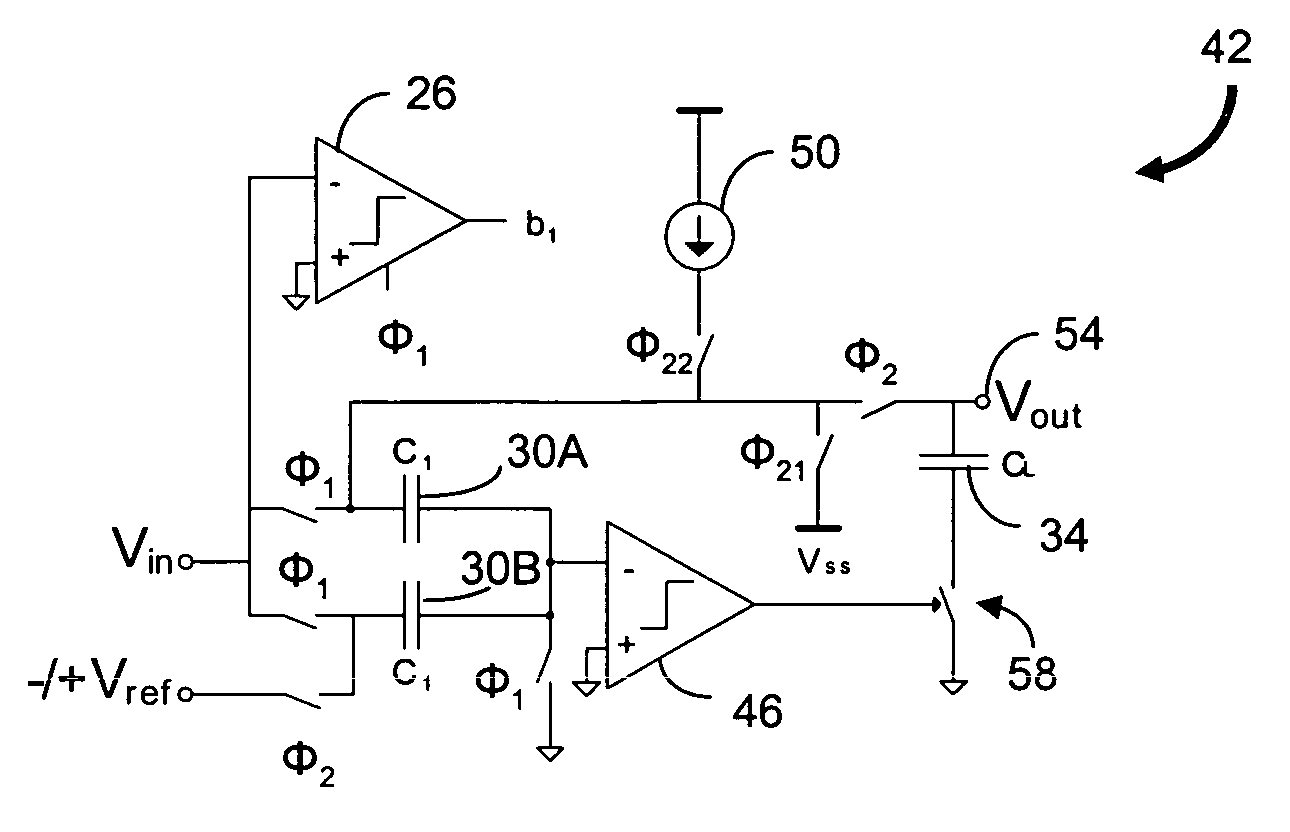

Comparator-based switched capacitor circuit for scaled semiconductor fabrication processes

ActiveUS7319425B2Electric signal transmission systemsAnalogue-digital convertersCapacitanceAudio power amplifier

Described is a switched capacitor circuit for performing an analog circuit function. Unlike conventional switched capacitor circuits employing operational amplifiers, the switched capacitor circuit uses a comparator and does not require direct feedback between the input and output of the comparator. The switched capacitor circuit includes a first and a second switched capacitance network, a comparator and a current source. The first switched capacitance network has an input terminal to receive a circuit input voltage during a first phase. The comparator has an input terminal in communication with the first switched capacitance network and an output terminal in communication with the second switched capacitance network through a switched terminal. The current source communicates with the switched capacitance networks and supplies a current to charge the networks during a second phase. The circuit can be used, for example, to provide high gain amplification in integrated circuits.

Owner:MASSACHUSETTS INST OF TECH

Reducing noise and/or power consumption in a switched capacitor amplifier sampling a reference voltage

ActiveUS7358801B2Amplifier modifications to reduce noise influenceAmplifier modifications to raise efficiencyAudio power amplifierSecondary stage

Owner:TEXAS INSTR INC

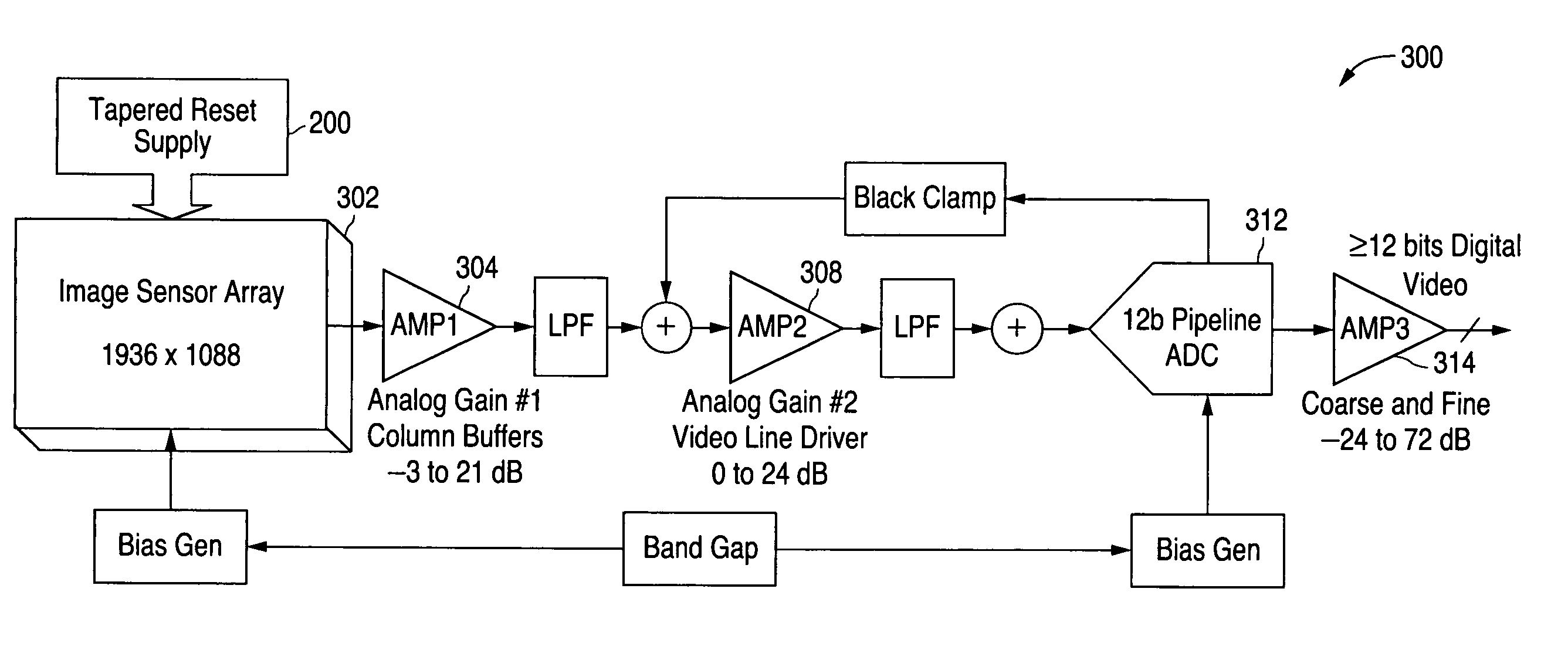

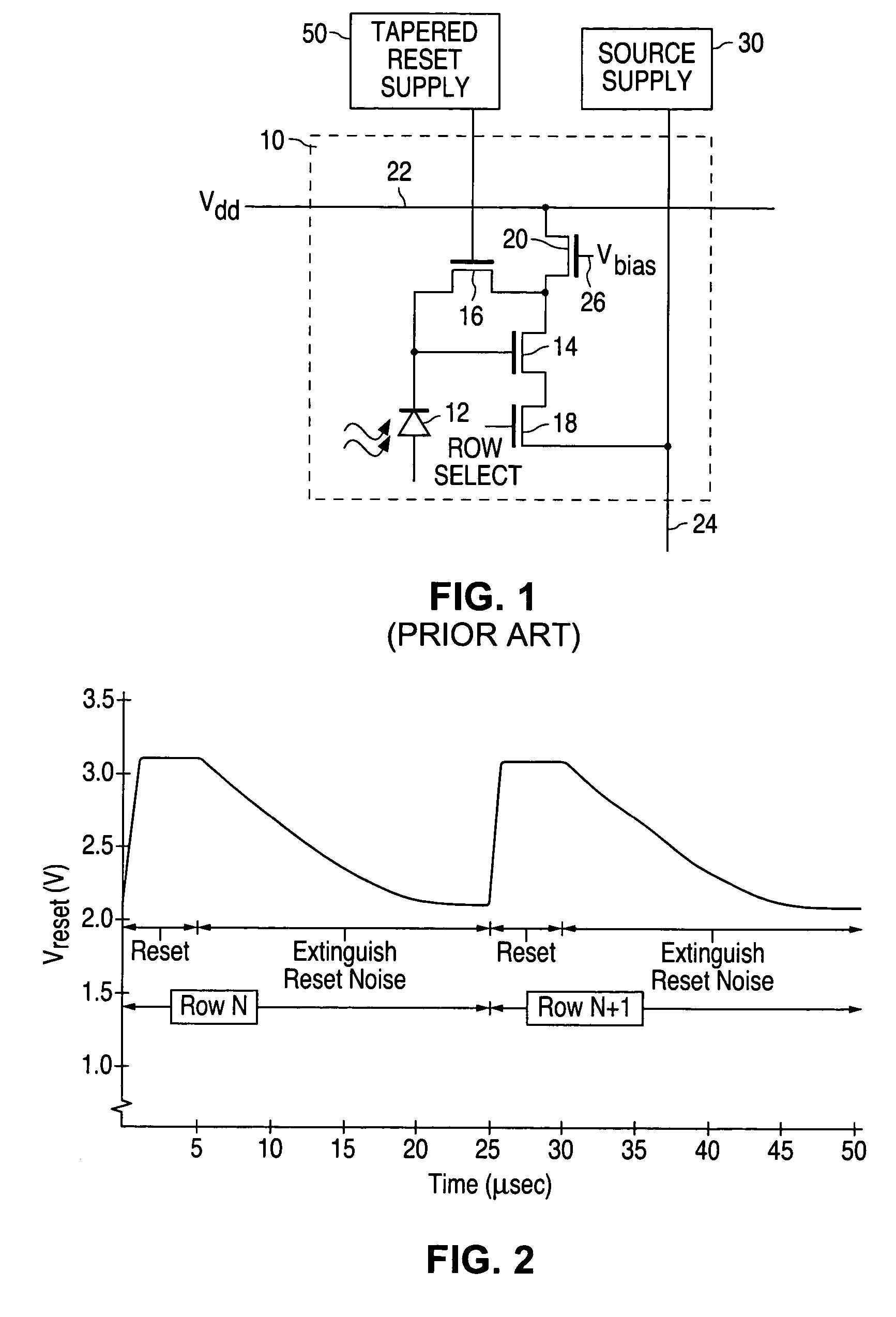

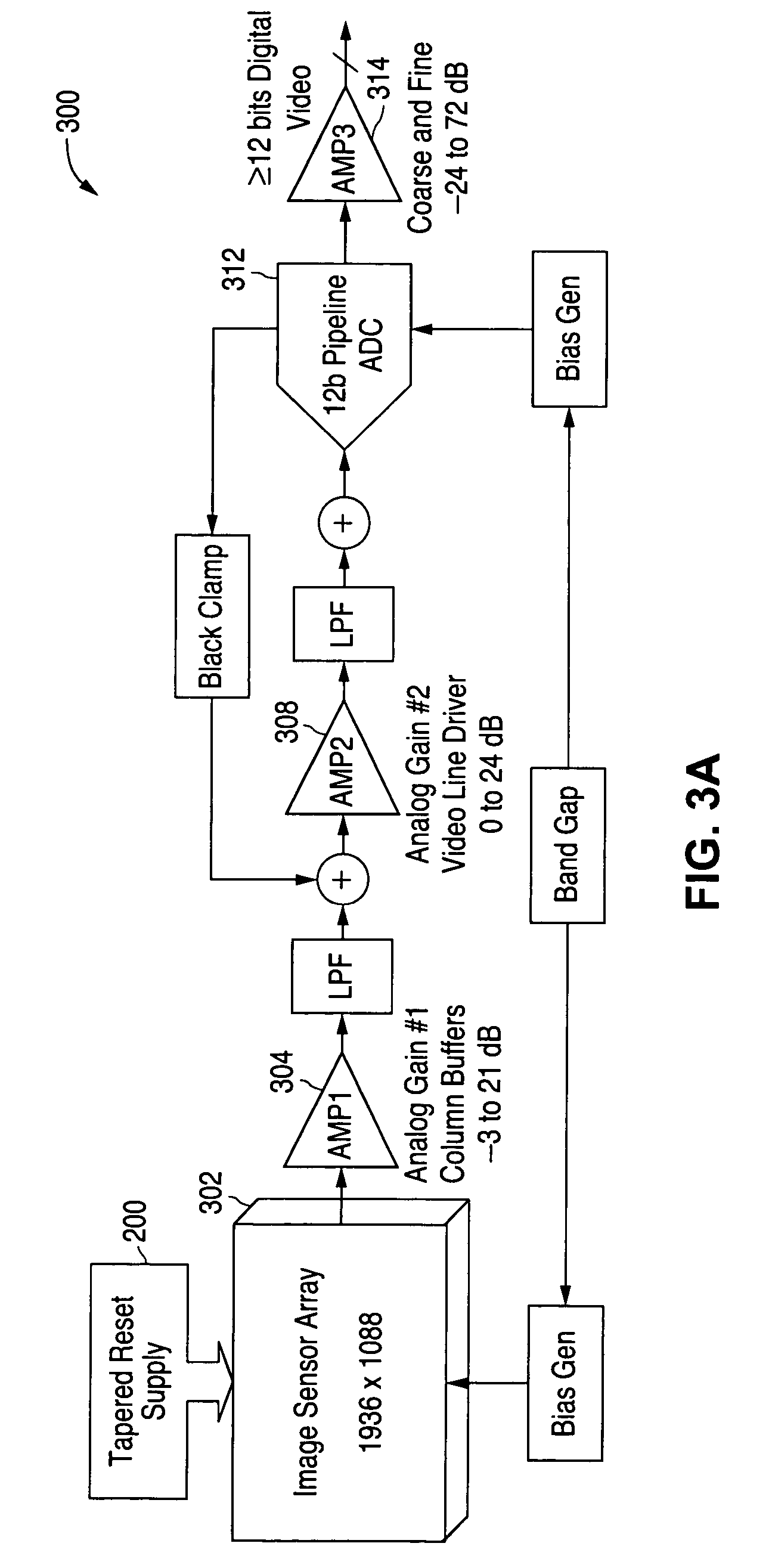

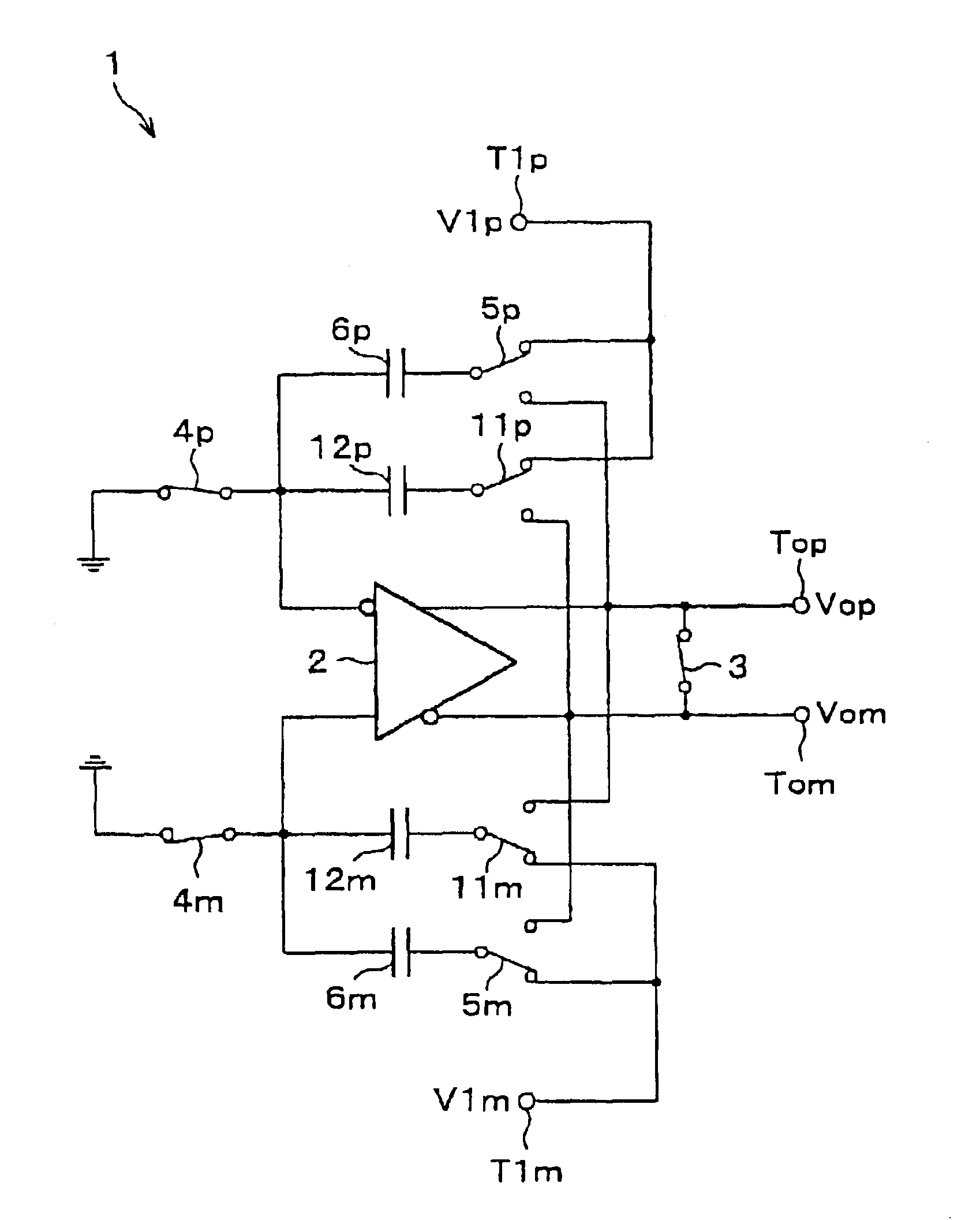

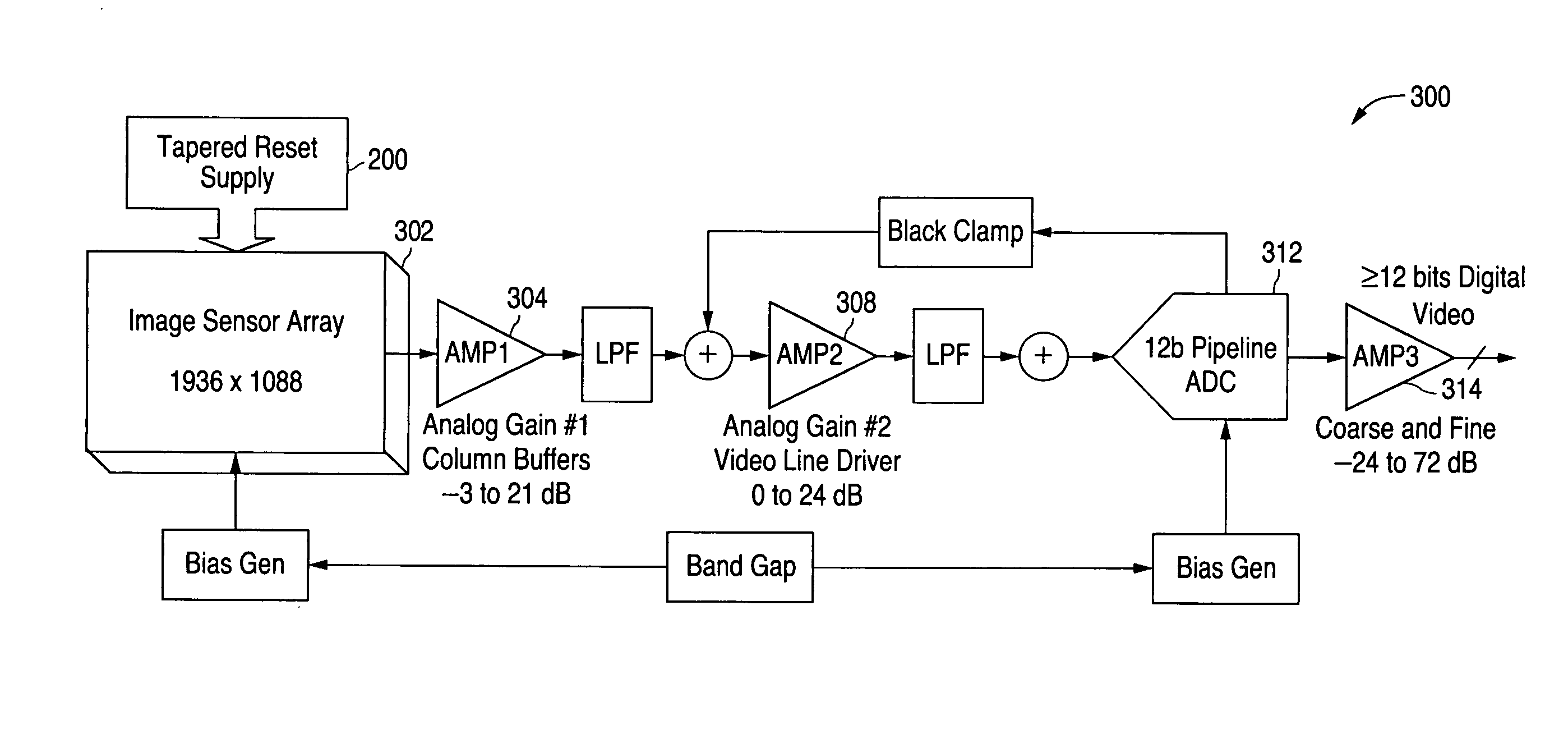

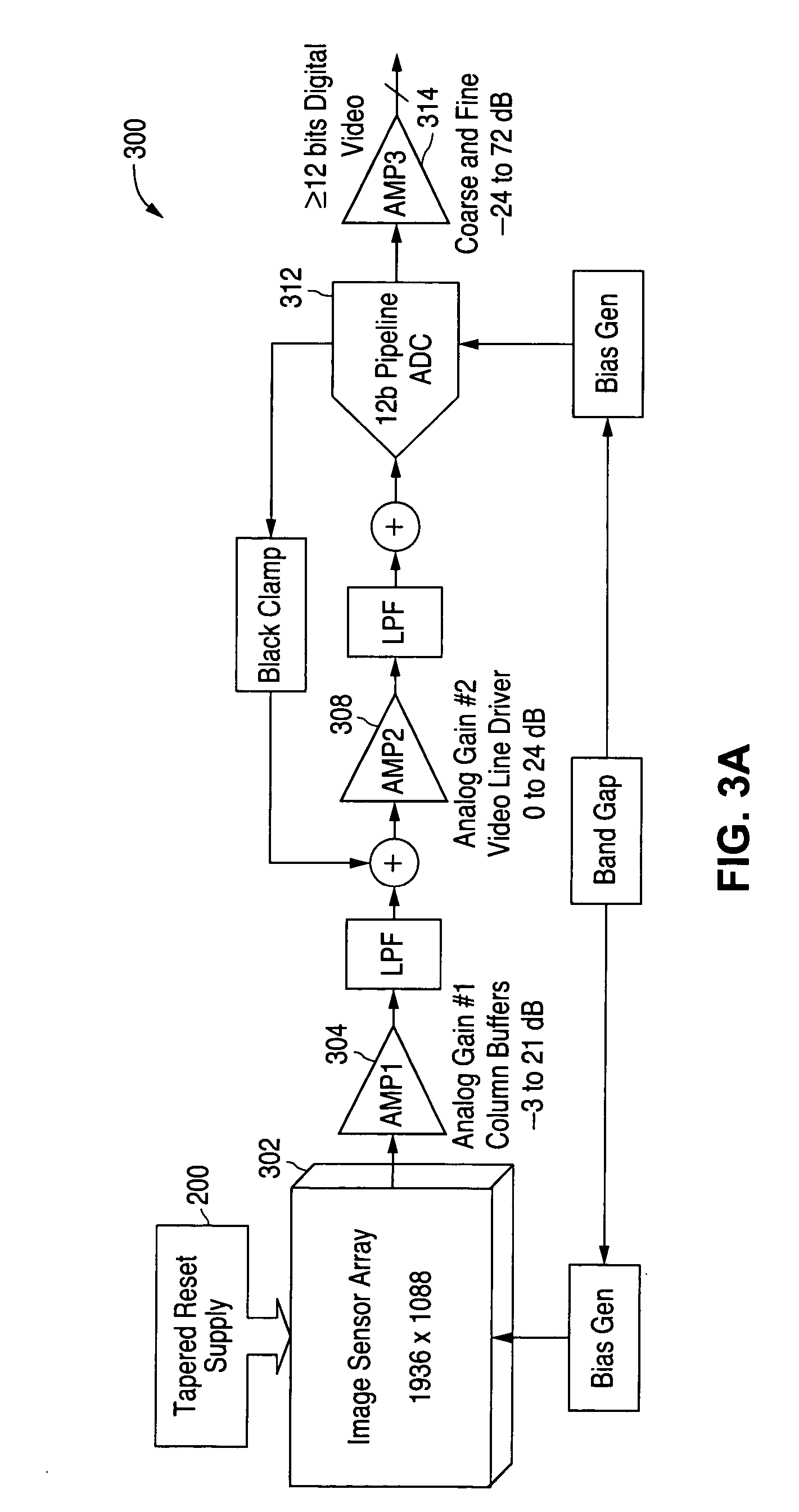

CMOS imaging system with low fixed pattern noise

A CMOS imager system including an active pixel sensor having an access supply which provides distributed feedback, a column buffer (having gain and FPN suppression), and an A / D converter co-located with the sensor such that the effective transmission path between the column buffer (or optional analog PGA) and the A / D converter acts as a resistor, rather than a reactance. The system may further include both an analog gain amplifier stage and a digital programmable amplifier stage.

Owner:SAMSUNG ELECTRONICS CO LTD

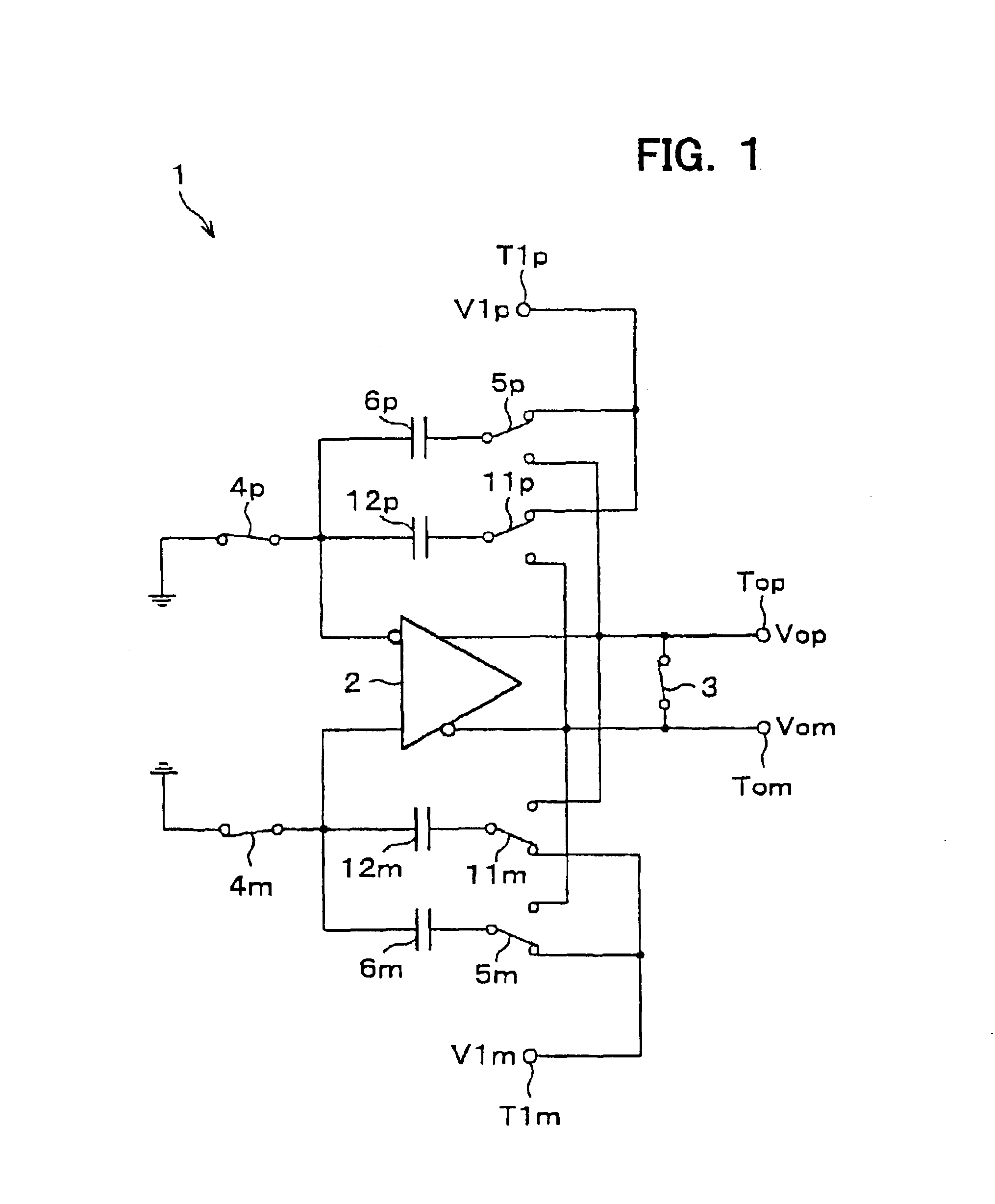

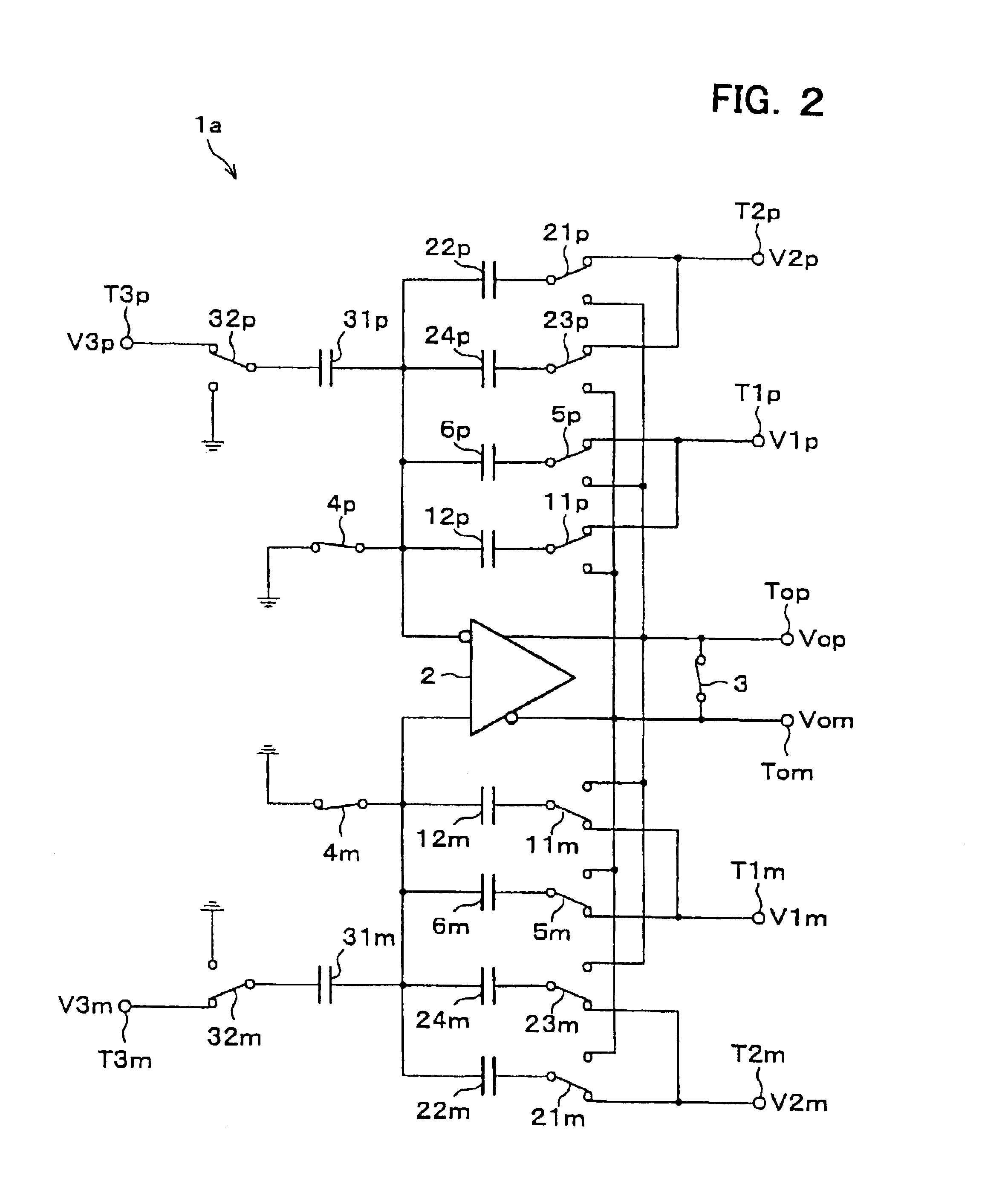

Switched-capacitor amplifier and analog interface circuit for charge coupled element adopting the same

InactiveUS6853241B2Reduction in capacitor ratioRaise the ratioCharge amplifiersTime-varying networkCapacitanceNegative feedback

In the hold phase, two negative feedback circuits constituted by the negative feedback capacitors 6p and 6m and two positive feedback circuits constituted by positive feedback capacitors are provided between an input terminal and an output terminal of an operational amplifier. Here, in a sampling phase before a hold phase, charges according an input signal V1p is stored in each of the capacitors, and charges according to an input signal V1p are stored in each of the capacitors. As a result, a gain of the switched capacitor amplifier circuit is derived from (Ca+C) / (Ca−Cx) wherein Ca indicates an electrostatic capacitance of the negative feedback capacitors, and Cx indicates an electrostatic capacitance of the positive feedback capacitors, and thus the gain can be increased without significantly increasing an electrostatic capacitance ratio.

Owner:SHARP KK

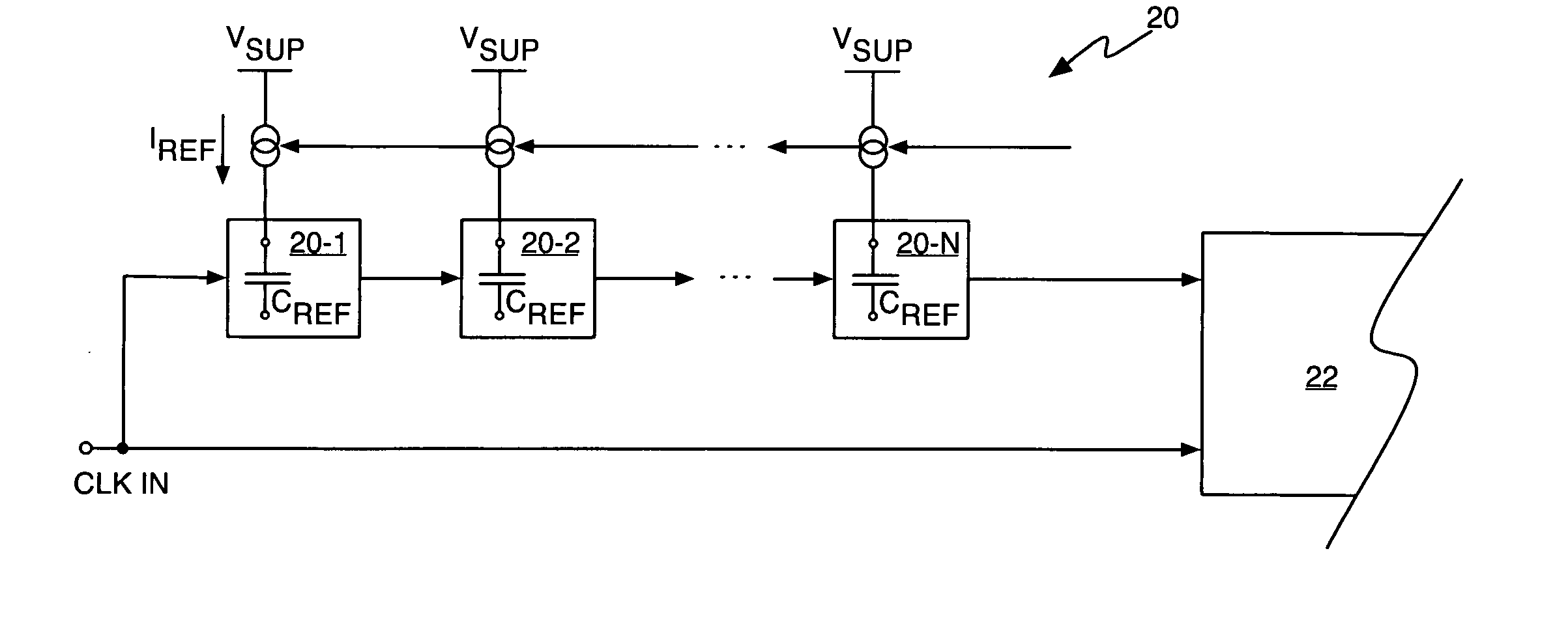

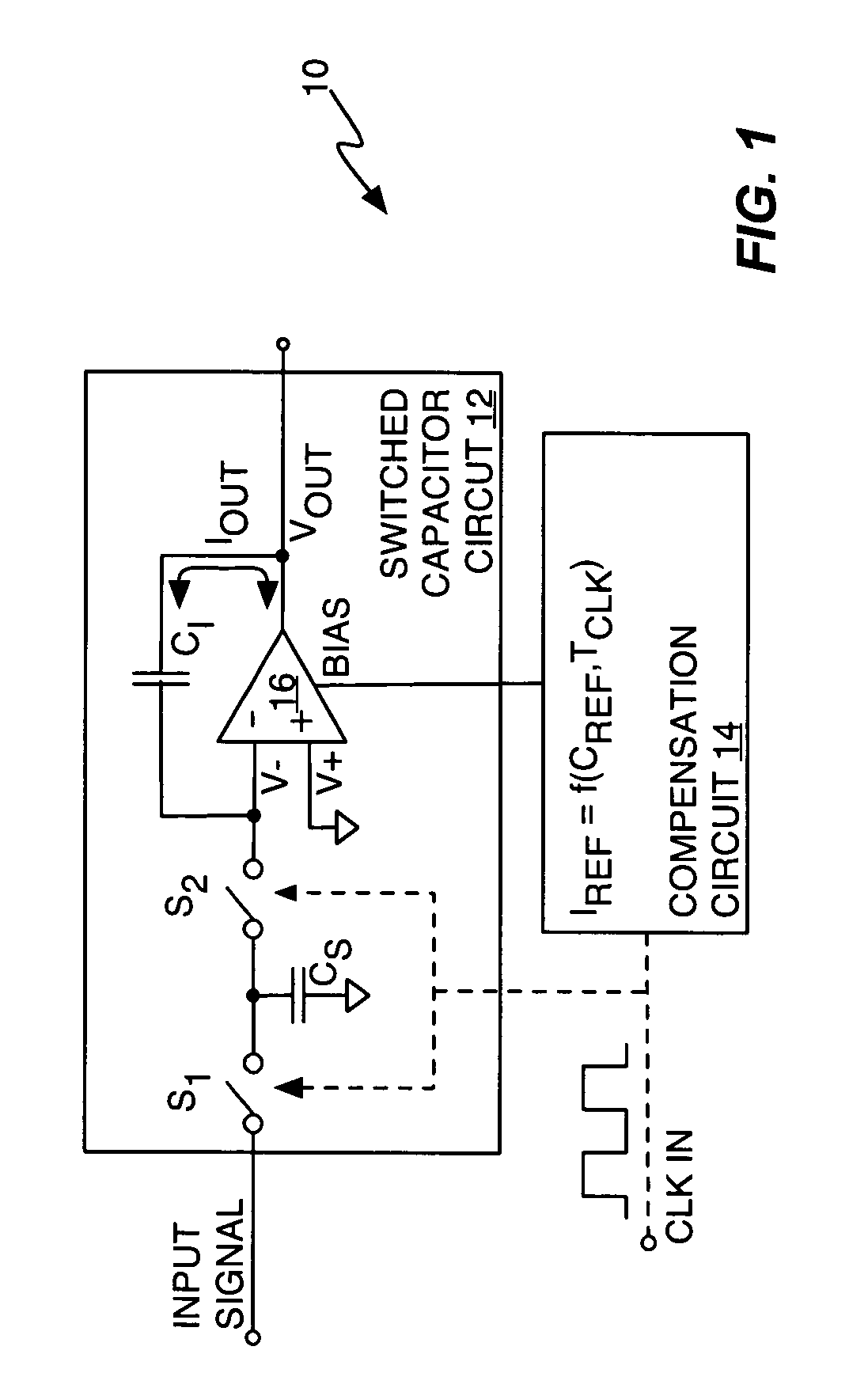

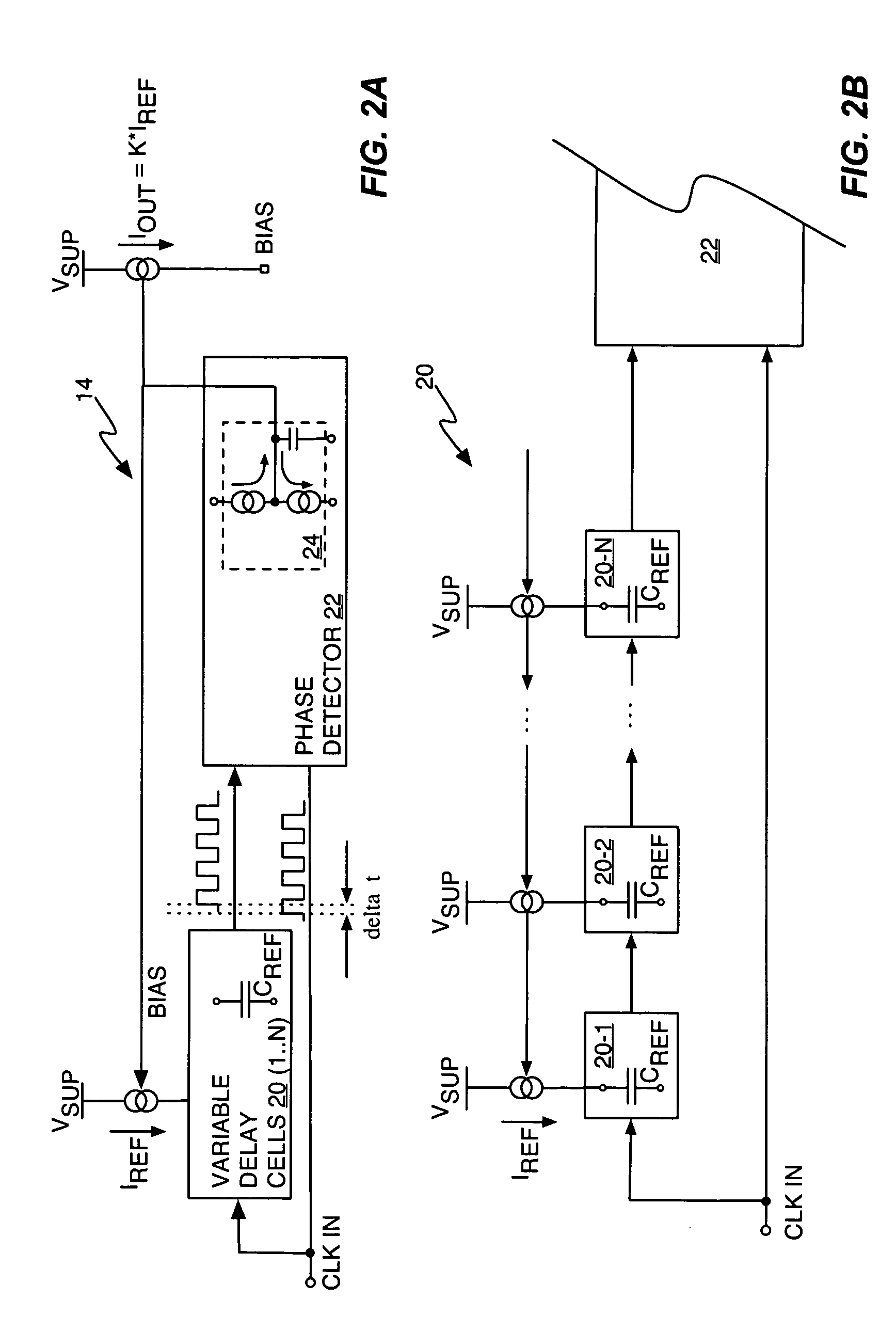

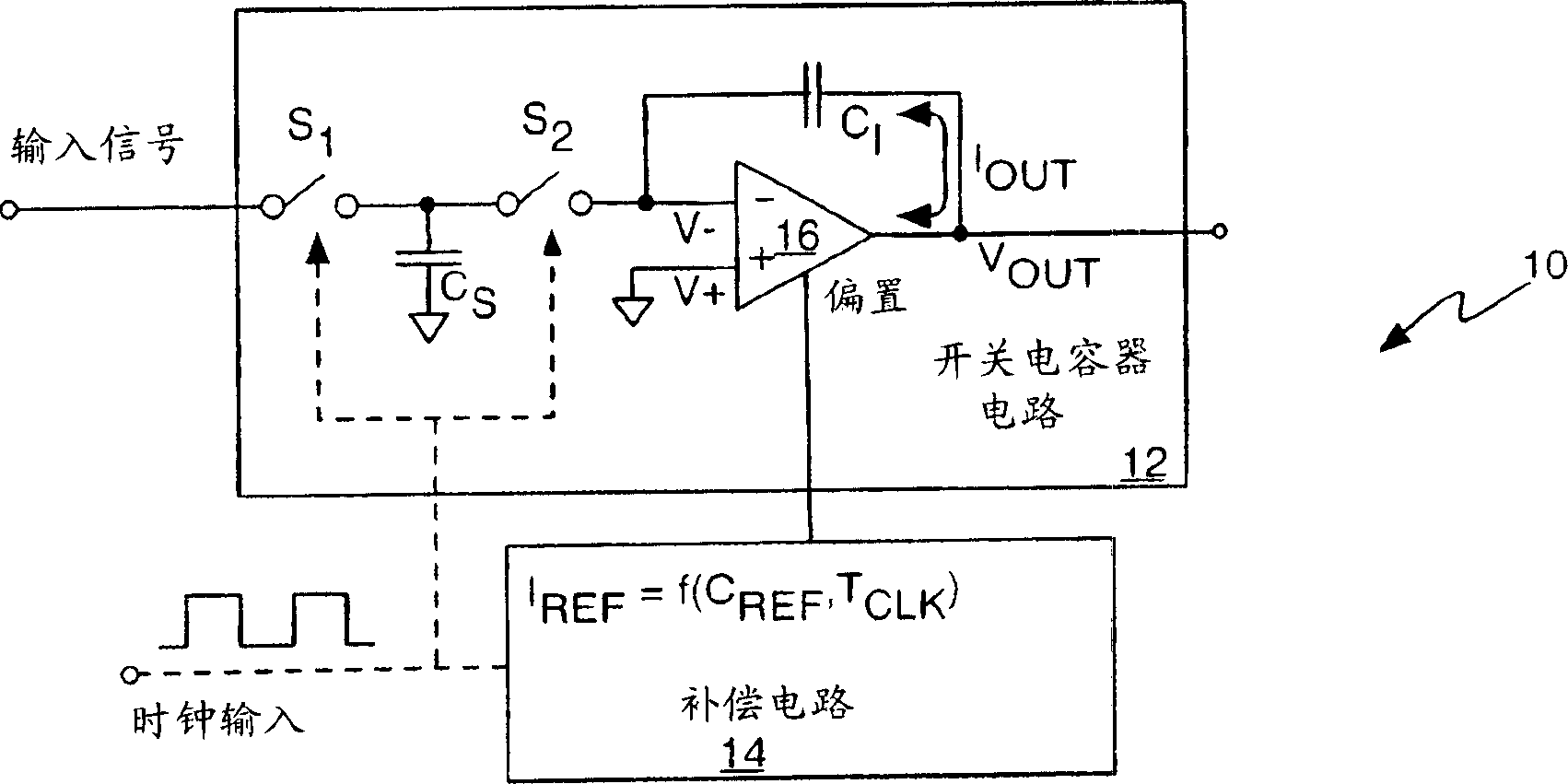

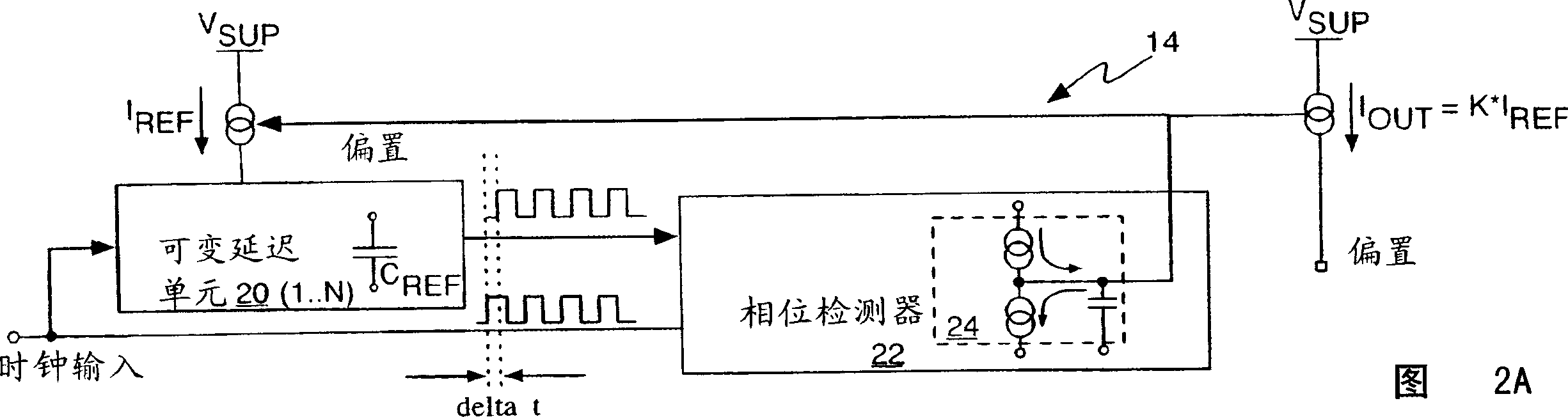

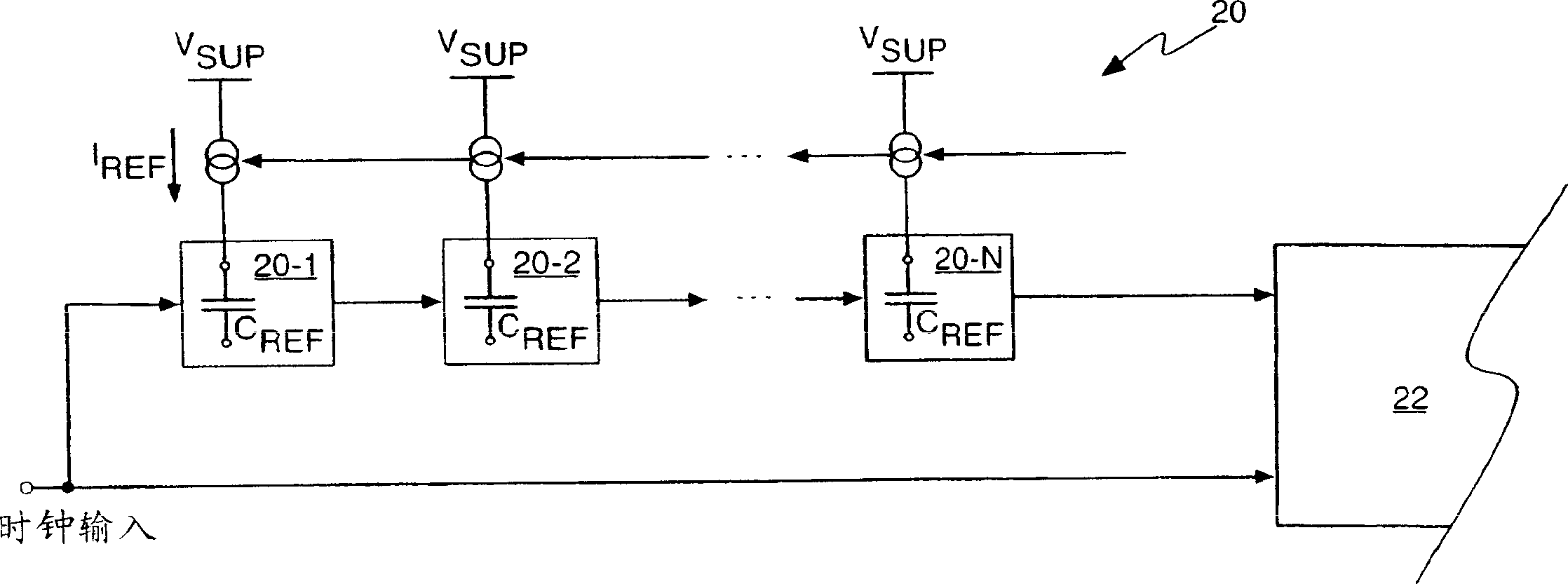

Switched capacitor circuit compensation apparatus and method

ActiveUS20050140422A1Easy to useIncrease currentElectric analogue storesDigital differential analysersCapacitanceLoop control

A compensated switched capacitor circuit comprises a switched capacitor circuit and a compensation circuit. The compensation circuit generates a reference current that varies under closed loop control to maintain a targeted slew rate for charging a reference capacitor that is determined by the input clock frequency. The switched capacitor circuit's output amplifier is configured such that its output current varies in proportion to the reference current. Thus, by configuring the reference capacitor to track the effective capacitance of the switched capacitor circuit, the settling time of the switched capacitor circuit may be made relatively insensitive to the value of and changes in the effective capacitance over a range of clock frequencies. The compensation circuit may include a clock reconditioning circuit to ensure that the switched capacitor circuit is clocked at a desired duty cycle.

Owner:TELEFON AB LM ERICSSON (PUBL)

Notch filter for ripple reduction in chopper stabilized amplifiers

ActiveUS20070170981A1Reduce ripple noiseFast signalAmplifier modifications to reduce noise influenceAmplifier modifications to raise efficiencyAudio power amplifierEngineering

A chopper-stabilized amplifier receiving an input signal includes a first operational transconductance amplifier having an input chopper and an output chopper for chopping an output signal produced by the first operational transconductance amplifier. A switched capacitor notch filter filters the chopped output signal by operating synchronously with the chopping frequency of output chopper to filter ripple voltages that otherwise would be produced by the output chopper. In one embodiment, a second operational transconductance amplifier amplifies the notch filter output. The input signal is fed forward, summed with the output of the second operational transconductance amplifier, and applied to the input of a fourth operational transconductance amplifier. Ripple noise and offset are substantially reduced.

Owner:TEXAS INSTR INC

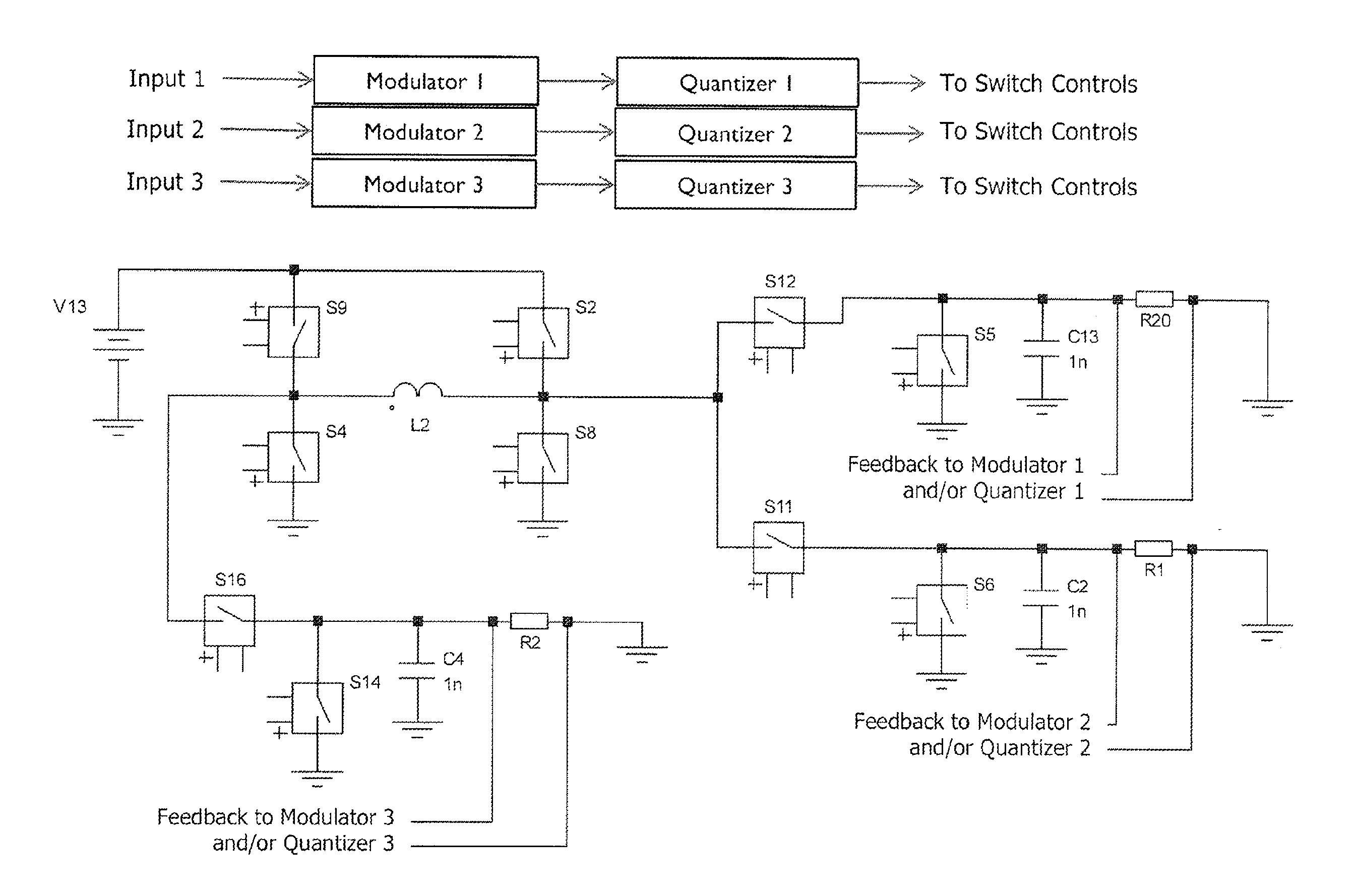

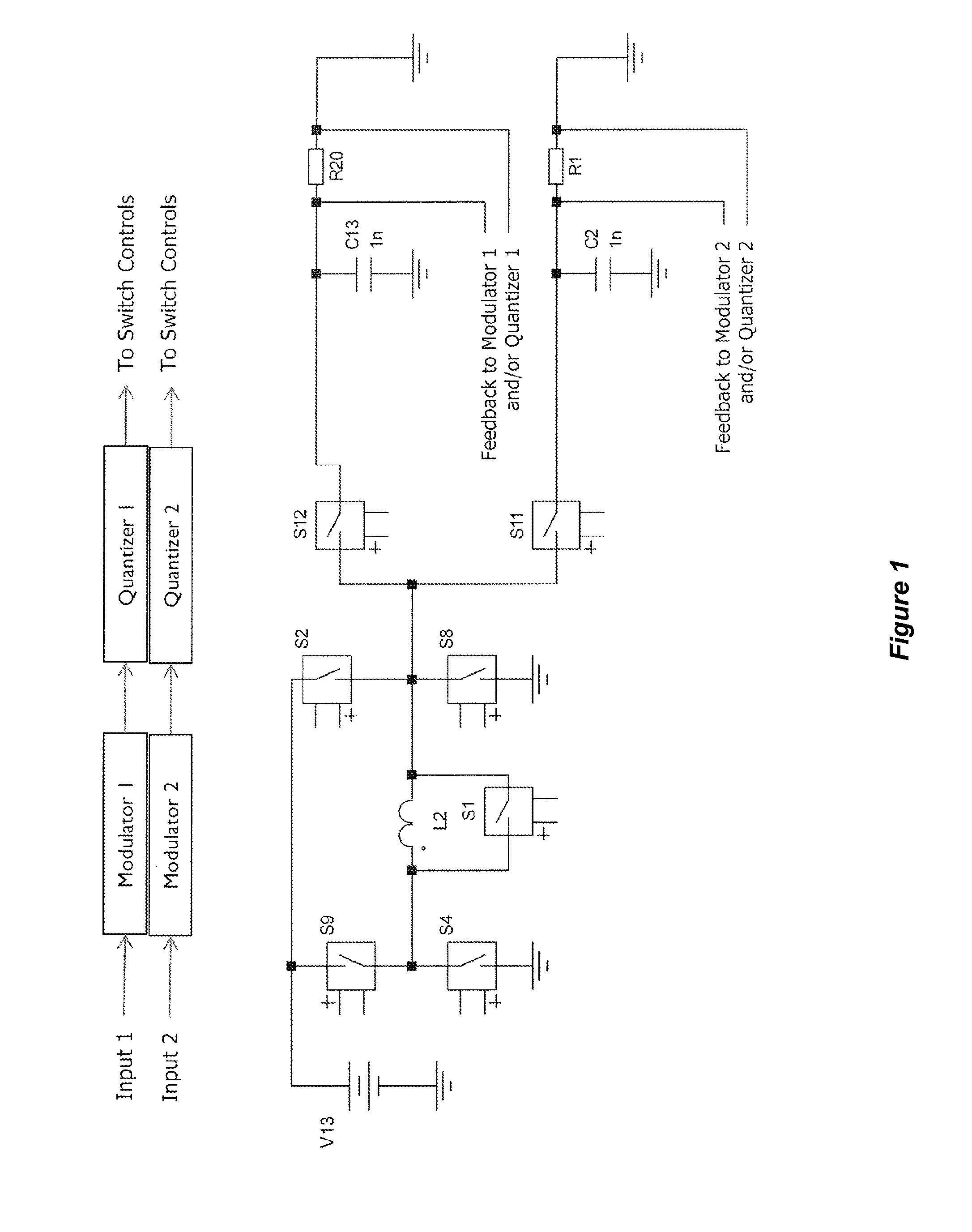

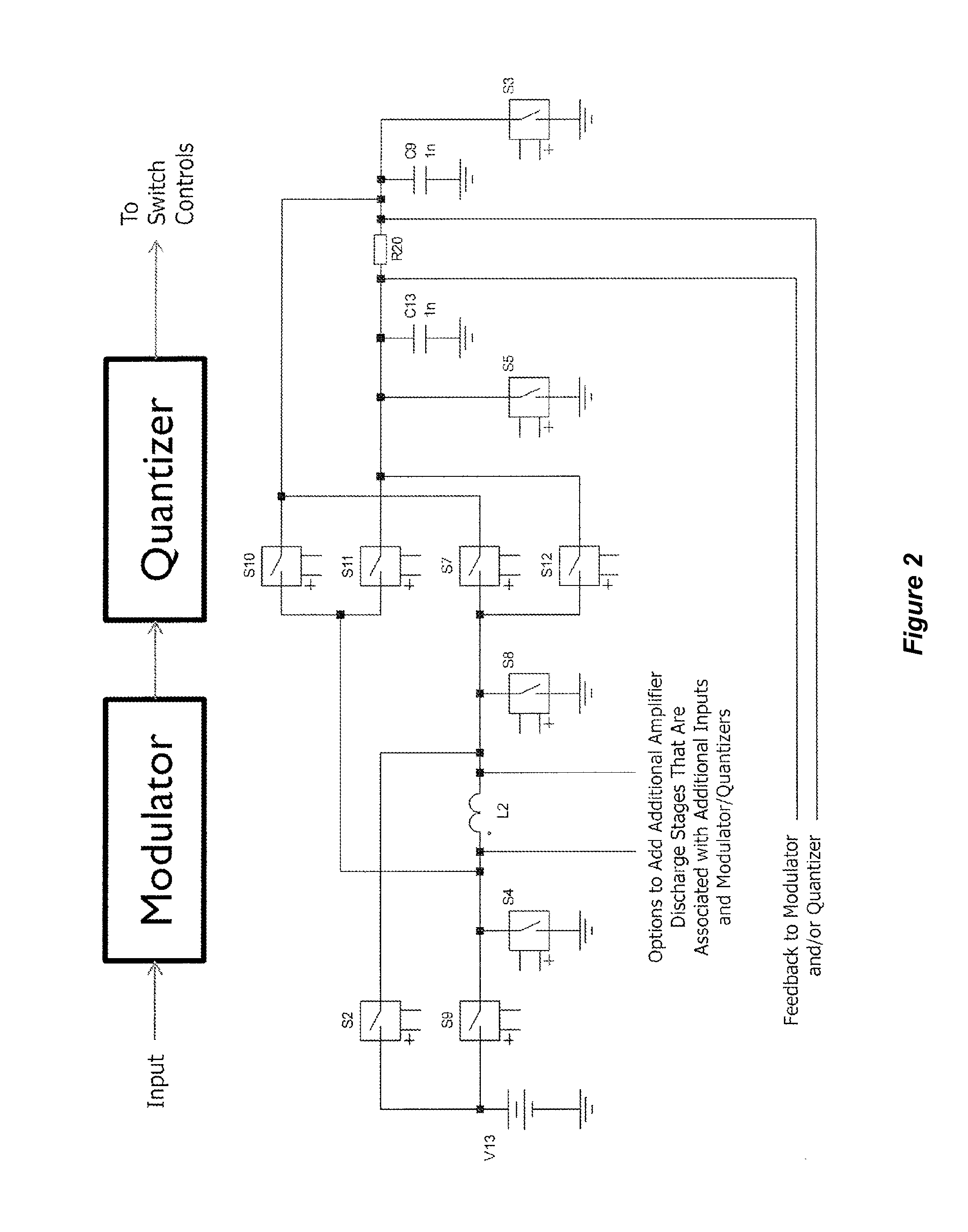

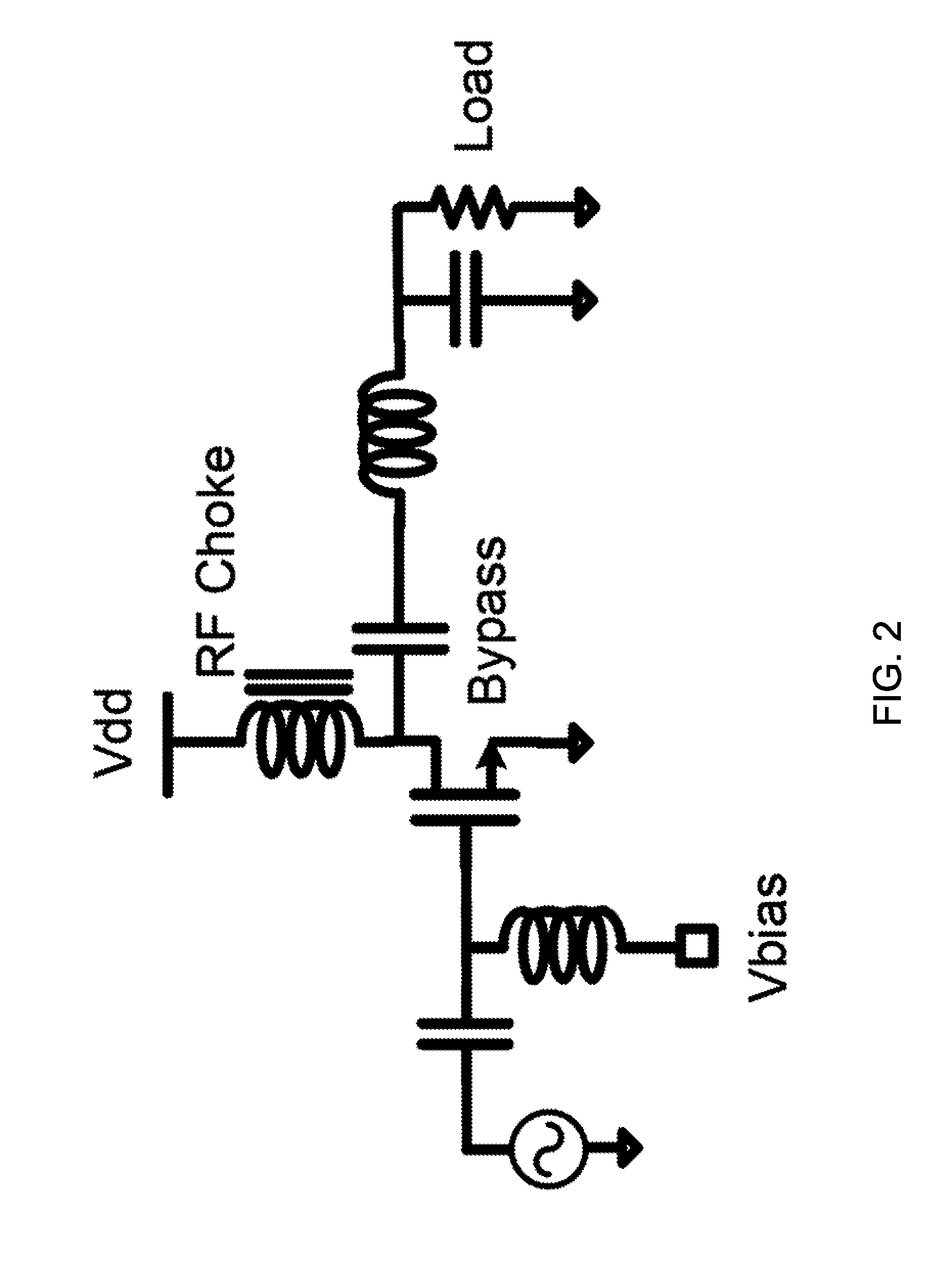

Resource pooling amplifier

ActiveUS20130082771A1Easy to useBoards/switchyards circuit arrangementsNegative-feedback-circuit arrangementsResource poolComputer architecture

A new type of amplifier, herein designated a resource pooling amplifier, involves extended usage of one or more inductors that is implemented by sharing. The sharing is either by switching the inductor or inductors among more than one load terminal at the same time (e.g., a bridged configuration or two different loads terminals with different polarity requirements) or by using the inductor or inductors for more than one purpose at different times. The inductor or inductors may be time shared such as by allocating different phases of a clock. The inductor or inductors may also be shared by monitoring load requirements and using the inductor or inductors only when needed (leaving other inductor cycles for other loads). In addition, inductor sharing may be implemented during different application requirements such as if two or more loads are not needed at the same time in a system. These types of sharing may be combined.

Owner:MAXIM INTEGRATED PROD INC

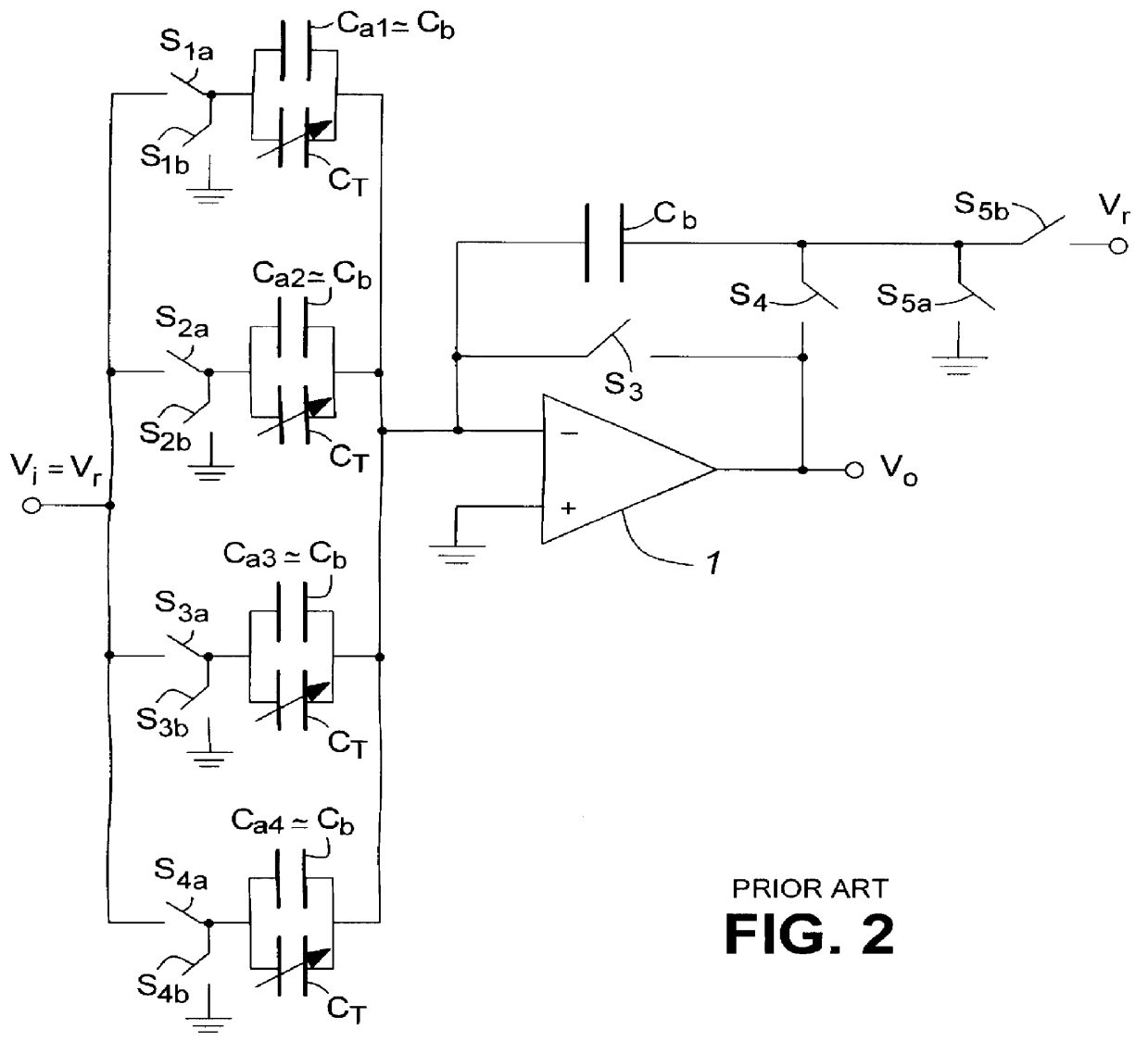

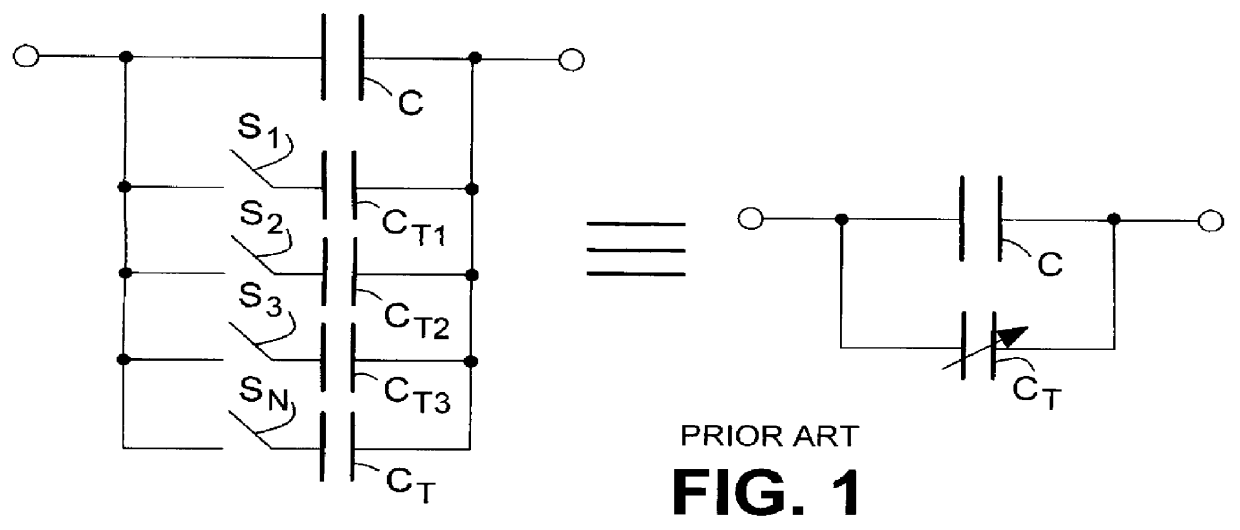

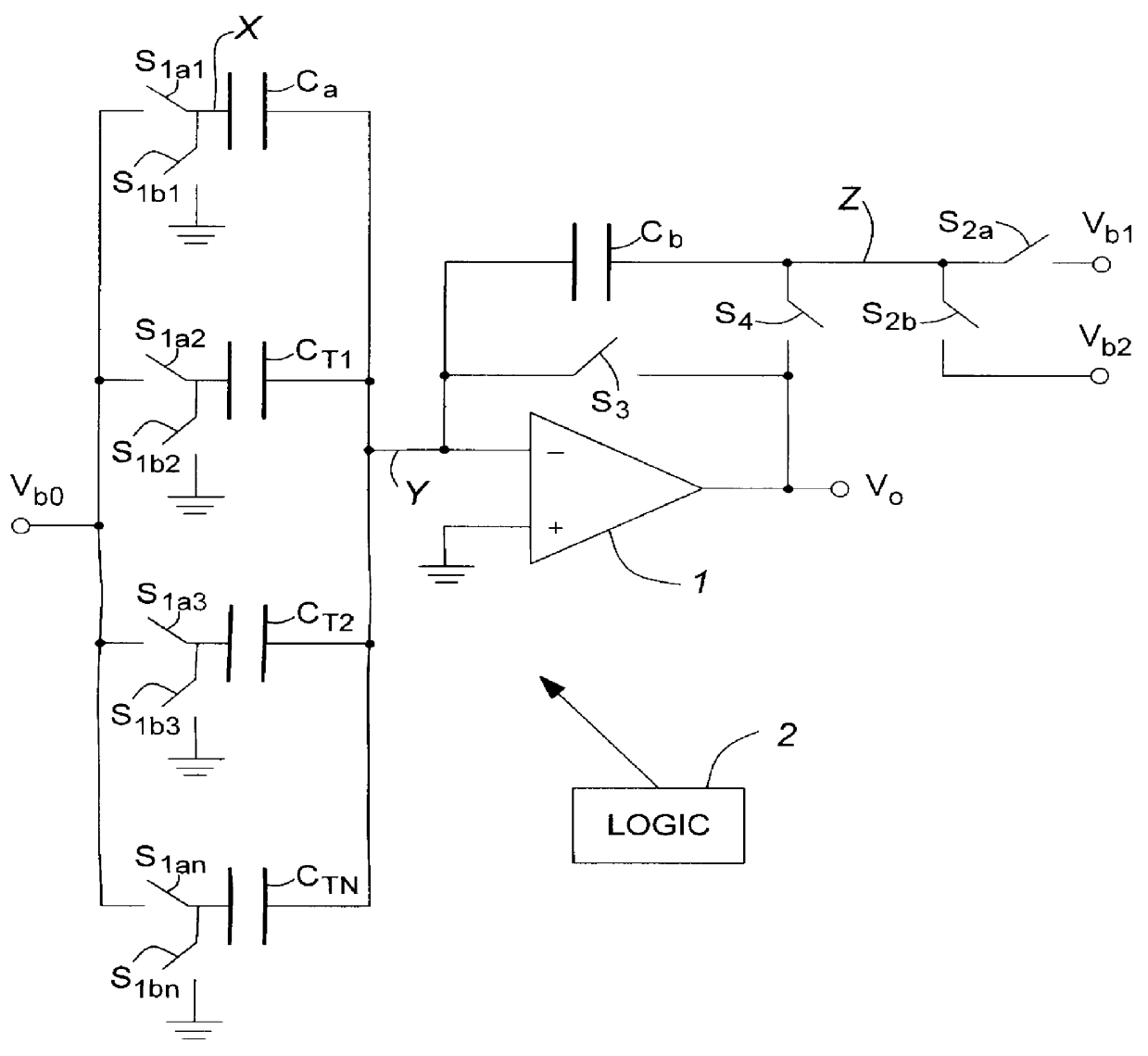

Generalized procedure for the calibration of switched capacitor gain stages

Within the field of integrated circuits used in amplifiers, a structure and improved method for calibrating a switched capacitor gain stage wherein the time required to self-calibrate a switched capacitor gain stage and the associated structure are reduced. The invention utilizes only a single calibration step which is performed while the output of the amplifier being calibrated is monitored. Instead of utilizing a plurality of capacitors Ca1-Can each in parallel with groups of trim capacitors CT, a single capacitor Ca is used and connected to switches S1a1 and S1b1. Further, instead of a group of trim capacitors CT being connected in parallel with the capacitor to be trimmed, each of plurality of trim capacitors CT1-CTN is connected between the input to the operational amplifier and a respective corresponding switch S1a2-S1aN to the input reference voltage node Vb0. As well, switches S1b2-S1bn connect the respective junctions between the trim capacitors CT1-CTN to ground.

Owner:PMC-SIERRA

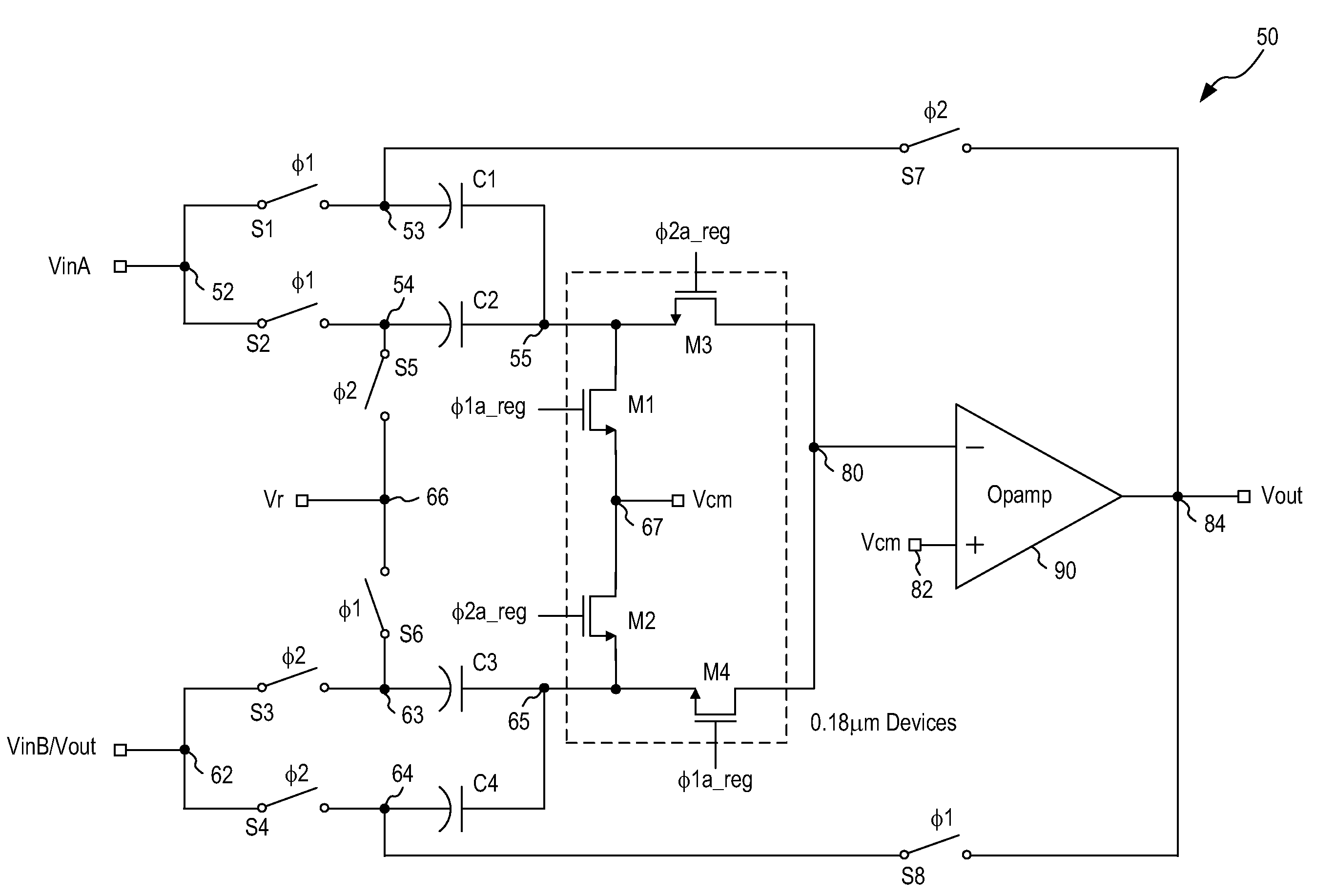

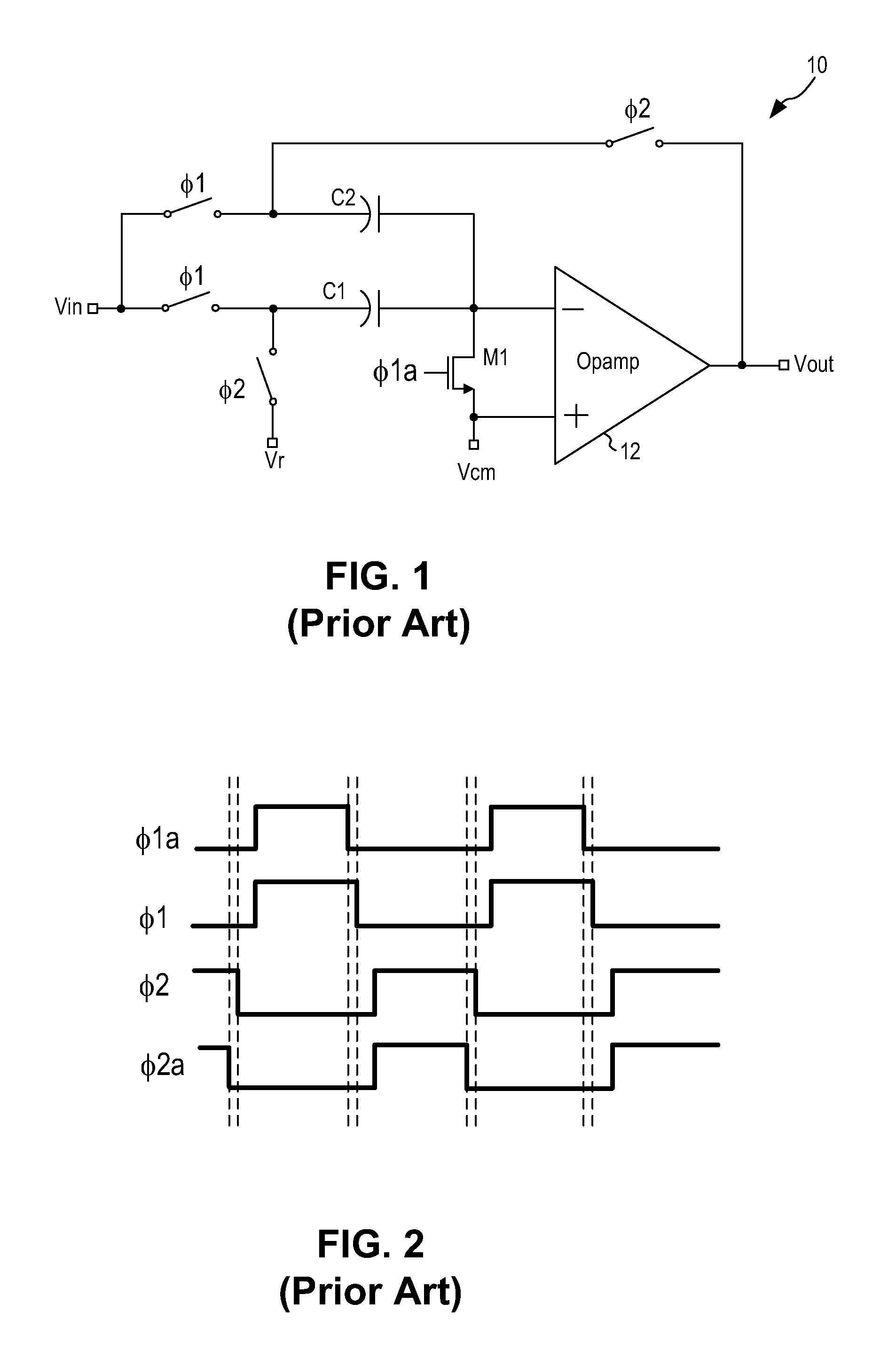

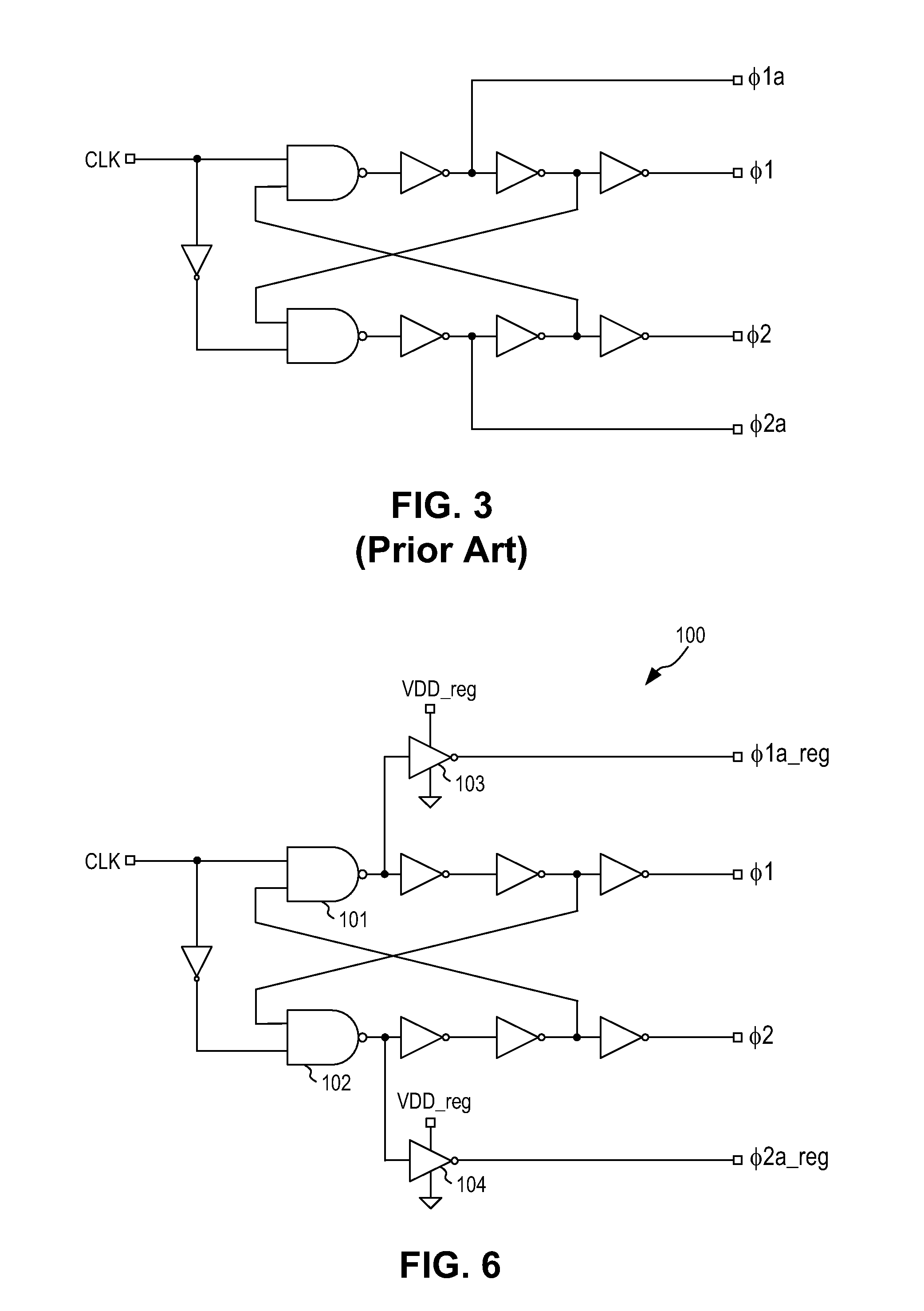

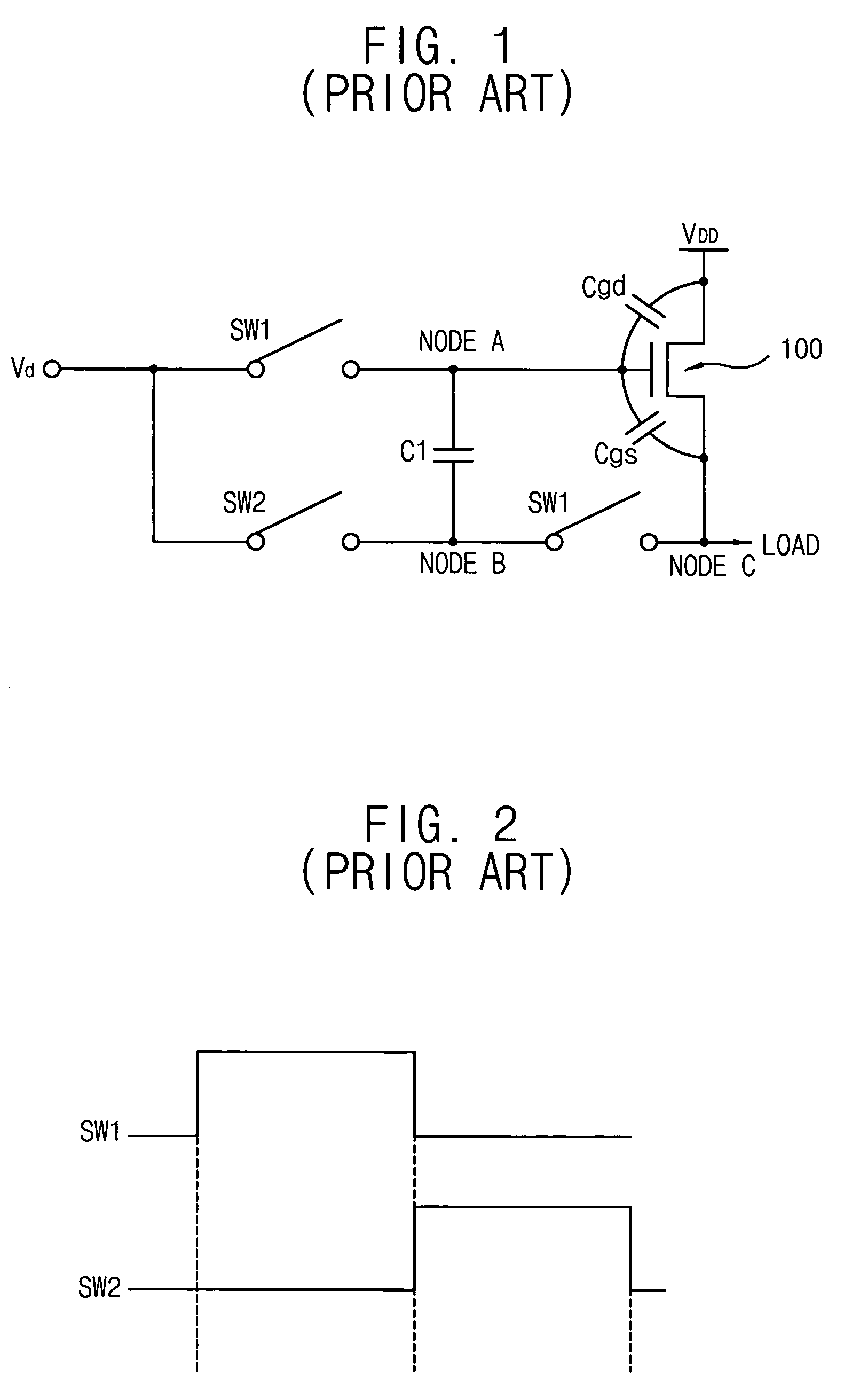

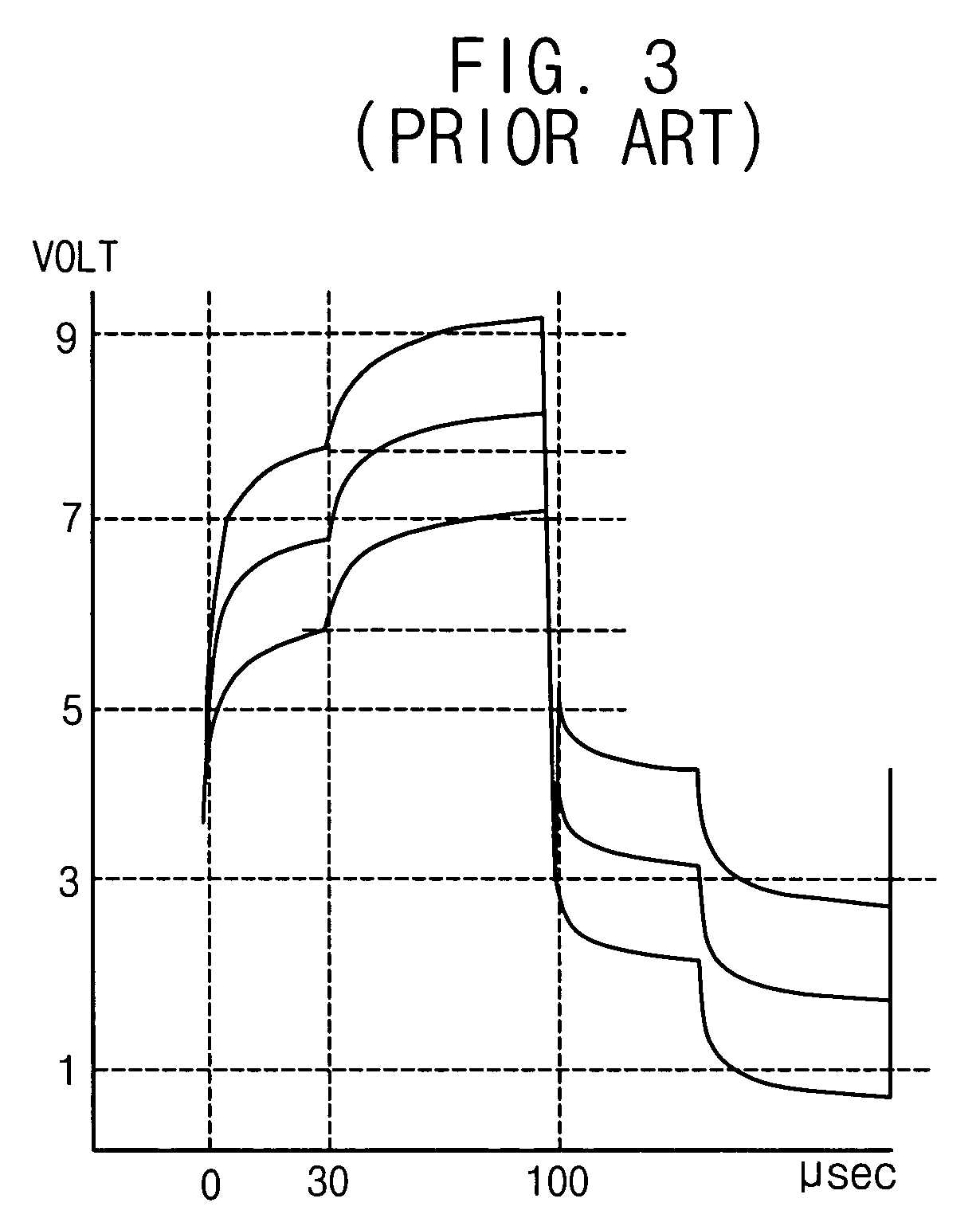

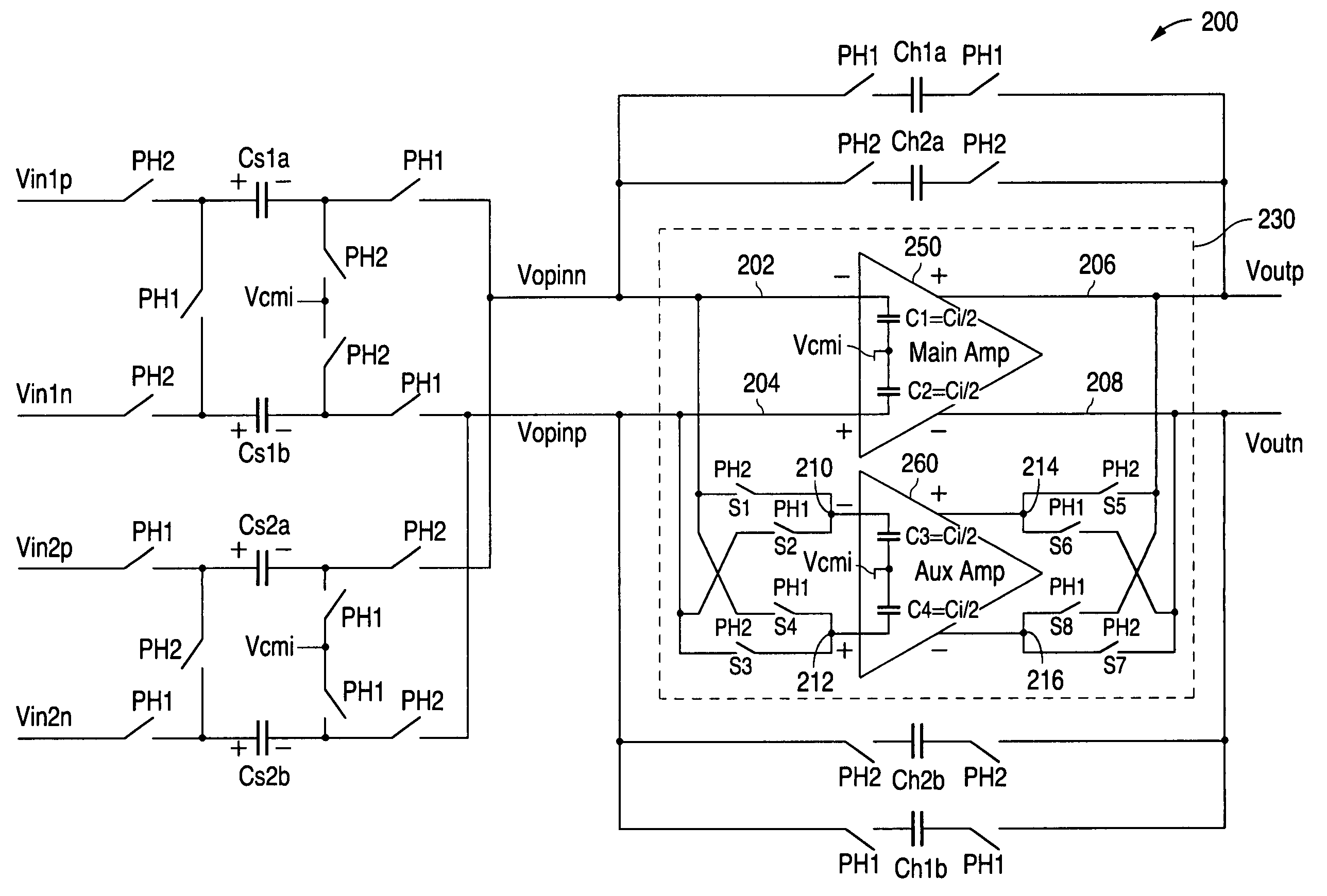

Regulated switch driving scheme in switched-capacitor amplifiers with opamp-sharing

ActiveUS7345530B1Amplifier modifications to raise efficiencyAmplifiers using switched capacitorsCapacitanceAudio power amplifier

A switched-capacitor amplifier circuit including first and second pairs of sampling capacitors for sampling a pair of input signals includes a voltage regulator coupled to receive a first reference voltage and generate a first regulated output voltage related to the first reference voltage and independent of a first power supply voltage; a clock signal generator generating first and second clock signals referenced to the first power supply voltage and third and fourth clock signals referenced to the first regulated output voltage; and a first set of switches coupling the bottom plates of the sampling capacitors to the amplifier, the first set of switches being controlled by the third and fourth clock signals. The circuit may further include a second set of switches coupling the top plates of the sampling capacitors to the input signals, the second set of switches being controlled by the first and second clock signals.

Owner:NAT SEMICON CORP

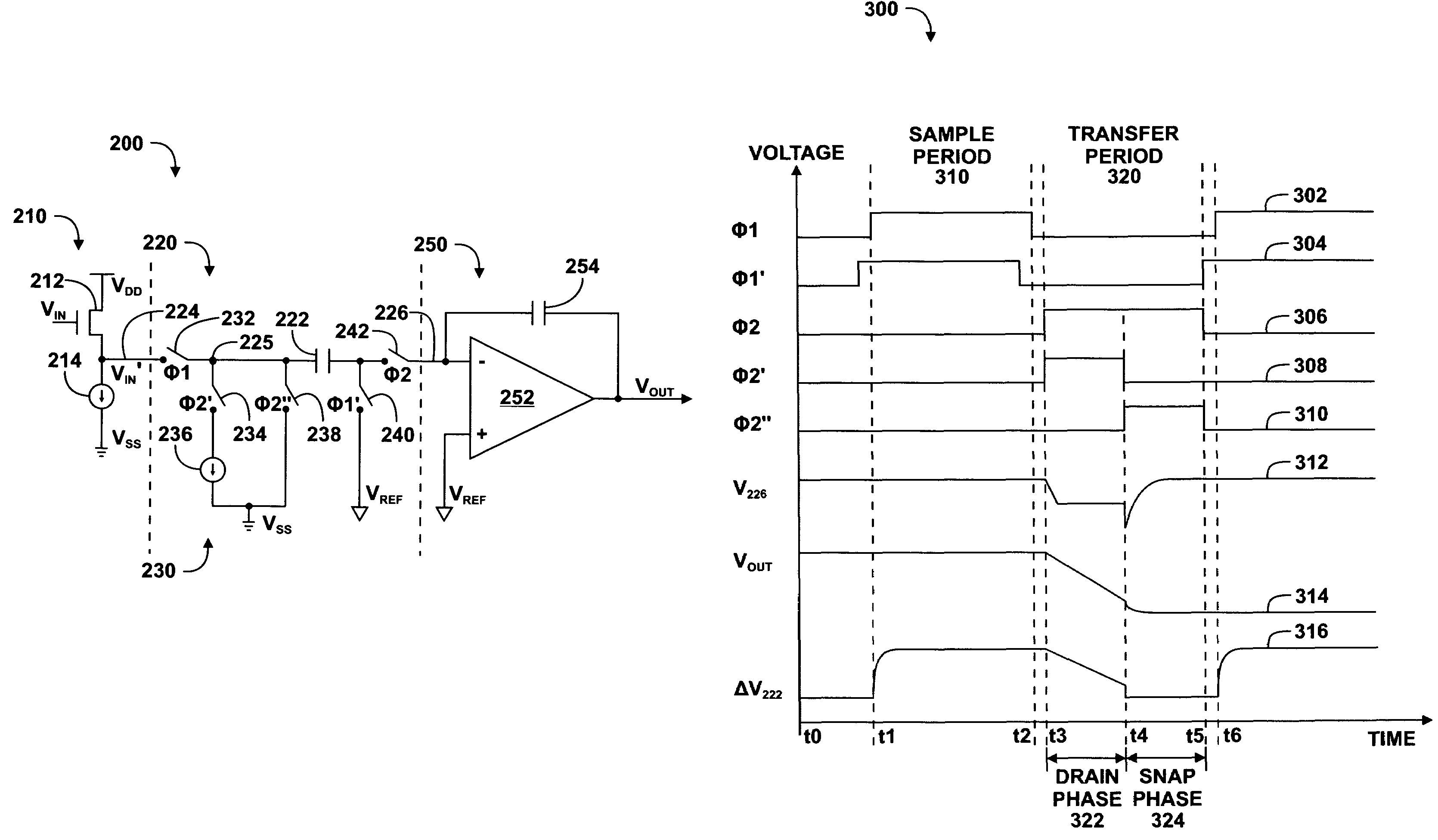

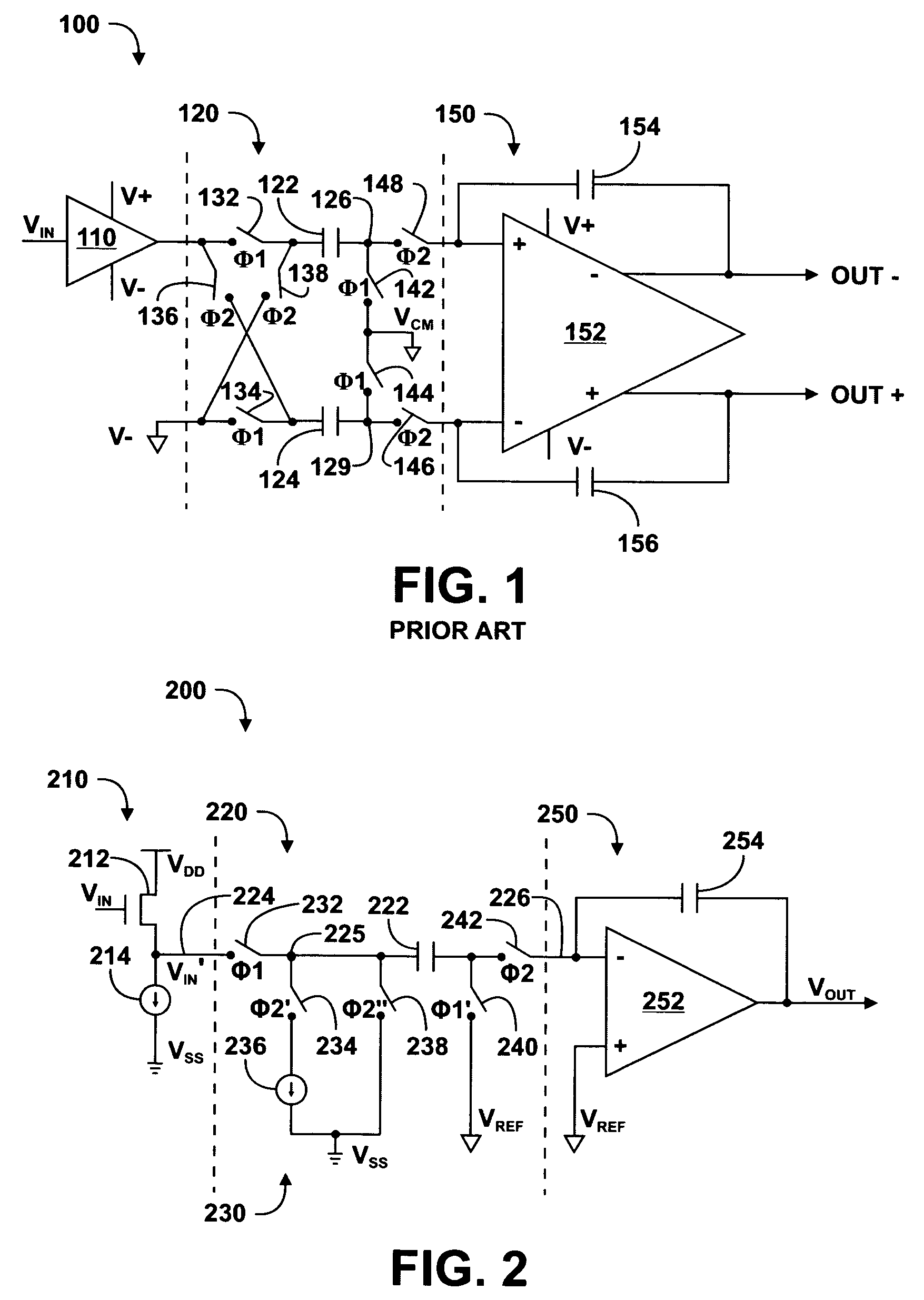

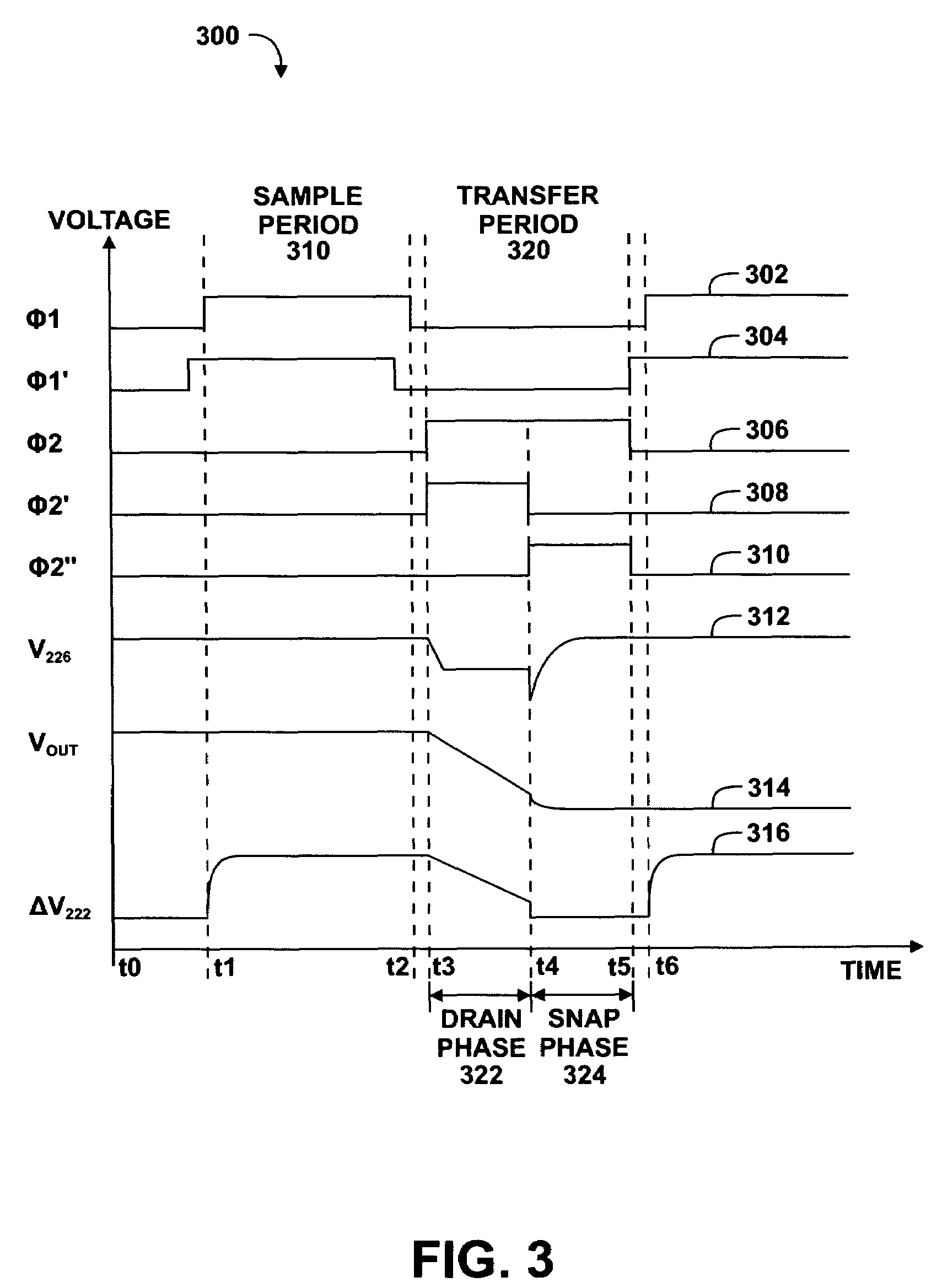

Switched capacitor input circuit and method therefor

InactiveUS7157956B2Computing operations for integral formationComputing operations for integration/differentiationIntegratorEngineering

A switched capacitor input circuit (200) includes an input buffer (210), a switched capacitor sampler circuit (220), and an integrator (250). The input buffer (210) has an input terminal for receiving an input voltage, and an output terminal. The switched capacitor sampler circuit (220) has an input terminal coupled to the output terminal of the input buffer (210), and an output terminal. The switched capacitor sampler circuit (220) includes a capacitor (222) and stores a charge proportional a voltage at the output terminal of the input buffer (210) in the capacitor (222) during a sample period, and transfers the charge from the capacitor (222) to the output terminal thereof during a transfer period subsequent to the sample period in a plurality of charge portions corresponding to a like plurality of phases of the transfer period. The integrator (250) has an input terminal coupled to the output terminal of the switched capacitor sampler circuit, and an output terminal for providing an output voltage signal.

Owner:SILICON LAB INC

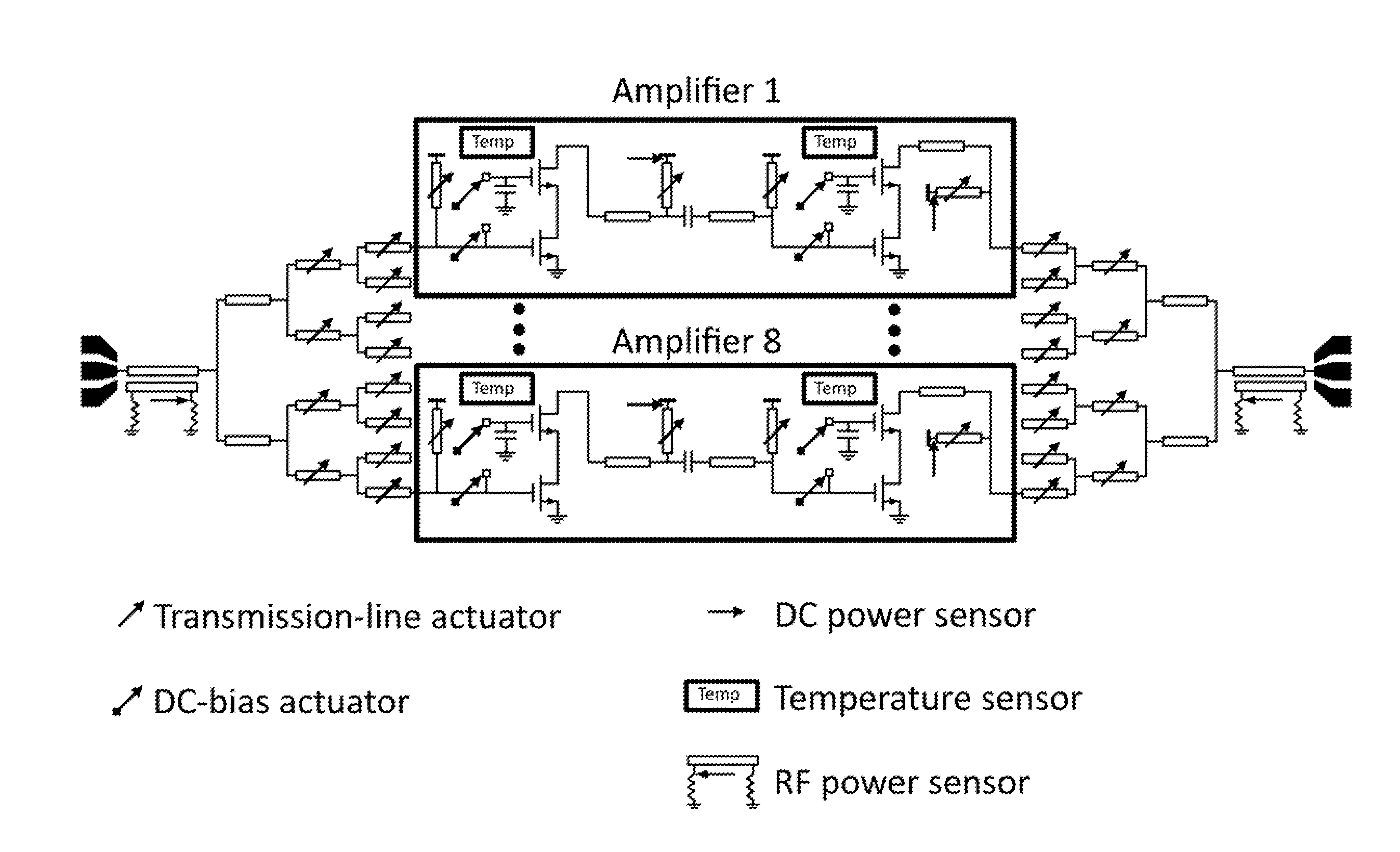

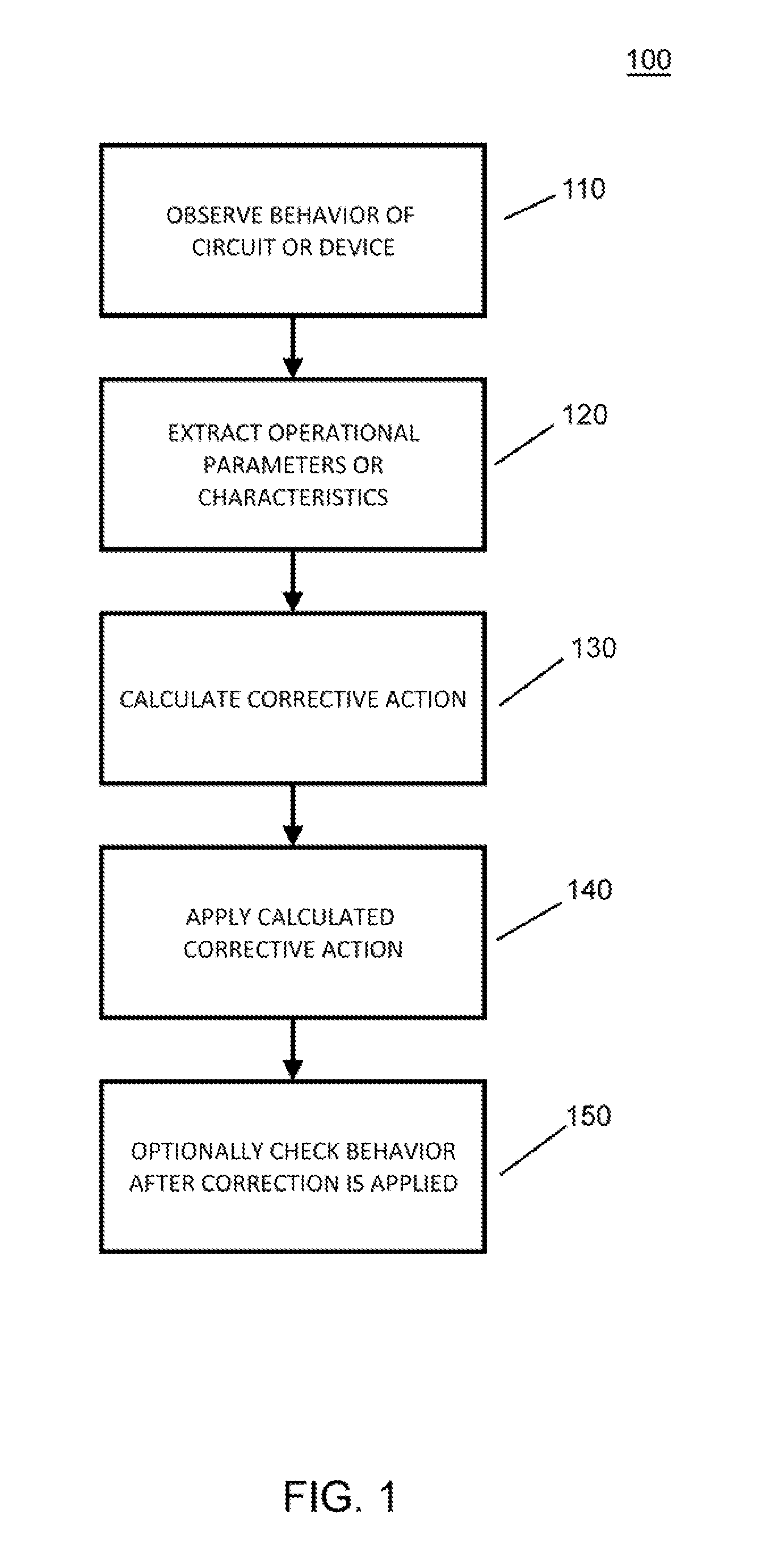

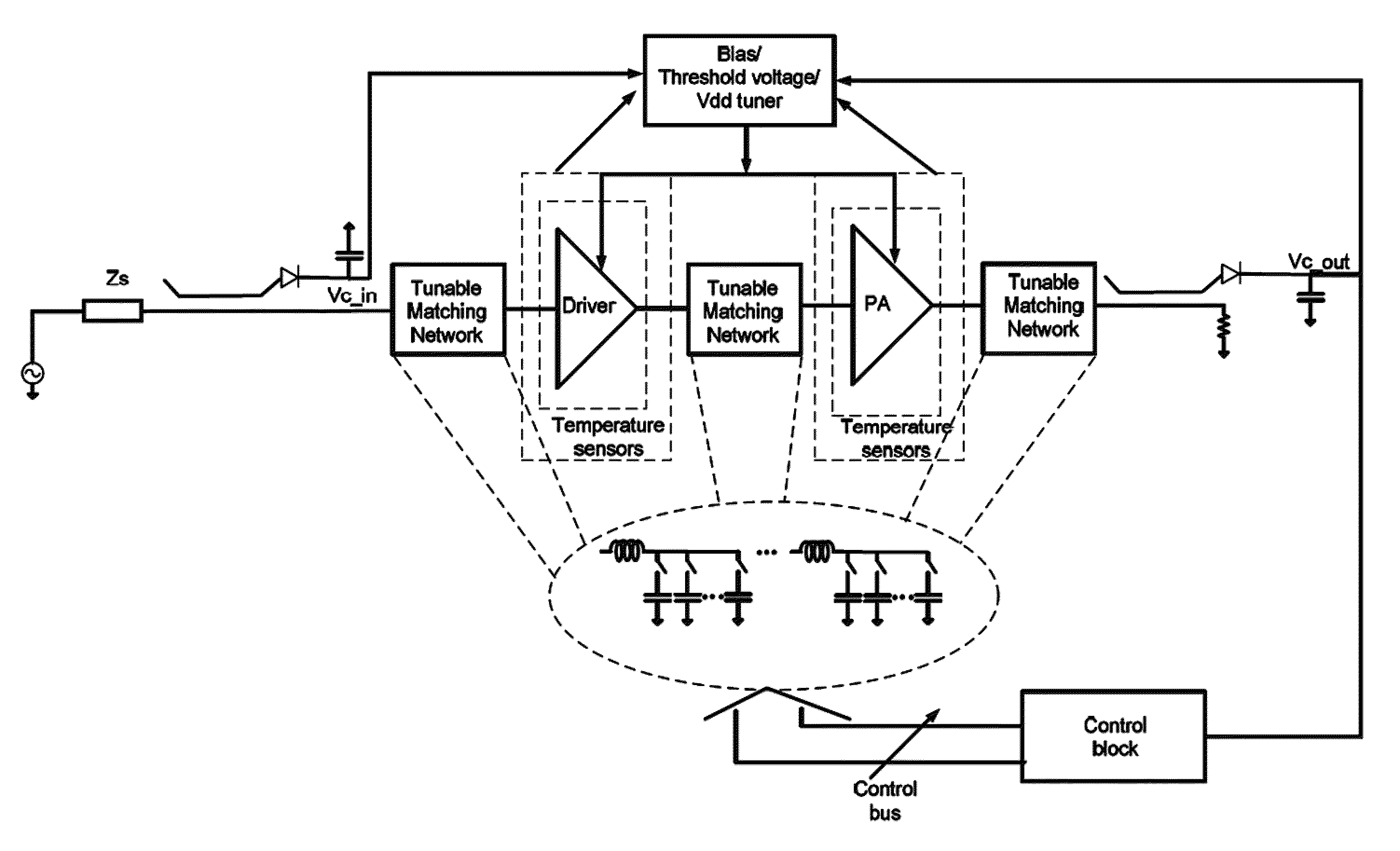

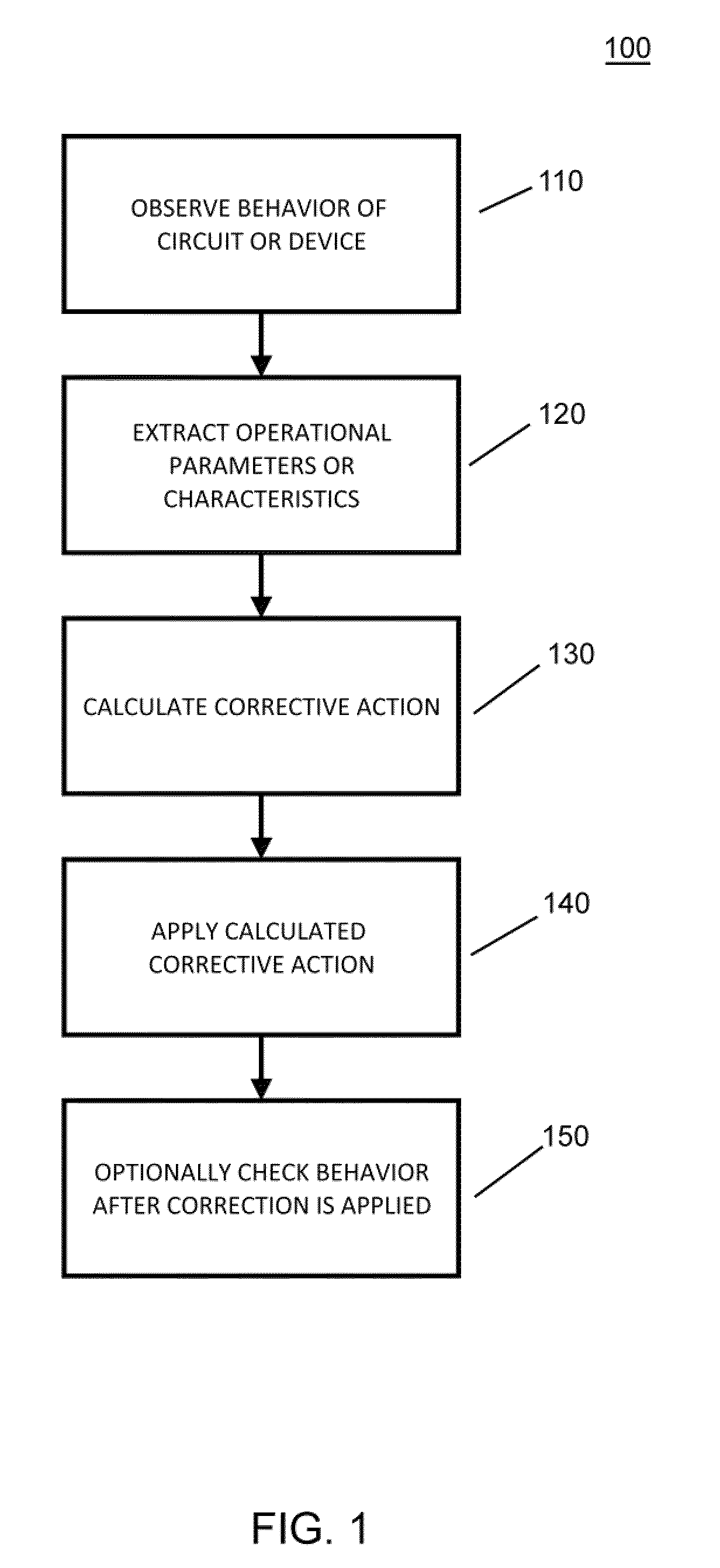

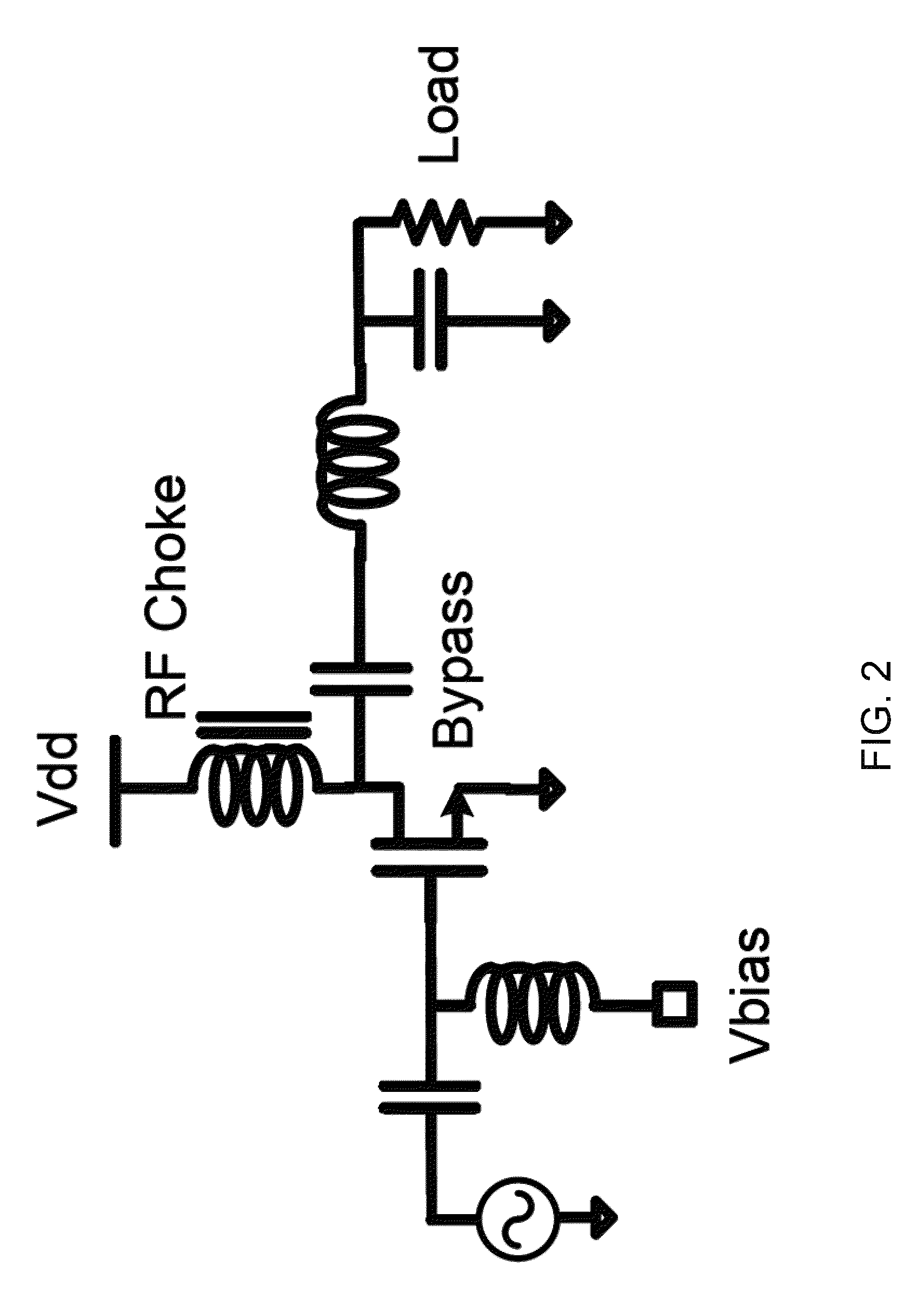

Self-healing power amplifier: methods and apparatus

ActiveUS20110140772A1Optimize power amplifier performance metricElectric devicesCurrent/voltage measurementPower sensorSelf-healing

An integrated power amplifier includes a divider and a combiner. The integrated power amplifier also includes two or more amplifiers. Each of the amplifier input terminals is electrically coupled to a divider output terminal and each of the amplifier output terminals is electrically coupled to a combiner input terminal. At least one power sensor is configured to provide a power amplifier performance metric. The divider and the combiner include a plurality of actuators. Each actuator has at least one actuator control terminal which is configured to provide an actuator setting. The actuators are configured via the actuator control terminals to optimize the power amplifier performance metric. Methods to simulate the operation of a self-healing power amplifier and a process for the operation of a self-healing circuit are also described.

Owner:CALIFORNIA INST OF TECH

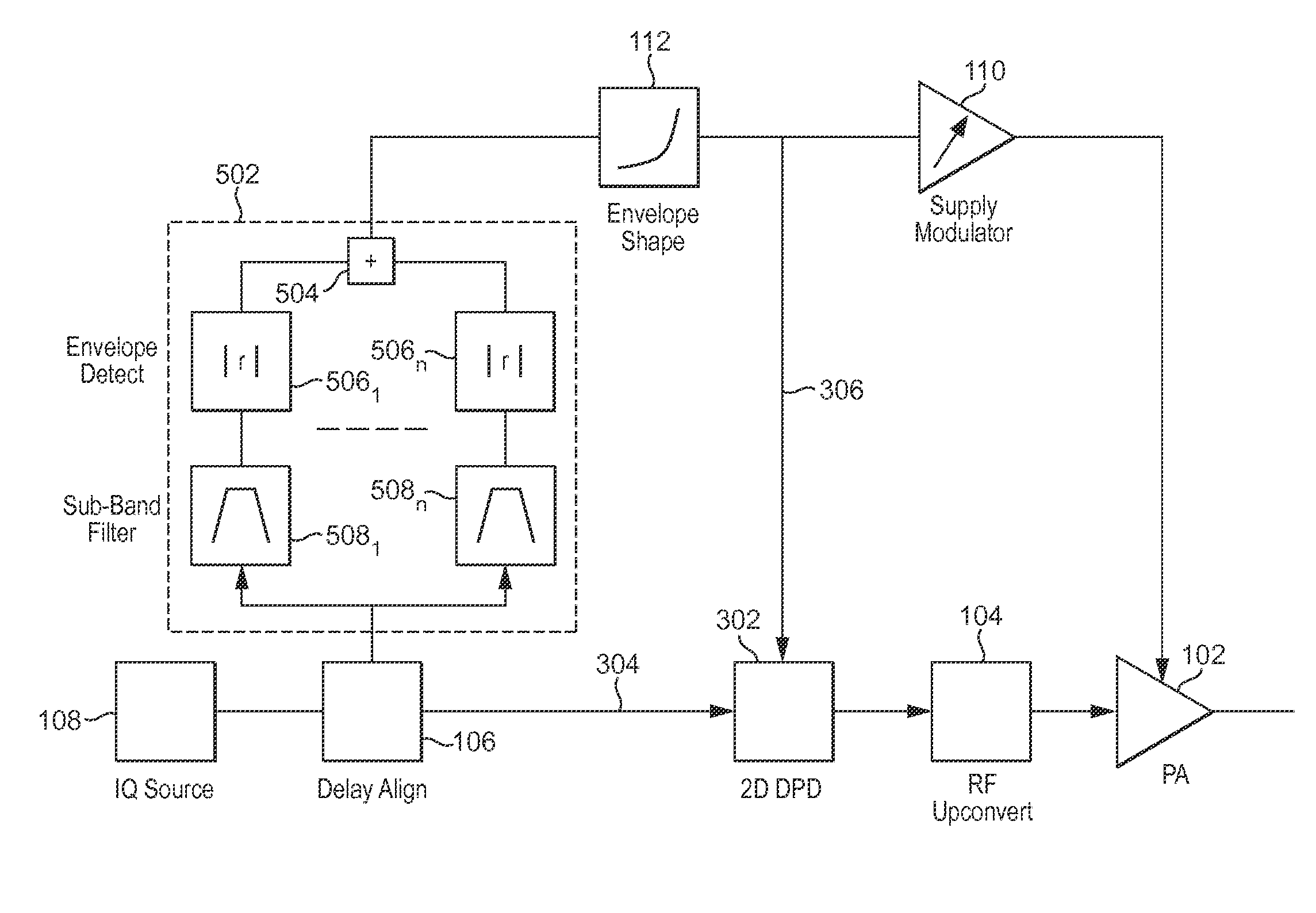

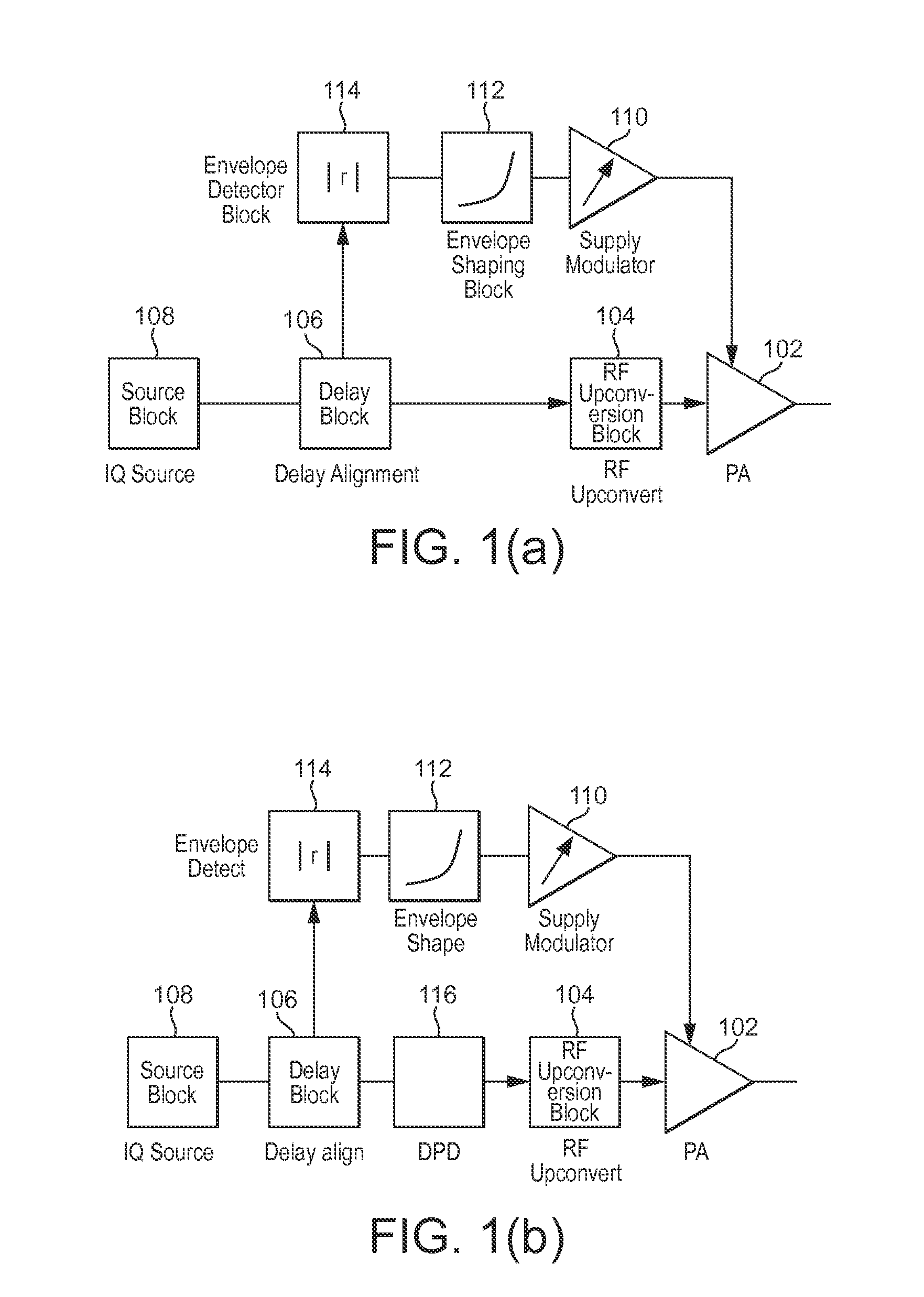

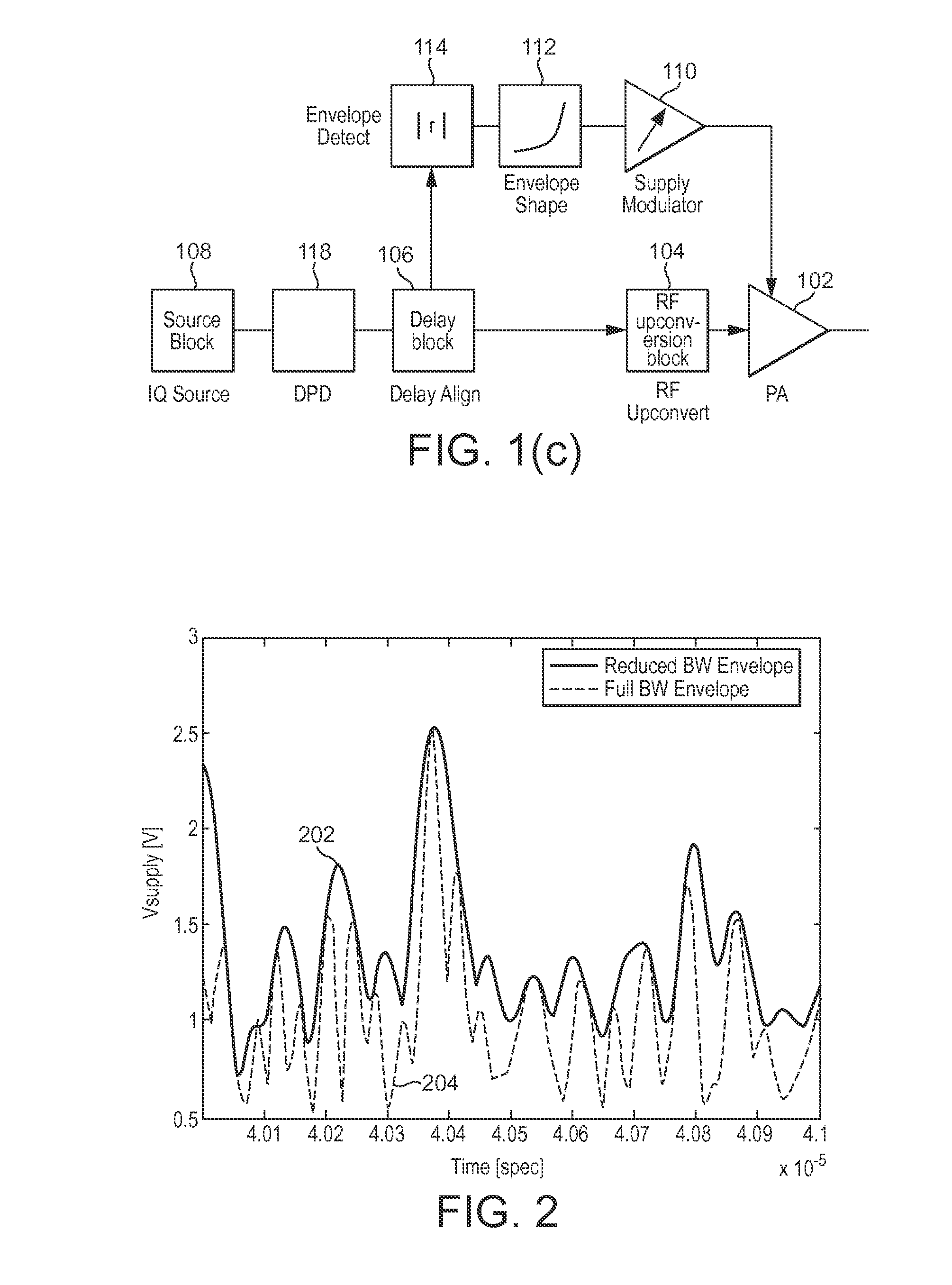

Reduced bandwith of signal in an envelope path for envelope tracking system

ActiveUS20150123735A1Amplifier modifications to reduce non-linear distortionHigh frequency amplifiersAudio power amplifierEngineering

An envelope tracking power amplifier system comprising an RF input path and an envelope path for providing a modulated power amplifier supply, further comprising a plurality of envelope detectors for detecting the envelope of a plurality of frequency bands of an input signal and each generating an output signal, and a combiner for combining the output of the envelope detectors.

Owner:SNAPTRACK

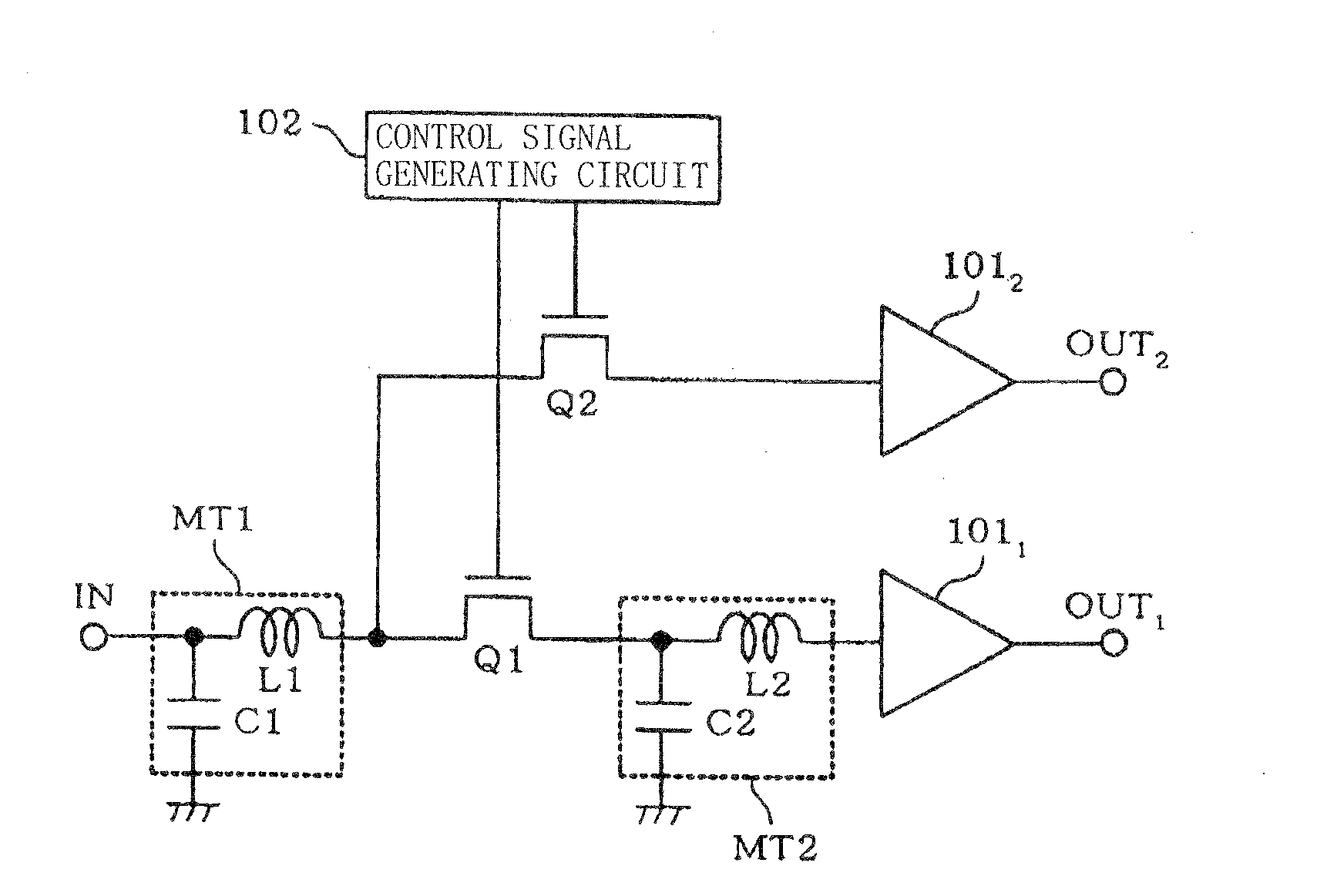

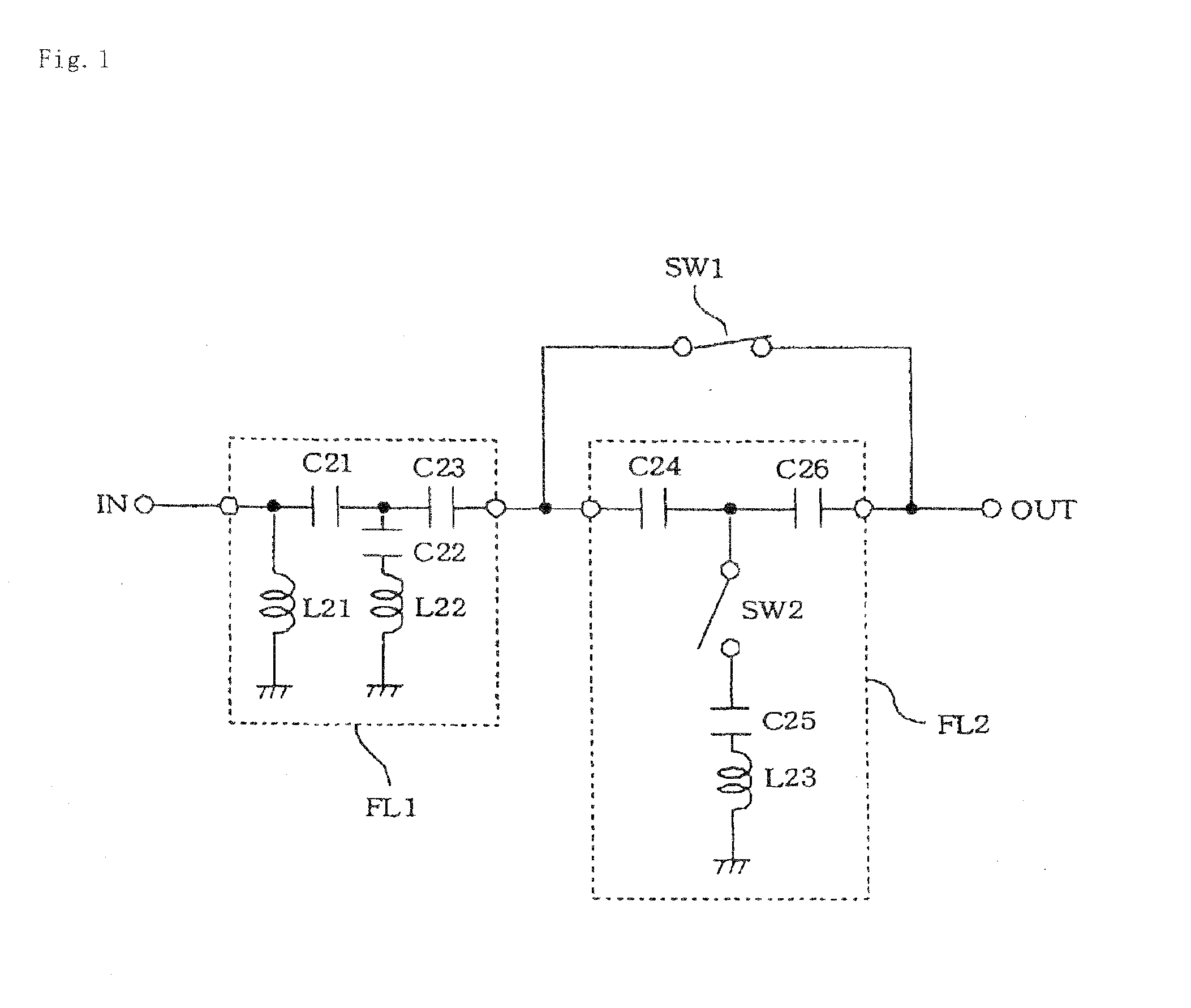

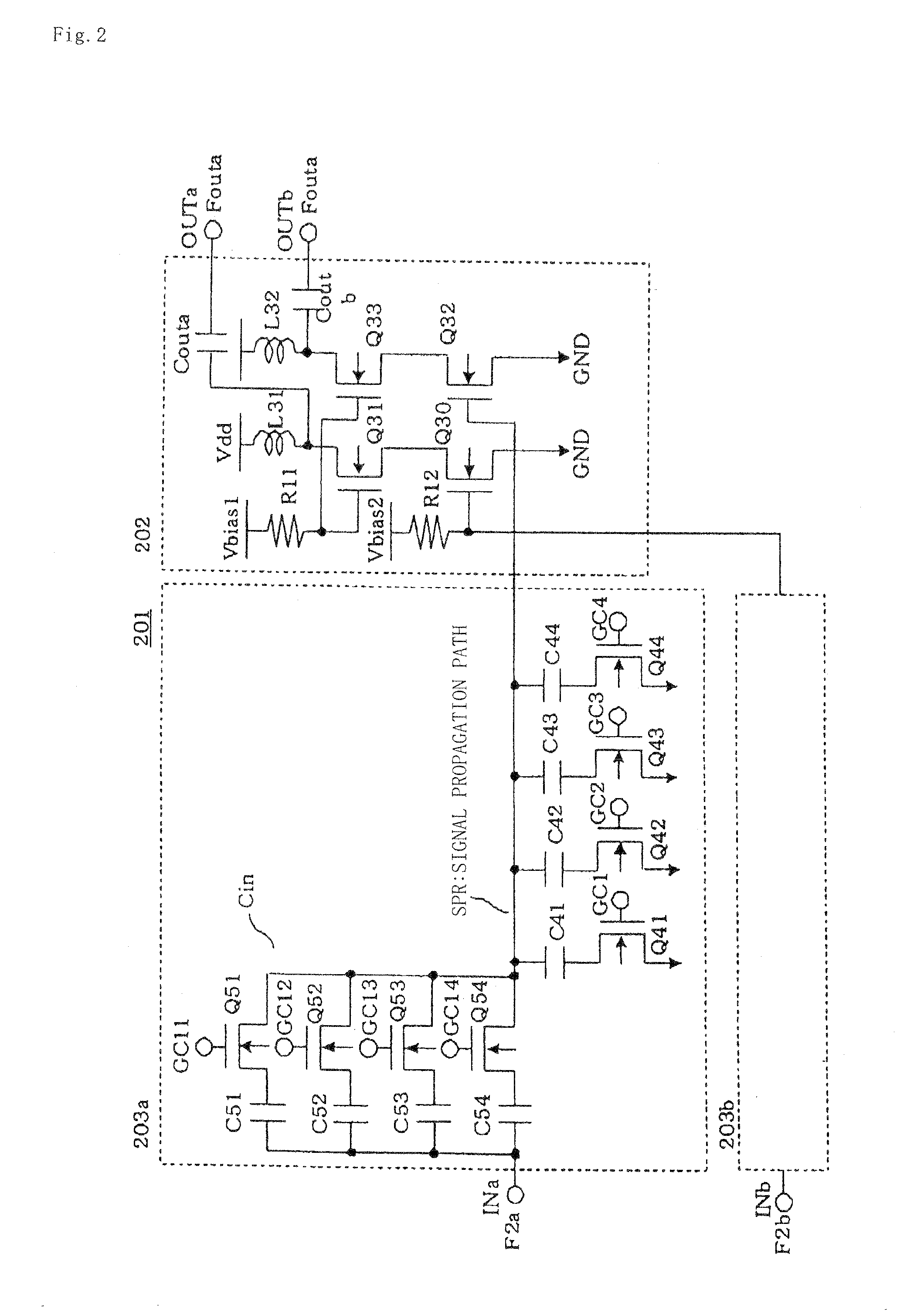

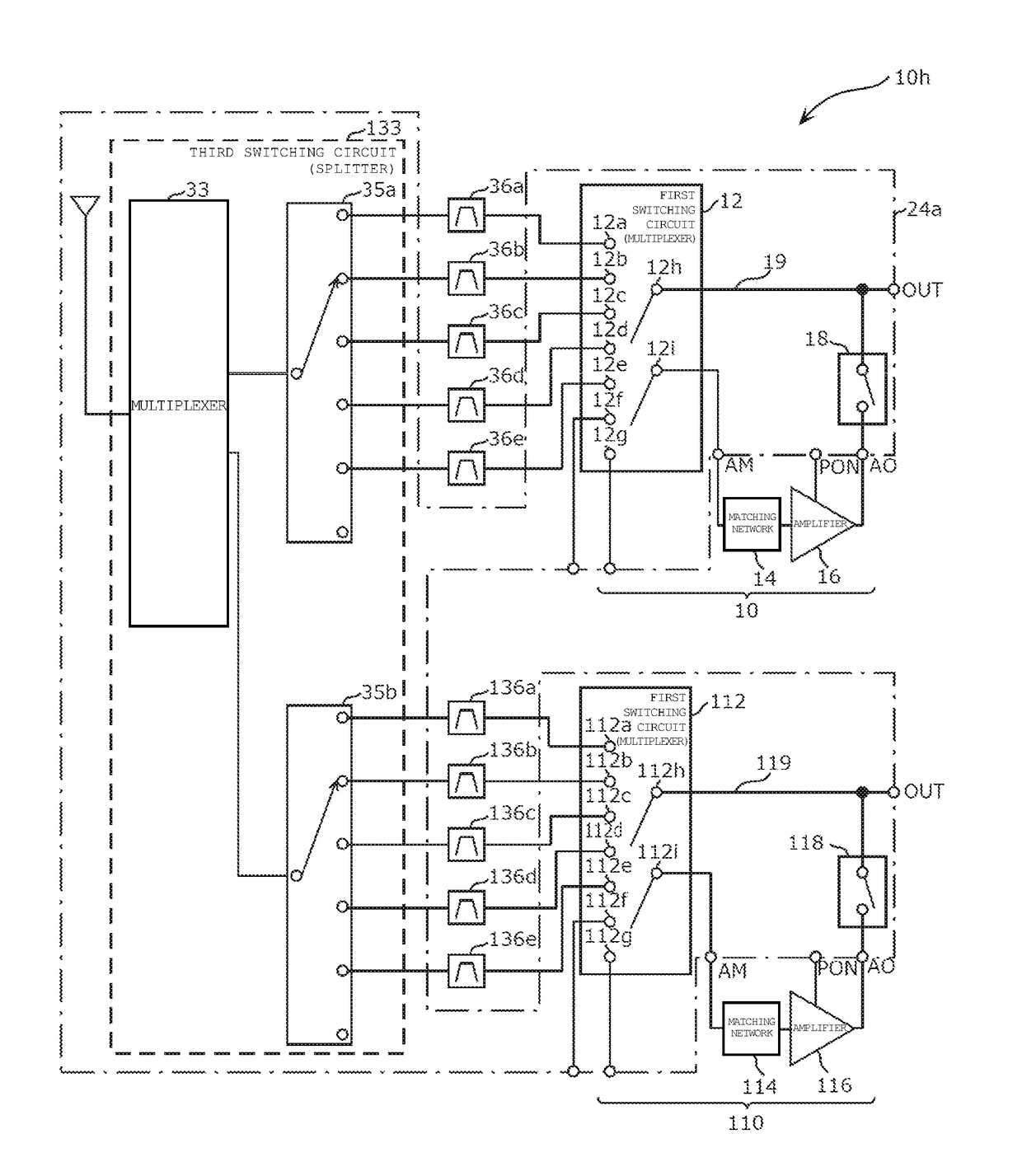

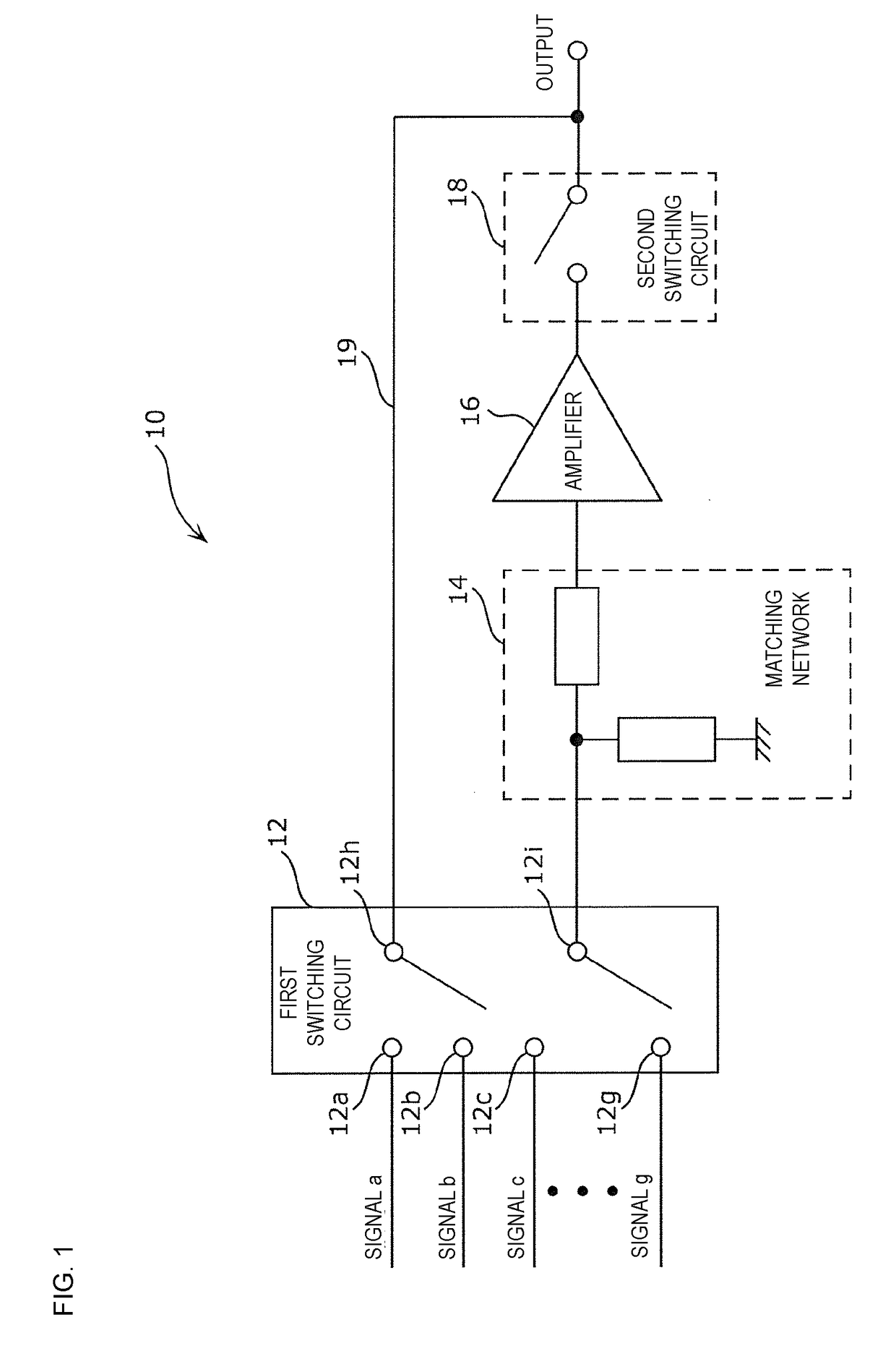

Amplification circuit

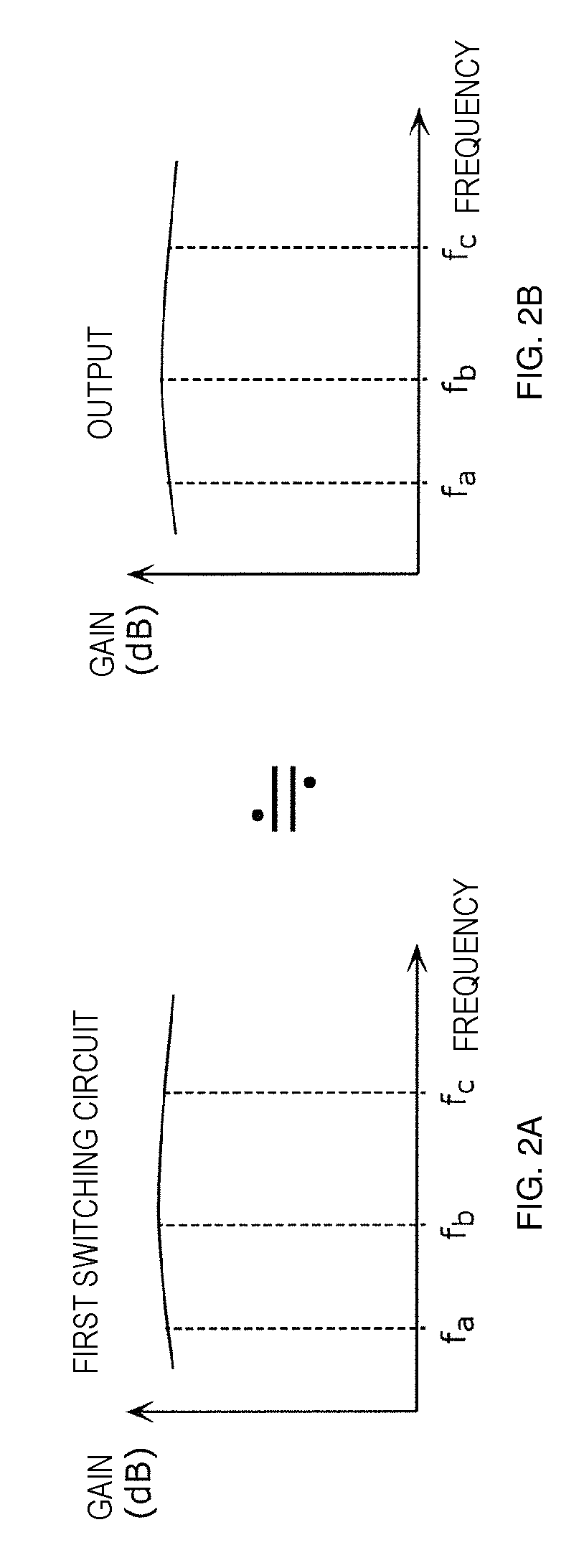

ActiveUS20100060354A1Wide dynamic rangeImprove signal qualityAmplifier combinationsAmplifiers using switched capacitorsAudio power amplifierControl signal

The present invention is aimed at realizing an amplifying circuit whose chip size is prevented from being significantly increased even if the number of compatible frequencies increases, and which has a wide dynamic range when it operates under a low voltage. The amplifying circuit includes a plurality of impedance converting circuits connected to each other by a switching circuit of a first type having a signal cutting-off function, a switching circuit of a second type connected to a path branched from an input side of the switching circuit of the first type, the switching circuit of the second type having a signal cutting-off function, amplifiers connected respectively to an output side of one of the impedance converting circuits in a final stage and to an output side of the switching circuit of the second type, and a control signal generating circuit for controlling connection / disconnection between said switching circuit of the first type and said switching circuit of the second type; wherein either one of the paths is selected to input a signal to one of the amplifiers.

Owner:RENESAS ELECTRONICS CORP

Self-healing power amplifier: methods and apparatus

An integrated power amplifier includes a divider and a combiner. The integrated power amplifier also includes two or more amplifiers. Each of the amplifier input terminals is electrically coupled to a divider output terminal and each of the amplifier output terminals is electrically coupled to a combiner input terminal. At least one power sensor is configured to provide a power amplifier performance metric. The divider and the combiner include a plurality of actuators. Each actuator has at least one actuator control terminal which is configured to provide an actuator setting. The actuators are configured via the actuator control terminals to optimize the power amplifier performance metric. Methods to simulate the operation of a self-healing power amplifier and a process for the operation of a self-healing circuit are also described.

Owner:CALIFORNIA INST OF TECH

Dual path chopper stabilized amplifier and method

ActiveUS7518440B1Economical lowAvoid performanceAmplifier modifications to raise efficiencyAmplifier modifications to reduce detrimental impedenceCapacitanceAudio power amplifier

A dual path chopper-stabilized amplifier (100) includes first (11) and second (11A) chopping / notch-filtering paths, each including an input chopper (9,9A), a transconductance amplifier (2,2A), and a notch filter (15,15A). Chopping and notch filtering in the first path are controlled by first (CHOPCLK) and second (FILTERCLK) clock signals, respectively. Chopping and notch filtering in the second path are controlled by the second (FILTERCLK) and first (CHOPCLK) clock signals, respectively. Outputs of the first (15) and second (15A) switched capacitor notch filters are combined to provide an amplifier output signal (23A,B) that updates a capacitance (C4) at 4 times the frequency of the filter clock signal, to thereby improve amplifier stability without increasing clock frequency.

Owner:TEXAS INSTR INC

Image sampling circuit with a blank reference combined with the video input

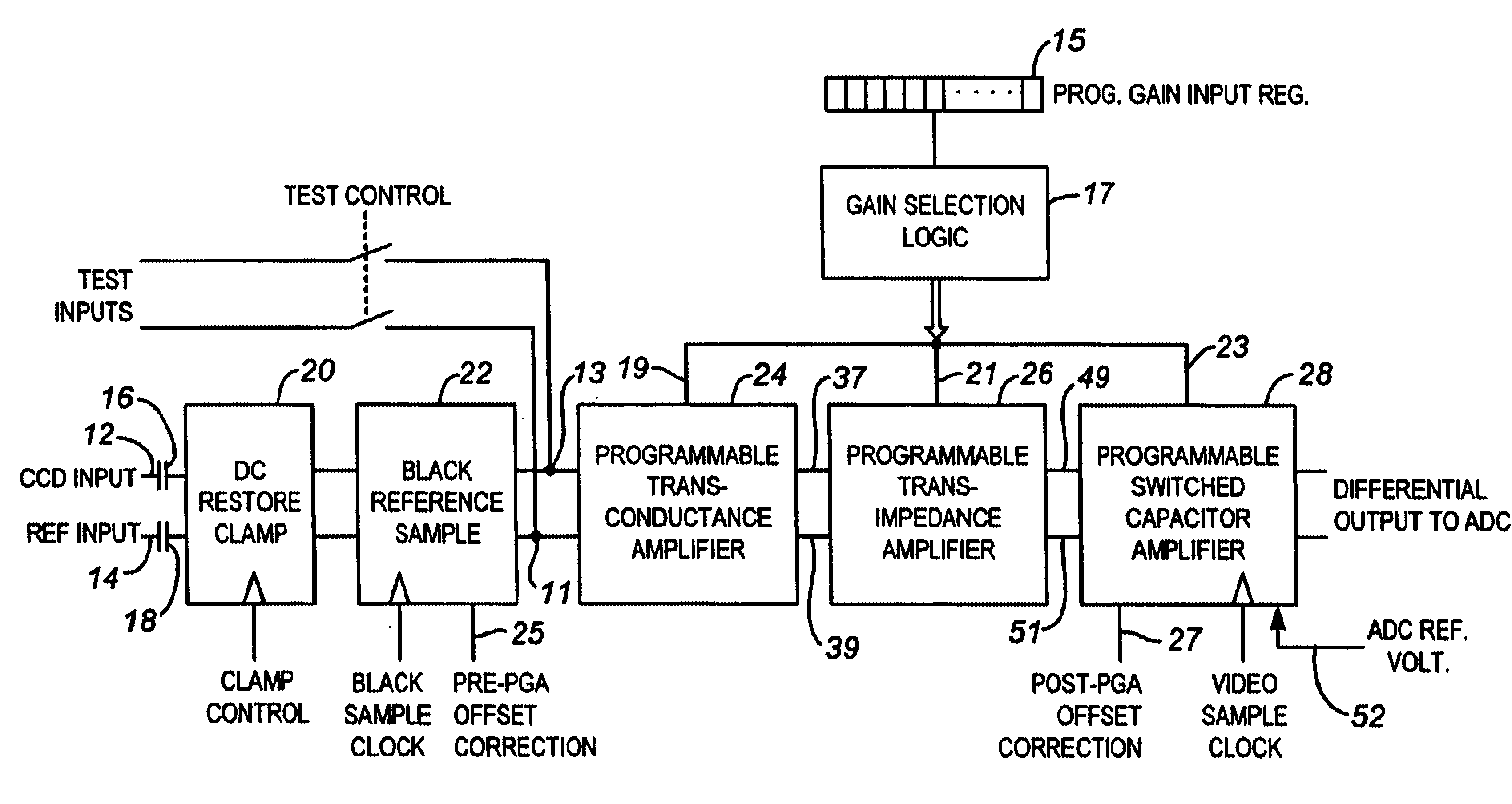

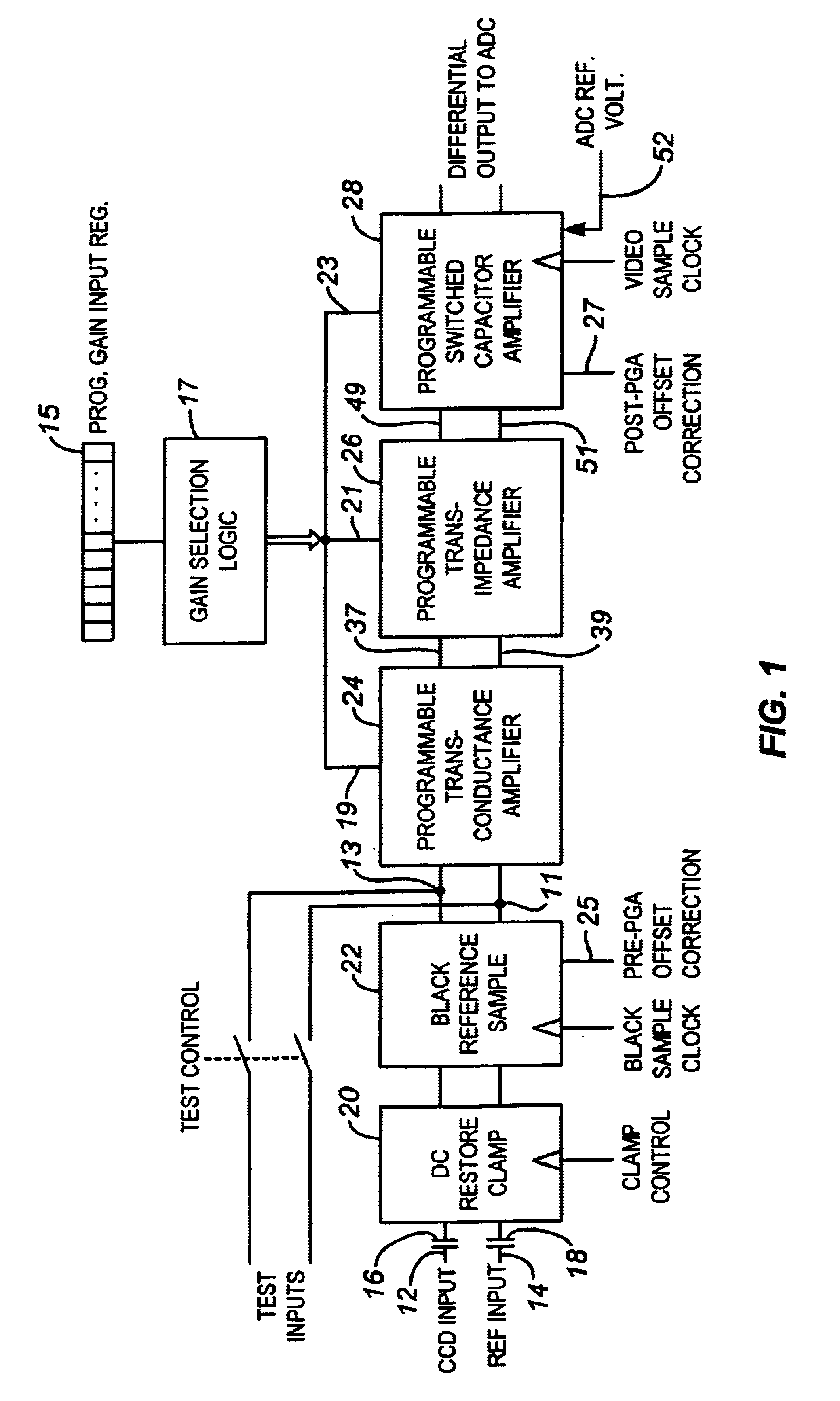

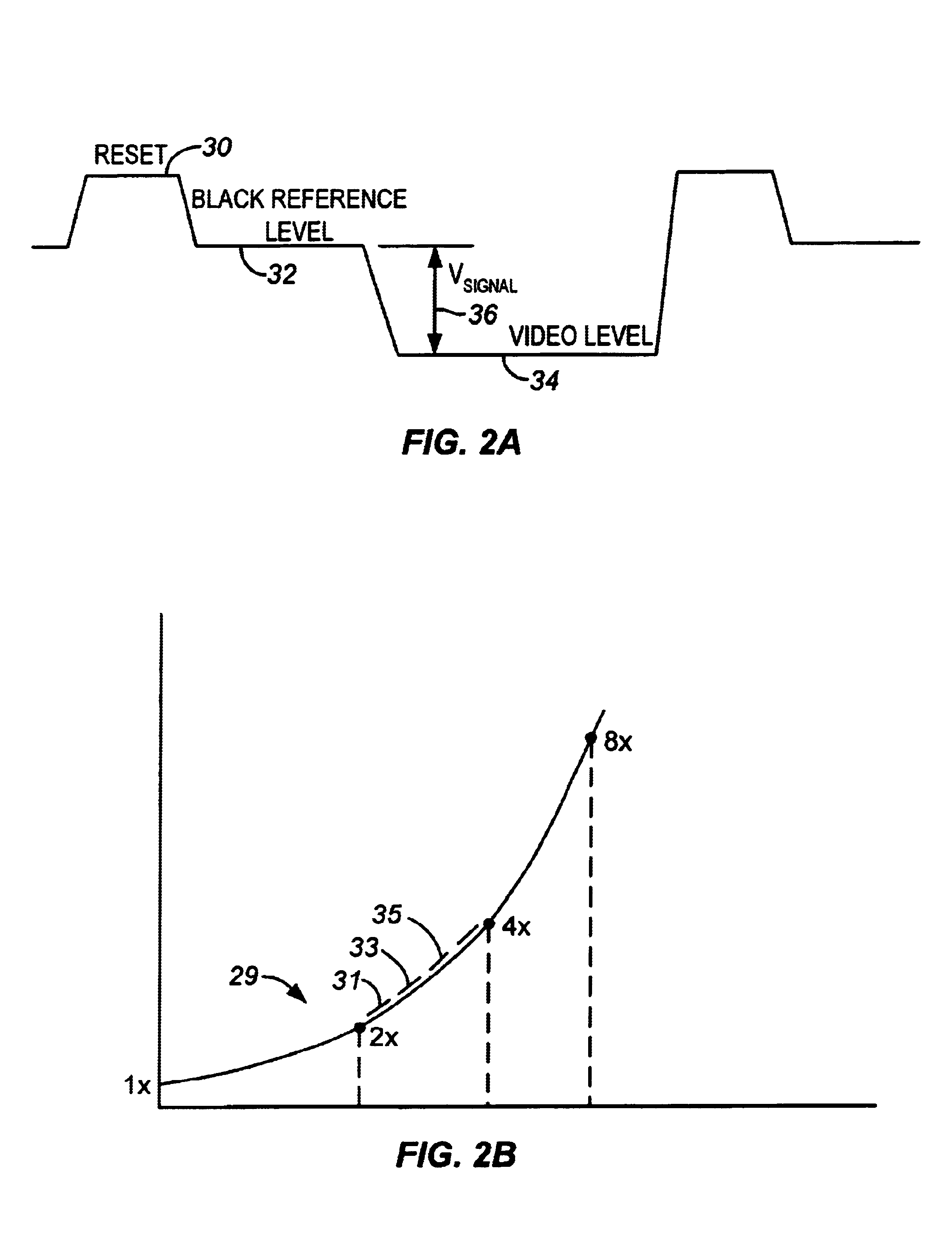

ActiveUS6952240B2Without adversely affectingEnhanced signalTelevision system detailsElectric signal transmission systemsCapacitanceAudio power amplifier

A programmable gain amplifier having three separately programmable amplifiers. A programmable transconductance amplifier is followed by a programmable transimpedance amplifier, then a programmable switched capacitor amplifier. In one embodiment, this programmable gain amplifier is implemented in an analog front-end (AFE) circuit. One AFE embodiment provides a coarse pre-gain offset a black reference level sampler, and a fine post-gain offset in the programmable switched capacitor amplifier. In one embodiment, an ADC reference is sampled, and is subtracted directly from the video signal in the switched capacitor amplifier so that the zero level of the video signal is made to correspond to the zero level of the ADC. In another embodiment, a piece-wise linear approximation of an exponential gain function is implemented by programming the transconductance and transimpedance amplifiers to provide exponential jumps in gain, while the switched capacitor amplifier is programmed to interpolate as needed between the exponential gain levels.

Owner:EXAR CORP

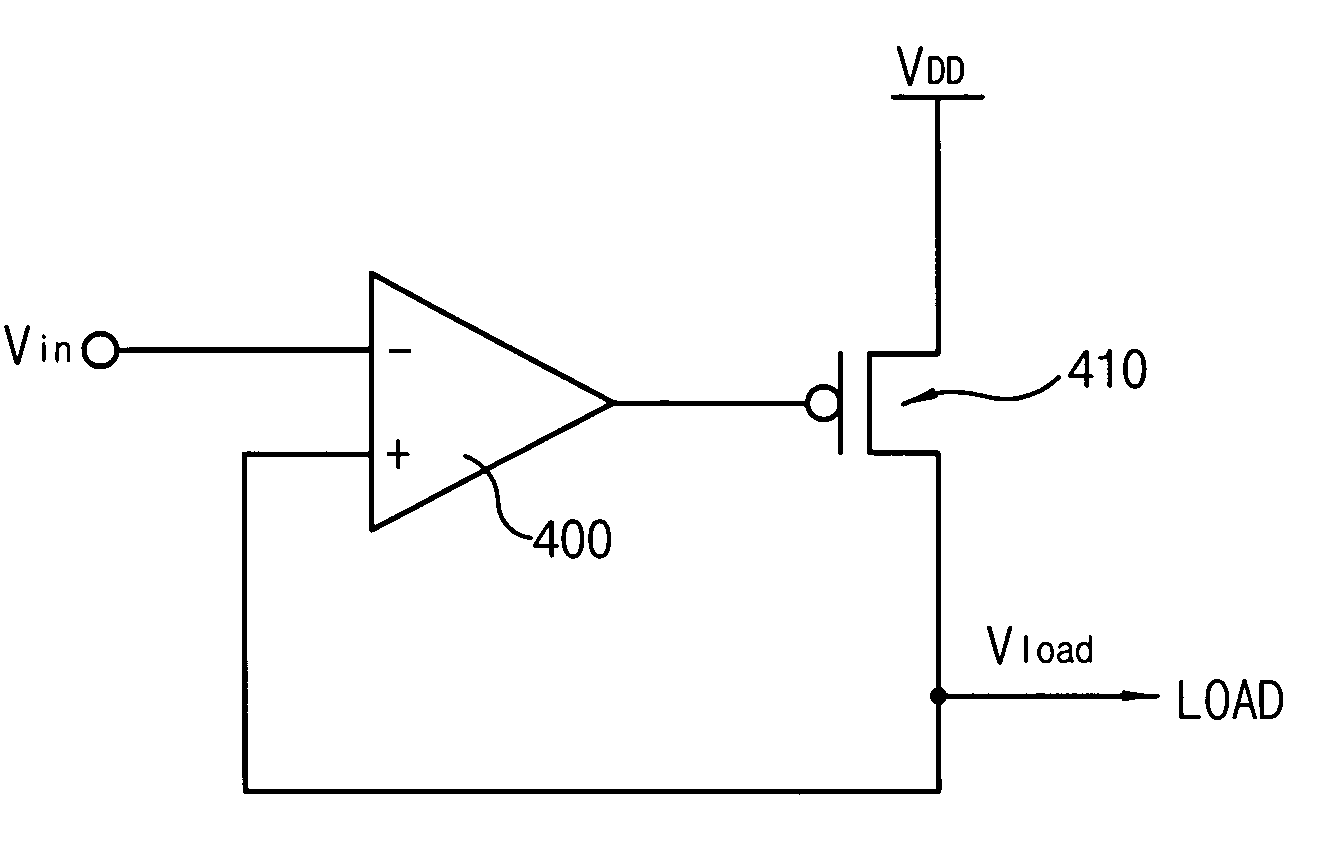

Analog buffer, display device having the same, and method of driving the same

ActiveUS20050258997A1Small sizeElectric signal transmission systemsCharge amplifiersDisplay deviceComparator

An analog buffer, display device having the same and a method of drving the same are provided. The analog buffer applies an analog voltage to a load. The analog buffer includes a comparator and a transistor. The comparator is configured to compare an input voltage provided from an external device with the analog voltage applied to the load. The transistor is turned on to electrically charge the load when the analog voltage is lower than the input voltage or turned on to electrically discharge the load when the analog voltage is higher than the input voltage, and turned off when the analog voltage becomes substantially the same as the input voltage.

Owner:SAMSUNG DISPLAY CO LTD

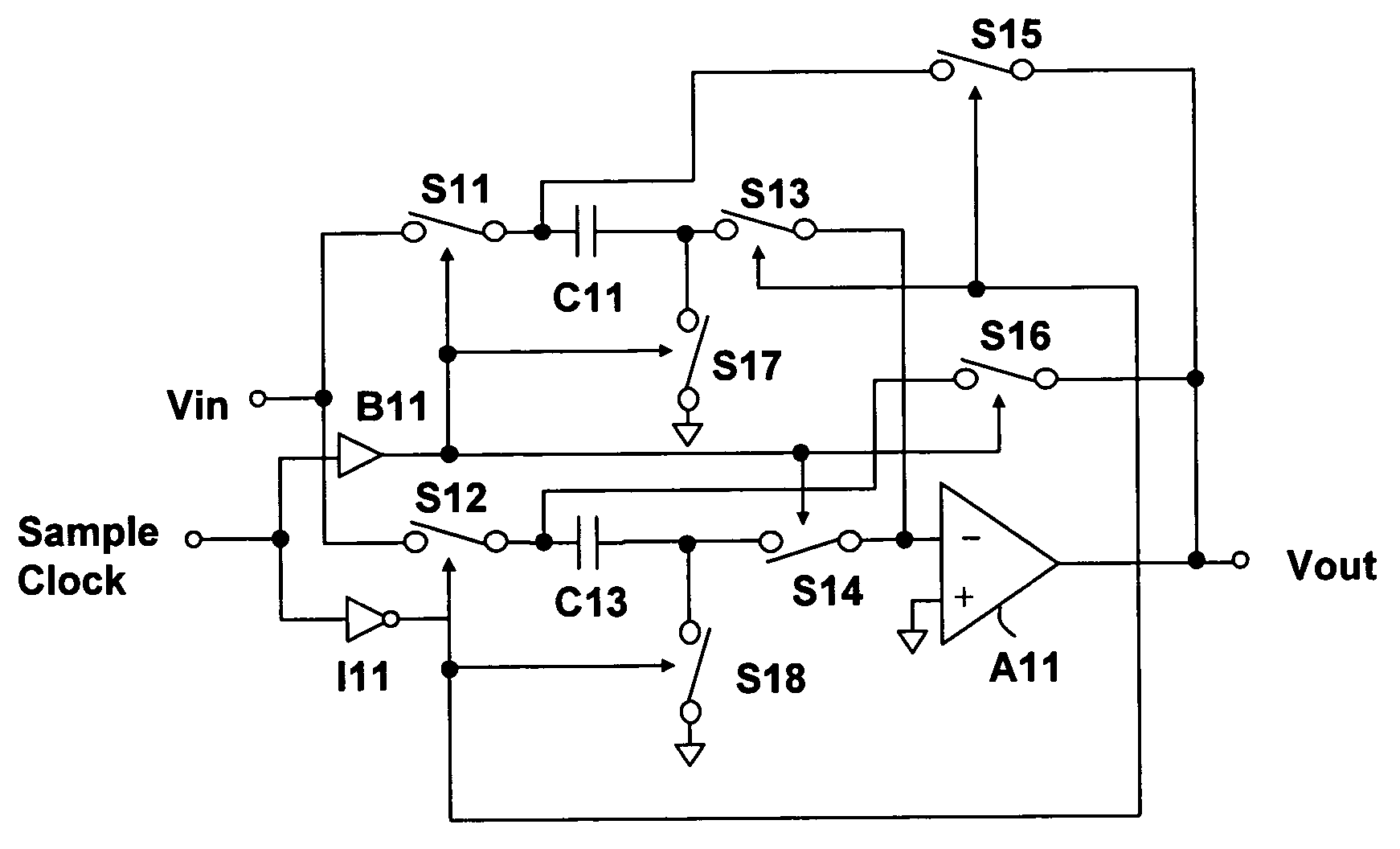

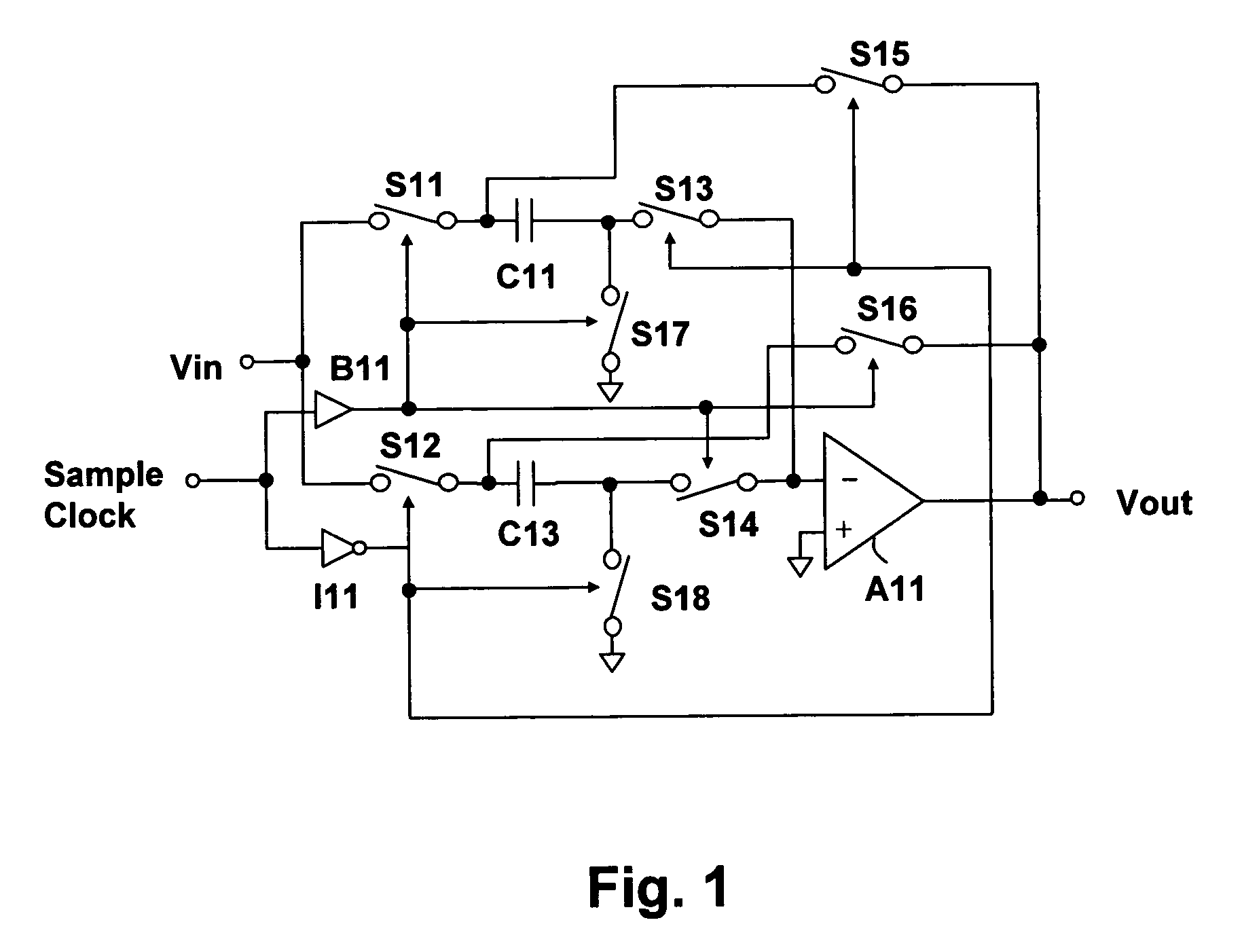

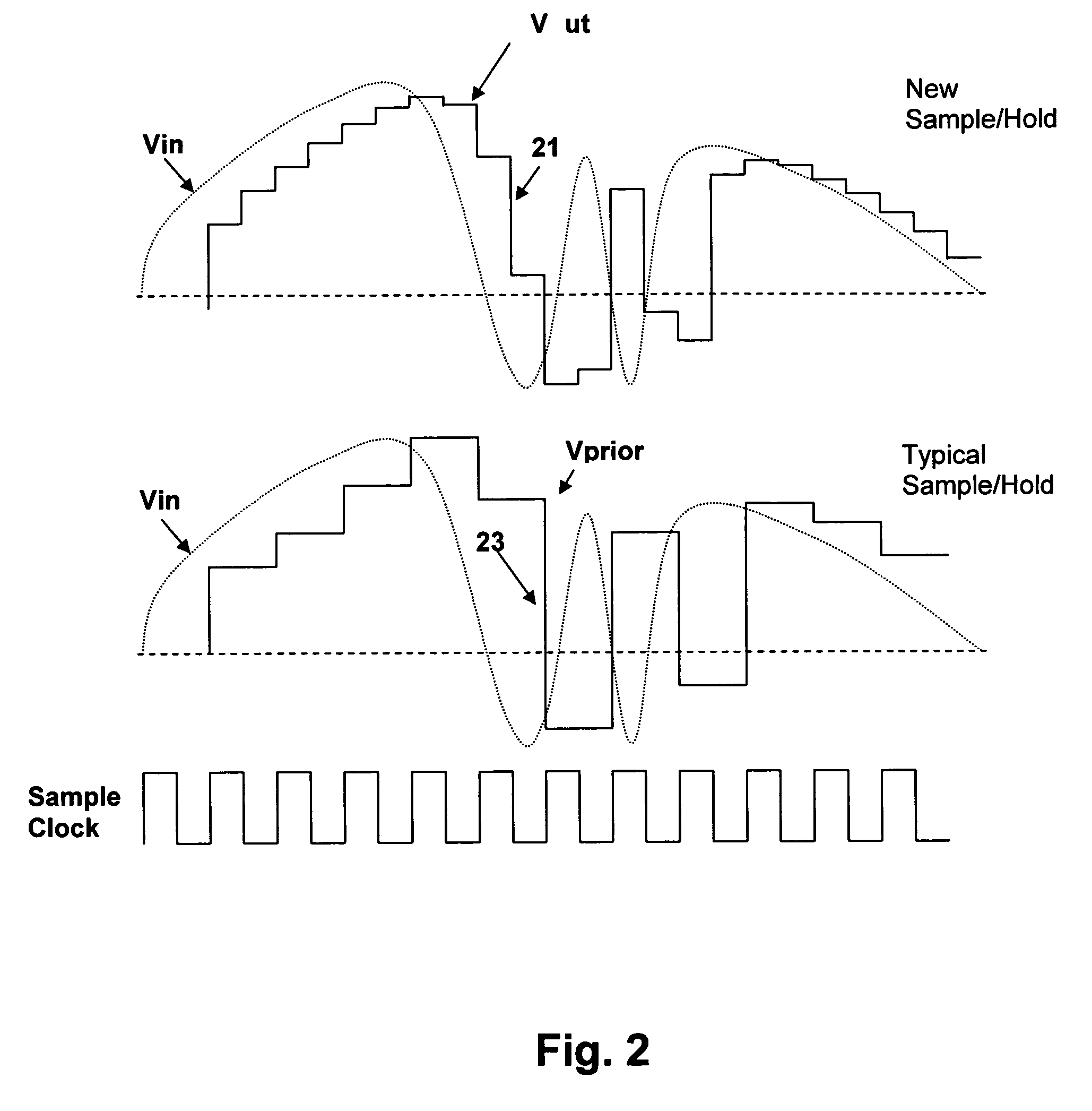

Switched-capacitor sample/hold having reduced amplifier slew-rate and settling time requirements

ActiveUS20050073351A1Lower conversion rateReduce errorsAnalogue/digital conversionComputing operations for integral formationCapacitanceNegative feedback

A switched-capacitor sample / hold circuit and method having reduced slew-rate and settling time requirements provides for lower-cost and / or lower-power implementation of sample / hold circuits and / or reduced error due to amplifier characteristics. The switched-capacitor sample / hold circuit incorporates a pair of capacitors that are alternatively and mutually-exclusively switched between an input sample position and an amplifier hold position, providing a dual sampled amplifier output signal that has reduced transitions at each sample interval. An alternative embodiment of the sample / hold circuit incorporates a fully-differential amplifier having a differential input and a differential output. Four capacitors are employed forming two of the dual sampled switched-capacitor circuits, one in each negative feedback path (inverted output to non-inverting input, non-inverted output to inverting input) of the amplifier. The two dual sampled switched-capacitor circuits are referenced to each other, providing fully differential operation and cancellation of error due to charge injection.

Owner:MICROCHIP TECH INC

Switched capacitor circuit with reduced common-mode variations

ActiveUS7012463B2Amplifier modifications to raise efficiencyDifferential amplifiersImpedance matchingFeedback circuits

A circuit with a common-mode dual output includes a feedback circuit connected to alternate the states of the dual output between an average output level and a desired common-mode level. The difference between the average and desired levels is proportional to a signal offset level. An impedance matching circuit is connected to the feedback circuit to adjust the signal offset level.

Owner:ANALOG DEVICES INC

Amplification circuit

ActiveUS20170302236A1Gated amplifiersAmplifier modifications to reduce temperature/voltage variationAudio power amplifierVariable-gain amplifier

An amplification circuit includes a first switching circuit that includes input terminals and first and second output terminals and that puts the second output terminal into an open state with respect to the input terminals while selectively putting the first output terminal into a state of being connected to any of the input terminals or selectively puts the second output terminal into a state of being connected to any of input terminals while putting the first output terminal into a state of being open with respect to the input terminals; a matching network that is connected to the first output terminal; an amplifier that is connected to an output side of the matching network; a second switching circuit that is connected to an output side of the amplifier; and a bypass path that electrically connects the second output terminal and an output terminal of the second switching circuit. The amplifier is a variable-gain amplifier.

Owner:MURATA MFG CO LTD

CMOS imaging system with low fixed pattern noise

ActiveUS20050068439A1Control performanceImprove efficiencyTelevision system detailsTelevision system scanning detailsCMOS sensorEngineering

A CMOS imager system comprising an active pixel sensor having an access supply which provides distributed feedback, a column buffer (having gain and FPN suppression), and an A / D converter co-located with the sensor such that the effective transmission path between the column buffer (or optional analog PGA) and the A / D converter acts as a resistor, rather than a reactance. The system may further include both an analog gain amplifier stage and a digital programmable amplifier stage.

Owner:SAMSUNG ELECTRONICS CO LTD

A switched capacitor circuit compensation apparatus and method

ActiveCN1898872AReference current increasesPulse automatic controlAmplifier modifications to reduce temperature/voltage variationCapacitanceLoop control

The compensation switched capacitor circuit includes a switched capacitor circuit and a compensation circuit. The compensation circuit generates a reference current that varies under closed loop control to maintain a target slew rate determined by the frequency of the input clock for charging the reference capacitor. The output amplifier of the switched capacitor circuit is configured such that its output current varies proportionally to the reference current. Thus, by configuring the reference capacitor to track the effective capacitance of the switched capacitor circuit, the settling time of the switched capacitor circuit can be made relatively insensitive to the value and variation of the effective capacitance over the clock frequency range. The compensation circuit may include a clock reconditioning circuit that clocks the switched capacitor circuit at a desired duty cycle.

Owner:TELEFON AB LM ERICSSON (PUBL)

Split amplifier architecture for cross talk cancellation

ActiveUS7250813B1Canceled outAmplifier modifications to raise efficiencyElectronic switchingAudio power amplifierControl signal

An amplifier circuit includes a first amplifier and a second amplifier and sets of switching devices controlled by a bistate control signal. The bistate control signal is in the first state to cause the first and second sets of switching devices to configure the first amplifier and the second amplifier in a positive parallel configuration and the bistate control signal is in the second state to cause the first and second sets of switching devices to configure the first amplifier and the second amplifier in a negative parallel configuration. When the bistate control signal switches states at each sample cycle of the amplifier circuit, the first amplifier and the second amplifier toggle between the positive parallel configuration and the negative parallel configurations to cancel out crosstalk signals stored at the positive and negative input terminals of the first and second amplifier circuit.

Owner:NAT SEMICON CORP

Popular searches

Switched capacitor networks Active element network Dc-amplifiers with dc-coupled stages Amplifiers with semiconductor devices only Amplifiers with impedence circuits Positive-feedback-circuit arrangements Low noise amplifier Color television details Oscillations generators Physical parameters compensation/prevention