Patents

Literature

411 results about "Fully differential amplifier" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

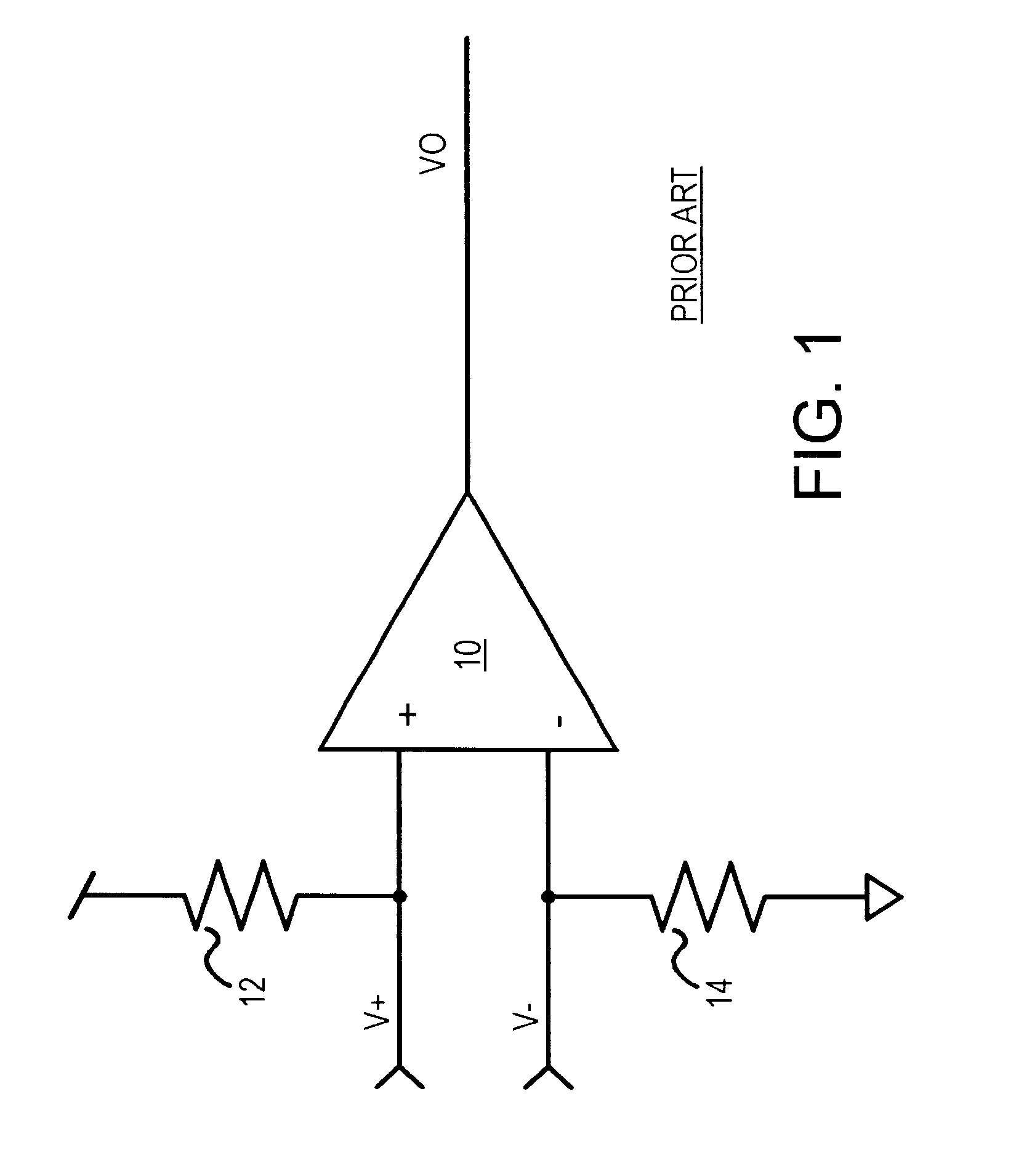

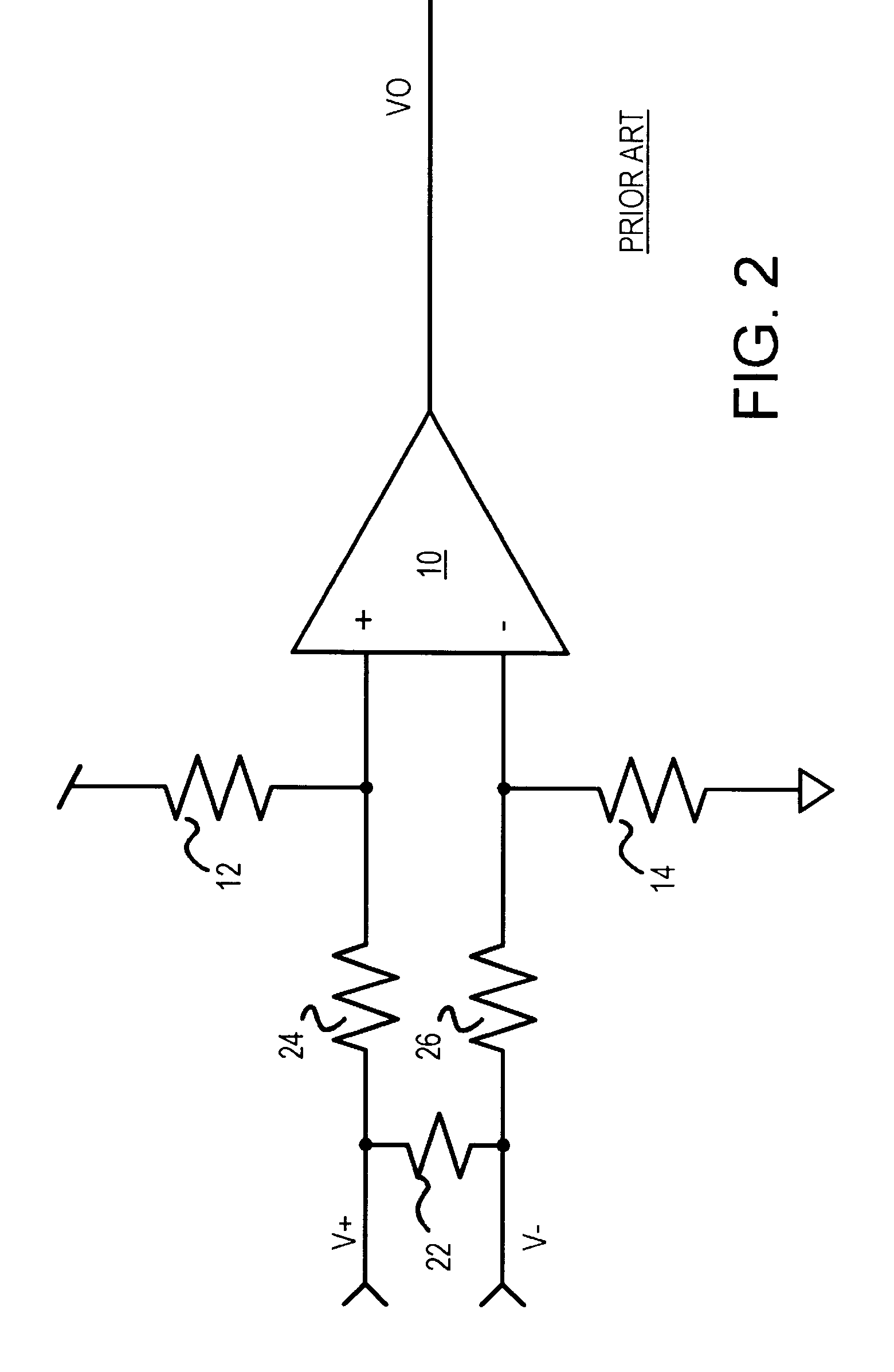

A fully differential amplifier (FDA) is a DC-coupled high-gain electronic voltage amplifier with differential inputs and differential outputs. In its ordinary usage, the output of the FDA is controlled by two feedback paths which, because of the amplifier's high gain, almost completely determine the output voltage for any given input.

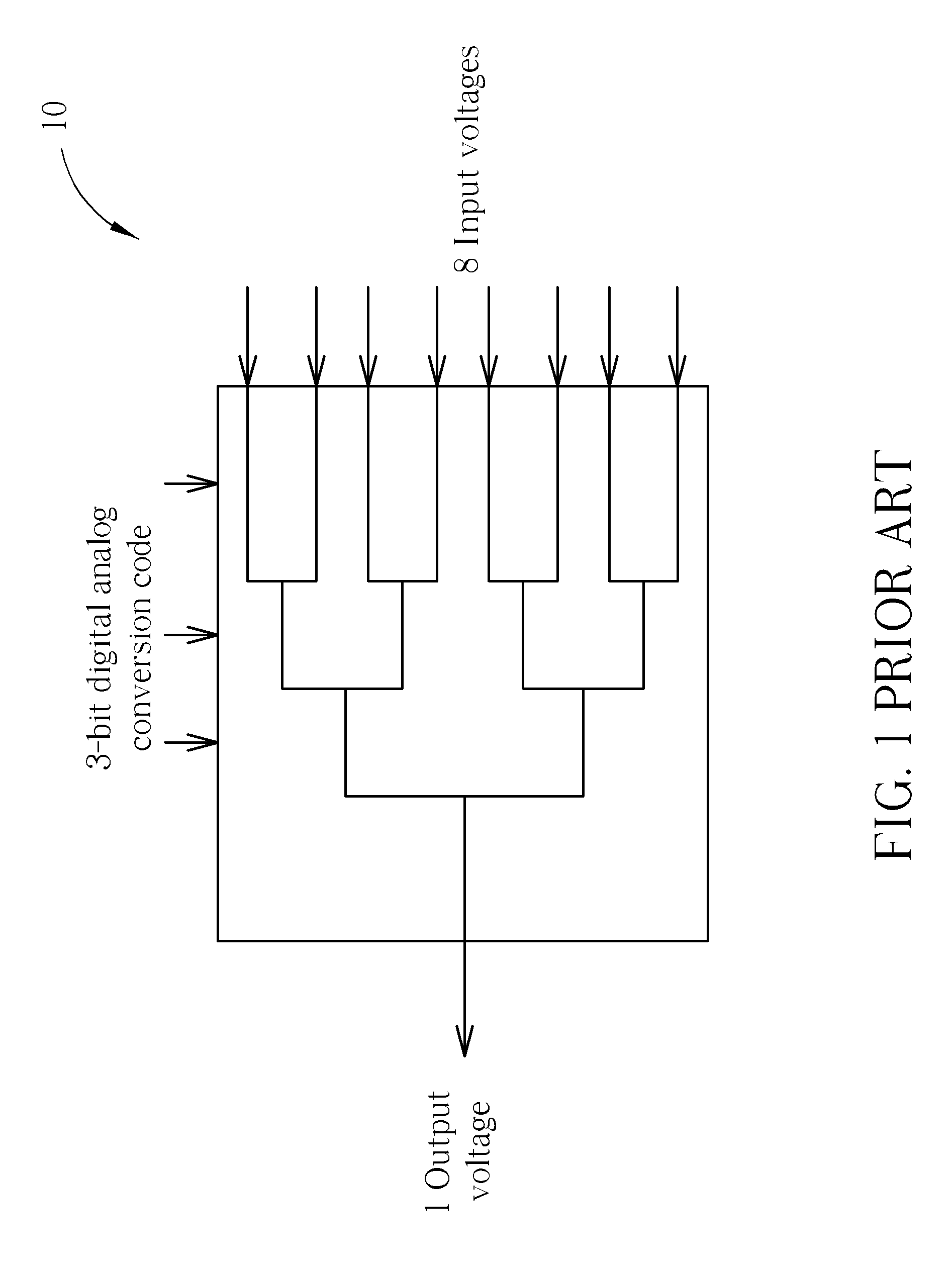

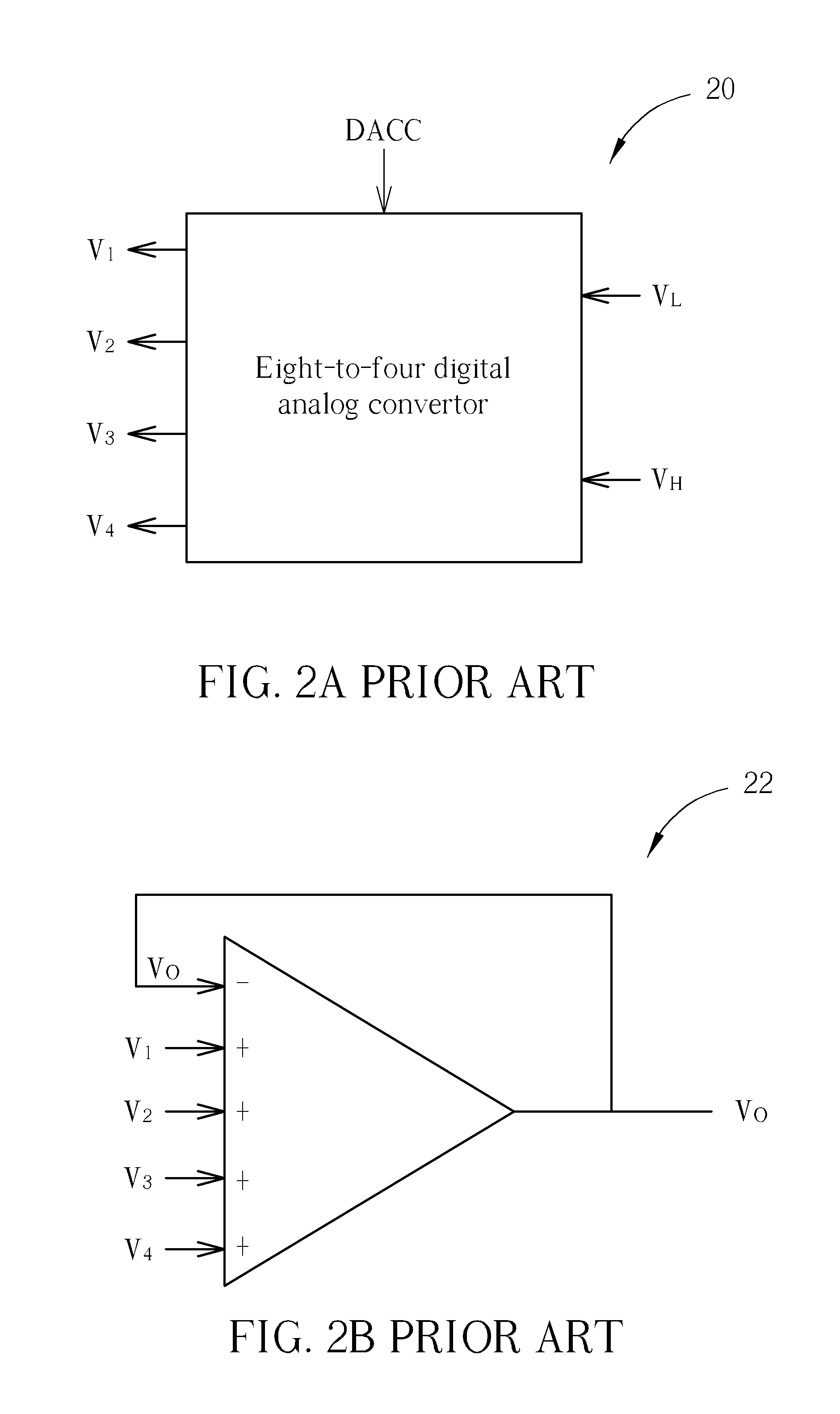

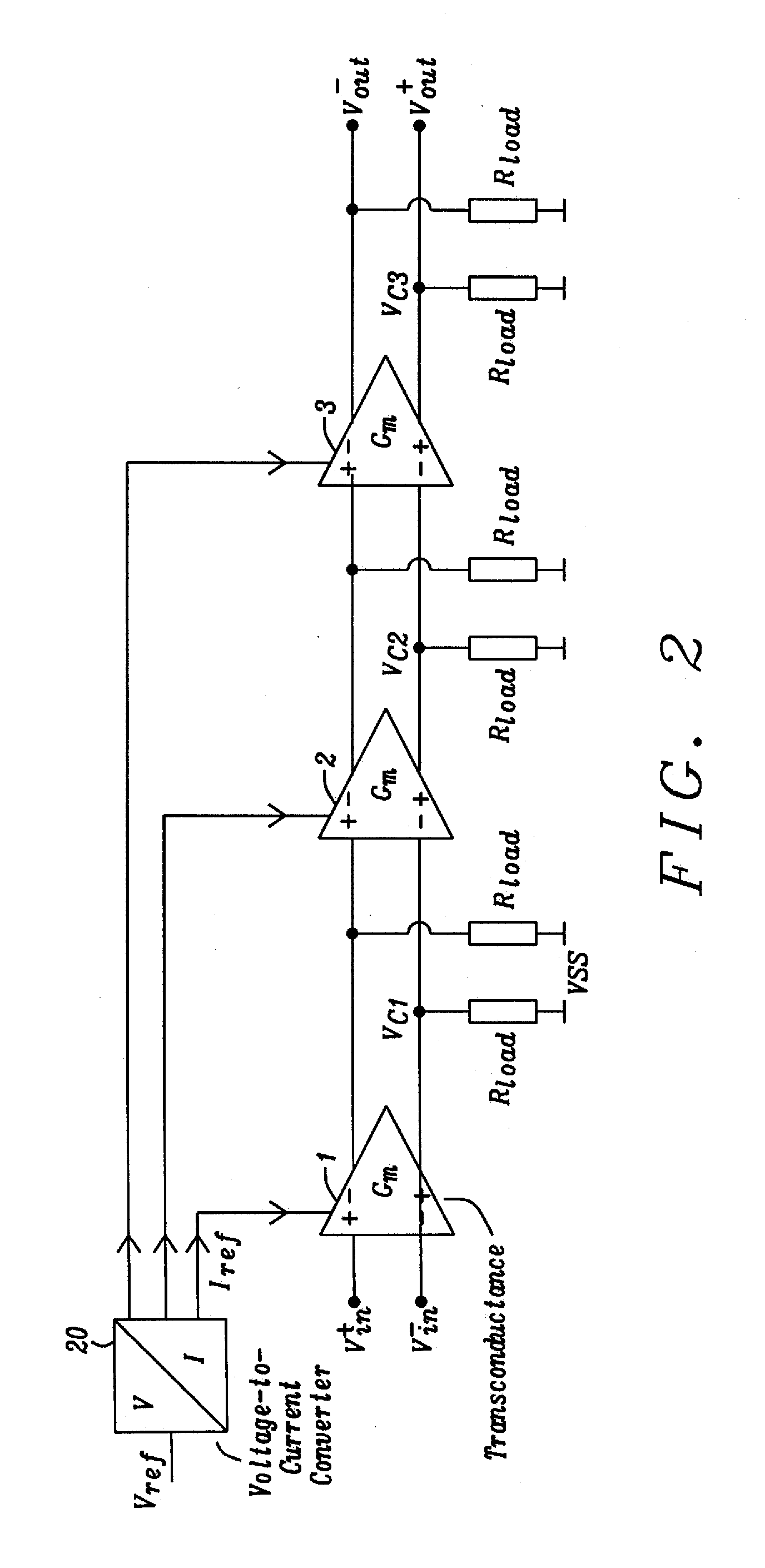

Multi-input differential amplifier with dynamic transconductance compensation

InactiveUS8643437B2Increase rangeHigh output voltage accuracyAmplifier combinationsDifferential amplifiersMulti inputEngineering

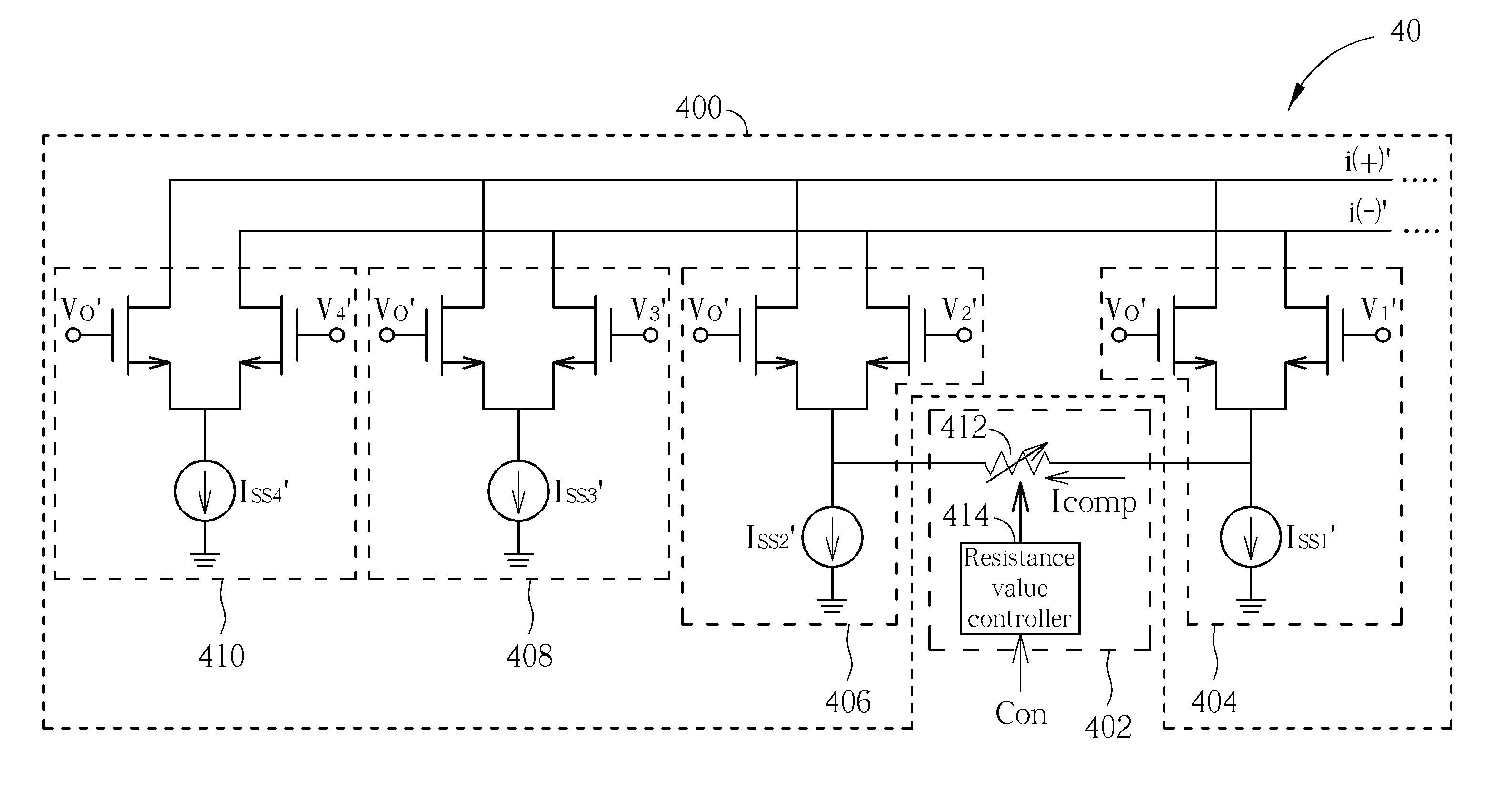

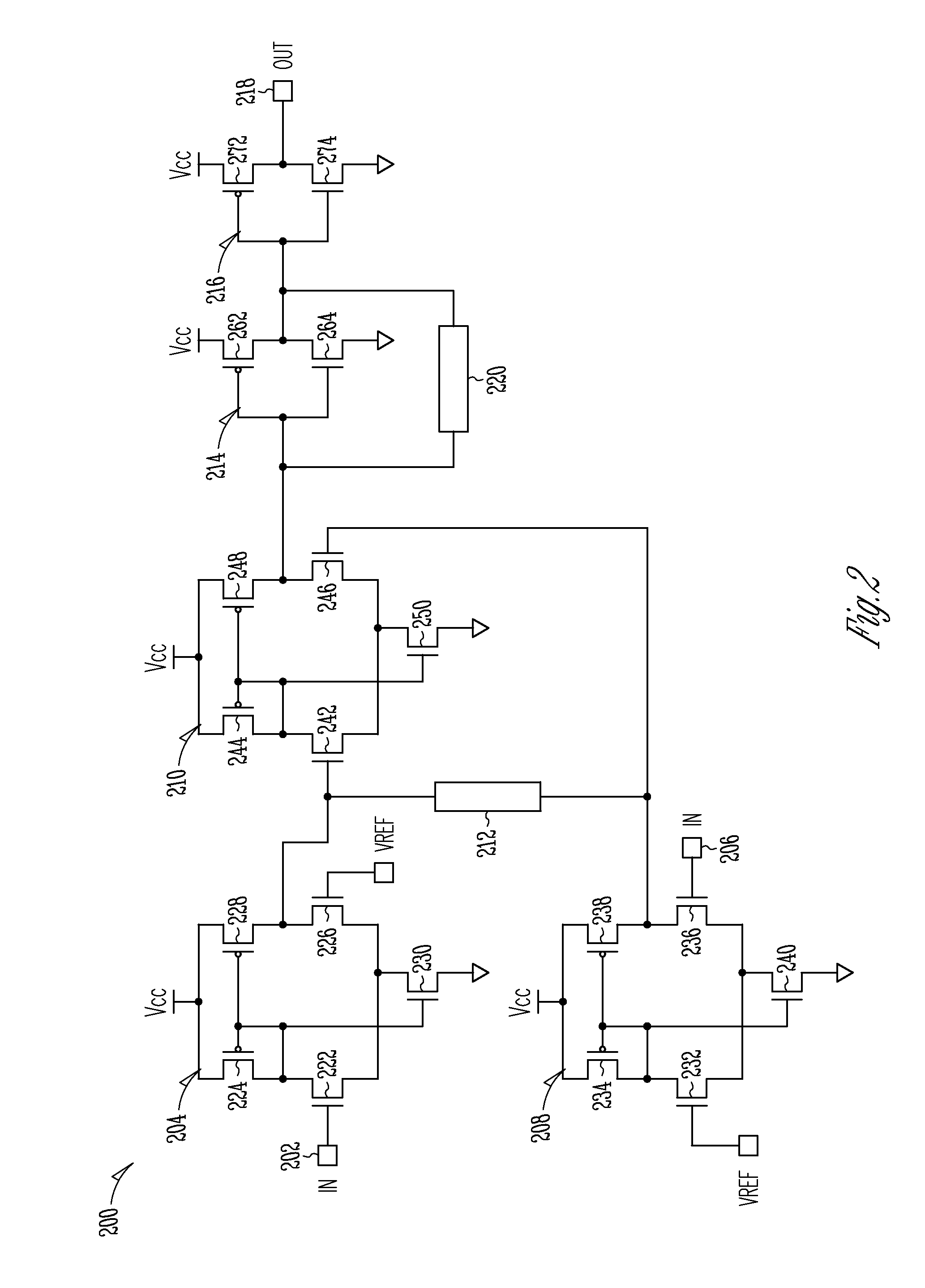

A multi-input differential amplifier with dynamic transconductance compensation is disclosed. The multi-input differential amplifier includes an input stage, an output stage and a transconductance compensation circuit. The input stage includes a plurality of differential input pairs, which includes a first differential input pair, a second differential input pair, a third differential input pair and a fourth differential input pair, for generating a pair of differential signals according to a first input signal, a second input signal, a third input signal, a fourth input signal, and an output signal. The output stage is utilized to generate the output signal in response to the pair of differential signals. The transconductance compensation circuit is coupled between the first and the second differential input pair, for compensating a first transconductance of the first differential input pair and a second transconductance of the second differential input pair.

Owner:NOVATEK MICROELECTRONICS CORP

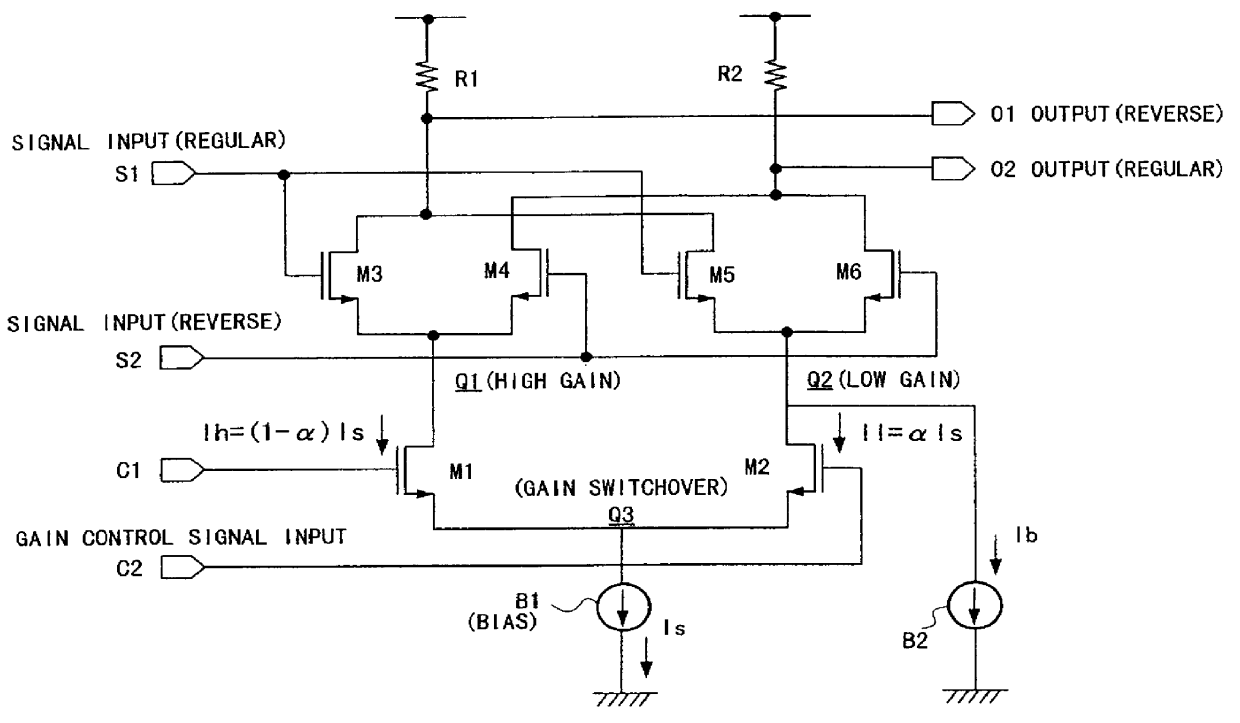

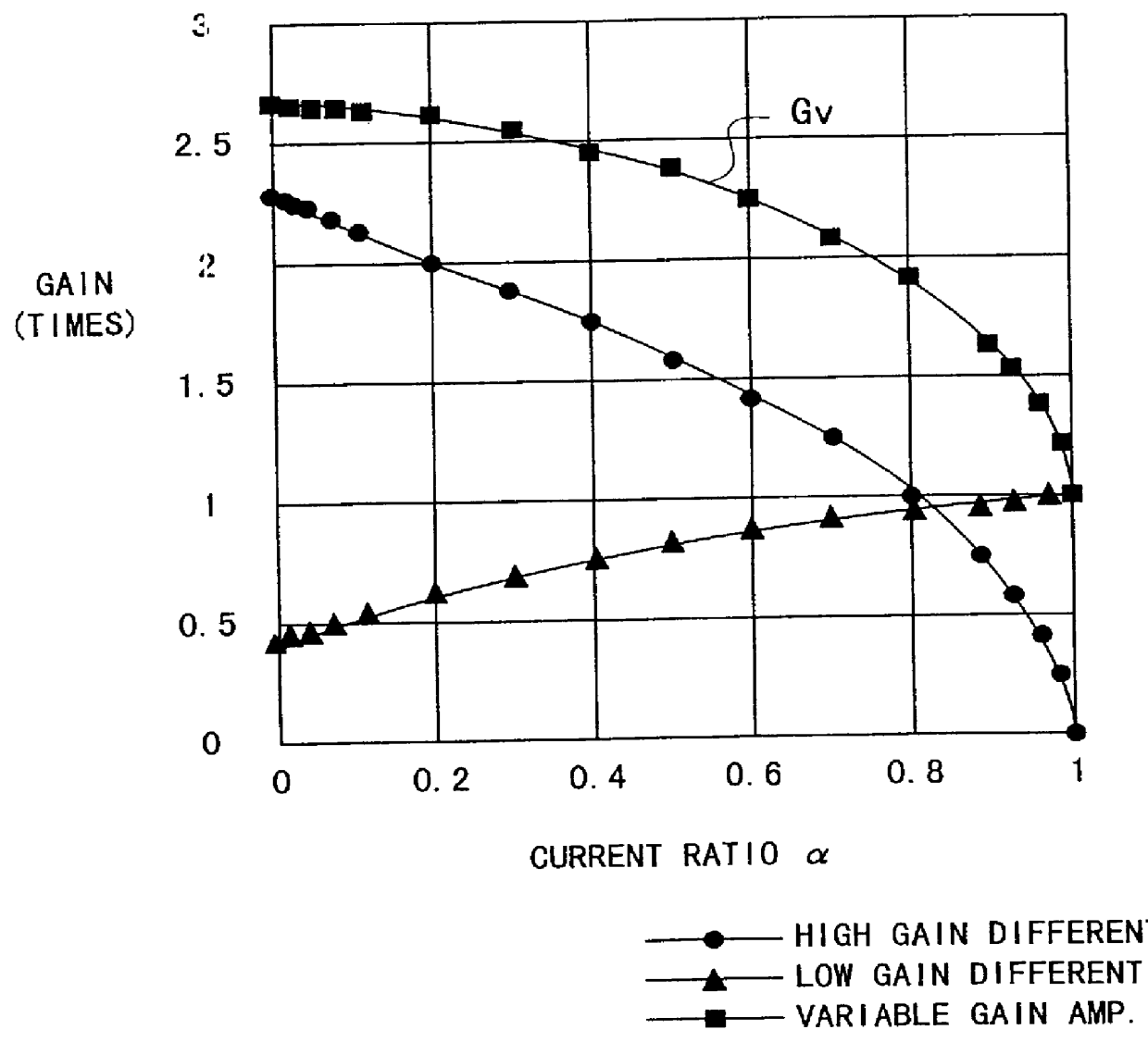

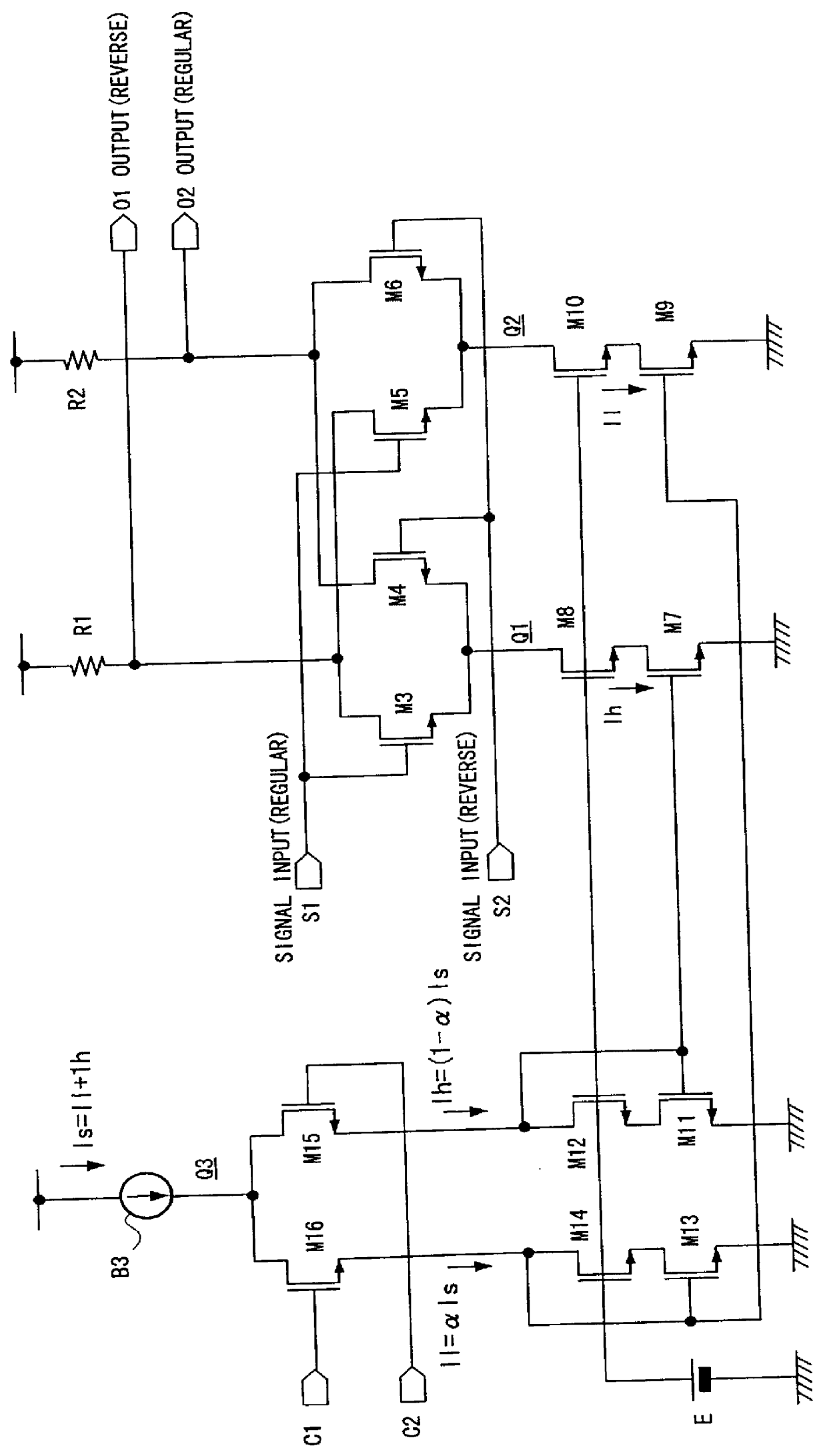

Variable gain amplifier

InactiveUS6163215AComputations using contact-making devicesGain controlAudio power amplifierVariable-gain amplifier

In a variable gain amplifier controlling a gain by using differential amplifiers with a gain control signal, a gain switchover differential amplifier or a bias circuit which composes a current mirror with the gain switchover differential amplifier is connected between a high and a low gain differential amplifier for the same bias current which are mutually connected to share load resistances for the same output polarity and a bias current source common to both of the differential amplifiers, to perform switchover operations of the high and the low differential amplifier by a gain control signal, and a current source which flows a fixed offset current through at least the low one of the high and the low differential amplifier is provided.

Owner:FUJITSU LTD

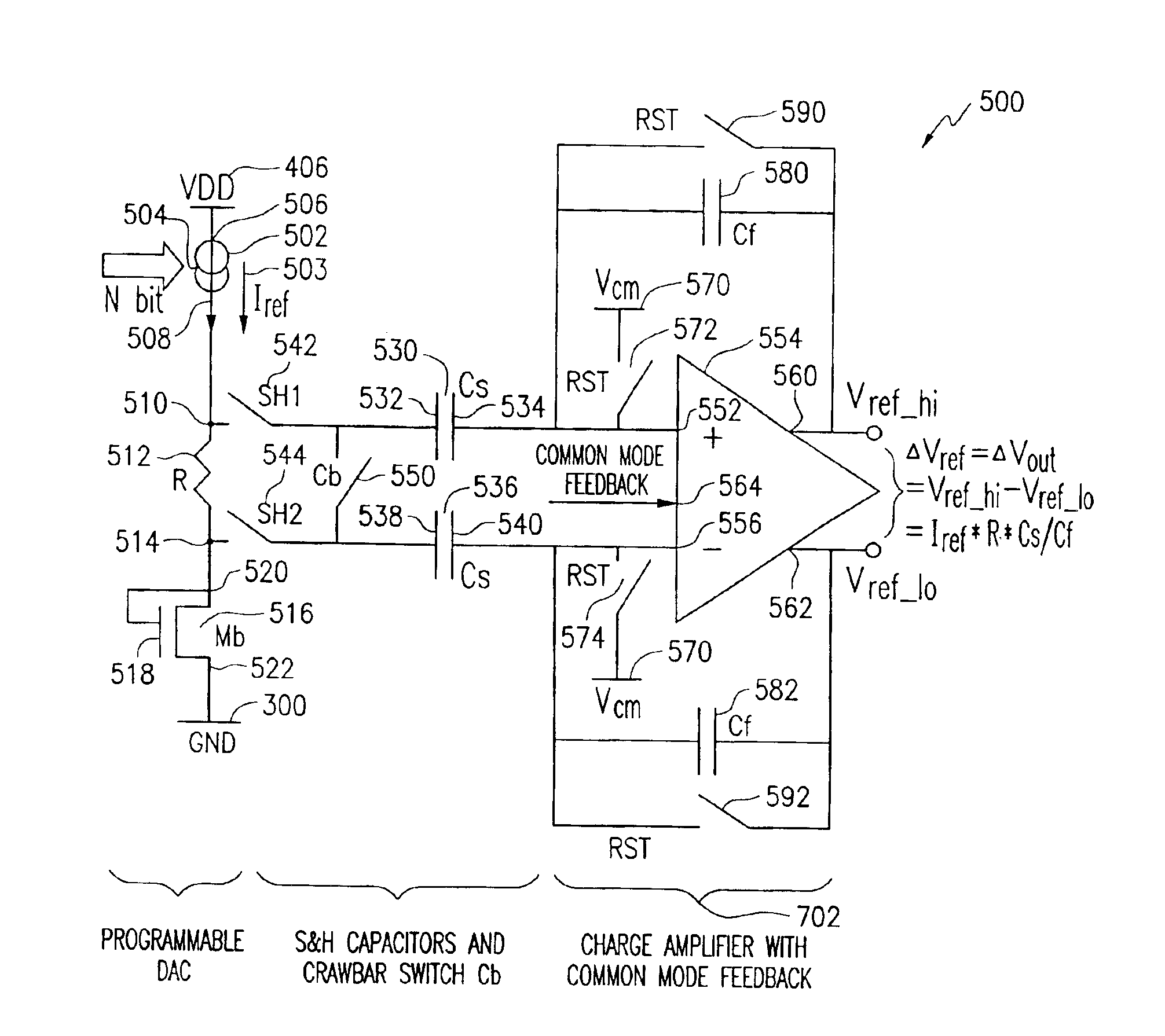

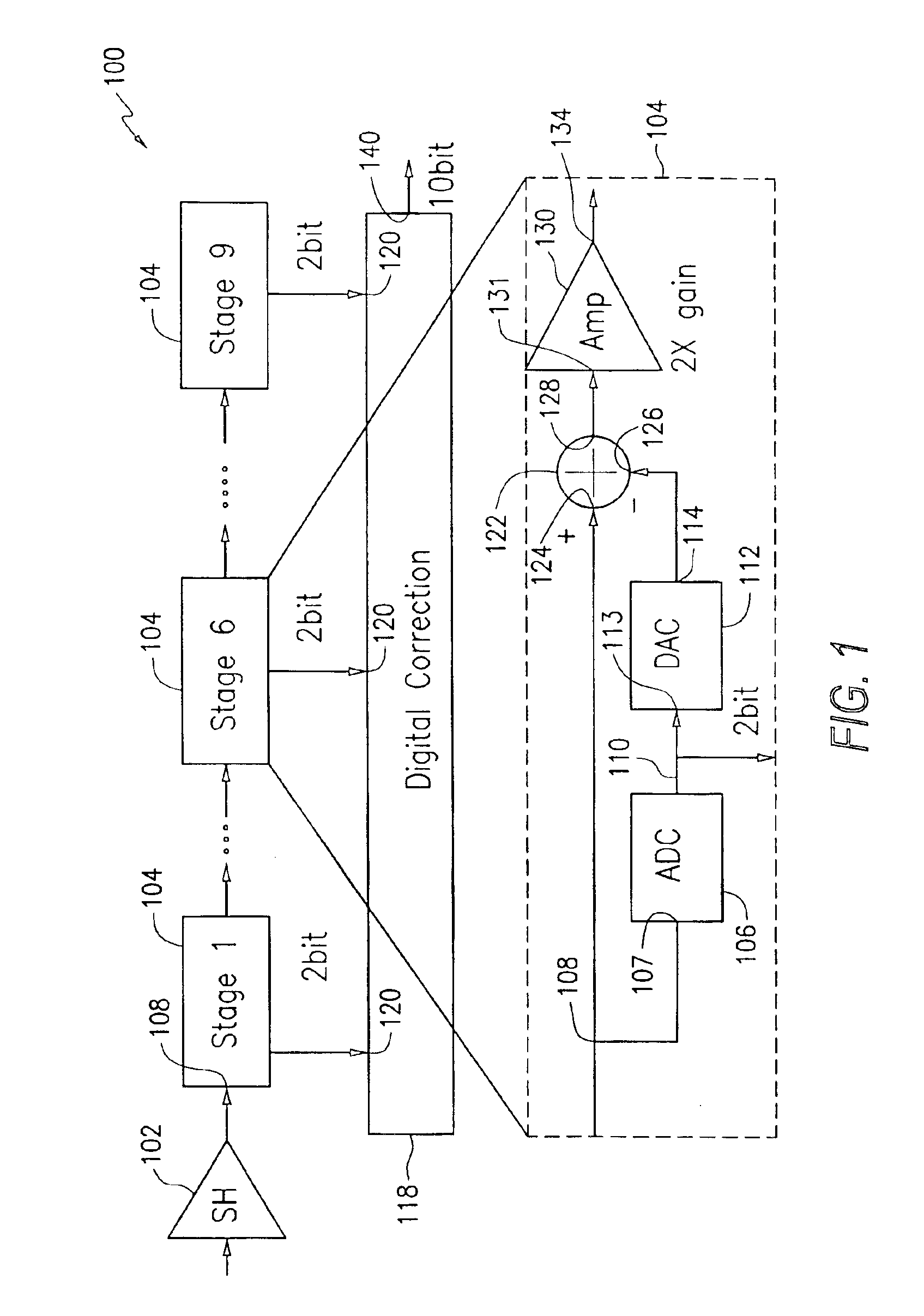

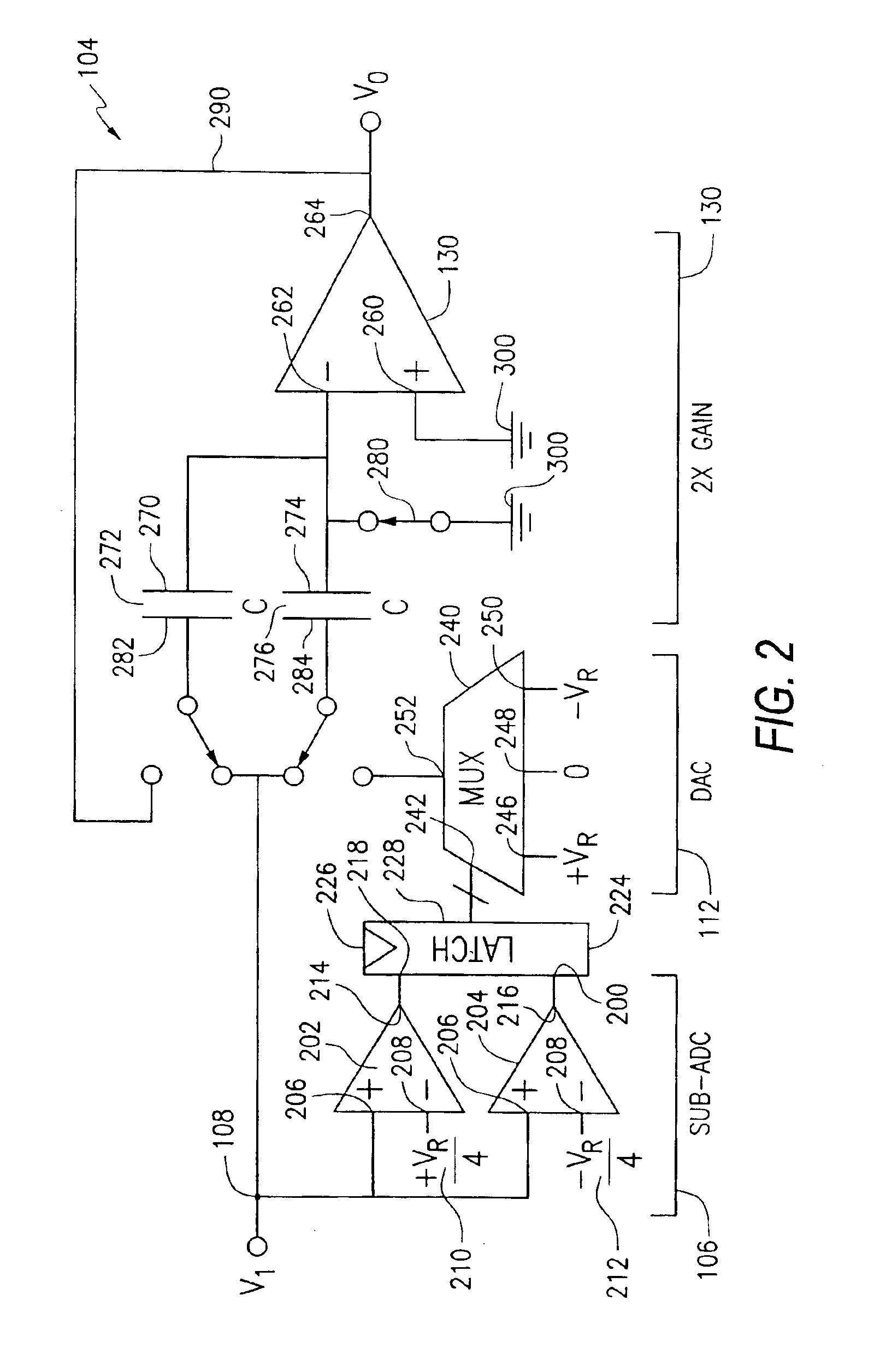

Fully differential reference driver for pipeline analog to digital converter

InactiveUS6909391B2Electric signal transmission systemsAnalogue-digital convertersCapacitanceVoltage reference

An analog to digital conversion (ADC) circuit is disclosed including a fully differential reference voltage source. The reference voltage source includes a programmable current supply adapted to drive a programmed current through a resistor so as to establish an initial reference voltage. The initial reference voltage is sampled onto a capacitive network during a first sampling time interval. The capacitive network is coupled to a differential input of a fully differential amplifier, and maintained at a differential output of the differential amplifier during a second output time interval. An output coupling between the differential output and differential input of the differential amplifier acts to maintain stability of the output voltage during the output time interval.

Owner:APTINA IMAGING CORP

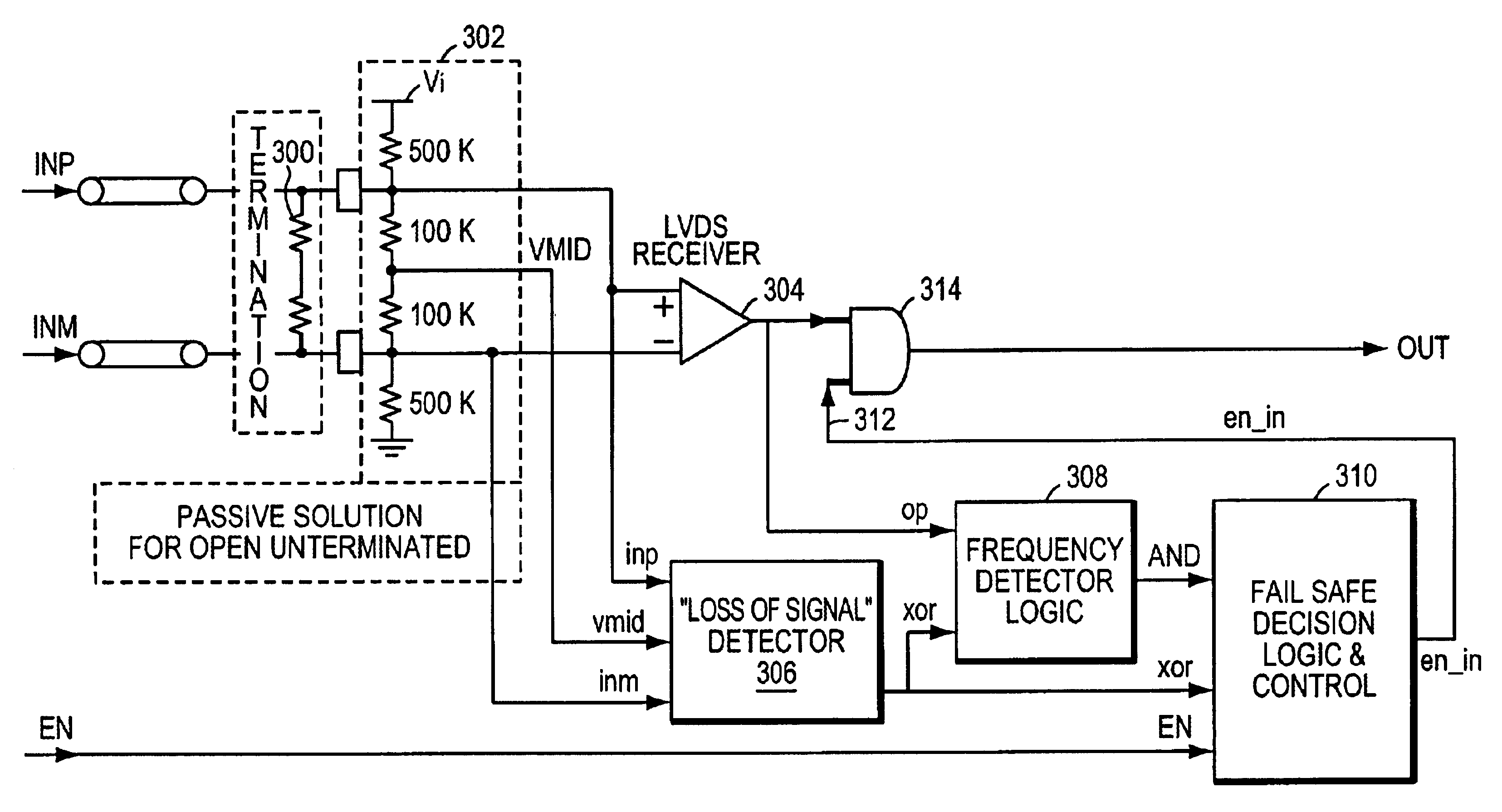

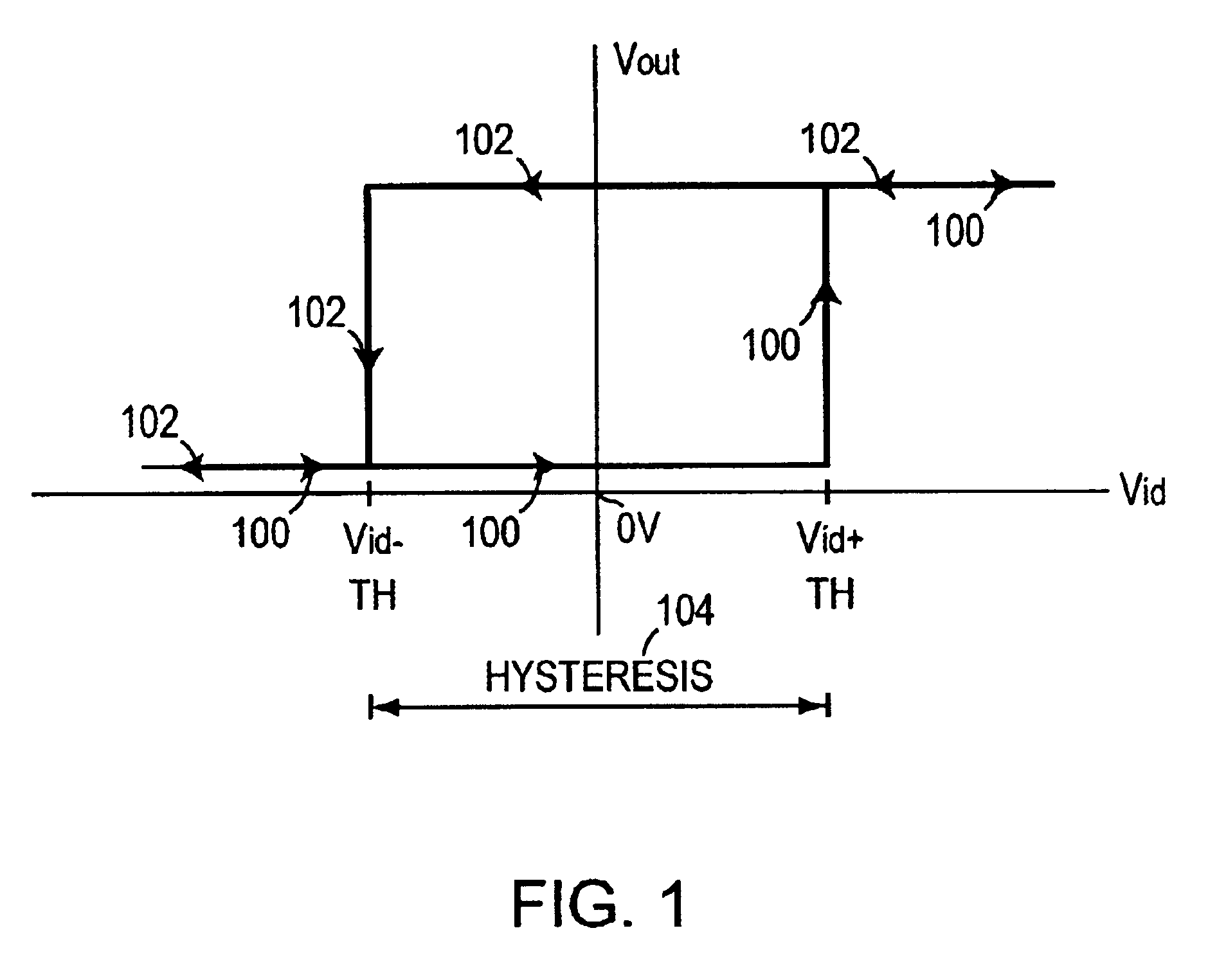

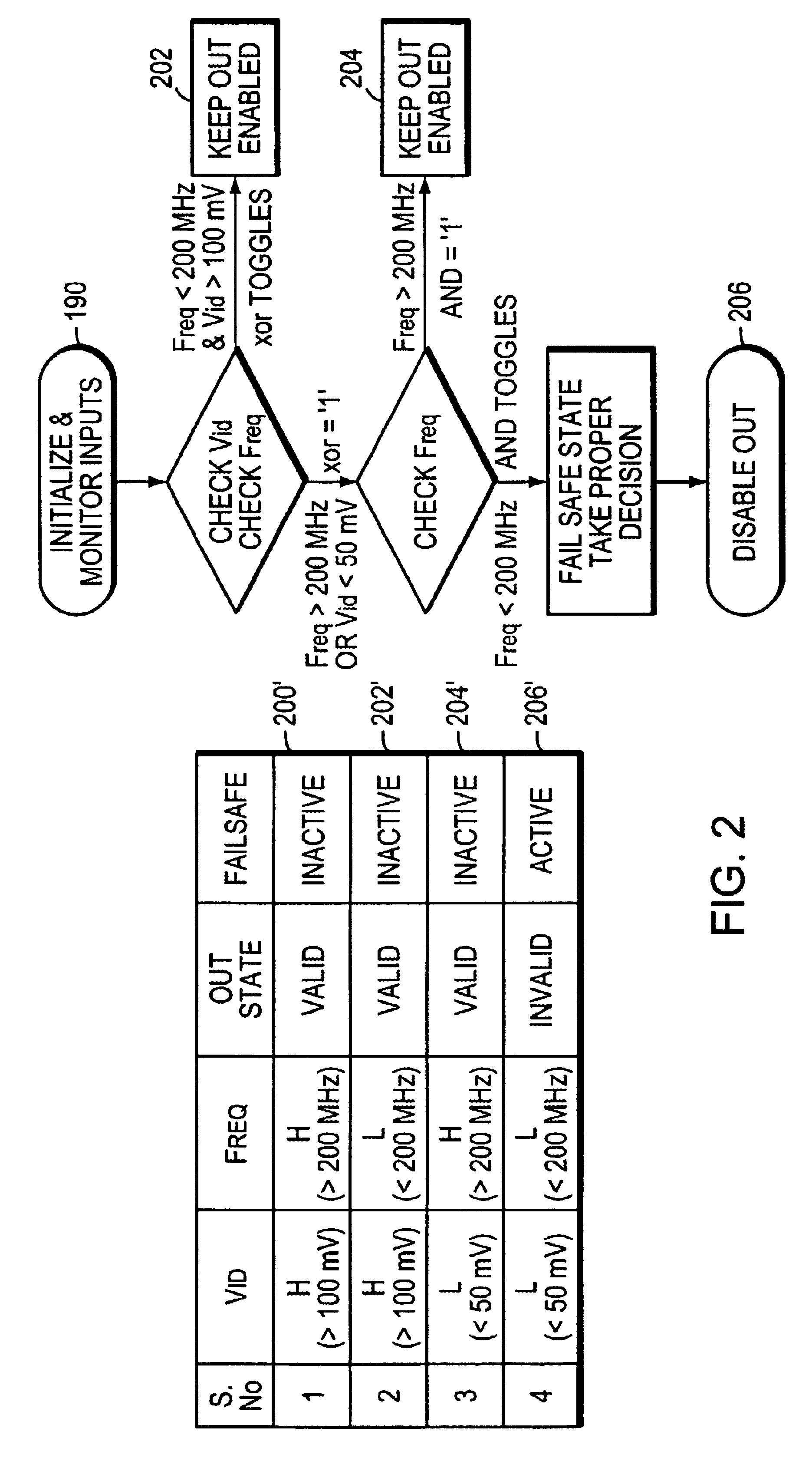

Failsafe differential amplifier circuit

InactiveUS6781456B2Not affect high-frequency performance of receiverFail-safe circuitsAmplifier combinationsAudio power amplifierSafety status

Differential input fail safe circuitry is disclosed that detects missing or too low differential signals combined with a frequency lower than a frequency limit where a final safe condition is detected and signaled. The output signal form the fail safe circuitry is held in a given state that is an invalid representation of the differential input signal. A frequency detector, complementary offsetting auxiliary amplifiers with limit frequency roll offs are used to detect the fail safe condition. In addition a delay circuit is used that requires the fail safe condition to exist for some time before the fail safe circuit is active. Initialization circuitry ensures a proper power up conditions where the circuitry is enabled to detect the fail safe conditions and guarantees a reliable fail safe irrespective of the previous state of the signal.

Owner:SEMICON COMPONENTS IND LLC

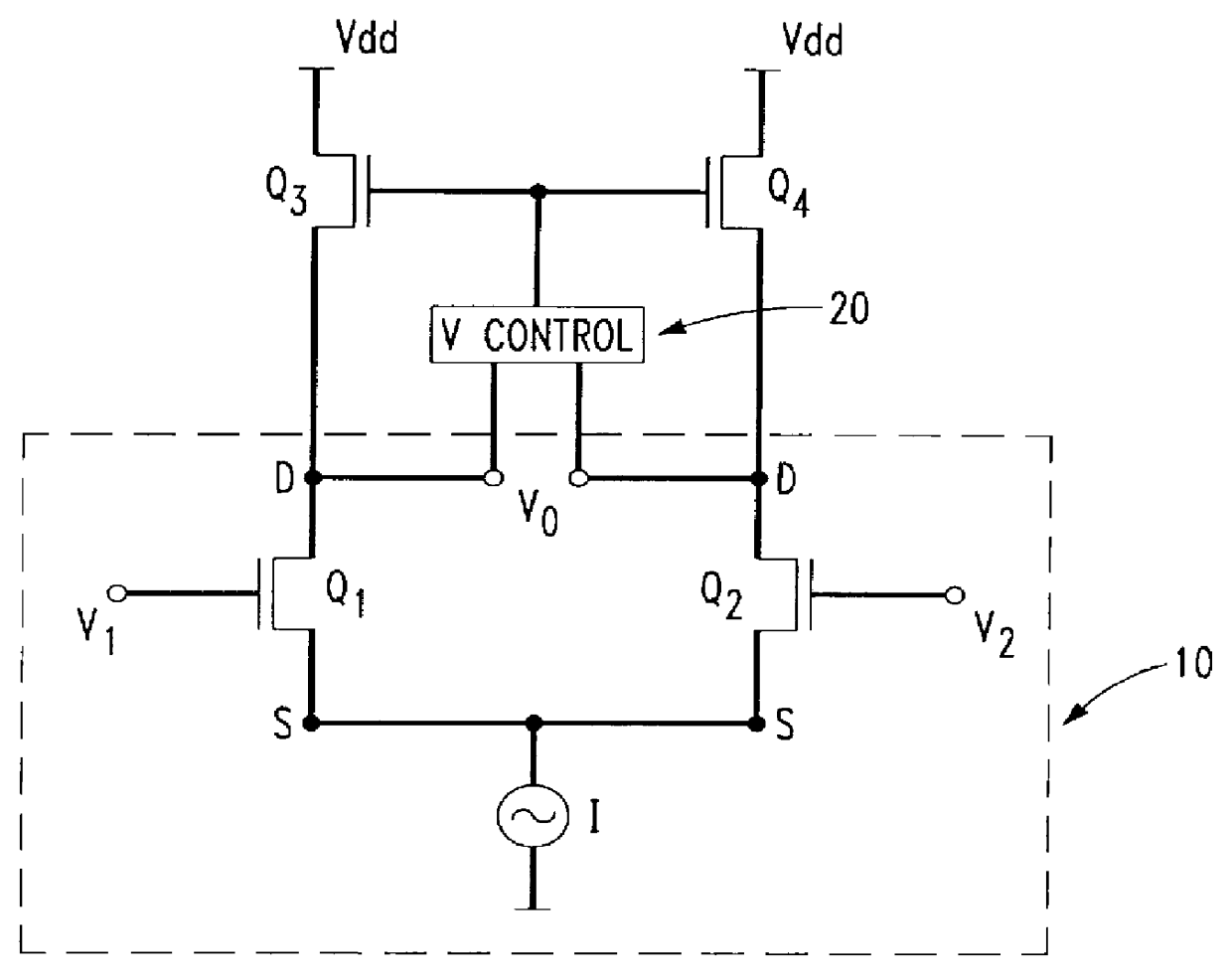

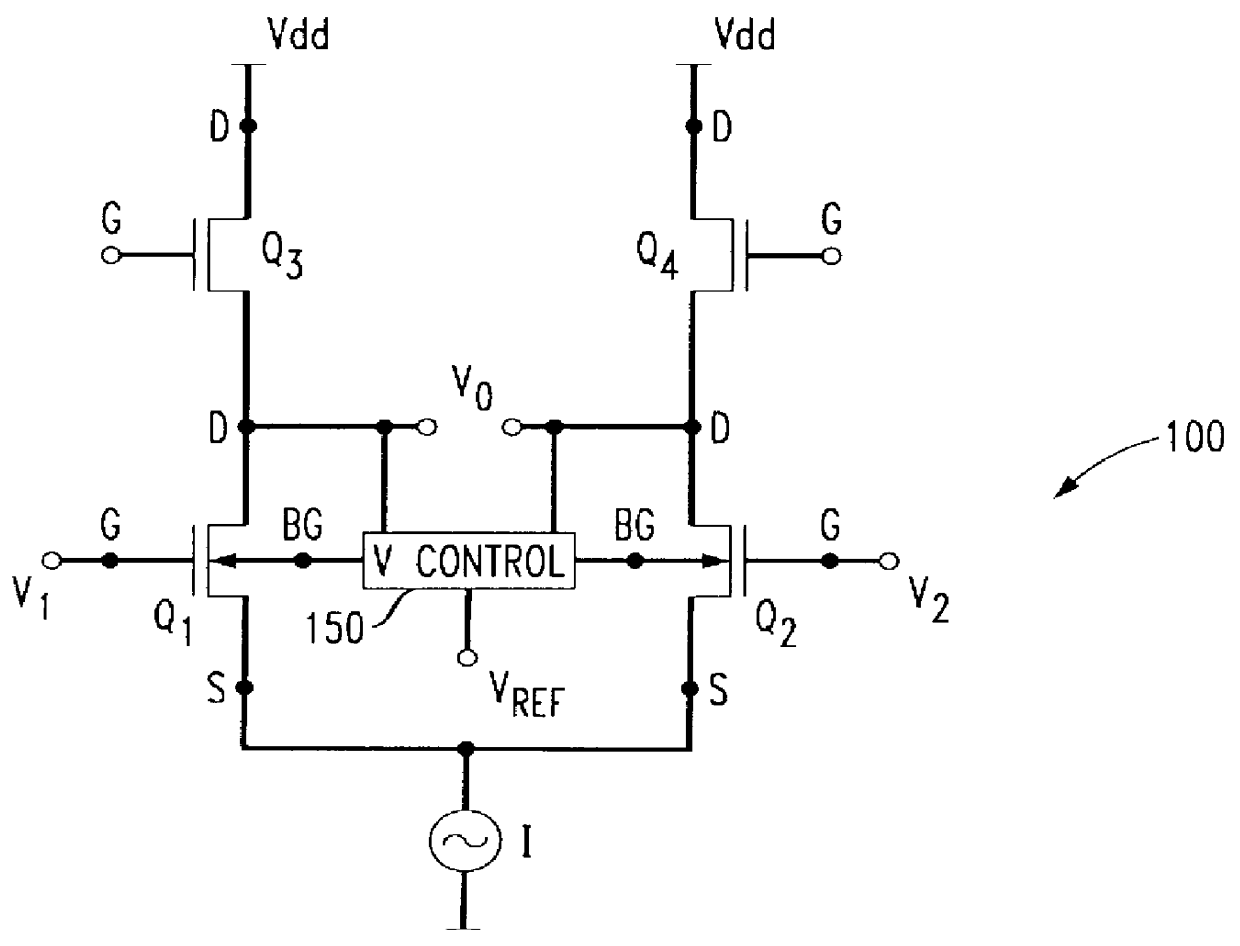

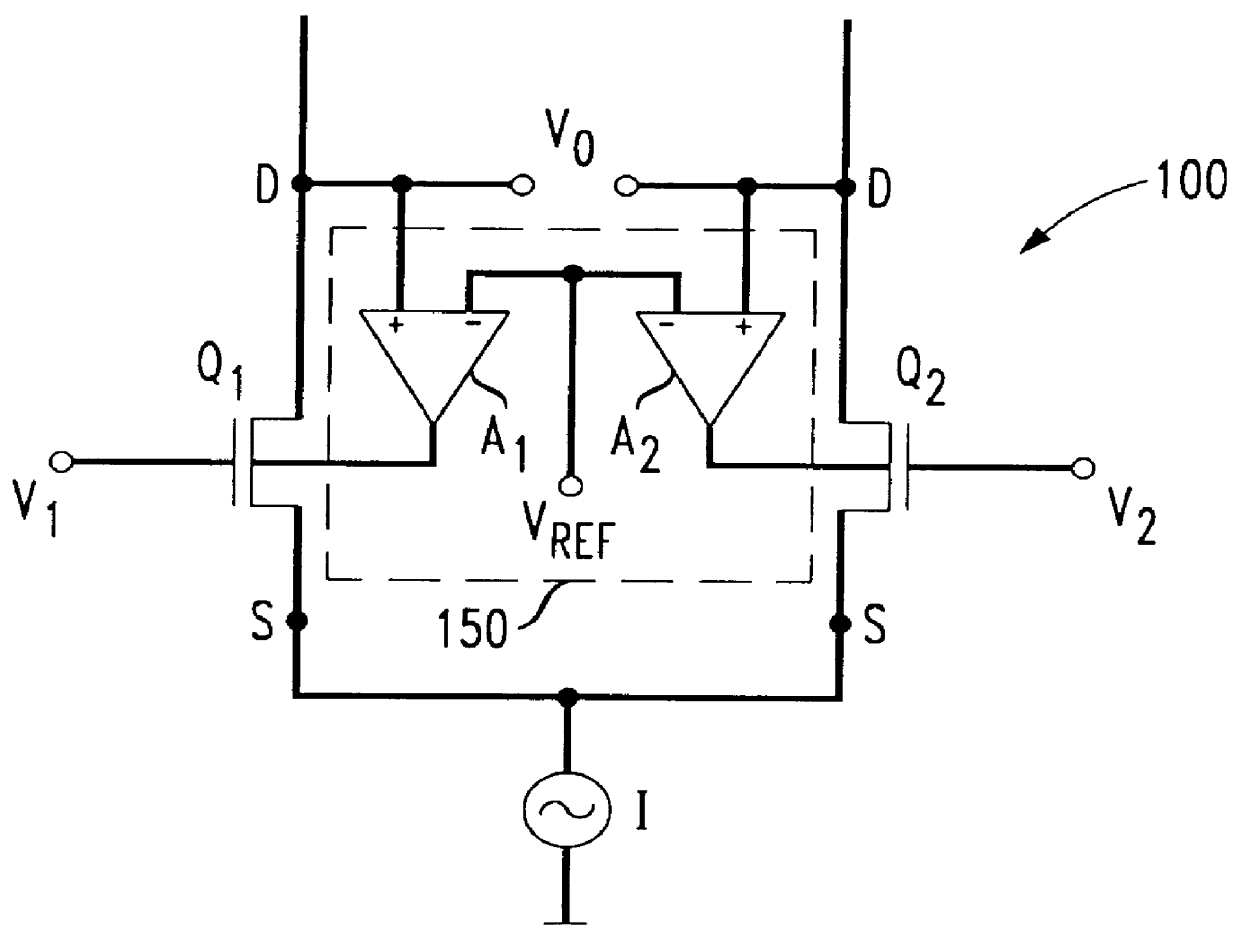

CMOS differential amplifier having offset voltage cancellation and common-mode voltage control

A differential amplifier for amplifying the difference between first and second input signals and producing therefrom a differential output signal. The differential amplifier includes first and second transistors connected to a common DC current source and receiving, at the transistor gate terminals, the respective first and second input signals. Each transistor has a common mode voltage associated therewith. A voltage control circuit generates control signals that are applied to the backgate terminals of the transistors to calibrate the differential output voltage and to adjust the common mode voltages of the transistors.

Owner:WSOU INVESTMENTS LLC +1

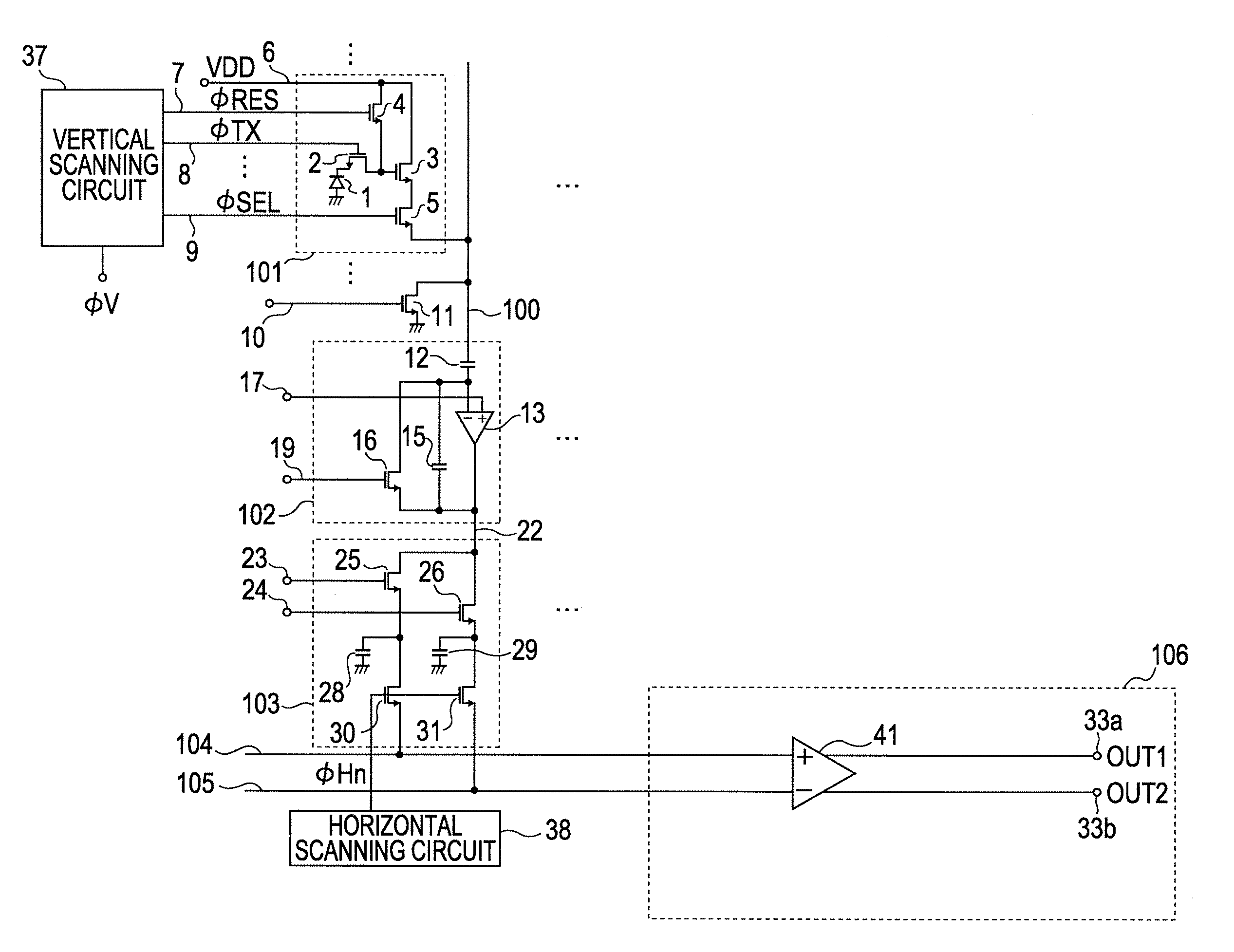

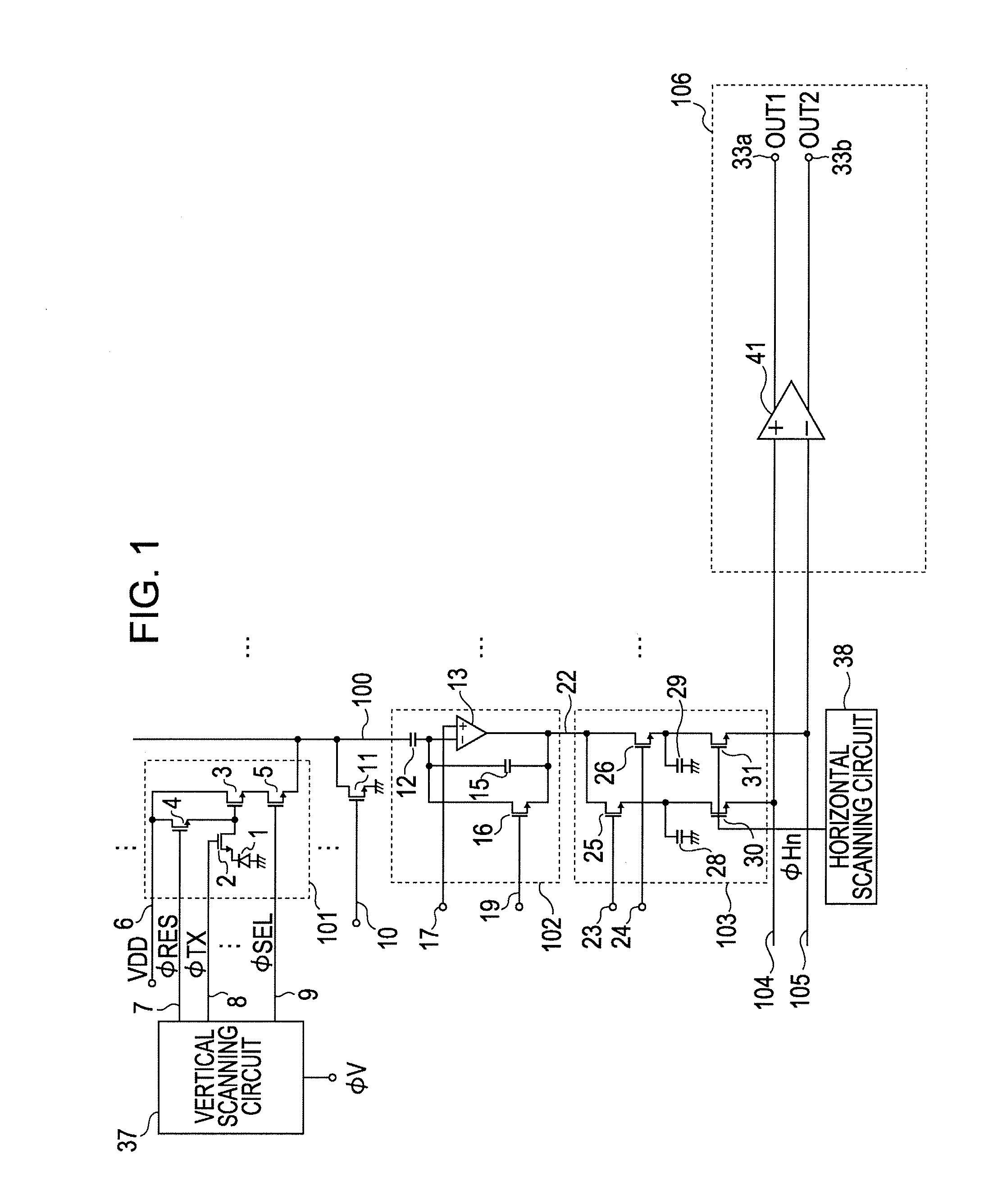

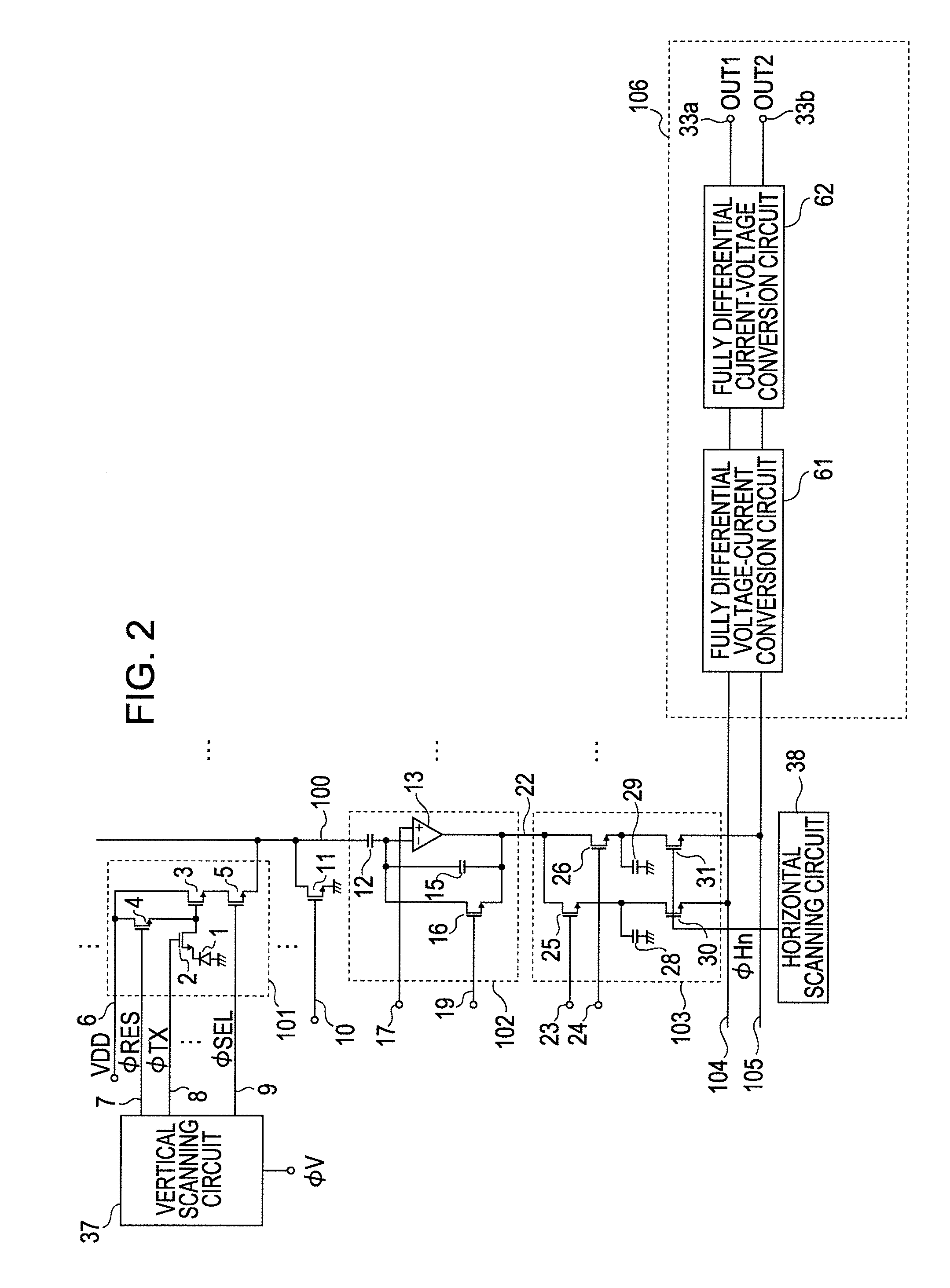

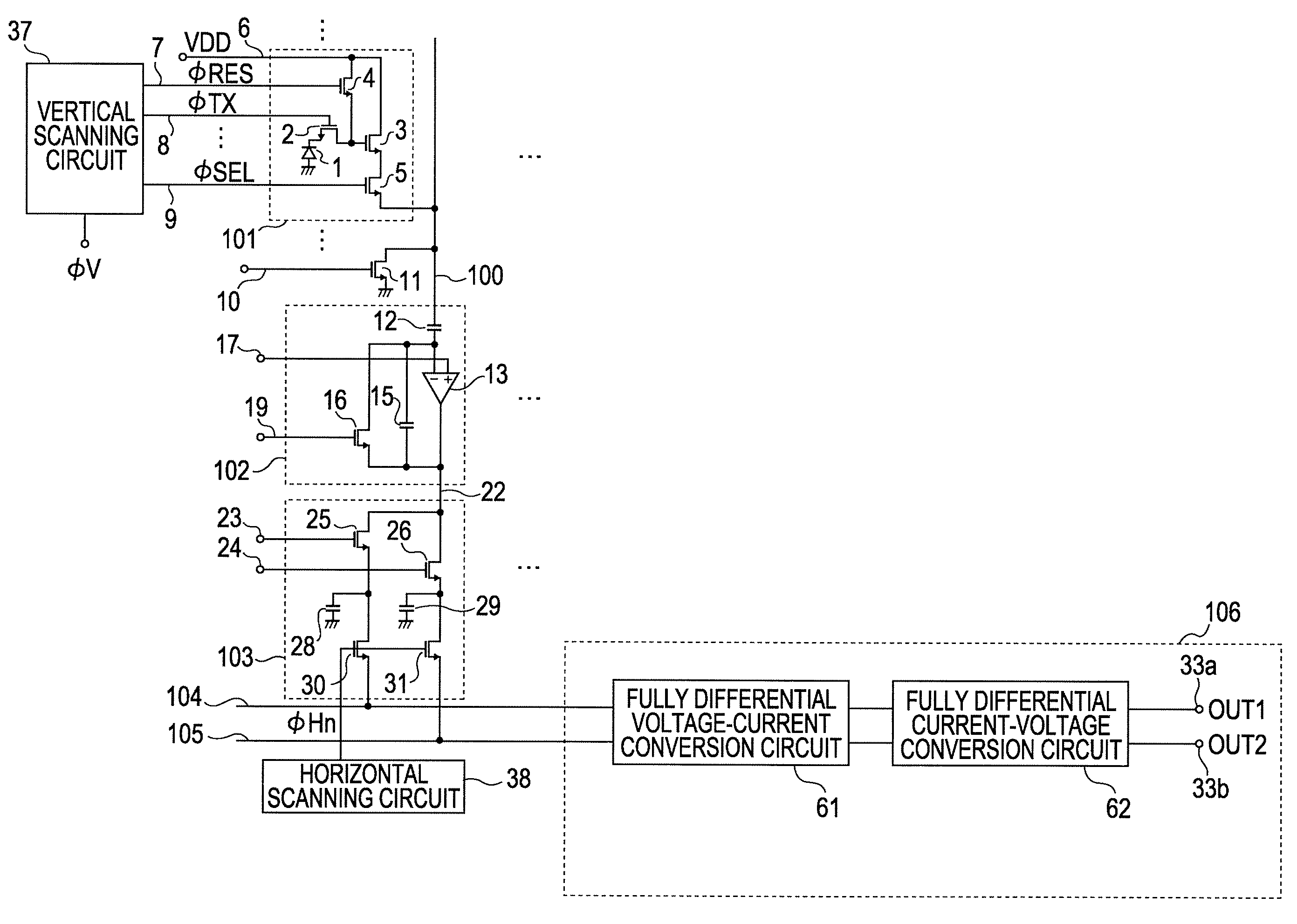

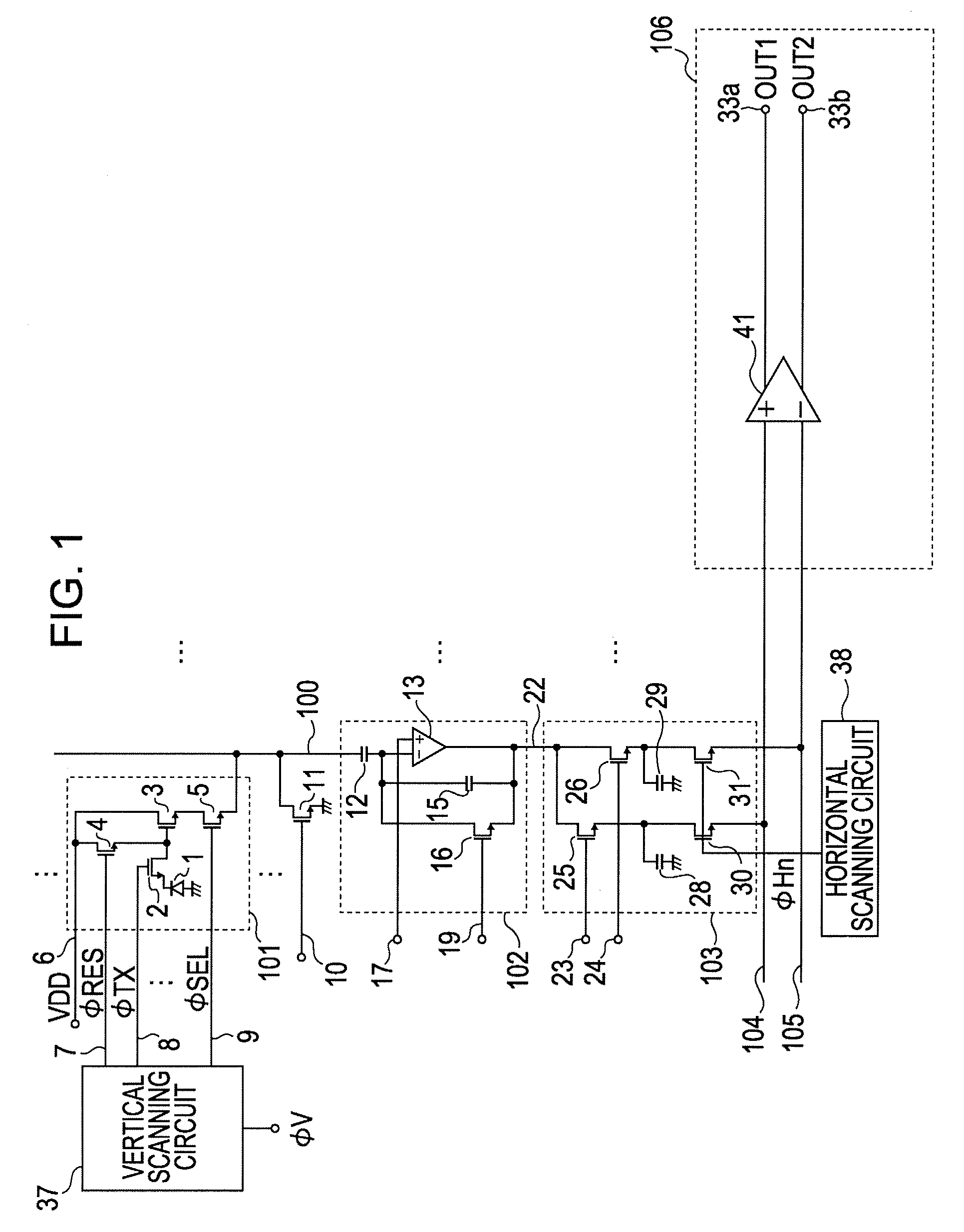

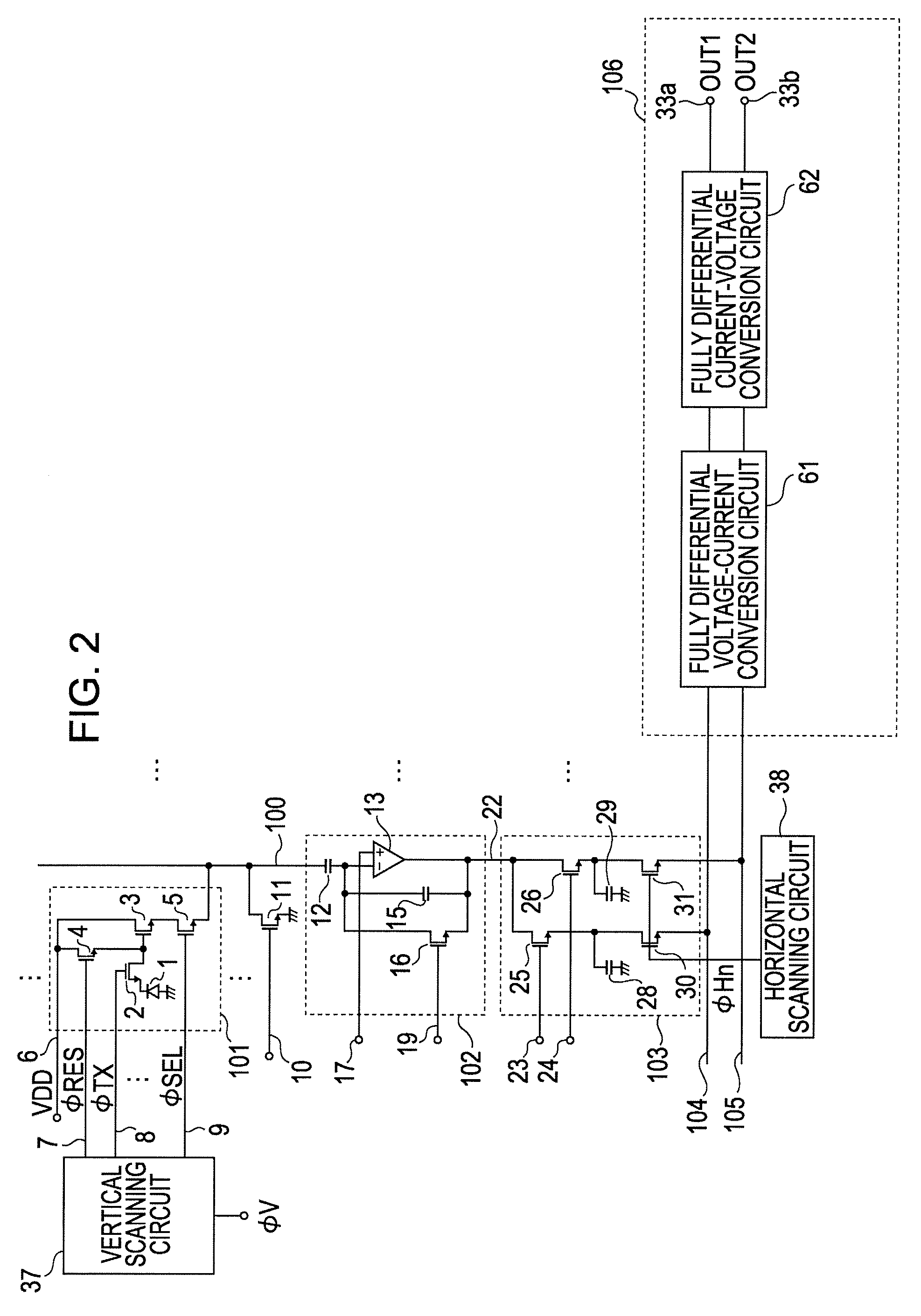

Photoelectric conversion apparatus and image sensing system

InactiveUS20080062295A1Decrease in reading speed can be suppressedReduce readTelevision system detailsTelevision system scanning detailsAudio power amplifierPhotoelectric conversion

To provide a configuration including a fully differential amplifier in which decrease in a reading speed can be suppressed. A photoelectric conversion apparatus according to the present invention includes a pixel area where a plurality of pixels are arranged; an amplifier configured to amplify a signal from the pixel area; a plurality of signal paths for transmitting the signals from the pixel area to the amplifier. The amplifier is a fully differential amplifier which includes a plurality of input terminals including a first input terminal and a second input terminal to which the signals from the plurality of signal paths are supplied and a plurality of output terminals including a first output terminal and a second output terminal and the input terminals and the output terminals have no feedback path provided therebetween.

Owner:CANON KK

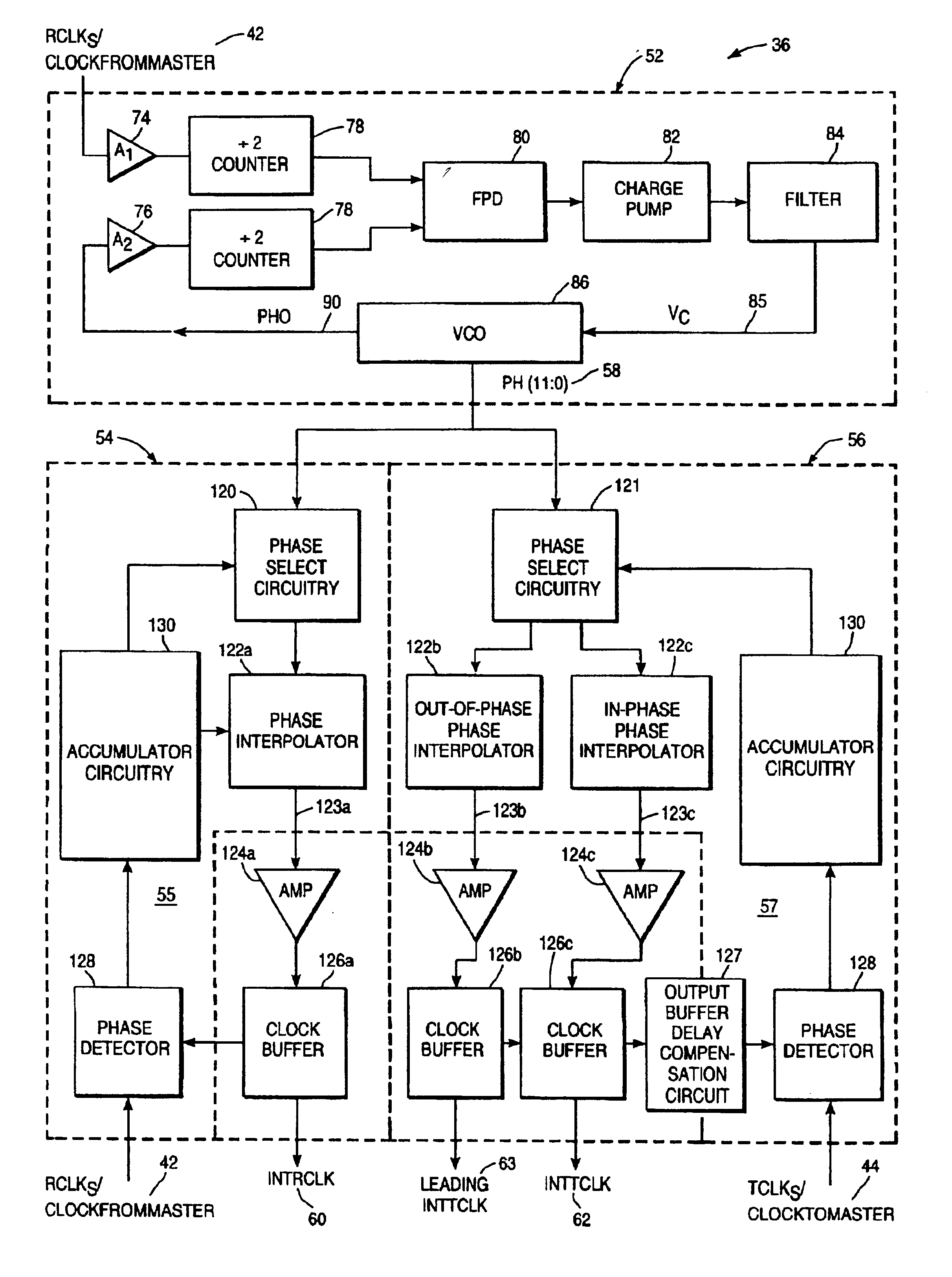

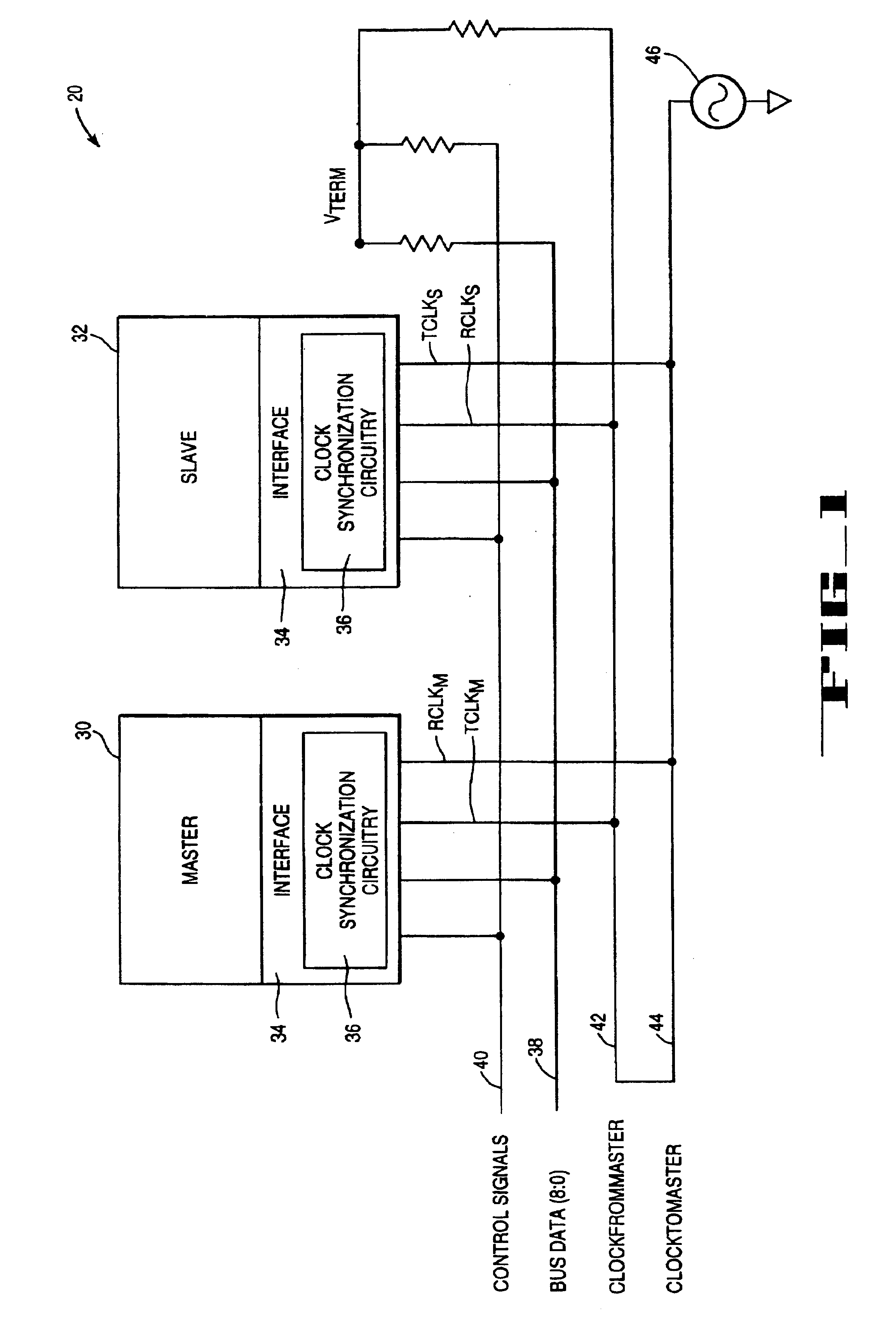

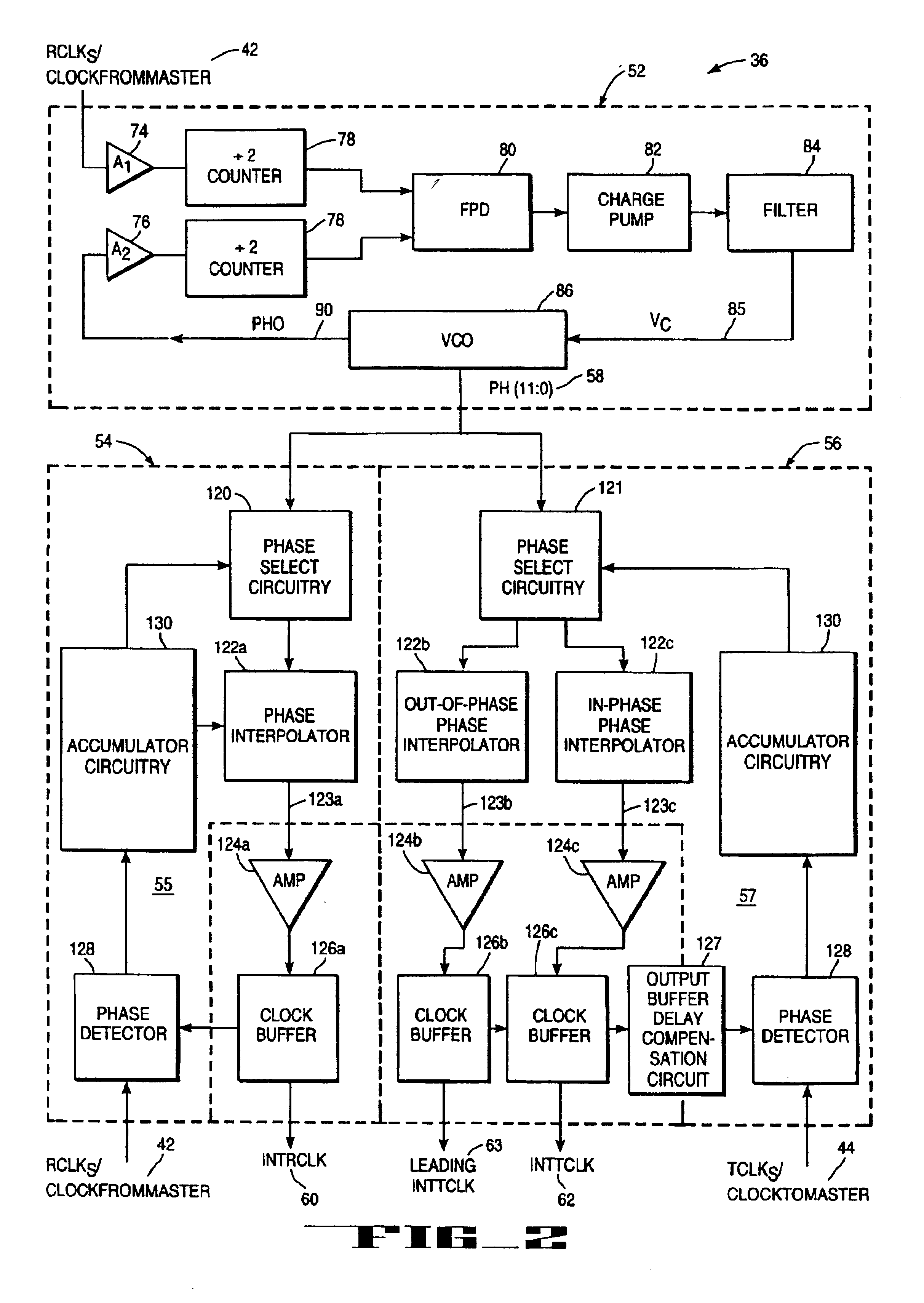

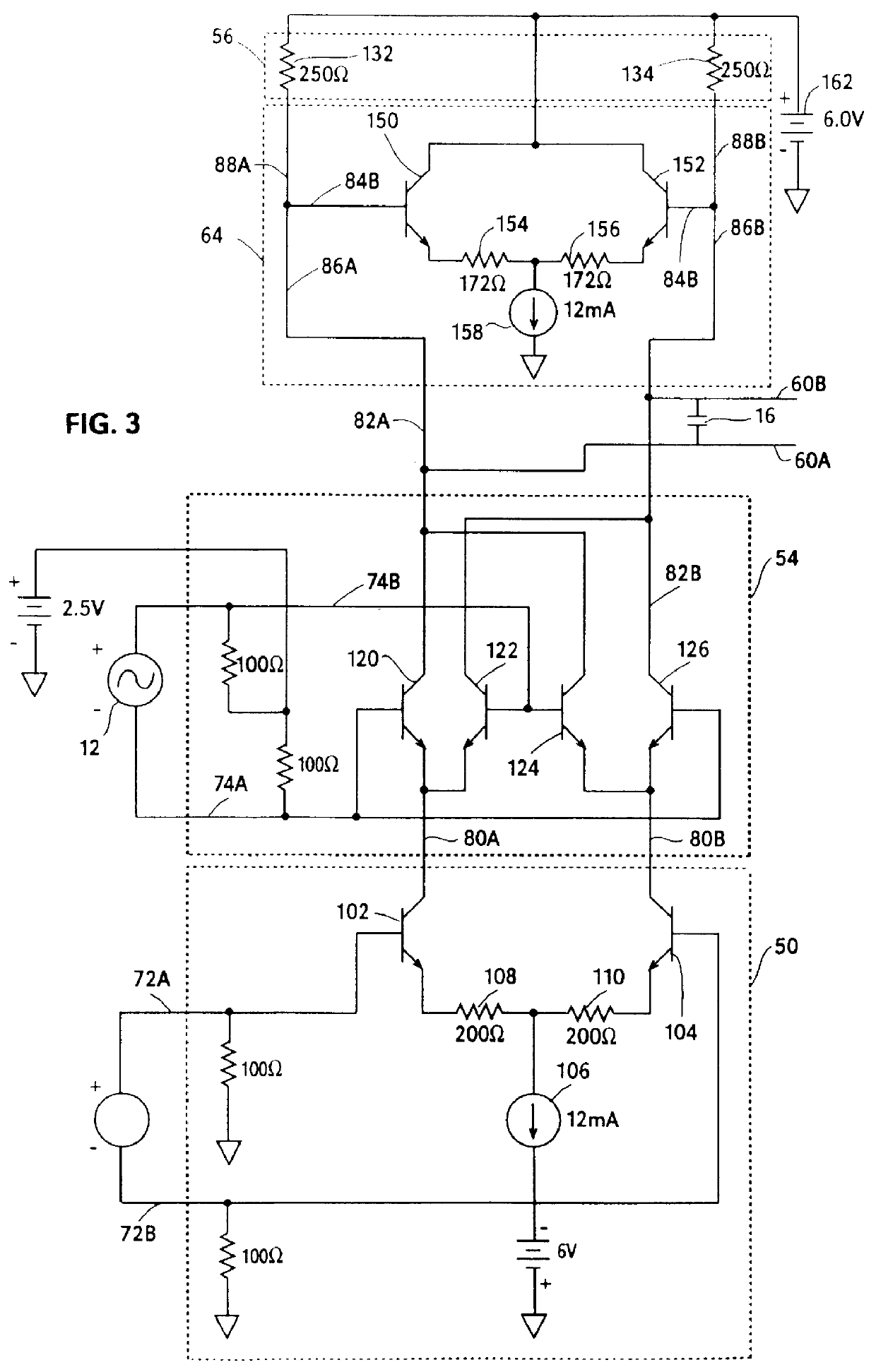

Delay stage circuitry for a ring oscillator

InactiveUSRE38482E1Easy to optimizePulse automatic controlTime-division multiplexEngineeringVoltage clamp

A ring oscillator includes an even-numbered plurality of ring coupled delay stages. Each delay stage includes a differential amplifier, a voltage clamping circuit, and a current source. The differential amplifier receives first and second input signals from a preceding delay stage. The differential amplifier provides a first output signal and a complementary second output signal at first and second nodes, respectively. The voltage clamping circuit is coupled between the first and second nodes to limit a peak-to-peak voltage swing of each of the first and second output signals. The current source is coupled to the differential amplifier and varies a bias current in accordance with a delay bias voltage.

Owner:RAMBUS INC

Active balun device

Owner:ELECTRONICS & TELECOMM RES INST

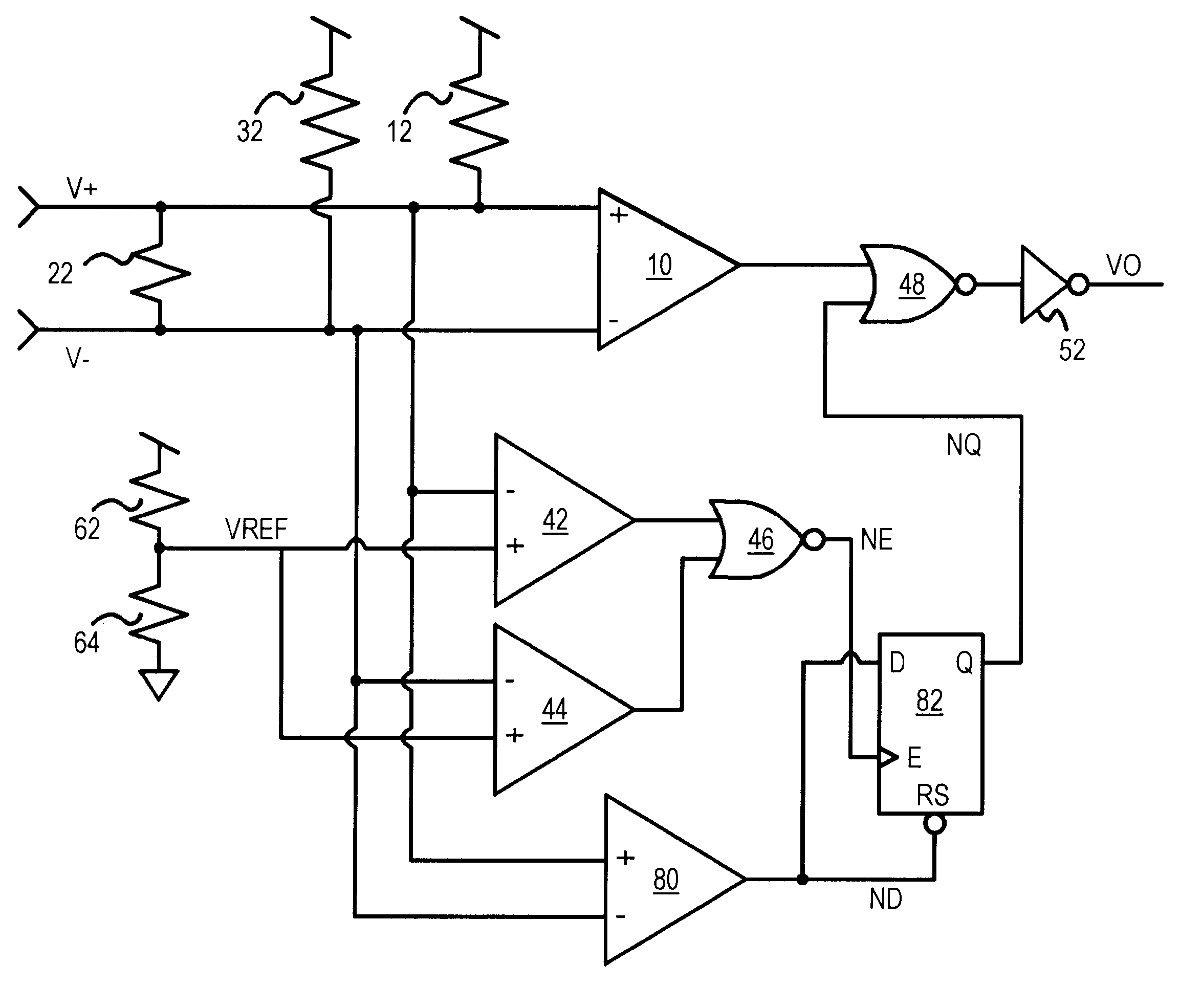

Active fail-safe detect circuit for differential receiver

InactiveUS6288577B1Multiple input and output pulse circuitsFail-safe circuitsNOR gateDifferential signaling

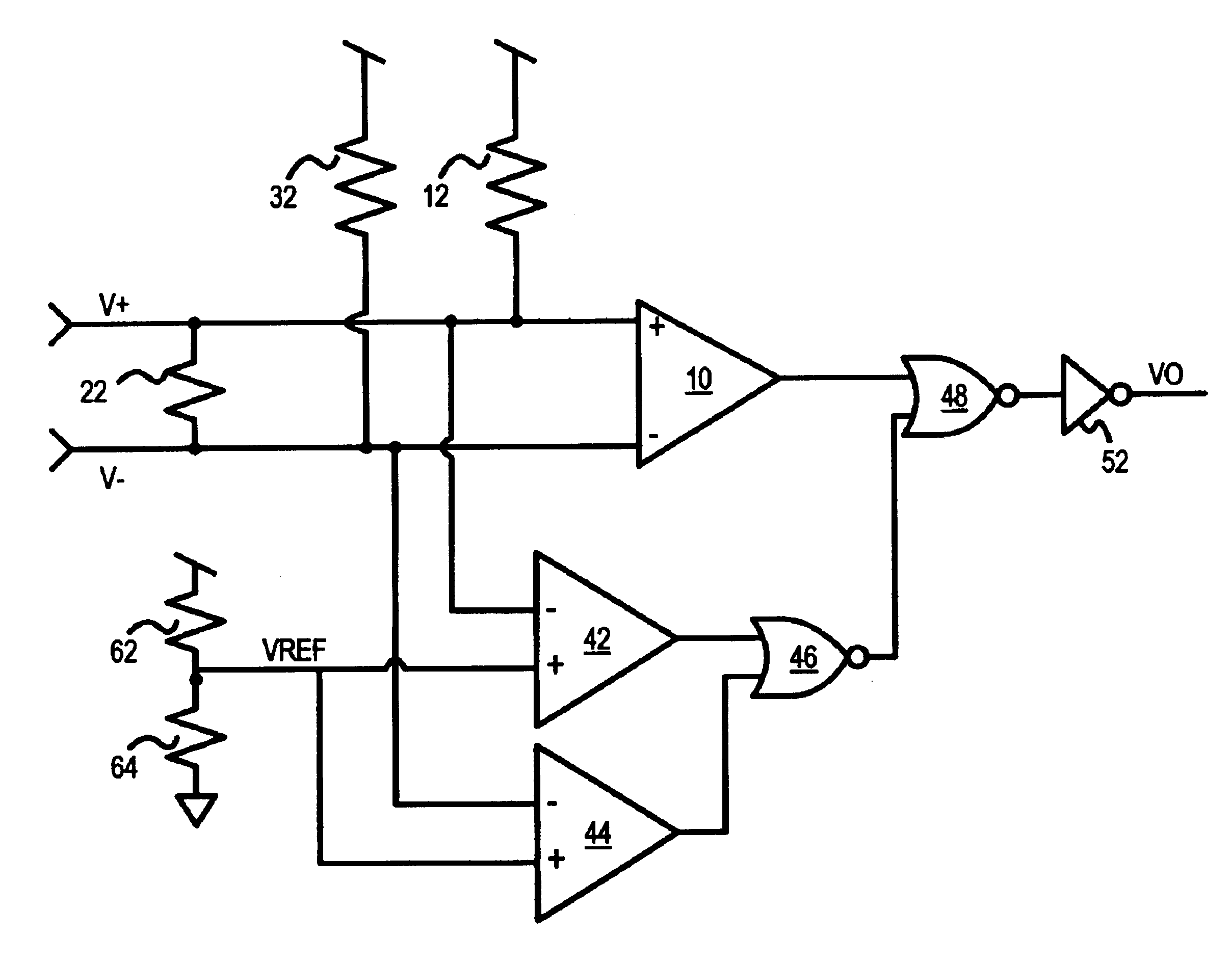

A fail-safe circuit for a differential receiver can tolerate high common-mode voltages. An output from a differential amplifier that receives a V+ and a V- differential signal can be blocked by a NOR gate when the fail-safe condition is detected, such as when the V+, V- lines are open. Pullup resistors pull V+, V- to Vcc when an open failure occurs. A pair of comparators receive a reference voltage on the non-inverting input. Once comparator outputs a high when the V+ line is above the reference voltage, and the other comparator outputs a high when the V- line is above the reference voltage. When both V+ and V- are above the reference voltage, the NOR gate blocks the output from the differential amplifier, providing a fail-safe. Since the reference voltage is very close to Vcc, a high common-mode bias can exist on V+, V- without falsely activating the fail-safe circuit.

Owner:DIODES INC

Differential amplifier, comparator, and A/D converter

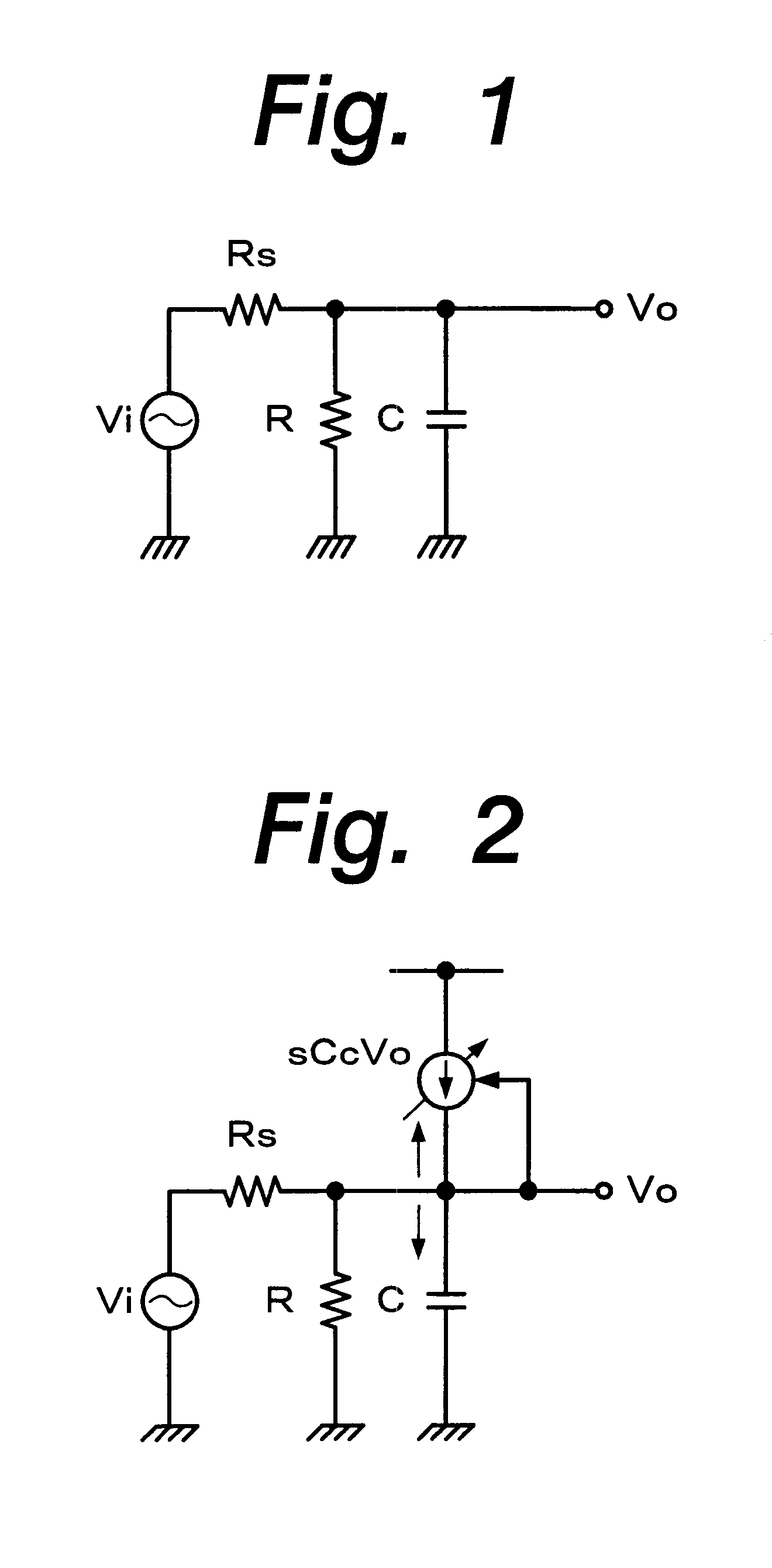

InactiveUS6369743B2Increase speedRun at high speedMultiple input and output pulse circuitsElectric signal transmission systemsCapacitanceBuck converter

An OTA circuit is disposed between a differential pair composed of NMOS transistors and an NMOS follower transistor that composes an output buffer circuit. The OTA circuit generates a compensation current that is equal to a current that flows in a capacitance formed between the gate and the drain of each of the differential pair transistors and that flows in the reverse direction thereof. The compensation current cancels the current that flows in the capacitance formed between the gate and the drain of each of the differential pair transistors. Thus, a differential amplifier that has a high accuracy and, high gain, and a wide frequency band and that operates at a low power voltage can be accomplished. Using a differential amplifier having a high gain and a wide frequency band, a comparator that operates at high speed and an A / D converter using such a comparator can be accomplished.

Owner:SONY CORP

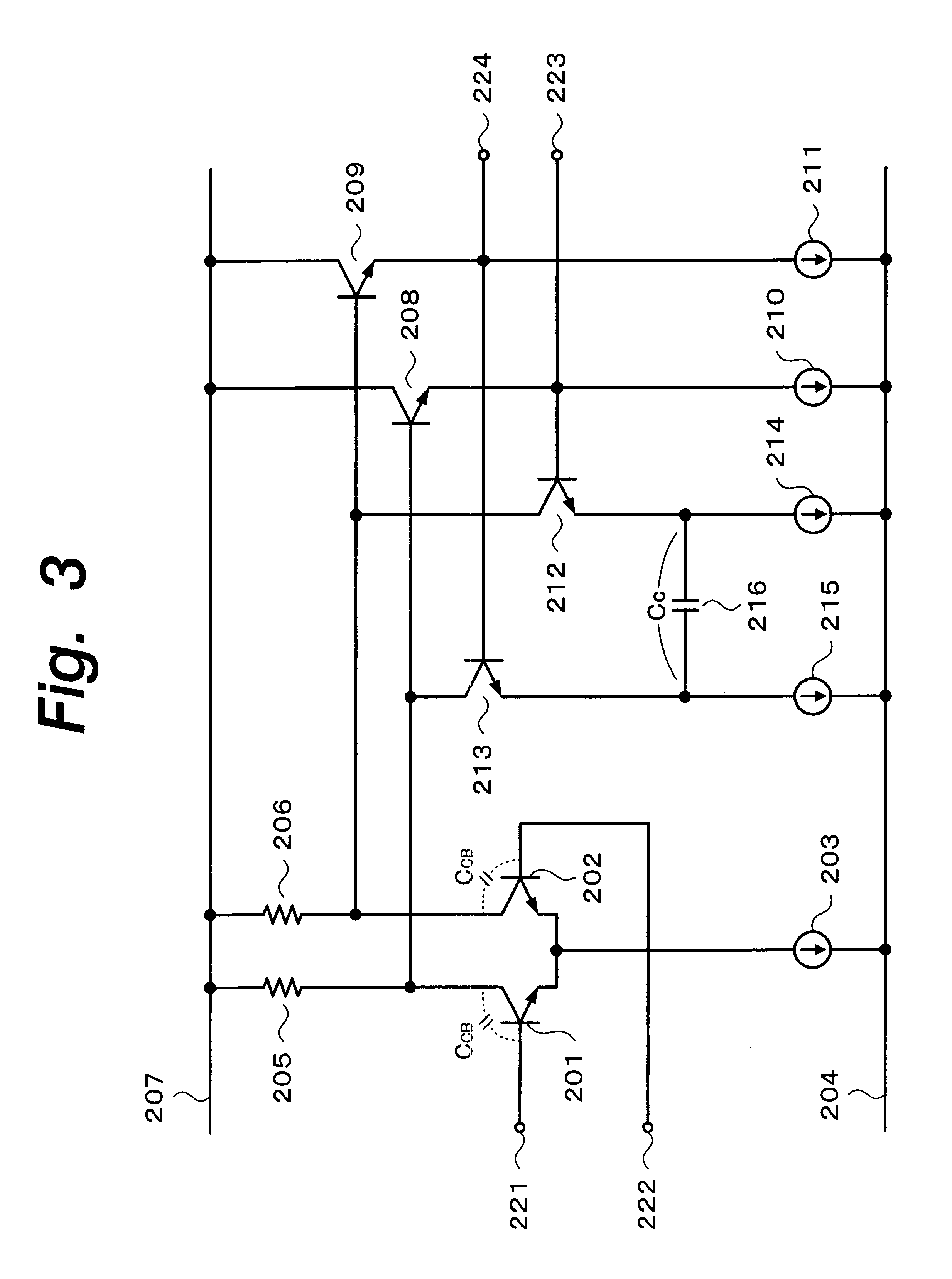

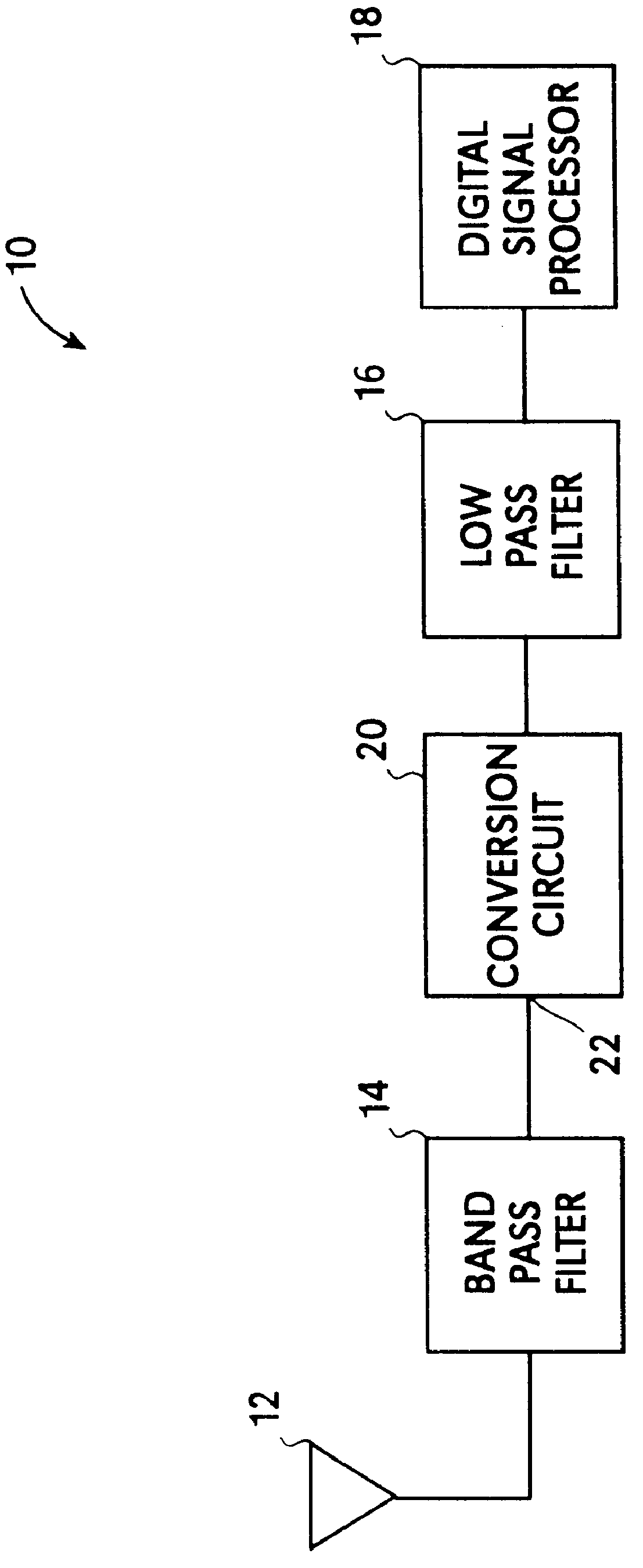

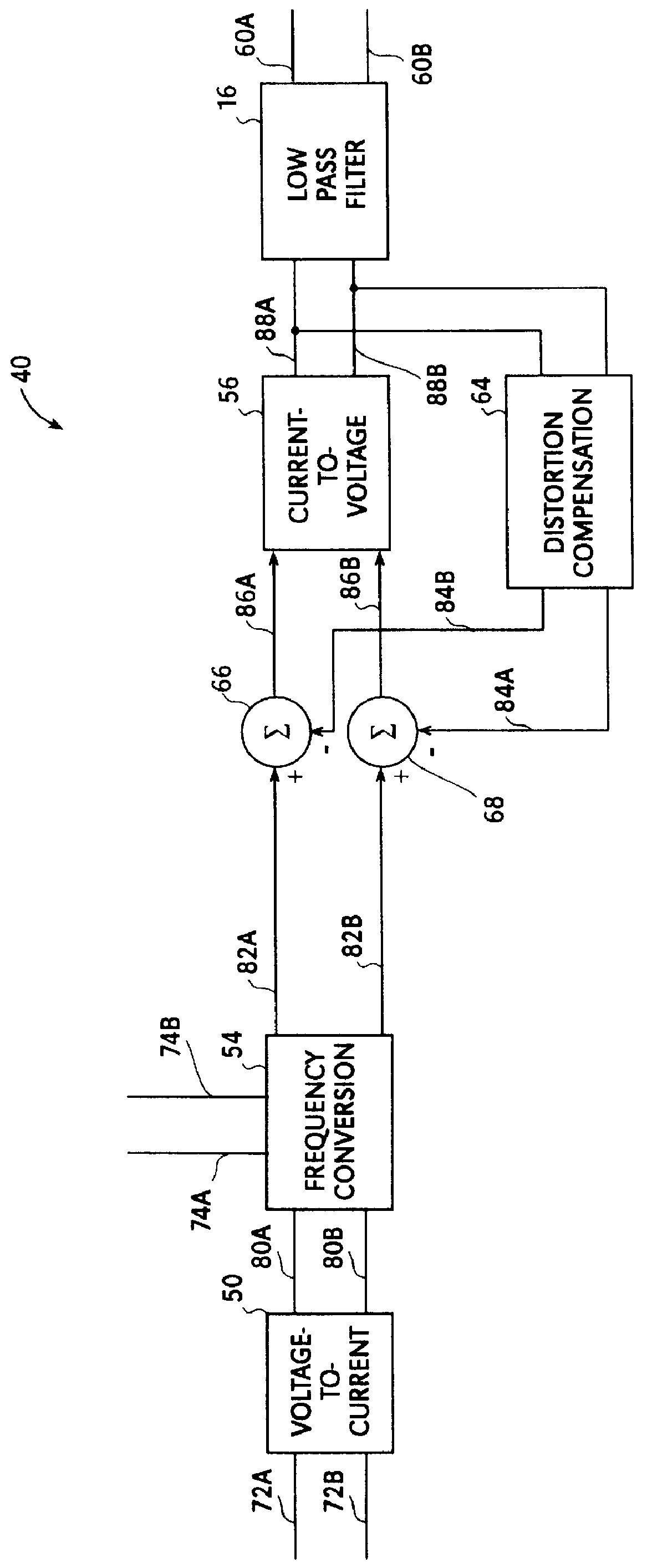

Direct conversion receiver with reduced even order distortion

InactiveUS6021323AReduce distortion problemsReduces even order distortionModulation transference balanced arrangementsRadio/inductive link selection arrangementsPhase currentsLinear component

A mixer for use in a direct conversion receiver includes a compensating differential amplifier which injects equal amplitude opposite phase currents with respect to even order distortion currents. The compensating differential amplifier utilizes an ideal current source. The mixer is an active mixer which utilizes four switching transistors. The even order distortion is introduced by non-linear components which demonstrate strong off-channel signals.

Owner:TELEDYNE SCI & IMAGING

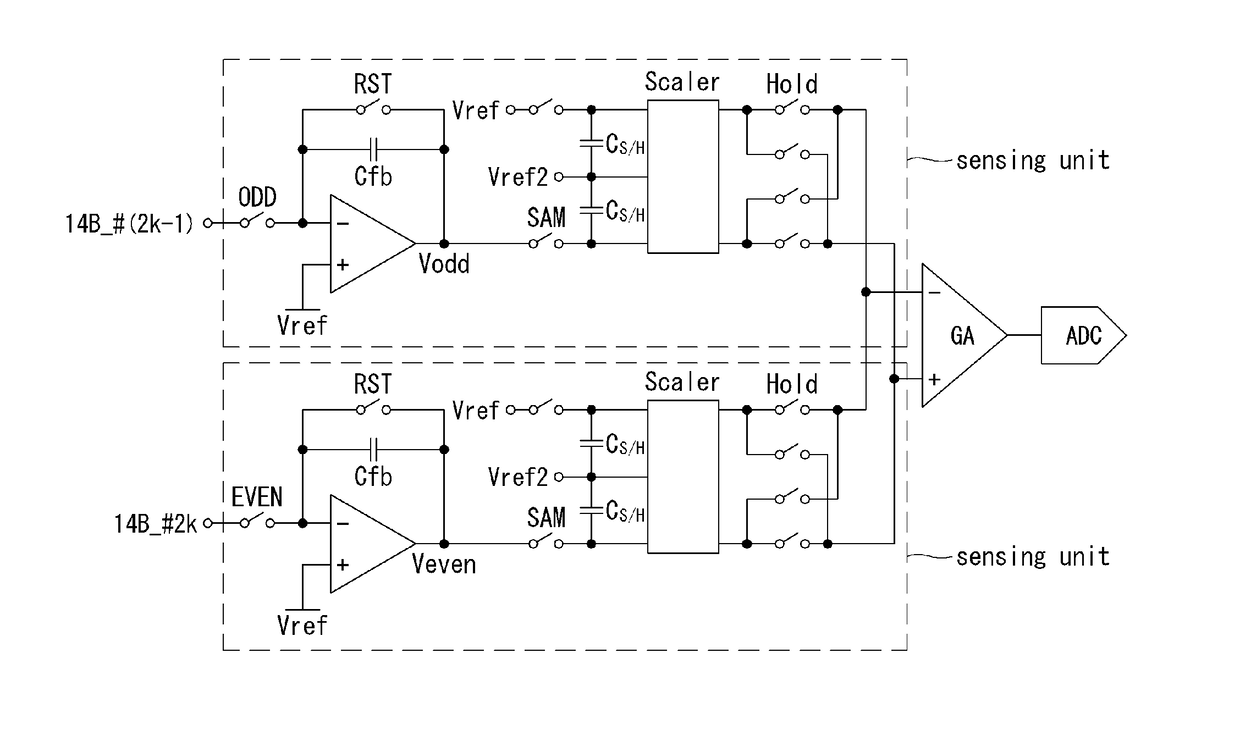

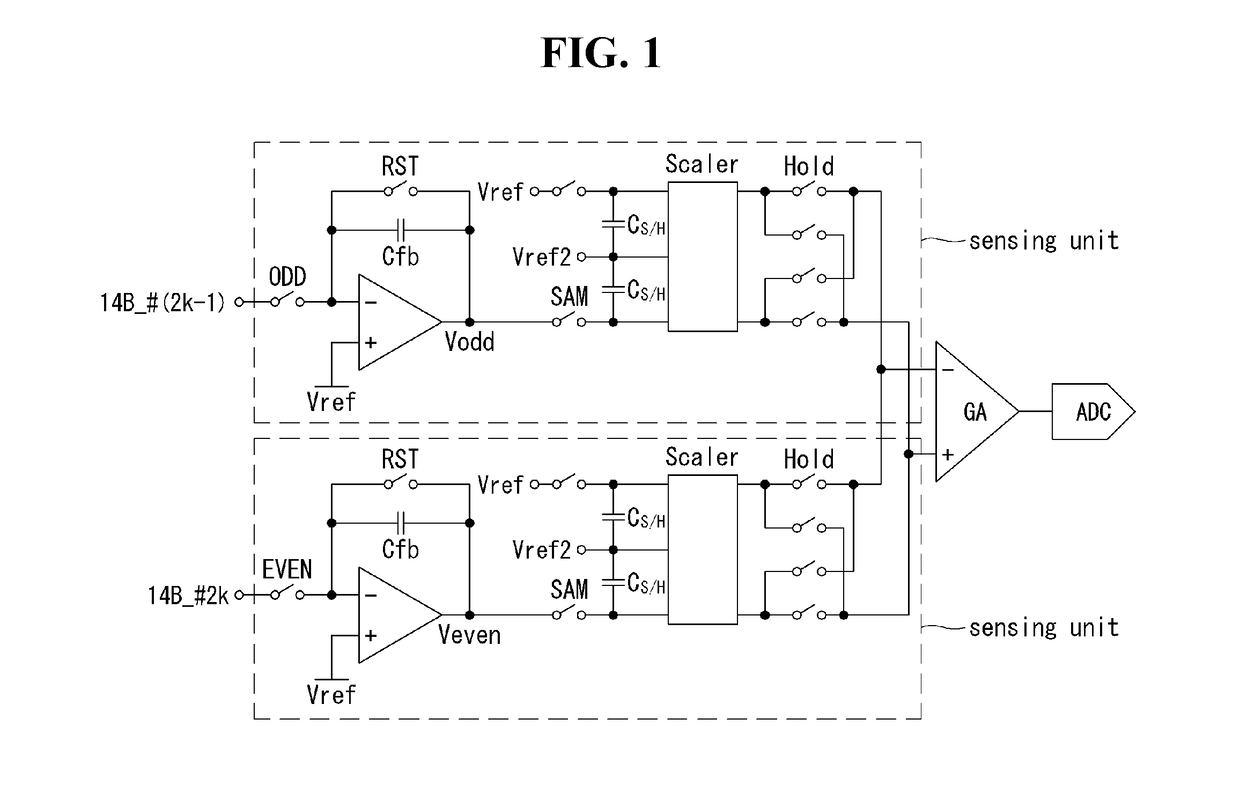

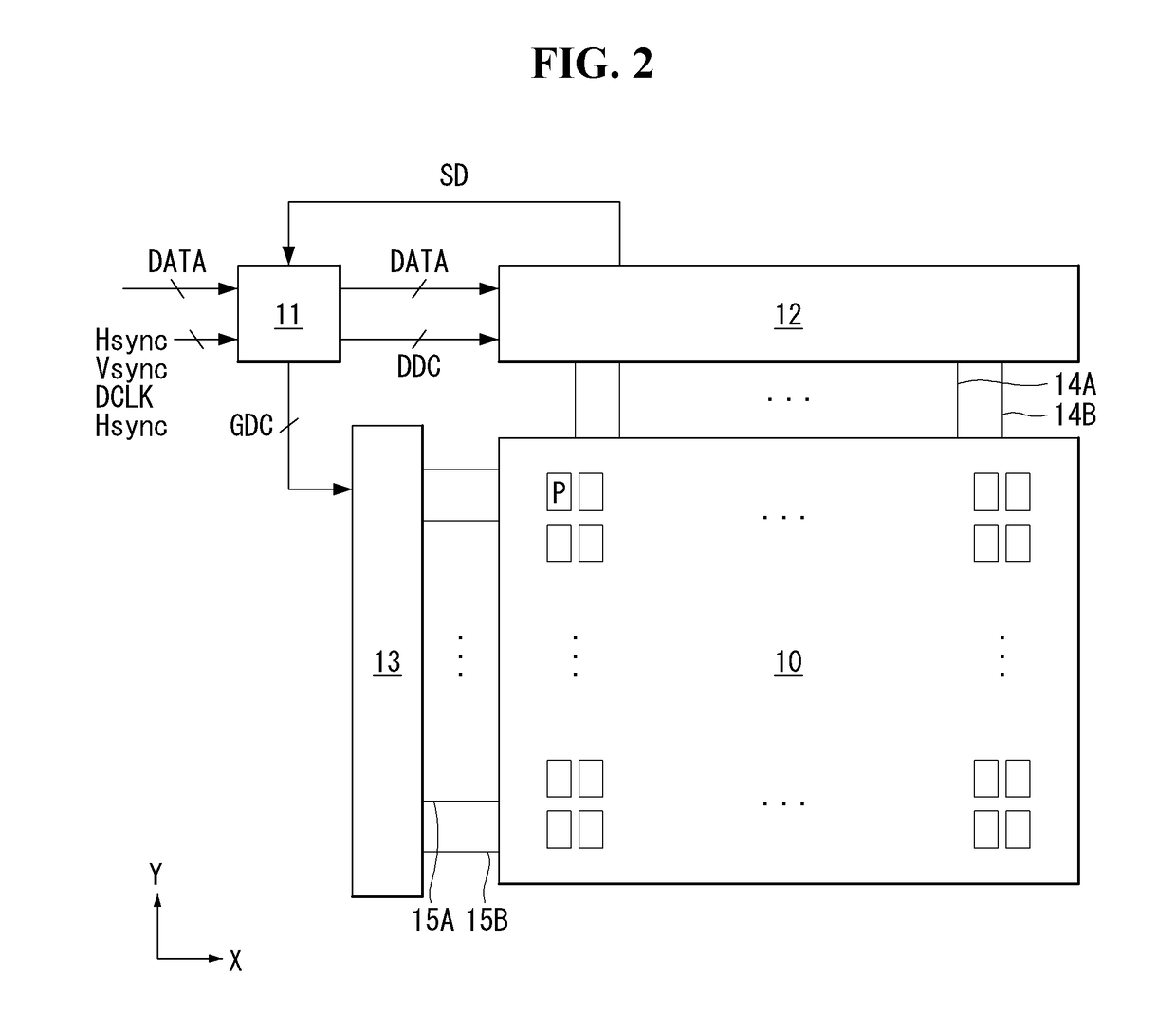

Organic light emitting display device

ActiveUS20180114815A1Reduce physical sizeReduce impactStatic indicating devicesElectroluminescent light sourcesIntegratorDisplay device

An organic light emitting display device in an embodiment of the present invention comprises a display panel equipped with a plurality of pixels each including an OLED and a driving TFT for driving the OLED and a sensing circuit connected to pixels through a sensing line and detecting driving characteristics of a corresponding pixel. The sensing circuit may comprise a plural sensing units including an integrator for integrating currents respectively flowing two adjacent sensing lines connected to inverting and non-inverting input terminals of a fully differential amplifier, a sampling unit for respectively sampling two integral outputs of the integrator and a scaler for regulating an operating range of outputs of the sampling unit, a differential amplifier for differentially amplifying one or more outputs of the scaler, and an ADC for converting an output of the differential amplifier into a digital sensing value.

Owner:LG DISPLAY CO LTD

Latched active fail-safe circuit for protecting a differential receiver

InactiveUS6650149B1Multiple input and output pulse circuitsFail-safe circuitsAudio power amplifierEngineering

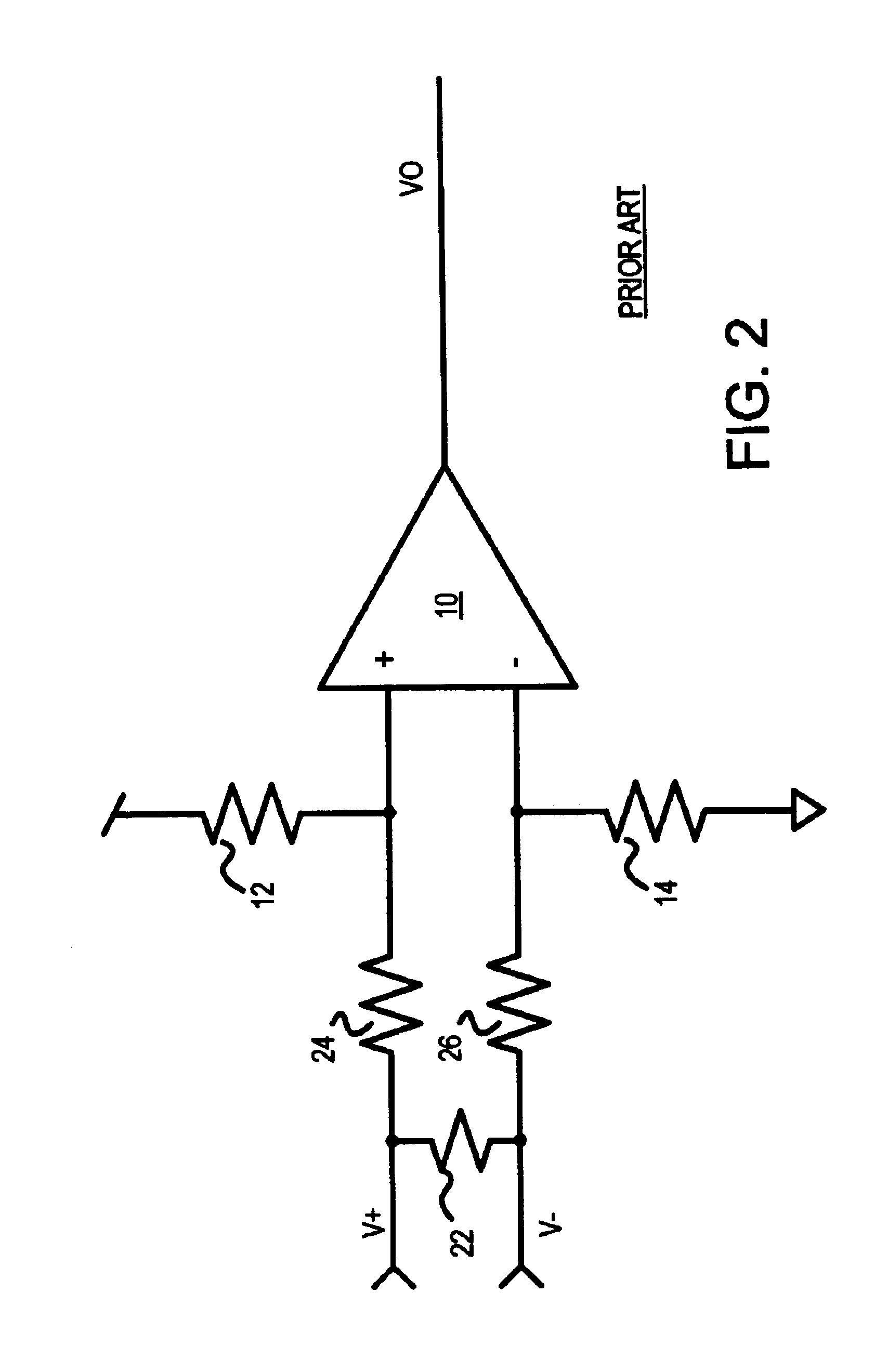

A fail-safe circuit for a differential receiver can tolerate noise. A latch is enabled when both differential inputs V+, V- rise above a reference voltage that is close to Vcc. The latch, once enabled, is set by an offset amplifier, signaling the fail-safe condition. The offset amplifier sets the latch when V+ is above or equal to V-. The differential amplifier has a small offset voltage to allow the latch to remain set when V+ and V- are equal in voltage. An output from a differential amplifier receiving V+ and V- can be blocked by a gate when the fail-safe condition is latched. Pullup resistors pull V+, V- to Vcc when an open failure occurs. The latch remains set when common-mode noise occurs on V+, V-, preventing noise from prematurely disabling the fail-safe condition. Such noise coupled into a broken cable is usually common-mode.

Owner:DIODES INC

Adaptive common mode bias for differential amplifier input circuits

Owner:GLOBALFOUNDRIES INC

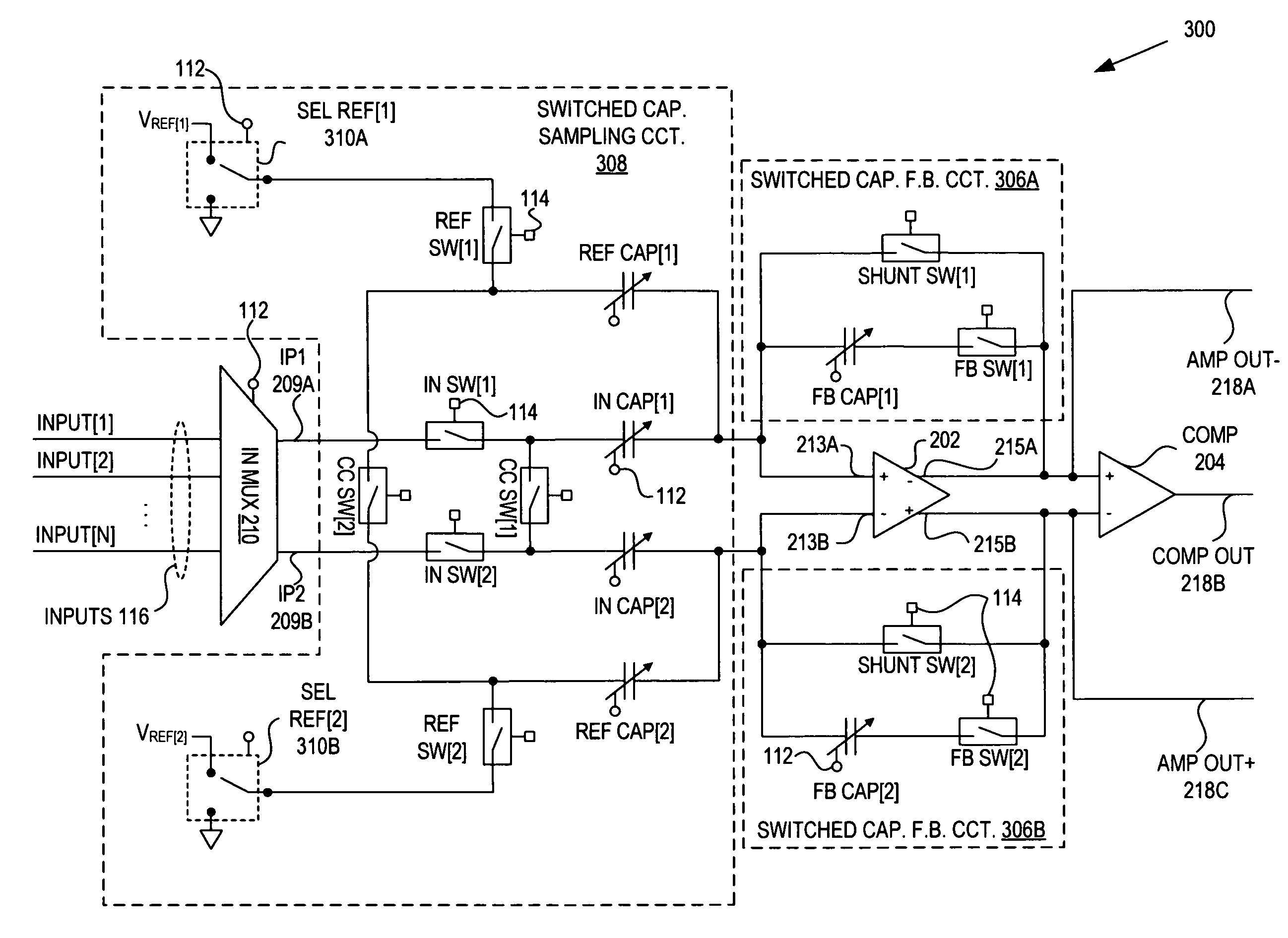

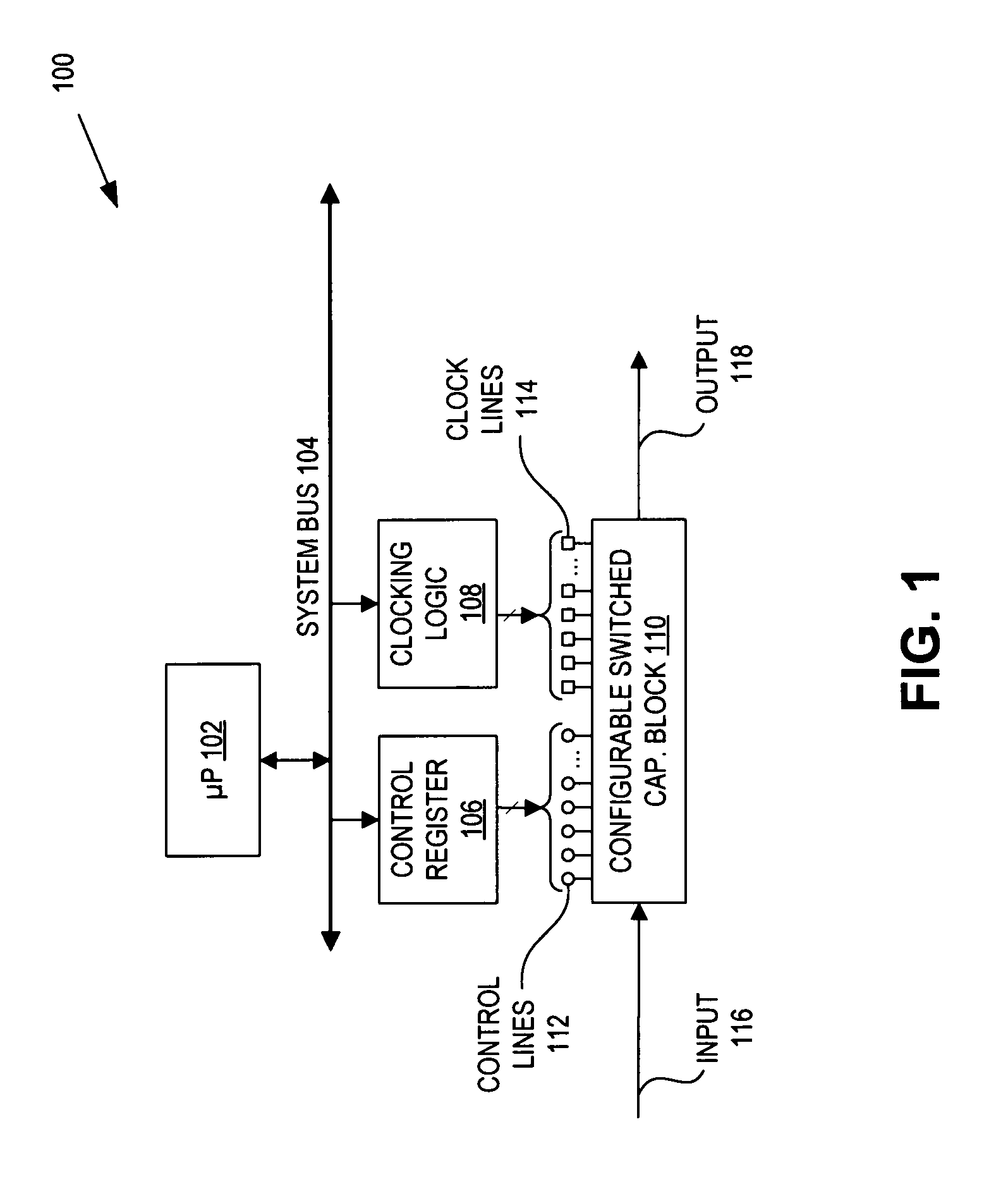

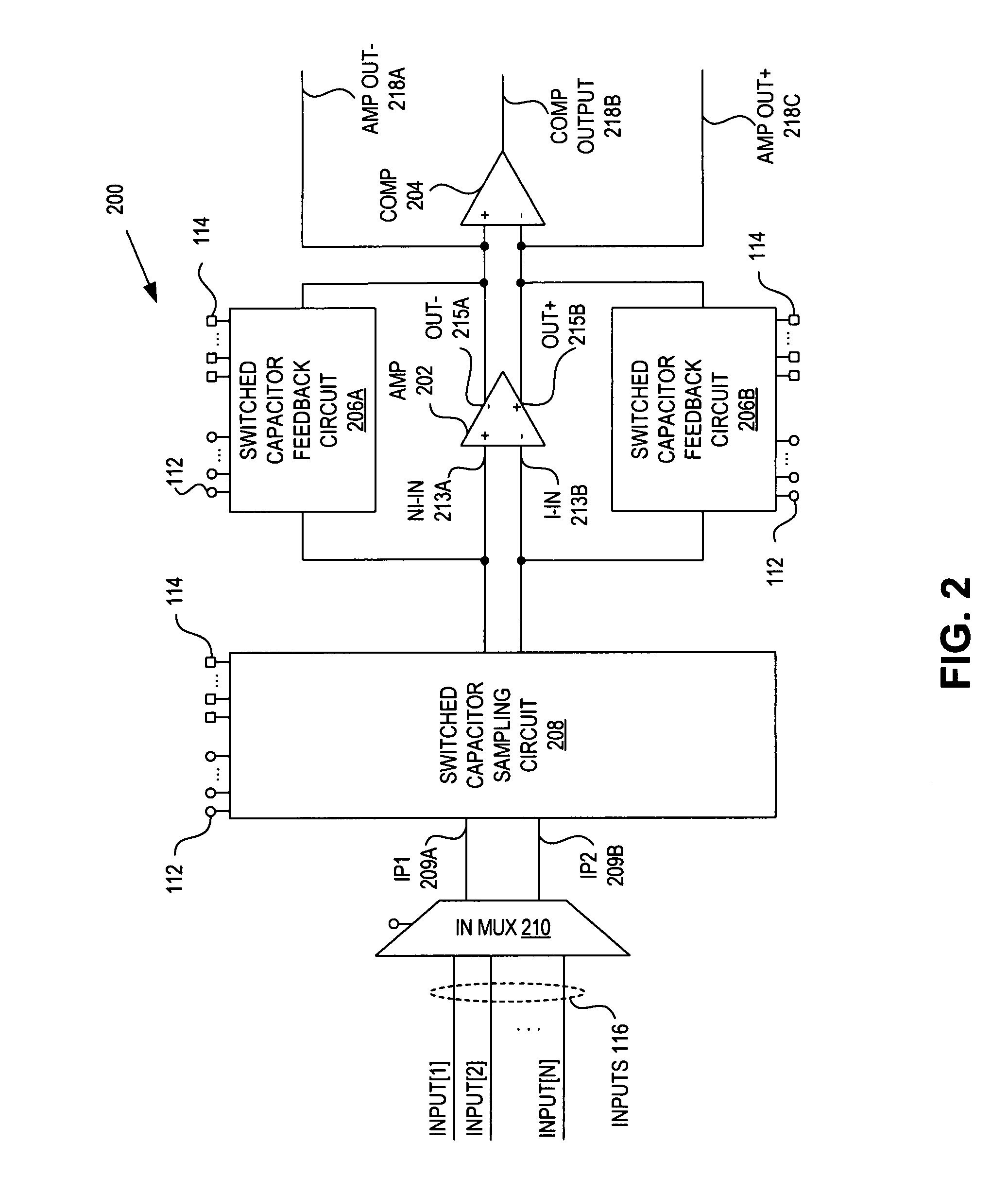

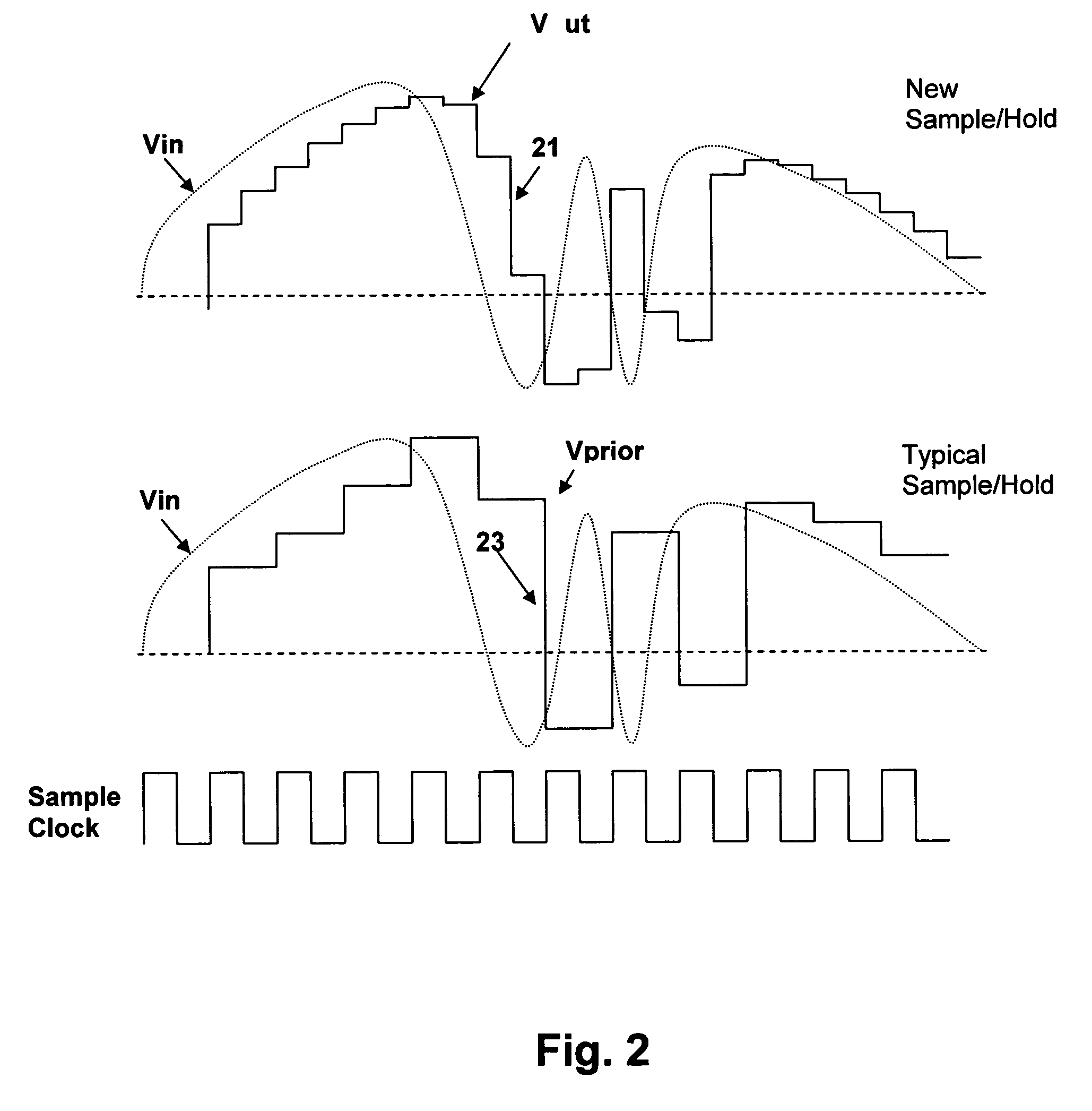

Configurable switched capacitor block

ActiveUS7679422B1Computing operations for integral formationElectric signal transmission systemsAudio power amplifierFeedback circuits

A configurable switched capacitor block includes a switched-capacitor (SC) sampling circuit, a fully differential amplifier, an SC feedback circuit, and a comparator. The SC sampling circuit is coupled to receive an input signal and to selectively generate a sampled signal to a differential input of the amplifier. The SC feedback circuit is coupled between the differential inputs and the differential outputs of the amplifier to selectively control a feedback of the amplifier. The comparator is coupled to the differential outputs of the amplifier to generate an output signal. The configurable switched capacitor block has multiple modes of operation which are selectable by programming the SC sampling circuit and the SC feedback circuit.

Owner:CYPRESS SEMICON CORP

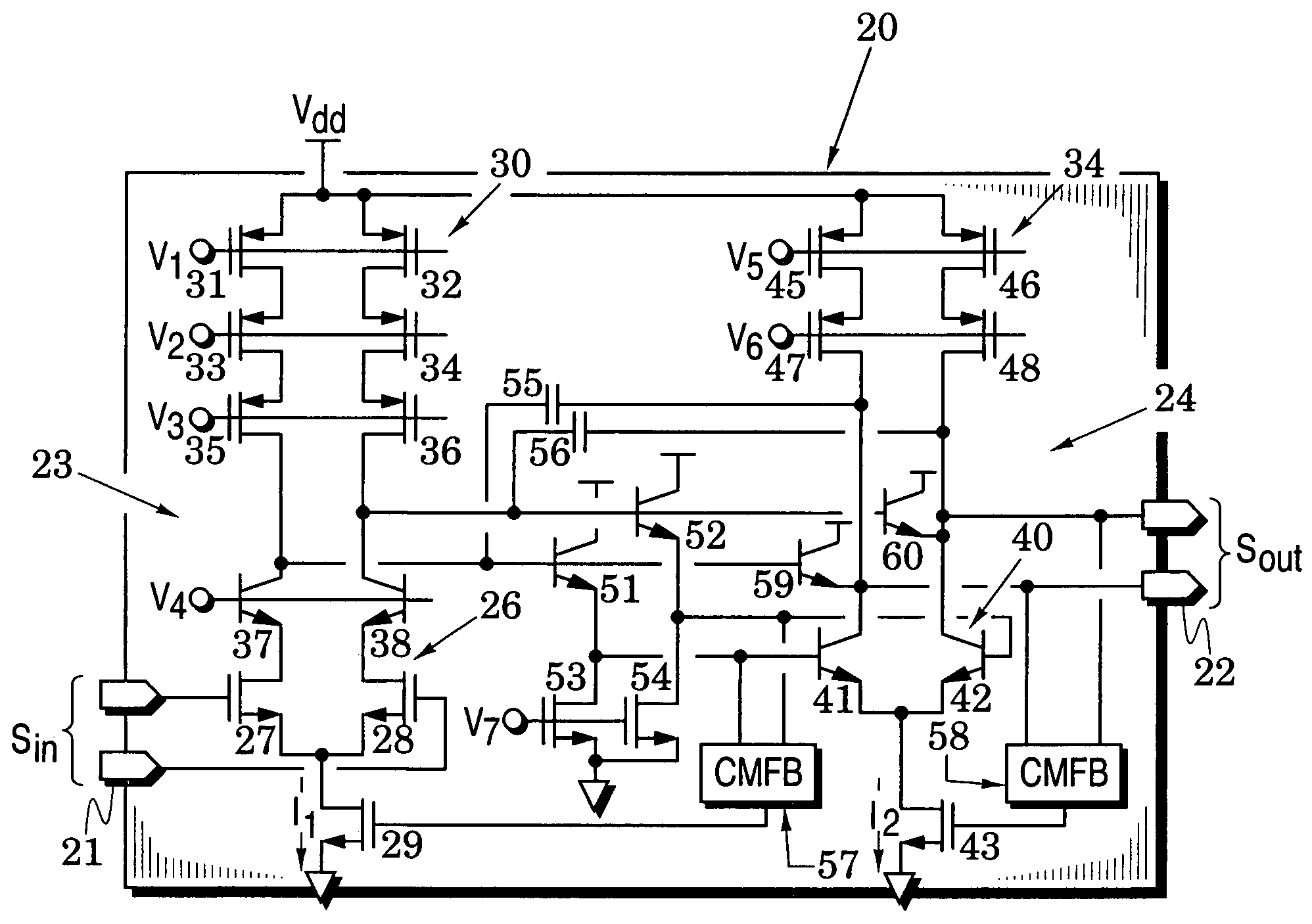

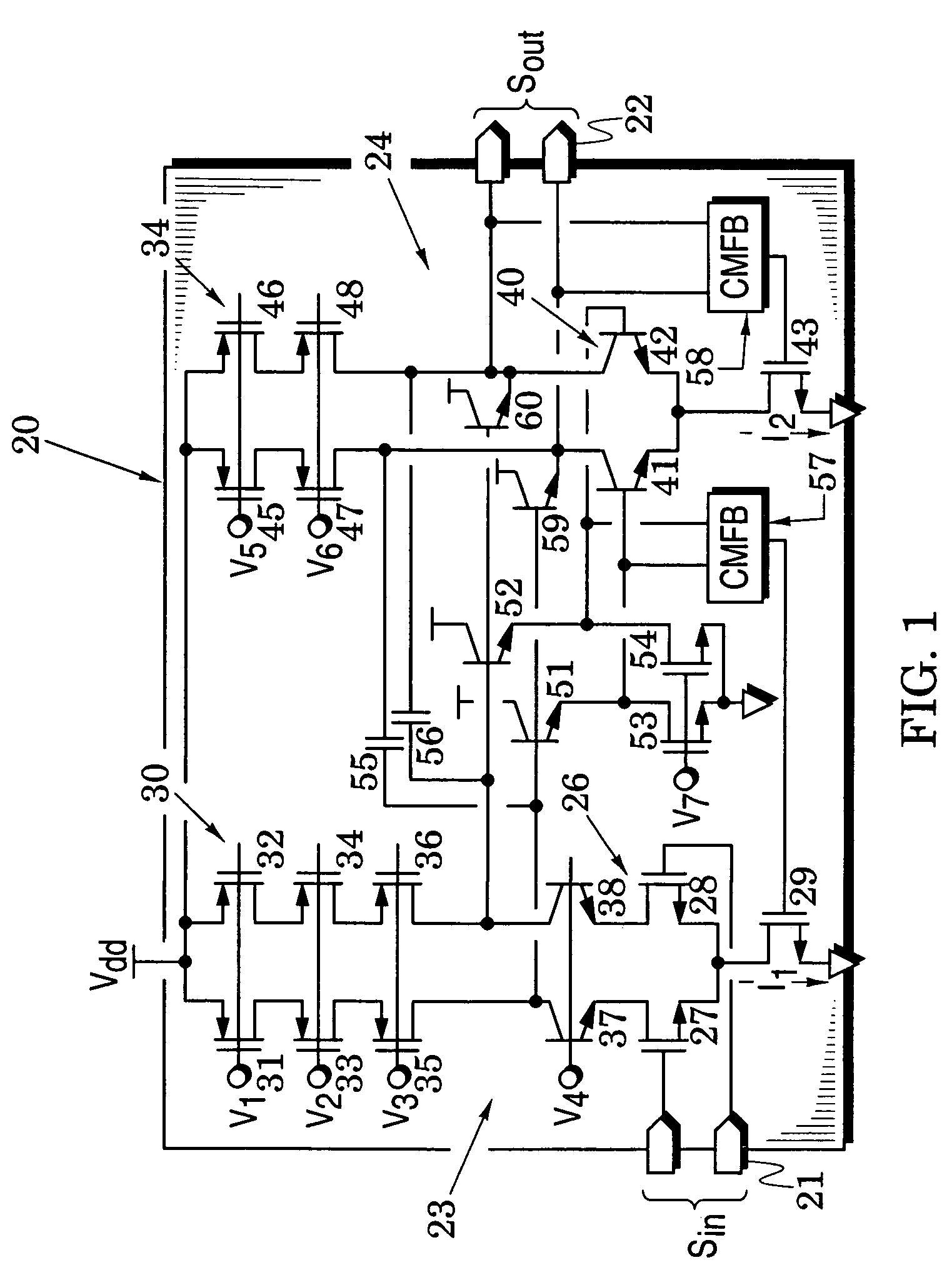

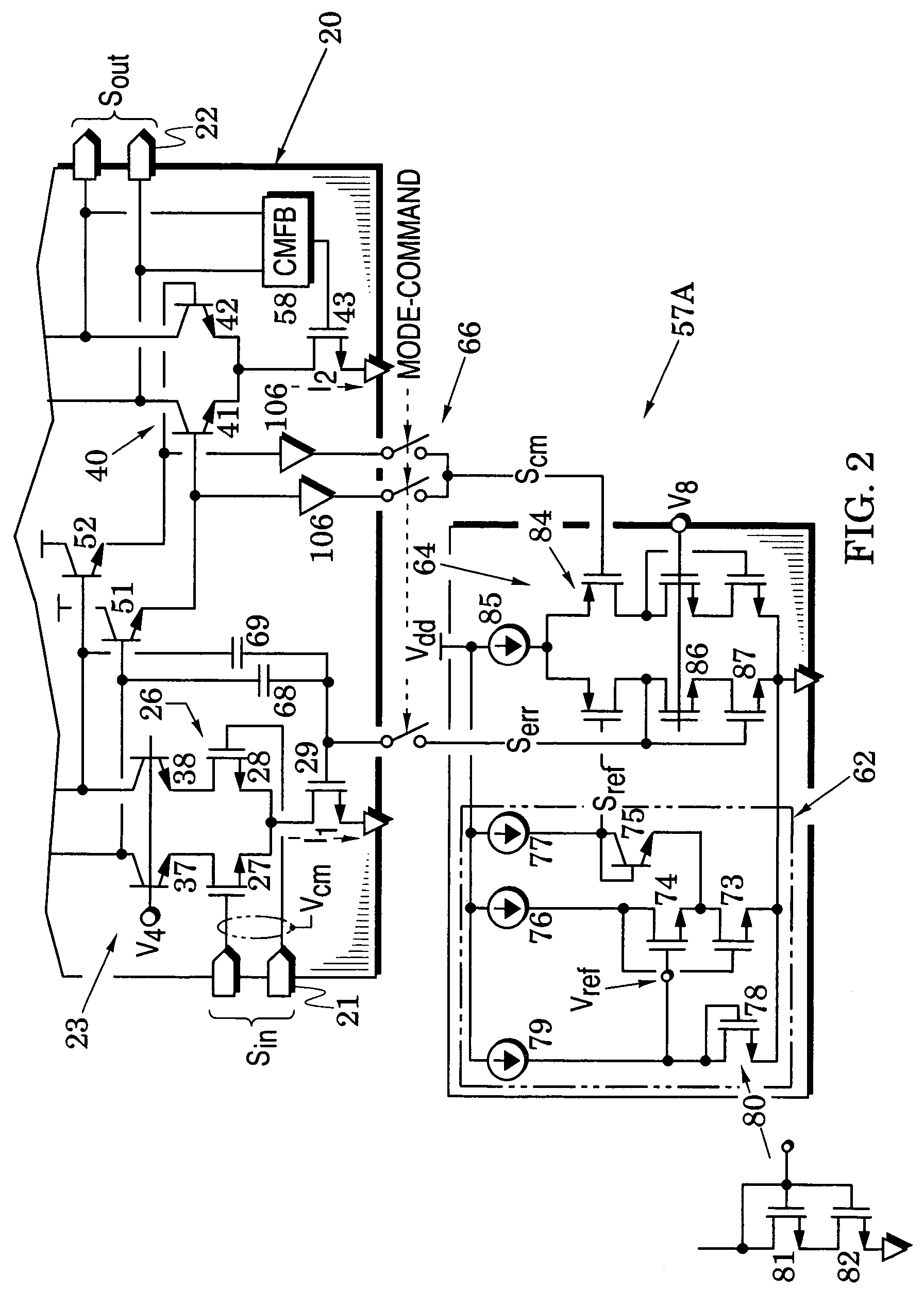

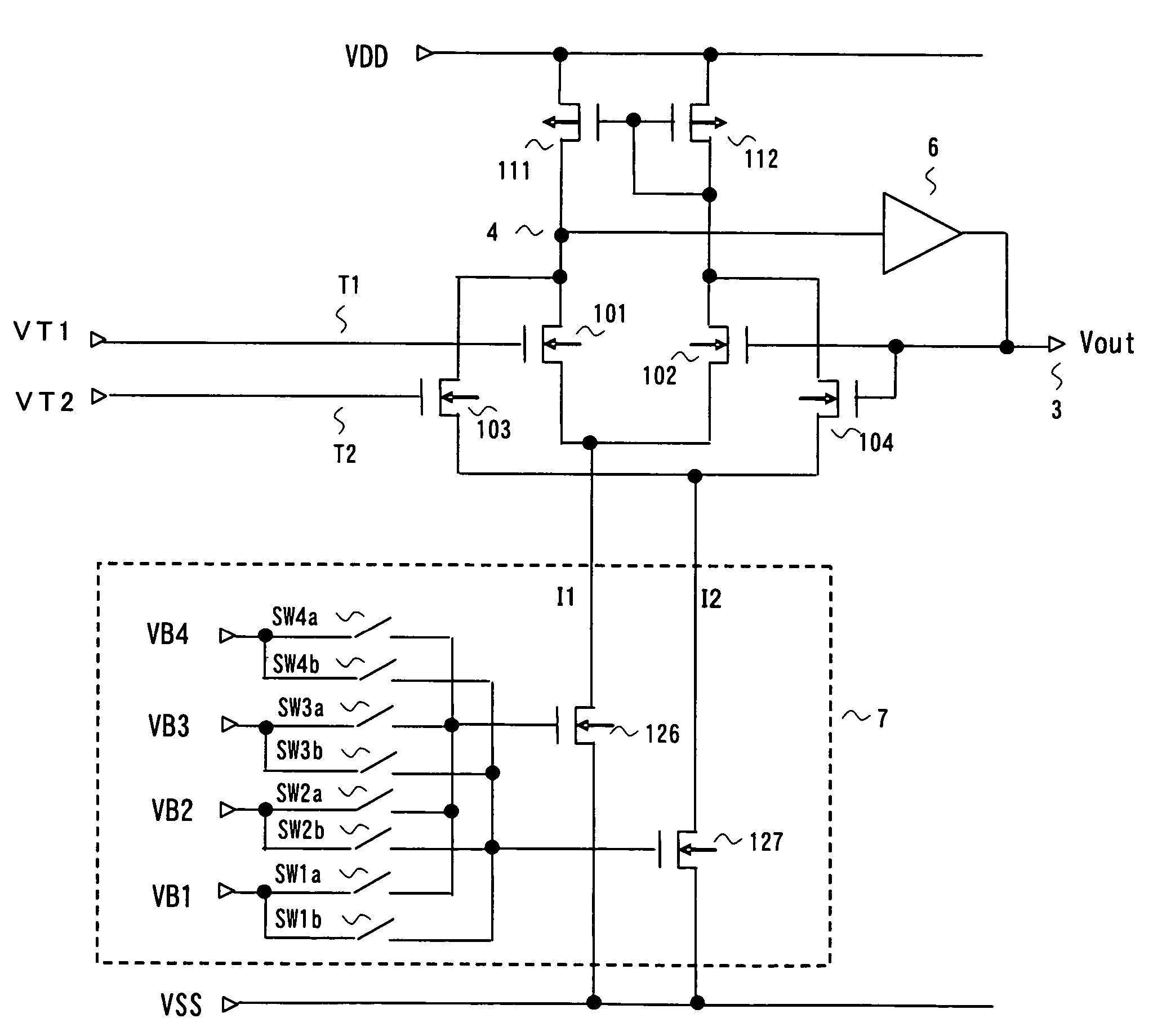

Differential amplifiers with enhanced gain and dynamic range

ActiveUS7253686B2Differential amplifiersDc-amplifiers with dc-coupled stagesAudio power amplifierEngineering

Differential amplifier embodiments are provided for amplifying input signals with enhanced gain and dynamic range. They include first and second amplifier stages and at least one common-mode feedback circuit that is arranged to mirror and adjust a tail current to control the common-mode level of a respective one of the stages. The stages are configured with cascode elements to obtain high impedances that enhance their signal gain and the common-mode feedback circuit is configured to controllably lower the output voltage of a current source that provides the tail current to thereby enhance the amplifier's dynamic range. The amplifier embodiments are particularly suited for use in applications where they must operate with reduced supply voltages and operate in alternating operational modes.

Owner:ANALOG DEVICES INC

Photoelectric conversion apparatus with fully differential amplifier

InactiveUS7808537B2Reduce readTelevision system detailsTelevision system scanning detailsAudio power amplifierEngineering

To provide a configuration including a fully differential amplifier in which decrease in a reading speed can be suppressed. A photoelectric conversion apparatus according to the present invention includes a pixel area where a plurality of pixels are arranged; an amplifier configured to amplify a signal from the pixel area; a plurality of signal paths for transmitting the signals from the pixel area to the amplifier. The amplifier is a fully differential amplifier which includes a plurality of input terminals including a first input terminal and a second input terminal to which the signals from the plurality of signal paths are supplied and a plurality of output terminals including a first output terminal and a second output terminal and the input terminals and the output terminals have no feedback path provided therebetween.

Owner:CANON KK

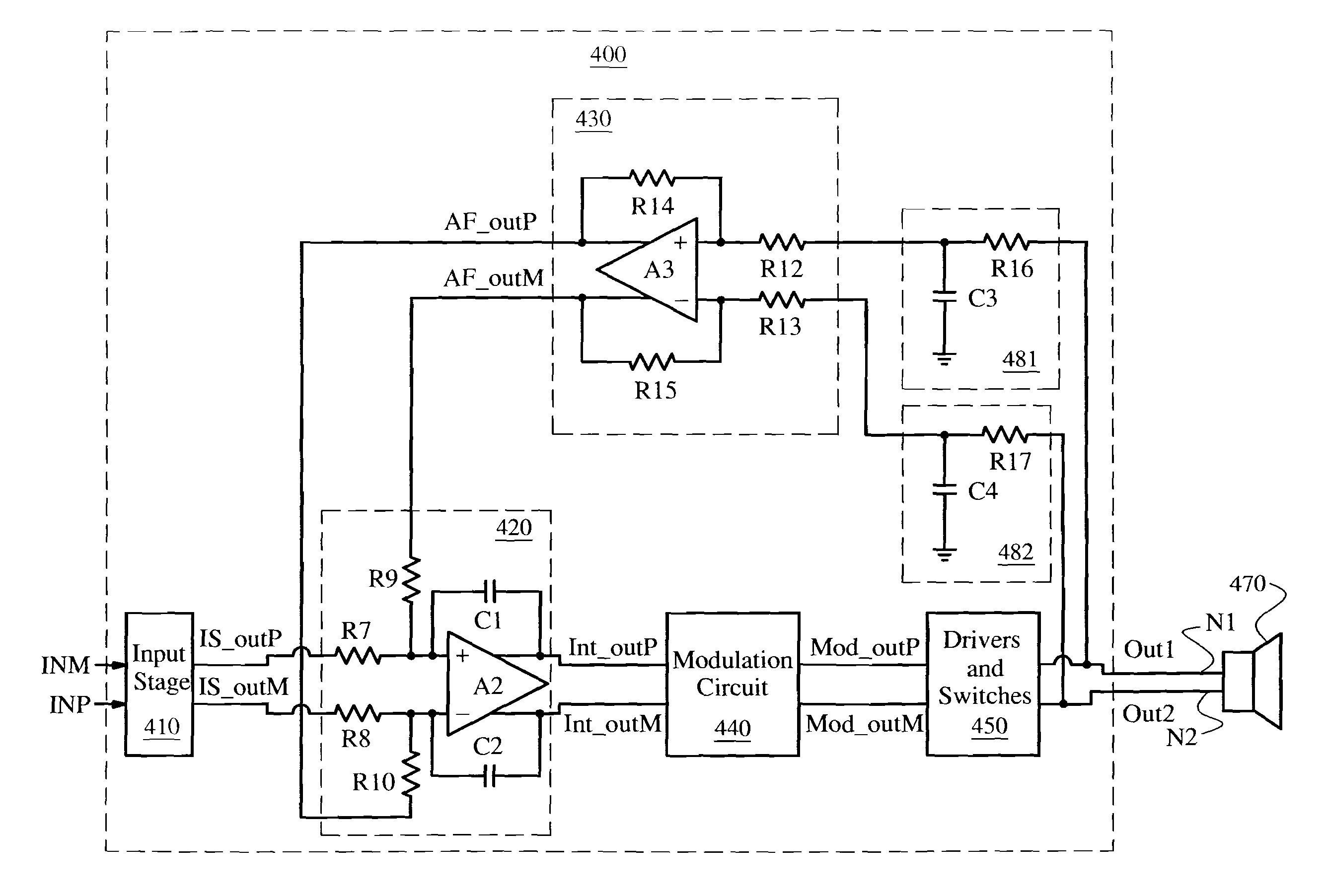

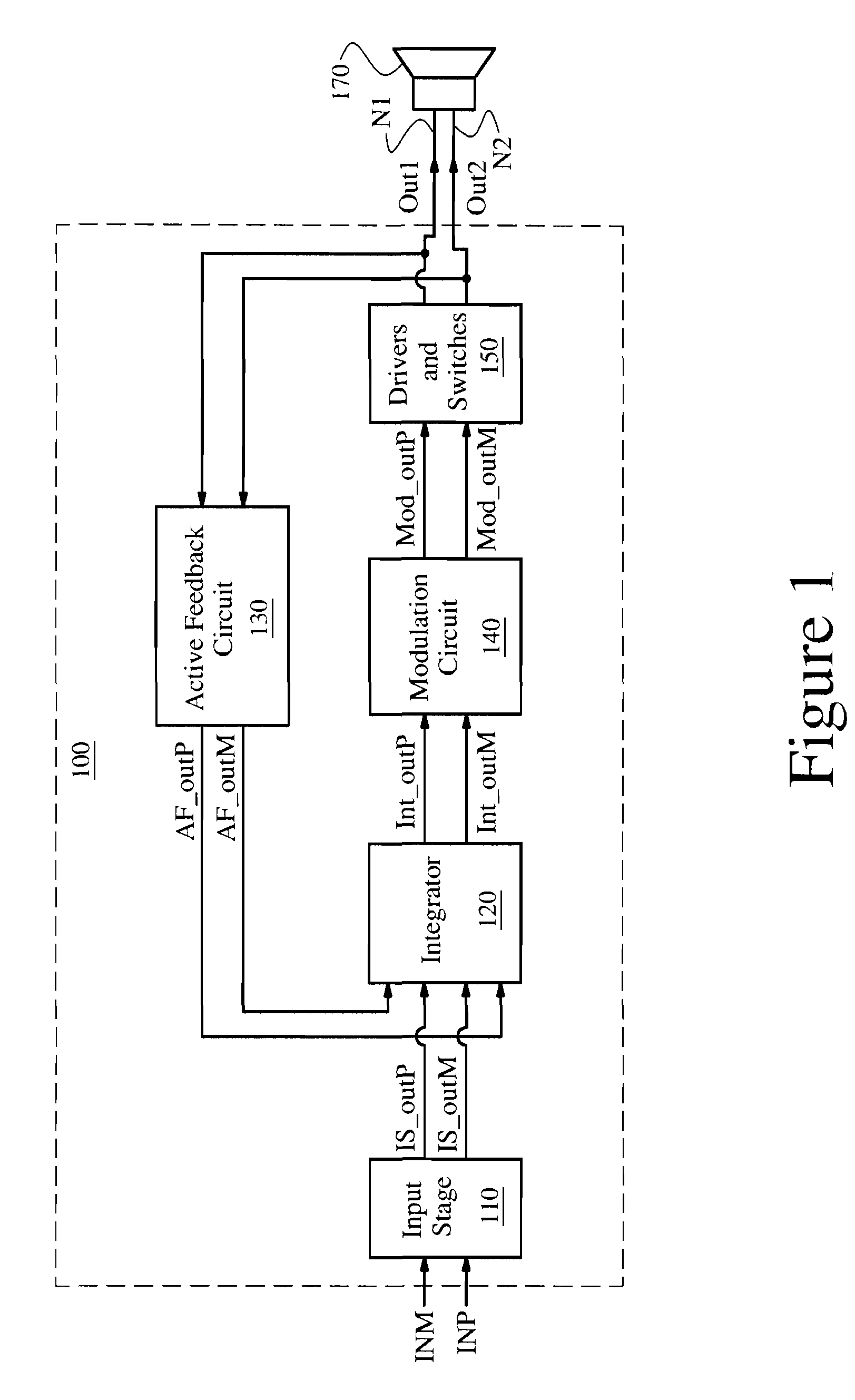

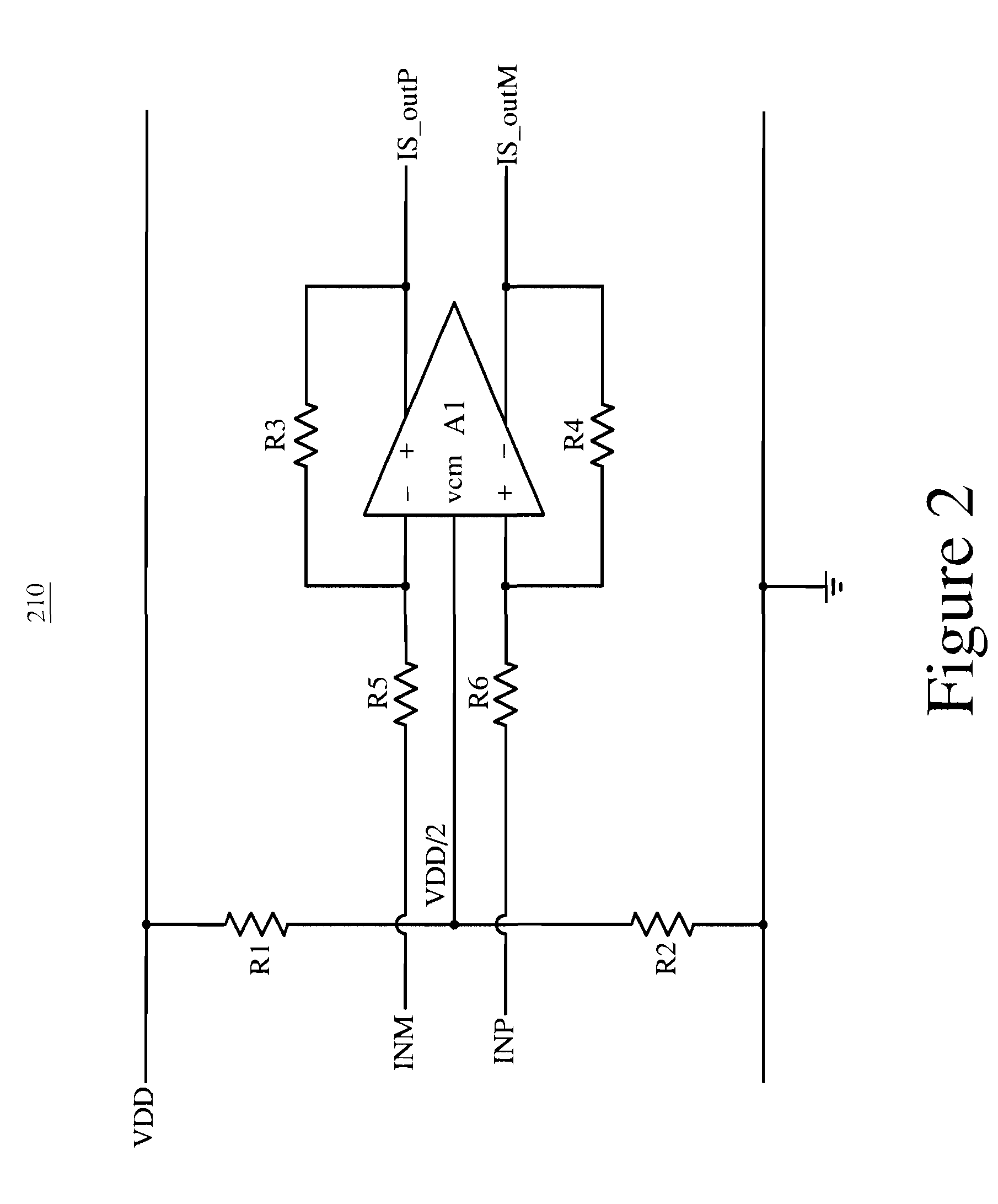

Class D audio power amplifier for mobile applications

ActiveUS7463089B1Negative-feedback-circuit arrangementsAmplifier modifications to raise efficiencyAudio power amplifierClass-D amplifier

A fully differential class D amplifier is provided. The class D amplifier includes an active amplifier in the feedback path of the modulator. In one embodiment, the class D amplifier includes a fully differential amplifier as an input buffer, in which a supply-independent reference voltage is used as the common mode voltage of the output of the fully differential amplifier. In one embodiment, the class D amplifier includes a pulse width modulation circuit that includes rail-to-rail comparators.

Owner:NAT SEMICON CORP

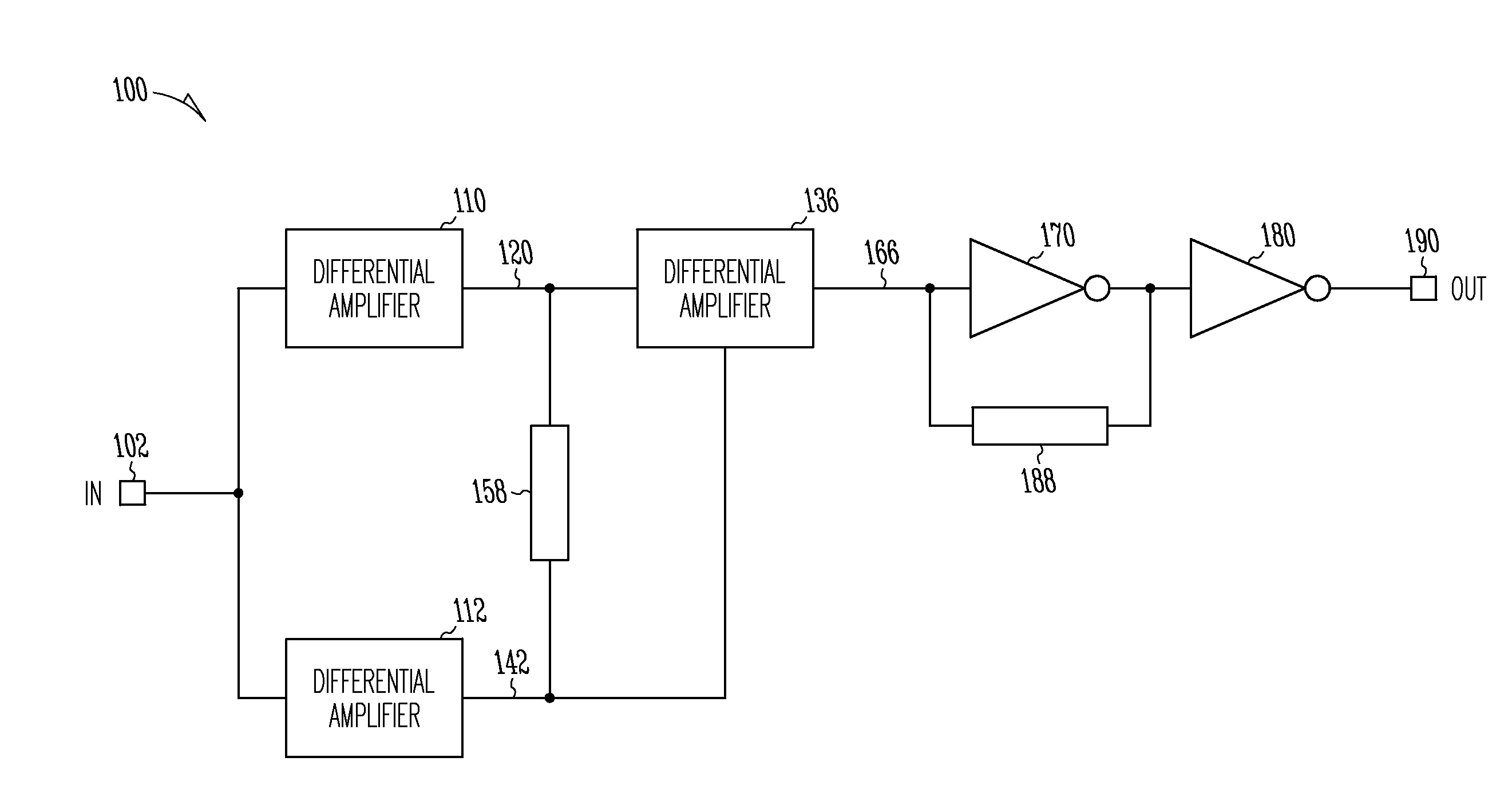

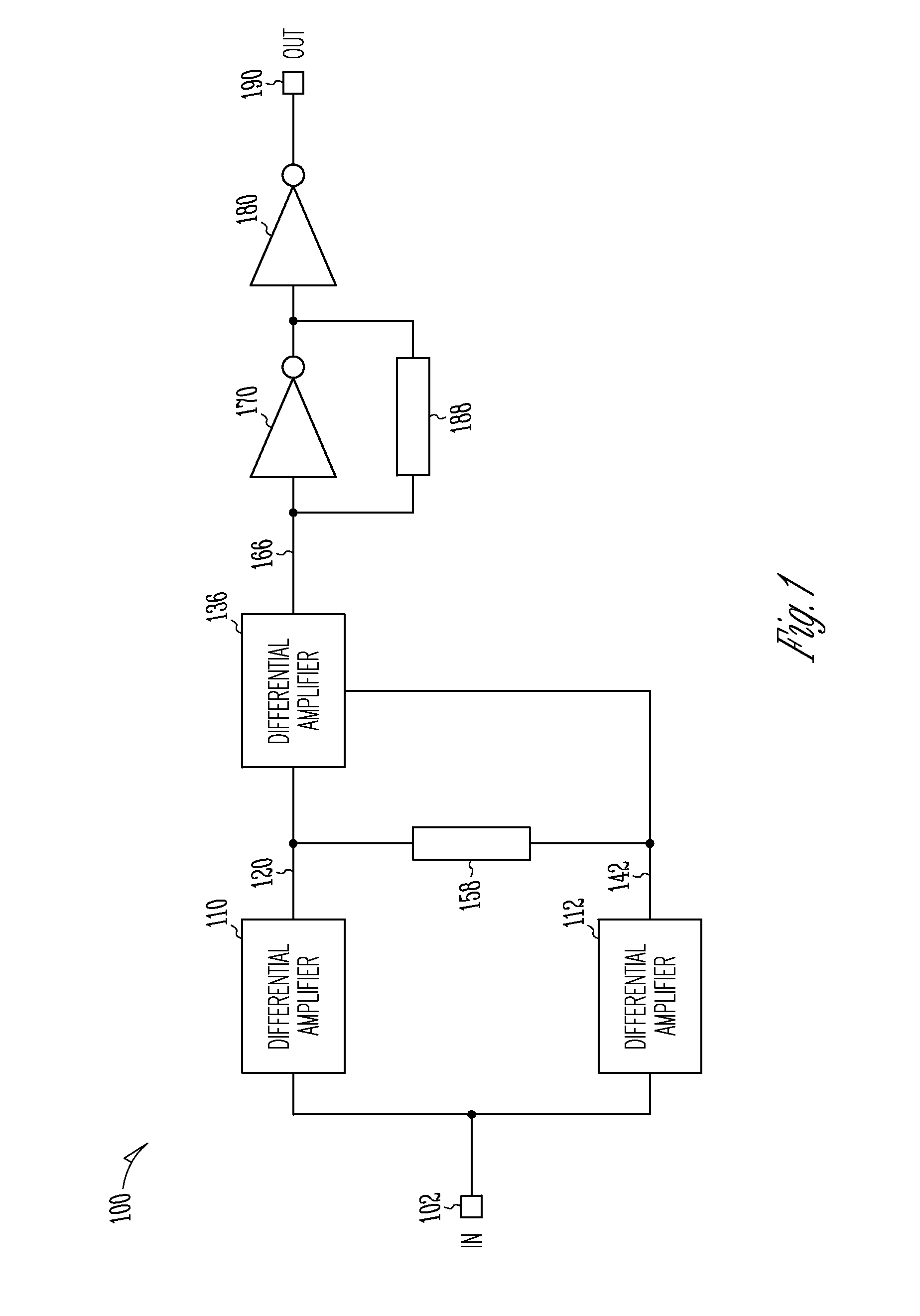

Input buffer apparatuses and methods

ActiveUS20140269118A1Digital storageDifferential amplifiersDifferential amplifierSignal amplification

Apparatuses and methods are disclosed, including an apparatus with a first differential amplifier to amplify an input signal into a first output signal, a second differential amplifier to amplify the input signal into a second output signal that is complementary to the first output signal, and a feedback resistance coupled between the first output signal and the second output signal. Additional apparatuses and methods are described.

Owner:MICRON TECH INC

Differential amplifier and drive circuit of display device using the same

InactiveUS20090231319A1Guaranteed high speed operationReduce power consumptionCathode-ray tube indicatorsDifferential amplifiersVoltage converterDriver circuit

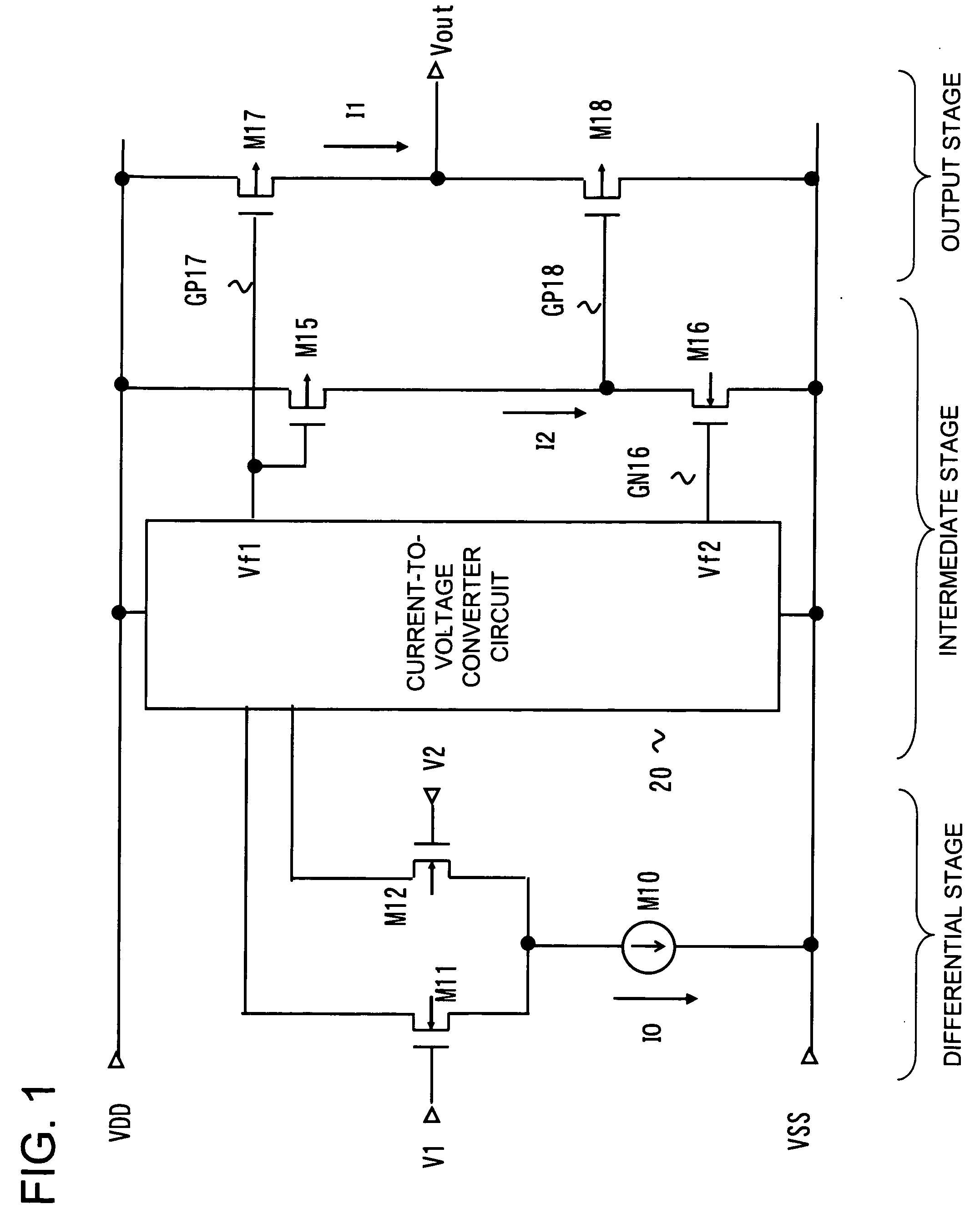

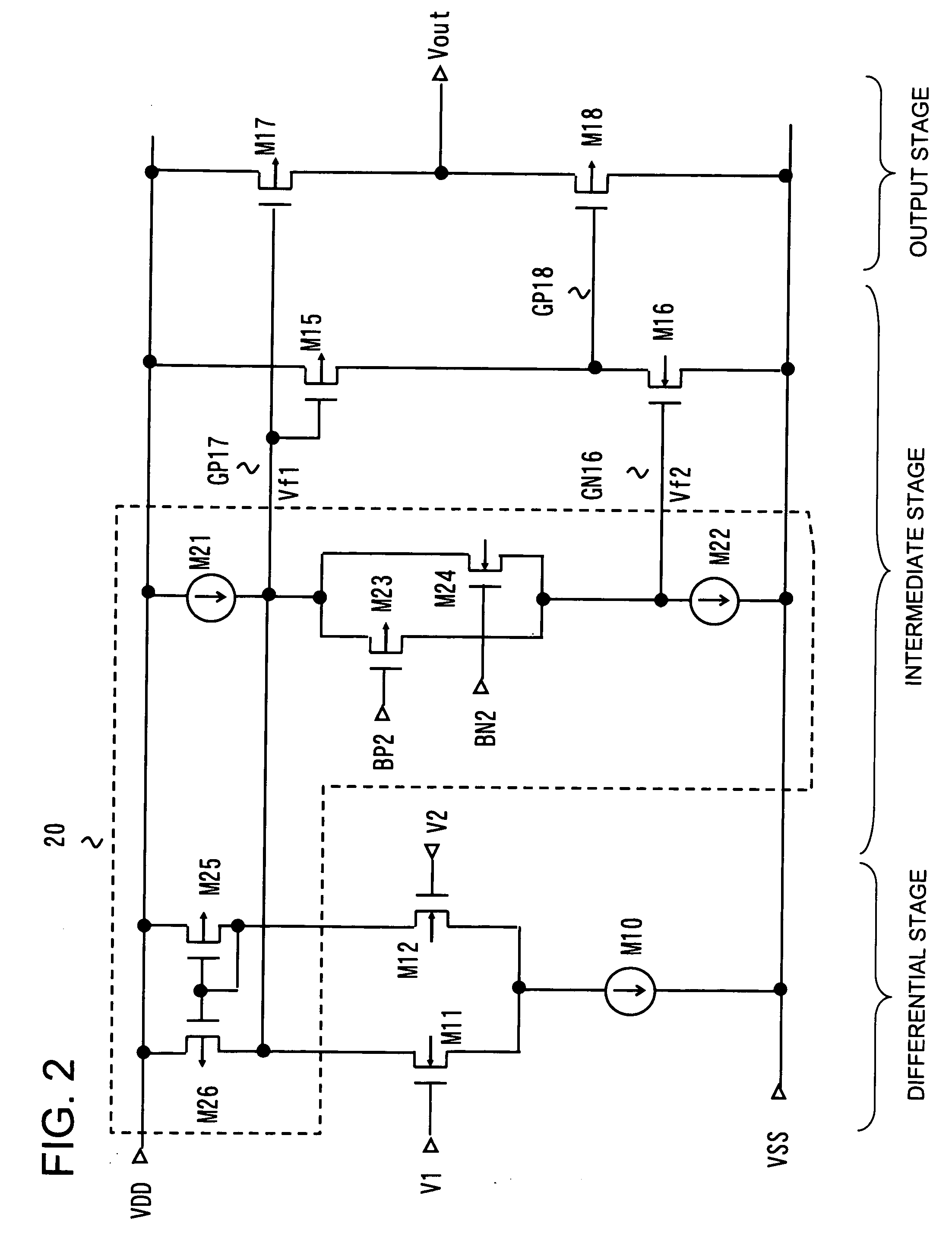

Disclosed is a differential amplifier of the present invention includes a differential pair differentially receiving a signal, a current source connected between a first voltage supply and the differential pair, for driving the differential pair, a current-to-voltage converter circuit receiving output currents of the differential pair and producing first and second voltage signals, first and second transistors of mutually different conductivity types connected in series between the first voltage supply and a second voltage supply and respectively receiving the first and second voltage signals at control terminals thereof, a third transistor connected between the second voltage supply and an output terminal and receiving the first voltage signal at a control terminal thereof, and a fourth transistor of the same conductivity type as that of the third transistor, the fourth transistor being connected between the output terminal and the first voltage supply and having a control terminal thereof connected to a connecting node between the first and second transistors.

Owner:RENESAS ELECTRONICS CORP

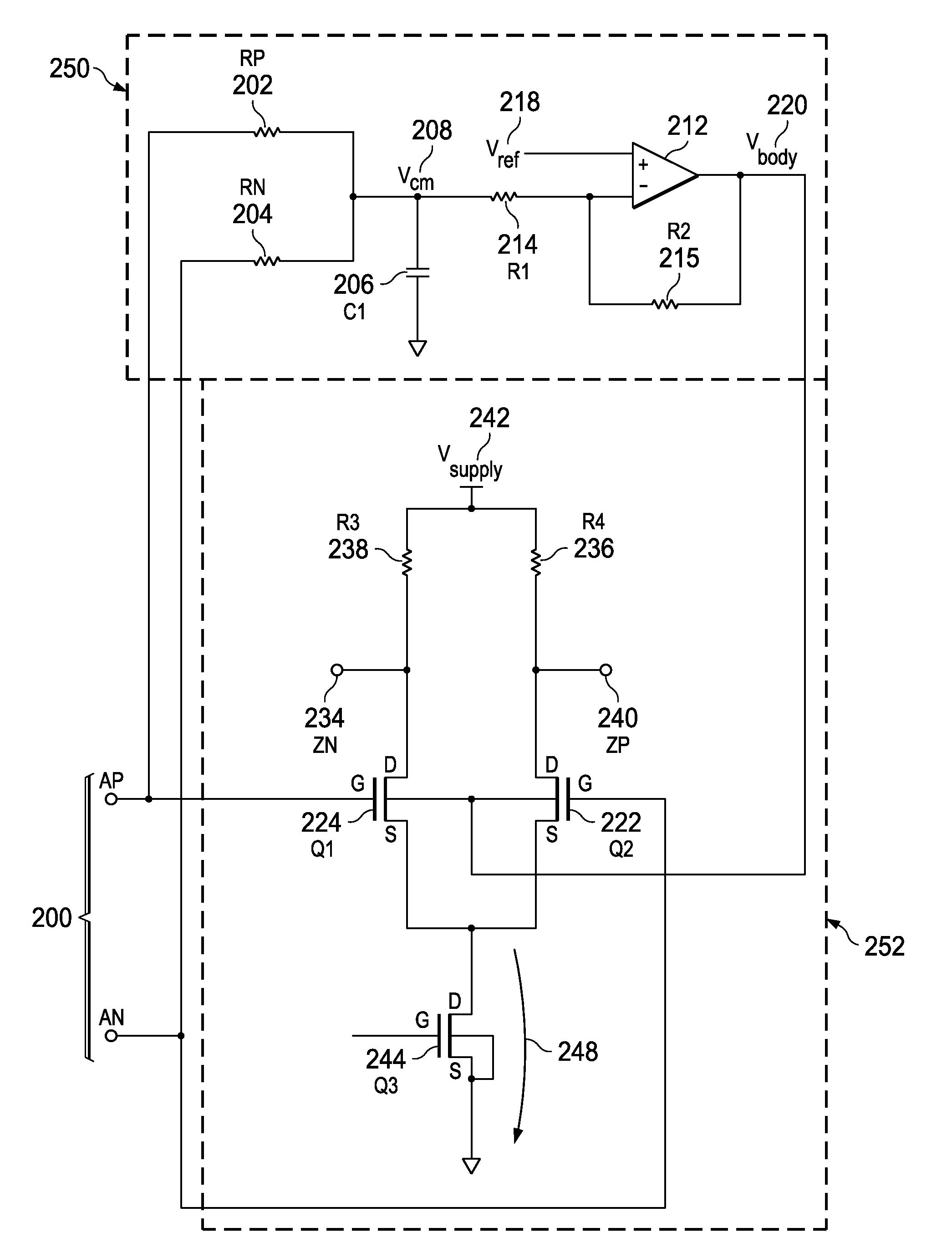

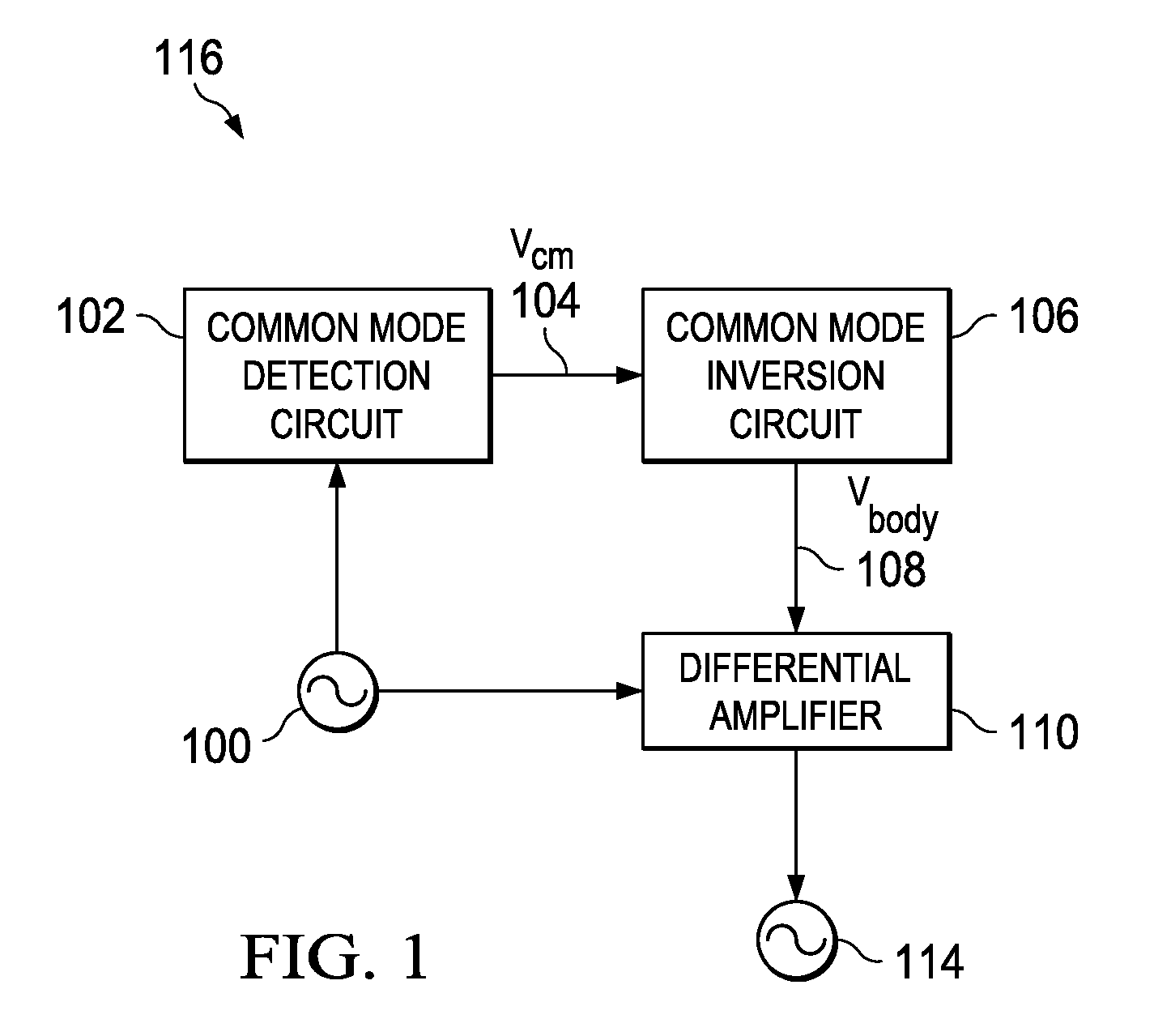

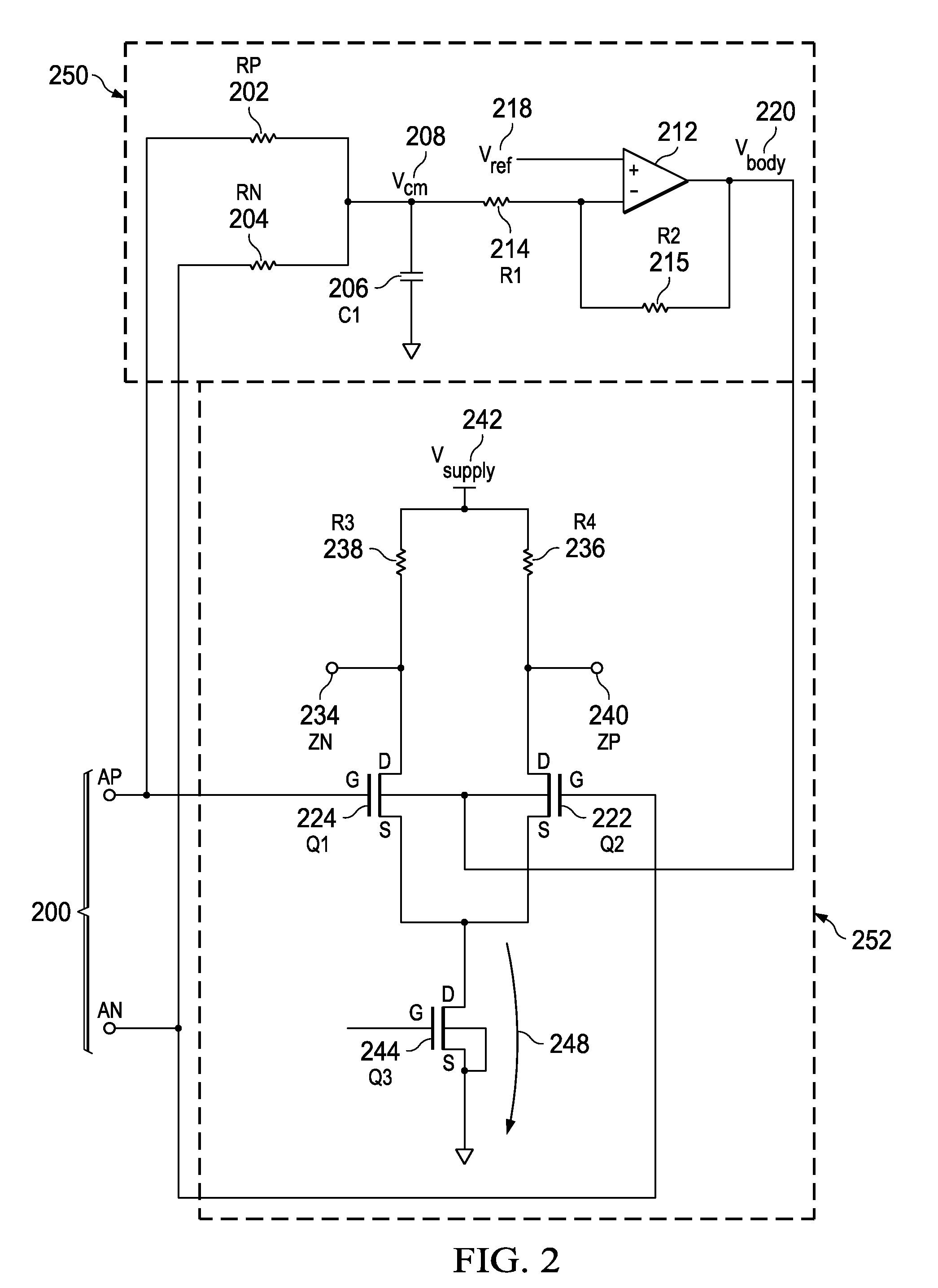

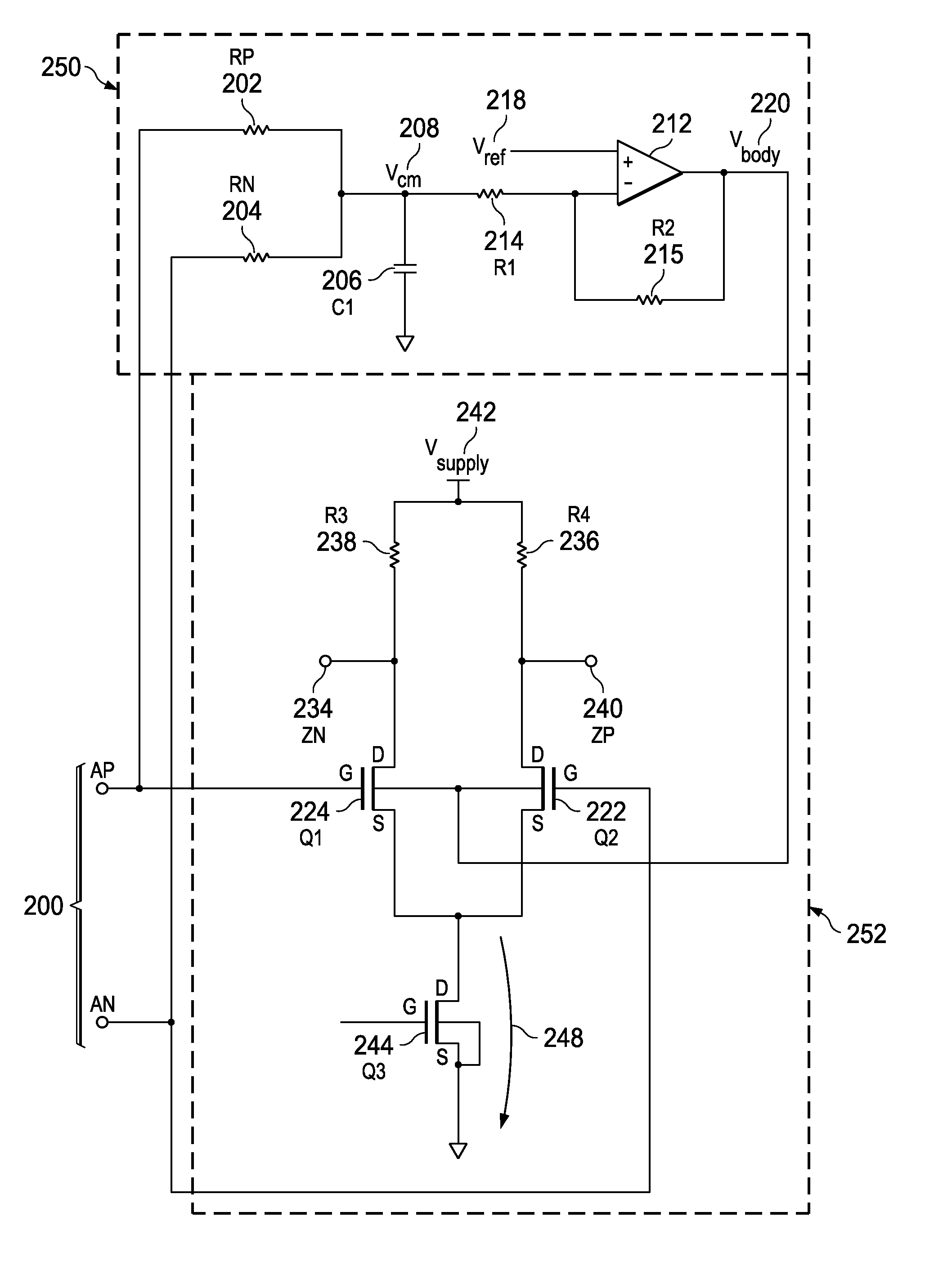

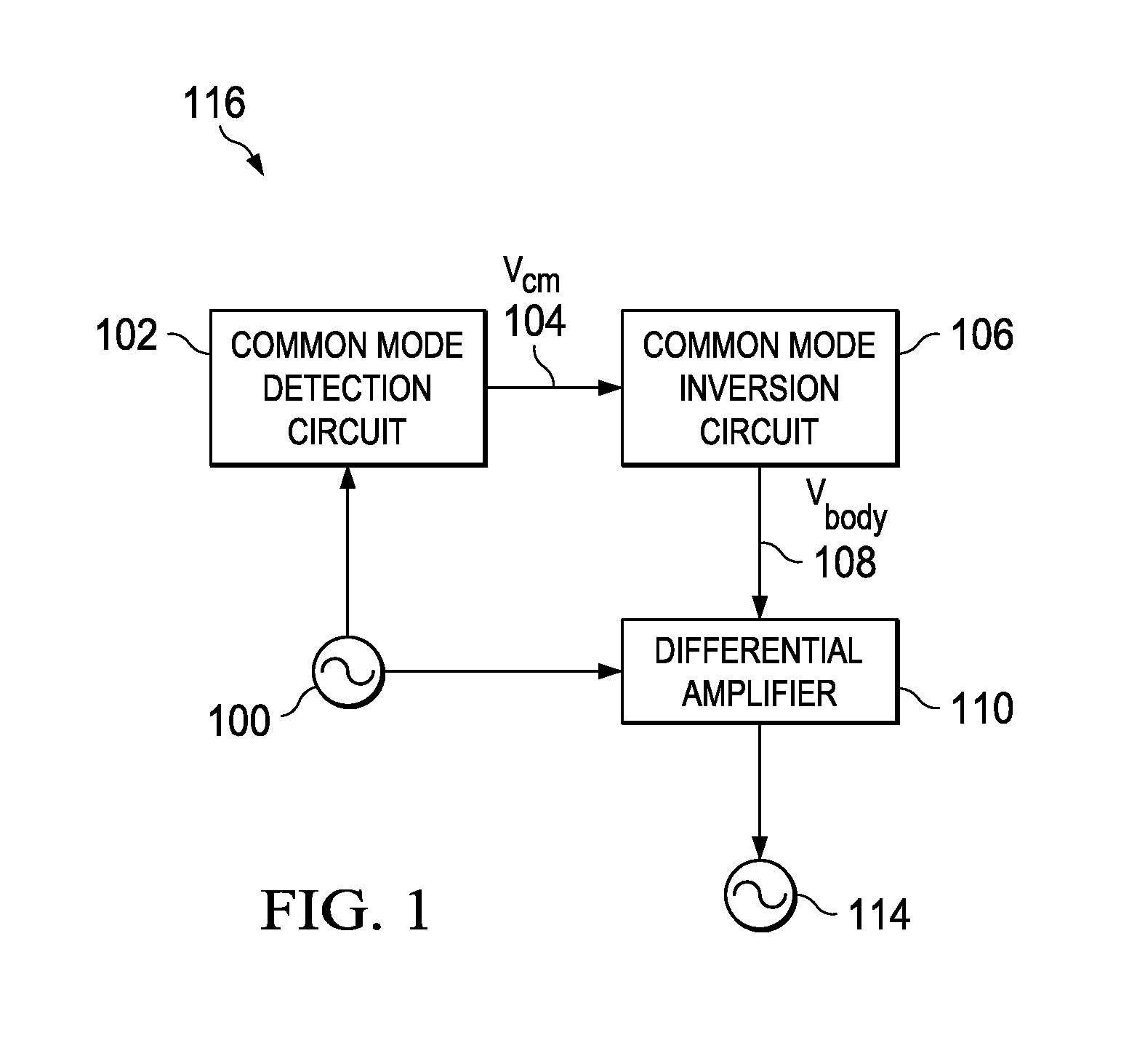

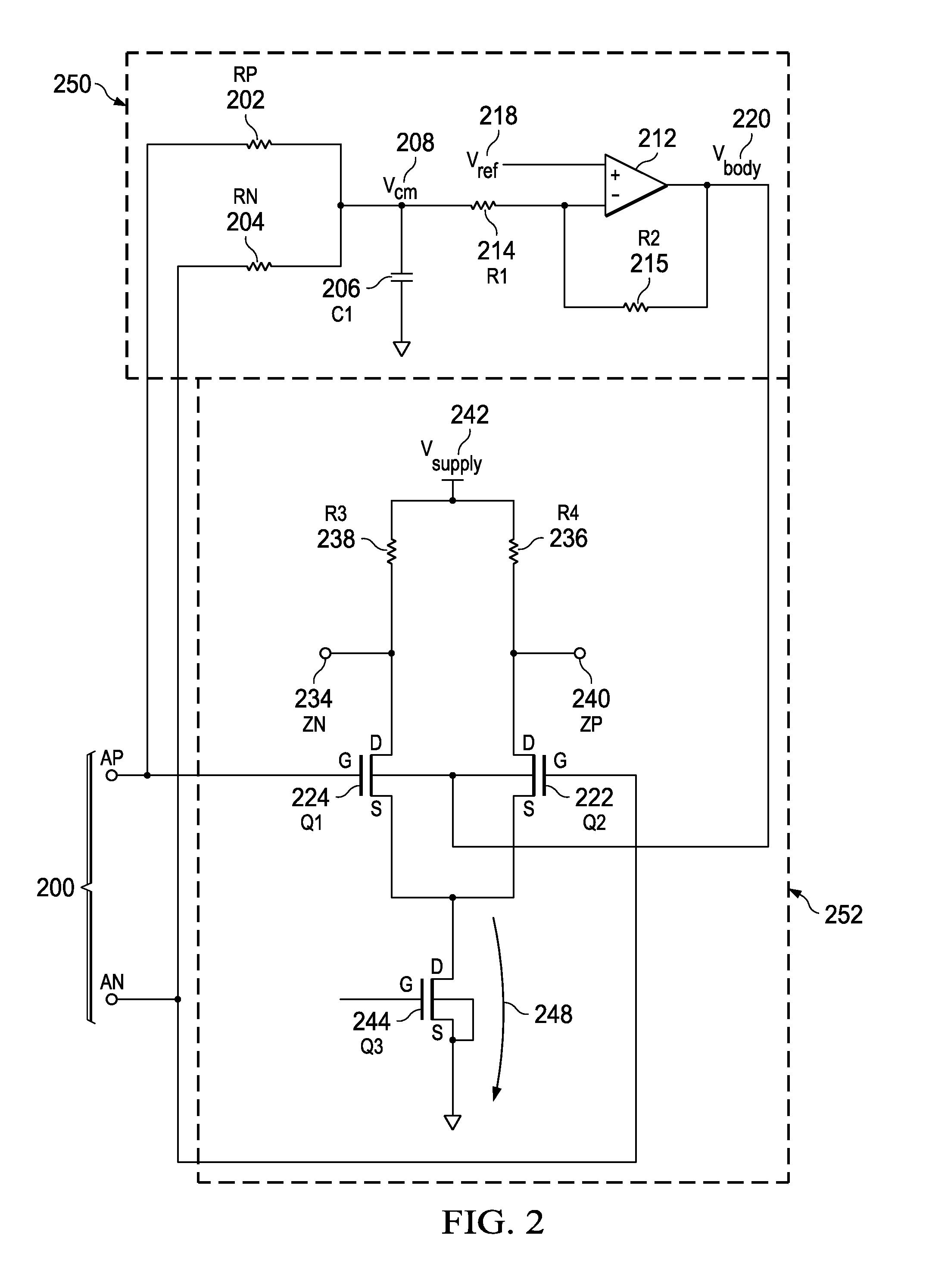

Adaptive common mode bias for differential amplifier input circuits

InactiveUS7893766B1Extend input common mode rangeDifferential amplifiersAmplifier detailsDifferential signalingSelf adaptive

A method and apparatus for extending the common mode range of a differential amplifier. A circuit has a common mode detection circuit, a common mode voltage inversion circuit, and a differential amplifier. The common mode detection circuit receives a differential signal and detects a common mode voltage. The common mode voltage inversion circuit is coupled to the common mode detection circuit. The common mode voltage inversion circuit has an input node that receives the common mode voltage and an output node that outputs body voltage, wherein the common mode voltage inversion circuit creates an inverse relationship between the common mode voltage and the body voltage. The differential amplifier includes a differential pair of transistors that have a pair of body terminals coupled to the output node of the common mode voltage inversion circuit.

Owner:GLOBALFOUNDRIES INC

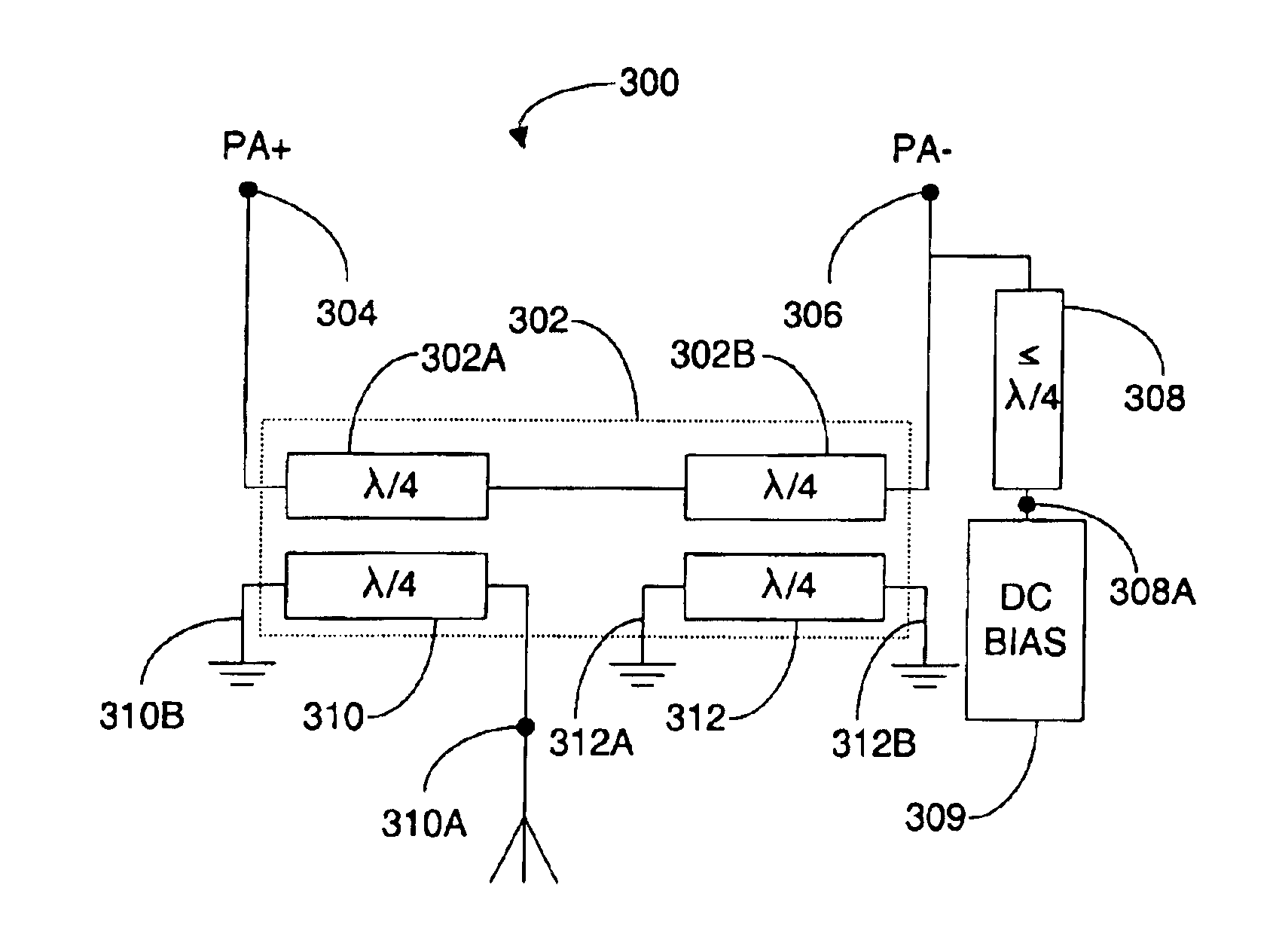

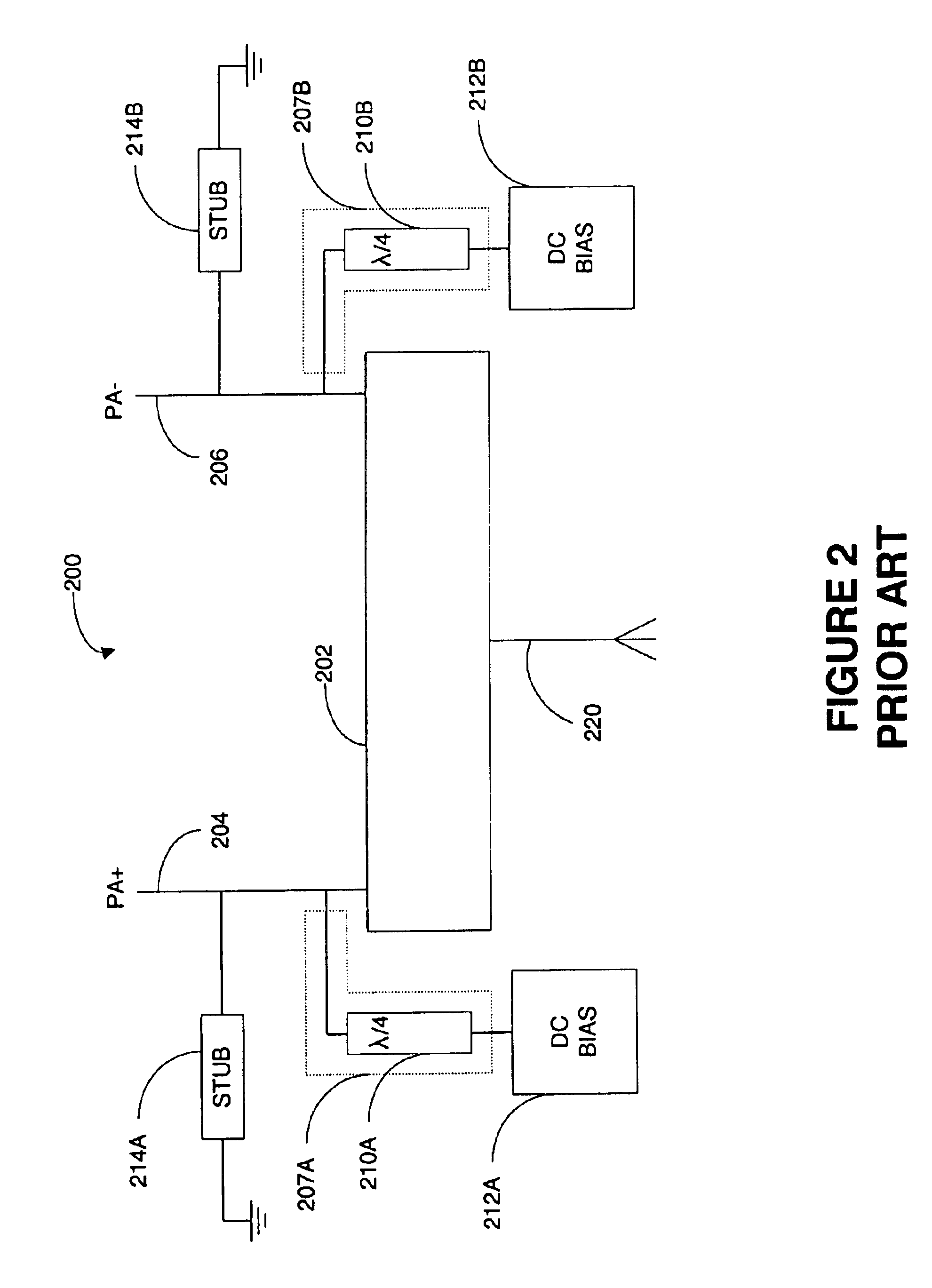

Single ended tuning of a differential power amplifier output

InactiveUS6844792B1Maximize signalMultiple-port networksOne-port networksElectrical conductorParasitic capacitance

A system and method for compensating a parasitic capacitance on a differential amplifier output includes a first differential output and a second differential output of the differential amplifier. The first differential output coupled to the second differential output by a first conductor that has a length of about one half wavelength. The first and the second differential outputs have a parasitic capacitance that can be measured. A second conductor is coupled to the first differential output. The second conductor having a length that is less than or equal to about one quarter wavelength and has an inductive reactance that offsets a capacitive reactance of the parasitic capacitance.

Owner:GATX VENTURES

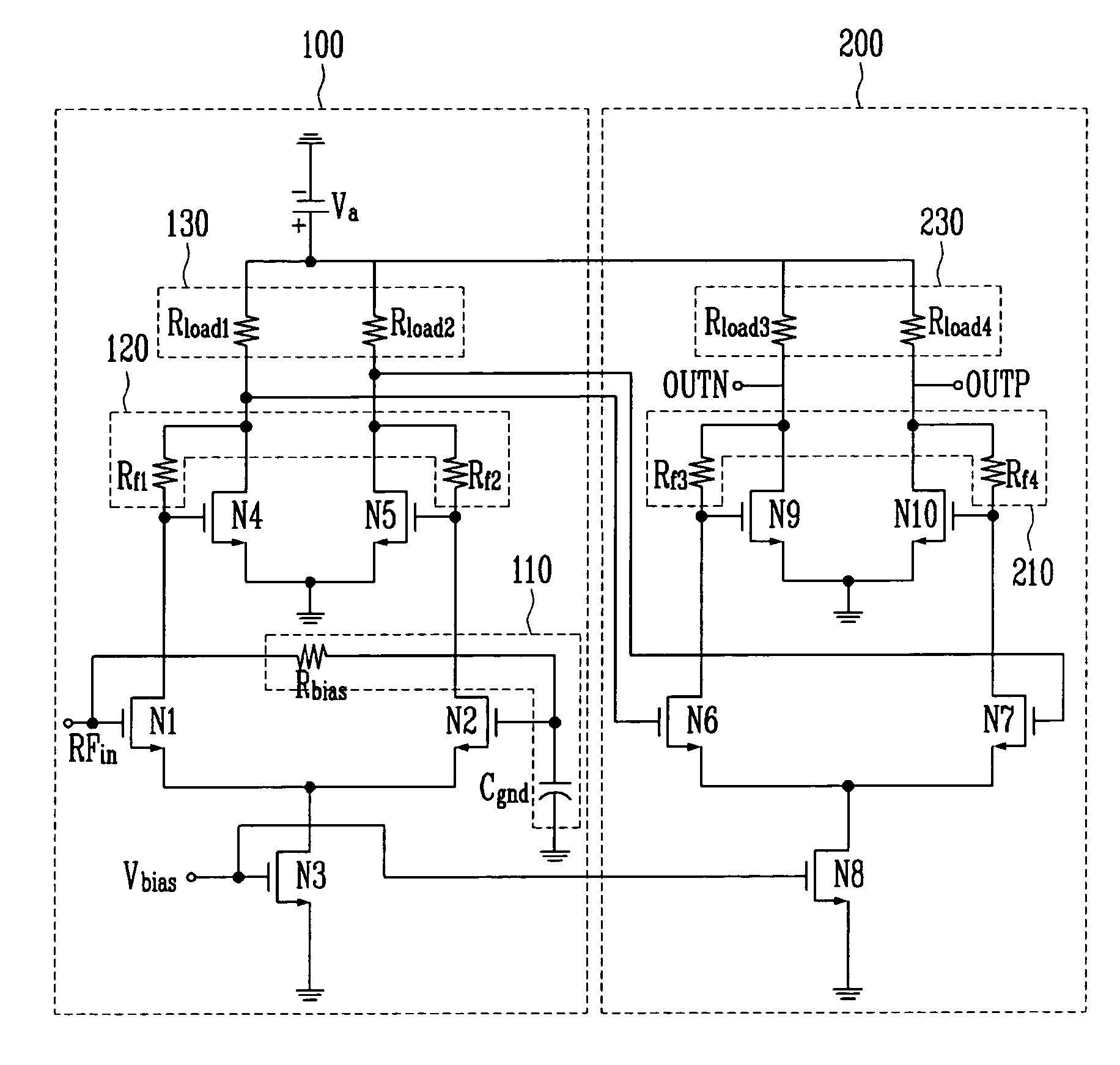

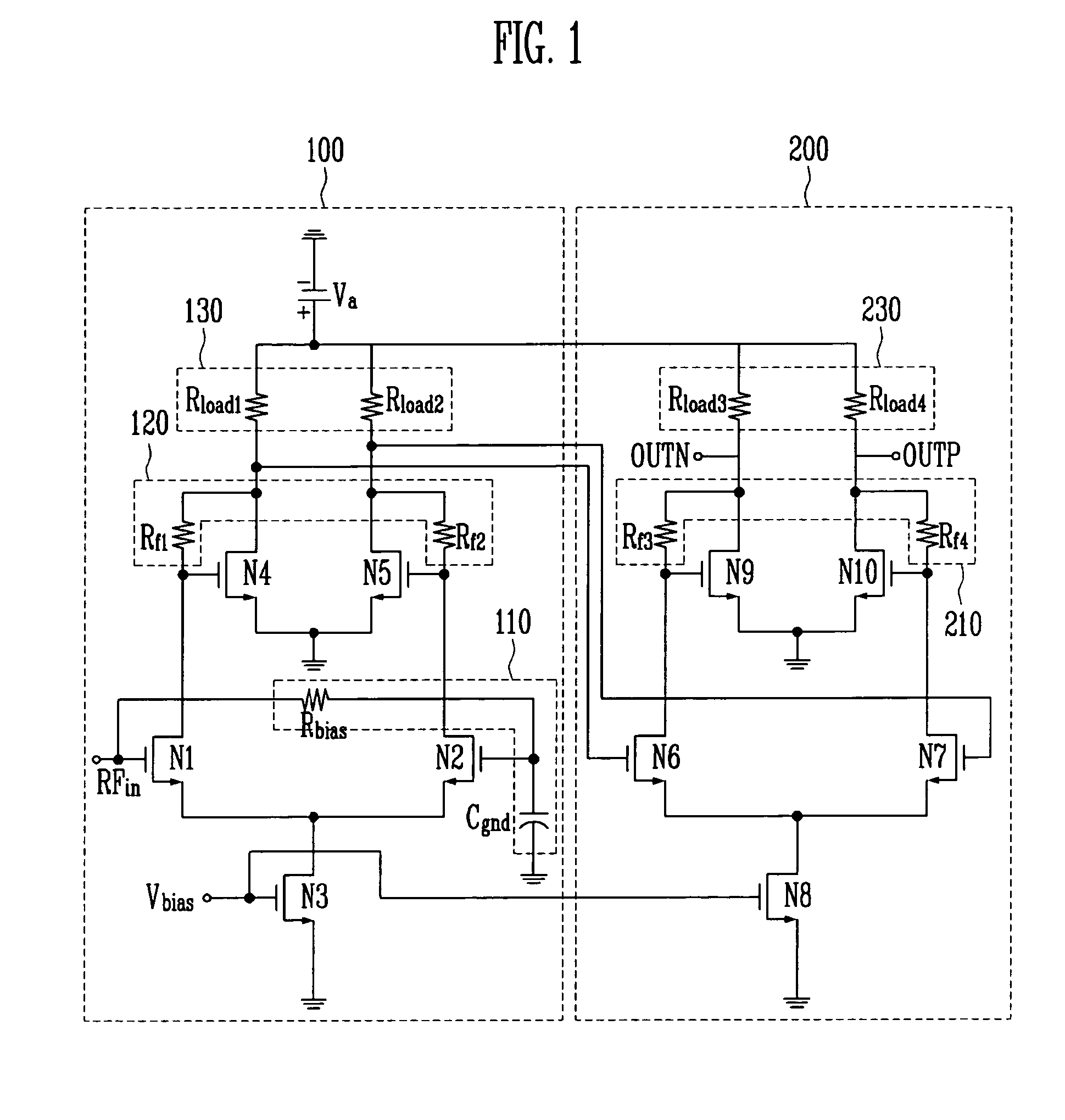

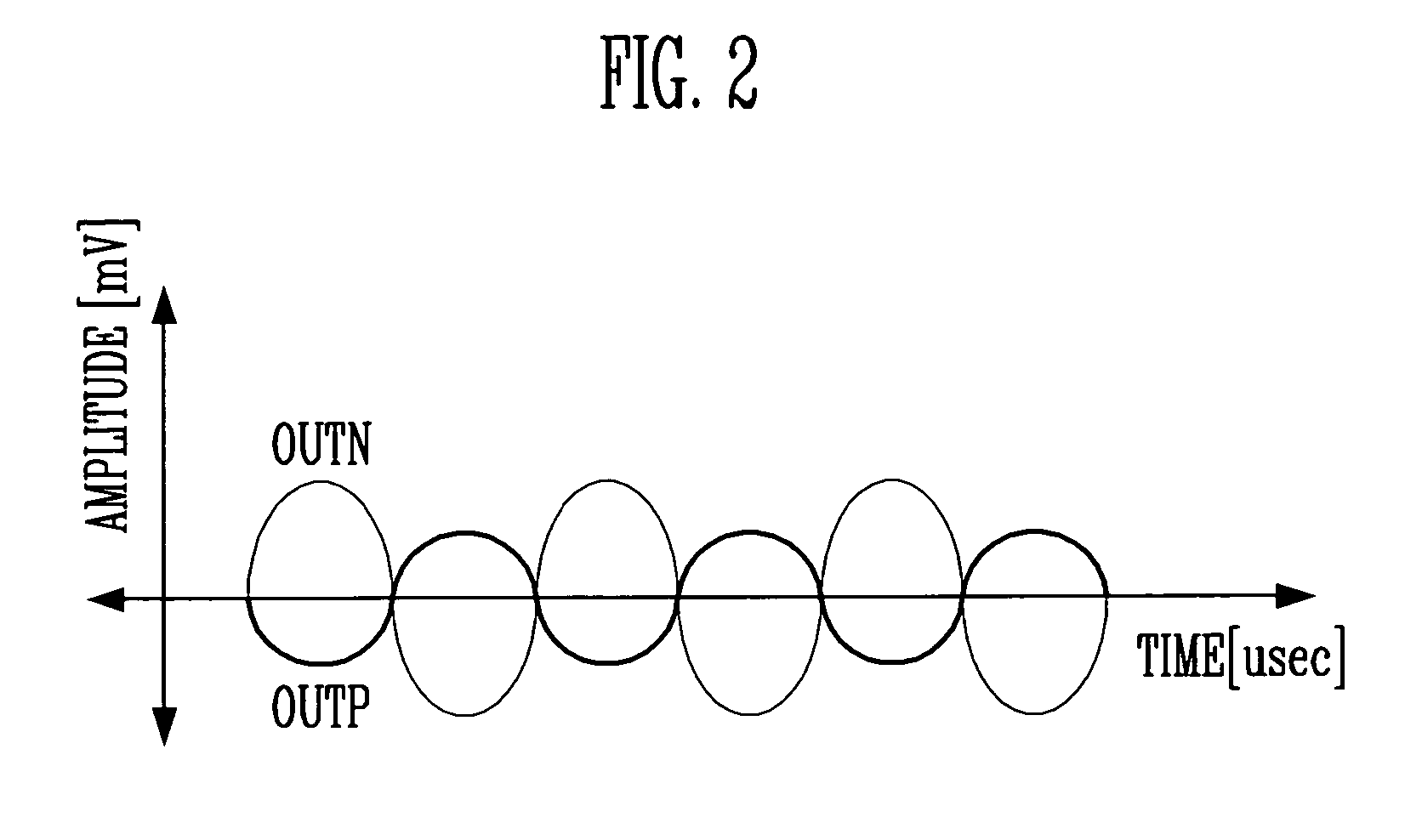

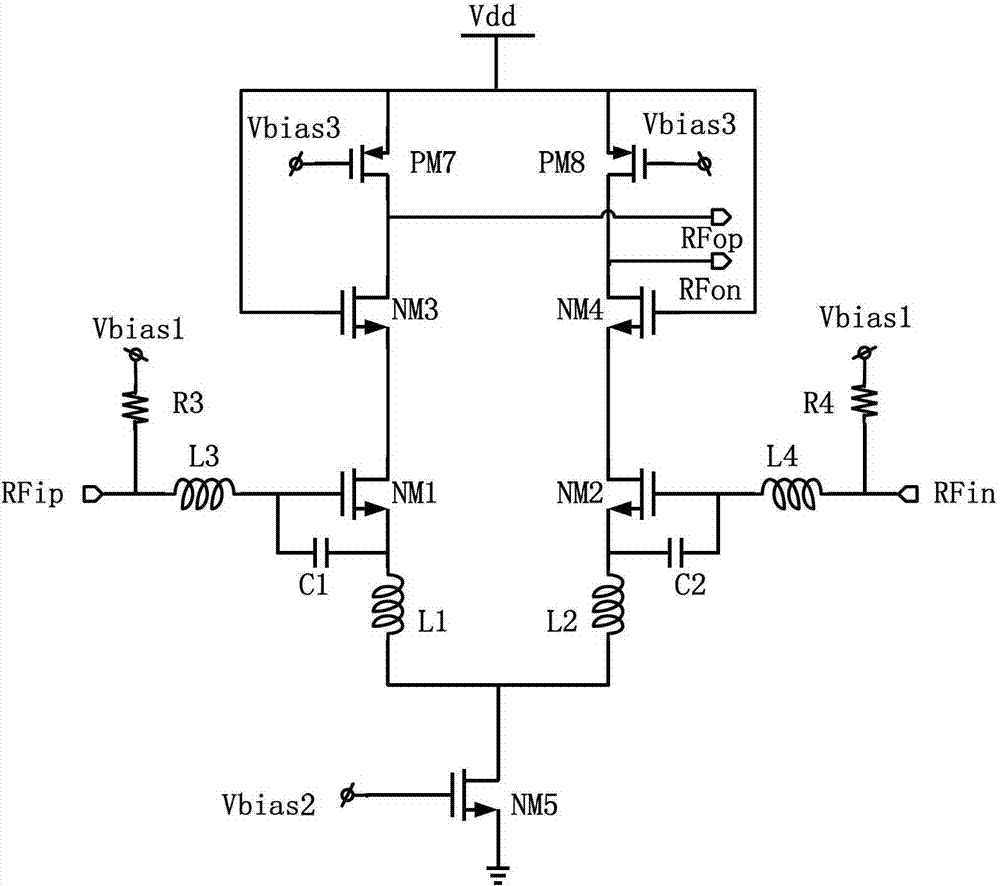

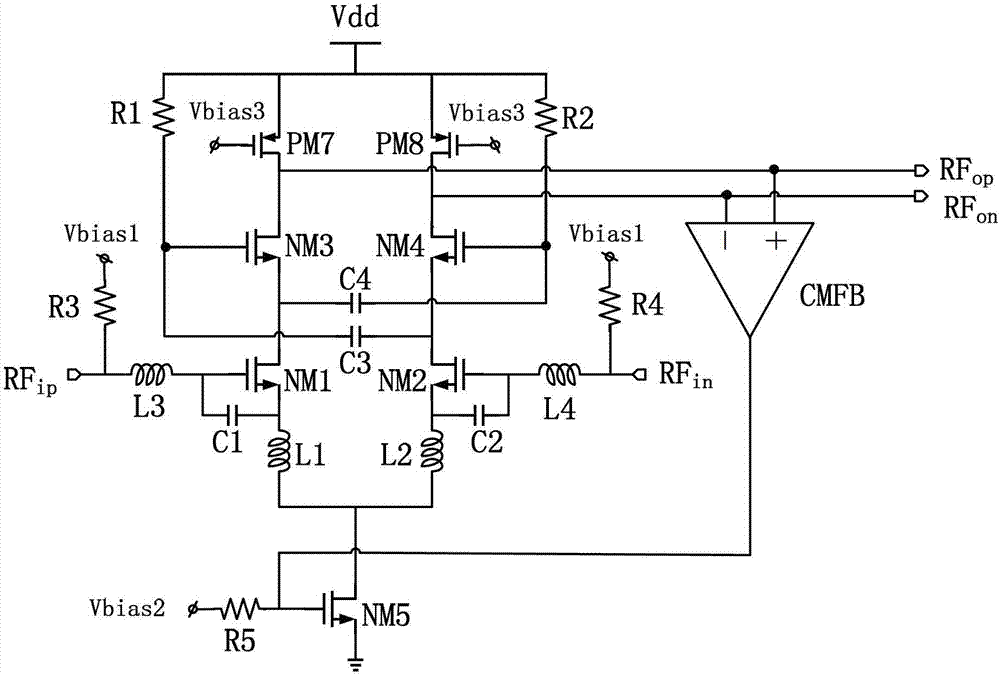

High-linearity low-noise amplifier

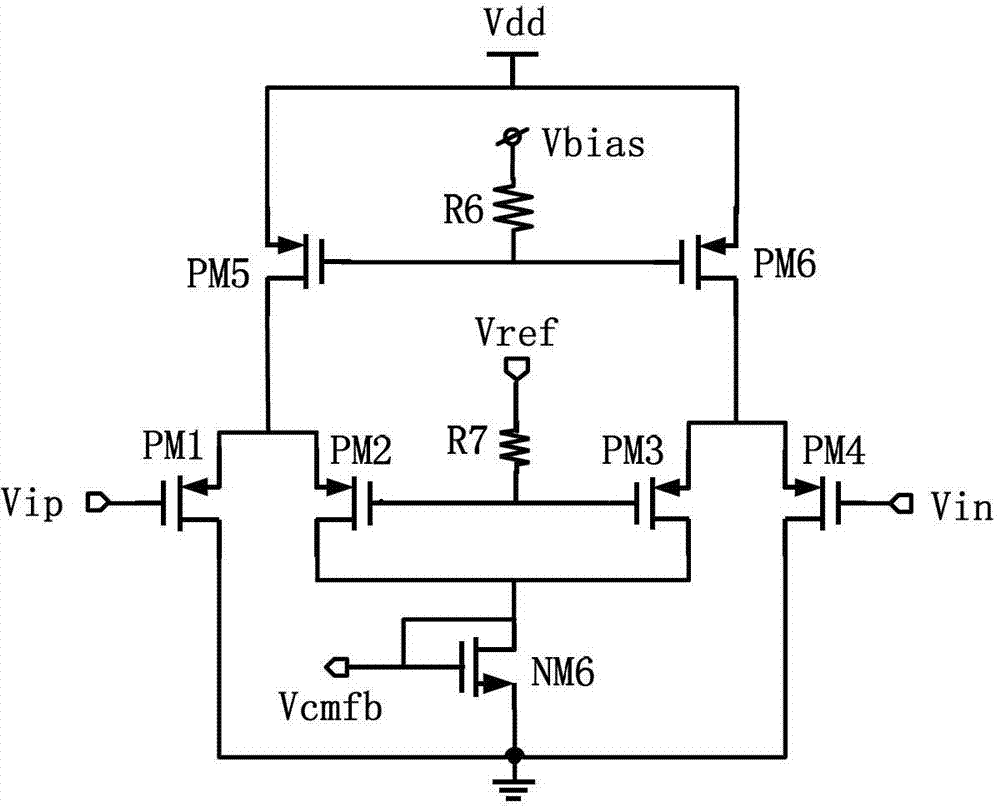

ActiveCN103248324AImprove linearityIncrease the overdrive voltageAmplifier modifications to reduce non-linear distortionAmplifier modifications to reduce noise influenceNonlinear distortionLow noise

The invention provides a high-linearity low-noise amplifier of the front end of an ultrahigh-frequency RFID (radio frequency identification) receiver. The amplifier detects two common levels from two differential output ends of a full-differential amplifier through a common-feedback circuit, bias current of the amplifier is adjusted validly and feedback voltage is outputted to a grid of a tail current source, and accordingly, overdrive voltage of the tail current source is increased, input current is increased and linearity is improved. Meanwhile, the problem of non-linear distortion caused by instability of the output common levels is solved. In addition, a coupling capacitor is crossed interstagely to increase power grain, and noise figure is reduced to improve noise performance. The high-linearity low-noise amplifier has the advantages of low noise figure, low power consumption, and high linearity, and solves the problem of carrier leak in ultrahigh-frequency RFID receivers and zero intermediate frequency receivers, and linearity of the low-noise amplifier is improved, so that weak available signals can be amplified linearly and distortionlessly in the process of receiving block signals.

Owner:NANJING UNIV OF POSTS & TELECOMM INST AT NANJING CO LTD

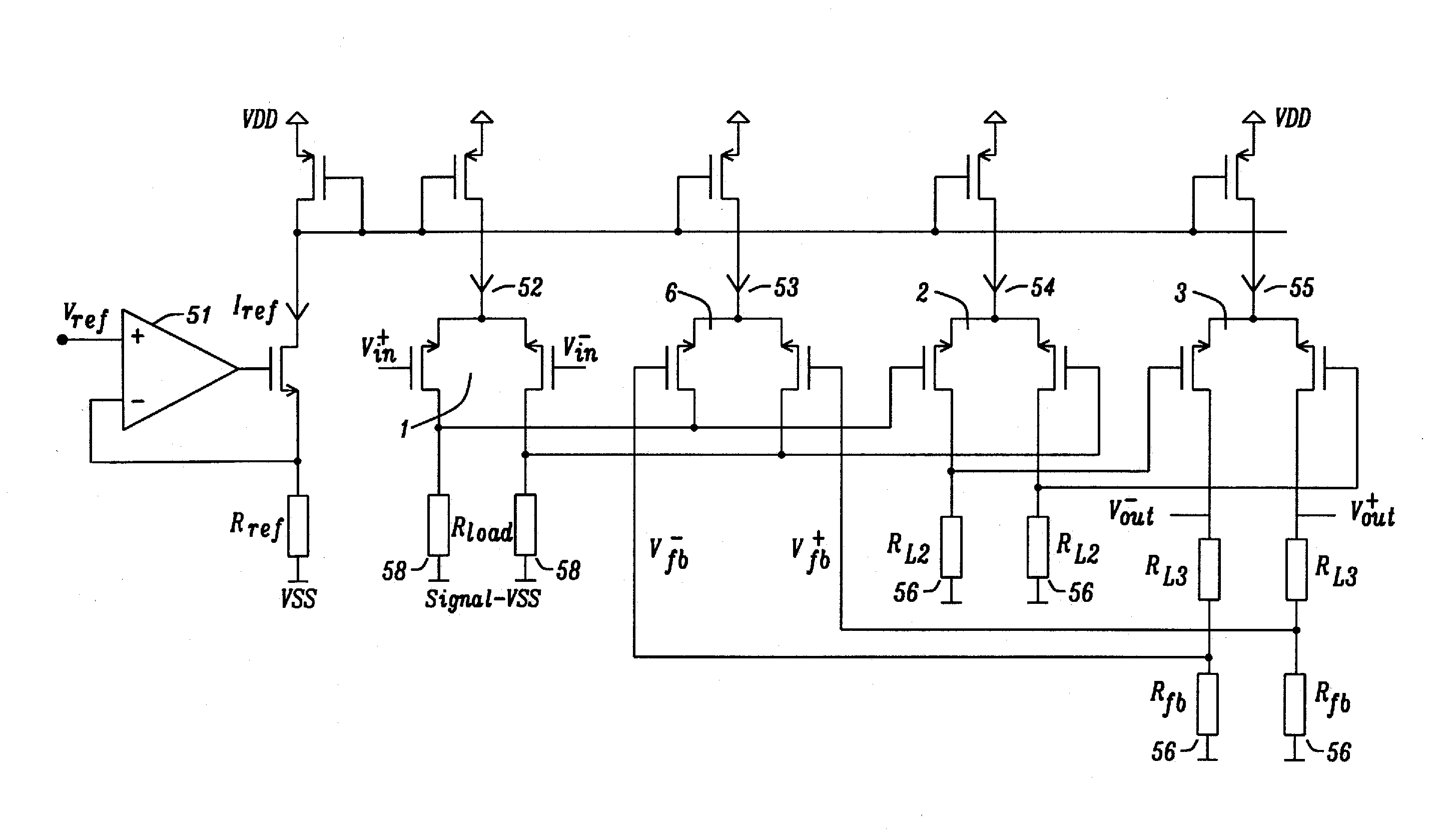

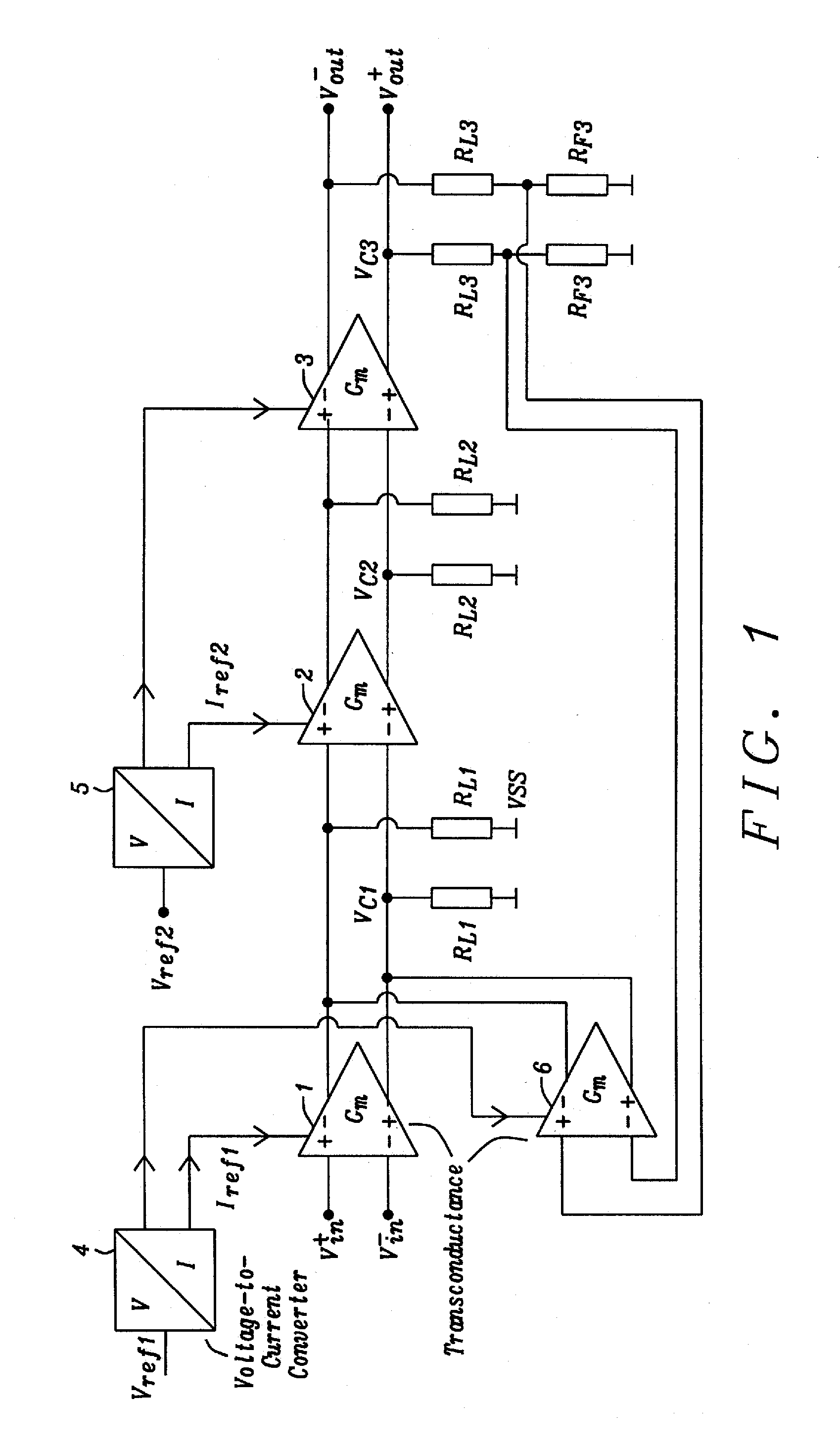

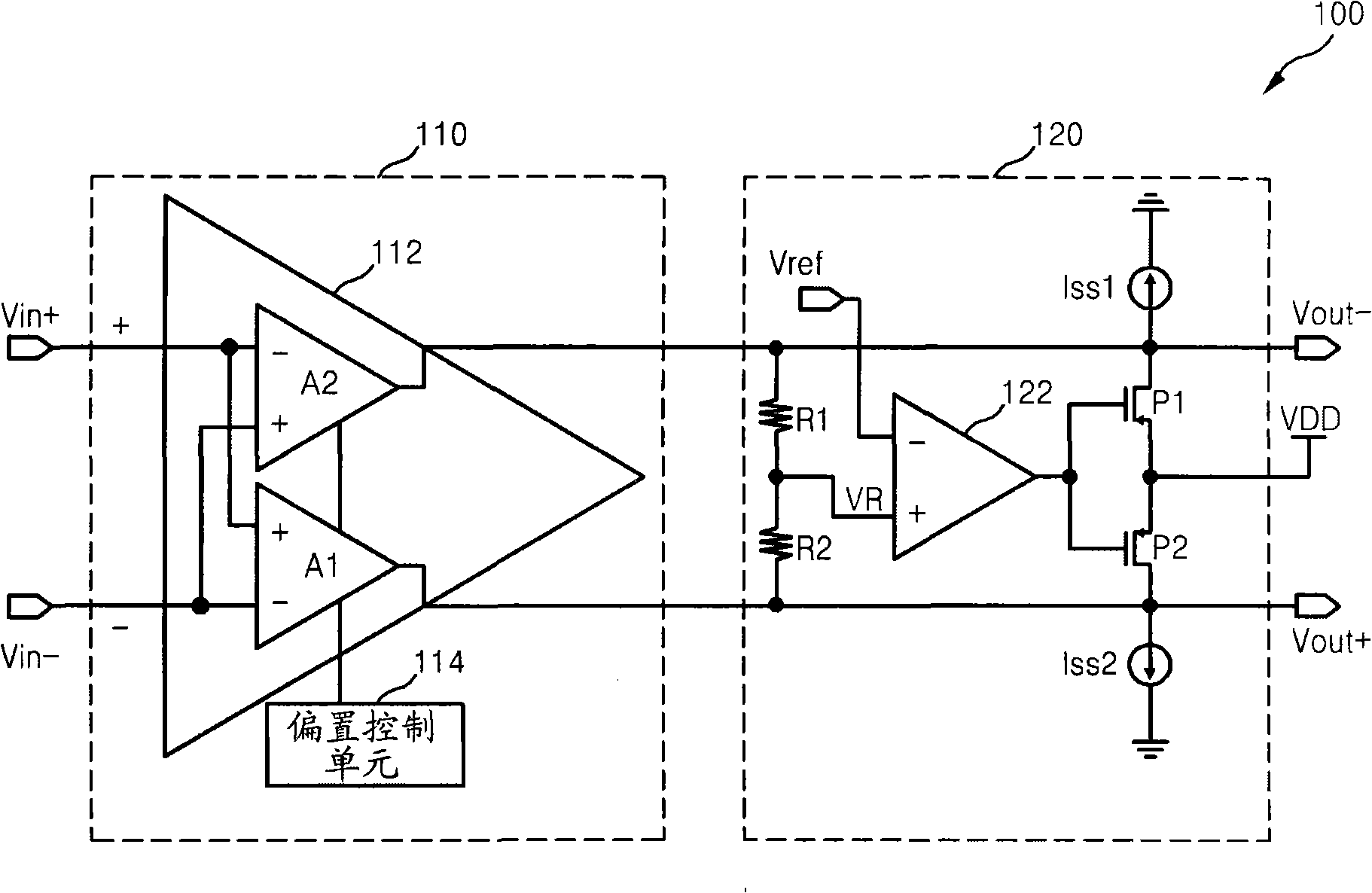

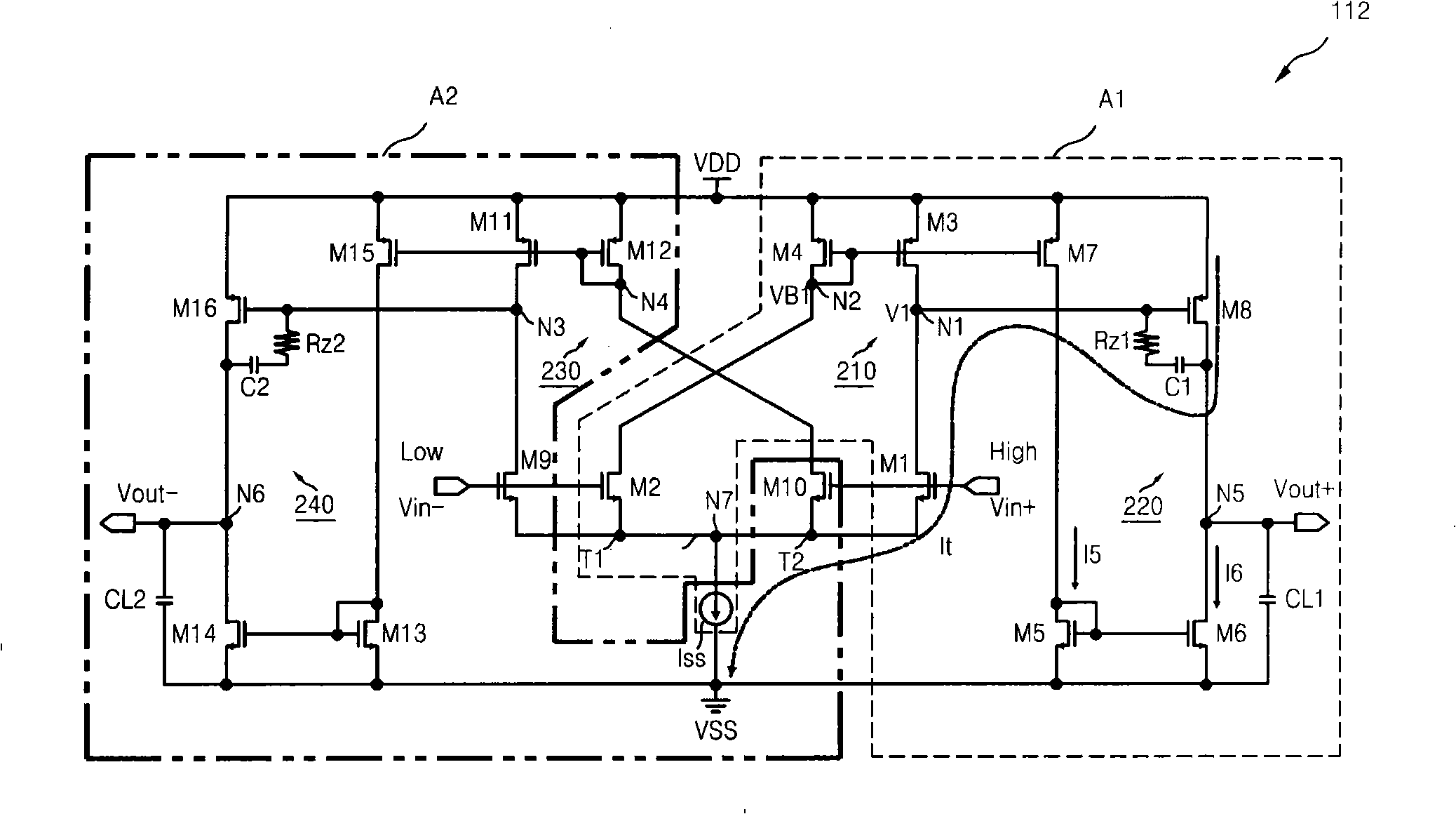

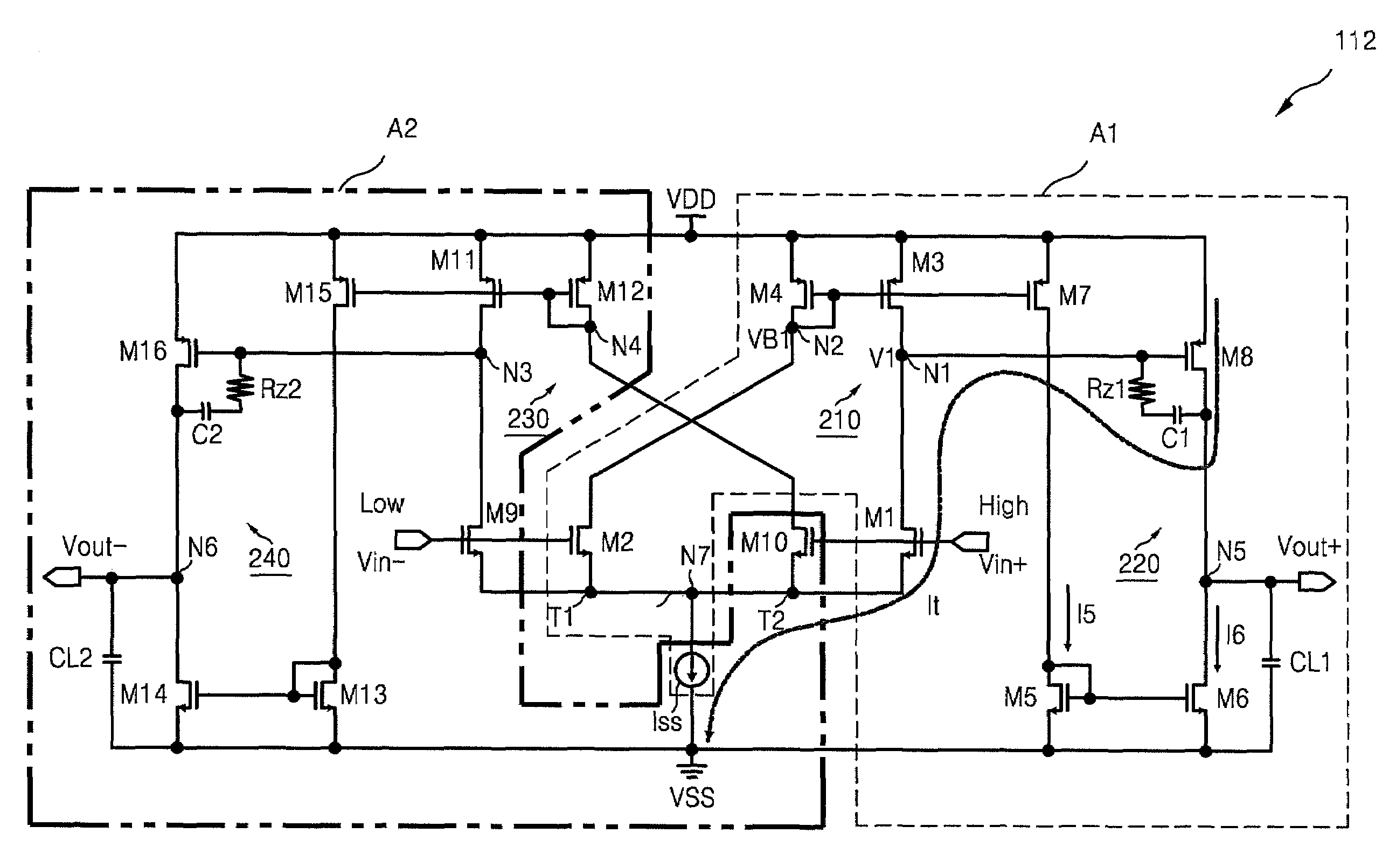

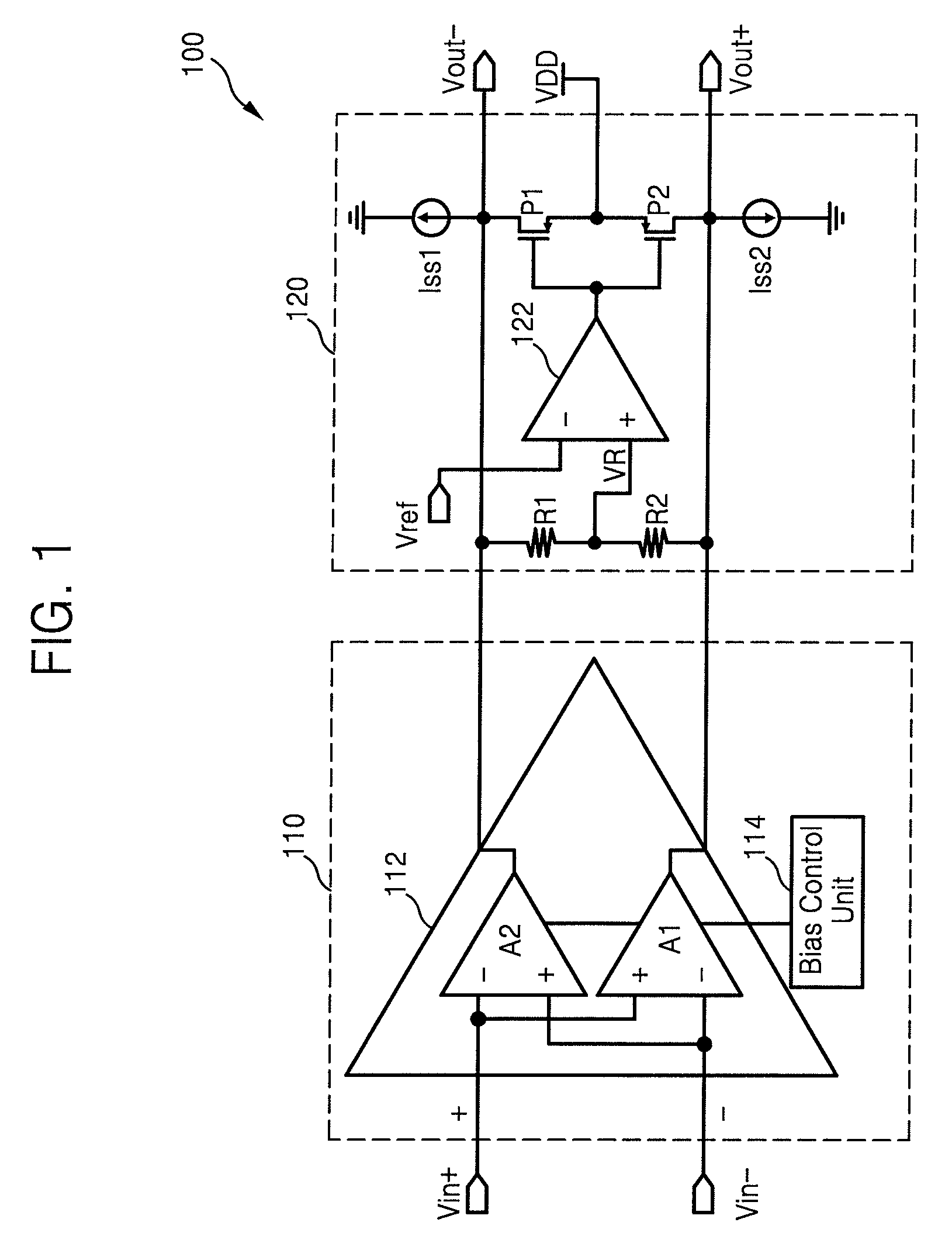

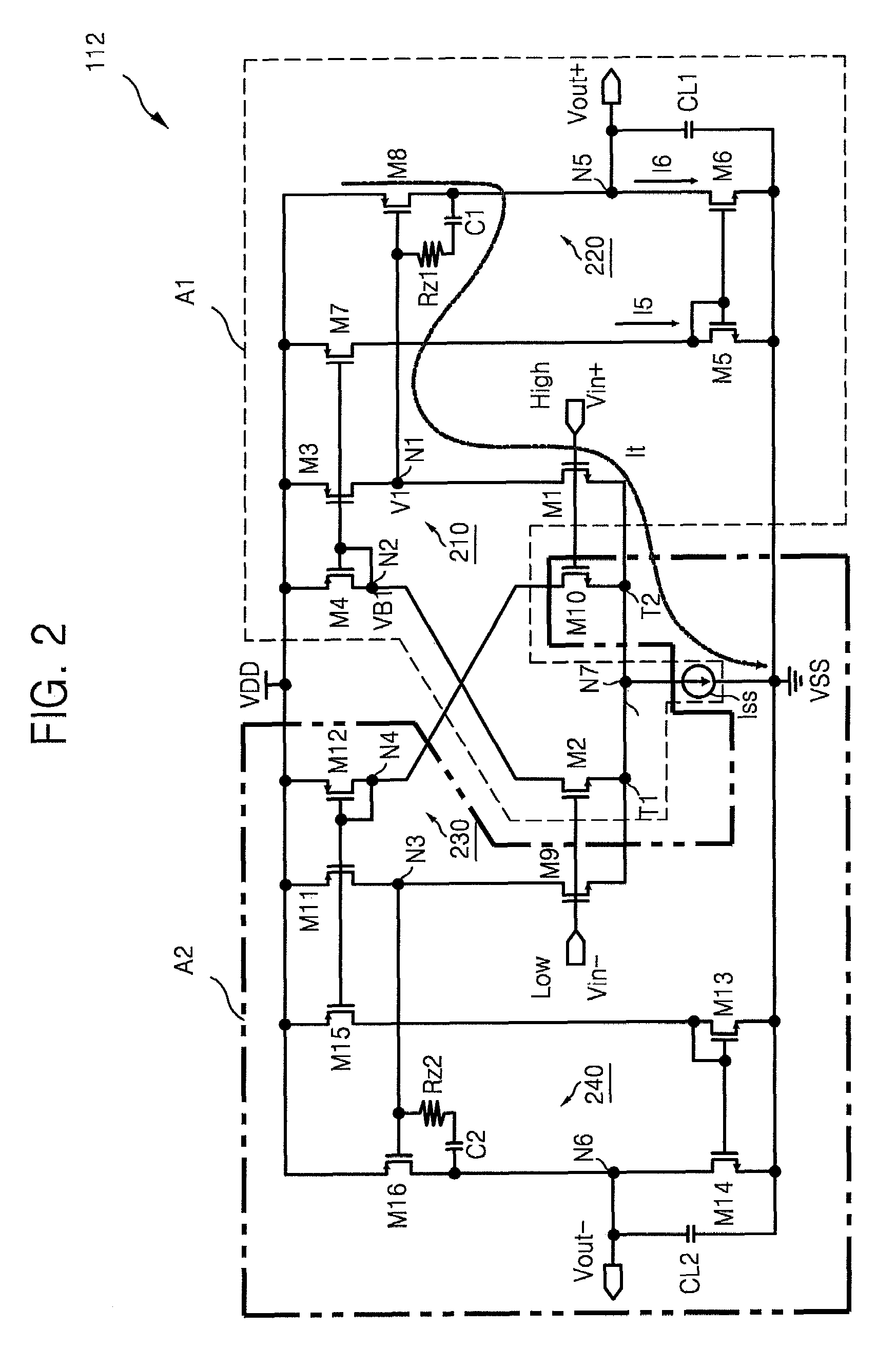

Multi-Stage Fully Differential Amplifier with Controlled Common Mode Voltage

ActiveUS20130169361A1Cancel noiseNoise minimizationAmplifier modifications to reduce noise influenceDifferential amplifiersLow noiseAudio power amplifier

Disclosed are systems and methods to achieve a low noise, fully differential amplifier with controlled common mode voltages at each stage output but without the requirement of a common mode feedback loop. Common mode voltages are adjusted by adjusting the currents flowing through the load impedances (bias currents) wherein the currents are derived from one or more voltage-to-current converters based on an impedance that matches to the load impedances of the stages of the amplifier. The amplifier invented is primarily used for amplification of low frequency signals. The amplifier has one or more gain stages applying only one conduction type of transistors of an IC technology that has the lowest transition frequency between 1 / f noise and white noise to achieve a low chopping or autozeroing frequency.

Owner:DIALOG SEMICONDUCTOR GMBH

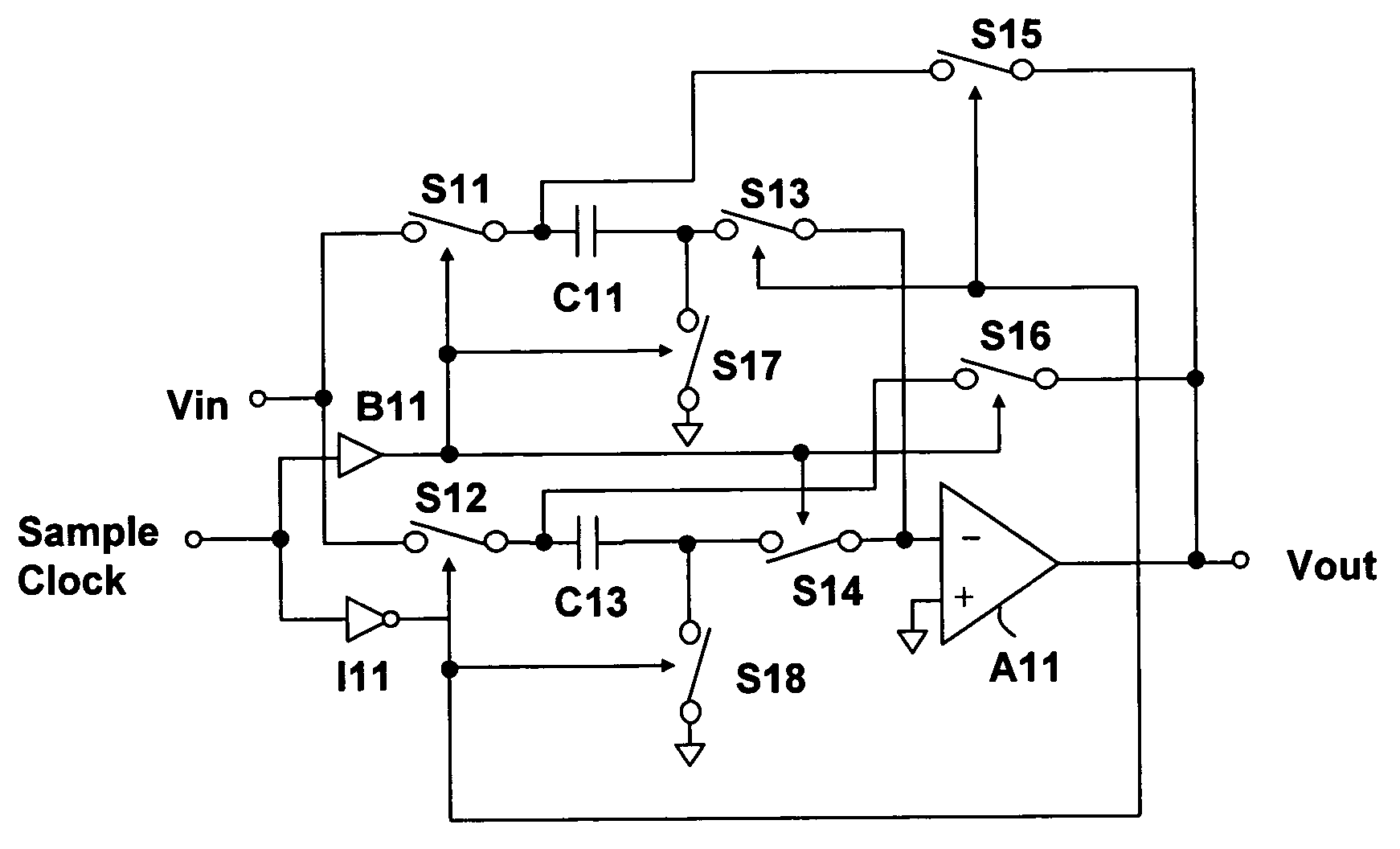

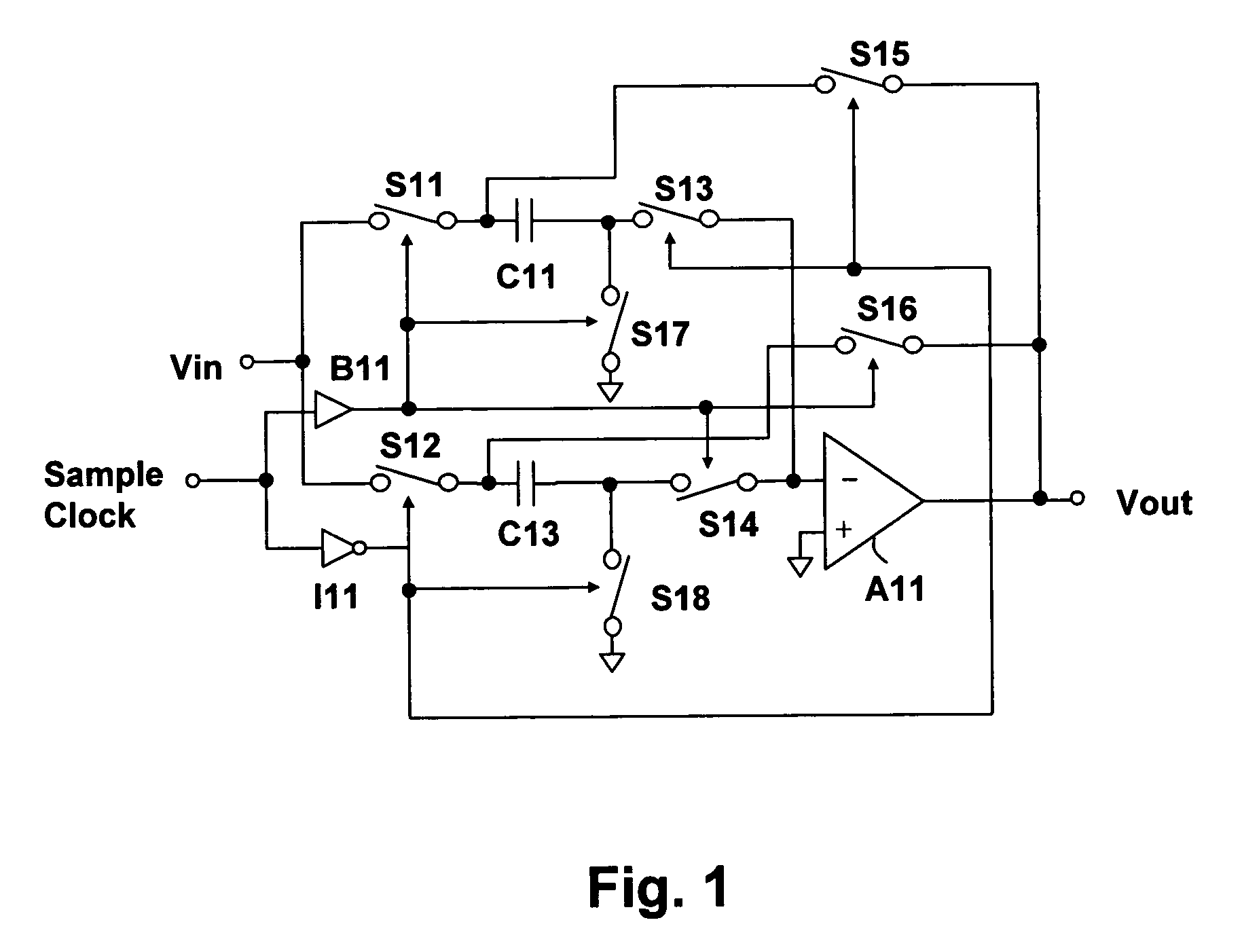

Switched-capacitor sample/hold having reduced amplifier slew-rate and settling time requirements

ActiveUS20050073351A1Lower conversion rateReduce errorsAnalogue/digital conversionComputing operations for integral formationCapacitanceNegative feedback

A switched-capacitor sample / hold circuit and method having reduced slew-rate and settling time requirements provides for lower-cost and / or lower-power implementation of sample / hold circuits and / or reduced error due to amplifier characteristics. The switched-capacitor sample / hold circuit incorporates a pair of capacitors that are alternatively and mutually-exclusively switched between an input sample position and an amplifier hold position, providing a dual sampled amplifier output signal that has reduced transitions at each sample interval. An alternative embodiment of the sample / hold circuit incorporates a fully-differential amplifier having a differential input and a differential output. Four capacitors are employed forming two of the dual sampled switched-capacitor circuits, one in each negative feedback path (inverted output to non-inverting input, non-inverted output to inverting input) of the amplifier. The two dual sampled switched-capacitor circuits are referenced to each other, providing fully differential operation and cancellation of error due to charge injection.

Owner:MICROCHIP TECH INC

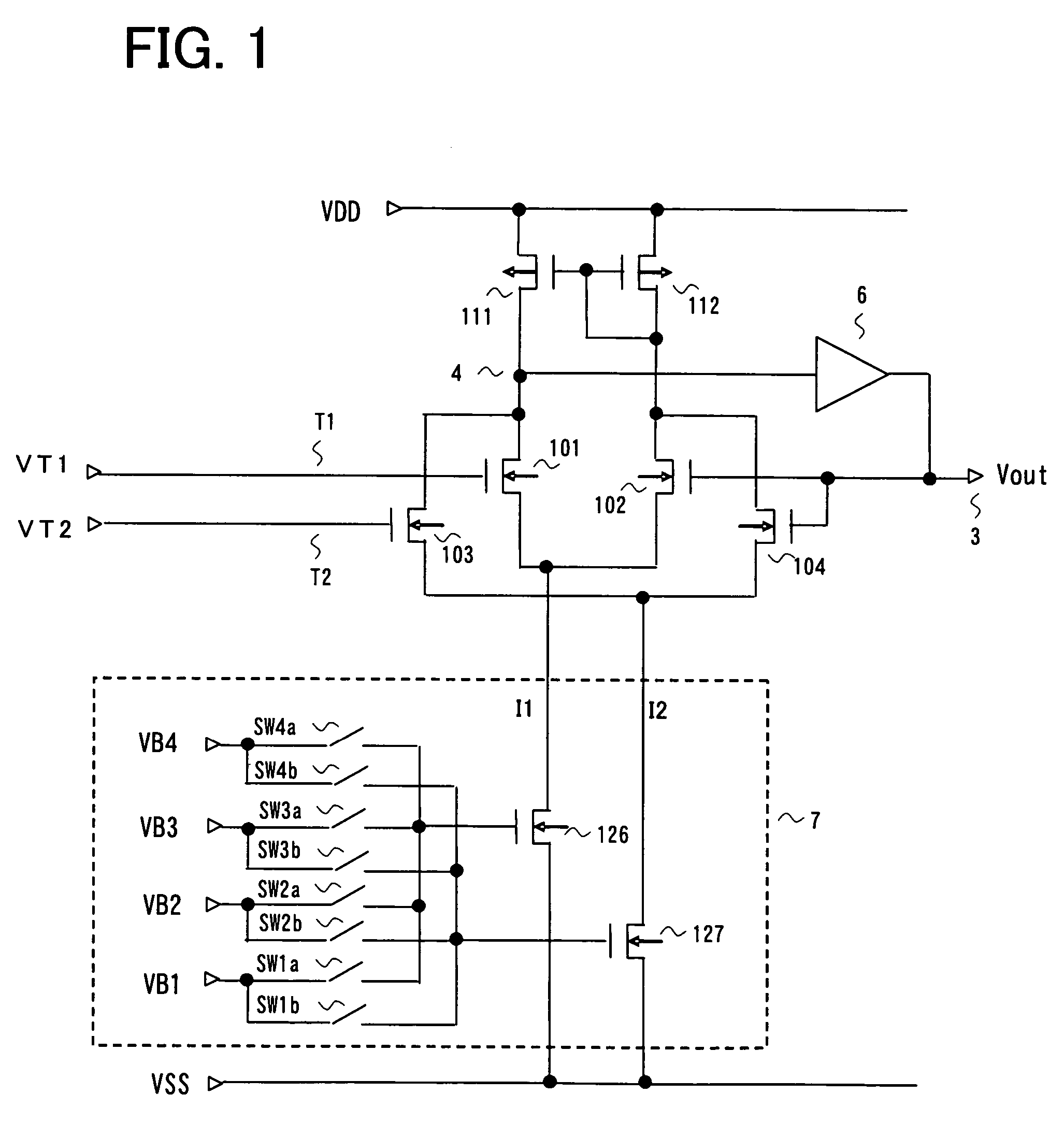

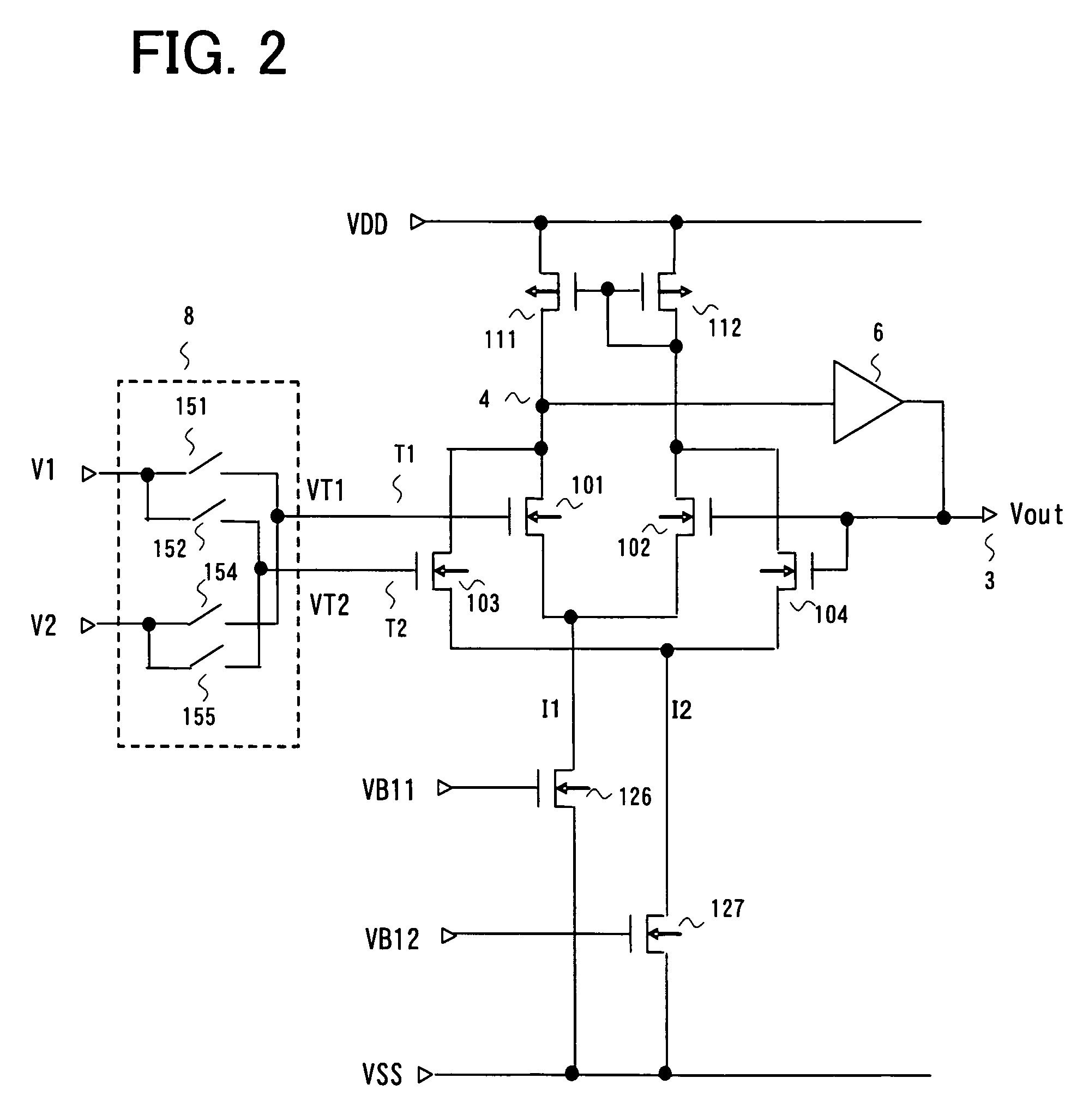

Differential amplifier and data driver employing the differential amplifier

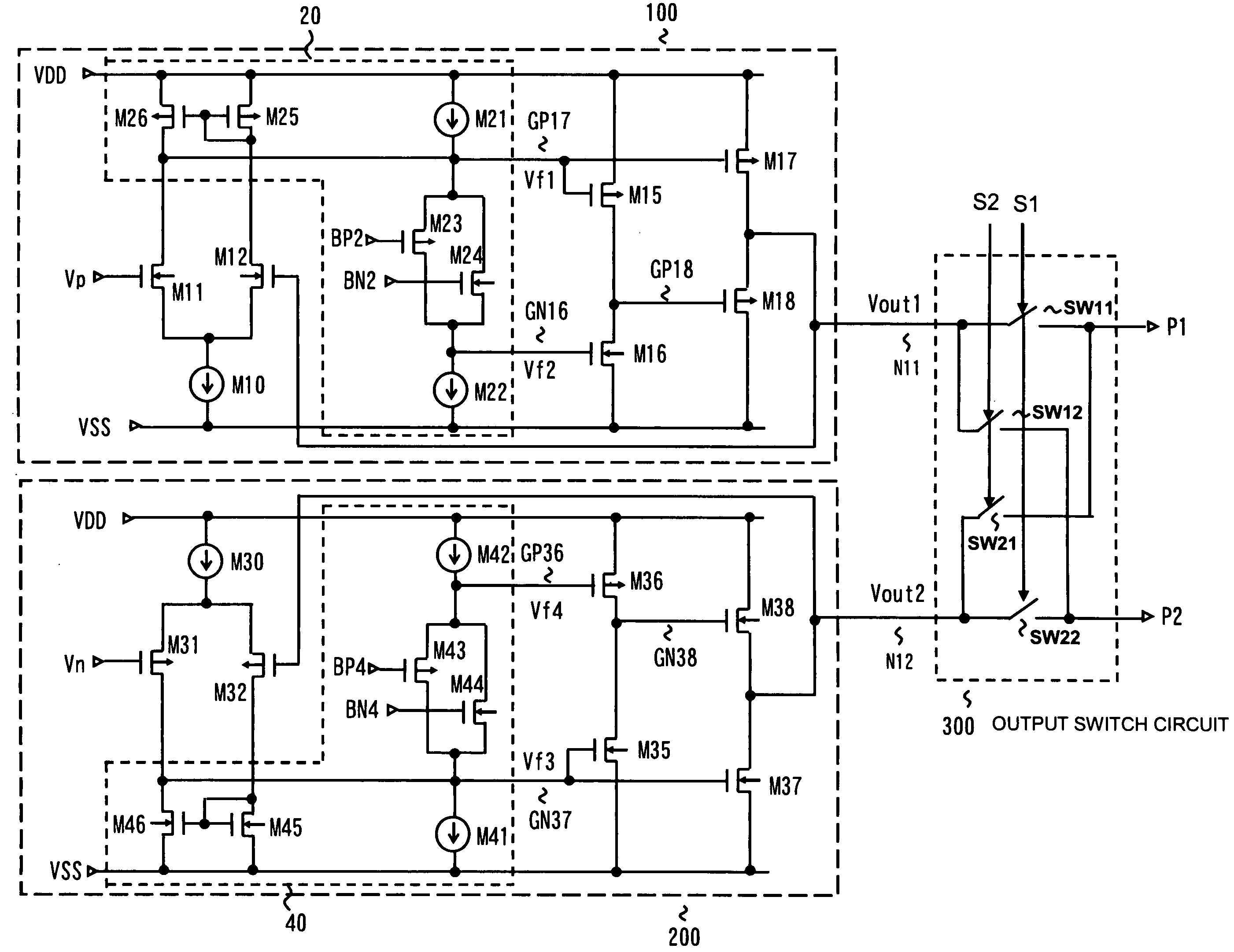

InactiveUS7368990B2Increase the number ofReduce displayPush-pull amplifiersElectric signal transmission systemsLoad circuitEngineering

Disclosed is a differential amplifier which includes first and second input terminals, an output terminal, first and second differential pairs, and first and second current sources for supplying currents to the first and second differential pairs. The first differential pair has first and second inputs of an input pair connected to the first input terminal and the output terminal, respectively. The second differential pair has first and second inputs of an input pair connected to the second input terminal the output terminal, respectively. The differential amplifier further includes a load circuit connected to output pairs of the first and second differential pairs for outputting a signal obtained on combining outputs of the first and second differential pairs from at least one of a pair of connection nodes between the output pairs of the first and second differential pairs and the load circuit, an amplifier stage supplied with at least one signal at a connection node of the output pairs of the first and second differential pairs and the load circuit to output a voltage at the output terminal, and a current control circuit controlling the first and second current sources for controlling the ratio of currents supplied to the first and second differential pairs.

Owner:RENESAS ELECTRONICS CORP +1

Fully differential class AB amplifier and amplifying method using single-ended, two-stage amplifier

InactiveCN101277095AHigh gainIncrease conversion rateDifferential amplifiersSingle-ended push-pull amplifiersAudio power amplifierEngineering

Owner:SAMSUNG ELECTRONICS CO LTD

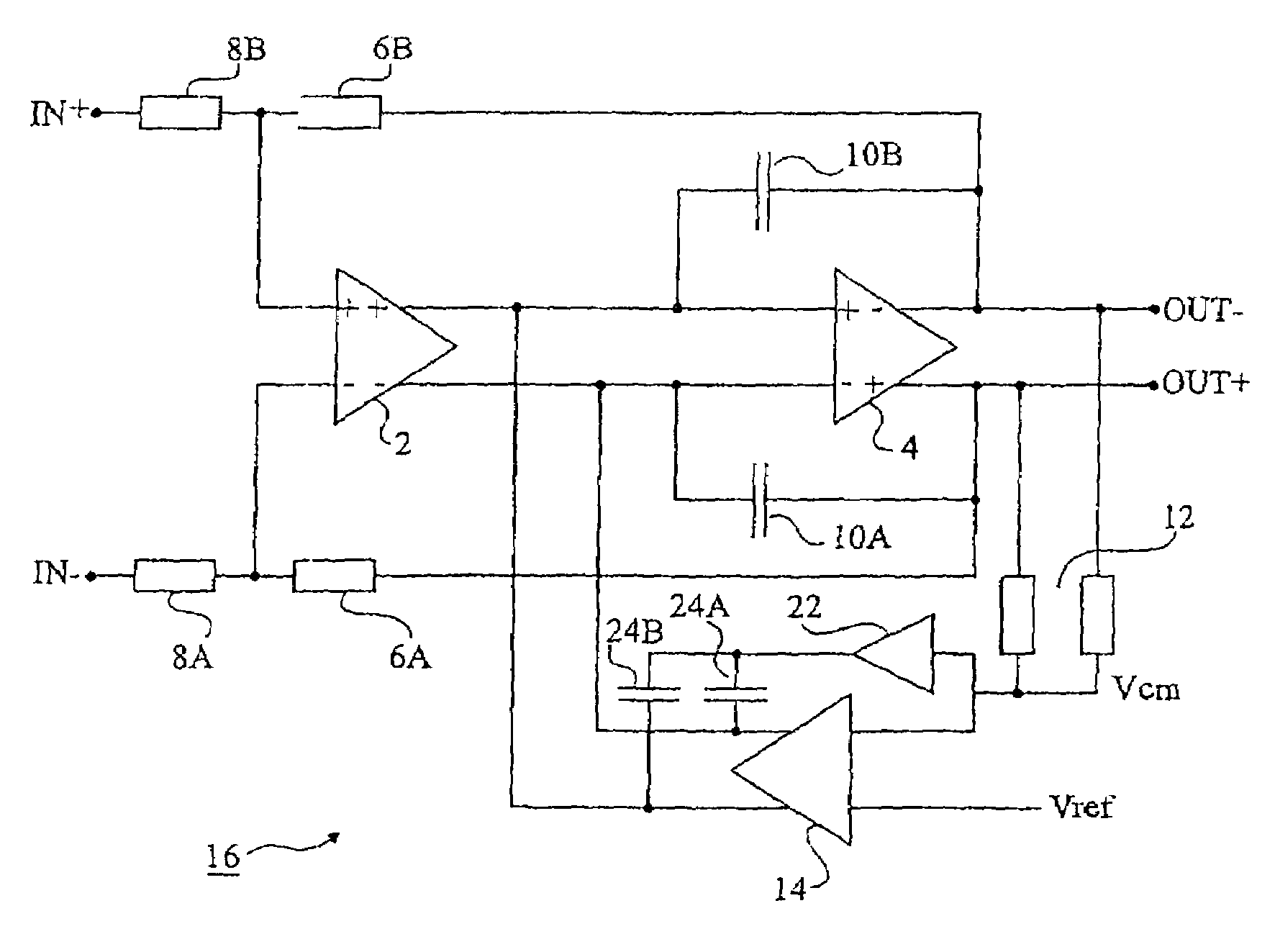

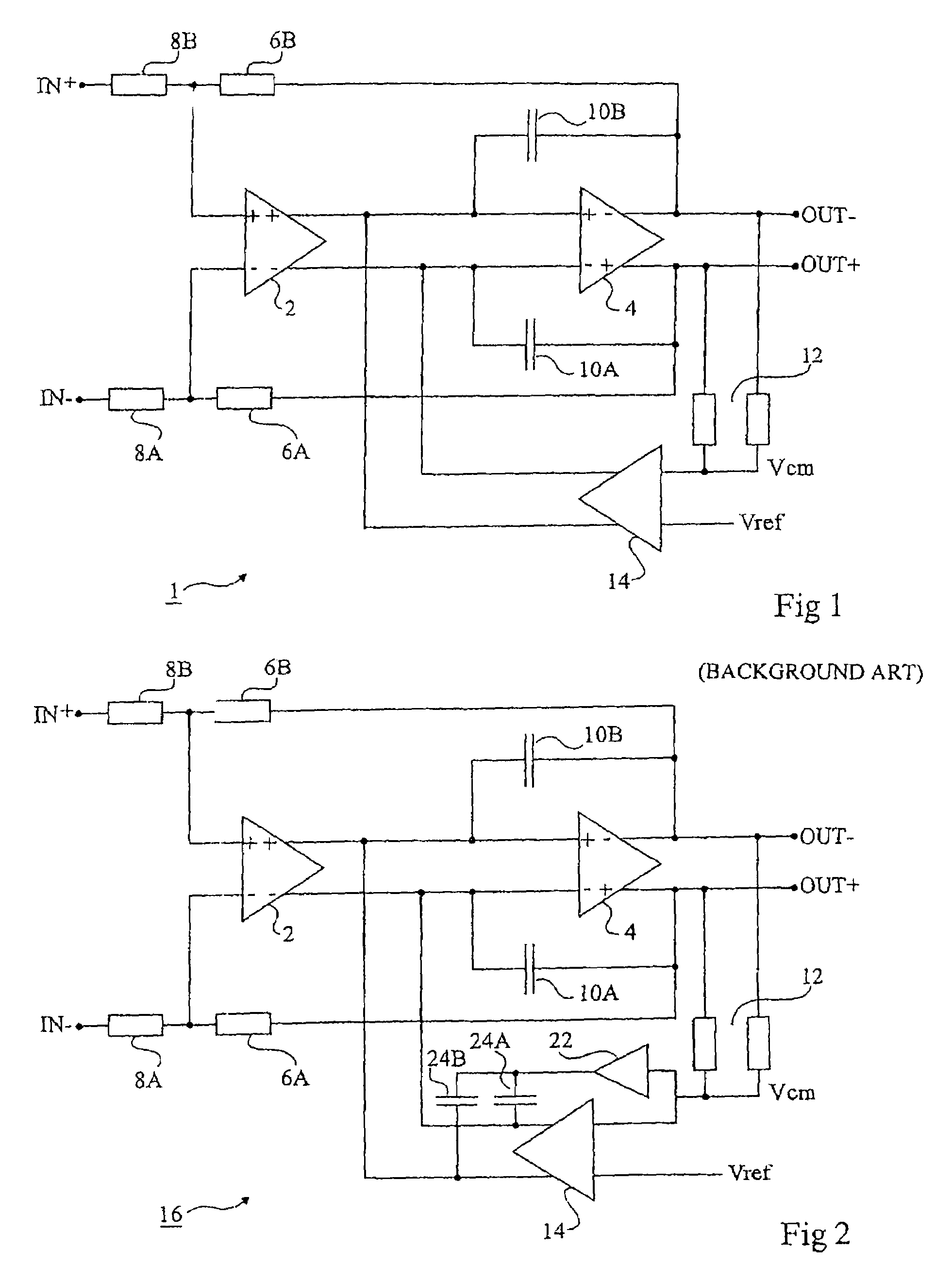

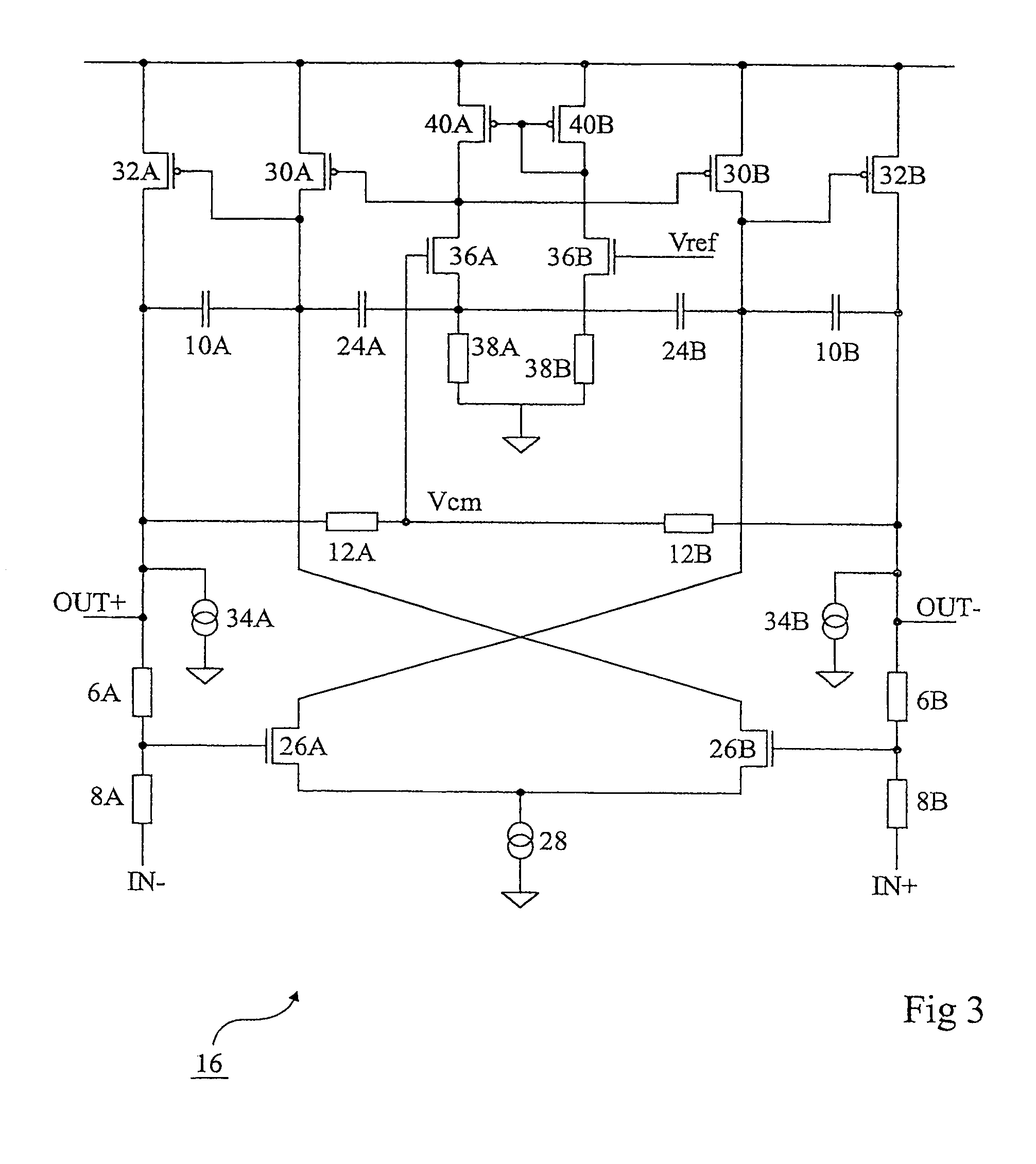

Differential amplifier with a common mode voltage loop

InactiveUS7071780B2Improve stabilityGuaranteed smooth progressAmplifier modifications to raise efficiencyAmplifier modifications to reduce detrimental impedenceAudio power amplifierPhase shifted

An amplifier circuit comprising an amplification chain having a differential output stage; a common mode correction block acting on the input of the output stage as a function of a common mode voltage at the output of said stage and introducing a phase shift between its input and its output for frequencies close to the cut-off frequency of the circuit; and, in parallel with the correction block, a means introducing no phase shift between its input and its output and having at frequencies greater than or equal to the circuit cut-off frequency an output impedance much smaller than the output impedance of the correction block.

Owner:ST ERICSSON SA

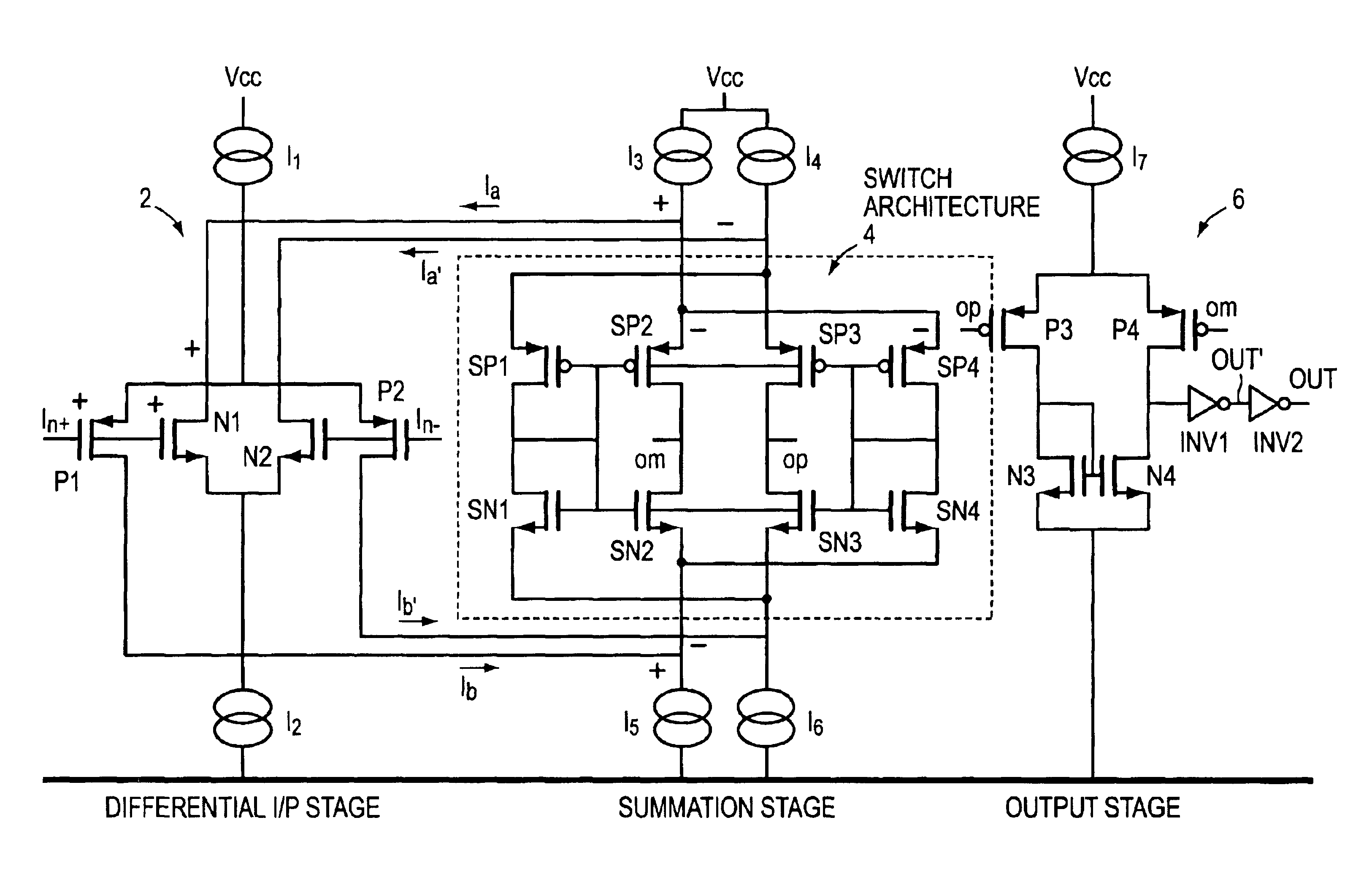

Fully differential class AB amplifier and amplifying method using single-ended, two-stage amplifier

InactiveUS7586373B2High gainReduce voltageDifferential amplifiersSingle-ended push-pull amplifiersAudio power amplifierEngineering

A fully differential amplifier includes a first single-ended current mirror type fully differential amplifier outputting a first output signal by two stage amplifying a difference between a first input signal and a second input signal and a second single-ended current mirror type fully differential amplifier outputting a second output signal by two stage amplifying a difference between the first input signal and the second input signal. A first tail of the first single-ended current mirror type fully differential amplifier and a second tail of the second single-ended current mirror type fully differential amplifier are connected to each other and the first output signal and the second output signal are differential signals.

Owner:SAMSUNG ELECTRONICS CO LTD

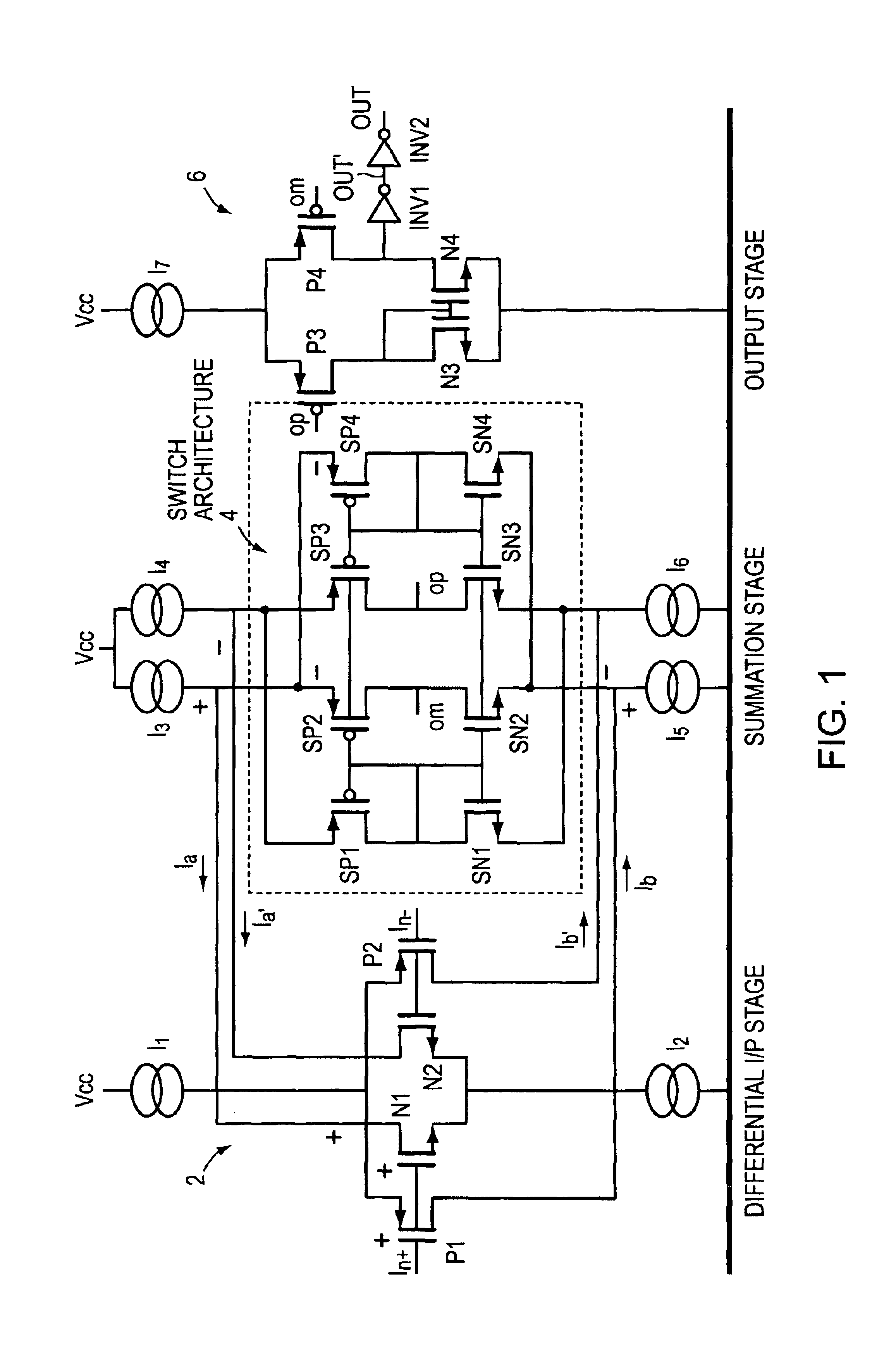

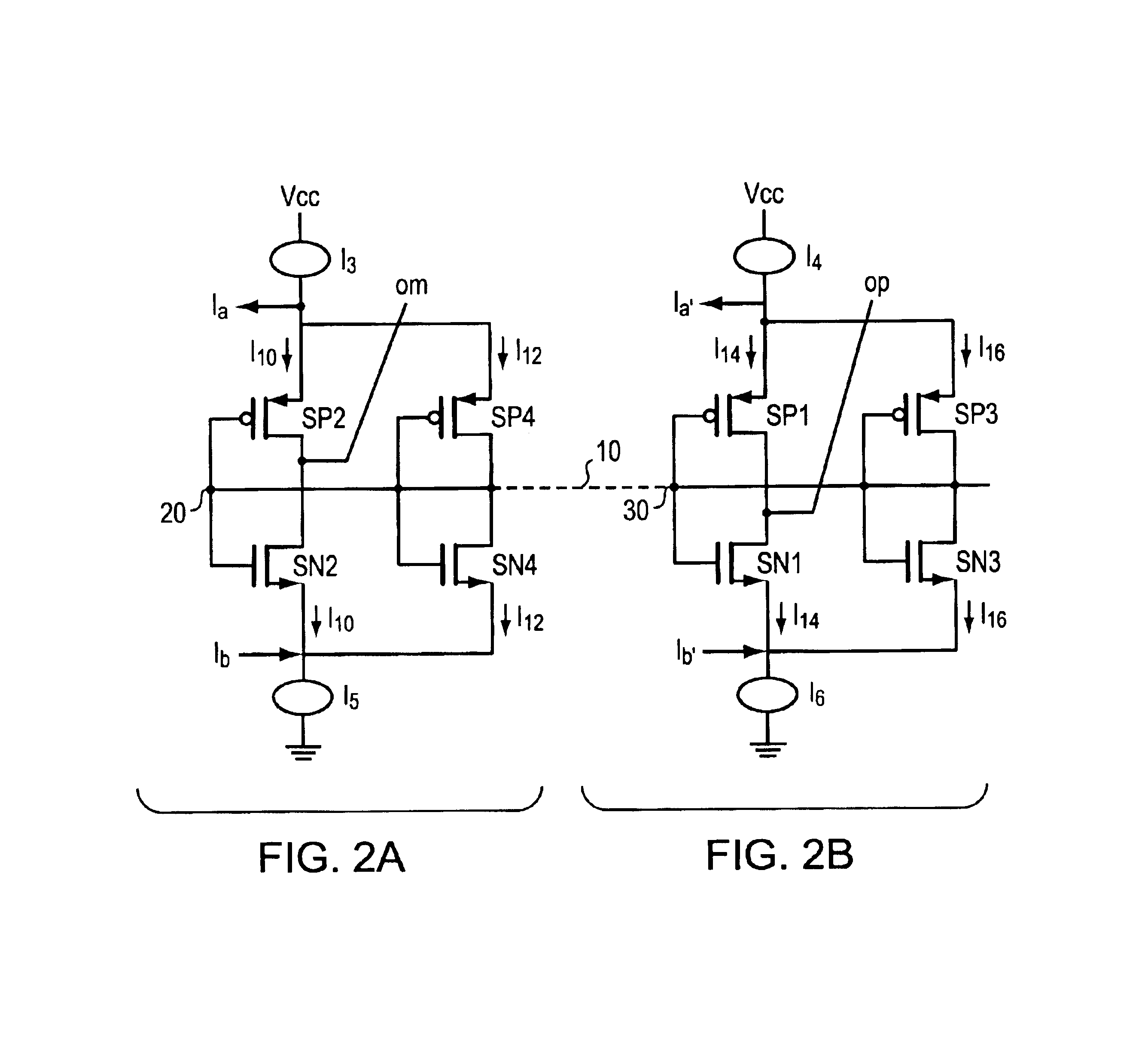

Low voltage, low power differential receiver

InactiveUS6970043B2Improves low Vcc performanceReduce jitterComputations using contact-making devicesComputing operations for multiplication/divisionLow voltageLow jitter

A folded common cascode circuit with symmetric parallel signal paths from the differential inputs to a single ended output provides a low skew, low jitter, low power, high speed differential amplifier. The signal paths on either side of the differential amplifier are made equal with equal loads along each path. Pairs of complementary NMOS and PMOS transistor pairs with parallel complementary biasing current mirroring stacks on the cascode circuitry have all their gates connected together. The layout maintains symmetrical parallel signal paths and symmetrical amplification and impedance loading from differential input to output. Output inverters provide a higher drive capability.

Owner:SEMICON COMPONENTS IND LLC