Patents

Literature

680results about How to "Guaranteed high speed operation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

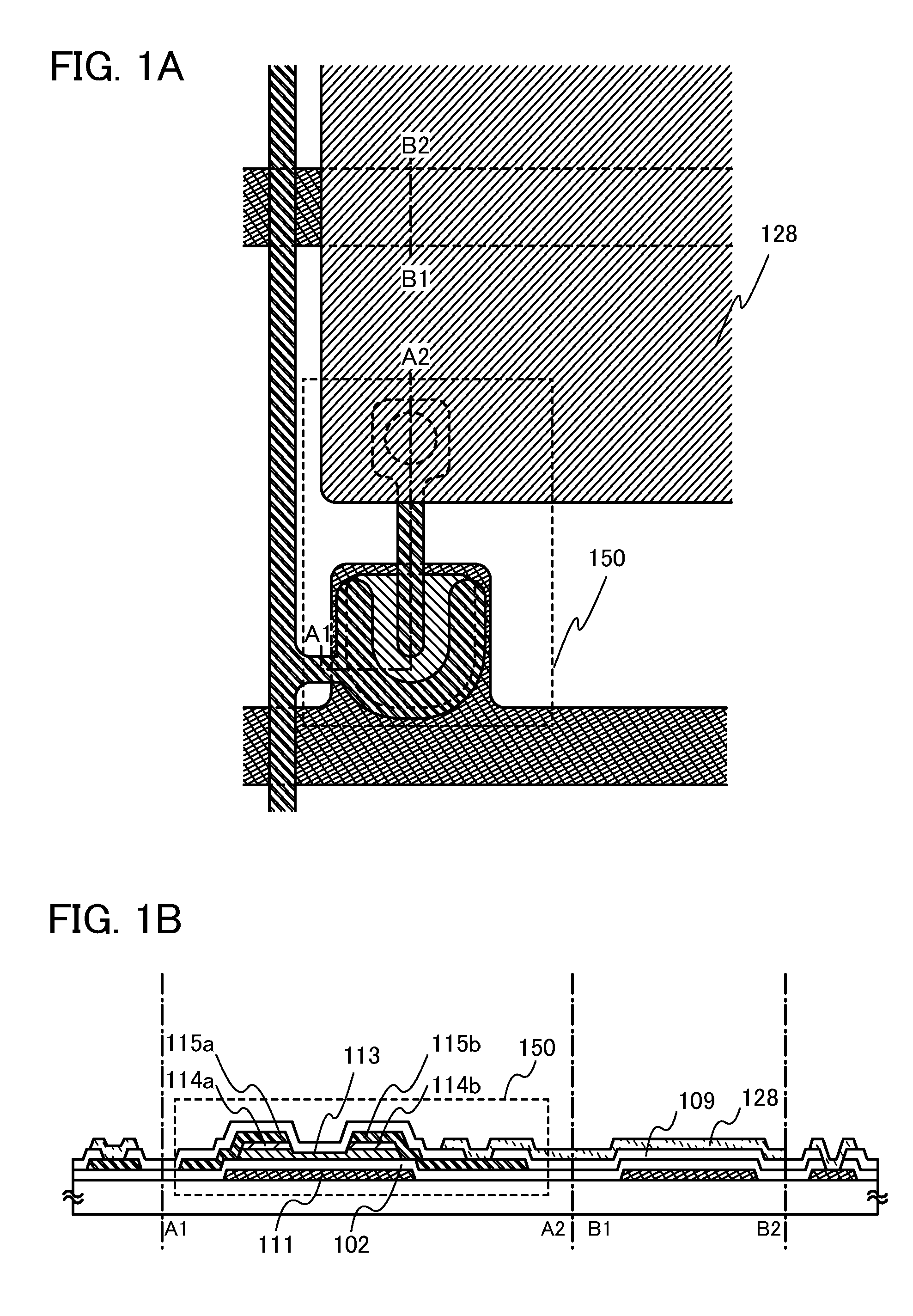

Semiconductor device and method for manufacturing the same

ActiveUS20100051949A1Small currentHigh on-off ratioTransistorStatic indicating devicesMetallic materialsOxygen deficient

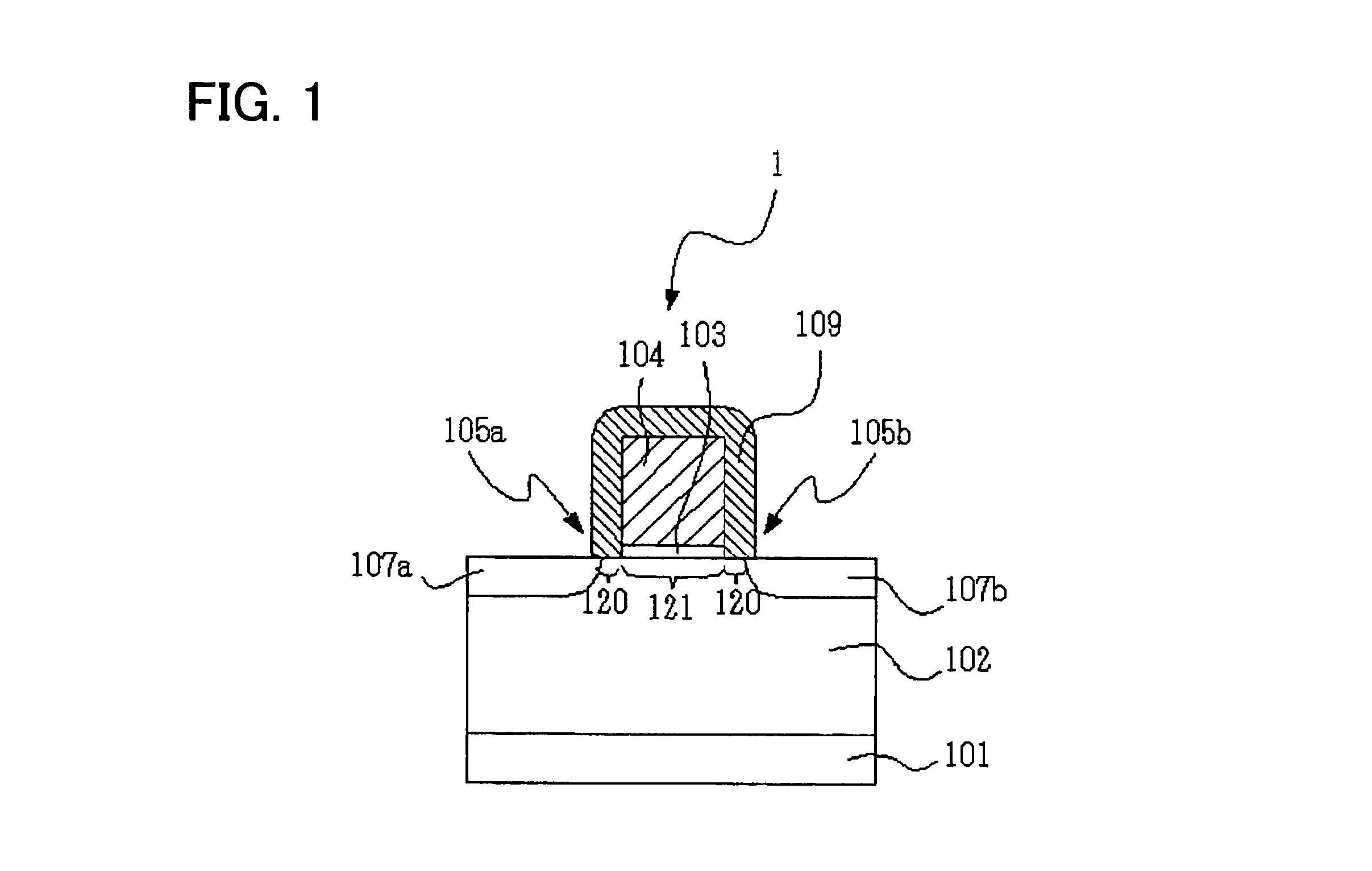

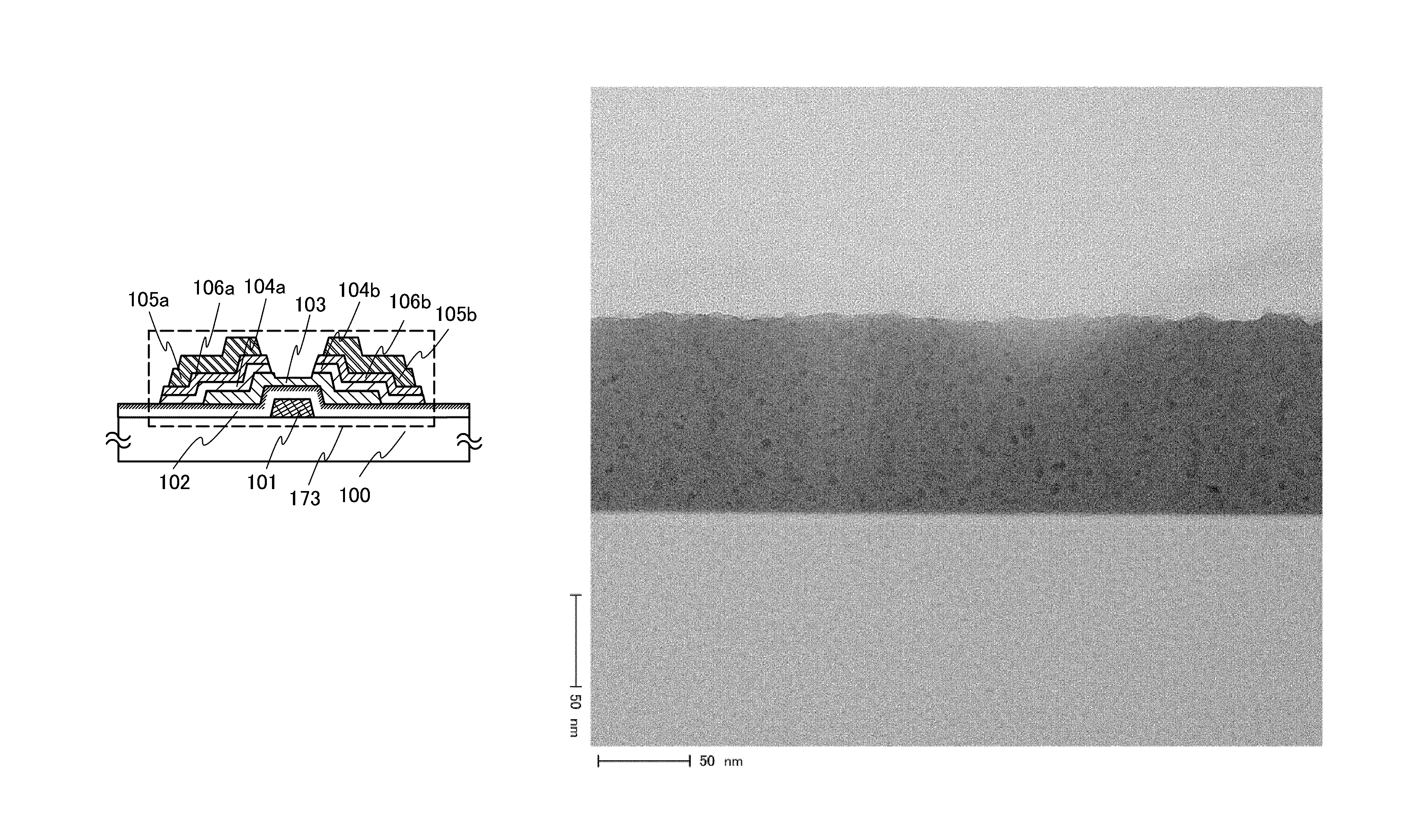

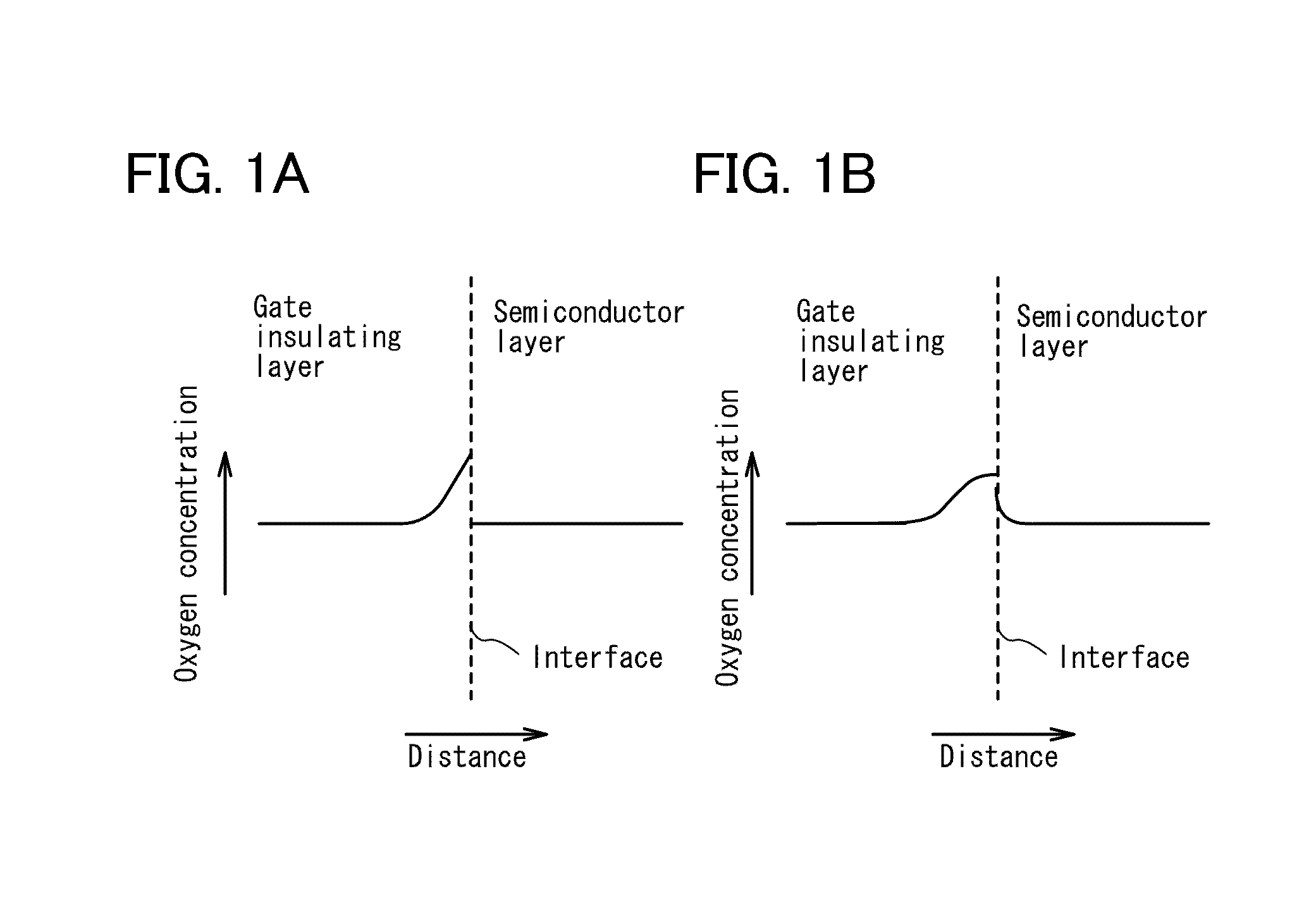

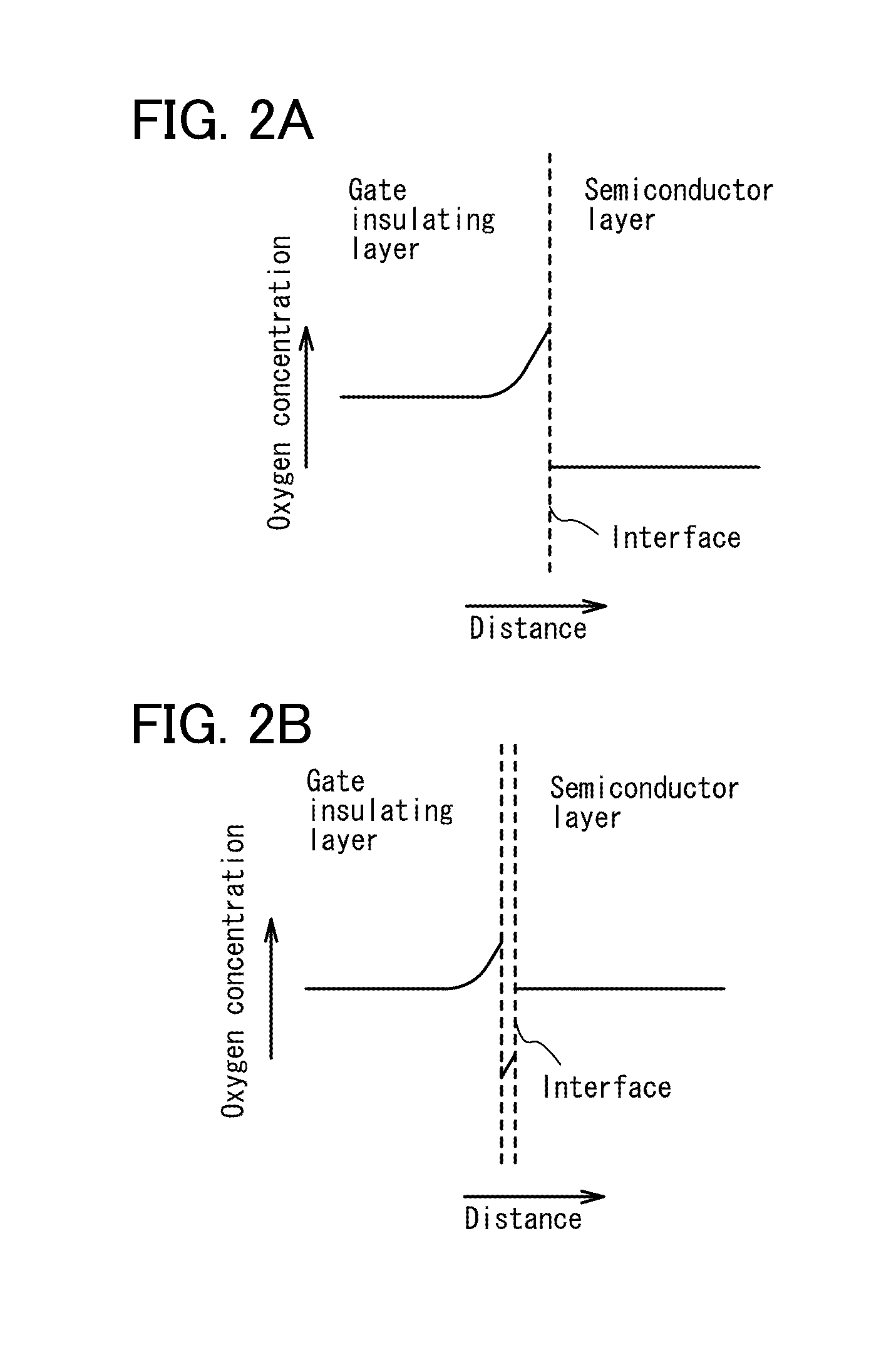

A thin film transistor structure in which a source electrode and a drain electrode formed from a metal material are in direct contact with an oxide semiconductor film may lead to high contact resistance. One cause of high contact resistance is that a Schottky junction is formed at a contact plane between the source and drain electrodes and the oxide semiconductor film. An oxygen-deficient oxide semiconductor layer which includes crystal grains with a size of 1 nm to 10 nm and has a higher carrier concentration than the oxide semiconductor film serving as a channel formation region is provided between the oxide semiconductor film and the source and drain electrodes.

Owner:SEMICON ENERGY LAB CO LTD

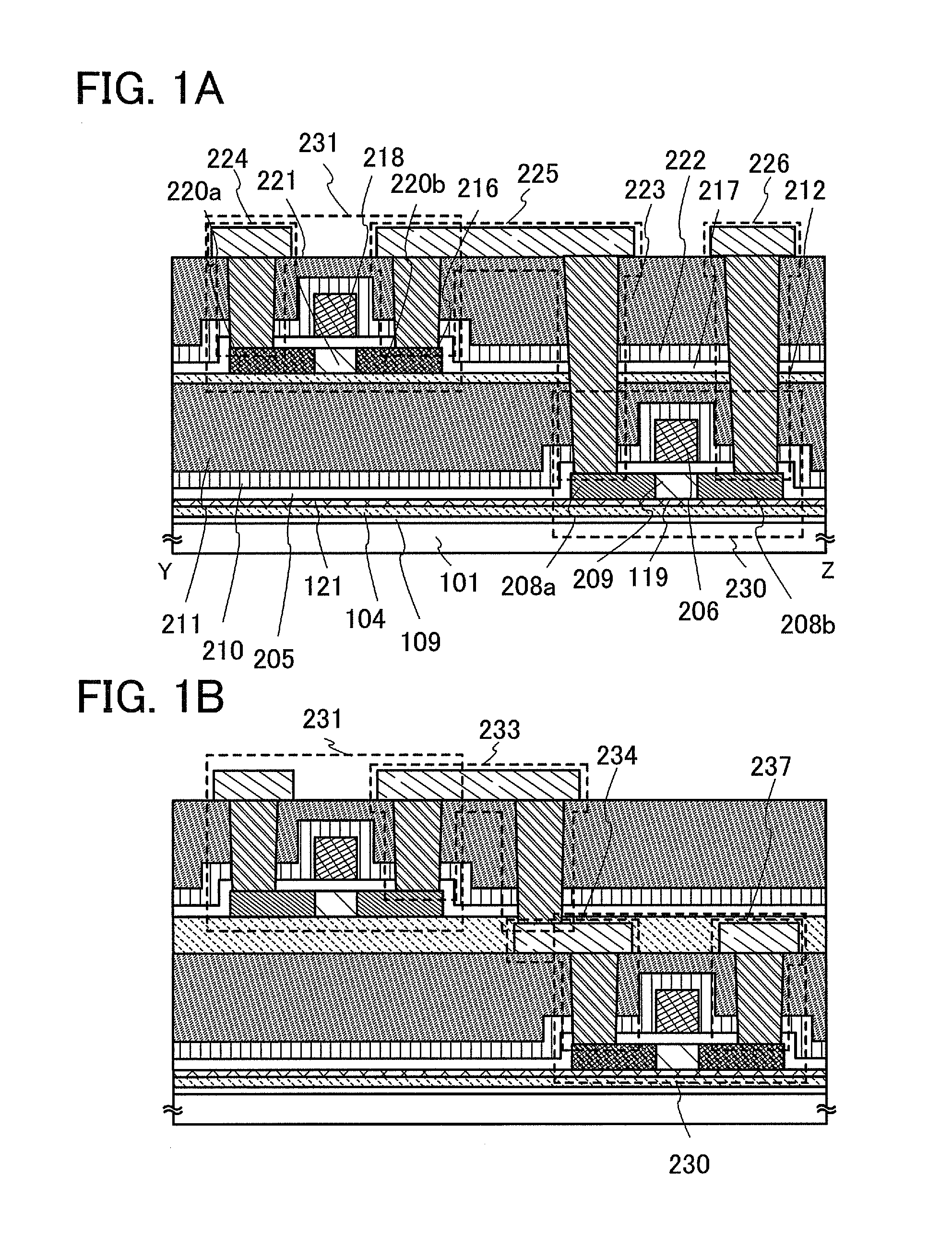

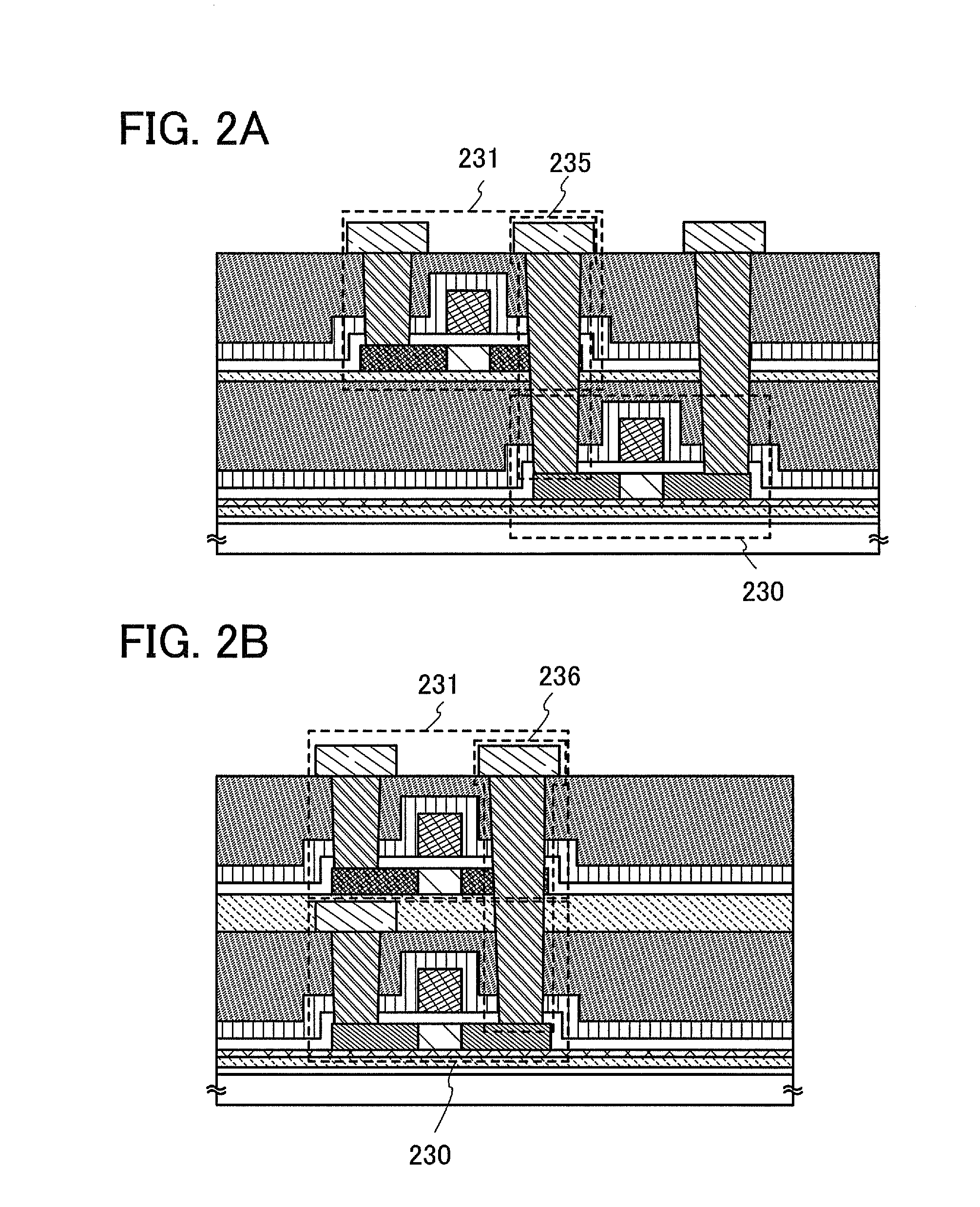

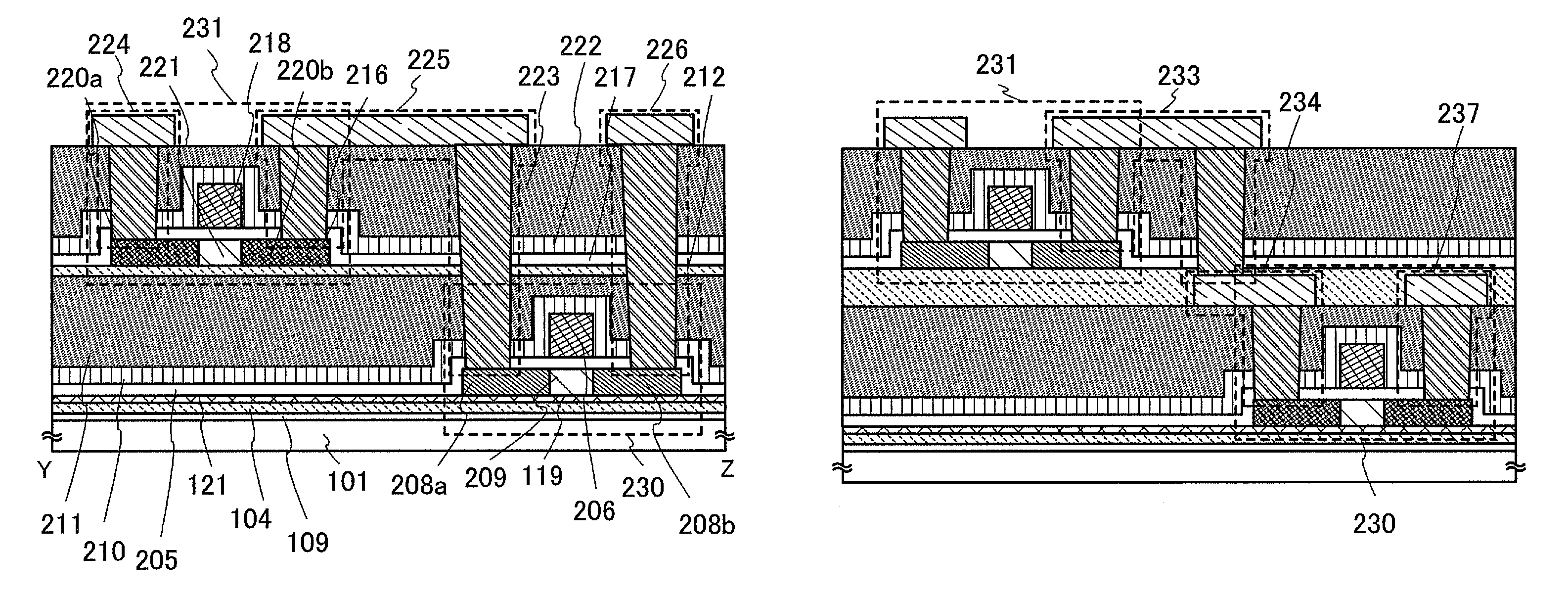

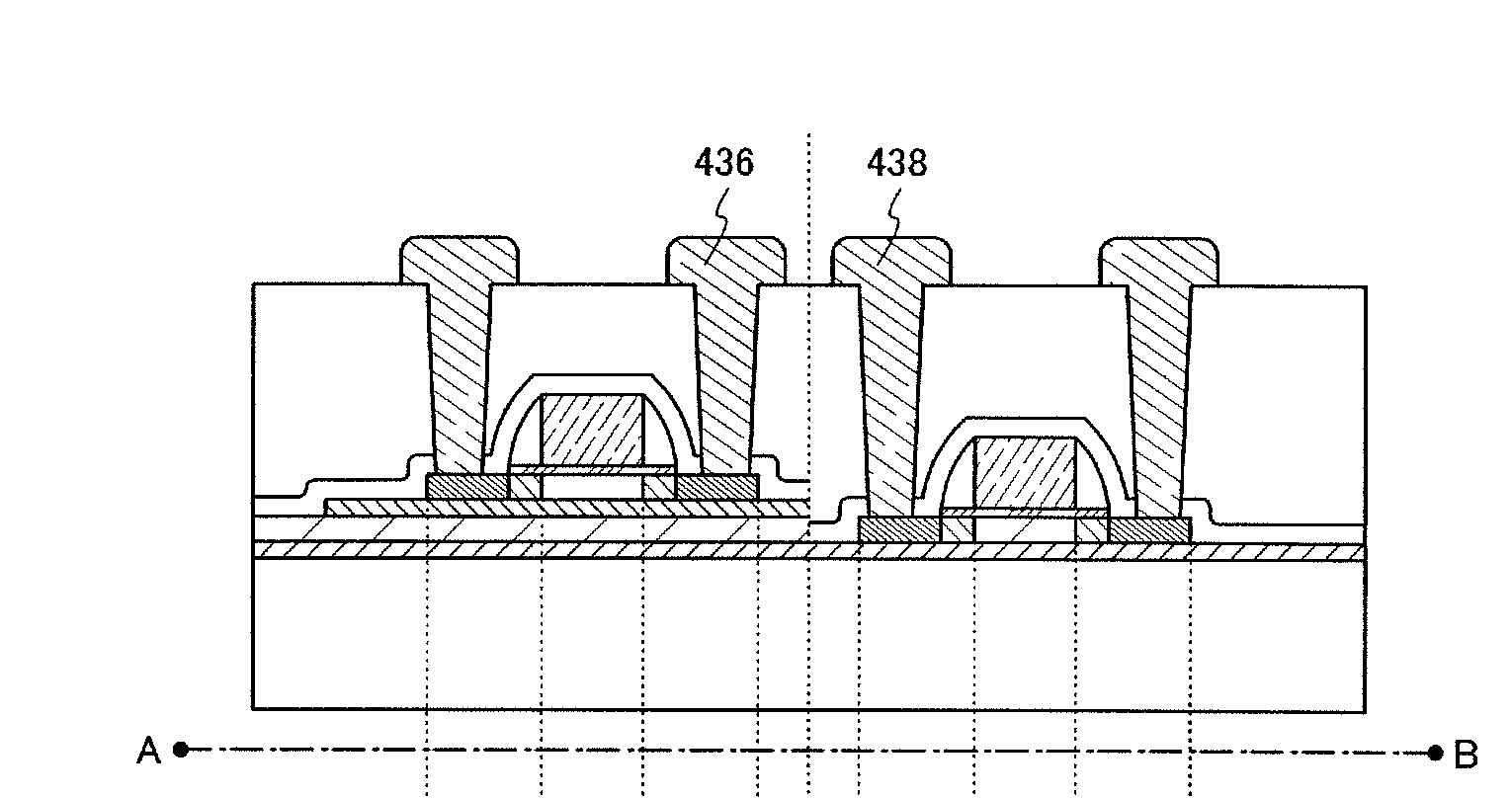

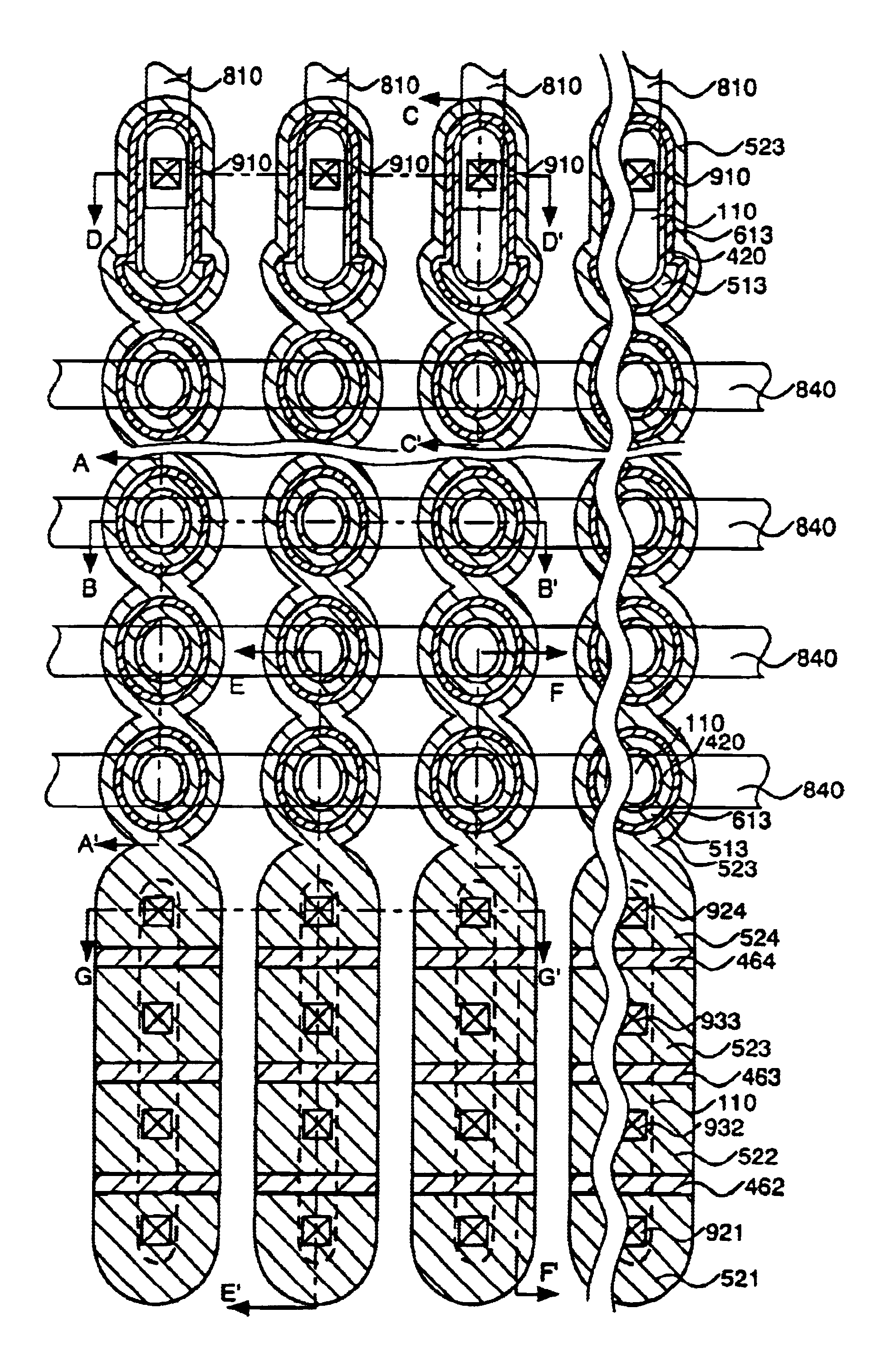

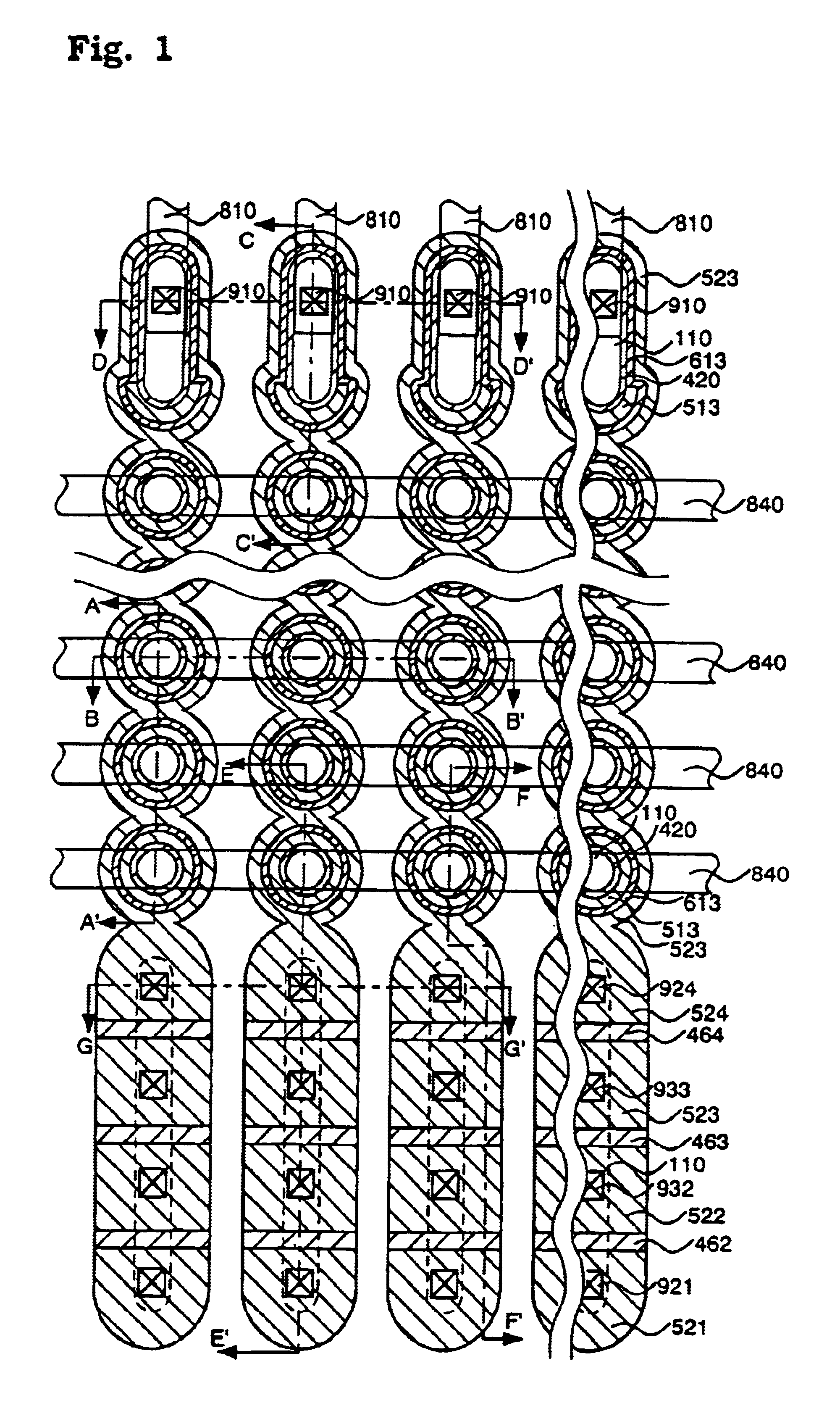

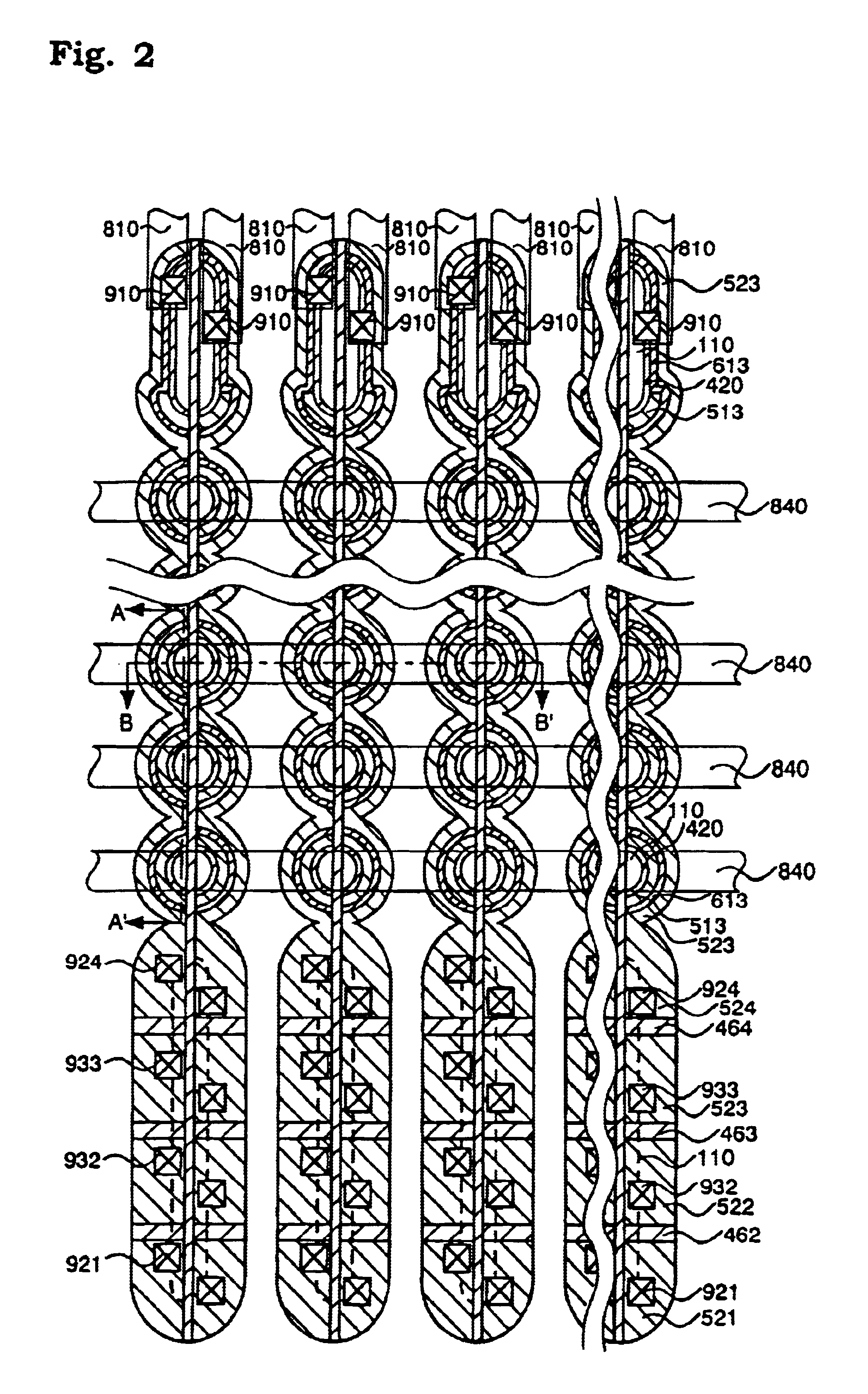

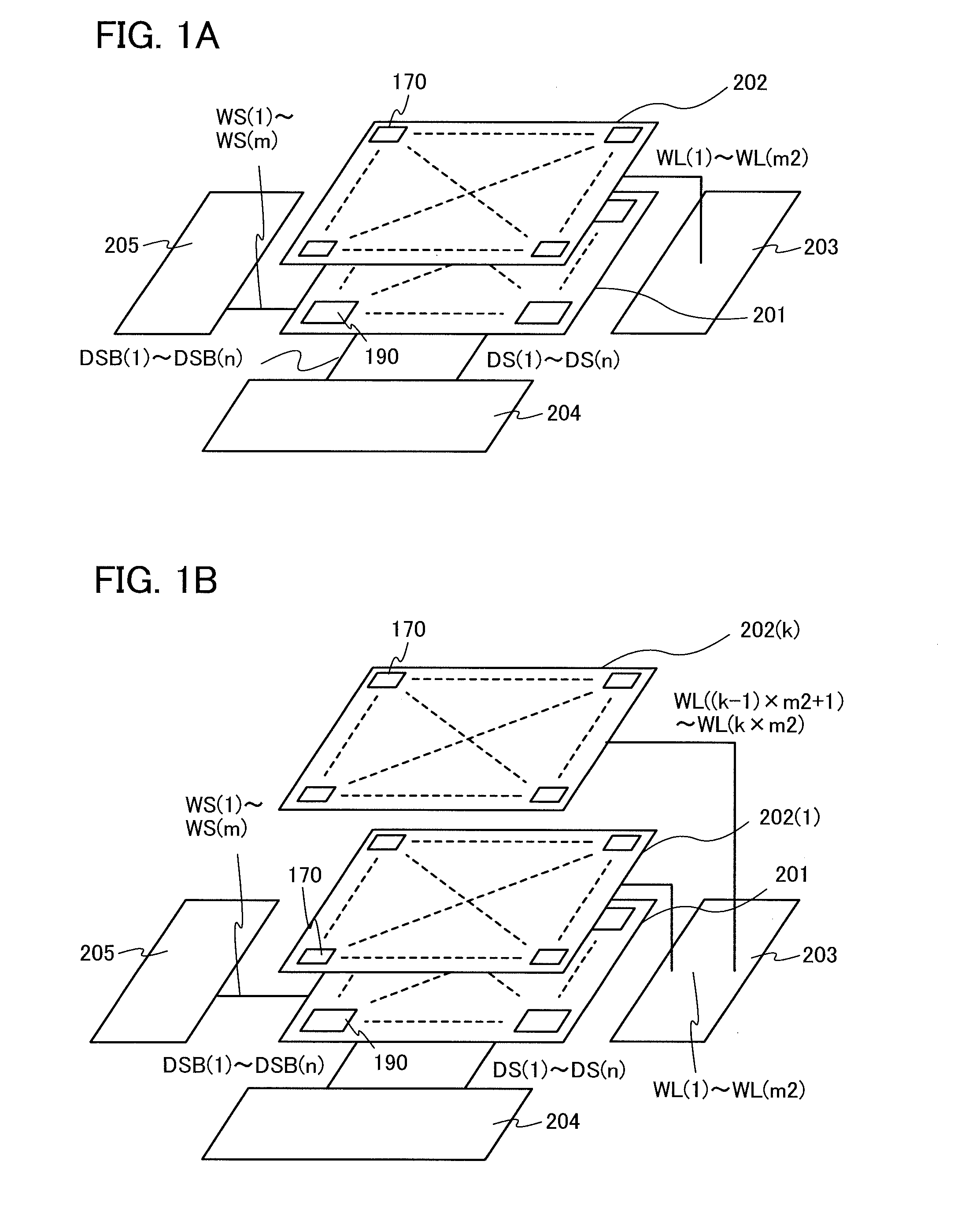

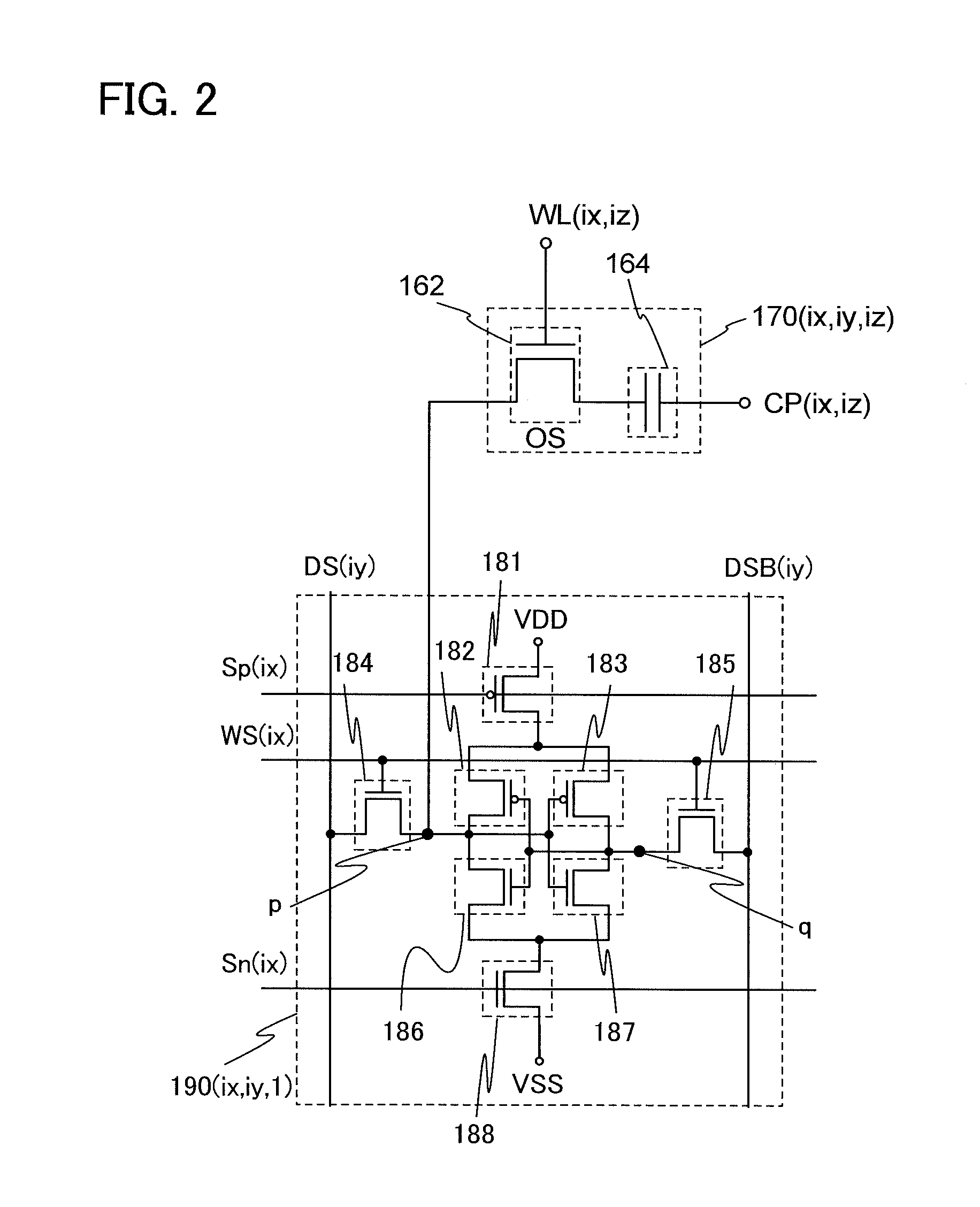

Semiconductor device

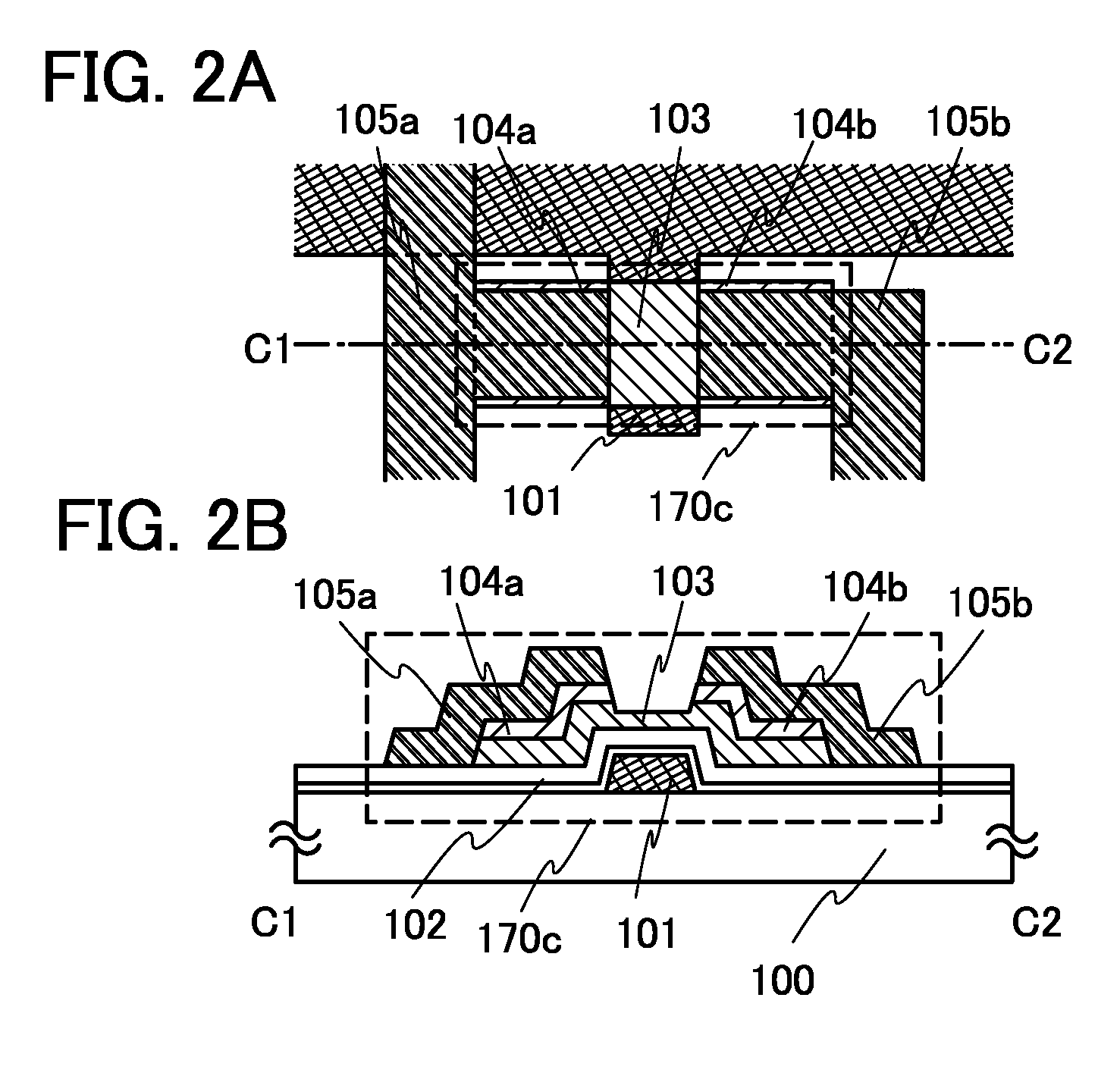

ActiveUS20090079000A1Difference in mobilityReduce power consumptionSemiconductor/solid-state device detailsSolid-state devicesDevice materialPlane orientation

An object is to realize high performance and low power consumption in a semiconductor device having an SOI structure. In addition, another object is to provide a semiconductor device having a high performance semiconductor element which is more highly integrated. A semiconductor device is such that a plurality of n-channel field-effect transistors and p-channel field-effect transistors are stacked with an interlayer insulating layer interposed therebetween over a substrate having an insulating surface. By controlling a distortion caused to a semiconductor layer due to an insulating film having a stress, a plane orientation of the semiconductor layer, and a crystal axis in a channel length direction, difference in mobility between the n-channel field-effect transistor and the p-channel field-effect transistor can be reduced, whereby current driving capabilities and response speeds of the n-channel field-effect transistor and the p-channel field-effect can be comparable.

Owner:SEMICON ENERGY LAB CO LTD

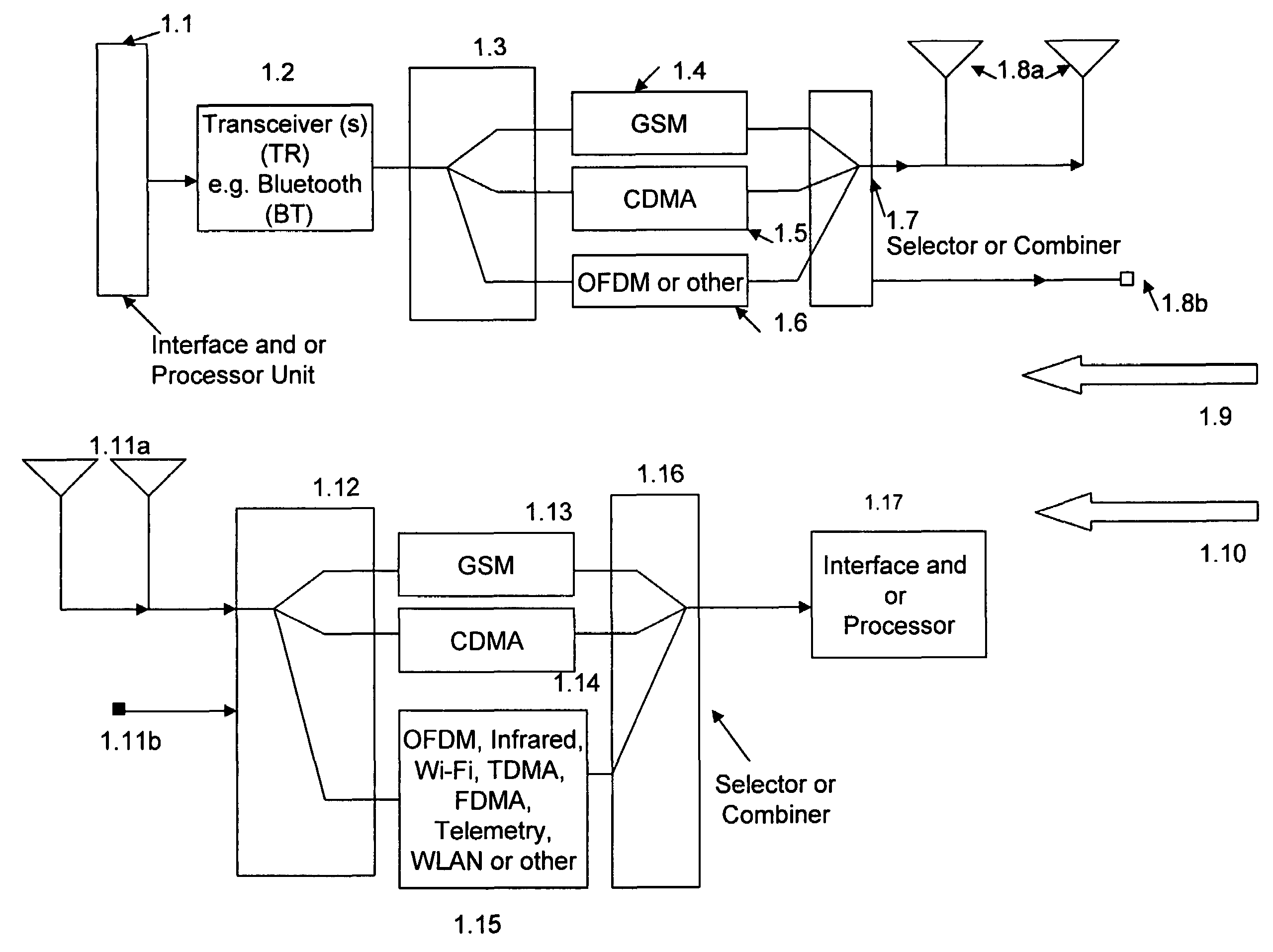

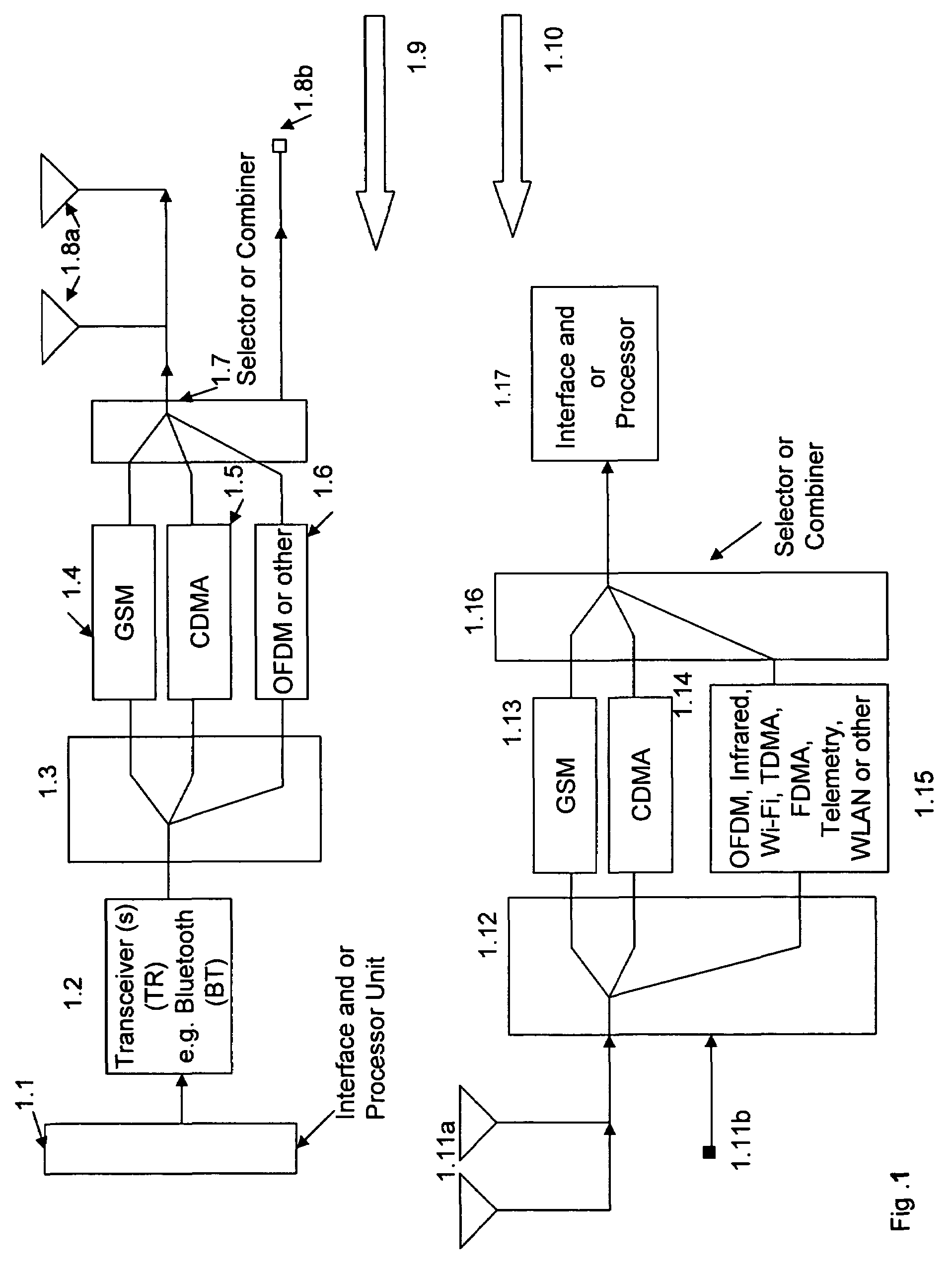

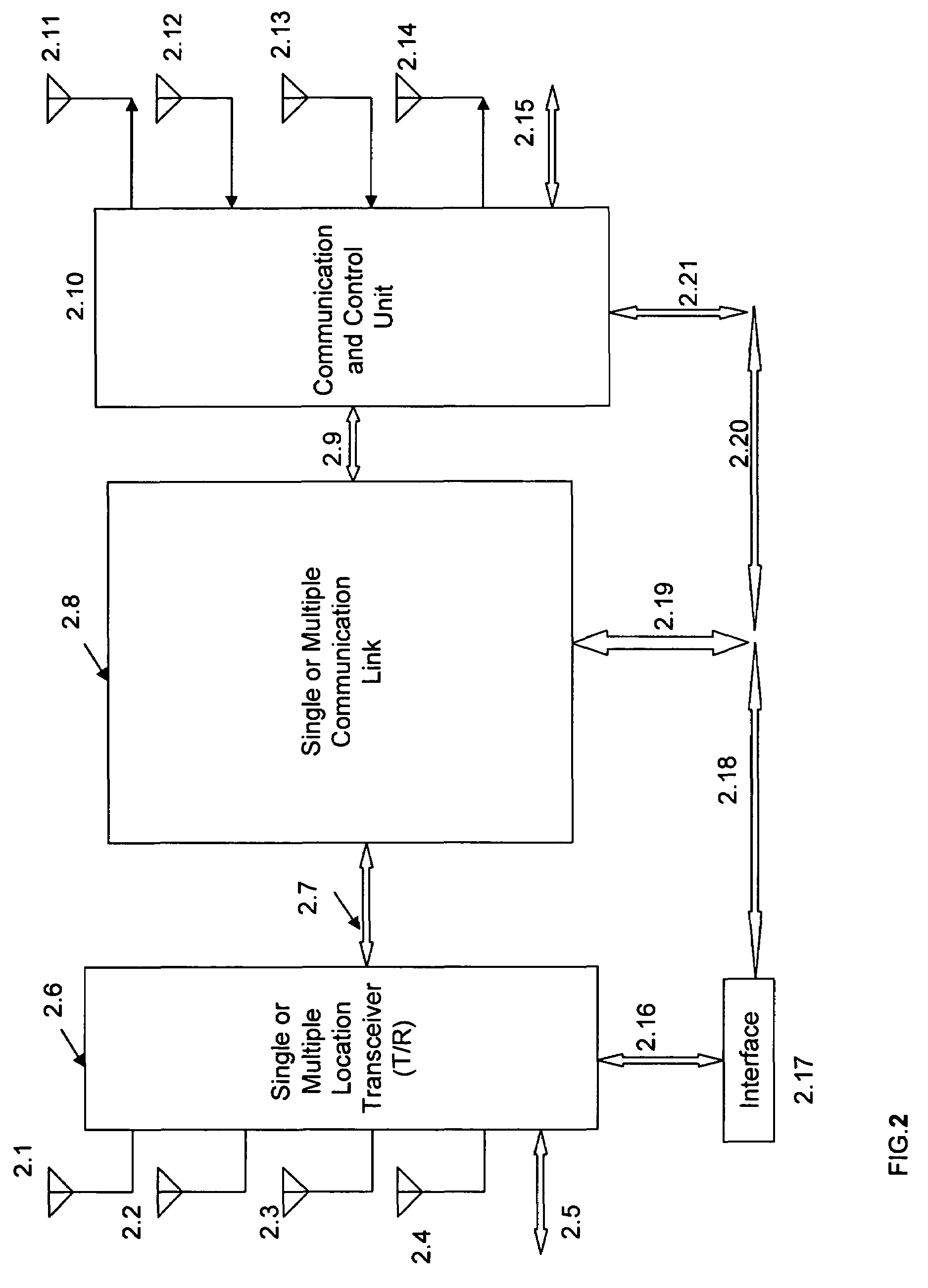

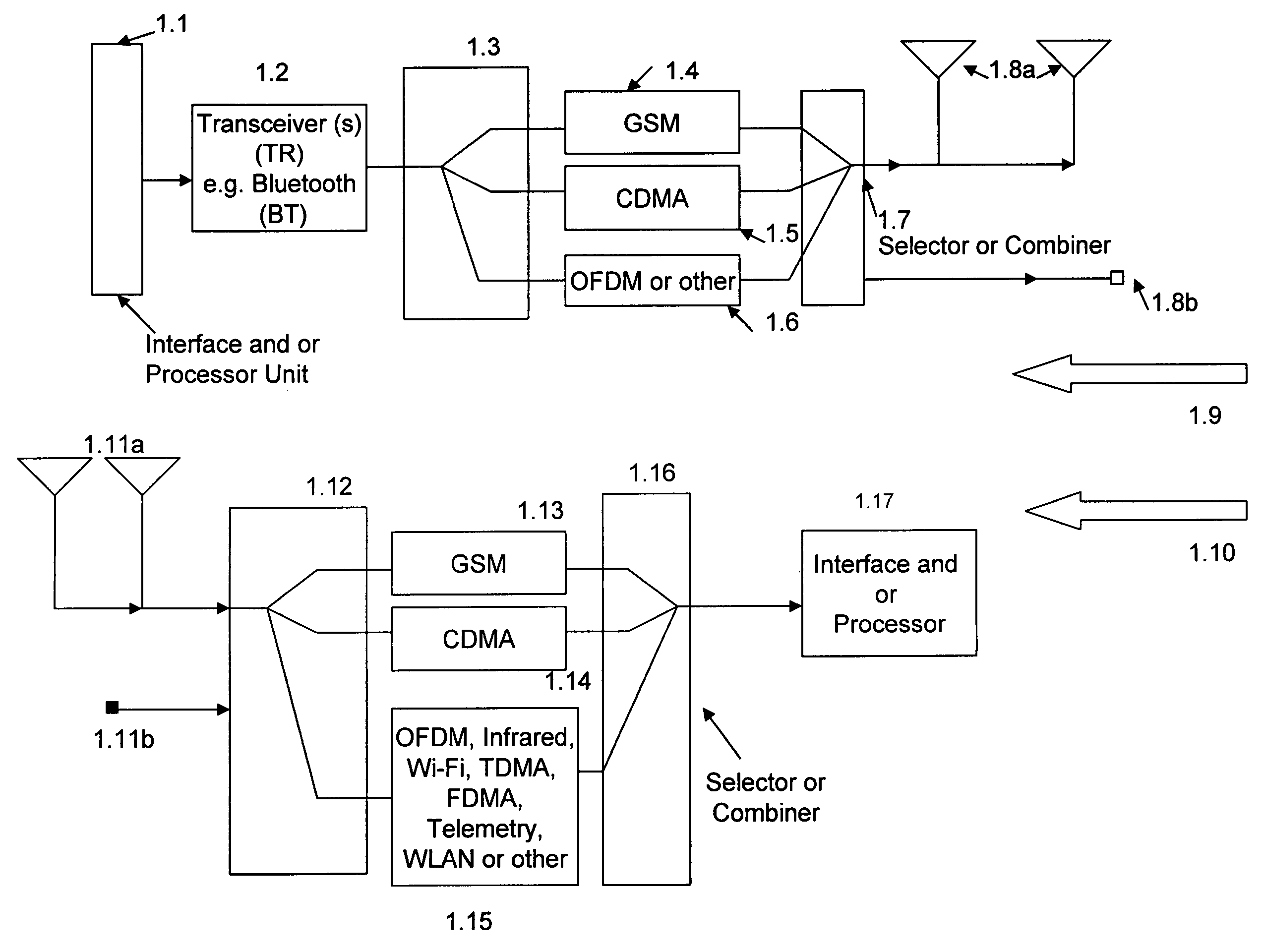

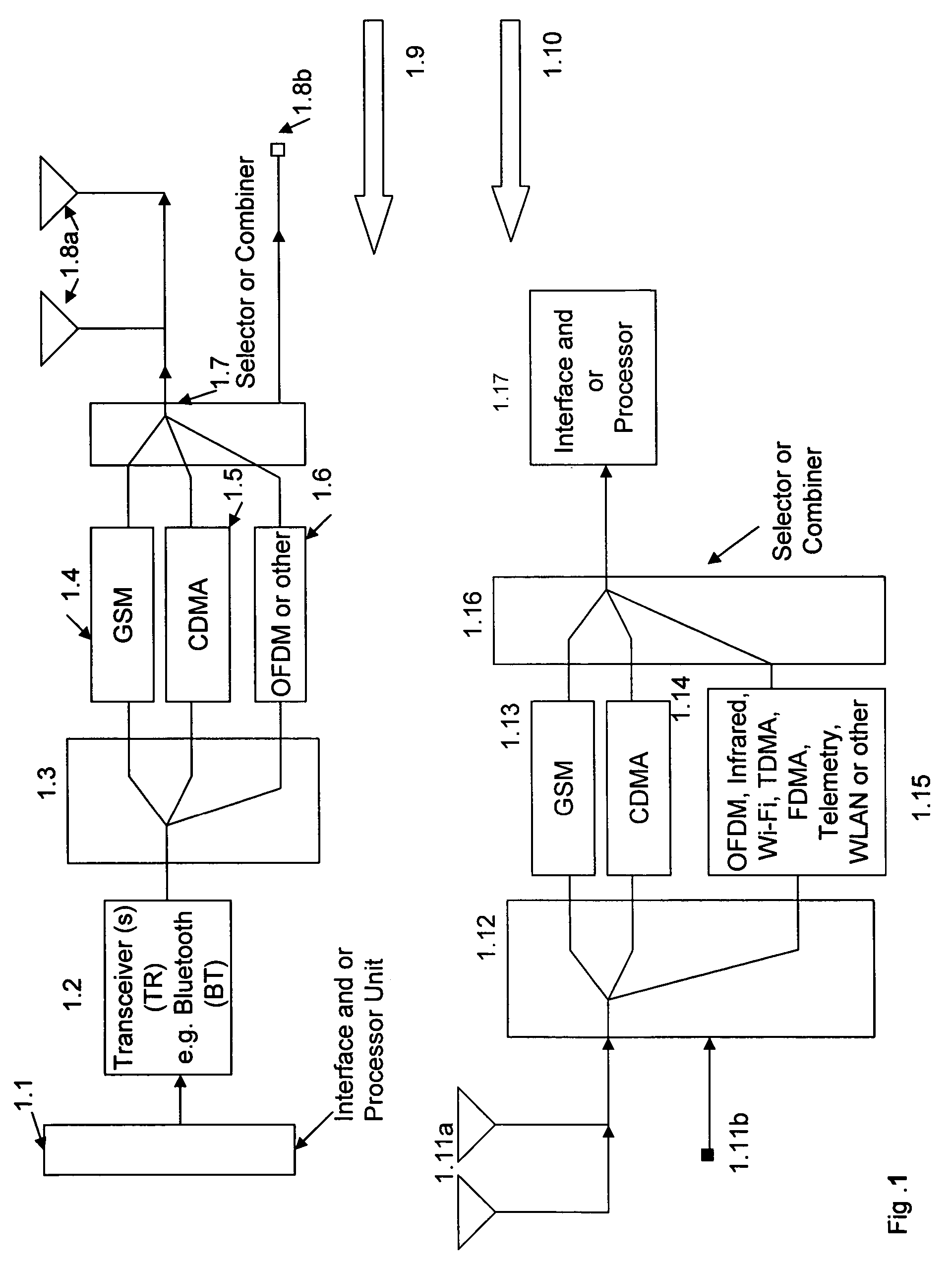

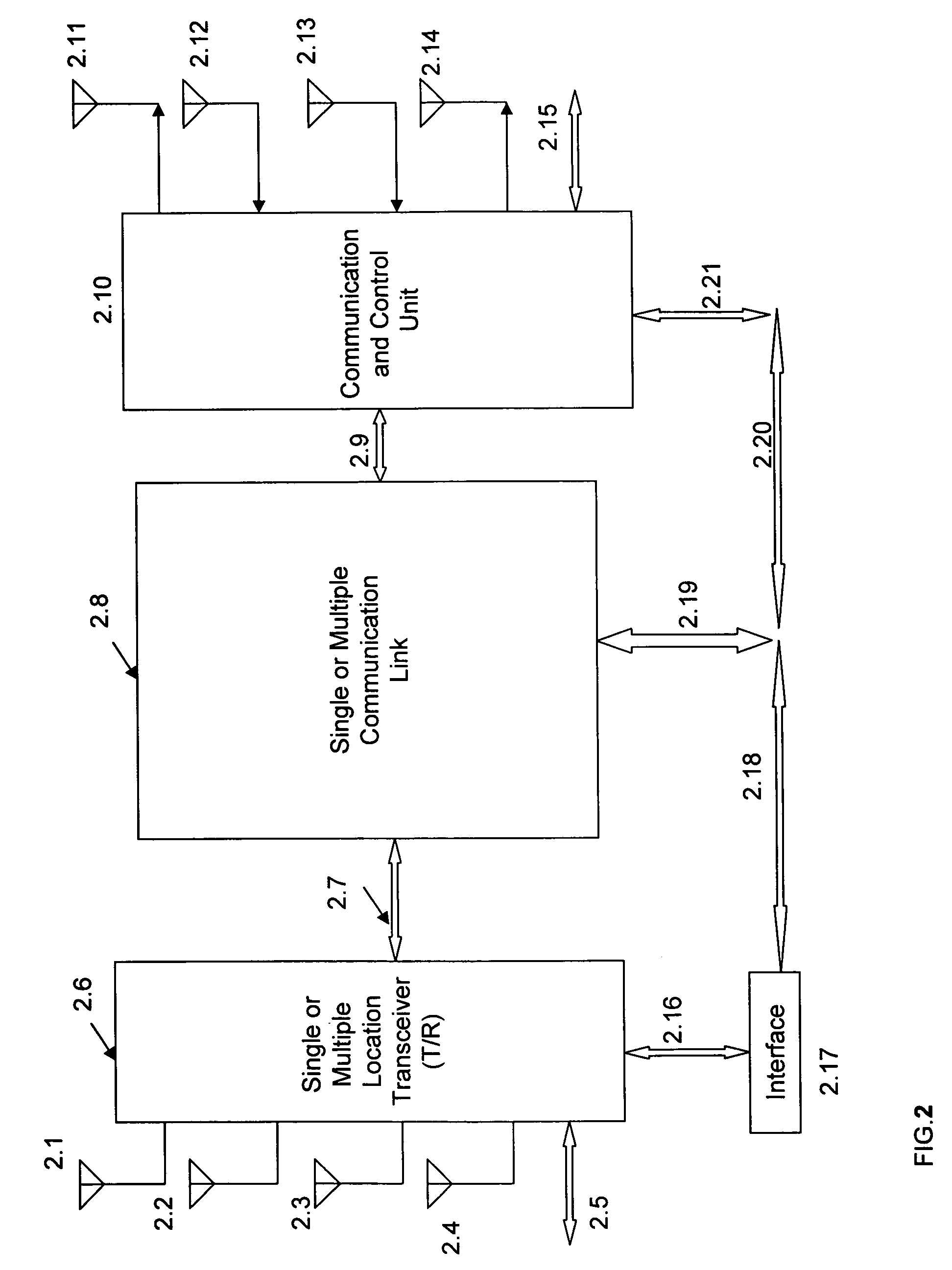

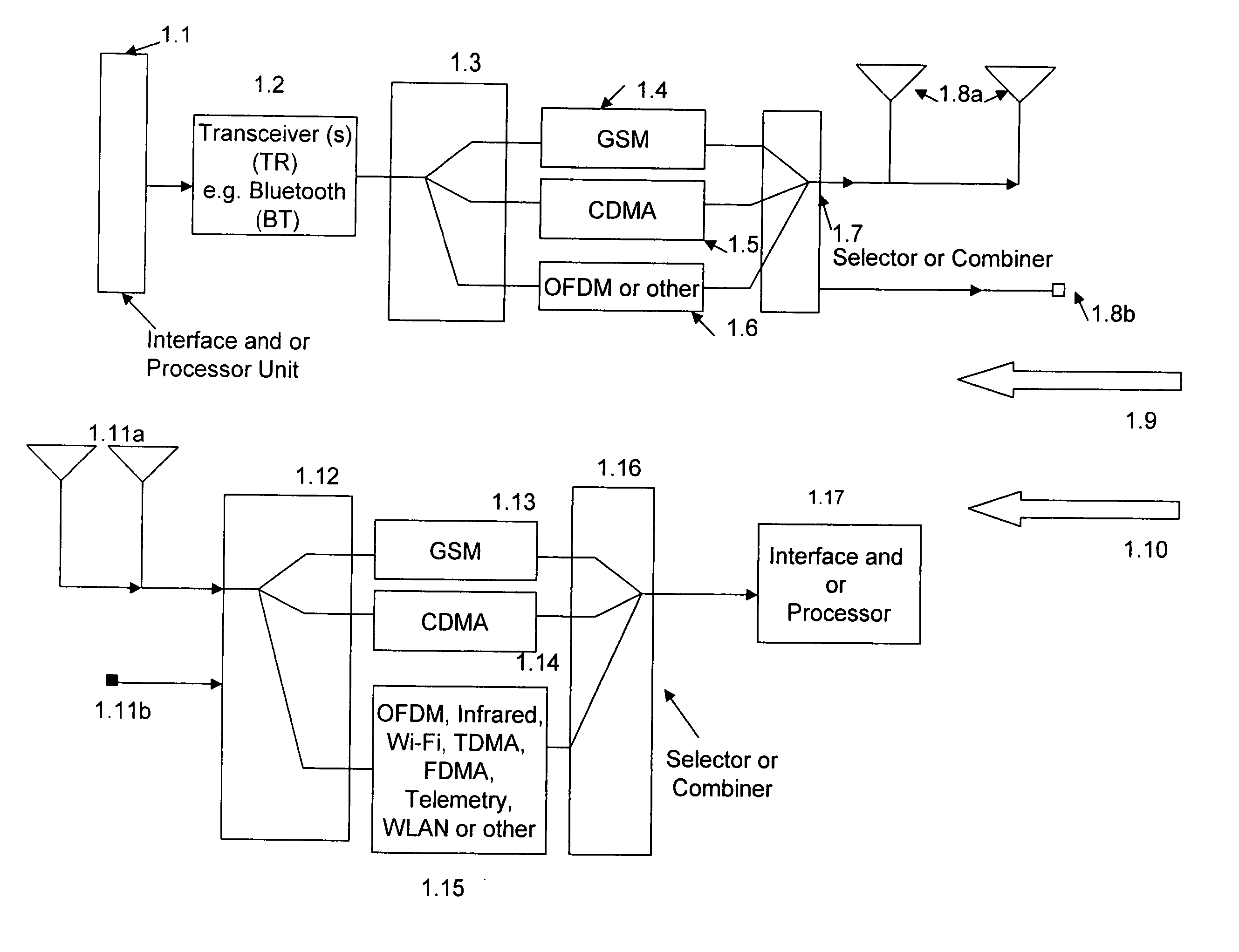

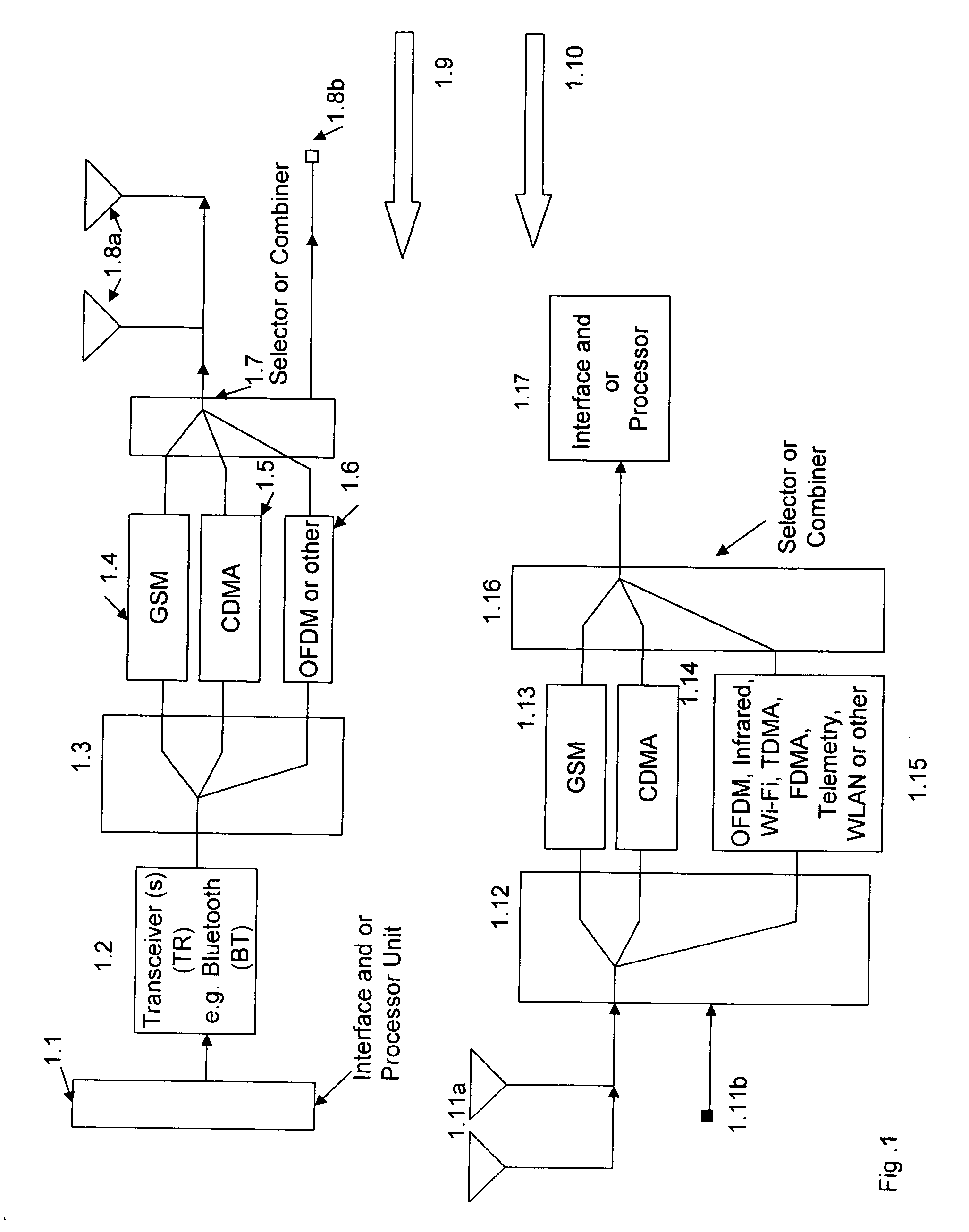

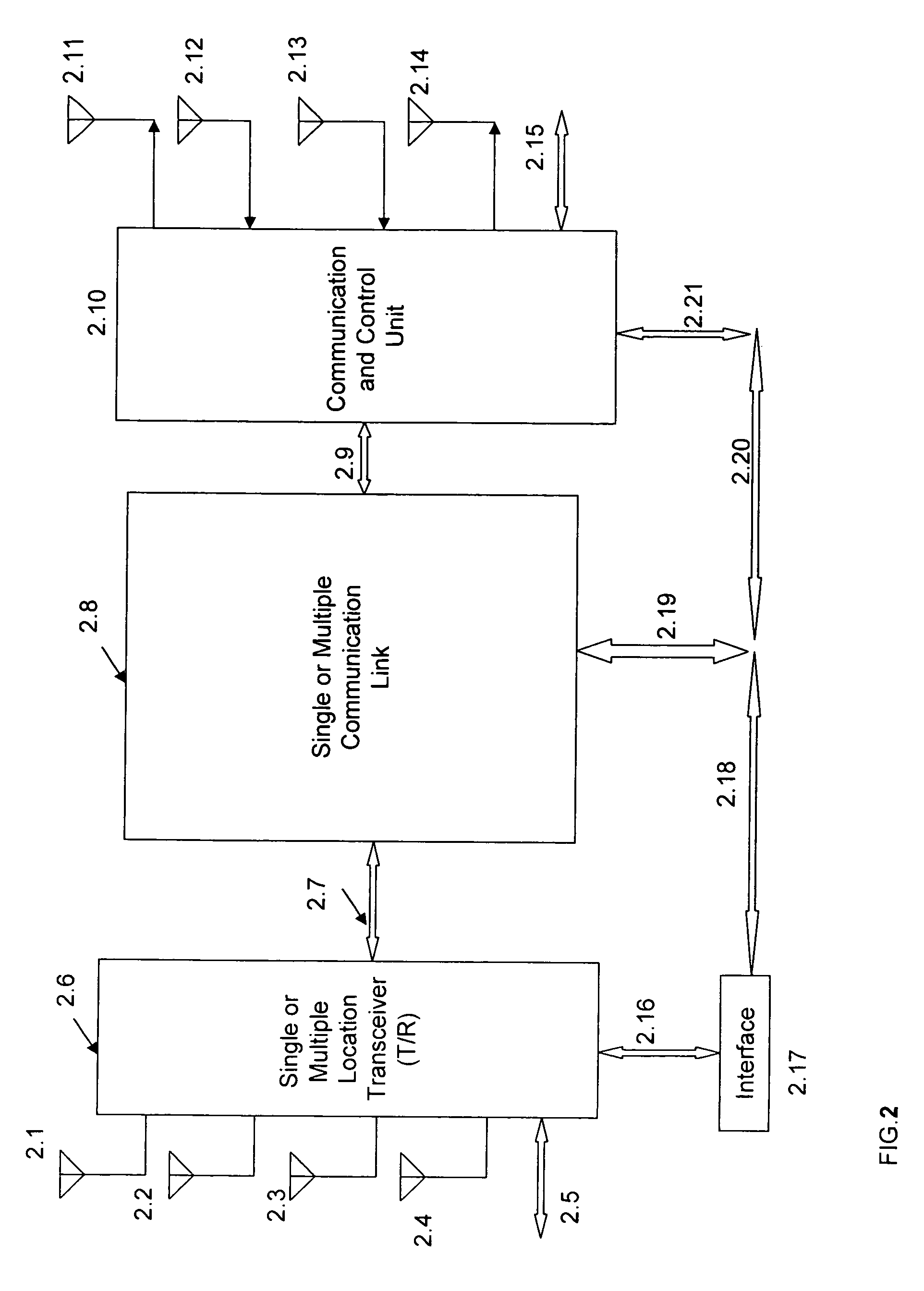

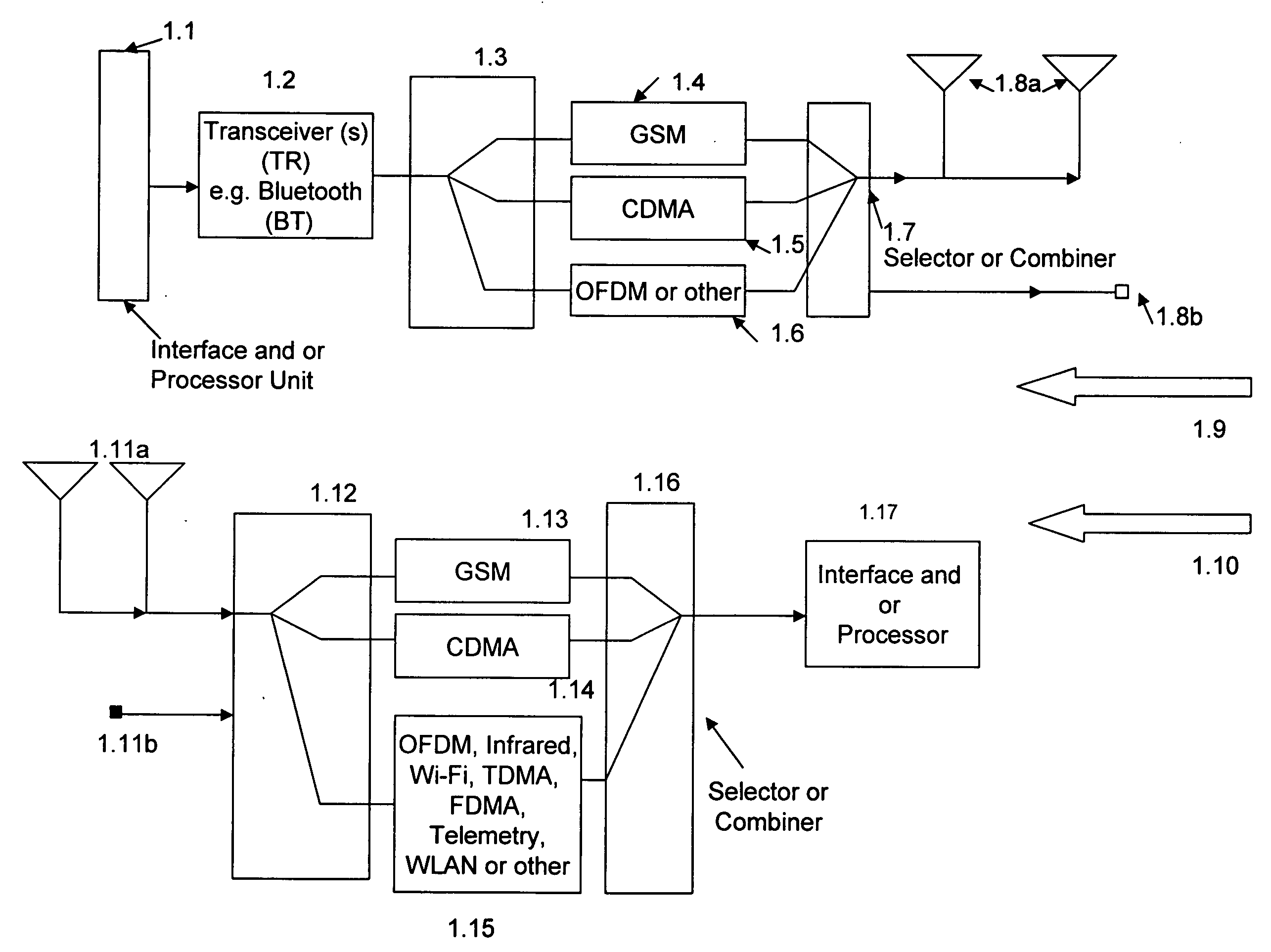

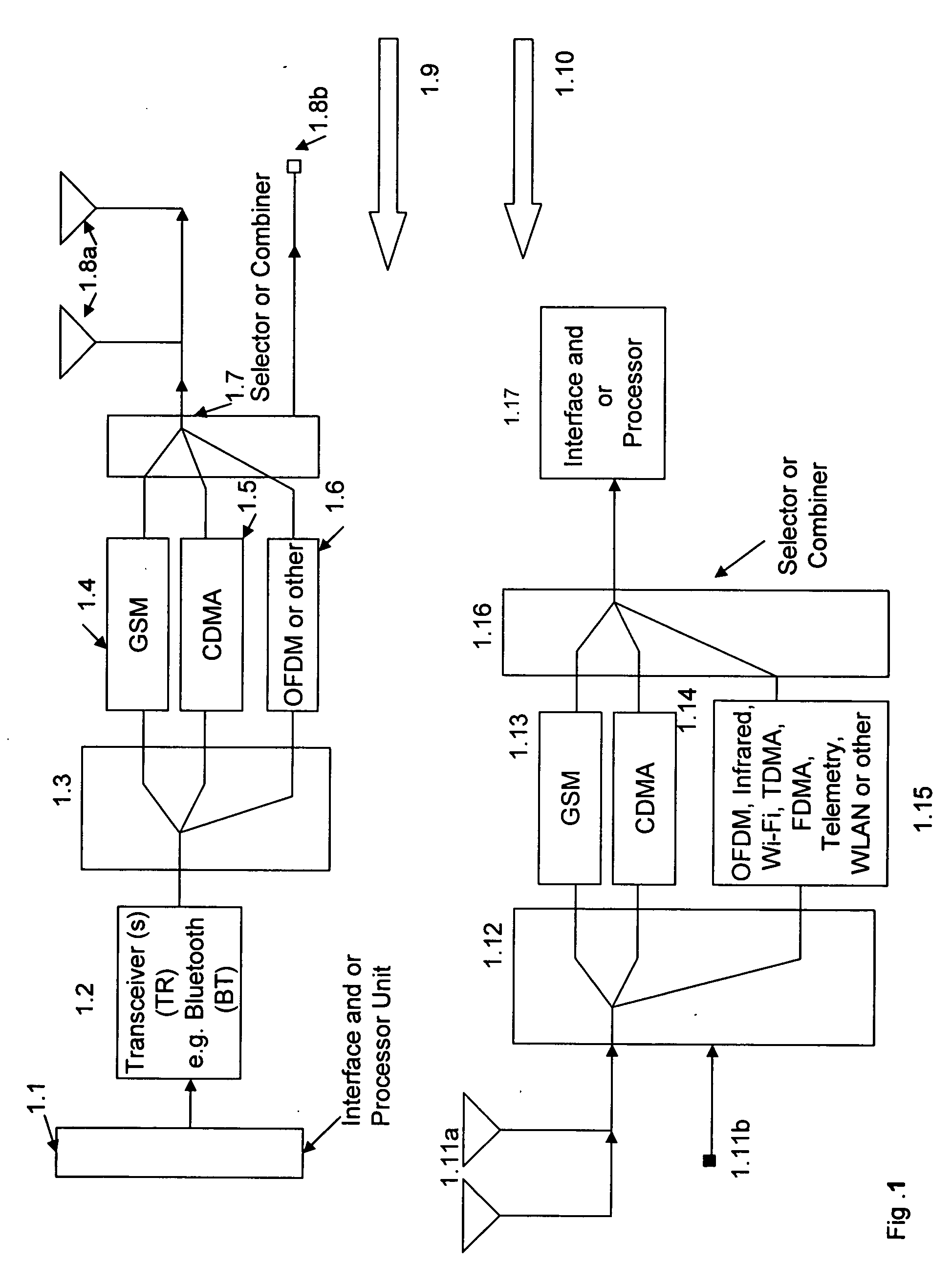

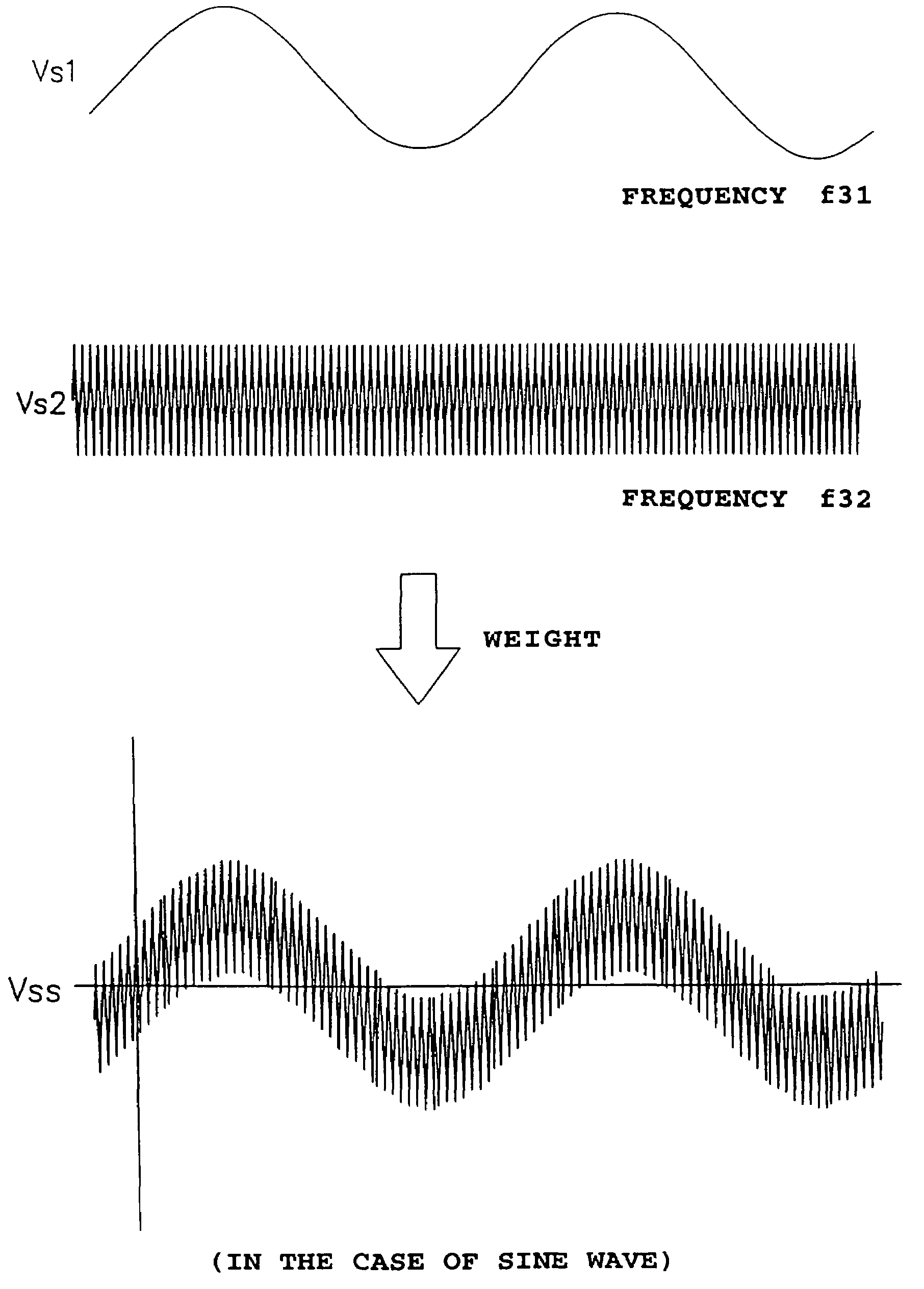

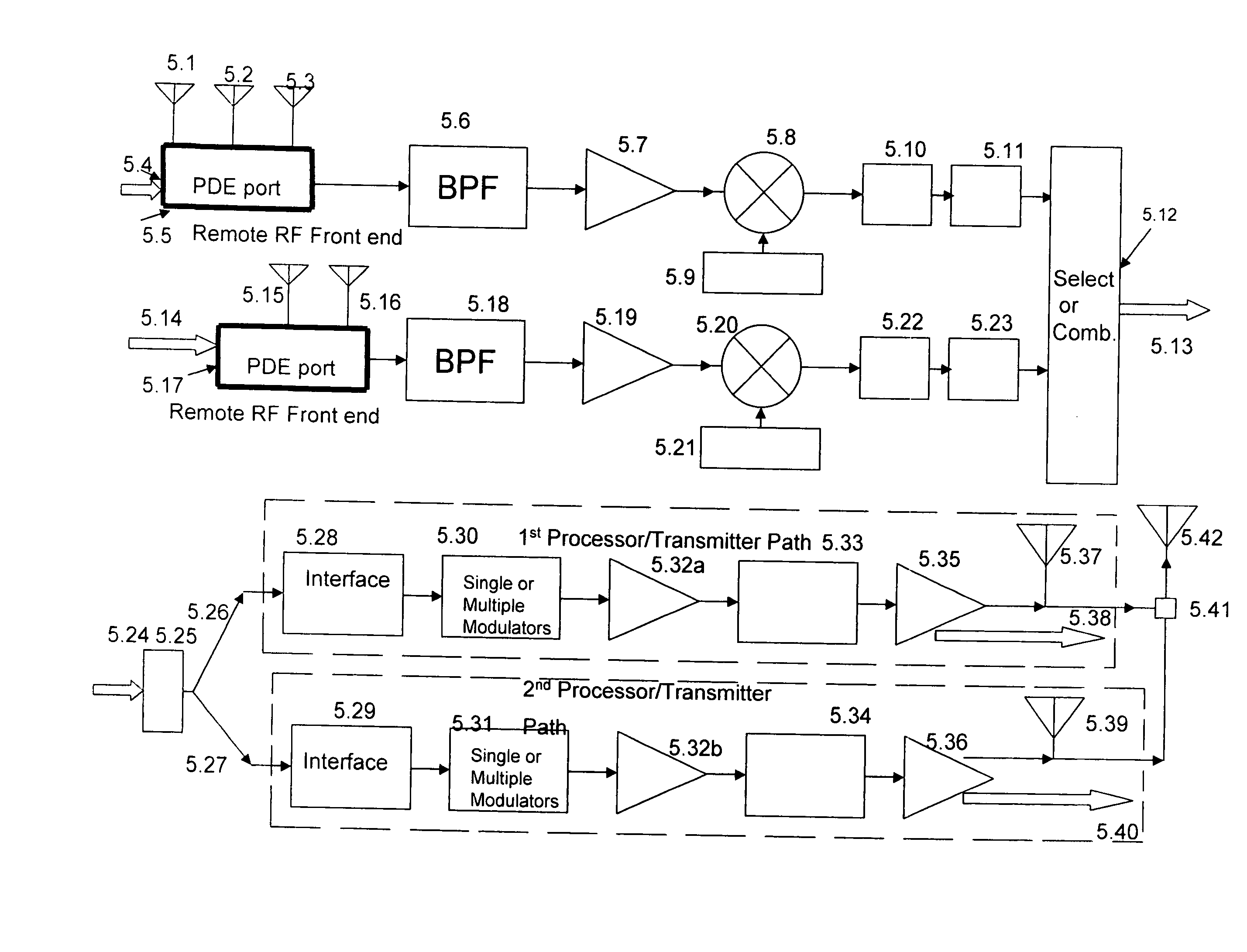

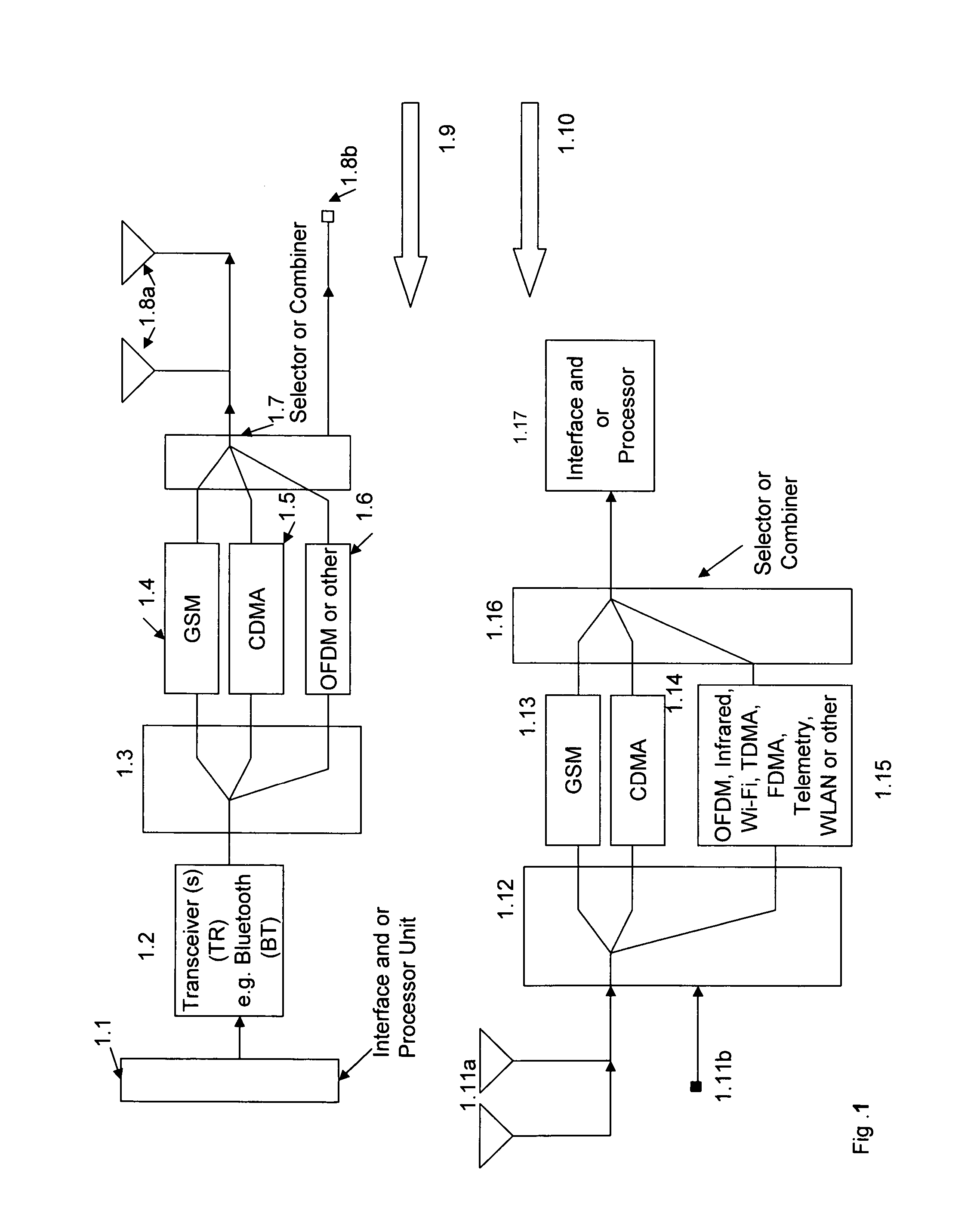

Location finder, tracker, communication and remote control system

ActiveUS7260369B2Expand coverageImprove performanceTelevision system detailsMultiple modulation transmitter/receiver arrangementsRemote controlControl system

A radio frequency identification (RFID) device, locator, wired and / or wireless communicator system comprising one or more than one antennas for receiving Radio Frequency (RF) signals from one or more RFID and or location determining and / or communication transmitters. The system has one or more receivers and demodulators for reception and demodulation of signals to baseband signals. A processor circuit processes the baseband signals and provides them to a cross-correlator circuit for cross-correlating the processed baseband signals and for generation of cross-correlated baseband signals. One or more modulators modulate the baseband signals and provide them to one or more transmitters. circuitry.

Owner:FEHER KAMILO

Semiconductor device

InactiveUS8044464B2Guaranteed high speed operationReduce power consumptionSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packagePlane orientation

Owner:SEMICON ENERGY LAB CO LTD

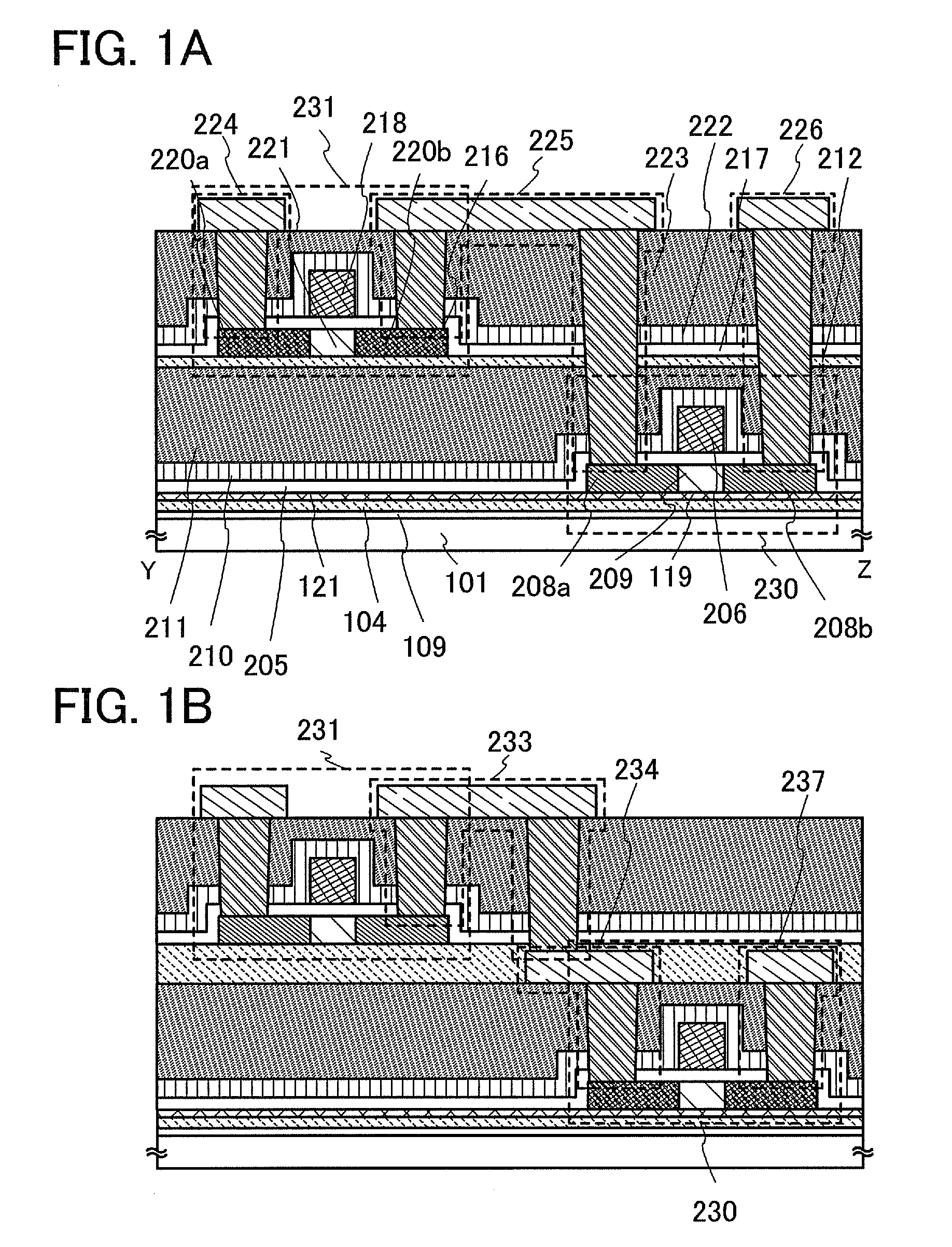

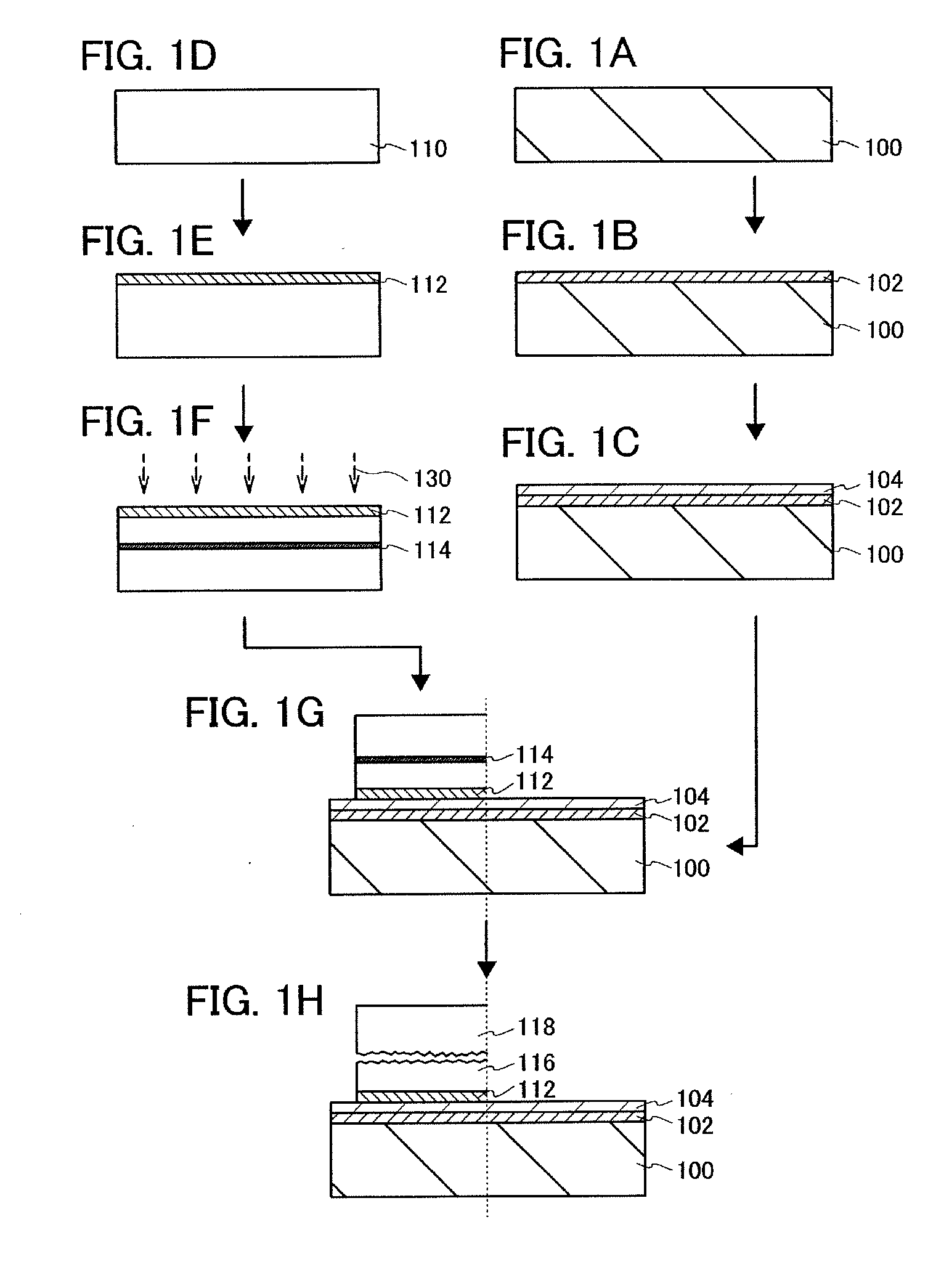

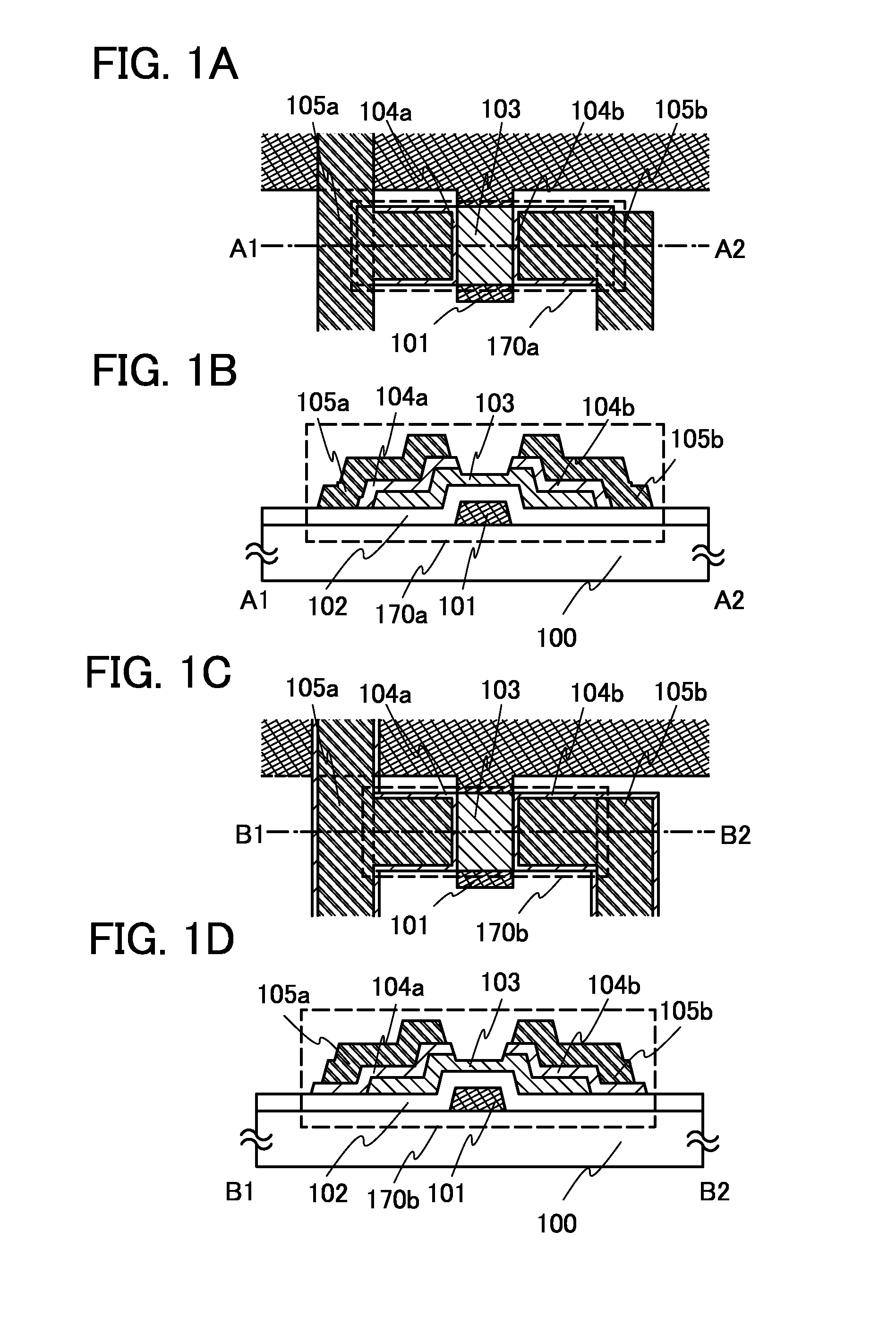

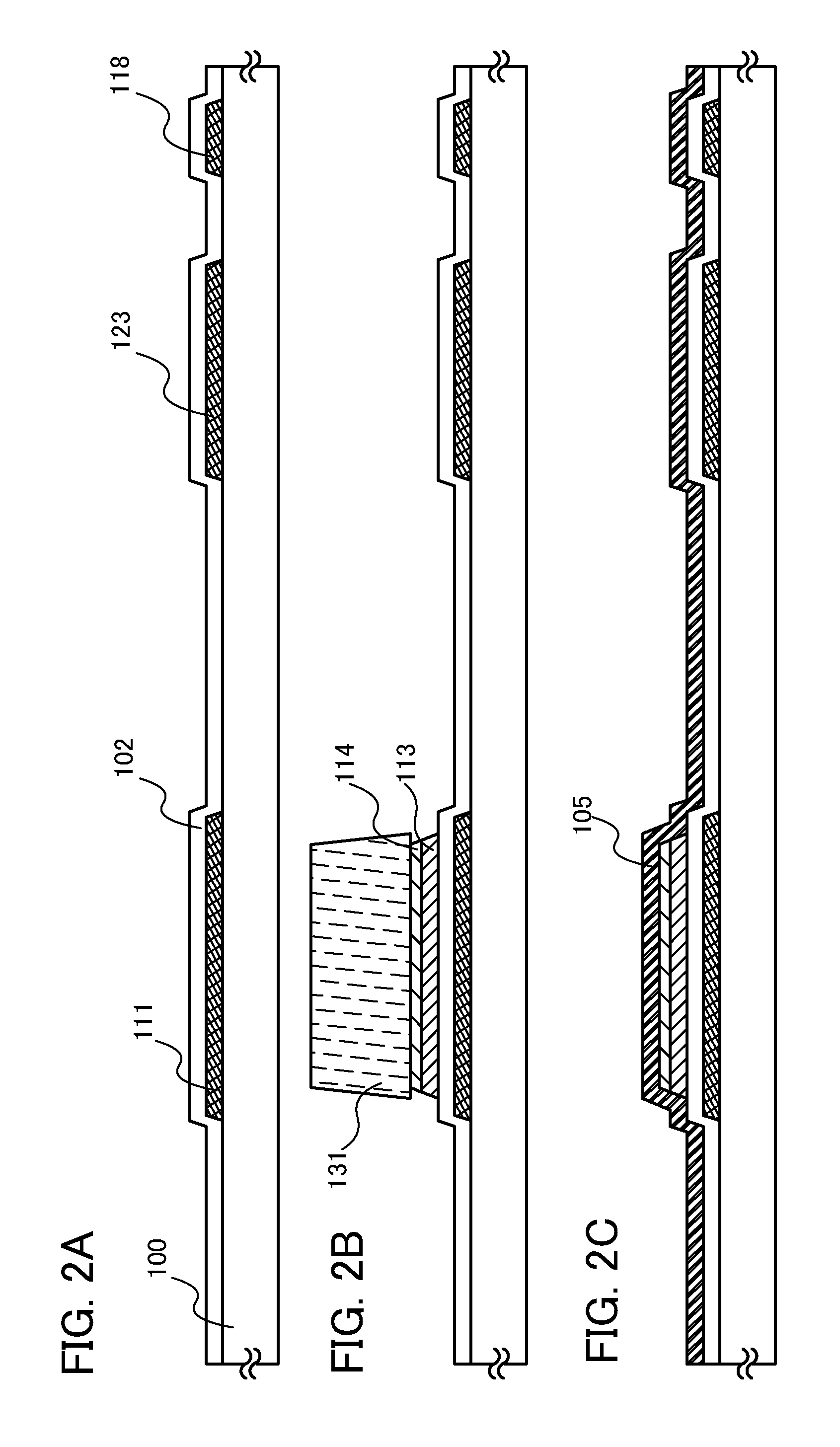

Semiconductor device and method for manufacturing the same

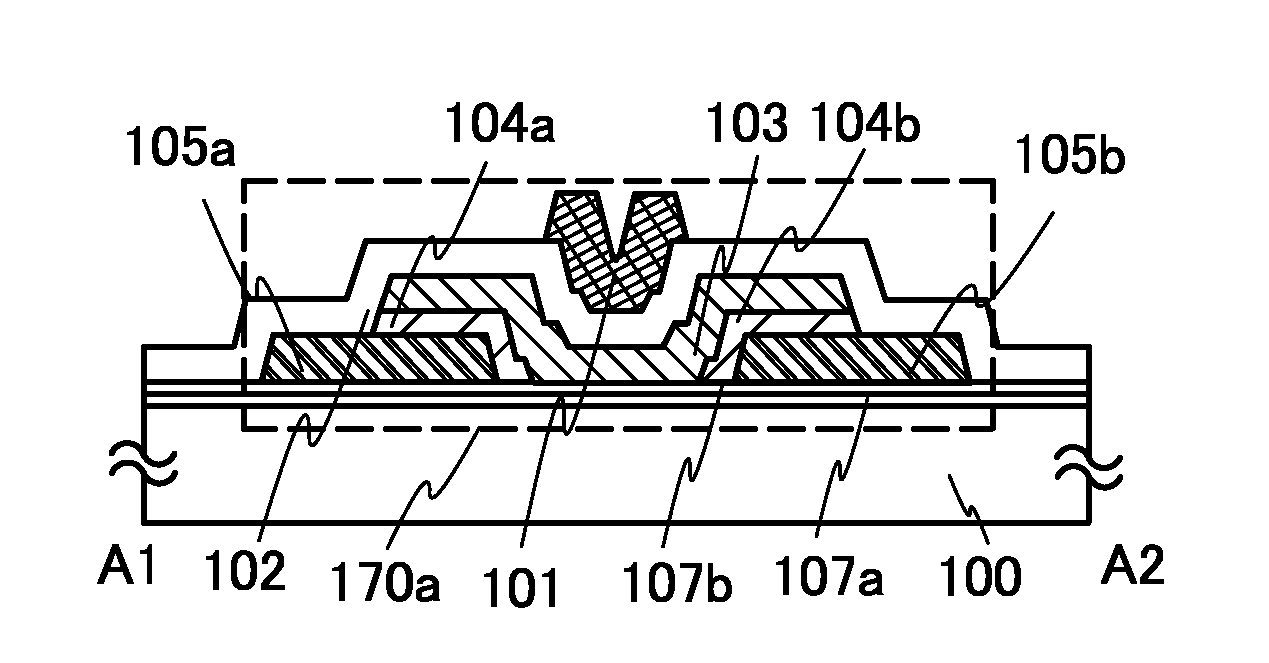

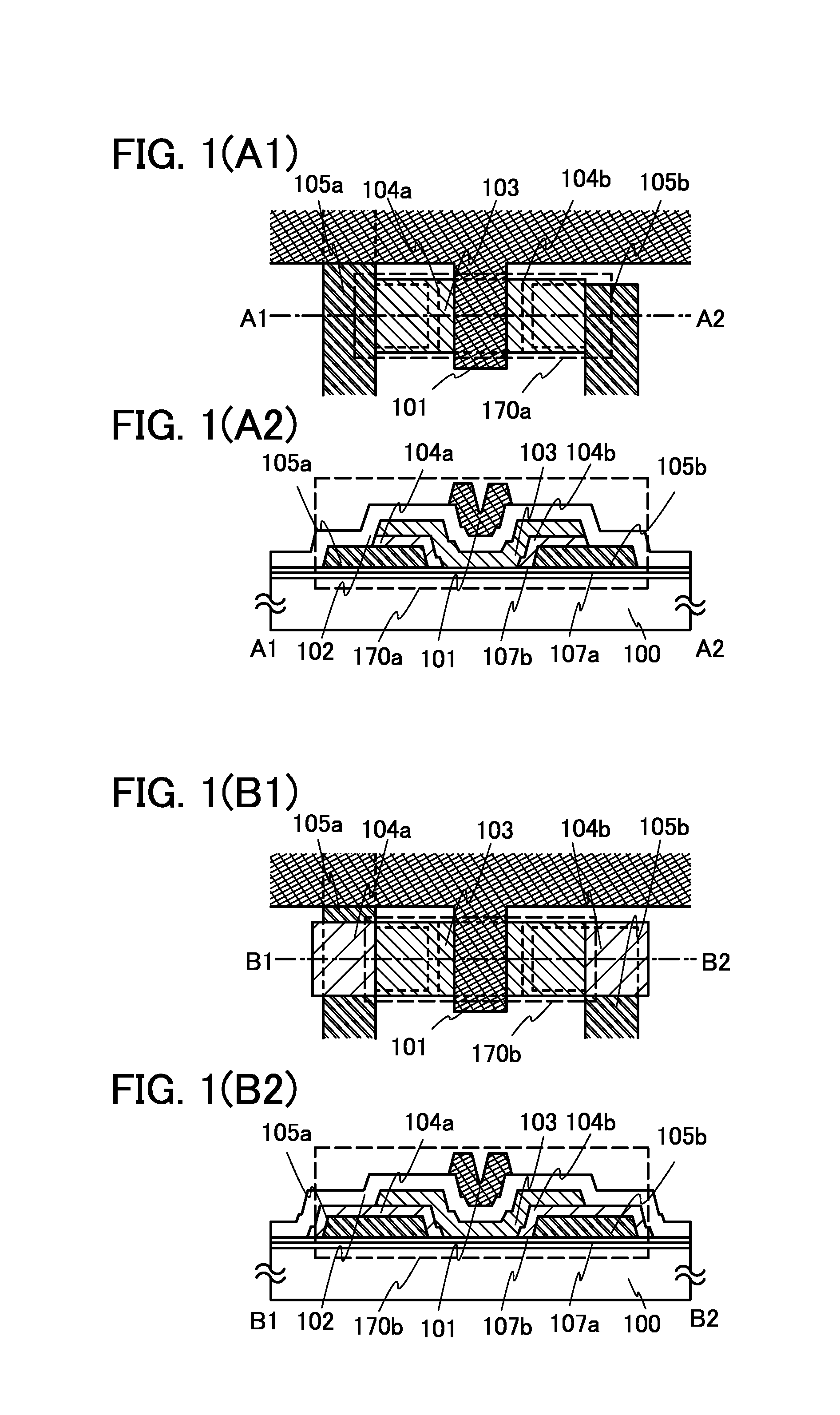

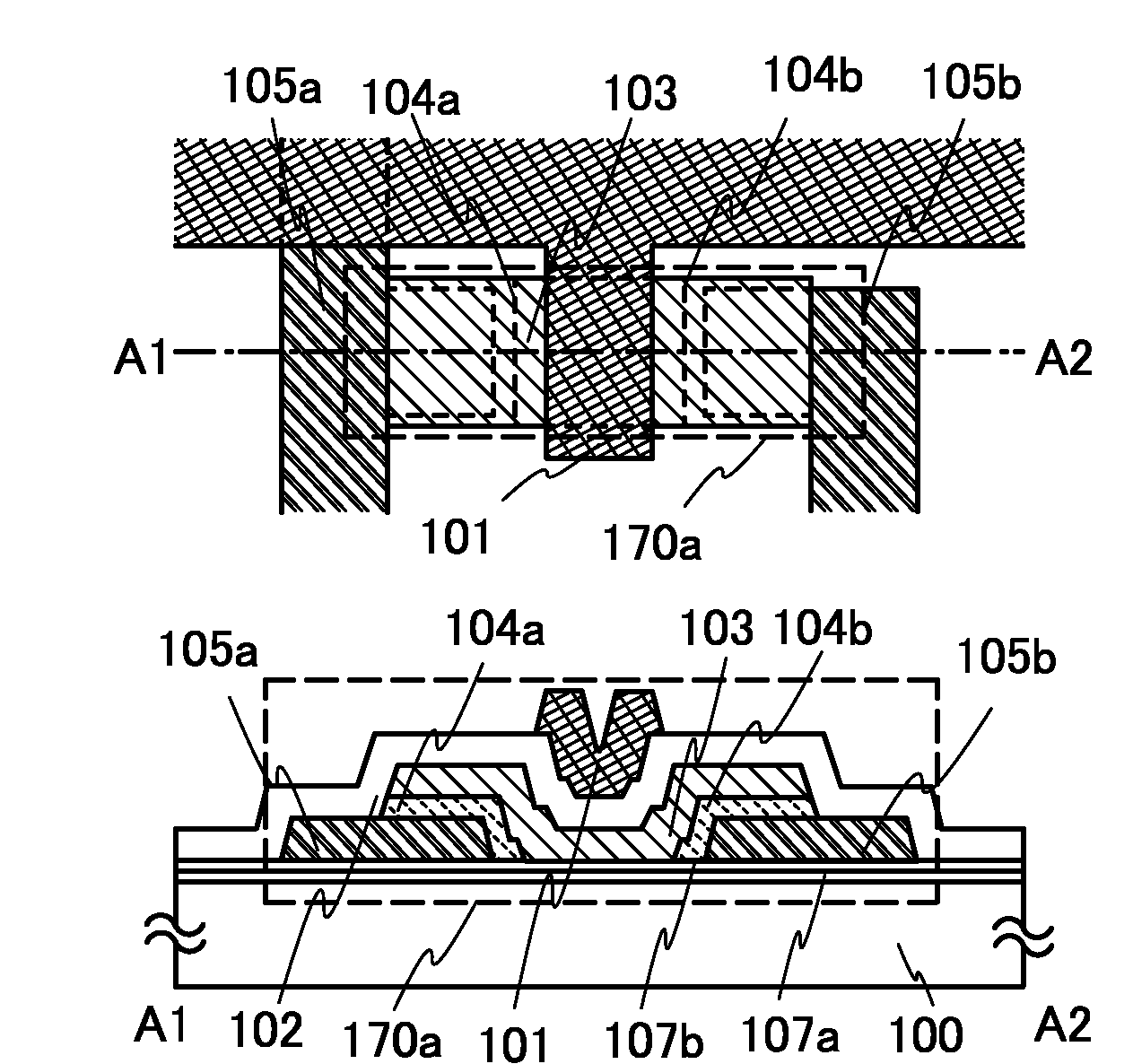

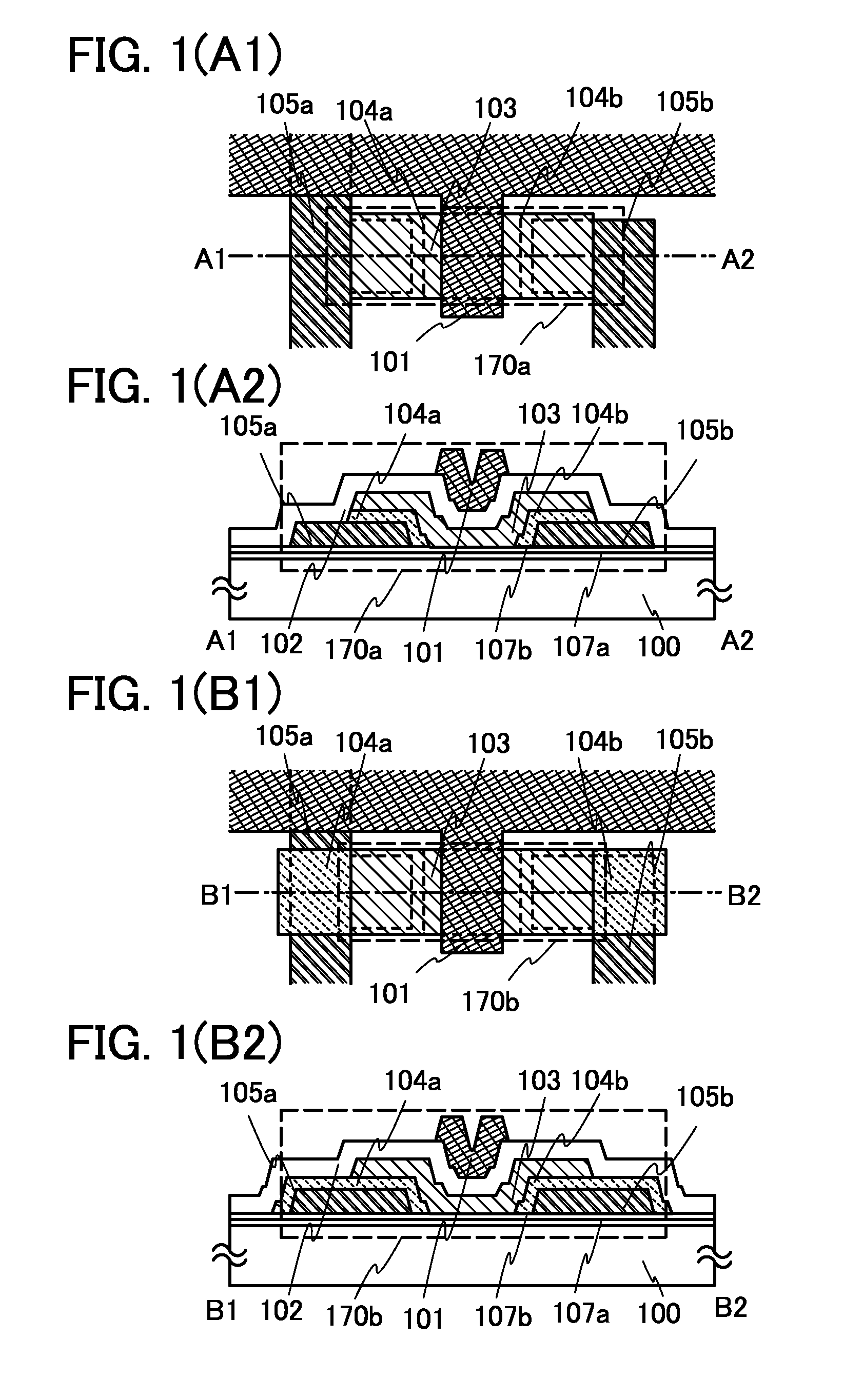

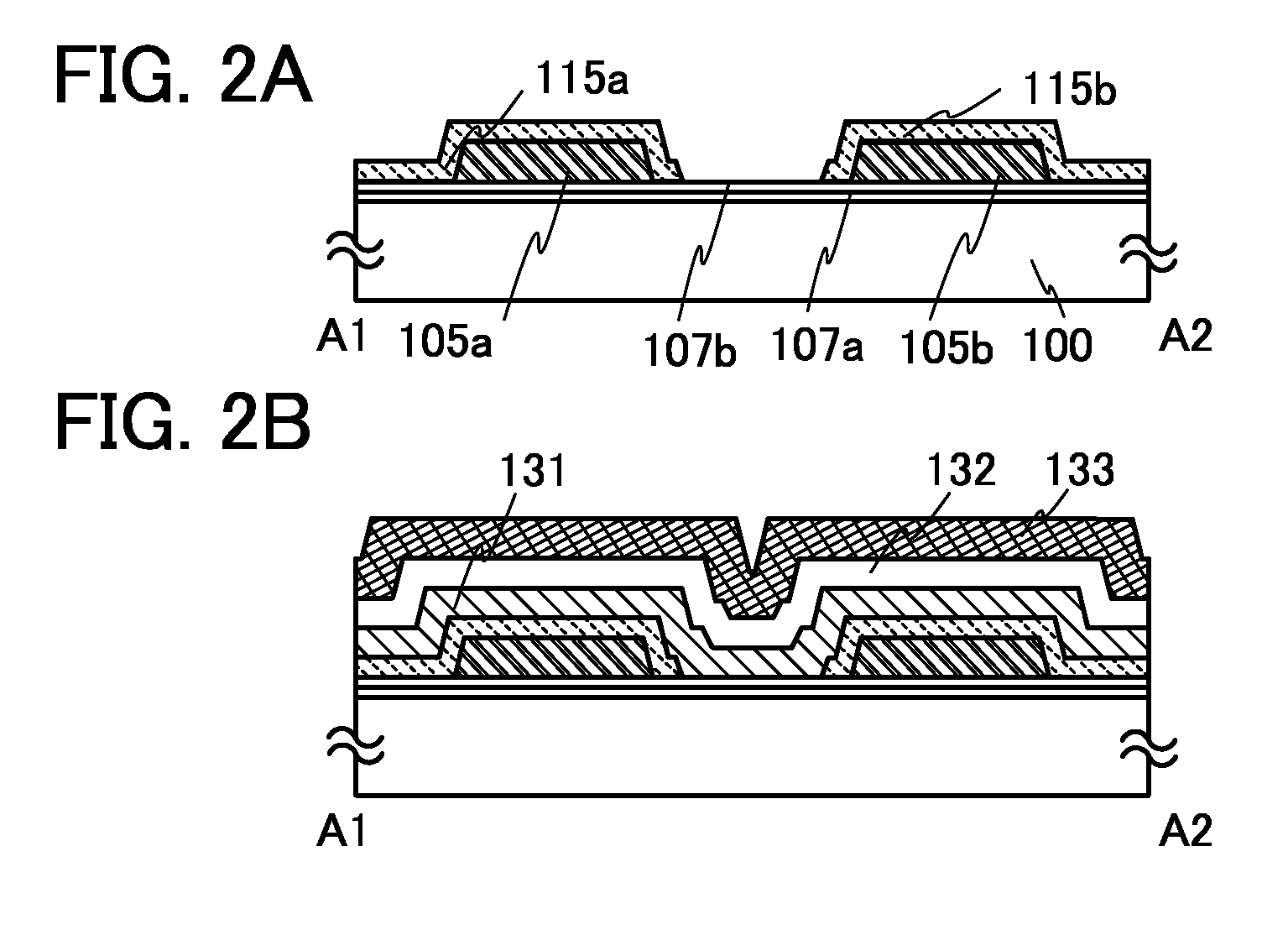

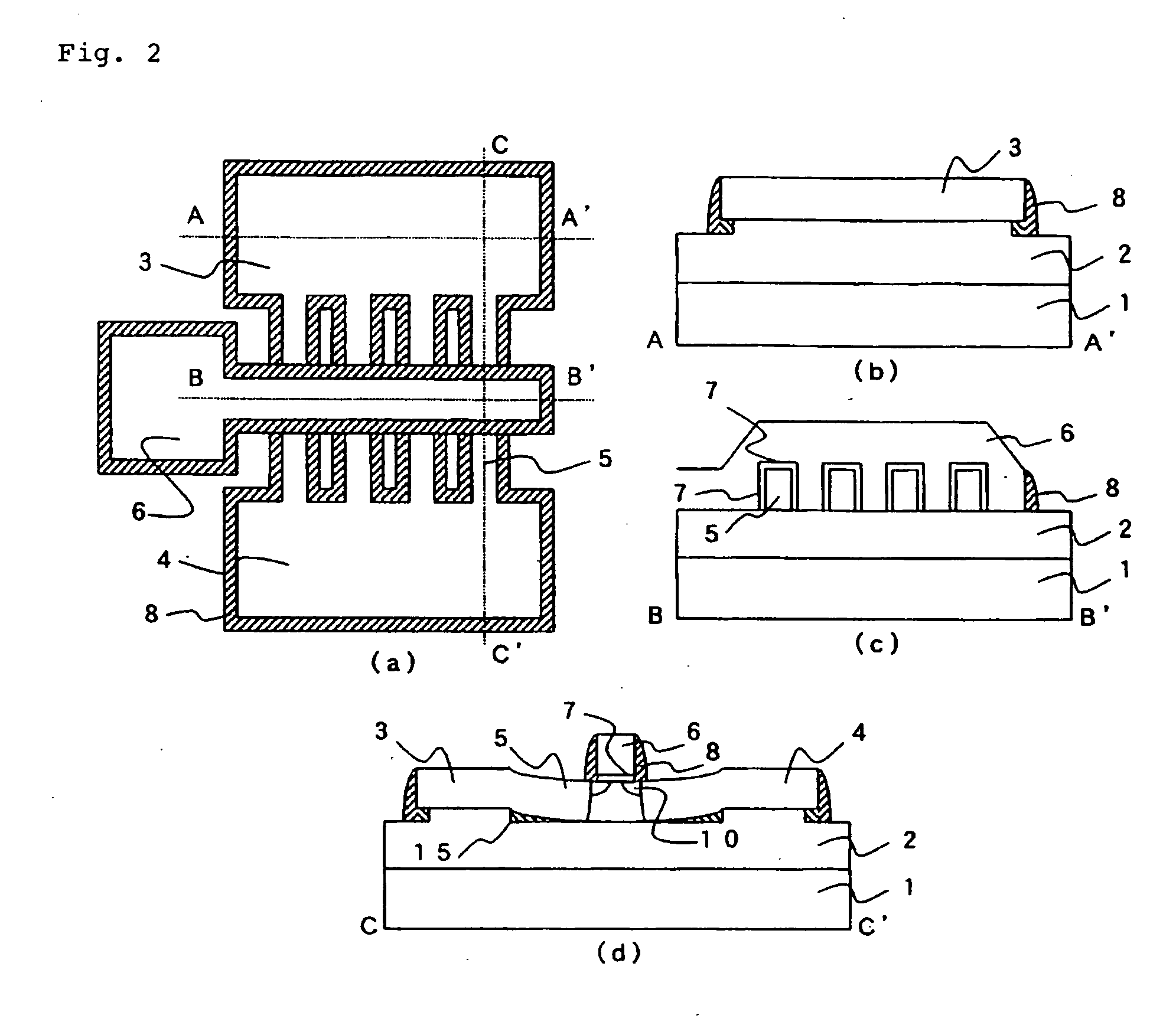

ActiveUS20100032665A1Easy to makeGuaranteed high speed operationTransistorElectroluminescent light sourcesOhmic contactCharge carrier

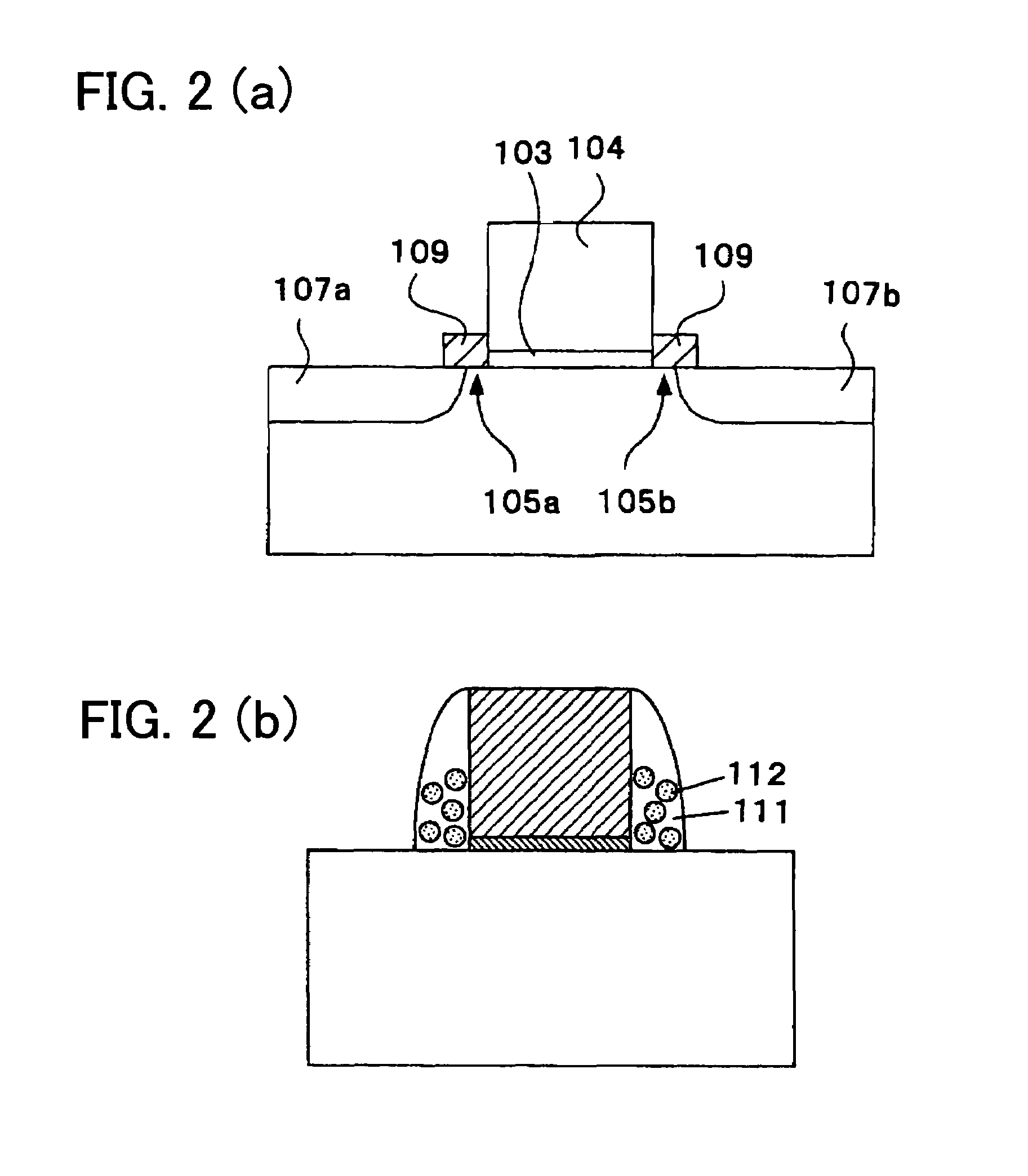

An embodiment is to include a staggered (top gate structure) thin film transistor in which an oxide semiconductor film containing In, Ga, and Zn is used as a semiconductor layer and a buffer layer is provided between the semiconductor layer and a source and drain electrode layers. The buffer layer having higher carrier concentration than the semiconductor layer is provided intentionally between the source and drain electrode layers and the semiconductor layer, whereby an ohmic contact is formed.

Owner:SEMICON ENERGY LAB CO LTD

Method for manufacturing semiconductor device, semiconductor device and electronic appliance

InactiveUS20090134397A1Guaranteed high speed operationReduce manufacturing costSolid-state devicesSemiconductor/solid-state device manufacturingDriver circuitDevice material

A non-single-crystal semiconductor layer is formed over a substrate, and then a single crystal semiconductor layer is formed over part of the non-single-crystal semiconductor layer. Thus, a semiconductor element of a region which requires a large area (e.g. a pixel region in a display device) can be formed using the non-single-crystal semiconductor layer, and a semiconductor element of a region which requires high speed operation (e.g. a driver circuit region in a display device) can be formed using the single crystal semiconductor layer.

Owner:SEMICON ENERGY LAB CO LTD

Multimode communication system

ActiveUS7280810B2Expand coverageImprove performanceElectric signal transmission systemsImage analysisModem deviceCommunications system

Multimode, multi-function, multiple modulator-demodulator (modem) system containing a fingerprint sensor, detection, identification, authentication, and processing device for one or multiple fingerprint information to activate one or multiple modulators for signal transmission and generation of authentication information signals. A location information receiver and a processor device for processing and combining the location information and fingerprint information activated signals with one or more additional user generated signals. Processed, combined signals are provided for filtering and / or spread spectrum encoding and / or cross-correlating and connection to one or more modulators and transmitters.

Owner:FEHER KAMILO

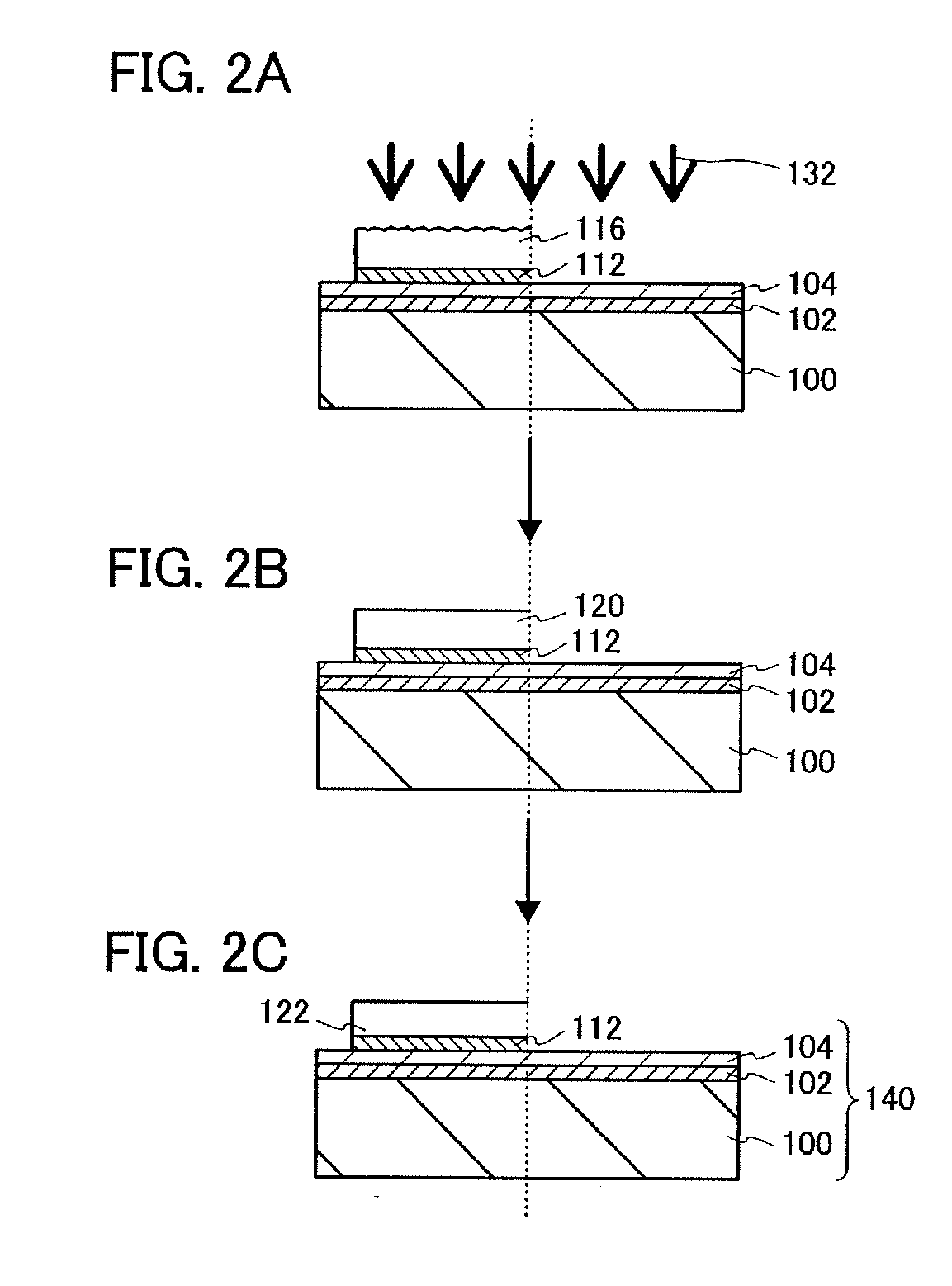

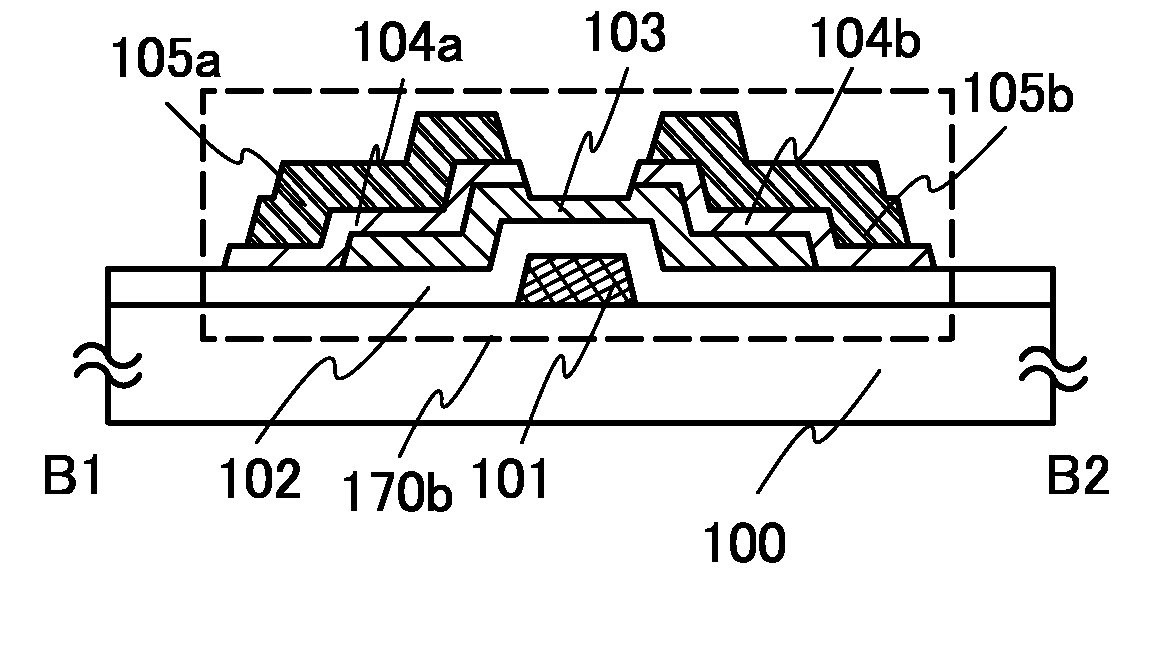

Semiconductor device and method for manufacturing the same

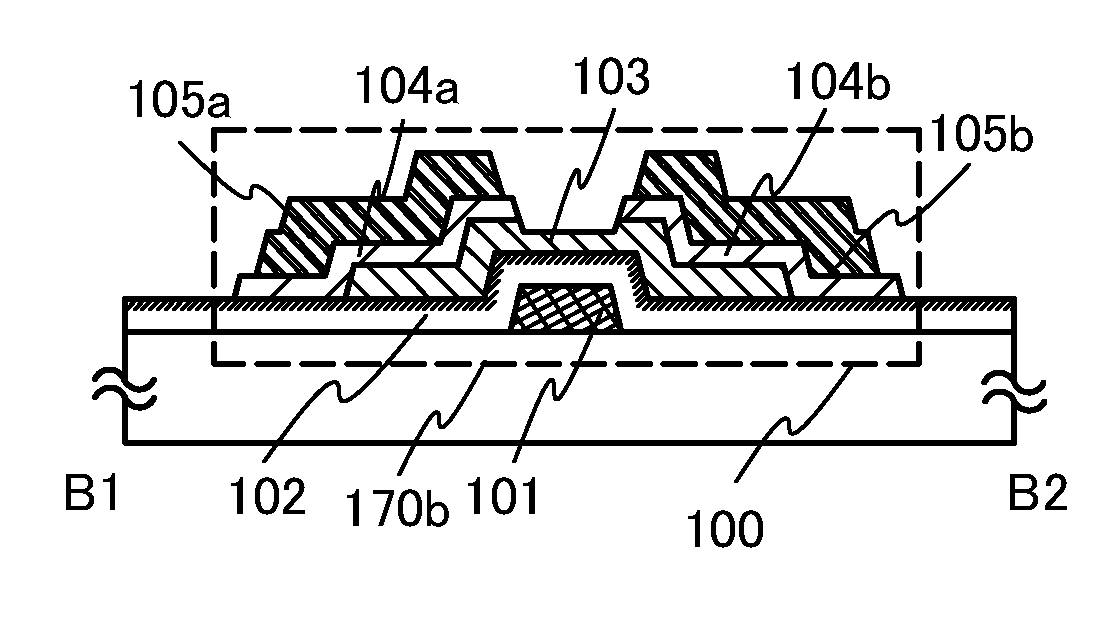

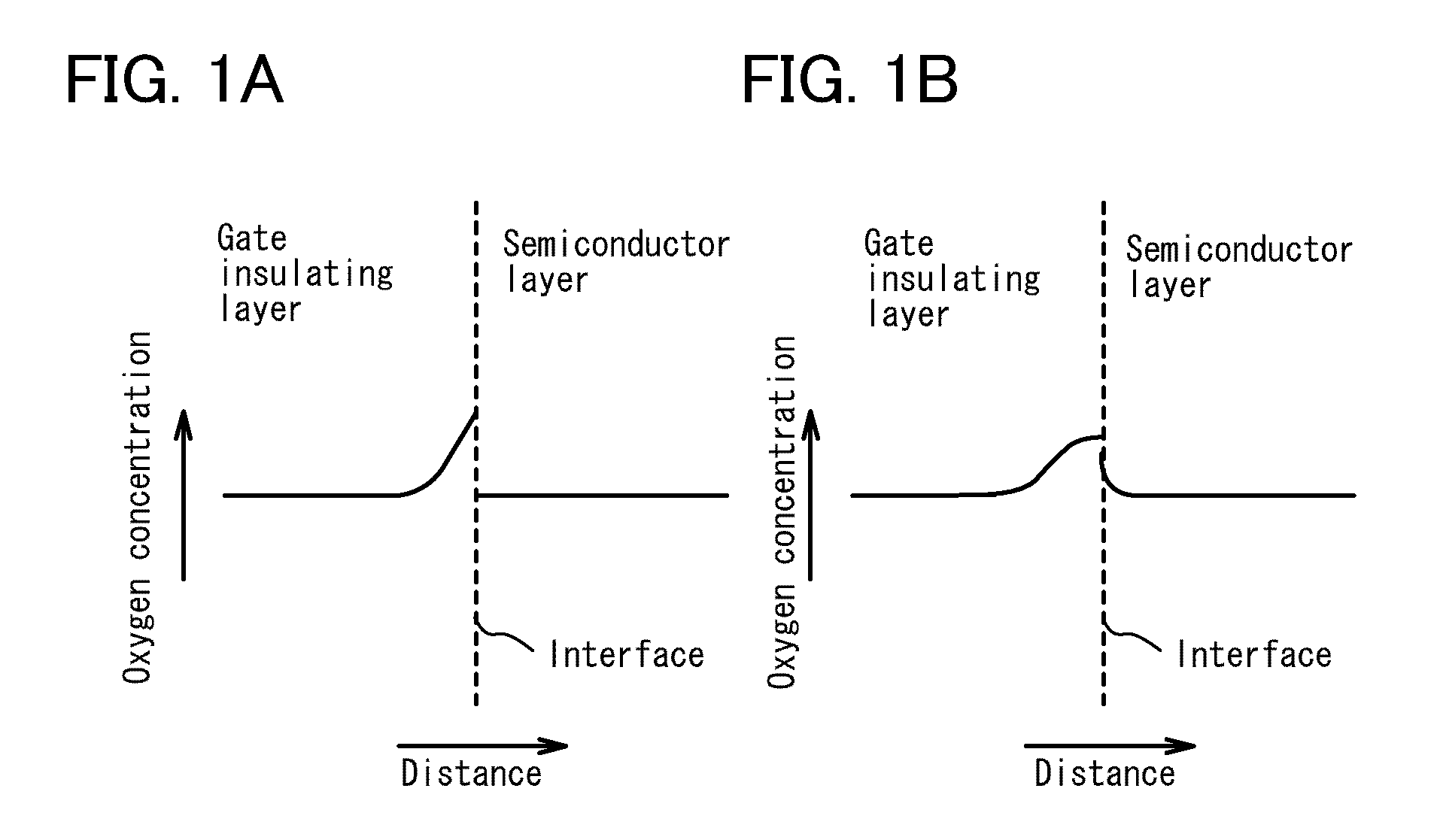

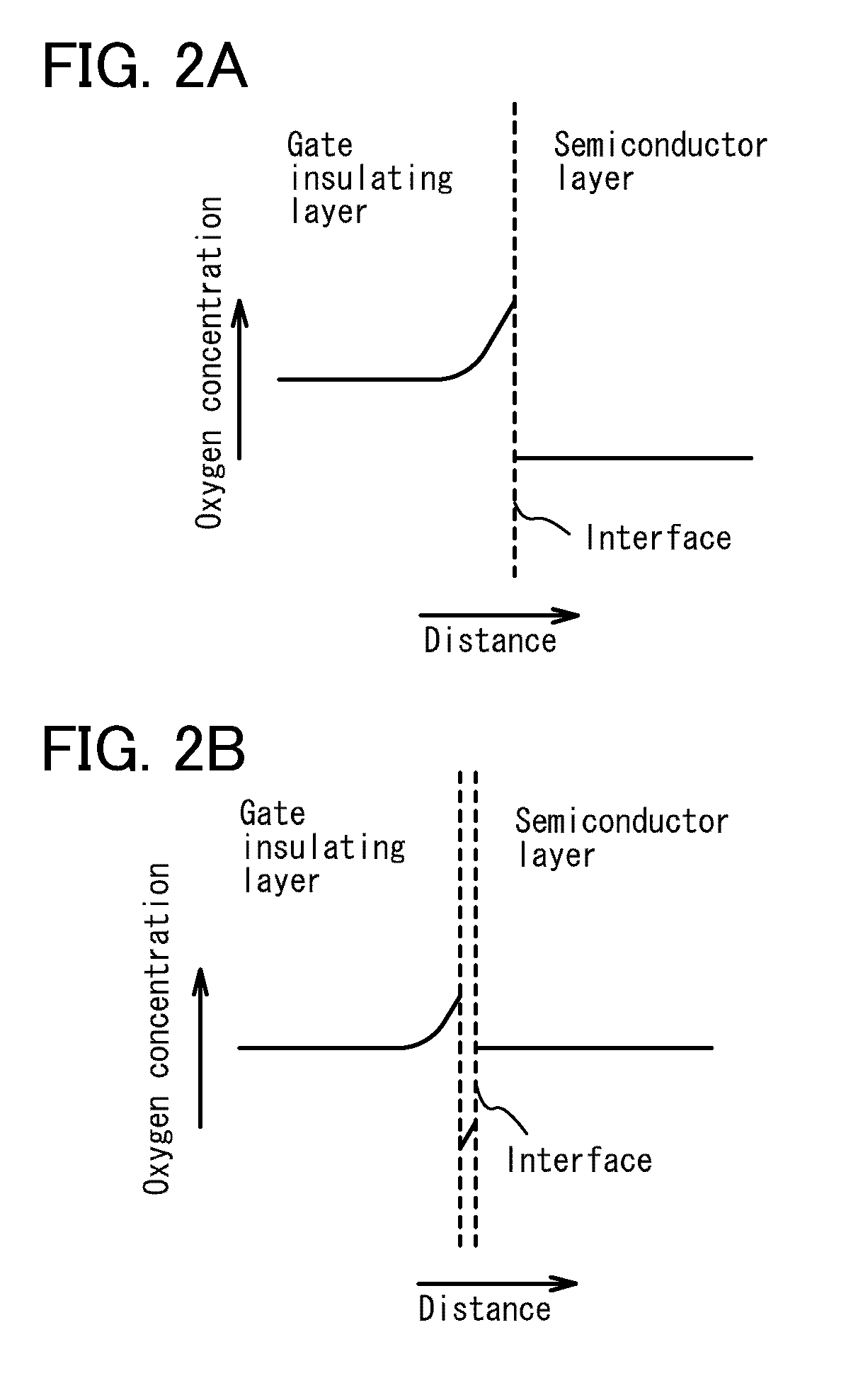

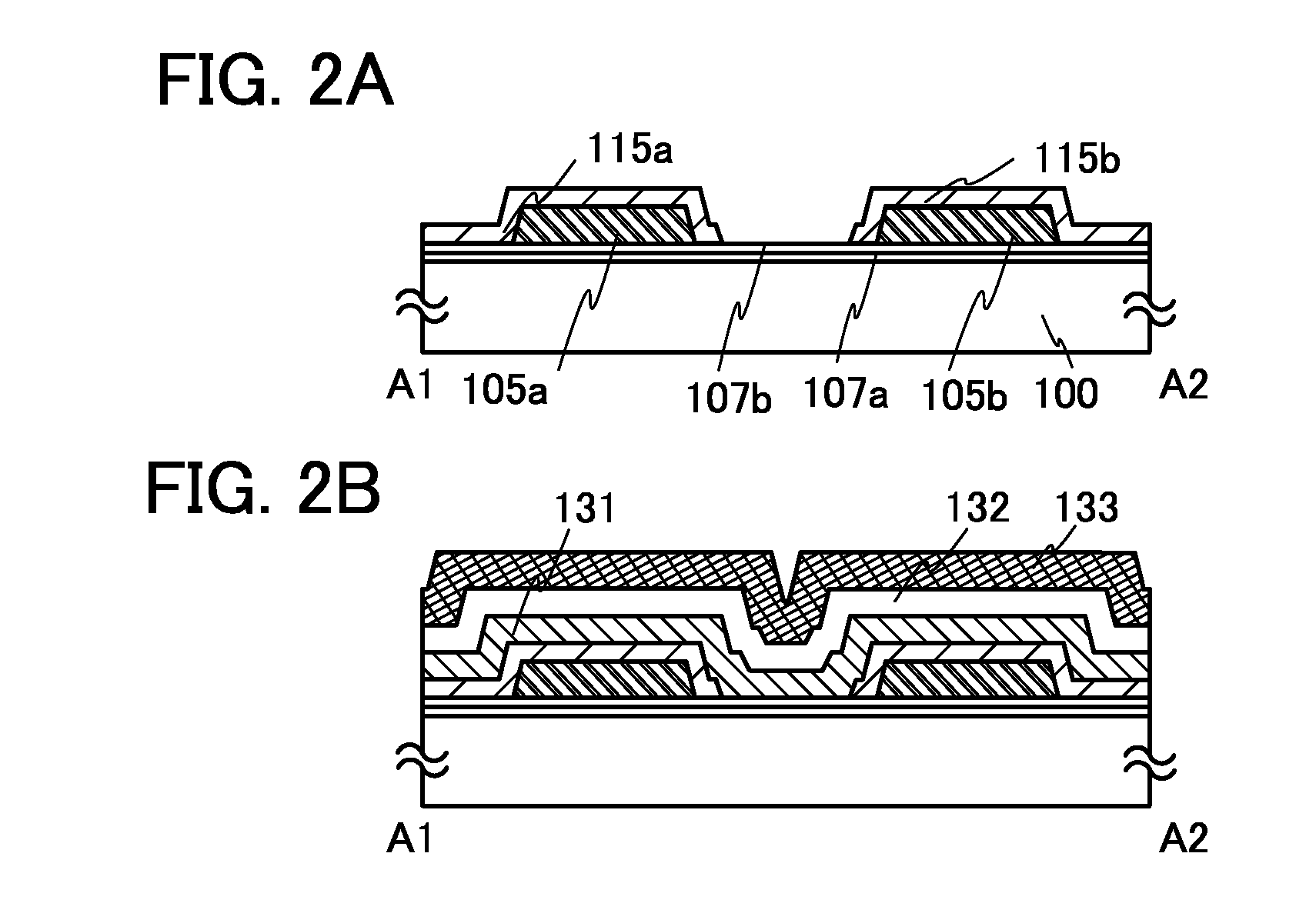

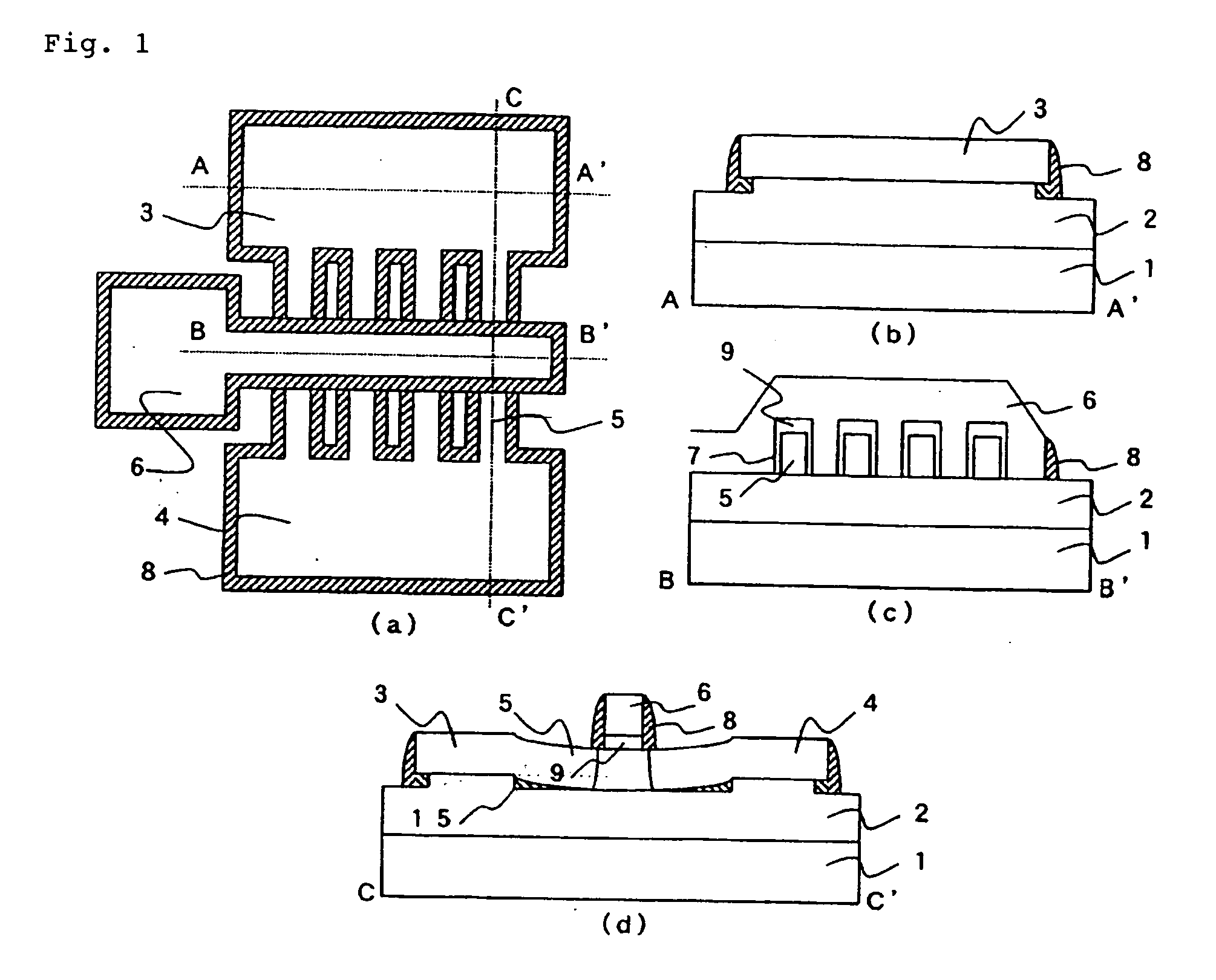

ActiveUS20100025679A1Small currentHigh on-off ratioStatic indicating devicesSolid-state devicesOhmic contactCharge carrier

An embodiment is to include an inverted staggered (bottom gate structure) thin film transistor in which an oxide semiconductor film containing In, Ga, and Zn is used as a semiconductor layer and a buffer layer is provided between the semiconductor layer and a source and drain electrode layers. The buffer layer having higher carrier concentration than the semiconductor layer is provided intentionally between the source and drain electrode layers and the semiconductor layer, whereby an ohmic contact is formed.

Owner:SEMICON ENERGY LAB CO LTD

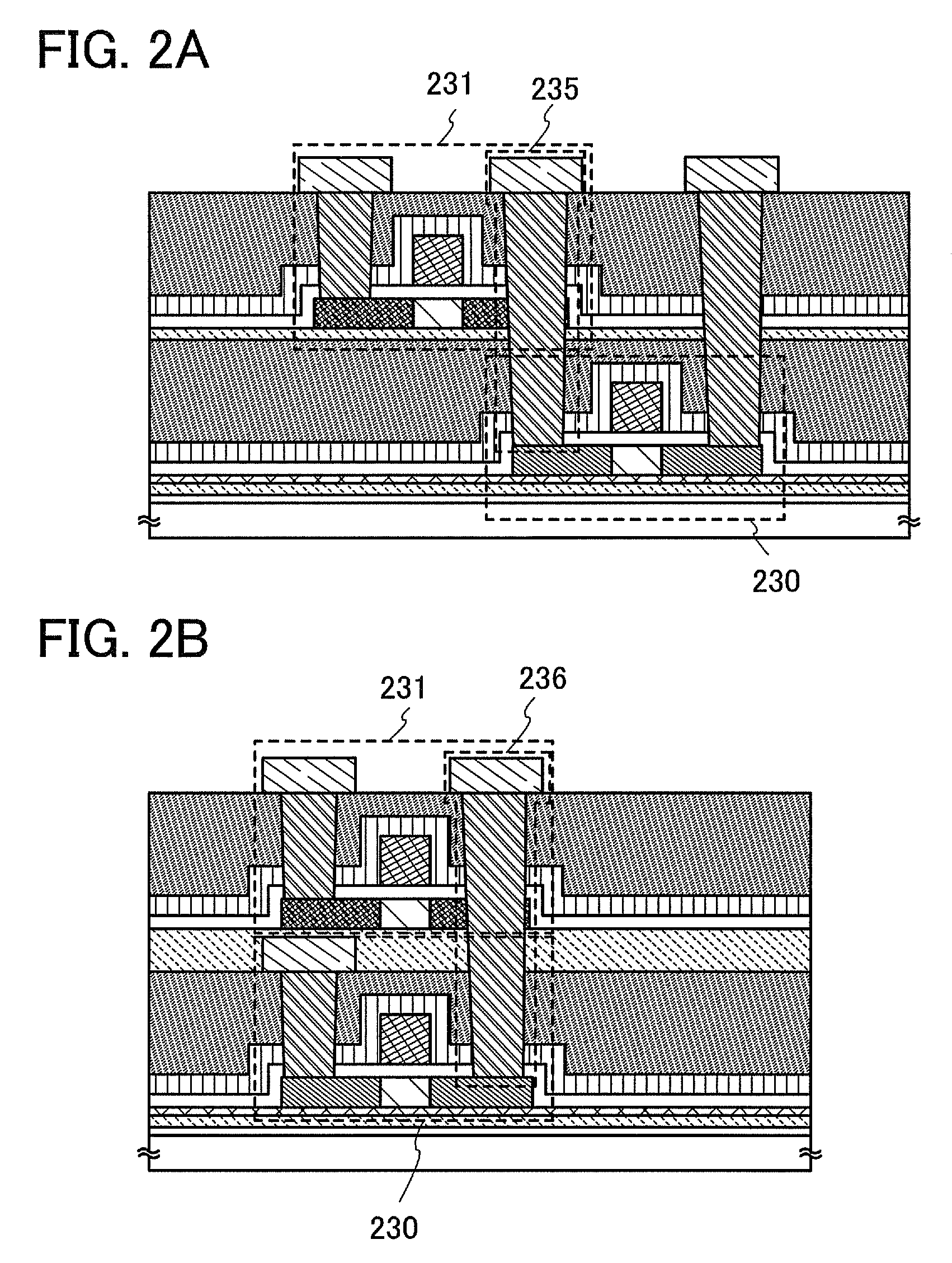

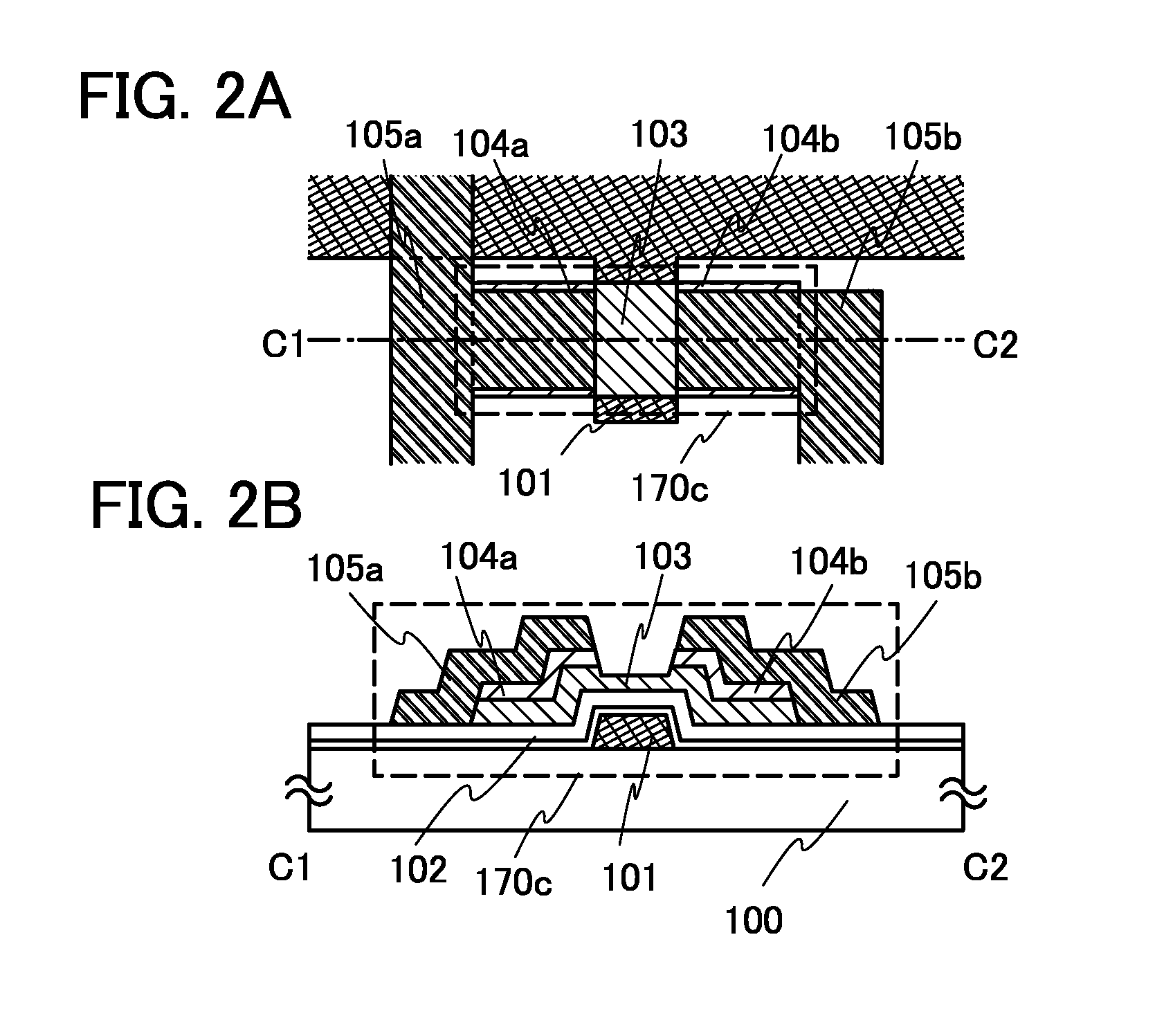

Semiconductor device and method for manufacturing the same

ActiveUS20100032668A1Easy to makeGuaranteed high speed operationTransistorSemiconductor/solid-state device manufacturingCharge carrierOhmic contact

An embodiment is to include a staggered (top gate structure) thin film transistor in which an oxide semiconductor film containing In, Ga, and Zn is used as a semiconductor layer and a buffer layer is provided between the semiconductor layer and a source and drain electrode layers. A metal oxide layer having higher carrier concentration than the semiconductor layer is provided intentionally as the buffer layer between the source and drain electrode layers and the semiconductor layer, whereby an ohmic contact is formed.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device and method for manufacturing the same

ActiveUS20100117073A1Small parasitic capacitanceHigh on-off ratioTransistorElectroluminescent light sourcesIndiumNitrogen

In a thin film transistor which uses an oxide semiconductor, buffer layers containing indium, gallium, zinc, oxygen, and nitrogen are provided between the oxide semiconductor layer and the source and drain electrode layers.

Owner:SEMICON ENERGY LAB CO LTD

Air based emergency monitor, multimode communication, control and position finder system

InactiveUS20070032246A1Extend coverageImprove performanceSpatial transmit diversityModulated-carrier systemsRadio frequencyTransceiver

Air based emergency monitor, multimode communication, control and position finder system with a receiver having multiple inputs for reception and demodulation of position finder signals to position finder baseband signals. One or more cameras or microphones or data signal generation devices, storage devices, and processors for recording or storing and processing of signals obtained from one or more cameras or microphones or data signal generation devices. A processor for processing input signals and for providing cross-correlated shaped in-phase and quadrature-phase baseband signals. Transceivers for multimode GSM, spread spectrum, CDMA, OFDM, TDMA and other signals. A receiver and demodulator for reception of modulated position finder radio frequency (RF) signals transmitted by a Global Positioning System (GPS) transmitter and a receiver and demodulator for reception of modulated position finder radio frequency (RF) signals transmitted by other than a GPS transmitter for providing the demodulated and receiver processed signal to an emergency unit. An air based position finding, signal monitor, control and emergency multimode communication system for use in one or more units located in or on airplanes, or helicopters, or unmanned vehicles (UV) or balloons or rockets, or missiles, or space shuttles or birds or other air based items with a multimode bit rate agile (BRA) and modulation demodulation (modem) format selectable (MFS) signal modulator.

Owner:FEHER KAMILO

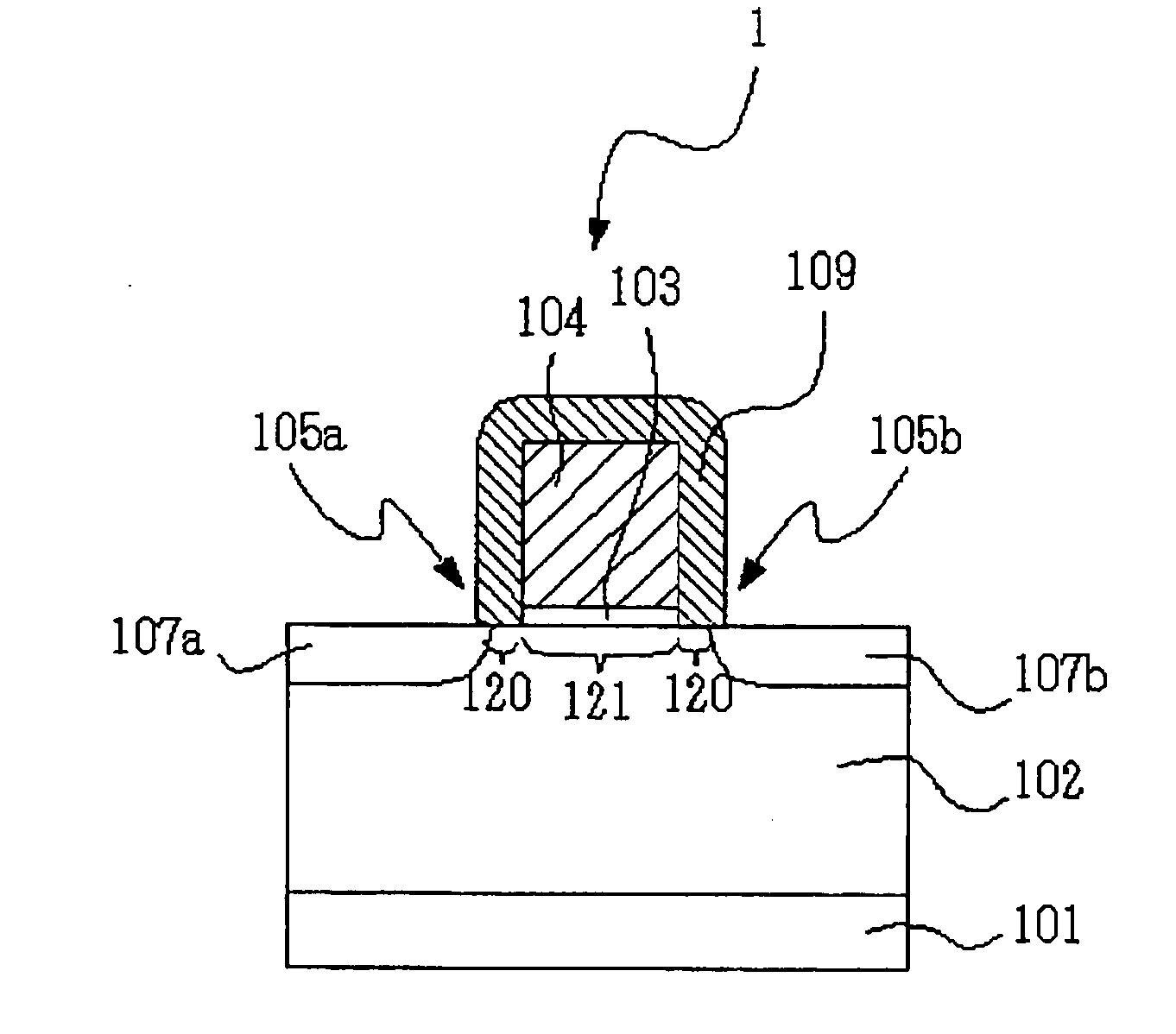

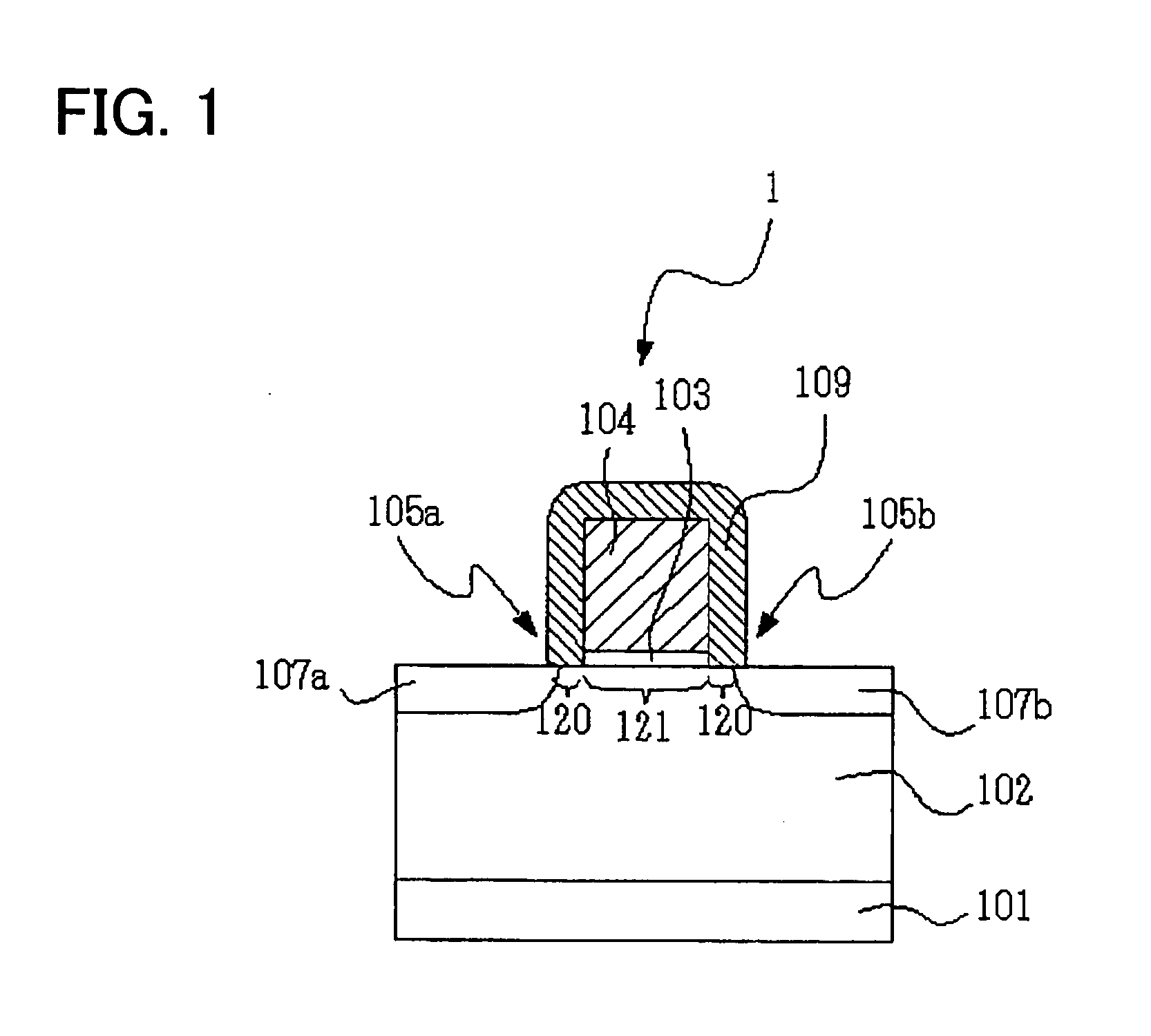

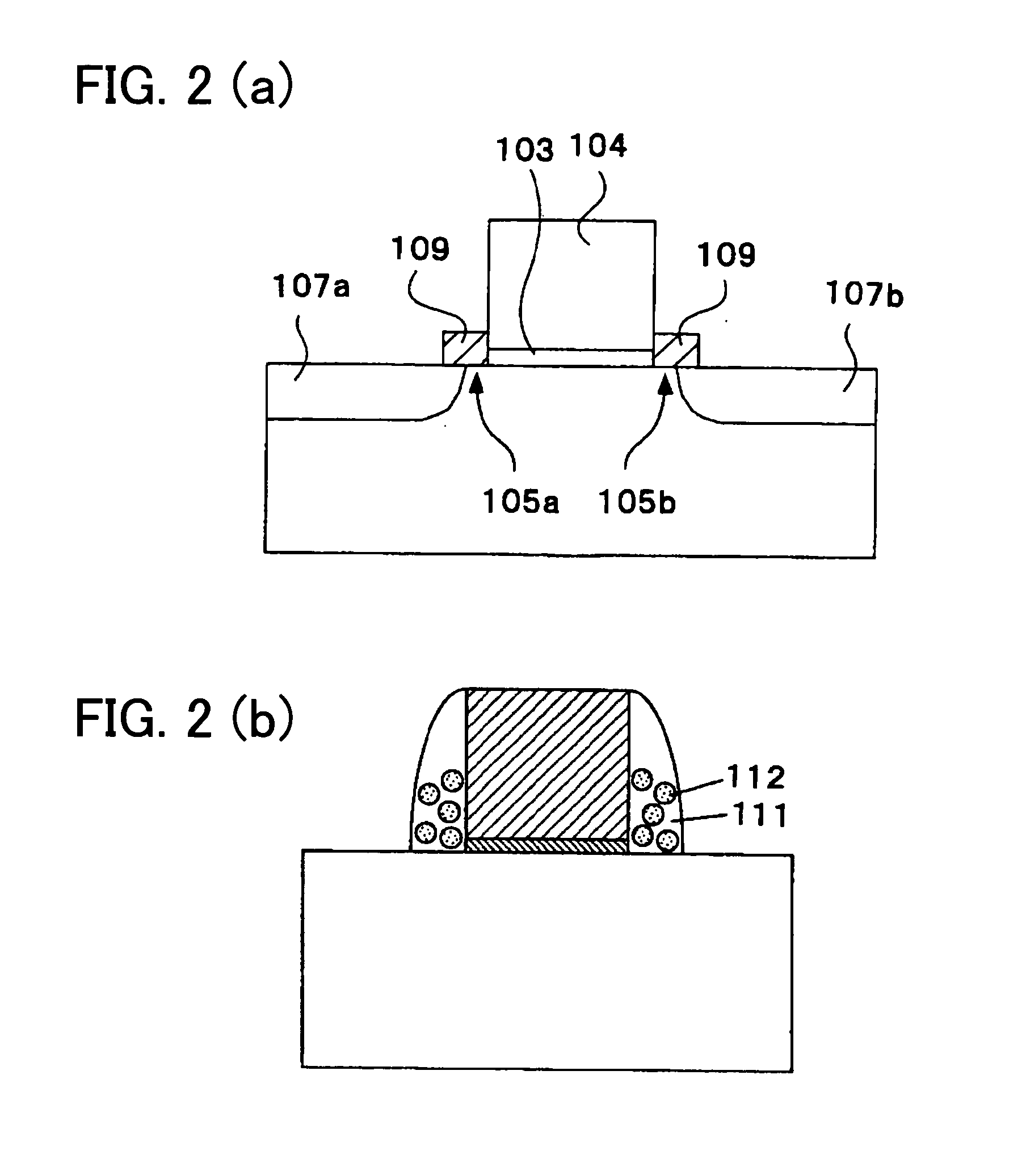

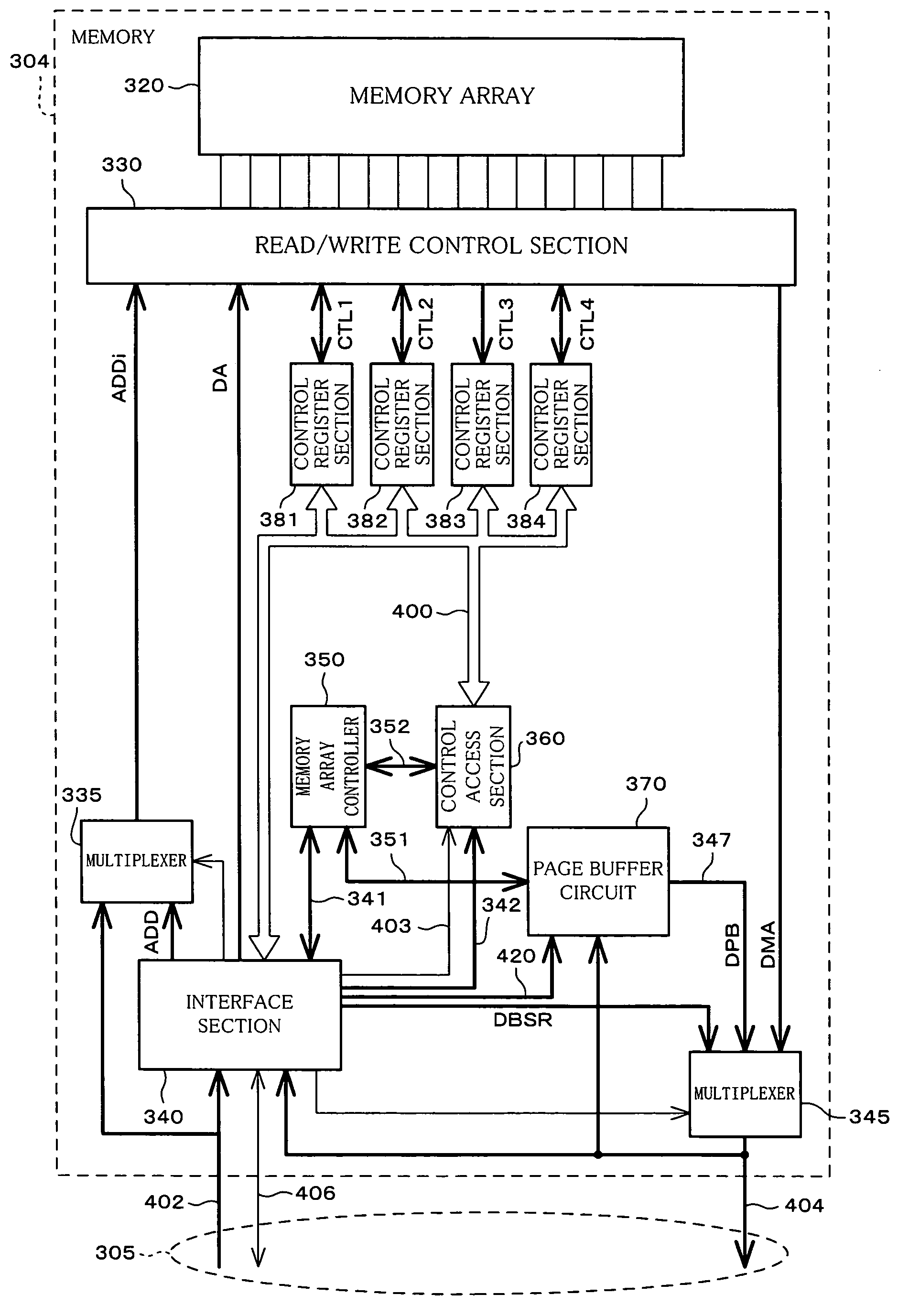

Writing control method and writing control system of semiconductor storage device, and portable electronic apparatus

InactiveUS20050002263A1Easily-realized finerSpeedup of writingTransistorSolid-state devicesSemiconductor storage devicesEngineering

A writing control system providing high-speed writing to a nonvolatile semiconductor storage device, includes (a) a plurality of memory elements each having: a gate electrode provided on a semiconductor layer with an intervening gate insulating film; a channel region provided beneath the gate electrode; a diffusion region provided on both sides of the channel region, having an opposite polarity to the channel region; and a memory functioning member, provided on both sides of the gate electrode, having a function of holding electric charges, (b) a memory array including a page buffer circuit, and (c) CPU controlling writing to the memory array. The CPU loads a first plane of the page buffer circuit with a first byte of data and writes with the first byte of data stored in the first plane. Further, the CPU writes a second byte of data into the second plane and writes the second byte of data having been stored in the second plane while writing the first byte of data having been stored in the first plane into the memory array.

Owner:SHARP KK

Semiconductor Device and Manufacturing Process Therefor

ActiveUS20070241414A1Less dislocation and defectControlled amount of strainTransistorSolid-state devicesManufacturing technologyDevice material

This invention relates to a semiconductor device having a beam made of a semiconductor to which strain is introduced by deflection, and a current is permitted to flow in the beam.

Owner:GK BRIDGE 1

Writing control method and writing control system of semiconductor storage device, and portable electronic apparatus

InactiveUS7050337B2The implementation process is simpleSpeedup of writingTransistorSolid-state devicesSemiconductor storage devicesHemt circuits

A writing control system providing high-speed writing to a nonvolatile semiconductor storage device, includes (a) a plurality of memory elements each having: a gate electrode provided on a semiconductor layer with an intervening gate insulating film; a channel region provided beneath the gate electrode; a diffusion region provided on both sides of the channel region, having an opposite polarity to the channel region; and a memory functioning member, provided on both sides of the gate electrode, having a function of holding electric charges, (b) a memory array including a page buffer circuit, and (c) CPU controlling writing to the memory array. The CPU loads a first plane of the page buffer circuit with a first byte of data and writes with the first byte of data stored in the first plane. Further, the CPU writes a second byte of data into the second plane and writes the second byte of data having been stored in the second plane while writing the first byte of data having been stored in the first plane into the memory array.

Owner:SHARP KK

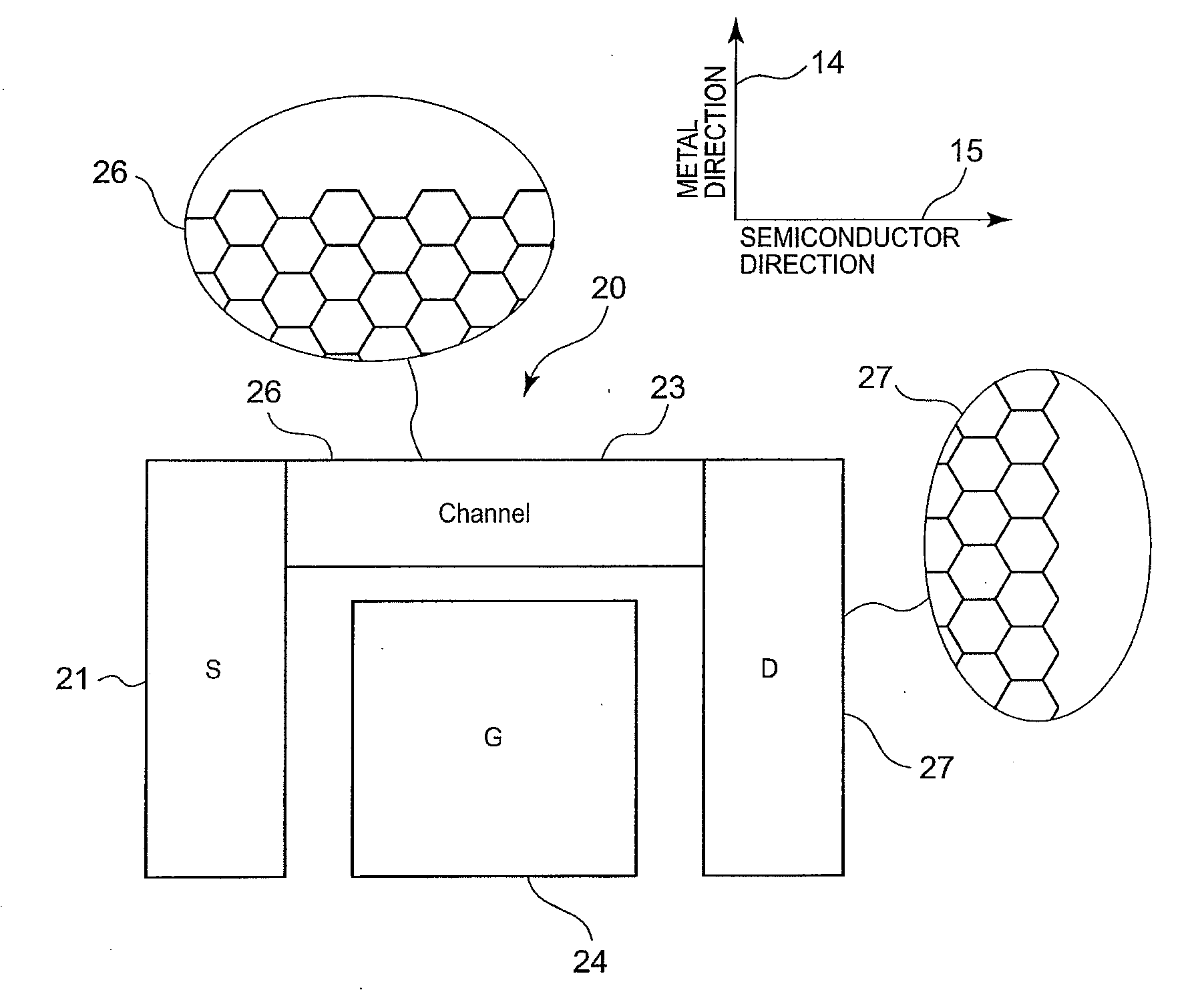

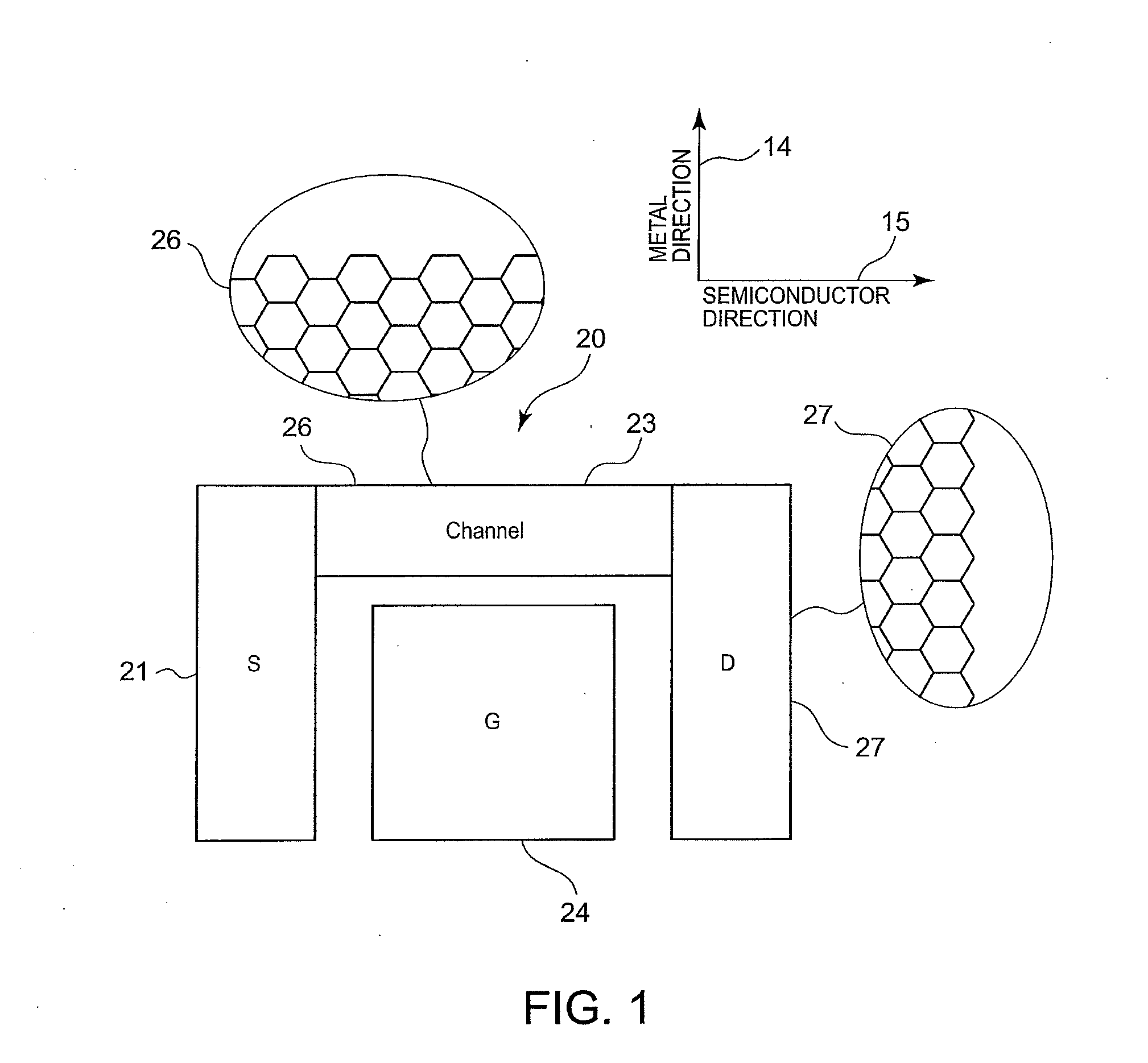

Semiconductor device using graphene and method of manufacturing the same

ActiveUS20100102292A1Guaranteed high speed operationReduce power consumptionTransistorNanoinformaticsInterconnectionGraphene

Owner:NEC CORP

Shift register circuit and image display comprising the same

InactiveUS20070247932A1Defective operation is preventedDrive capability is prevented being loweredStatic indicating devicesDigital storageShift registerProcessor register

In a shift register circuit, a defective operation while an output signal is not outputted and a drive capability lowering while the output signal is outputted are prevented. A unit shift register comprises a first transistor for supplying a clock signal inputted to a first clock terminal to an output terminal, and the first transistor is driven by a drive circuit. A second transistor is connected between the gate of the first transistor and the output terminal and has a gate connected to the first clock terminal. The second transistor connects the gate of the first transistor to the output terminal based on the clock signal when the gate of the first transistor is at L (Low) level.

Owner:MITSUBISHI ELECTRIC CORP

Medical diagnostic and communication system

InactiveUS20070032832A1Expand coverageImprove performanceSpatial transmit diversityModulated-carrier systemsHeart pacemakersEmergency rooms

Cardiac stimulation device and wireless communication system, without magnetic detection or magnetic control of the heart pacemaker parameters, having leads for carrying stimulating pulses to and or from one or more electrodes located in a heart and a pulse generator configured to generate stimulation pulses. In certain embodiments and environments the heart pacemaker could operate in an emergency room, even during Magnetic Resonance Imaging (MRI) diagnostic studies. A processor for connection of the stimulating pulses to and / or from one or more spread spectrum transmitter-receiver (T / R) circuits and / or from a signal processing network for receiving said stimulation pulses and for providing cross-correlated in-phase and quadrature-phase baseband signals. One or more modulators and demodulators for transmission and / or reception of one or more spread spectrum and / or cross-correlated signals.

Owner:FEHER KAMILO

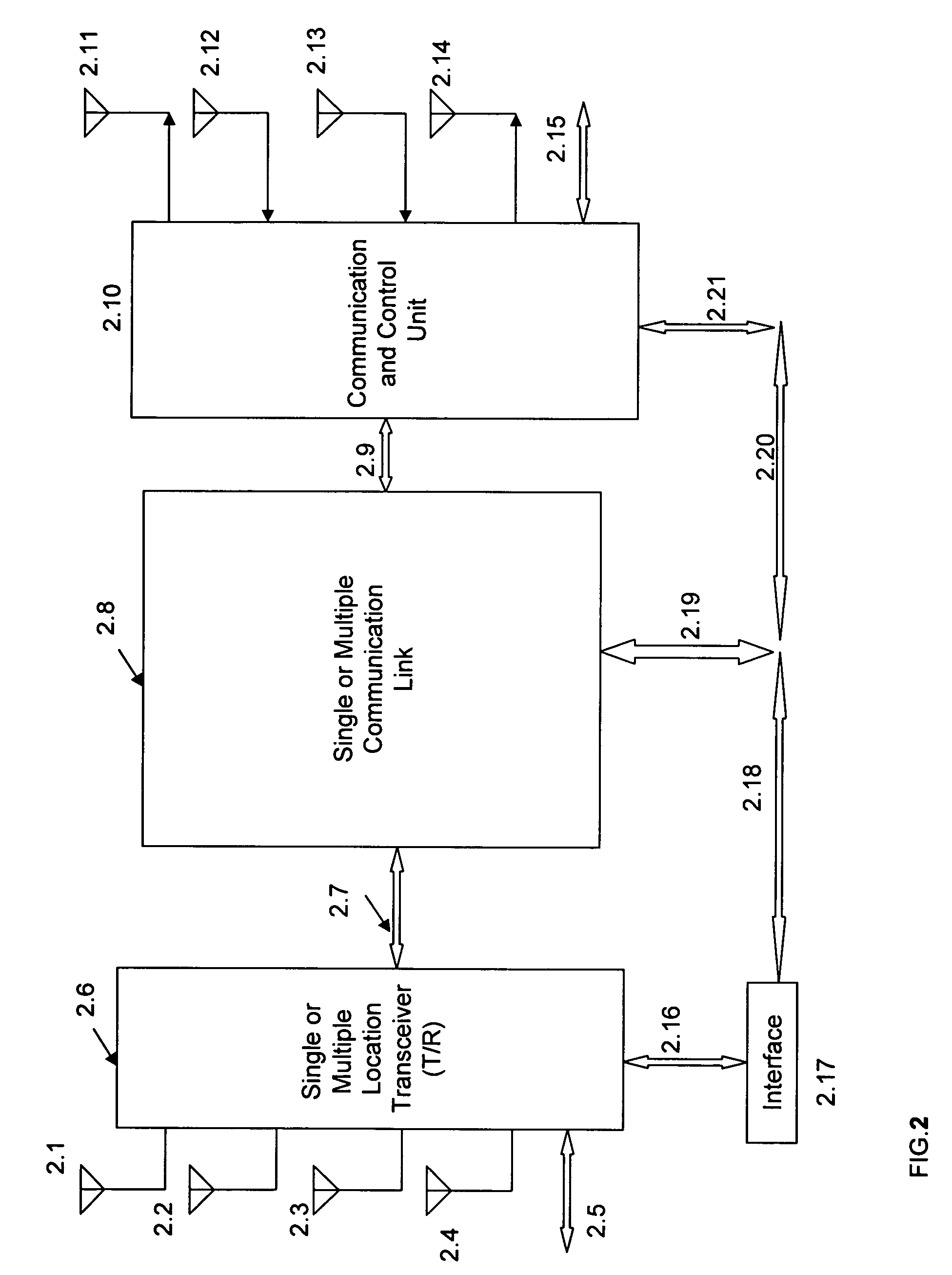

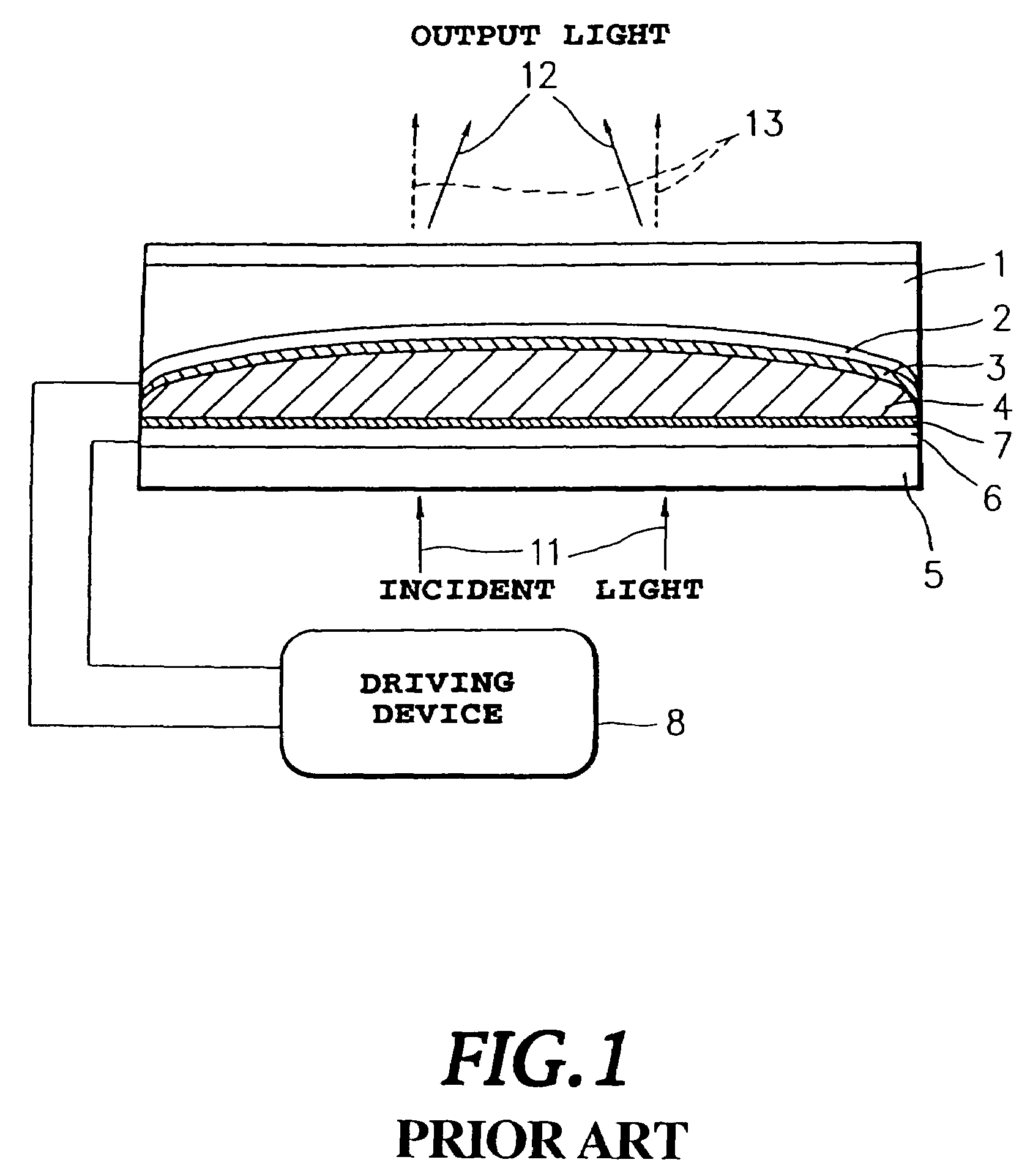

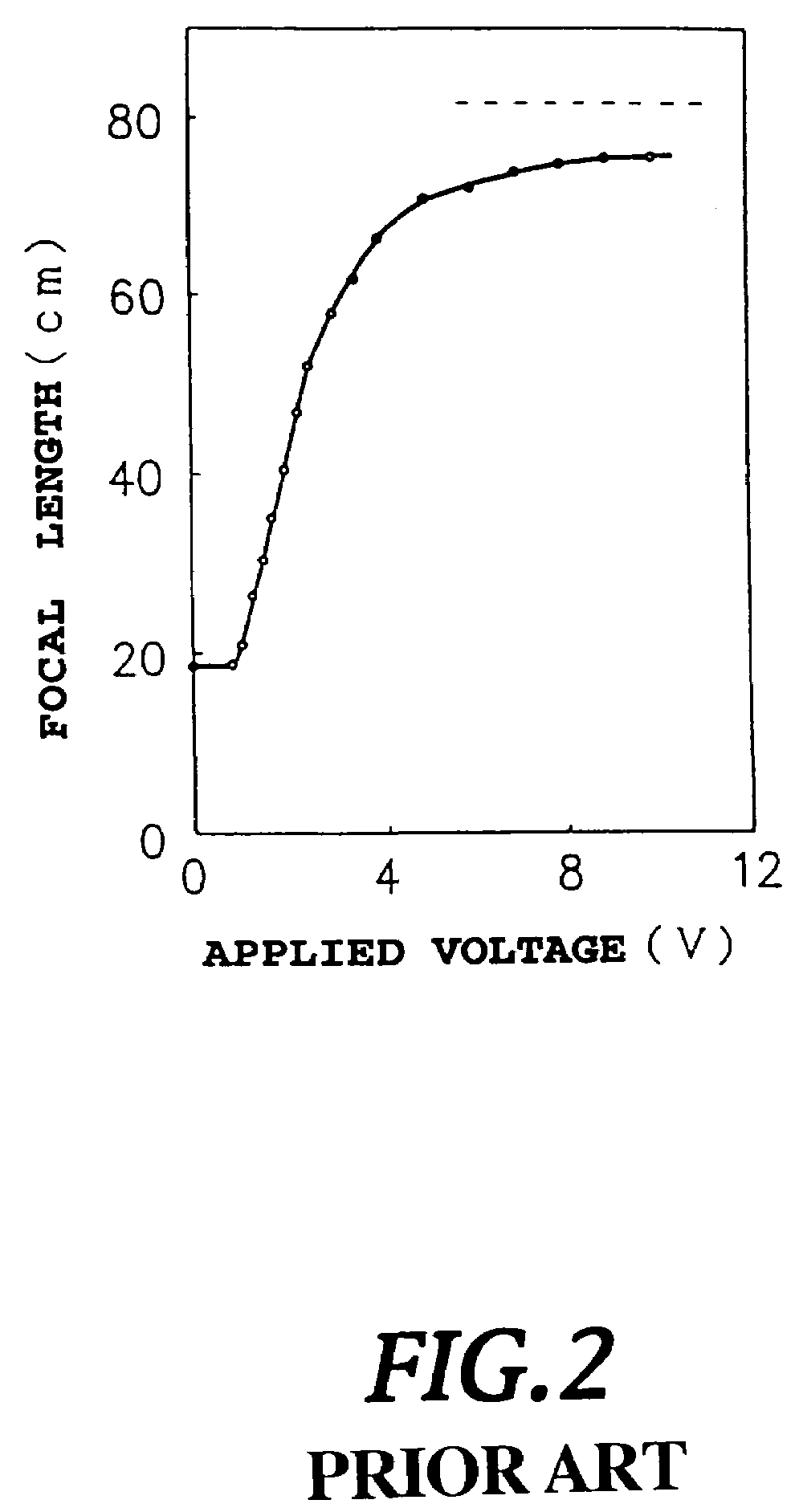

Optical device and three-dimensional display device

InactiveUS7209097B2Increase speedImprove uniformityStatic indicating devicesSteroscopic systemsRefractive indexDielectric contrast

An optical device includes a transparent material layer having a desired curved surface configuration, a layer including a variable refractive index material having a dielectric constant anisotropy, at least two transparent electrodes arranged to sandwich the transparent material layer and the variable refractive index material, and a driving device supplying a voltage including driving frequencies f1 and f2 between the transparent electrodes. The difference Δ∈ in the dielectric constant of the variable refractive index material due to the anisotropy is positive at one of the driving frequencies and negative at the other driving frequency.

Owner:NIPPON TELEGRAPH & TELEPHONE CORP

Semiconductor device and method for manufacturing the same

ActiveUS20120273780A1Comparatively-easy manufacturing processGuaranteed high speed operationStatic indicating devicesSolid-state devicesPower semiconductor deviceOhmic contact

An embodiment is to include an inverted staggered (bottom gate structure) thin film transistor in which an oxide semiconductor film containing In, Ga, and Zn is used as a semiconductor layer and a buffer layer is provided between the semiconductor layer and a source and drain electrode layers. The buffer layer having higher carrier concentration than the semiconductor layer is provided intentionally between the source and drain electrode layers and the semiconductor layer, whereby an ohmic contact is formed.

Owner:SEMICON ENERGY LAB CO LTD

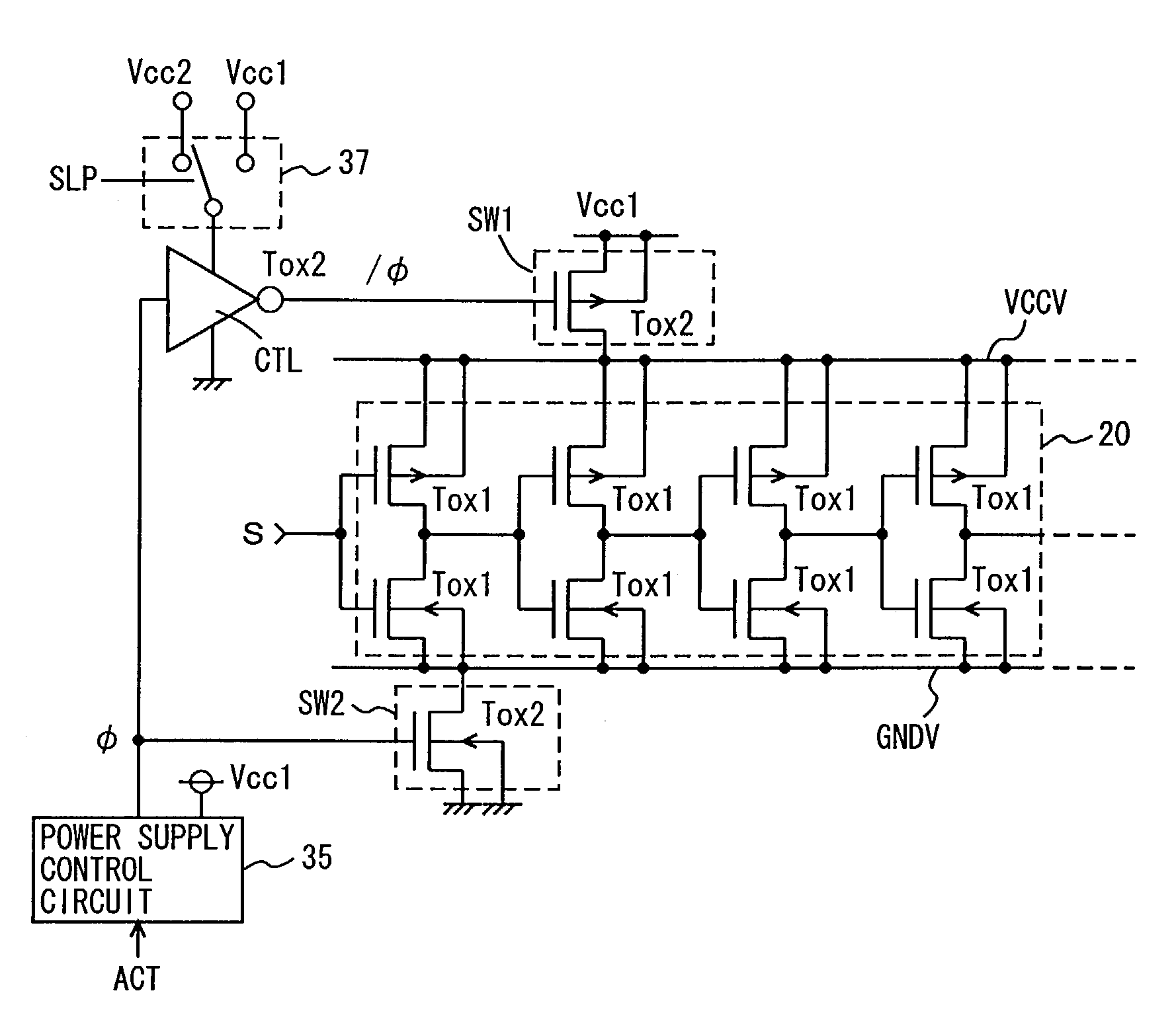

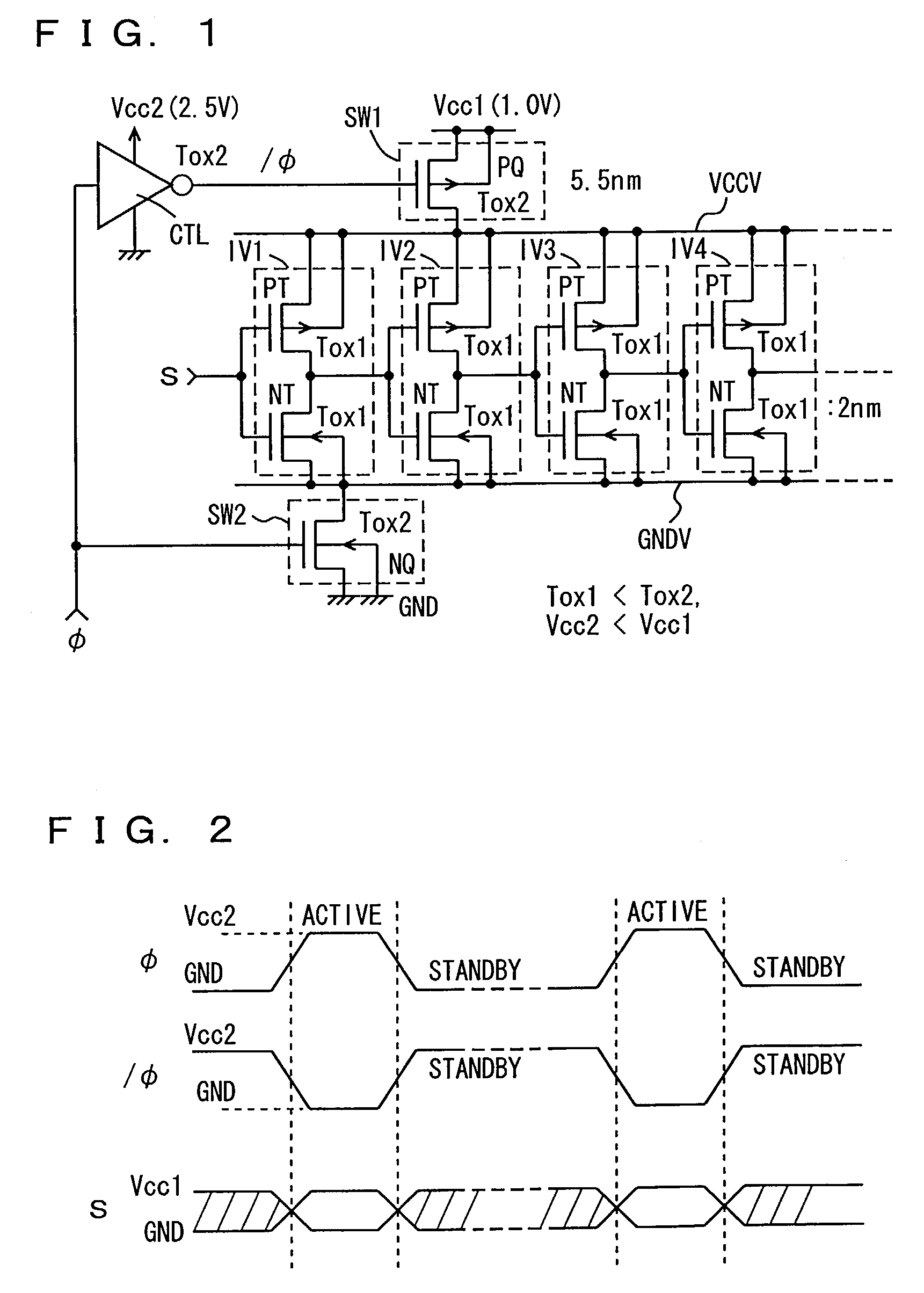

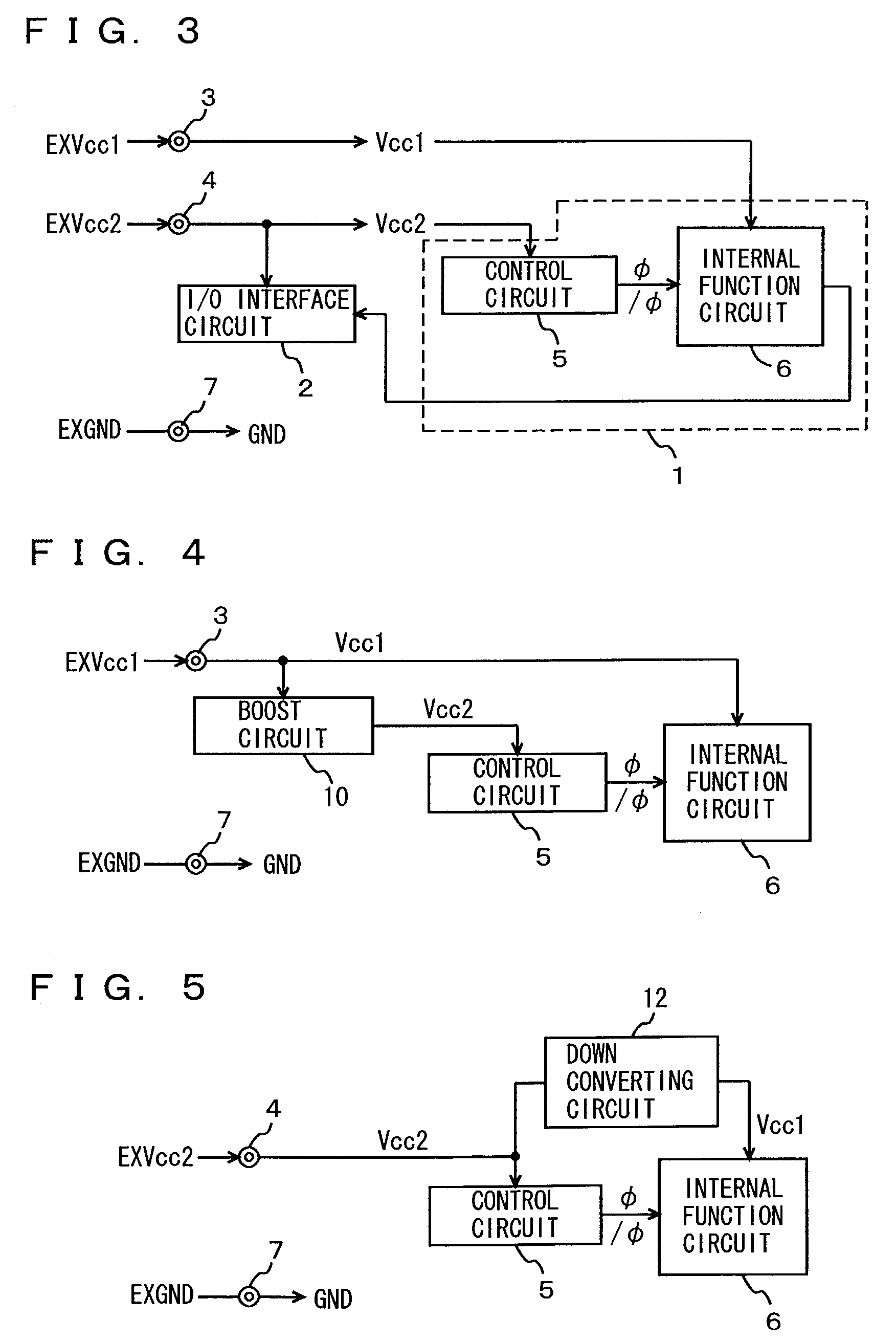

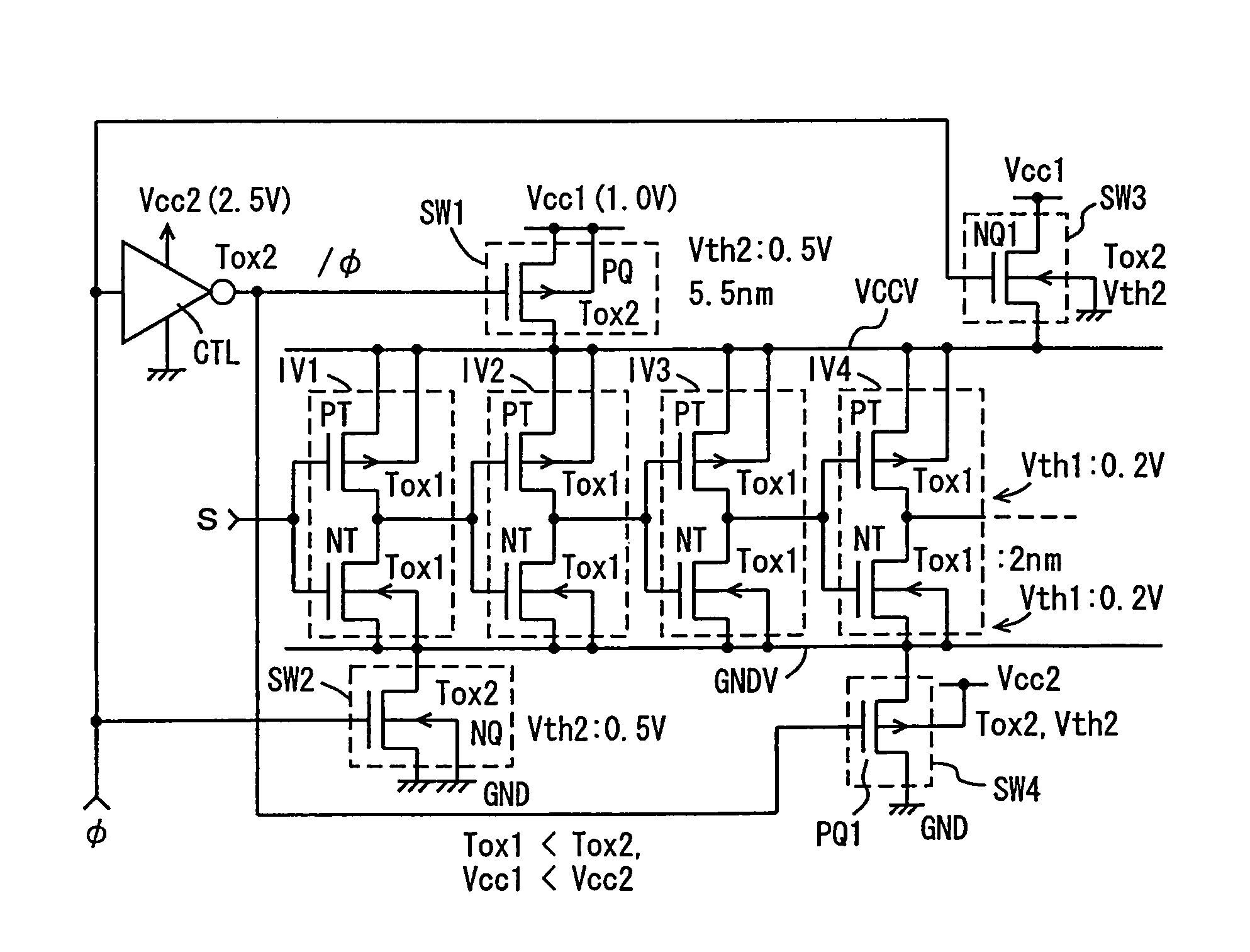

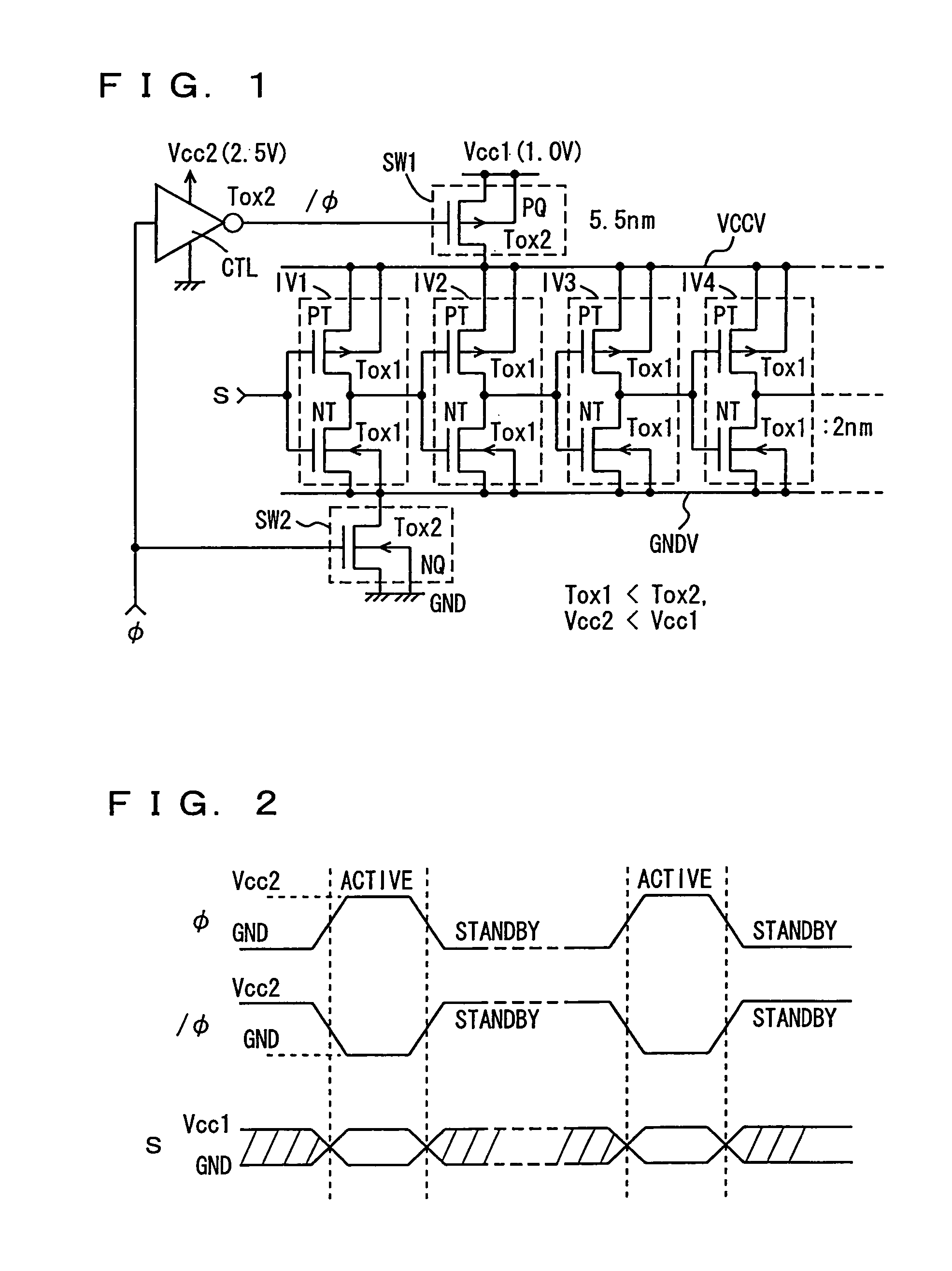

Low power consumption MIS semiconductor device

InactiveUS7042245B2Total current dropSimple circuit configurationTransistorReliability increasing modificationsCurrent consumptionLogic gate

A logic gate is constructed of an insulated gate field effect transistor (MIS transistor) having a thin gate insulation film. An operation power supply line to the logic gate is provided with an MIS transistor having a thick gate insulation film for switching the supply and stop of an operation power source voltage. A voltage of the gate of the power source switching transistor is made changing in an amplitude greater than an amplitude of an input and an output signal to the logic gate. Current consumption in a semiconductor device configured of MIS transistor of a thin gate insulation film can be reduced and an power source voltage thereof can be stabilized.

Owner:RENESAS ELECTRONICS CORP

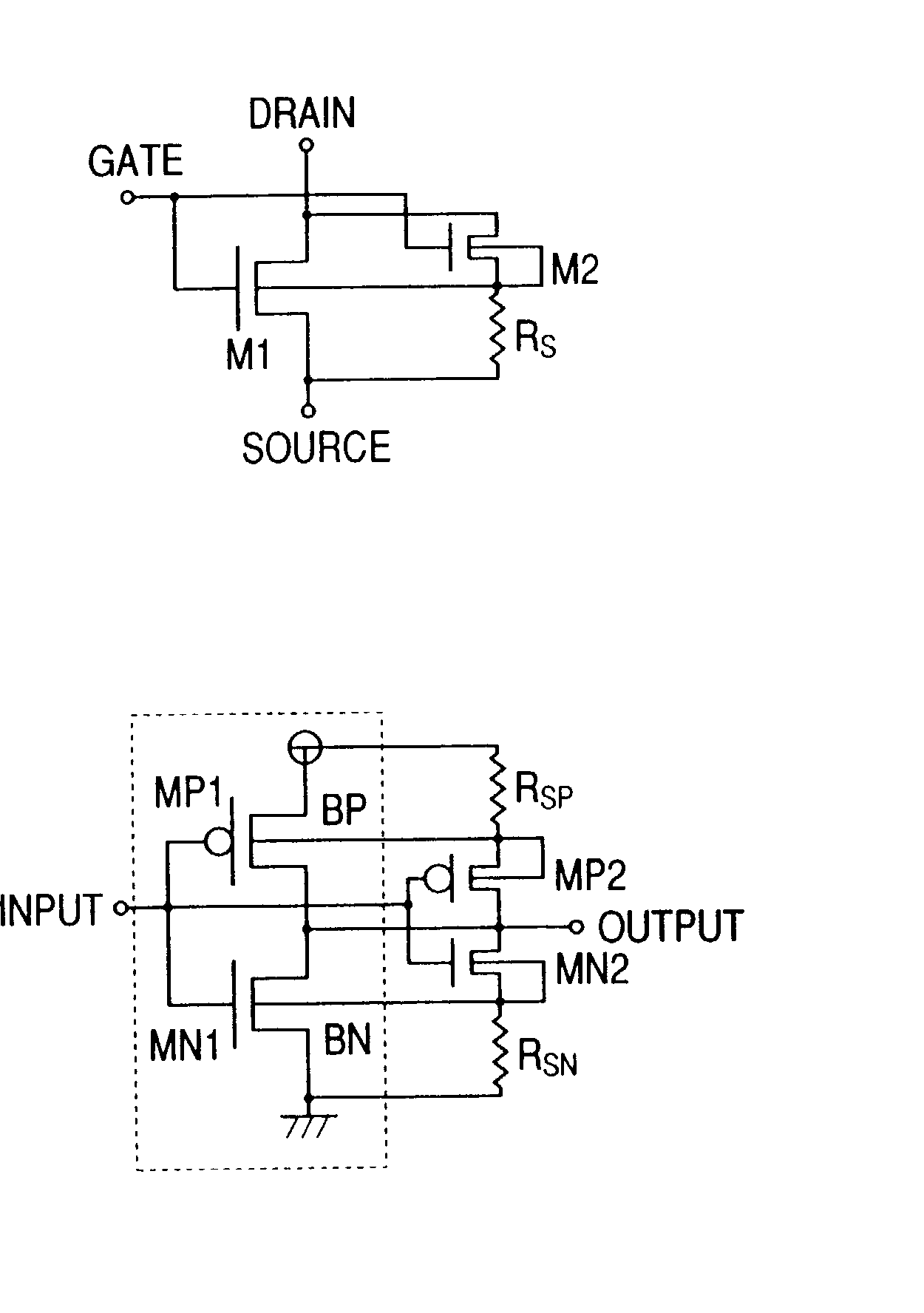

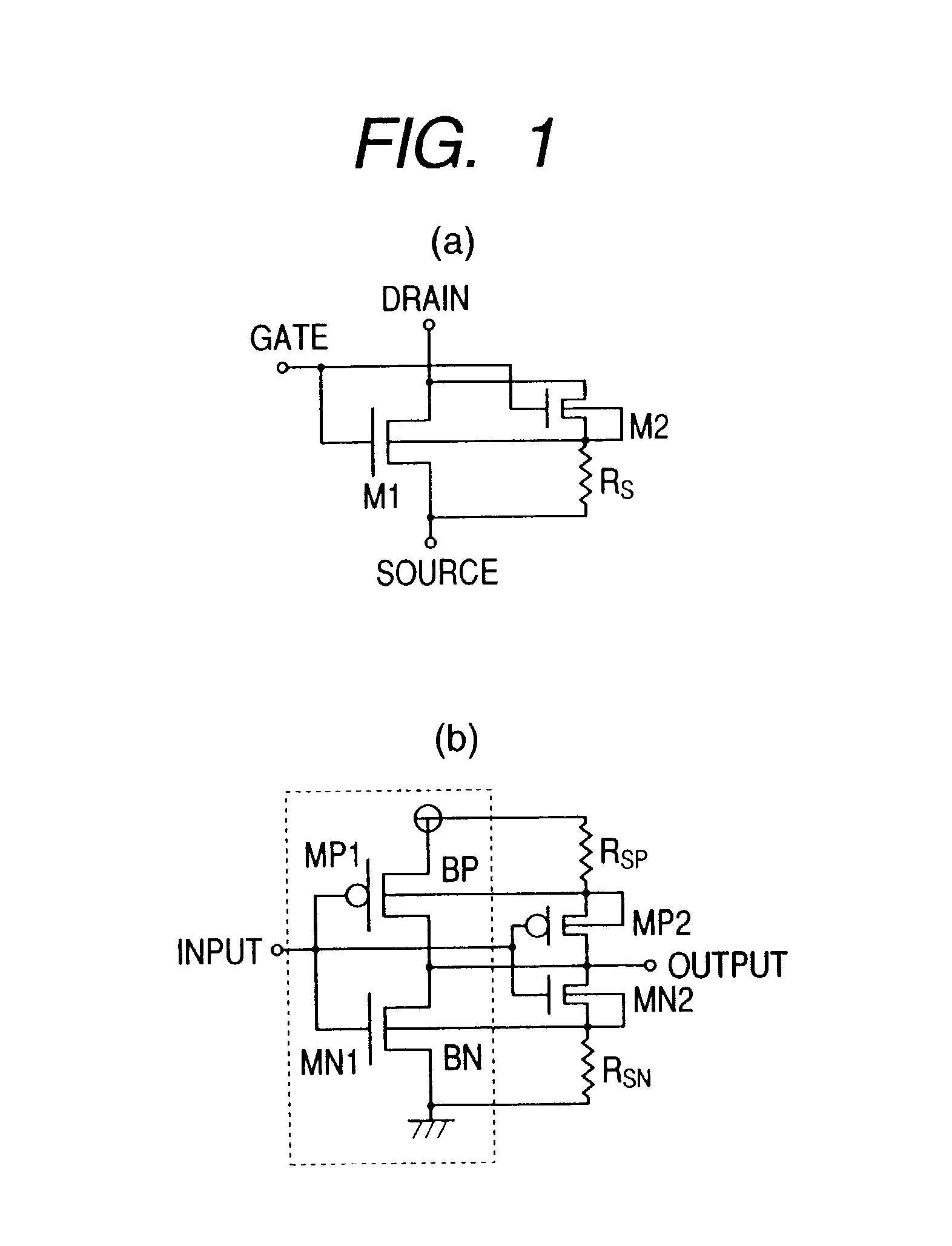

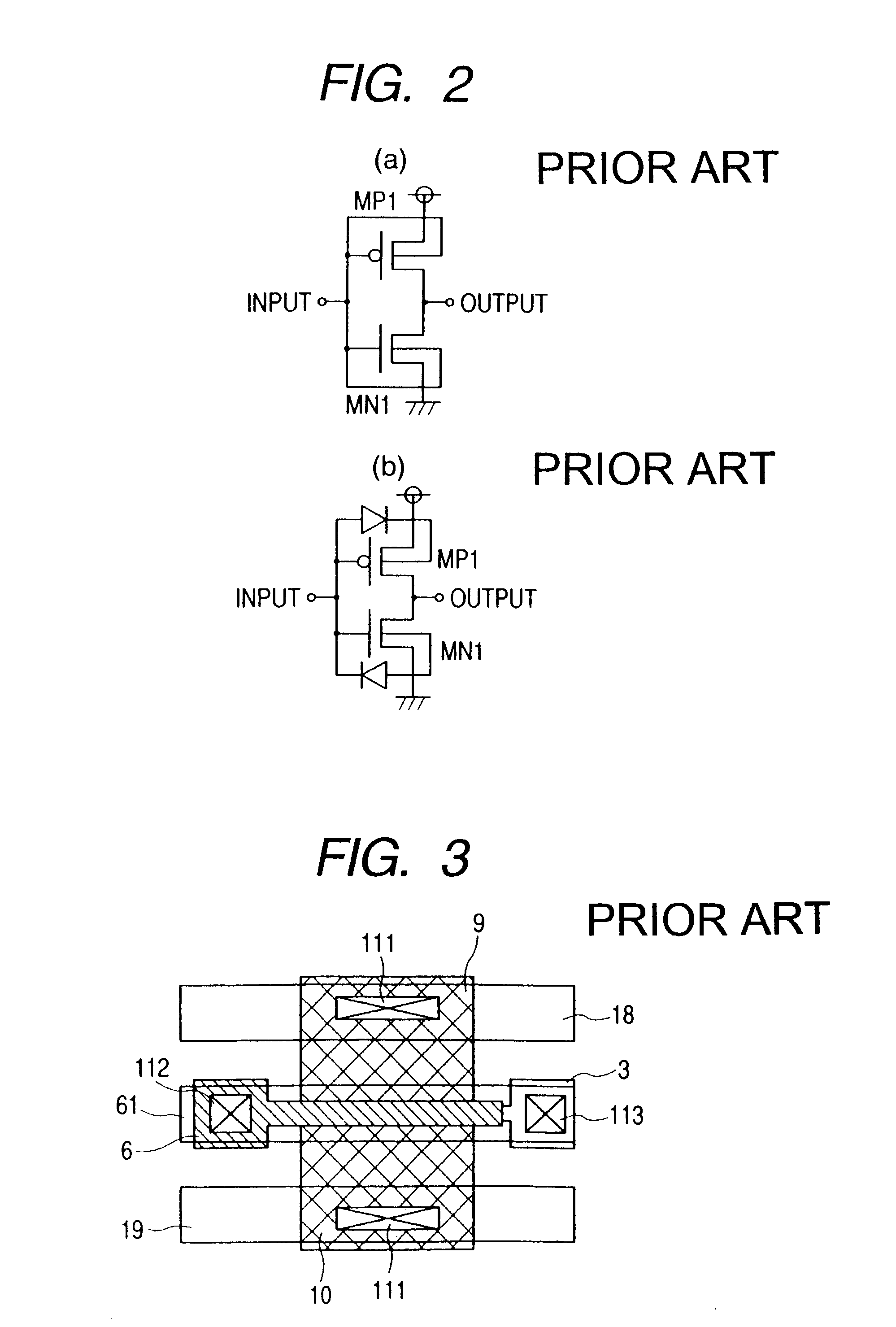

Semiconductor integrated circuit and method for manufacturing the same

InactiveUS20020195623A1Low voltageGreat currentTransistorSolid-state devicesFloating body effectIntegrated circuit

A semiconductor integrated circuit according to the present invention comprises a MOS transistor formed on an SOI substrate and a subsidiary transistor provided between a body node and a drain node of the MOS transistor and sharing a gate electrode with the MOS transistor, whereby body potential of the MOS transistor is controlled by gate and drain potentials. Accumulated body charge in a non-conducting state in the semiconductor integrated circuit is extracted by a resistor formed between the body node and a source, whereby various phenomena caused by floating body effect are eliminated. Since the body potential of the MOS transistor can be varied without creating an undesirable leakage current path, and hence without limitations to supplied voltage, its threshold voltage can be made variable so as to follow change in an input signal, thereby making it possible to achieve higher speed and lower voltage operation of the semiconductor integrated circuit. According to the present invention, it is possible to eliminate floating body effect, which is the greatest problem with an SOI transistor formed on an SOI substrate, and also to achieve lower voltage and greater current operation of a transistor without posing limitations to supplied voltage and without causing the problem of leakage current.

Owner:HITACHI LTD

GPS and non GPS position finder, emergency, MIMO, spread spectrum, CDMA, GSM and OFDM

InactiveUS20070032266A1Expand coverageImprove performanceSpatial transmit diversitySubstation equipmentEngineeringGlobal Positioning System

Global Positioning System (GPS) and non GPS position finder, emergency, multiple input multiple output (MIMO), multimode, spread spectrum, code division multiple access (CDMA), Global Mobile System or Global System Mobile (GSM) and orthogonal frequency division multiplex (OFDM) communication systems. Position finder and emergency communication multiple input multiple output (MIMO) system and a receiver having multiple inputs for reception and demodulation of position finder signals to position finder baseband signals. A processor for processing position finder signals with a signal containing an emergency number. A processors for processing signals to provide cross-correlated shaped in-phase and quadrature-phase baseband signals, spread spectrum and OFDM baseband signals. A control unit for control and selection of one of the jointly processed signals and a selector for providing the selected signal to a modulator. A modulator for modulating the selected signal and for connecting the modulated signal to a multiple output signal transmitter for signal transmission. A demodulator connected to the emergency receiver for demodulation of the modulation format selectable (MFS) and bit rate agile (BRA) modulated signal with at least one demodulator filter which has a mis-match with the corresponding filter of the modulator.

Owner:FEHER KAMILO

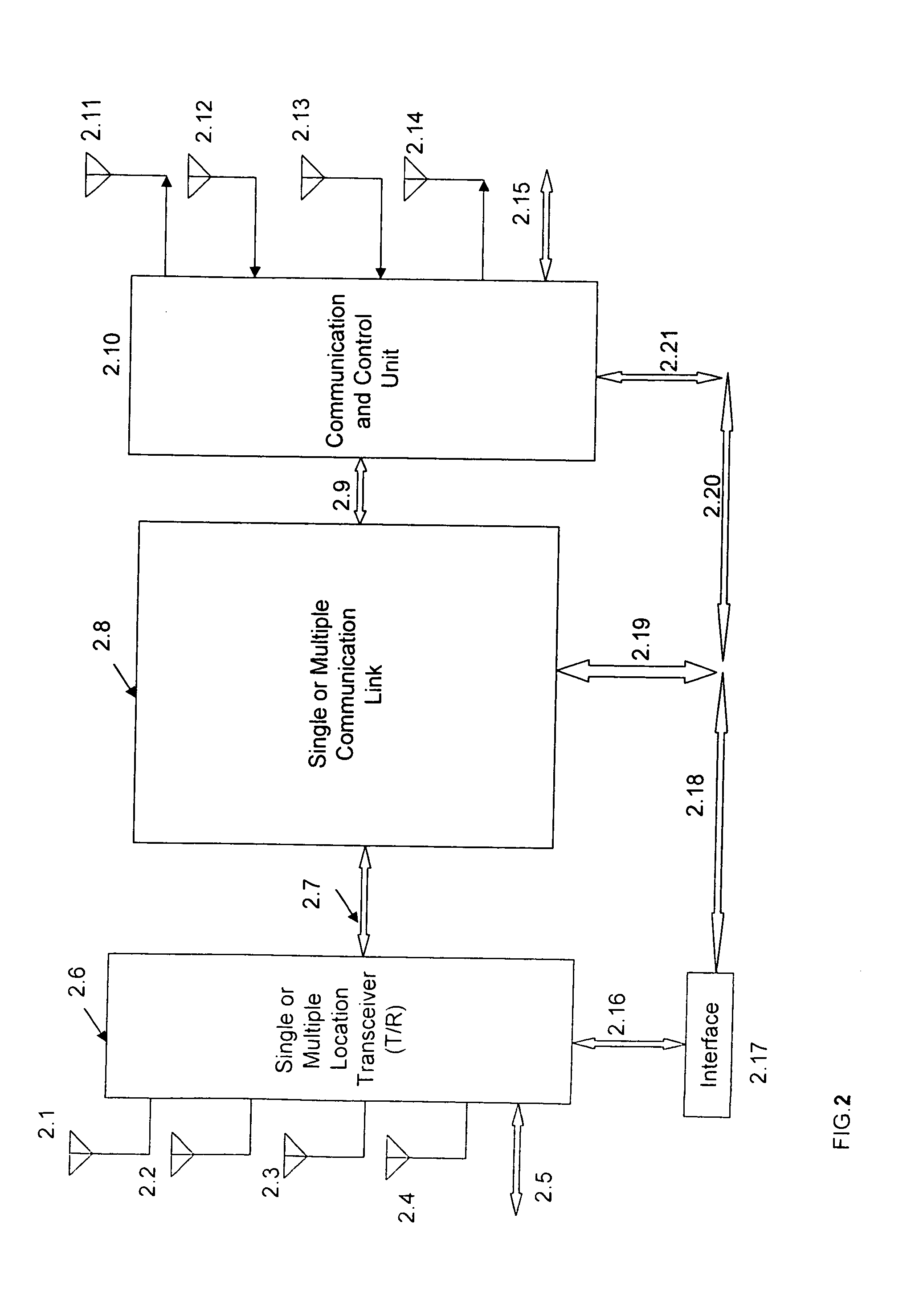

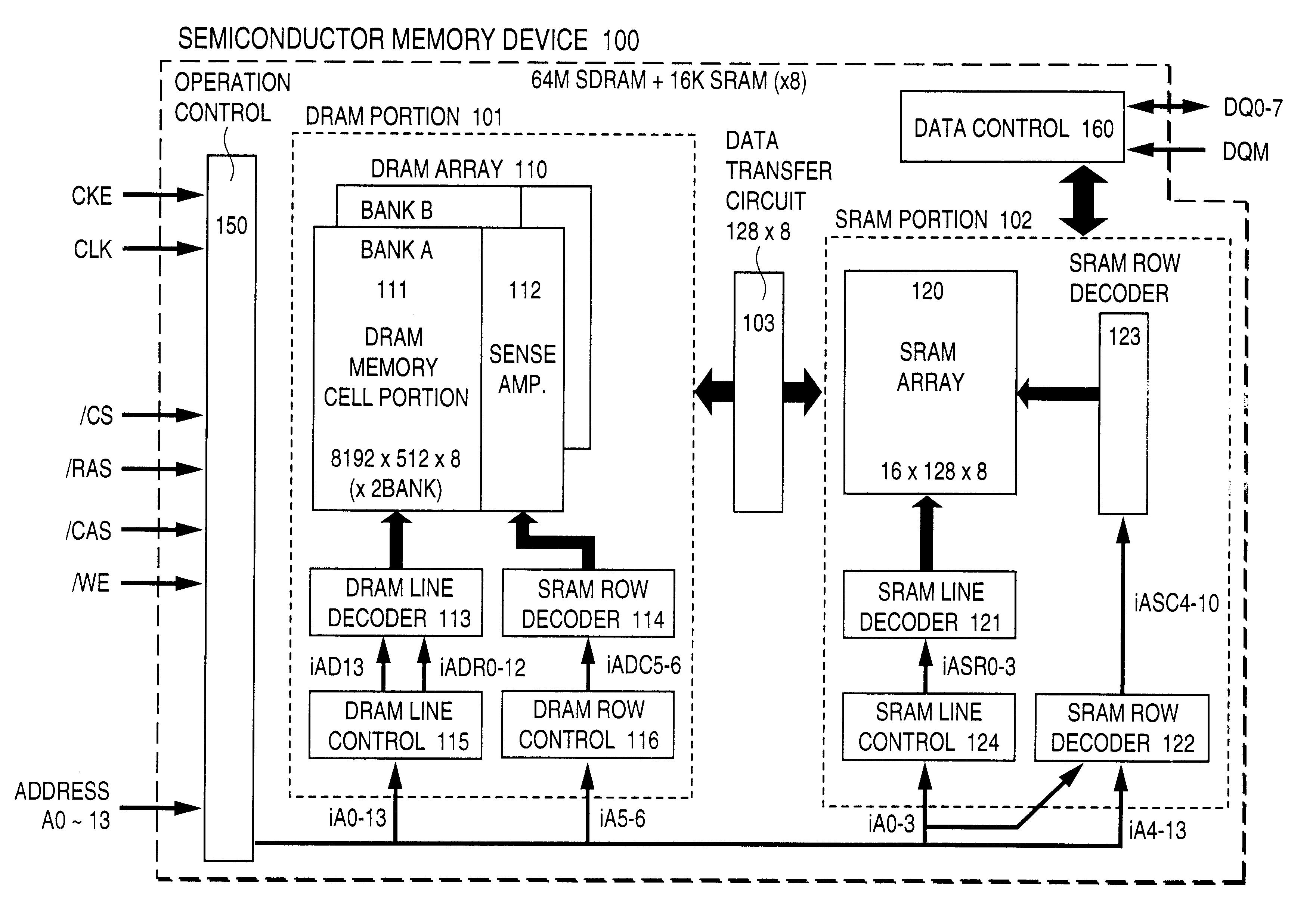

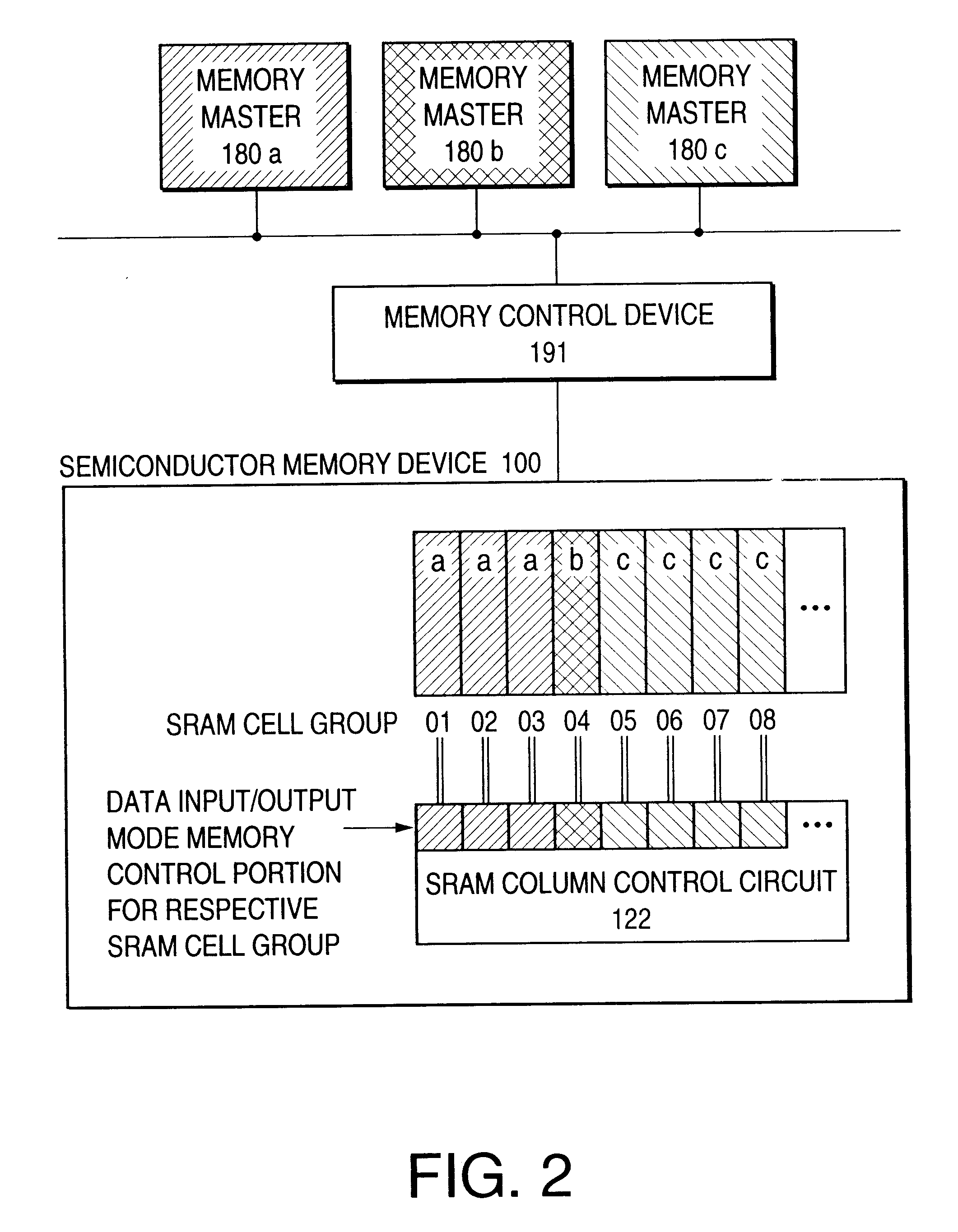

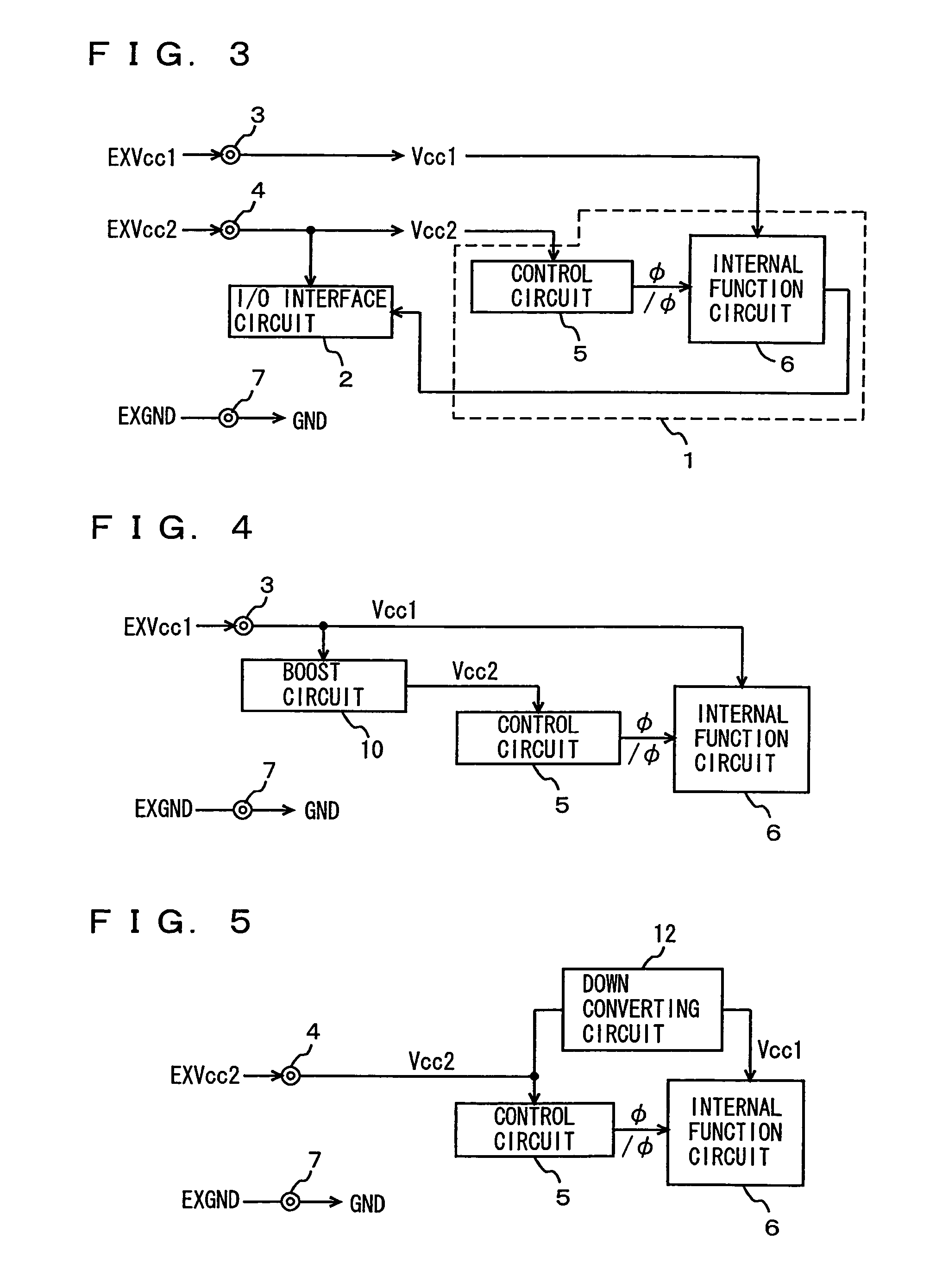

Semiconductor integrated circuit device

InactiveUS6453400B1Guaranteed high speed operationOptimize the numberMemory adressing/allocation/relocationDigital storageComputer scienceSemiconductor

A semiconductor integrated circuit device is comprised a main memory portion constituted with memory cells arranged in a plurality of rows and in a plurality of columns and a sub memory portion constituted with memory cells arranged in a plurality of rows and in a plurality of columns, wherein at least one of address input terminals assigning rows or columns of the main memory portion and at least one of address input terminals assigning rows or columns of the sub memory portion are commonly used and a total number of address input terminals is equal to or smaller than the number of address input terminals assigning rows or columns of the main memory portion. Therefore, the semiconductor integrated circuit device of the present invention has a main memory suitable for being accessed from a plurality of data processors.

Owner:RENESAS ELECTRONICS CORP

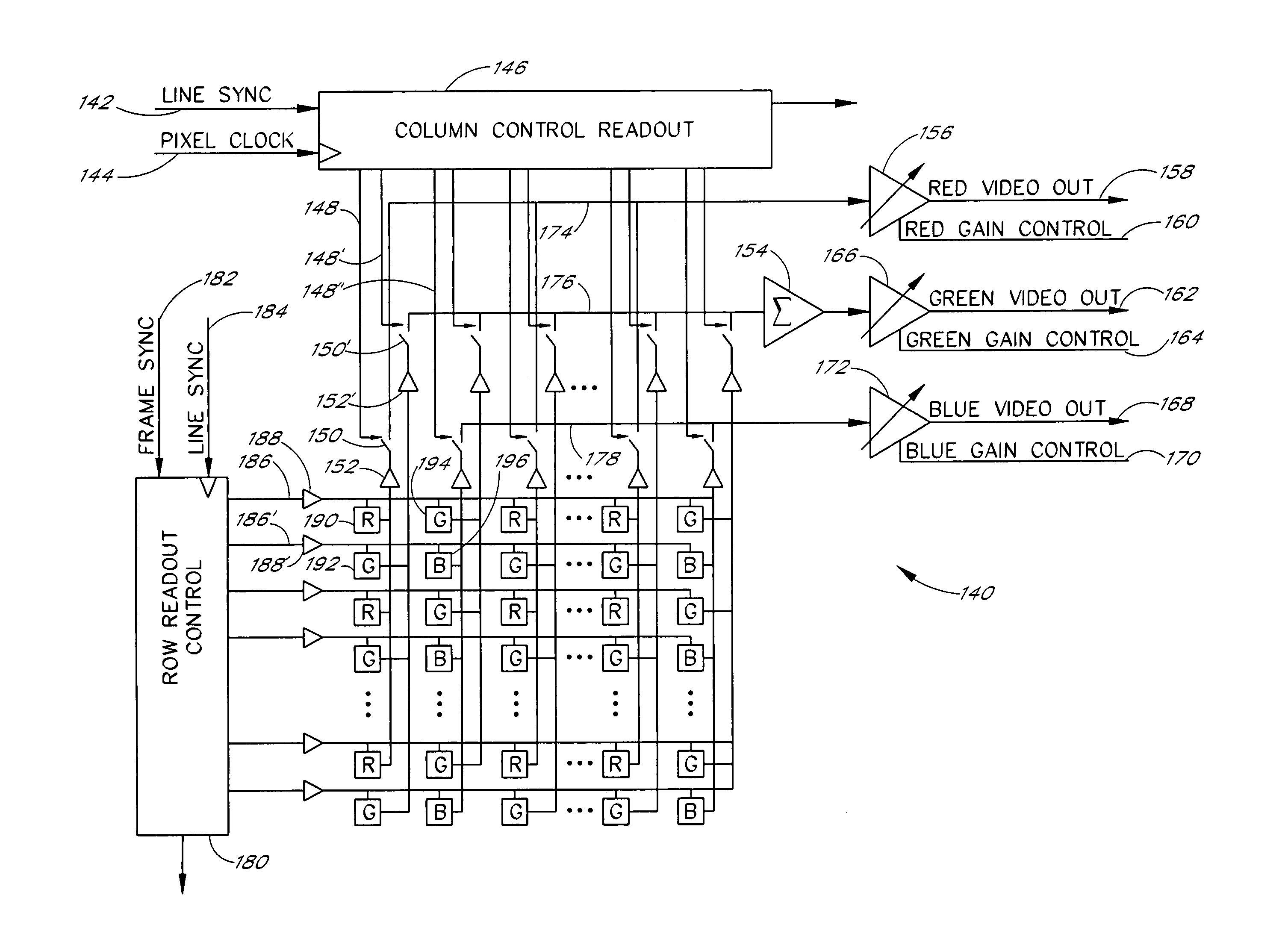

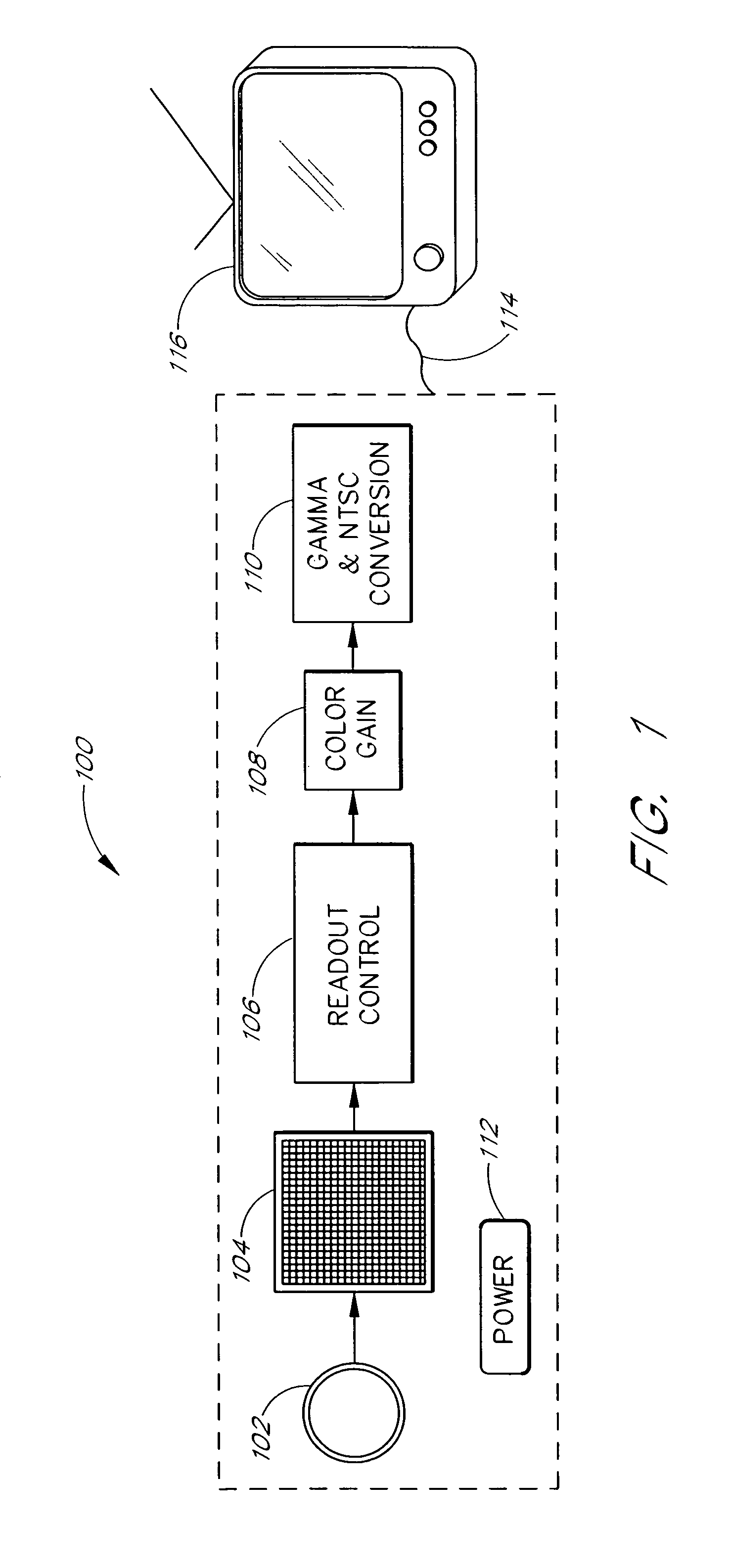

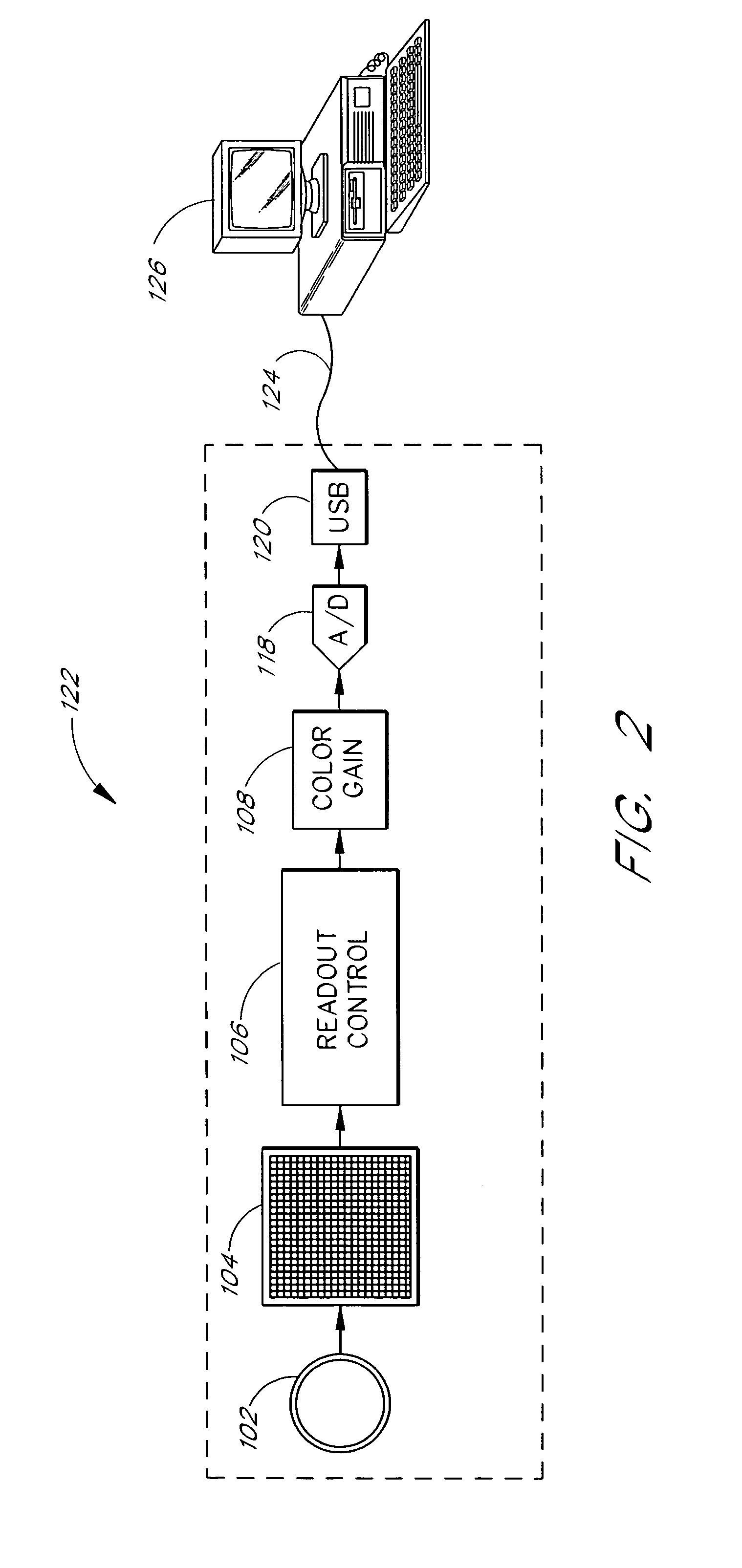

Method and apparatus for color interpolation

InactiveUS7133073B1Guaranteed high speed operationEasy to integrateTelevision system detailsTelevision system scanning detailsColor interpolationControl circuit

An imaging method and system that flexibly accesses light sensor elements and processes imaging signals. The imaging system comprises an array of pixel sensor cells, an array controller and a readout control circuit. The imaging system provides color interpolation.

Owner:GULA CONSULTING LLC

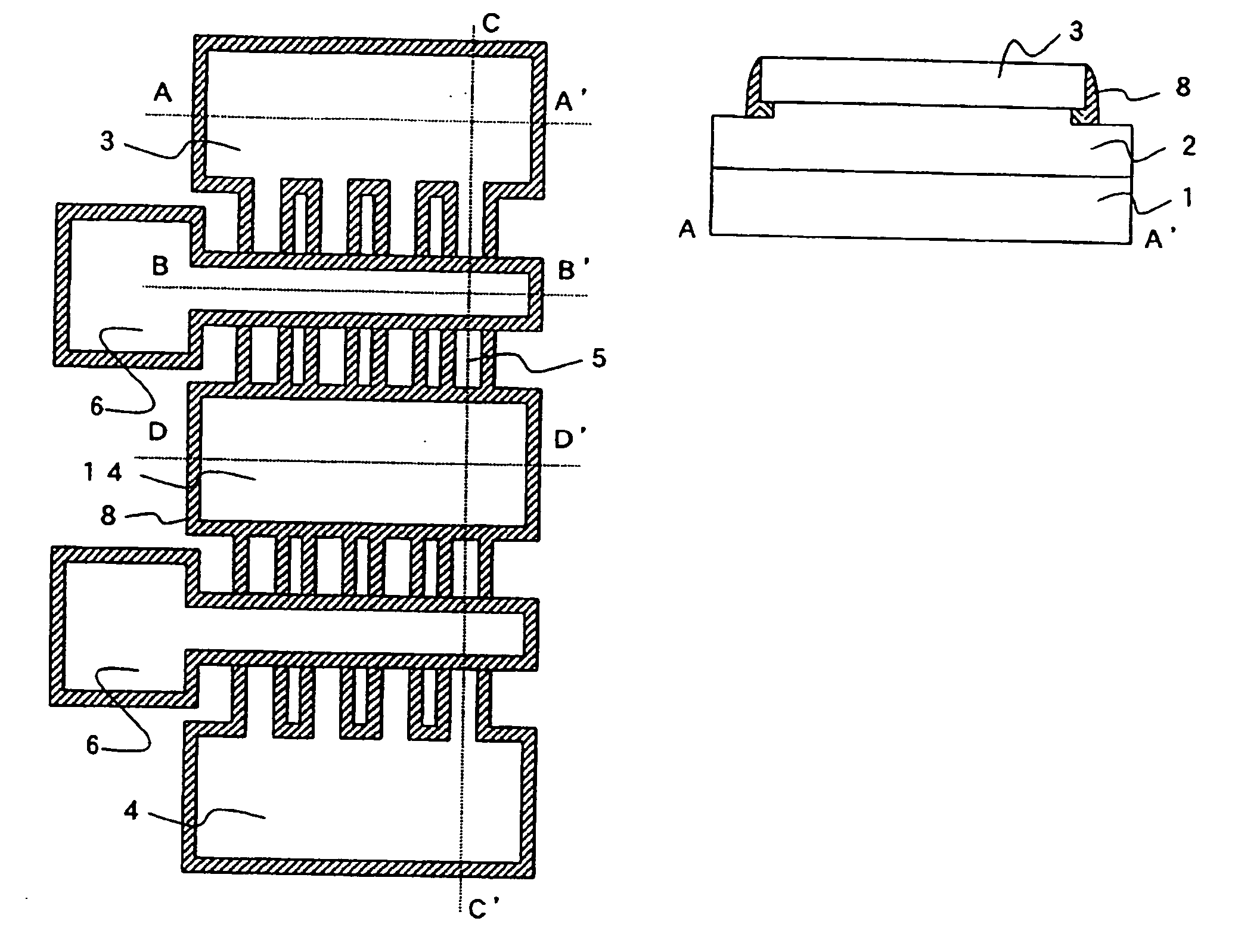

Semiconductor memory with gate at least partially located in recess defined in vertically oriented semiconductor layer

InactiveUS6933556B2Increase capacitanceSuppress mutationTransistorSolid-state devicesSemiconductorSemiconductor memory

A semiconductor memory comprises: a first conductivity type semiconductor substrate and one or more memory cells each constituted of an island-like semiconductor layer having a recess on a sidewall thereof, a charge storage layer formed to entirely or partially encircle a sidewall of the island-like semiconductor layer, and a control gate formed on the charge storage layer, wherein at least one charge storage layer of said one or more memory cells is partially situated within the recess formed on the sidewall of the island-like semiconductor layer.

Owner:SAMSUNG ELECTRONICS CO LTD +1

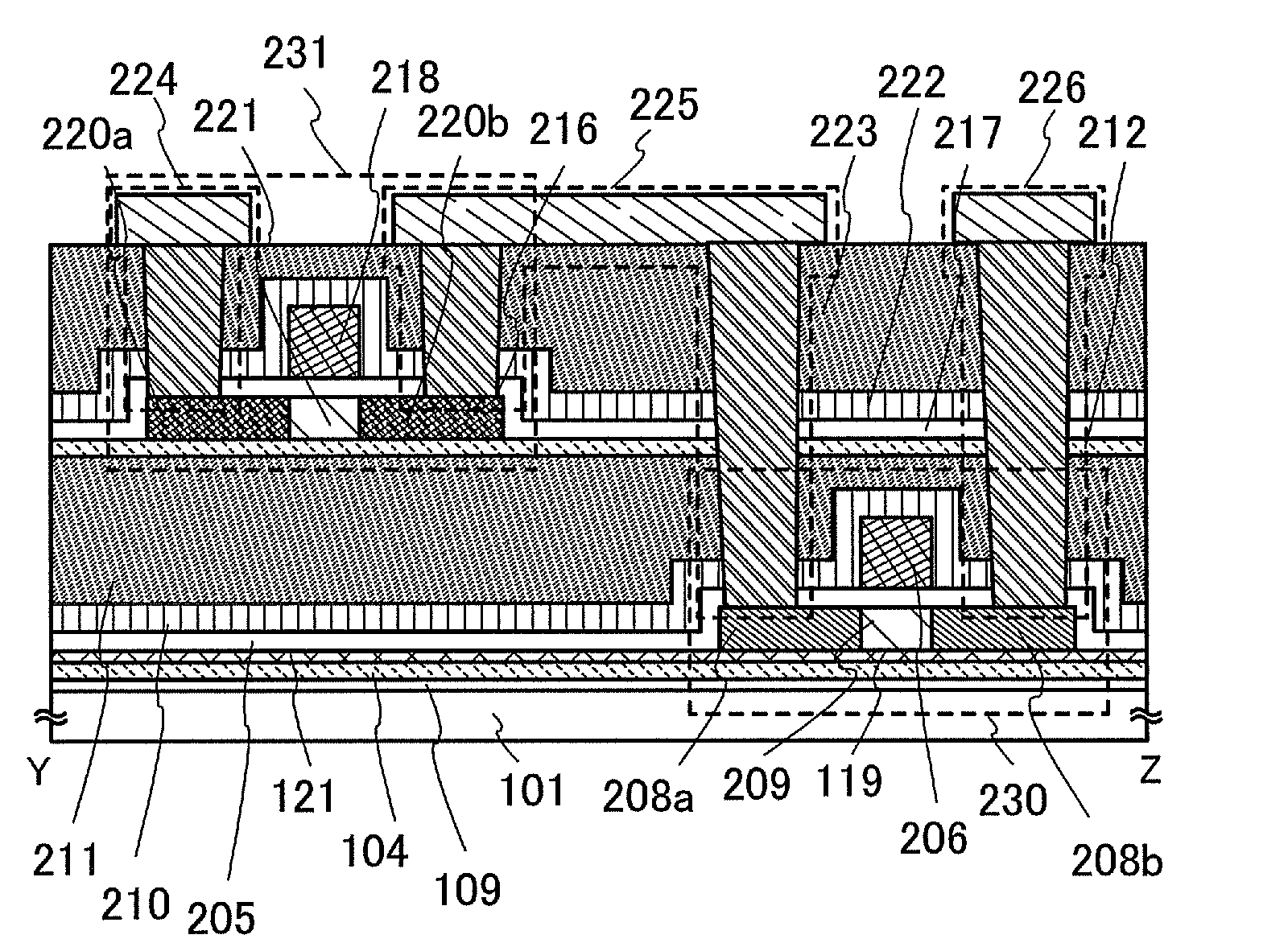

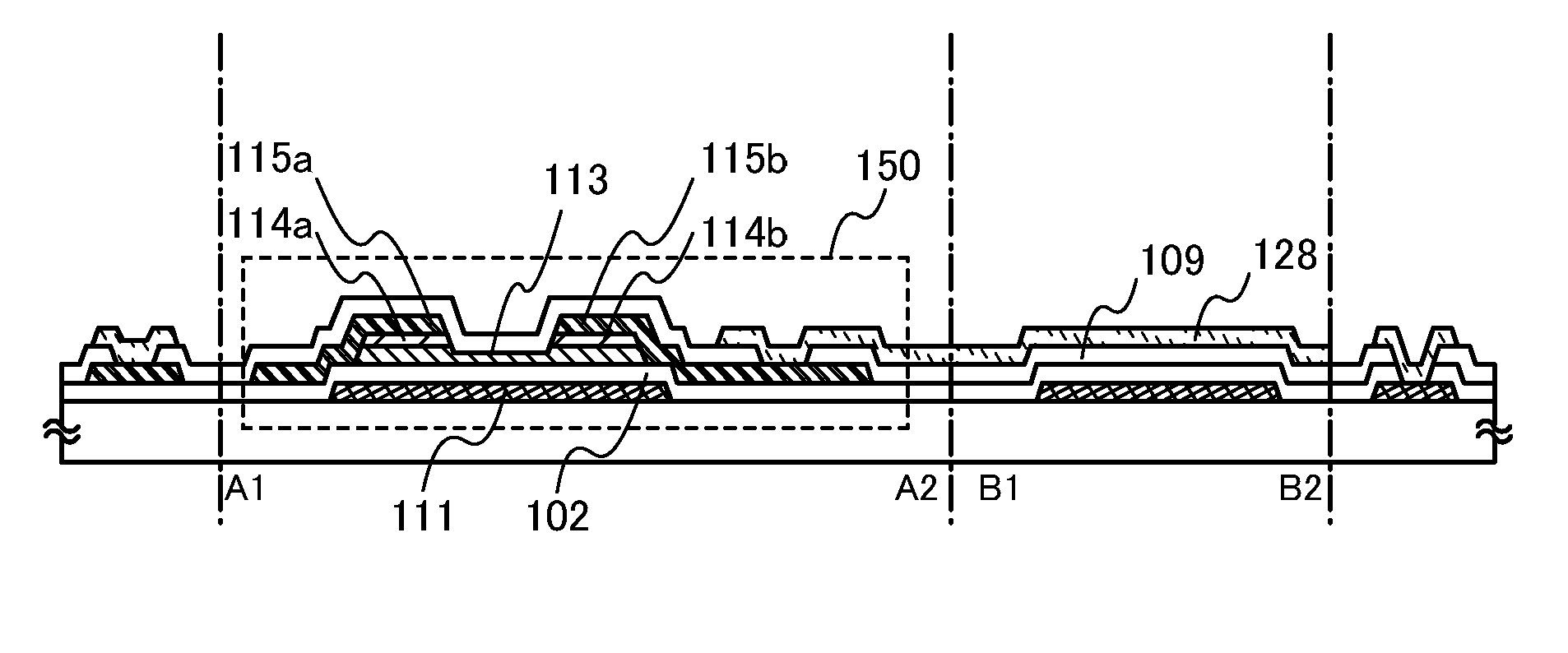

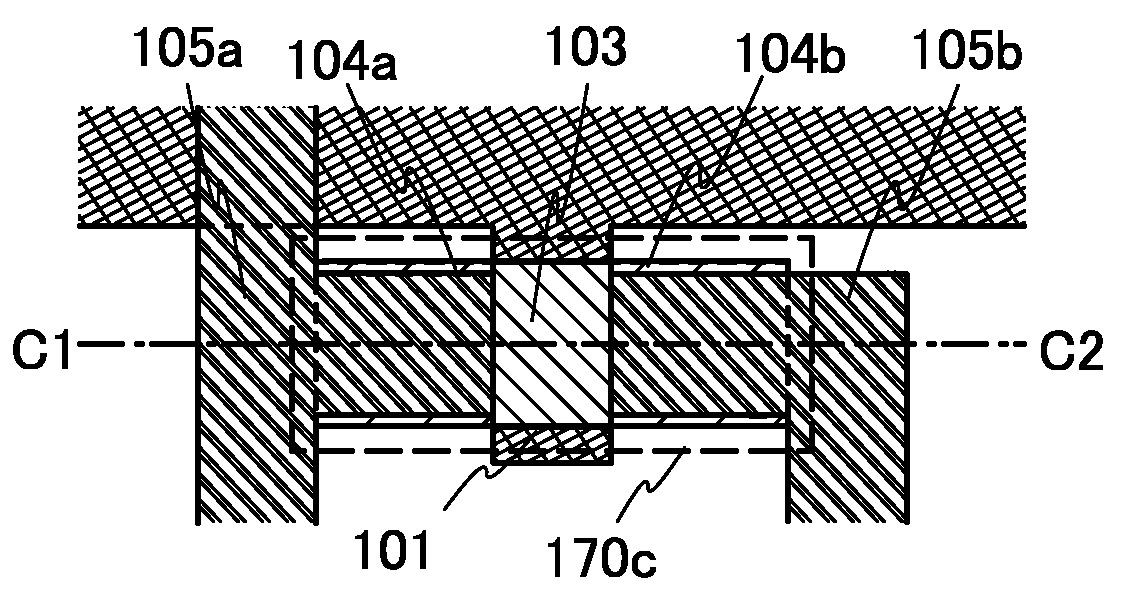

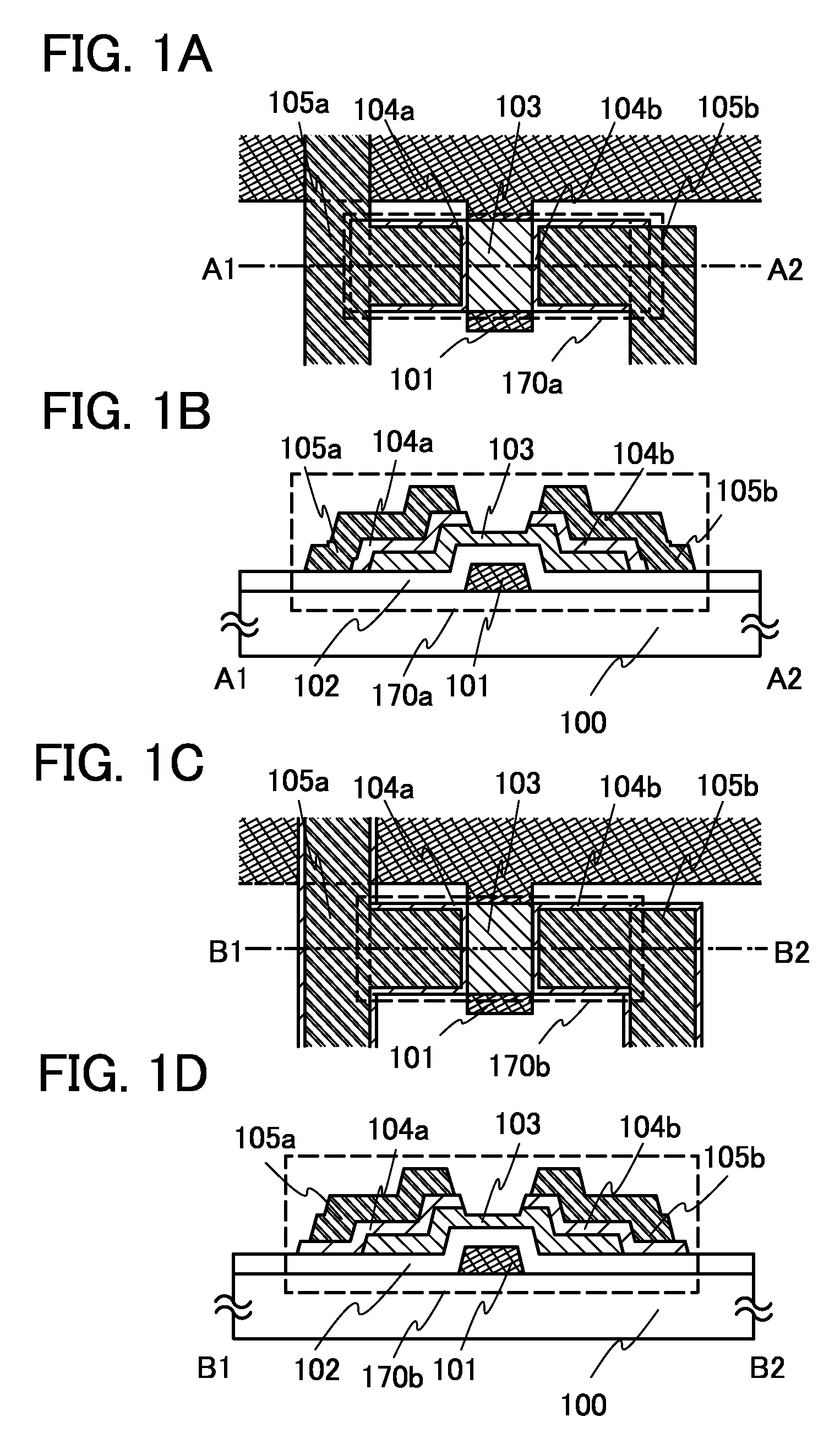

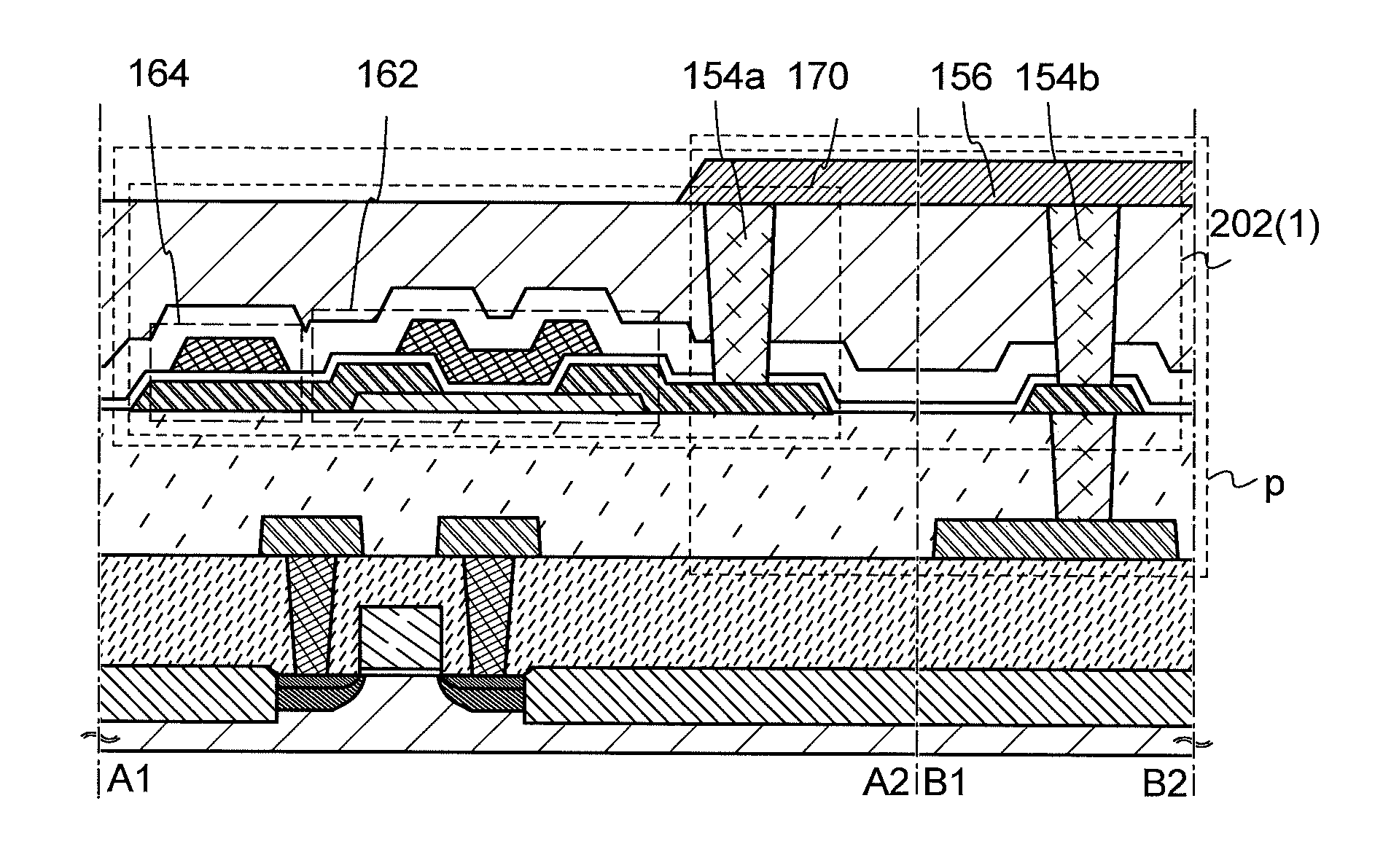

Semiconductor device

ActiveUS20120112257A1Reduce power consumptionFrequency of refresh can be lowTransistorSolid-state devicesDriver circuitDevice material

Provided is a semiconductor device with a novel structure in which stored data can be retained even when power is not supplied, and which does not have a limitation on the number of writing. The semiconductor device includes both a memory circuit including a transistor including an oxide semiconductor (in a broader sense, a transistor whose off-state current is sufficiently small), and a peripheral circuit such as a driver circuit including a transistor including a material other than an oxide semiconductor (that is, a transistor capable of operating at sufficiently high speed). Further, the peripheral circuit is provided in a lower portion and the memory circuit is provided in an upper portion, so that the area and size of the semiconductor device can be decreased.

Owner:SEMICON ENERGY LAB CO LTD

Low power consumption MIS semiconductor device

InactiveUS7355455B2Total current dropSimple circuit configurationTransistorReliability increasing modificationsCurrent consumptionLogic gate

A logic gate is constructed of an insulated gate field effect transistor (MIS transistor) having a thin gate insulation film. An operation power supply line to the logic gate is provided with an MIS transistor having a thick gate insulation film for switching the supply and stop of an operation power source voltage. A voltage of the gate of the power source switching transistor is made changing in an amplitude greater than an amplitude of an input and an output signal to the logic gate. Current consumption in a semiconductor device configured of MIS transistor of a thin gate insulation film can be reduced and an power source voltage thereof can be stabilized.

Owner:RENESAS ELECTRONICS CORP

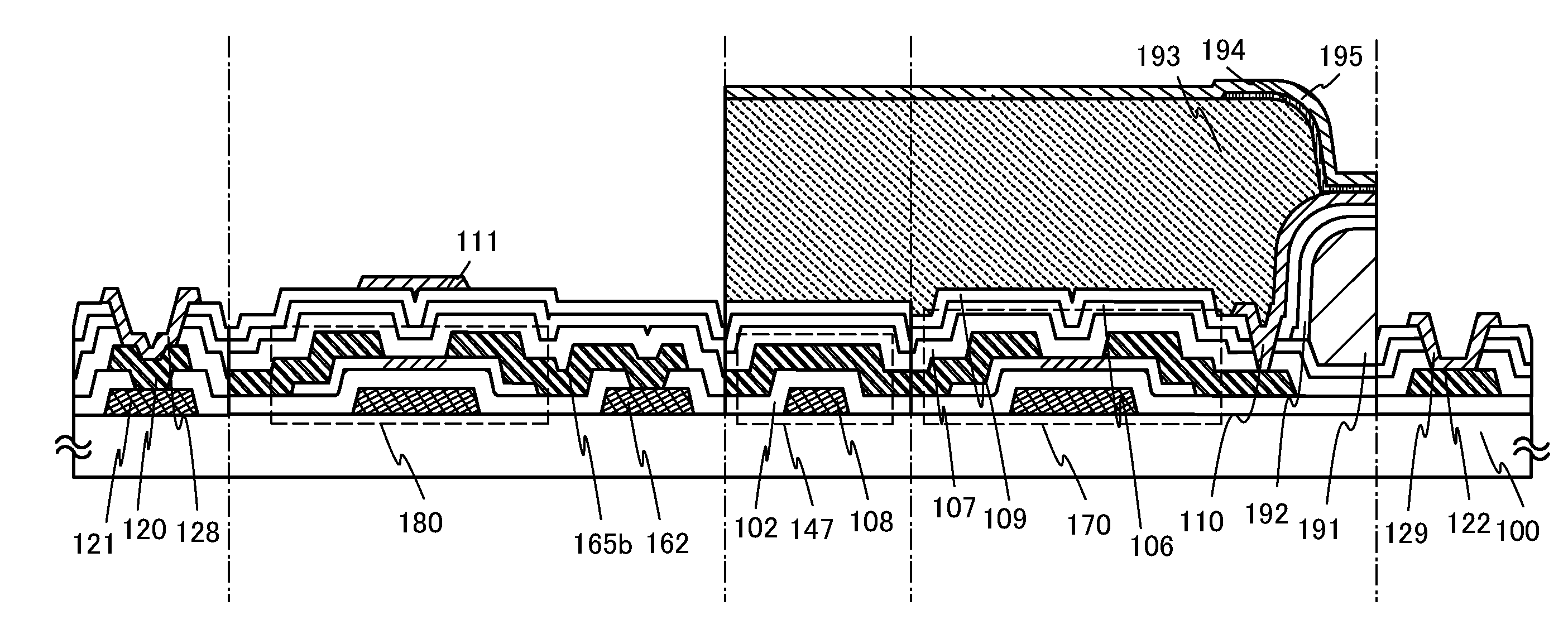

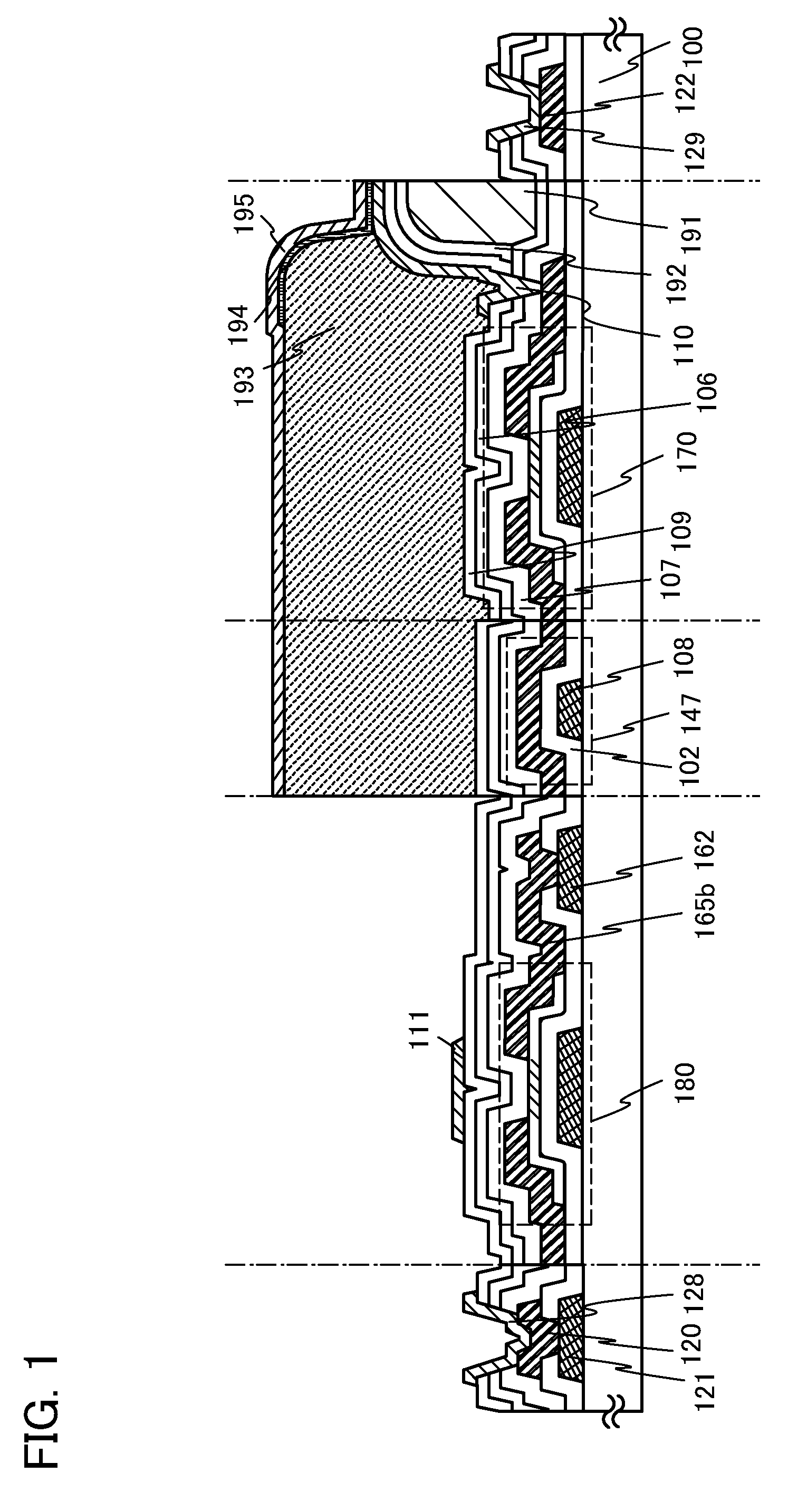

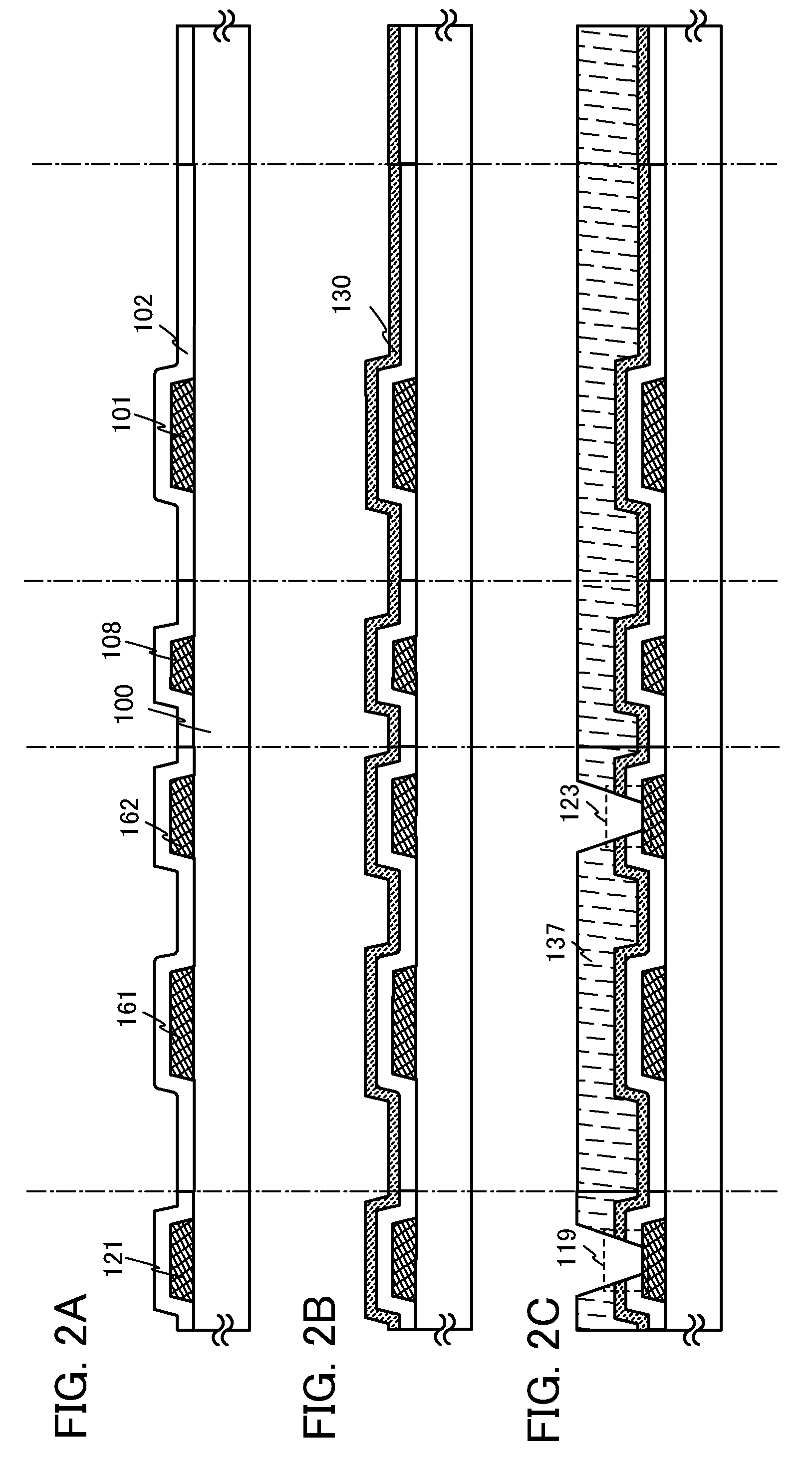

Light-emitting device and manufacturing method thereof

ActiveUS20110062434A1Excellent electrical propertiesImprove reliabilityFinal product manufactureSolid-state devicesEngineeringLight emitting device

An object of the invention is to improve the reliability of a light-emitting device. Another object of the invention is to provide flexibility to a light-emitting device having a thin film transistor using an oxide semiconductor film. A light-emitting device has, over one flexible substrate, a driving circuit portion including a thin film transistor for a driving circuit and a pixel portion including a thin film transistor for a pixel. The thin film transistor for a driving circuit and the thin film transistor for a pixel are inverted staggered thin film transistors including an oxide semiconductor layer which is in contact with a part of an oxide insulating layer.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device comprising an oxide semiconductor layer

ActiveUS9082857B2Easy to makeGuaranteed high speed operationTransistorStatic indicating devicesMetallic materialsOxygen deficient

A thin film transistor structure in which a source electrode and a drain electrode formed from a metal material are in direct contact with an oxide semiconductor film may lead to high contact resistance. One cause of high contact resistance is that a Schottky junction is formed at a contact plane between the source and drain electrodes and the oxide semiconductor film. An oxygen-deficient oxide semiconductor layer which includes crystal grains with a size of 1 nm to 10 nm and has a higher carrier concentration than the oxide semiconductor film serving as a channel formation region is provided between the oxide semiconductor film and the source and drain electrodes.

Owner:SEMICON ENERGY LAB CO LTD

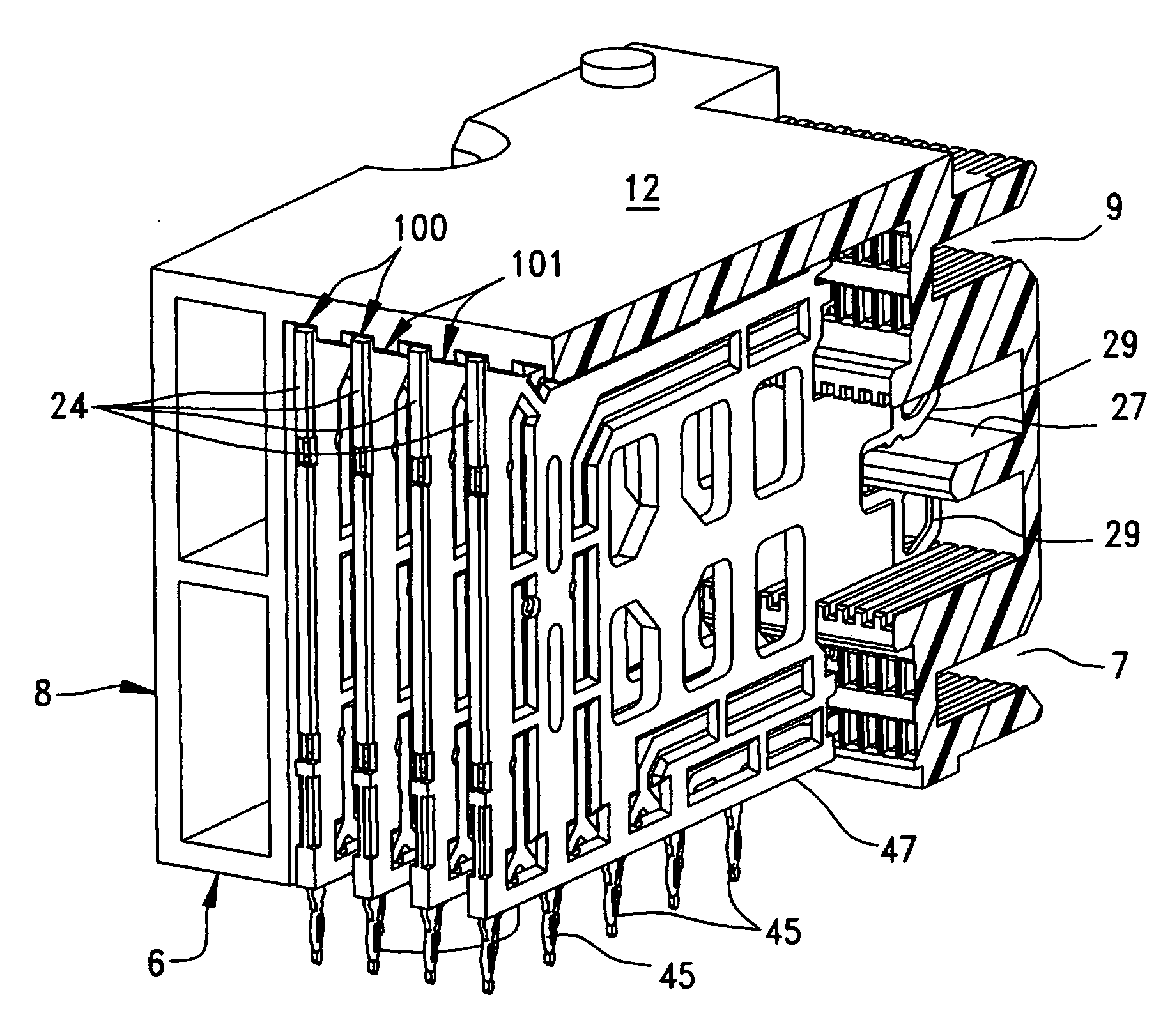

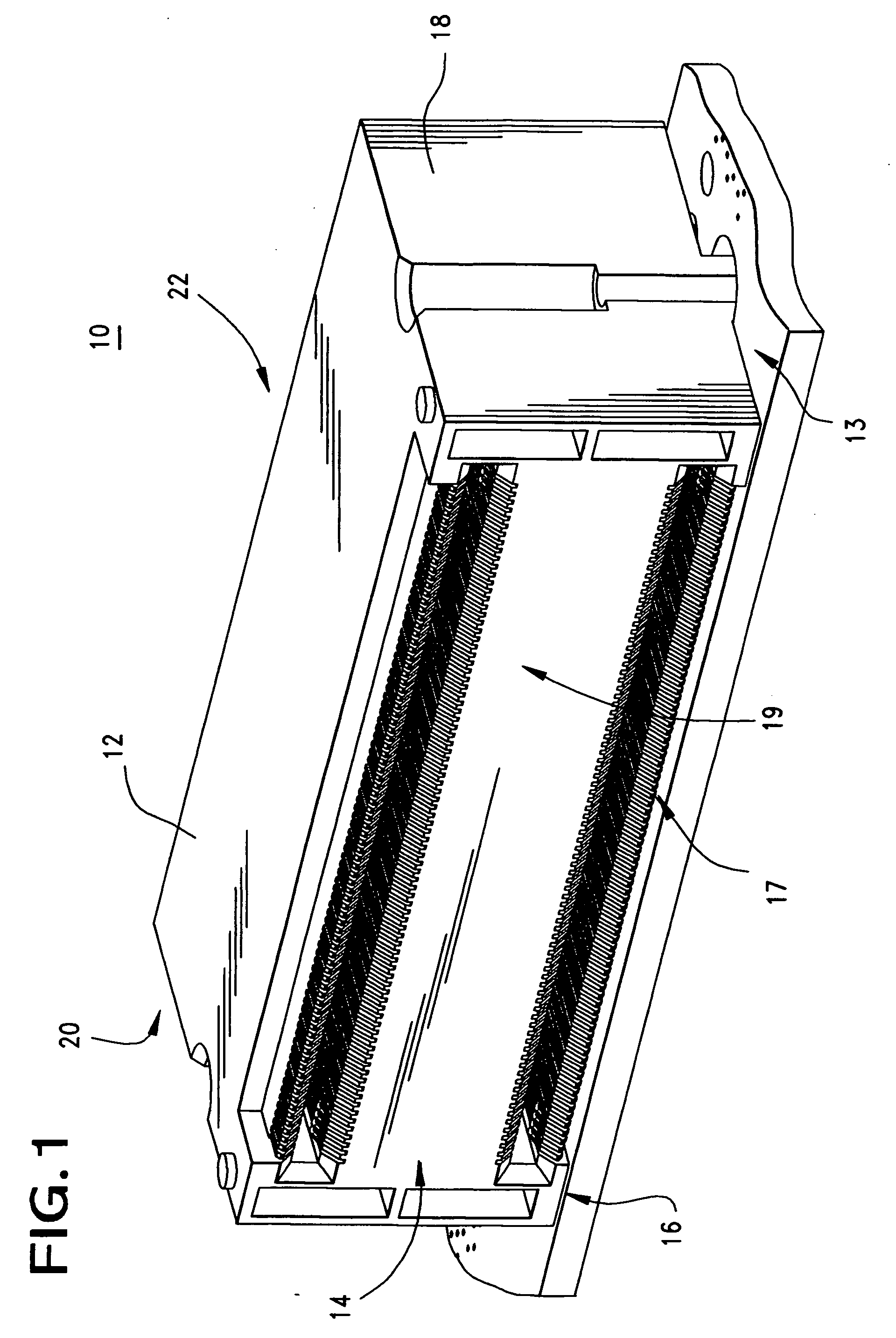

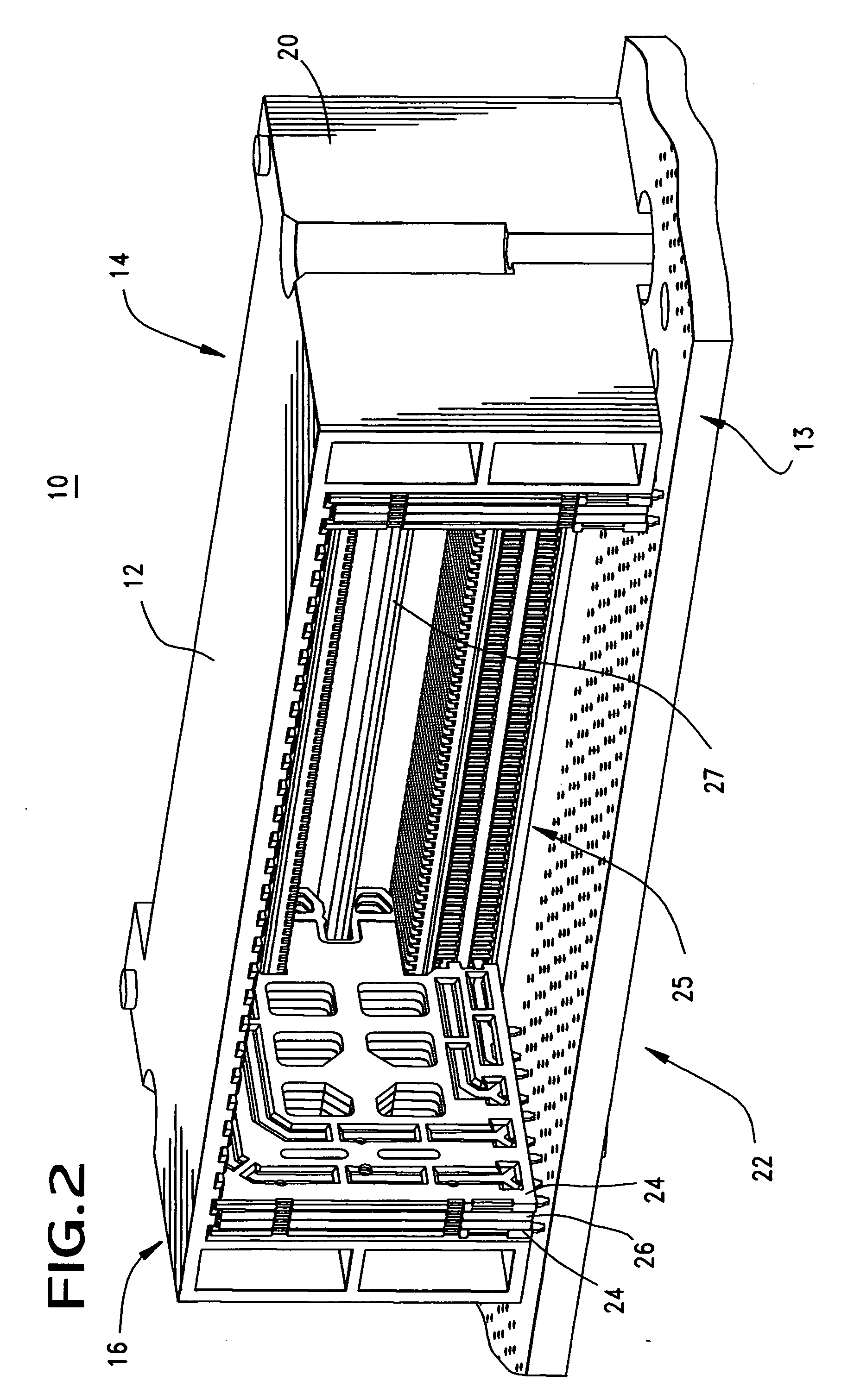

Differential signal connector with wafer-style construction

ActiveUS20060189212A1Easy to manufactureGuaranteed high speed operationElectrically conductive connectionsCross-talk/noise/interference reductionEngineeringMultiple layer

Stacked receptacles in a connector that each provide side-by-side differential signal contacts, are attached to a circuit board without additional width to accommodate multiple layers of differential signals by using connector wafer inserts that rotate the side-by-side positioned differential signal contacts to front-to-back contacts.

Owner:MOLEX INC