Patents

Literature

2033 results about "Current consumption" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Systems and methods for monitoring data and bandwidth usage

ActiveUS20100017506A1Assess restrictionMultiple digital computer combinationsResource consumptionResource utilization

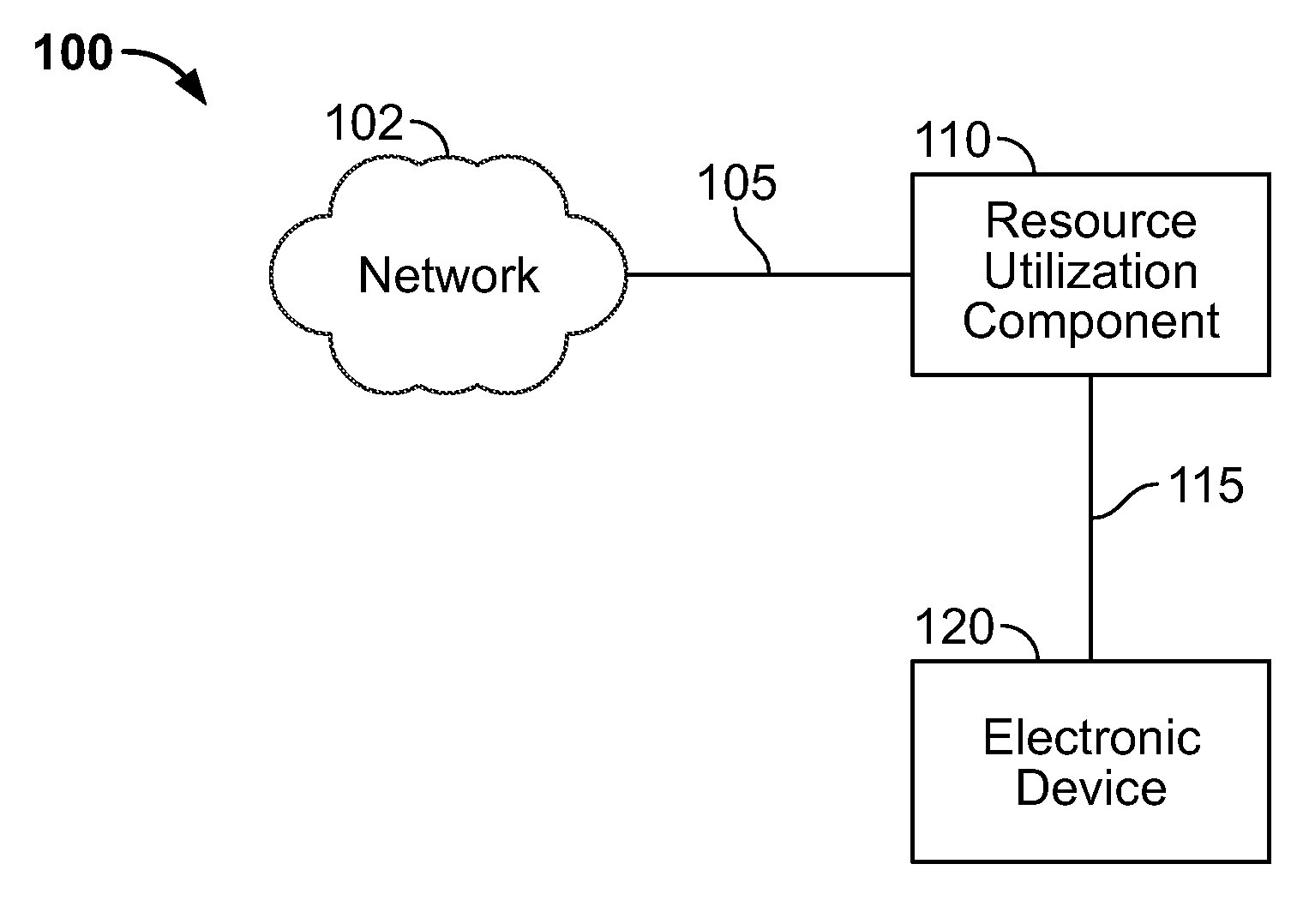

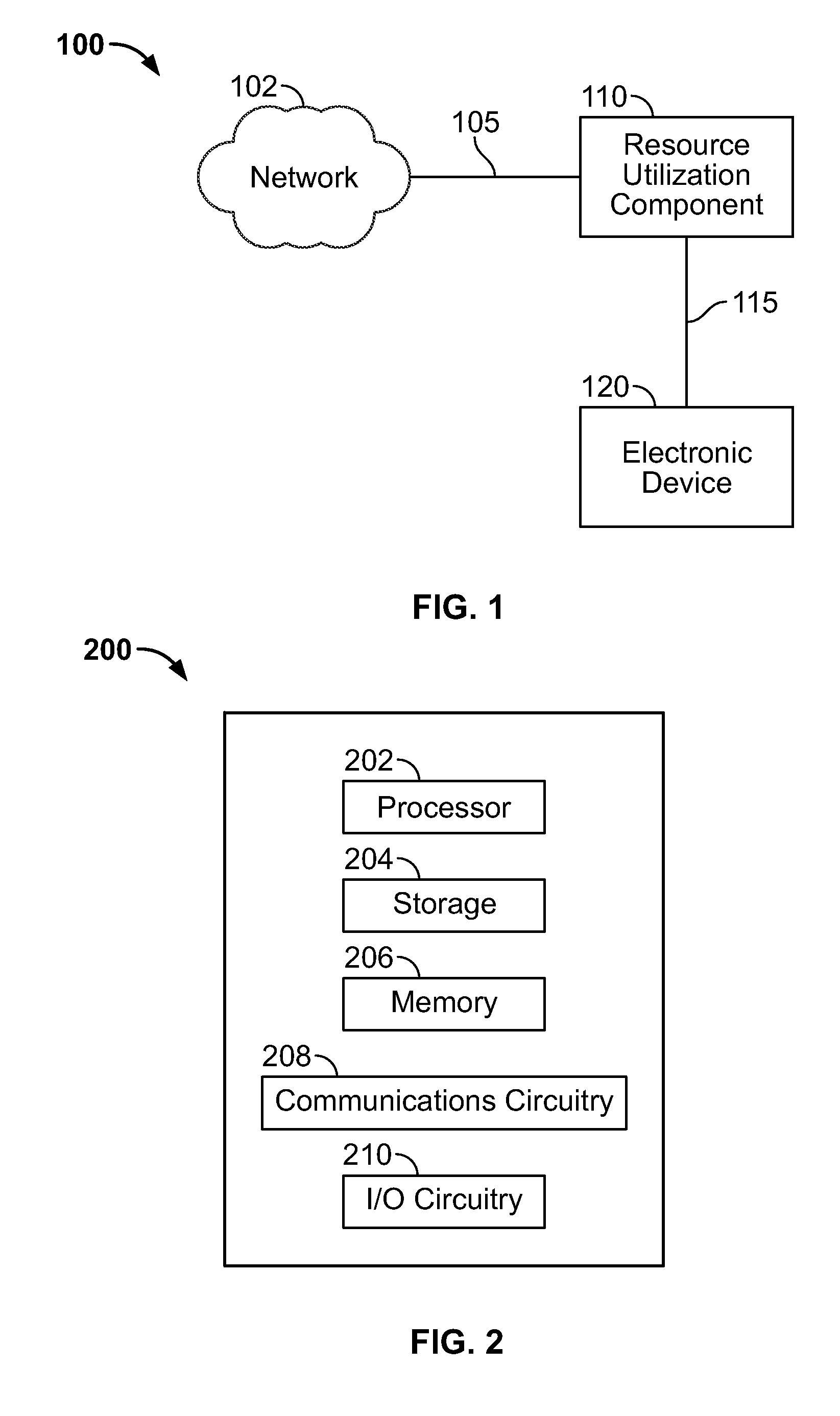

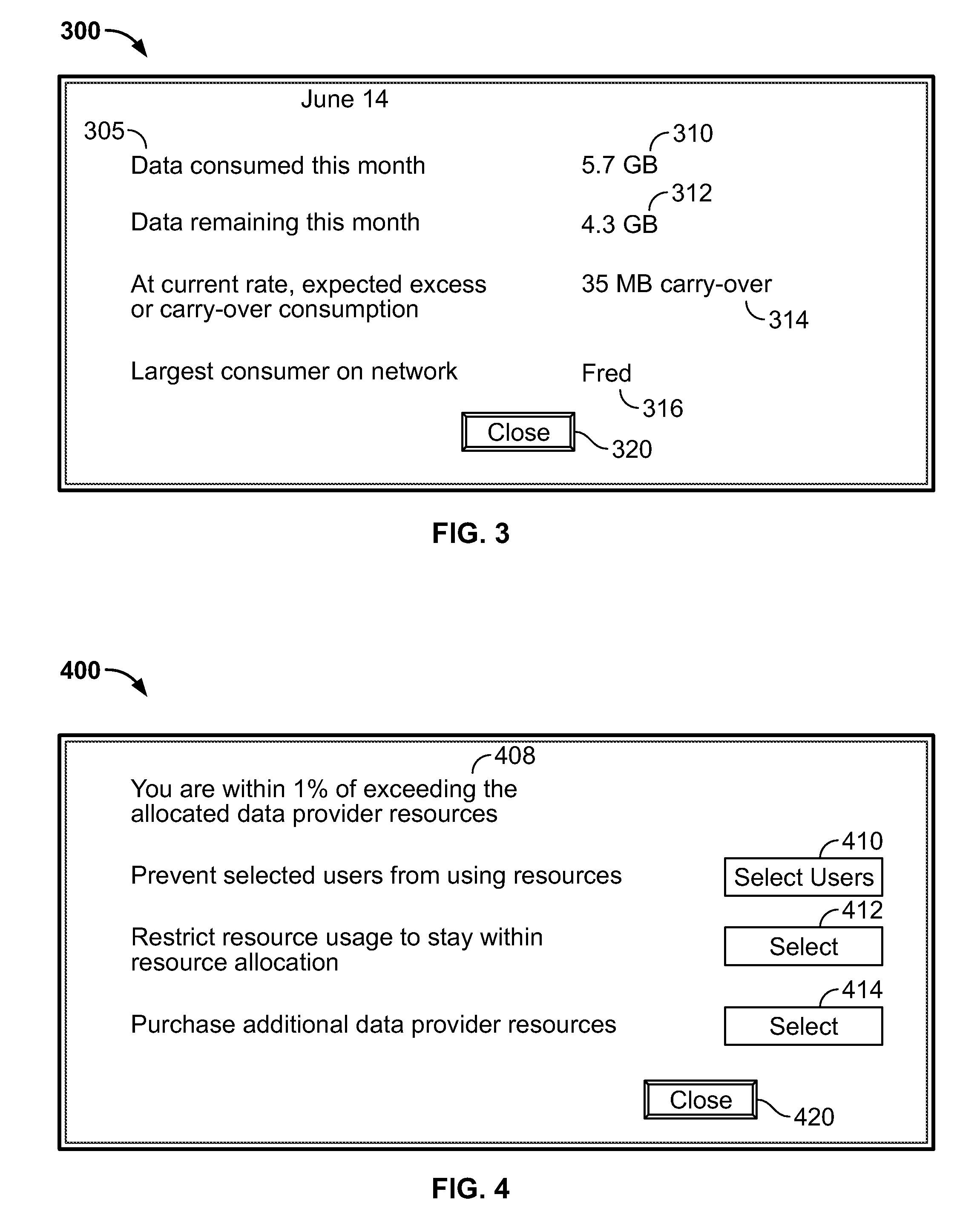

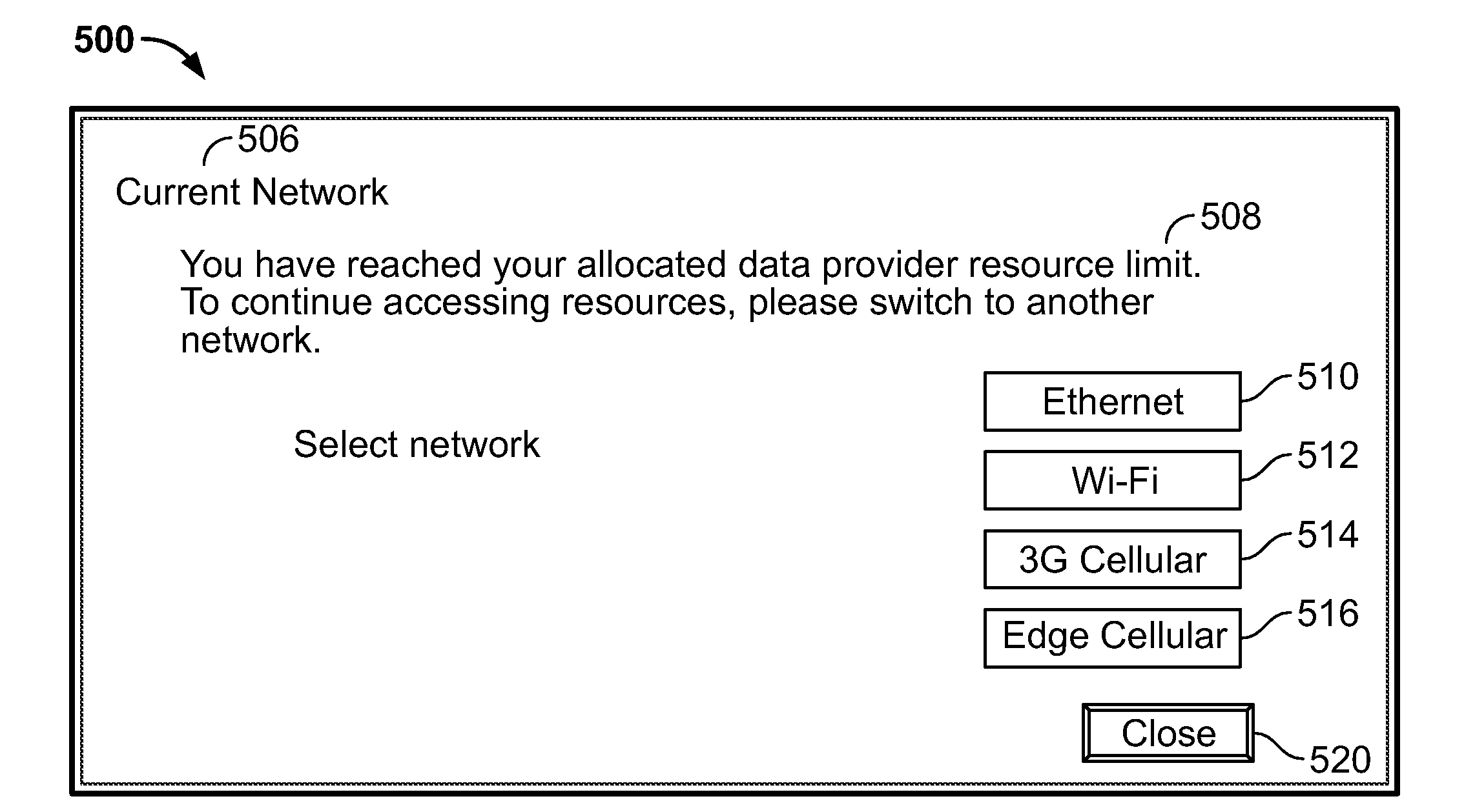

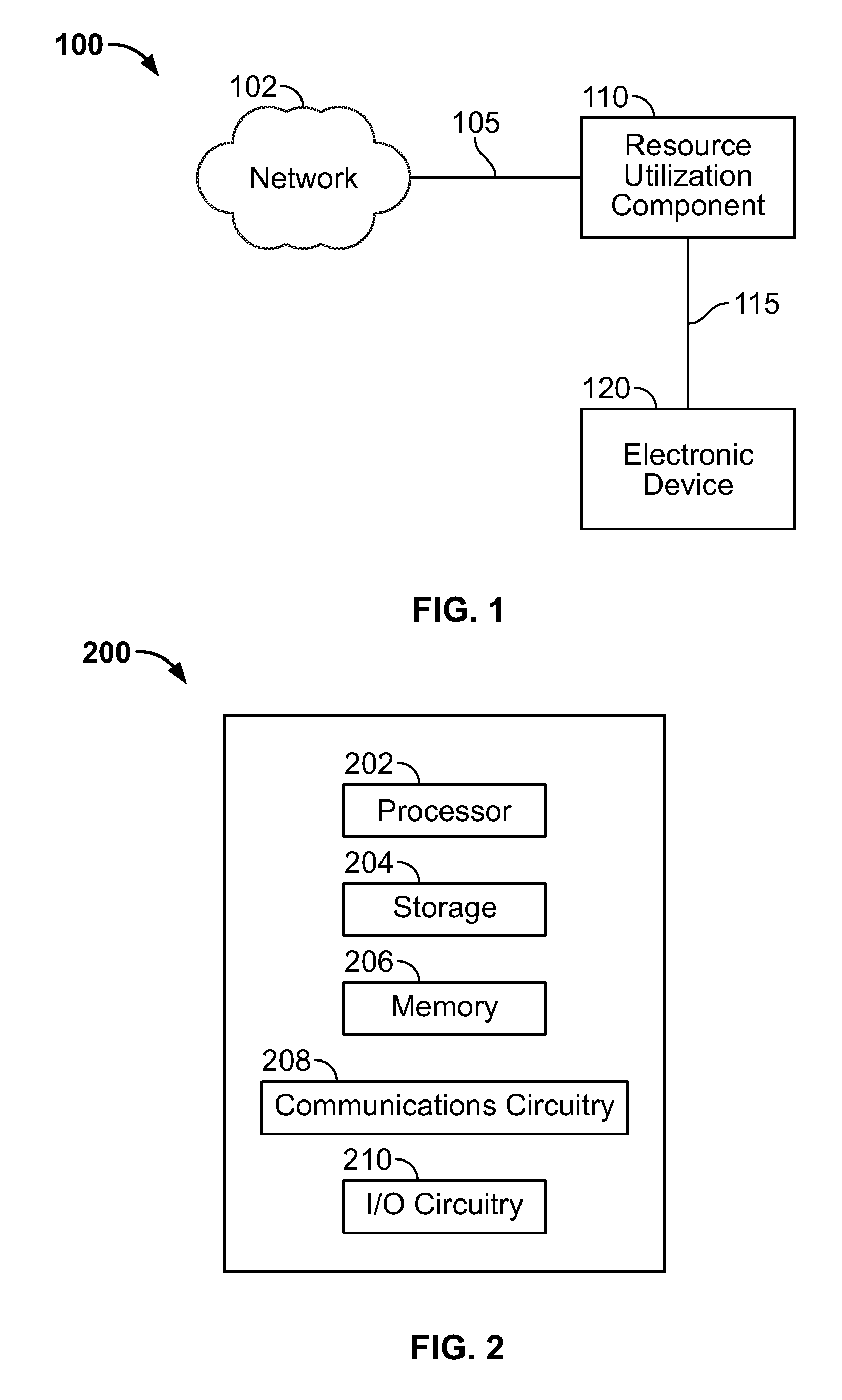

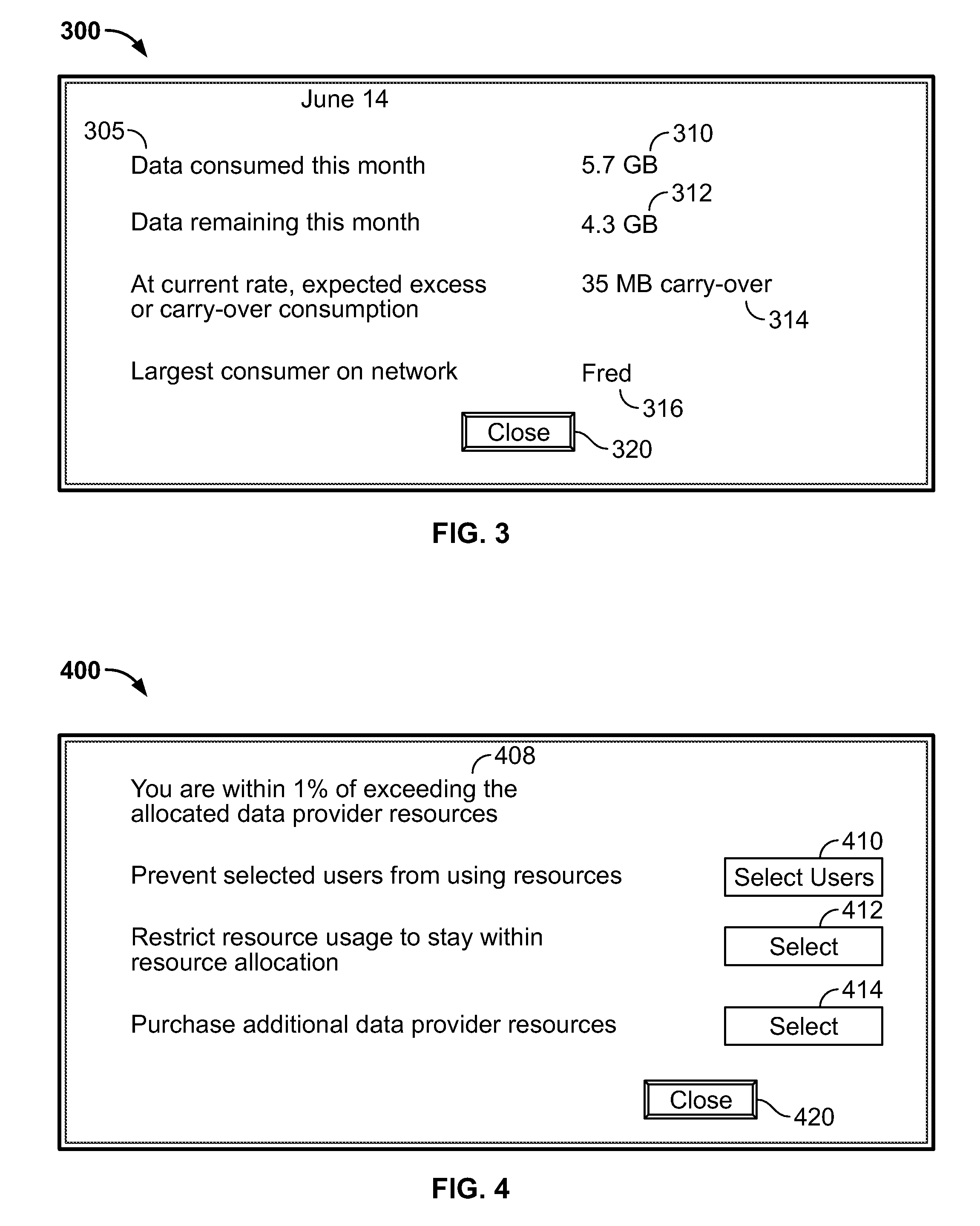

Access to a communications network may be provided via a data provider that may charge for access. In some cases, the access fee may be related to the amount of network resources consumed (e.g., amount of data downloaded or bandwidth used). In some cases, a user may have access to a particular amount of data provider resources and be required to pay an additional fee for using resources in excess of the particular amount. To assist the user in managing his data resource consumption, a resource utilization component may provide different alerts and notices informing the user of current consumption, expected future consumption, and recommendations for reducing data provider resources consumed (e.g., stopping particular processes or data provider requests, such as downloading media). If several electronic devices in a network are connected to the same data provider resources, a network component may manage the data provider resource use among the several electronic devices (e.g., allow only particular users or devices access).

Owner:APPLE INC

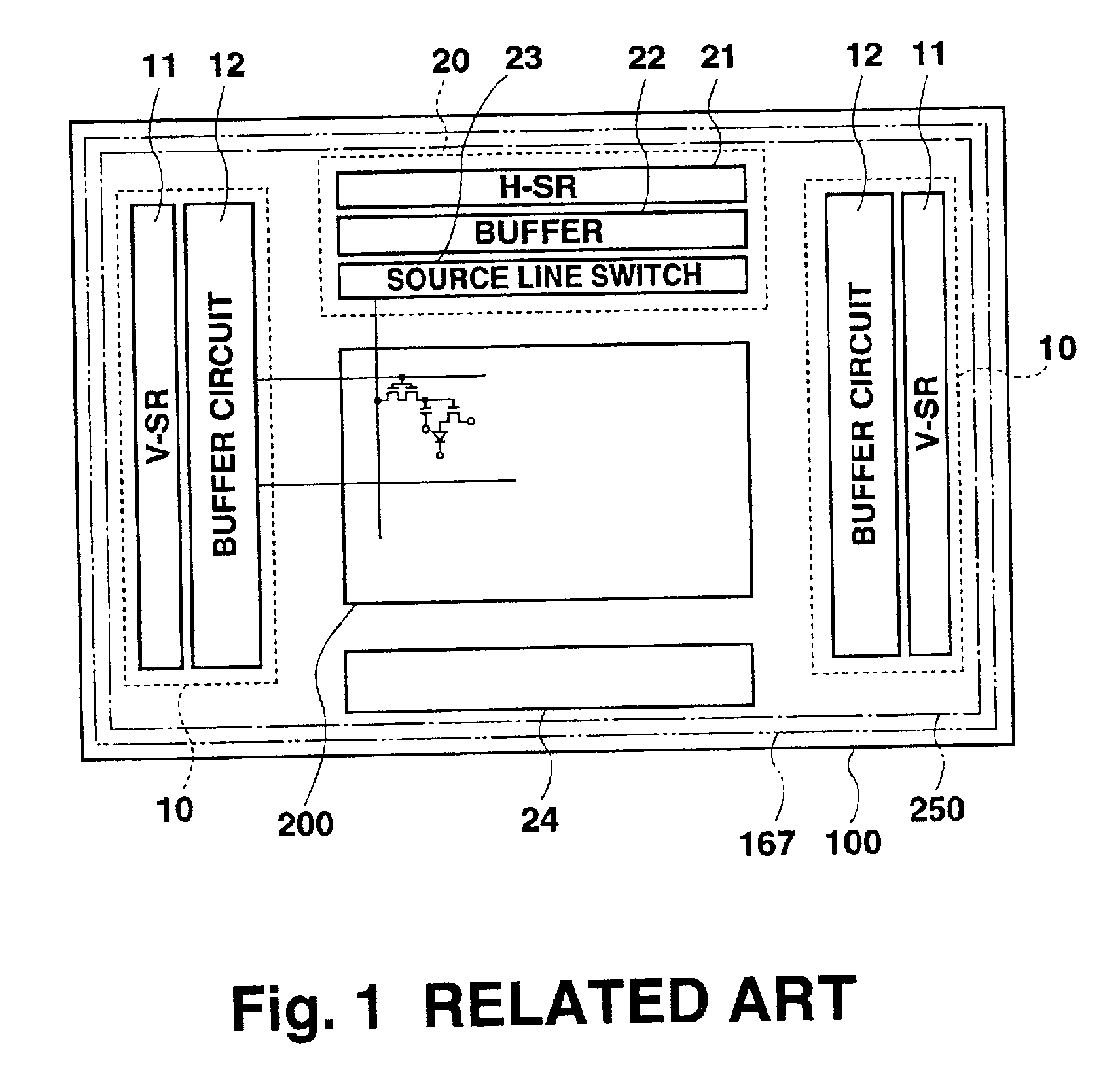

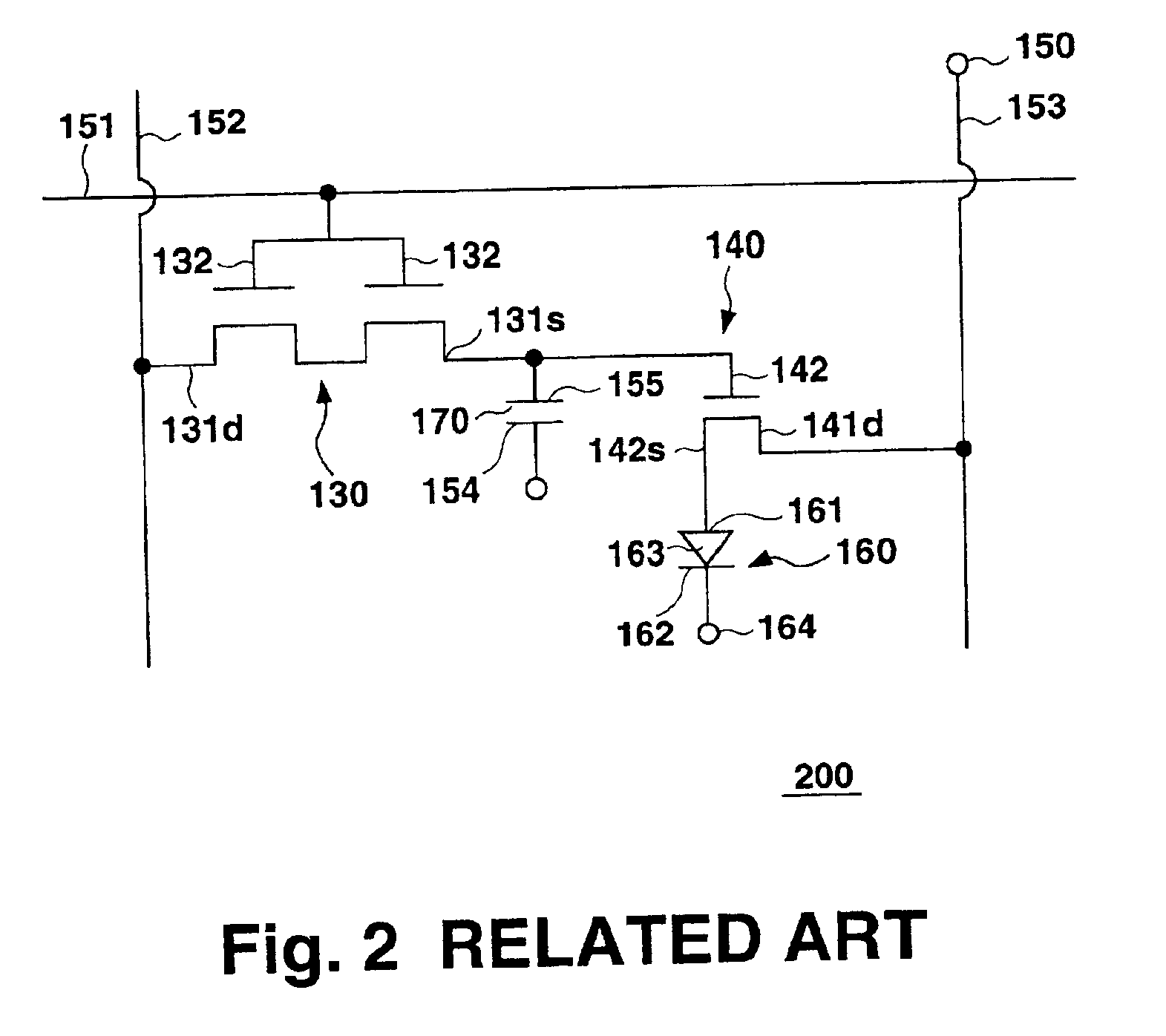

Electroluminescence display device

InactiveUS6940214B1Simple structureInhibition of characteristic changesDischarge tube luminescnet screensElectric discharge tubesDisplay deviceCurrent consumption

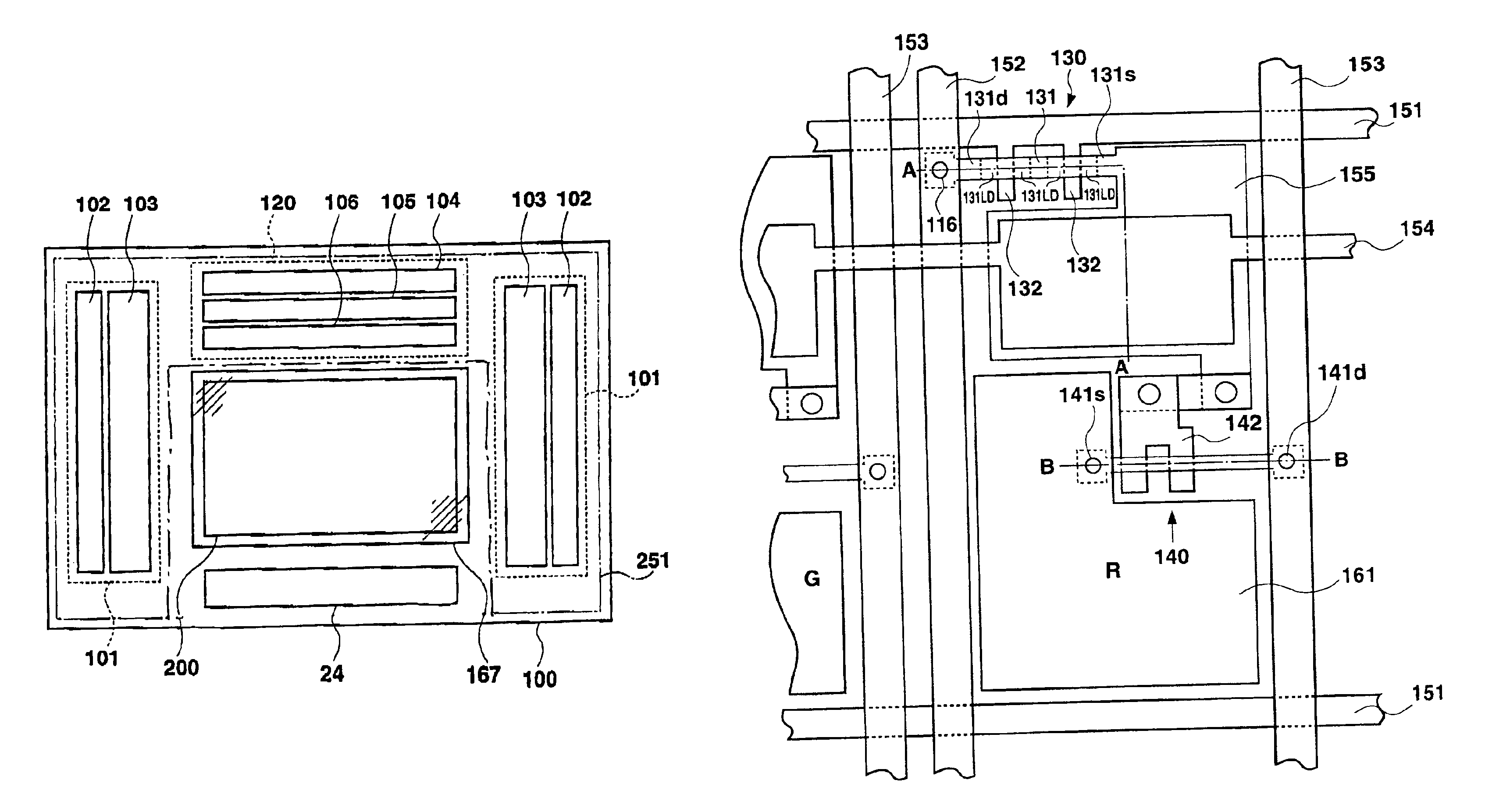

An insulator substrate (110) is provided with a display pixel region (200) comprising an electroluminescence element (160) having a cathode (167), emissive layer (166), and anode (161), and with first and second TFTs for driving the element. Surrounding the display pixel region (200), a peripheral drive circuit region (251) having a third TFT for driving each pixel is further provided on the insulator substrate (110). The cathode (167) is disposed in a region other than the peripheral drive circuit region (251). With this arrangement, generation of a back channel by applying the EL element potential to the cathode is prevented in a complementary TFT employed in the peripheral drive circuit region for controlling the display region, thereby suppressing changes in threshold values due to such back channel generation. As a result, an EL display device with reduced generation of penetration current and minimized increased current consumption is achieved.

Owner:SANYO ELECTRIC CO LTD

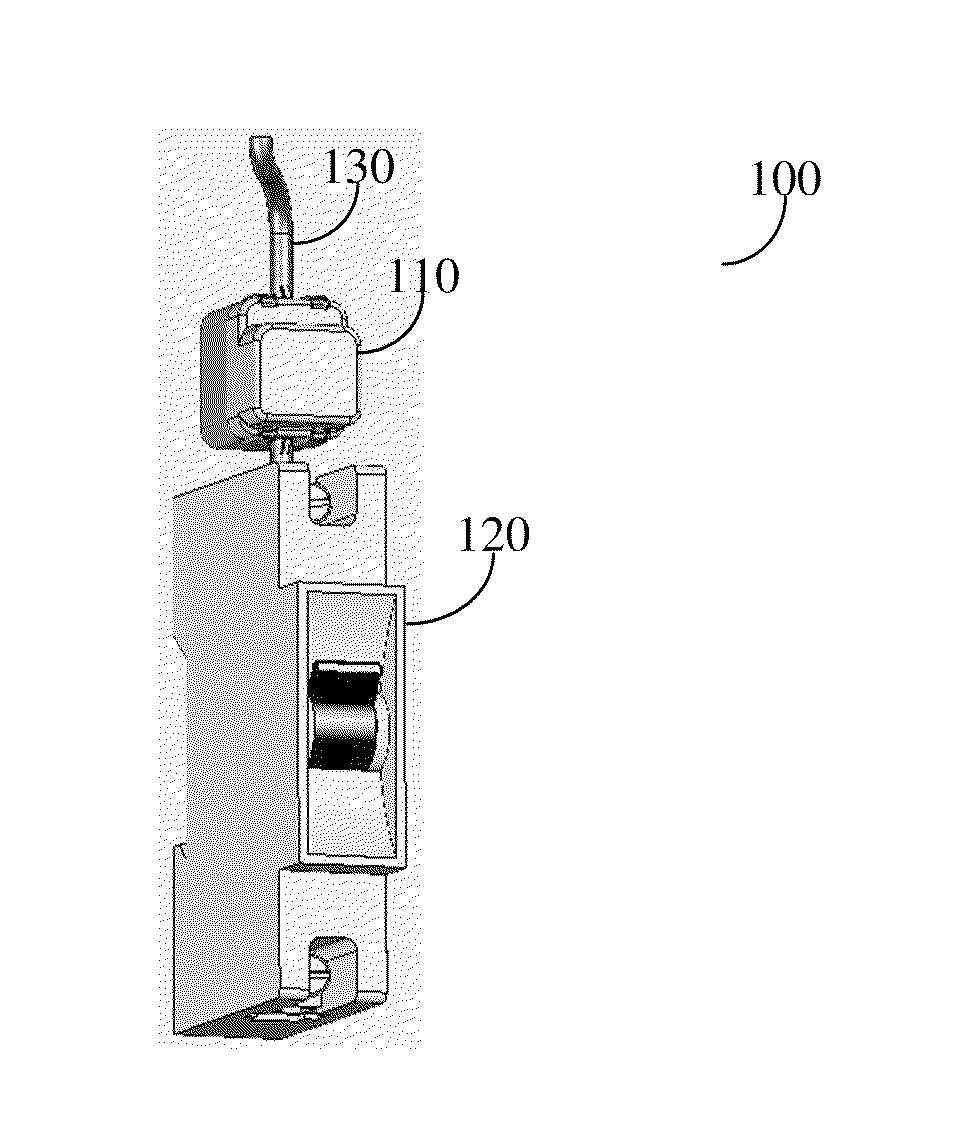

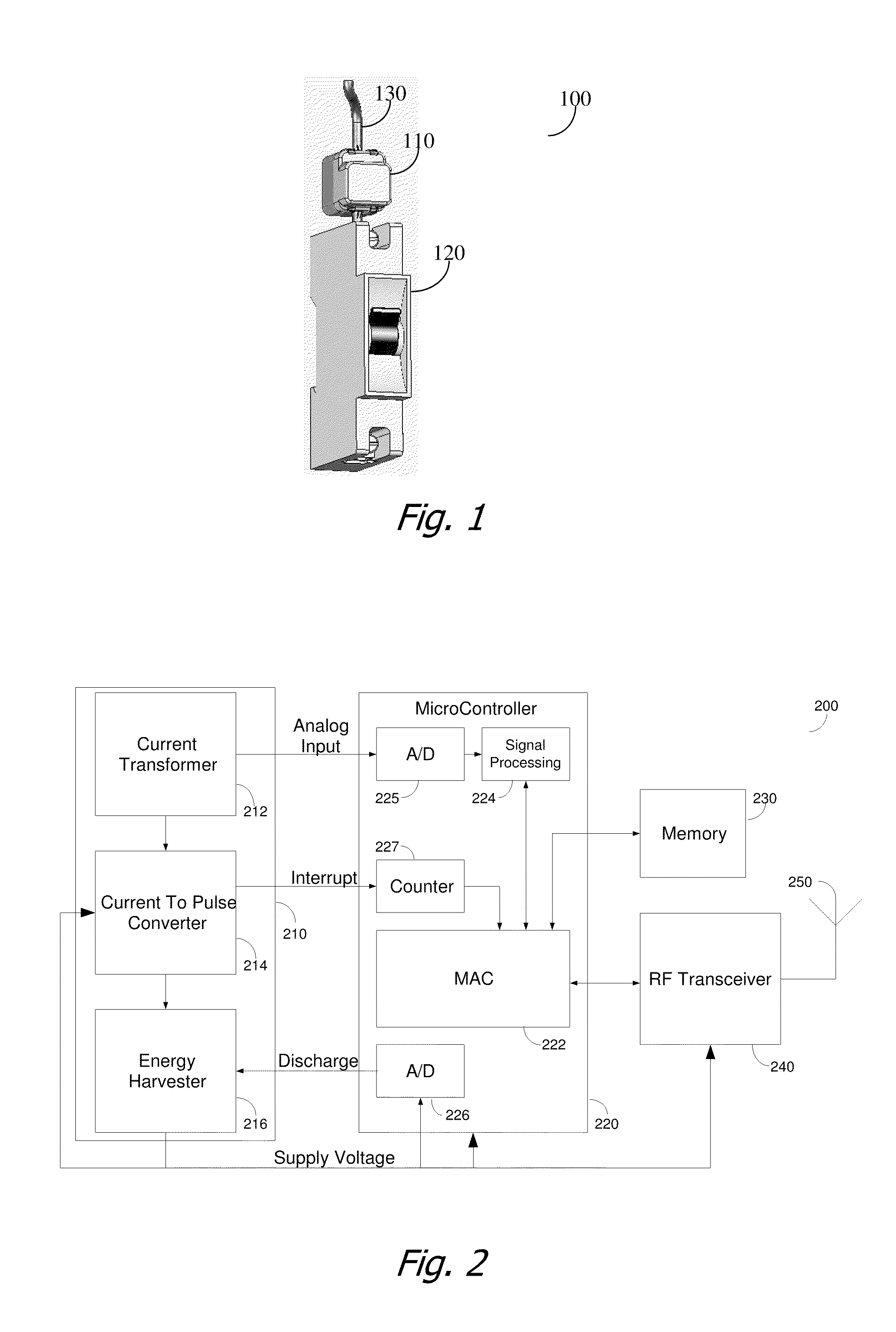

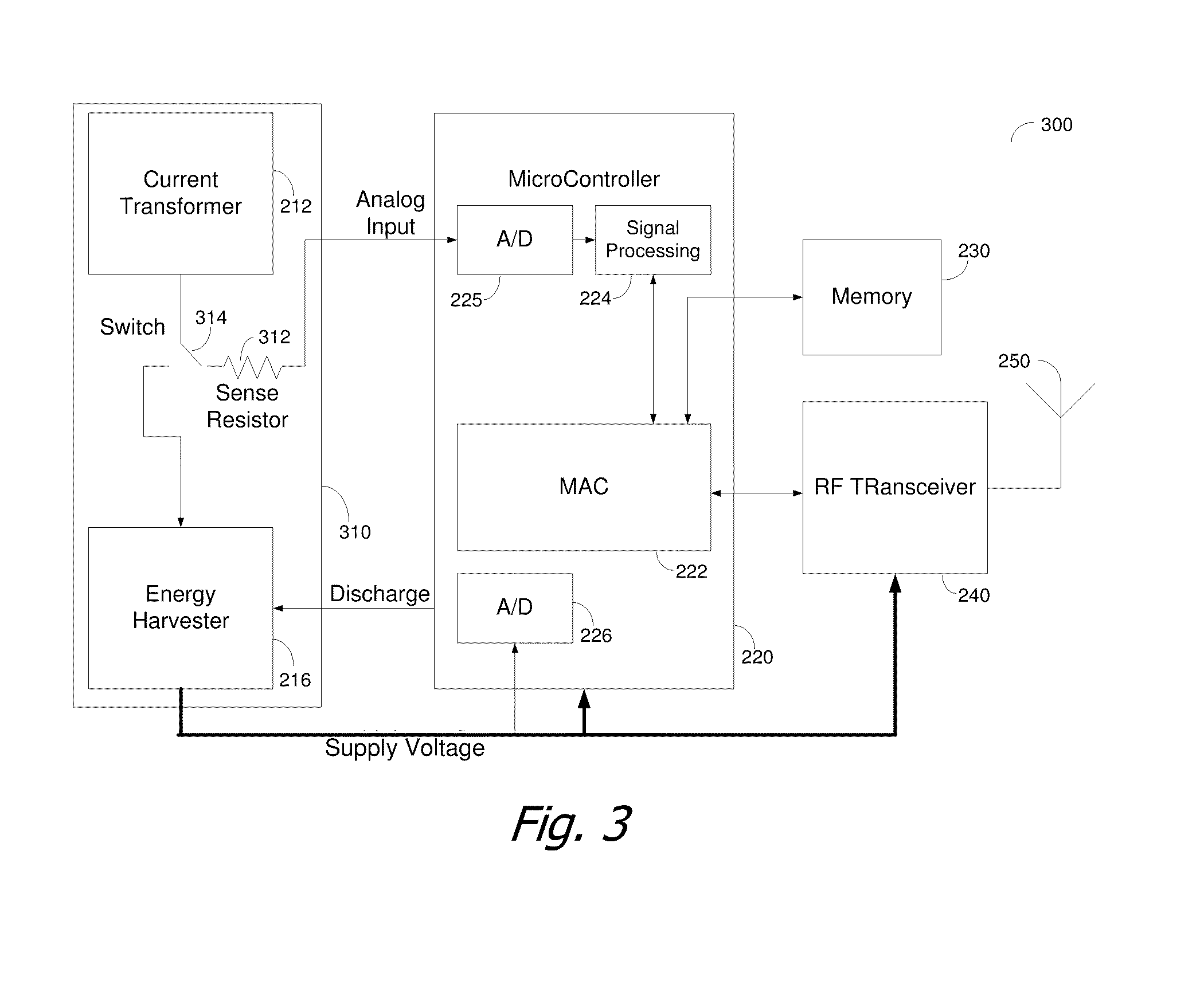

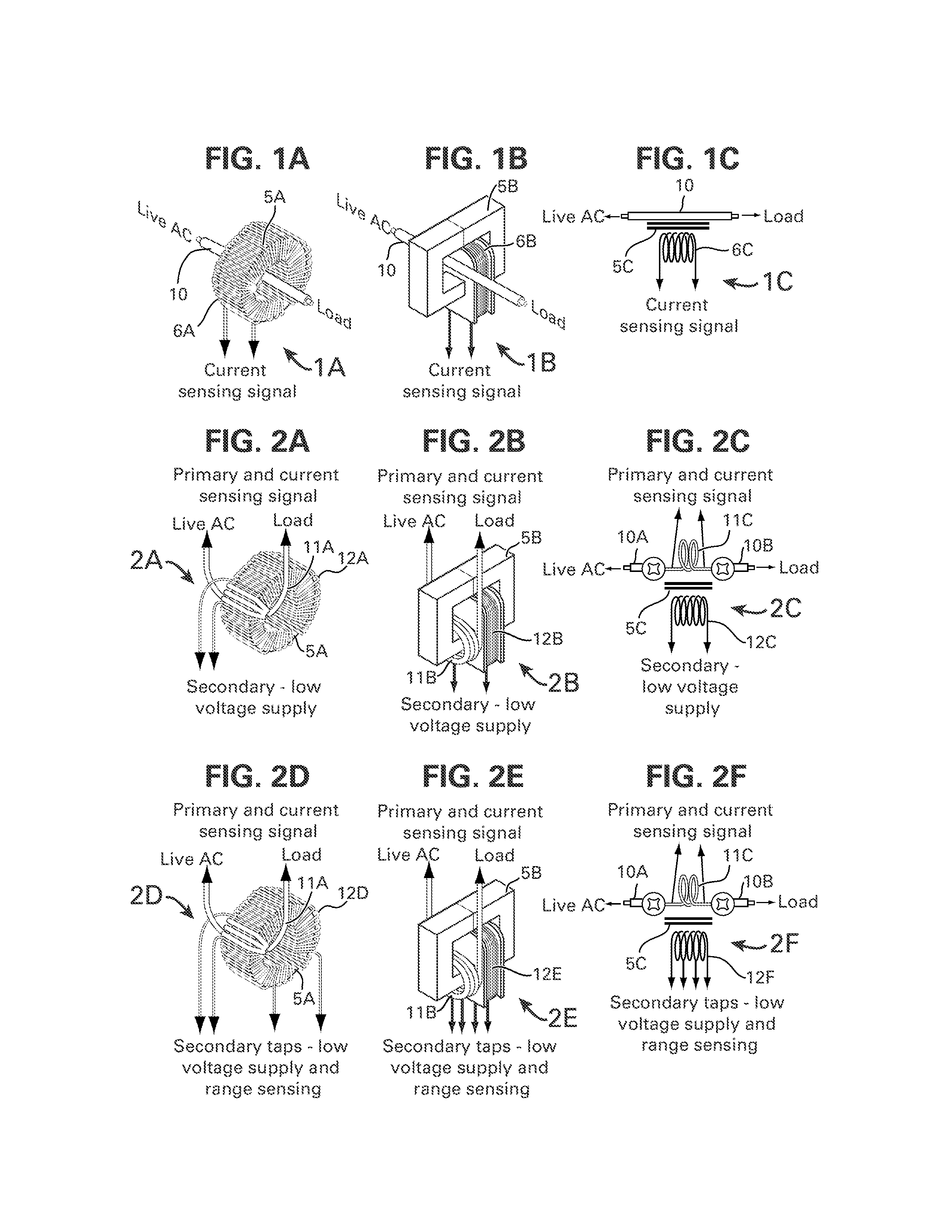

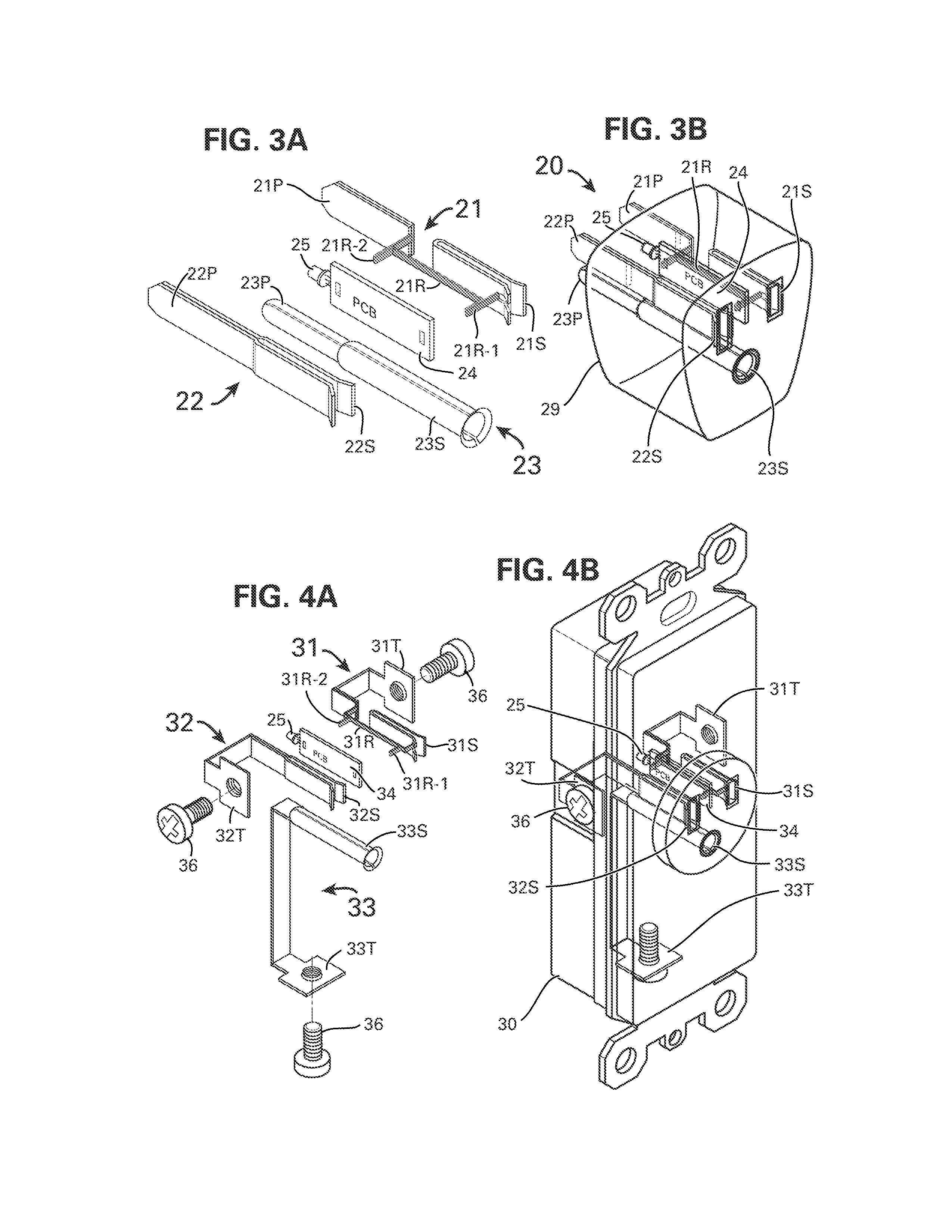

Circuit Tracer

A circuit tracer for use with circuit breakers equipped with sensors capable of sensing at least a change in the power consumption of the circuit and transmitting, preferably wirelessly, such information. The information is received directly or indirectly by a circuit tracer having a display, the display showing all the circuit breakers equipped with the sensors. Upon changing the load of an electricity outlet, such as a wall outlet, a light source, HVAC, pump, electrical machinery, etc., the sensor equipped circuit breaker provides an indication of such power or current consumption change to the circuit tracer. This allows the user of the circuit tracer to associate on the circuit tracer the circuit breaker with the specific electricity outlet. The association information may be saved on a central server or database for future use.

Owner:PANORAMIC POWER

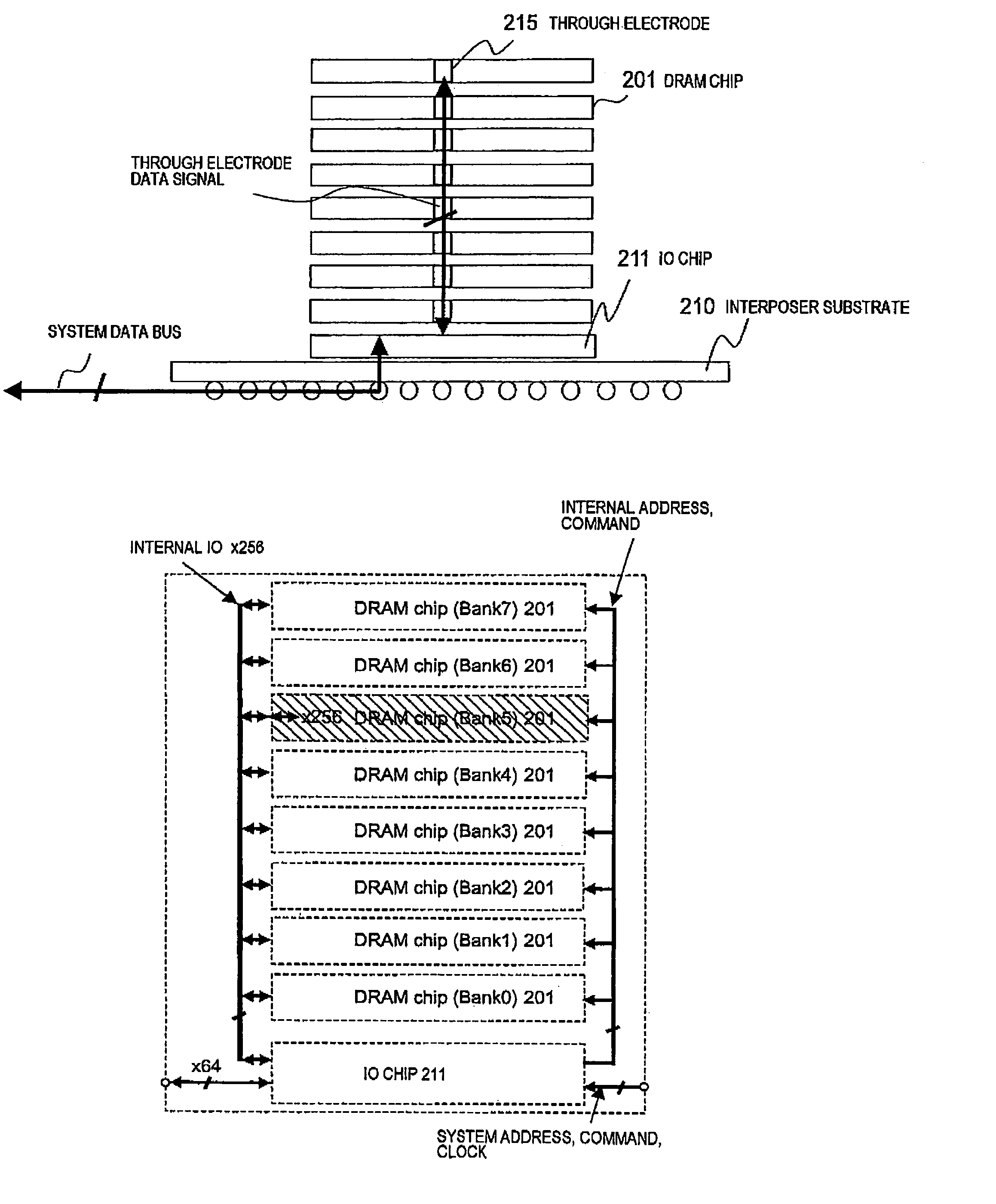

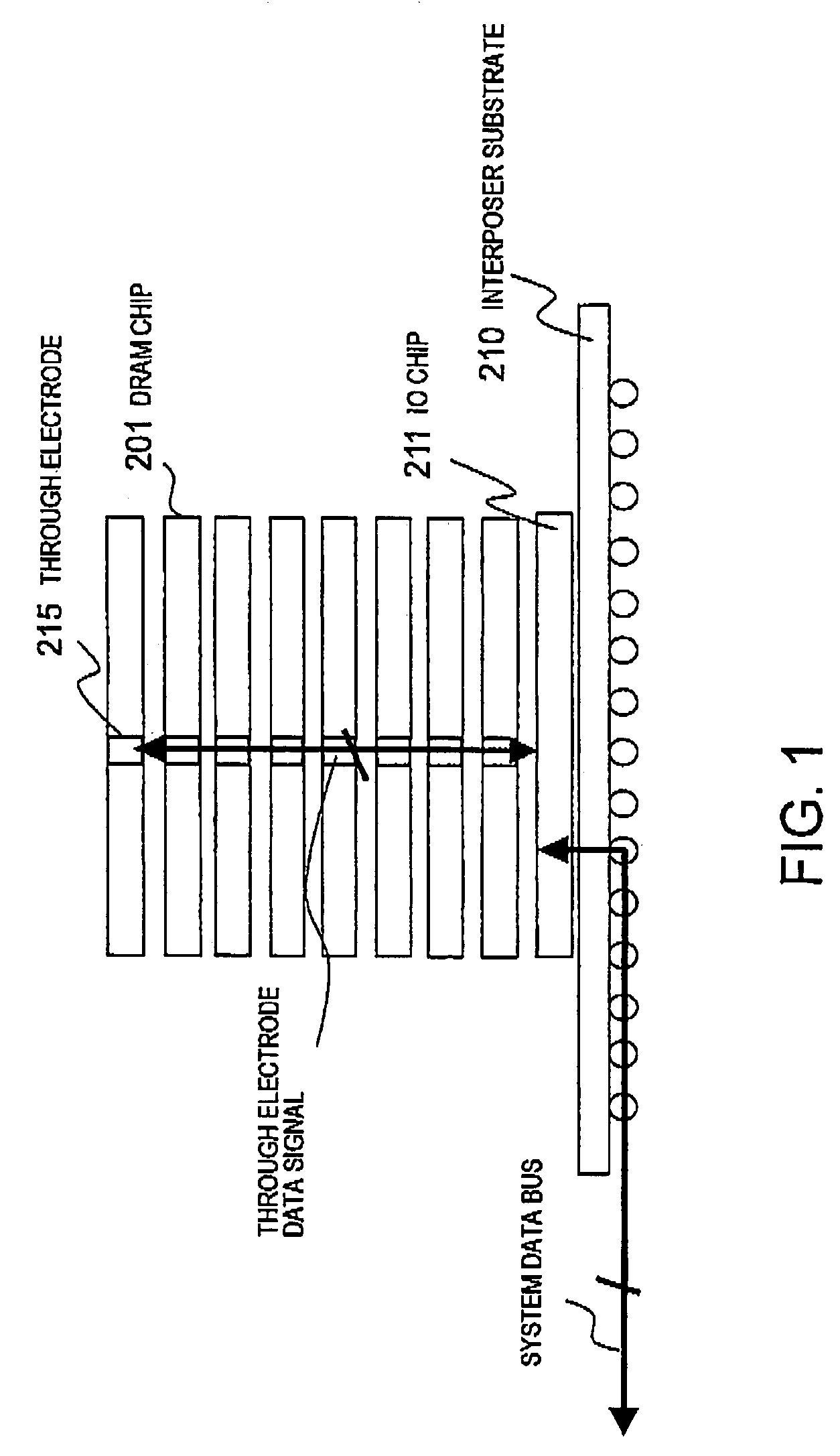

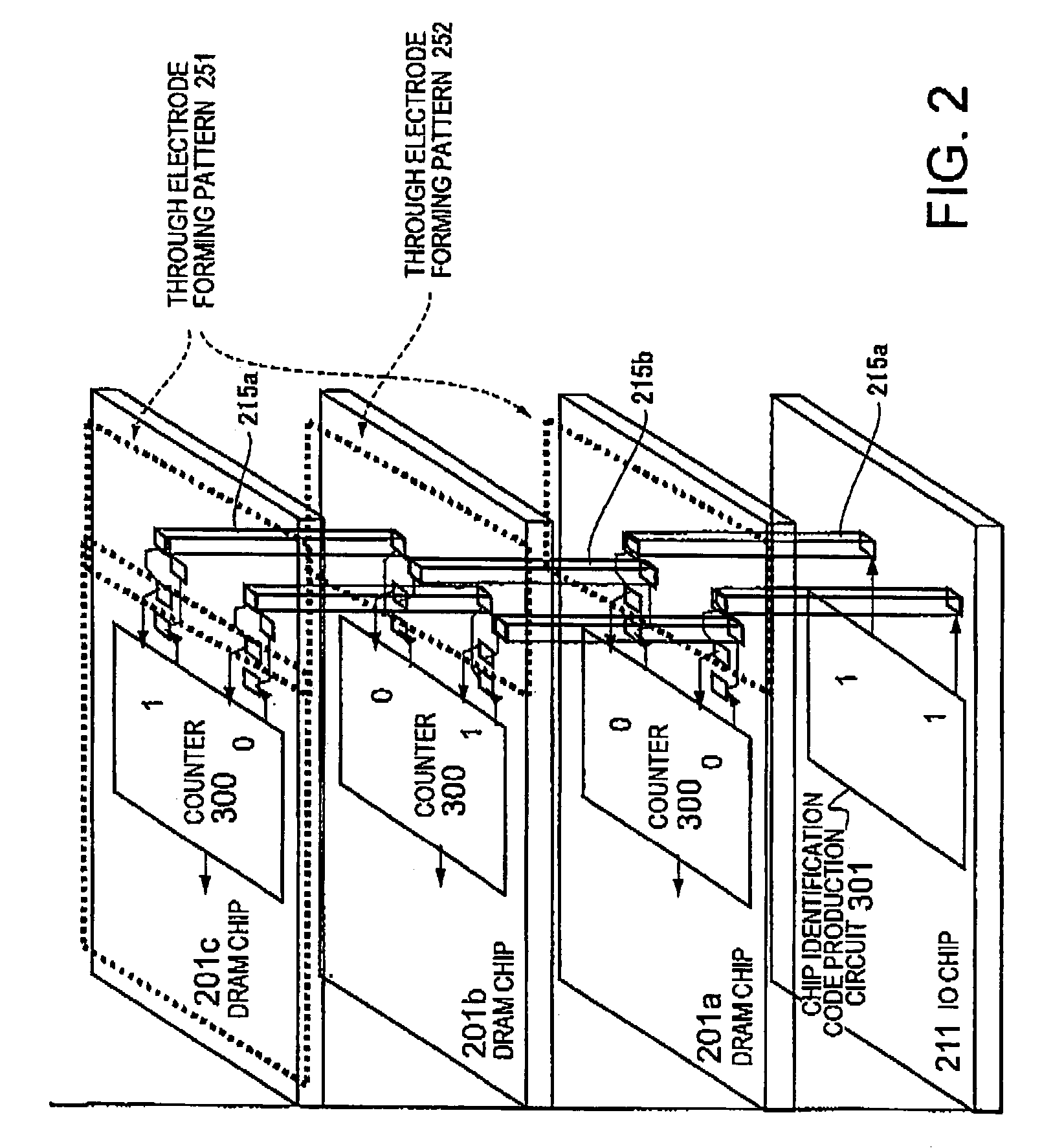

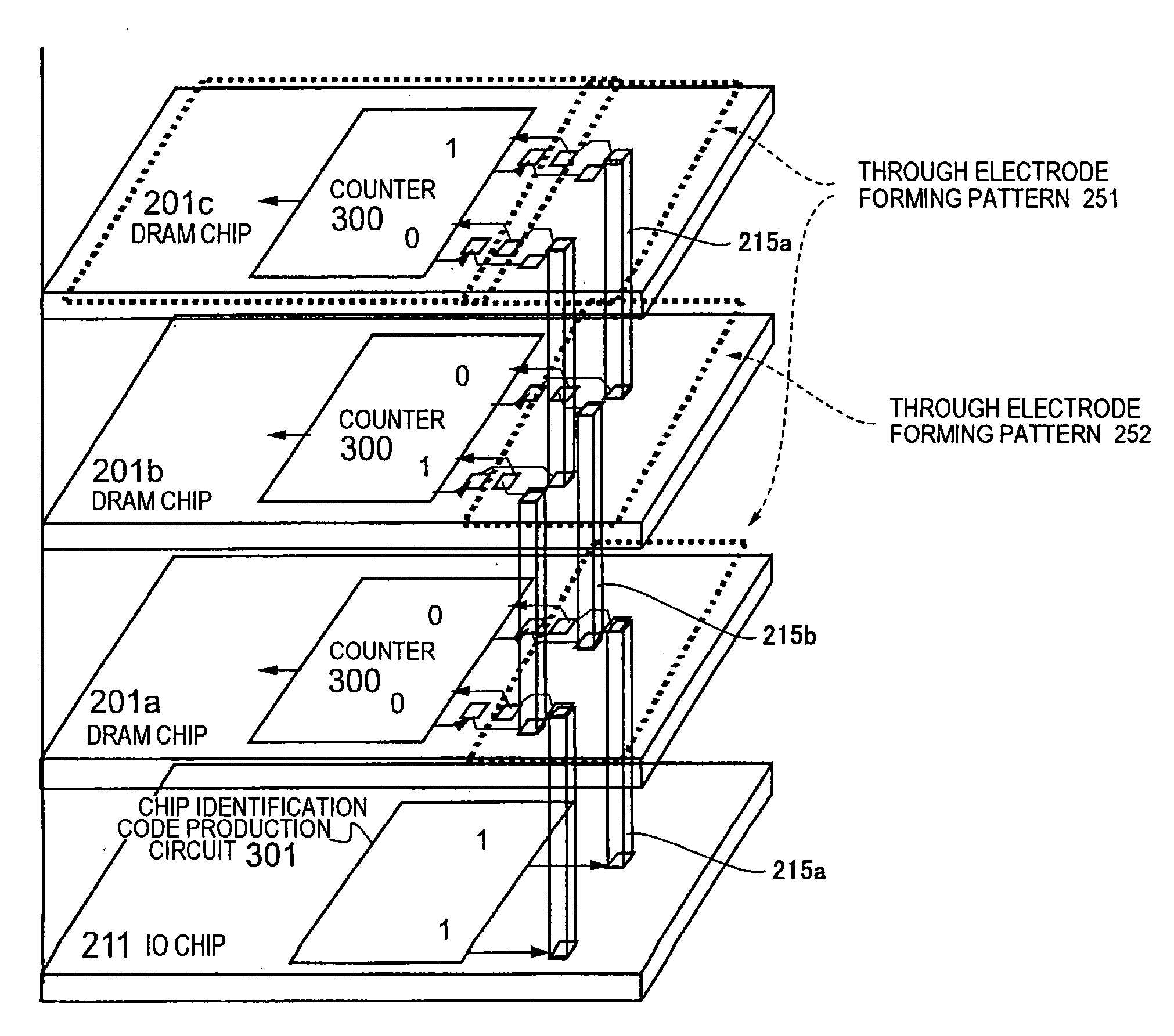

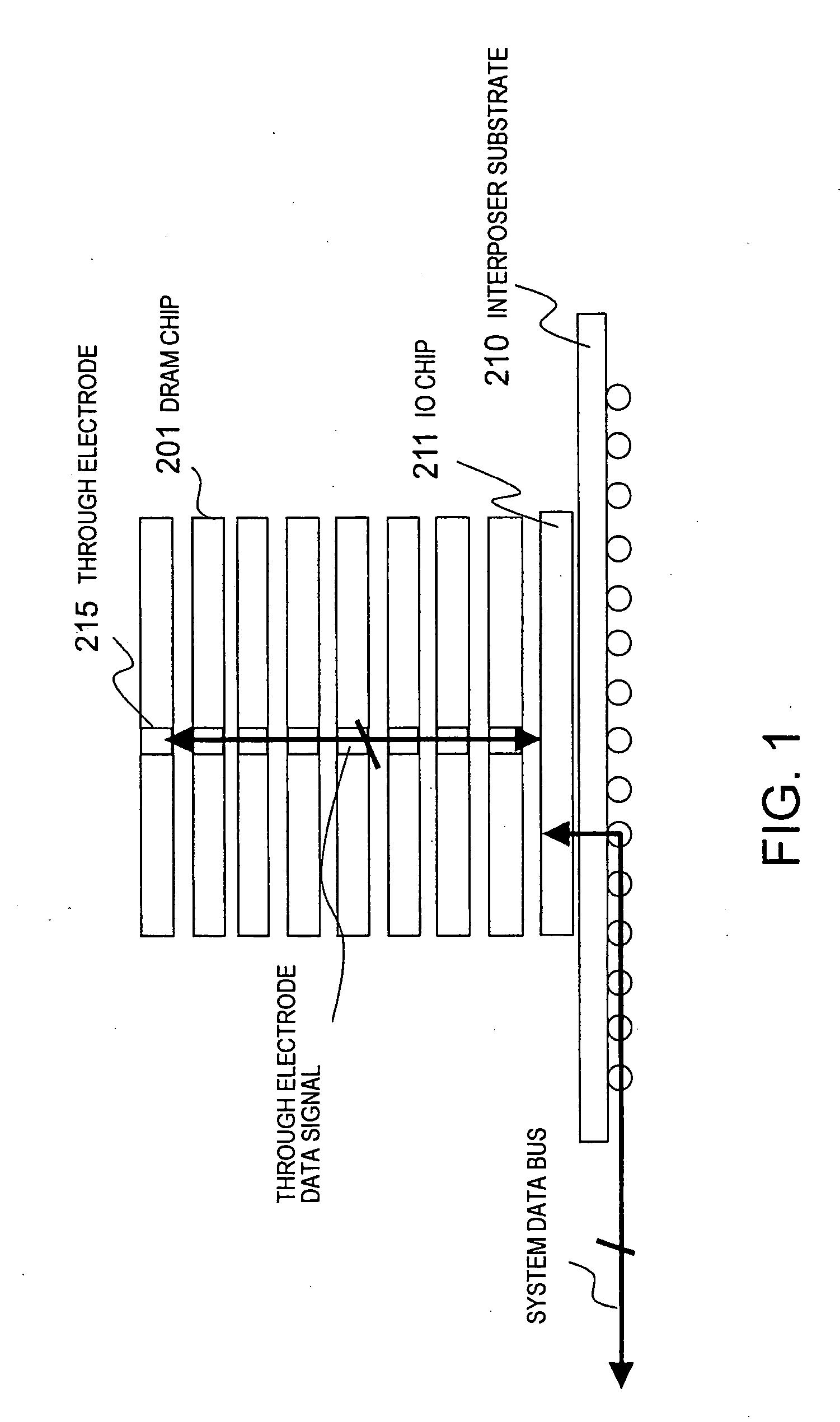

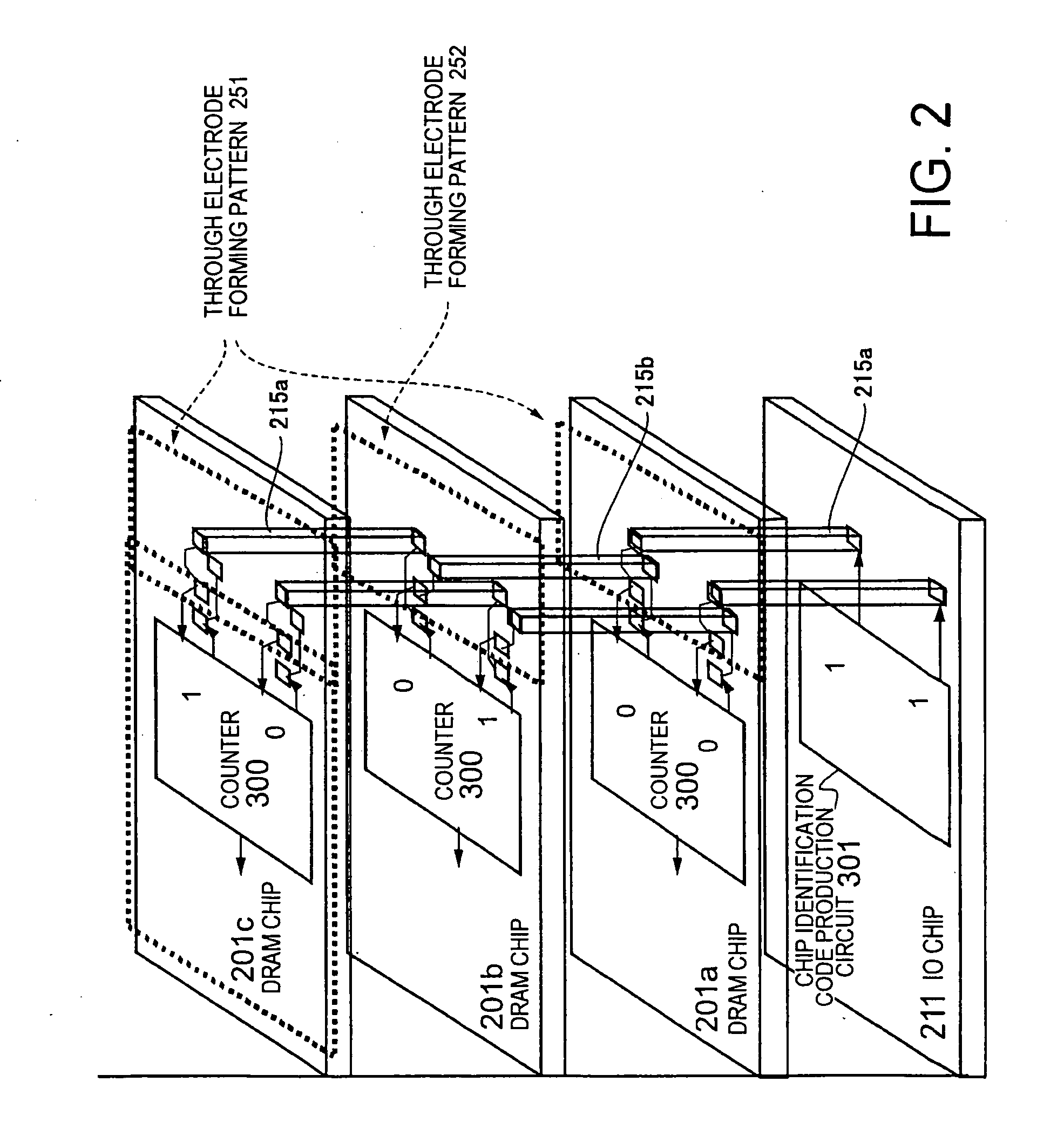

Memory module and memory system

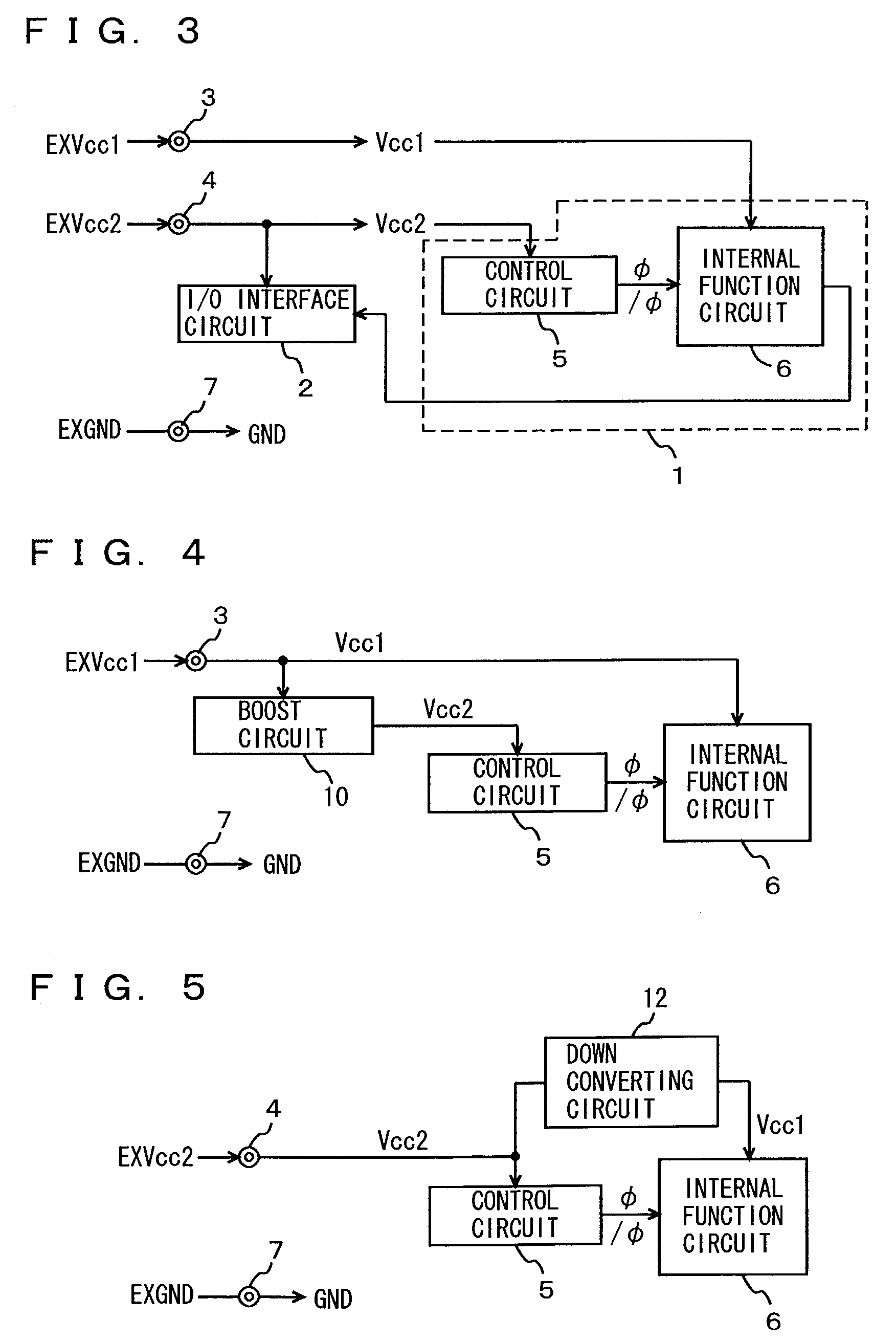

ActiveUS7123497B2Increase chanceVarious problemDomestic stoves or rangesLighting and heating apparatusData signalComputer module

In a memory module including a plurality of DRAM chips which transmit / receive a system data signal with a predetermined data width and at a transfer rate and which transmit / receive an internal data signal having a larger data width and a lower transfer rate as compared with the system data signal, it has become clear that there is a restriction on the transfer rate of the system data signal and that speeding-up cannot be expected. A current consumption in a plurality of DRAMs constituting the memory module is large, and this is also a factor for hindering the speeding-up. There is obtained a memory module in which a plurality of DRAM chips are stacked on an IO chip and in which each DRAM chip is connected to the IO chip by a through electrode and which comprises a constitution for mutually converting the system data signal and the internal data signal in each DRAM chip by the IO chip. In this constitution, a wiring between the DRAM chips can be shortened, and DLL having a large current consumption may be disposed only on the IO chip.

Owner:LONGITUDE LICENSING LTD

Systems and methods for monitoring data and bandwidth usage

ActiveUS8706863B2Assess restrictionData switching by path configurationResource utilizationData provider

Access to a communications network may be provided via a data provider that may charge for access. In some cases, the access fee may be related to the amount of network resources consumed (e.g., amount of data downloaded or bandwidth used). In some cases, a user may have access to a particular amount of data provider resources and be required to pay an additional fee for using resources in excess of the particular amount. To assist the user in managing his data resource consumption, a resource utilization component may provide different alerts and notices informing the user of current consumption, expected future consumption, and recommendations for reducing data provider resources consumed (e.g., stopping particular processes or data provider requests, such as downloading media). If several electronic devices in a network are connected to the same data provider resources, a network component may manage the data provider resource use among the several electronic devices (e.g., allow only particular users or devices access).

Owner:APPLE INC

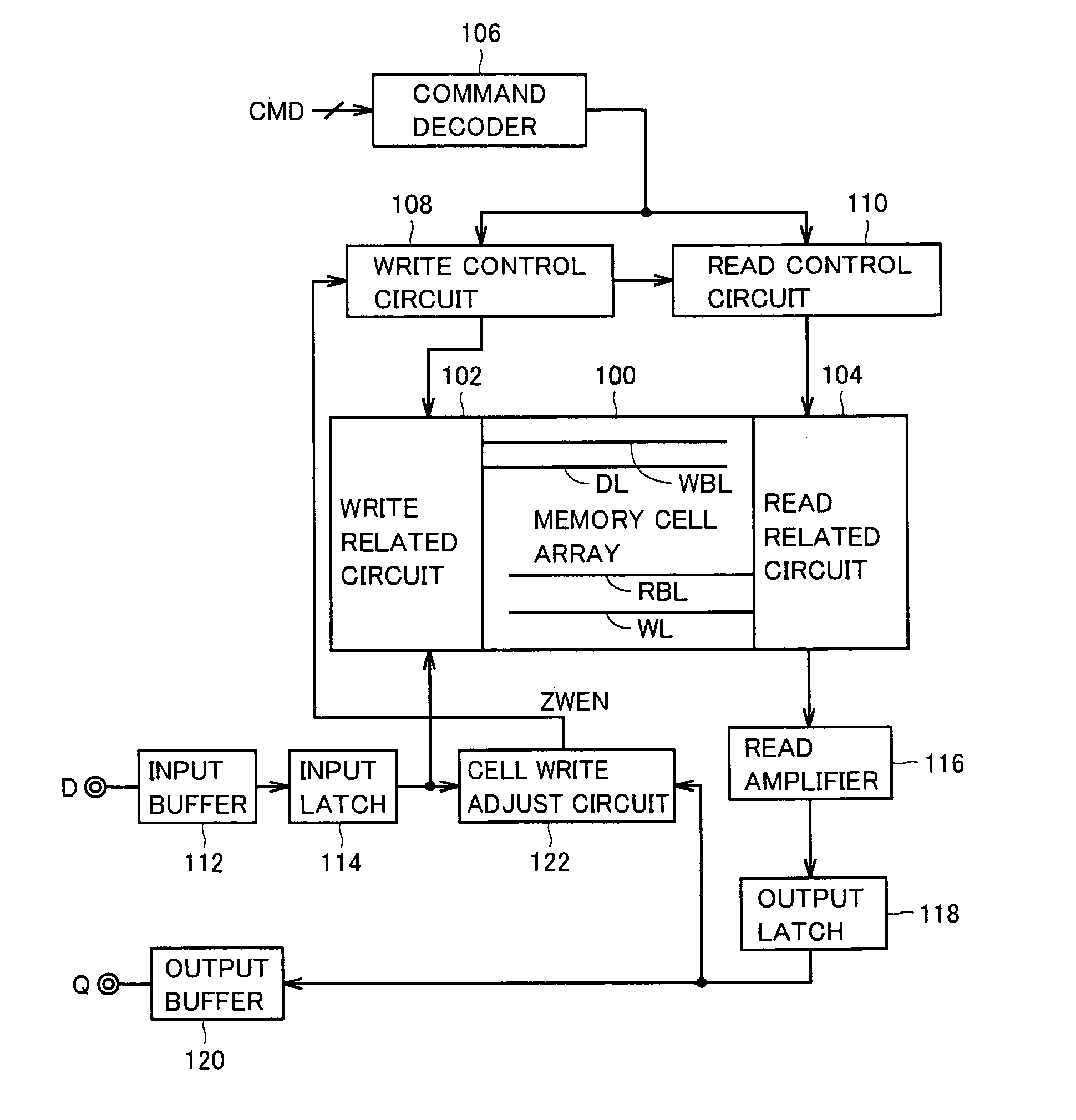

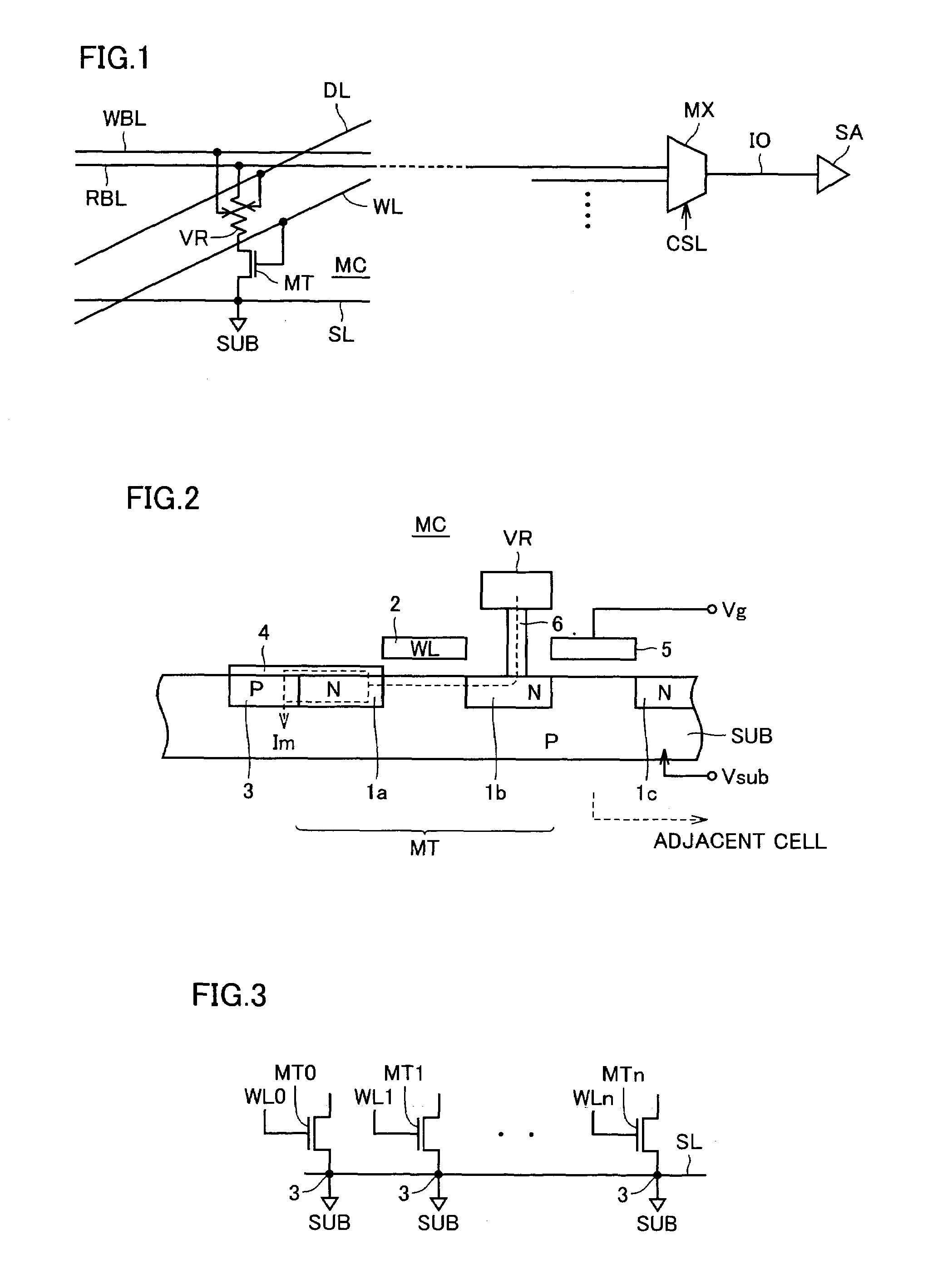

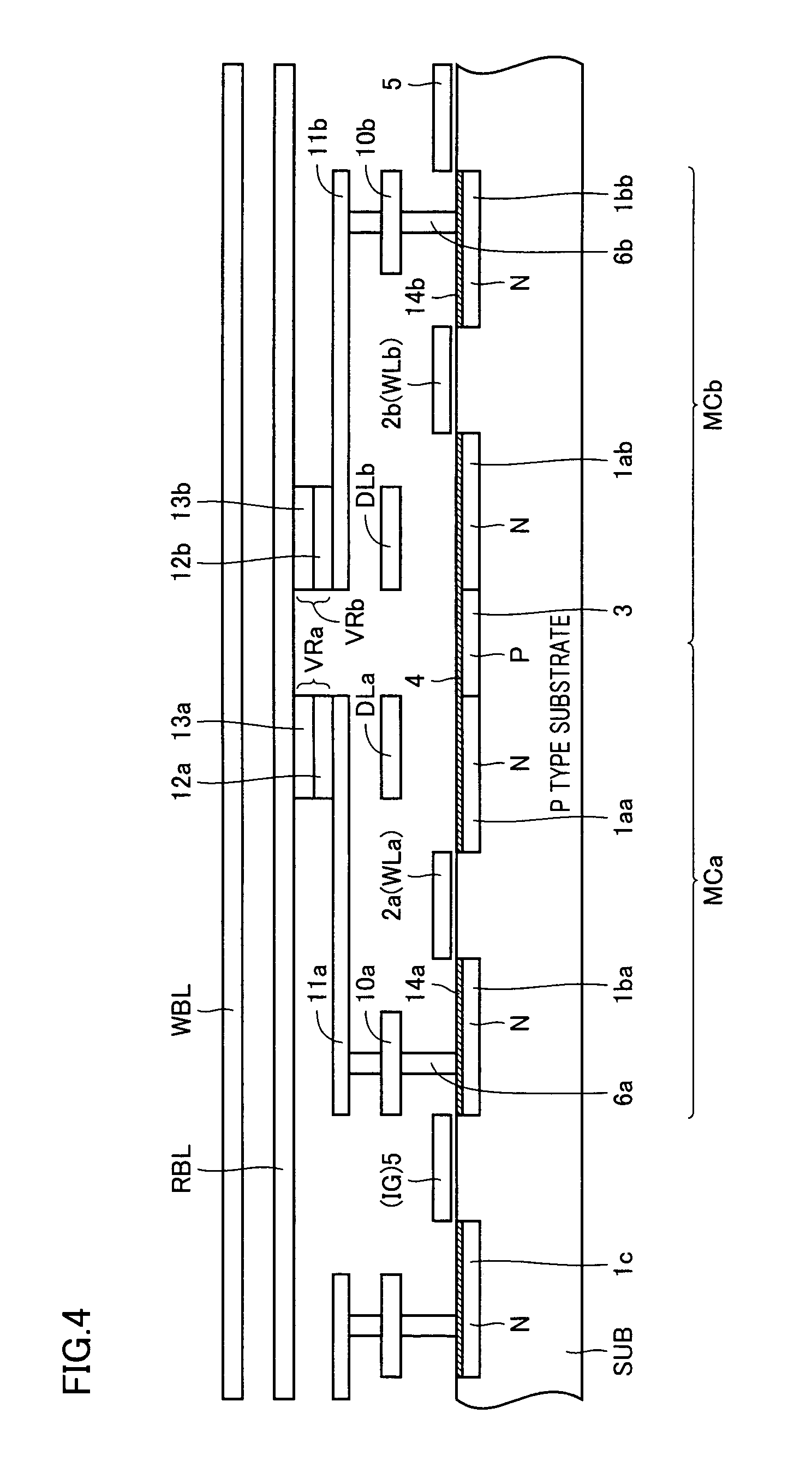

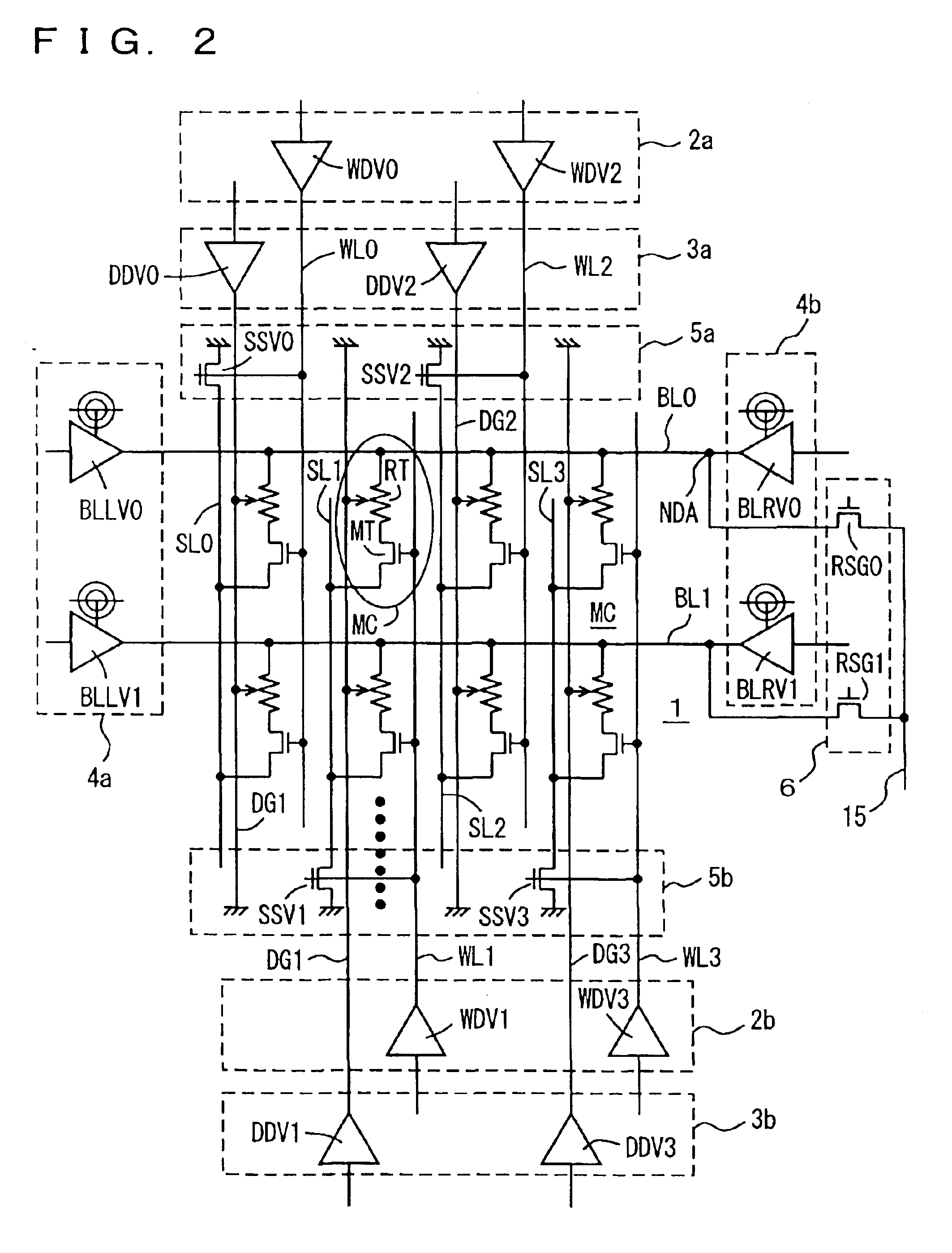

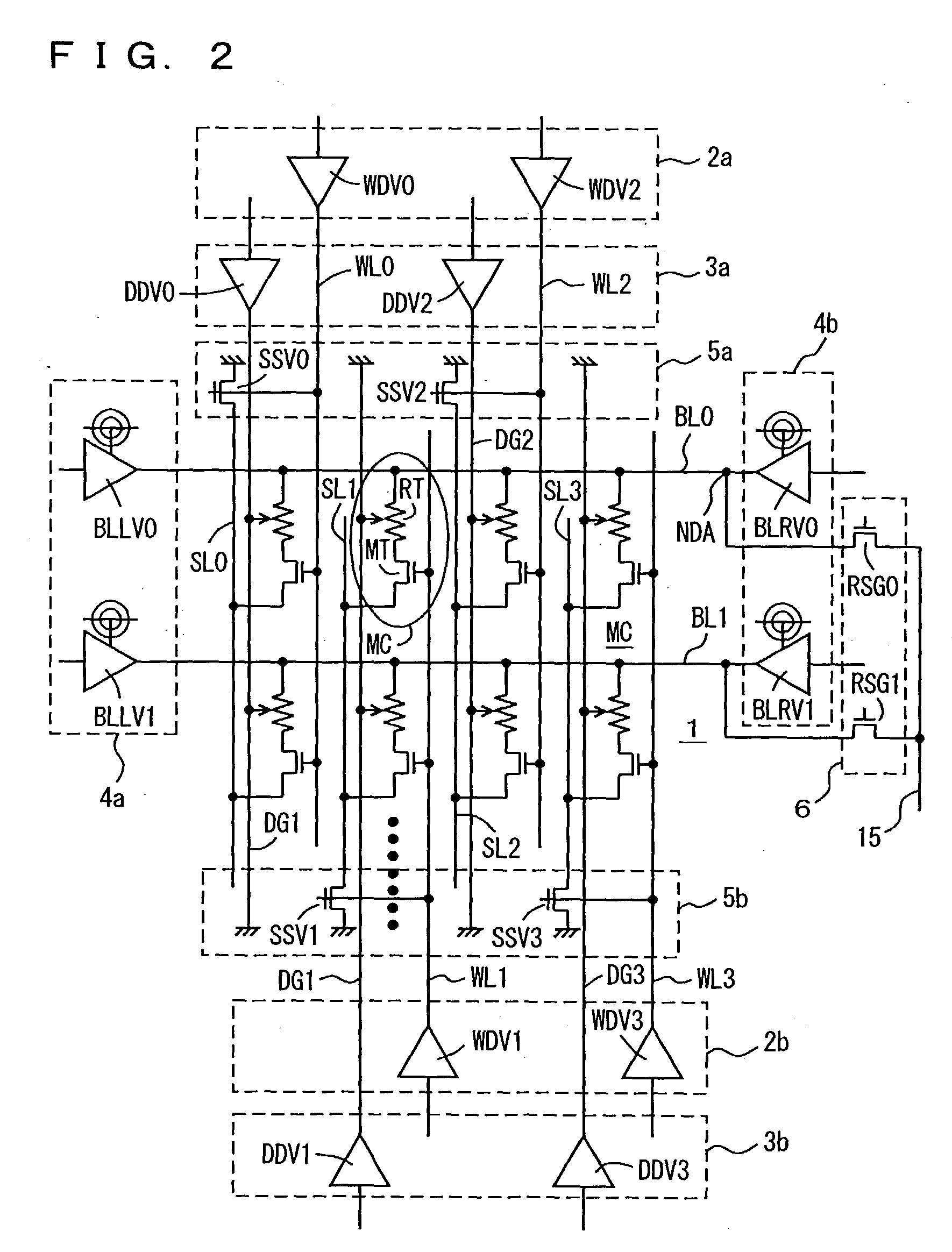

Non-volatile semiconductor memory device allowing concurrent data writing and data reading

A write bit line and a read bit line are provided separately for a memory cell. A source line connecting to the memory cell is formed of a source impurity region the same in conductivity type as a substrate region. A memory cell transistor and the source impurity region are connected by a metal interconnection line of a low resistance. A rise in the source line potential can be prevented, and a memory cell current can reliably be generated according to storage data. Further, fast data reading can be achieved. Additionally, by performing precharging and data amplification in a unit of read bit line, the load of the read bit line can be alleviated to achieve fast reading. An accessing time of a non-volatile semiconductor memory device that uses a variable resistance element as a storage element is reduced without increasing the current consumption.

Owner:RENESAS ELECTRONICS CORP

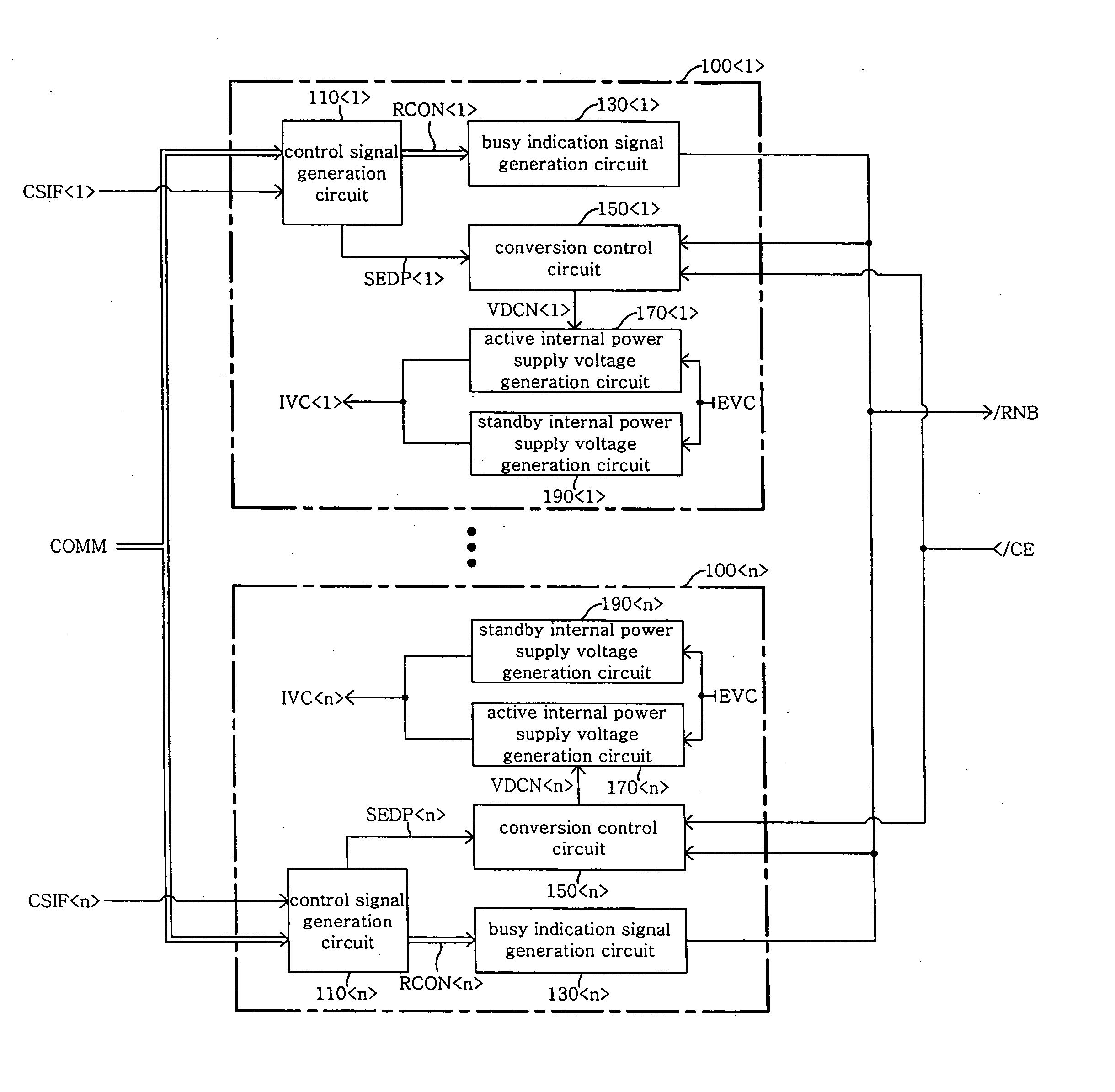

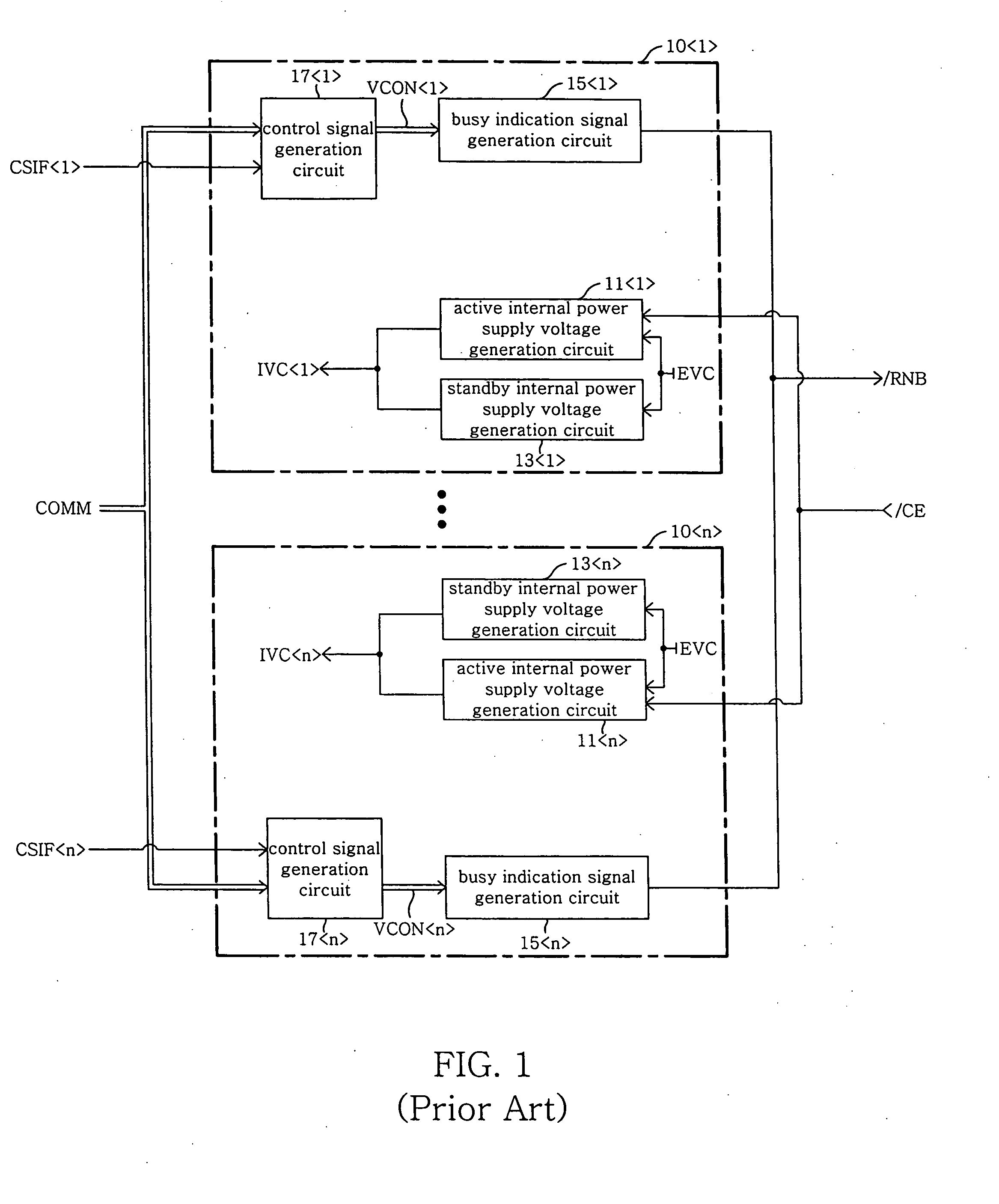

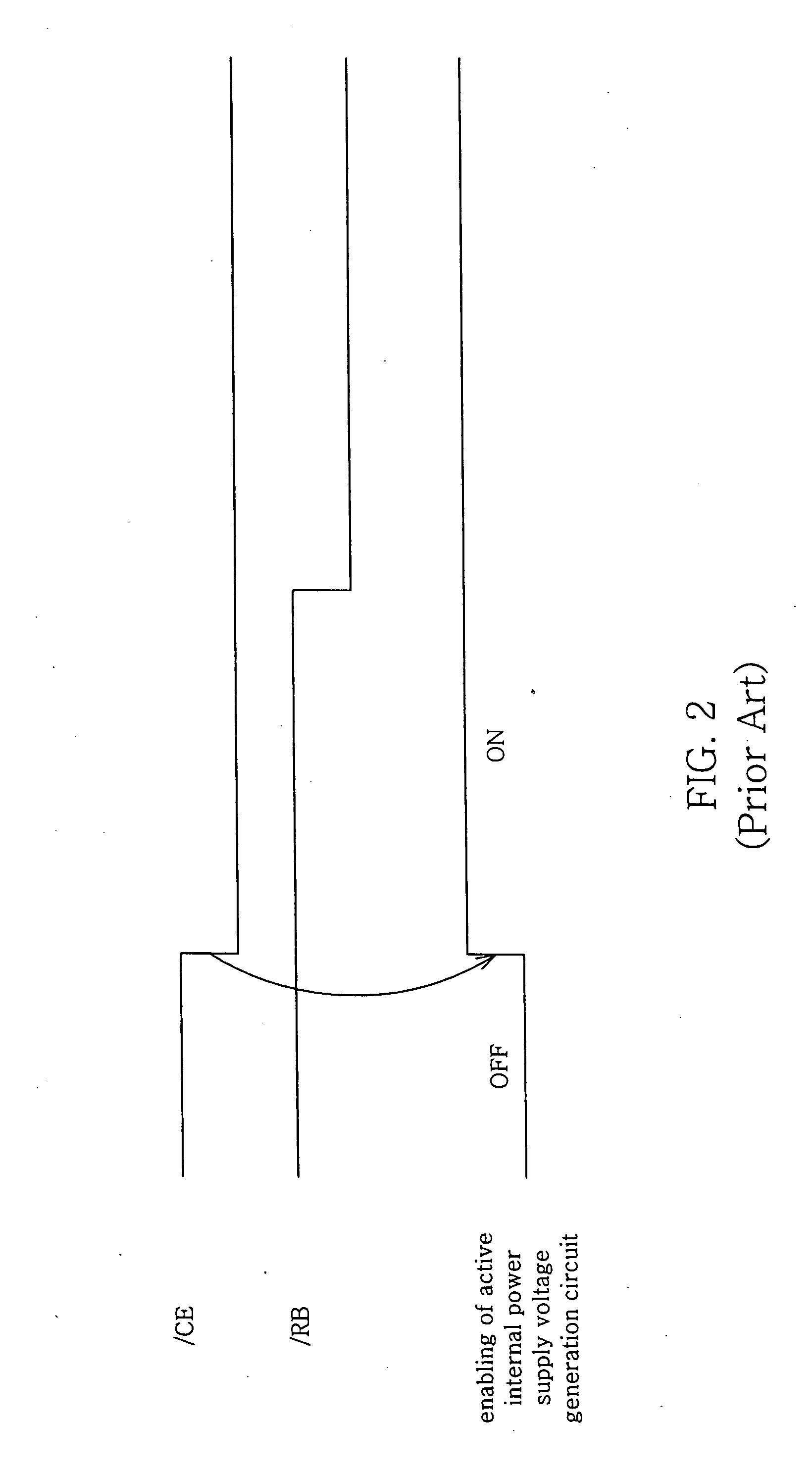

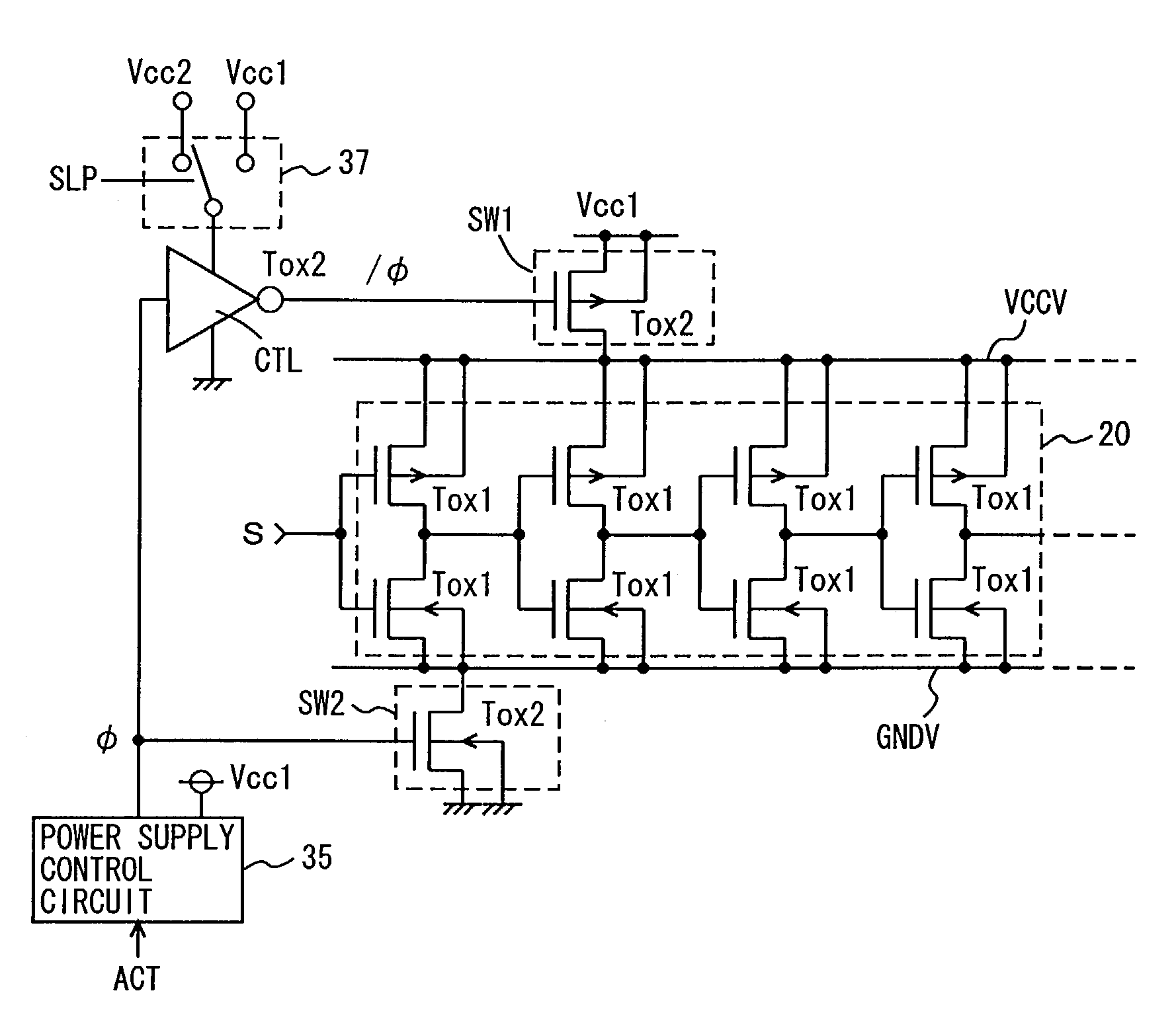

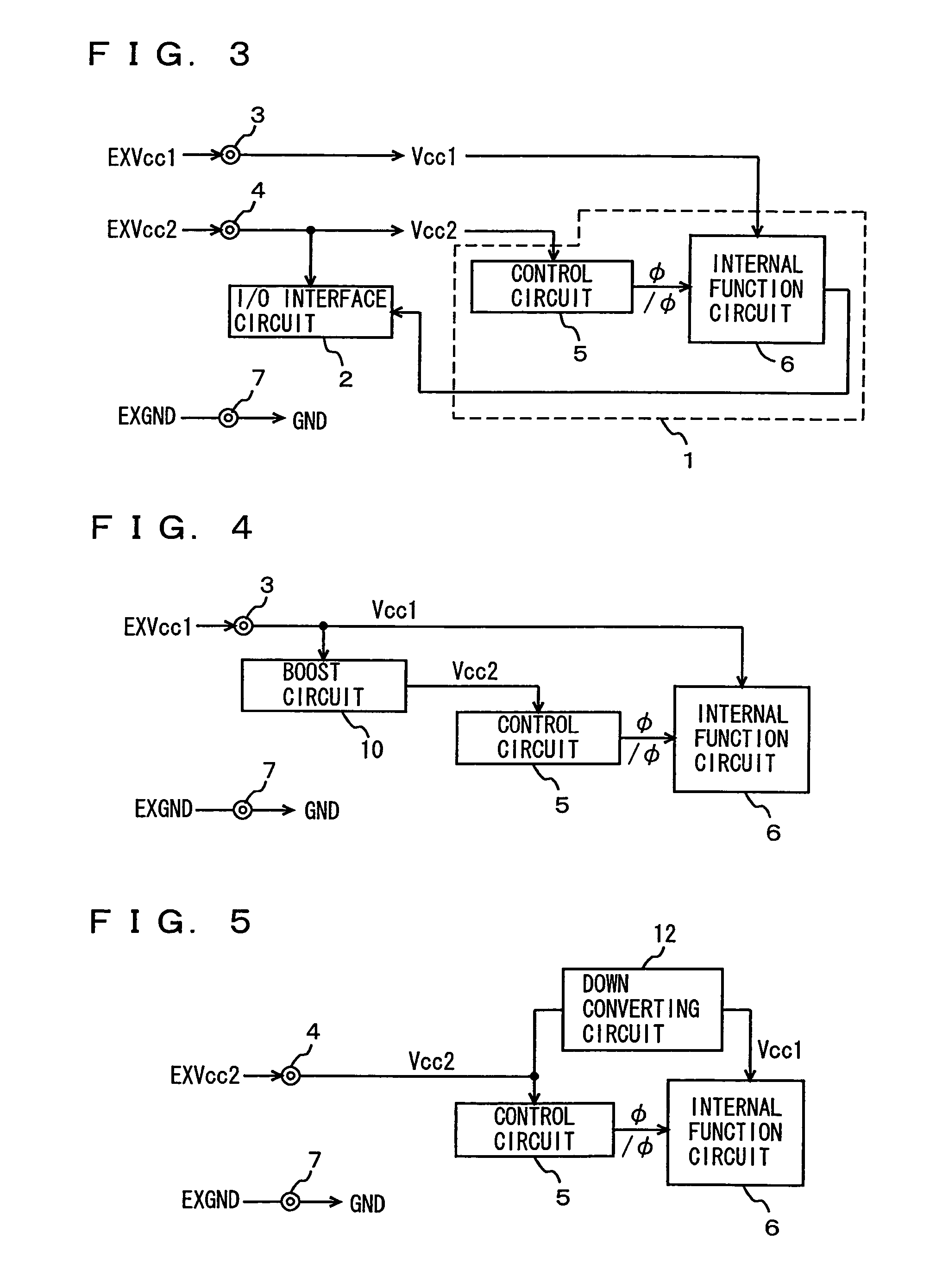

Multi-chip semiconductor memory device having internal power supply voltage generation circuit for decreasing current consumption

A multi-chip semiconductor memory device may comprise of a plurality of memory chips sharing a predetermined chip enable signal. Each of the plurality of memory chips may comprise of an active internal power supply generation circuit configured to convert an external power supply voltage into an internal power supply voltage and to be disabled in response to deactivation of a predetermined drive control signal. Each of the plurality of memory chips may also comprise of a conversion control circuit for generating the drive control signal, wherein the drive control signal is deactivated in an interval in which any of the plurality of memory chips is in an active interval.

Owner:SAMSUNG ELECTRONICS CO LTD

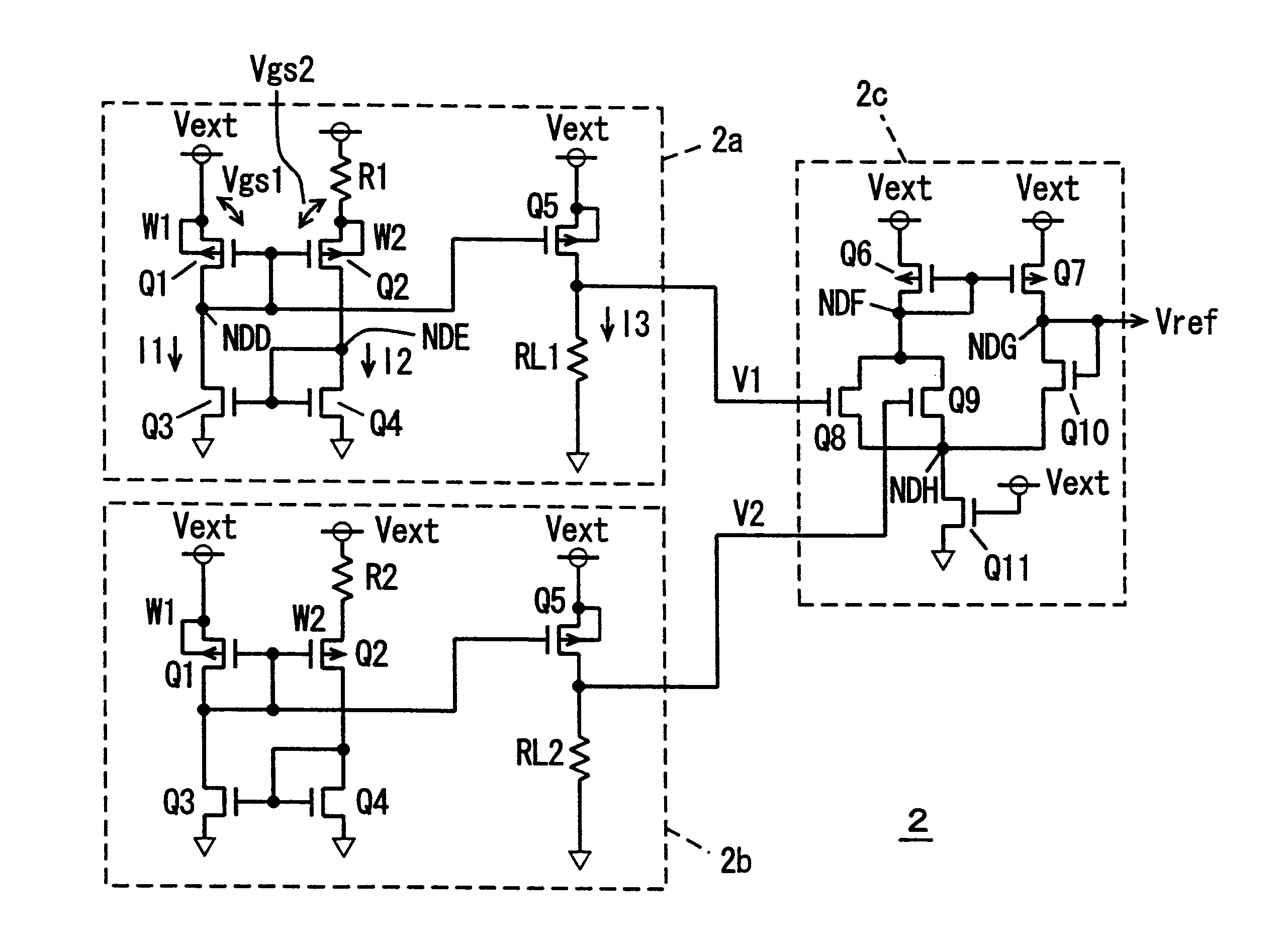

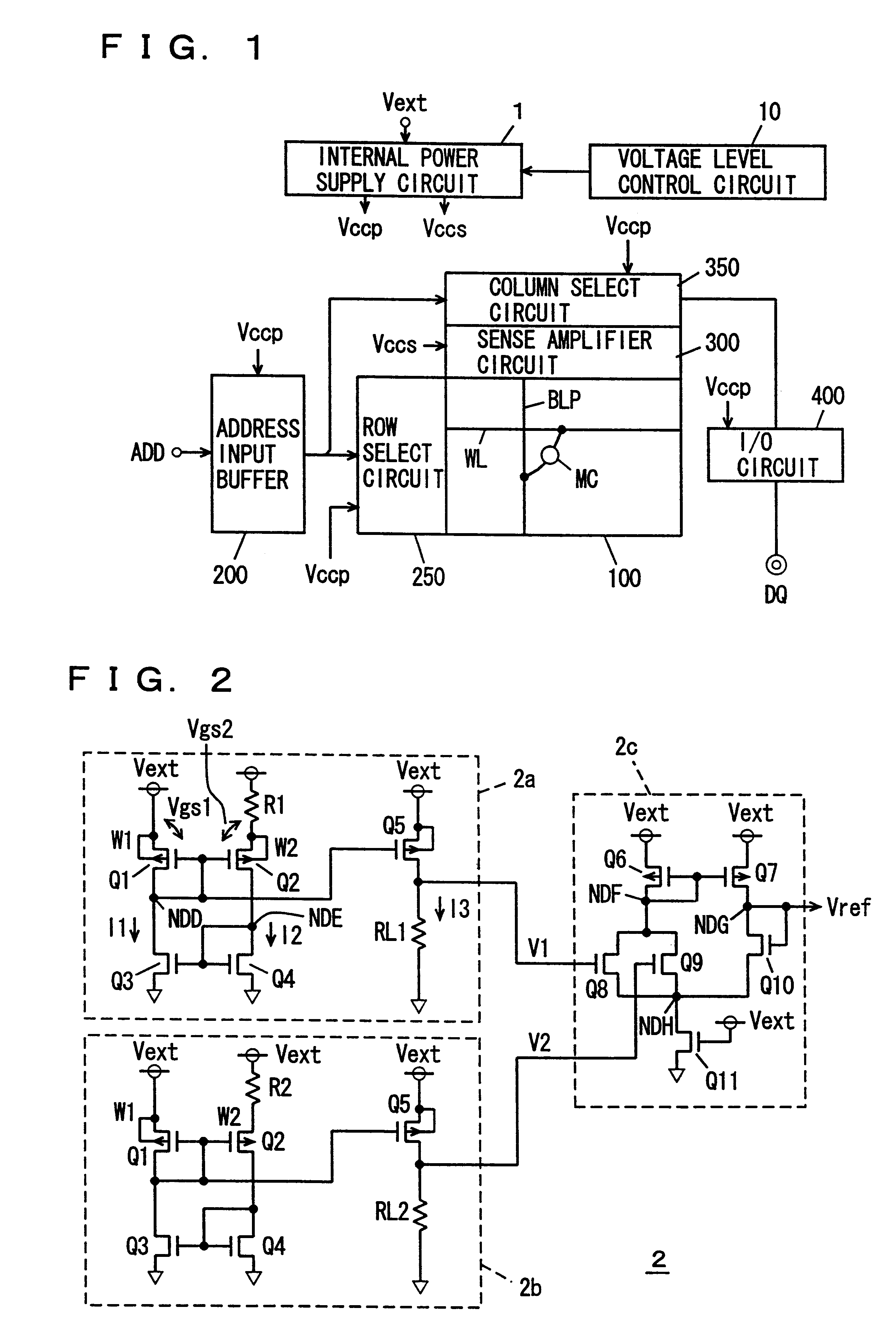

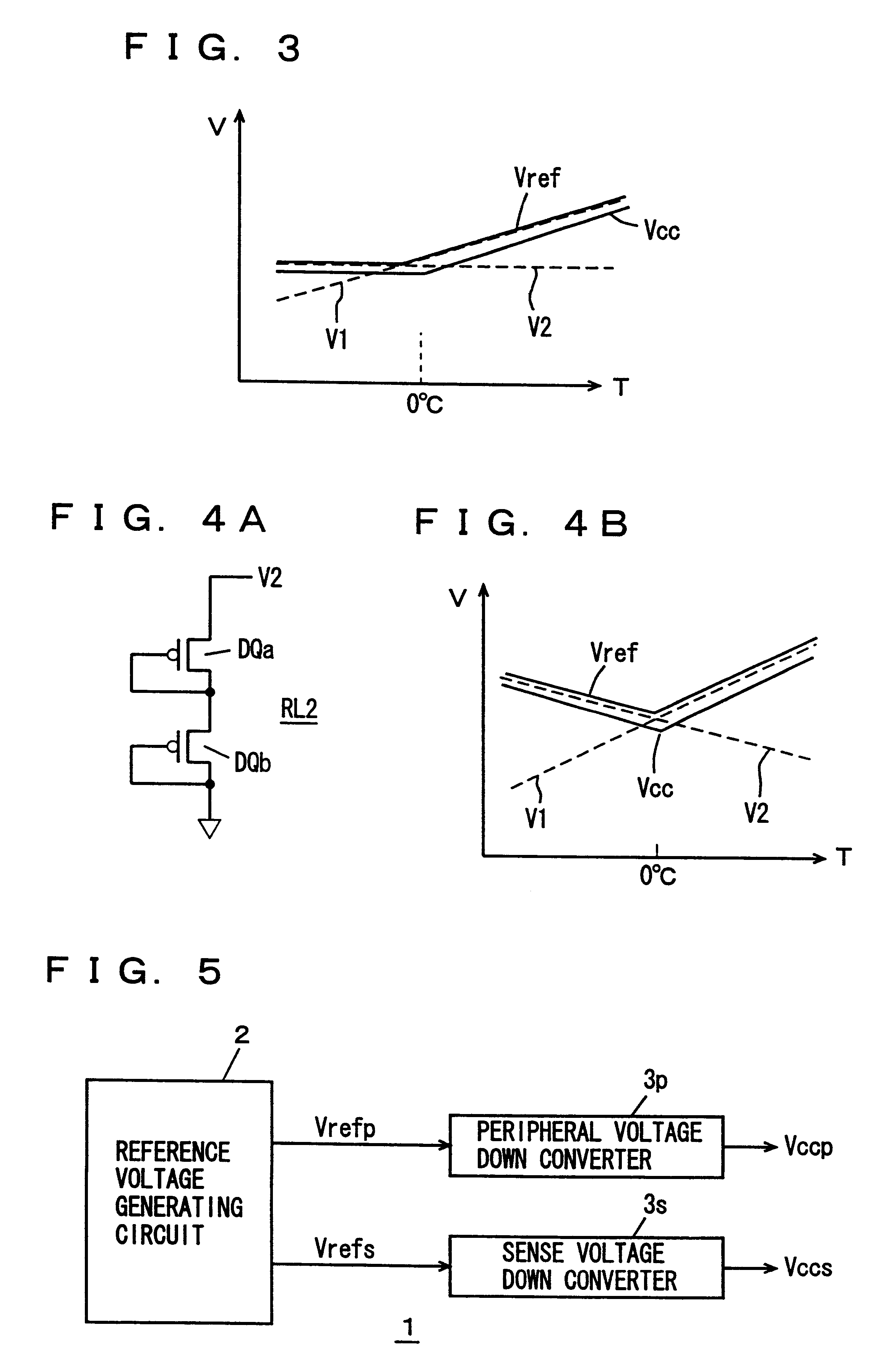

Semiconductor device having an internal voltage generating circuit

An internal power supply circuit produces an internal power supply voltage from an external power supply voltage. A voltage level control circuit controls a voltage level and a temperature characteristic of the internal power supply voltage generated by the internal power supply circuit. The internal power supply circuit produces the internal power supply voltage having a negative or zero temperature characteristic in a low temperature region and a positive temperature characteristic in a high temperature region. The voltage level control circuit includes a structure optimizing a capacitance value of a sense power supply line stabilizing capacitance for driving a sense amplifier circuit, a level converting circuit determining the lowest operable region of the external power supply voltage of the internal power supply circuit, or a structure forcedly operating the internal voltage down converter upon power-on. The internal power supply voltage at a desired level is stably produced with a small occupied area and a low current consumption.

Owner:MITSUBISHI ELECTRIC CORP

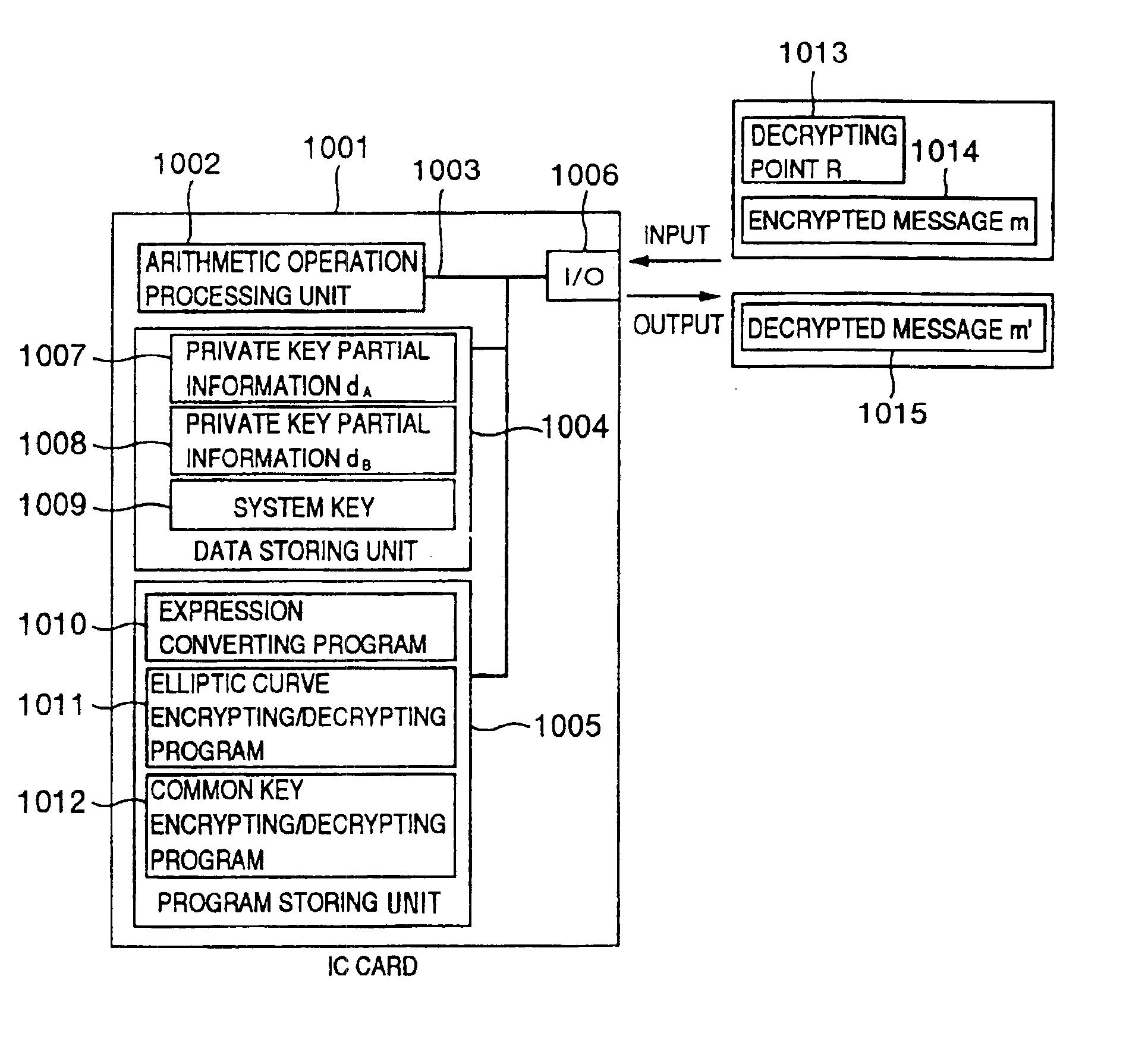

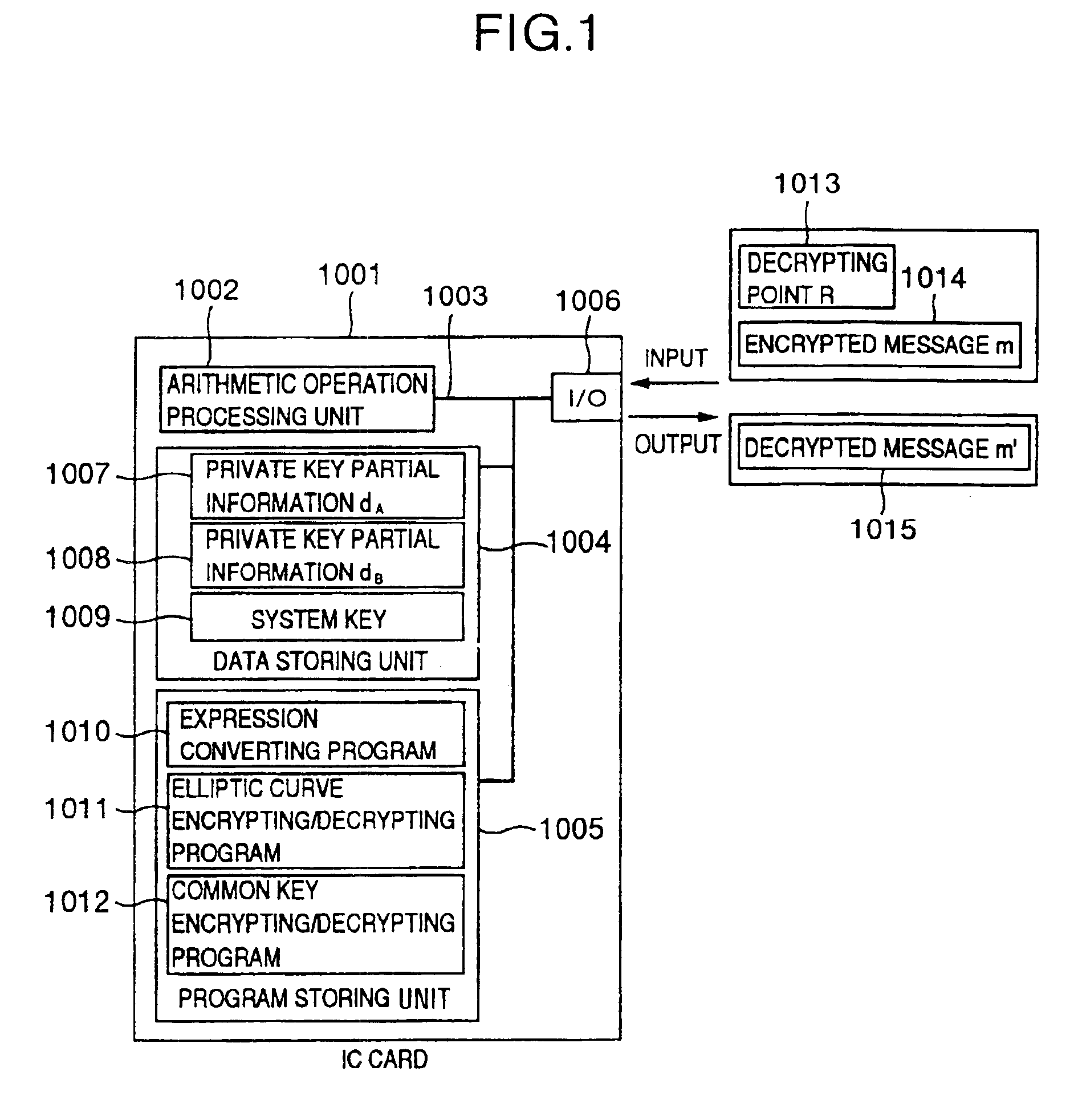

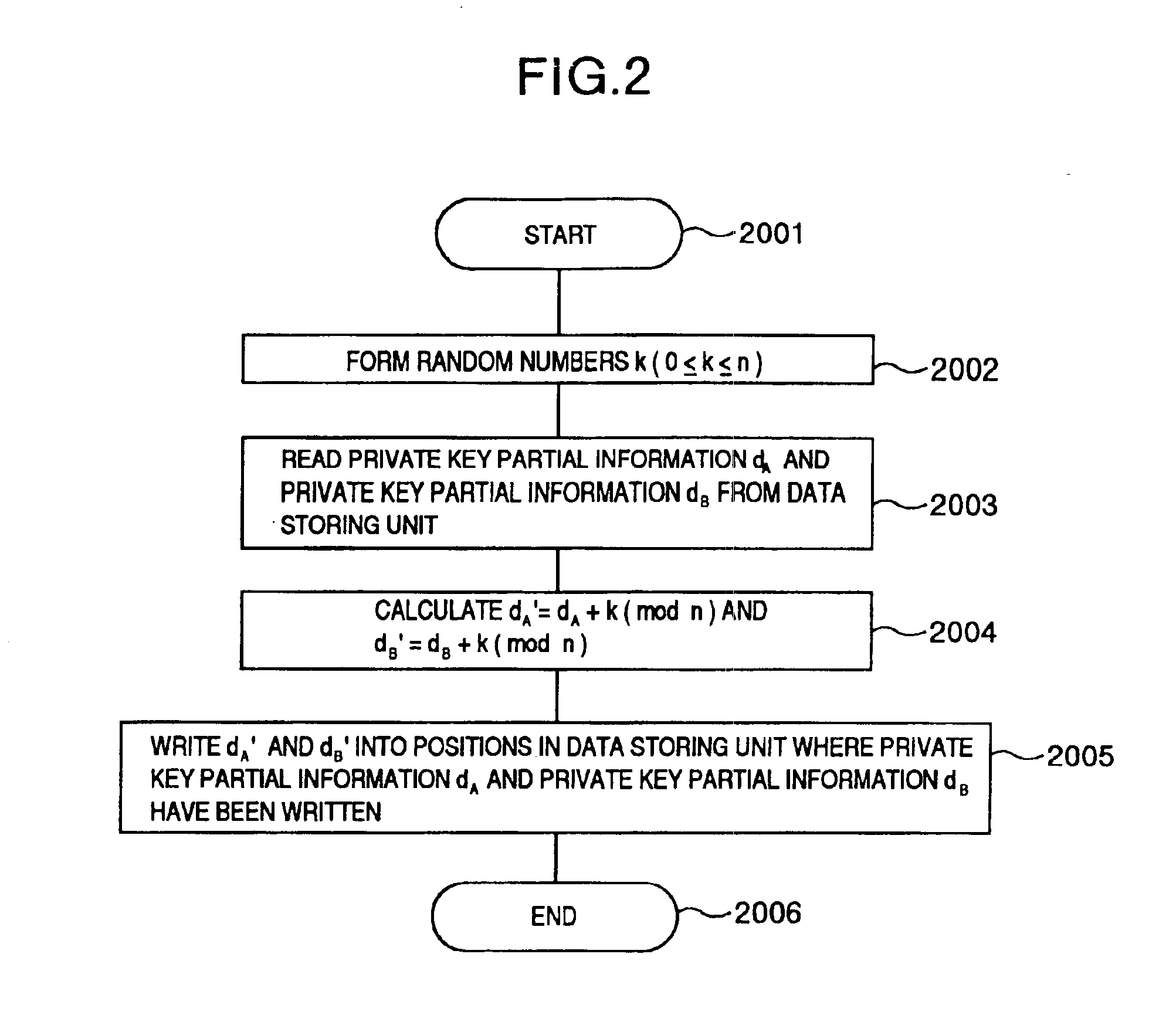

Processing apparatus, program, or system of secret information

InactiveUS6873706B1Reduce correlationTotal current dropKey distribution for secure communicationPublic key for secure communicationComputer hardwarePower analysis

To provide a secure cryptographic device such as an IC card which can endure TA (Timing Attack), DPA (Differential Power Analysis), SPA (Simple Power Analysis), or the like as an attaching method of presuming secret information held therein, when the secret information held in the card or another information which is used in the secret information or an arithmetic operation using such secret information when such an arithmetic operation is performed is shown by a plurality of expressing methods and the arithmetic operation is performed, thereby making an arithmetic operation processing method different each time the arithmetic operation is performed and making each of an arithmetic operation time, an intensity of a generated electromagnetic wave, and a current consumption different.

Owner:HITACHI LTD

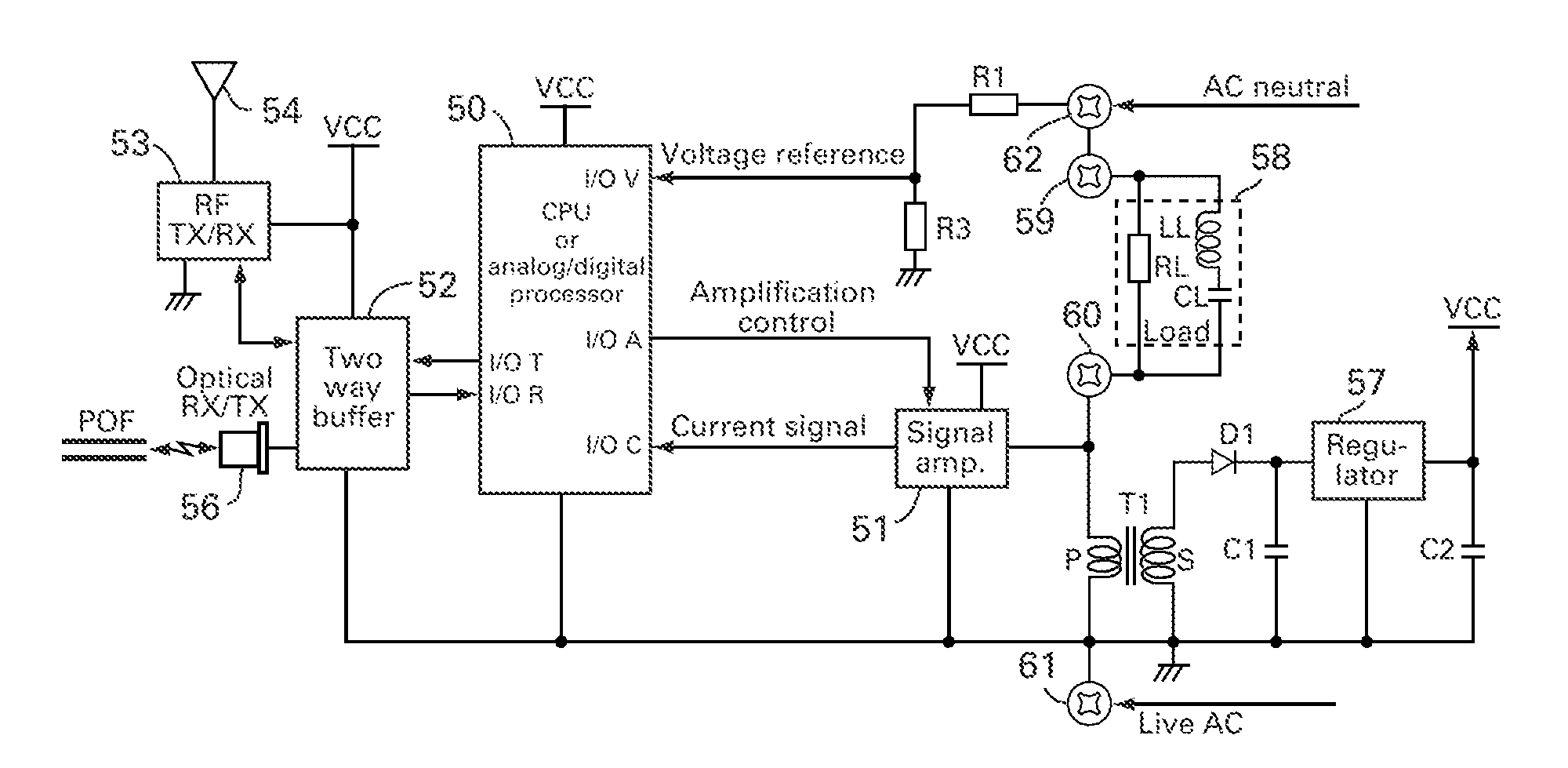

Apparatus for employing low ohmic alloy conductors and method for simplifying current drain data retrieval

ActiveUS20130183043A1Decrease in Q-factorSmallAc-dc conversionTransformers/inductances coils/windings/connectionsElectrical conductorData retrieval

Apparatus and method for measuring current drain and reporting power consumption using current transformer with primary windings made of low ohmic alloy, enabling the use of the secondary coil to power the sensing and reporting circuits eliminating the power wasted by AC-DC power adaptors used for the current sensors. The saving is substantial as the current sensors will not drain a current when the AC outlets are disconnected from a load or when the load is switched off. The apparatus using low ohmic alloy is extended to the structuring of terminals, including power pins, power sockets and combinations to provide a low ohmic sensing elements in AC plugs, outlets, adaptors and extension cables with multi outlets, dissipating the heat from the sensing elements by the plugs and the larger metal heat dissipation.

Owner:ELBEX VIDEO LTD

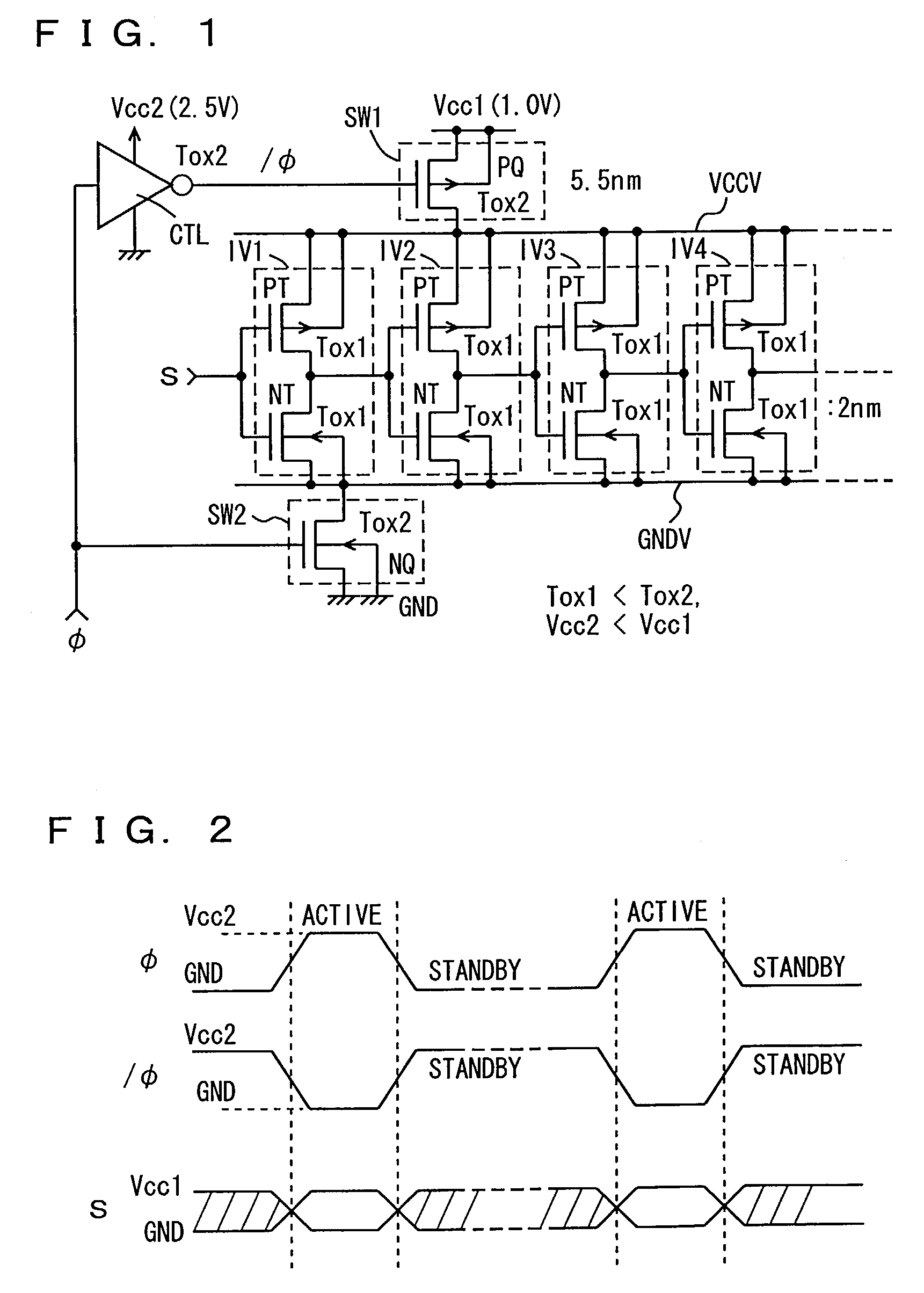

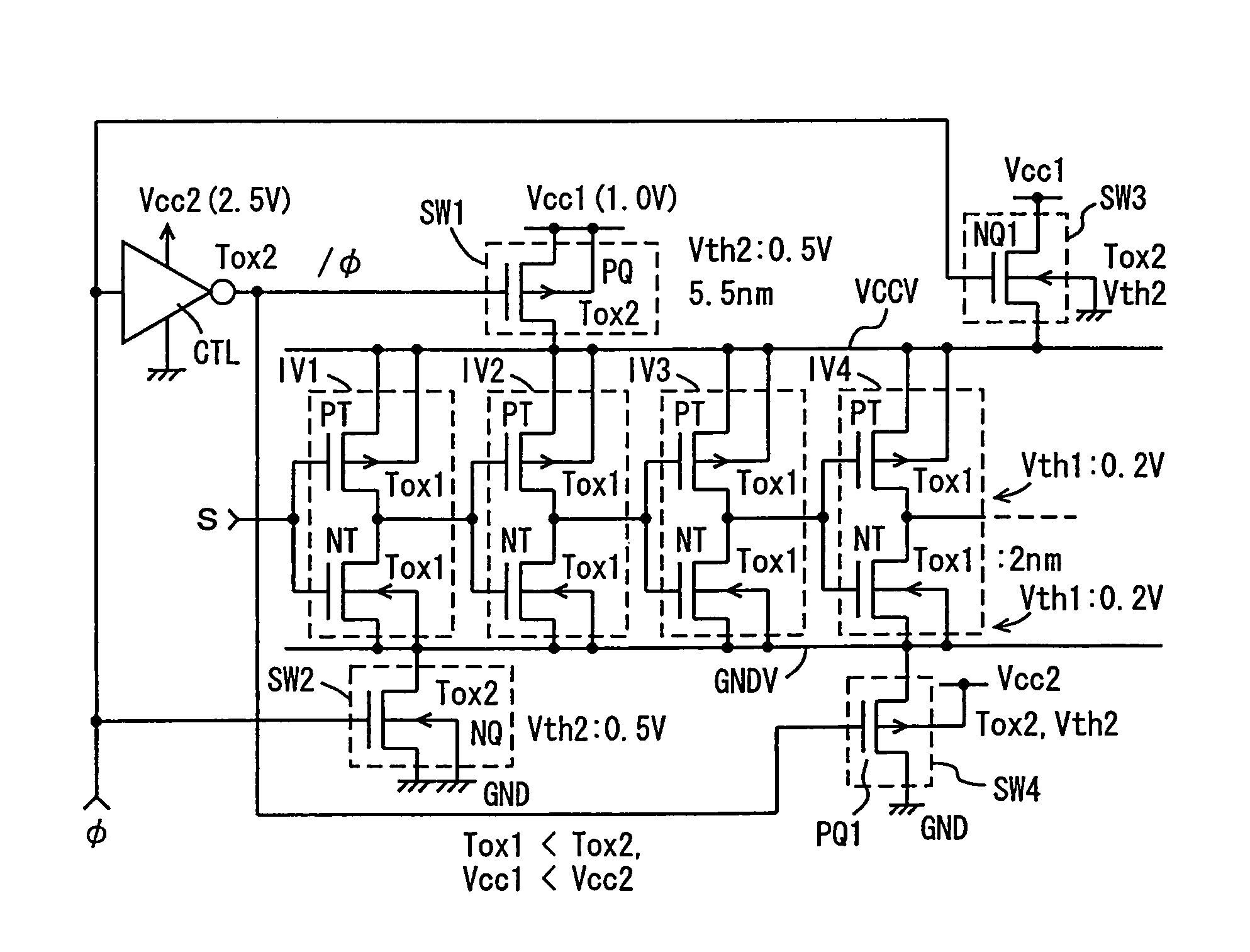

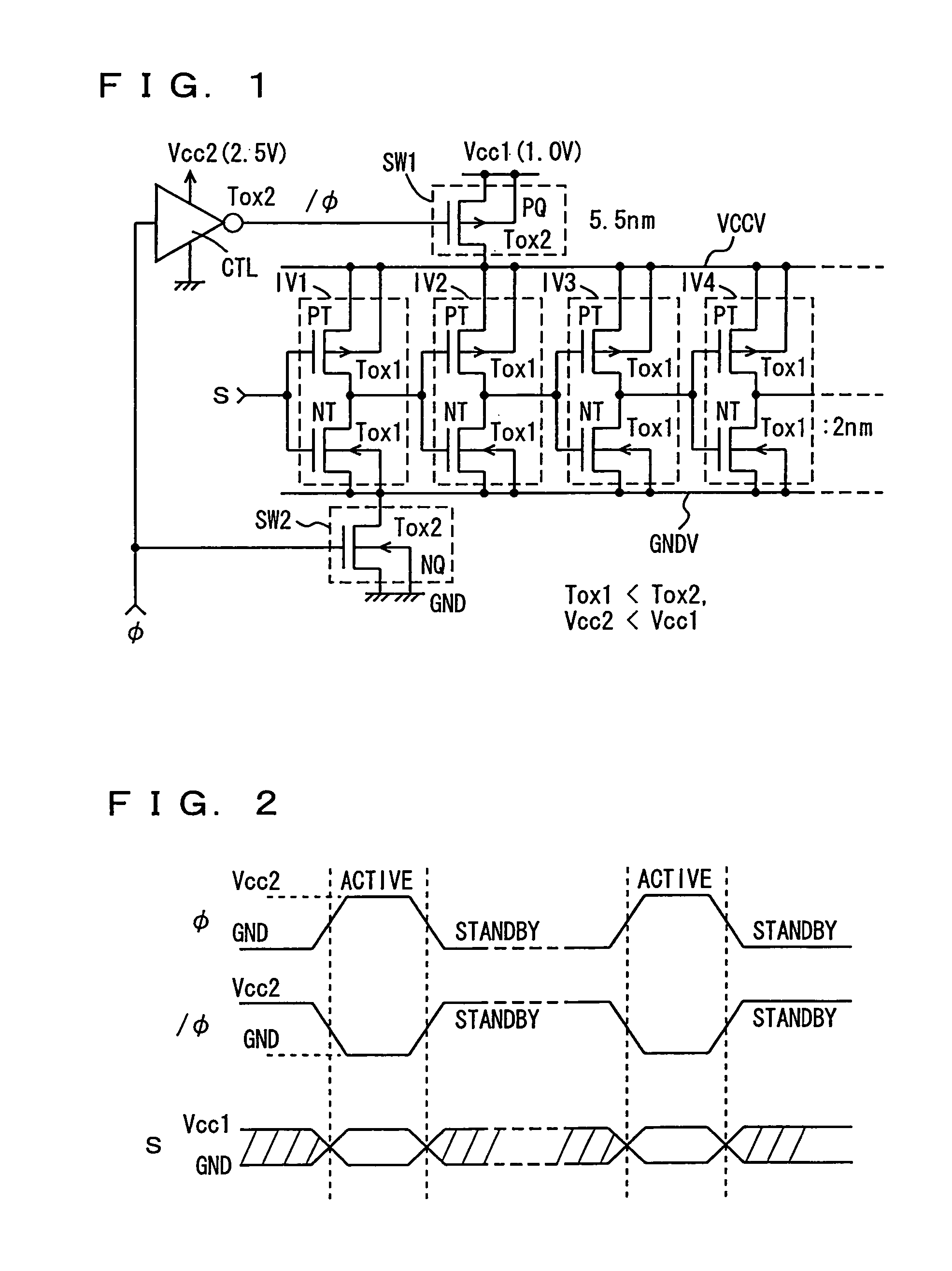

Low power consumption MIS semiconductor device

InactiveUS7042245B2Total current dropSimple circuit configurationTransistorReliability increasing modificationsCurrent consumptionLogic gate

A logic gate is constructed of an insulated gate field effect transistor (MIS transistor) having a thin gate insulation film. An operation power supply line to the logic gate is provided with an MIS transistor having a thick gate insulation film for switching the supply and stop of an operation power source voltage. A voltage of the gate of the power source switching transistor is made changing in an amplitude greater than an amplitude of an input and an output signal to the logic gate. Current consumption in a semiconductor device configured of MIS transistor of a thin gate insulation film can be reduced and an power source voltage thereof can be stabilized.

Owner:RENESAS ELECTRONICS CORP

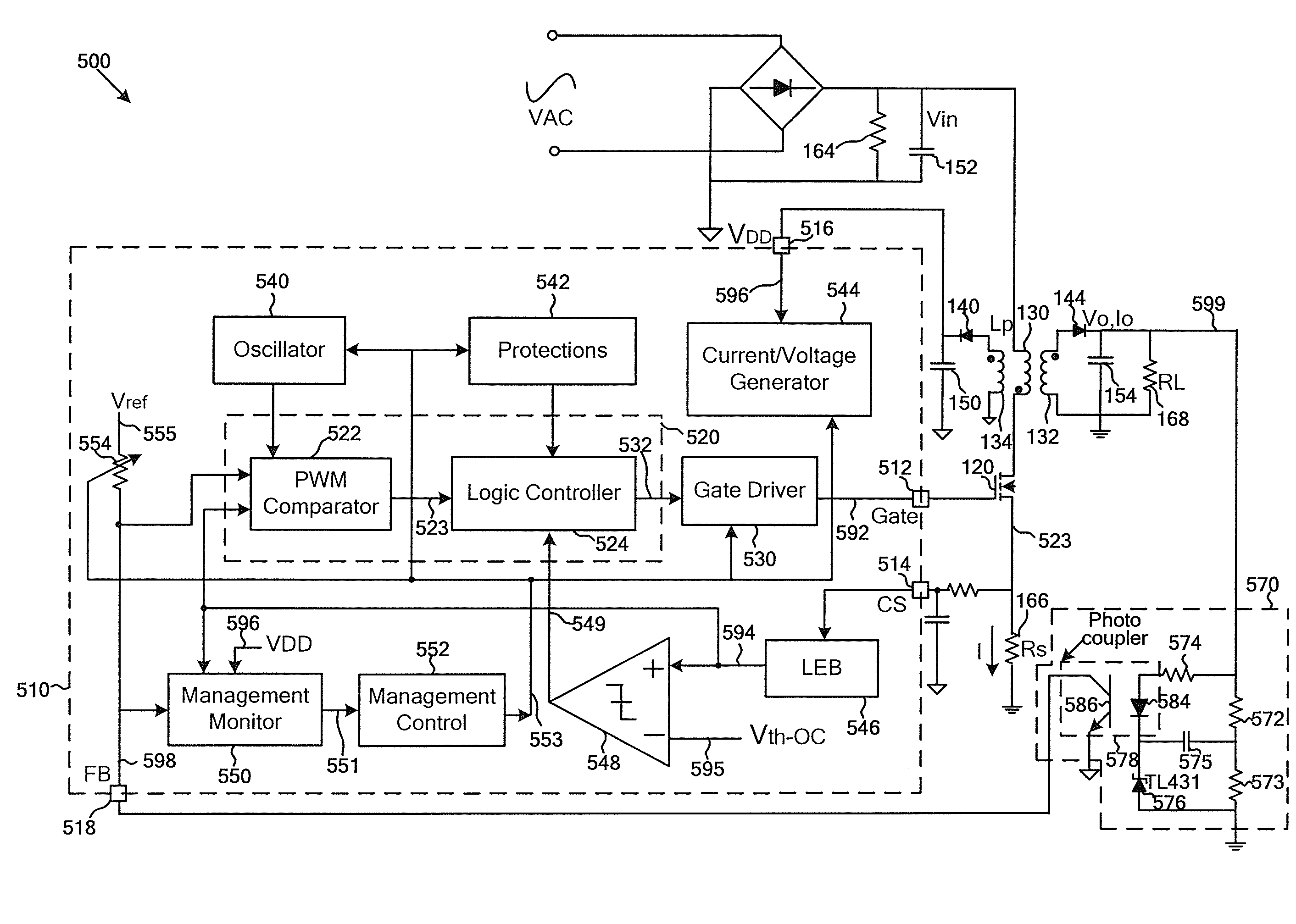

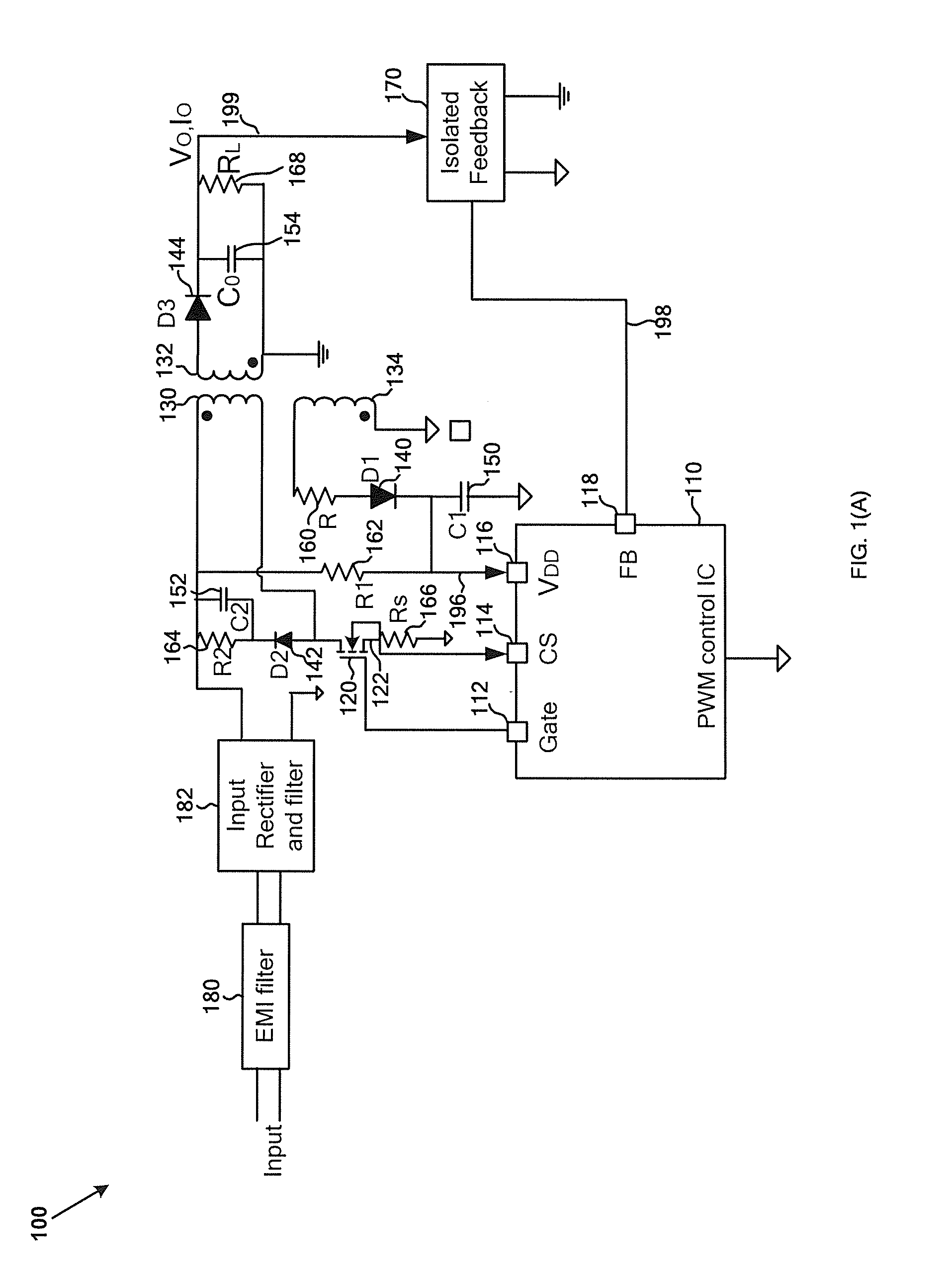

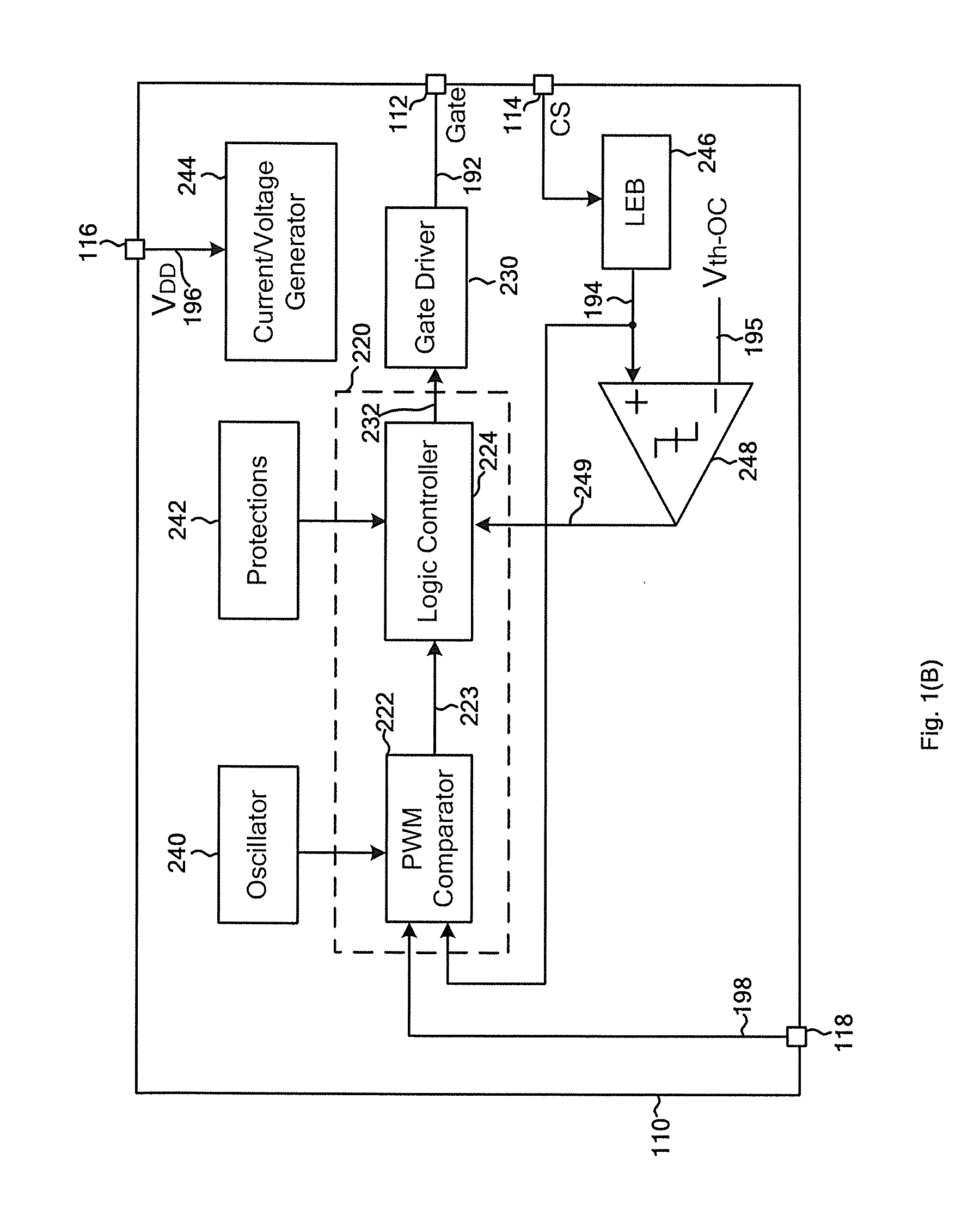

Systems and methods for adjusting current consumption of control chips to reduce standby power consumption of power converters

ActiveUS20130003421A1Reduce standby power consumptionReduce power consumptionEfficient power electronics conversionAc-dc conversionTime segmentControl signal

System and method for regulating a power conversion system. For example, a system controller includes a signal generator and one or more power-consumption components. The signal generator is configured to receive a feedback signal related to an output signal of the power conversion system, a current sensing signal and an input voltage, and to generate a control signal based on at least information associated with the feedback signal, the current sensing signal and the input voltage. The power-consumption components are configured to receive the control signal. The signal generator is further configured to determine whether the feedback signal is smaller than a feedback threshold for a first predetermined period of time, the current sensing signal is smaller than a current sensing threshold for a second predetermined period of time, and the input voltage is smaller than a first threshold for a third predetermined period of time in magnitude.

Owner:ON BRIGHT ELECTRONICS SHANGHAI

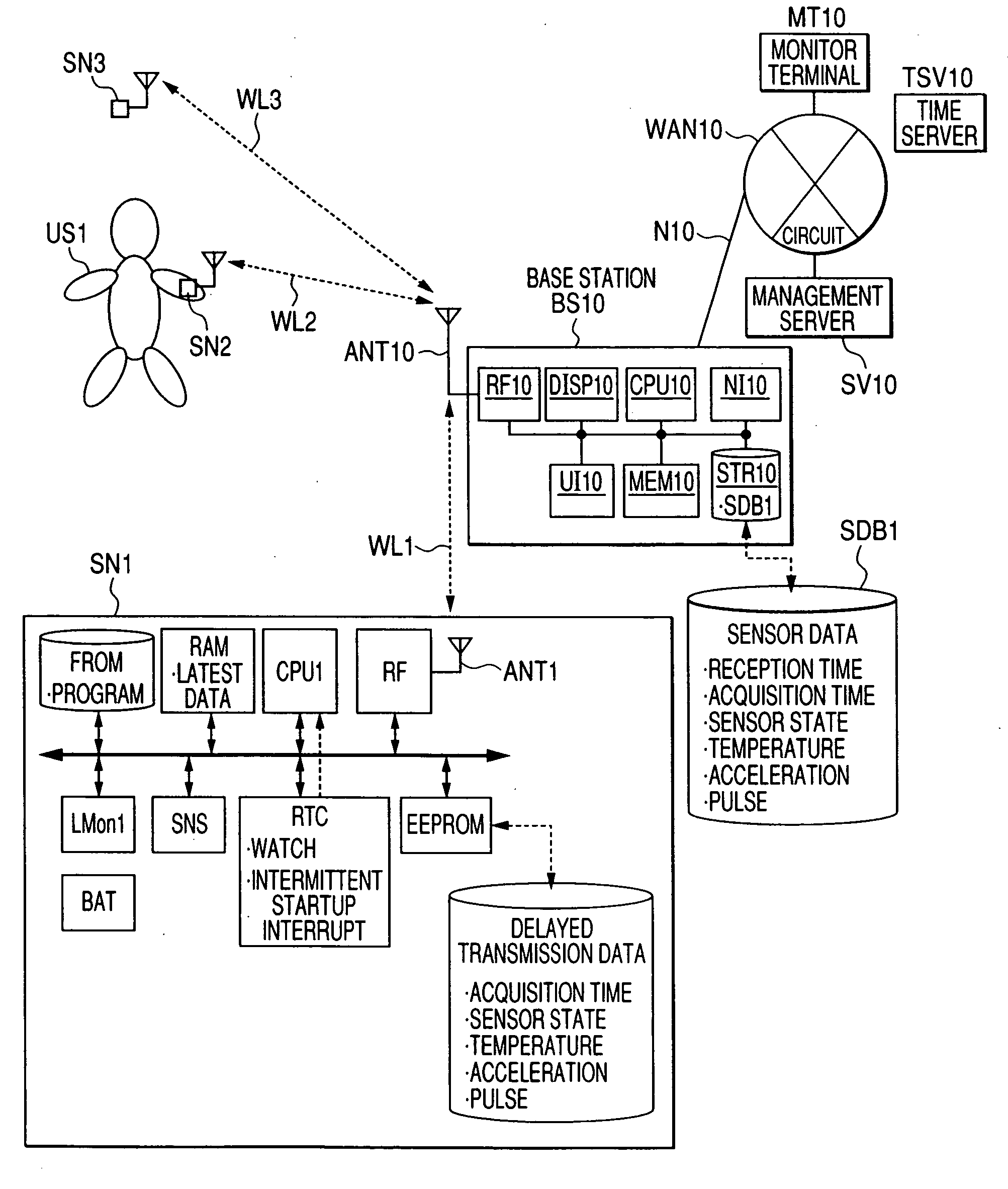

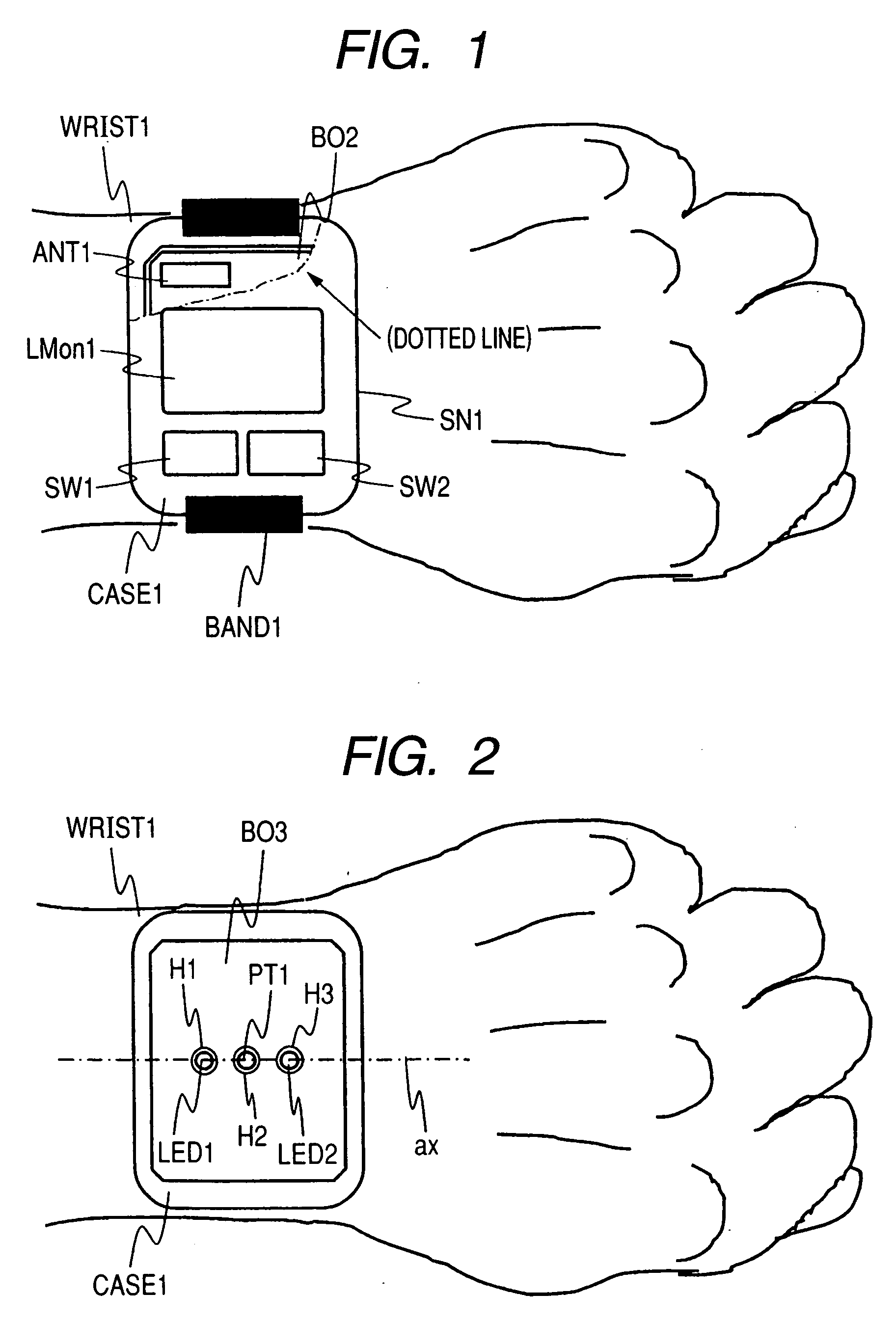

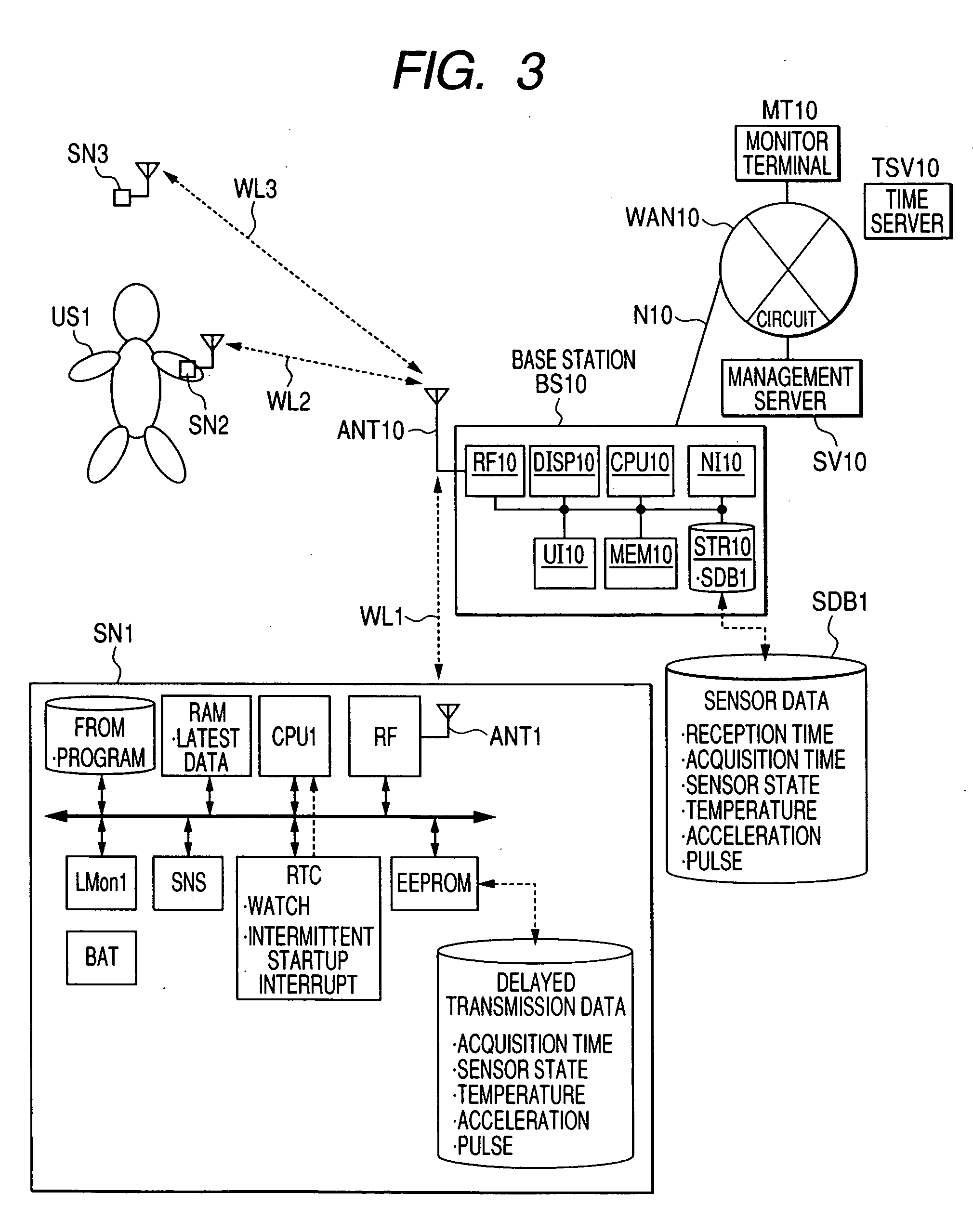

Sensor node, base station, sensor network and sensing data transmission method

InactiveUS20070159321A1High precisionAvoid lostPower managementMeasurement devicesSensing dataSensor node

To provide suppressing loss of sensing data while suppressing current consumption at a sensor node, a sensor node is started at a predetermined interval, a sensor measures data (P143), the measurement data is sent to a base station (P144), a state of wireless communication with the base station is determined (P145), and if the wireless communication state is not suitable for data transmission, the data is stored in a sensor node storage device (P147), whereas if the wireless communication state is suitable for data transmission, the data stored in the storage device is transmitted (P148).

Owner:HITACHI LTD

Memory module and memory system

ActiveUS20060262587A1Increase chanceTotal current dropDomestic stoves or rangesLighting and heating apparatusData signalTerm memory

In a memory module including a plurality of DRAM chips which transmit / receive a system data signal with a predetermined data width and at a transfer rate and which transmit / receive an internal data signal having a larger data width and a lower transfer rate as compared with the system data signal, the transfer rate of the system data signal is restricted. Current consumption in DRAMs constituting the memory module is large, hindering speed increases. For this memory module, a plurality of DRAM chips are stacked on an IO chip. Each DRAM chip is connected to the IO chip by a through electrode, and includes a constitution for mutually converting the system data signal and the internal data signal in each DRAM chip by the IO chip. Therefore, wiring between the DRAM chips can be shortened, and DLL having a large current consumption may be disposed only on the IO chip.

Owner:LONGITUDE LICENSING LTD

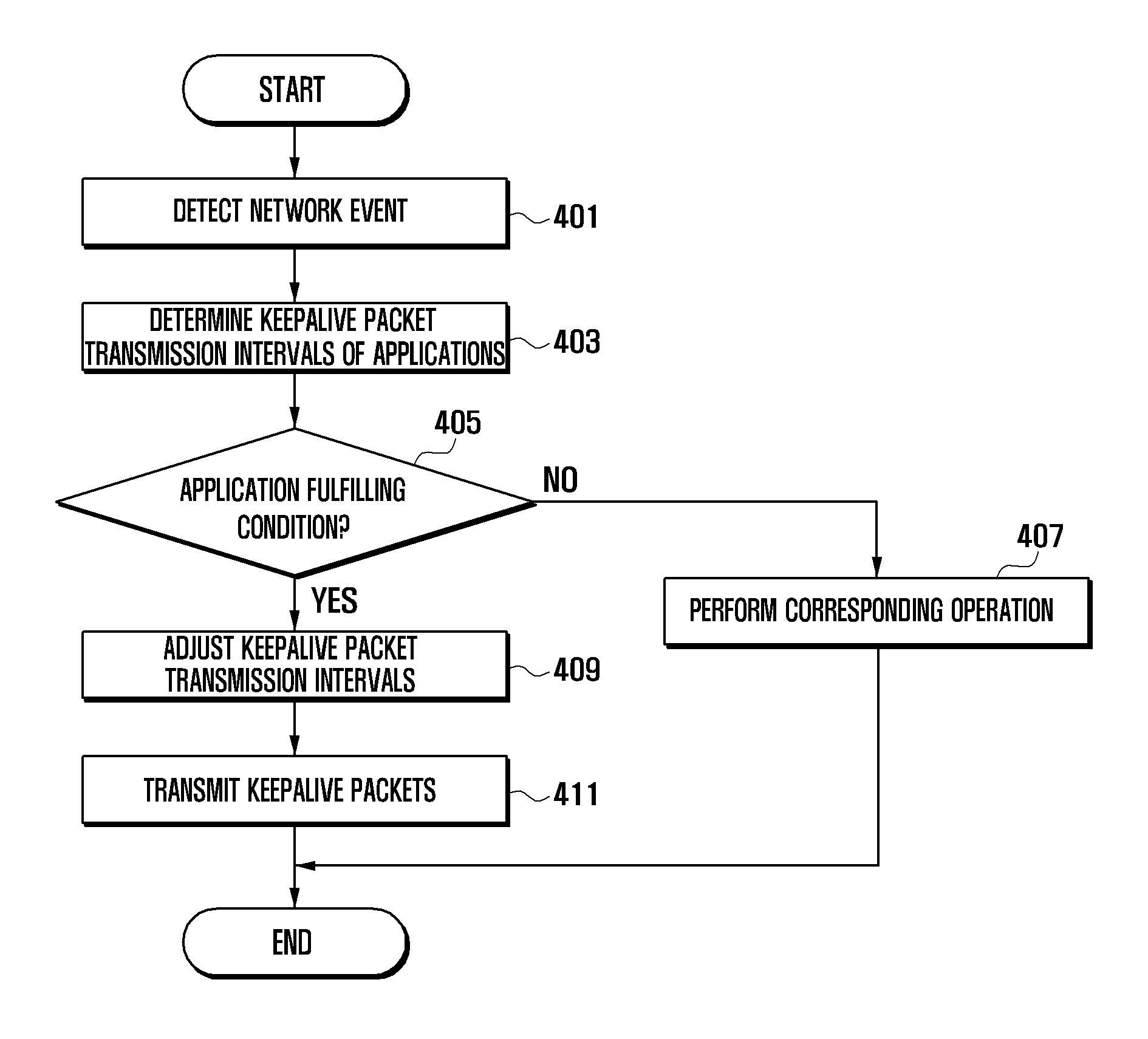

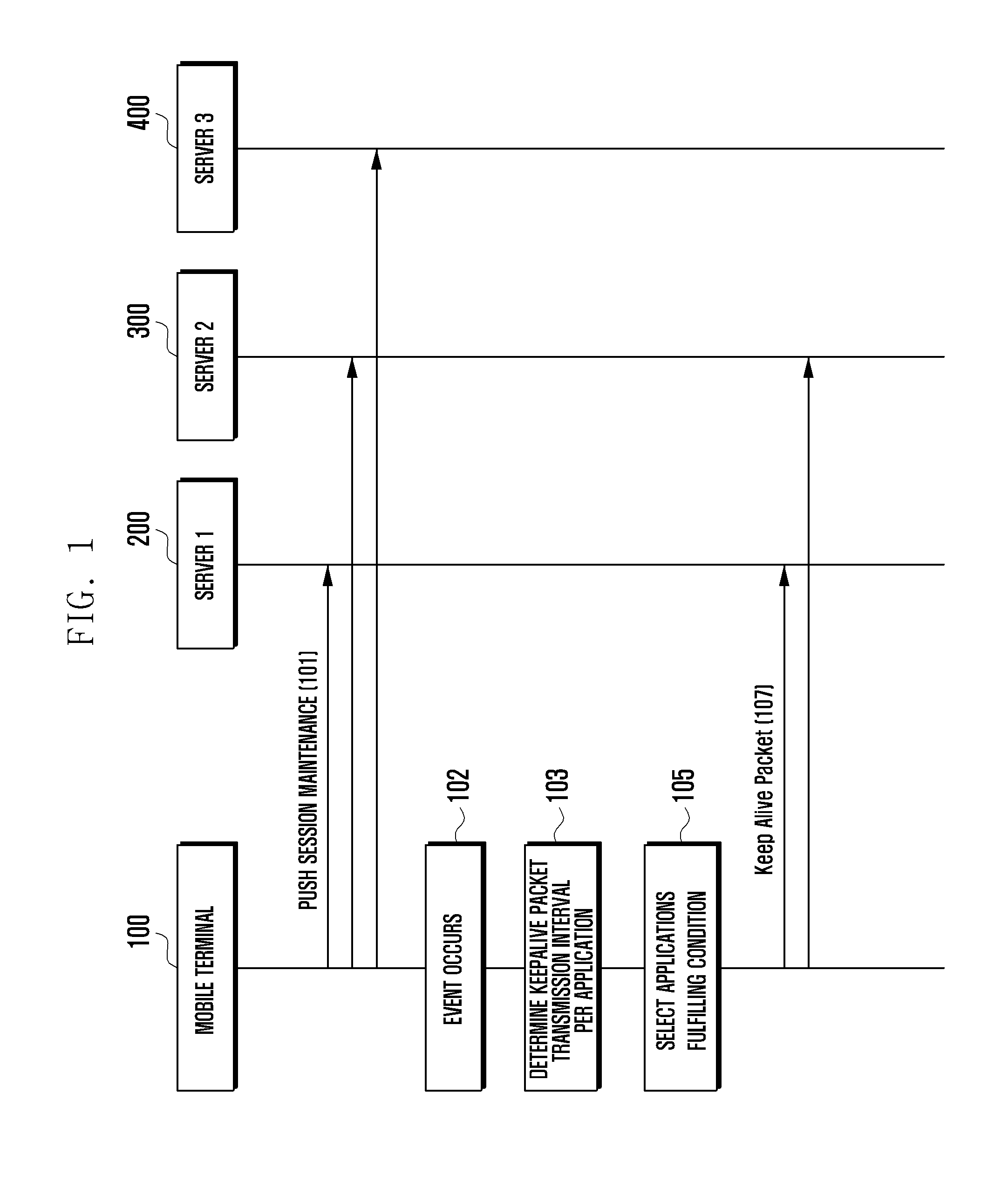

Keep-alive packet transmission method and apparatus of mobile terminal

InactiveUS20120170496A1Total current dropCurrent consumptionPower managementTransmission systemsComputer networkEngineering

A method and an apparatus for synchronizing the keep-alive packet transmission timings of the direct push applications are provided to improve an electric current consumption characteristic. The method includes detecting a network event, synchronizing transmission timings of keep-alive packets of direct push applications with reference to an occurrence time of the network event, and transmitting the keep-alive packets of the direct push application at a synchronized transmission timing simultaneously.

Owner:SAMSUNG ELECTRONICS CO LTD

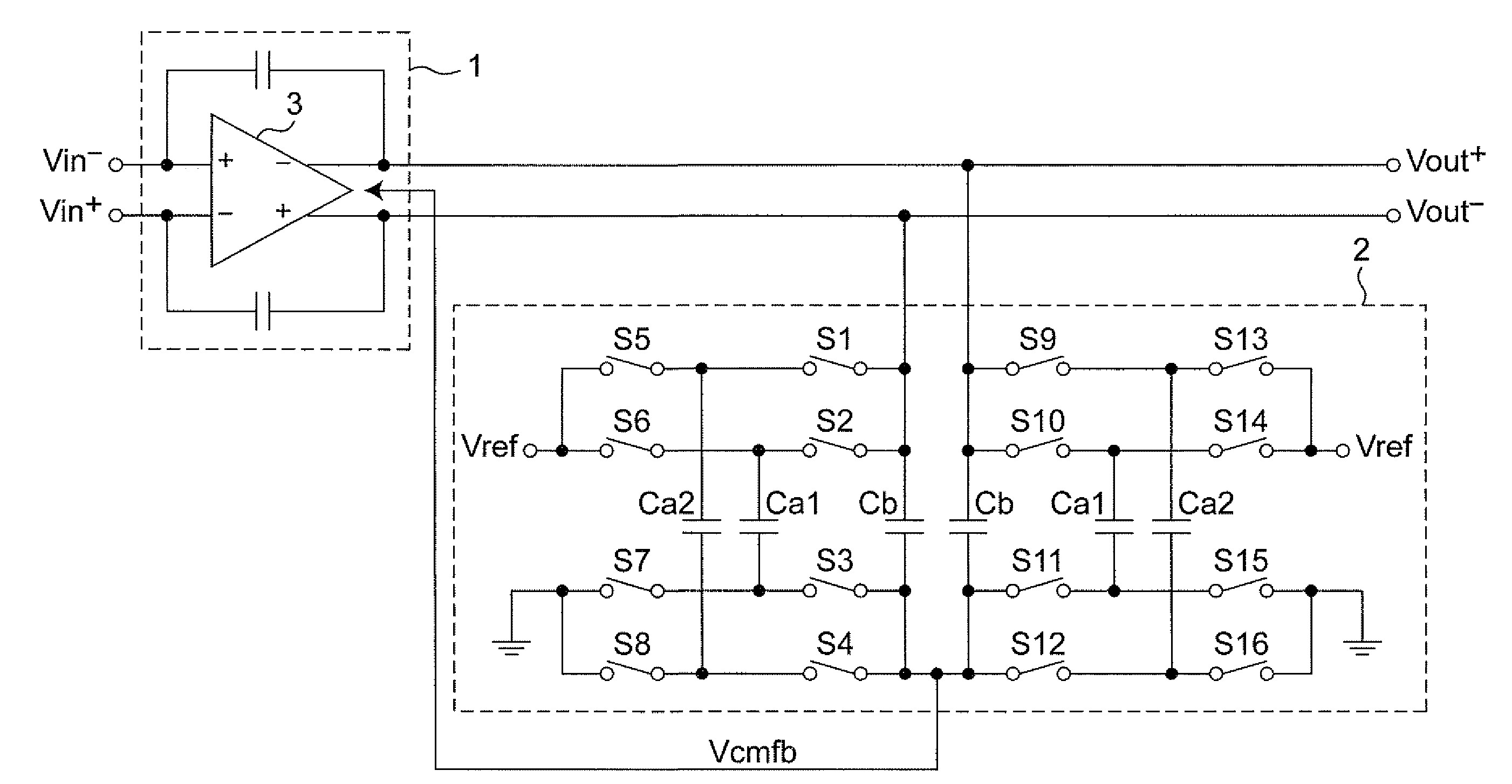

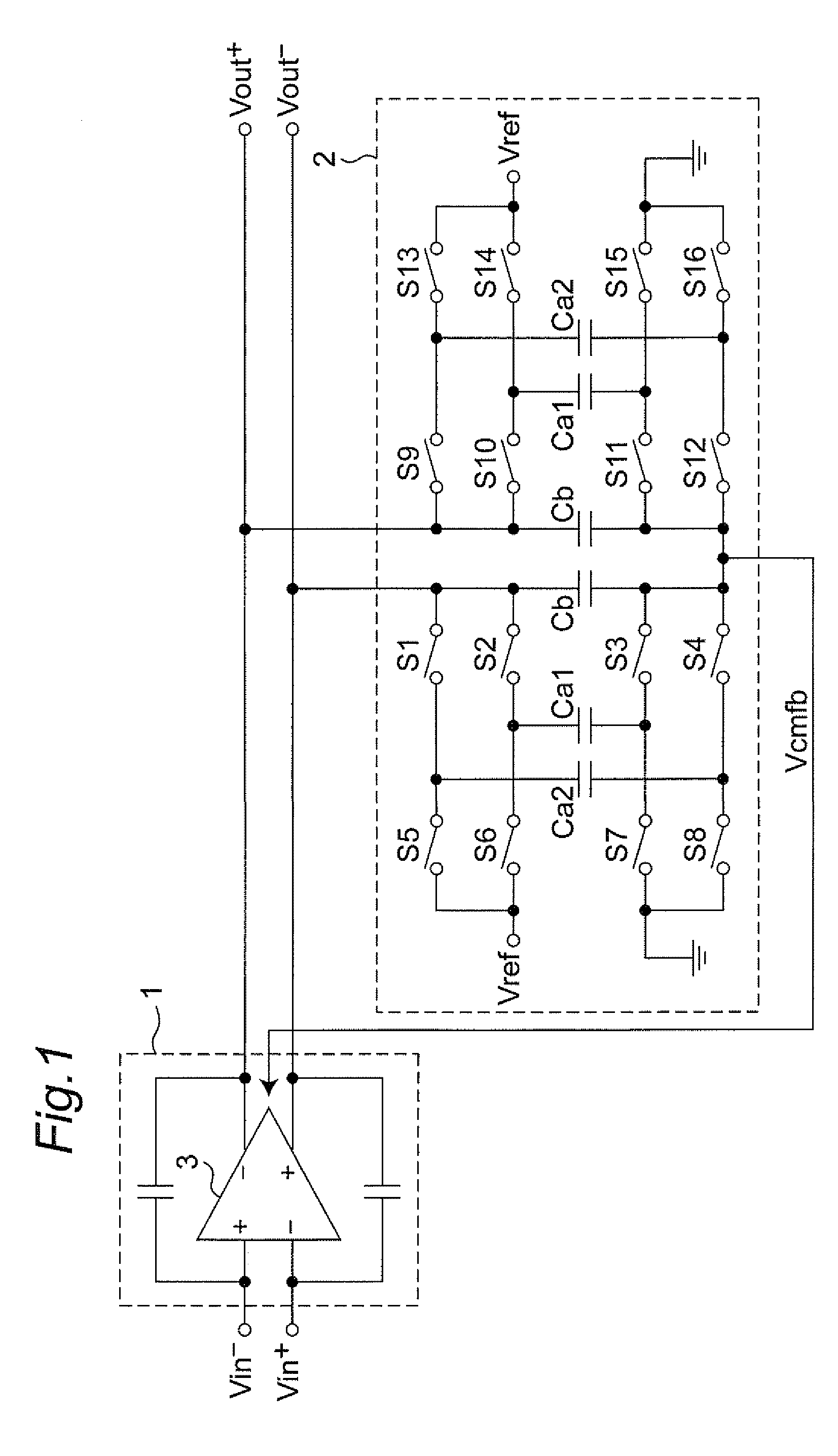

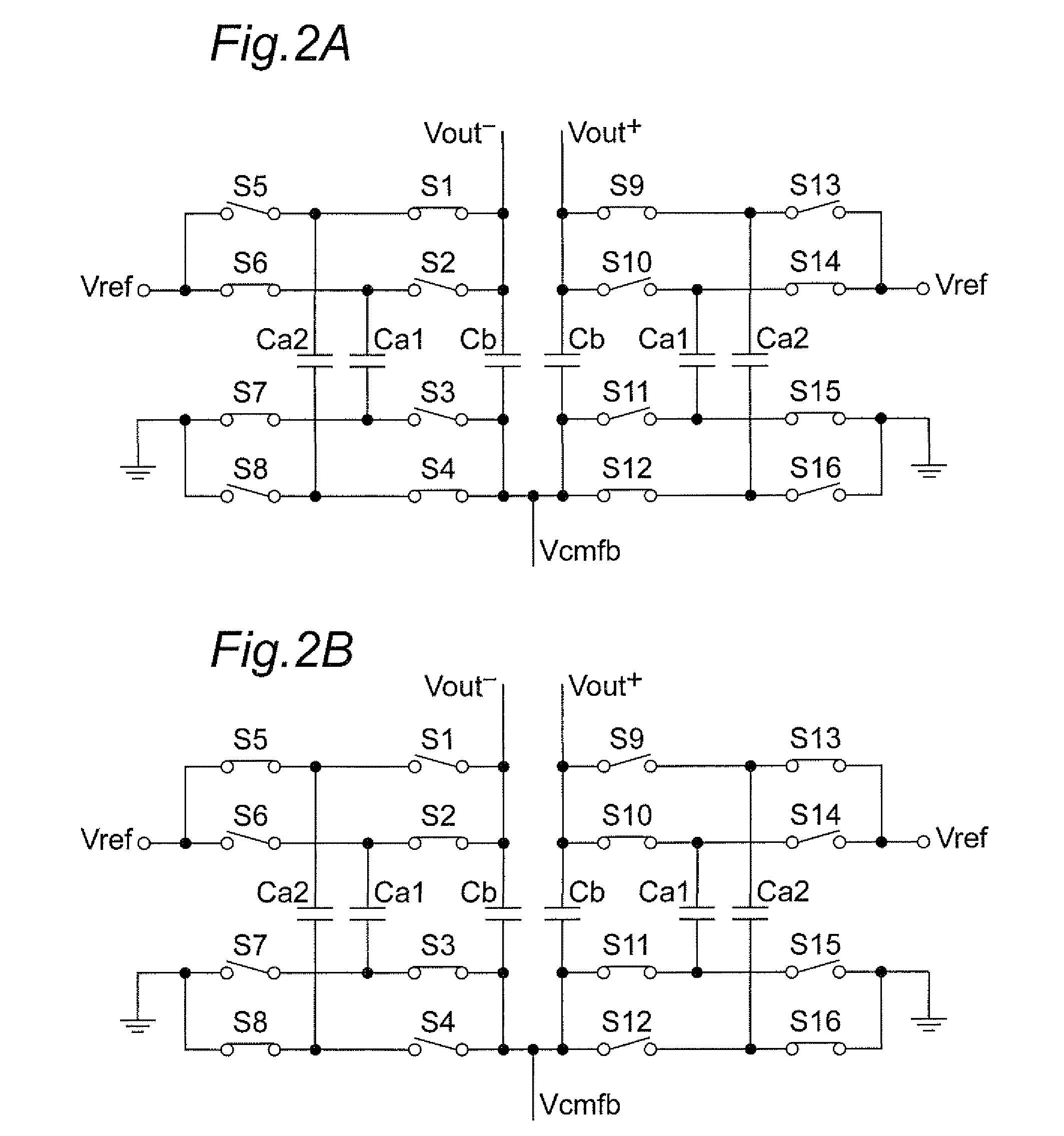

Discrete time amplifier circuit and analog-digital converter

ActiveUS20090115523A1Simple circuit configurationShorten convergence timeElectric signal transmission systemsAnalogue-digital convertersAudio power amplifierA d converter

The present invention is intended to attain simplified circuit configuration and low current consumption in a discrete time amplifier circuit and an AD converter, to improve the convergence from the transient response state to the steady state of the amplifier circuit and to reduce noise and distortion owing to the variation in the output common-mode voltage. The discrete time amplifier circuit and the AD converter are provided with a switched-capacitor common-mode feedback (CMFB) circuit capable of detecting and feeding back the output common-mode voltage at every sampling timing in the case that the circuit operates at double sampling timing (every ½ cycle).

Owner:SOCIONEXT INC

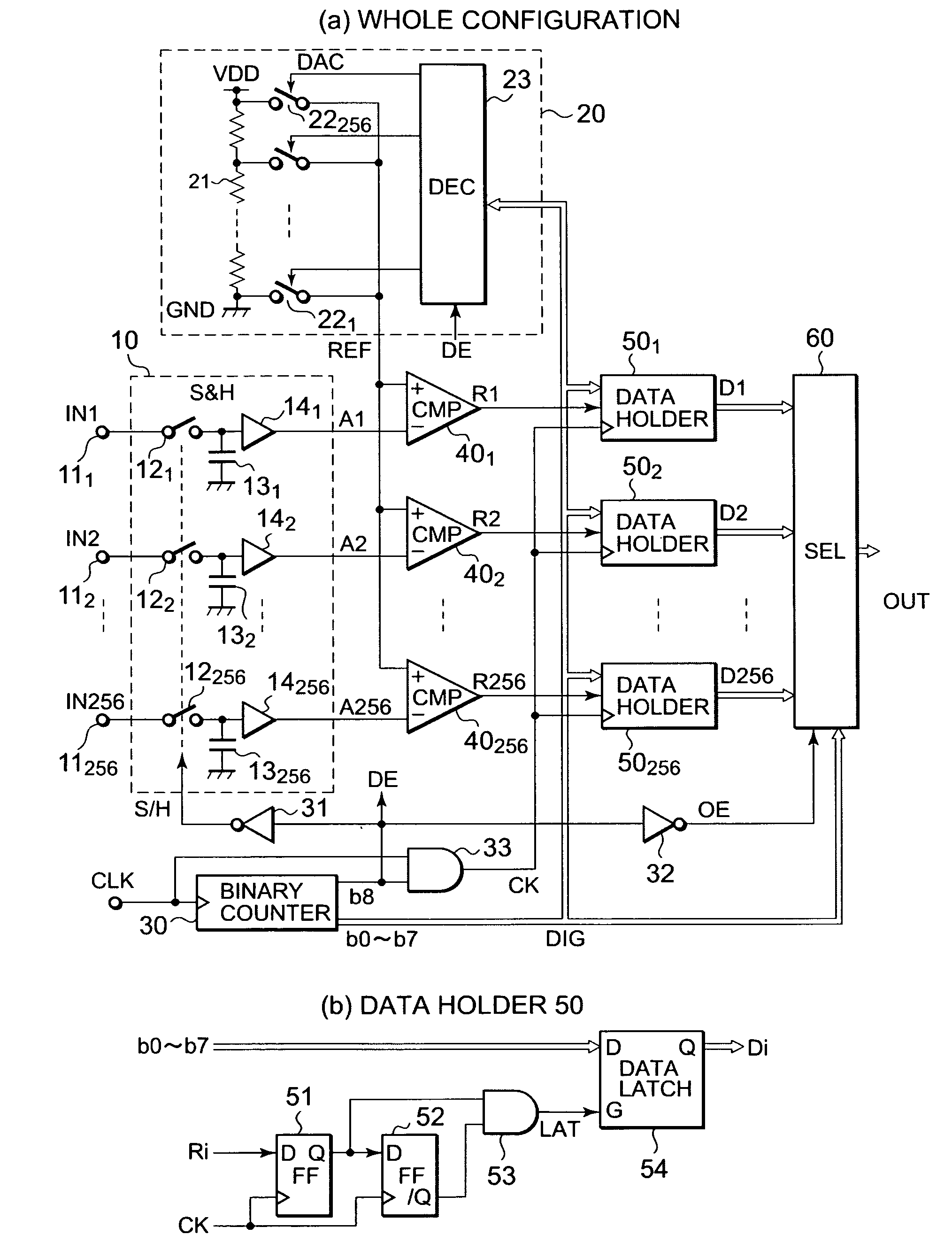

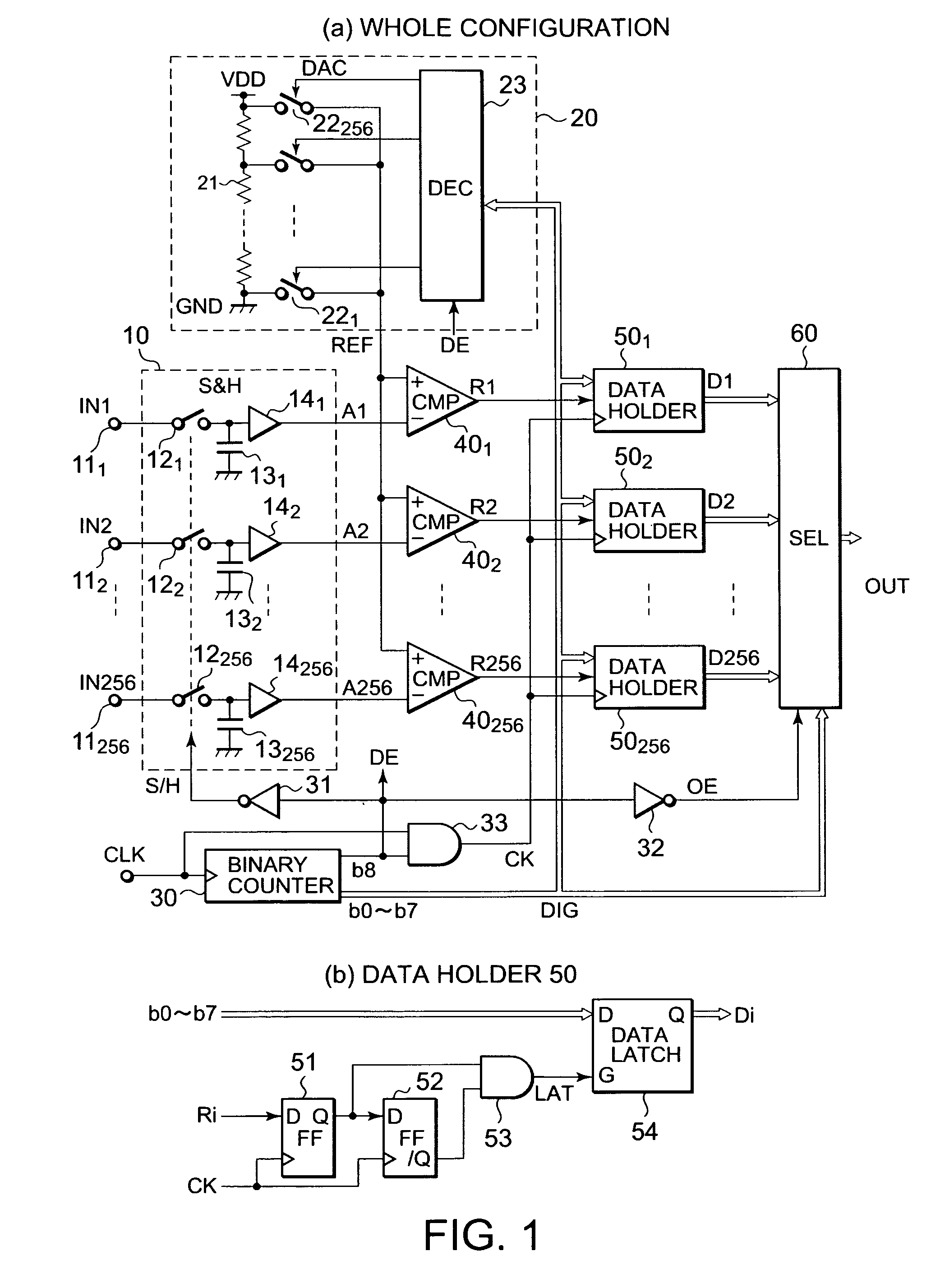

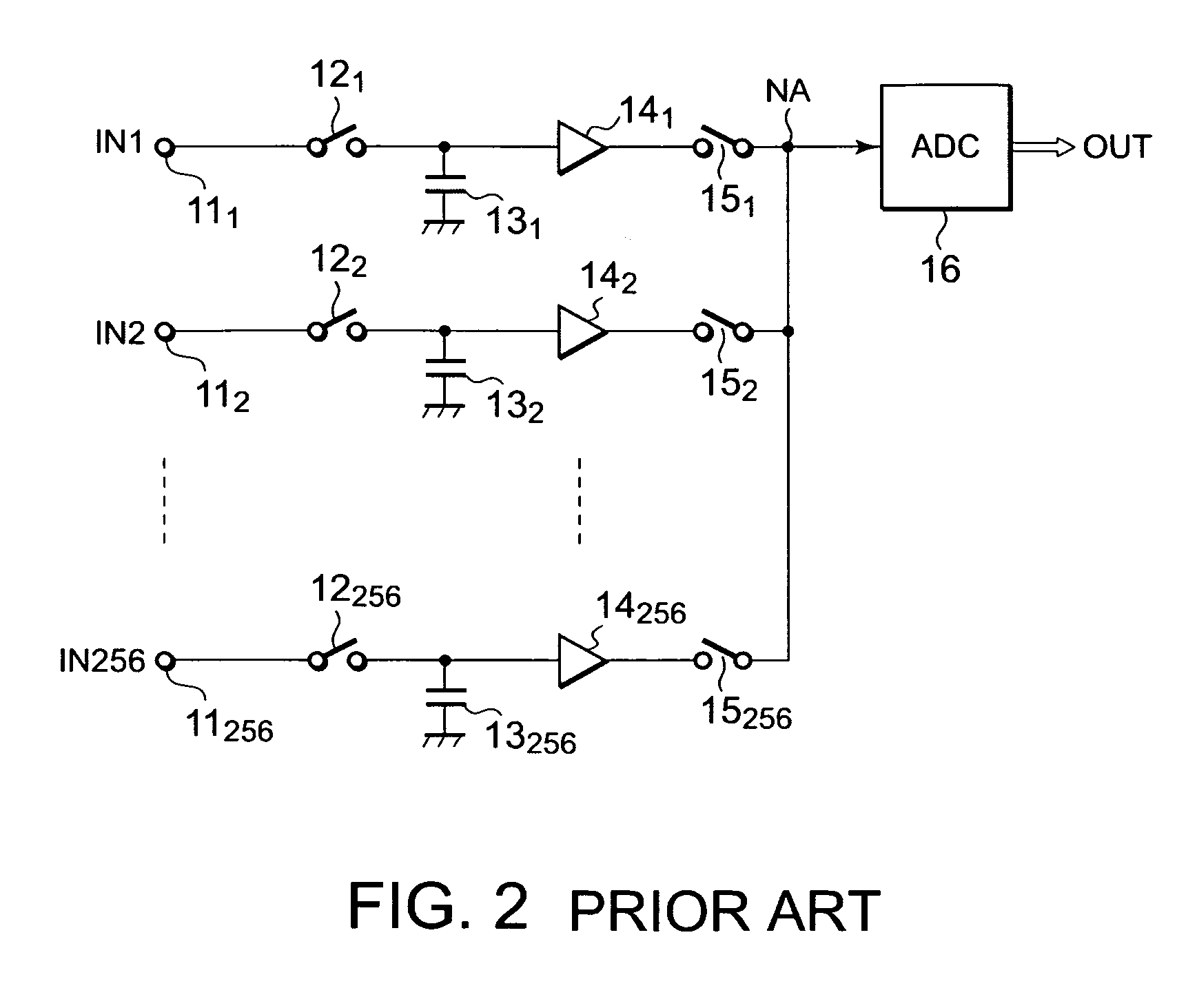

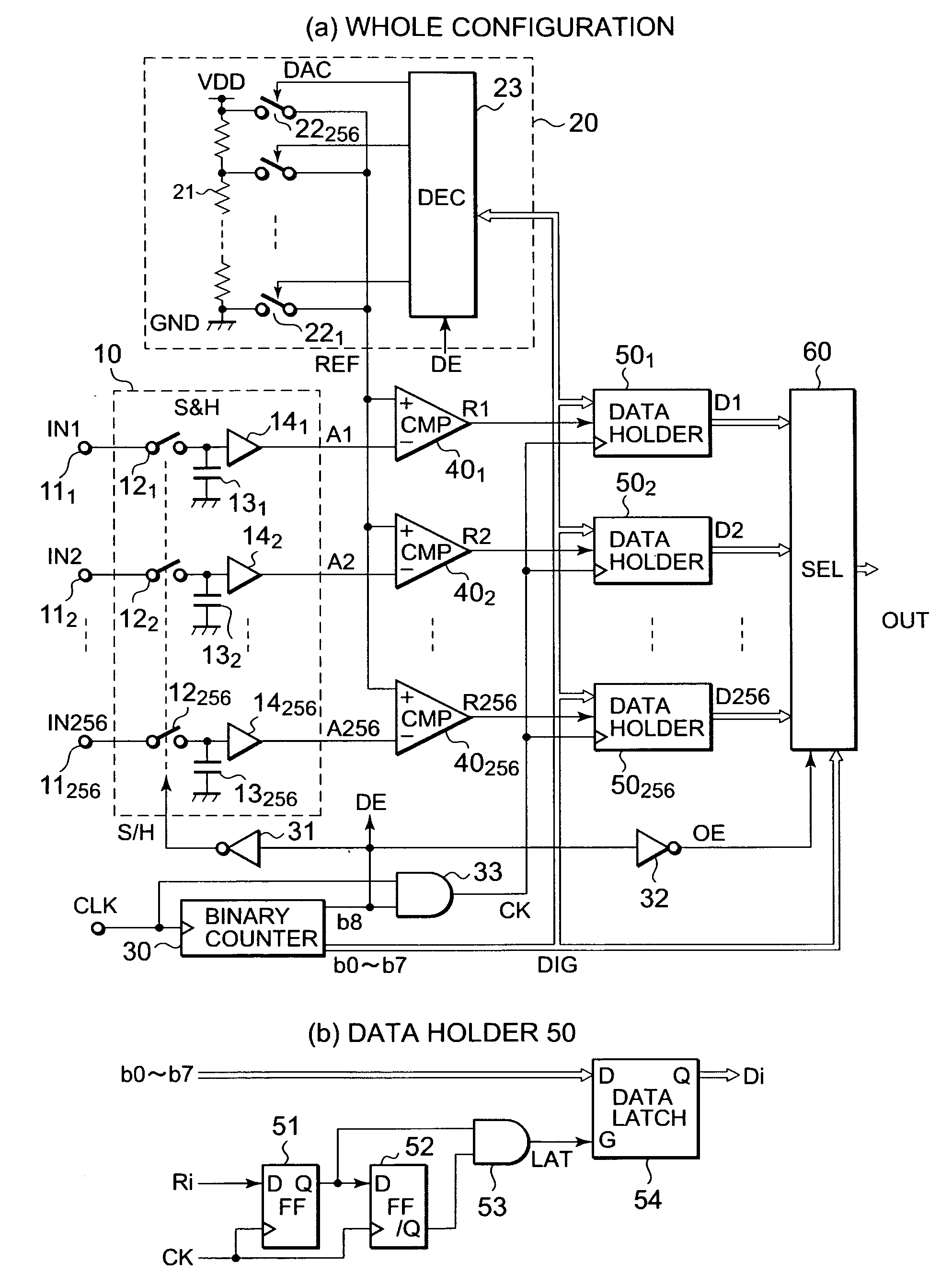

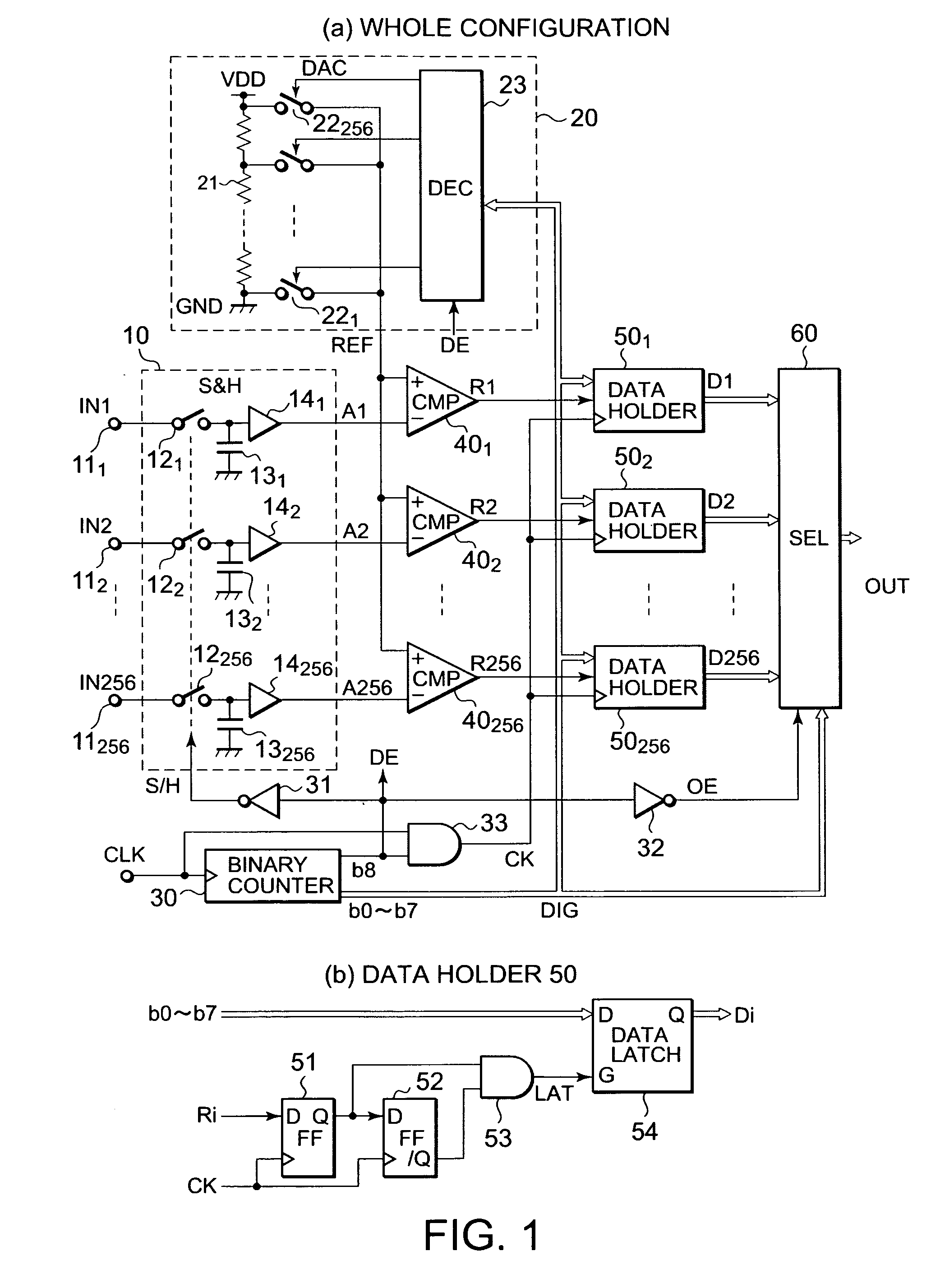

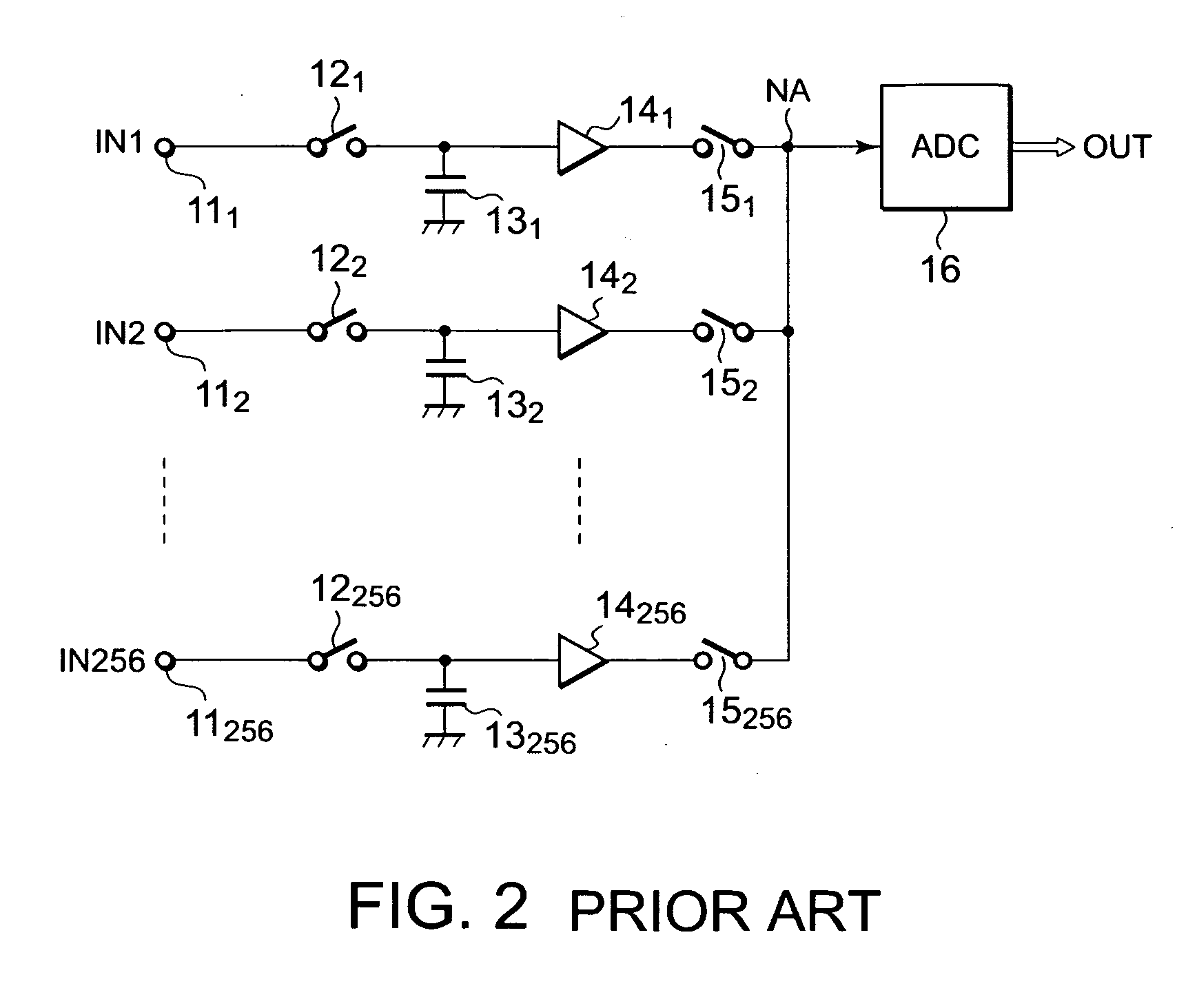

Analog-digital converter circuit

ActiveUS7372390B2Reduced conversion timeSimple circuit configurationElectric signal transmission systemsAnalogue-digital convertersMulti inputCurrent consumption

The present invention provides a multi-input A / D converter circuit capable of shorting a conversion time without increasing its layout area and current consumption. When a most significant bit of a binary counter is “L”, individual input signals are sampled by a sample and hold unit, and digital signals held in respective data holders are sequentially selected by a selector. When the most significant bit is brought to “H”, the respective input signals are held as analog signals and compared with each of reference voltages produced corresponding to a digital signal by a DAC. When decision signals outputted from comparators are changed from “L” to “H”, the digital signal at that time is held in the individual data holders as digital signals.

Owner:LAPIS SEMICON CO LTD

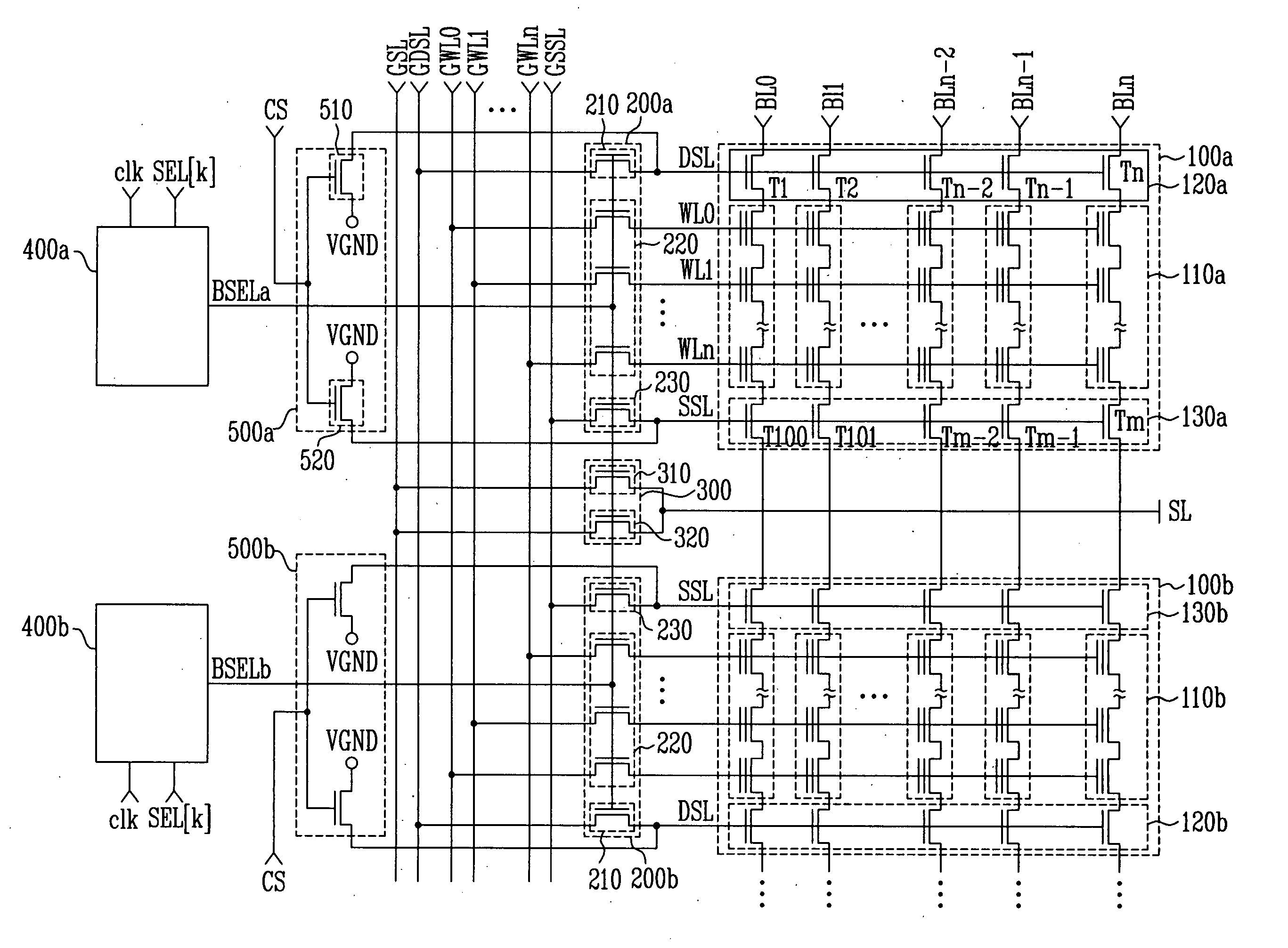

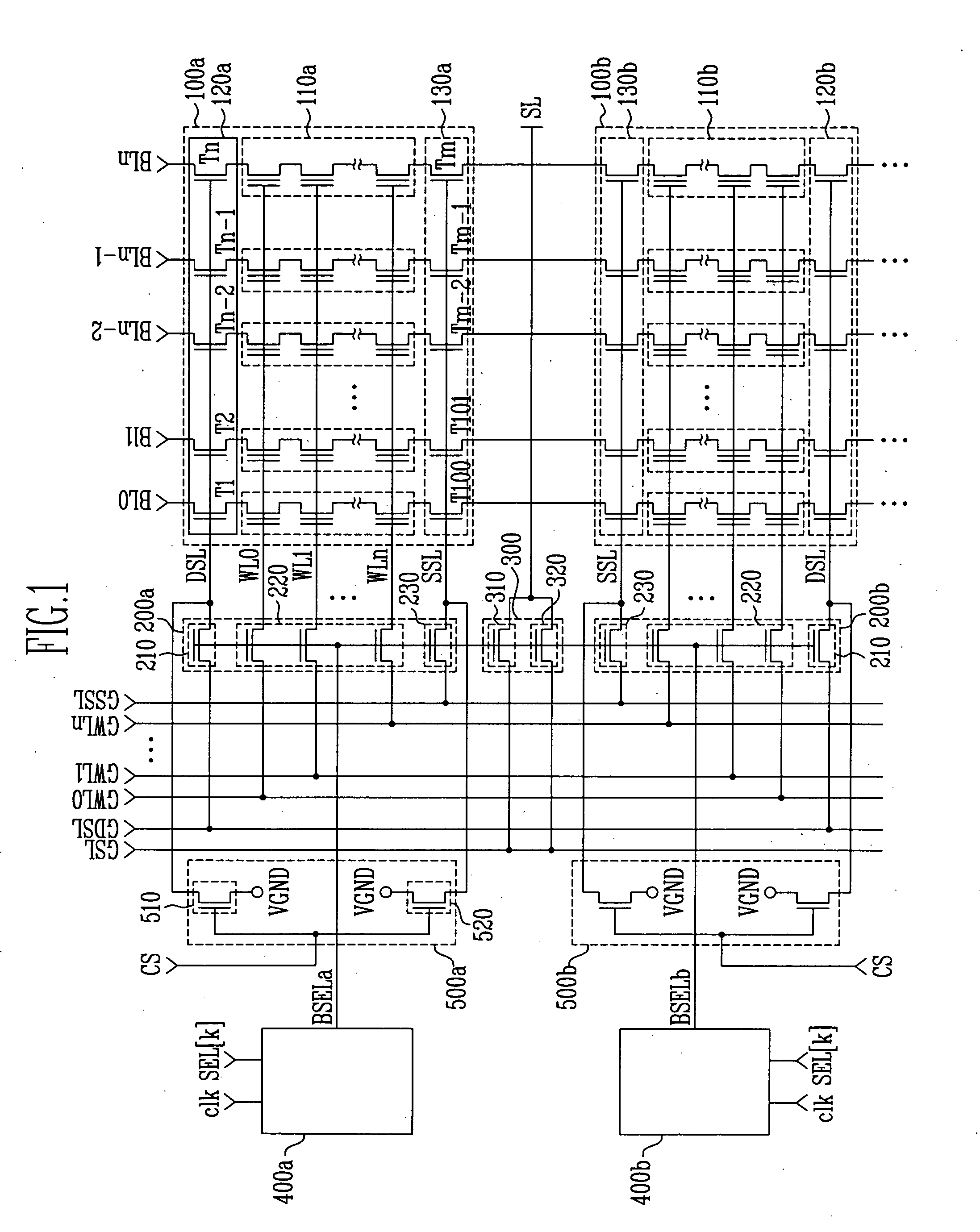

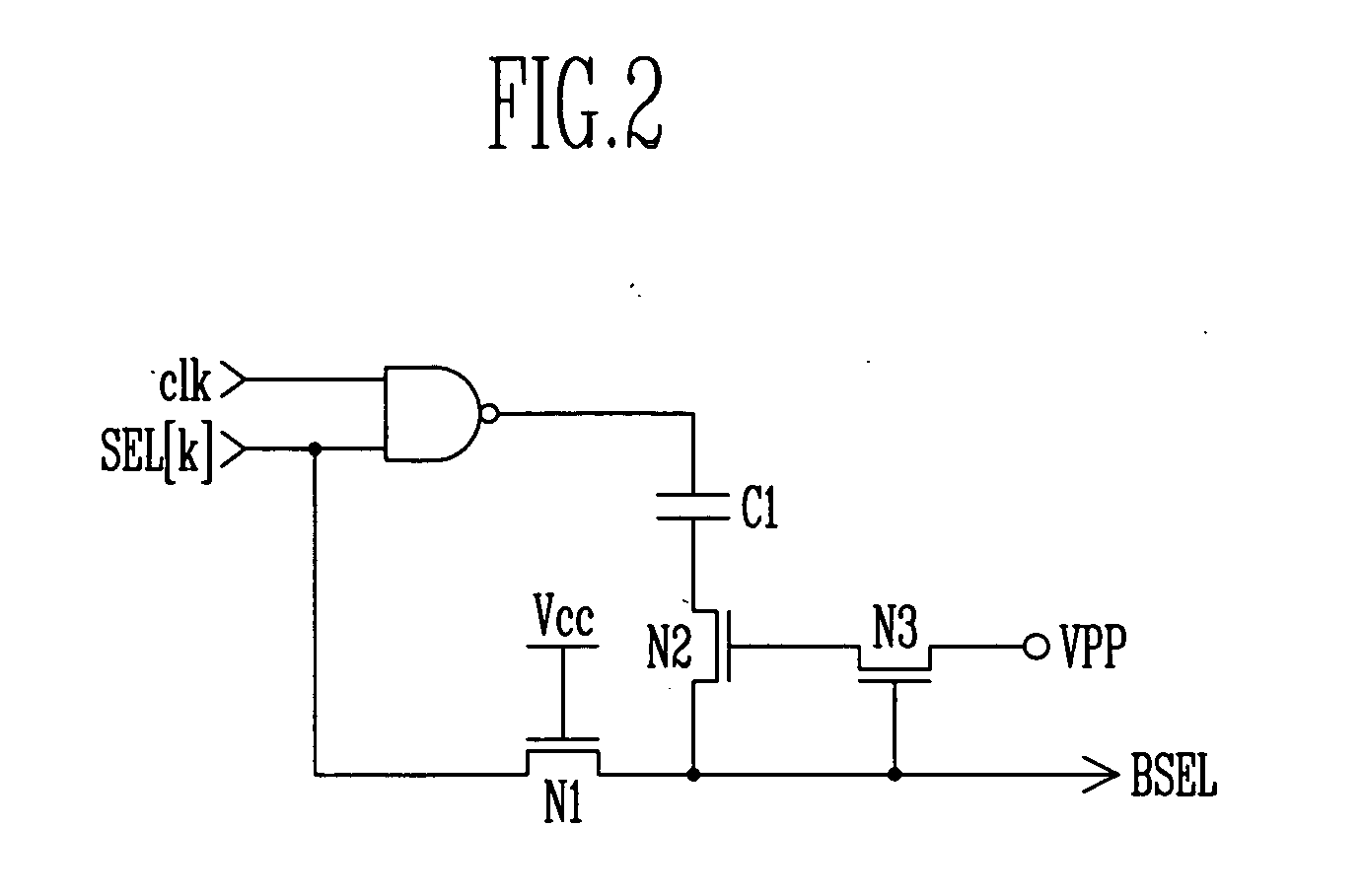

NAND flash memory device and method of programming the same

Provided is directed to a NAND flash memory device and a method of programming the same, which can improve integration of the device by removing a common source line connecting with a source line coupled to a plurality of cell blocks, control a voltage applied to a source line by each cell block, and rise a precharge level in a channel area by applying a pumping voltage to the source line relatively having low capacitance instead of a bitline having a large capacitance, and as a result of those, the NAND flash memory device can reduce disturbance, use a lower voltage than a power supply voltage on the bitline, which leads to reduce a current consumption.

Owner:STMICROELECTRONICS SRL +1

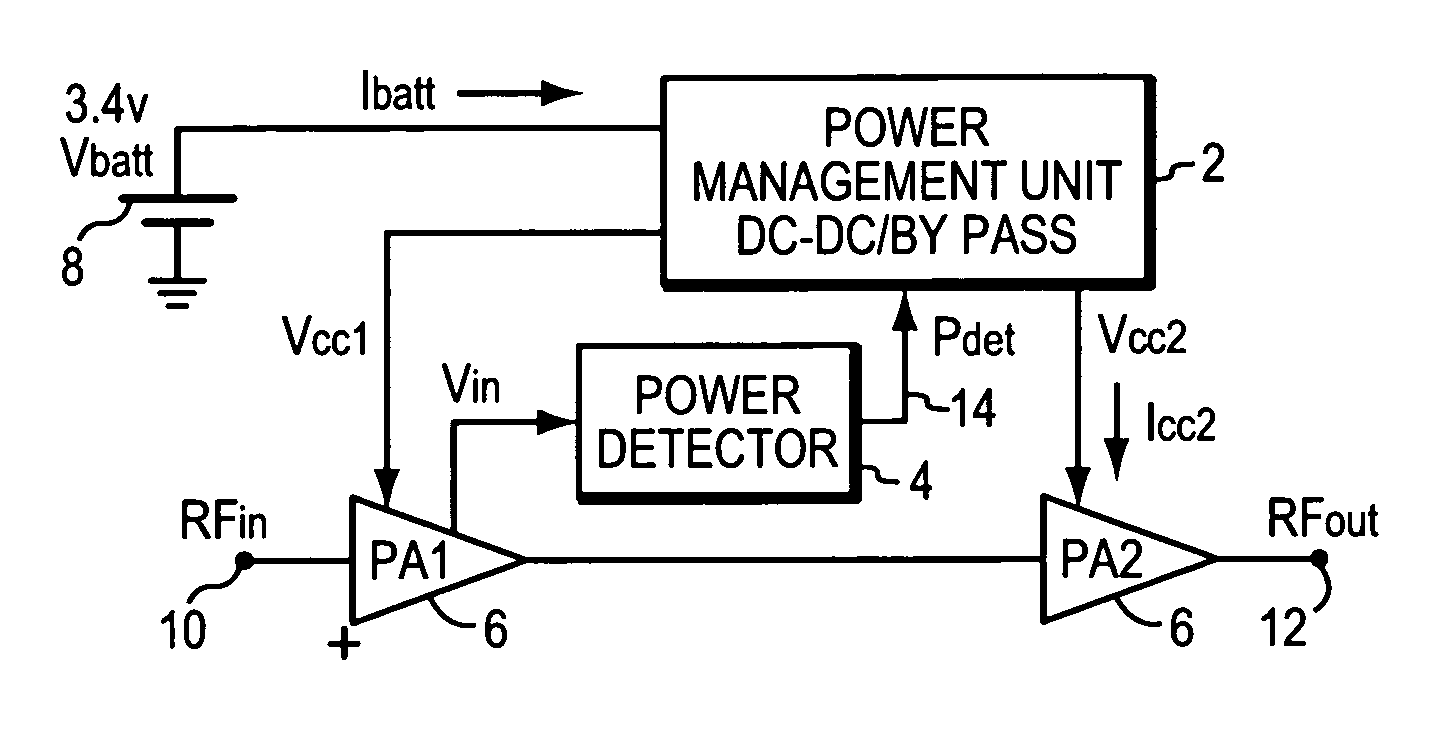

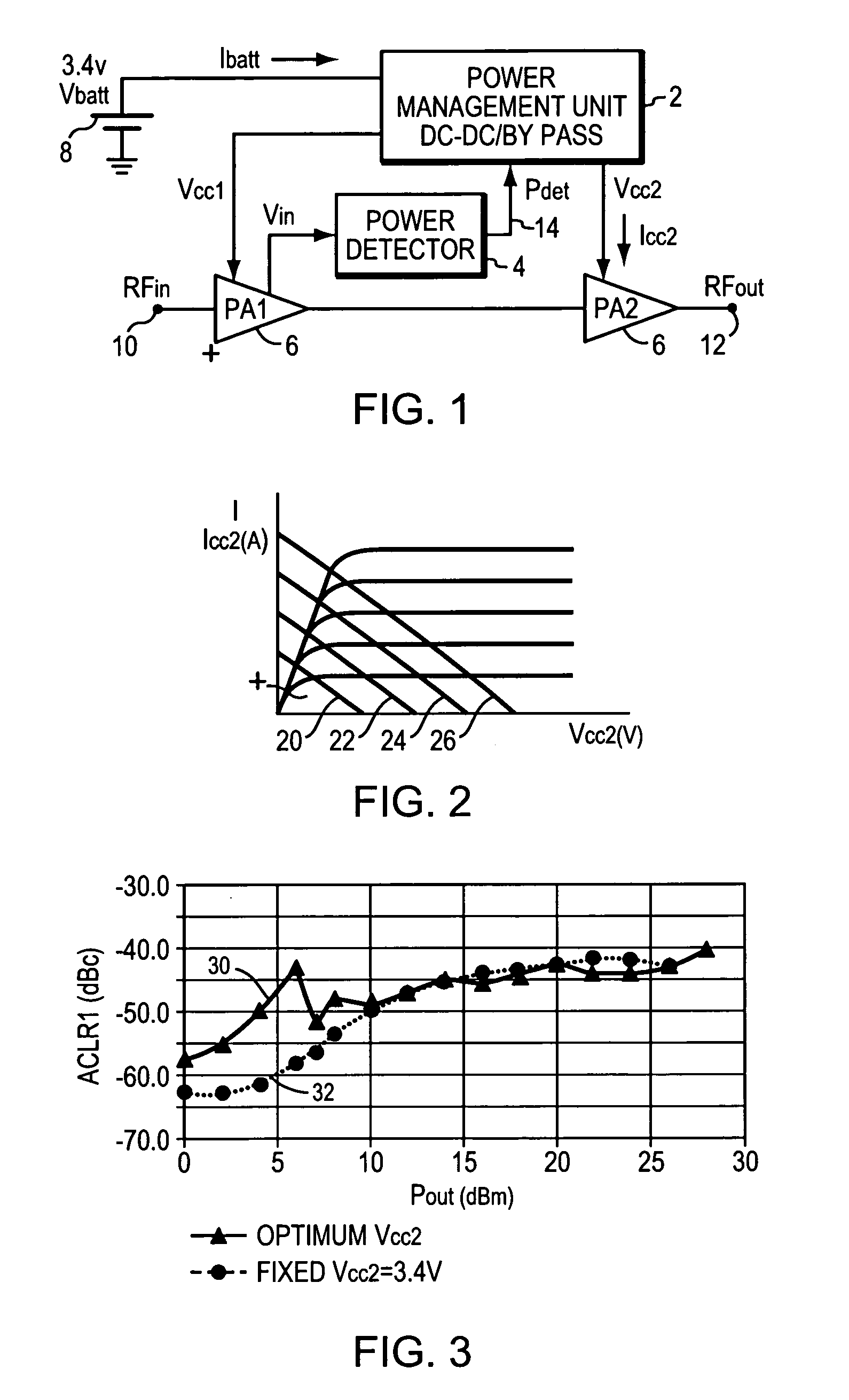

Power amplifier with close-loop adaptive voltage supply

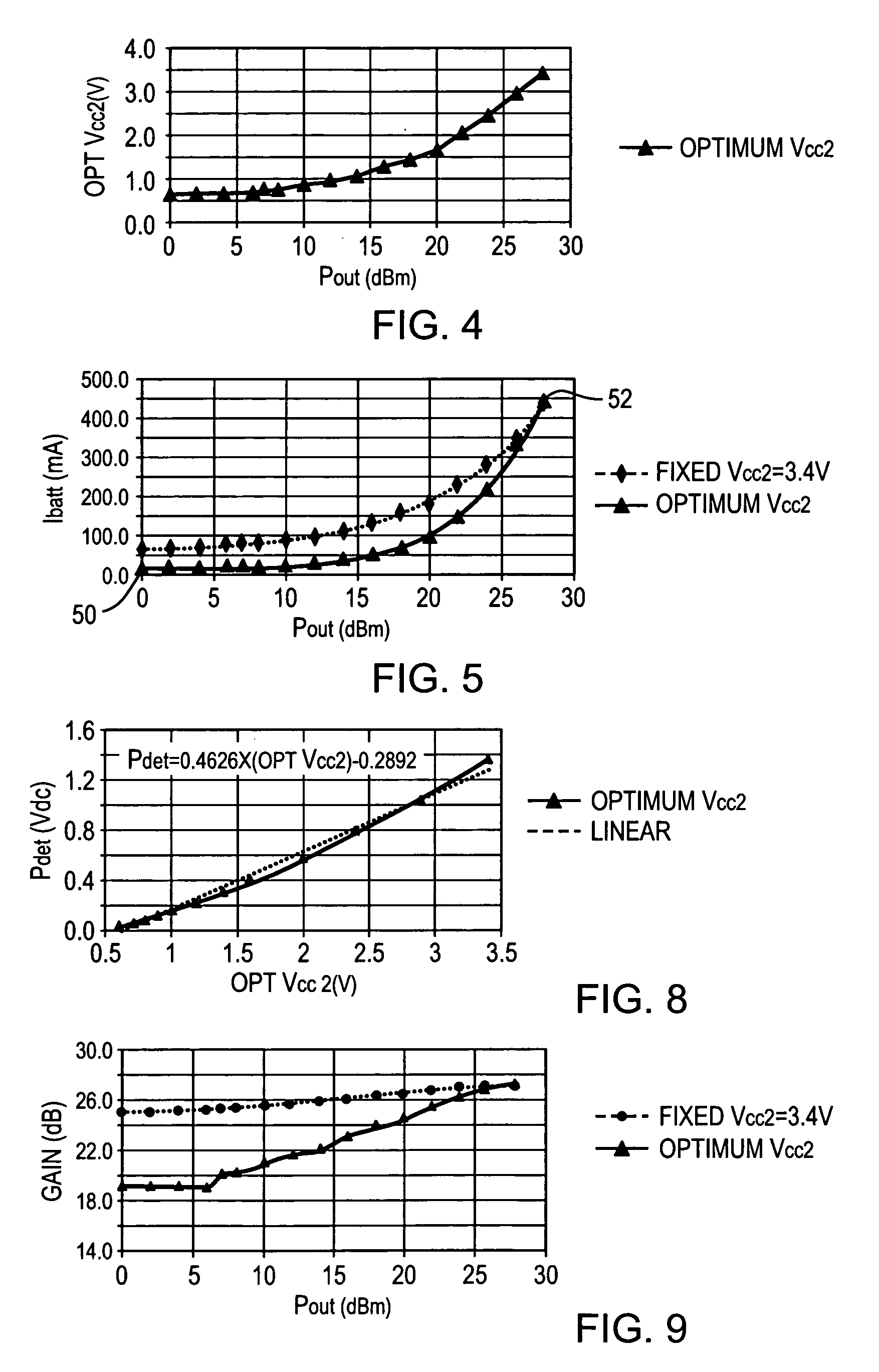

InactiveUS20070182490A1Conserve battery lifeReduce current consumptionGain controlAmplifier detailsControl signalPower detector

A two- (or multi) stage power amplifier receives a variable RF input signal, and outputs an optimized. RF output signal from, for example, a mobile handset. The output power level from the handset is predetermined, as known in the art, by the received control signal from a base station. The first power amplifier stage amplifies the variable RF input signal and outputs an RF signal, Vin, to a power detector circuit and an RF signal to the second or next amplifier stage. The power detect circuit amplifies the Vin signal and rectifies that signal with a linearly biased diode and provides a detect signal to a DC to DC converter. The converter responds by providing an optimum voltage bias, which is linearly related to the DC voltage detect signal from the power detector, to the output stage, and, if desired, to the first and / or other stages of the power amplifier that optimizes the output power level while meeting the required linearity specification. The battery current consumption is optimized through this automatic, dynamically control of the supply voltage for the power amplifier at each output power level through the DC to DC converter.

Owner:SEMICON COMPONENTS IND LLC

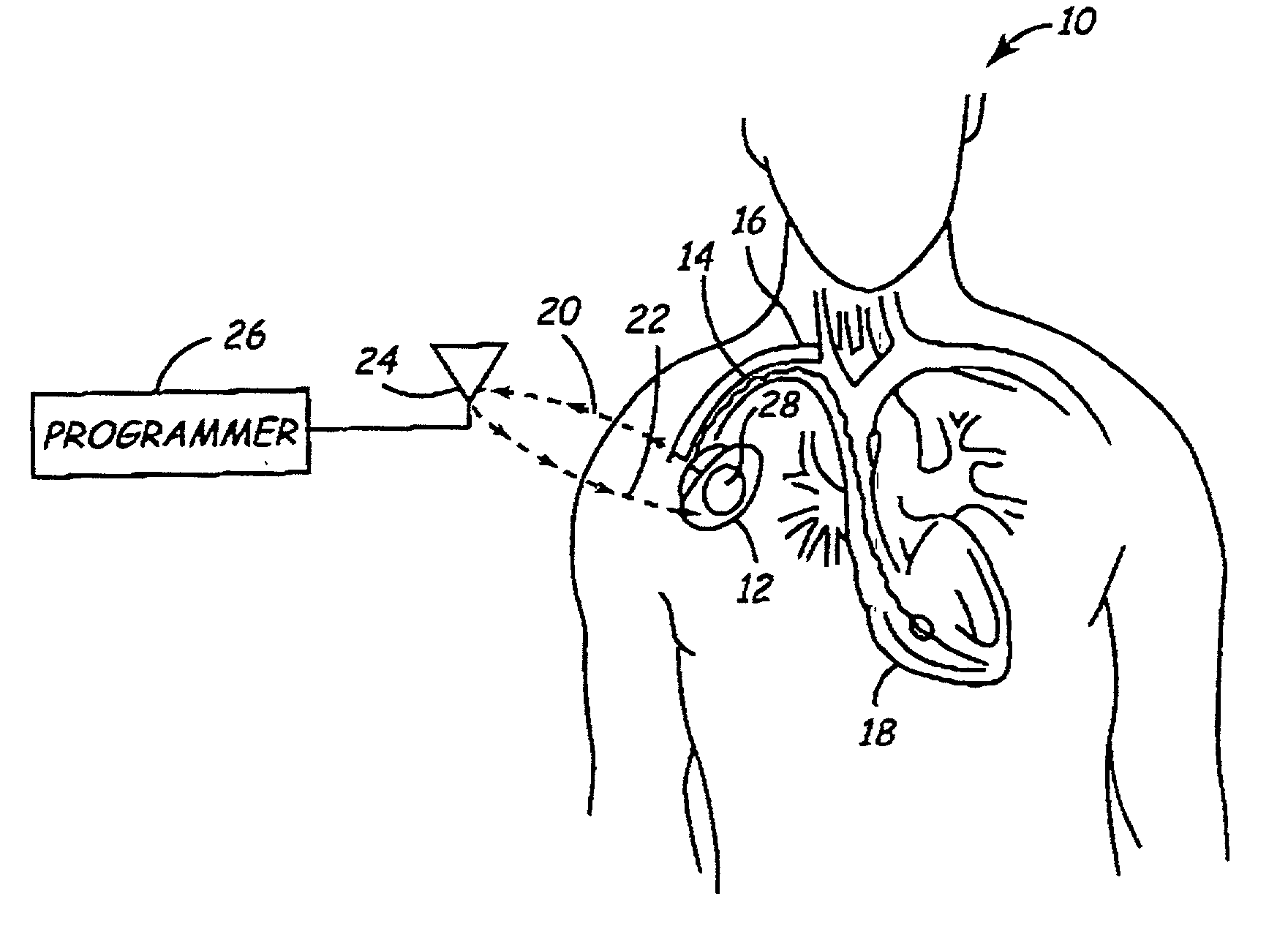

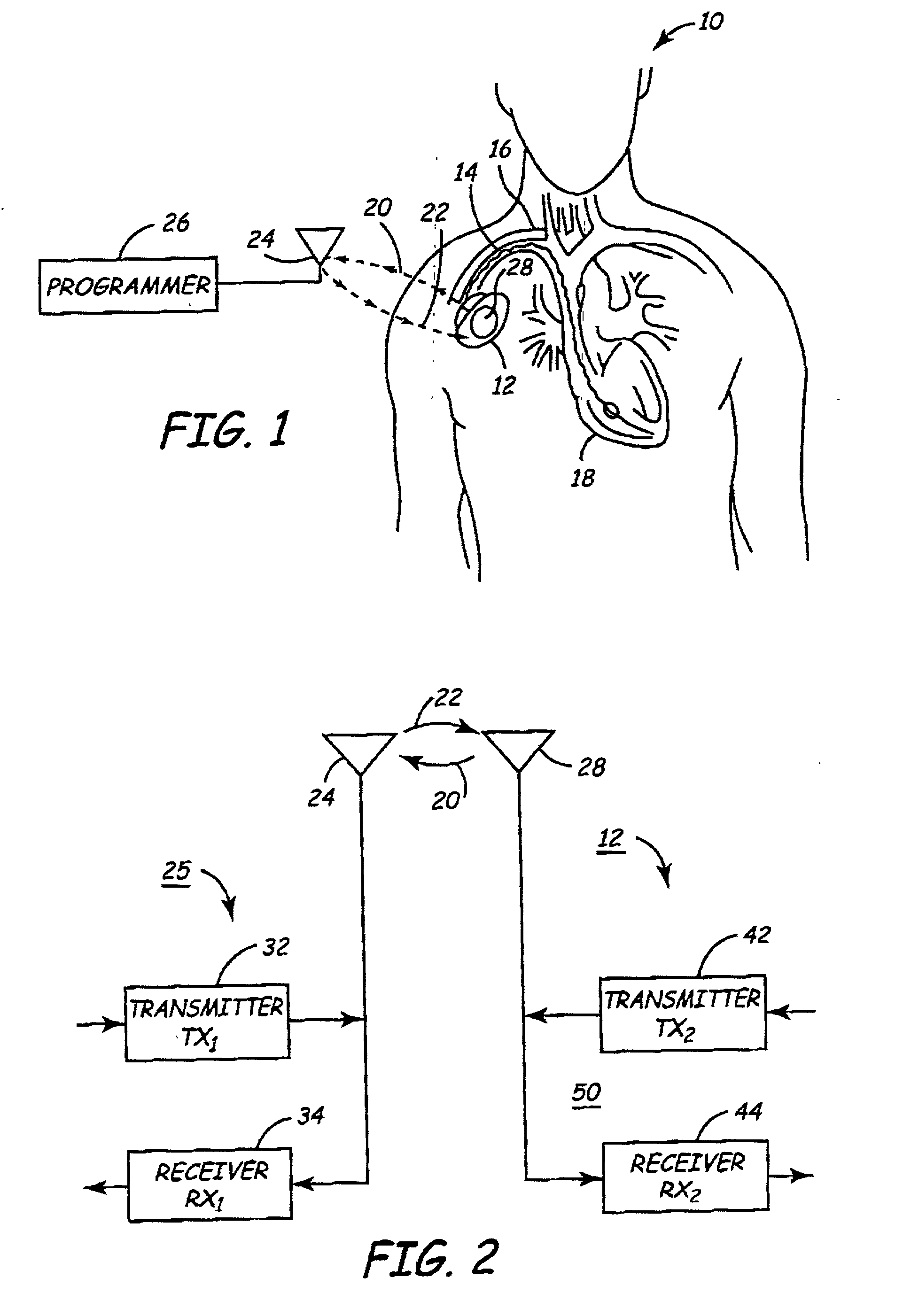

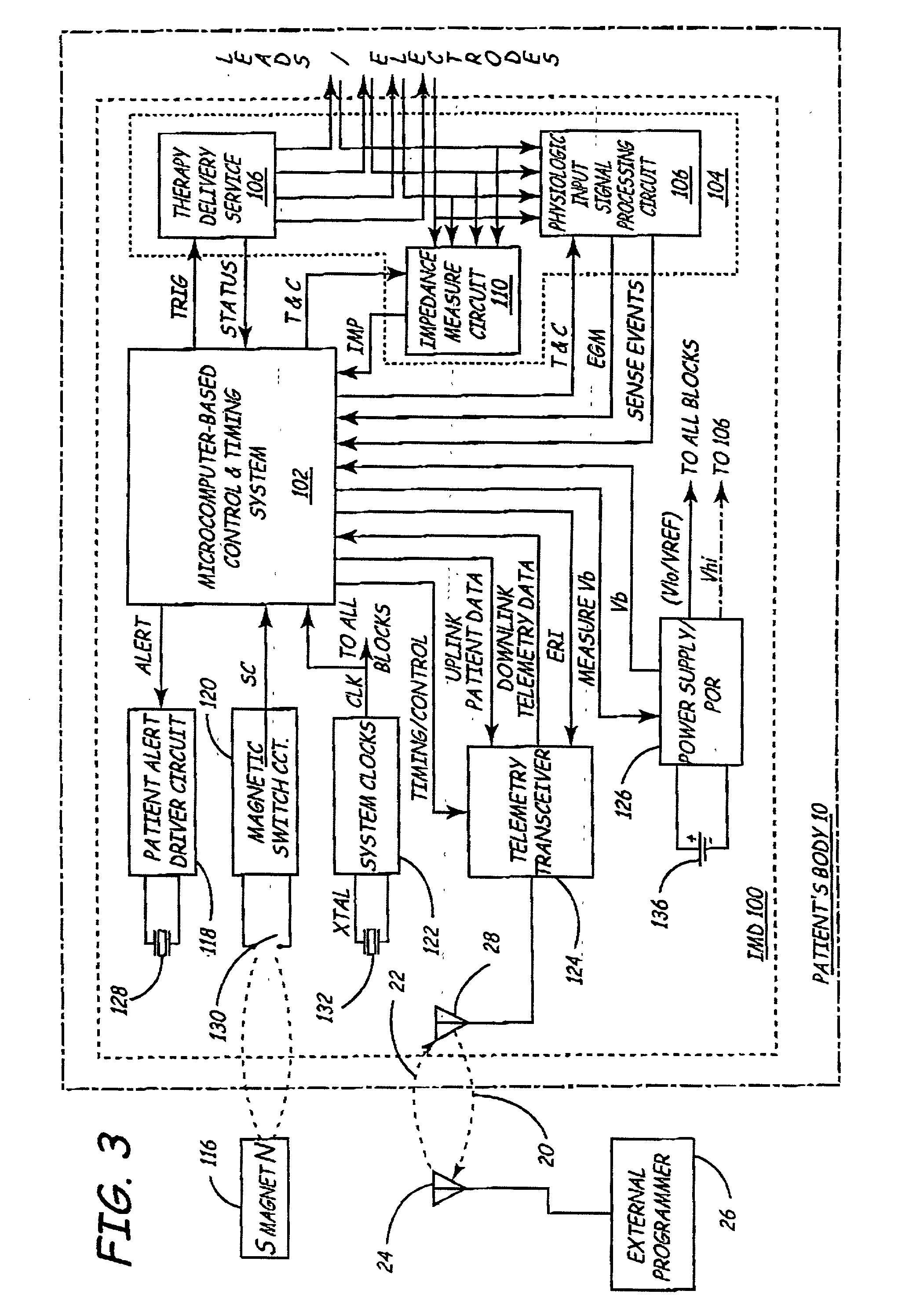

System and method for determining remaining battery life for an implantable medical device

A system and method for determining a remaining life estimate of the remaining battery life of a battery of an implantable medical device (IMD). The IMD battery preferably exhibits a highly reproducible monotonically decreasing discharge curve. The estimated remaining life estimates are derived by periodically measuring battery voltage, and estimating the estimated past current drain of the IMD comprising an average of the sum of the quiescent current drain and therapy delivery current drain, and determining the estimated remaining longevity from the measured voltage and the estimated past current drain.

Owner:MEDTRONIC INC

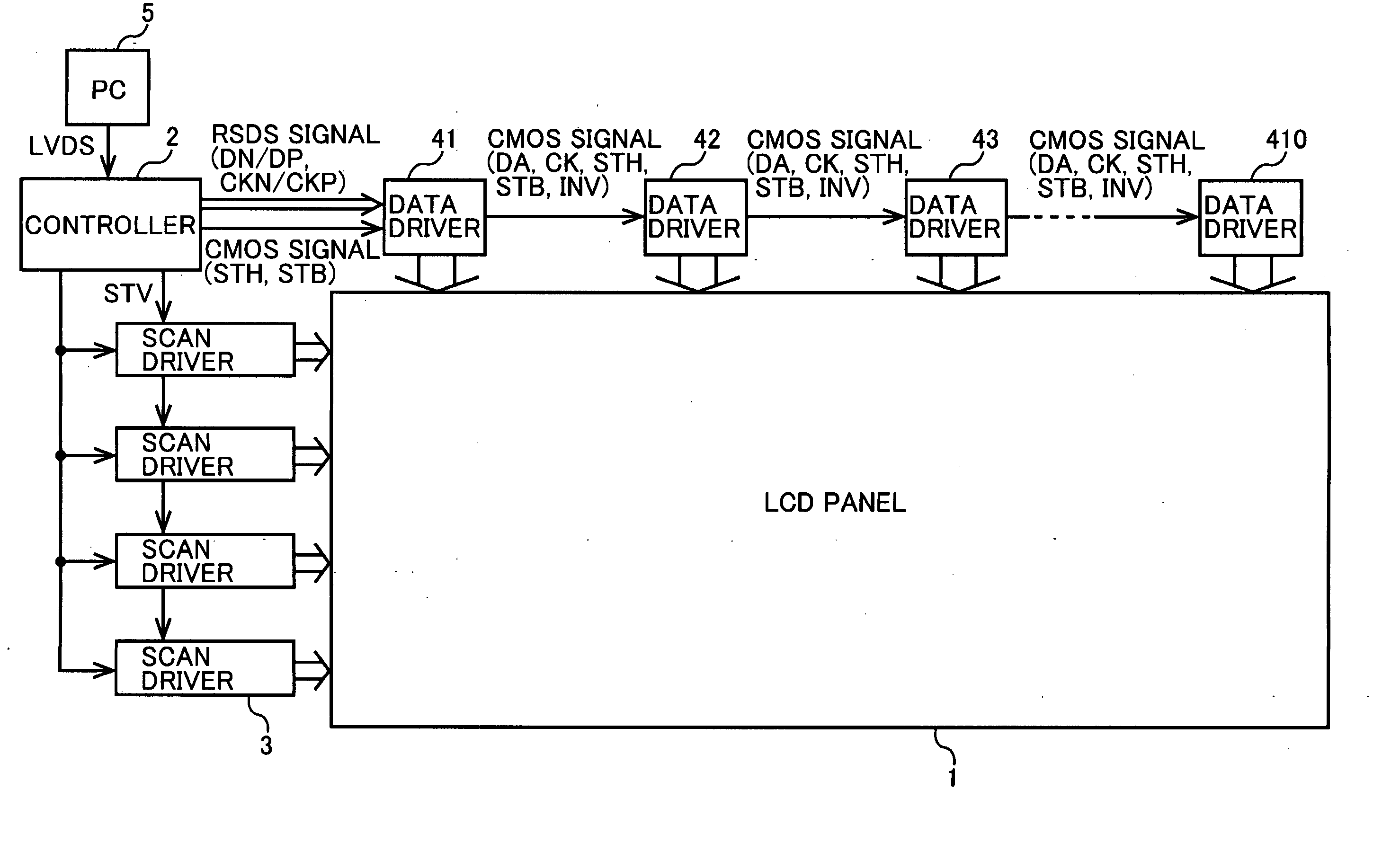

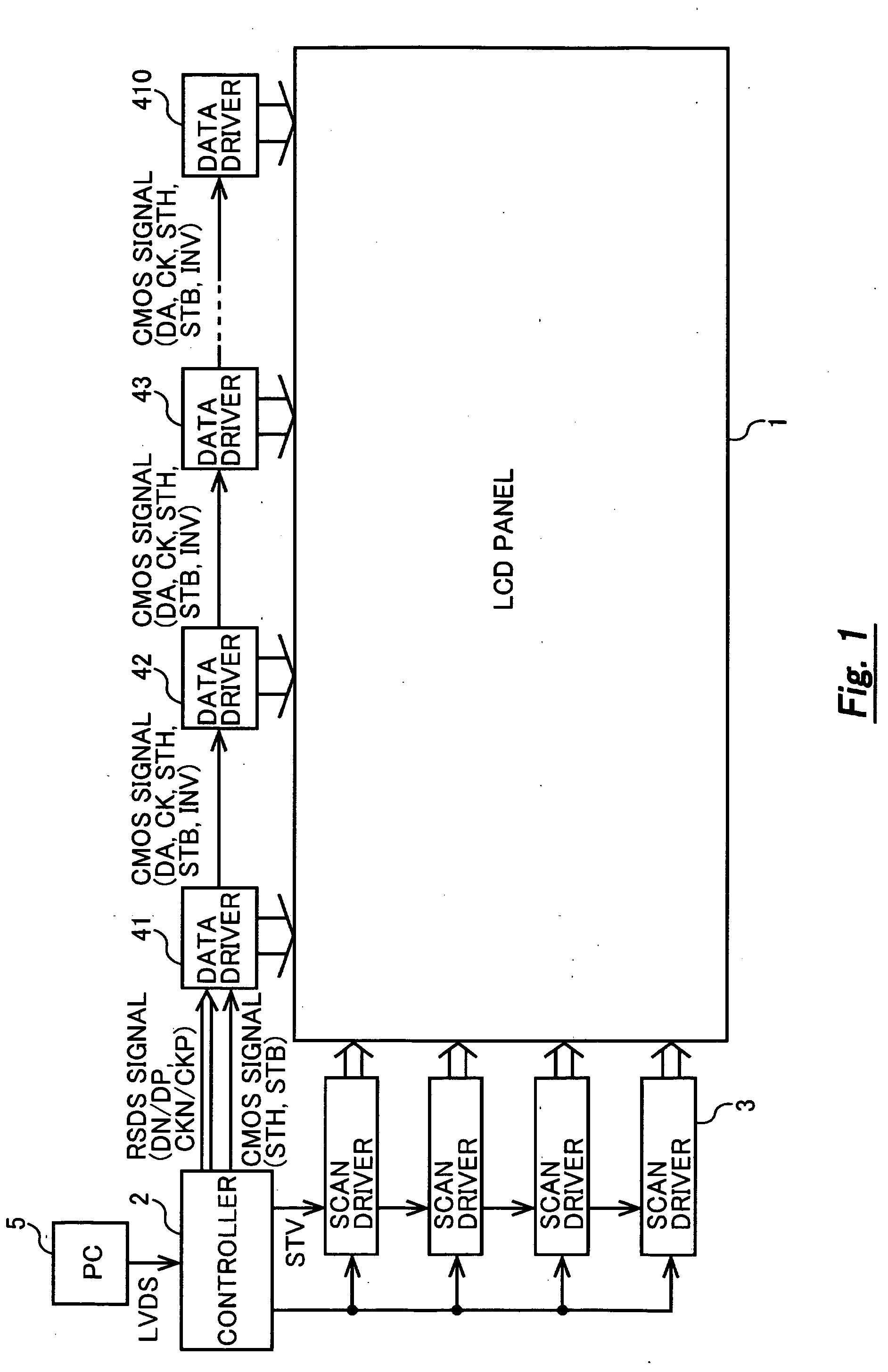

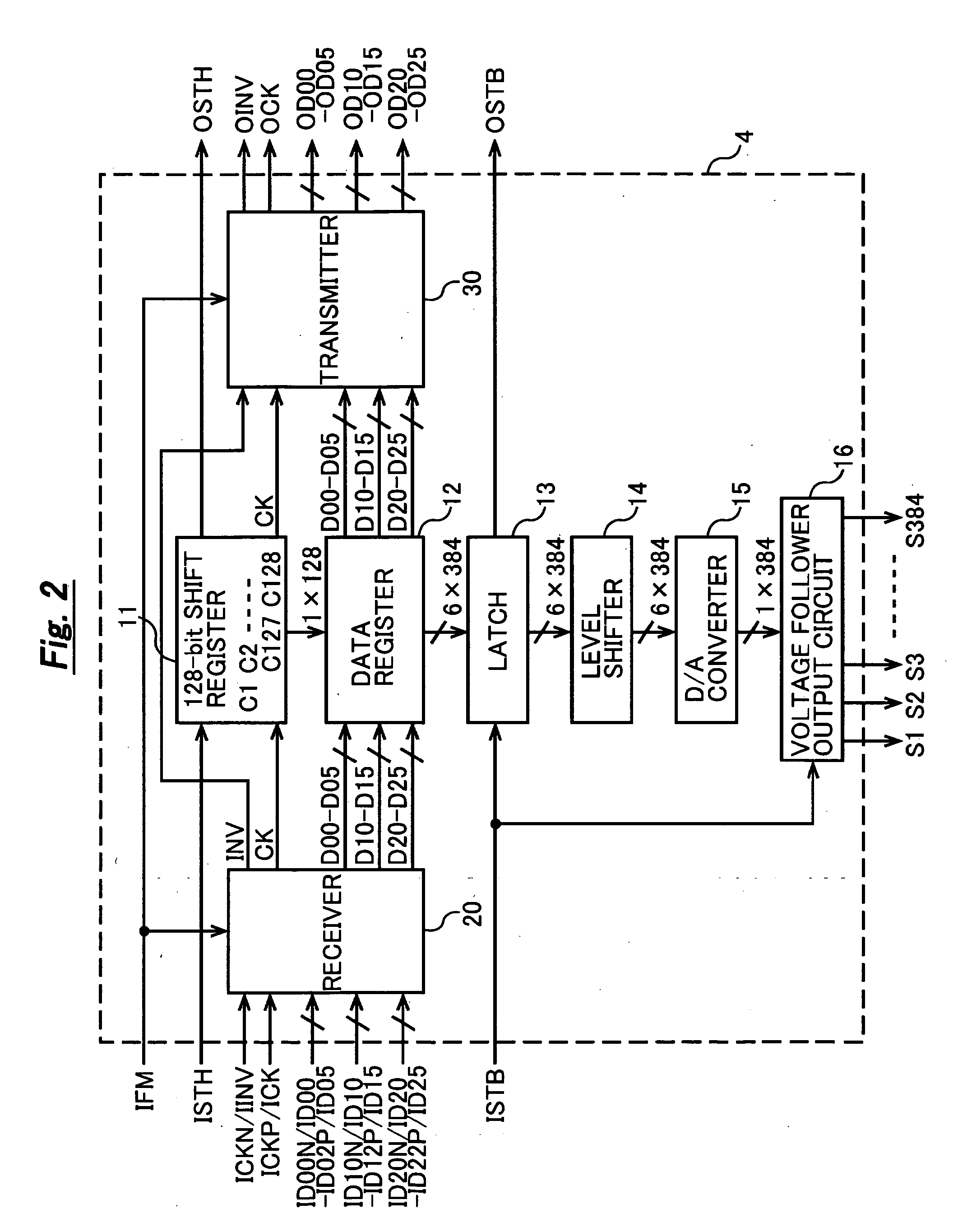

Data transfer method and electronic device

ActiveUS20050219189A1Large amplitudeObtaining adequateCathode-ray tube indicatorsInput/output processes for data processingCMOSTiming margin

The present invention provides a liquid-crystal display device that is able to reduce EMI, current consumption, and so forth in an interchip transfer of display data, a timing signal, and so forth and to provide an appropriate timing margin. In an interchip transfer of display data, a timing signal, and so forth that uses a plurality of data drivers, a certain data driver is used as a data driver. When the data driver is used in a first stage, an internal receiver is made to function as an RSDS receiver by fixing the IFM terminal at the “H” level. The received RSDS signal constitutes a CMOS signal that has been divided into two by the receiver and is output by the transmitter. Here, a data inversion signal is generated and output by the transmitter. When the data driver is used in the second or subsequent stage, the internal receiver is made to function as a CMOS receiver by fixing the IFM terminal at the “L” level. The received CMOS signal is output after being subjected to inversion control by means of the data inversion signal by the receiver and transmitter.

Owner:AU OPTRONICS CORP

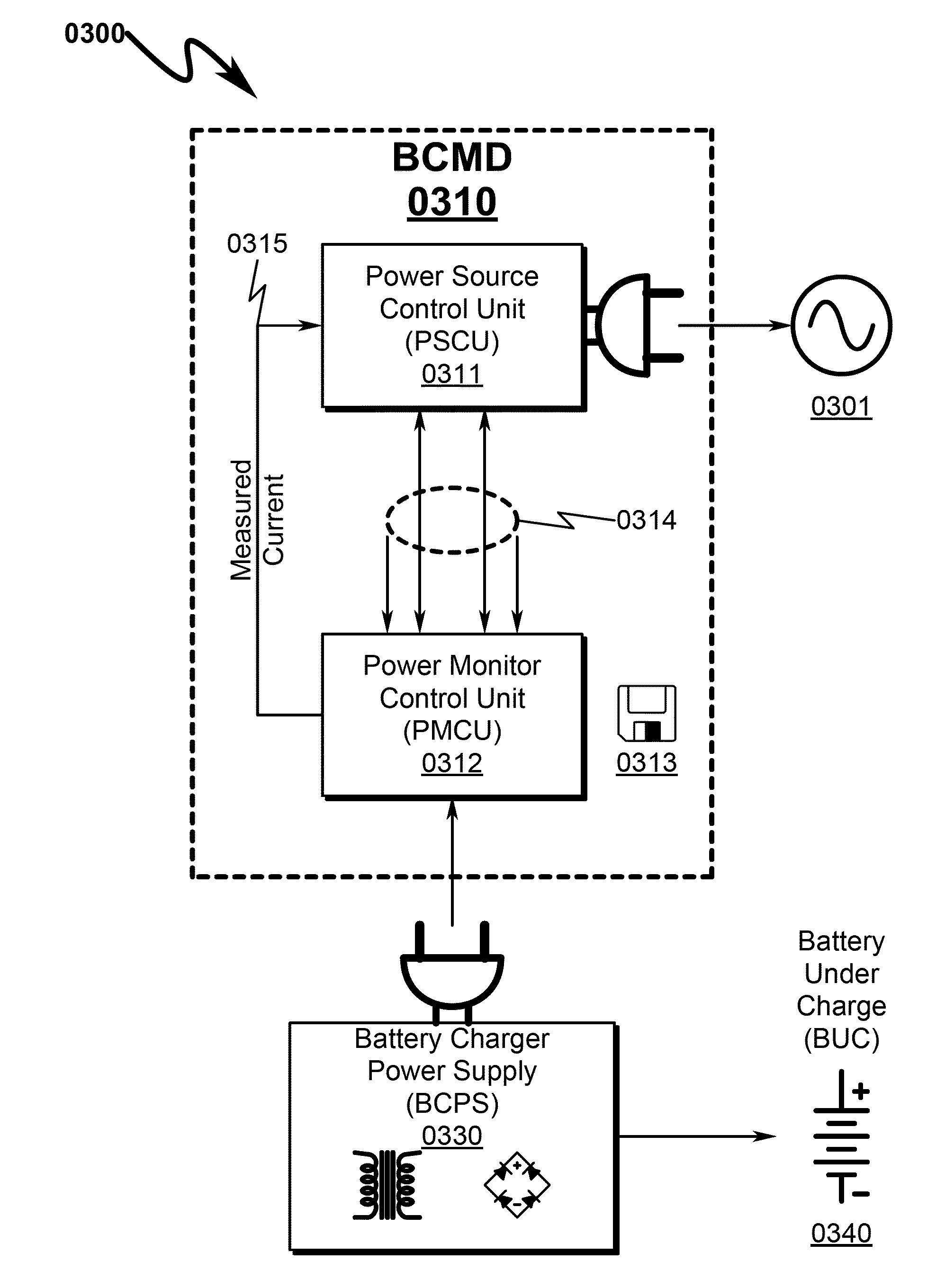

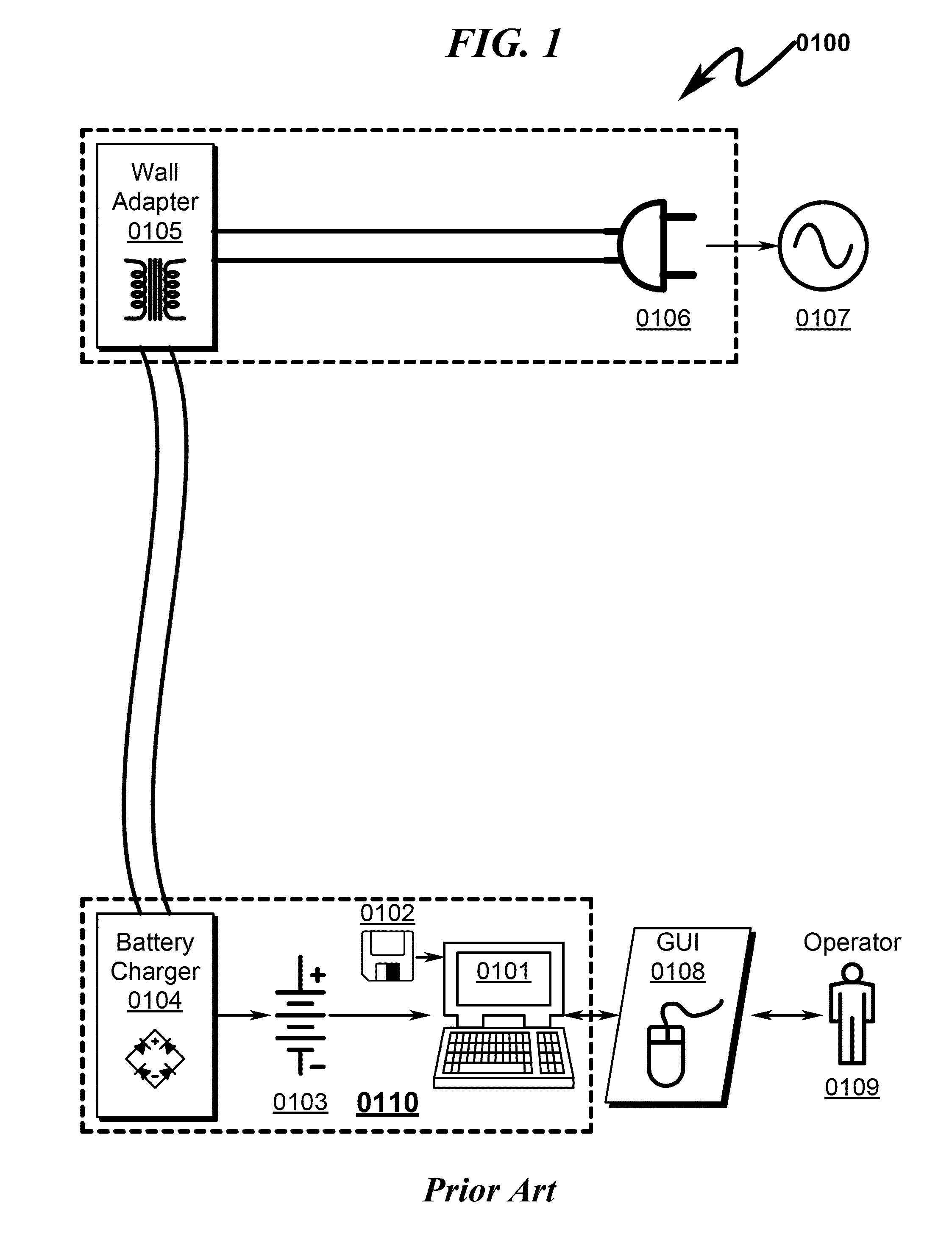

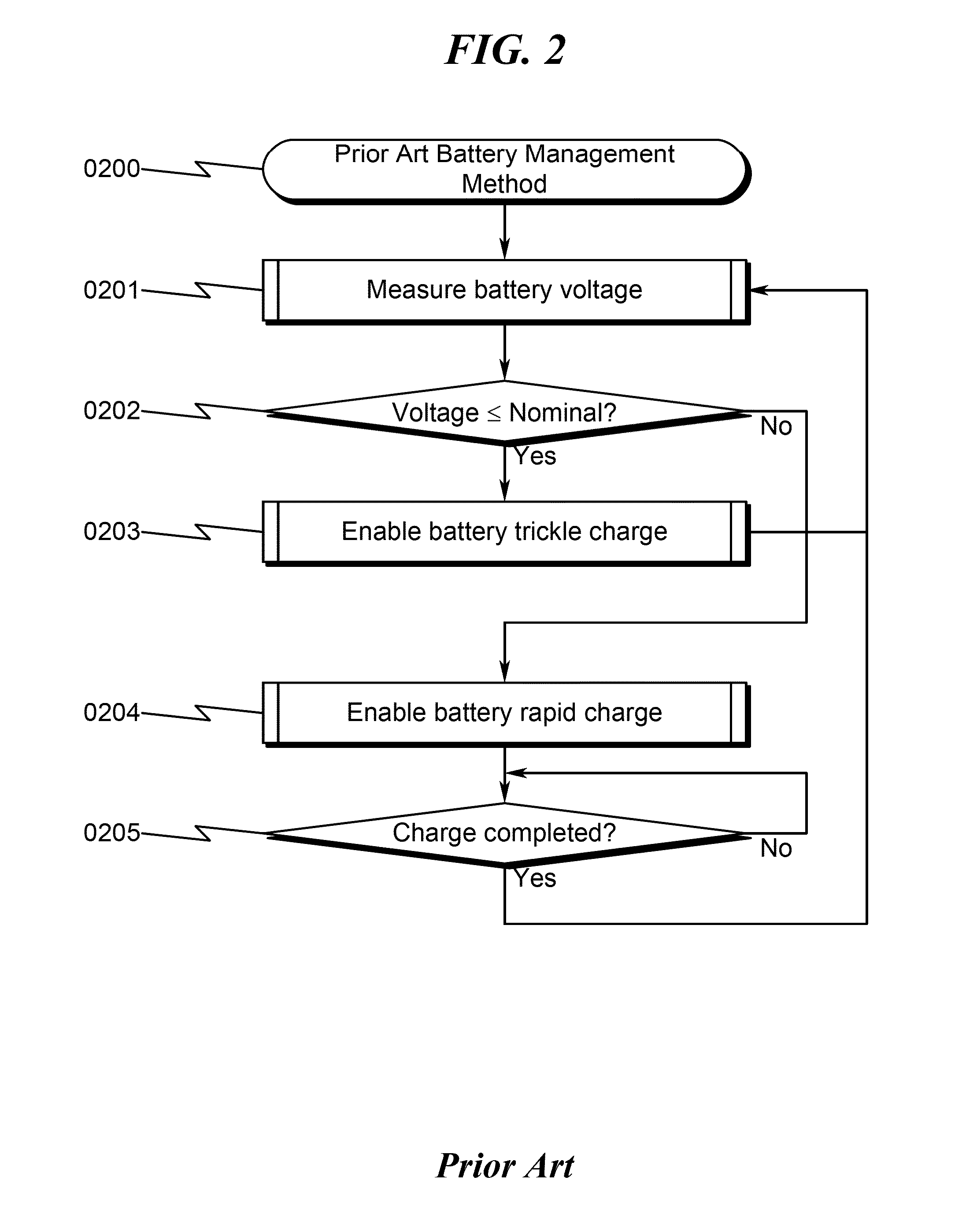

Battery charger management system and method

ActiveUS20130214730A1Extend battery lifeElectric powerNetwork connectionsBattery chargeElectrical battery

A battery charger management system / method implementing indirect execution of battery charging profiles is disclosed. The system utilizes a power source control unit (PSCU) to selectively switch a power supply source to a battery charging power supply (BCPS) that charges a battery. A power monitor control unit (PMCU) monitors the current consumed by the BCPS and reports this to the PSCU. The BCPS current consumption provides the PSCU a profile of the charging characteristics of the battery attached to the BCPS, allowing identification of the battery type and a determination of the optimal charging profile for the battery in its current charge state. The power source to the BCPS is switched by the PCCU in accordance with the determined optimal charging profile to optimally charge the battery. The PSCU may operate independently or in conjunction with wireless commands received from a mobile communication device (MCD).

Owner:ADVANERGY

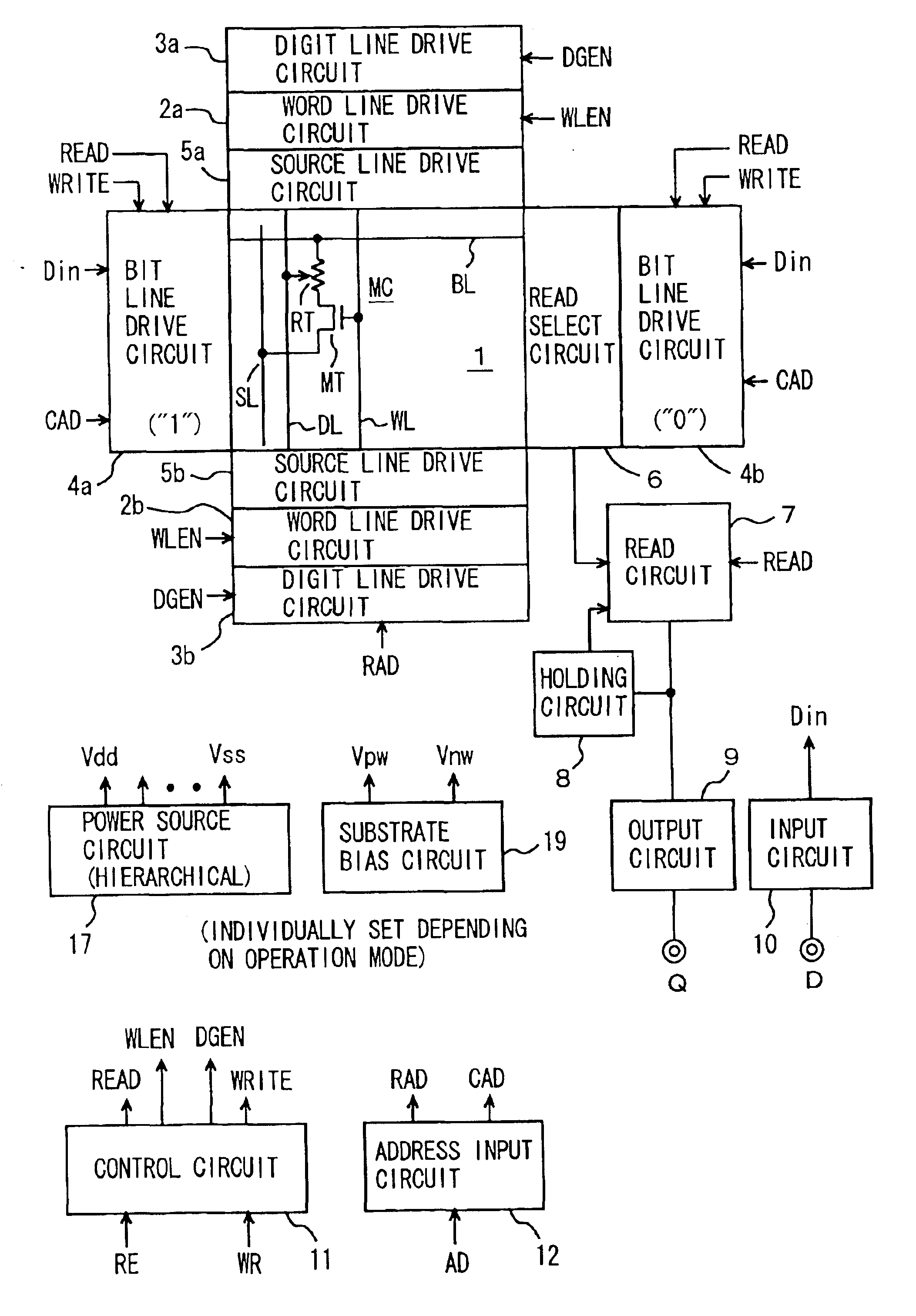

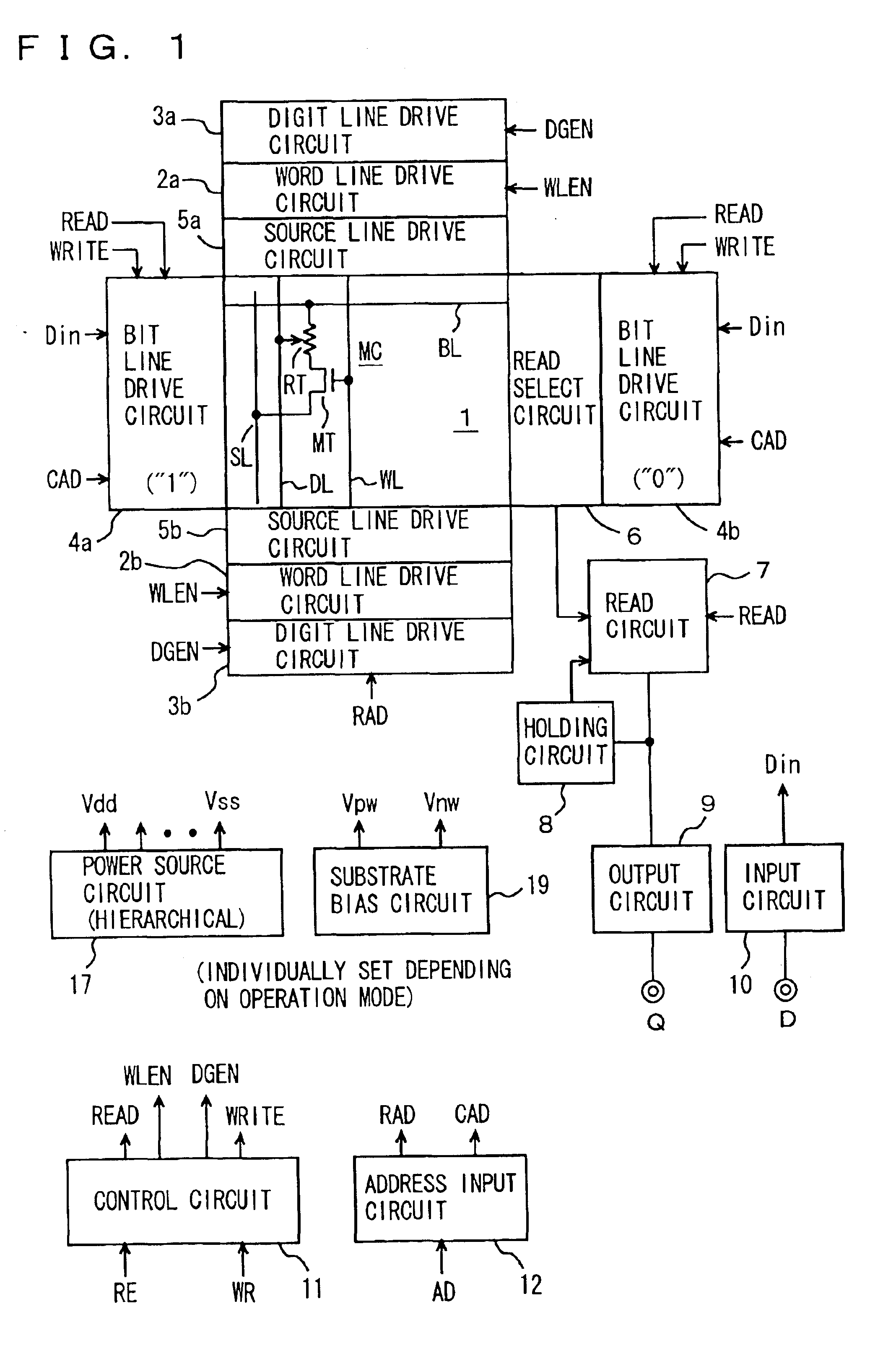

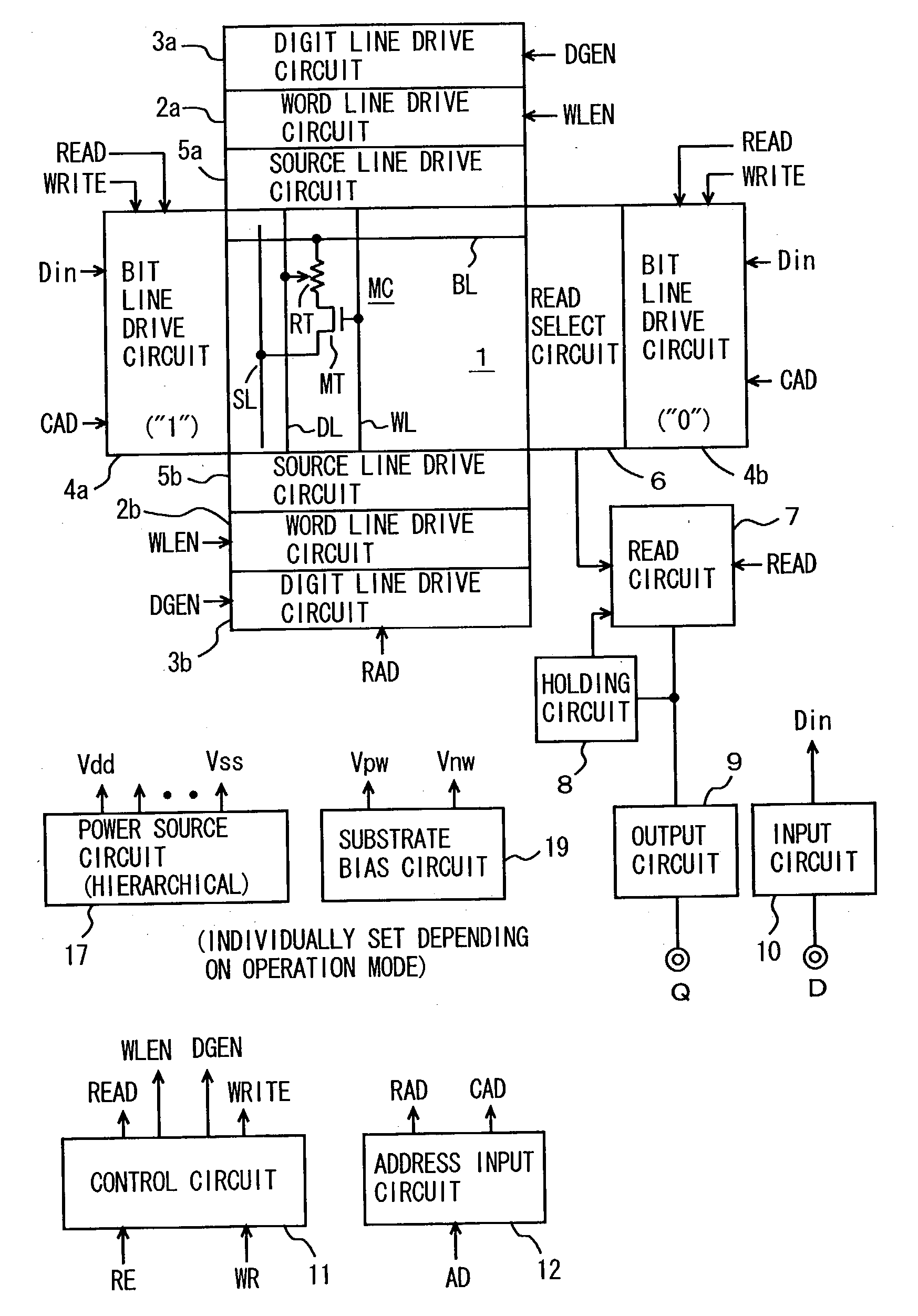

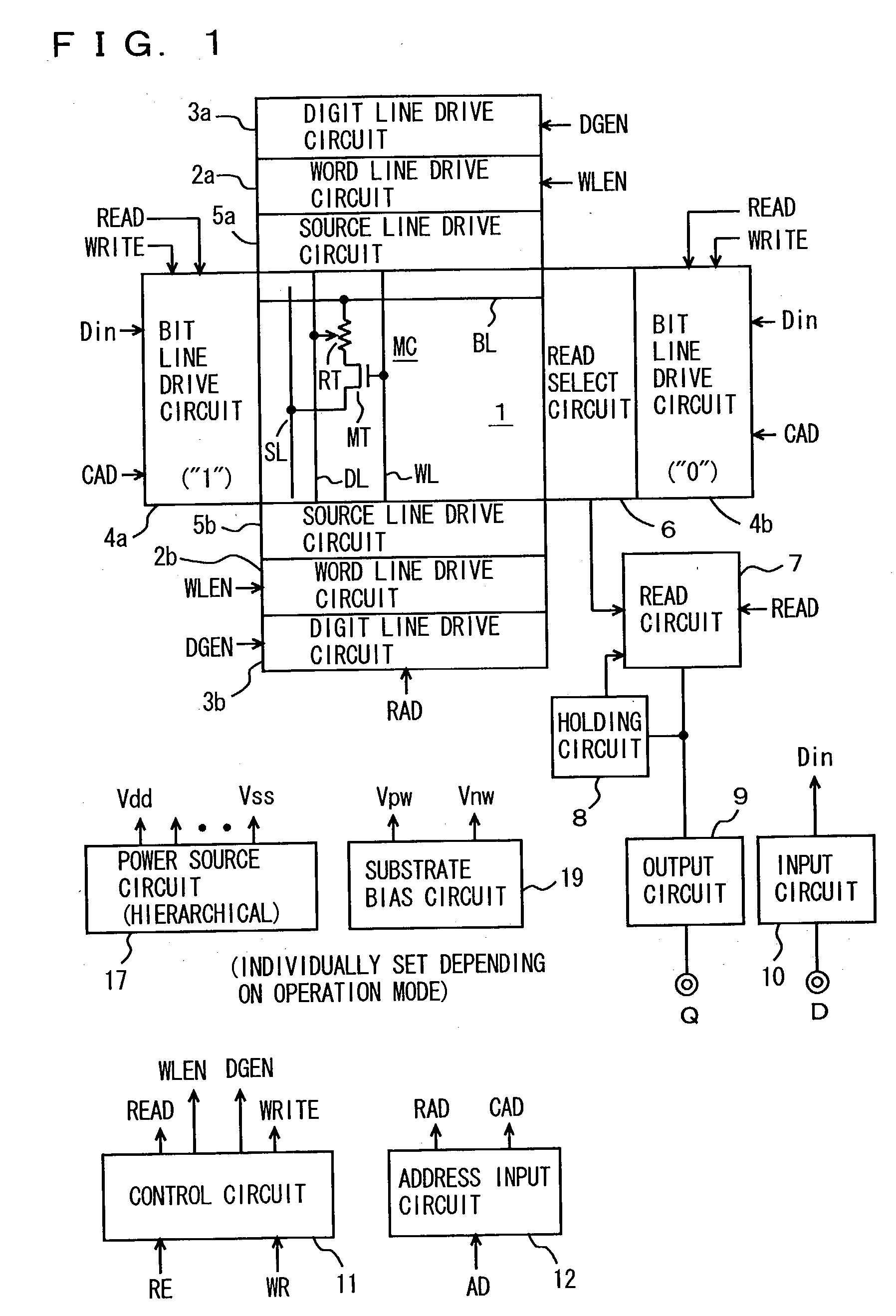

Semiconductor memory device operating with low current consumption

In a resistance value variable memory, substrate voltages and / or substrate biases of a digit line drive circuit, a word line drive circuit and a bit line drive circuit for a memory cell array are changed in accordance with an operation mode. A driving power on signal lines connected to memory cells can be increased, and a leakage current during standby can be reduced without increasing a circuit layout area.

Owner:RENESAS ELECTRONICS CORP

Low power consumption MIS semiconductor device

InactiveUS7355455B2Total current dropSimple circuit configurationTransistorReliability increasing modificationsCurrent consumptionLogic gate

A logic gate is constructed of an insulated gate field effect transistor (MIS transistor) having a thin gate insulation film. An operation power supply line to the logic gate is provided with an MIS transistor having a thick gate insulation film for switching the supply and stop of an operation power source voltage. A voltage of the gate of the power source switching transistor is made changing in an amplitude greater than an amplitude of an input and an output signal to the logic gate. Current consumption in a semiconductor device configured of MIS transistor of a thin gate insulation film can be reduced and an power source voltage thereof can be stabilized.

Owner:RENESAS ELECTRONICS CORP

Analog-digital converter circuit

ActiveUS20070188367A1Reduced conversion timeSimple circuit configurationElectric signal transmission systemsAnalogue-digital convertersMulti inputA d converter

The present invention provides a multi-input A / D converter circuit capable of shorting a conversion time without increasing its layout area and current consumption. When a most significant bit of a binary counter is “L”, individual input signals are sampled by a sample and hold unit, and digital signals held in respective data holders are sequentially selected by a selector. When the most significant bit is brought to “H”, the respective input signals are held as analog signals and compared with each of reference voltages produced corresponding to a digital signal by a DAC. When decision signals outputted from comparators are changed from “L” to “H”, the digital signal at that time is held in the individual data holders as digital signals.

Owner:LAPIS SEMICON CO LTD

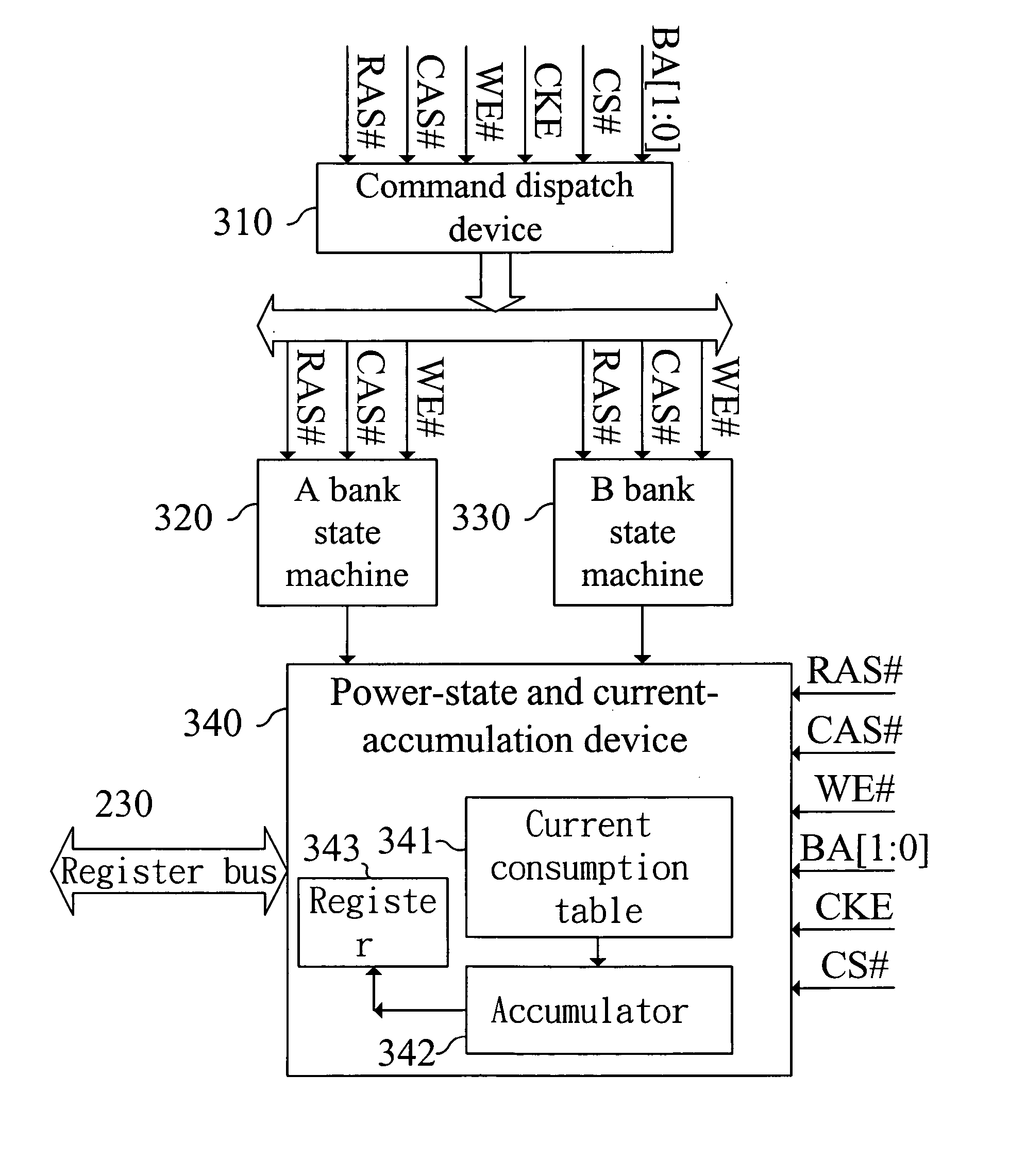

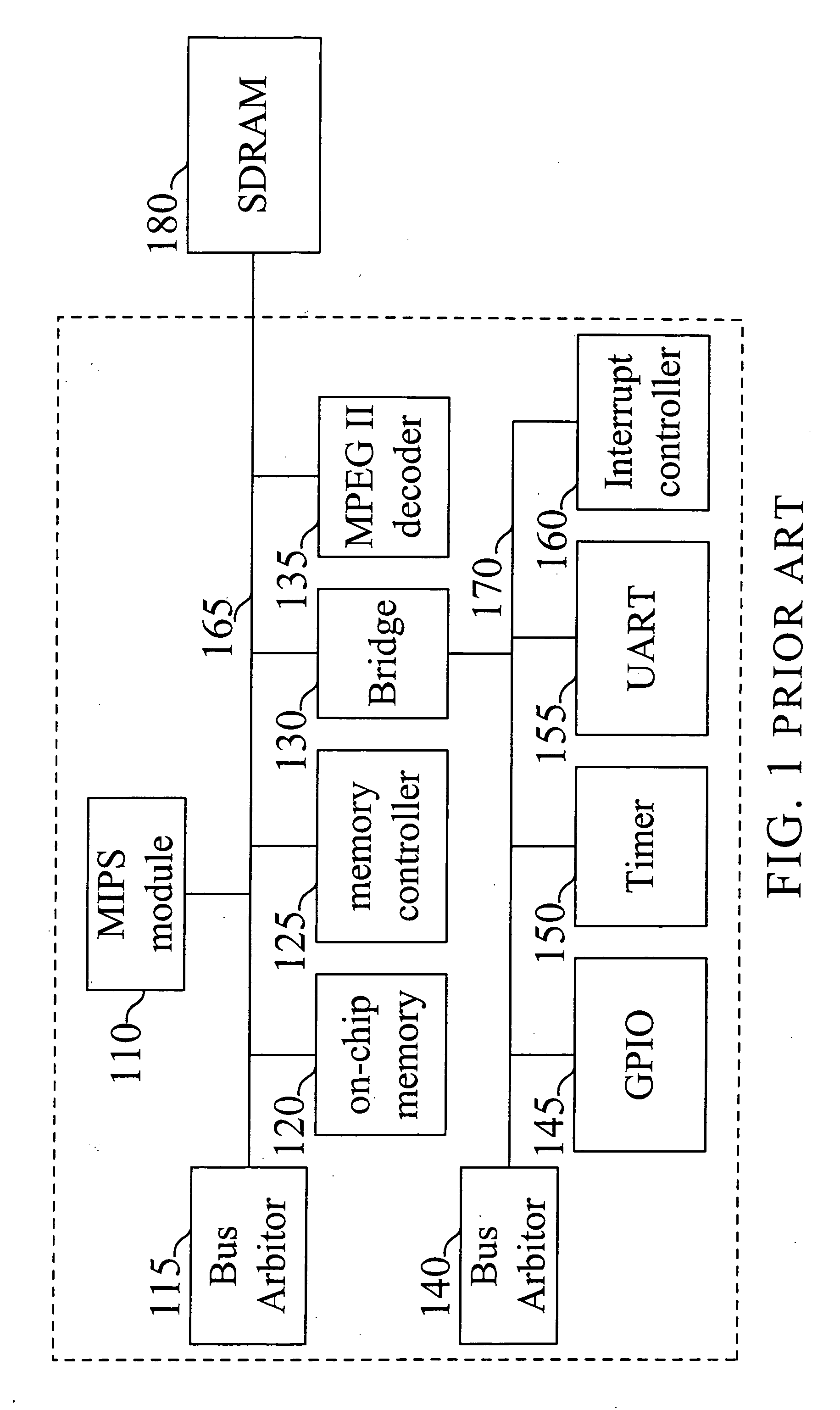

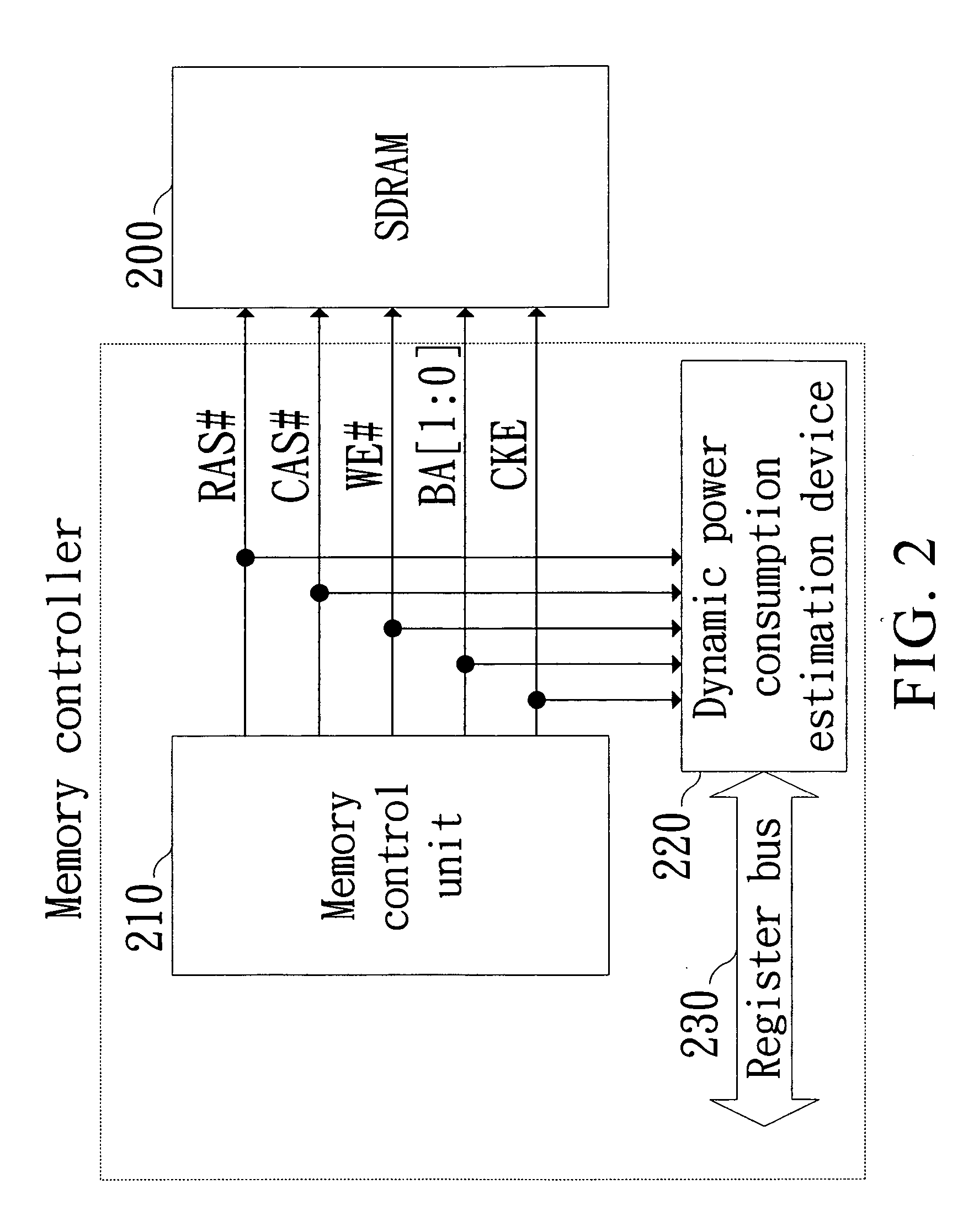

Memory controller capable of estimating memory power consumption

ActiveUS20050152212A1Accurate estimateDigital data processing detailsHardware monitoringControl signalRandom access memory

A memory controller capable of estimating memory power consumption includes a memory control unit, a command dispatch device, plural bank state machines and a power-state and current-accumulation device. The memory control unit generates control signals based on a memory access command sent by a system for accessing a synchronous dynamic random access memory (SDRAM). The command dispatch device synchronously receives the control signals sent by the controller to the SDRAM. The plural bank state machines are connected to the command dispatch device to receive the control signals dispatched by the command dispatch device and accordingly determine whether to transfer its internal state or not. The power-state and current-accumulation device determines on which state the SDRAM is in accordance with states of the plural band state machines, thereby computing current consumption of the SDRAM.

Owner:SUNPLUS TECH CO LTD

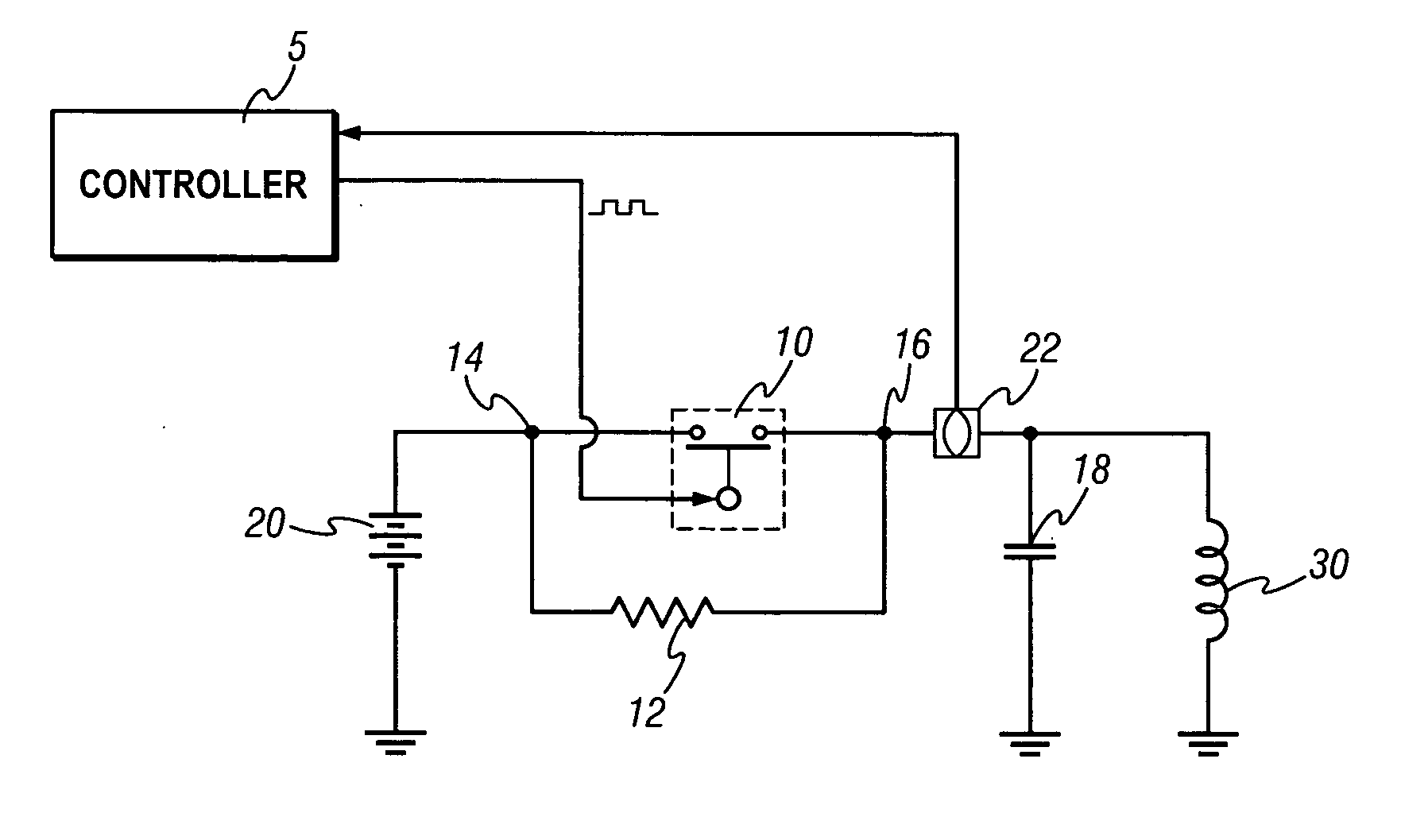

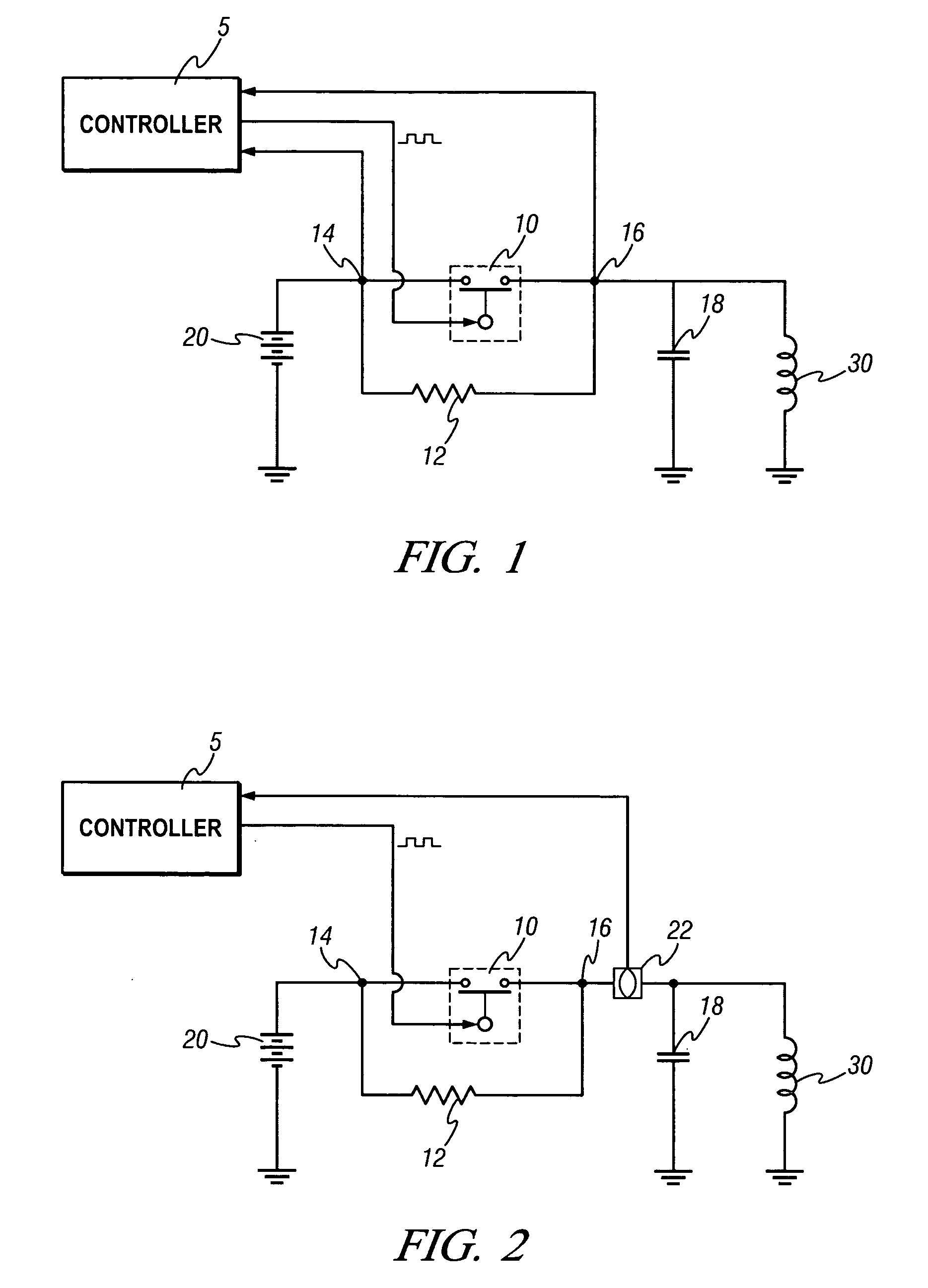

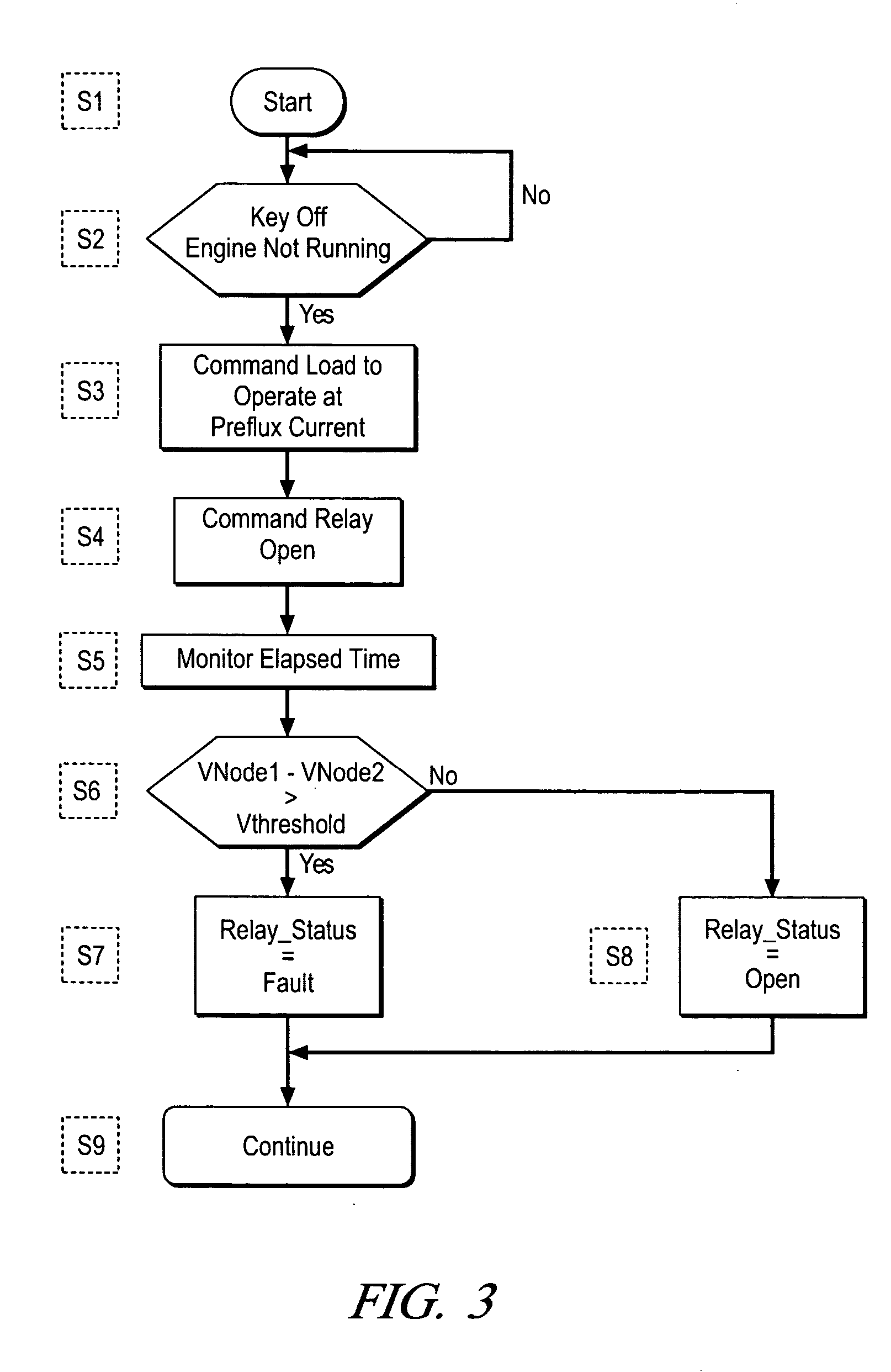

System and method for monitoring an electrical power relay in a hybrid electric vehicle

InactiveUS20070115604A1Electric switchesTesting electric installations on transportElectricityElectrical resistance and conductance

A method and system to monitor a high voltage power relay operable to conduct electrical power from a source to a load, during each vehicle shutdown event. The system includes the electrical relay with a resistive device, electrically connected in parallel circuit, a controllable electrical load device, and a sensing device. A controller is connected to the electrical relay and each sensing device, and operable to identify a low electrical load condition at the load. The controller commands the load to operate at a known current draw level, commands the relay open, and monitors a change in power to the load device when the relay is commanded open. The electrical relay is functioning properly when the change in electrical power to the load exhibits a known profile over time, when the electrical relay is controlled to the commanded-open position.

Owner:GM GLOBAL TECH OPERATIONS LLC

Semiconductor memory device operating with low current consumption

Owner:RENESAS ELECTRONICS CORP

Device and method for radio transmitters

InactiveUS6047168AReduce saturationLimiting bandwidth of outputResonant long antennasGain controlLow noisePower detector

The present invention relates to a device and a method in a transmitter stage in a radio transmitter for modulating and amplifying an information signal for further transmission through a radio channel. The transmitter stage in the radio transmitter comprises a converting device (5) PCH, an amplifier control device (8) PAC, a power detector (13) and a power amplifier (2). Examples of the problems solved by the present invention are difficulties in reducing the power consumption, non-linearities in the output signal when using non-linear amplifiers in radio transmitters, and achieving a high signal-to-noise ratio in the output signal without connecting filter arrangements after such an amplifier. The solution according to the inventive method and device utilizes an information signal which has in earlier steps been divided in its polar components: a phase reference component signal (Ephr) and an amplitude component signal (Aamp). The phase reference component phase modulates a low noise high power signal source which has a constant amplitude. The amplitude of the obtained signal is then formed in an amplifier, which is controllable with the amplitude component signal (Aamp). Its current consumption is registered and compared to a control value for the current. The amplifier is controlled towards this control value.

Owner:OPTIS WIRELESS TECH LLC

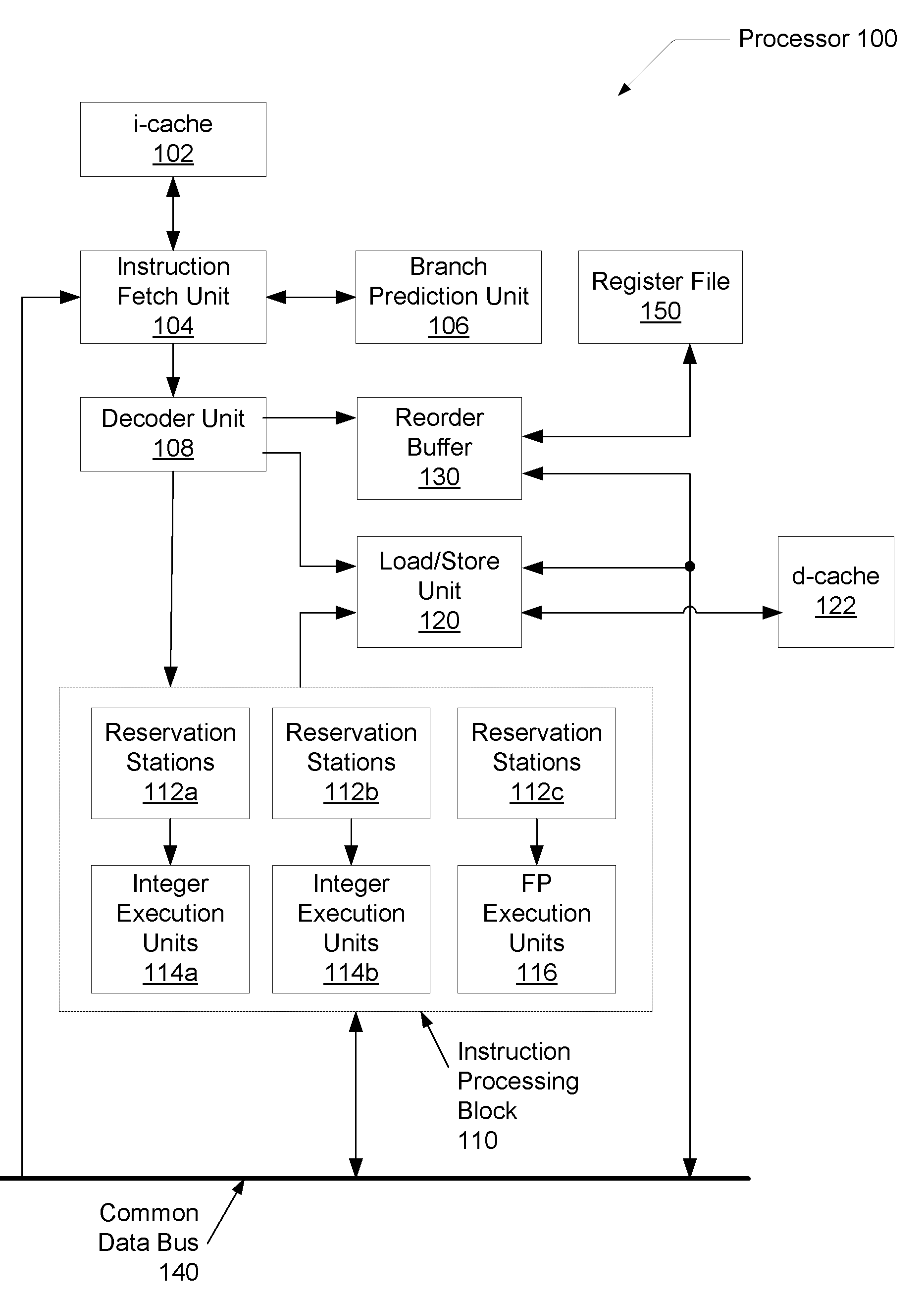

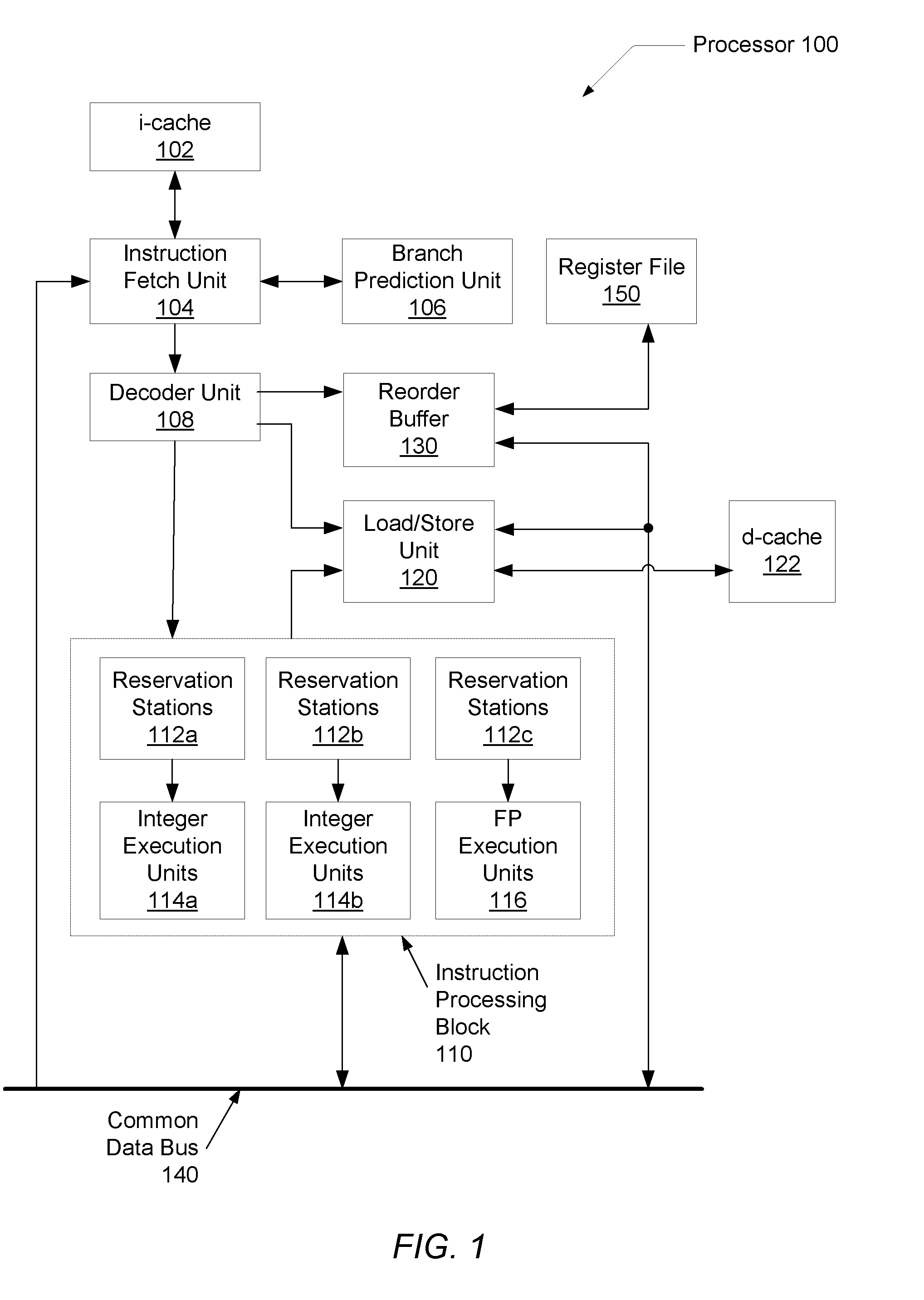

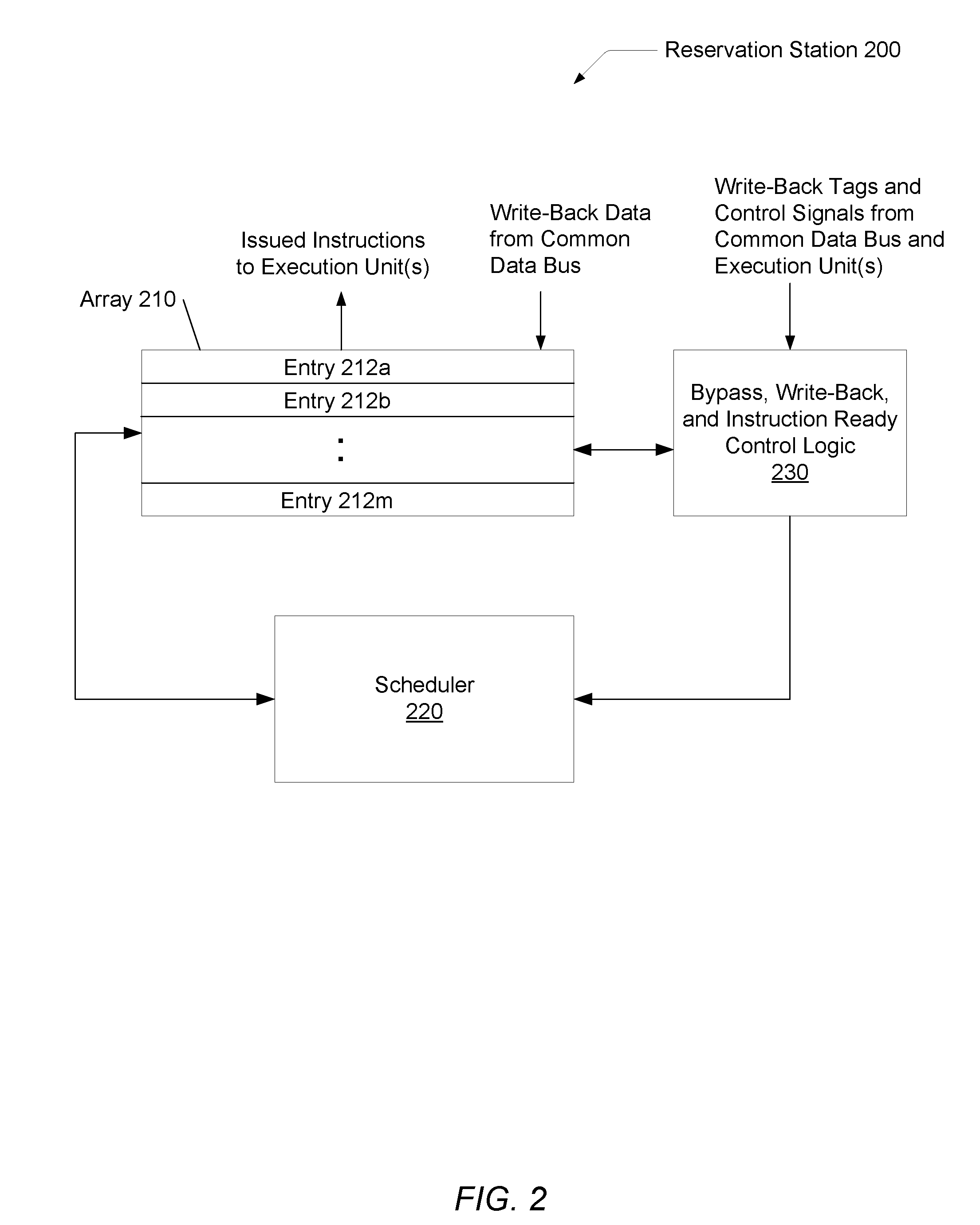

Voltage droop mitigation through instruction issue throttling

ActiveUS20090300329A1Reduce voltage dropVolume/mass flow measurementDigital computer detailsCapacitanceHash function

A system and method for providing a digital real-time voltage droop detection and subsequent voltage droop reduction. A scheduler within a reservation station may store a weight value for each instruction corresponding to node capacitance switching activity for the instruction derived from pre-silicon power modeling analysis. For instructions picked with available source data, the corresponding weight values are summed together to produce a local current consumption value and this value is summed with any existing global current consumption values from corresponding schedulers of other processor cores yielding an activity event. The activity event is stored. Hashing functions within the scheduler are used to determine both a recent and an old activity average using the calculated activity event and stored older activity events. Instruction issue throttling occurs if either a difference between the old activity average and the recent activity average exceed a first threshold or the recent activity average exceeds a second threshold.

Owner:ADVANCED MICRO DEVICES INC