Patents

Literature

547results about How to "Current consumption" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

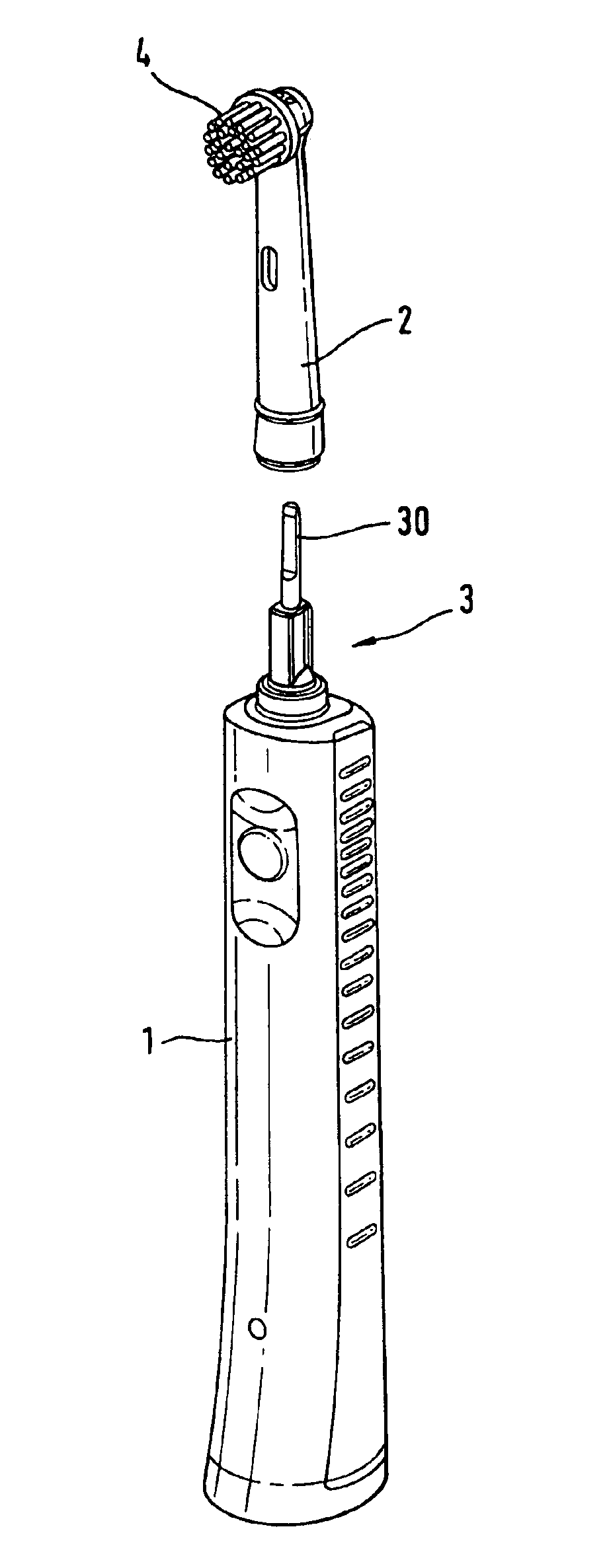

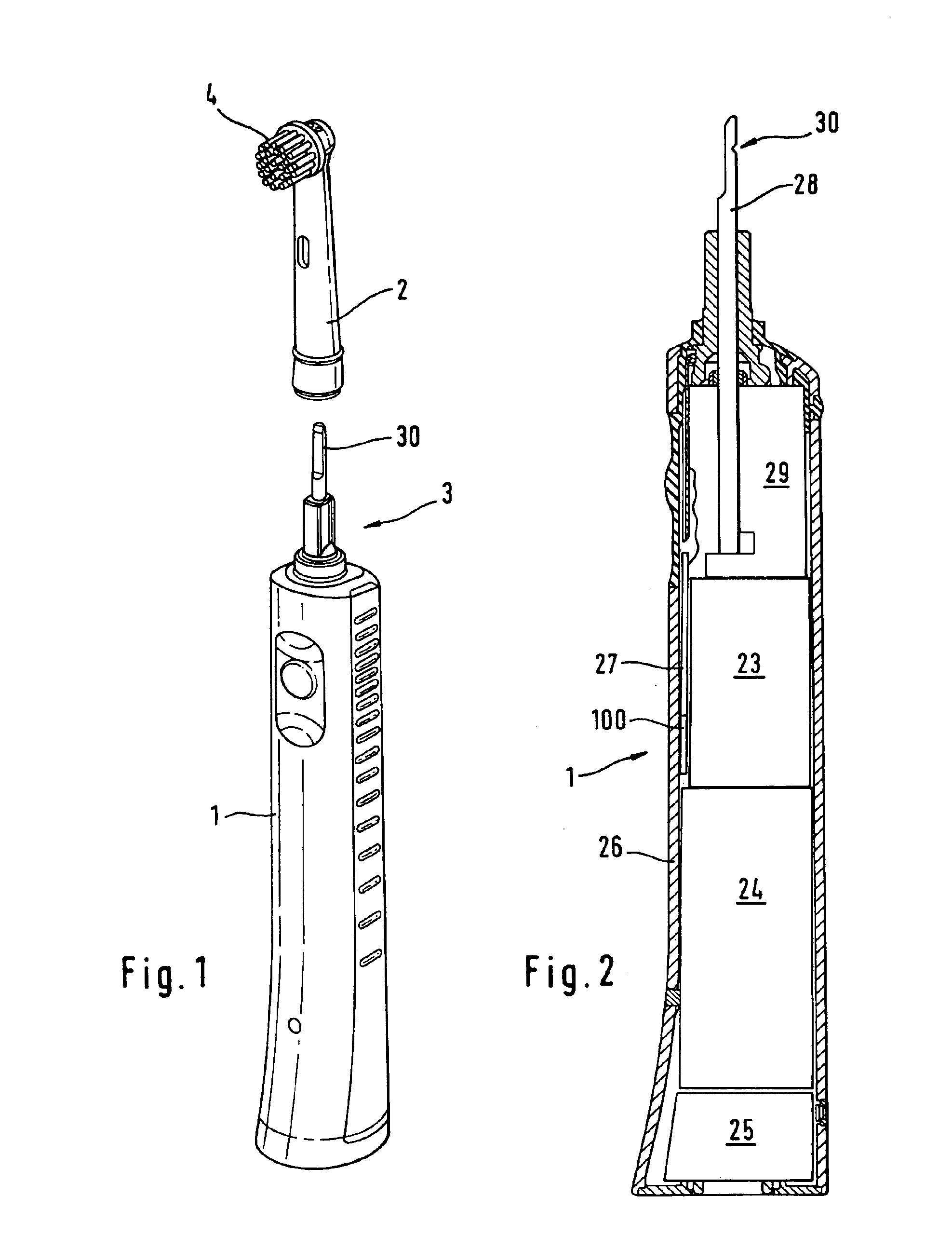

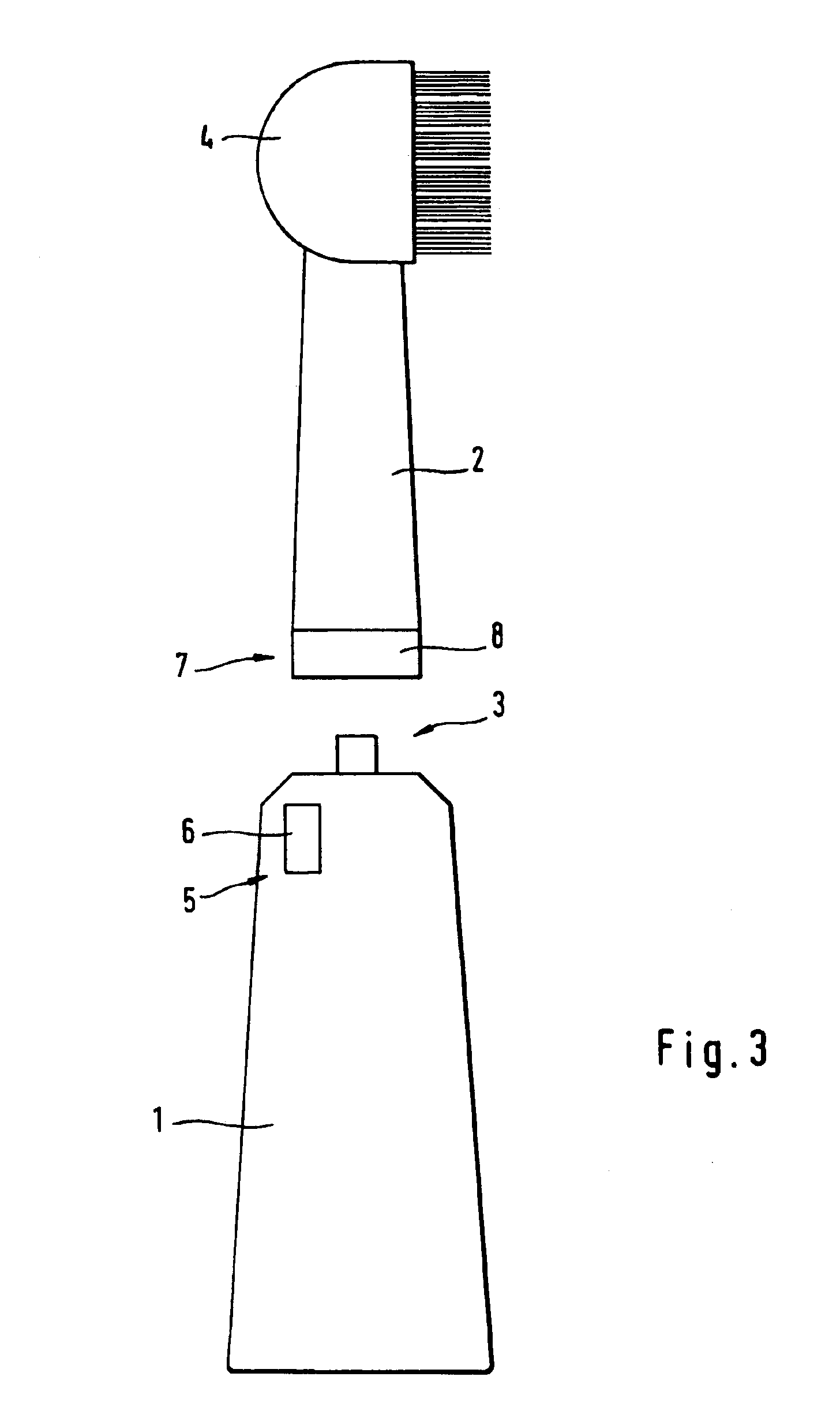

Electric dental cleaning device

The invention is directed to a dental cleaning device. It relates in particular to a handle section of an electric toothbrushing device, with a coupling section for coupling various cleaning tools thereto, a drive mechanism for driving the coupled cleaning tool, and a control device for controlling the drive mechanism. The invention further relates to such cleaning tools. According to the invention the handle section includes an electronic interlock device which is deactivated by an encoded interlock canceling element on the cleaning tool only when the cleaning tool is coupled to the handle section (FIG. 4).

Owner:BRAUN GMBH

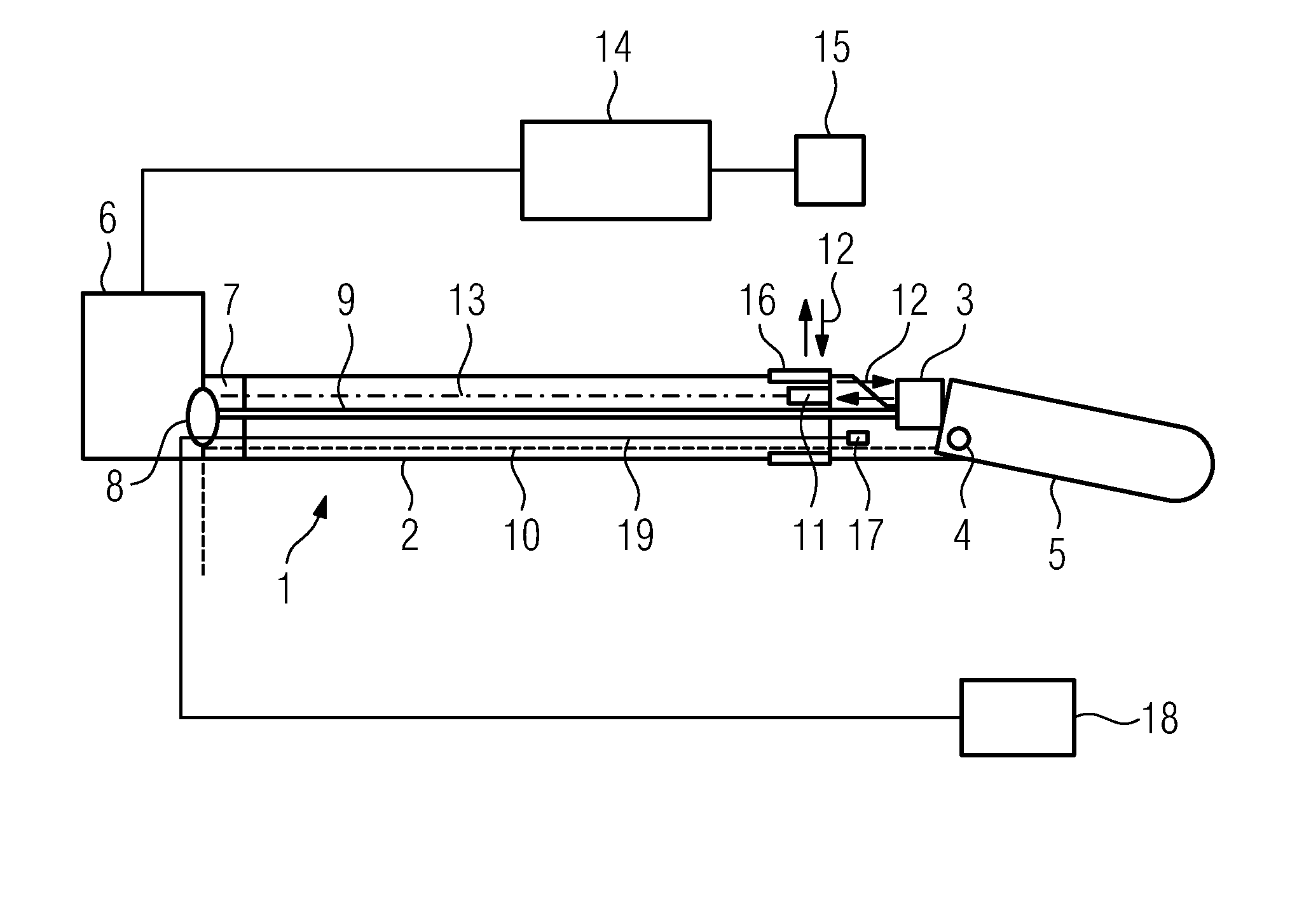

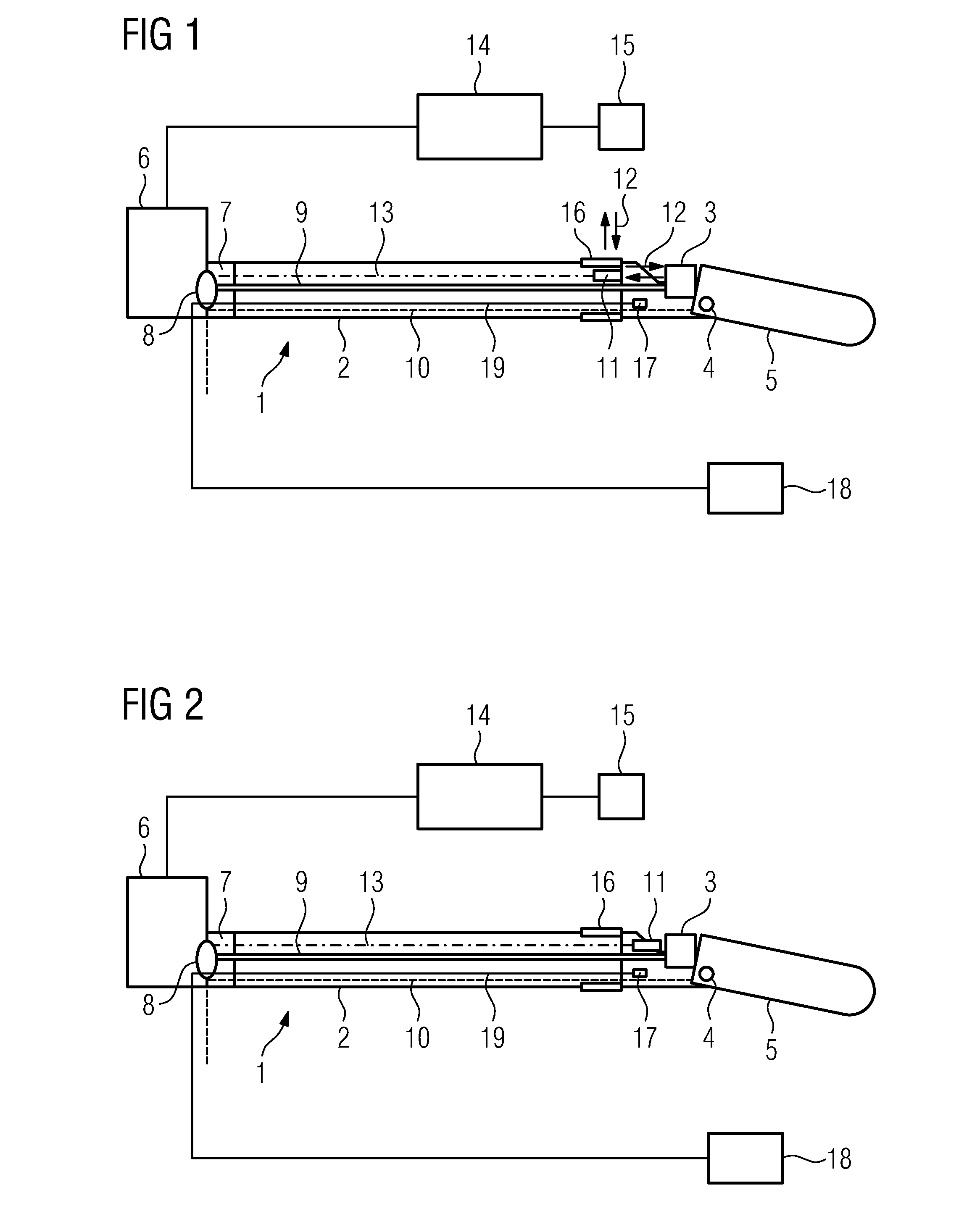

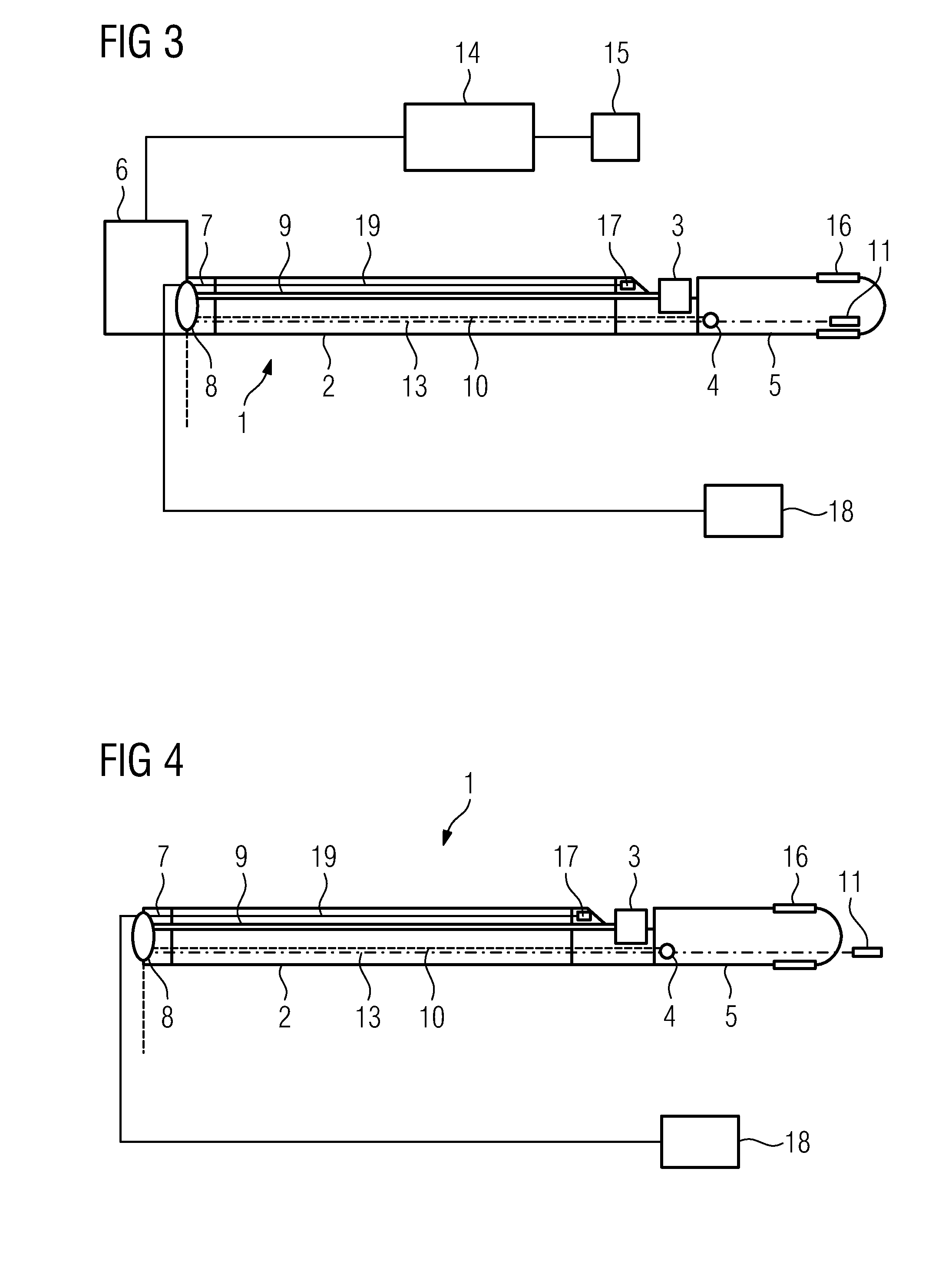

Catheter and medical apparatus as well as method for assisting an intervention to remove plaque

InactiveUS20100241147A1Good removal effectPrecise and high-resolution visualizationMagnetic measurementsCannulasImage sensorImaging Signal

Owner:SIEMENS HEALTHCARE GMBH

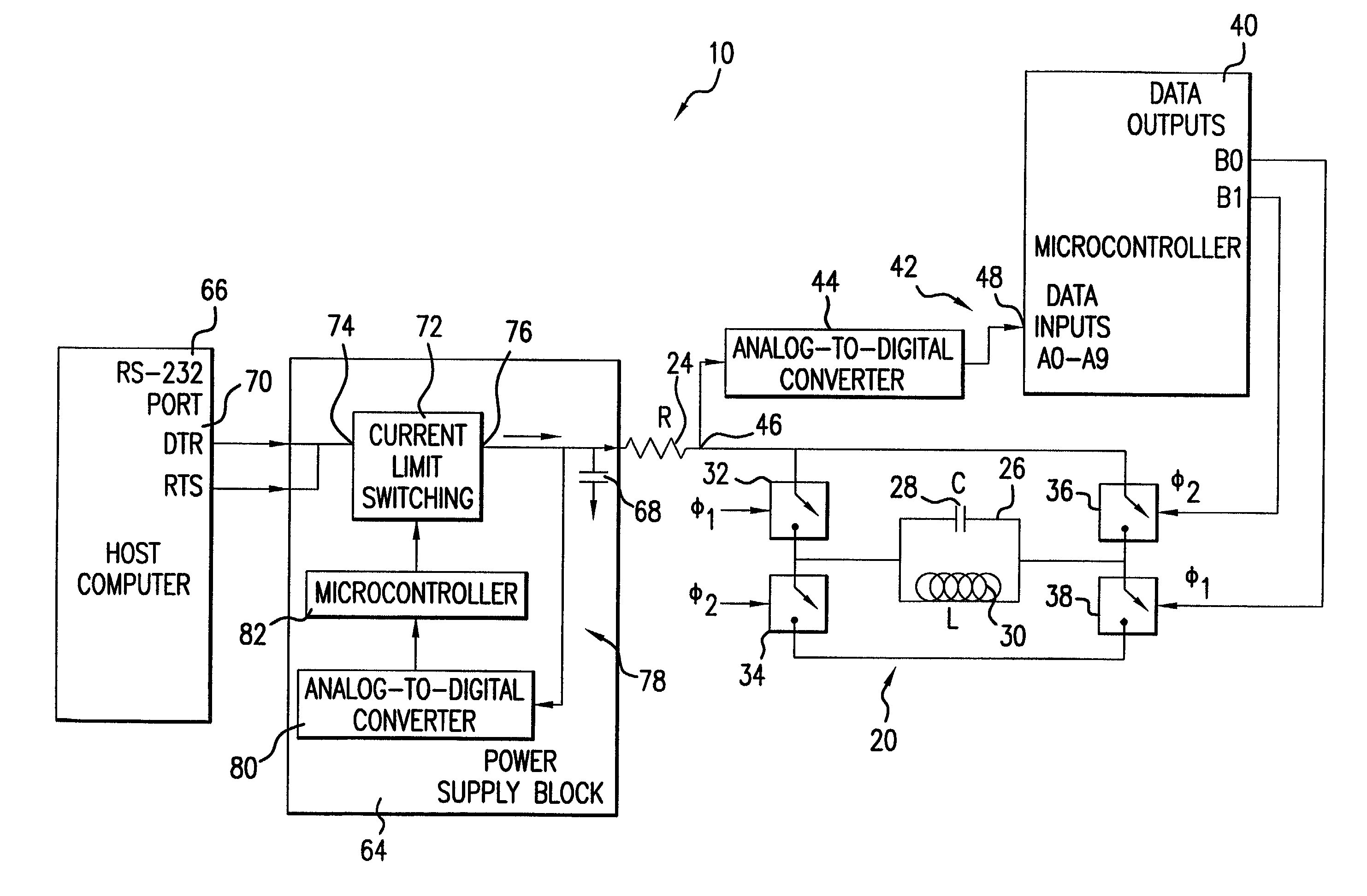

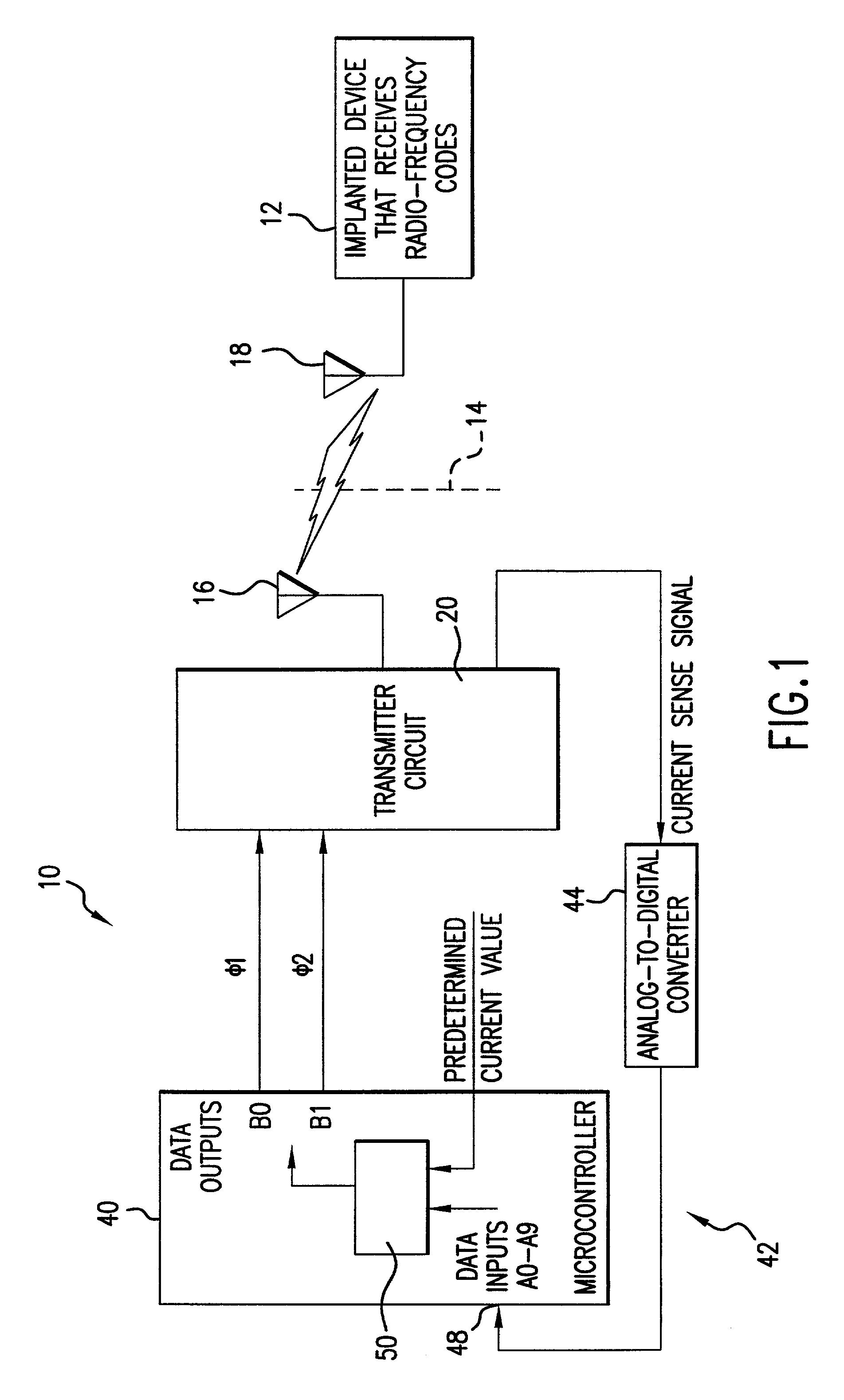

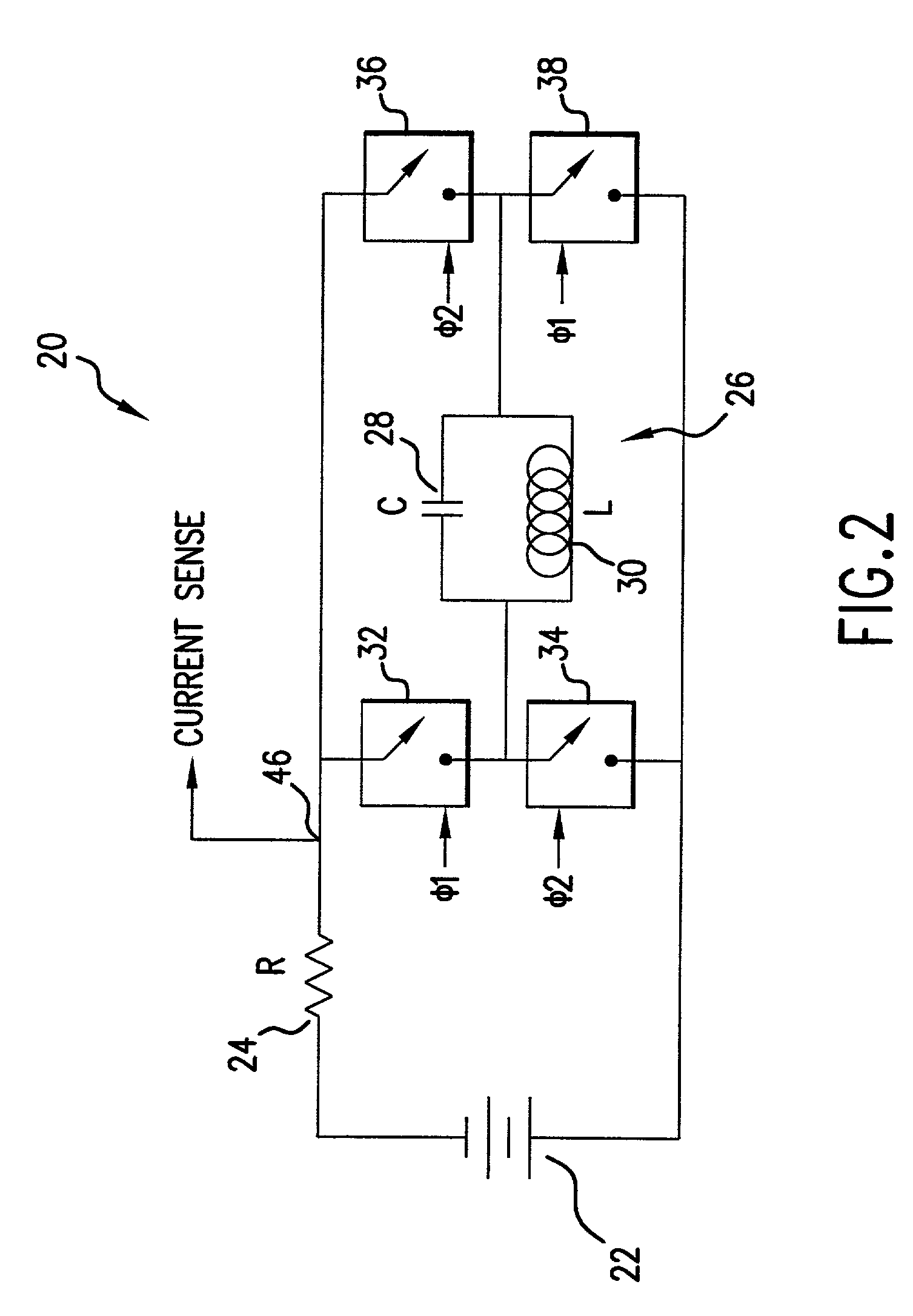

Transmitter system for wireless communication with implanted devices

ActiveUS7151914B2Low power operationCurrent consumptionResonant long antennasElectrotherapyMaximum levelFeedback circuits

A transmitter system for wireless communication with implanted medical devices includes a transmitter circuit having a resonant network the resonant frequency of which is adjusted by a feedback circuit in order to minimize the current drain from the power source and maximizing the power source life. The transmitter system may be powered by a power supply block which uses commonly available RS-232 signals of a host computer as a raw power source, combined with a high value storage capacitor to provide power for the wireless medical data programmer. A feedback circuit monitors the charging current as well as voltage impressed across the storage capacitor in order to maintain the charging current at maximum level during the charging time and in order to stop the charging once the full charge of the storage capacitor has been reached.

Owner:MEDTRONIC INC

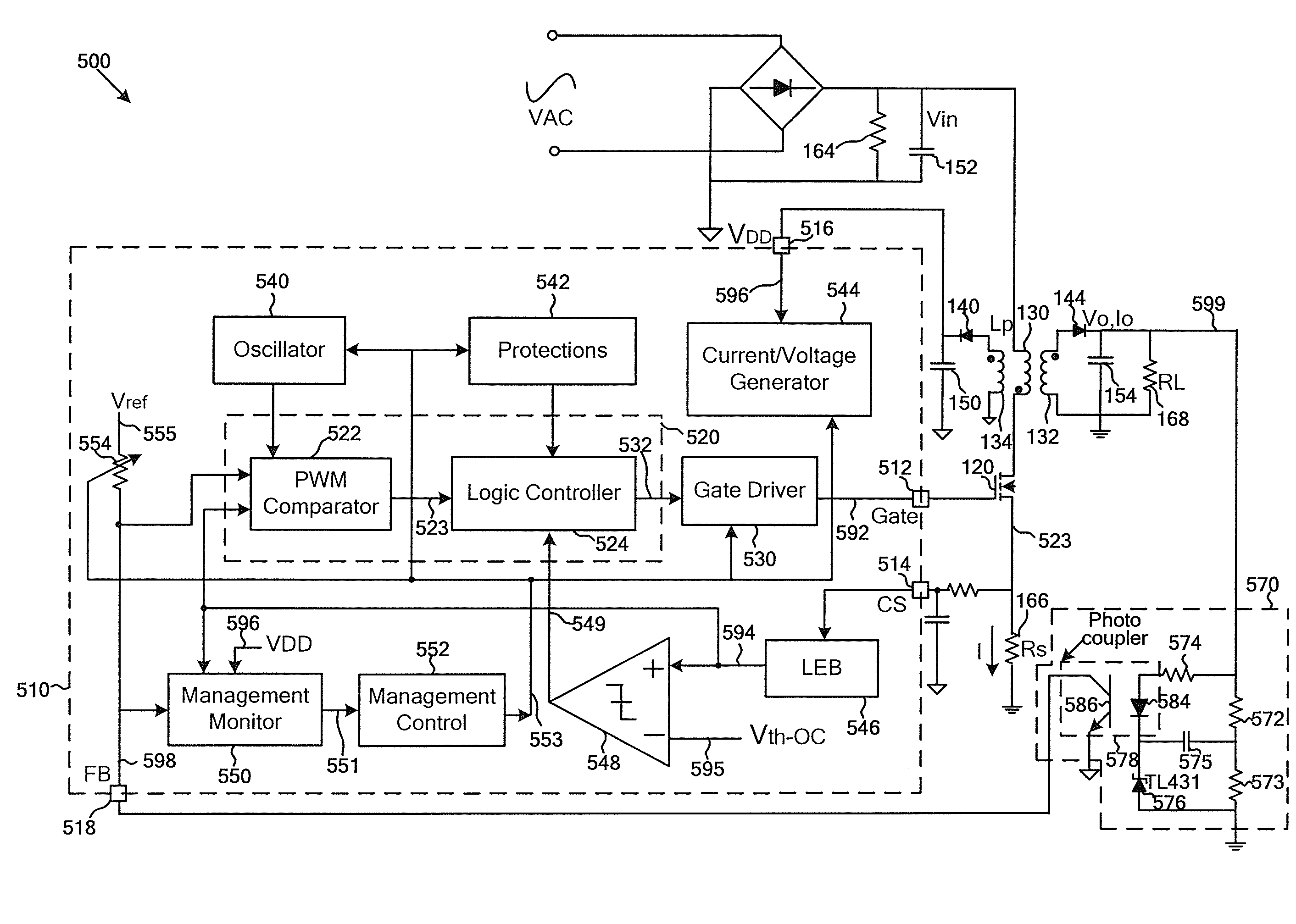

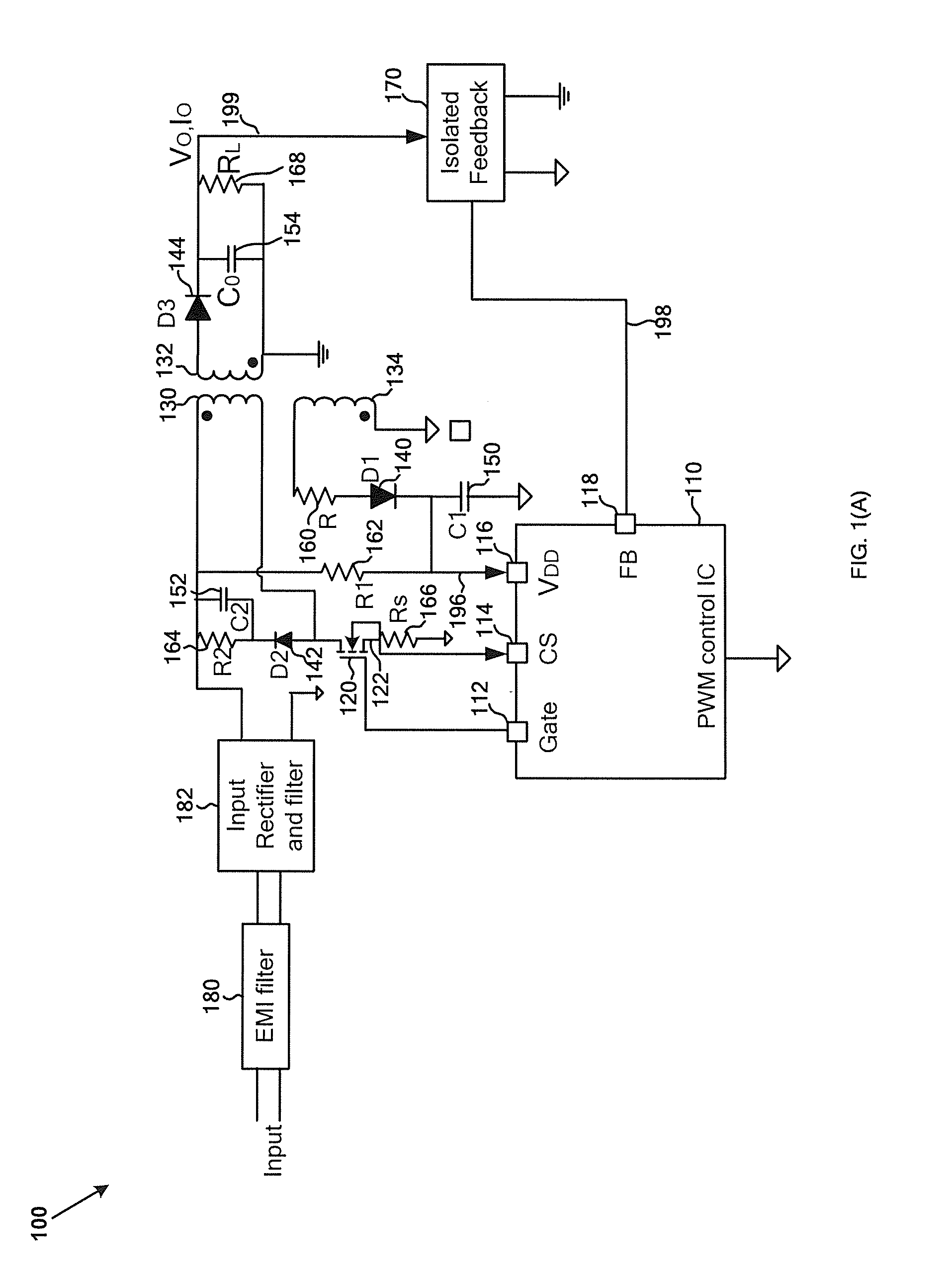

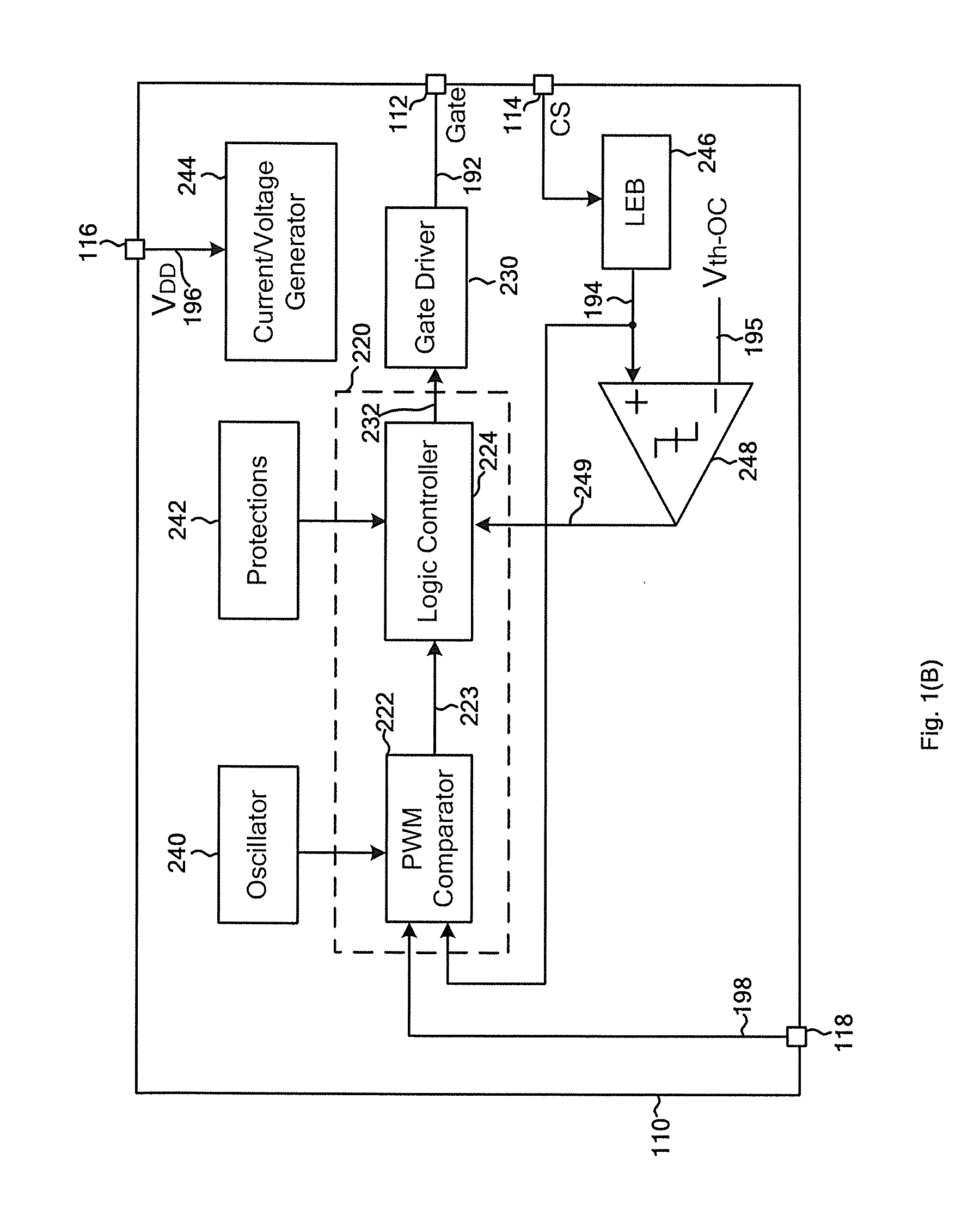

Systems and methods for adjusting current consumption of control chips to reduce standby power consumption of power converters

ActiveUS20130003421A1Reduce standby power consumptionReduce power consumptionEfficient power electronics conversionAc-dc conversionTime segmentControl signal

System and method for regulating a power conversion system. For example, a system controller includes a signal generator and one or more power-consumption components. The signal generator is configured to receive a feedback signal related to an output signal of the power conversion system, a current sensing signal and an input voltage, and to generate a control signal based on at least information associated with the feedback signal, the current sensing signal and the input voltage. The power-consumption components are configured to receive the control signal. The signal generator is further configured to determine whether the feedback signal is smaller than a feedback threshold for a first predetermined period of time, the current sensing signal is smaller than a current sensing threshold for a second predetermined period of time, and the input voltage is smaller than a first threshold for a third predetermined period of time in magnitude.

Owner:ON BRIGHT ELECTRONICS SHANGHAI

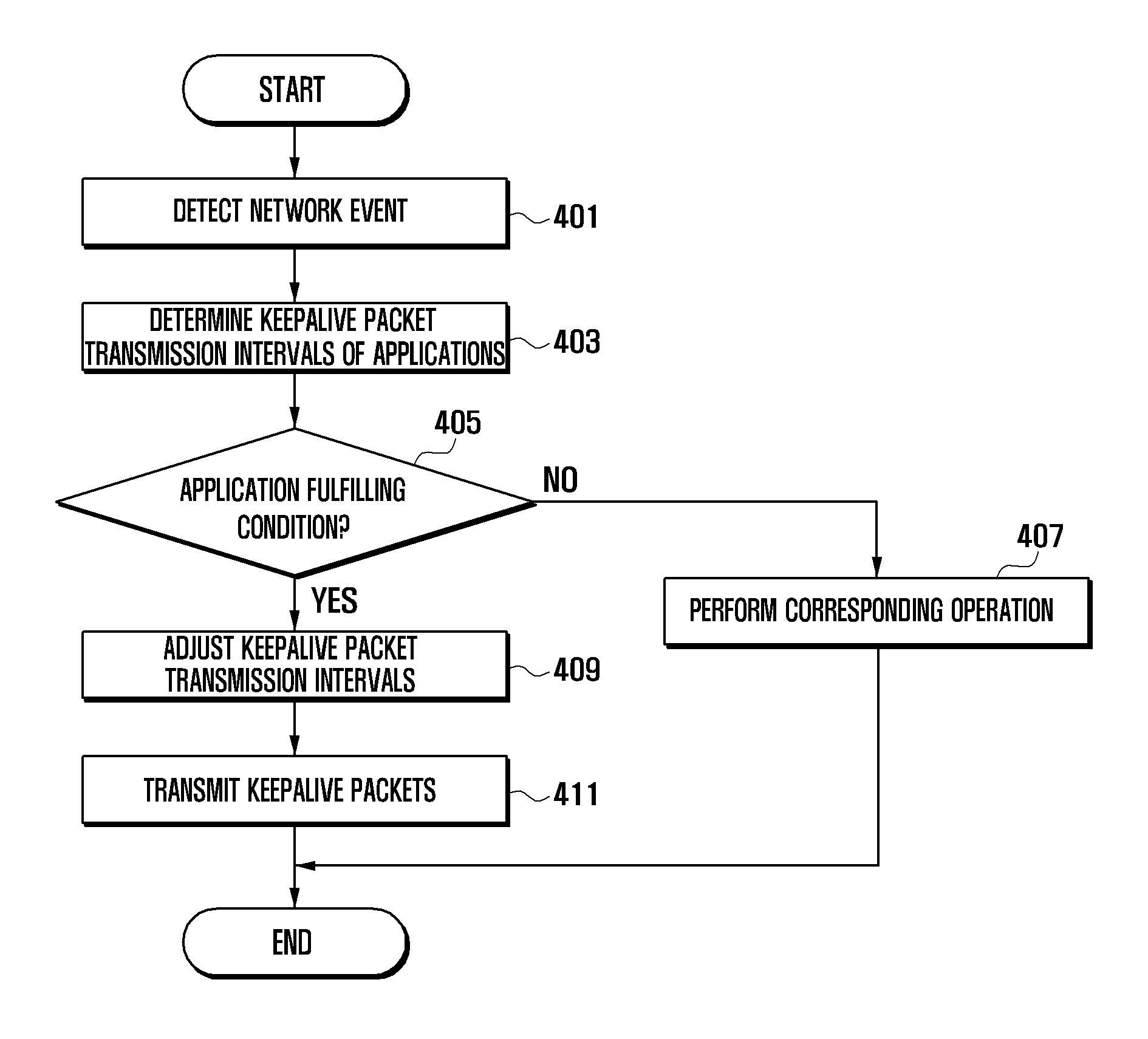

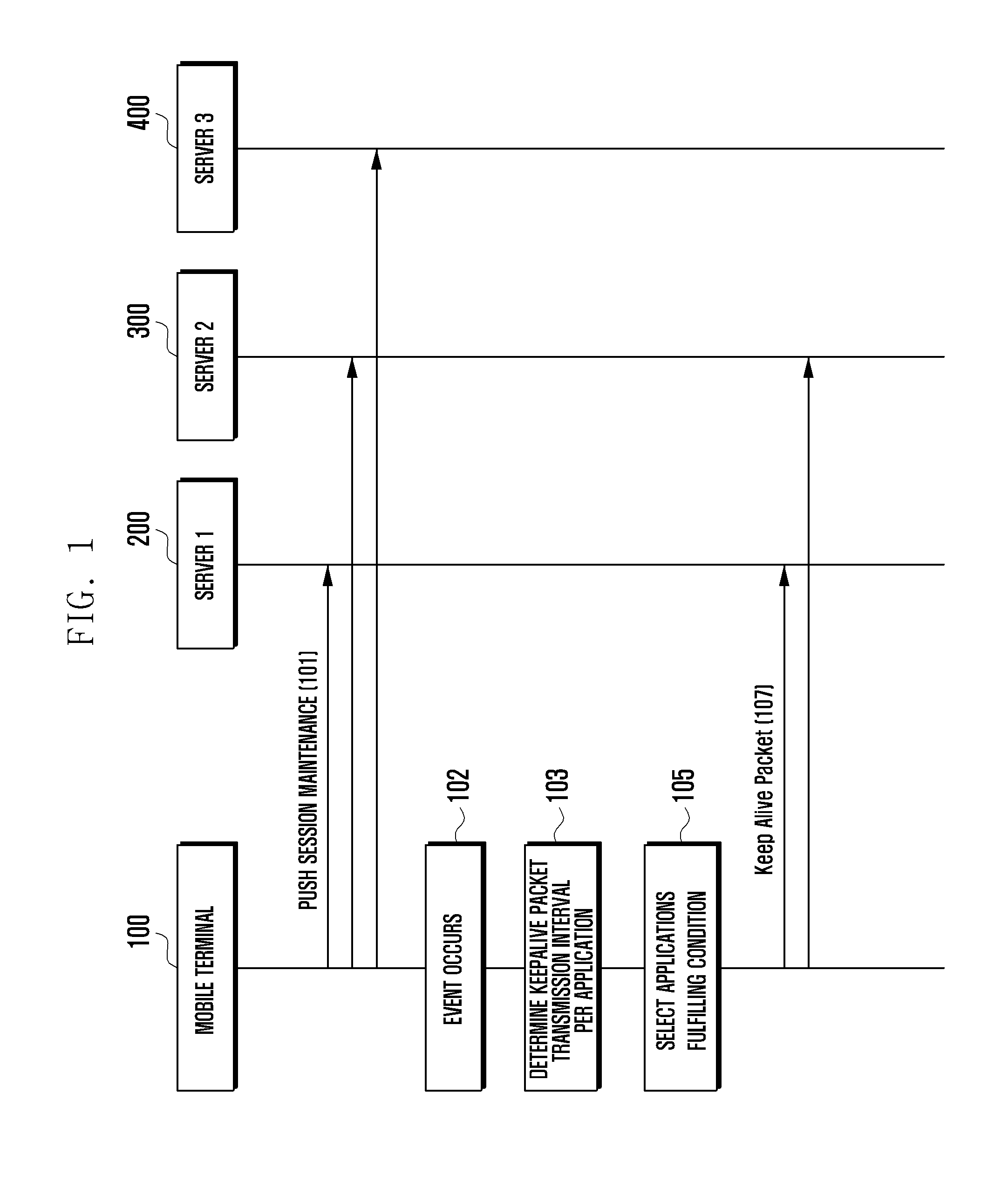

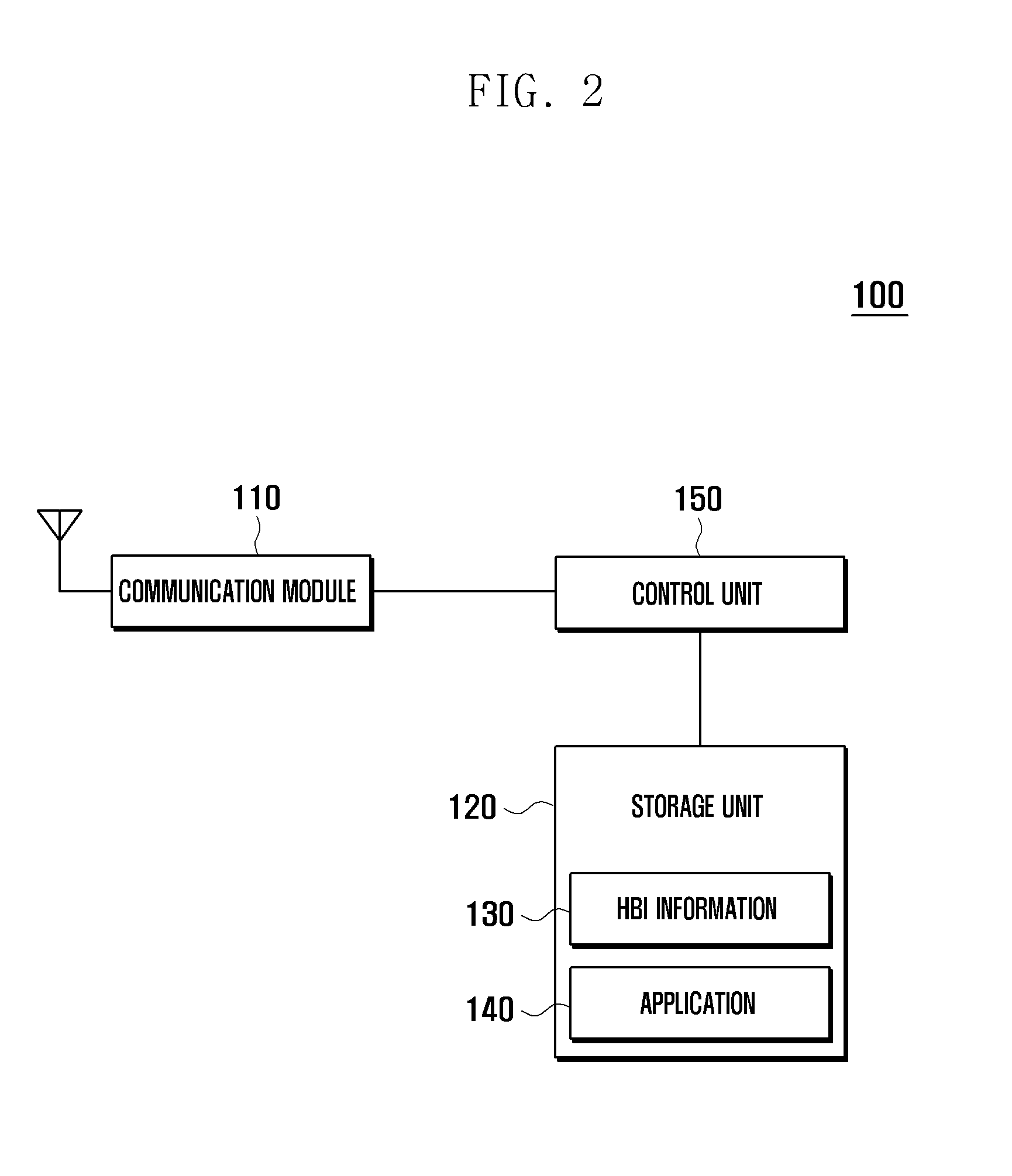

Keep-alive packet transmission method and apparatus of mobile terminal

InactiveUS20120170496A1Total current dropCurrent consumptionPower managementTransmission systemsComputer networkEngineering

A method and an apparatus for synchronizing the keep-alive packet transmission timings of the direct push applications are provided to improve an electric current consumption characteristic. The method includes detecting a network event, synchronizing transmission timings of keep-alive packets of direct push applications with reference to an occurrence time of the network event, and transmitting the keep-alive packets of the direct push application at a synchronized transmission timing simultaneously.

Owner:SAMSUNG ELECTRONICS CO LTD

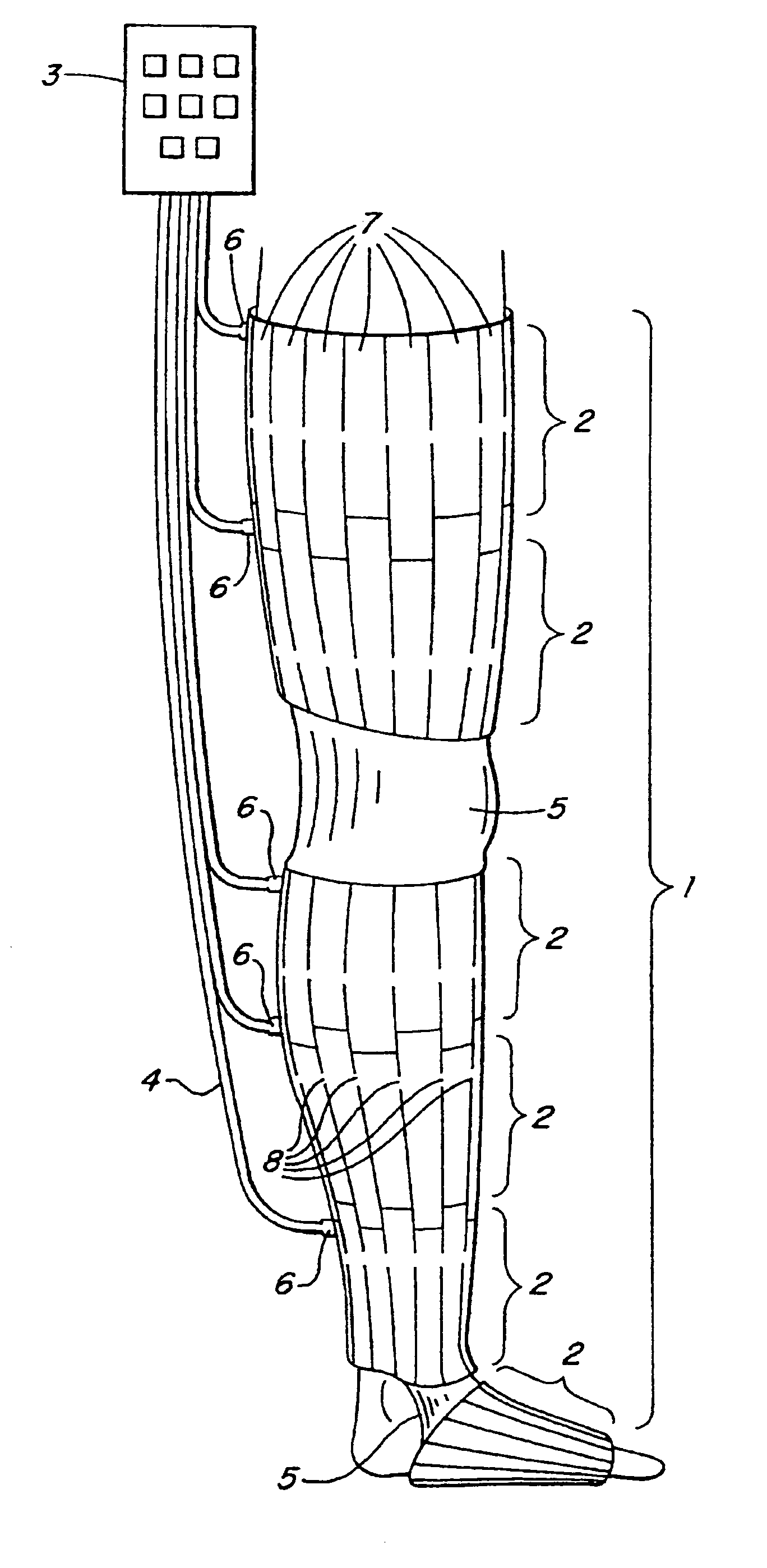

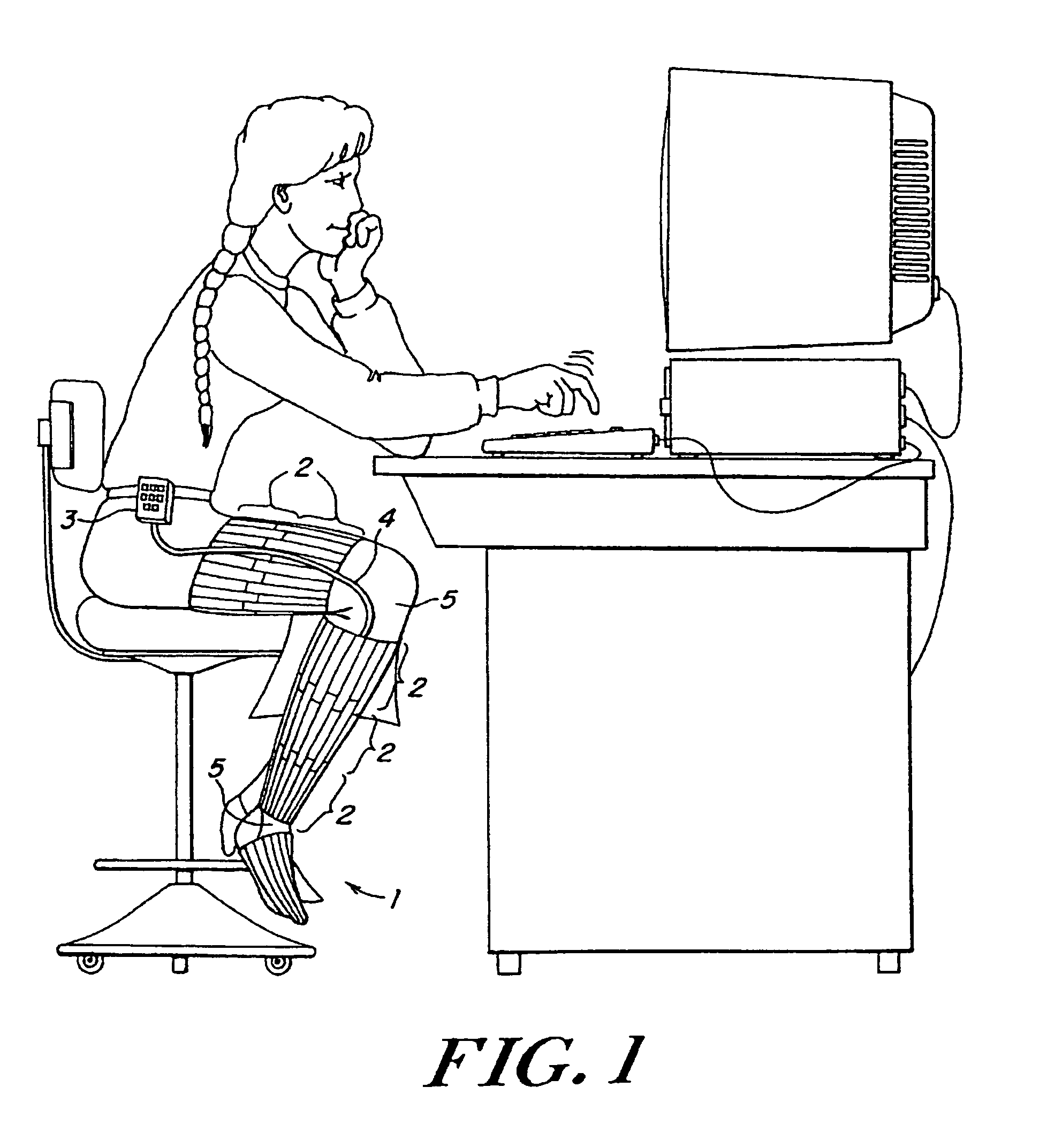

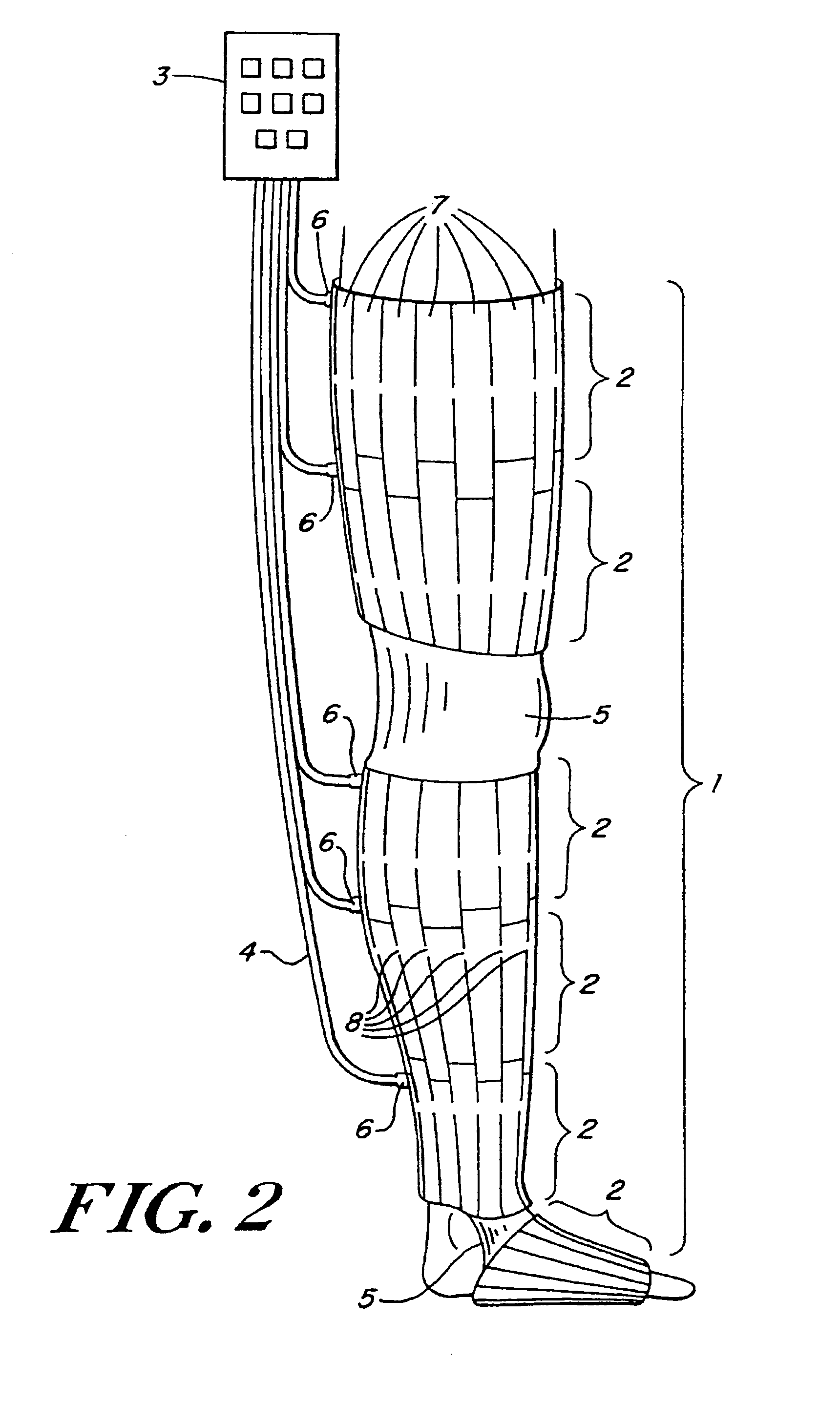

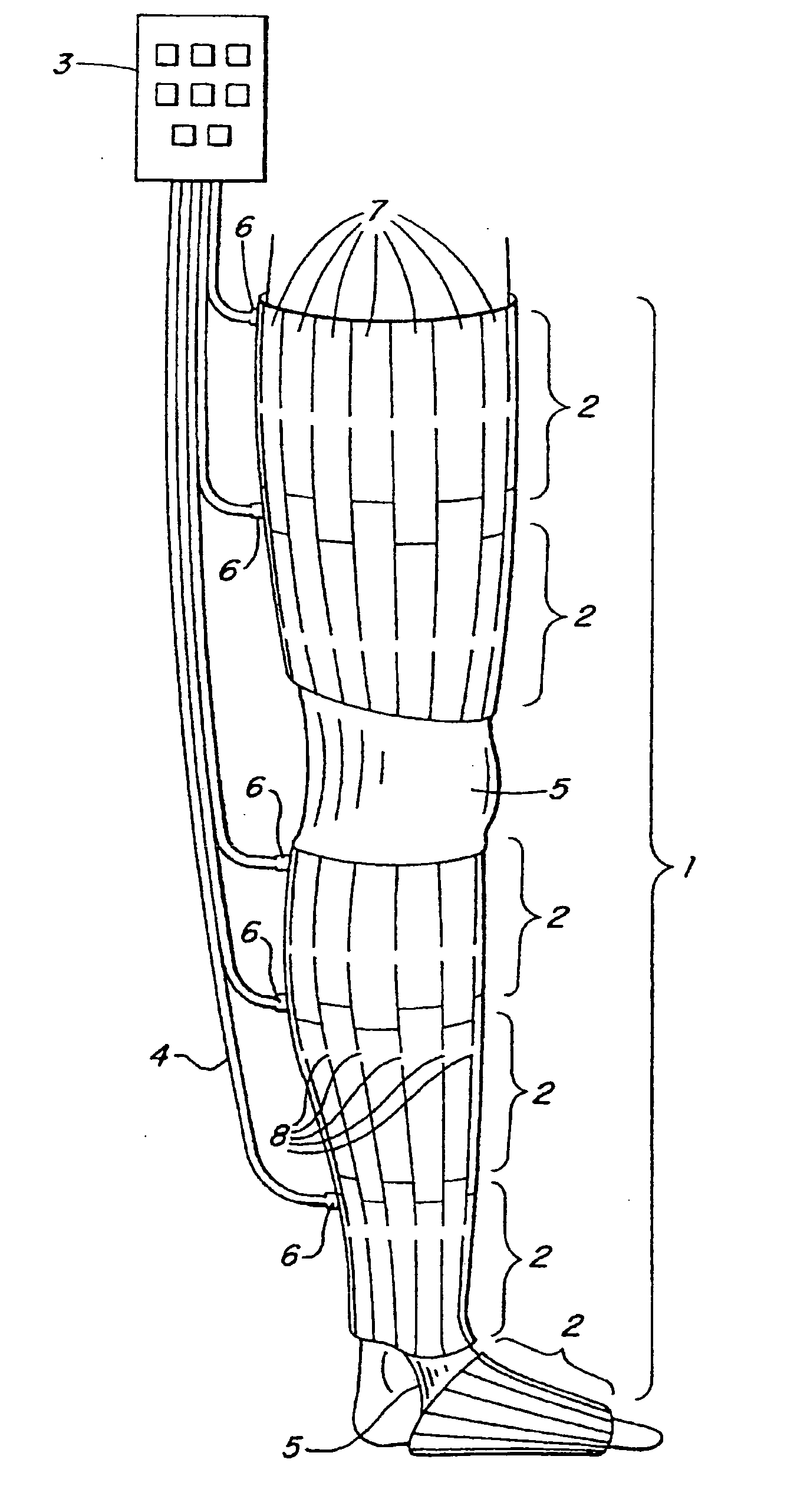

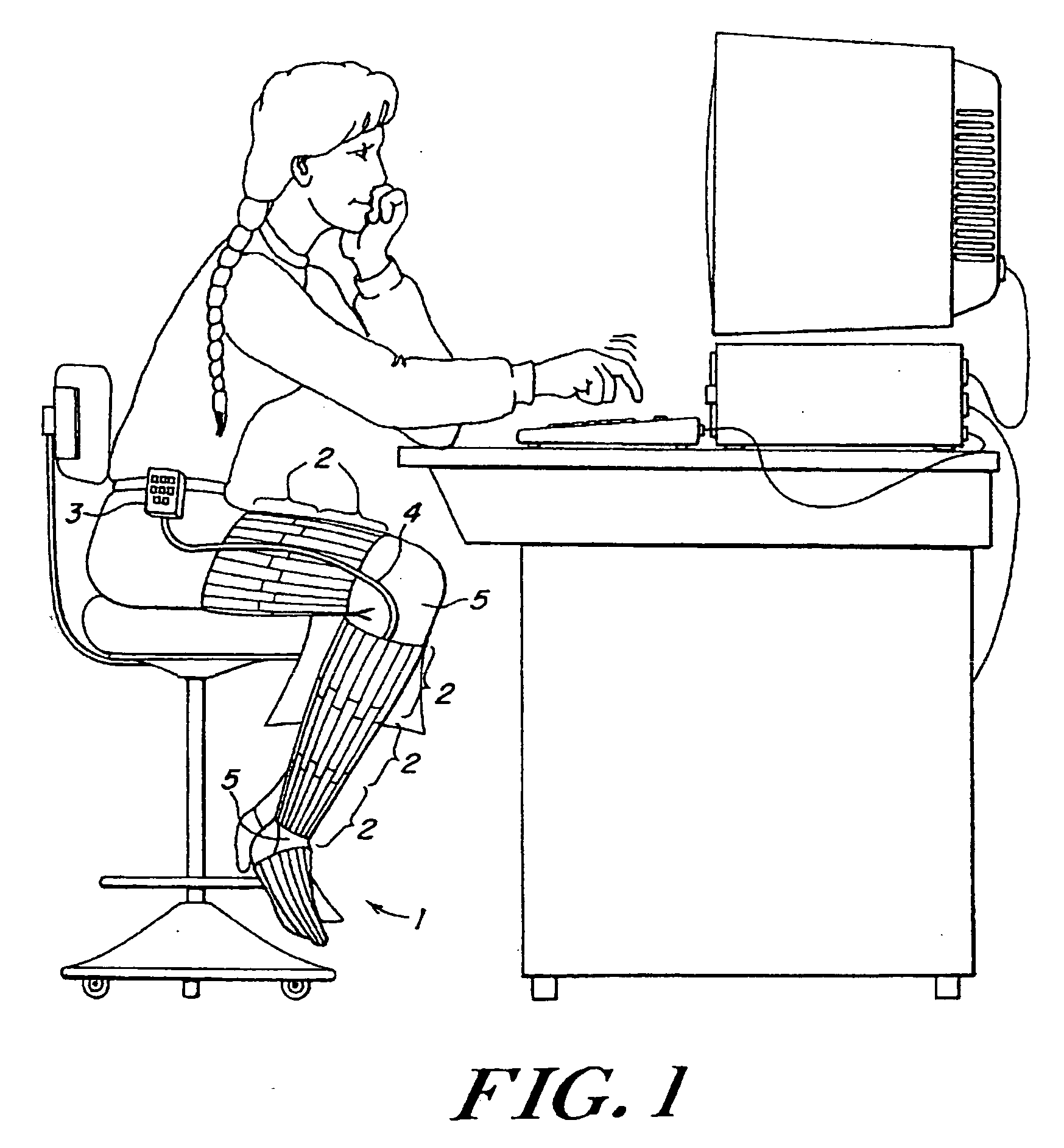

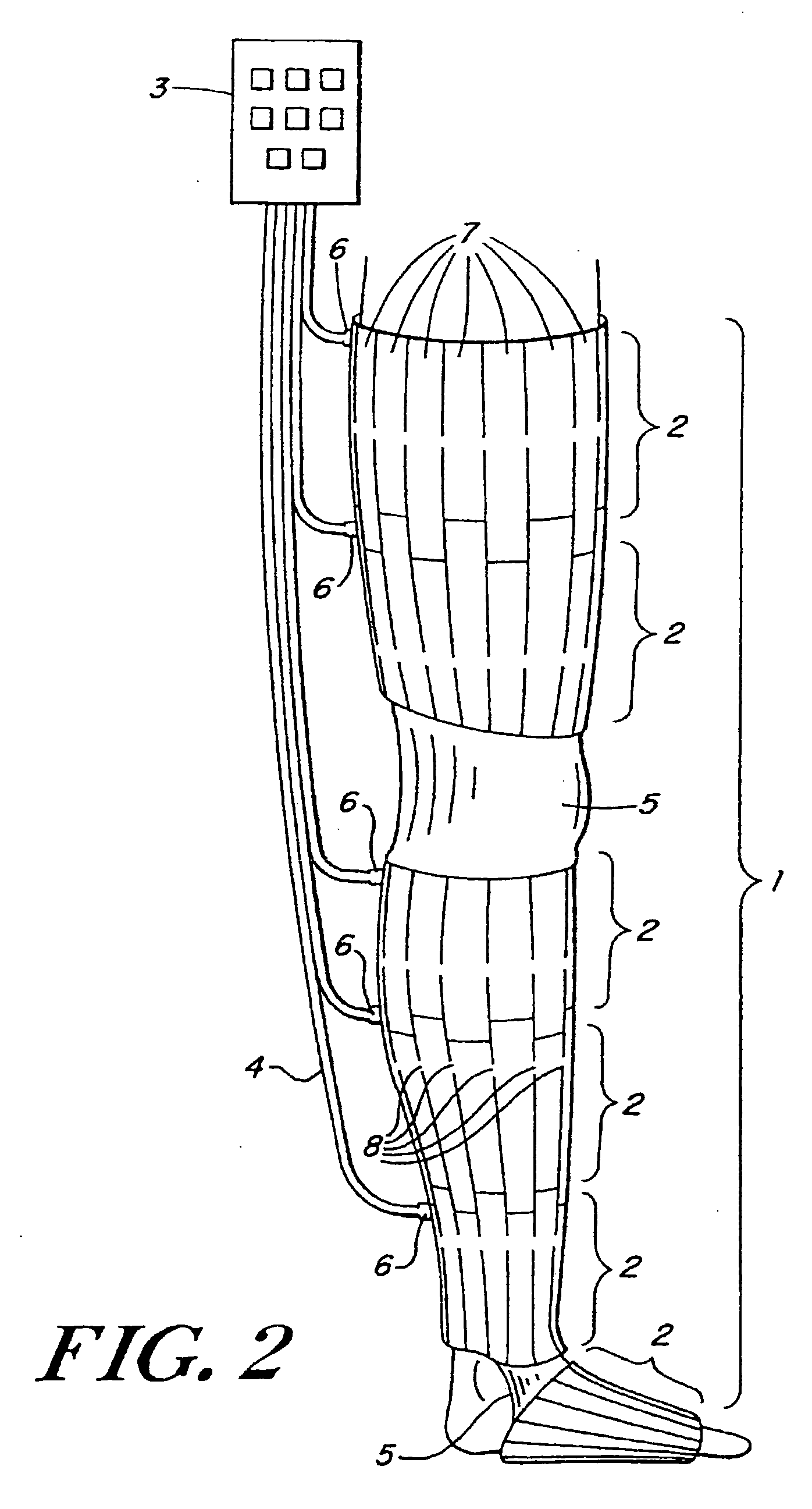

Automatic portable pneumatic compression system

InactiveUS7063676B2Improve compactnessReduce power consumptionPneumatic massageChiropractic devicesHand heldCatheter

An automatic portable ambulant miniaturized system for applying pneumatic pressure to a body limb including a portable ambulant hand-held fluid source unit, a conduit for delivering fluid generated by the unit, and a sleeve coupled to the conduit and adapted to envelop a body limb. The sleeve contains one or more individually inflatable cells, each cell being subdivided into two or more longitudinally extending confluent compartments along the axis of the body limb. The compartments are inflated and deflated essentially simultaneously by the portable fluid source unit.

Owner:ZIMMER SURGICAL

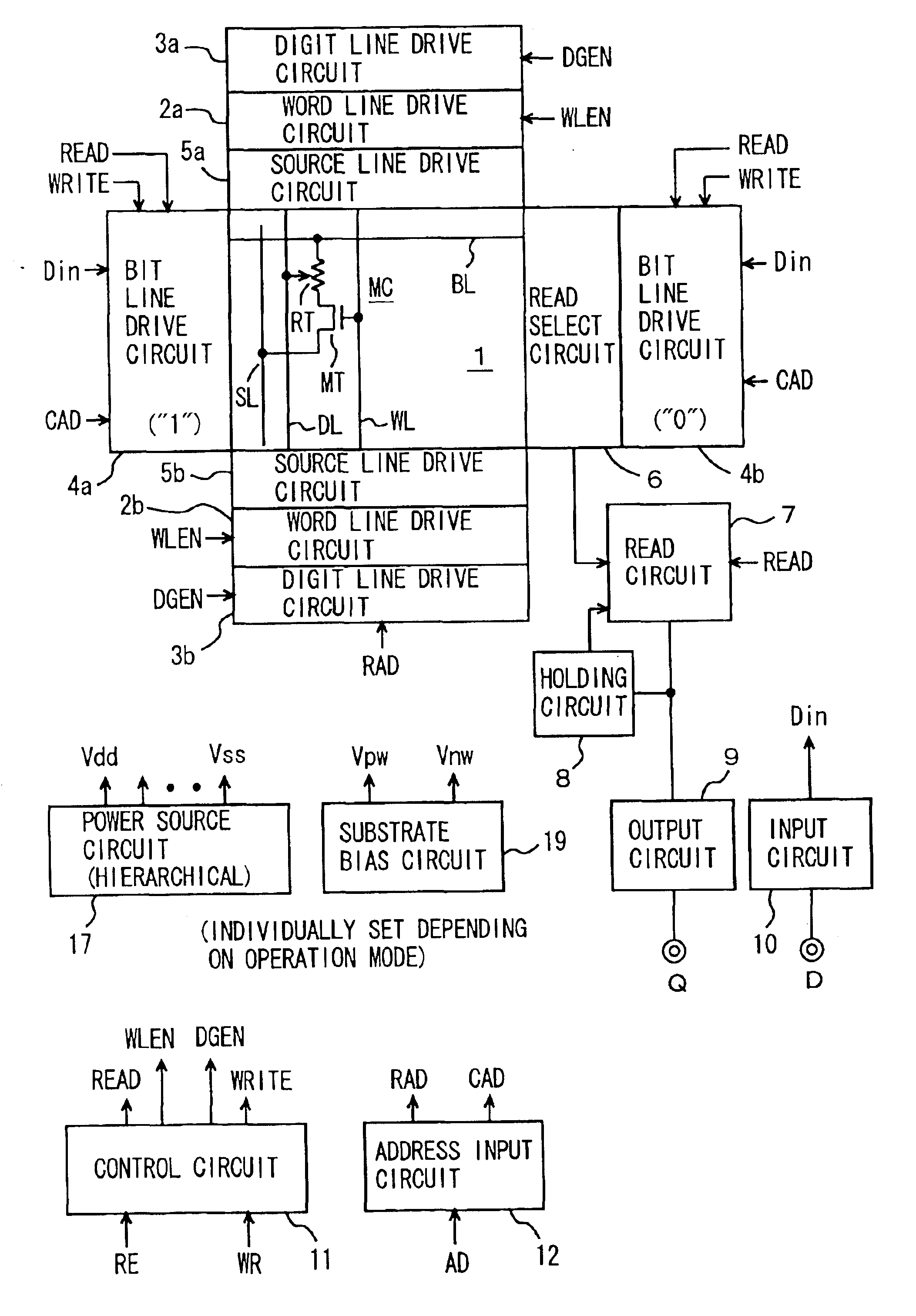

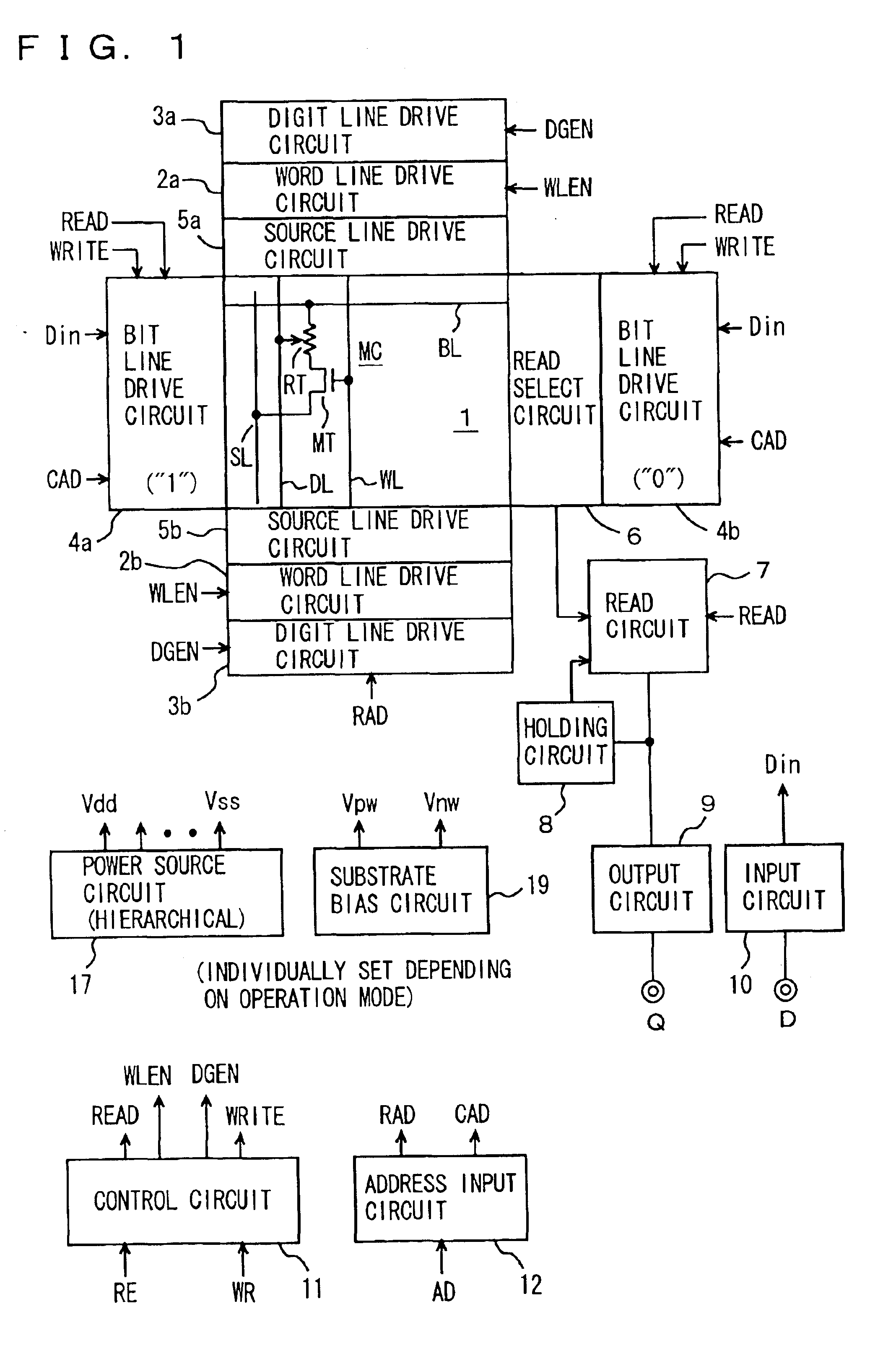

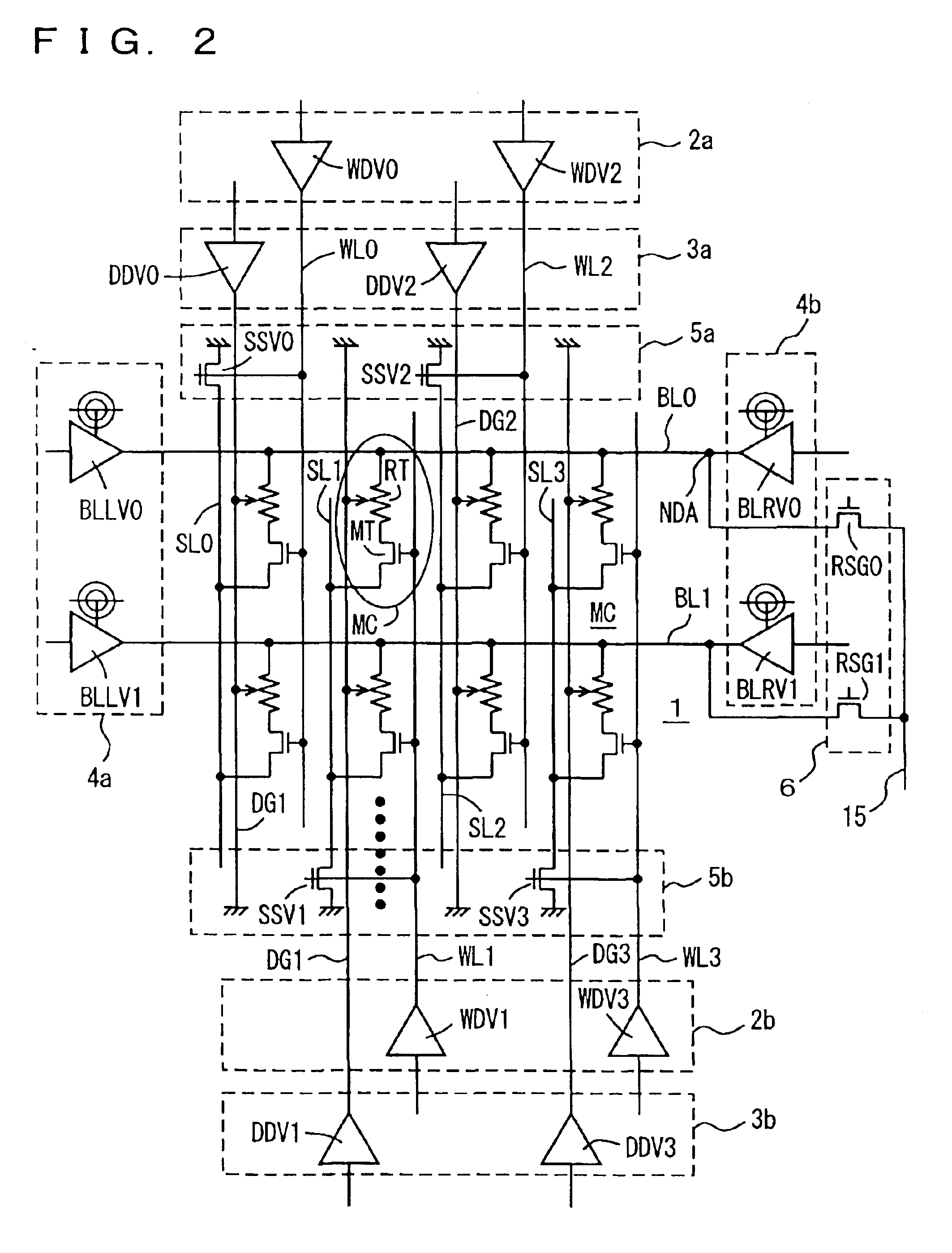

Semiconductor memory device operating with low current consumption

In a resistance value variable memory, substrate voltages and / or substrate biases of a digit line drive circuit, a word line drive circuit and a bit line drive circuit for a memory cell array are changed in accordance with an operation mode. A driving power on signal lines connected to memory cells can be increased, and a leakage current during standby can be reduced without increasing a circuit layout area.

Owner:RENESAS ELECTRONICS CORP

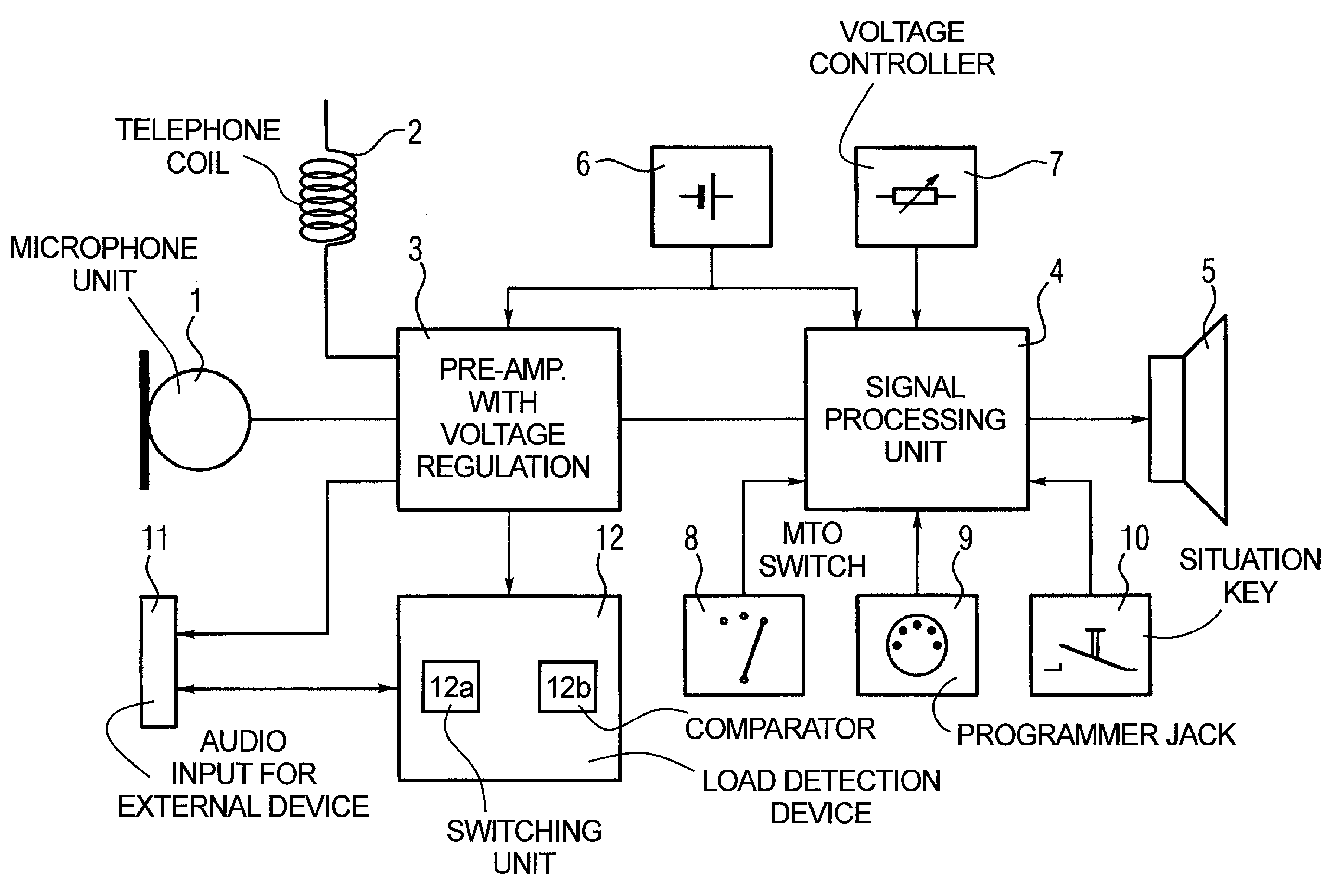

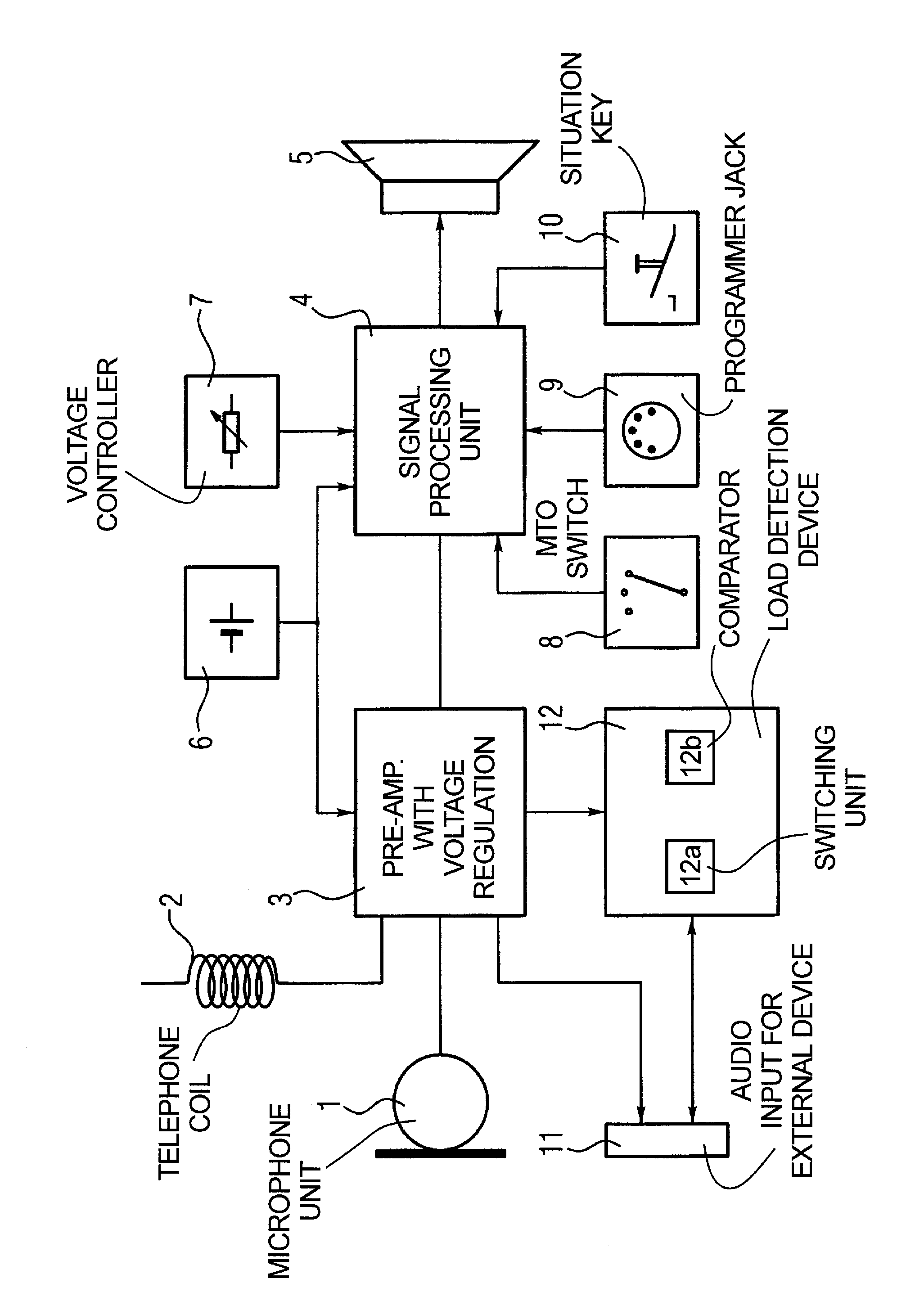

Hearing aid device and operating method for automatically switching voltage supply to a connected external device

ActiveUS7333624B2Comfortable designImprove satisfactionEar supported setsHearing aid batteryAudio power amplifier

In a hearing aid device and operating method with automatic switching of the hearing aid voltage supply for an external component connected to an audio input of he hearing aid via a single audio voltage supply contact. A load detection device measures the electrical load at the audio input and switches either the unregulated voltage of the hearing aid battery or the regulated voltage of a voltage regulator in a preamplifier of the hearing aid to the audio input dependent on the measured load.

Owner:SIVANTOS PTE LTD

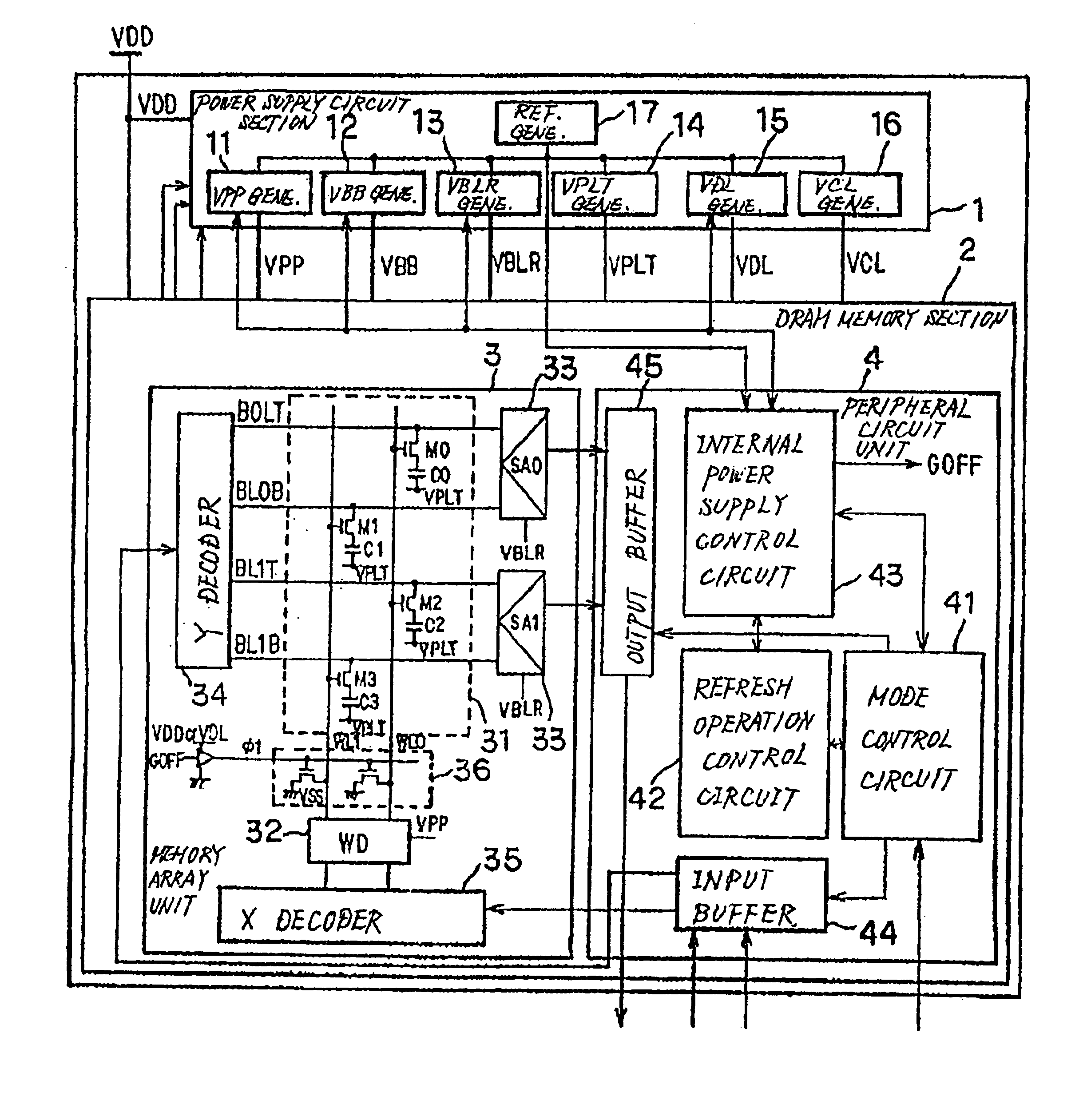

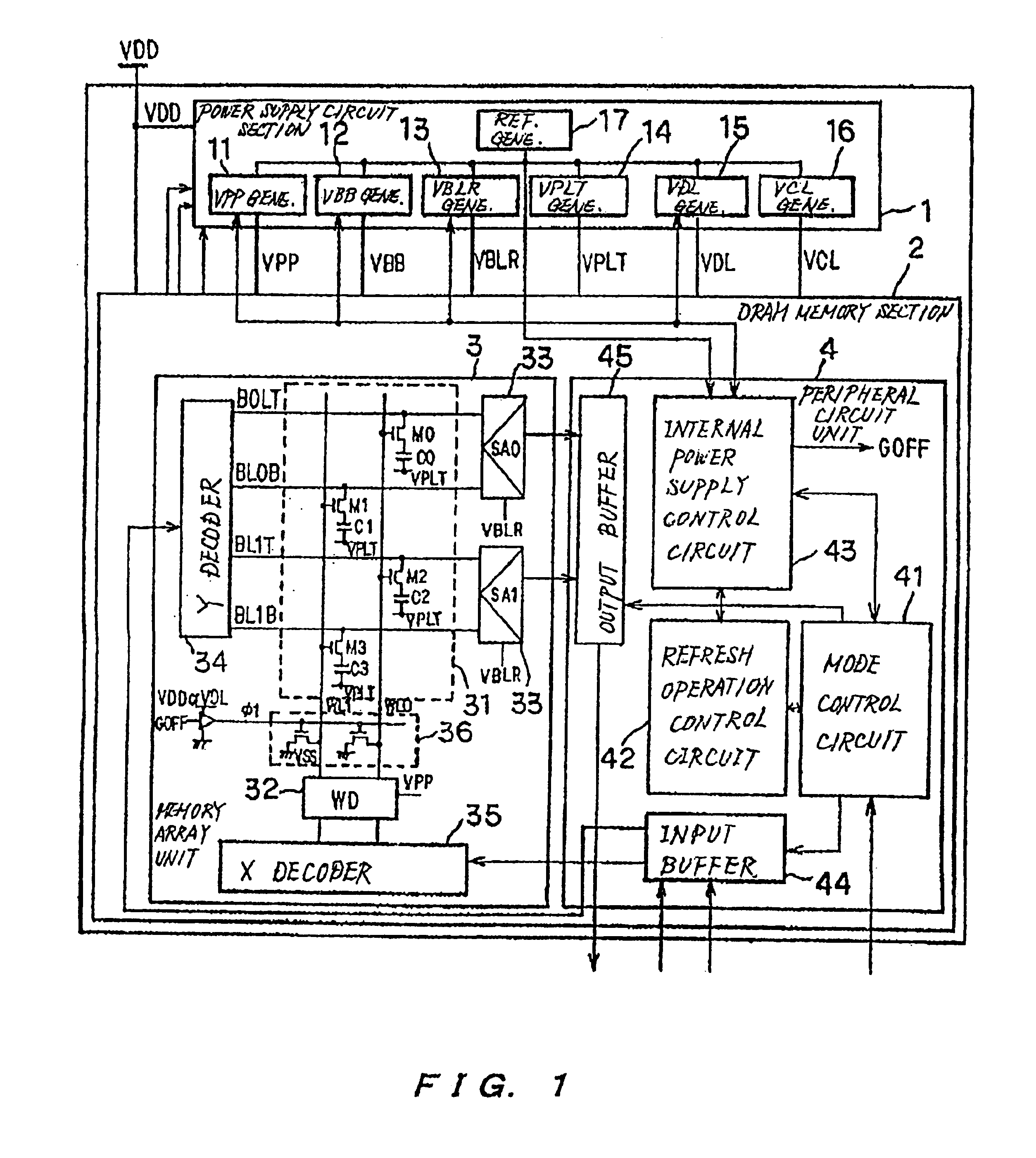

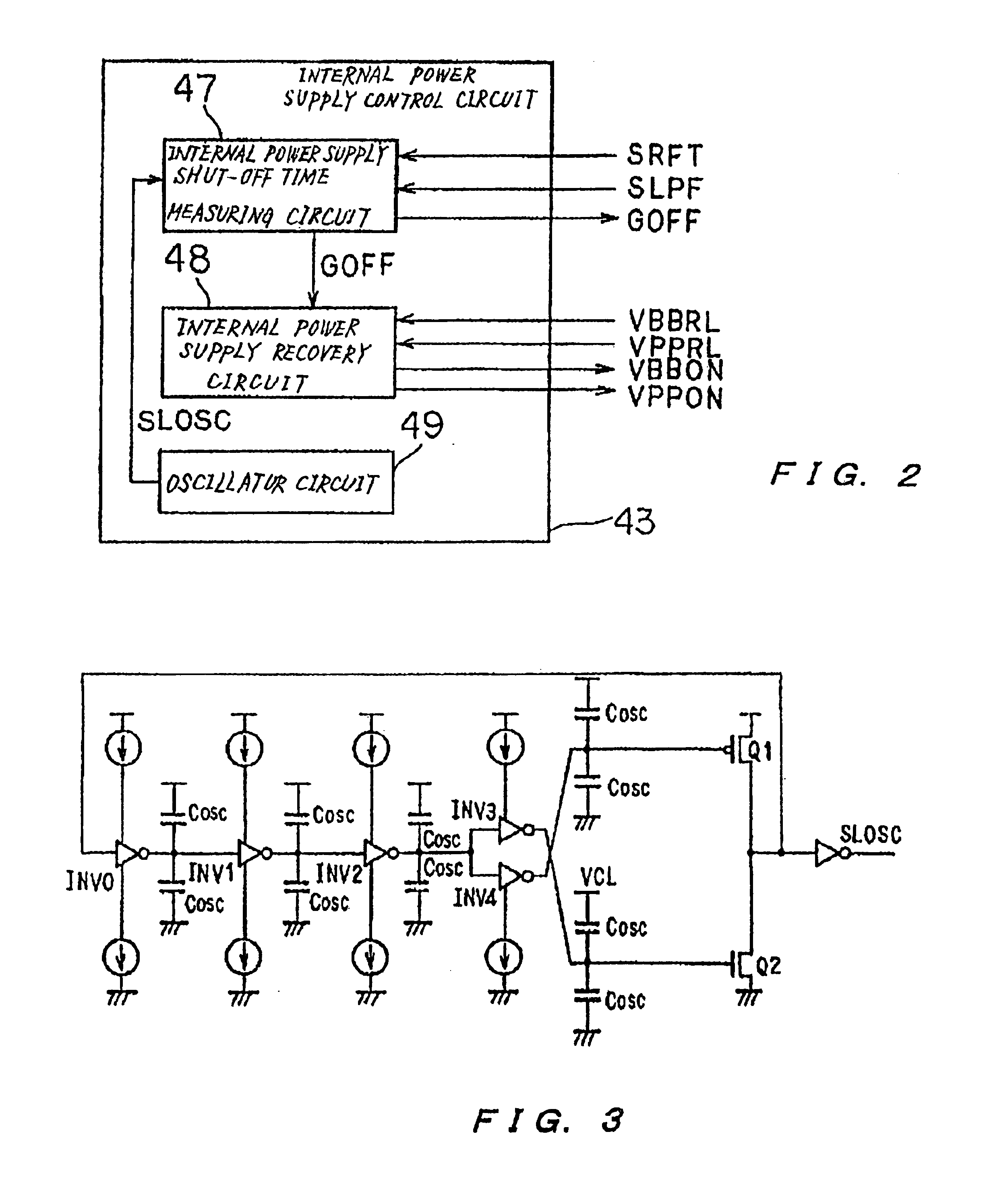

Semiconductor memory device control method and semiconductor memory device

ActiveUS6990031B2Reducing average current consumptionTotal current dropDigital storageBit lineEngineering

In a semiconductor memory device which requires a refresh operation, a control method stops supplying a word line voltage which is a boosted voltage higher than an external supply voltage, a memory array substrate voltage which is a negative voltage supplied to a semiconductor substrate, and a bit line precharge voltage for use in reproducing data held in memory cells for a predetermined period at the end of each refresh operation. In this event, voltage output terminals of the word line and memory array substrate voltages are respectively driven to a ground potential. For recovering these voltages, the delivery of the word line voltage is stopped until the memory array substrate voltage rises to some extent.

Owner:LONGITUDE LICENSING LTD

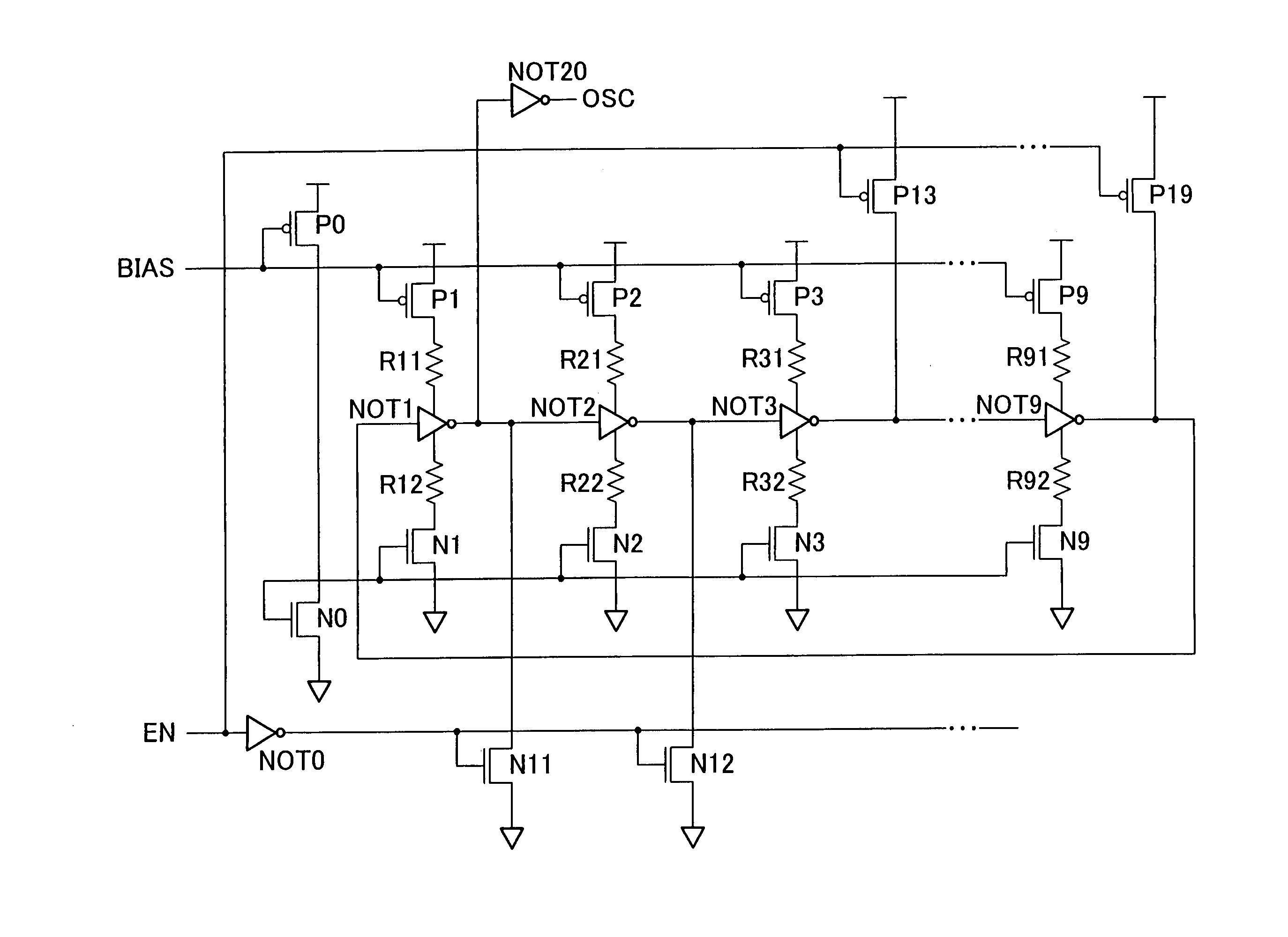

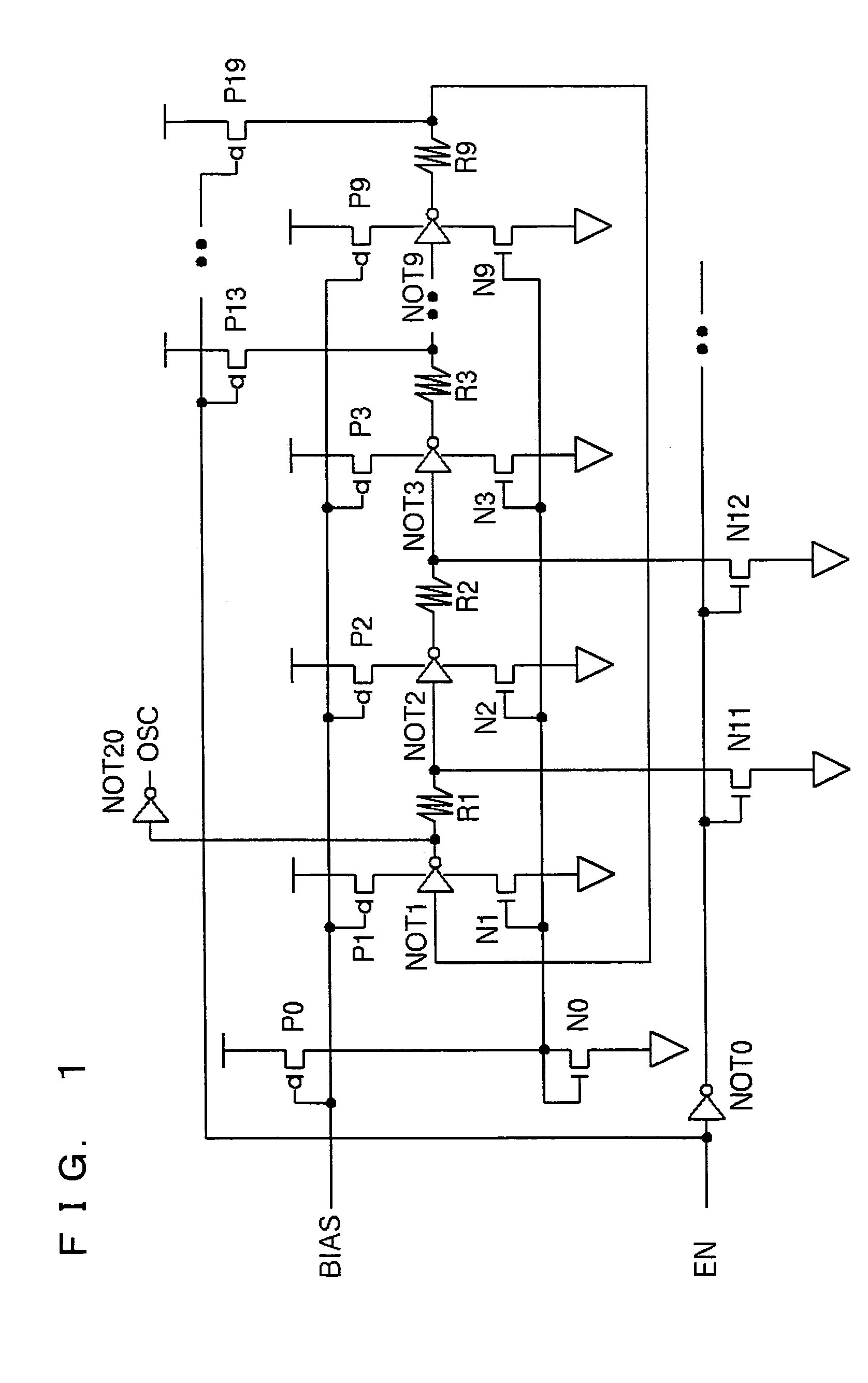

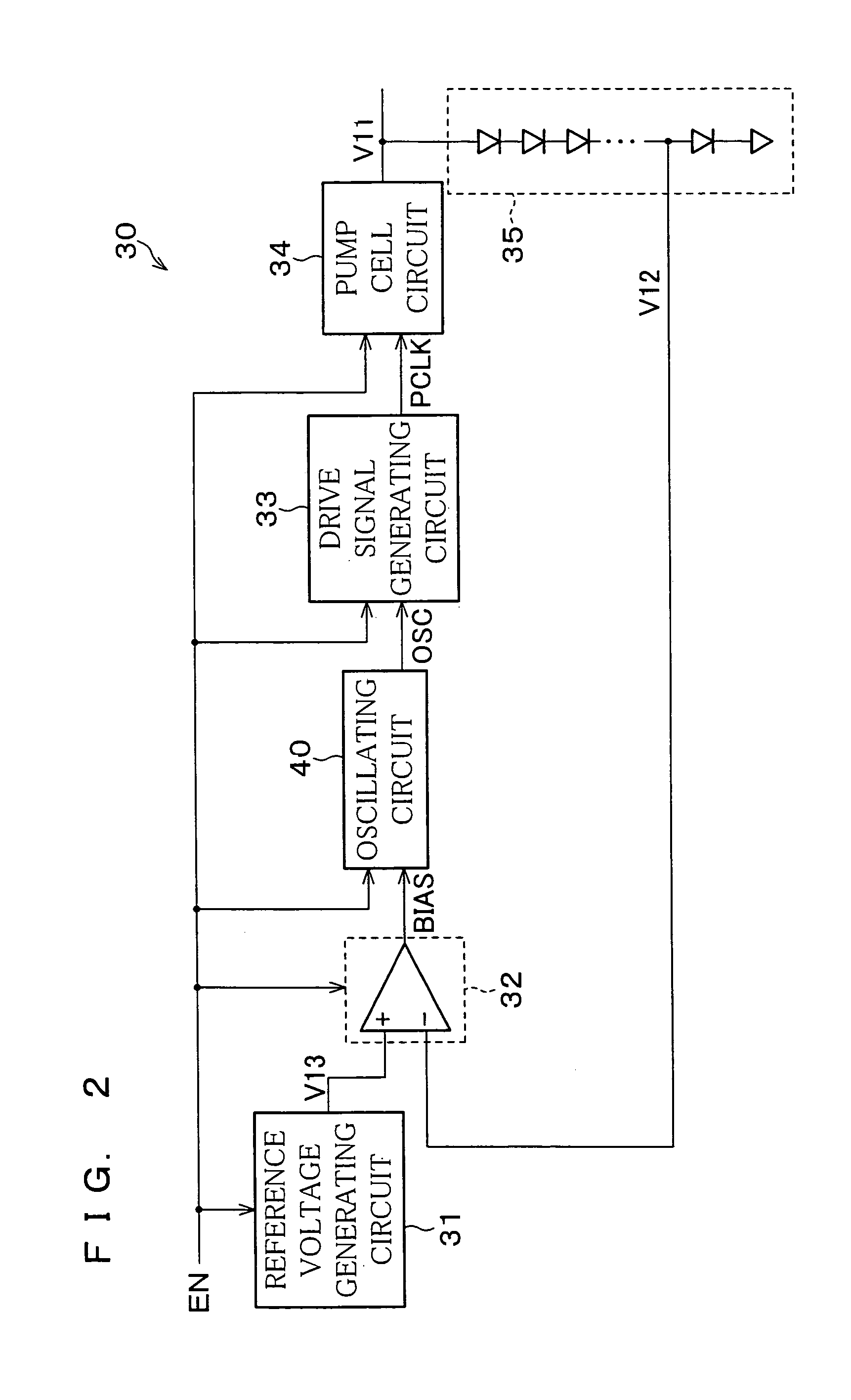

Oscillating circuit, booster circuit, nonvolatile memory device, and semiconductor device

InactiveUS7180794B2Suppress the variation in the oscillating frequencies of an output signalChange in resistancesSolid-state devicesRead-only memoriesPower inverterEngineering

In a ring oscillator constituting an oscillating circuit, resistor circuits are used as delay circuits to be connected to respective inverters. That is, the inverters and the resistors are connected in series so that the resistor is provided between the adjacent inverters. With the arrangement, it is possible to provide an oscillating circuit which is less dependent on any of power supply voltages, temperatures, and manufacturing variations, while maintaining a characteristic in which the oscillating frequency decreases as an output voltage of a booster circuit increases.

Owner:TAMIRAS PER PTE LTD LLC

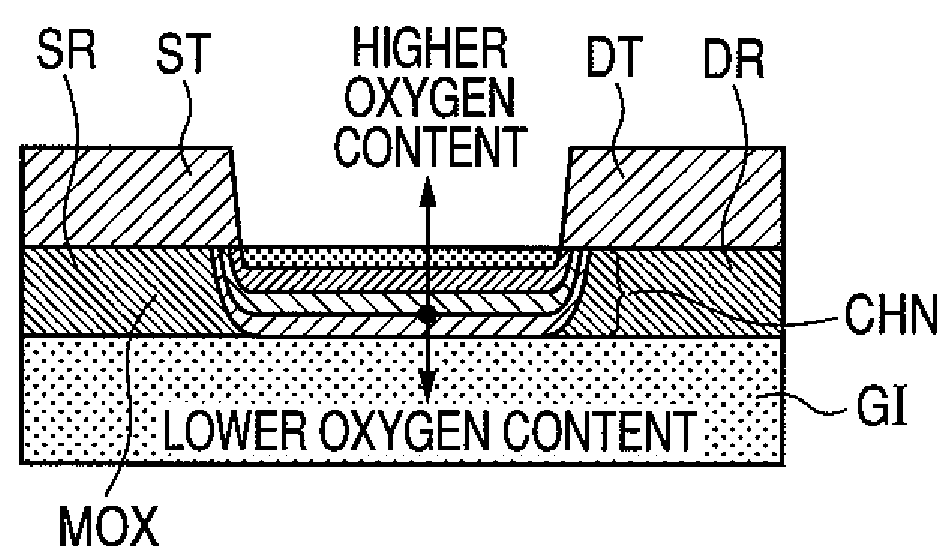

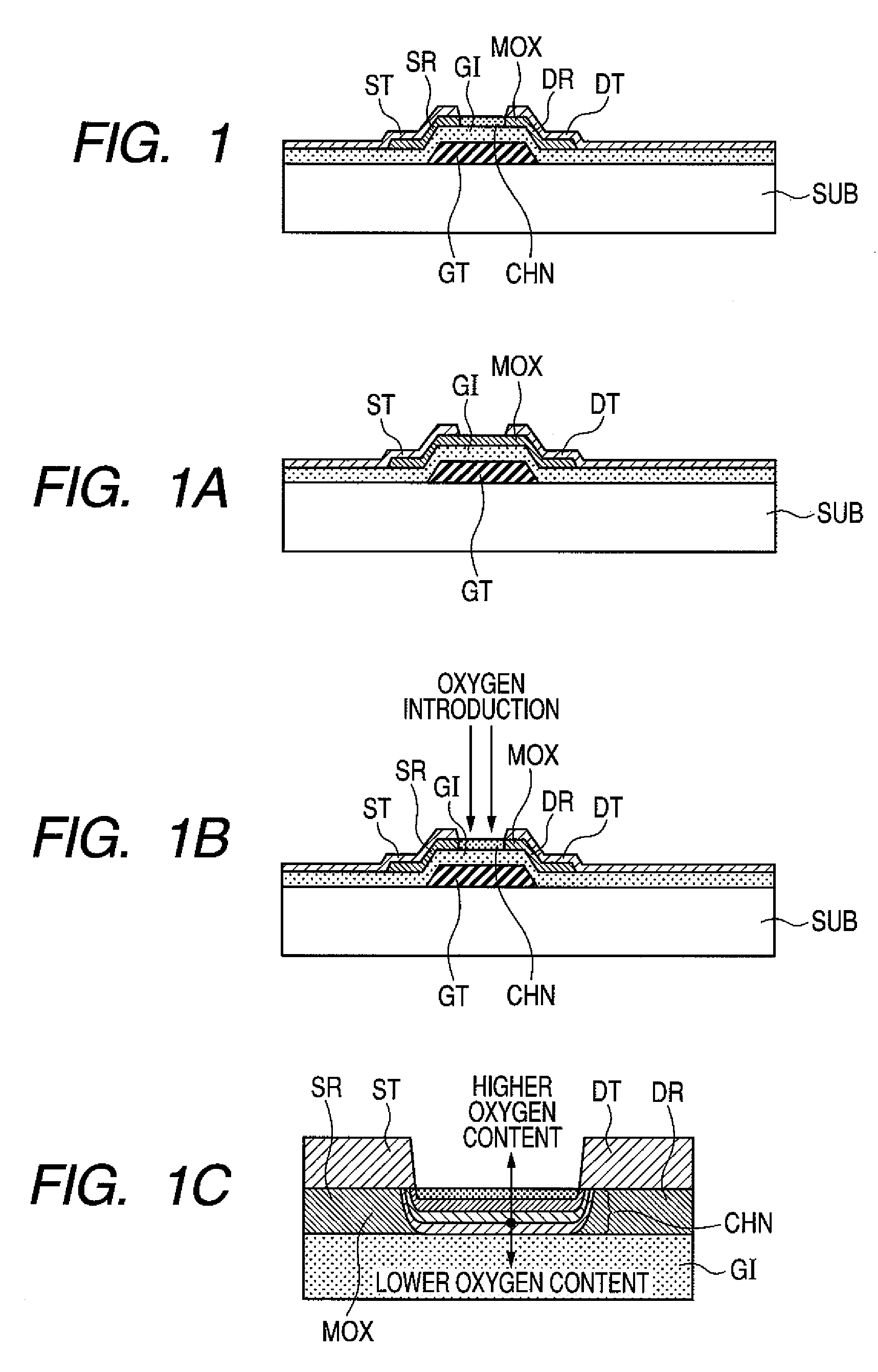

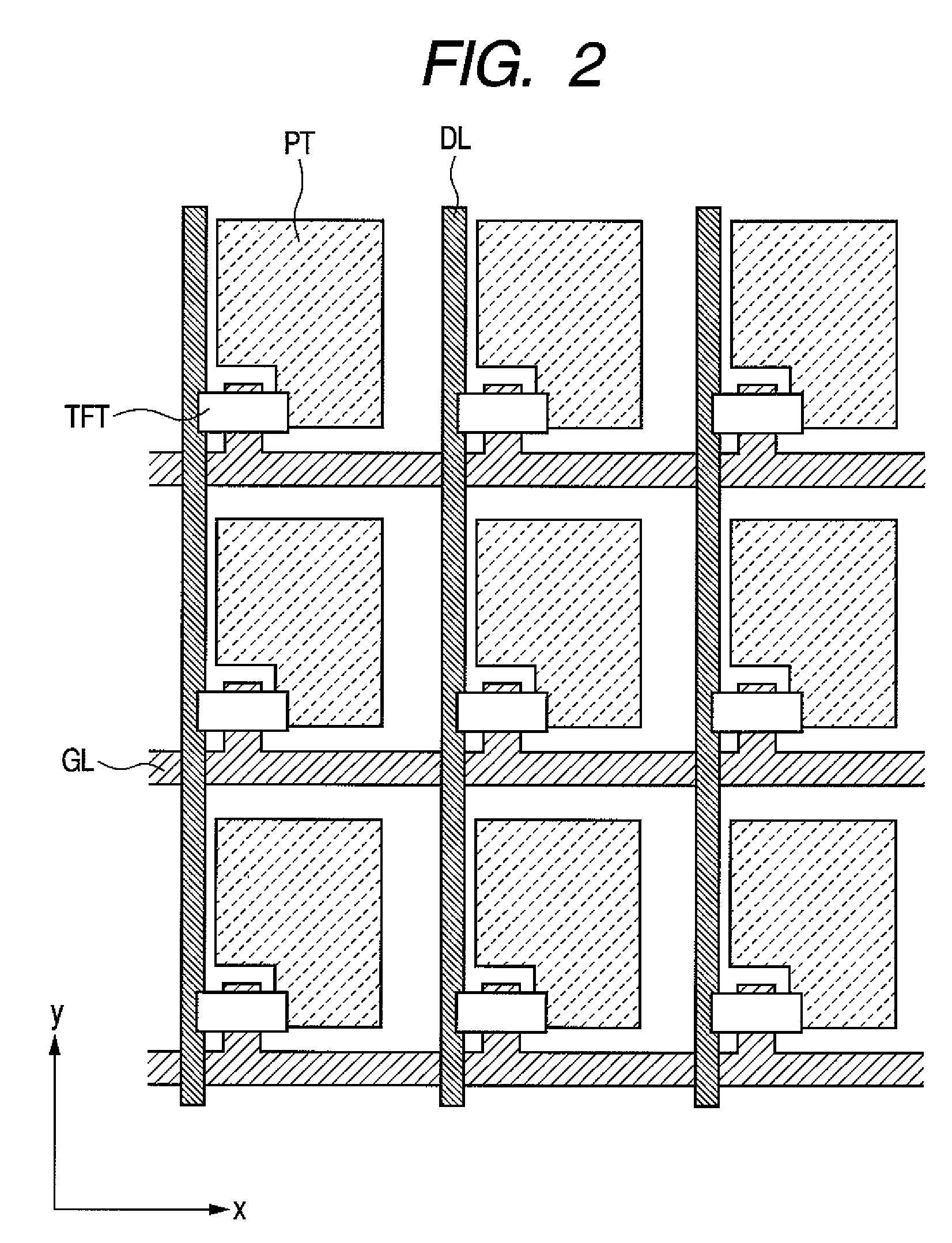

Semiconductor device and method for manufacturing the same

InactiveUS7977675B2Improve featuresReduce allocationSolid-state devicesSemiconductor/solid-state device manufacturingOxygen contentField-effect transistor

A metallic oxide semiconductor device with high performance and small variations. It is a field effect transistor using a metallic oxide film for the channel, which includes a channel region and a source region and comprises a drain region with a lower oxygen content than the channel region in the metallic oxide, in which the channel region exhibits semiconductor characteristics and the oxygen content decreases with depth below the surface.

Owner:HITACHI LTD

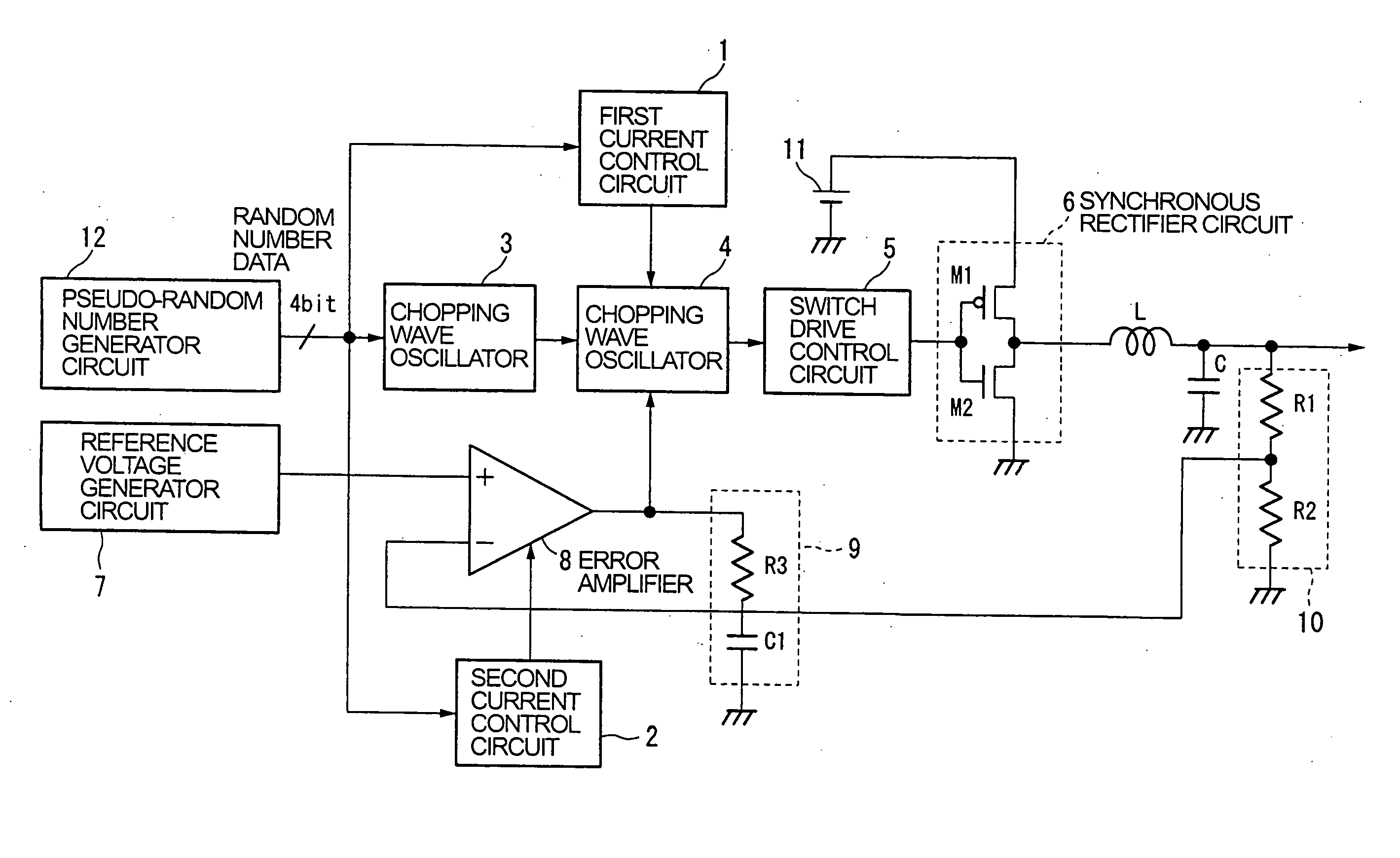

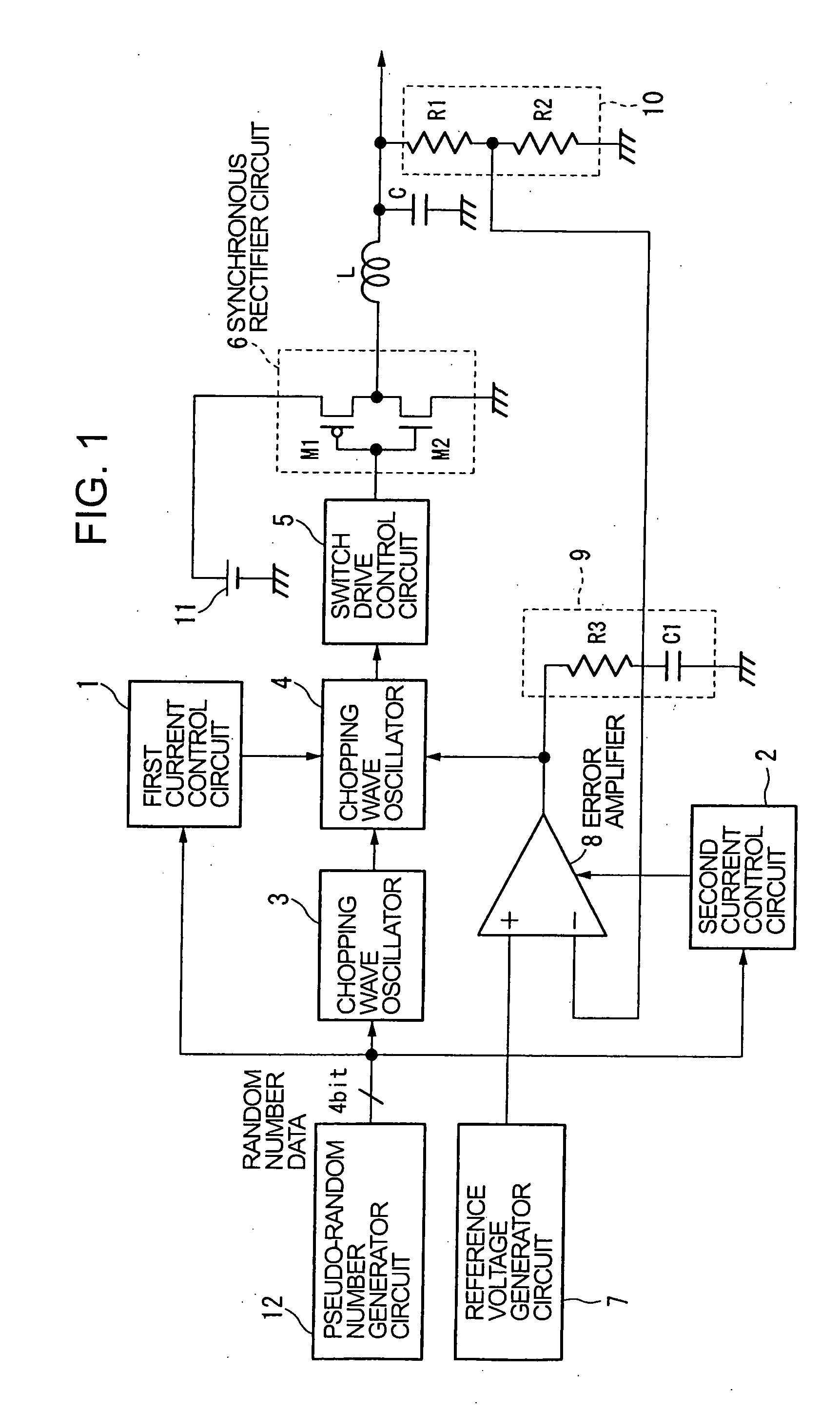

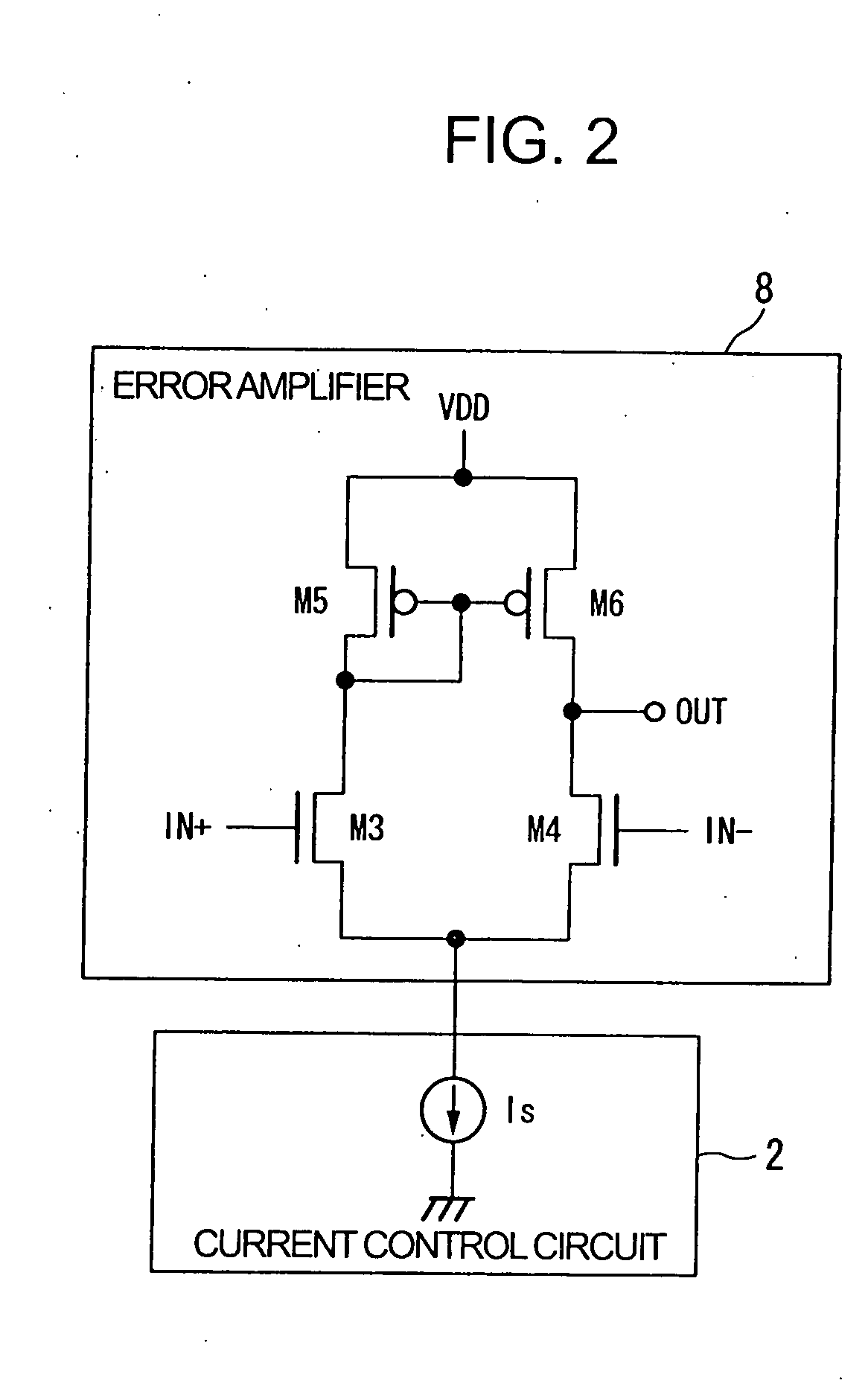

Switching power source apparatus

InactiveUS20070210776A1Reduce consumption currentReduce effectDc-dc conversionElectric variable regulationSwitching powerControl circuit

There is provided a switching power supply device which is capable of reducing an influence of noises and also reducing a consumption current of a control circuit. A pseudo-random number generator circuit (12) generates random number data for determining frequencies of switching signals of MOS transistors (M1) and (M2). A chopping wave oscillation frequency (a frequency of a switching signal) of a chopping wave oscillator (3) randomly changes according to the random number data that is generated by the pseudo-random number generator circuit (12). A current control circuit (1) and a current control circuit (2) control consumption currents that flow in the chopping wave oscillator (3) and an error amplifier (8) according to a change (a change in the frequency of the switching signal) in the random number data that is generated by the pseudo-random number generator circuit (12).

Owner:SEIKO INSTR INC

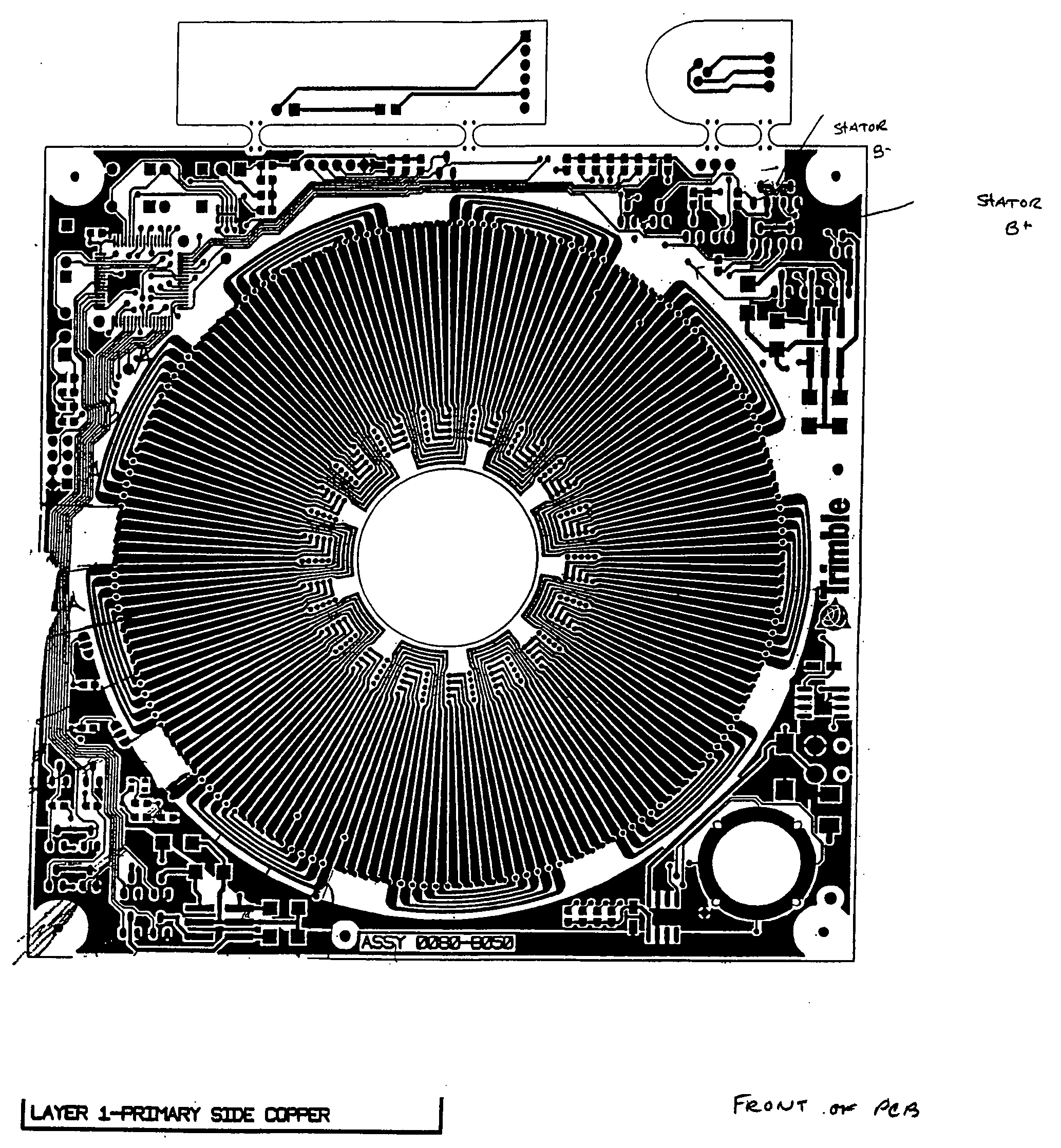

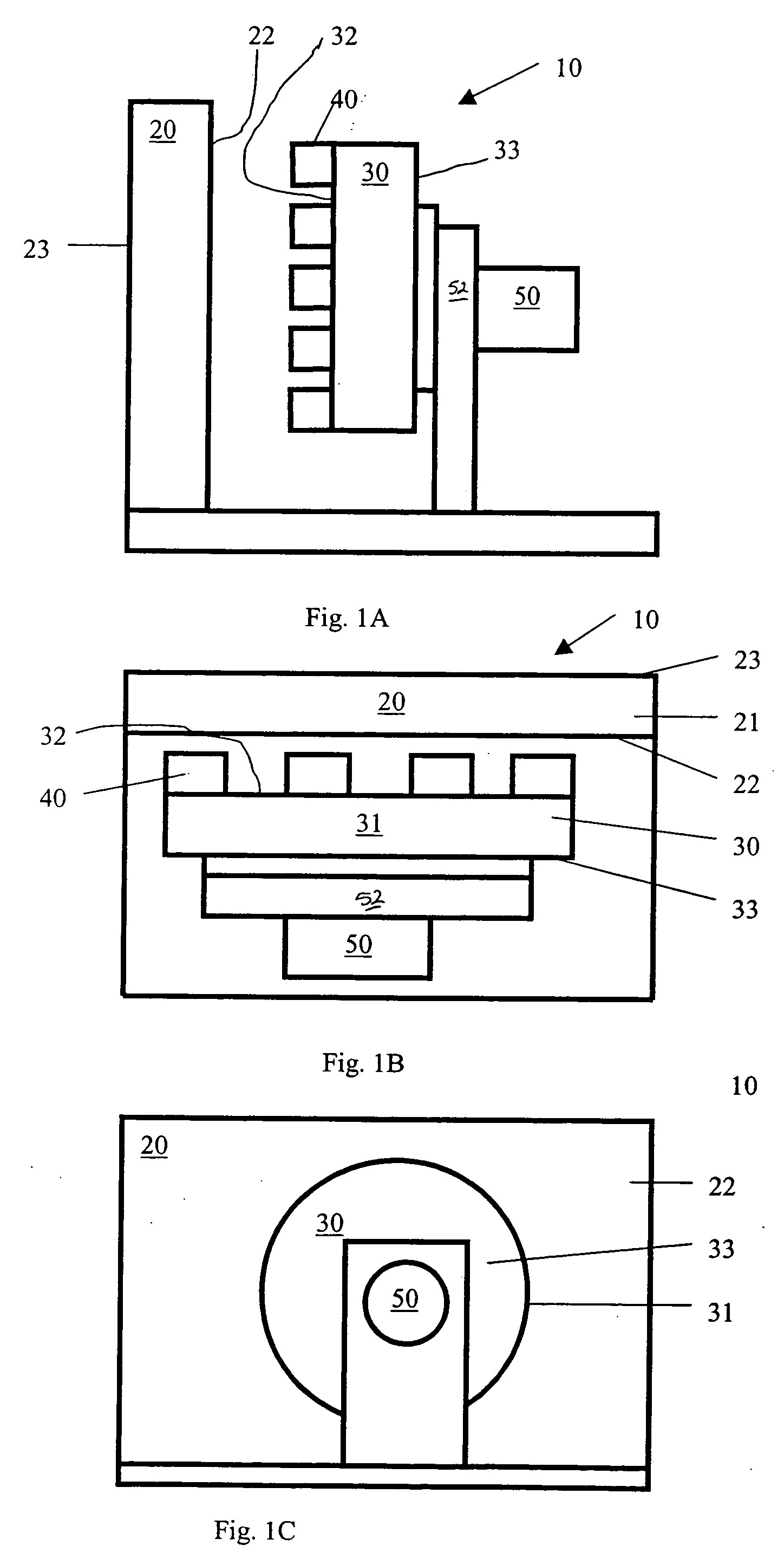

Printed circuit board motor

InactiveUS20060055265A1Easy to controlCurrent consumptionAssociation with control/drive circuitsMagnetic circuit rotating partsElectrical conductorAverage current

A printed circuit board motor is disclosed. The motor comprises a rotor plate embedded with magnets, an axle, and a printed circuit board stator. The printed circuit board comprises two conductors printed on the same surface or on opposite surfaces of the printed circuit board The two conductors produce alternating “square wave” patterns. The printed circuit board circuitry causes the direction of the current flow to reverse at intervals. The rotor rotates in response to the current flow in the stator. The rotation rate can be accurately controlled. The torque and average current consumption can be controlled by “chopping” the current with high frequency modulation whose duty cycle is proportional to the torque and average current consumption which will prolong the battery life of the motor.

Owner:TRIMBLE NAVIGATION LTD

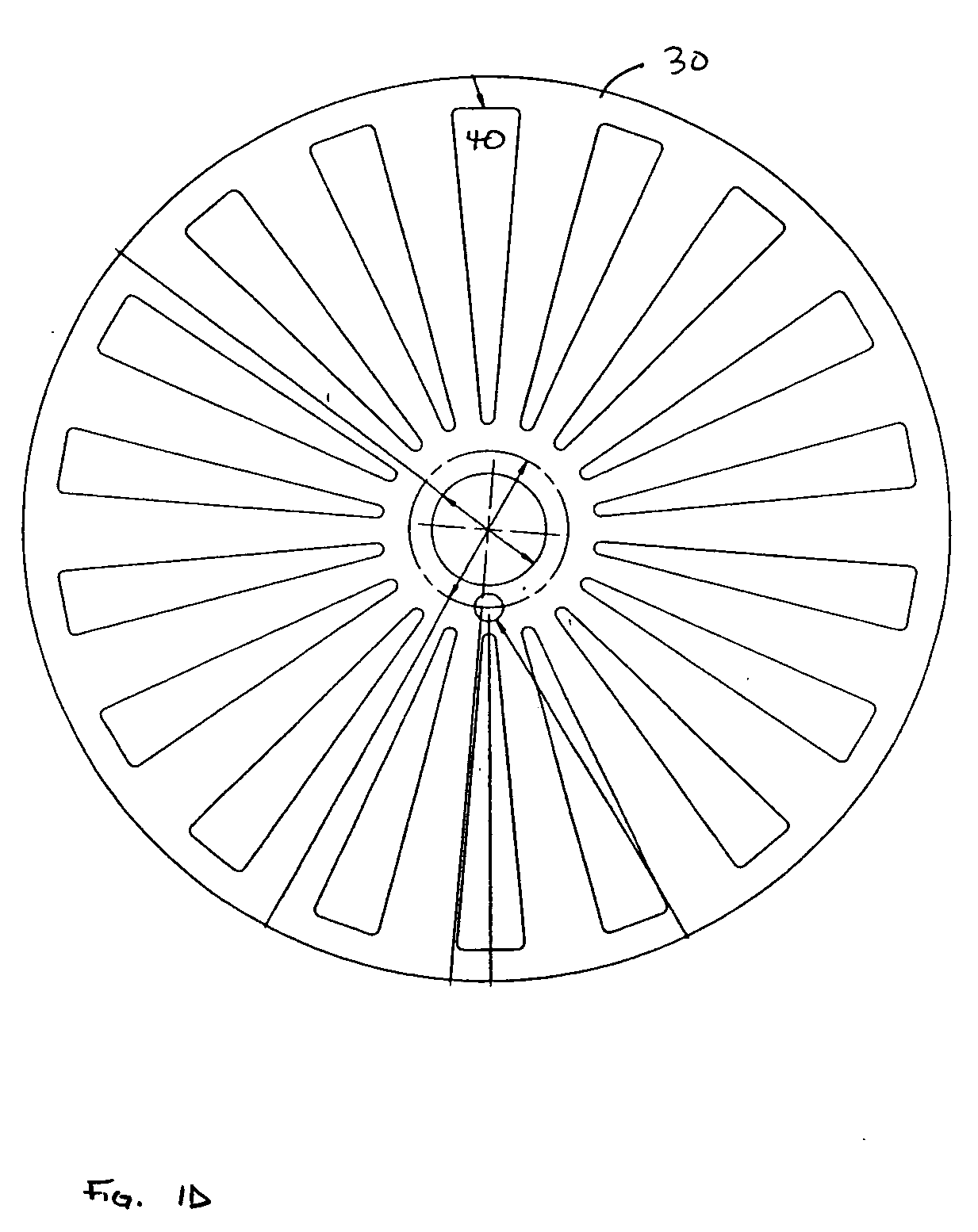

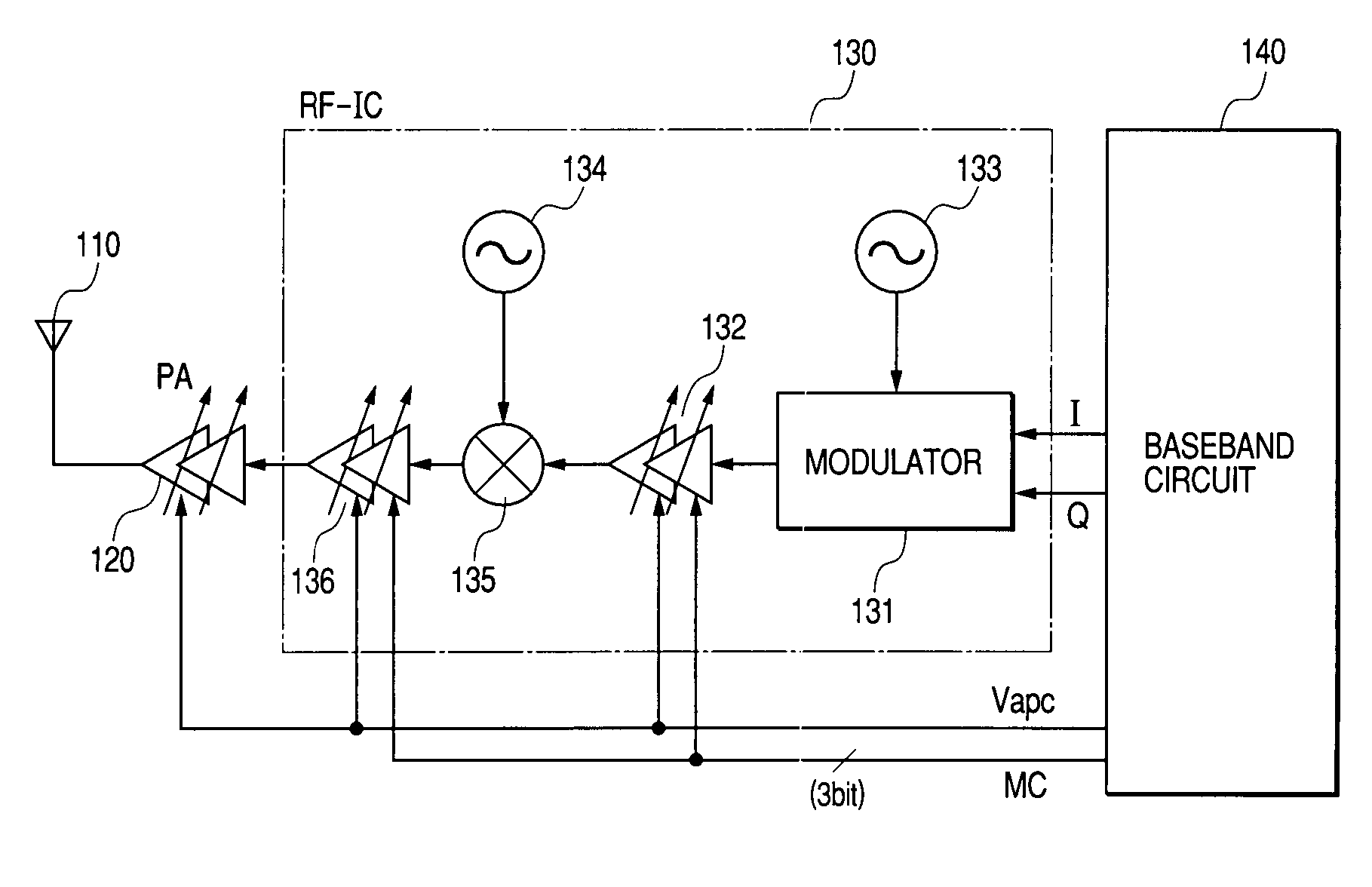

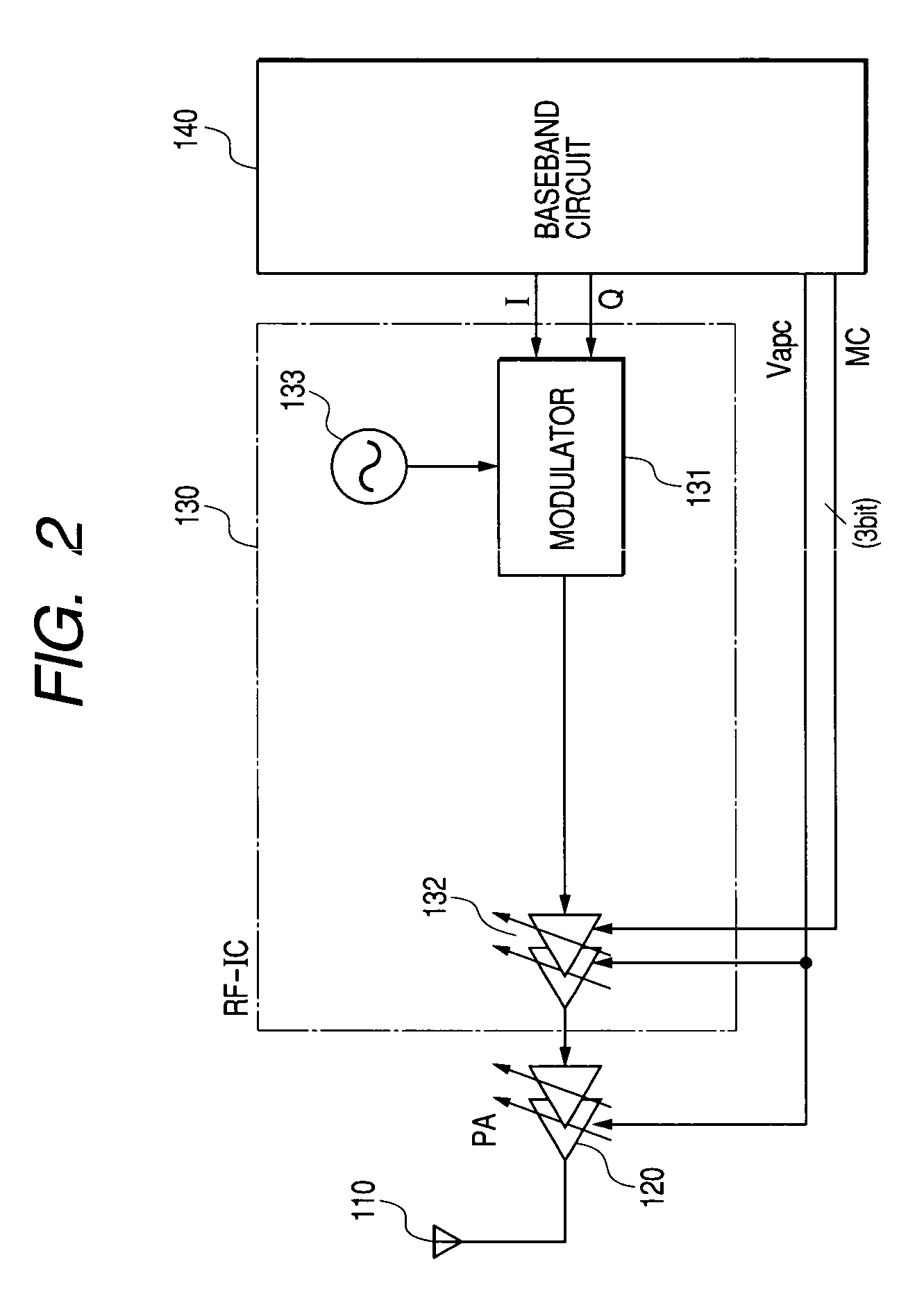

Semiconductor integrated circuit device and wireless communication system

InactiveUS7116949B2Total current dropImprove dynamic rangeResonant long antennasGain controlCurrent consumptionEngineering

The dynamic range is changed by switching a current applied to an amplifying circuit to obtain the minimum ICP required to keep linearity with the number of multiplexes even when the number of multiplexes of data is changed by switching the operation current of the amplifying circuits of the transmission system and also supplying the information about number of multiplexes of data to be transmitted to the amplifying circuits of the transmission system from the baseband circuit. Thereby, the signal can be transmitted without distortion even when the number of multiplexes increases and the current of the amplifying circuit may be reduced when the number of multiplexes is small in order to reduce the current consumption in the communication semiconductor integrated circuit device which can form a wireless communication system of the code division multiplex system such as W-CDMA system.

Owner:RENESAS ELECTRONICS CORP

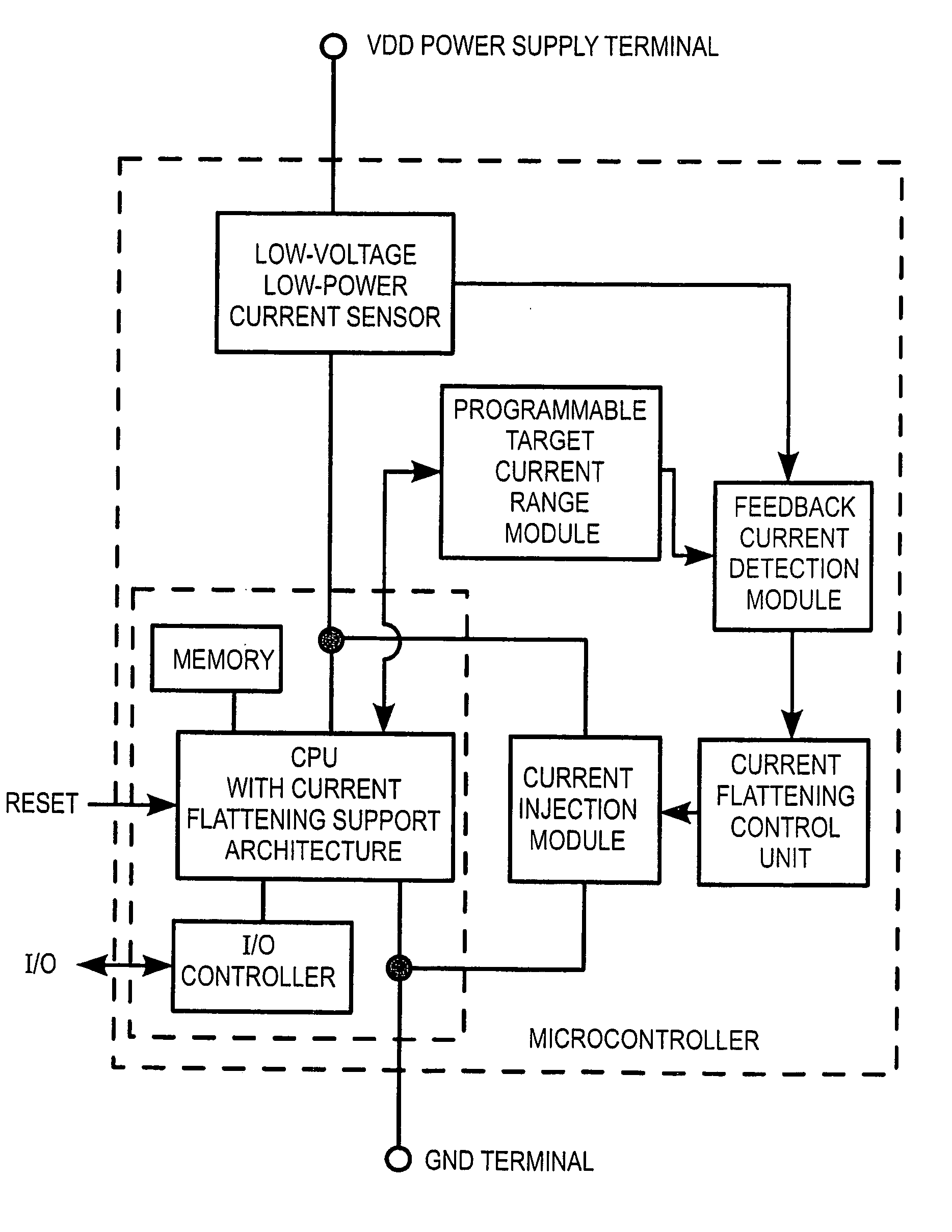

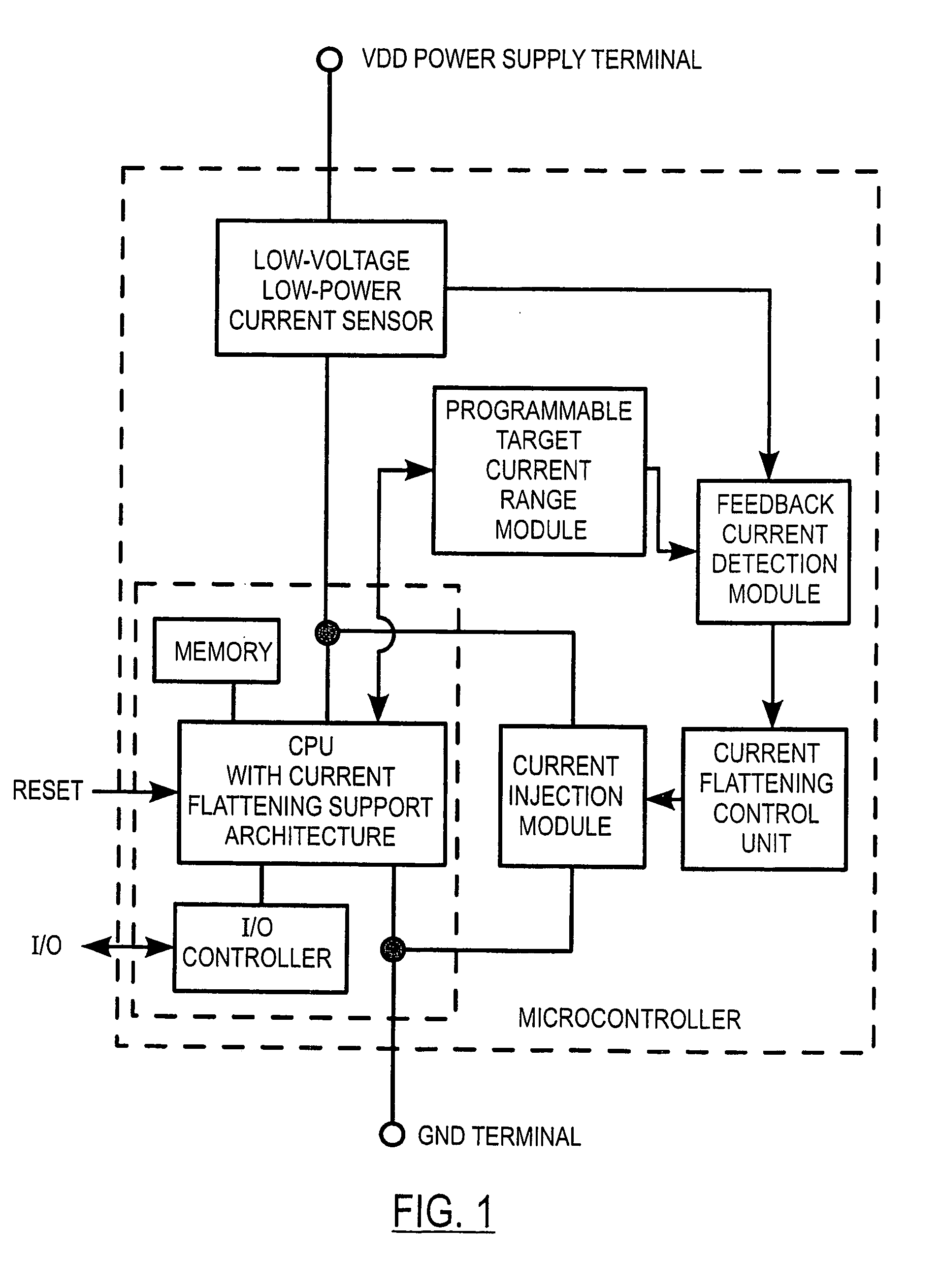

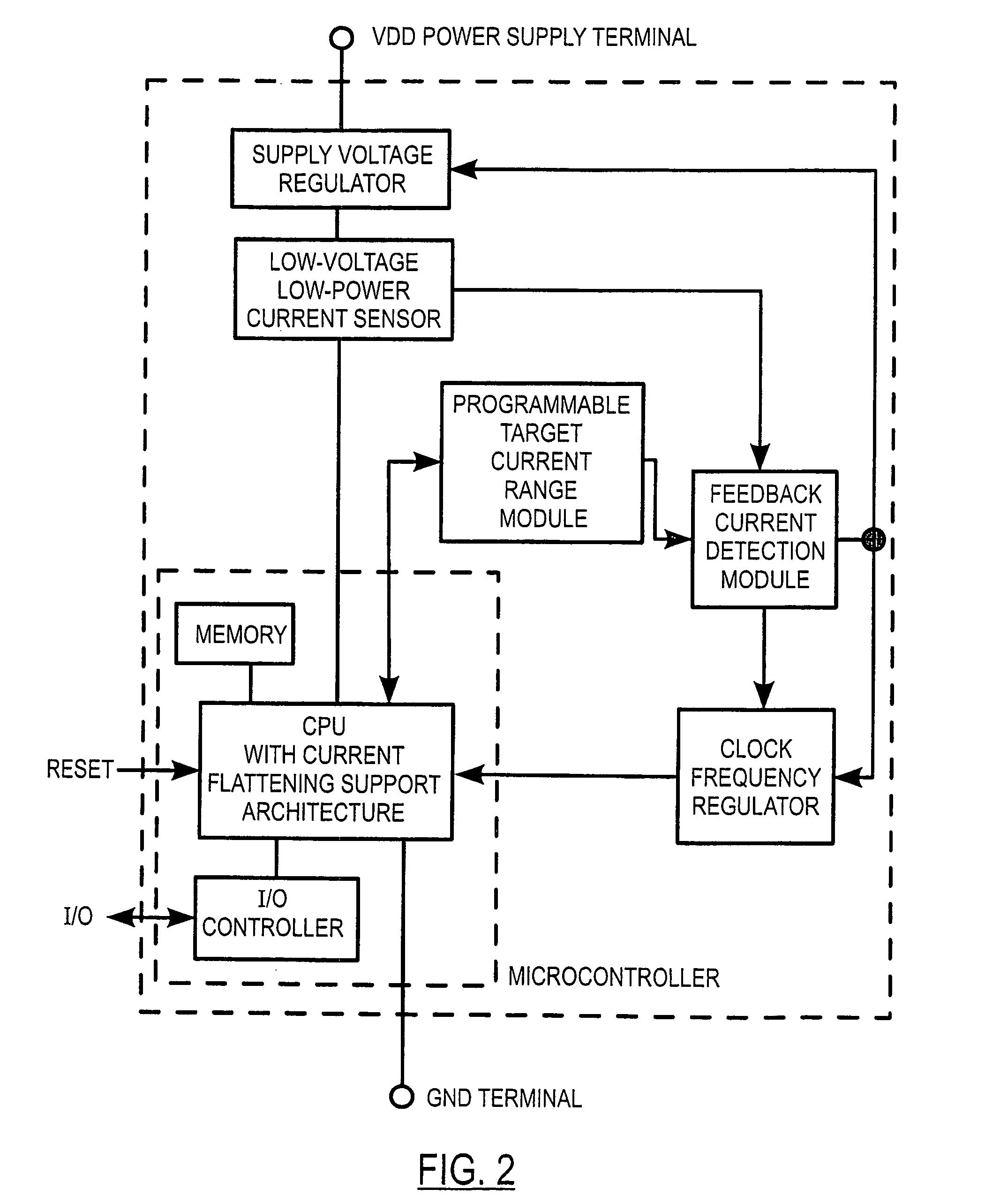

Current flattening and current sensing methods and devices

InactiveUS20070076890A1Flattening total current consumptionCurrent consumptionDigital data processing detailsHardware monitoringReference currentCurrent sensor

Flattening total current consumption of system having processing core and power supply input by current sensing within system at power supply input and controlling system current consumption such that system current is reduced if over reference current threshold, and increased if below reference current threshold. Inject additional current through digital injections cells working higher frequencies, by increasing switching activity, by increasing voltage supply to core, and by increasing operating frequency of processor core. Feedback signal indicates current consumption of system. Current consumption similarly decreased. Current sensed by mirroring input current inline with power supply input and compensating for voltage drop introduced by mirroring using opposing field effect transistors and maintaining outputs at same voltage through feedback control loop. Processor core may be general purpose processor core or cryptographic processor core. System may be system-on-chip or system-on-package. System includes processor core and current flattening device based on method. Also, current flattening device and current sensor. On chip current sensor sensing current draw of processor core.

Owner:GREGORI STEFANO +1

Portable ambulant pneumatic compression system

An automatic portable ambulant miniaturized system for applying pneumatic pressure to a body limb including a portable ambulant hand-held fluid source unit, a conduit for delivering fluid generated by the unit, and a sleeve coupled to the conduit and adapted to envelop a body limb. The sleeve contains one or more individually inflatable cells, each cell being subdivided into two or more longitudinally extending confluent compartments along the axis of the body limb. The compartments are inflated and deflated essentially simultaneously by the portable fluid source unit.

Owner:ZIMMER SURGICAL

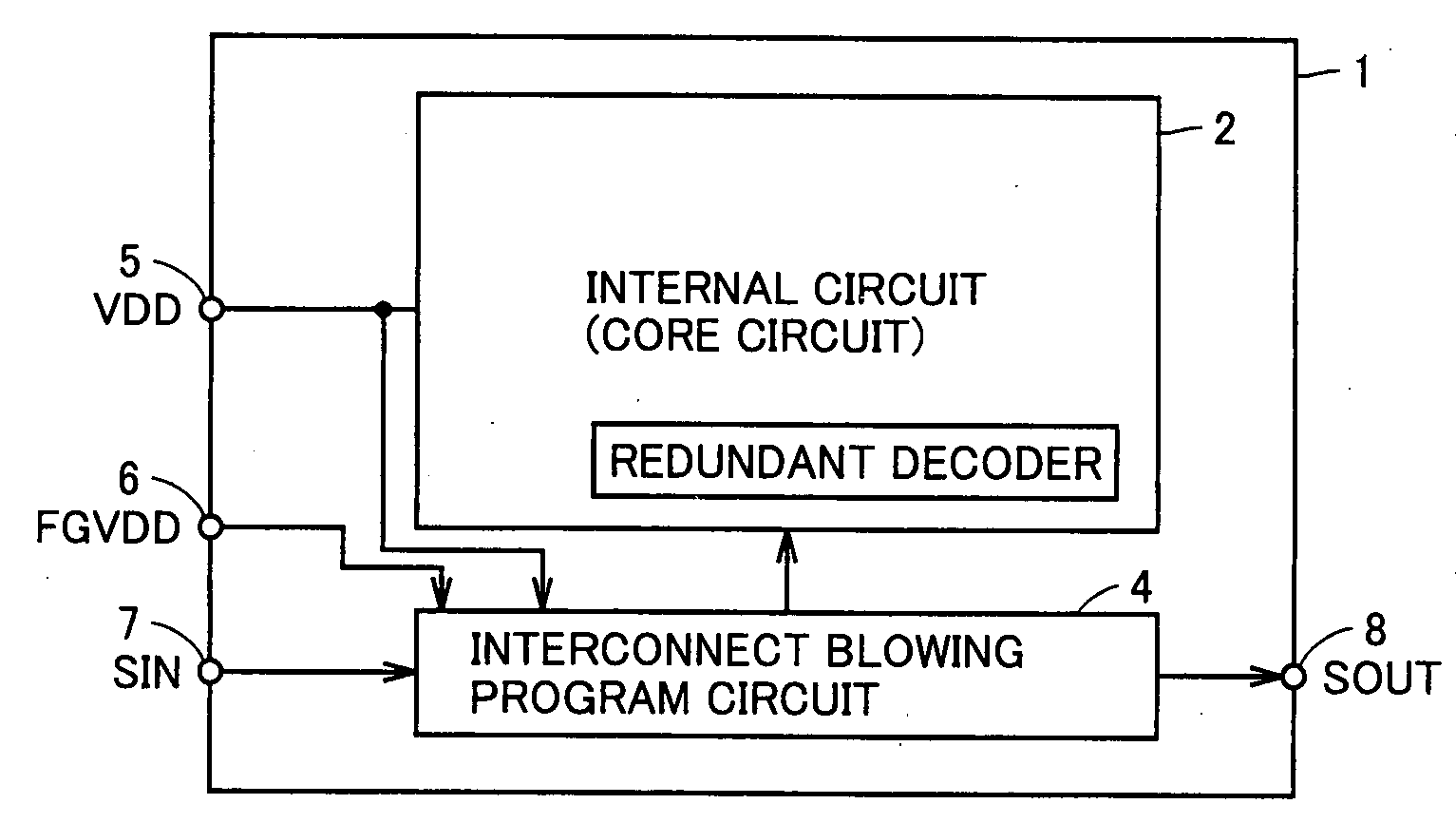

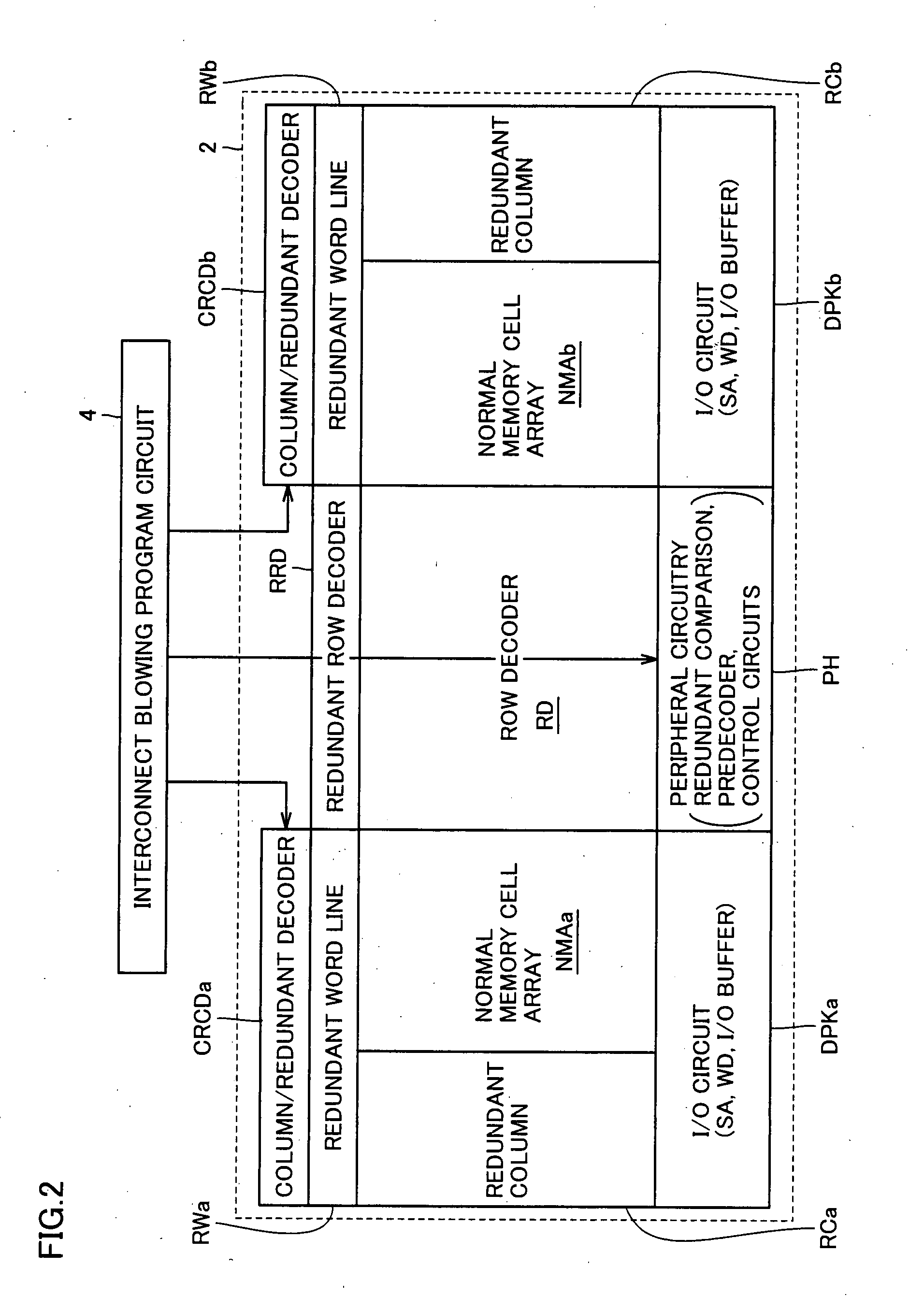

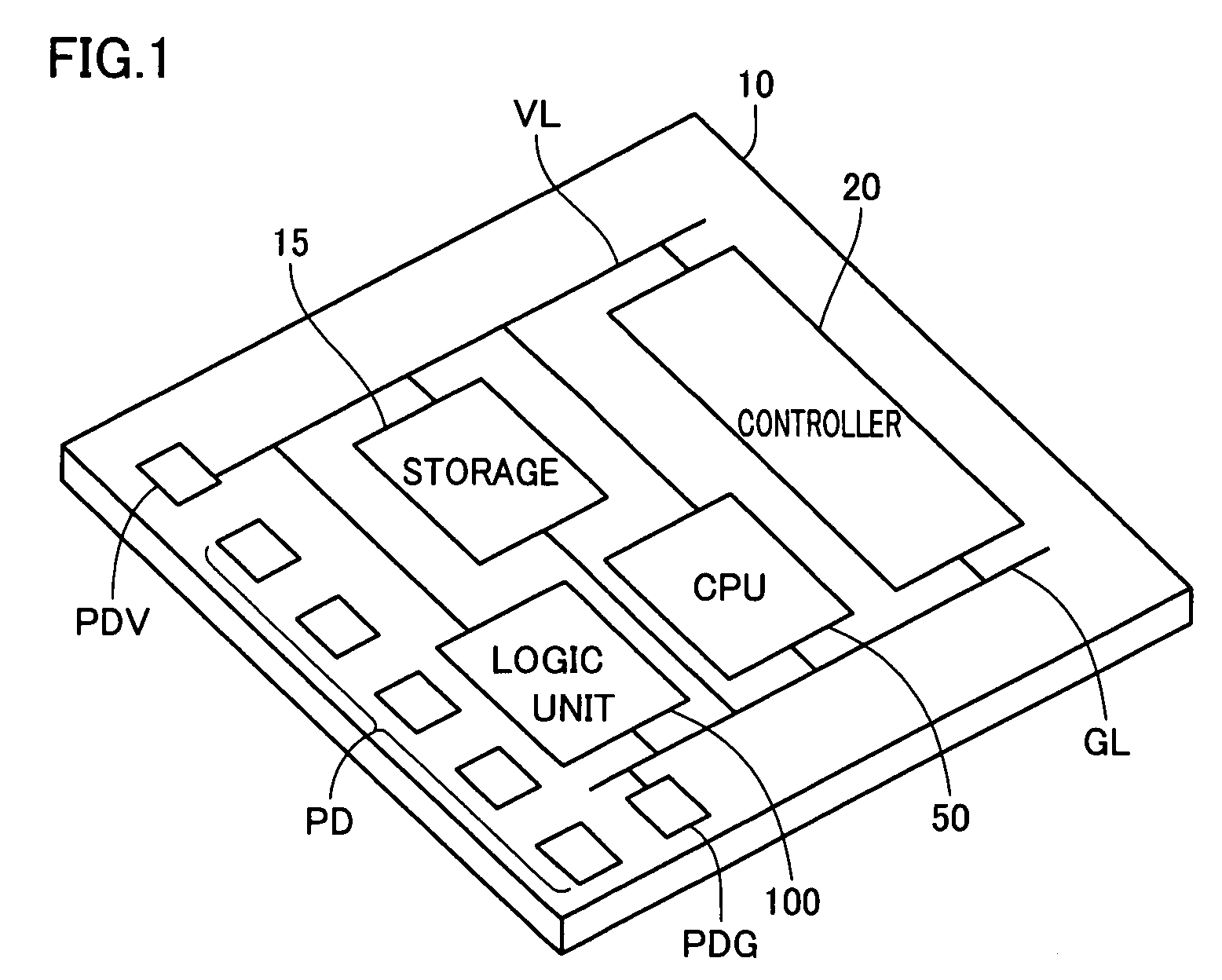

Semiconductor device

ActiveUS20070280012A1Small footprintLower average currentSemiconductor/solid-state device detailsSolid-state devicesMetal interconnectDevice material

In fuse program circuits, fuse element FS is implemented using metal interconnect at third or higher layer of multilayer metal interconnect. In each fuse program circuit, program information and fuse select information are sequentially transferred using a scan flip-flops, and fuses are selectively and electrically blown one by one. The fuse program circuit provided with fuse elements that can be programmed even after packaging is implemented with low power consumption and a low occupation area.

Owner:RENESAS ELECTRONICS CORP

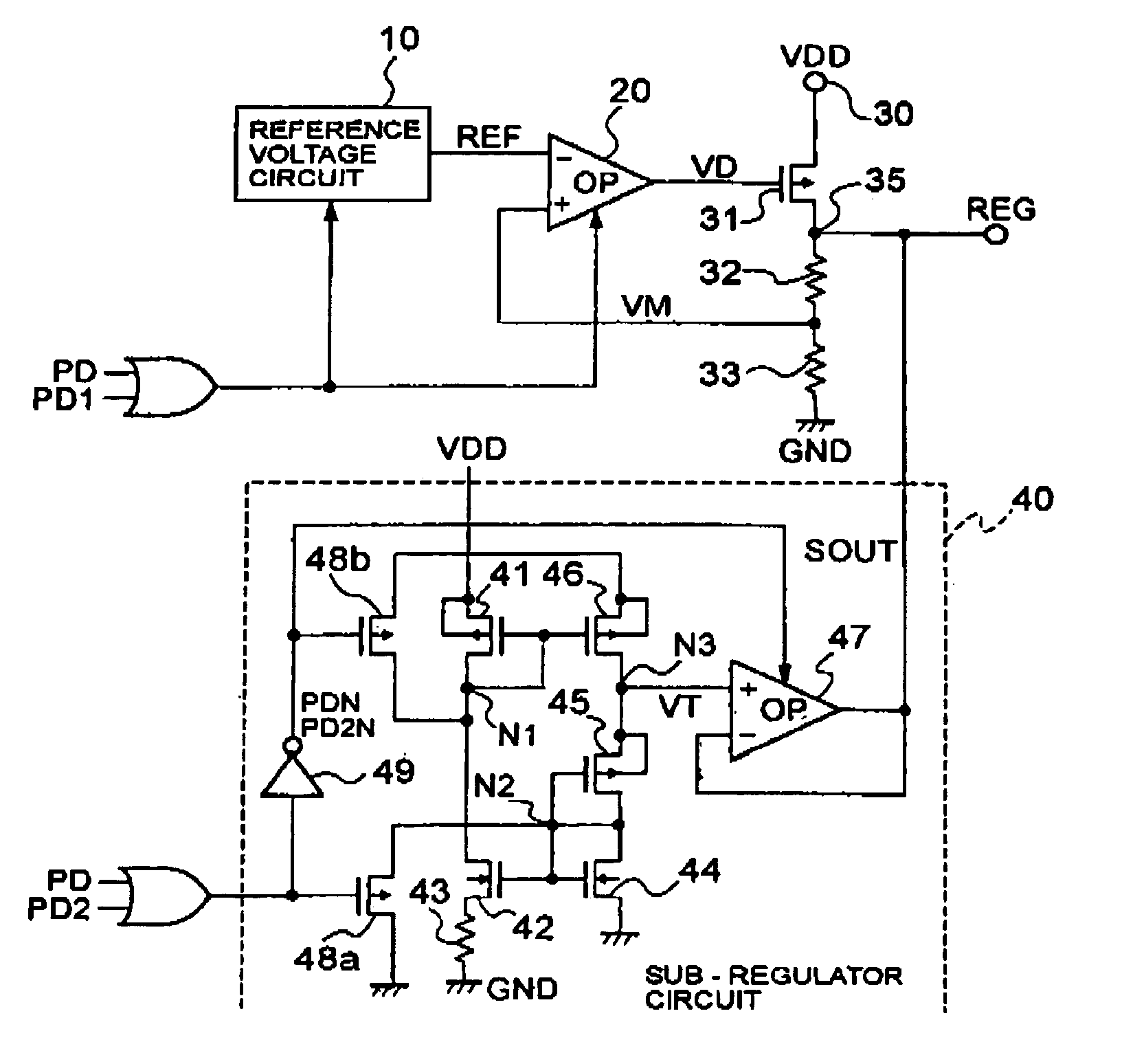

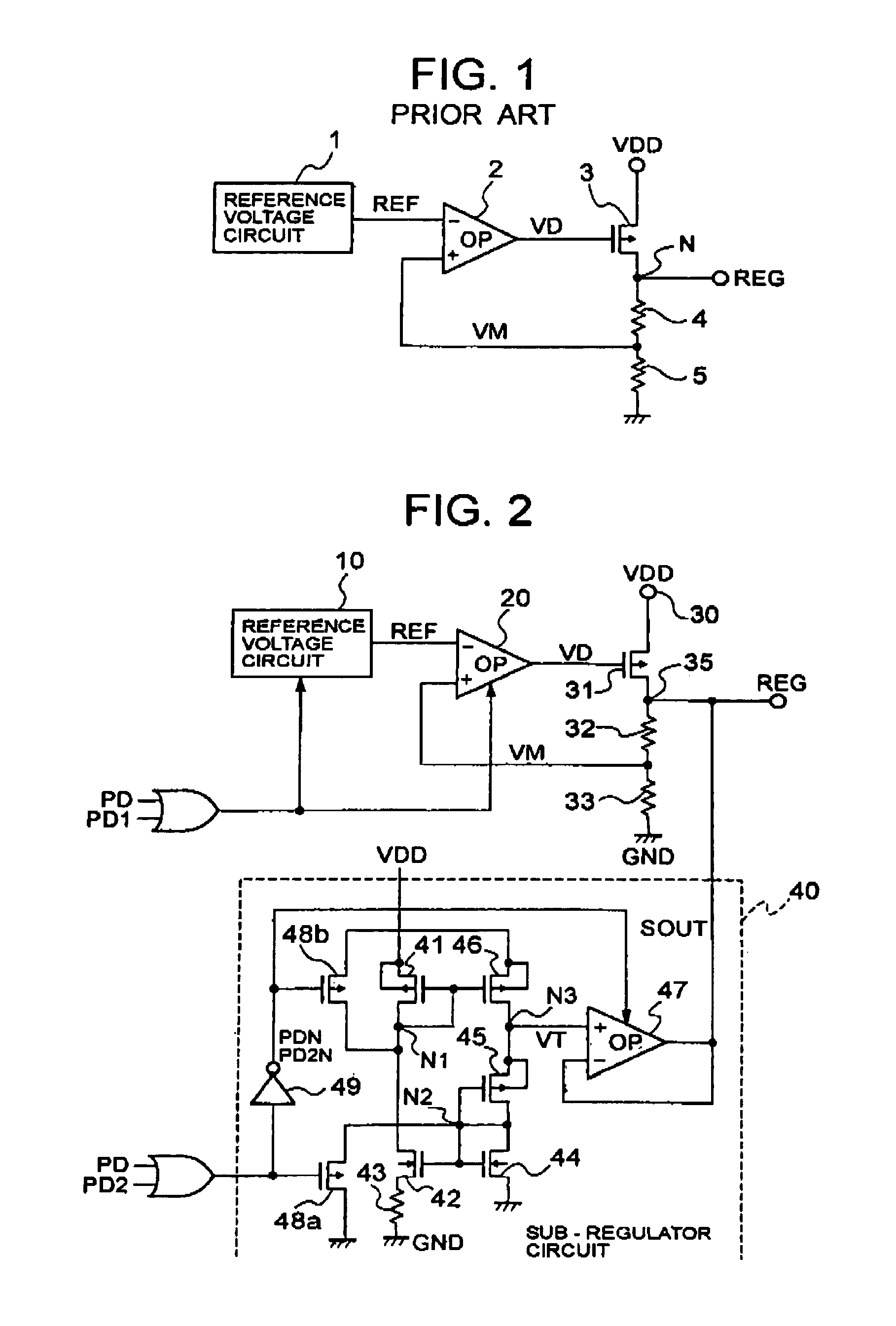

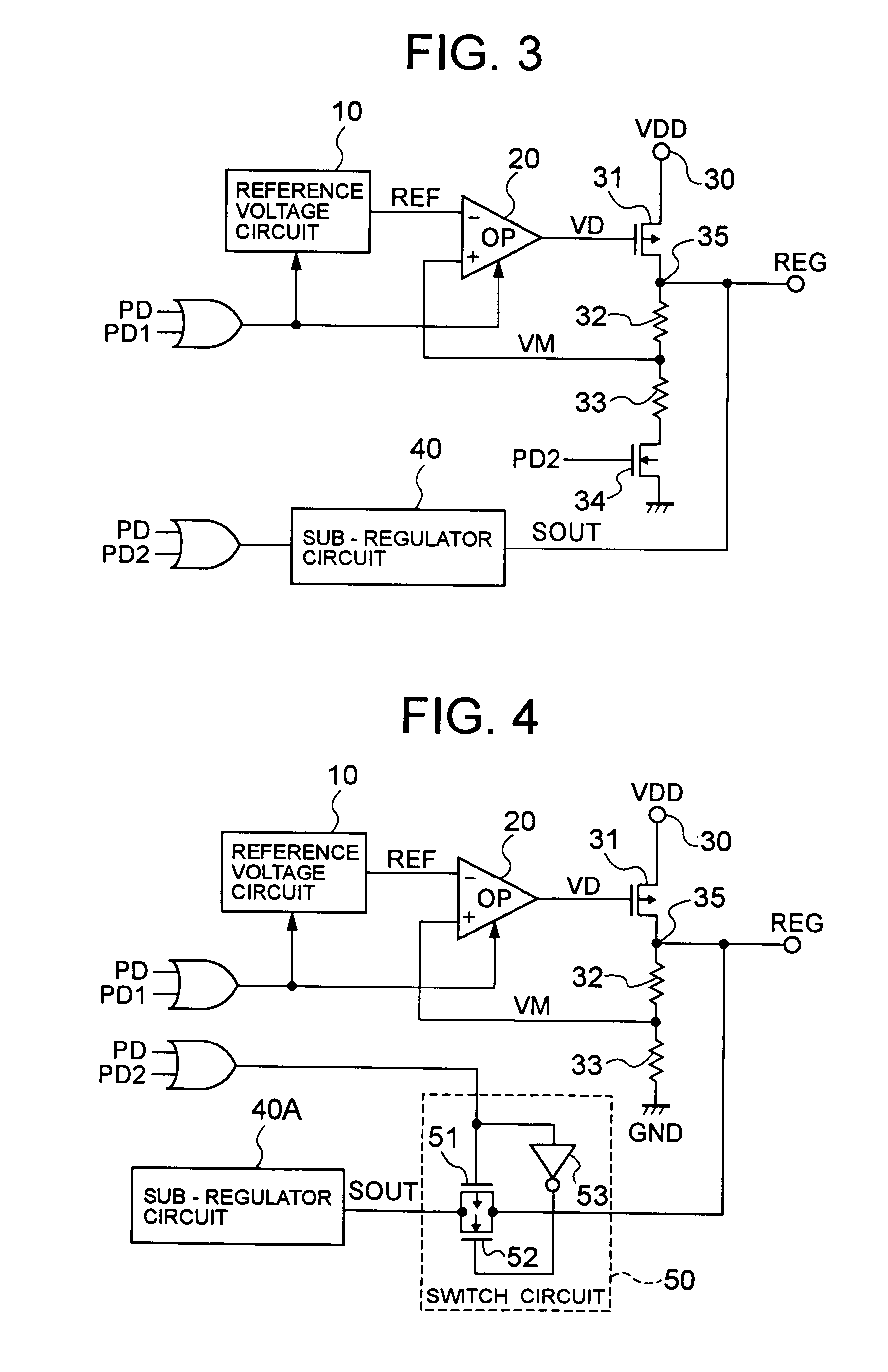

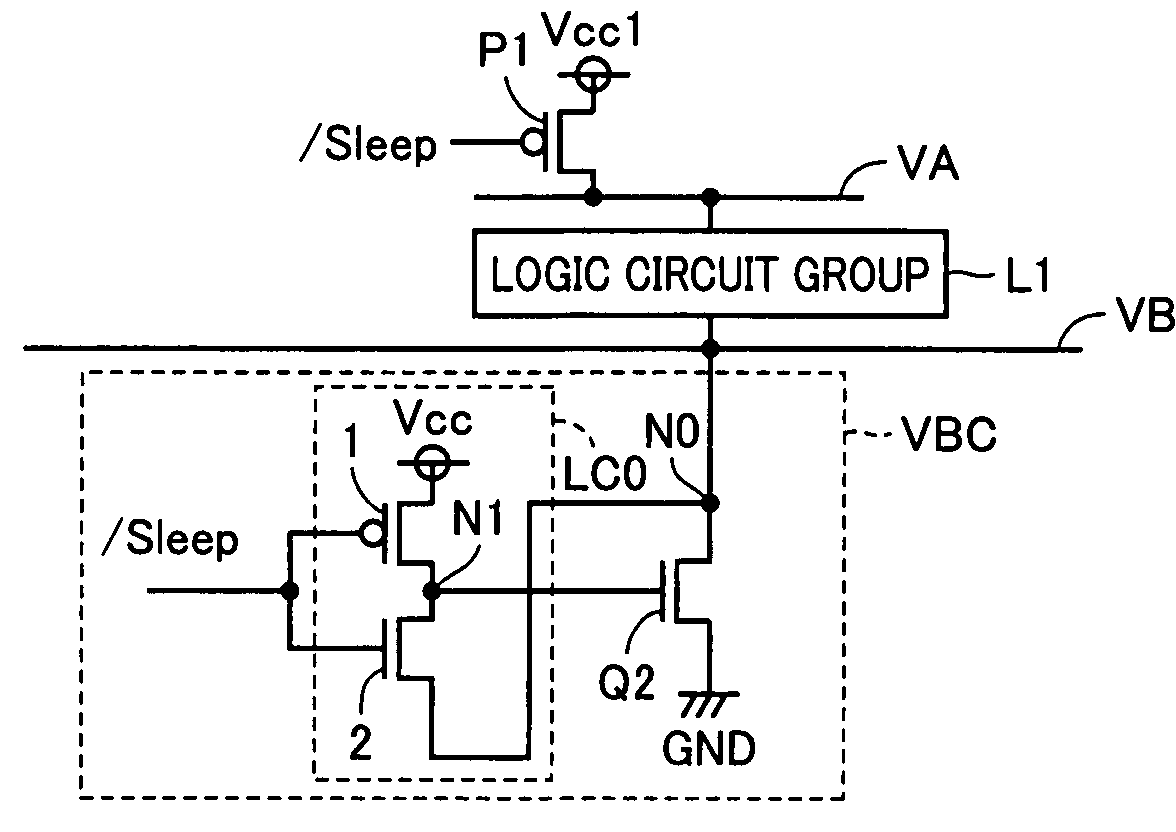

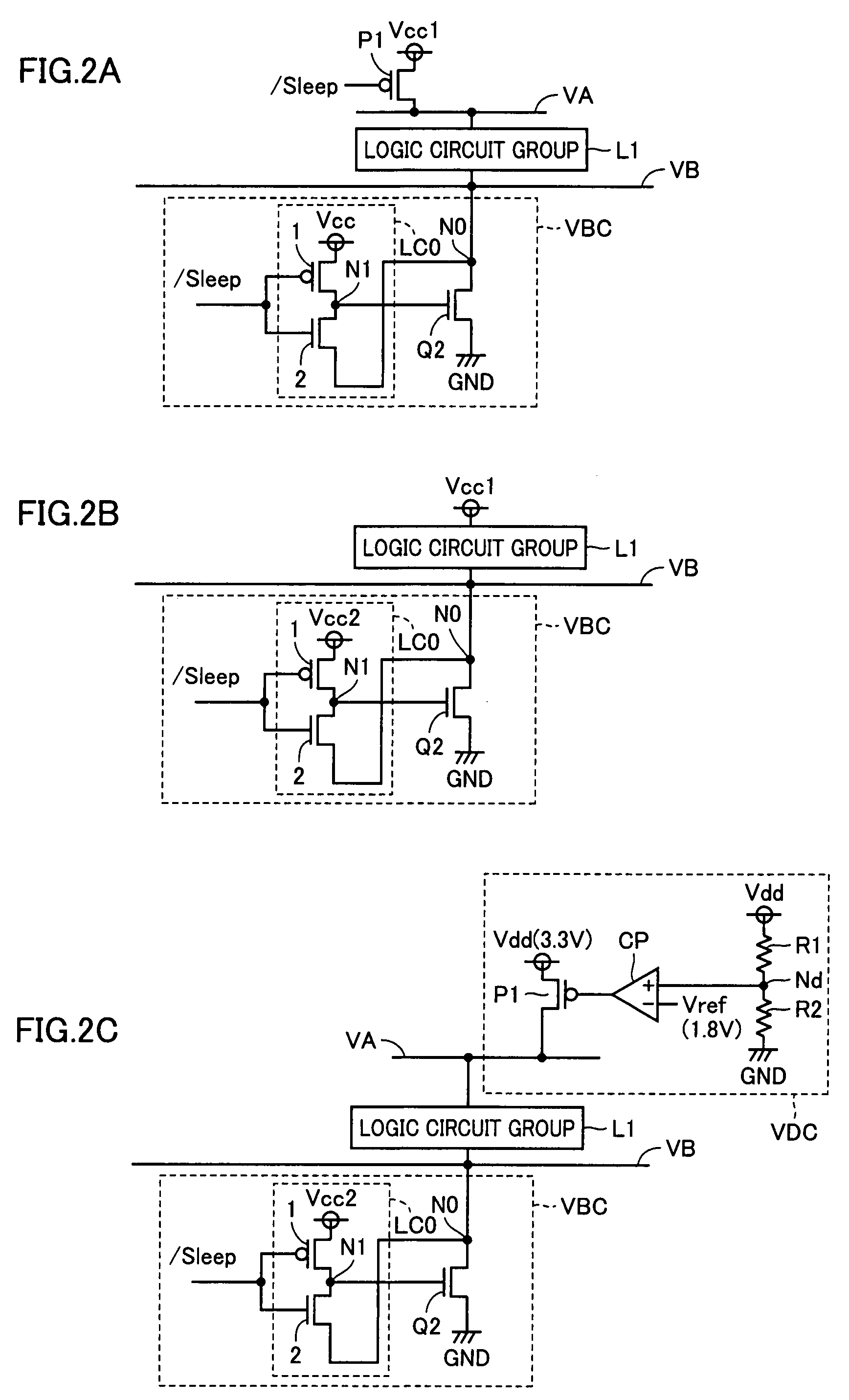

Voltage regulator

ActiveUS7193399B2Current consumptionTotal current dropPackagingShakersOperation modeVoltage reference

Consumption current is reduced for a voltage regulator in sleep mode. In normal operation mode, a sub-regulator circuit is ceased from operating according to a power-down signal, which allows an operation amplifier to compare between a reference voltage outputted from a reference voltage circuit and a monitor voltage generated by a voltage-dividing circuit. Based on a detection voltage as a comparison result, a PMOS is controlled to regulate an internal power voltage such that the monitor voltage becomes equal to the reference voltage. In sleep mode, the reference voltage circuit and operational amplifier is ceased from operating, to start up the sub-regulator circuit. A slight current, restricted by a resistance, flows through a PMOS of the sub-regulator circuit. The same magnitude of current is supplied from the PMOS constituting a current mirror to a PMOS, etc. of a threshold-voltage output circuit. The threshold voltage, at a node between the PMOS constituting the current mirror and the PMOS of the threshold-voltage output circuit, is power-amplified by a voltage follower and outputted through an output terminal.

Owner:LAPIS SEMICON CO LTD

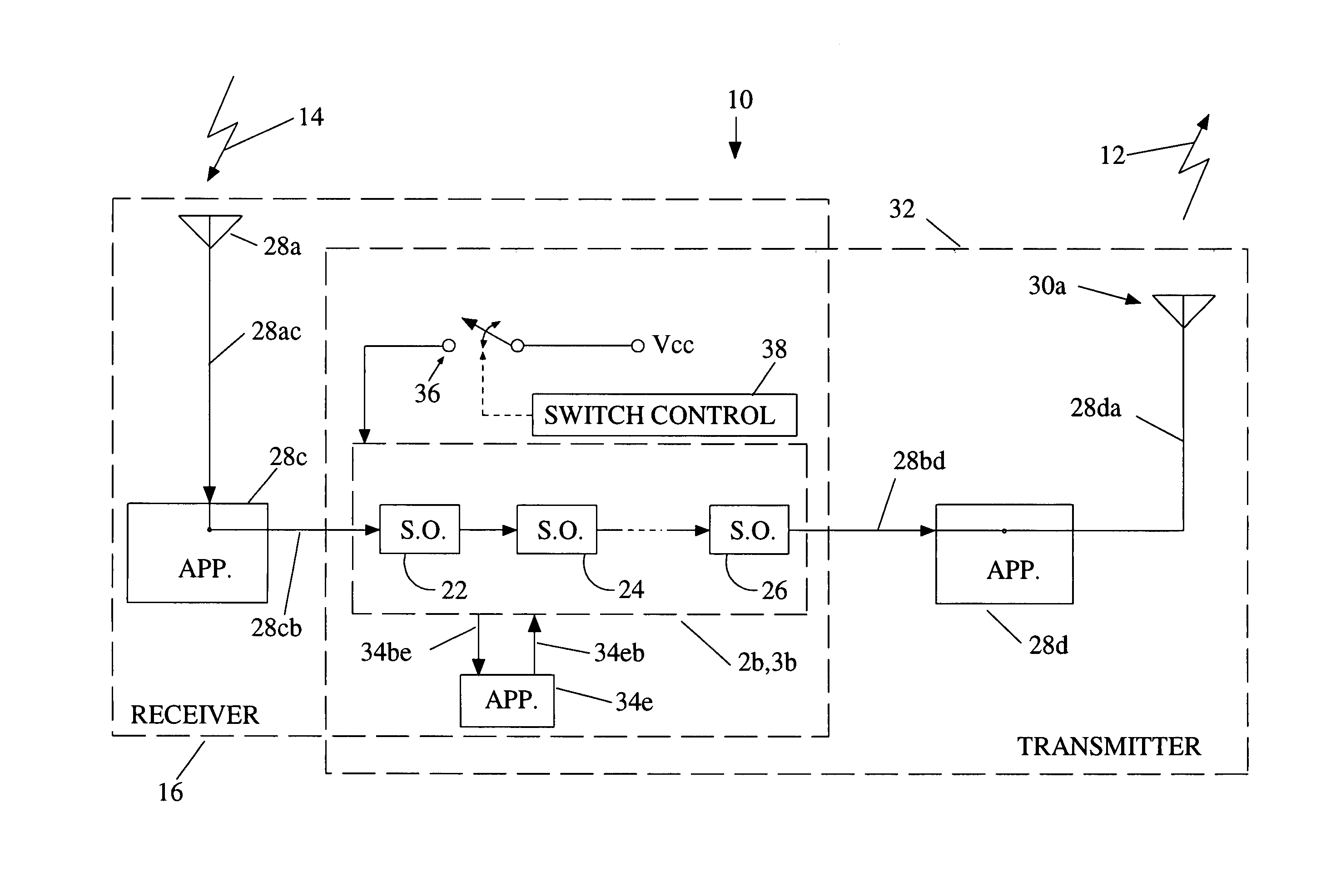

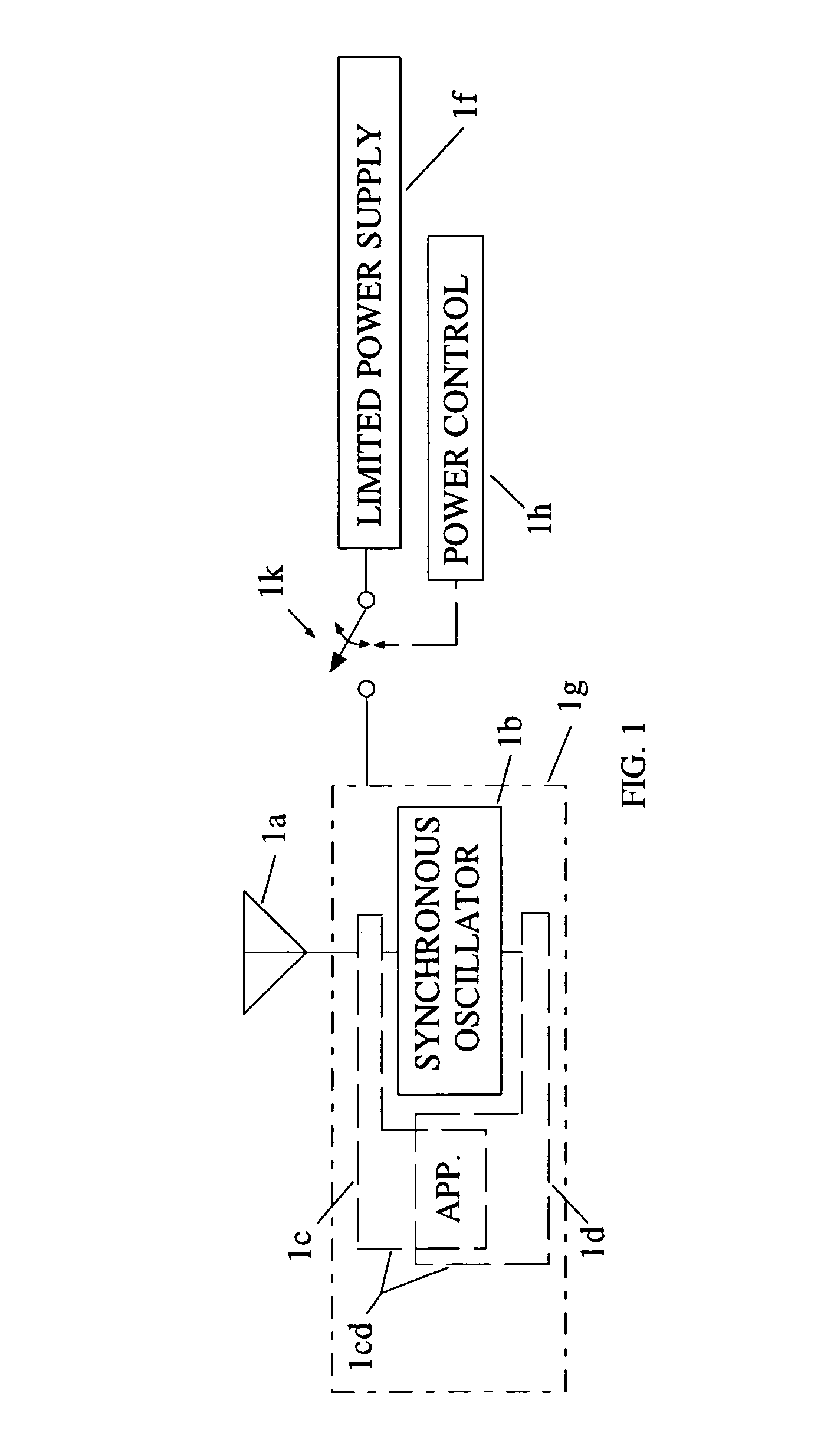

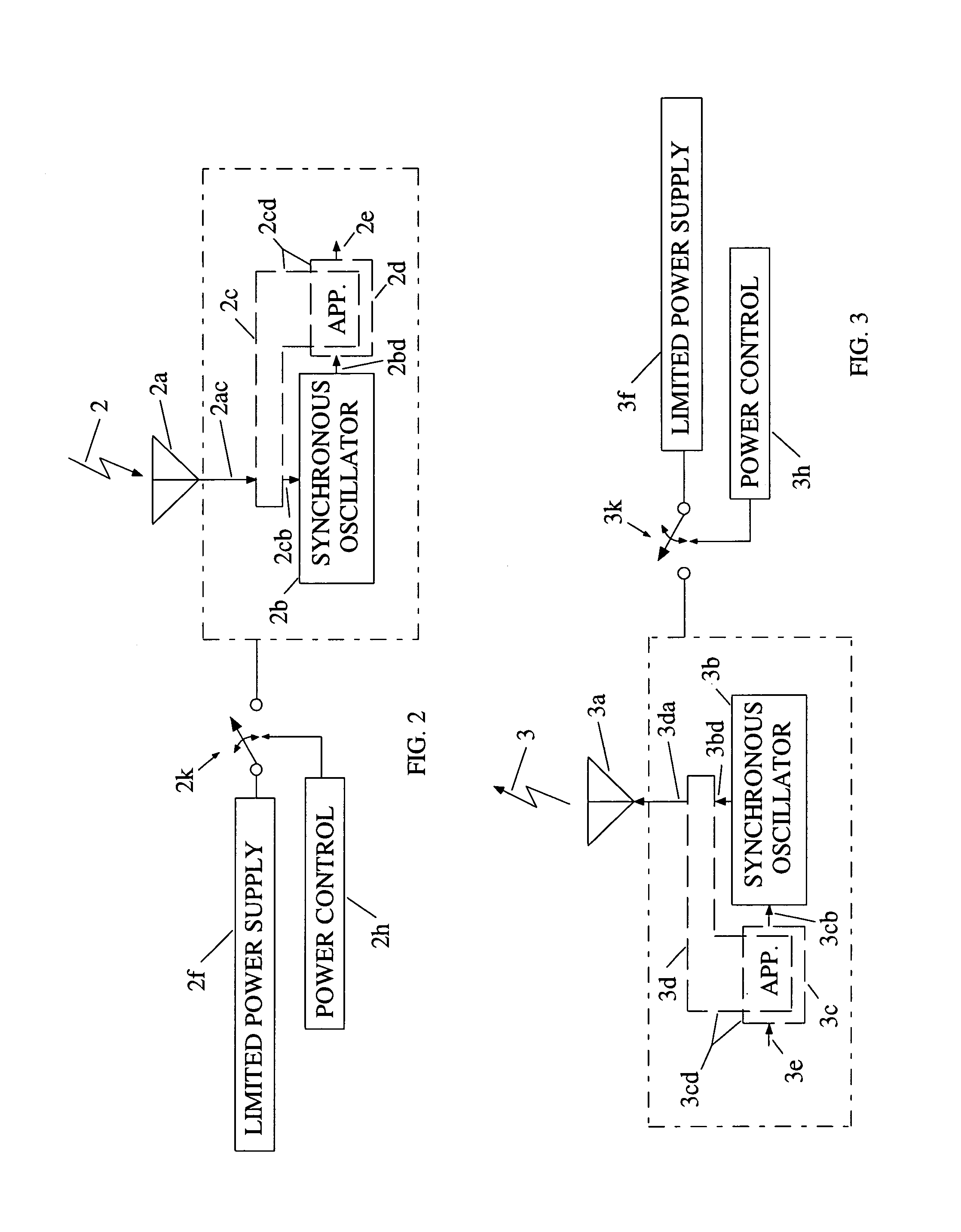

Oscillator coupled to an antenna and an application

ActiveUS7106246B1Improve power efficiencyLong period of timeRadio wave reradiation/reflectionTag antennaRadio frequency

A radio frequency device has an antenna for capturing an incoming signal for processing by the device or for radiating an outgoing signal from the device and a signal processor having one or more synchronous oscillators responsive to an input signal for providing an amplified output signal without using much power. An application is a radio frequency (RF) transponder (tag) for receiving an RF signal from an interrogator includes a tag antenna for receiving the RF signal from the interrogator and a receiver section connected to the tag antenna wherein the receiver consumes a significantly lower amount of power than conventional receiver technologies by using one or more synchronous oscillators.

Owner:LINDELL KEVIN W

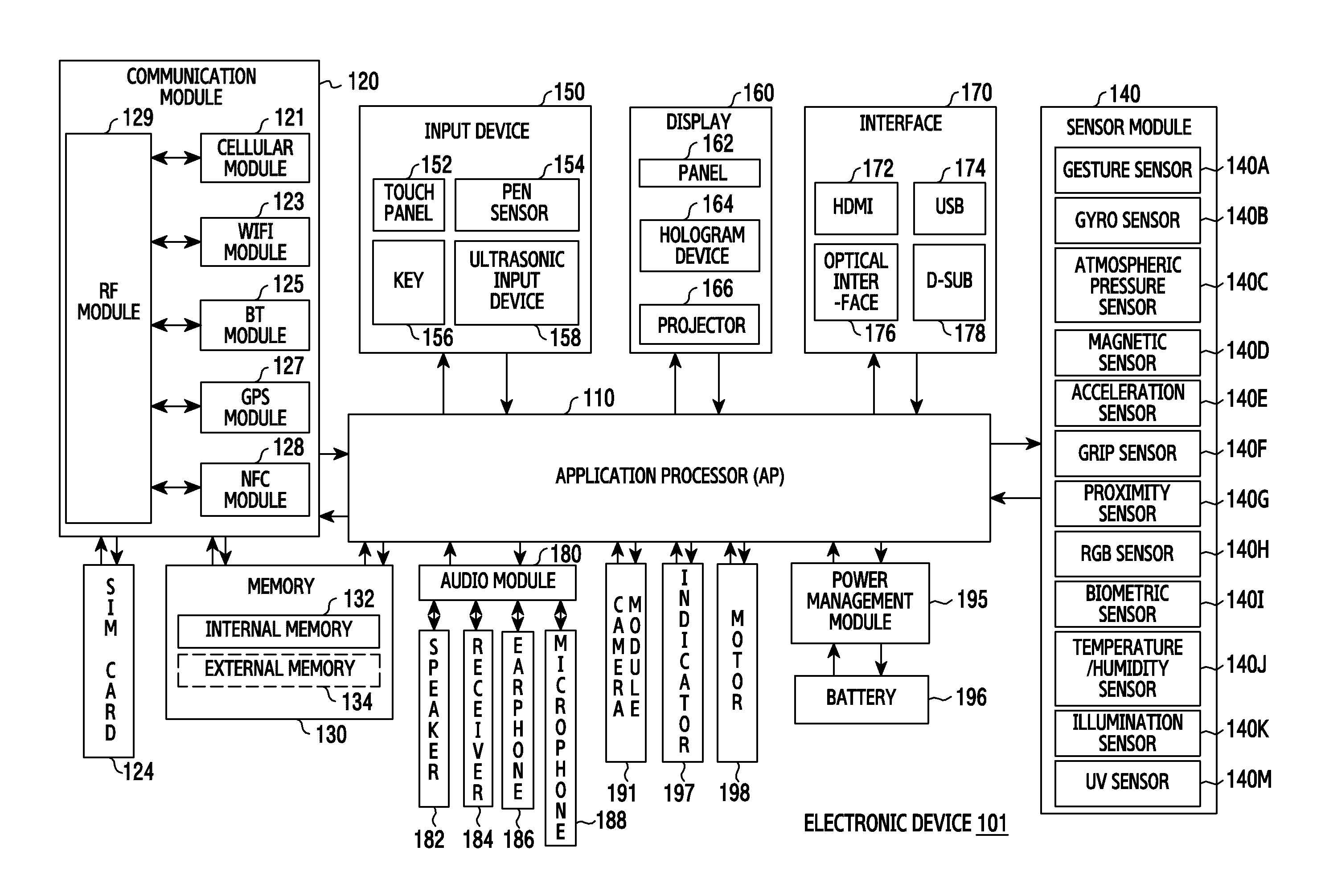

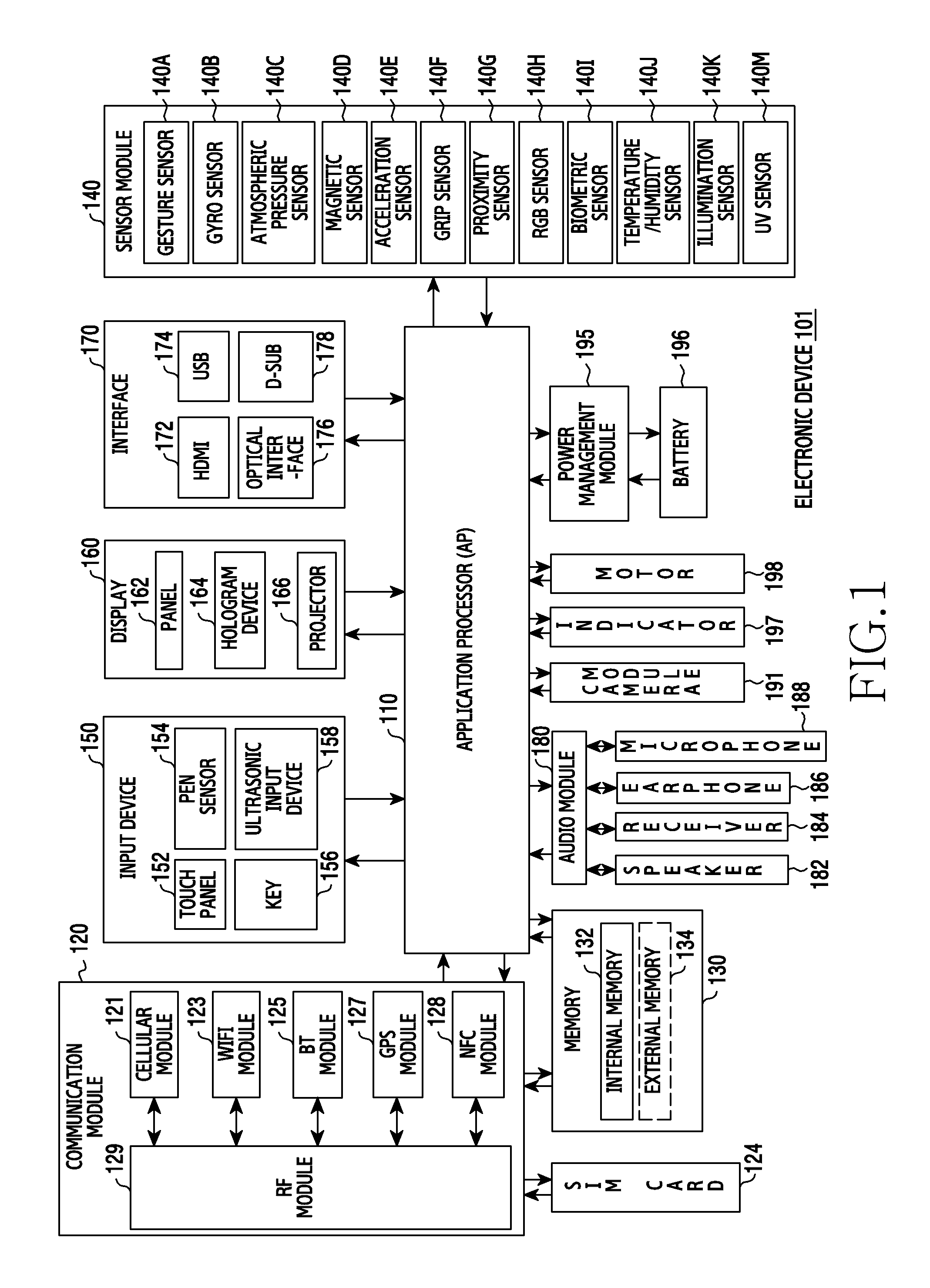

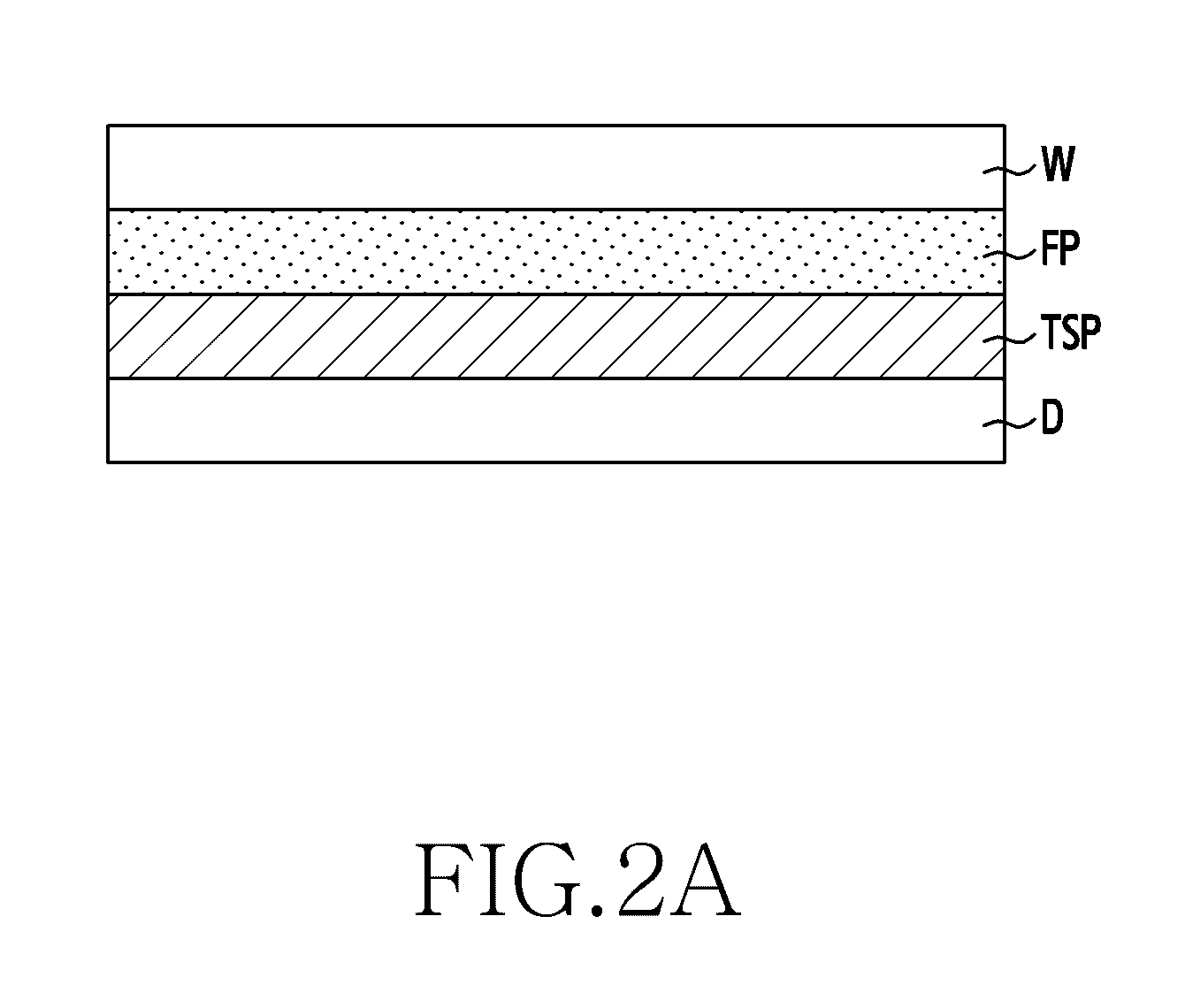

Electronic device with touch sensor and driving method therefor

ActiveUS20170024597A1Lower performance requirementsReduced usabilityStatic indicating devicesDigital data authenticationPattern recognitionDisplay device

An electronic device having a fingerprint verification function is provided. The electronic device includes a display; a touch recognition sensor pattern for recognizing a touch input on the display; a fingerprint recognition sensor pattern for recognizing a fingerprint input on the display; and a processor functionally connected to the display, the touch recognition sensor pattern and the fingerprint recognition sensor pattern. The processor determines whether a fingerprint recognition mode is executed, and selectively activates the touch recognition sensor pattern and the fingerprint recognition sensor pattern according to whether the determined fingerprint recognition mode is executed.

Owner:SAMSUNG ELECTRONICS CO LTD

Clamp circuit

InactiveUS6737905B1Reduce areaLow costPulse automatic controlSolid-state devicesLevel shiftingLinear region

Owner:DENSO CORP

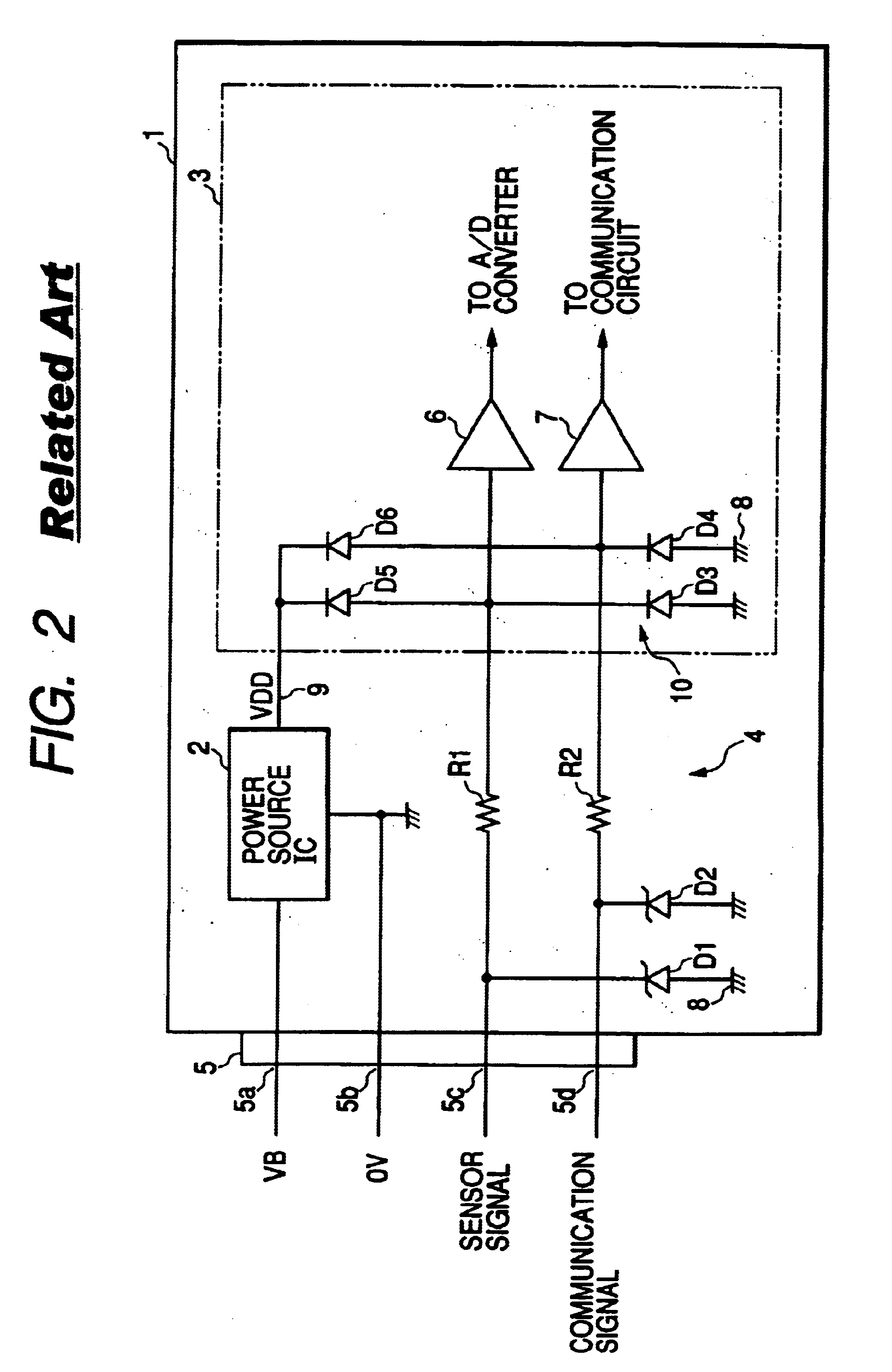

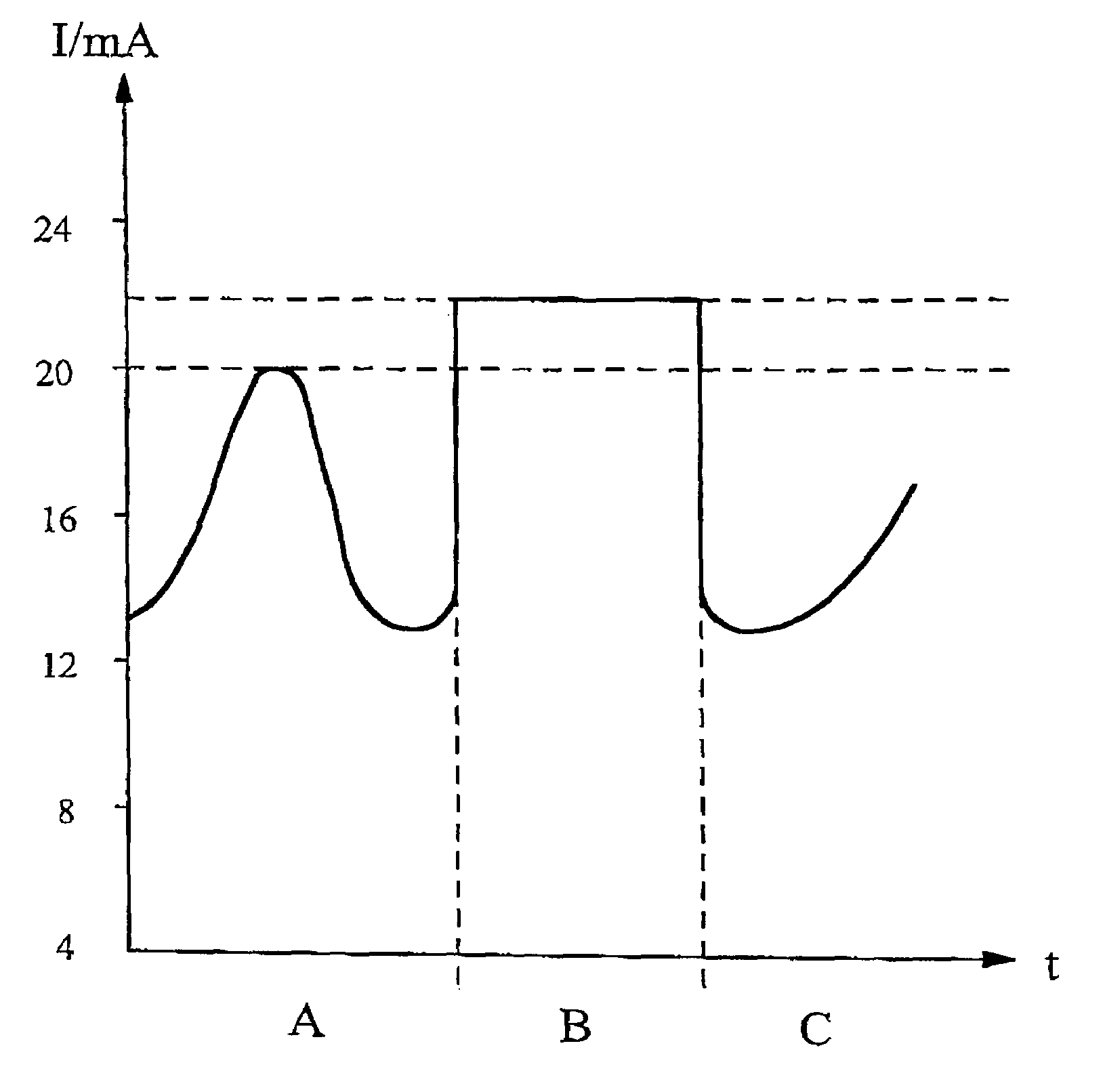

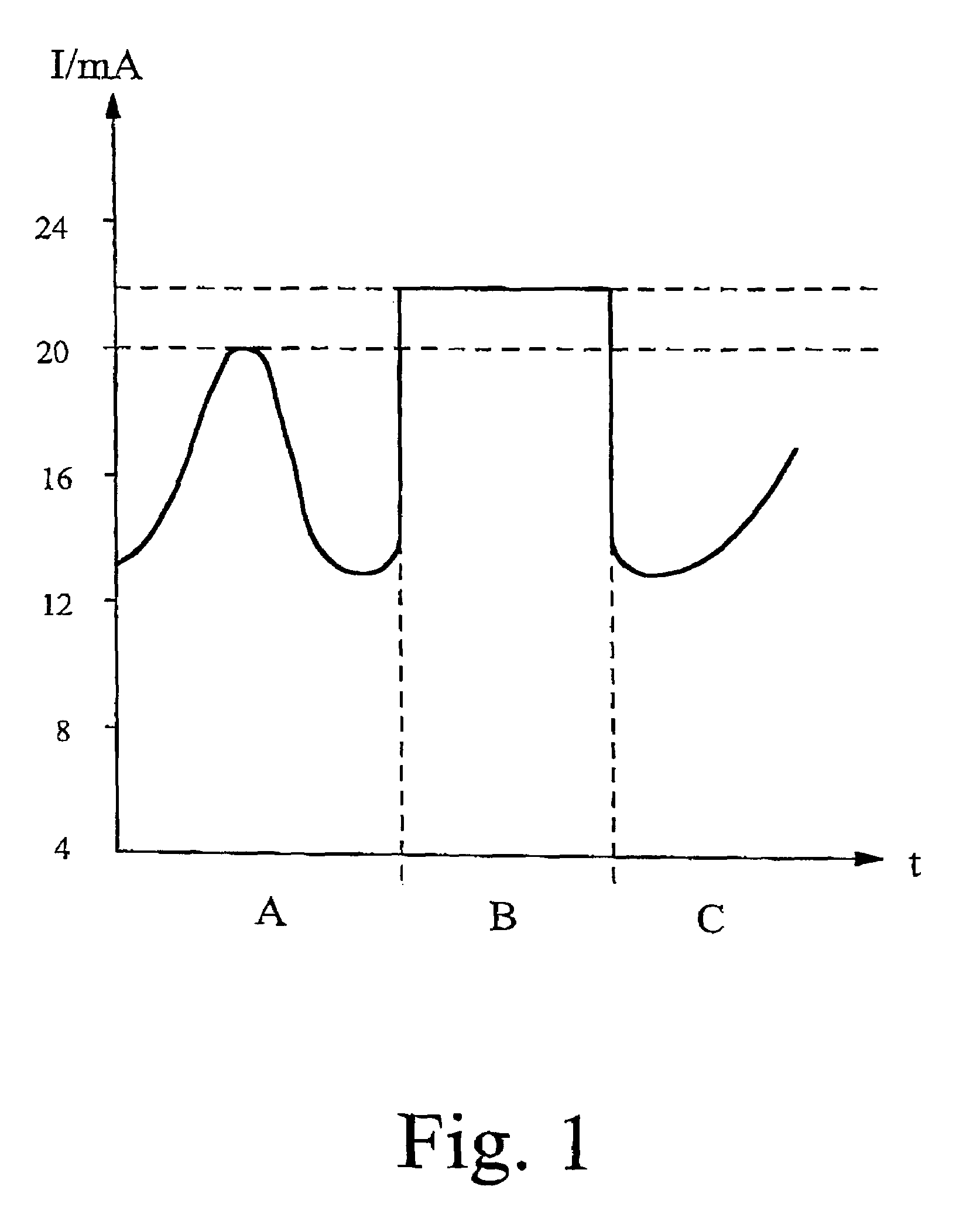

Electric device and method for operating an electric device

InactiveUS7162651B2Current consumptionShorten the timeVolume/mass flow measurementPower supply for data processingElectrical devicesEngineering

An electric device features a two-wire interface which two-wire interface serves to feed electric power to the electric device and also to transmit a signal, with the maximum power drawn via the two-wire interface in normal operation being restricted to a predefined upper limit. The permissible maximum power consumption of the electric device is automatically and temporarily increased beyond the predefined upper limit when the electric device is switched into a special operational function mode. The length of time in which the electric device is in the special operational function mode can thus be reduced.

Owner:KROHNE MESSTECHNICK GMBH & CO KG

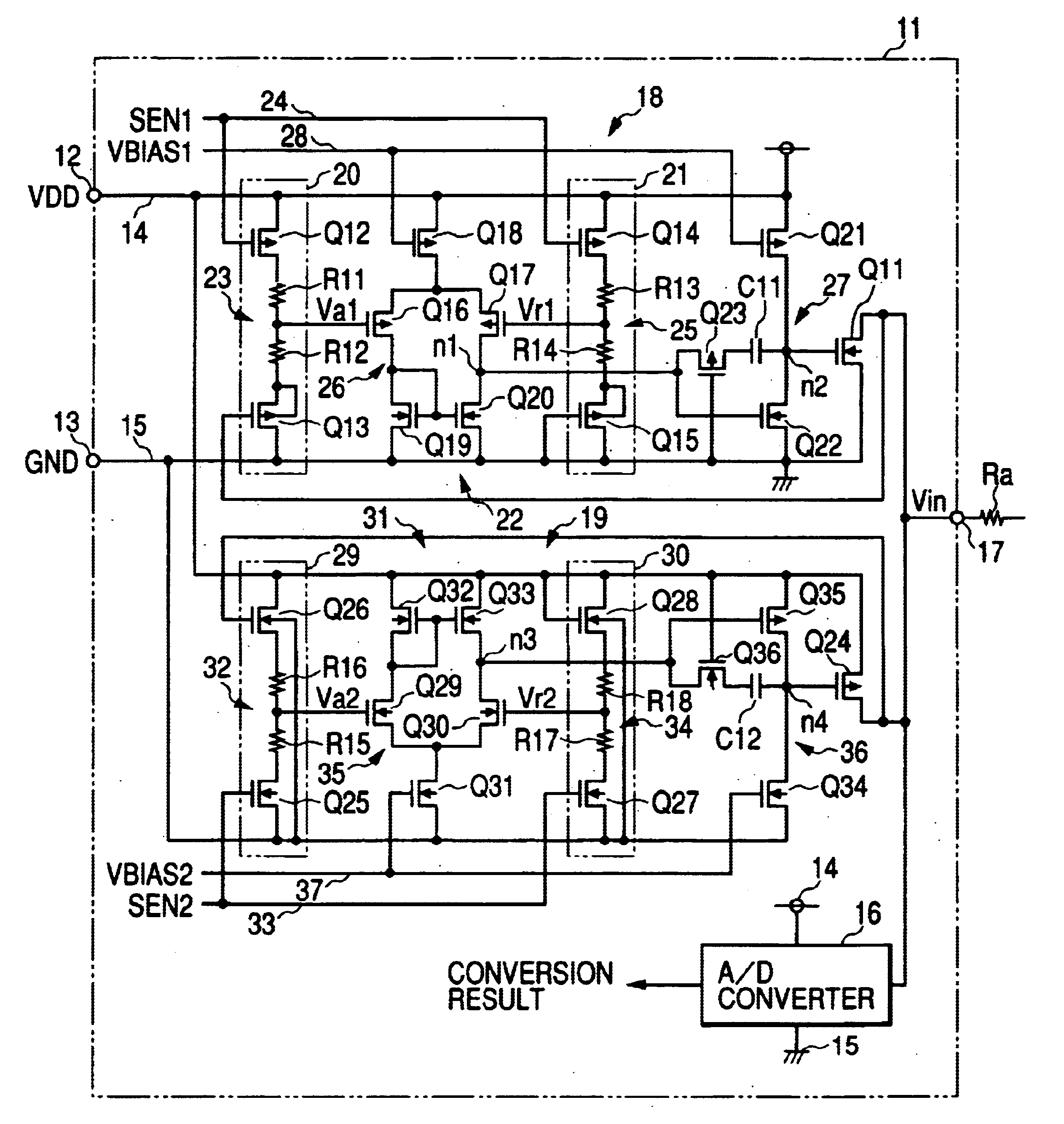

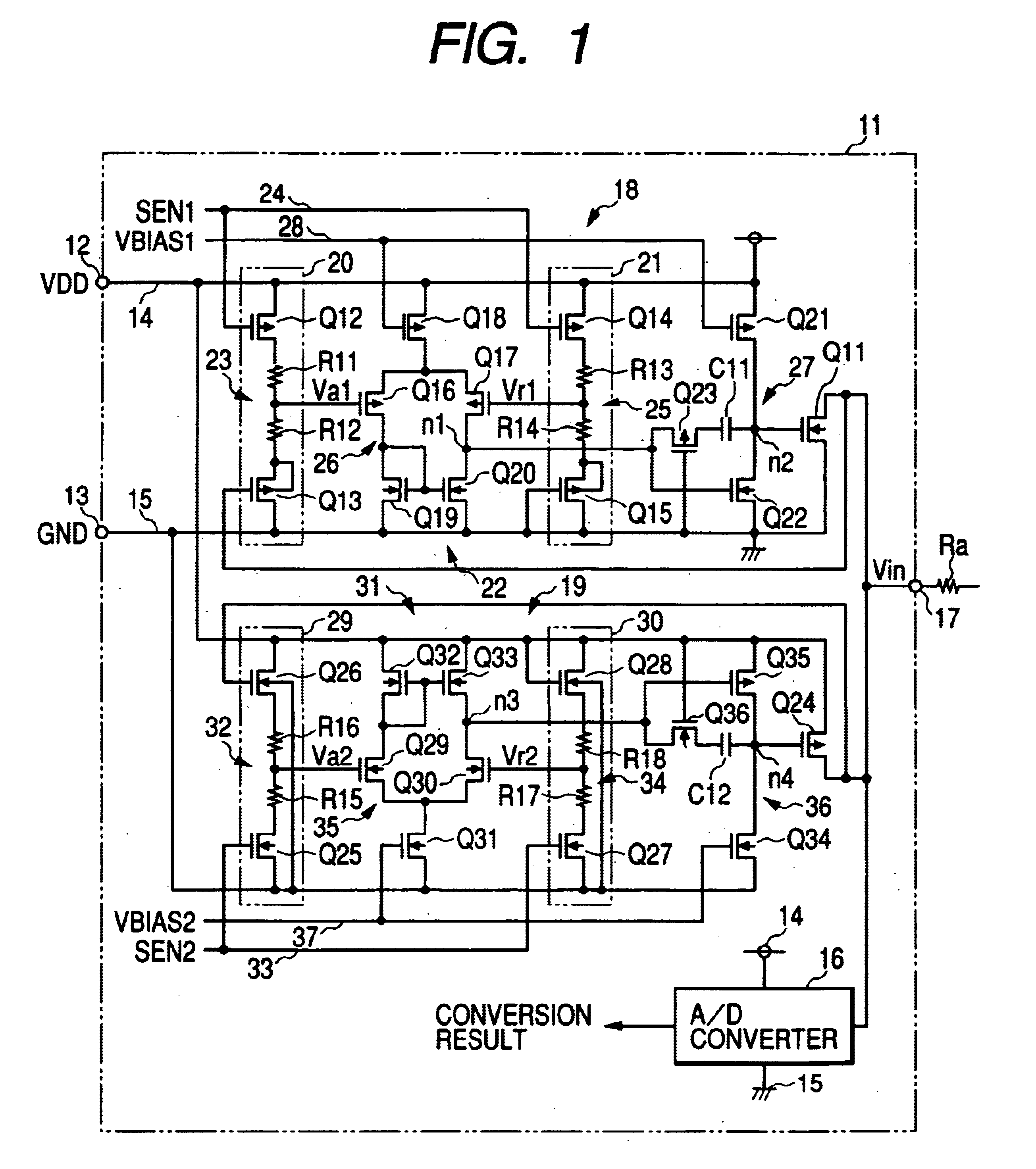

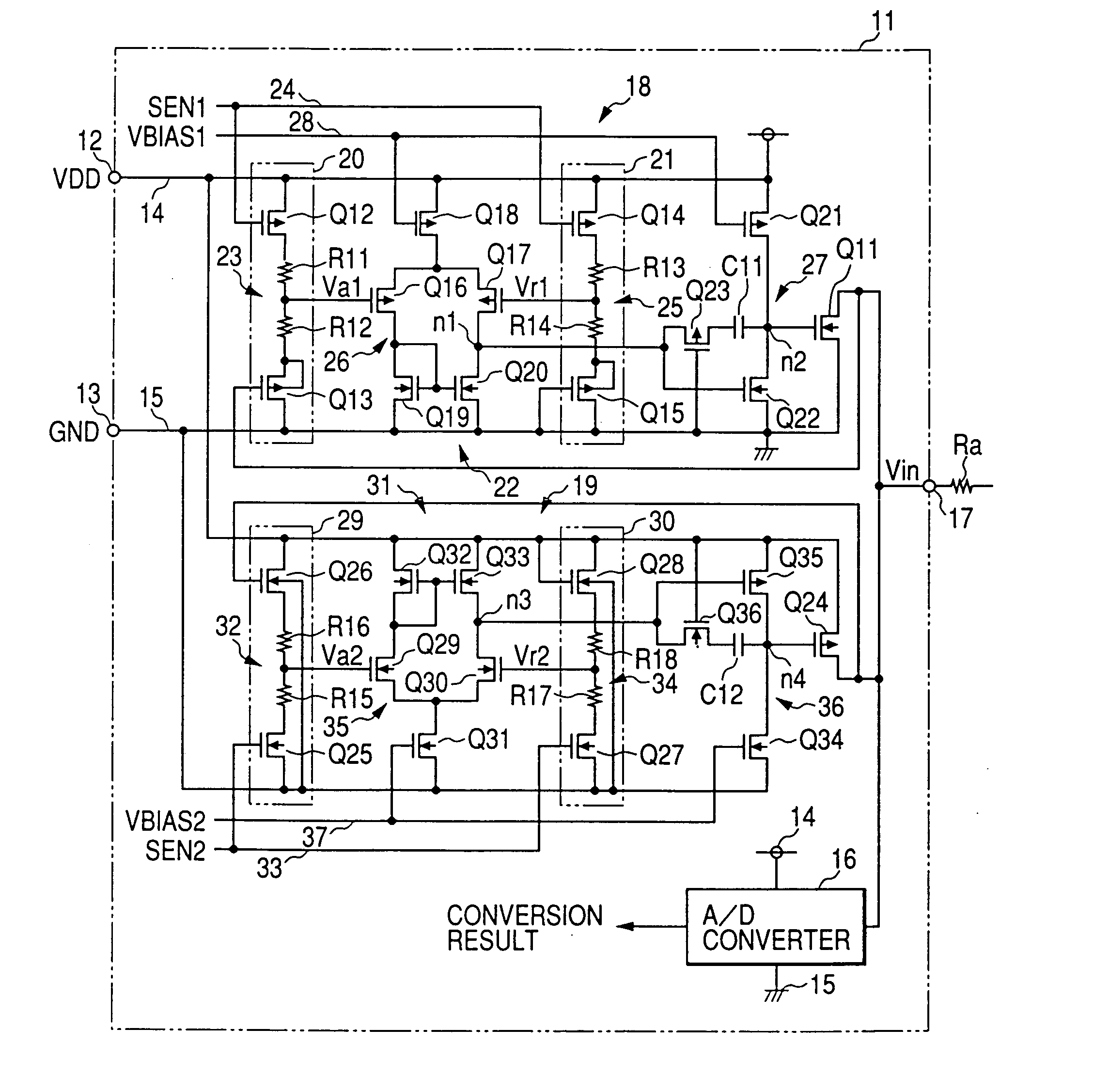

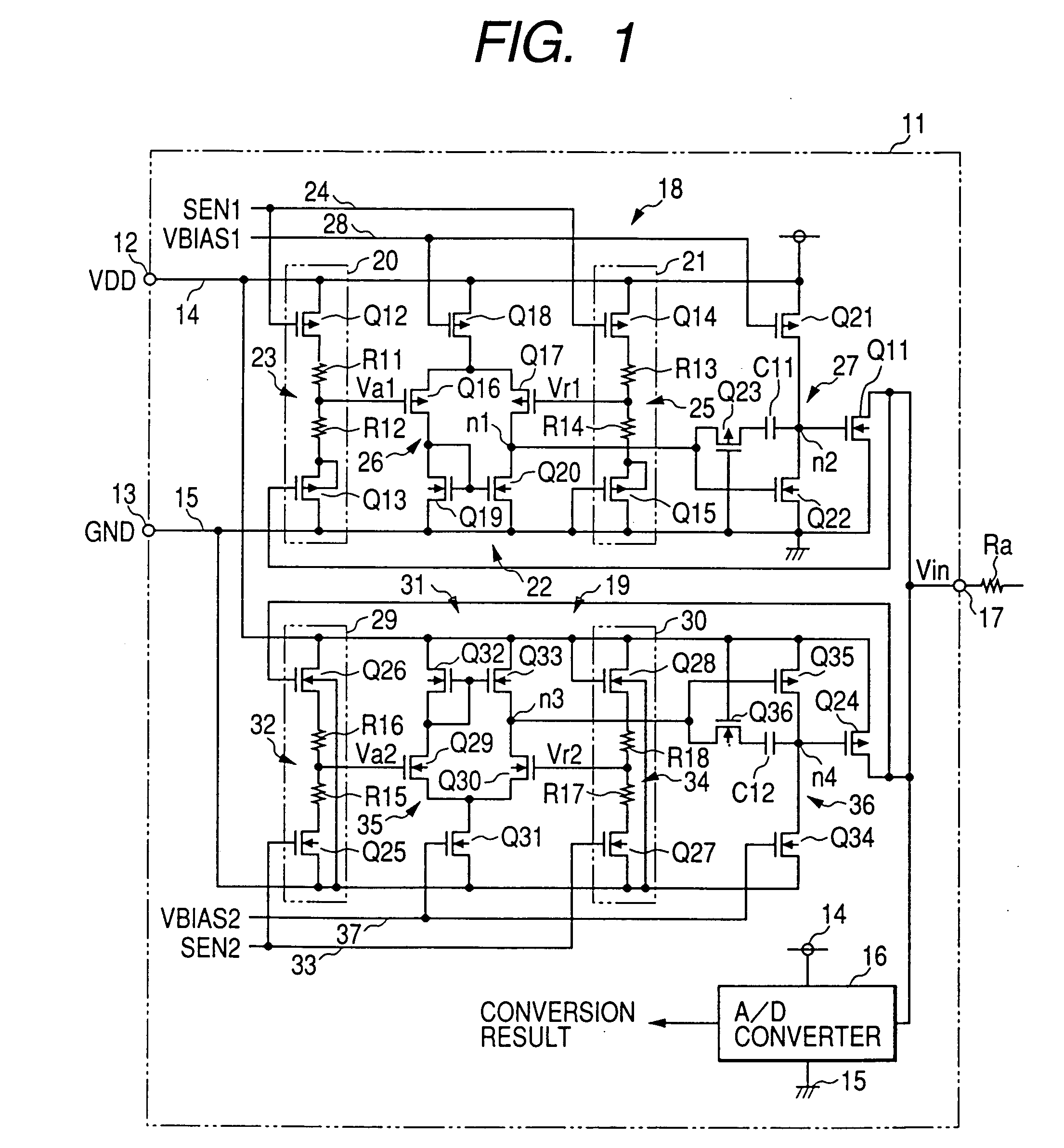

Clamp circuit

InactiveUS20040080352A1Reduce areaLow costPulse automatic controlSolid-state devicesElectrical resistance and conductanceLevel shifting

The clamp circuit clamps an input voltage at prescribed higher and lower clamp voltages which are stabilized under a temperature fluctuation. Transistors Q12 and Q14 are switched on in their linear region. In a lower voltage clamp circuit 18, an Vin detecting circuit 20 outputs Va1 by level-shifting Vin by Q13 and voltage-divides by series resistance circuit 23 the level-shifted Vin, while a reference voltage generating circuit 21 outputs Vr1 by level-shifting 0 V by Q15 and voltage-divides by series resistance circuit 25 the level-shifted voltage. Q11 is switched on, when a comparator 22 determines that Va1 descends and goes across Vr1. Here, Q12 is of the same characteristics as Q14, while Q13 is of the same characteristics as Q15. Further, the resistance of the circuits 23 is the same as that of the circuit 25. The higher voltage clamp circuit 19 is similar to the circuit 18.

Owner:DENSO CORP

Semiconductor device reducing power consumption in standby mode

InactiveUS7436205B2Reduce power consumptionReduce in quantityReliability increasing modificationsPower reduction by control/clock signalElectricityControl signal

A voltage supply control circuit is arranged between a true ground voltage and a pseudo ground line. In an active mode, first and second control signals are at the “H” and “L” levels, respectively. In response to this, a first switch is turned on so that a first node is electrically coupled to a power supply voltage, and attains the “H” level. Further, a second switch is turned on to couple electrically the ground voltage to a second node. In a standby mode, the first and second control signals are at the “L” and “H” levels, respectively. In response to this, a third switch is turned on to couple electrically the first and second nodes together. Since the power supply voltage was electrically coupled to the first node according to the turn-on of the first switch in the active mode, the path of the control signal including the first node to the switch has accumulated charged charges.

Owner:RENESAS ELECTRONICS CORP

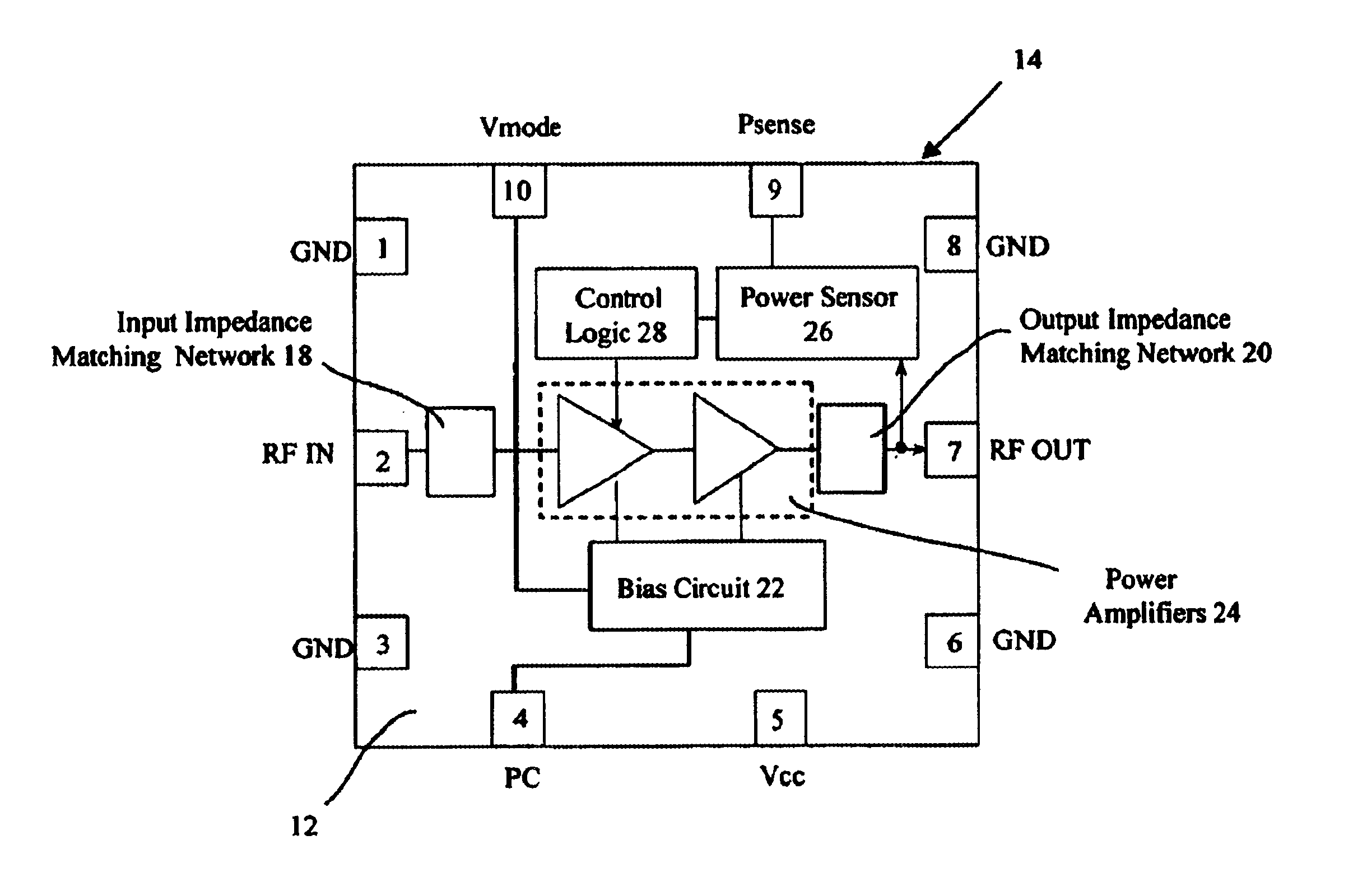

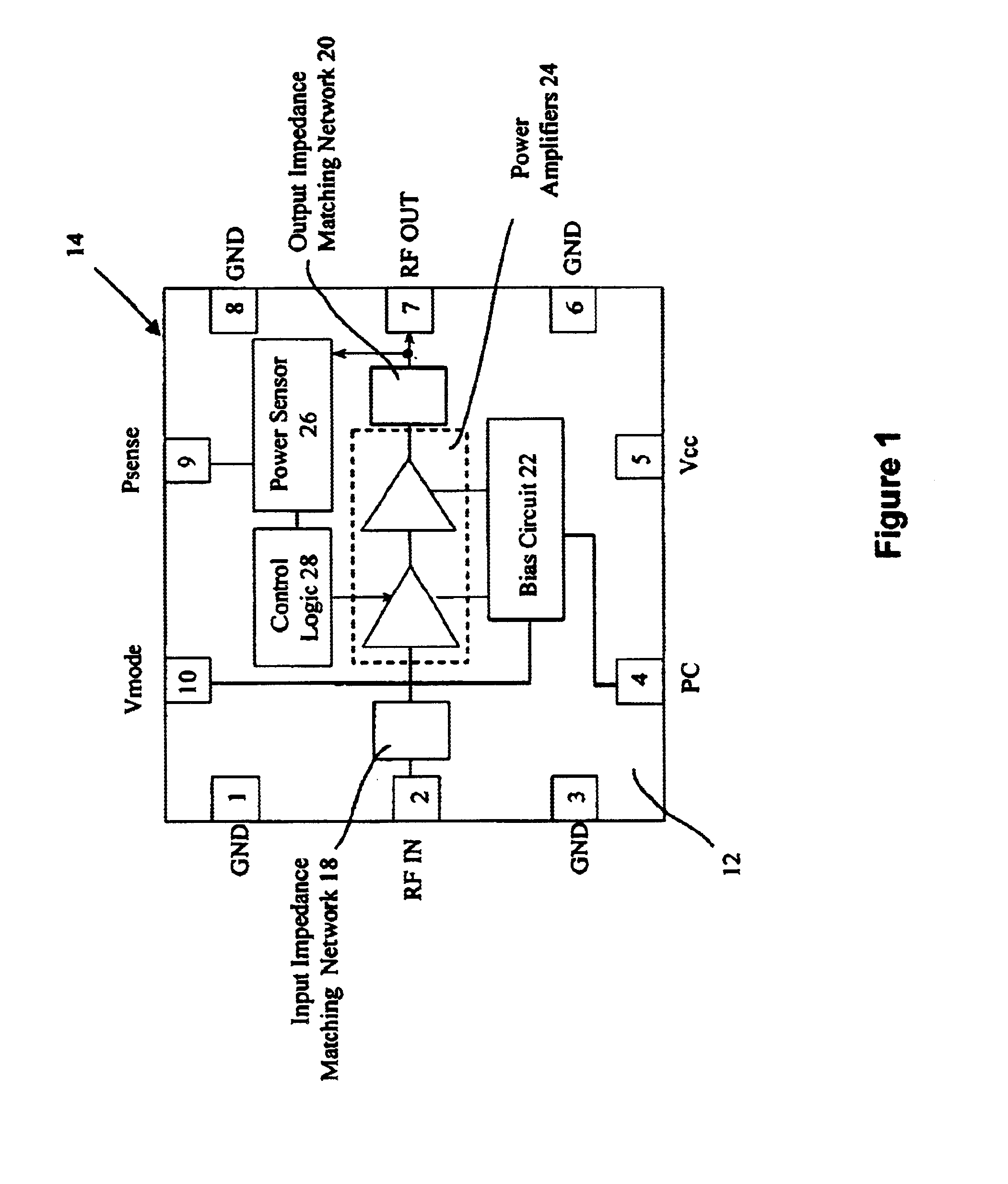

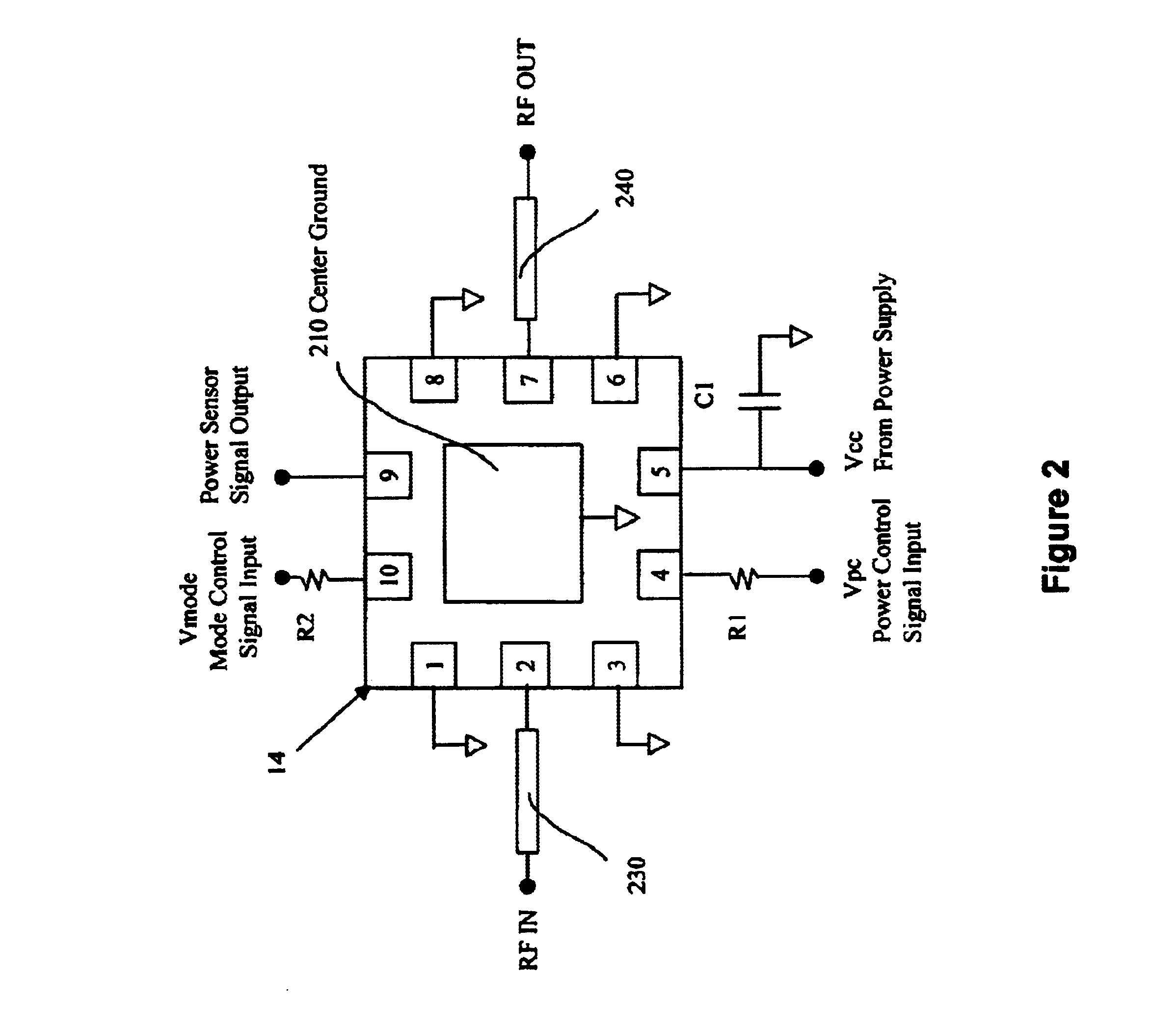

Integrated power amplifier module with power sensor

InactiveUS6847262B2Easy to controlHighly linear output powerGain controlSemiconductor/solid-state device detailsPower sensorAudio power amplifier

A power amplifier module for amplifying radio frequency signals includes first, second, third and fourth corner ground pads positioned at each corner of the power amplifier module; a radio frequency input pad positioned between the first and second corner ground pads; a radio frequency output pad positioned between the third and fourth corner ground pads; and a power amplifier circuit centrally positioned on the power amplifier module, the power amplifier having an input coupled to the radio frequency input pad and an output coupled to the radio frequency output pad.

Owner:MICRO MOBIO

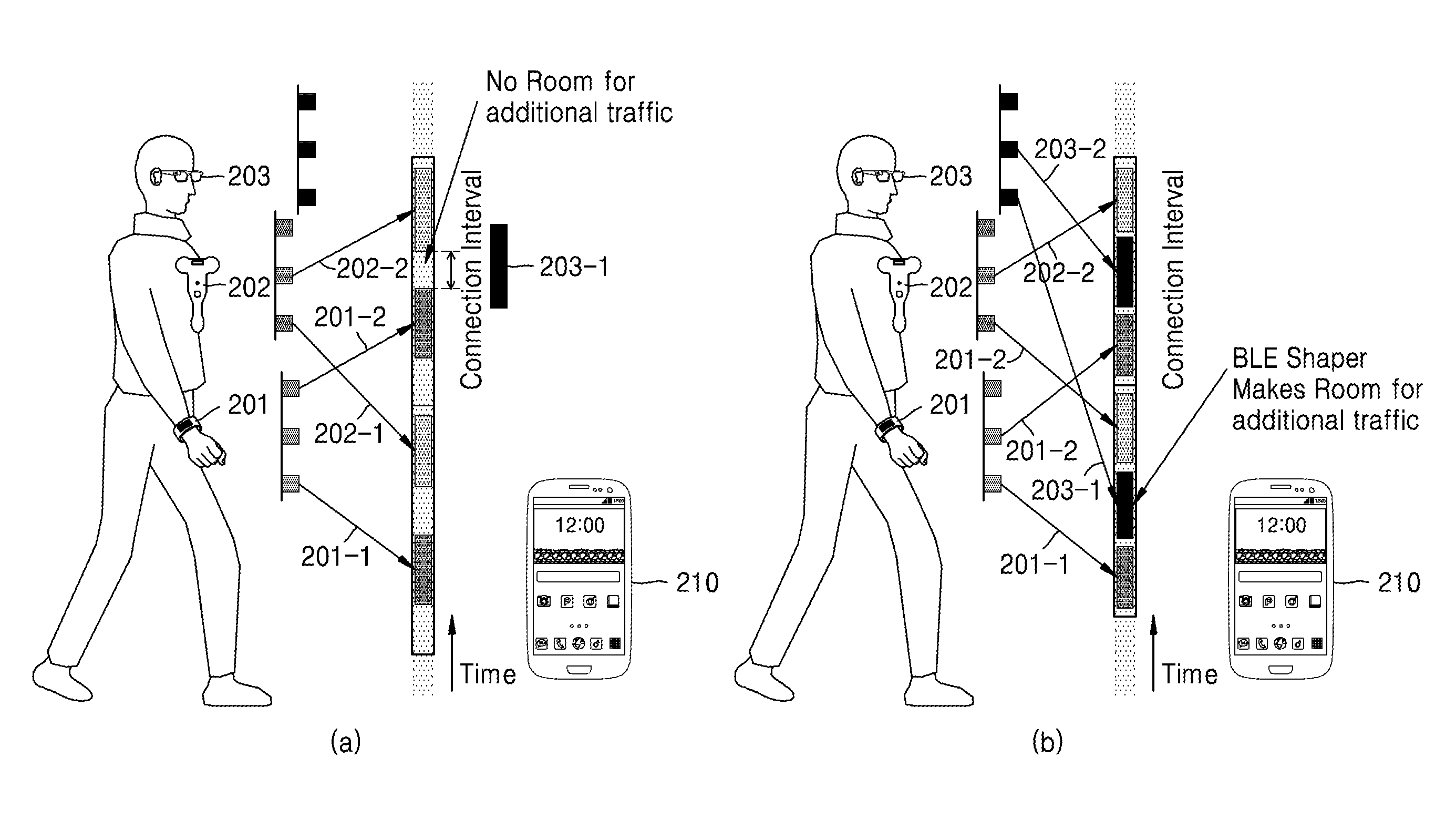

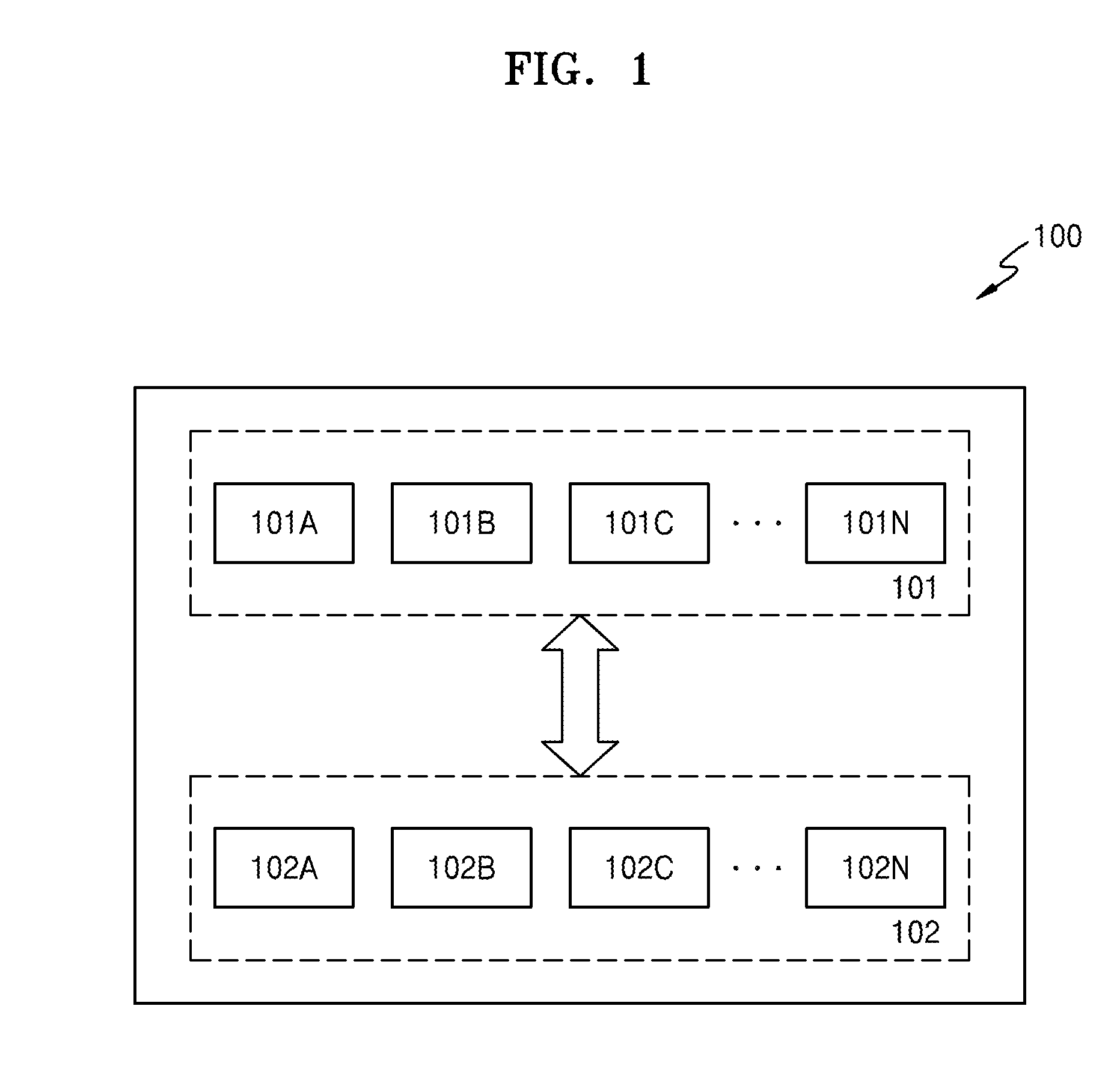

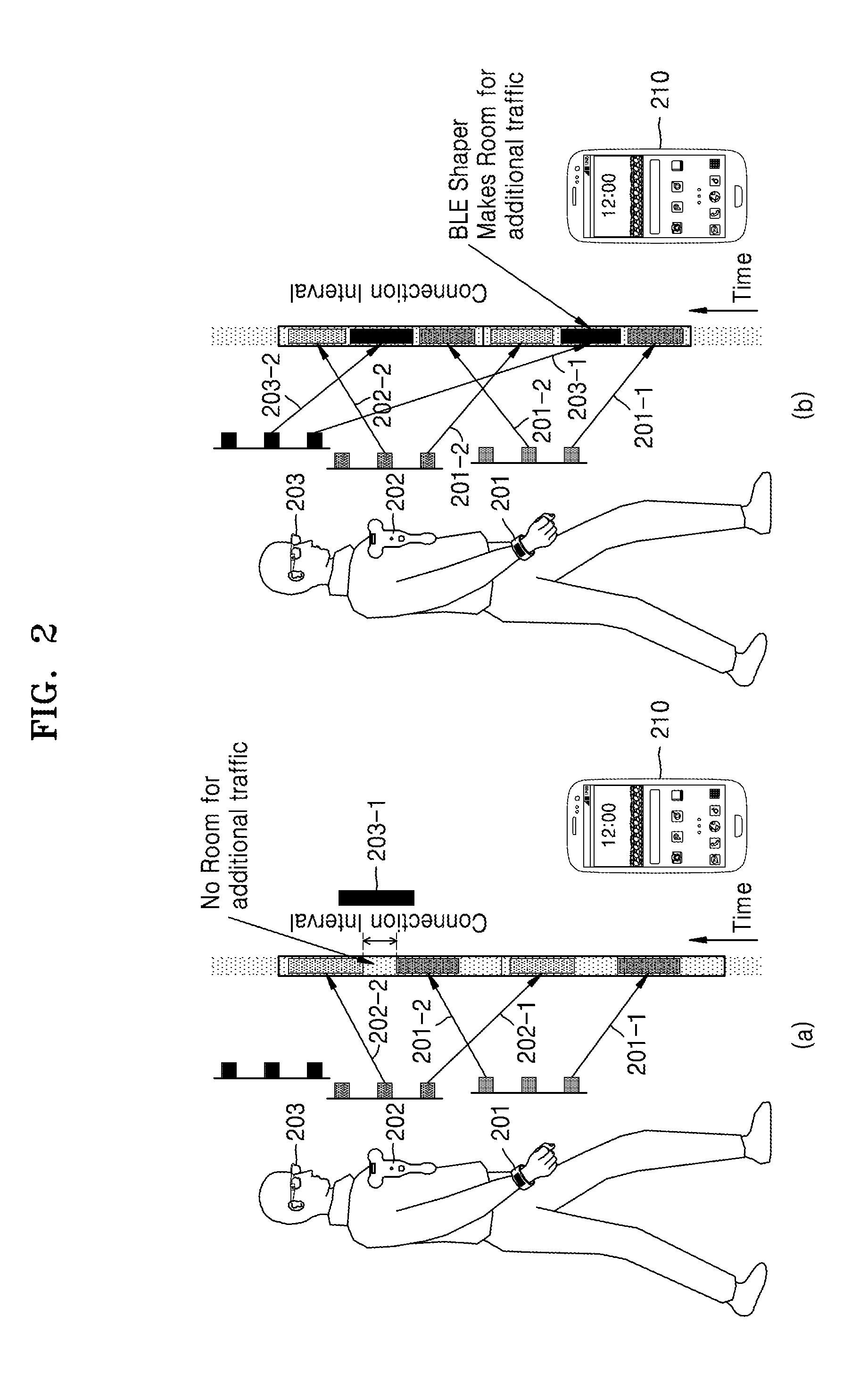

Method of dynamically managing ble communications in wireless communication network and system thereof

InactiveUS20160014550A1Current consumptionWeaken energyPower managementNetwork topologiesComputer networkDynamic management

The present disclosure discloses method and system for dynamically managing communications in a Bluetooth Low Energy (BLE) network. The method comprises: obtaining one or more BLE connection parameters of one or more slave devices in communication with a master device; detecting change information in the BLE network; dynamically determining one or more updated BLE connection parameters of the one or more slave devices based on the one or more BLE connection parameters and the change information; and controlling the communication between the one or more slave devices and the master device according to the dynamically determined one or more updated BLE connection parameters.

Owner:SAMSUNG ELECTRONICS CO LTD

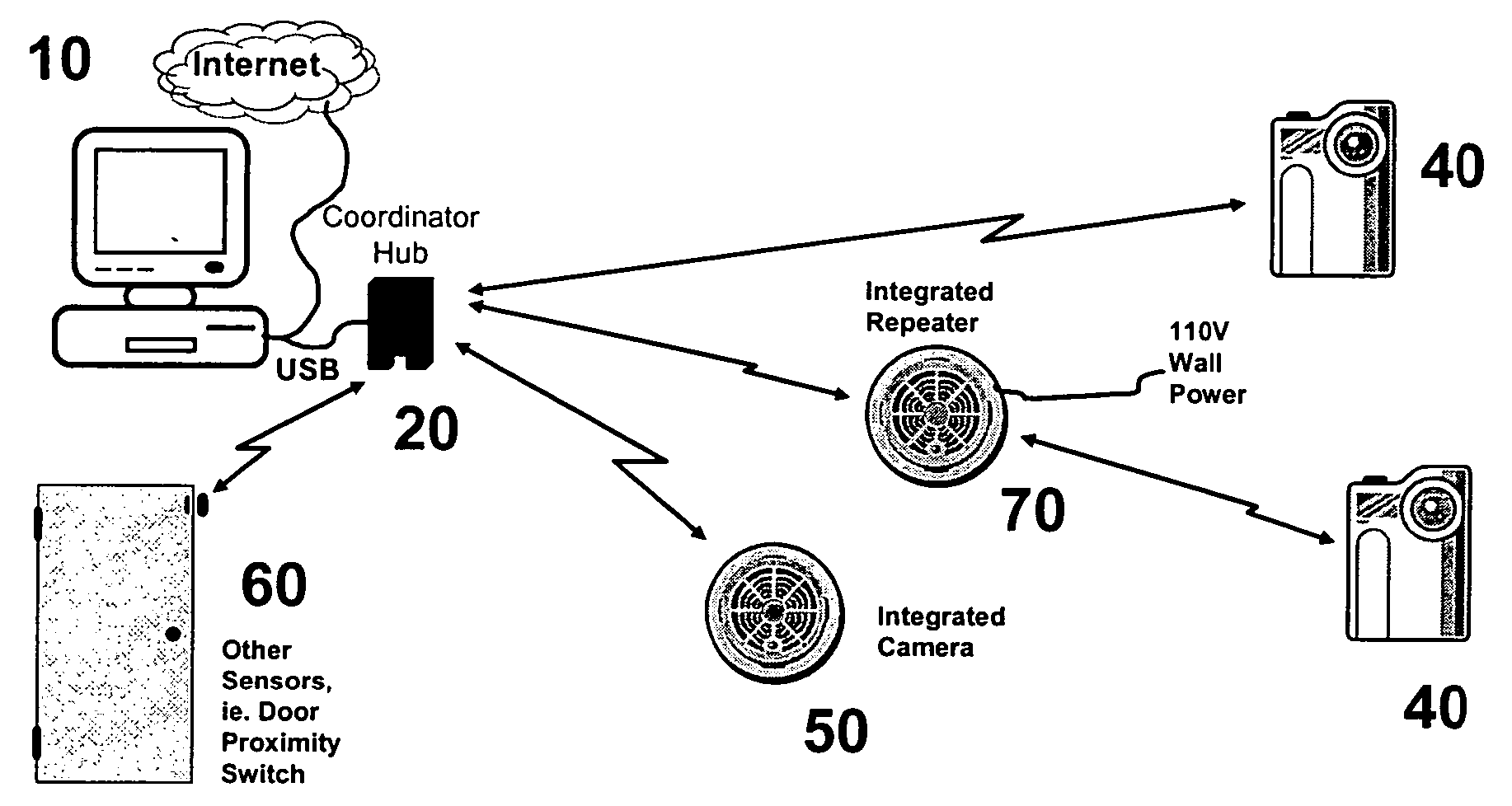

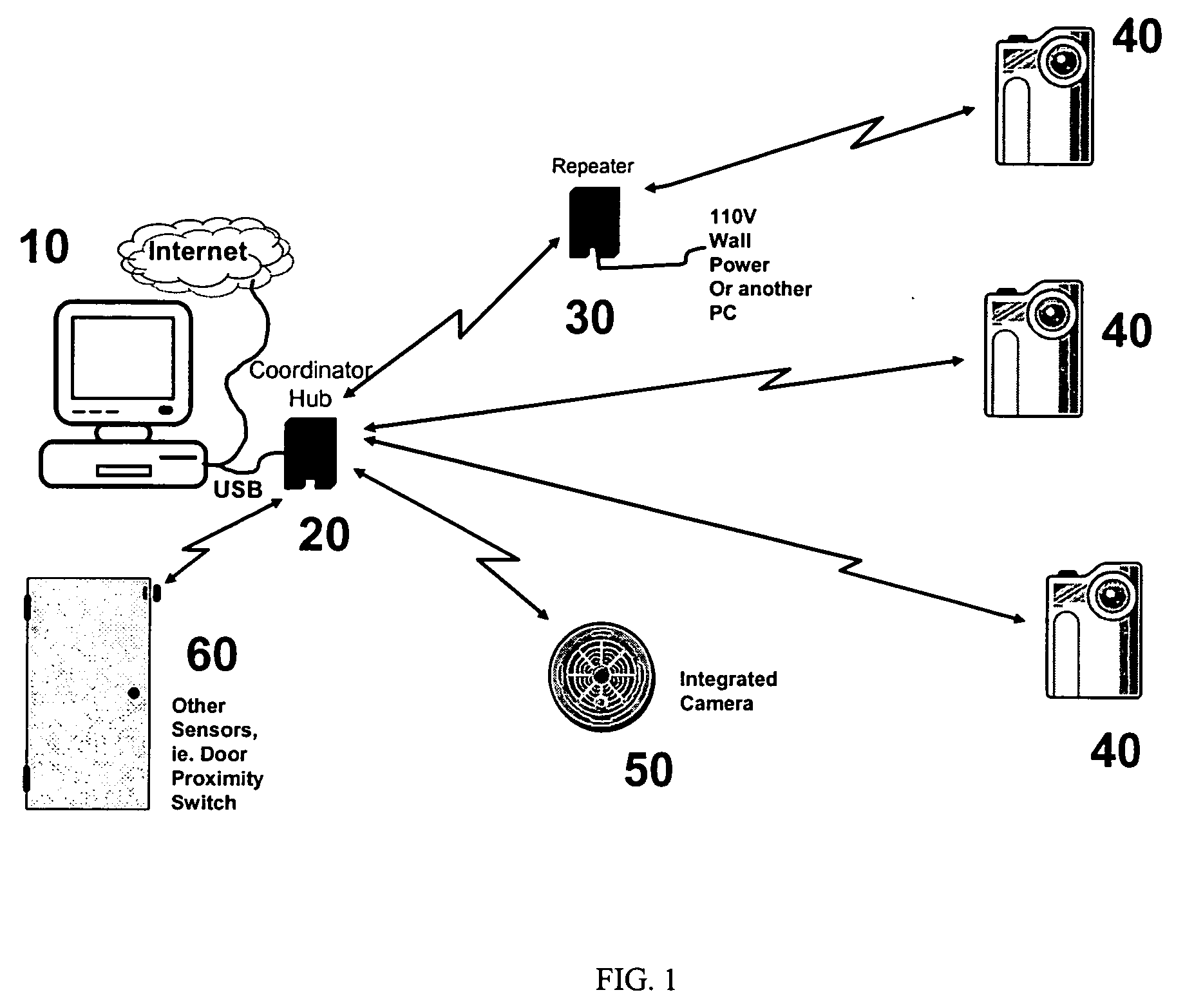

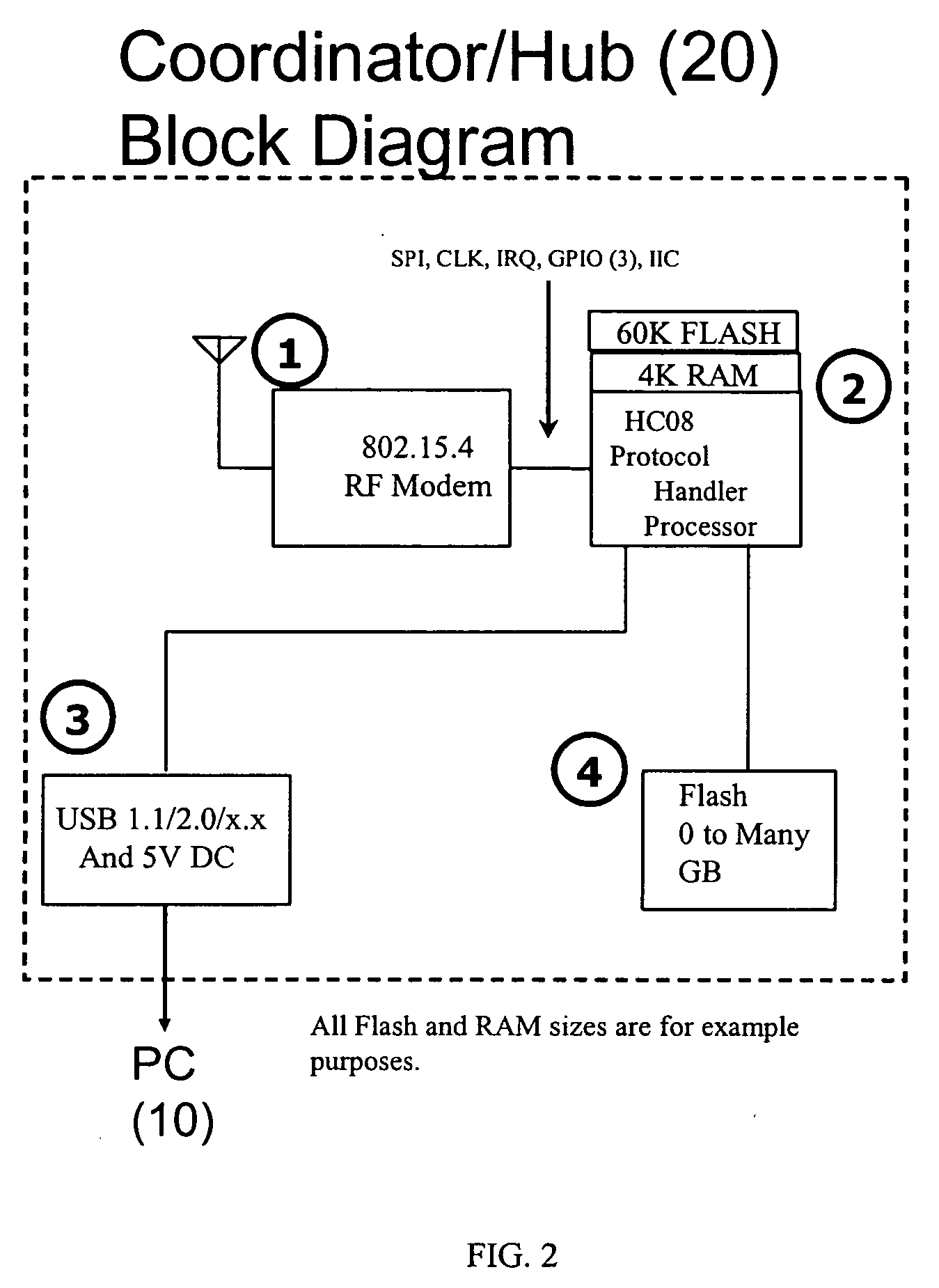

System and method for communicating over an 802.15.4 network

InactiveUS20060088018A1Low powerSimple setupTelevision system detailsError preventionModem deviceComputer vision

A method of reducing data transfer while increasing image information over an 802.15.4 network includes obtaining an image with a sensor, modulating a representation of the image using a first 802.15.4 modem, sending the representation of the image to a coordinator, demodulating the representation of the image using a second 802.15.4 modem, and digitally enhancing at least one of the representation of the image and the image. A system for communication over an 802.15.4 network includes a sensor for obtaining data, the size of the data being at least an order of magnitude greater than the size of an 802.15.4 packet, a first 802.15.4 modem coupled to the sensor, a buffer for temporarily storing the data to allow transmission of portions of the data; the buffer being coupled to the sensor, a coordinator coupled to the sensor, the coordinator being capable of communicating with a computer, and a second 802.15.4 modem coupled to the coordinator.

Owner:SIMPLE WORKS

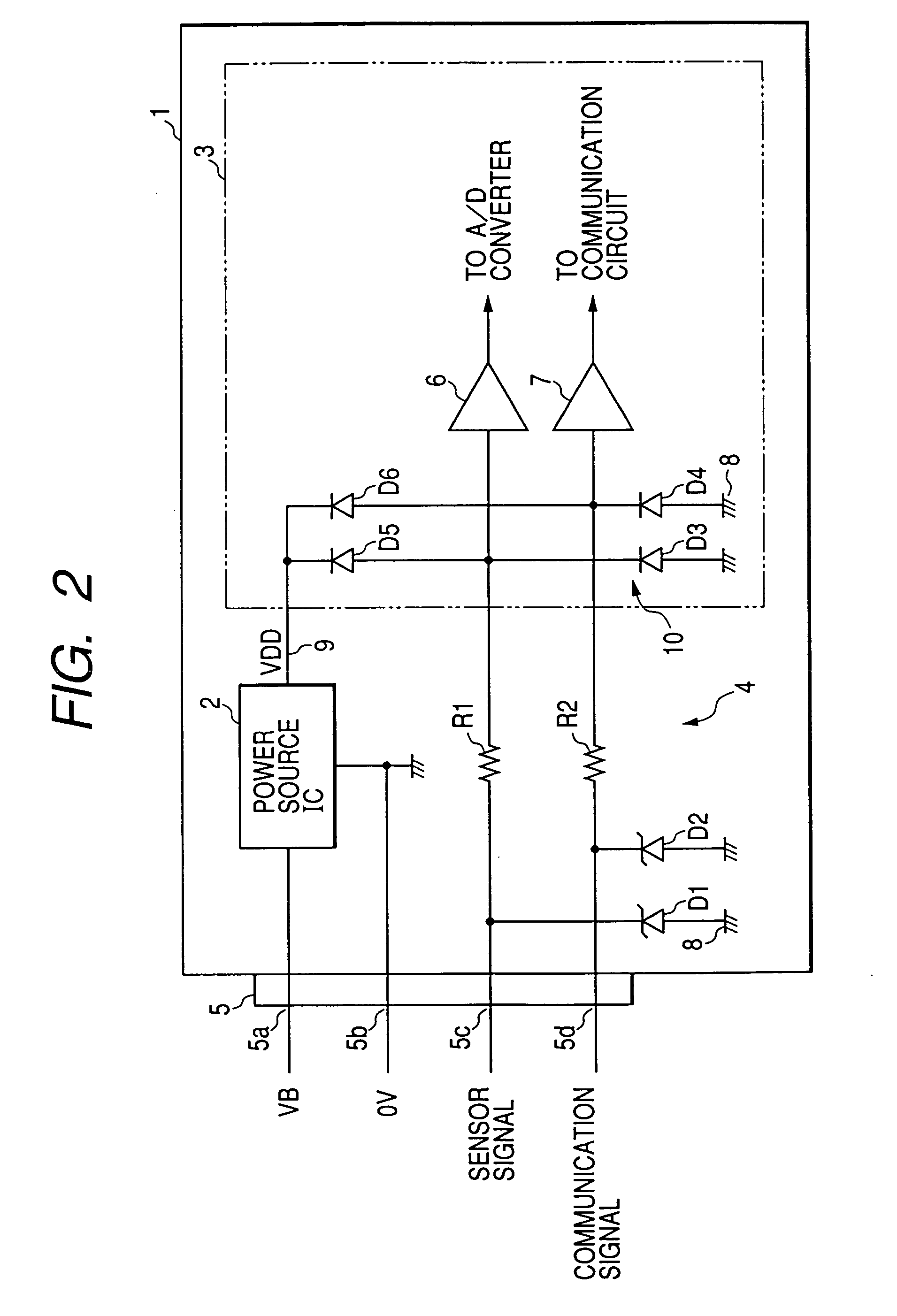

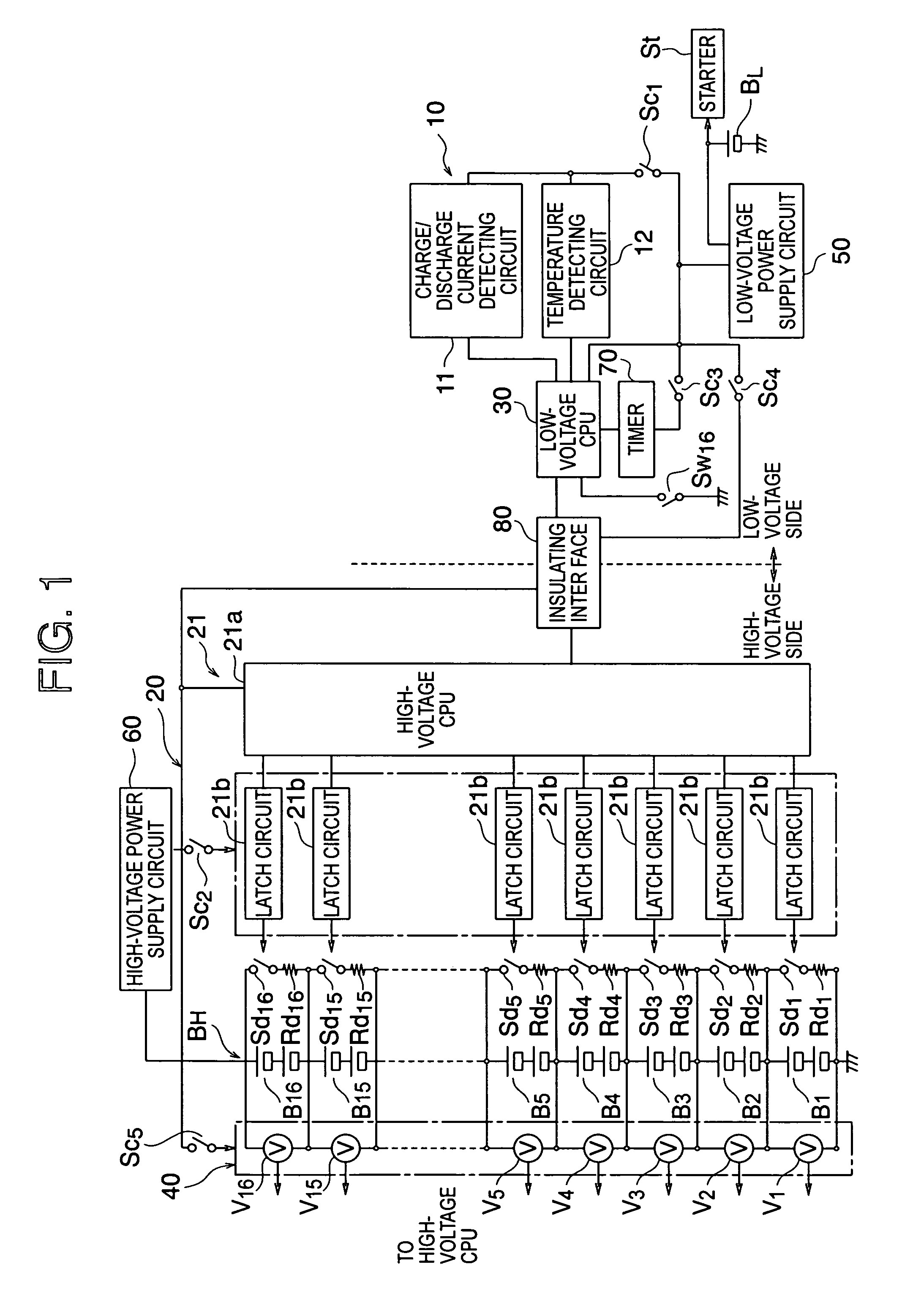

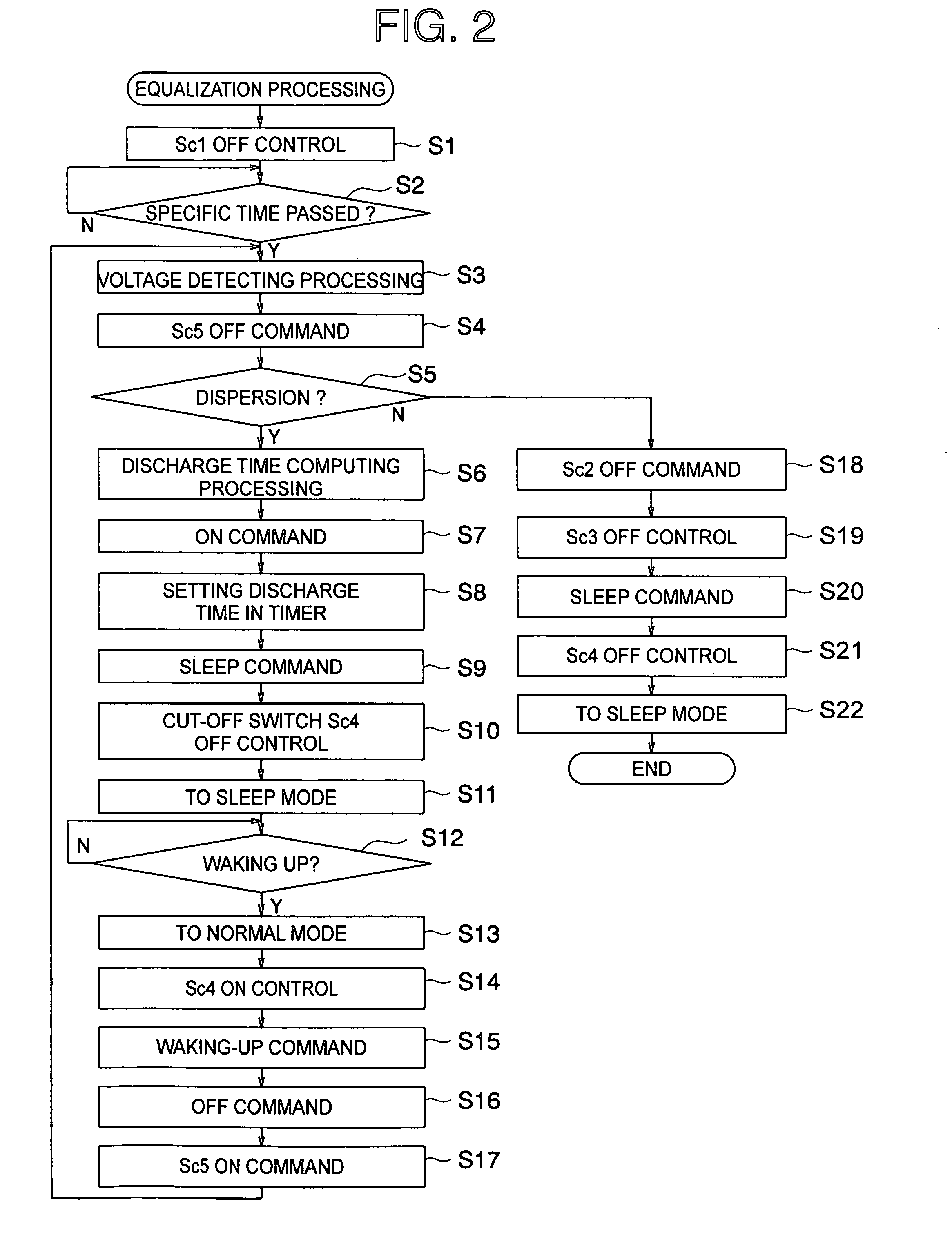

Battery control device

ActiveUS20070120529A1Current is limitedCurrent consumptionCharge equalisation circuitElectric devicesLow voltageElectrical battery

The battery control device includes: a state detecting means which acts by receiving electric power from an on-vehicle low-voltage battery having a supply voltage lower than that of an on-vehicle high-voltage battery composed of a plurality of unit cells connected together in series and detects a state of the on-vehicle high-voltage battery to monitor the on-vehicle high-voltage battery; an equalizing means for equalizing a voltage of each unit cell; and a control means which acts by receiving electric power from the on-vehicle low-voltage battery and starts to control the equalizing means in response to turning-off of an ignition switch, wherein the control means cuts electric power supply supplied from the on-vehicle low-voltage battery to the state detecting means after the turning-off of the ignition switch and before the control means starts to control the equalizing means.

Owner:YAZAKI CORP

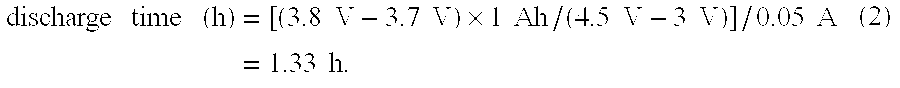

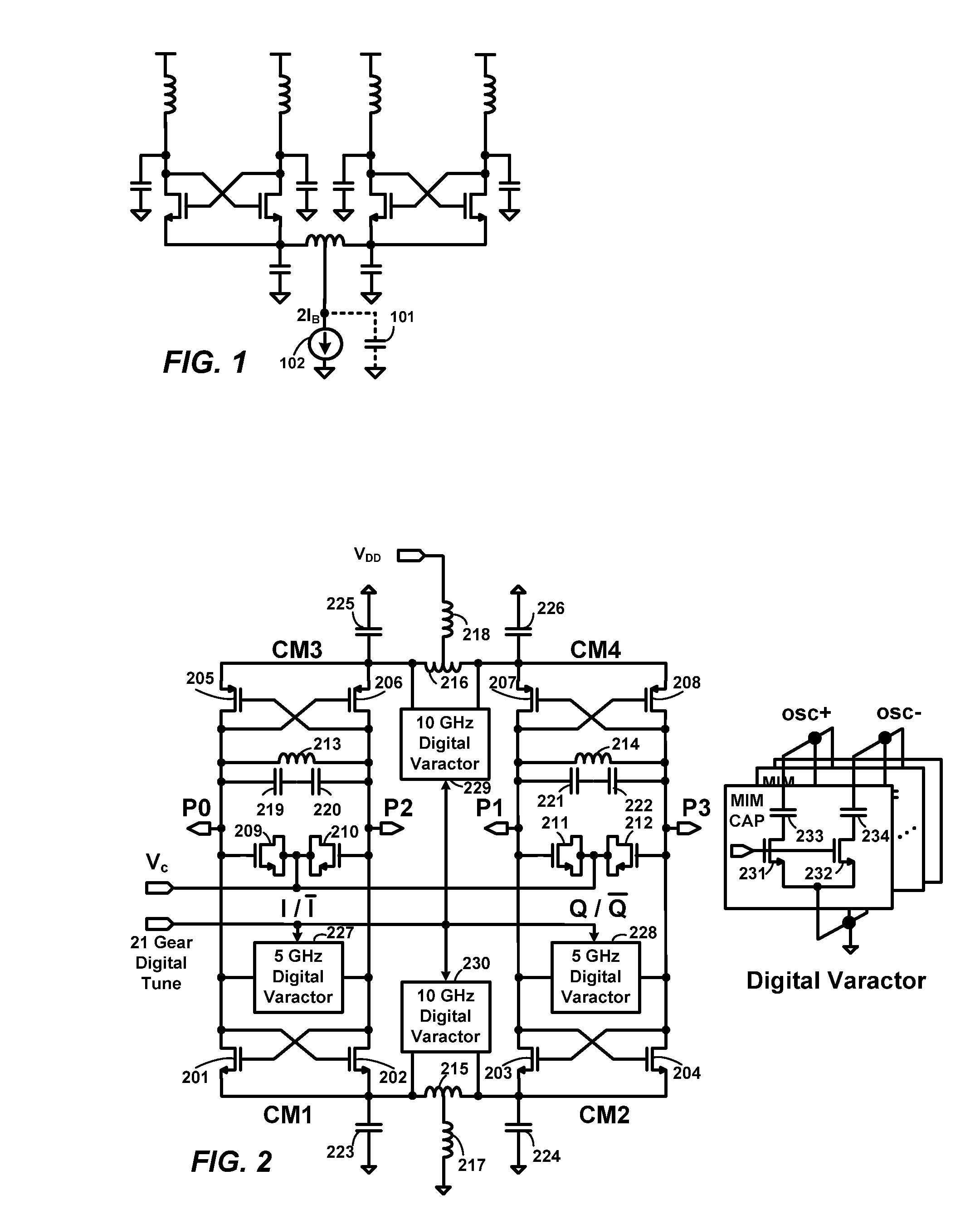

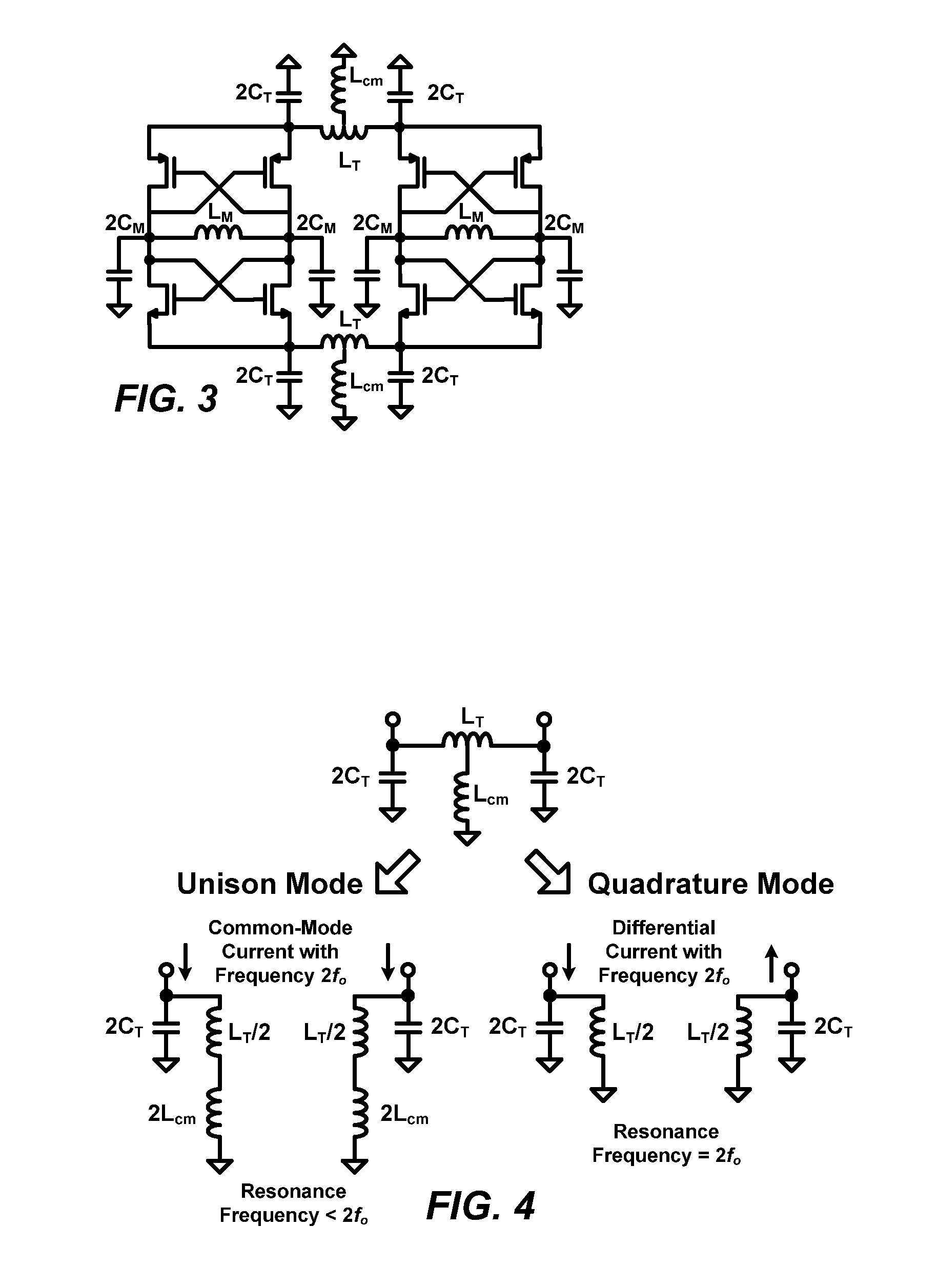

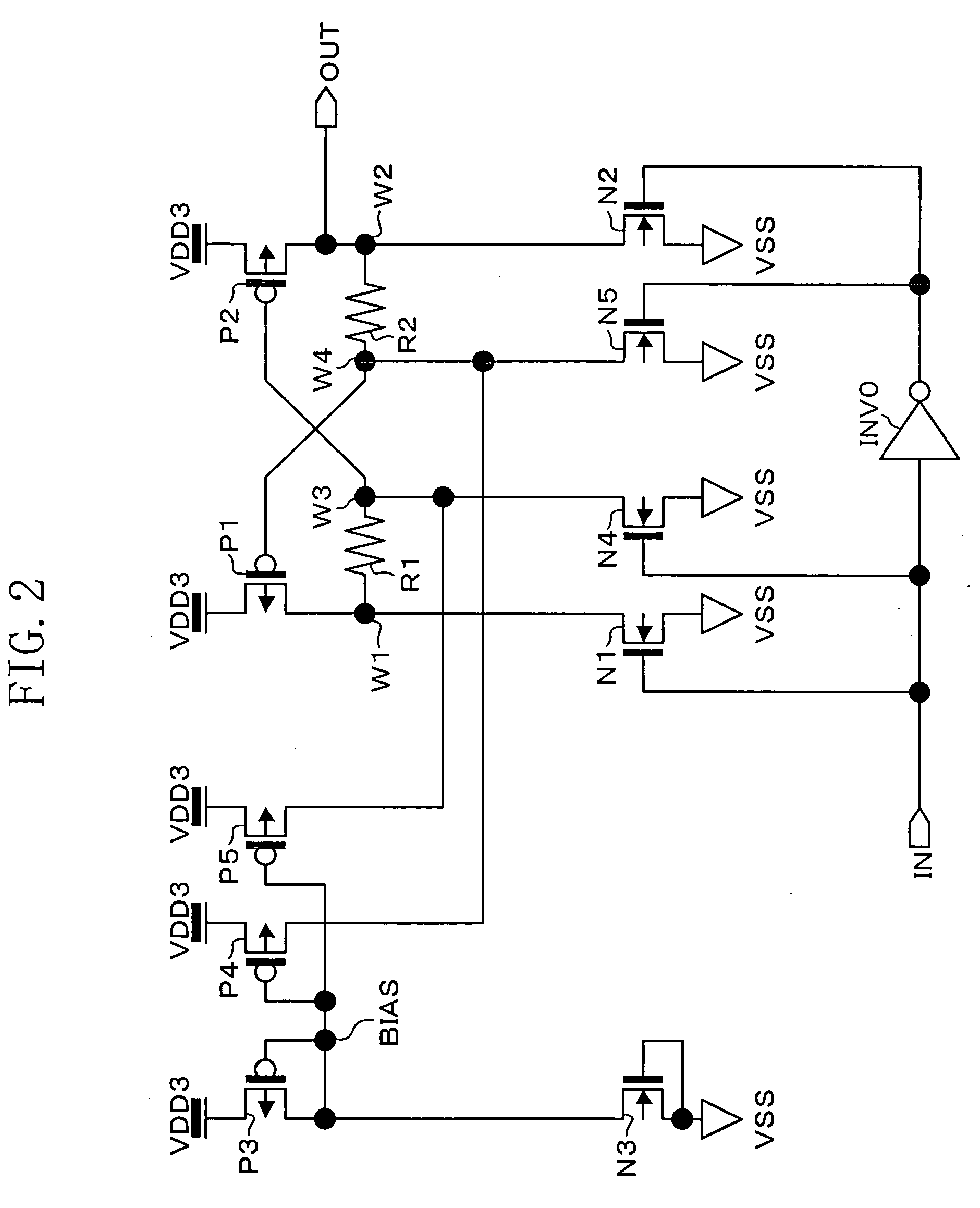

Low Phase-Noise Oscillator

InactiveUS20080143446A1Reduce impactTotal current dropPulse automatic controlElectric pulse generatorPhase noiseCoupling

A tail-tank coupling technique combines two complementary differential LC-VCOs to form a quadrature LC-VCO. The technique reduces phase noise by providing additional energy storage for noise redistribution and by cancelling noise injected by transistors when they operate in the triode region. The resulting noise factor is close to the theoretical minimum 1+γ, similar to a differential LC-VCO driven by an ideal noiseless current source. However, its figure-of-merit is higher, due to the absence of voltage head-room being consumed by a current source. The optimal ratio of tail-tank capacitor to main-tank capacitor for minimizing phase noise is approximately 0.5. The method can be extended to combine any even number of LC tanks resonating at fo and 2fo to form an integrated oscillator producing quadrature phase at frequency fosc and differential output at 2fosc.

Owner:WILLSON ALAN N JR

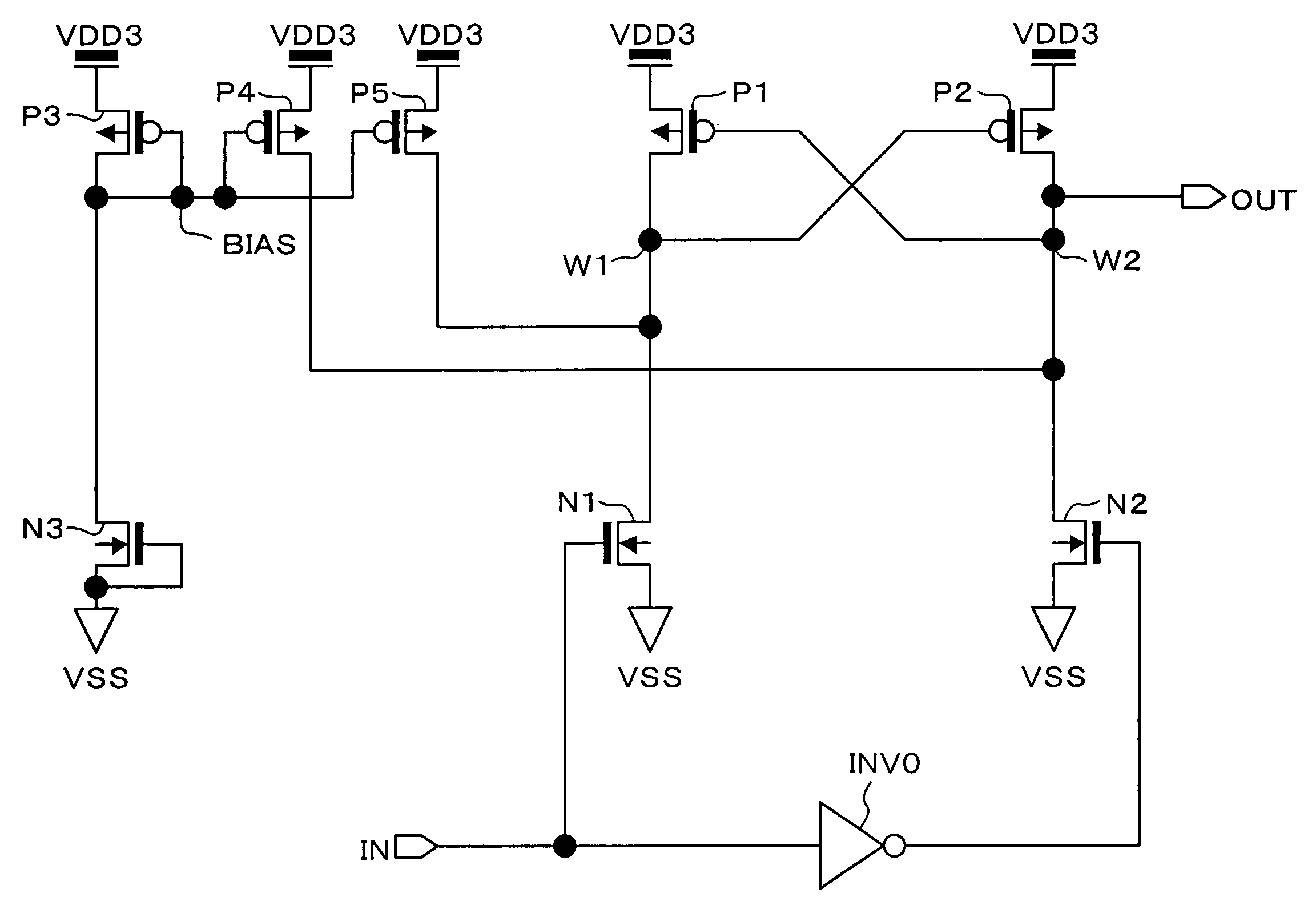

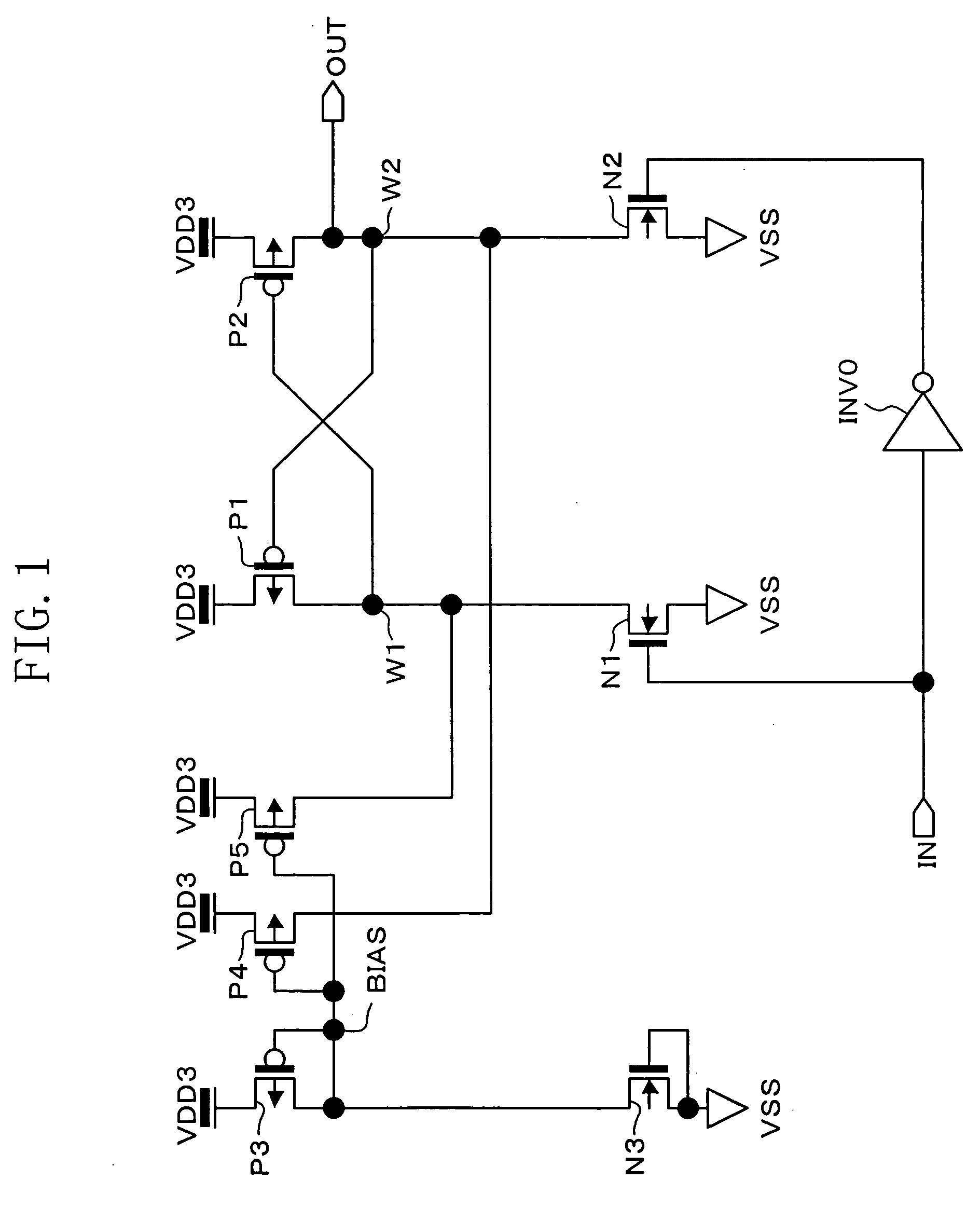

Level shifter

InactiveUS20060208759A1Increase resistanceCarry-out quicklyElectronic switchingElectric pulse generatorEngineeringVoltage source

In a level shifter, OFF leakage currents flow through two N-type transistors for signal input even when they are OFF. However, another N-type transistor serving as an OFF leakage generation circuit and three P-type transistors serving as current mirrors, which constitute a current conversion circuit, supply to the signal-input transistors a current equivalent to or greater than the OFF leakage currents flowing through the signal-input transistors when they are OFF, thereby canceling the OFF leakage currents. Therefore, one of nodes which is at H level is surely fixed to a potential equal to a higher voltage supply. Thus, the level shifter surely operates with a high speed even when large OFF leakage currents flow through the signal-input transistors.

Owner:SOCIONEXT INC