Patents

Literature

135results about "Shakers" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

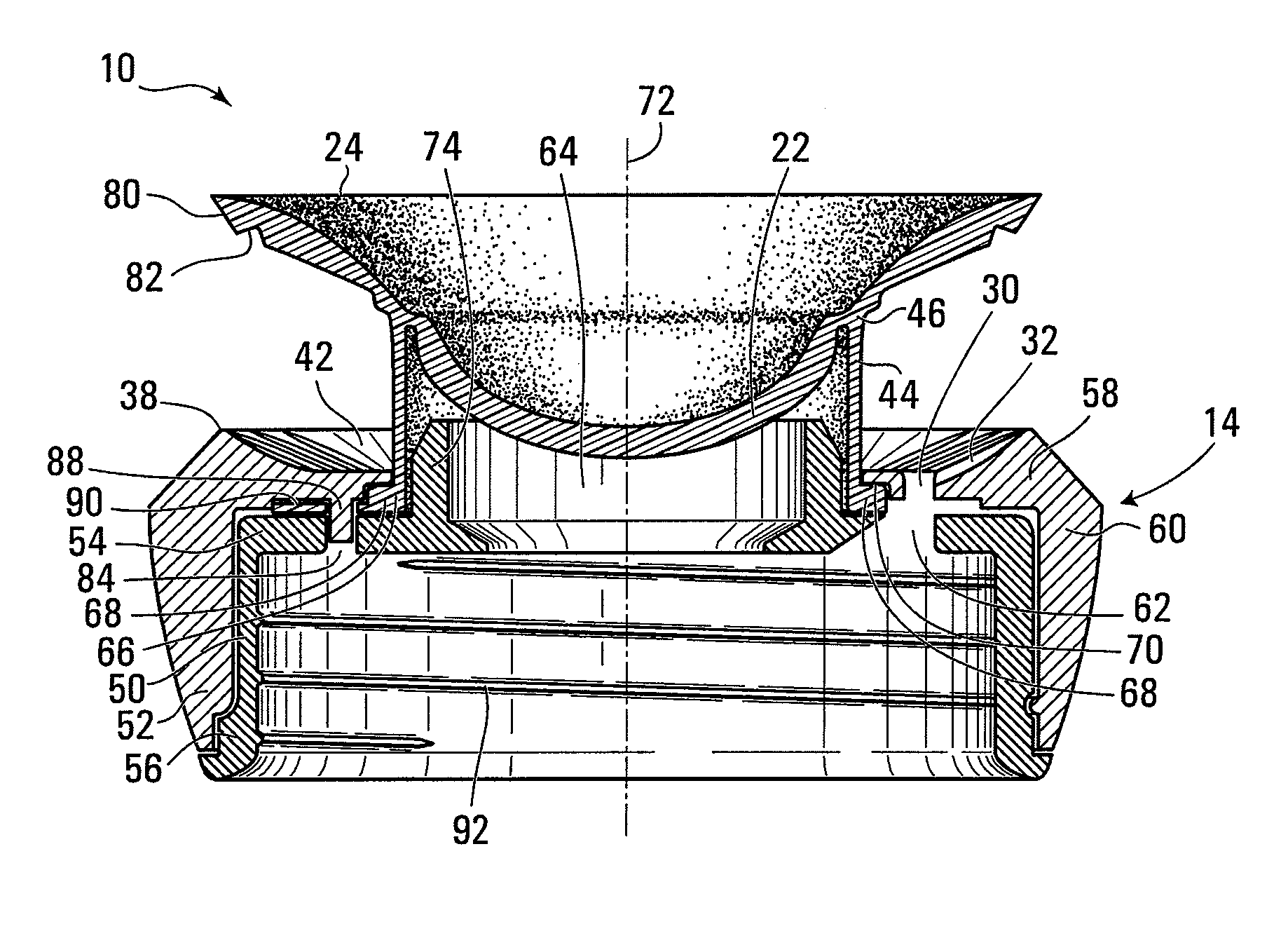

Reconfigurable metered material dispenser

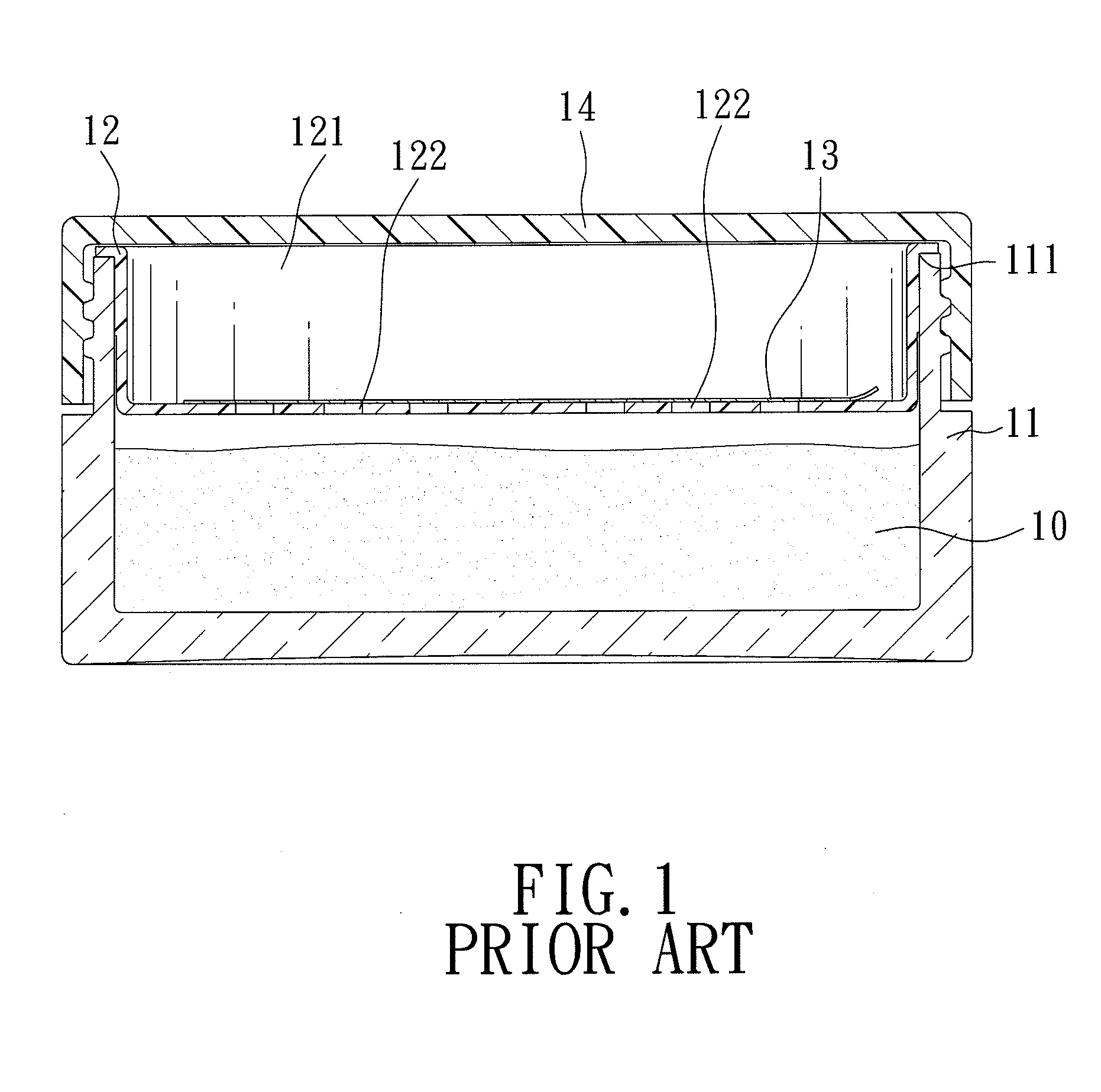

A dispenser is provided for delivering a controlled quantity of a granular material. The dispenser includes a container assembly, a diffuser and a metering cup. The container includes a reservoir which supports a disposable cartridge of granular material. The cartridge is supported in the reservoir so as to define a passageway therebetween. A nozzle is defined for the outflow of material from the cartridge. The diffuser is disposed on one end of the container and includes a plurality of apertures. The metering cup is disposed on the opposite end of the container and has an open end adapted to receive granular material. Adjustment of the axial spacing between the nozzle and metering cup varies the quantity of granular material collected in the cup. The granular material is dispensed by inverting the container to a second orientation, such that material flows out of the metering cup, through the passageway and out of the diffuser. The nozzle may serve as a piercing mechanism for opening the disposable cartridge upon its insertion into the reservoir.

Owner:RESTAURANT TECH

All-purpose dispenser

ActiveUS7086569B2Minimize possibility of migratory infestationClosuresRefuse receptaclesBiomedical engineeringWaste disposal

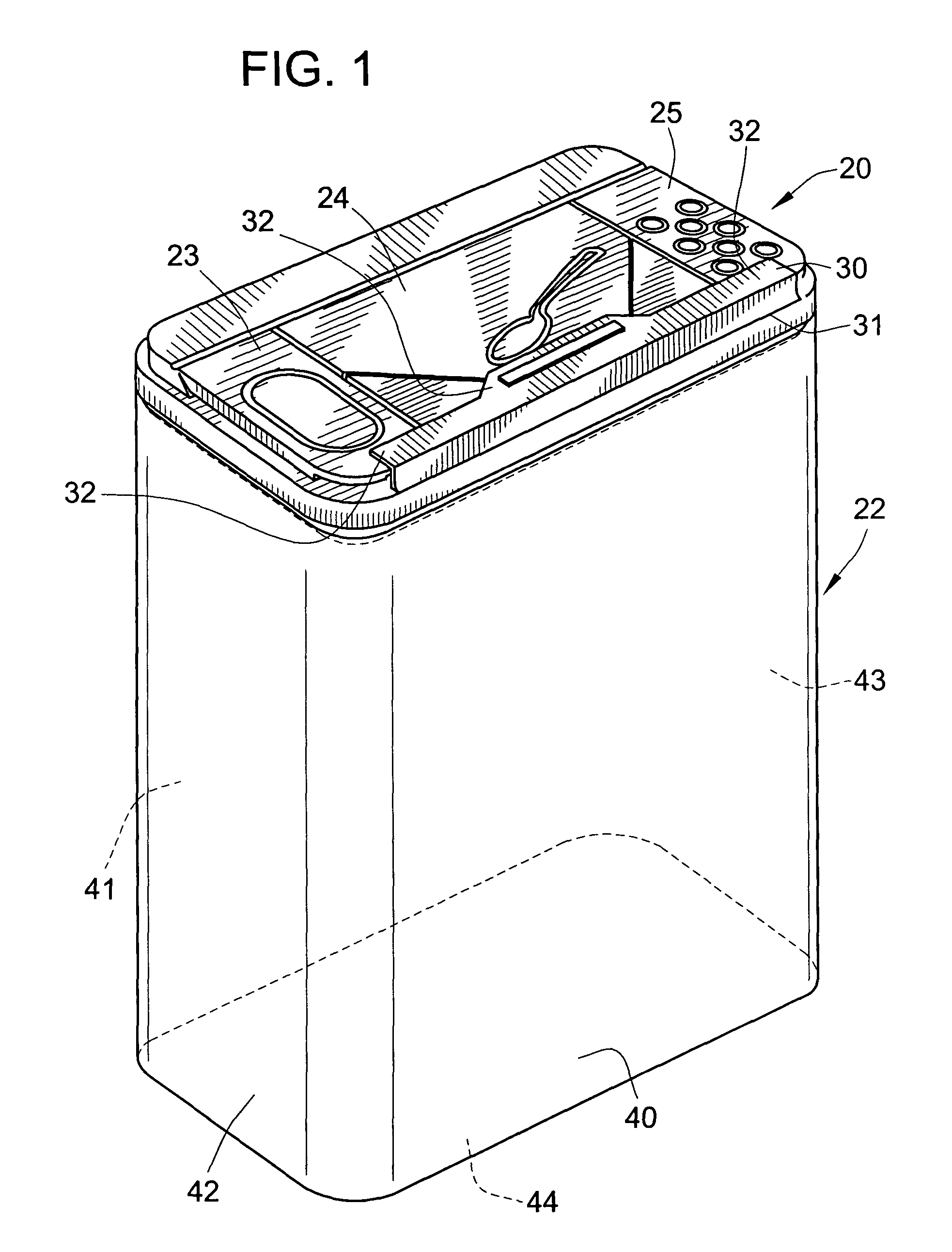

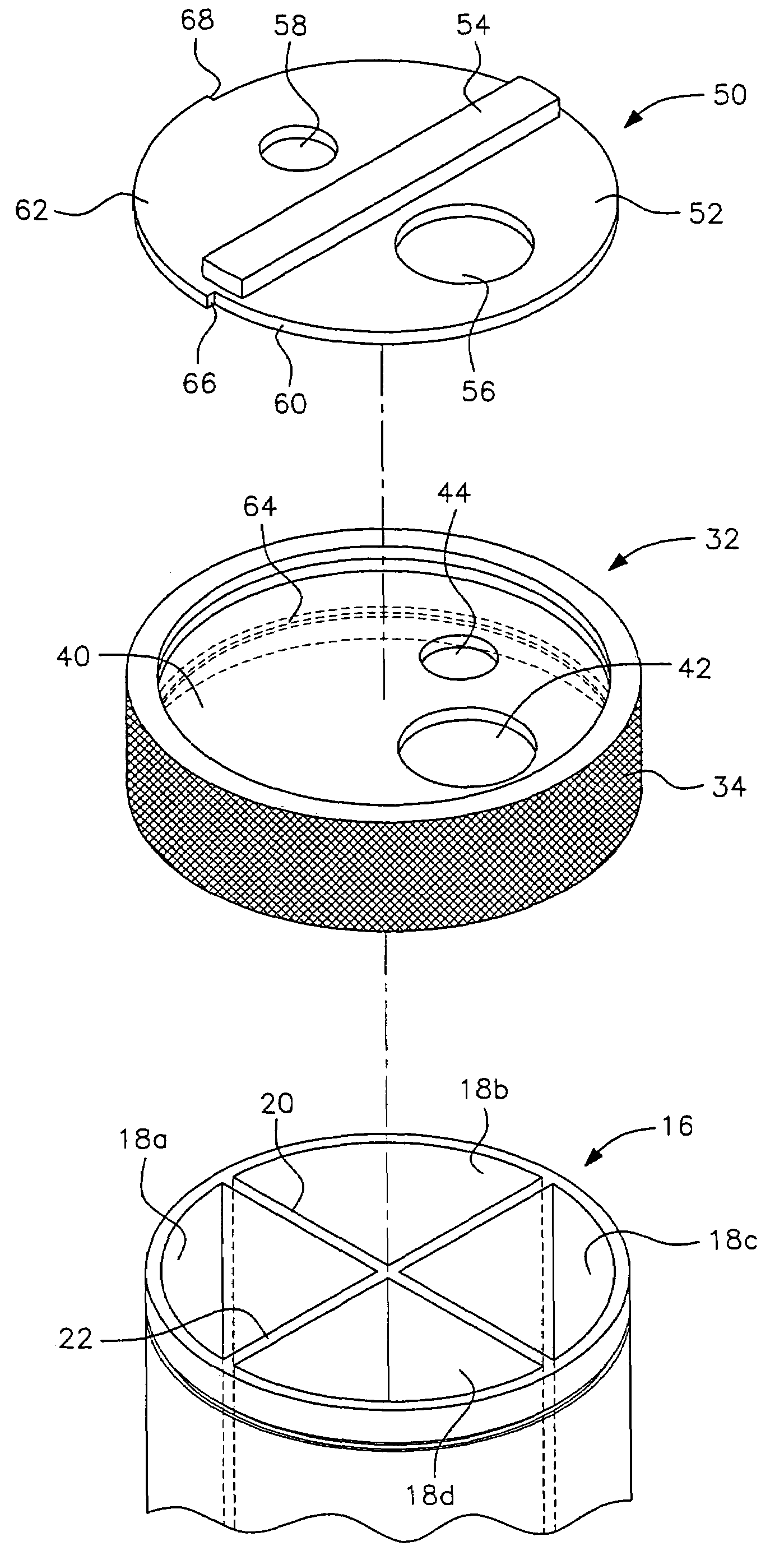

Dispenser including a cartridge module and a powder or liquid dispensing agent arranged in the cartridge module. Dispensing occurs when the dispenser is jarred which causes the dispensing agent to pass through one or more dispenser openings in a lower wall of the cartridge module. For example, when the dispenser is mounted to an inner surface of a pivotable lid of a waste disposal can, closure of the lid against a base of the can causes a jarring impact on the lid which results in an amount of the dispensing agent falling through the dispensing opening(s). The lid can also be manually tapped when closed to jar the dispenser.

Owner:MUNCHKIN INC

Reusable bottle stopper

A bottle stopper is provided having a cylindrical body formed of a resilient, flexible, elastic material that includes a first cylindrical section adapted to be inserted into an opening of a bottle in sealing engagement with the bottle and a second cylindrical section disposed adjacent the first cylindrical section for extending above the opening of the bottle when the first cylindrical section is inserted in sealing engagement with the bottle. An air passageway is disposed adjacent and extends longitudinally along substantially at least the length of the first cylindrical section and along the internal periphery of the cylindrical body. A visual indicator, preferably a spout, is disposed on an outer surface of the second cylindrical section for identifying the relative location of the air passageway with respect to the visual indicator.

Owner:HALEYS CORKER INC

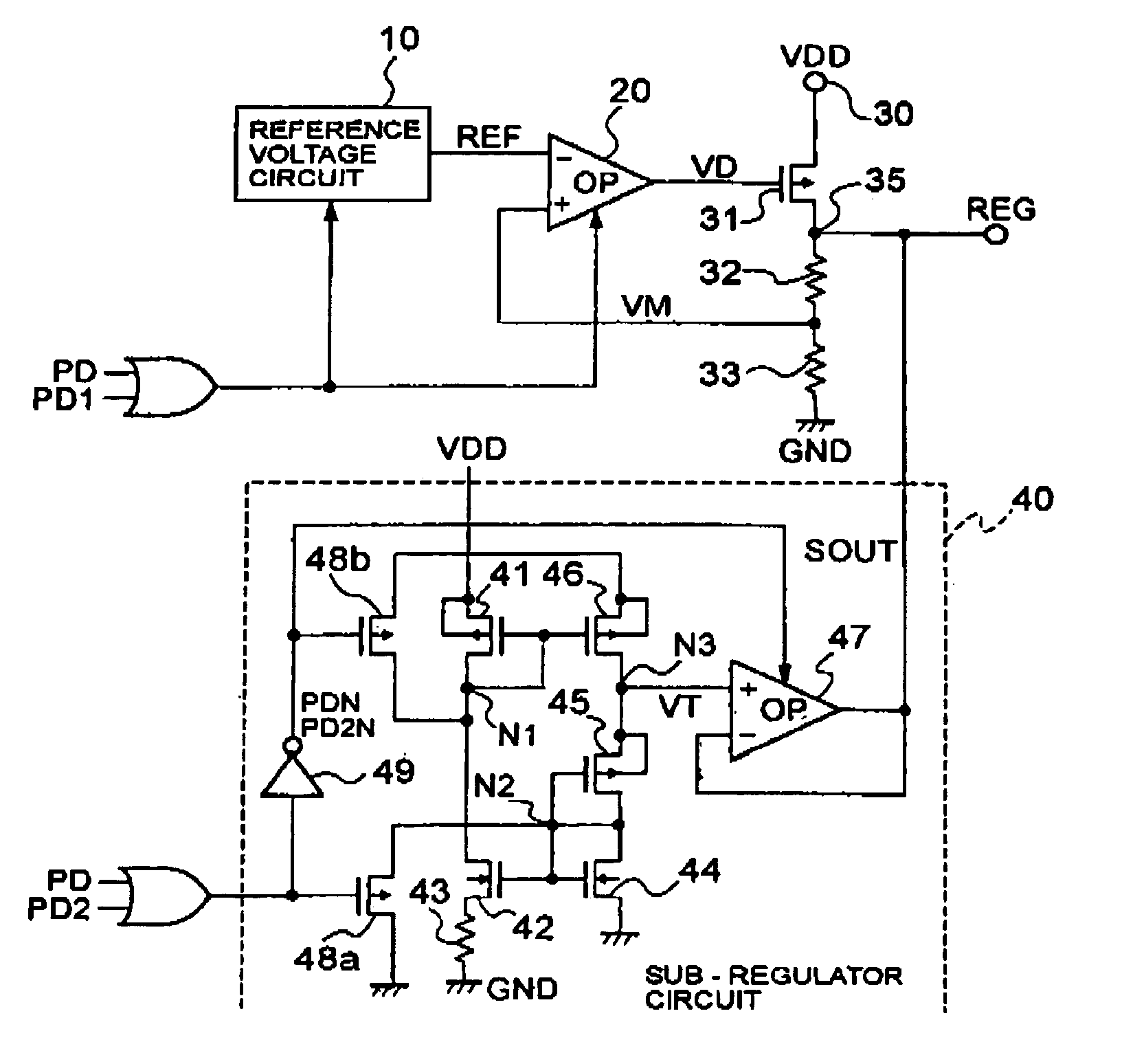

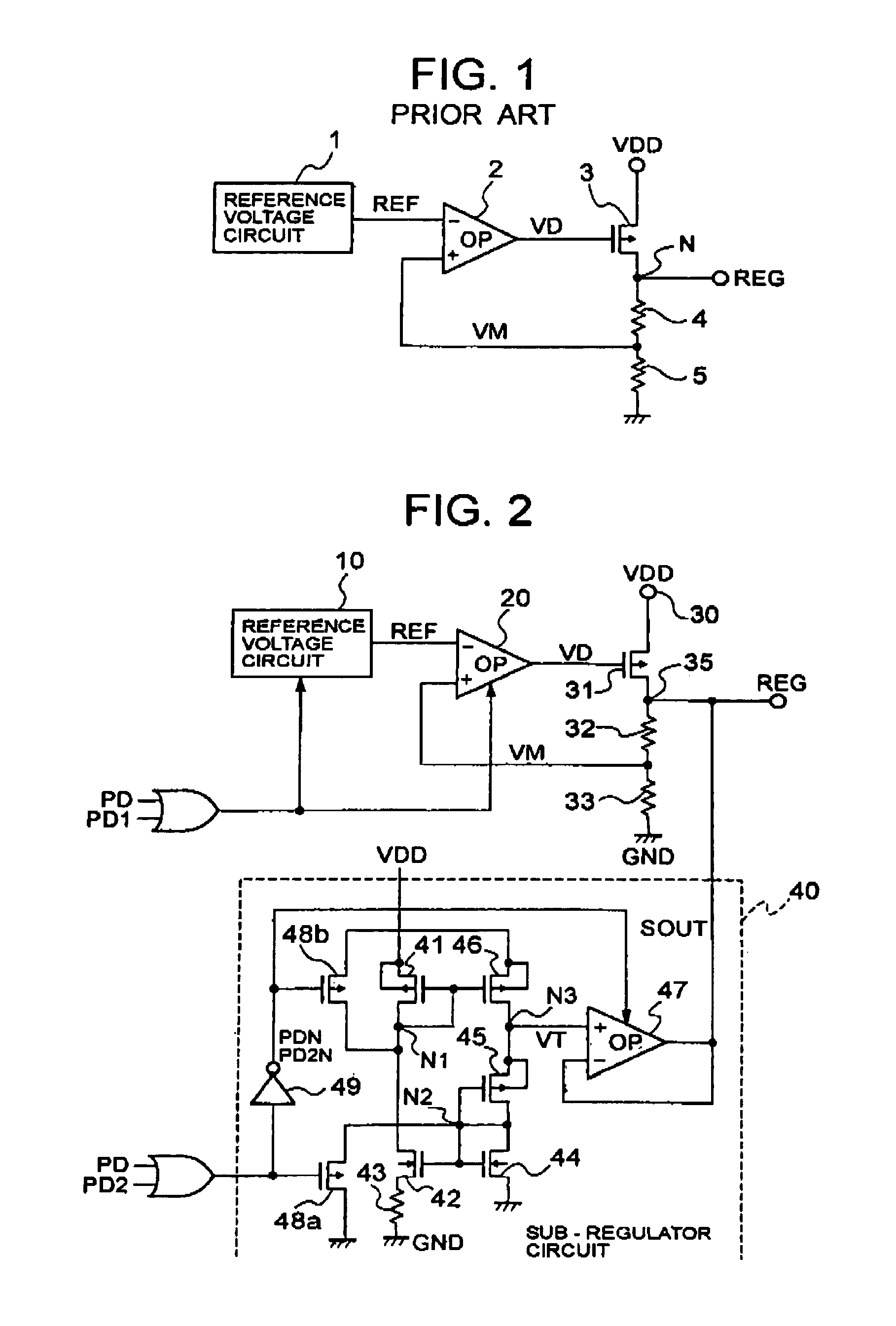

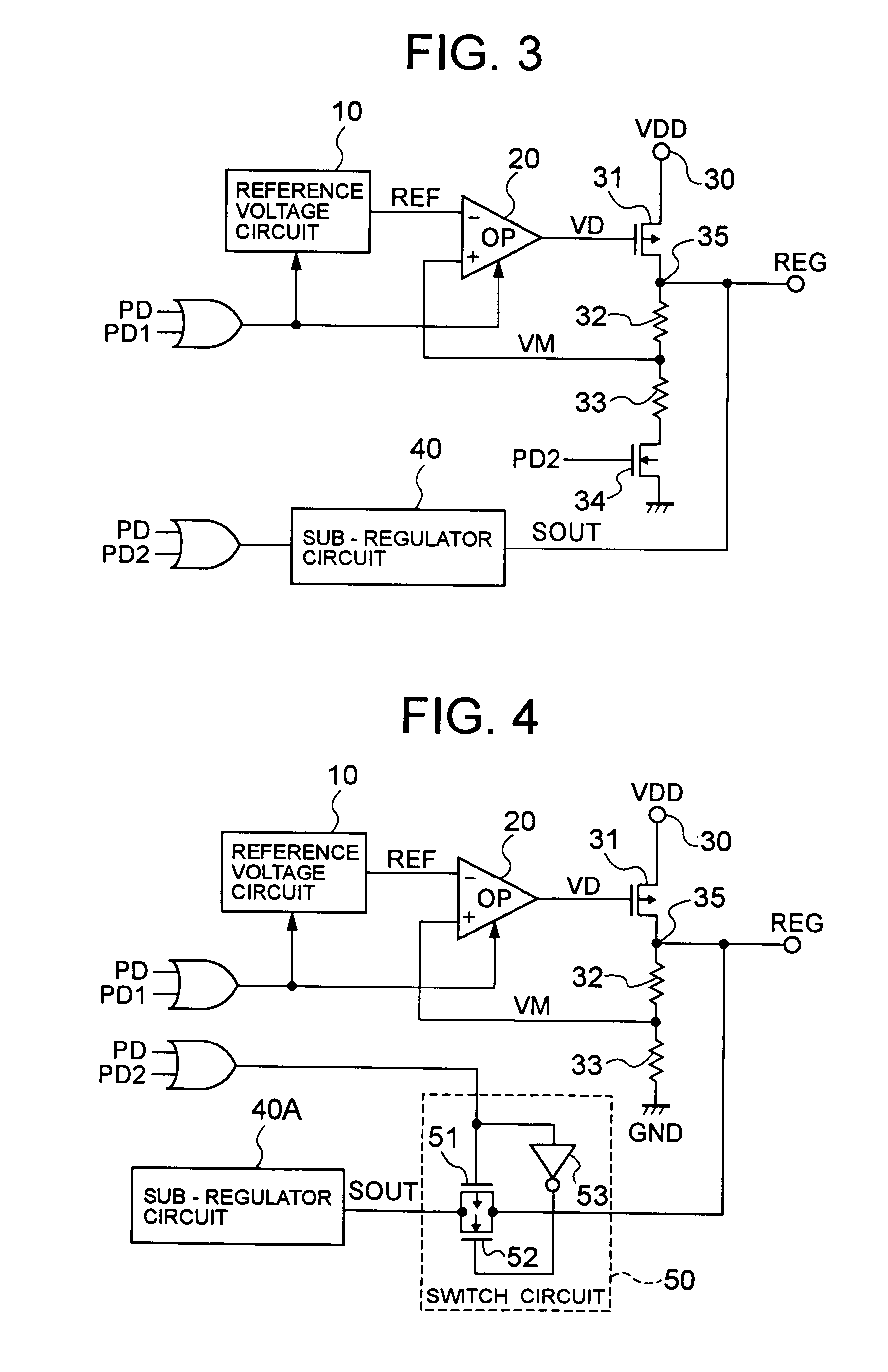

Voltage regulator

ActiveUS7193399B2Current consumptionTotal current dropPackagingShakersOperation modeVoltage reference

Consumption current is reduced for a voltage regulator in sleep mode. In normal operation mode, a sub-regulator circuit is ceased from operating according to a power-down signal, which allows an operation amplifier to compare between a reference voltage outputted from a reference voltage circuit and a monitor voltage generated by a voltage-dividing circuit. Based on a detection voltage as a comparison result, a PMOS is controlled to regulate an internal power voltage such that the monitor voltage becomes equal to the reference voltage. In sleep mode, the reference voltage circuit and operational amplifier is ceased from operating, to start up the sub-regulator circuit. A slight current, restricted by a resistance, flows through a PMOS of the sub-regulator circuit. The same magnitude of current is supplied from the PMOS constituting a current mirror to a PMOS, etc. of a threshold-voltage output circuit. The threshold voltage, at a node between the PMOS constituting the current mirror and the PMOS of the threshold-voltage output circuit, is power-amplified by a voltage follower and outputted through an output terminal.

Owner:LAPIS SEMICON CO LTD

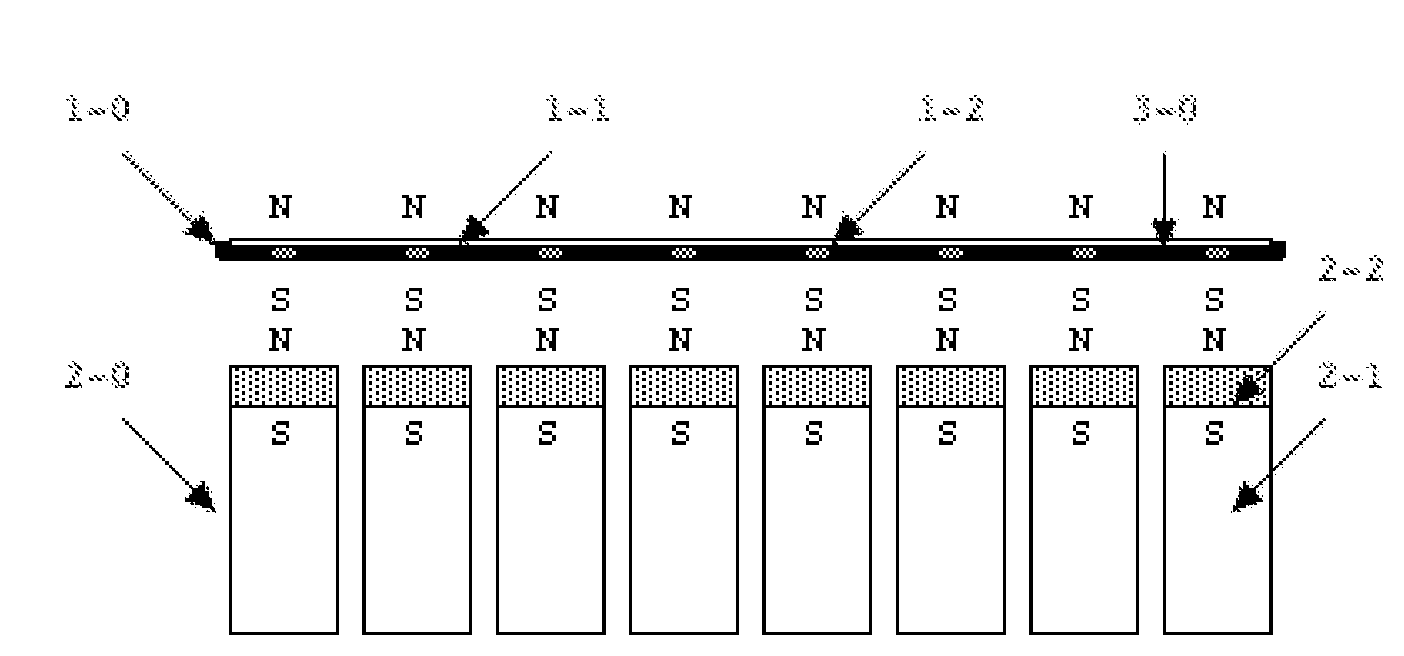

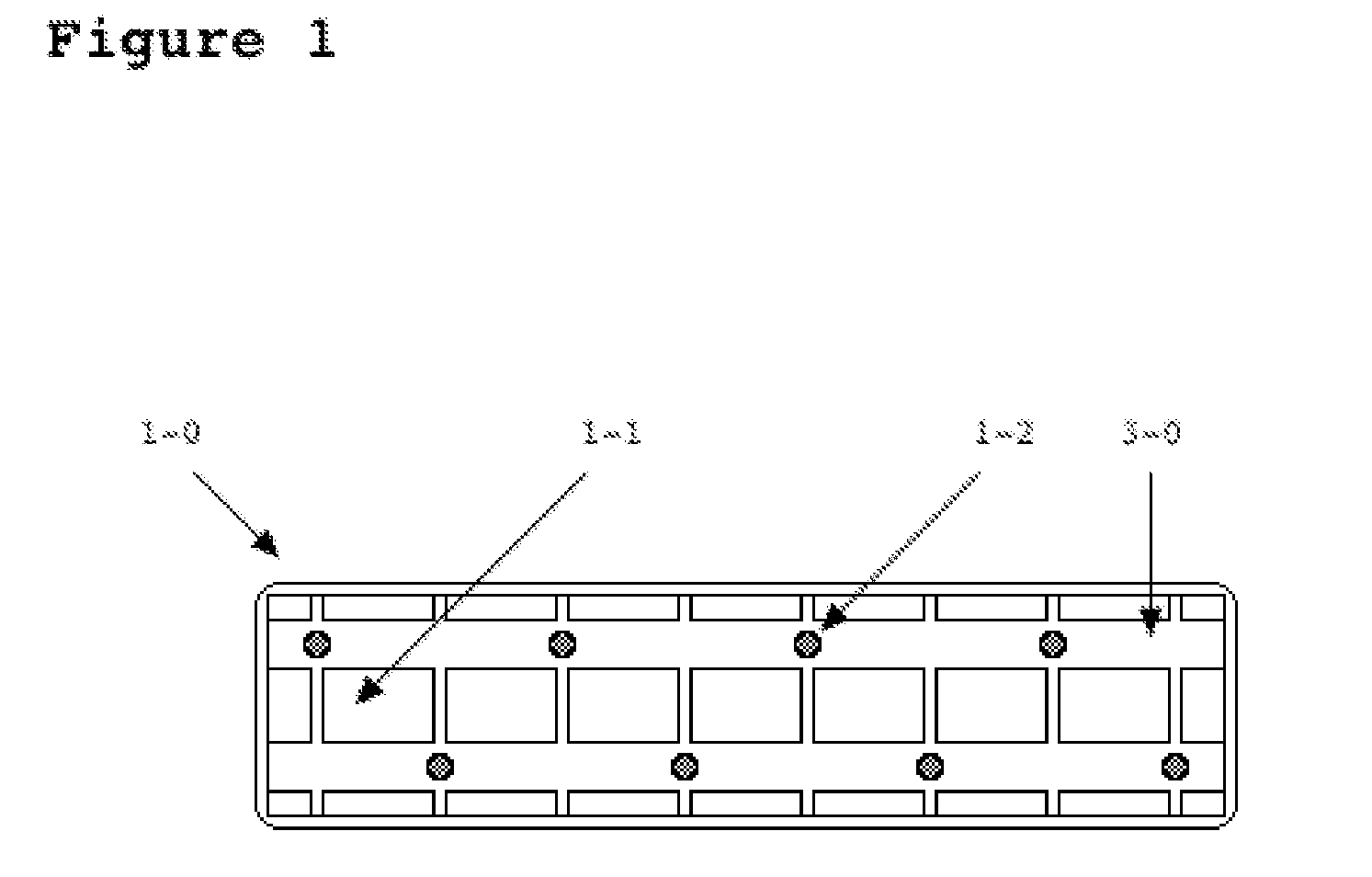

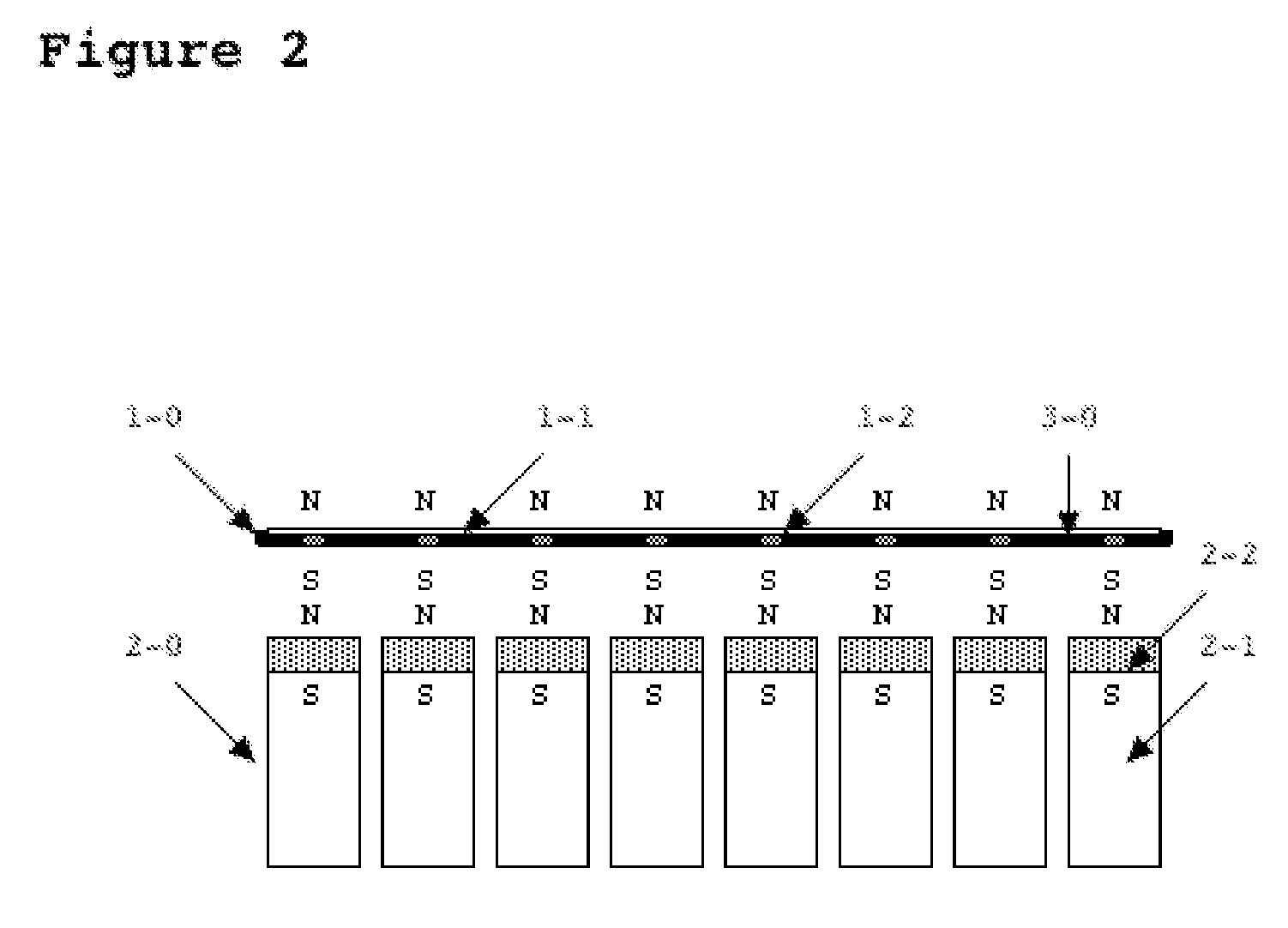

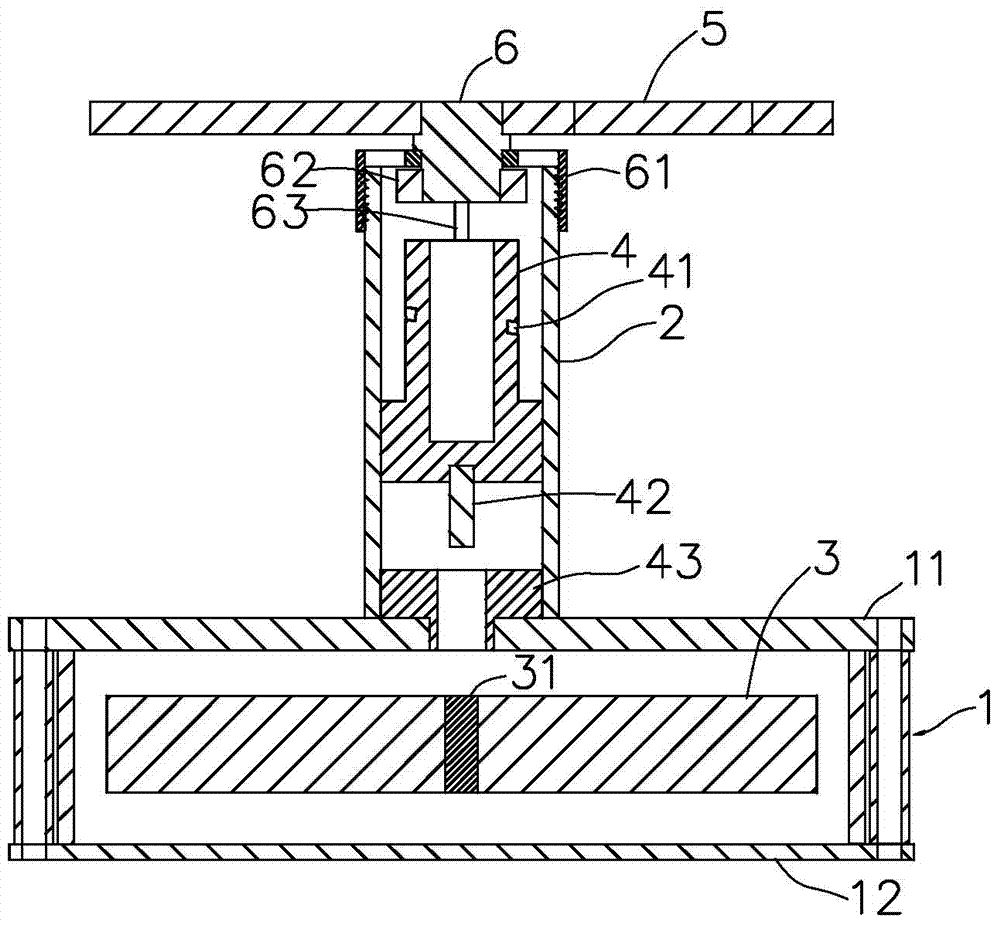

Self-sealing auto-aligning magnetically-hanging spice dispenser

A hanging spice dispenser comprises a plate assembly and a container assembly for storing spices. The plate assembly comprises a non-magnetic planer plate and a plurality of magnetic elements embedded at pre-determined locations. The container assembly comprises a generally cylindrical spice container, a removable cap and a magnetic element. Magnetic attraction force between the magnetic element of the container assembly and the magnetic element of the plate assembly is exerted when the container assembly is placed in proximity to the plate assembly. The container assembly is capable of detaching from the bottom surface of the plate assembly when force is applied to the container assembly. The removable cap and the plate assembly form self-seal in order to prevent air and moisture from entering into the generally cylindrical container. This invention relates to spice dispensers, and the principal use of the invention is for dispensing spices in a kitchen.

Owner:SUNATORI GO SIMON

Tamper evident multiple door closure

A server lid for a container with an integral tear strip tamper evident feature. A tear strip for the tamper evident feature is molded as an adjunct to a base member which forms the closure. The tear strip is joined to the base by at least one frangible web, and hinges about the frangible web to overlie front edges of one or more flaps formed in the server lid. Ultrasonic welds connect the overlying tear strip to the flaps or adjacent the flaps for providing a tamper evident feature.

Owner:JL CLARK INC

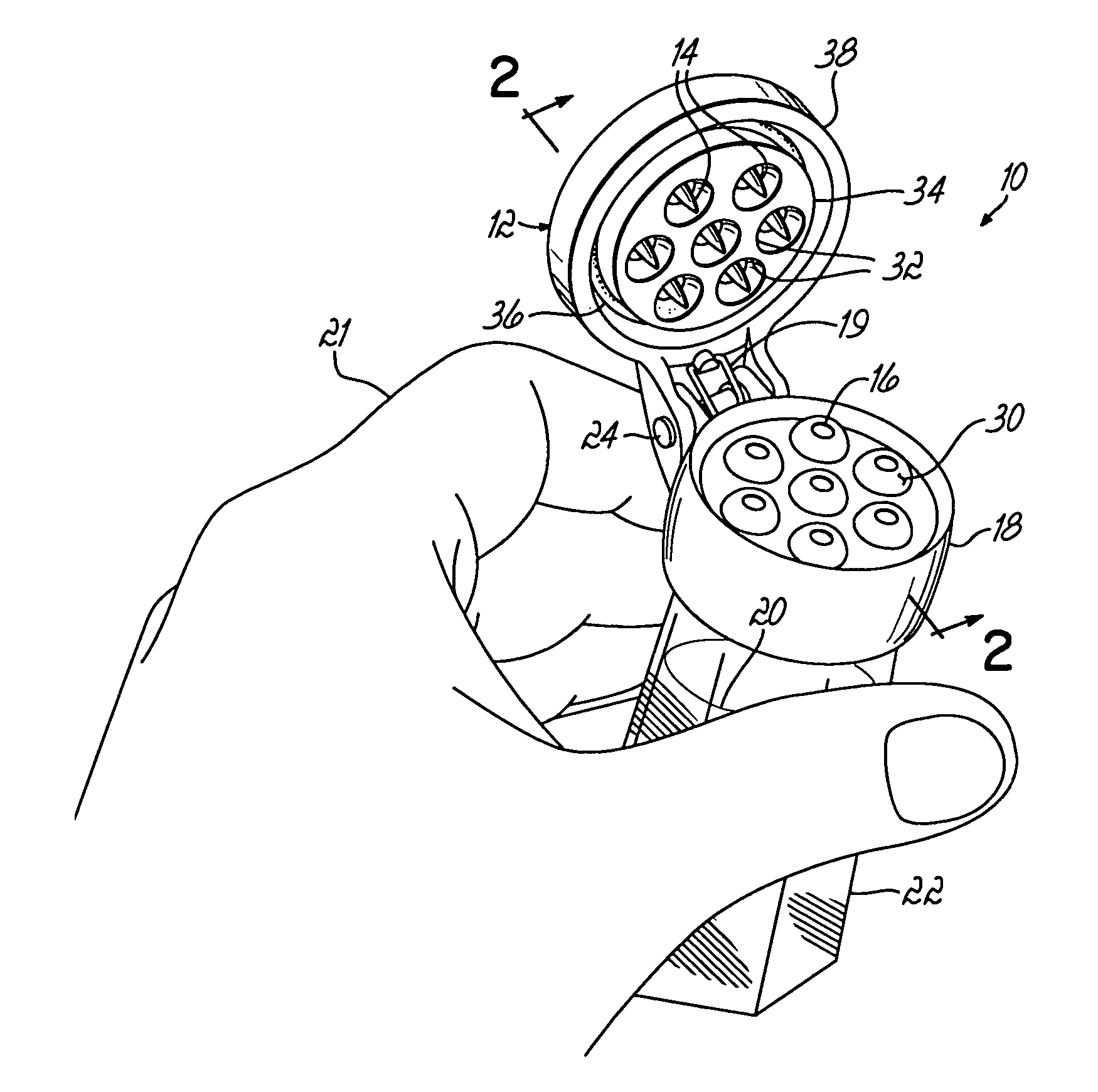

Multiple compartment pill dispenser

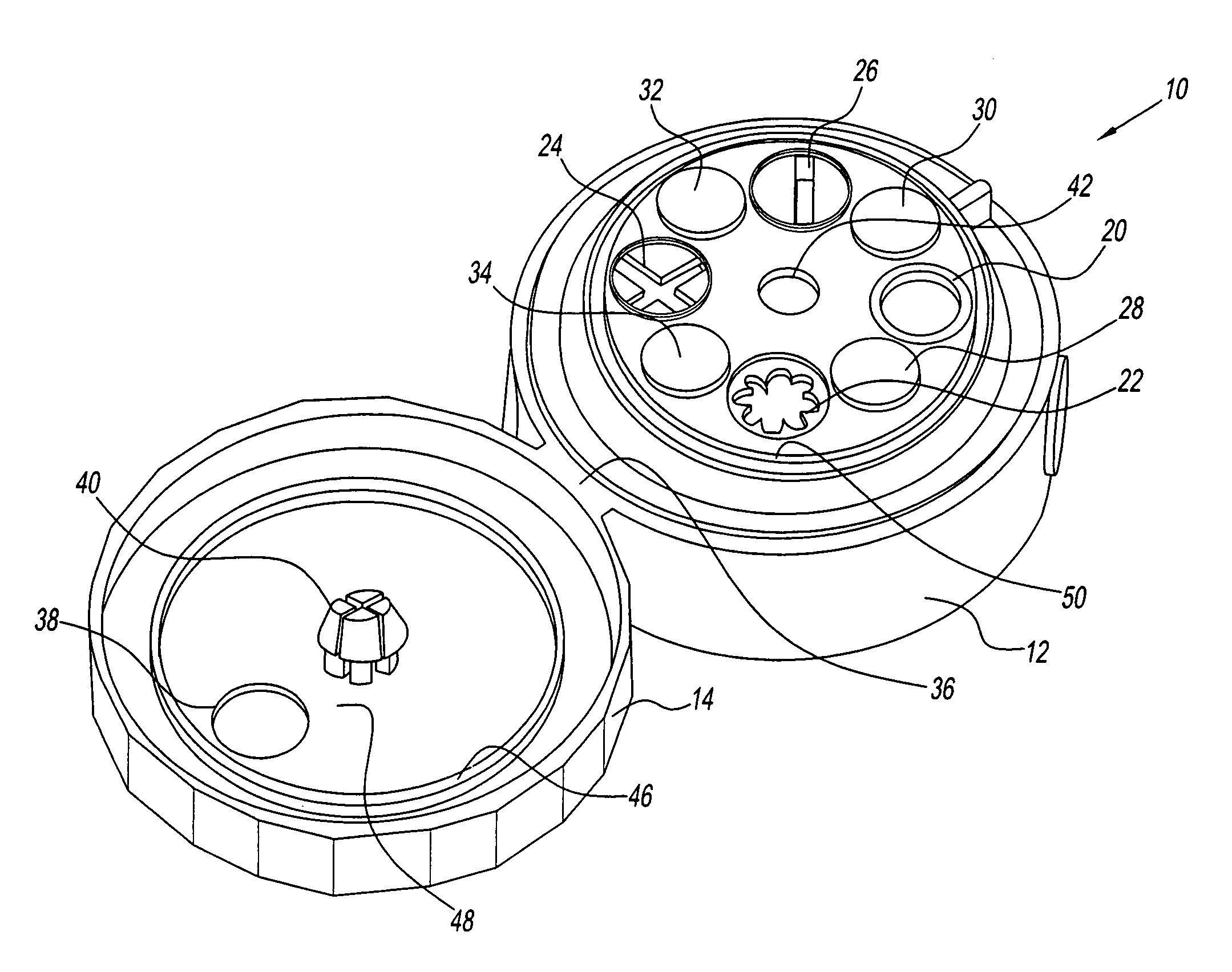

InactiveUS7240795B2Small article dispensingCoin-freed apparatus detailsEngineeringMechanical engineering

The multiple compartment pill dispenser has a rotatable cap mechanism having two holes associated with the cap which are displaceable to be aligned with each of the compartments of the dispenser. There are two standard sized holes, one for small pills and one for large pills. The dial cap mechanism is used to rotate one of the two holes into alignment with a particular pill compartment and allow a pill to be dispensed therefrom. As a closure device, an alignment plate is rotatably mounted in the cap mechanism. The alignment plate also includes two different sized holes, identical in diameter, respectively, to the two holes in the cap mechanism.

Owner:LEE JAMES M

Reusable bottle stopper

A bottle stopper is provided having a cylindrical body formed of a resilient, flexible, elastic material that includes a first cylindrical section adapted to be inserted into an opening of a bottle in sealing engagement with the bottle and a second cylindrical section disposed adjacent the first cylindrical section for extending above the opening of the bottle when the first cylindrical section is inserted in sealing engagement with the bottle. An air passageway is disposed adjacent and extends longitudinally along substantially at least the length of the first cylindrical section and along the internal periphery of the cylindrical body. A visual indicator, preferably a spout, is disposed on an outer surface of the second cylindrical section for identifying the relative location of the air passageway with respect to the visual indicator.

Owner:HALEYS CORKER INC

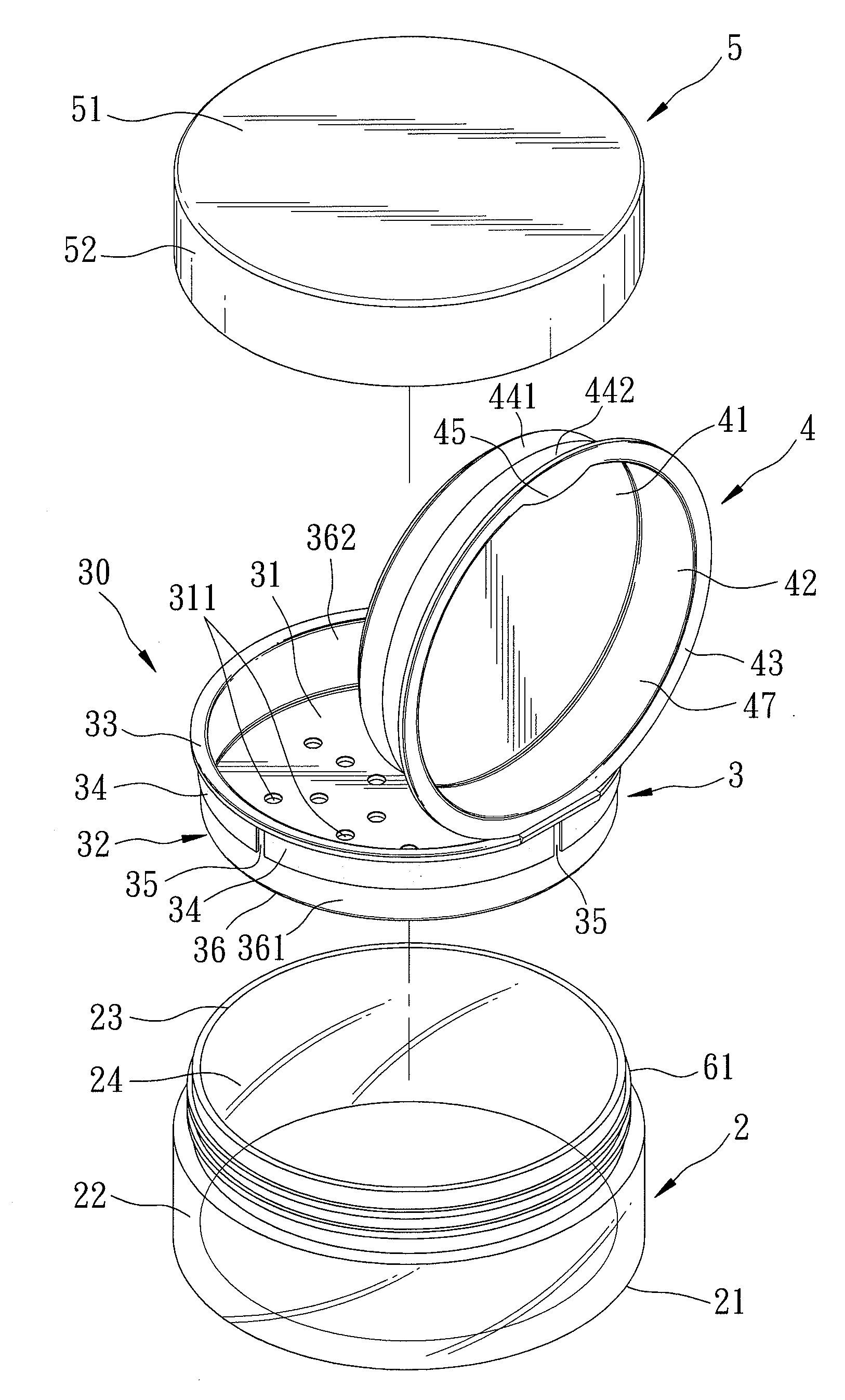

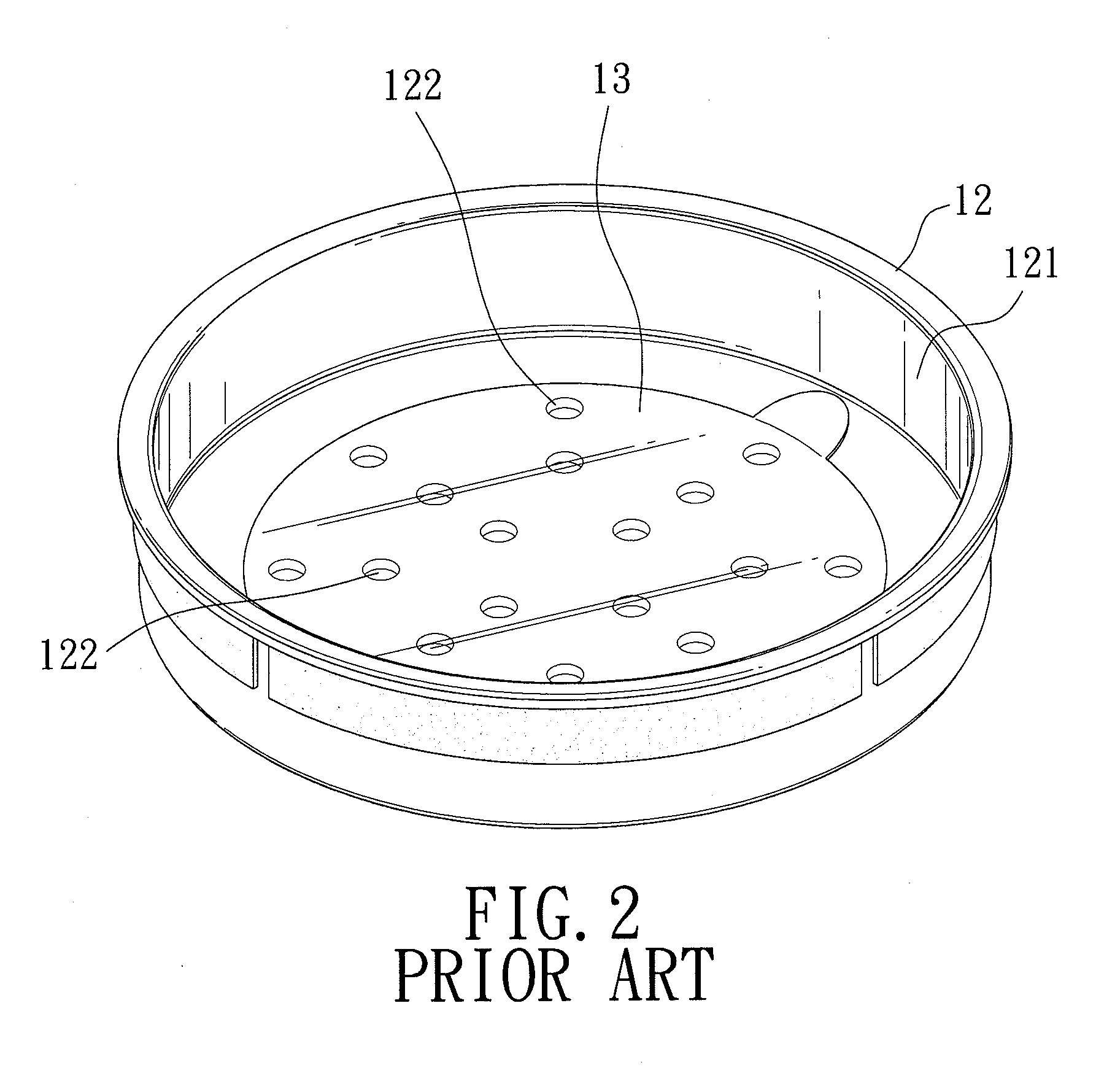

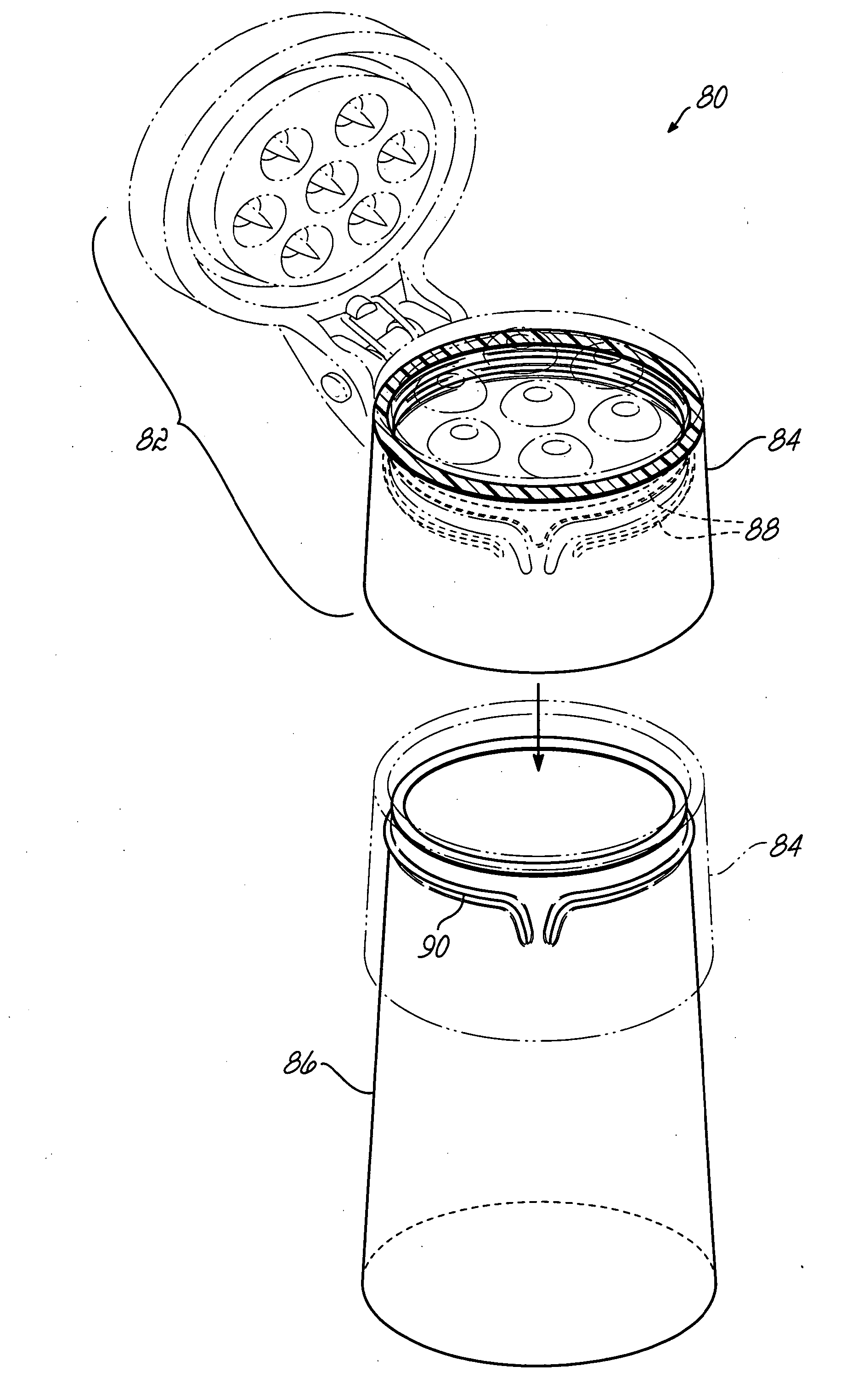

Sifter dish insert for cosmetic package

A sifter insert for the neck of a powder jar is secured above the product reservoir and below the cap of the jar. The insert has a central concave dish for supporting a quantity of powder product, and a channel around the perimeter of the dish. The insert is secured in the neck such that the dish is spaced below the bottom of the cap. Slots in the channel permit the flow of powder from the reservoir into the channel when the jar is inverted with the cap closed, and from the channel onto the dish when the inverted jar is righted. Powder in the dish is accessed by the user upon removal of the cap. The cap is then closed and the jar shaken to return excess powder from the dish to the reservoir through the slots in the channel.

Owner:ELC MANAGEMENT LLC

Condiment shaker

InactiveUS7100806B2Less incidenceLimited amountClosuresLiquid flow controllersEngineeringMechanical engineering

Owner:SURE SHAKE

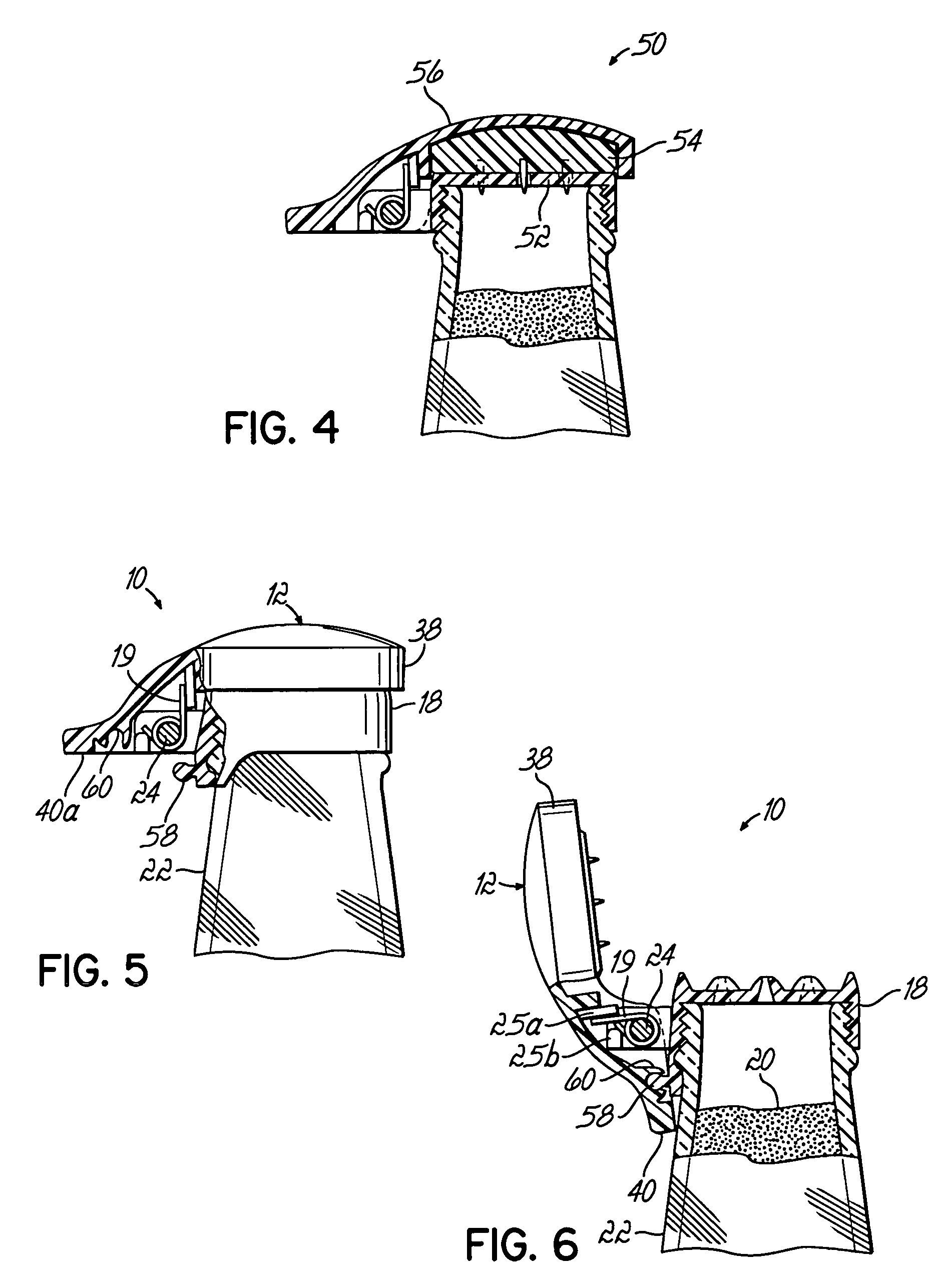

Powder Container

A powder container includes a container body and first and second insert members. The container body has an inner space for disposal of powder therein. The first insert member has a first surrounding wall inserted fittingly into the inner space, and a first bottom wall formed with at least one through hole. The second insert member has a second bottom wall inserted into the inner space and disposed on the first bottom wall, and a second surrounding wall extending upwardly from the second bottom wall and disposed fittingly and disengageably on the first surrounding wall of the first insert member for blocking passage of the powder to an external environment through the at least one through hole.

Owner:LAI JENN SHYANG

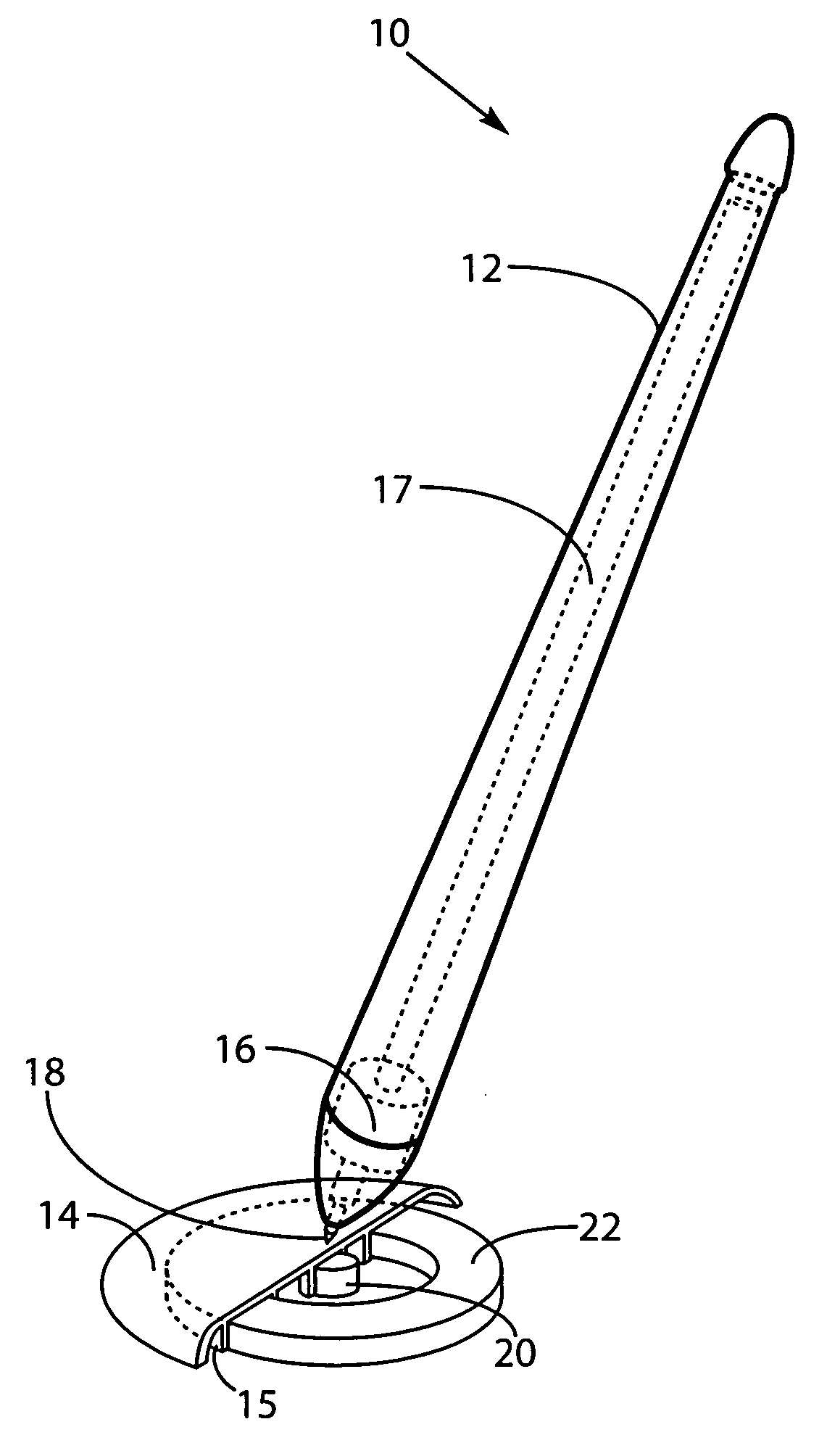

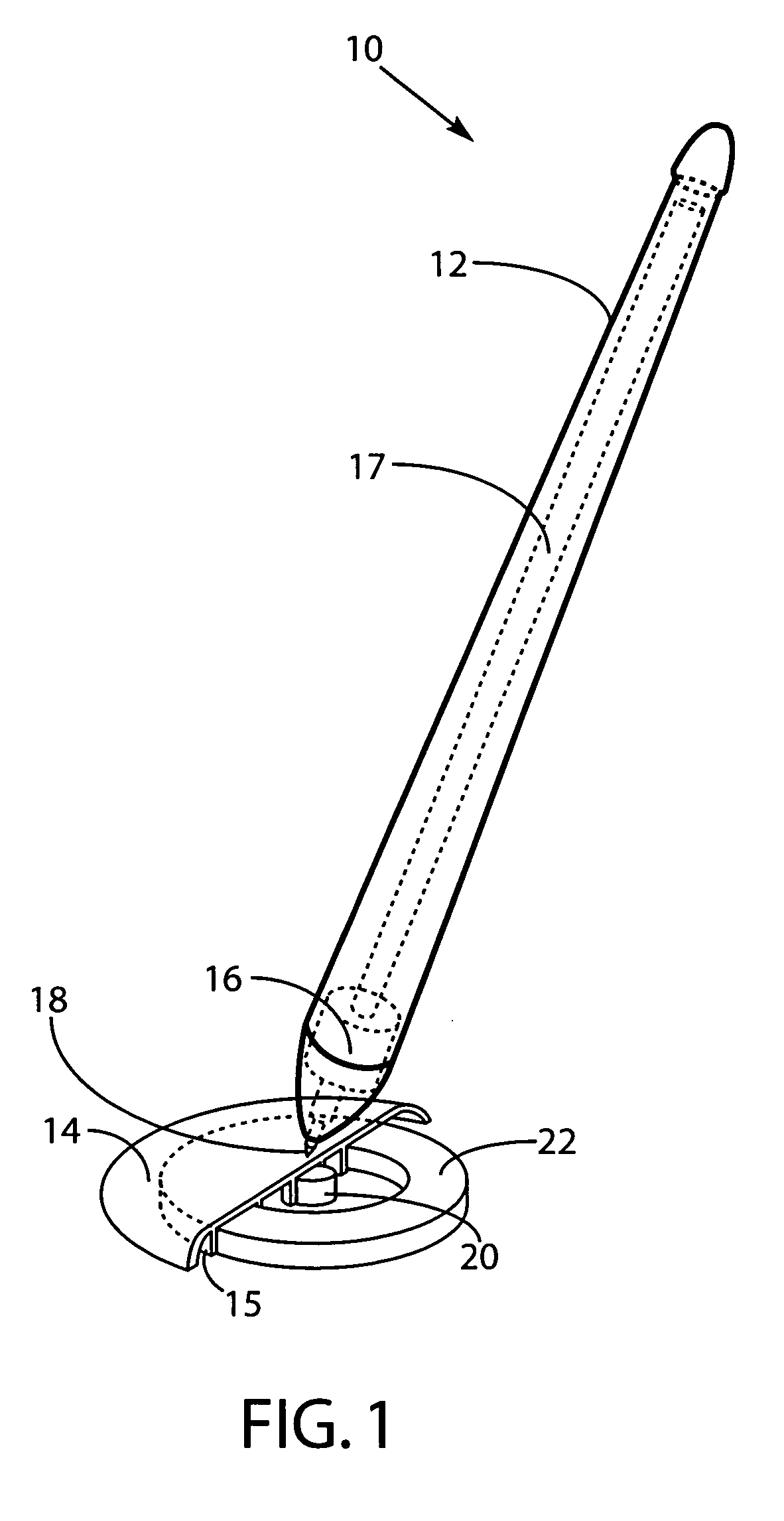

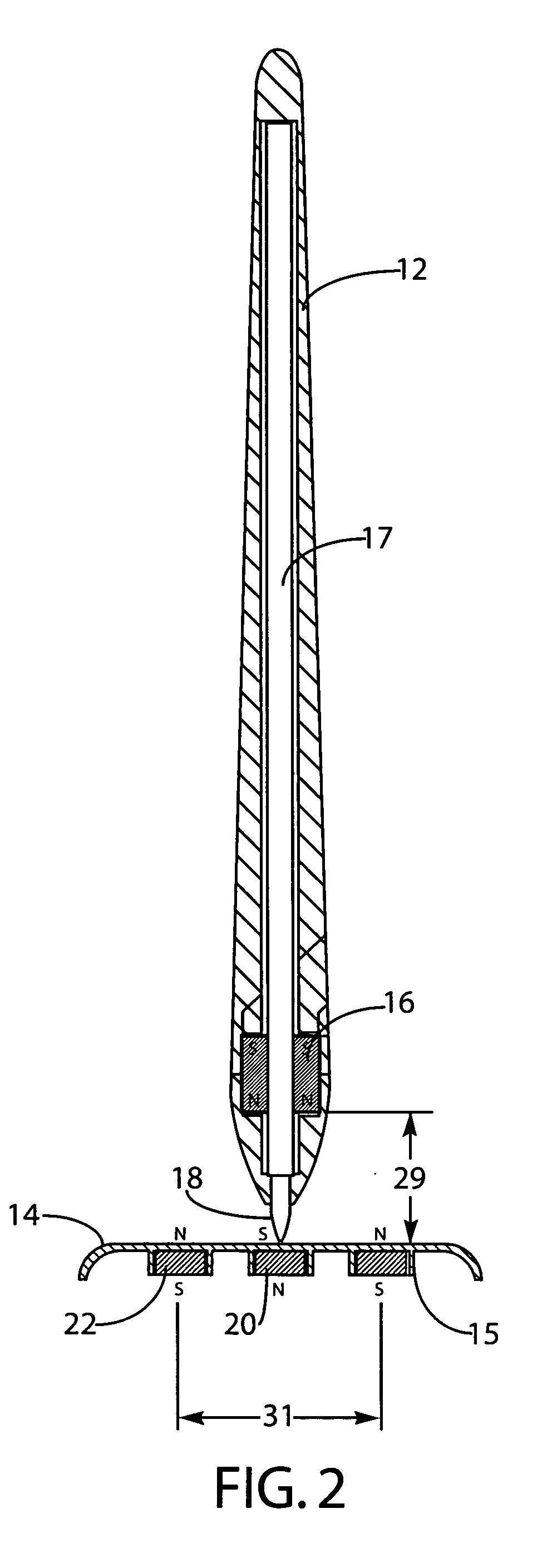

Self-balancing magnetic objects

A magnetically self balancing pen and base includes a base member housing a disk magnet and a concentric ring magnet having a predetermined inside diameter. The pen assembly has a barrel, an elongated ink cartridge with a magnetically attractable tip, and an annular magnet disposed inside the barrel and around the elongated ink cartridge. The annular magnet is located proximal but separated from the magnetically attractable tip with the end proximal the tip having a polarity equal to that of an upper surface of the ring magnet in the base.

Owner:RAMOS ALEX SORIANO

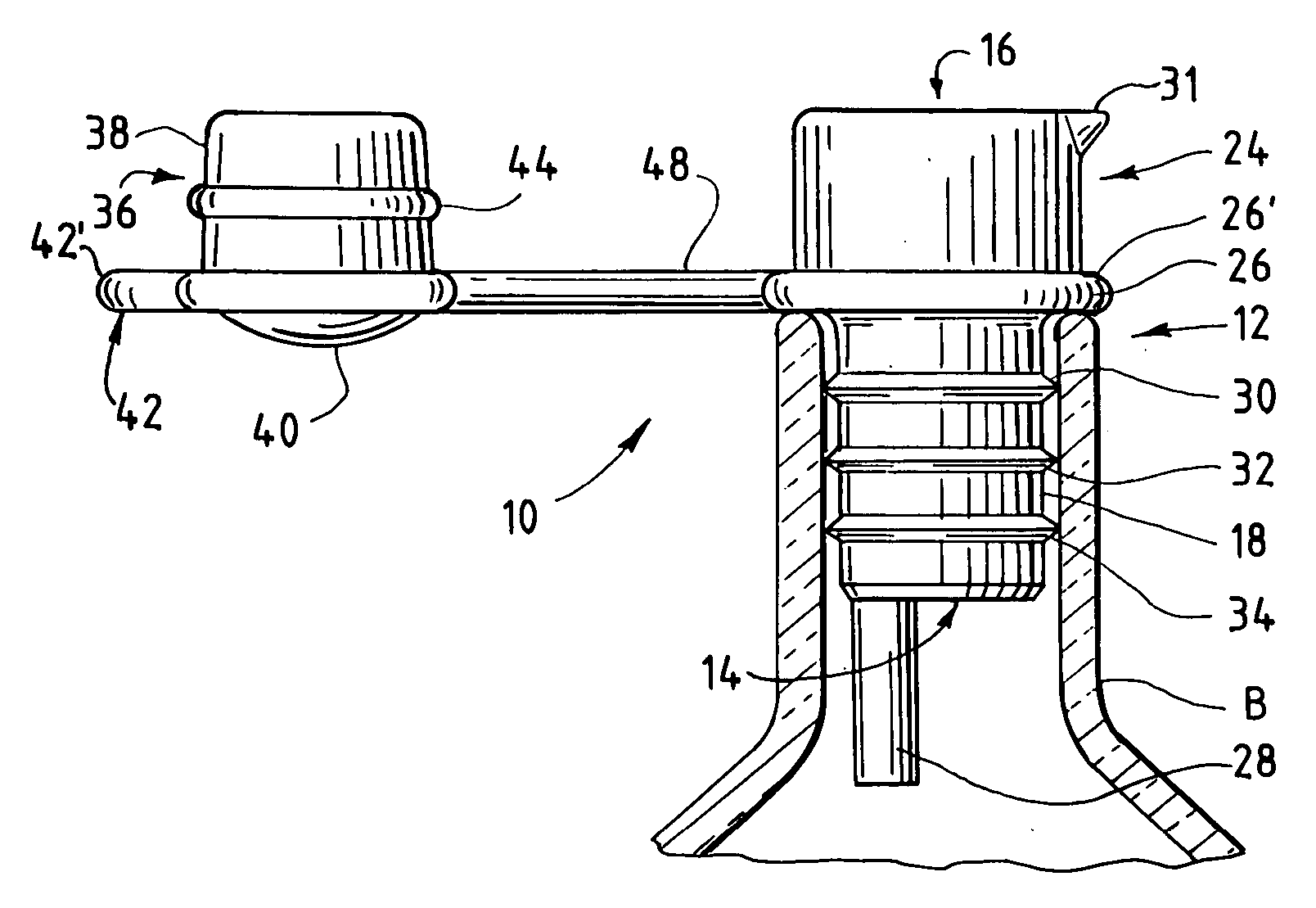

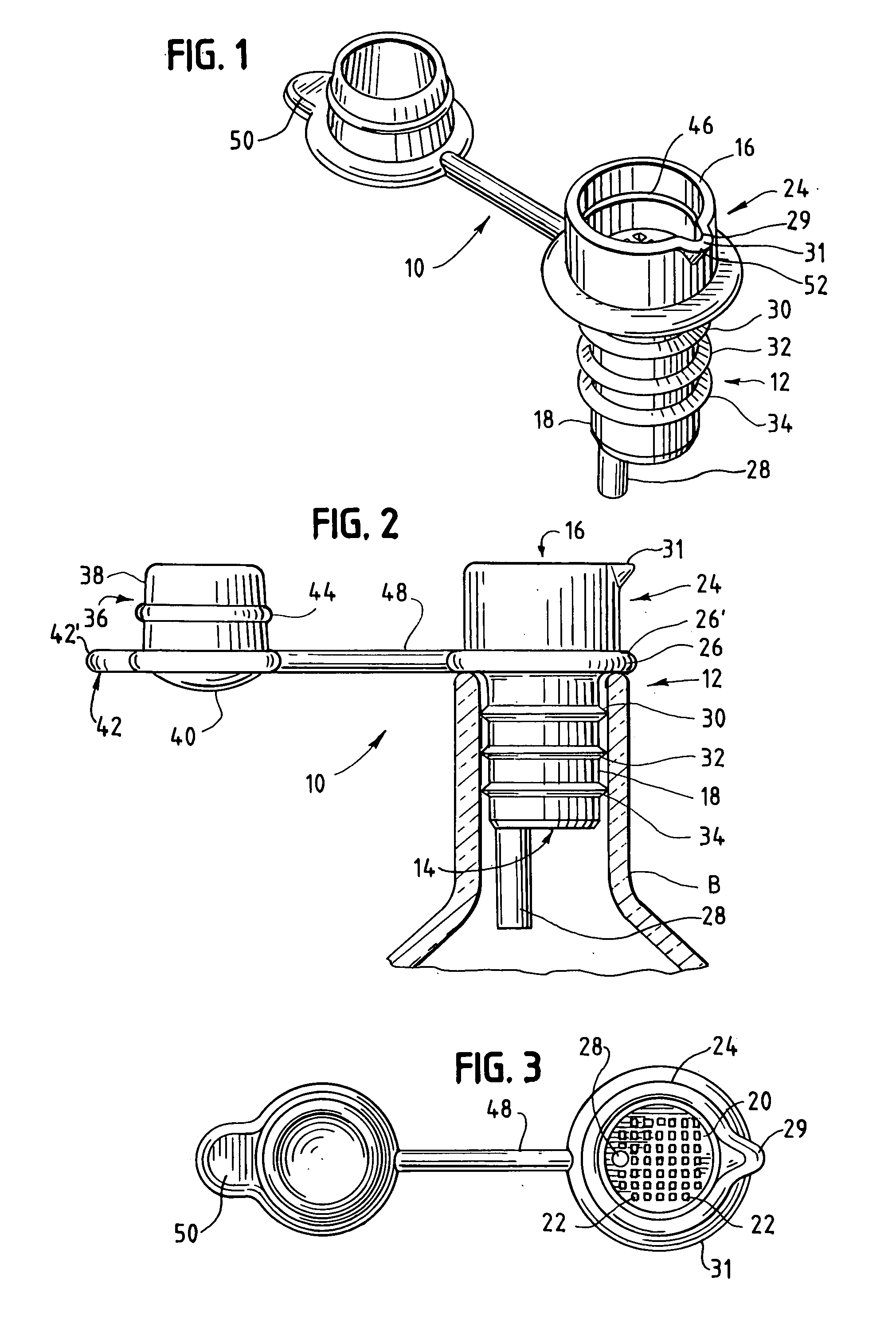

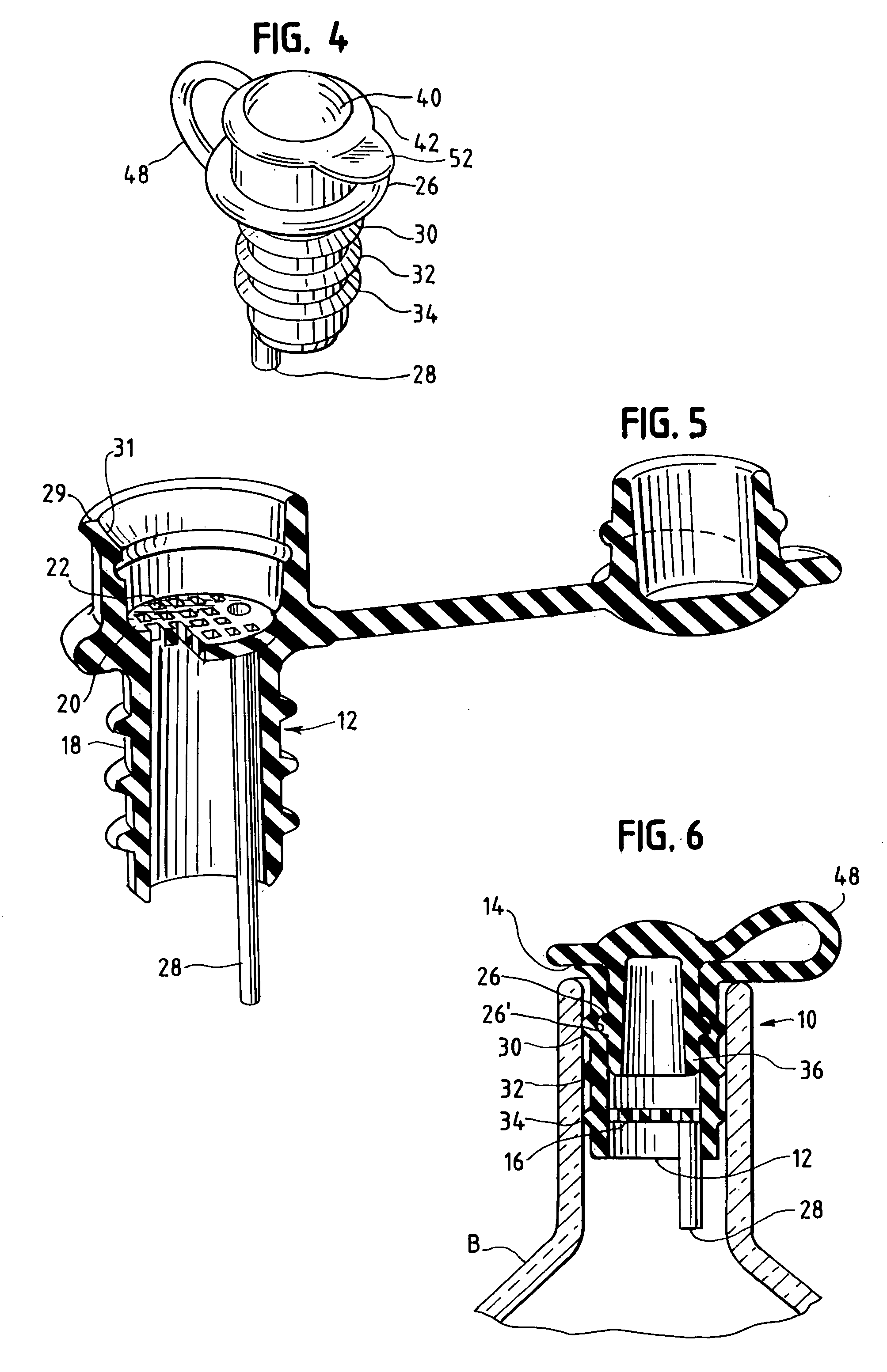

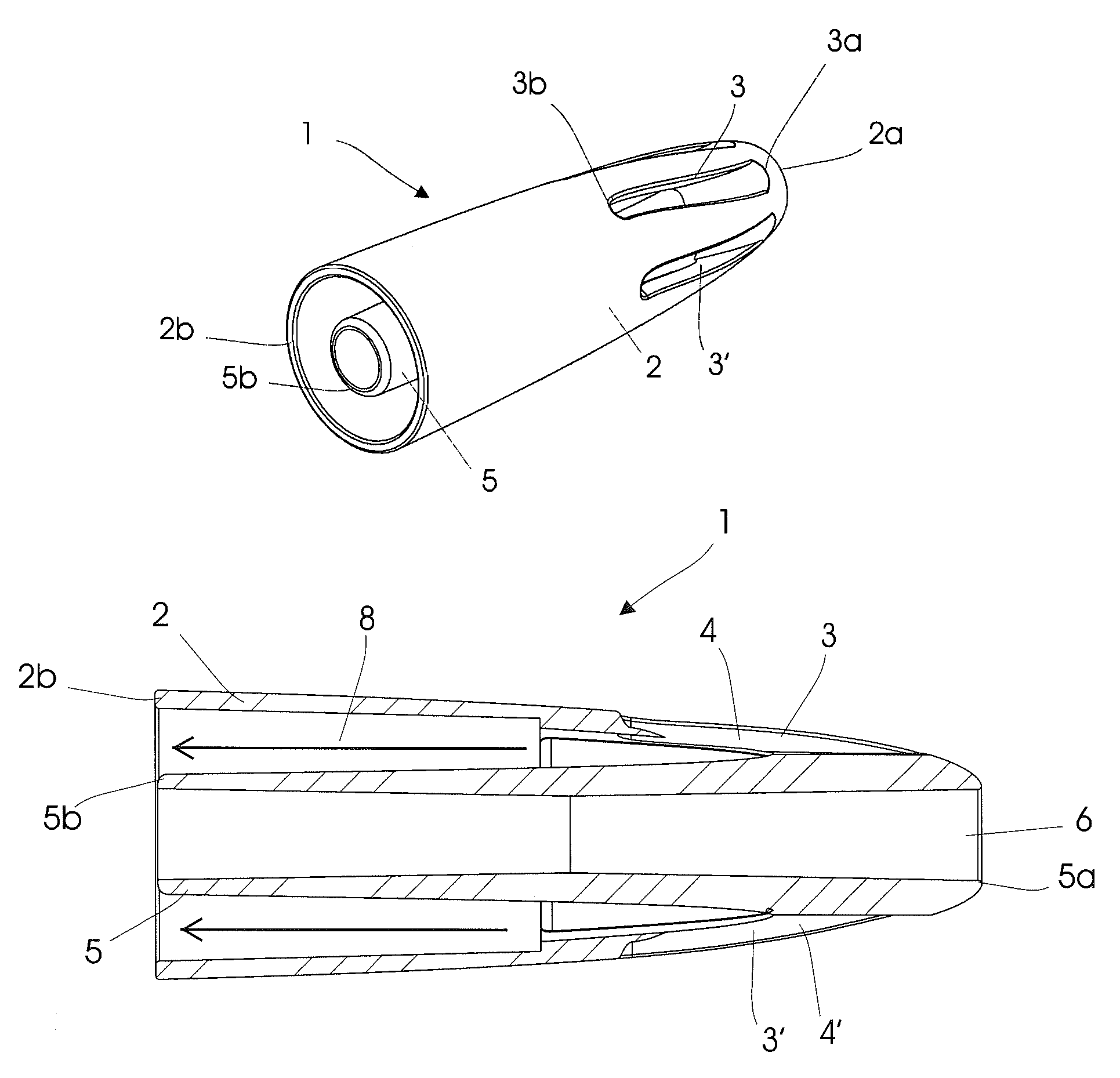

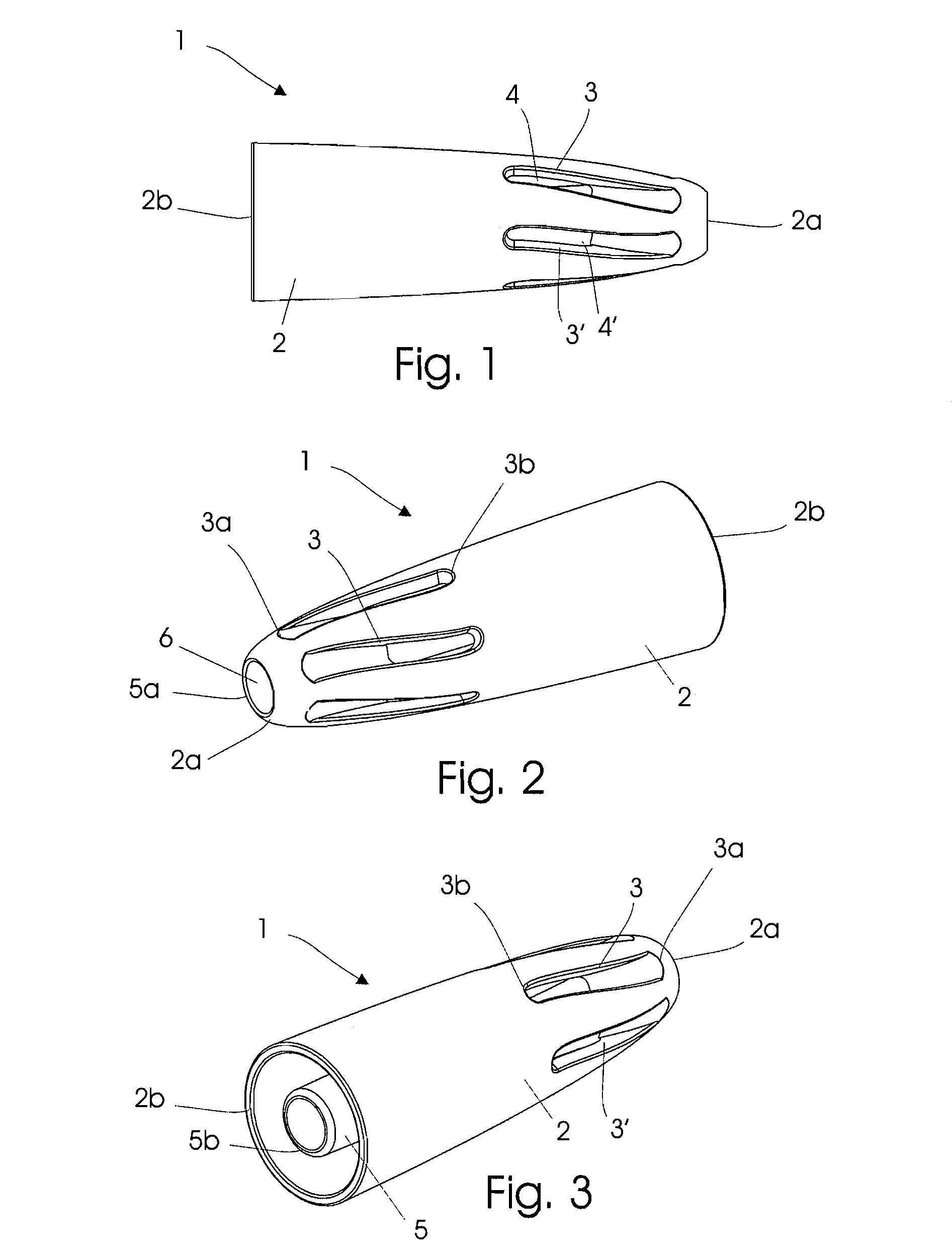

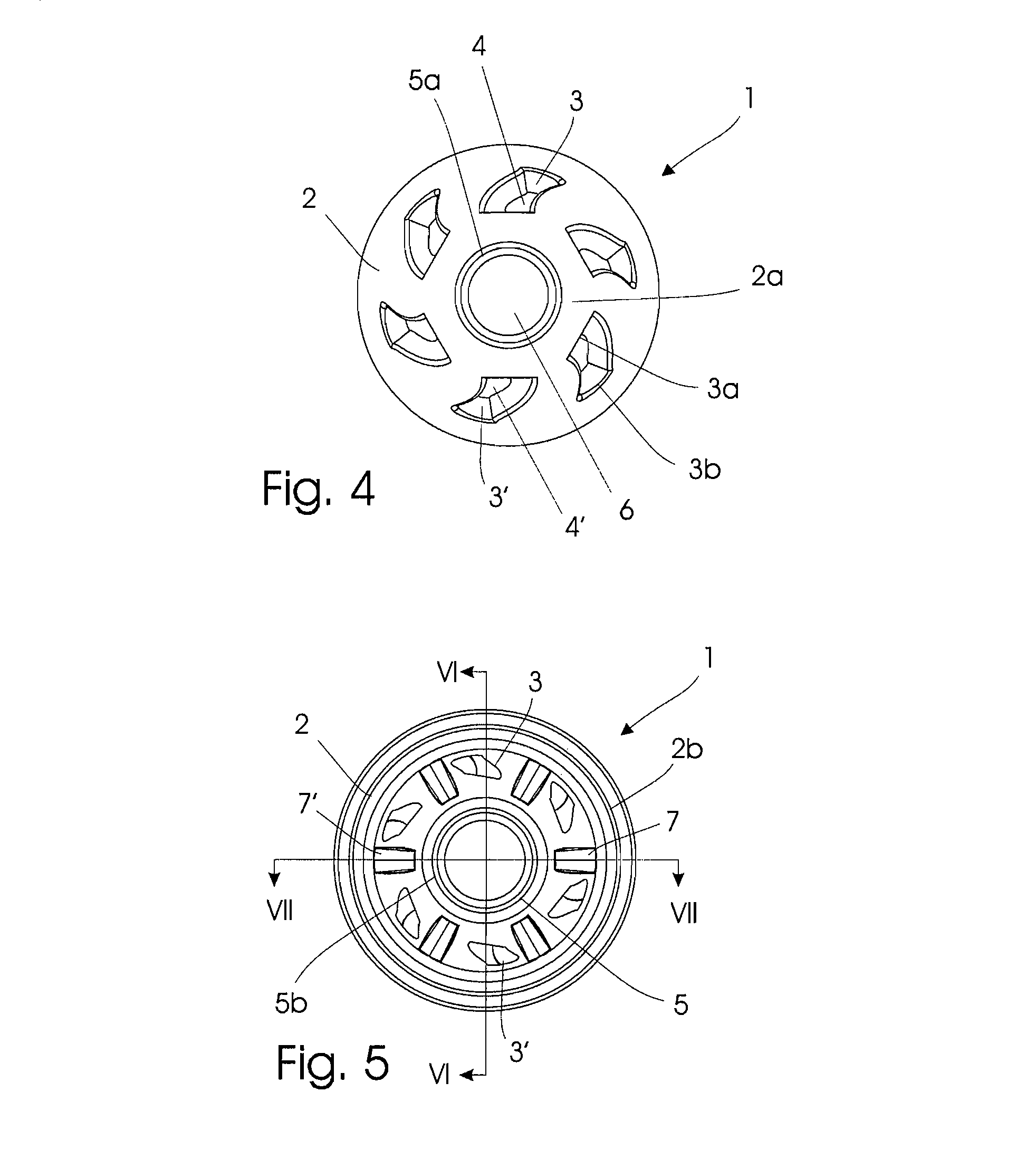

Pouring insert

InactiveUS8413858B2Maximizes liquid-air interfaceSimple and cost-effectiveClosuresFlow mixersEngineeringBottle

A pouring insert is provided for insertion into a container outlet, for example a bottleneck, for aerating liquids pored from the container. This is achieved by a combination of a hollow, tapering jacket with a hollow pipe axially disposed within it. The jacket features a plurality of elongated slots penetrating the jacket and allowing for liquid / air flow therethrough. The invention furthermore relates to a bottle pourer having a spout and the pouring insert described herein. The invention also relates to the use of the pouring insert and of the bottle pourer for aerating wine. Finally, the present invention relates to a method of manufacturing the pouring insert by injection molding.

Owner:IDEAS DENMARK

Metal and plastic dispensing lid

A serving lid for use with a container having a threaded upper exterior is provided. The serving lid includes a metal lid, a plastic liner, and a metal cap. The metal lid has a skirt, a lid top with a sidewall and convex cover, and a shoulder between the lid top and skirt. The skirt has a curled bottom and the lid top includes a lid dispensing port. The plastic liner has a flange is abutted against the shoulder and a distal end is clamped under the curled end to secure the plastic liner within the metal lid. A threaded interior of the plastic liner mates with the threaded upper exterior neck of the plastic container. The metal cap has a cap dispensing port and is rotatably coupled to the lid top.

Owner:JL CLARK INC

Sift-resistant dispensing closure

A sift-resistant dispensing closure is disclosed. The sift-resistant dispensing closure includes a base, a lid and a hinge connecting the lid to the base. The base contains a circular end wall, a cylindrical skirt extending downward from the periphery of the end wall, and a sift deck elevated from the upside of the circular end wall. The sift deck contains a deck surface surrounded by a first snap bead and a first sealing surface, and pouring holes formed on the deck surface. The lid contains a second snap bead and a second sealing surface that are formed on the underside of the lid and engage with the first snap bead and first sealing surface, respectively, to form a seal around the sift deck when the lid is in a closed position.

Owner:WEATHERCHEM

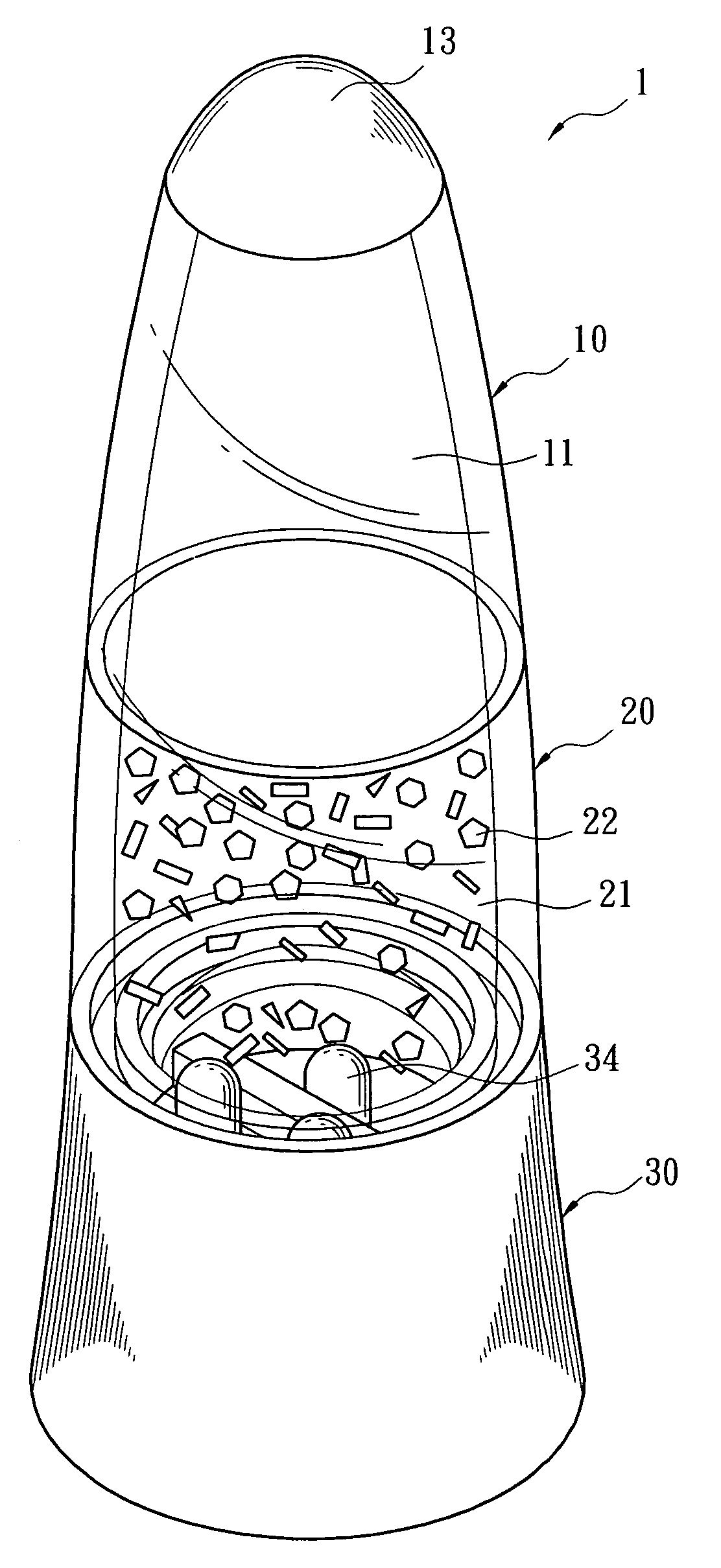

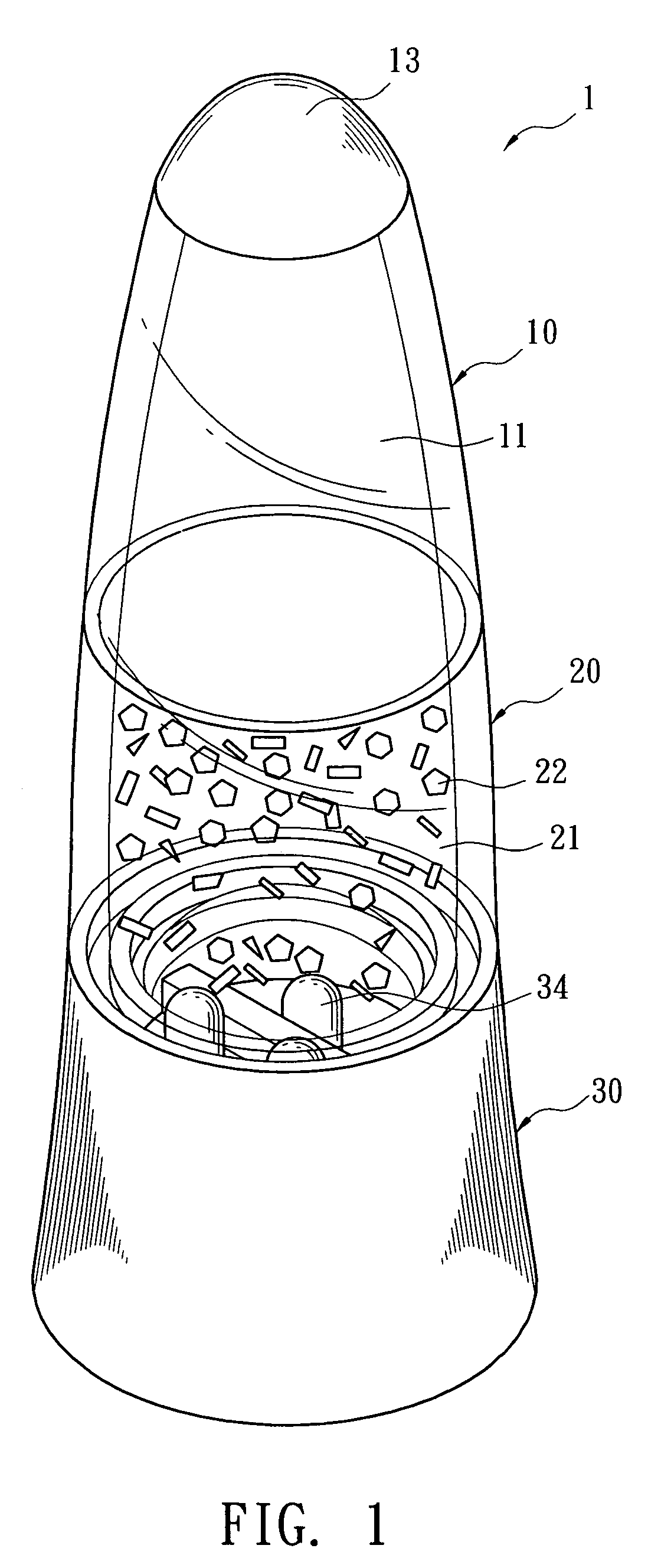

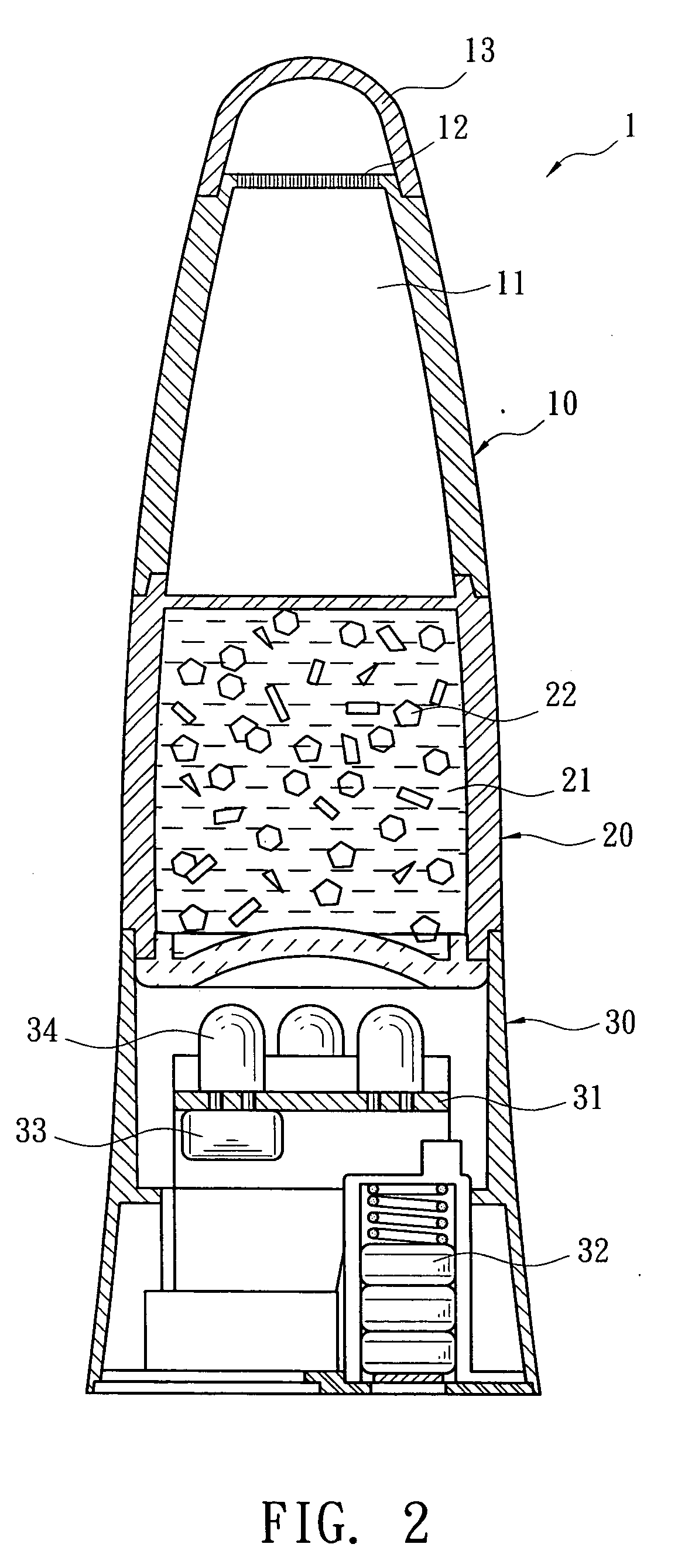

Spice bottle

A spice bottle includes a spice container, a transparent liquid container and an container for electronic parts. The spice container is disposed on upper part of the spice bottle with holes facing upwards. The transparent liquid container is filled with transparent liquid with a plurality of differently colored lustrous foil fragments flowing therein for display. The container for electronic parts is disposed with a circuit board, a battery holder, a vibration switch and a plurality of LED (light-emitting diode) lamps. Light emitted from the LED lamps illuminates into the transparent liquid container. When the spice bottle is shaken for pouring spices out, the lustrous foil fragments inside the transparent liquid container is simultaneously driven to flow freely. At the same time, the LED lamps are turned on by the vibration switch for emitting light into the transparent liquid container so as to show dynamic lighting effect caused by reflection of the lustrous foil fragments.

Owner:LIN MING KUEI

Powder delivery system

InactiveUS20120080457A1Efficient removalNegates needClosuresLiquid flow controllersDelivery systemMaterials science

A delivery system for delivery of powders to targeted areas. Various embodiments include a powder delivery train that mates with standard-sized powder containers. Another embodiment includes a bellows container that contains the powder and propels the powder through the powder delivery train. Another embodiment integrates the powder delivery train with the sifter cap and enables the powder delivery tube to be stowed within the powder container.

Owner:POWDERWAND

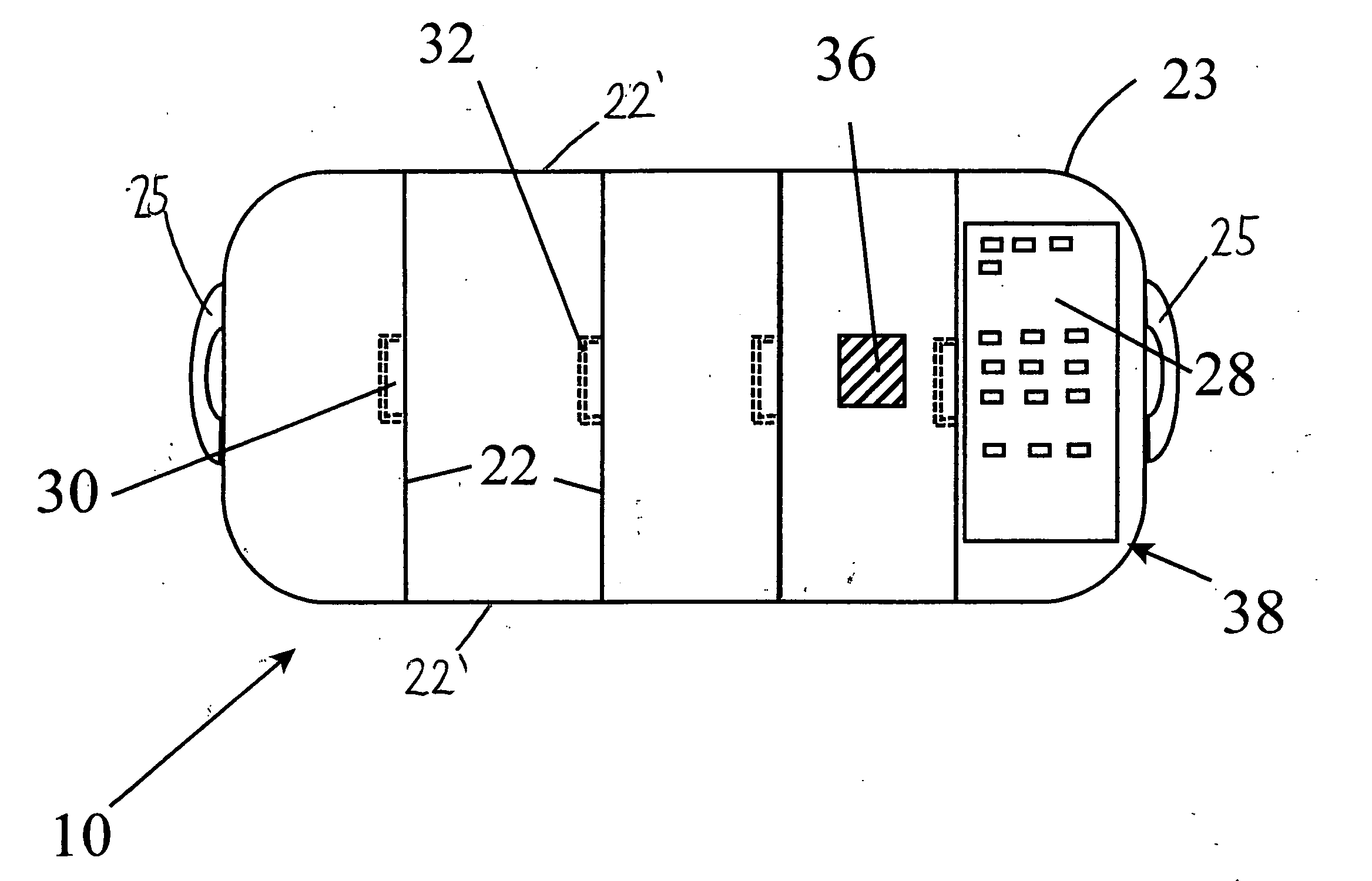

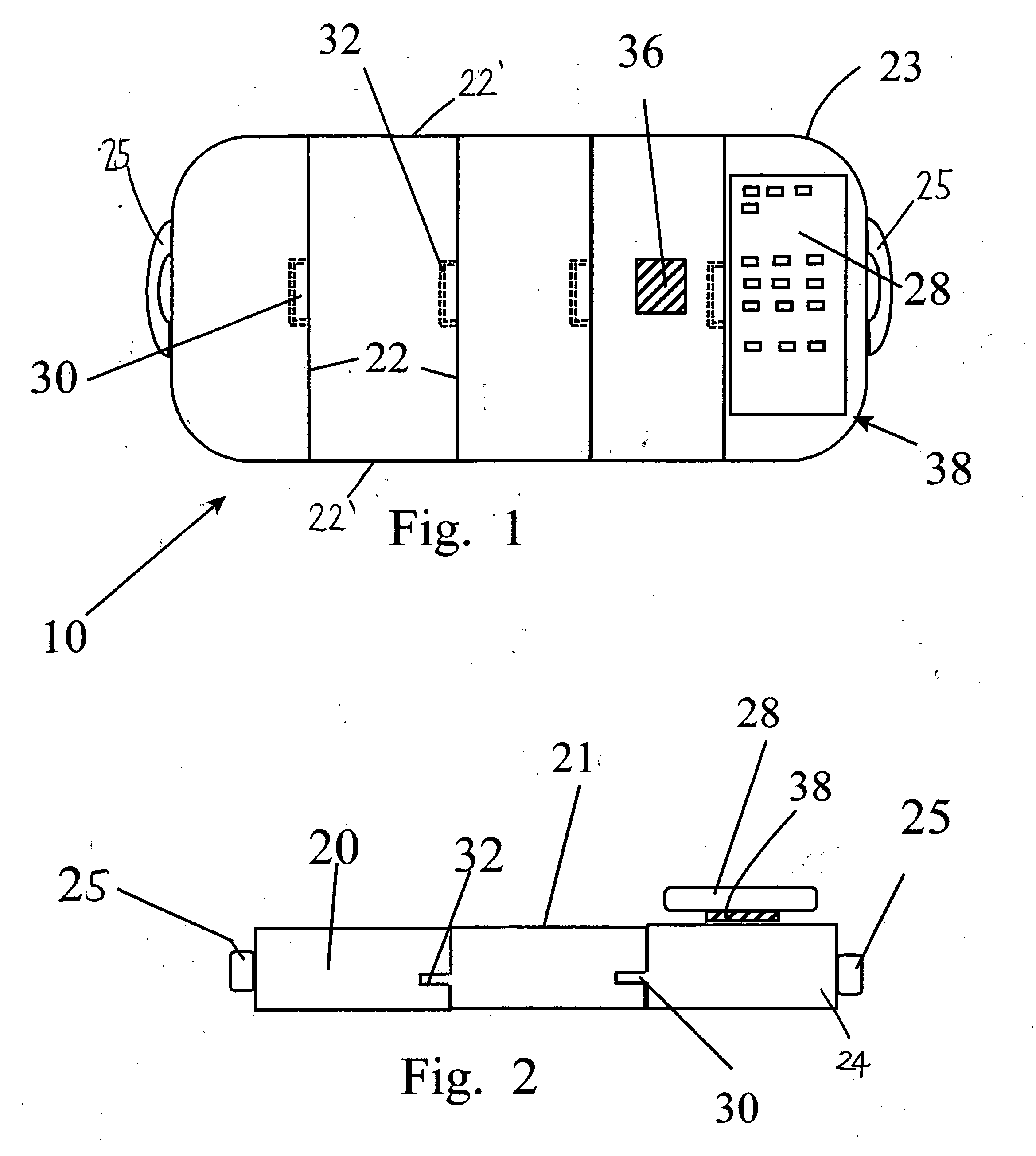

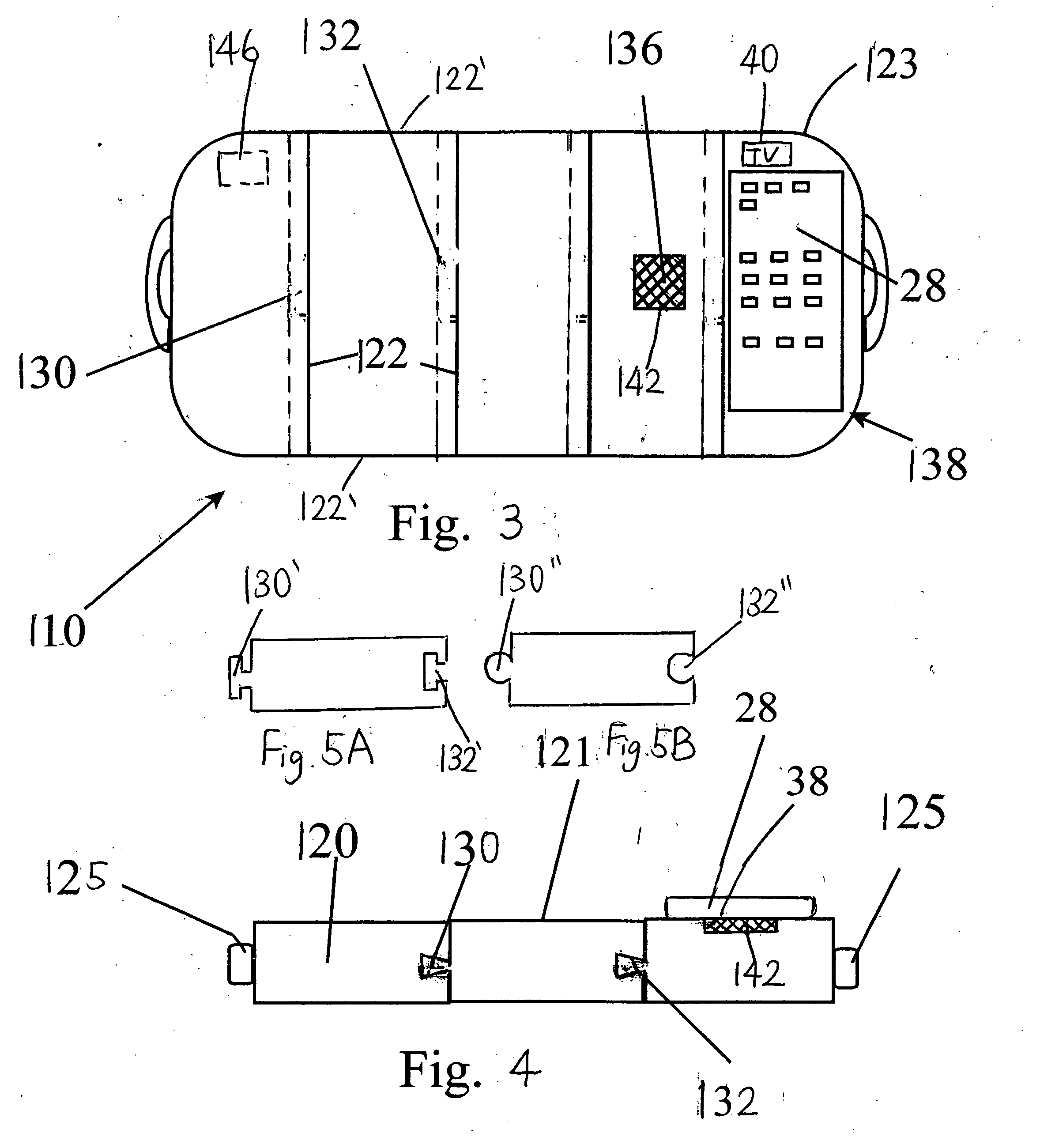

Expandable remote control organizer

A compartmentalized organizer for accommodating one or more remote controls. The organizer has a plurality of discrete compartments which are substantially identical but variable with respect to size. Each compartment has a substantially rectangular shape, with both male and female connectors. The male connector is laterally disposed on the opposing side from the female connector allowing the compartments to be laterally arranged in releasably connectable fashion. The remotes are situated on the top panel of each compartment to allow line of sight transmission while still positioned on the compartment. Signaling means may be provided to allow for communication between compartments and the remote controls accommodated thereon.

Owner:TAWANAPOOR ALI

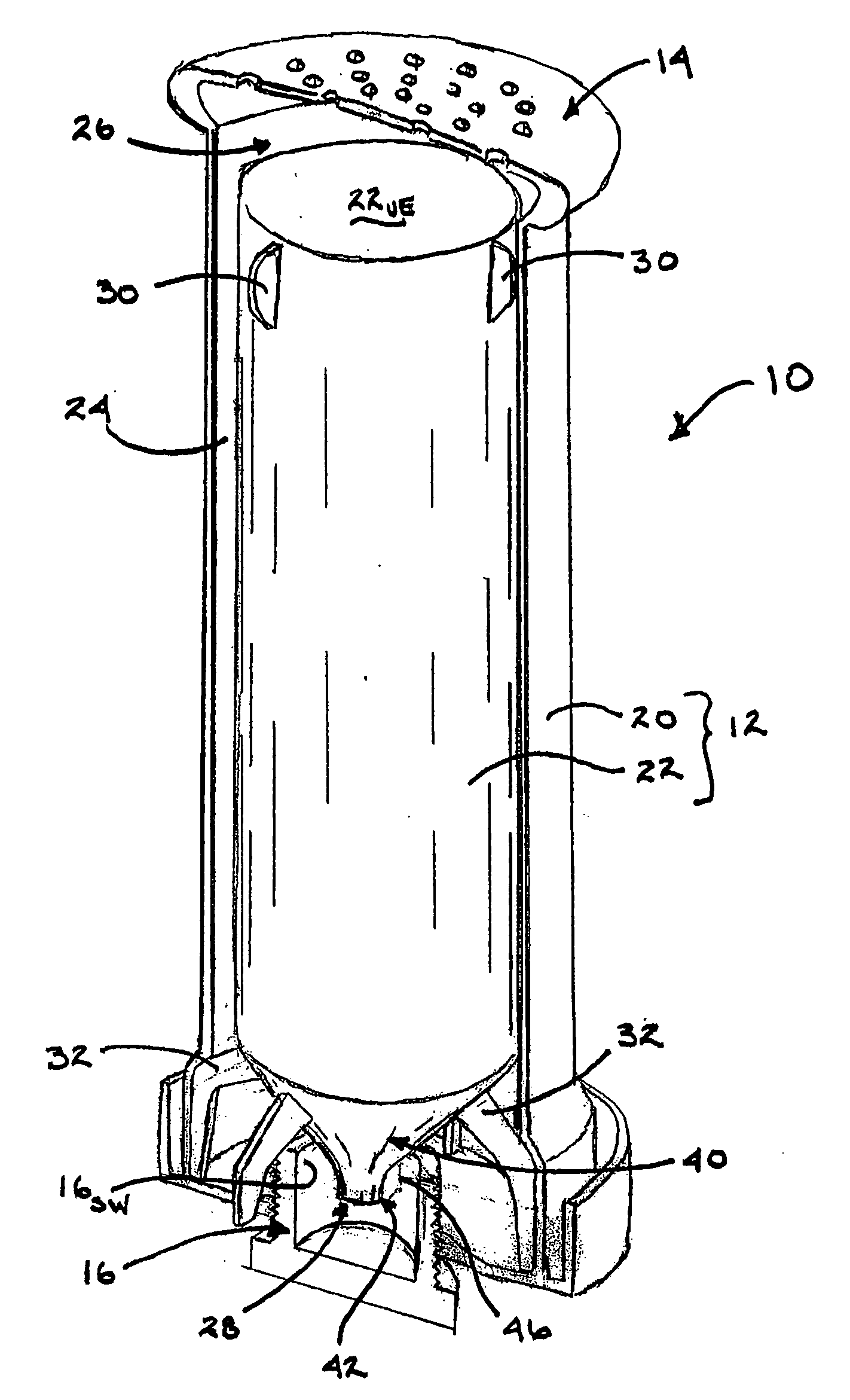

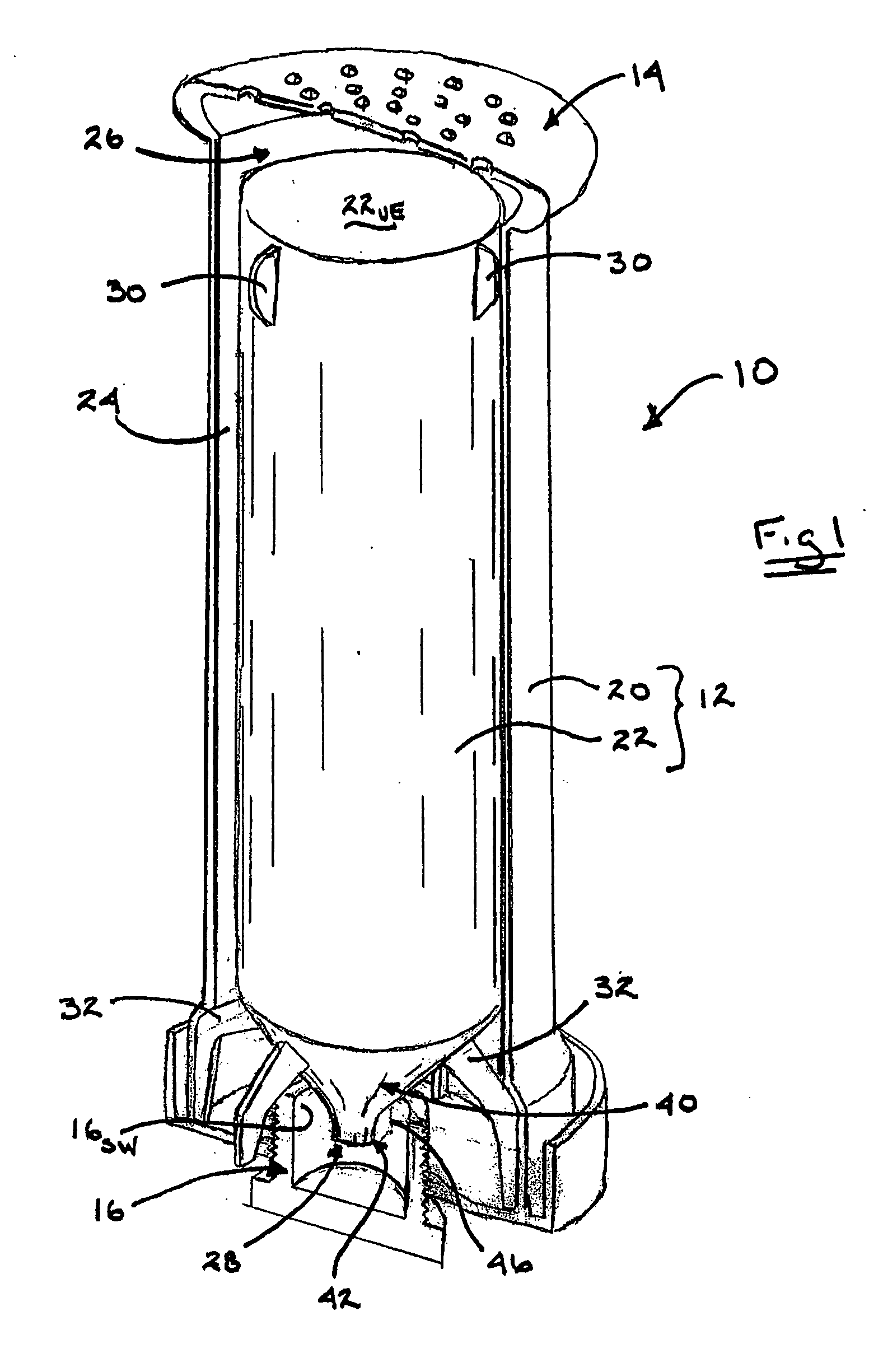

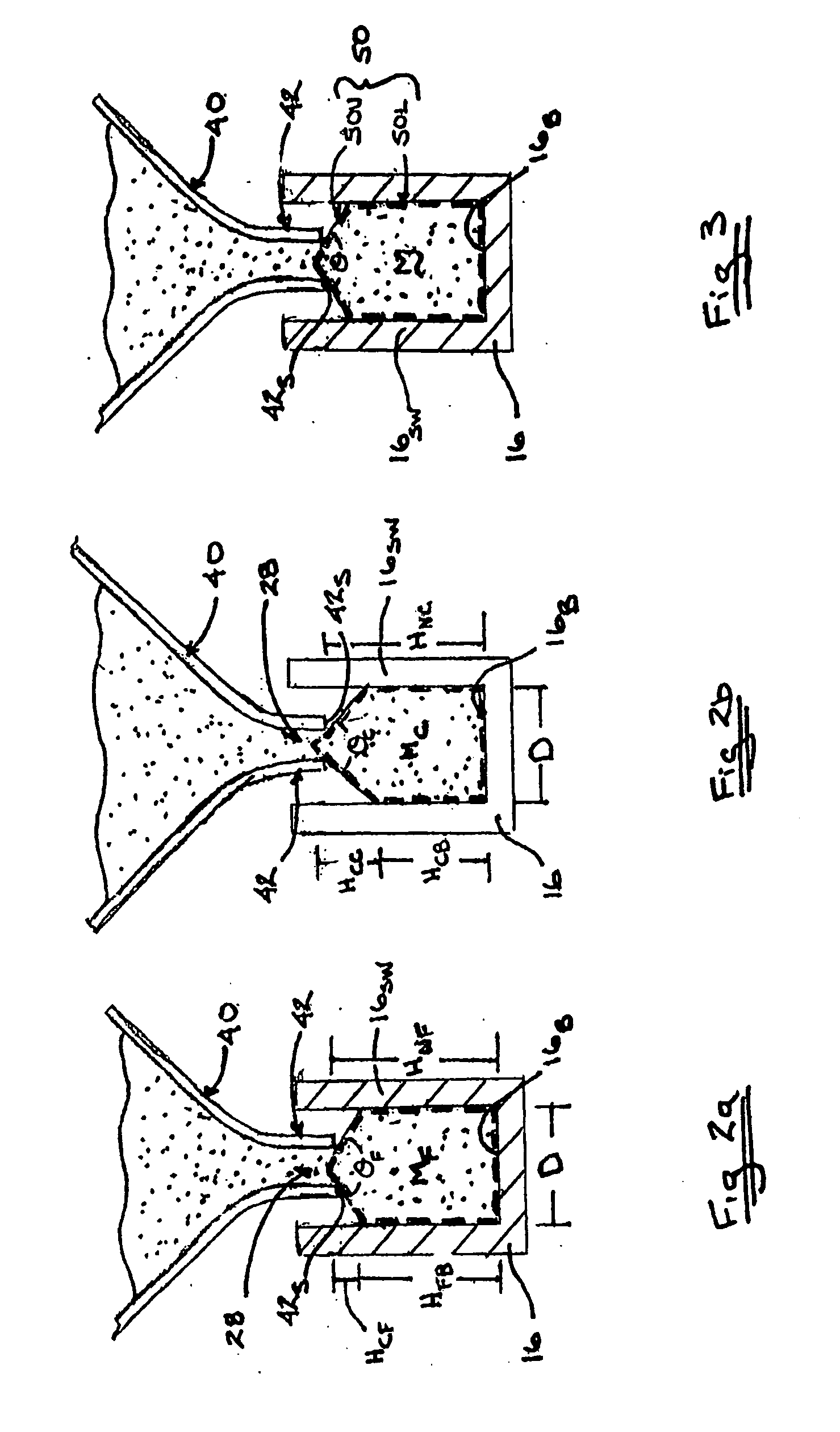

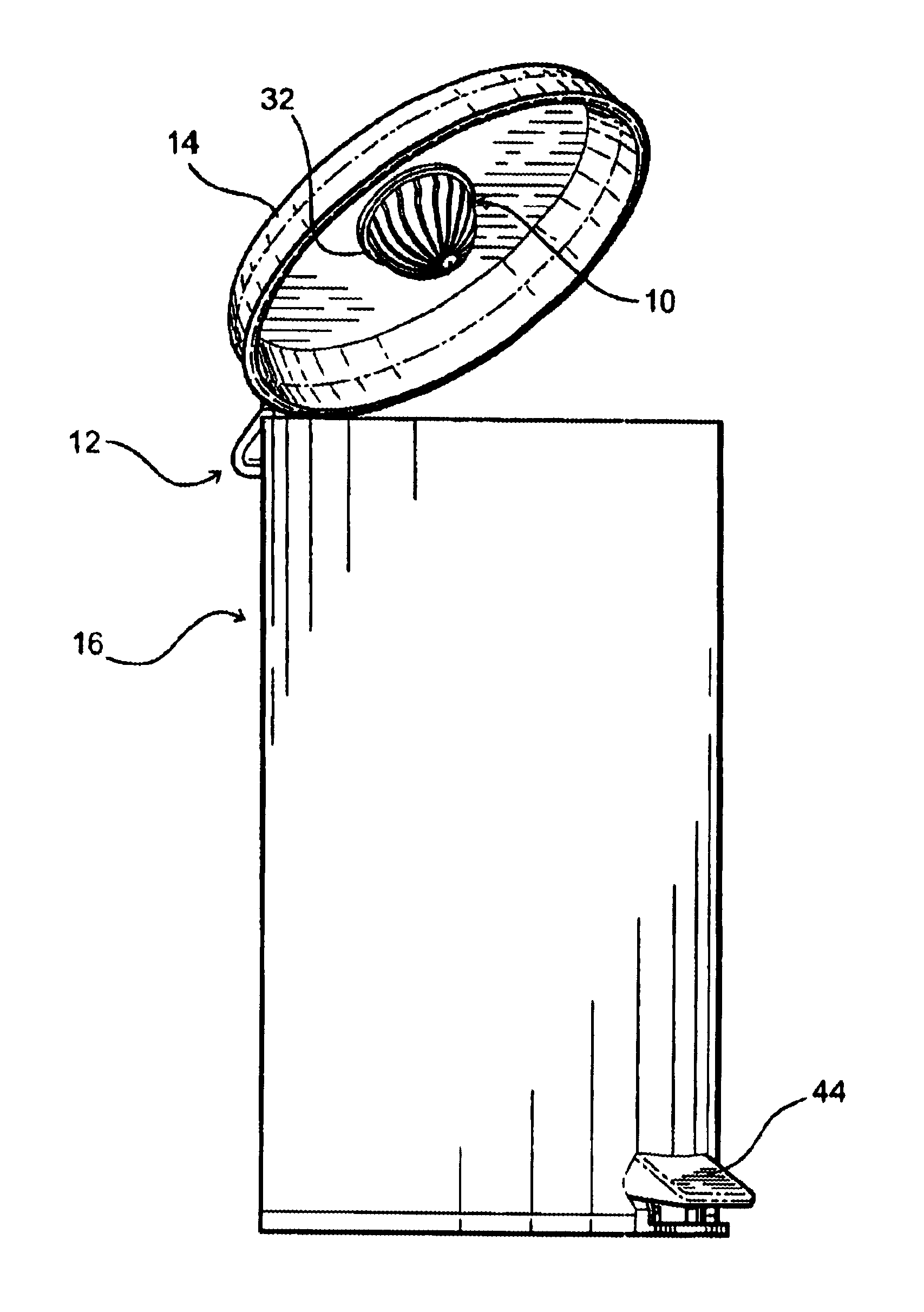

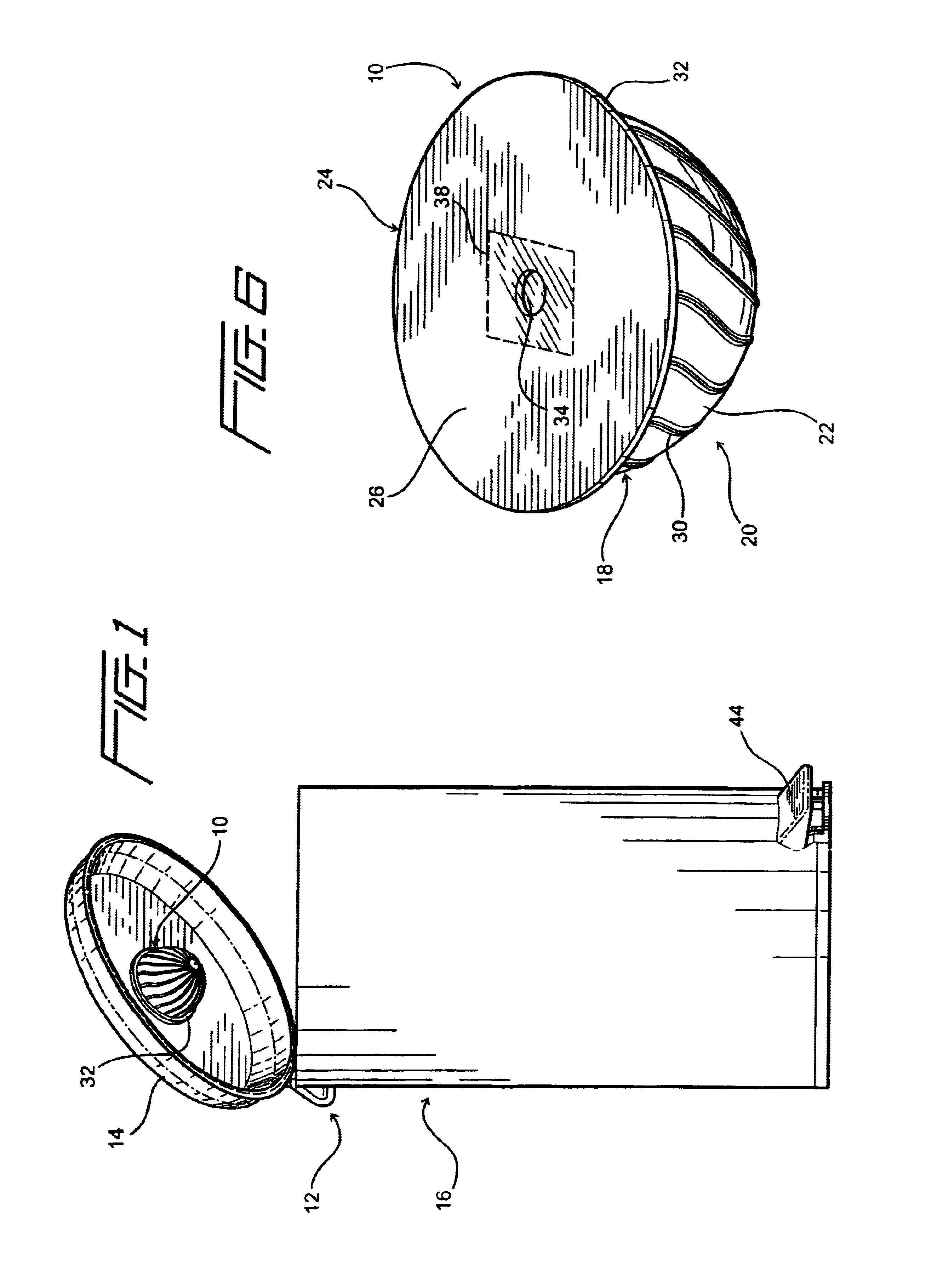

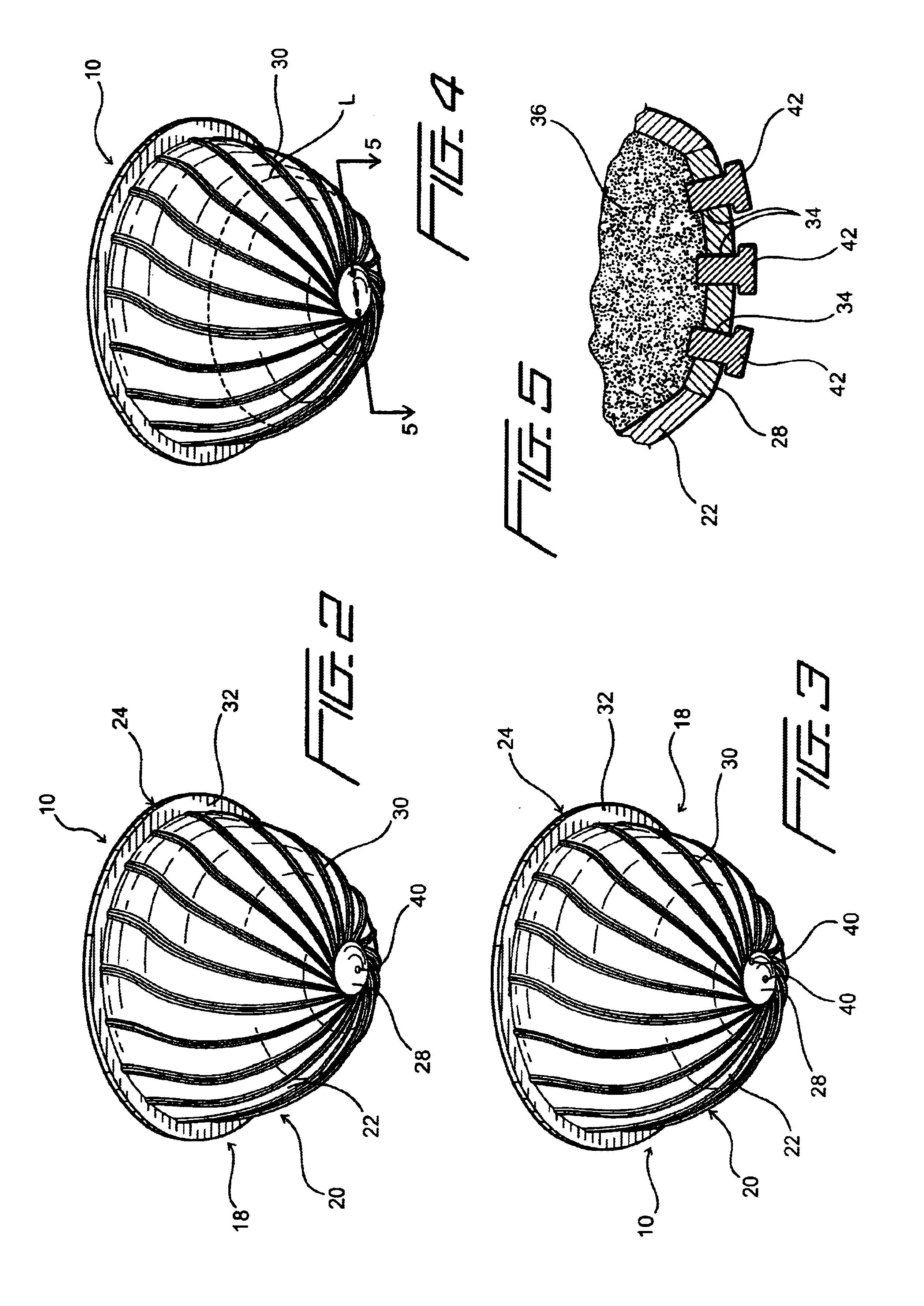

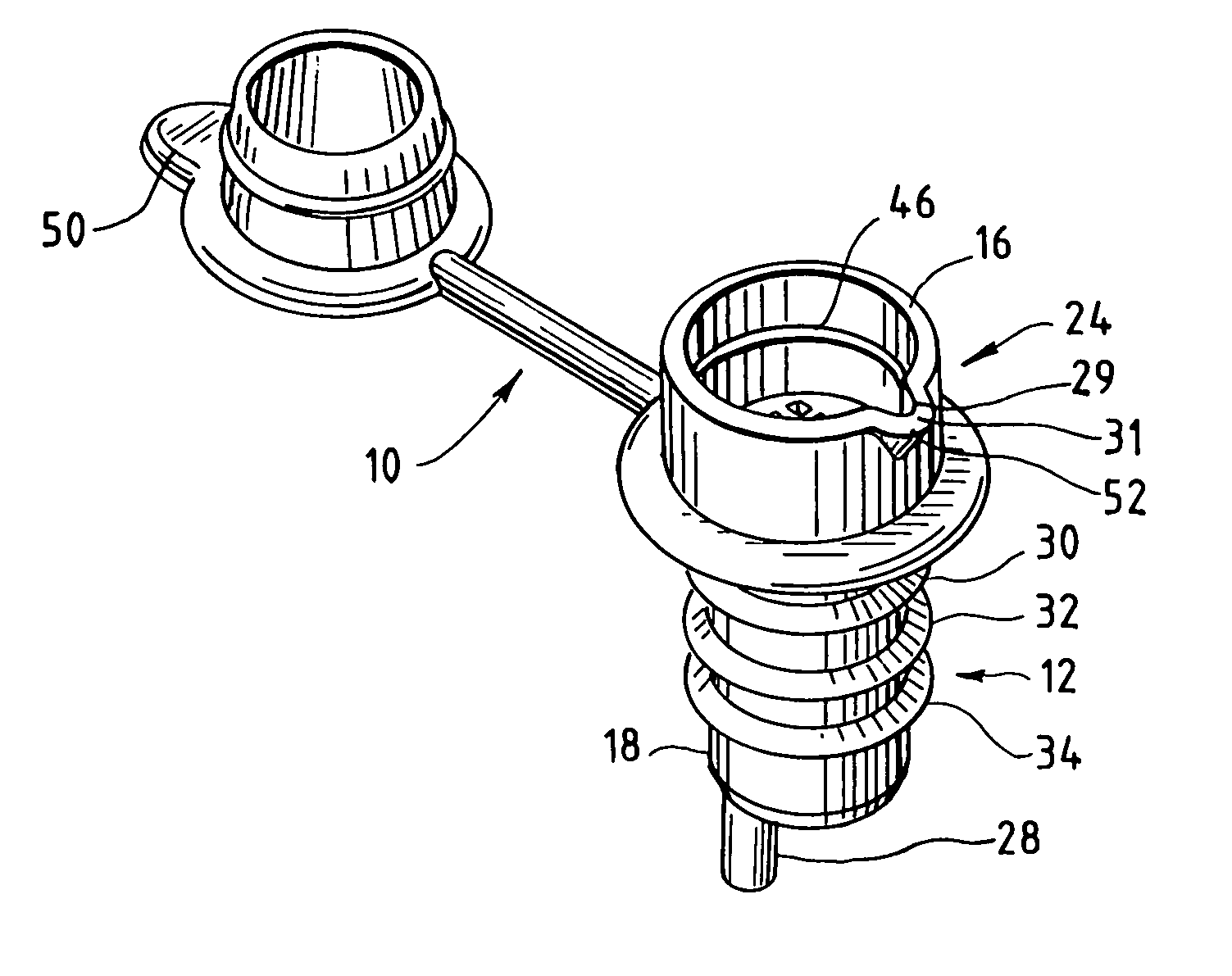

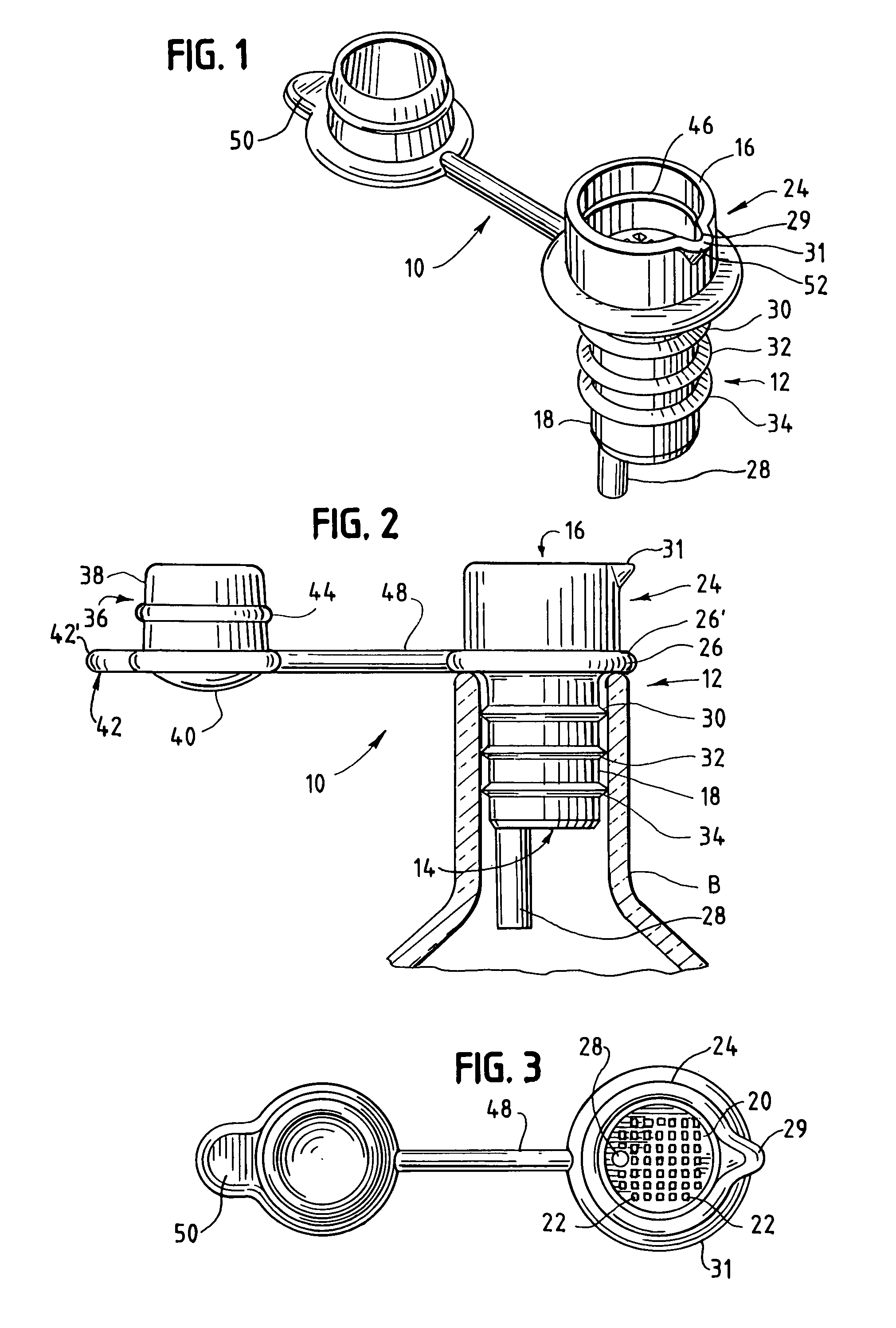

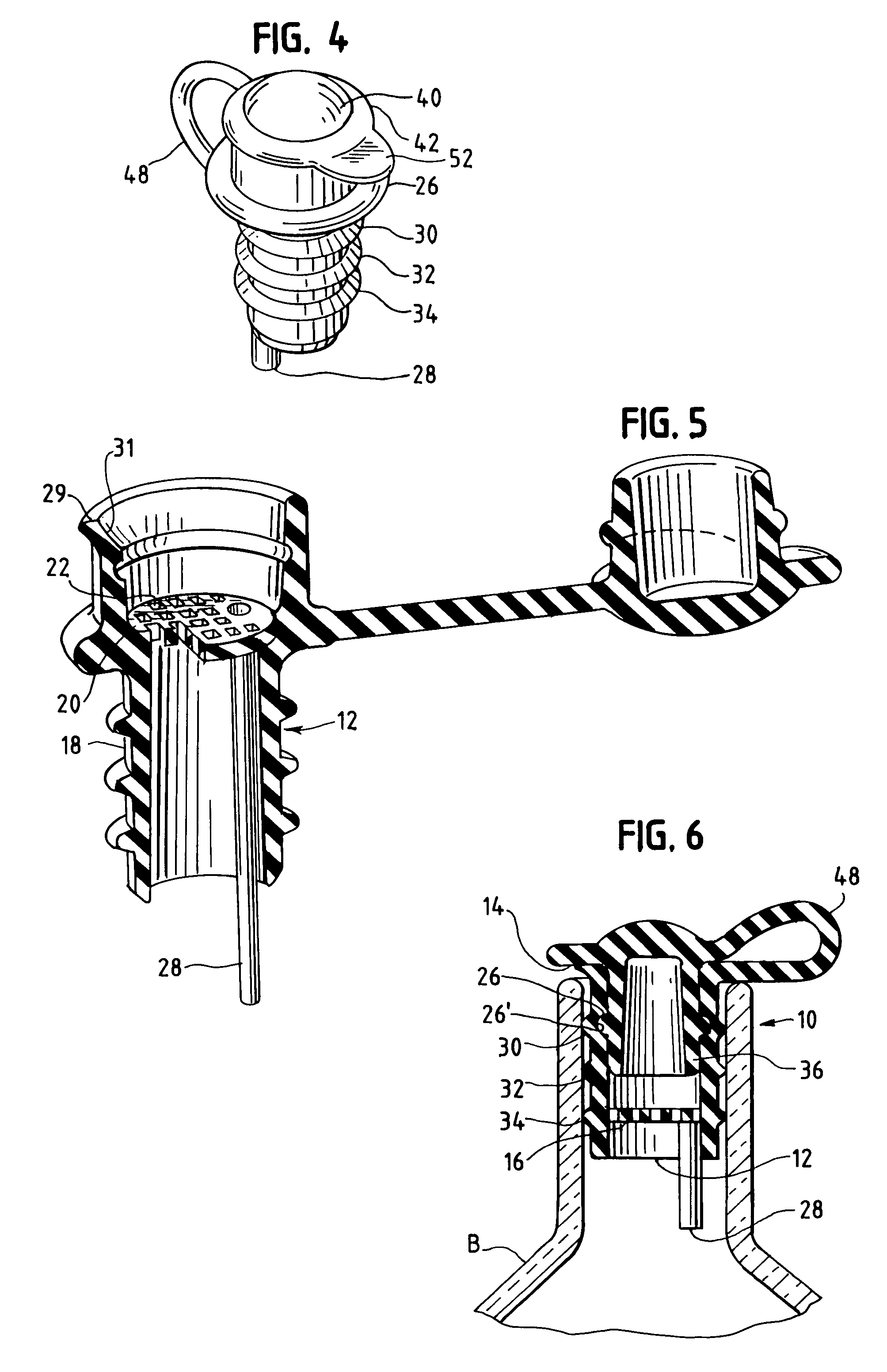

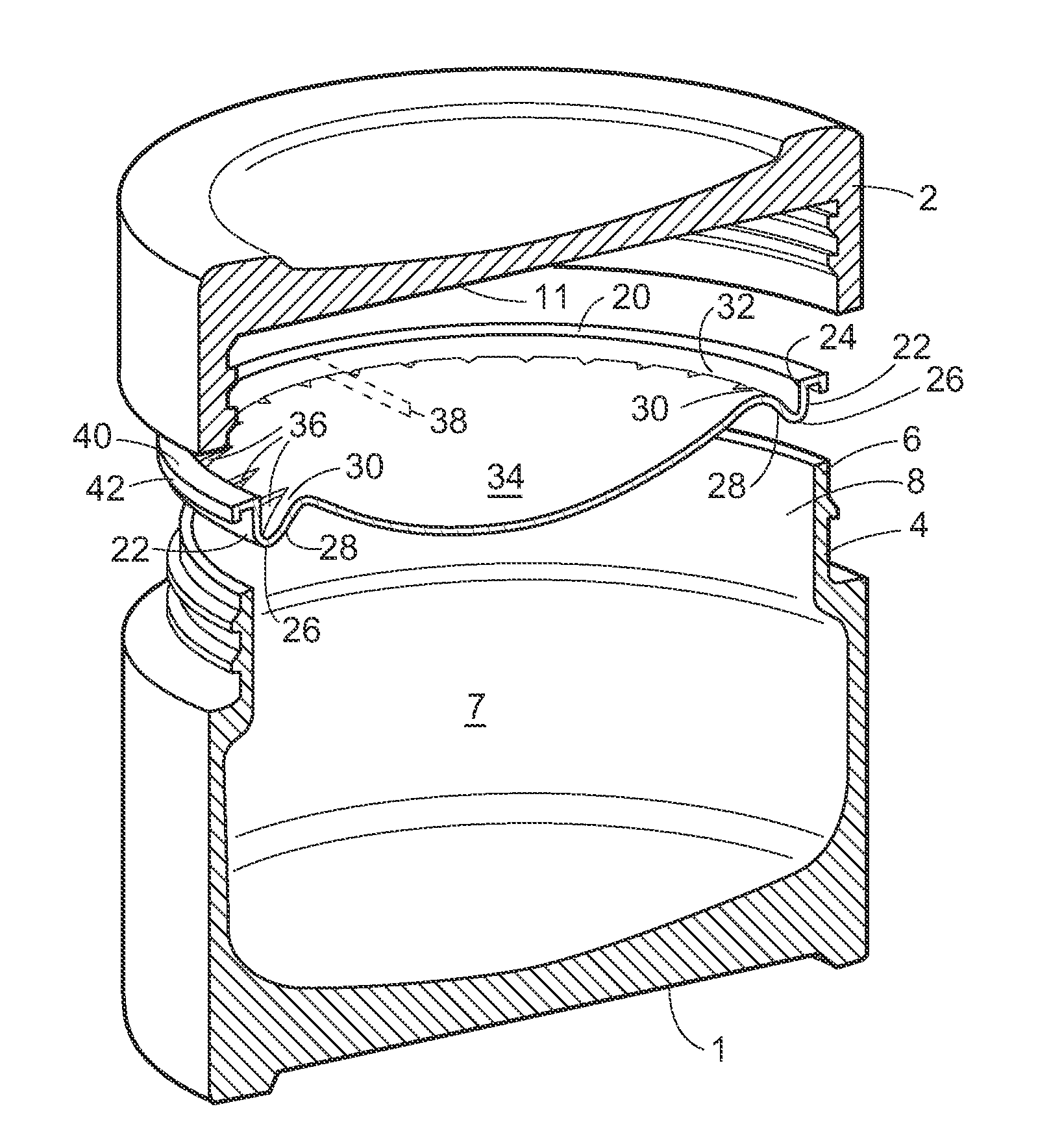

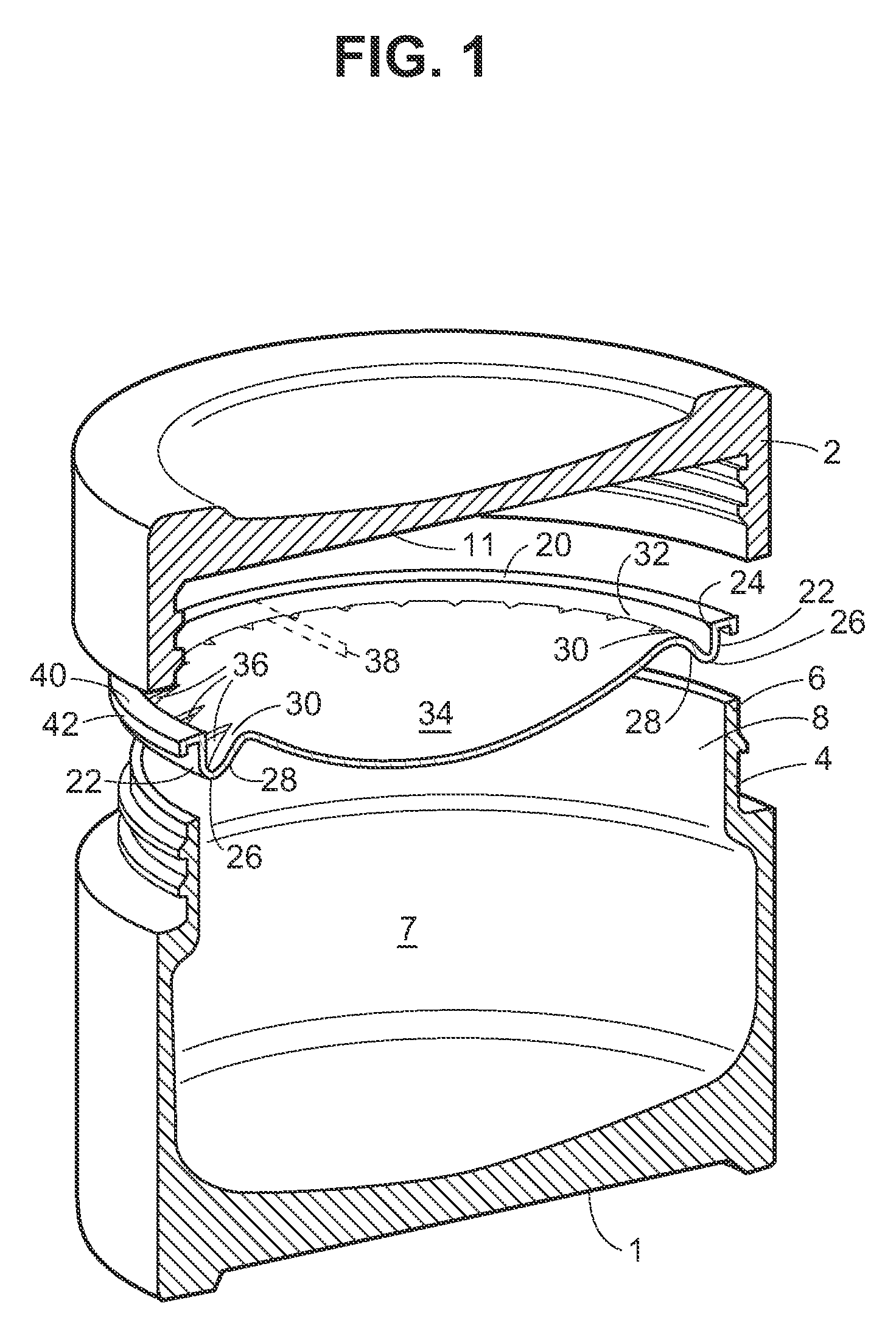

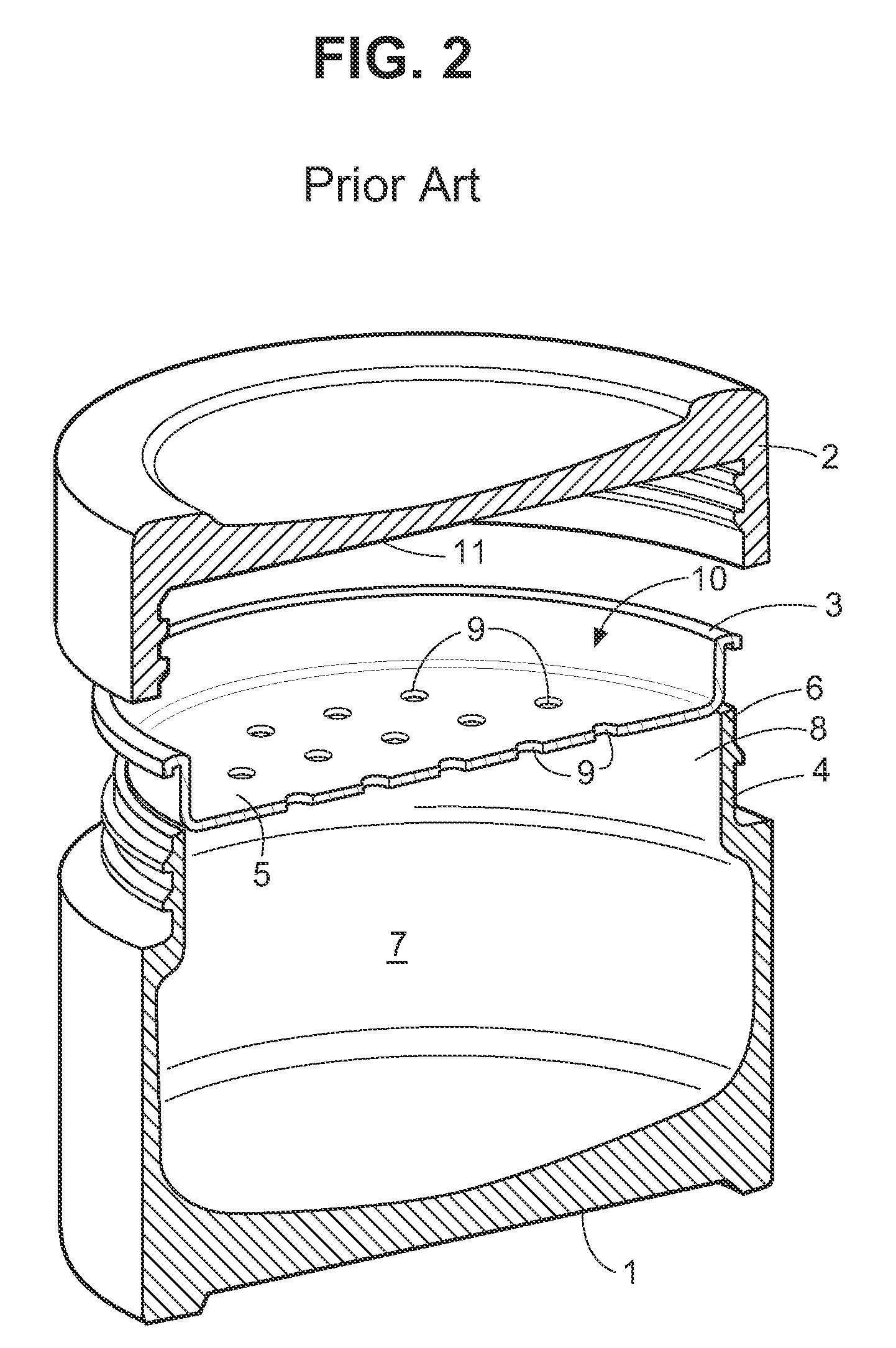

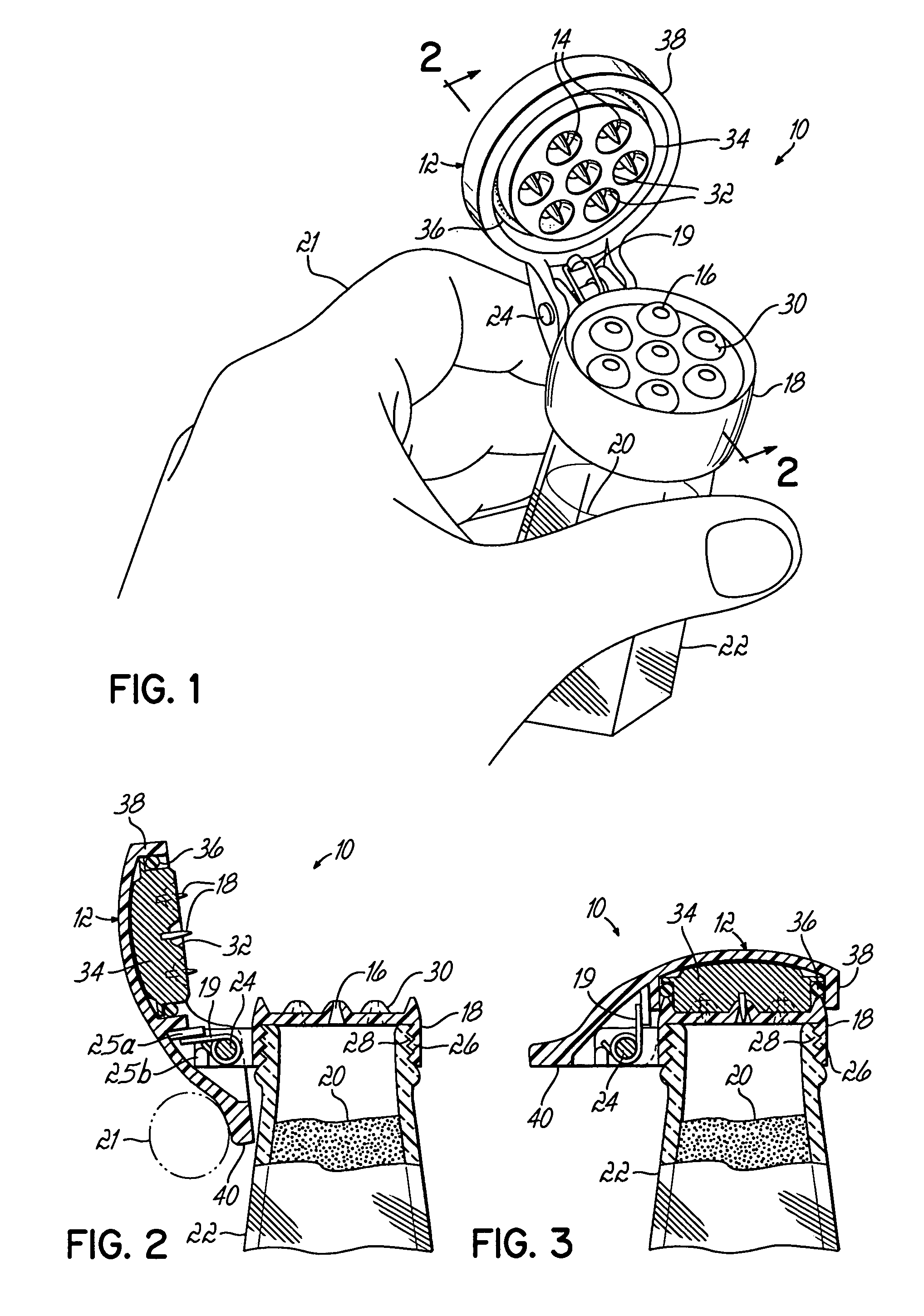

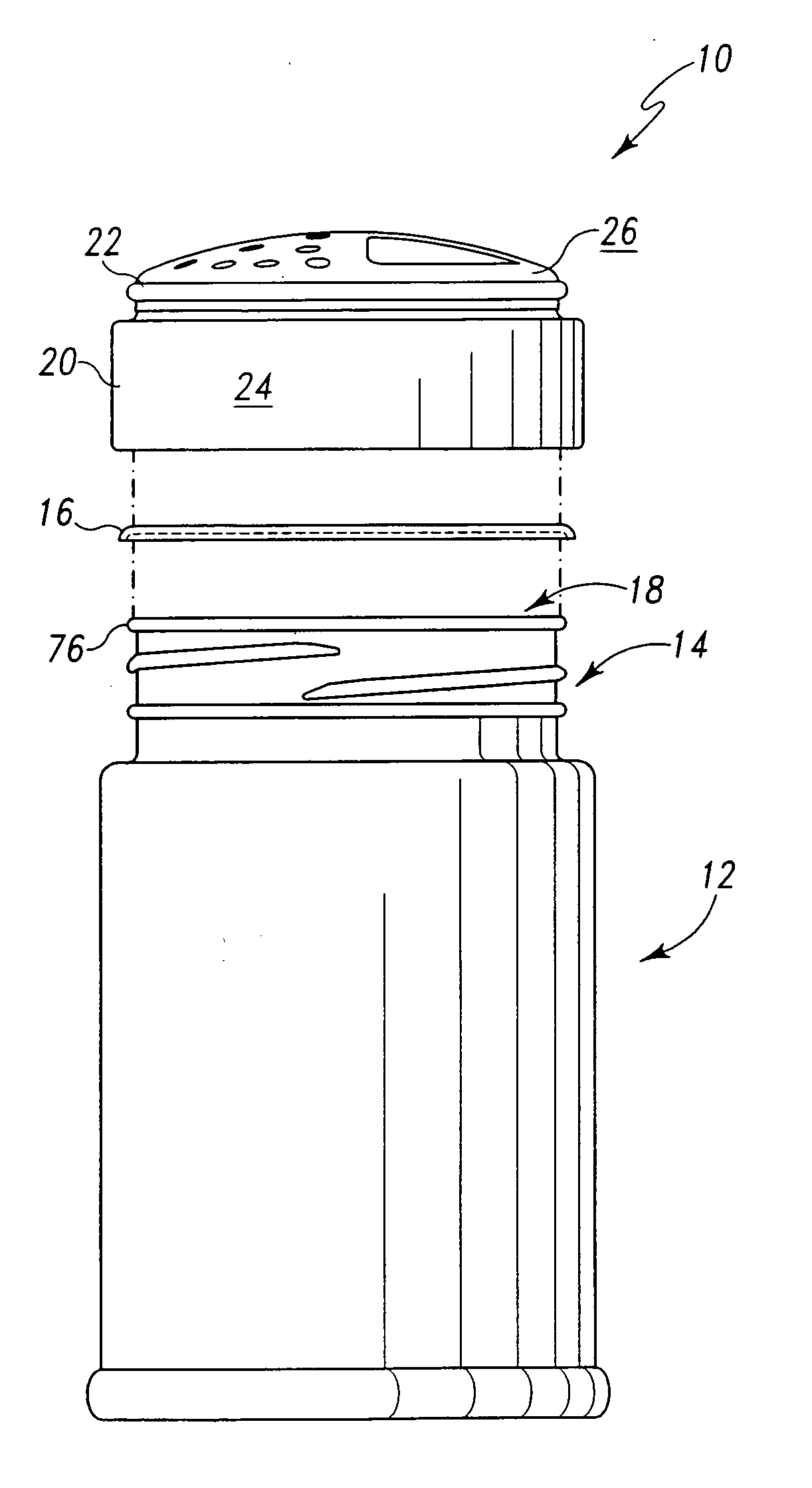

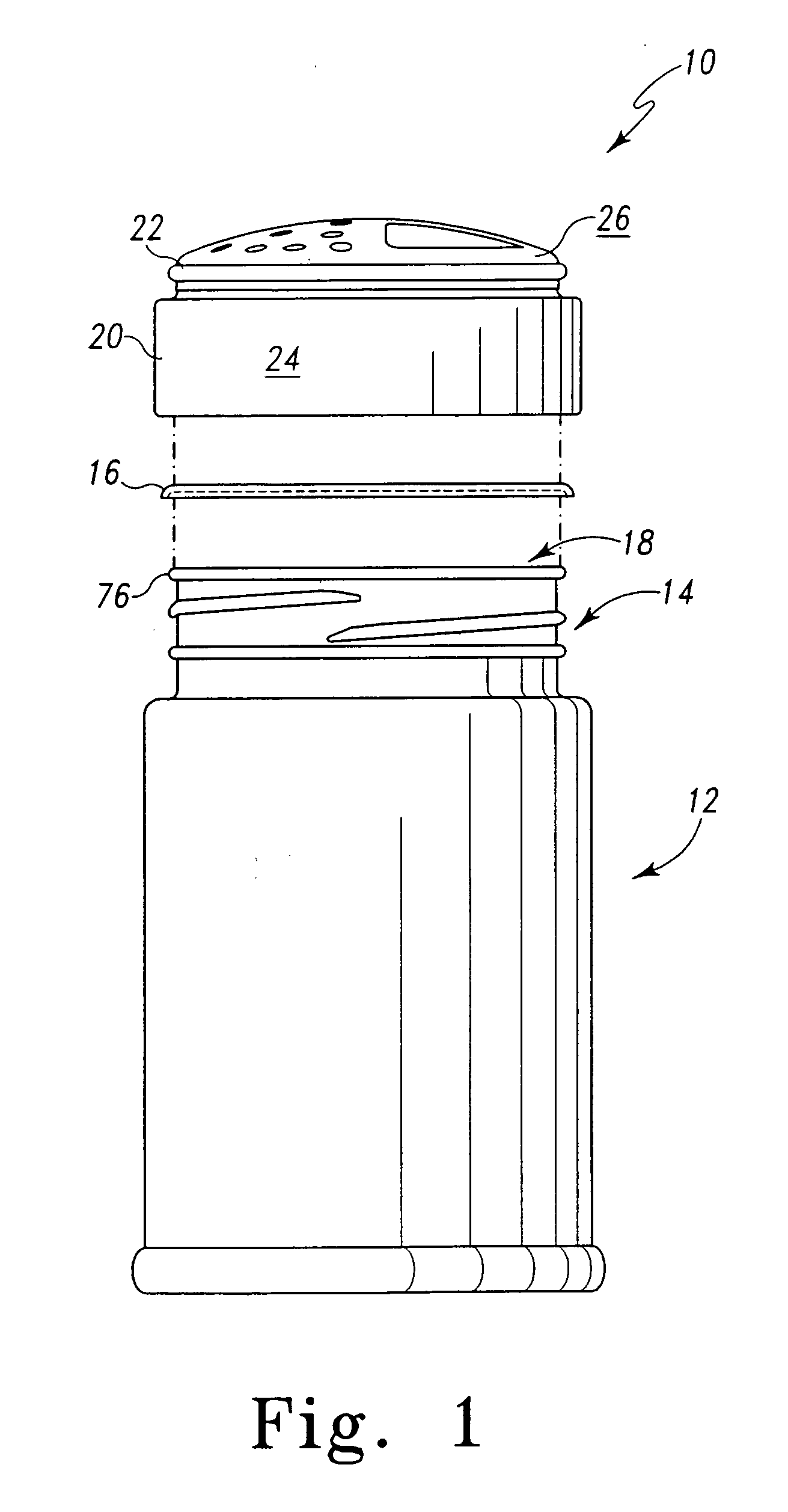

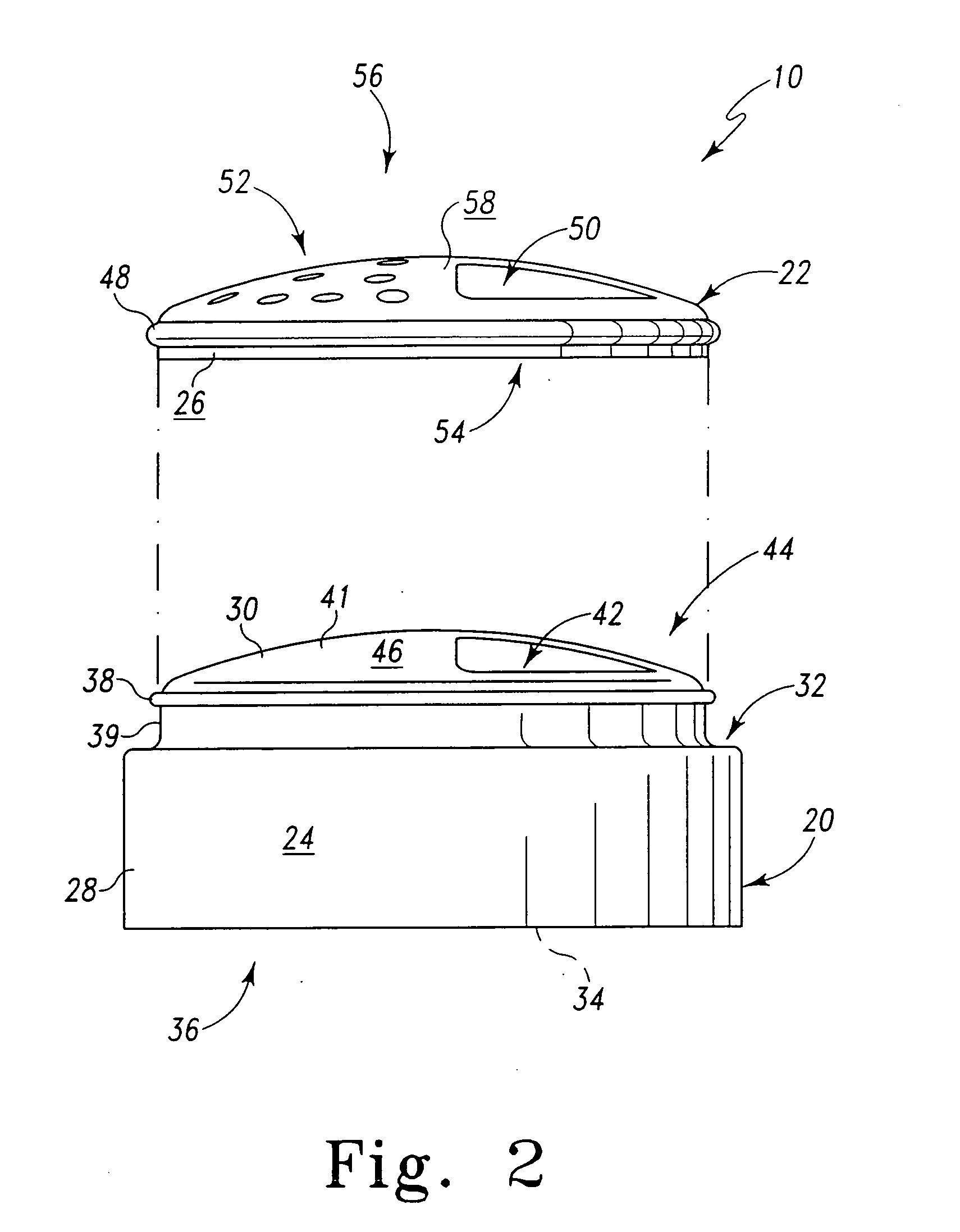

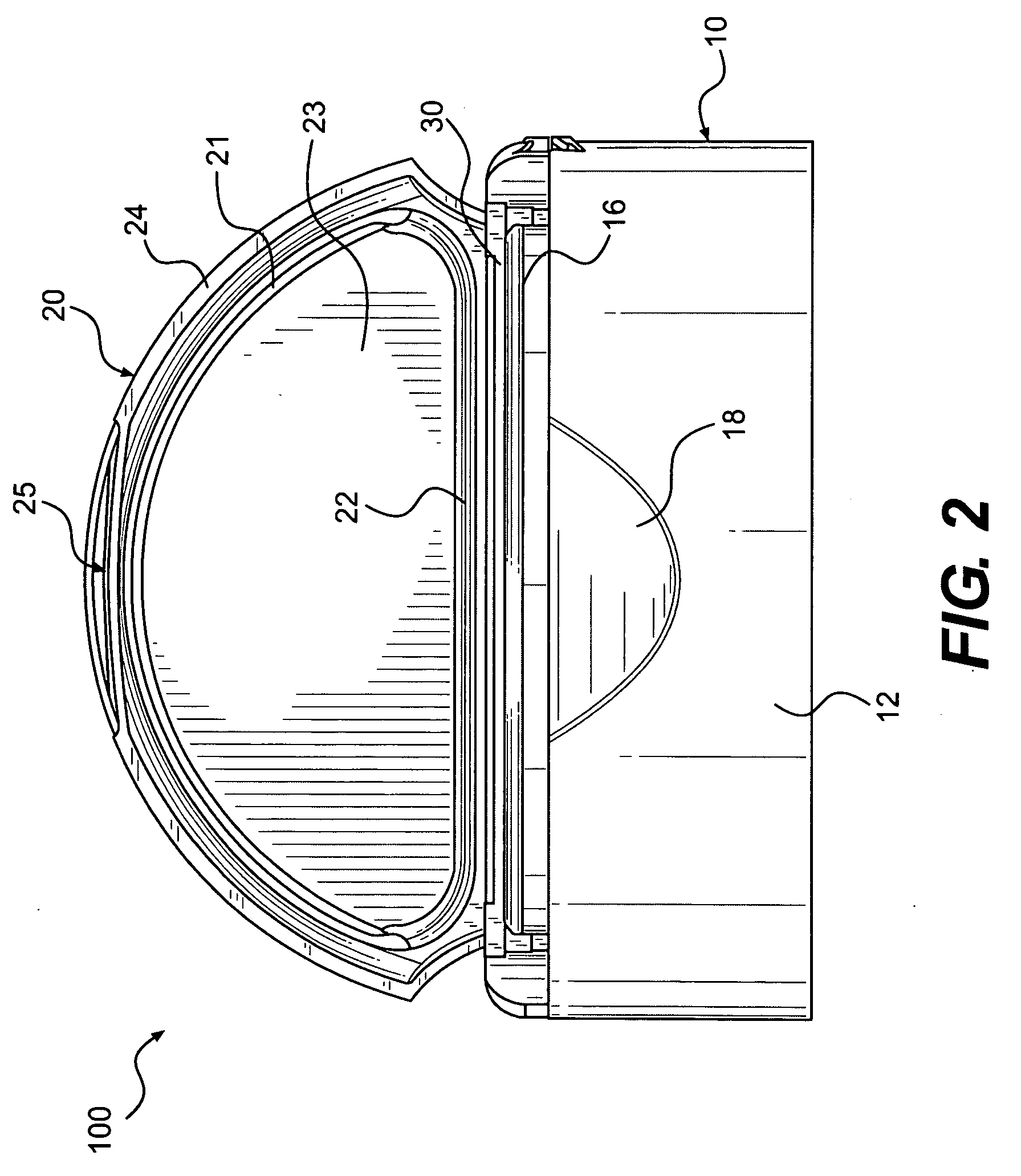

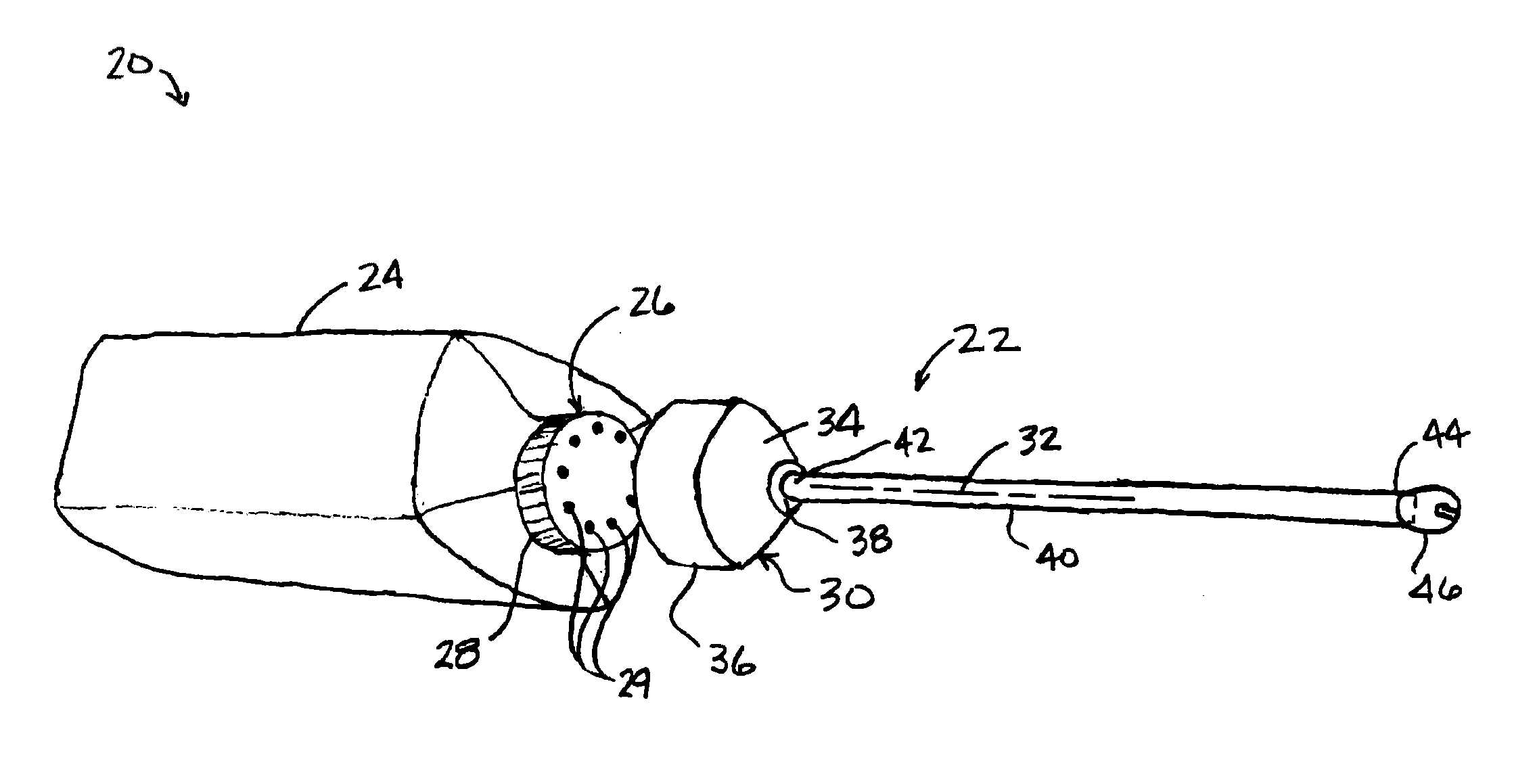

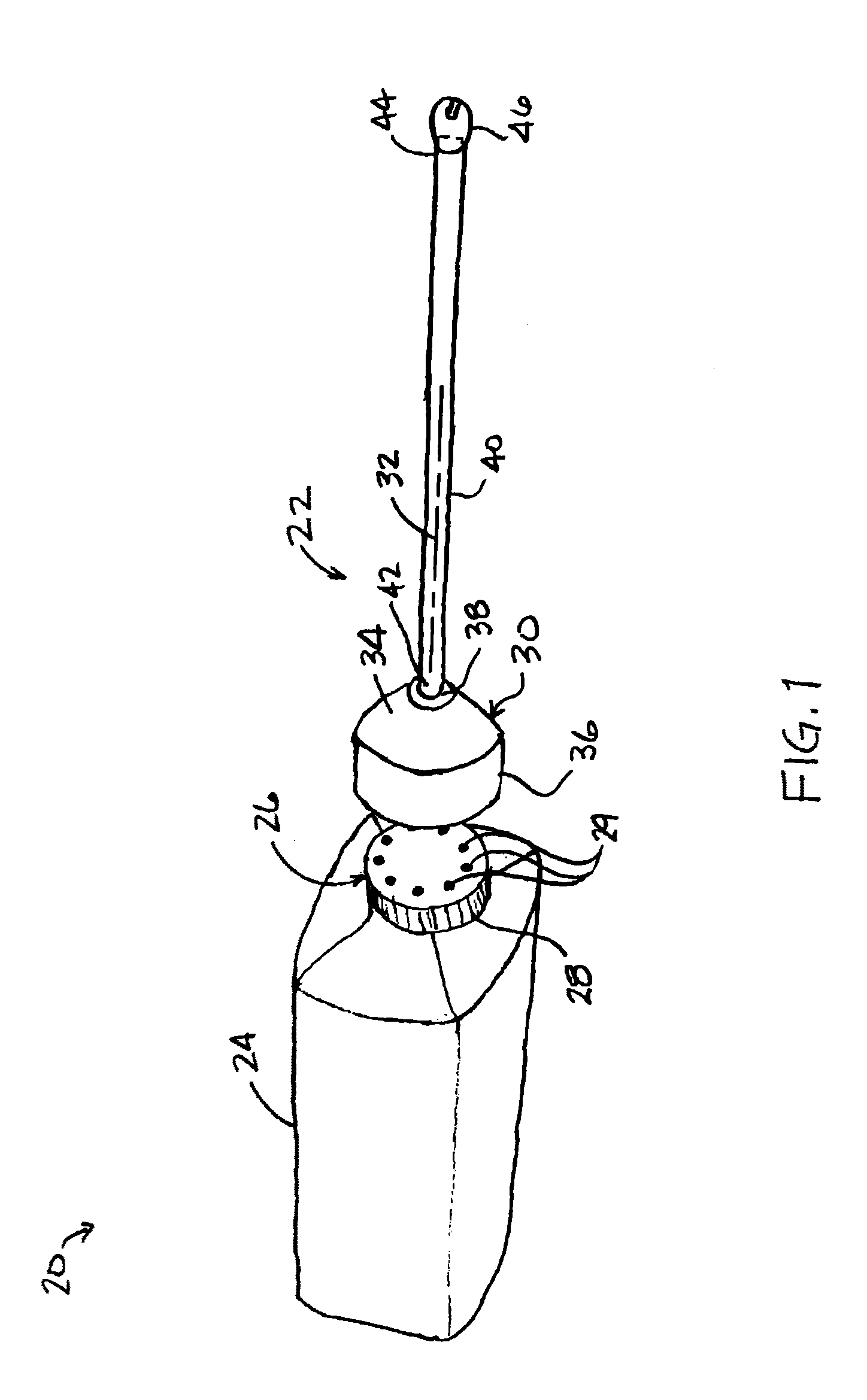

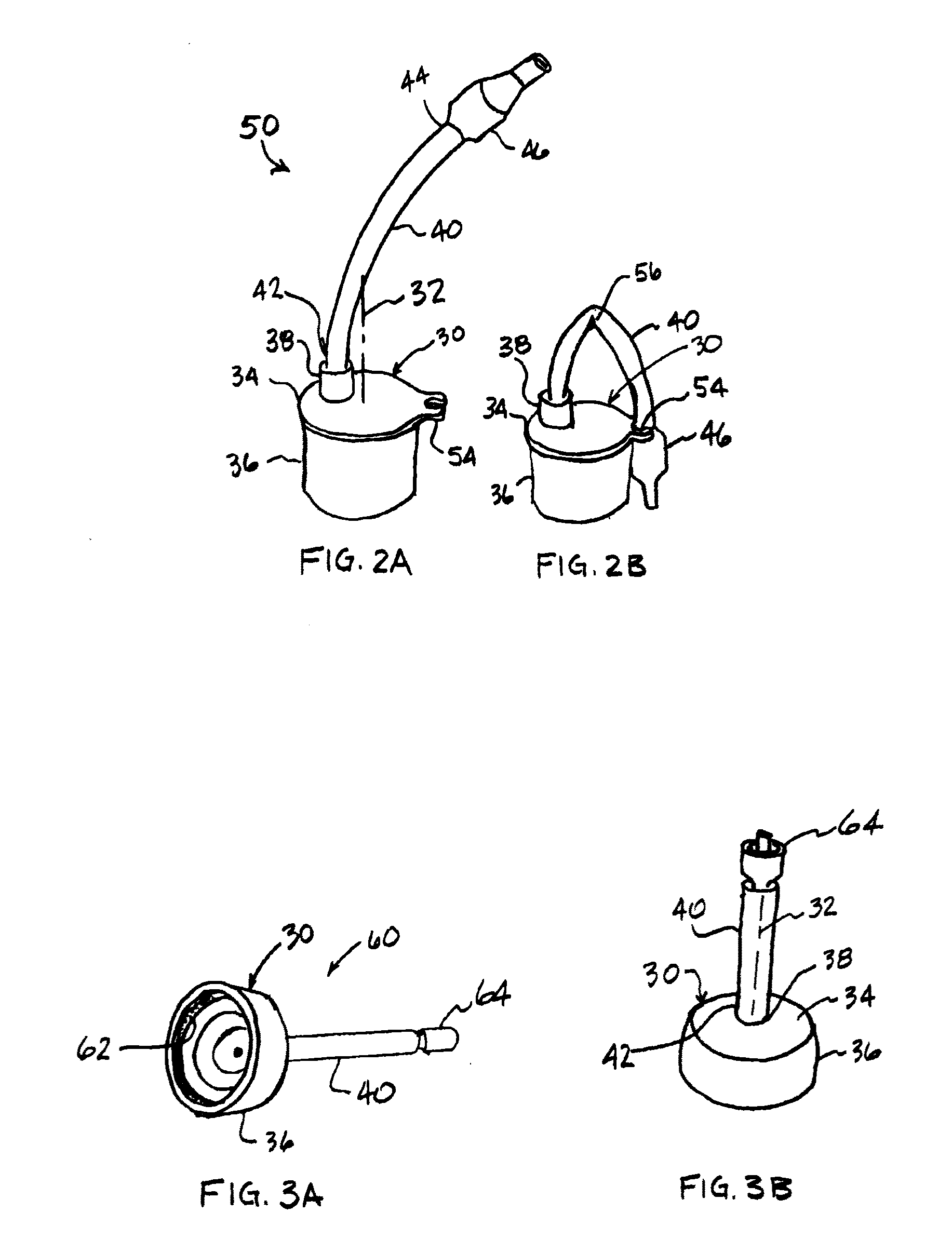

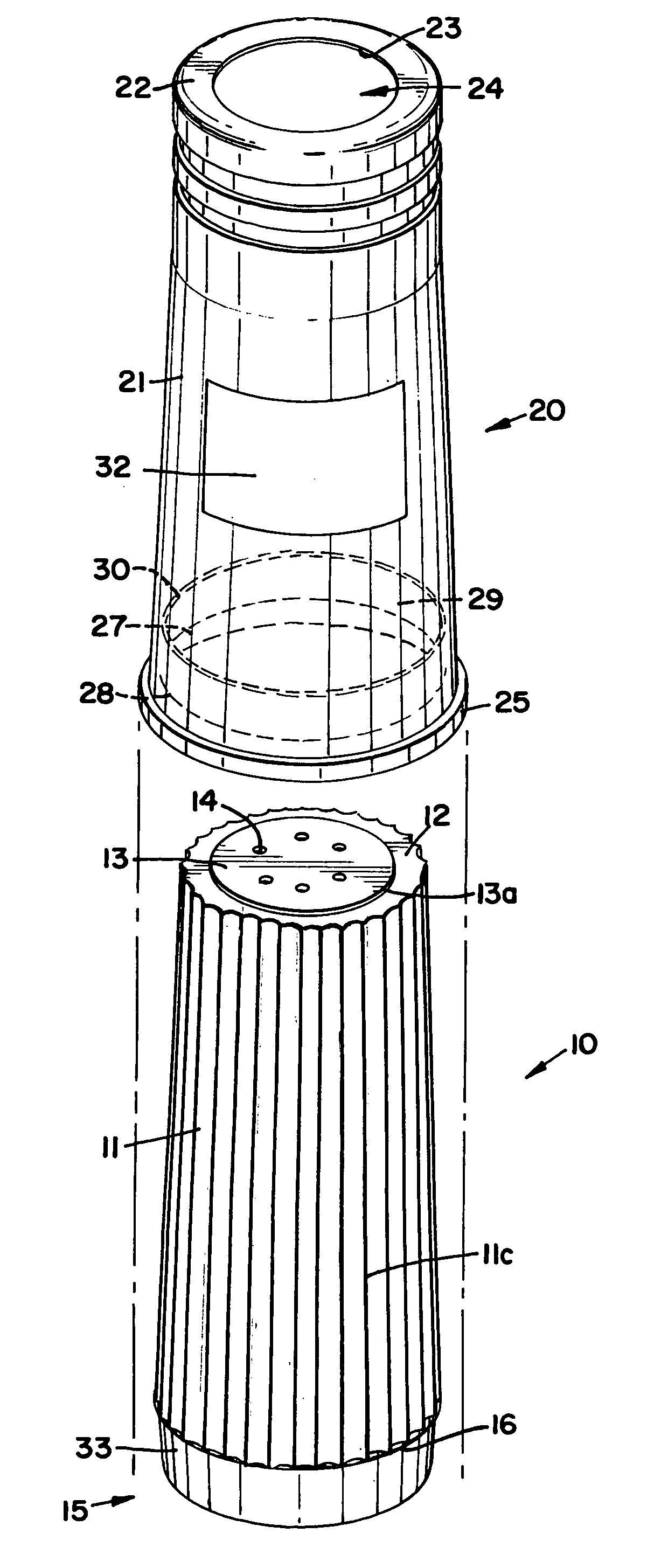

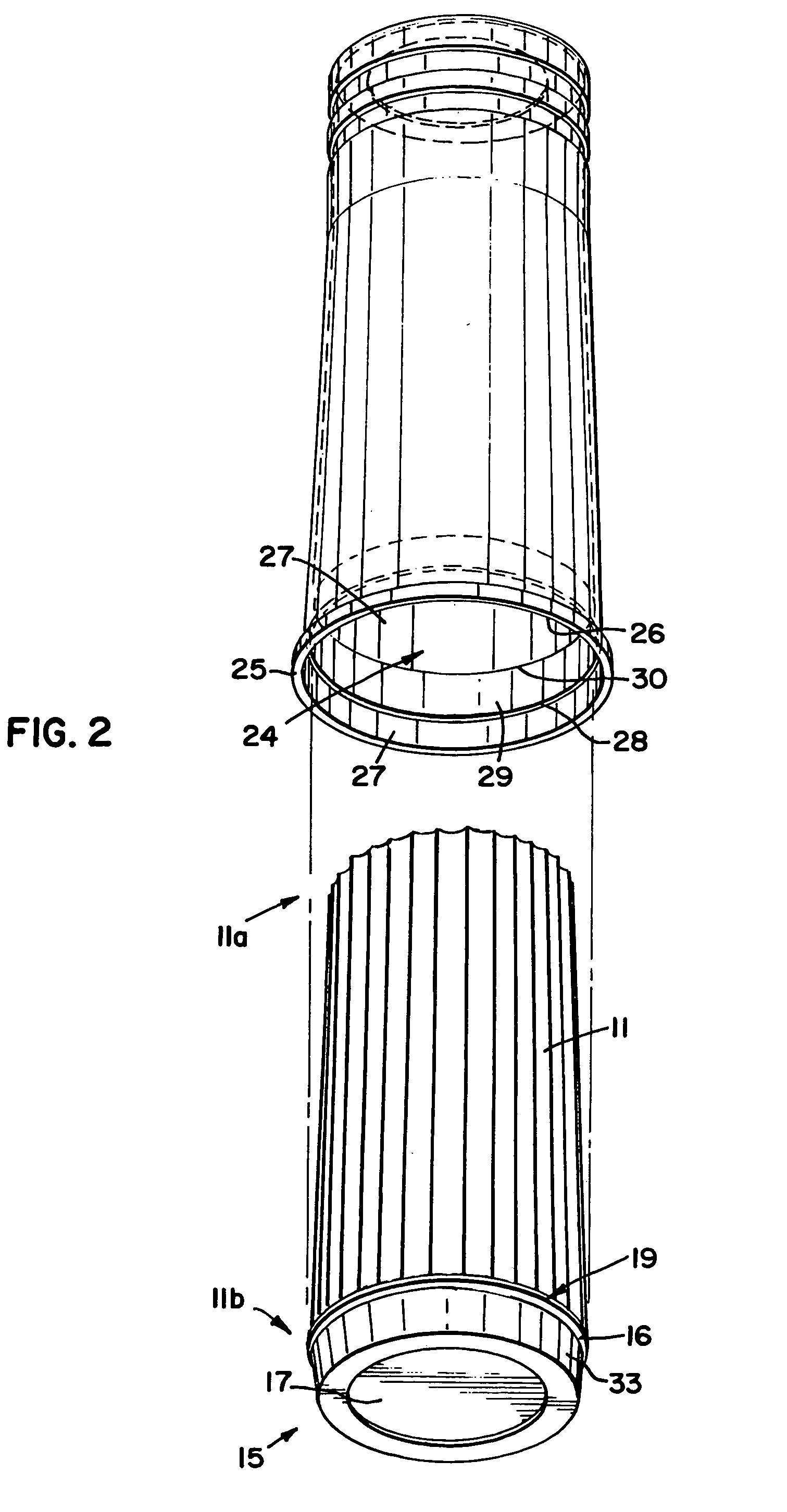

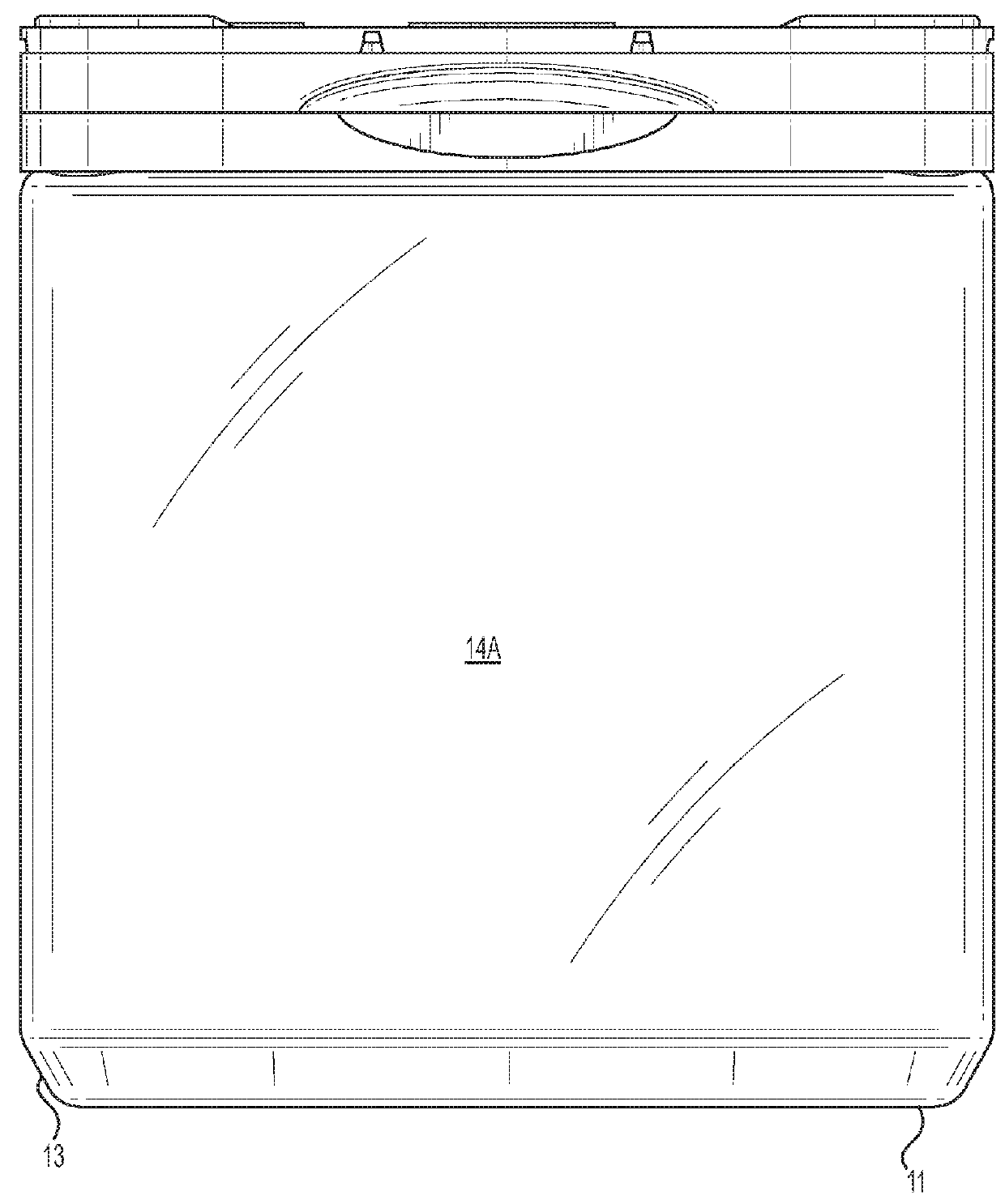

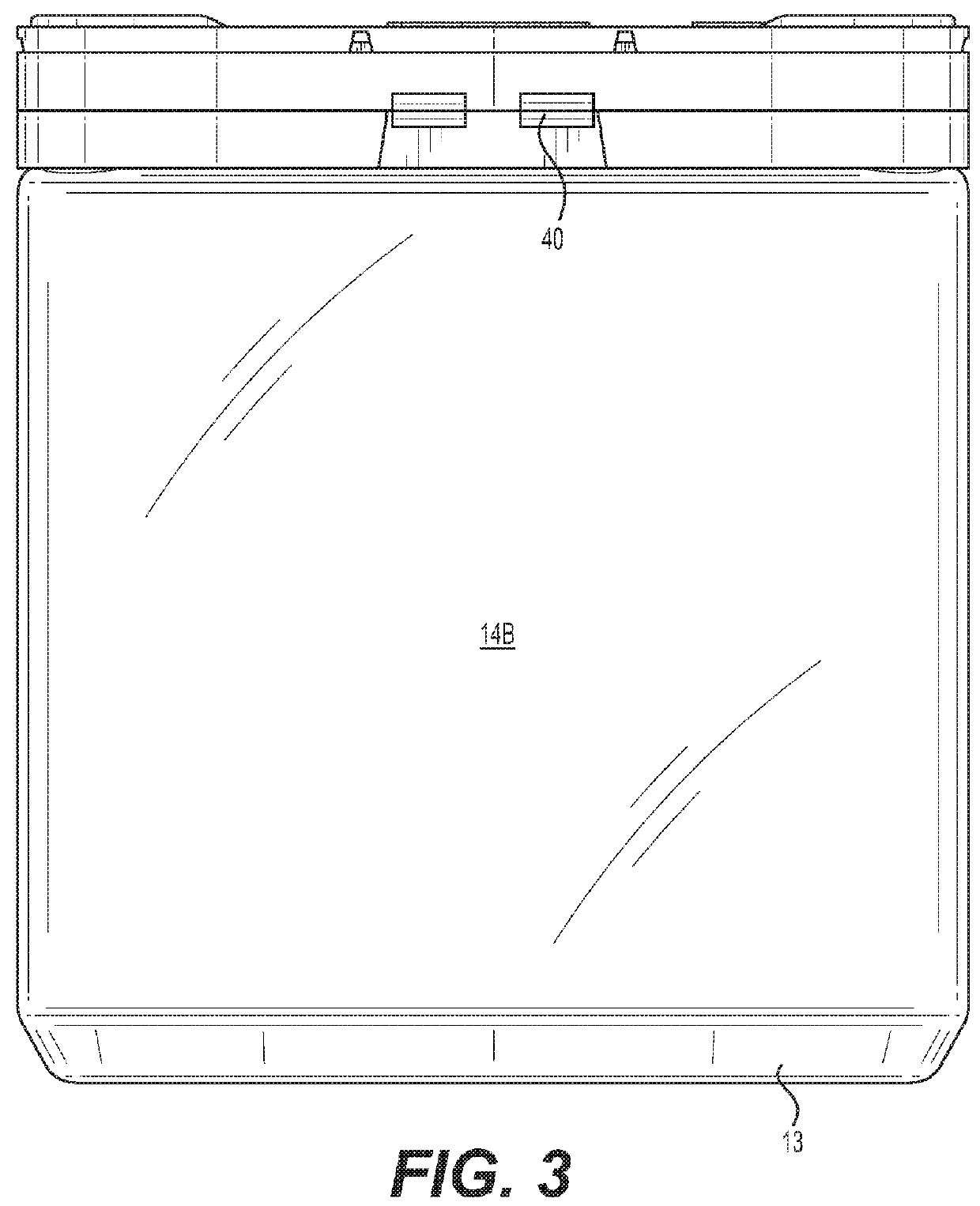

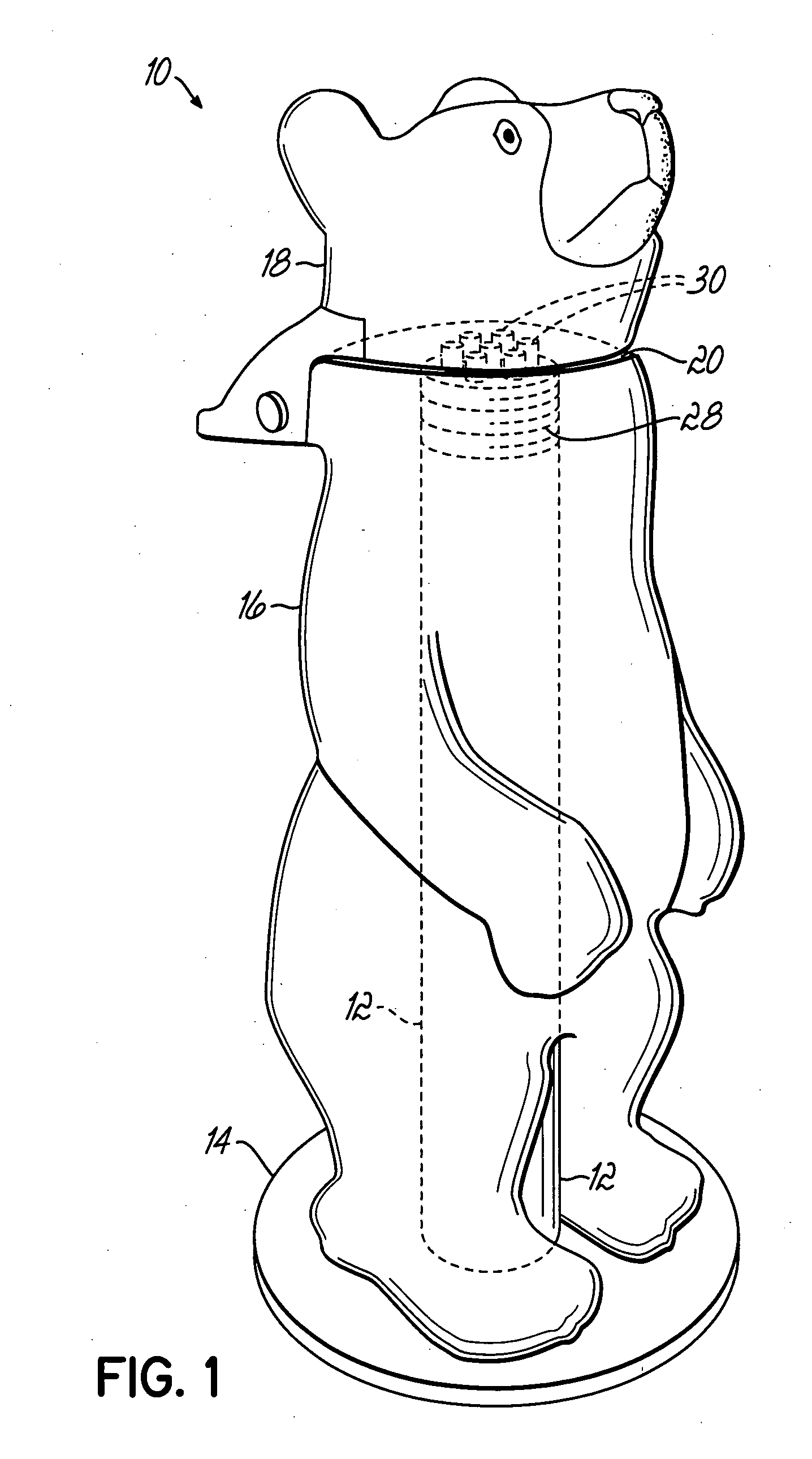

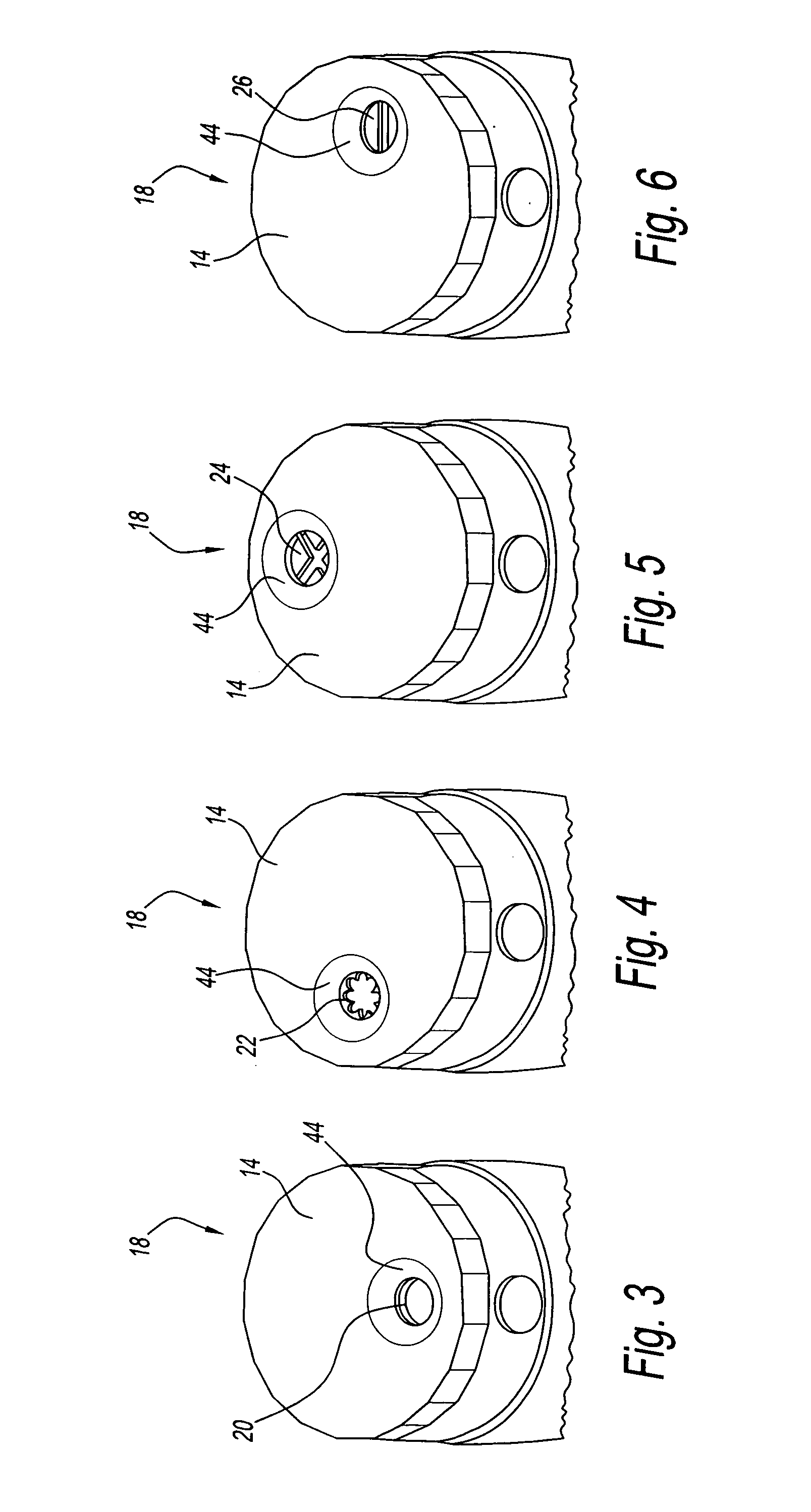

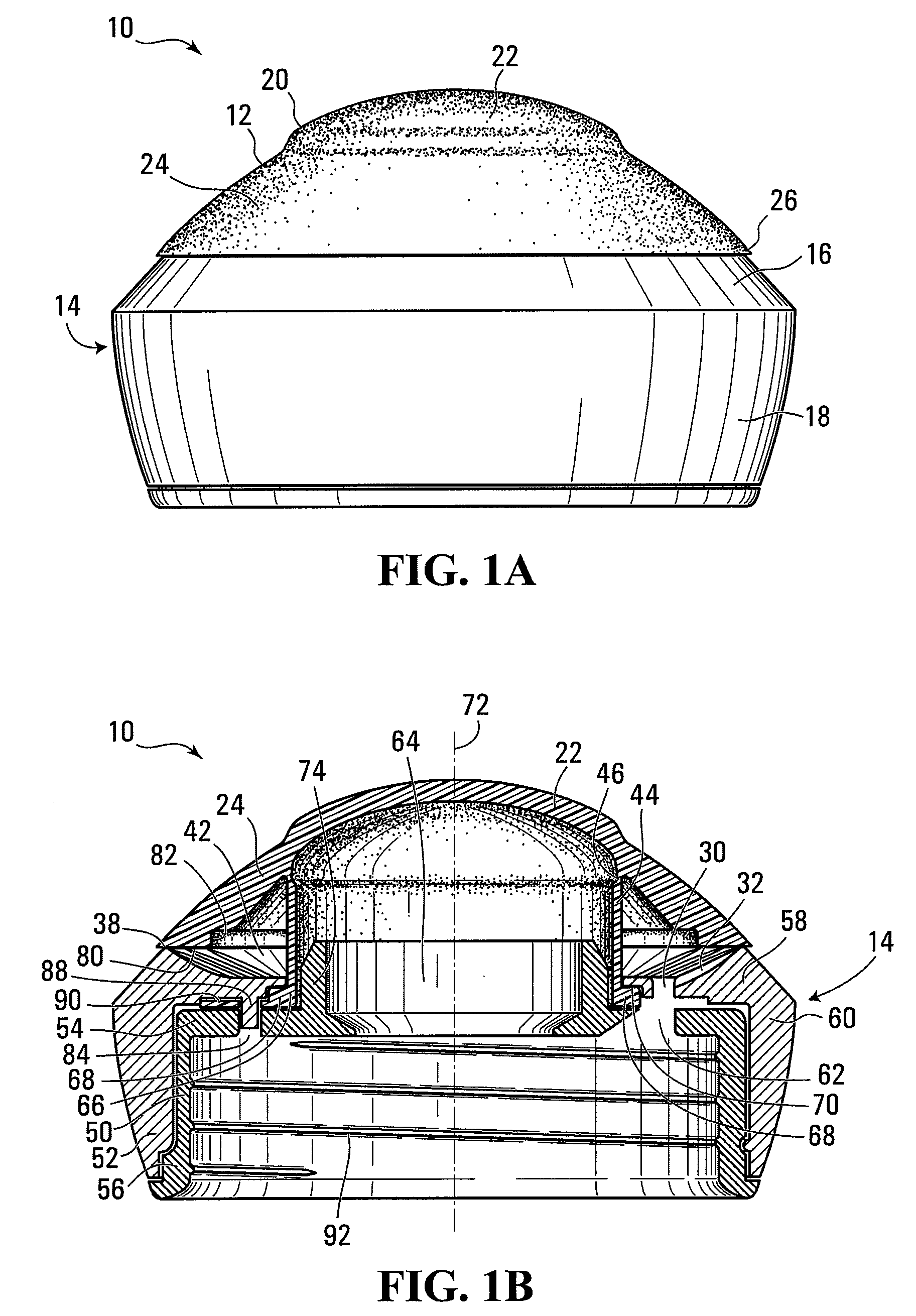

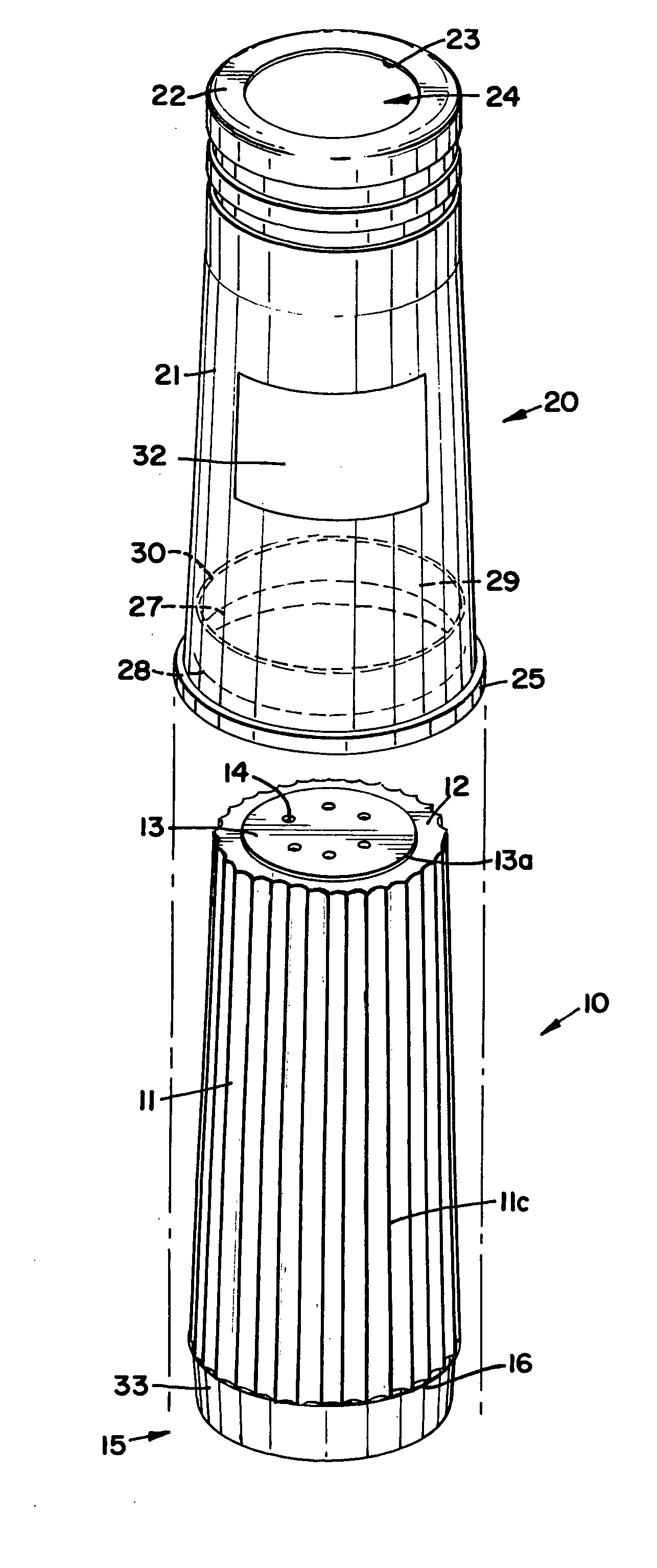

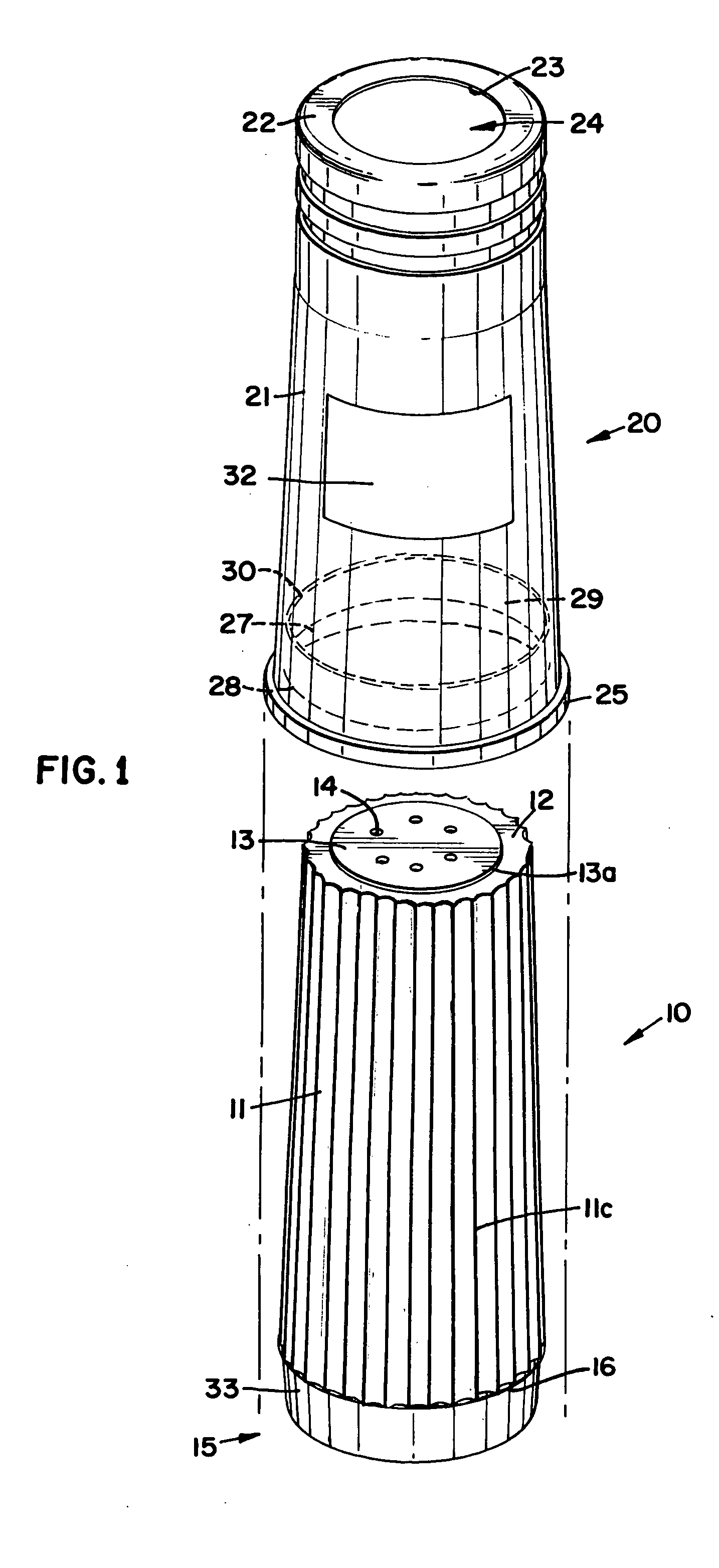

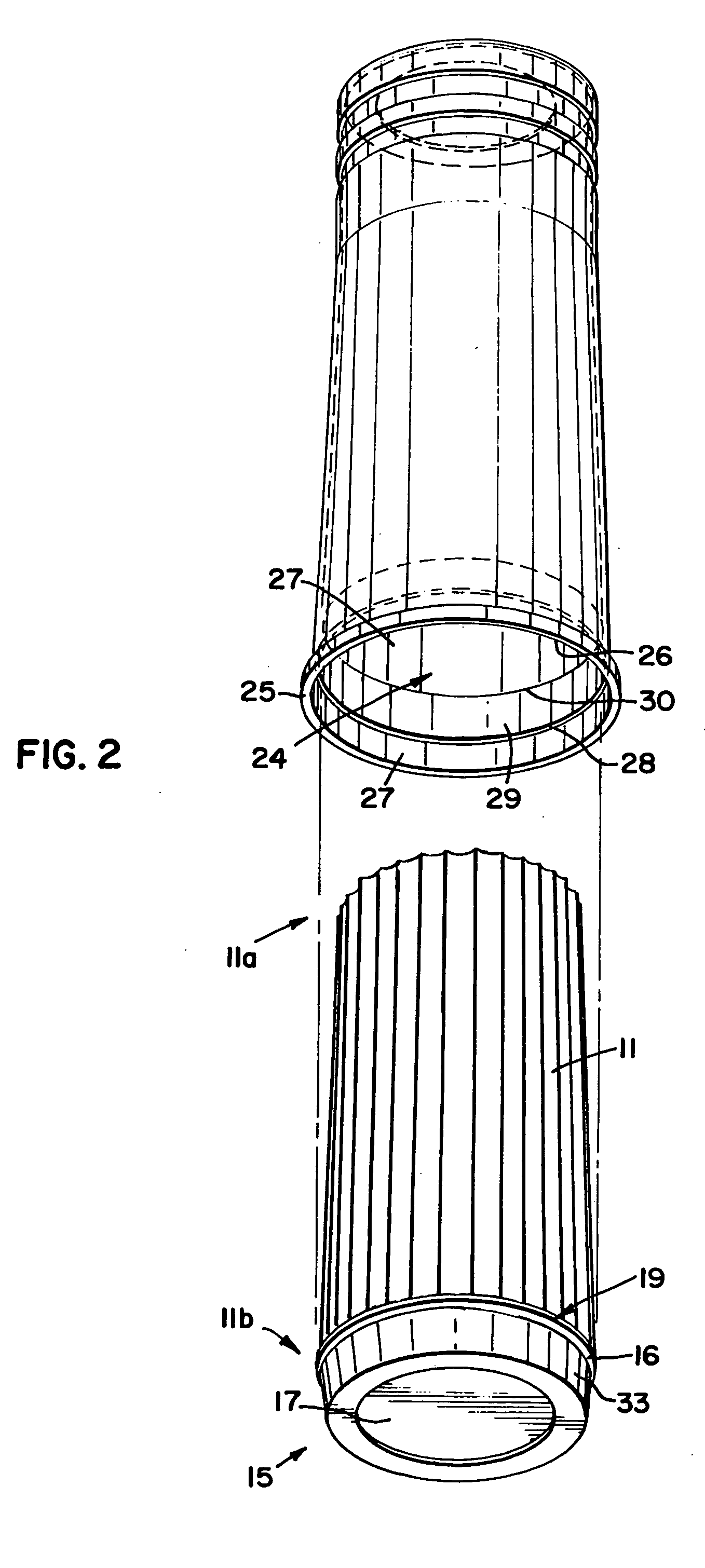

Disposable condiment shaker and decorative sleeve

A disposable, tamper-resistant condiment shaker (10) containing a condiment (37) is supported within a cavity (24) of a decorative sleeve (20) to provide a more aesthetically pleasing condiment dispensing assembly (100). The sleeve (20) includes a securing member (29, 42, 44) to support the shaker (10) within the cavity (24). When the condiment supply within the shaker (10) has become depleted, the shaker (10) may be removed from the sleeve (20), discarded, and replaced with a new shaker (10). This cartridge type loading and refilling of the condiment (37) eliminates the need to pour condiment (37) into a dispenser.

Owner:HORMEL FOODS

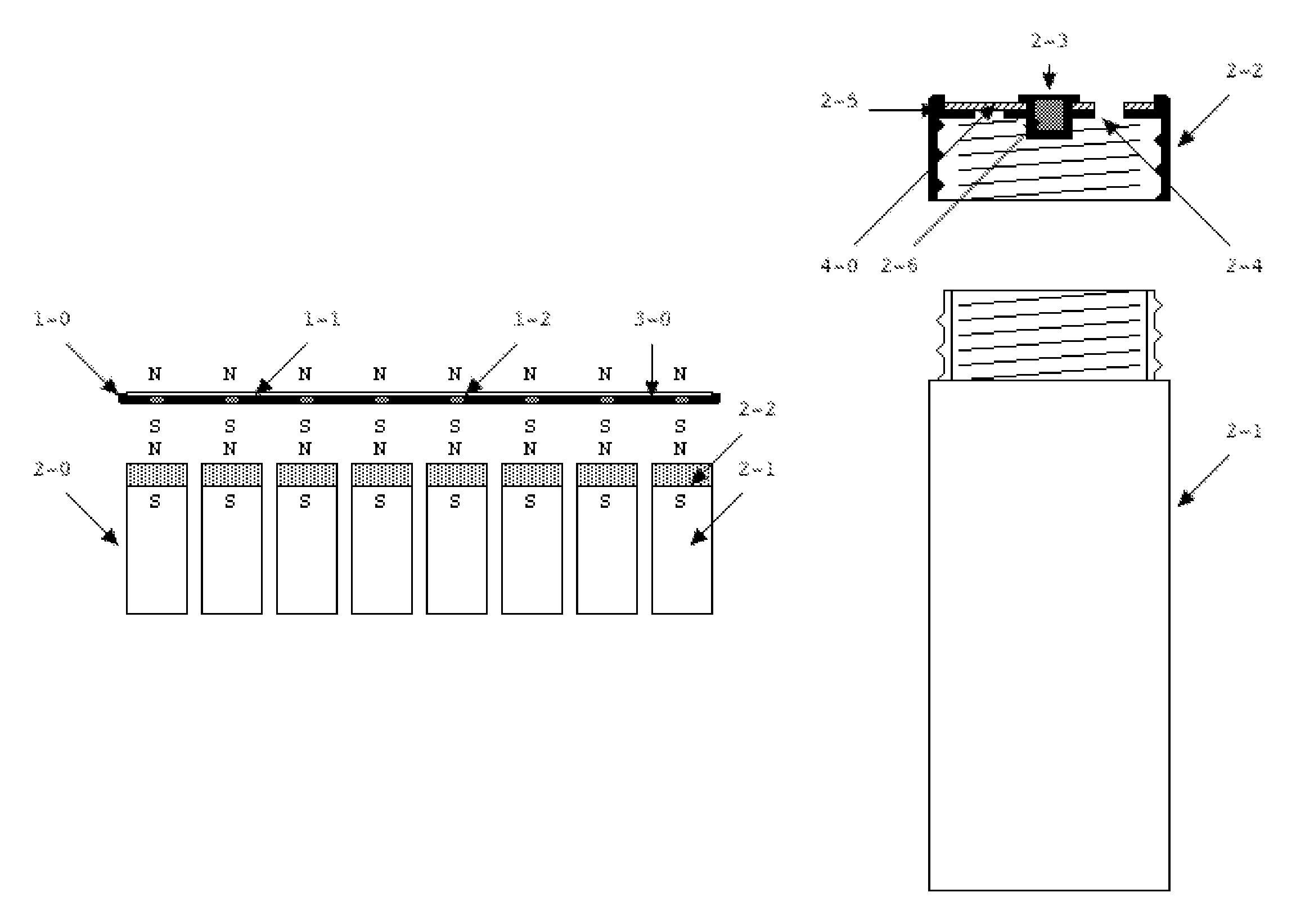

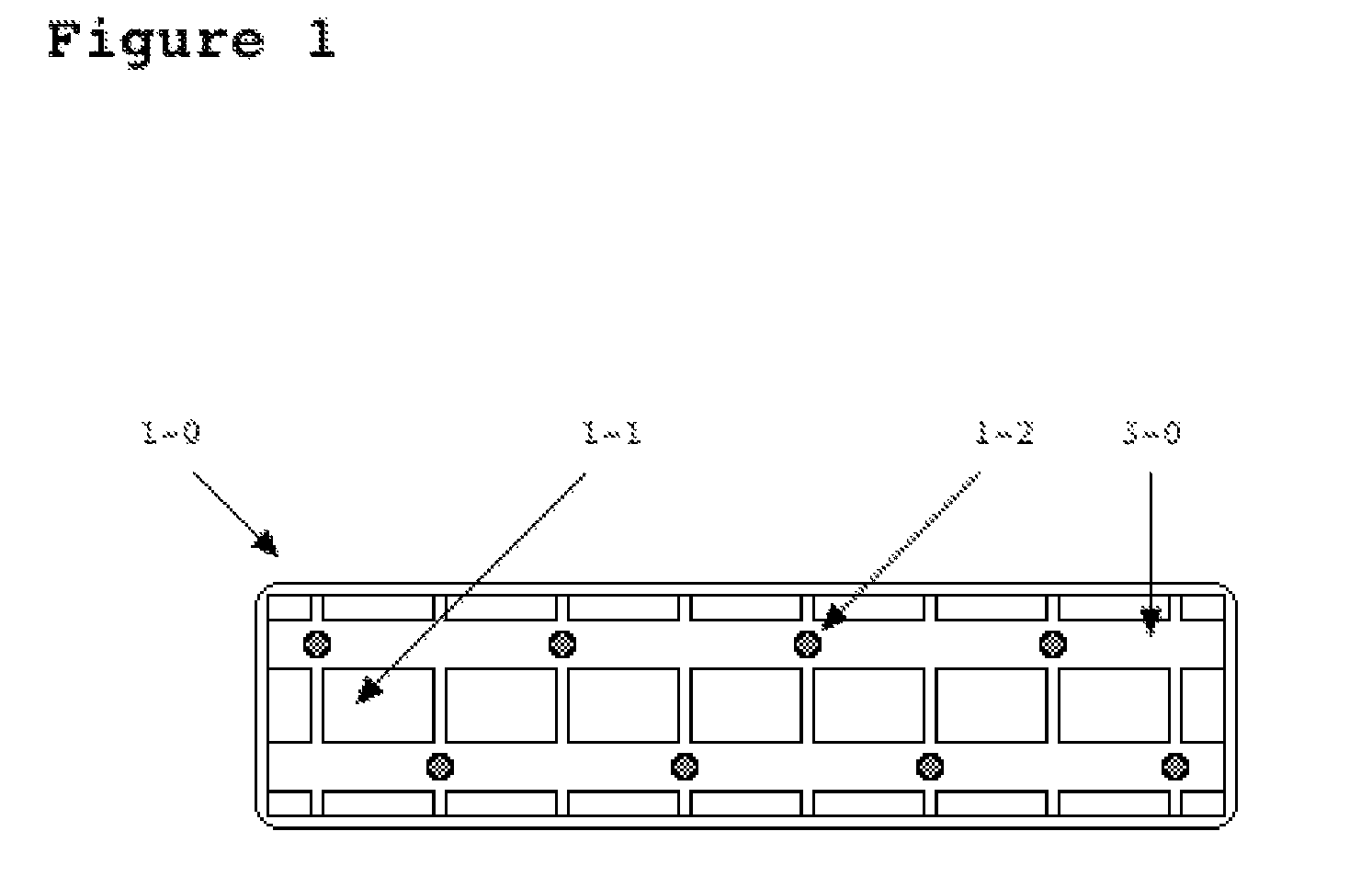

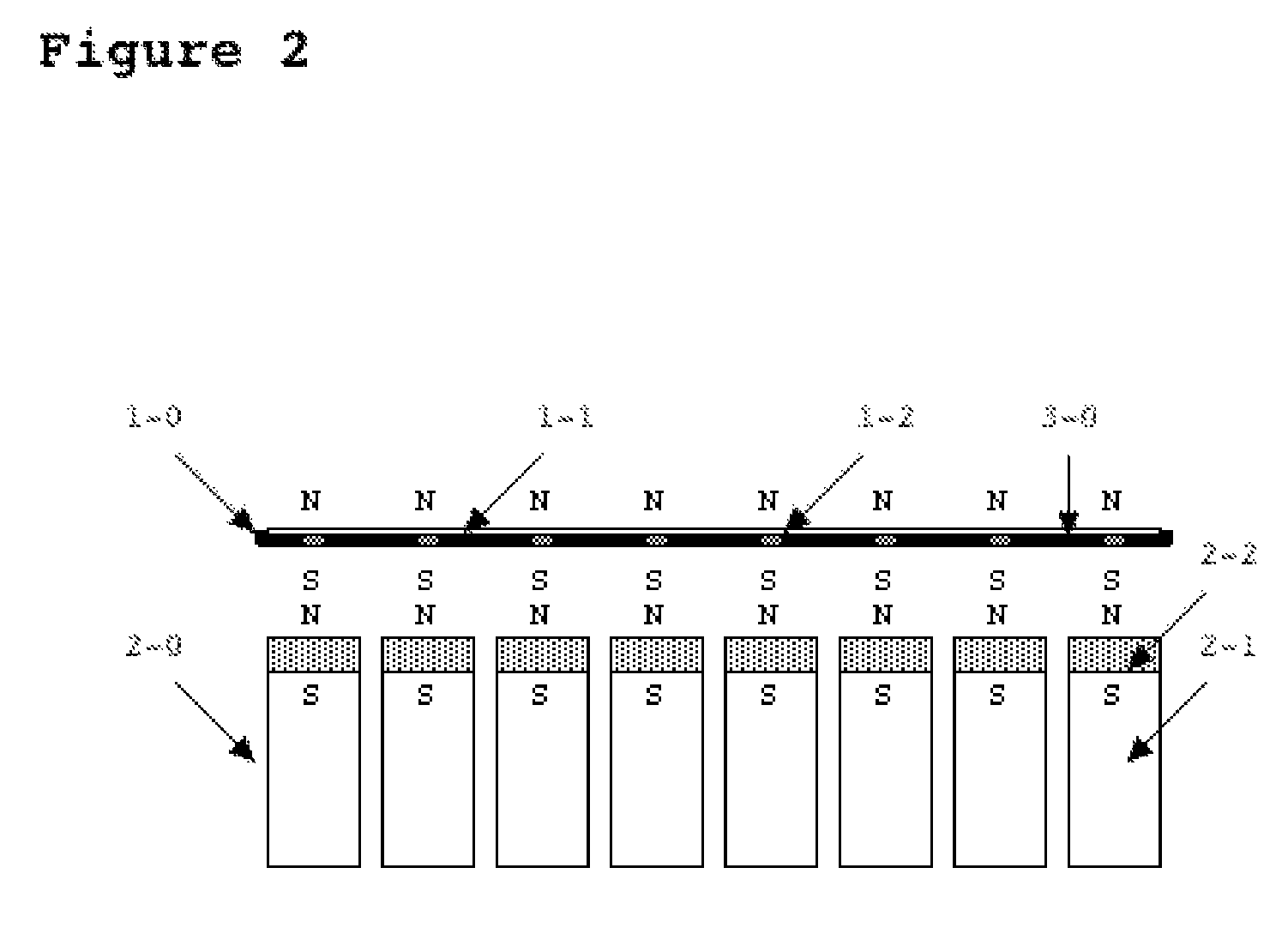

Self-Sealing Auto-Aligning Magnetically-Hanging Spice Dispenser

A hanging spice dispenser comprises a plate assembly and a container assembly for storing spices. The plate assembly comprises a non-magnetic planer plate and a plurality of magnetic elements embedded at pre-determined locations. The container assembly comprises a generally cylindrical spice container, a removable cap and a magnetic element. Magnetic attraction force between the magnetic element of the container assembly and the magnetic element of the plate assembly is exerted when the container assembly is placed in proximity to the plate assembly. The container assembly is capable of detaching from the bottom surface of the plate assembly when force is applied to the container assembly. The removable cap and the plate assembly form self-seal in order to prevent air and moisture from entering into the generally cylindrical container. This invention relates to spice dispensers, and the principal use of the invention is for dispensing spices in a kitchen.

Owner:SUNATORI GO SIMON

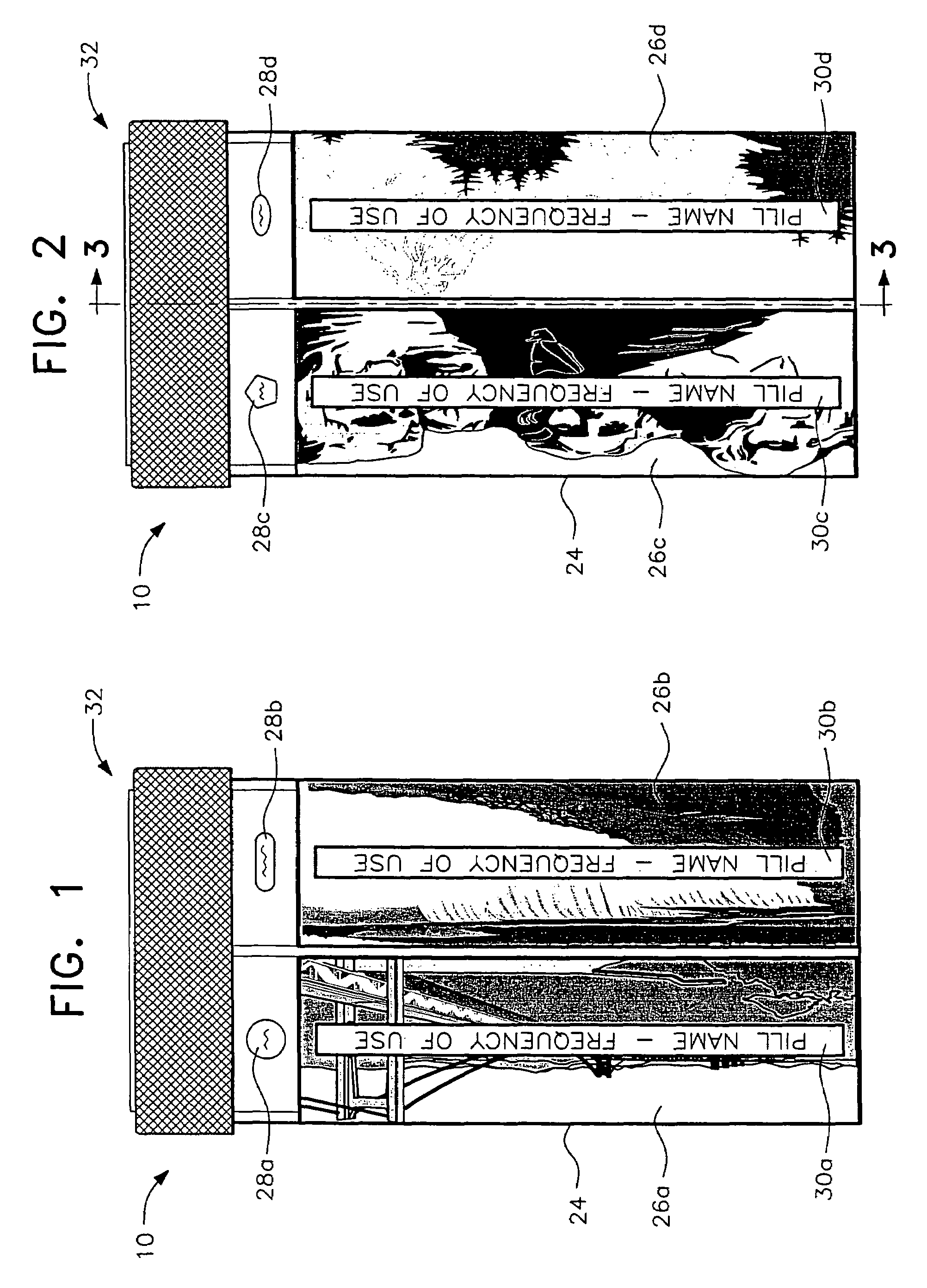

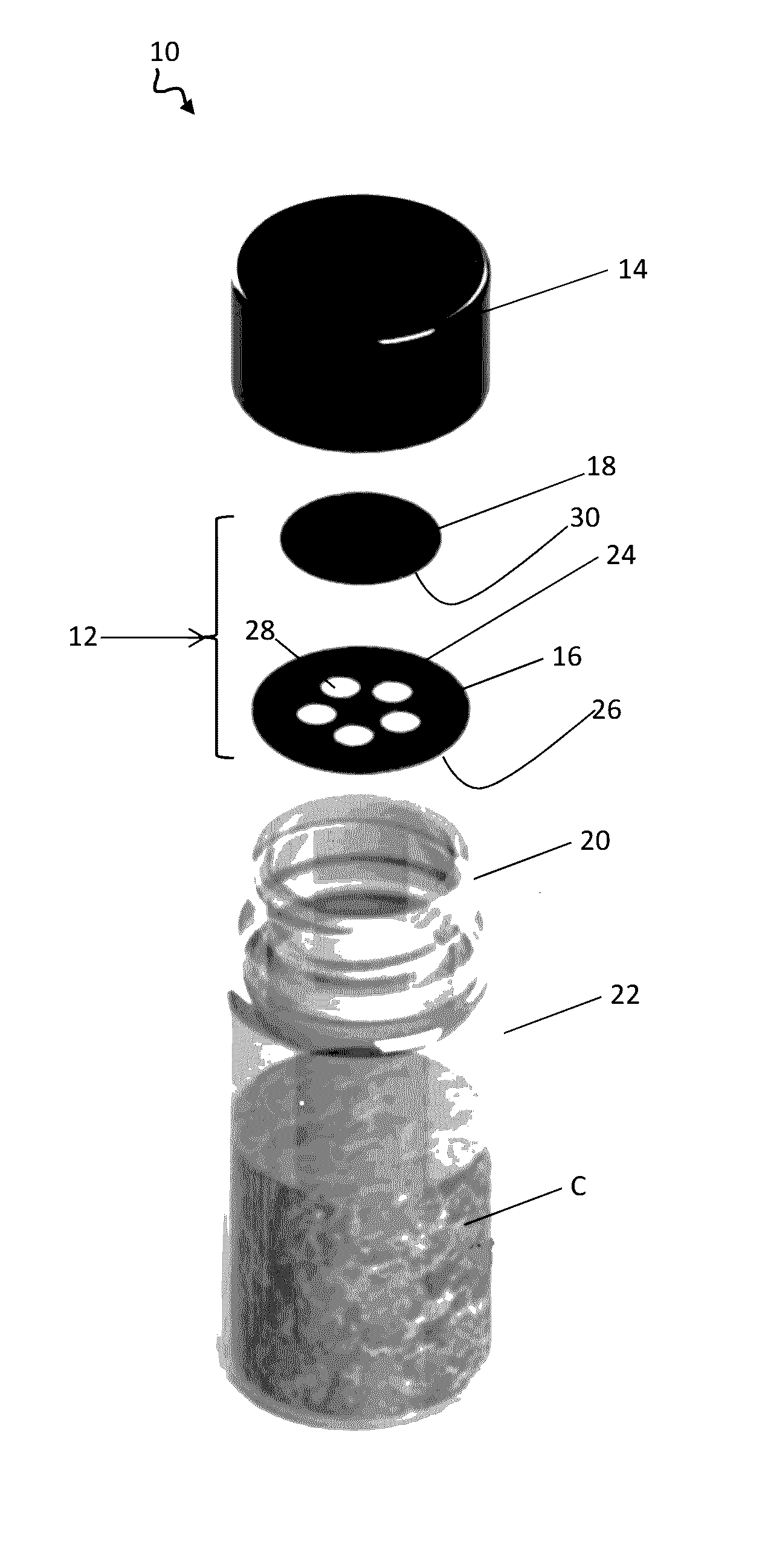

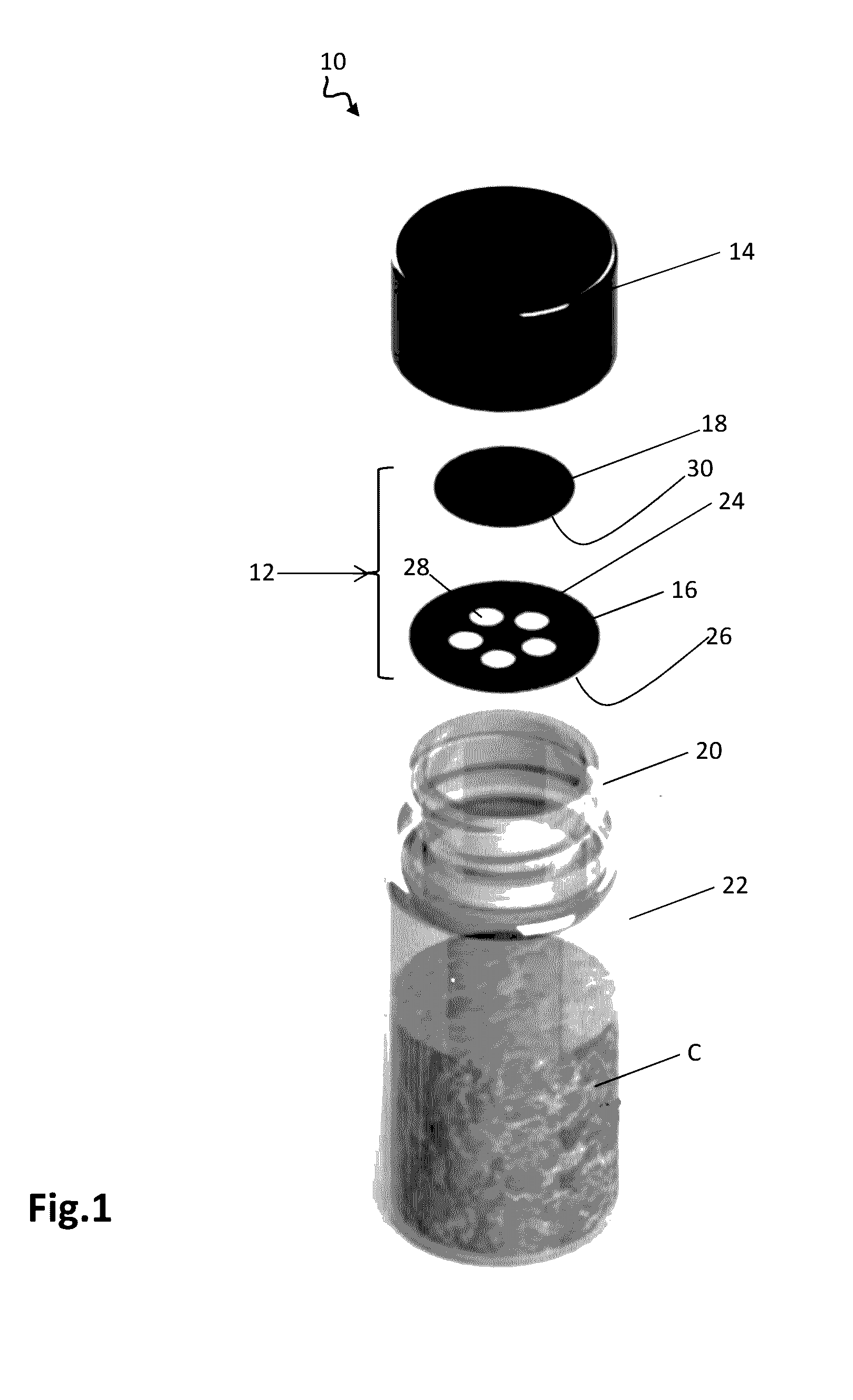

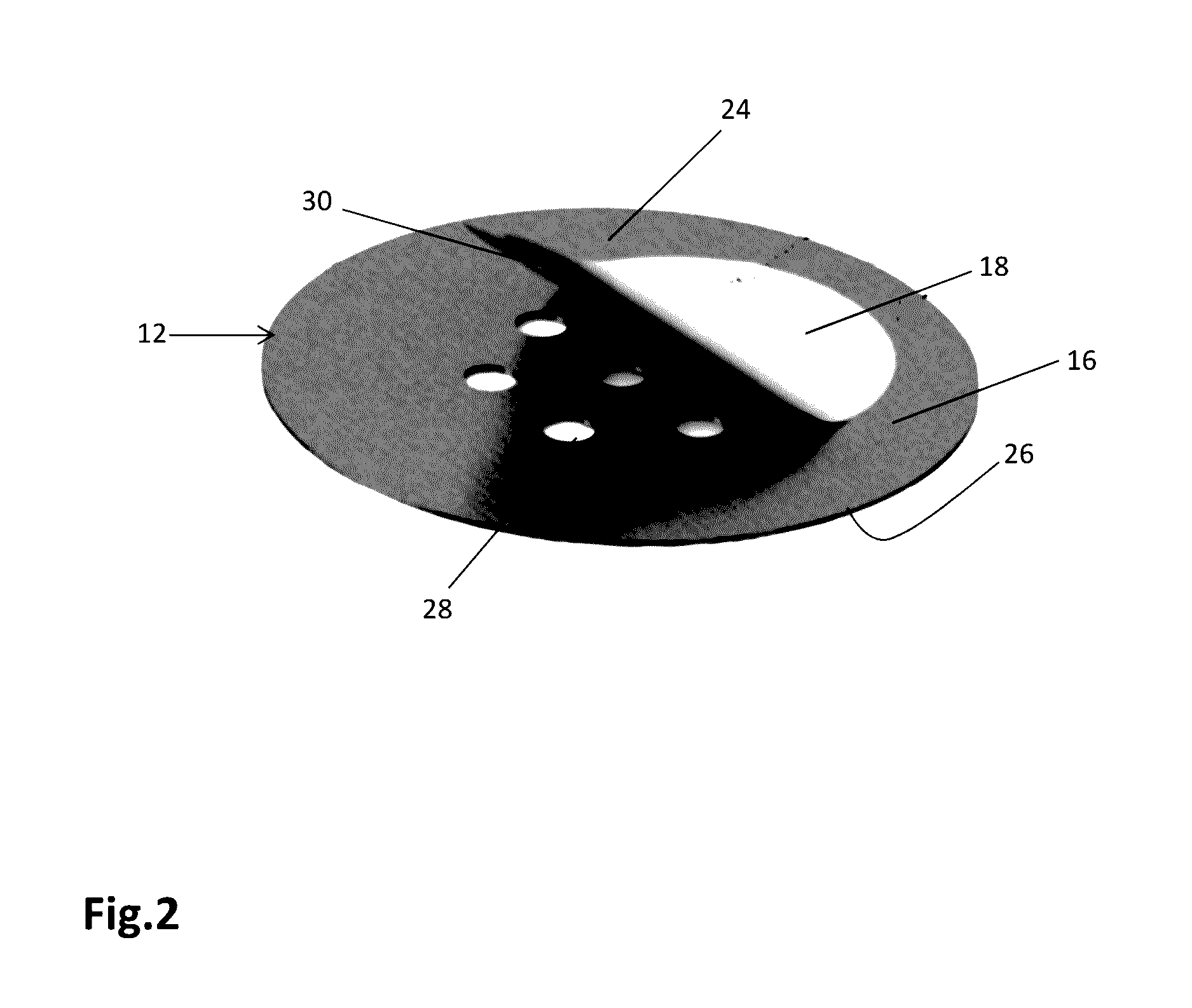

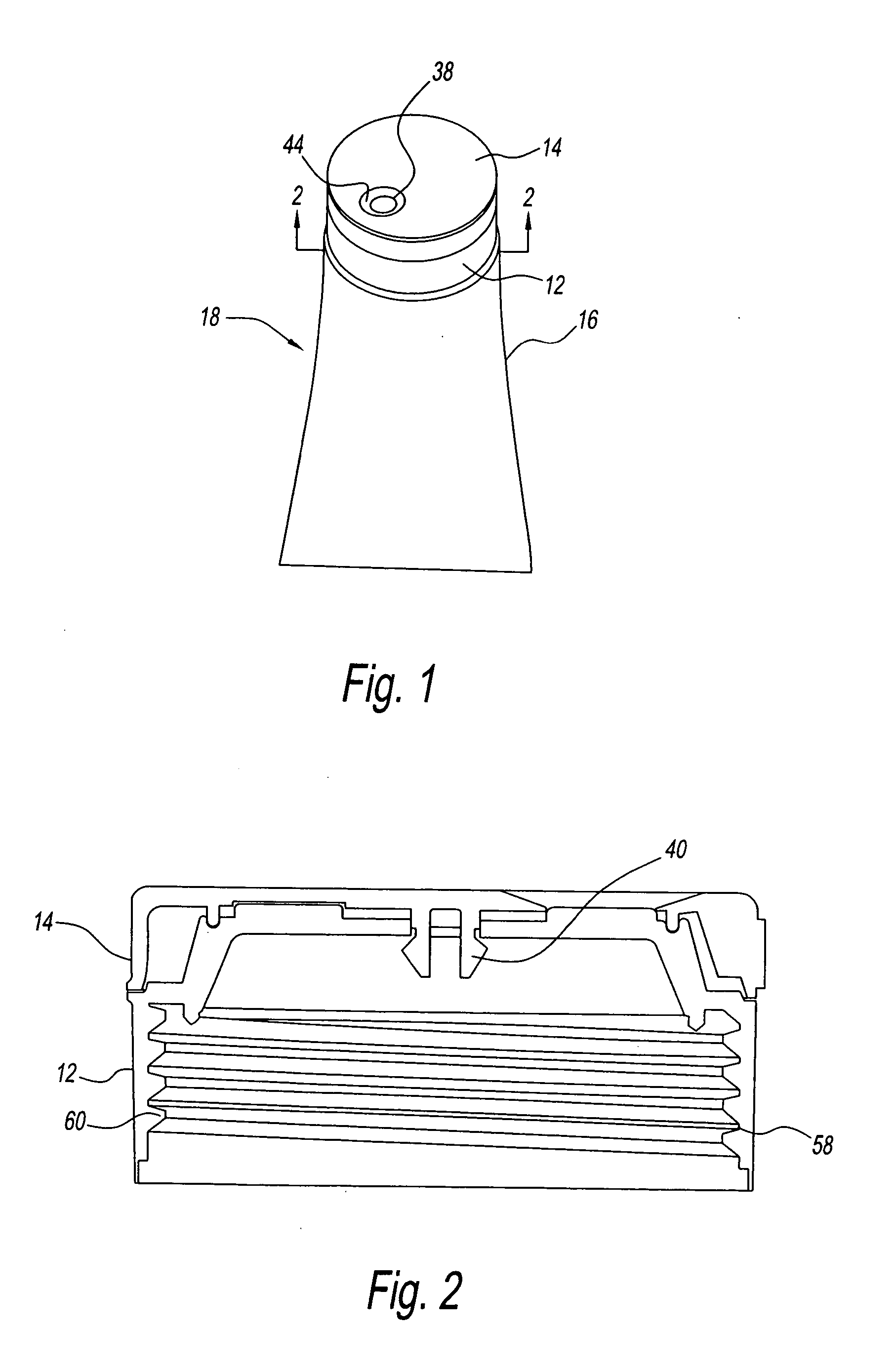

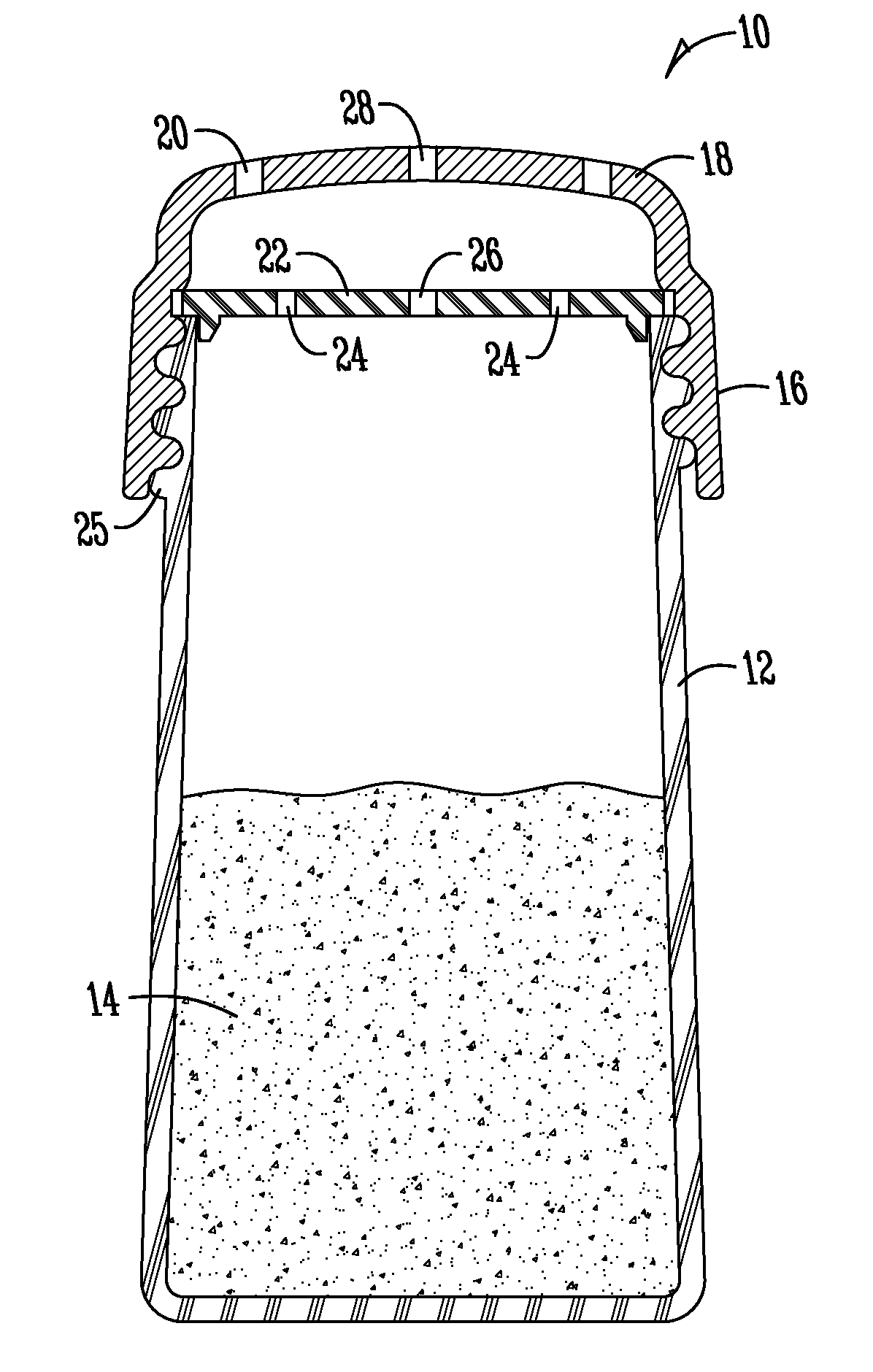

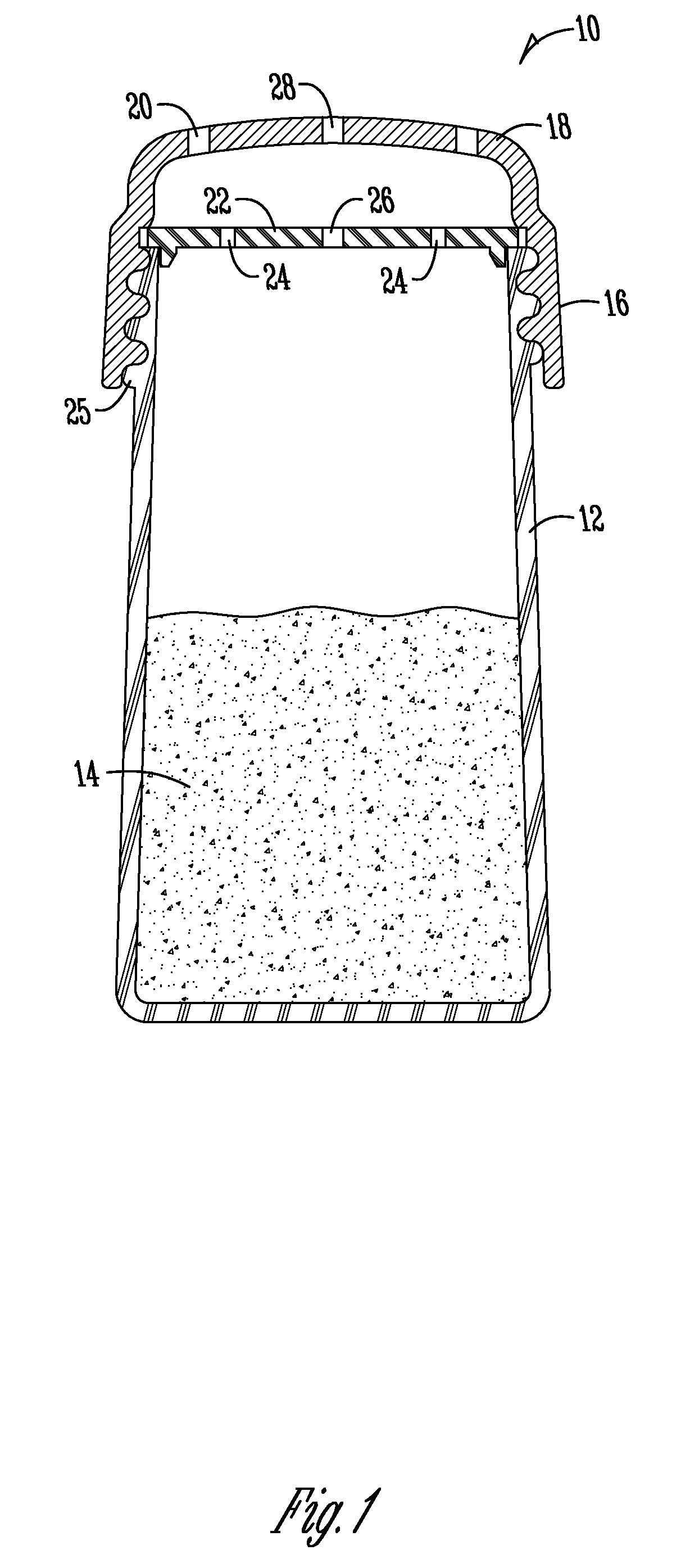

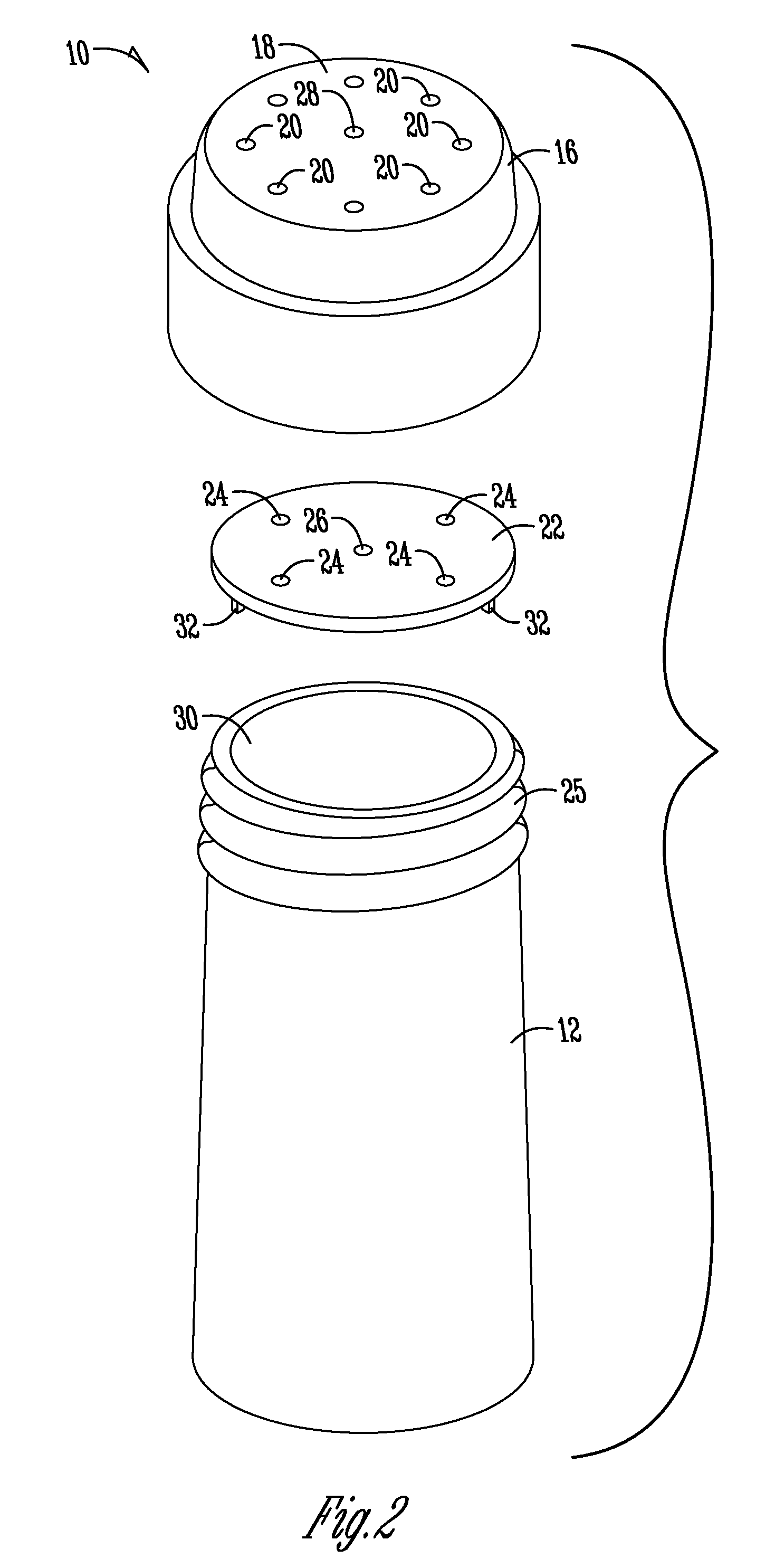

Shaker top with freshness seal and method of making same

A shaker top for dispensing products in a container, including a top unit having a peelable protective cover affixed upon a dispensing liner having at least one perforation, the top unit affixed to a mouth of a container. A method of manufacturing a shaker top with a peelable protective cover, including the steps of affixing a peelable protective cover upon a dispensing liner, assembling a top unit including the peelable protective cover and the dispensing liner, affixing the top unit to a mouth of a container, and covering the container with a cap. A shaker top with a peelable protective cover attached to a container, manufactured by the method of manufacture. A method of using a container having a shaker top with a freshness seal.

Owner:SELIG GRAND RAPIDS LLC

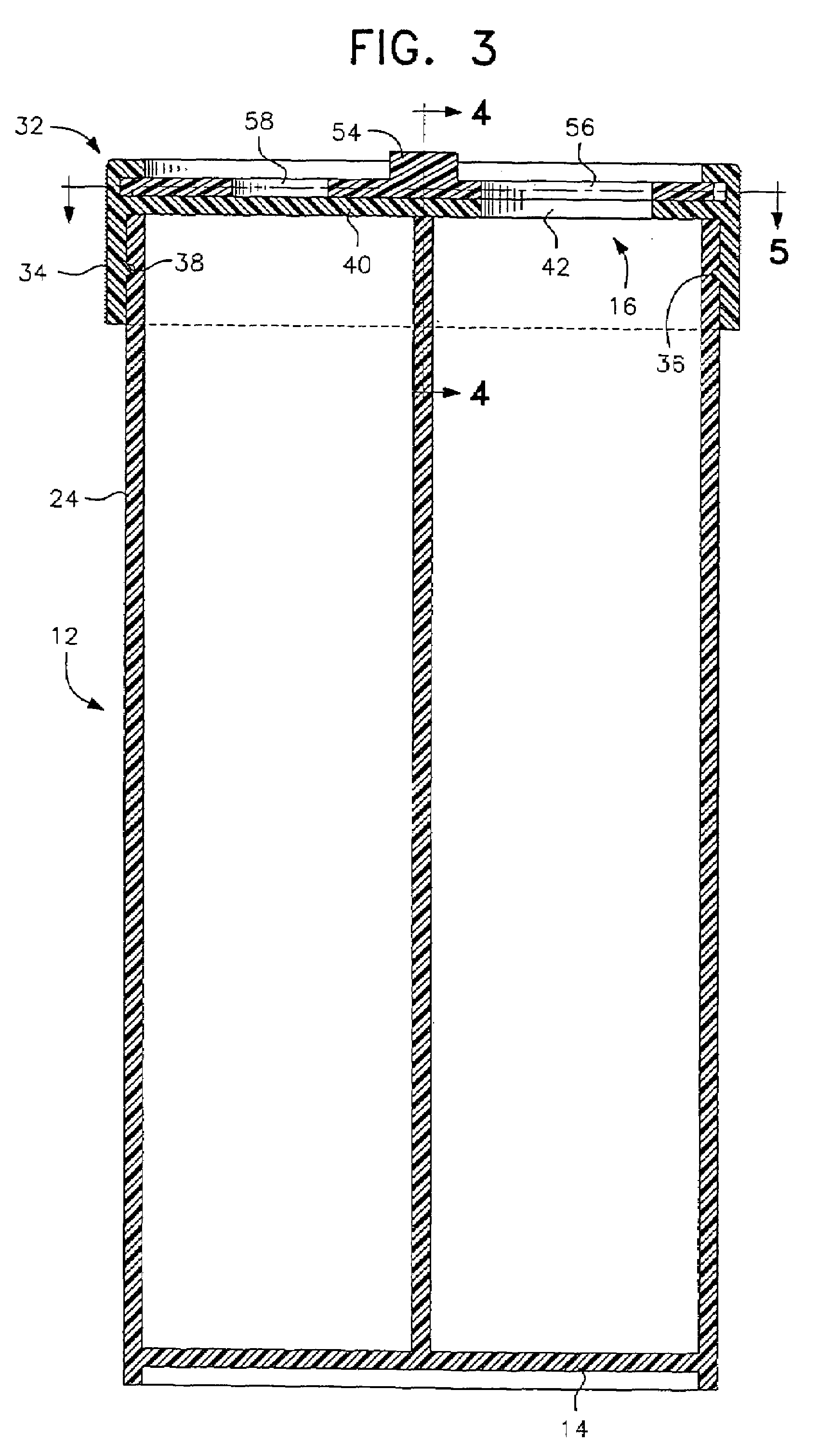

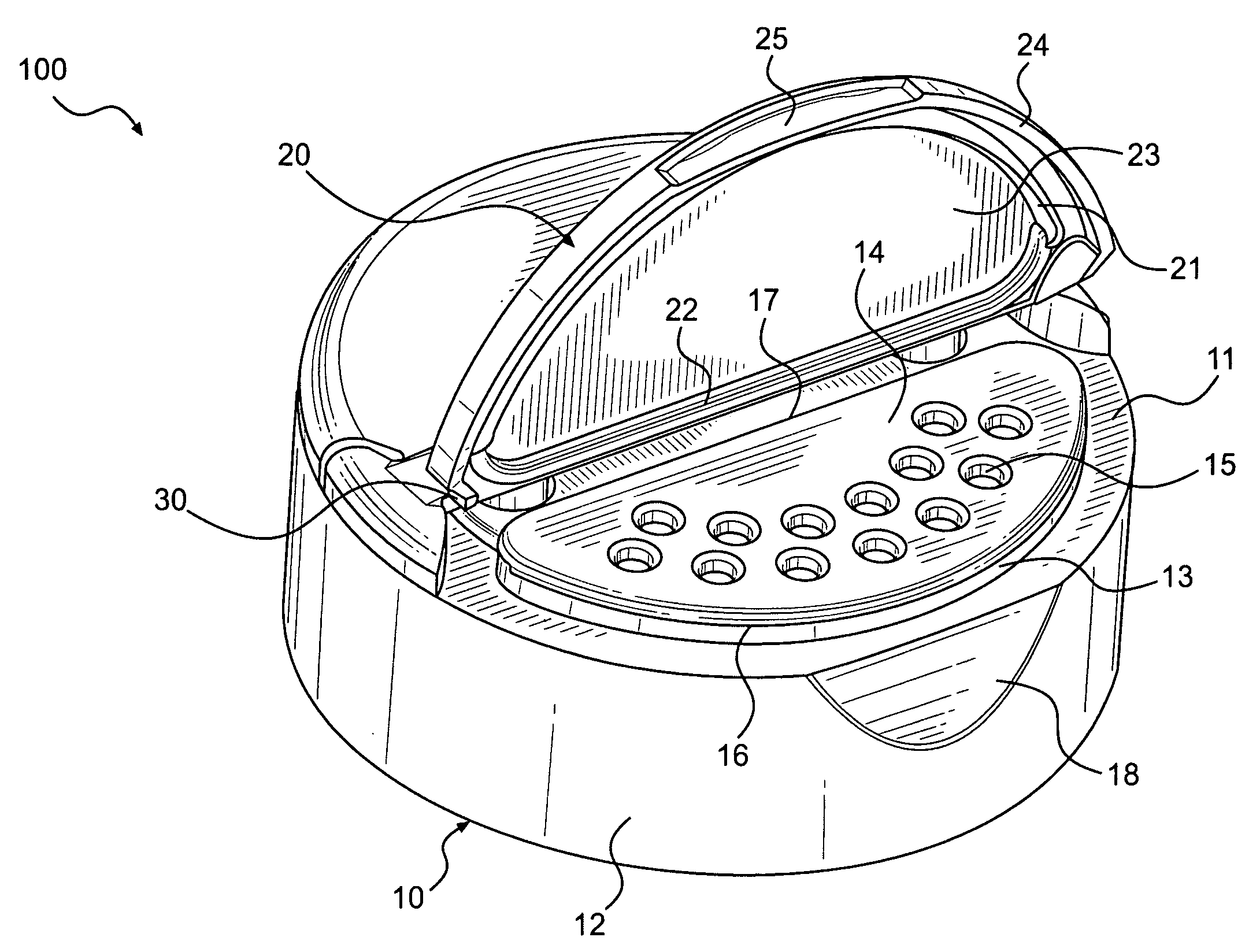

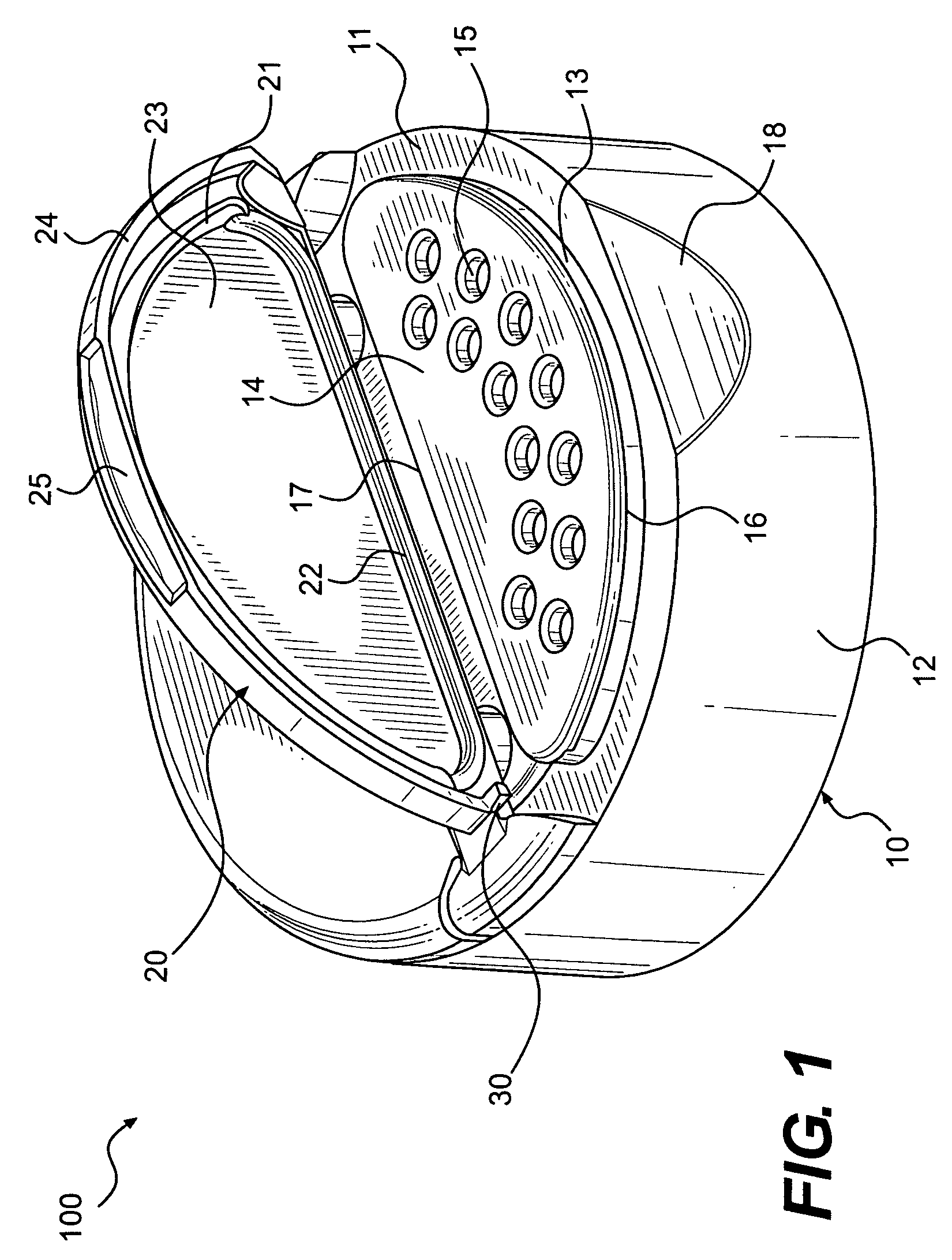

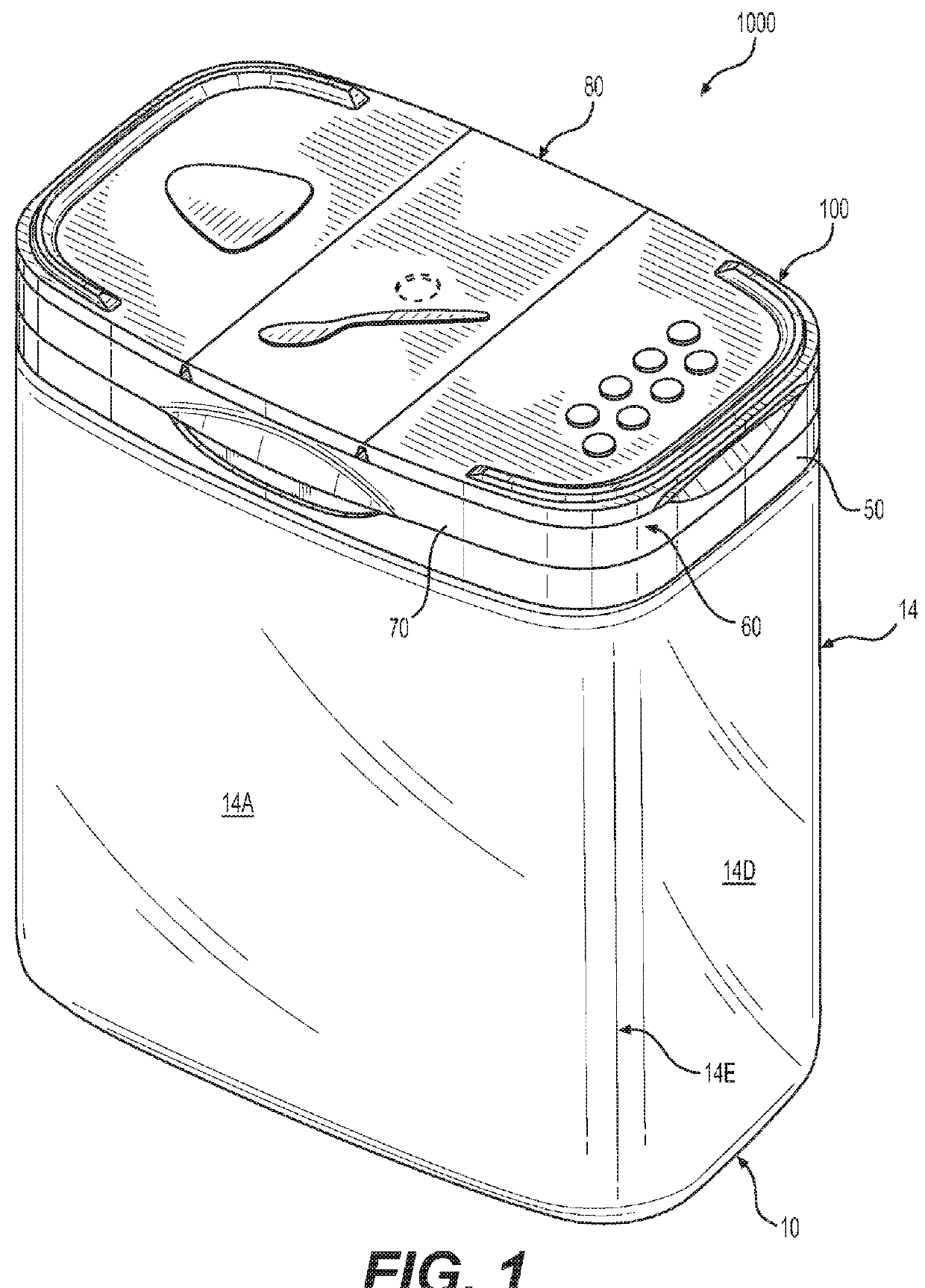

Three door lid and container utilizing the same

Container having a container body comprising a bottom, a rim and a lid securing portion located adjacent the rim. A lid includes a lid base sized and configured to secure the lid to the lid securing portion of the container body and a lid door assembly movably mounted to the lid base. The lid door assembly includes a main door that can assume at least a closed position with respect to the lid base and an open position with respect to the lid base, a first side door that can assume at least a closed position with respect to the main door and an open position with respect to the main door, and a second side door that can assume at least a closed position with respect to the main door and an open position with respect to the main door.

Owner:MCCORMICK & CO INC

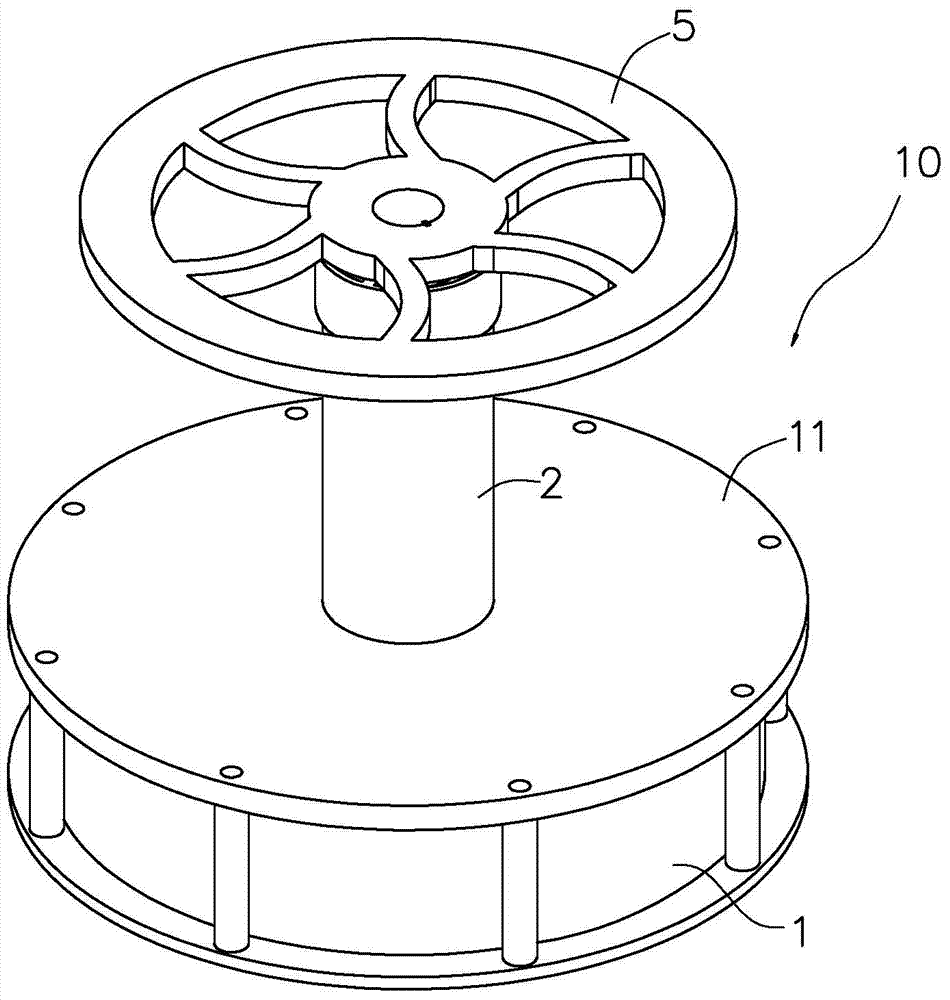

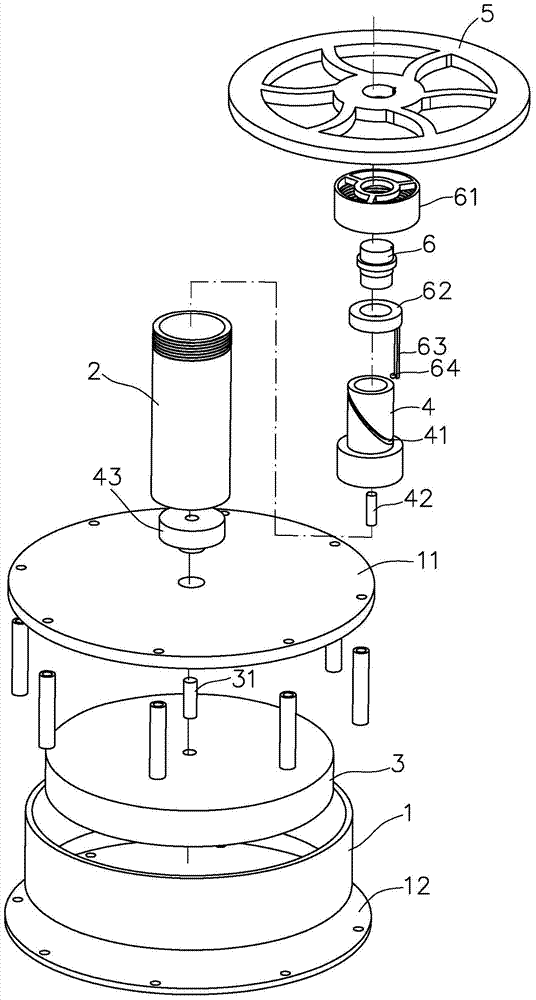

Stirling engine and cup cover and cup with same

The invention provides a stirling engine. The stirling engine comprises a first cylinder, a second cylinder, an air moving piston and a power piston. The stirling engine is characterized in that the bottom end of the power piston is arranged to a magnet, and a guide groove is obliquely formed in the periphery or the inner wall of the power piston; a driving block which is in match with the magnet by magnetic attracting through a clearance manner is arranged on the air moving piston; a flywheel is arranged on the top end of the second cylinder through a rotating shaft; the rotating direction of the flywheel is perpendicular to the moving direction of the power piston; the rotating shaft is downwards connected with a driving rod; the end part of the driving rod is arranged in the guide groove and can move along the guide groove. The invention further discloses a cup cover and a cup which are both provided with the engine. Compared with the prior art, the stirling engine has the advantages that the power piston drives the flywheel through the driving rod to rotate in the horizontal direction, so that the structure and type of the existing stirling engine model is enriched; the whole structure is compact, and the design is nice.

Owner:NINGBO XIAYUAN TECH +1

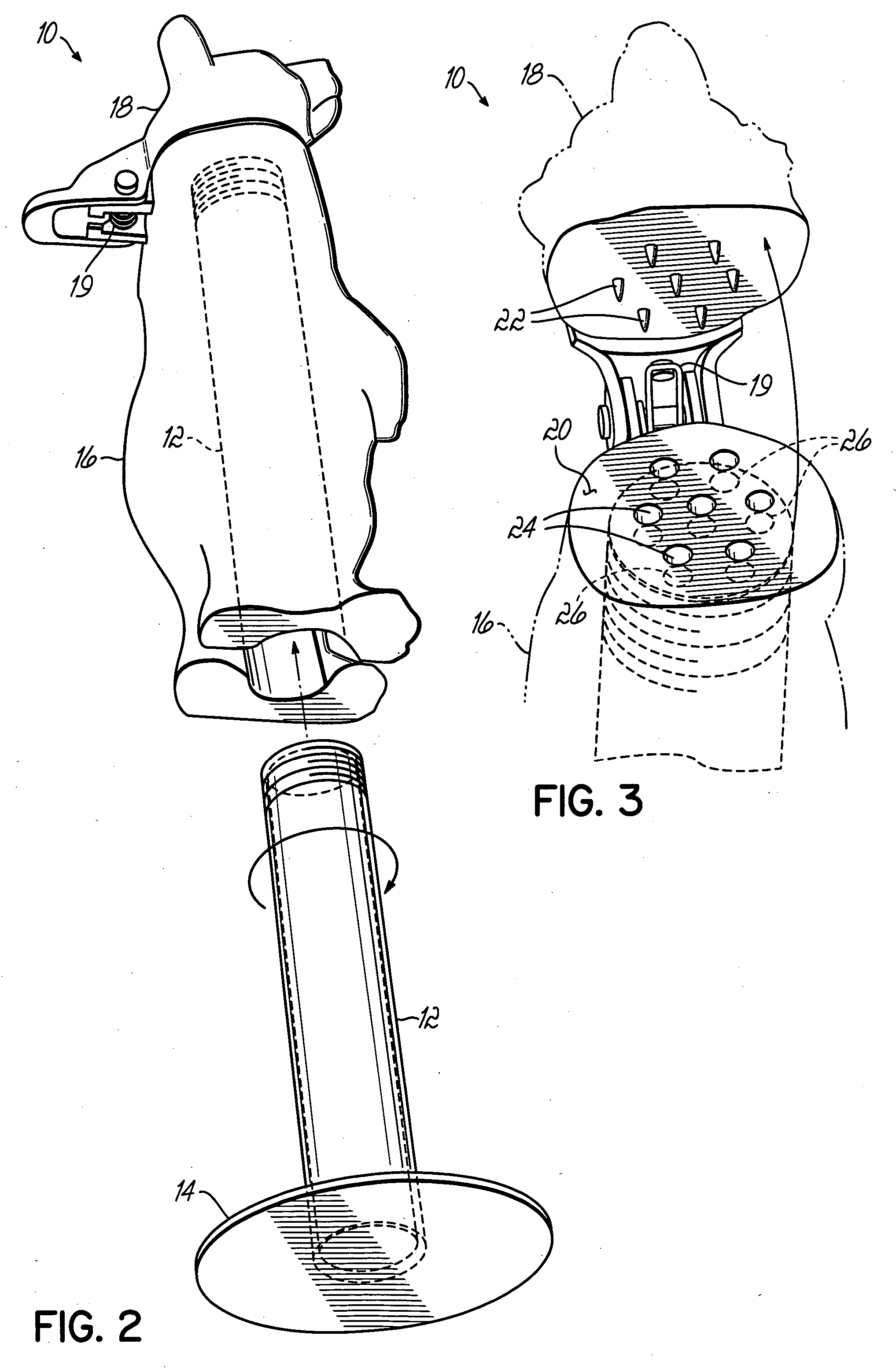

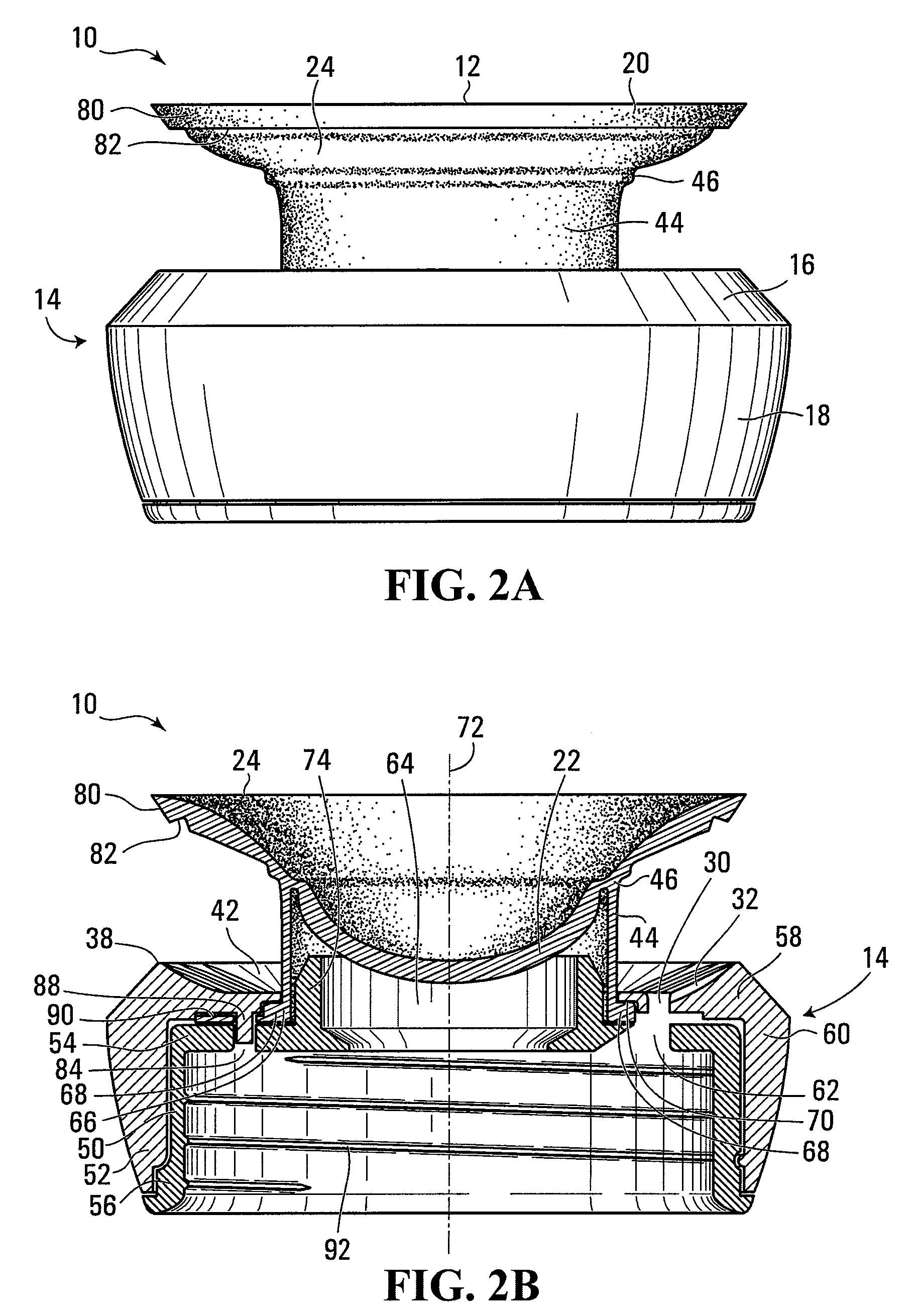

Condiment cartridge

InactiveUS20060201974A1Increase is affectedClosuresLiquid transferring devicesEngineeringMechanical engineering

A condiment shaker includes an inner container that may be inserted into an outer container. The inner container contains the condiment and may be removed and replaced during refilling. The inner container may include a base to lend support to the containers when assembled. Where desired, a handle grip, flip top lid and prongs for dislodging material in the container may be used to facilitate pouring of the condiment.

Owner:SURE SHAKE

One-piece multiorifice closure

Owner:PECHINEY PLASTIC PACKAGING

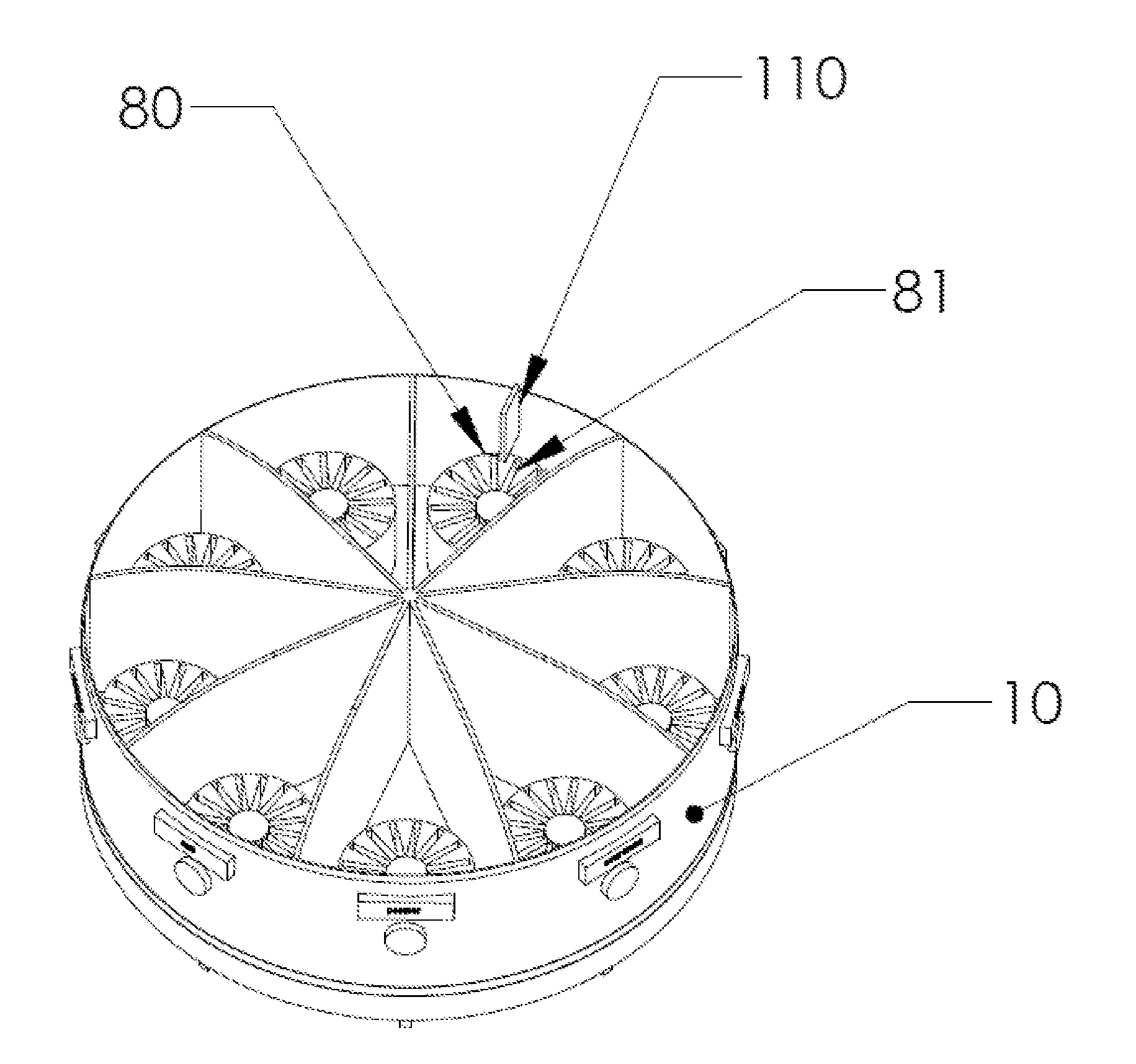

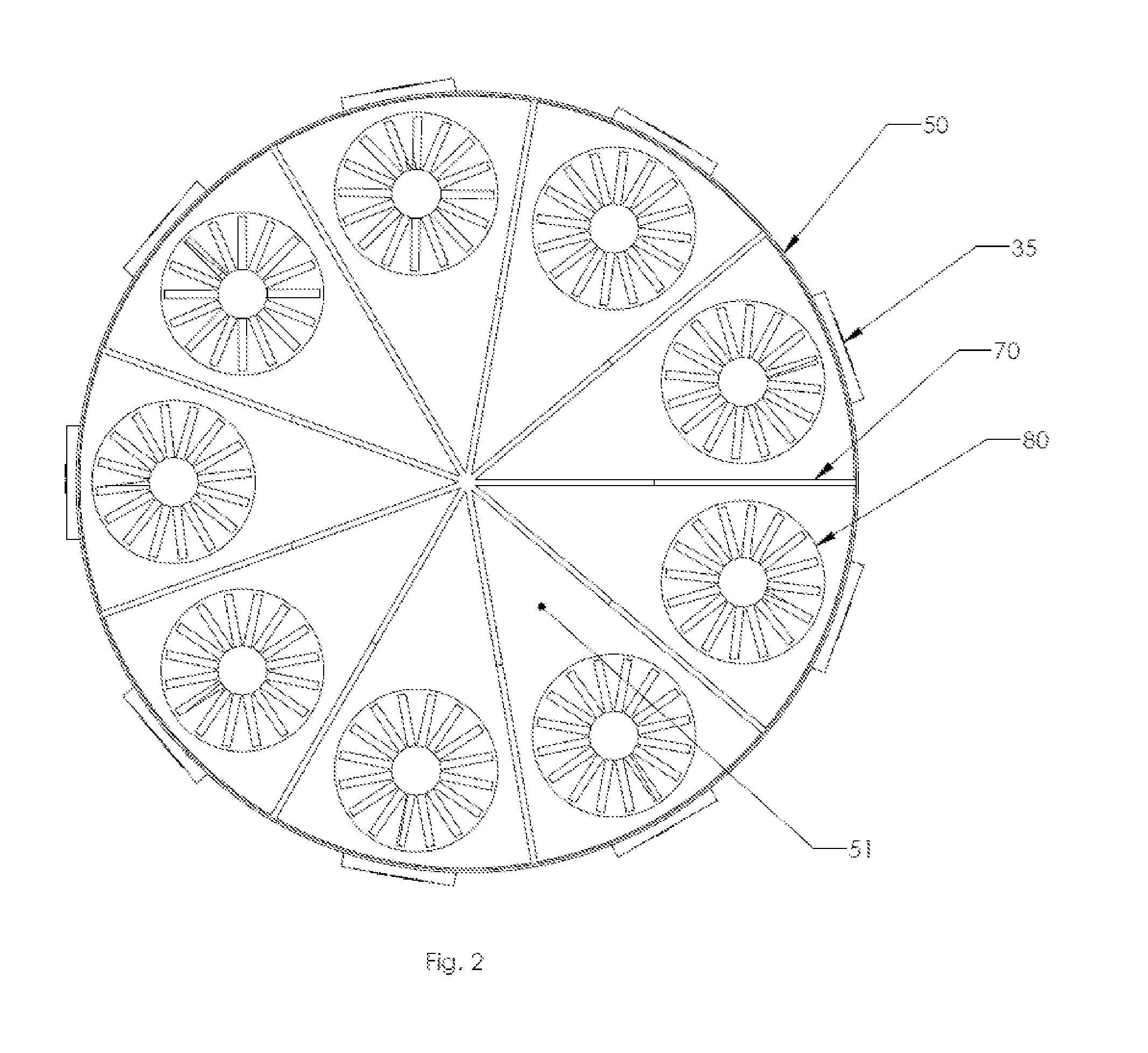

Condiment packet dispenser

ActiveUS8727178B1Easy refillEfficient storagePowdered material dispensingRecord information storageSpur gearElectric motor

A condiment packet dispenser that includes a cylindrical shaped housing containing an open top with a plurality of radially partitioned chambers. Each chamber contains a cylindrical shaped container that stores individual condiment packets in a radial manner. The dispenser is operated by pushing a button which sends a signal to a motor control board. The motor control board powers a motor having a spur gear which turns the selected condiment container until the condiment packet is aligned with a drop chute. The packet then falls thru the drop chute and is available for picking up by the customer. There is also a cylindrical shaped top lid which is removable when new condiments need to be loaded to replenish the dispenser. The condiment dispenser sits on top of a base stand that may either be rigidly mounted or may be rotated to choose a condiment.

Owner:CARTER IRENE +1

Cap for a condiment container

The invention provides a cap for a container for storing condiments for human consumption. The cap comprises a member having a top portion with a peripheral wall that has means for retaining the cap onto the container extending downwardly for covering the mouth of the container, the top portion having dispensing openings for allowing passage of the condiments. The cap comprises a seal having a top portion comprising a central portion, a flange portion extending around the central portion for overlapping the dispensing openings of the member and a central peripheral wall extending downwardly from the top portion and having a lower end mountable to the member. In use, the seal is moveable between a closed position, wherein the flange portion covers the dispensing openings for preventing passage of the condiments outwards from the interior of the container, and an open position, wherein the flange portion and the flange portion frees the dispensing openings for allowing passage of the condiments outwards from the interior of the container.

Owner:TRUDEAU 1889

Reduced flow salt shaker

InactiveUS20100276441A1Avoid cakingEasy to cleanOpening closed containersBottle/container closureEngineeringMechanical engineering

Owner:PORDY WILLIAM T +2

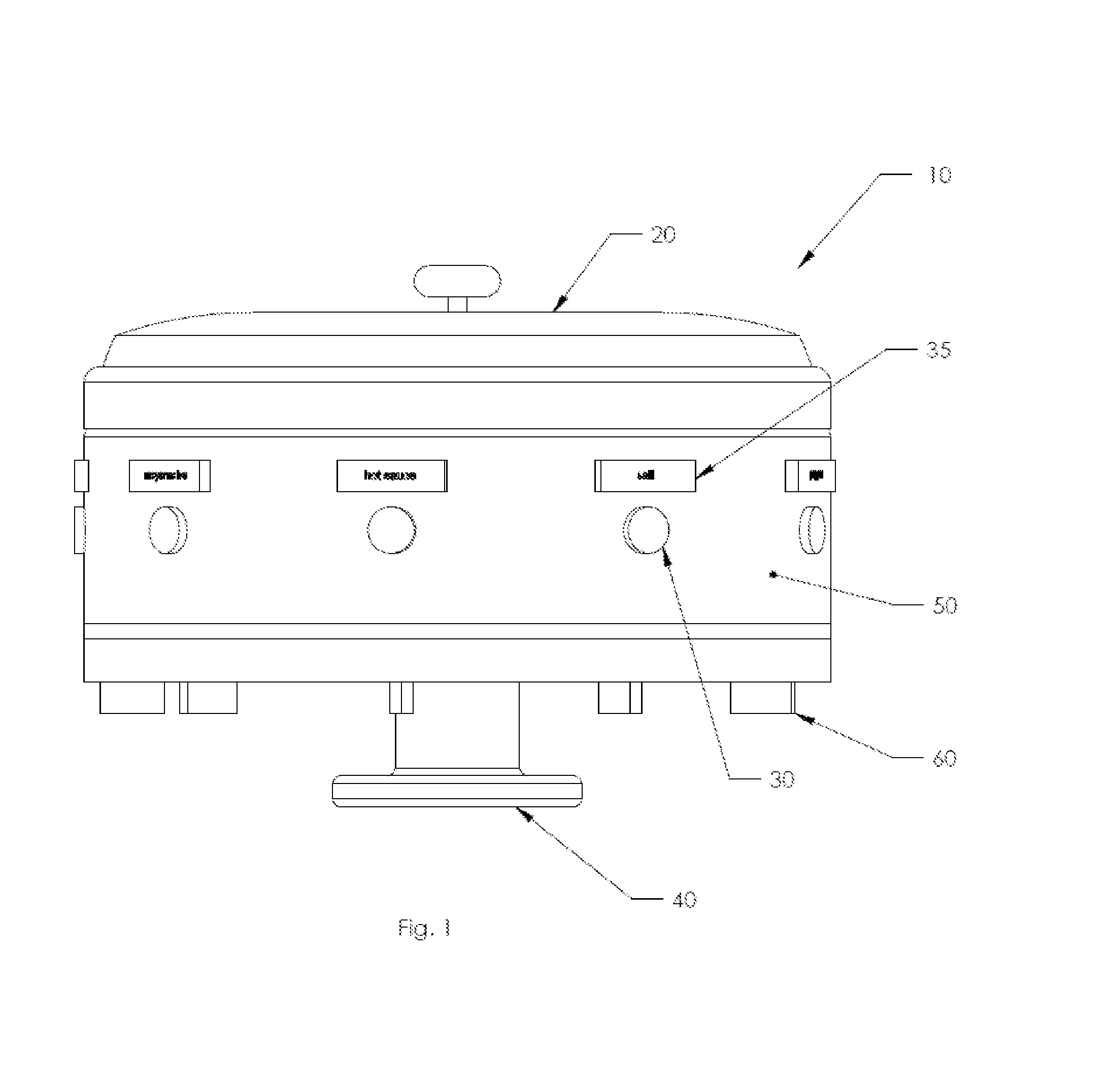

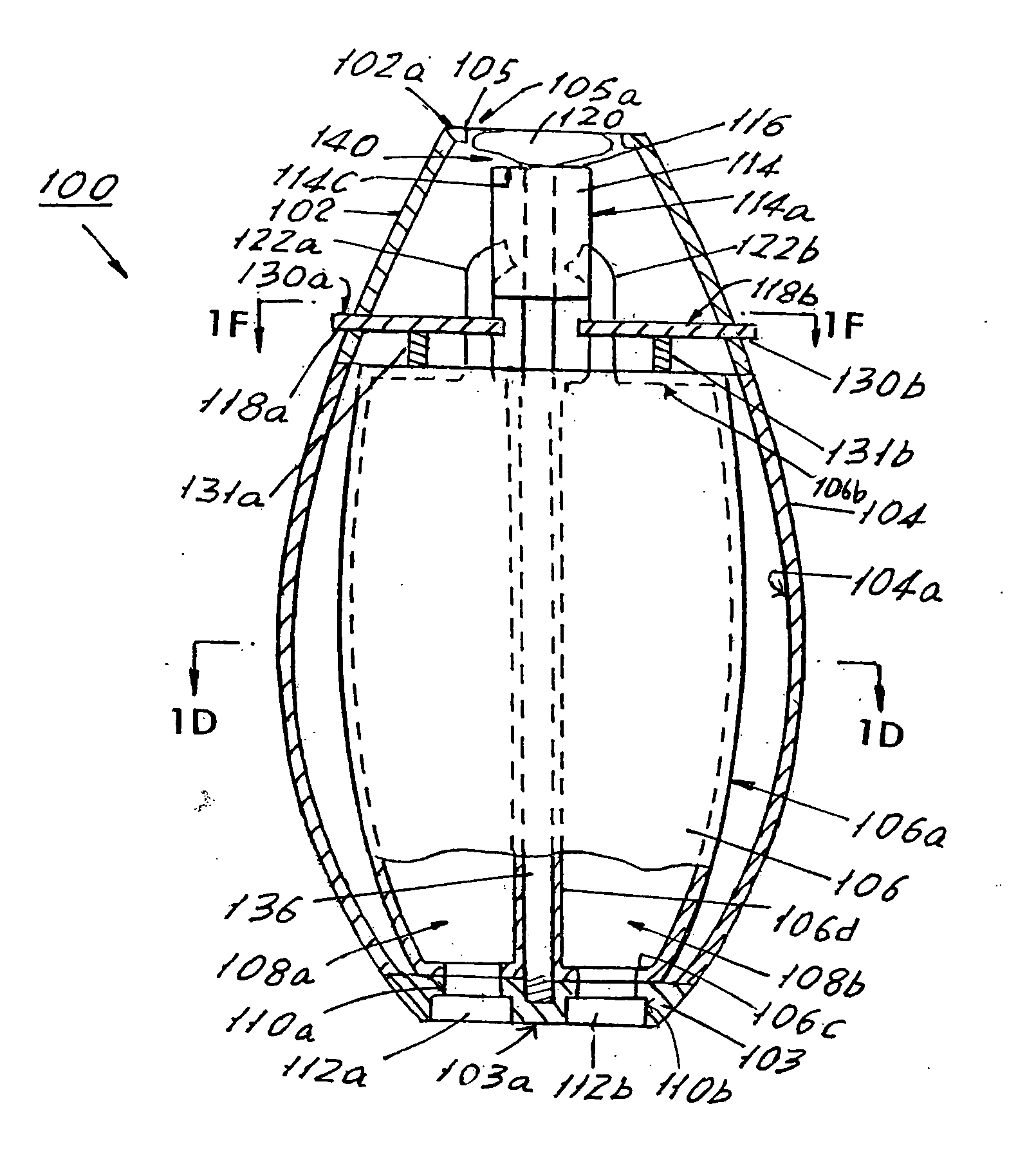

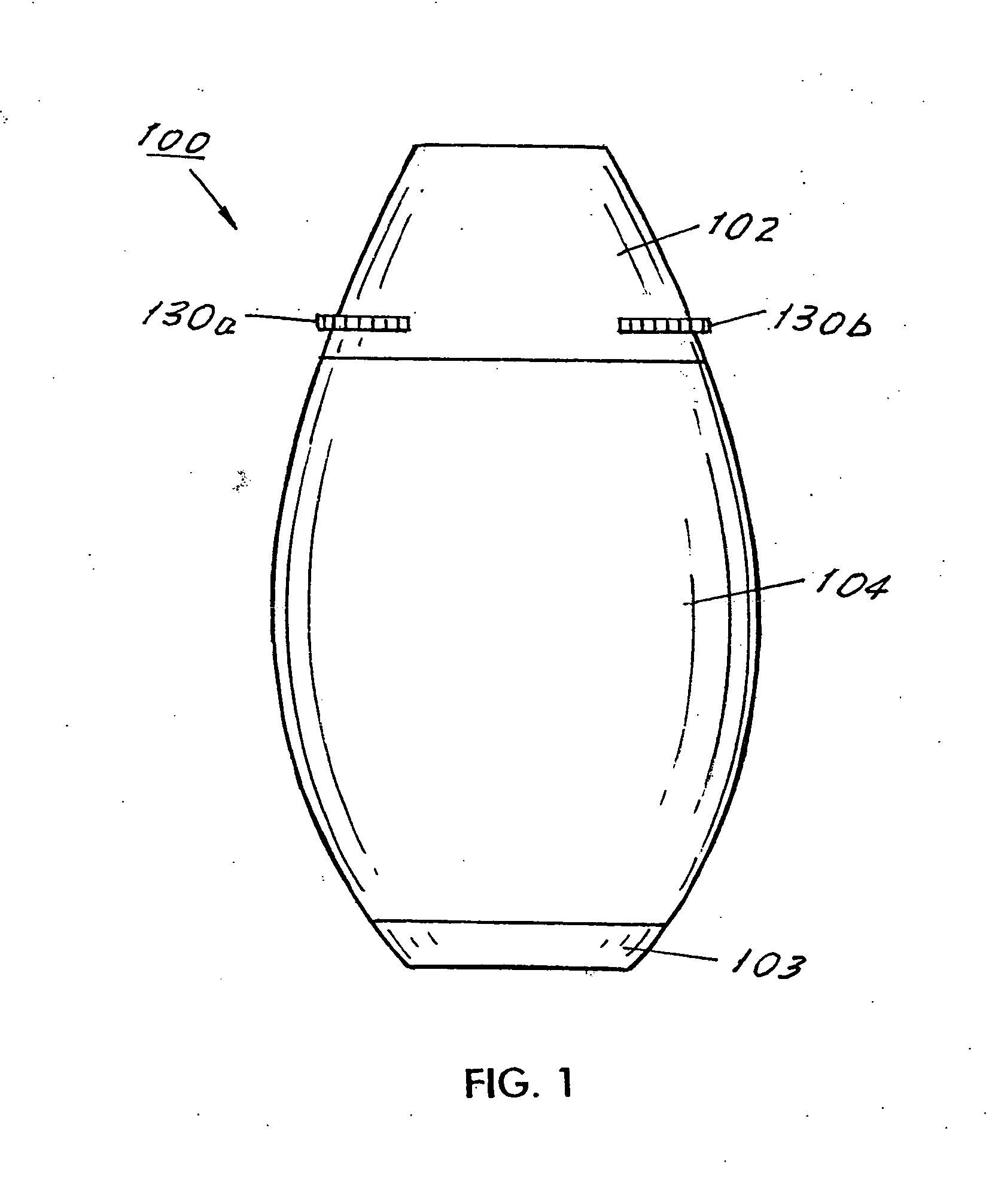

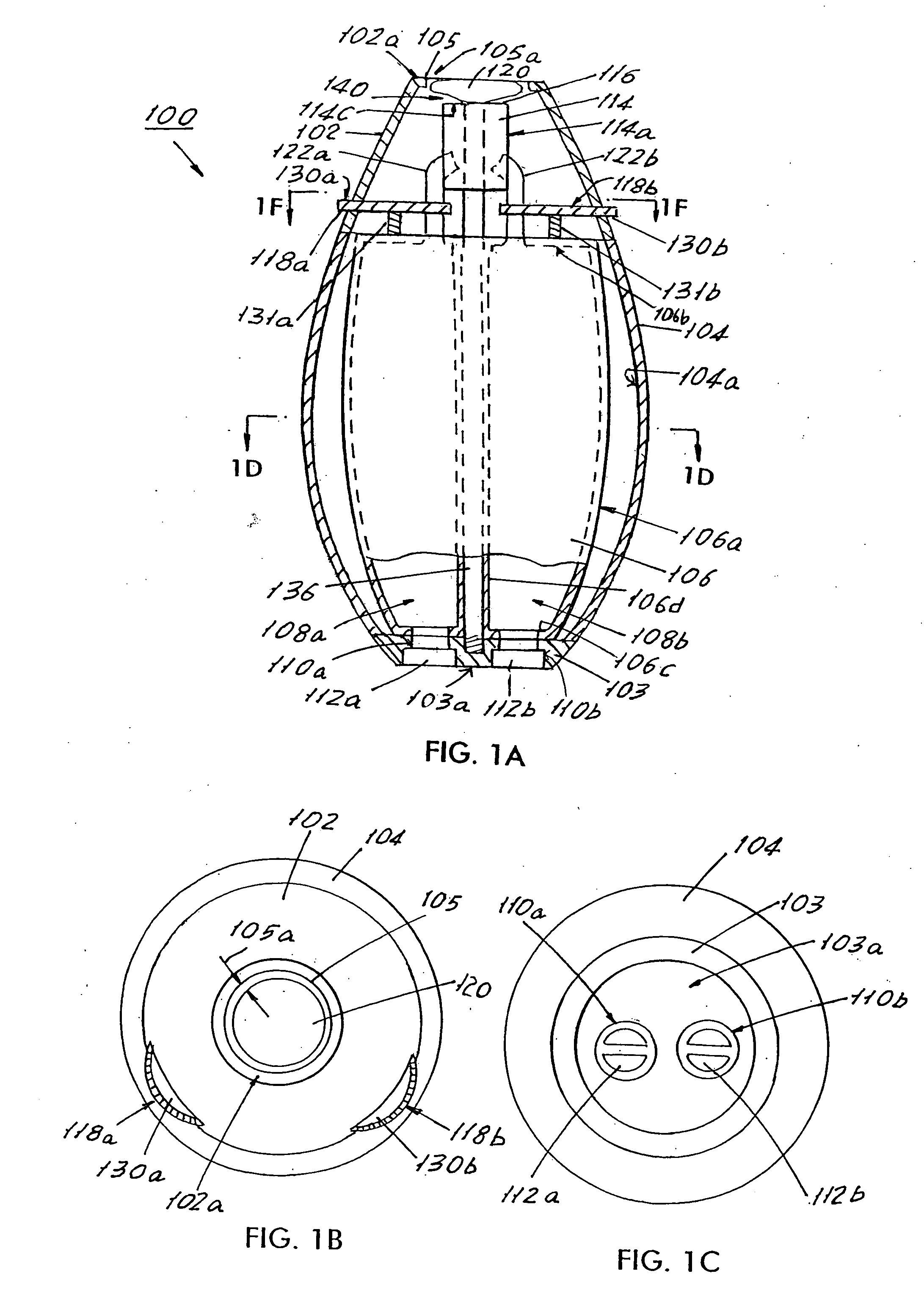

Condiment dispenser

A condiment dispenser includes one or more condiment chambers for holding condiments. Each condiment chamber is connected to a common discharge chamber or to a respective discharge chamber, the discharge chamber(s) having an outlet for dispensing condiments from the condiment chamber(s). Each connection may be formed through a respective tube. A flow control mechanism may control the flow from a condiment chamber to a discharge chamber. The mechanism may be a dial that is operable to compress and decompress the tube. The dial may move between numerous positions and retain any position between uses. A dispersing element may be positioned respective to the outlet of a discharge chamber to control the dispensing and dispersing of condiments. In an example operation, the flow control mechanism(s) are adjusted to a desired flow and the dispenser is inverted, causing condiment(s) to flow from the condiment chamber(s) and into the discharge chamber(s), where the condiments are dispensed and dispersed.

Owner:SAHA ATANU

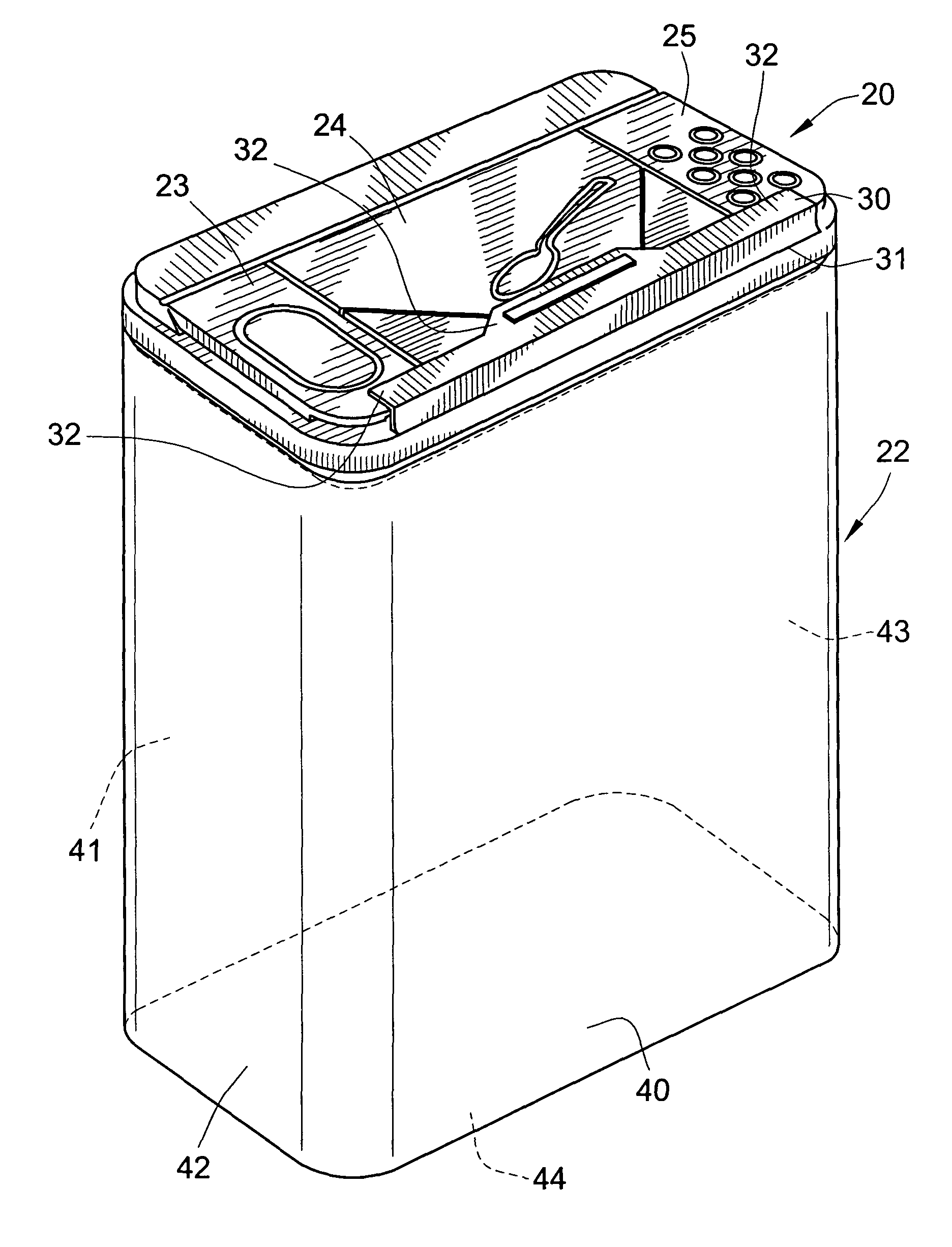

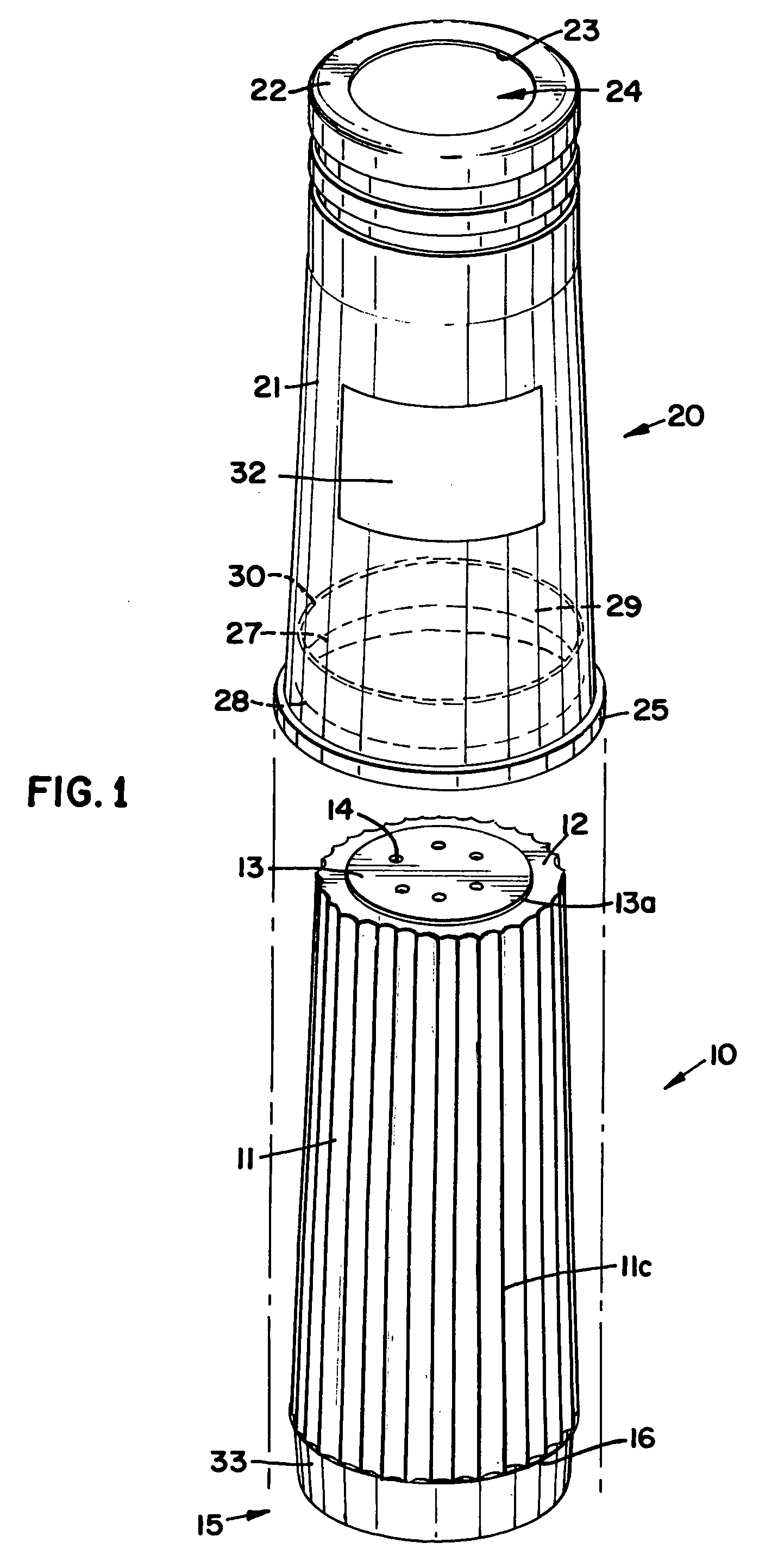

Disposable condiment shaker and decorative sleeve

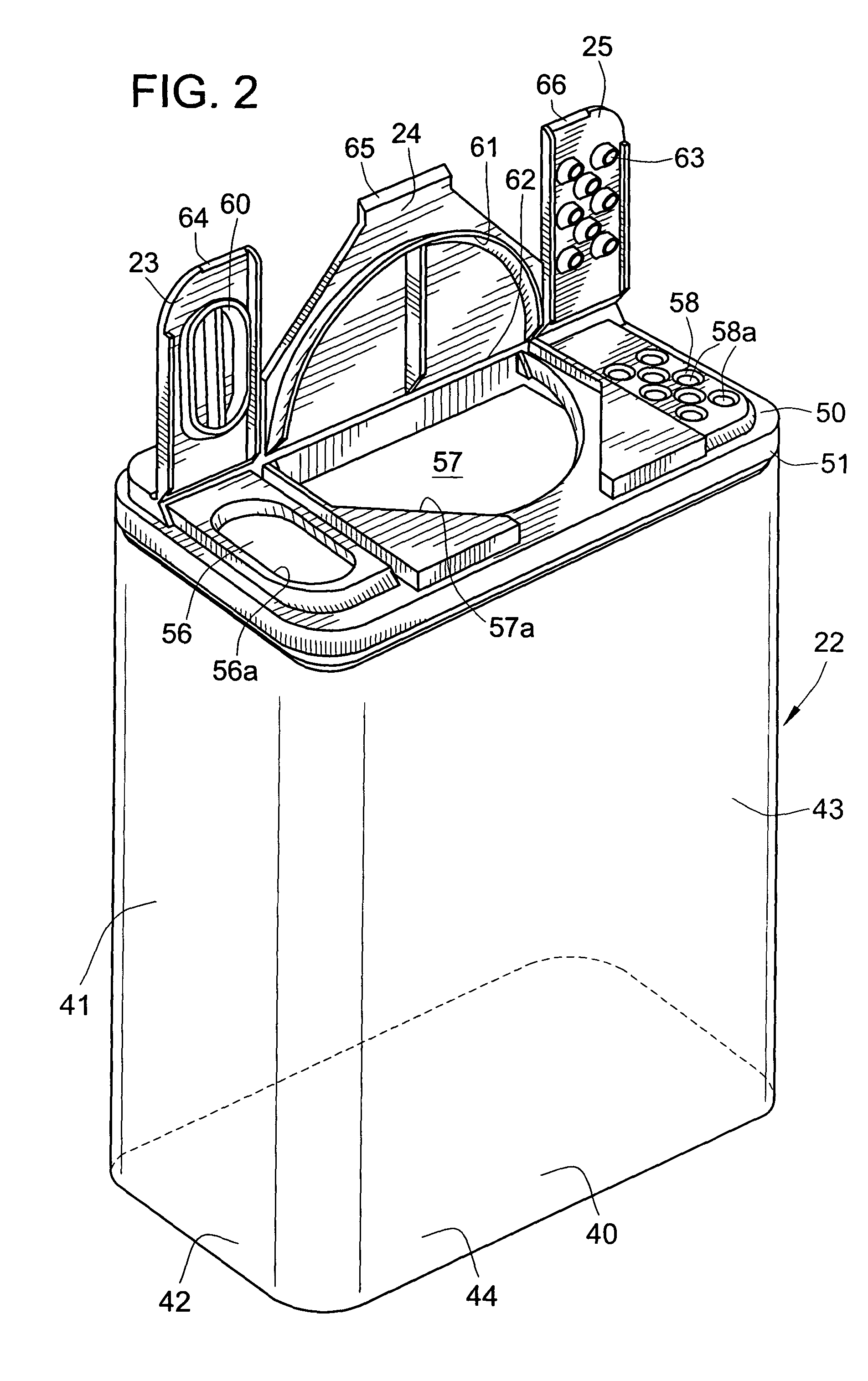

InactiveUS20050161466A1Prevent openingOpening closed containersBottle/container closureBiomedical engineering

A disposable, tamper-resistant condiment shaker (10) containing a condiment (37) is supported within a cavity (24) of a decorative sleeve (20) to provide a more aesthetically pleasing condiment dispensing assembly (100). The sleeve (20) includes a securing member (29, 42, 44) to support the shaker (10) within the cavity (24). When the condiment supply within the shaker (10) has become depleted, the shaker (10) may be removed from the sleeve (20), discarded, and replaced with a new shaker (10). This cartridge type loading and refilling of the condiment (37) eliminates the need to pour condiment (37) into a dispenser.

Owner:HORMEL FOODS