Patents

Literature

1078results about How to "Avoid switching" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

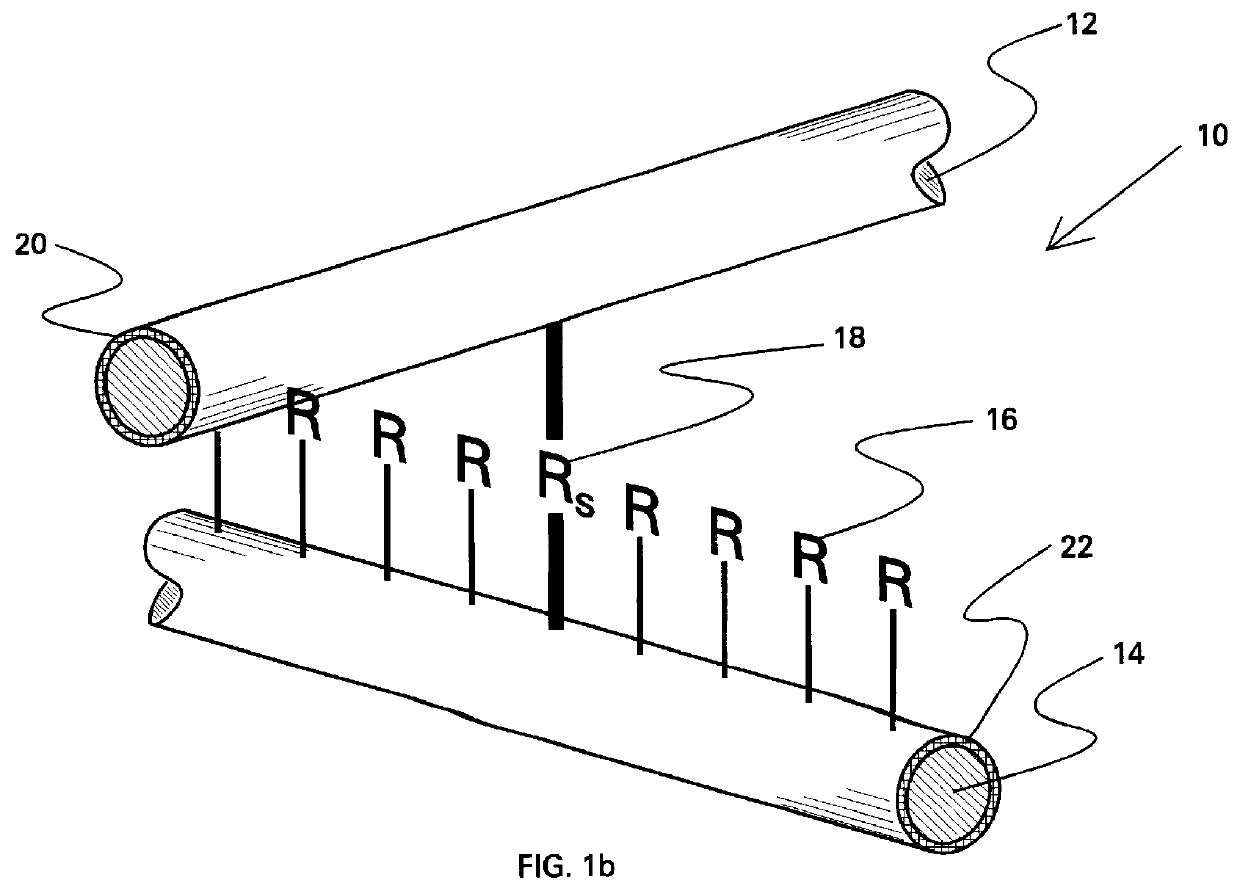

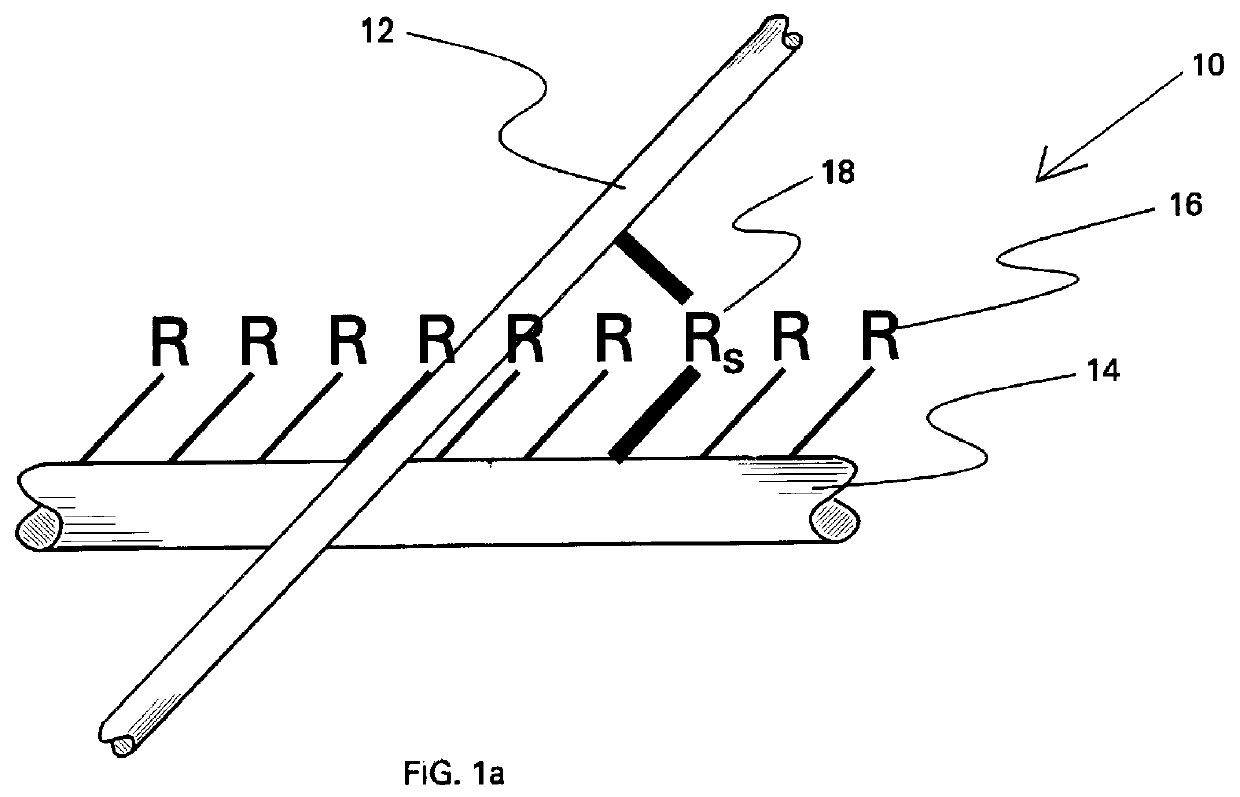

Molecular wire crossbar memory

InactiveUS6128214AAvoid switchingReduce power consumptionNanoinformaticsSolid-state devicesResistorNon symmetric

A molecular wire crossbar memory (MWCM) system is provided. The MWCM comprises a two-dimensional array of a plurality of nanometer-scale devices, each device comprising a junction formed by a pair of crossed wires where one wire crosses another and at least one connector species connecting the pair of crossed wires in the junction. The connector species comprises a bi-stable molecular switch. The junction forms either a resistor or a diode or an asymmetric non-linear resistor. The junction has a state that is capable of being altered by application of a first voltage and sensed by application of a second, non-destructive voltage.

Owner:RGT UNIV OF CALIFORNIA +1

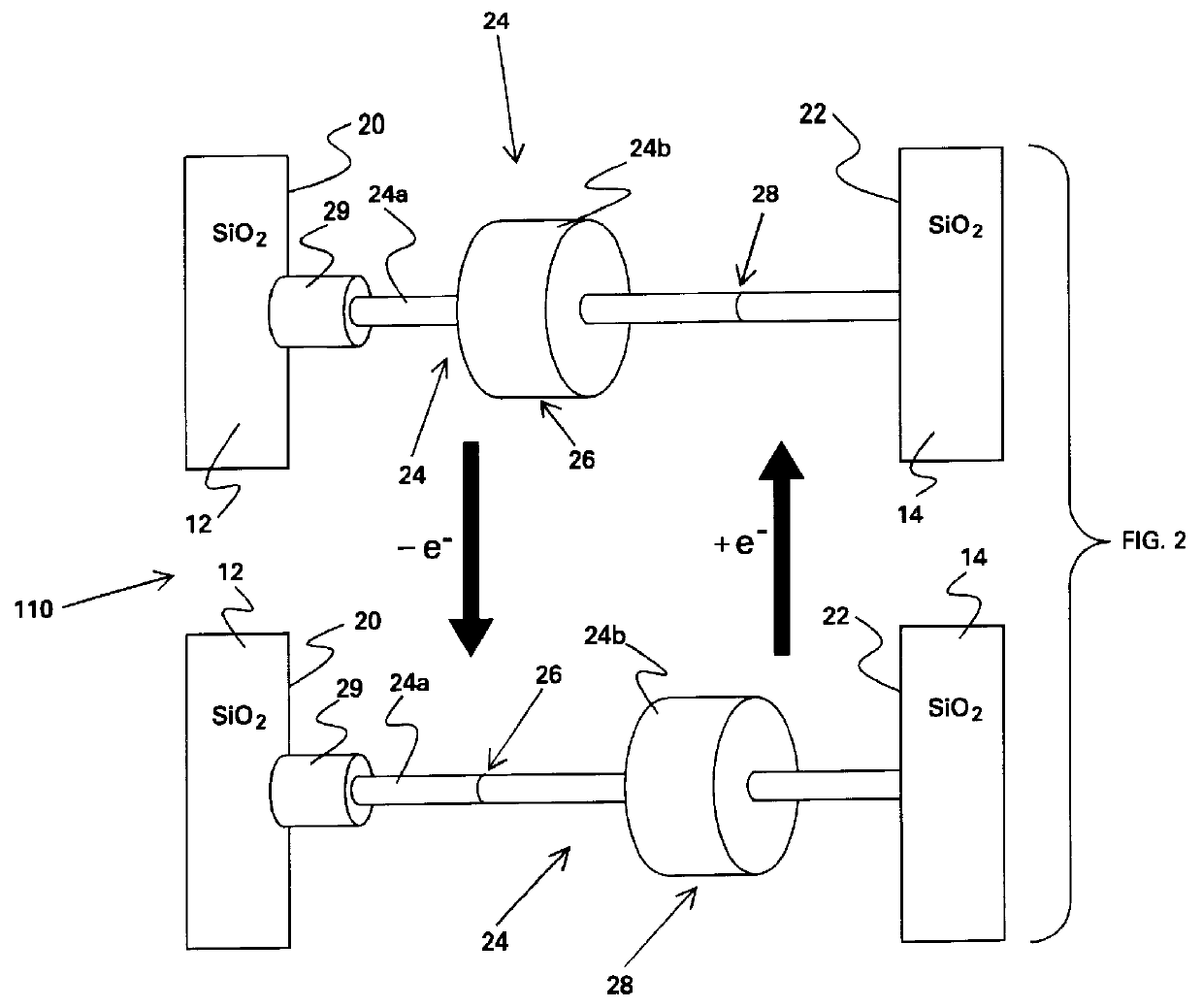

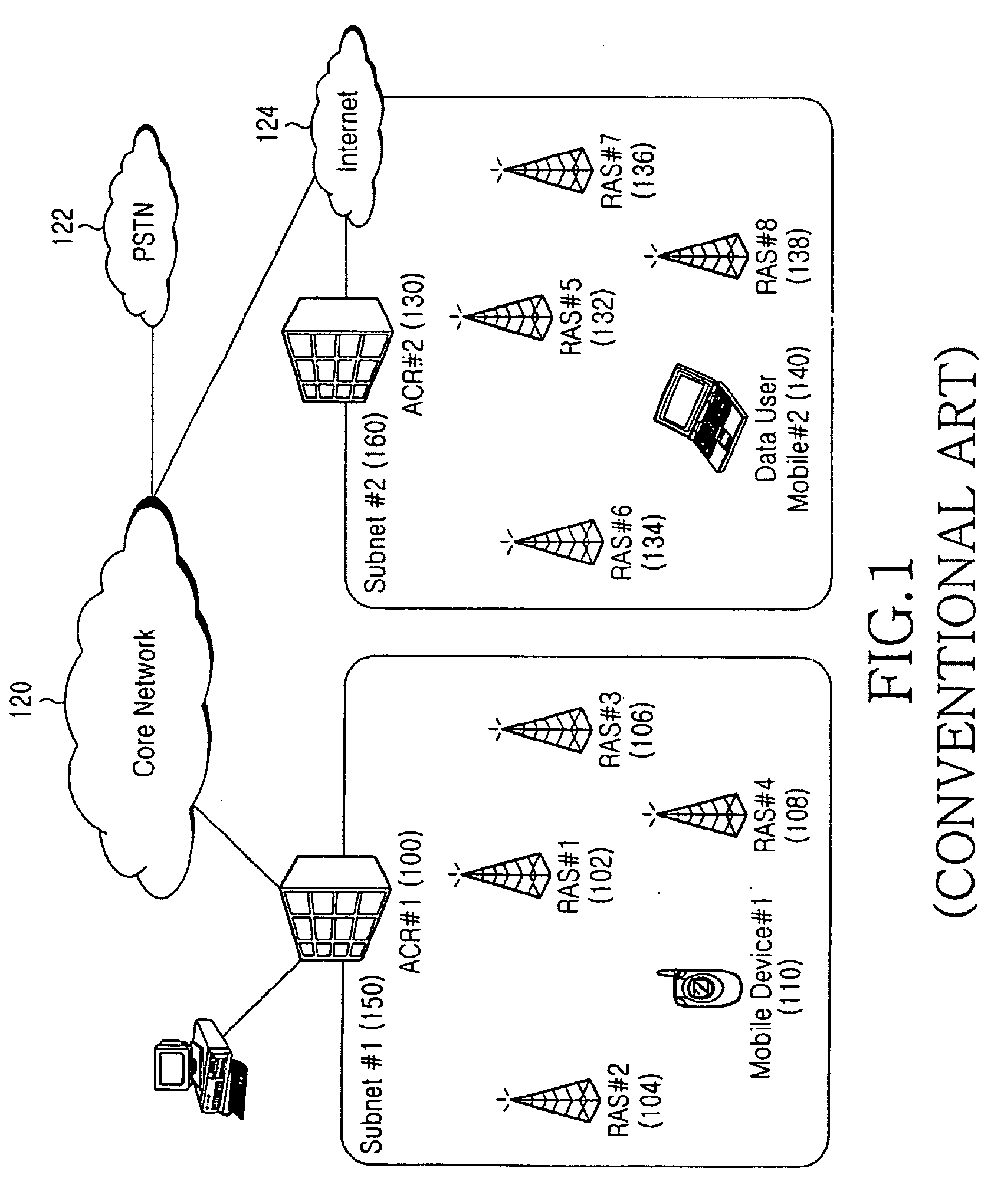

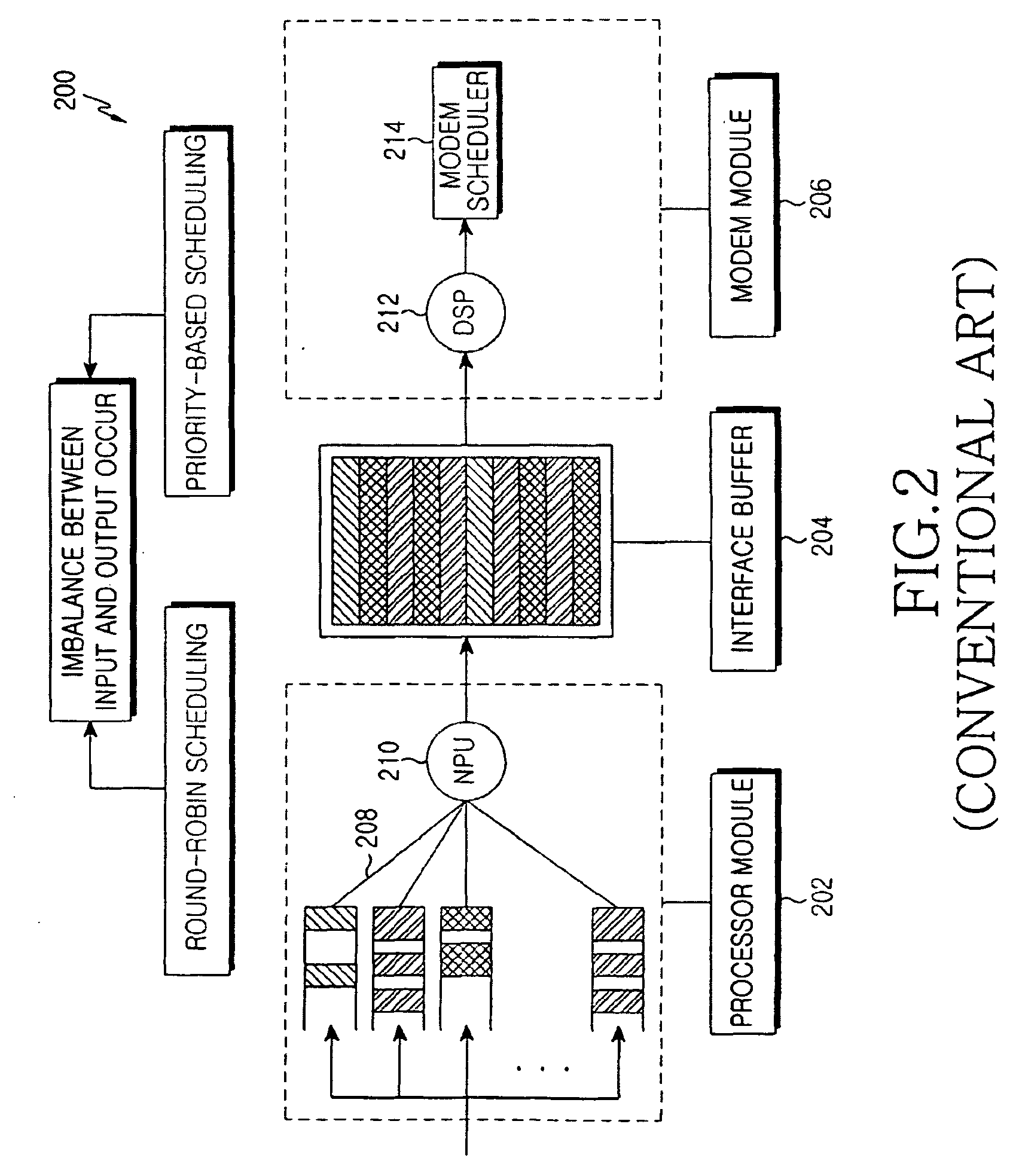

Method and apparatus for managing a buffer in a communication system

ActiveUS20080130670A1Prevent unnecessary switchingAvoid switchingError preventionTransmission systemsQuality of serviceCommunications system

A method and apparatus for managing a buffer of a Radio Access Station (RAS) in a communication system are provided. An available buffer space determiner sets a threshold for each service class for scheduling packet input / output of the buffer according to priority of a service class, estimates and stores, upon receipt of a packet at the buffer, an available space size of the buffer after the packet reception, compares the estimated available space size of the buffer with a first threshold corresponding to a first service class indicative of a service class of the packet, and schedules packet input / output of the buffer according to the comparison result. A processor module schedules packet input / output of the buffer according to an output of the available buffer space determiner. The present invention can improve quality of services through service differentiation based on priorities of service classes and buffer management based on characteristics of the corresponding service traffics.

Owner:SAMSUNG ELECTRONICS CO LTD

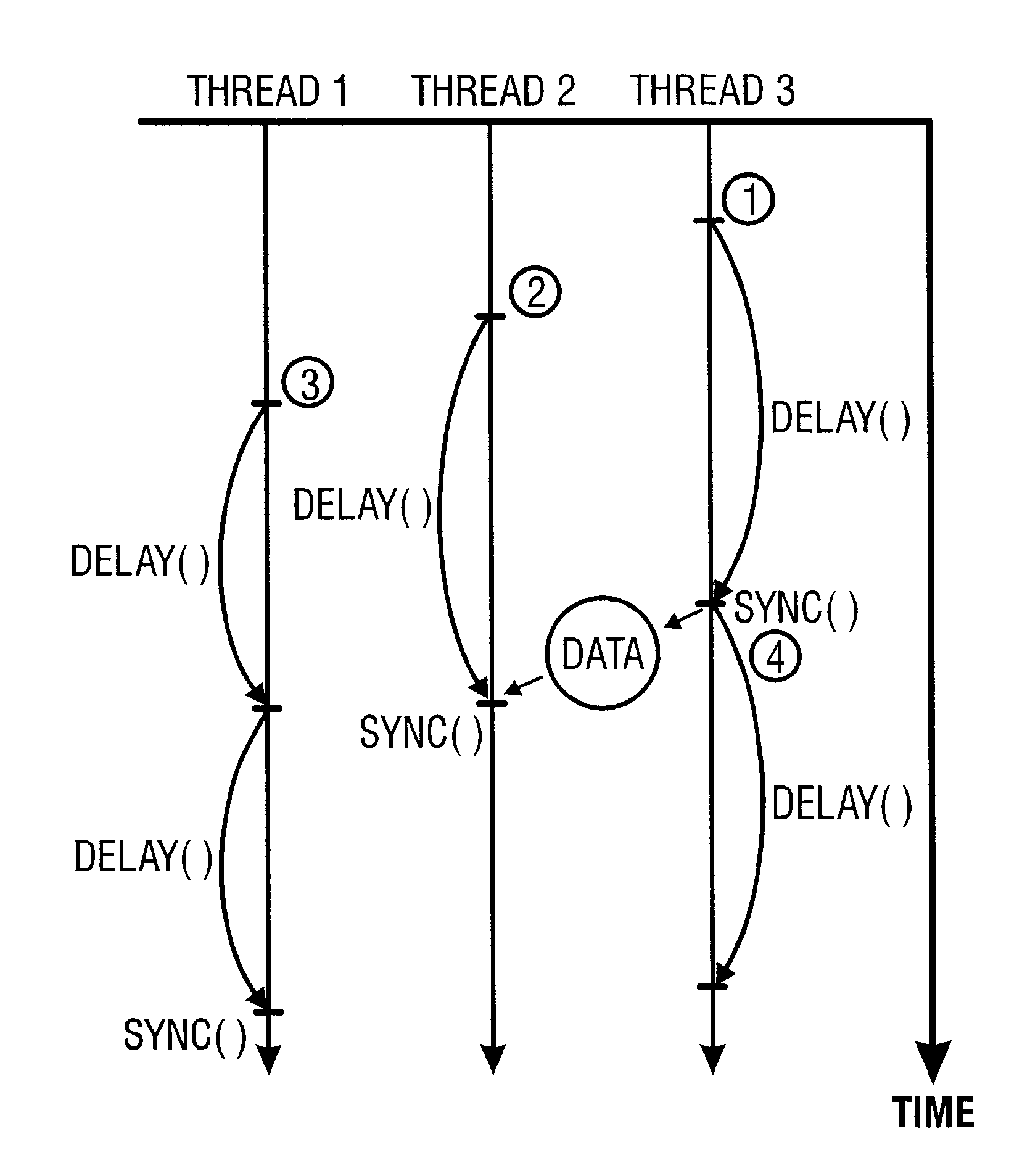

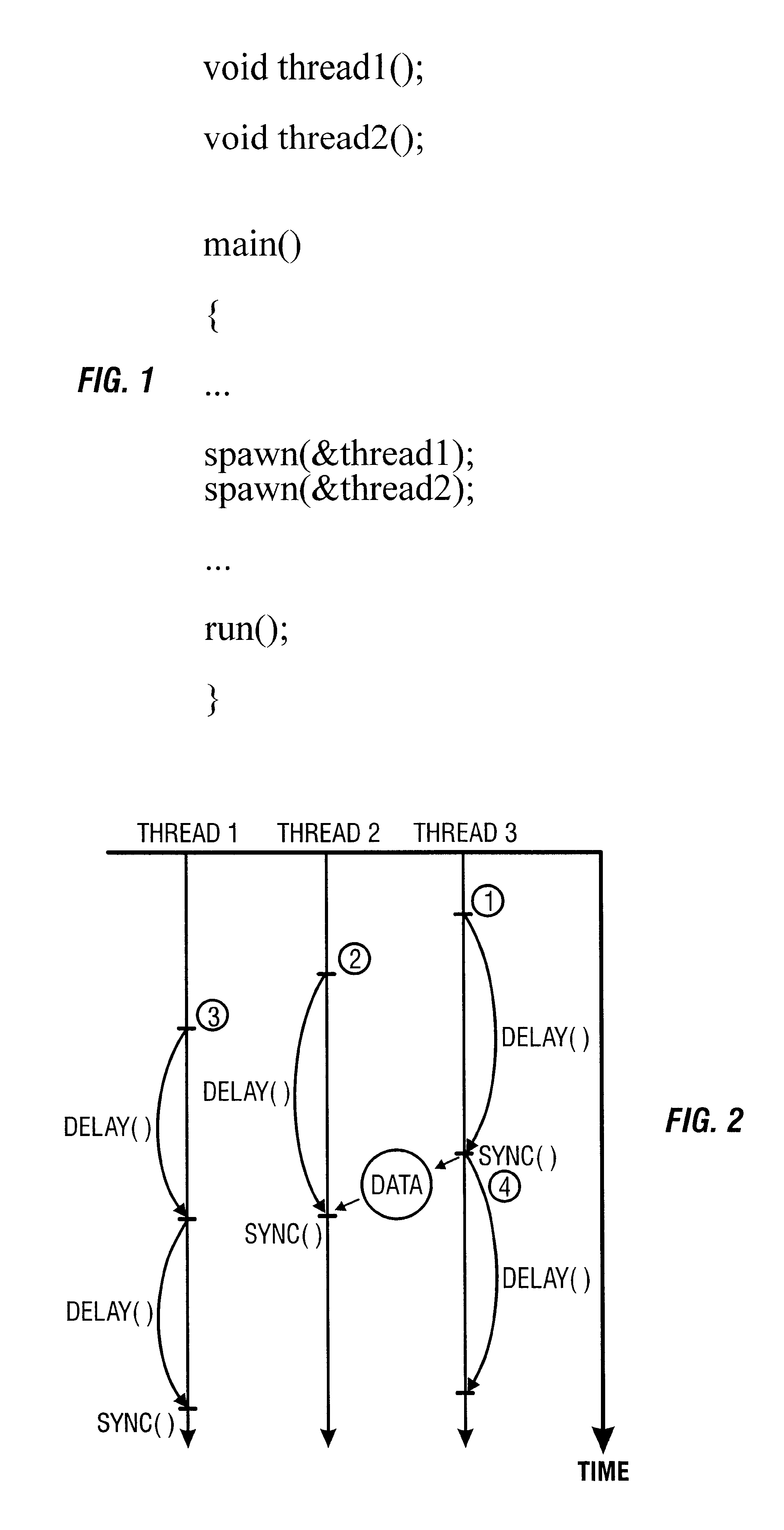

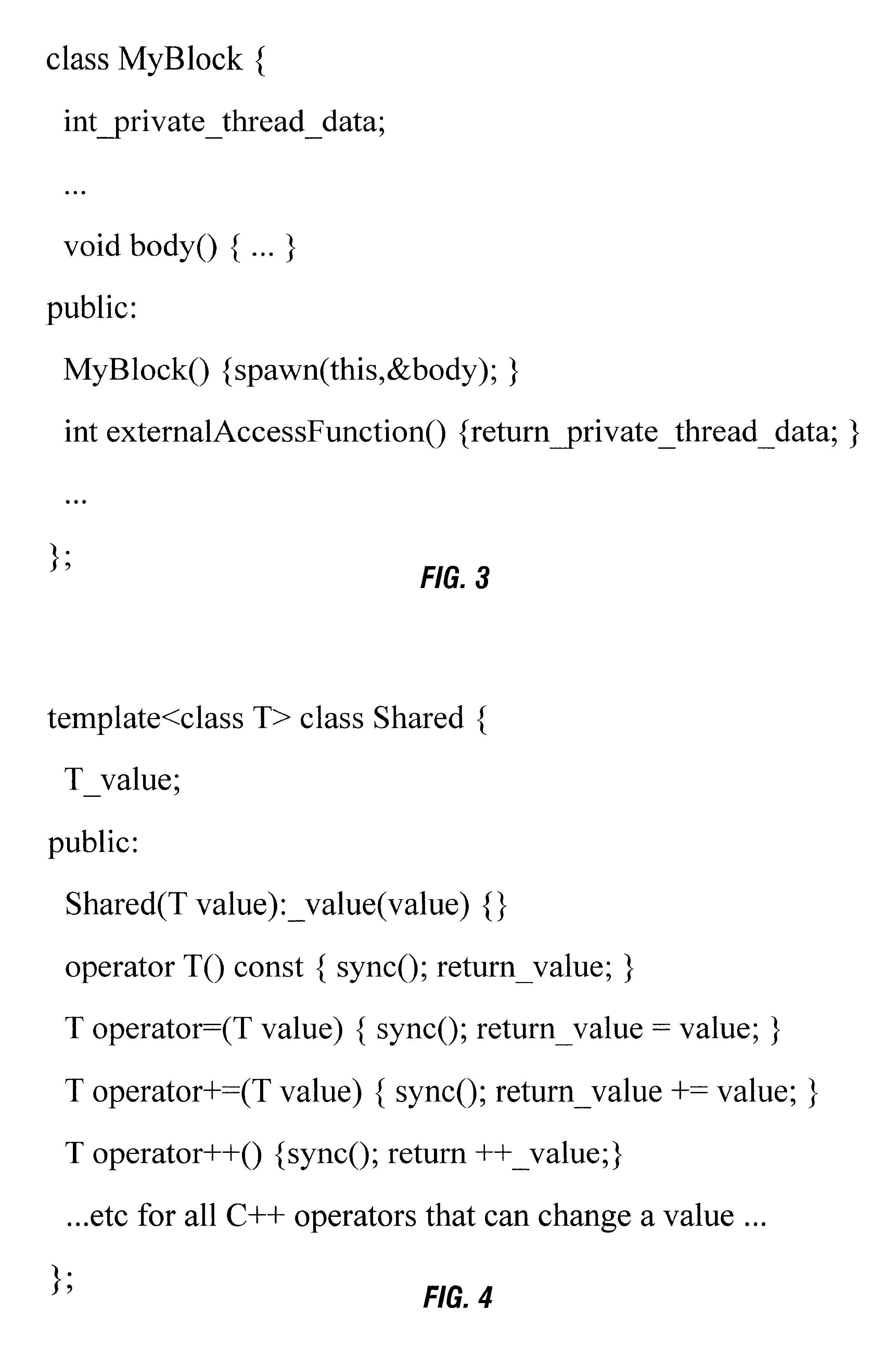

Concurrent timed digital system design method and environment

InactiveUS6952825B1Improve Simulation EfficiencyAvoid switchingMultiprogramming arrangementsSoftware designSystems designCommunications system

The present invention relates to the design of an essentially digital system. As one example of digital systems, these may perform real-time transformations on time discrete digitized samples of analogue quantities. An example of such a system is a digital communication system. The transformations on the data can be specified in a programming language and executed on a processor such as a programmable processor or directly on application specific hardware. In accordance with the present invention the digital system is described as a set of threads in a description language. Alternative names for a thread are tasks and processes. The set of threads defines a representation or model of the digital system. In accordance with the present invention, the representation or model is preferably executable at each stage of the design independent of the current level of abstraction of that representation or model. With description language is meant a programming language. In accordance with the present invention each of the threads has a variable having an assignable value which represents the “local time” of said thread, i.e. a time associated only with that thread, which can be used for sequencing the processing of that thread with respect to other threads. With the word “local” is meant that the time is an attribute of the thread only. In accordance with the present invention a means is provided for the designer to assign a delay to each thread or operation within a thread, this delay representing for instance the processing time for the respective operation or thread on a processing engine, e.g. a computer. By this means, not only can the processing of threads be scheduled but also the designer may assign a value representative of an elapsed time for the processing of a thread or operation on a processing engine. In addition, the threads may be refined concurrently, while still keeping their local time so that after the refining process the new representation of the digital system is executable, i.e. the processing of the refined threads can be scheduled without divergence from the specification.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

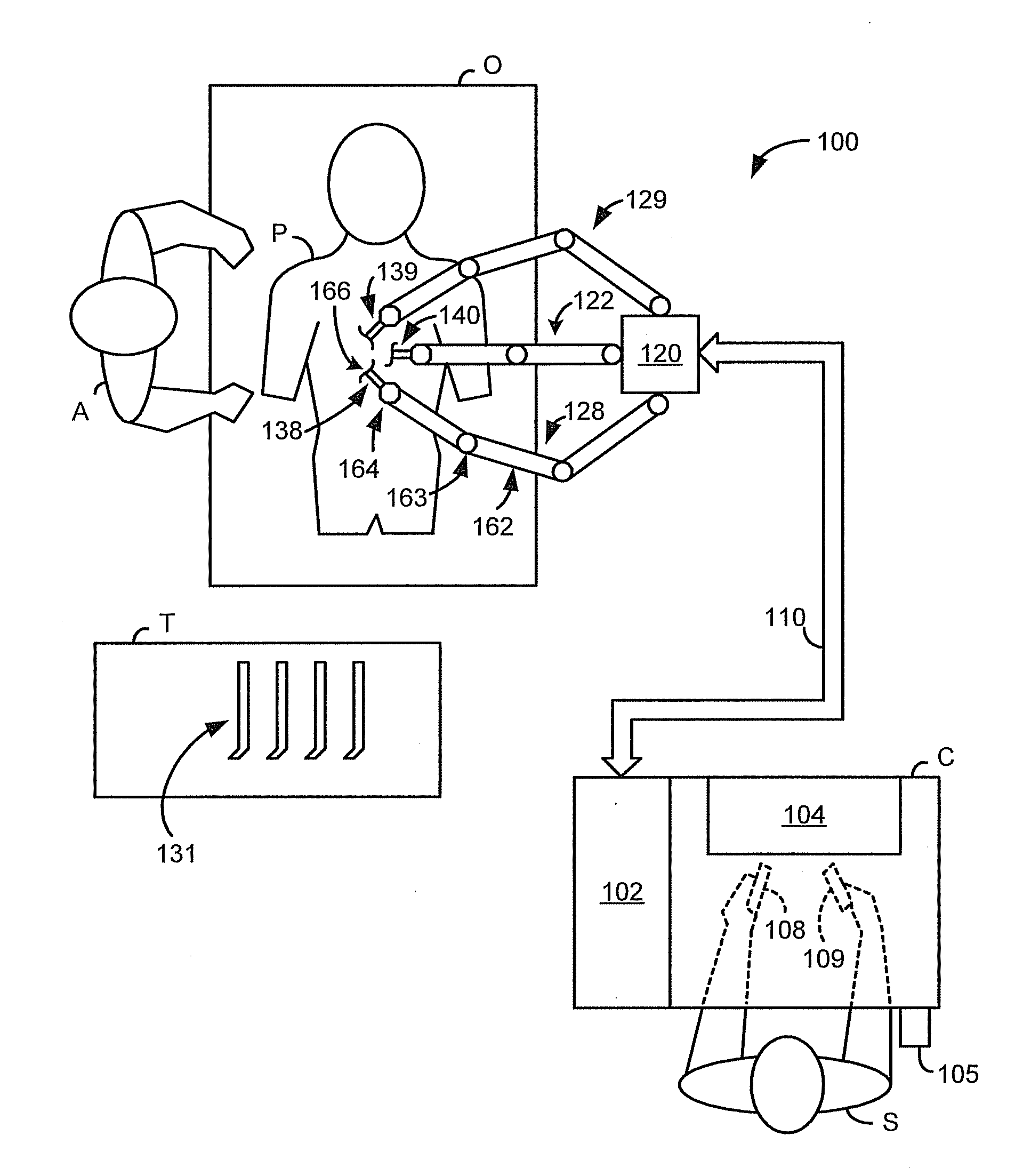

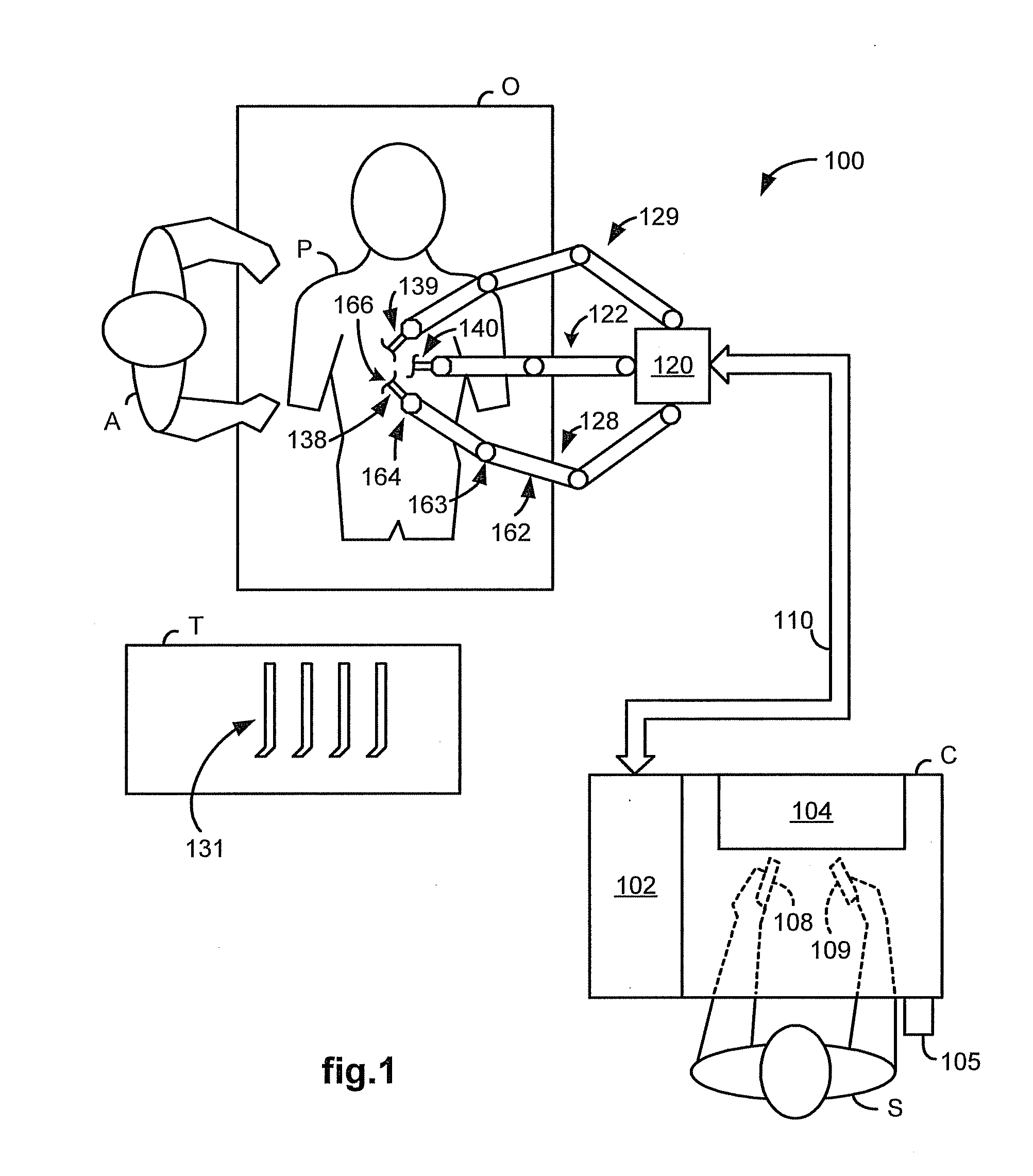

Medical robotic system with dynamically adjustable slave manipulator characteristics

ActiveUS20090062813A1Improve surgeon performanceImprove medical performanceProgramme controlProgramme-controlled manipulatorManipulatorEngineering

A slave manipulator manipulates a medical device in response to operator manipulation of an input device through joint control systems. The stiffness and strength of the slave manipulator are adjustable according to criteria such as the mode of operation of the slave manipulator, the functional type of the medical device currently being held by the slave manipulator, and the current phase of a medical procedure being performed using the slave manipulator by changing corresponding parameters of the control system. For safety purposes, such changes are not made until it is determined that it can be done in a smooth manner without causing jerking of the medical device. Further, an excessive force warning may be provided to surgery staff when excessive forces are being commanded on the slave manipulator for more than a specified period of time.

Owner:INTUITIVE SURGICAL OPERATIONS INC

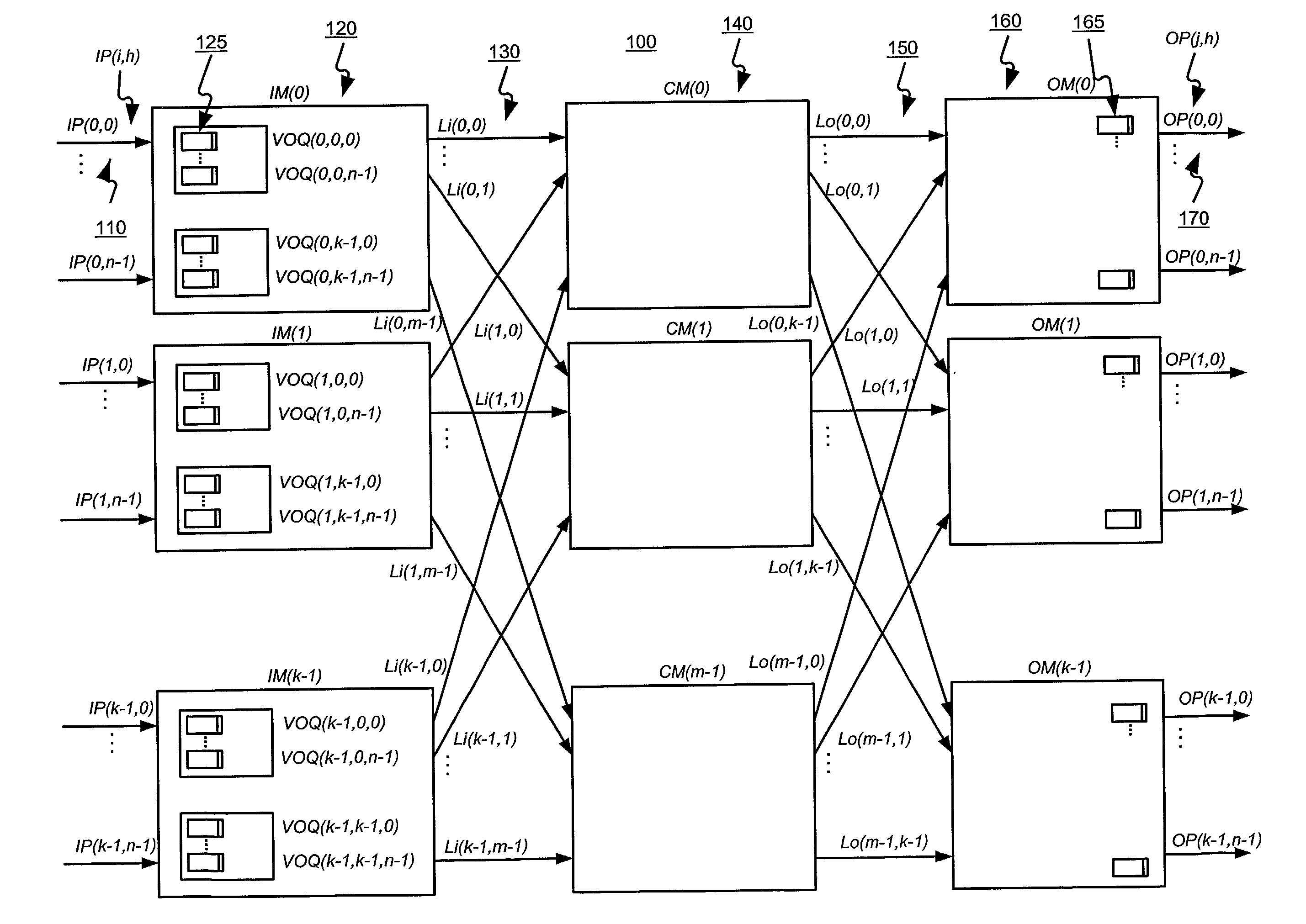

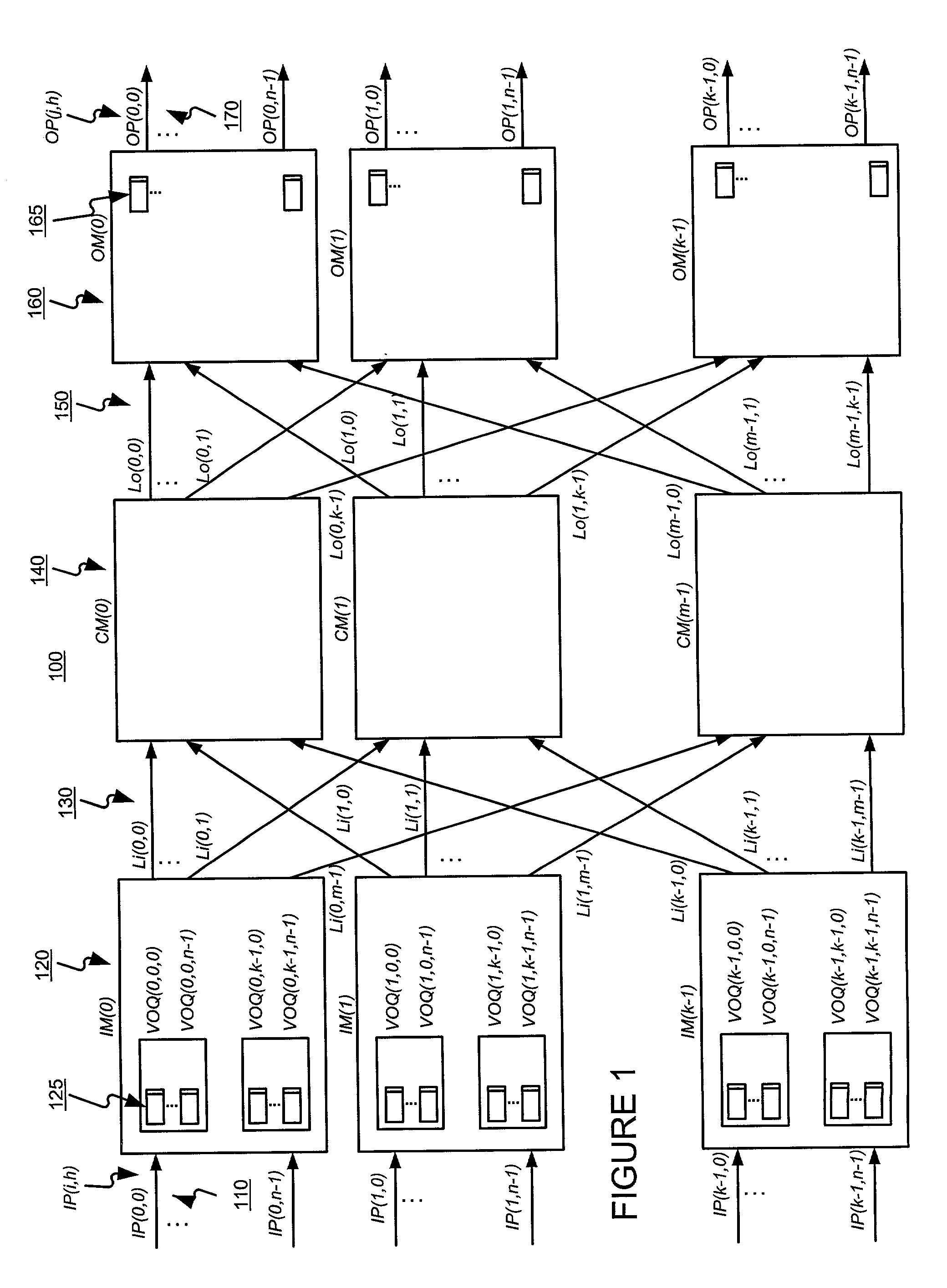

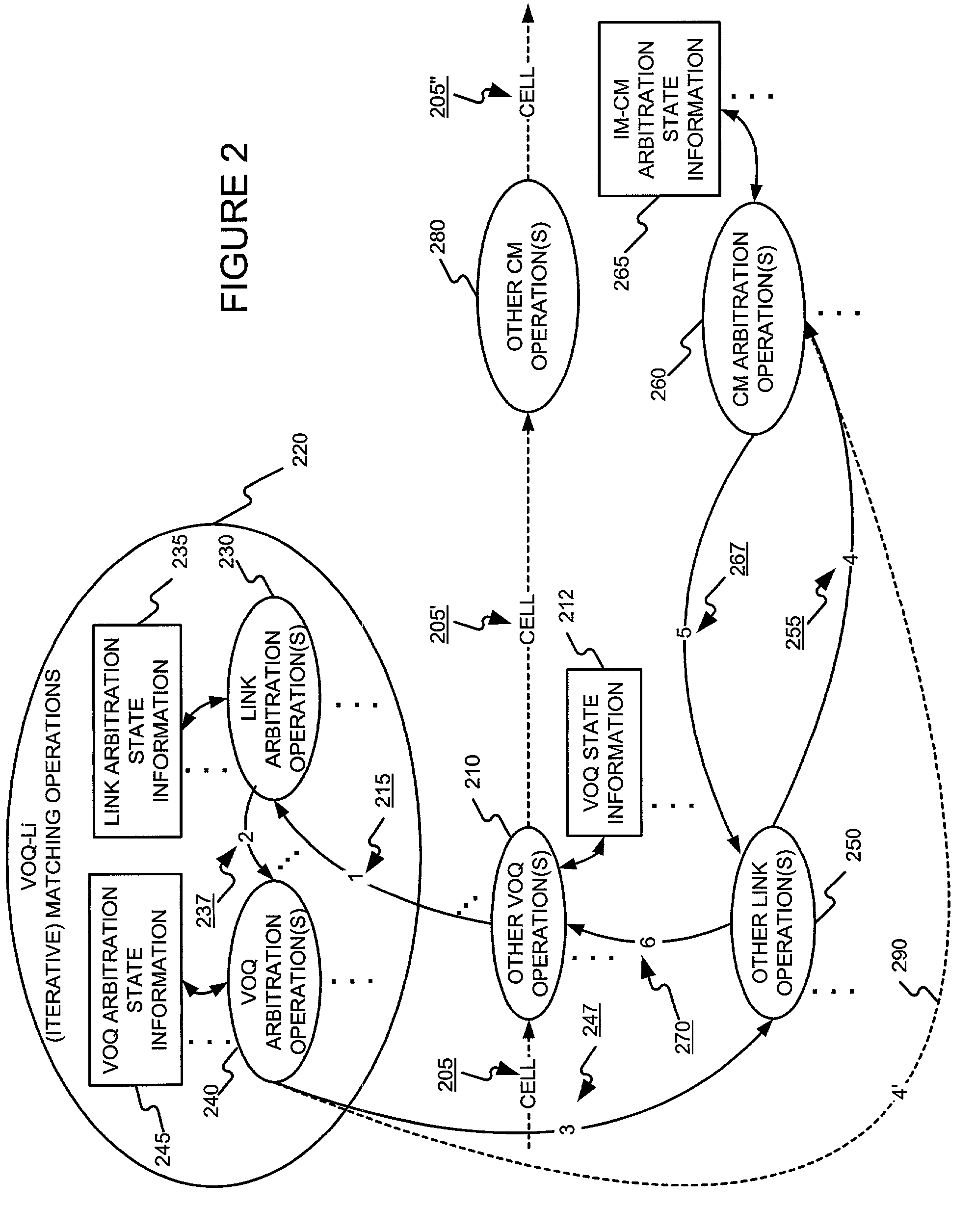

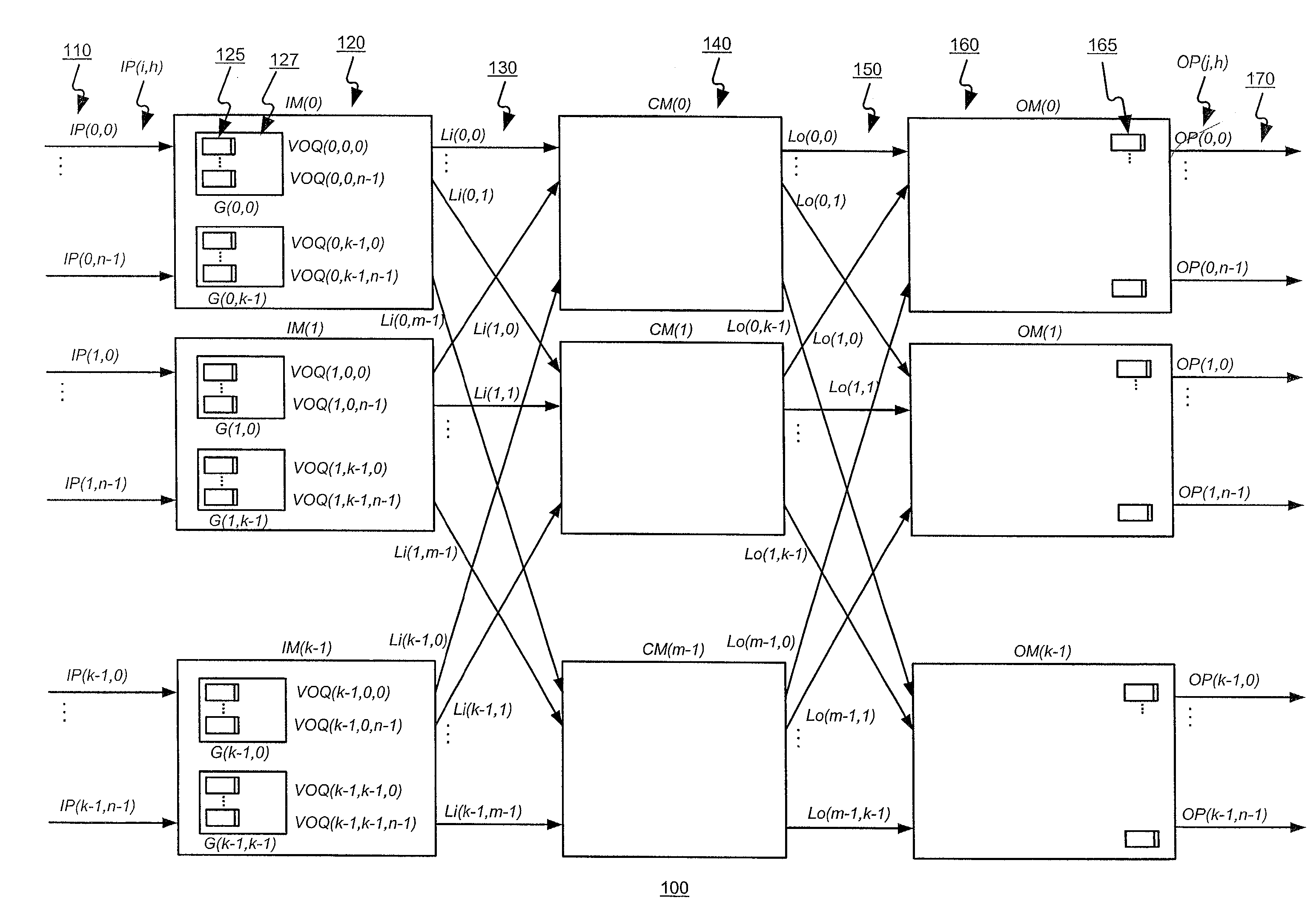

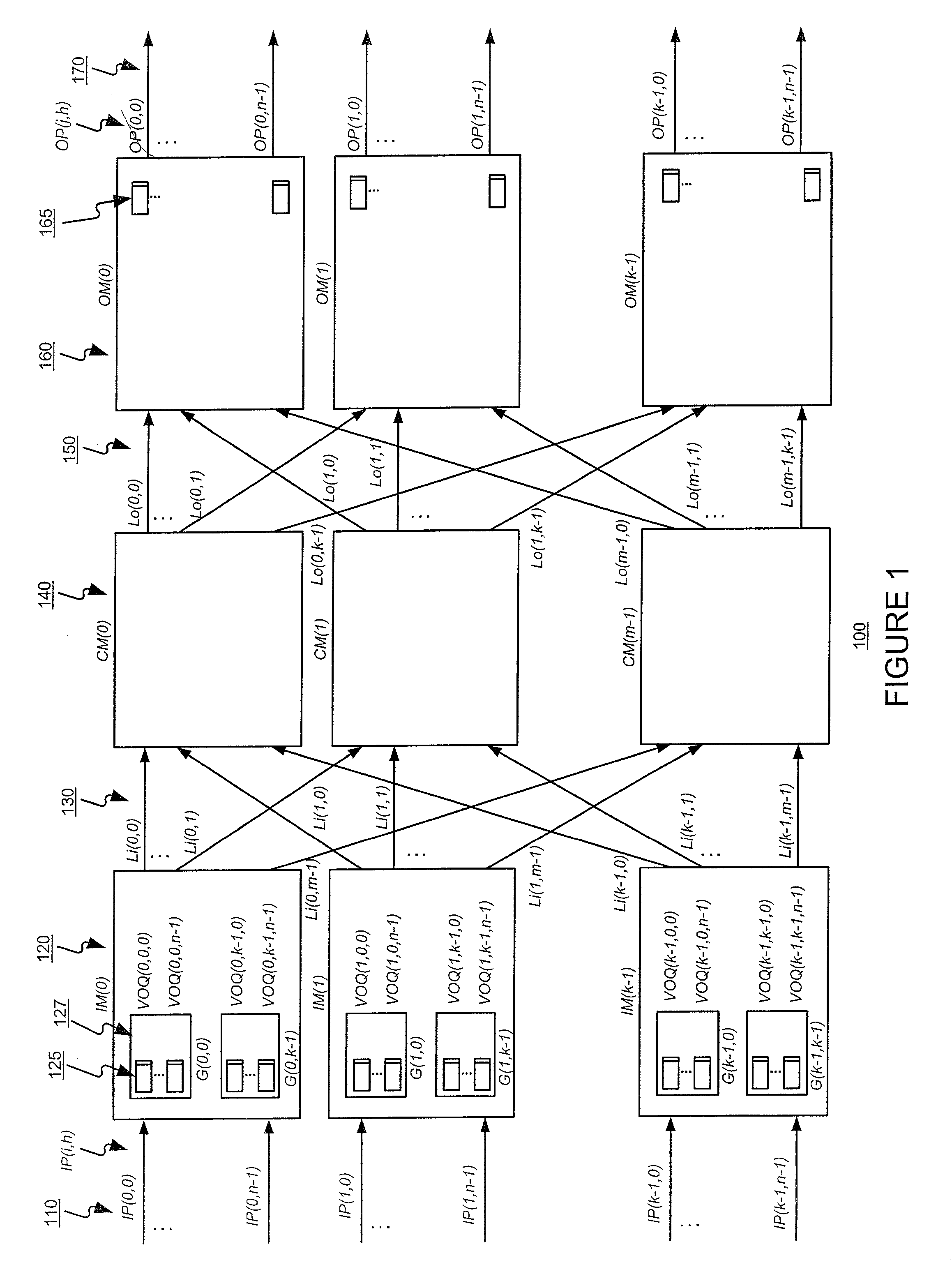

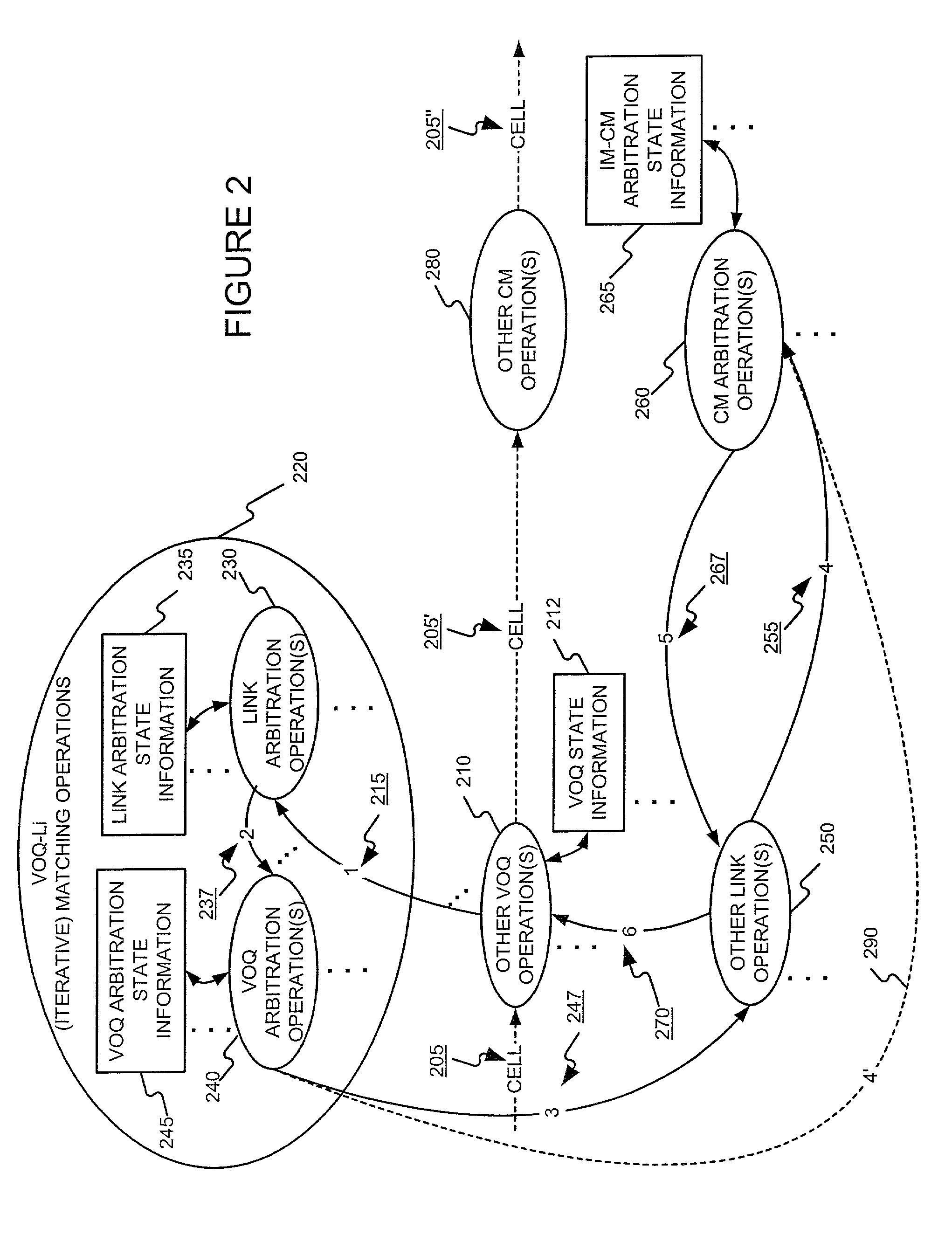

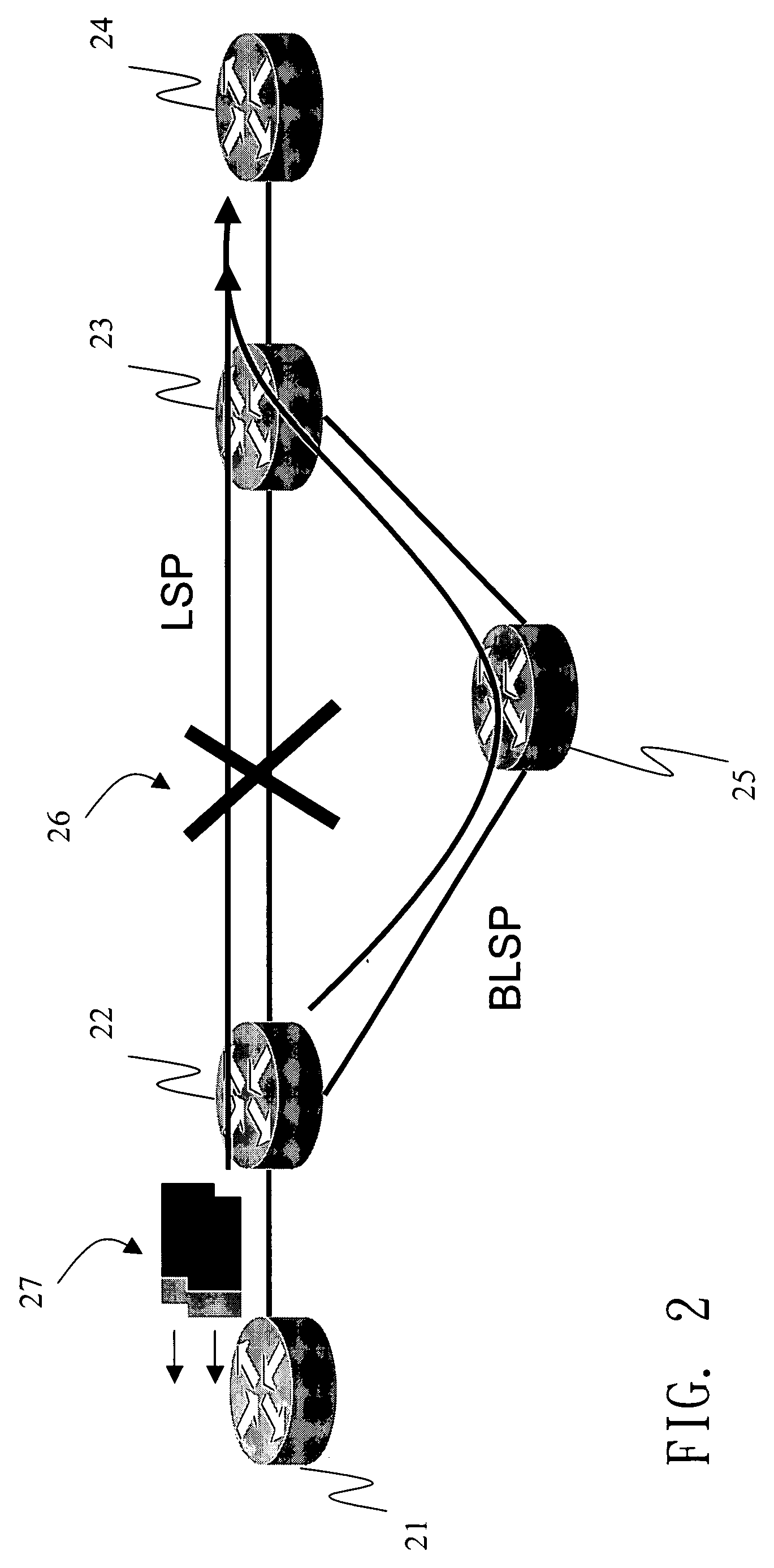

Scheduling the dispatch of cells in multistage switches

InactiveUS7173931B2Improve throughputAvoid switchingTime-division multiplexData switching by path configurationSecondary stageMulti phase

A multiple phase cell dispatch scheme, in which each phase uses a simple and fair (e.g., round robin) arbitration methods, is described. VOQs of an input module and outgoing links of the input module are matched in a first phase. An outgoing link of an input module is matched with an outgoing link of a central module in a second phase. The arbiters become desynchronized under stable conditions which contributes to the switch's high throughput characteristic. Using this dispatch scheme, a scalable multiple-stage switch able to operate at high throughput, without needing to resort to speeding up the switching fabric and without needing to use buffers in the second stage, is possible. The cost of speed-up and the cell out-of-sequence problems that may occur when buffers are used in the second stage are therefore avoided.

Owner:POLYTECHNIC INST OF NEW YORK

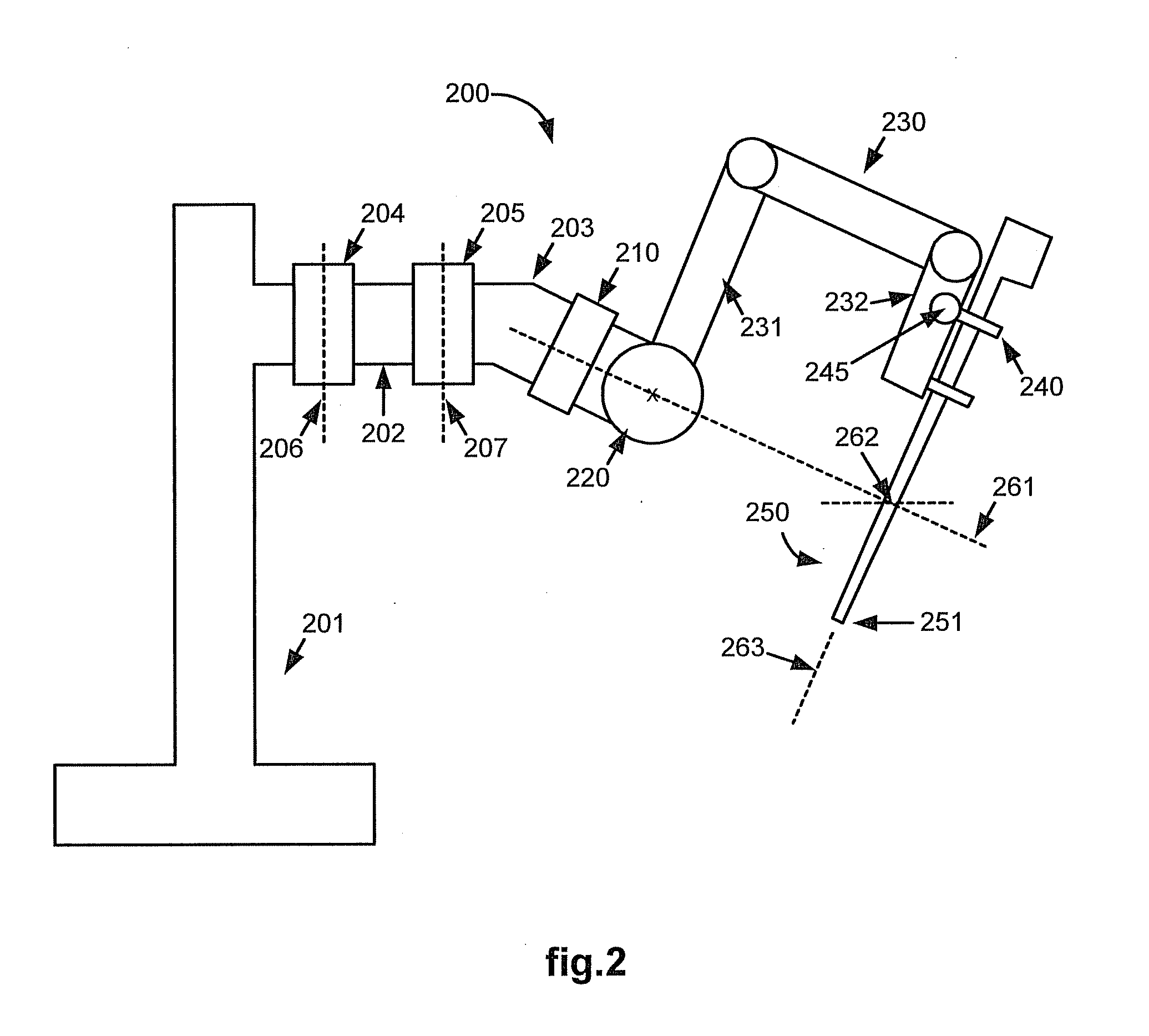

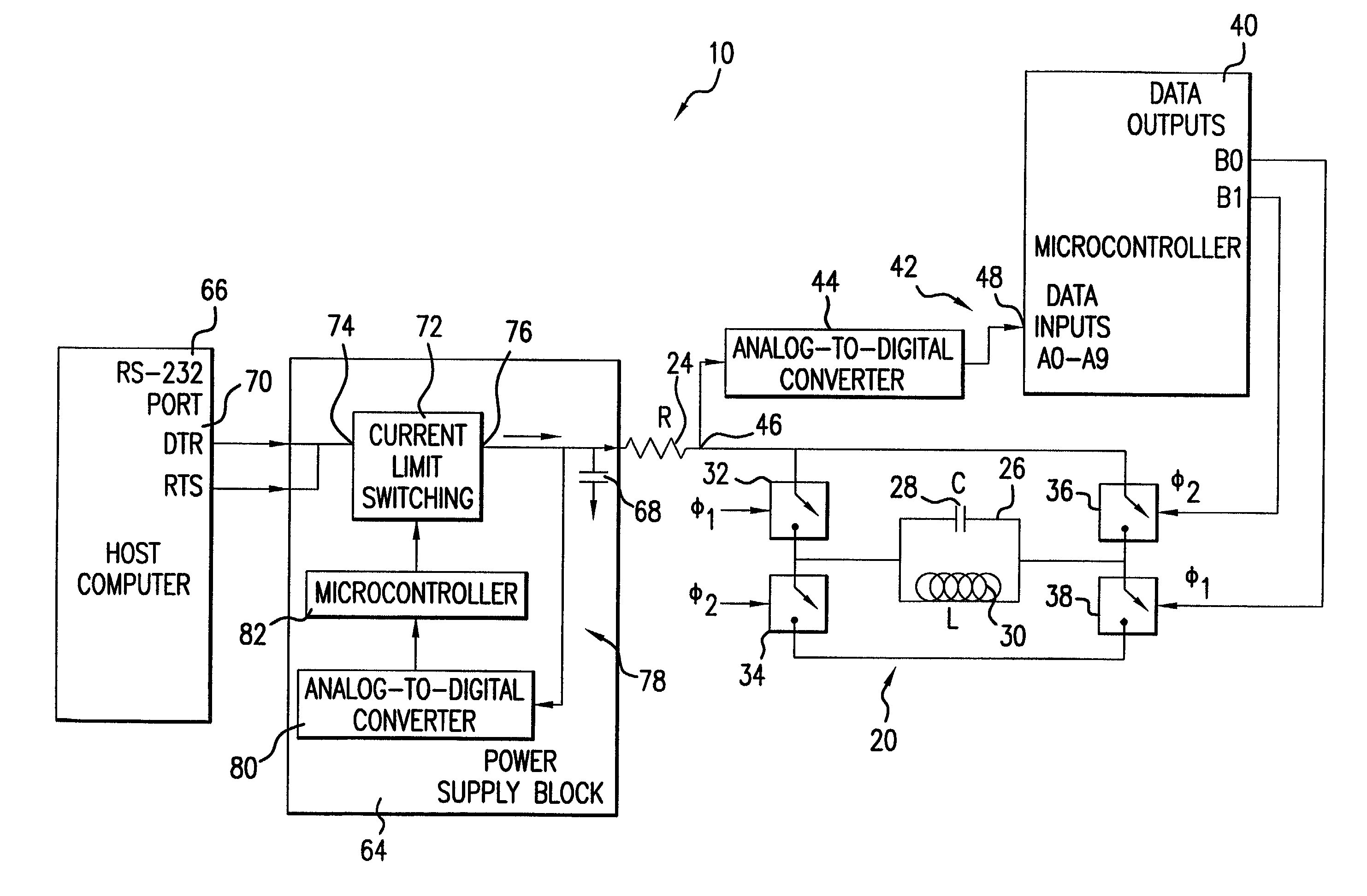

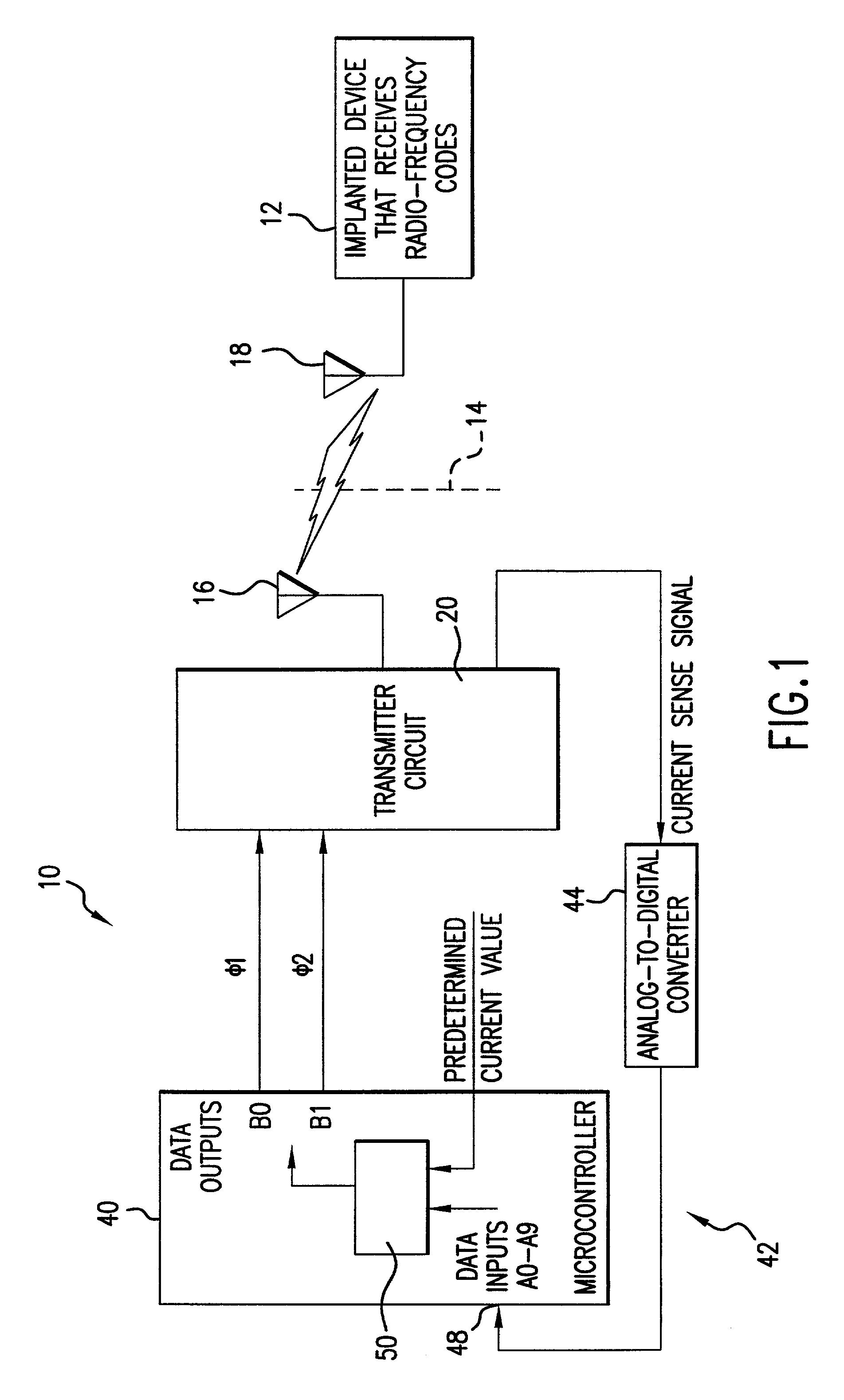

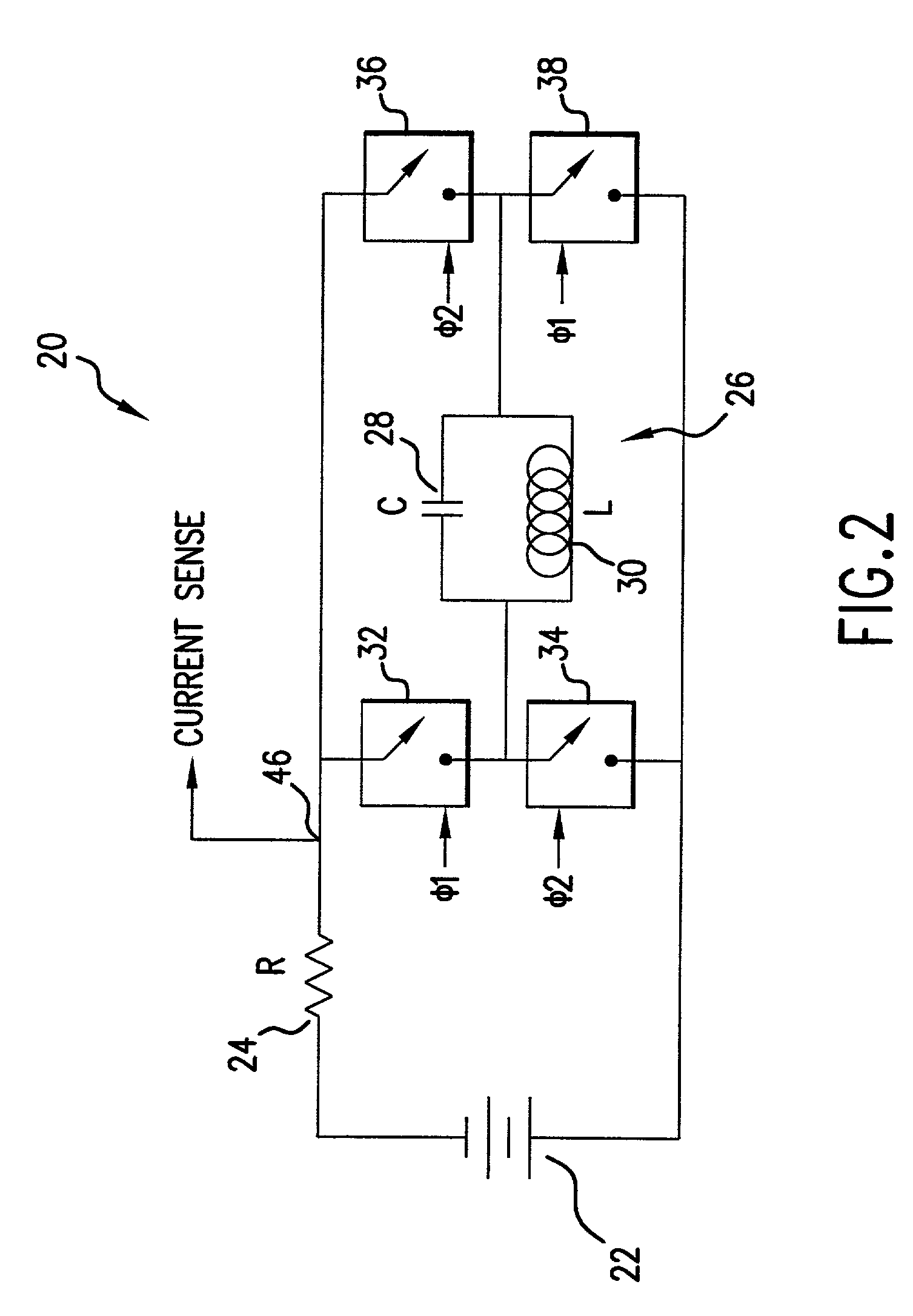

Transmitter system for wireless communication with implanted devices

ActiveUS7151914B2Low power operationCurrent consumptionResonant long antennasElectrotherapyMaximum levelFeedback circuits

A transmitter system for wireless communication with implanted medical devices includes a transmitter circuit having a resonant network the resonant frequency of which is adjusted by a feedback circuit in order to minimize the current drain from the power source and maximizing the power source life. The transmitter system may be powered by a power supply block which uses commonly available RS-232 signals of a host computer as a raw power source, combined with a high value storage capacitor to provide power for the wireless medical data programmer. A feedback circuit monitors the charging current as well as voltage impressed across the storage capacitor in order to maintain the charging current at maximum level during the charging time and in order to stop the charging once the full charge of the storage capacitor has been reached.

Owner:MEDTRONIC INC

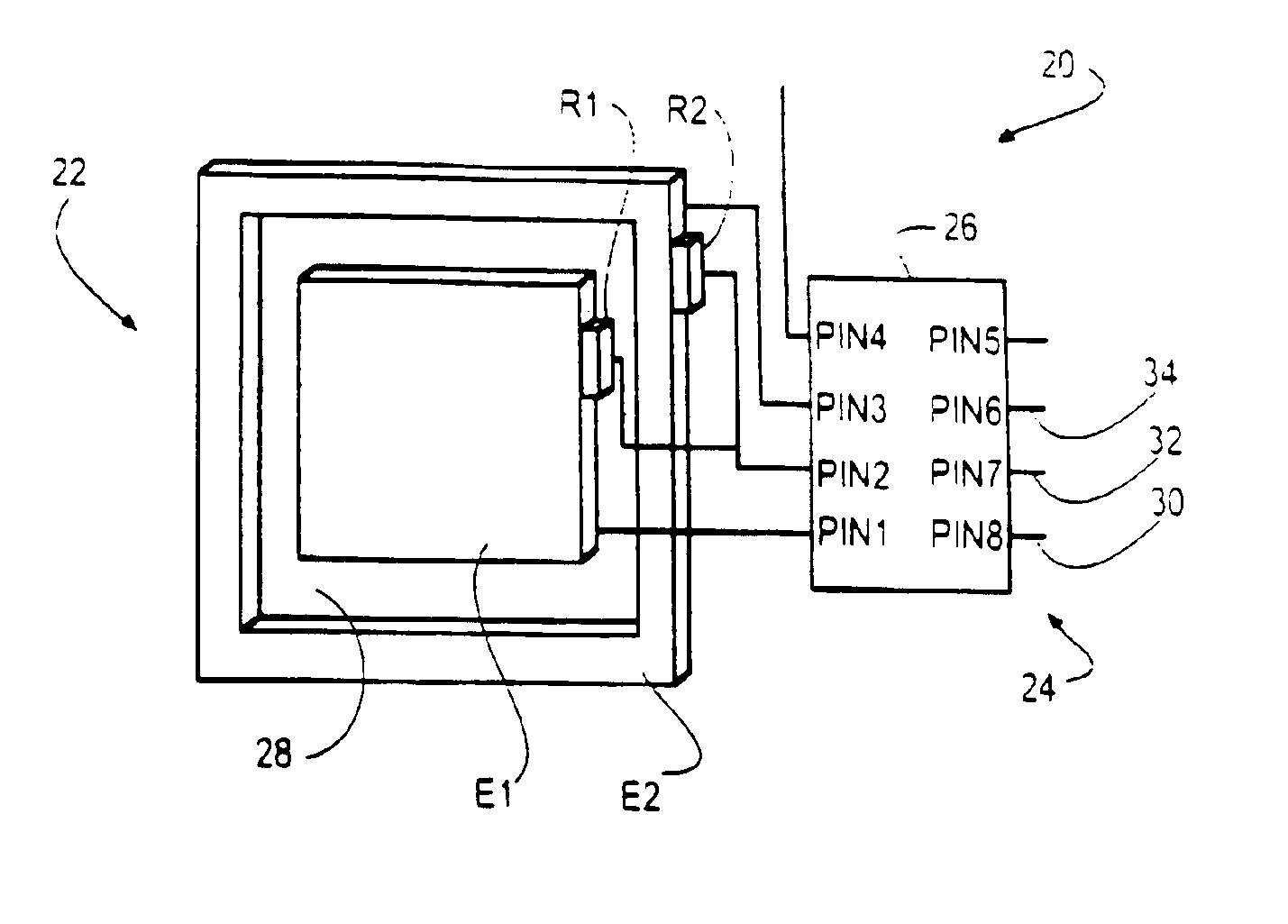

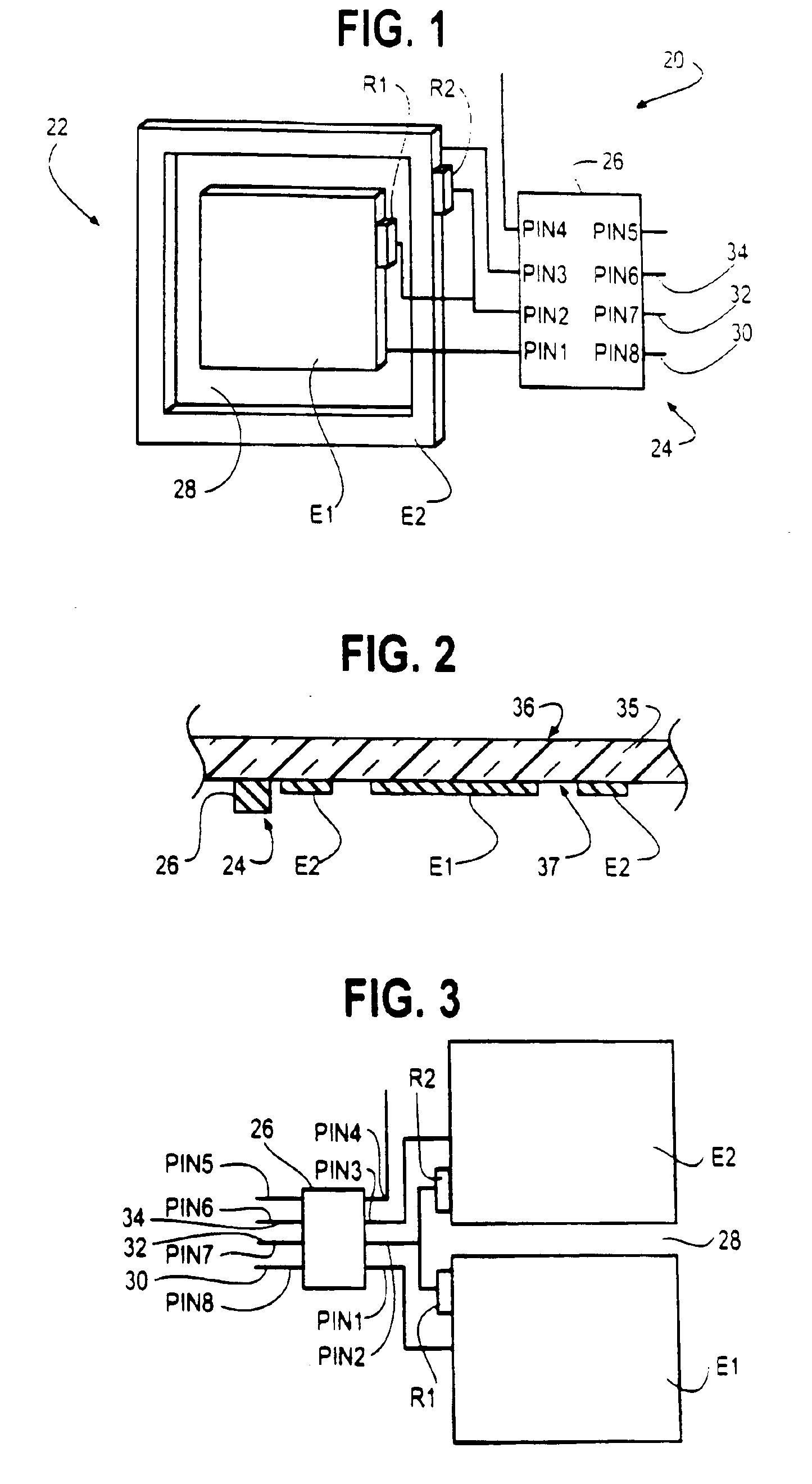

Touch switch with integral control circuit

InactiveUS7030513B2Prevent unintended switch actuationAvoid switchingInput/output for user-computer interactionBatteries circuit arrangementsControl signalTouchpad

A touch switch apparatus for detecting the presence of an object such as a human appendage, the apparatus having a touch pad and a local control circuit connected to the touch pad and to a controlled device. The touch pad preferable includes a first electrode and a second electrode spaced from and surrounding the first electrode. The control circuit is preferably in integrated circuit form. A signal is provided to the touch pad to generate an electric field thereabout. Introduction of a stimulus near the touch pad disturbs the electric field. The control circuit detects the electric field disturbance in and generates a control signal in response.

Owner:TOUCHSENSOR TECH

High Frequency Power MESFET Gate Drive Circuits

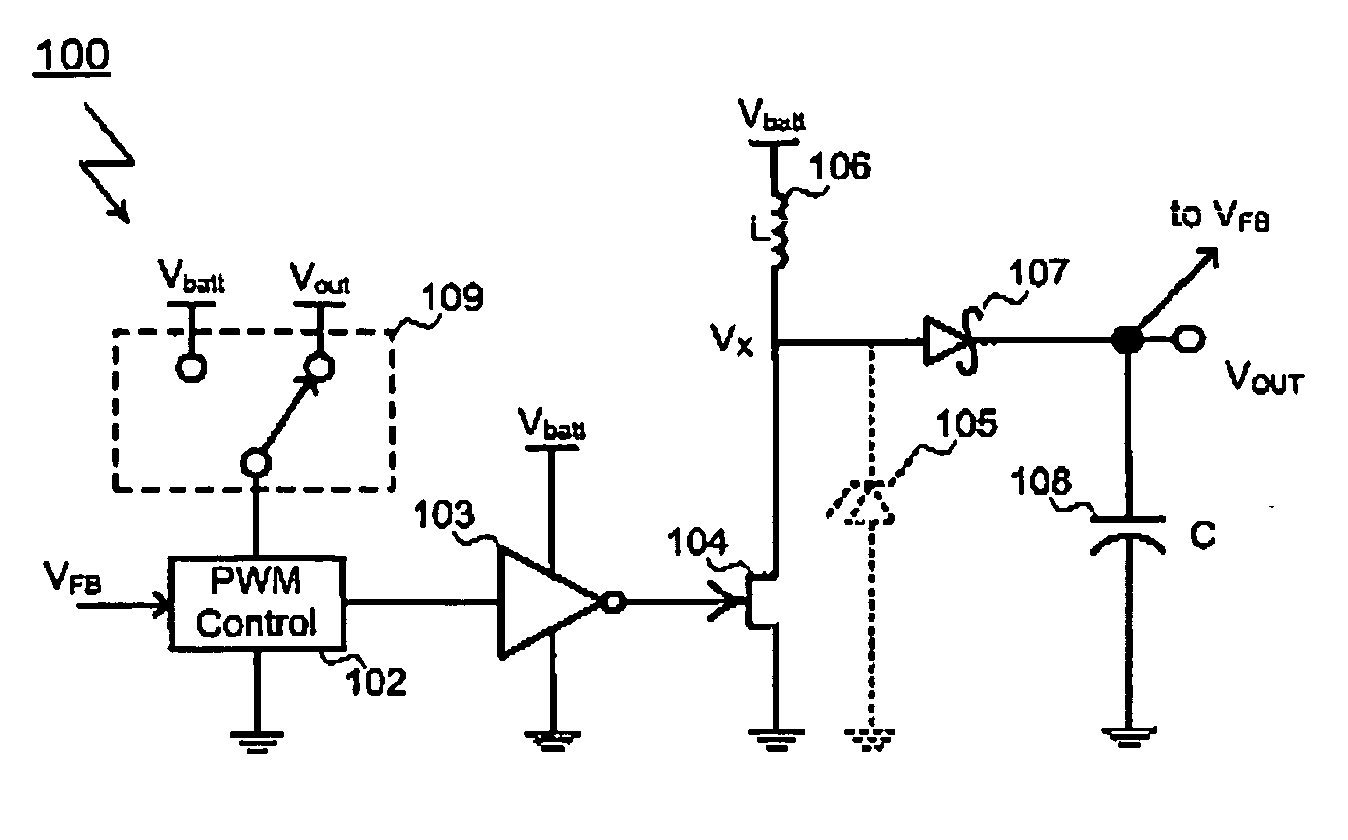

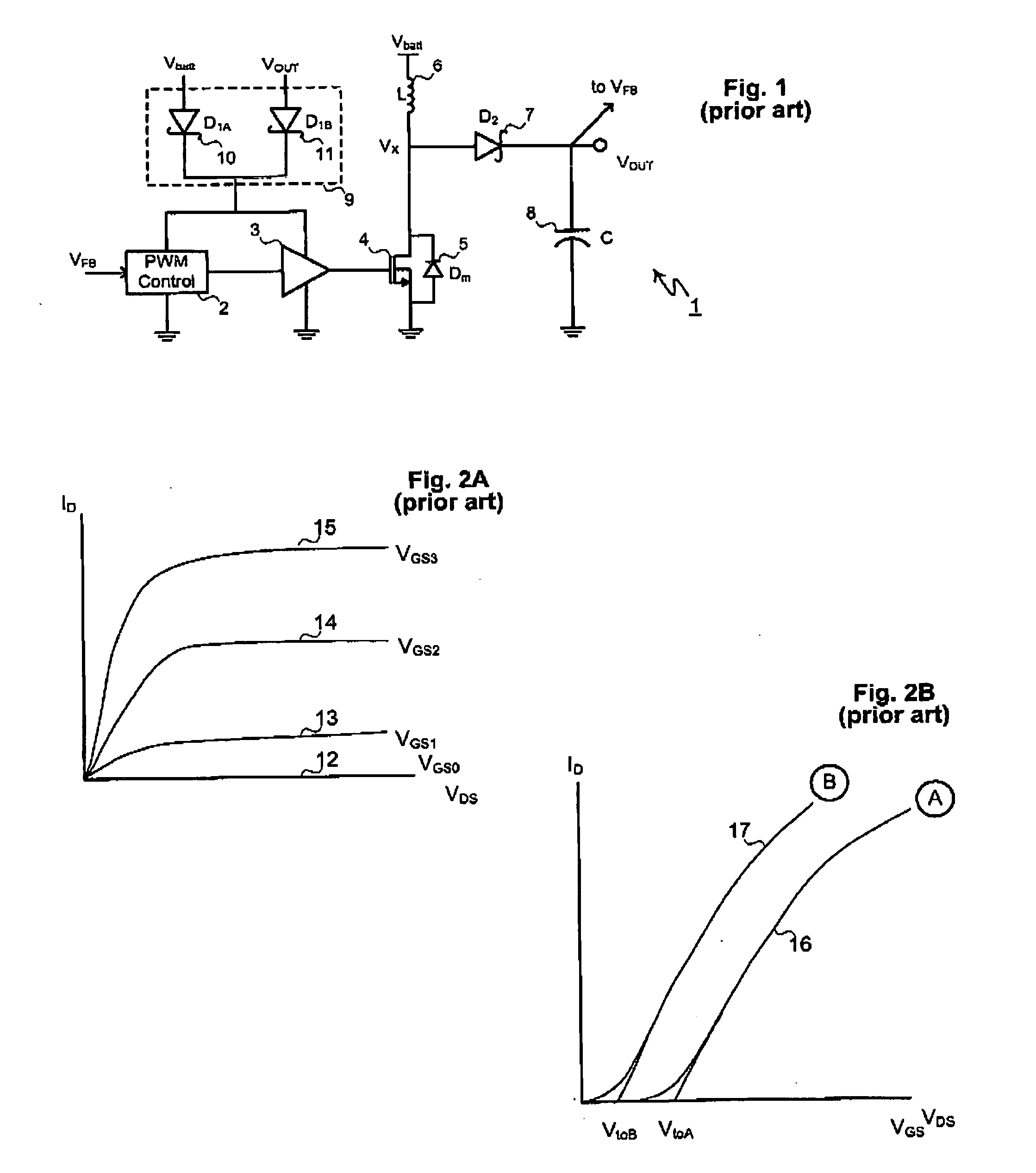

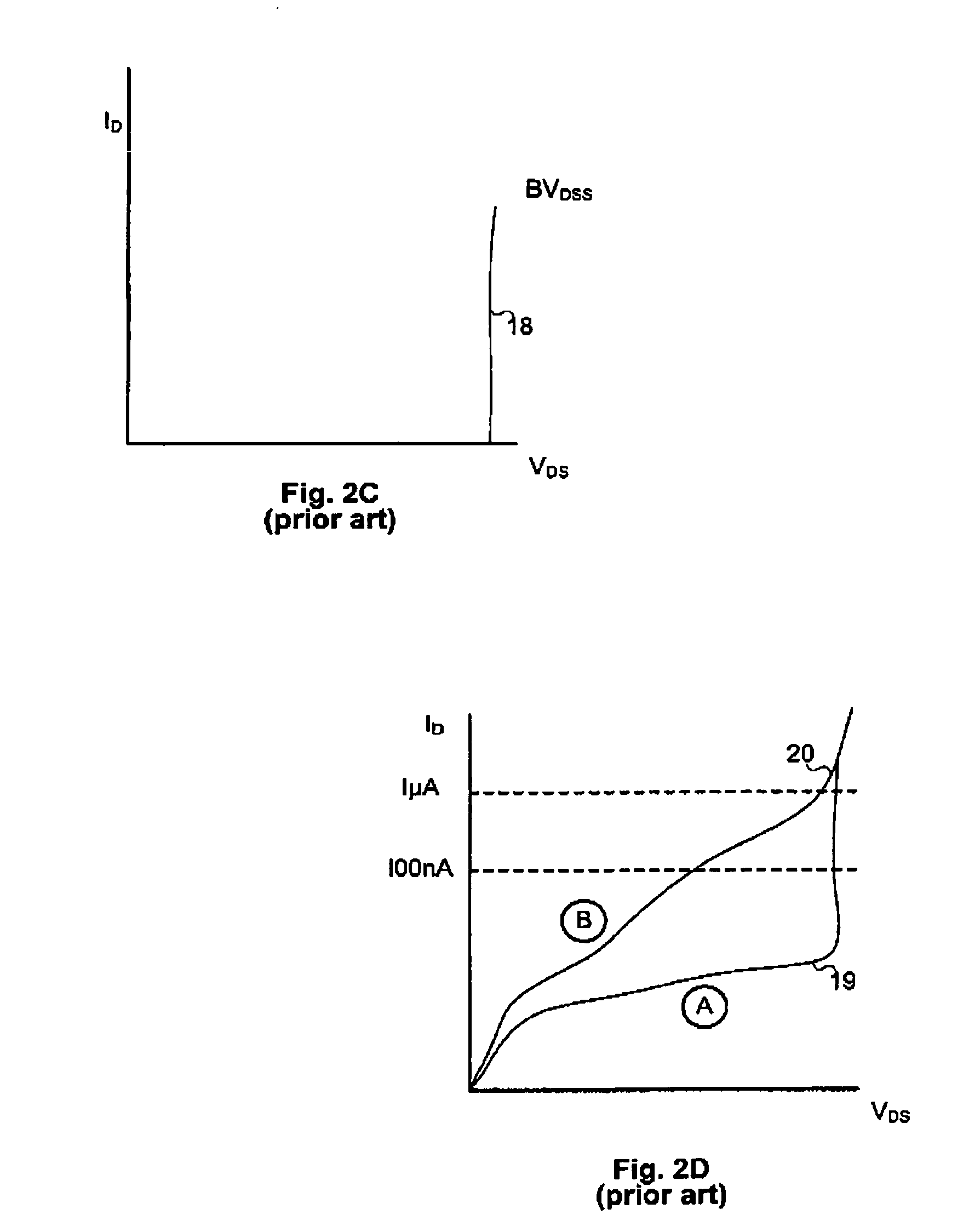

InactiveUS20070146020A1Lower on-resistanceRobust avalancheTransistorDc-dc conversionDriver circuitHigh frequency power

A series of gate drive circuits for MESFETs are provided. The gate drive circuits are intended to be used in switching regulators where at least one switching device is an N-channel MESFET. For regulators of this type, the gate drive circuits provide gate drive at the correct voltage to ensure that MESFETs are neither under driven (resulting in incorrect circuit operation) nor over driven (resulting in MESFET damage or excess current or power loss).

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

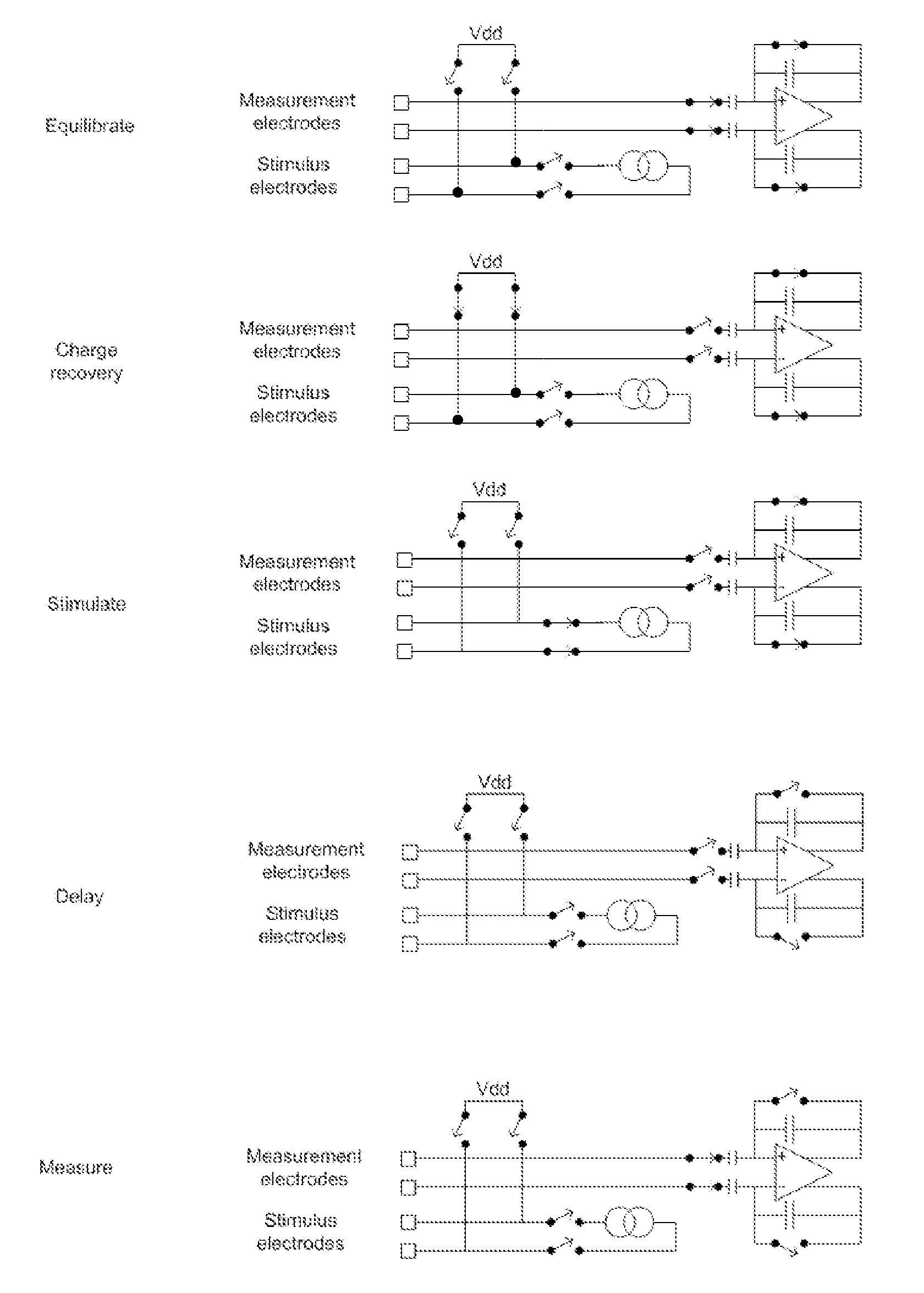

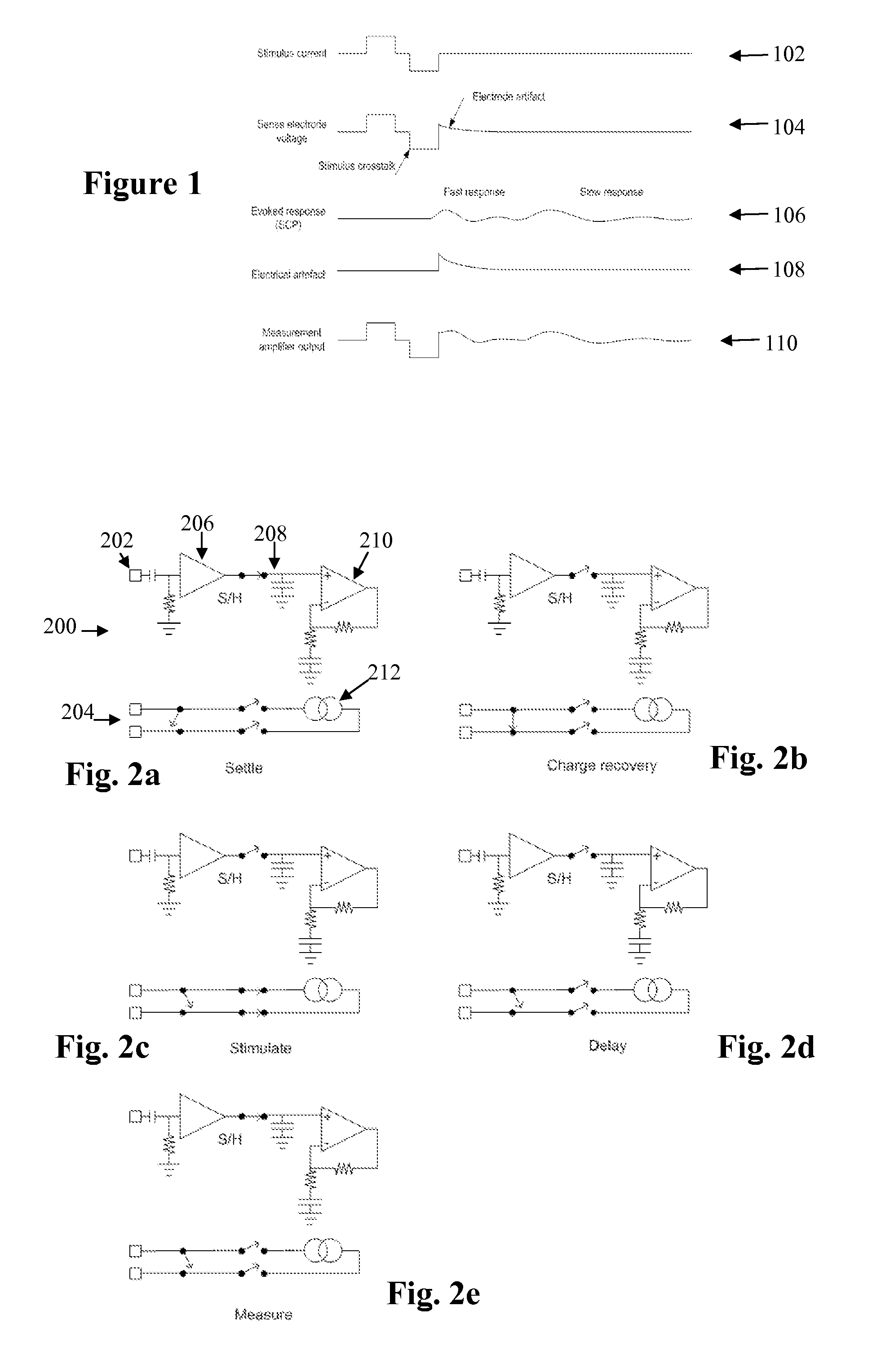

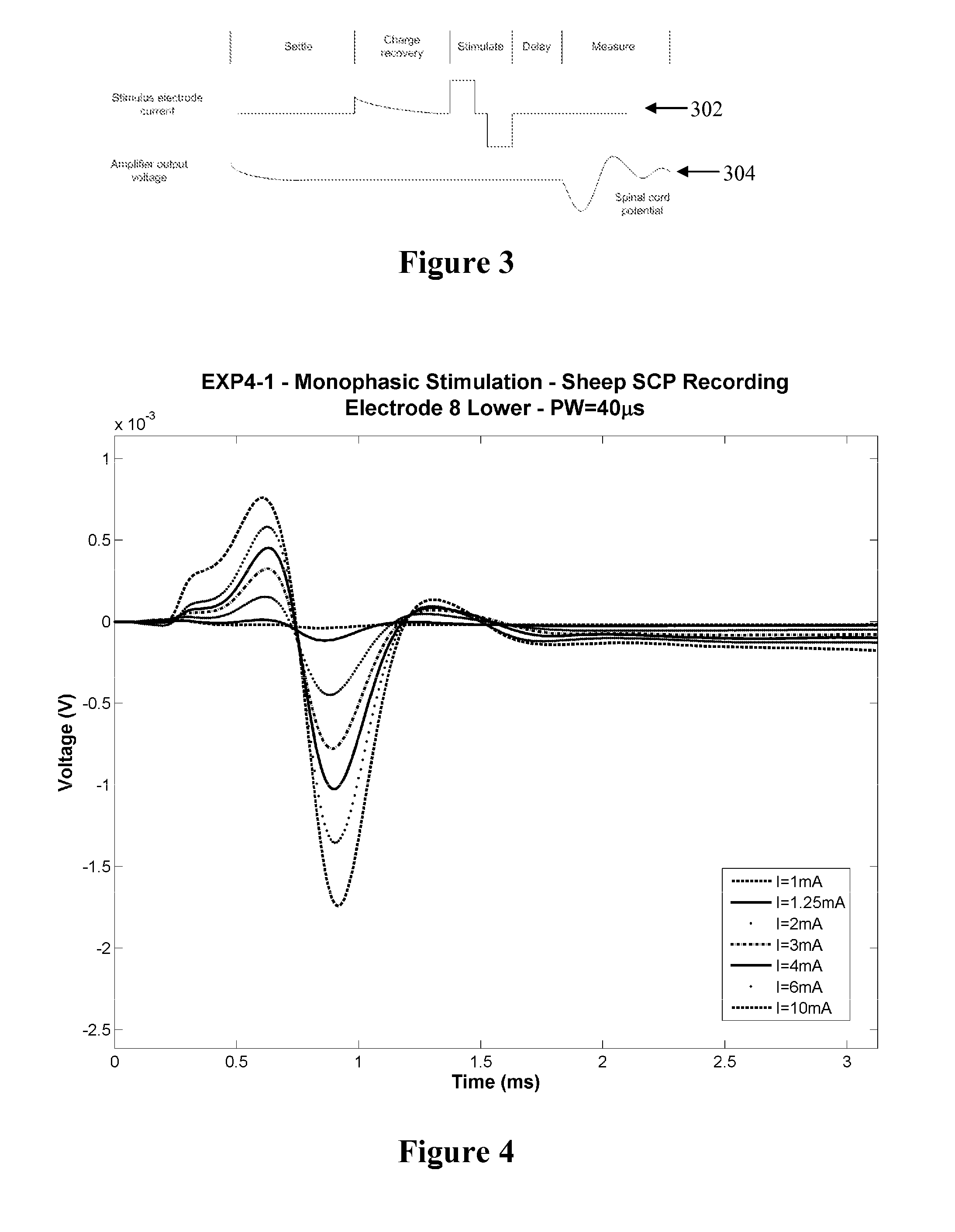

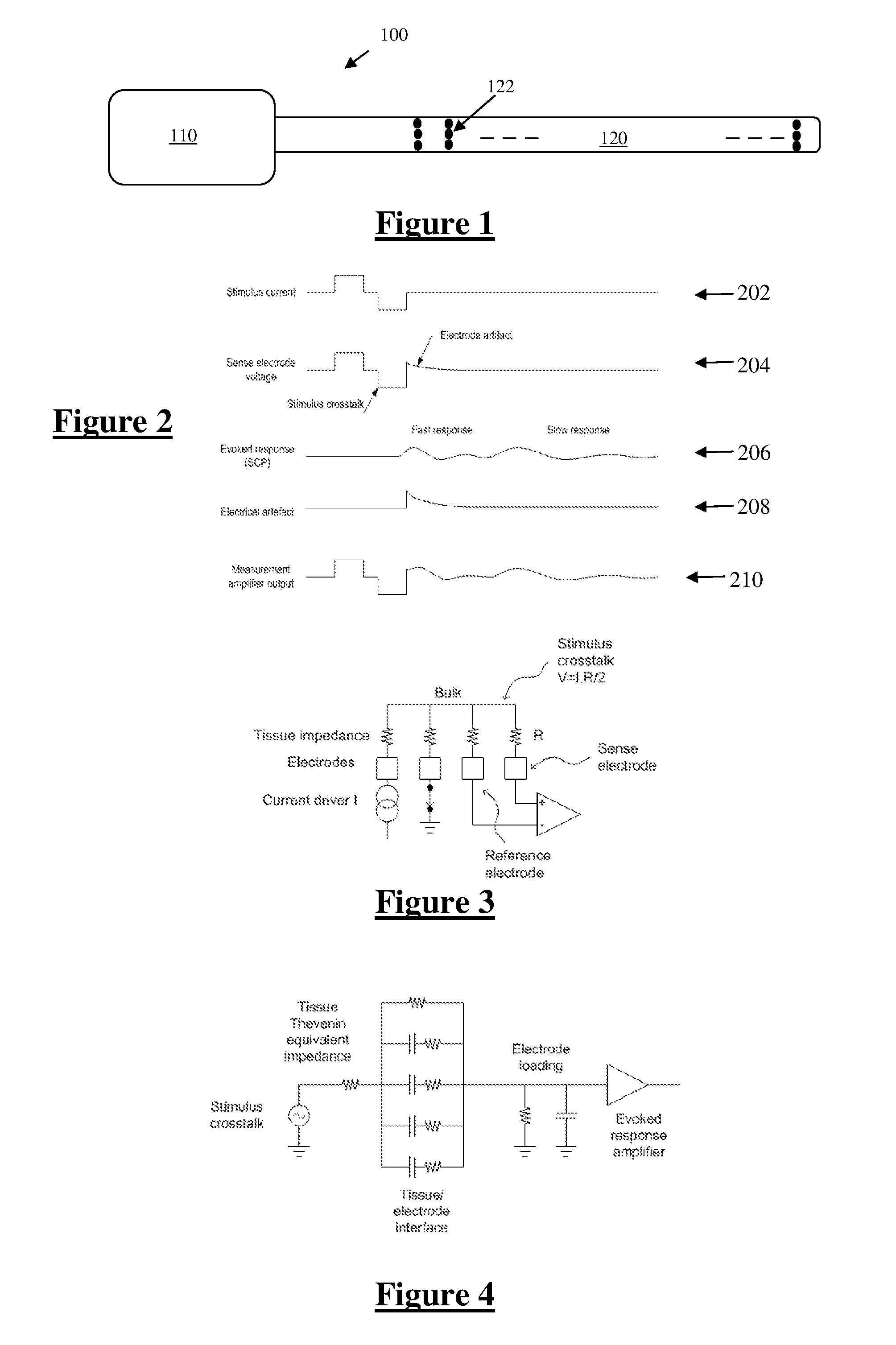

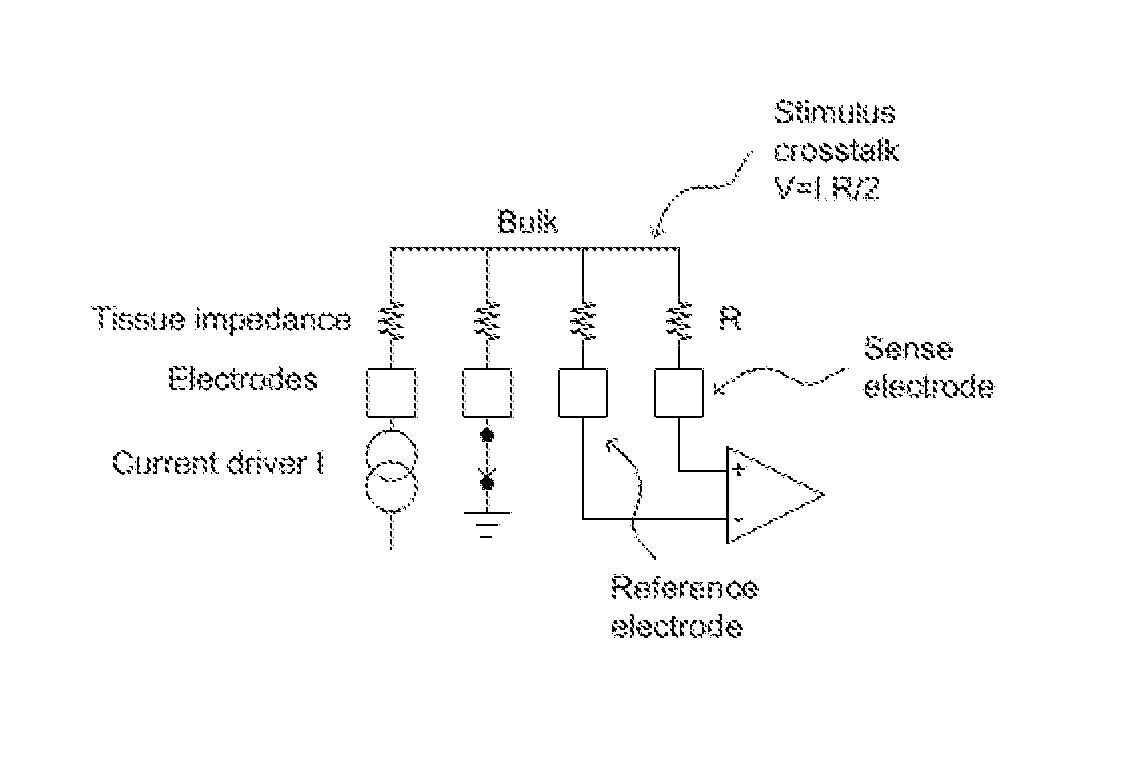

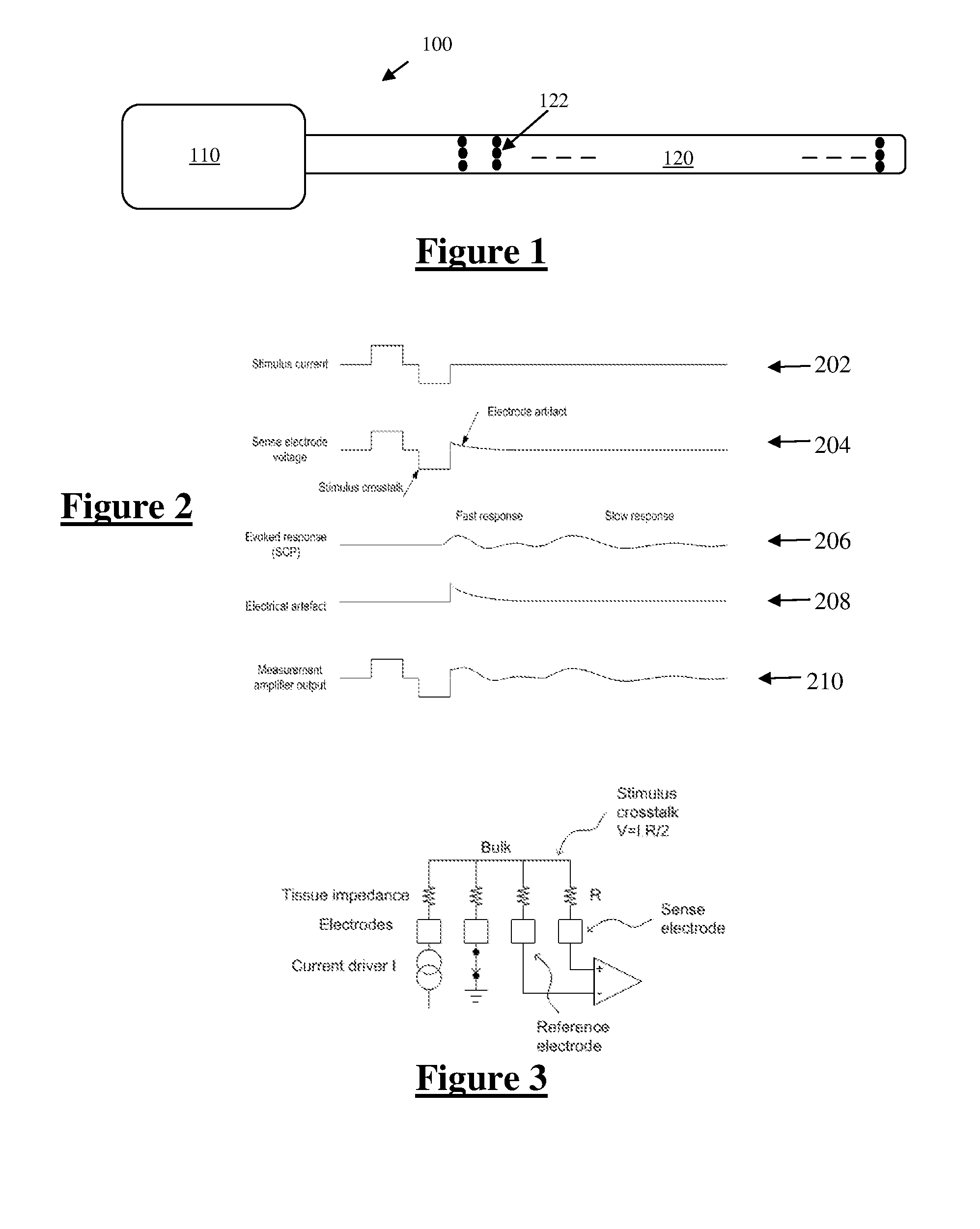

Method and apparatus for measurement of neural response

A method for measuring a neural response to a stimulus. Measurement circuitry is settled prior to a stimulus, by connecting a sense electrode to the measurement circuitry to allow the measurement circuitry to settle towards a bio-electrically defined steady state. Charge is recovered on stimulus electrodes by short circuiting the stimulus electrodes to each other. An electrical stimulus is then applied from the stimulus electrodes to neural tissue, while keeping the sense electrode disconnected from the measurement circuitry. After the stimulus, a delay is imposed during which the stimulus electrodes are open circuited and the sense electrode is disconnected from the measurement circuitry and from the stimulus electrodes. After the delay, a neural response signal present at the sense electrode is measured by connecting the sense electrode to the measurement circuitry.

Owner:SALUDA MEDICAL PTY LTD

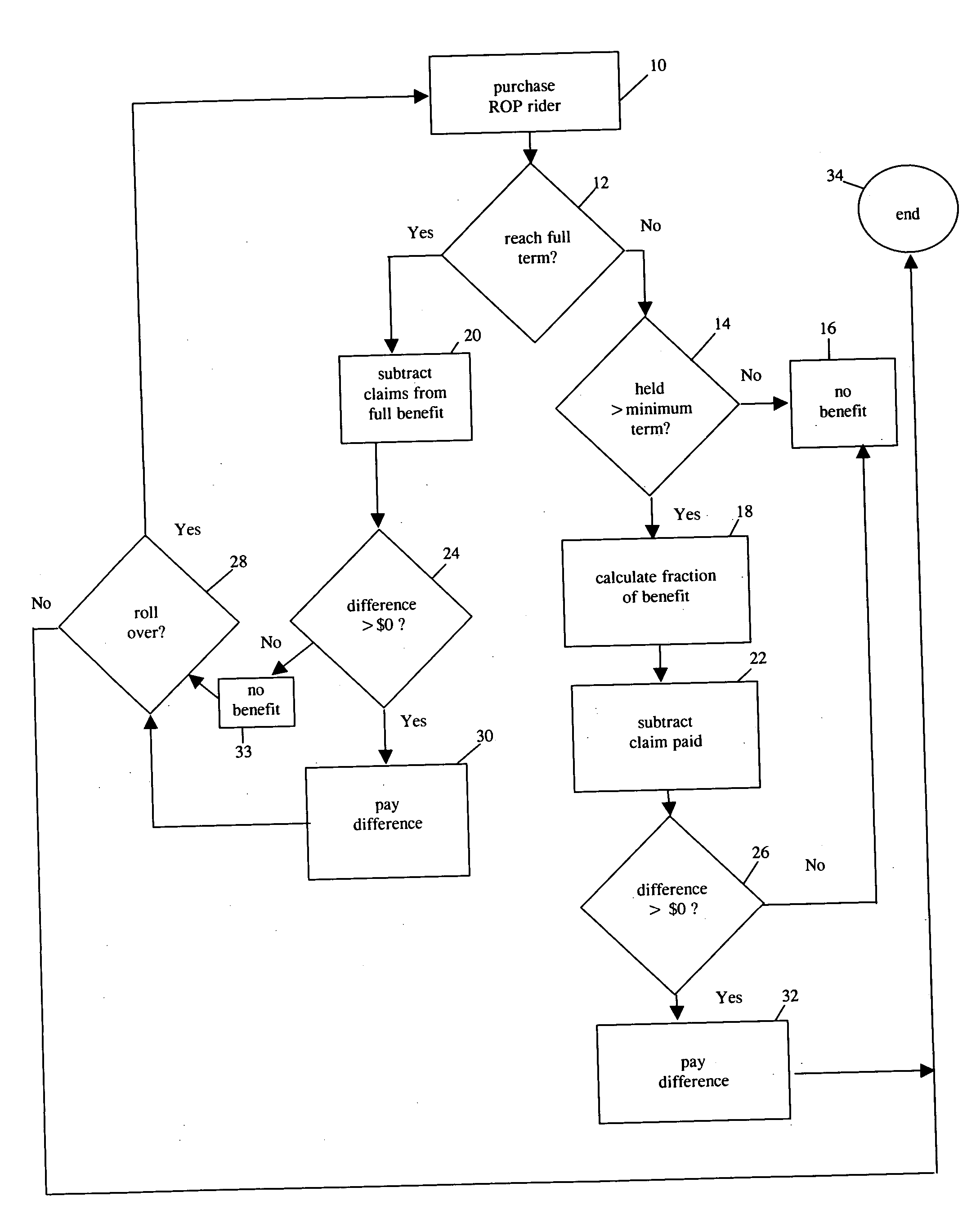

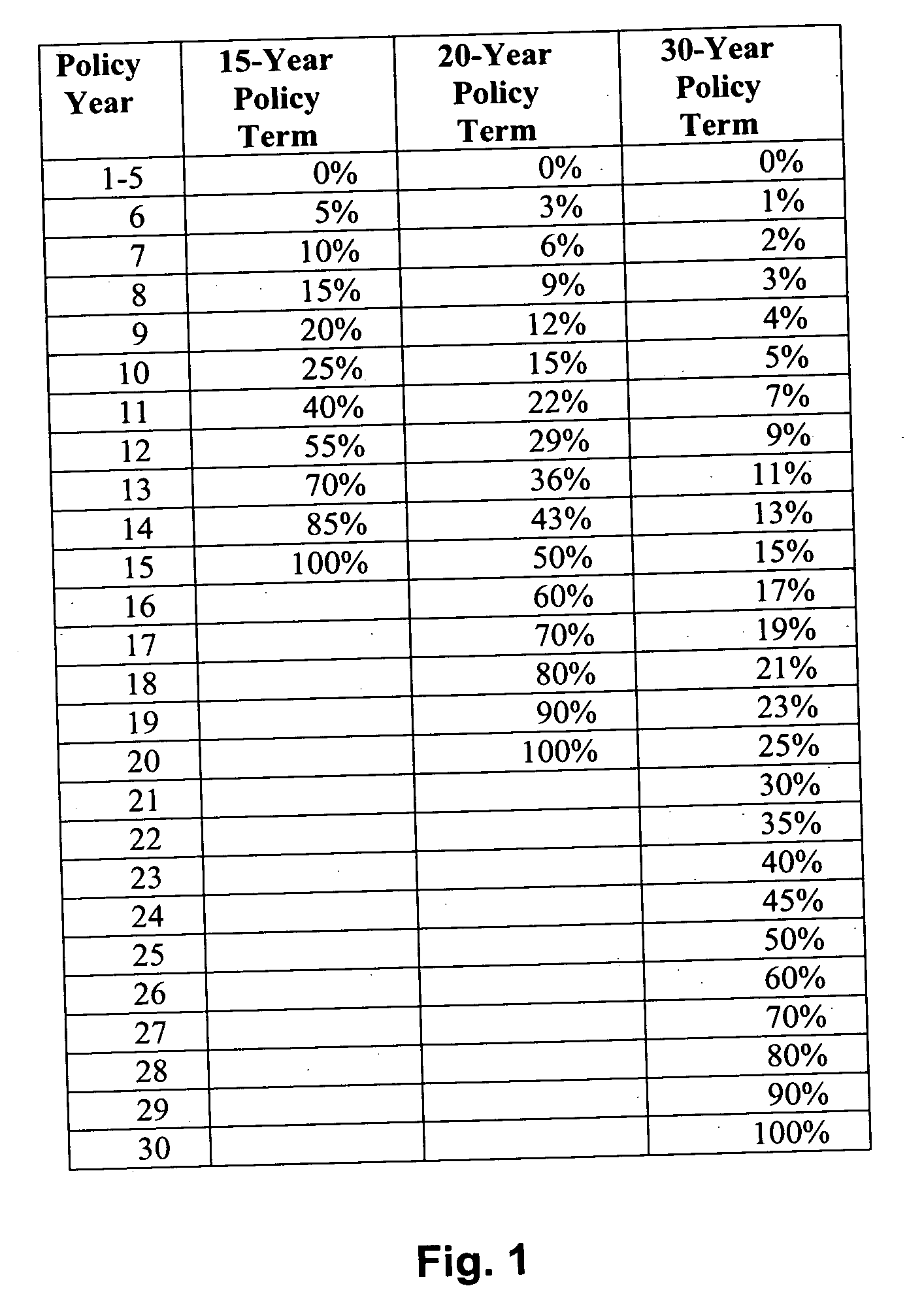

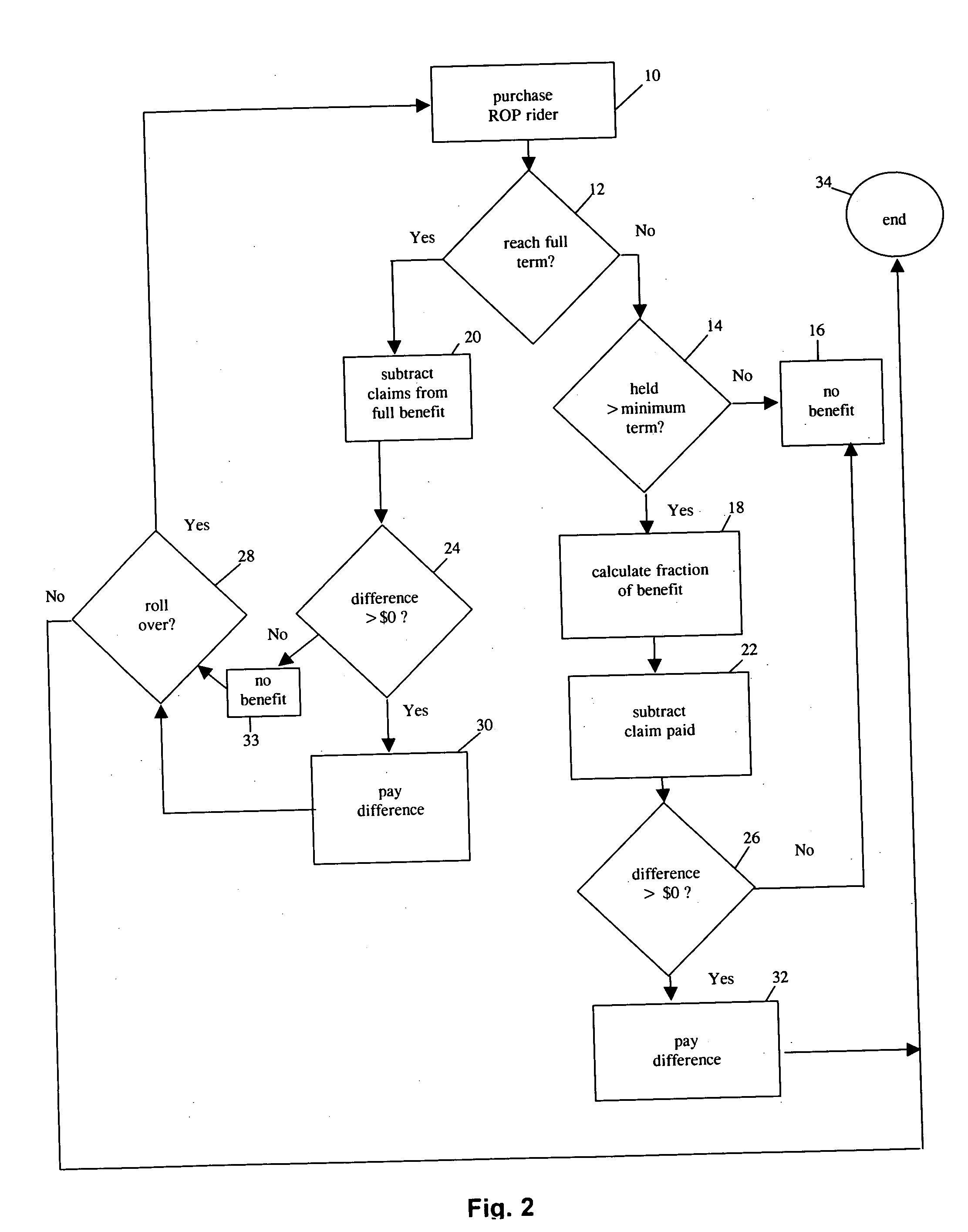

Return-of-premium insurance system and method

Owner:DSD HLDG LLC

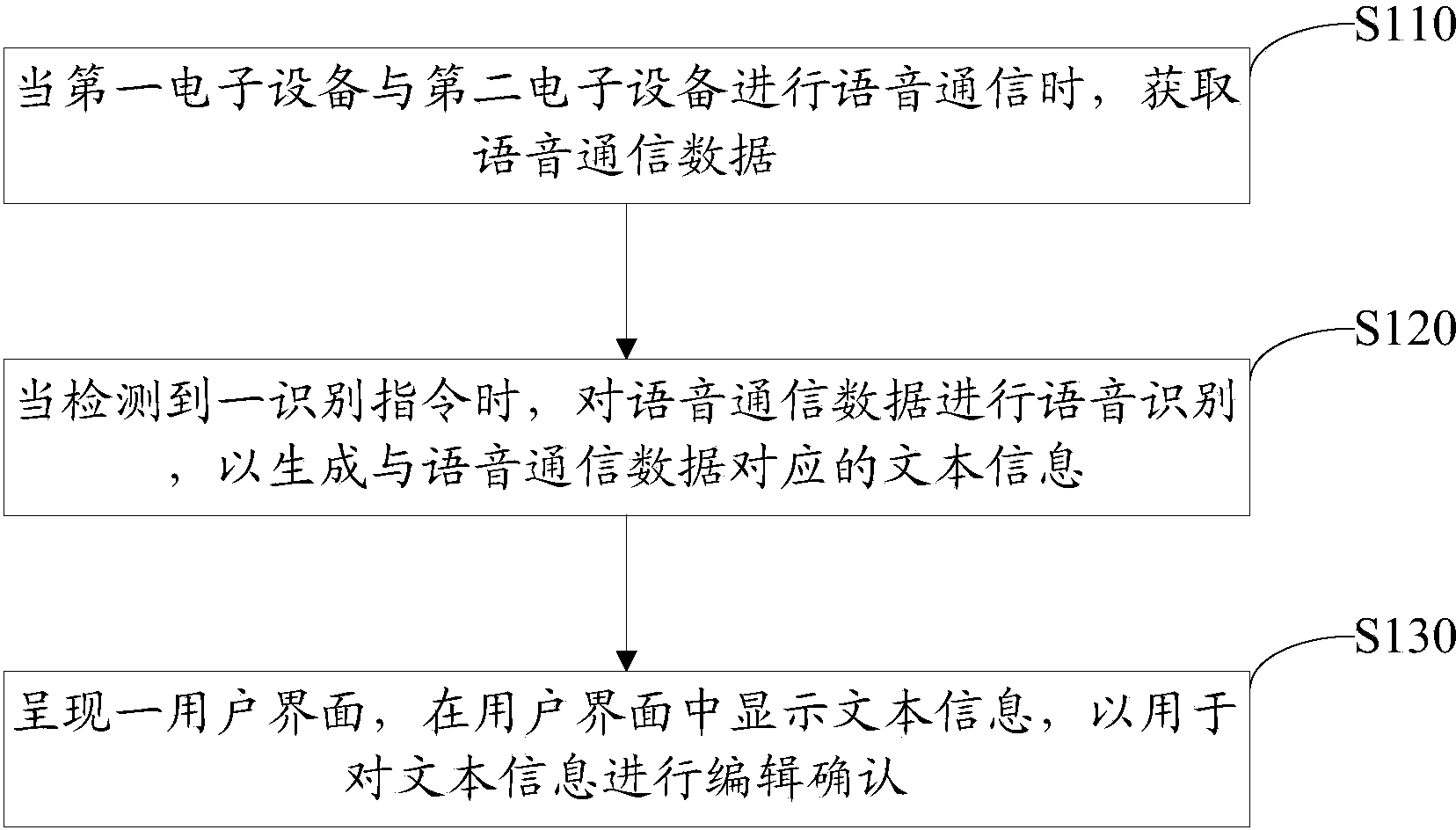

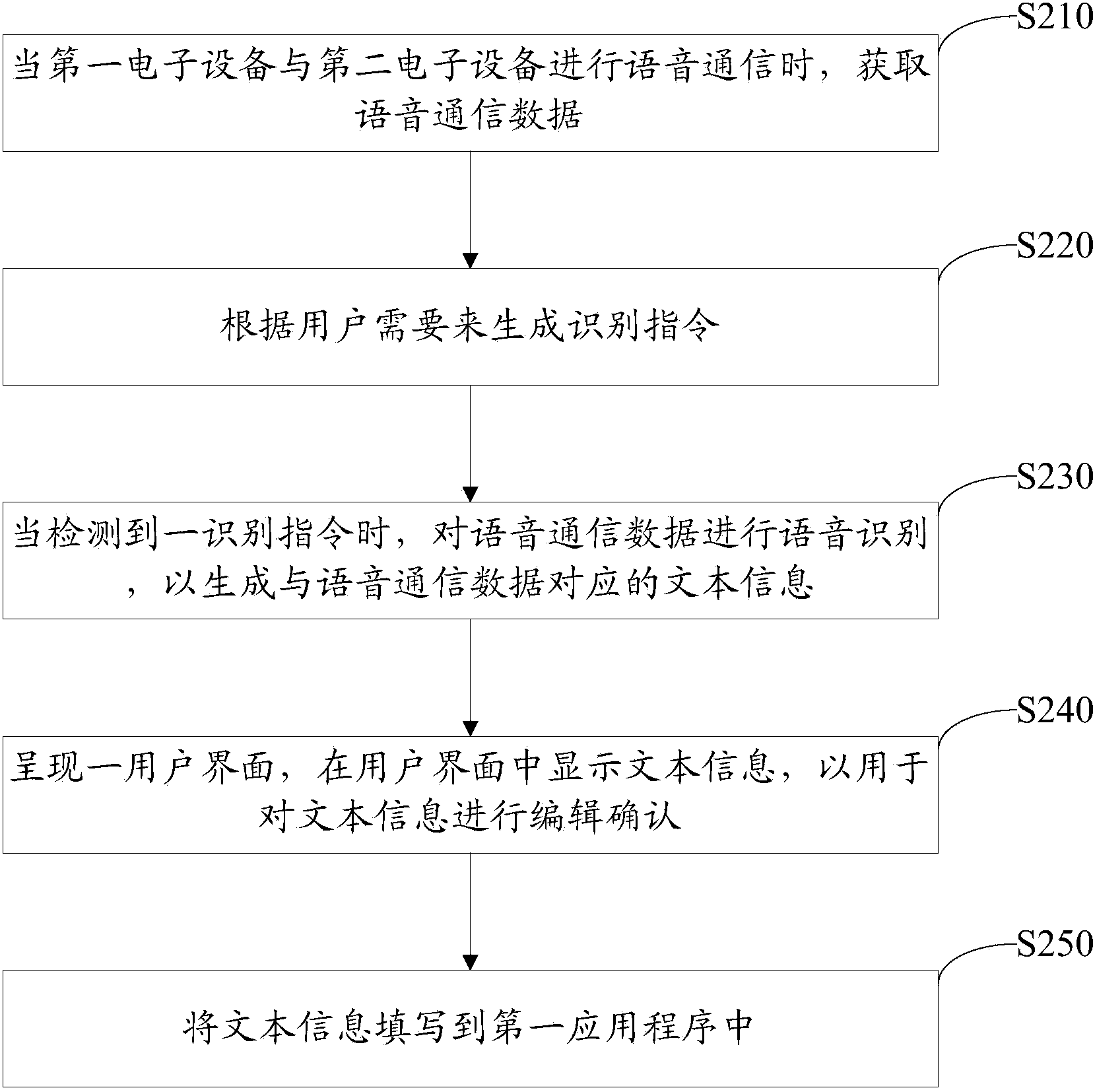

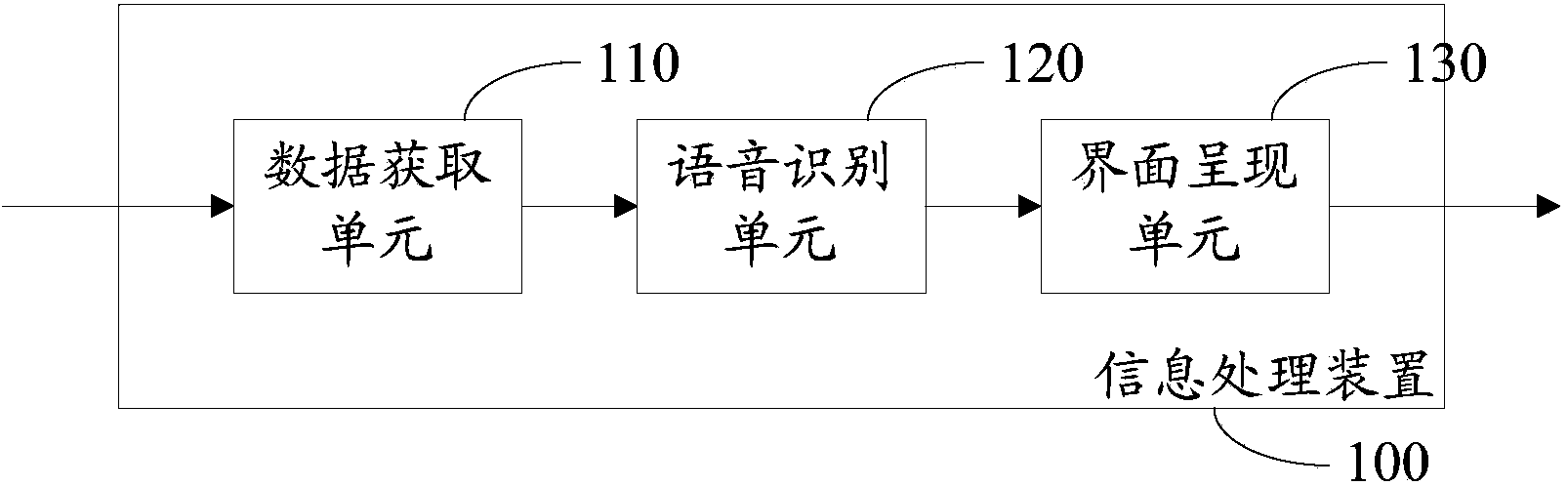

Information processing method and information processing device

InactiveCN103841268AAvoid switchingImprove experienceInput/output for user-computer interactionSubstation equipmentSpeech soundComputer hardware

The invention discloses an information processing method and an information processing device. The information processing method is applied to first electronic equipment which can be in voice communication with second electronic equipment. The information processing method comprises the steps that when the first electronic equipment is in voice communication with the second electronic equipment, voice communication data are obtained; when an identification command is detected, the voice communication data are subjected to voice identification so as to generate text messages corresponding to the voice communication data; a user interface is presented, and the text messages are shown in the user interface so as to be compiled and determined. The information processing method can flexibly and conveniently record information, the problem that a user has to switch communication operation and information record in order to record information in the process of voice communication is solved, and user experience is improved.

Owner:LENOVO (BEIJING) CO LTD

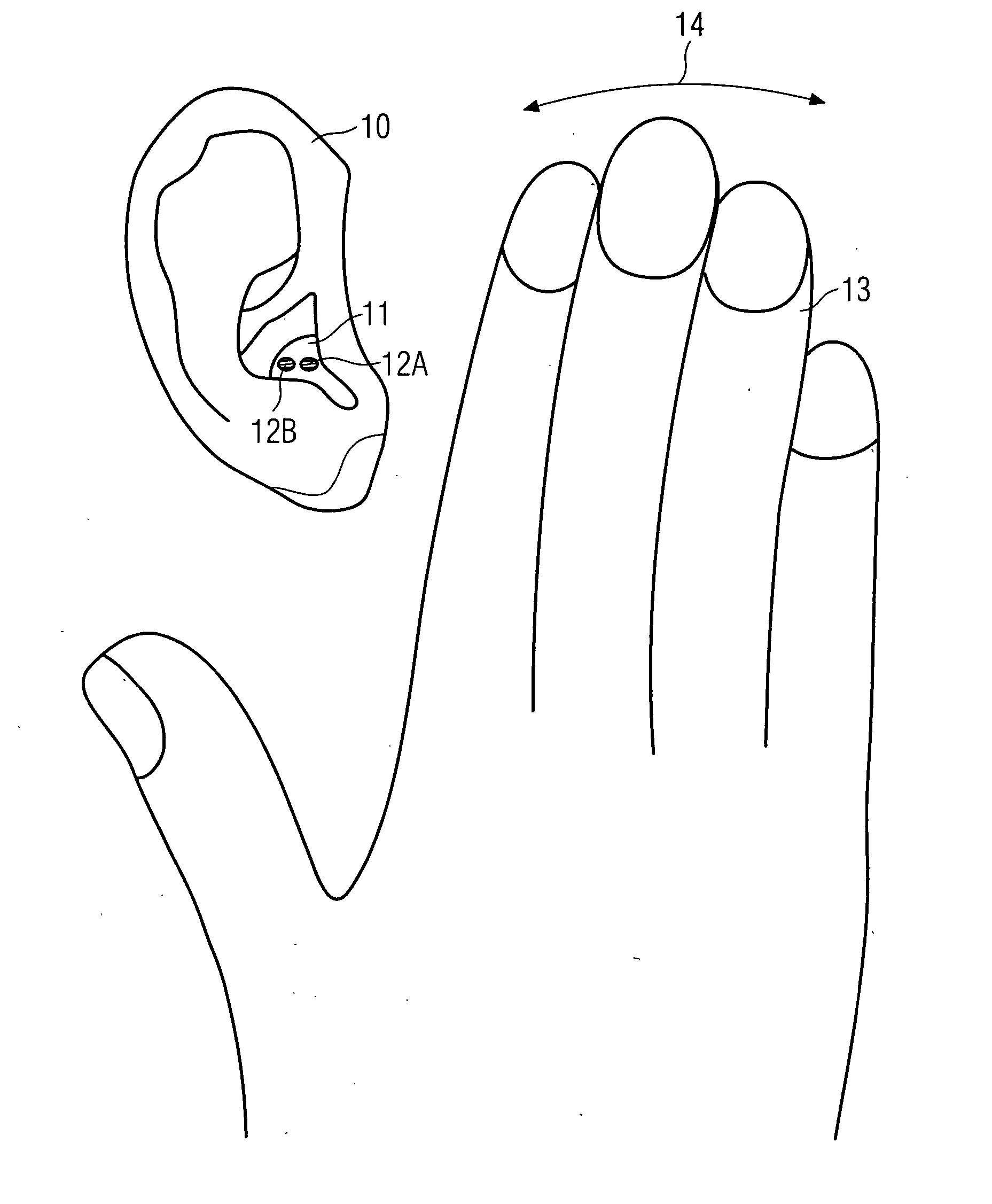

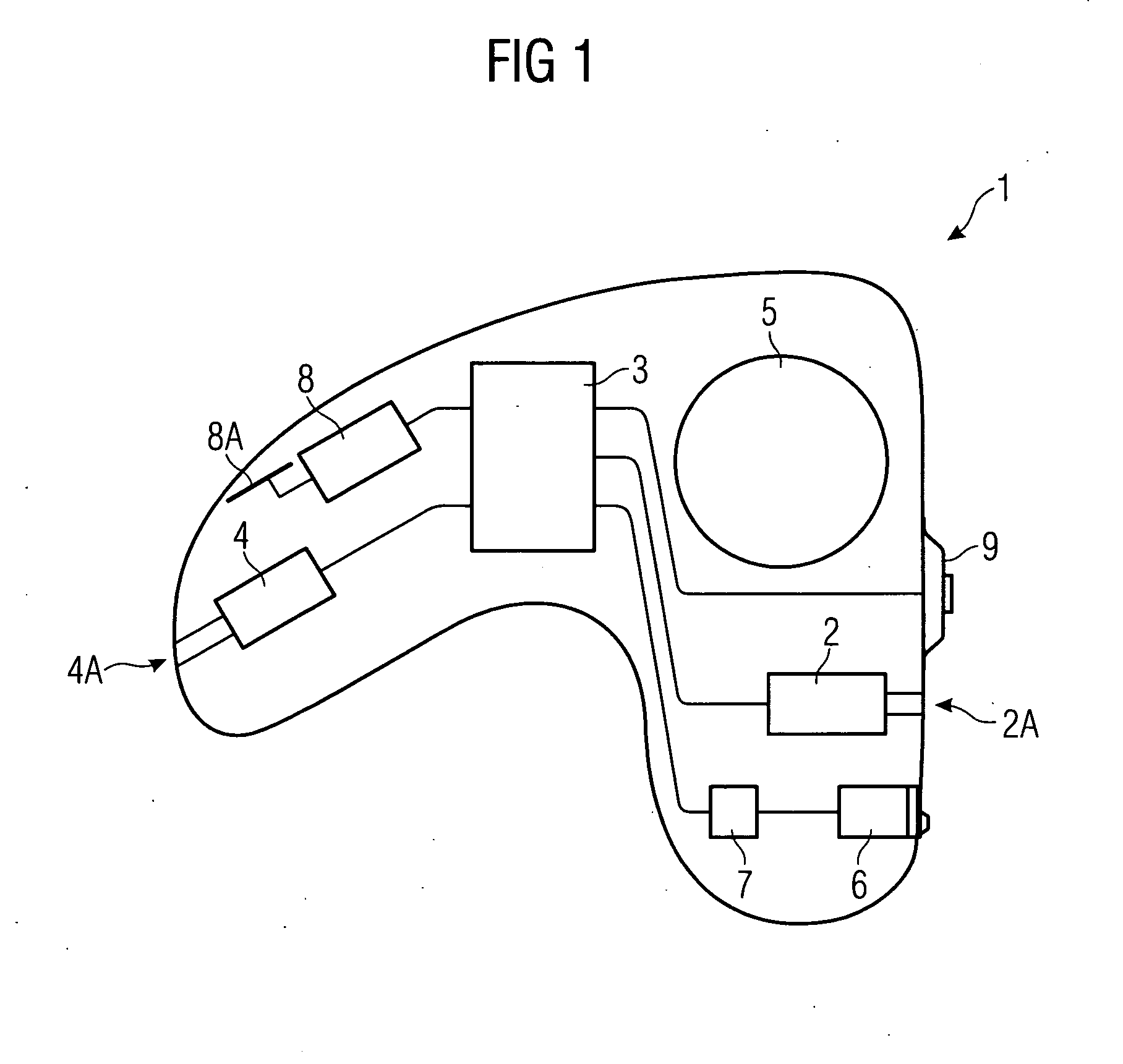

Hearing aid

ActiveUS20050238190A1Avoid failureAvoid switchingManually-operated gain controlEar supported setsProximity sensorRemote control

The increasing miniaturization of hearing aids means that less and less space is available for accommodating controls (9). It is thus proposed that, at least one proximity sensor (6; 12A, 12B) be provided on a hearing aid (1; 11) so as to enable an operating function to be performed even without touching a control directly. For operation of a hearing aid (1; 11) in accordance with the invention, in addition to the hearing aid (1; 11) itself, no further technical aids such as remote control, magnets etc. have to be worn as well.

Owner:SIVANTOS PTE LTD

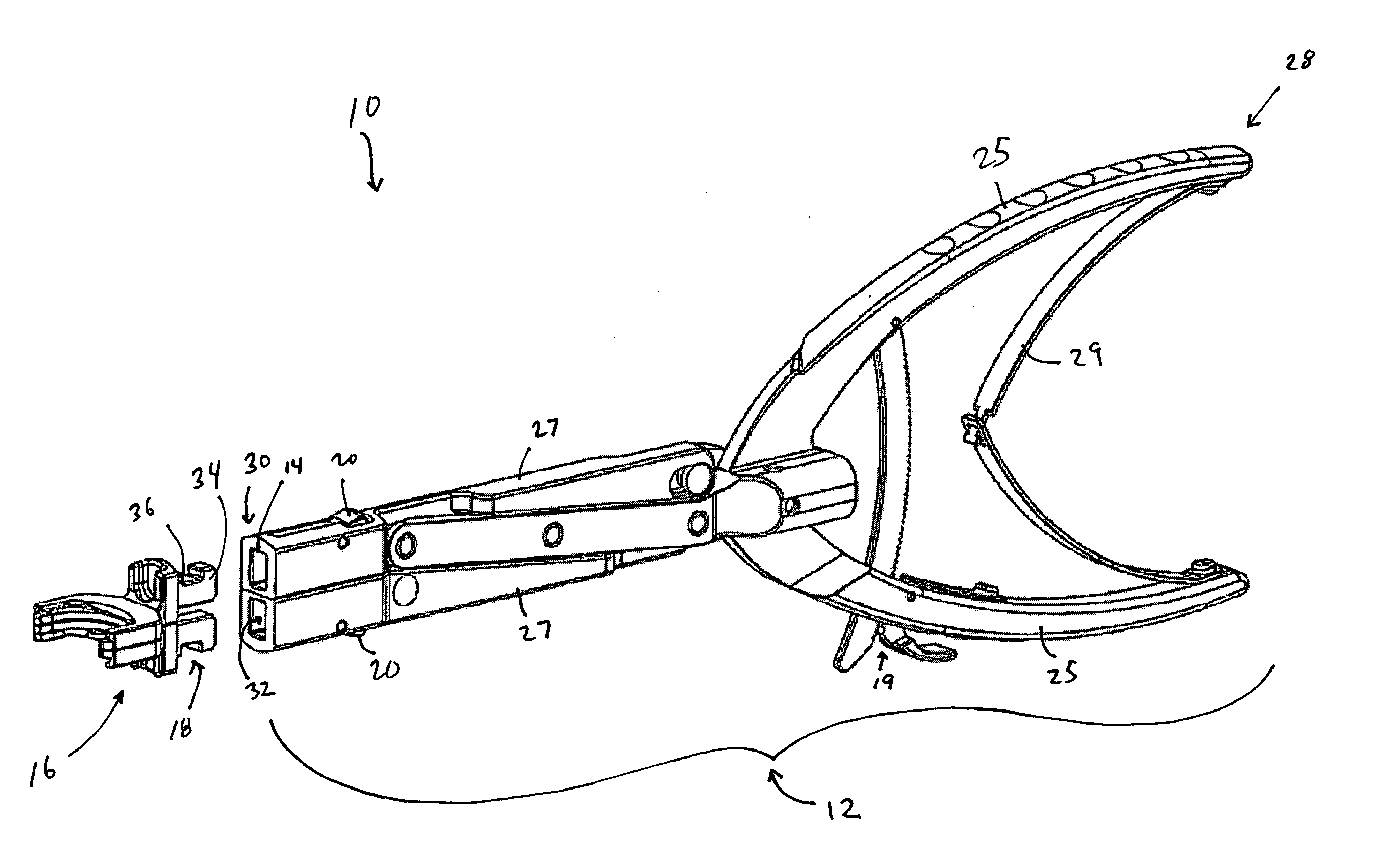

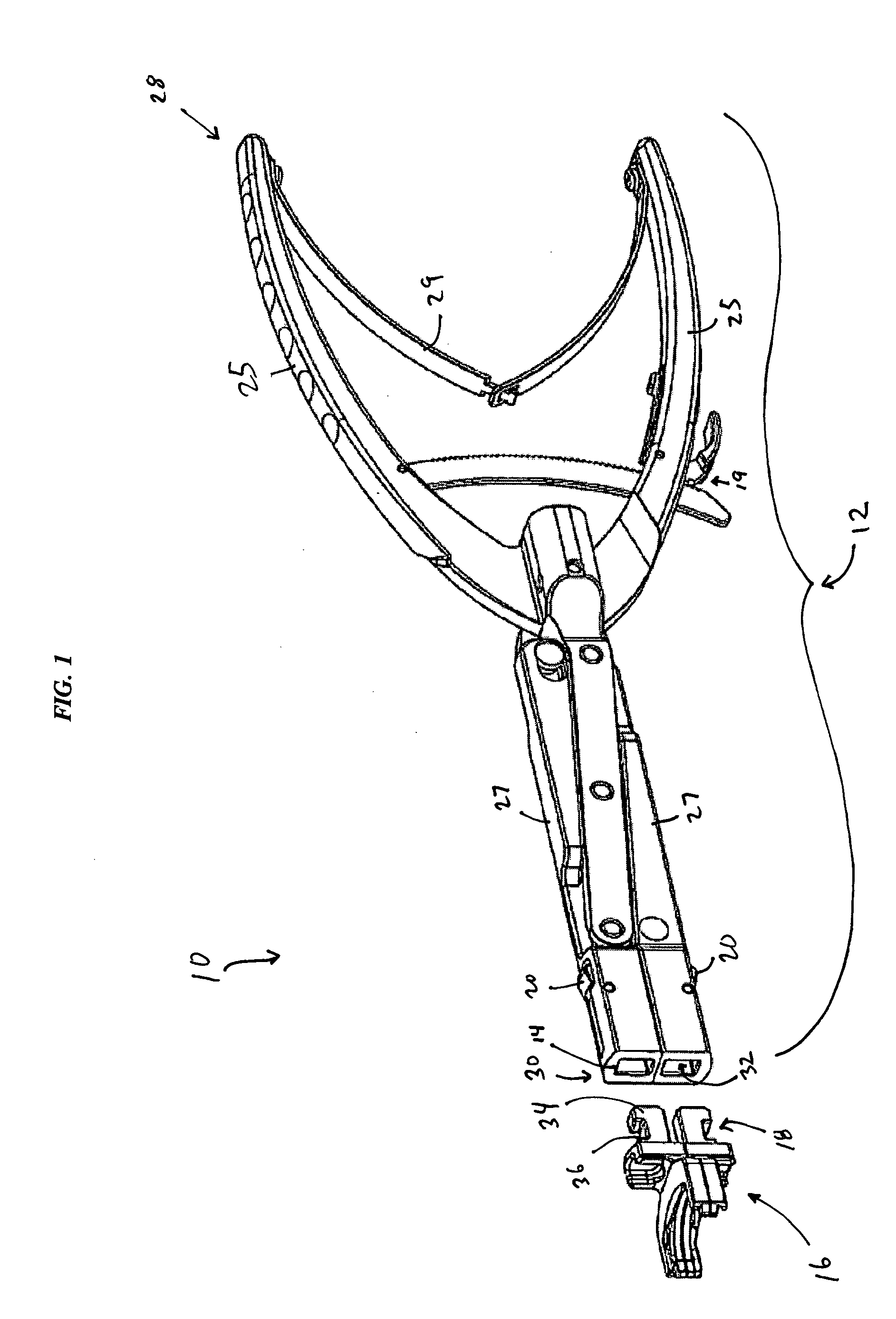

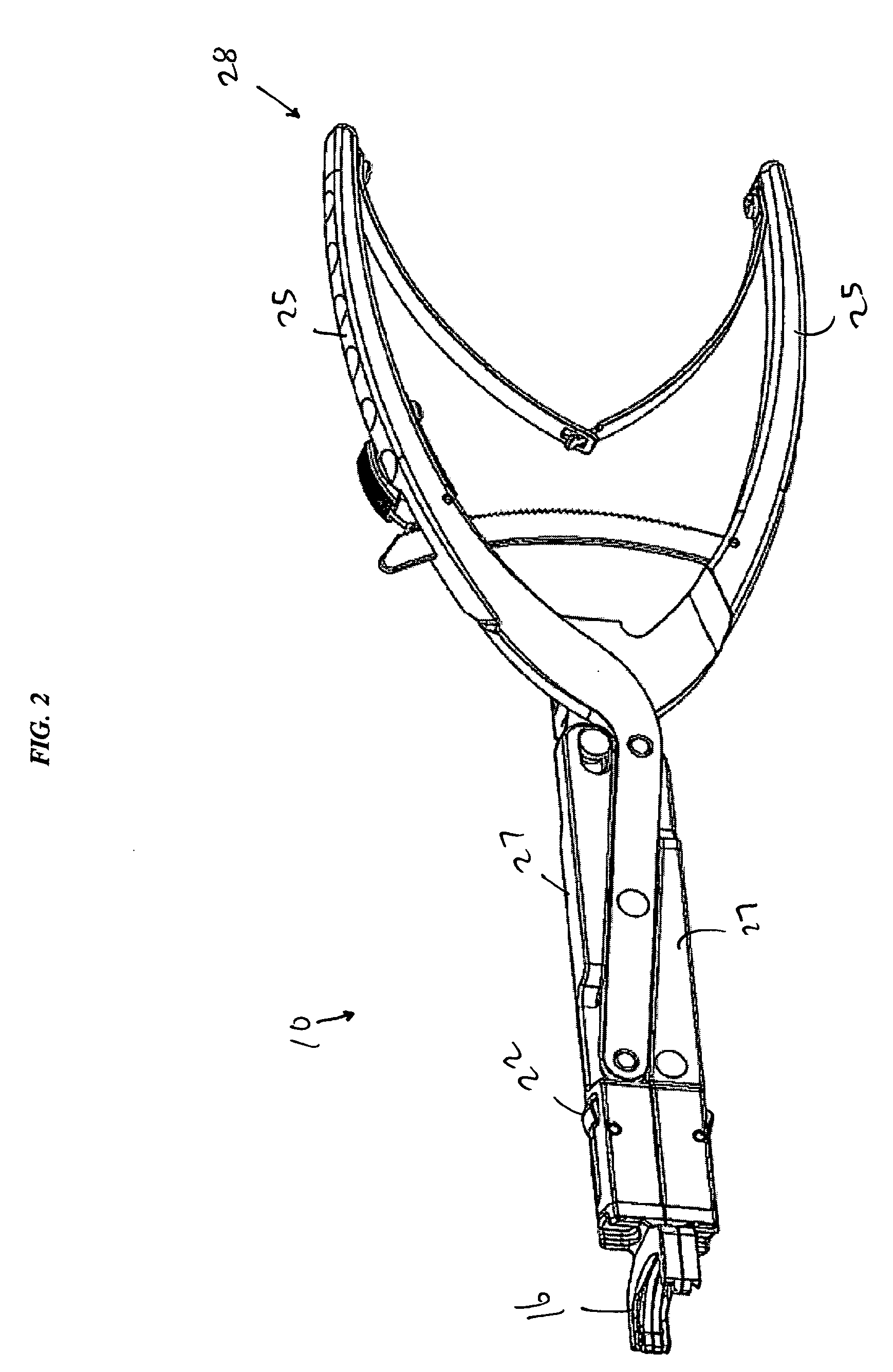

Modular medical tool and connector

ActiveUS20060074432A1Increase contactEffective protectionSpinal implantsOsteosynthesis devicesLocking mechanismEngineering

Modular medical instruments and kits are provided, having, a tool body portion with a first mating element at one end. A removable and replaceable modular end effector having a second mating element is matable with the first mating element. The instrument further includes a selectively engageable locking mechanism having a lever arm with a first portion associated with the body portion and a claw portion matingly engageable with a portion of the second mating element of the end effector, the locking mechanism being effective to secure the end effector to the body portion of the modular medical instrument. The invention can be particularly useful for providing a secure connection between the modular end effector and the body portion, yet provide ease of interchangeability between modular end effectors

Owner:DEPUY SYNTHES PROD INC

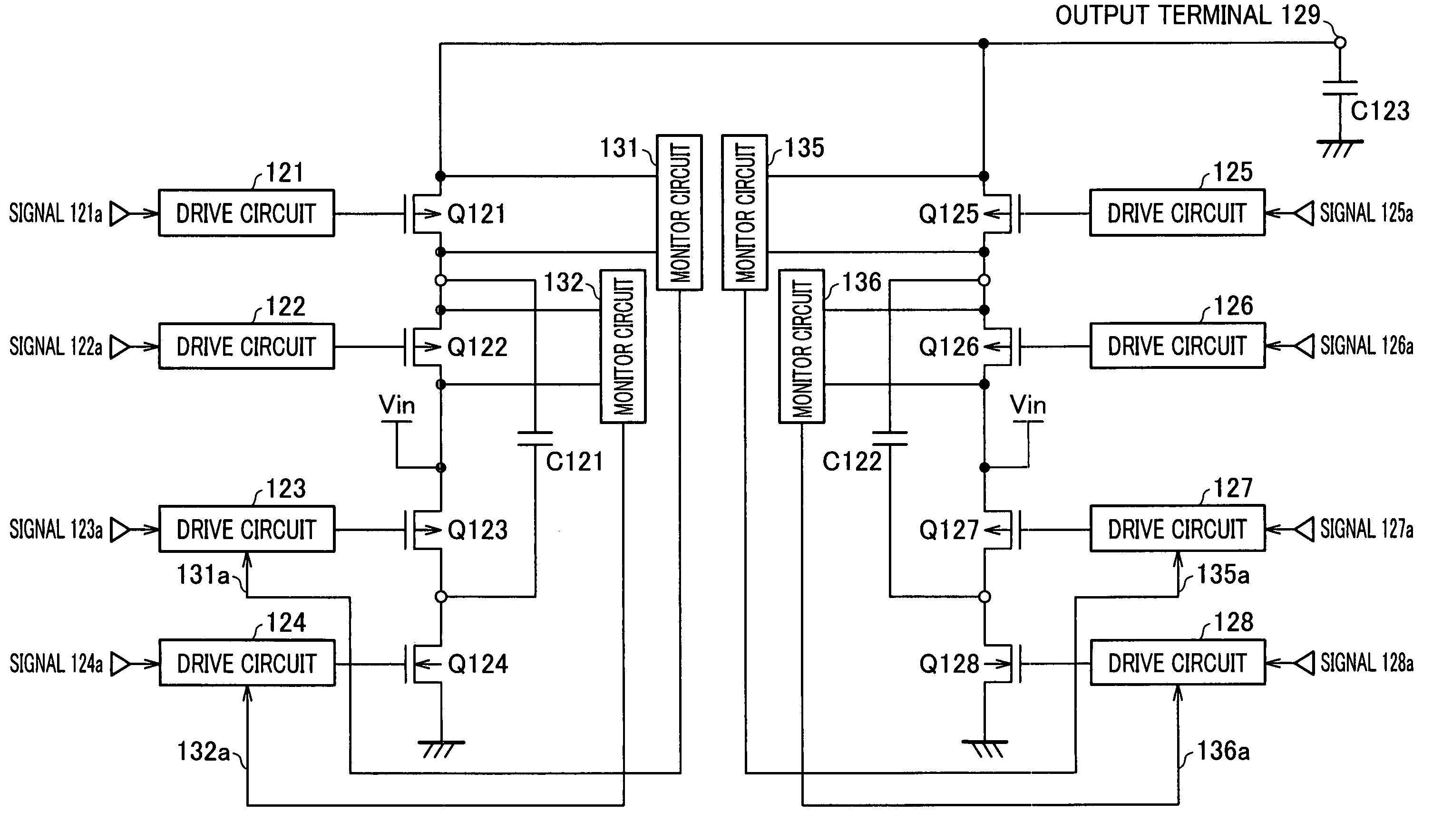

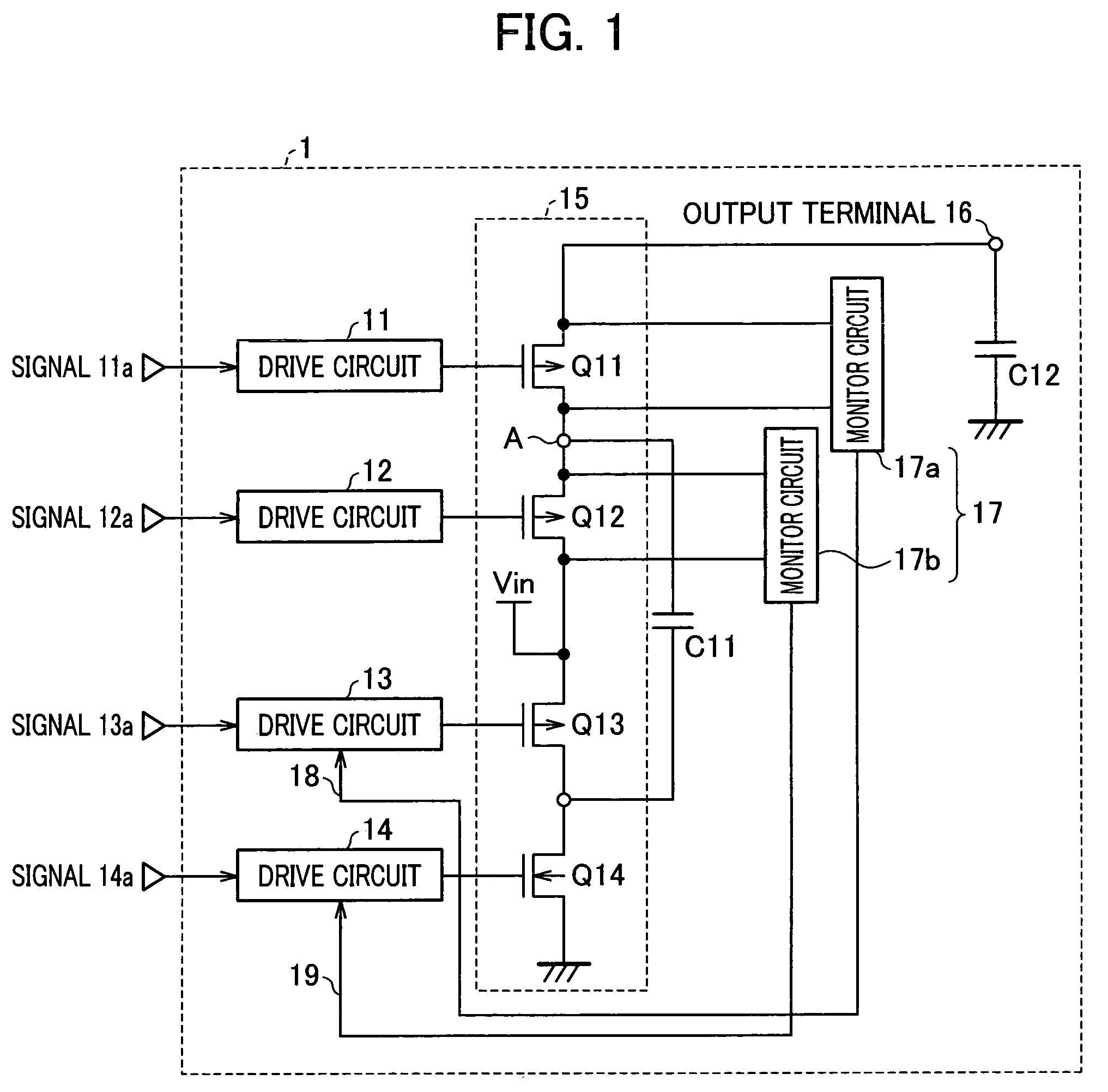

Charge pump DC/DC converter circuit

ActiveUS7224591B2Increase the on-resistanceAvoid switchingAc-dc conversionApparatus without intermediate ac conversionPotential differenceSemiconductor

Owner:SHARP KK

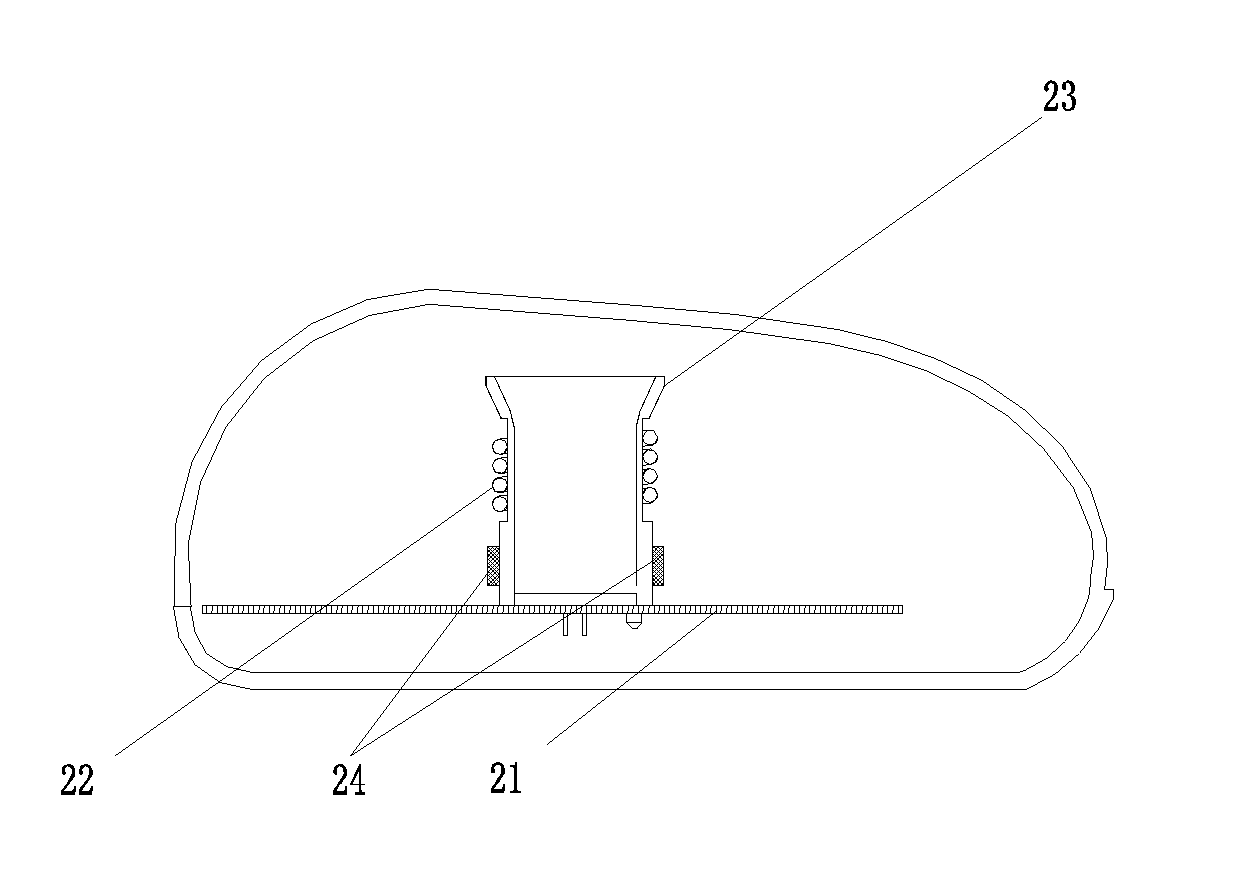

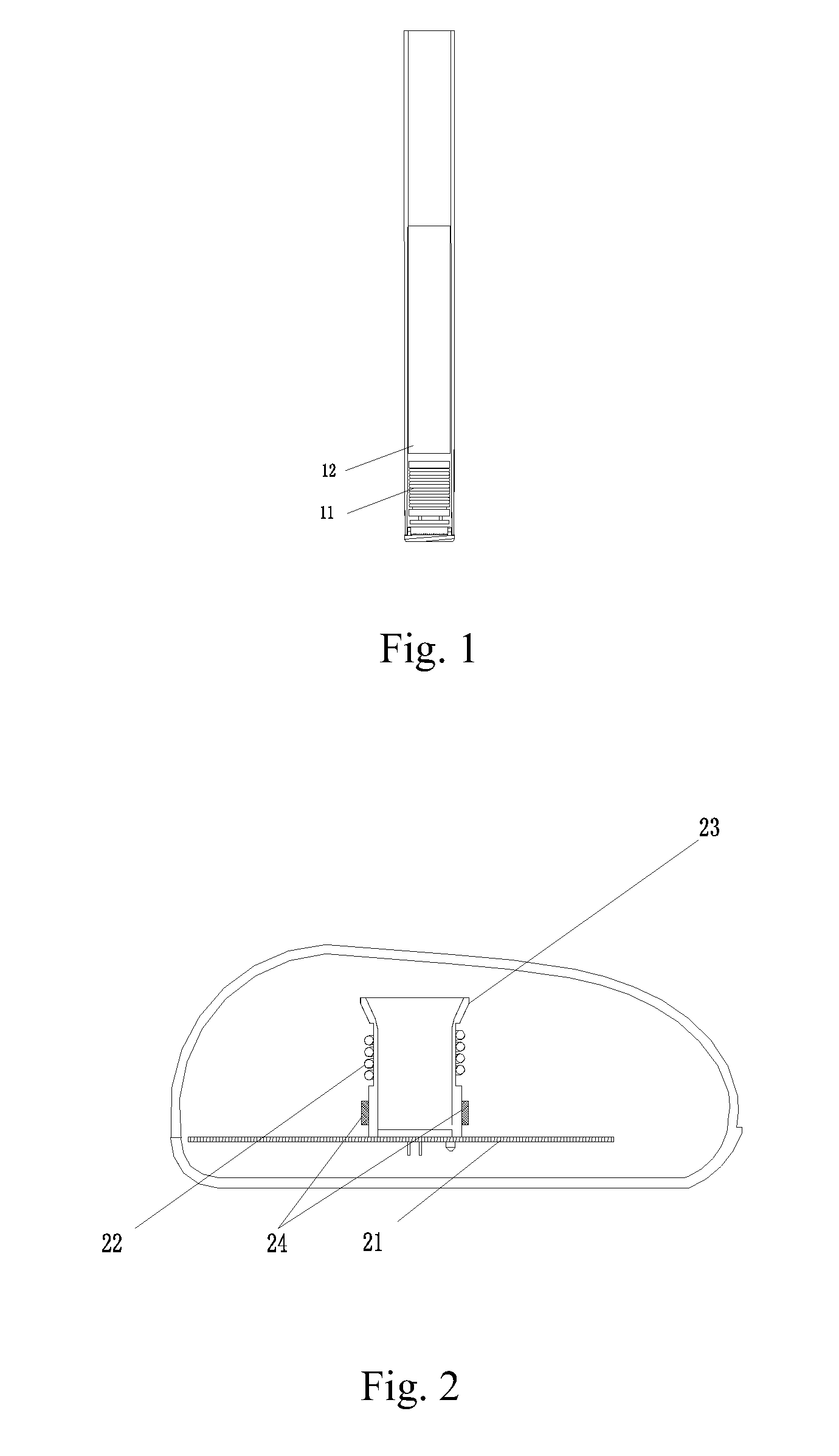

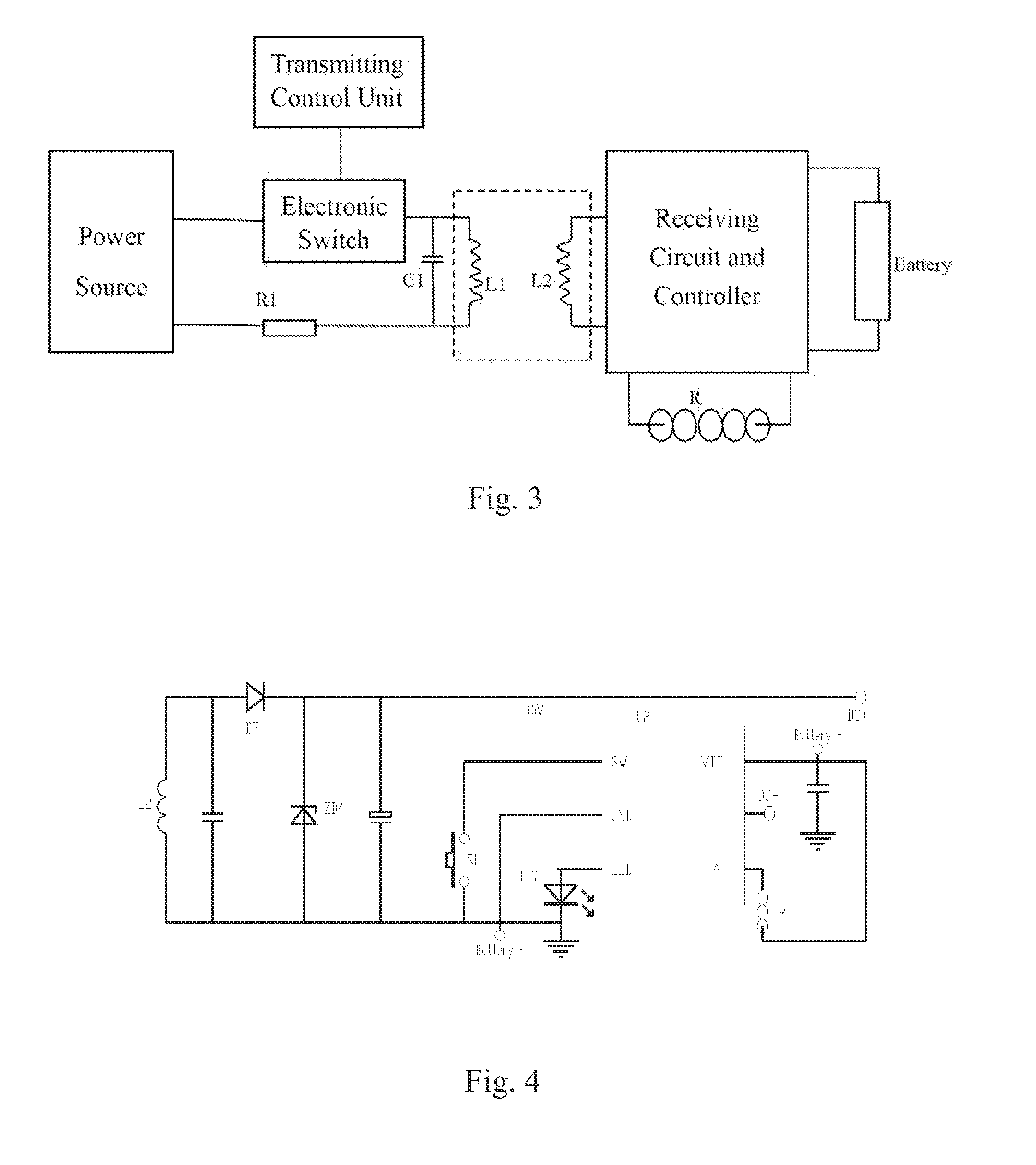

Wireless charging device

InactiveUS20130300350A1Improve efficiencyLow calorific valueTobacco devicesElectric powerElectricityElectrical resistance and conductance

A wireless charging device comprises an electronic switch and a transmitting coil (L1) electrically connected with a power source in sequence. A control end of the electronic switch is connected with a transmitting control unit. The wireless charging device further comprises a current limiting resistance (R1) connected in serial with the transmitting coil. The wireless charging device further comprises a compensation capacitor (C1) connected in parallel with the transmitting coil. An insert total electromagnetic coupling structure is further employed for charging. Such wireless charging device is particularly suitable for electronic cigarette, with low cost, stable and reliable working status and high efficiency, and specific heat sink is not required.

Owner:KIMREE HI TECH

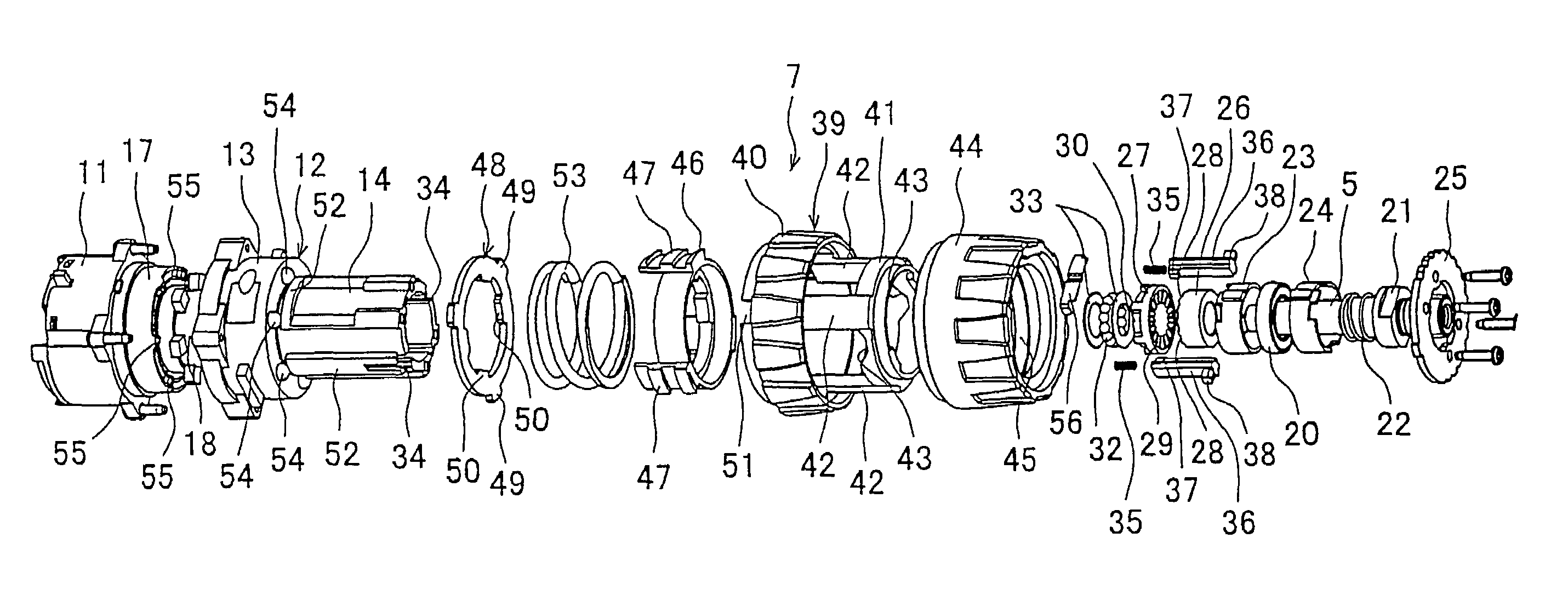

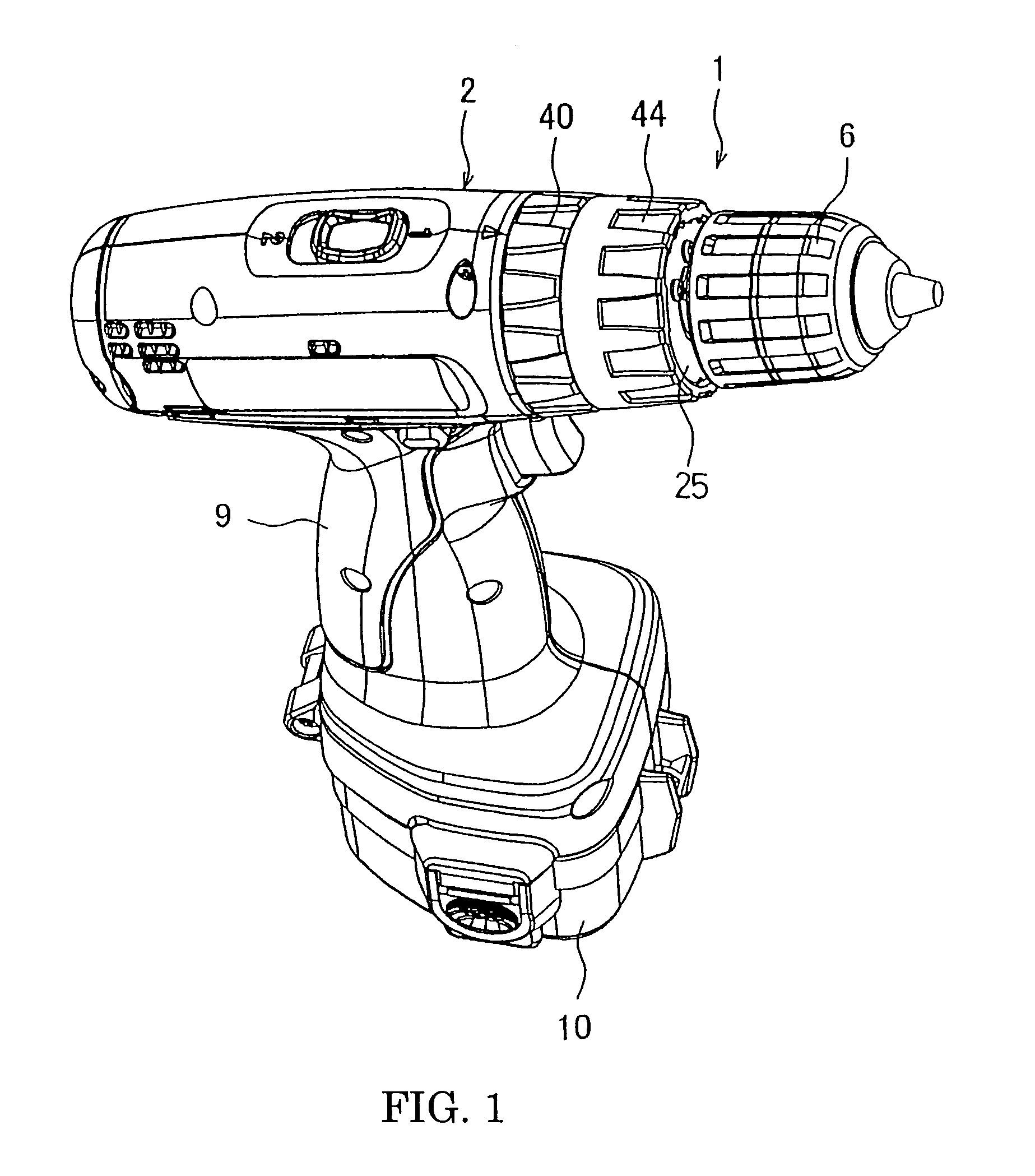

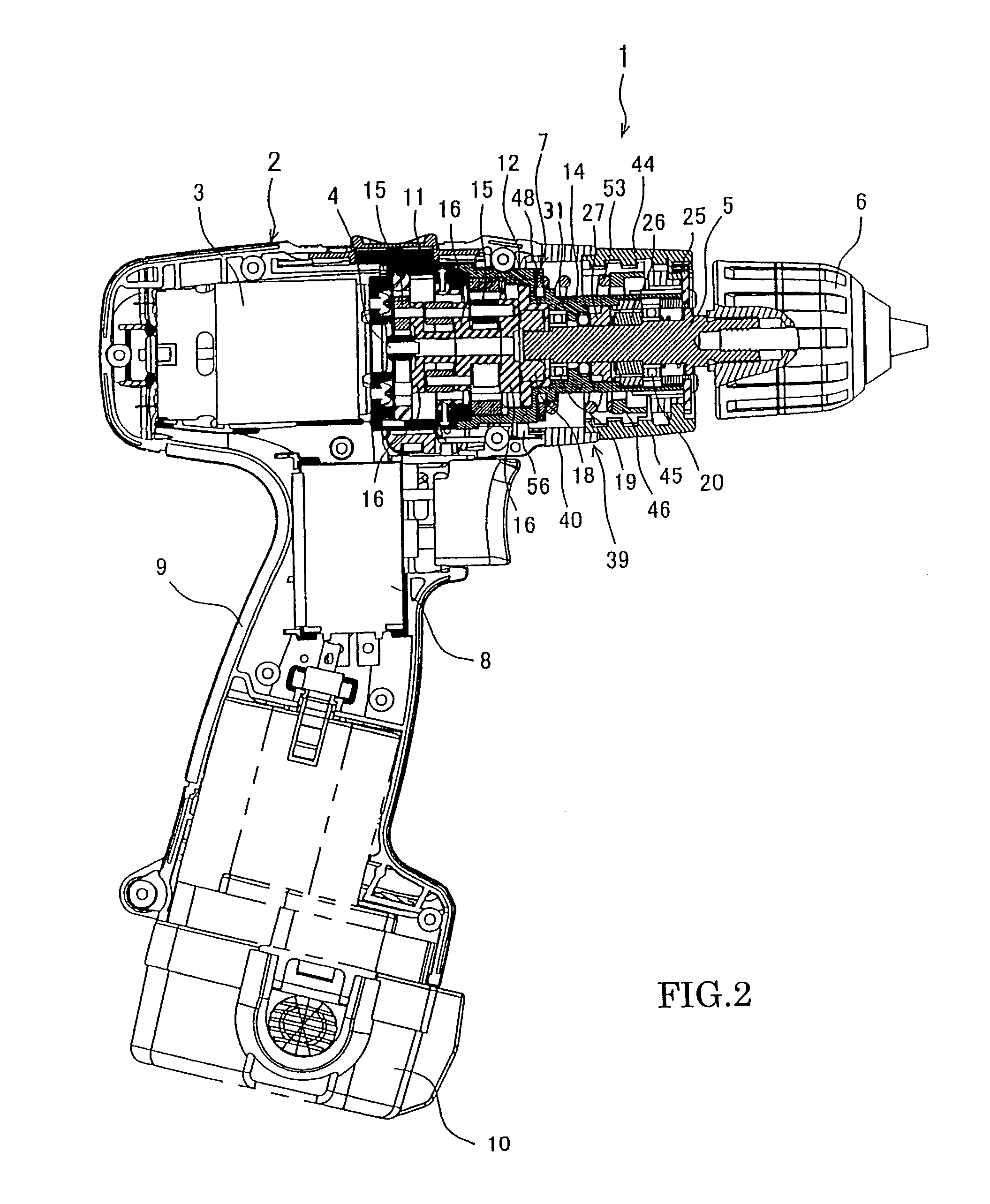

Driver drill

ActiveUS7201235B2Prevent erroneous clutch operationImprove reliabilityDrilling rodsConstructionsGear wheelCoil spring

A driver drill that can effectively prevent erroneous clutch operation in a drill mode is provided. A flat washer positioned between steel balls for locking an internal gear and a coil spring is rotatable by rotative operation of a mode-change ring. Also, protruding streaks are provided on a small-diameter unit of a second gear case around which a flat washer is externally mounted. The protruding streaks interfere with internal projections on an inner circumference of the flat washer at its predetermined rotating position to regulate a forward movement of the flat washer. When a drill mode is selected with the mode-change ring, the flat washer is locked by the protruding streaks.

Owner:MAKITA CORP

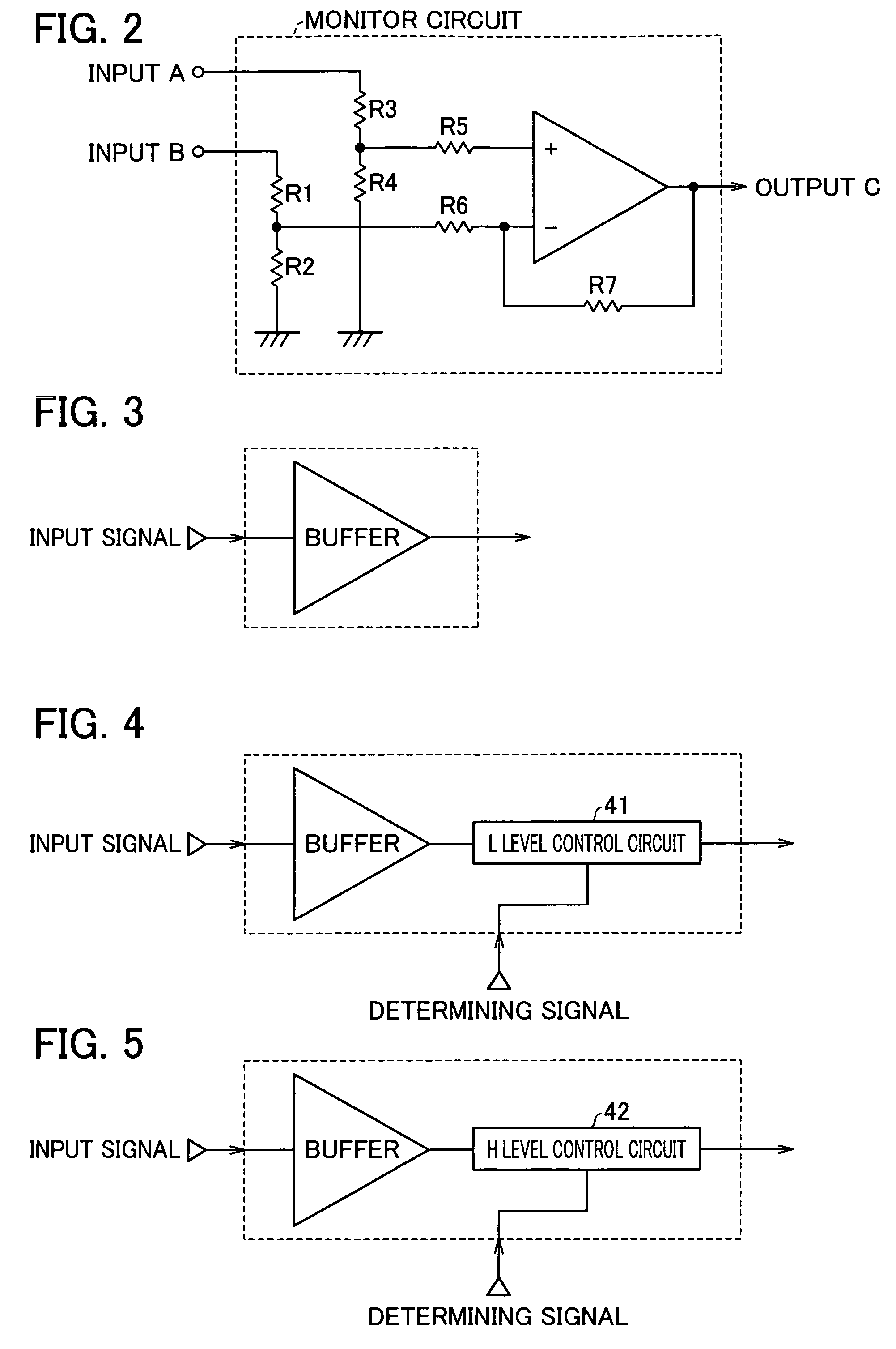

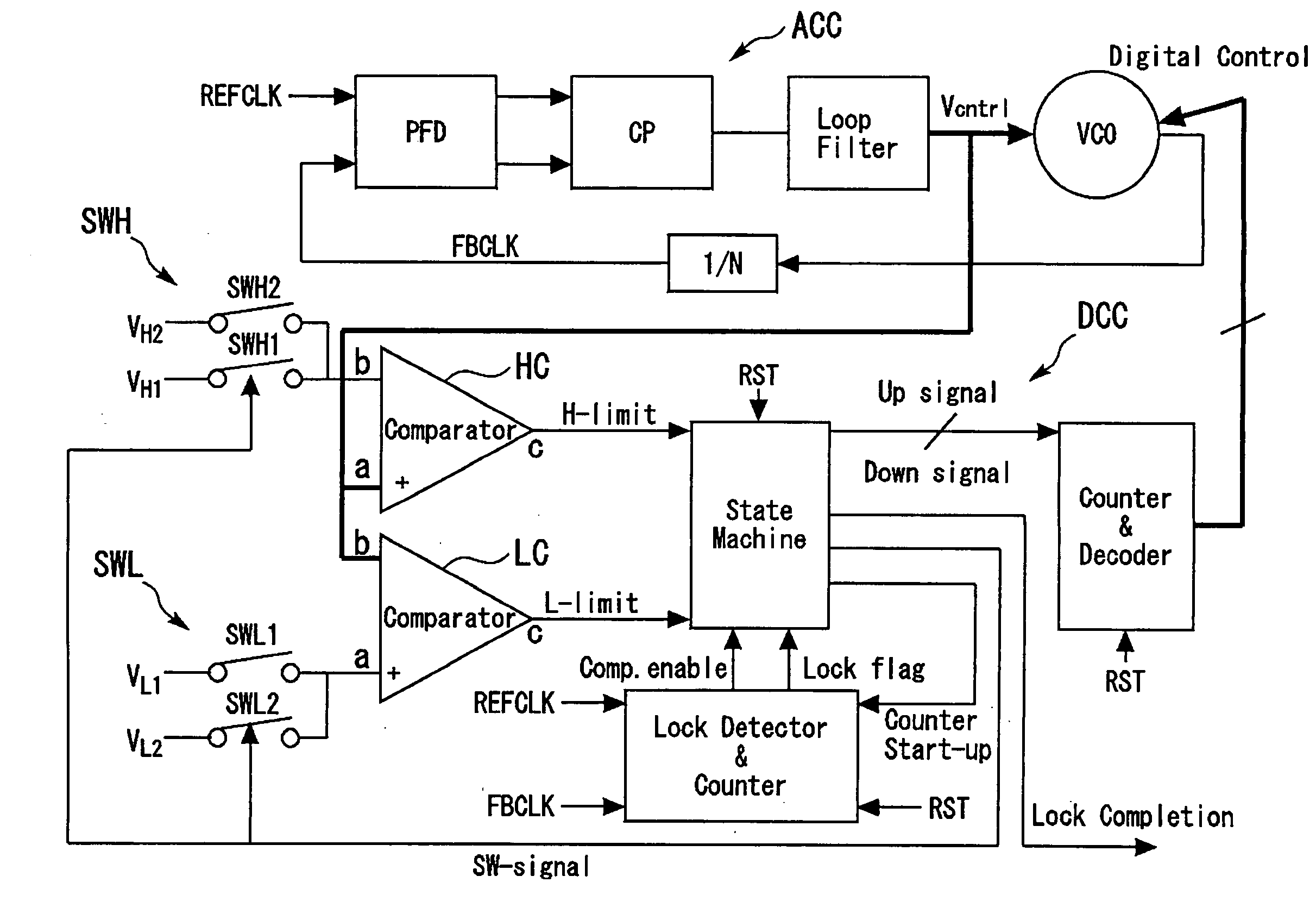

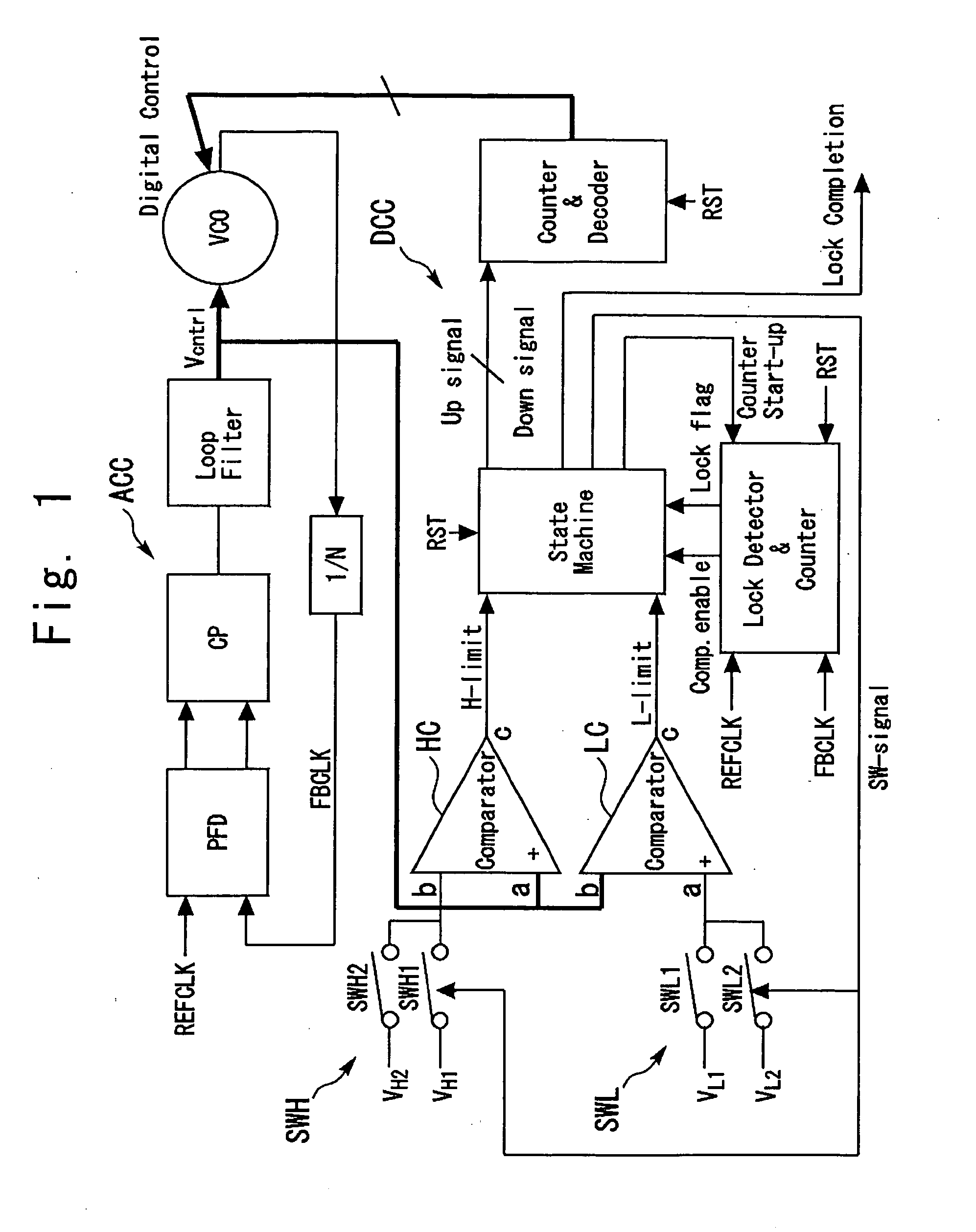

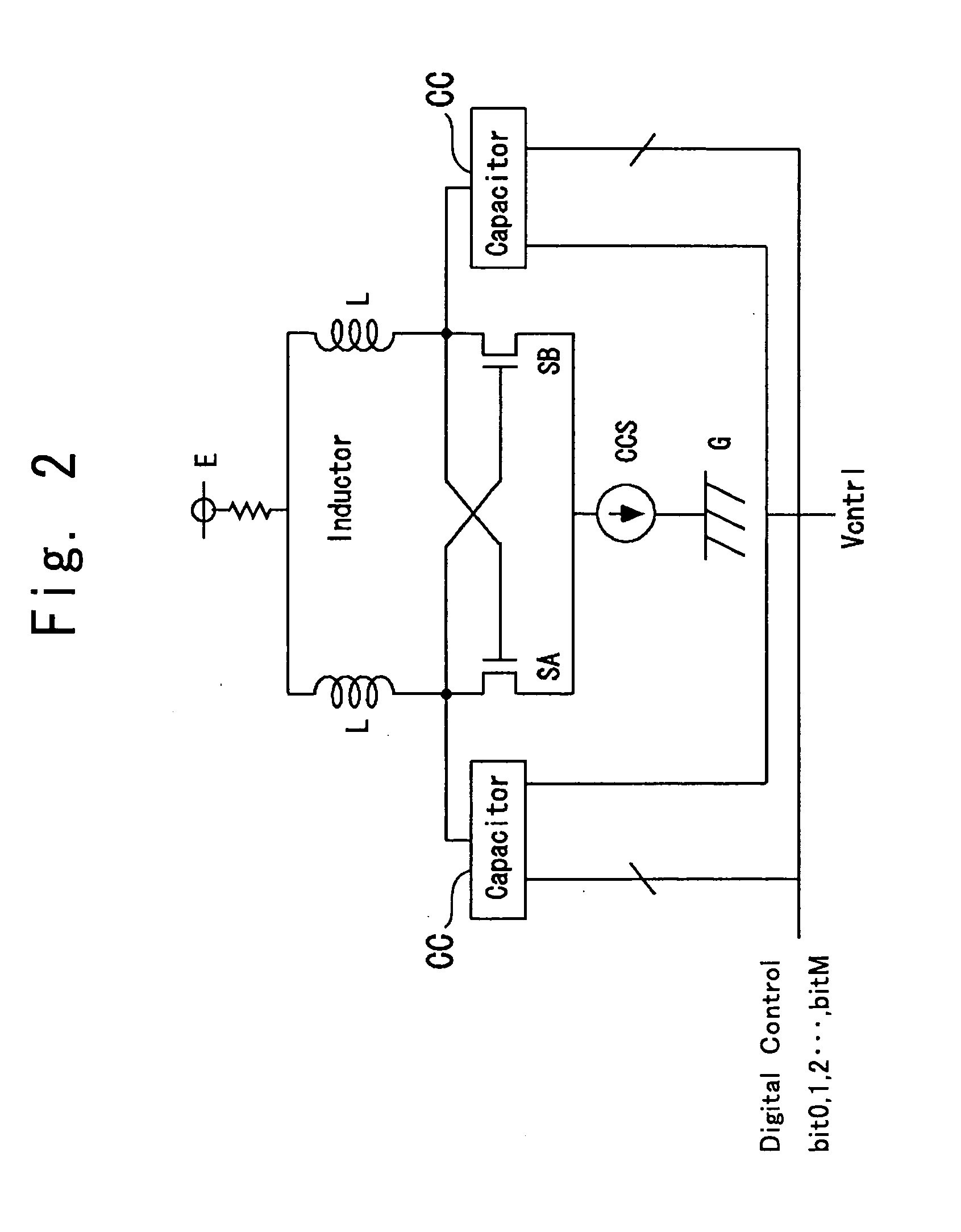

Automatic frequency correction PLL circuit

ActiveUS20050226357A1Prevent unnecessary switchingAvoid switchingPulse automatic controlPulse generation by logic circuitsEngineeringComparator

An automatic frequency correction phase-locked loop (PLL) circuit includes an analog control circuit and a digital control circuit. The digital control circuit includes a High-side comparator and a Low-side comparator which receive an analog control voltage, a state monitor circuit, and a counter and decoder circuit. At least one of the High-side comparator and the Low-side comparator includes a threshold switching circuit which selectively gives a first threshold and a second threshold having different. When the analog control voltage remains between the High-side threshold and the Low-side threshold in a state in which the threshold switching circuit gives the first threshold, the threshold switching circuit switches the first threshold to the second threshold and expands the interval between the High-side threshold and the Low-side threshold.

Owner:MITSUBISHI ELECTRIC CORP

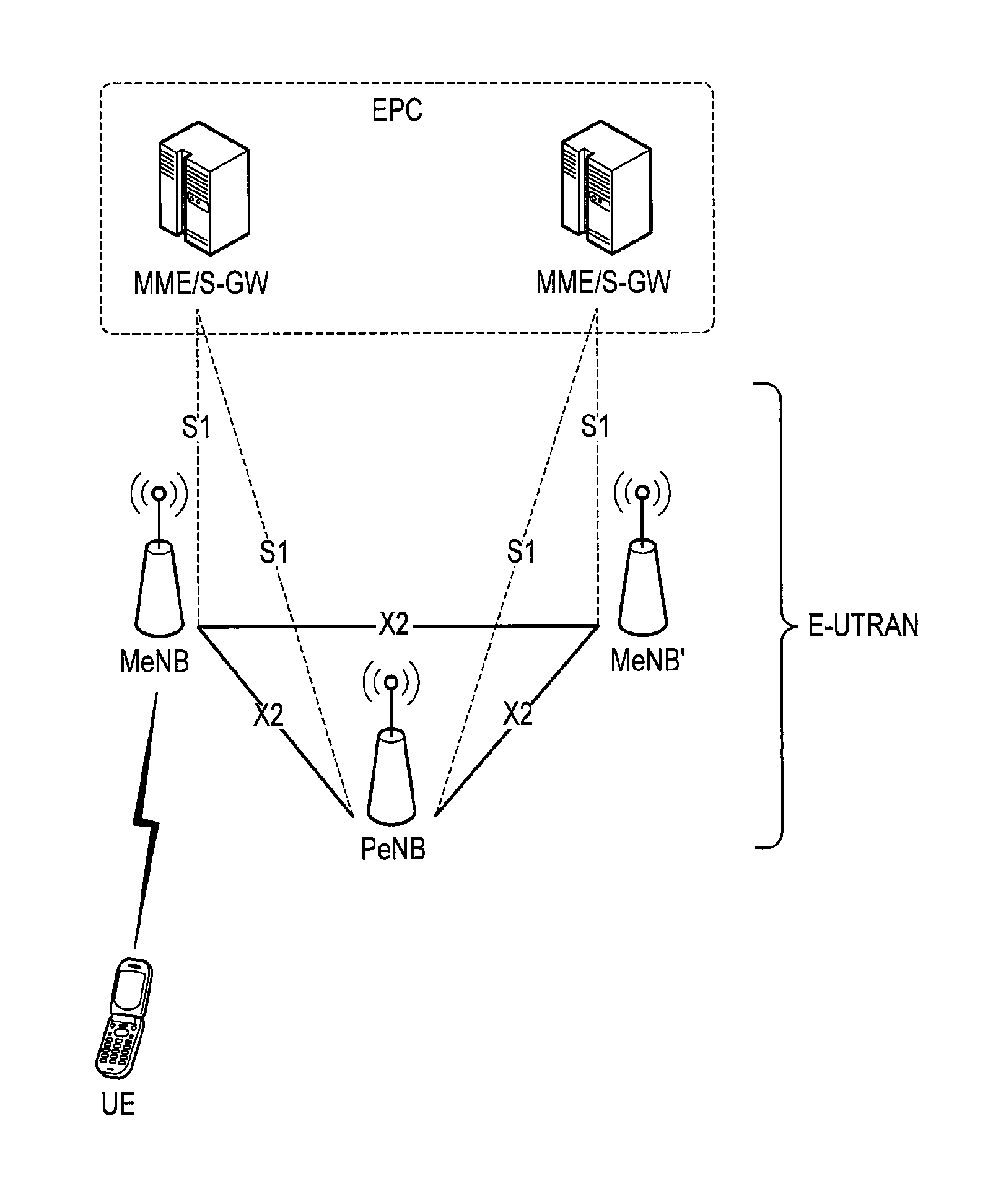

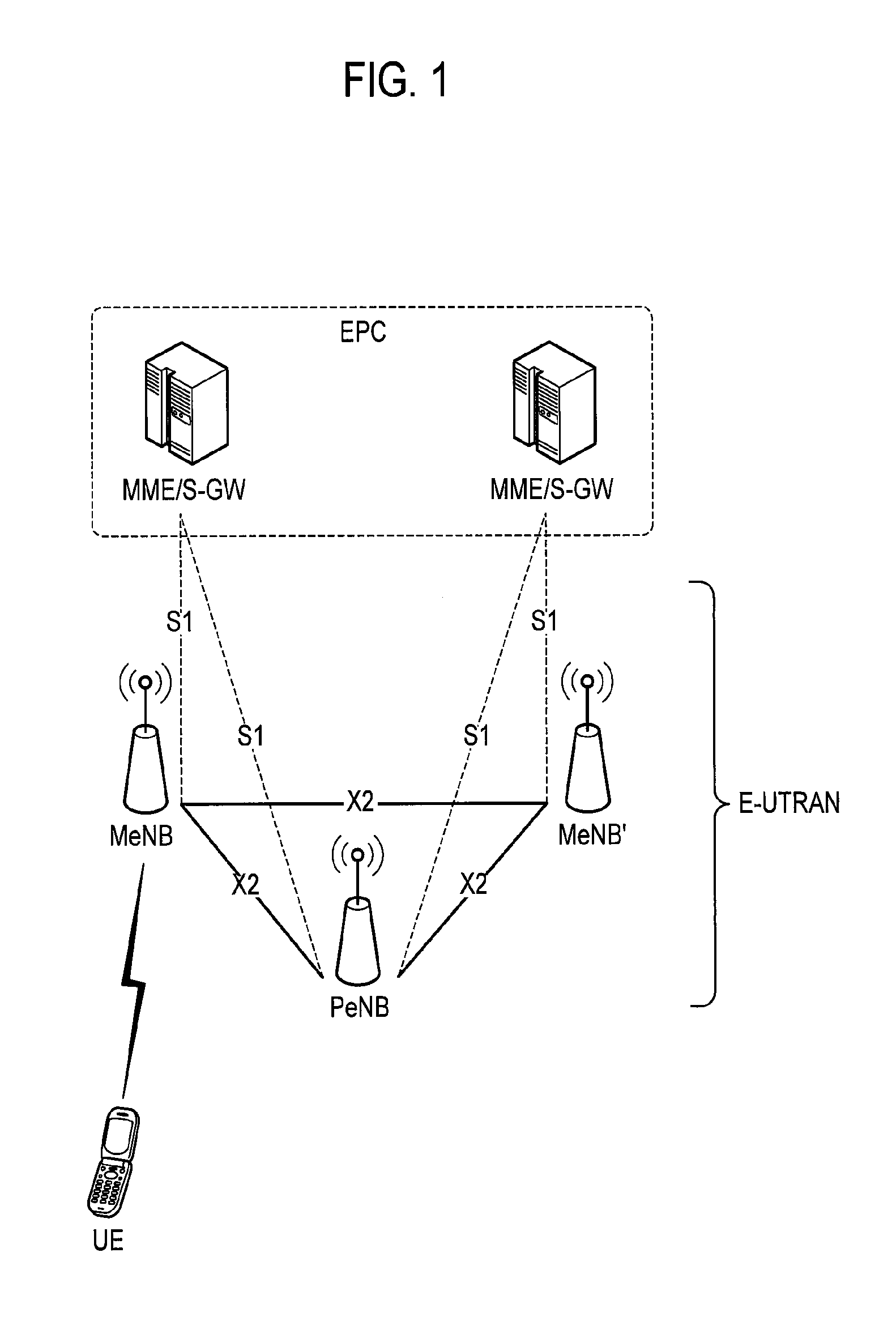

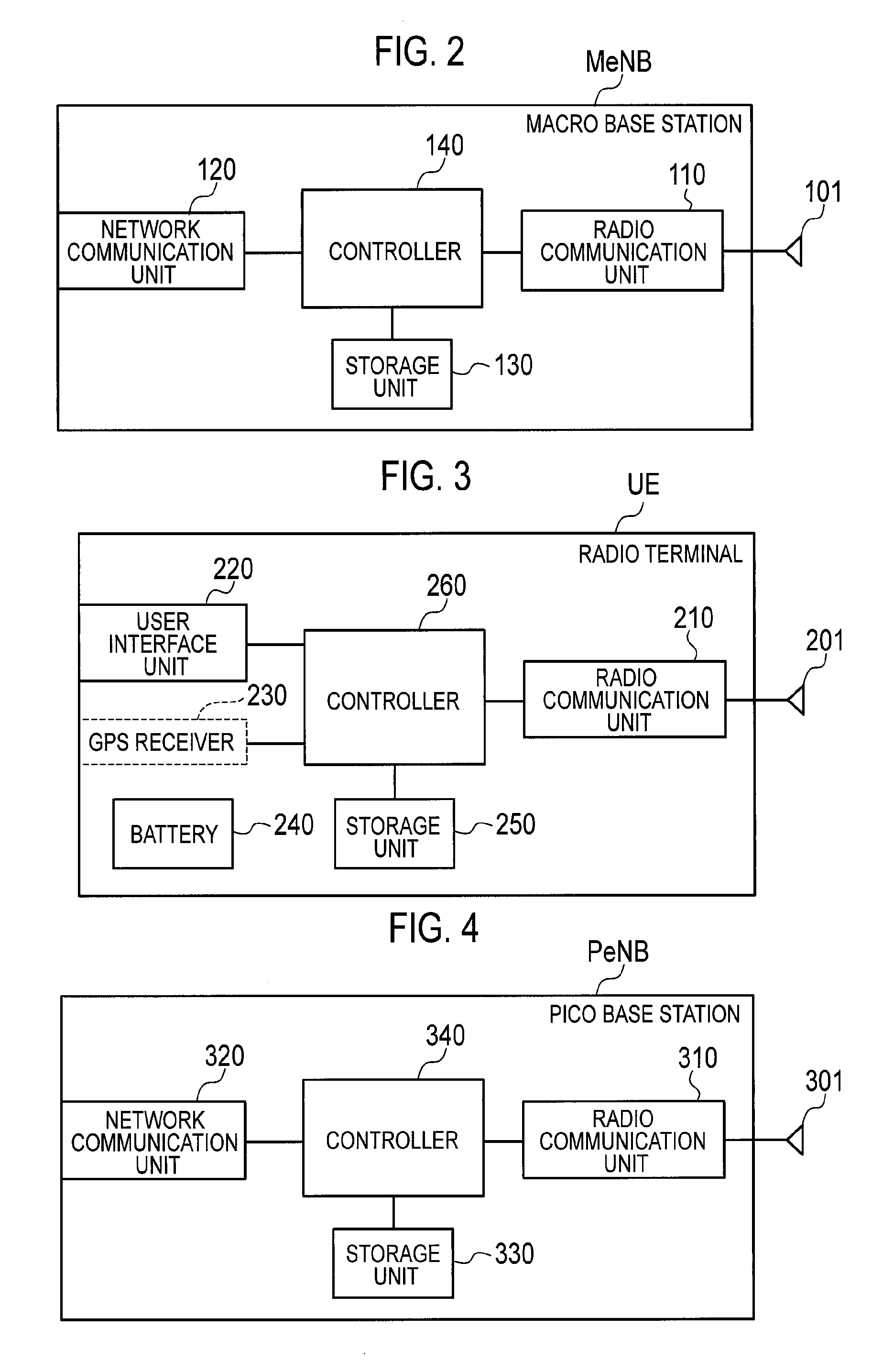

Mobile communication method

InactiveUS20130171995A1Prevent unnecessary switchingAvoid switchingNetwork traffic/resource managementNetwork topologiesCommunication unitComputer terminal

A radio terminal UE according to one embodiment includes a radio communication unit 210 configured to receive a plurality of parameters including a first parameter for high-speed movement and a second parameter for non-high-speed movement as parameters for processing for switching to a neighboring base station from a base station connected to the radio terminal, and a controller 260 configured to acquire movement speed information indicating a movement speed of the radio terminal and to select a parameter corresponding to the movement speed information. The first parameter is configured to inhibit processing for switching to a Pico base station PeNB which is included in the neighboring base stations.

Owner:KYOCERA CORP

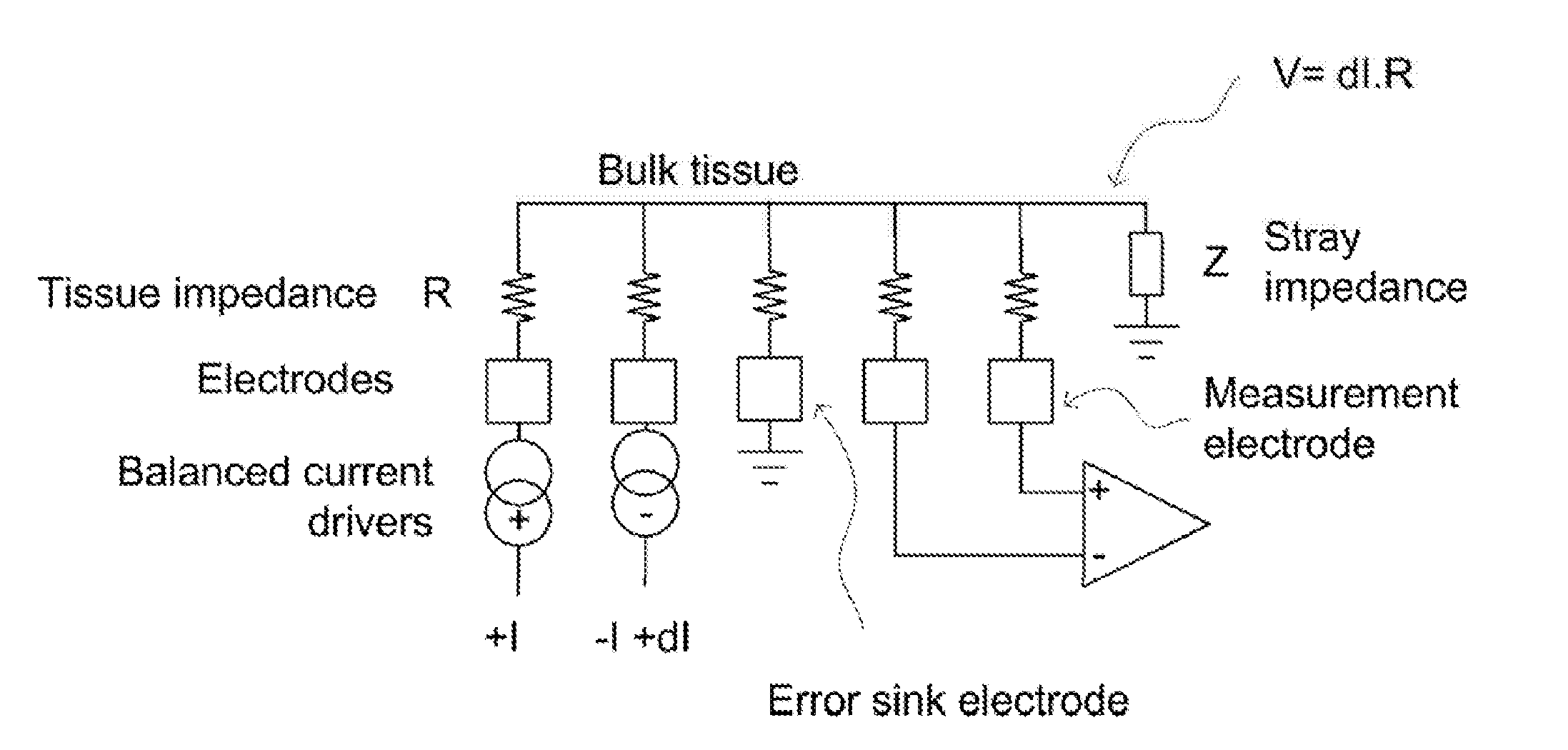

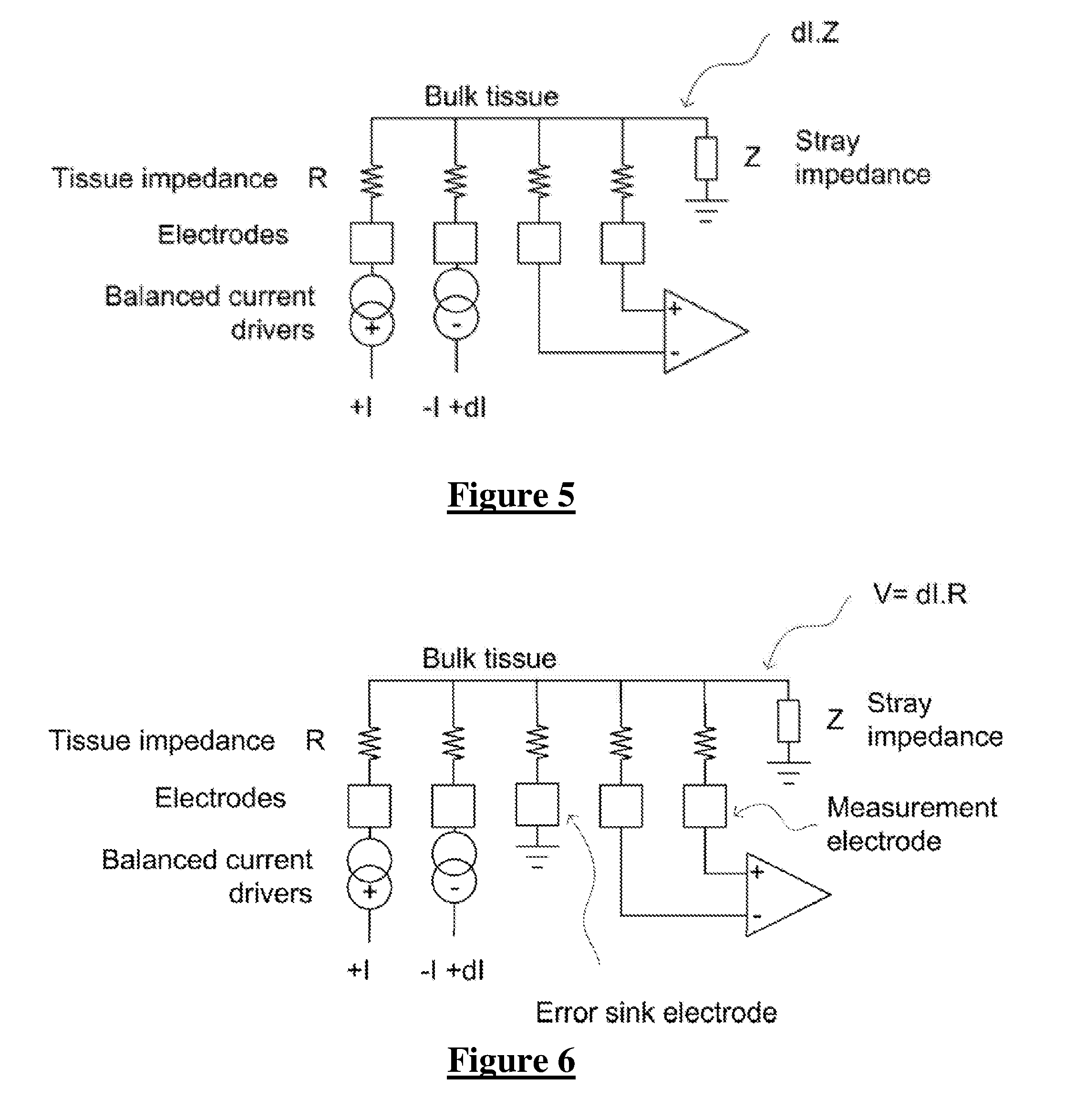

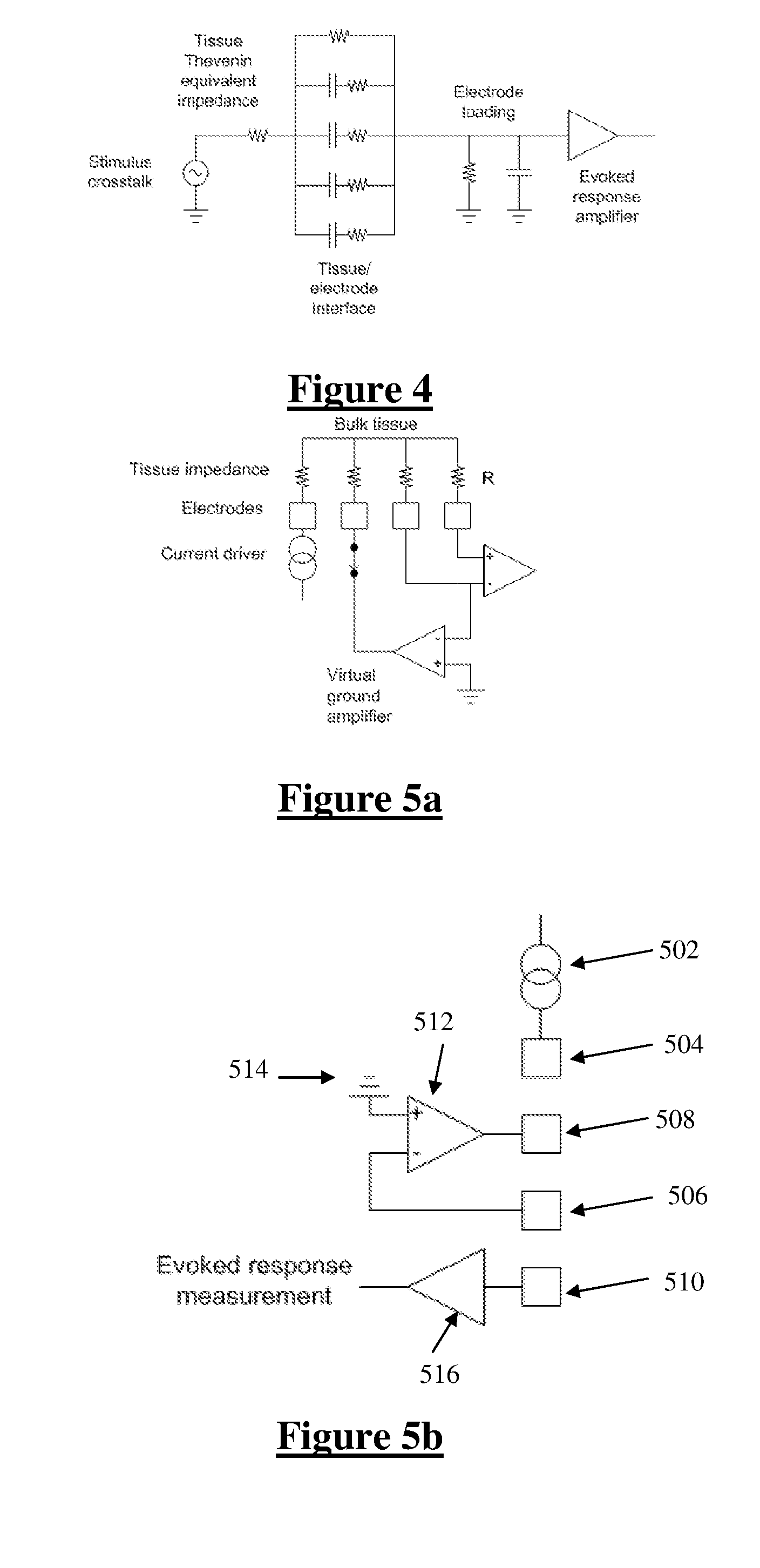

Method and System for Controlling Electrical Conditions of Tissue II

A method for controlling electrical conditions of tissue in relation to a current stimulus. A first current produced by a first current source is delivered to the tissue via a current injection electrode. A second current drawn by a second current source is extracted from the tissue via a current extraction electrode. The second current source is matched with the first current source so as to balance the first current and the second current. A ground electrode which is proximal to the current injection electrode and the current extraction electrode is grounded, to provide a ground path for any mismatch current between the first current and second current. A response of the tissue to the current stimulus is measured via at least one measurement electrode.

Owner:SALUDA MEDICAL PTY LTD

Method and System for Controlling Electrical Conditions of Tissue

ActiveUS20150313487A1Reduce artefactReduce interactionElectrotherapySensorsAudio power amplifierImplanted device

An implantable device for controlling electrical conditions of body tissue. A feedback sense electrode and a compensation electrode are positioned proximal to the tissue to make electrical contact with the tissue. A feedback amplifier is referenced to ground, and takes as an input a feedback signal from the feedback sense electrode. The output of the feedback amplifier is connected to the compensation electrode. The feedback amplifier thus drives the neural tissue via the compensation electrode in a feedback arrangement which seeks to drive the feedback signal to ground, or other desired electrical value.

Owner:SALUDA MEDICAL PTY LTD

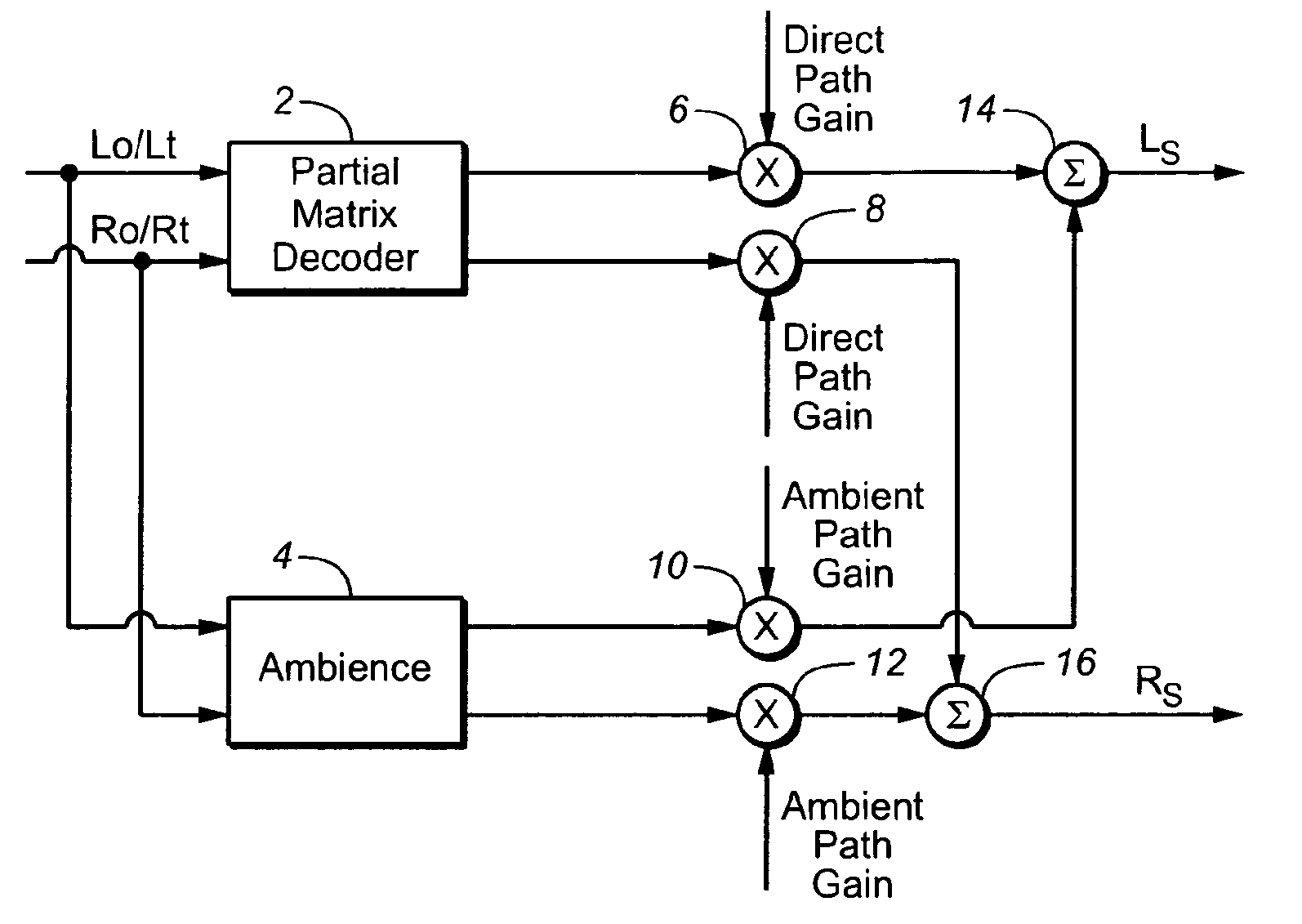

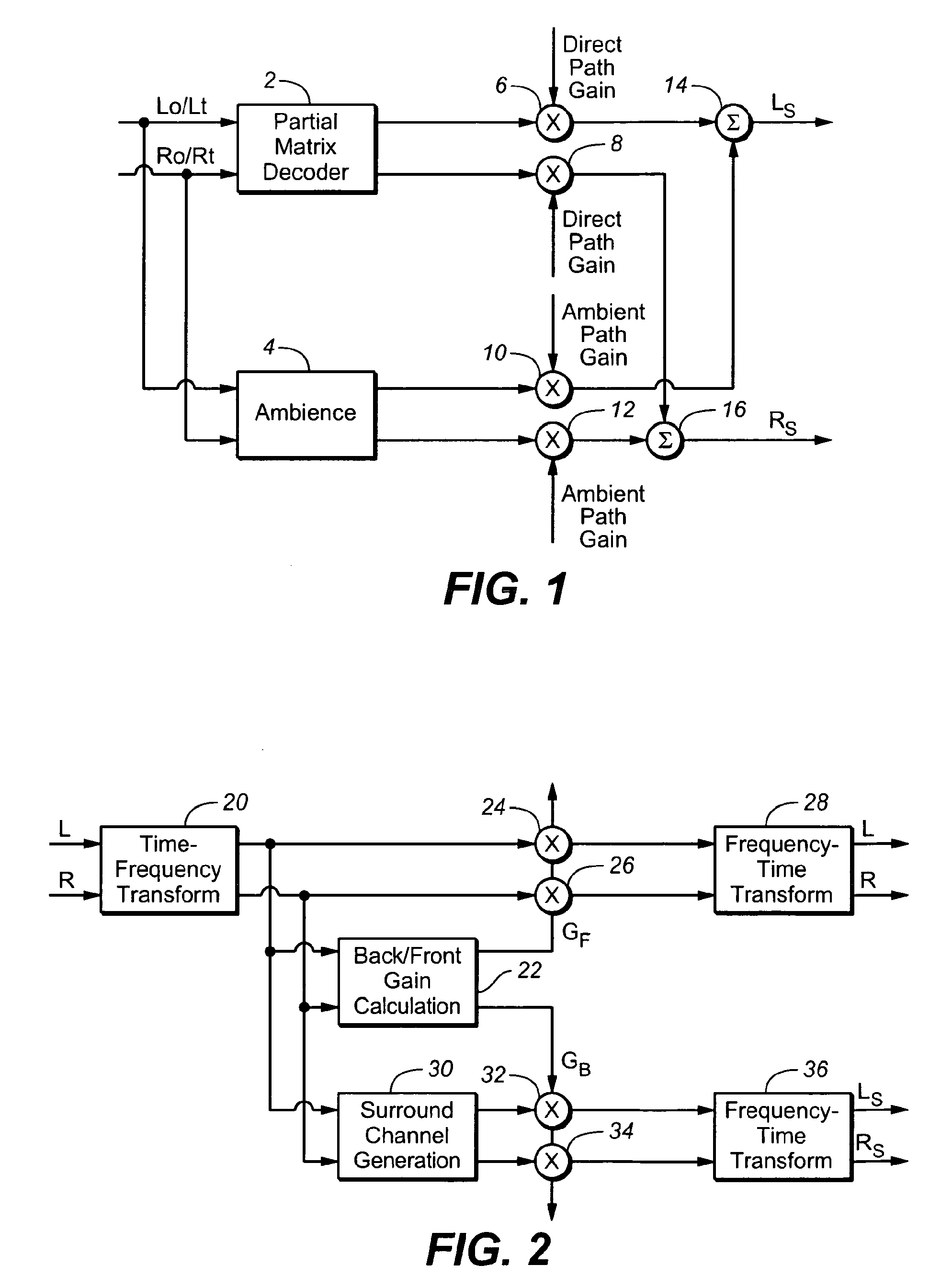

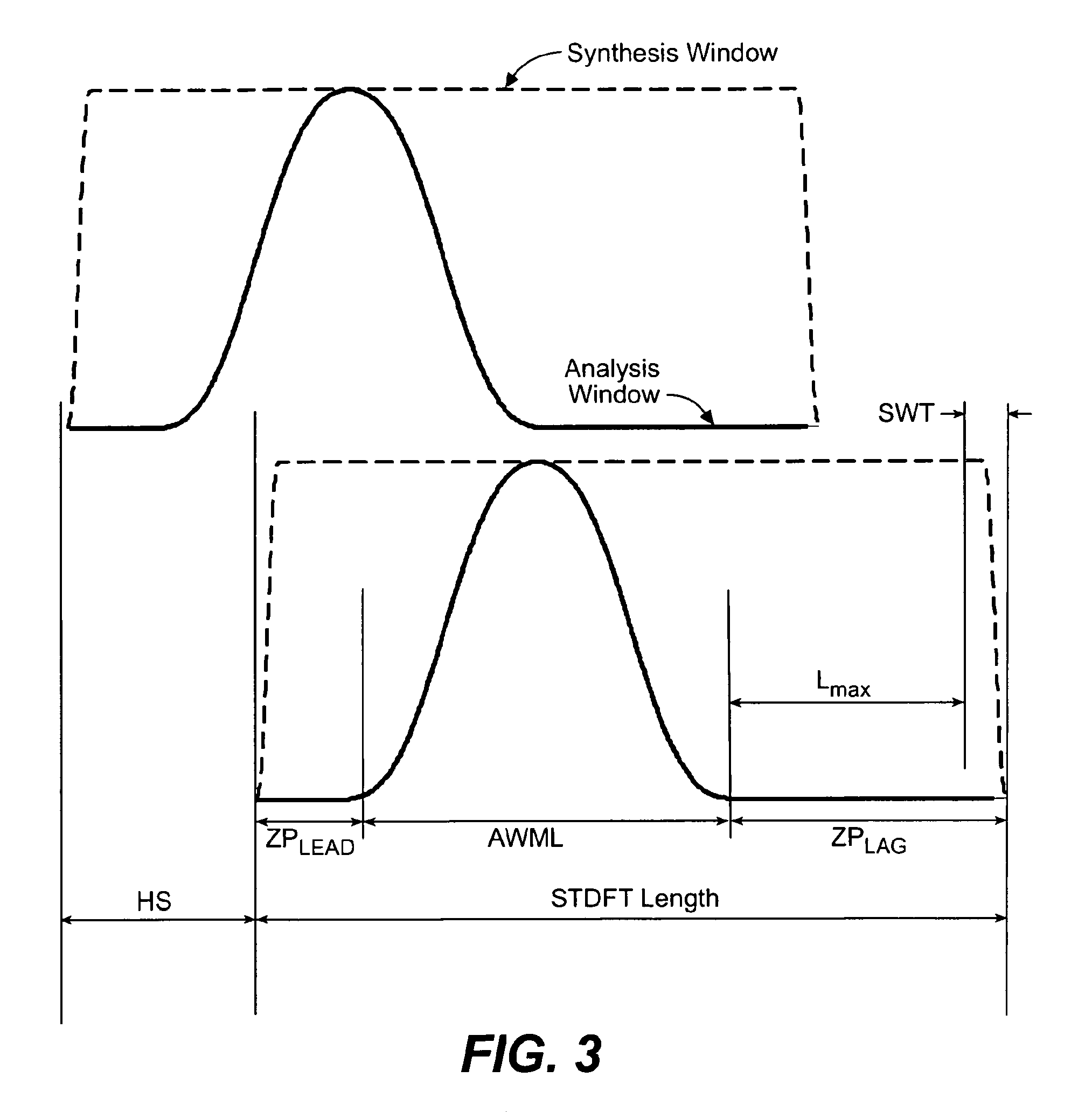

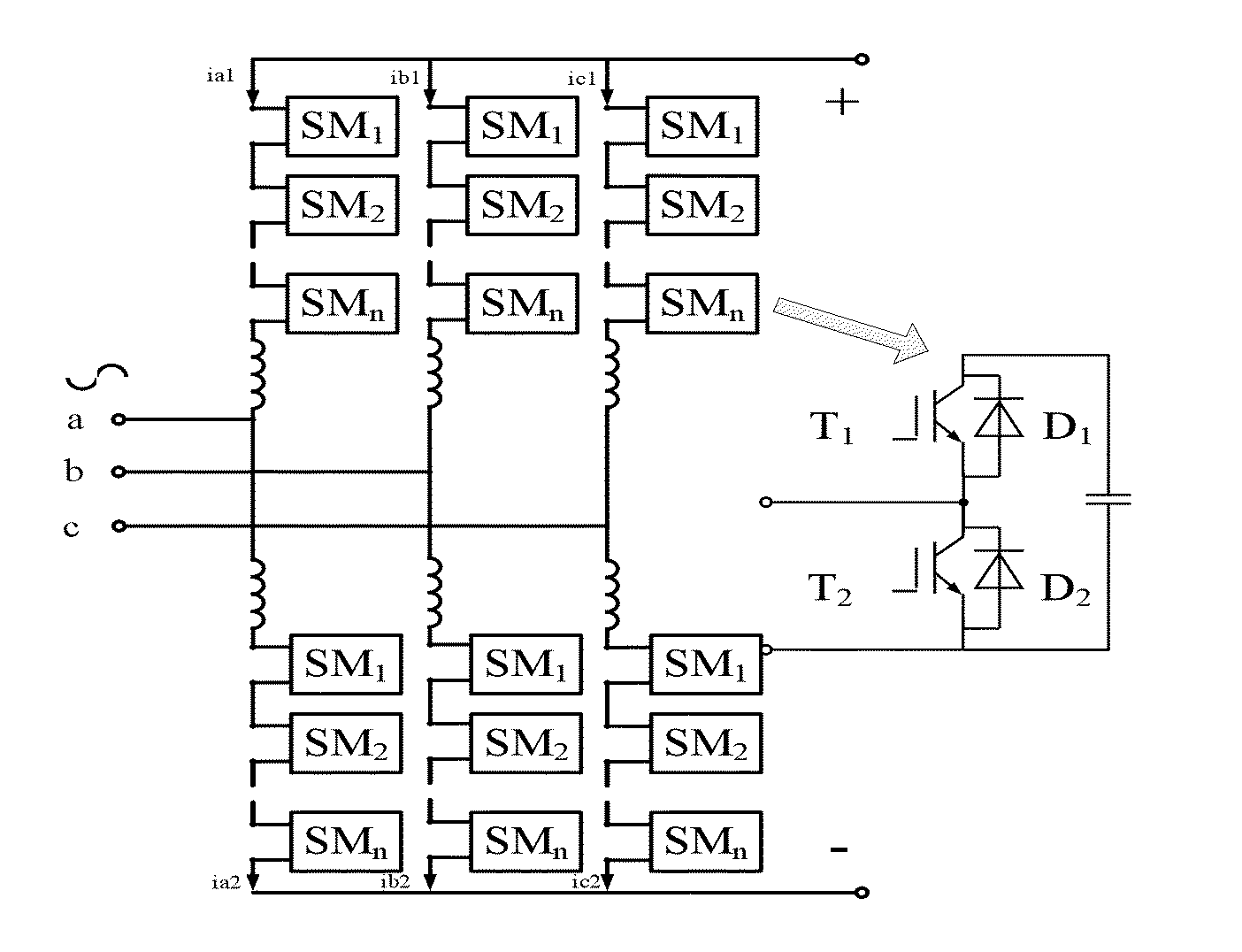

Hybrid Derivation of Surround Sound Audio Channels By Controllably Combining Ambience and Matrix-Decoded Signal Components

InactiveUS20100177903A1Avoid switchingIncrease widthSpeech analysisTwo-channel systemsCorrelation filterDecorrelation

Ambience signal components are obtained from source audio signals, matrix-decoded signal components are obtained from the source audio signals, and the ambience signal components are controllably combined with the matrix-decoded signal components. Obtaining ambience signal components may include applying at least one decorrelation filter sequence. The same decorrelation filter sequence may be applied to each of the input audio signals or, alternatively, a different decorrelation filter sequence may be applied to each of the input audio signals.

Owner:DOLBY LAB LICENSING CORP

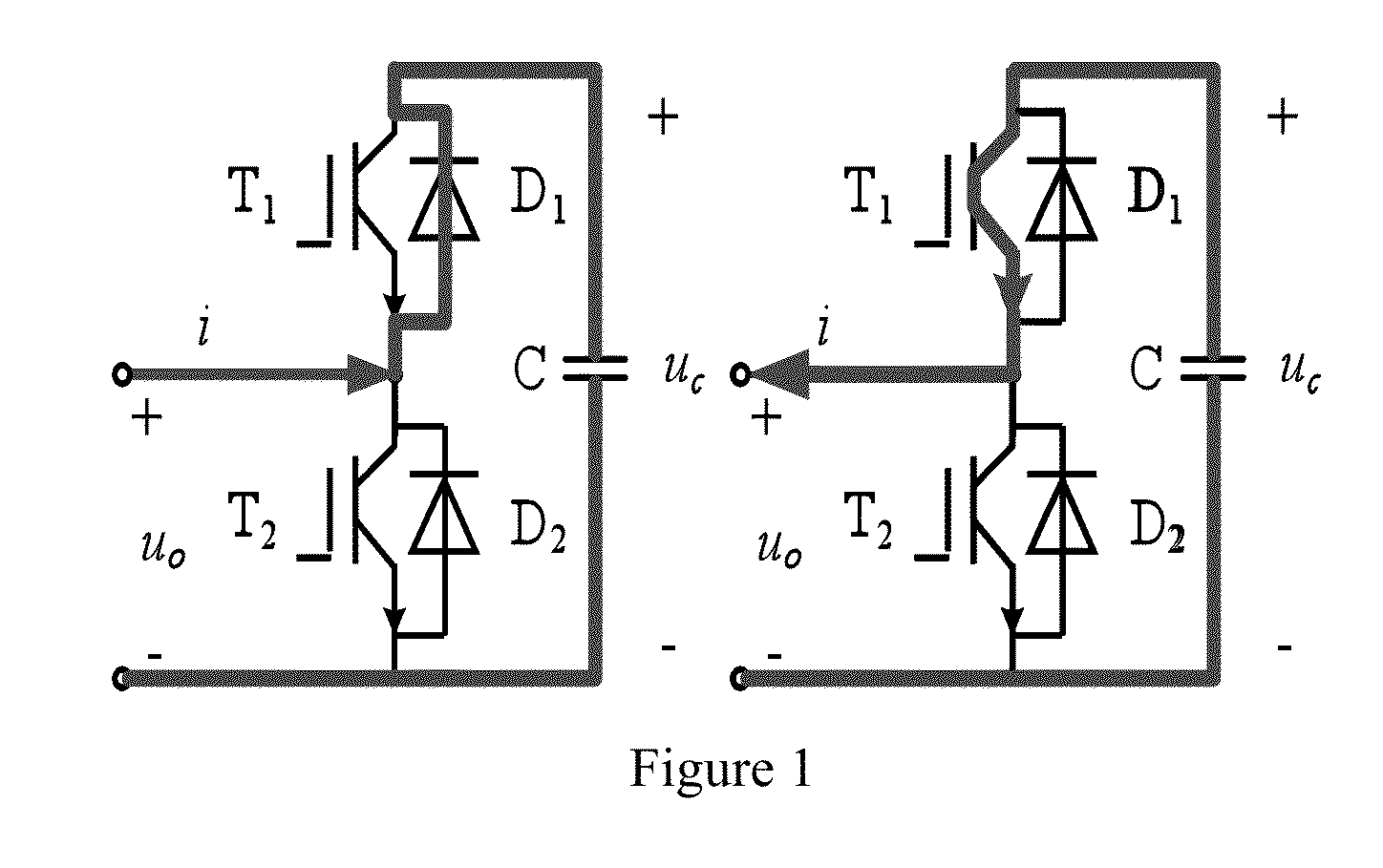

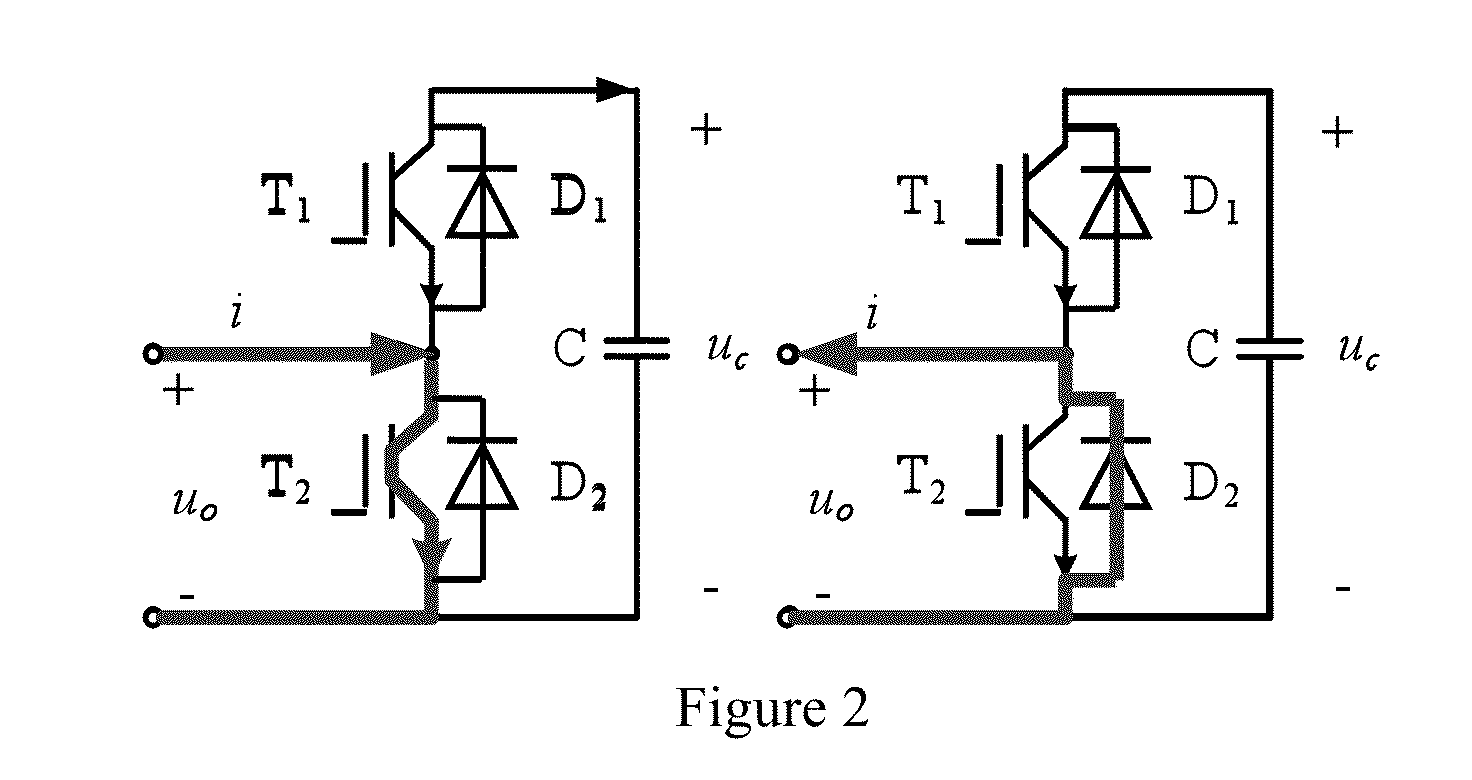

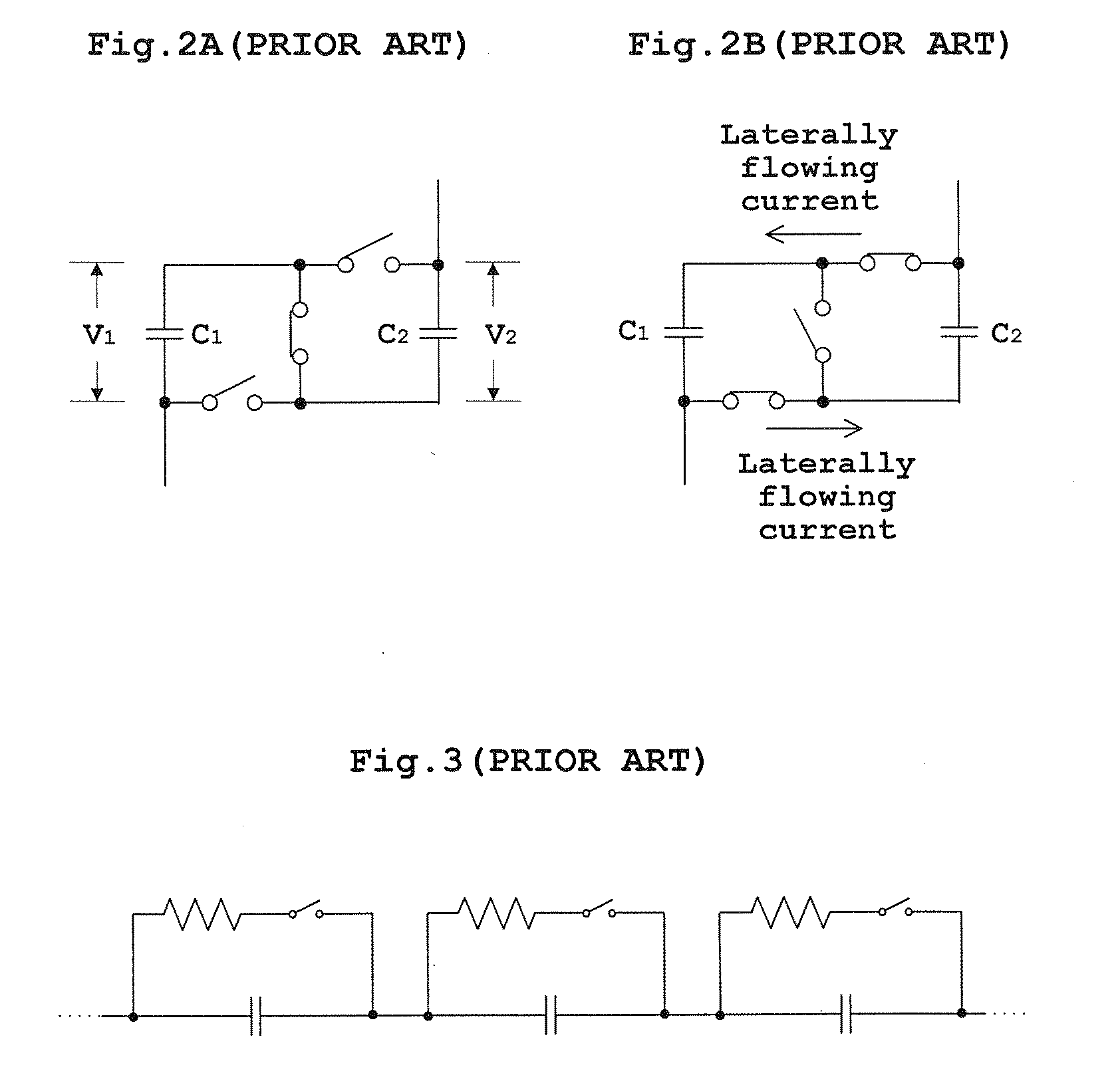

Voltage balancing control method for modular multilevel converter

InactiveUS20140002048A1Reduce switching frequencyAvoid switchingAc-dc conversionElectric variable regulationHigh voltage igbtCapacitor voltage

The present invention relates to Voltage balancing control method for modular multilevel converter is characterized that, it includes some steps as follows:1) Determine the leg current direction is positive or negative;2) Find out the highest sub module on output state whose capacitor voltage amplitude is the maximum, and find out that on bypass state whose capacitor voltage amplitude is the minimum;3) Determine whether the sub module inputs or bypass operation; this method avoided switching arbitrariness of the sub module, and decreased the switching frequency of the sub module. The capacitor voltage balancing control of the sub module proposed by the method is more suitable to be applied in the field of high voltage and large capacity converter that has large numbers of sub modules.

Owner:CHINA ELECTRIC POWER RES INST

Scheduling the dispatch of cells in non-empty virtual output queues of multistage switches using a pipelined hierarchical arbitration scheme

InactiveUS20030021266A1Improve throughputMinimize timeData switching by path configurationCircuit switching systemsDistributed computingVirtual Output Queues

Owner:POLYTECHNIC INST OF NEW YORK

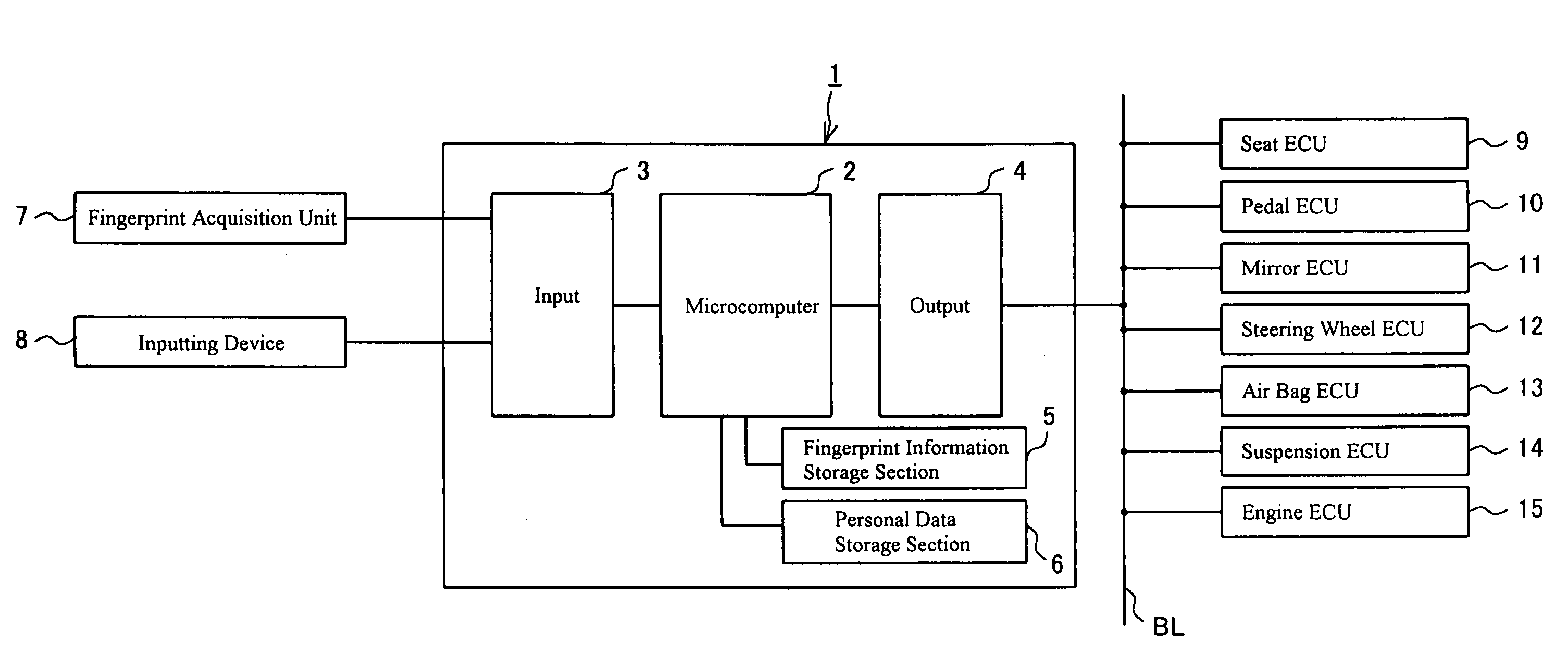

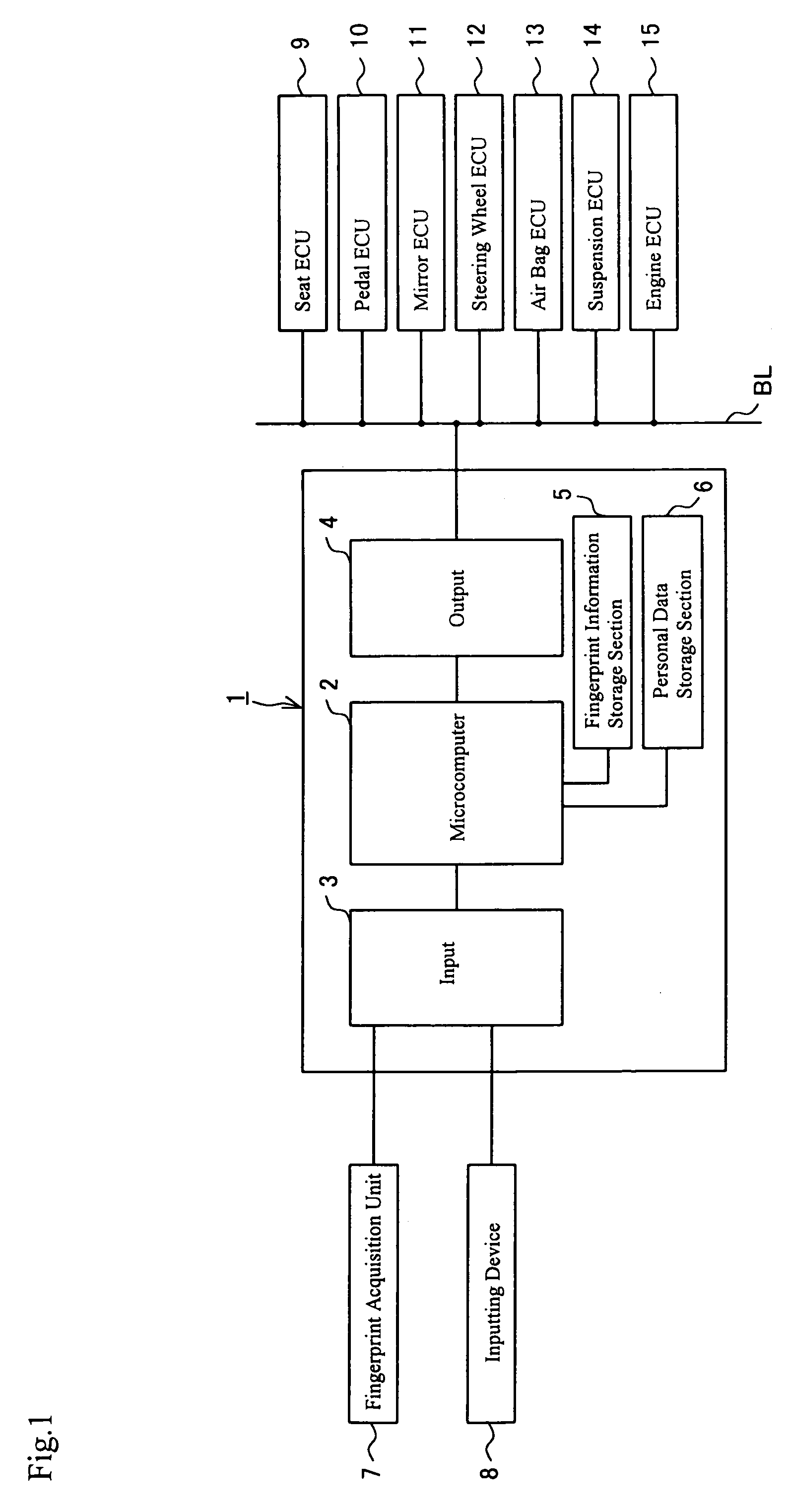

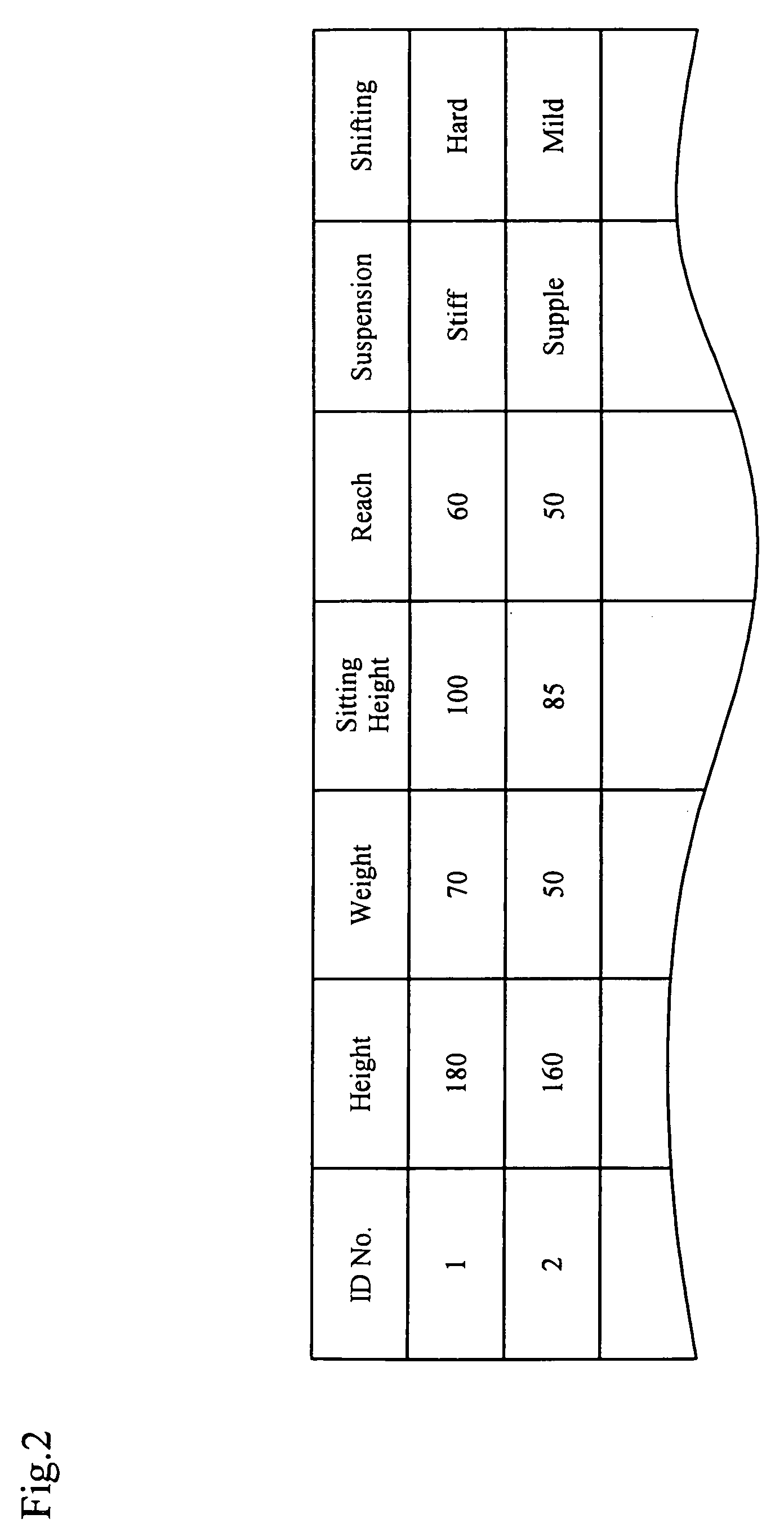

Vehicle environment control device

InactiveUS7228213B2Operation is notAvoid switchingVehicle fittingsDigital data processing detailsDriver/operatorFingerprint

A vehicle environment control device for recognizing and controlling the state of vehicle-associated equipment and a vehicle environment has a personal data storage section for storing user's personal data associated with users of the vehicle M, a fingerprint information storage section for storing information about fingerprints of authorized users thereof, a section for identifying a user based on fingerprint information, a section for reading personal data (such as a physique) of the identified user thereof from the personal data storage section and a section for setting the vehicle M to be an environment suitable for the user (such as setting a seat position) based on the read personal data, resulting in improved convenience of a driver or occupants in using a vehicle.

Owner:FUJITSU GENERAL LTD

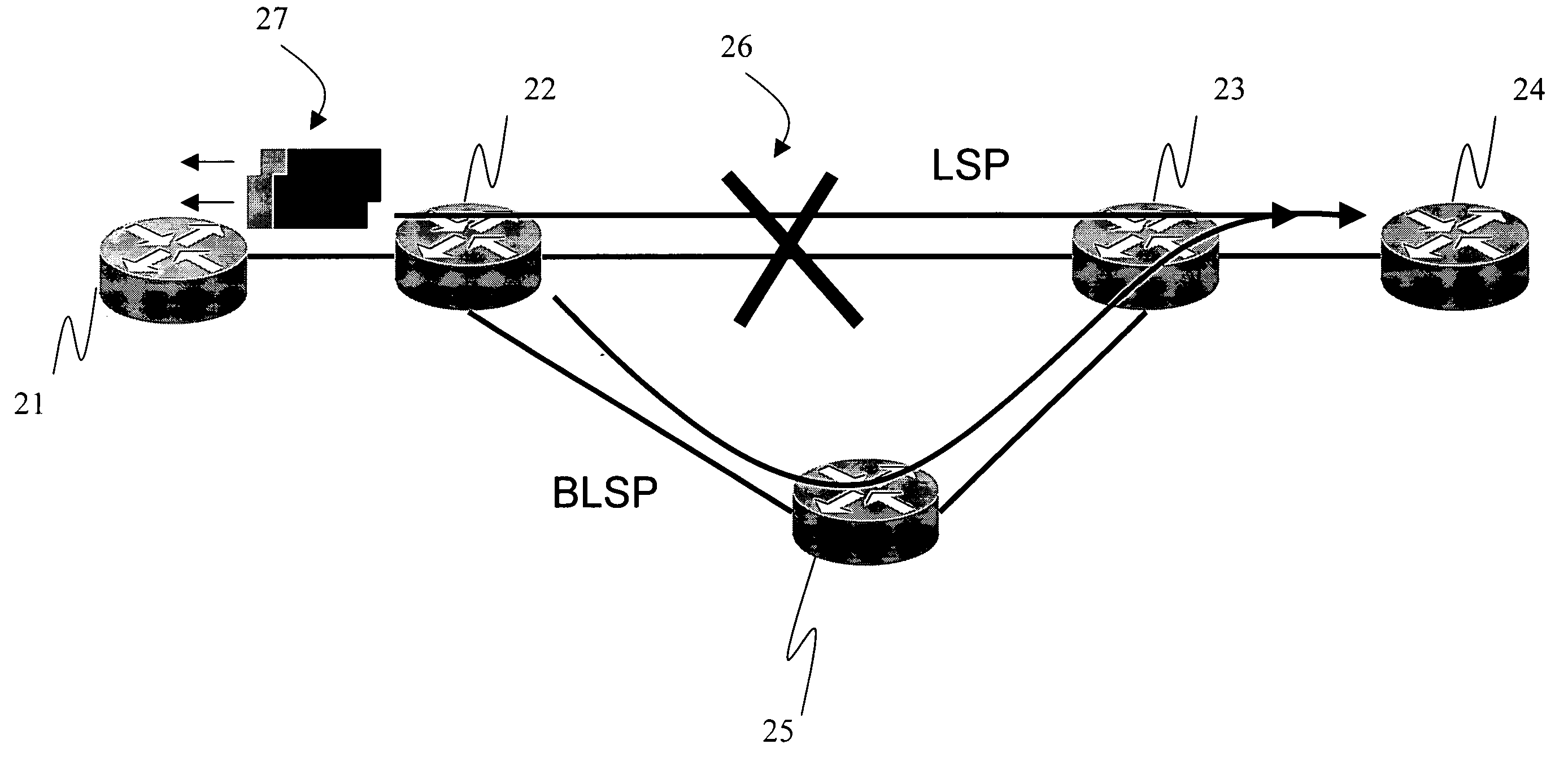

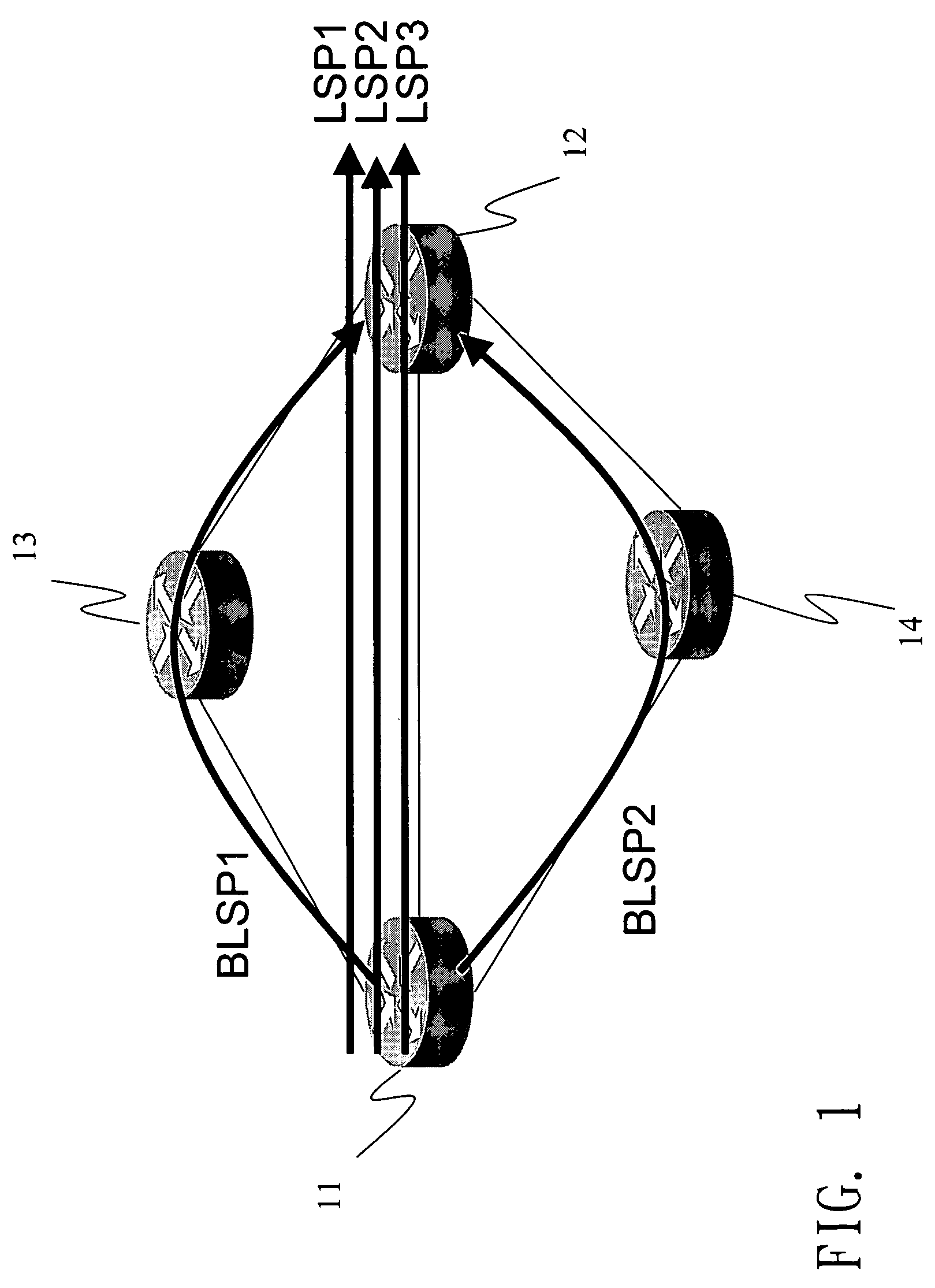

Method for MPLS link protection

InactiveUS20050152269A1Improve bandwidth utilizationShort service interrupted timeLaser detailsError preventionReal-time computingBackup

A method for MPLS link protection pre-builds backup LSP. When the LSP breaks down, it can redirect the LSP to the backup LSP within the minimal time and rearrange an auxiliary LSP after breaking down for a default time. By the guiding and the rearrangement, the method prevents the service of the MPLS from being unavailable when the MPLS breaks down and optimizes the utilization of the MPLS resources.

Owner:IND TECH RES INST

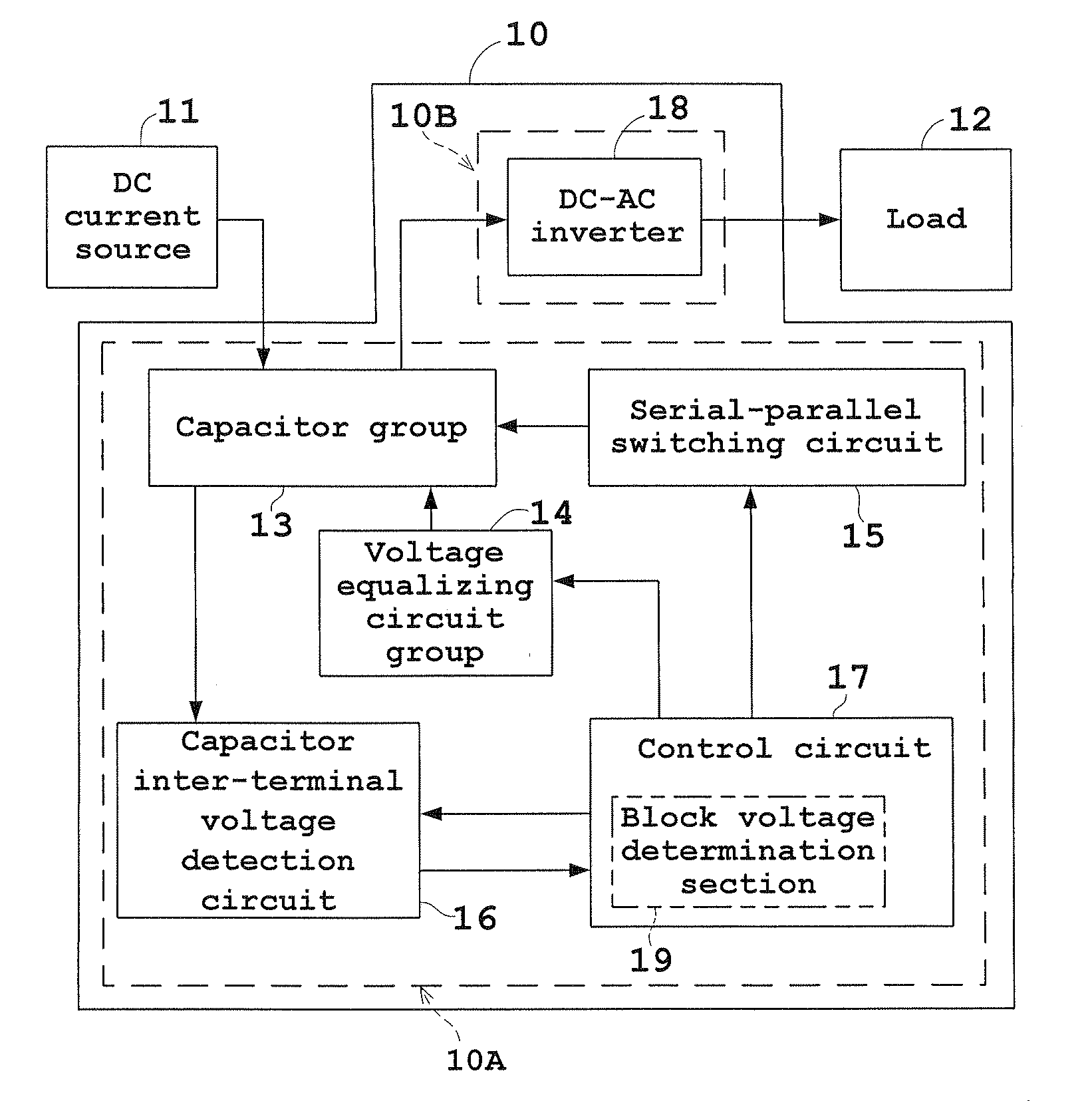

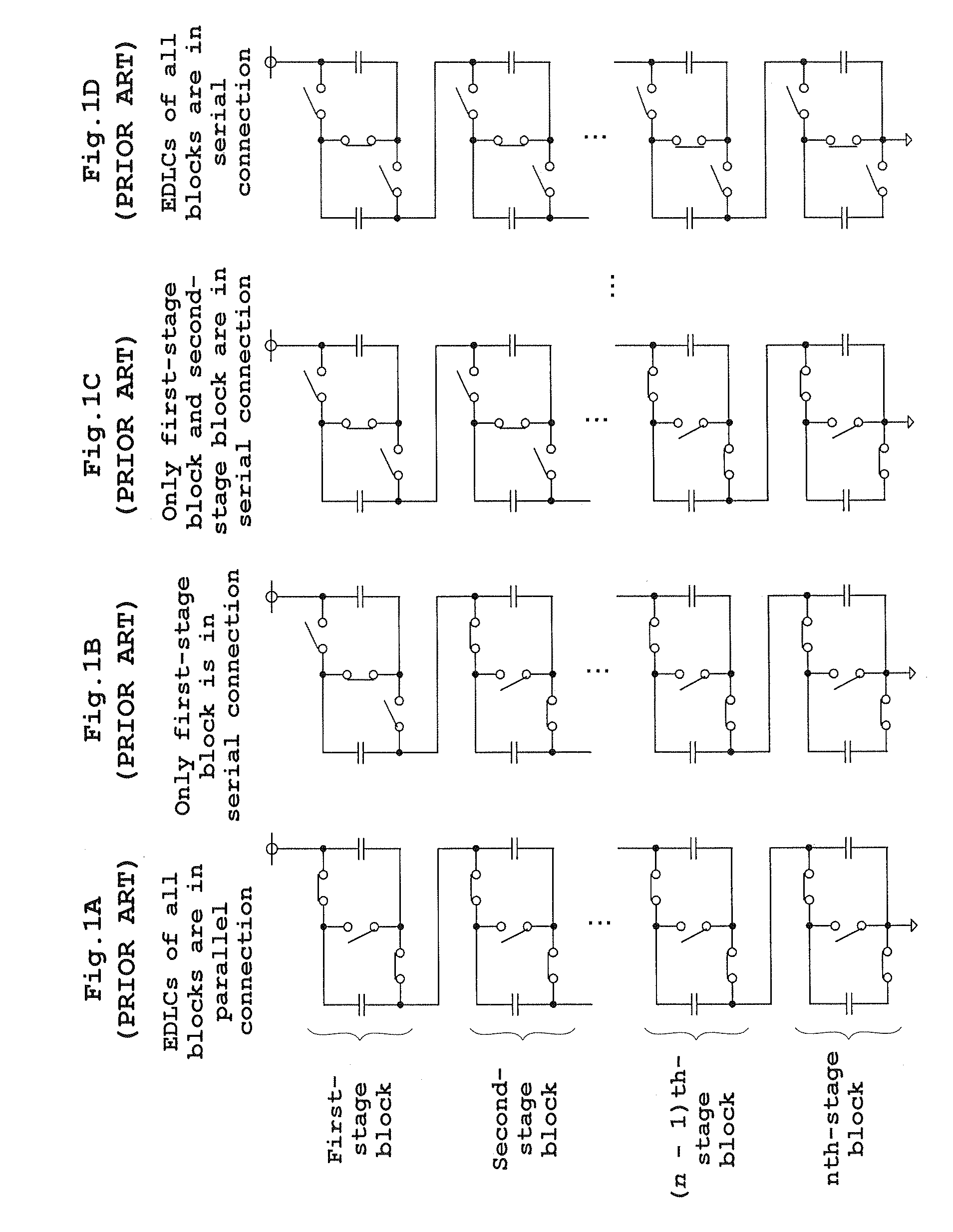

Electric power storage system using capacitors and control method thereof

InactiveUS20090134851A1High voltageSignificantly affecting the charging/discharging characteristicsHybrid capacitorsParallel/serial switchingDischarge efficiencyElectricity

In an electric power storage system according to the present invention, in the case of charging, a plurality of capacitors of each circuit block of the electric power storage system are switched to a serial connection to initiate the charging. When the output voltage of power storage means reaches the maximum input voltage of DC-AC conversion means, each capacitor of a number j of circuit blocks is switched to a parallel connection in order of higher block voltage. Also up to the time when the maximum input voltage is reached again, each capacitor of a number j of circuit blocks is switched to a parallel connection in order of higher block voltage. In the case of discharging, pluralities of capacitors of each circuit block of the electric power storage system are switched to a parallel connection to initiate the discharging. When the output voltage of power storage means reaches the minimum input voltage of DC-AC conversion means, each capacitor of a number k of circuit blocks is switched to a serial connection in order of higher block voltage. Also up to the time when the minimum input voltage is reached gain, each capacitor of a number k of circuit blocks is switched to a serial connection in order of higher block voltage. Accordingly, the electric power storage system is hardly affected by the capacitance error of the capacitors, and charging / discharging efficiency can be improved.

Owner:LIMITED COMPANY TM

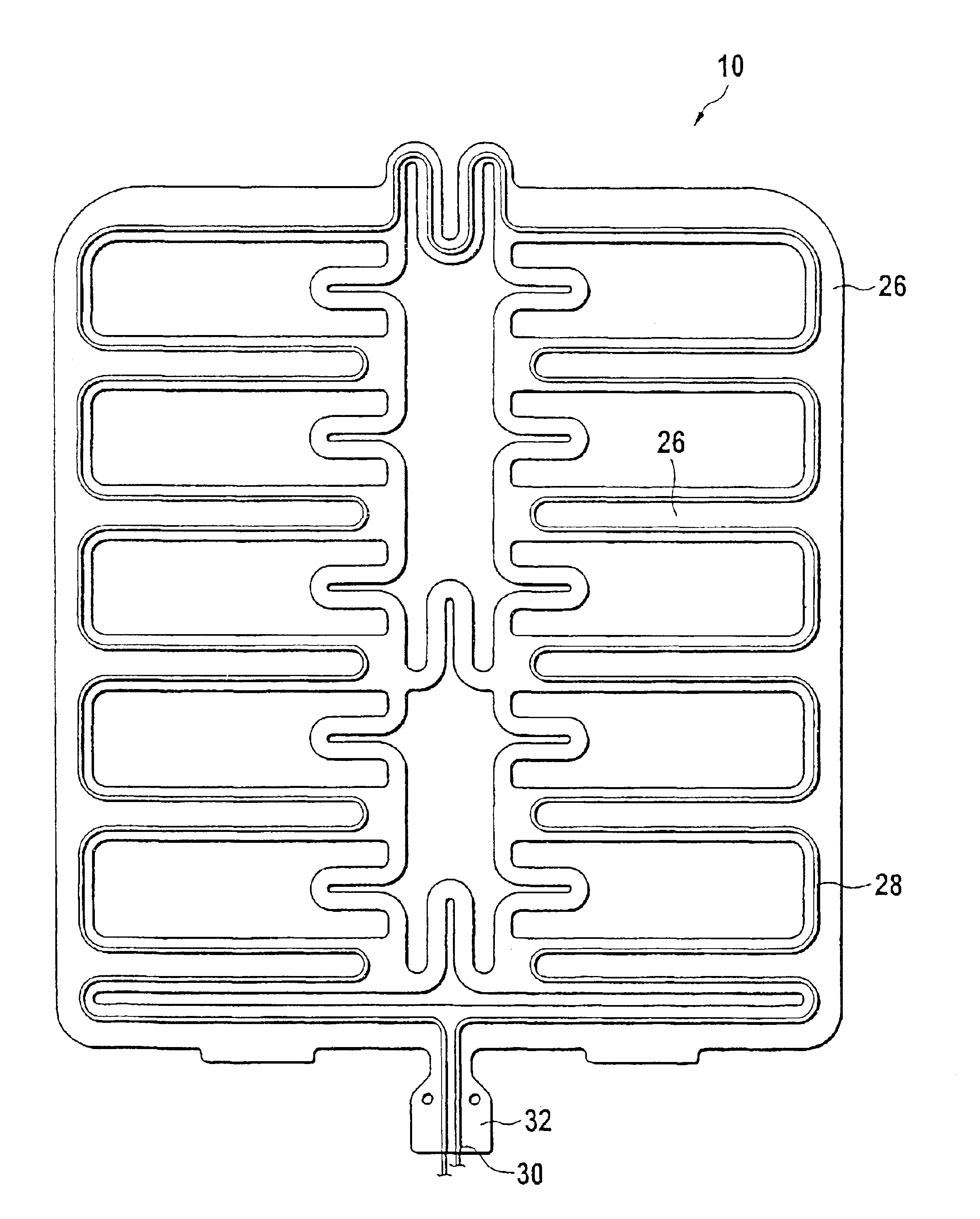

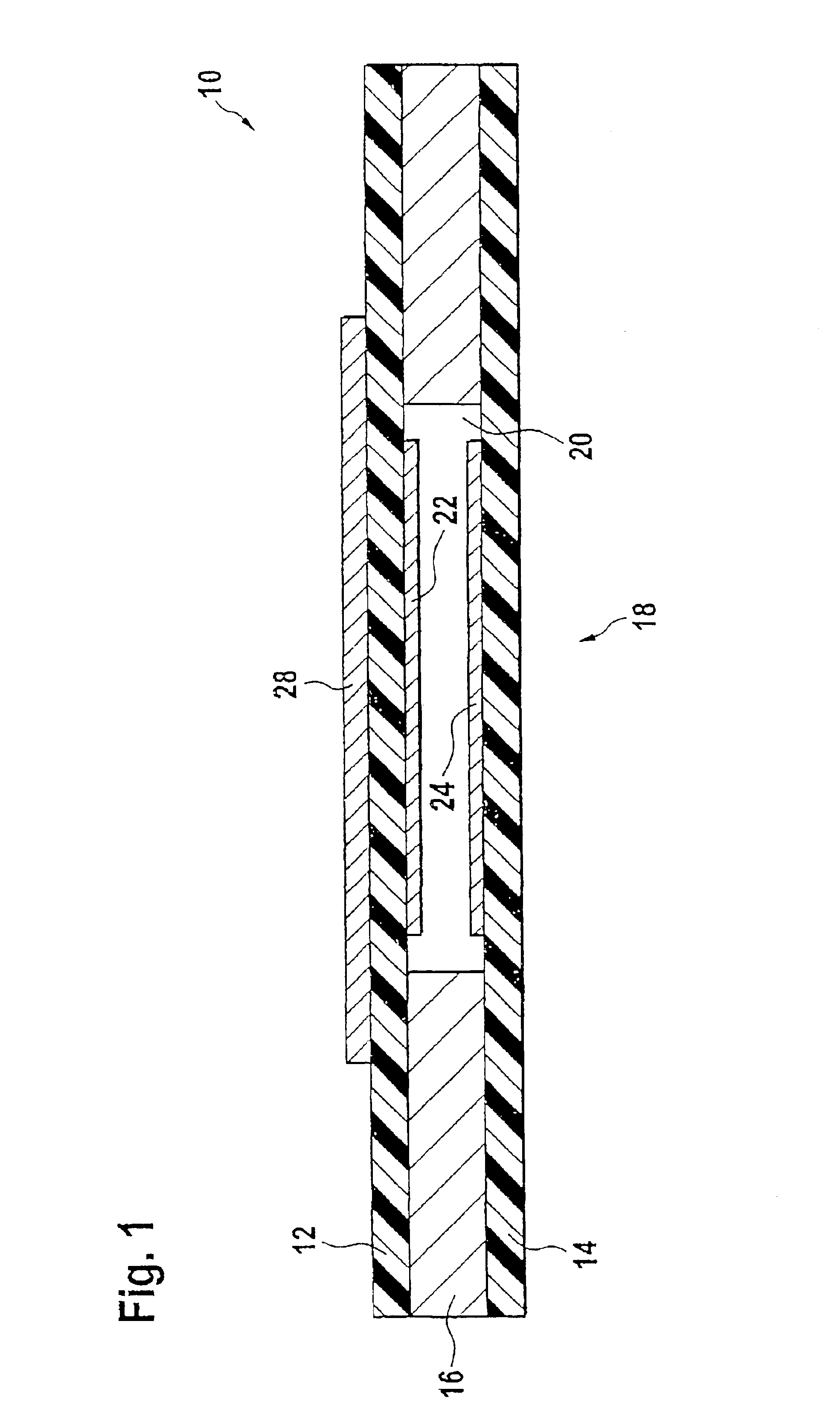

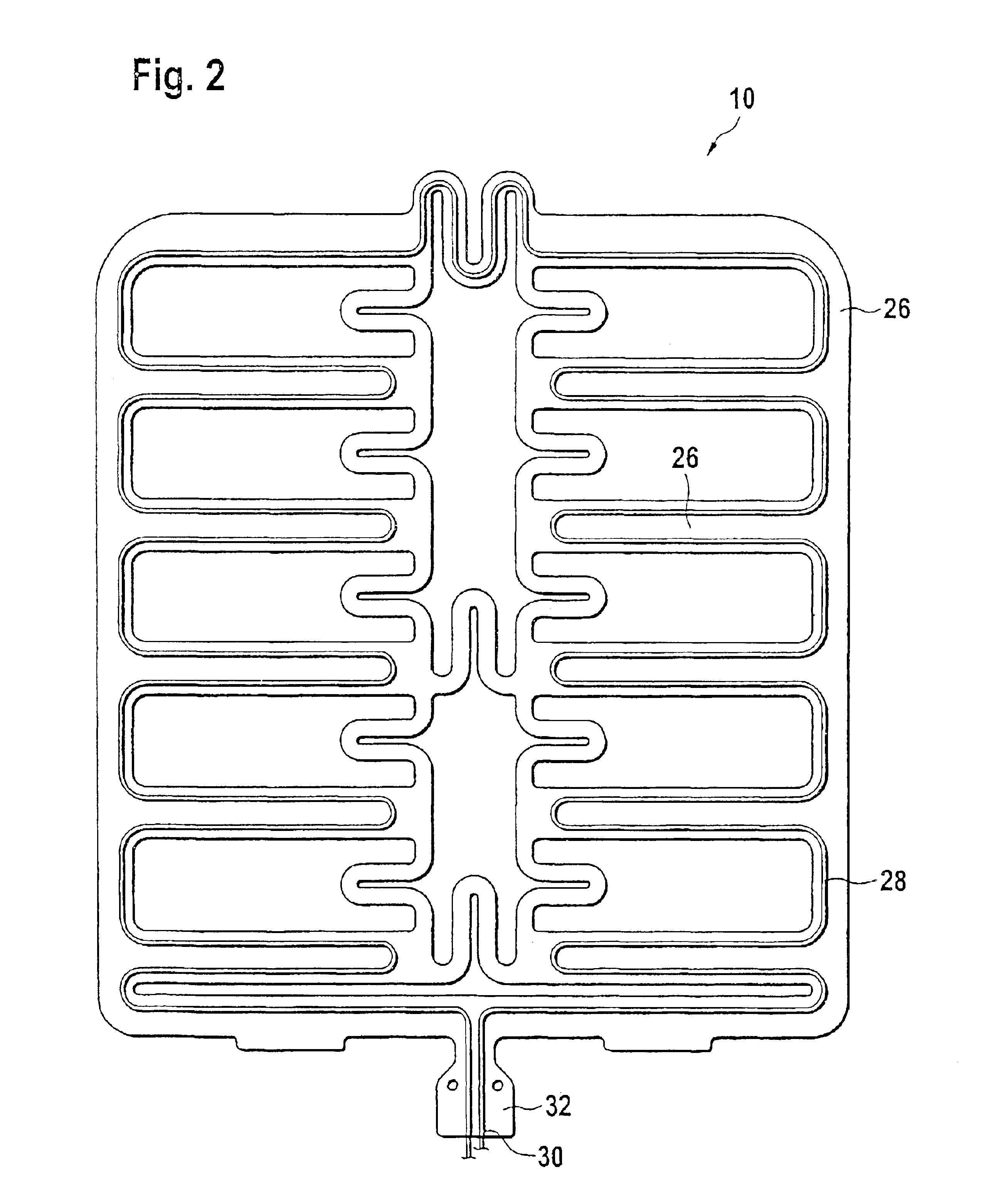

Combined sensor and heating element

InactiveUS6906293B2High electric resistanceFacilitate assemblyStuffed mattressesSpring mattressesHeating elementElectrical conductor

A combined sensor arid heating element includes a sensor mat having several active regions interconnected by flexible connection strips. The flexible connection strips each include two carrier foils laminated together having contact arrangements arranged in the active regions at the inside of the carrier foils. Each flexible connection strips further include a heat conductor directly applied to an outer side of one of the carrier foils.

Owner:IEE INT ELECTRONICS & ENG SA

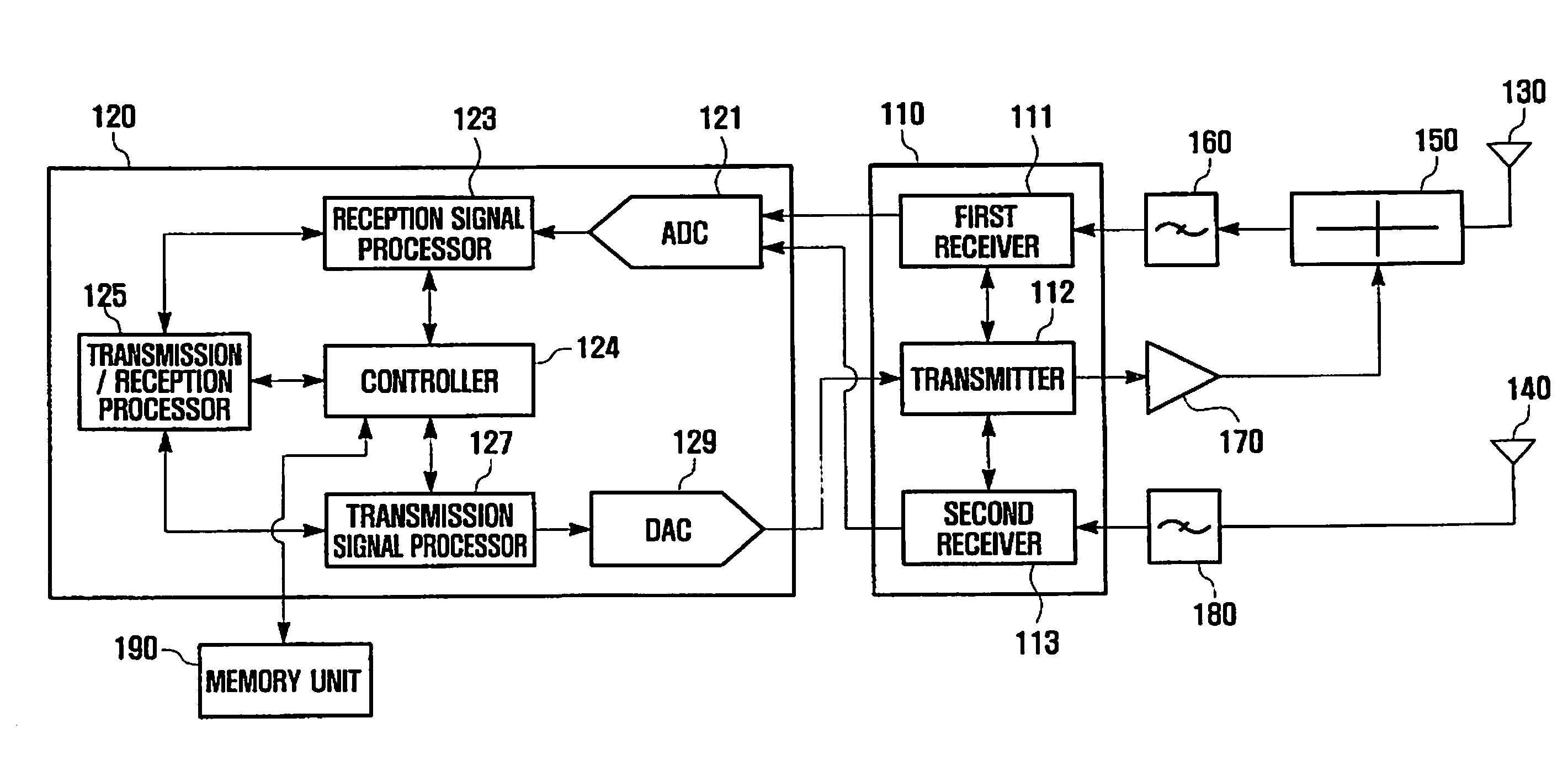

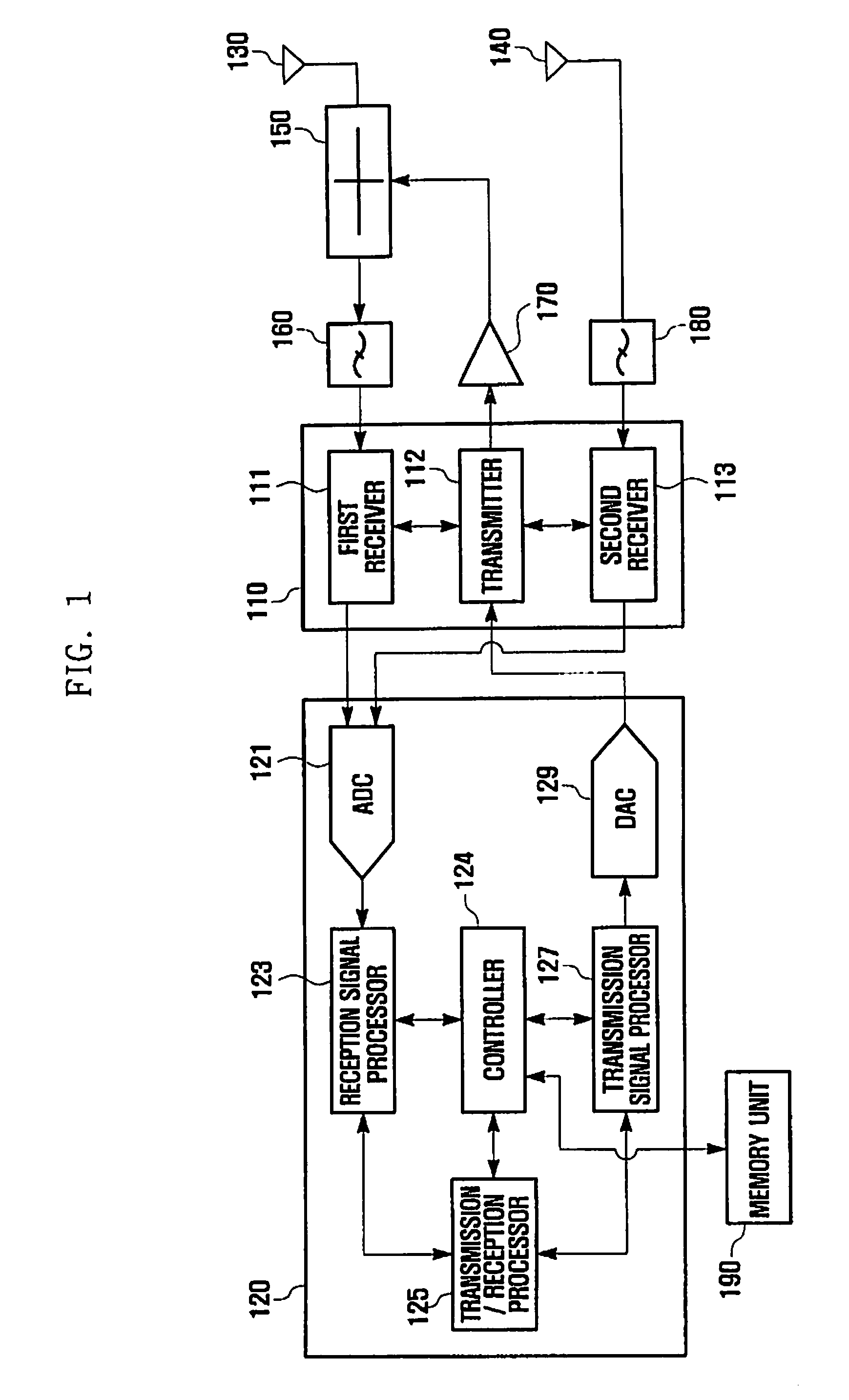

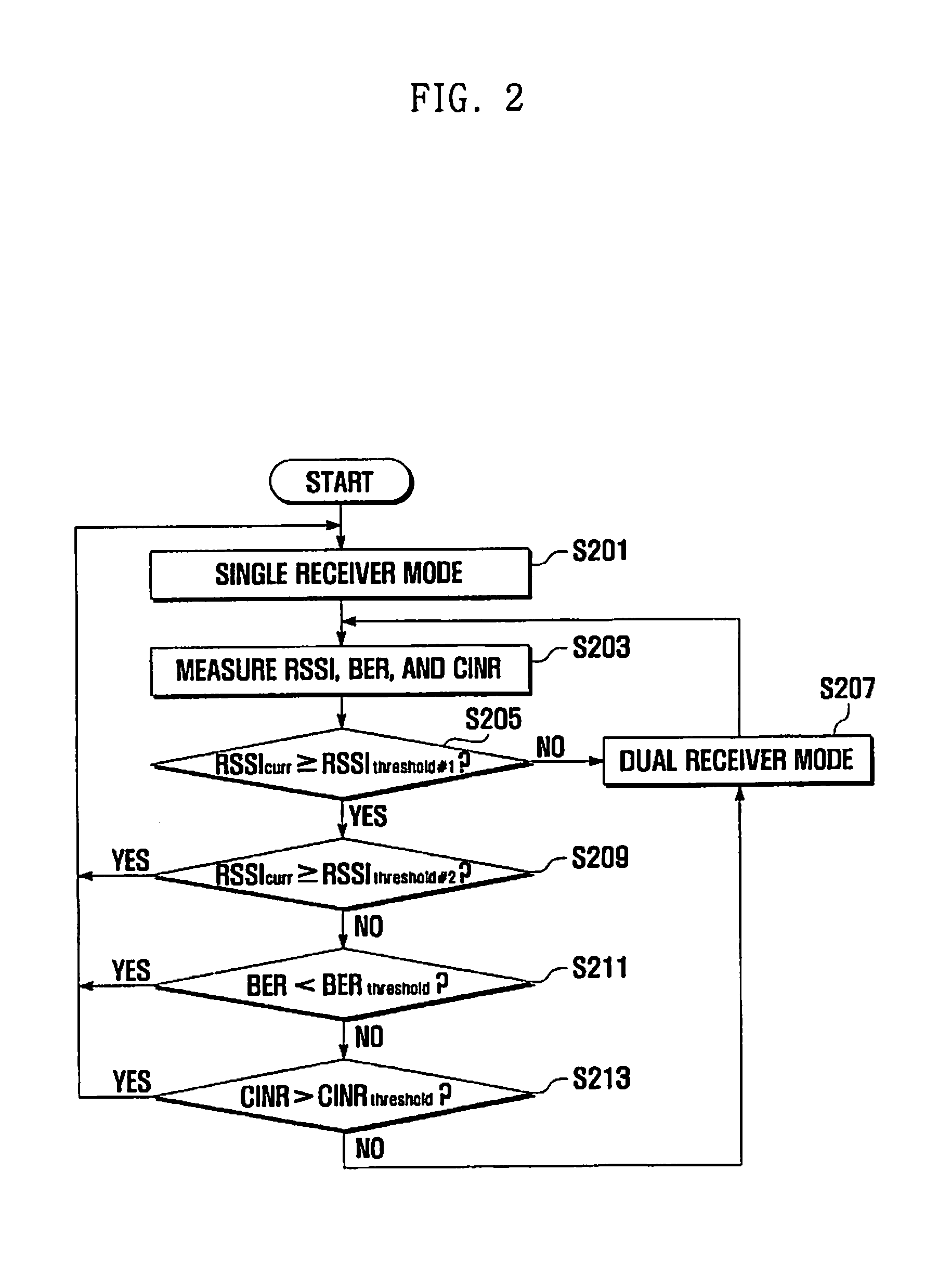

Method for selecting receiver mode of mobile terminal with two receivers

InactiveUS20080090606A1High sensitivityReduce power consumptionPower managementSpatial transmit diversityEngineeringSelf adaptive

Provided is a method for selecting a receiver mode of a mobile terminal having two receivers and that can receive a signal using either or both of the two receivers depending on a channel environment. A method for selecting a receiver mode of a wireless communication terminal having at least two receivers includes computing at least one parameter for determining the receiver mode from a received signal; comparing the at least one parameter with a preset threshold; and selecting one only of a single receiver mode in which either of the two receivers is activated and a dual receiver mode in which both of the receivers are activated according to the comparison result. The method enables a receiver mode to switch between single and dual receiver modes adaptively according to a wireless environment, thus achieving stable signal reception without compromising reception sensitivity.

Owner:SAMSUNG ELECTRONICS CO LTD

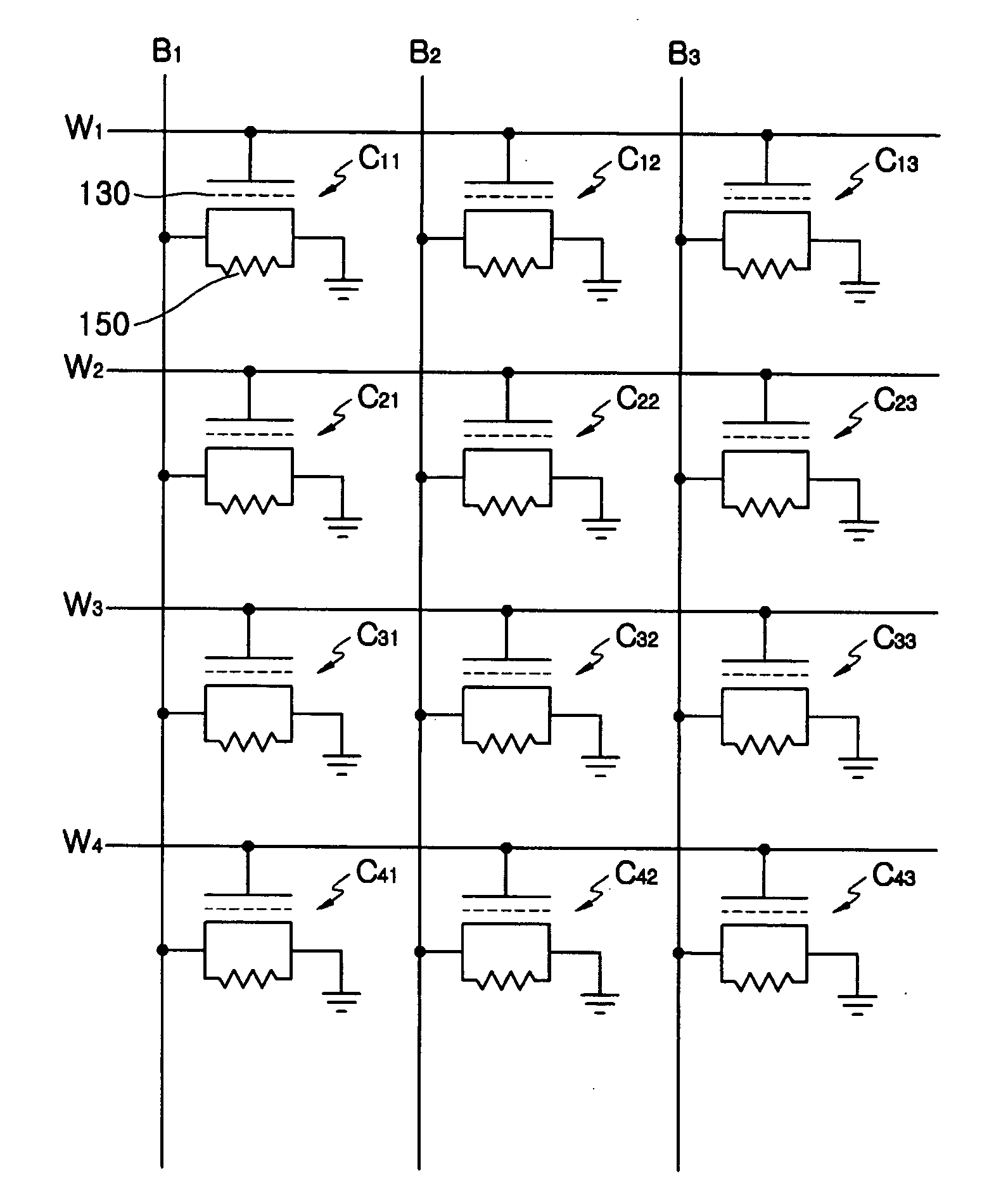

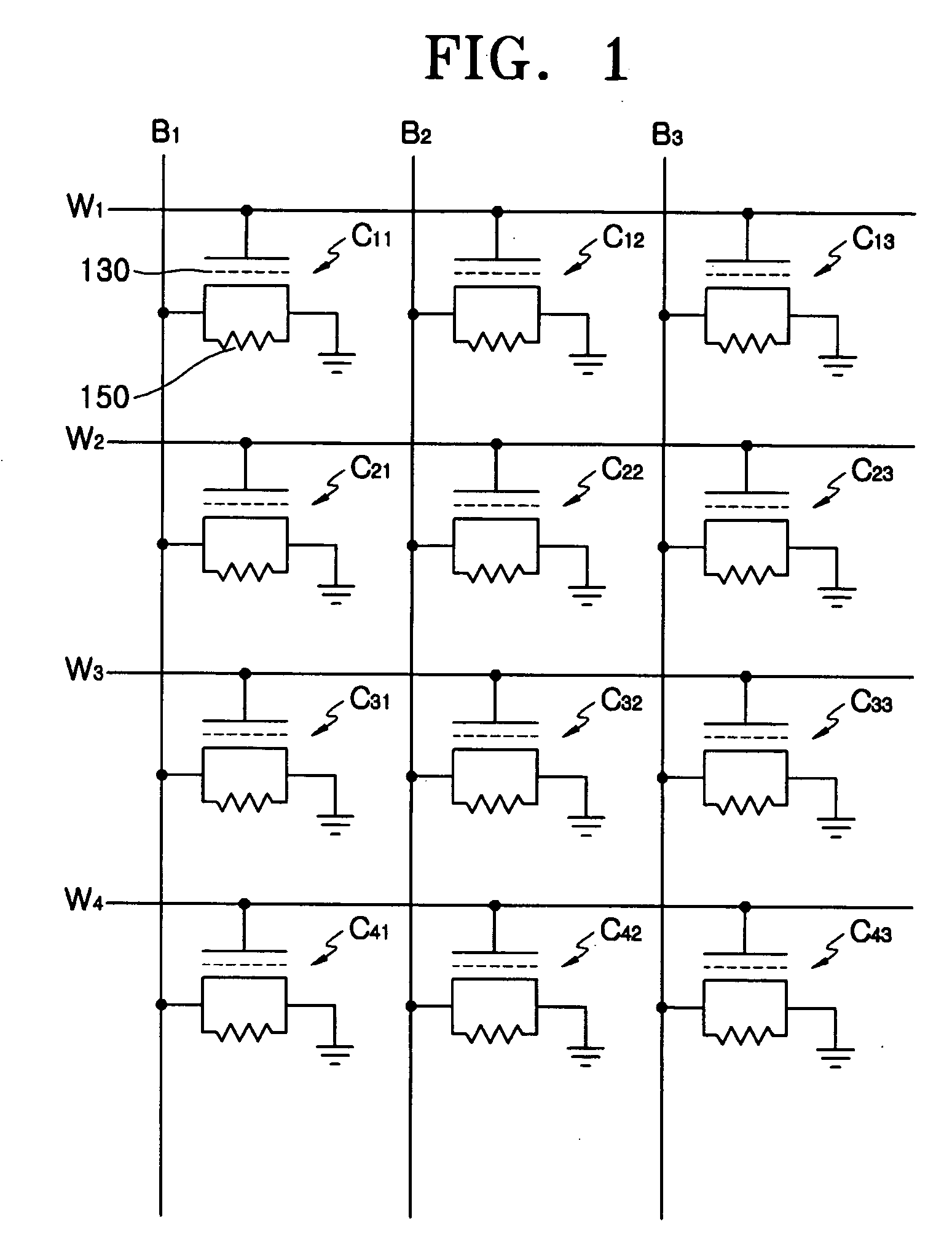

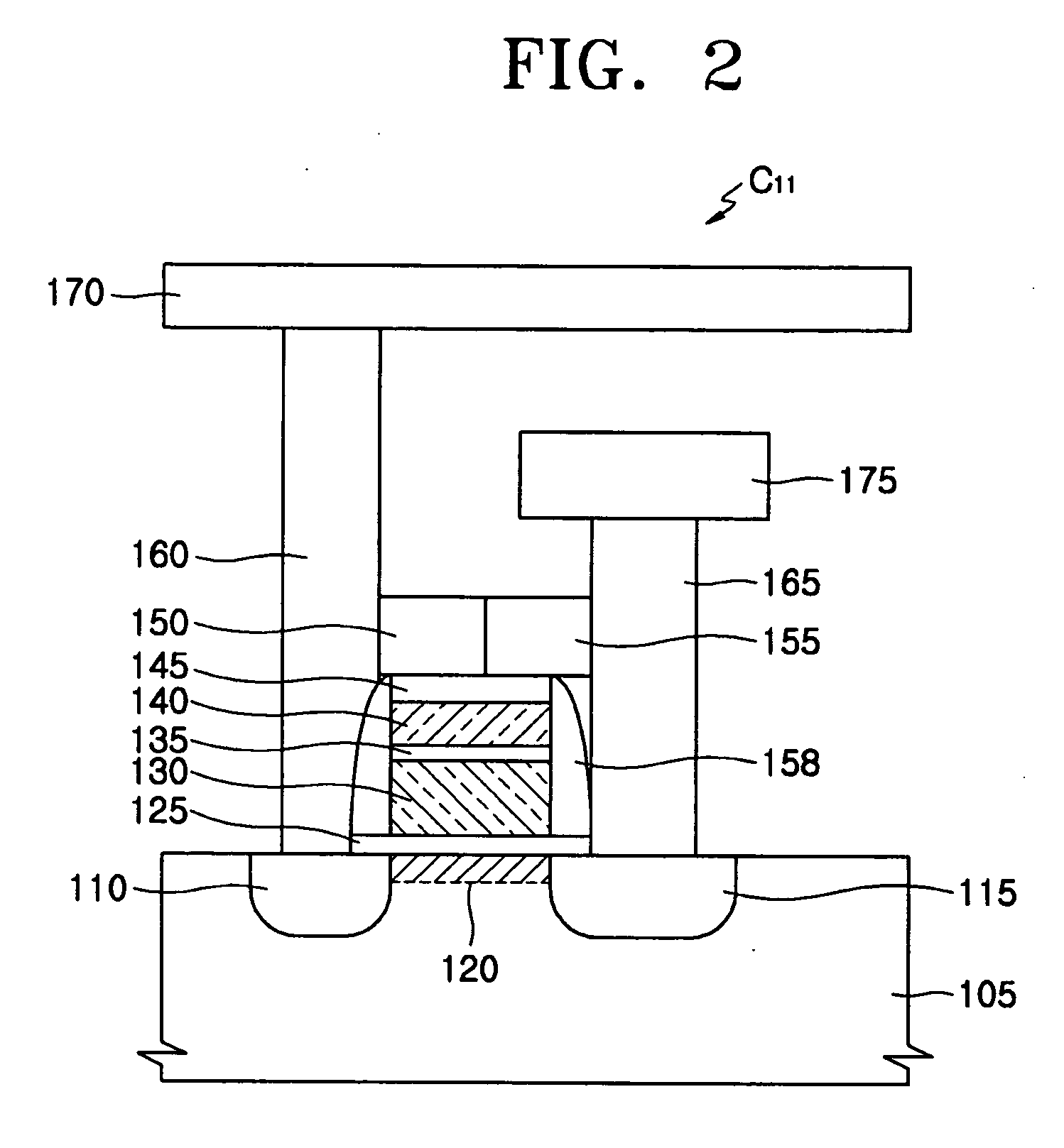

NOR-type hybrid multi-bit non-volatile memory device and method of operating the same

A hybrid multi-bit memory device may include a plurality of unit cells arranged in a matrix of a plurality of rows and columns. Each of the unit cells may include a first memory unit and a second memory unit. The first and second memory unit may share a source and a drain. The first memory unit of each unit cell arranged in each row may be connected to one of a plurality of word lines, and the drain of each unit cell arranged in each column may be connected to one of a plurality of bit lines.

Owner:SAMSUNG ELECTRONICS CO LTD

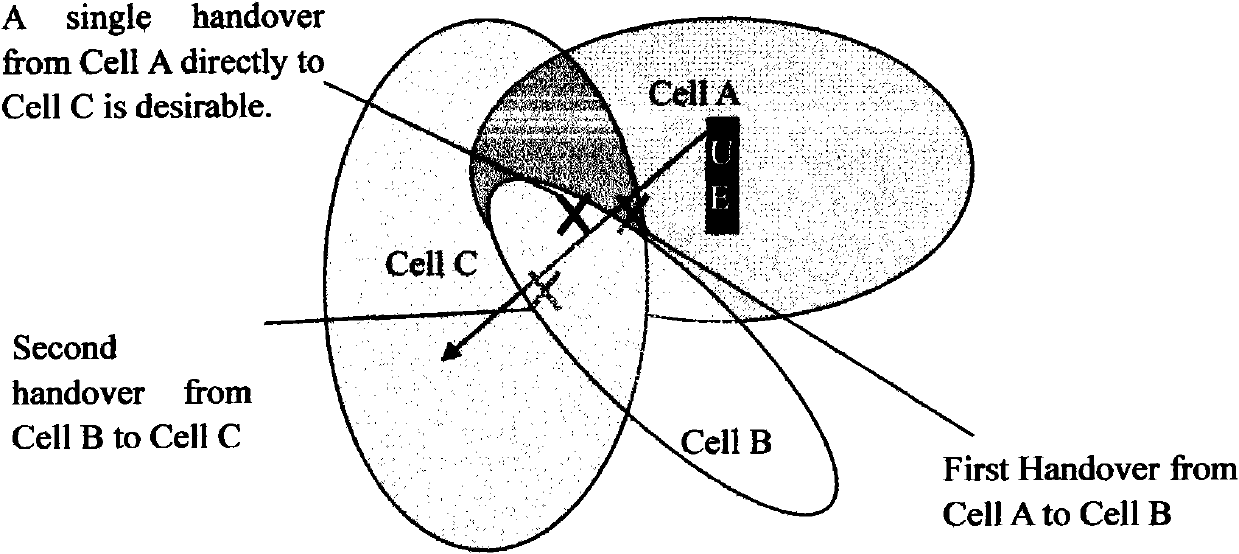

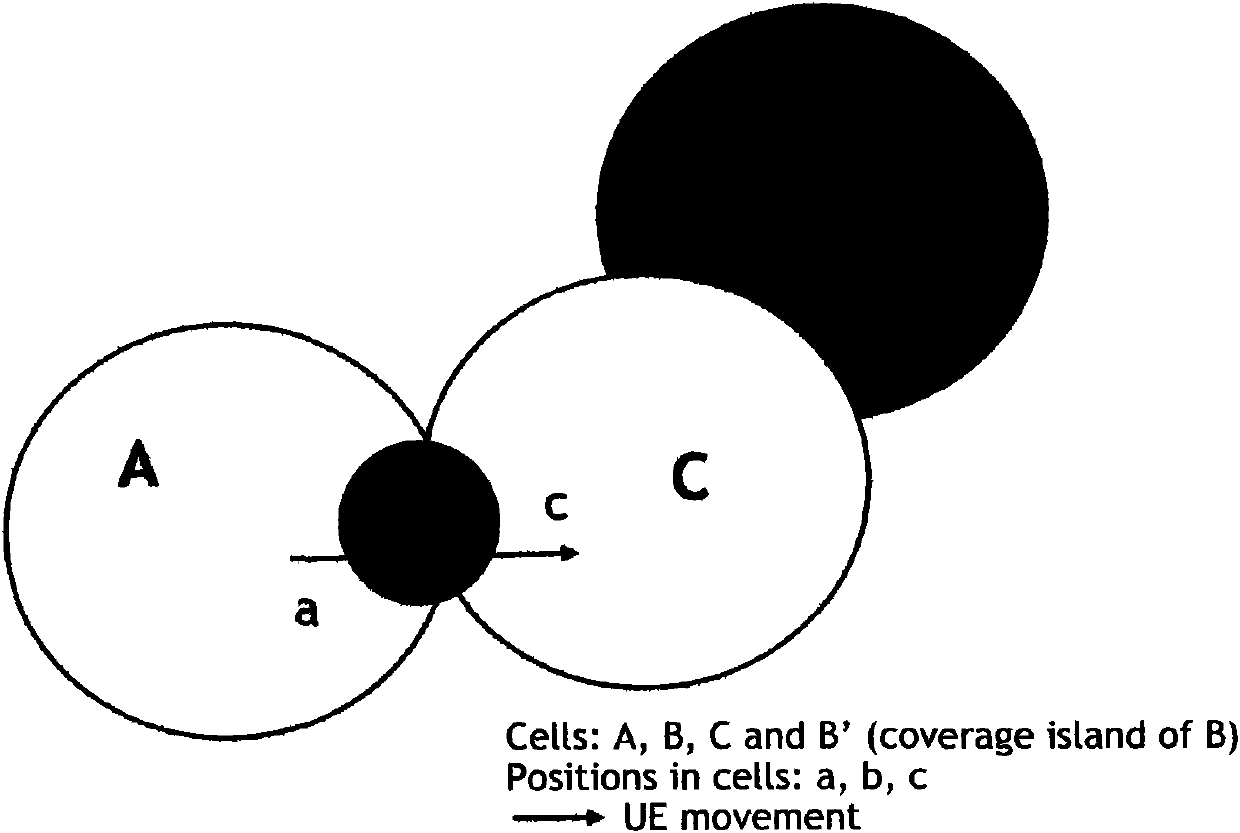

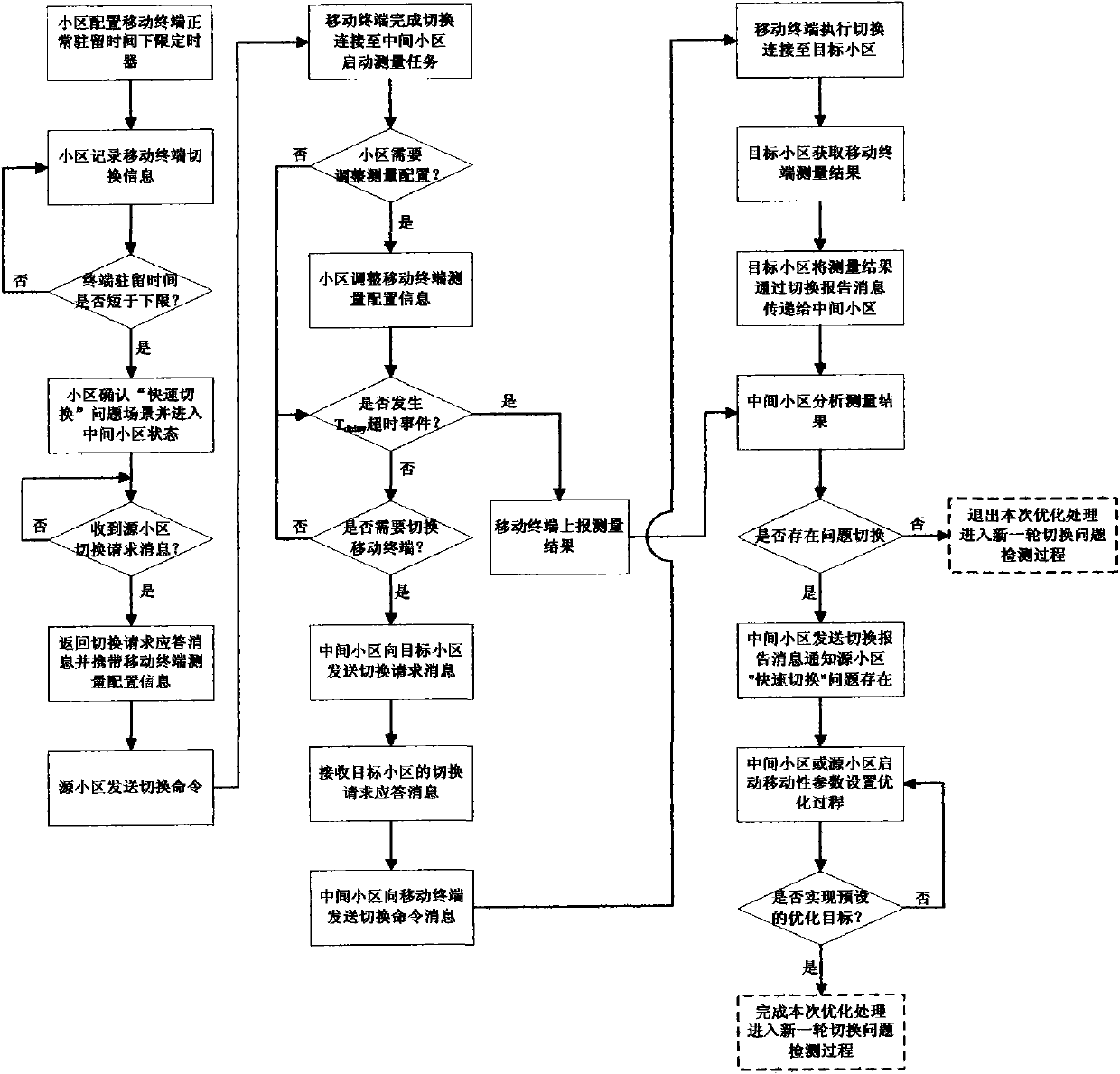

Cooperative measurement and switching setting optimization method among multiple cells in mobile communication network

ActiveCN102026232AImprove performanceIncrease capacityNetwork traffic/resource managementCommunications systemMobile communication systems

The invention provides a cooperative measurement and switching setting optimization method among multiple cells in a mobile communication network. The cooperative measurement and switching setting optimization method requires that the multiple cells positioned on a network side cooperatively control a mobile terminal to complete radio link measurement in specified cell coverage areas, and the specified cell coverage areas are target areas of the multiple cells trying to carry out intercell switching optimization. An intercell cooperative measurement mechanism enables a source cell starting the measurement to acquire a measuring result of the mobile terminal from other cells and assists the source cell to detect the necessity of switching and the reasonability of mobile parameter setting, and if the source cell discovers unnecessary switching exists among cooperative cells or the mobile parameter setting is unreasonable, the source cell can notify information to the cooperative cells so as to trigger the optimization process of the mobile parameter setting; and finally, the multiple cooperative cells can prevent unreasonable switching by modifying parameters, thereby achieving the optimization of the integral mobile function of the mobile communication network and realizing the enhancement of the property and the capacity of a mobile communication system.

Owner:北京万海云科技有限公司