Patents

Literature

148results about How to "Reduce input capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

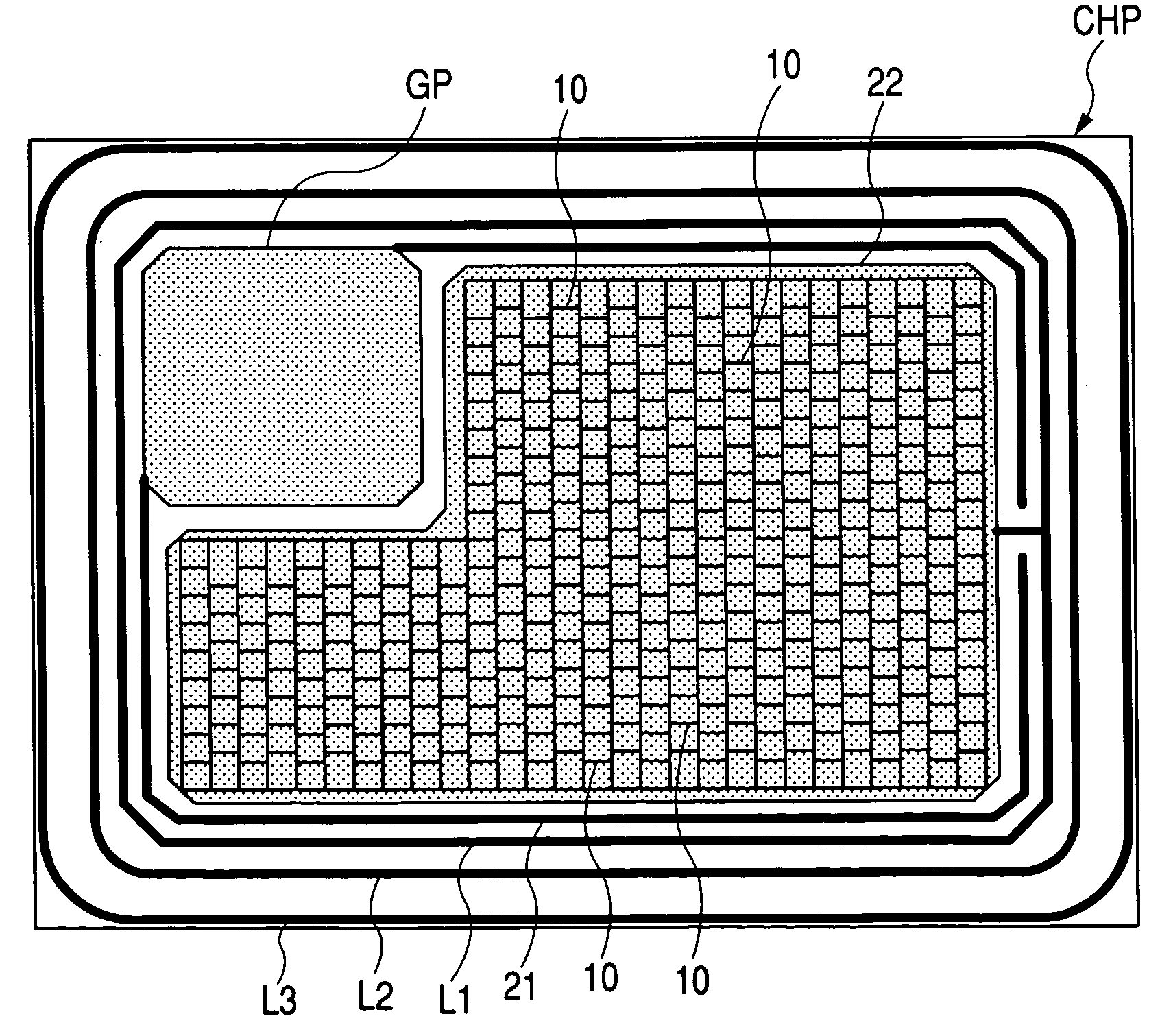

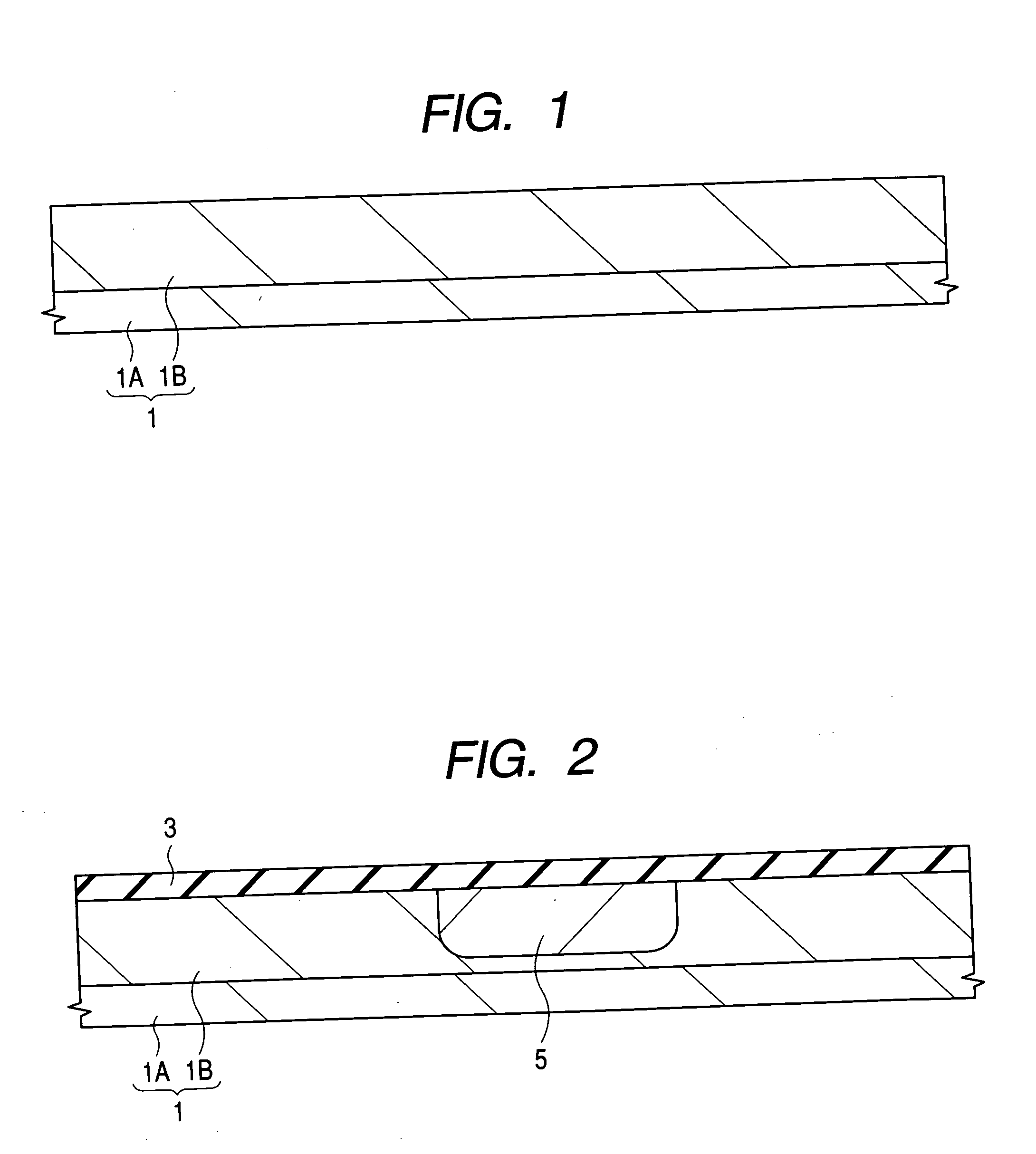

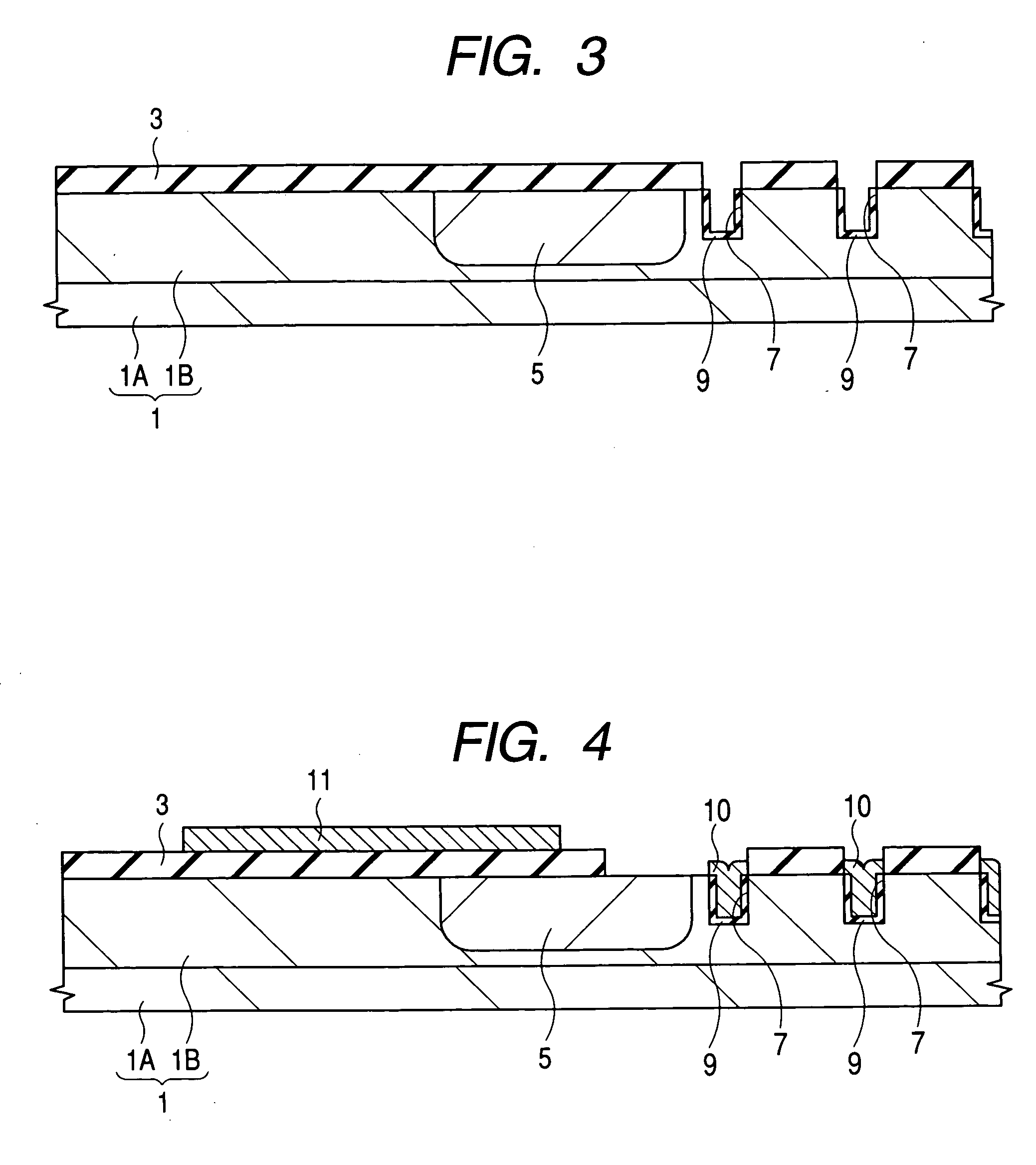

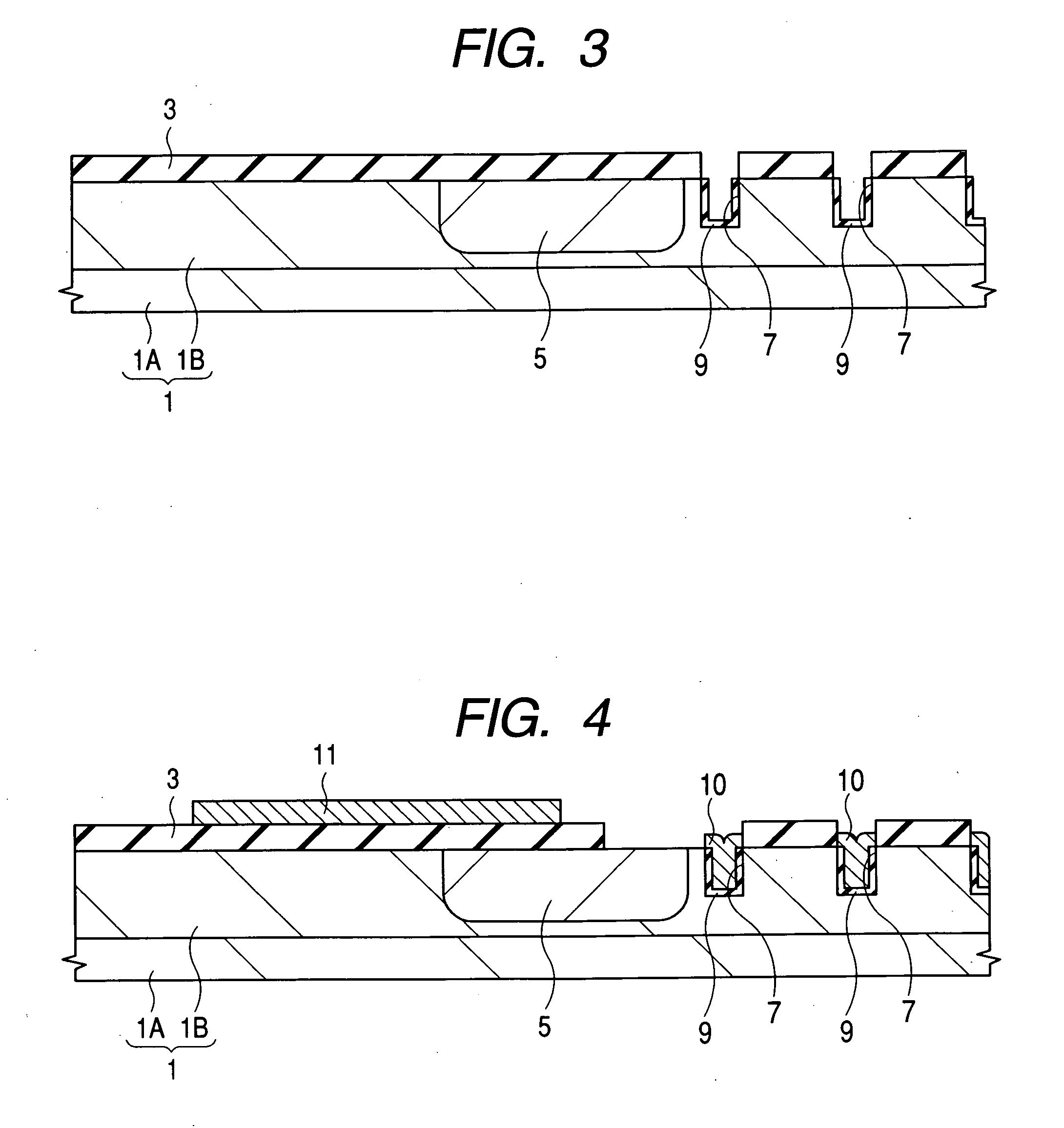

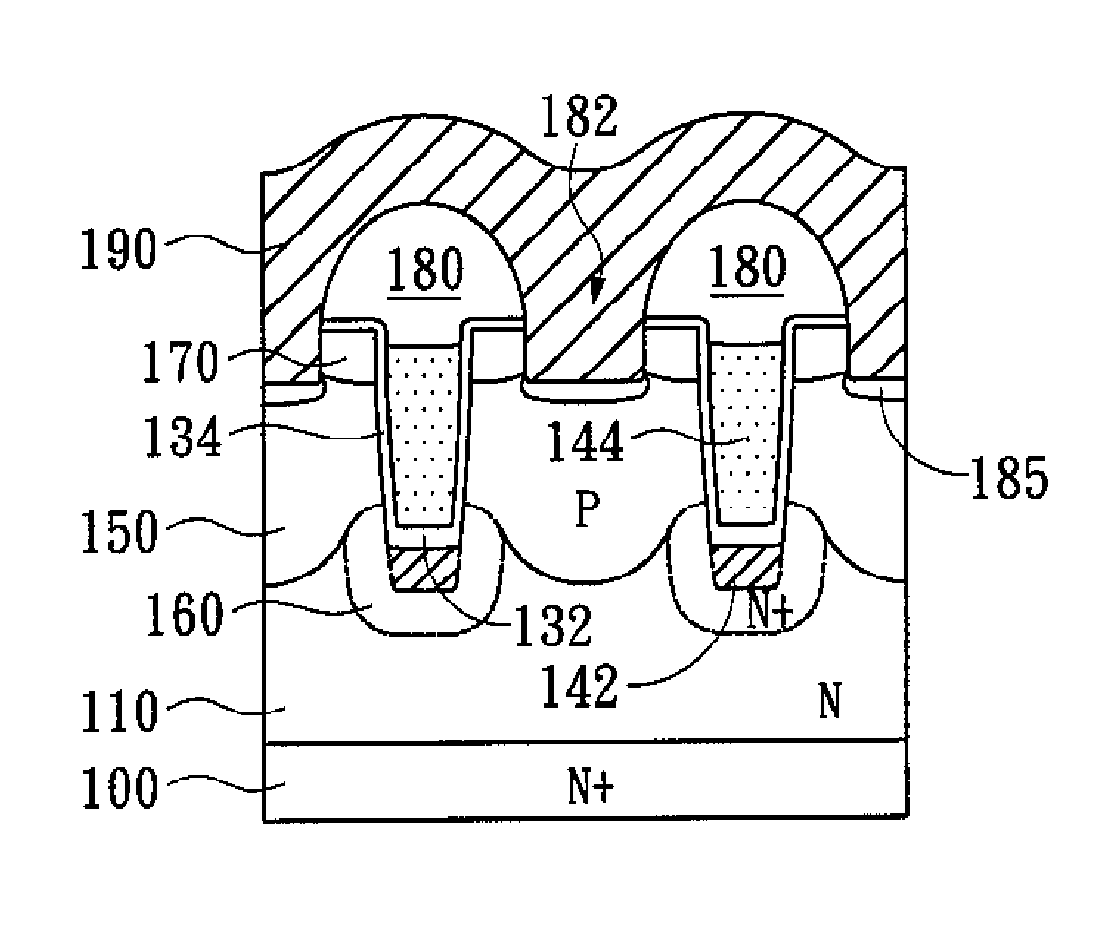

Semiconductor device and a method of manufacturing the same

InactiveUS20050029584A1Easy to integrateReduce resistanceSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceFeedback capacitance

A technology is provided to reduce ON-resistance, and the prevention of punch through is achieved with respect to a trench gate type power MISFET. Input capacitance and a feedback capacitance are reduced by forming a groove in which a gate electrode is formed so as to have a depth as shallow as about 1 μm or less, a p−type semiconductor region is formed to a depth so as not to cover the bottom of the groove, and a p-type semiconductor region higher in impurity concentration than the p−type semiconductor region is formed under a n+type semiconductor region serving as a source region of the trench gate type power MISFET, causing the p-type semiconductor region to serve as a punch-through stopper layer of the trench gate type power MISFET.

Owner:RENESAS TECH CORP

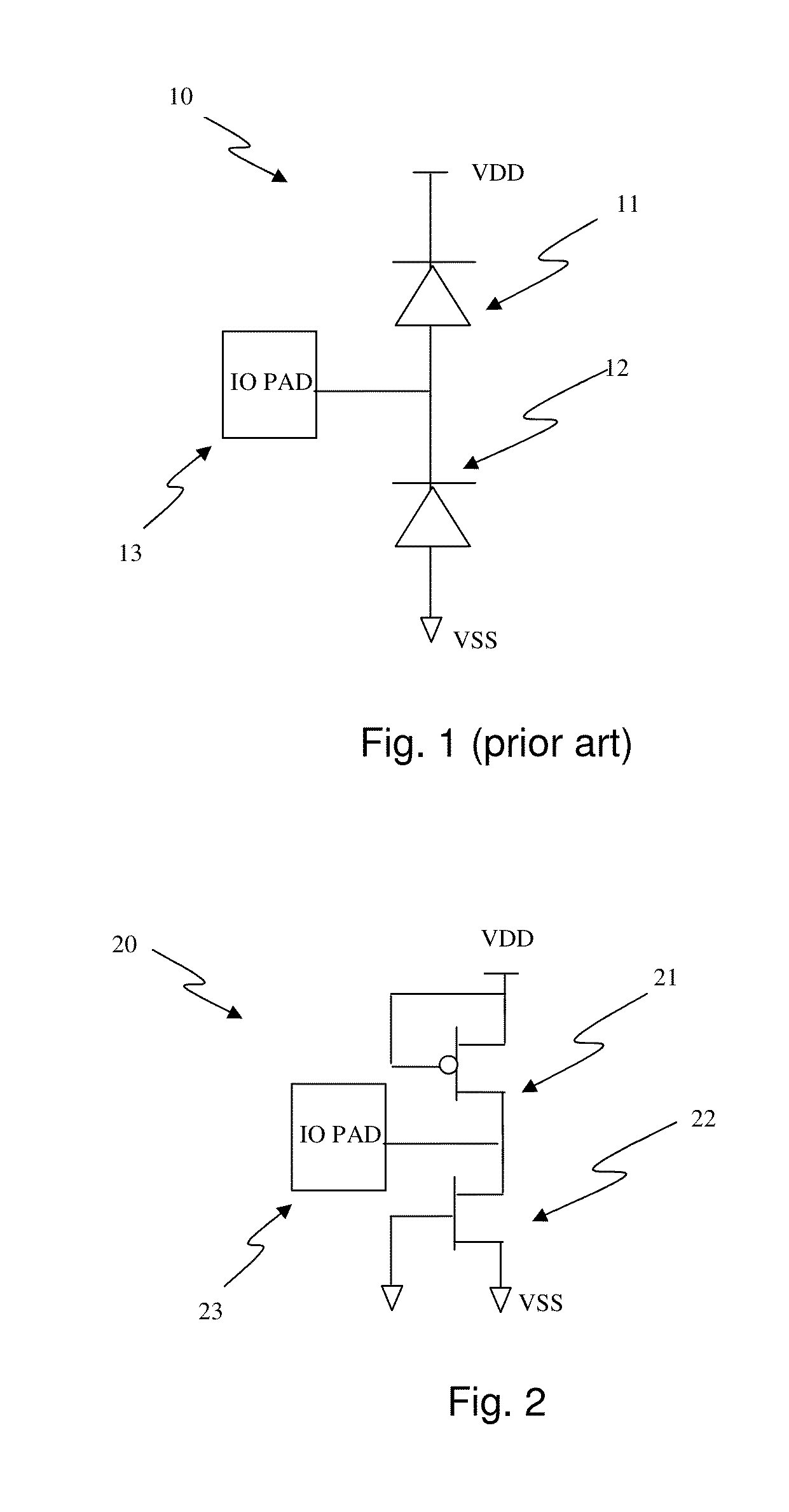

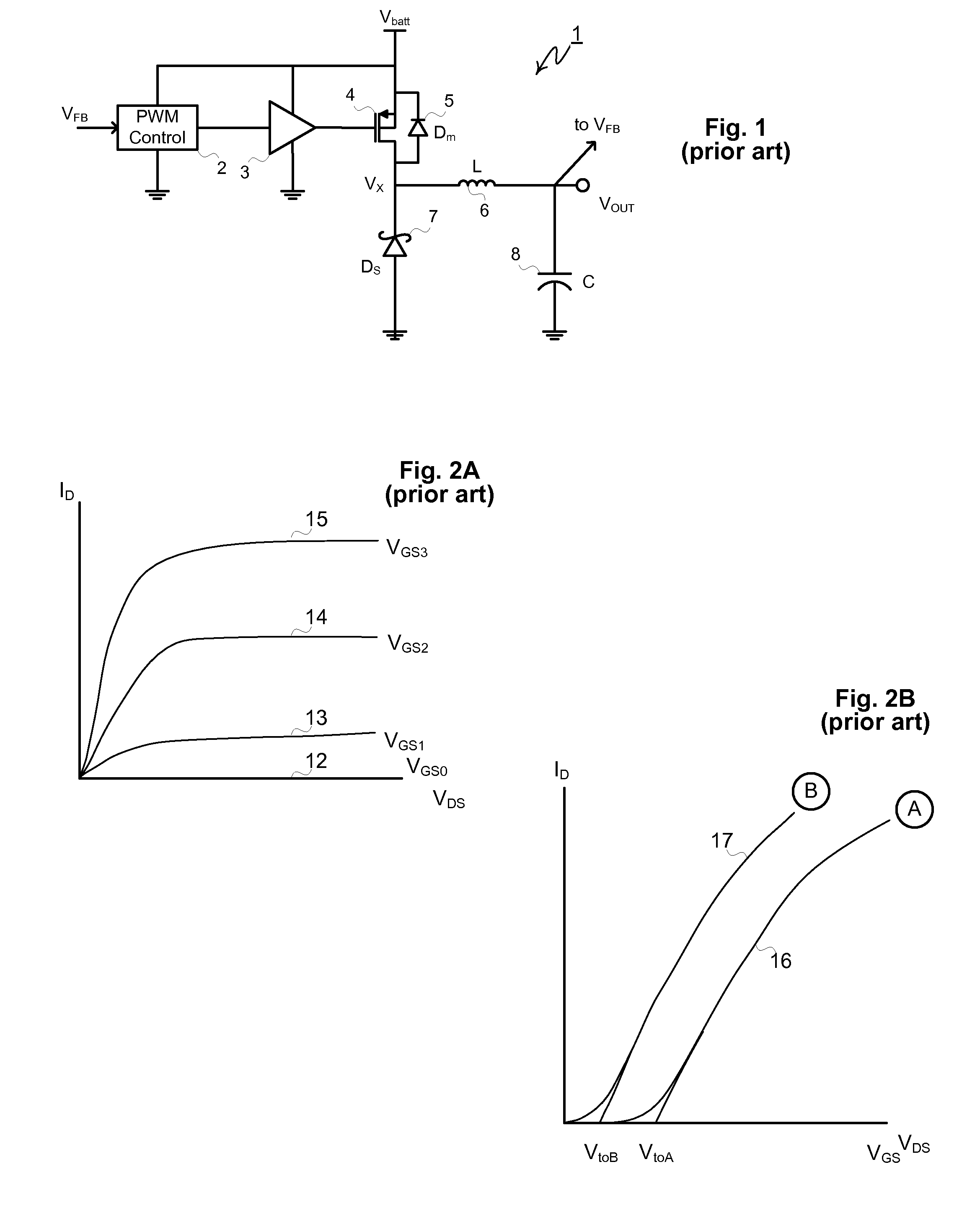

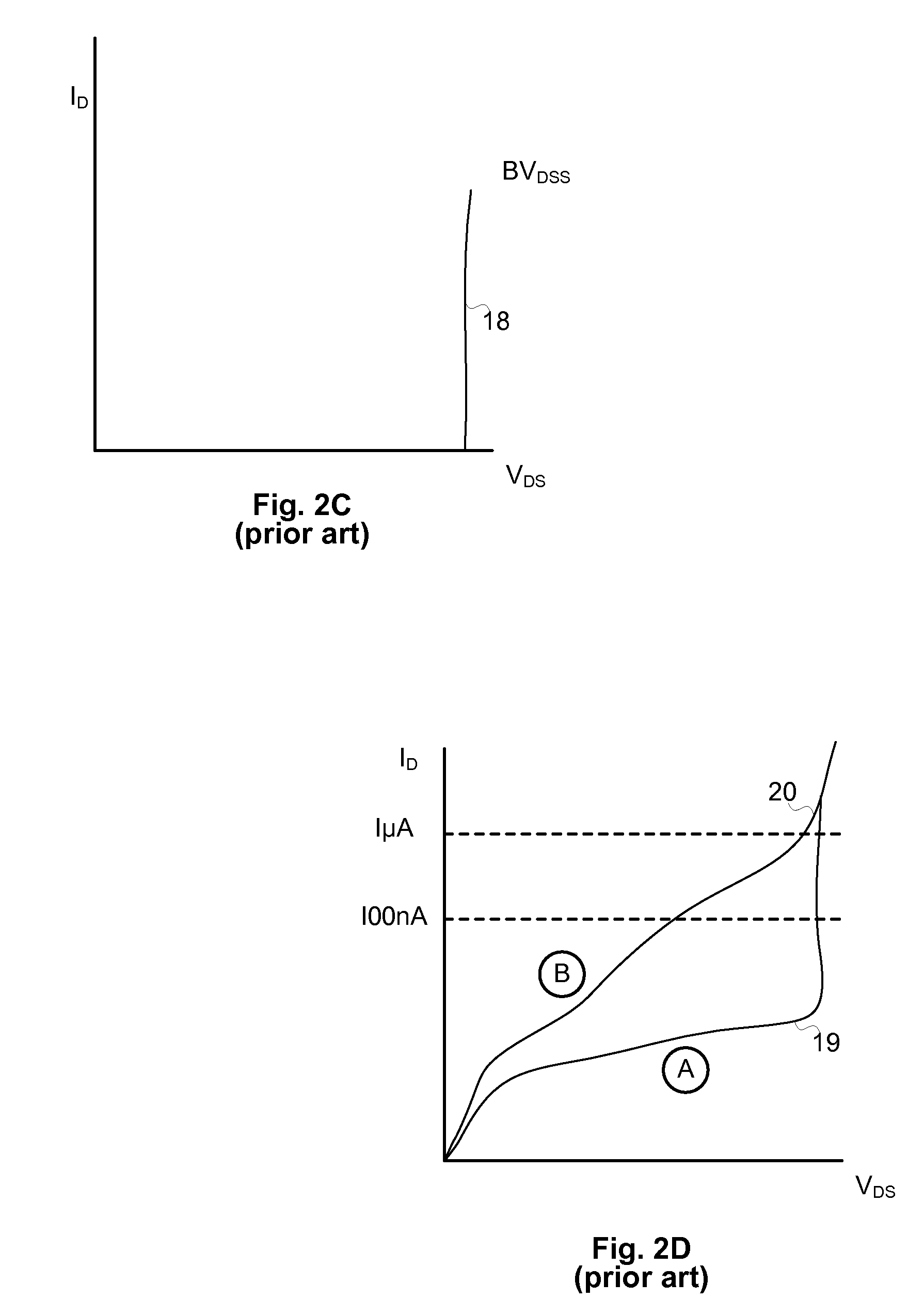

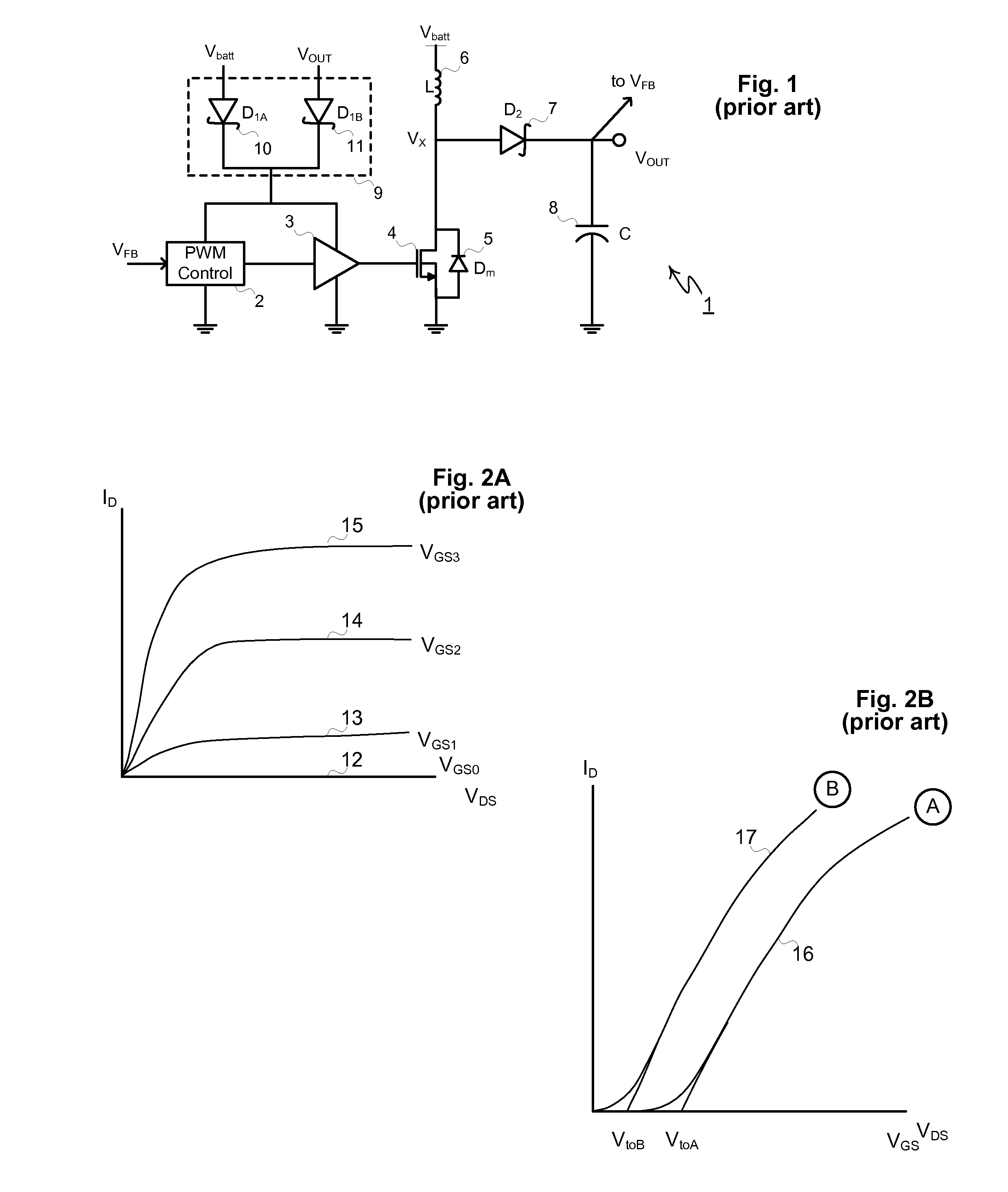

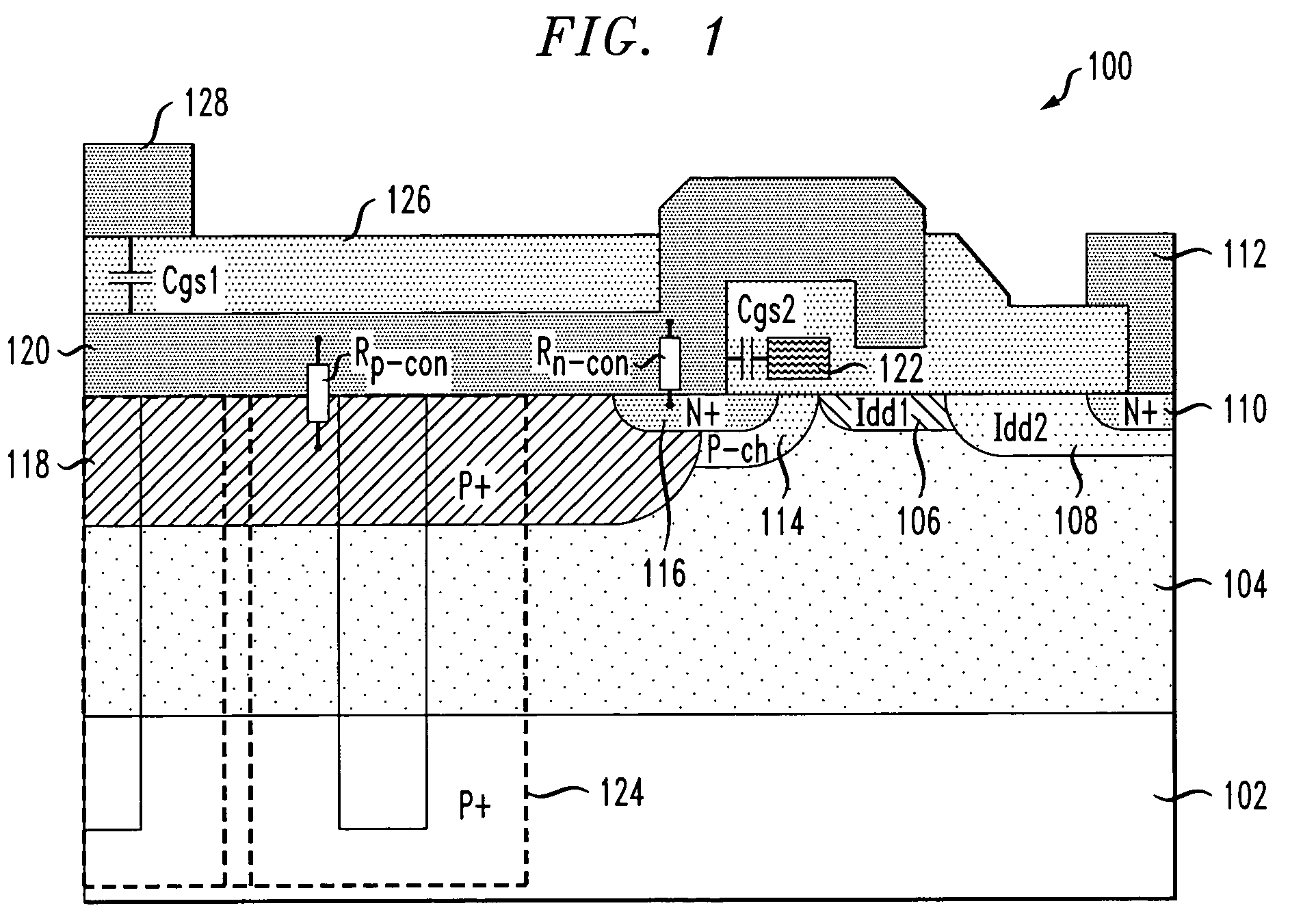

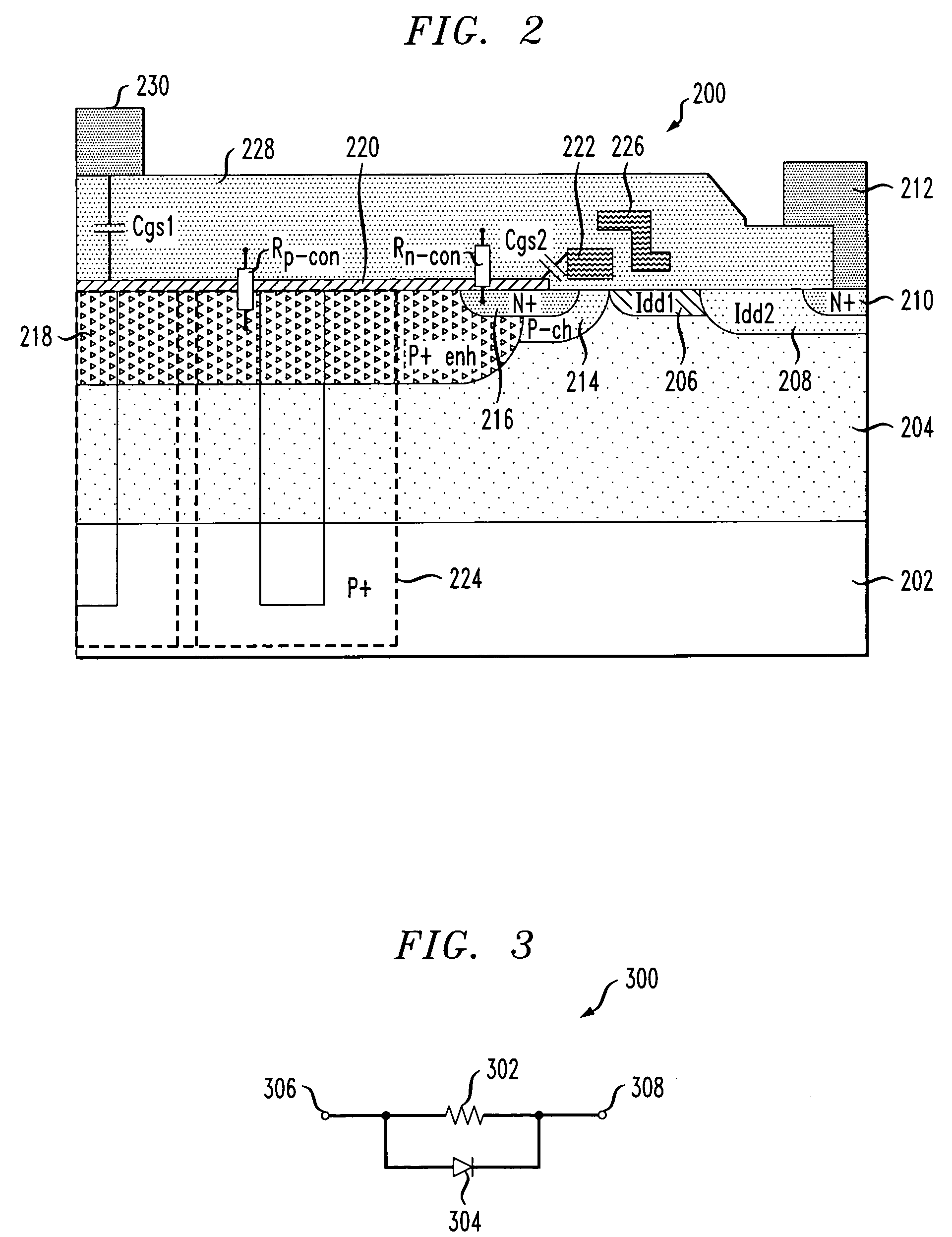

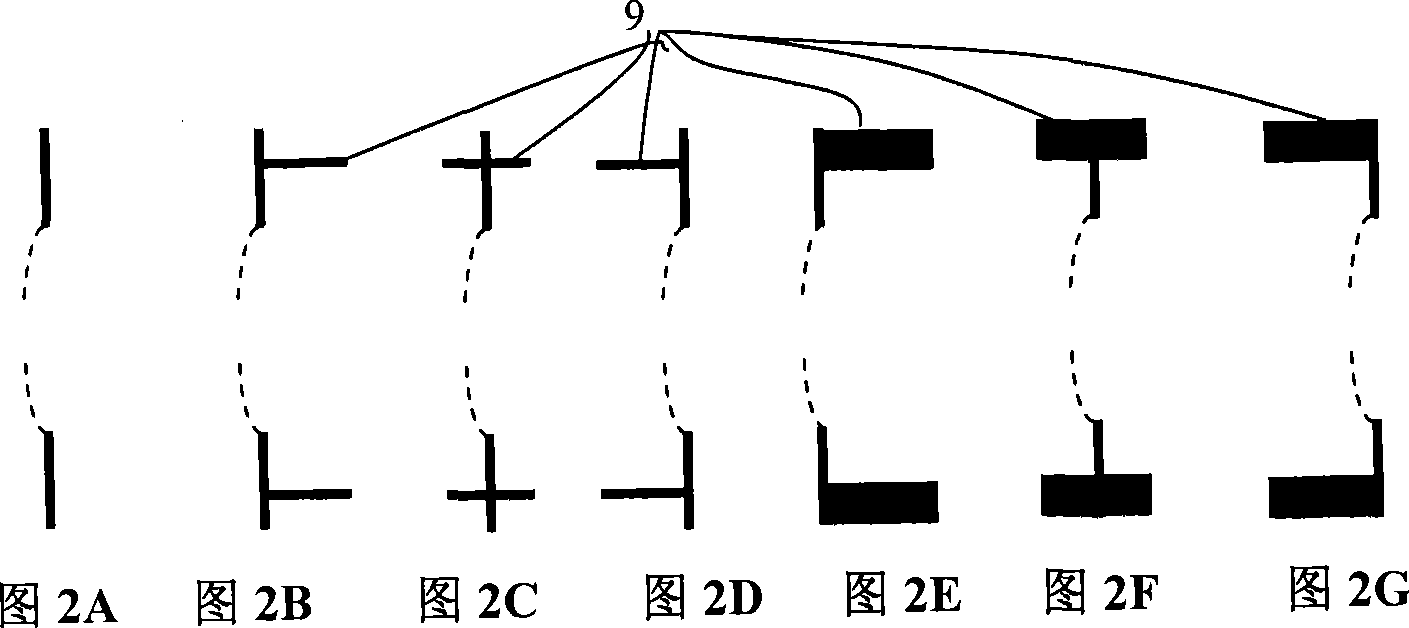

High Frequency Power MESFET Gate Drive Circuits

InactiveUS20070146020A1Lower on-resistanceRobust avalancheTransistorDc-dc conversionDriver circuitHigh frequency power

A series of gate drive circuits for MESFETs are provided. The gate drive circuits are intended to be used in switching regulators where at least one switching device is an N-channel MESFET. For regulators of this type, the gate drive circuits provide gate drive at the correct voltage to ensure that MESFETs are neither under driven (resulting in incorrect circuit operation) nor over driven (resulting in MESFET damage or excess current or power loss).

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

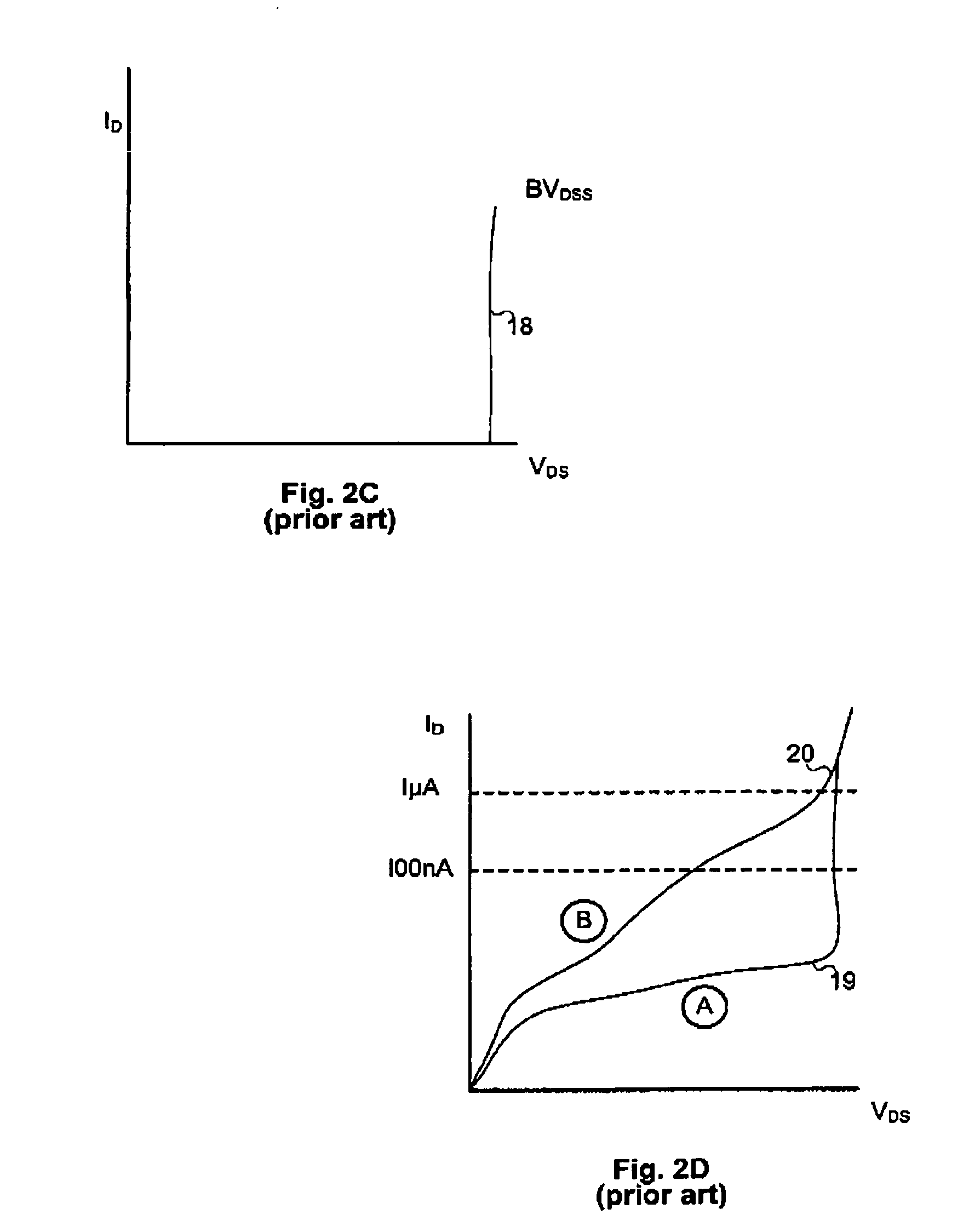

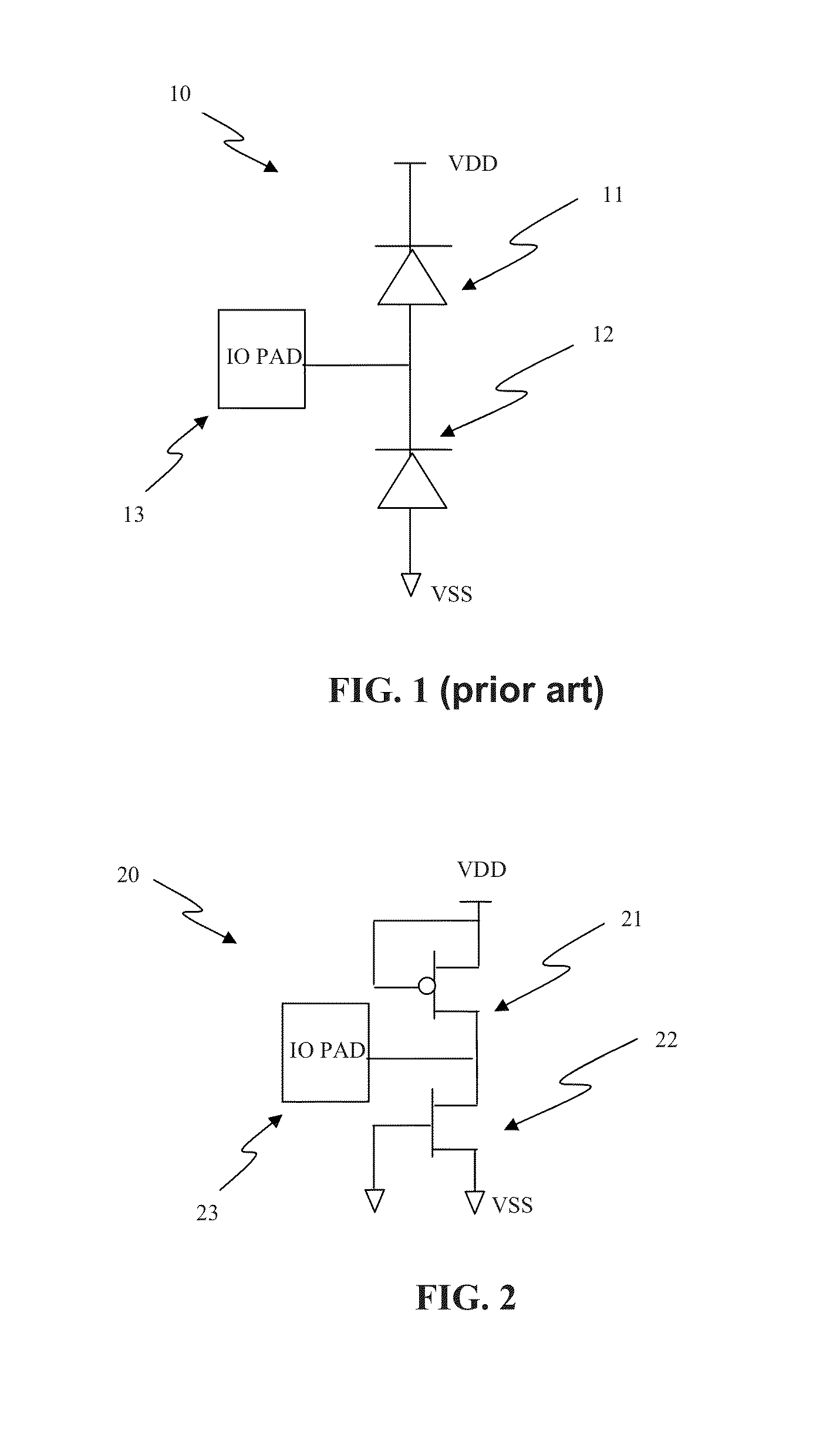

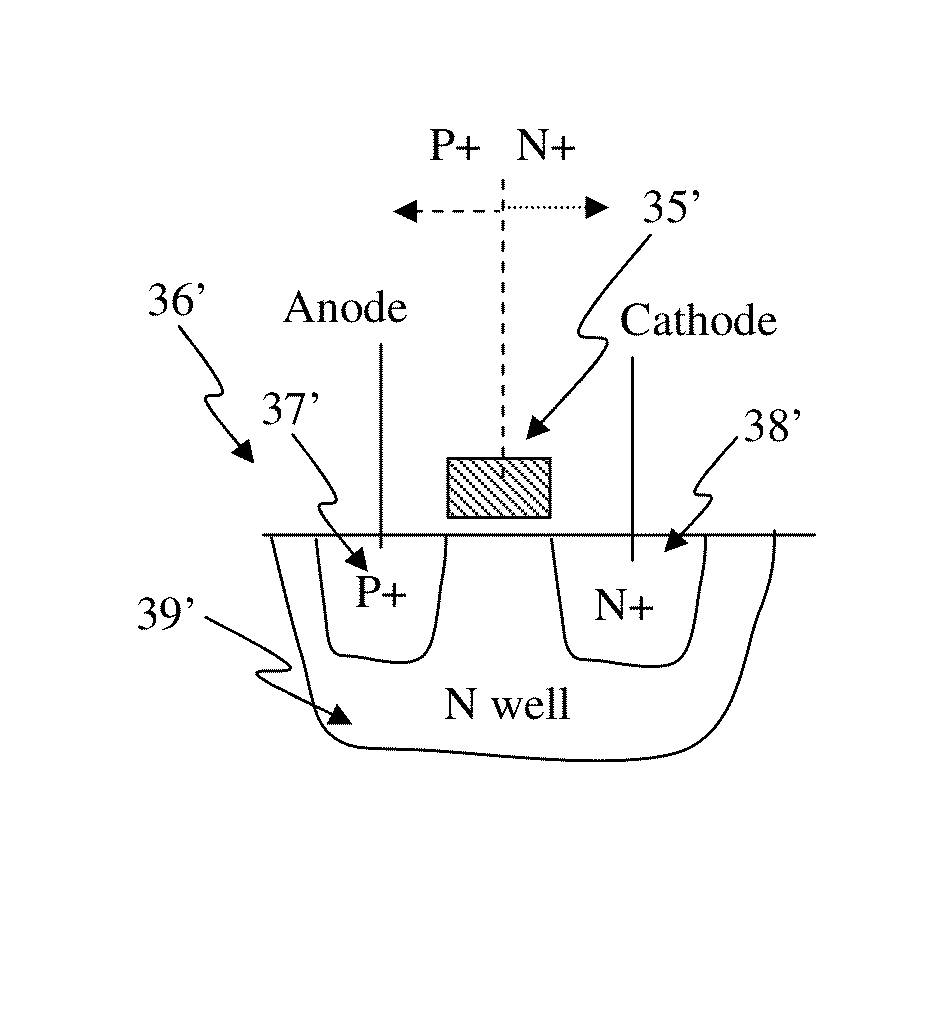

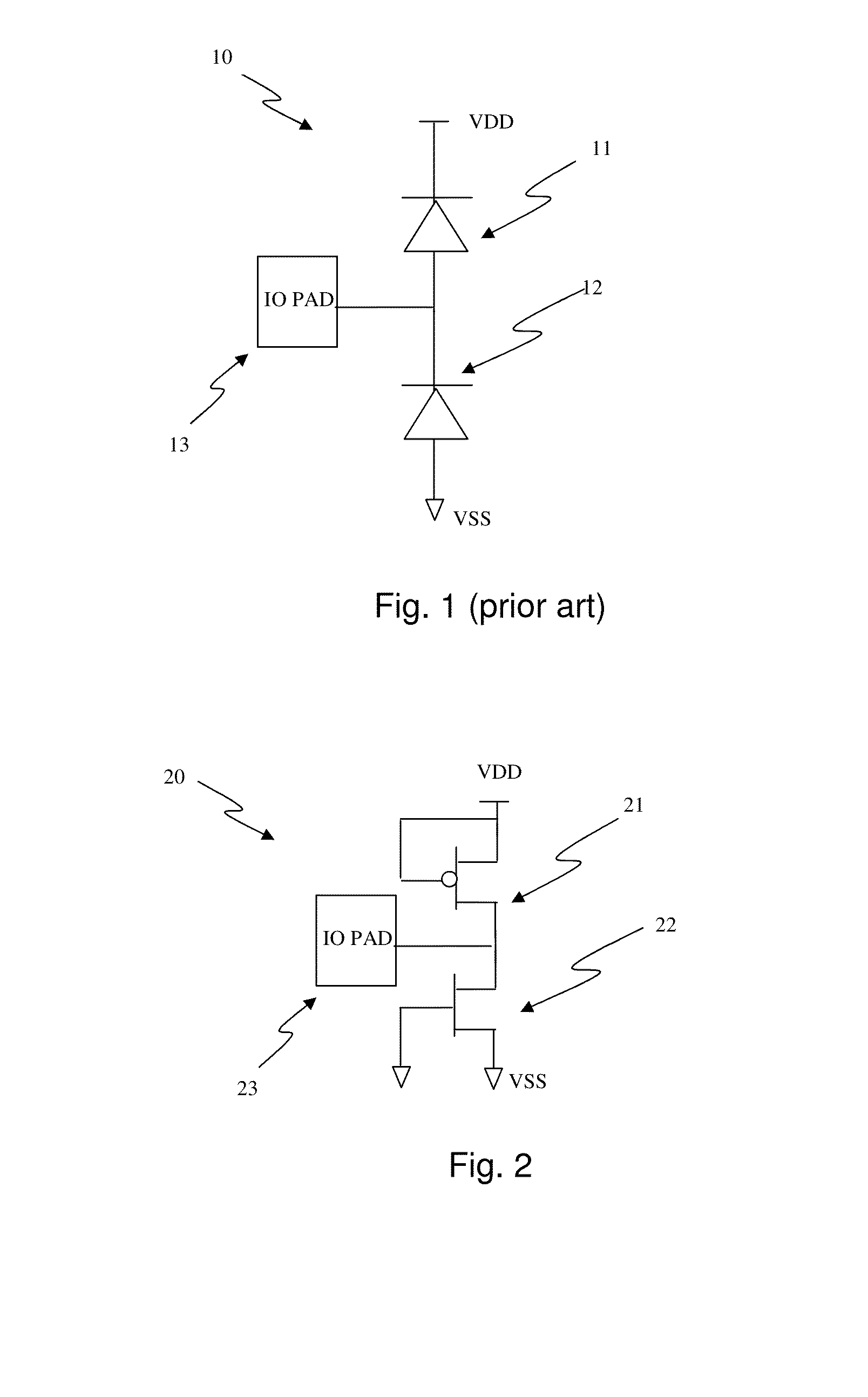

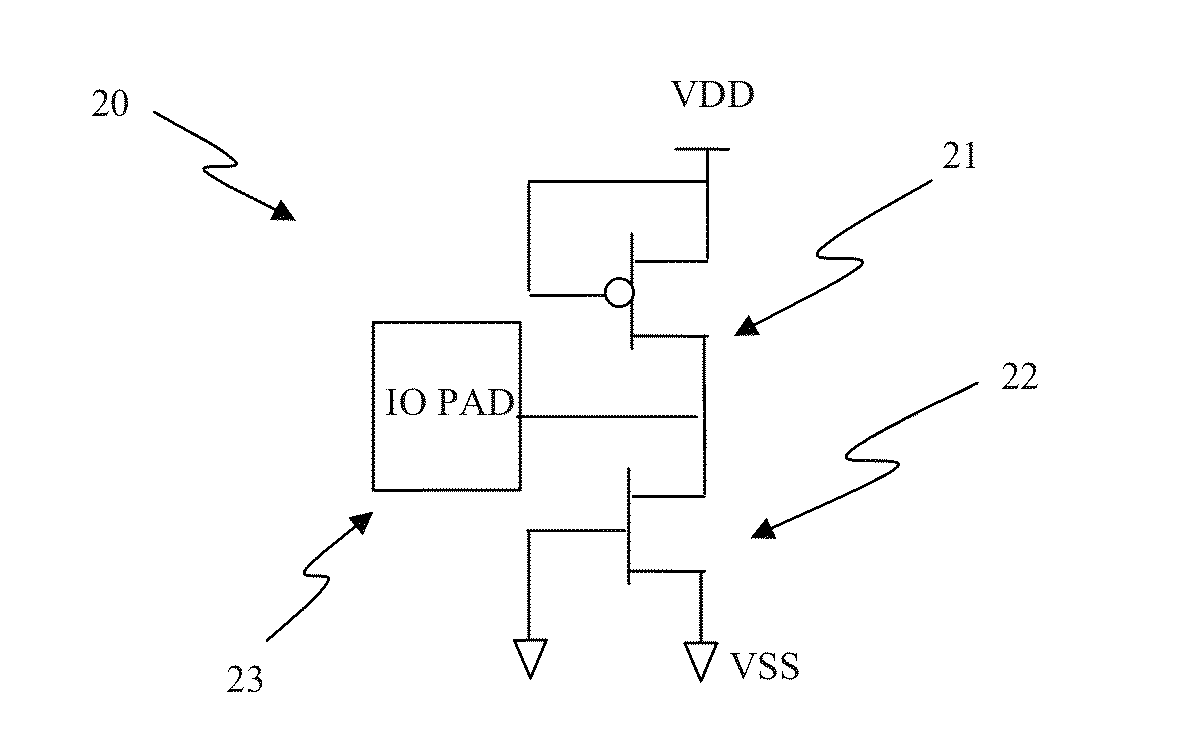

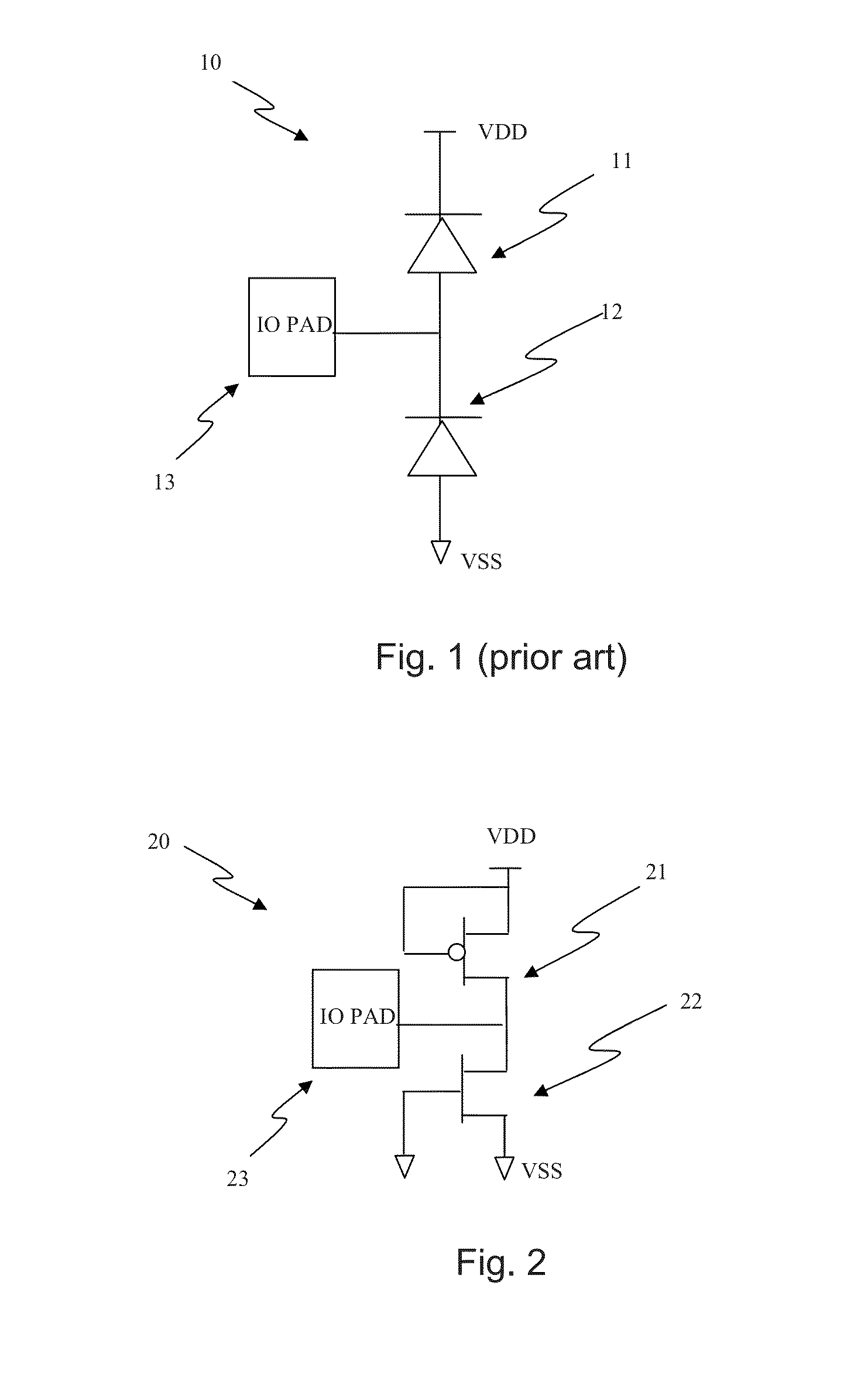

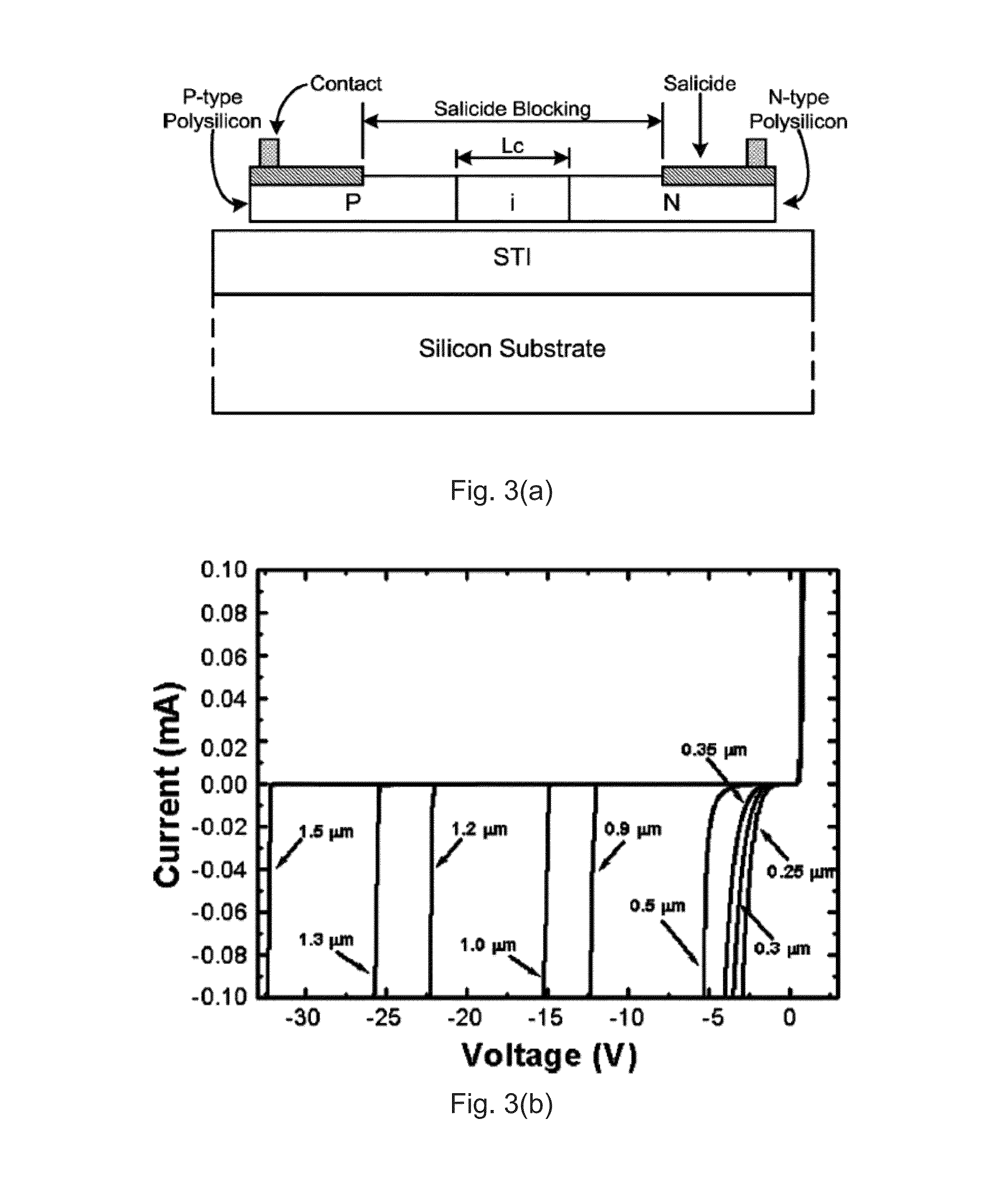

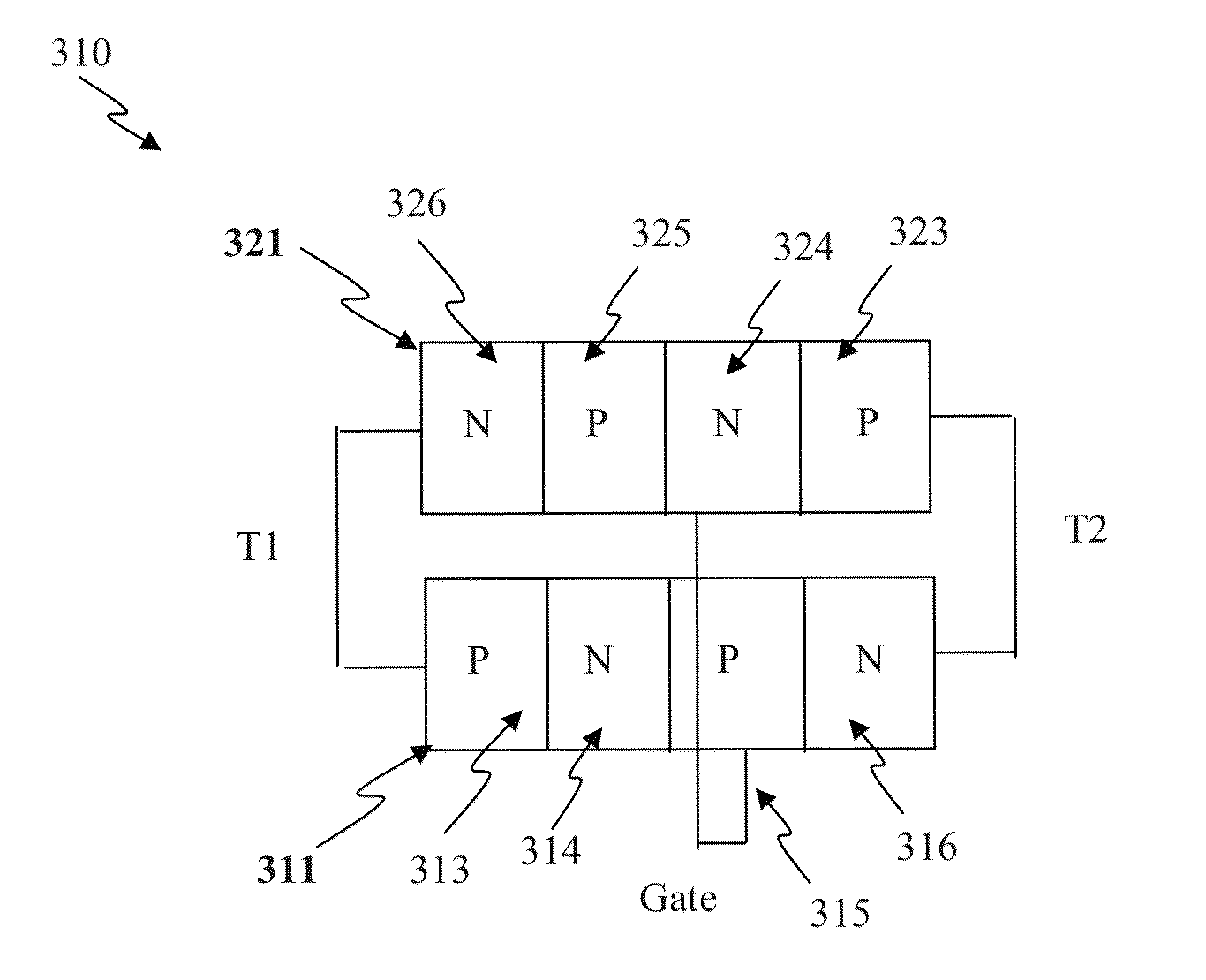

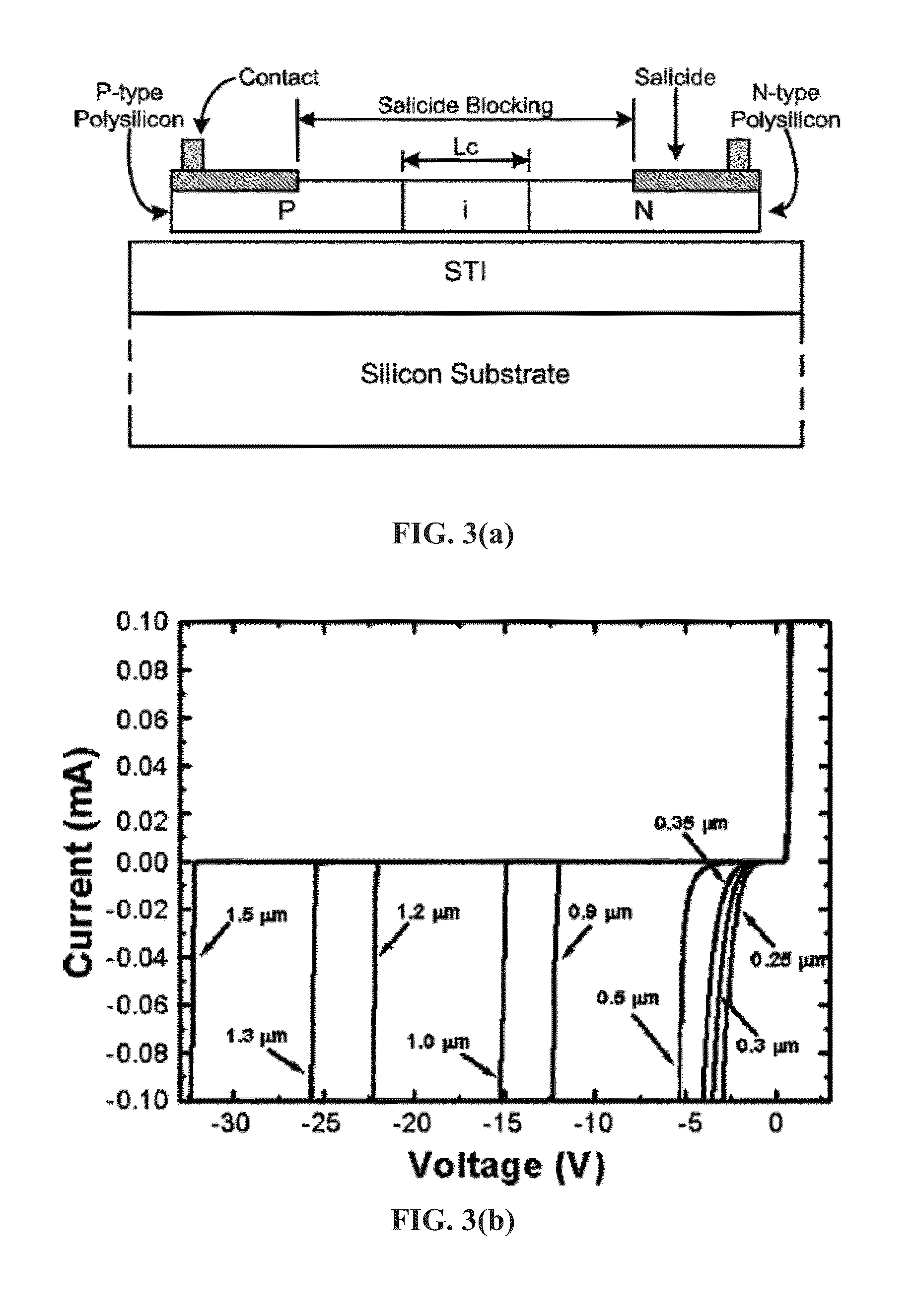

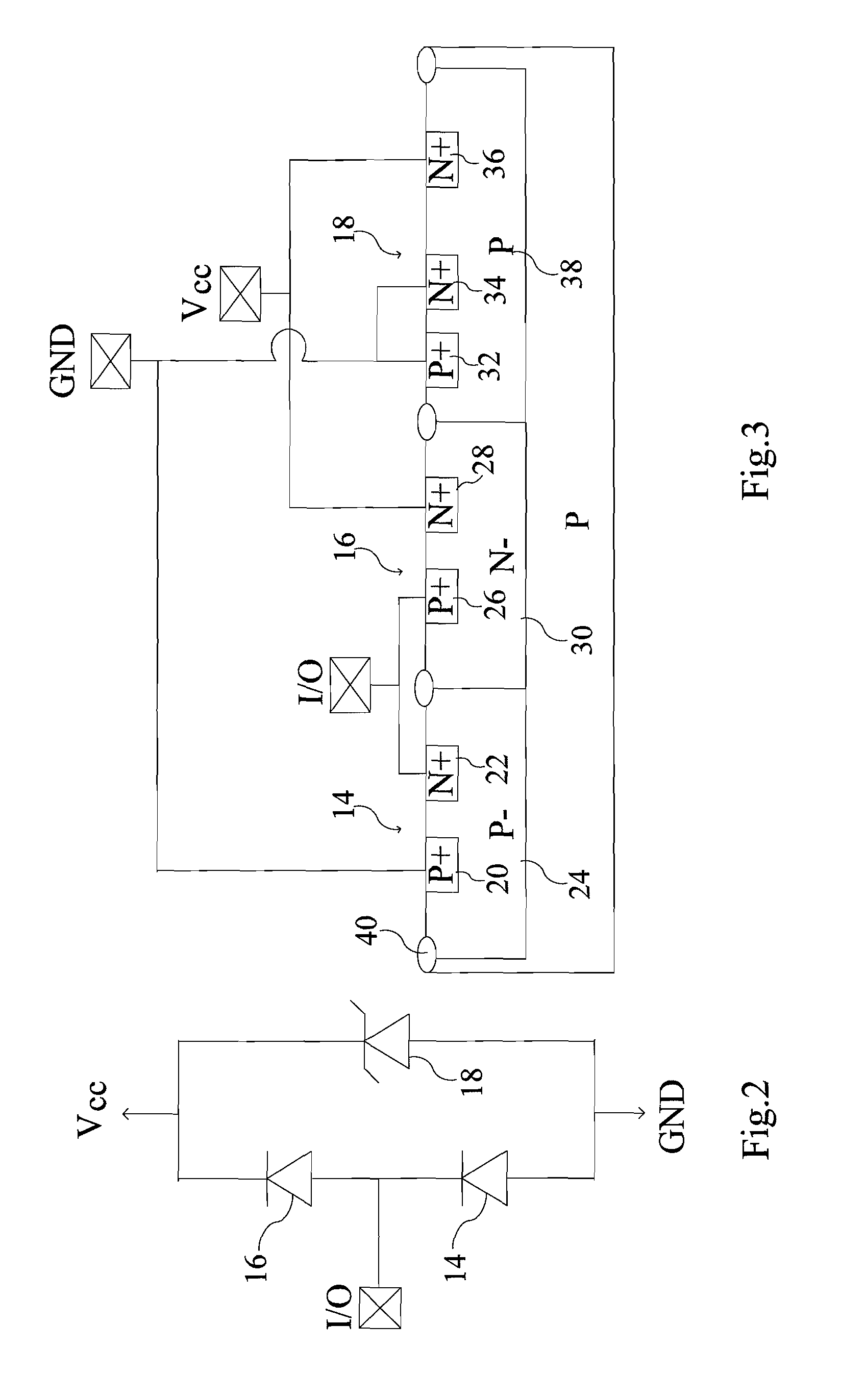

Structures and techniques for using mesh-structure diodes for electro-static discharge (ESD) protection

ActiveUS20130200488A1Improve immunityReduce input capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingLOCOSBlocking layer

An Electro-Static Discharge (ESD) protection using at least one I / O pad with at least one mesh structure of diodes provided on a semiconductor body is disclosed. The mesh structure has a plurality of cells. At least one cell can have a first type of implant surrounded by at least one cell with a second type of implant in at least one side of the cell, and at least cell can have a second type of implant surrounded by at least one cell with a first type of implant in at least one side of the cell. The two types of implant regions can be separated with a gap. A silicide block layer (SBL) can cover the gap and overlap into the both implant regions to construct P / N junctions on the polysilicon or active-region body on an insulated substrate. Alternatively, the two types of implant regions can be isolated by LOCOS, STI, dummy gate, or SBL on silicon substrate. The regions with the first and the second type of implants can be coupled to serve as the first and second terminal of a diode, respectively. The mesh structure can have a first terminal coupled to the I / O pad and a first terminal coupled to a first supply voltage.

Owner:ATTOPSEMI TECH CO LTD

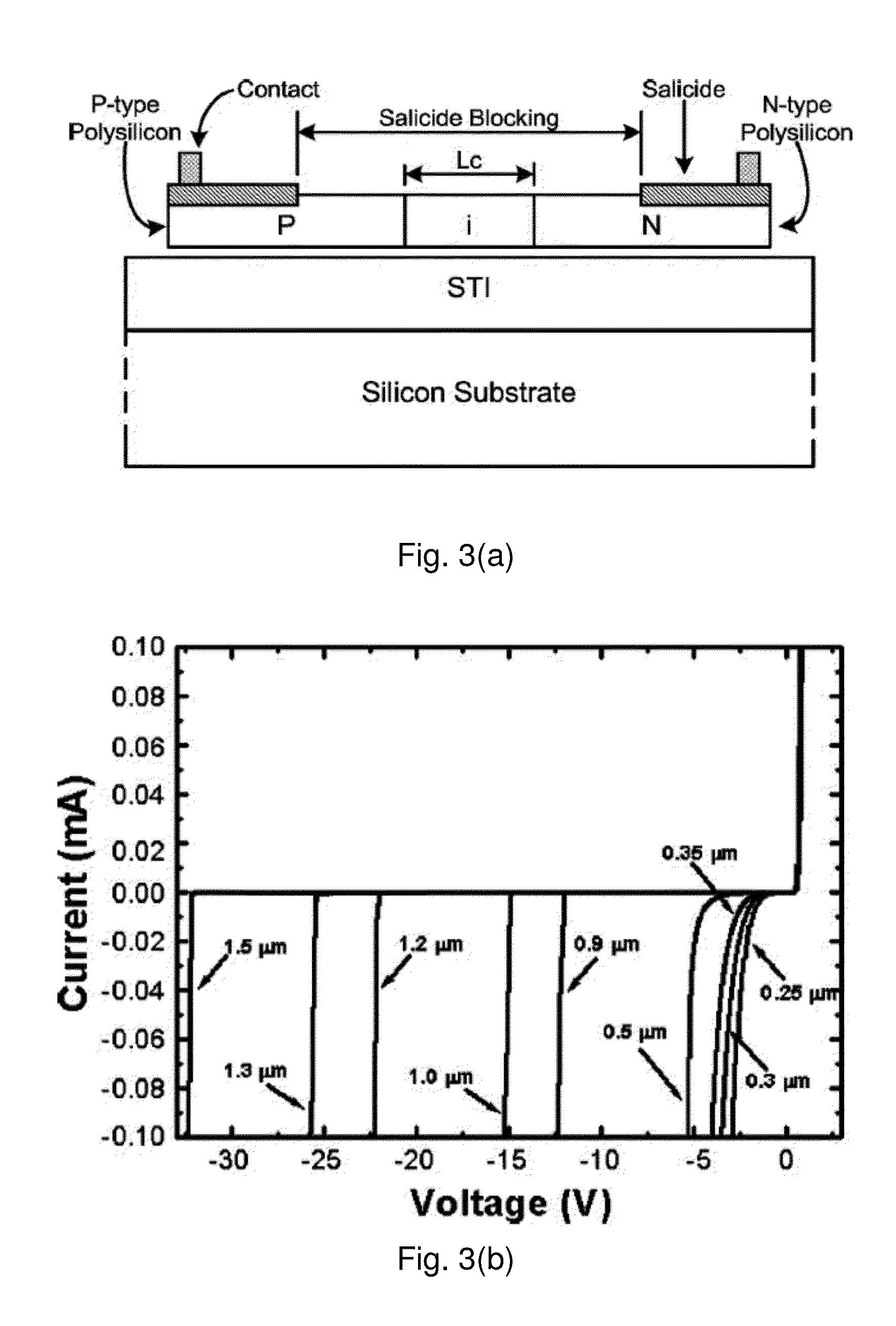

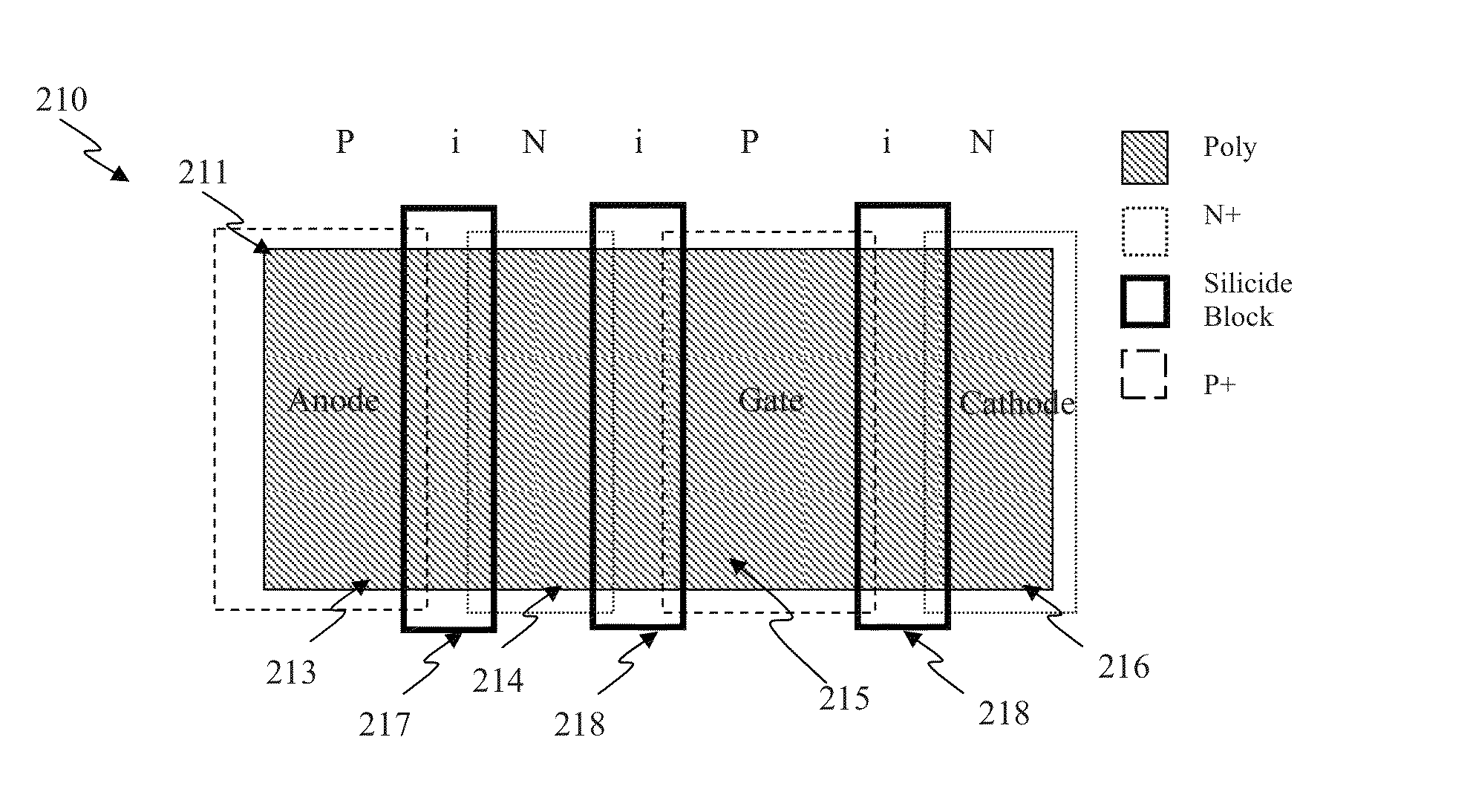

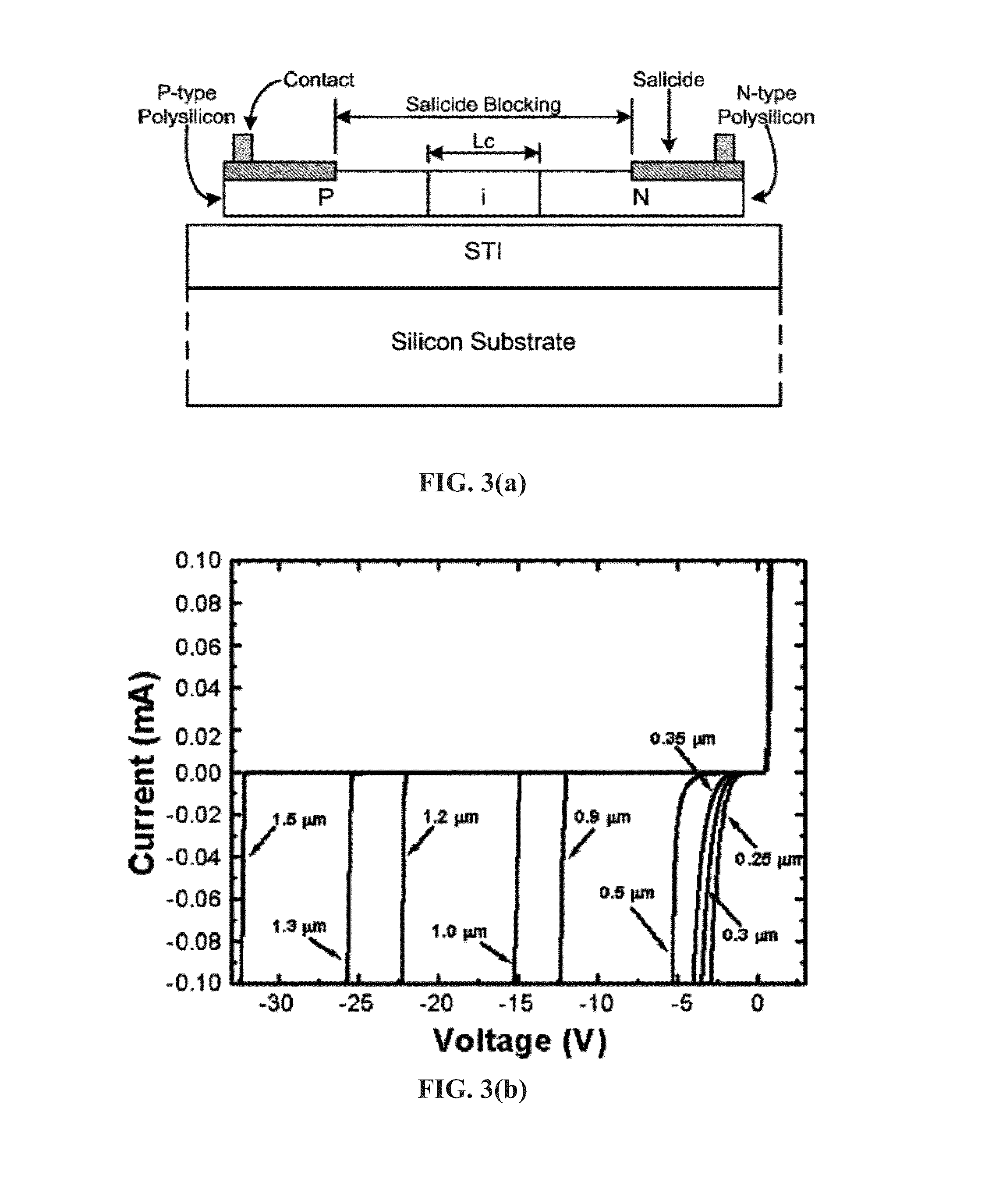

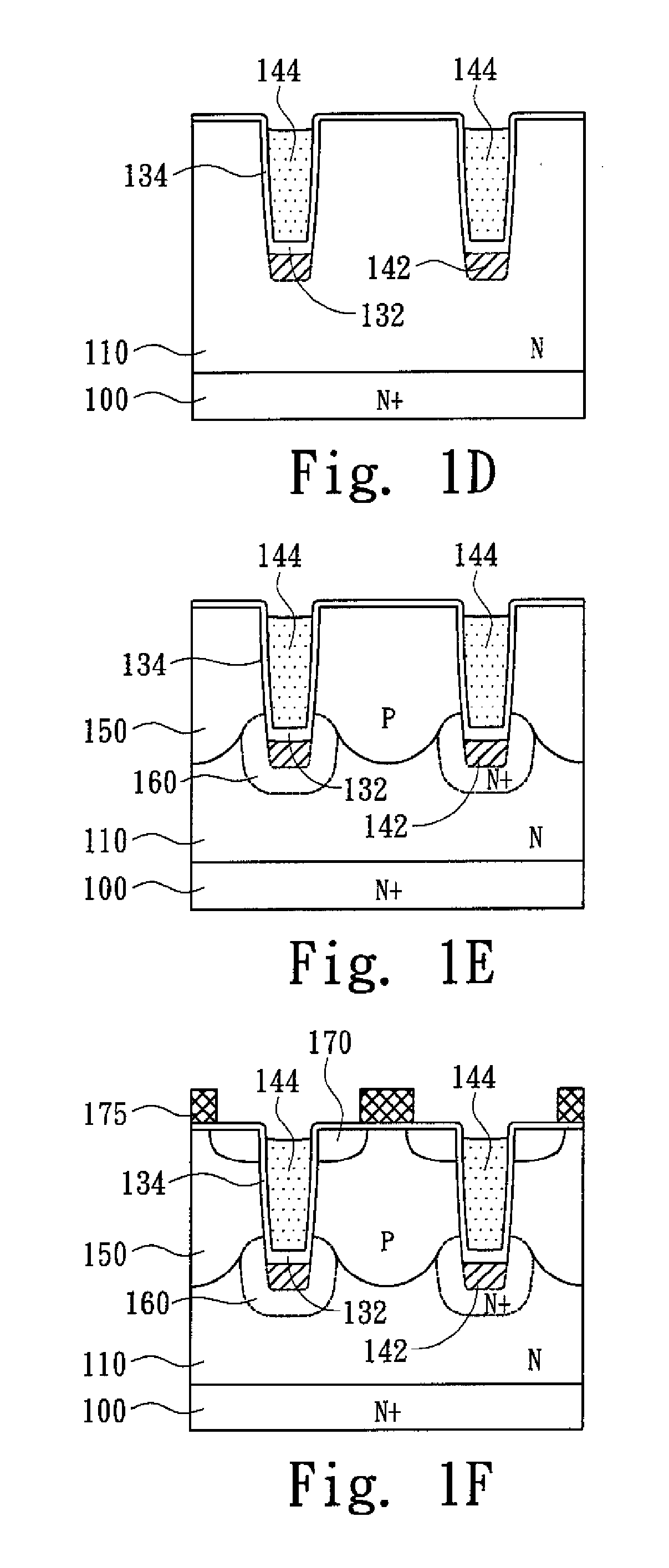

Structures and techniques for using semiconductor body to construct SCR, DIAC, or triac

ActiveUS20140131764A1Improve immunityReduce input capacitanceTransistorSemiconductor/solid-state device manufacturingDIACSilicon-controlled rectifier

Switch devices, such as Silicon Controlled Rectifier (SCR), DIAC, or TRIAC, on a semiconductor body are disclosed. P / N junctions can be built on a semiconductor body, such as polysilicon or active region body on an insulated substrate, with a first implant in one end and a second implant in the other end. The first and second implant regions are separated with a space. A silicide block layer can cover the space and overlap into both implant regions to construct P / N junctions in the interface.

Owner:ATTOPSEMI TECH CO LTD

Structures and techniques for using semiconductor body to construct bipolar junction transistors

ActiveUS20140131711A1High ESD immunityReduce input capacitanceTransistorSolid-state devicesBlock layerBipolar junction transistor

A bipolar junction transistor built with a mesh structure of cells provided on a semiconductor body is disclosed. The mesh structure has at least one emitter cell with a first type of implant. At least one emitter cell has at least one side coupled to at least one cell with a first type of implant to serve as collector of the bipolar. The spaces between the emitter and collector cells are the intrinsic base of a bipolar device. At least one emitter cell has at least one vortex coupled to at least one cell with a second type of implant to serve as the extrinsic base of the bipolar. The emitter, collector, or base cells can be arbitrary polygons as long as the overall geometry construction can be very compact and expandable. The implant regions between cells can be separated with a space. A silicide block layer can cover the space and overlap into at least a portion of both implant regions.

Owner:ATTOPSEMI TECH CO LTD

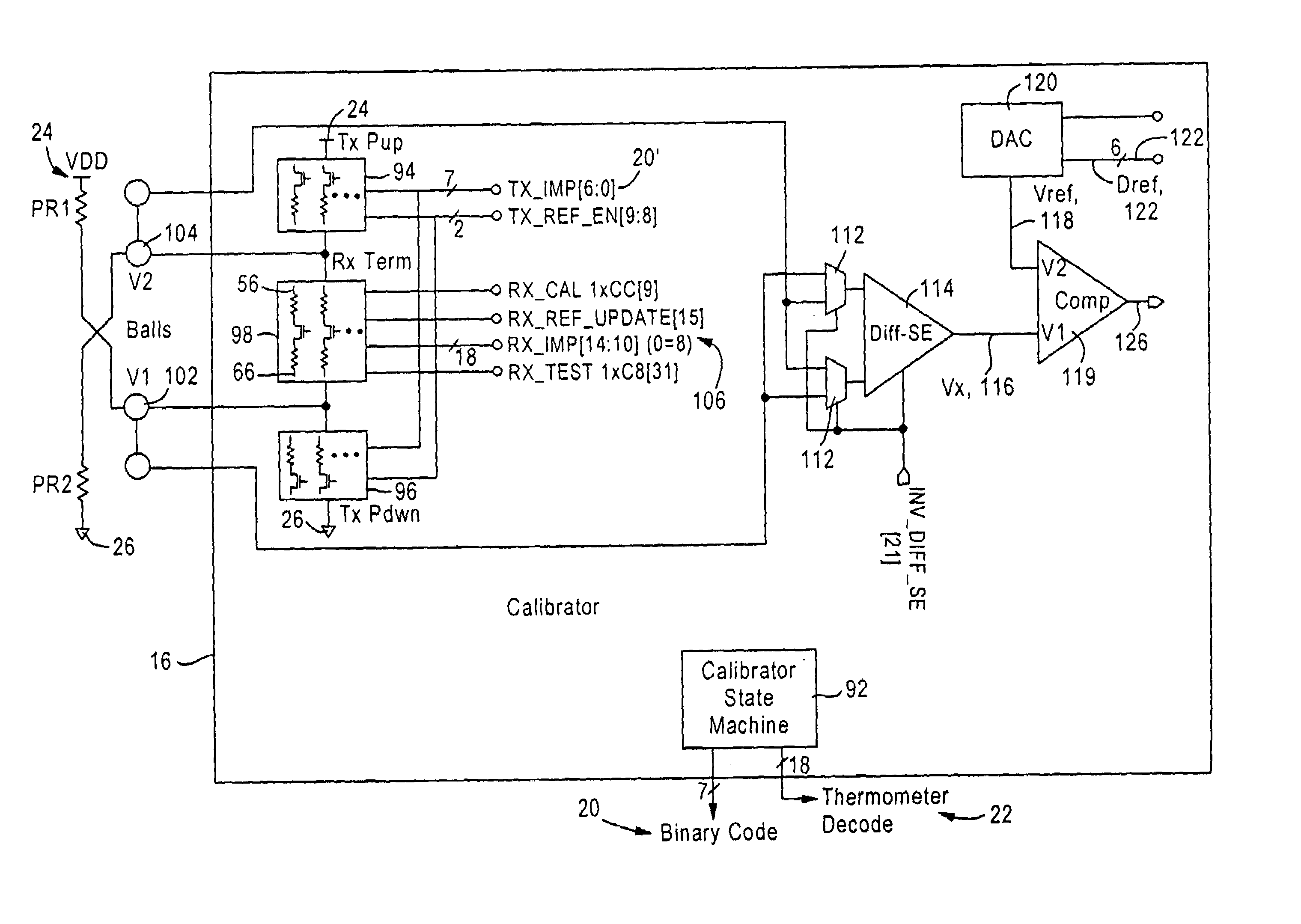

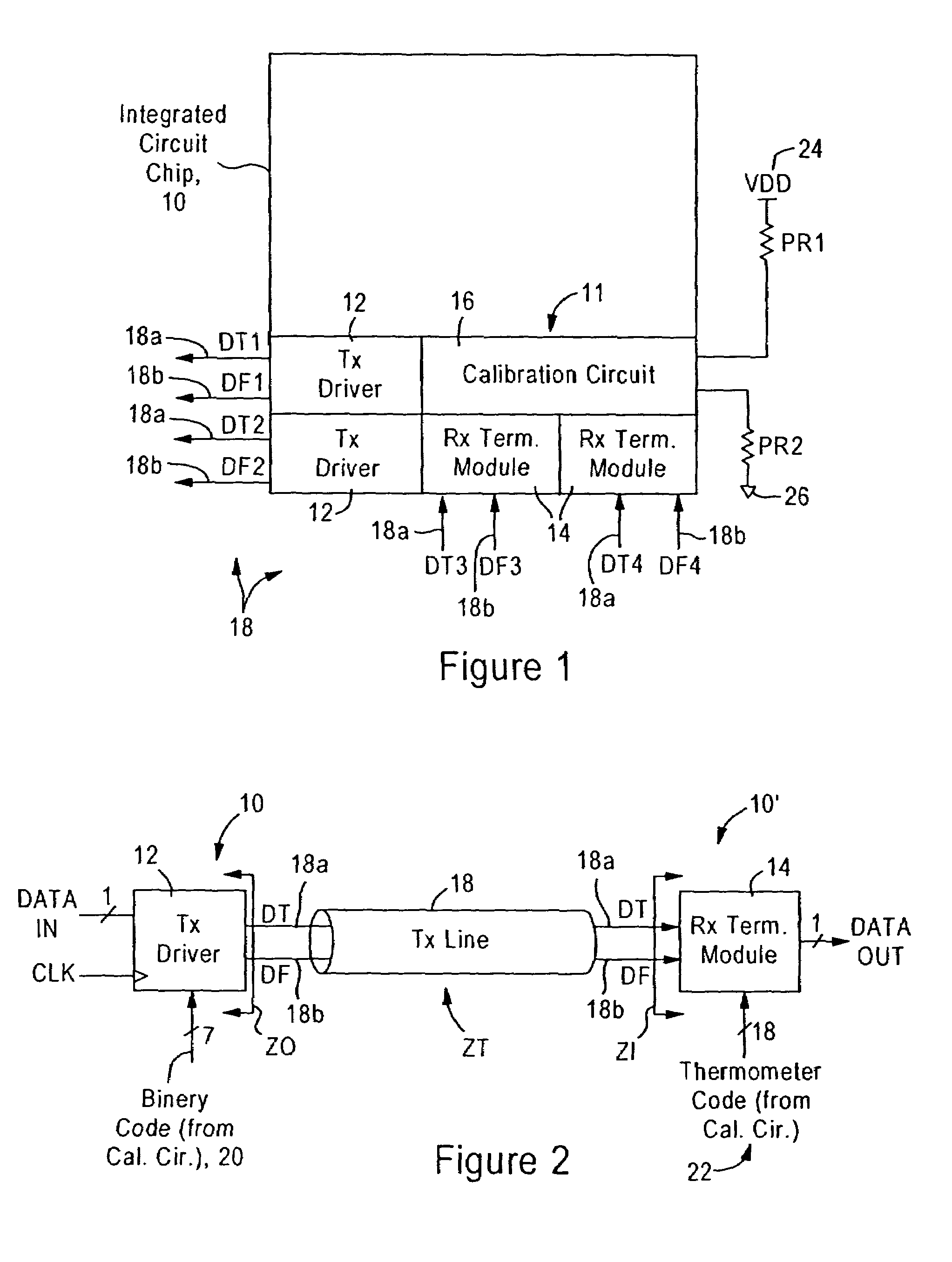

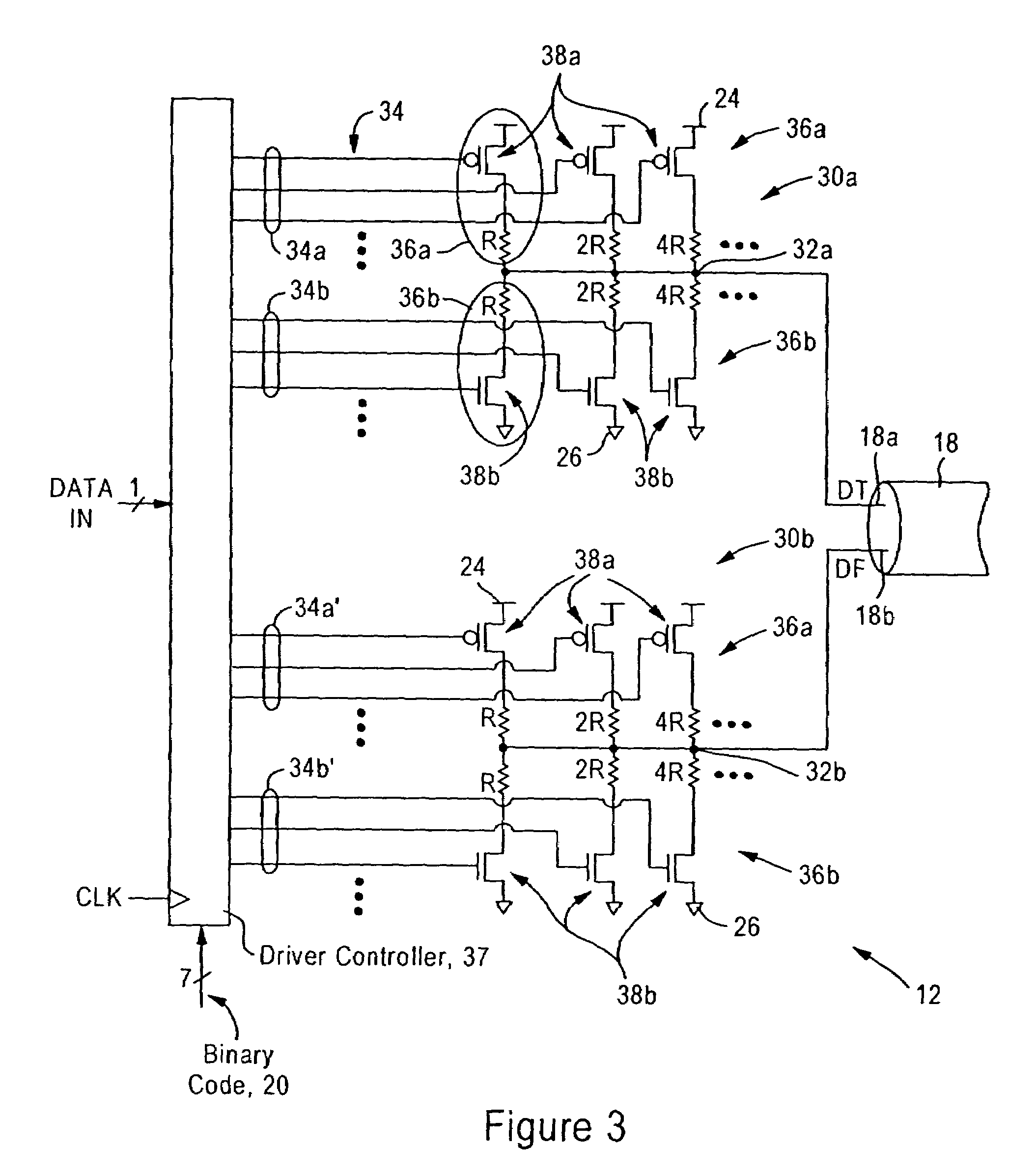

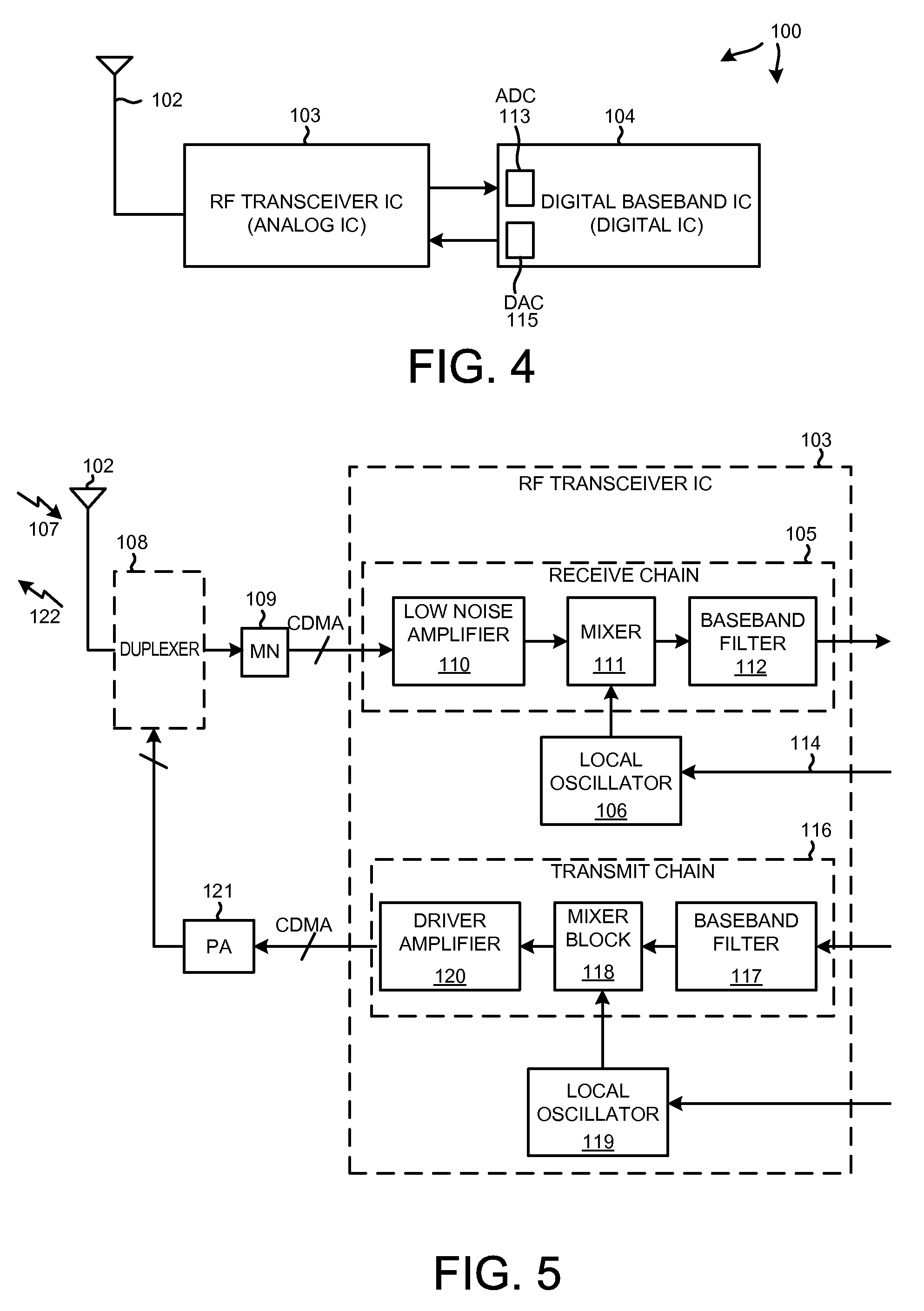

Voltage mode transceiver having programmable voltage swing and external reference-based calibration

ActiveUS7135884B1Reduce input capacitanceImprove the level ofInput/output impedence modificationReliability increasing modificationsExternal referenceInput impedance

An integrated device includes a voltage mode transmit driver for matching an output impedance to an output transmission line based on a binary code, an input termination module configured for matching an input impedance to an input transmission line based on an input impedance calibration value using thermometer-based decoding. The voltage mode transmit driver includes, for each differential output signal, a resistor network circuit having pull-up circuits and pull-down circuits for changing the voltage on the differential output signal, and having binary weighted resistance values relative to each other. The input termination module includes pull-up circuits and pull-down circuits having inverse hyperbolic resistance values relative to each other, and using thermometer-based decoding to ensure a linear change in input impedance during transitions in the input impedance calibration value. A calibration circuit generates the binary code and the input impedance calibration value based on replicas of the pull-up and pull-down circuits.

Owner:MEDIATEK INC

Structures and techniques for using mesh-structure diodes for electro-static discharge (ESD) protection

InactiveUS20140133056A1High ESD immunityReduce input capacitanceSemiconductor/solid-state device detailsSolid-state devicesLOCOSImplant

An Electro-Static Discharge (ESD) protection using at least one I / O pad with at least one mesh structure of diodes provided on a semiconductor body is disclosed. The mesh structure has a plurality of cells. At least one cell can have a first type of implant surrounded by at least one cell with a second type of implant in at least one side of the cell, and at least cell can have a second type of implant surrounded by at least one cell with a first type of implant in at least one side of the cell. The two types of implant regions can be separated with a gap. A silicide block layer (SBL) can cover the gap and overlap into the both implant regions to construct P / N junctions on the polysilicon or active-region body on an insulated substrate. Alternatively, the two types of implant regions can be isolated by LOCOS, STI, dummy gate, or SBL on silicon substrate. The regions with the first and the second type of implants can be coupled to serve as the first and second terminal of a diode, respectively. The mesh structure can have a first terminal coupled to the I / O pad and a first terminal coupled to a first supply voltage.

Owner:ATTOPSEMI TECH CO LTD

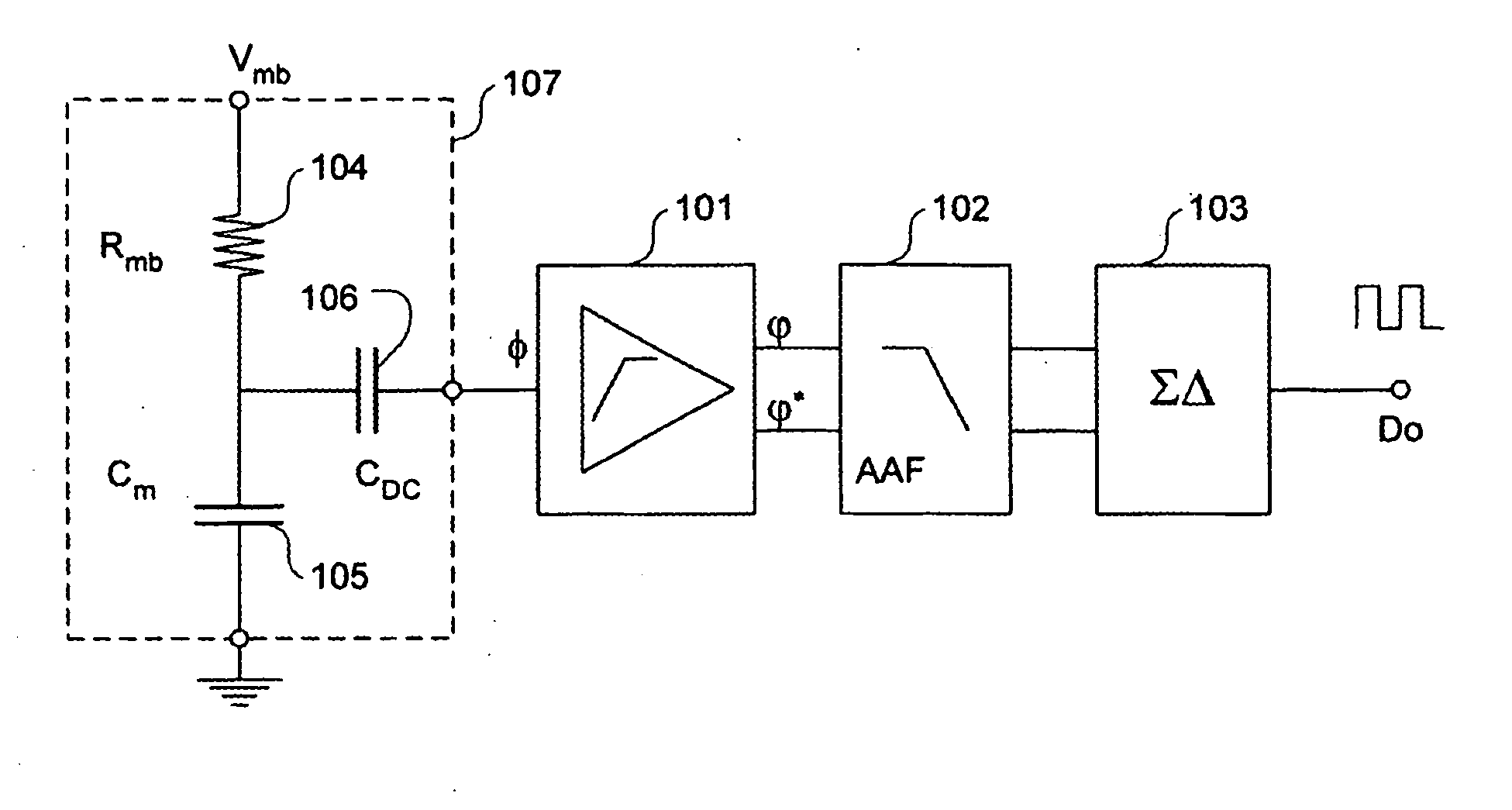

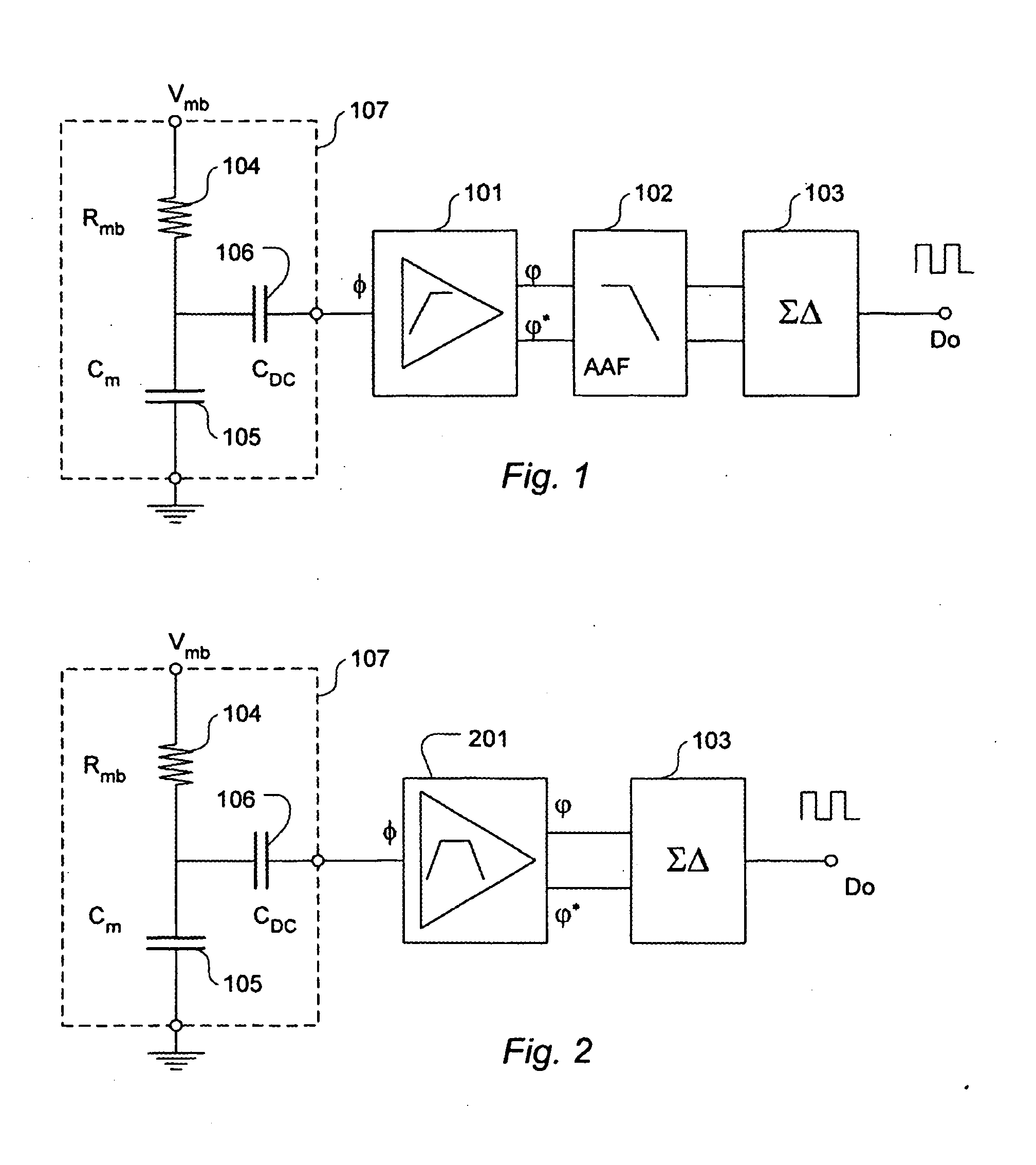

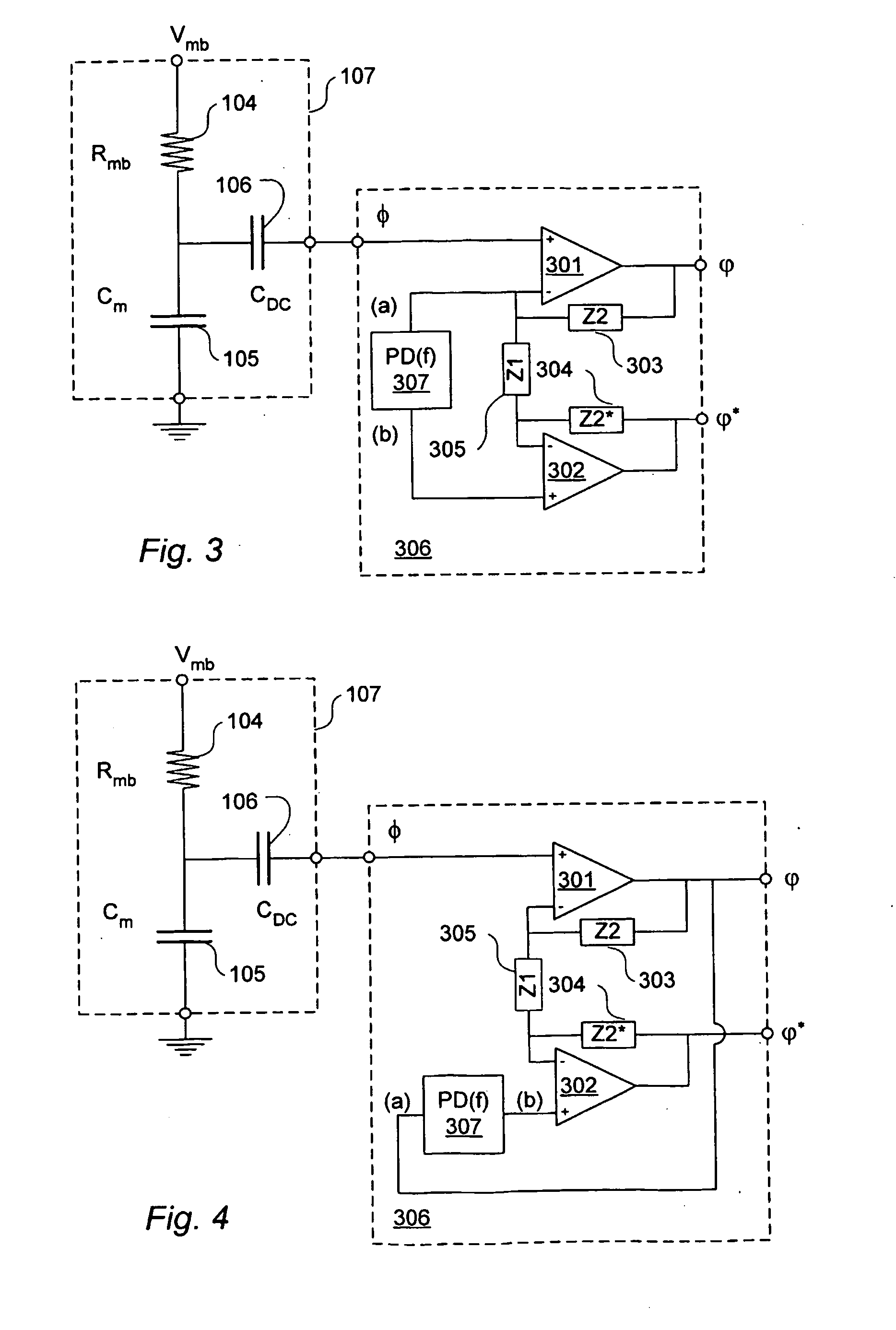

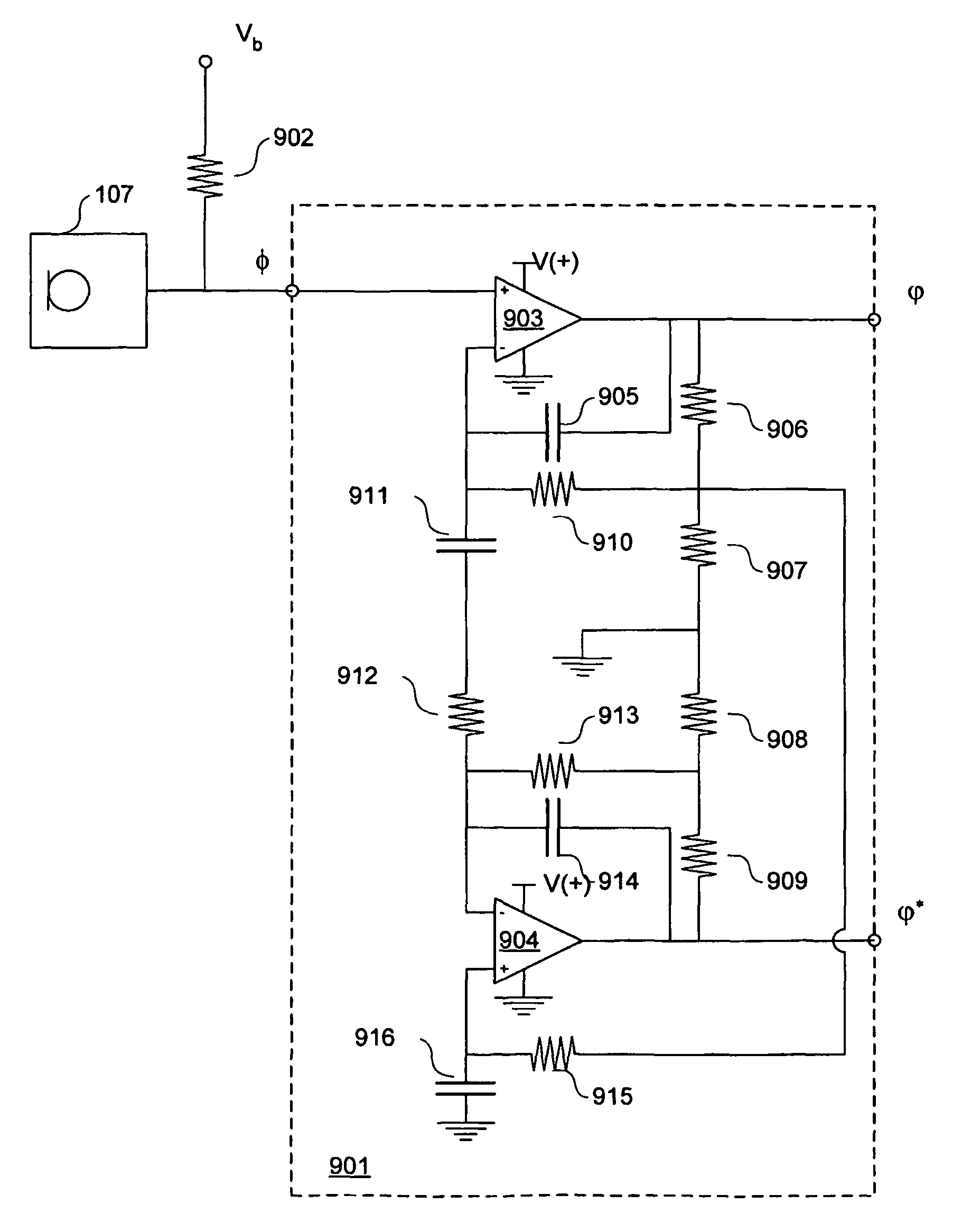

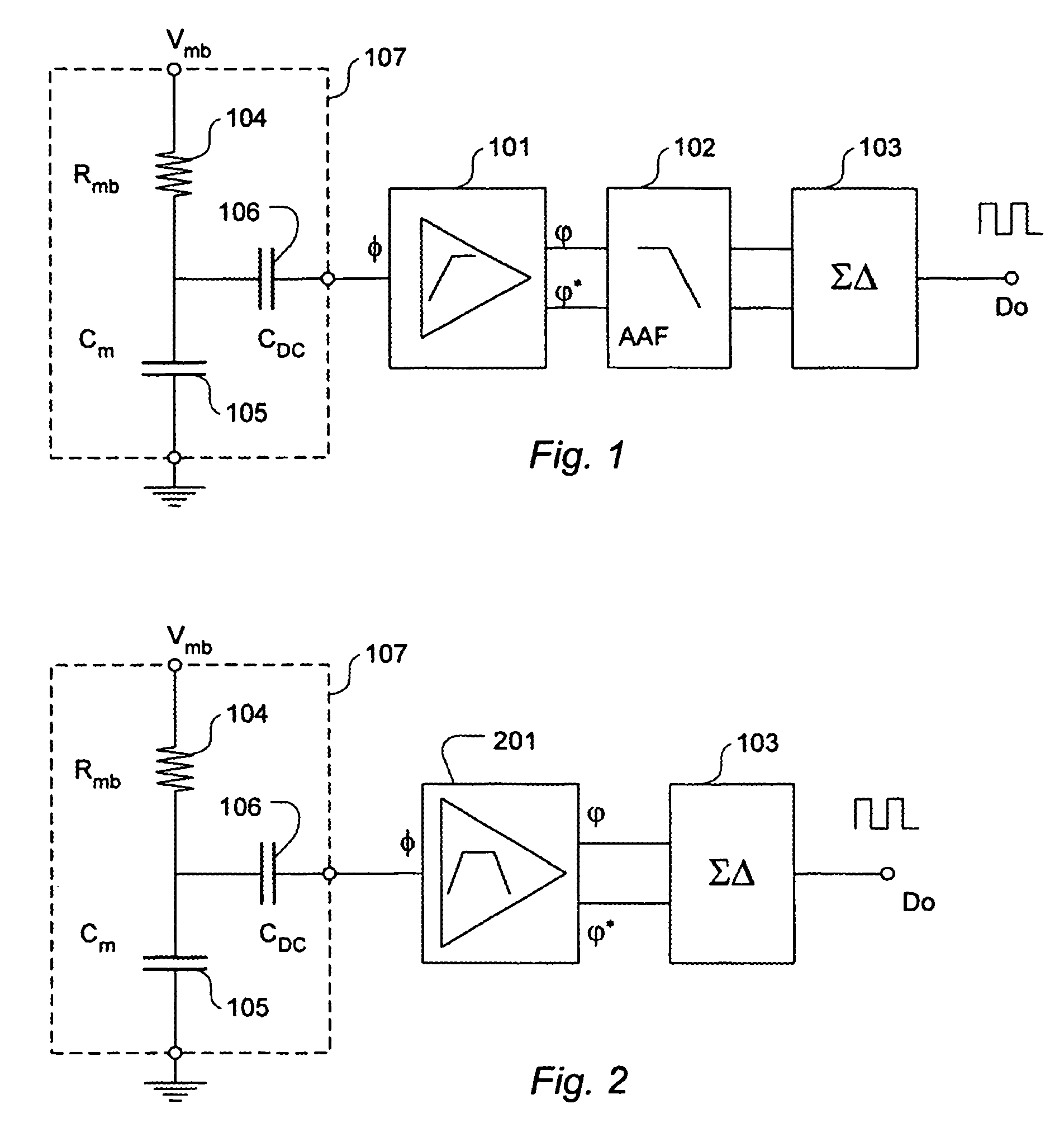

Digital microphone

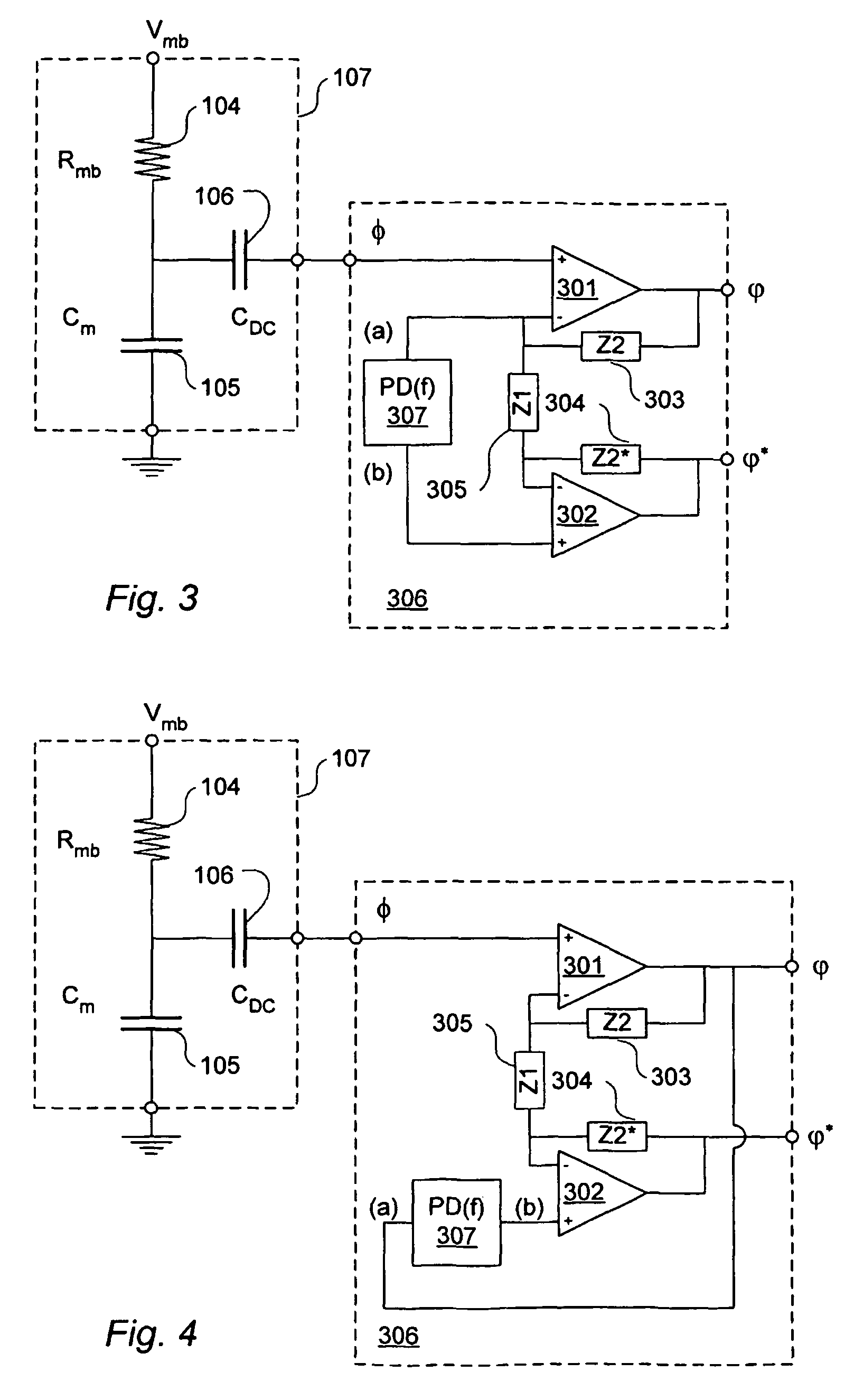

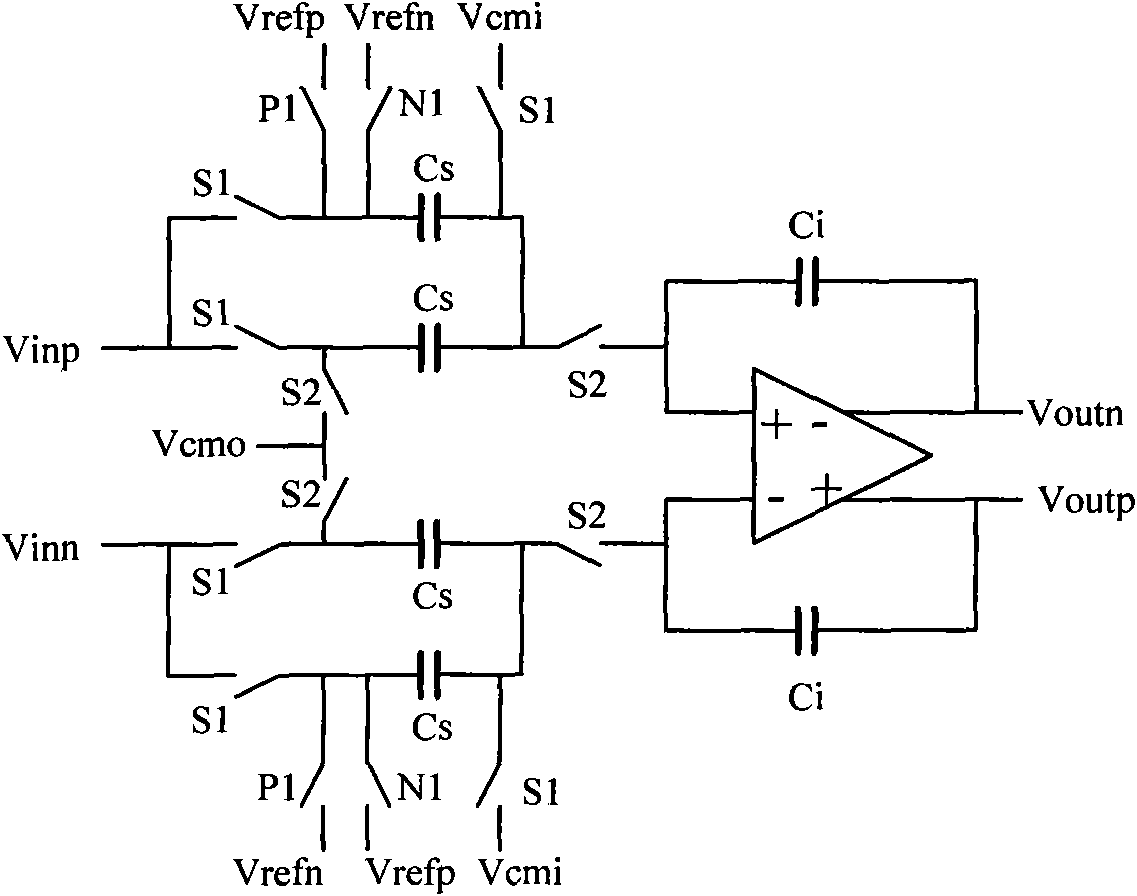

ActiveUS20090316935A1High input impedanceLarge common mode rejection ratioAmplifier modifications to reduce non-linear distortionNegative-feedback-circuit arrangementsA d converterAnti-aliasing

An integrated circuit, configured to process microphone signals, where the integrated circuit comprises: a preamplifier (306) with an amplifier section (301) which has a first input (φ) and a second input (φ*) and an output (φ), and with a feedback filter network (Z1; Z1, Z1*, Z2) coupled between the output (φ; φ, φ*) and the second input (φ′); where the first input (φ) to the amplifier section (301) has an input impedance which by means of the input impedance of the amplifier section is substantially isolated from the feedback network with respect to input impedance; and where the preamplifier has a frequency-gain transfer function which suppress low frequencies; and an analogue-to-digital converter coupled to receive an anti-aliasing filtered input signal and providing a digital output signal (Do).

Owner:ANALOG DEVICES INC

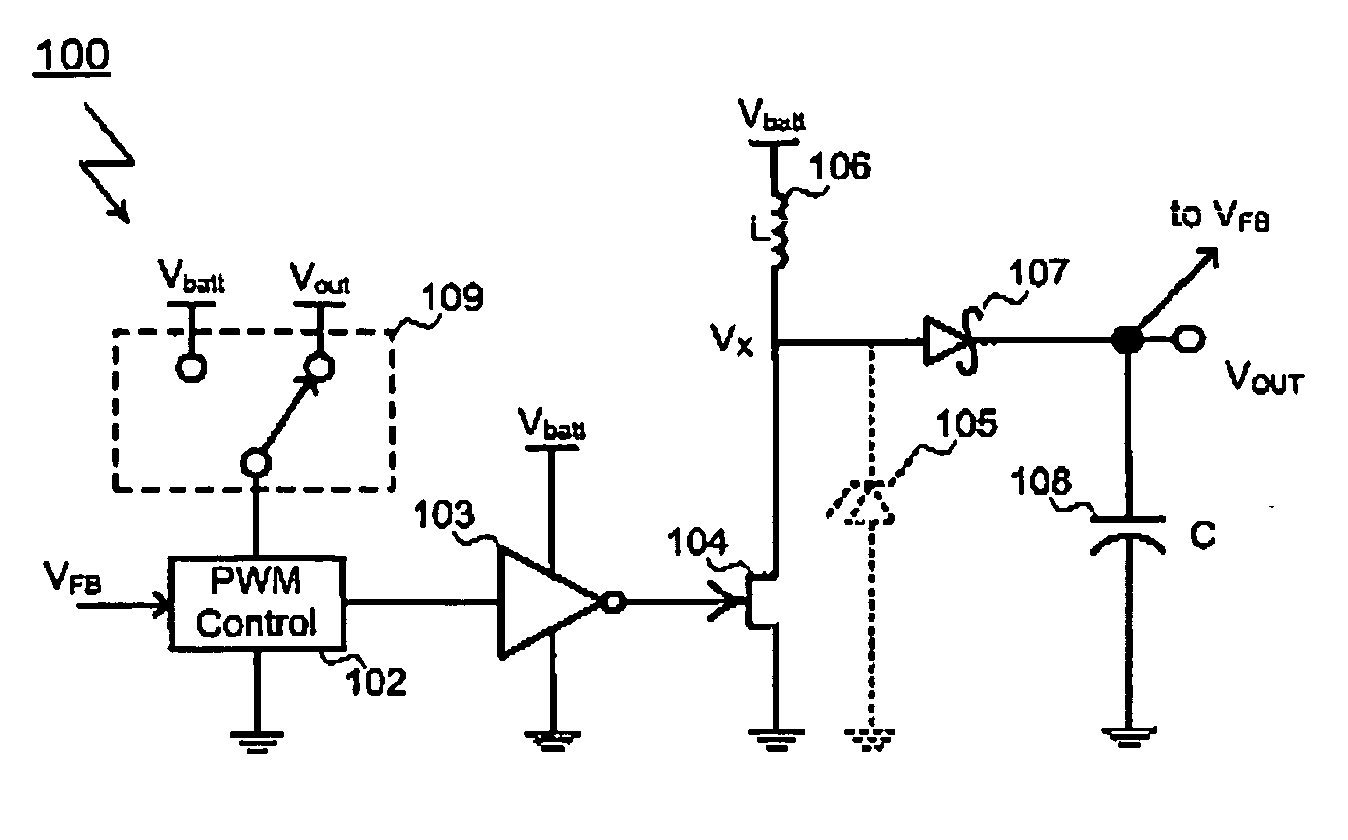

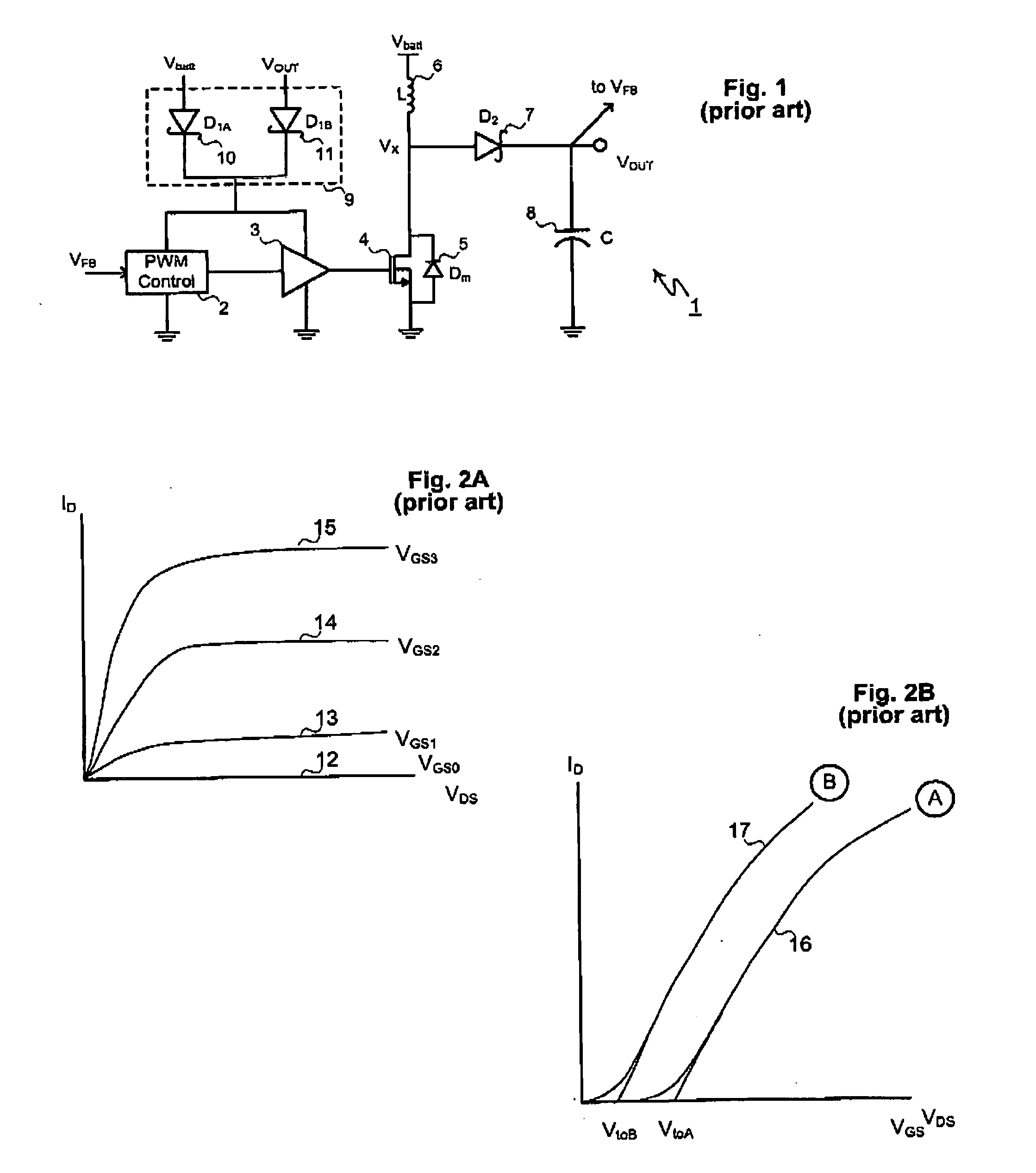

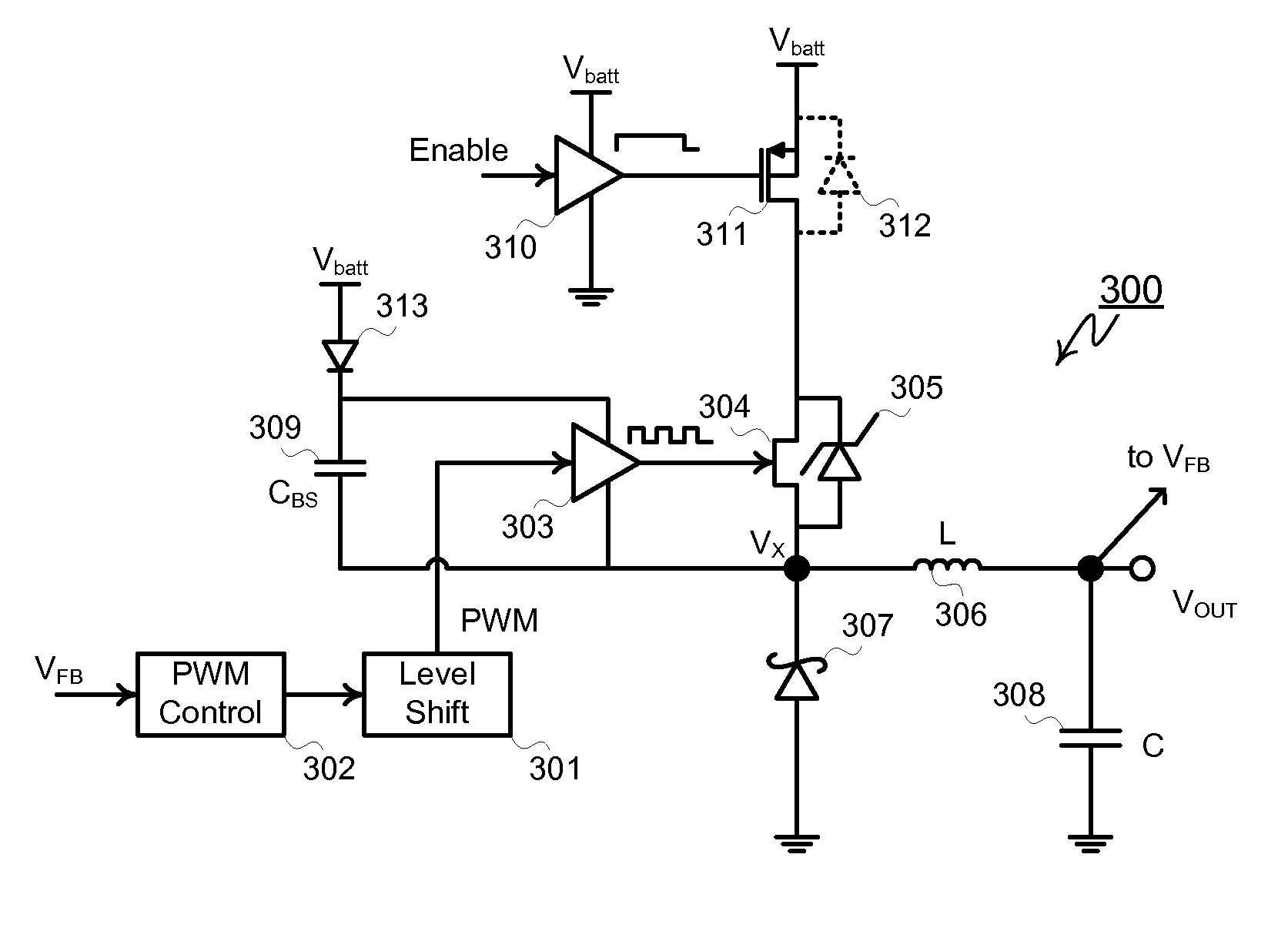

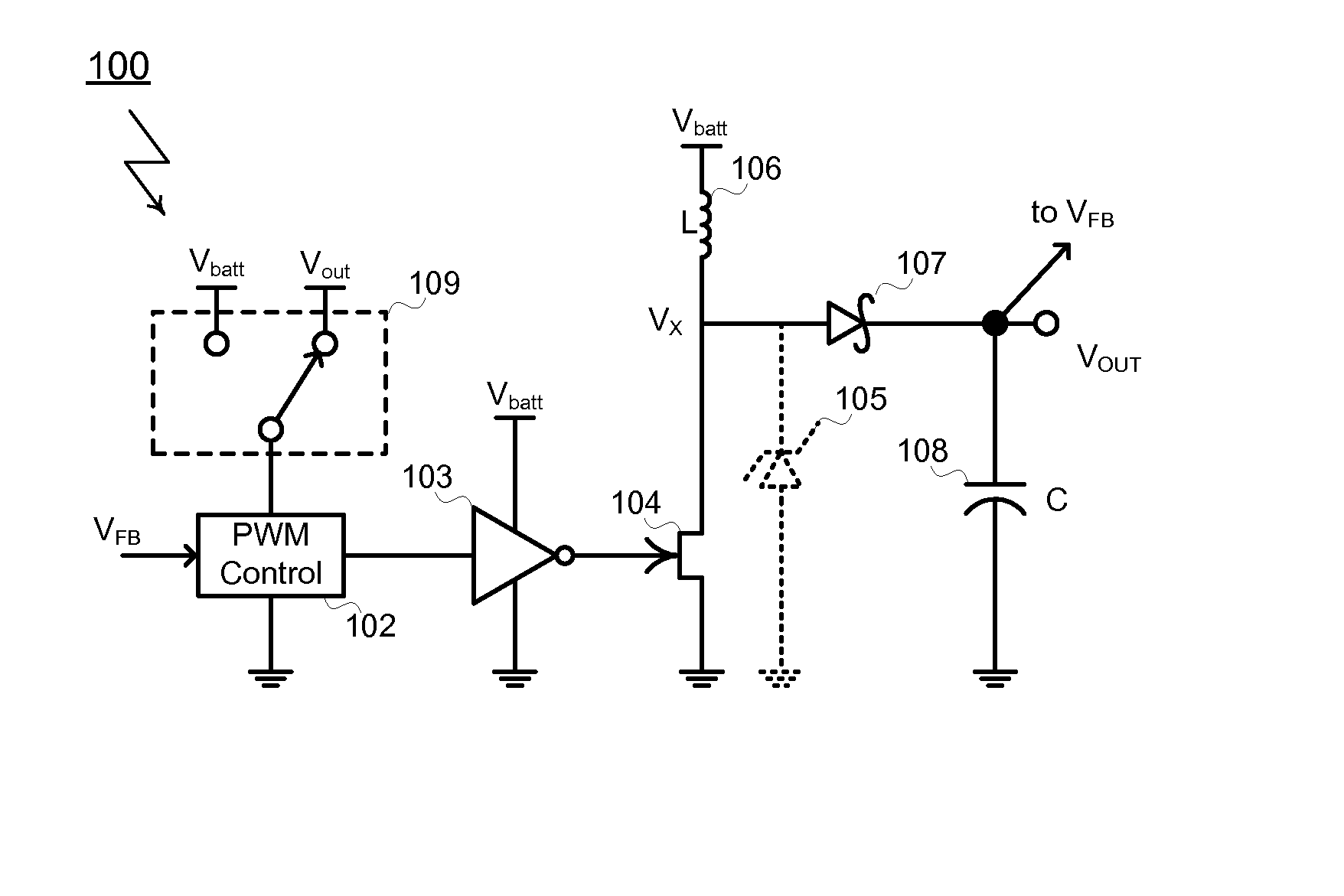

High-Frequency Buck Converter that Includes a Cascode MESFET-MOSFET Power Switch

InactiveUS20080191679A1Lower on-resistanceLow off-state drain leakageDc-dc conversionElectric variable regulationMOSFETElectrical battery

A Buck converter that includes a cascode switch comprising a series connected MESFET and MOSFET power switch. The cascode power switch is typically connected in between a power source and a node Vx. The node Vx is connected to an output node via an inductor and to ground via a Schottky diode or a second MESFET or both. A control circuit drives the MESFET (and the second MESFET) so that the inductor is alternately connected to the battery and to ground. The MOSFET is switched off during sleep or standby modes to minimize leakage current through the MESFET. The MOSFET is therefore switched at a low frequency compared to the MESFET and does not contribute significantly to switching losses in the converter.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

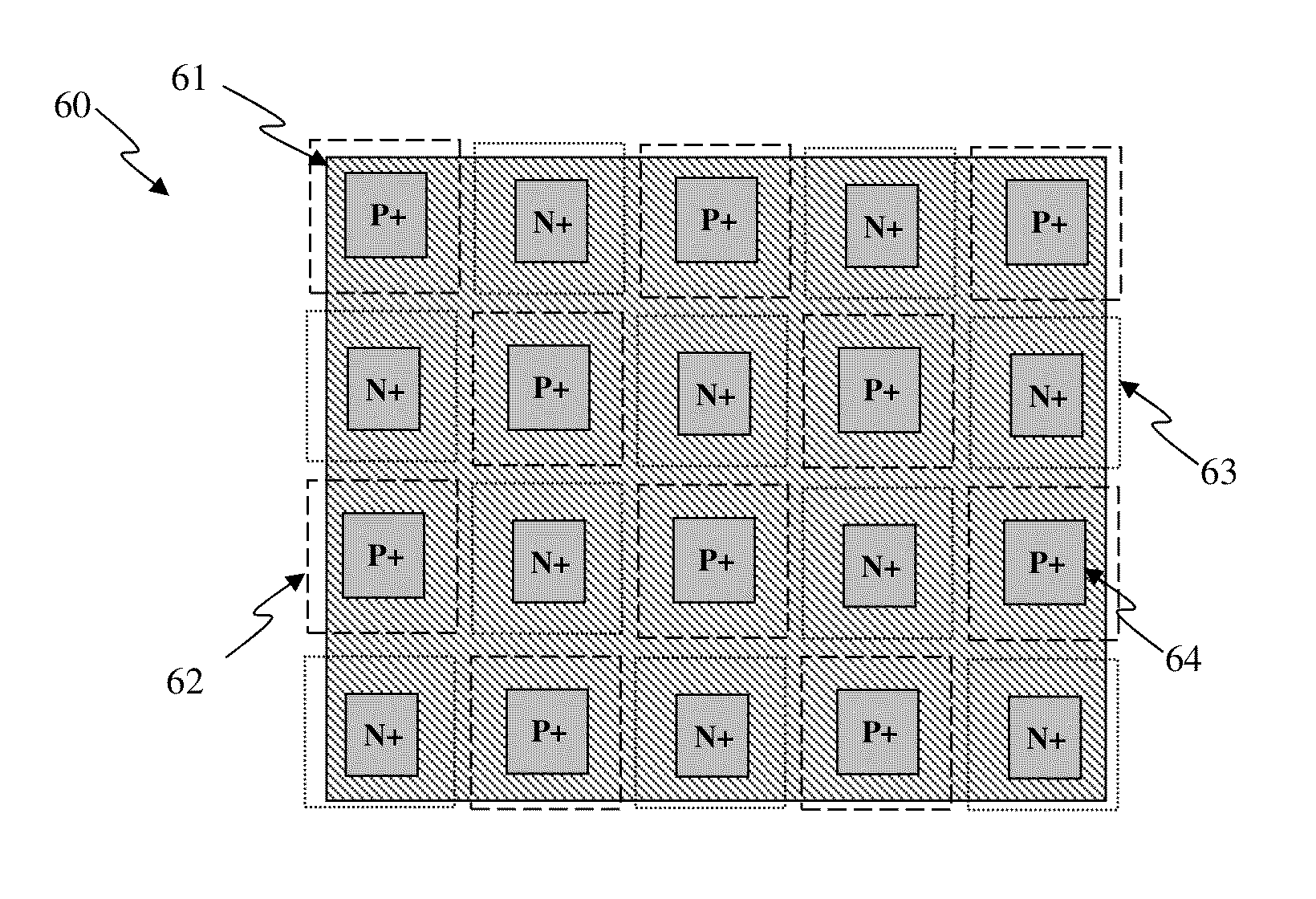

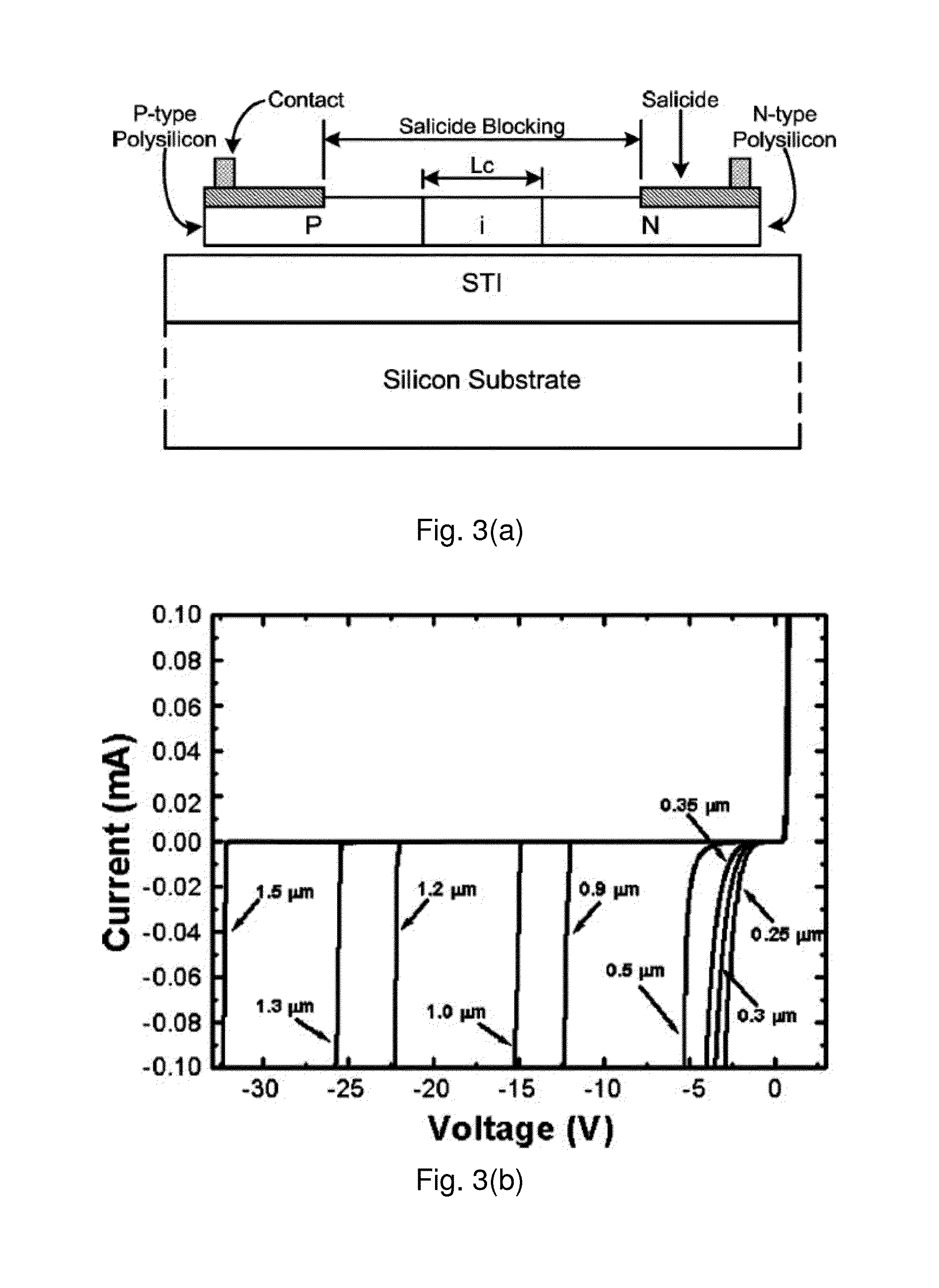

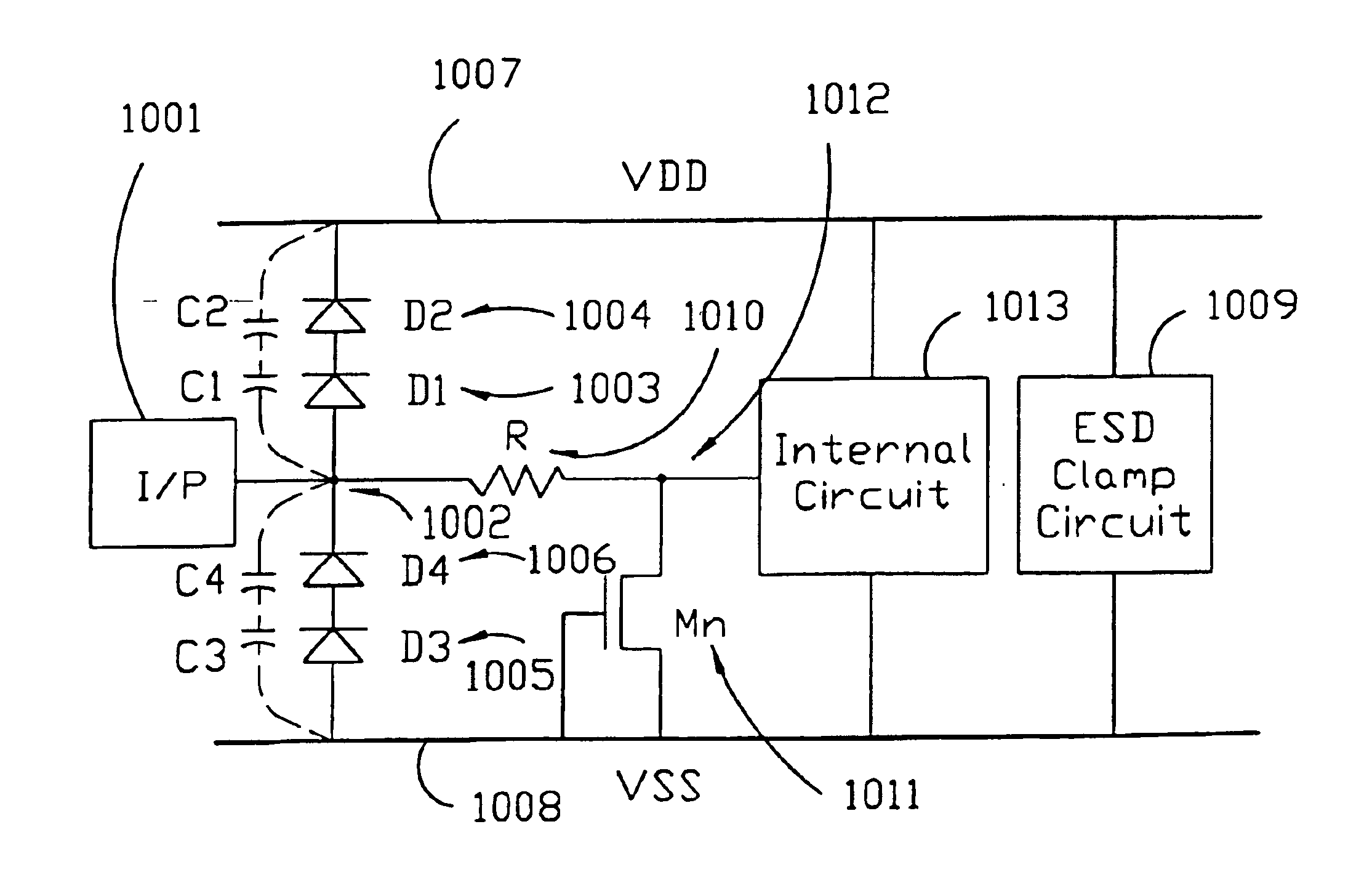

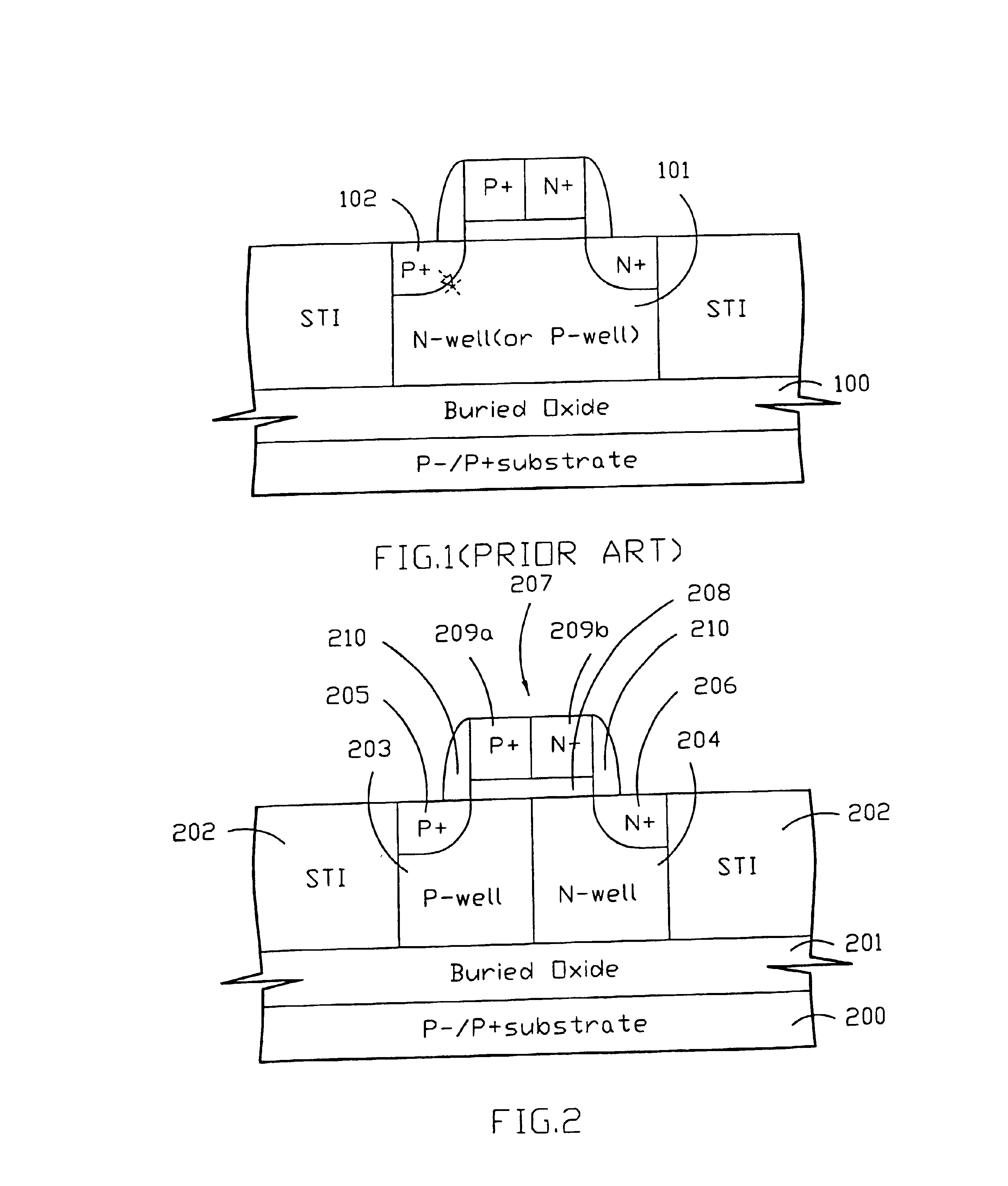

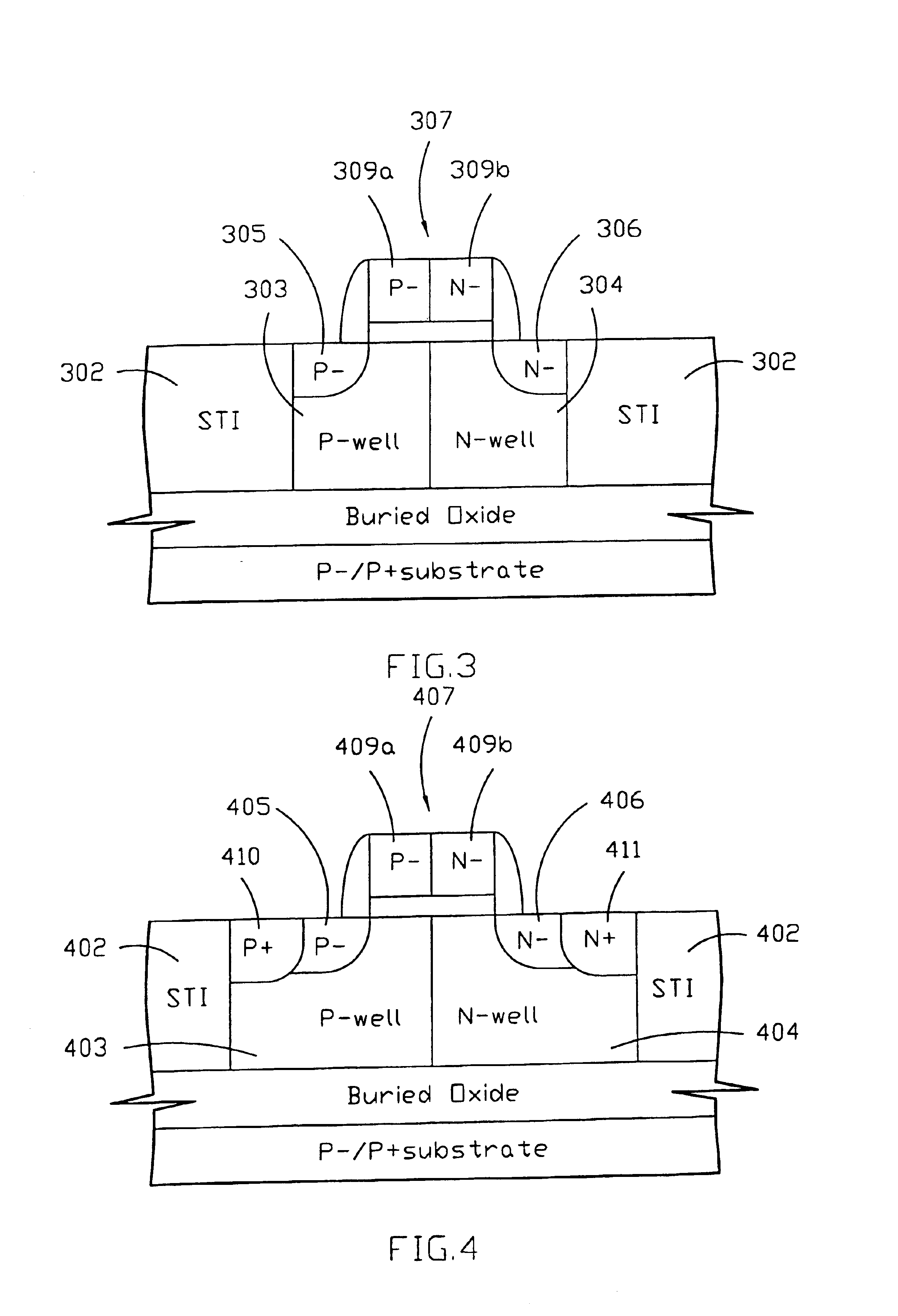

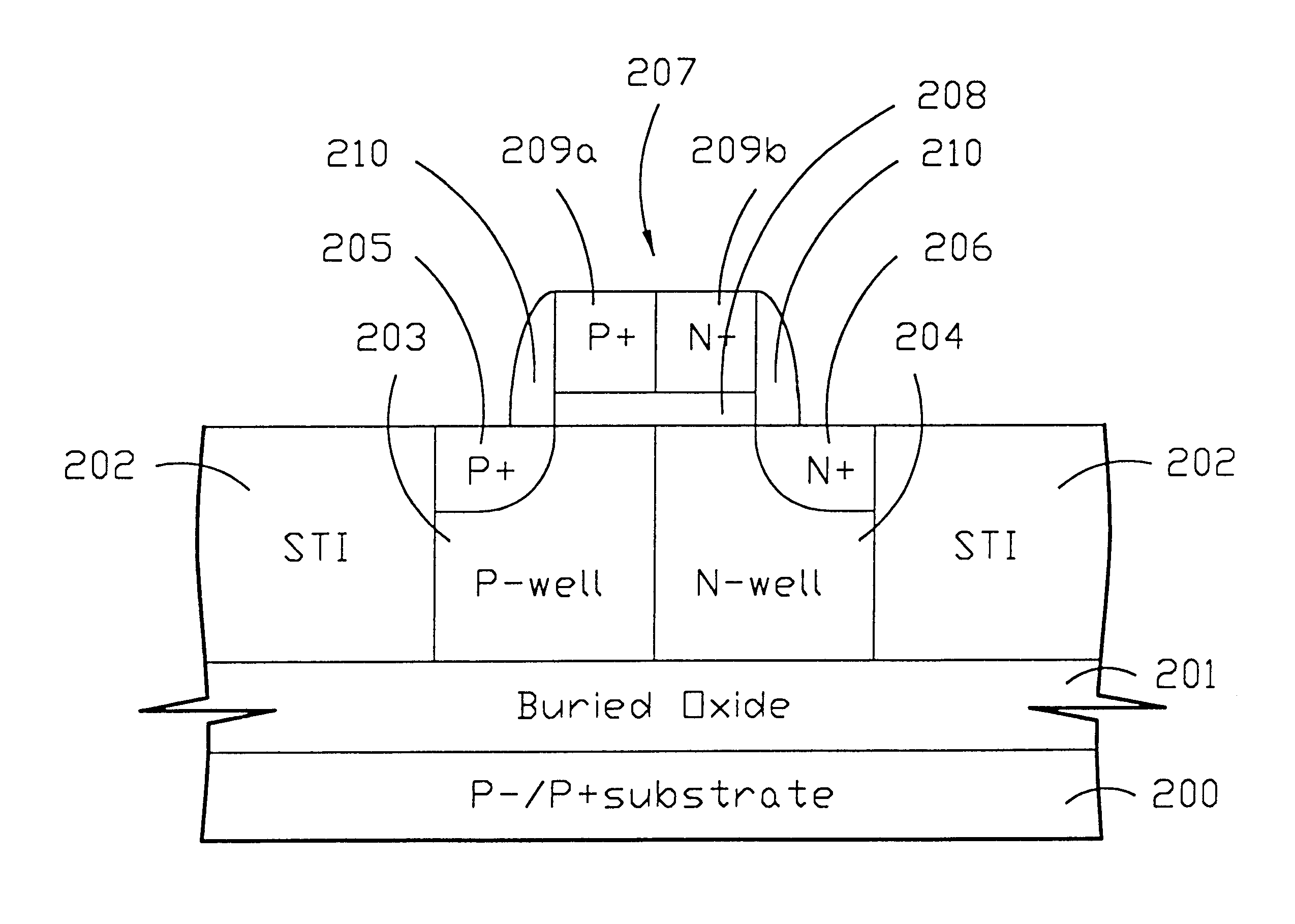

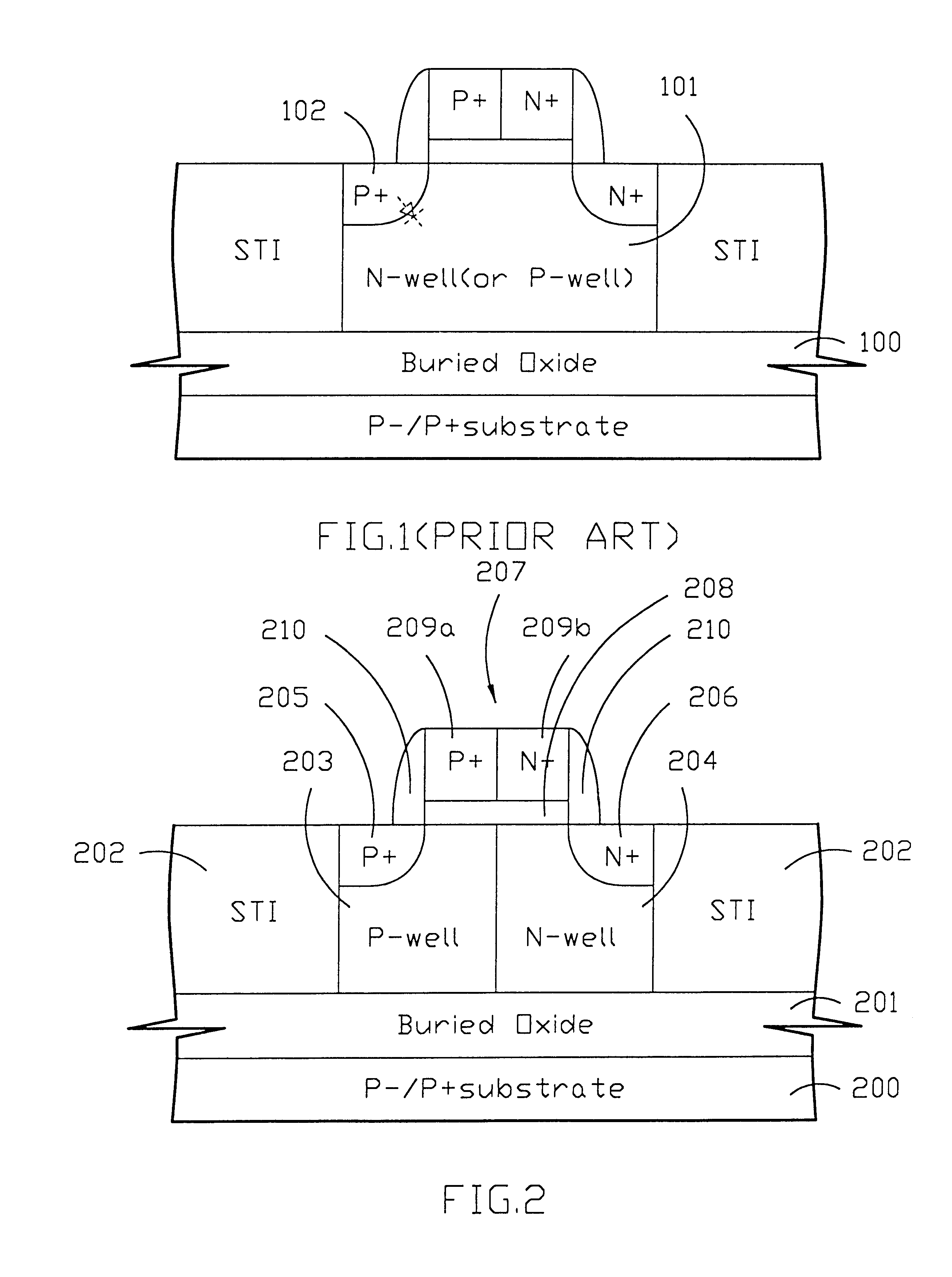

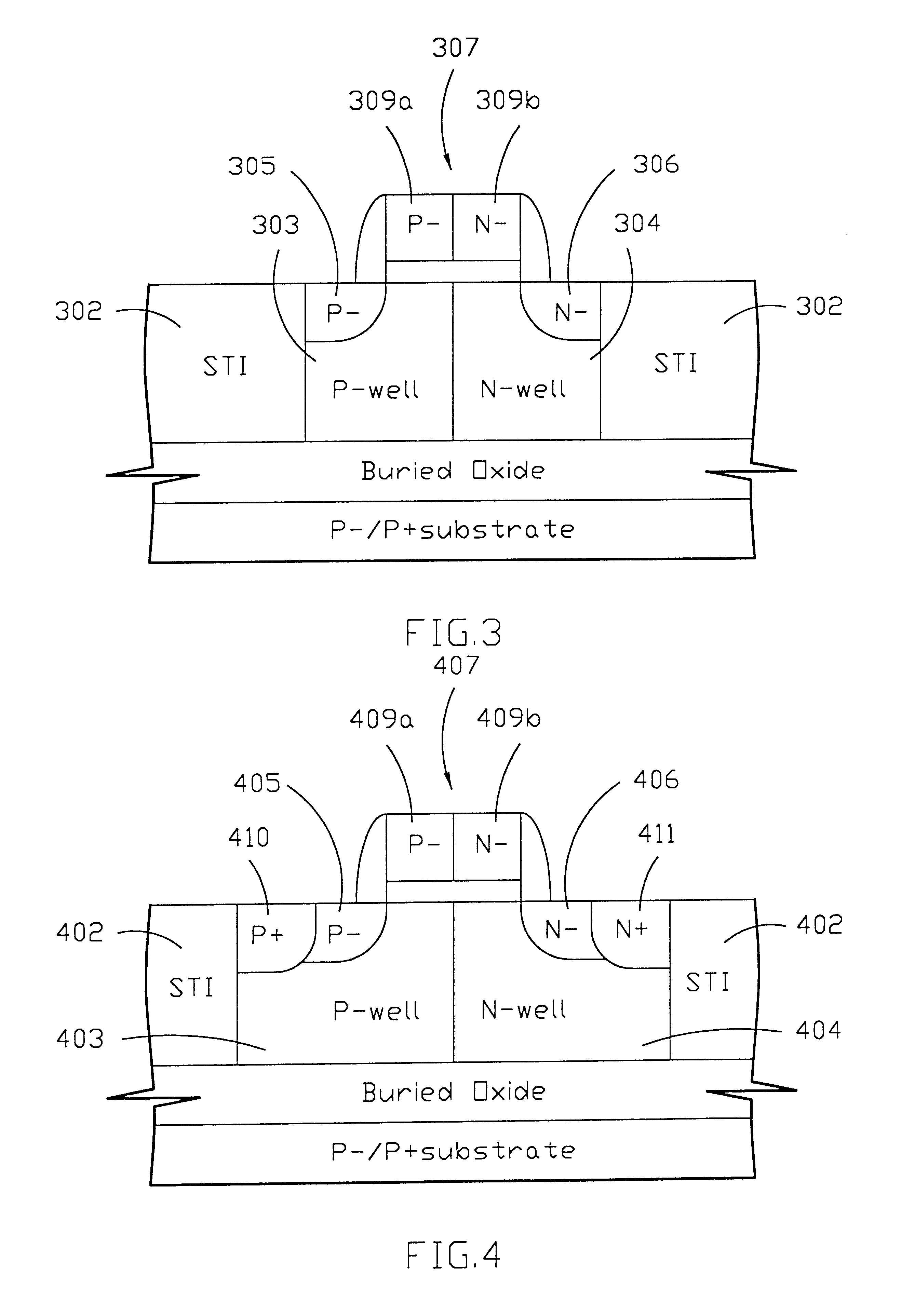

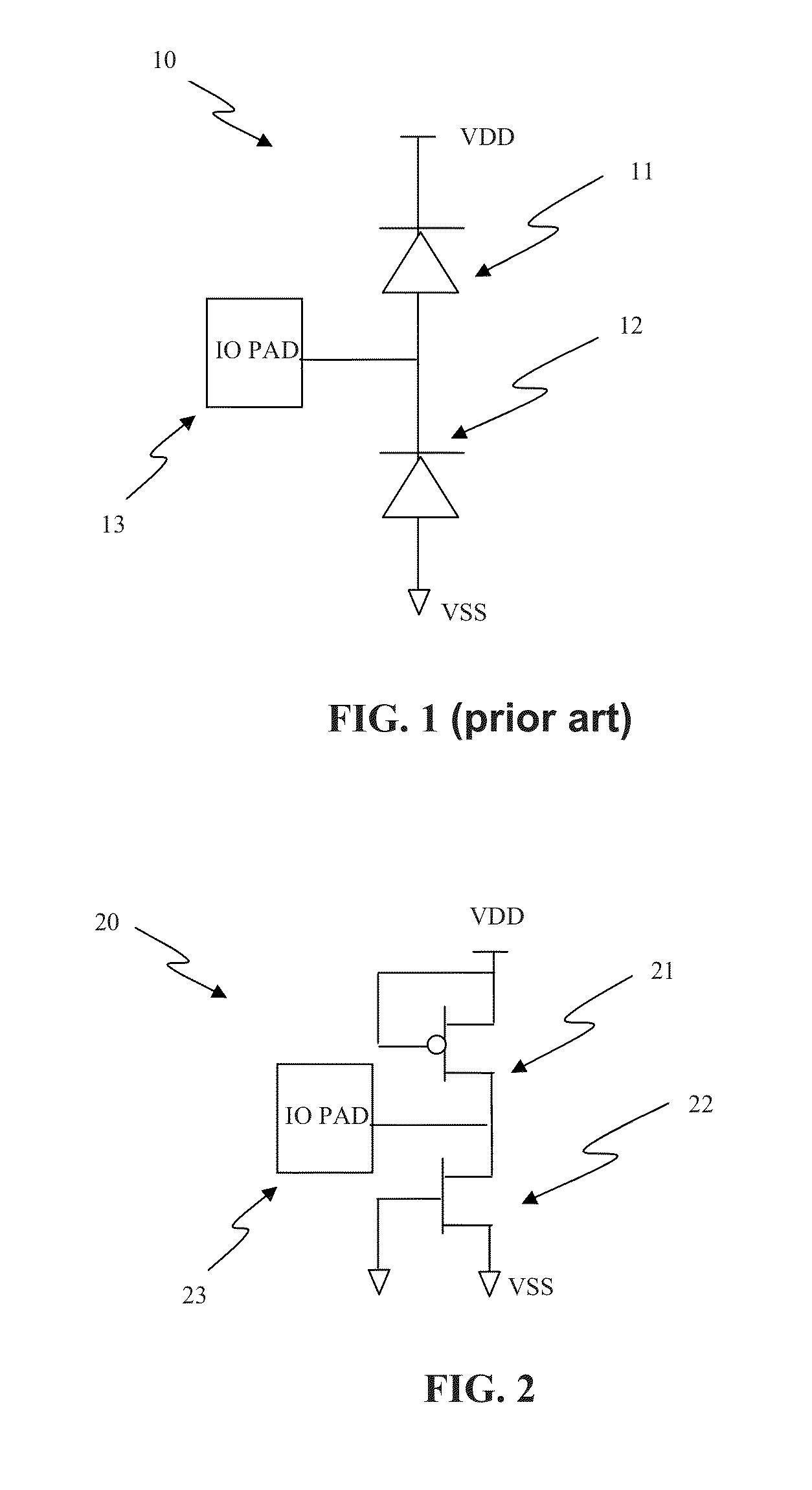

Silicon-on-insulator diodes and ESD protection circuits

InactiveUS6861680B2Reduce power densityHigh protection levelTransistorSolid-state devicesCapacitanceSilicon on insulator

A silicon-on-insulator (SOI) gated diode and non-gated junction diode are provided. The SOI gated diode has a PN junction at the middle region under the gate, which has more junction area than a normal diode. The SOI non-gated junction diode has a PN junction at the middle region thereof, and also has more junction area than a normal diode. The SOI diodes of the present invention improve the protection level offered for electrical overstress (EOS) / electrostatic discharge (ESD) due to the low power density and heating for providing more junction area than normal ones. The I / O ESD protection circuits, which comprise primary diodes, a first plurality of diodes, and a second plurality of diodes, all of which are formed of the present SOI diodes, could effectively discharge the current when there is an ESD event. And the ESD protection circuits, which comprise more primary diodes, could effectively reduce the parasitic input capacitance, so that they can be used in the RF circuits or HF circuits. The proposed gated diode and non-gated diode can be fully process-compatiable to general partially-depleted or fully-depleted silicon-on-insulator CMOS processes.

Owner:UNITED MICROELECTRONICS CORP

DC-DC Converter that Includes a High Frequency Power MESFET Gate Drive Circuit

InactiveUS20080203991A1Lower on-resistanceLow off-state drain leakageTransistorDc-dc conversionDc dc converterHigh frequency power

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

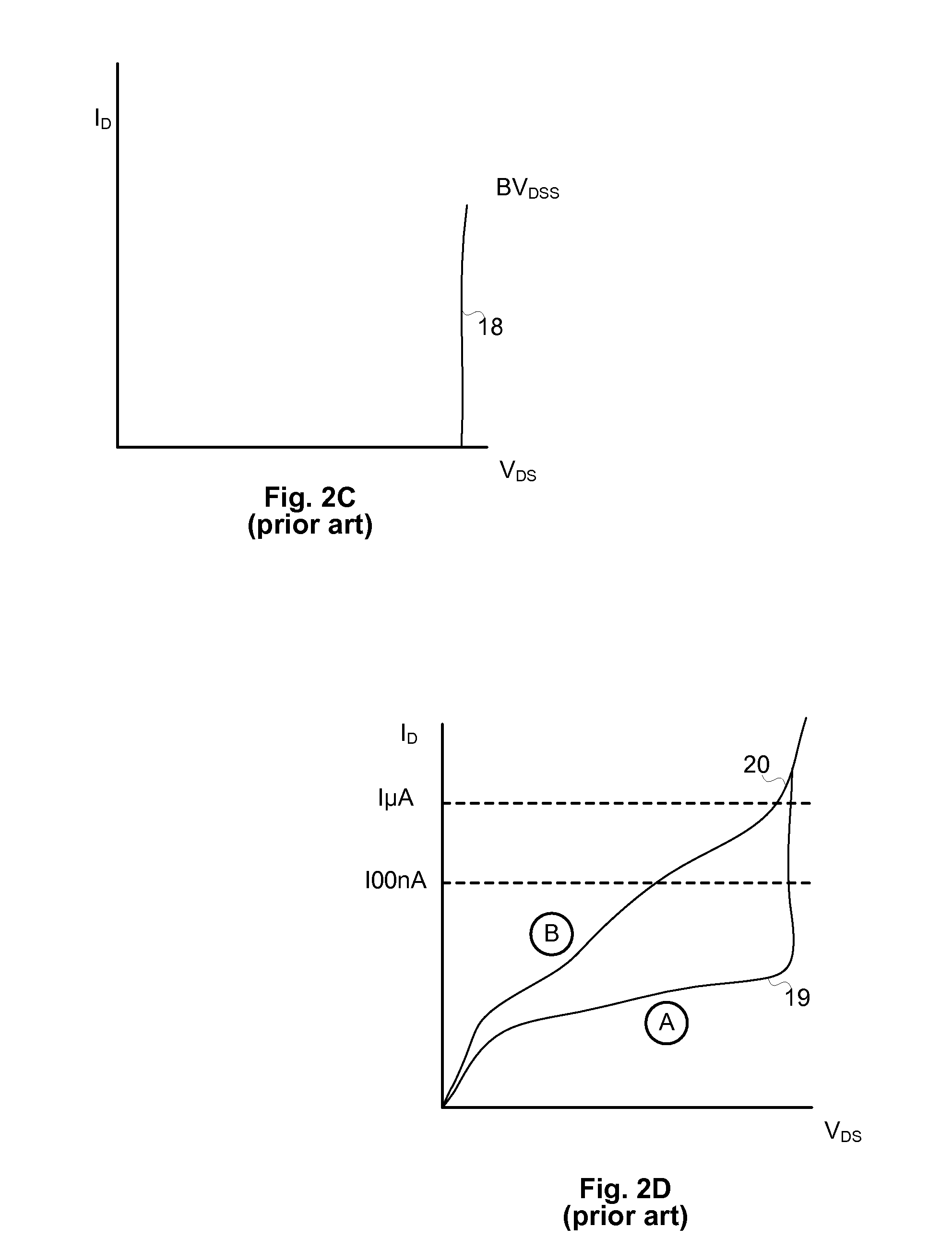

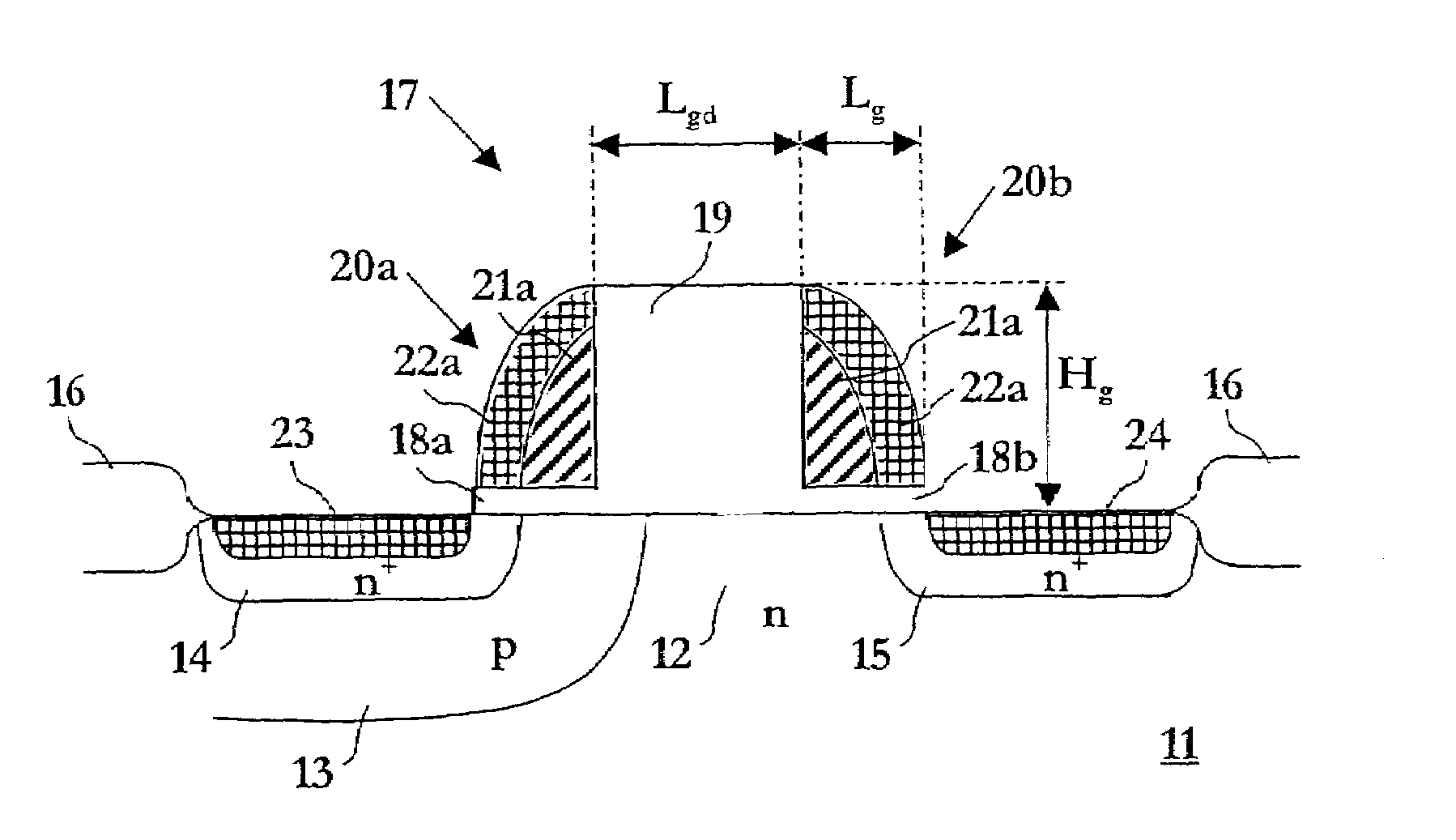

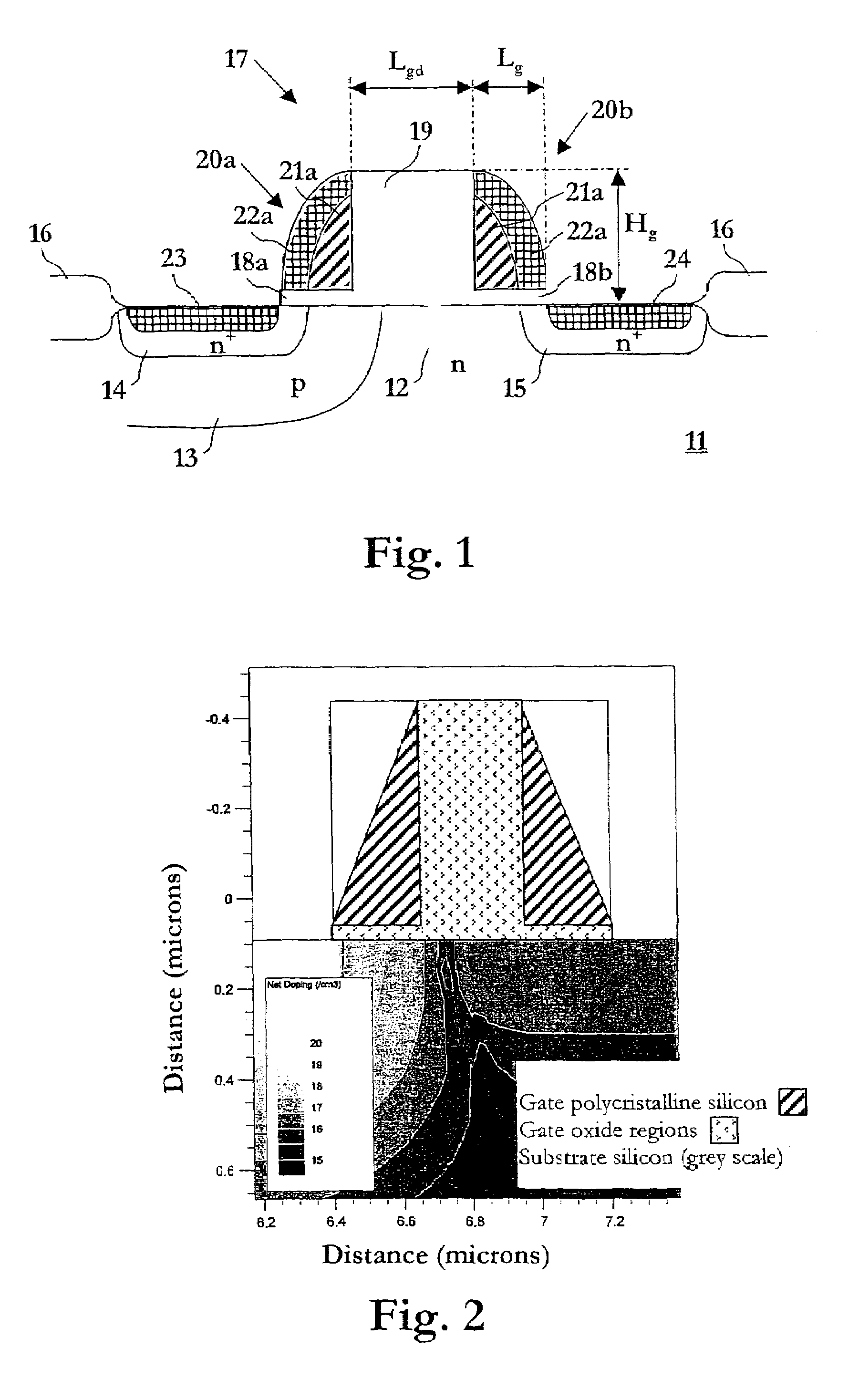

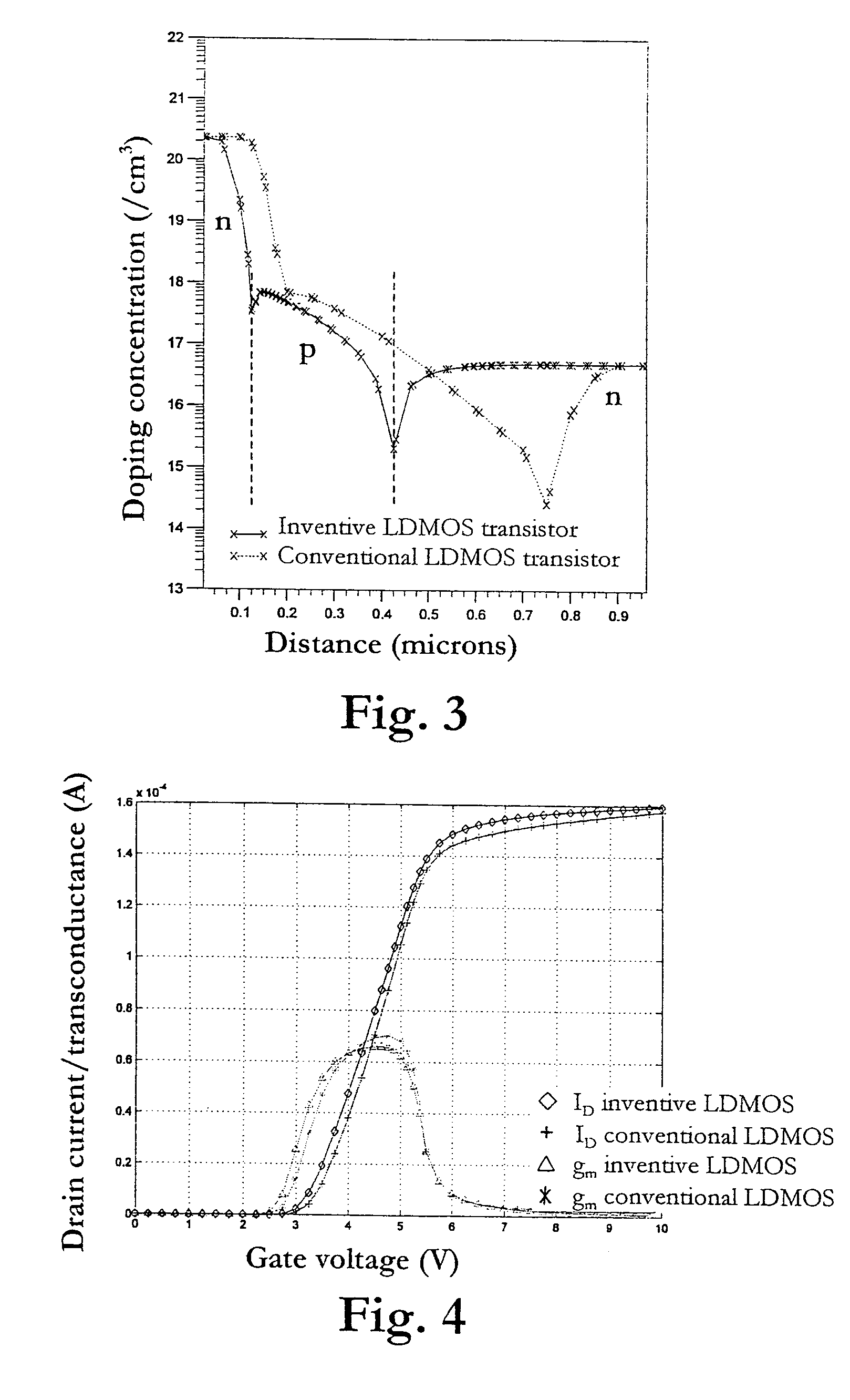

LDMOS transistor device employing spacer structure gates

InactiveUS7391080B2Increase speedShorten the lengthSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSInsulation layer

Owner:INFINEON TECH AG

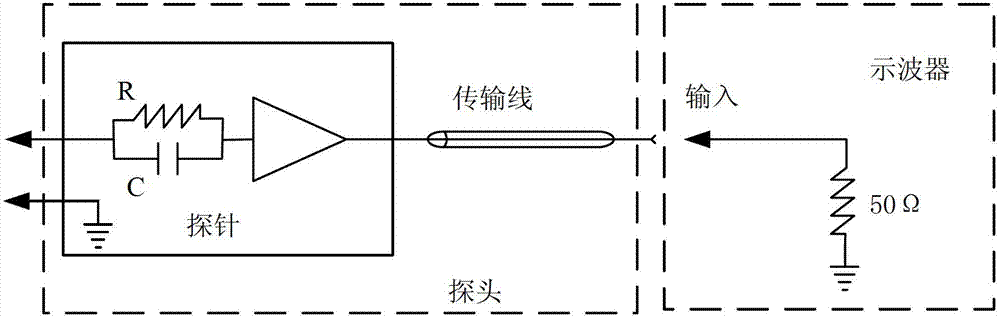

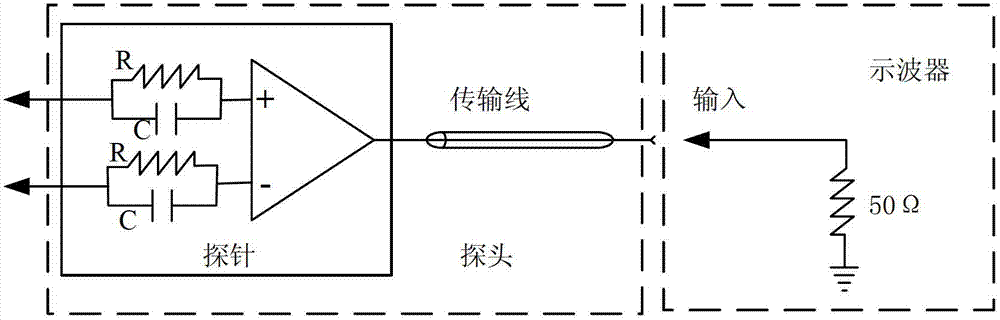

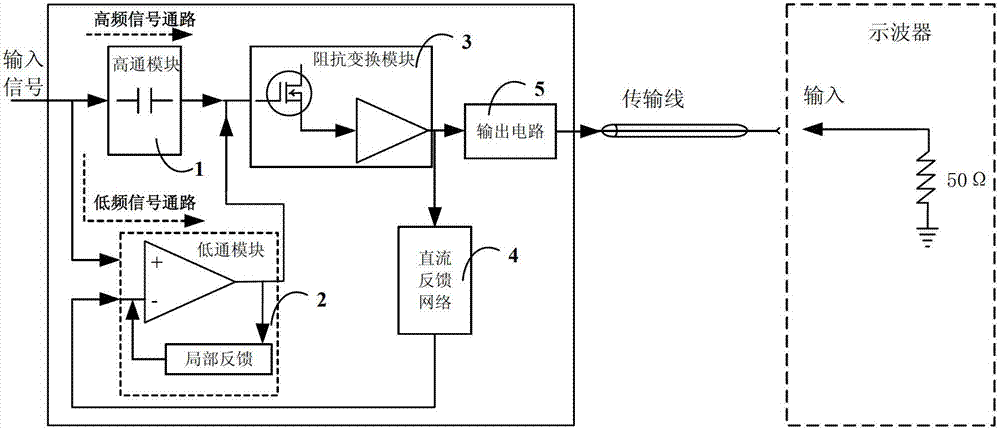

Single-ended active probe circuit of digital oscilloscope

InactiveCN102735887AReduce input capacitanceLow output impedanceMeasurement leads/probesCapacitanceInput impedance

The invention discloses a single-ended active probe circuit of a digital oscilloscope, which combines high-speed signal completeness test requirements and combines an existing component based on a broadband testing principle for analyzing a single-ended active probe. Through an impedance conversion module, the requirements of the single-ended active probe in high input impedance, smallest input capacitance and small output impedance are realized; simultaneously, through an output circuit, the single-ended active probe circuit can be matched with the input impedance of 50 ohm of the oscilloscope.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

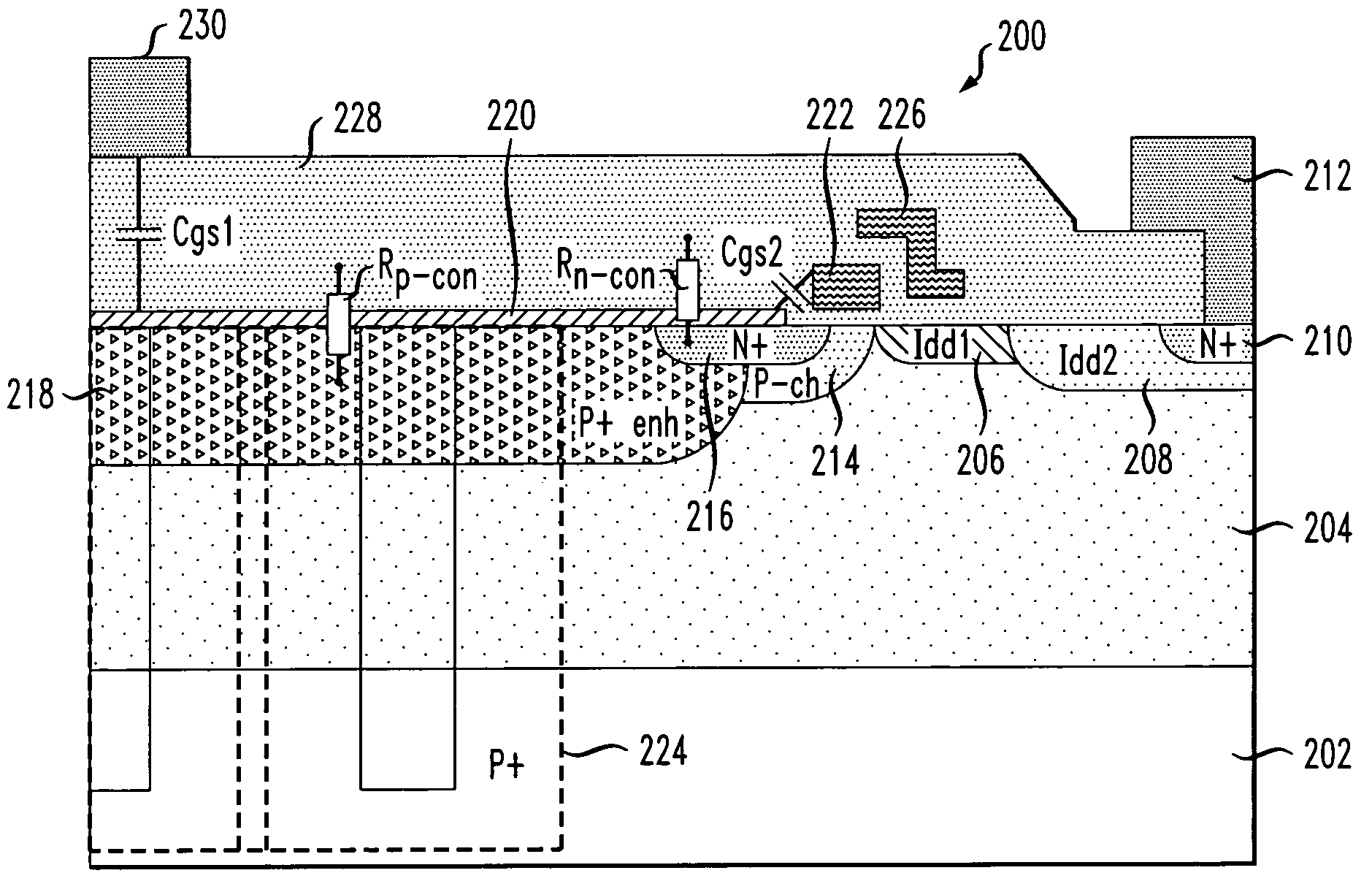

Metal-oxide-semiconductor device with enhanced source electrode

ActiveUS7126193B2Reduce input capacitanceImprove device performanceSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical connectionSemiconductor

An MOS device is formed including a semiconductor layer of a first conductivity type, a first source / drain region of a second conductivity type formed in the semiconductor layer, and a second source / drain region of the second conductivity type formed in the semiconductor layer and spaced apart from the first source / drain region. A gate is formed proximate an upper surface of the semiconductor layer and at least partially between the first and second source / drain regions. The MOS device further includes at least one contact, the at least one contact including a silicide layer formed on and in electrical connection with at least a portion of the first source / drain region, the silicide layer extending laterally away from the gate. The contact further includes at least one insulating layer formed directly on the silicide layer.

Owner:CICLON SEMICON DEVICE

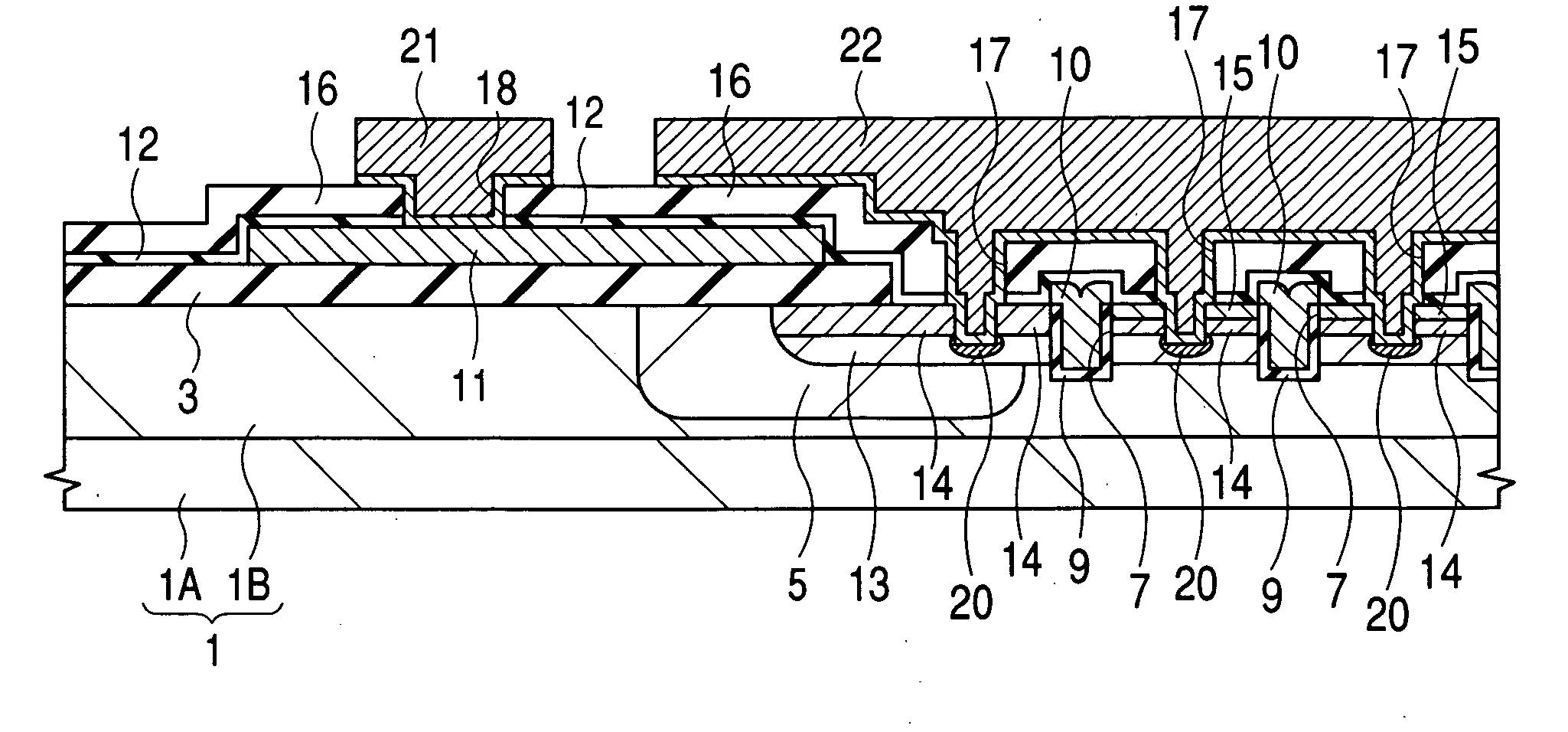

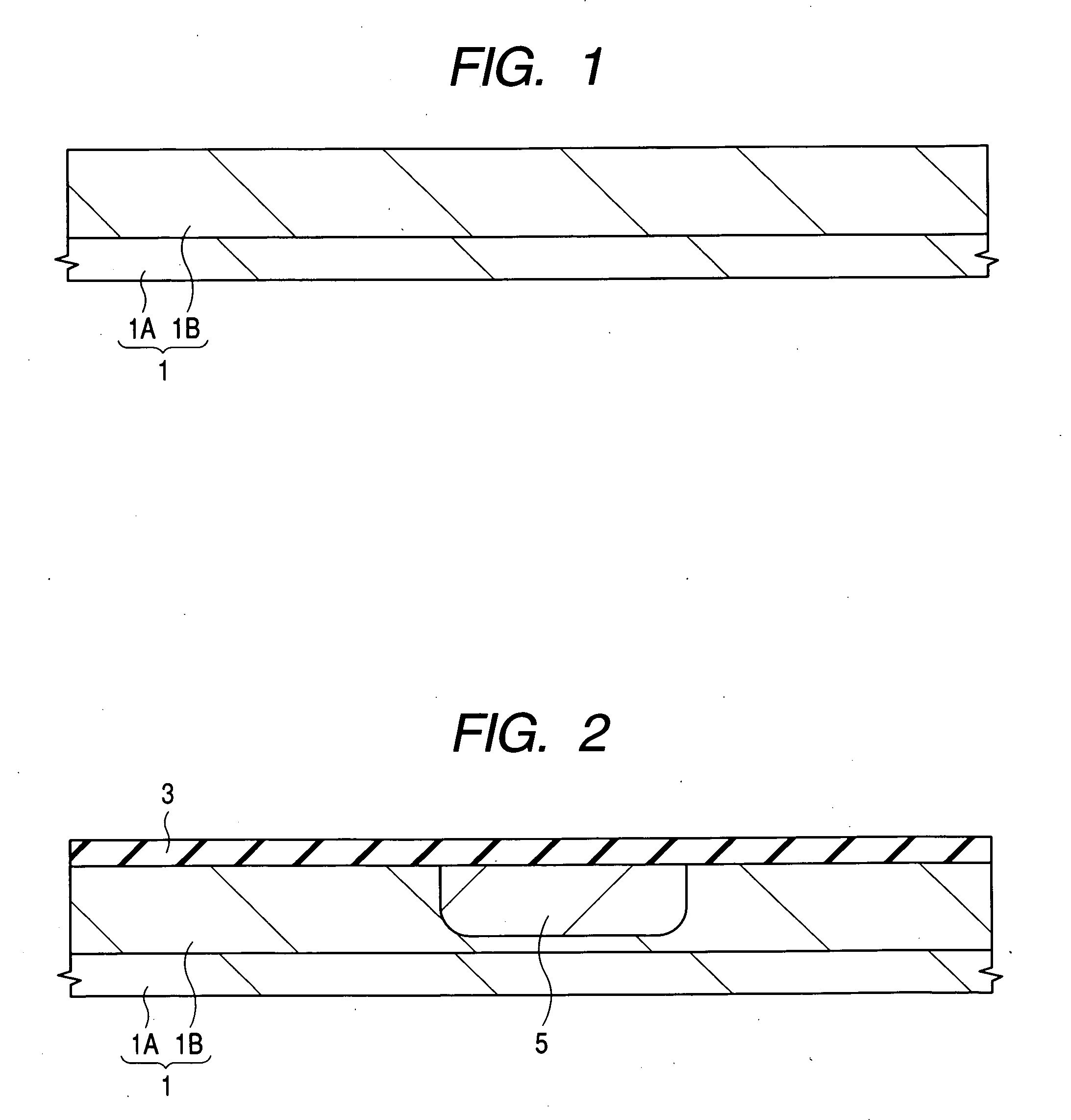

Semiconductor device and a method of manufacturing the same

InactiveUS20070120194A1Easy to integrateReduce resistanceSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceDevice material

A technology is provided to reduce ON-resistance, and the prevention of punch through is achieved with respect to a trench gate type power MISFET. Input capacitance and a feedback capacitance are reduced by forming a groove in which a gate electrode is formed so as to have a depth as shallow as about 1 μm or less, a p− type semiconductor region is formed to a depth so as not to cover the bottom of the groove, and a p-type semiconductor region higher in impurity concentration than the p− type semiconductor region is formed under a n+ type semiconductor region serving as a source region of the trench gate type power MISFET, causing the p-type semiconductor region to serve as a punch-through stopper layer of the trench gate type power MISFET.

Owner:RENESAS TECH CORP

Silicon-on-insulator diodes and ESD protection circuits

InactiveUS6894324B2More junction areaReduce power densityTransistorSemiconductor/solid-state device detailsCapacitanceSilicon on insulator

A silicon-on-insulator (SOI) gated diode and non-gated junction diode are provided. The SOI gated diode has a PN junction at the middle region under the gate, and which has more junction area than a normal diode. The SOI non-gated junction diode has a PN junction at the middle region thereof, and then also has more junction area than a normal diode. The SOI diodes of the present invention improve the protection level offered for electrical overstress (EOS) / electrostatic discharge (ESD) due to the low power density and heating for providing more junction area than normal ones. The I / O ESD protection circuits, which comprise primary diodes, a first plurality of diodes, and a second plurality of diodes, all of which are formed of the present SOI diodes, could effectively discharge the current when there is an ESD event. And, the ESD protection circuits, which comprise more primary diodes, could effectively reduce the parasitic input capacitance, so that they can be used in the RF circuits or HF circuits. The proposed gated diode and non-gated diode can be fully process-compatiable to general partially depleted or fully-depleted silicon-on-insulator CMOS processes.

Owner:UNITED MICROELECTRONICS CORP

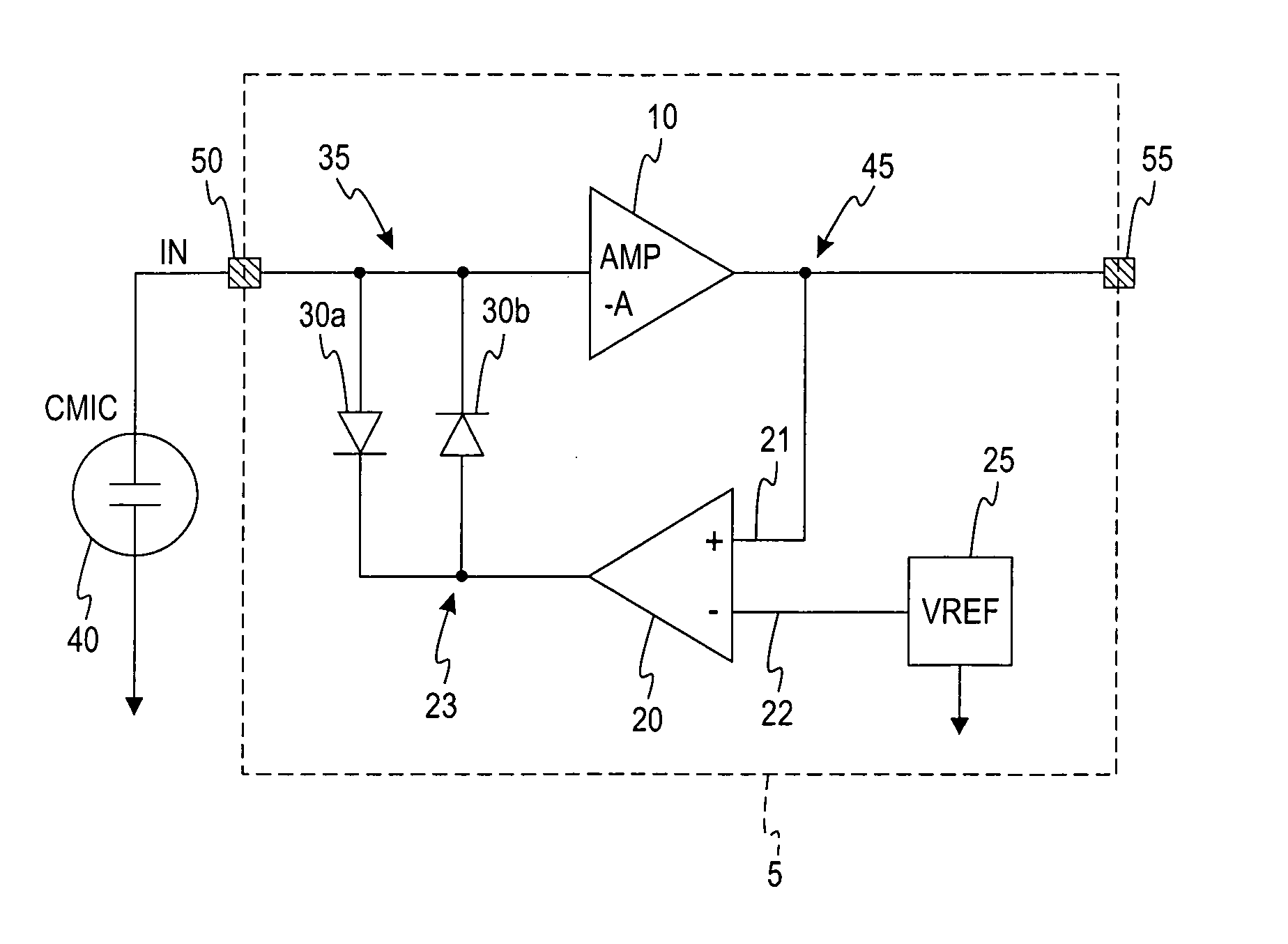

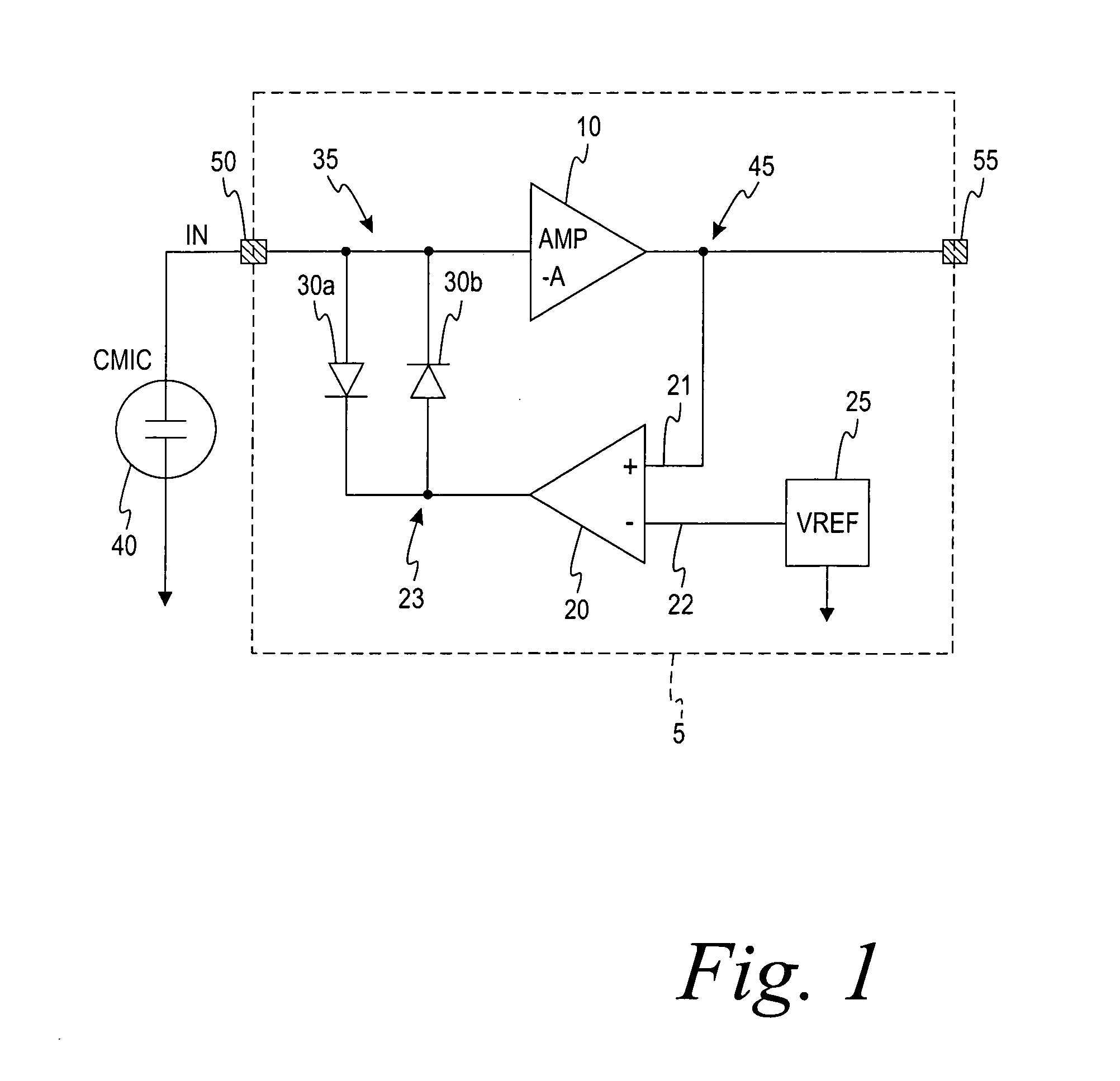

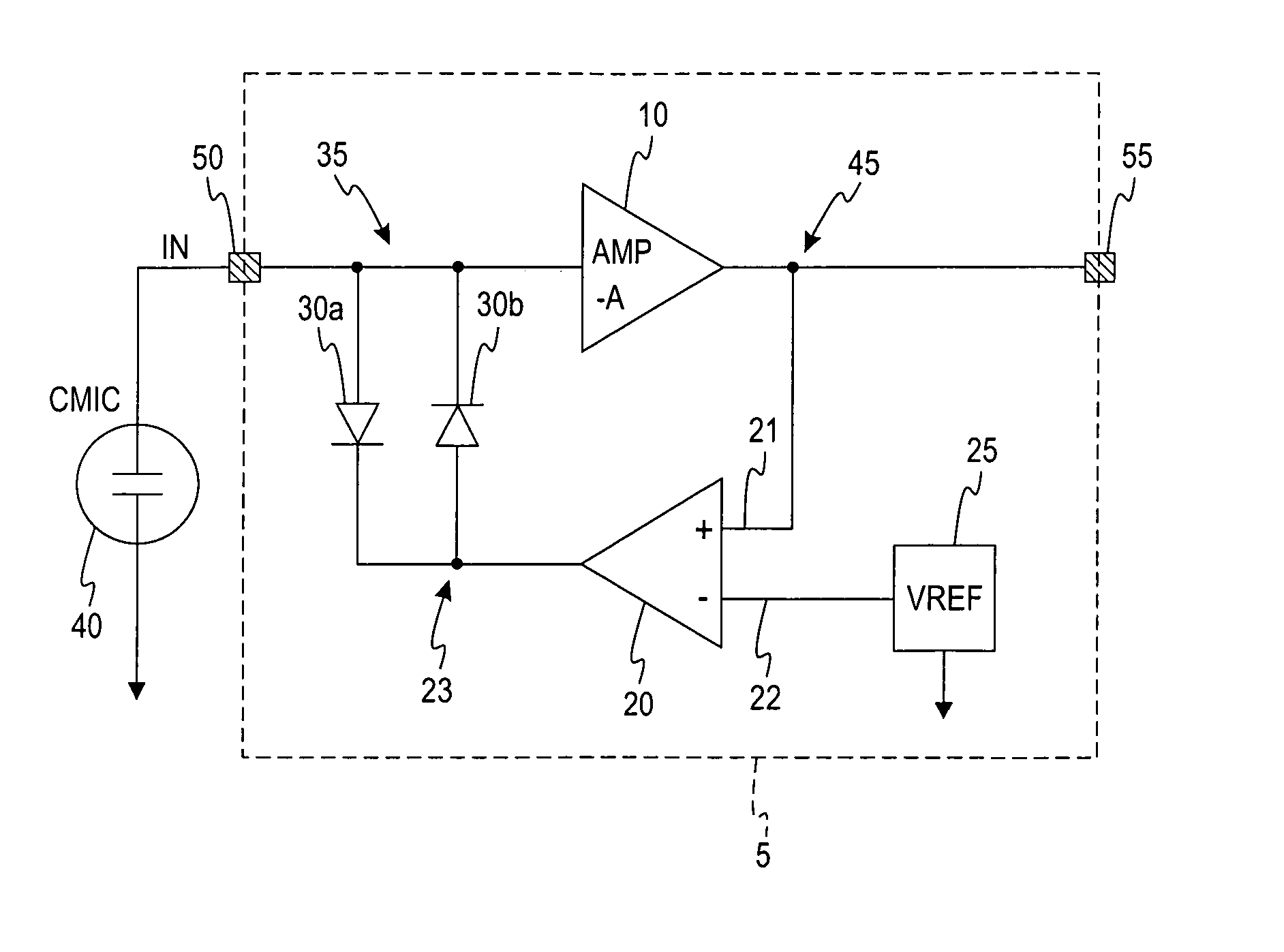

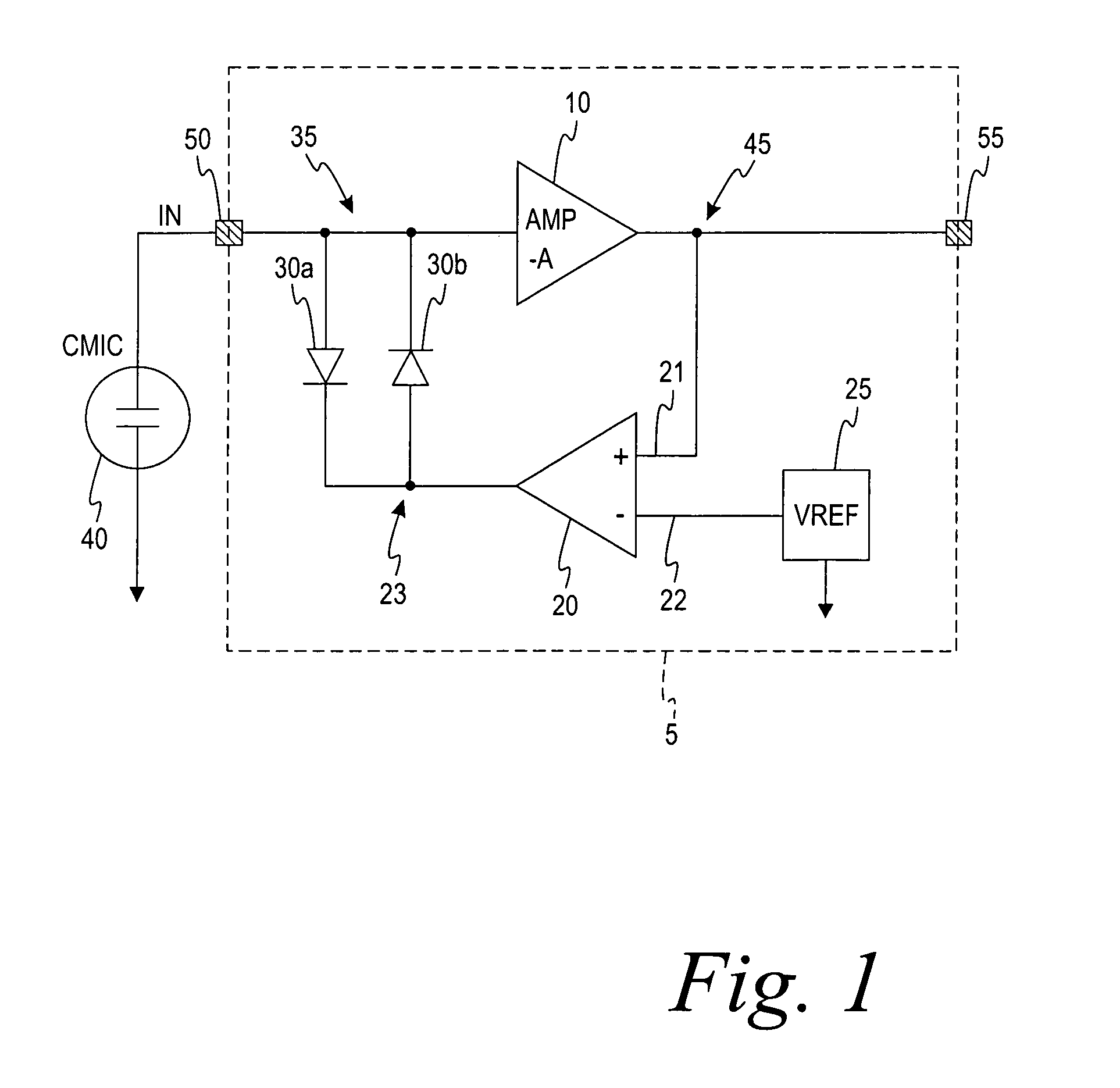

Amplifier circuit for capacitive transducers

ActiveUS20050151589A1Load minimizationLow noise amplification/bufferingAmplifier modifications to reduce noise influenceAmplifier modifications to reduce temperature/voltage variationAudio power amplifierEngineering

An amplifier circuit for capacitive transducers, such as miniature electret or condenser microphones, wherein the amplifier circuit comprises bias control means adapted to improve settling of the amplifier circuit. Another aspect of the invention relates to a miniature condenser microphone and a monolithic integrated circuit comprising an amplifier circuit according to the present invention. The present invention provides amplifier circuits of improved performance by resolving traditionally conflicting requirements of maintaining a large input resistance of the amplifier circuit to optimize its noise performance and provide fast settling of the amplifier circuit.

Owner:TDK CORPARATION

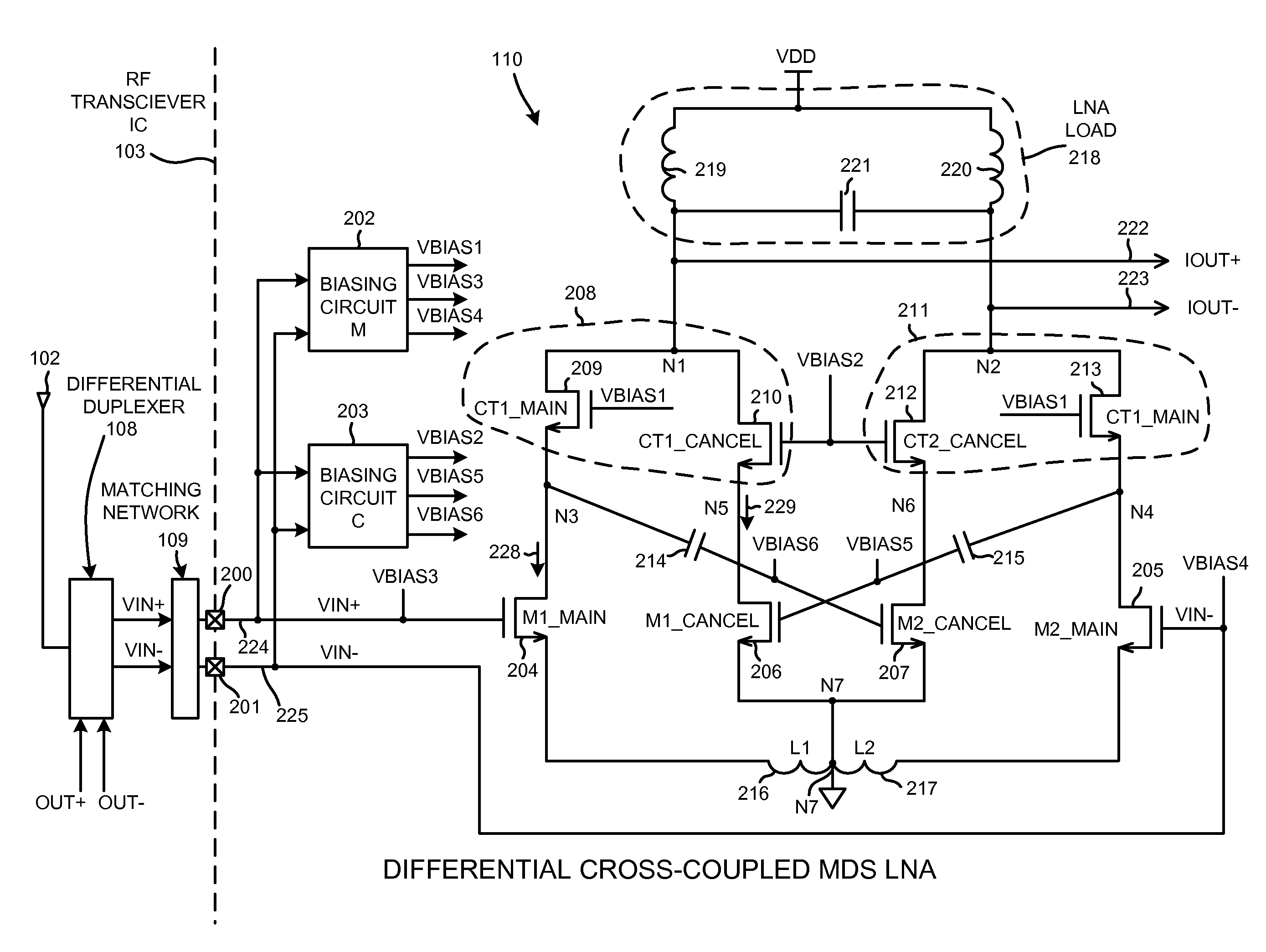

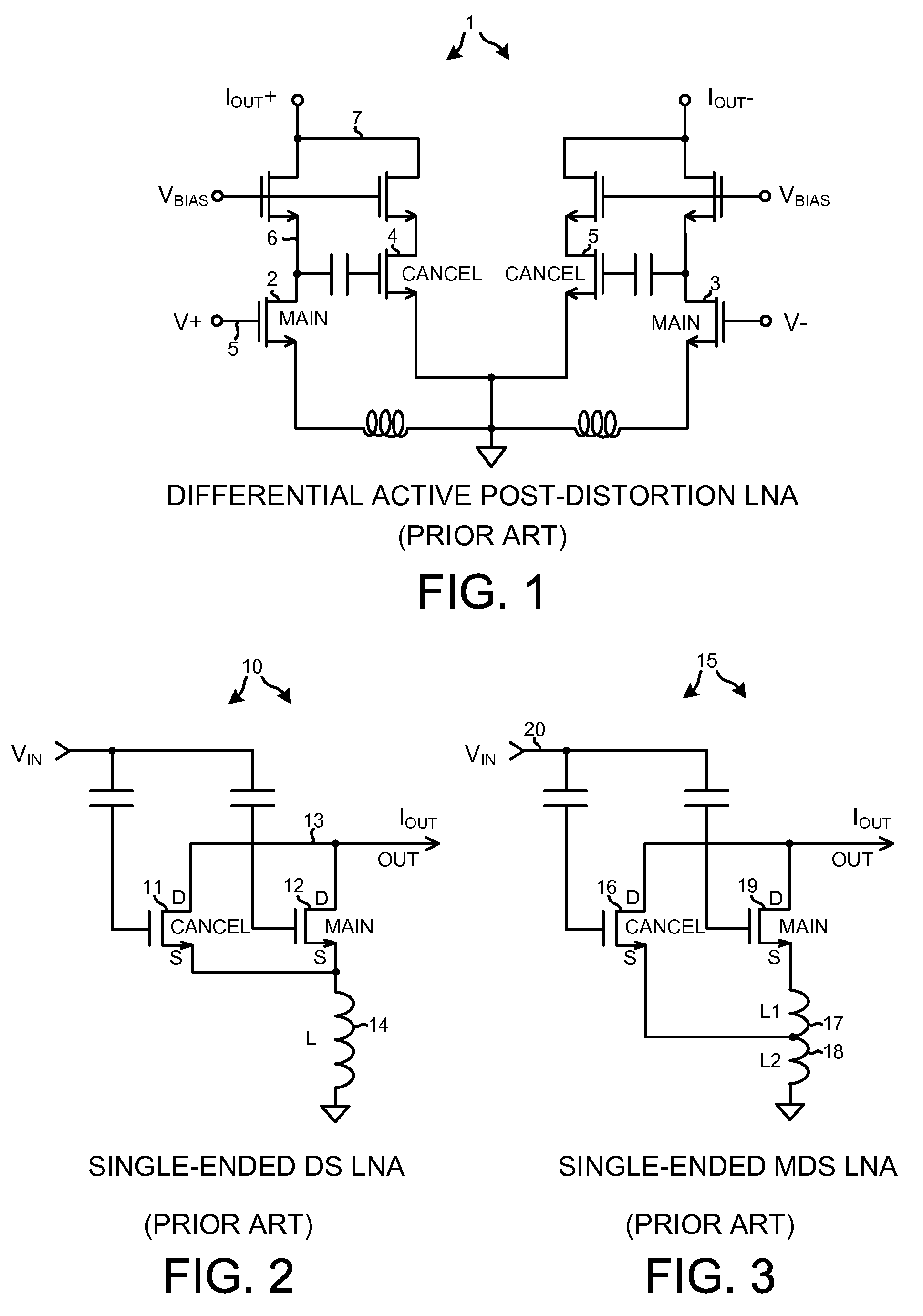

Low noise and low input capacitance differential MDS LNA

ActiveUS7944298B2Weakening rangeReduce input capacitanceGain controlDifferential amplifiersCapacitanceLow noise

A differential low noise amplifier (LNA) involves two main amplifying transistors biased in saturation, and two cancel transistors biased in sub-threshold. In one example, the gates of the cancel transistors are coupled to the drains of main transistors, in a symmetrical and cross-coupled fashion. The main transistors are source degenerated. Because the gates of cancel transistors are not coupled to the differential input leads of the LNA, the input capacitance of the LNA is reduced. Noise introduced into the LNA output due to the cancel transistors being biased in the sub-threshold region is reduced because there are two stages. The first stage involves the main transistors, and the second stage involves the cancel transistors. By increasing the gain of the first stage and decreasing the gain of the second stage, overall LNA gain is maintained while reducing the noise that the sub-threshold biased transistors contribute to the LNA output.

Owner:QUALCOMM INC

Amplifier circuit for capacitive transducers

ActiveUS7634096B2Load minimizationLow noise amplification/bufferingAmplifier modifications to reduce noise influenceAmplifier modifications to reduce temperature/voltage variationAudio power amplifierCondenser microphone

An amplifier circuit for capacitive transducers, such as miniature electret or condenser microphones, wherein the amplifier circuit comprises bias control means adapted to improve settling of the amplifier circuit. Another aspect of the invention relates to a miniature condenser microphone and a monolithic integrated circuit comprising an amplifier circuit according to the present invention. The present invention provides amplifier circuits of improved performance by resolving traditionally conflicting requirements of maintaining a large input resistance of the amplifier circuit to optimize its noise performance and provide fast settling of the amplifier circuit.

Owner:TDK CORPARATION

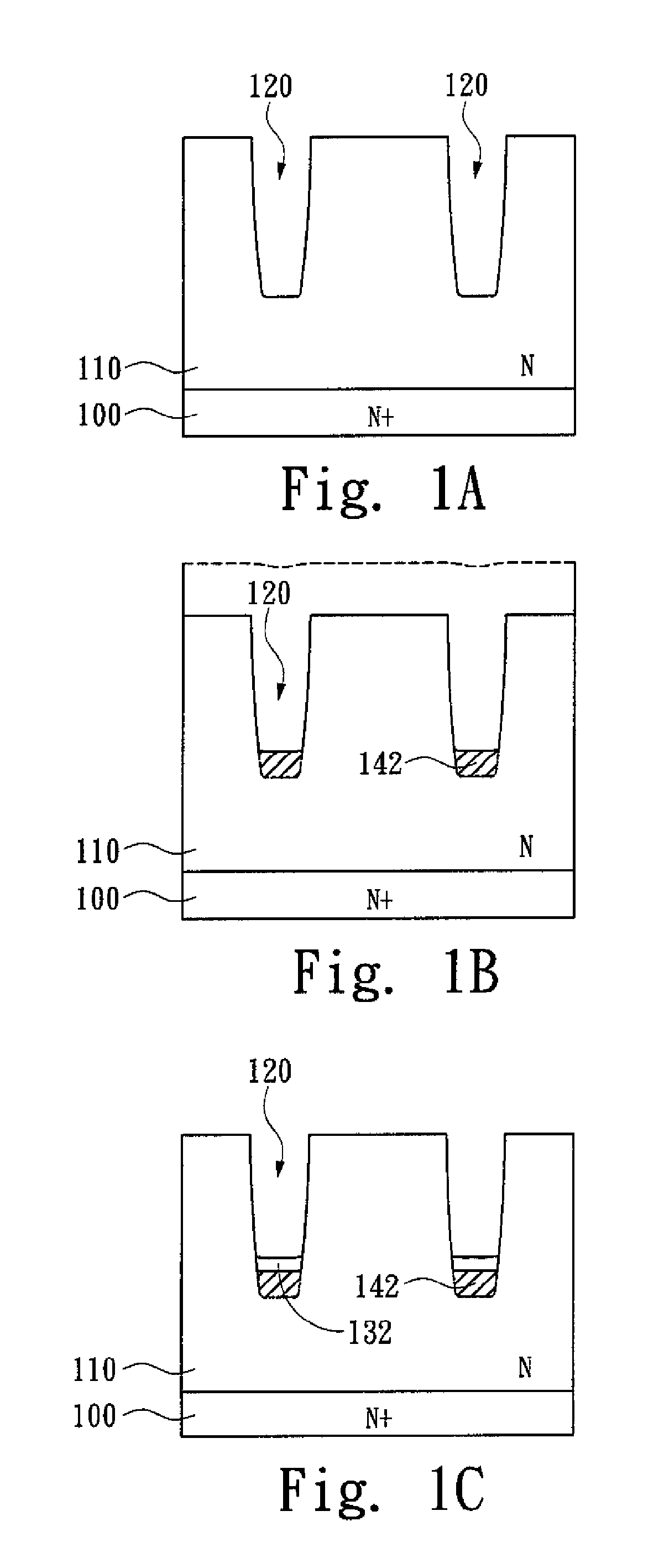

Power semiconductor device with trench bottom polysilicon and fabrication method thereof

ActiveUS20110298042A1Increased switching lossesReduce input capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceDopant

A power semiconductor device comprising a base, a trench, a heavily doped polysilicon structure, a polysilicon gate, a gate dielectric layer, and a heavily doped region is provided. The trench is formed in the base. The heavily doped polysilicon structure is formed in the lower portion of the trench. At least a side surface of the heavily doped polysilicon structure touches the naked base. The polysilicon gate is located in the upper portion of the trench. The gate dielectric layer is interposed between the polysilicon gate and the heavily doped polysilicon structure. The dopants in the heavily doped polysilicon structure are diffused outward to form a heavily doped region.

Owner:SUPER GROUP SEMICON

Structures and techniques for using semiconductor body to construct SCR, DIAC, or TRIAC

Switch devices, such as Silicon Controlled Rectifier (SCR), DIAC, or TRIAC, on a semiconductor body are disclosed. P / N junctions can be built on a semiconductor body, such as polysilicon or active region body on an insulated substrate, with a first implant in one end and a second implant in the other end. The first and second implant regions are separated with a space. A silicide block layer can cover the space and overlap into both implant regions to construct P / N junctions in the interface.

Owner:ATTOPSEMI TECH CO LTD

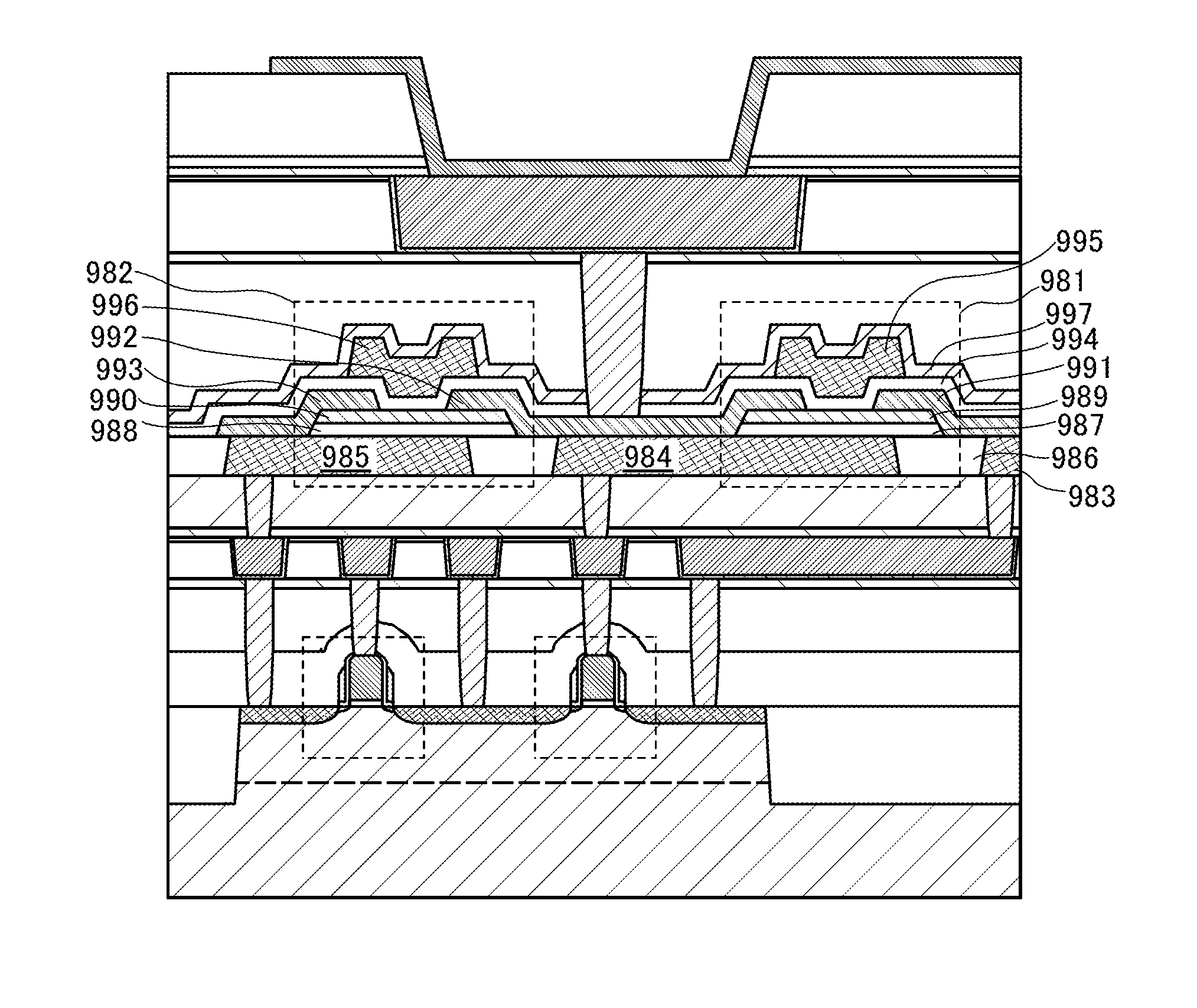

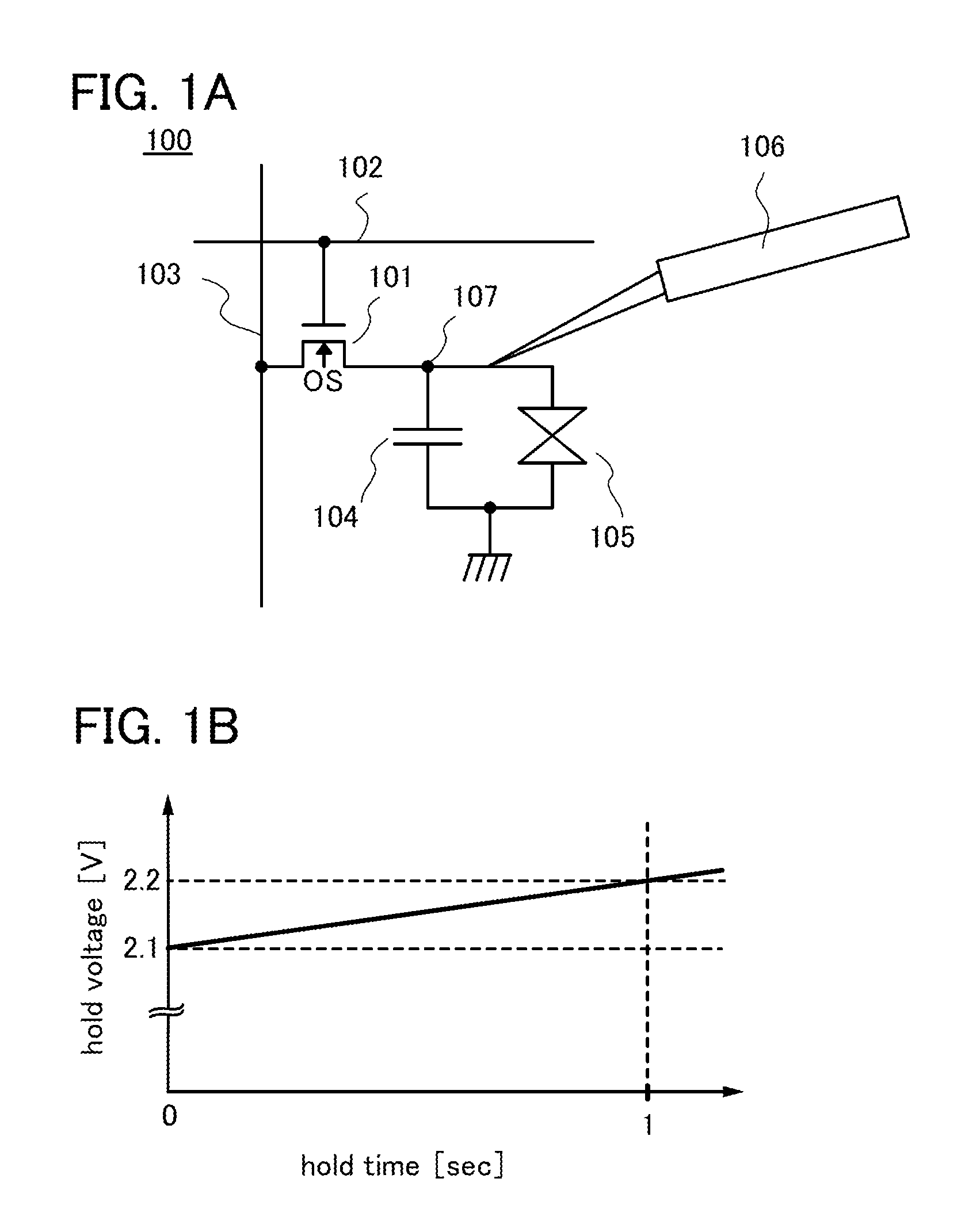

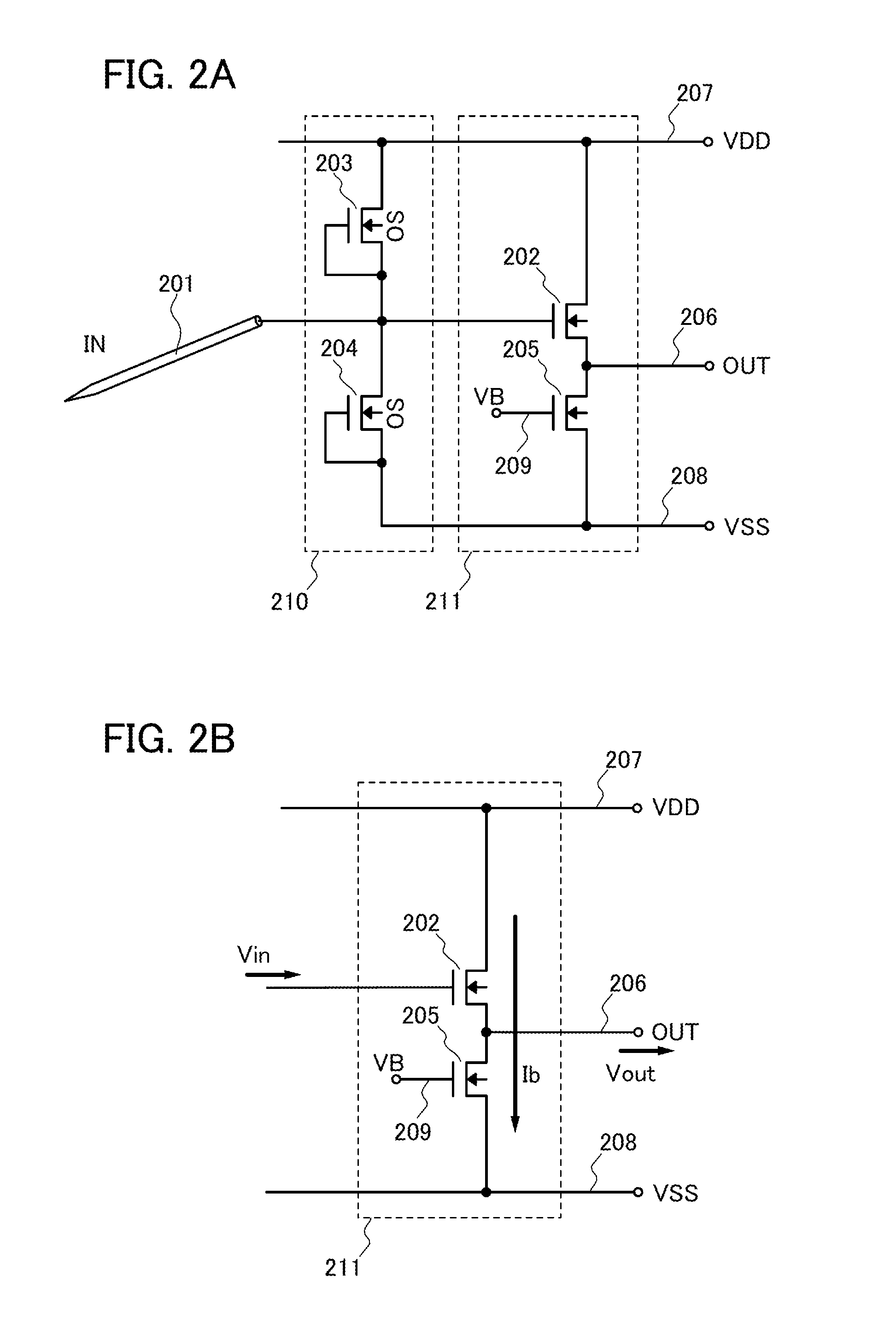

Measurement device

ActiveUS20130314074A1Accurate voltage measurementReduce leakage currentOverload protection arrangementsElectrical testingElectrical resistance and conductanceMeasurement device

To provide a measurement device which allows long-term accurate measurement of voltage without adversely affecting a device under test, by ensuring a predetermined level of resistance to ESD and reducing leakage current. A measurement device includes a probe needle for contacting a device under test, a first FET for detecting voltage of the device under test, and a protection circuit for protecting the first FET from static electricity. The protection circuit includes a second FET having an oxide semiconductor film as a channel formation region.

Owner:SEMICON ENERGY LAB CO LTD

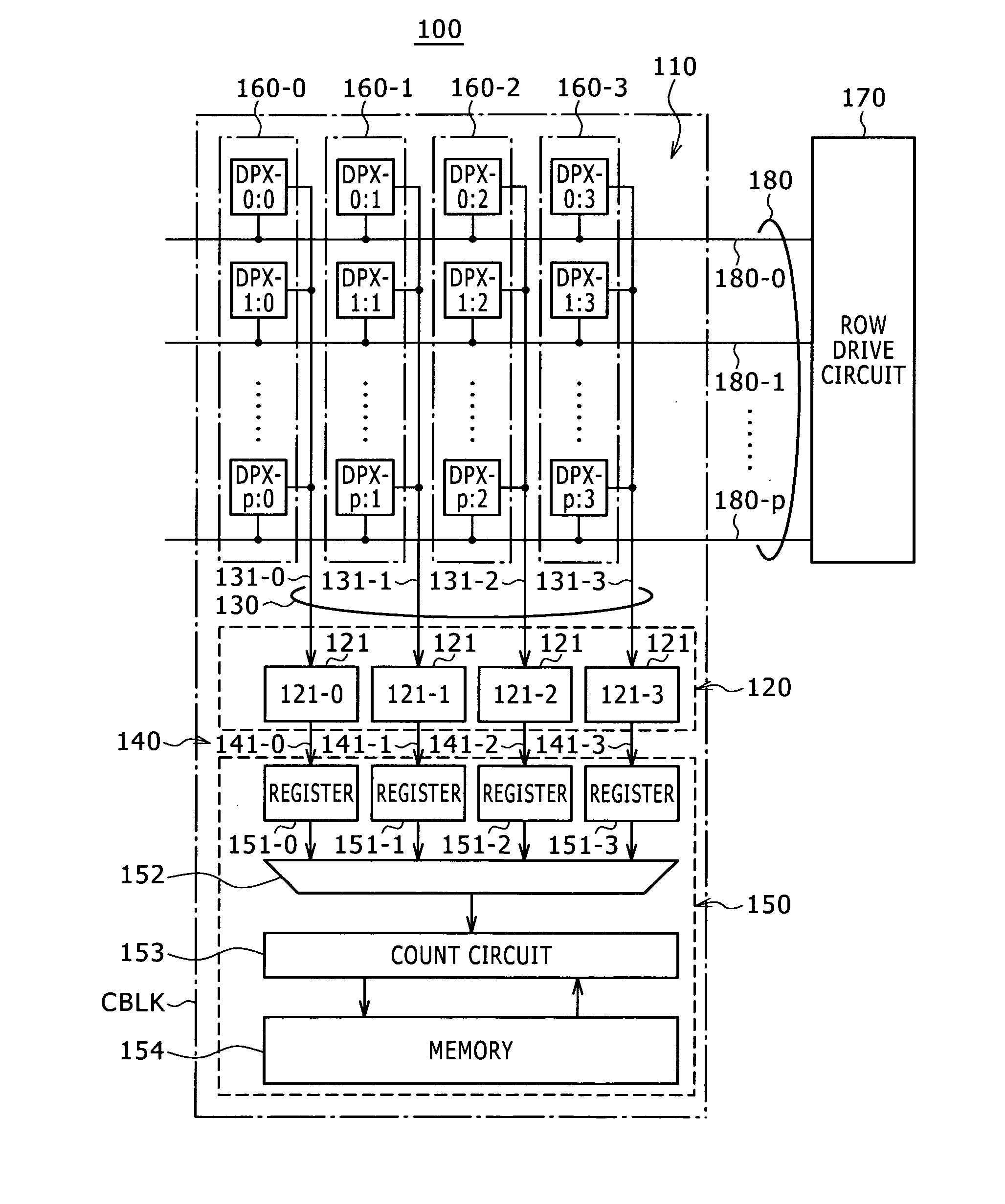

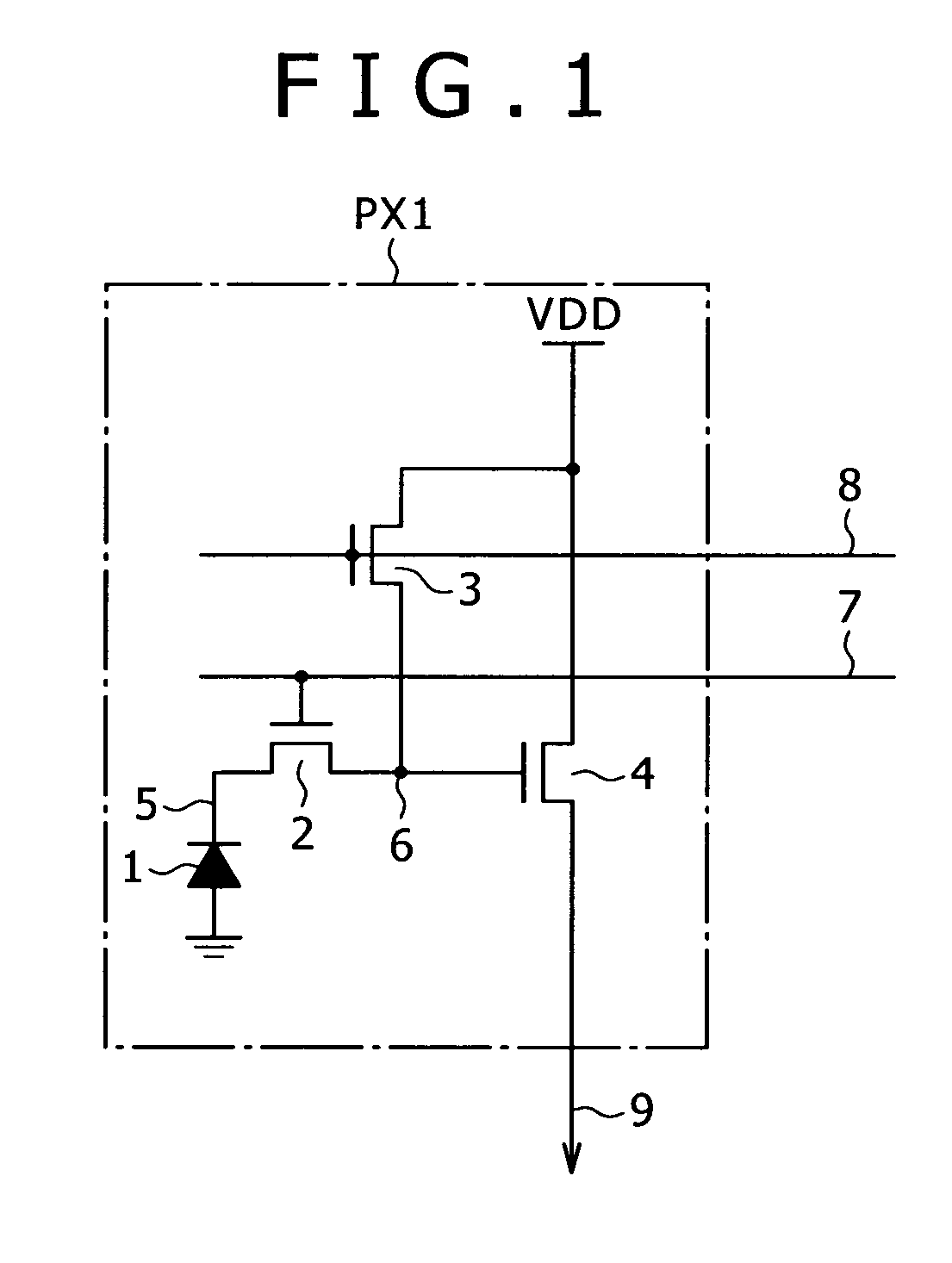

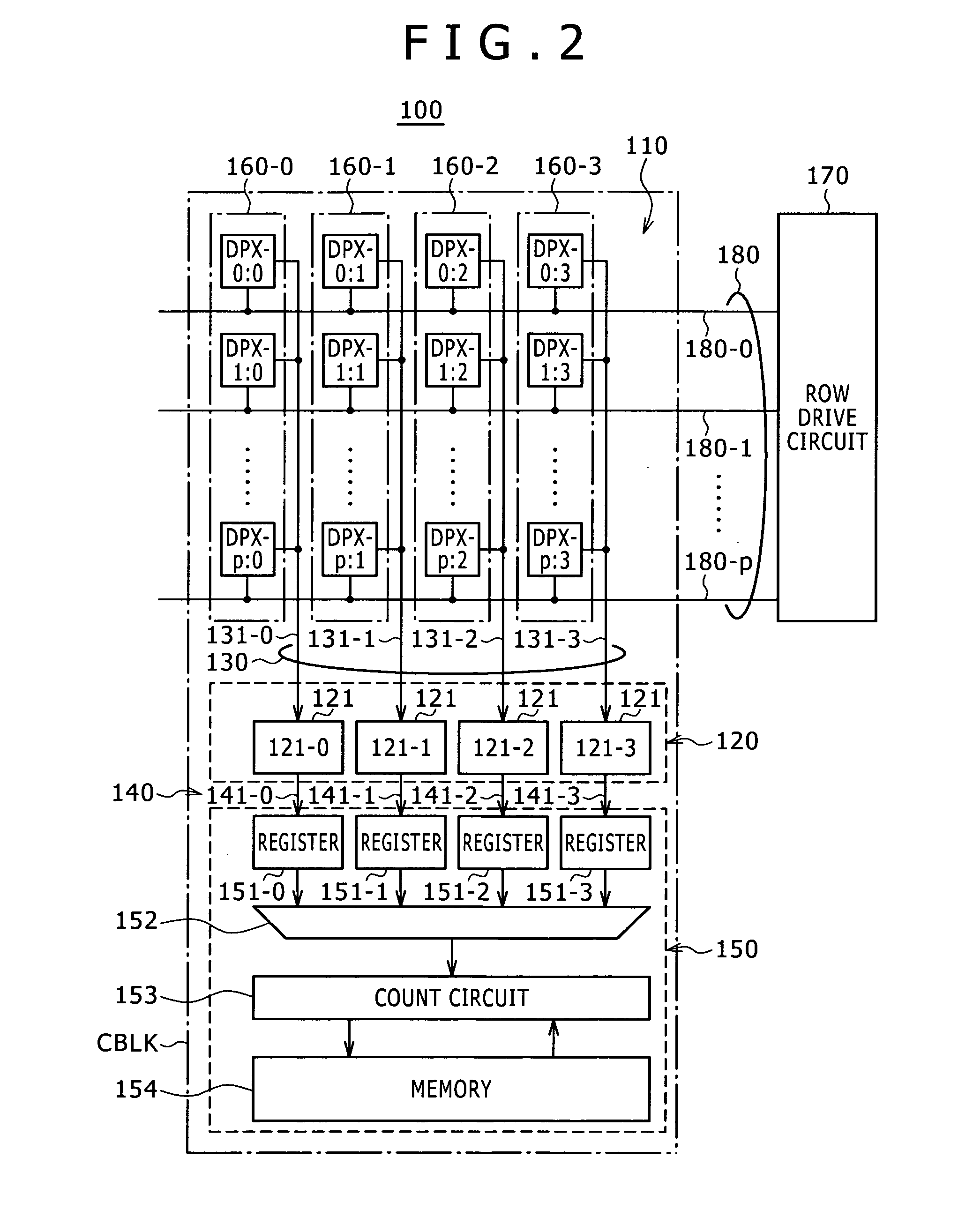

Imaging element and camera system

ActiveUS20110134264A1Reduce gate capacitanceReduce parasitic capacitanceTelevision system detailsTelevision system scanning detailsPhotodiodeSilicon on insulator

An imaging element includes an amplifying transistor. A signal charge from the photodiode is transferable to the gate of amplifying transistor, the photodiode being within a semiconductor substrate. The source and drain of the amplifying transistor are electrically isolated from a semiconductor substrate, wherein the source is within a well or the source and drain are within a silicon-on-insulator layer.

Owner:SONY SEMICON SOLUTIONS CORP

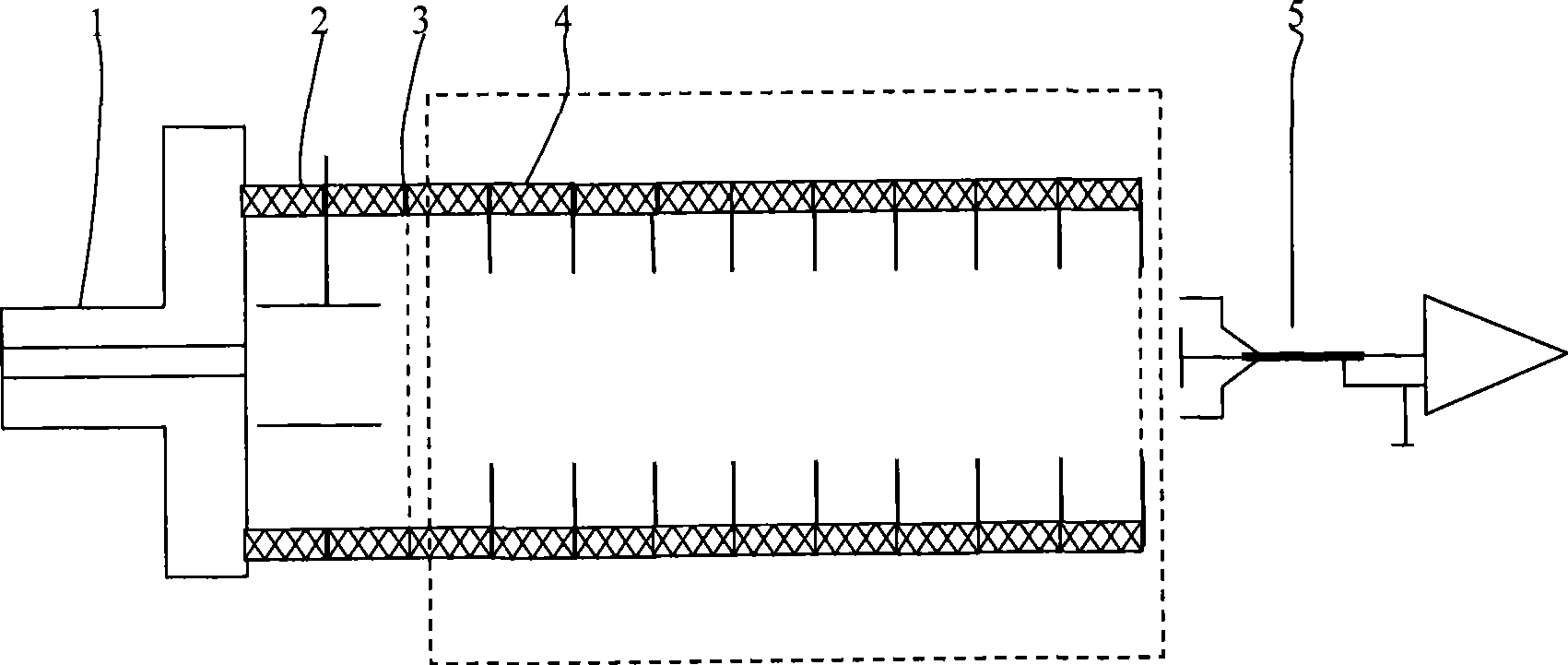

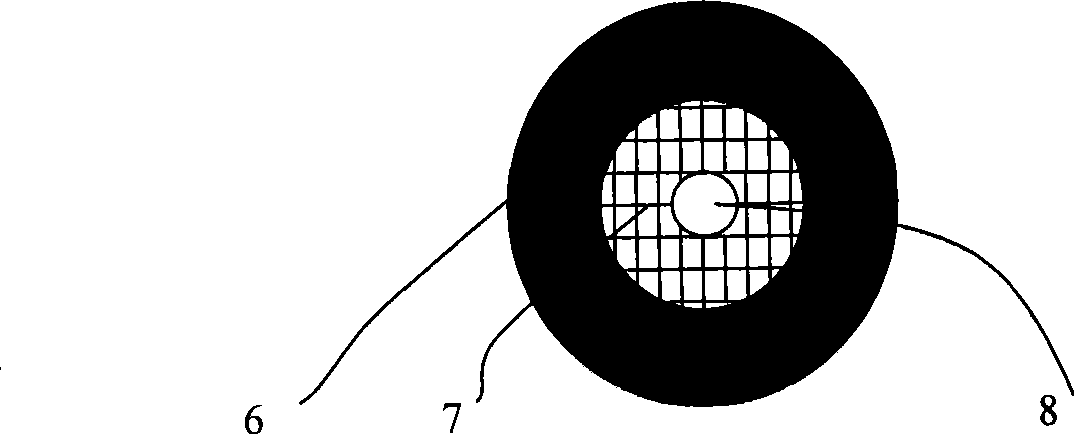

Migration tube structure used for ion mobility spectrometer

ActiveCN101471222AImprove pass rateReduce input capacitanceMaterial analysis by electric/magnetic meansParticle separator tube detailsPole pieceSpectrometer

The invention discloses a transfer tube structure for ion mobility spectrometers, comprising electrical pole pieces which are arranged at interval and an insulated portion, wherein, the electrical pole pieces are netted sheet metals with radians and tapers. In addition, the radian or taper portion of the electrical pole piece is provided with a mesh with higher transparency. Because of the above structure of the invention, an electric field which has evener focusing center on the periphery is to be formed on the transfer district portion, because of the toroidal structure of the electrode periphery, the influence of the extraneous electric field to the transfer electric field can be screened. Because the electrode is netted and has a circular hole in the middle, which focus and gather the ions which are not moved at the axial center as much as possible, and the ions which move toward the direction of axial center can be completely and transparently pass by.

Owner:NUCTECH CO LTD

Digital microphone

ActiveUS7899196B2Reduce input capacitanceLarge output signalAmplifier modifications to reduce non-linear distortionNegative-feedback-circuit arrangementsAnti-aliasingAudio power amplifier

Owner:ANALOG DEVICES INC

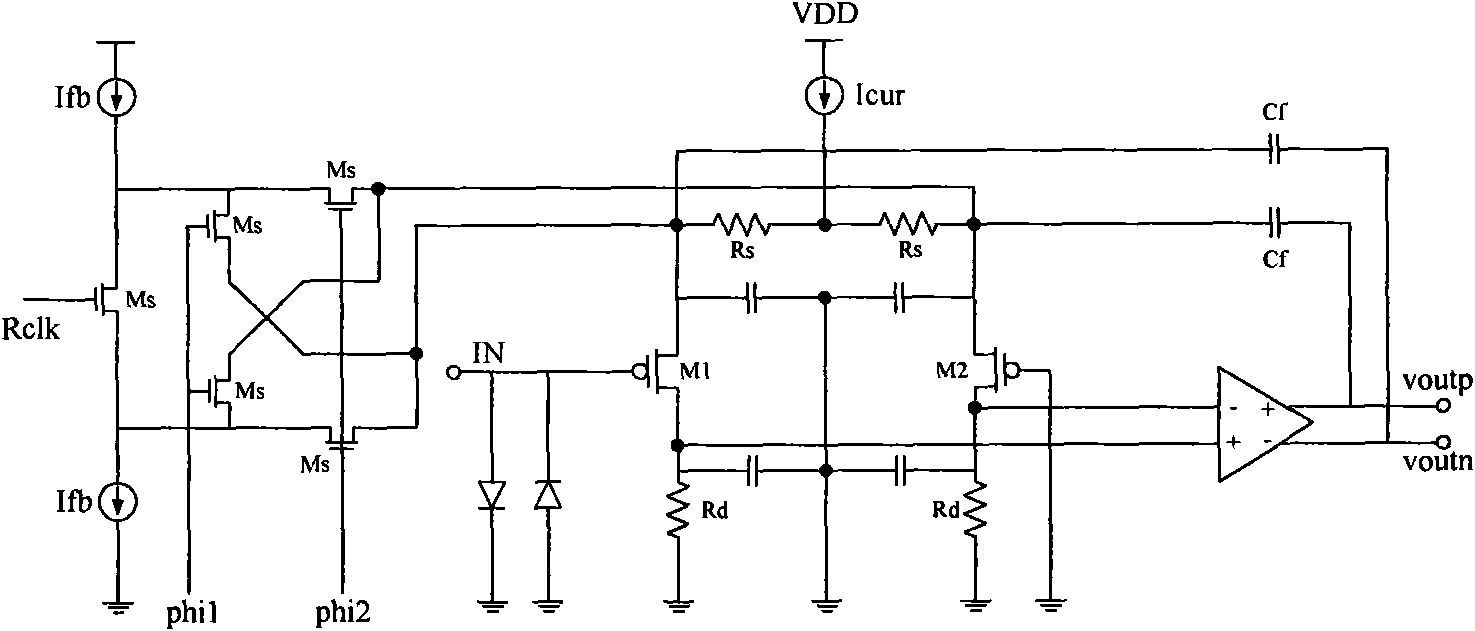

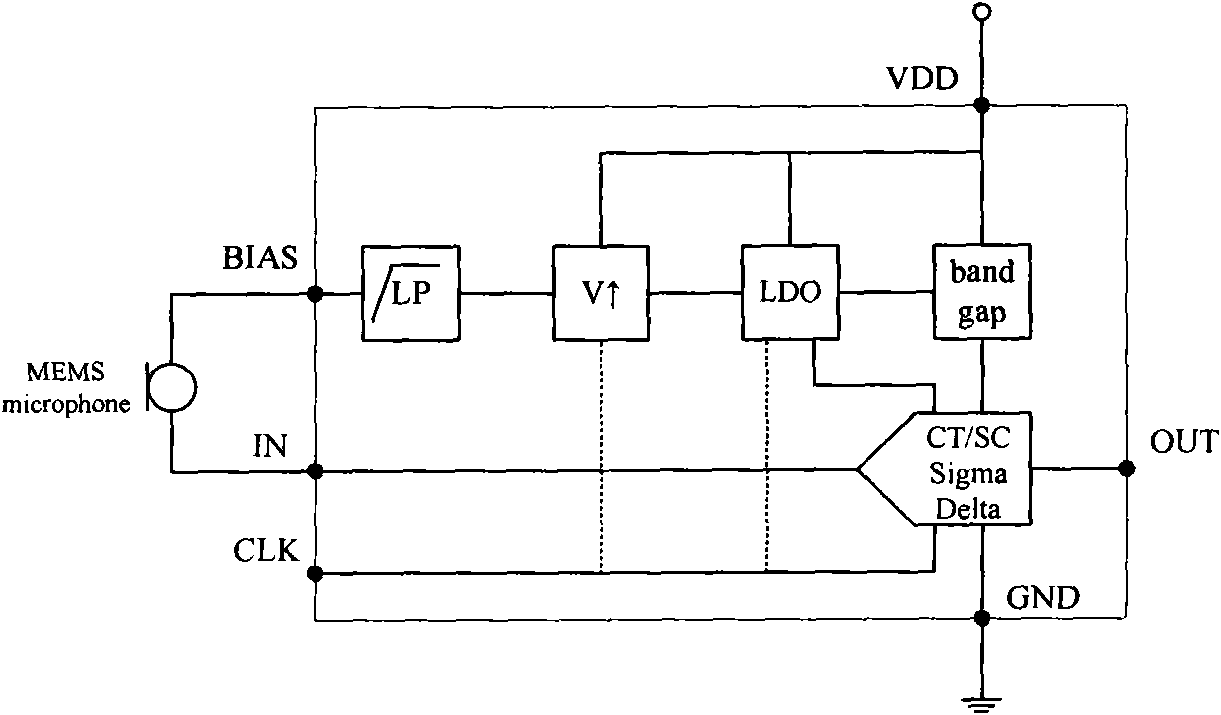

Digital preamplifier for MEMS microphone

InactiveCN101640829ADetermine the gain magnificationReduce input capacitanceDifferential amplifiersTransducer circuitsAnti jammingAudio frequency

The invention relates to a digital preamplifier for an MEMS microphone, which comprises an Sigma Delta modulator and an MEMS polarization voltage generation module, wherein a first-stage integrator ofthe Sigma Delta modulator adopts a structure of a continuous time integrator, and various stages of integrators after the second stage adopt a structure of a switched-capacitor integrator; an input end of the continuous time integrator adopts a gate differential input circuit; and a wake source of the gate differential input circuit is connected with an integrating resistor and a feedback currentof the continuous time integrator respectively. The digital preamplifier meets the requirement of a new-generation advanced audio system on the input end, greatly promotes the anti-jamming ability ofthe conventional analog signal transmission path, improves the transmission quality of analog signals, and reduces physical space and design cost.

Owner:INST OF ACOUSTICS CHINESE ACAD OF SCI

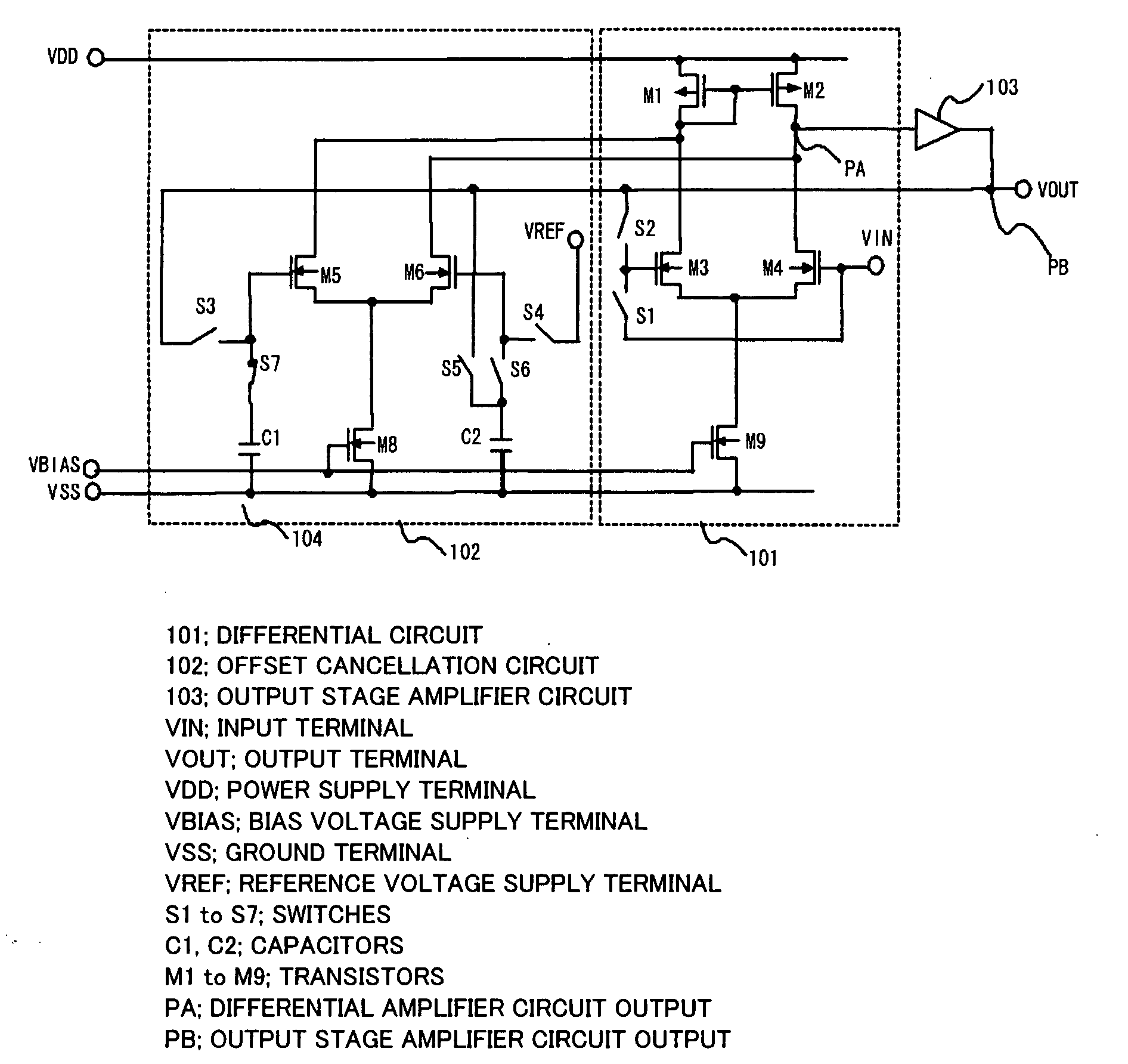

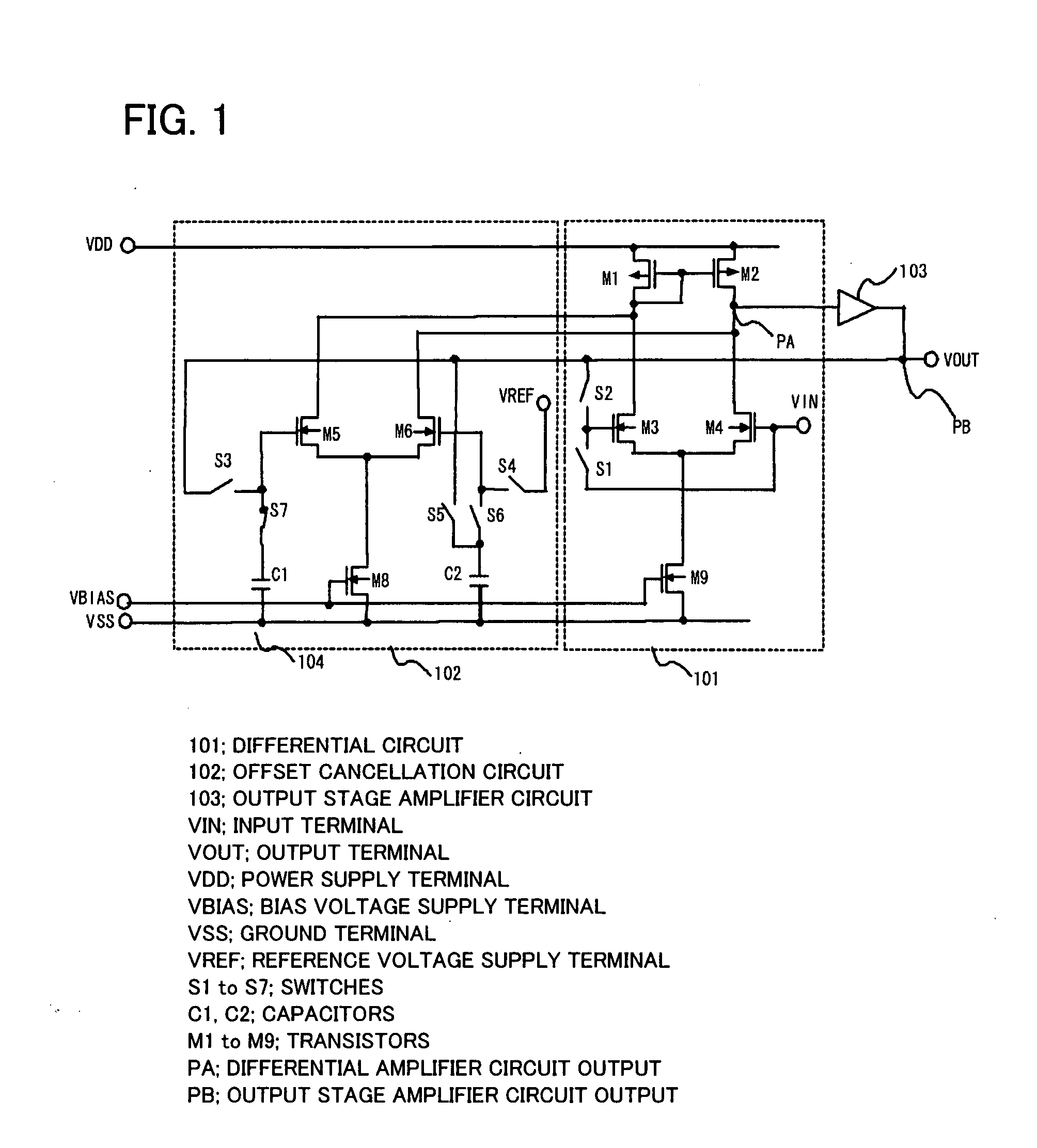

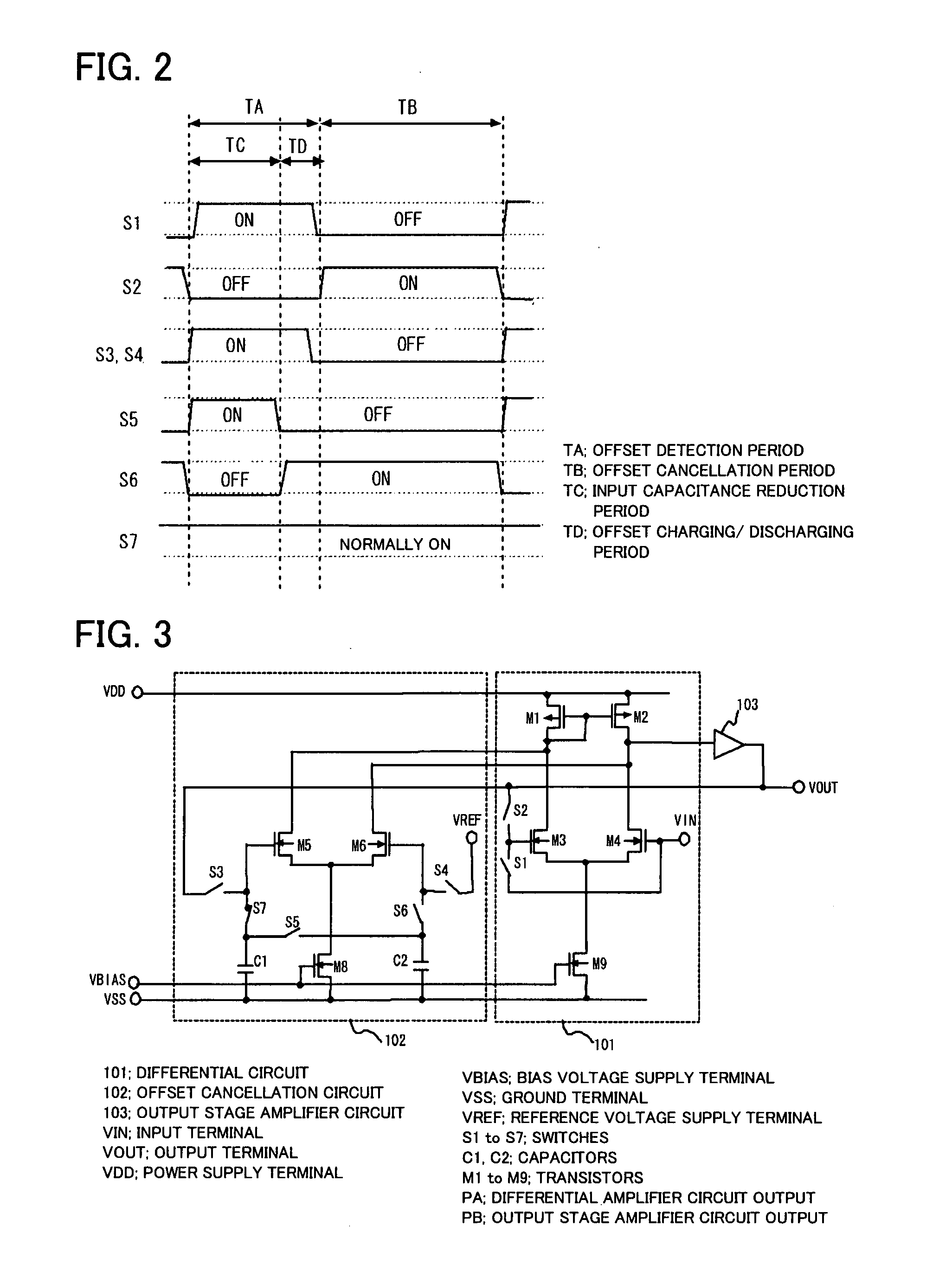

Offset cancellation amplifier, display employing the offset cancellation amplifier and method for controlling the offset cancellation amplifier

InactiveUS20070200620A1Reduction in output accuracyImprove accuracyAmplifier modifications to raise efficiencyAmplifier with semiconductor-devices/discharge-tubesLoad circuitAudio power amplifier

Disclosed is an offset cancellation amplifier which includes a first differential pair, second differential pair, a common load circuit for the two differential pairs, current sources, an amplifier stage, and first and second capacitors. The first capacitor is connected to the gate of one transistor of the first differential pair. During a first period of a data output period, an output voltage and the reference voltage are supplied to the gates of the first differential pair, the second capacitor is disconnected from the gate of the other transistor of the first differential pair. In this state, the output voltage is accumulated in the first and second capacitors. An input voltage is supplied in common to the gates of the second differential pair During the second period, the second capacitor is disconnected from the first capacitor and connected to the gate of the other transistor of the first differential pair. The output voltage is accumulated in the first capacitor, while the reference voltage is accumulated in the second capacitor. During the third period, the gates of the first differential pair cease to be supplied with the output voltage and with the reference voltage, respectively, and are supplied with the voltages accumulated in the first and second capacitors, respectively. The gates of the second differential pair are supplied with the output voltage and with the input voltage, respectively.

Owner:NEC CORP

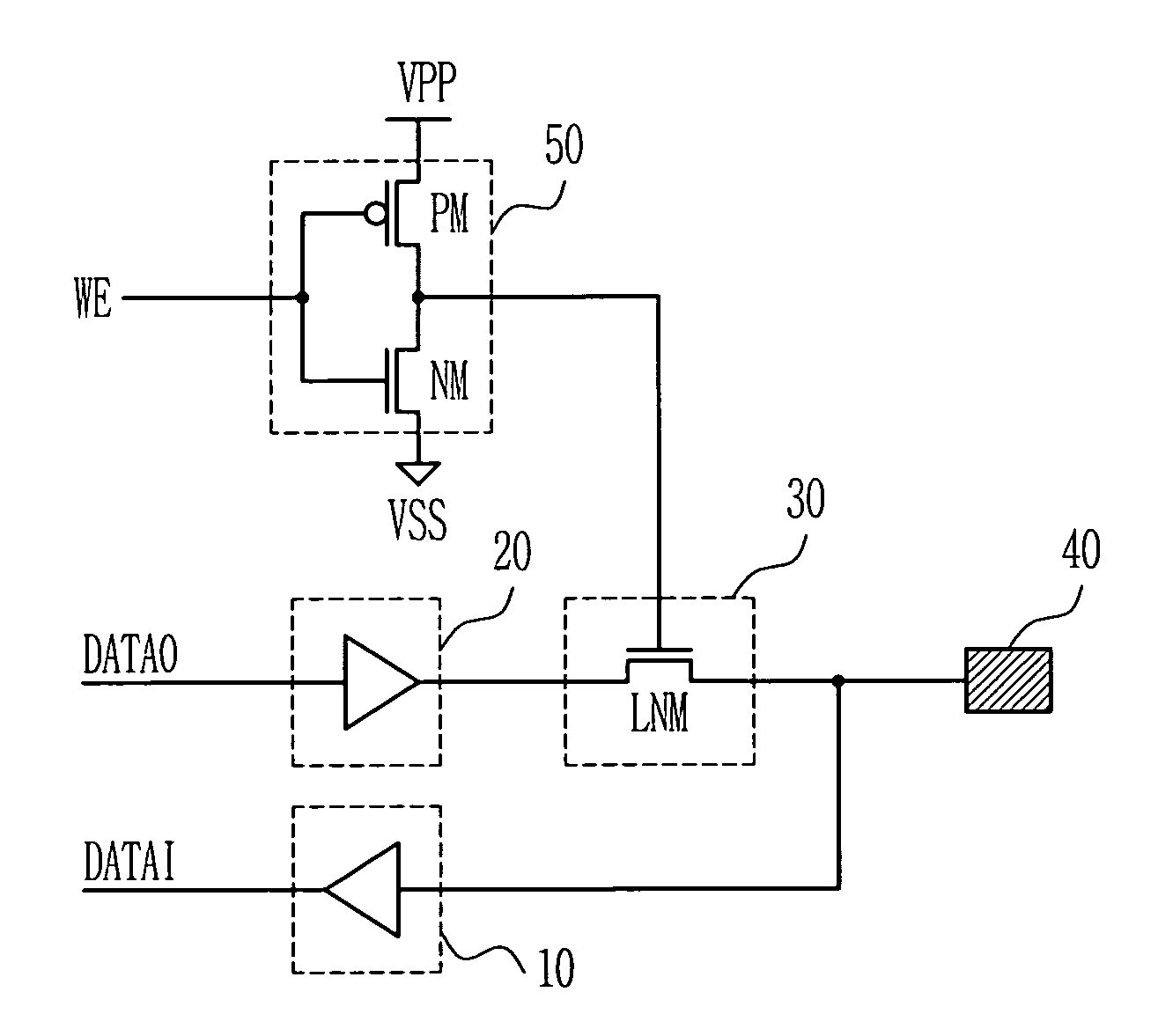

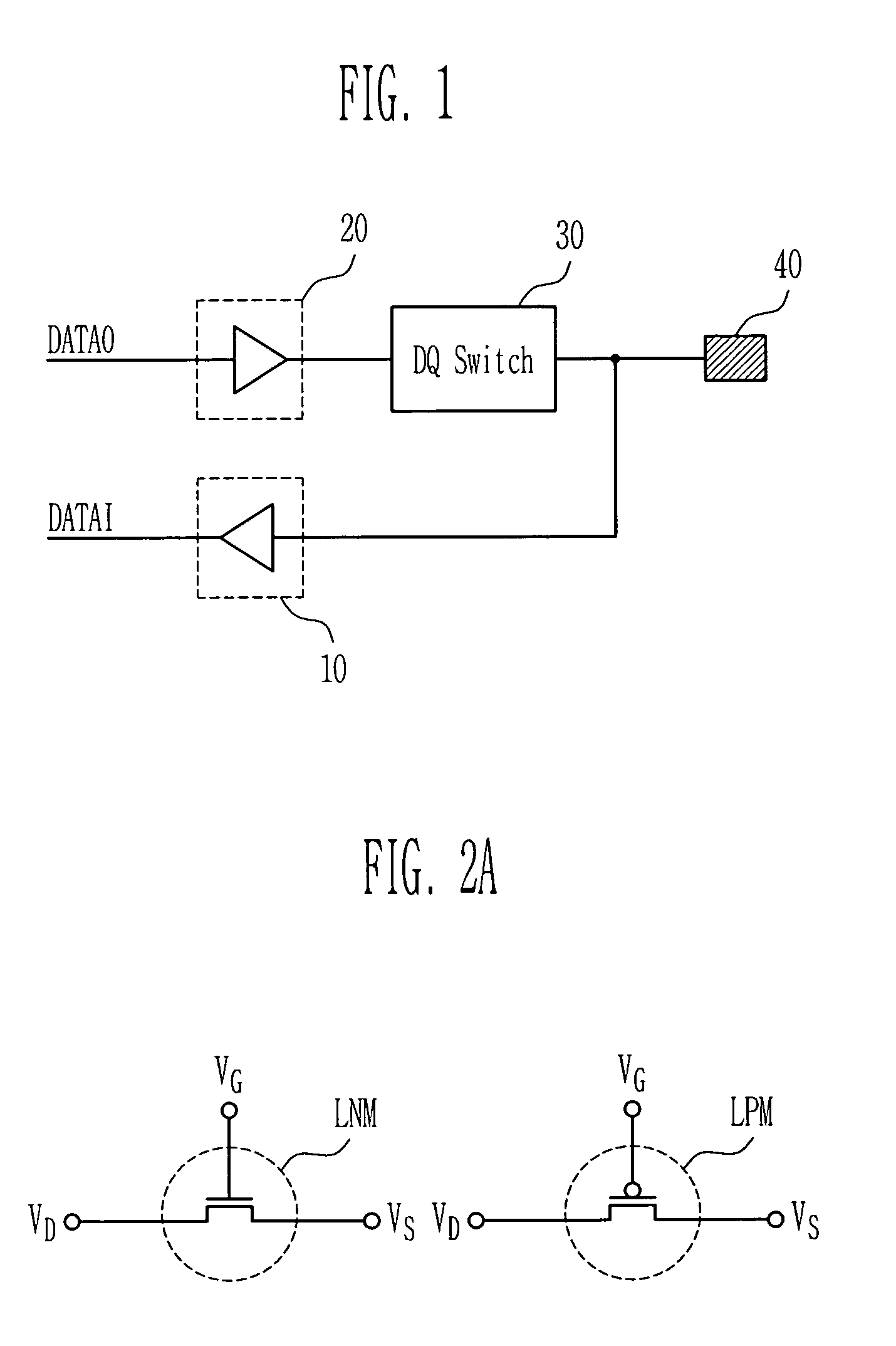

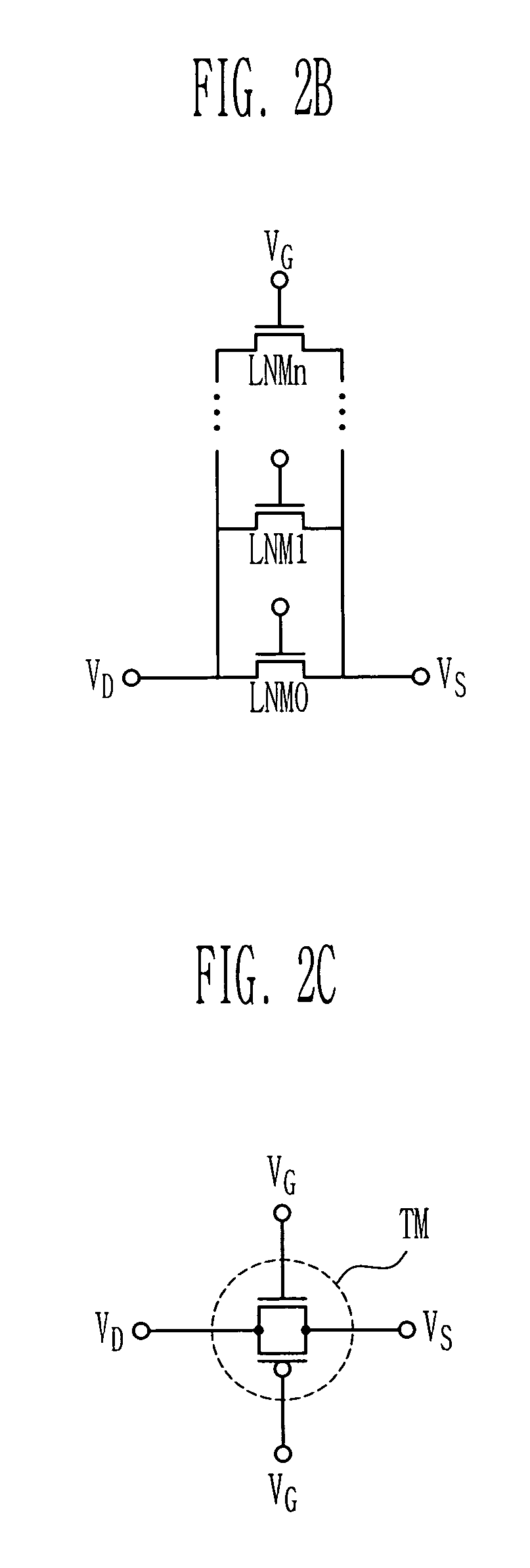

Input and output driver

InactiveUS7012449B2Reduce input capacitanceEfficient reductionDigital storageLogic circuits using specific componentsCapacitance

An input and output driver is disclosed which includes comprising a DQ switch capable of reducing a total input capacitance Cin by electrically isolating an output driver from a DQ pad using the DQ switch in a writing mode to reduce the capacitance due to the output driver.

Owner:SK HYNIX INC

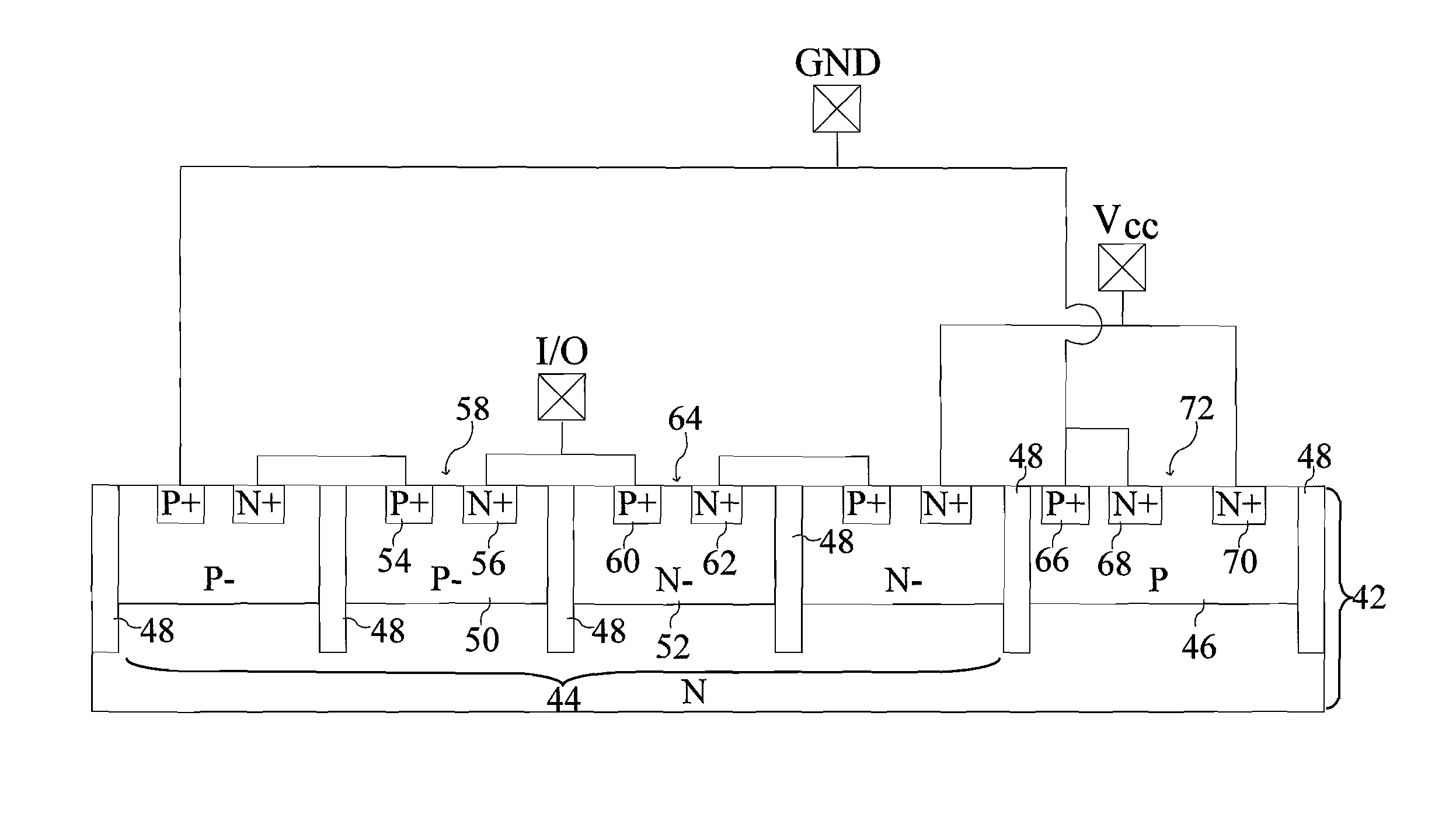

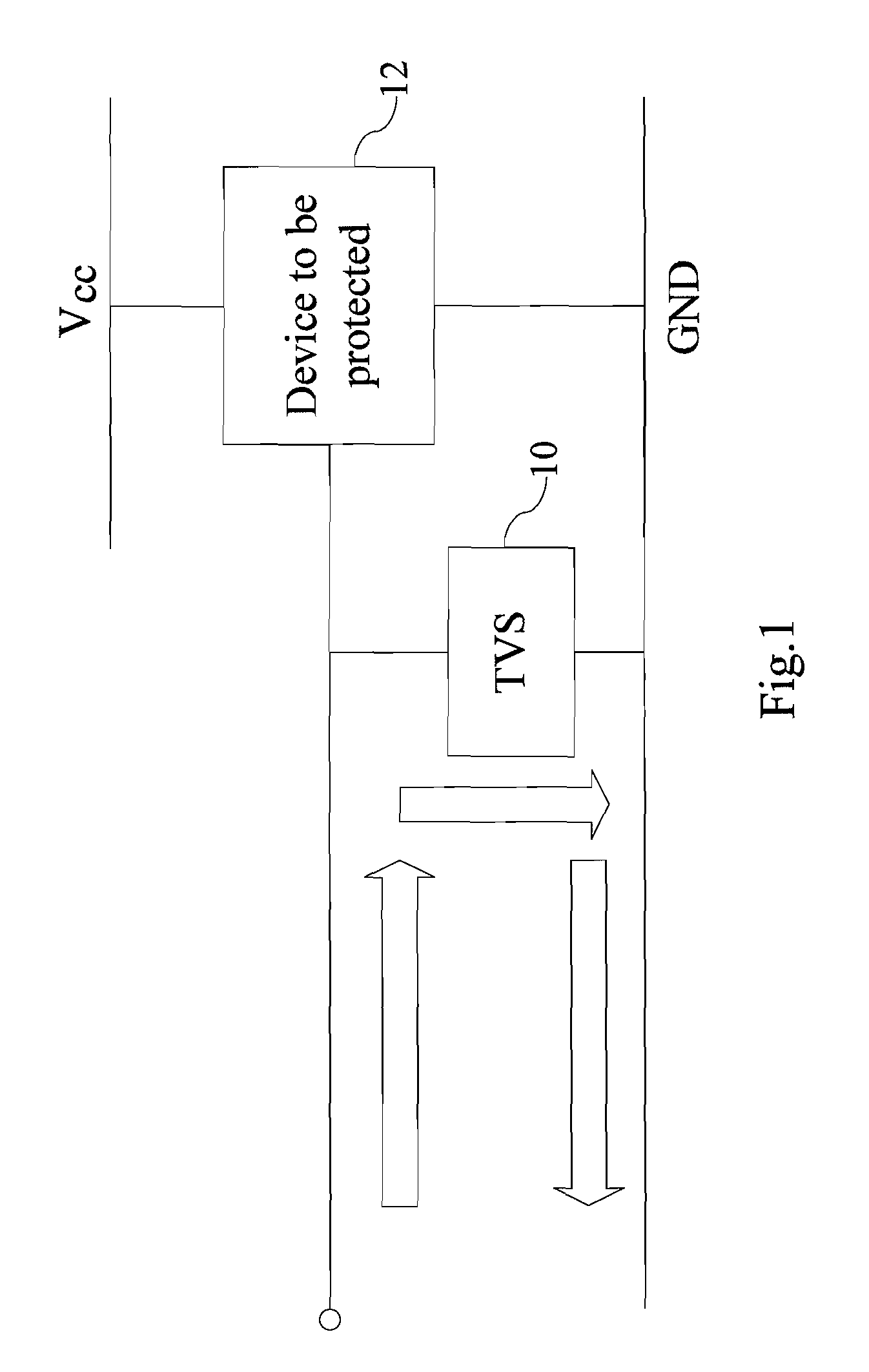

Lateral transient voltage suppressor with ultra low capacitance

ActiveUS20120012973A1Reduce input capacitanceGood signal effectSemiconductor/solid-state device detailsSolid-state devicesCapacitanceSuppressor

A lateral transient voltage suppressor with ultra low capacitance is disclosed. The suppressor comprises a first type substrate and at least one diode cascade structure arranged in the first type substrate. The cascade structure further comprises at least one second type lightly doped well and at least one first type lightly doped well, wherein there are two heavily doped areas arranged in the second type lightly doped well and the first type lightly doped well. The cascade structure neighbors a second type well, wherein there are three heavily doped areas arranged in the second type well. The suppressor further comprises a plurality of deep isolation trenches arranged in the first type substrate and having a depth greater than depths of the second type lightly doped well, the second type well and the first type lightly doped well. Each doped well is isolated by trenches.

Owner:AMAZING MICROELECTRONICS

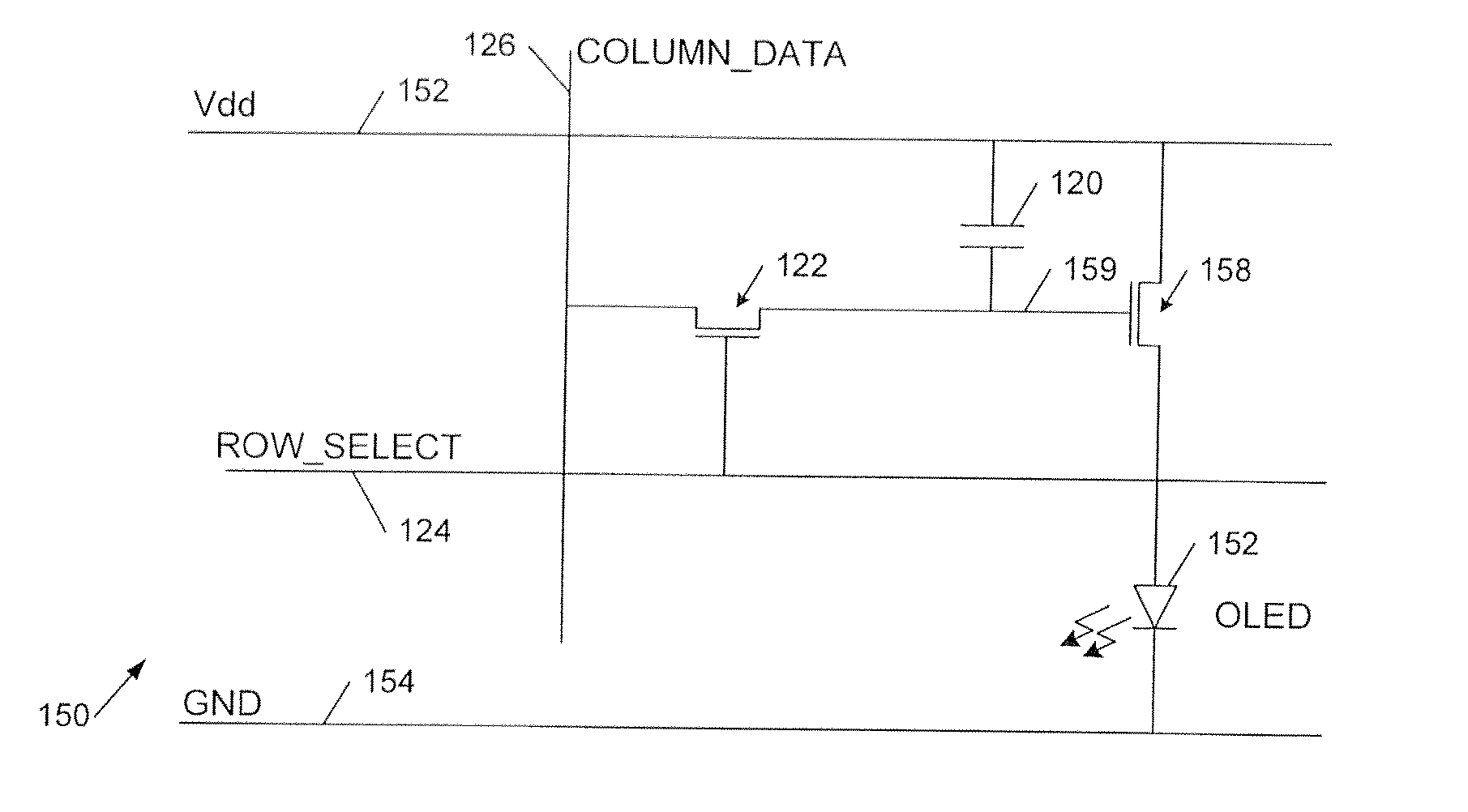

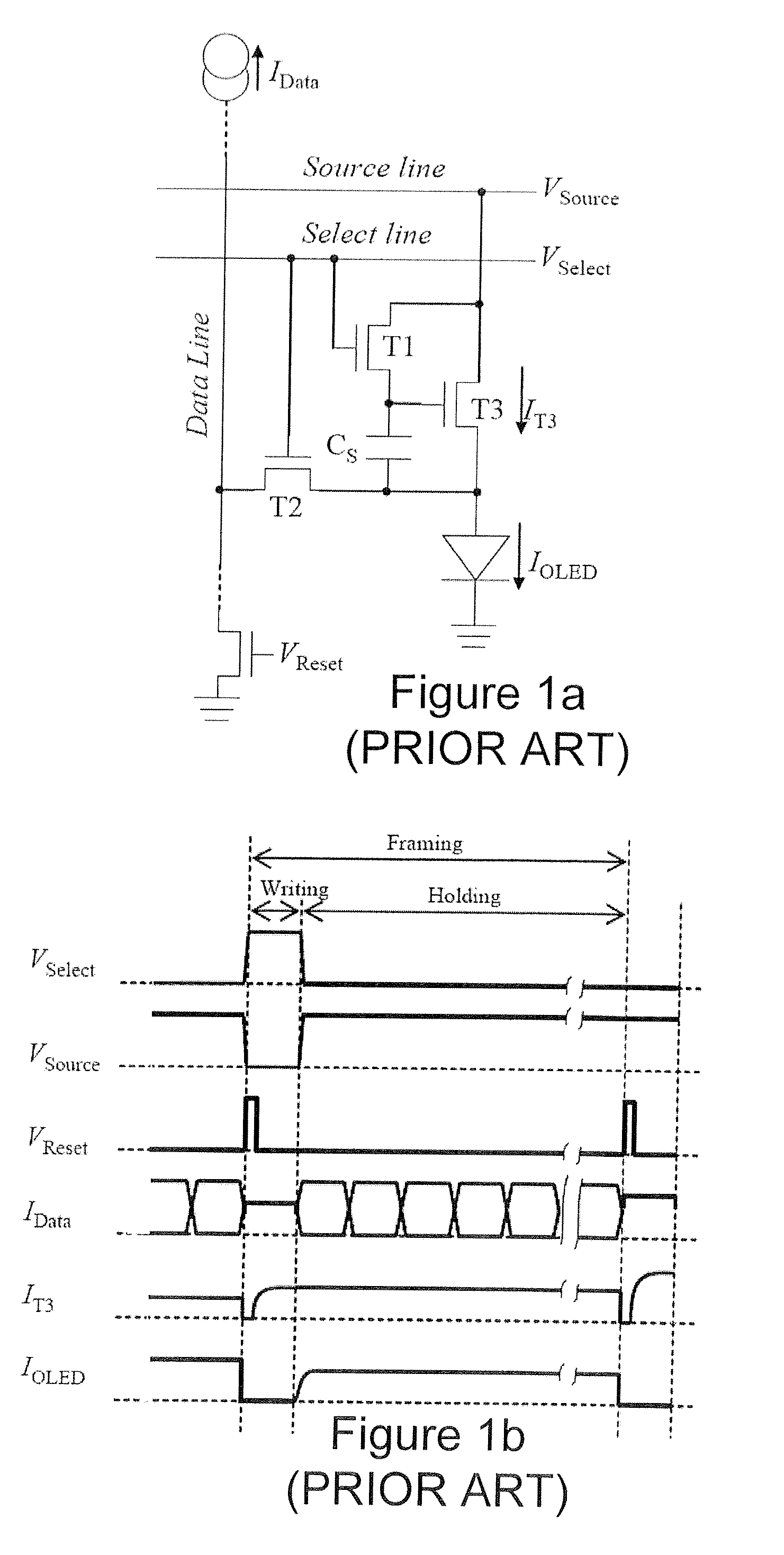

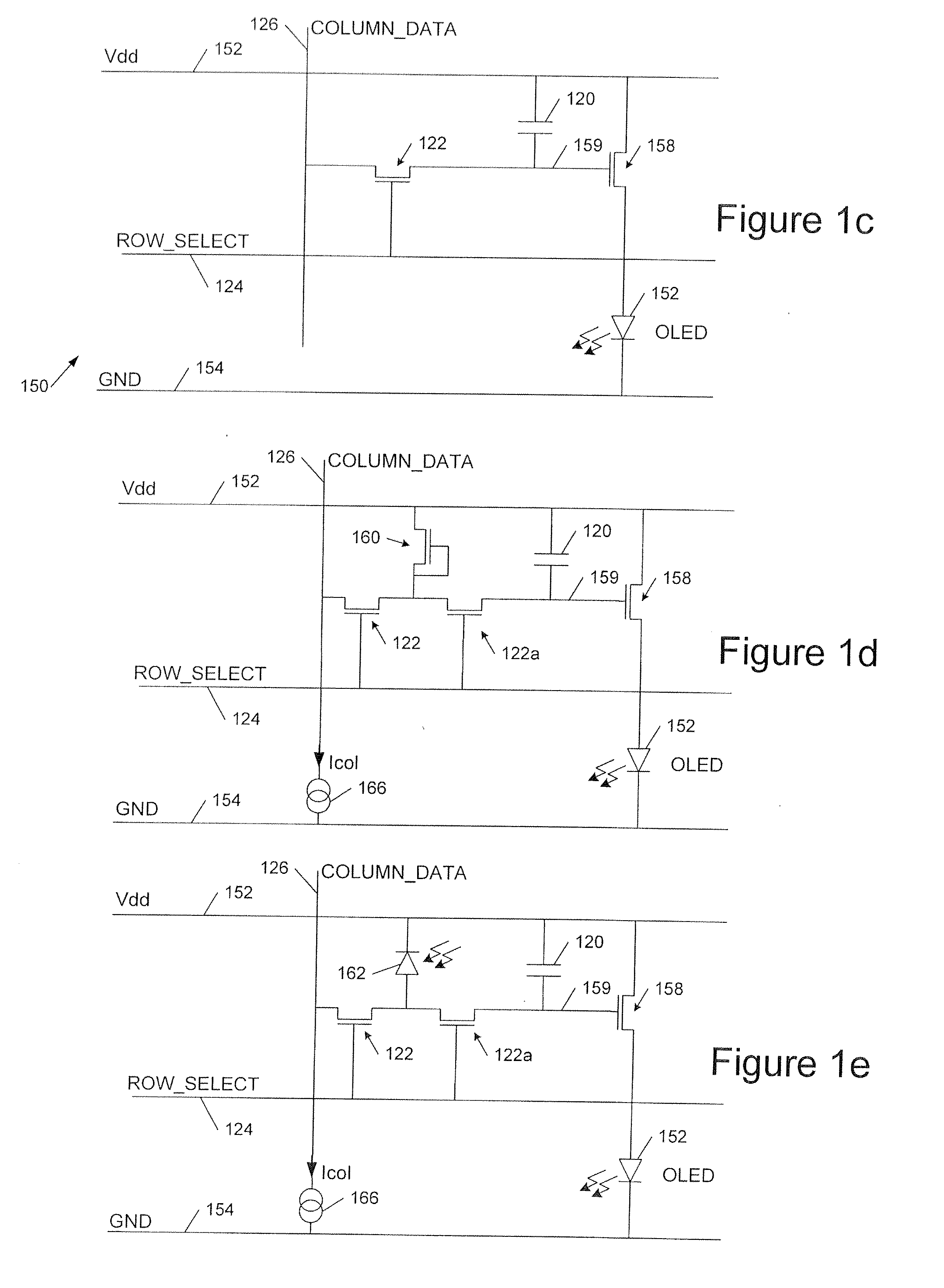

Active Matrix OLED Displays and Driver Therefor

InactiveUS20110181561A1Increase capacitanceReduce capacitanceSolid-state devicesCathode-ray tube indicatorsDriver circuitCapacitance

A display has a plurality of organic light emitting diode (OLED) pixels each with an associated pixel driver circuit, a plurality of select lines and a plurality of data lines. Each pixel driver circuit is coupled to a select line and to a data line. The pixel driver circuit includes a drive transistor configured to drive an OLED and a select transistor having a first terminal coupled to a select line and a second terminal coupled to a data line, wherein one of the terminals of said select transistor comprises a gate connection of said select transistor and wherein the other terminal comprises one of a drain and a source connection of said select transistor, and wherein said select transistor comprises source, drain and gate regions, wherein said gate region at least partially overlaps said source and drain regions, and wherein an area of said overlap of said gate region with one of said source region and said drain region is greater than an area of said overlap with the other region so that a capacitance between said gate connection and one of said drain and source connections is less than a capacitance between said gate connection and the other connection.

Owner:CAMBRIDGE DISPLAY TECH LTD