Patents

Literature

281results about "Logic circuits using specific components" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

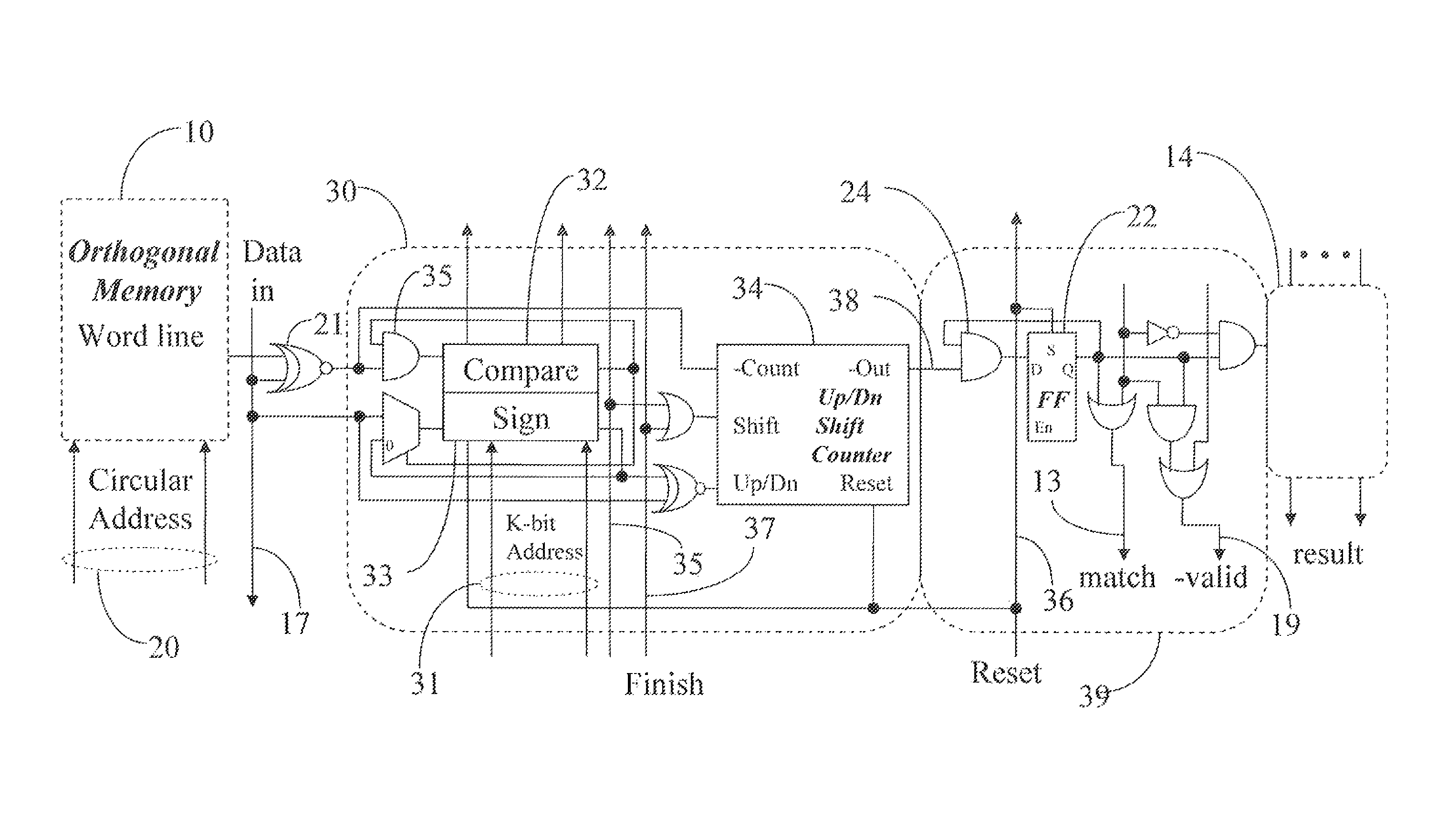

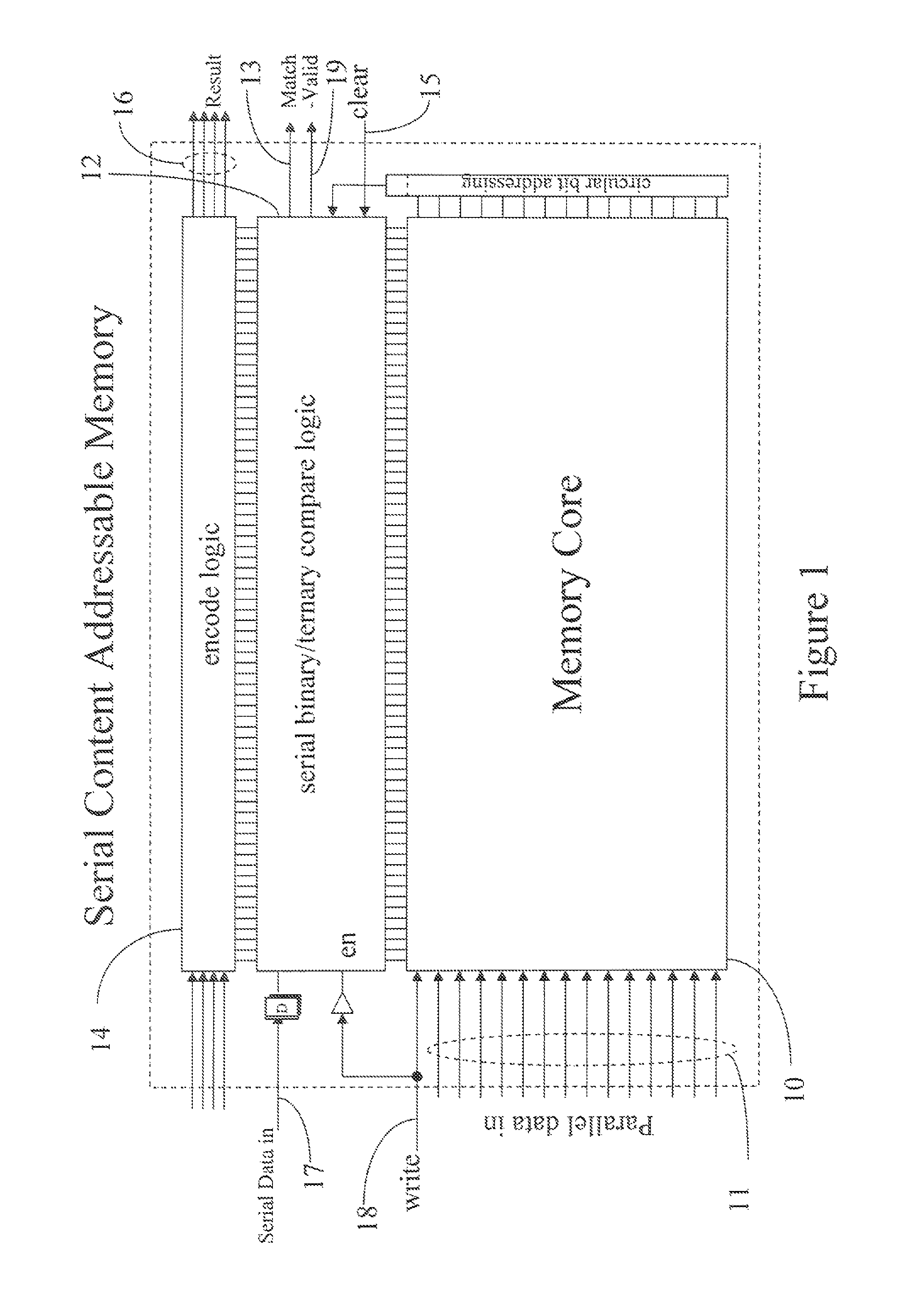

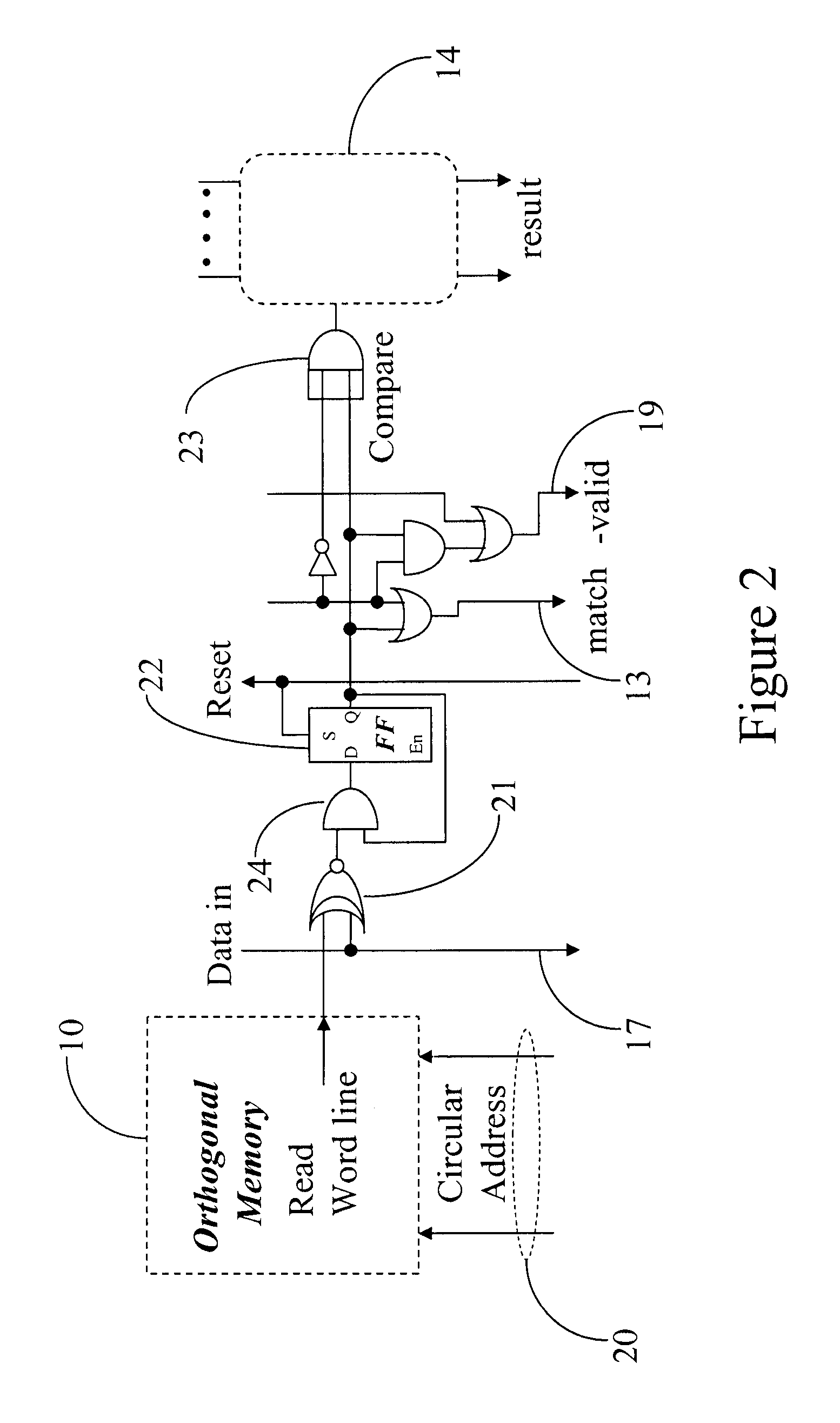

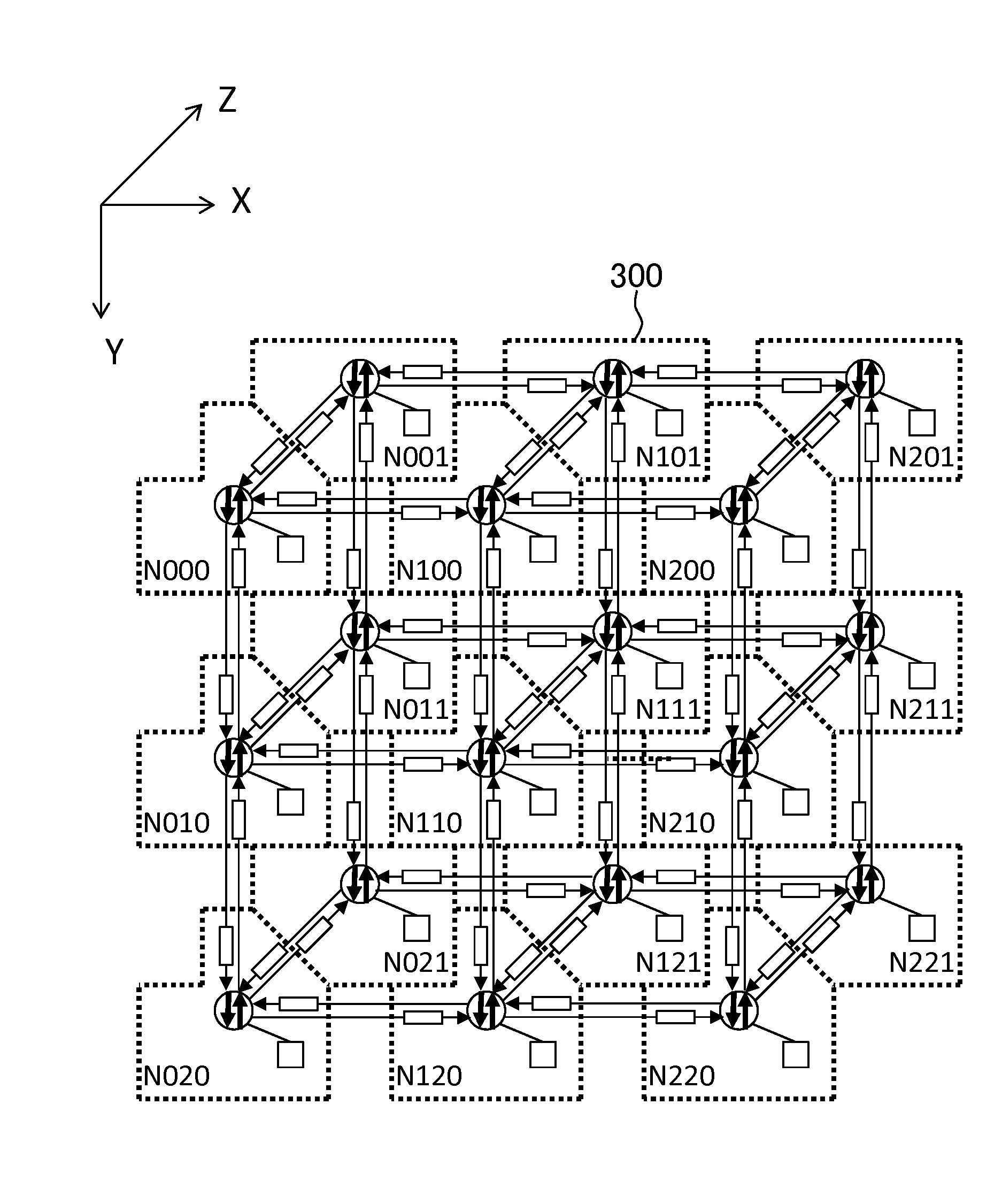

Nearest neighbor serial content addressable memory

A digital design and technique may be used to implement a Manhattan Nearest Neighbor content addressable memory function by augmenting a serial content addressable memory design with additional memory and counters for bit serially accumulating in parallel and subsequently comparing in parallel all the Manhattan distances between a serially inputted vector and all corresponding vectors resident in the CAM. Other distance measures, besides a Manhattan distance, may optionally be used in conjunction with similar techniques and designs.

Owner:COOKE LAURENCE H

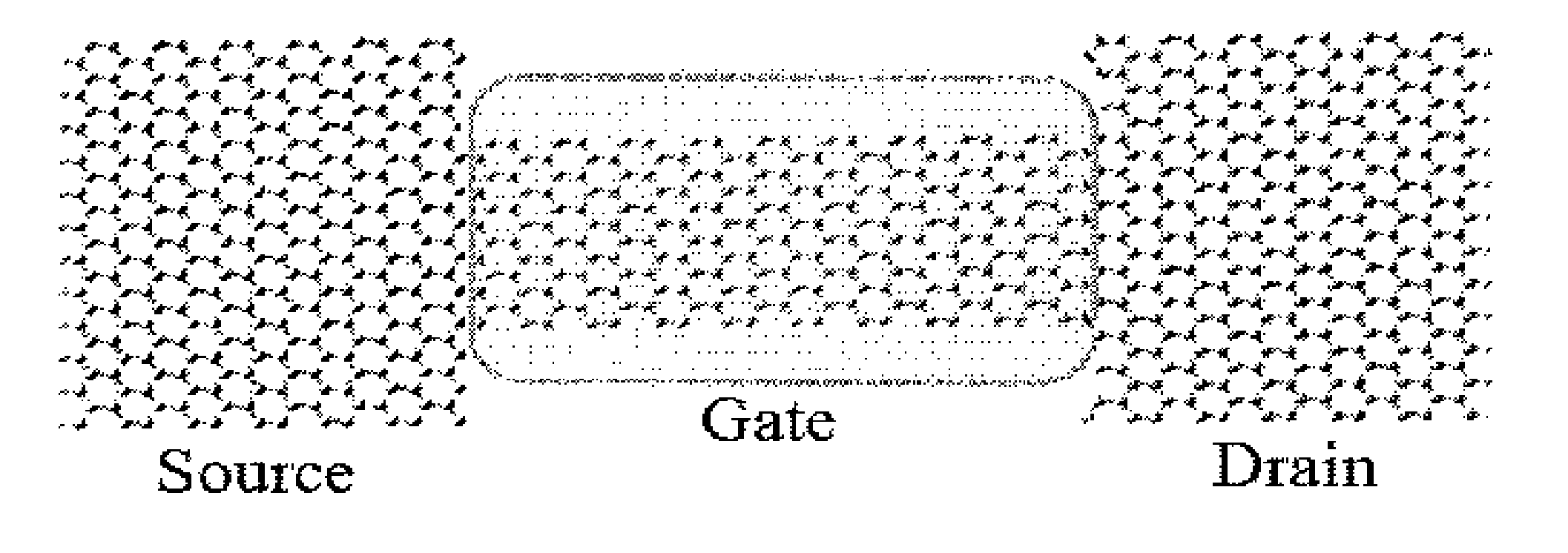

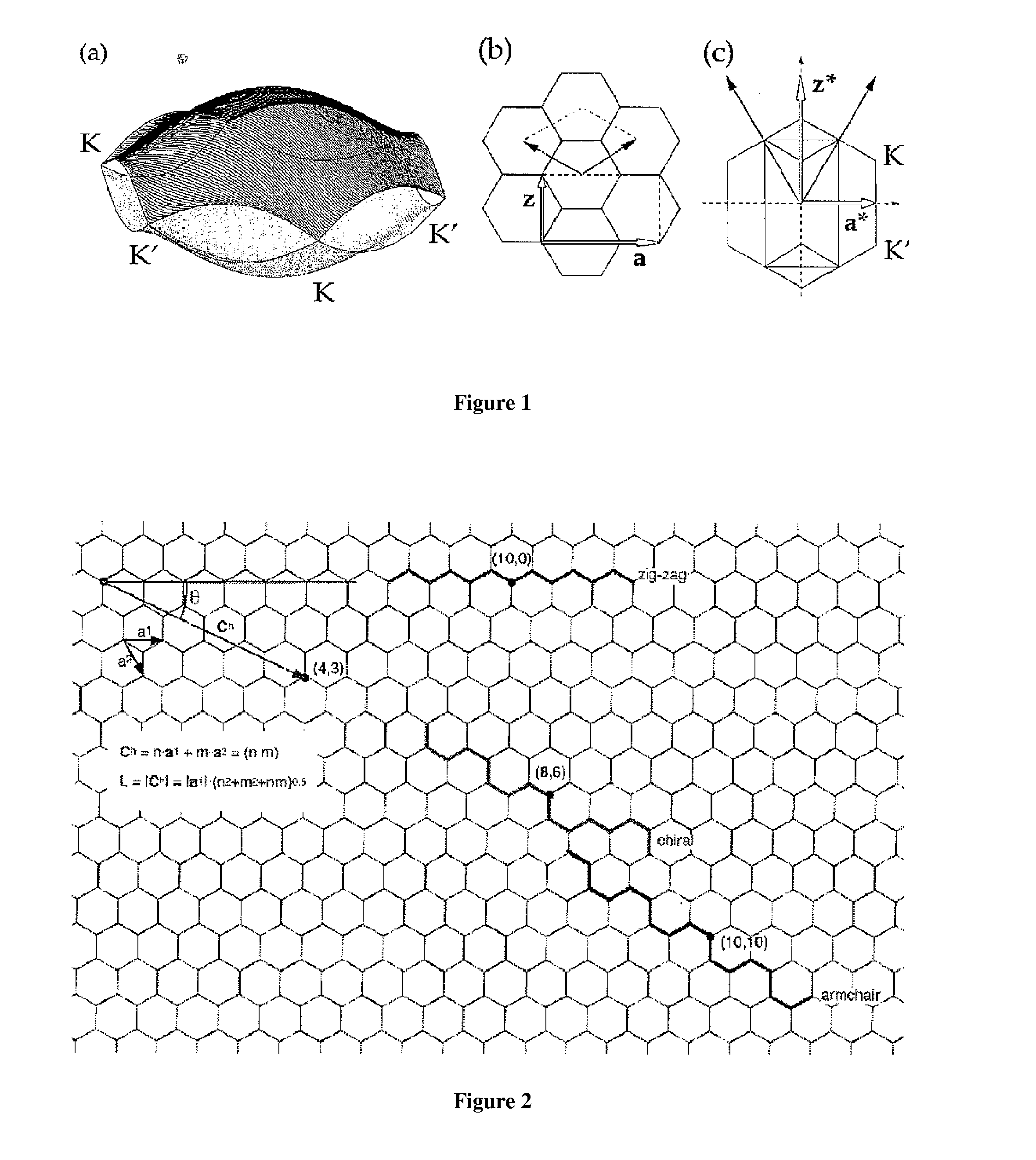

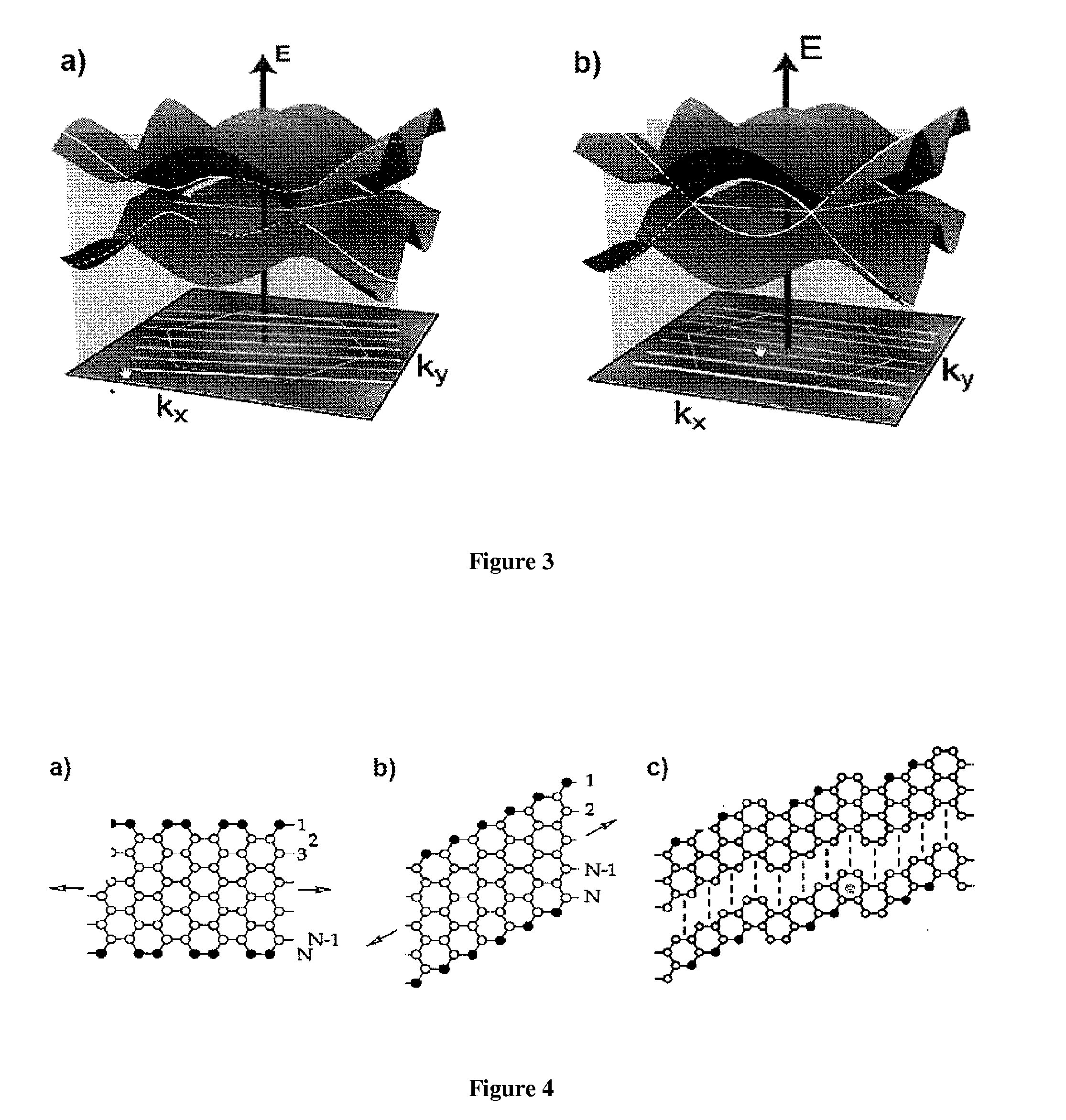

Monolithically-Integrated Graphene-Nano-Ribbon (GNR) Devices, Interconnects and Circuits

InactiveUS20090174435A1Logic circuits characterised by logic functionNanoinformaticsGraphene nanoribbonsElectronic component

The invention discloses new and advantageous uses for carbon / graphene nanoribbons (GNRs), which includes, but is not limited to, electronic components for integrated circuits such as NOT gates, OR gates, AND gates, nano-capacitors, and other transistors. More specifically, the manipulation of the shapes, sizes, patterns, and edges, including doping profiles, of GNRs to optimize their use in various electronic devices is disclosed.

Owner:UNIV OF VIRGINIA

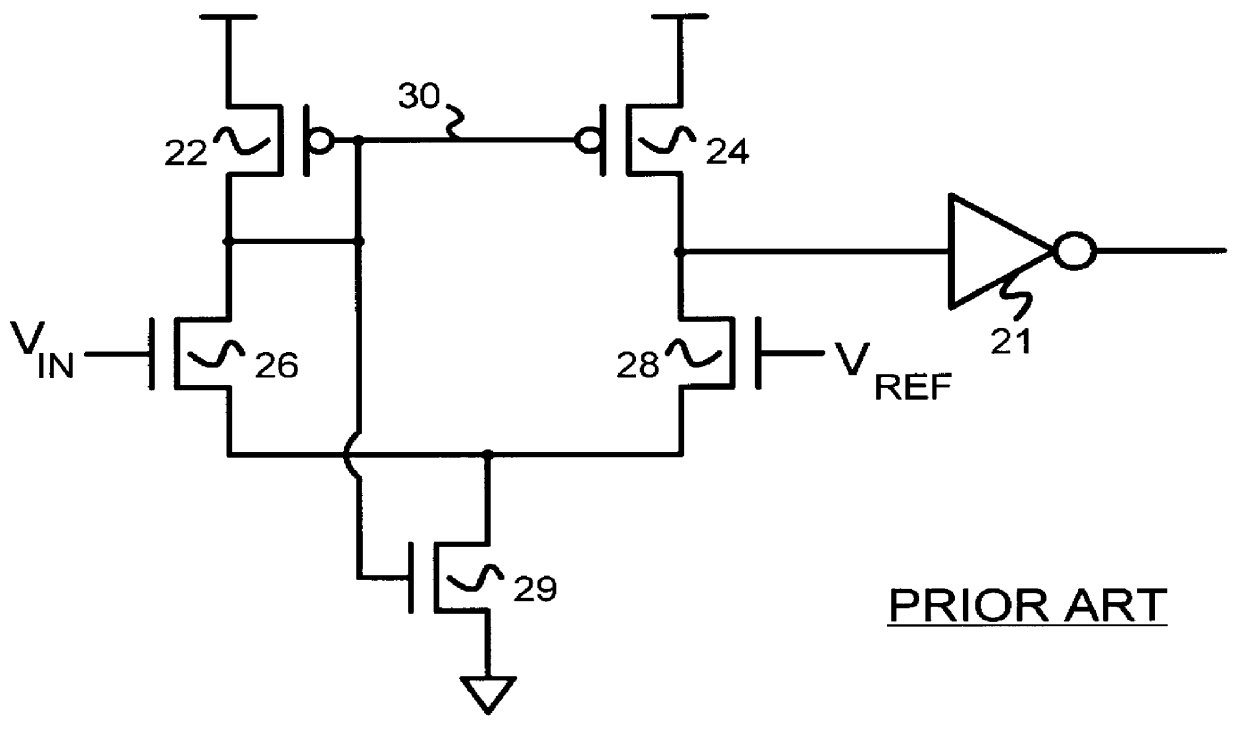

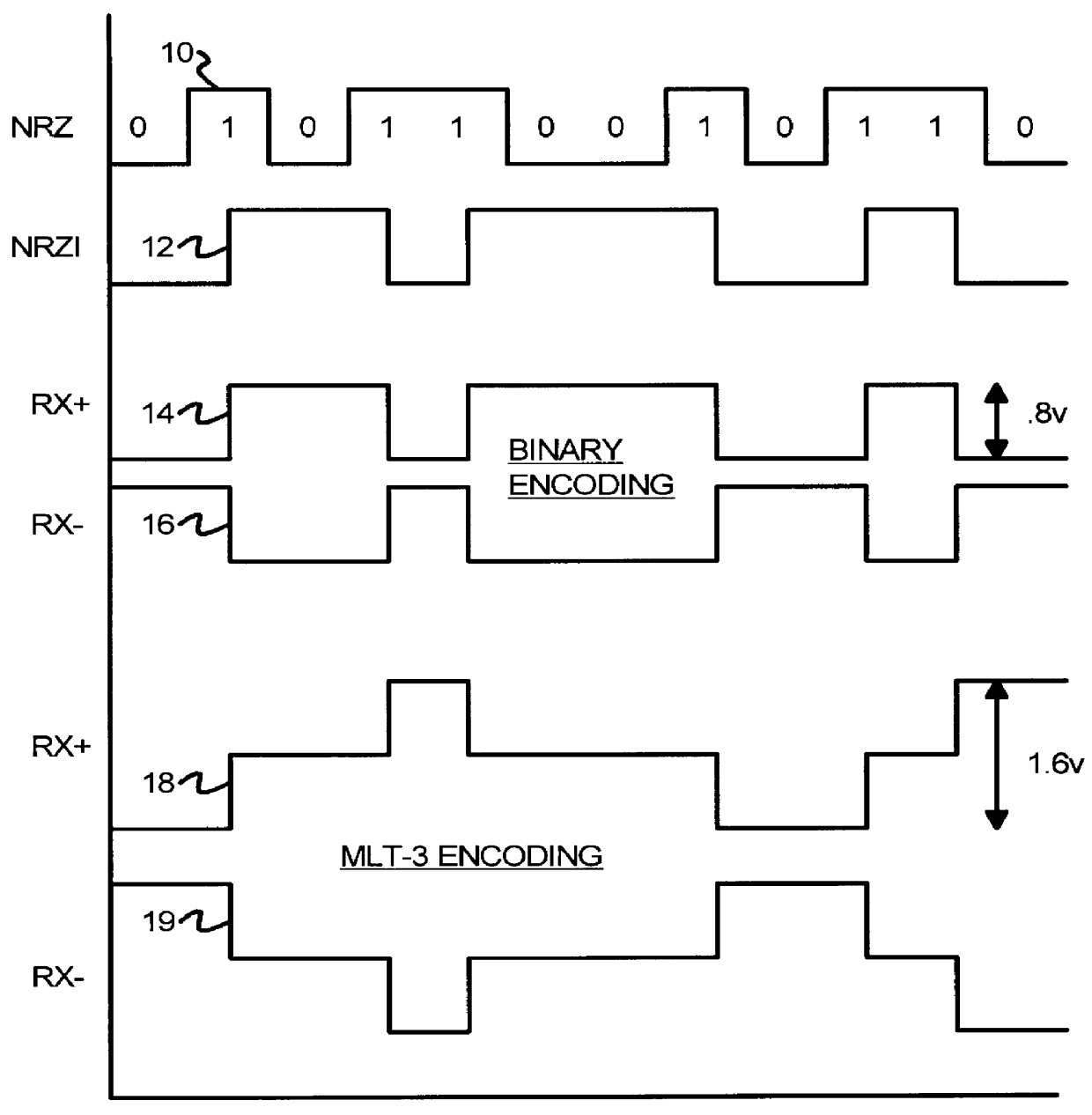

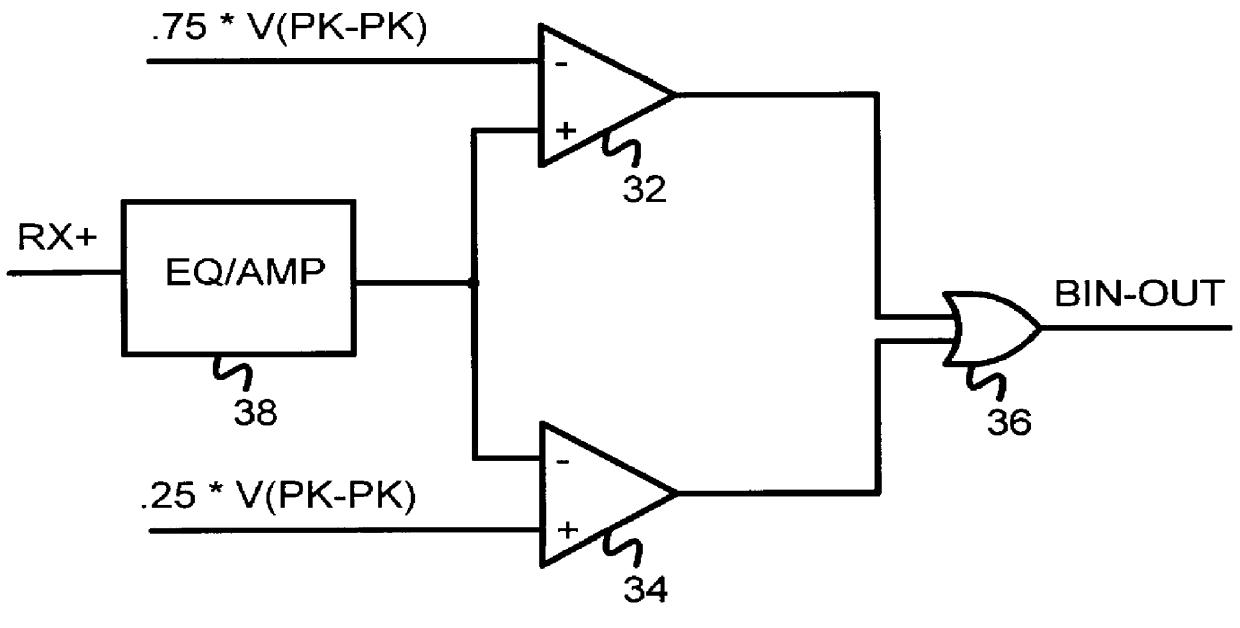

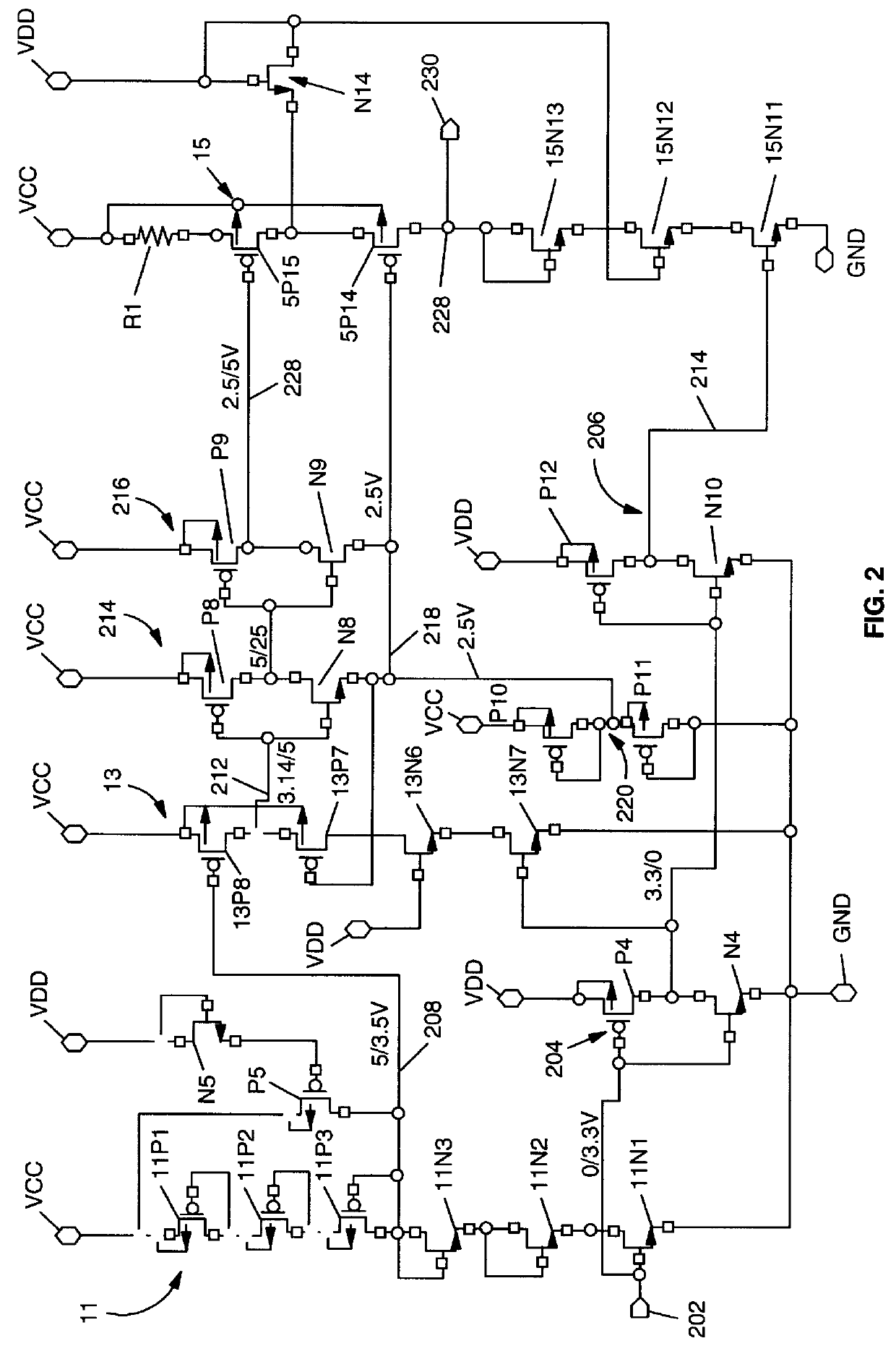

Self-biasing CMOS PECL receiver with wide common-mode range and multi-level-transmit to binary decoder

InactiveUS6049229AReduced Power RequirementsSimplify interconnect routingLogic circuits characterised by logic functionLogic circuits coupling/interface using field-effect transistorsThree levelEmitter-coupled logic

A pseudo-emitter-coupled-logic (PECL) receiver has a wide common-mode range. Two current-mirror CMOS differential amplifiers are used. One amplifier has n-channel differential transistors and a p-channel current mirror, while the second amplifier has p-channel differential transistors and an n-channel current mirror. When the input voltages approach power or ground, one type of differential transistor continues to operate even when the other type shuts off. The outputs of the two amplifiers are connected together and each amplifier receives the same differential input signals. The tail-current transistor is self-biased using the current-mirror's gate-bias. This self biasing of each amplifier eliminates the need for an additional voltage reference and allows each amplifier to adjust its biasing over a wide input-voltage range. Thus the common-mode input range is extended using self biasing and complementary amplifiers. The complementary self-biased comparators can be used for receiving binary or multi-level-transition (MLT) inputs by selecting different voltage references for threshold comparison. Using the same reference on both differential inputs eliminates a second reference for multi-level inputs having three levels. Thus binary and MLT inputs can be detected and decoded by the same decoder.

Owner:DIODES INC

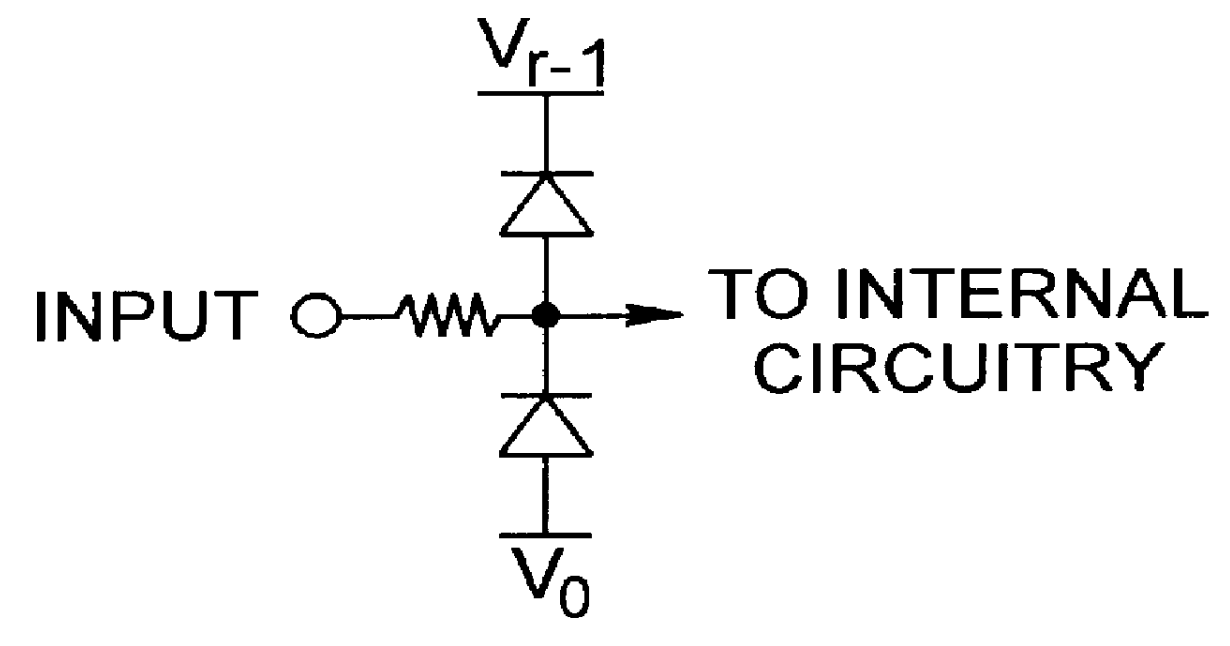

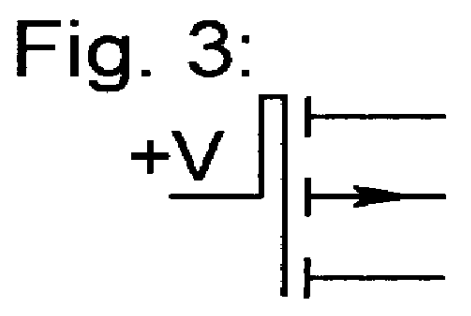

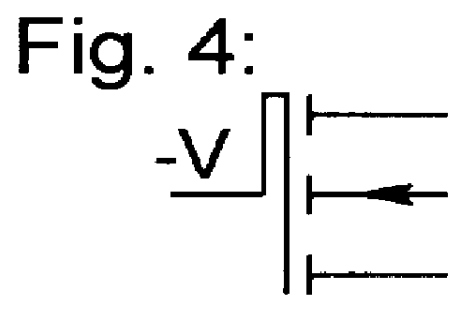

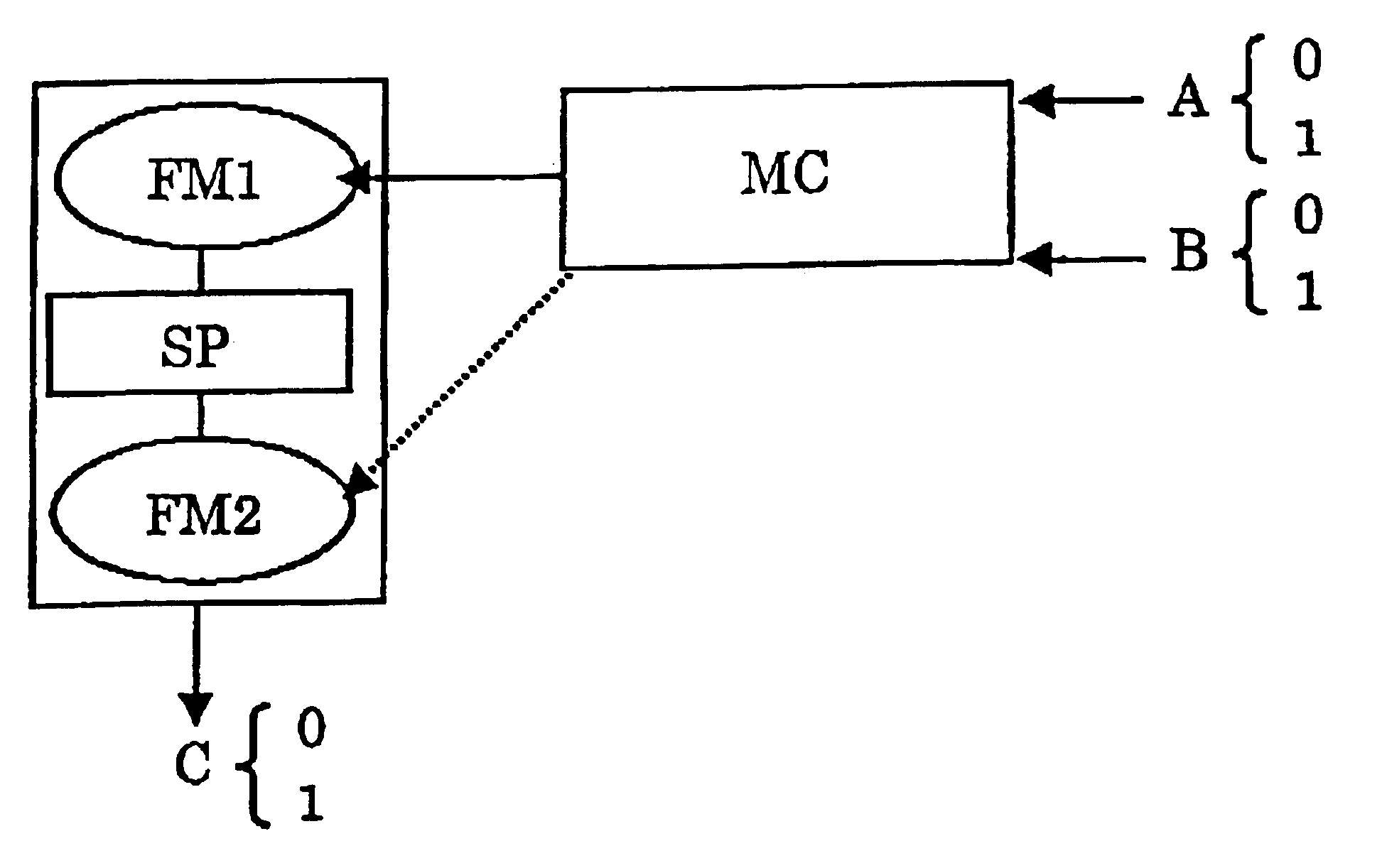

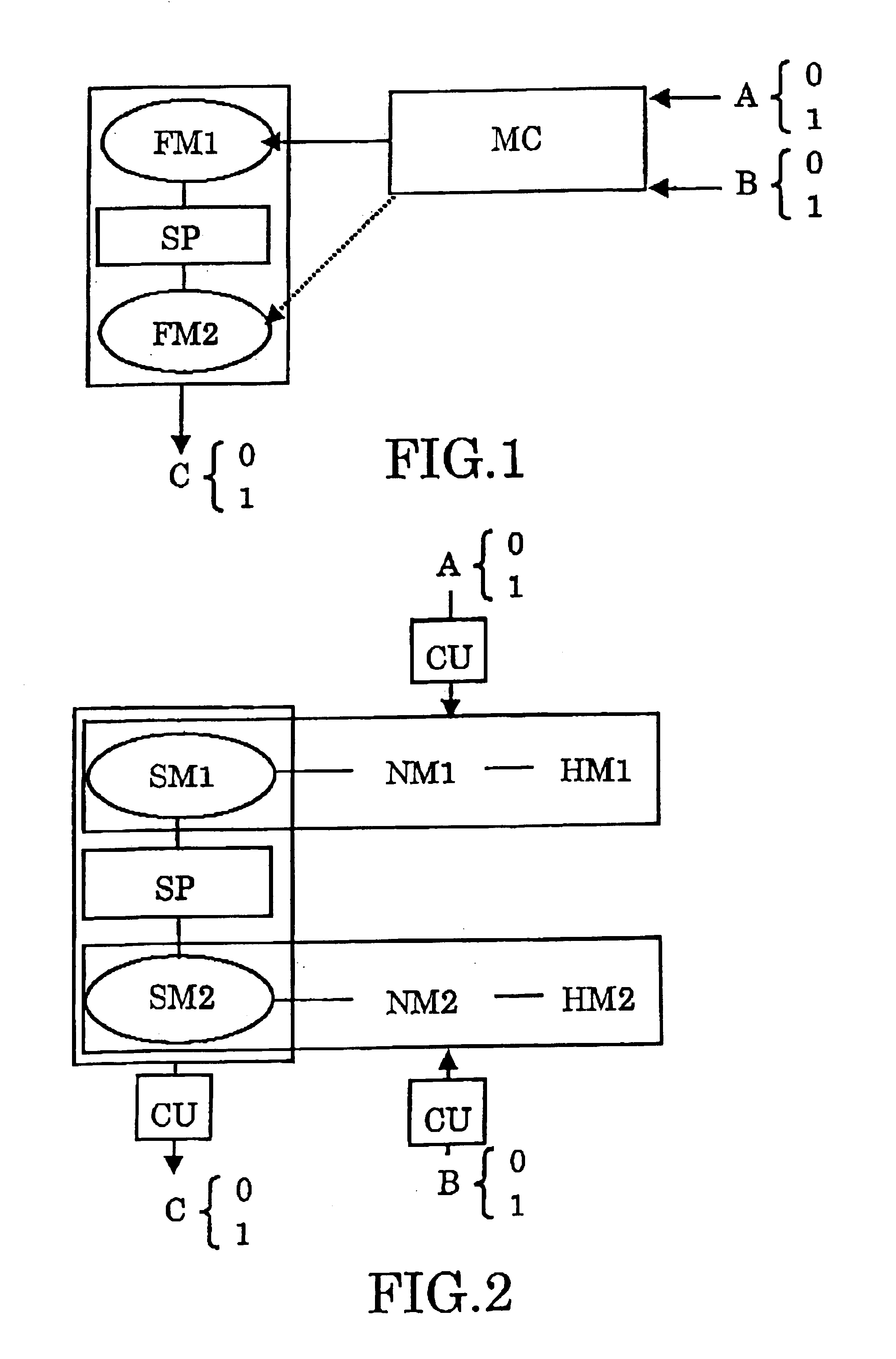

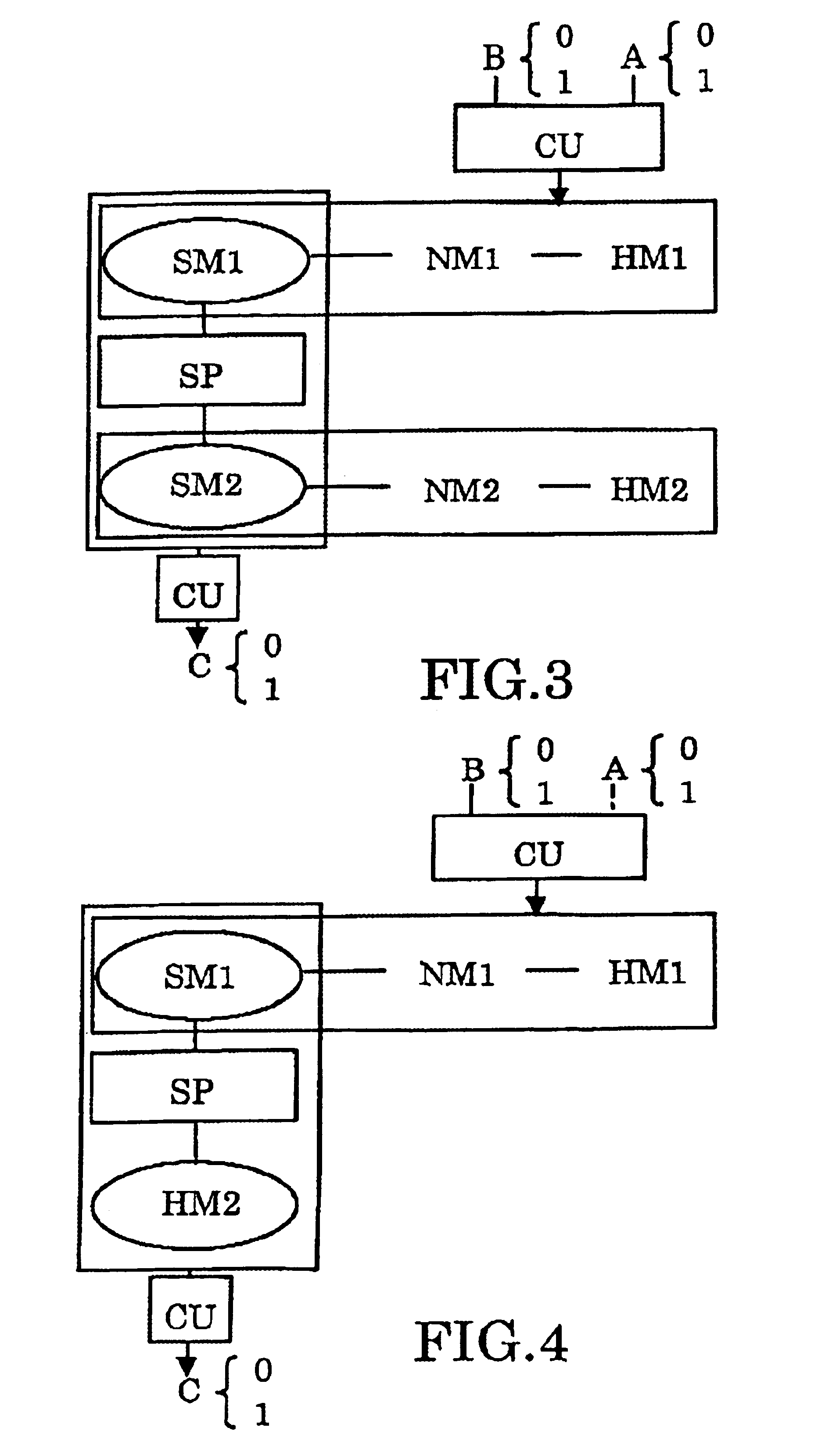

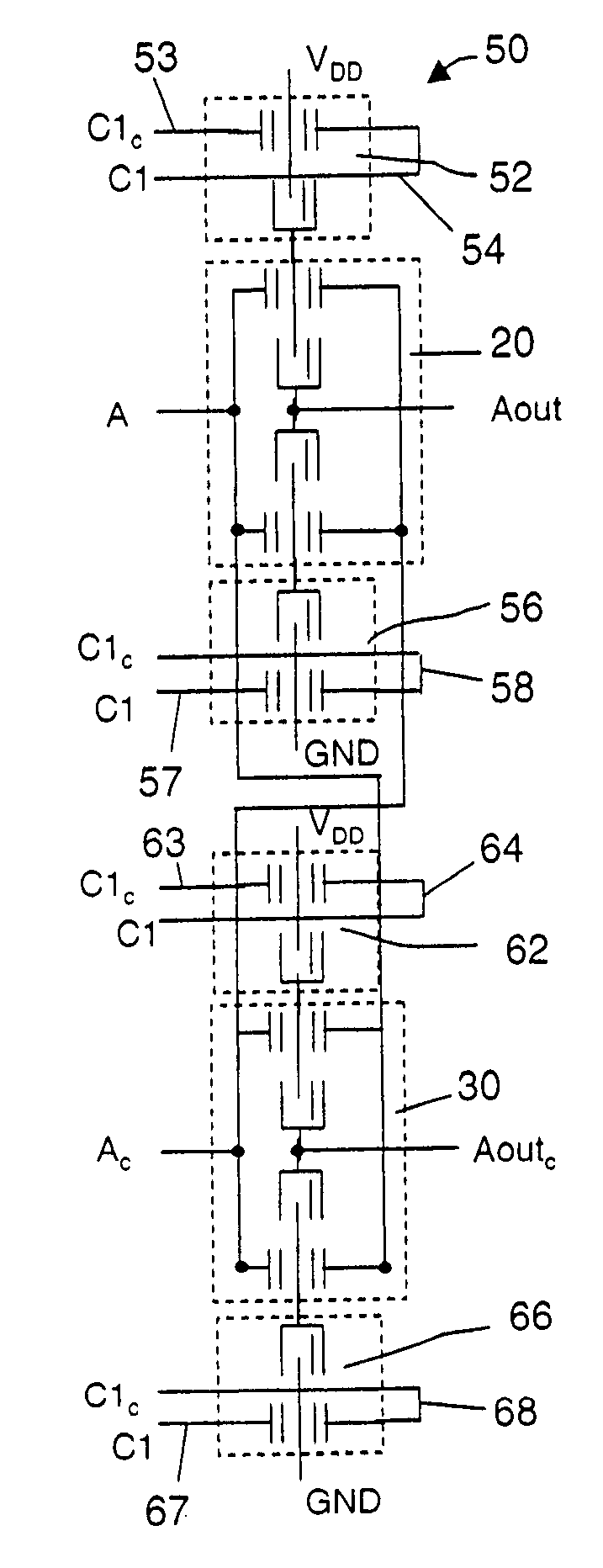

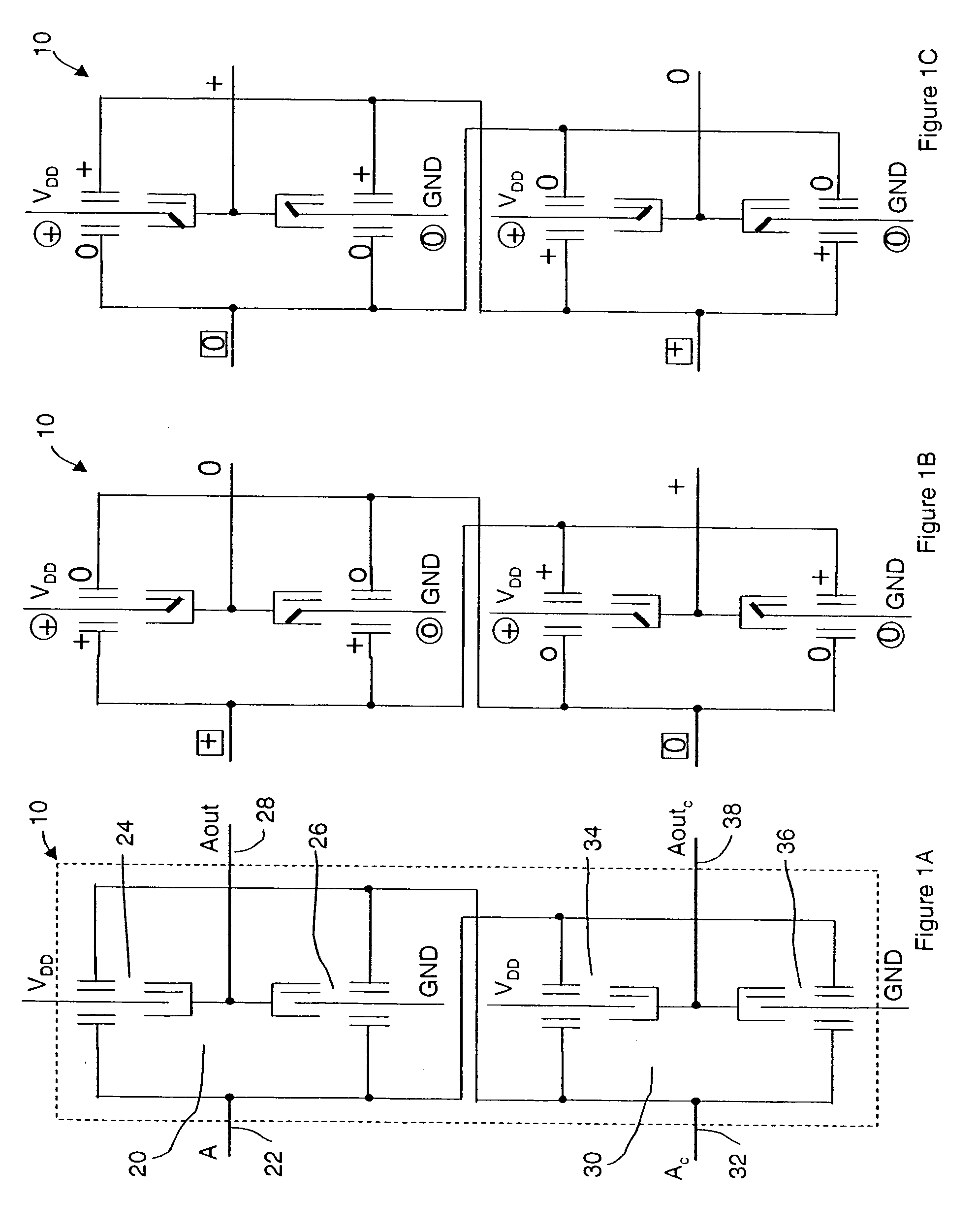

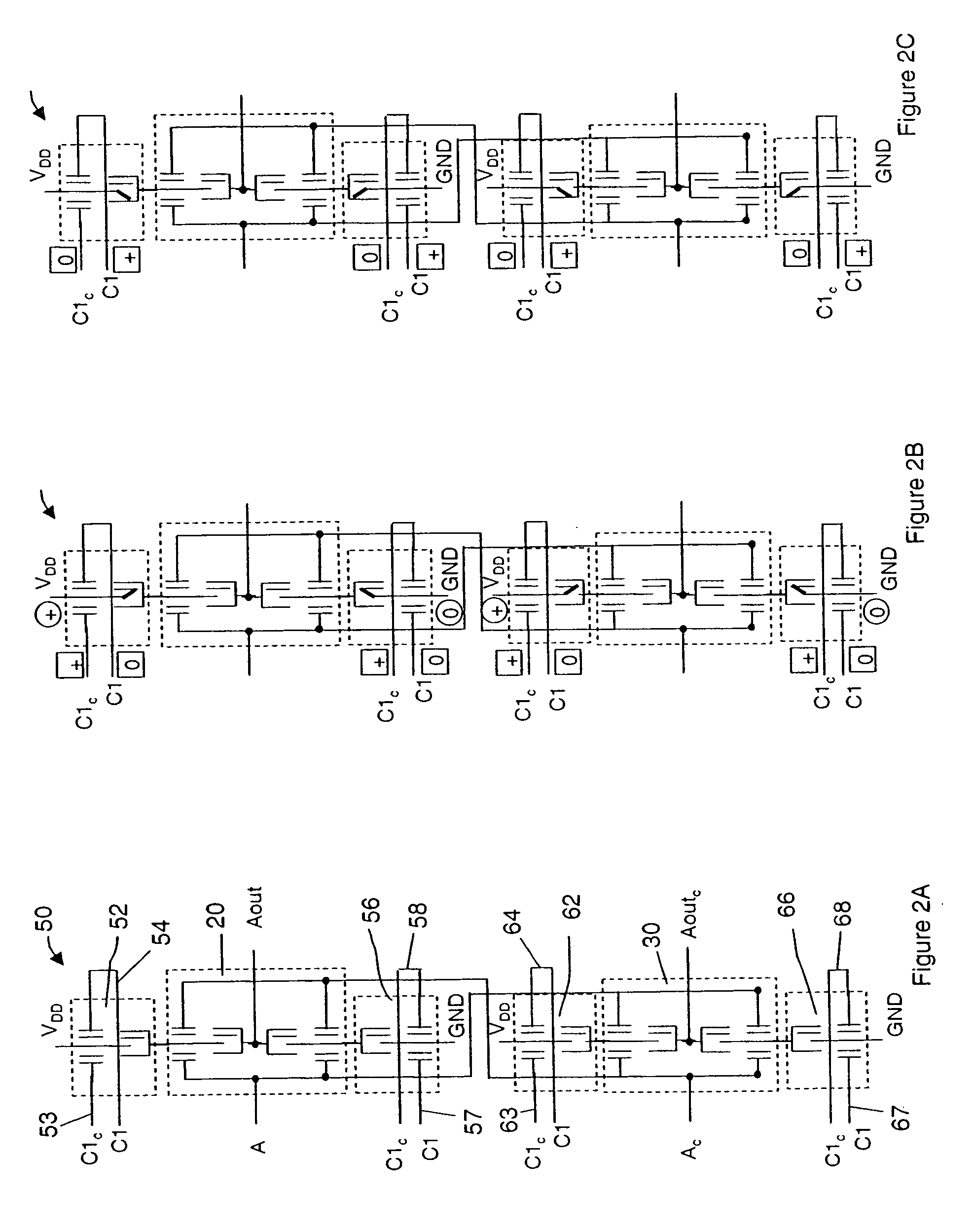

Multiple-valued logic circuit architecture; supplementary symmetrical logic circuit structure (SUS-LOC)

InactiveUS6133754AEasy to copyEasy transferPower consumption reductionLogic circuits characterised by logic functionMany-valued logicLogic synthesis

Circuit structure and resulting circuitry for multiple-valued logic. The circuit structure allows the design and fabrication of any r-valued logic function of n-places where r is an integer greater than 1 and n is an integer greater than 0. This structure is called SUpplementary Symmetrical LOgic Circuit structure (SUS-LOC). In circuits incorporating SUS-LOC, circuit branches are realized that uniquely deliver circuit response and output. For some circuits, and due to the operating characteristics of the switch elements, additional circuit elements, or stages, must be incorporated to prevent "back biasing." SUS-LOC is fully active. Only active elements perform logic synthesis and those components not directly related to logic synthesis, such as resistors and / or other passive loads, are relegated the task of circuit protection. The fabrication of r-valued, multi-valued, or multiple-valued logic circuits, designed using the definitions of the SUS-LOC structure can be accomplished with known techniques, materials, and equipment.

Owner:OMNIBASE LOGIC

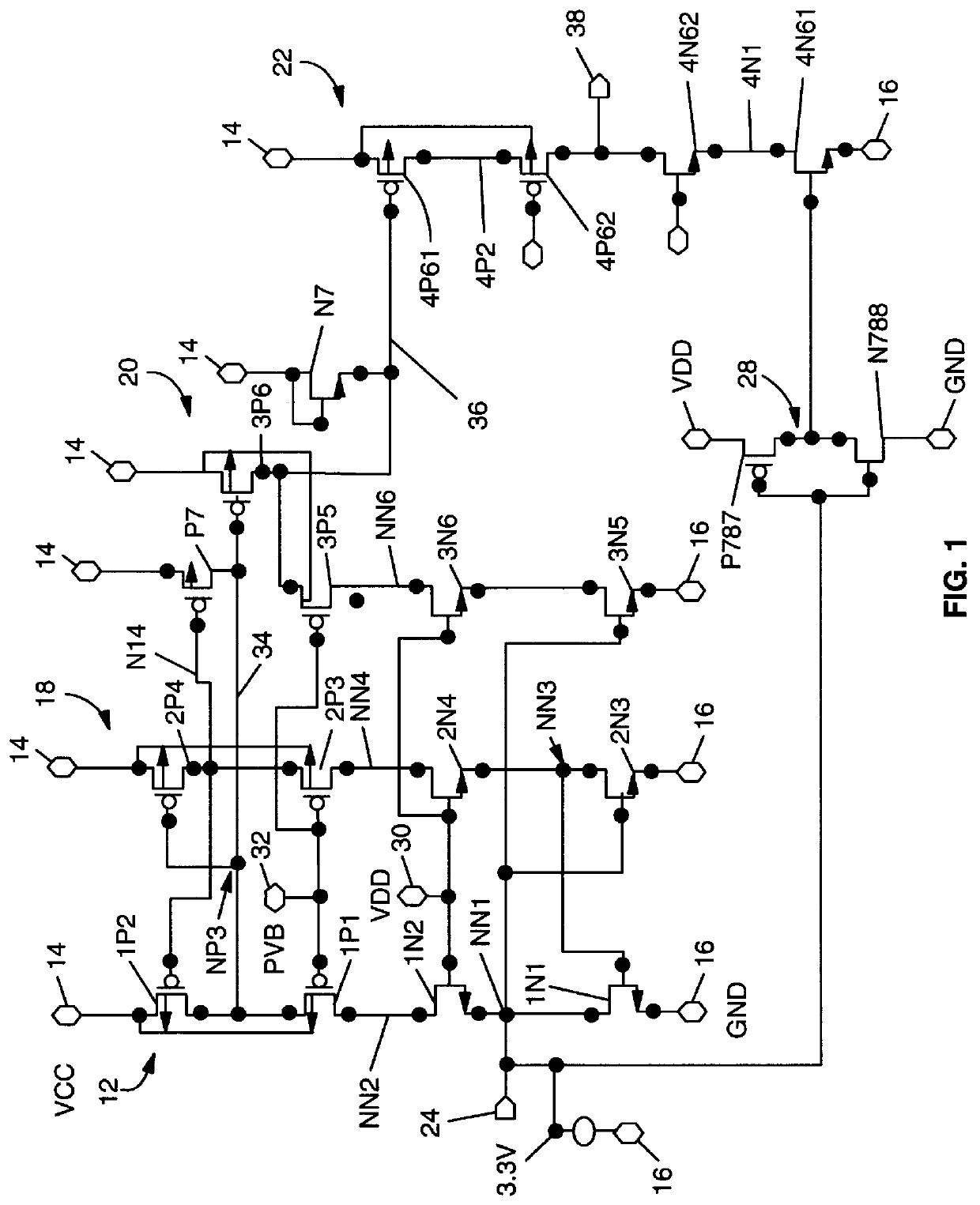

Low voltage CMOS circuit for on/off chip drive at high voltage

InactiveUS6031394AAvoid failureReliability increasing modificationsLogic circuits characterised by logic functionCMOSCascode

A low voltage CMOS circuit and method provide output current ability meeting multimode requirements of high voltage off-chip drivers while protecting the CMOS devices from various breakdown mechanisms. The circuit and method utilize intermediate voltages between two power rails and voltage division techniques to limit the voltages to acceptable limits for drain-to-source, gate-to-drain, and gate-to-source of CMOS devices in any chosen technology. The circuit comprises first and second CMOS cascode chains connected between a high voltage power rail, e.g 5 volt and a reference potential power rail, e.g. ground. Each CMOS cascode chain comprises first and second p-type MOS devices in series with first and second n-type MOS devices. An input circuit is coupled to a node at the midpoint of the first CMOS cascode chain. A bias voltage, typically 3.3 volts is connected to the NMOS devices in the first and CMOS cascode chains. A second bias voltage is coupled to the PMOS devices in the first and second CMOS cascode chains. An output is provided from the second CMOS cascode chain to a third CMOS cascode chain for purposes of providing sufficient pullup capability to drive an output circuit comprising a fourth CMOS cascode chain between the high and reference potentials without exceeding the breakdown mechanisms for any MOS device in the CMOS cascode chains.

Owner:GOOGLE LLC

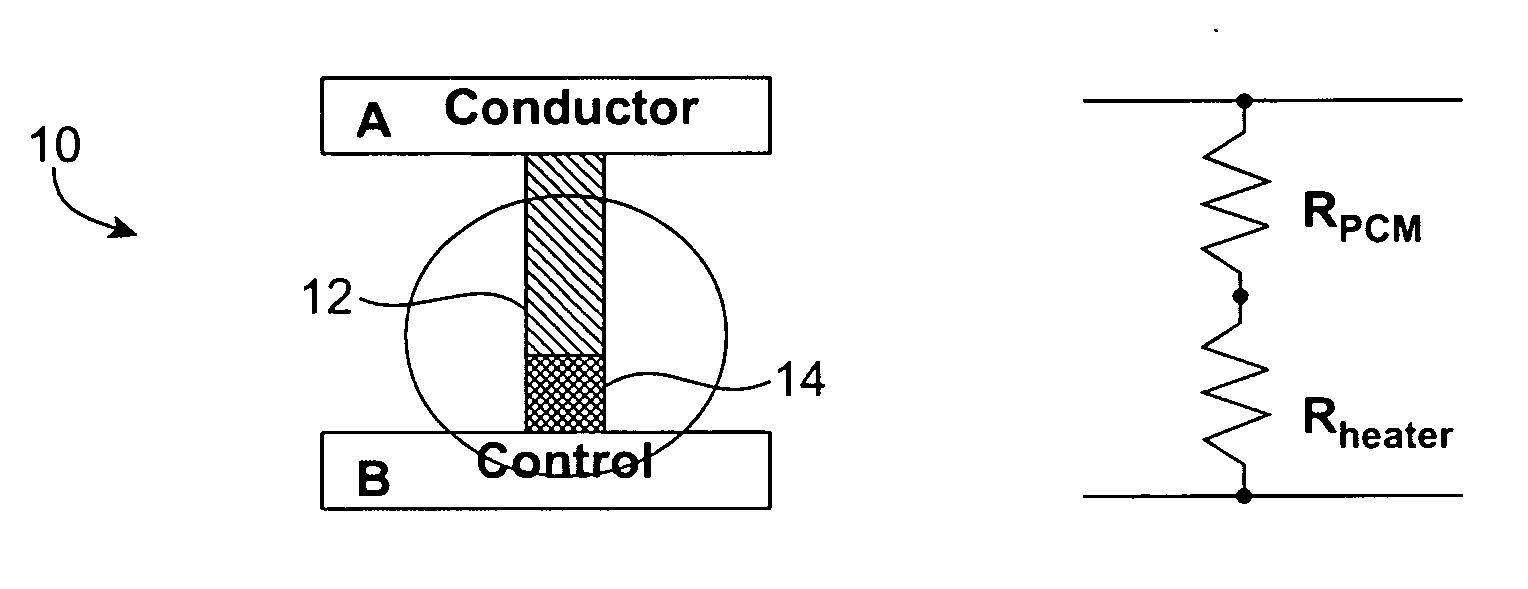

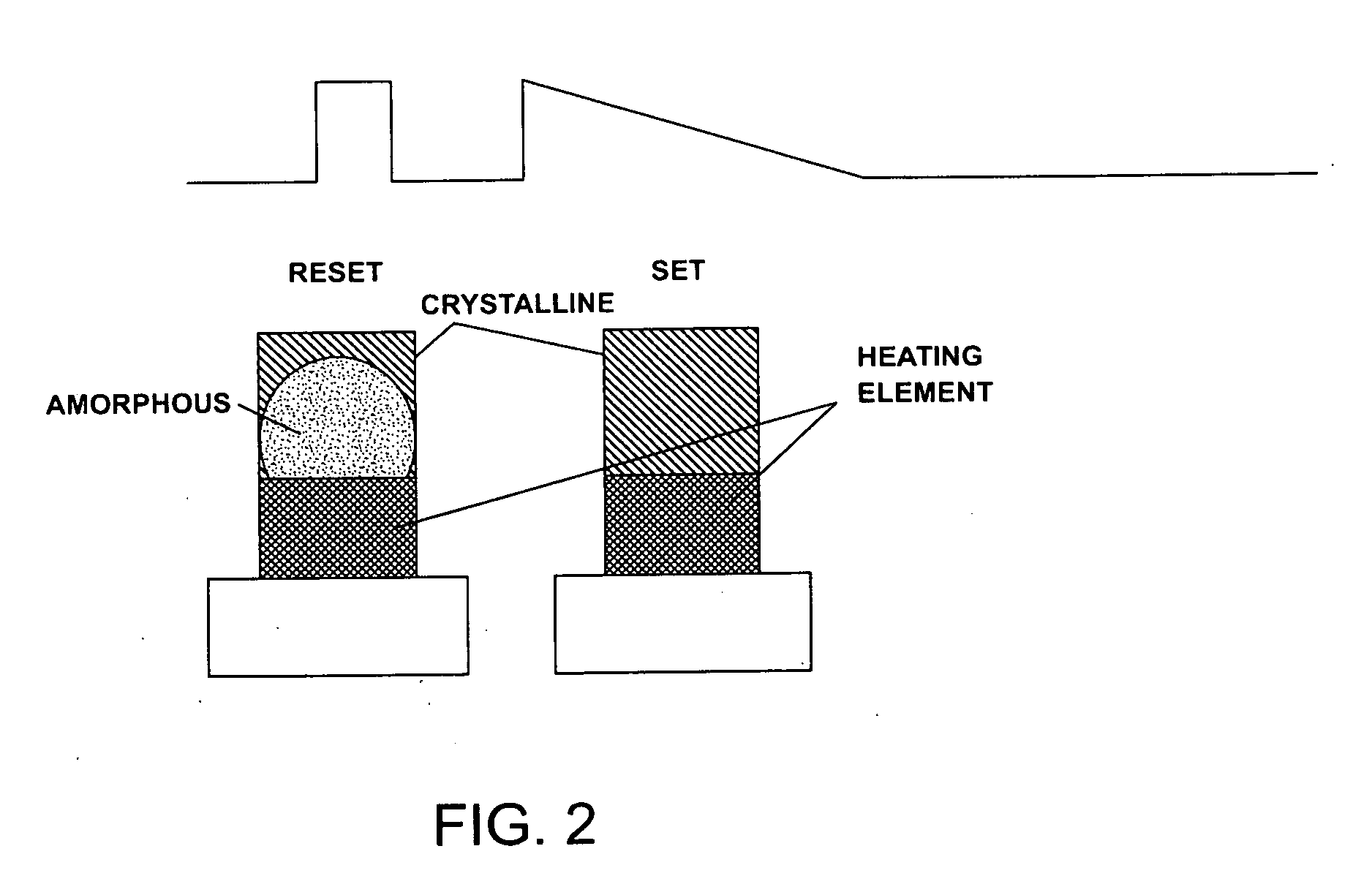

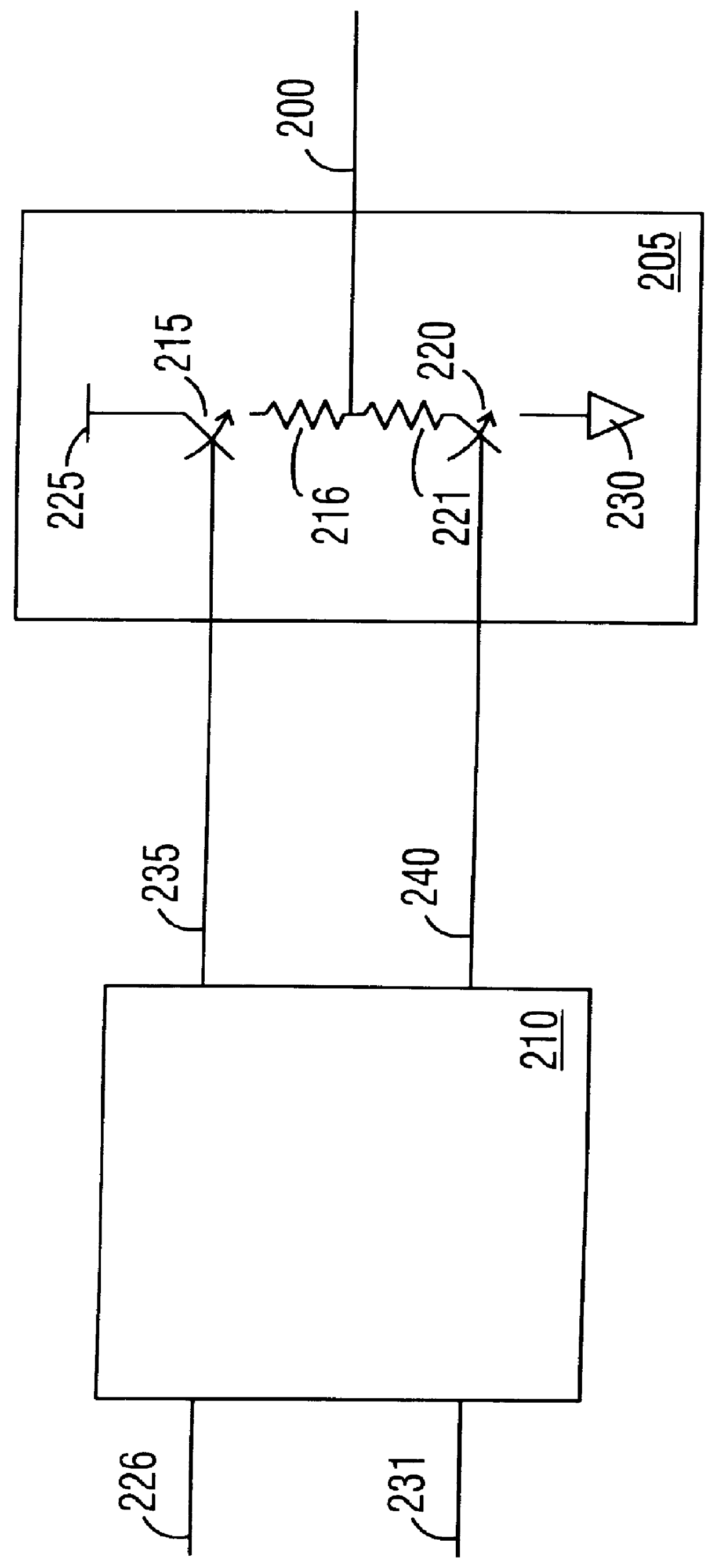

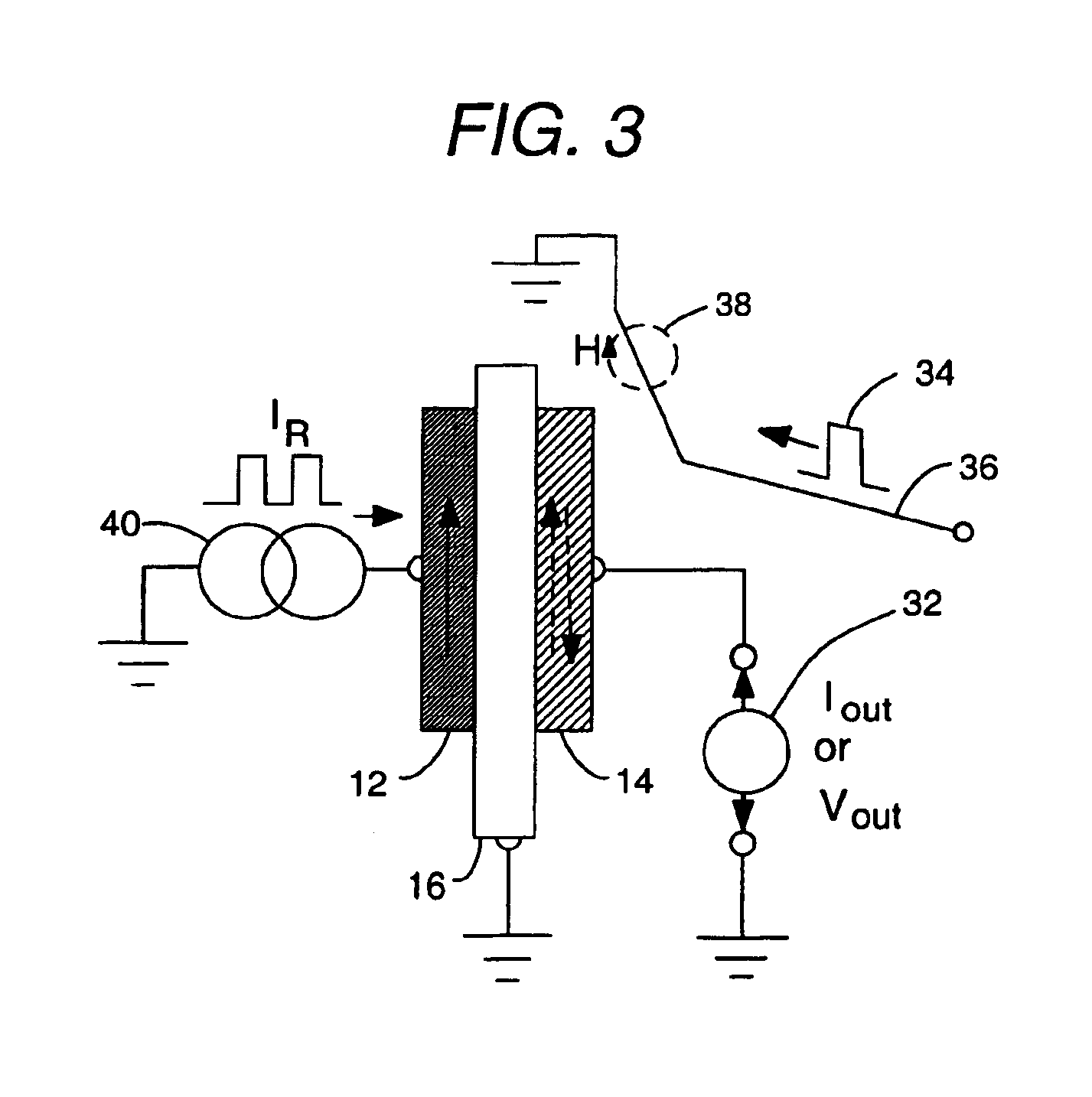

Multi-terminal phase change devices

InactiveUS20070096071A1Reduce capacitanceReduce resistanceDigital storageBulk negative resistance effect devicesCapacitanceElectrical resistance and conductance

Phase change devices, and particularly multi-terminal phase change devices, include first and second active terminals bridged together by a phase-change material whose conductivity can be modified in accordance with a control signal applied to a control electrode. This structure allows an application in which an electrical connection can be created between the two active terminals, with the control of the connection being effected using a separate terminal or terminals. Accordingly, the resistance of the heater element can be increased independently from the resistance of the path between the two active terminals. This allows the use of smaller heater elements thus requiring less current to create the same amount of Joule heating per unit area. The resistance of the heating element does not impact the total resistance of the phase change device. The programming control can be placed outside of the main signal path through the phase change device, reducing the impact of the associated capacitance and resistance of the device.

Owner:AGATE LOGIC BEIJING

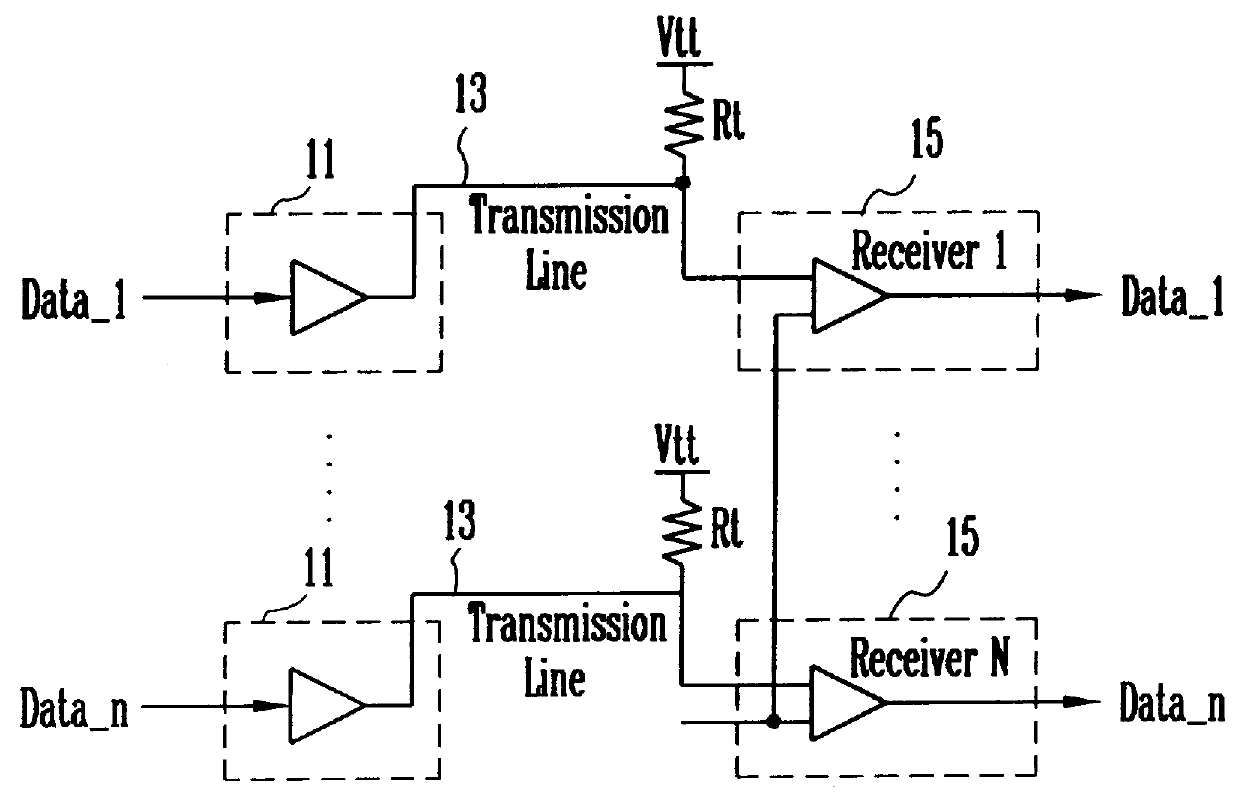

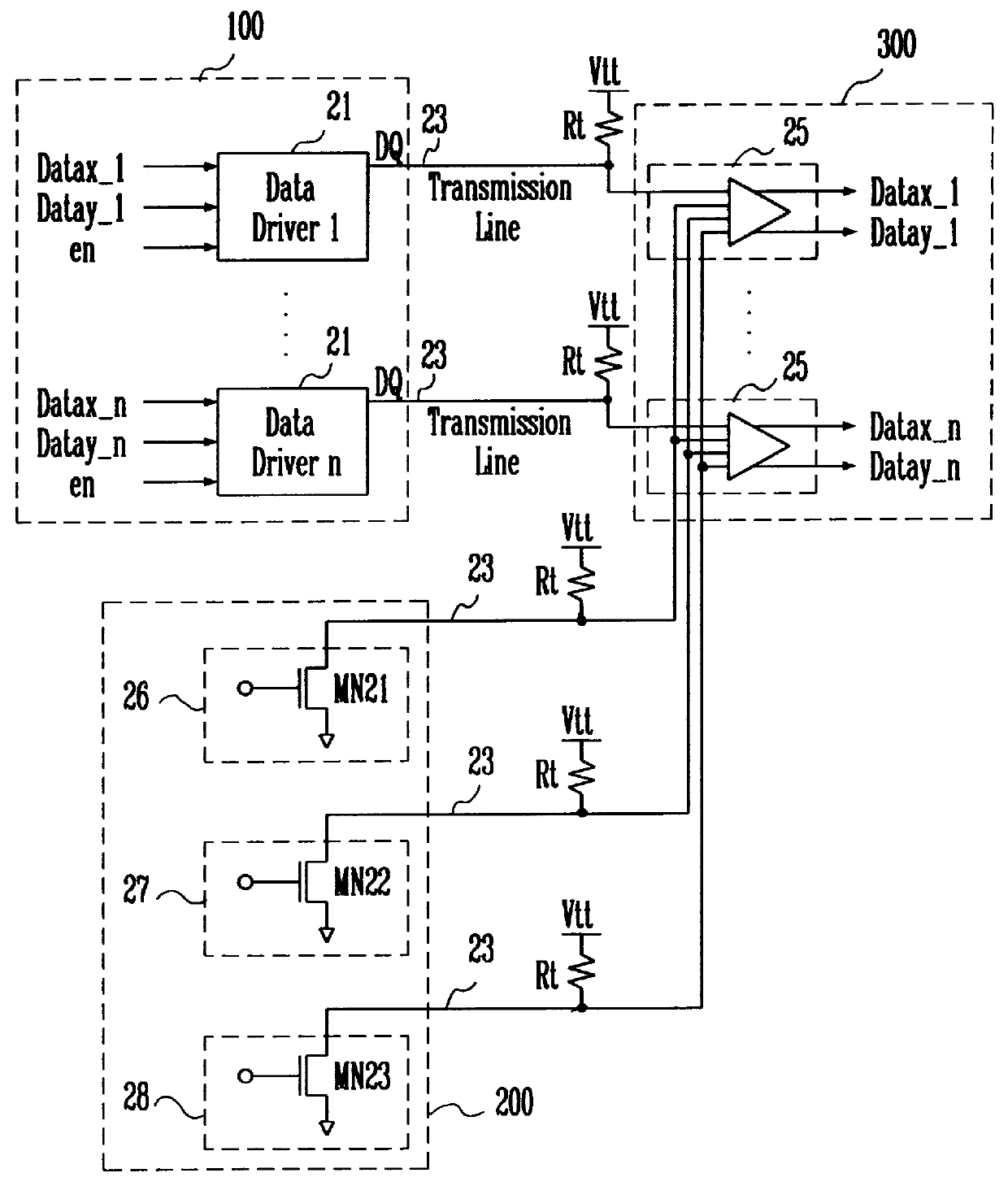

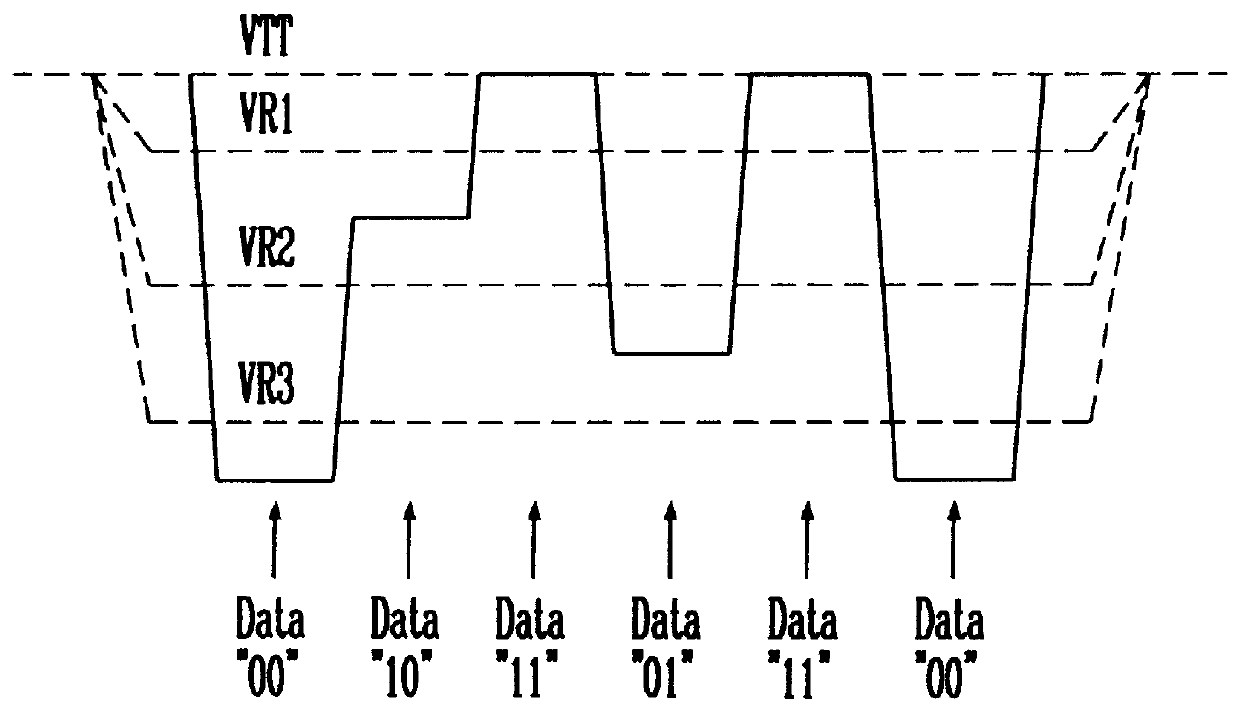

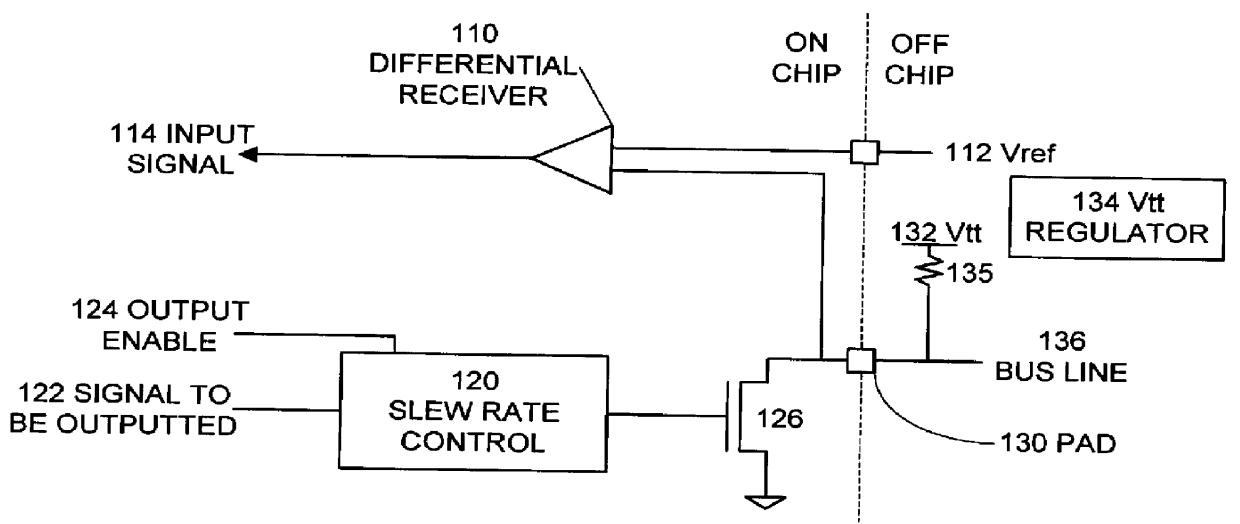

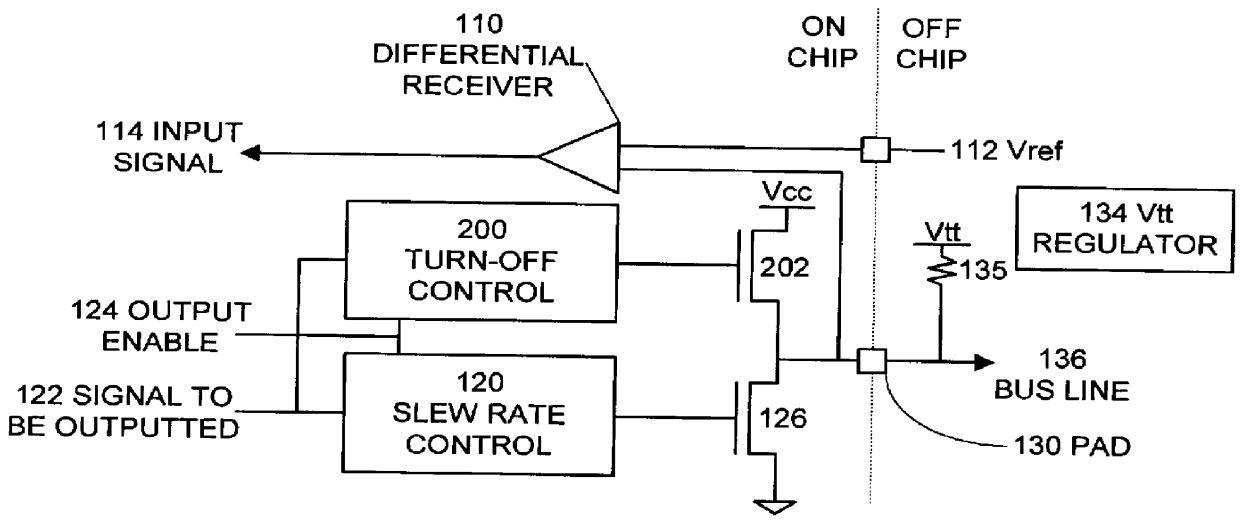

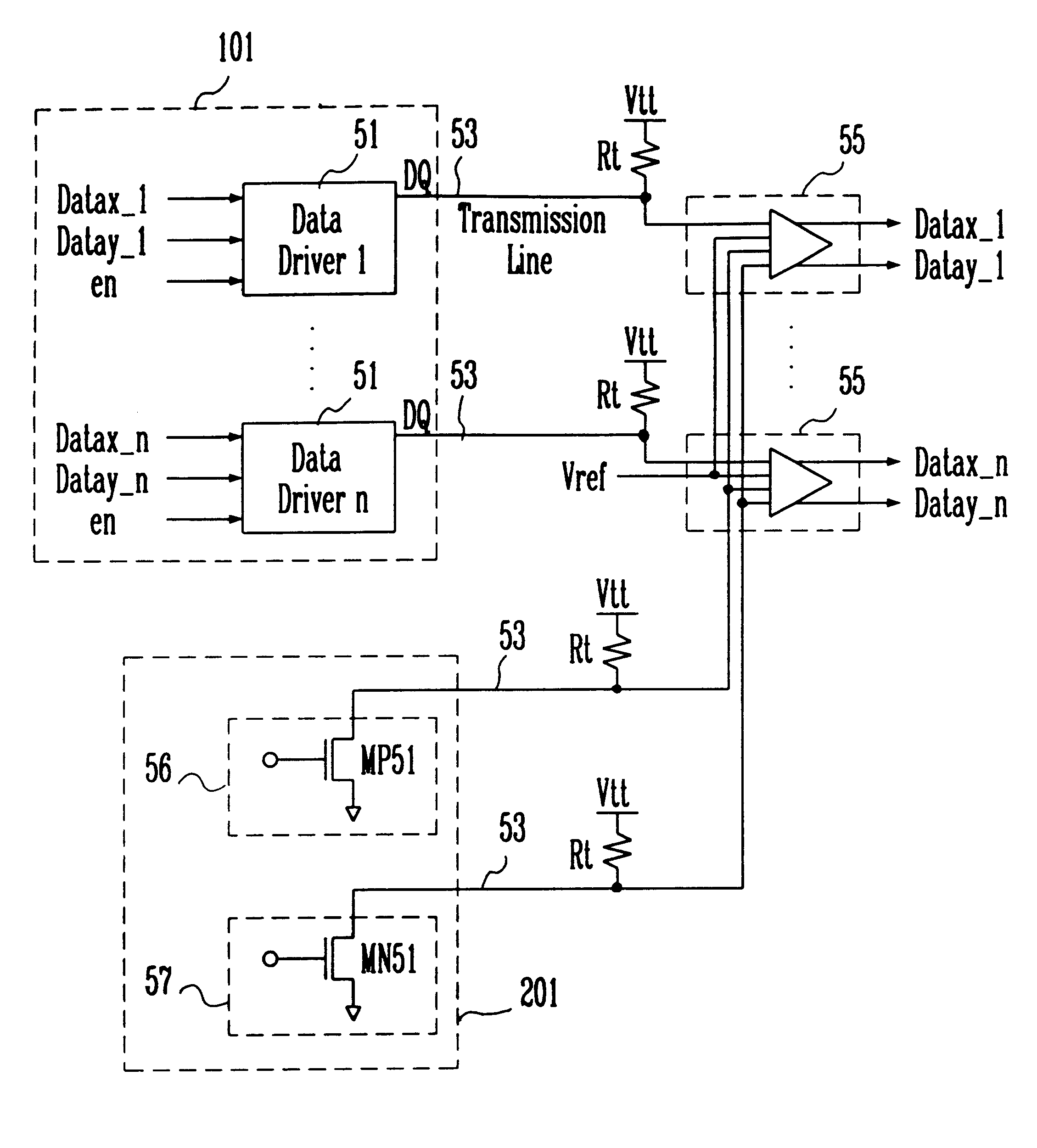

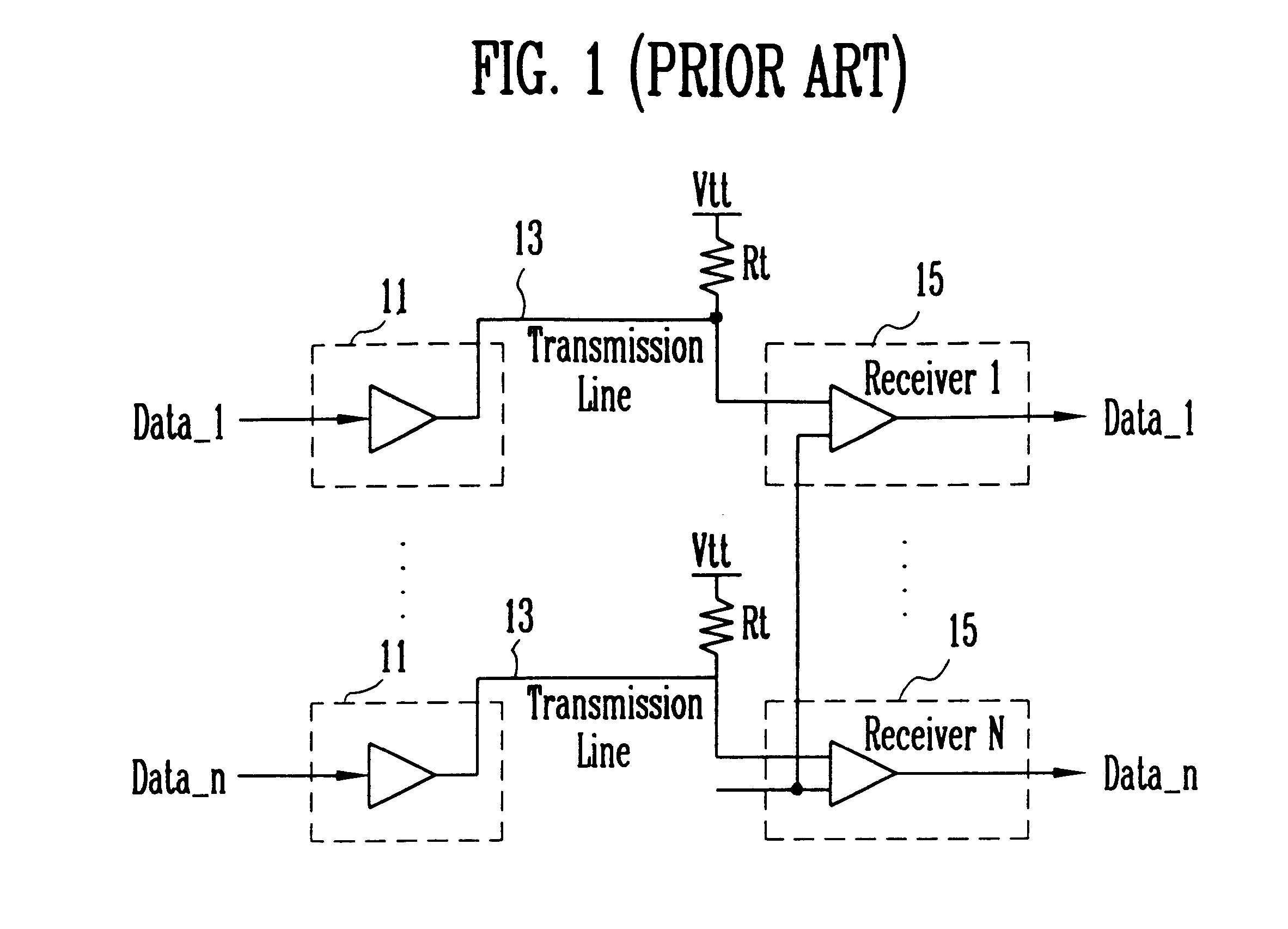

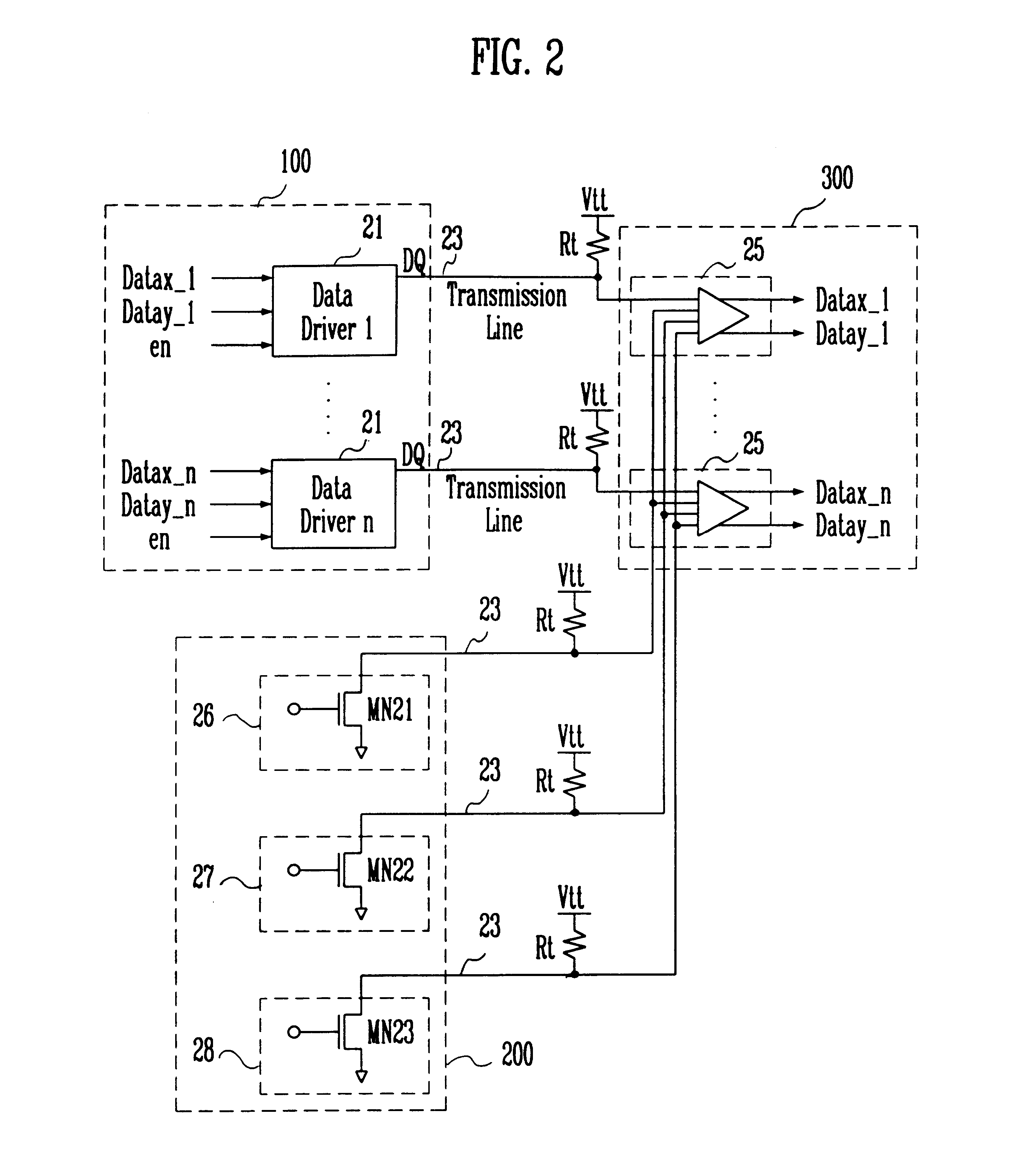

High speed interface apparatus

InactiveUS6140841AElectric signal transmission systemsElectric analogue storesThree levelData signal

The present invention discloses a much higher speed interface apparatus which comprises a data driving means for decoding two-bit data signals using them as inputs to output four-level data signals; a reference voltage generating means for generating three-level reference voltages to discriminate the voltage levels of the four-level data signals; and a receiver means for comparing the four-level data signals and the three-level reference voltage signals using them as inputs and for encoding the resulting signals to output two data signals.

Owner:HYUNDAI ELECTRONICS IND CO LTD

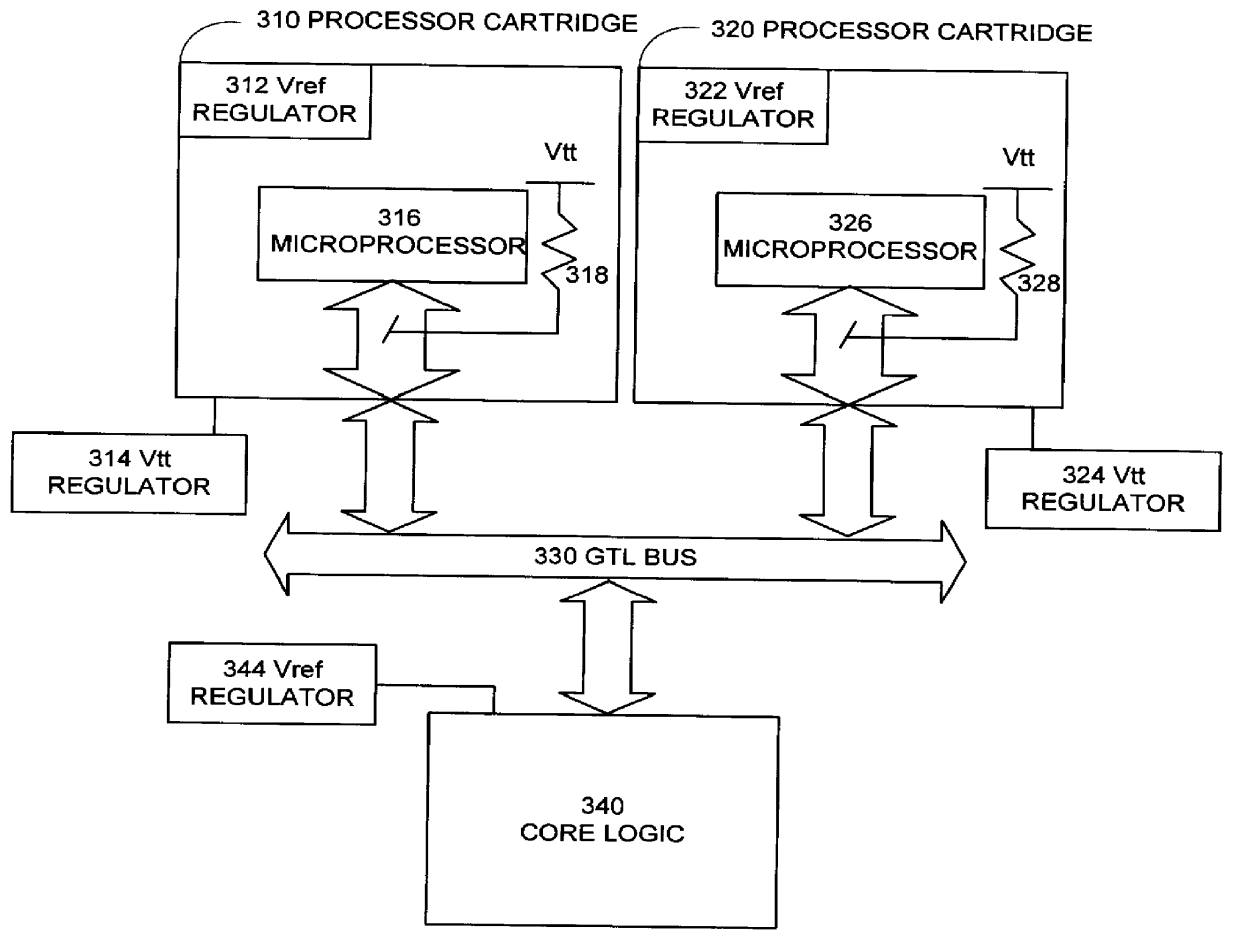

Method for providing two modes of I/O pad termination

InactiveUS6040714AReliability increasing modificationsLogic circuits coupling/interface using field-effect transistorsDual modeEngineering

The present invention provides a method of providing two different modes of operation for an output driver on an integrated circuit. A first mode provides an open drain driver, such as an enhanced GTL+ driver, for high-speed data transmission. A second mode provides a totem pole output driver, such as a TTL or a LVTLL driver, which does not require additional circuitry for external terminations, as is required for open drain drivers. Thus, one embodiment of the present invention can be characterized as a method of providing a dual mode output from an integrated circuit. This method includes receiving an output mode signal indicating an enhanced GTL+ output mode or a totem pole output mode. This method also includes providing an enhanced GTL+ output signal if the mode signal indicates the enhanced GTL+ output mode, and providing a totem pole output signal if the mode signal indicates the totem pole output mode. Another embodiment of the present invention can be described as a method for providing a dual mode output from an integrated circuit. This method includes providing to the integrated circuit an output mode signal indicating a first output mode or a second output mode. It also includes coupling an output pin of the integrated circuit to an open drain bus with an active termination if the mode signal indicates the first mode, and coupling an output pin of the integrated circuit to an unterminated bus if the mode signal indicates the second output mode.

Owner:MICRON TECH INC

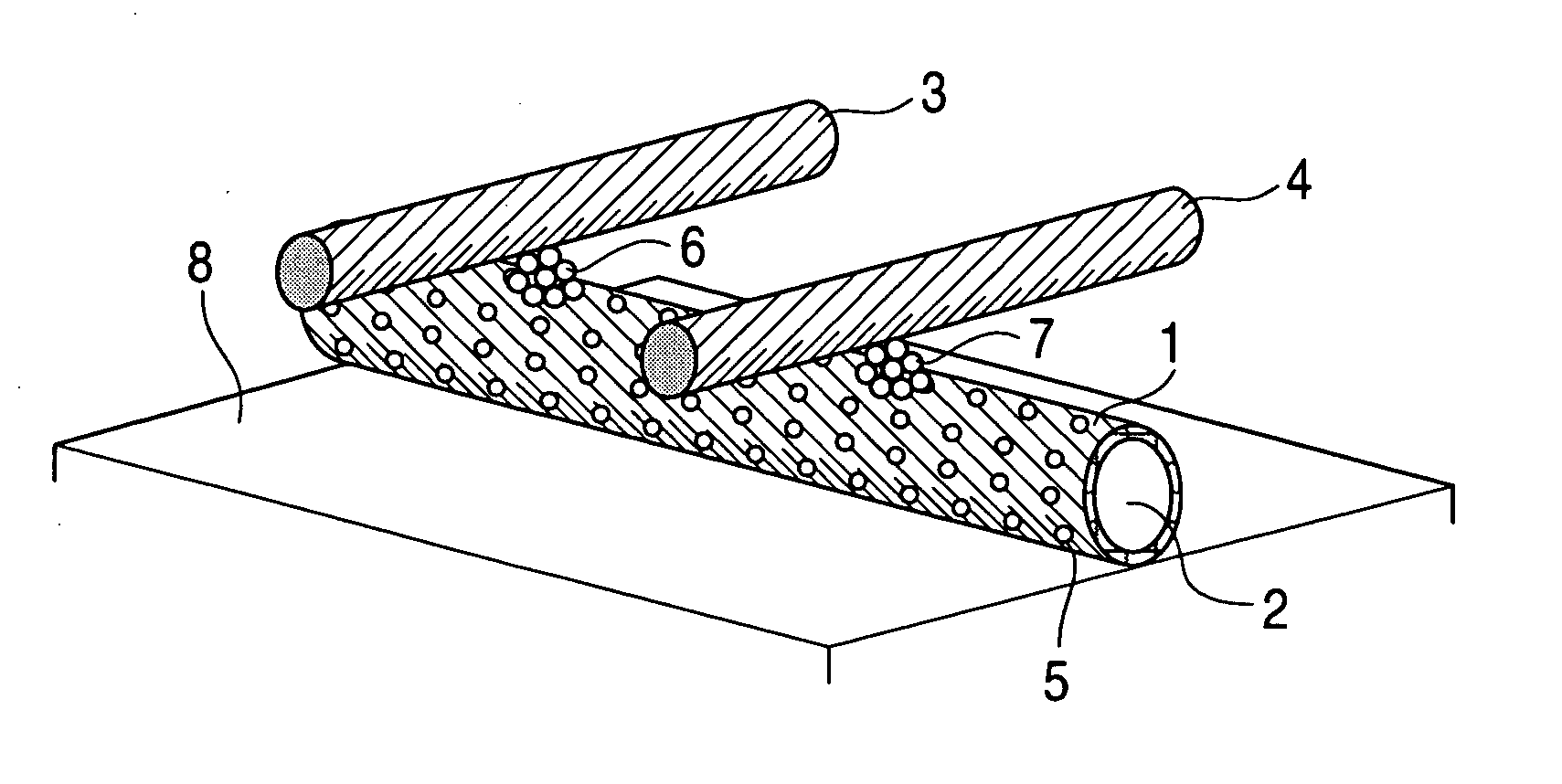

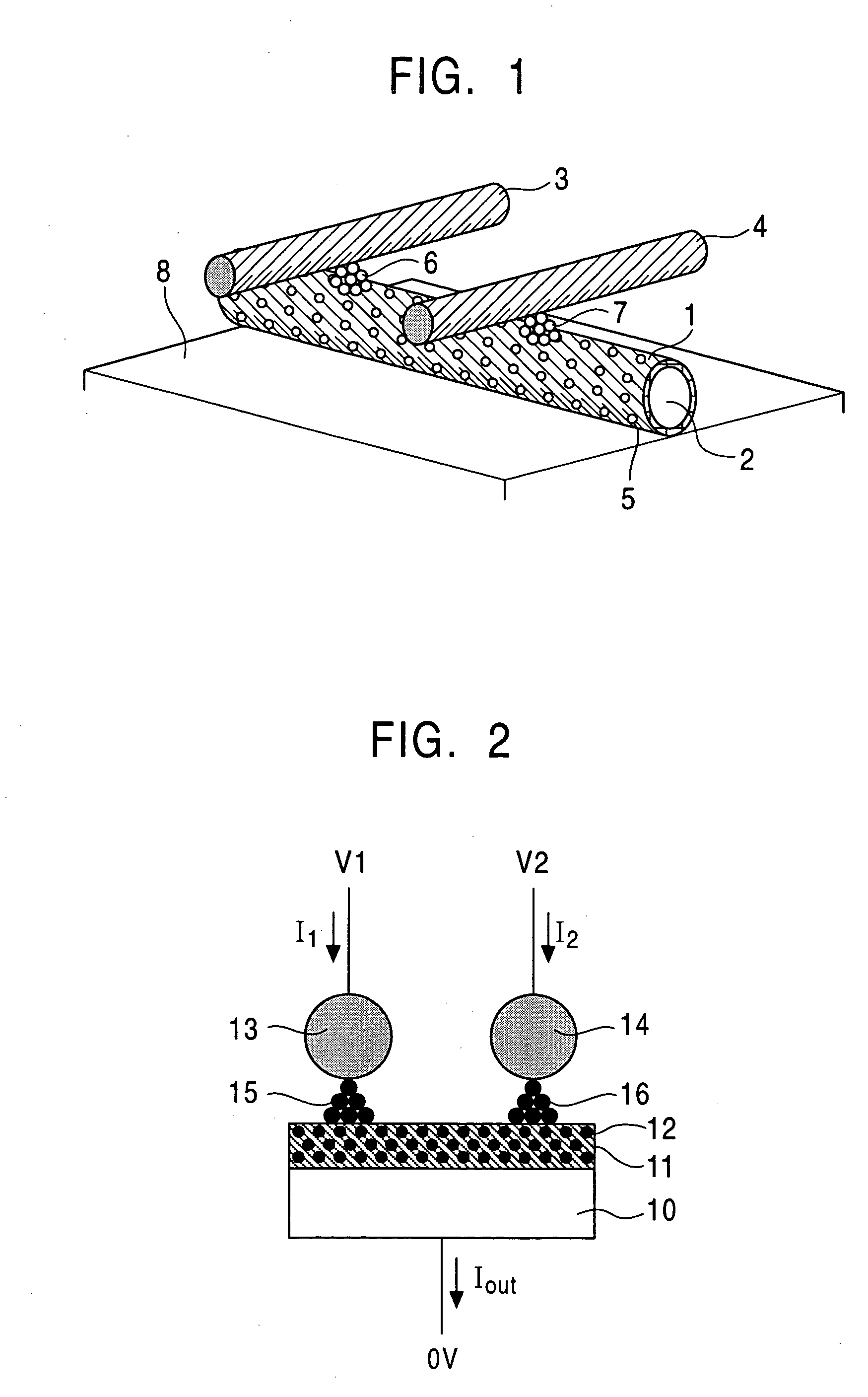

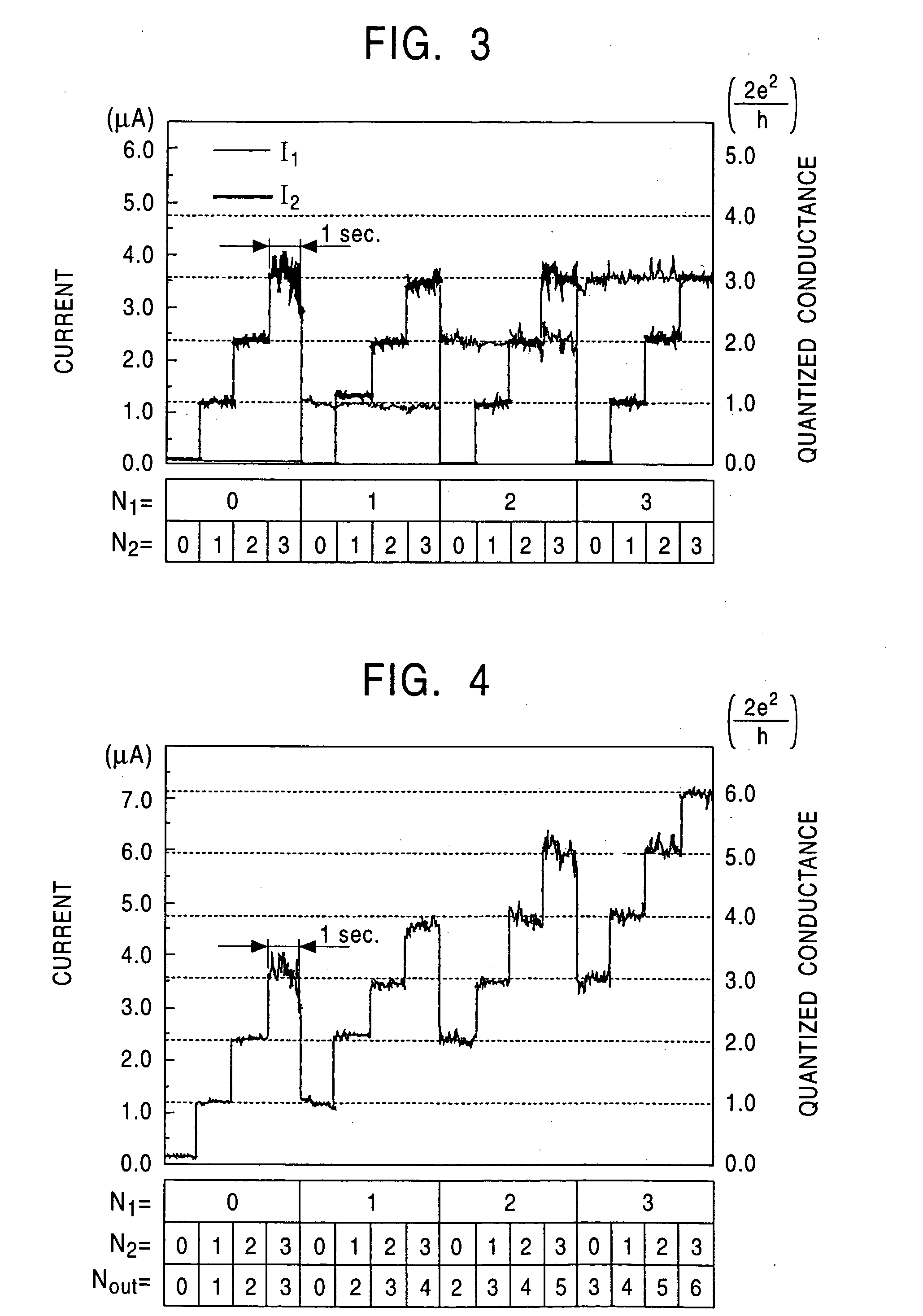

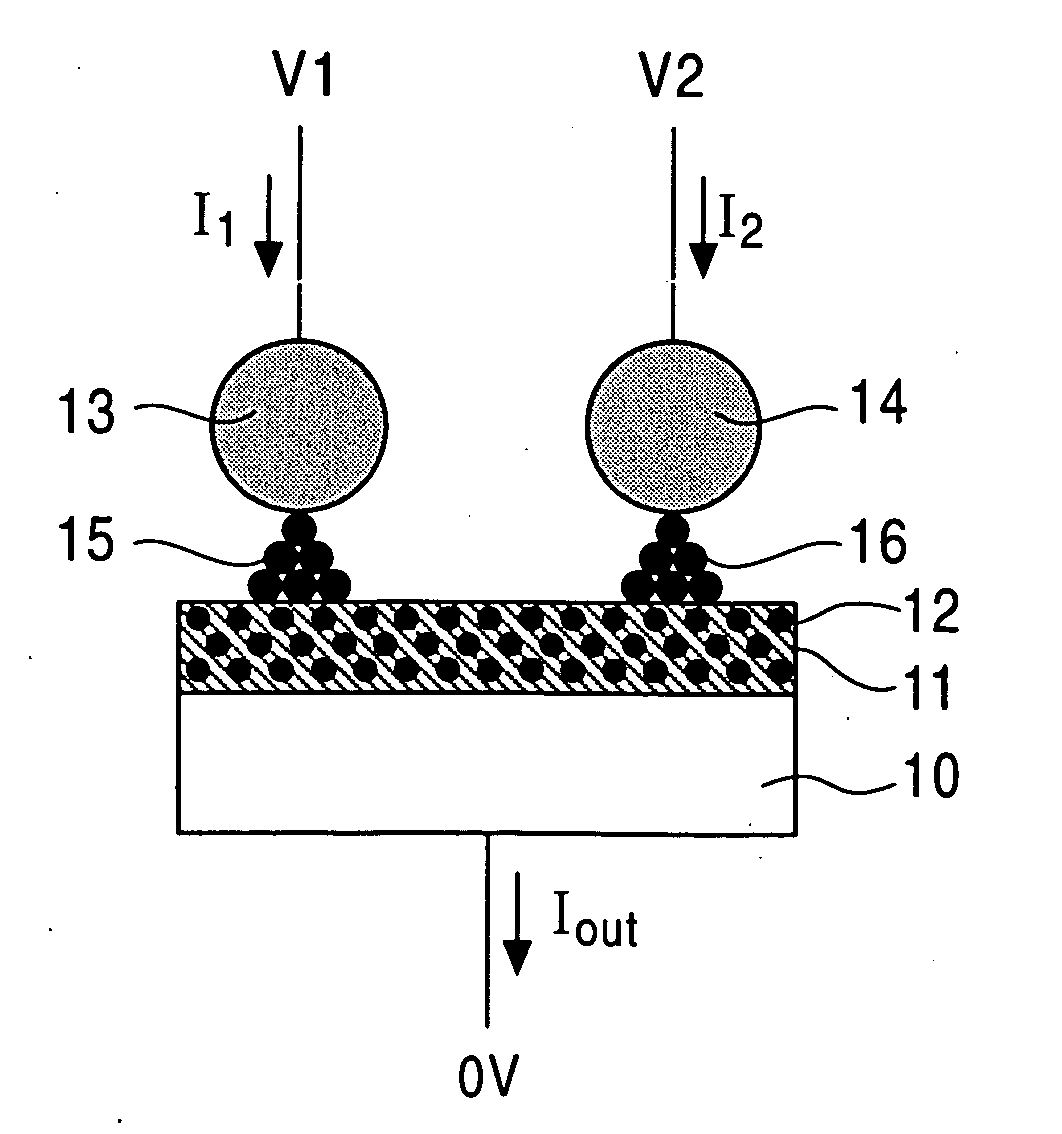

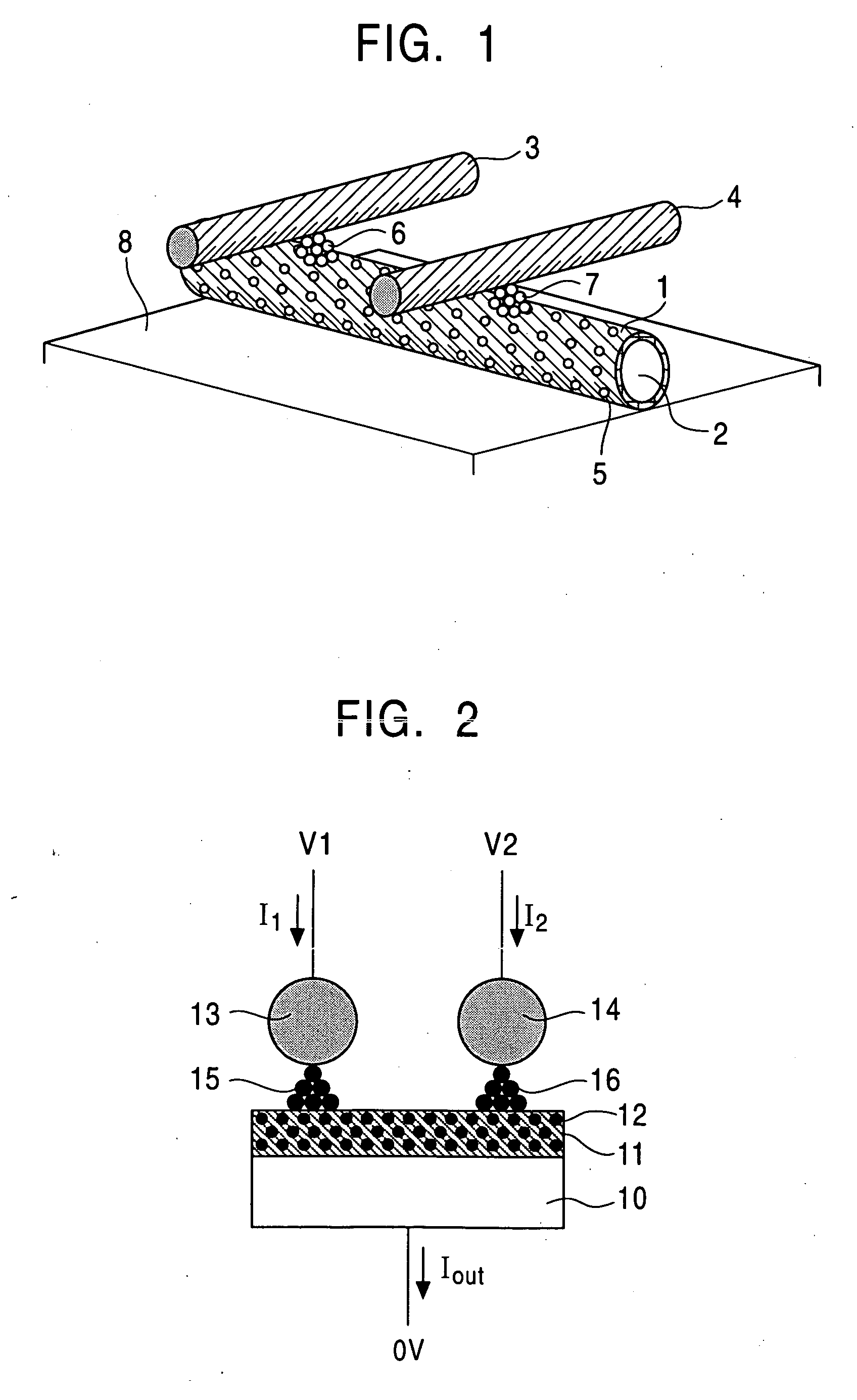

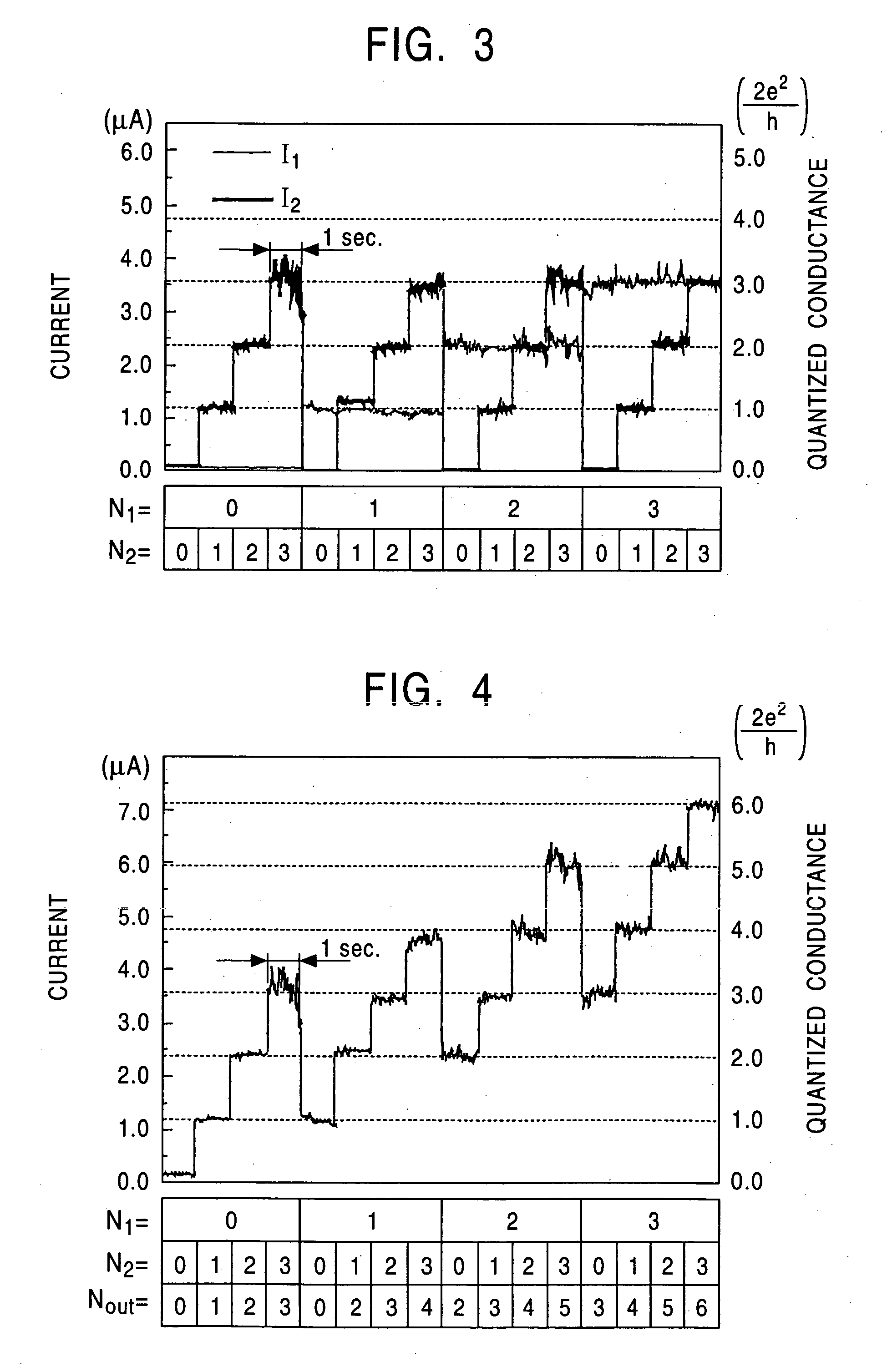

Point contact array, not circuit, and electronic circuit comprising the same

A NOT circuit realized using an atomic switch serving as a two terminal device and including a first electrode made of a compound conductive material having ionic conductivity and electronic conductivity and a second electrode made of a conductive substance. Ag2S, Ag2Se, Cu2S, or Cu2Se is preferably used as the compound conductive material.

Owner:JAPAN SCI & TECH CORP

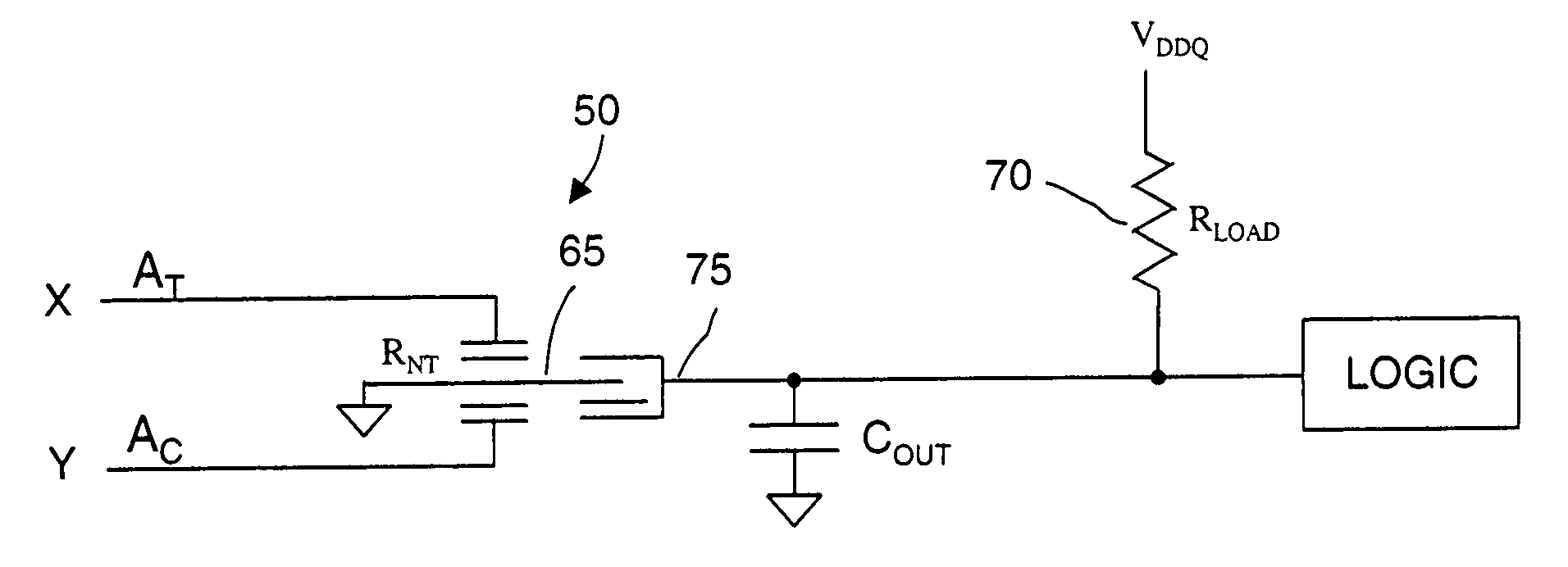

Nanotube-based logic driver circuits

InactiveUS20050280436A1Sufficient currentReliability increasing modificationsNanoinformaticsDriver circuitPush pull

Nanotube based logic driver circuits. These include pull-up driver circuits, push-pull driver circuits, tristate driver circuits, among others. Under one embodiment, an off-chip driver circuit includes a differential input having first and second signal links, each coupled to a respective one of two differential, on-chip signals. At least one output link is connectable to an off-chip impedance load, and at least one switching element has an input node, an output node, a nanotube channel element, and a control structure disposed in relation to the nanotube channel element to controllably form and unform an electrically conductive channel between said input node and said output node. The input node is coupled to a reference signal and the control structure is coupled to the first and second signal links. The output node is coupled to the output link, and the channel element is sized to carry sufficient current to drive said off-chip impedance load.

Owner:NANTERO

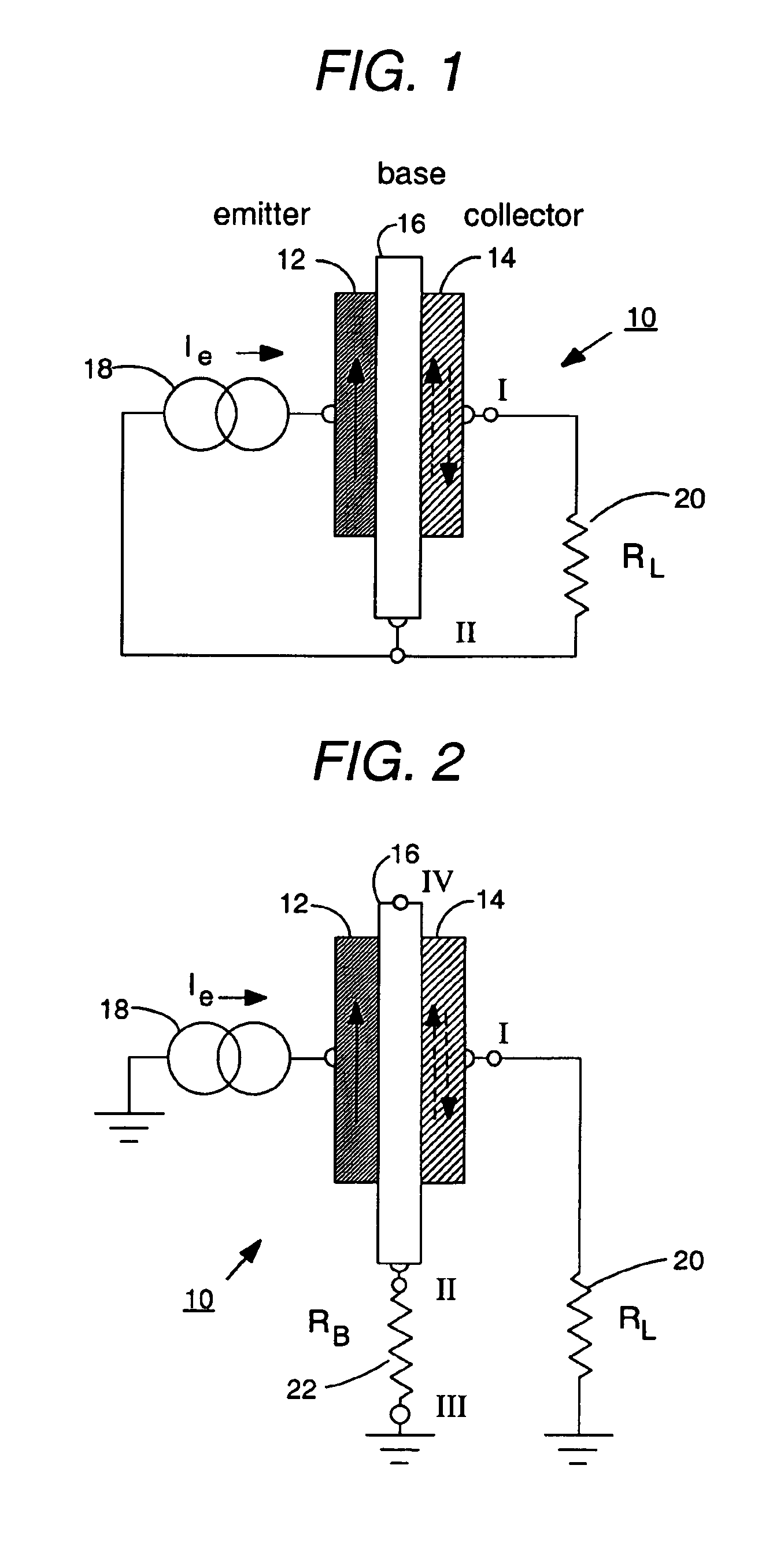

Magnetic logic element and magnetic logic element array

A magnetic logic element comprises a magnetic logic element cell having; a first and second magnetic parts; a MR intermediate part provided between the first and second magnetic parts. The magnetic logic element further includes a magnetization controlling part that controls a relation of directions of magnetizations of the first and second magnetic parts in accordance with a combination of a first binary input data and a second binary input data. A binary output data can be read by detecting a magnetoresistance effect of the first and second magnetic parts through the MR intermediate part.

Owner:KIOXIA CORP

Tri-state circuit using nanotube switching elements

InactiveUS20060255834A1Logic circuits characterised by logic functionNanoelectromechanical switchesCMOSEngineering

Nanotube-based logic circuitry is disclosed. Tri-stating elements add an enable / disable function to the circuitry. The tri-stating elements may be provided by nanotube-based switching devices. In the disabled state, the outputs present a high impedance, i.e., are tri-stated, which state allows interconnection to a common bus or other shared communication lines. In embodiments wherein the components are non-volatile, the inverter state and the control state are maintained in the absence of power. Such an inverter may be used in conjunction with and in the absence of diodes, resistors and transistors or as part of or as a replacement to CMOS, biCMOS, bipolar and other transistor level technologies.

Owner:NANTERO

Point contact array, not circuit, and electronic circuit using the same

There are provided a point contact array, in which a plurality of point contacts are arranged, each point contact electrically and reversibly controlling conductance between electrodes and being applicable to an arithmetic circuit, a logic circuit, and a memory device, a NOT circuit, and an electronic circuit using the same. A circuit includes a plurality of point contacts each composed of a first electrode made of a compound conductive material having ionic conductivity and electronic conductivity and a second electrode made of a conductive substance. The conductance of each point contact is controlled to realize the circuit. Ag2S, Ag2Se, Cu2S, or Cu2Se is preferably used as the compound conductive material. When a semiconductor or insulator material is interposed between the electrodes, a crystal or an amorphous material of GeSx, GeSex, GeTex, or WOx (0<x<100) is preferably used as the semiconductor or insulator material. A NOT circuit is realized using a device which includes an atomic switch serving as a two-terminal device, the device including a first electrode made of a compound conductive material having ionic conductivity and electronic conductivity and a second electrode made of a conductive substance, and capable of controlling conductance between the electrodes.

Owner:JAPAN SCI & TECH CORP

High speed interface apparatus

The present invention discloses a much higher speed interface apparatus which comprises a data driving means for decoding two-bit data signals using them as inputs to output four-level data signals; a reference voltage generating means for generating three-level reference voltages to discriminate the voltage levels of the four-level data signals; and a receiver means for comparing the four-level data signals and the three-level reference voltage signals using them as inputs and for encoding the resulting signals to output two data signals.

Owner:HYUNDAI ELECTRONICS IND CO LTD

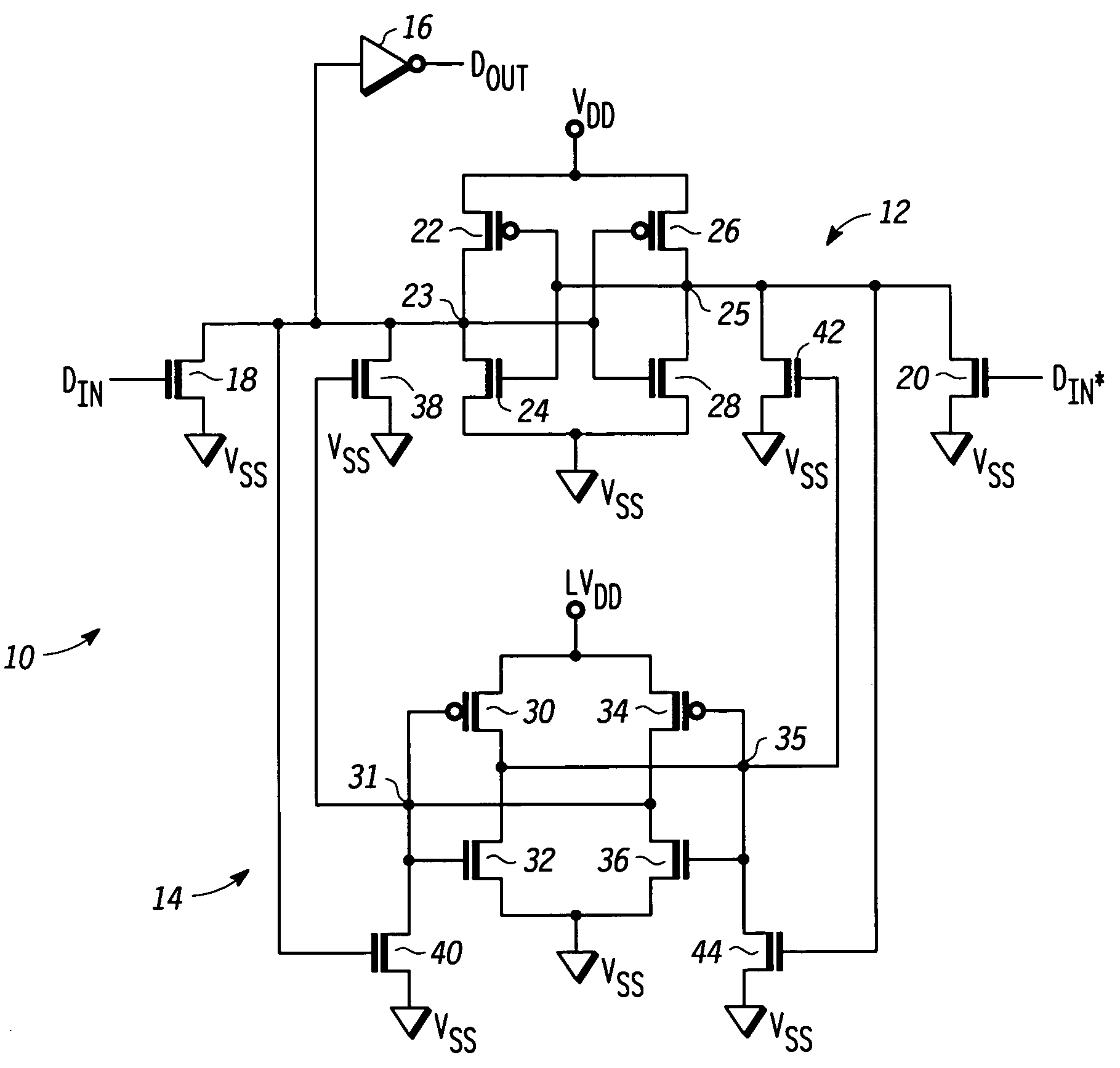

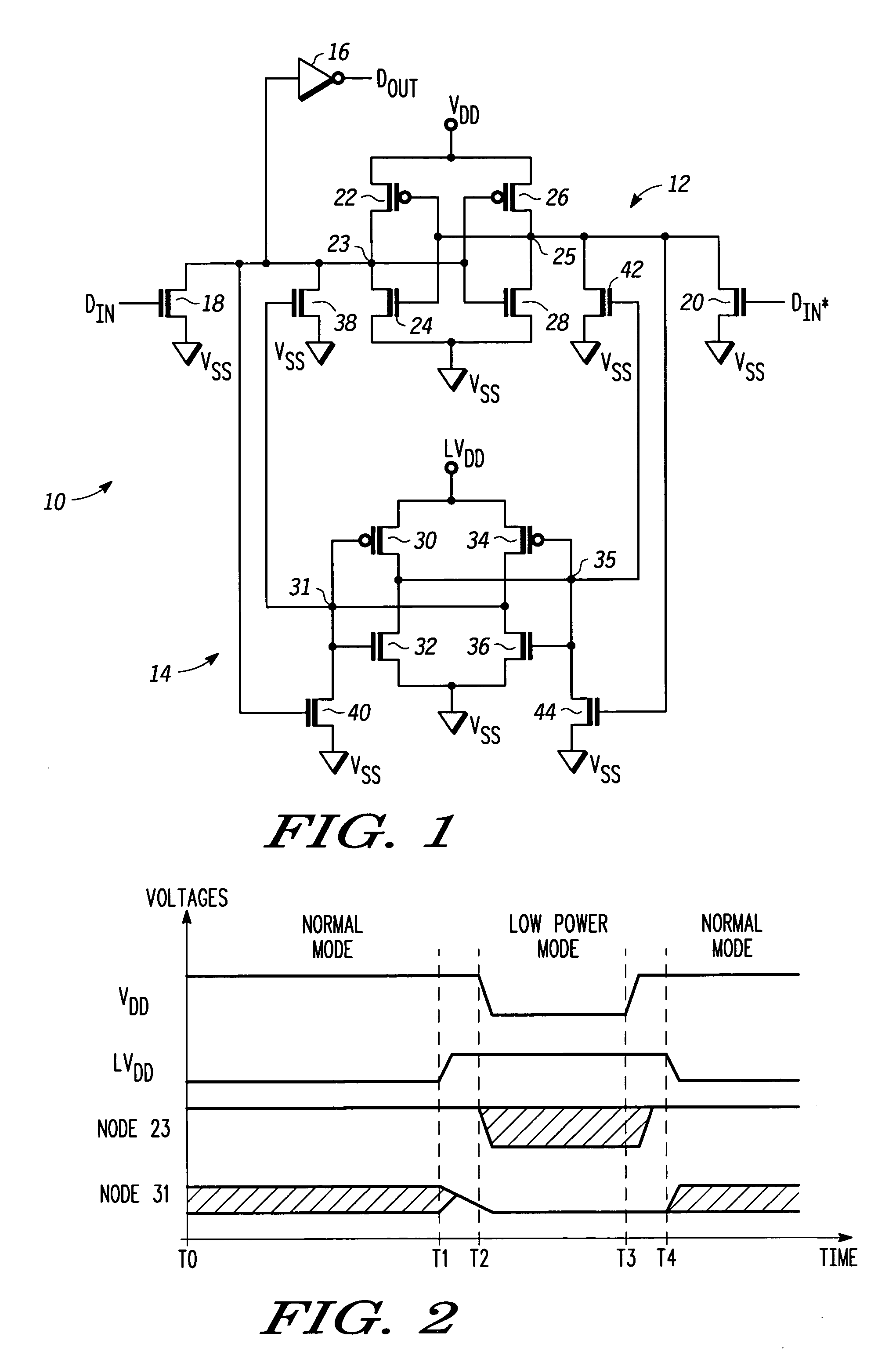

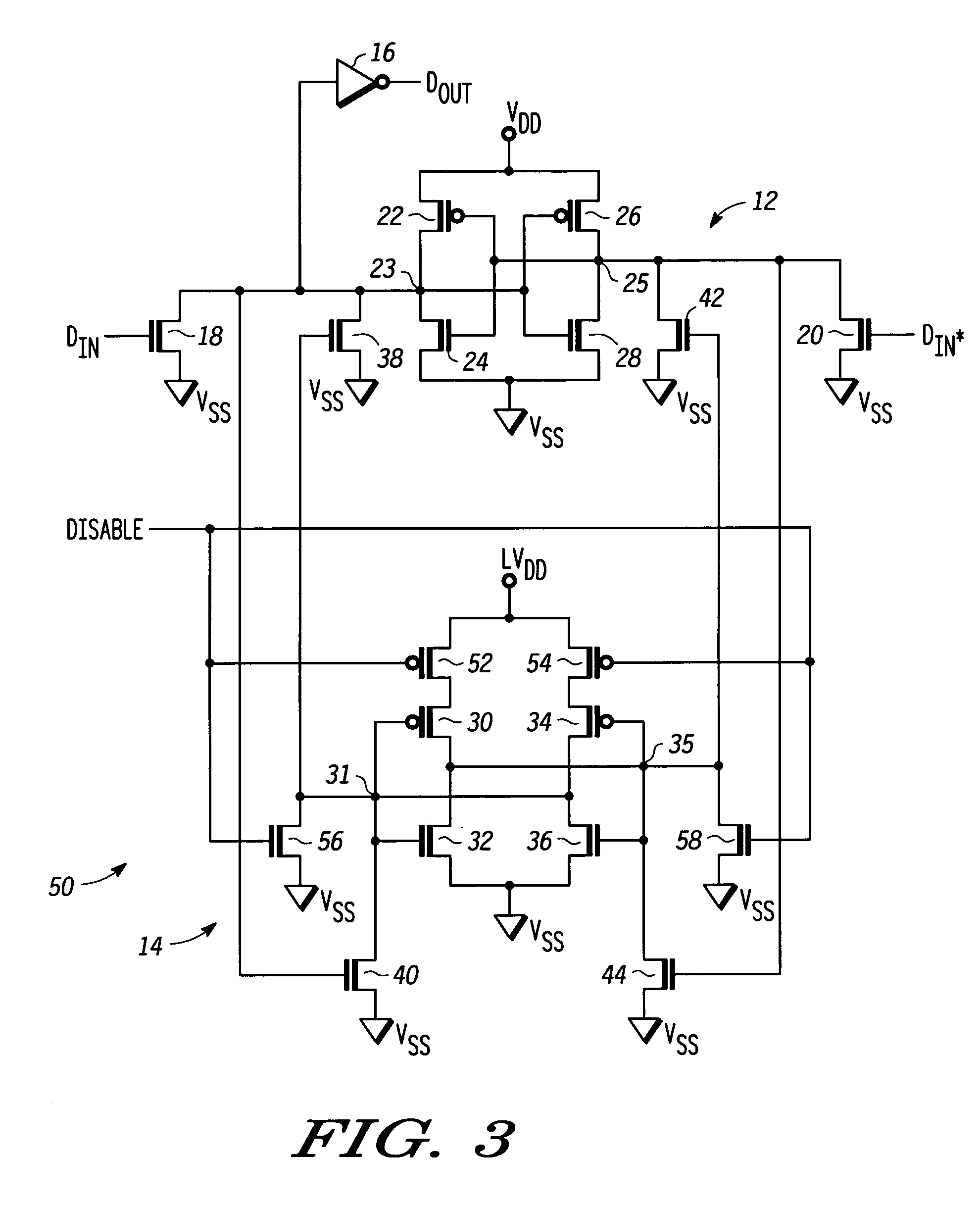

Integrated circuit having a low power mode and method therefor

ActiveUS7215188B2Power reduction by control/clock signalPulse automatic controlPower modeEngineering

Owner:VLSI TECH LLC

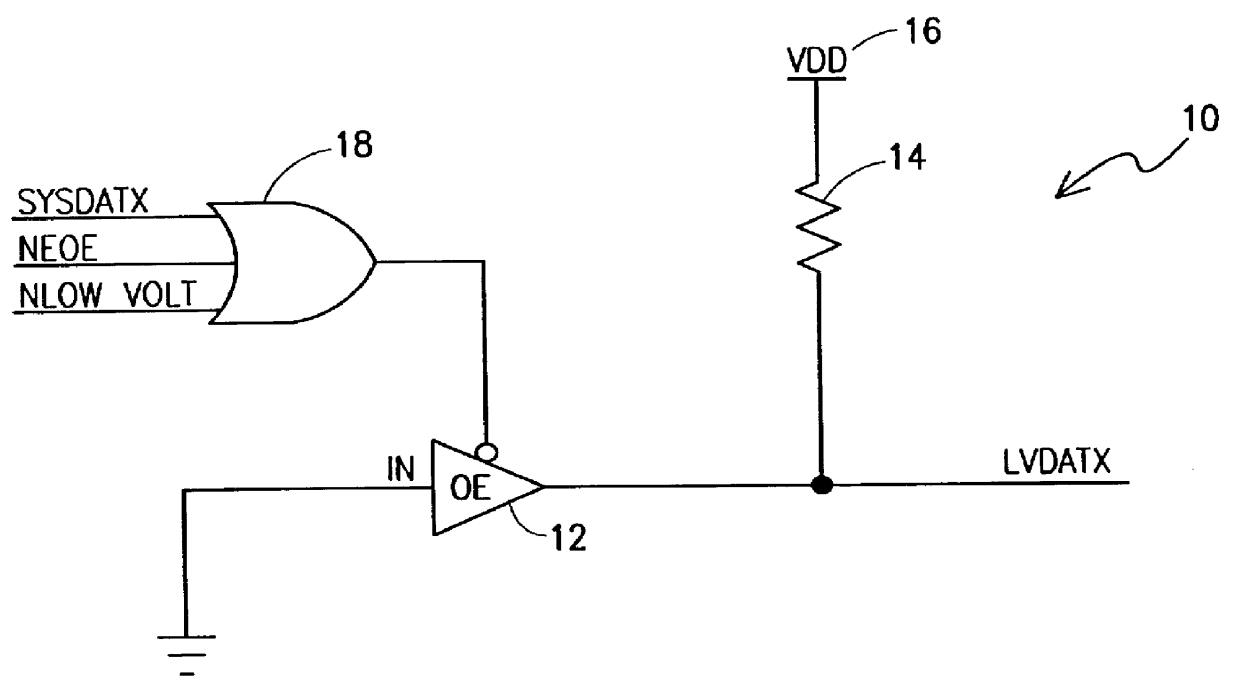

Voltage translator circuit which allows for variable low voltage signal translation

InactiveUS6160421ALogic circuits using specific componentsLogic circuit interface arrangementsVoltage converterLow voltage

A variable low voltage signal translator uses a driver for outputting a low voltage signal translation. A control circuit is coupled to the driver for enabling and disabling the driver wherein the control circuit has an input coupled to the signal to be translated. One terminal of the pull-up resistor is coupled to an output of the driver. A second terminal of the pull-up resistor is coupled to a voltage supply which provides the low voltage level of the variable low voltage signal translator.

Owner:MICROCHIP TECH INC

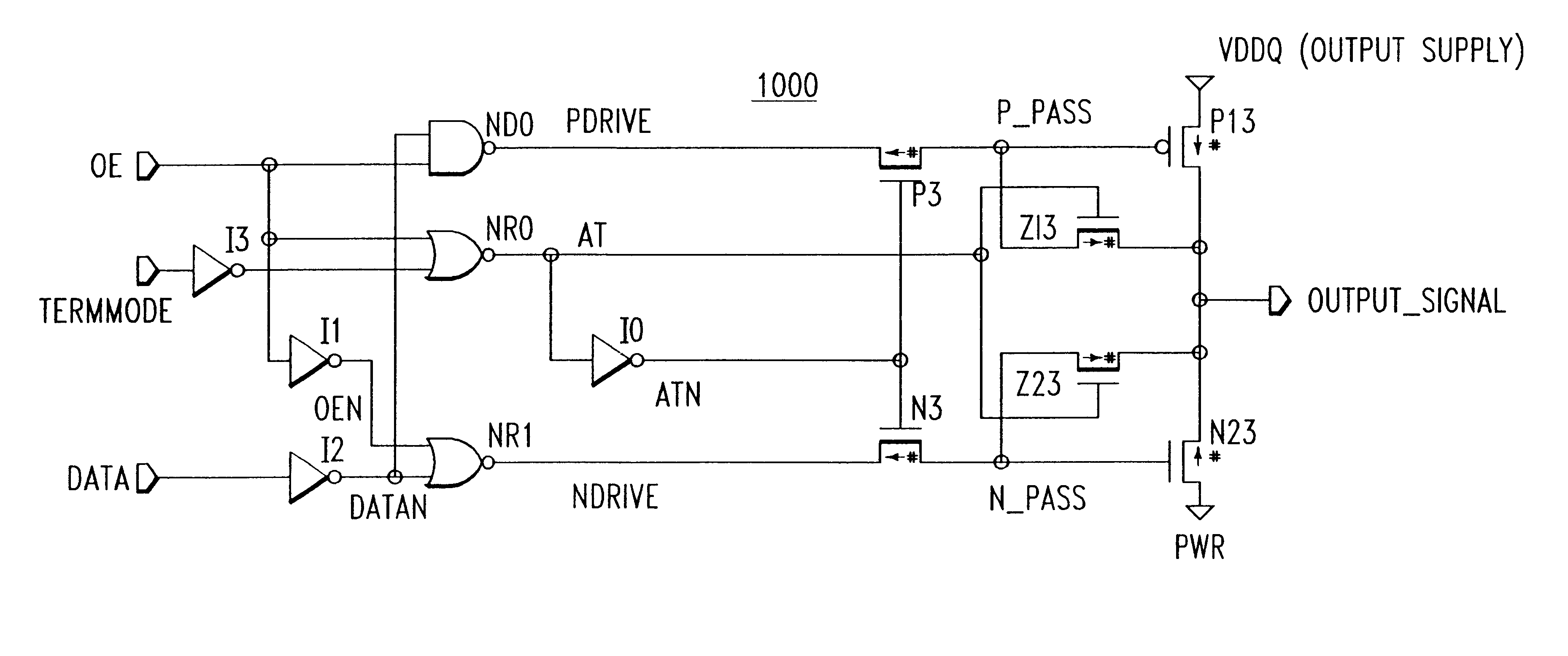

Method and apparatus for programmable active termination of input/output devices

InactiveUS6501293B2Reliability increasing modificationsBaseband system detailsOutput deviceEngineering

A method and apparatus for providing programmable active termination of transmission lines with substantially reduced DC power consumption.

Owner:GLOBALFOUNDRIES INC

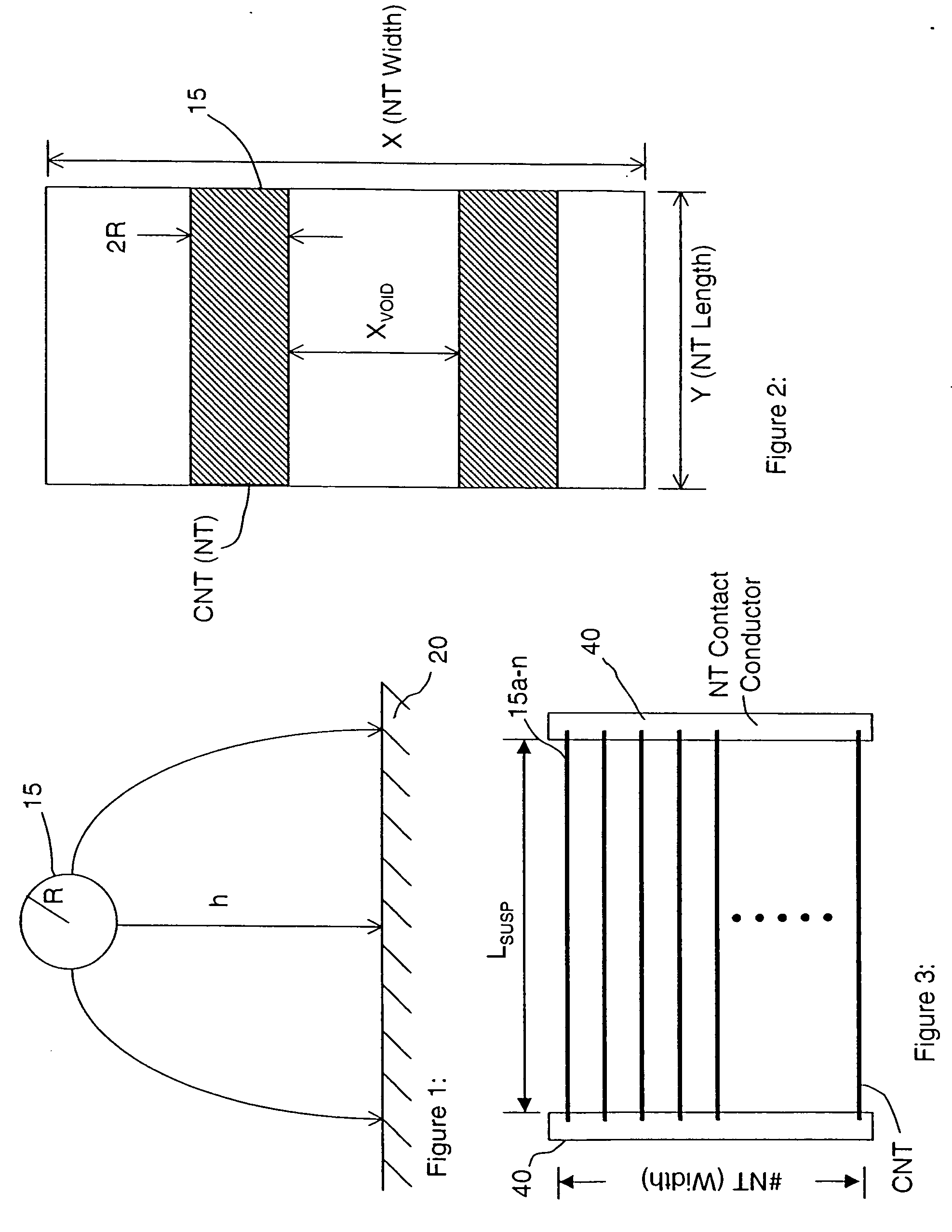

Nanoeletromechanical switch and logic circuits formed therefrom

A nanoelectromechanical (NEM) switch is formed on a substrate with a source electrode containing a suspended electrically-conductive beam which is anchored to the substrate at each end. This beam, which can be formed of ruthenium, bows laterally in response to a voltage applied between a pair of gate electrodes and the source electrode to form an electrical connection between the source electrode and a drain electrode located near a midpoint of the beam. Another pair of gate electrodes and another drain electrode can be located on an opposite side of the beam to allow for switching in an opposite direction. The NEM switch can be used to form digital logic circuits including NAND gates, NOR gates, programmable logic gates, and SRAM and DRAM memory cells which can be used in place of conventional CMOS circuits, or in combination therewith.

Owner:NAT TECH & ENG SOLUTIONS OF SANDIA LLC

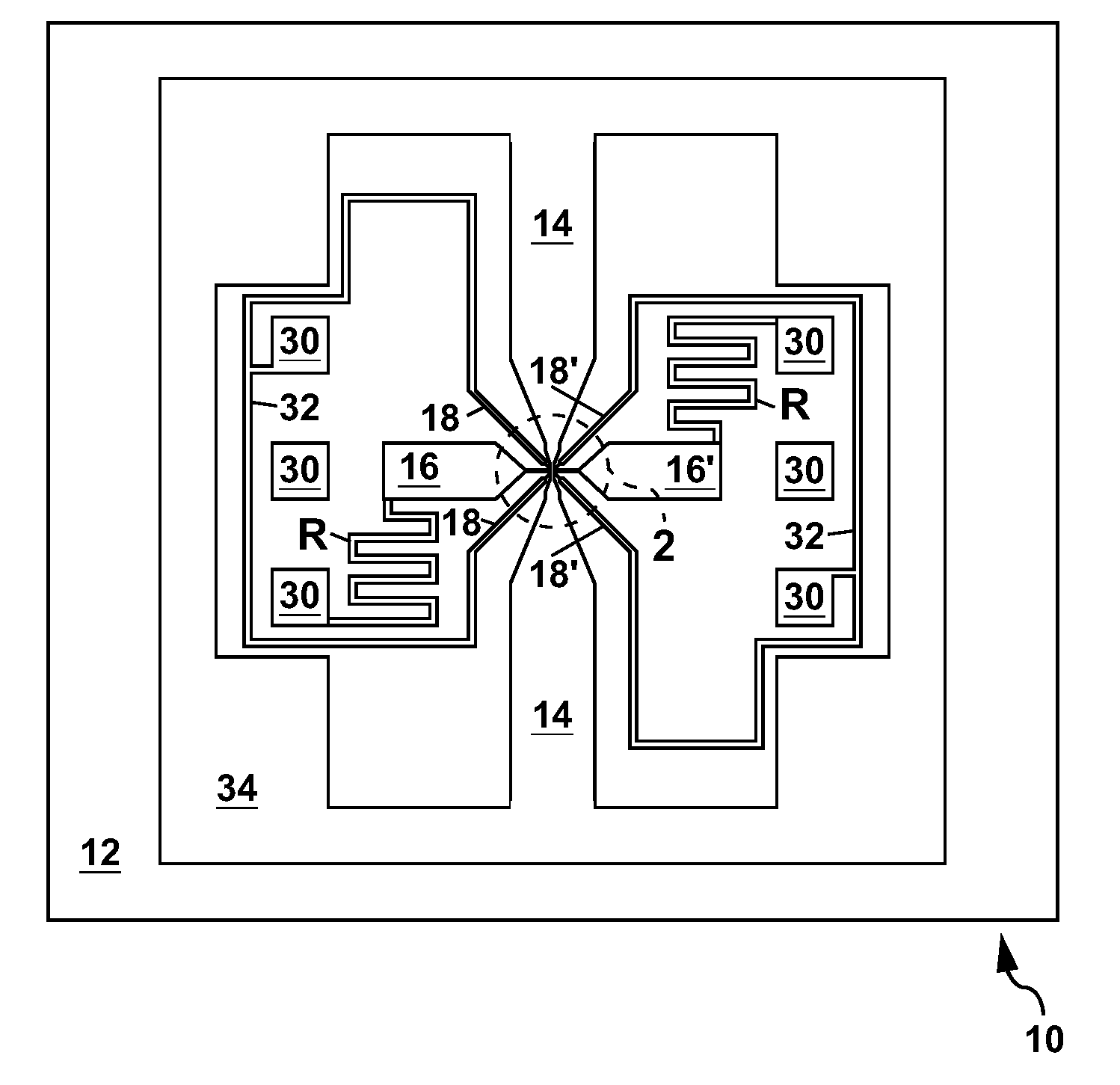

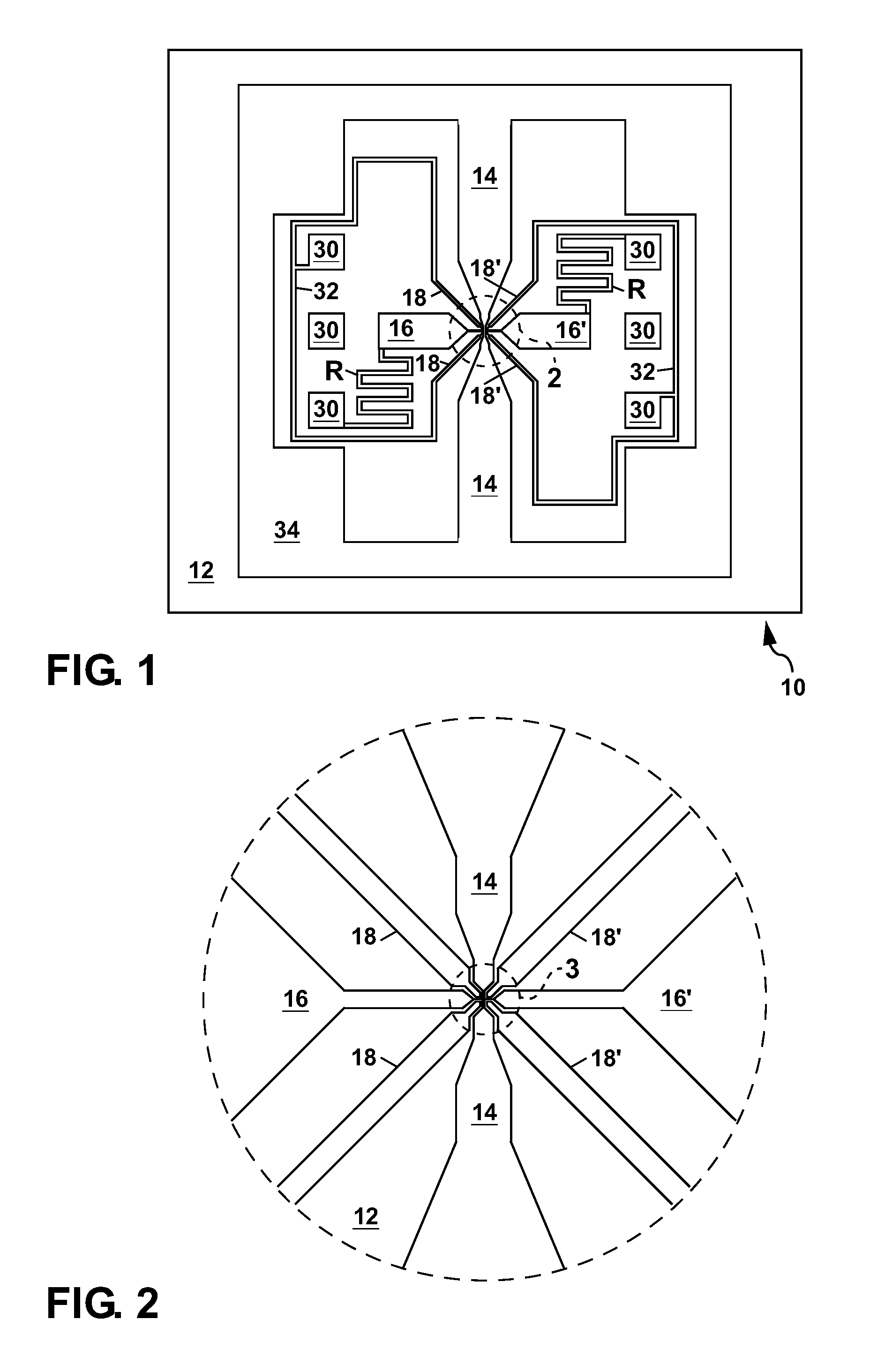

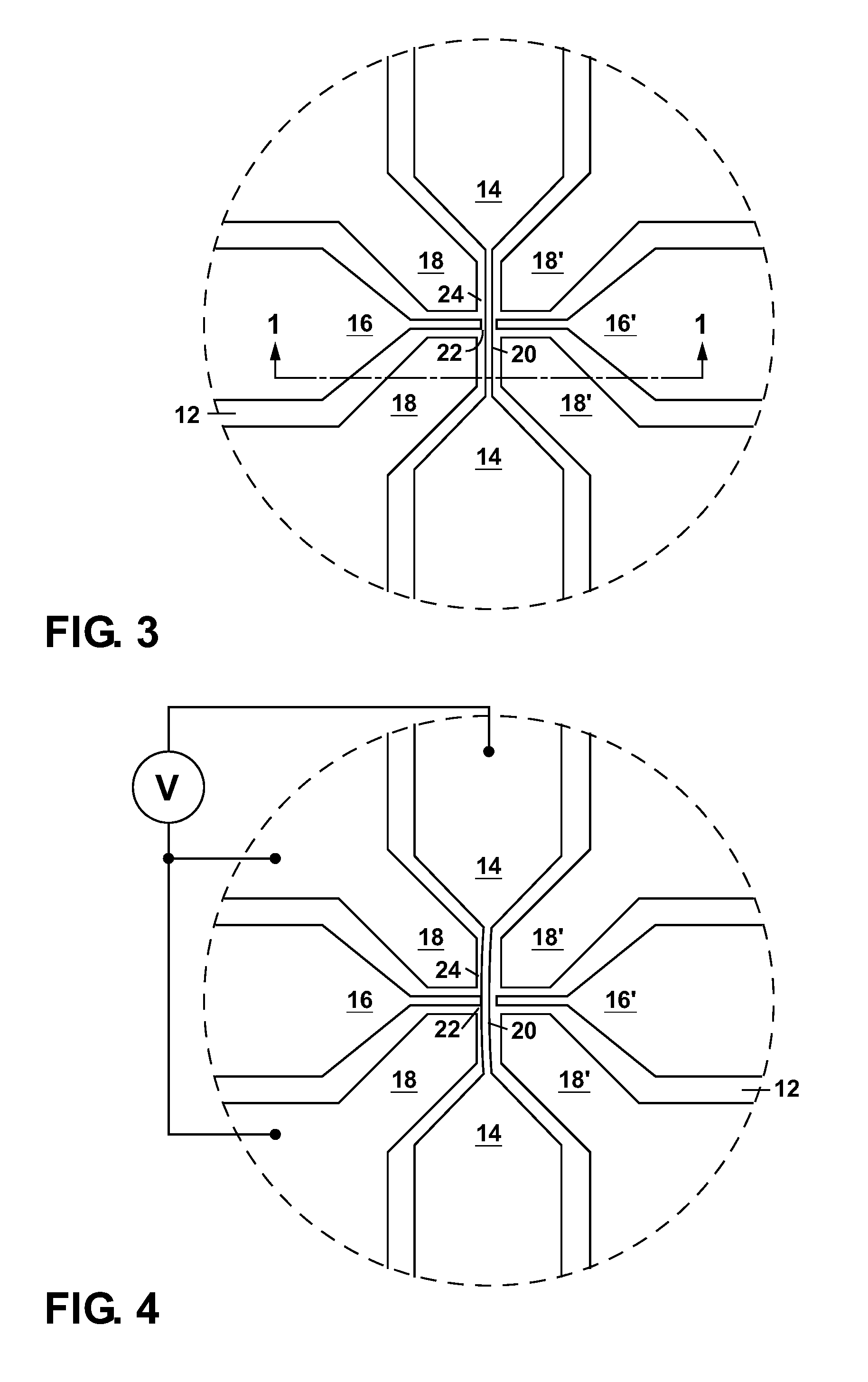

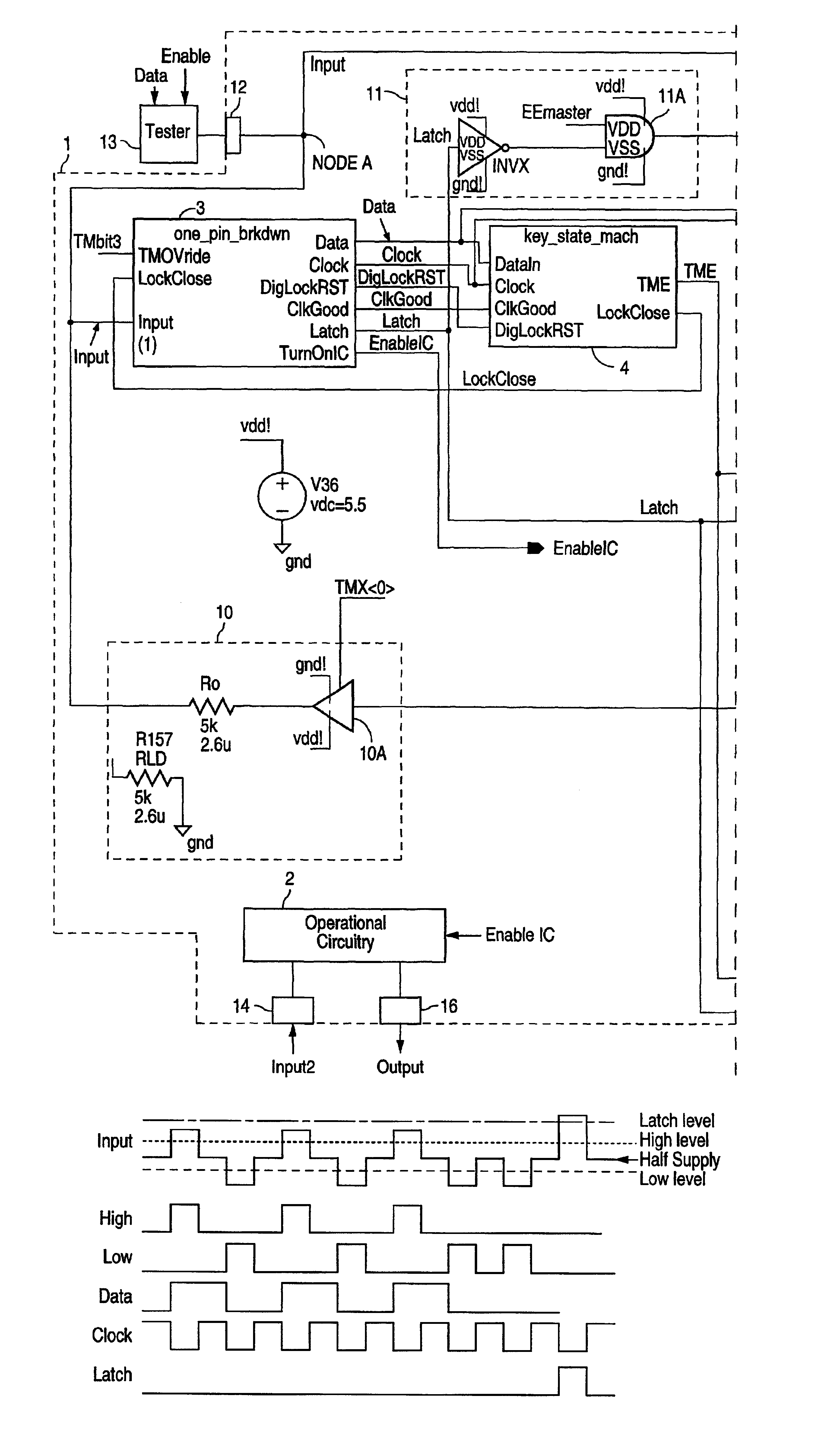

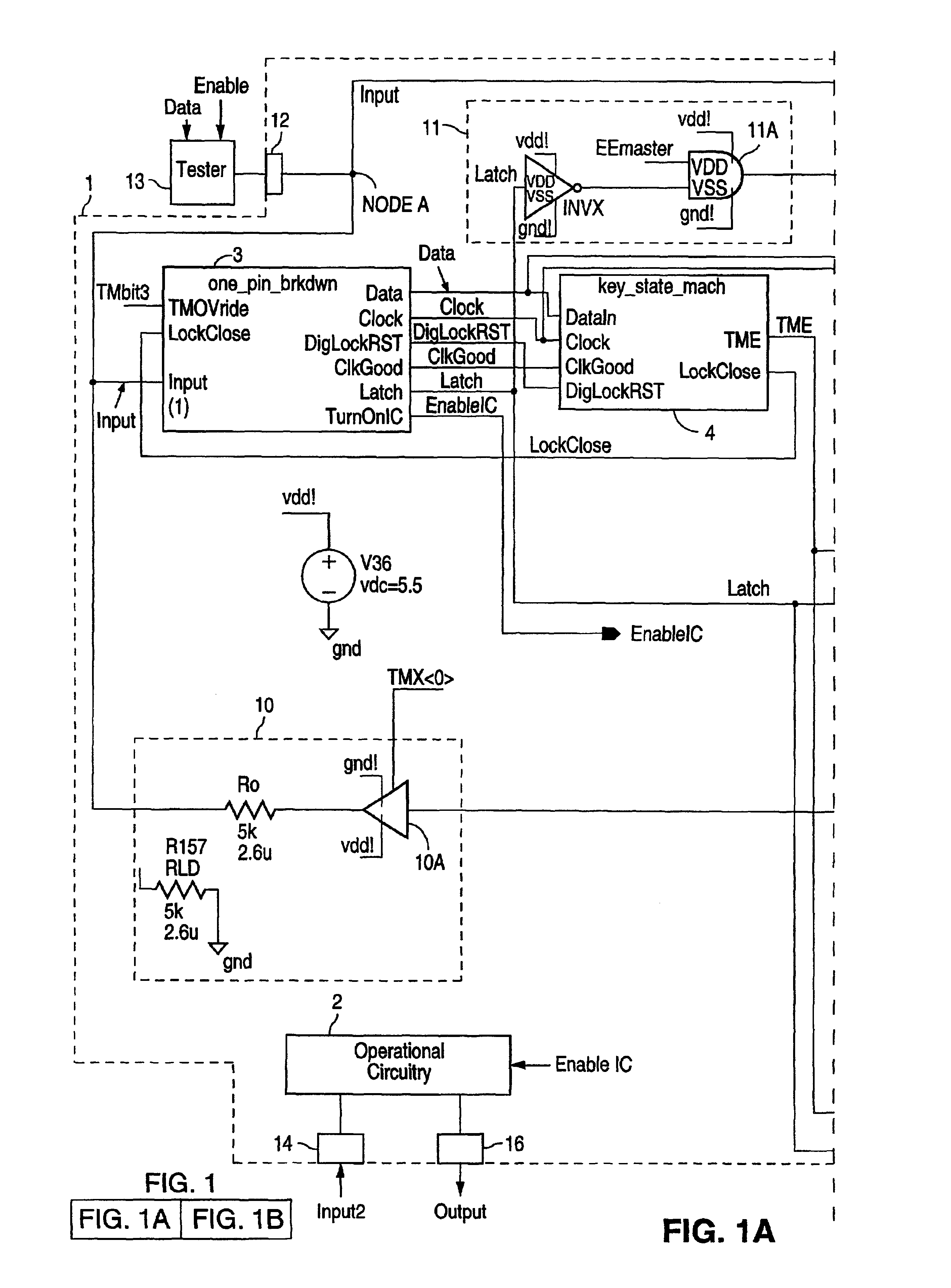

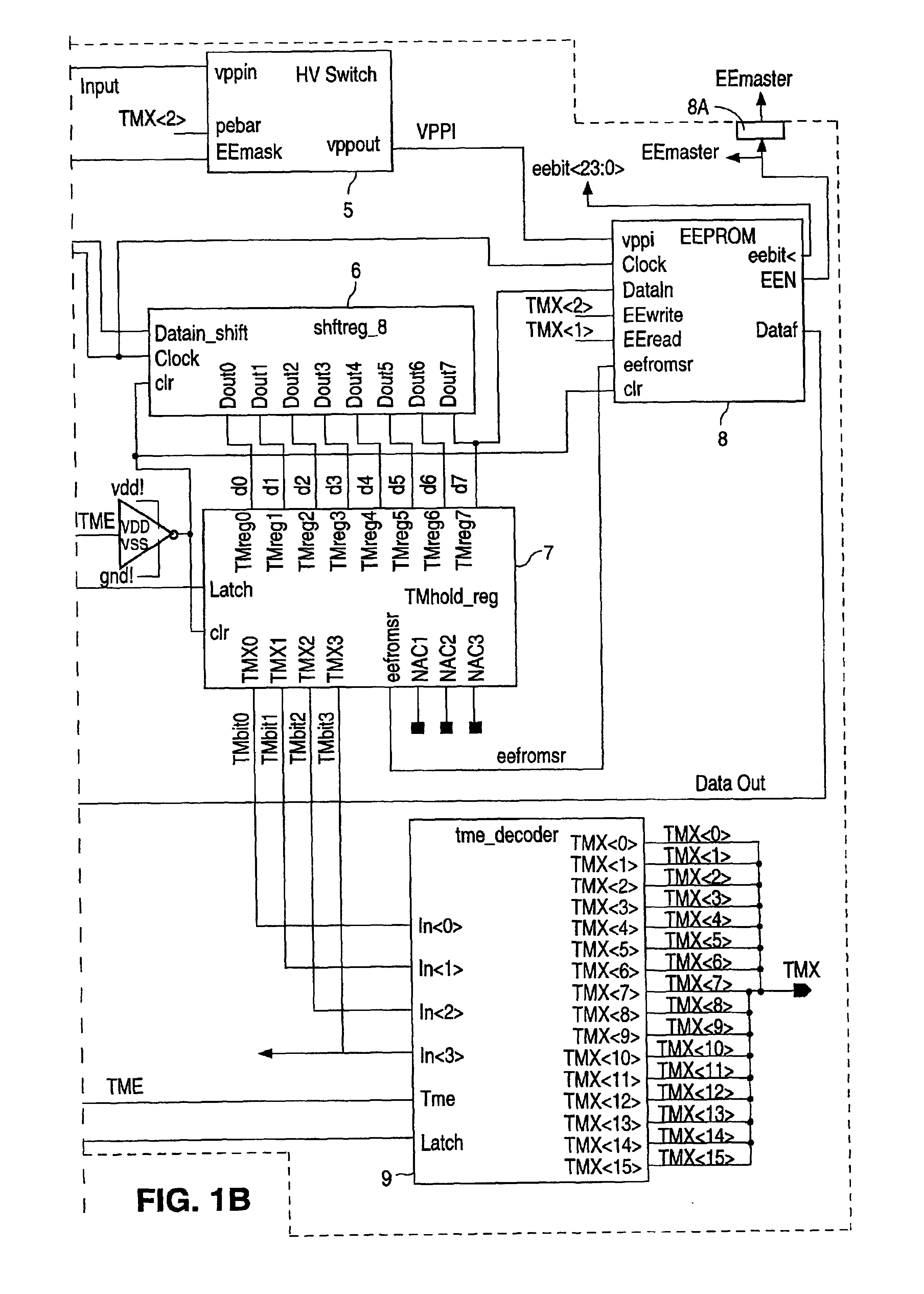

Integrated circuit and method for testing same using single pin to control test mode and normal mode operation

InactiveUS6888765B1Reduce power consumptionDigital circuit testingDigital storageControl signalNormal mode

An integrated circuit including operational circuitry operable in response to at least one control signal asserted to an external node from an external source, and test circuitry coupled to the external node and the operational circuitry. In response to data asserted to the external node from an external source, the test circuitry enters a test mode in which it tests, configures, or reconfigures the operational circuitry. The test circuitry also asserts to the operational circuitry each control signal received at the external node (or an amplified or translated version thereof). Other aspects of the invention include test circuitry for use in a circuit having an access node and methods for performing on-chip testing, configuration, and control of operational circuitry within a chip in response to test data and at least one control signal asserted from an external source to an external node.

Owner:NAT SEMICON CORP

Predriver logic circuit

A buffer for enabling a signal to be applied to a bus. The buffer includes a first transistor coupled to a bus and a voltage supply. The logic buffer includes a first logic circuit which has an input coupled to receive a data signal and adapted to charge a terminal of the transistor at a first rate in response to a transition in the data signal. A second logic circuit charges the terminal at a faster rate during an initial transition period, until a first preselected condition is met. The buffer also includes a third logic circuit to charge the terminal at a second faster rate during a final transition period, after a second preselected condition is met. A method for controlling a voltage level of a signal applied to a terminal of a transistor includes charging the terminal at a fast rate until a first preselected condition is met. The terminal is then charged at a slower rate, until a second preselected condition is met, at which time the terminal is charged at a second fast rate, which is also greater than the slower rate.

Owner:INTEL CORP

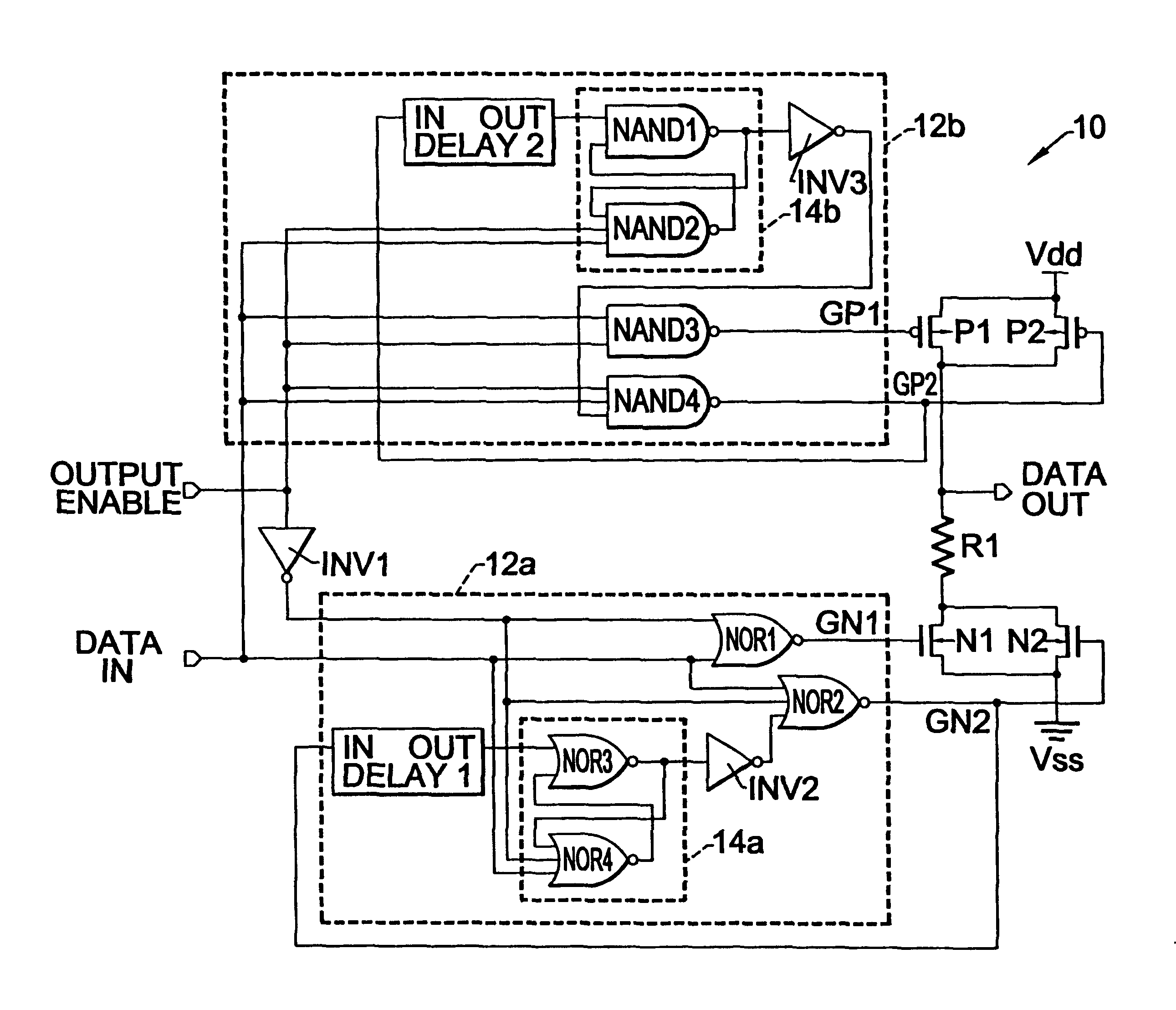

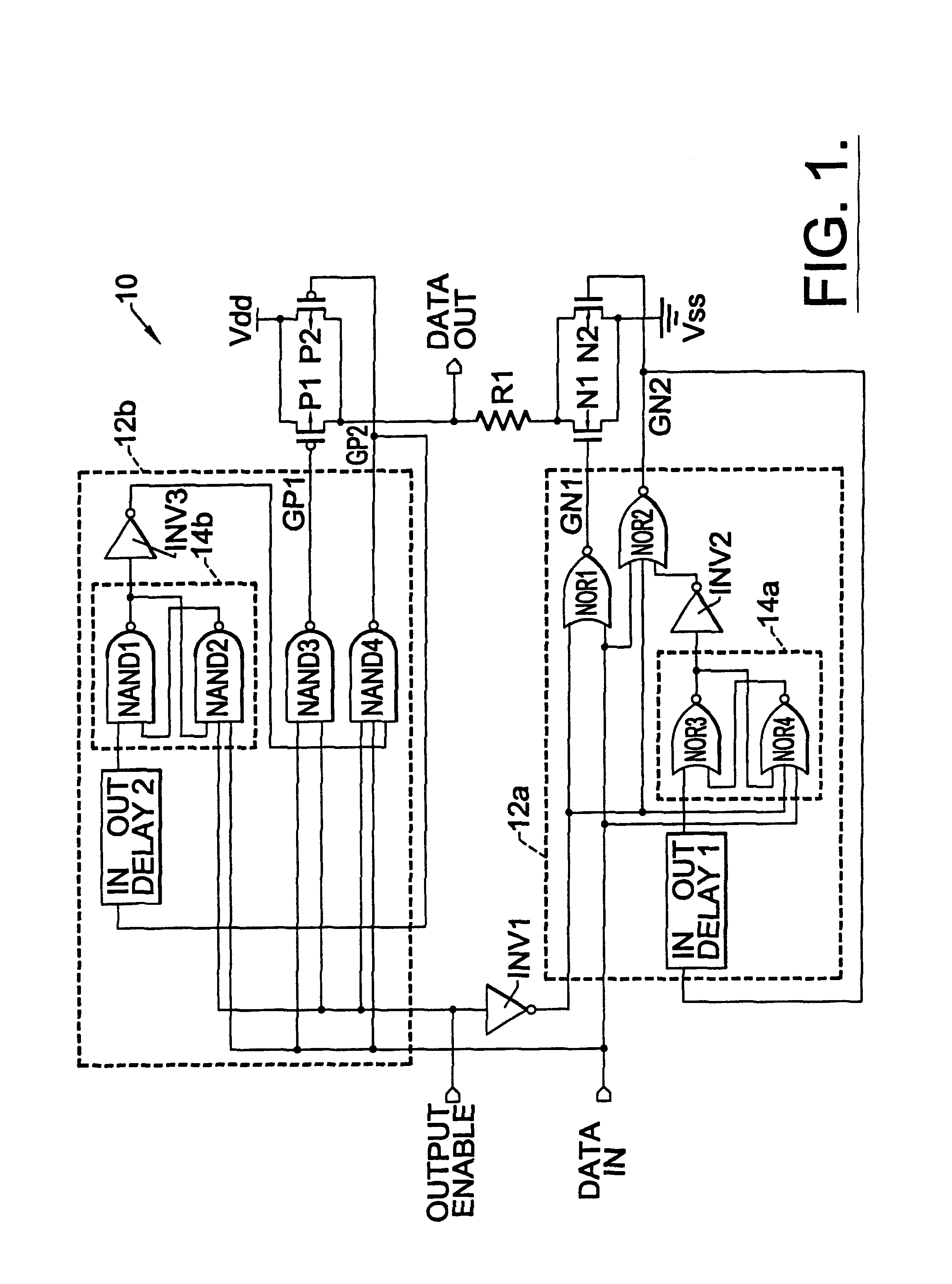

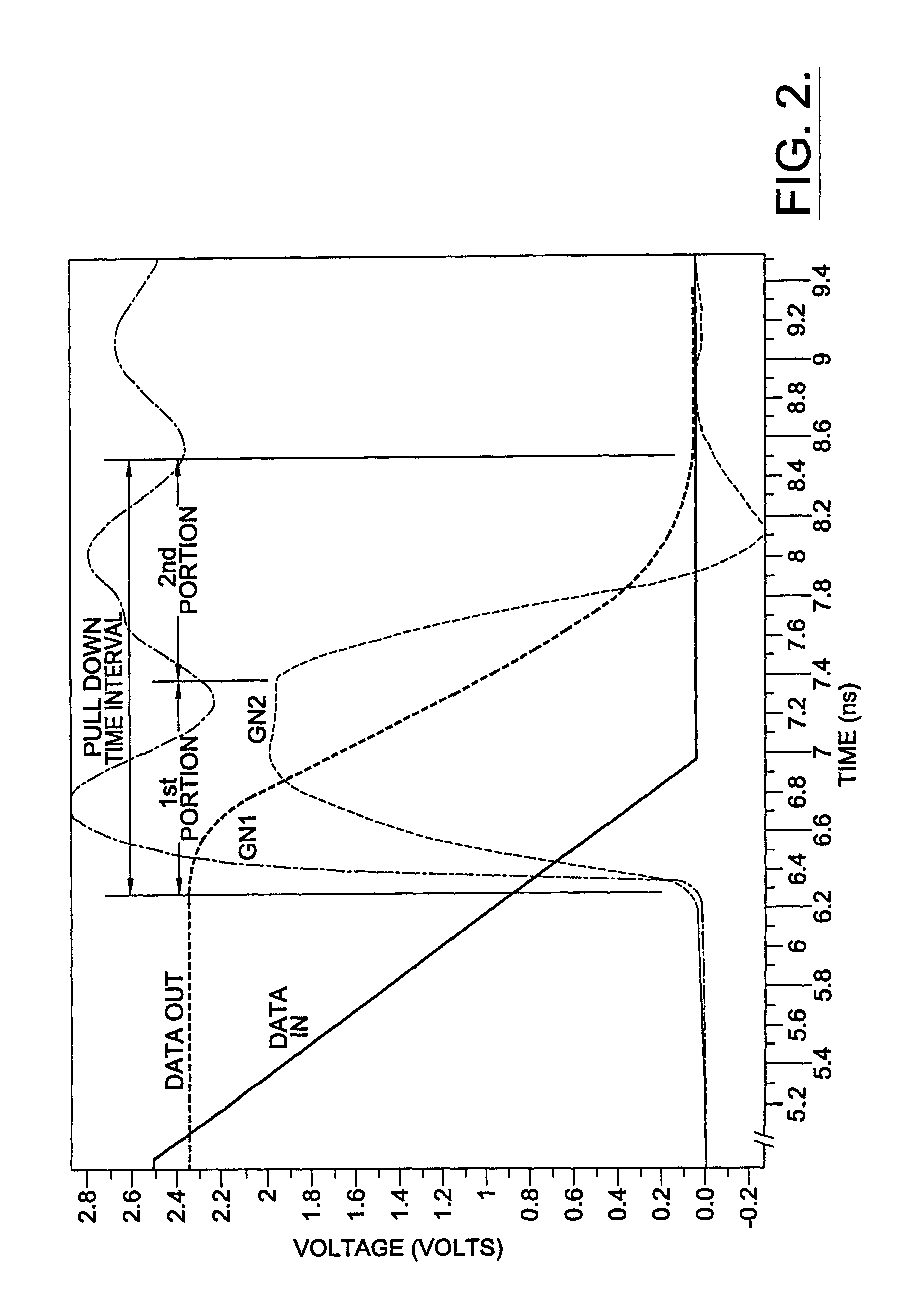

Integrated circuit output buffers having feedback switches therein for reducing simultaneous switching noise and improving impedance matching characteristics

InactiveUS6242942B1Reliability increasing modificationsElectronic switchingEngineeringImpedance matching

Integrated circuit output buffers include pull-down an pull-up circuits and a control circuit that utilizes a preferred feedback circuit to facilitate a reduction in simultaneous-switching noise during pull-down and pull-up operations and also improve the impedance matching characteristics of the output buffers during DC conditions. The preferred feedback circuit also limits the degree to which external noise can influence operation of the control circuit. Each of the pull-down and pull-up circuits may comprise a respective pair of primary and secondary transistors. The pull-down circuit is preferably configured so that the primary and secondary pull-down transistors (e.g., NMOS transistors) are electrically coupled to an output signal line (through an ESD protection resistor) and a first reference signal line (e.g., Vss). The control circuit is designed to activate the pull-down circuit by turning on both the primary and secondary pull-down transistors during a leading portion of the pull-down time interval and by turning off the secondary pull-down transistor during a trailing portion of the pull-down time interval using a first feedback switch that is electrically coupled in series between the output signal line and a gate electrode of the secondary pull-down transistor so that a signal representing a potential of said output signal line can be passed through the first feedback switch to the gate electrode of the secondary pull-down transistor.

Owner:INTEGRATED DEVICE TECH INC

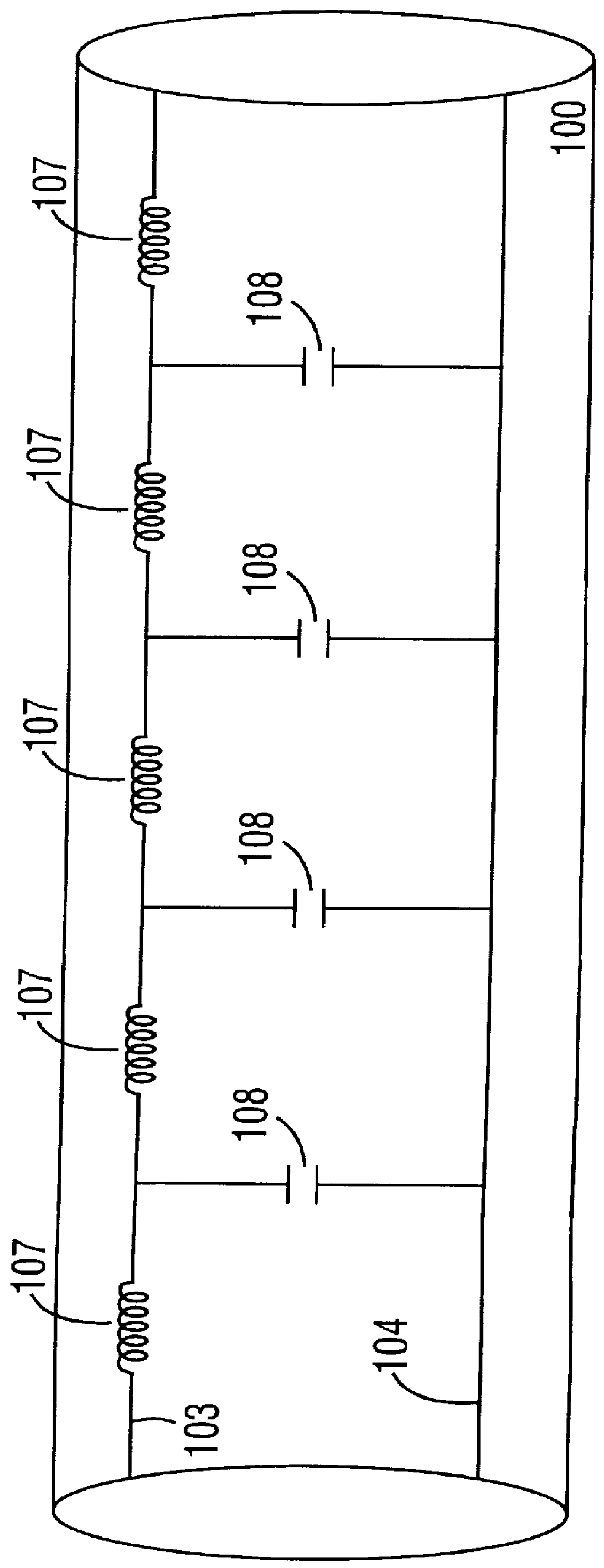

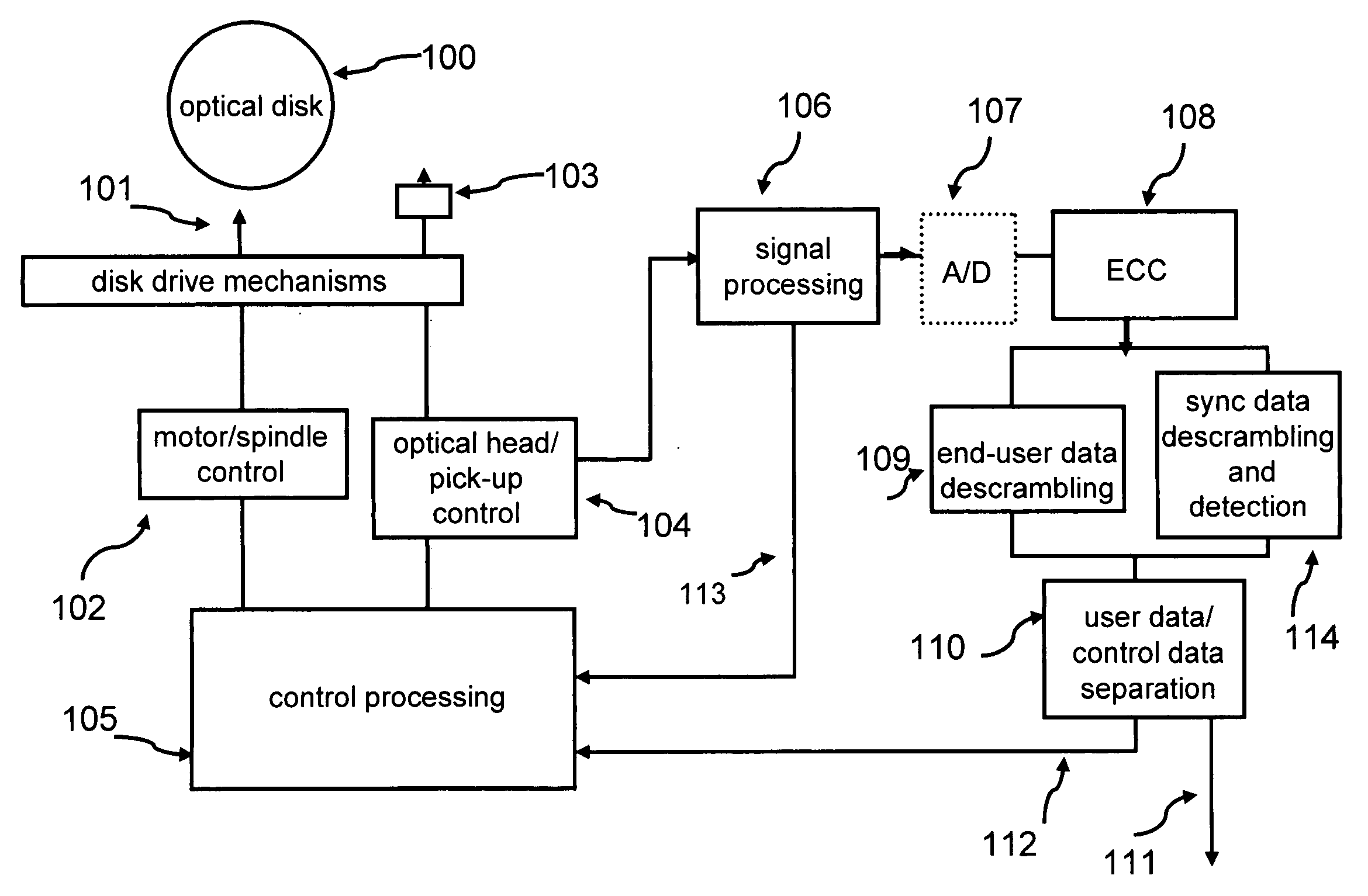

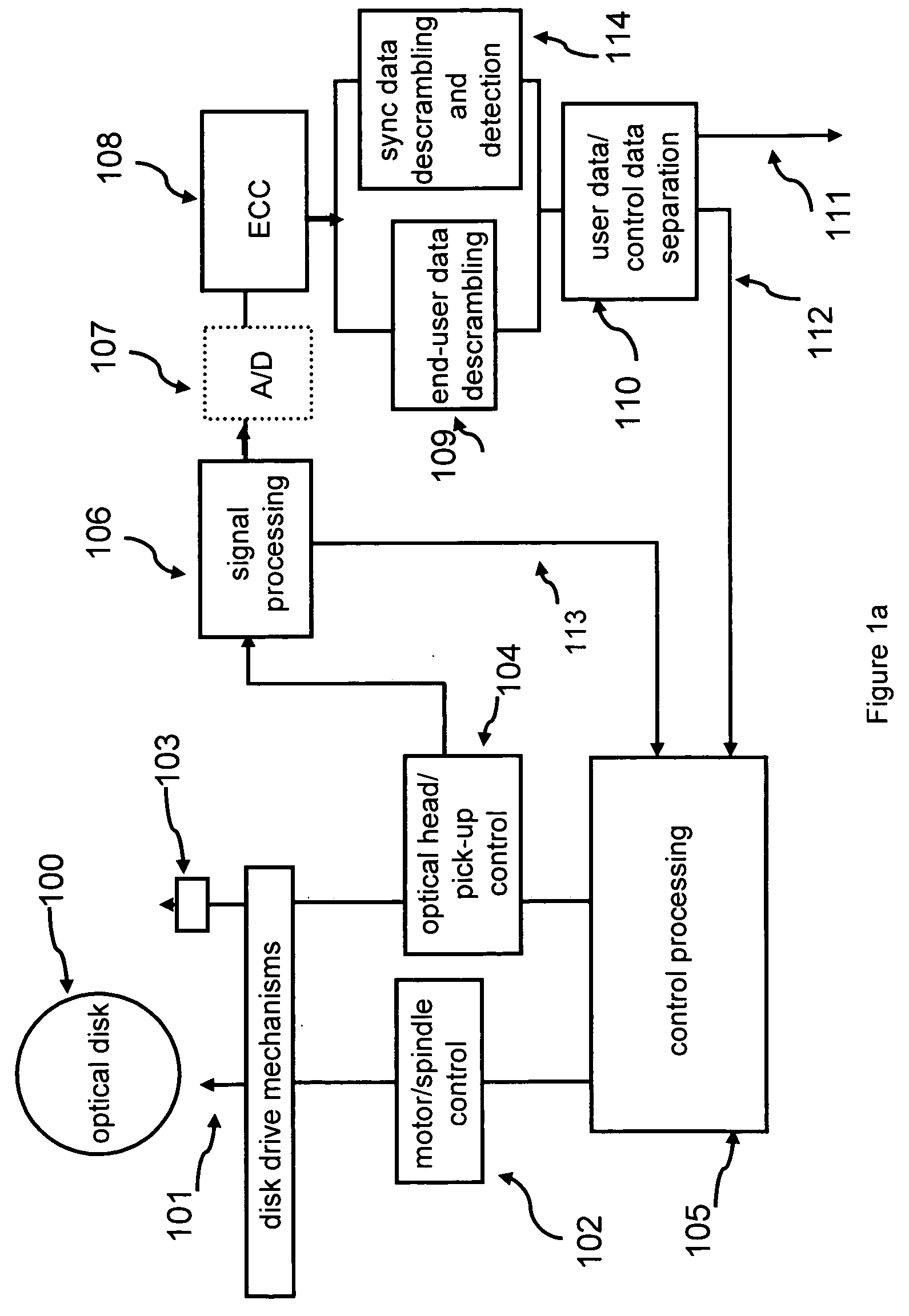

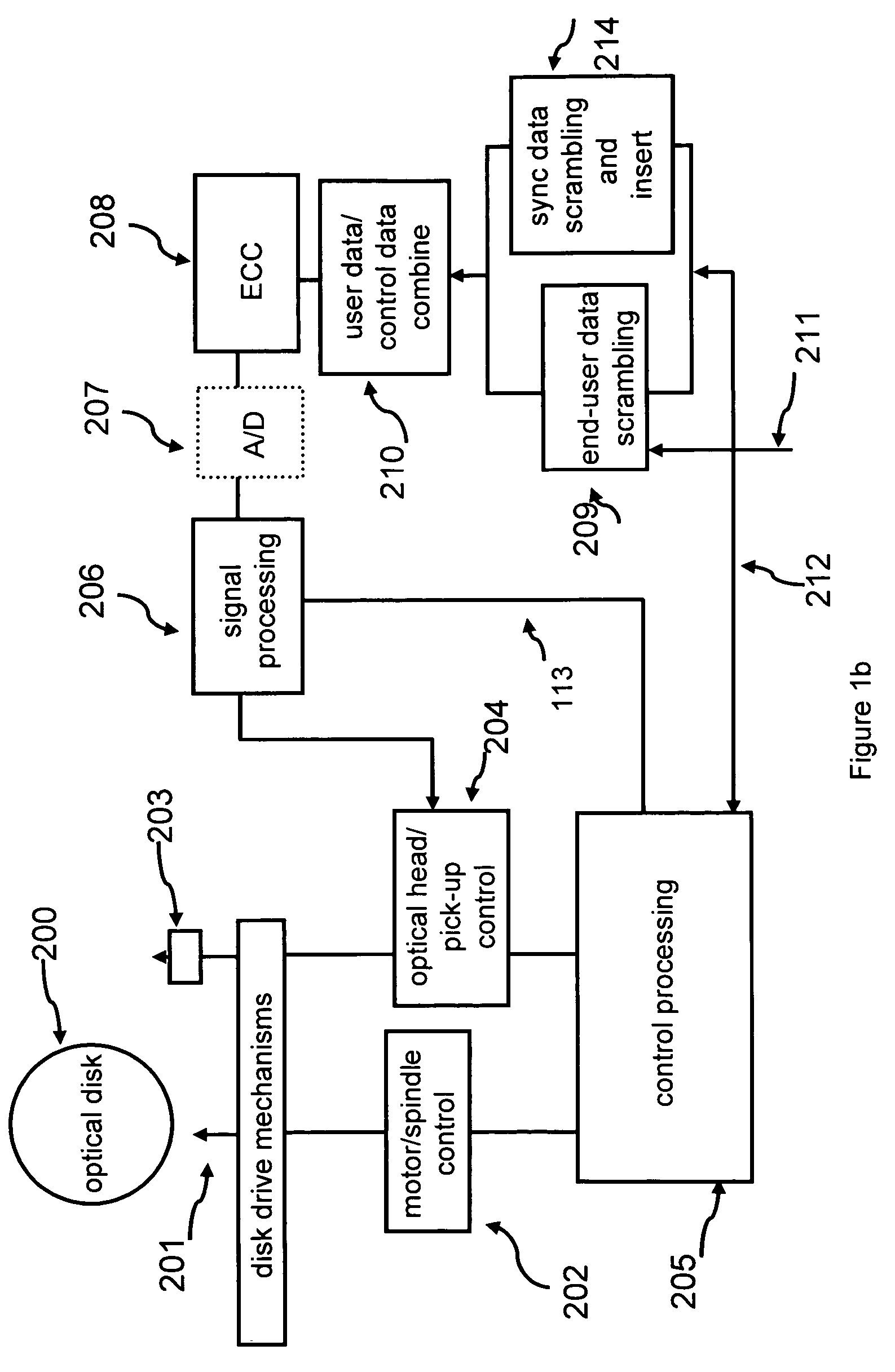

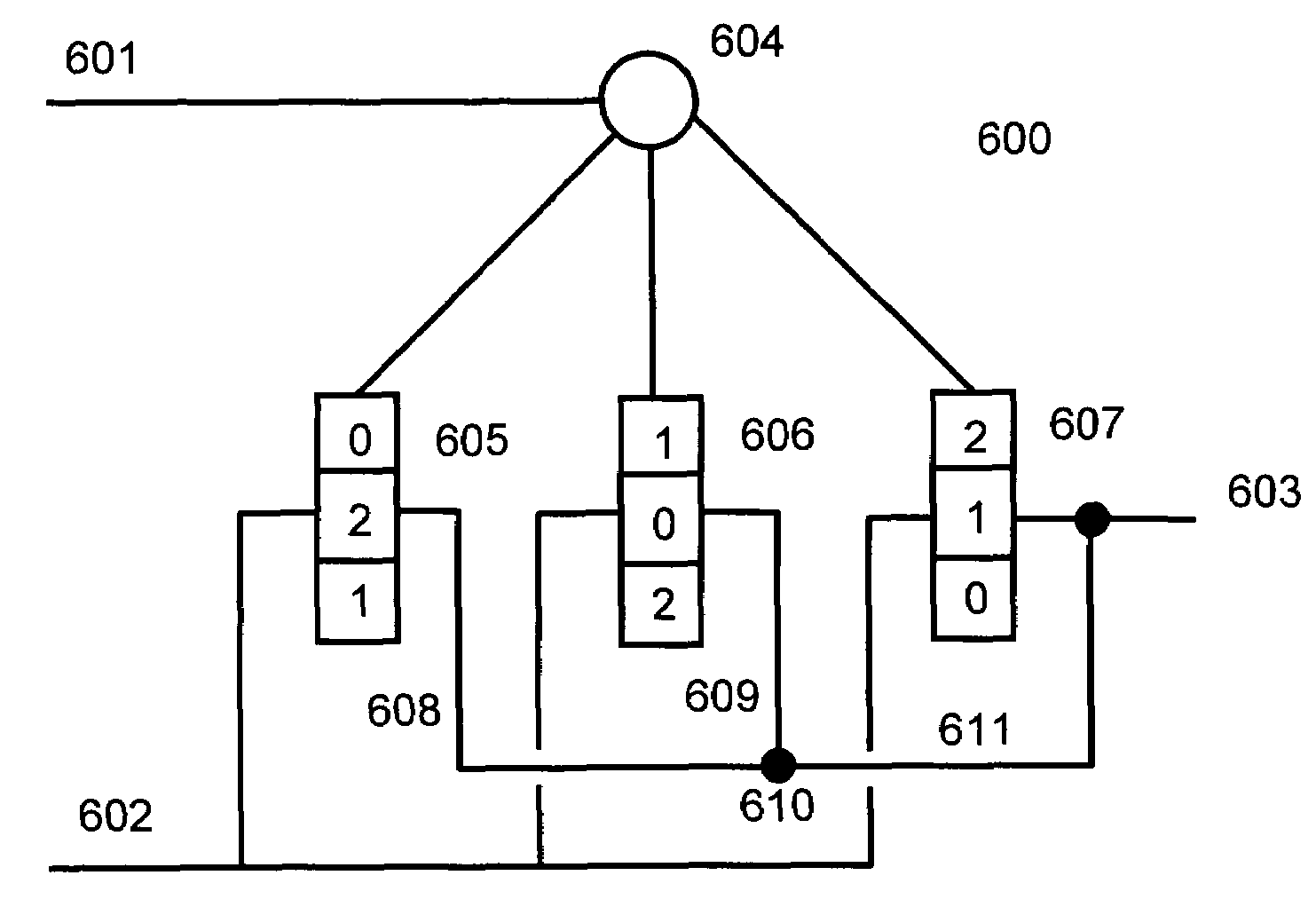

Multi-valued scrambling and descrambling of digital data on optical disks and other storage media

InactiveUS20060164883A1Good correlationError detection/correctionOptical discsDigital dataCorrection code

Method and apparatus for writing scrambled multi-value data to a physical media and for reading scrambled multi-value data from a physical media, are disclosed. The physical media can be an optical disk. The scrambling can be performed by a multi-valued LFSR scrambler and the descrambling can be performed by a multi-valued LFSR descrambler. Further, the multi-valued data that is scrambled can include synchronization data and / or user data. Error correction coding can be used during the writing process and processing to correct for errors can be used during the reading process. Also, methods and apparatus for synchronizing multi-valued data written to and read from physical media are disclosed. Multi-value correlation methods and apparatus are also disclosed.

Owner:TERNARYLOGIC

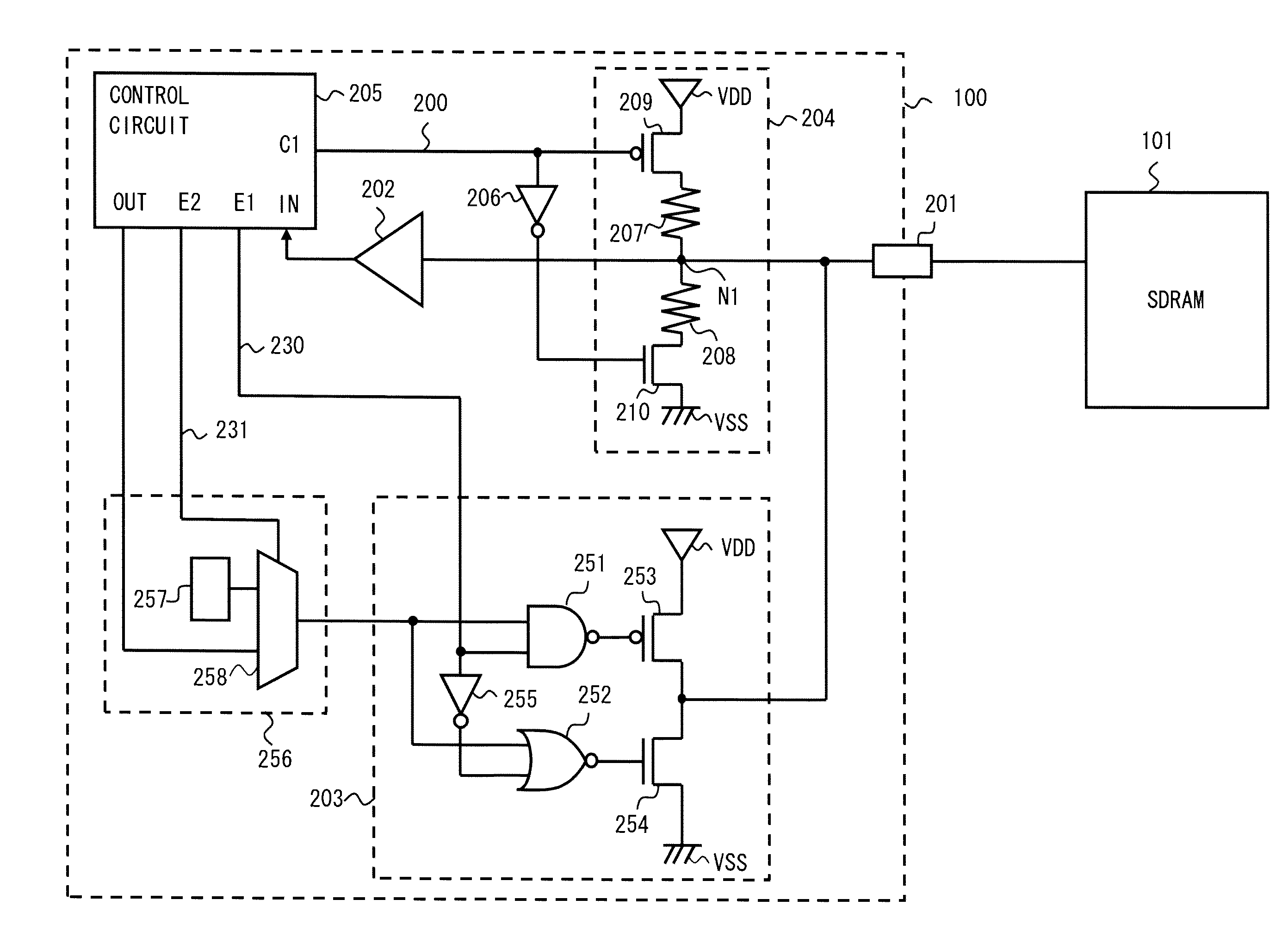

Semiconductor integrated circuit

ActiveUS7999572B2Reduce noiseReduced amplificationInput/output impedence modificationEnergy efficient ICTData selectionControl circuit

Provided is a semiconductor integrated circuit according to an exemplary aspect of the present invention including a data transmitting circuit that transmits data in parallel through a plurality of signal lines and a data receiving circuit that receives the data. The data transmitting circuit includes a plurality of data output circuits that output the data in a data transmission mode or set an output to a high impedance state in a HiZ mode, a plurality of data selection circuits that select one of the data and fixed data and output the selected data to the data output circuits, and a control circuit that controls the data output circuits to output the fixed data during a period between a time when a mode is switched from the HiZ mode to the data transmission mode and a time when the data output circuits start to output the data.

Owner:RENESAS ELECTRONICS CORP

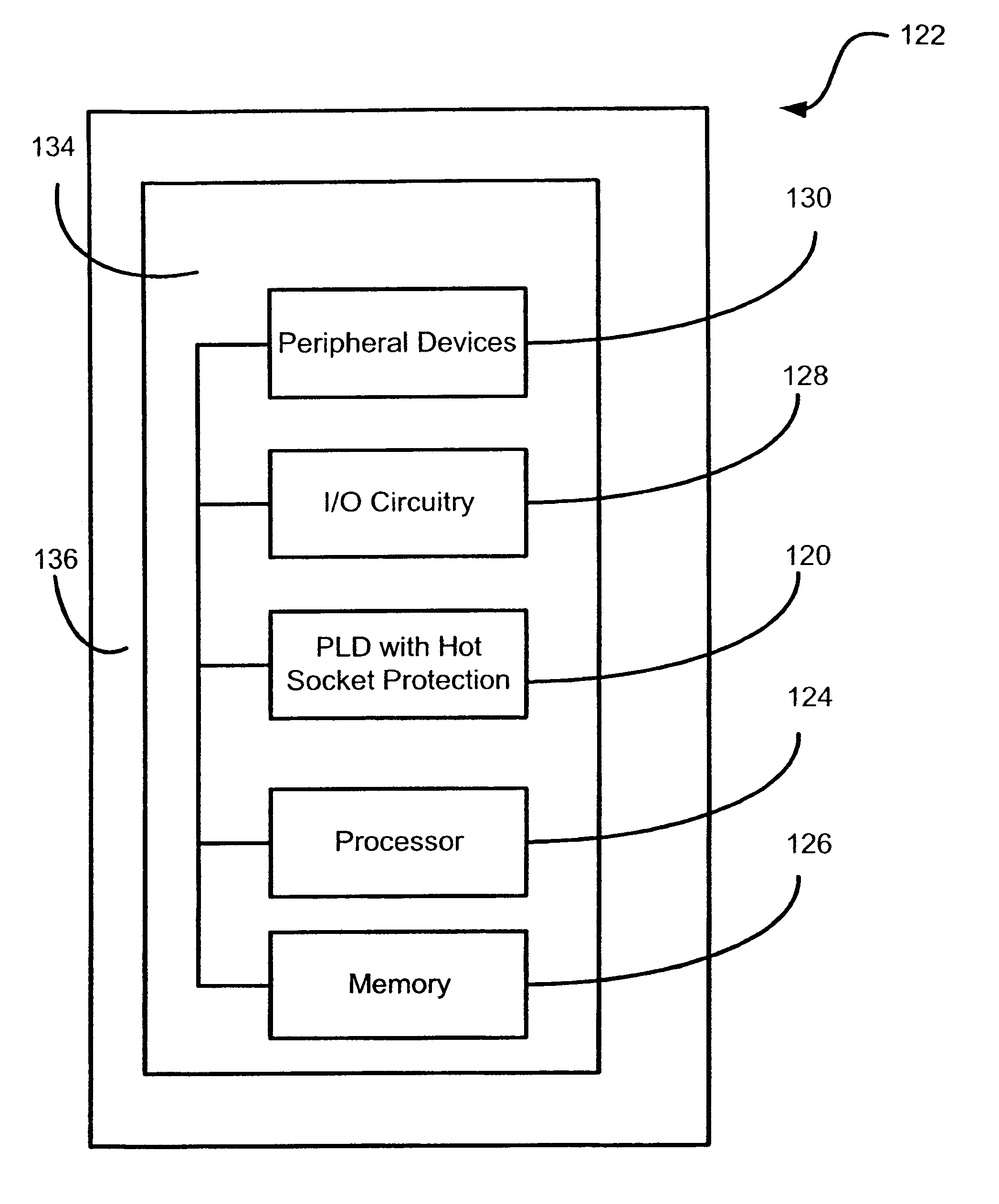

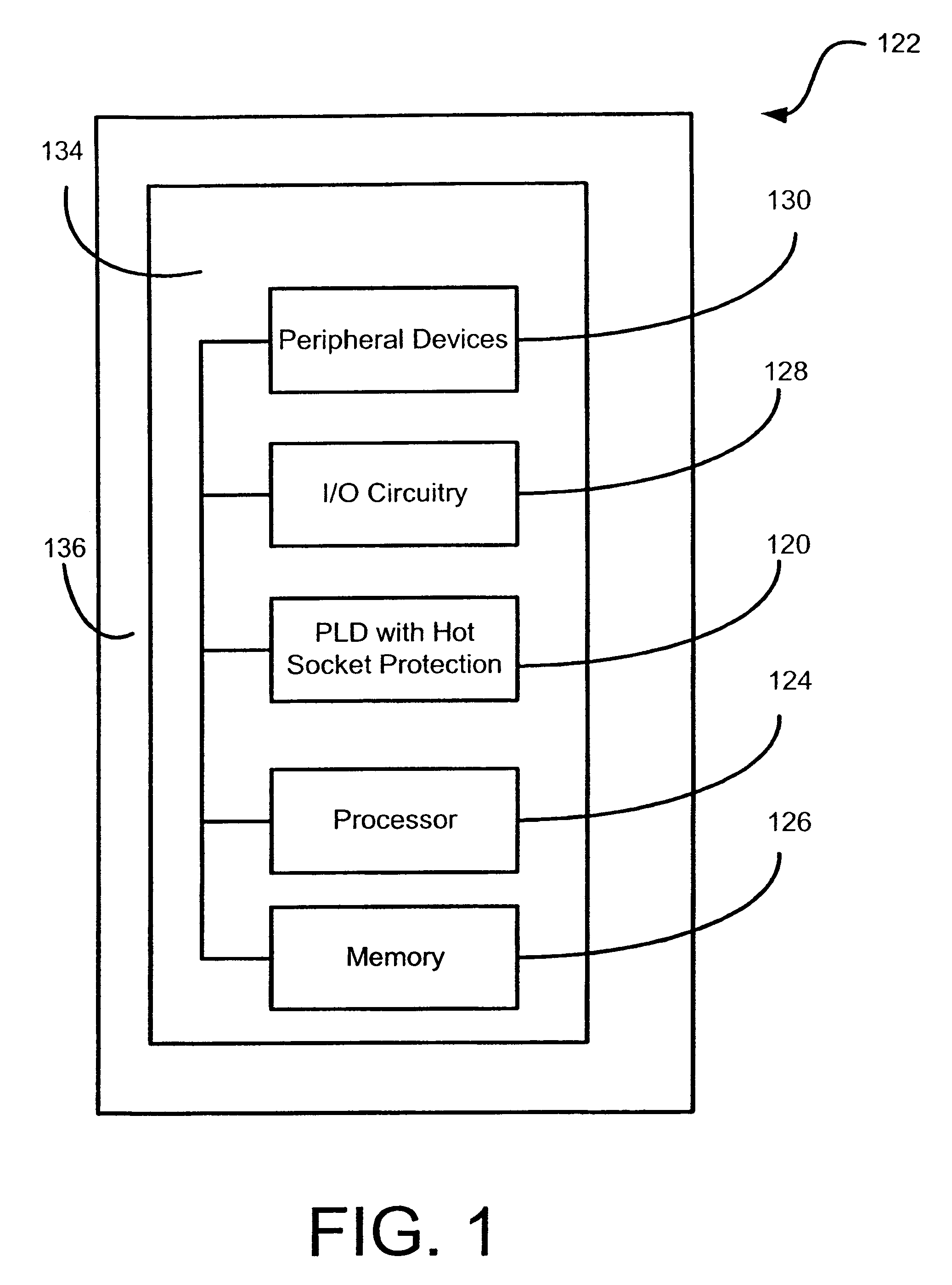

Method and apparatus for protecting a circuit during a hot socket condition

InactiveUS6972593B1Increase valueReliability increase in field effect transistorsLogic circuits using specific componentsHot swappingEngineering

The hot socket detect circuit of the present invention includes a well bias circuit and three hot socket detect blocks. If the output of any of the three hot socket detect blocks is a digital high signal then the output of the hot socket detect circuit is a digital high signal. The digital high signal indicates that a hot socket condition exists.

Owner:ALTERA CORP

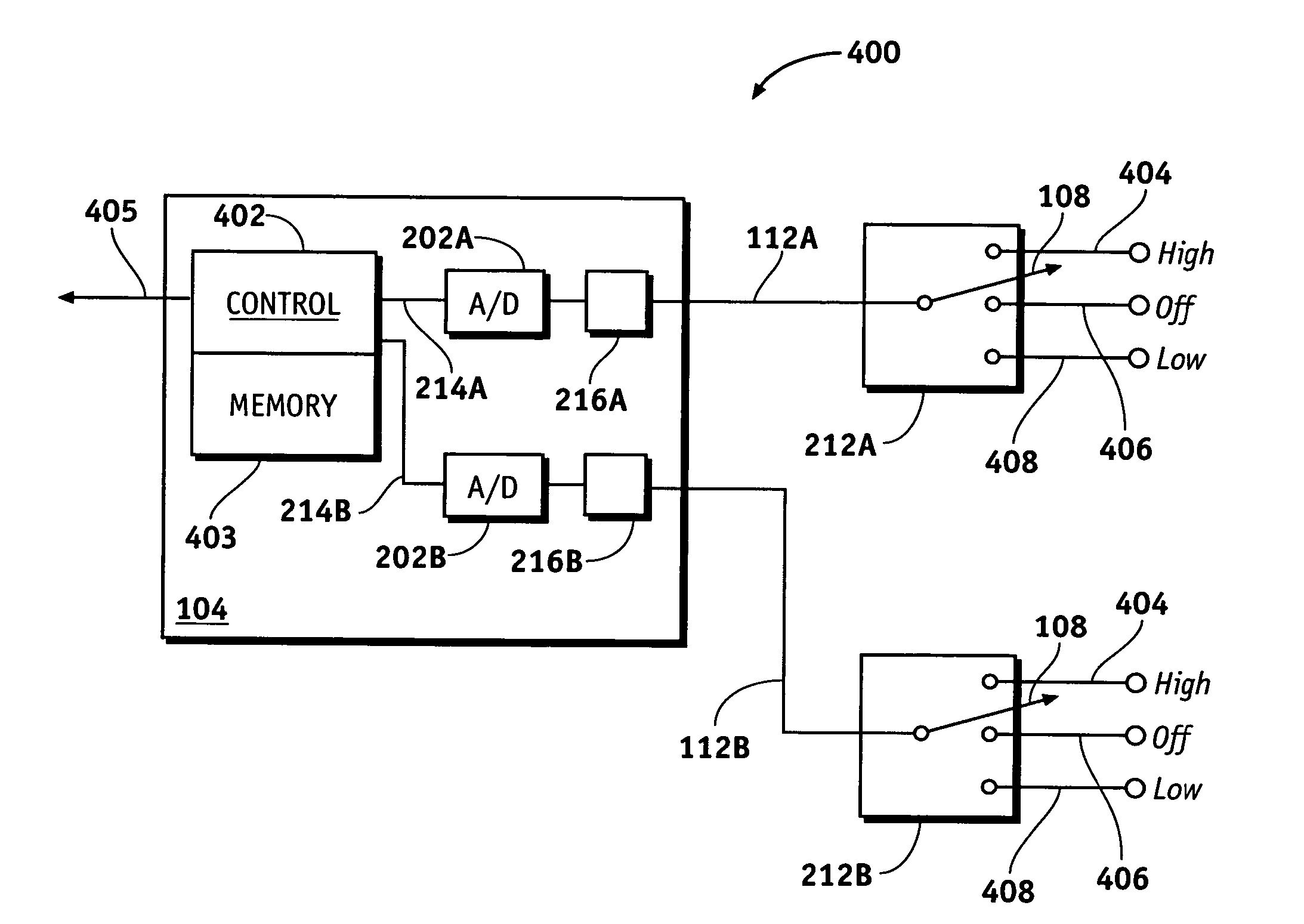

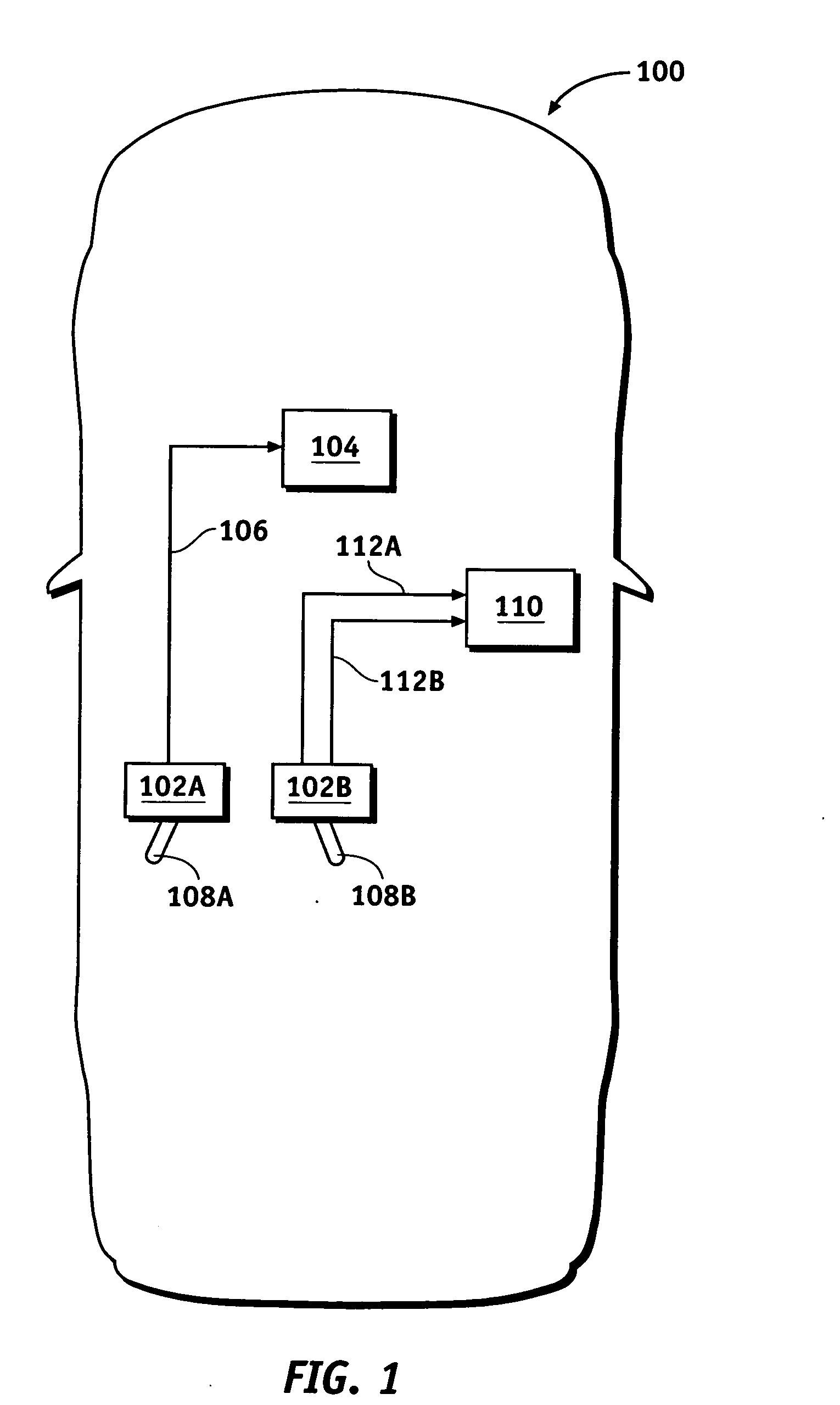

Methods and systems for multi-state switching using multiple ternary switching inputs

InactiveUS20060082386A1Electric switchesLogic circuits using specific componentsCombined useEngineering

Systems, methods and devices are described for placing a controlled device into a desired operating state in response to the position of a multi-position actuator. Two or more switch contacts provide input signals representative of the position of the actuator. Control logic then determines the desired state for -the controlled device based upon the input signals received. The desired operating state is determined from any number of operating states defined by the input values. In various embodiments, ternary switching may be used alone or in combination with binary switching to efficiently implement multi-state rotary or linear switches capable of identifying six, eight, nine, twelve, eighteen, twenty-six, twenty-seven or any other number of switchable states.

Owner:GM GLOBAL TECH OPERATIONS LLC

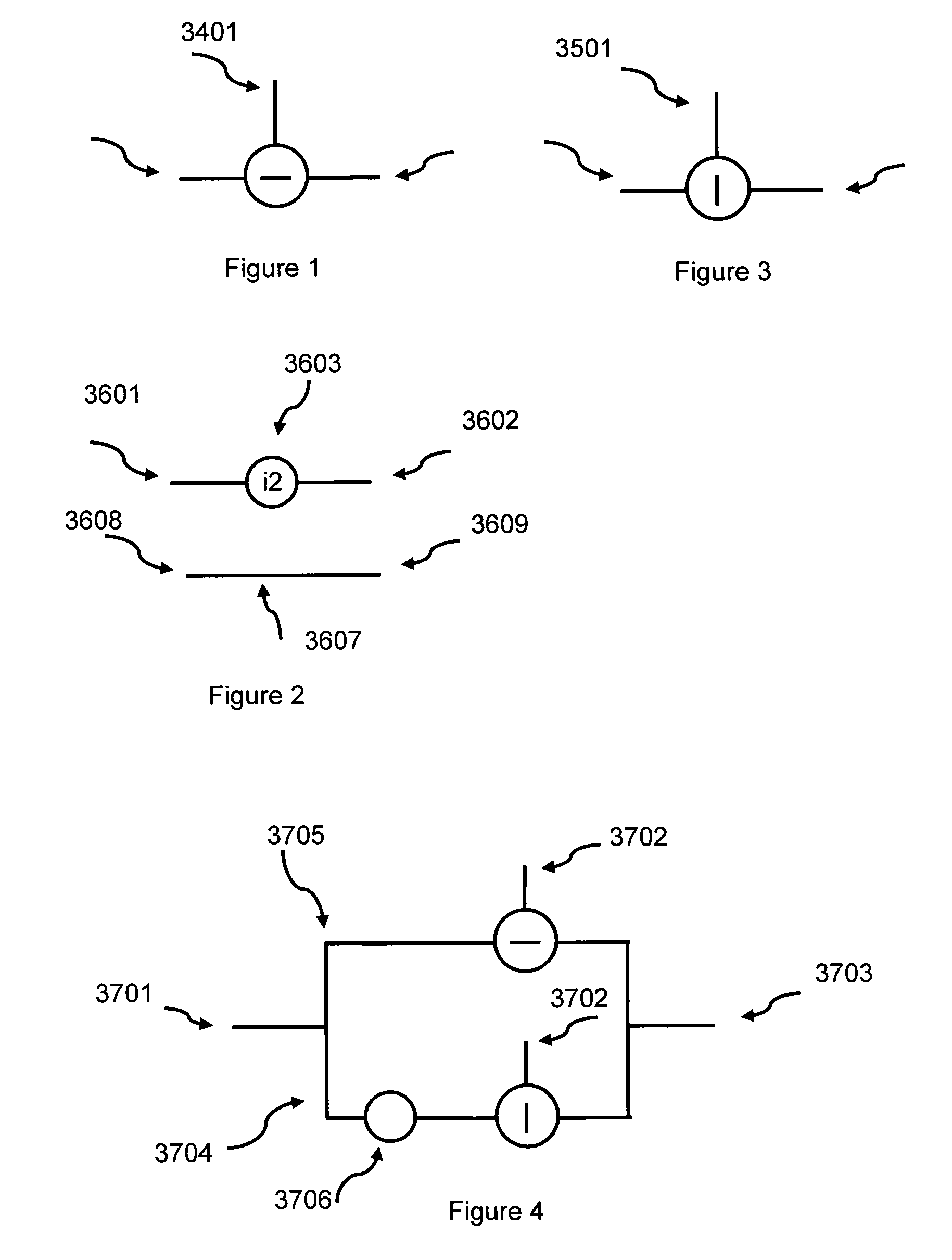

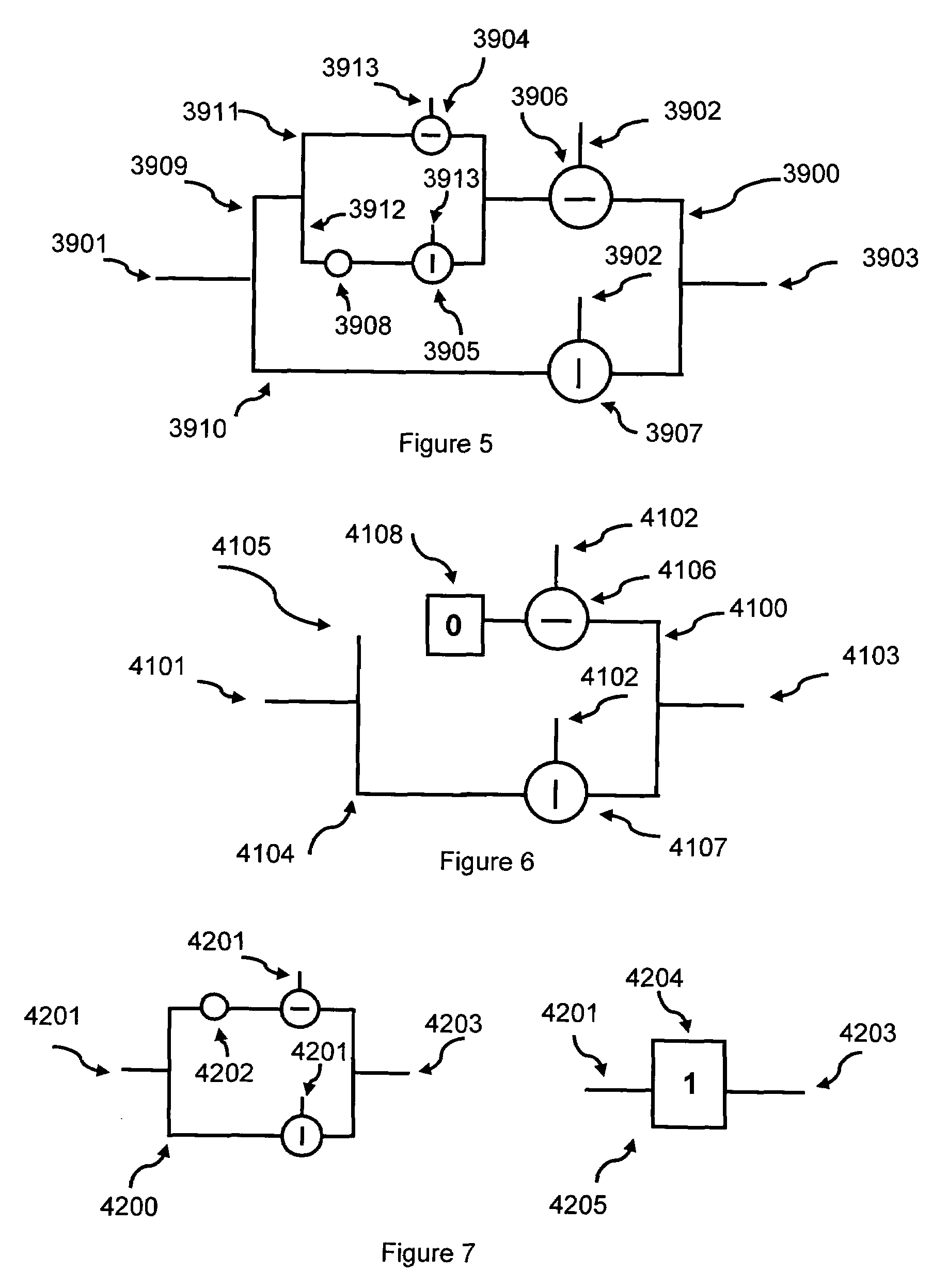

Single and composite binary and multi-valued logic functions from gates and inverters

InactiveUS7218144B2Minimum propagation timePractical to useLogic circuits characterised by logic functionMultistate logicEngineeringMany-valued logic

Owner:TERNARYLOGIC

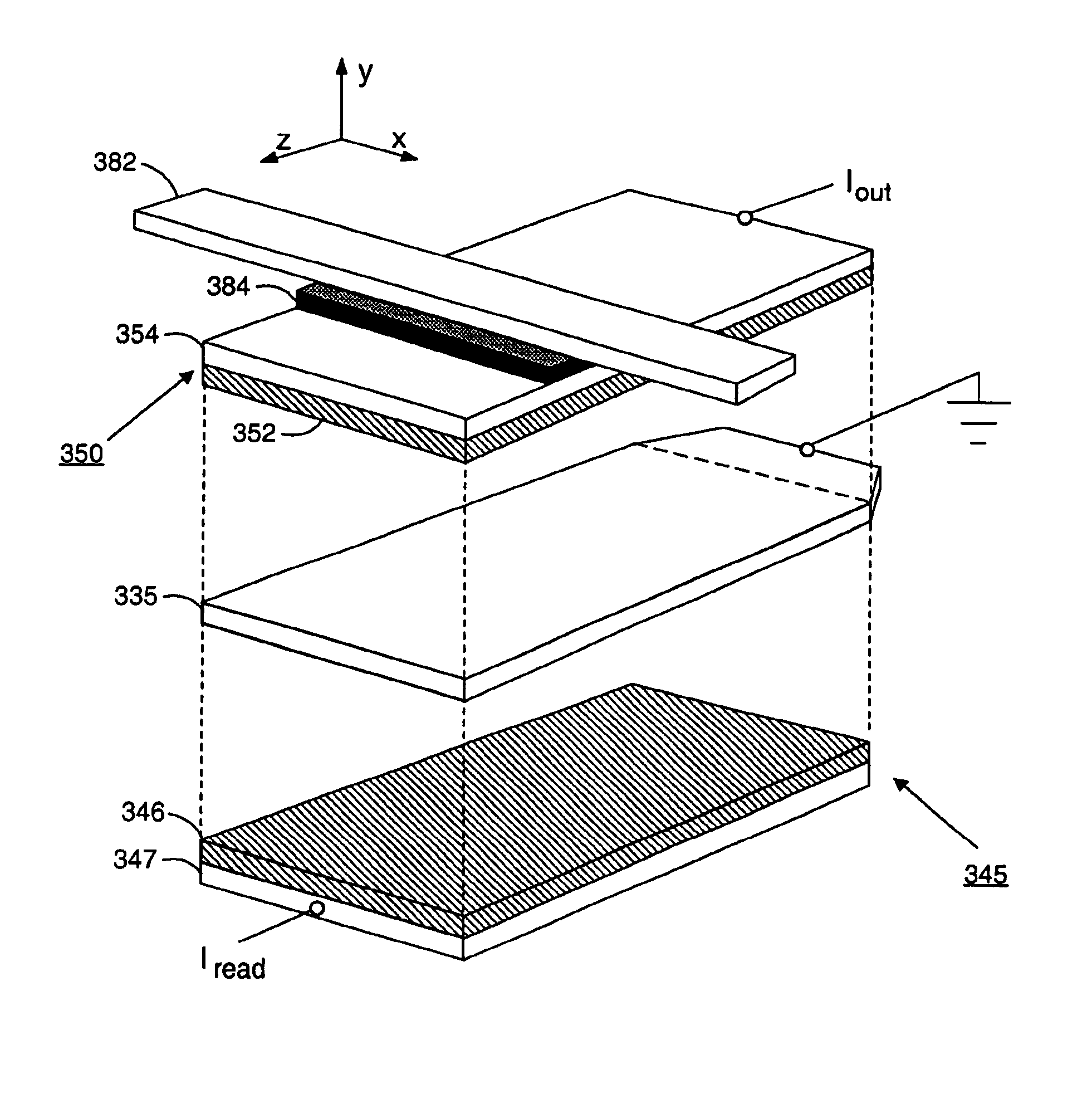

Stacked hybrid semiconductor-magnetic spin based memory

InactiveUS6870761B2Improve isolationImprove noiseSolid-state devicesMagnetic field measurement using galvano-magnetic devicesEngineeringSemiconductor

A new nonvolatile hybrid memory cell stacked architecture is provided. The cells are comprised of magnetic spin storage elements stacked on top of each other on a silicon substrate, as well as one or two semiconductor FET isolation elements.

Owner:SEAGATE TECH INT

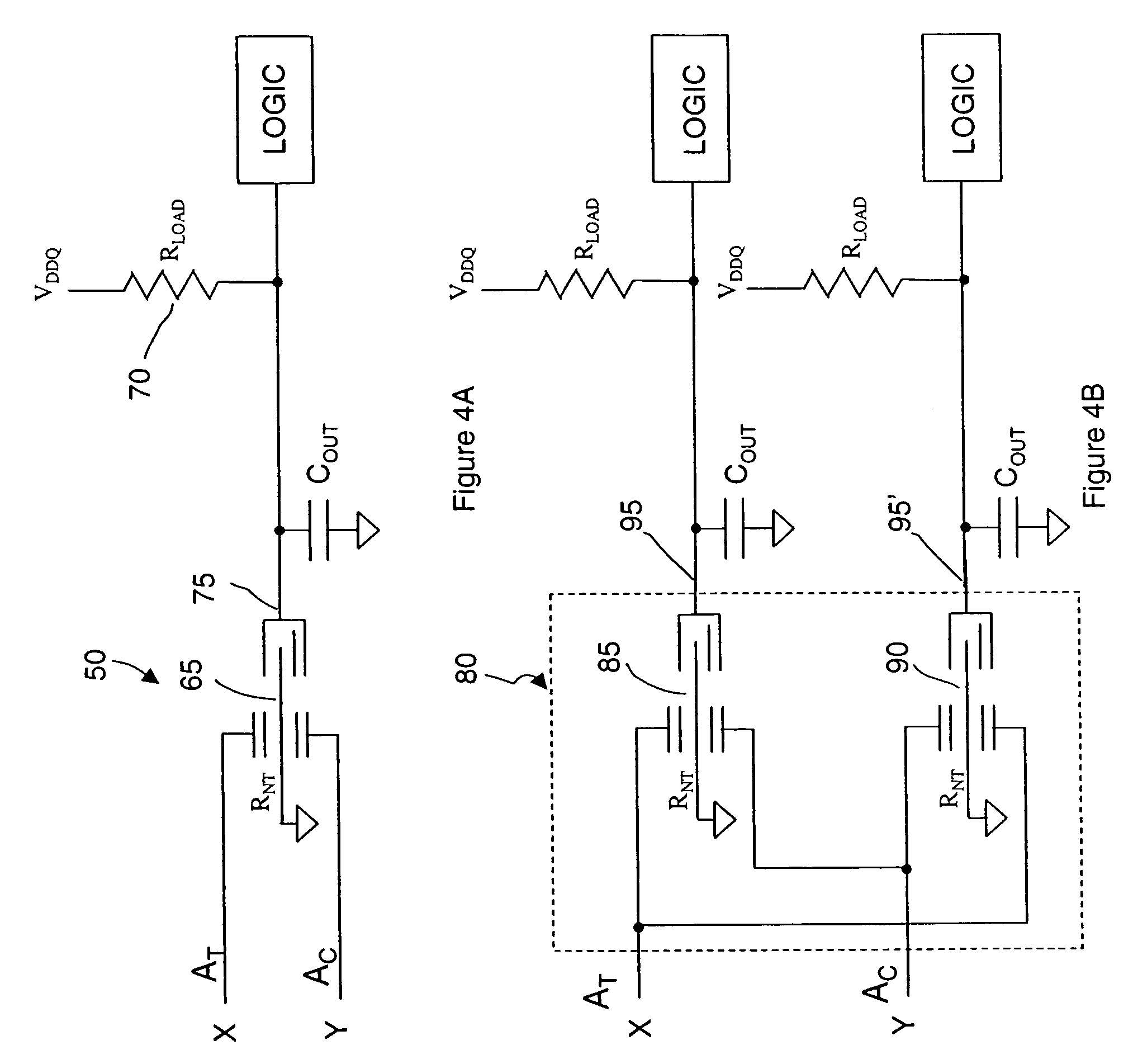

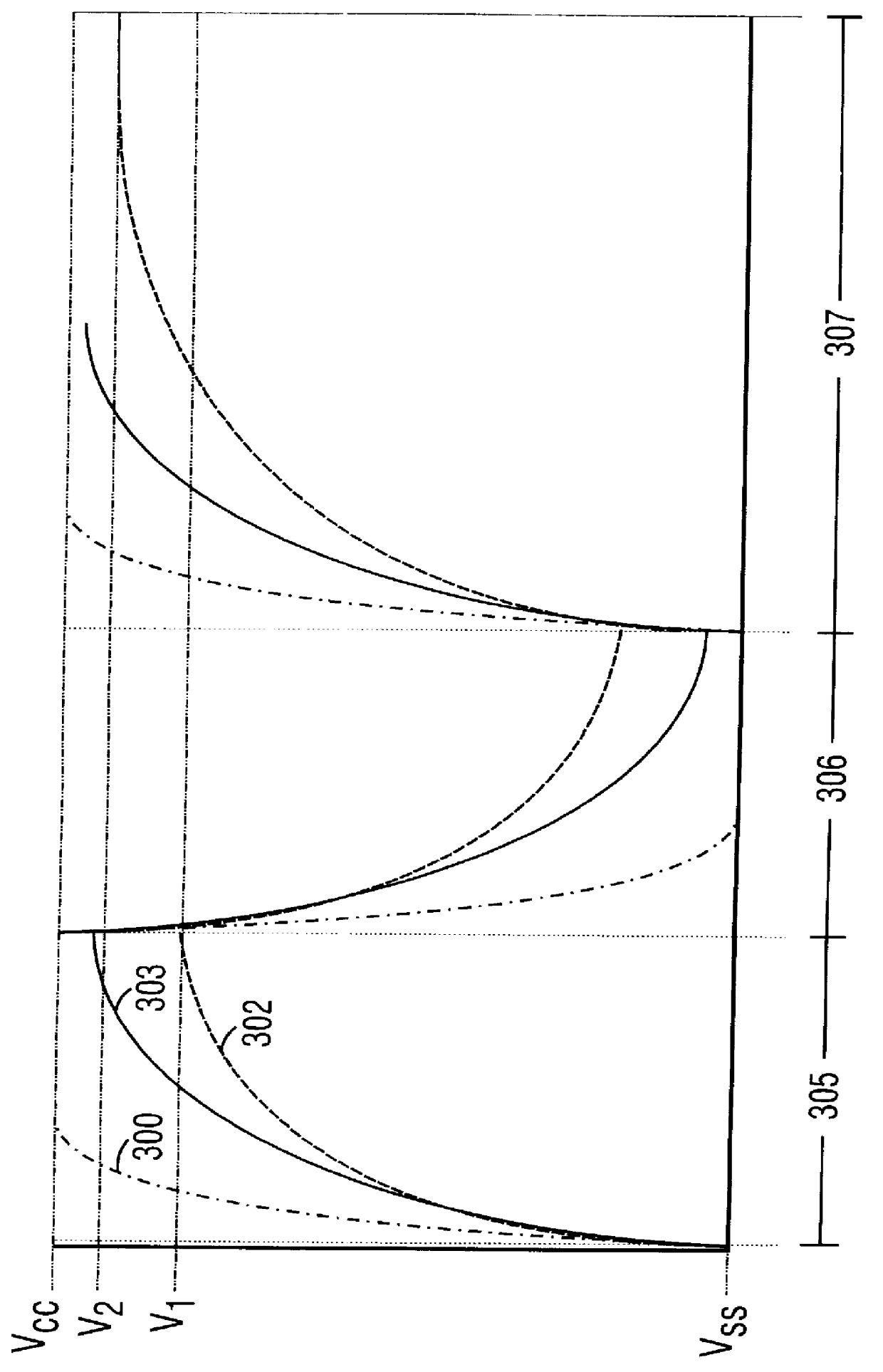

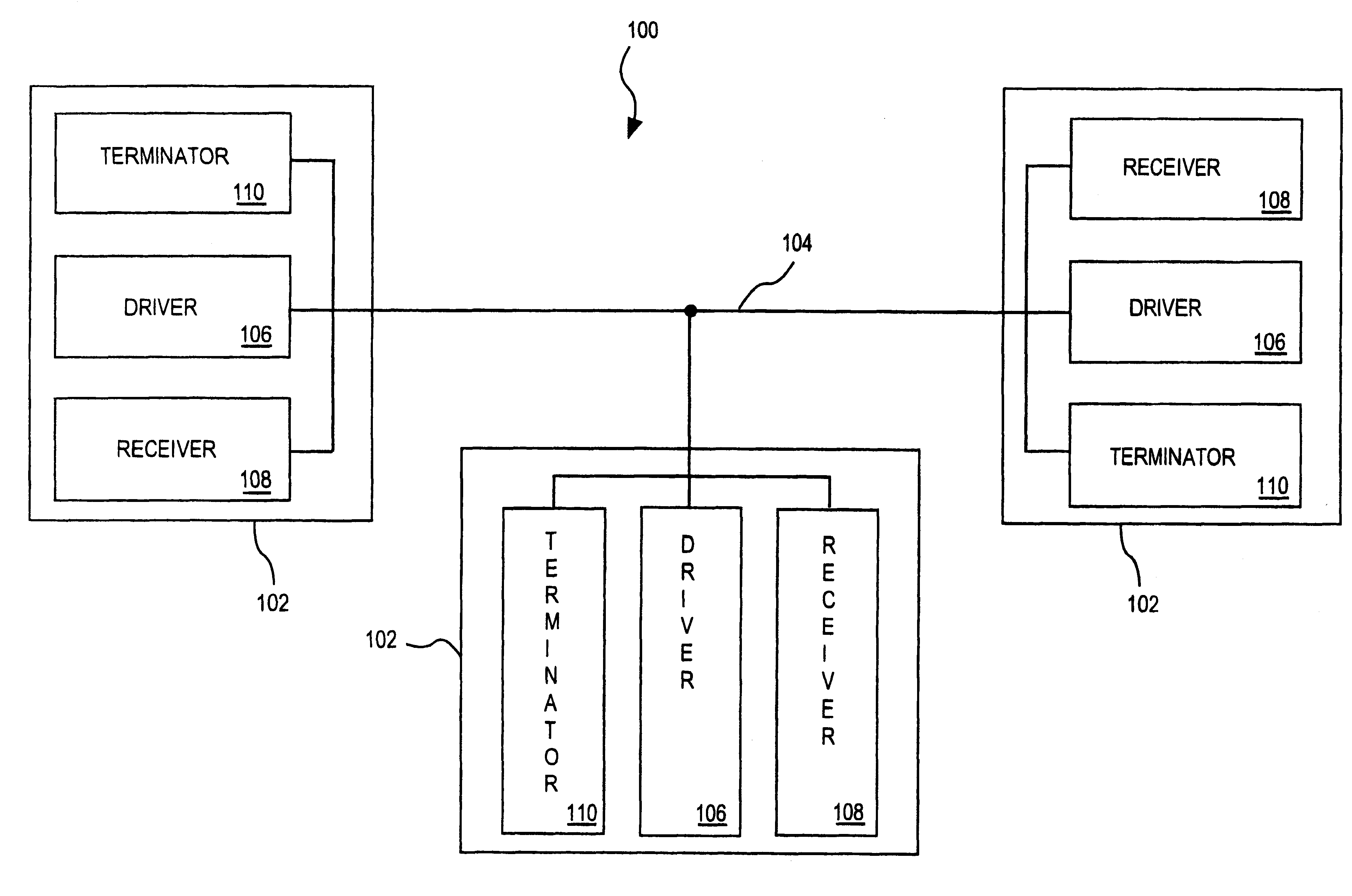

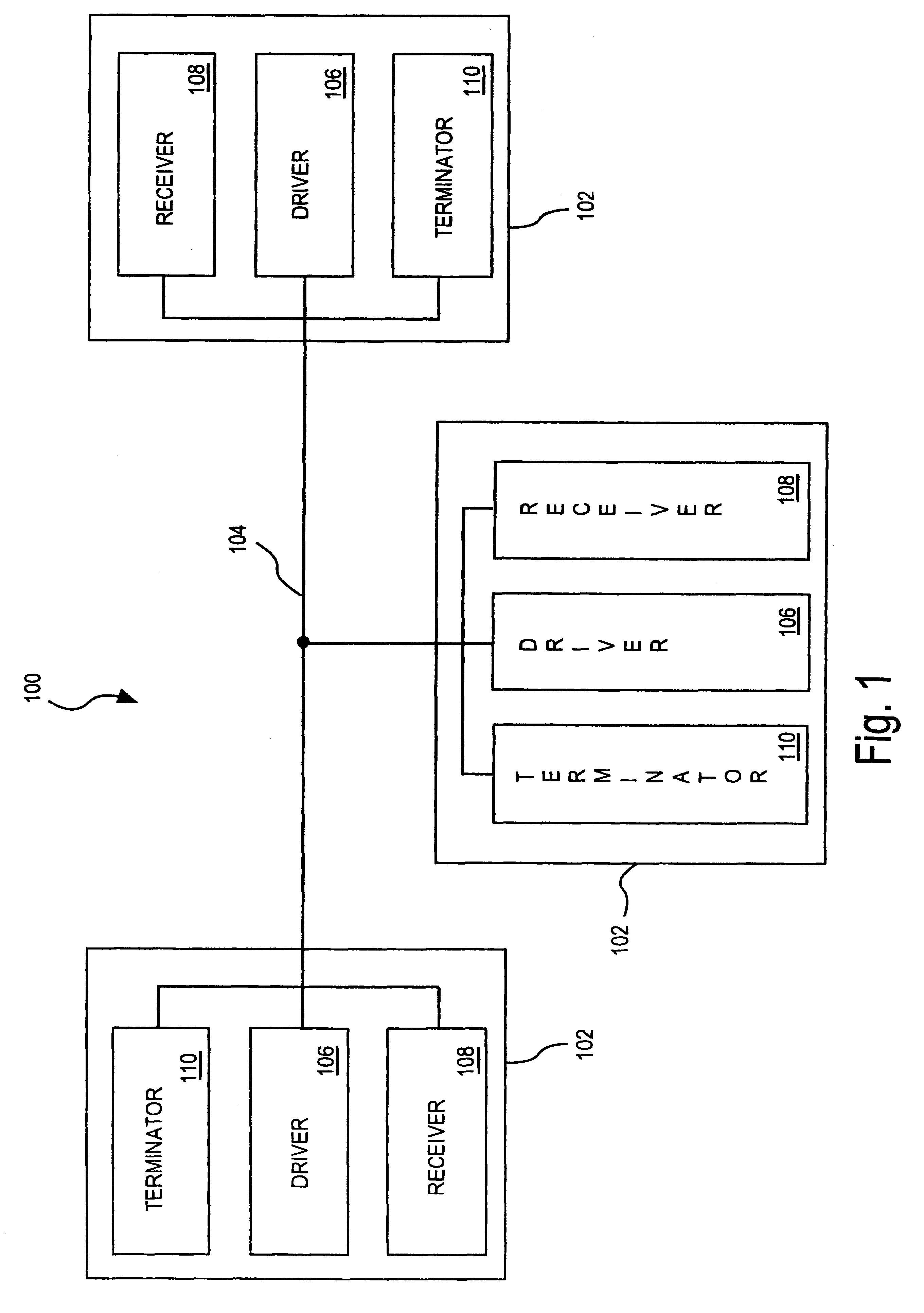

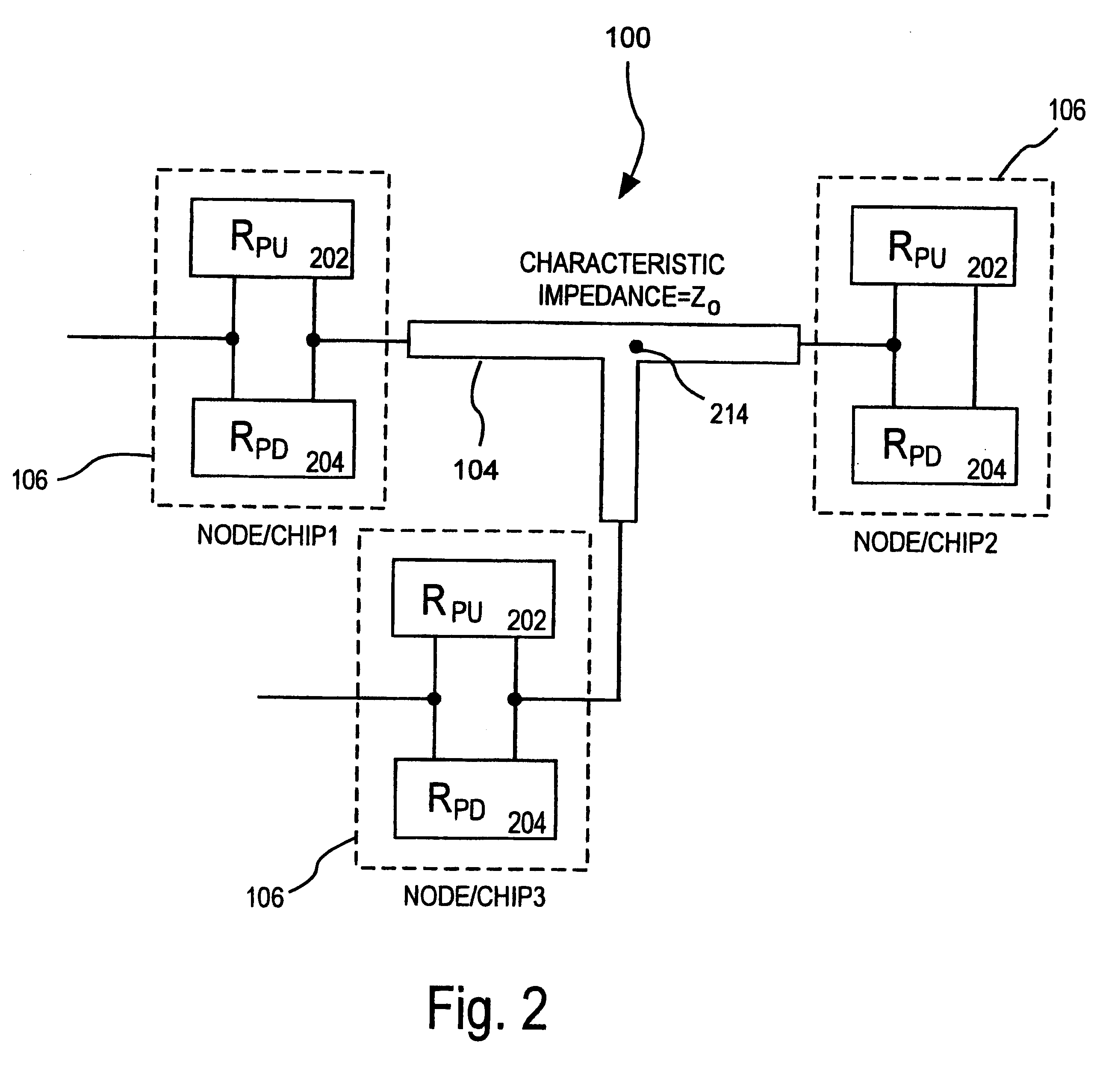

Termination of transmission lines using simultaneously enabled pull-up and pull-down circuits

InactiveUS6275062B1Reliability increasing modificationsElectronic switchingDriver circuitElectrical resistance and conductance

An information handling system includes a plurality of transmission lines coupled together at one end and having a characteristic impedance, a driver circuit coupled to one of the transmission lines, and at least one receiver circuit coupled to the transmission lines. At least one driver circuit includes pull-up and pull-down circuits each having output resistances. The parallel combination of the pull-up and pull-down resistances matches the characteristic impedance of the transmission line. When the driver is used to terminate the transmission line, the pull-up and pull down circuits are enabled at approximately the same time, thus terminating the line. On-chip terminators may alternatively be used for termination, the terminators either including pull-up and pull-down circuits substantially similar to those described for the drivers, or may include a single resistance tied to a voltage other than an upper or lower rail. A method for managing the information handling system described above includes terminating each node by causing either an on-chip terminator or a driver to go into a terminating mode, thus causing the termination of the line using an output resistance that matches the characteristic impedance of the transmission line.

Owner:SUN MICROSYSTEMS INC

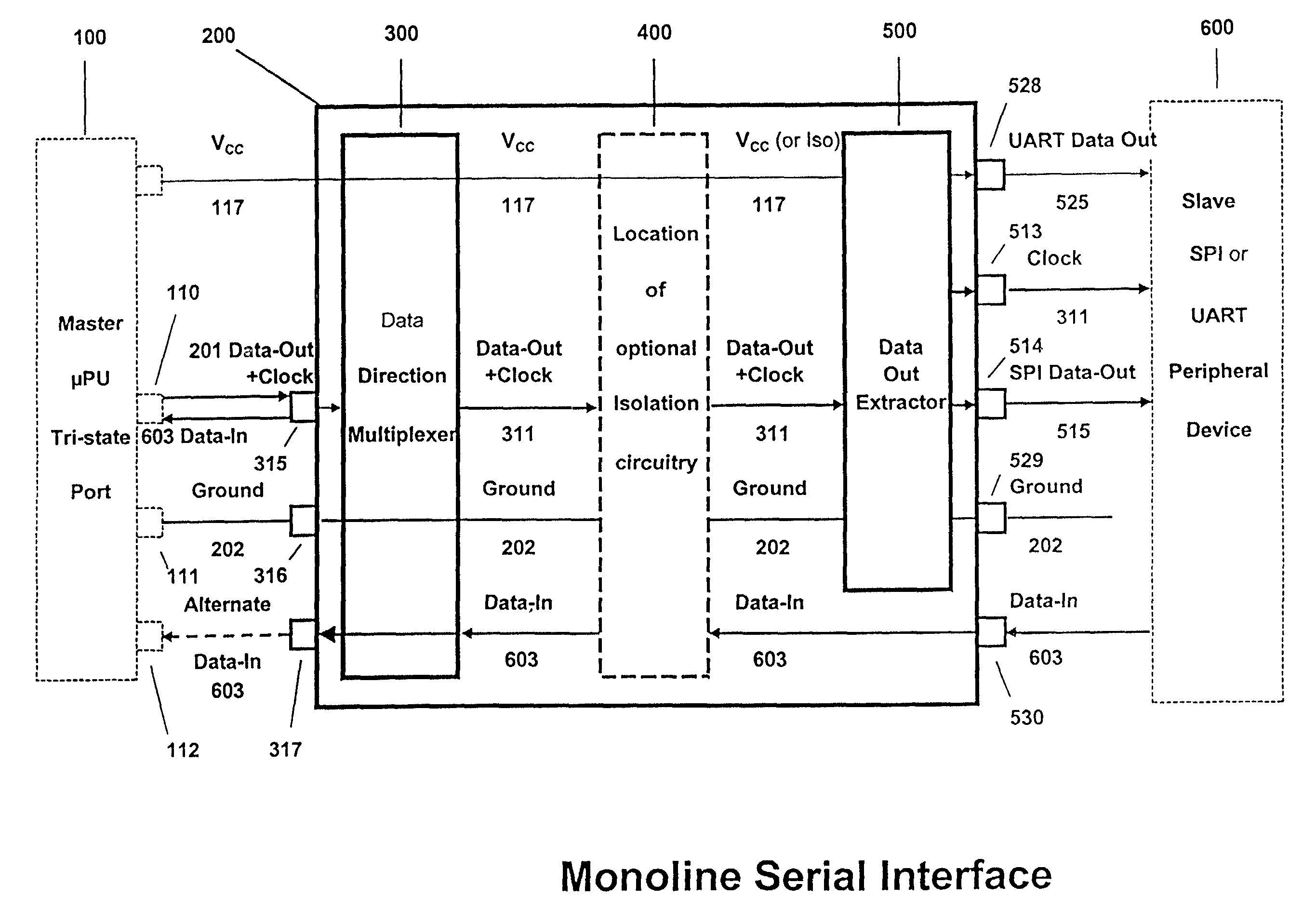

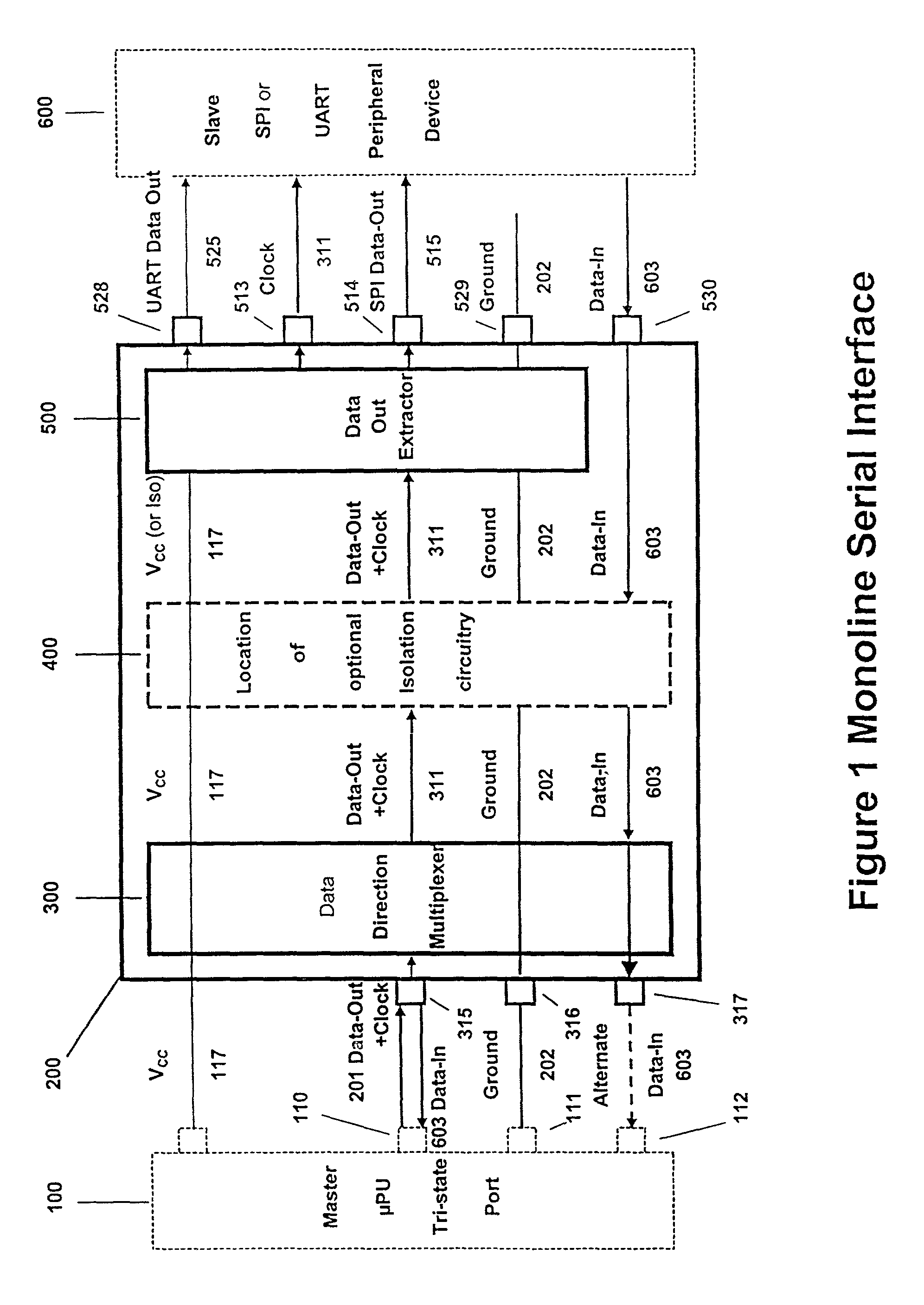

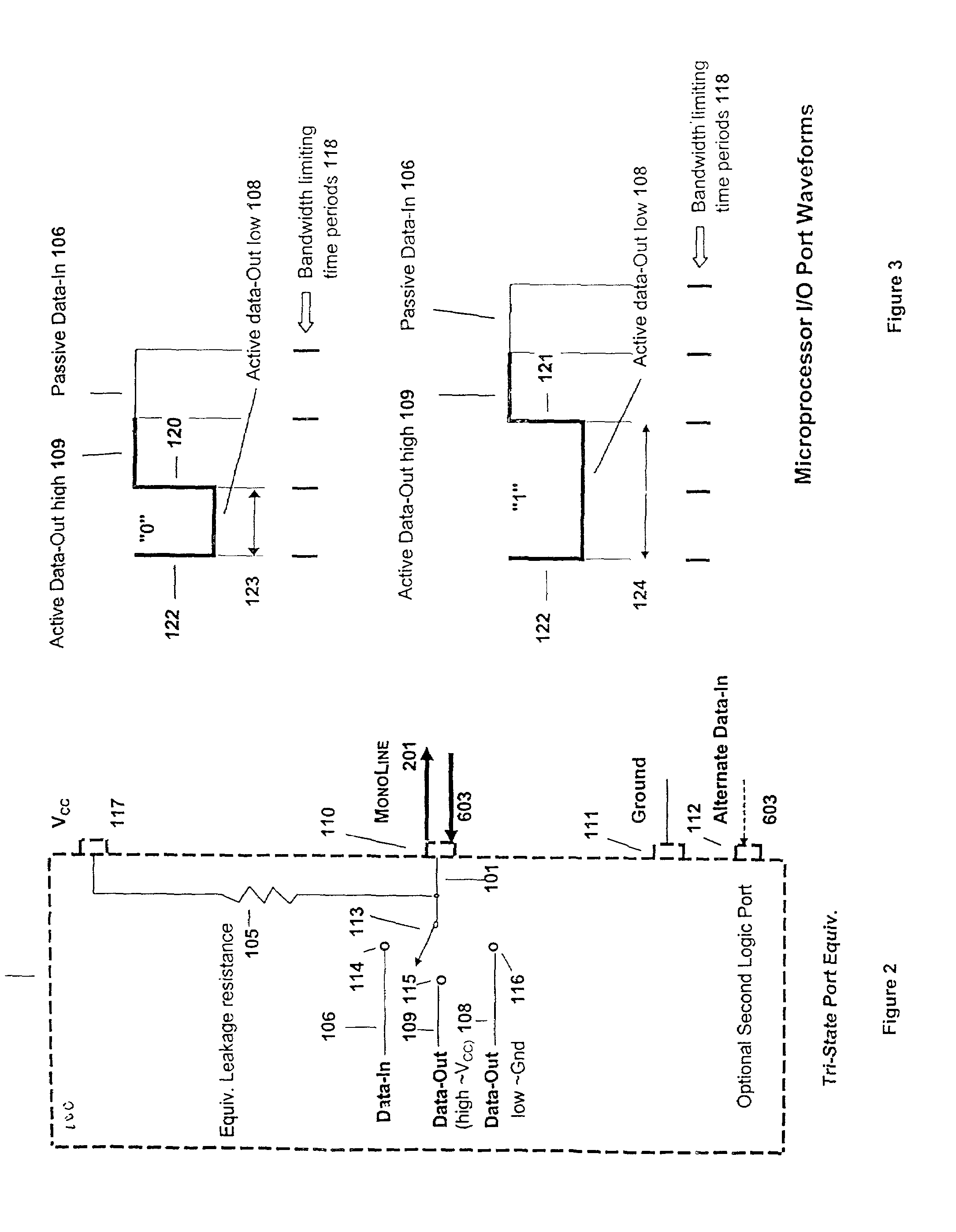

Apparatus, method and signal set for monoline serial interface

InactiveUS7028105B2Programme controlReliability increasing modificationsData exchangeSignaling protocol

Circuit, apparatus, method, and signal set for sending and controlling bi-directional data flow between a microprocessor (or other device) and a peripheral device having a standard UART-based, SPI-based, or similar interface over a single input / output (I / O) port line, utilizing the differences of the instantaneous source impedance of the I / O port line operating with data in and data out states. Circuit, apparatus, method, and signal set for separating the 1-wire data into standard 2-wire and 3-wire UART-based, SPI-based, or similar interfaces for use with unmodified peripheral devices. The exchange of data on a bit-by-bit or analog basis, with insignificant return delay, allows operation independent of any signaling protocol.

Owner:ELECTRONICS SOLUTIONS

Semiconductor device

An object of the present invention is to realize an example of configuration that approximately represents a state of quantum spin in a semiconductor device where components as a basic configuration unit are arrayed so as to search a ground state of Ising model. There is disclosed a semiconductor device provided with plural units each of which is equipped with a first memory cell that stores a value which represents one spin of the Ising model by three or more states, a second memory cell that stores an interaction coefficient showing interaction from another spin which exerts interaction on the one spin and a logical circuit that determines the next state of the one spin on the basis of a function having a value which represents a state of the other spin and the interaction coefficient as a constant or a variable.

Owner:HITACHI LTD