Patents

Literature

1287results about "Logic circuit interface arrangements" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

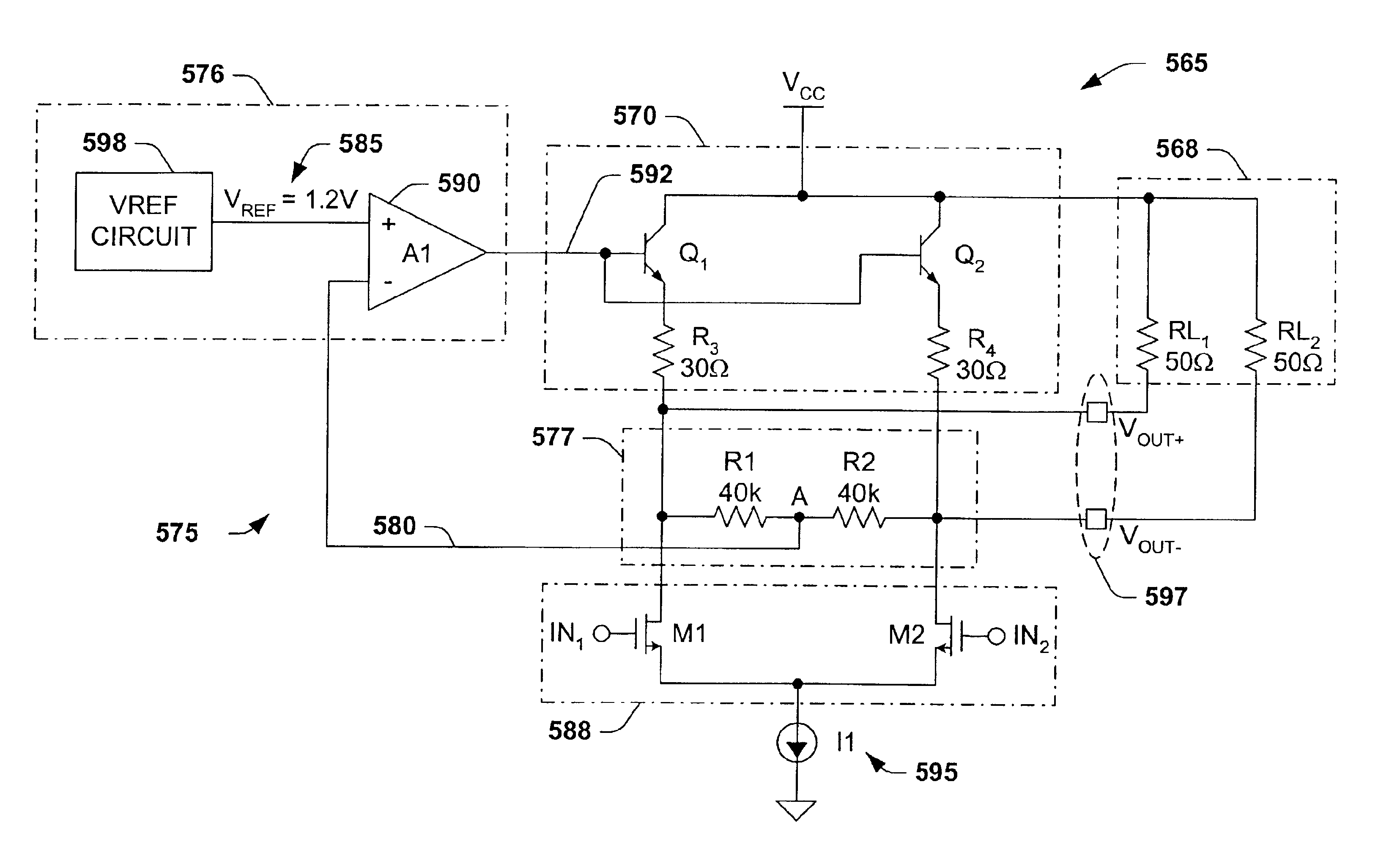

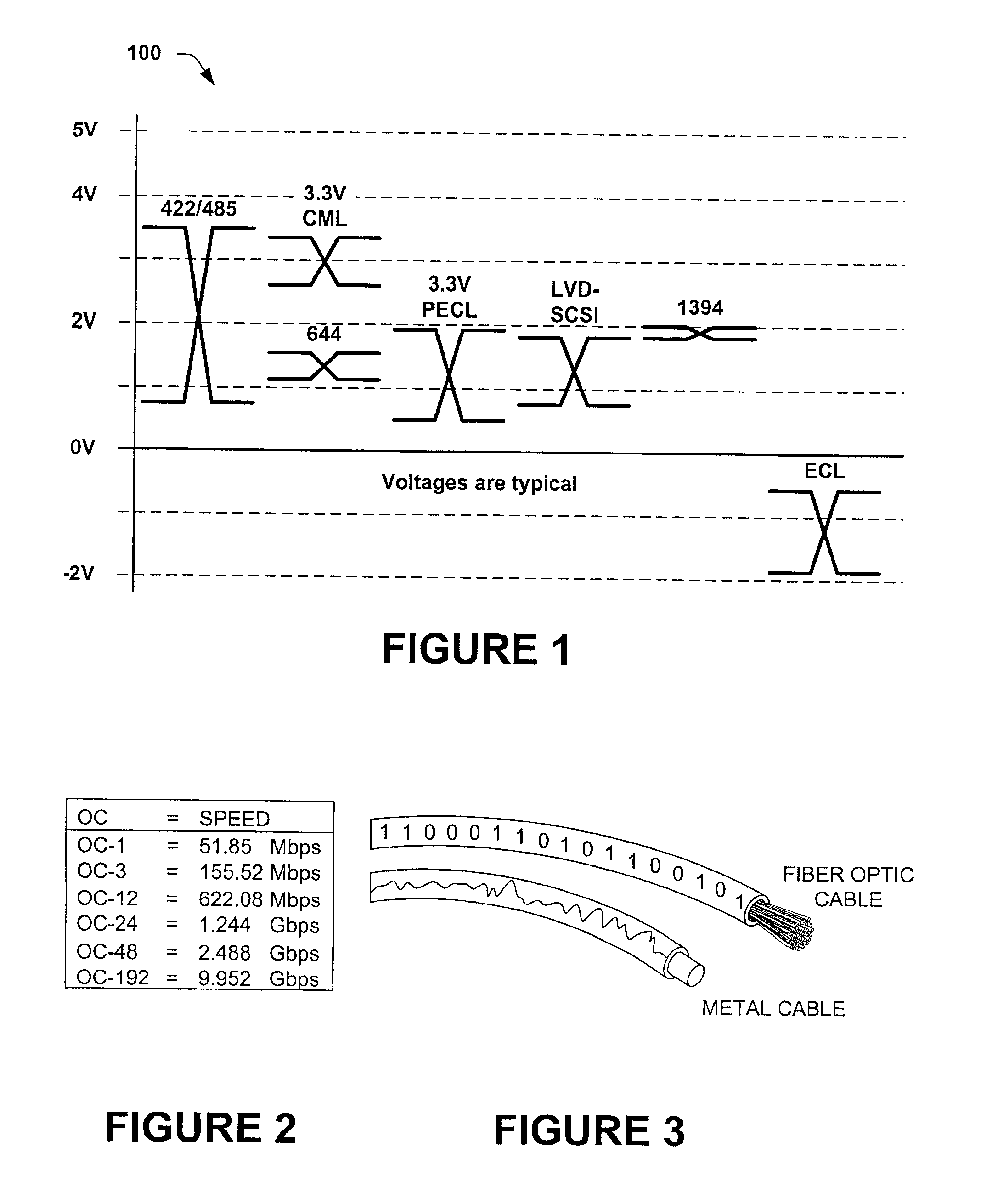

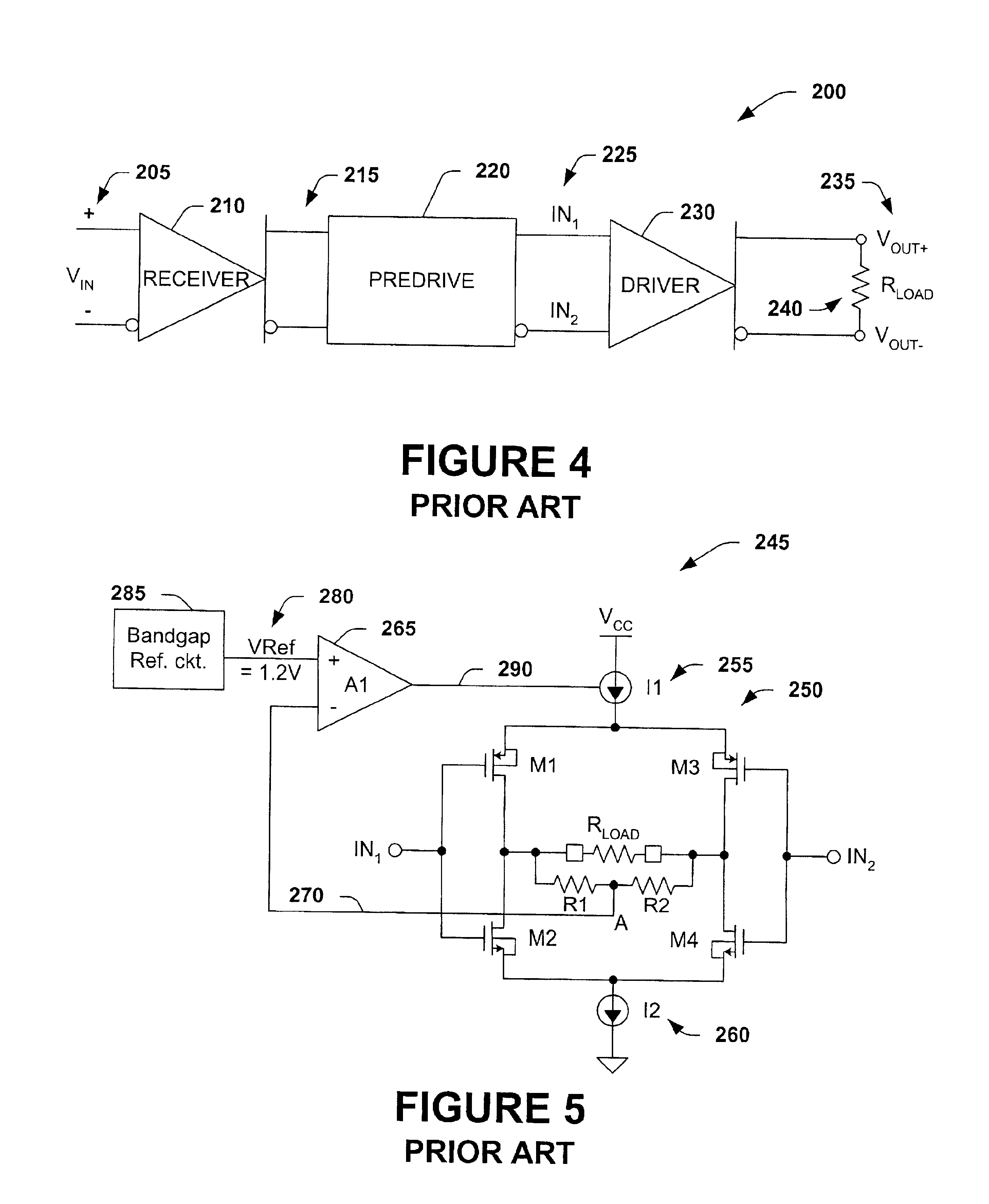

Interchangeable CML/LVDS data transmission circuit

InactiveUS6847232B2Easy to operateReduce input voltageLogic circuits coupling/interface using field-effect transistorsAmplifier with semiconductor-devices/discharge-tubesDriver circuitTransceiver

A system and method is described for a driver circuit used for high speed data transmission in LVDS and CML transceiver device applications. The transceivers are intended to receive a low voltage differential input signal and interchangeably drive a standard LVDS load with a TIA / EIA-644 compliant LVDS signal, and a standard CML load with a standard CML compatible signal. The driver circuit operates at speeds up to 1.36 Gbps, making it compatible with the OC-24 signaling rate for optical transmission. To accomplish this, the driver uses a mixed combination of voltage and current mode drive sections in the output circuit when coupled to LVDS loads, and when the driver is coupled to CML loads, operates purely in a current mode using only the current mode drive section. MOS transistors and a current source are used in the current mode switch portion to switch the drive with a constant current at the high speeds, and NPN transistors in the voltage mode output portion provide variable impedance for the output circuit. A common mode compensation circuit using a feedback voltage from the load generates a compensation signal for variable impedance control of the NPN transistors to yield a regulated voltage for the common mode dc voltage.

Owner:TEXAS INSTR INC

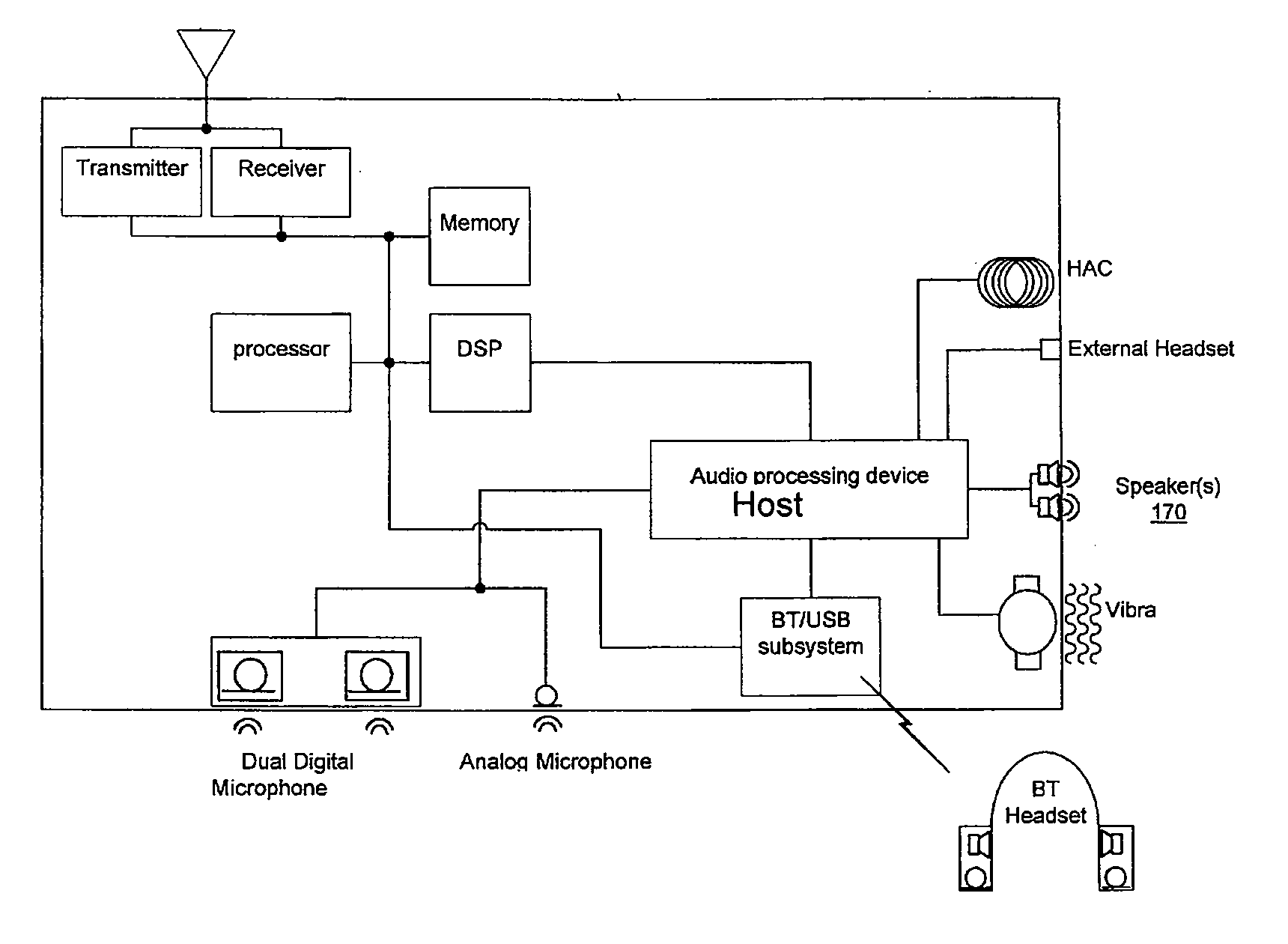

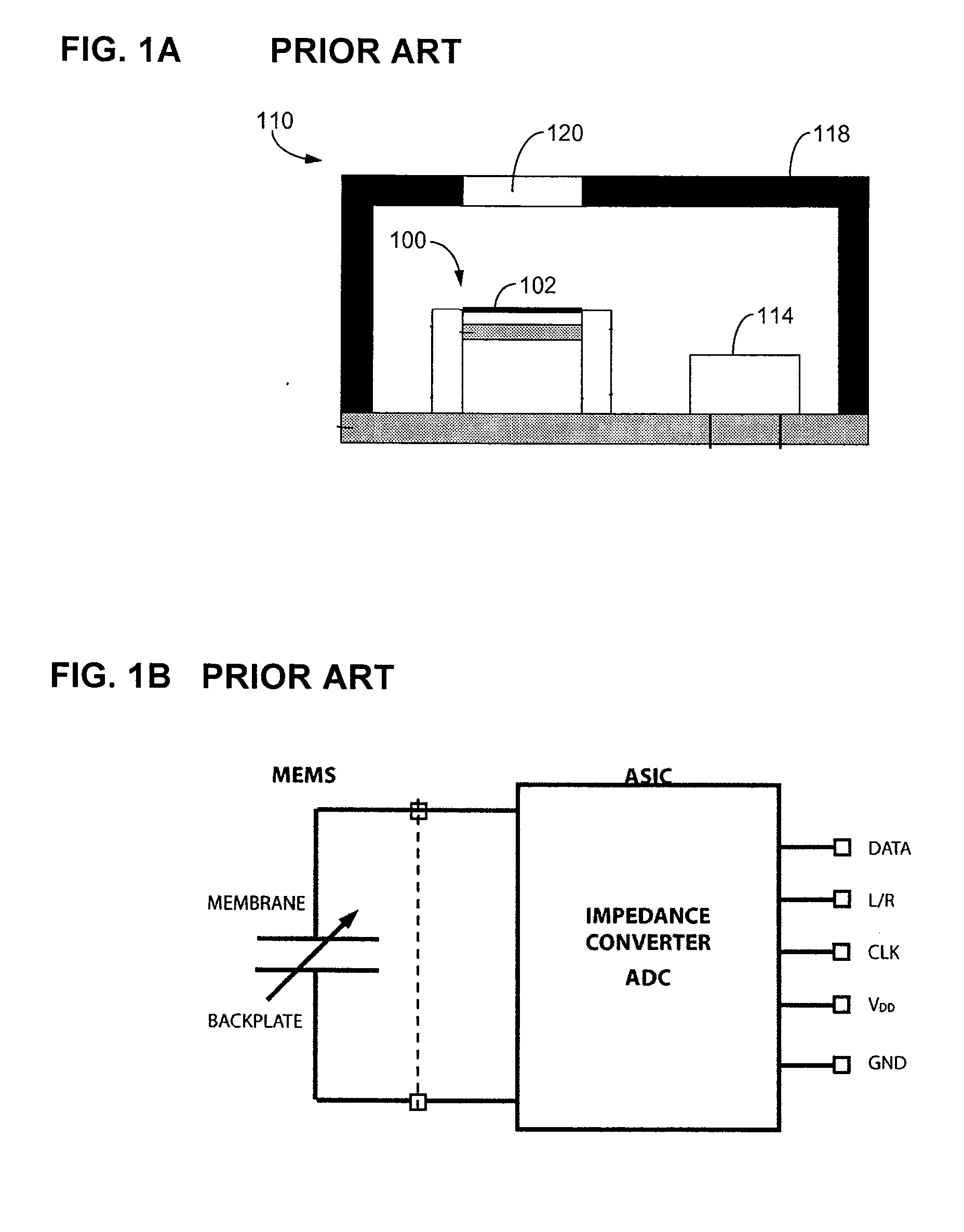

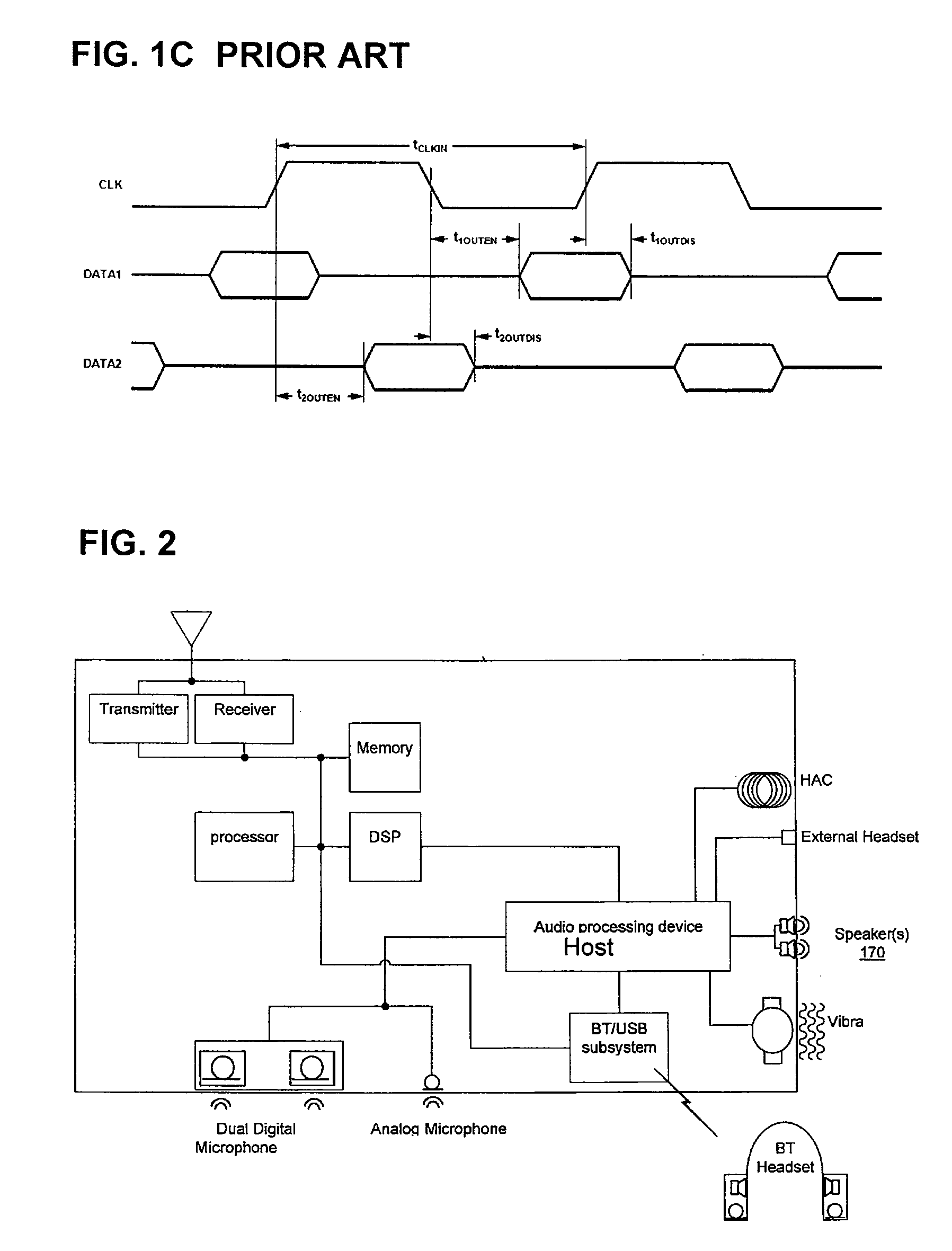

System and A Method For Streaming PDM Data From Or To At Least One Audio Component

InactiveUS20130058495A1Shorten the counting processReduce in quantityMicrophonesLoudspeakersData connectionControl data

An electronic circuit, a digital audio component, an interface system and a method for streaming PDM data from or to at least one audio element are provided. The electronic circuit comprises a VDD connection for receiving a VDD potential, a GND connection for receiving a potential numerically lower than said VDD potential, a CLK connection for receiving a clock signal having a high and a low part, a DATA connection for communicating said PDM data to or from a host and / or another such electronic circuit, an L / R connection for receiving a DC potential designating whether to communicate substantially synchronously with said high part or said low part of said clock signal. The electronic circuit further comprises an I / O circuit configured for communicating control data via said L / R connection.

Owner:KNOWLES ELECTRONICS INC

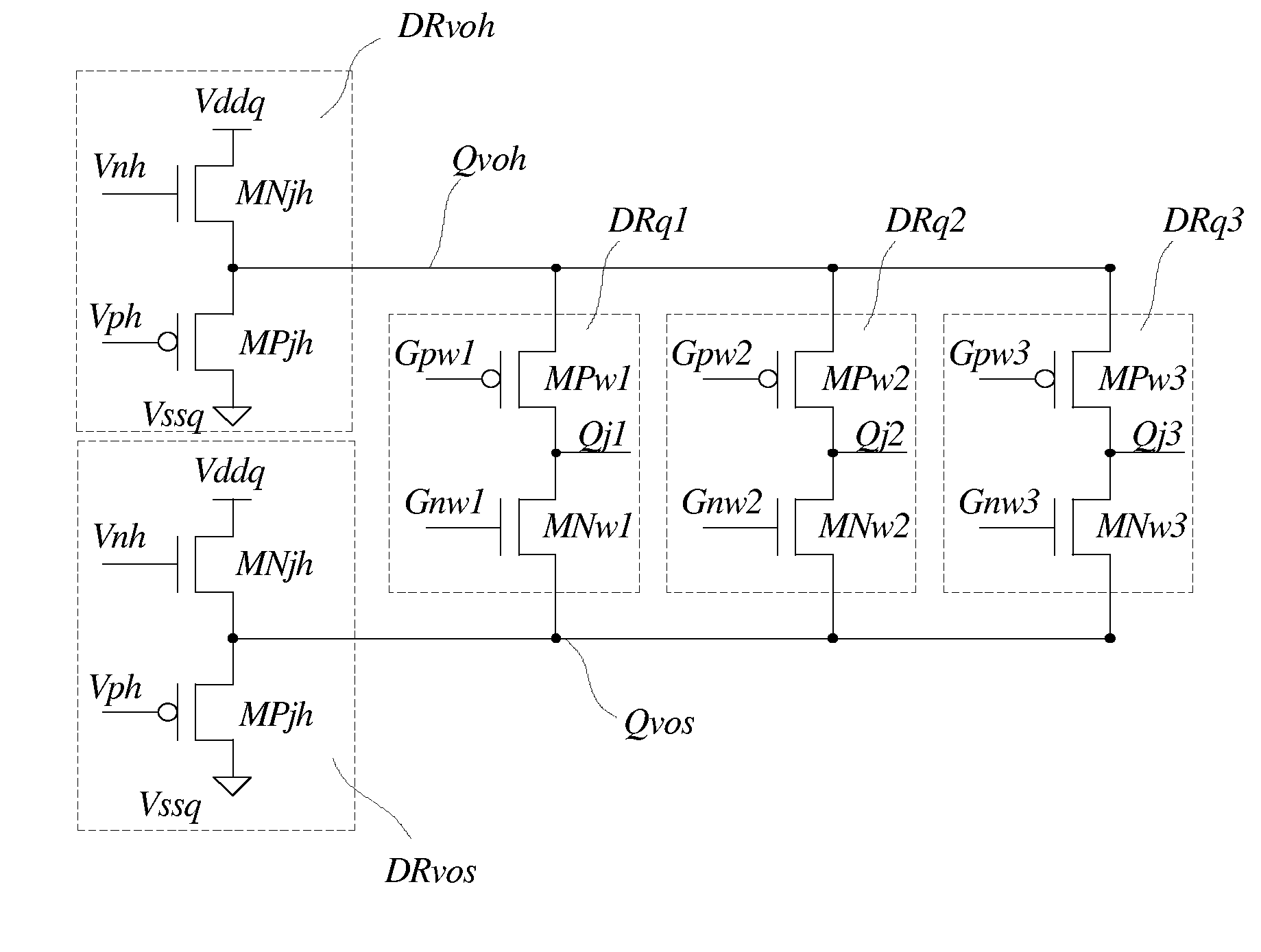

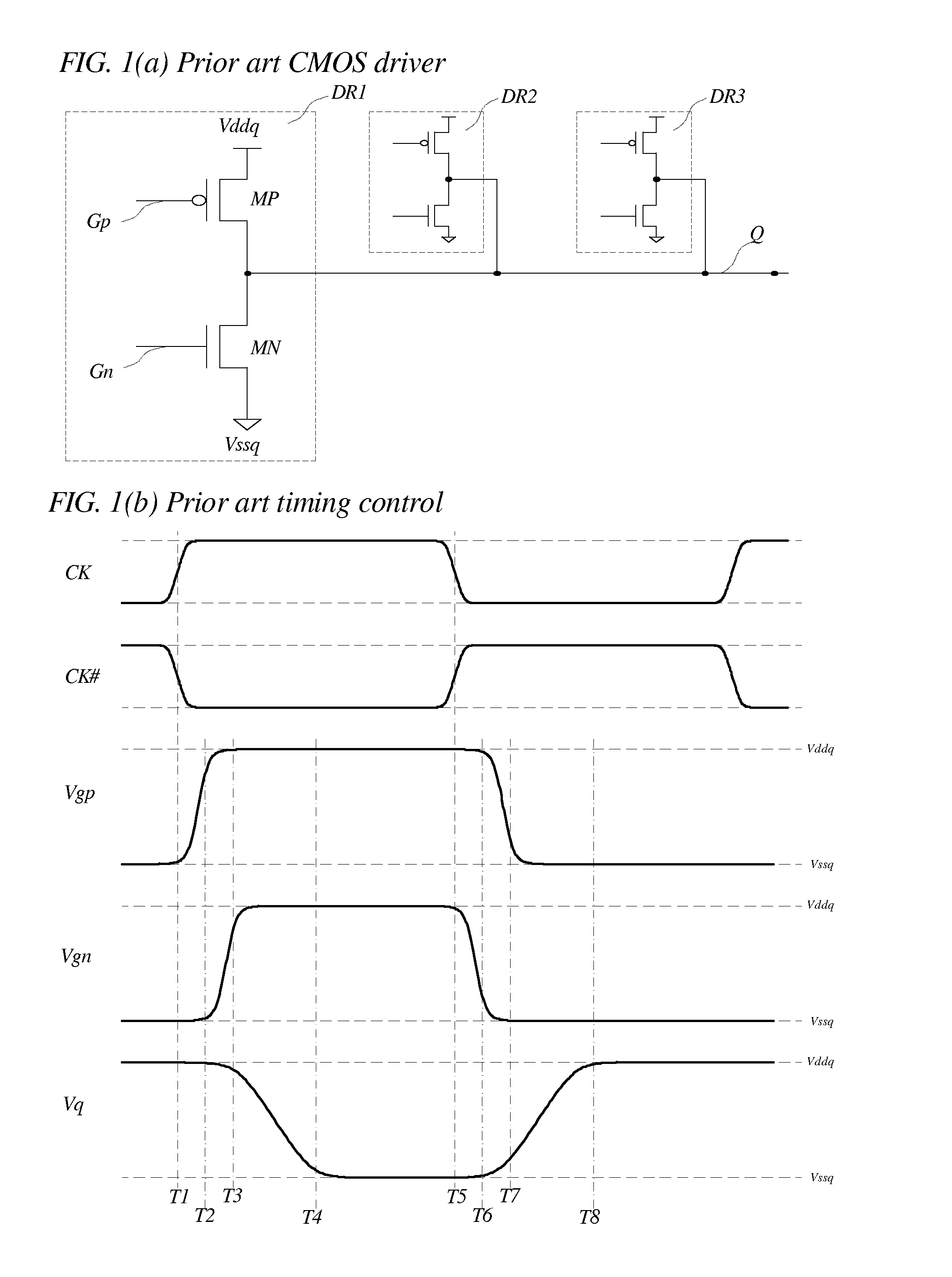

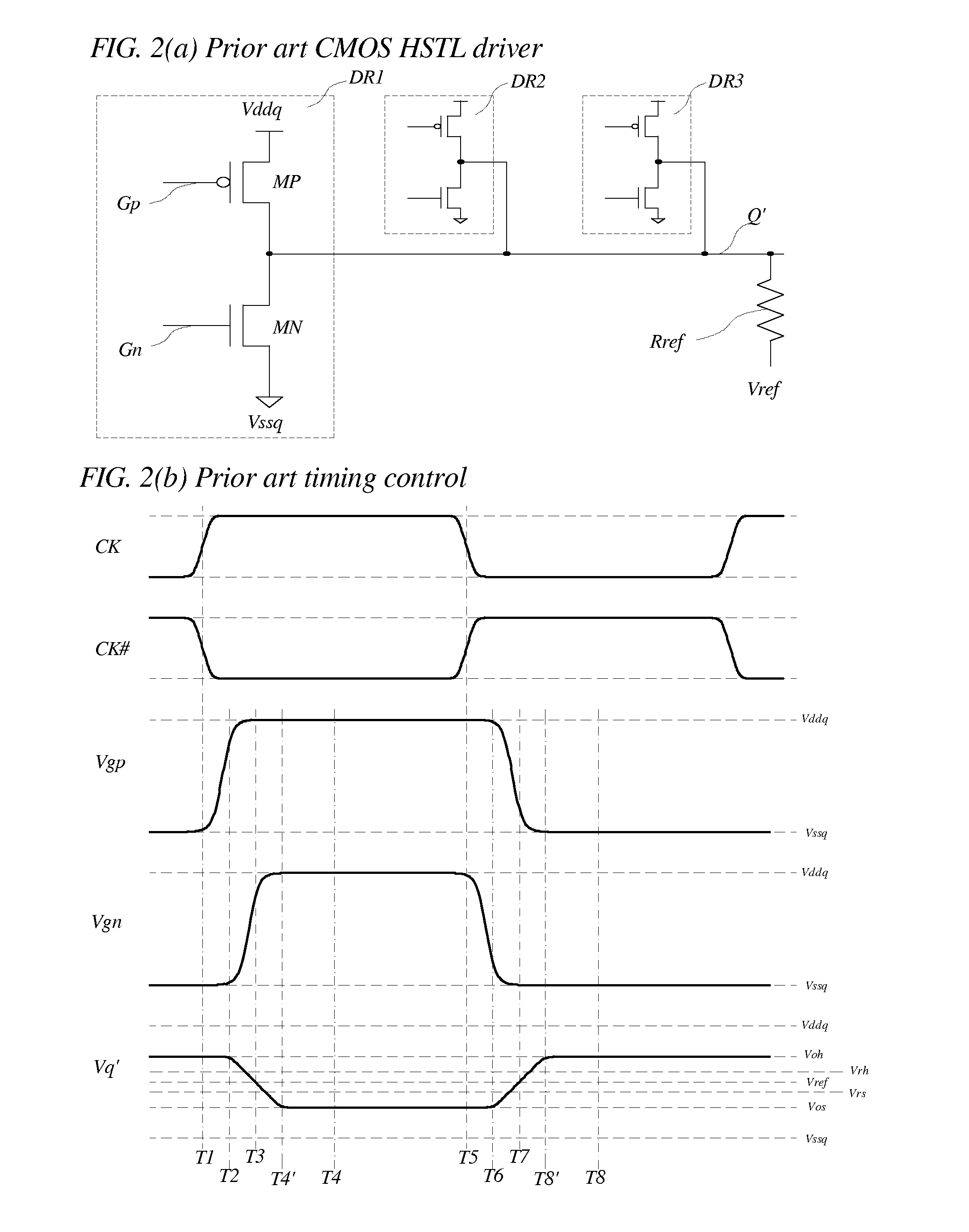

High performance low power multiple-level-switching output drivers

InactiveUS20080129348A1Less power consumptionAvoiding switching noise problemElectric pulse generatorOscillations generatorsImage resolutionEngineering

Long existing performance, noise, and power consumption problems of prior art output drivers are solved by using n-channel transistors as pull up transistors and / or p-channel transistors as pull down transistors for high performance output drivers. Output drivers of the present invention can be fully compatible with HSTL, SSTL, LVDS, MIPI, or MDDI interfaces without using termination resistors. High resolution switching applications are also made possible without consuming much power. Output drivers of the present invention provide excellent solutions to support high performance interface while consuming much lower power.

Owner:UNIRAM TECH

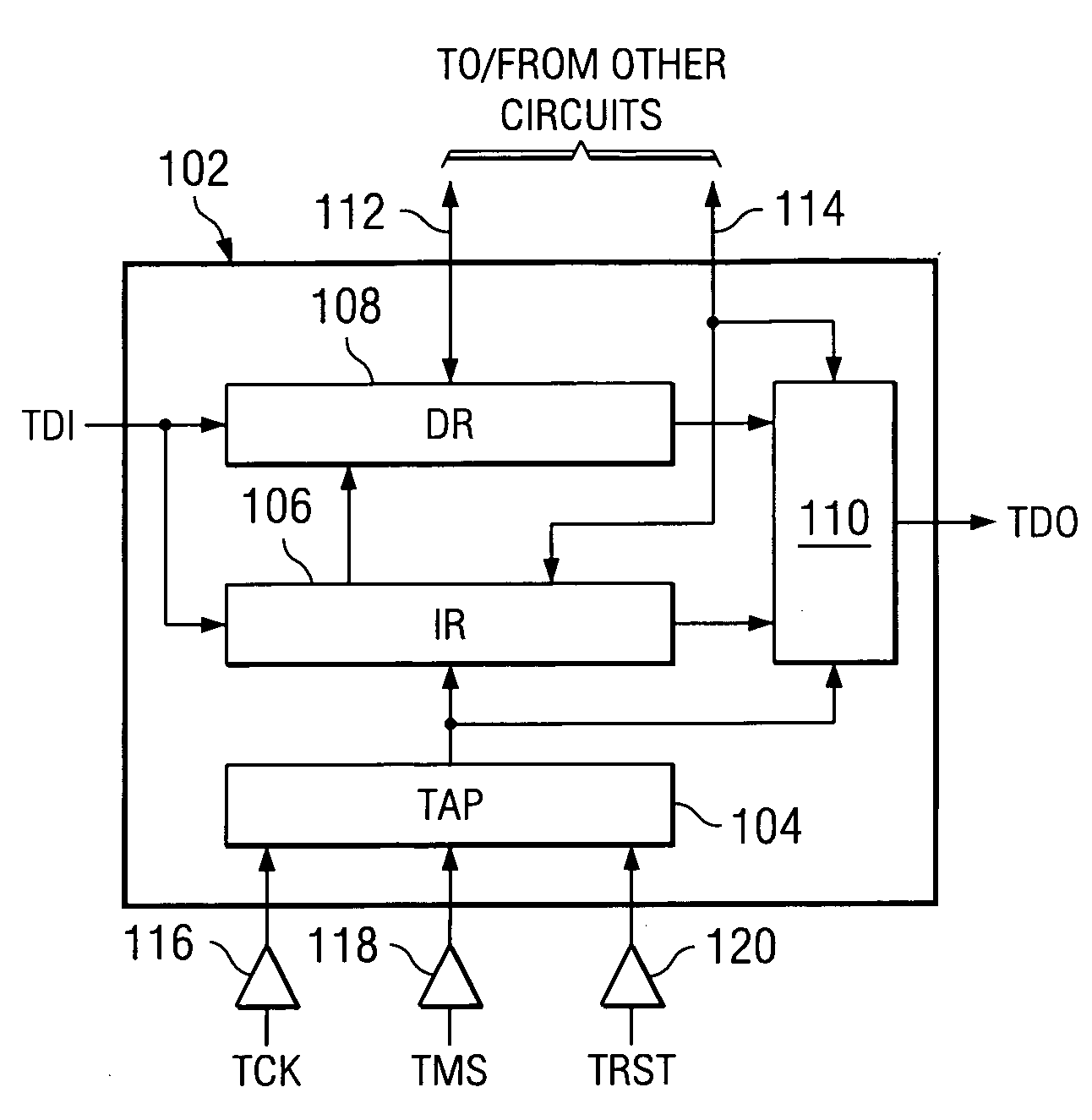

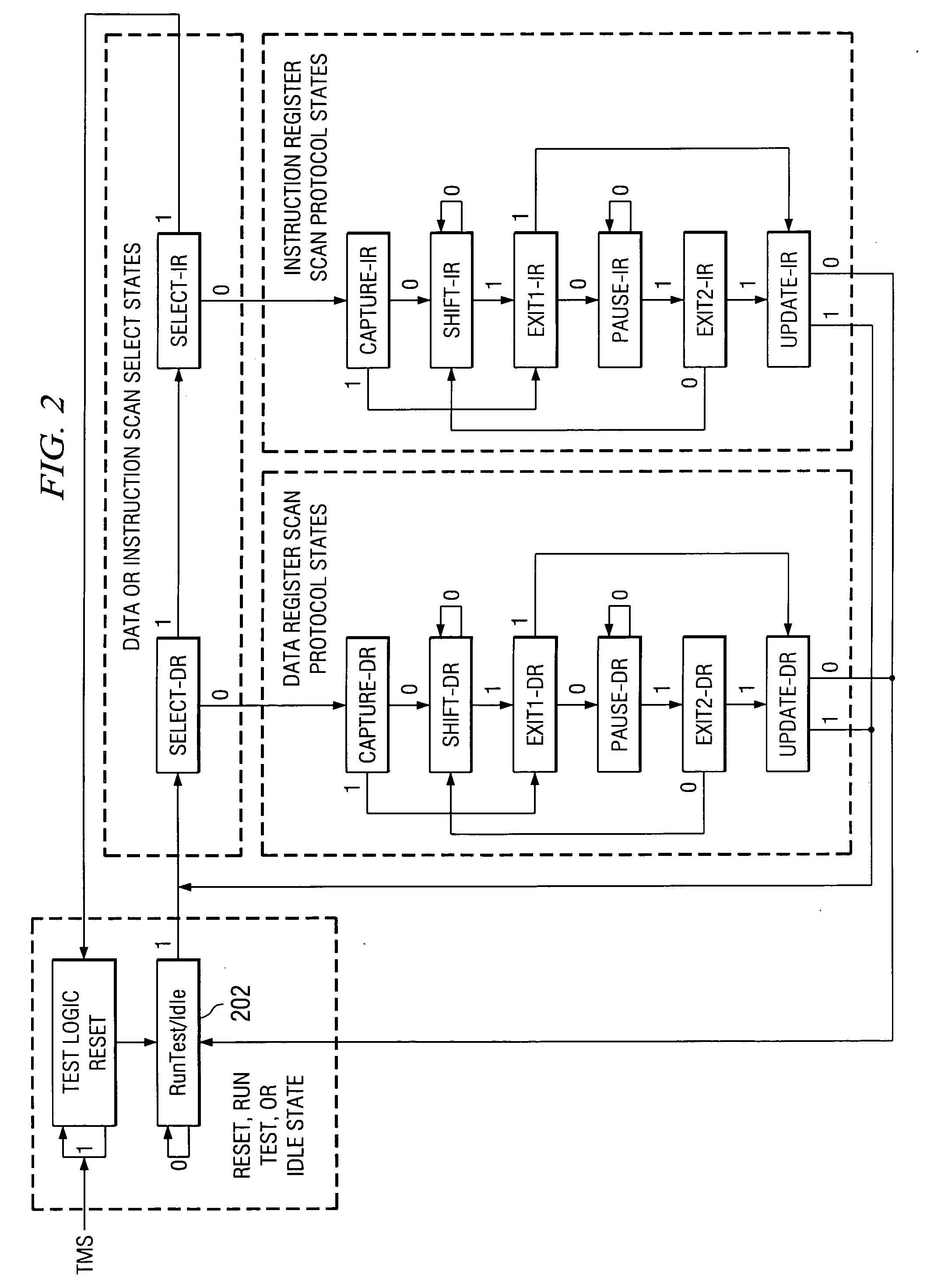

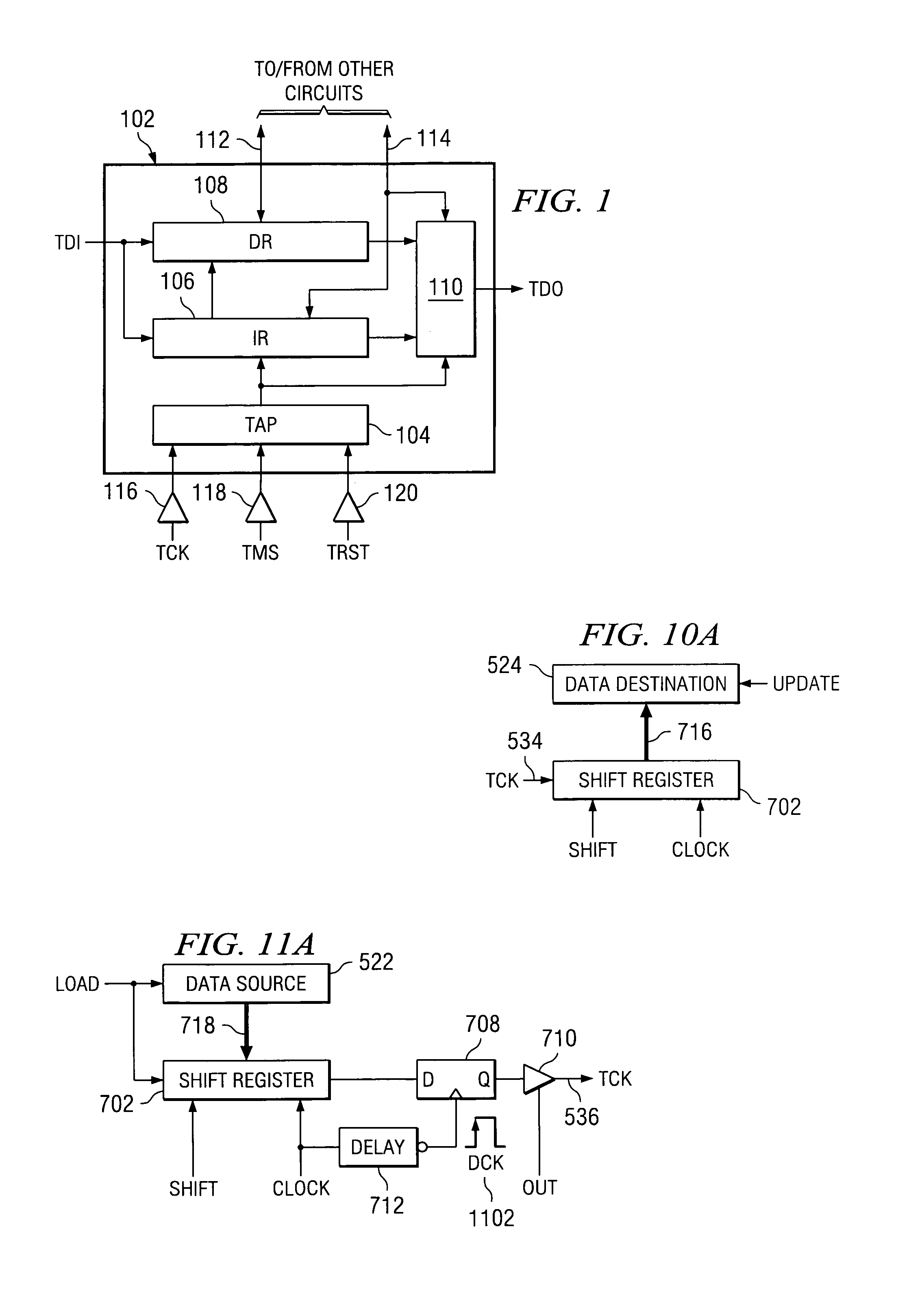

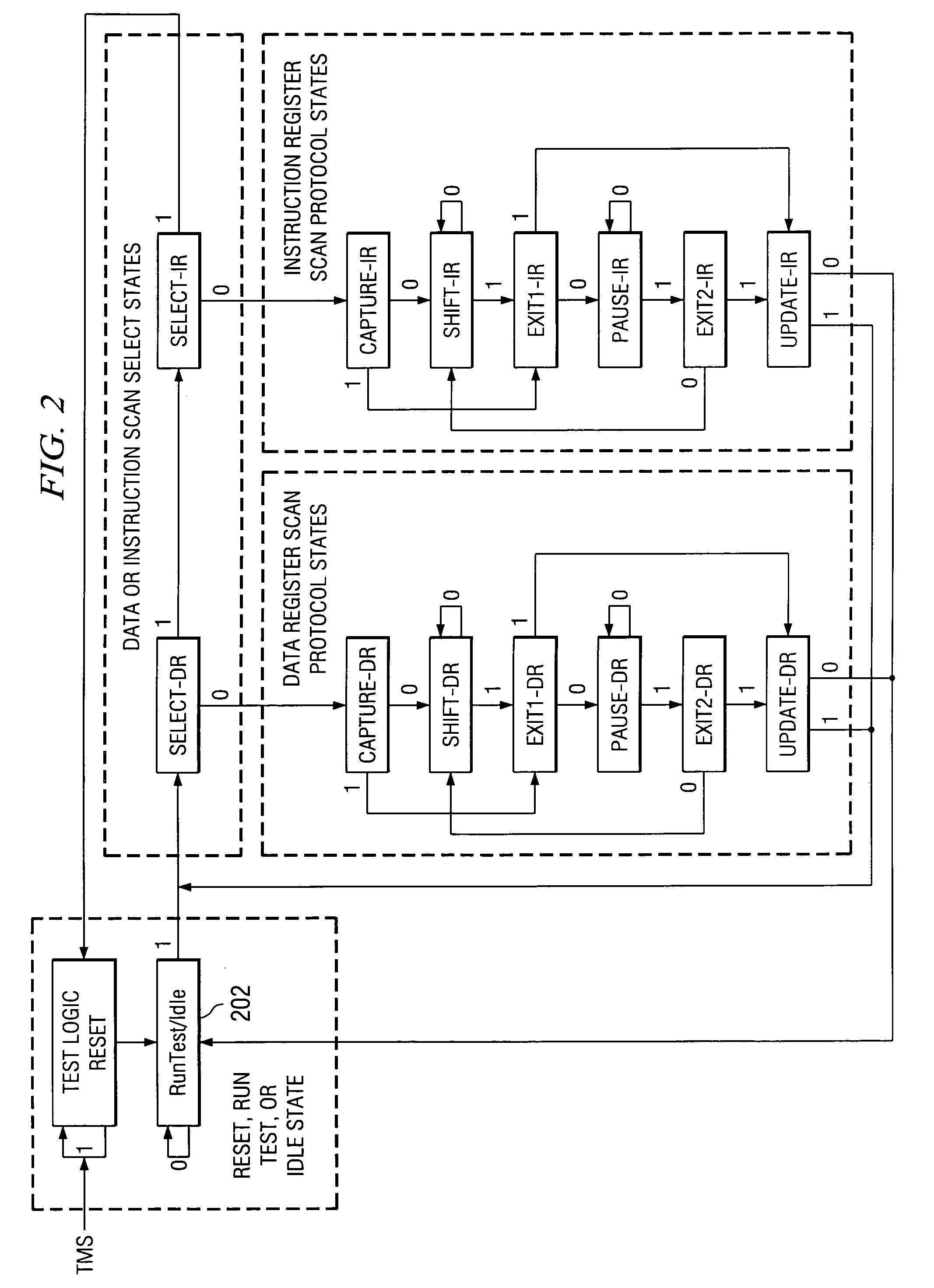

Serial I/O using JTAG TCK and TMS signals

ActiveUS20050204225A1Electronic circuit testingGenerating/distributing signalsGeneral purposeData signal

The present disclosure describes a novel method and apparatus of using the JTAG TAP's TMS and TCK terminals as a general purpose serial Input / Output (I / O) bus. According to the present disclosure, the TAP's TMS terminal is used as a clock signal and the TCK terminal is used as a bidirectional data signal to allow serial communication to occur between; (1) an IC and an external controller, (2) between a first and second IC, or (3) between a first and second core circuit within an IC.

Owner:TEXAS INSTR INC

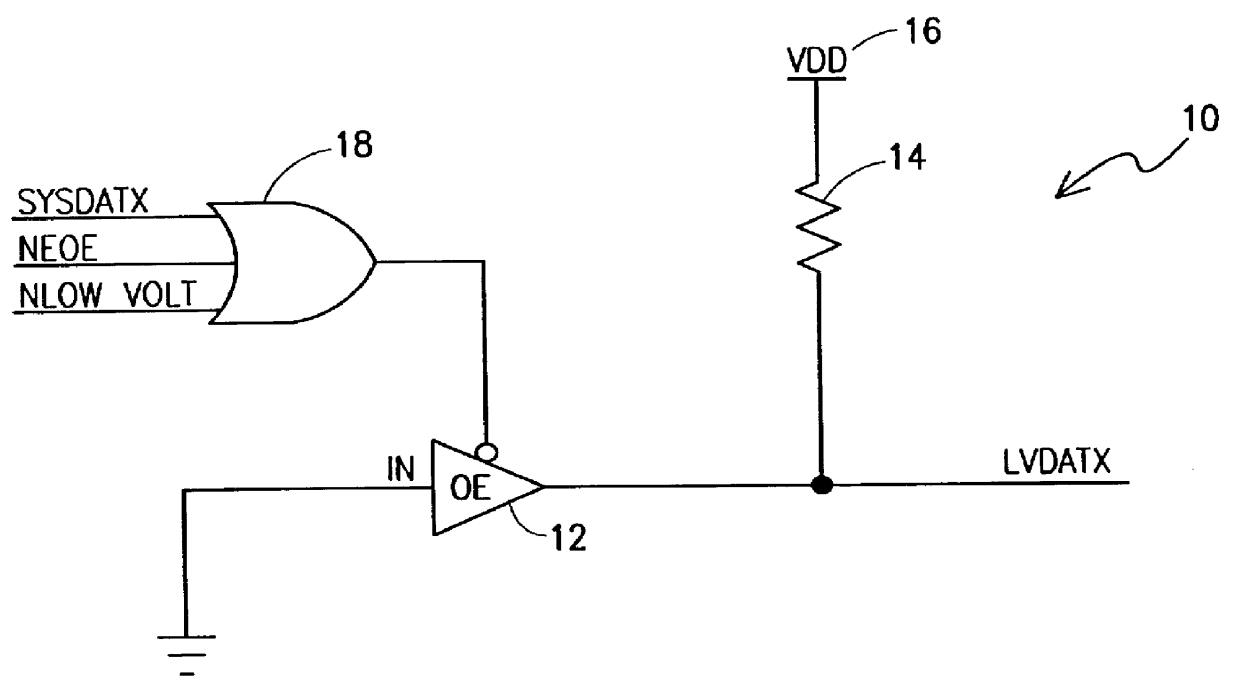

Voltage translator circuit which allows for variable low voltage signal translation

InactiveUS6160421ALogic circuits using specific componentsLogic circuit interface arrangementsVoltage converterLow voltage

A variable low voltage signal translator uses a driver for outputting a low voltage signal translation. A control circuit is coupled to the driver for enabling and disabling the driver wherein the control circuit has an input coupled to the signal to be translated. One terminal of the pull-up resistor is coupled to an output of the driver. A second terminal of the pull-up resistor is coupled to a voltage supply which provides the low voltage level of the variable low voltage signal translator.

Owner:MICROCHIP TECH INC

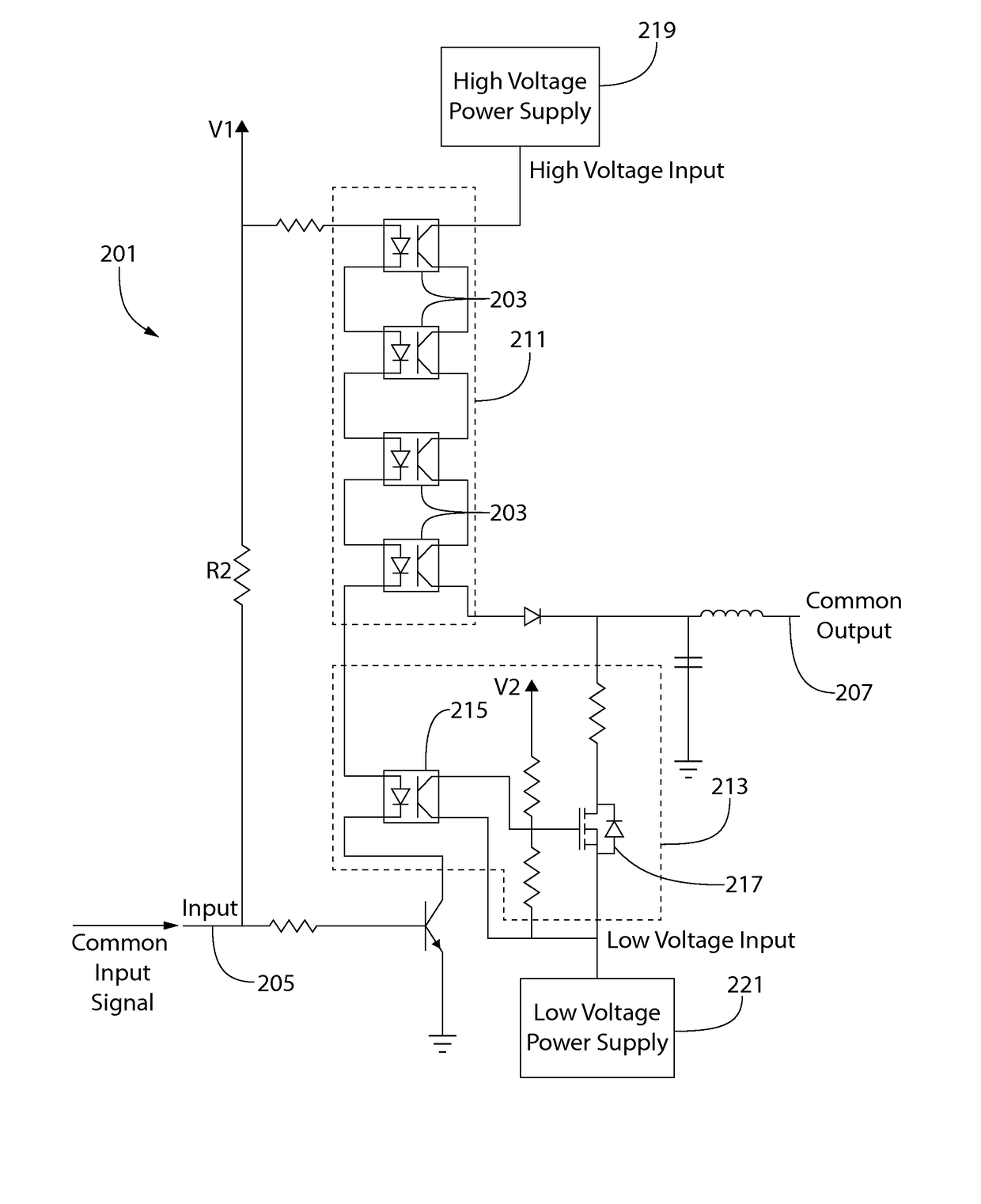

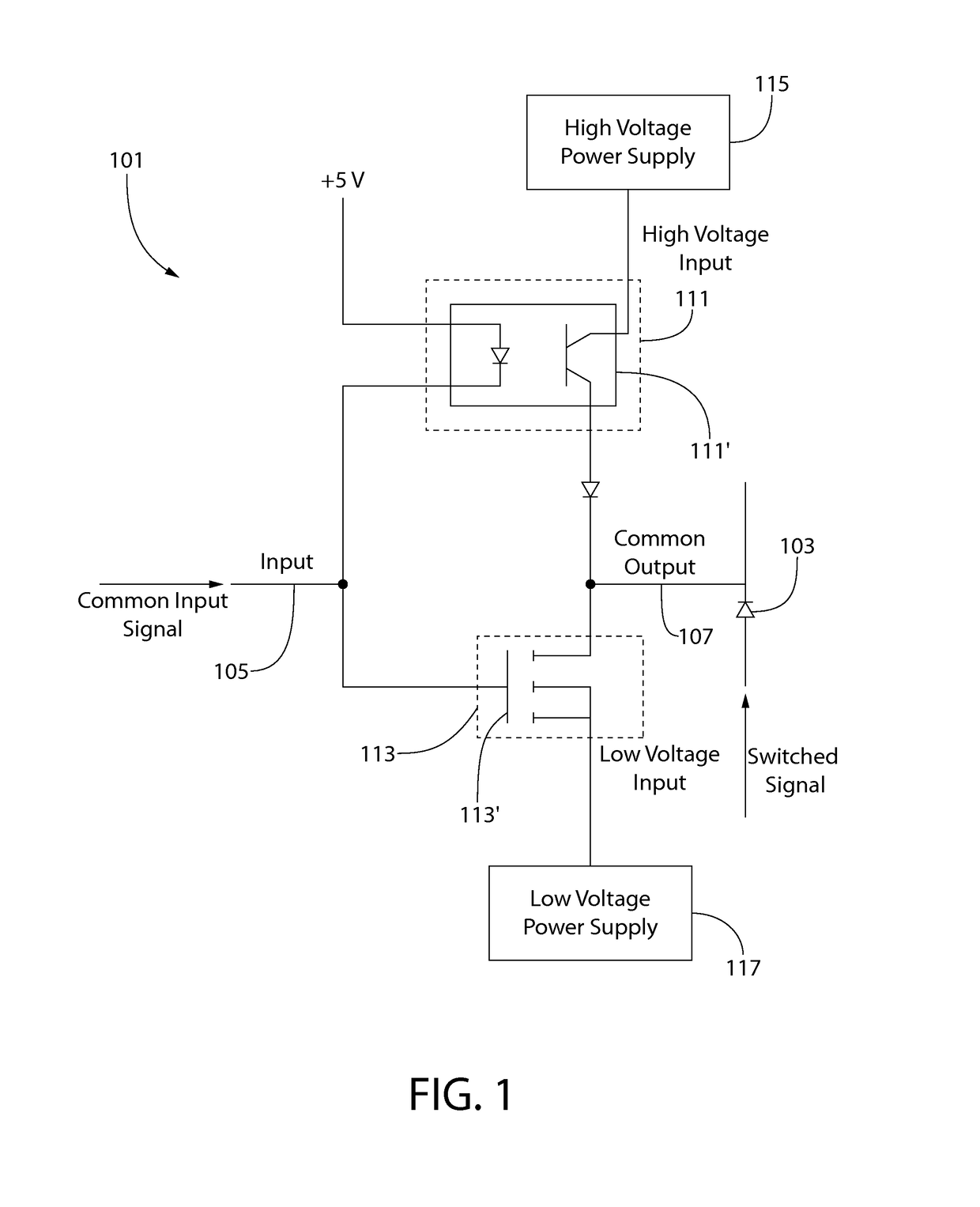

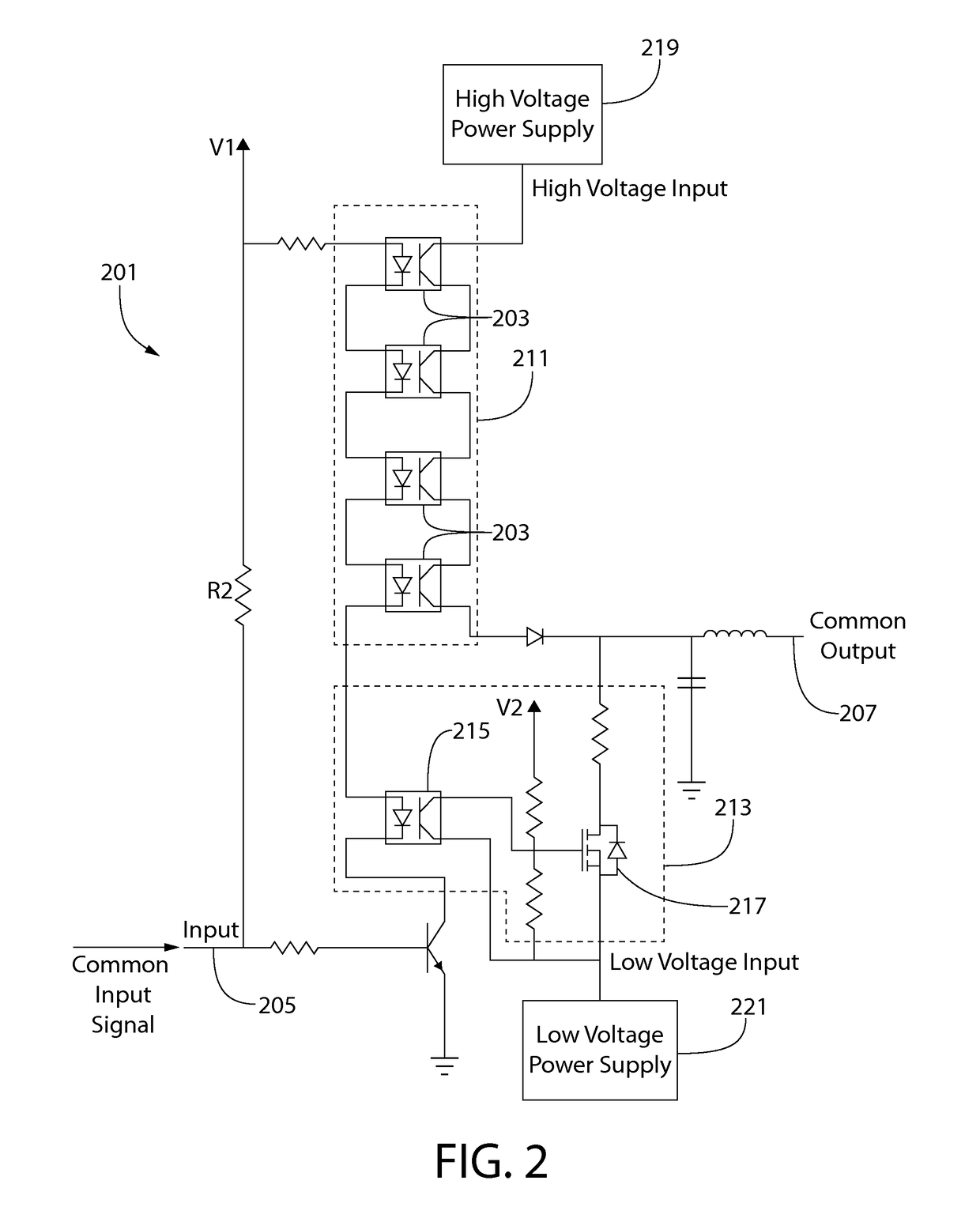

High speed high voltage switching circuit

ActiveUS9755641B1Logic circuit coupling arrangementsElectronic switchingPower switchingElectronic switch

A control circuit for an electronic switch includes a first power switch receiving a common input signal and a first voltage input and a second power switch receiving the common input signal and a second voltage input. The first and second power switches switchably connect the first voltage input and the second voltage input, respectively, to a common output in response to the common input signal. The second voltage input is opposite in polarity to the first voltage input, and the first power switch and the second power switch are configured to asynchronously connect the first voltage input and the second voltage input, respectively, to the common output in response to the common input signal, the electronic switch being switched according to the first voltage input or the second voltage input being connected to the common output.

Owner:RENO TECH

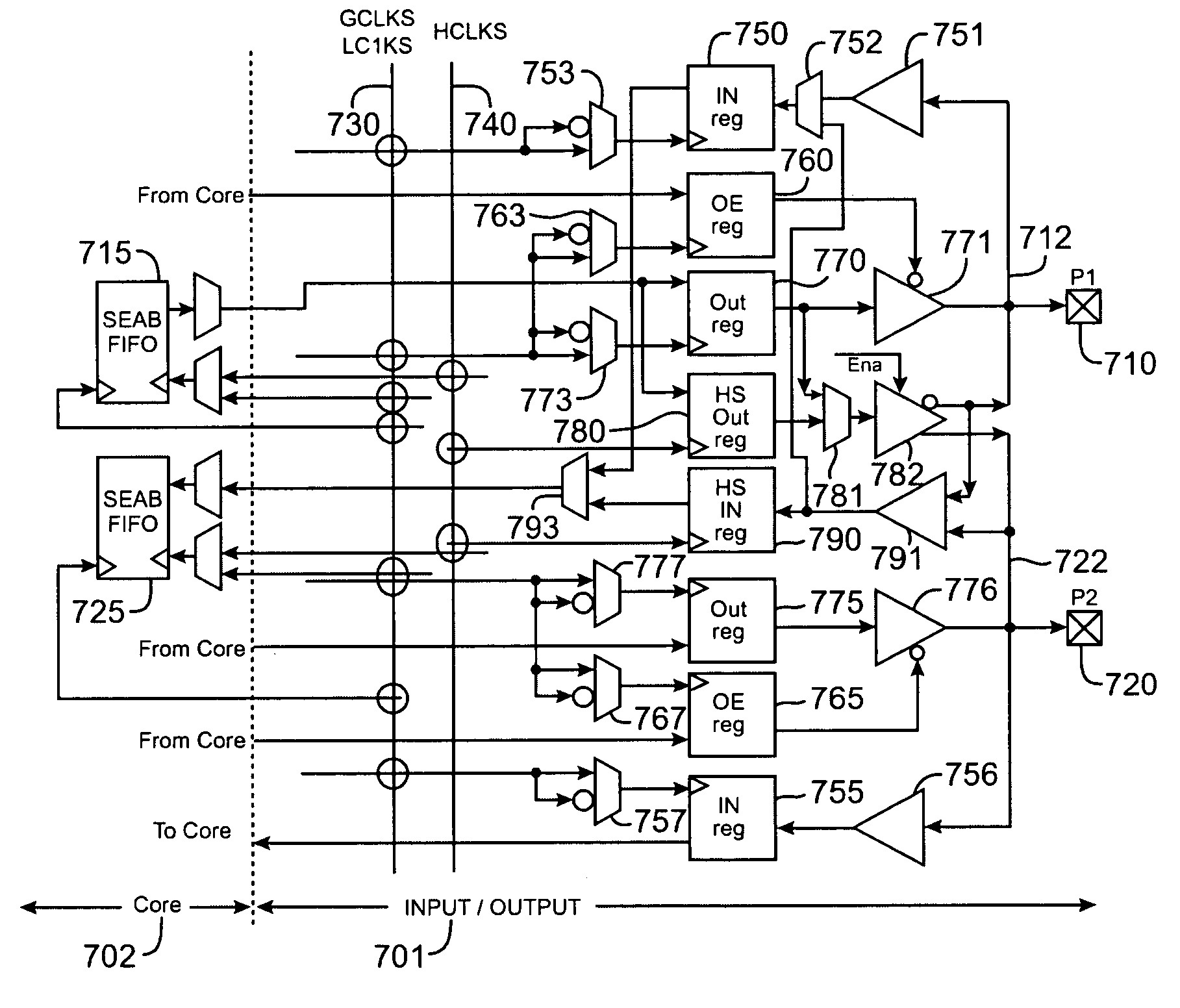

Programmable high speed I/O interface

InactiveUS7116135B2High-speed inputHigh-speed outputProgrammable logic circuit arrangementsElectric pulse generatorBoundary testingLow speed

Methods and apparatus for providing either high-speed, or lower-speed, flexible inputs and outputs. An input and output structure having a high-speed input, a high-speed output, a low or moderate speed input, and an low or moderate speed output is provided. One of the input and output circuits are selected and the others are deselected. The high-speed input and output circuits are comparatively simple, in one example having only a clear signal for a control line input, and are able to interface to lower speed circuitry inside the core of an integrated circuit. The low or moderate speed input and output circuits are more flexible, for example, having preset, enable, and clear as control line inputs, and are able to support JTAG boundary testing. These parallel high and lower speed circuits are user selectable such that the input output structure is optimized between speed and functionality depending on the requirements of the application.

Owner:ALTERA CORP

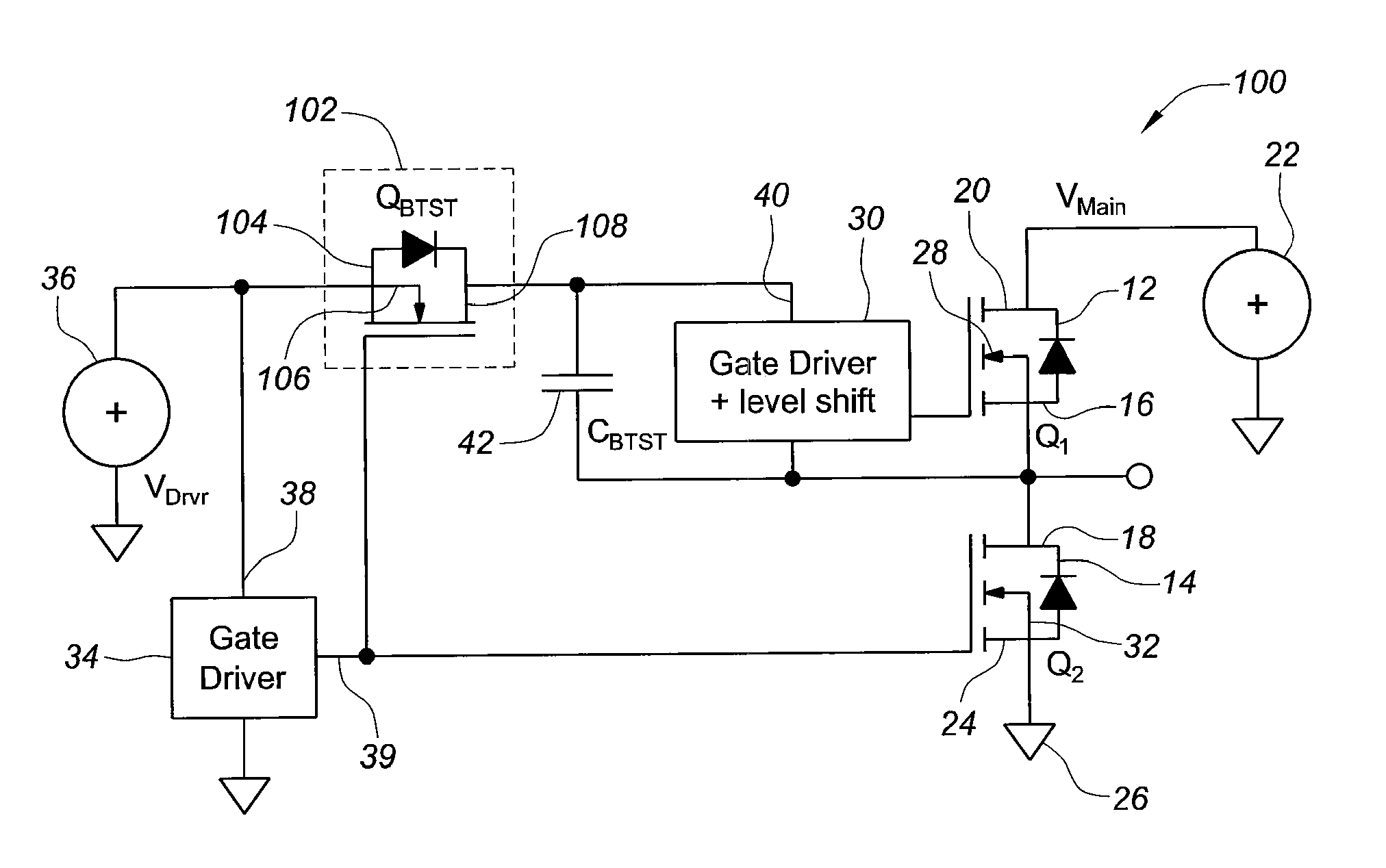

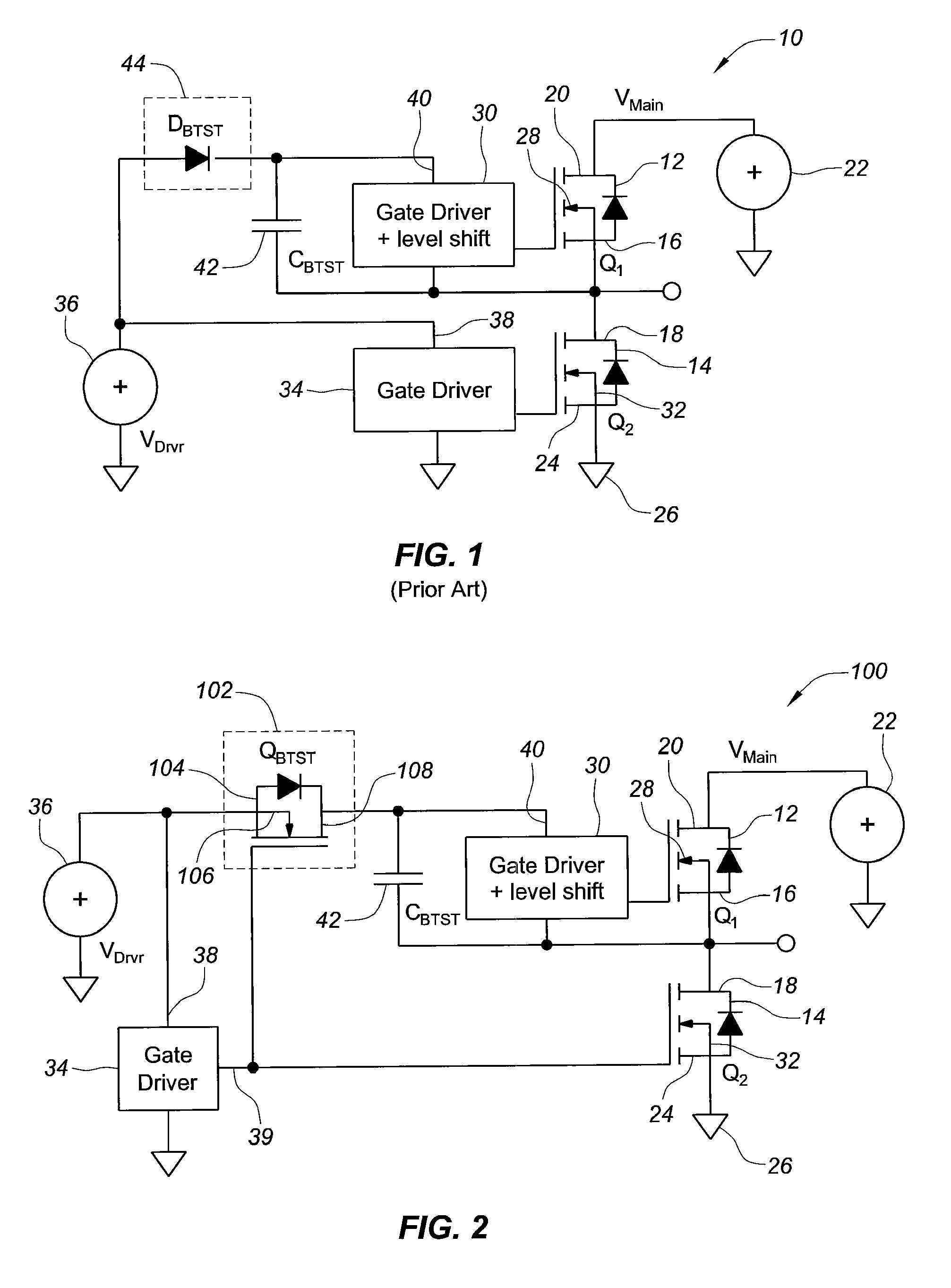

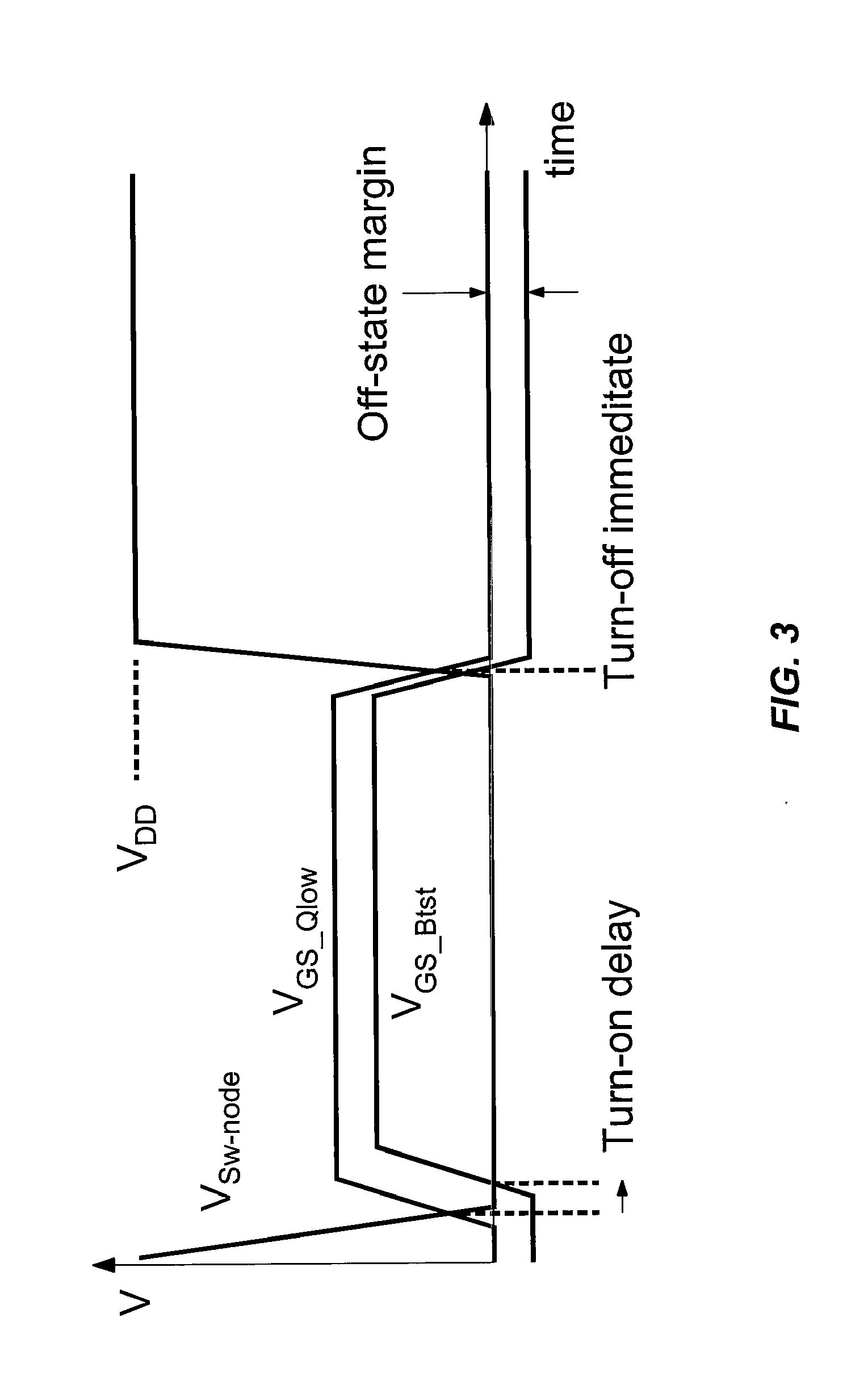

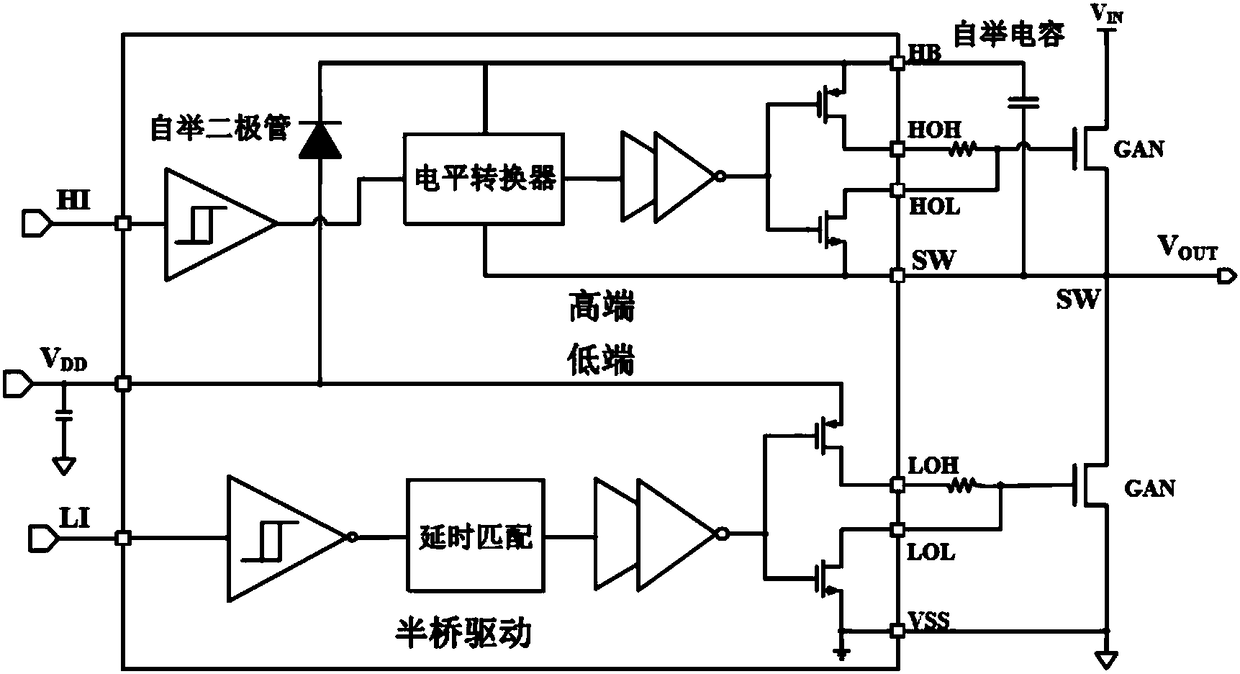

High voltage zero qrr bootstrap supply

ActiveUS20160105173A1Improve switching performanceReduce lossesTransistorElectronic switchingEngineeringVoltage source

An electrical circuit arranged in a half bridge topology. The electrical circuit includes a high side transistor; a low side transistor; a gate driver and level shifter electrically coupled to a gate of the high side transistor; a gate driver electrically coupled to a gate of the low side transistor; a capacitor electrically coupled in parallel with the gate driver and level shifter; a voltage source electrically coupled to an input of the gate driver and level shifter and an input of the gate driver; and, a bootstrap transistor electrically coupled between the voltage source and the capacitor. A GaN field-effect transistor is synchronously switched with a low side device of the half bridge circuit.

Owner:EFFICIENT POWER CONVERSION CORP

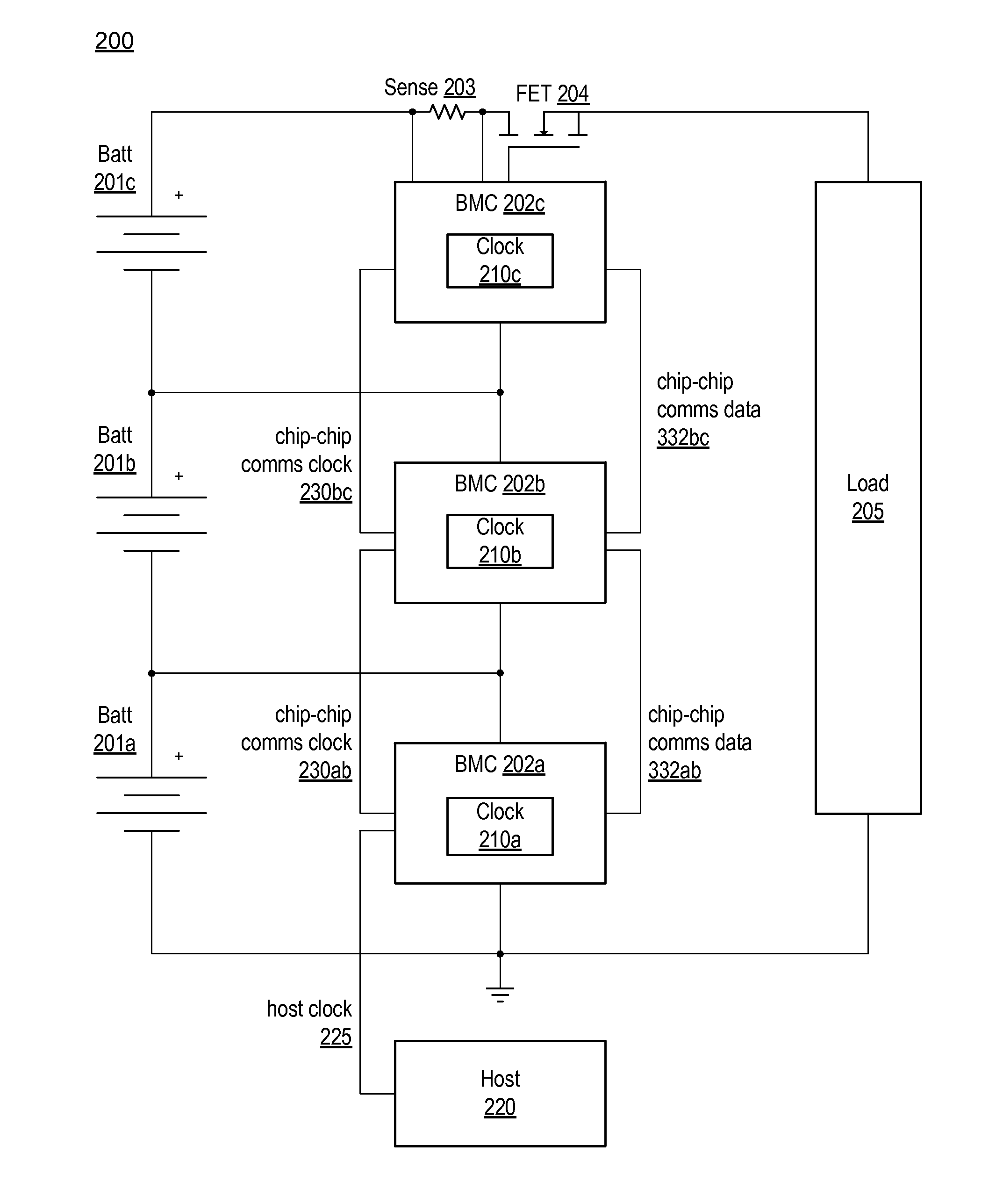

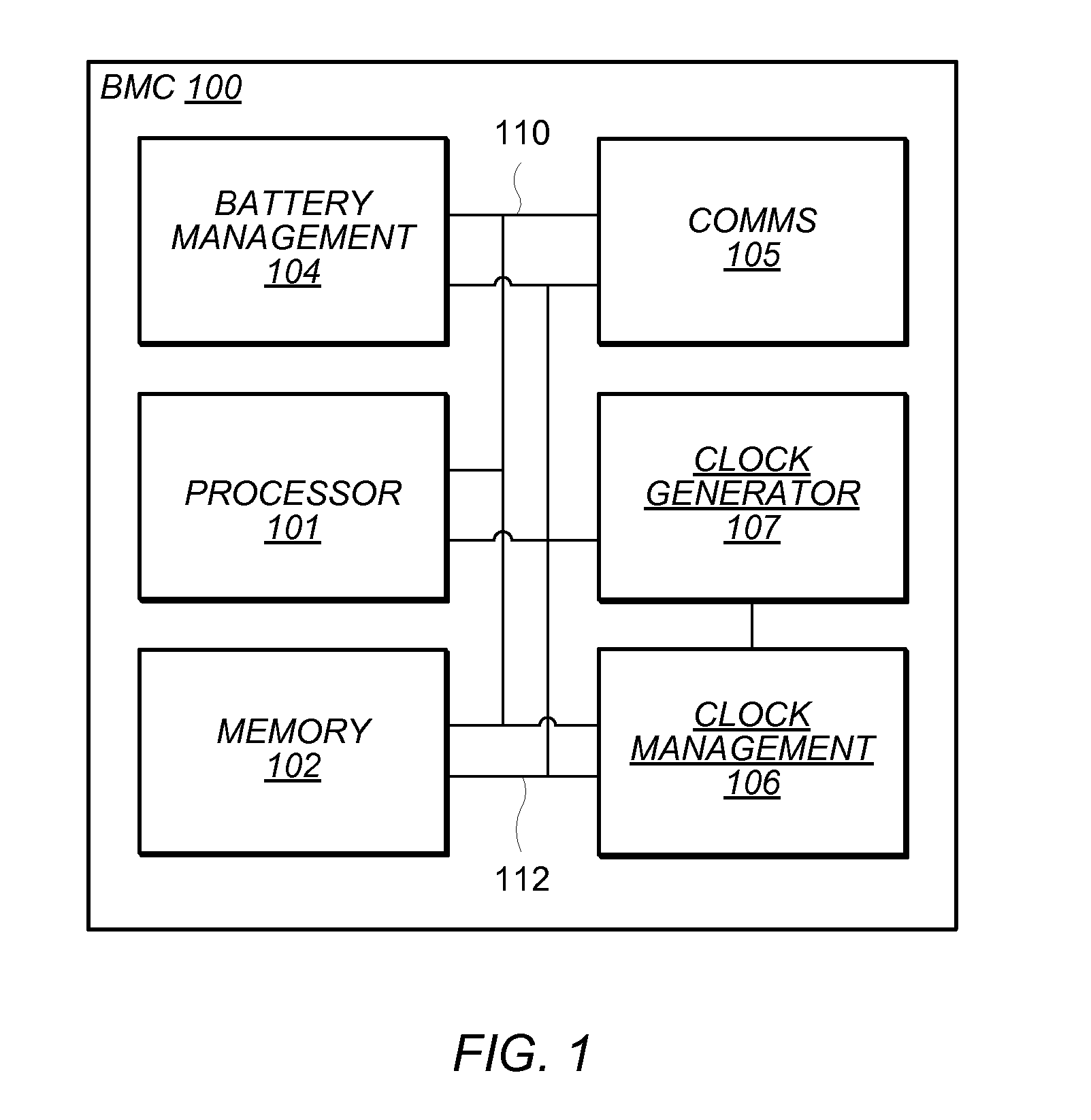

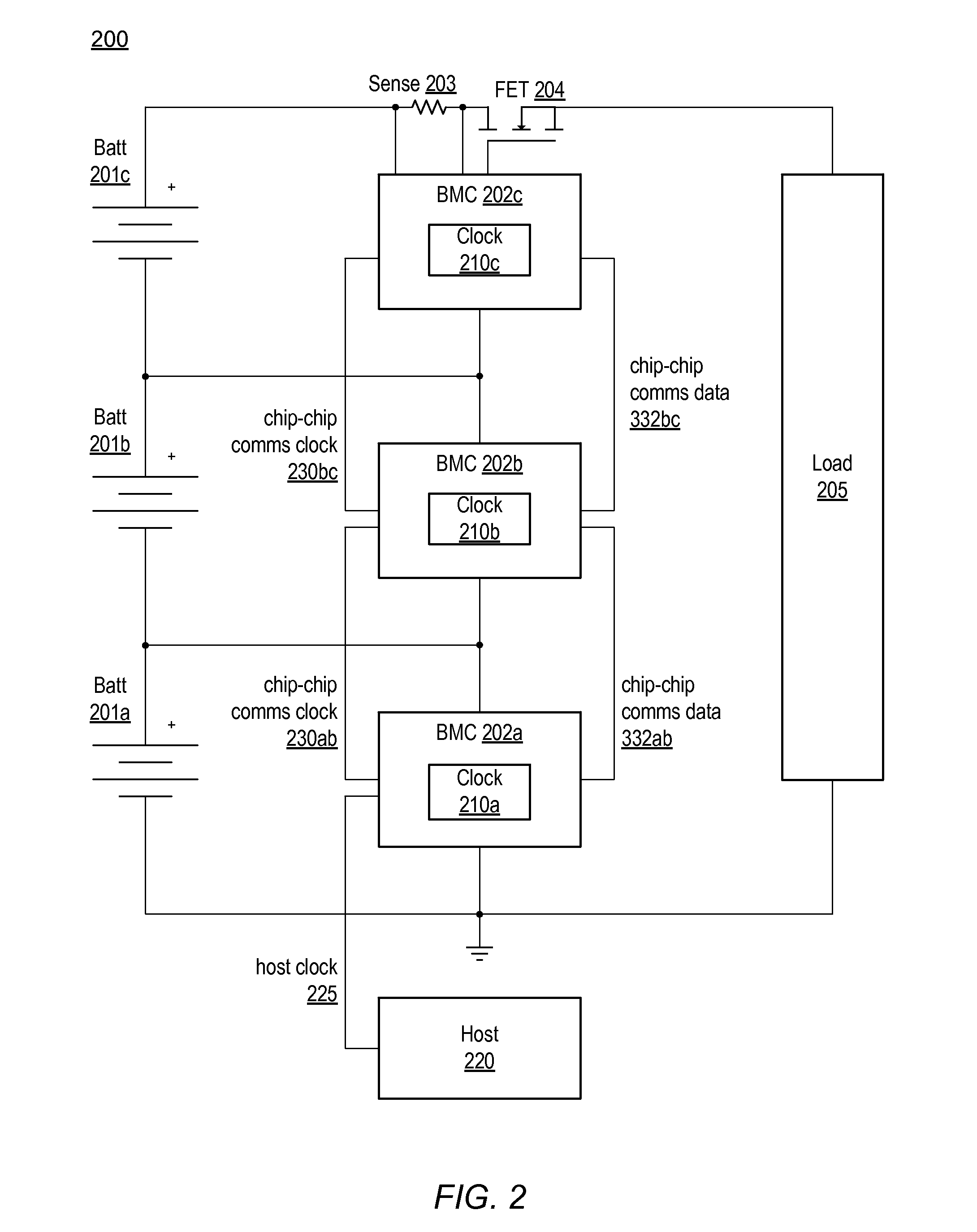

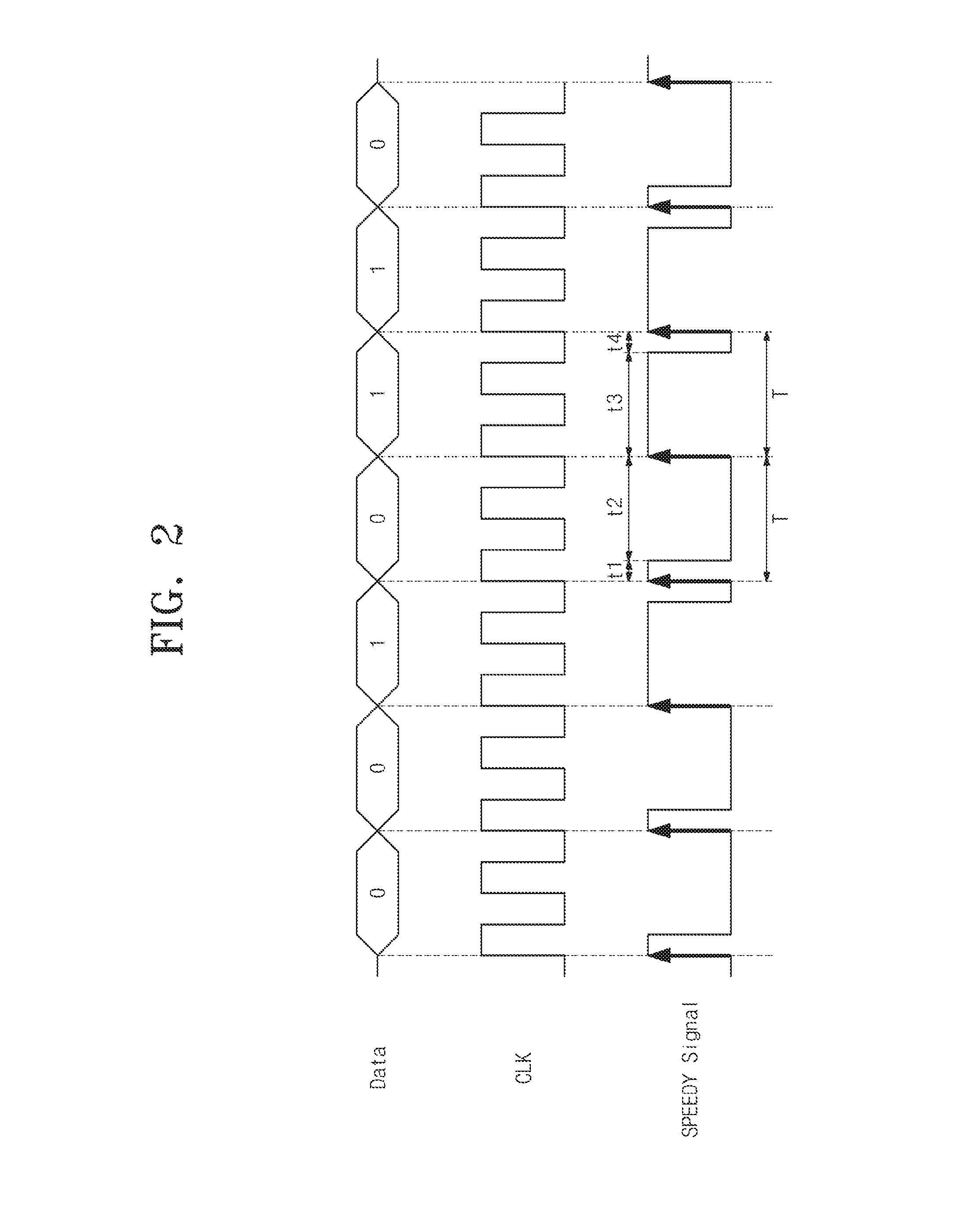

Method for clock calibration

A system may include a plurality of devices, wherein each device of the plurality of devices has a respective clock source. A first device of the plurality of devices may be configured to generate a first clock signal. A second device of the plurality of devices may be configured to generate a second clock signal, receive the first clock signal from the first device, and modify a first frequency of the first clock signal. The second device may be further configured to adjust a second frequency of the second clock signal dependent upon the modified first frequency of the first clock signal.

Owner:APPLE INC

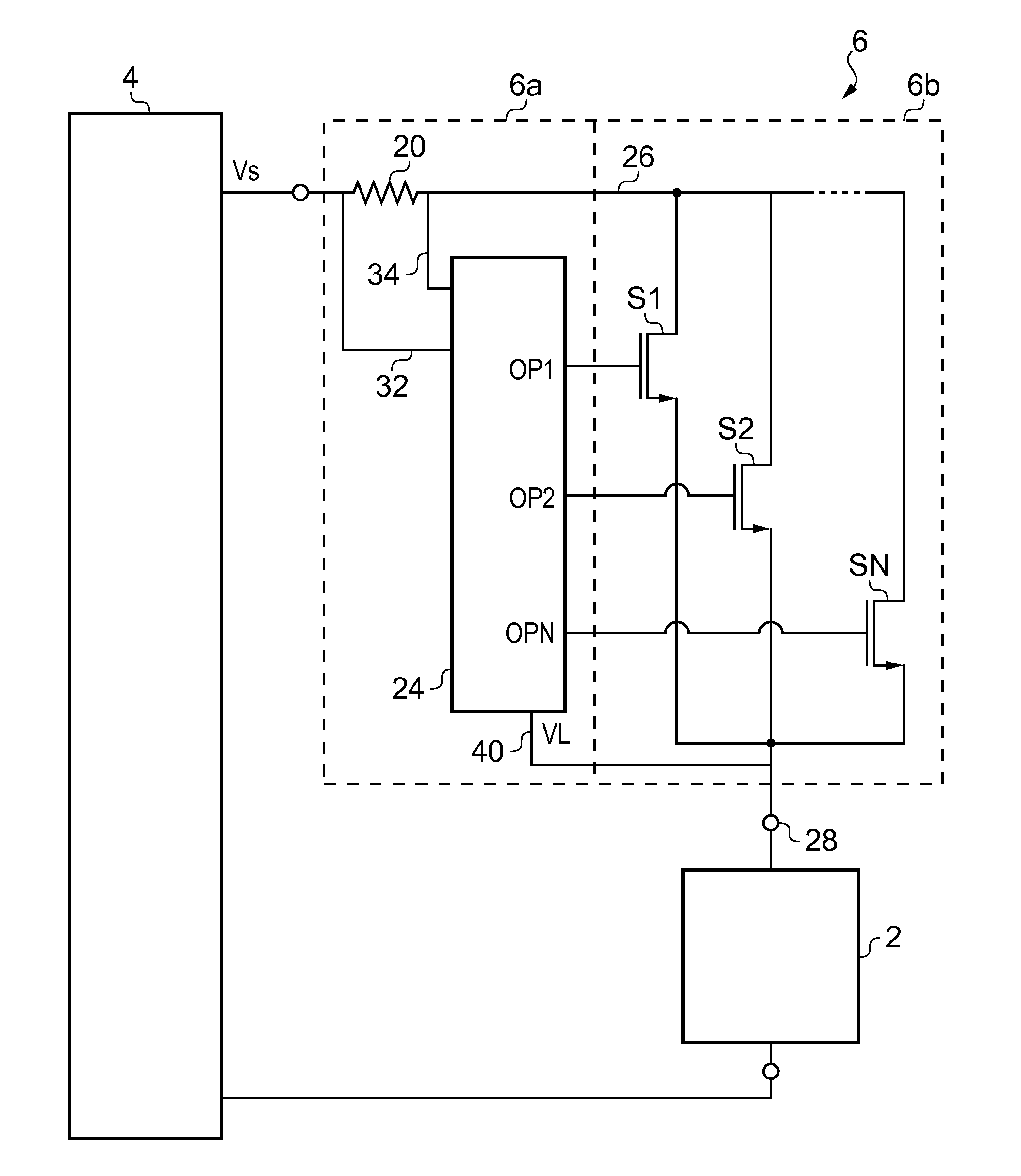

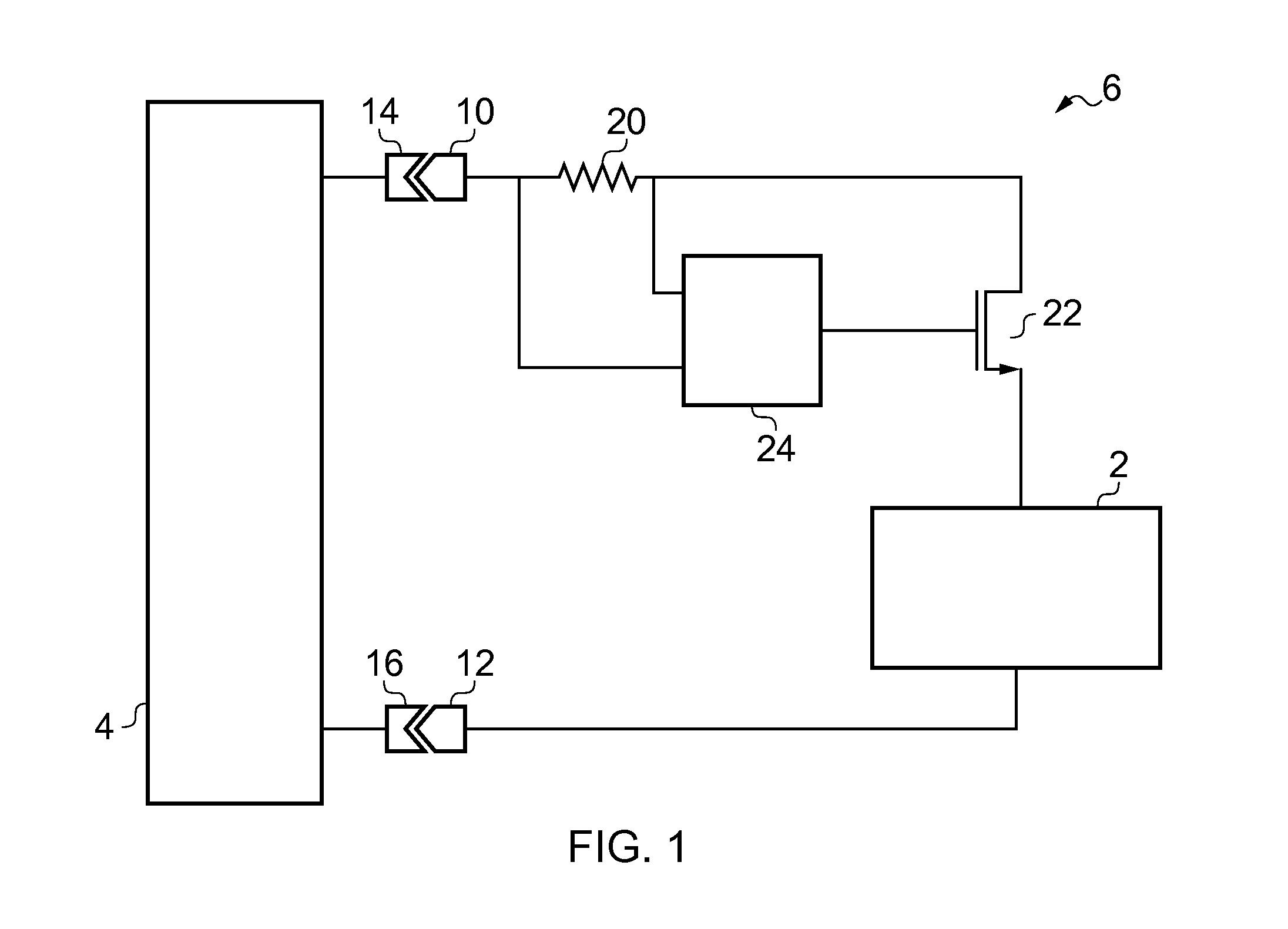

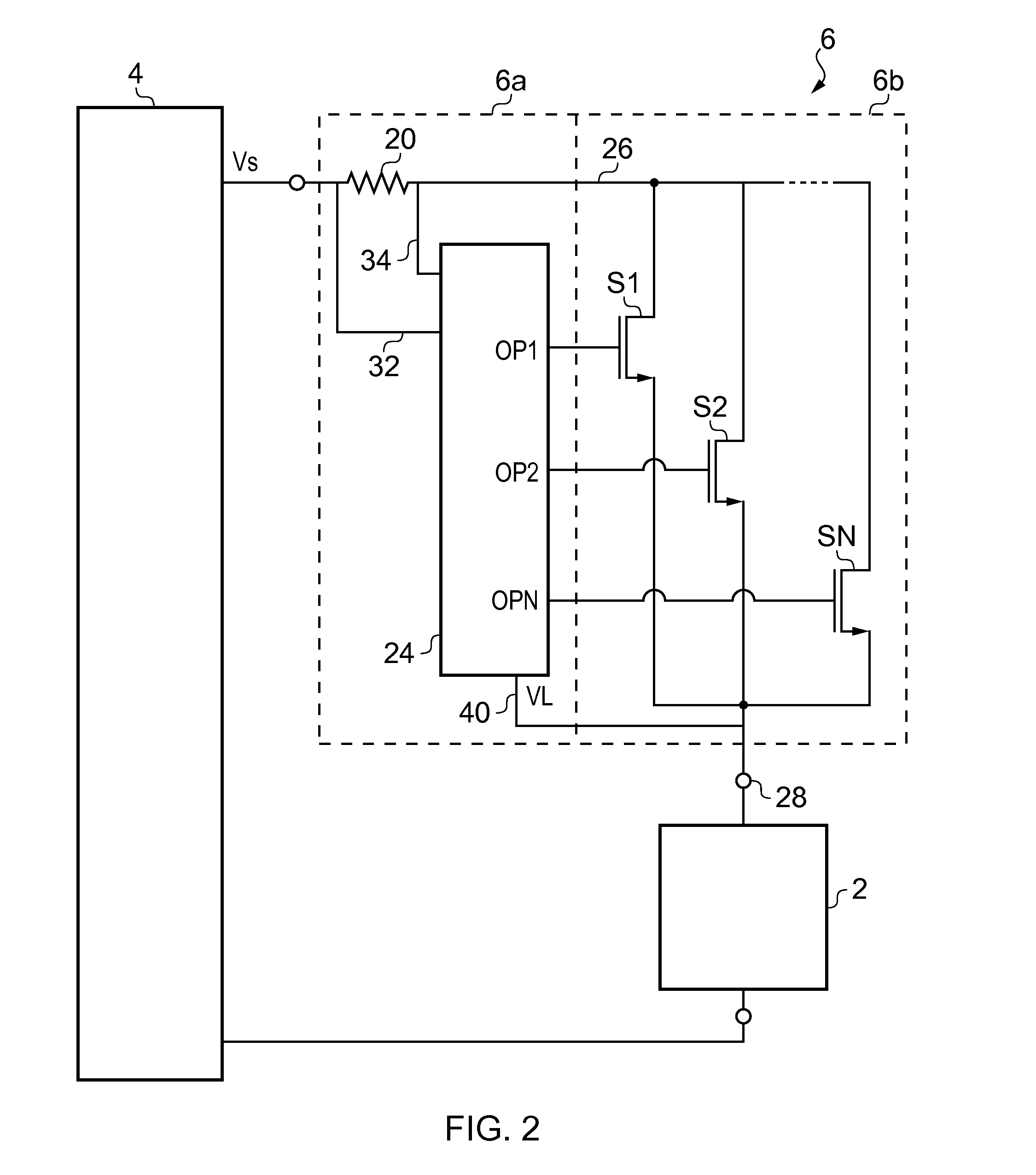

Connection device

ActiveUS20130088278A1Low drain to source resistancePerform less-wellTransistorElectronic switchingElectrical and Electronics engineeringEngineering

Owner:ANALOG DEVICES INC

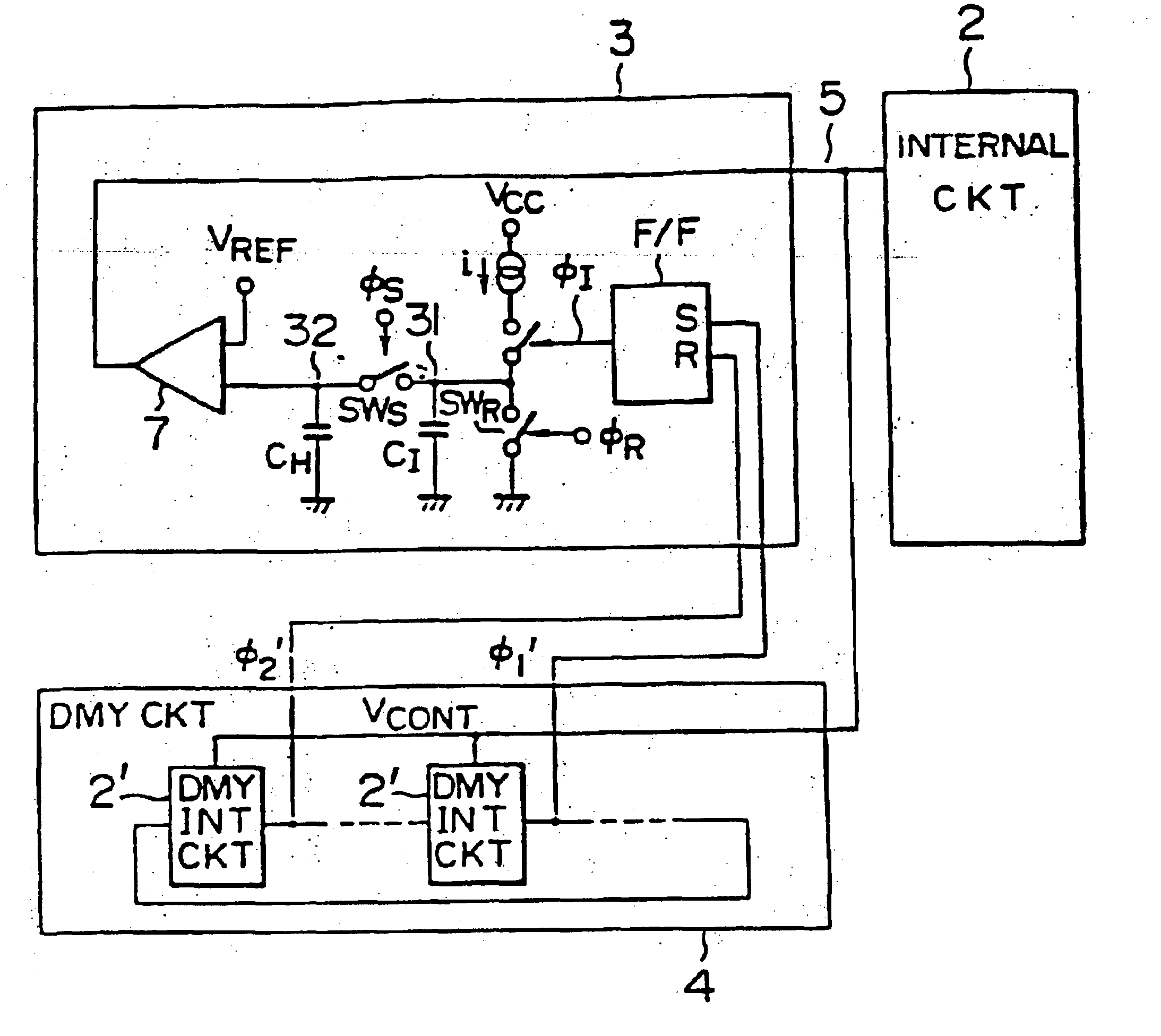

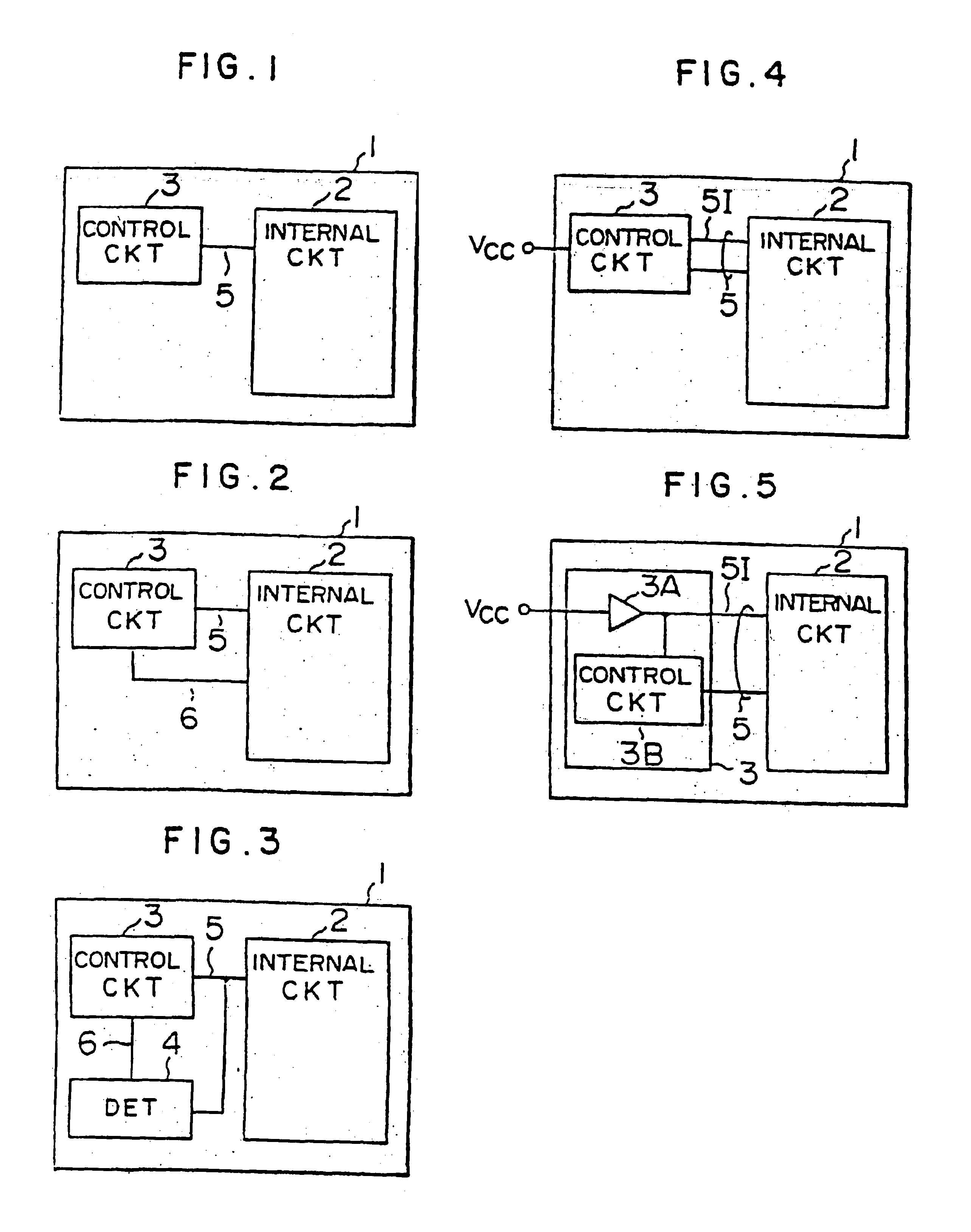

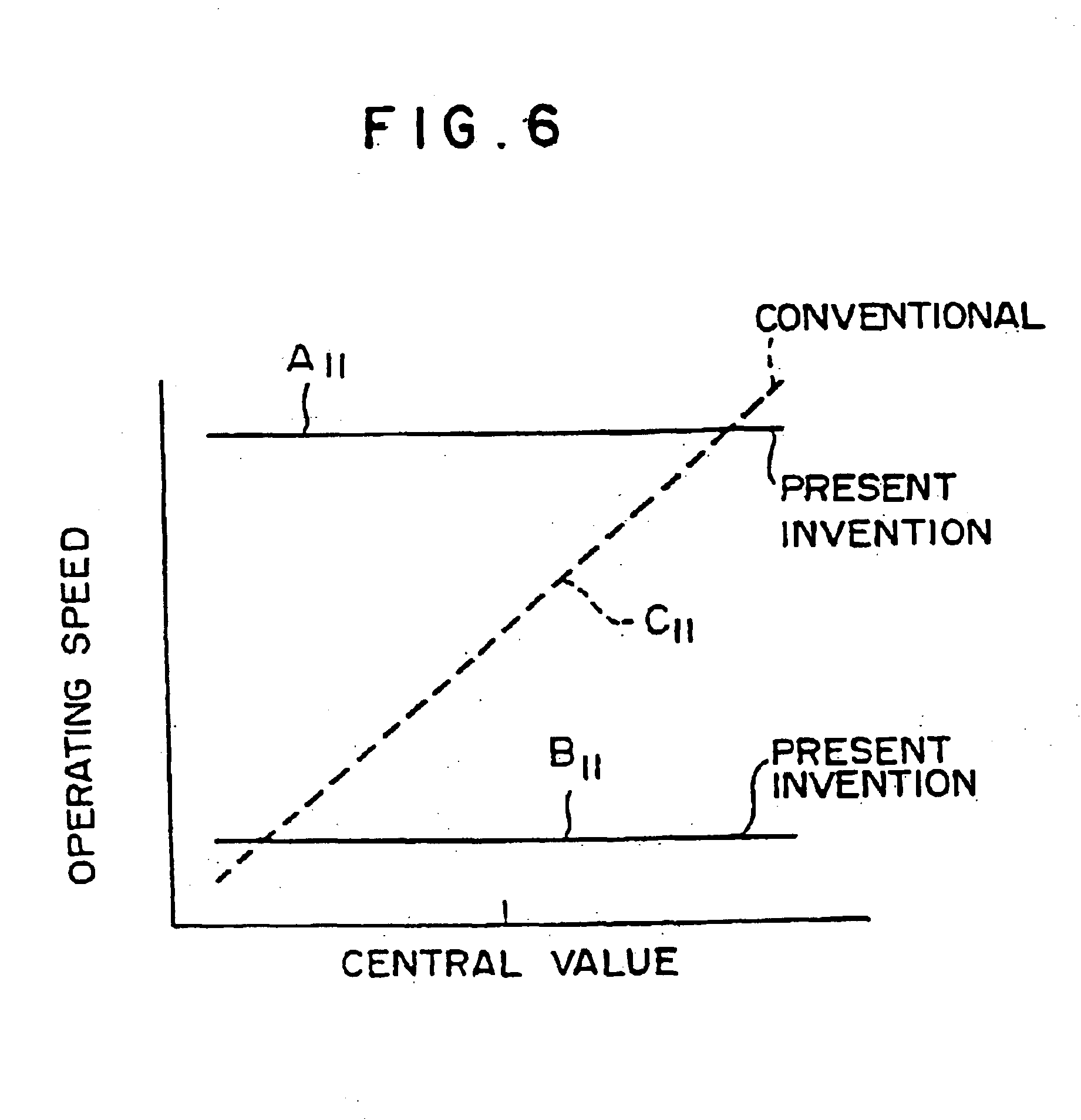

Semiconductor device incorporating internal power supply for compensating for deviation in operating condition and fabrication process conditions

InactiveUS6970391B2Improve stabilityImprove reliabilitySwitching accelaration modificationsReliability increasing modificationsPower semiconductor deviceSemiconductor chip

A semiconductor integrated circuit comprises a semiconductor chip, a power supply terminal provided on the semiconductor chip for receiving a voltage from an external power supply source, an internal circuit provided on the semiconductor chip, a power supply circuit provided on the semiconductor chip for transforming an external power supply voltage received from the power supply terminal for supplying a source voltage resulting from the voltage transformation to the internal circuit, and a control circuit provided on the semiconductor chip for controlling the power supply circuit, wherein the control circuit includes external power supply voltage detecting means and / or temperature detecting means and responds to the signal from the external power supply voltage detecting means and / or the temperature detecting means by changing the power supply voltage to the internal circuit to thereby maintain the operating speed of the internal circuit to be constant.

Owner:RENESAS TECH CORP

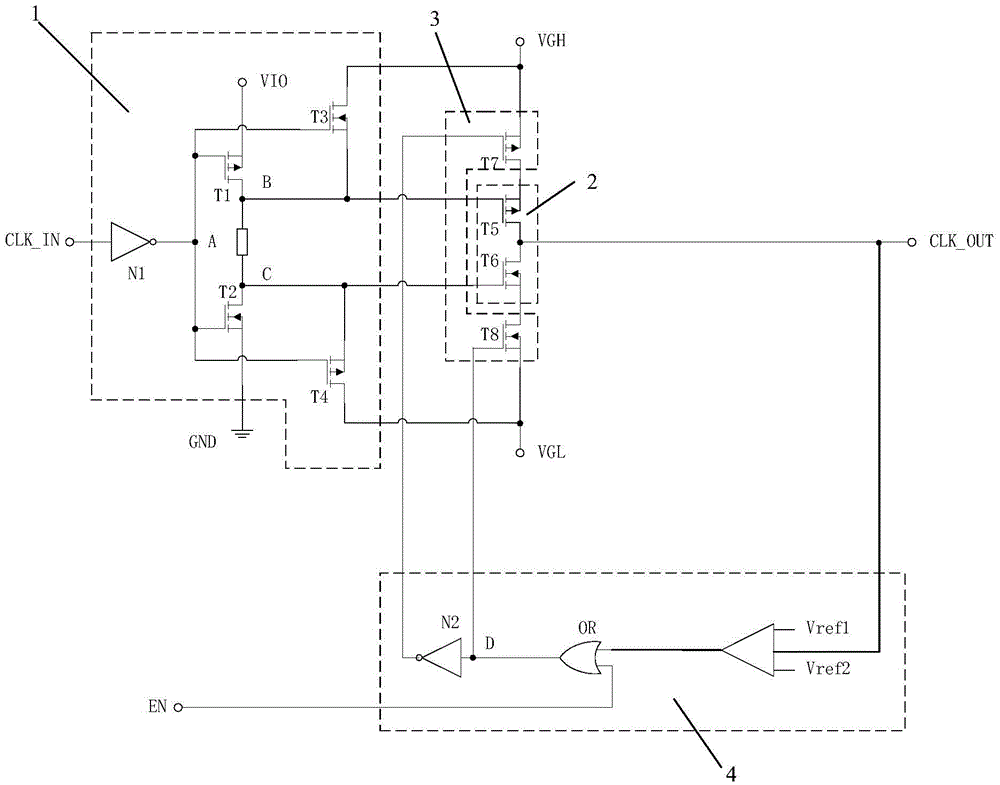

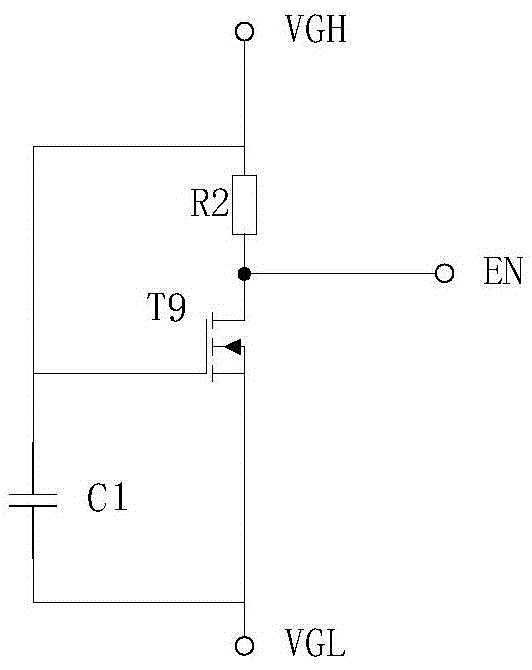

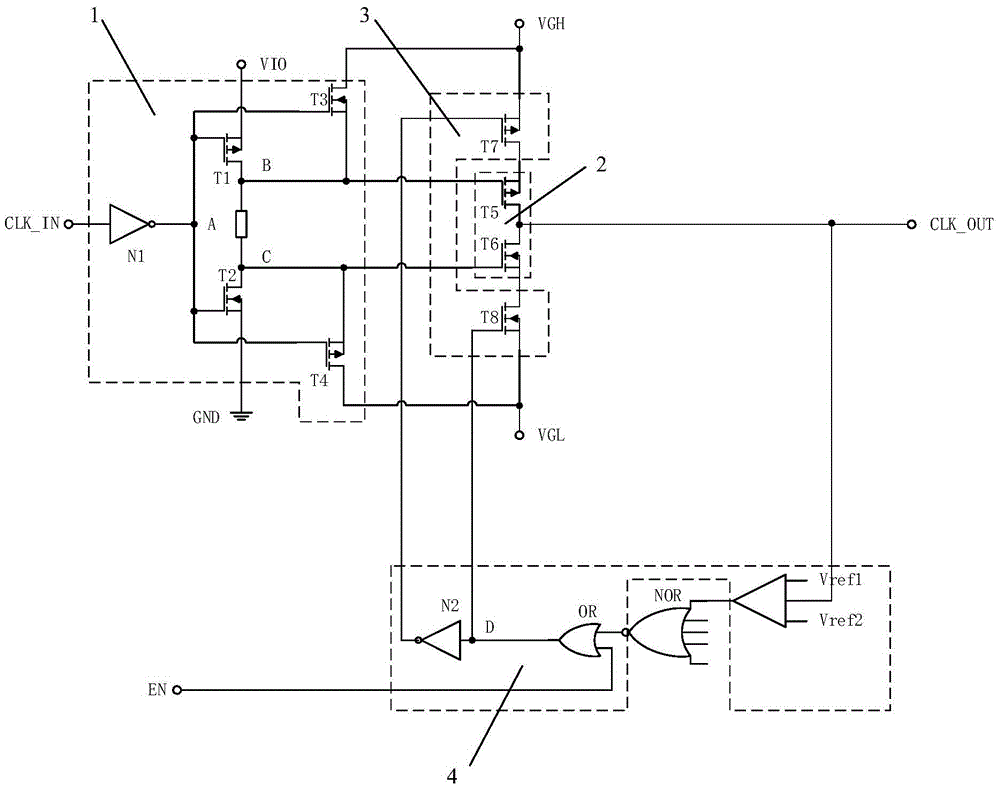

Level offset unit, level offset circuit and drive method, and grid drive circuit

ActiveCN105632438AAvoid burnsStatic indicating devicesLogic circuit interface arrangementsComputer moduleEngineering

The invention provides a level offset unit, a level offset circuit and drive method, and a grid drive circuit, belonging to the display technology field. The level offset unit comprises a logic control module, an output module, an output control module and a feedback module, wherein the logic control module is connected to a start up power supply, a driving power supply, an input signal terminal and an output module; the feedback module is connected to an enabling signal terminal, a signal output terminal and an output control module; the output control module is connected to the output module and the driving power supply; and the output module is connected to the signal output terminal. The feedback module of the level offset unit controls the output module to start up and switch off through the enabling terminal and the signal input terminal. If the signals outputted by the two level offset units are short circuited, the feedback module controls the output control module of the level offset circuit to be disconnected, so that the output module outputs the high impedance so as to avoid the burning of the gate driver, which causes the potential safety hazard.

Owner:BOE TECH GRP CO LTD +1

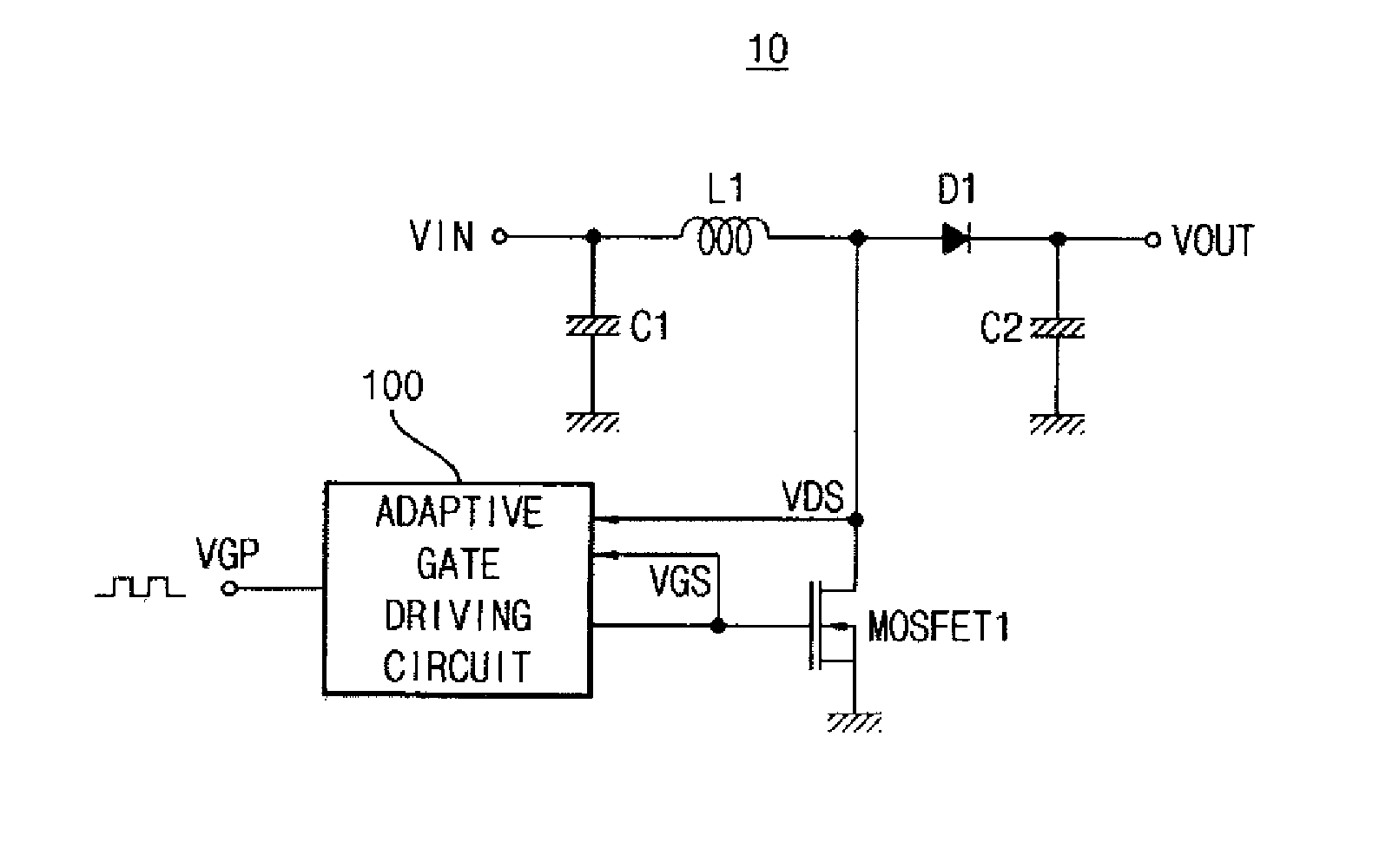

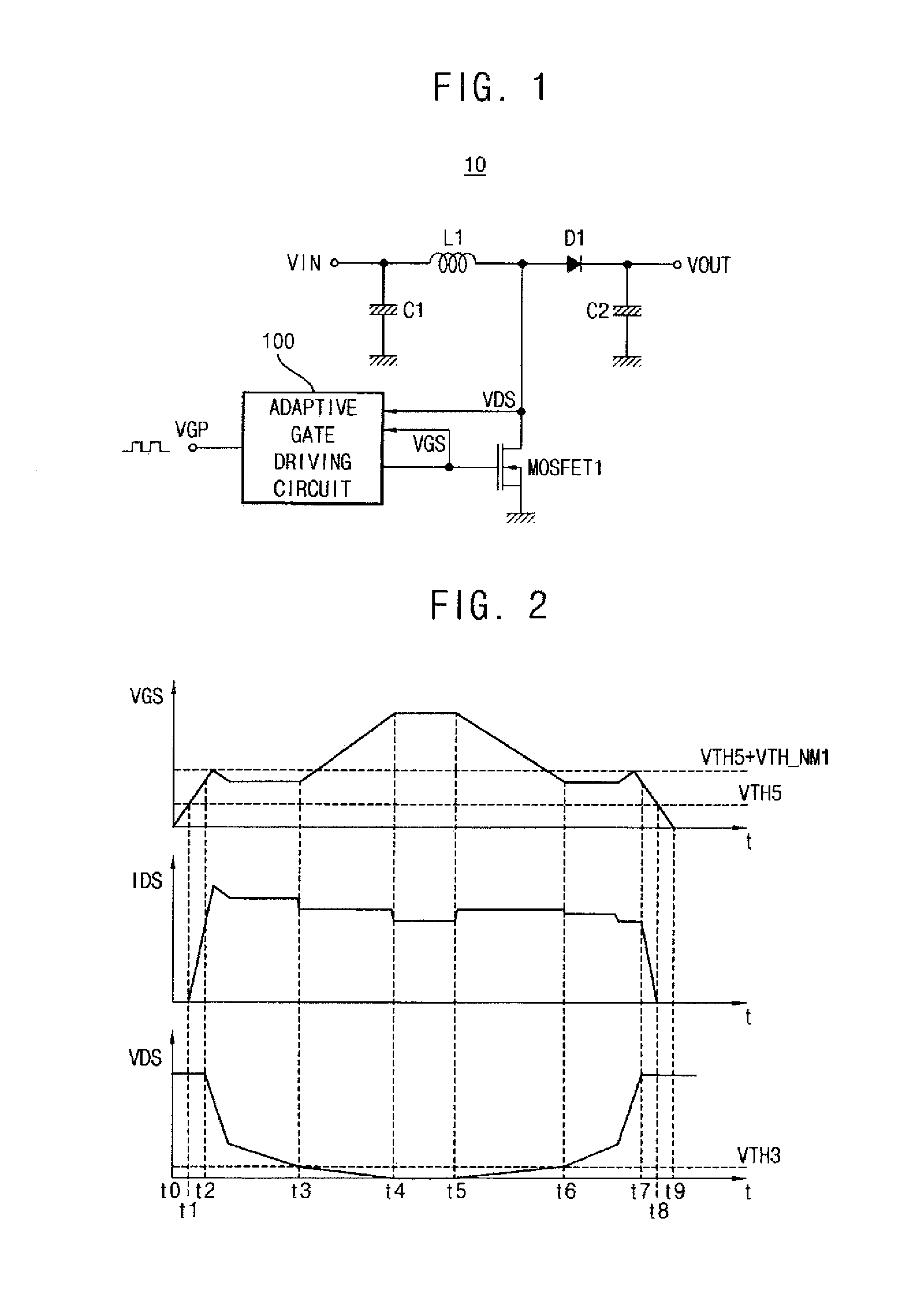

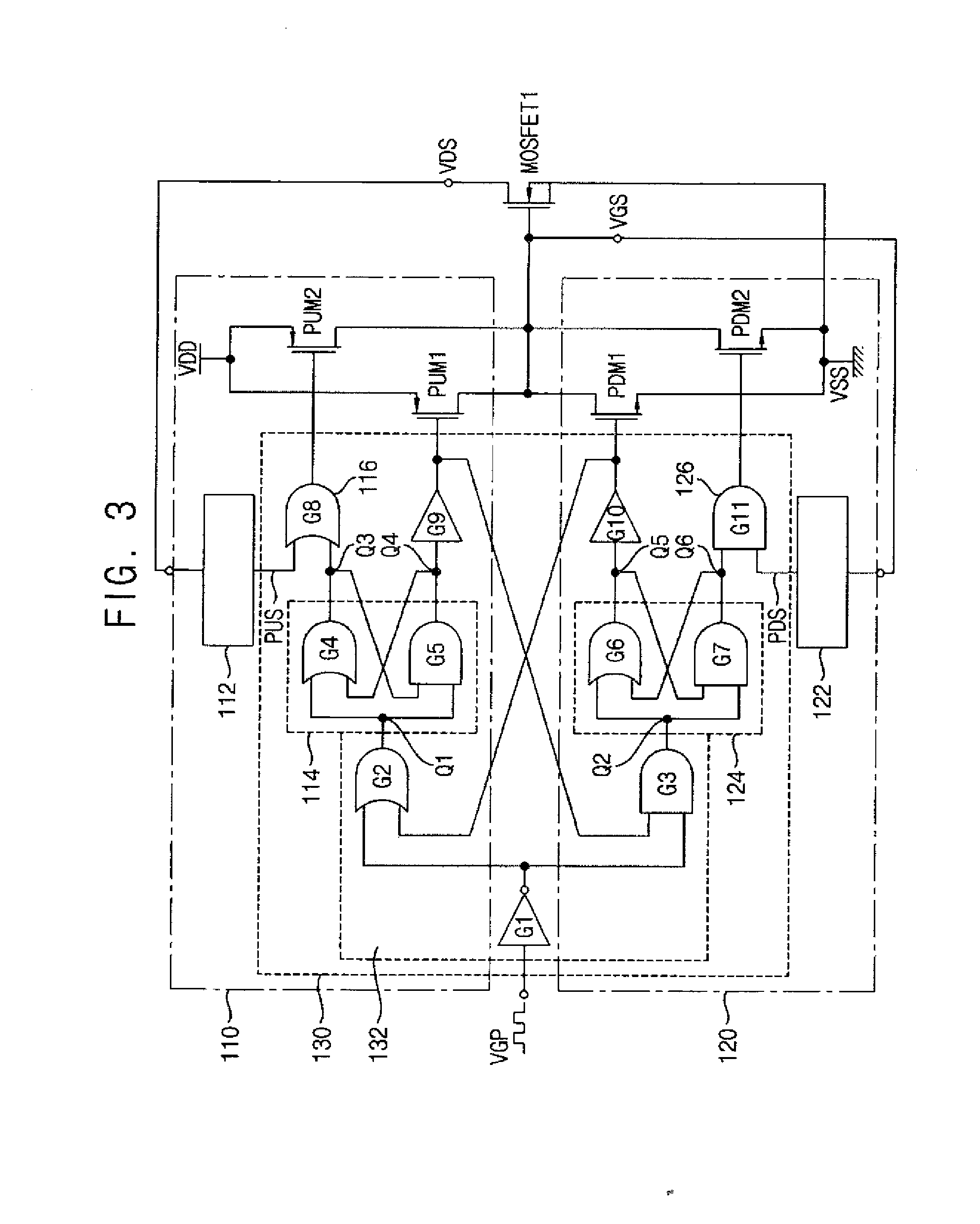

Circuit for driving gate of power mos transistor

ActiveUS20140015501A1EMI suppressionAvoid failureDc-dc conversionElectronic switchingDriver circuitTransistor

A circuit for driving a gate of a power MOS transistor includes an adaptive pull-up unit and an adaptive pull-down unit. The adaptive pull-up unit is connected between a first power source voltage and the gate of the power MOS transistor. The adaptive pull-up unit maximizes pull-up current driving ability. The adaptive pull-down unit is connected between a second power source voltage and the gate of the power MOS transistor. The adaptive pull-down unit maximizes pull-down current driving ability.

Owner:SAMSUNG ELECTRONICS CO LTD

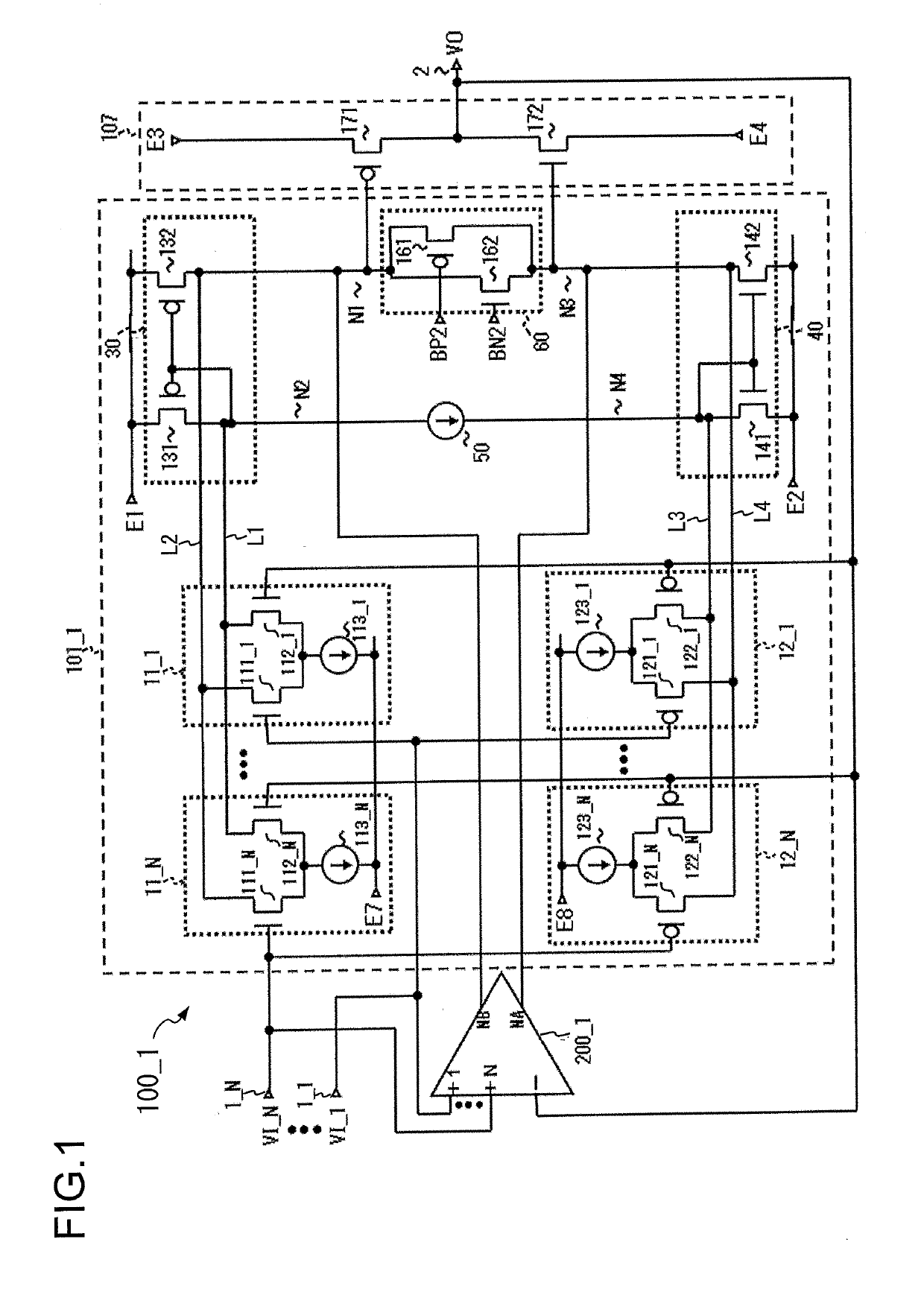

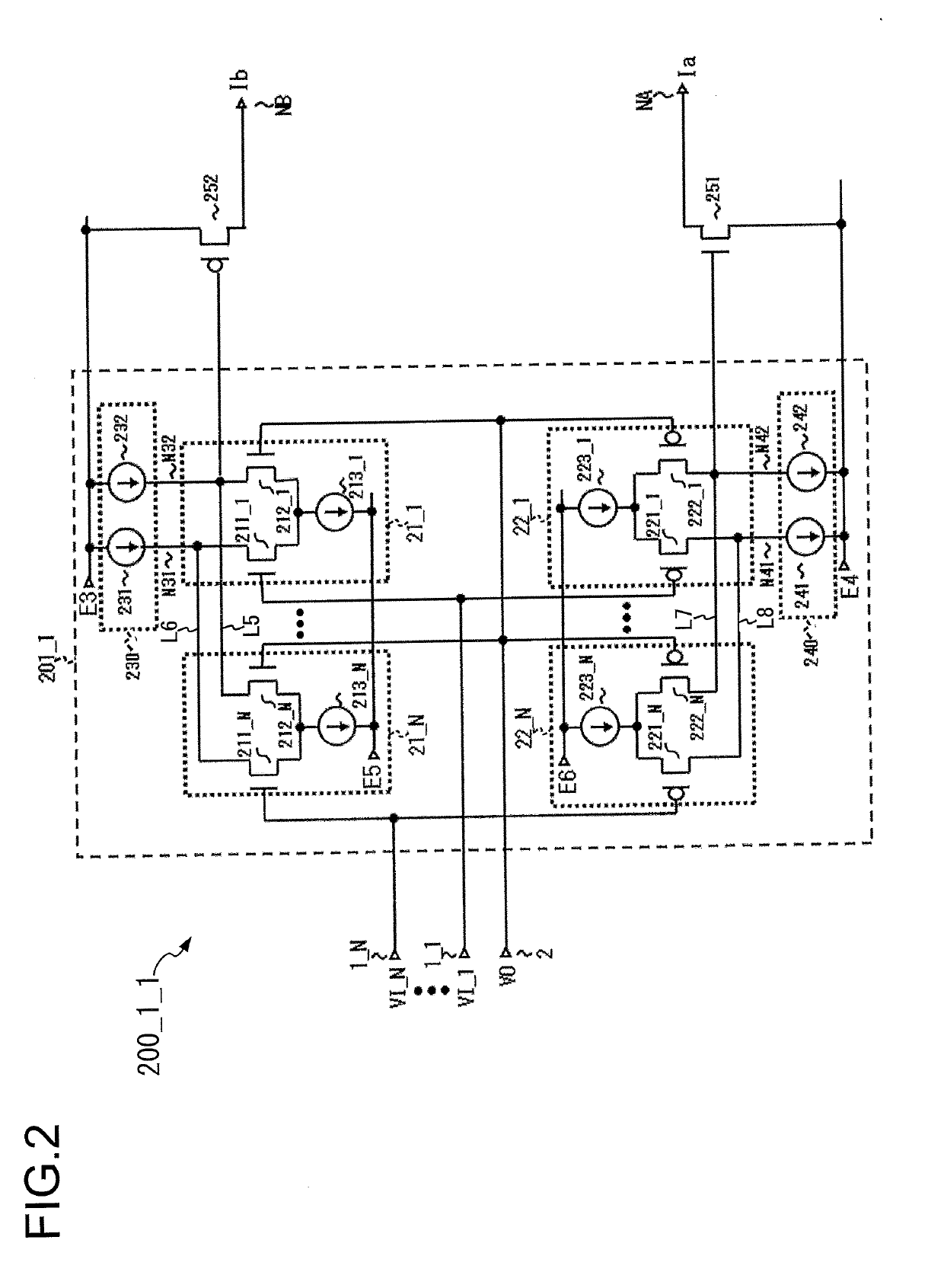

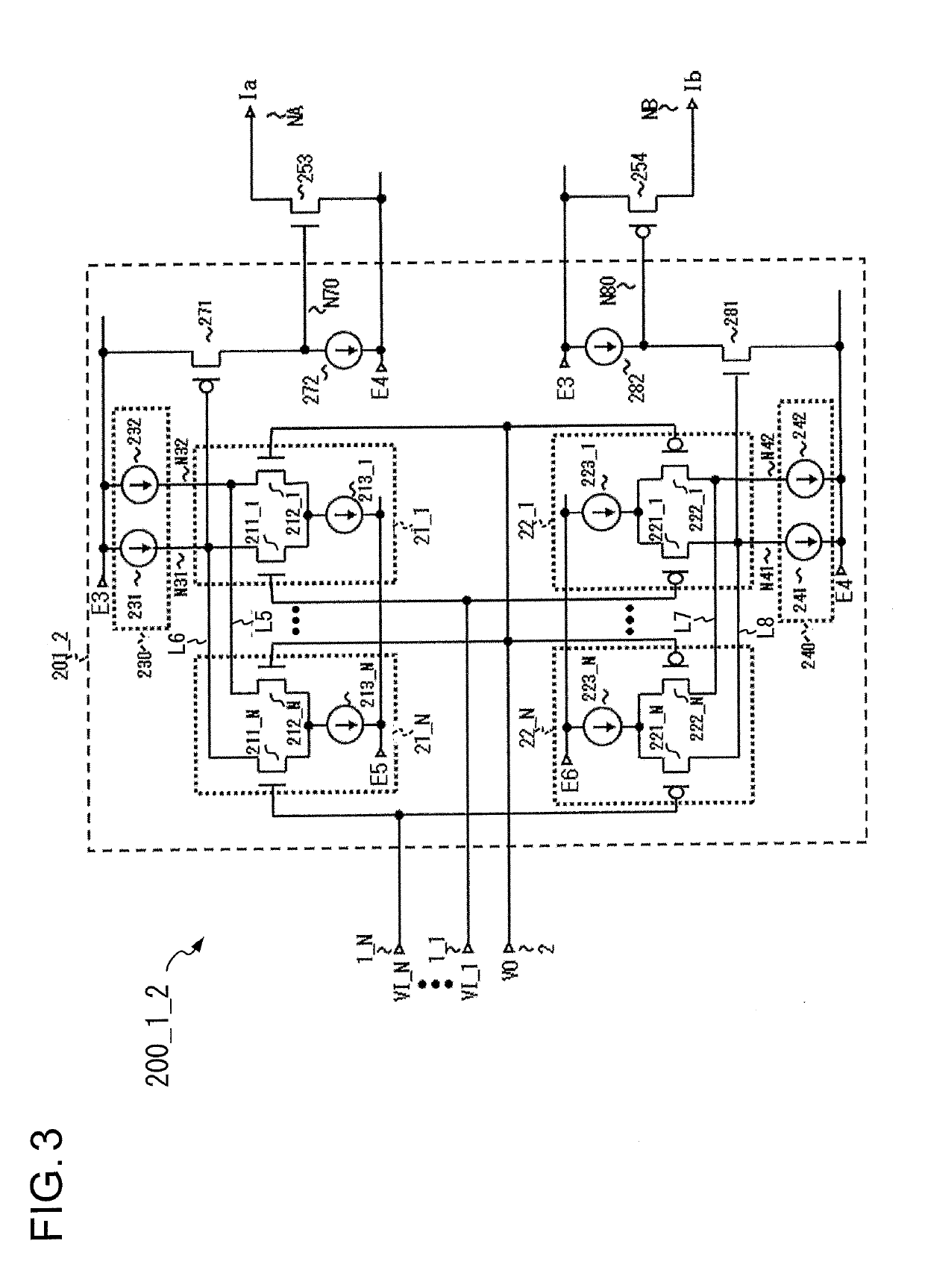

Semiconductor device

ActiveUS20190221153A1Improve accuracyStatic indicating devicesDigital storagePower semiconductor devicePower flow

A current corresponding to the difference between an input signal voltage and an output signal voltage is generated as an amplification acceleration current. The amplification acceleration current is sent to an output node of a current mirror, which drives a transistor in an output amplifier stage, and therefore added to a current to drive the transistor in the output amplifier stage.

Owner:LAPIS SEMICON CO LTD

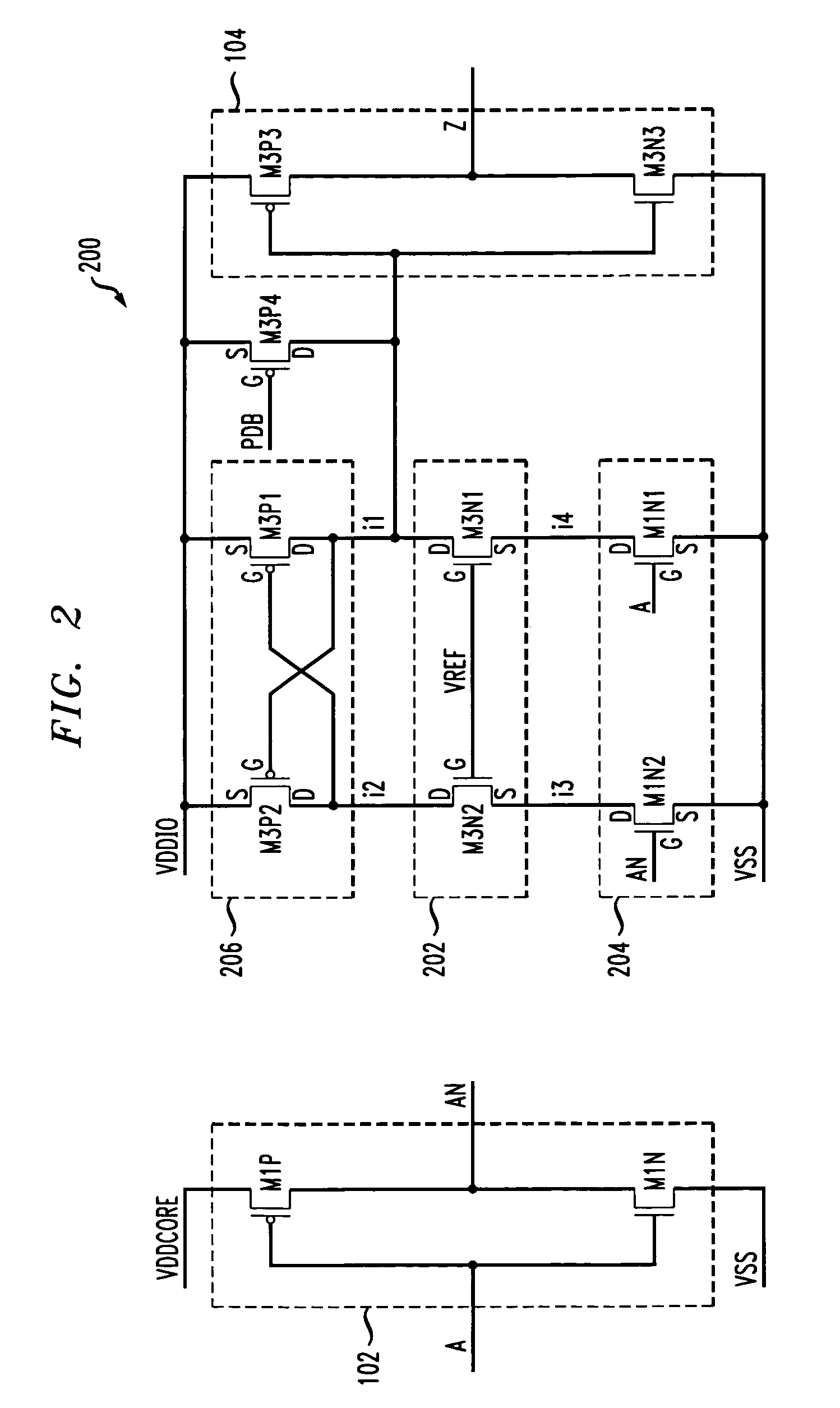

Voltage level translator circuit with wide supply voltage range

ActiveUS7397279B2Constant propagation delayWide voltage rangePulse automatic controlApparatus without intermediate ac conversionVoltage amplitudeEngineering

A voltage level translator circuit for translating an input signal referenced to a first voltage supply to an output signal referenced to a second voltage supply includes an input stage for receiving the input signal, the input stage including at least one transistor device having a first threshold voltage associated therewith. The voltage level translator circuit further includes a latch circuit operative to store a signal representative of a logic state of the input signal, the latch circuit including at least one transistor device having a second threshold voltage associated therewith, the second threshold voltage being greater than the first threshold voltage. A voltage clamp circuit is connected between the input stage and the latch circuit. The voltage clamp circuit is operative to limit a voltage across the input stage, an amplitude of the voltage across the input stage being controlled as a function of a voltage difference between the first and second voltage supplies.

Owner:AVAGO TECH INT SALES PTE LTD

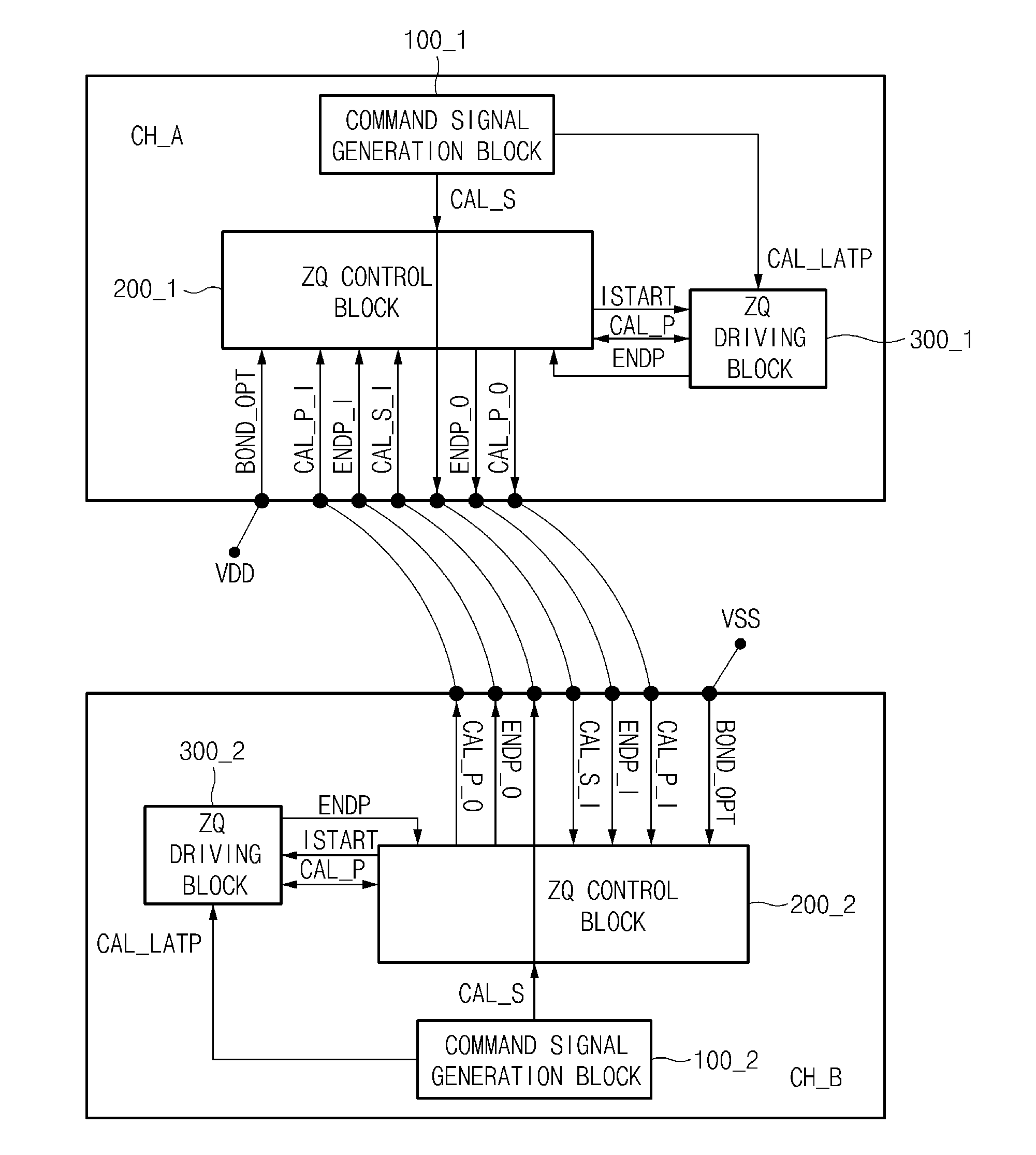

Semiconductor device

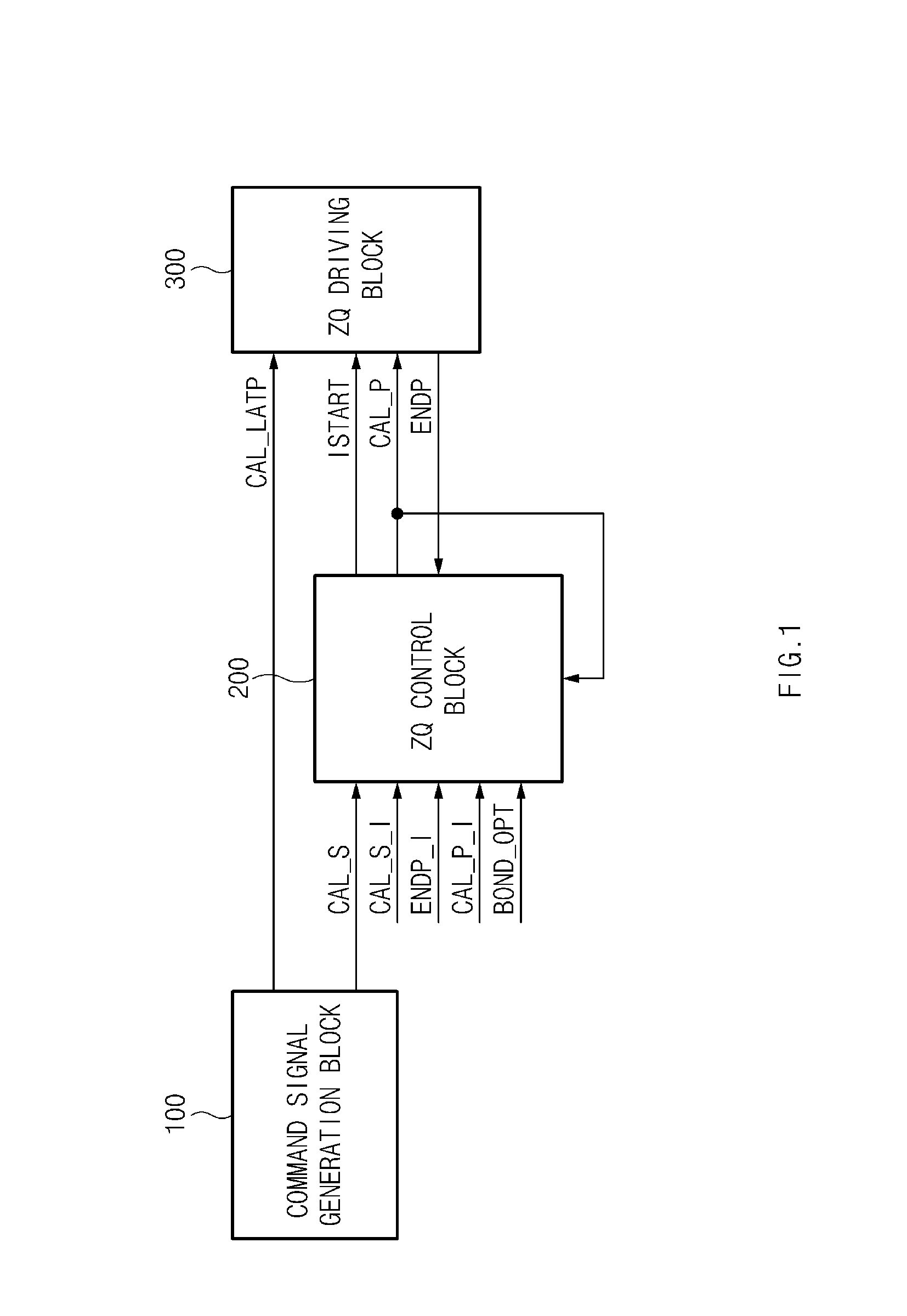

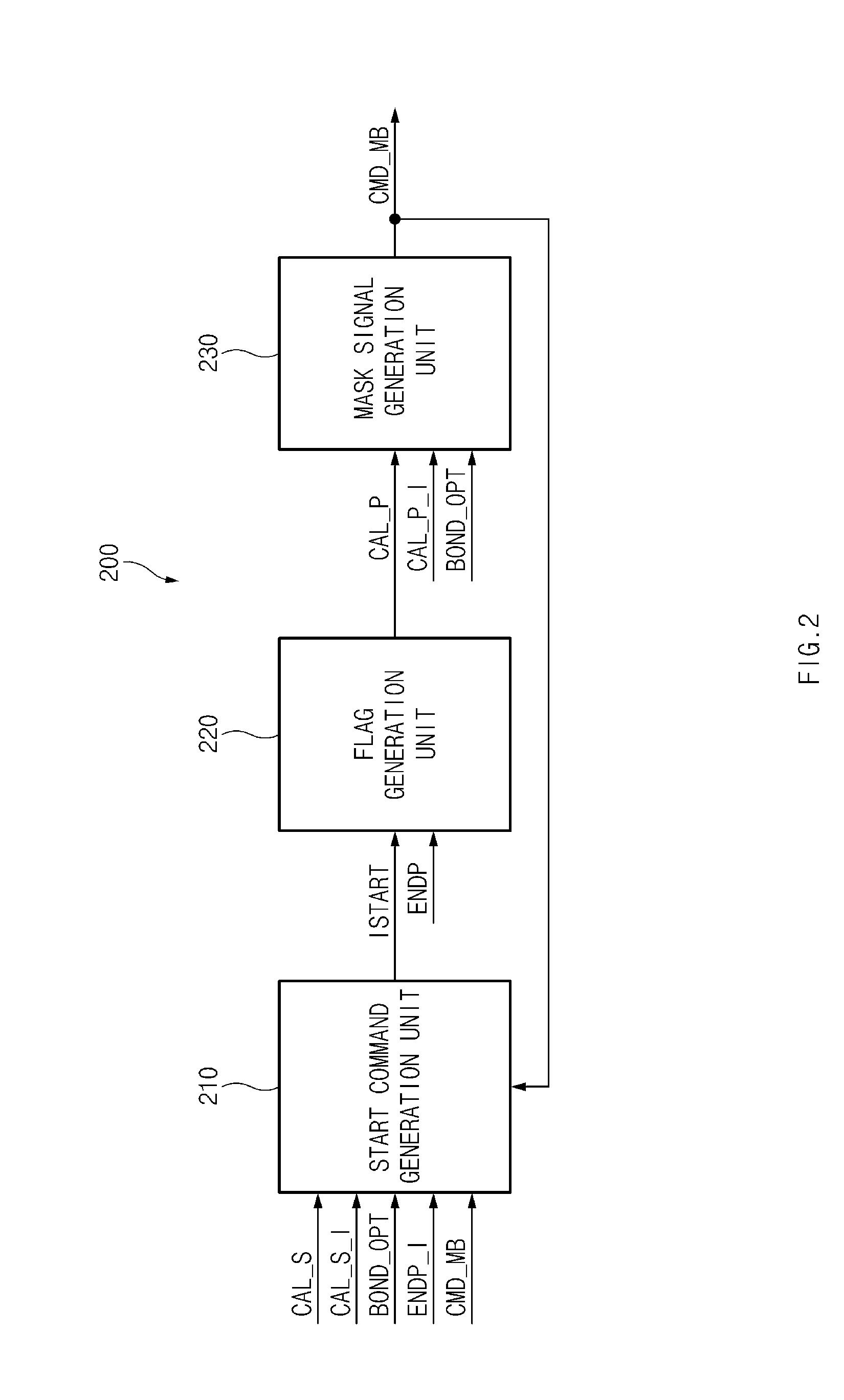

A semiconductor device may include a first channel provided in a first die. The semiconductor device may include a second channel provided in a second die and disposed adjacent to the first channel, and configured to exchange signals and data with the first channel. The first channel and the second channel may receive and output calibration-related signals from and to each other through bonding, and may share calibration start signals. The calibration start signal may be respectively generated in the first channel and the second channel.

Owner:SK HYNIX INC

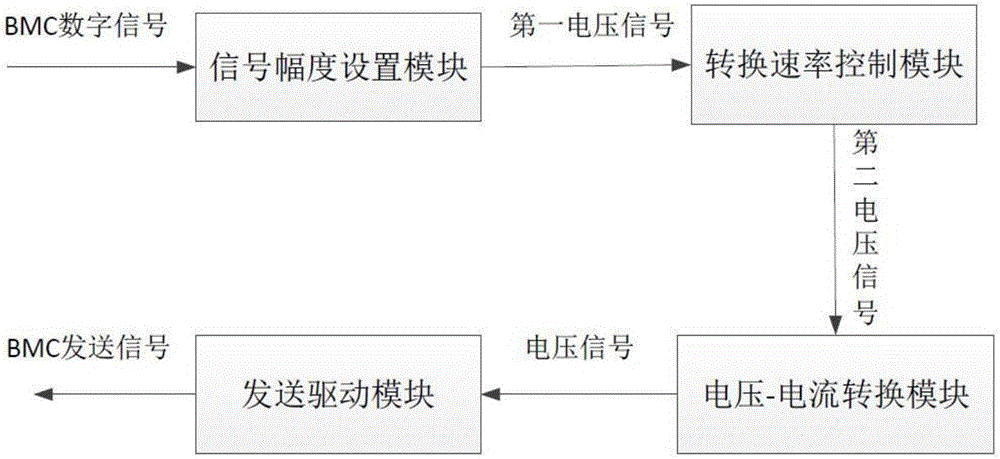

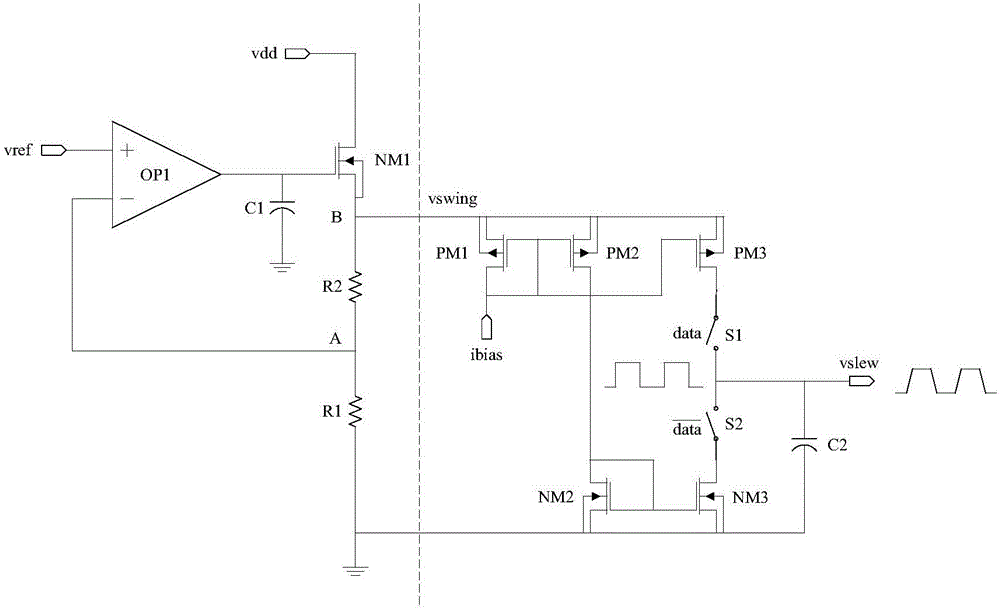

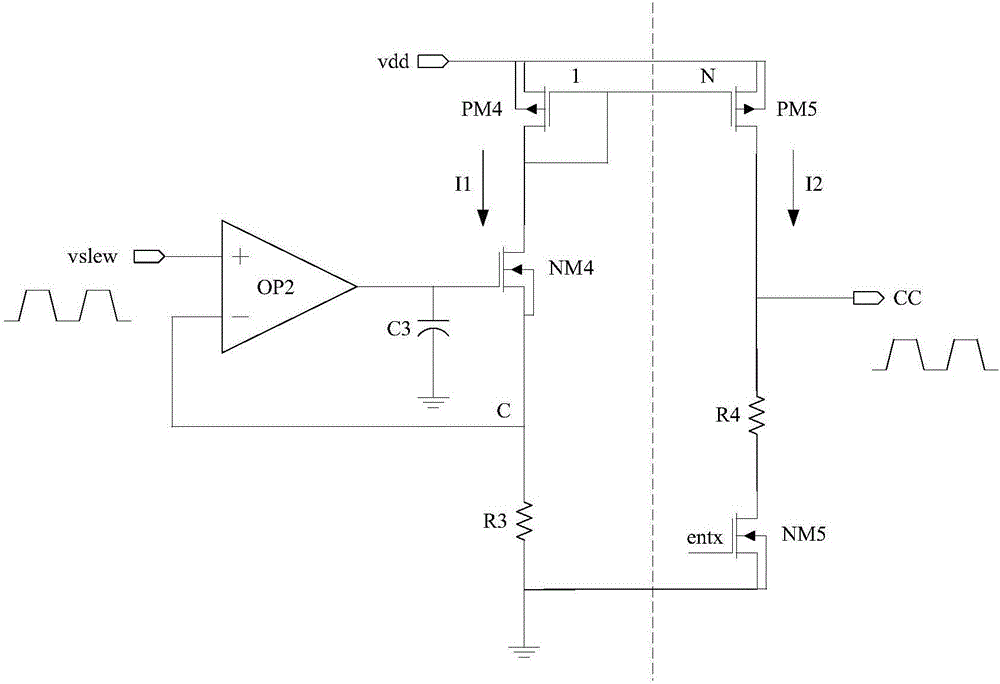

BMC signal sending device for USB PD communication

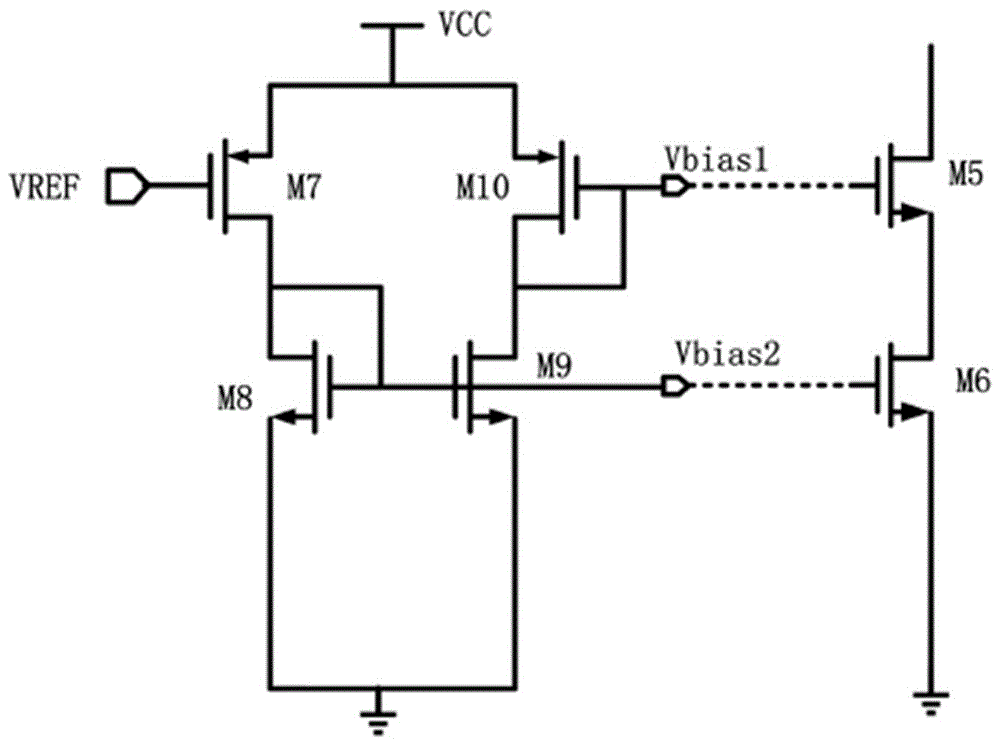

PendingCN106055507AEasy to integrateLow technical barriers to designElectric digital data processingLogic circuit interface arrangementsVoltage amplitudeDesign technology

The invention discloses a BMC signal sending device for USB PD communication. The device comprises a signal amplitude setting module, a conversion rate control module, a voltage-current conversion module and a sending driving module which are connected in sequence. The signal amplitude setting module is used for setting the voltage amplitude of a BMC sending signal and generating a first voltage signal; the conversion speed control module is used for controlling the high-low level conversion speed of the first voltage signal and generating a second voltage signal with the amplitude same as that of the first voltage signal and the conversion speed different from that of the first voltage signal; the voltage-current conversion module is used for converting the second voltage signal into a current signal; the sending driving module is used for converting the current signal into a BMC sending signal and transmitting the BMC sending signal to a CC line. The BMC signal sending device conforming to USB PD and USB Type-C protocol specifications is provided for USB PD communication of electronic equipment with a USB Type-C interface, the device is low in design technology limit and flexible and easy to debug; in addition, the device can be integrated to a silicon wafer easily, no any off-chip element is needed, and therefore the device has the good market application value.

Owner:ZHUHAI ISMARTWARE TECH CO LTD

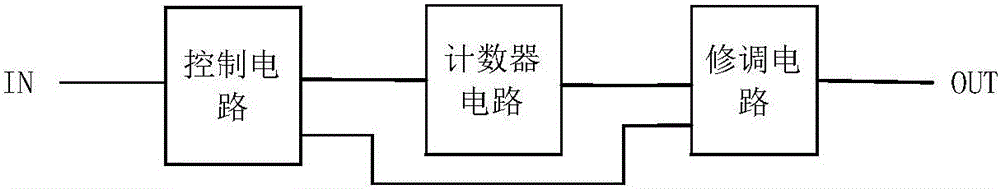

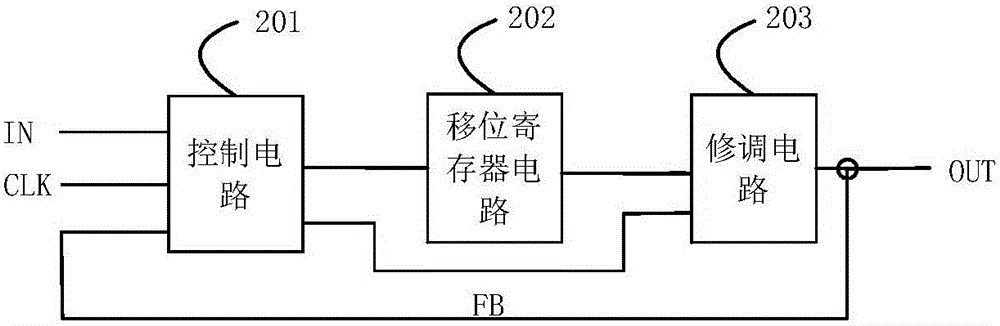

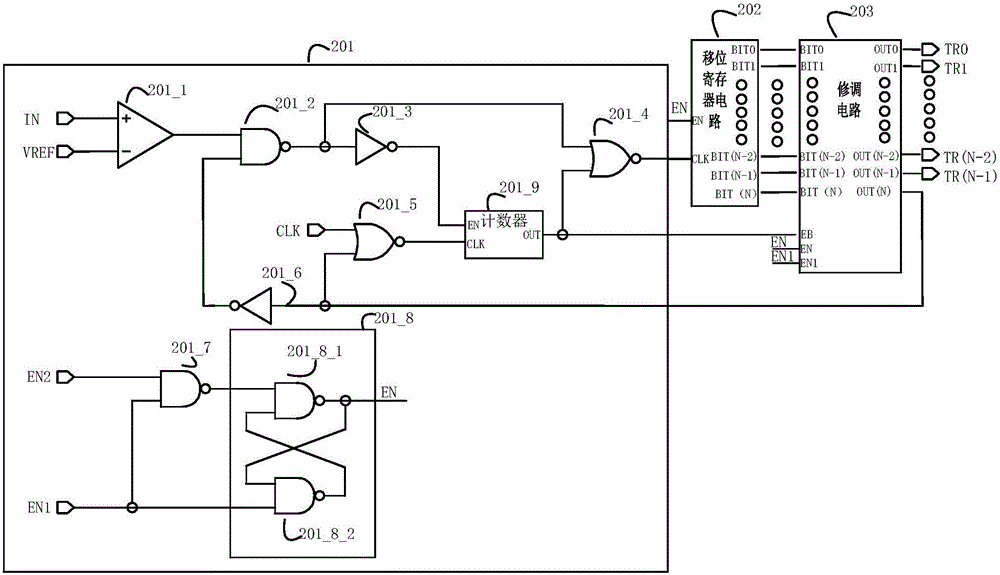

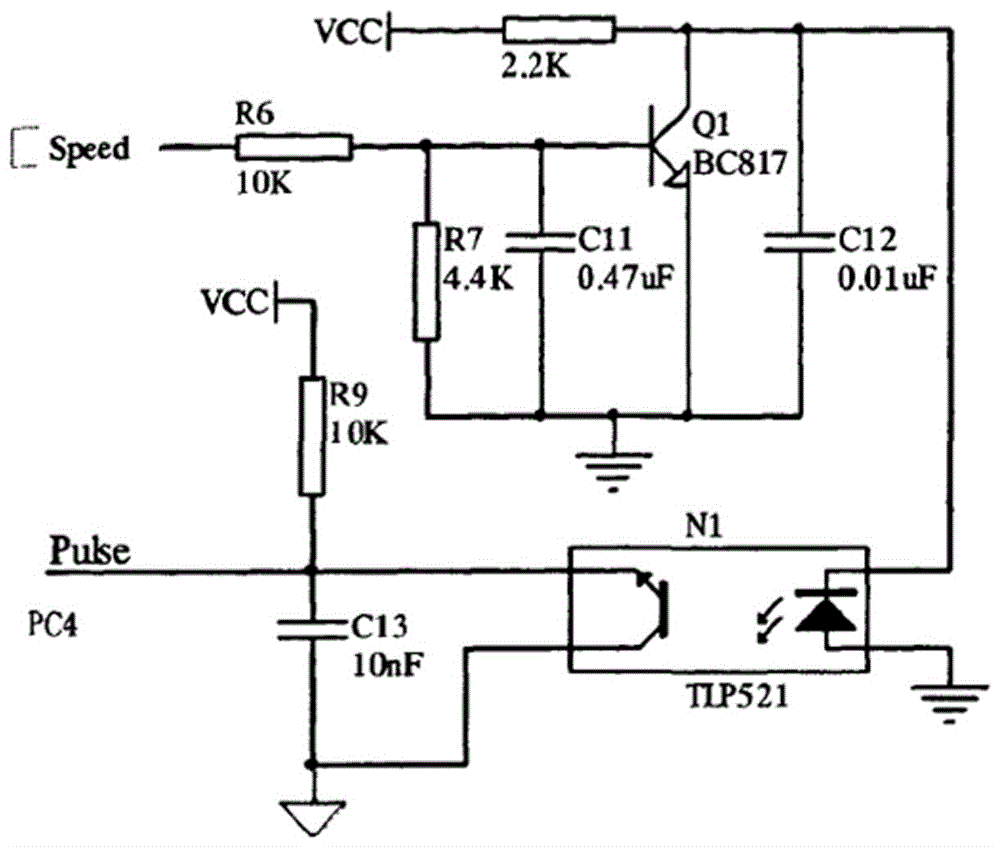

Digital trimming system based on pin multiplexing

ActiveCN105897249AAvoid false trimmingReduced pin countLogic circuit interface arrangementsVIT signalsFeedback circuits

The invention discloses a digital trimming system based on pin multiplexing. The digital trimming system comprises a control circuit connected with a trimming input pulse signal. The output end of the control circuit is connected with a shift register circuit and a trimming circuit. The output end of the shift register circuit is connected with the input end of the trimming circuit. A trimming feedback circuit is connected between the output end of the trimming circuit and the input end of the control circuit. It is not required to specially use a pin of a chip as a trimming pin but to directly multiplex the function pin of the chip so that the number of the pins of the chip may decrease. The shift register circuit mainly converts the number of the pulses of the input trimming signal into a control signal to a specific bit required to be trimmed. The trimming circuit mainly receives the trimming signal of the specific bit of the shift register circuit, fuses the fuse of a corresponding bit, latches a trimming result, and outputs the trimming result to a module of which the chip is required to be trimmed. The digital trimming system may prevent erroneous trimming of the chip in a normal operating state after trimming finishes.

Owner:HUNAN ADVANCECHIP ELECTRONICS TECH CO LTD

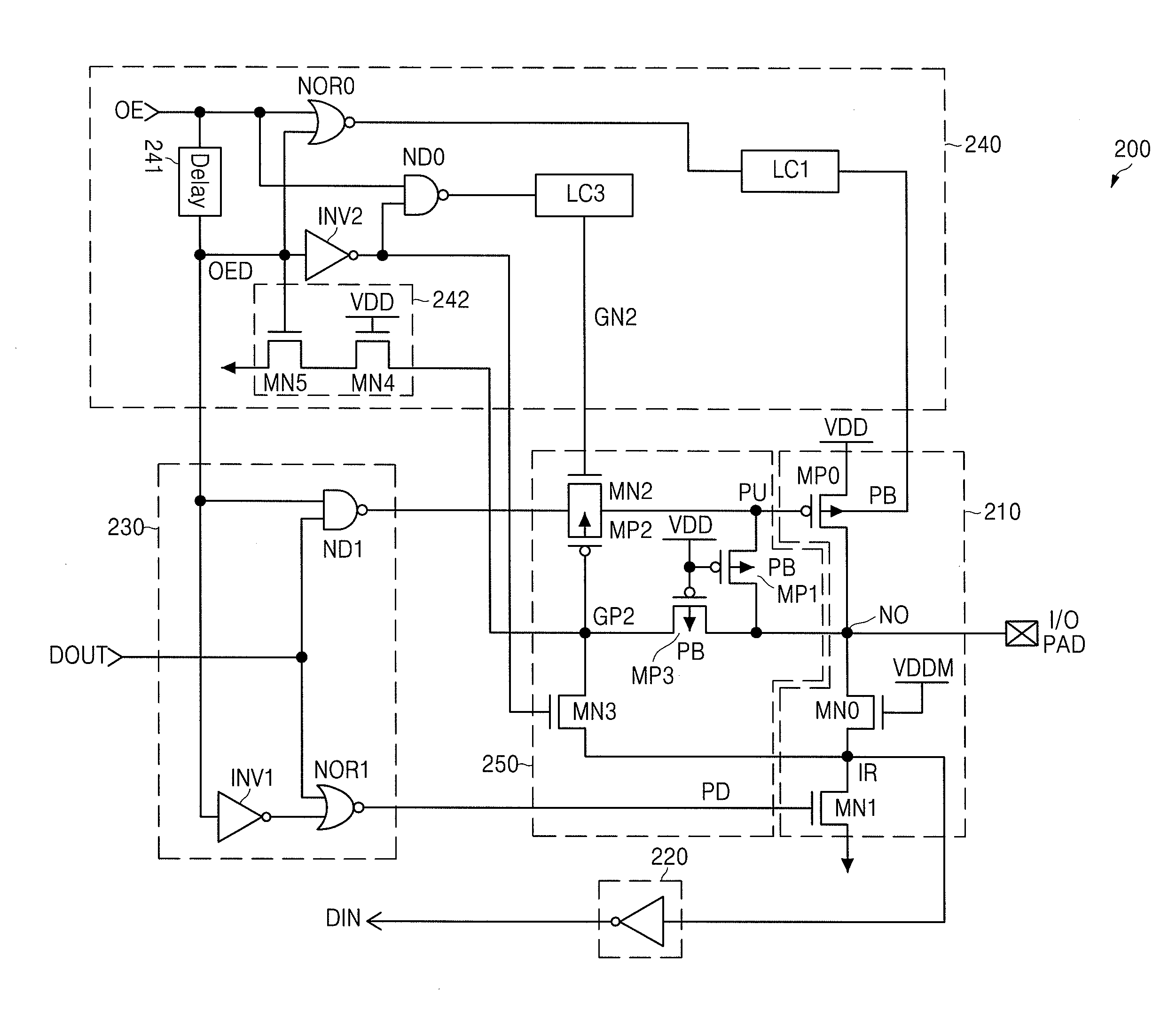

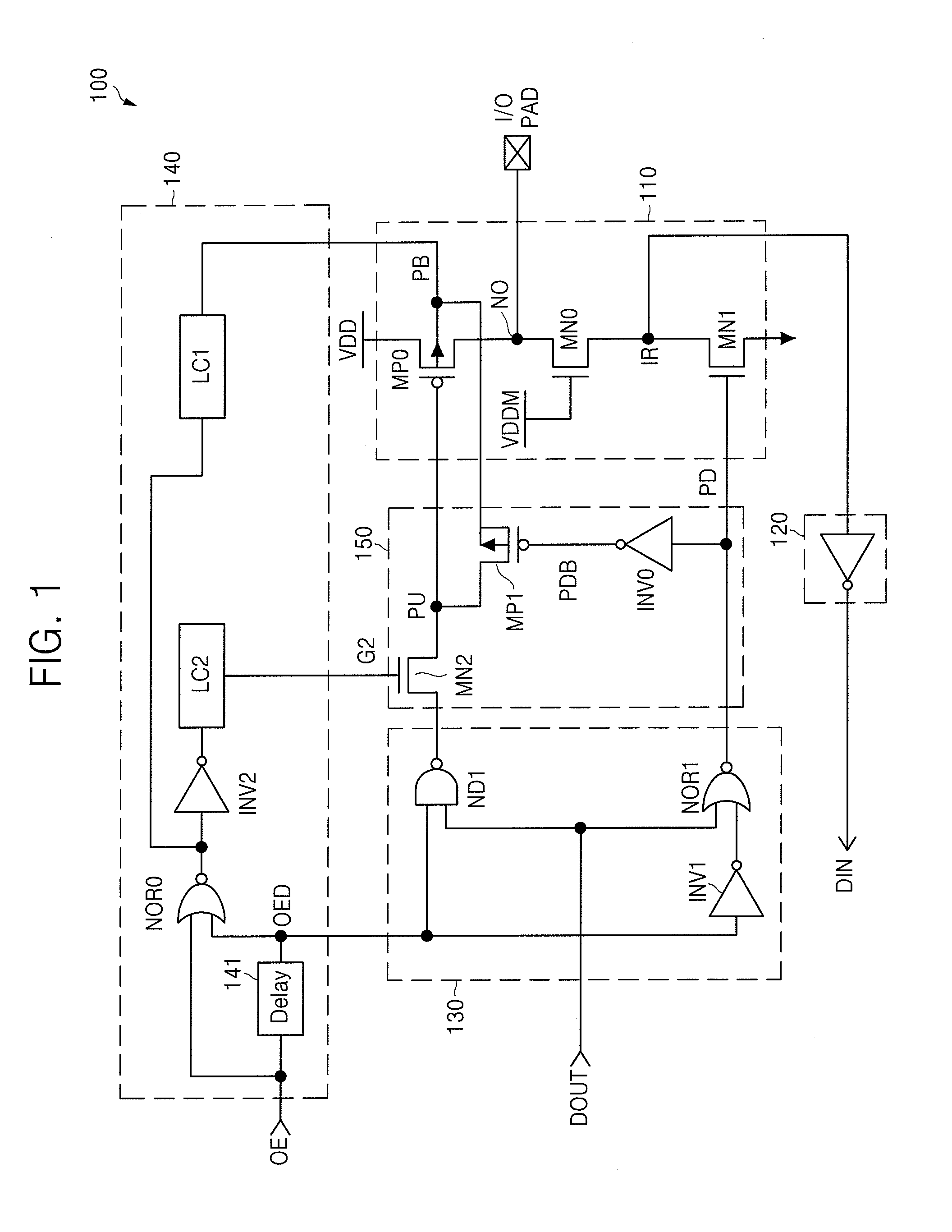

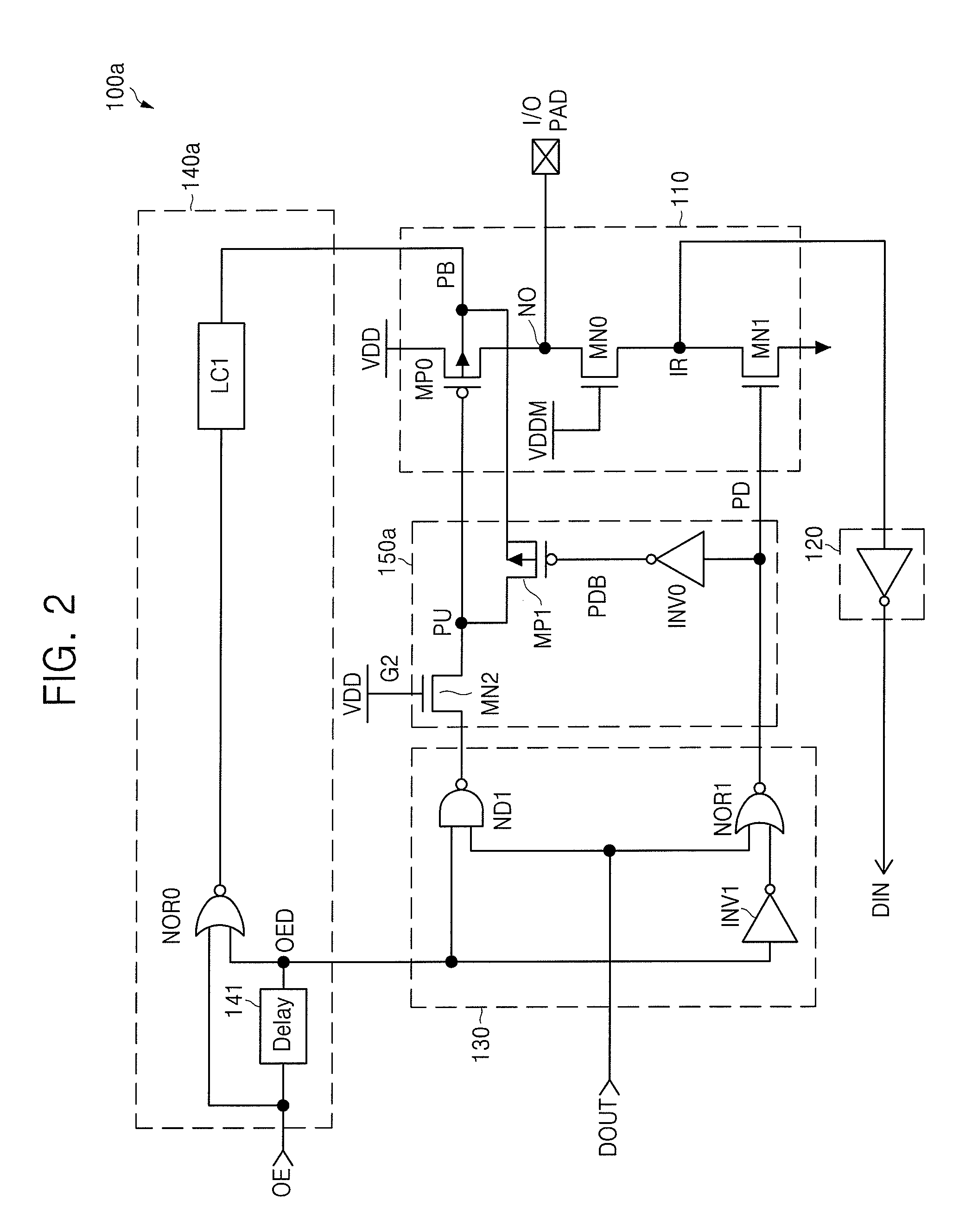

Input/output circuit and integrated circuit apparatus including the same

ActiveUS20100271069A1Preventing and reducing leakage currentLow reliabilityDigital storageBaseband systemsEngineeringControl circuit

An input / output circuit includes an I / O node connected to a pull up and pull down circuit having a pull up and pull down transistors. Data is sent and received at through the I / O node. A level shifter provides voltages including a supply voltage and a high voltage higher than the supply voltage. A signal control circuit controls the voltage level applied to the pull up and pull down circuit. During a data input mode, data is received at the I / O node and the pull up transistor is biased at the high voltage to cut off the pull up transistor. During a data output mode, data is output at the I / O node and the pull down transistor pulls down the I / O node to ground when the output data is low, and the pull up transistor is activated when the output data is high.

Owner:SAMSUNG ELECTRONICS CO LTD

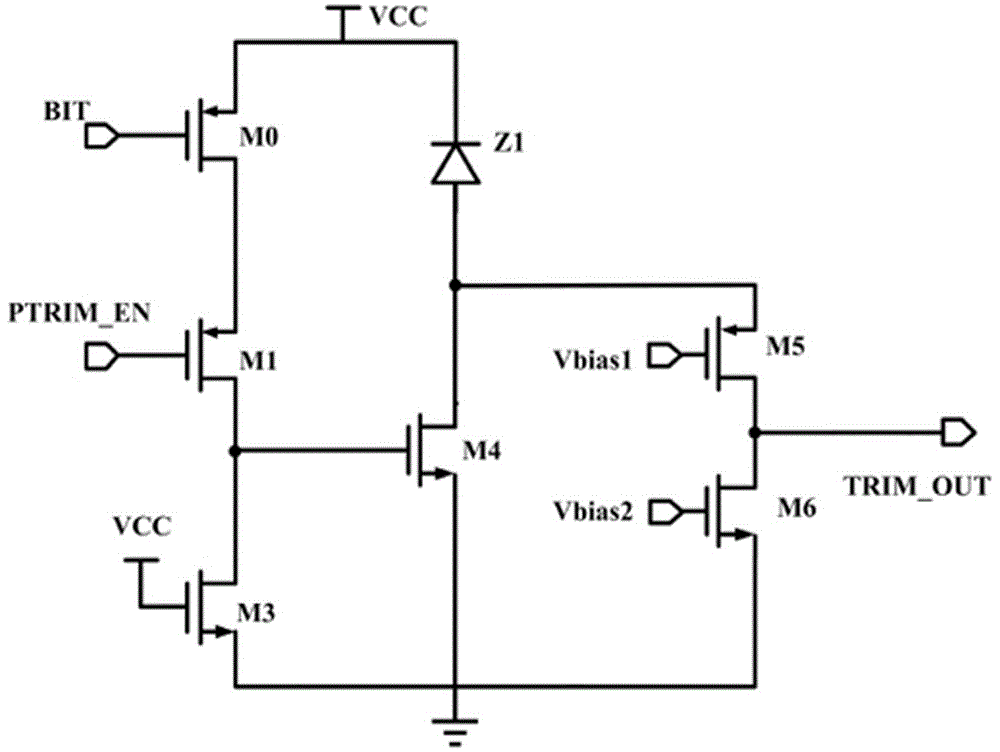

High-performance switching power supply chip trimming circuit

InactiveCN107528576AGood production process compatibilityLow priceLogic circuit interface arrangementsOvervoltageHysteresis

A high-performance switching power supply chip trimming circuit is suitable for the power supply field. Trim circuit consists of anti-fuse trim unit circuit, bias circuit, control pin UV / OV module circuit, high voltage current source, trim mode switching circuit, line voltage latch overvoltage detection circuit, latch hysteresis overvoltage circuit composition. The diode anti-fuse trimming scheme is adopted. After trimming, the chip has good production process compatibility, and is inexpensive to implement, avoids the influence of packaging, and has higher precision.

Owner:许亚夫

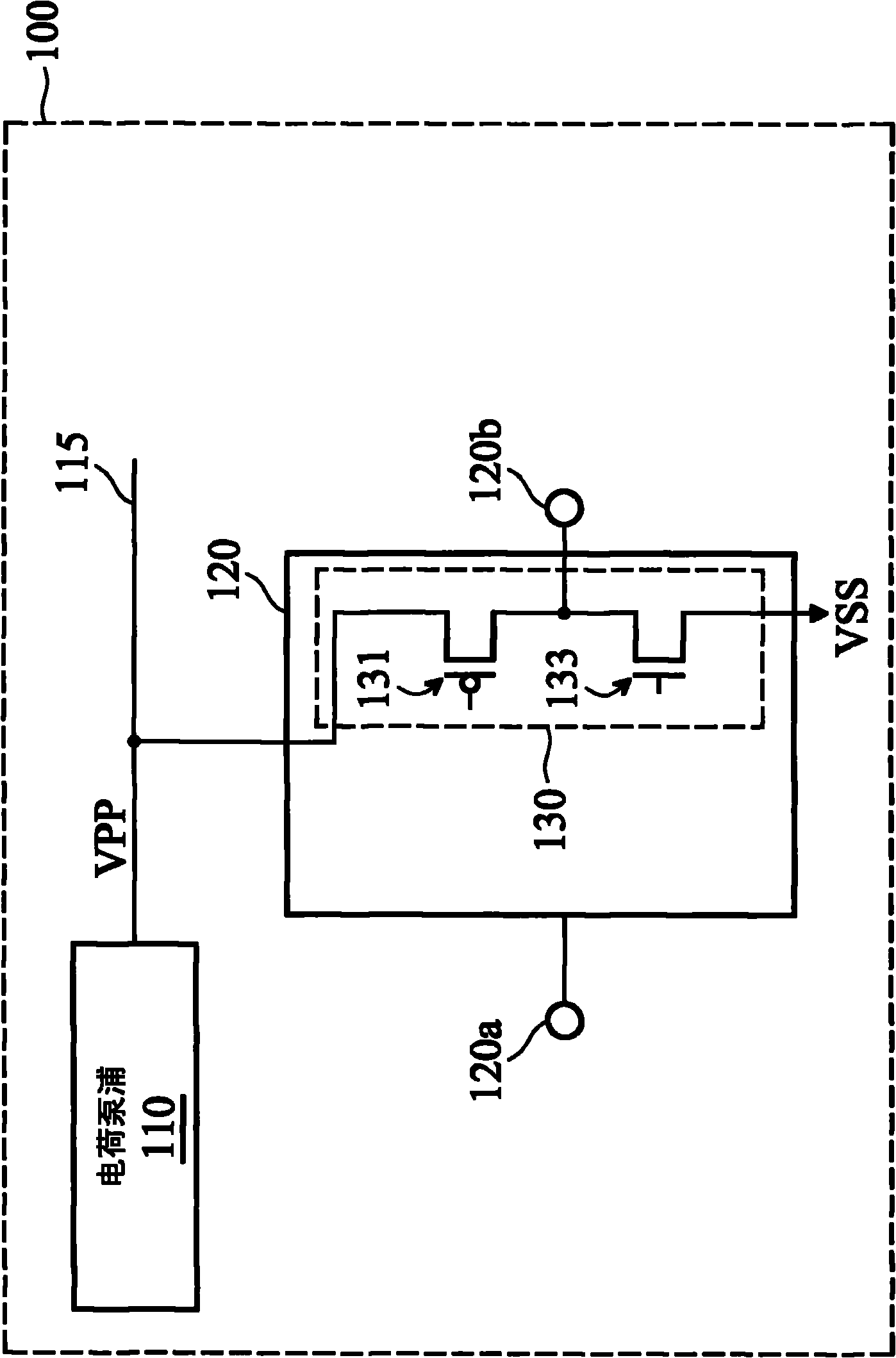

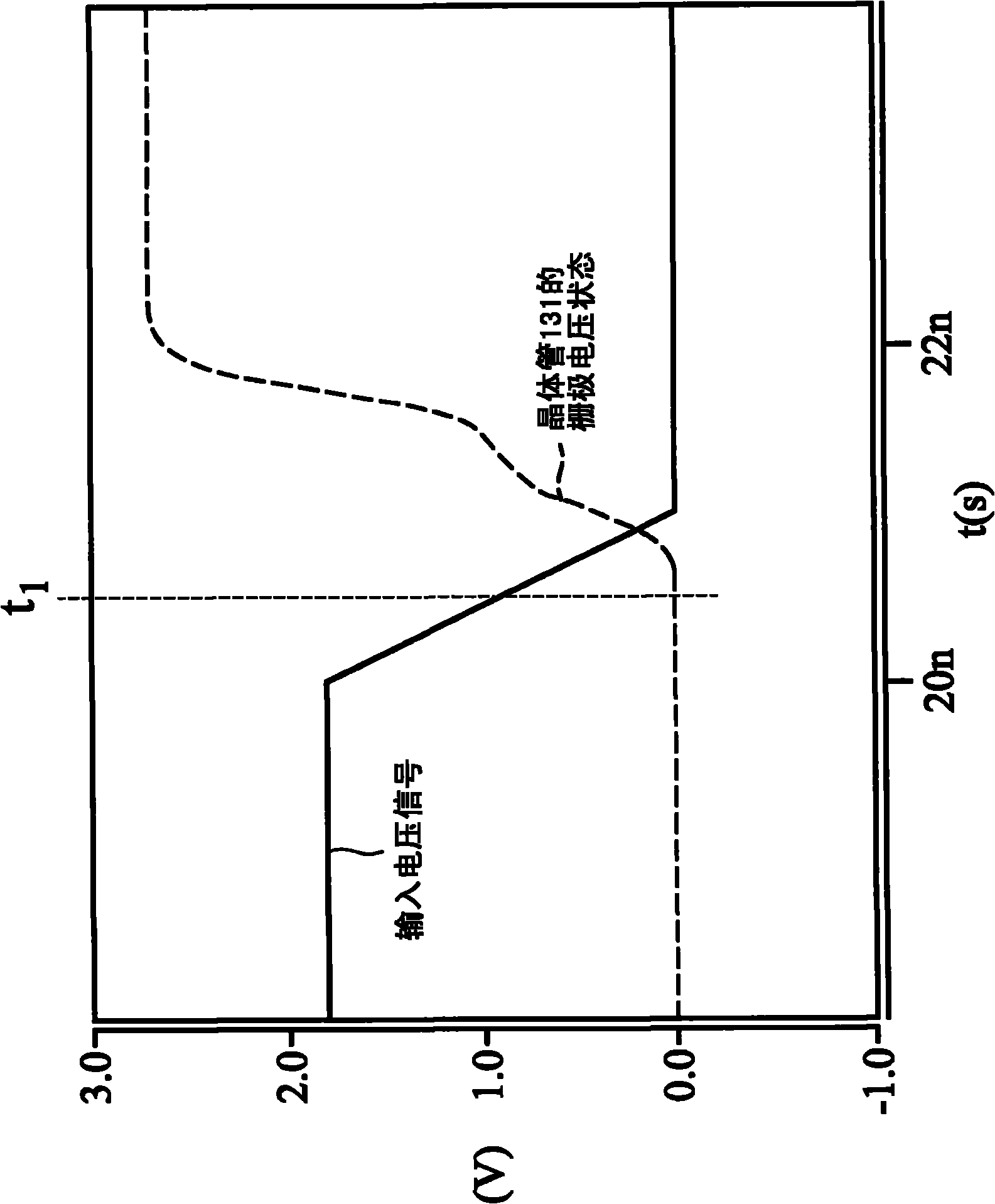

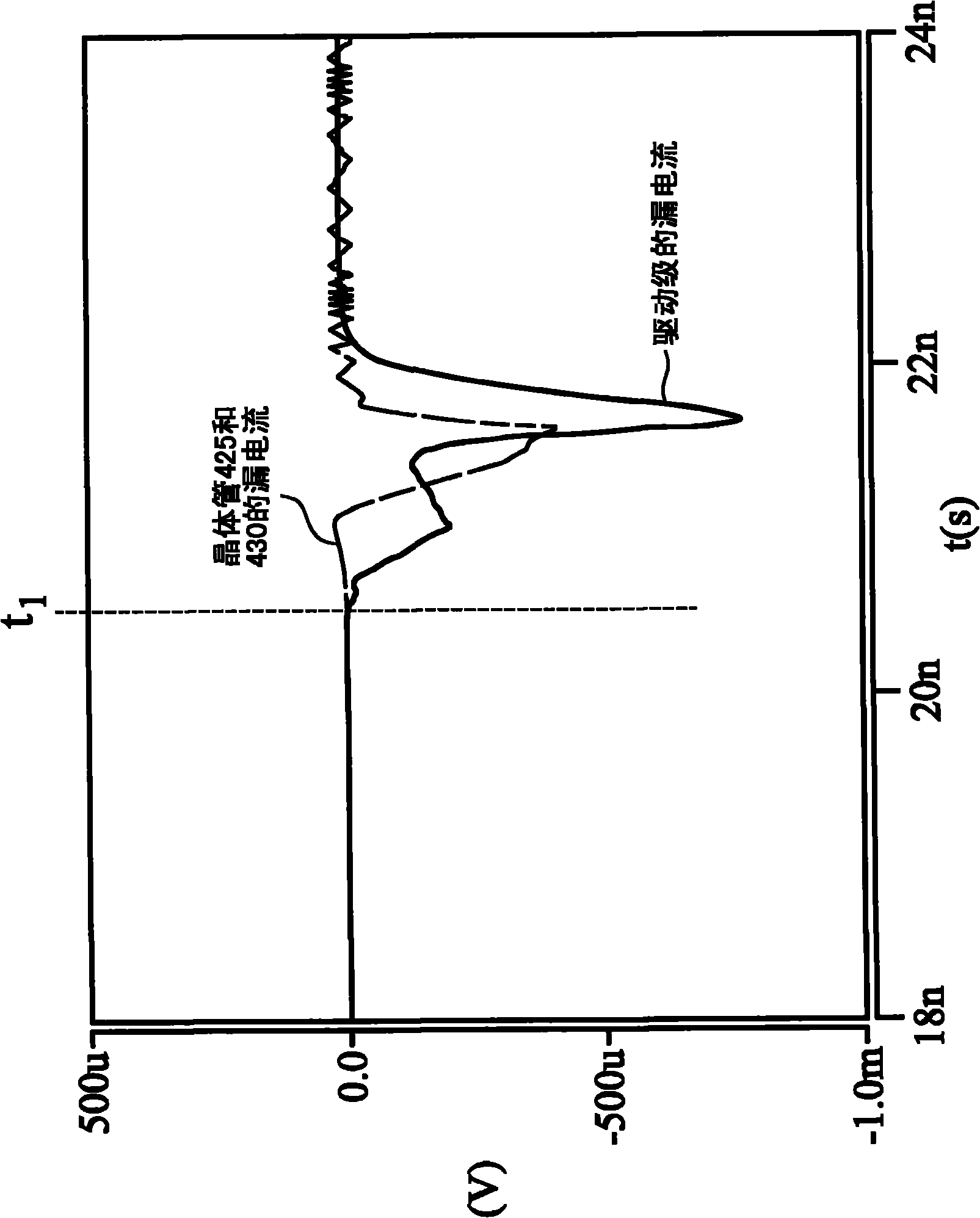

Level shifters, integrated circuits, systems, and method for operating the level shifters

ActiveCN101860356AAvoid damageElectrical componentsLogic circuit interface arrangementsEngineeringState switching

The present invention provides level shifters, integrated circuits, systems, and a method for operating the level shifters. The level shifter includes an input end being capable of receiving an input voltage signal. The input voltage signal includes a first state transition from a first voltage state to a second voltage state. An output end can output an output voltage signal having a second state transition from a third voltage state to the second voltage state corresponding to the first state transition of the input voltage signal. A driver stage is coupled between the input end and the output end. The driver stage includes a first transistor and a second transistor. Substantially immediately from a time corresponding to about a mean of voltage levels of the first voltage state and the second voltage state, the second voltage state is substantially free from being applied to a gate of the first transistor so as to substantially turn off the first transistor. The present invention can avoid the flash device, the transistor and / or circuit damage under a high voltage operation.

Owner:TAIWAN SEMICON MFG CO LTD

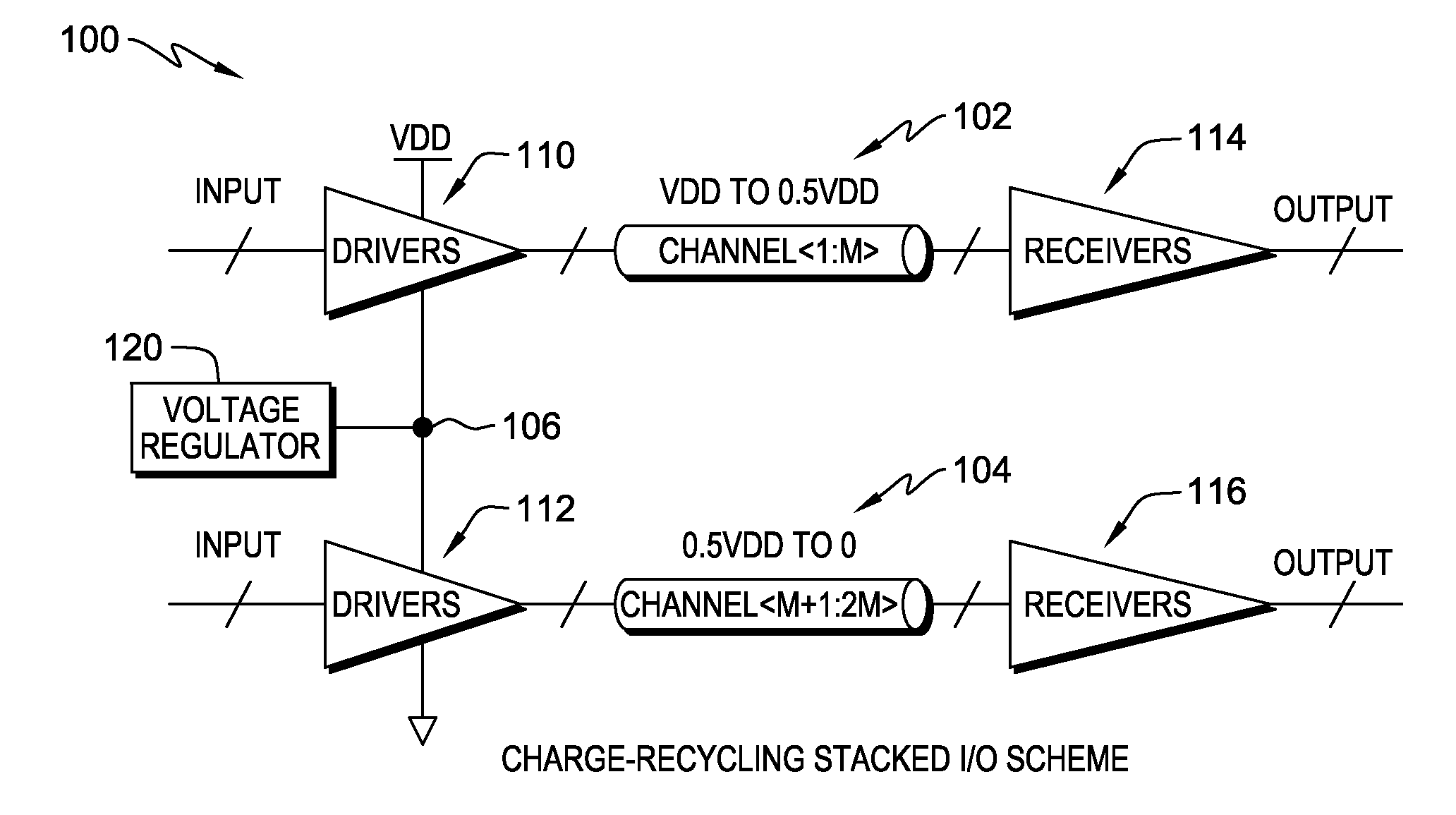

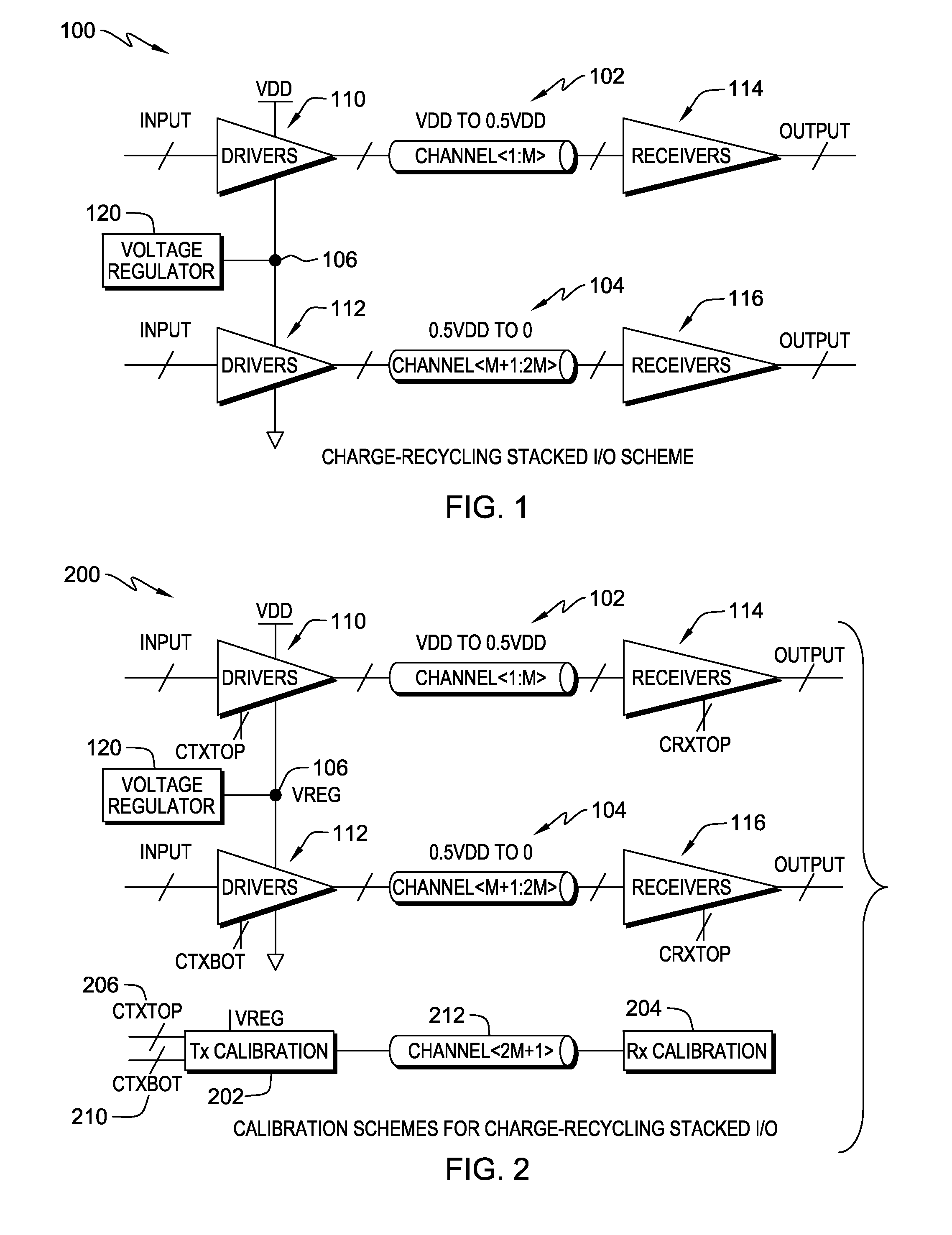

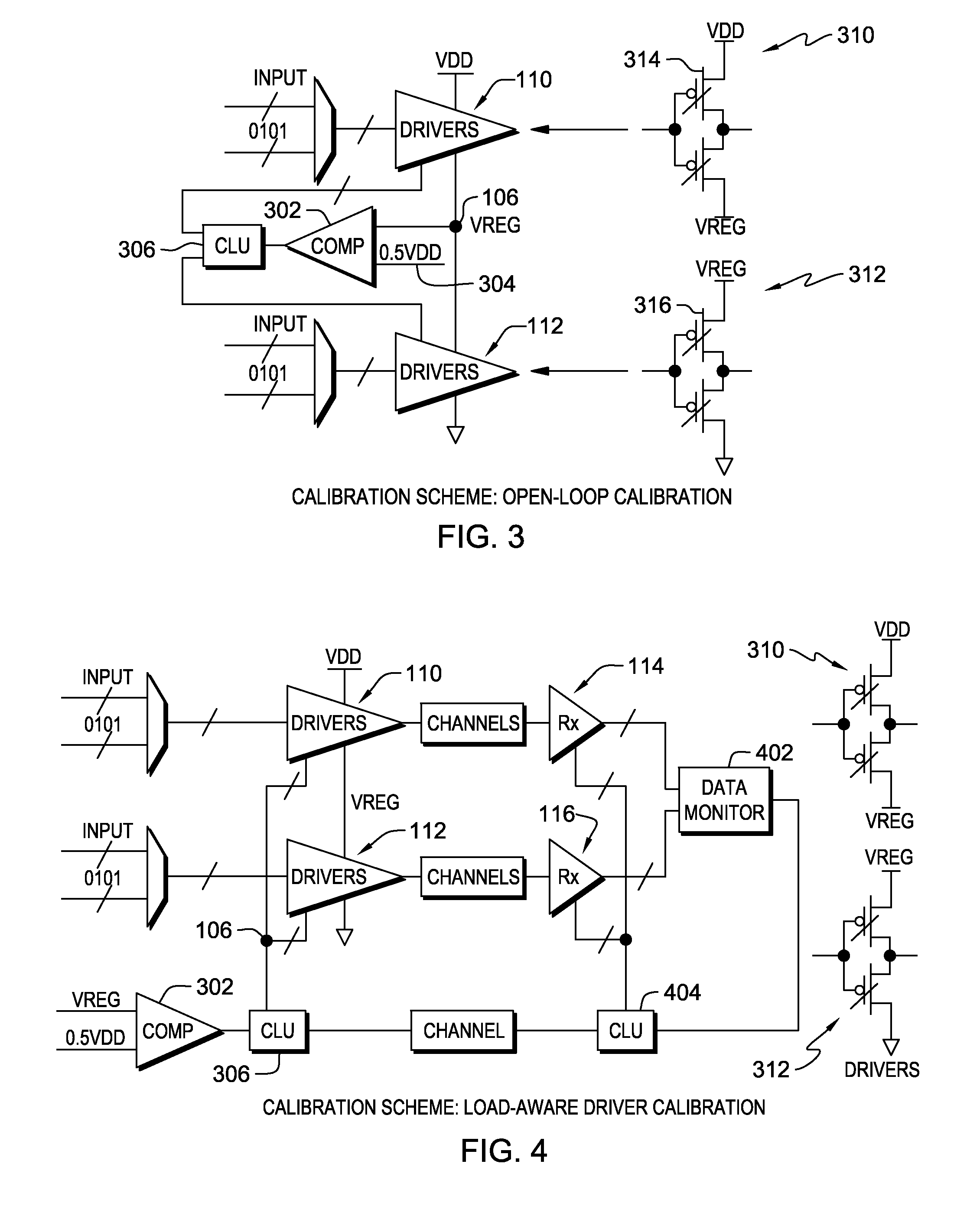

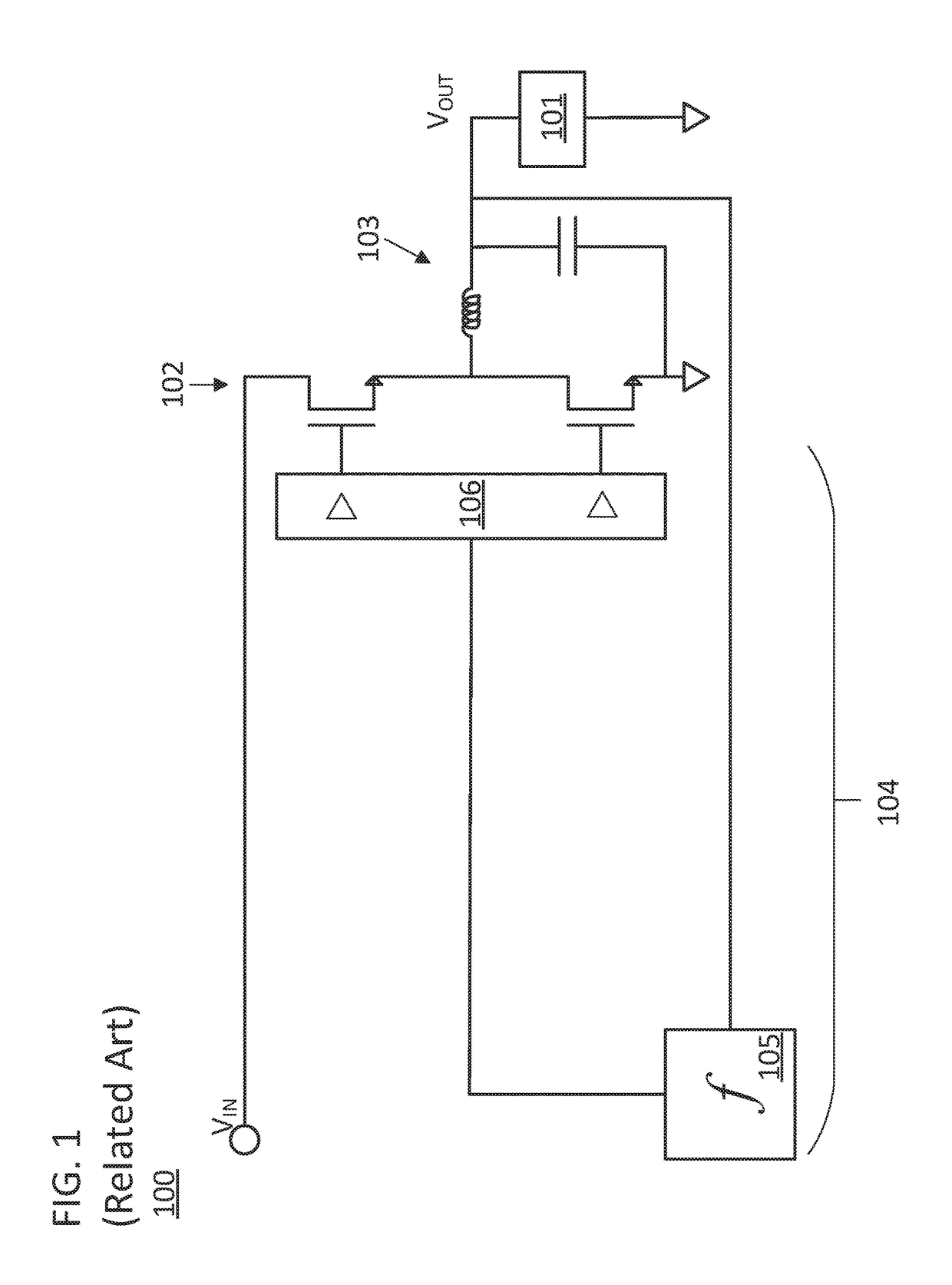

Calibration schemes for charge-recycling stacked voltage domains

ActiveUS20140176198A1Reduced strengthHigh strengthPower reduction by energy recoveryPower reduction by adiabatic operationVoltage regulationEngineering

A method and system are disclosed for calibrating a mid-voltage node in an integrated circuit including an input-output circuit having charge-recycling stacked voltage domains including at least first and second voltage domains. In one embodiment, the method comprises transmitting data through the input-output circuit, including transmitting a first portion of the data across the first voltage domain, and transmitting a second portion of the data across the second voltage domain. The method further comprises measuring a specified characteristic of the data transmitted through the input-output circuit; and based on the measured specified characteristic, adjusting a voltage of said mid-voltage node to a defined value. The voltage of the mid-voltage node may be adjusted to accomplish a number of objectives, for example, to achieve a desired trade-off between power and performance, or so that the two voltage domains have the same performance.

Owner:GLOBALFOUNDRIES US INC

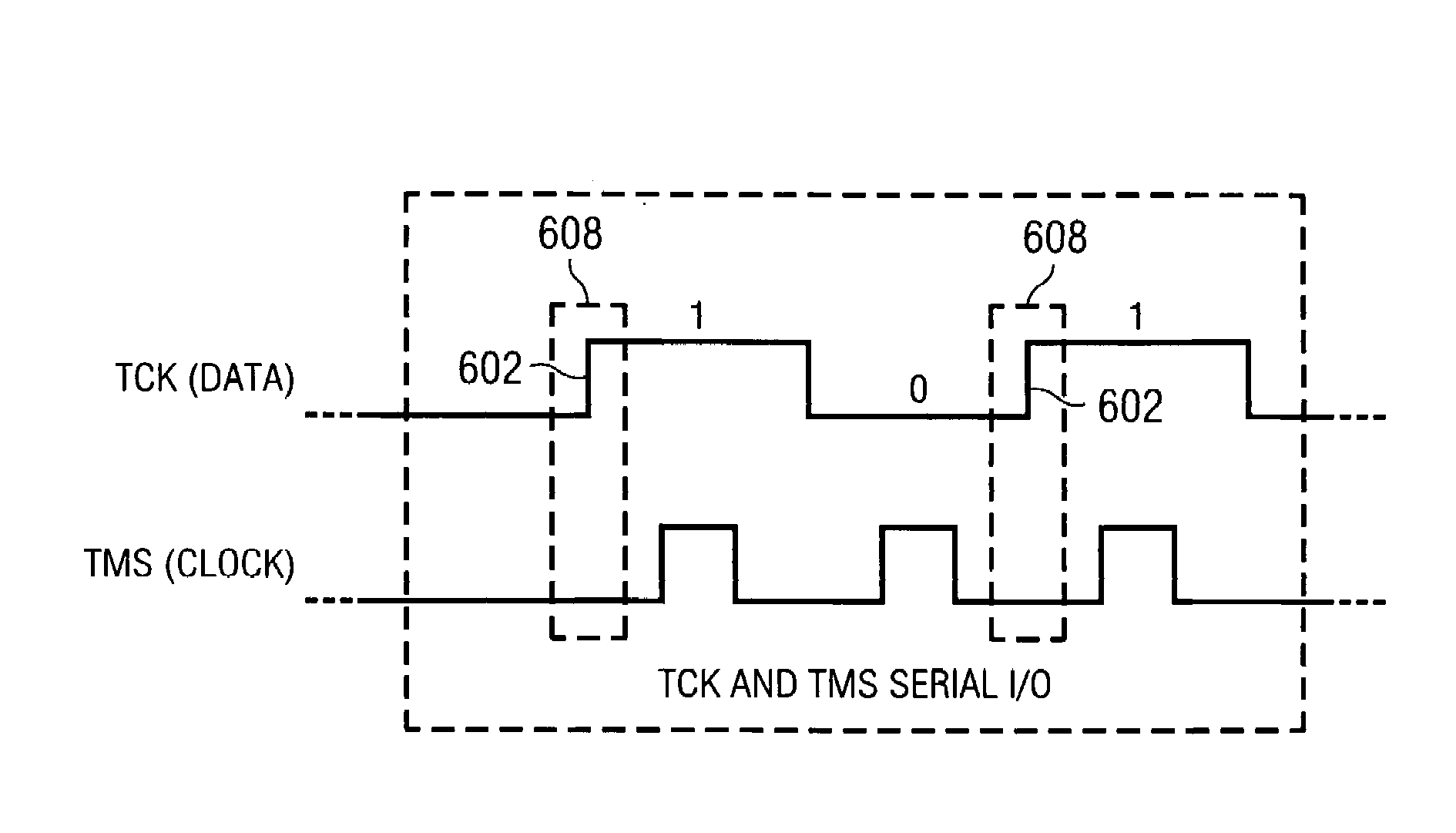

Serial data I/O on JTAG TCK with TMS clocking

ActiveUS7404128B2Electronic circuit testingGenerating/distributing signalsGeneral purposeData signal

The present disclosure describes a novel method and apparatus of using the JTAG TAP's TMS and TCK terminals as a general purpose serial Input / Output (I / O) bus. According to the present disclosure, the TAP's TMS terminal is used as a clock signal and the TCK terminal is used as a bidirectional data signal to allow serial communication to occur between; (1) an IC and an external controller, (2) between a first and second IC, or (3) between a first and second core circuit within an IC.

Owner:TEXAS INSTR INC

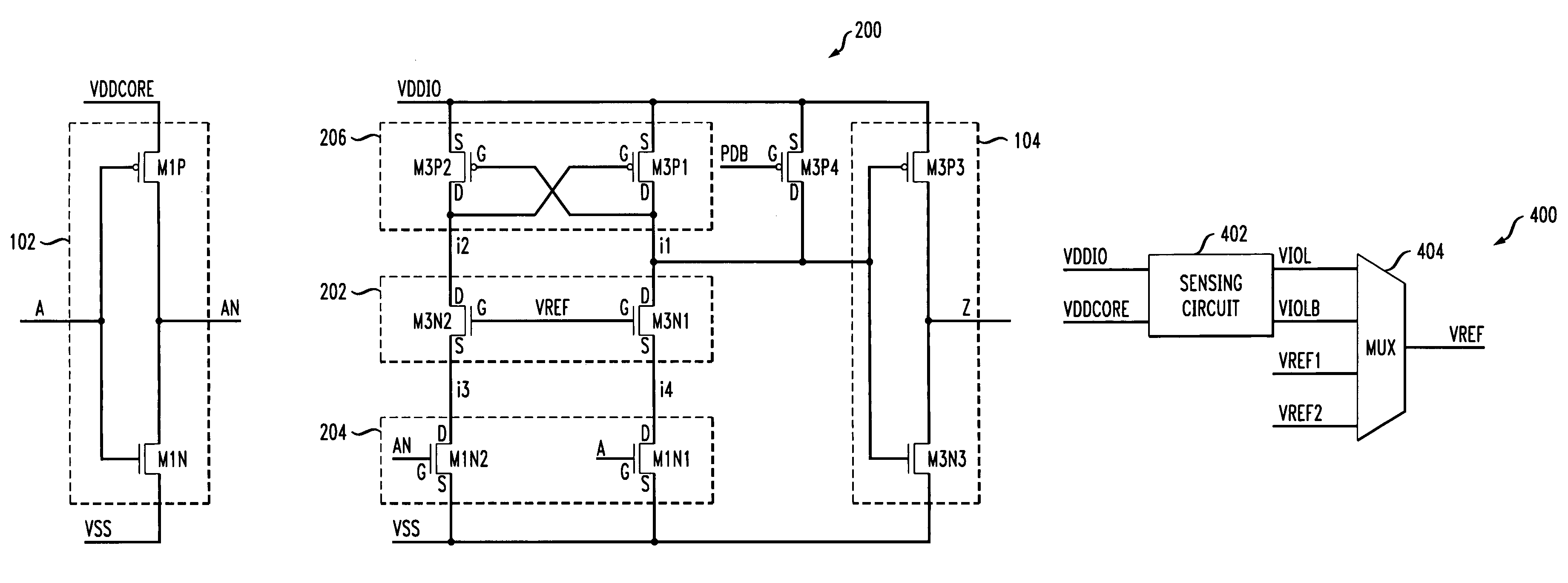

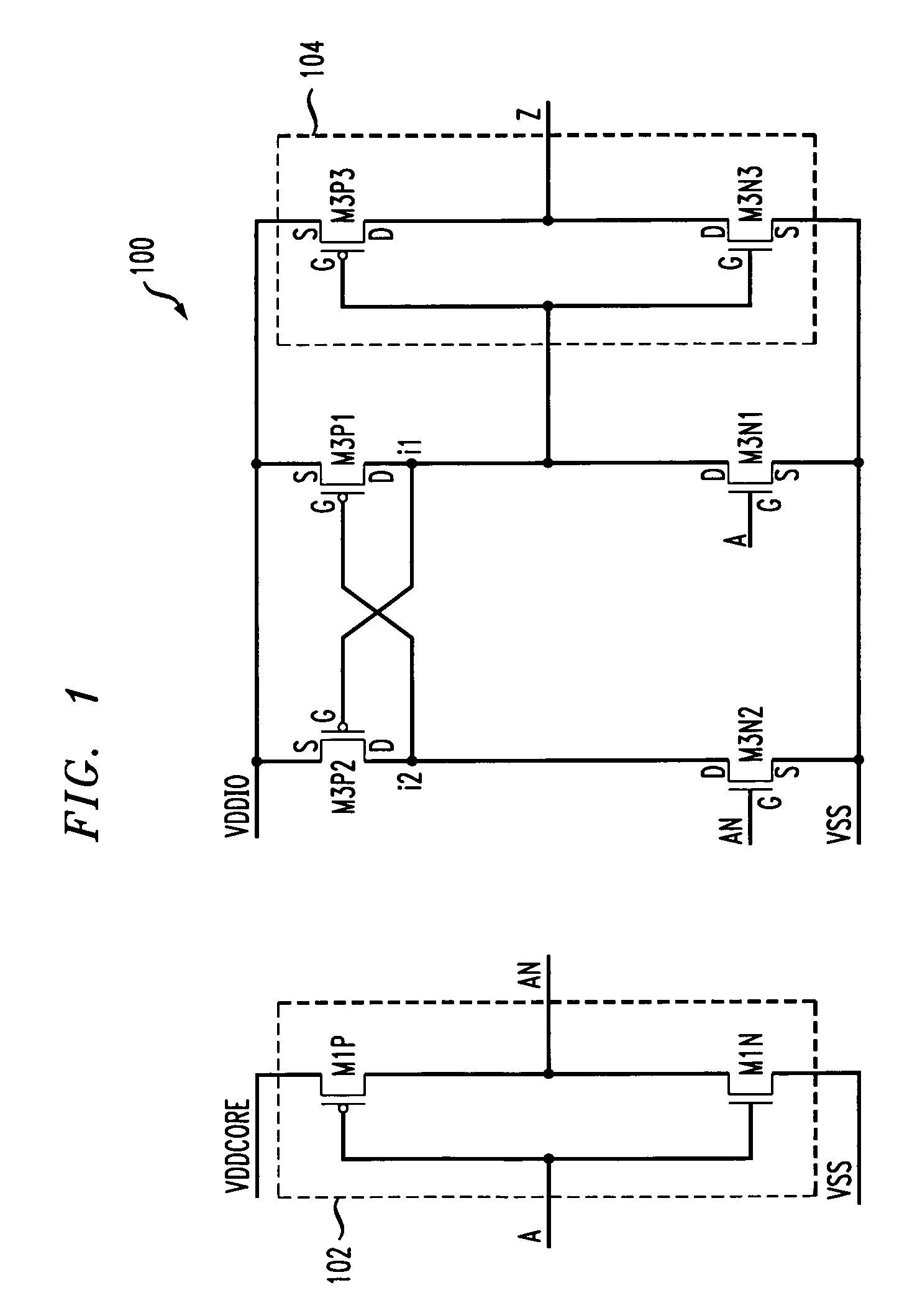

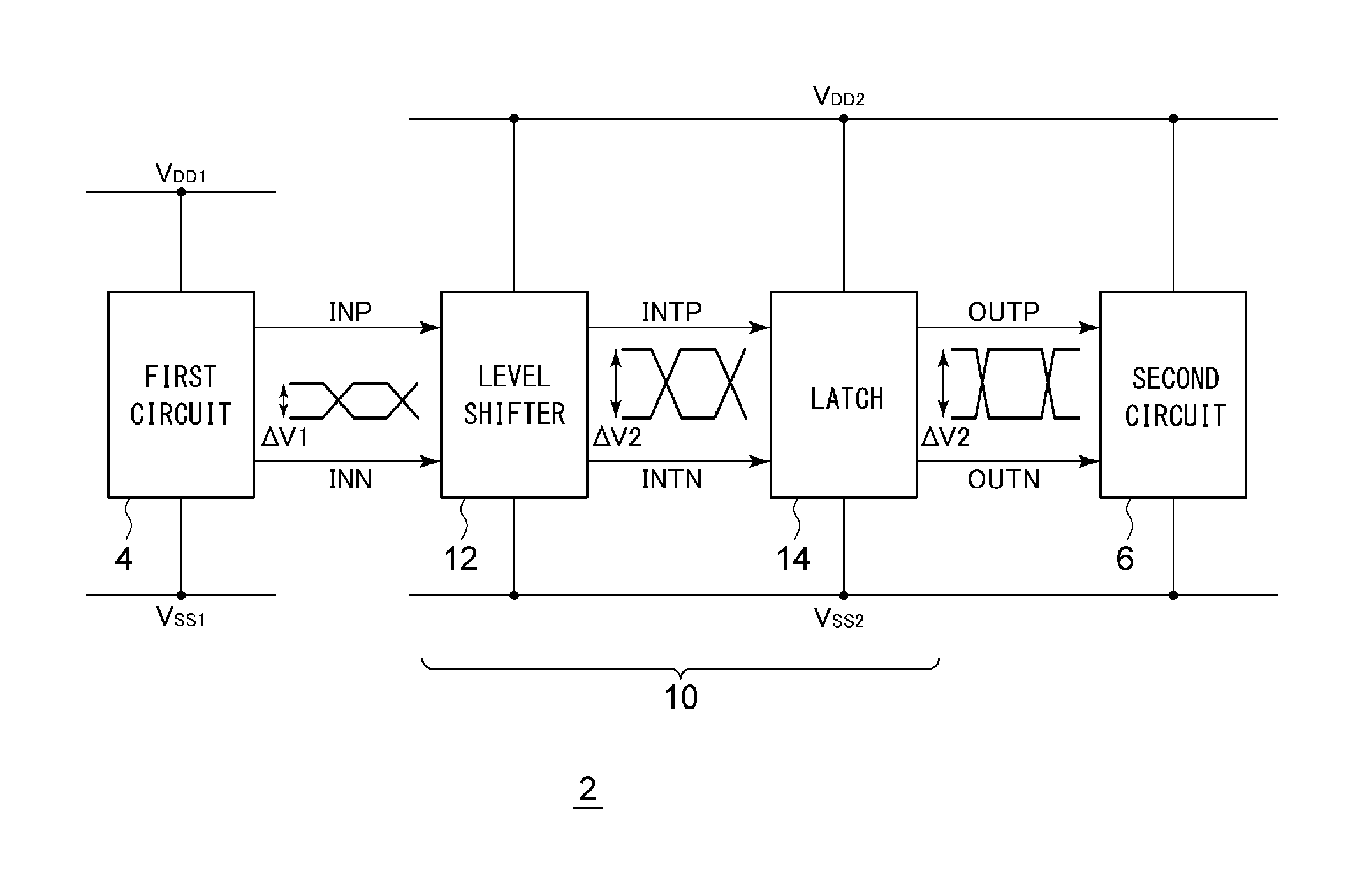

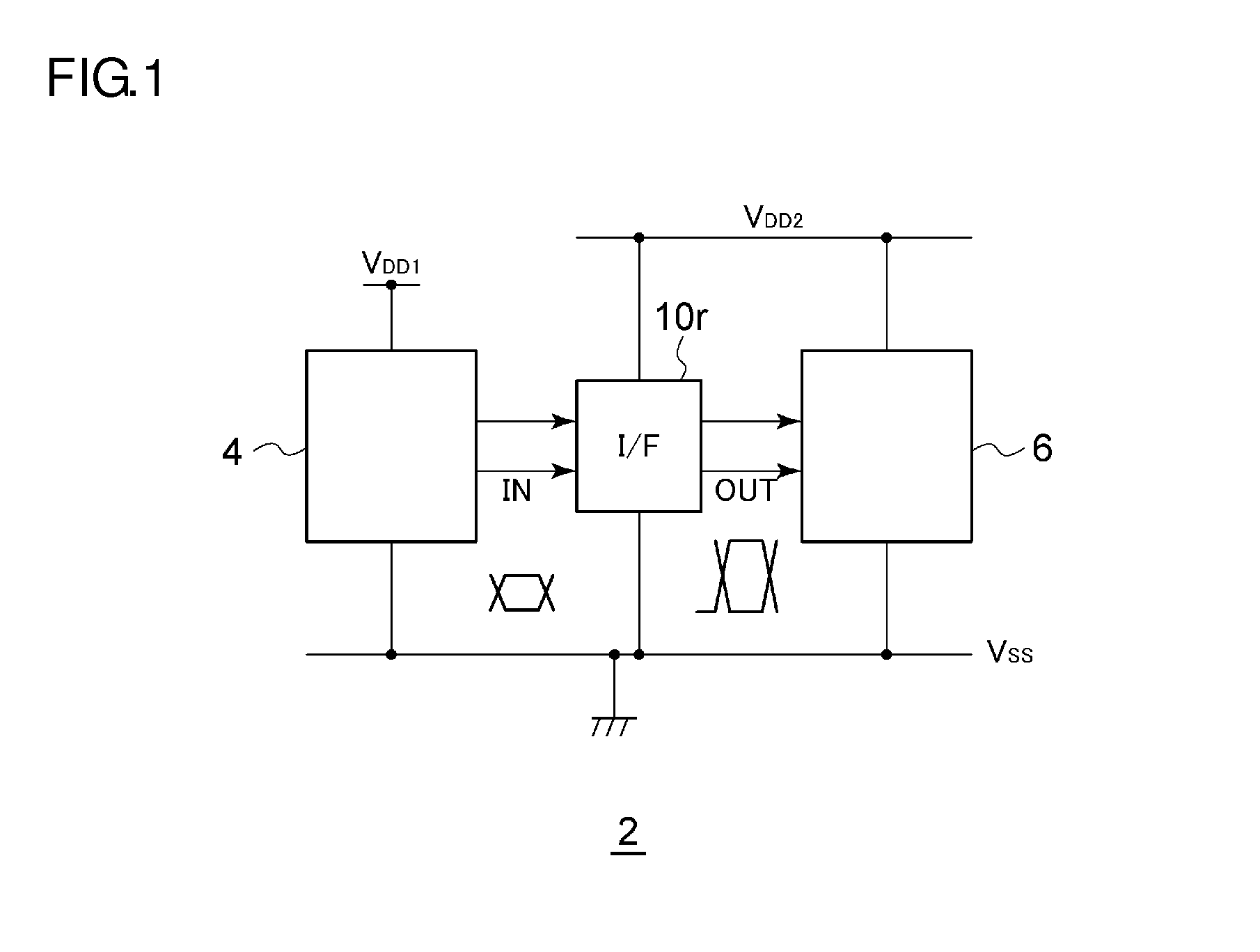

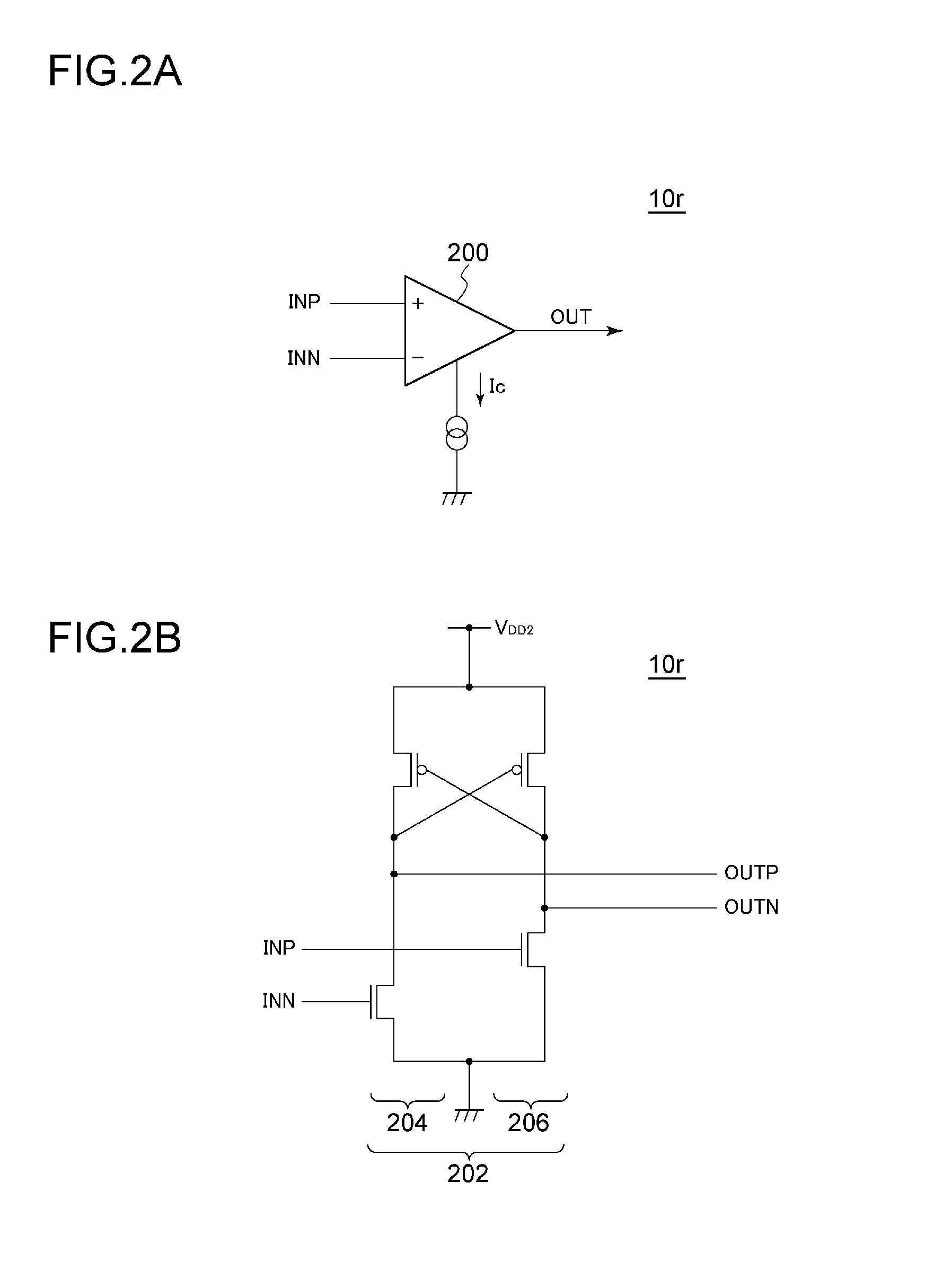

Interface circuit

ActiveUS20150381180A1Reduce power consumptionIncrease speedInput/output impedence modificationPulse automatic controlVoltage amplitudeCMOS

An interface circuit receives an input signal IN having a first voltage amplitude from a first circuit, and outputs an output signal OUT having a second voltage amplitude to a second circuit. A level shifter comprises a first CMOS inverter and a second CMOS inverter which are cross-coupled, and a current limiting circuit that limits a current that flows through the first CMOS inverter and the second CMOS inverter, and converts the input signal IN into an intermediate signal INT which is a differential signal. A latch circuit receives the intermediate signal INT from the level shifter, and switches its state according to the positive signal and the negative signal of the intermediate signal INT.

Owner:ROHM CO LTD

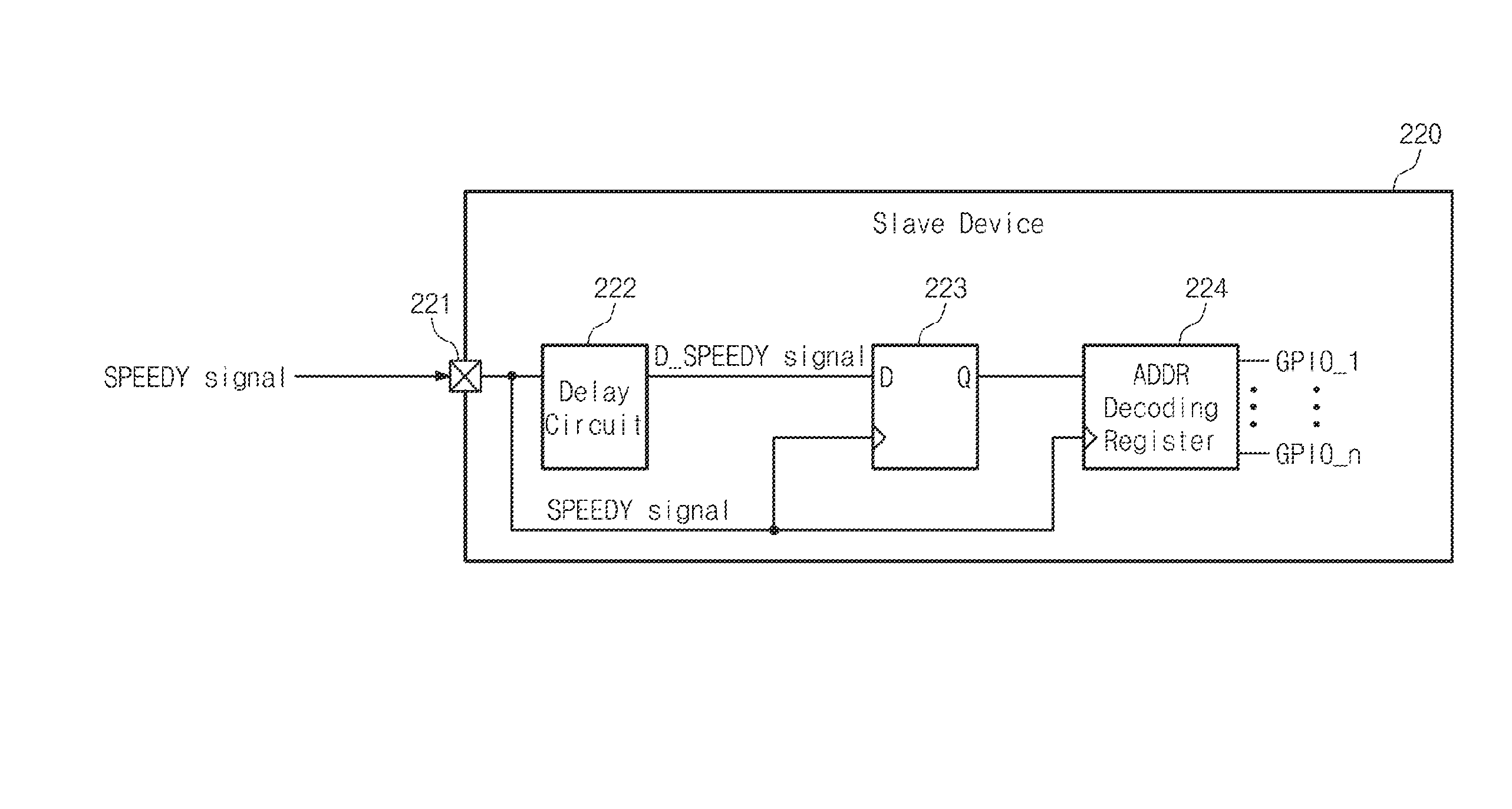

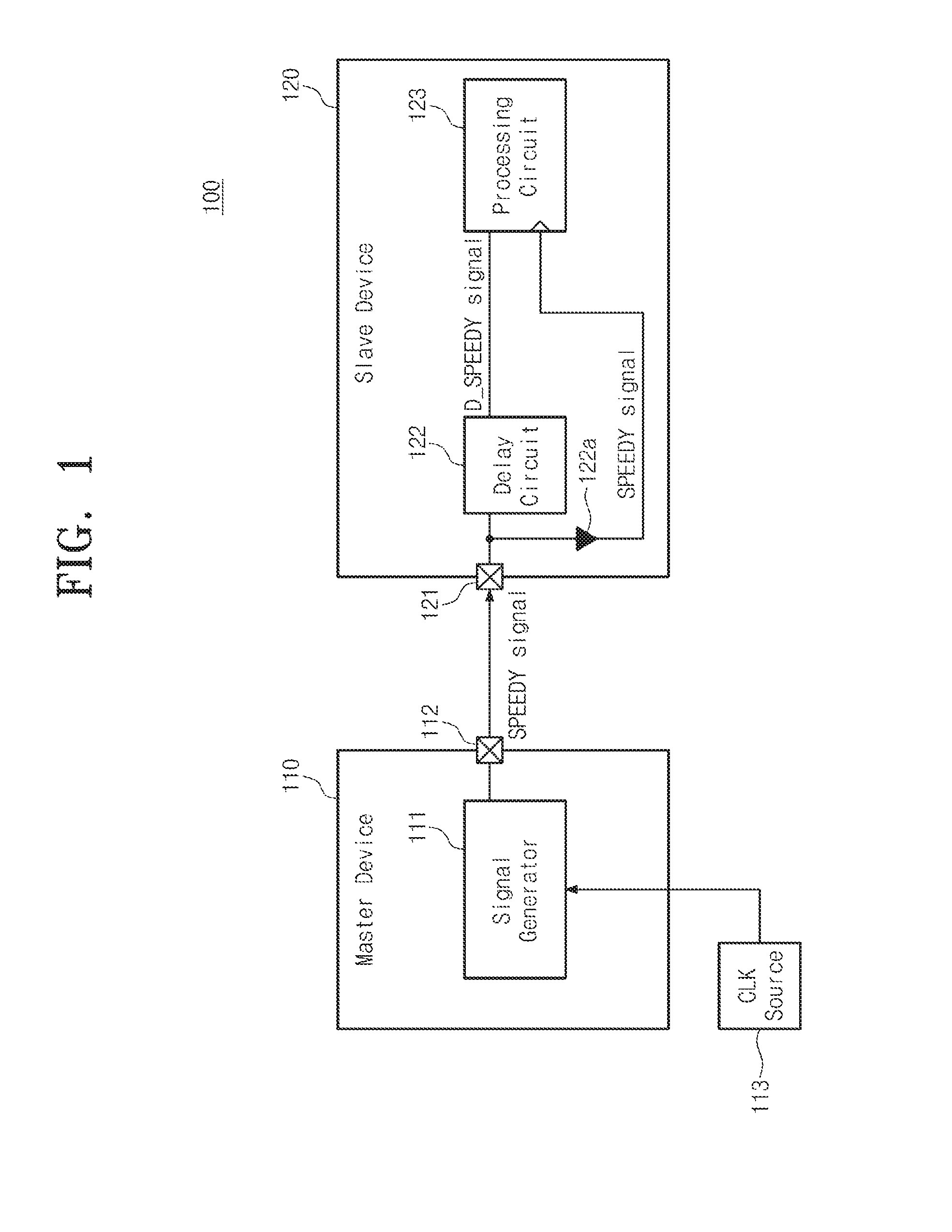

Device including a single wire interface and a data processing system having the same

ActiveUS20170060791A1Digital storageEnergy efficient computingData processing systemComputer science

A system including: a master device configured to generate a first signal having a periodic pulse, wherein the first signal includes data; and a slave device including a pin, a delay circuit, a buffer, and a processing circuit, wherein the slave device receives the first signal at the pin, delays the first signal with the delay circuit to generate a second signal having a first delay, delays the first signal with the buffer to generate a third signal having a second delay, and reads the data from the second signal using the third signal at the processing circuit.

Owner:SAMSUNG ELECTRONICS CO LTD

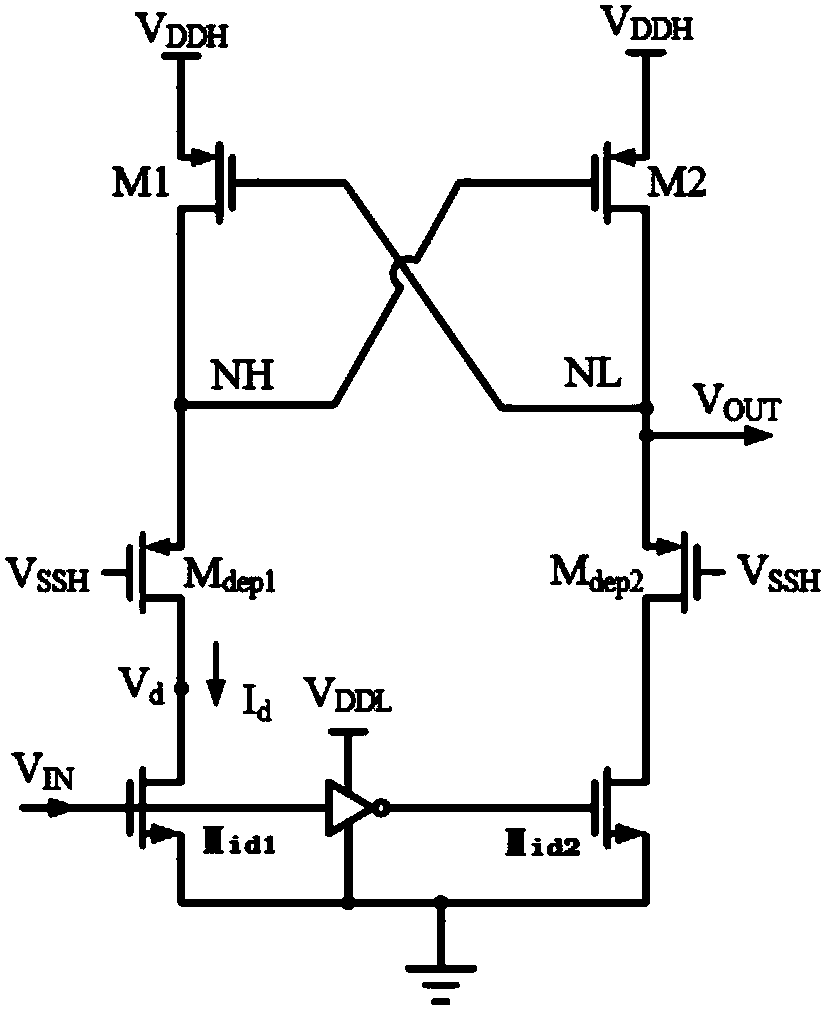

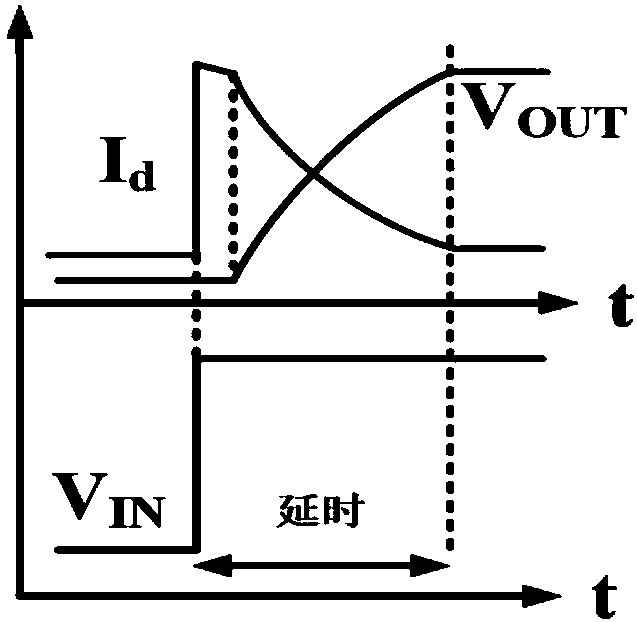

High-speed high-voltage level conversion circuit applied to GaN gate drive

ActiveCN108155903ASmall sizeReduce power consumptionLogic circuit interface arrangementsEngineeringP channel

The invention discloses a high-speed high-voltage level conversion circuit applied to a GaN gate drive. The high-speed high-voltage level conversion circuit comprises an input circuit, a first PMOS (P-channel Metal Oxide Semiconductor) transistor, a level conversion circuit and a shaping circuit, wherein a first end of the input circuit is connected to a first end of the level conversion circuit at a first node; a second end of the input circuit is connected to a drain electrode of the first PMOS transistor at a second node; a gate electrode of the first PMOS transistor is connected to a firstpower line; a source electrode of the first PMOS transistor is connected to a second end of the level conversion circuit at a third node; the level conversion circuit is connected to a second power line; a second end of the level conversion circuit is connected to an input end of the shaping circuit at the third node; the shaping circuit is connected to the first power line and the second power line; an output end of the shaping circuit is connected to a first end of a power device at a fourth node; and the power device is connected to the first power line and the third power line.

Owner:拓尔微电子股份有限公司

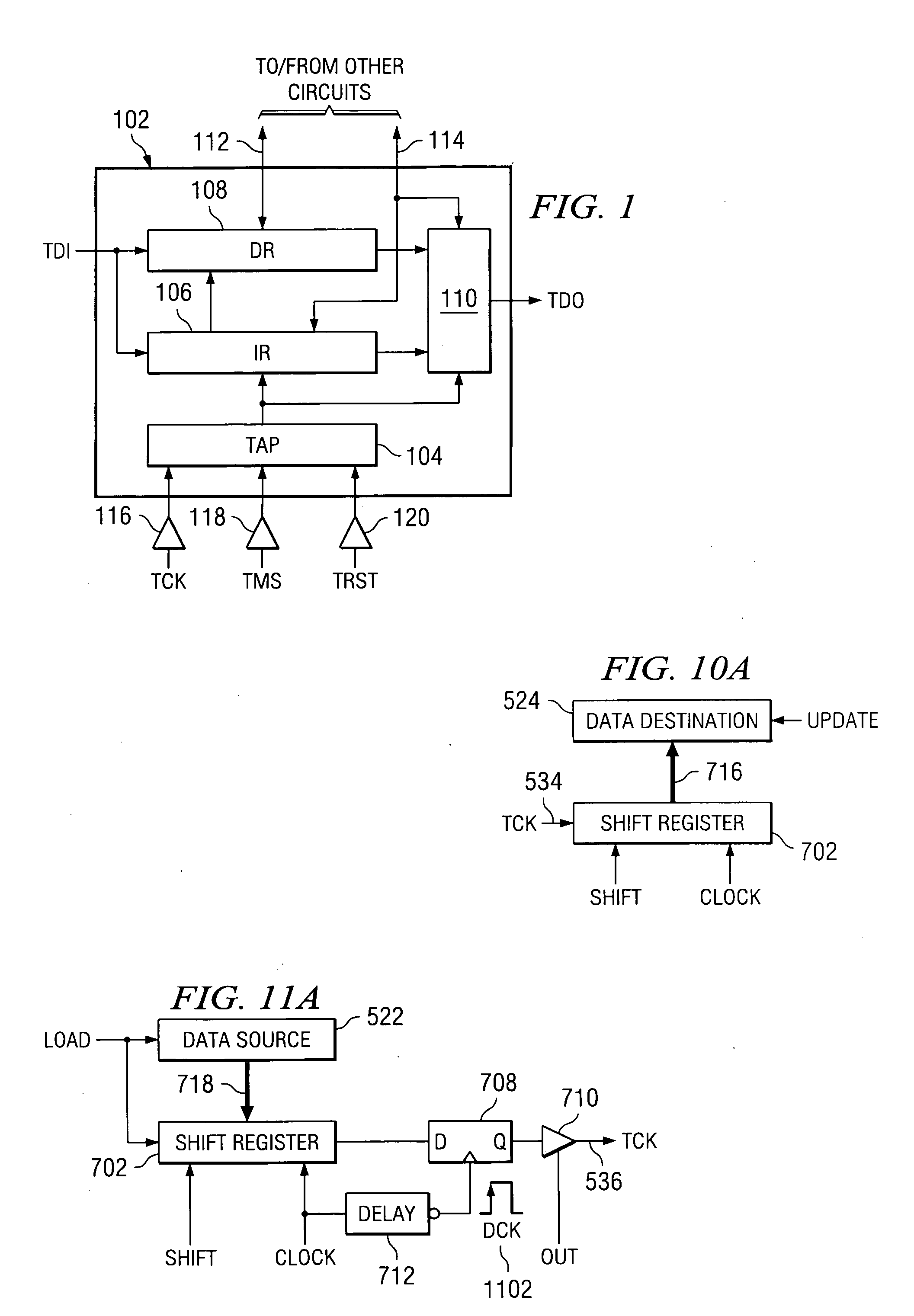

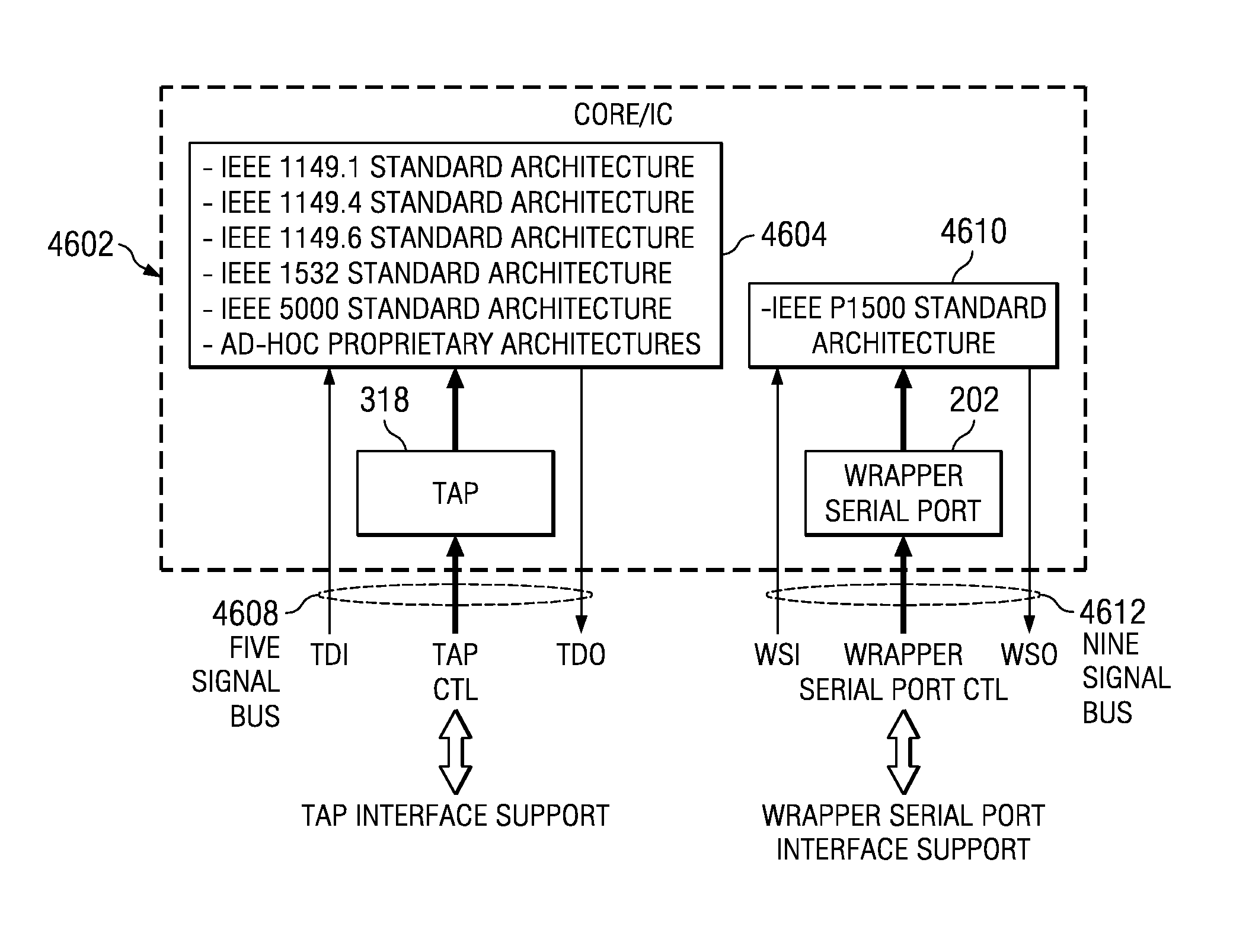

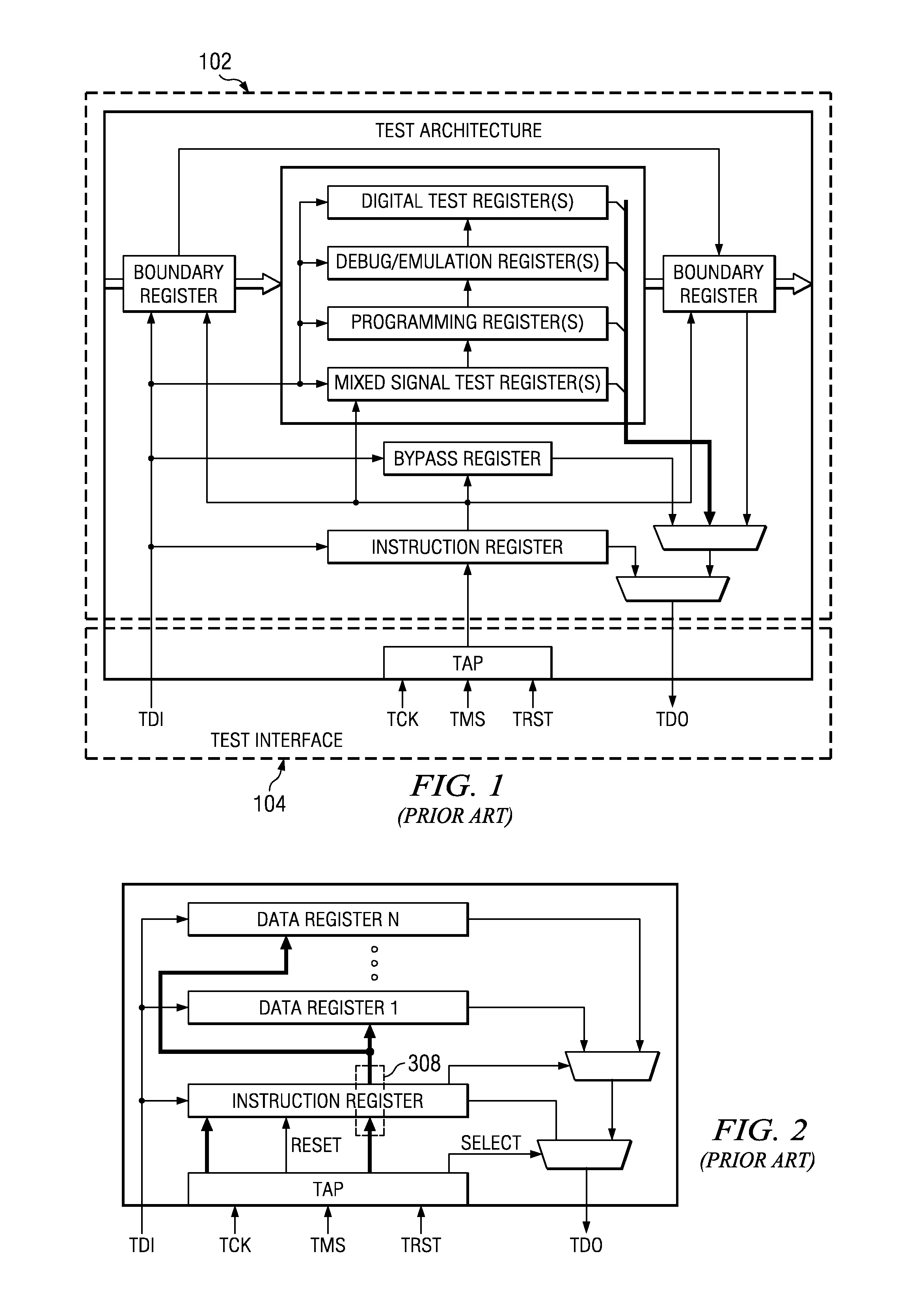

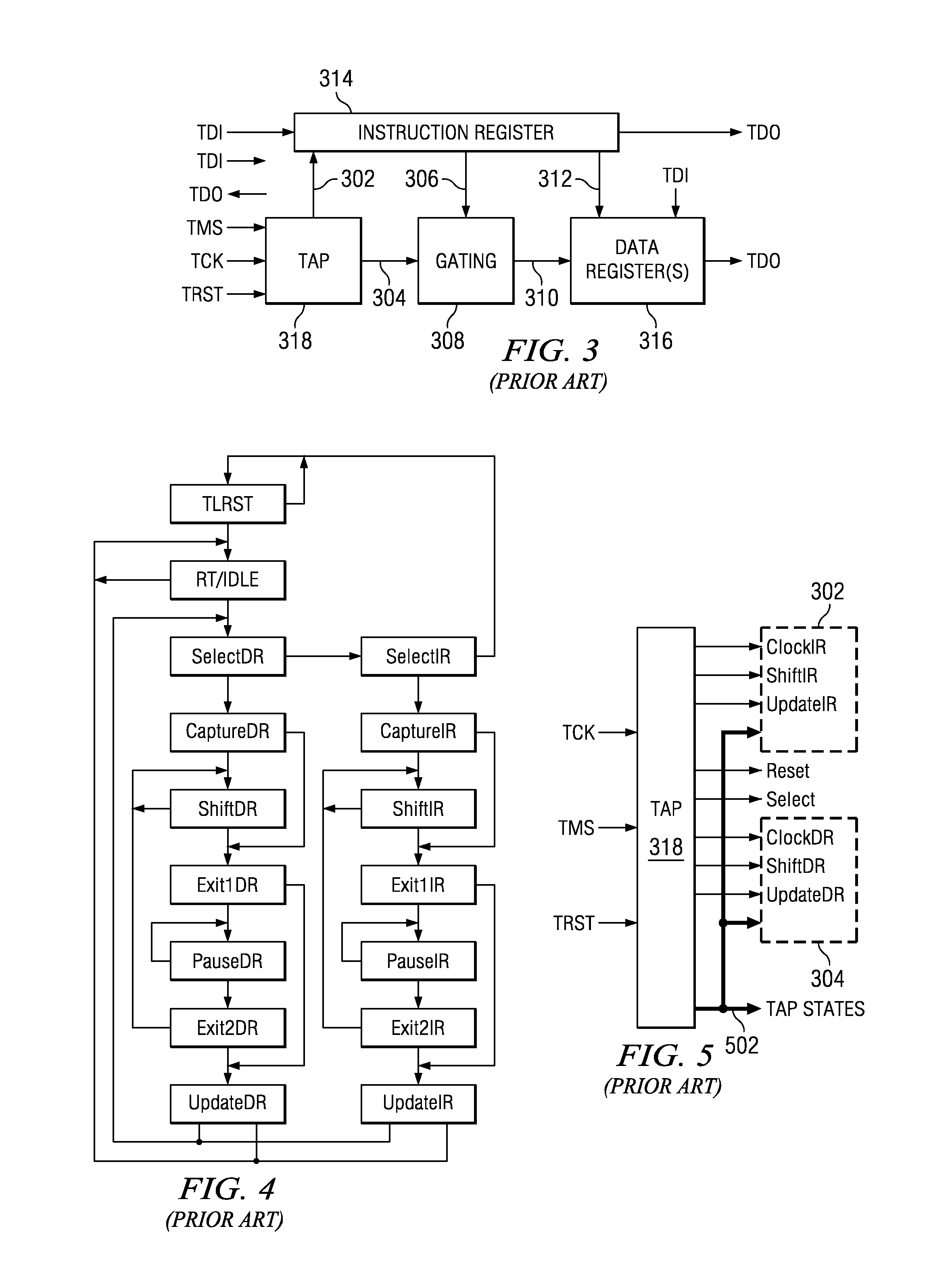

IEEE 1149.1 and p1500 test interfaces combined circuits and processes

ActiveUS20080250287A1Electronic circuit testingGenerating/distributing signalsComputer hardwareControl signal

In a first embodiment a TAP of IEEE standard 1149.1 is allowed to commandeer control from a WSP of IEEE standard P1500 such that the P1500 architecture, normally controlled by the WSP, is rendered controllable by the TAP. In a second embodiment (1) the TAP and WSP based architectures are merged together such that the sharing of the previously described architectural elements are possible, and (2) the TAP and WSP test interfaces are merged into a single optimized test interface that is operable to perform all operations of each separate test interface. One approach provides for the TAP to maintain access and control of the TAP instruction register, but provides for a selected data register to be accessed and controlled by either the TAP+ATC or by the discrete CaptureDR, UpdateDR, TransferDR, ShiftDR, and ClockDR WSP data register control signals.

Owner:TEXAS INSTR INC

Bi-directional signal level shift circuit

InactiveUS20050122154A1Less spaceSmall sizePulse automatic controlLogic circuits coupling/interface with bidirectional operationEngineeringOperating voltage

A circuit for shifting a level between two bidirectional signals having different voltage levels. The circuit includes a first analog switch including a first switching control terminal connected to first directional signal stage, a first input terminal connected to a first level of operating voltage, and a first output terminal connected to a second directional signal stage, for performing a switching operation for the first input terminal and the first output terminal based on a state of logic level of a signal from the second directional signal stage. The circuit also includes a second analog switch including a second switching control terminal connected to the first directional signal stage, a second input terminal connected to a second level of operating voltage, and a second output terminal connected to the first directional signal stage for performing a switching operation for the second input terminal and the second output terminal based on a state of a logic level of a signal from the first directional signal stage.

Owner:SAMSUNG ELECTRONICS CO LTD

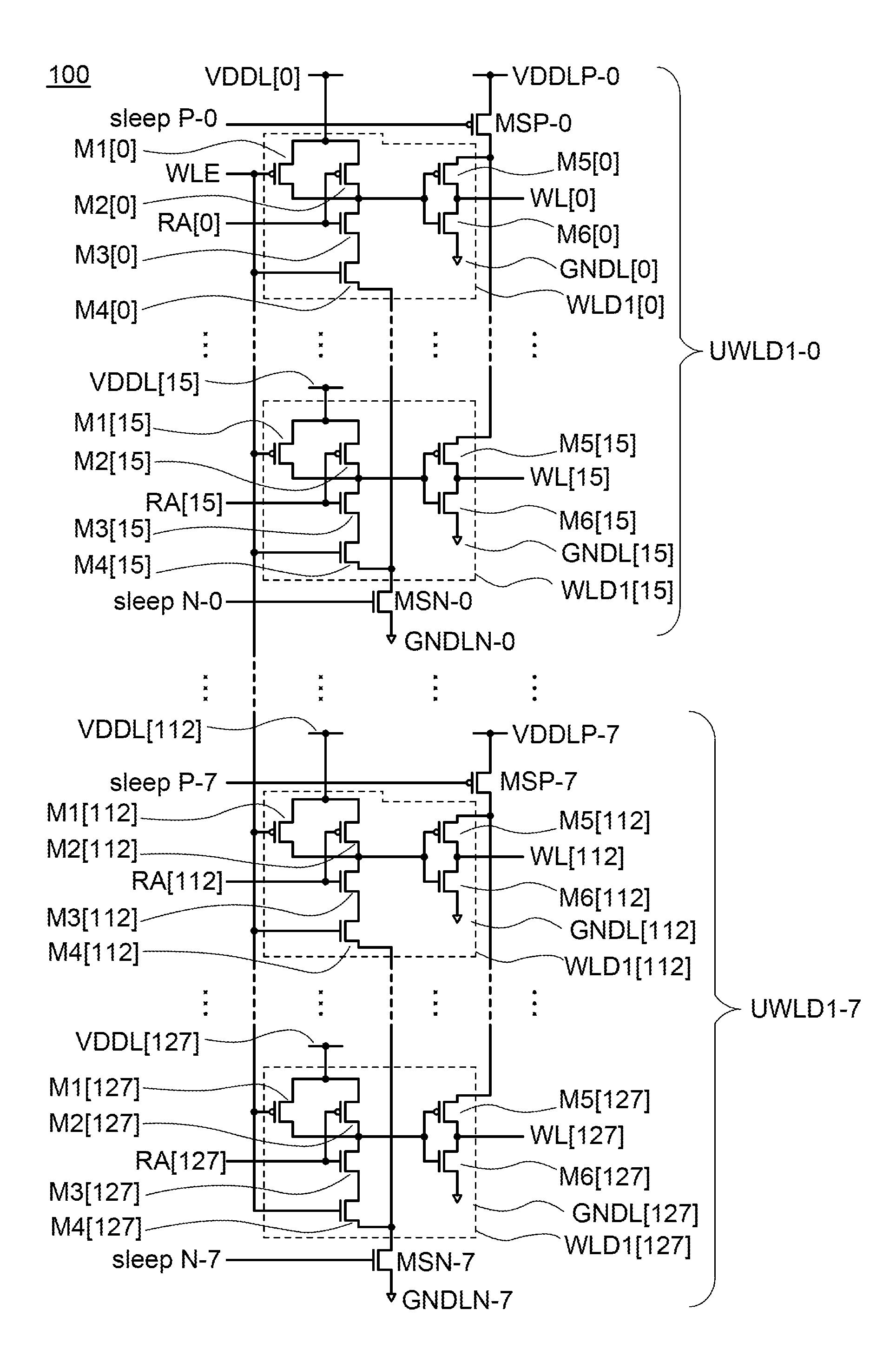

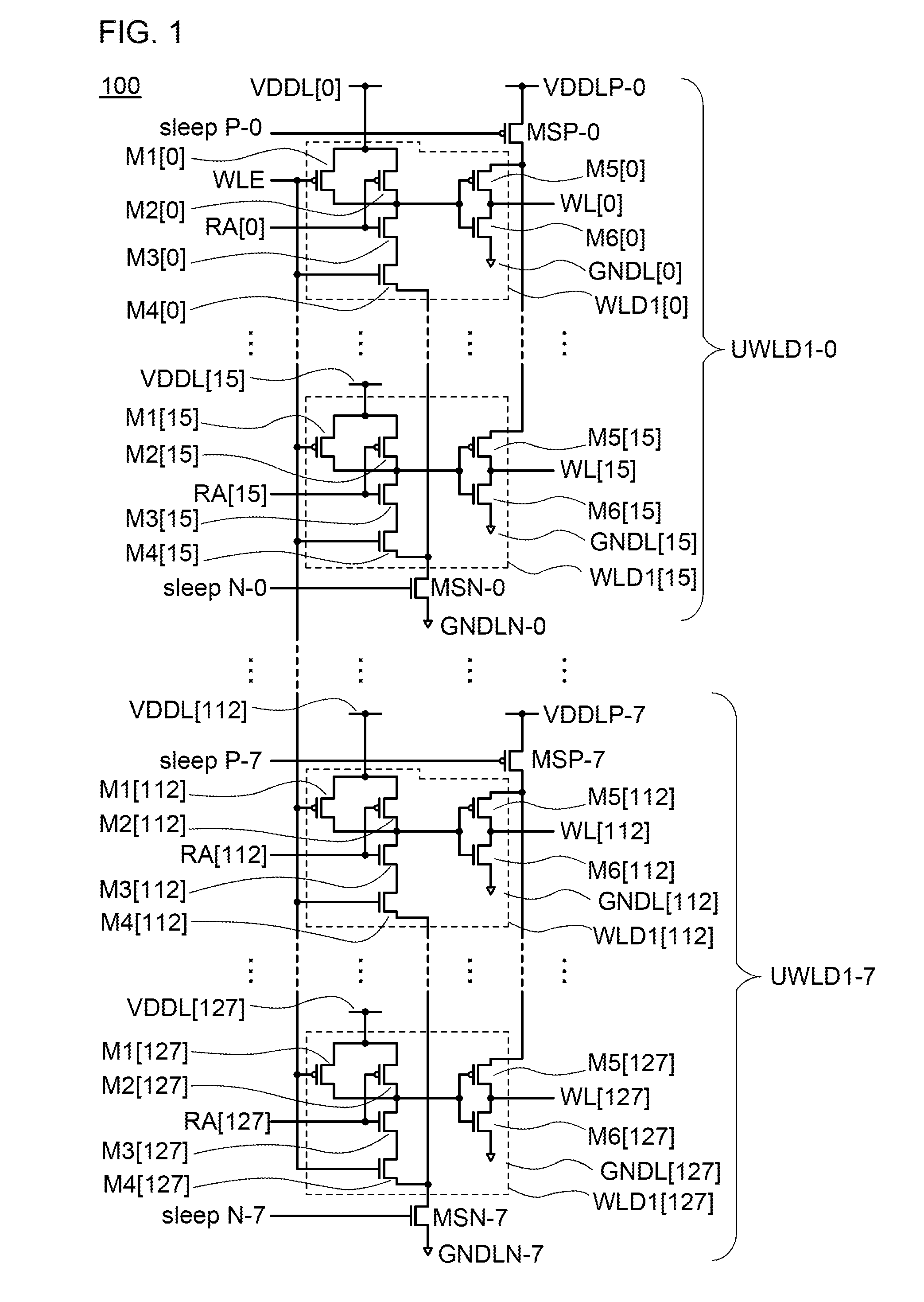

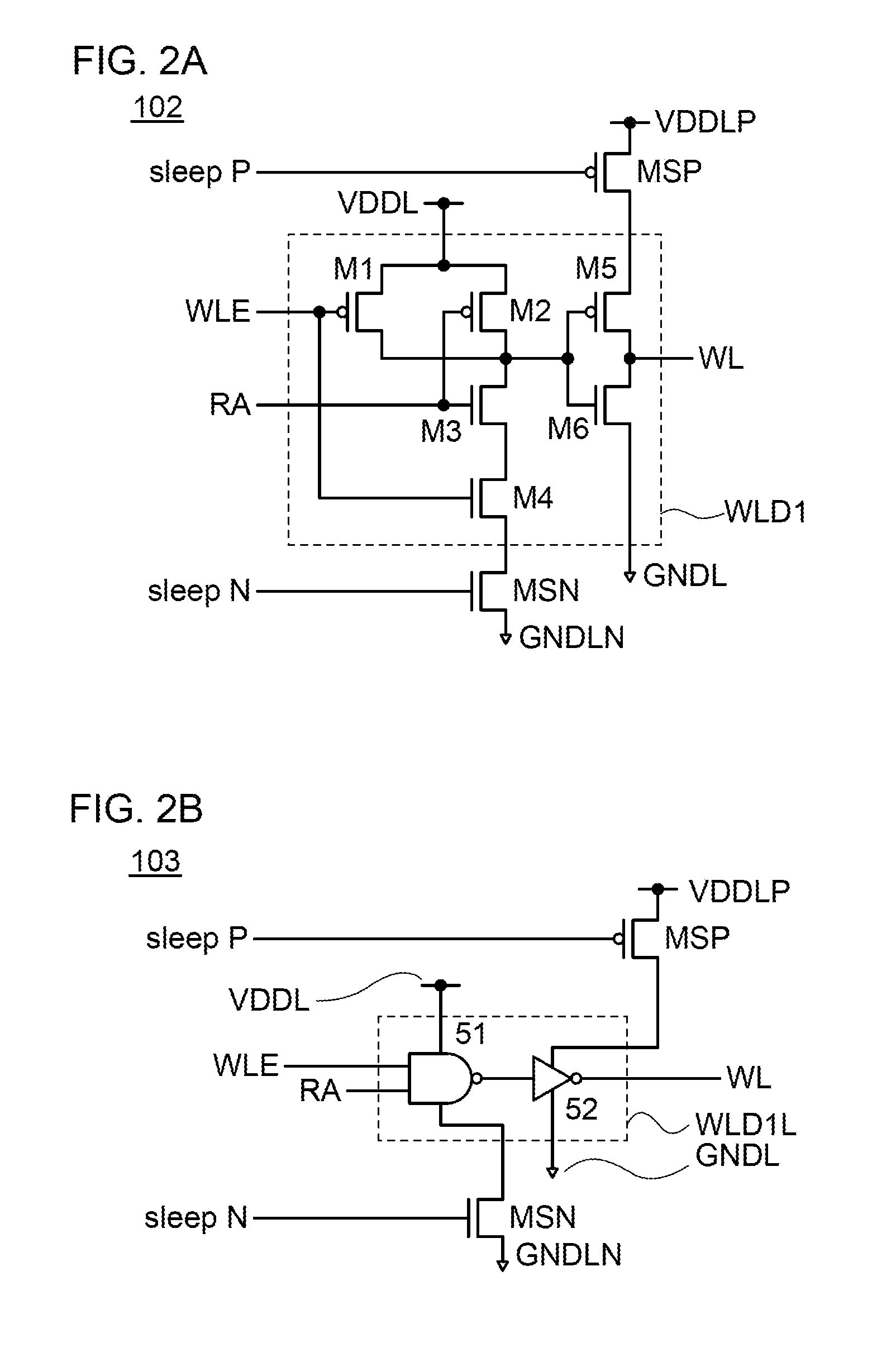

Semiconductor device or electronic device including the same

ActiveUS20160233866A1Reduce power consumptionSmall sizePower consumption reductionDigital storagePower semiconductor deviceDriver circuit

A semiconductor device with lower power consumption and an electronic device including the same are provided. To reduce leakage current flowing in a word line driver circuit, a switching element is provided, specifically, between the word line driver circuit and a high or low voltage power source. When there is no memory access, the switching element is turned off, thereby interrupting application of voltage (or current) from the high or low voltage power source to the word line driver circuit. Furthermore, to reduce the stand-by power due to precharge of a bit line, a switching element is provided in a bit line driver circuit, specifically, between the bit line and a high or low voltage power source. When there is no memory access, the switching element is turned off, thereby interrupting application of voltage (or current) from the high or low voltage power source to the bit line driver circuit.

Owner:SEMICON ENERGY LAB CO LTD

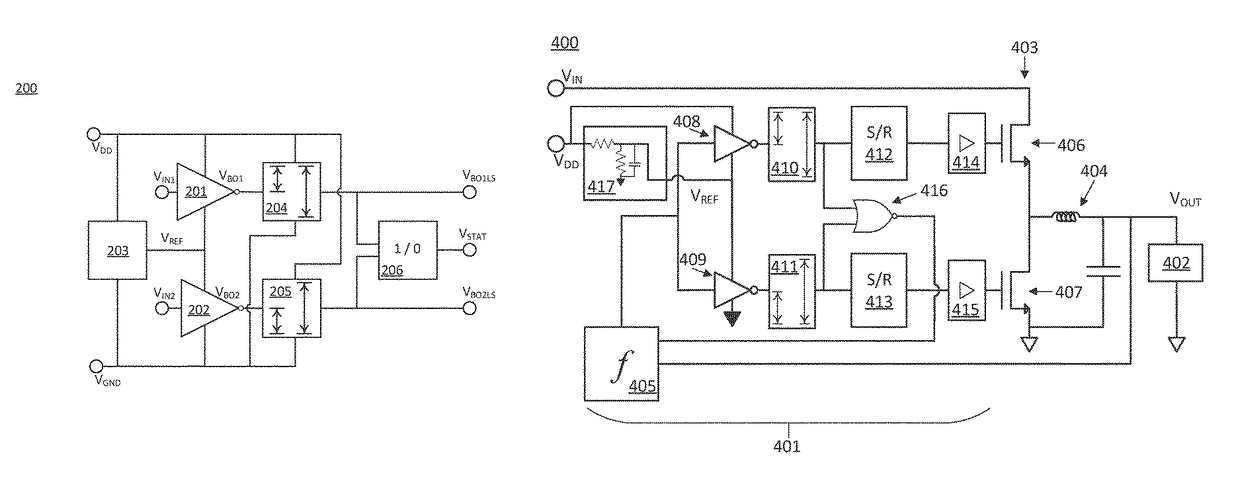

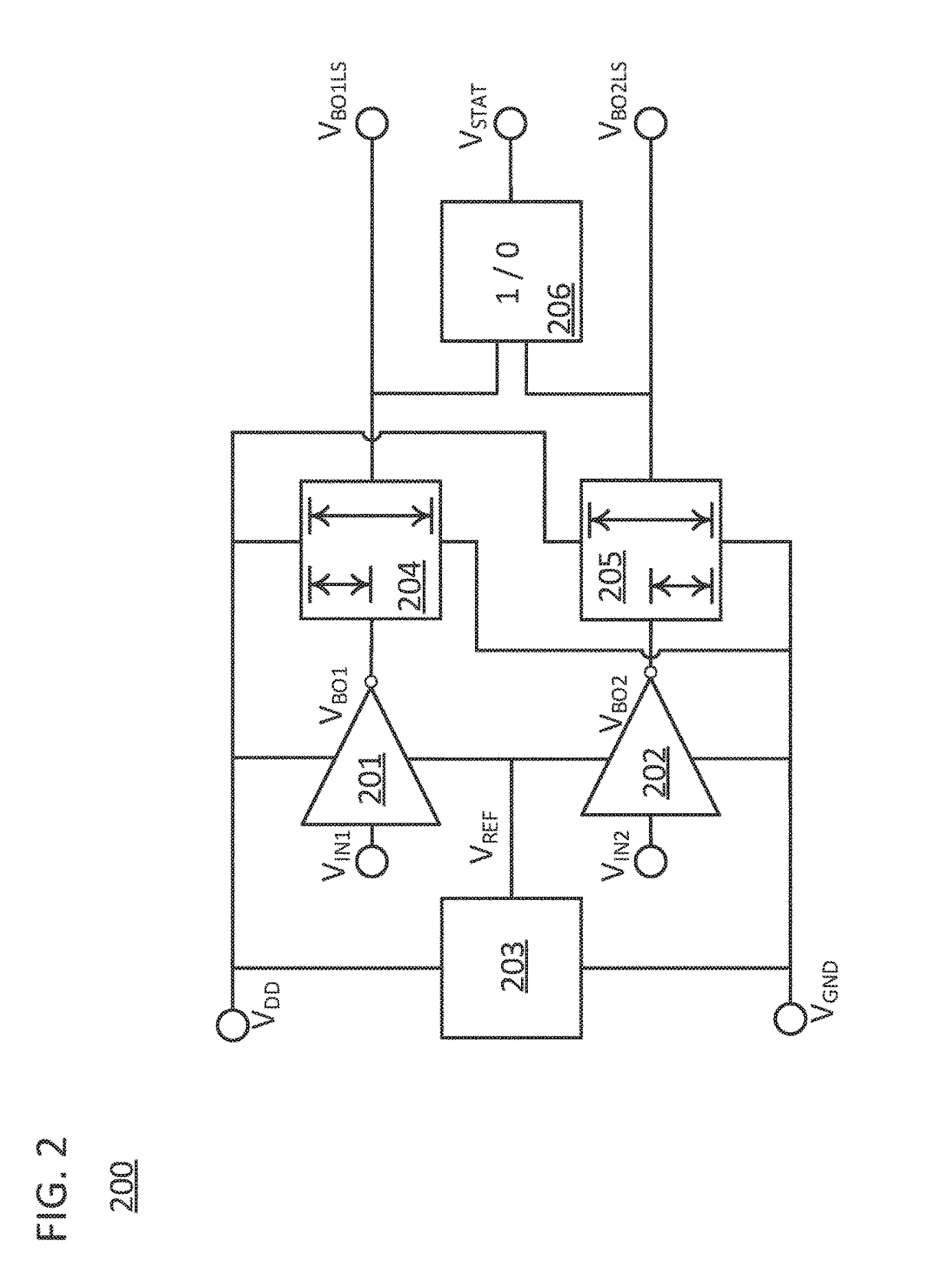

High speed tri-level input power converter gate driver

ActiveUS9712058B1Efficient power electronics conversionDc-dc conversionLevel shiftingVoltage reference

Various methods and devices that involve electronic circuits are disclosed. A disclosed method includes buffering an input signal using a first buffer. The first buffer is powered by a supply voltage and a reference voltage. The method also includes buffering the input signal using a second buffer. The second buffer is powered by the reference voltage and a ground voltage. The method also includes level shifting a first buffer output signal of the first buffer to a voltage range using a first level shifter, and level shifting a second buffer output signal of the second buffer to the voltage range using a second level shifter. The voltage range is larger than a delta between the supply voltage and the reference voltage. The reference voltage is greater than one quarter of the supply voltage and less than three quarters of the supply voltage.

Owner:SILANNA ASIA

Popular searches

Transmission line coupling arrangements Stereophonic circuit arrangements Microphones signal combination Loudspeaker signals distribution Line-transmission Logic circuits using elementary logic circuit components Input/output processes for data processing Electrical testing Secondary cells Safety/protection battery circuits