Patents

Literature

72results about "Logic circuits coupling/interface with bidirectional operation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

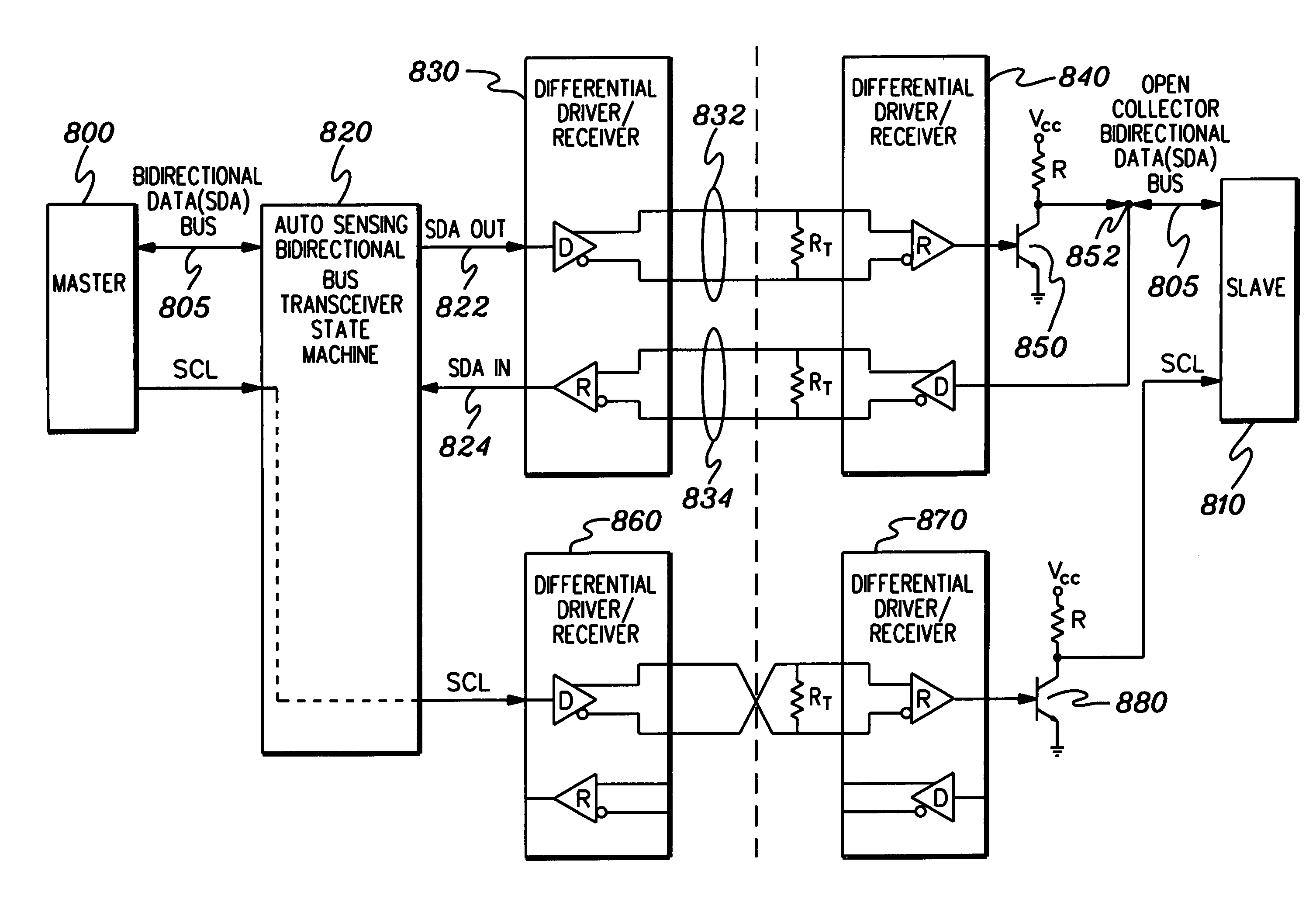

System, method and program product for extending range of a bidirectional data communication bus

InactiveUS7088137B2Logic circuits coupling/interface with bidirectional operationRepeater/relay circuitsCommunications systemControl line

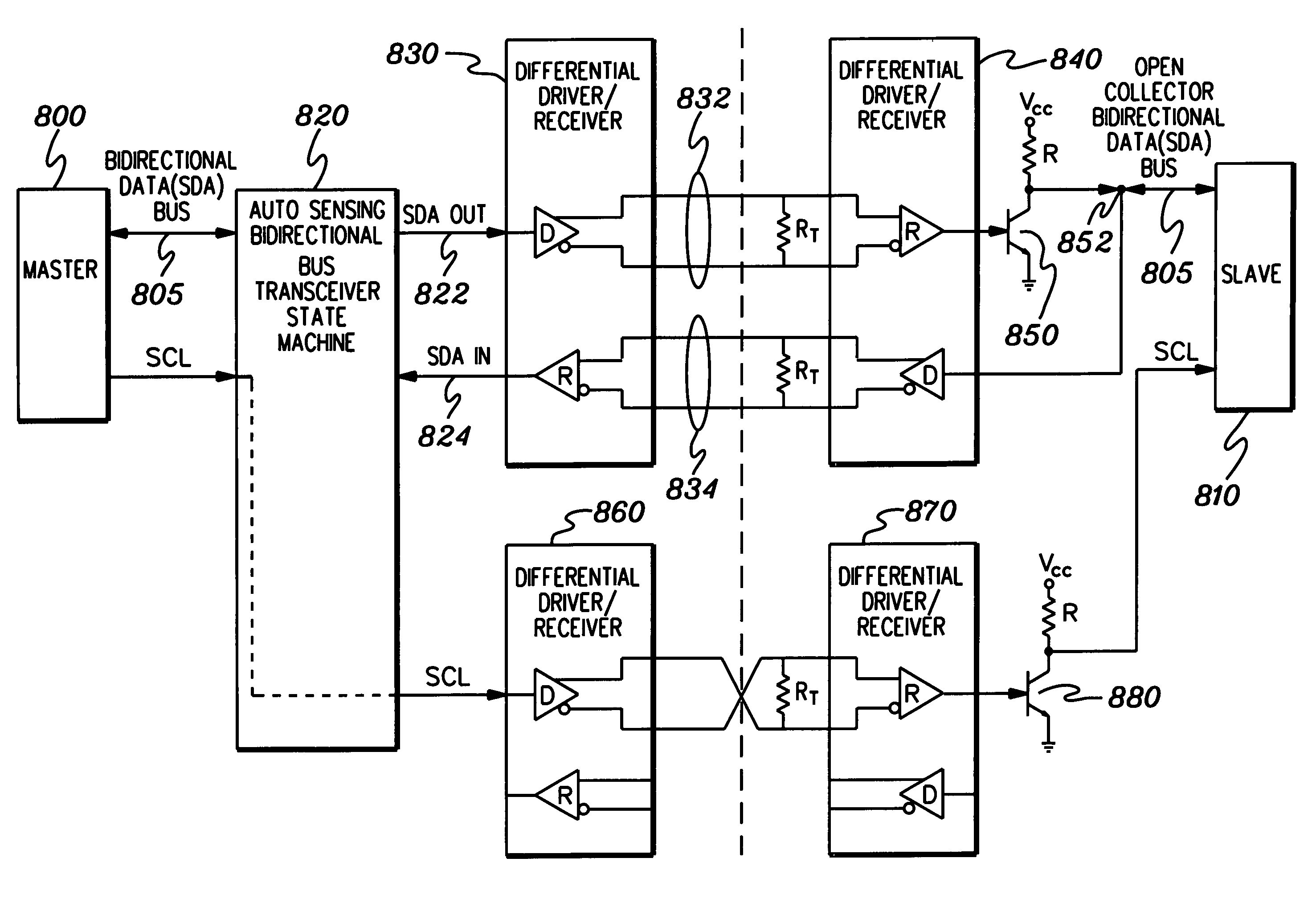

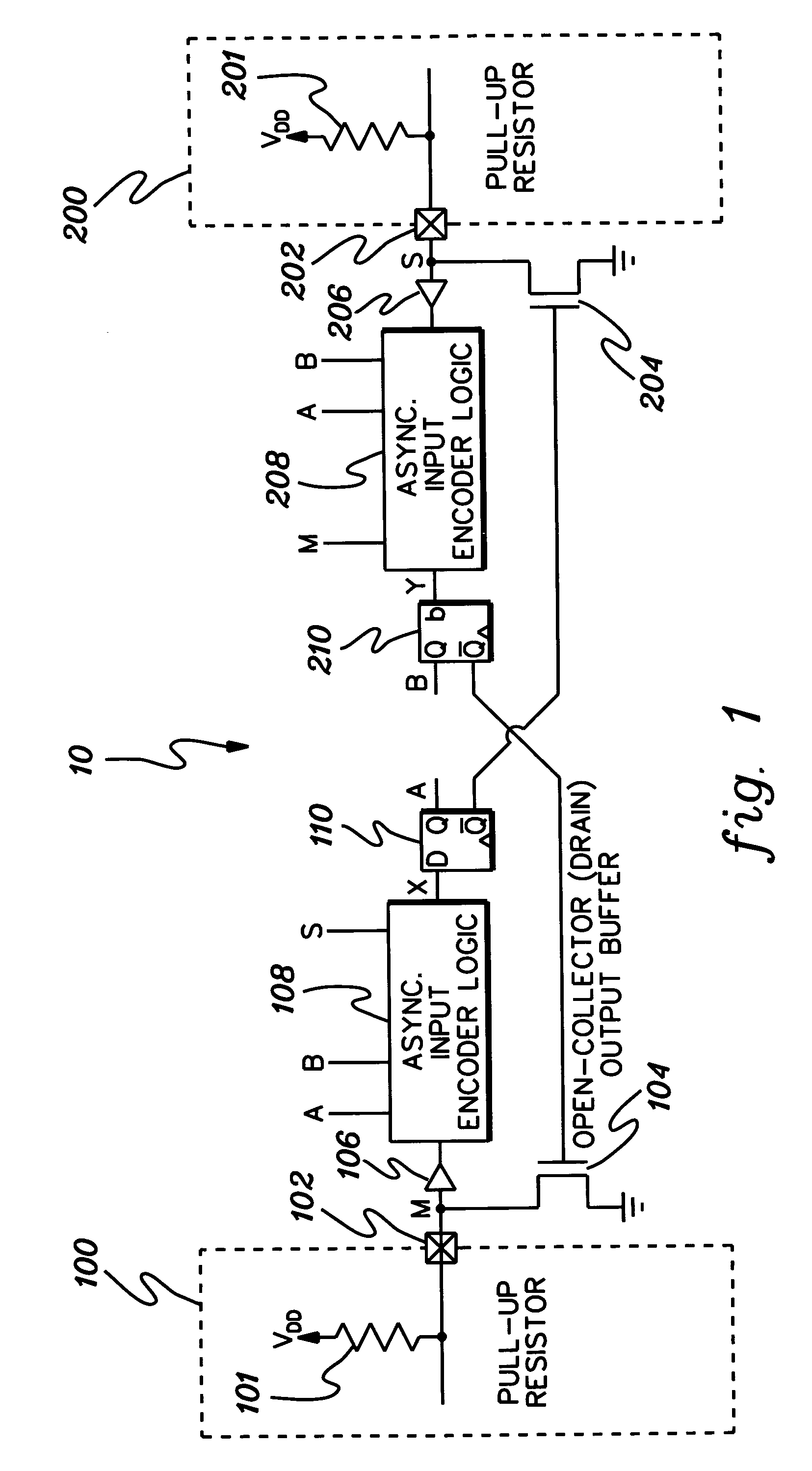

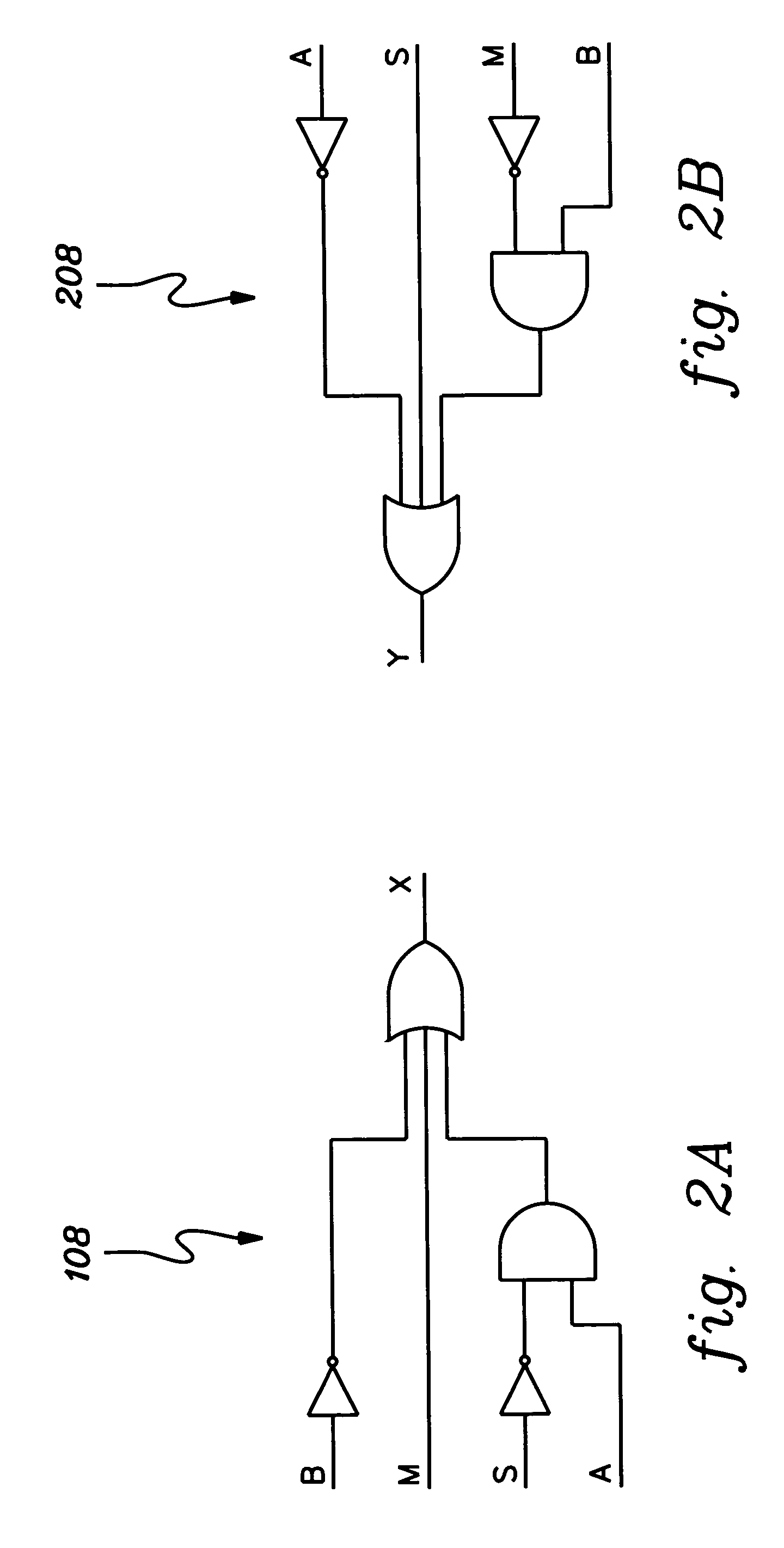

A communication system, method and program product are provided for establishing an extended bidirectional communication bus between a first device and a second device. The communication system includes decomposition logic for decomposing a single line, bidirectional data communication bus into a unidirectional transmit data communication bus and a unidirectional receive data communication bus. A differential communication subsystem is connected to the two unidirectional buses for extending the length thereof, and recomposition circuitry is connected to the differential communication subsystem for recombining the extended unidirectional transmit data communication bus and the extended unidirectional receive data communication bus to reestablish the single line, bidirectional data communication bus. The decomposition logic, differential communication subsystem and recomposition circuitry are implemented transparent to the first device and the second device and without use of a data direction control line.

Owner:INT BUSINESS MASCH CORP

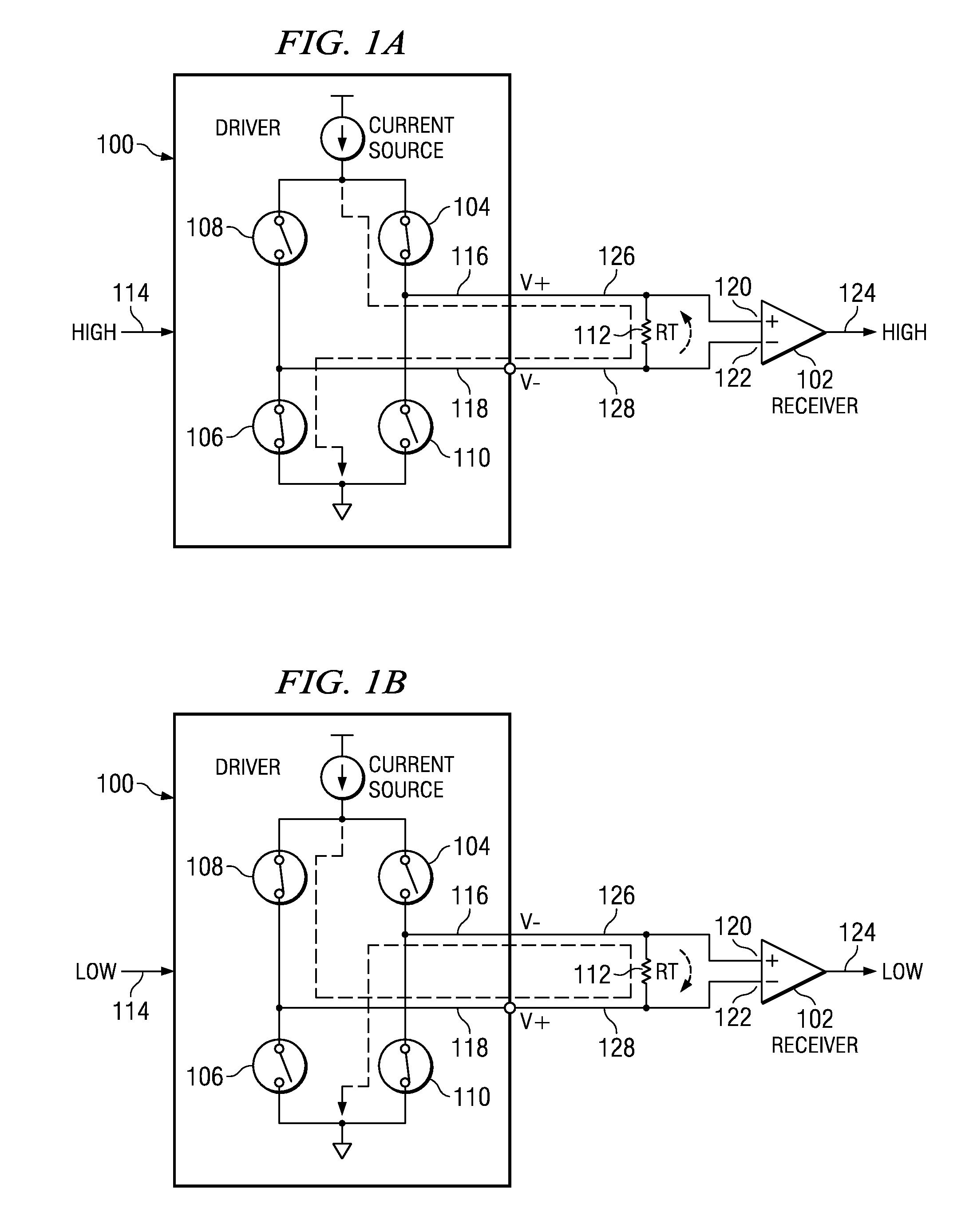

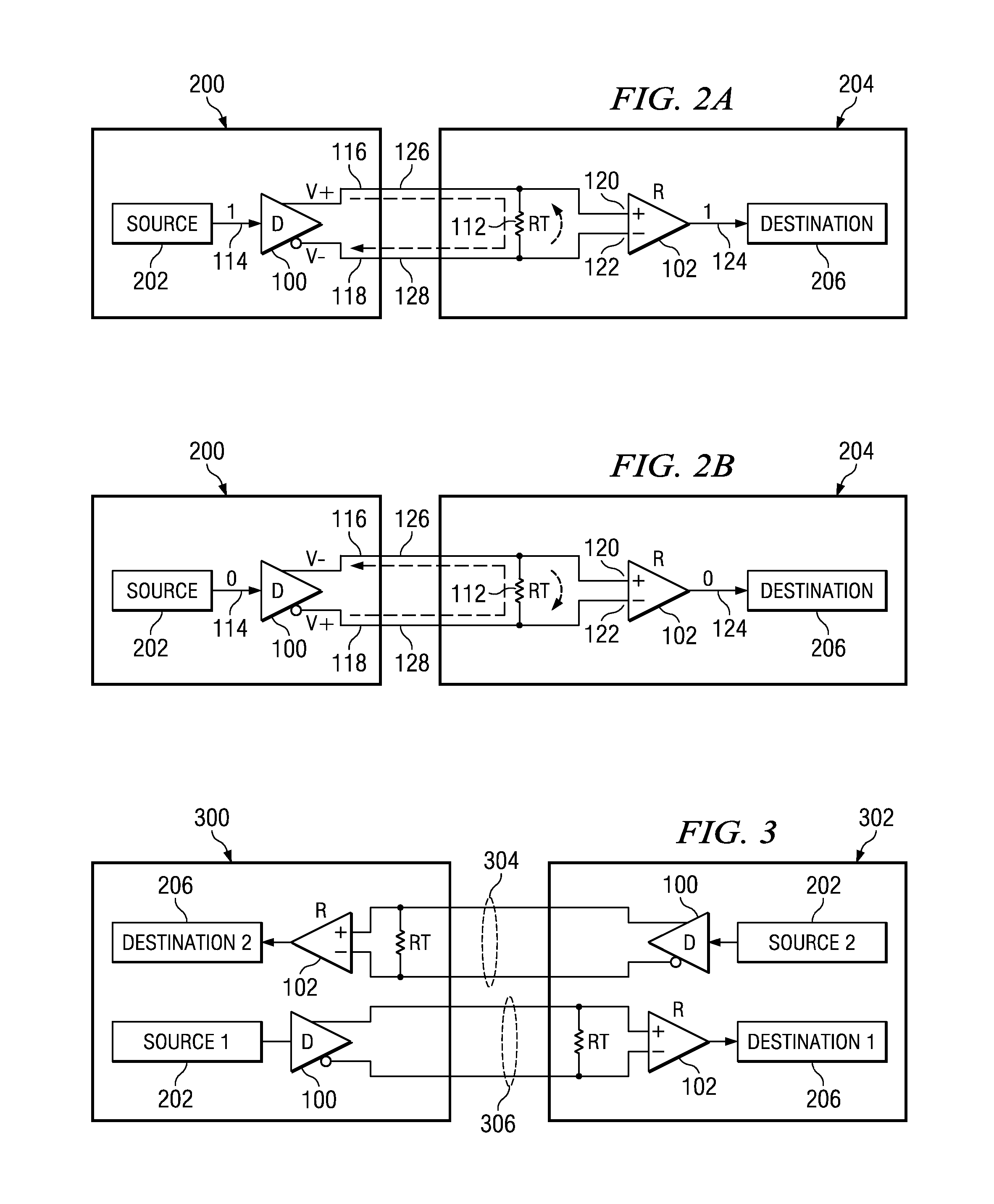

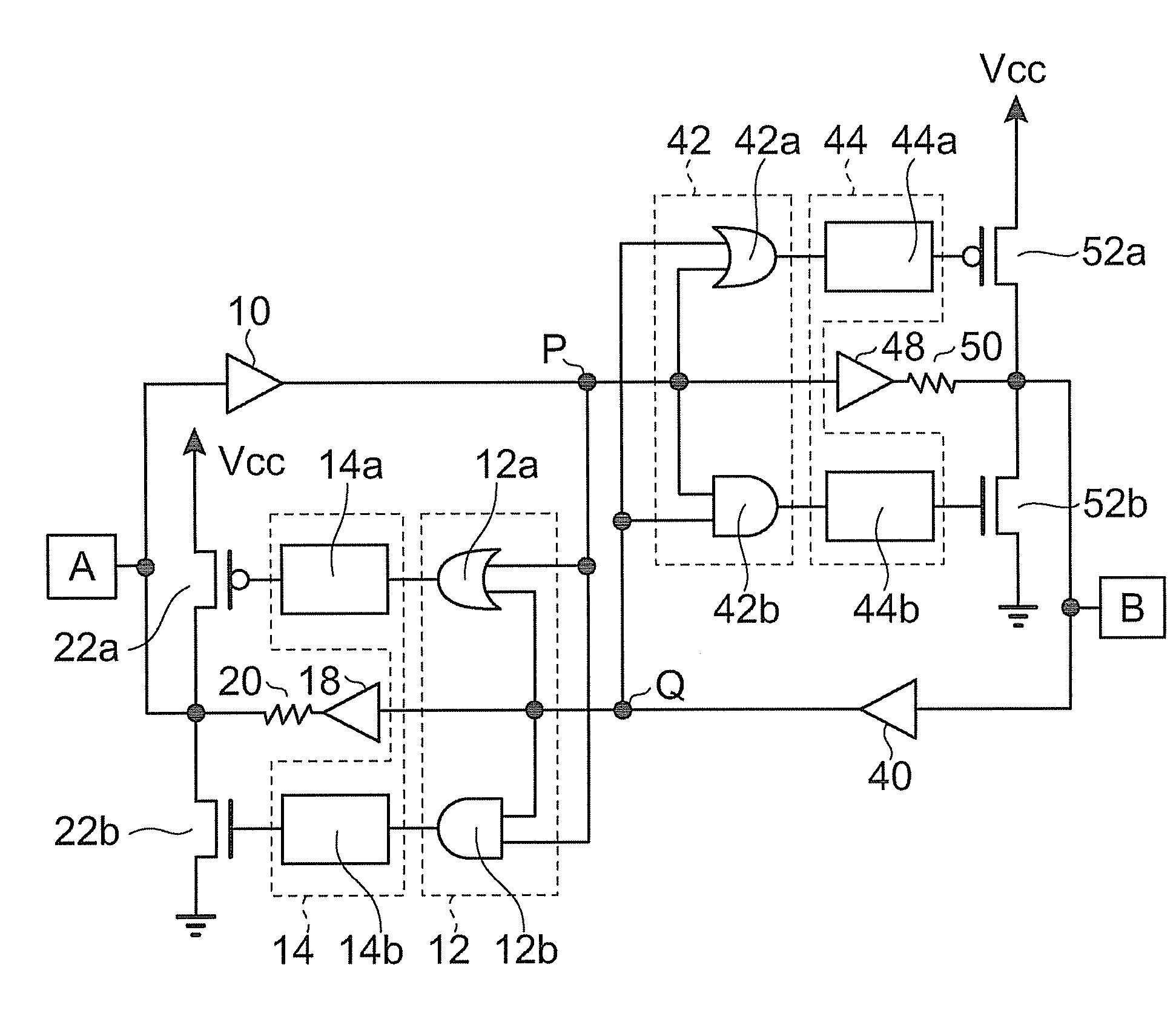

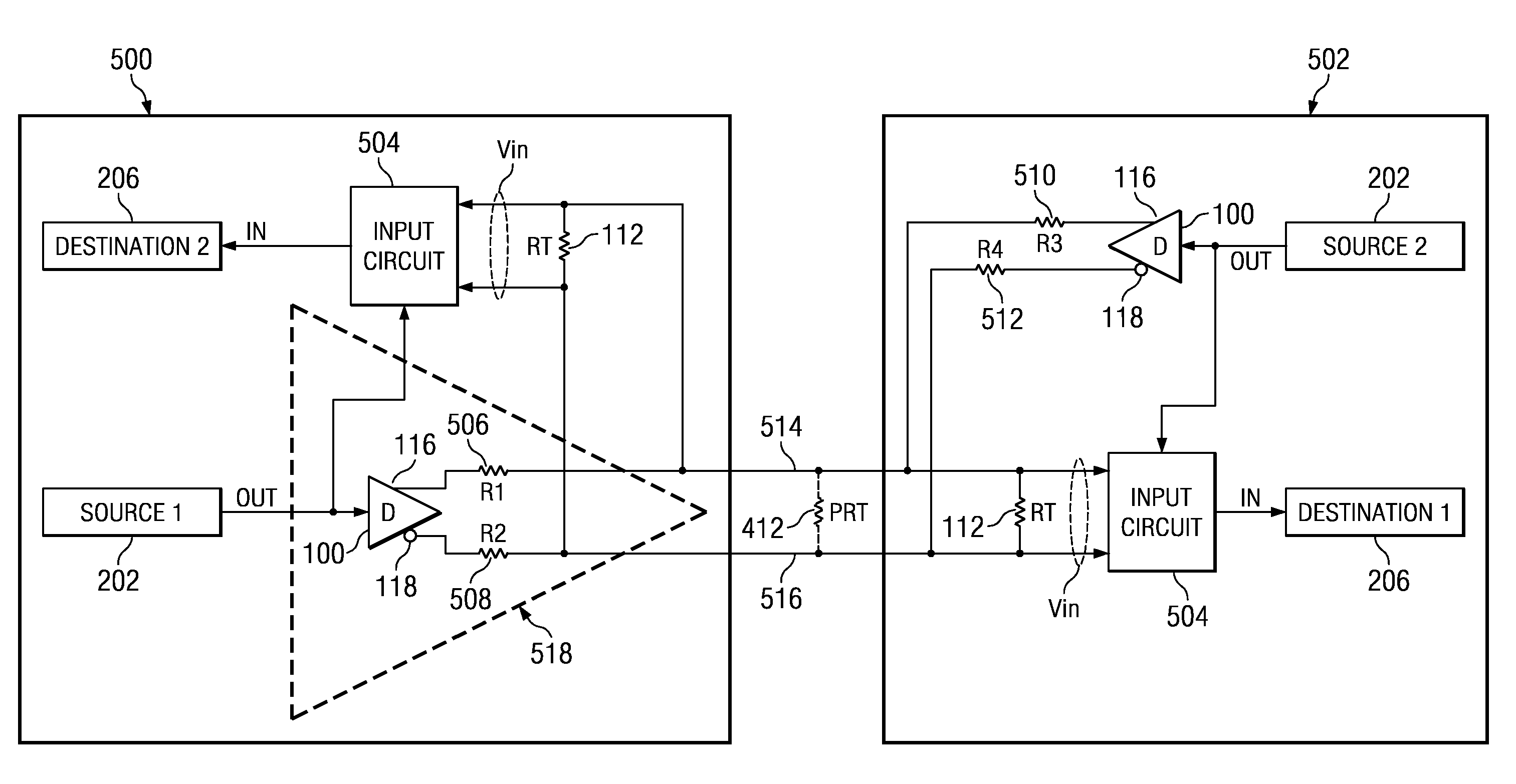

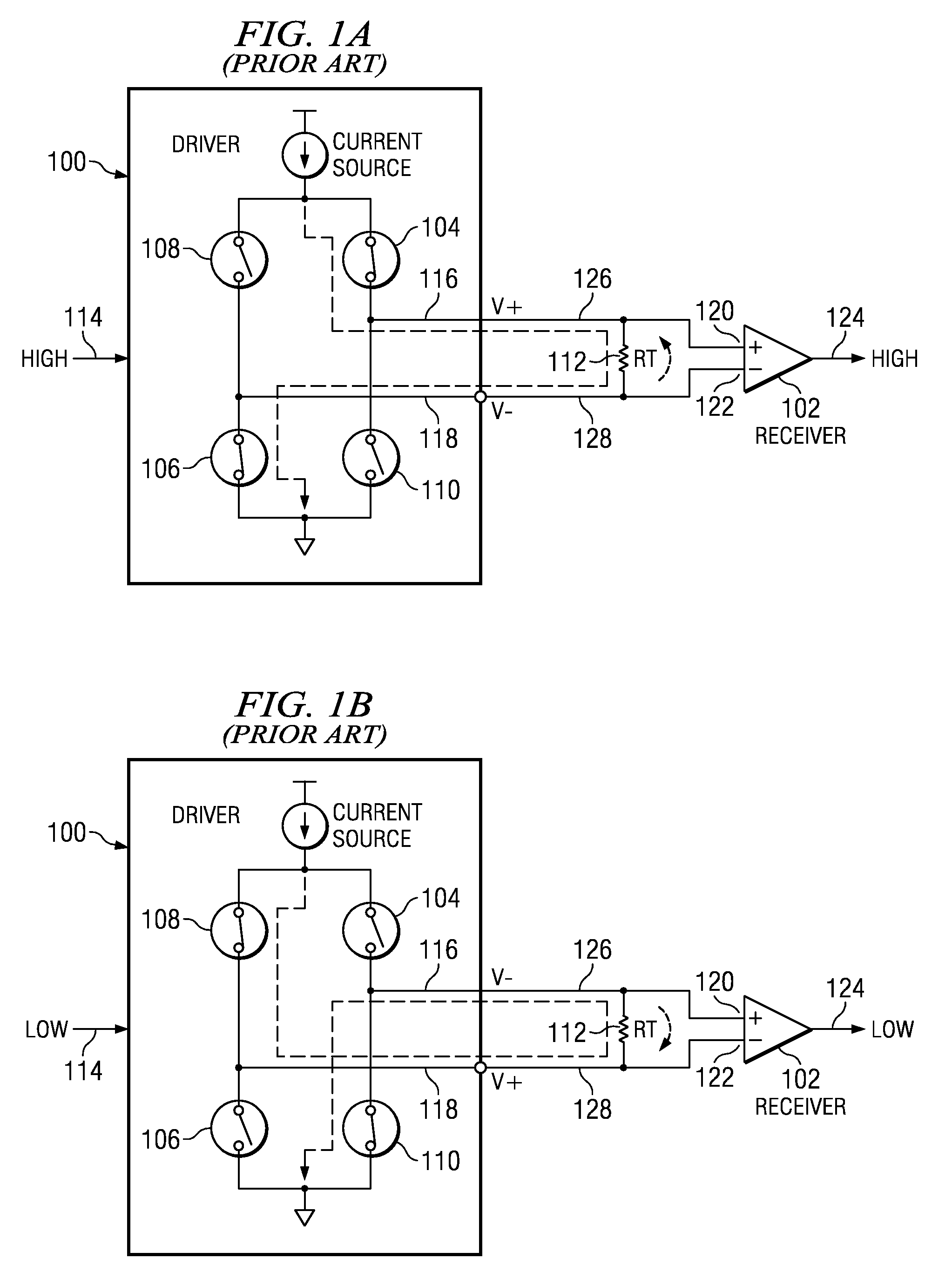

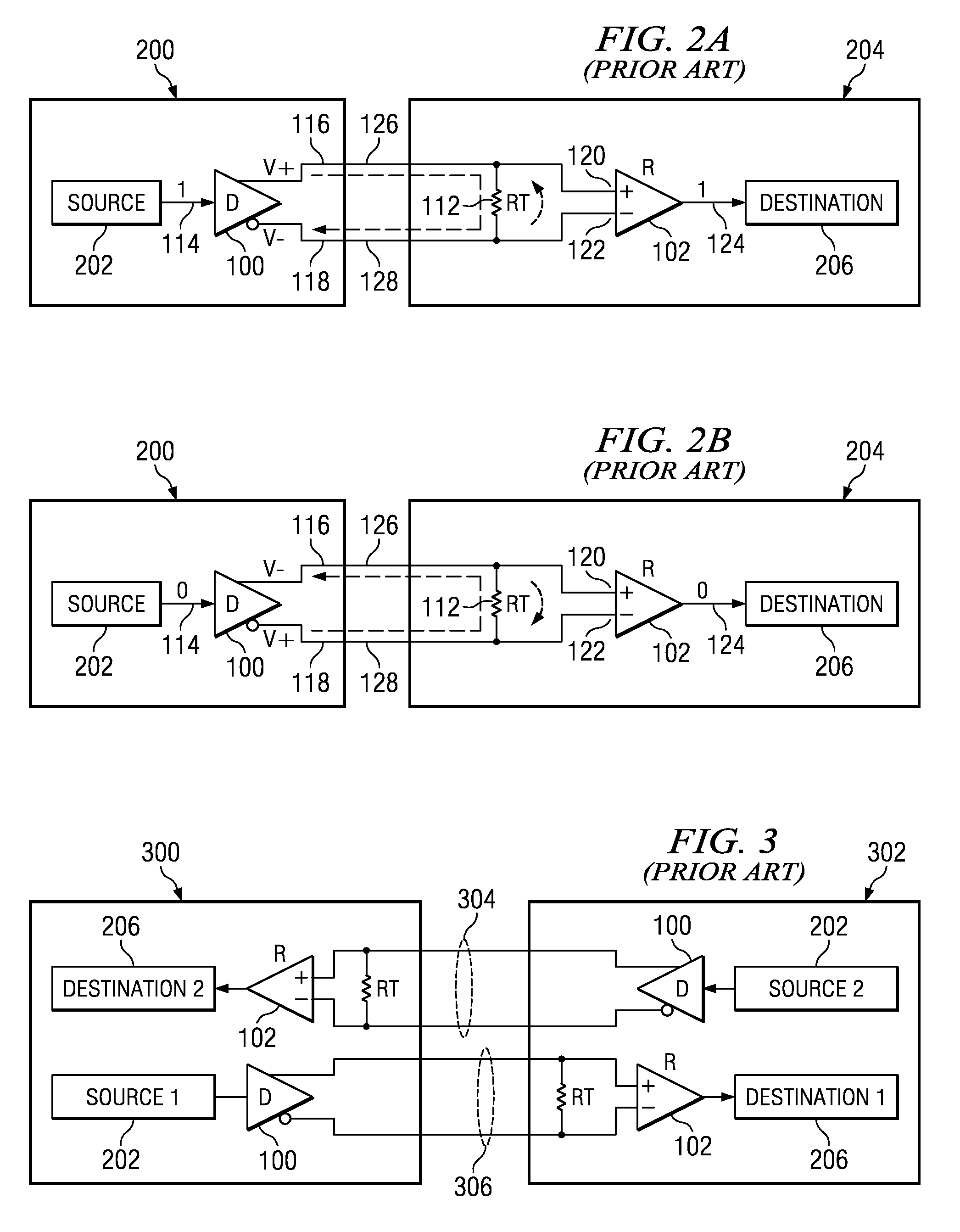

Simultaneous LVDS I/O signaling method and apparatus

ActiveUS20070103205A1Reliability increasing modificationsLogic circuits coupling/interface with bidirectional operationMultiplexerEngineering

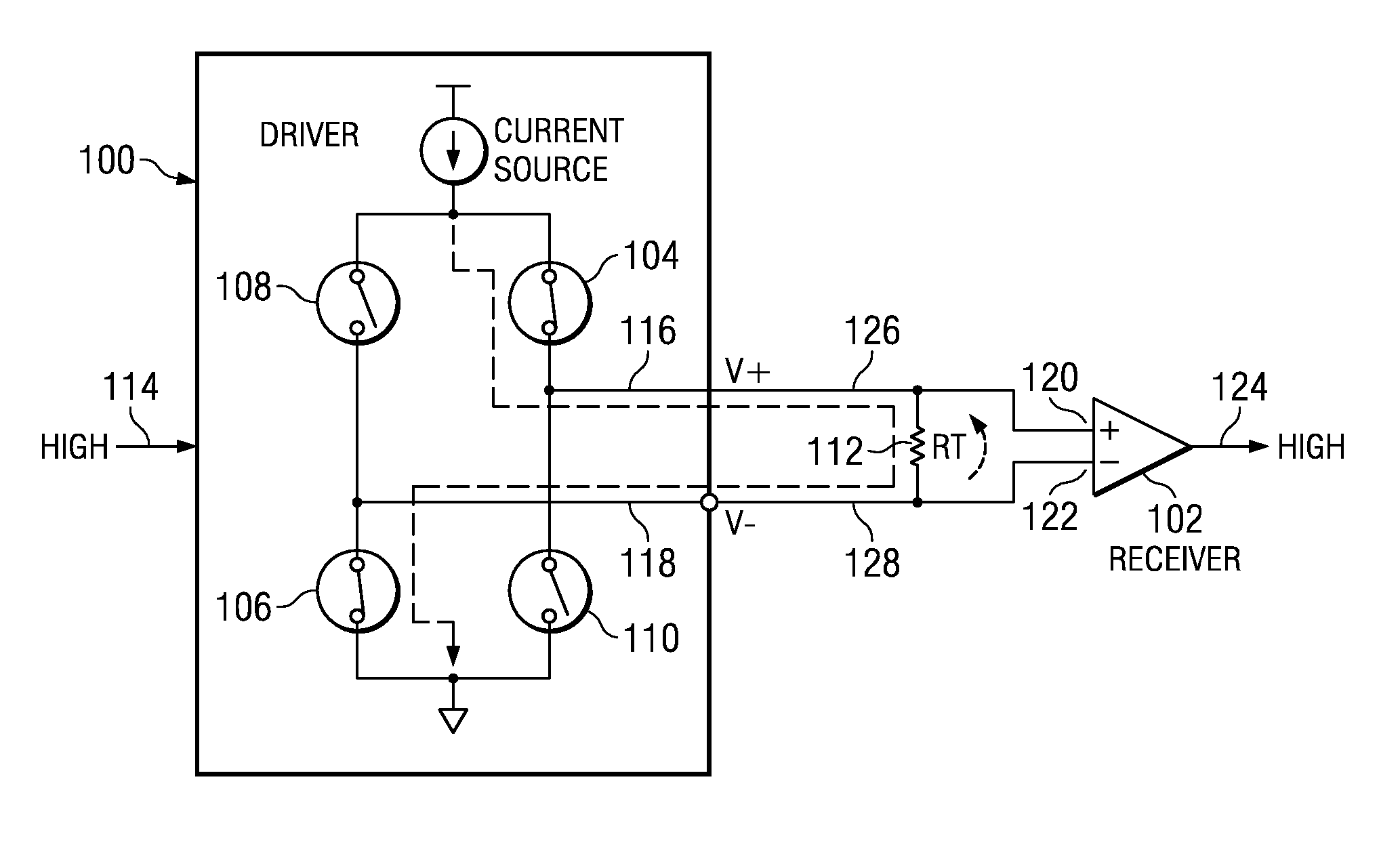

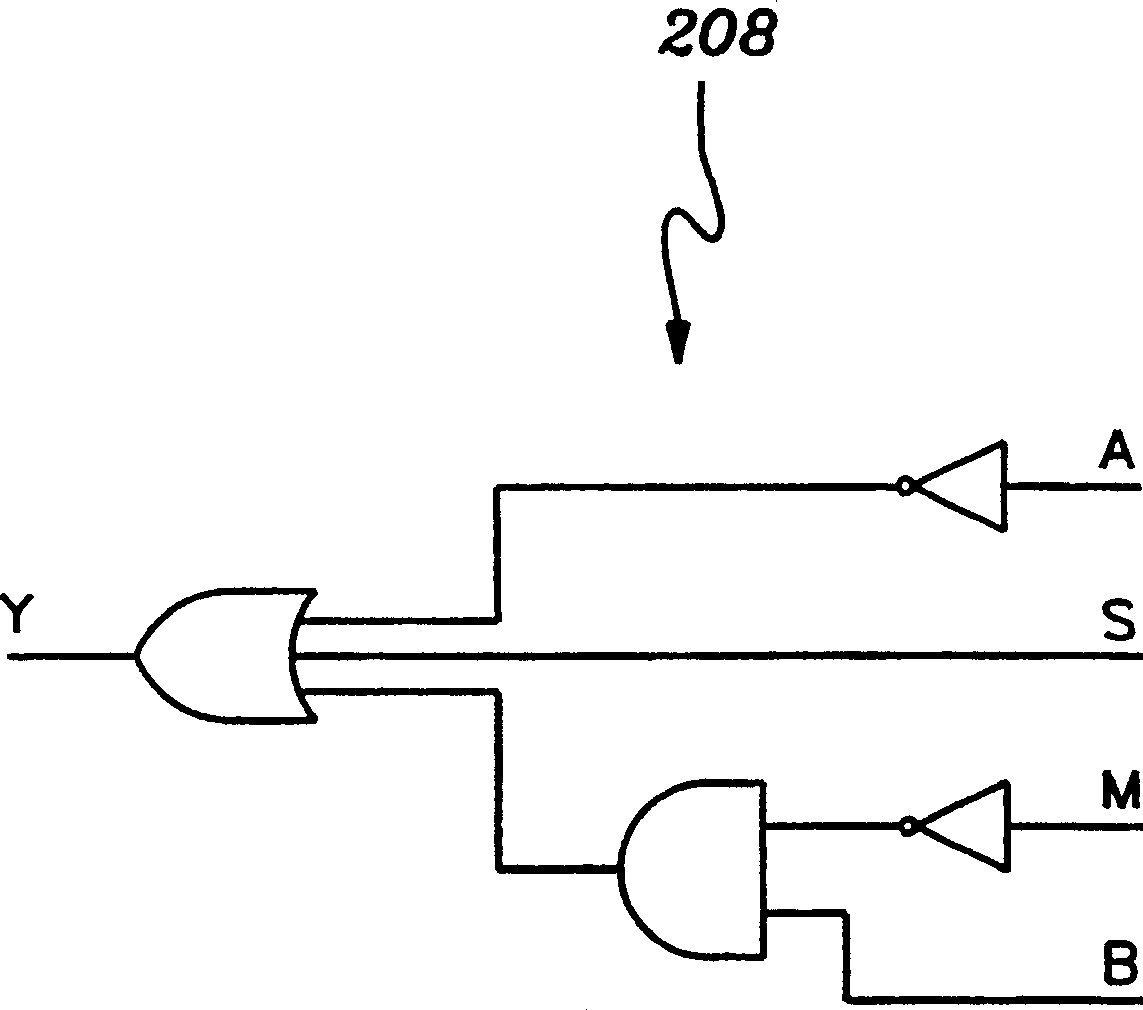

First and second devices may simultaneously communicate bidirectionally with each other using only a single pair of LVDS signal paths. Each device includes an input circuit and a differential output driver connected to the single pair of LVDS signal paths. An input to the input circuit is also connected to the input of the driver. The input circuit may also receive an offset voltage. In response to its inputs, the input circuit in each device can use comparators, gates and a multiplexer to determine the logic state being transmitted over the pair of LVDS signal paths from the other device. This advantageously reduces the number of required interconnects between the first and second devices by one half.

Owner:TEXAS INSTR INC

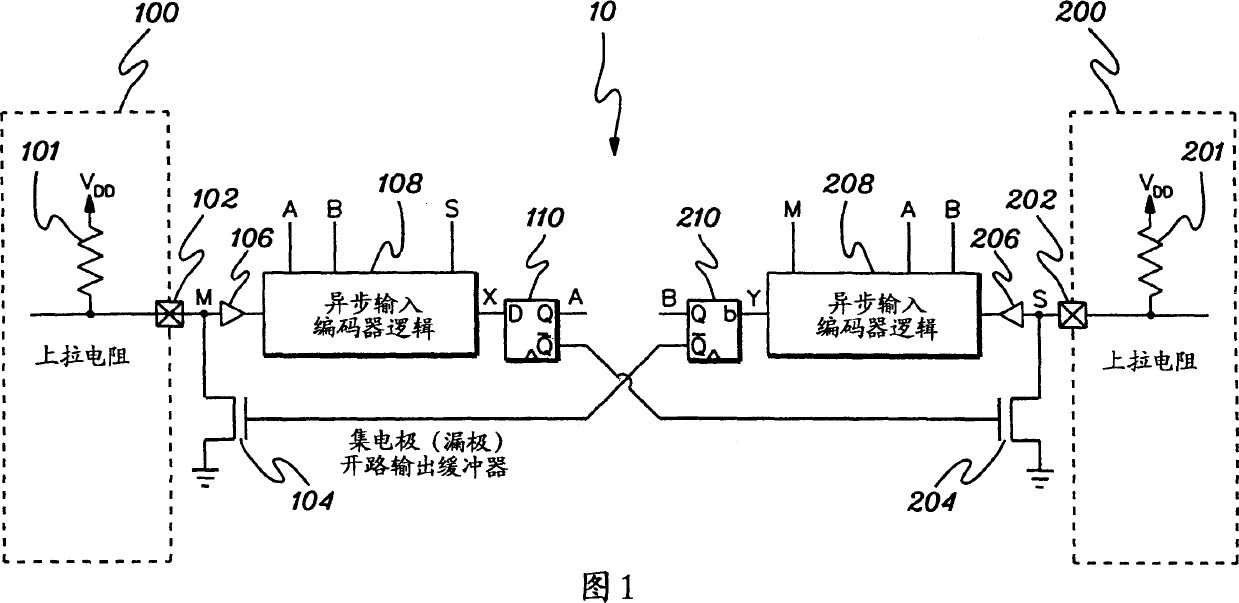

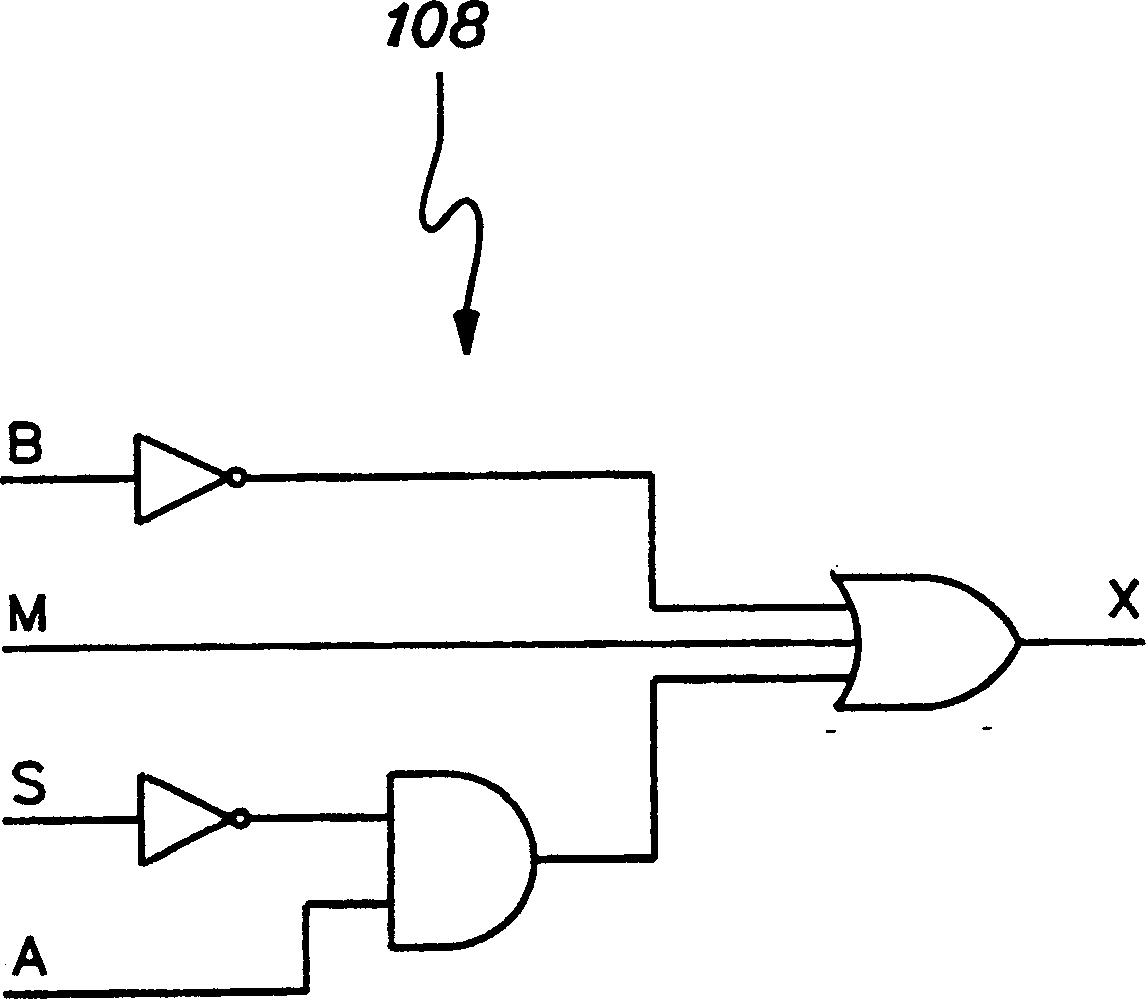

System, and method for extending range of a bidirectional data communication bus

InactiveCN1694425ALogic circuits coupling/interface with bidirectional operationRepeater/relay circuitsCommunications systemDecomposition

A communication system, method and program product are provided for establishing an extended bidirectional communication bus between a first device and a second device. The communication system includes decomposition logic for decomposing a single line, bidirectional data communication bus into a unidirectional transmit data communication bus and a unidirectional receive data communication bus. A differential communication subsystem is connected to the two unidirectional buses for extending the length thereof, and recomposition circuitry is connected to the differential communication subsystem for recombining the extended unidirectional transmit data communication bus and the extended unidirectional receive data communication bus to reestablish the single line, bidirectional data communication bus. The decomposition logic, differential communication subsystem and recomposition circuitry are implemented transparent to the first device and the second device and without use of a data direction control line.

Owner:INT BUSINESS MASCH CORP

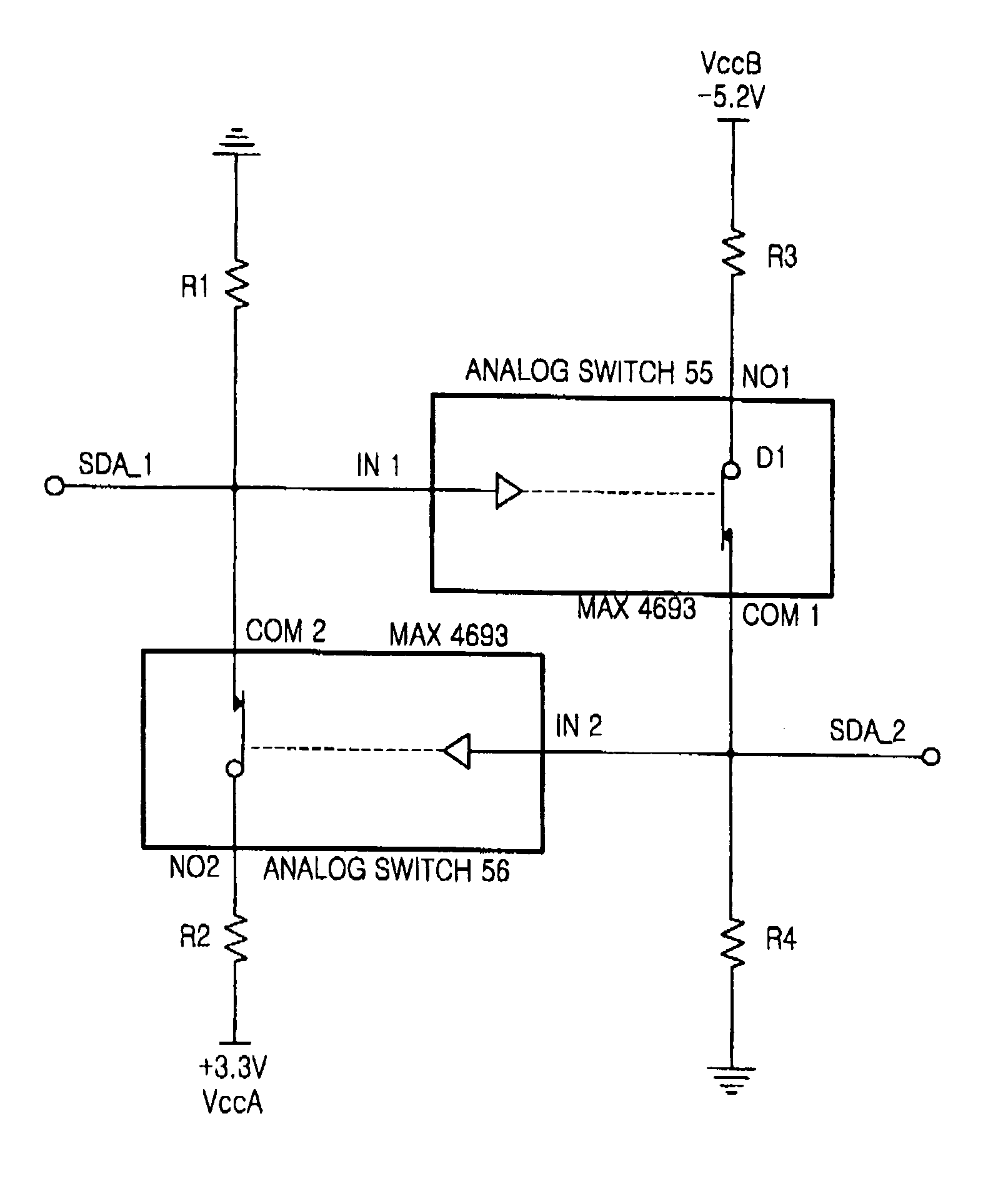

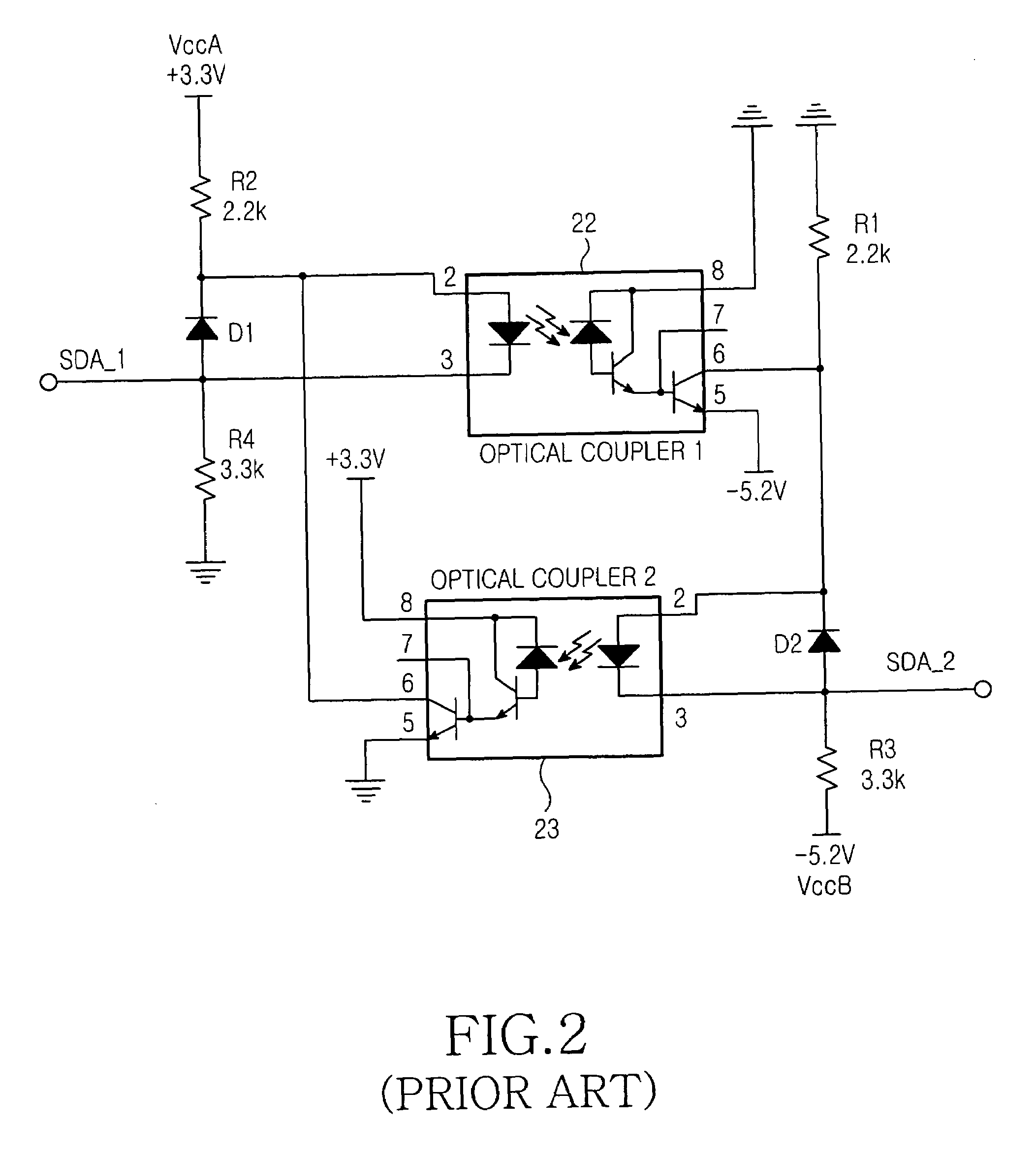

Bi-directional signal level shift circuit

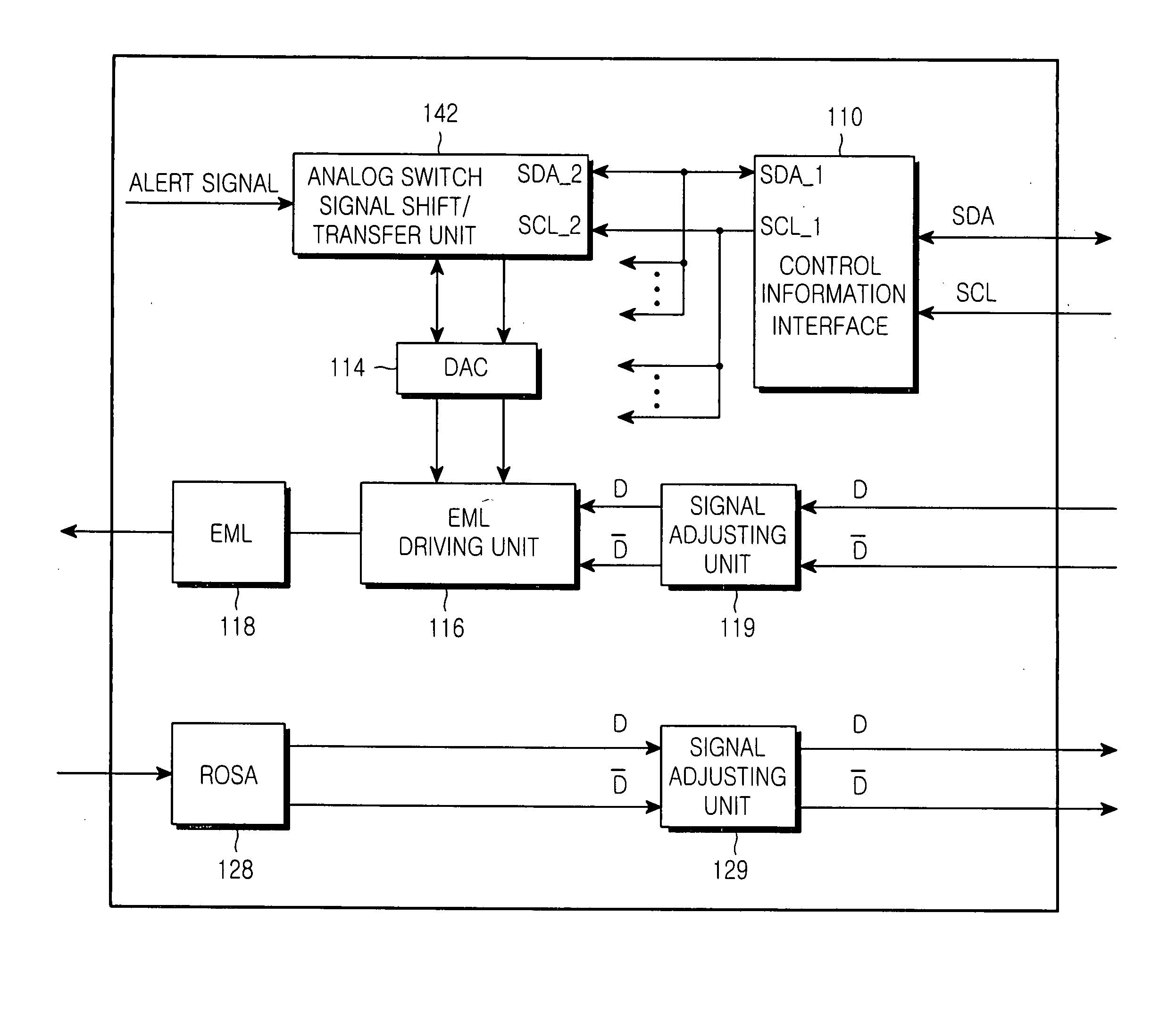

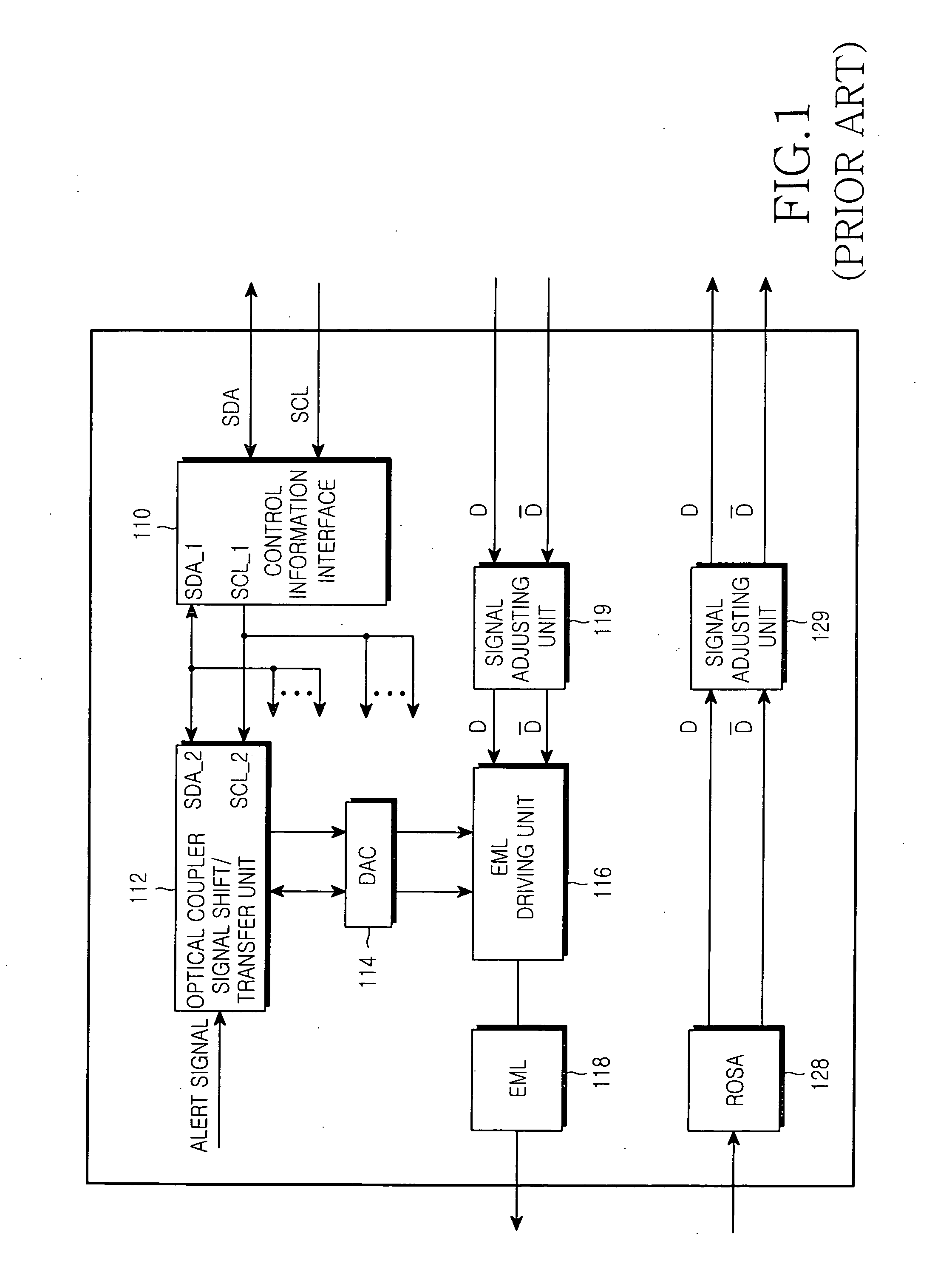

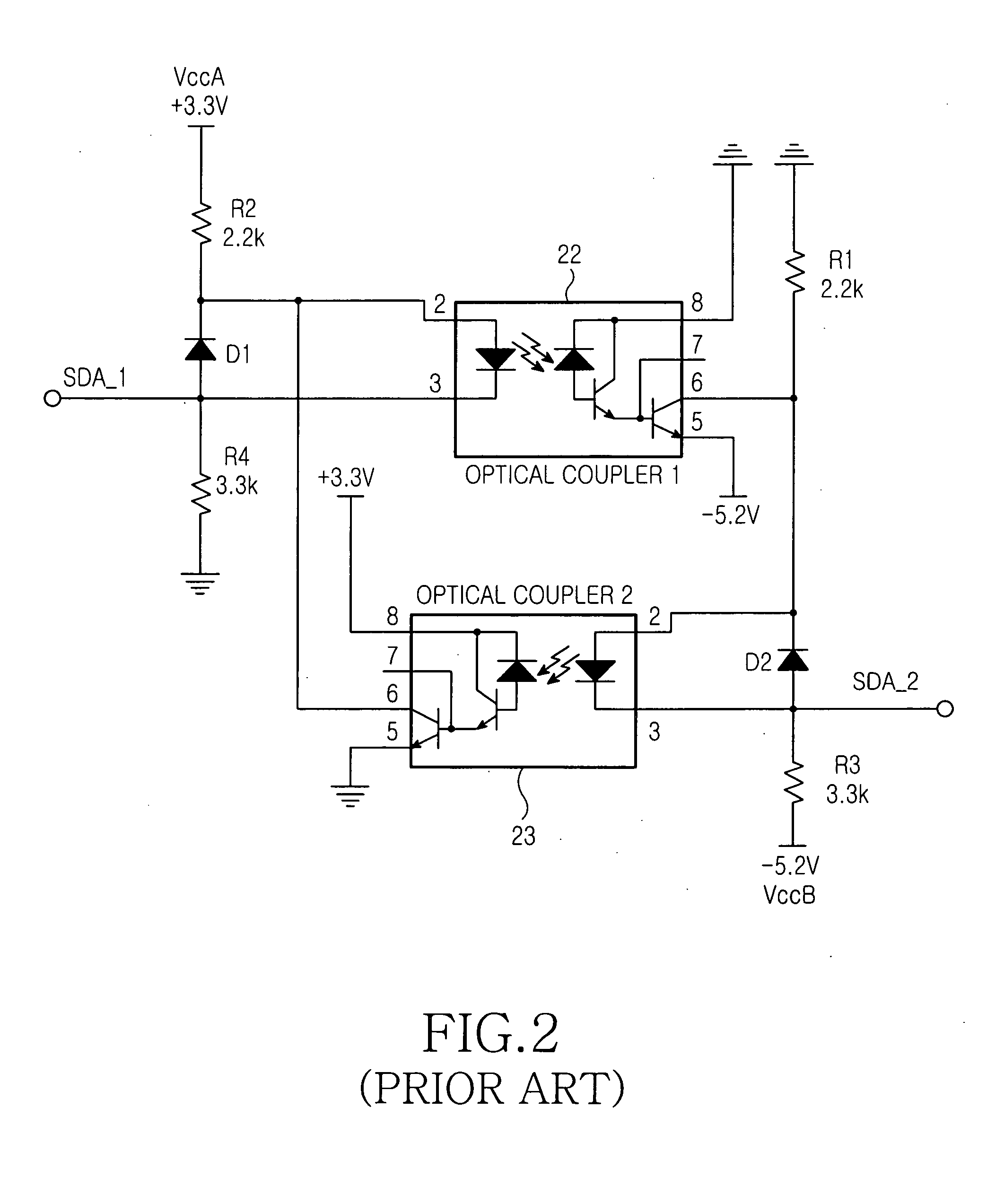

InactiveUS20050122154A1Less spaceSmall sizePulse automatic controlLogic circuits coupling/interface with bidirectional operationEngineeringOperating voltage

A circuit for shifting a level between two bidirectional signals having different voltage levels. The circuit includes a first analog switch including a first switching control terminal connected to first directional signal stage, a first input terminal connected to a first level of operating voltage, and a first output terminal connected to a second directional signal stage, for performing a switching operation for the first input terminal and the first output terminal based on a state of logic level of a signal from the second directional signal stage. The circuit also includes a second analog switch including a second switching control terminal connected to the first directional signal stage, a second input terminal connected to a second level of operating voltage, and a second output terminal connected to the first directional signal stage for performing a switching operation for the second input terminal and the second output terminal based on a state of a logic level of a signal from the first directional signal stage.

Owner:SAMSUNG ELECTRONICS CO LTD

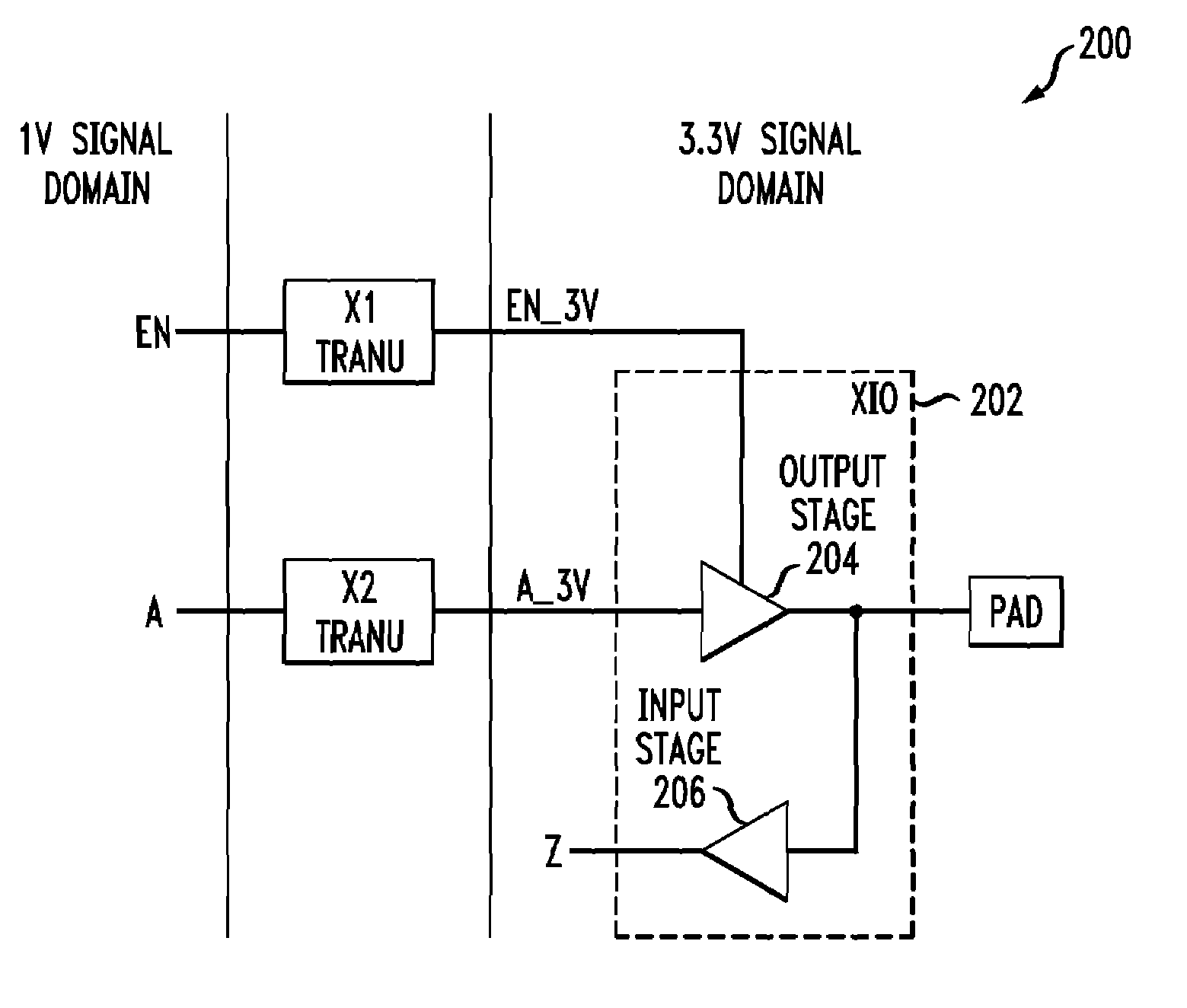

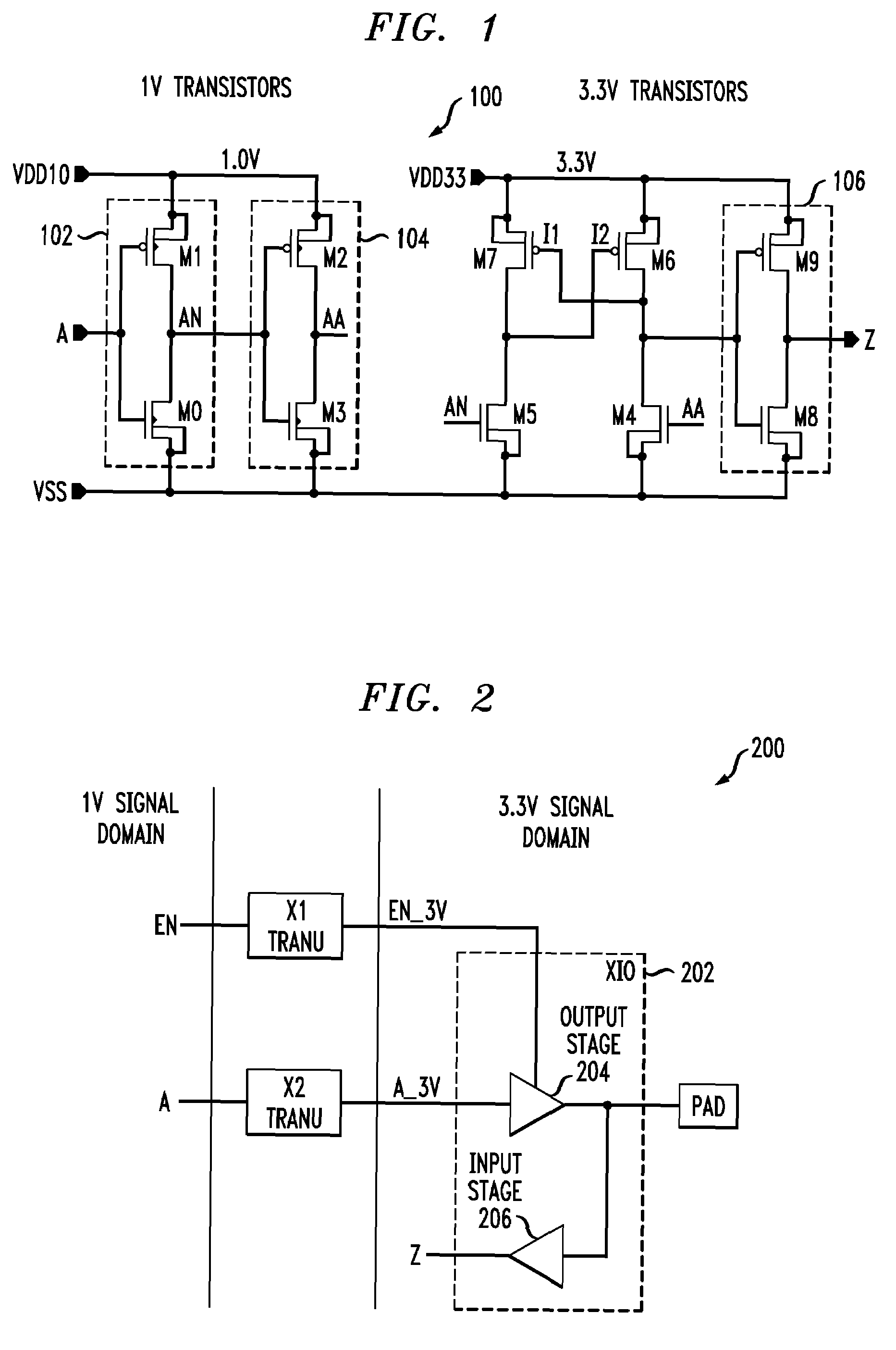

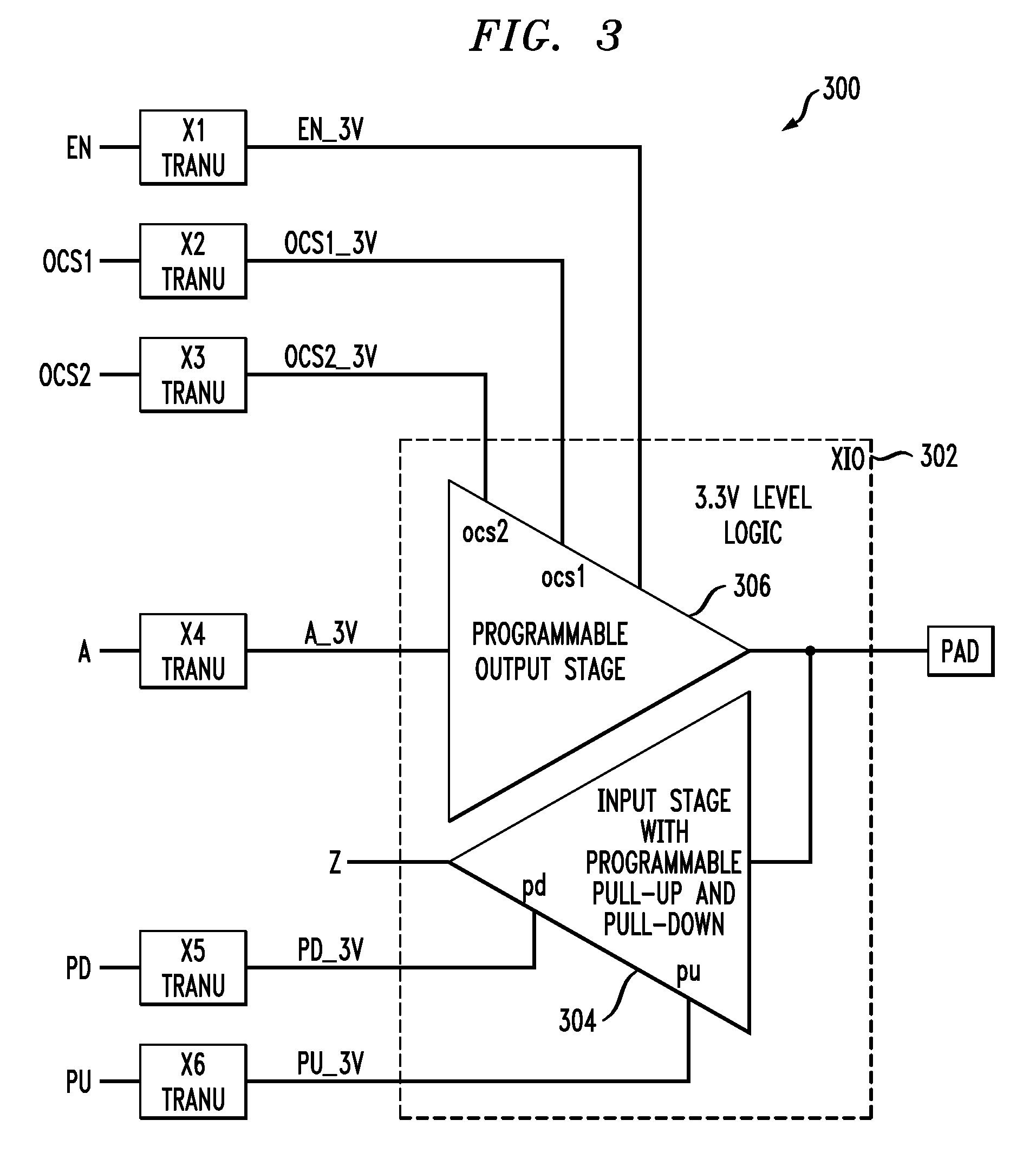

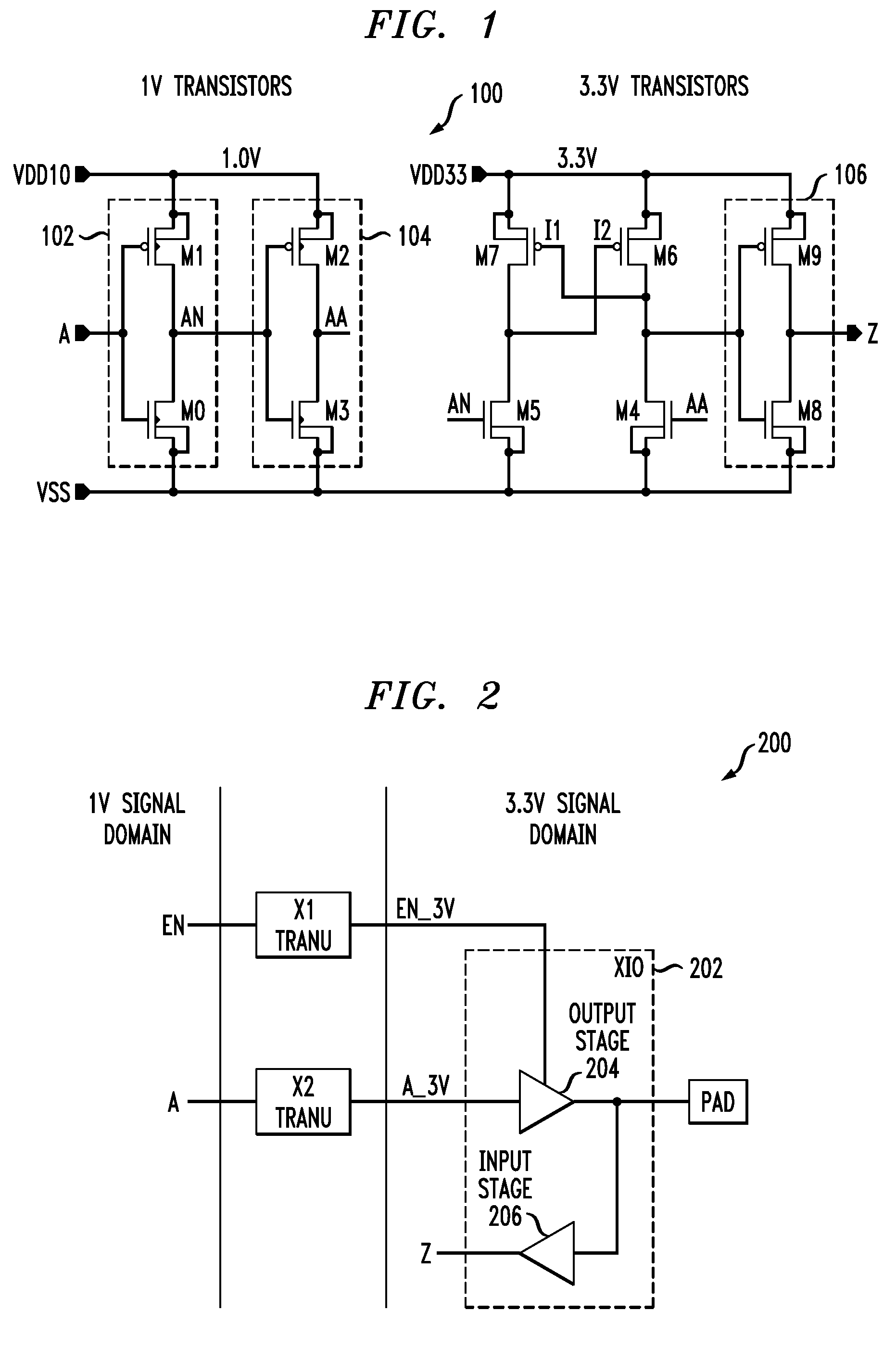

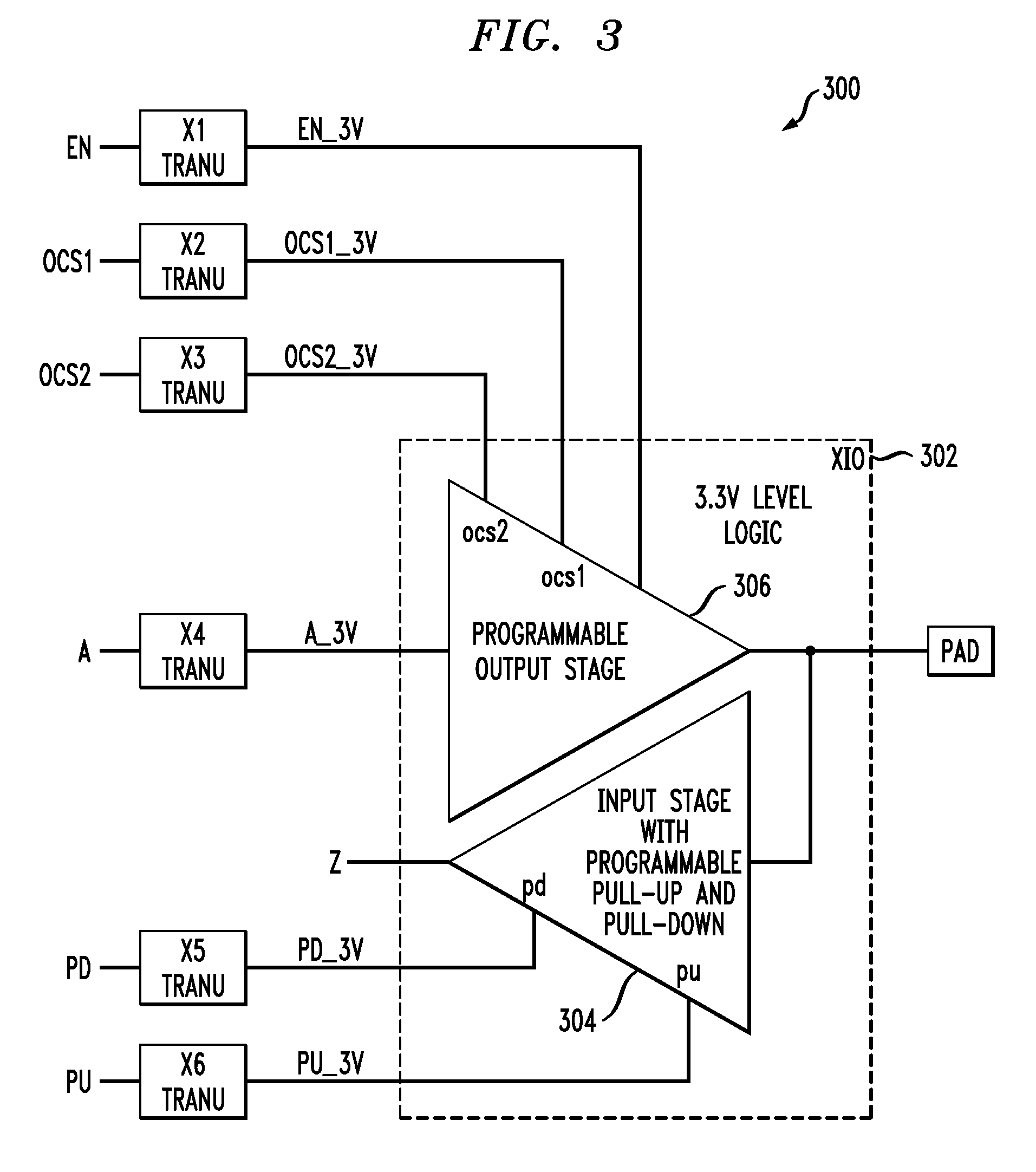

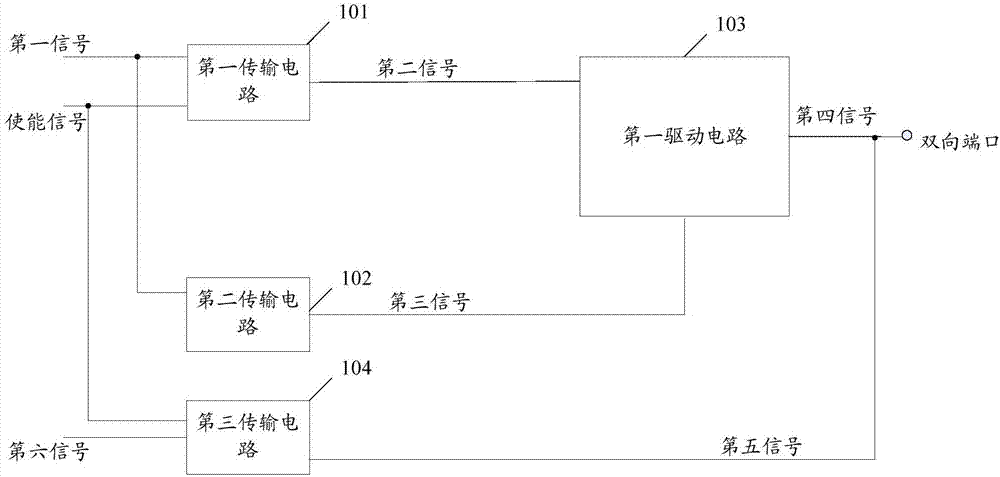

Buffer circuit having multiplexed voltage level translation

ActiveUS7498860B2Reduce chip areaSmall sizeProgrammable logic circuit arrangementsLogic circuits coupling/interface with bidirectional operationControl signalEngineering

A buffer circuit is selectively operative in one of at least a first mode and a second mode as a function of a first control signal supplied to the buffer circuit. The buffer circuit includes interface circuitry operative to receive at least second and third control signals referenced to a first voltage level, and to generate an output signal referenced to a second voltage level, the second voltage level being greater than the first voltage level. The output signal is a function of the second control signal in the first mode and is a function of the third control signal in the second mode. The buffer circuit further includes at least first and second circuit portions coupled to the interface circuitry, each of the first and second circuit portions including at least one control input operative to receive the output signal generated by the interface circuitry.

Owner:GENERAL ELECTRIC CO +1

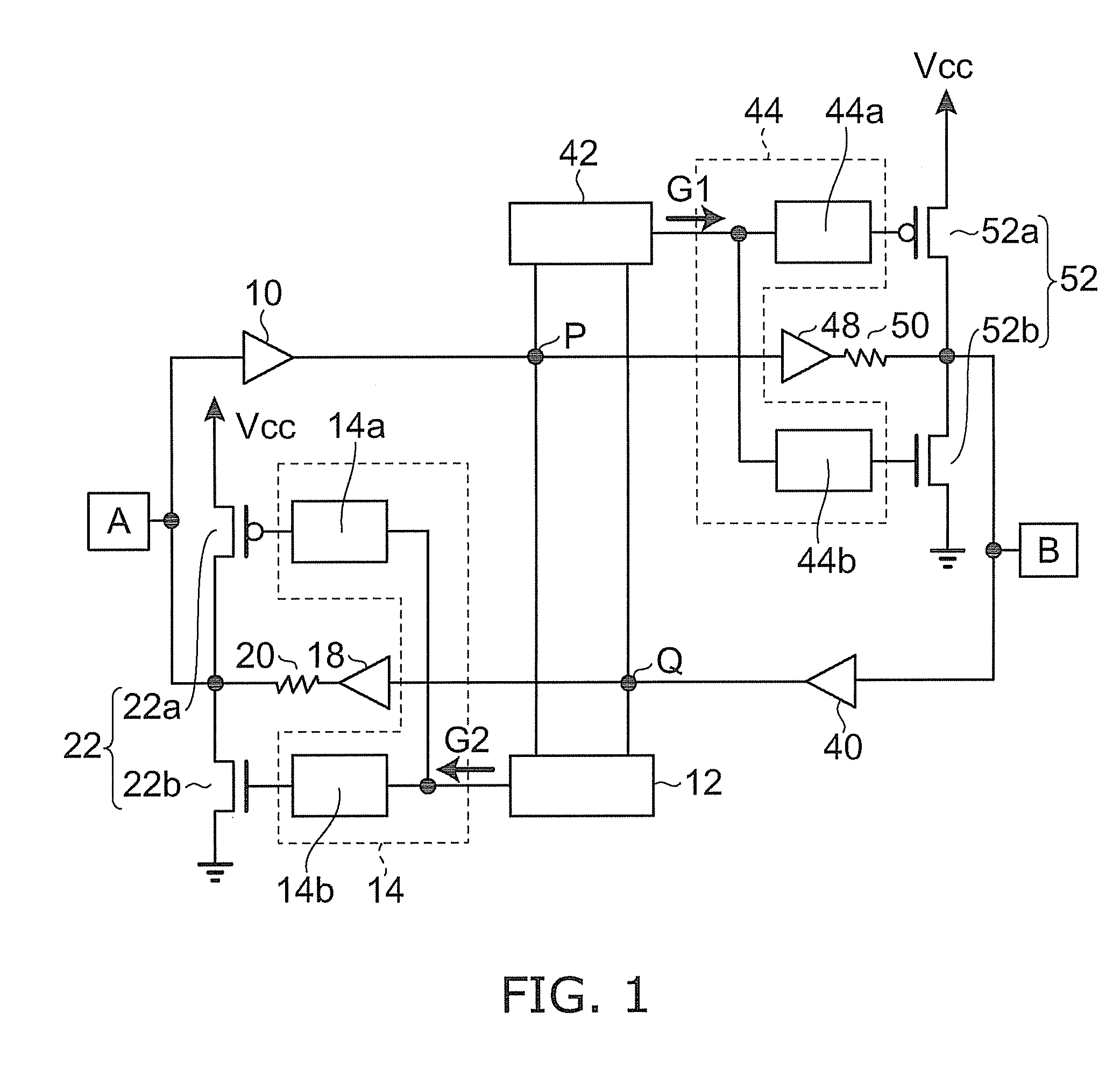

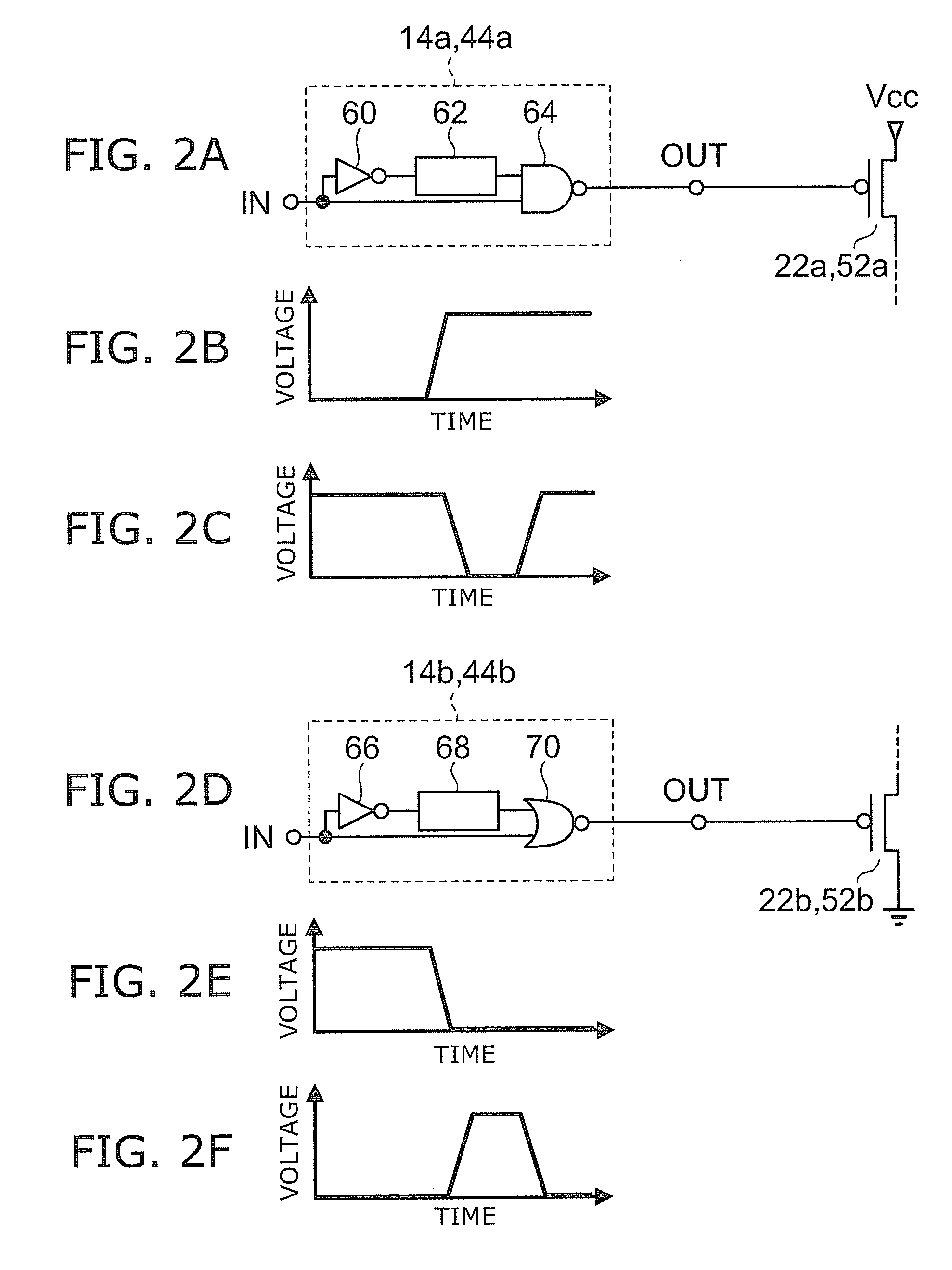

Bidirectional buffer circuit and signal level conversion circuit

InactiveUS20090295429A1Logic circuits coupling/interface with bidirectional operationControl signalEngineering

A bidirectional buffer circuit includes a first terminal, a second terminal, a first output buffer to which a signal from the first terminal is input and which outputs the signal to the second terminal, a first one-shot buffer control circuit outputting a first control signal according to an earlier arriving signal out of a signal from the first terminal and a signal from the second terminal, a first one-shot buffer temporarily driving the second terminal by the first control signal, a second output buffer to which a signal from the second terminal is input and which outputs the signal to the first terminal, a second one-shot buffer control circuit outputting a second control signal according to an earlier arriving signal out of a signal from the first terminal and a signal from the second terminal, and a second one-shot buffer temporarily driving the first terminal by the second control signal.

Owner:KK TOSHIBA

System, method and program product for extending range of a bidirectional data communication bus

InactiveUS20050258865A1Logic circuits coupling/interface with bidirectional operationRepeater/relay circuitsCommunications systemDecomposition

A communication system, method and program product are provided for establishing an extended bidirectional communication bus between a first device and a second device. The communication system includes decomposition logic for decomposing a single line, bidirectional data communication bus into a unidirectional transmit data communication bus and a unidirectional receive data communication bus. A differential communication subsystem is connected to the two unidirectional buses for extending the length thereof, and recomposition circuitry is connected to the differential communication subsystem for recombining the extended unidirectional transmit data communication bus and the extended unidirectional receive data communication bus to reestablish the single line, bidirectional data communication bus. The decomposition logic, differential communication subsystem and recomposition circuitry are implemented transparent to the first device and the second device and without use of a data direction control line.

Owner:IBM CORP

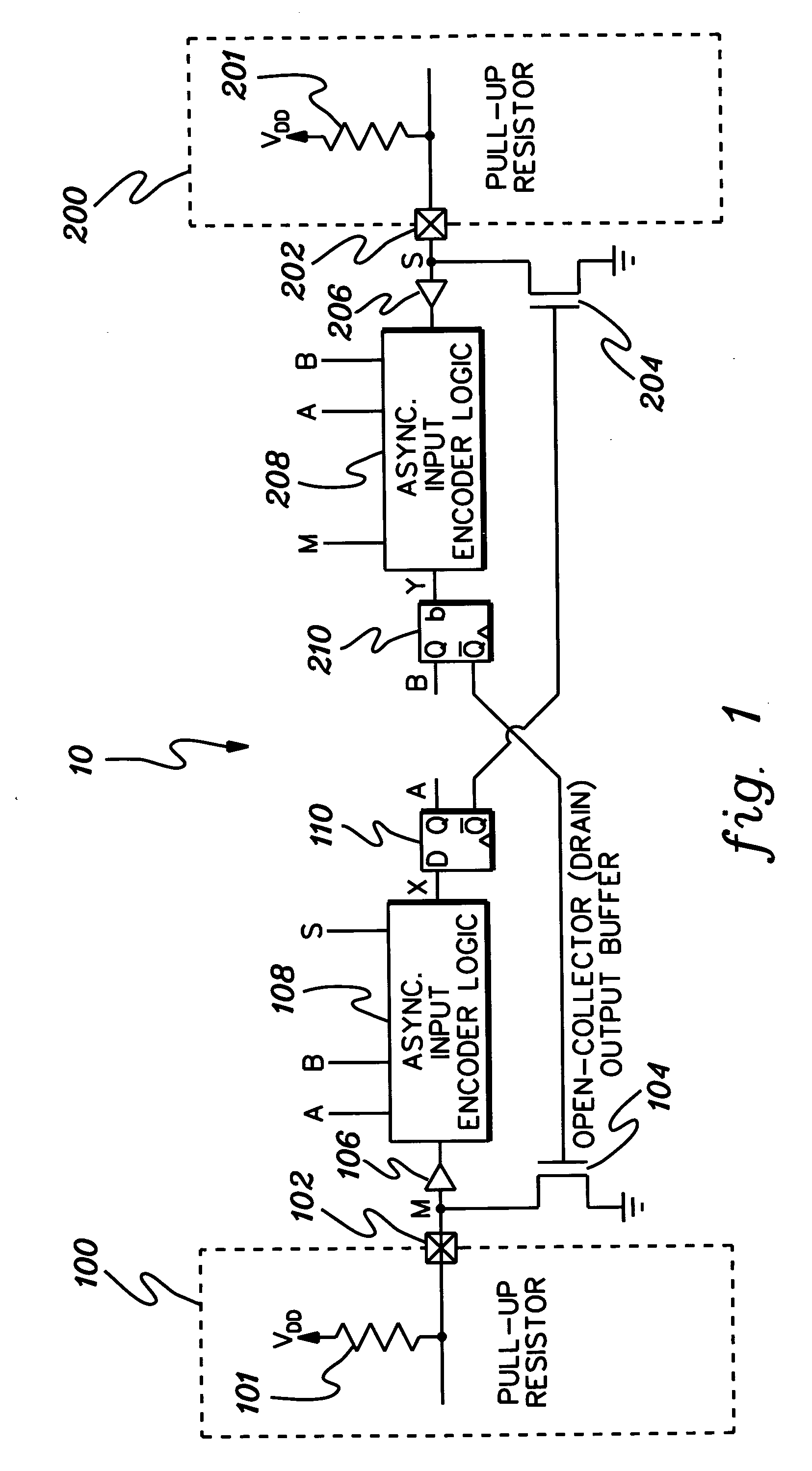

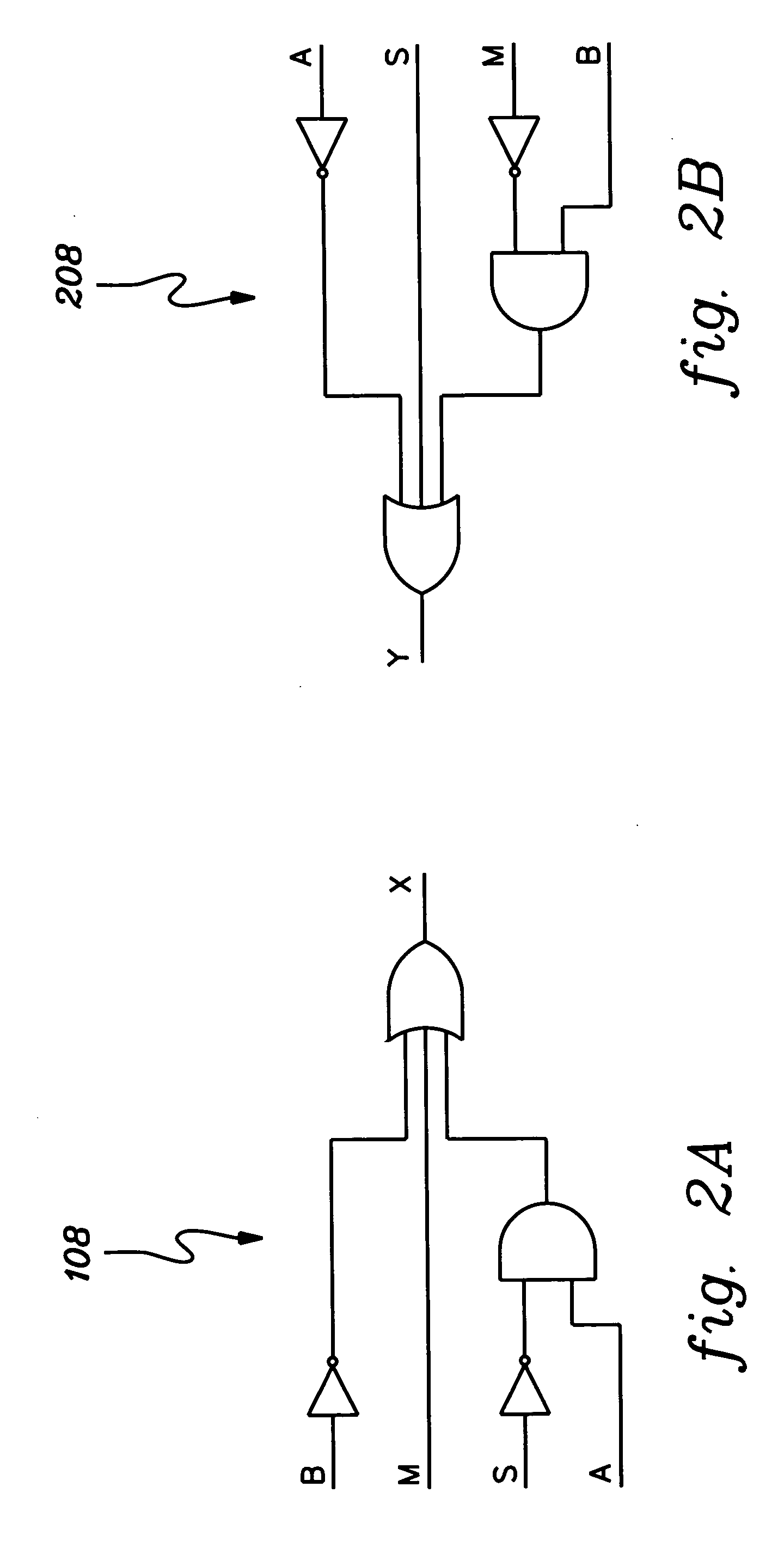

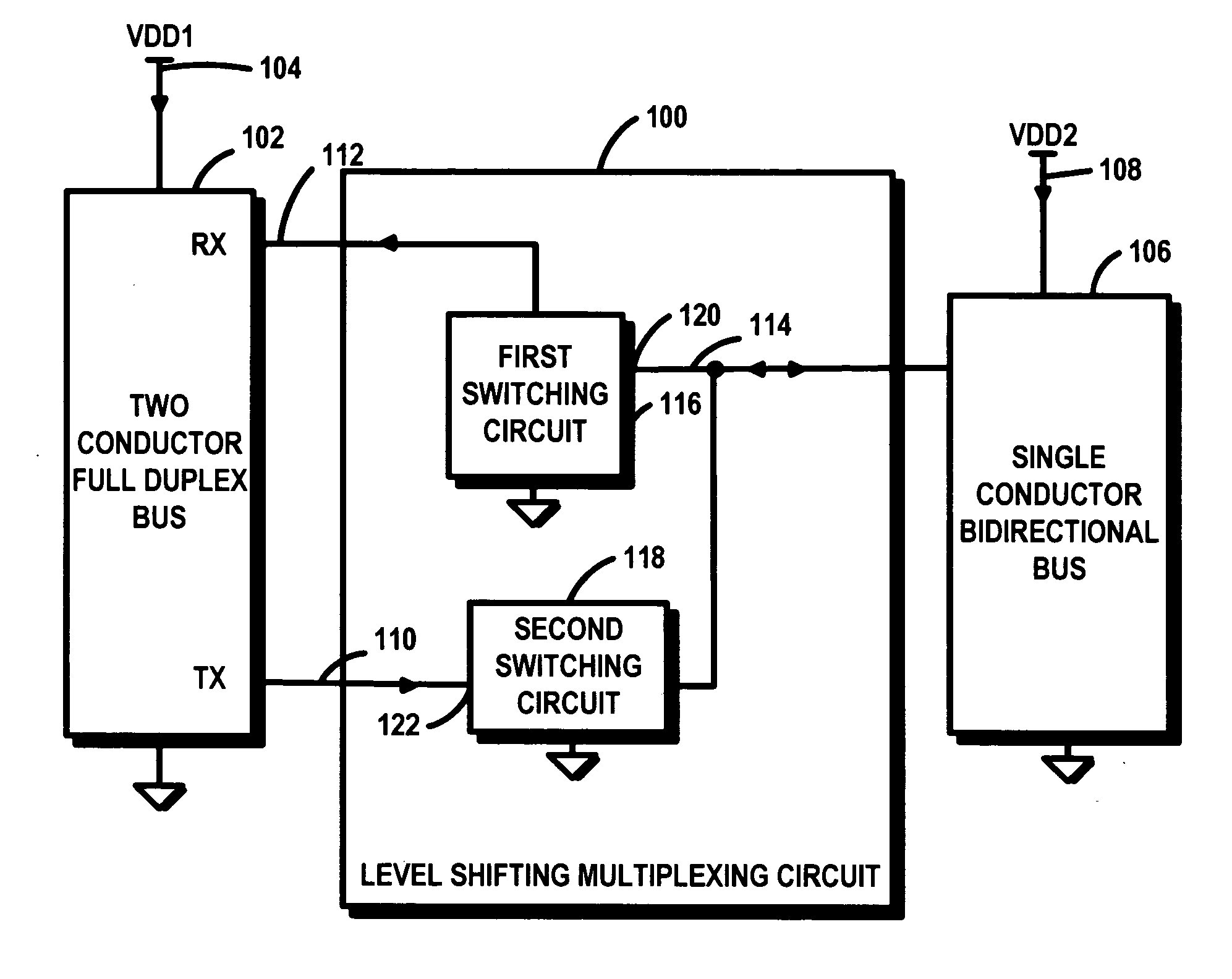

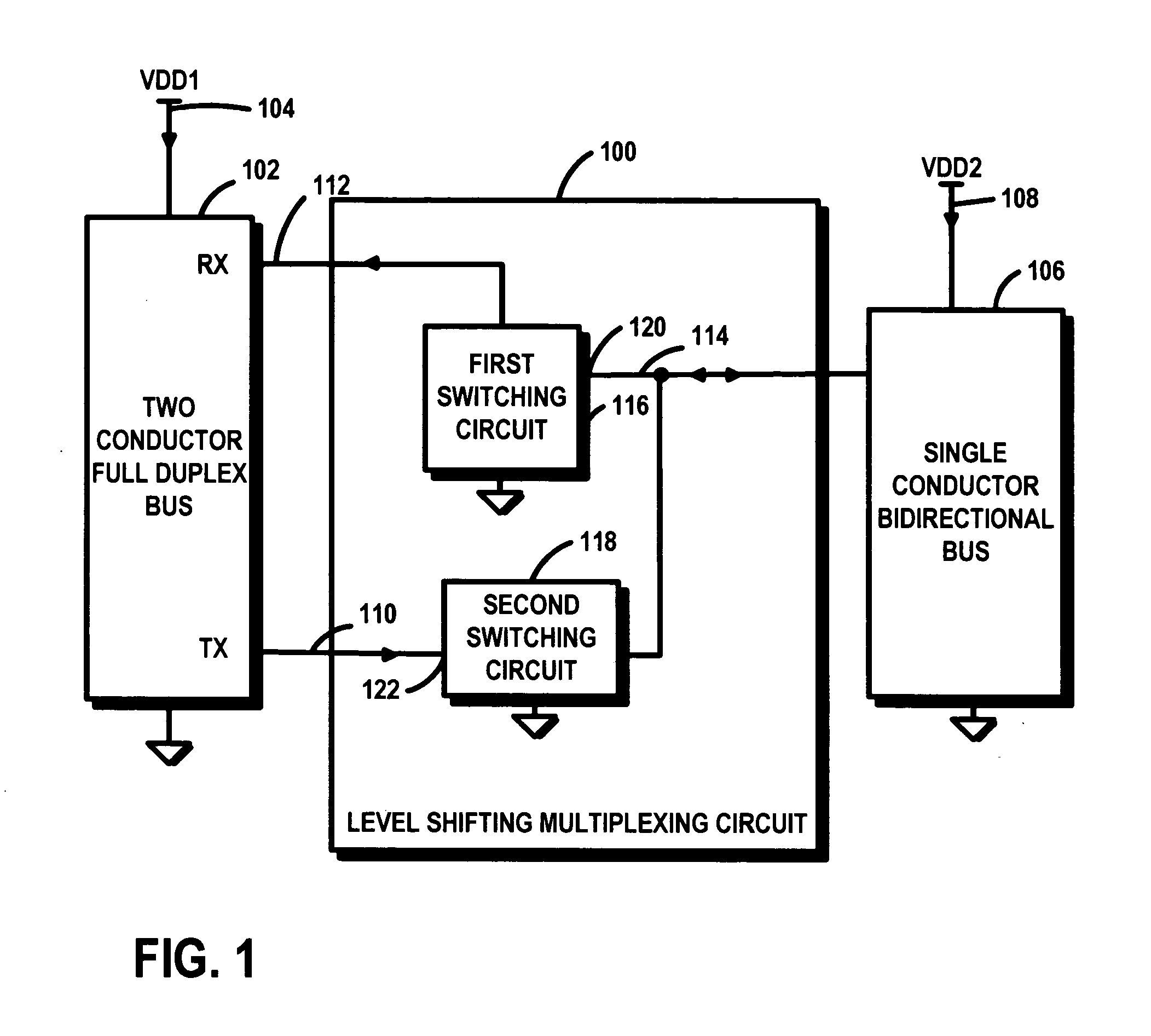

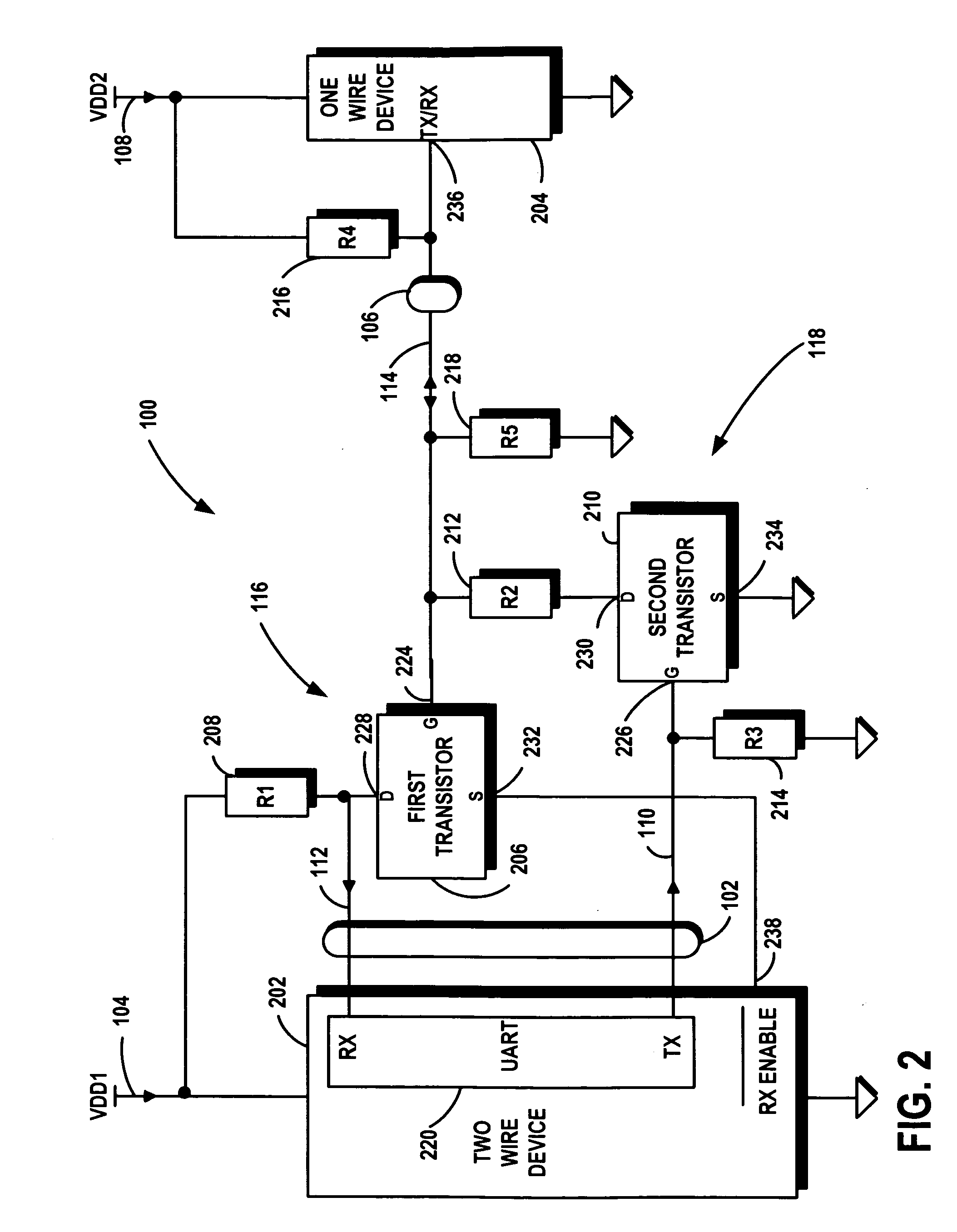

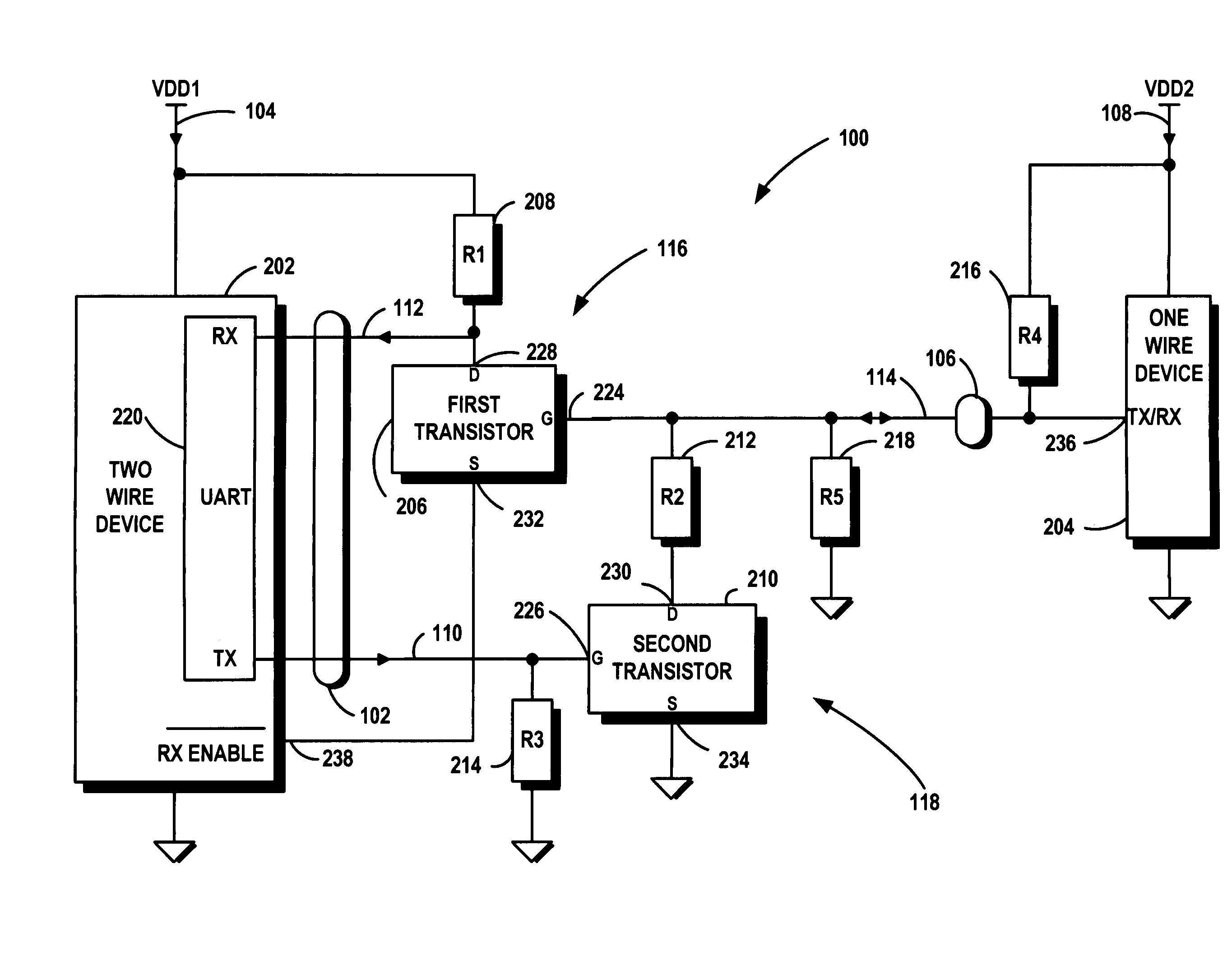

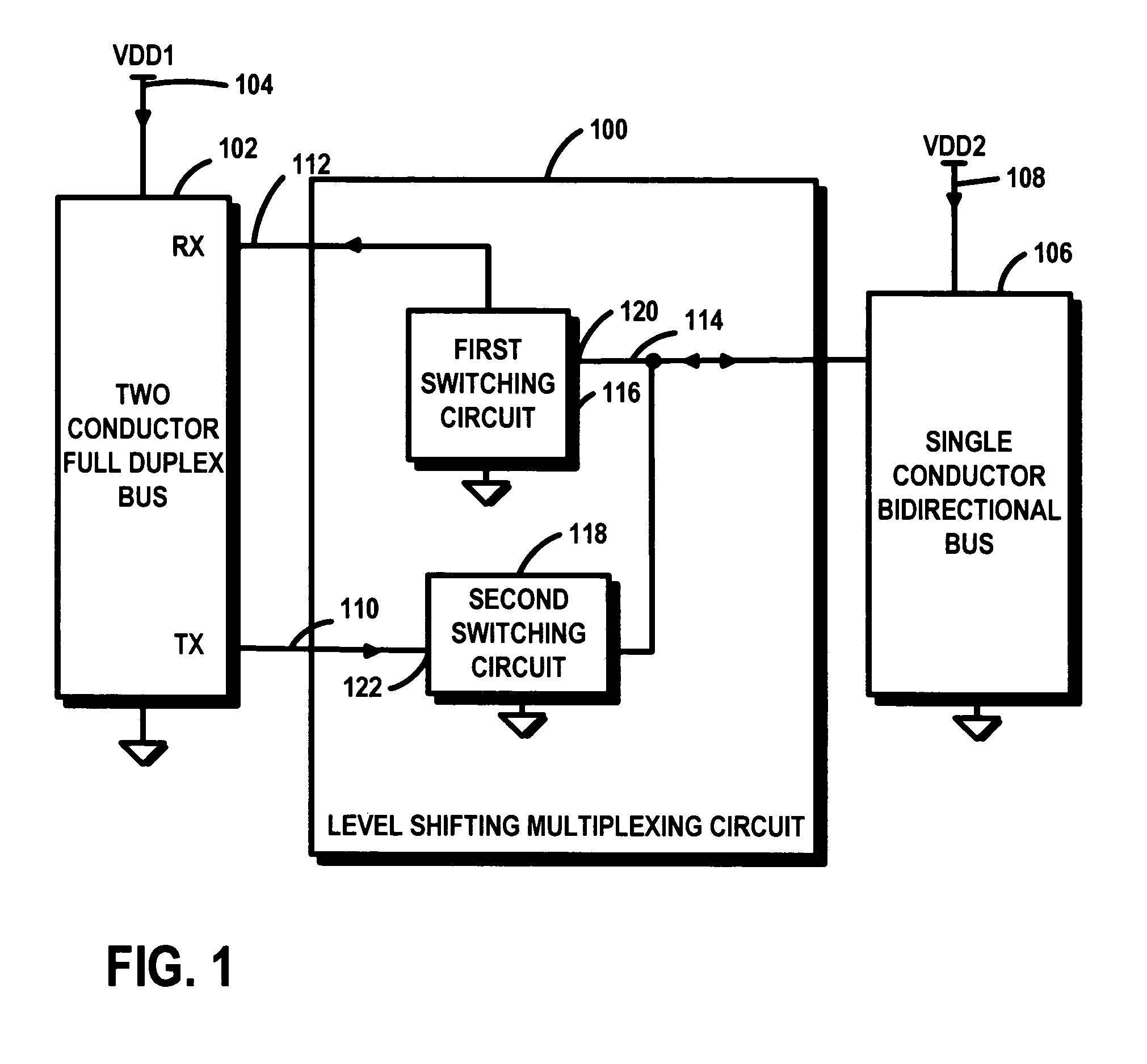

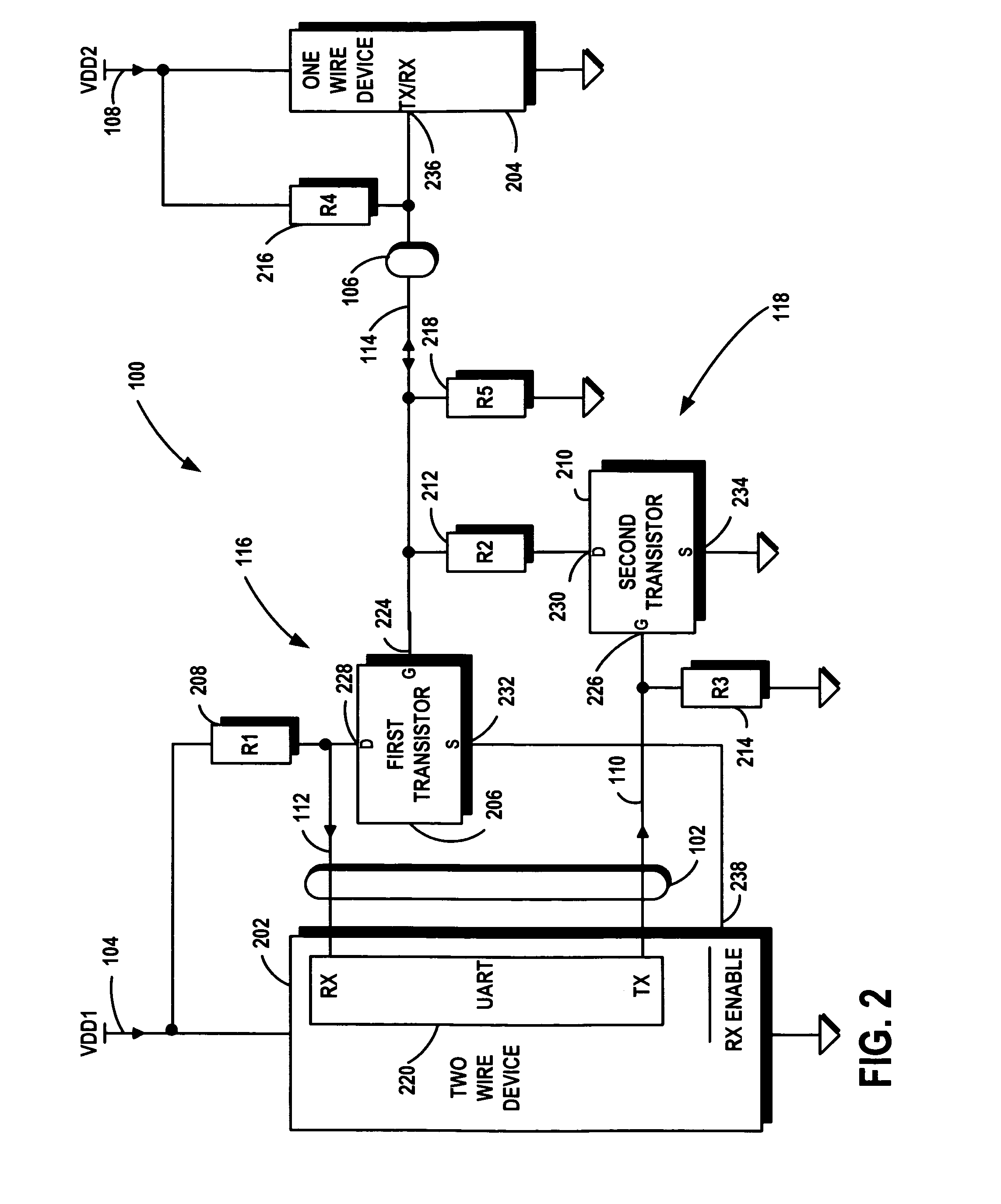

Level shifting multiplexing circuit for connecting a two conductor full duplex bus to a bidirectional single conductor bus

InactiveUS20070182449A1Logic circuits coupling/interface with bidirectional operationLogic circuits coupling/interface using field-effect transistorsVoltageLevel shifting

A level shifting multiplexing circuit provides an interface between a two conductor full duplex bus (two conductor bus) and a single conductor bidirectional half duplex bus (single conductor bus) where the two conductor bus is operates at a first supply voltage and the single conductor bus operates at a second supply voltage. A first switching circuit connected between the single conductor bus and the reception conductor of the two conductor bus is configured to provide a low logic signal to the reception conductor when a first switching voltage threshold is exceeded and to provide a high logic signal, otherwise. A second switching circuit connected between the single conductor bus and the transmission conductor of the two conductor bus is configured to provide a voltage less than the first switching voltage threshold when voltage at the transmission conductor exceeds a second switching voltage threshold unless a high logic signal is received on the single conductor bus. The second switching circuit is further configured to provide a voltage greater than the first switching voltage when the transmission conductor voltage exceeds the second switching voltage threshold unless a low logic signal is received on the single conductor bus.

Owner:KYOCERA CORP

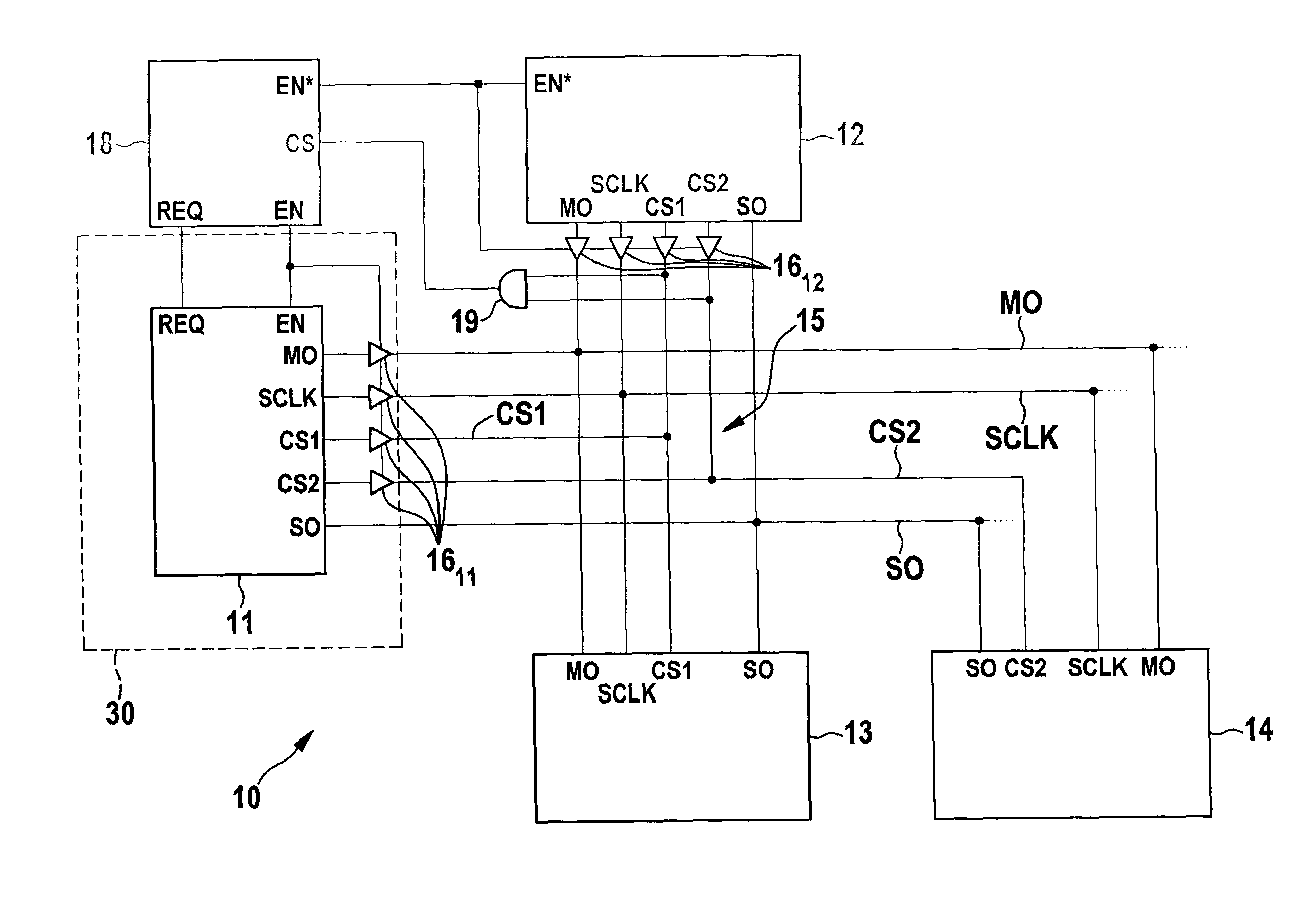

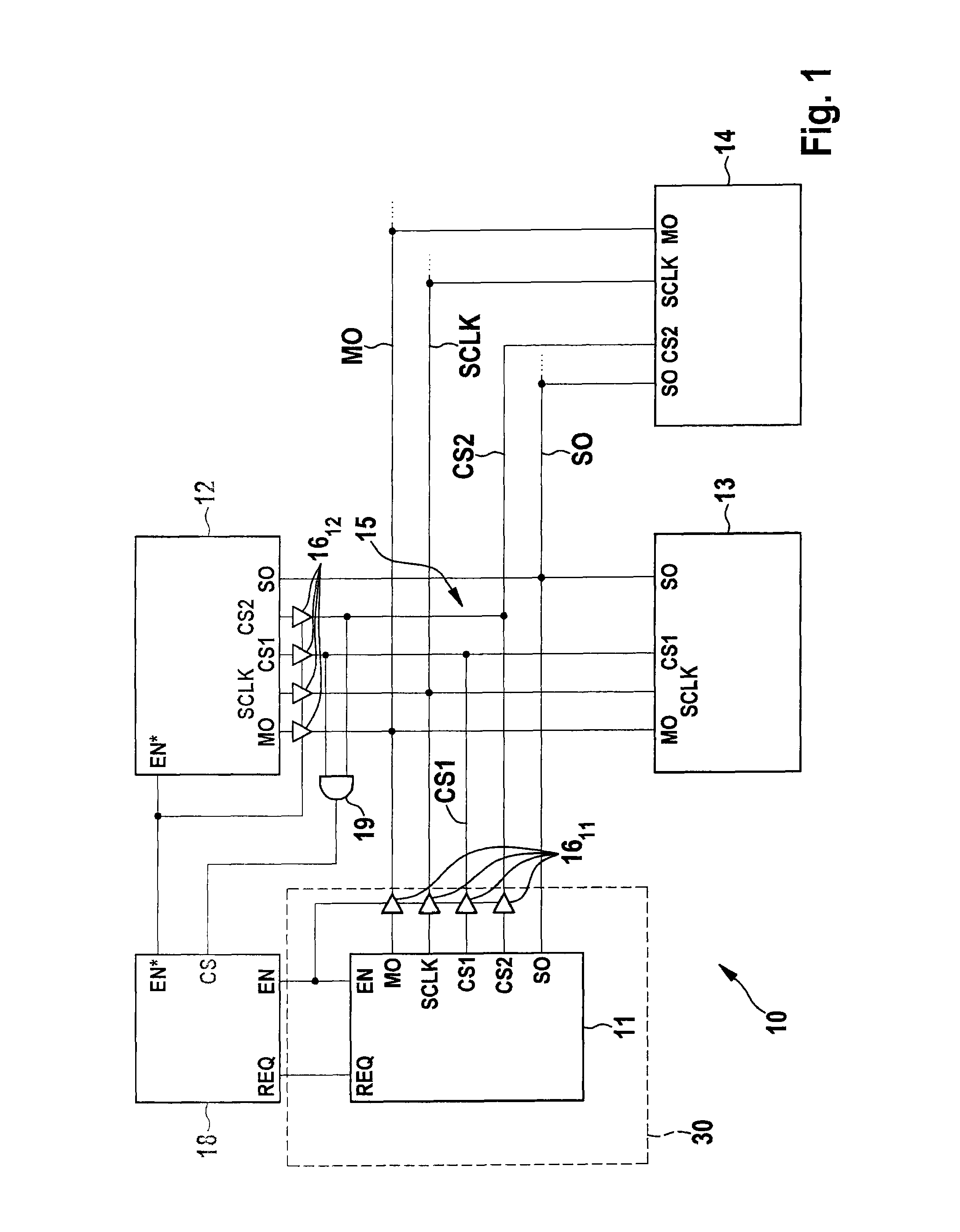

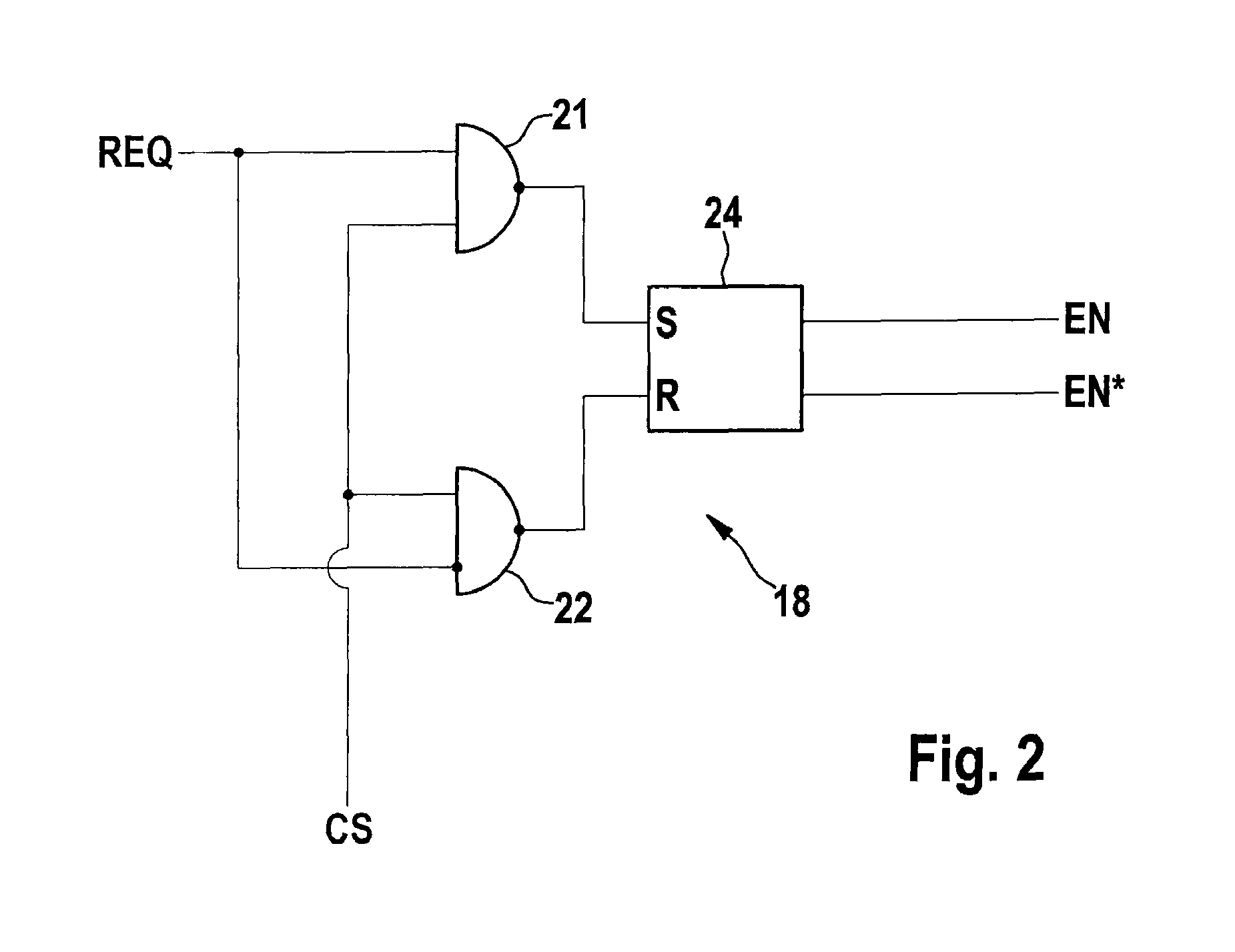

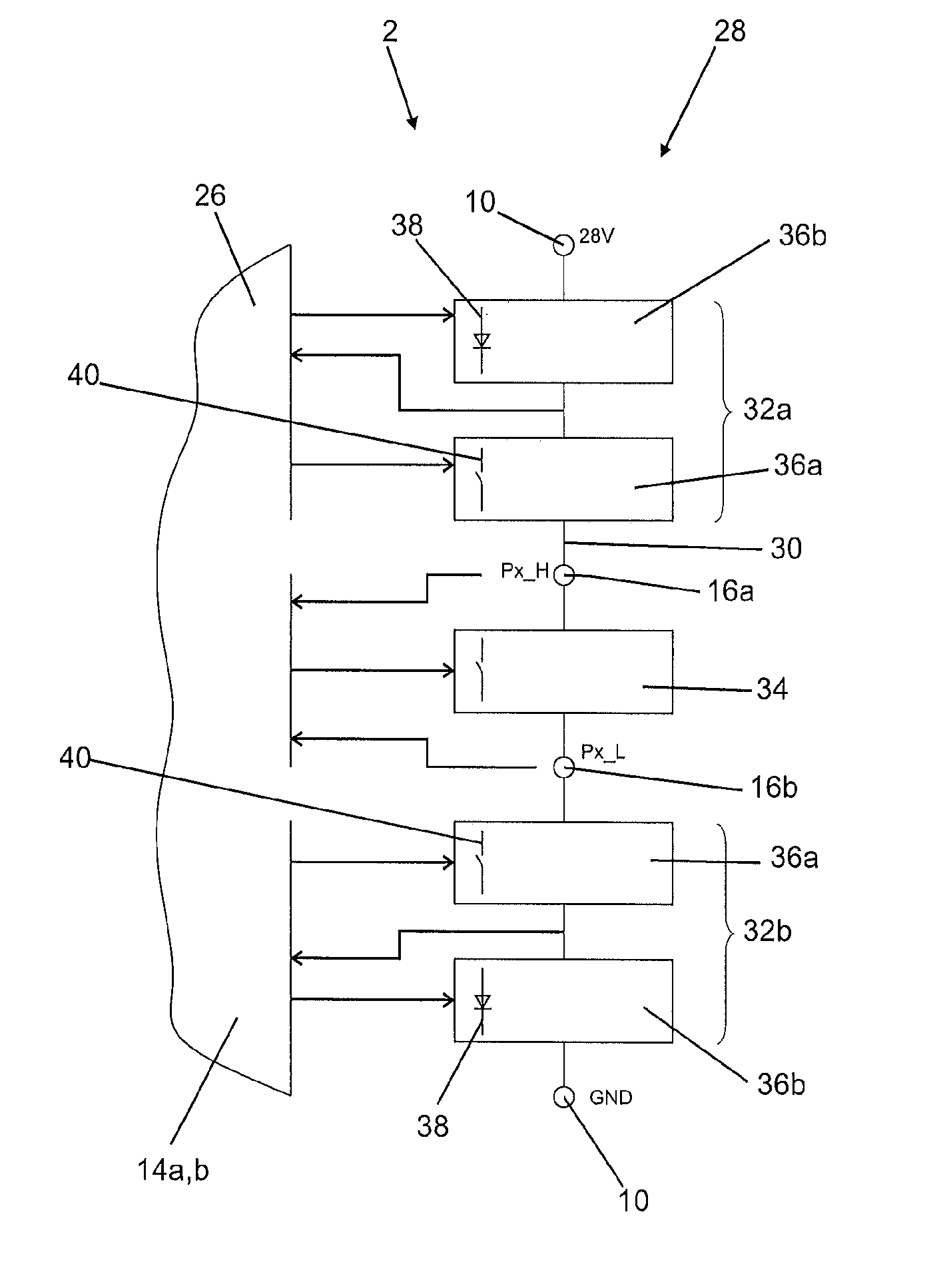

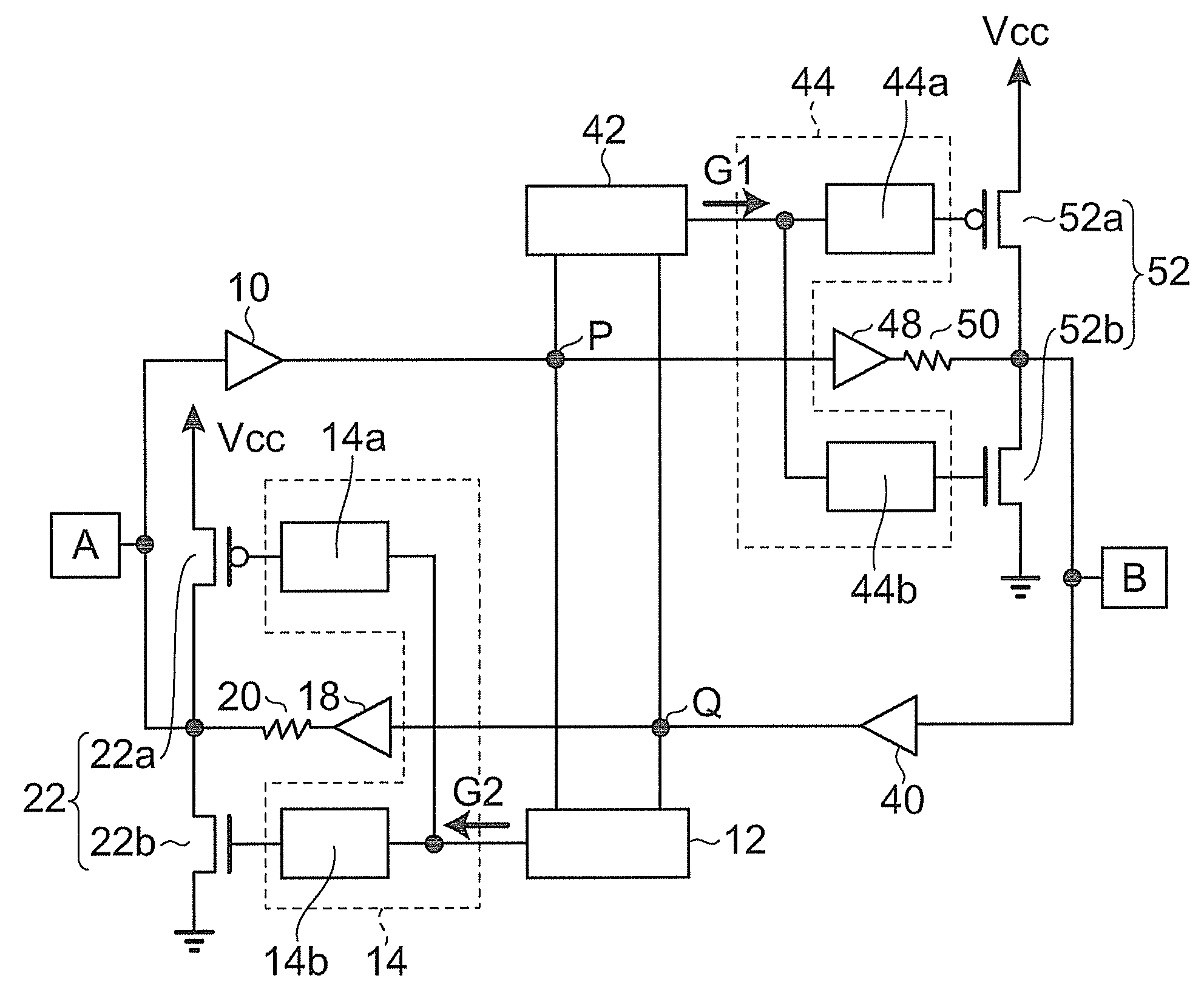

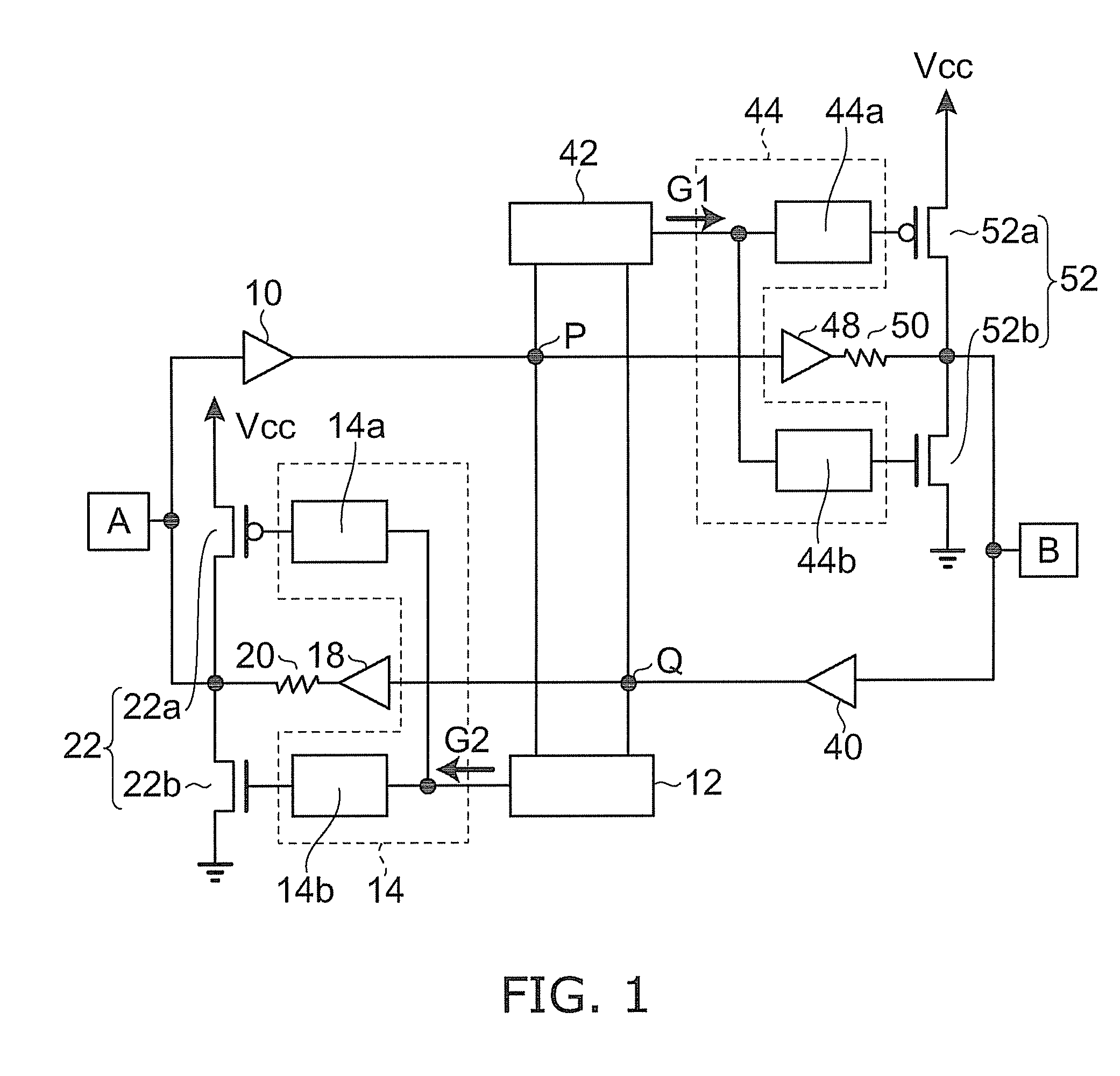

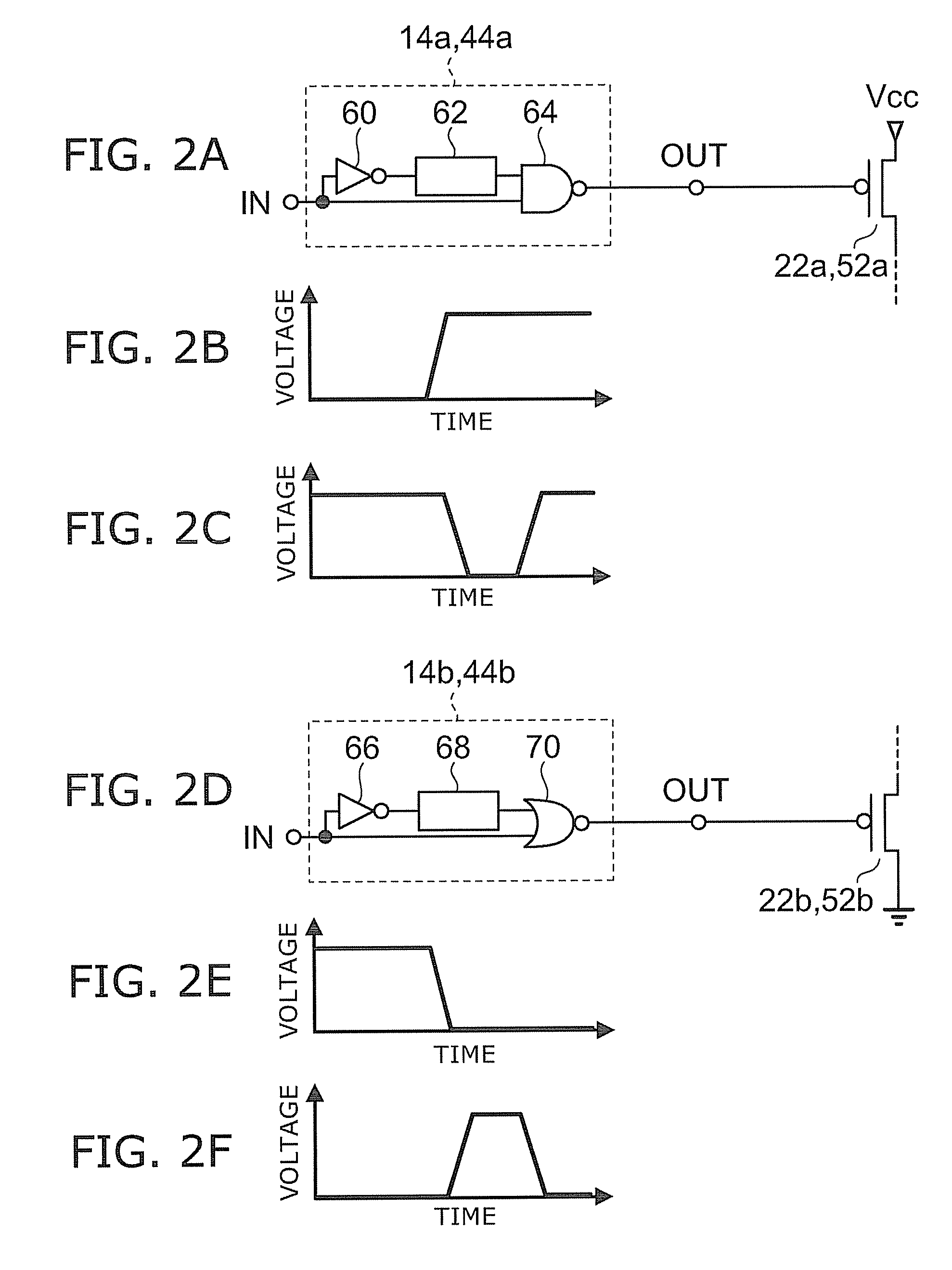

Electrical circuit for transmitting signals between two masters and one or more slaves

ActiveUS8892799B2Reliability increasing modificationsLogic circuits coupling/interface with bidirectional operationEngineeringMaster data

An electrical circuit for transmitting signals between two masters and one or more slaves is described. The two masters and the slave or slaves are connected to one another via a bus system. At least one master data signal can be generated by each of the two masters, which signal can be received by the slave or slaves. A three-state gate is present at each of the outputs of the two masters at which the respective master data signal is present. The three-state gates are effective either as closed or as open switches. The three-state gates are activated in such a way that the three-state gate associated with the one of the two masters acts as a closed switch, and the three-state gate associated with the other of the two masters acts as an open switch.

Owner:ROBERT BOSCH GMBH

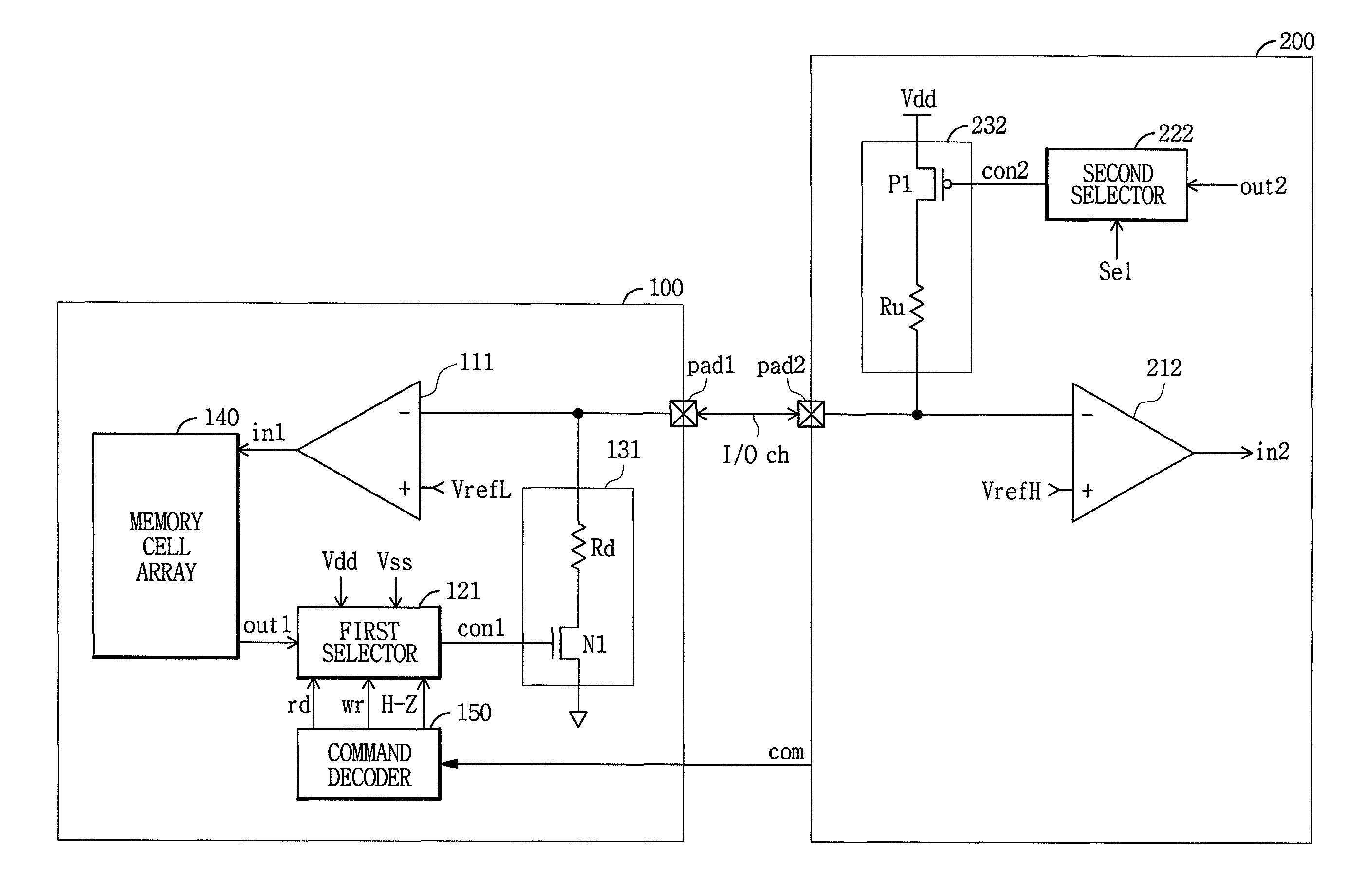

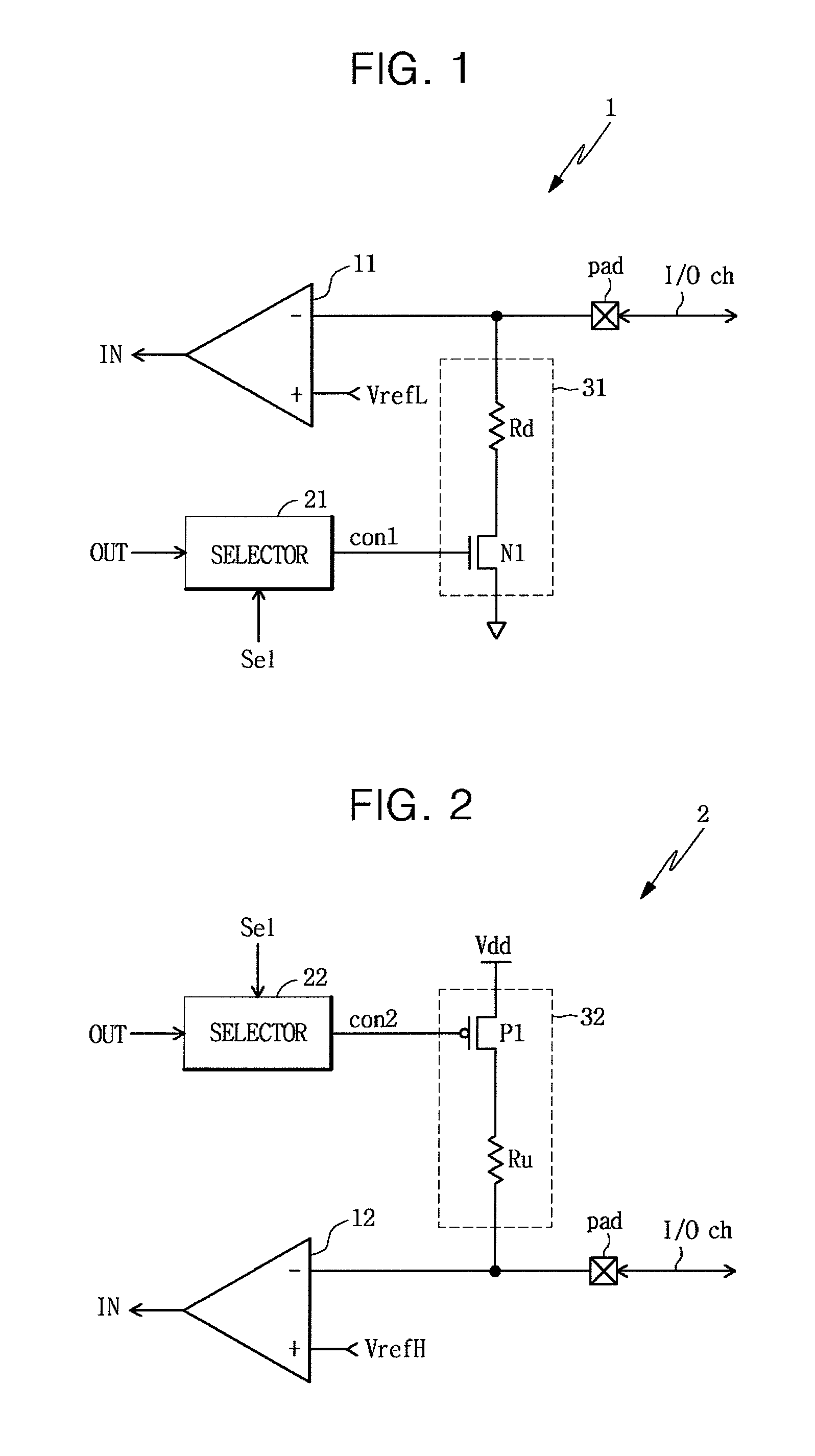

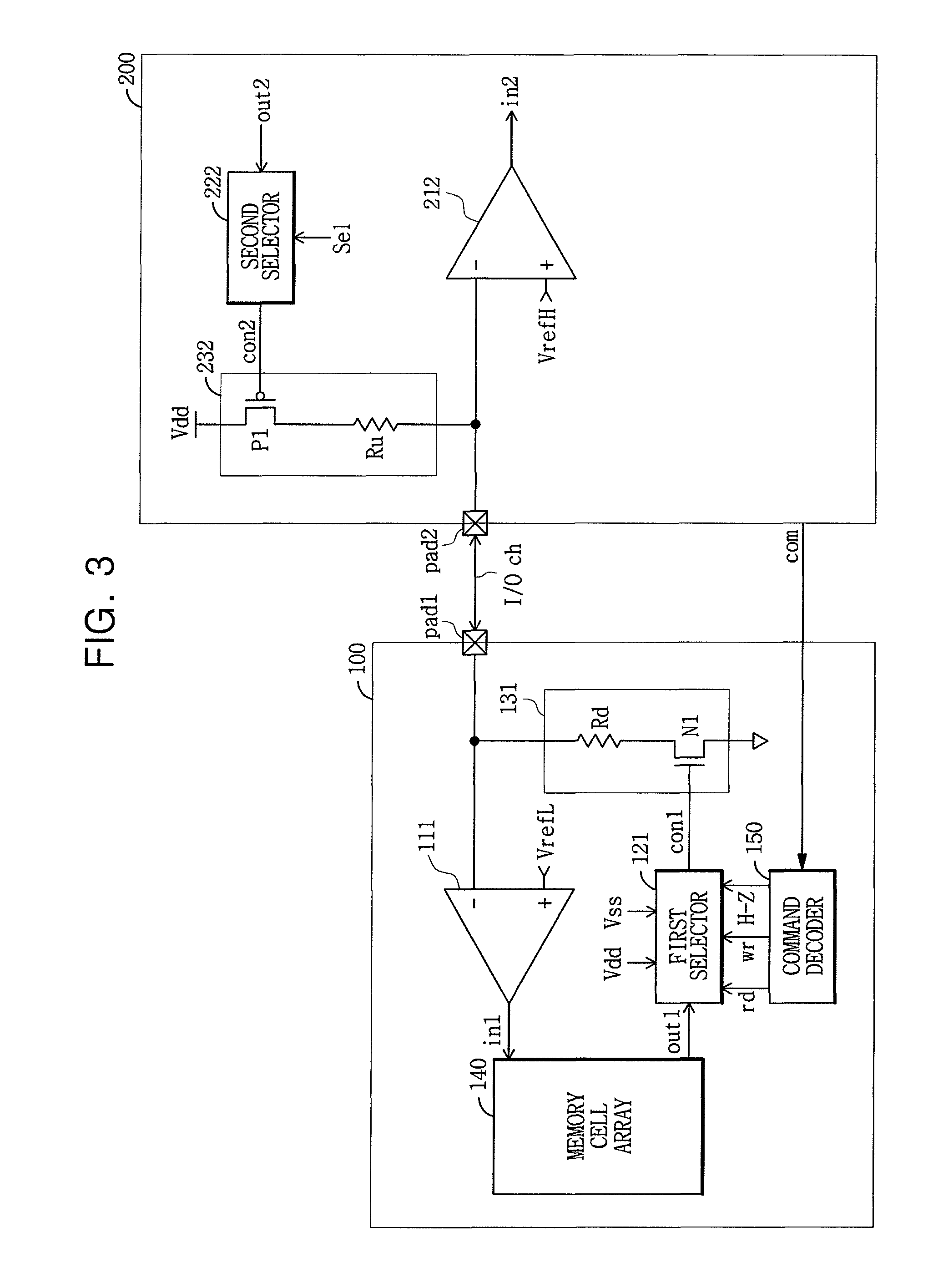

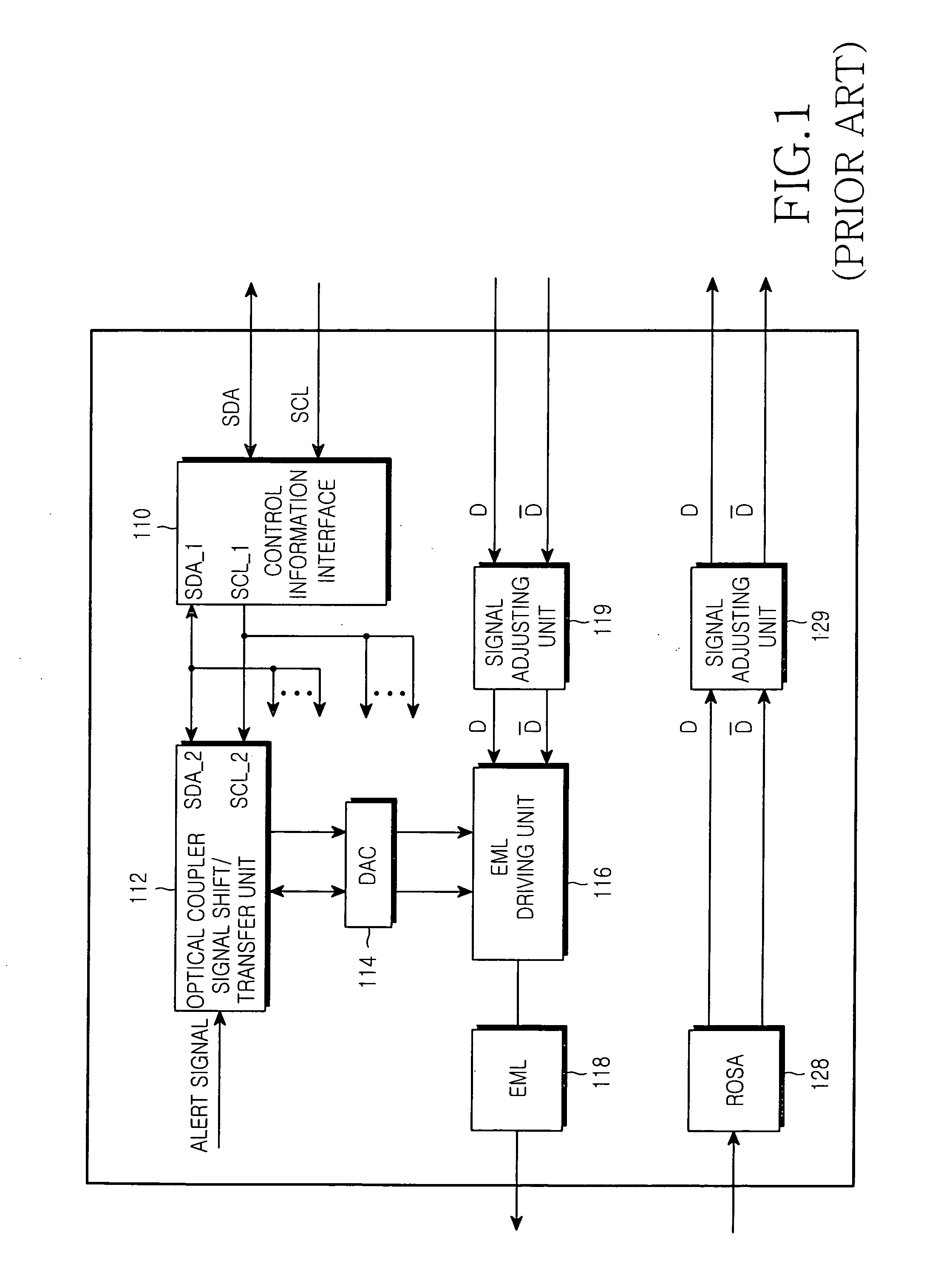

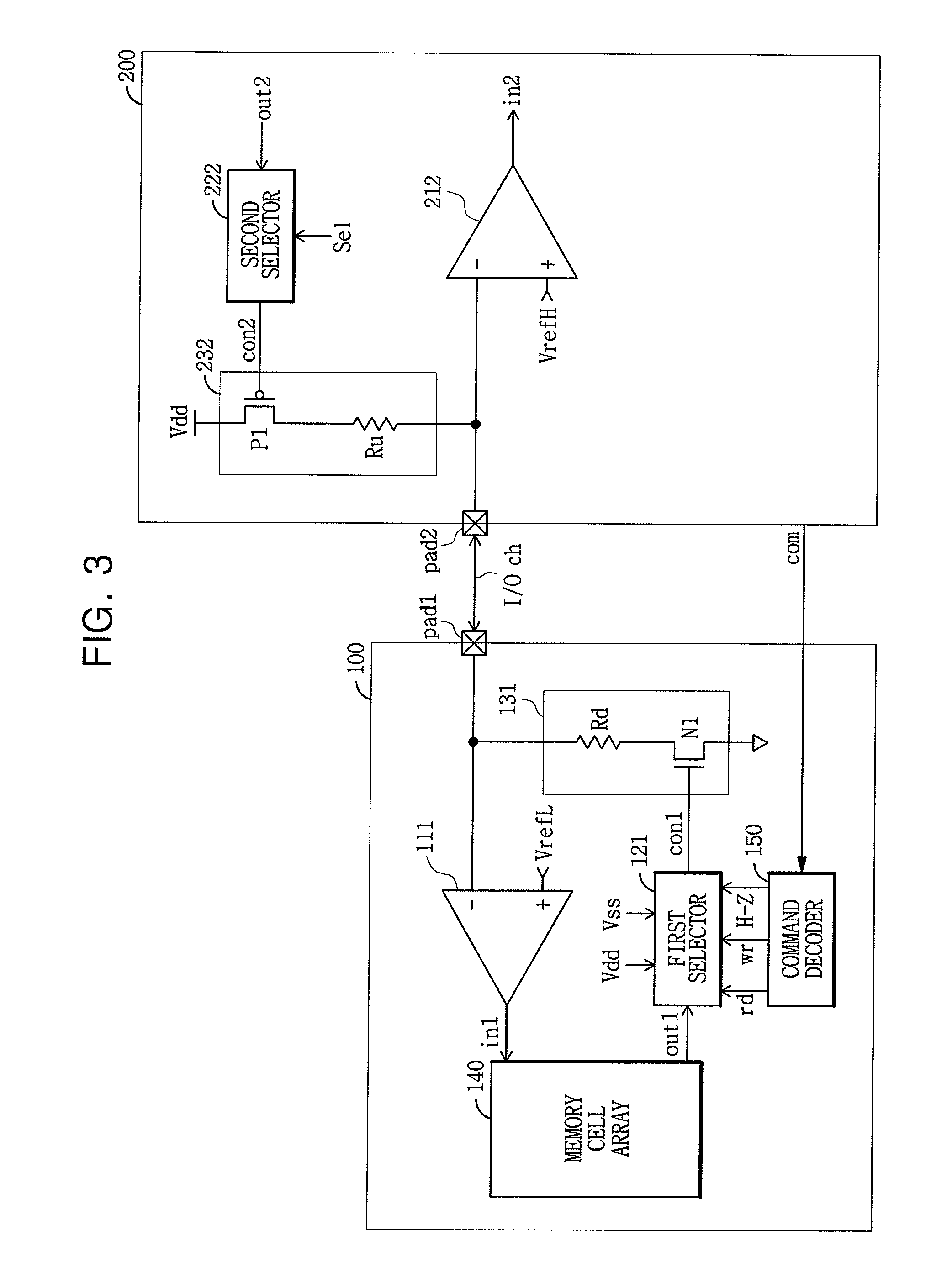

Transceiver system, semiconductor device thereof, and data transceiving method of the same

ActiveUS8149015B2Reliability increasing modificationsLogic circuits coupling/interface with bidirectional operationTransceiverElectrical conductor

A transceiver system includes a first semiconductor device having a first input / output (I / O) pad connected with an I / O channel and a second semiconductor device having a second I / O pad connected with the I / O channel. The first semiconductor device is configured to terminate the first I / O pad with a first voltage when data is received, and maintain the first I / O pad and the I / O channel at the first voltage when data is transmitted. The second semiconductor device is configured to terminate the second I / O pad with a second voltage higher than the first voltage when data is received, and maintain the second I / O pad and the I / O channel at the second voltage when data is transmitted.

Owner:SAMSUNG ELECTRONICS CO LTD

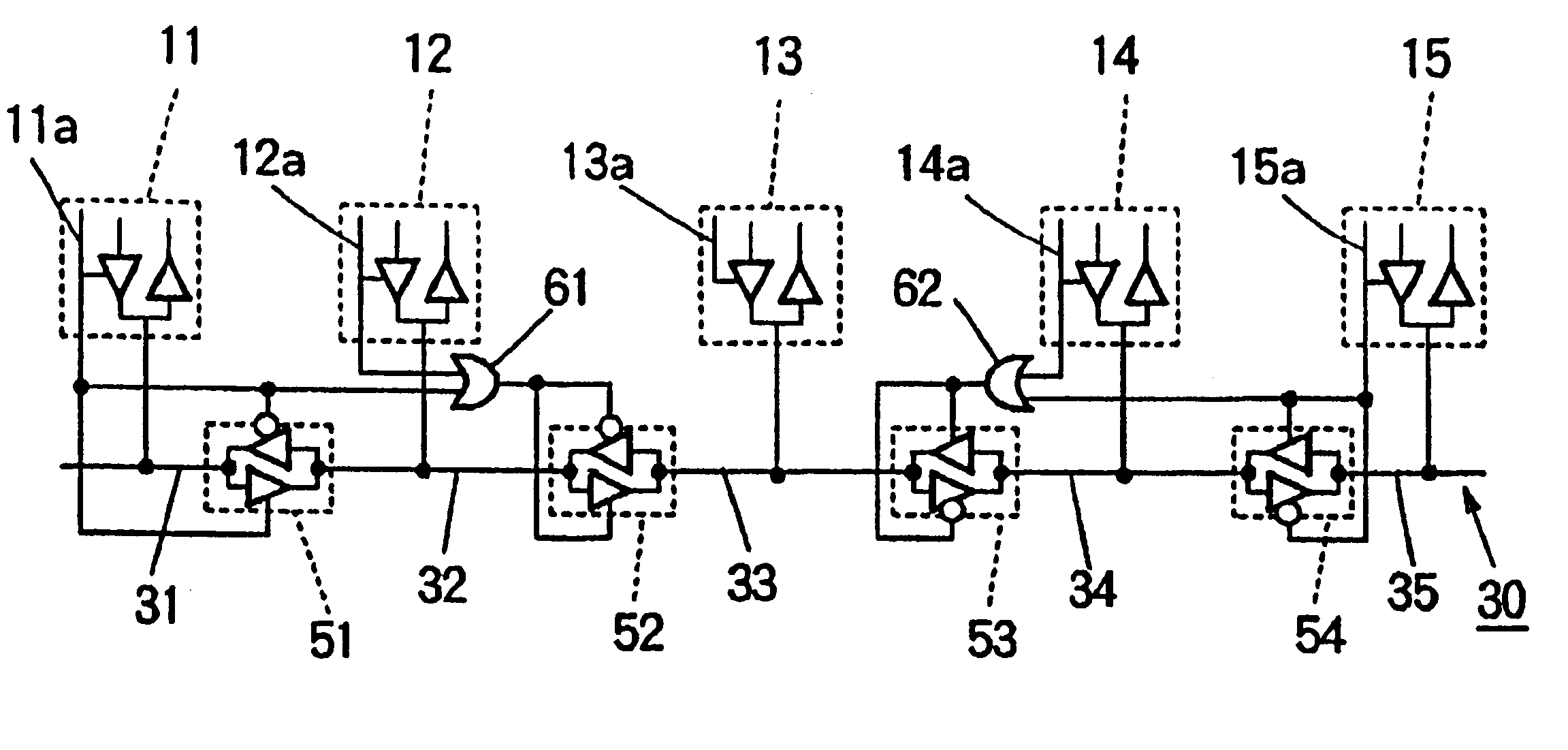

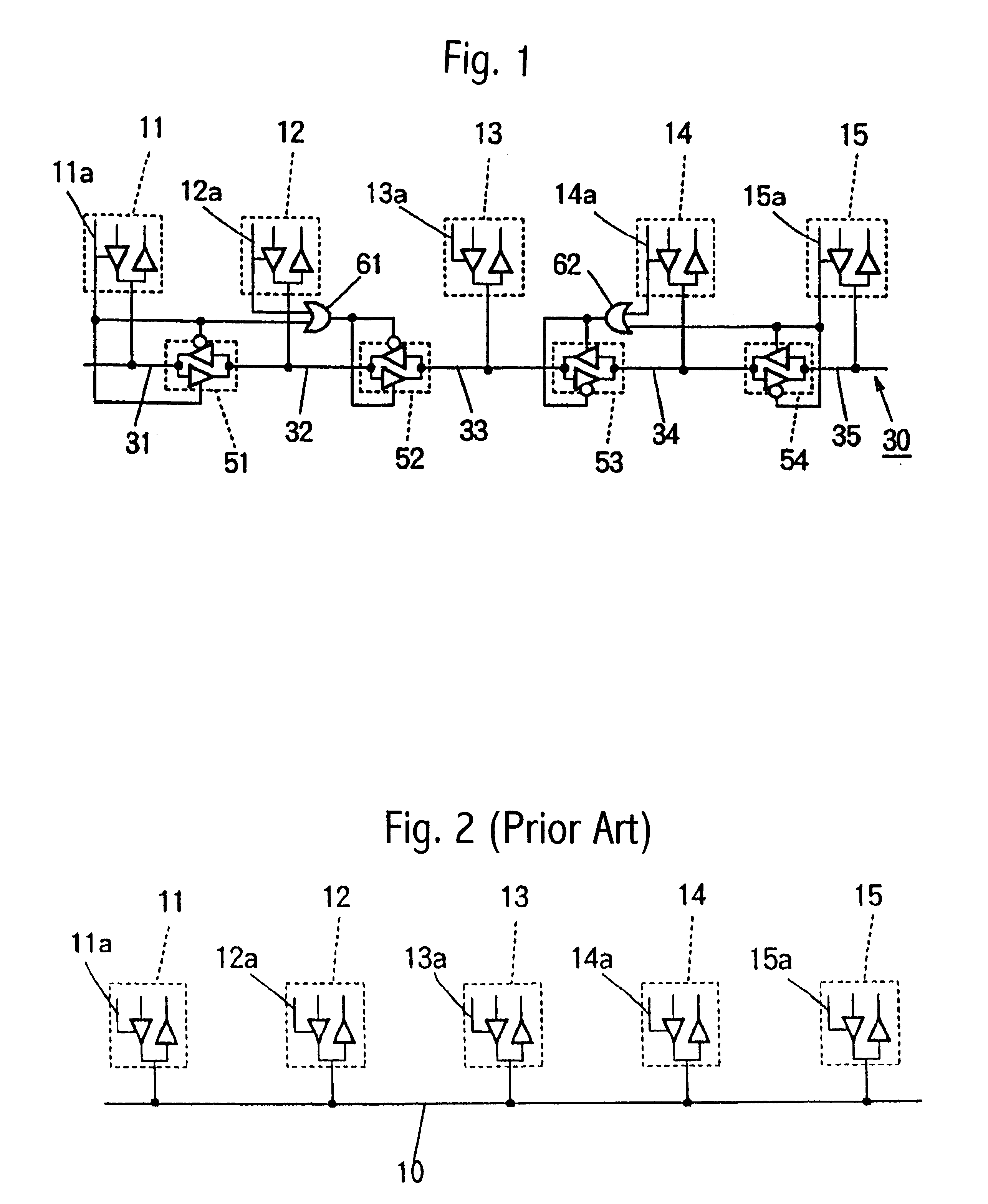

Bidirectional signal control circuit

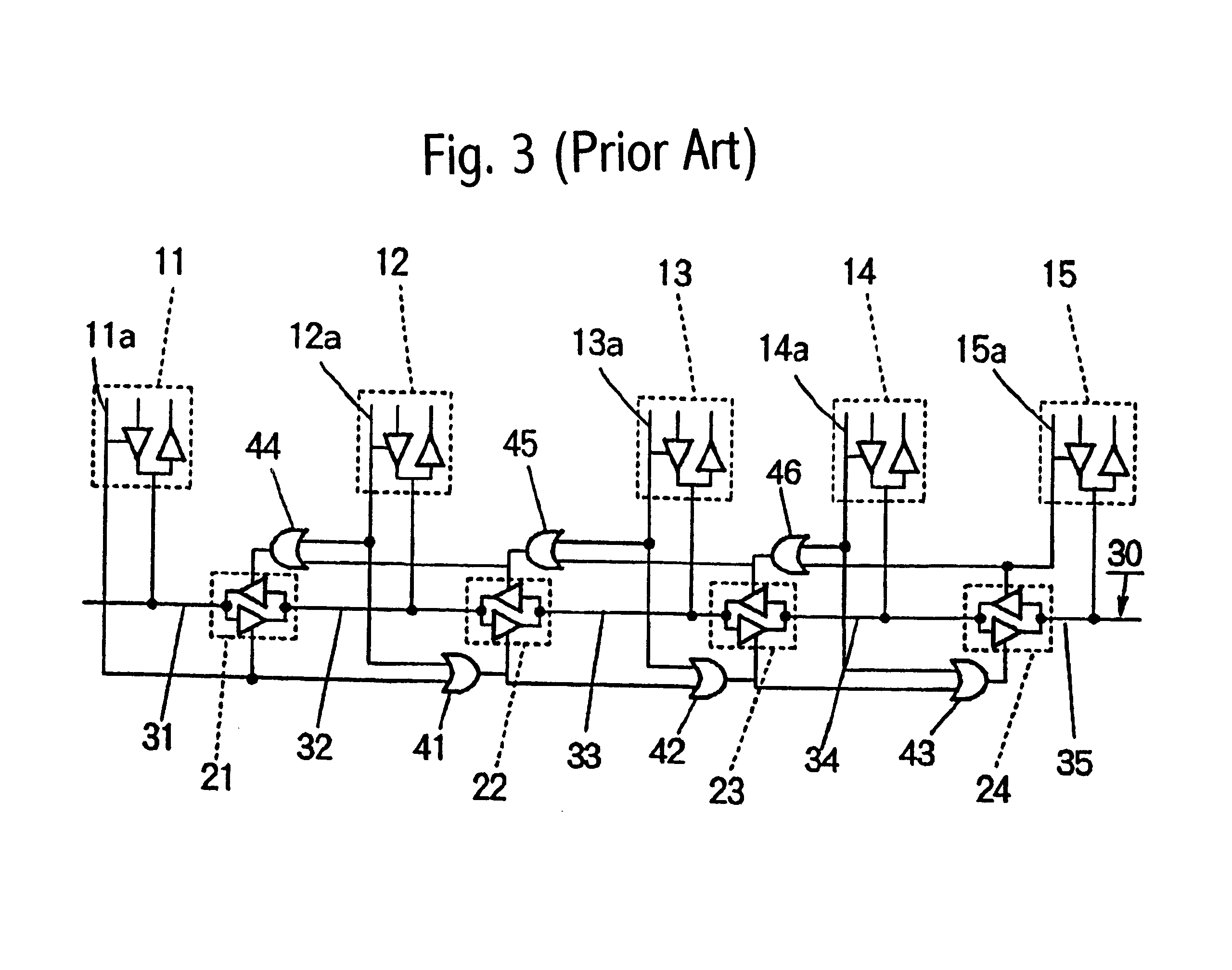

InactiveUS6633179B1Logic circuits coupling/interface with bidirectional operationSolid-state devicesControl signalData signal

A wire used for transferring bidirectional signals is divided into a plurality of sub line segments. These sub line segments are classified into groups. Further, bidirectional buffers are provided between respective adjacent sub wires. The direction of transfer of a signal by each of the bidirectional buffers is controlled based on at least one of control signals used to control drivers for respectively outputting data signals to the sub line segments.< / PTEXT>

Owner:LAPIS SEMICON CO LTD

Bidirectional level conversion circuit and bilateral level conversion chip

PendingCN109687862AReduce areaLow costLogic circuits coupling/interface with bidirectional operationLogic circuit interface arrangementsEngineeringVoltage

Owner:SHANGHAI AWINIC TECH CO LTD

Bi-directional signal level shift circuit

InactiveUS7202727B2Pulse automatic controlLogic circuits coupling/interface with bidirectional operationEngineeringOperating voltage

A circuit for shifting a level between two bi-directional signals having different voltage levels. The circuit includes a first analog switch including a first switching control terminal connected to first directional signal stage, a first input terminal connected to a first level of operating voltage, and a first output terminal connected to a second directional signal stage, for performing a switching operation for the first input terminal and the first output terminal based on a state of logic level of a signal from the second directional signal stage. The circuit also includes a second analog switch including a second switching control terminal connected to the first directional signal stage, a second input terminal connected to a second level of operating voltage, and a second output terminal connected to the first directional signal stage for performing a switching operation for the second input terminal and the second output terminal based on a state of a logic level of a signal from the first directional signal stage.

Owner:SAMSUNG ELECTRONICS CO LTD

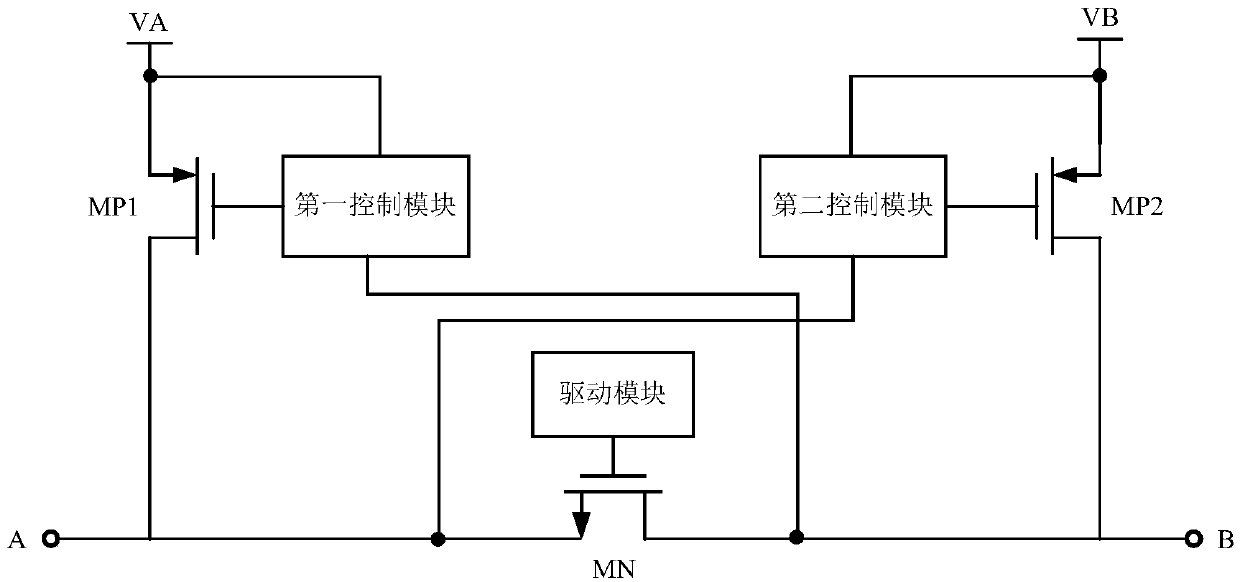

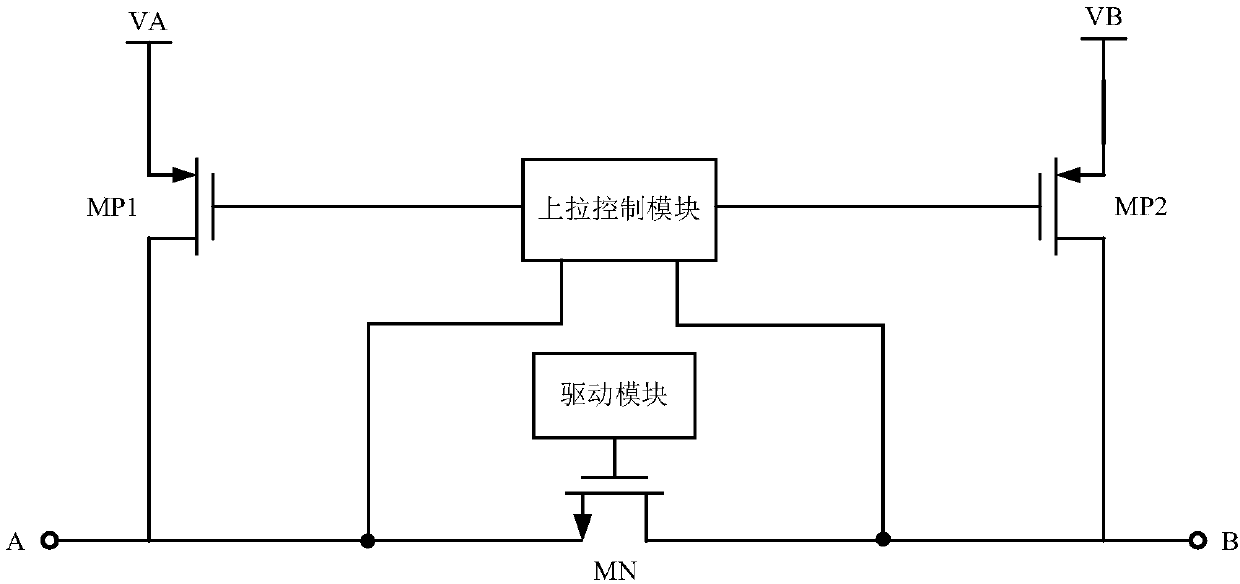

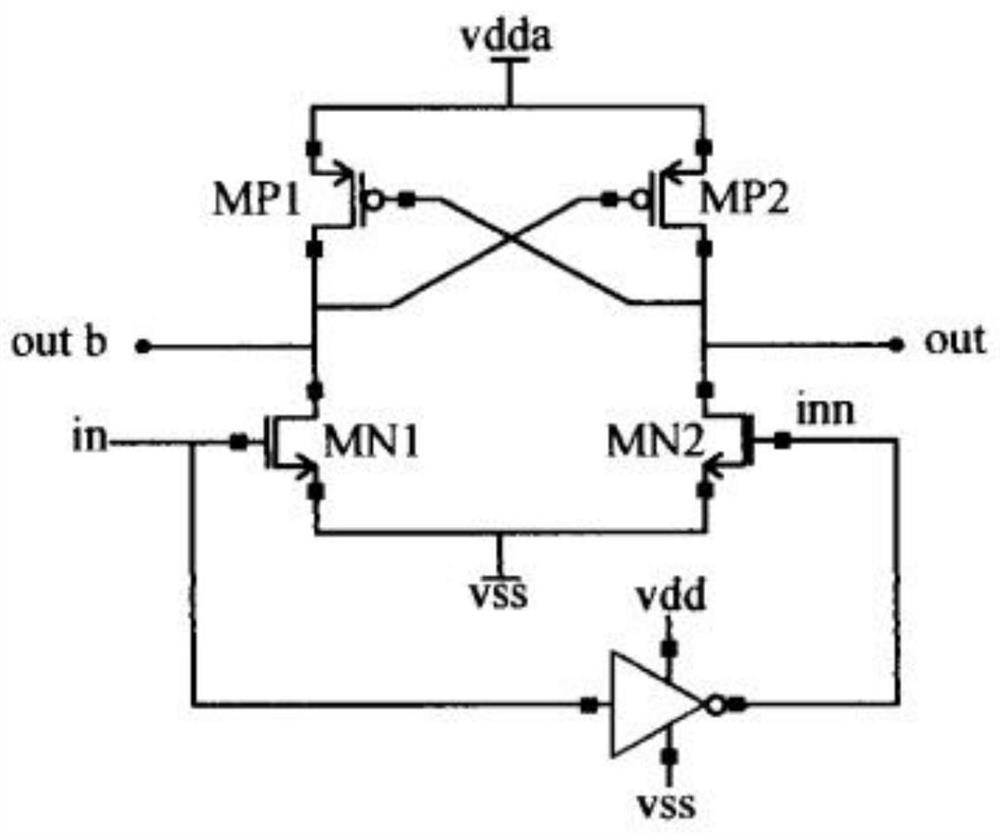

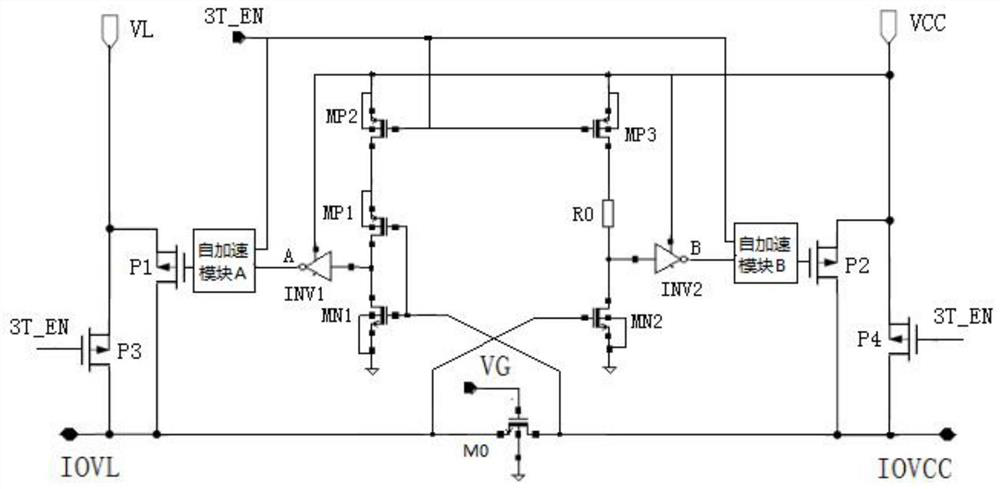

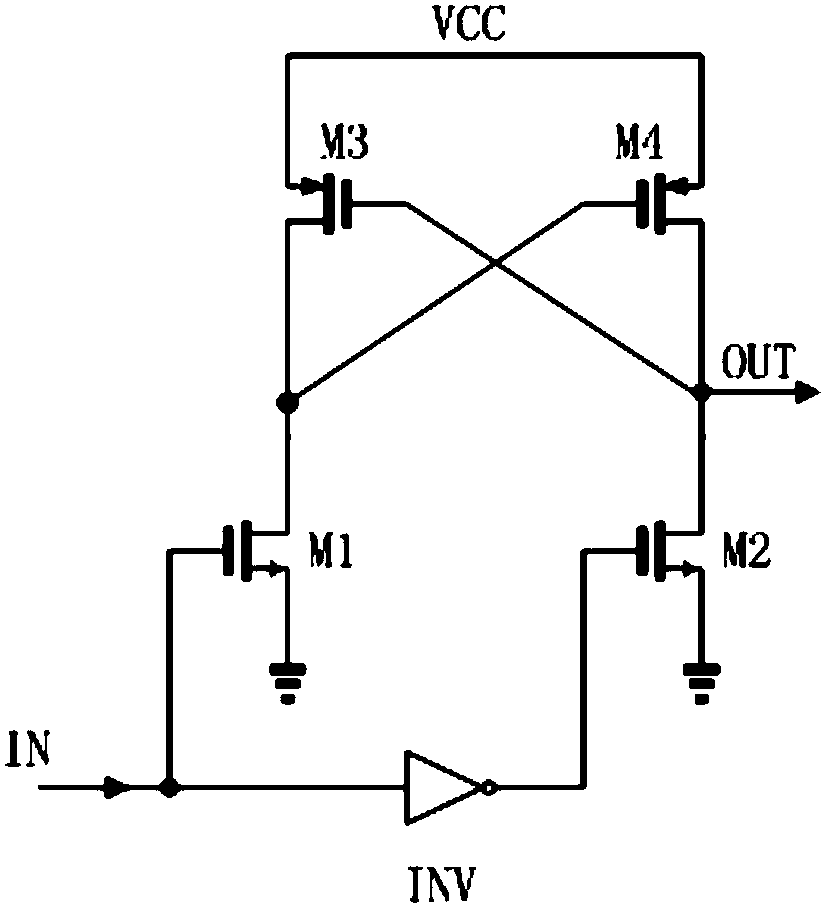

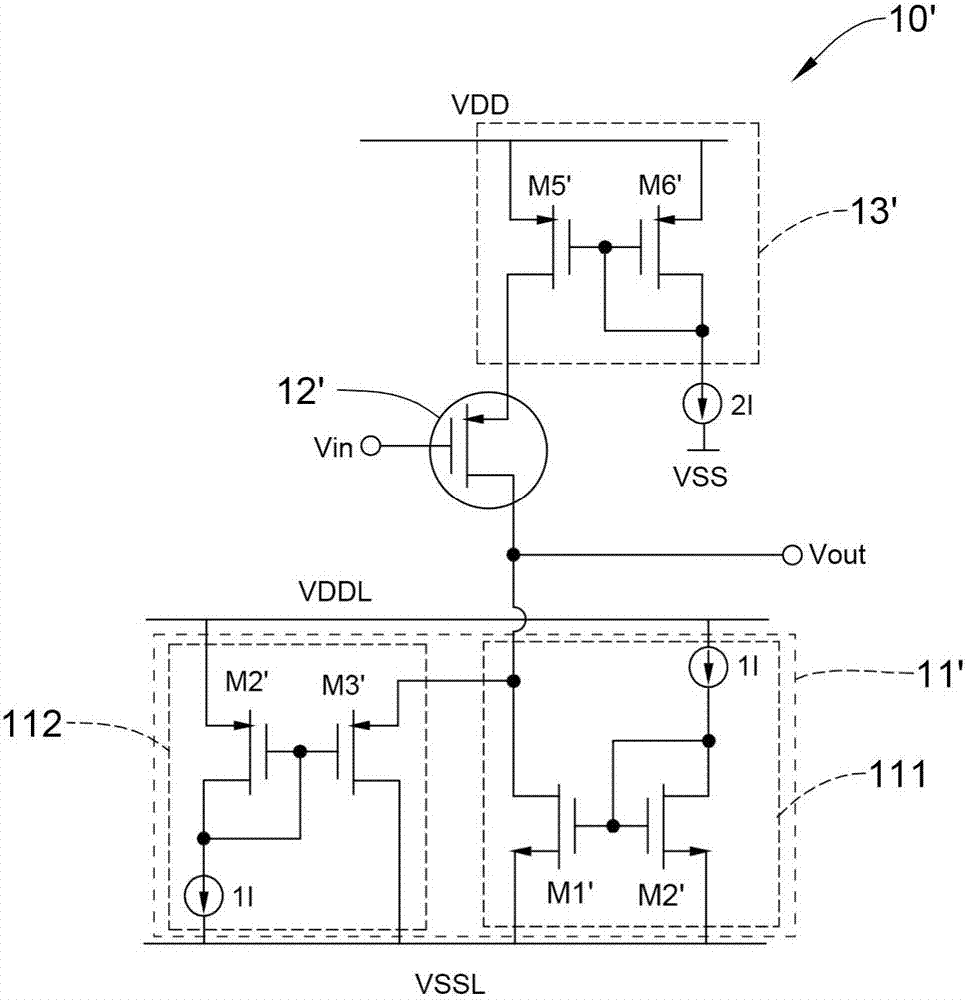

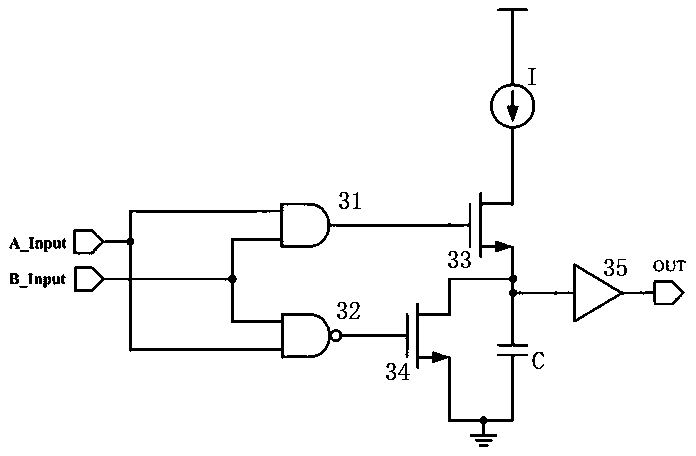

Self-induction and self-acceleration bidirectional level conversion circuit

ActiveCN111817705ASimple structureImprove workabilitySwitching accelaration modificationsPower reduction in field effect transistorsLevel shiftingLow voltage

The invention discloses a self-induction and self-acceleration bidirectional level conversion circuit, and belongs to the technical field of electronic circuits. The circuit is simple in structure, good in working performance, high in conversion speed and higher in working frequency under the common CMOS process; not only can conversion be carried out between specific double-path power supply voltages, but also a relatively wide voltage conversion range is achieved; and an independent direction control bidirectional conversion function is built in, so that the device can sense and control thedata flow direction, and a direction control pin is not needed. Not only can a low voltage be converted into a high voltage, but also the high voltage can be converted into the low voltage. Digital level conversion and matching work among most of current systems can be well completed. The circuit is less affected by temperature, power supply voltage and process. Therefore, the self-induction and self-acceleration bidirectional level conversion circuit applied to the field of signal transmission provided by the invention can greatly improve the level conversion efficiency, and has an importantapplication value.

Owner:58TH RES INST OF CETC

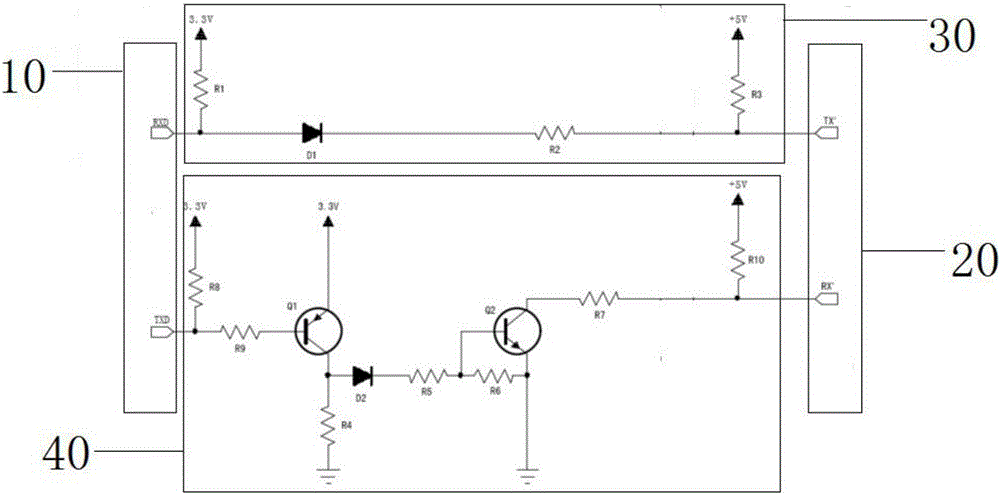

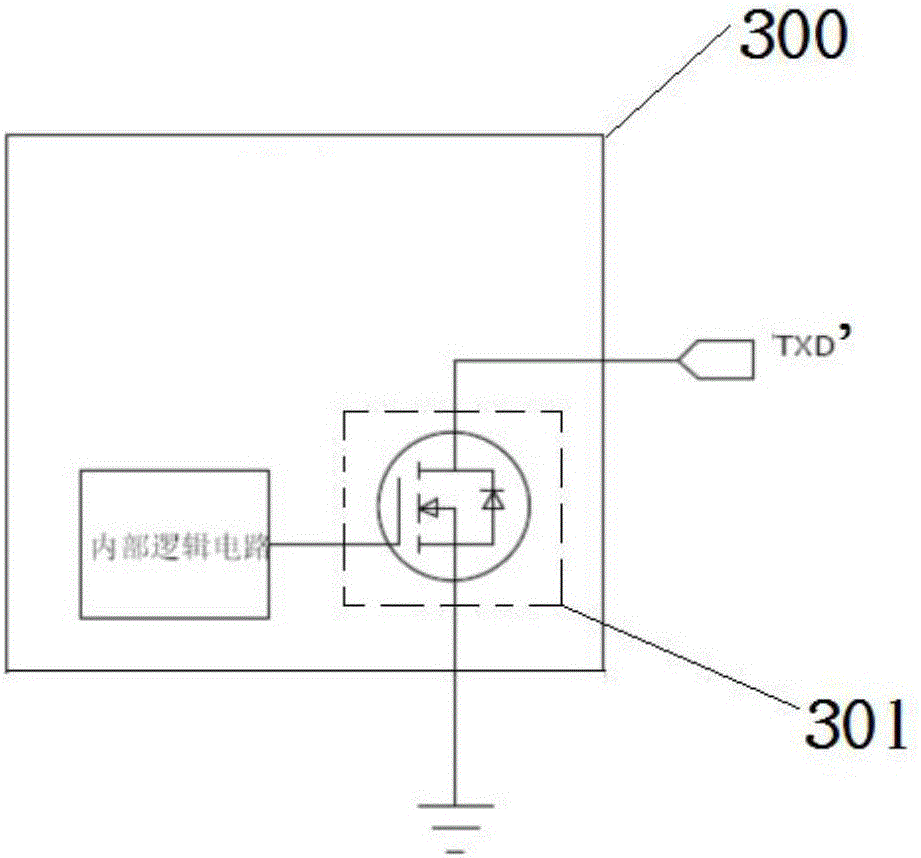

Communication isolation and level switching circuit

PendingCN106712764ASolve the communication functionAvoid damageLogic circuits coupling/interface with bidirectional operationFail-safe circuitsHigh pressurePull-up resistor

The invention discloses a communication isolation and level switching circuit. The communication isolation and level switching circuit is separately connected with a battery and a host, and comprises a first branch and a second branch; the first branch comprises a diode D1, a pull-up resistor R1 and a pull-up resistor R3; and the second branch comprises an audion Q1, an audion Q2, a pull-up resistor R8 and a pull-up resistor R10. By means of the communication isolation and level switching circuit disclosed by the invention, the communication function between MCUs having different power supply voltage can be solved; and the problem that the battery can be damaged due to the fact that high voltage of the host is supplied to the battery when the host is abnormal can be prevented.

Owner:SUNWODA ELECTRONICS

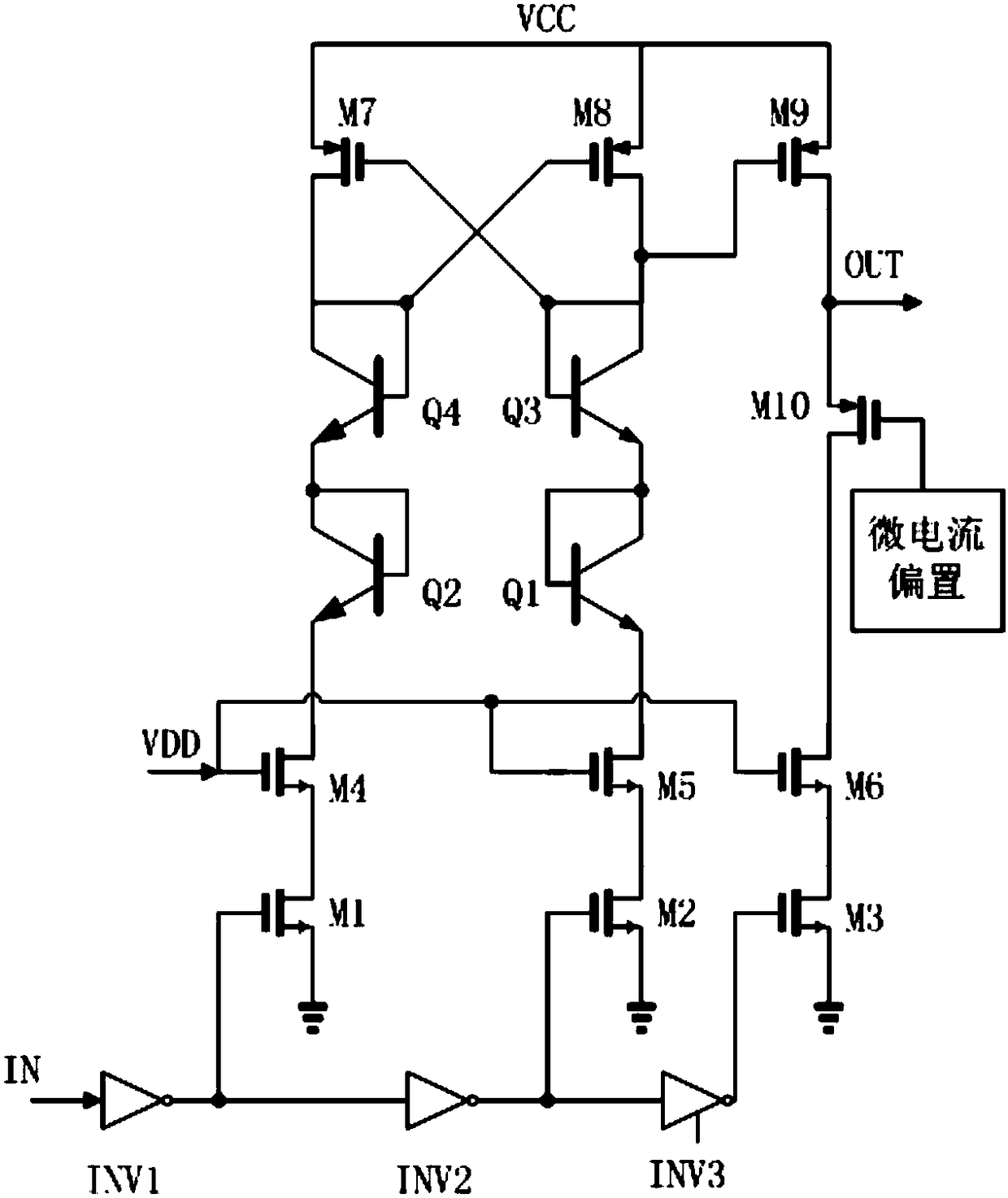

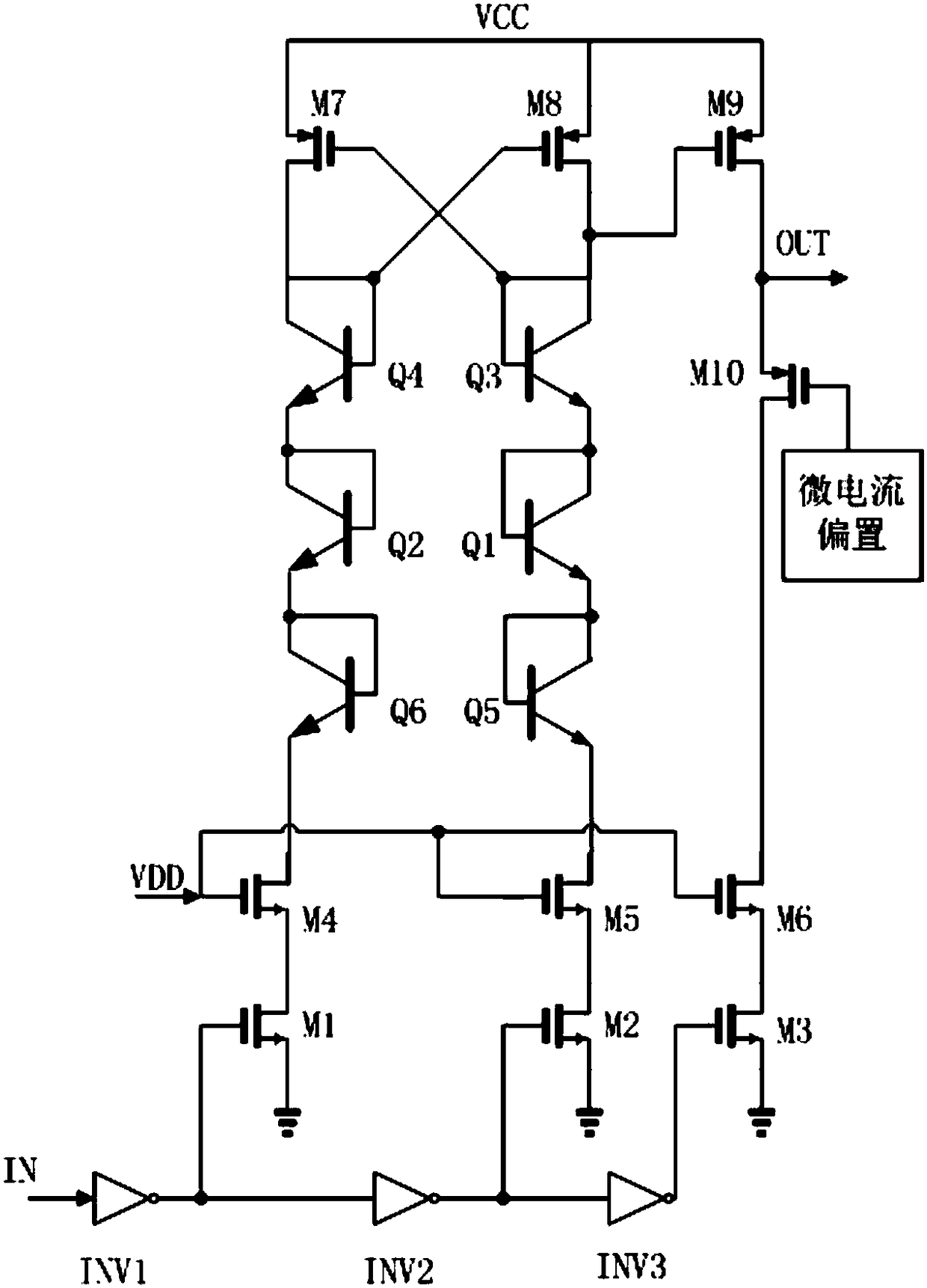

Level translation circuit

PendingCN108233917AImprove reliabilityGuaranteed to workLogic circuits coupling/interface with bidirectional operationFail-safe circuitsCircuit reliabilityEngineering

The invention discloses a level translation circuit. The circuit comprises a first phase inverter, a second phase inverter, a third phase inverter, a first NMOS tube, a second NMOS tube, a third NMOStube, a fourth NMOS tube, a fifth NMOS tube, a sixth NMOS tube, a first PMOS tube, a second PMOS tube, a primary NPN tube set, a third PMOS tube, and a fourth PMOS tube, wherein the primary NPN tube set comprises a first NPN tube and a second NPN tube. The level translation circuit can enable working points of all MOS tubes to not exceed the breakdown voltage thereof when the external power voltage of the level translation circuit exceeds the breakdown voltage of the internal MOS tube, thereby enabling the circuit to work in the safety working voltage range; the required level translation performance can be guarantee, and the circuit reliability can be improved to guarantee the normal work of the circuit.

Owner:上海安其威微电子科技有限公司

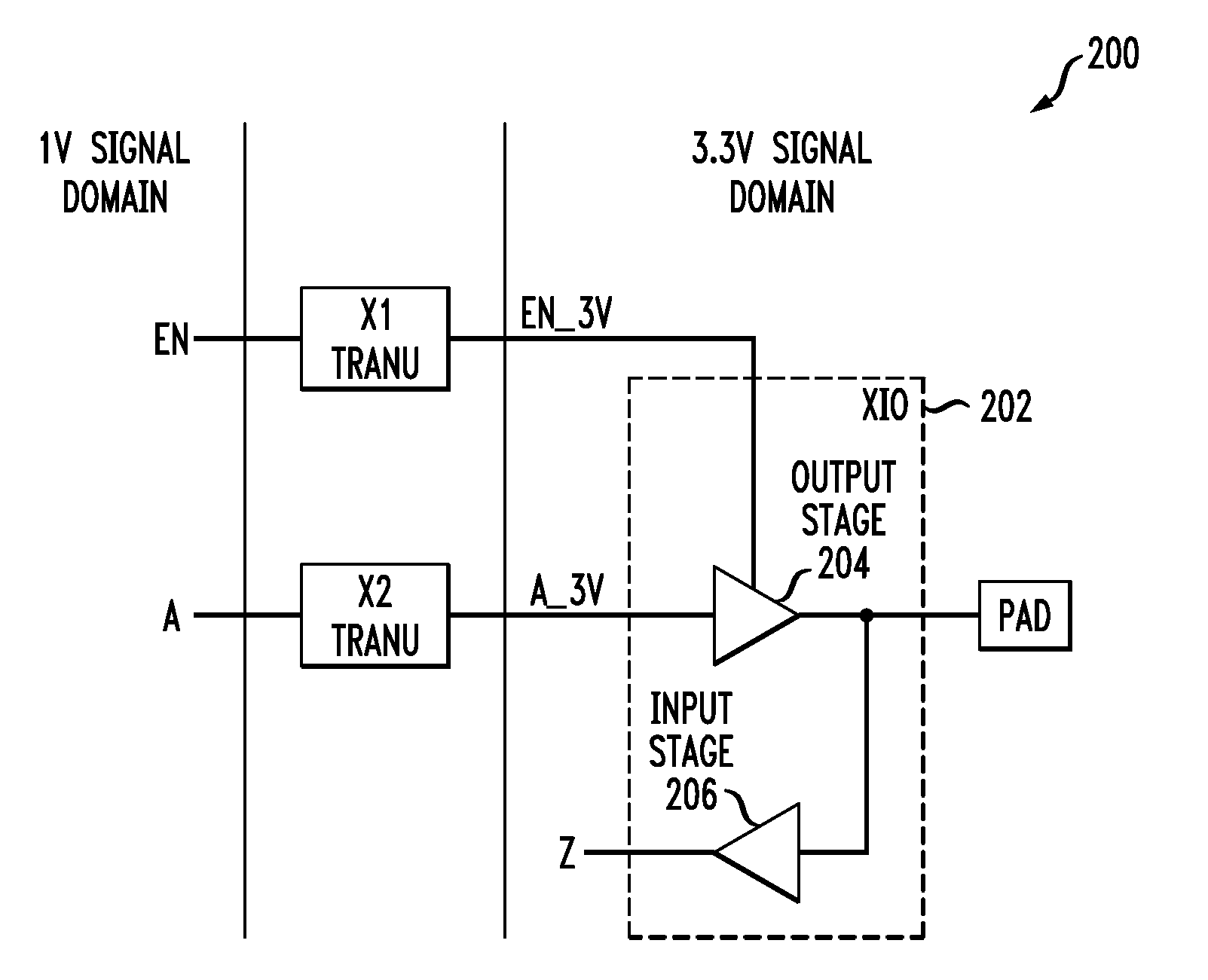

LVDS input circuit with connection to input of output driver

ActiveUS7453283B2Reliability increasing modificationsLogic circuits coupling/interface with bidirectional operationMultiplexerLogic state

First and second devices may simultaneously communicate bidirectionally with each other using only a single pair of LVDS signal paths. Each device includes an input circuit and a differential output driver connected to the single pair of LVDS signal paths. An input to the input circuit is also connected to the input of the driver. The input circuit may also receive an offset voltage. In response to its inputs, the input circuit in each device can use comparators, gates and a multiplexer to determine the logic state being transmitted over the pair of LVDS signal paths from the other device. This advantageously reduces the number of required interconnects between the first and second devices by one half.

Owner:TEXAS INSTR INC

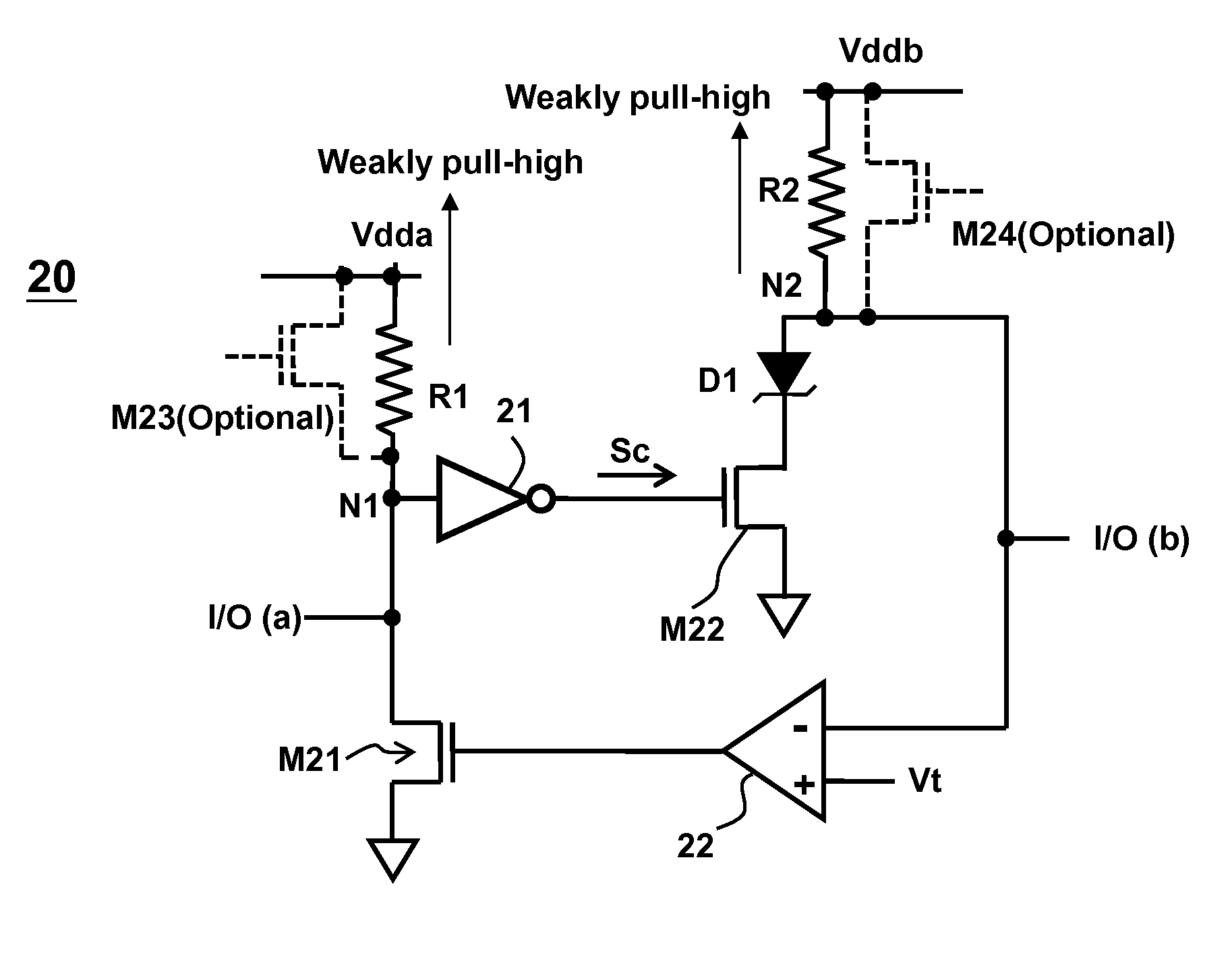

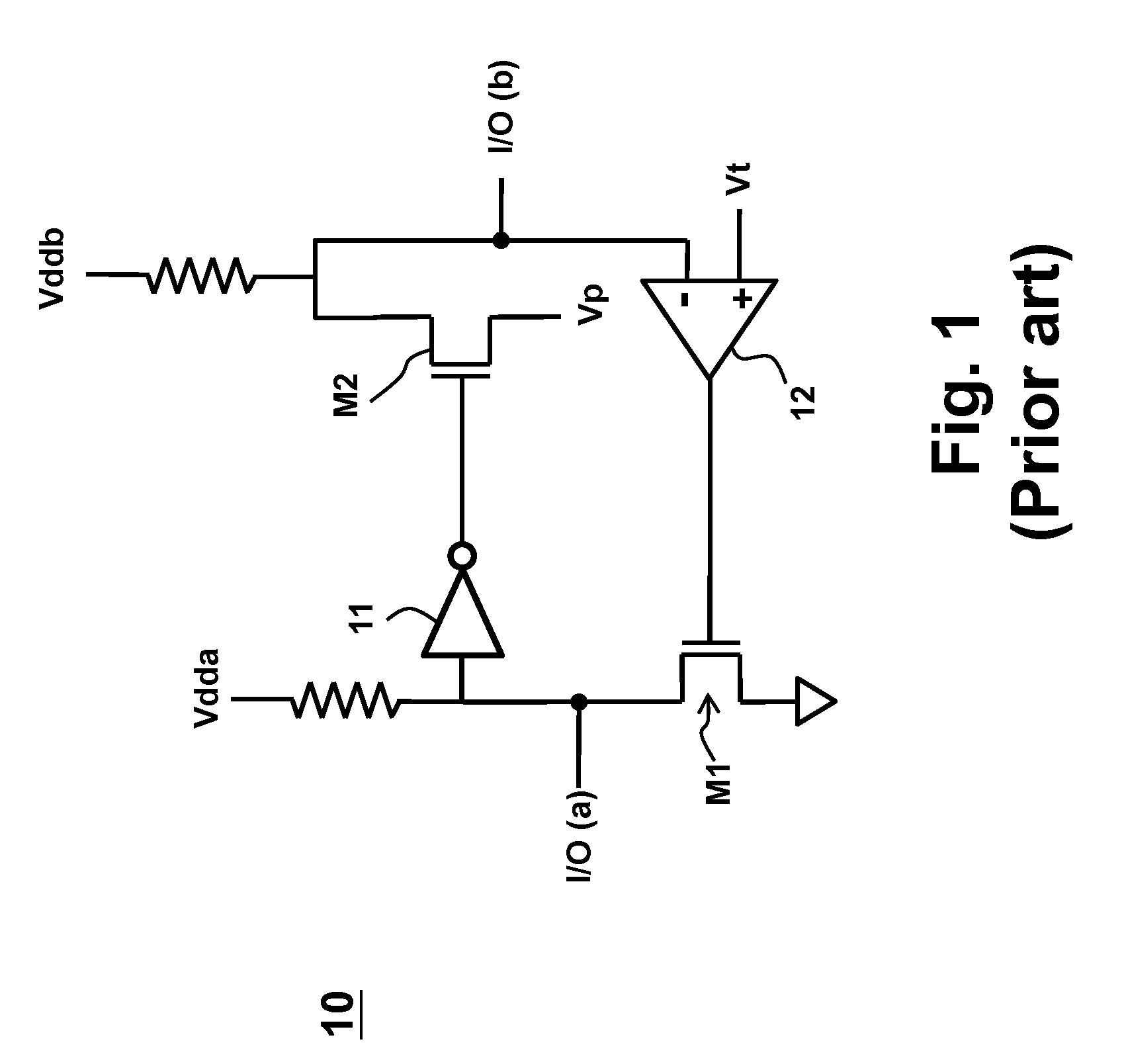

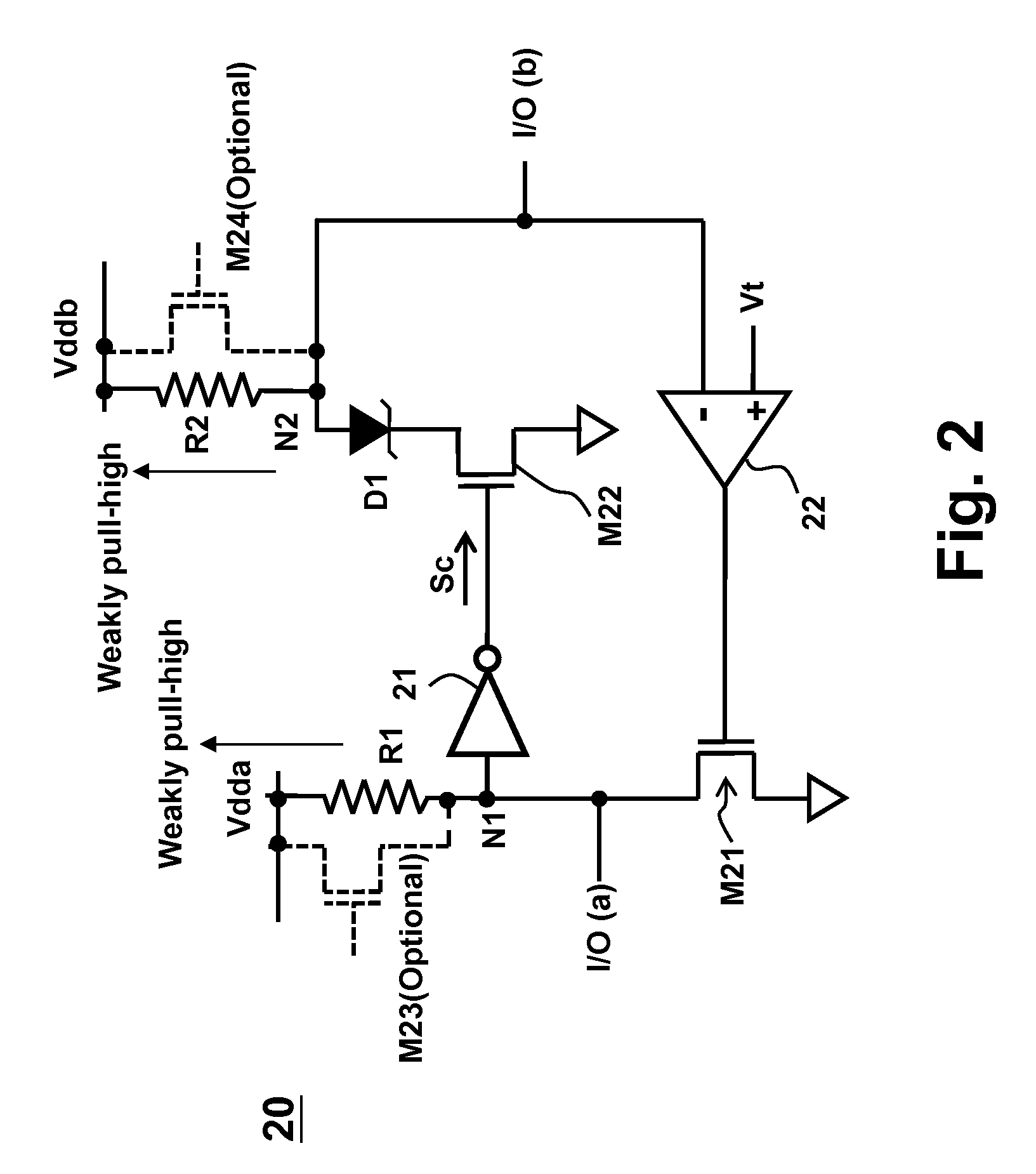

Bidirectional level shifter

InactiveUS8917112B1Logic circuits characterised by logic functionPulse automatic controlVoltage referenceVoltage source

The invention provides a bidirectional level shifter which includes: a first signal terminal; a second signal terminal; a first switch, coupled between the first signal terminal and ground; an inverter receiving a signal from the first signal terminal; a Schottky diode including an anode and a cathode, the anode receiving a signal from the second signal terminal; a second switch, coupled between the cathode of the Schottky diode and the ground; a comparing circuit, comparing a reference voltage and a voltage at the second signal terminal to control the first switch, wherein the reference voltage is lower than a forward bias voltage of the Schottky diode; a first voltage source coupled to the first common node; and a second voltage source coupled to the second common node.

Owner:RICHTEK TECH

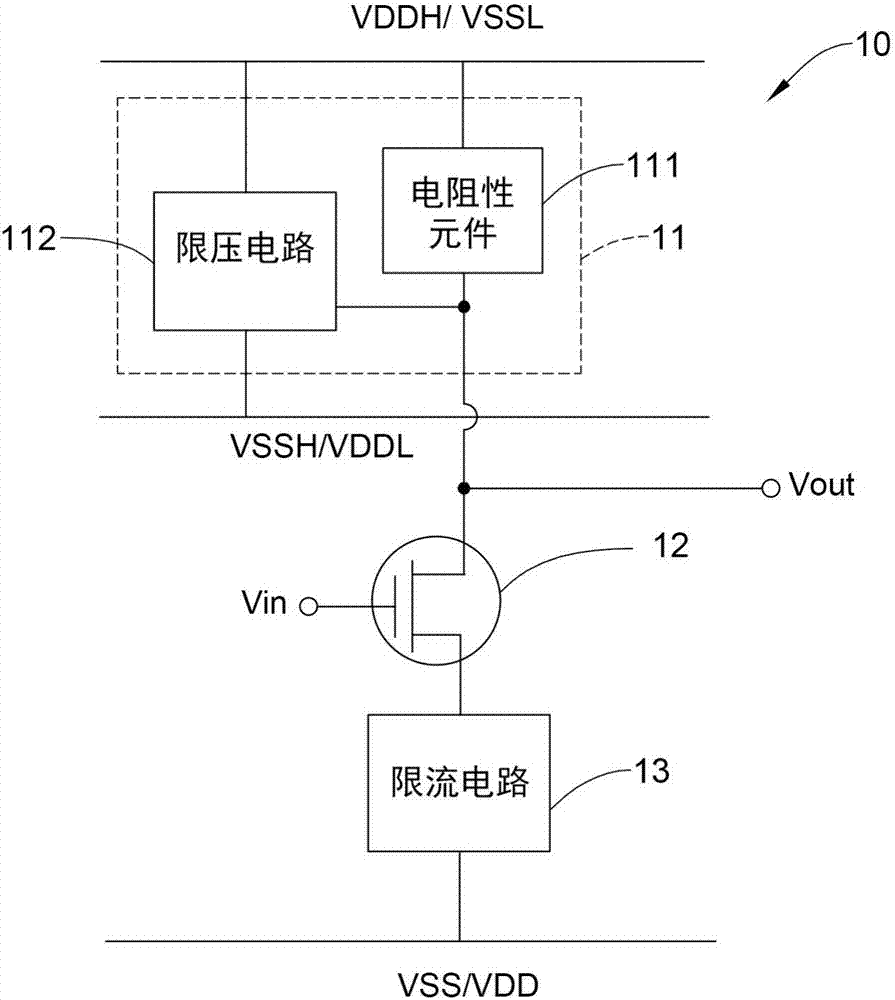

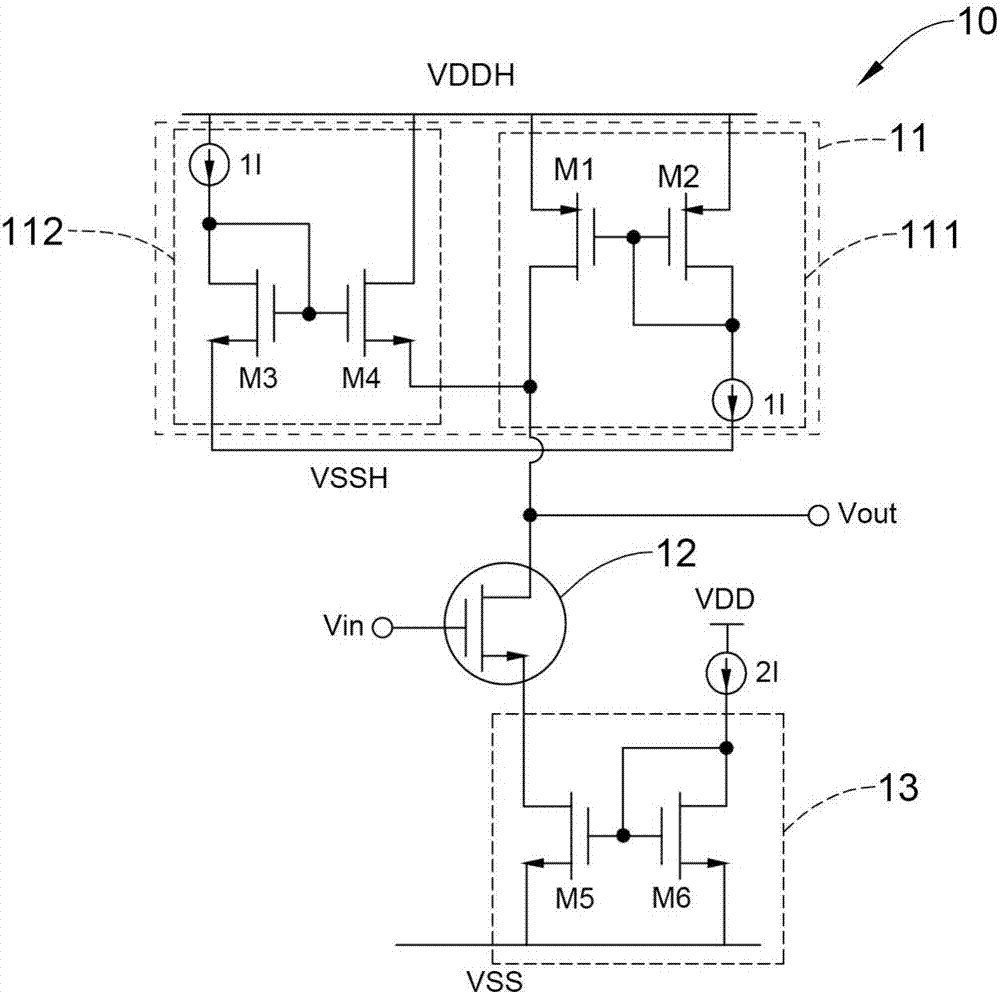

Voltage level shift circuit

ActiveCN107317578AReduce layout areaReduce manufacturing costLogic circuits coupling/interface with bidirectional operationCurrent limitingPower switching

The invention discloses a voltage level shift circuit comprising a voltage clamping unit operating between the highest level voltage and a first low level voltage of a first system power supply, a current-limiting circuit coupled to the second low level voltage of the first system power supply, and a single power switching transistor coupled to the voltage clamping unit and the current-limiting circuit, wherein the first low level voltage is higher than the second low level voltage. When the single power switching transistor is not turned on, the output voltage is pulled up to the highest level voltage of the first system power supply; when the single power switching transistor is powered on, the current-limiting circuit limits the breakover current of the single power switching transistor to a value not exceeding a current upper limit, the condition that the voltage clamping unit does not need to be provided with the other high withstand power transistor is ensured, and thus the output voltage is clamped at the first low level voltage.

Owner:ADVANCED ANALOG TECH INC

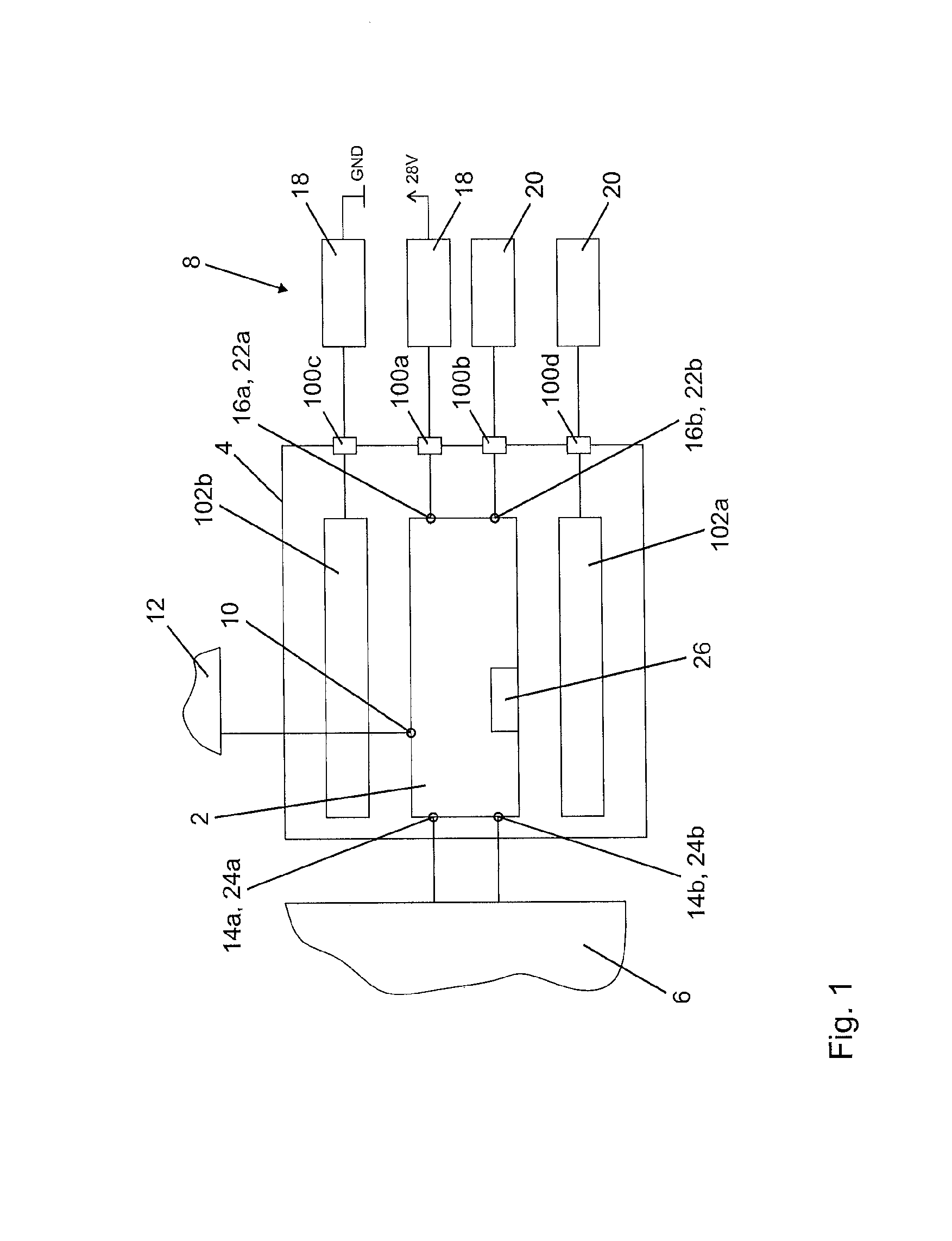

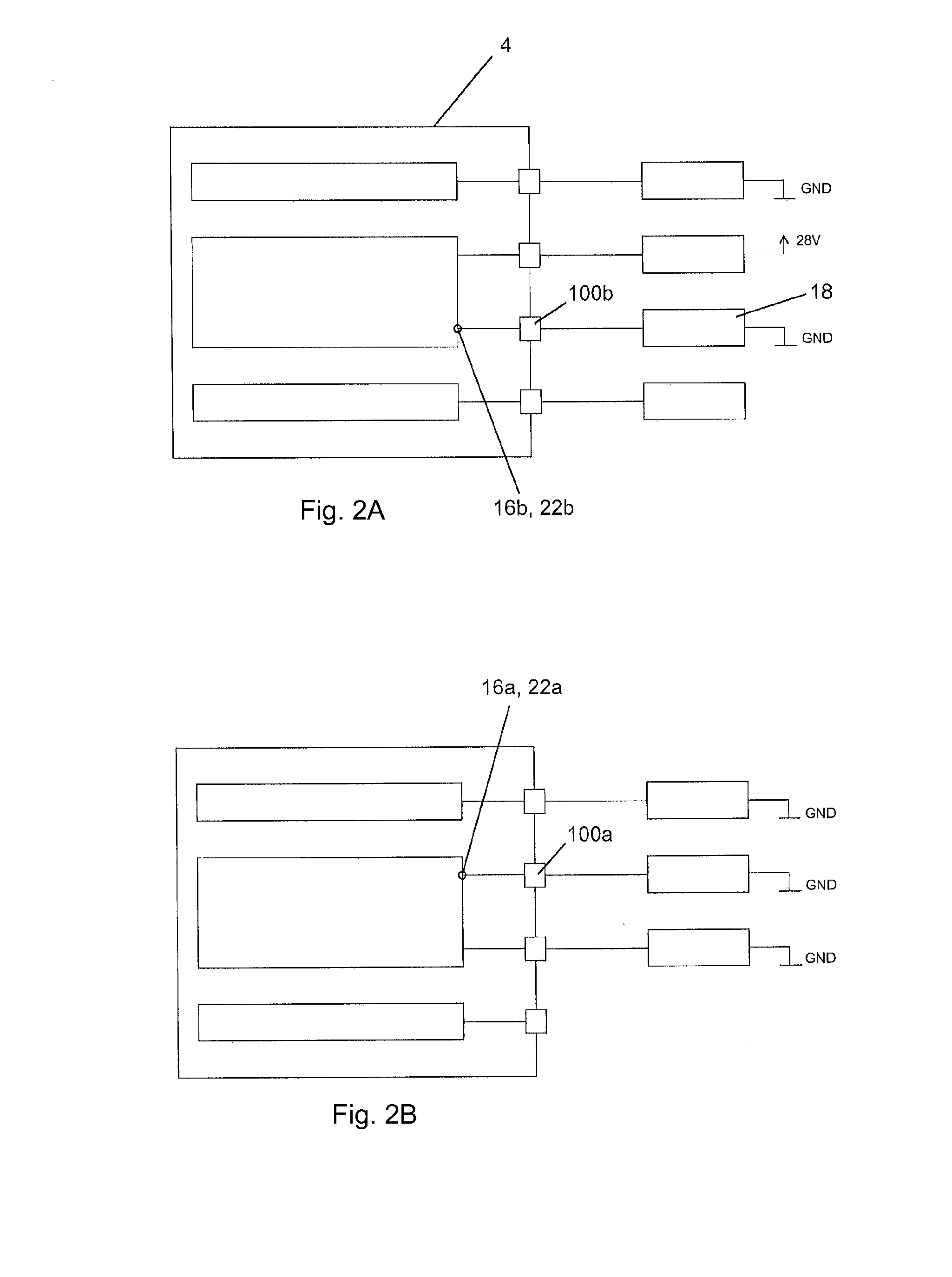

Configurable interface circuit

ActiveUS20150162907A1Reduce in quantityReduce spacingProgramme controlProgrammable logic circuit arrangementsEngineeringPower circuits

The present invention relates to an interface circuit for intermediate connection between a logic circuit and a power circuit, having a supply connection for connection to a power supply, contains two logic connections, which are configurable as logic input or logic output, and two power connections, which are configurable as power input or power output, and a configuration unit for the corresponding configuration, wherein the power input can be read by the logic output and the power output can be driven by the logic input.The present invention further relates to an interface module, having at least two power connections, contains at least one interface circuit, the power connections of which interface circuit are routed to the power connections of the interface module.

Owner:DIEHL AEROSPACE GMBH

Bidirectional buffer circuit and signal level conversion circuit

InactiveUS7839172B2Logic circuits coupling/interface with bidirectional operationControl signalControl circuit

A bidirectional buffer circuit includes a first terminal, a second terminal, a first output buffer to which a signal from the first terminal is input and which outputs the signal to the second terminal, a first one-shot buffer control circuit outputting a first control signal according to an earlier arriving signal out of a signal from the first terminal and a signal from the second terminal, a first one-shot buffer temporarily driving the second terminal by the first control signal, a second output buffer to which a signal from the second terminal is input and which outputs the signal to the first terminal, a second one-shot buffer control circuit outputting a second control signal according to an earlier arriving signal out of a signal from the first terminal and a signal from the second terminal, and a second one-shot buffer temporarily driving the first terminal by the second control signal.

Owner:KK TOSHIBA

Buffer Circuit Having Multiplexed Voltage Level Translation

ActiveUS20080238399A1Reduce chip areaSmall sizeProgrammable logic circuit arrangementsLogic circuits coupling/interface with bidirectional operationMultiplexingControl signal

A buffer circuit is selectively operative in one of at least a first mode and a second mode as a function of a first control signal supplied to the buffer circuit. The buffer circuit includes interface circuitry operative to receive at least second and third control signals referenced to a first voltage level, and to generate an output signal referenced to a second voltage level, the second voltage level being greater than the first voltage level. The output signal is a function of the second control signal in the first mode and is a function of the third control signal in the second mode. The buffer circuit further includes at least first and second circuit portions coupled to the interface circuitry, each of the first and second circuit portions including at least one control input operative to receive the output signal generated by the interface circuitry.

Owner:GENERAL ELECTRIC CO +1

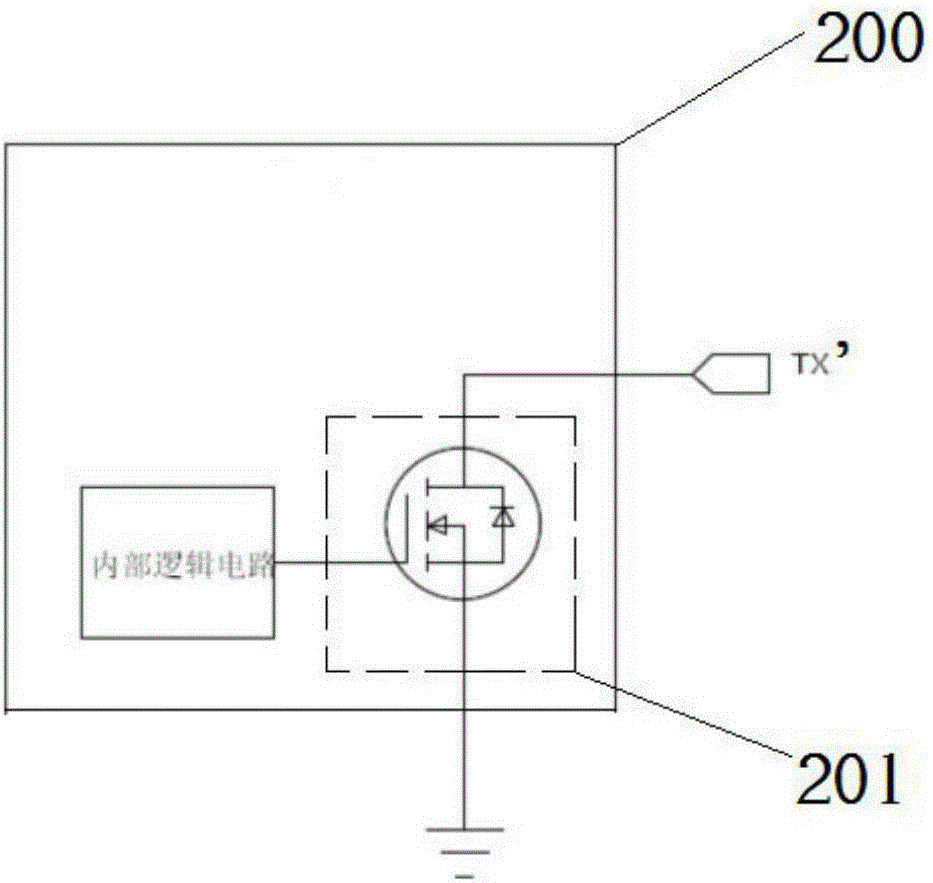

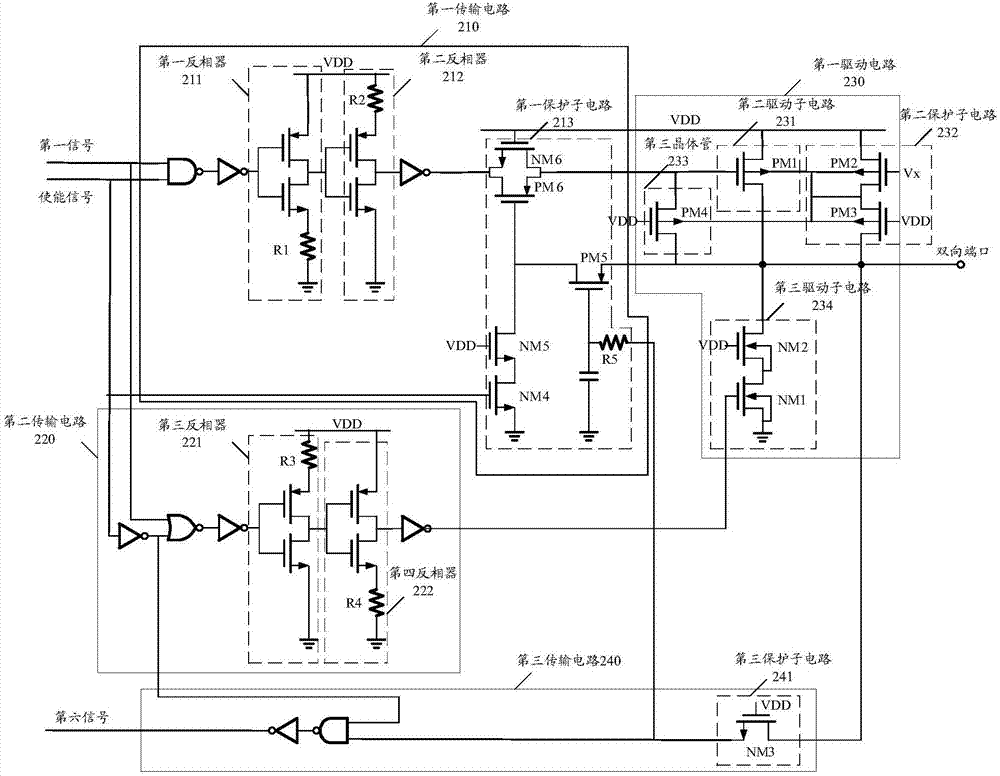

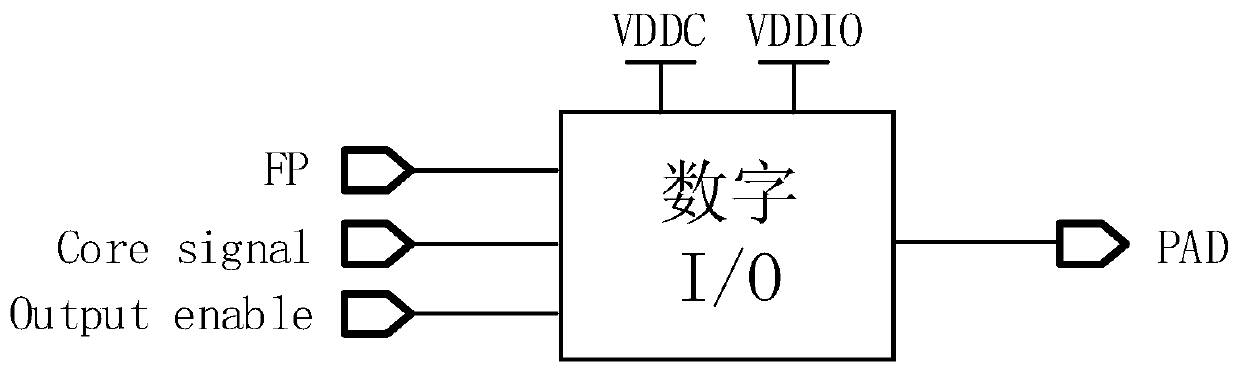

Bidirectional interface circuit

PendingCN107395192AReduce leakage currentImprove robustnessLogic circuits coupling/interface with bidirectional operationLogic circuits coupling/interface using field-effect transistorsSoftware engineeringHemt circuits

The invention discloses a bidirectional interface circuit, which comprises a first transmission circuit, a second transmission circuit, a first drive circuit and a third transmission circuit. When an enable signal is in a first level state, the first transmission circuit carries out time delay and phase reversal on a received first signal and then, outputs a second signal; the second transmission circuit carries out time delay and phase reversal on the received first signal, and then, outputs a third signal; the first drive circuit receives the second signal and the third signal, and outputs a fourth signal from a bidirectional interface based on the second signal and the third signal; and when the enable signal is in a second level state, the third transmission circuit receives a fifth signal from the bidirectional interface and outputs a sixth signal based on the fifth signal.

Owner:SHANGRUI MICROELECTRONICS SHANGHAI

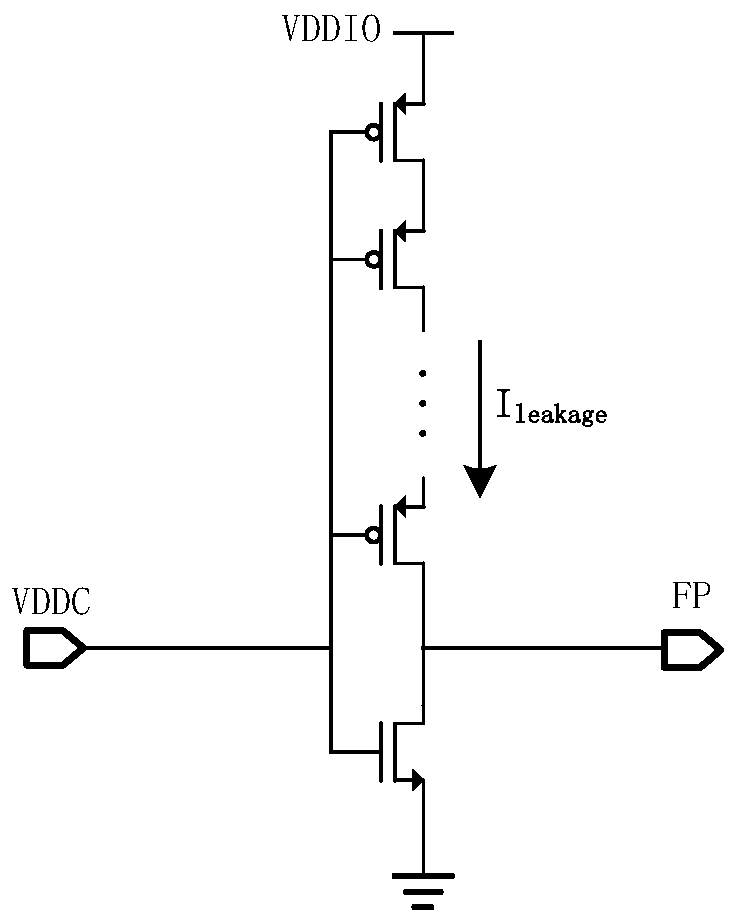

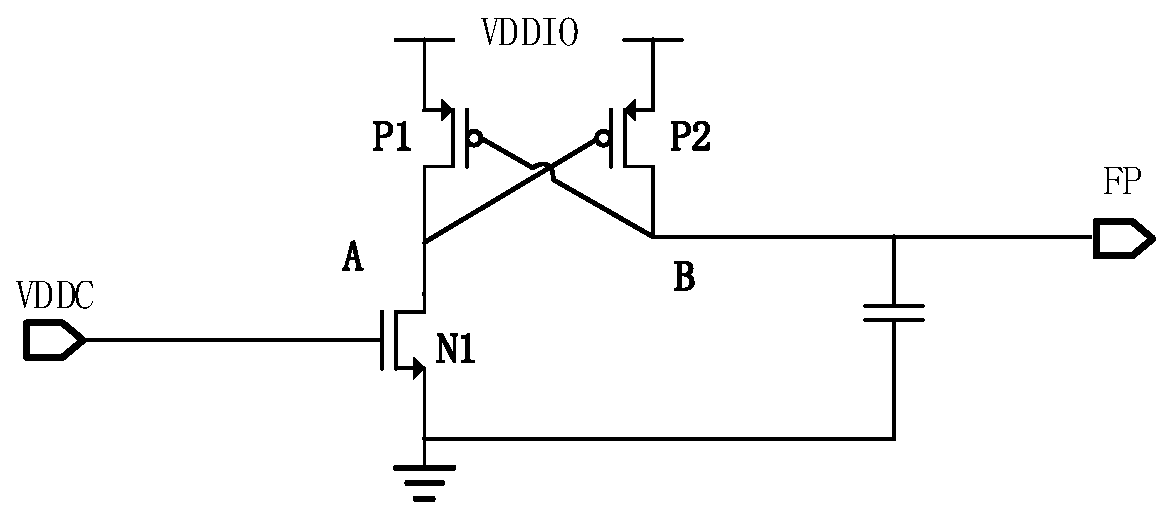

Power supply power-on module

PendingCN111106822AReduce power consumptionPrevent leakagePower reduction in field effect transistorsPower reduction by control/clock signalControl signalControl theory

The invention discloses a power supply power-on module. The power supply power-on module is used for controlling the on-off state of digital I / O. The power supply power-on module is characterized by comprising a VDDC power supply, a VDDIO power supply, a pull-down MOS transistor N1, a first transmission MOS transistor P1, a second transmission MOS transistor P2 and a time delay unit, the grid electrode of the pull-down MOS tube N1 is connected with the VDDC power supply, the source electrode of the pull-down MOS tube N1 is grounded, and the drain electrode of the pull-down MOS tube N1 is connected with a node A; source electrodes of the first transmission MOS tube P1 and the second transmission MOS tube P2 are simultaneously connected with the VDDIO power supply, drain electrodes of the first transmission MOS tube P1 and the second transmission MOS tube P2 are respectively connected with a node A and a node B, grid electrodes of the first transmission MOS tube P1 and the second transmission MOS tube P2 are respectively connected with the node B and the node A, and the node A and the node B are mutually reverse signals. And the node B is connected with a control signal FP. Accordingto the power supply power-on module provided by the invention, the generated control signal FP can correctly open or close the digital I / O, so that electric leakage of the digital I / O can be avoided,and electric leakage of the power supply power-on module in the prior art is also avoided.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT

Simultaneous LVDS I/O signaling method and apparatus

ActiveUS20090033372A1Multiple input and output pulse circuitsReliability increasing modificationsMultiplexerSingle pair

First and second devices may simultaneously communicate bidirectionally with each other using only a single pair of LVDS signal paths. Each device includes an input circuit and a differential output driver connected to the single pair of LVDS signal paths. An input to the input circuit is also connected to the input of the driver. The input circuit may also receive an offset voltage. In response to its inputs, the input circuit in each device can use comparators, gates and a multiplexer to determine the logic state being transmitted over the pair of LVDS signal paths from the other device. This advantageously reduces the number of required interconnects between the first and second devices by one half.

Owner:TEXAS INSTRUMENTS INC

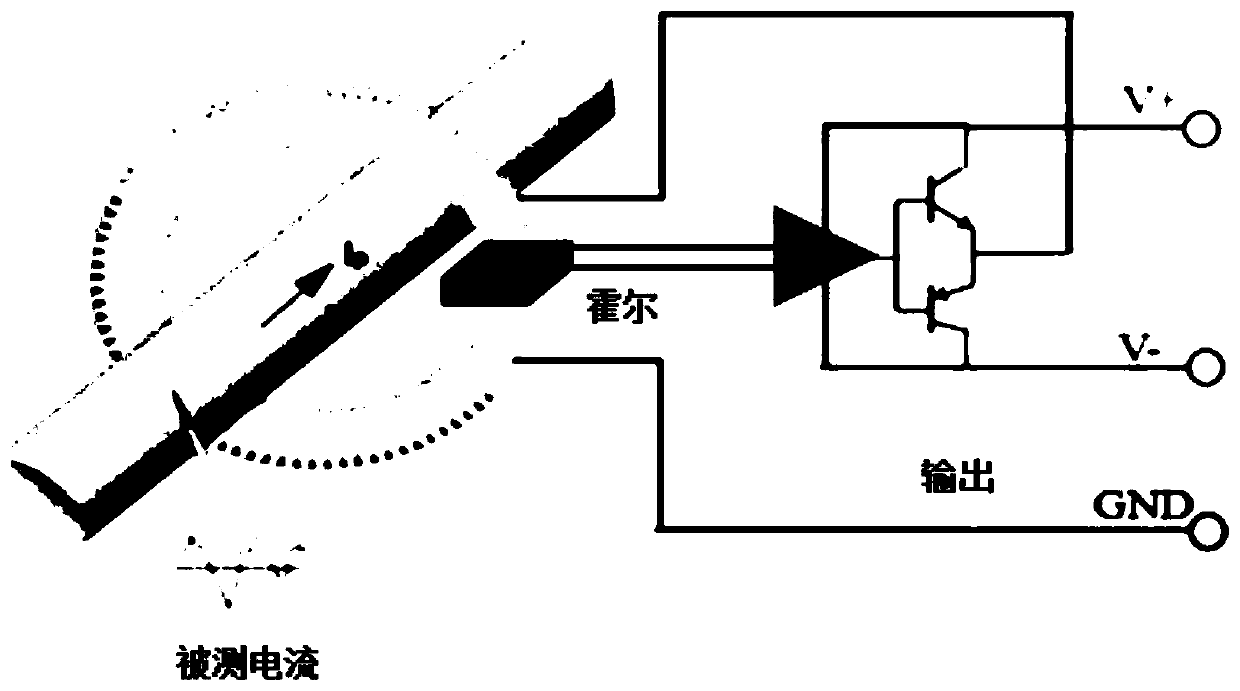

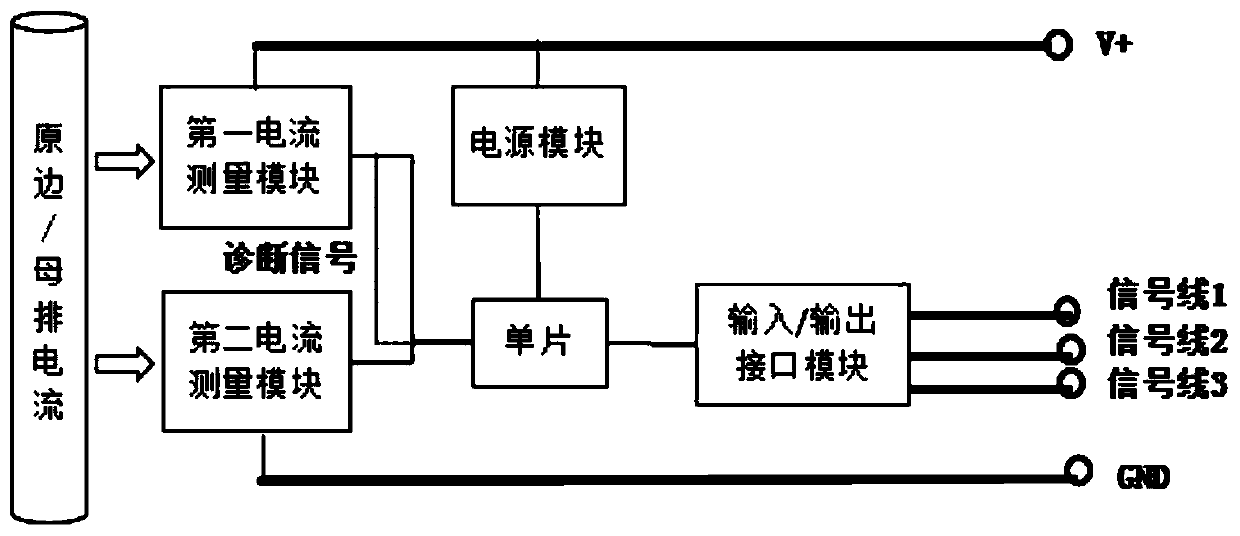

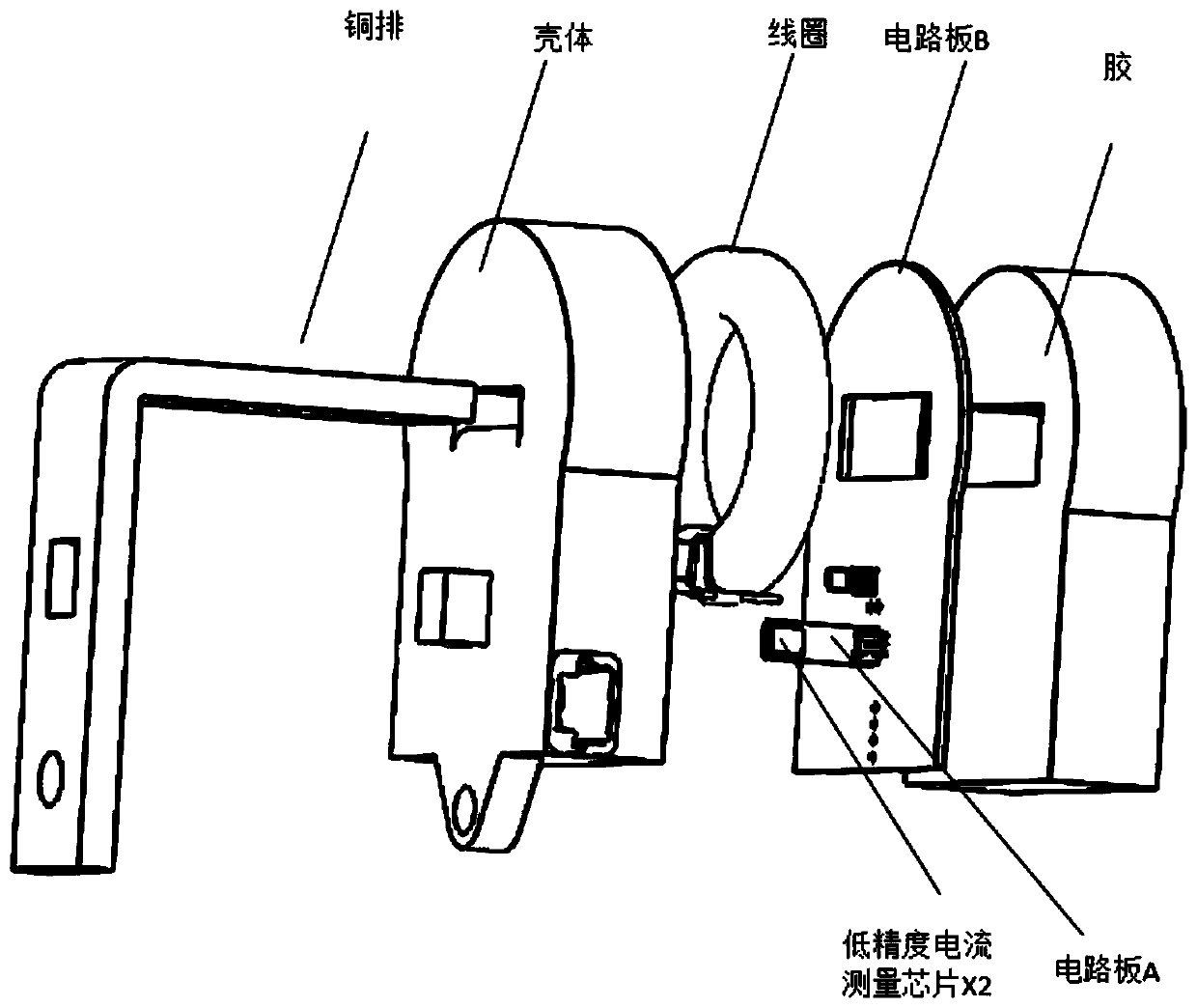

H-bridge drive circuit and current sensor based on H-bridge drive circuit

InactiveCN111162775ARealize high-precision measurementLow costLogic circuits coupling/interface with bidirectional operationElectrical measurement instrument detailsEngineeringHemt circuits

The invention discloses an H-bridge driving circuit which comprises a first operational amplifier, a second operational amplifier, N first NPN triodes, N first PNP triodes, N second NPN triodes, N second PNP triodes, a first resistor, a second resistor and a sampling resistor. The invention further discloses a current sensor, the current sensor comprises a first current measurement module, a second current measurement module and a processor, and the first current measurement module comprises the H-bridge drive circuit, a magnetic sensitive unit and a coil. Under the condition of unidirectionalpower supply, high-precision measurement of bidirectional large current is realized, the cost is low, and the functional safety level of the sensor is improved.

Owner:陈玲

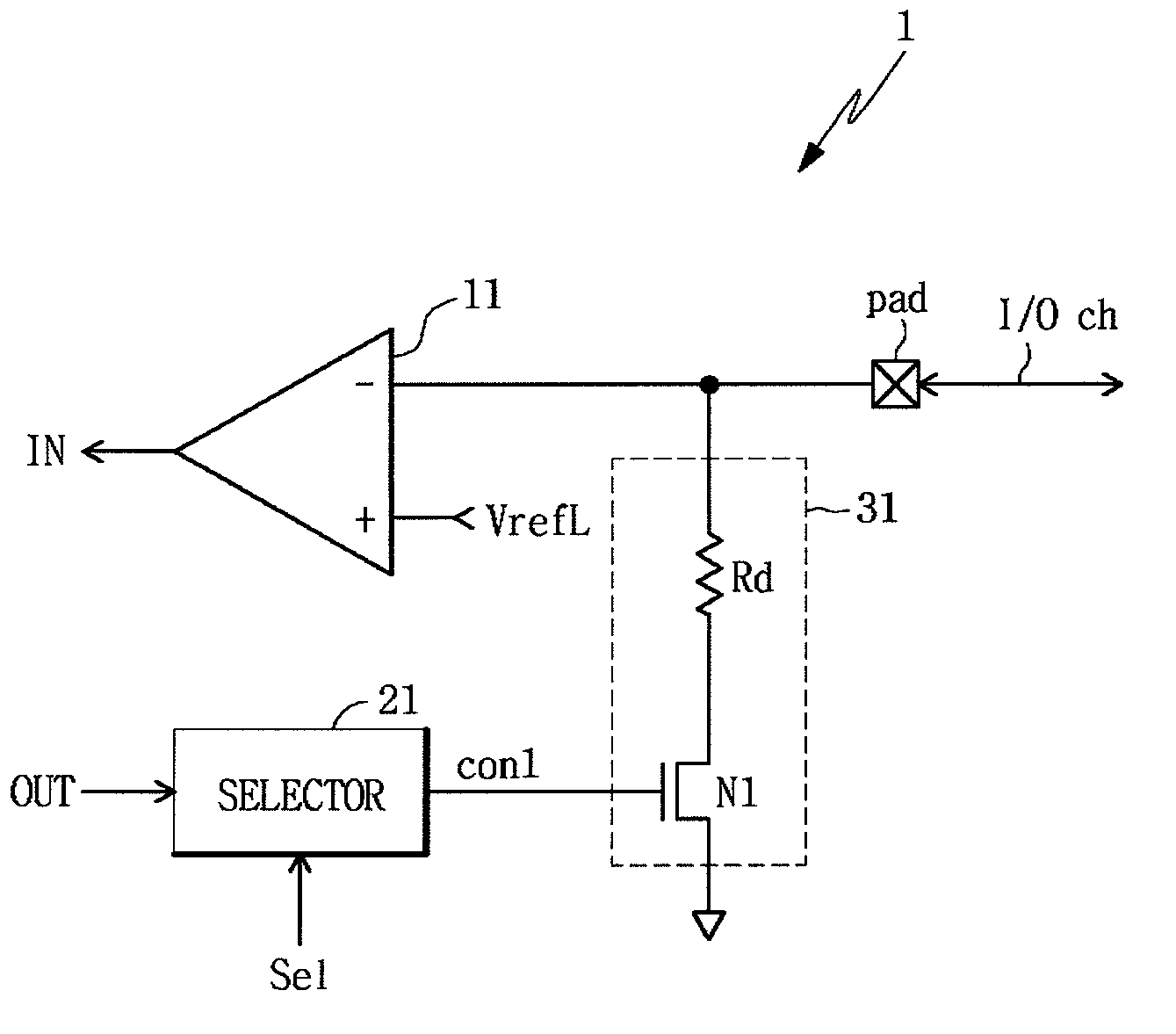

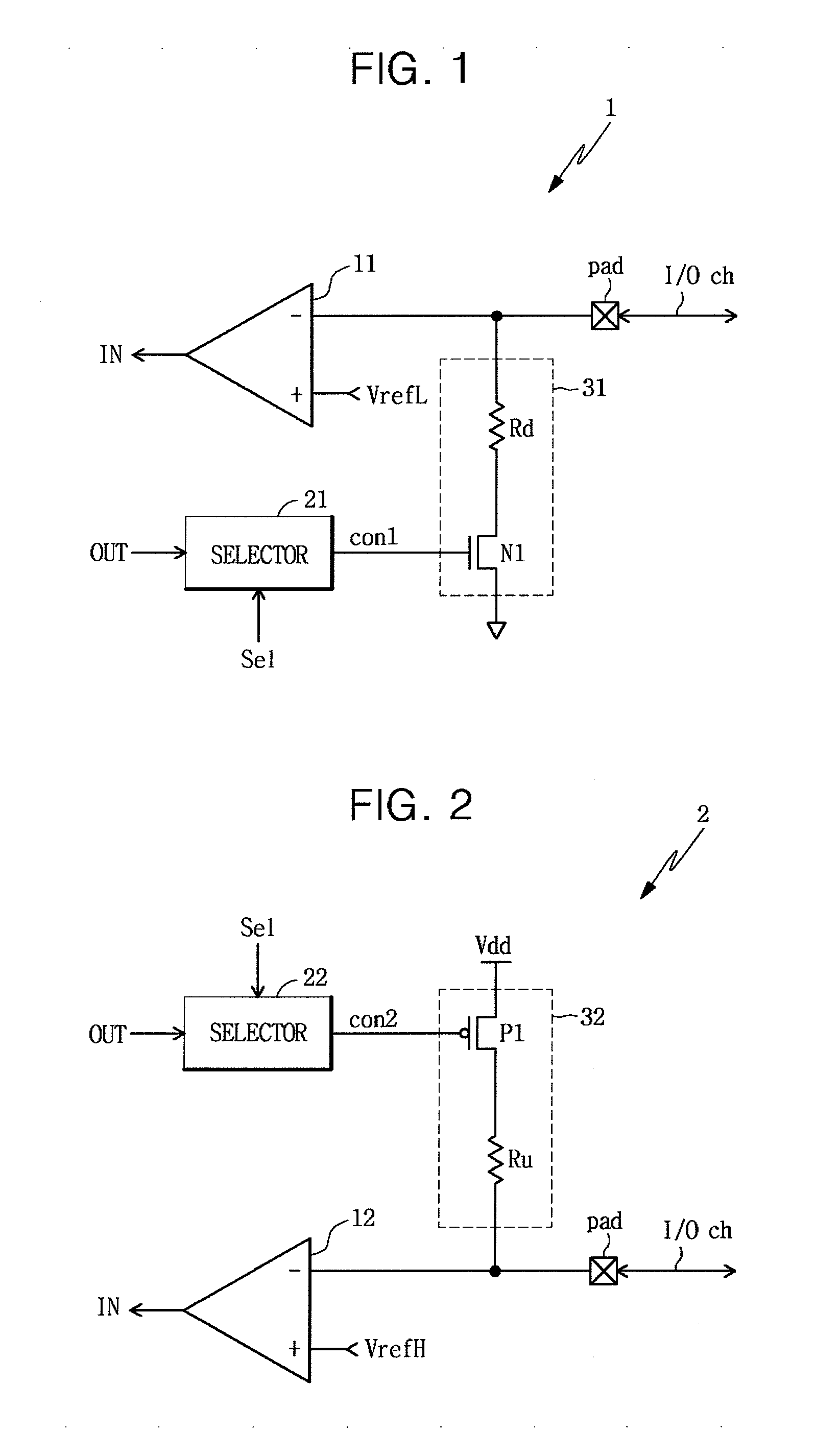

Transceiver system, semiconductor device thereof, and data transceiving method of the same

ActiveUS20110057684A1Reliability increasing modificationsLogic circuits coupling/interface with bidirectional operationTransceiverElectrical conductor

A transceiver system includes a first semiconductor device having a first input / output (I / O) pad connected with an I / O channel and a second semiconductor device having a second I / O pad connected with the I / O channel. The first semiconductor device is configured to terminate the first I / O pad with a first voltage when data is received, and maintain the first I / O pad and the I / O channel at the first voltage when data is transmitted. The second semiconductor device is configured to terminate the second I / O pad with a second voltage higher than the first voltage when data is received, and maintain the second I / O pad and the I / O channel at the second voltage when data is transmitted.

Owner:SAMSUNG ELECTRONICS CO LTD

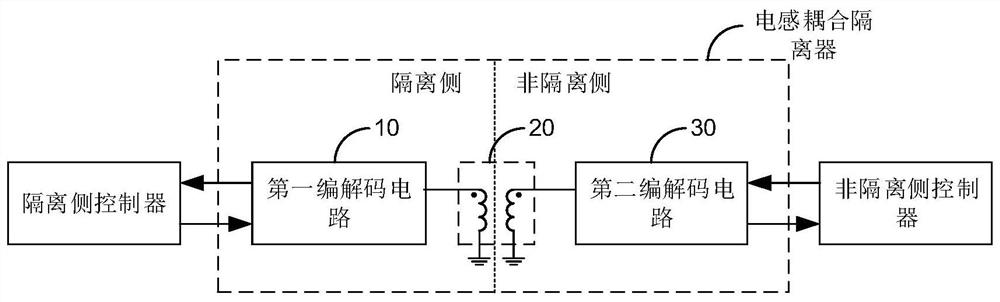

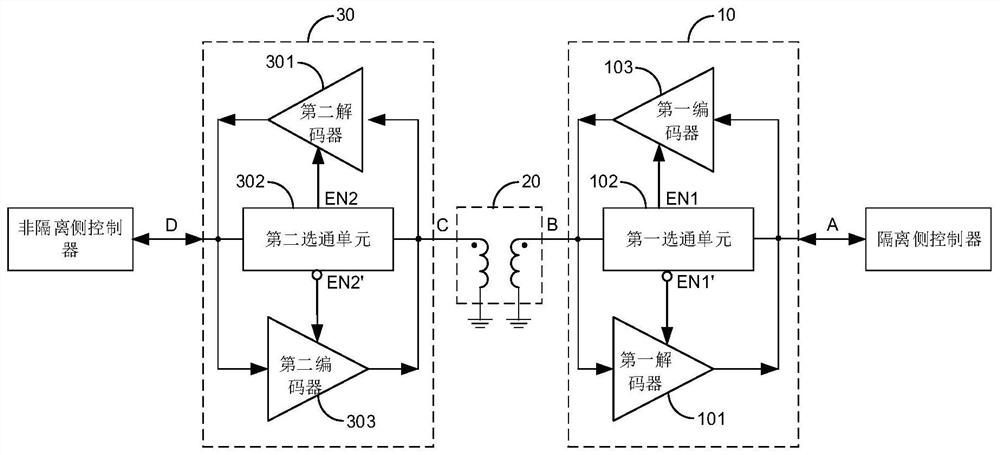

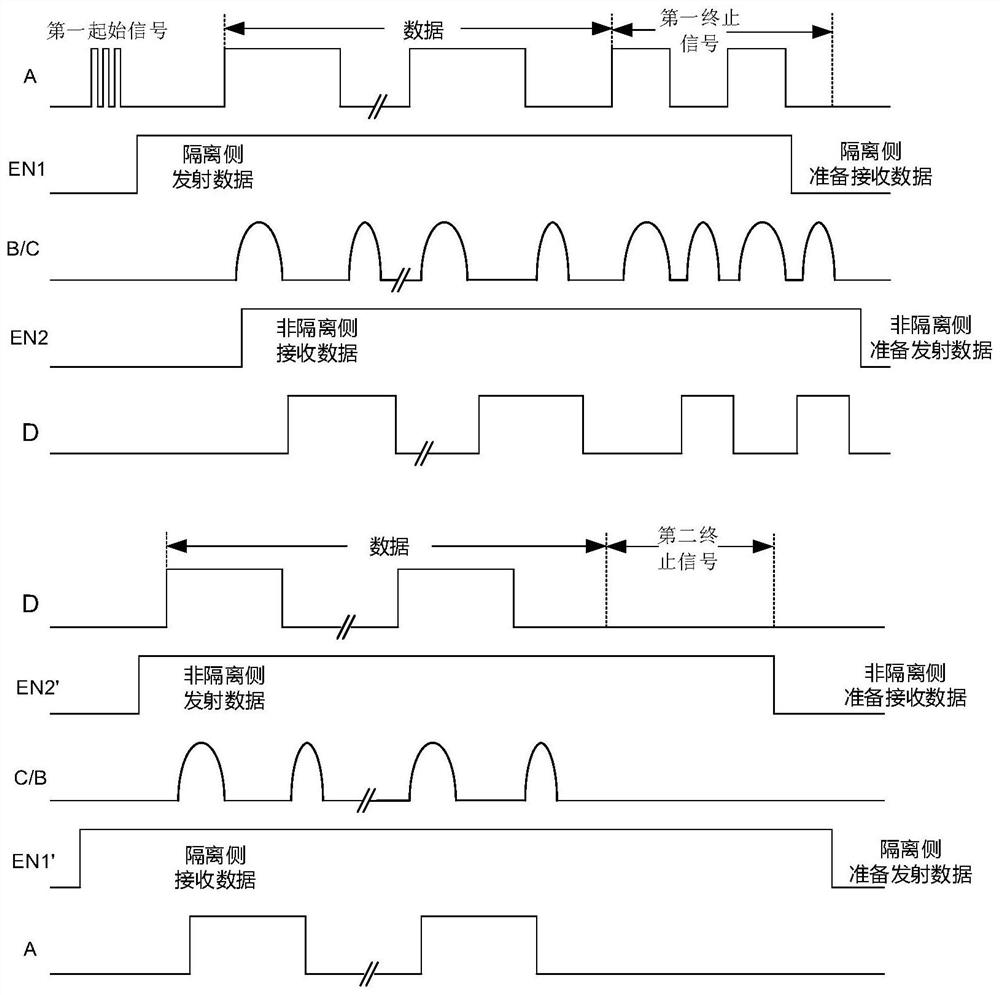

Inductively coupled isolator, high-voltage signal acquisition system and industrial control system

PendingCN111697960AReduce footprintLogic circuit coupling arrangementsLogic circuits coupling/interface with bidirectional operationIsolatorHemt circuits

The invention discloses an inductive coupling isolator, which comprises: a coupling inductor pair; a first encoding and decoding circuit which is used for transmitting first data to a second encodingand decoding circuit through the coupling inductor pair when a first starting signal is received, wherein when a first termination signal is received, sending the first data to the second encoding anddecoding circuit is stopped, and a non-isolated side controller is notified to prepare to send the second data; and a second encoding and decoding circuit which is used for receiving the first data,notifying the non-isolated side controller to prepare to send second data when receiving the first termination signal, and transmitting the second data to the first encoding and decoding circuit through the coupling inductor pair, wherein when a second termination signal is received, sending the second data to the first encoding and decoding circuit is stopped, and an isolation side controller isnotified to send the data of the next period by using the second termination signal. Only one coupling inductor pair is used in the isolator, so that the space volume occupied by the inductive couplercan be reduced.

Owner:HANGZHOU RUIMENG TECH

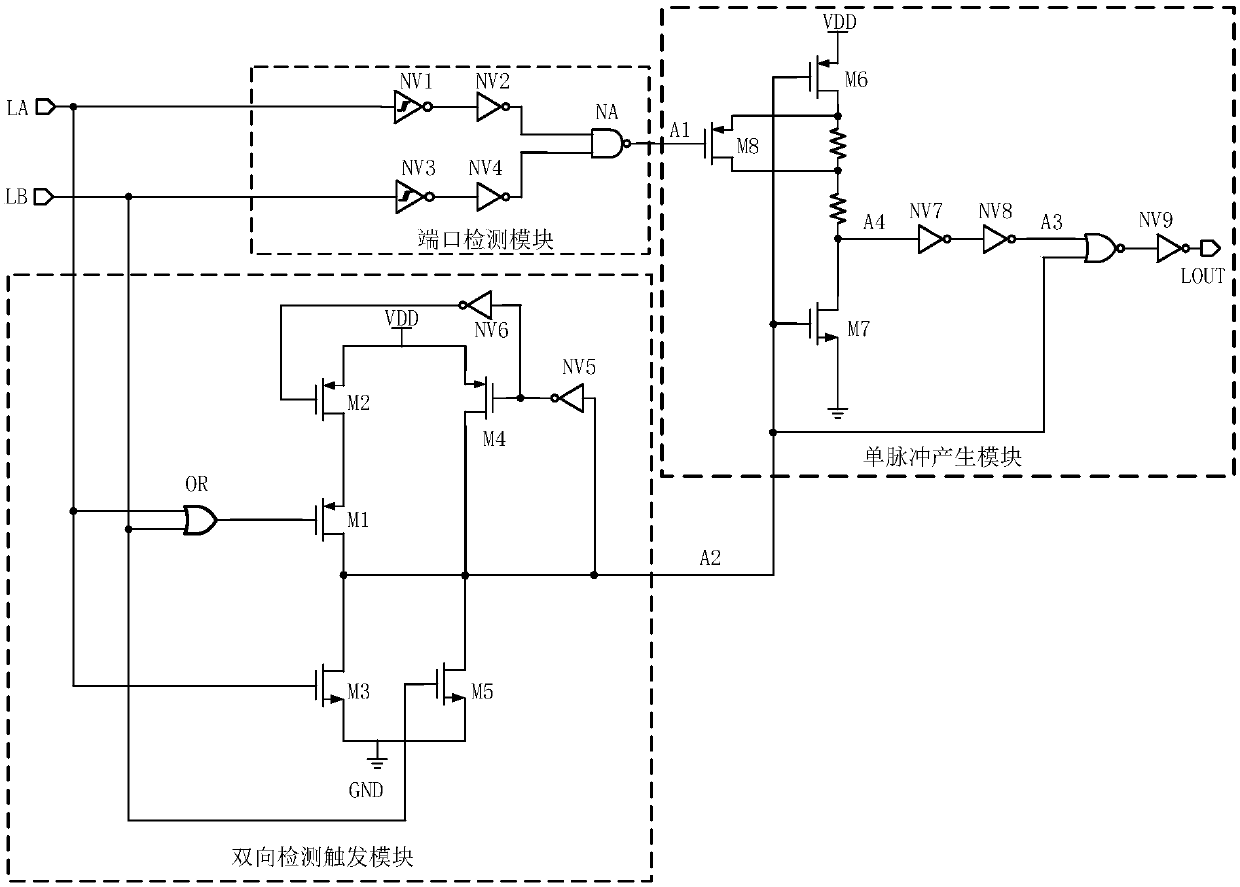

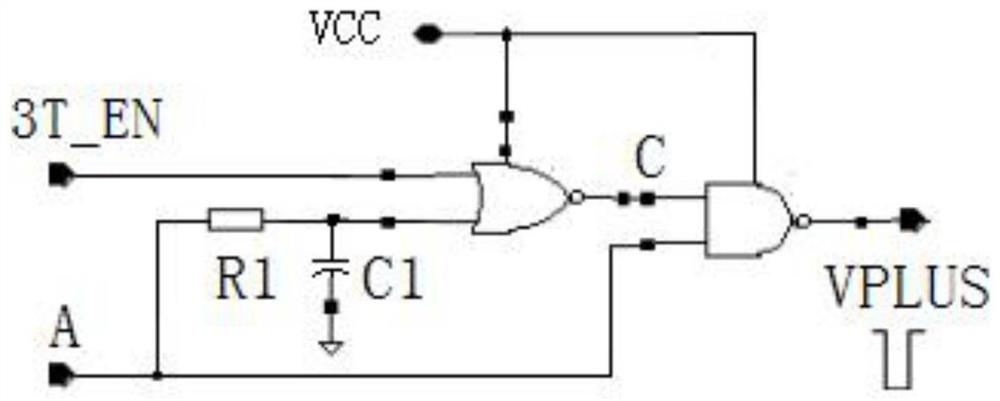

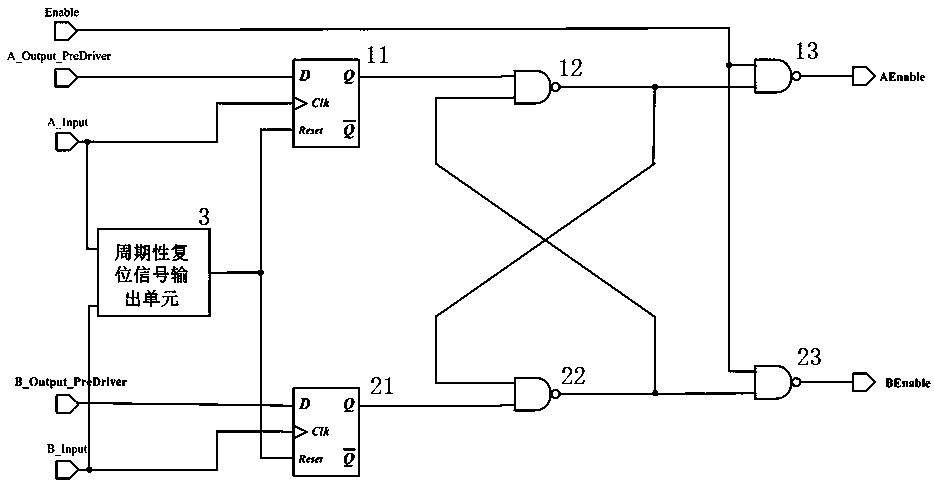

Automatic direction detection circuit of bidirectional transmission interface

ActiveCN110995244AReduce lossHighlight substantivePower reduction in field effect transistorsLogic circuits coupling/interface with bidirectional operationSignal onBidirectional transmission

The invention discloses an automatic direction detection circuit of a bidirectional transmission interface. The automatic direction detection circuit comprises a D trigger, a primary NAND gate and a final NAND gate which are configured corresponding to signal input and output on any side, a pre-driving signal is accessed to the D end of the D trigger; an input signal is accessed to a Clk end of the D trigger; the Q end of the D trigger outputs enable signals on the corresponding side sequentially through the primary NAND gate and the final NAND gate, the detection circuit is provided with periodic reset units connected to the Reset end of the D trigger based on input signals on the two sides, and the output ends of the primary NAND gates on the two sides are connected to one input end of the primary NAND gate on the other side in a jumper mode. By applying the detection circuit design, whether the output of the side is opened or not can be periodically detected through the rising edgeor the falling edge of the input side signal, and the enable signal can be reset; hardware loss of automatic direction recognition is greatly reduced, and flexibility of automatic direction recognition is improved.

Owner:3PEAK INC

Level shifting multiplexing circuit for connecting a two conductor full duplex bus to a bidirectional single conductor bus

InactiveUS7288962B2Logic circuits coupling/interface with bidirectional operationLogic circuits coupling/interface using field-effect transistorsMultiplexingLevel shifting

A level shifting multiplexing circuit provides an interface between a two conductor full duplex bus (two conductor bus) and a single conductor bidirectional half duplex bus (single conductor bus) where the two conductor bus is operates at a first supply voltage and the single conductor bus operates at a second supply voltage. A first switching circuit connected between the single conductor bus and the reception conductor of the two conductor bus is configured to provide a low logic signal to the reception conductor when a first switching voltage threshold is exceeded and to provide a high logic signal, otherwise. A second switching circuit connected between the single conductor bus and the transmission conductor of the two conductor bus is configured to provide a voltage less than the first switching voltage threshold when voltage at the transmission conductor exceeds a second switching voltage threshold unless a high logic signal is received on the single conductor bus. The second switching circuit is further configured to provide a voltage greater than the first switching voltage when the transmission conductor voltage exceeds the second switching voltage threshold unless a low logic signal is received on the single conductor bus.

Owner:KYOCERA CORP

Popular searches

Electric pulse generator Logic circuits using elementary logic circuit components Input/output processes for data processing Duplex signal operation Bus networks Computation using denominational number representation Electronic switching Oscillations generators Baseband systems Electric digital data processing