Patents

Literature

124results about How to "High speed output" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

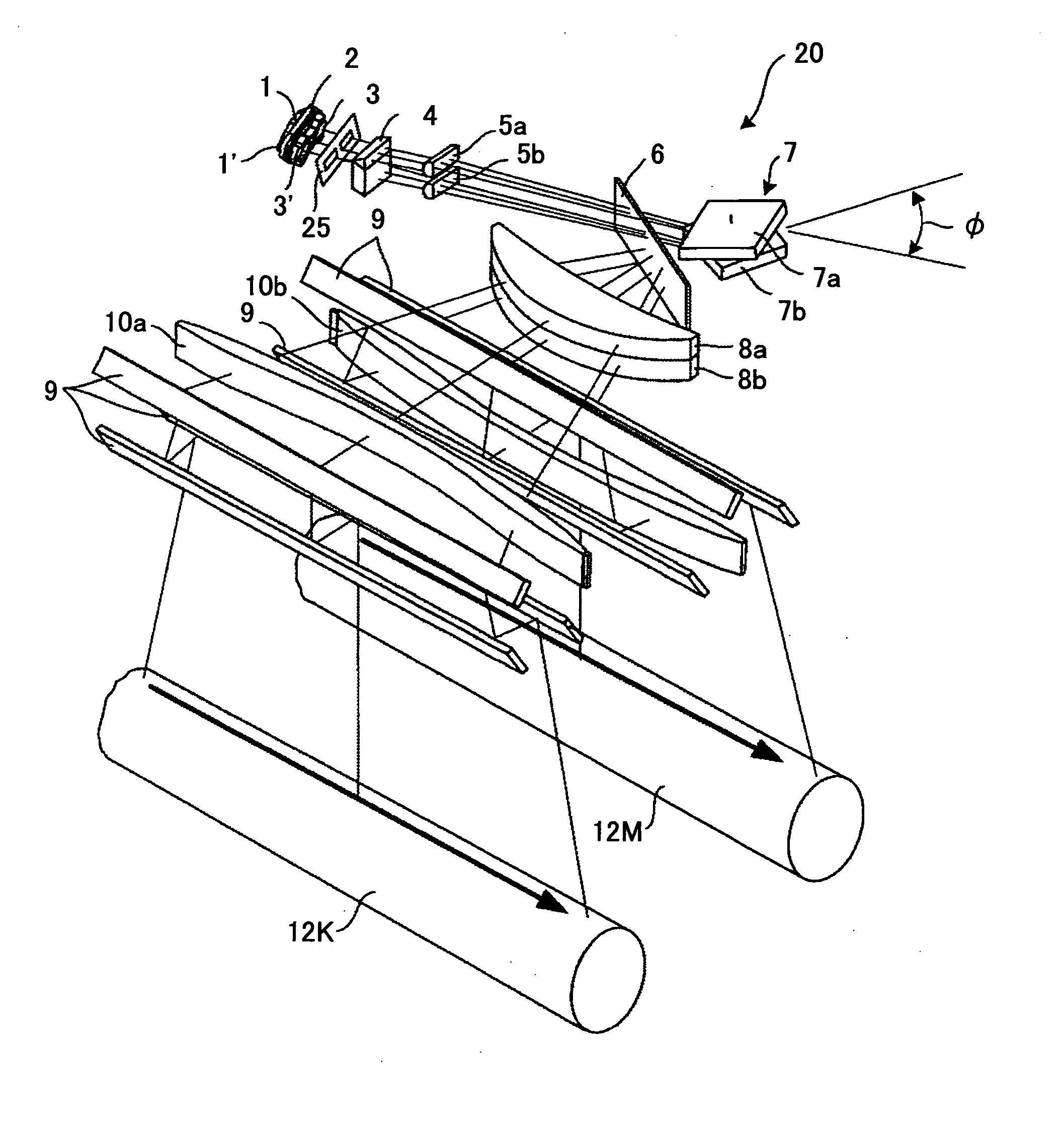

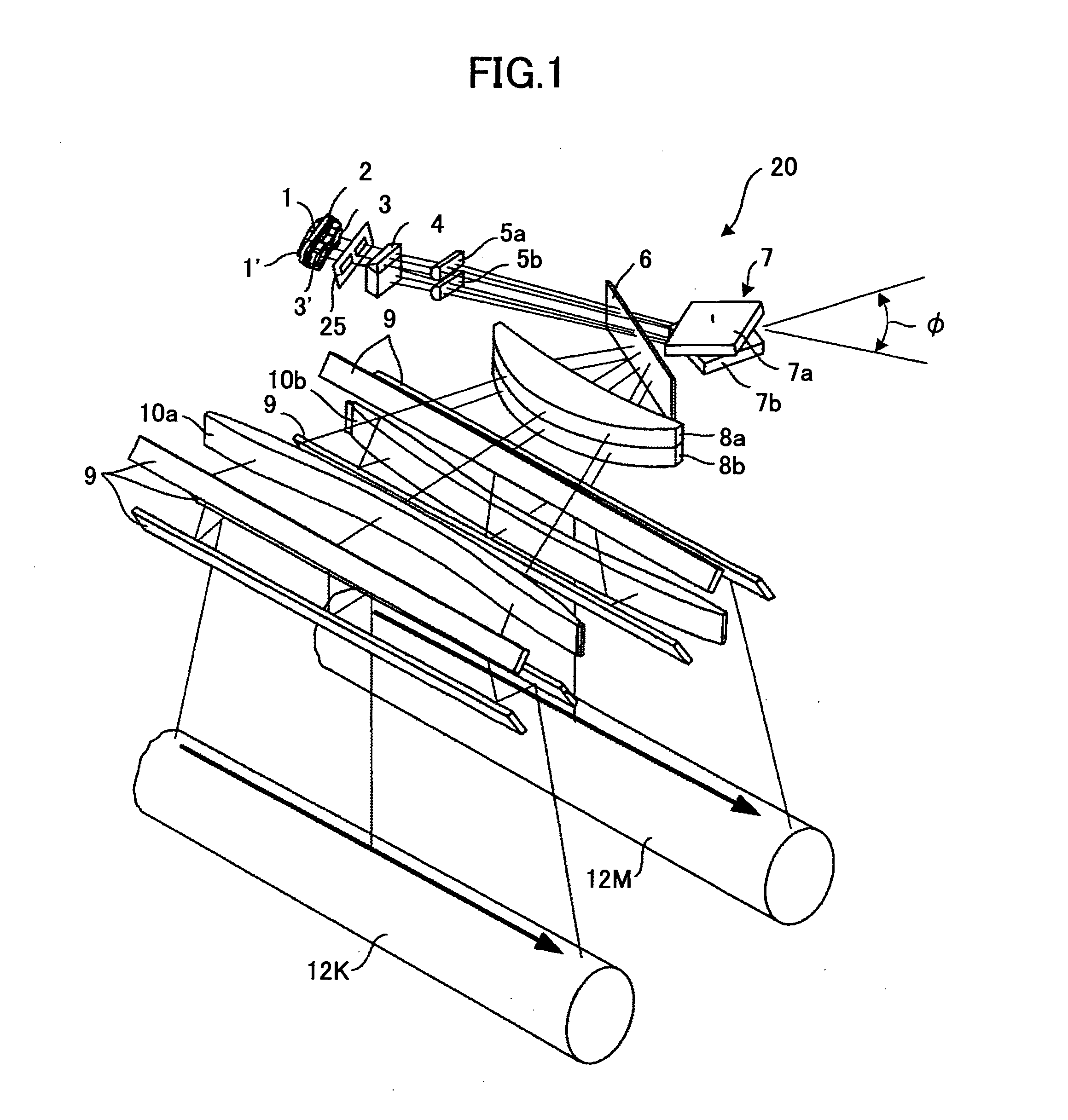

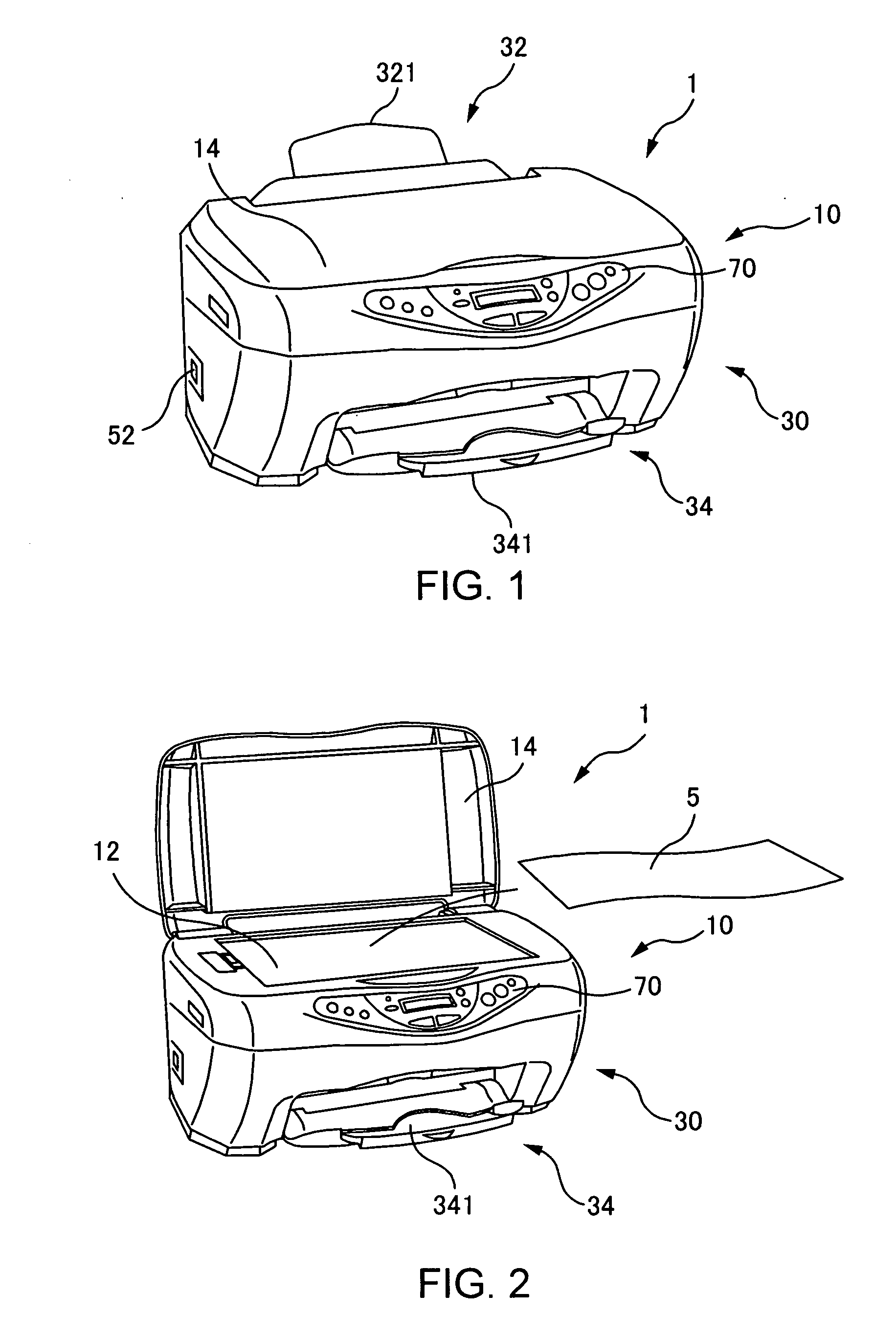

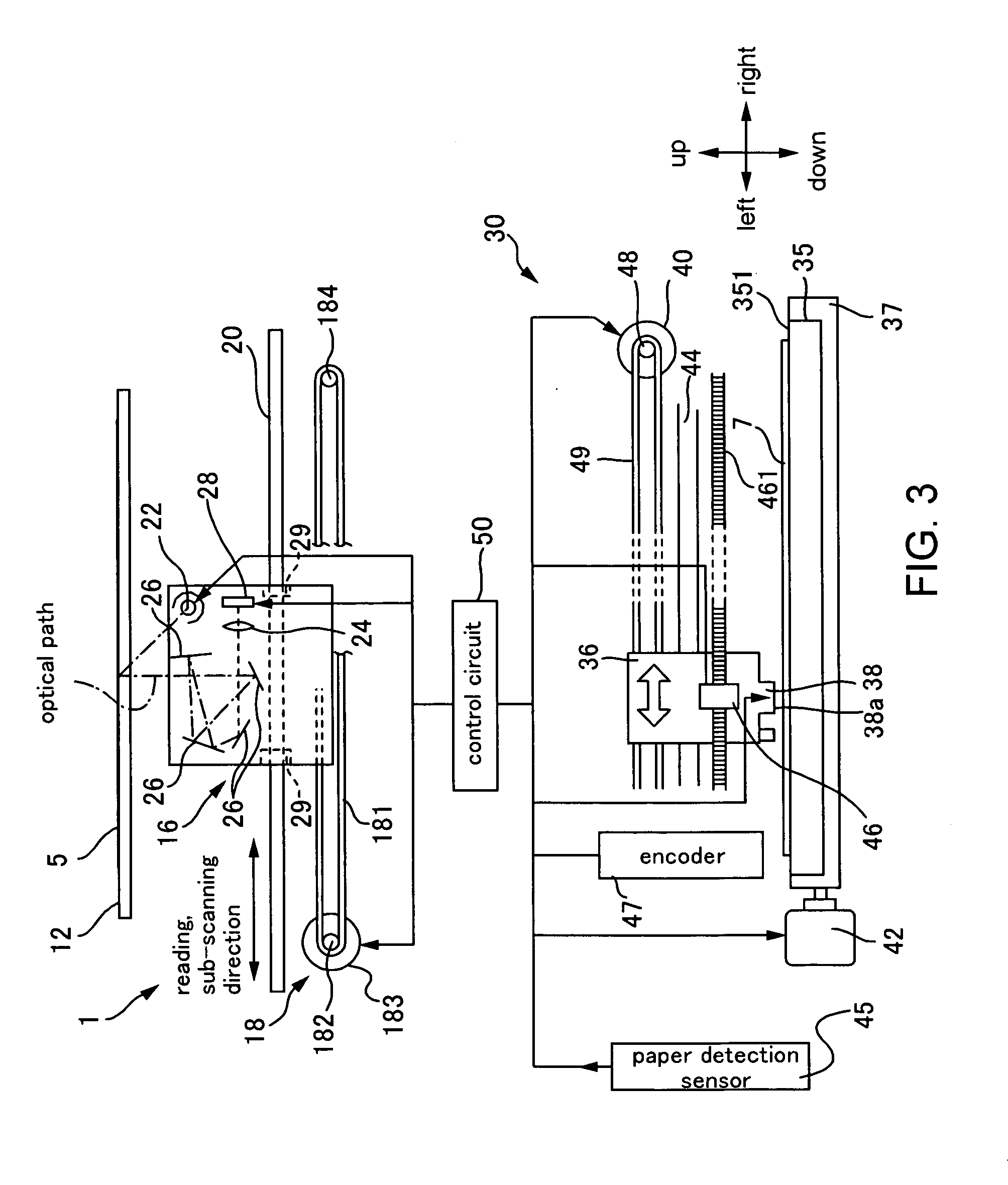

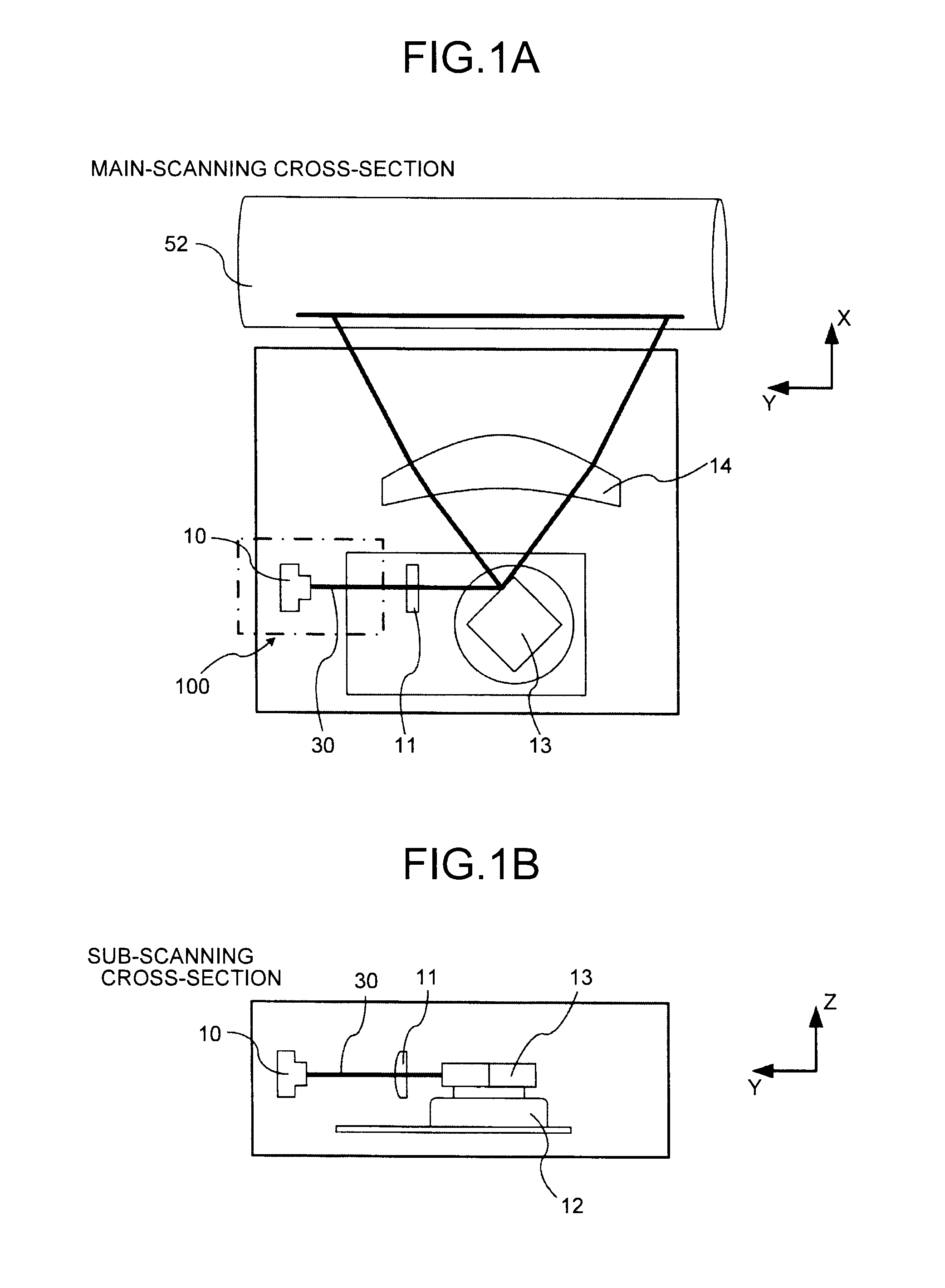

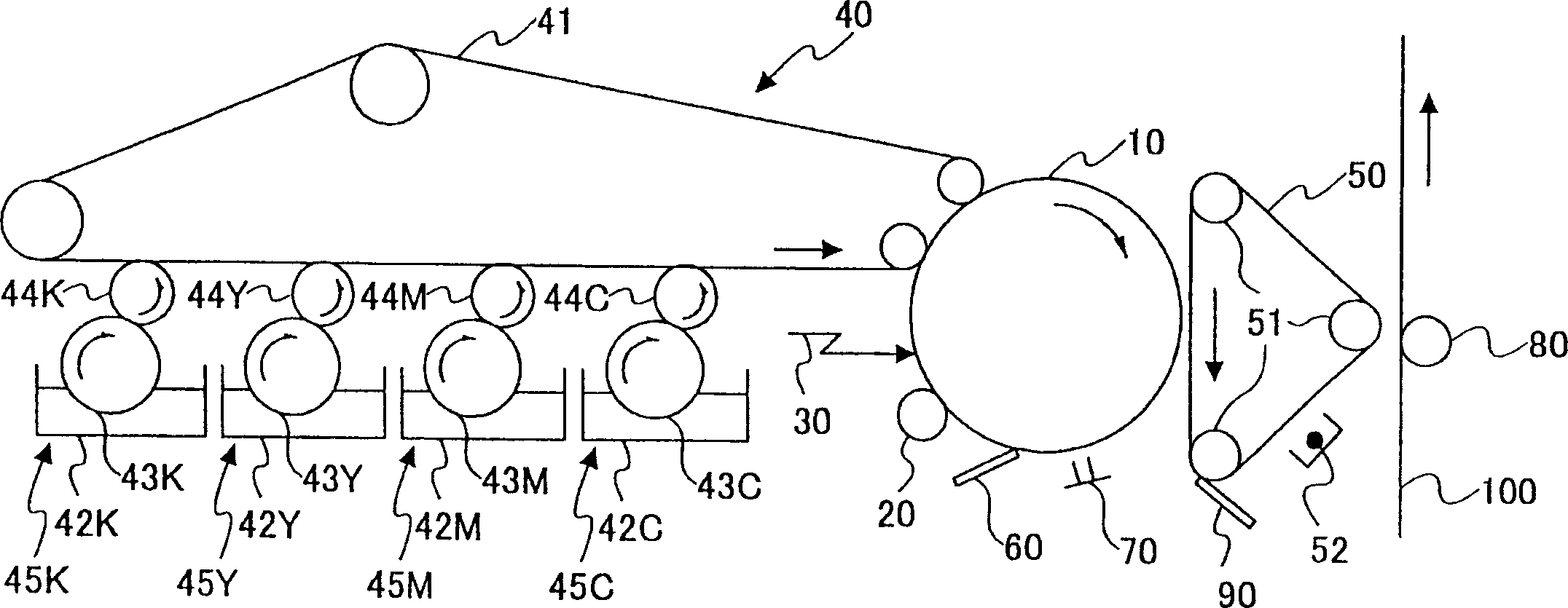

Optical scanner and image forming apparatus

InactiveUS20070058255A1Easy to useHigh quality imagingDiffraction gratingsOptical scannersLight beam

An optical scanner includes a light source; a deflecting unit that deflects and scans a light beam emitted from the light source; a scanning optical system that focuses the light beam deflected and scanned onto different surfaces to be scanned; and a light quantity correcting unit that corrects a light quantity of the light beam. The light quantity correcting unit changes light quantity correction data used for correcting the light quantity of the light beam for each of the surfaces. The light quantity correction data is dependent on positions in a main scanning direction.

Owner:RICOH KK

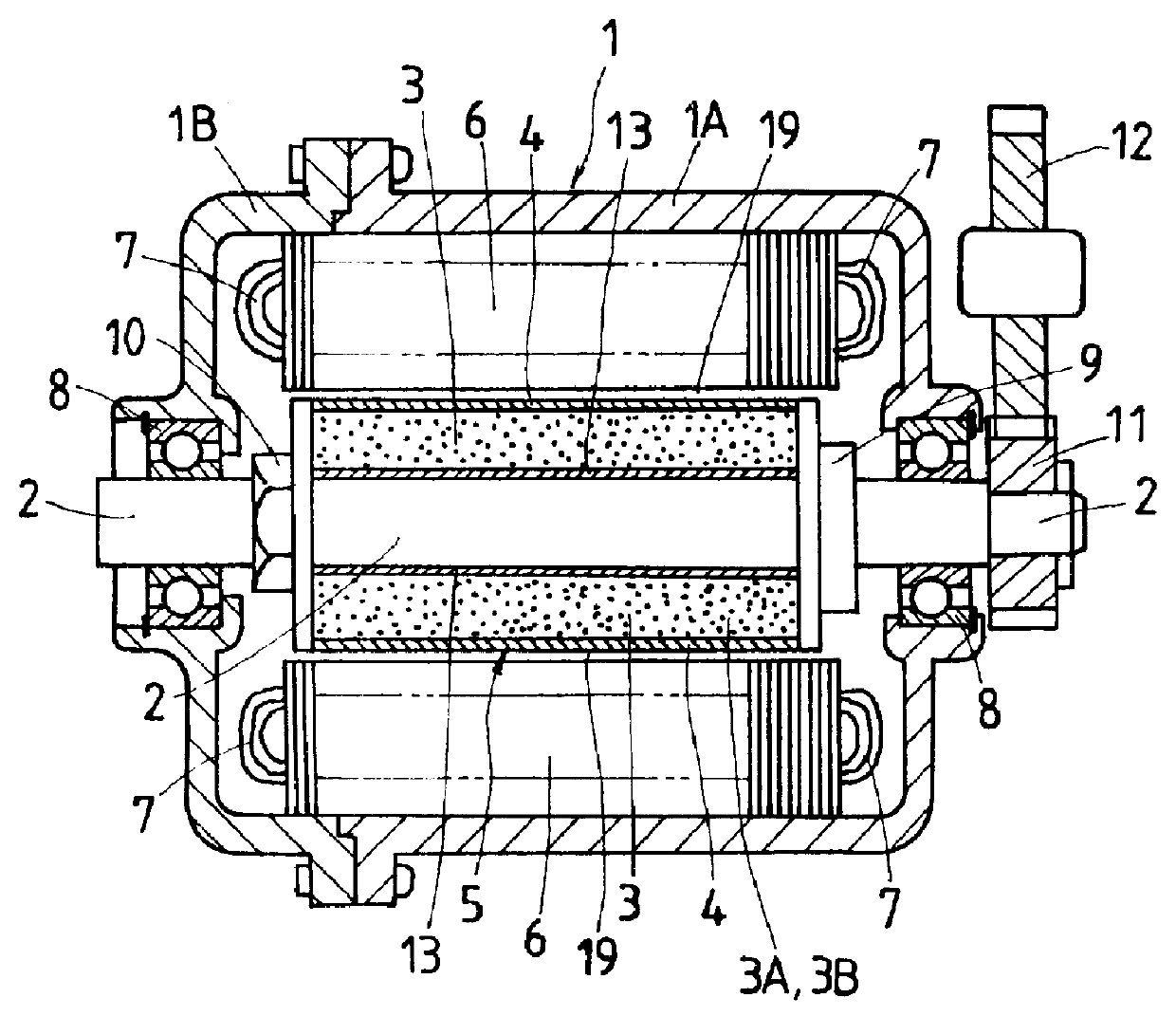

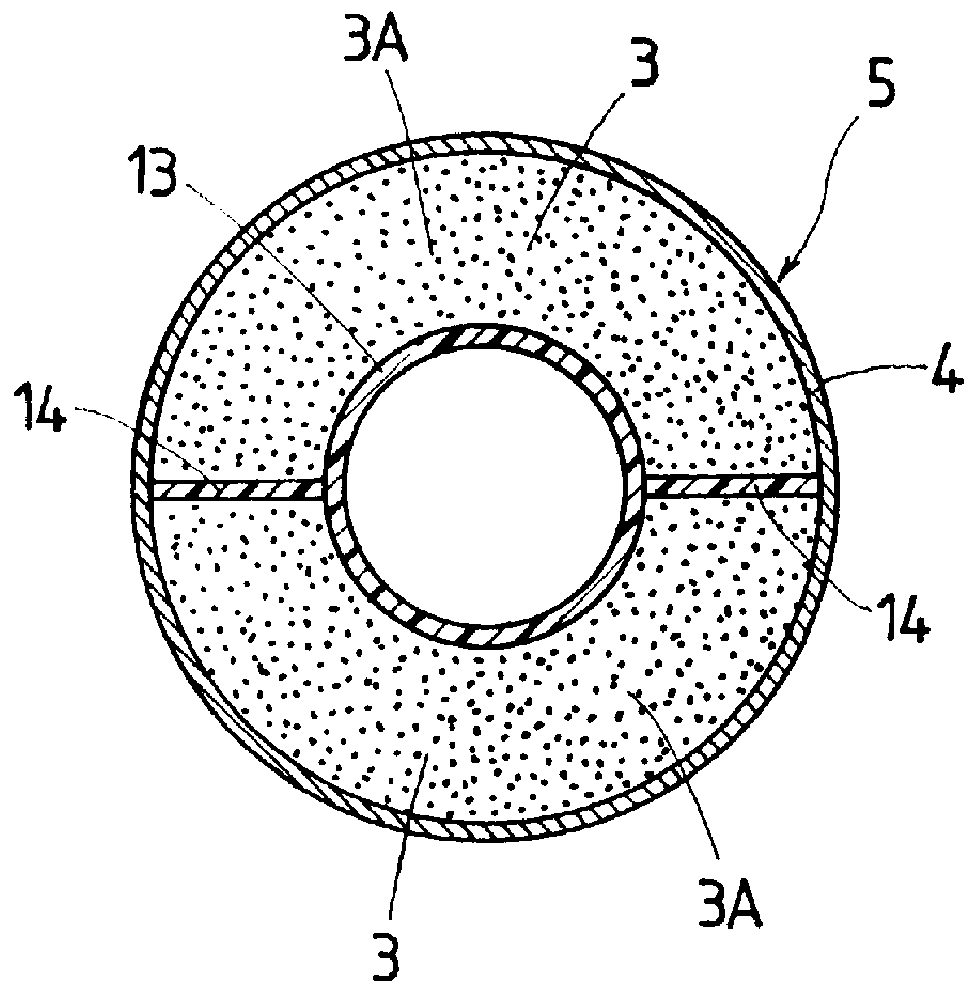

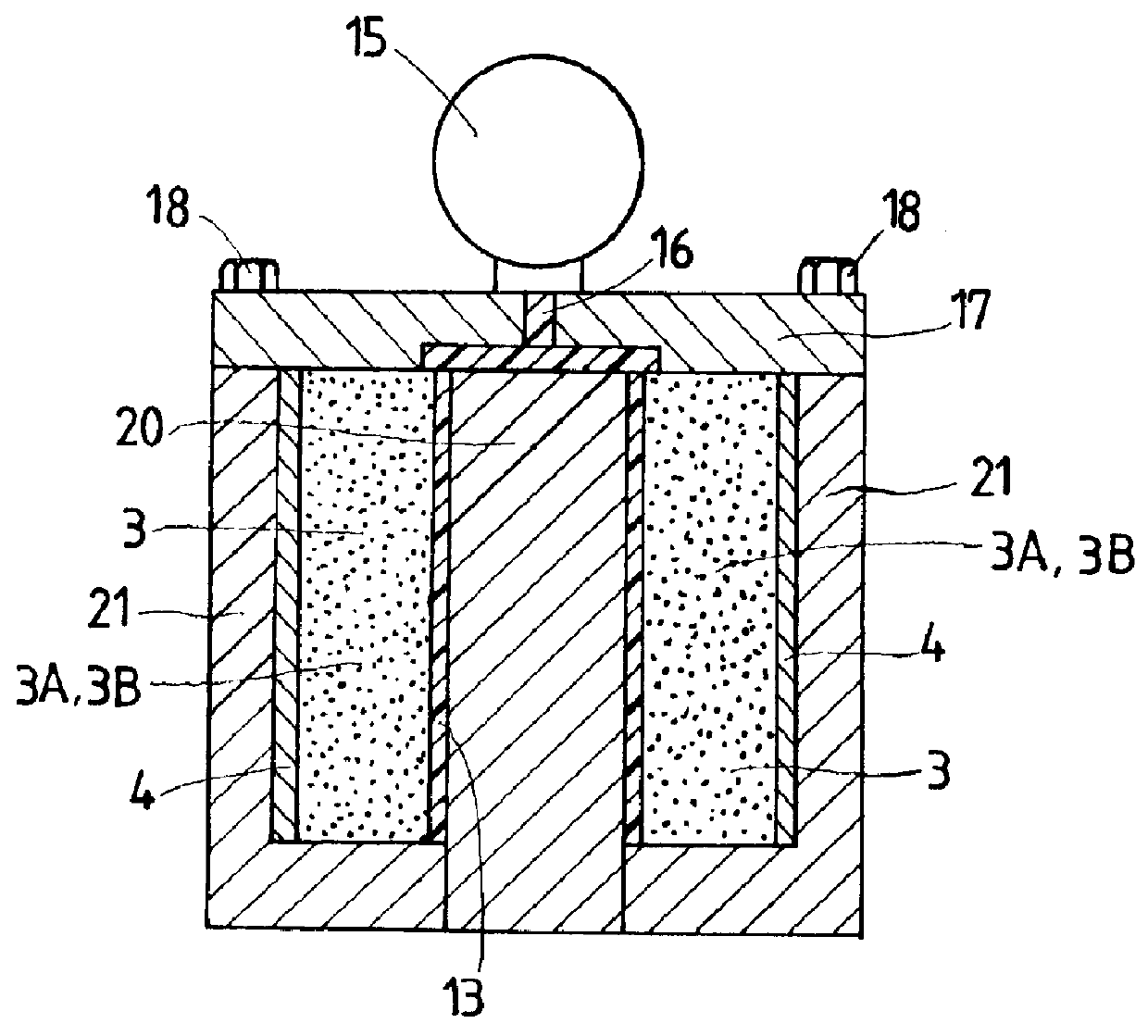

Structure of rotor for generators and method of manufacturing the same rotor

InactiveUS6144130AReduce manufacturing costImprove permeabilityMagnetic circuit rotating partsMagnetic circuit characterised by magnetic materialsFiberEngineering

Owner:ISUZU MOTORS LTD

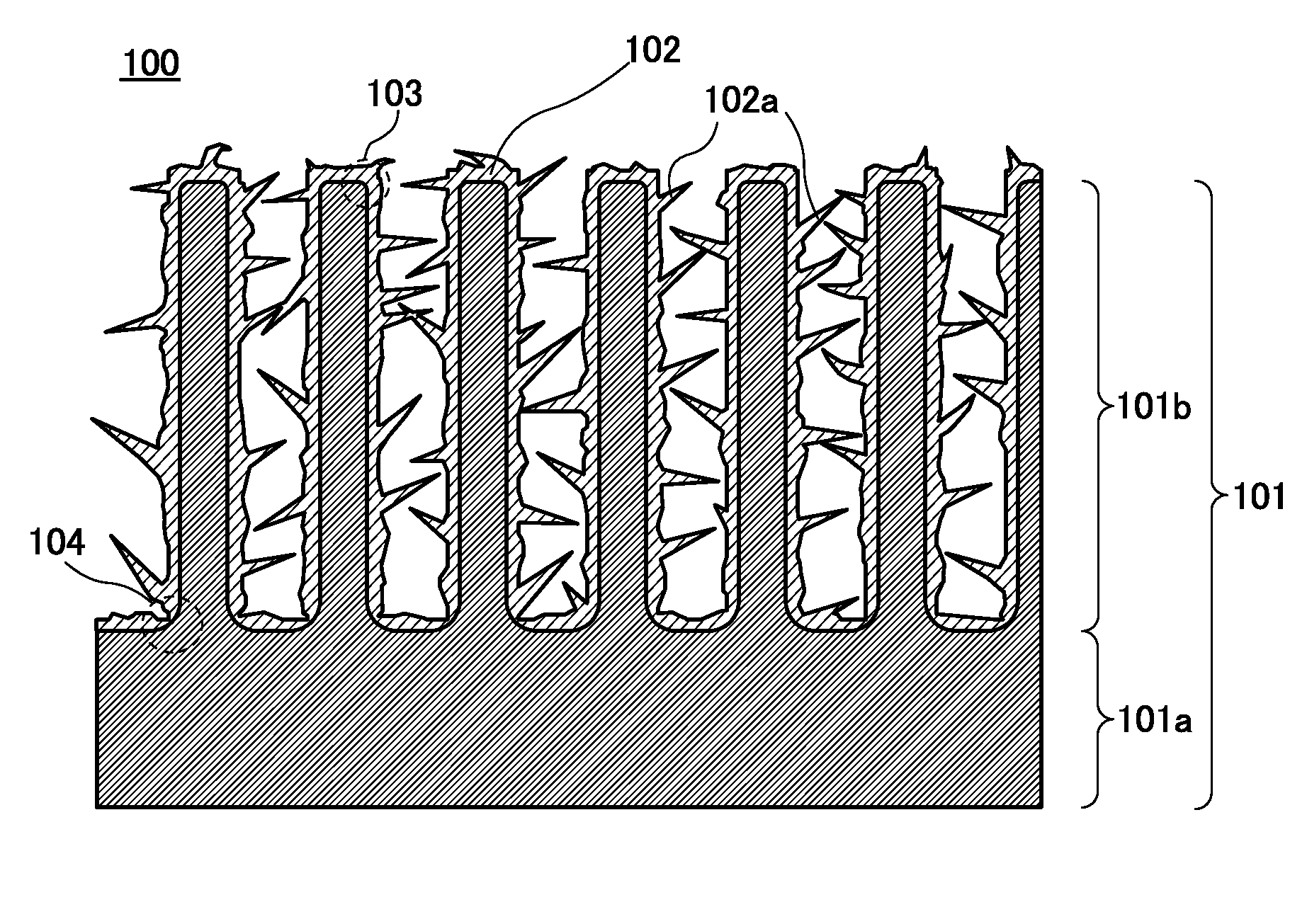

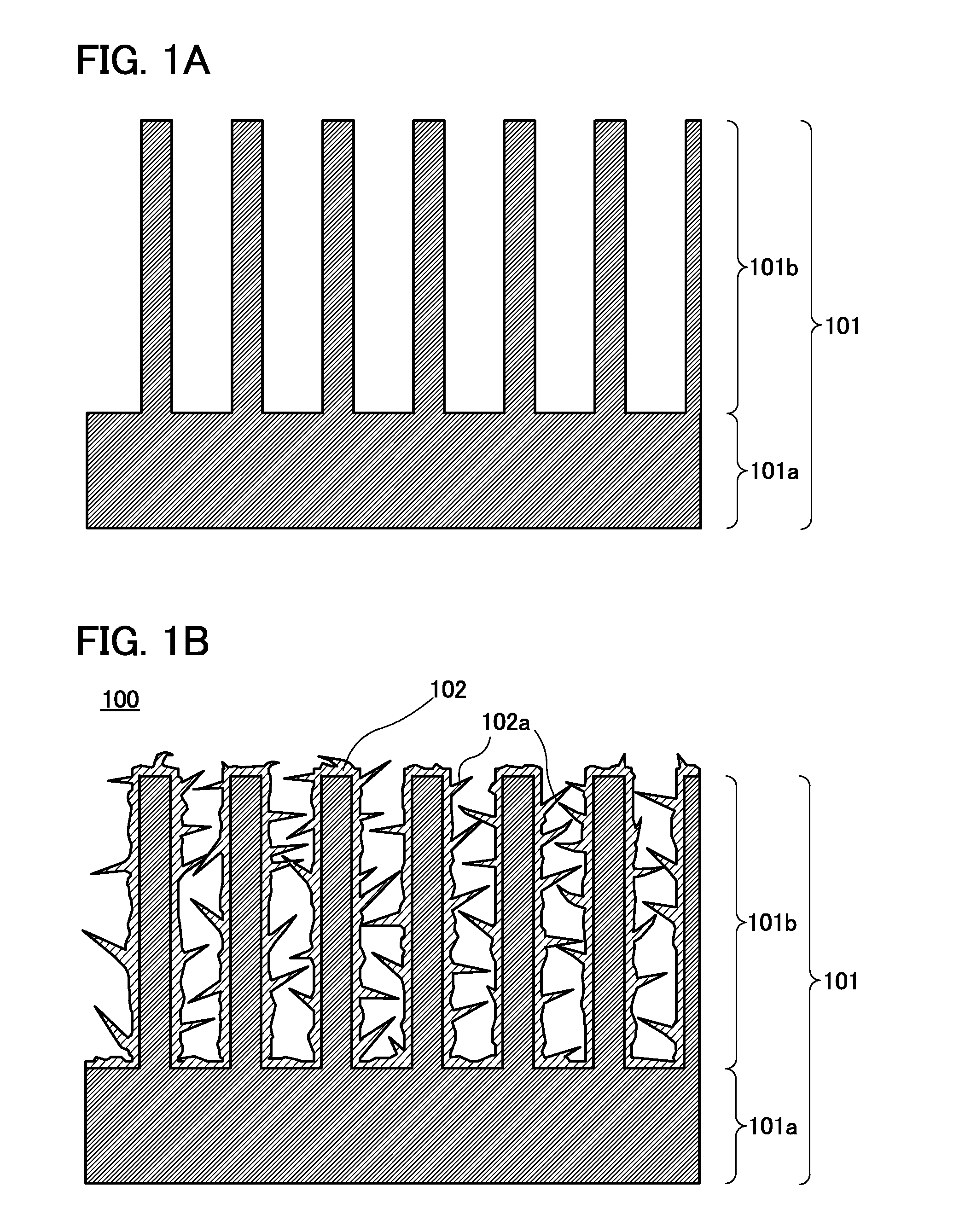

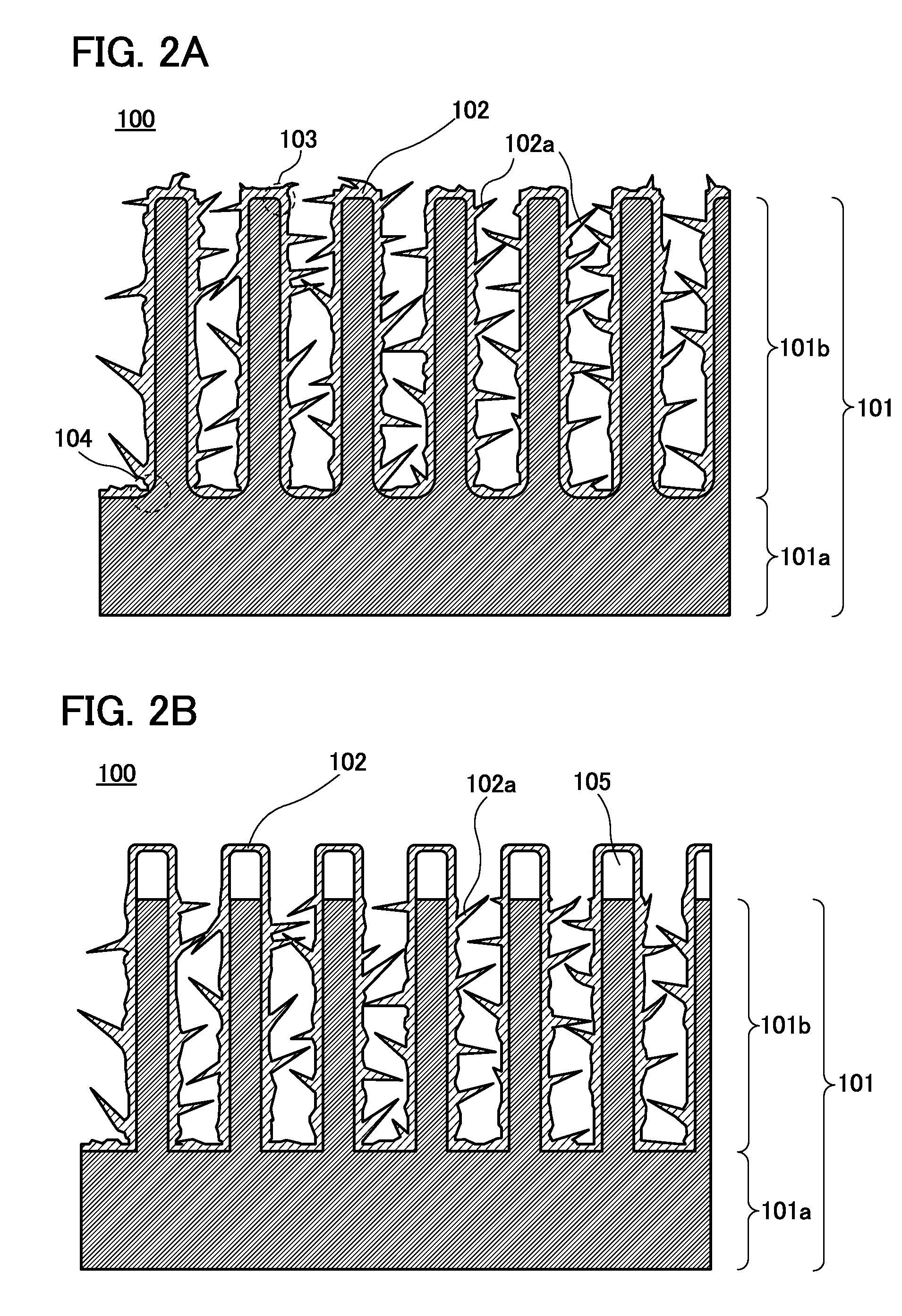

Negative electrode for non-aqueous secondary battery, non-aqueous secondary battery, and manufacturing methods thereof

InactiveUS20130164612A1High-speed outputIncrease volumeElectrolysis componentsVolume/mass flow measurementWhiskersTitanium

A non-aqueous secondary battery which has high charge-discharge capacity, can be charged and discharged at high speed, and has little deterioration in battery characteristics due to charge and discharge is provided. A negative electrode includes a current collector and an active material layer. The current collector includes a plurality of protrusion portions extending in a substantially perpendicular direction and a base portion connected to the plurality of protrusion portions. The protrusion portions and the base portion are formed using the same material containing titanium. Top surfaces and side surfaces of the protrusion portions and a top surface of the base portion are covered with the active material layer. The active material layer includes a plurality of whiskers. The active material layer may be covered with graphene.

Owner:SEMICON ENERGY LAB CO LTD

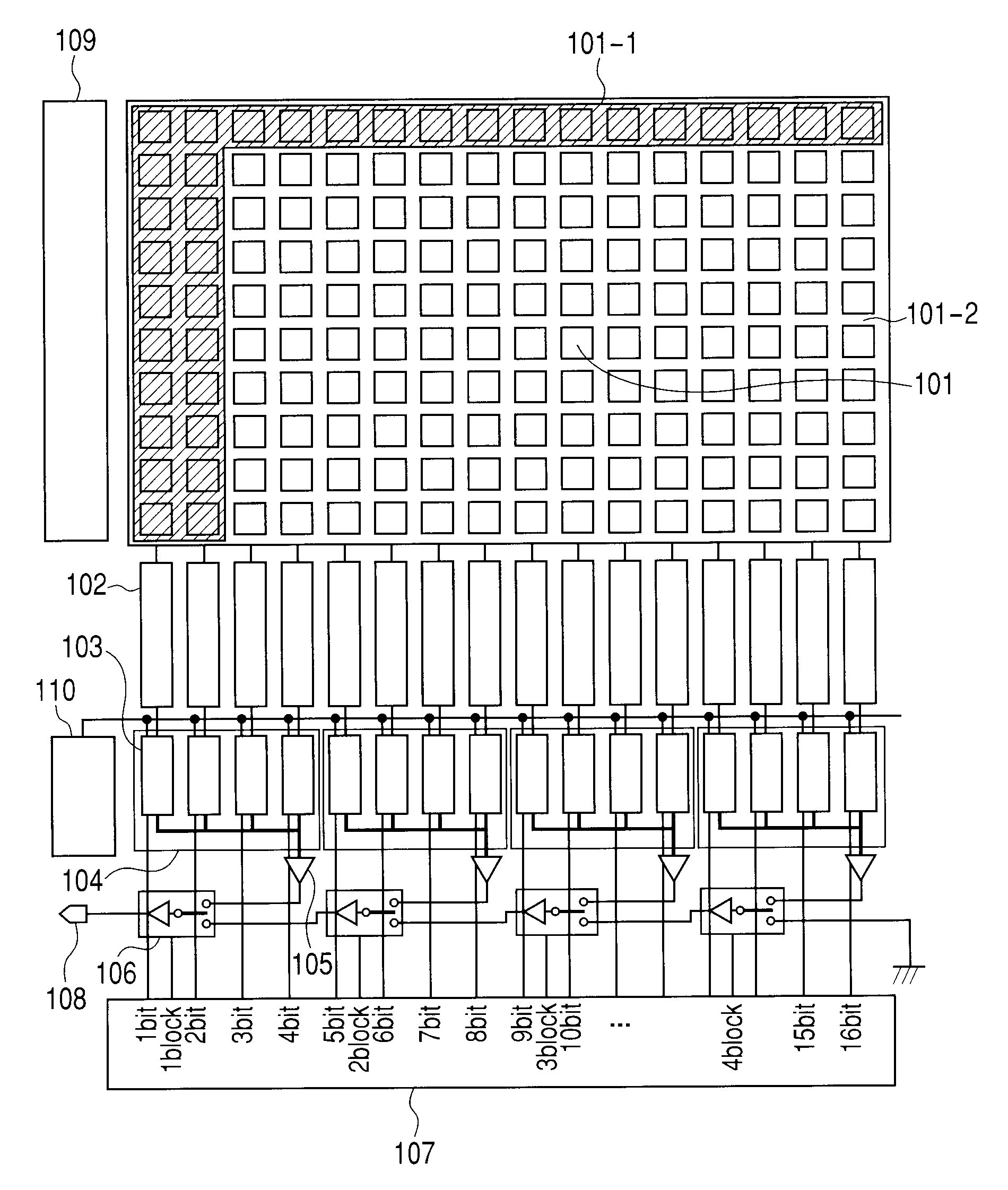

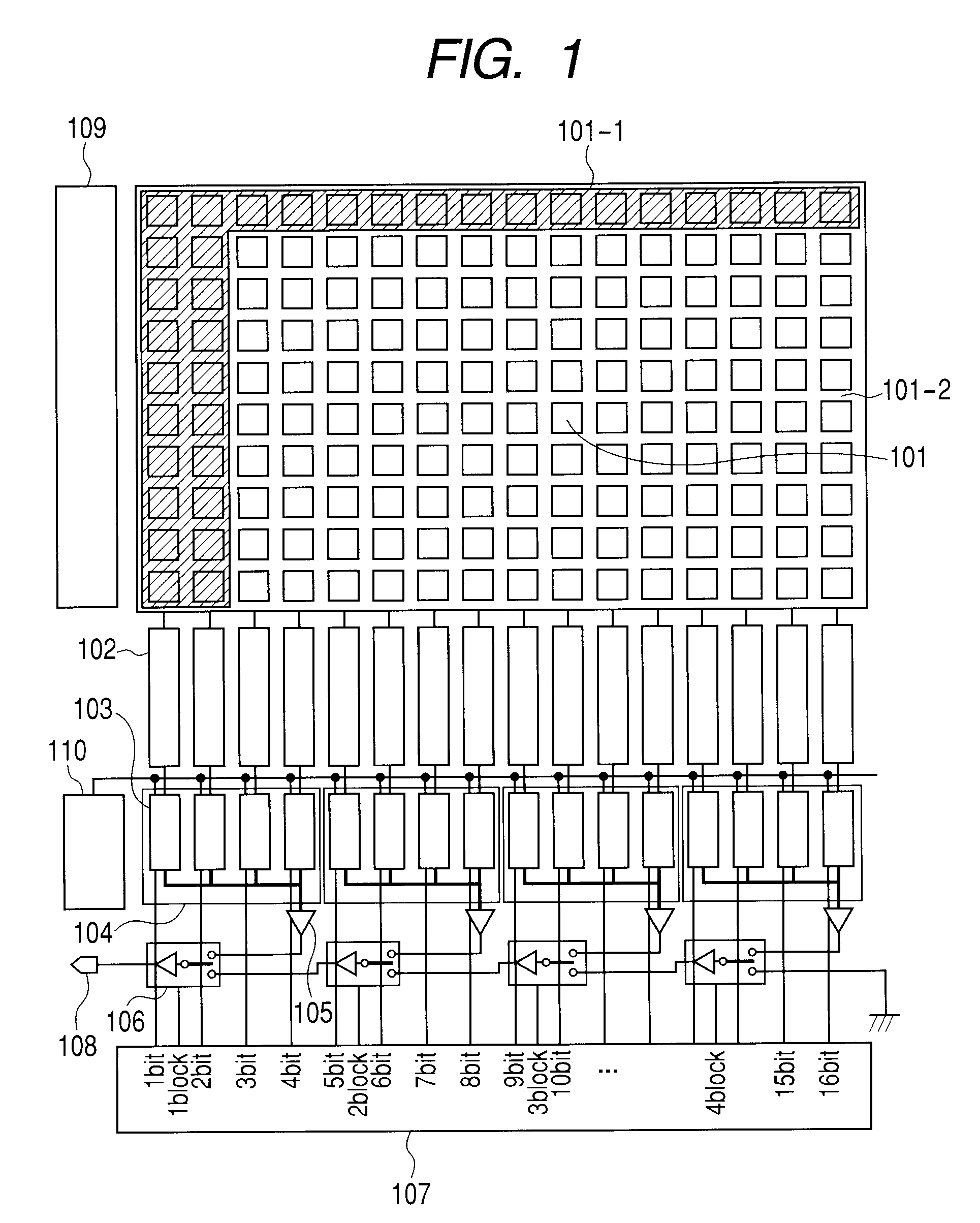

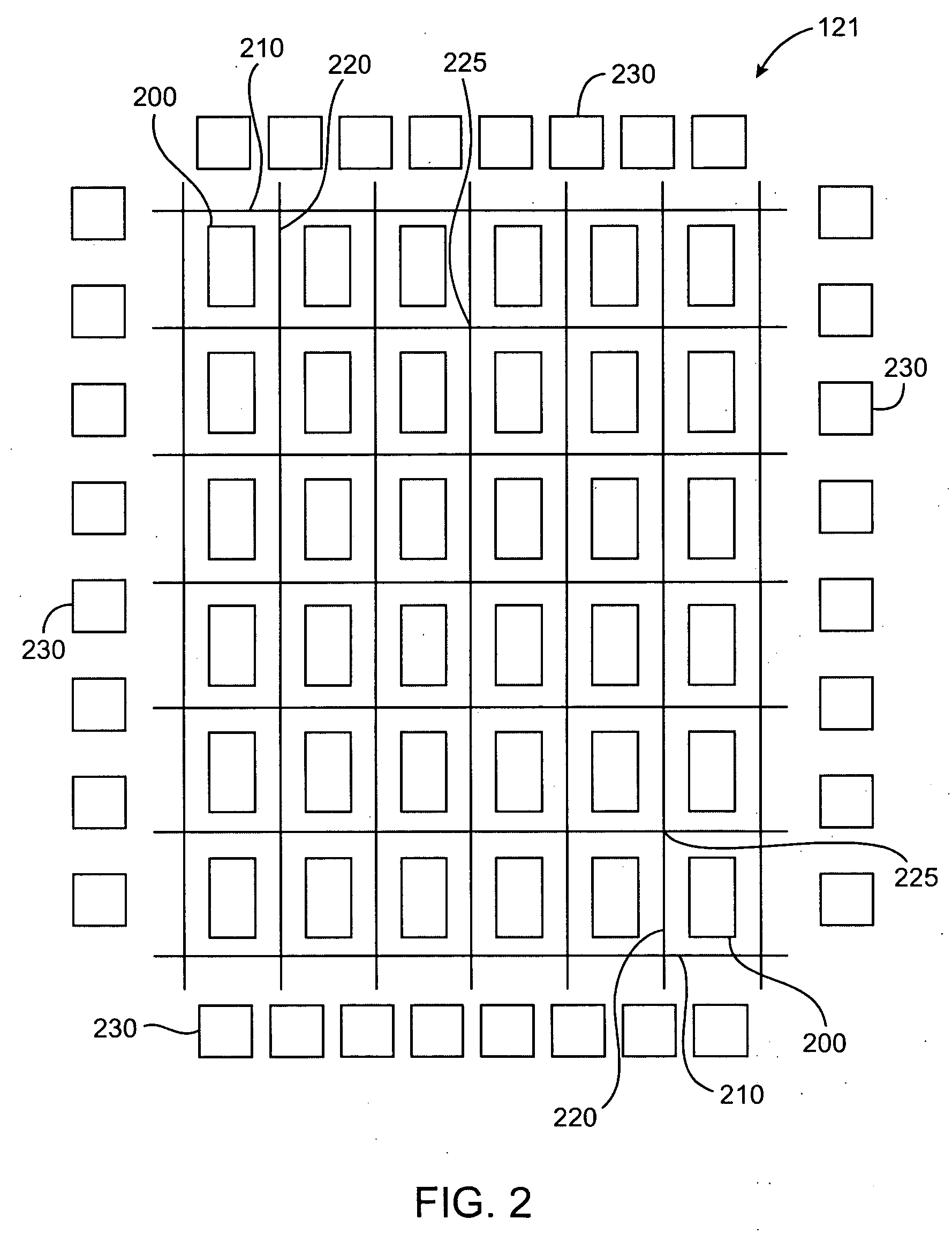

Solid-state imaging apparatus including pixel matrix with selectable blocks of output lines and imaging system using the solid-state imaging apparatus

ActiveUS8325260B2High-speed outputTelevision system detailsTelevision system scanning detailsDigital storageAnalog signal

Owner:CANON KK

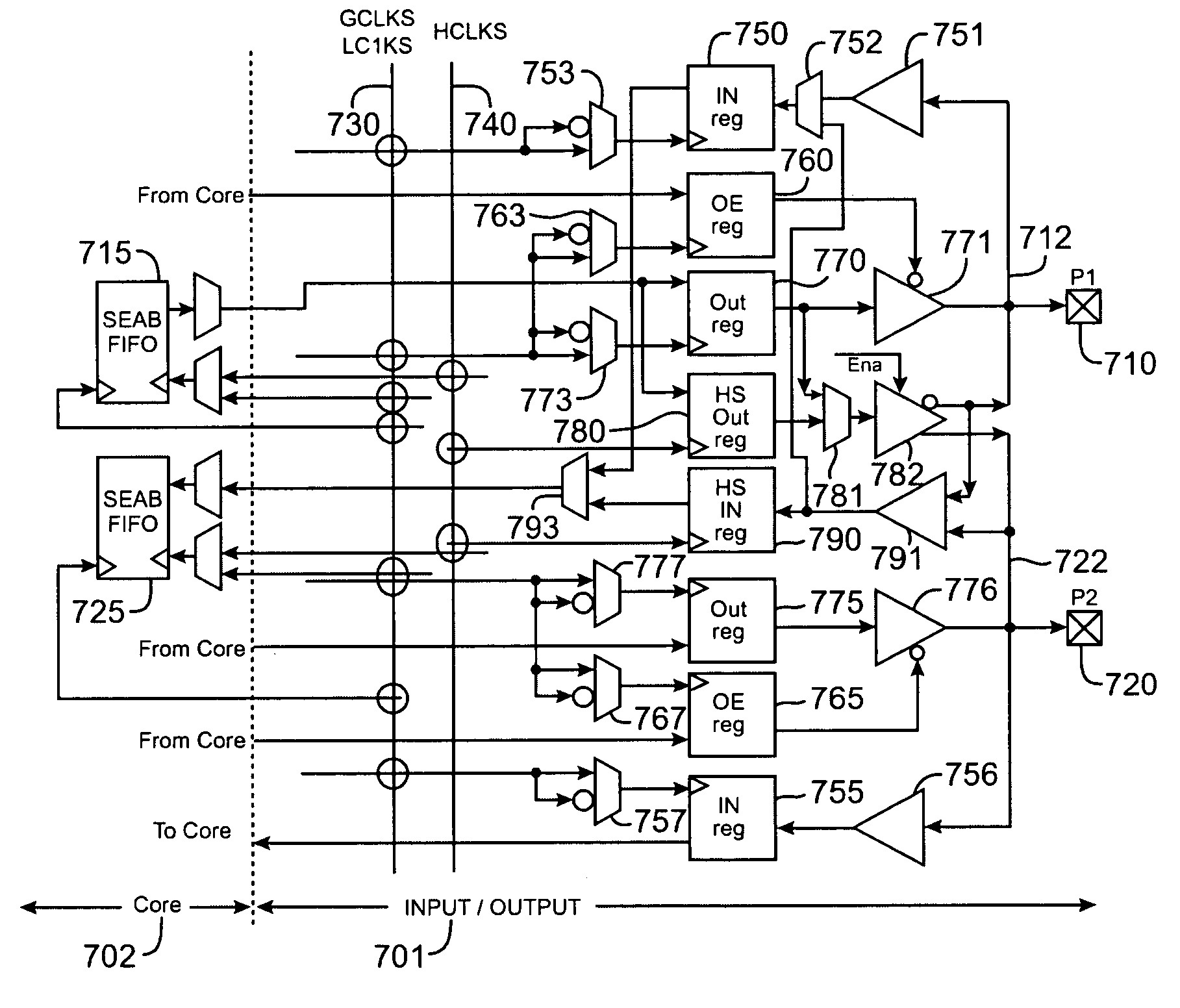

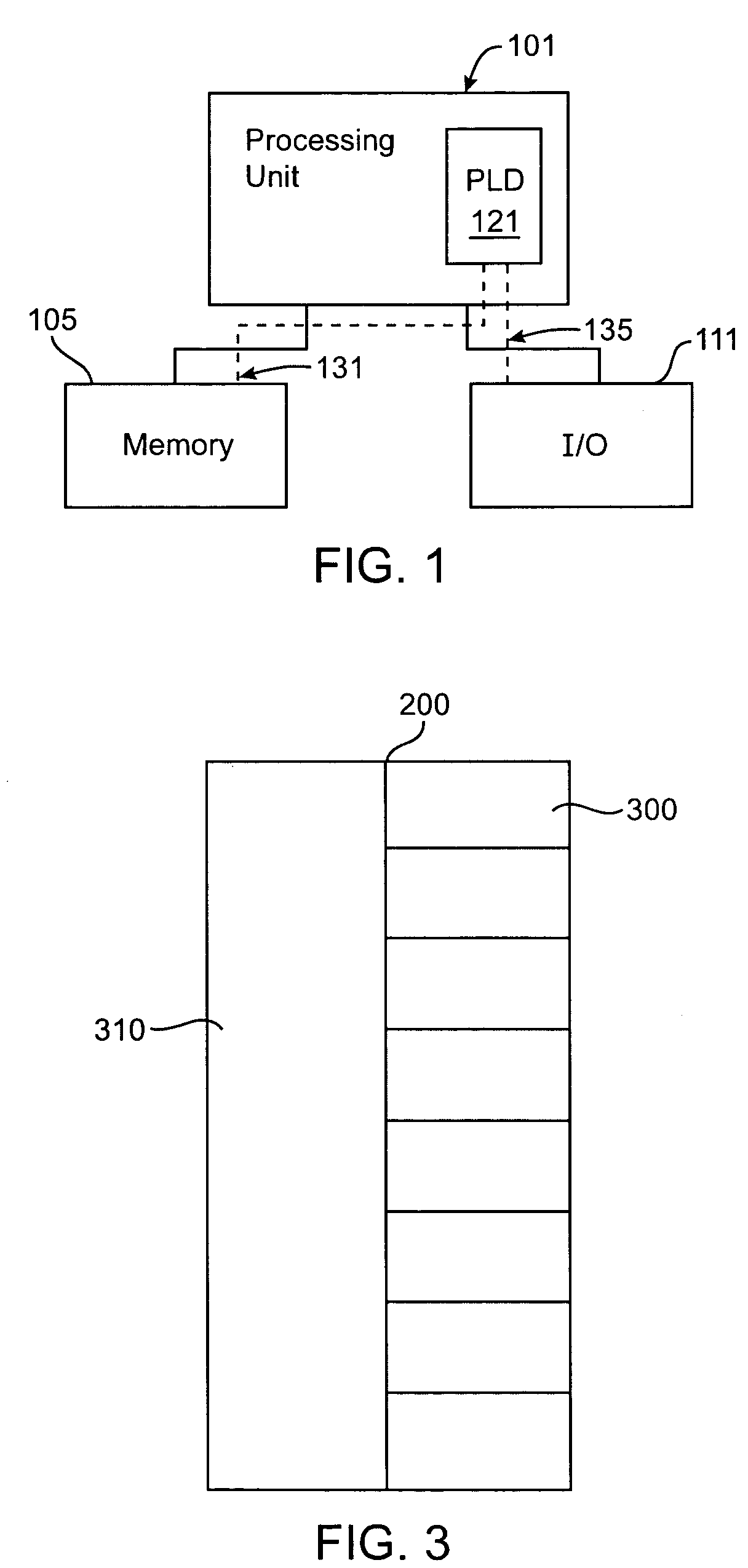

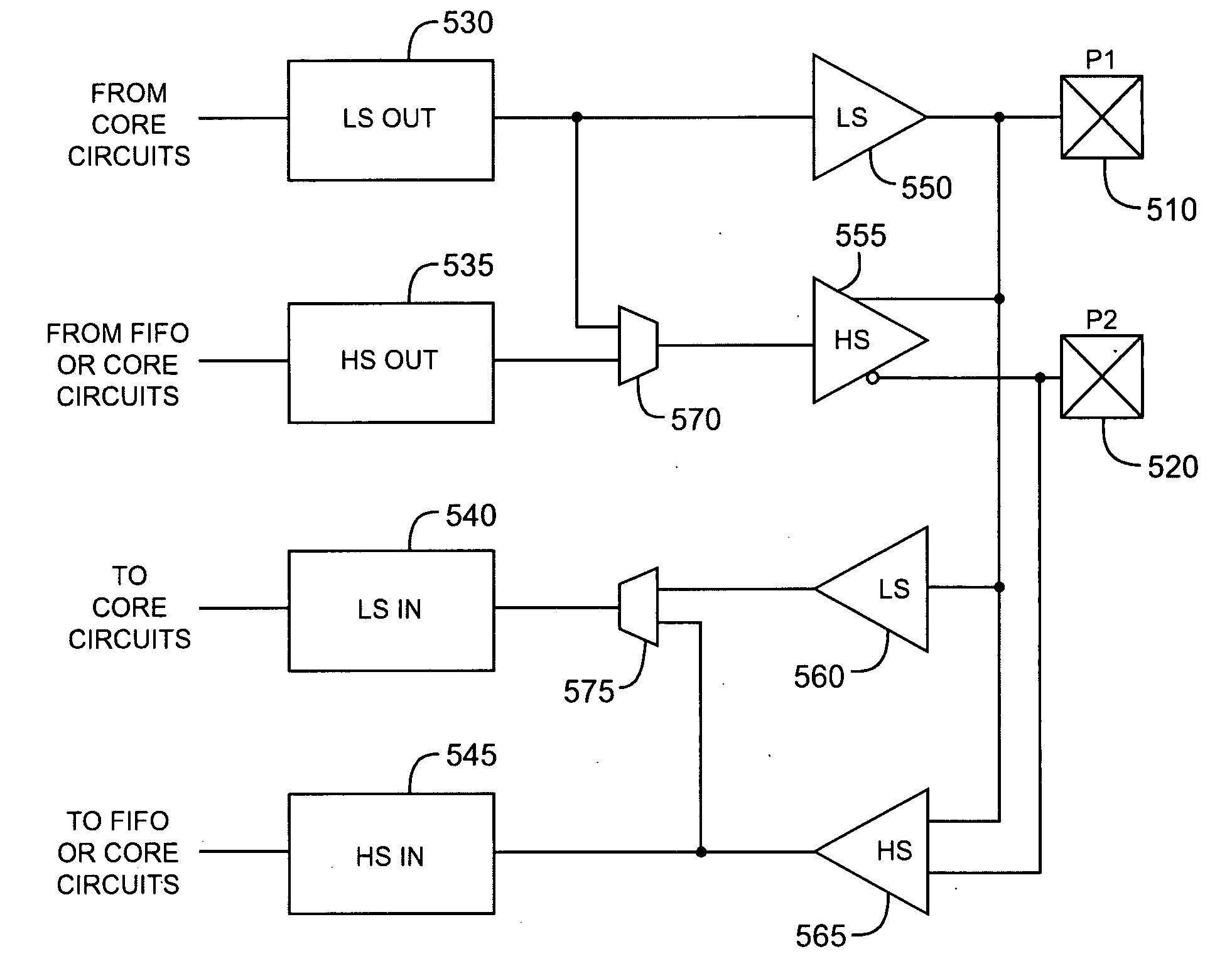

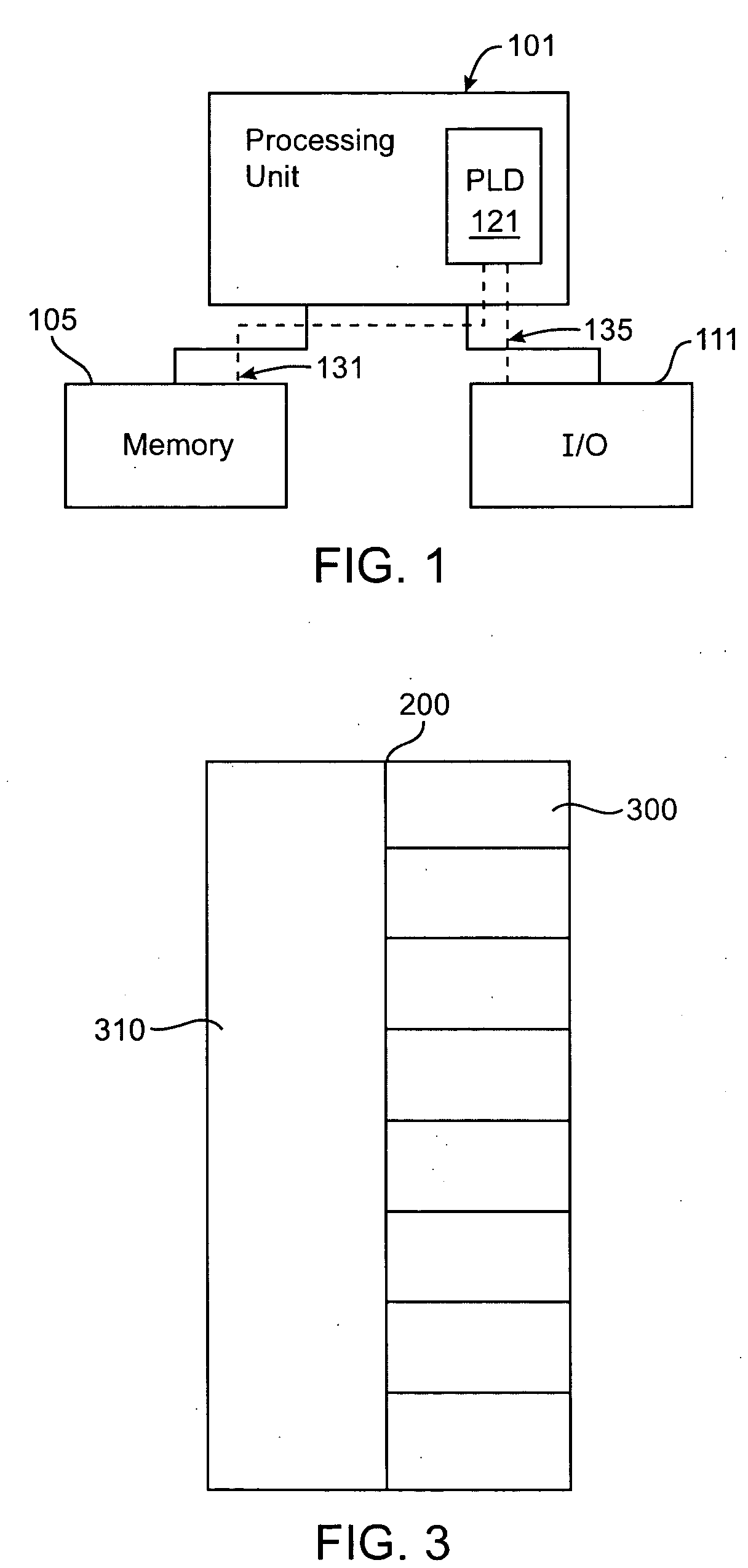

Programmable high speed I/O interface

InactiveUS7116135B2High-speed inputHigh-speed outputProgrammable logic circuit arrangementsElectric pulse generatorBoundary testingLow speed

Methods and apparatus for providing either high-speed, or lower-speed, flexible inputs and outputs. An input and output structure having a high-speed input, a high-speed output, a low or moderate speed input, and an low or moderate speed output is provided. One of the input and output circuits are selected and the others are deselected. The high-speed input and output circuits are comparatively simple, in one example having only a clear signal for a control line input, and are able to interface to lower speed circuitry inside the core of an integrated circuit. The low or moderate speed input and output circuits are more flexible, for example, having preset, enable, and clear as control line inputs, and are able to support JTAG boundary testing. These parallel high and lower speed circuits are user selectable such that the input output structure is optimized between speed and functionality depending on the requirements of the application.

Owner:ALTERA CORP

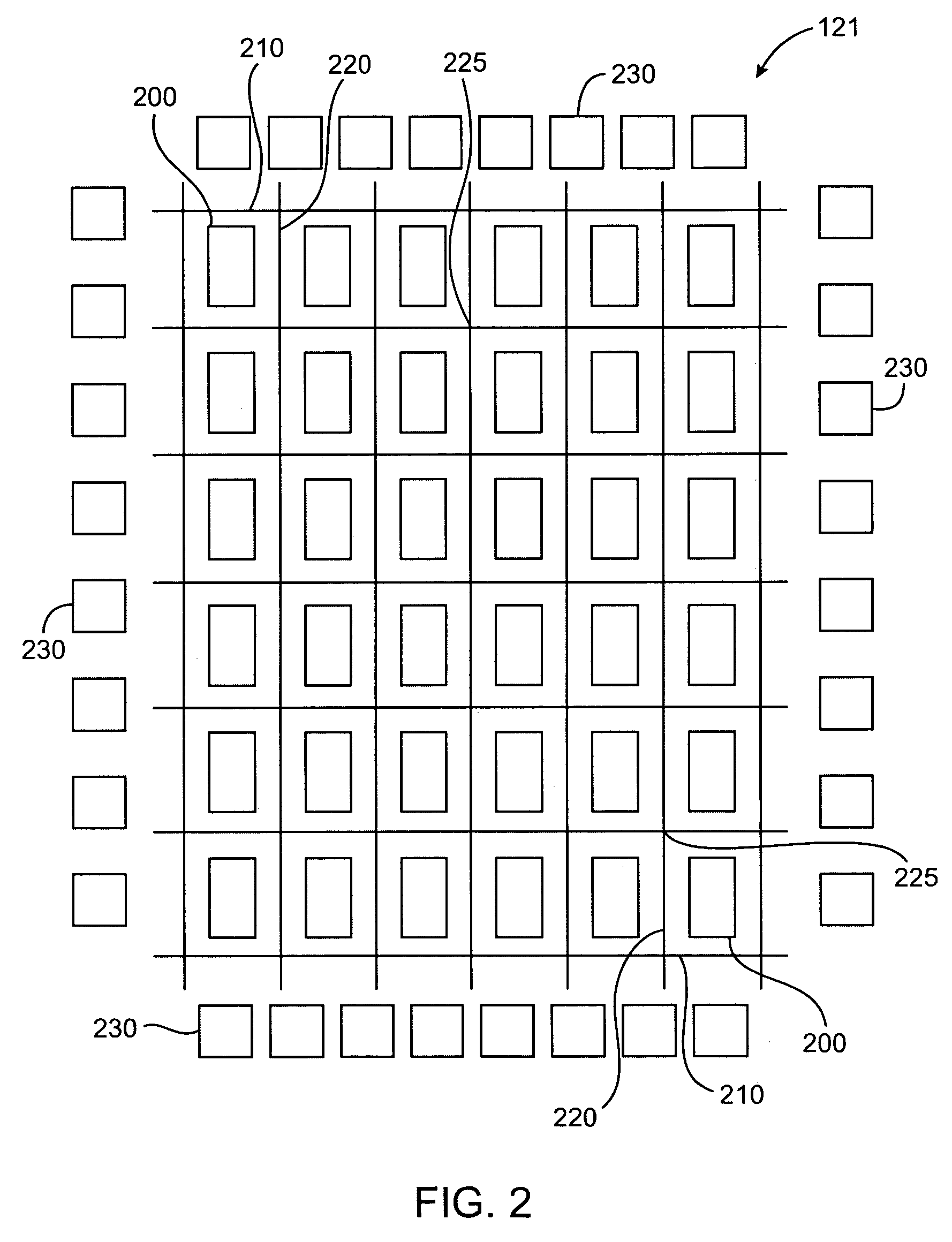

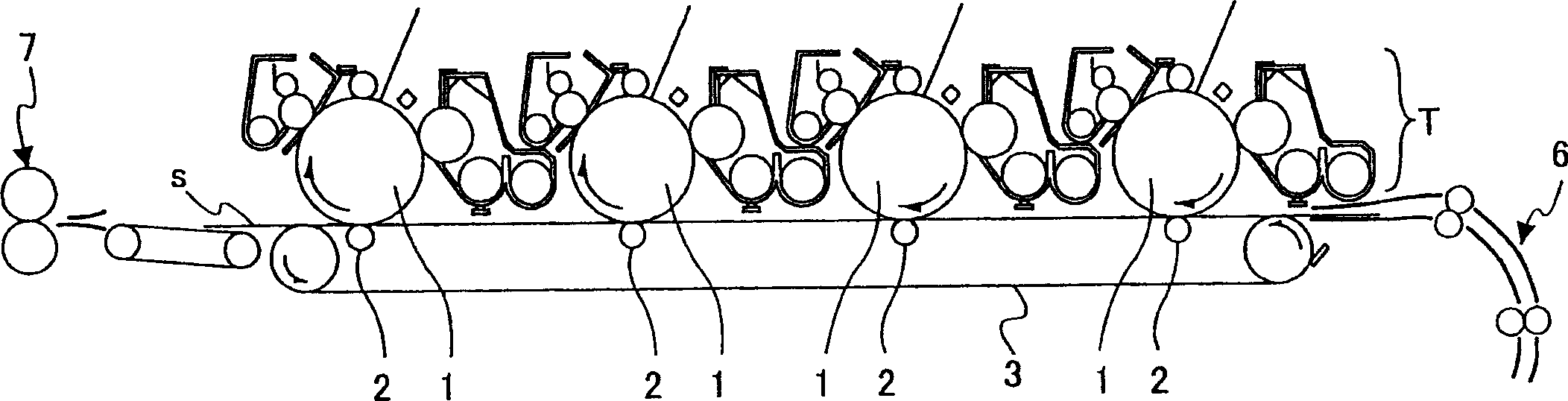

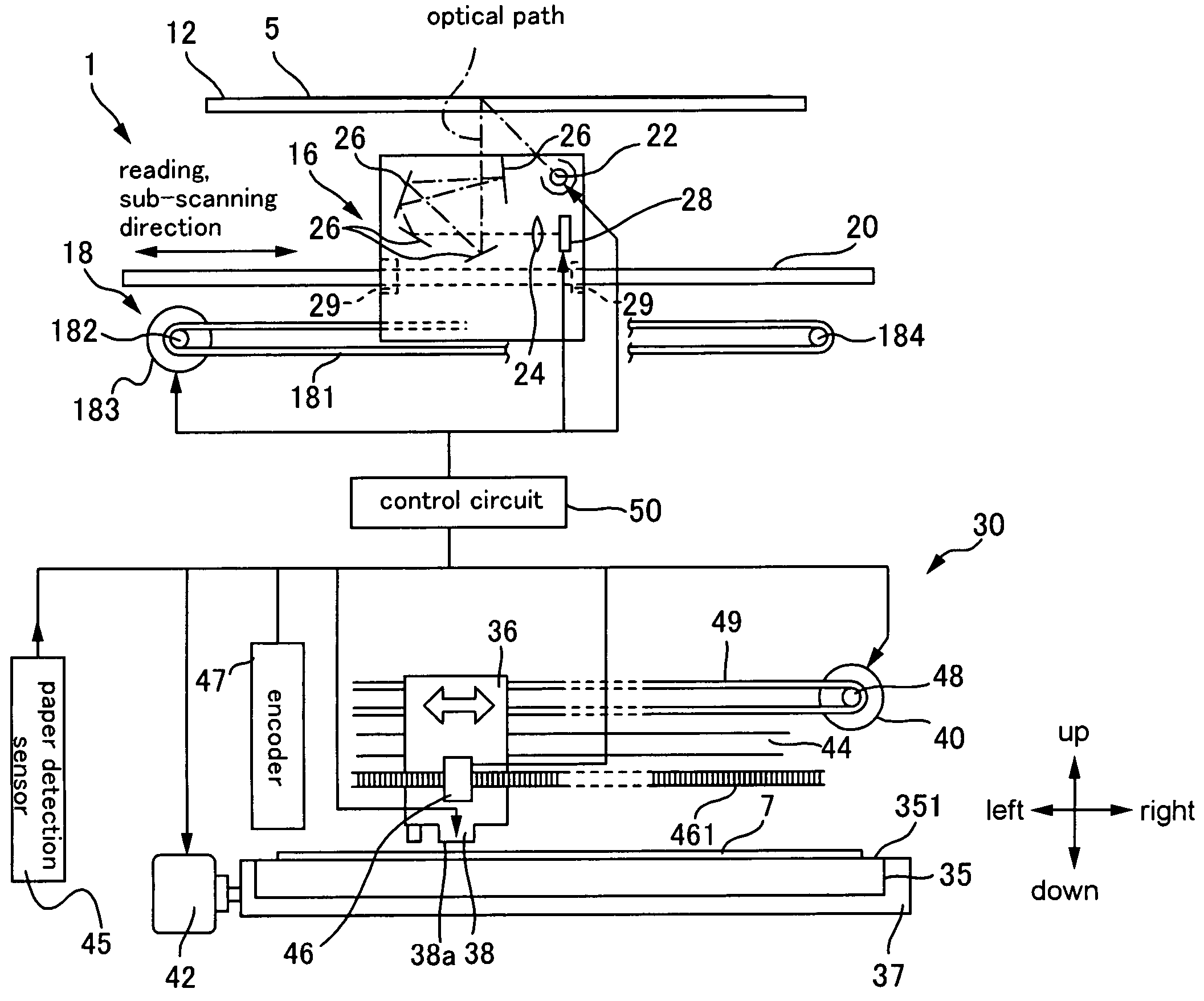

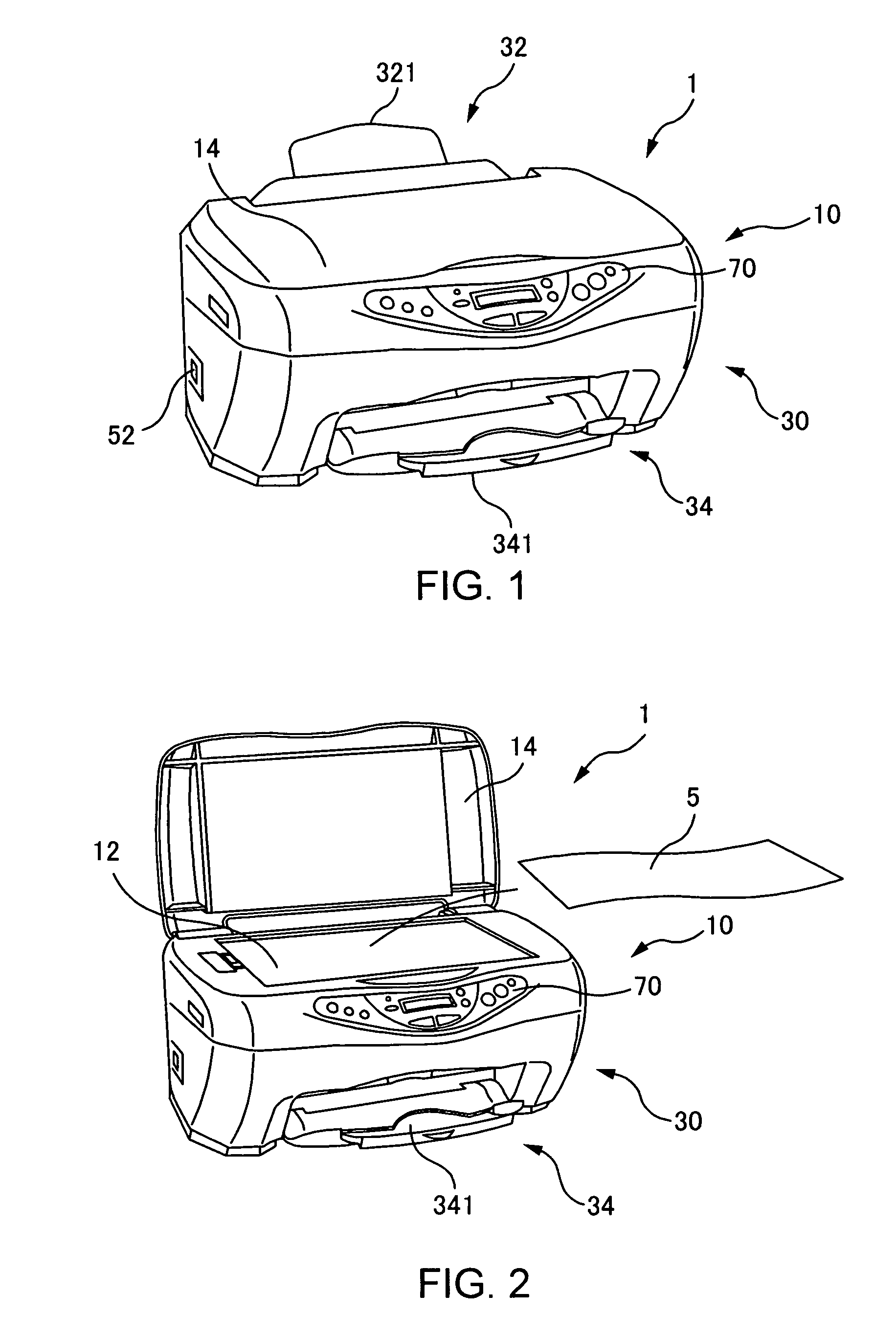

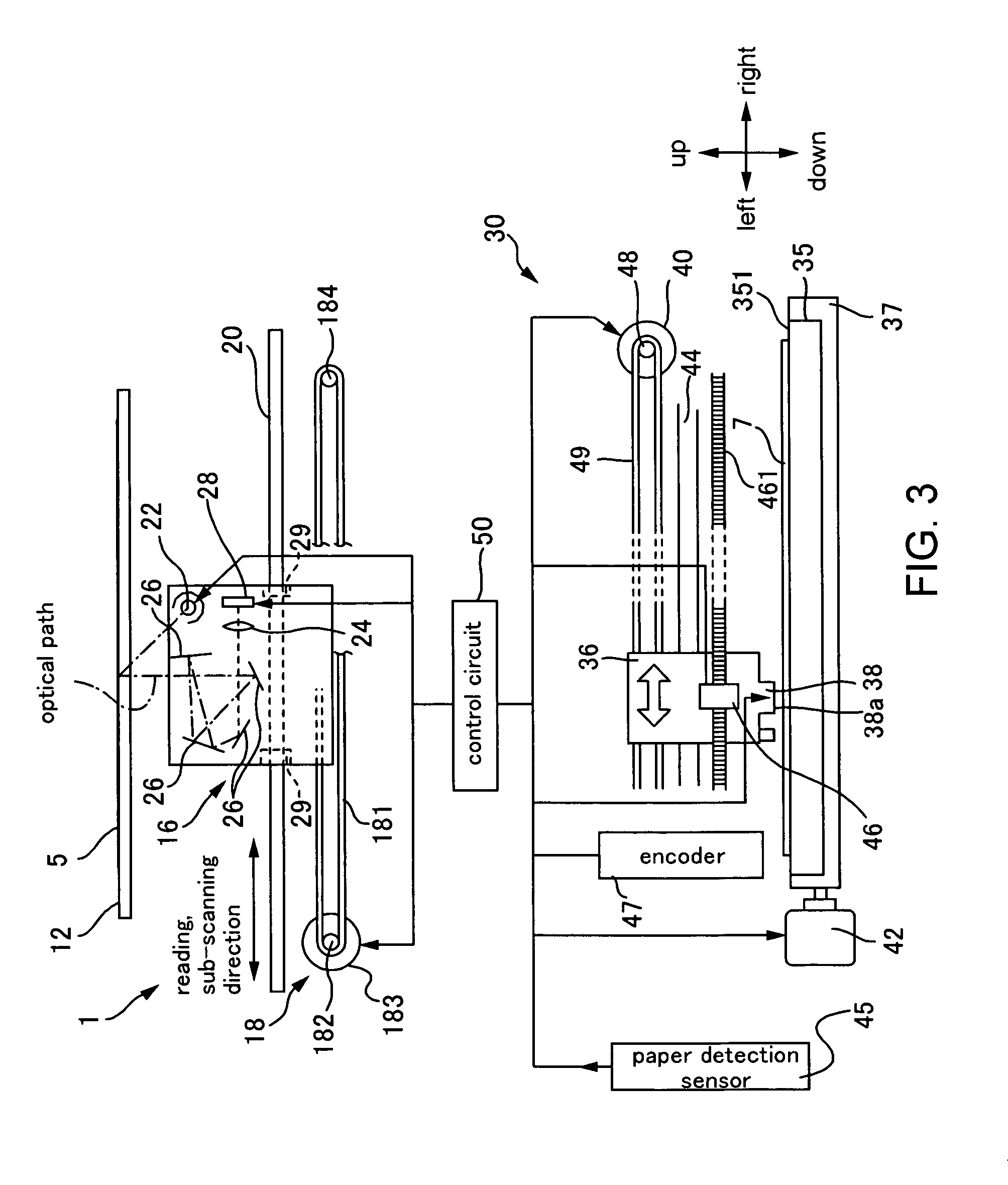

Recording apparatus

ActiveUS20050099660A1High-speed outputReduce generationDigitally marking record carriersVisual representation by matrix printersComputer scienceData generator

A recording apparatus, and so forth, capable of outputting at high speed is provided. Second recording data that are stored in a memory based on data obtained by a data obtaining section are transferred to a data generator via a second transfer path, and based on the second recording data that have been transferred, the data generator generates first recording data for performing recording on a medium.

Owner:SEIKO EPSON CORP

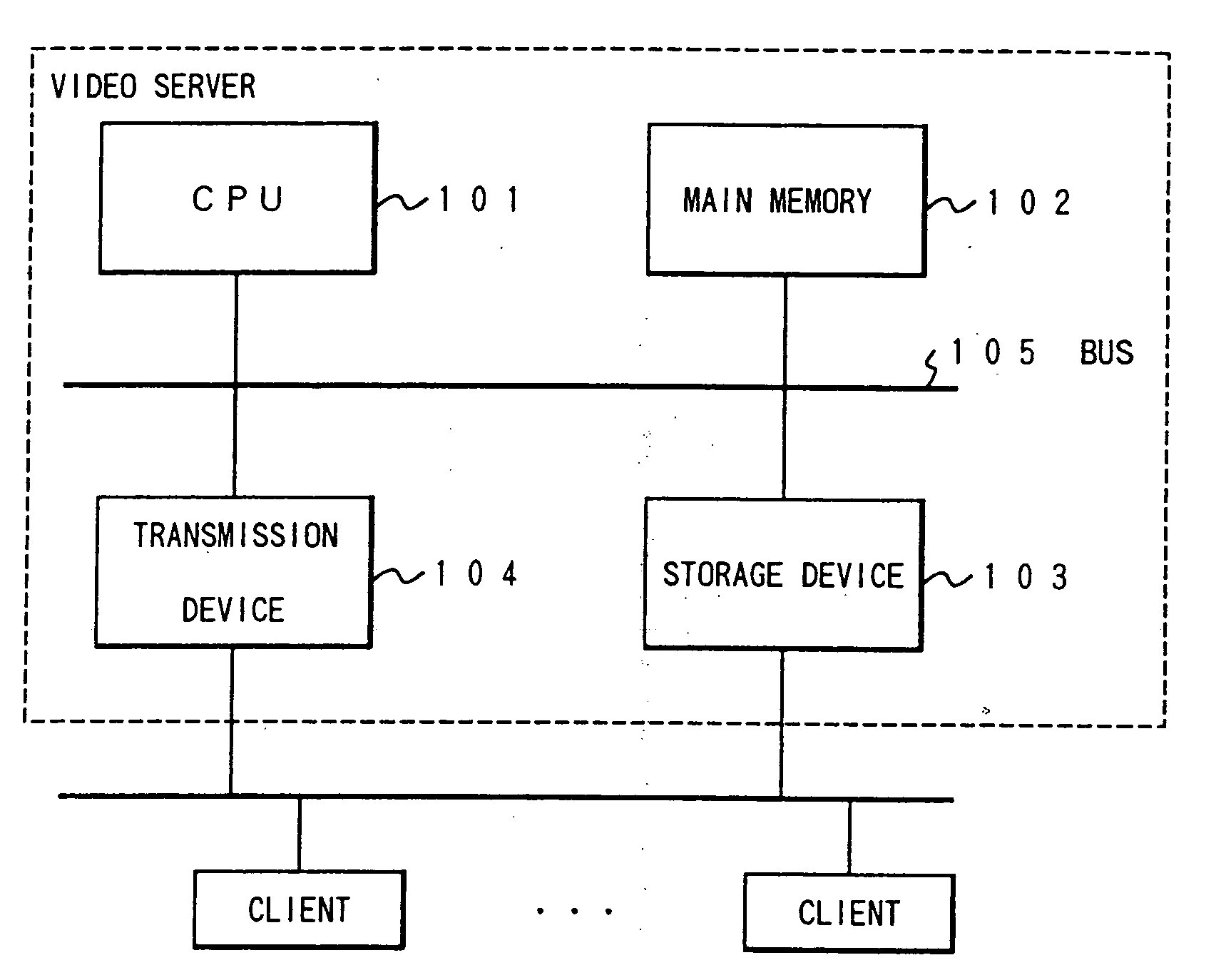

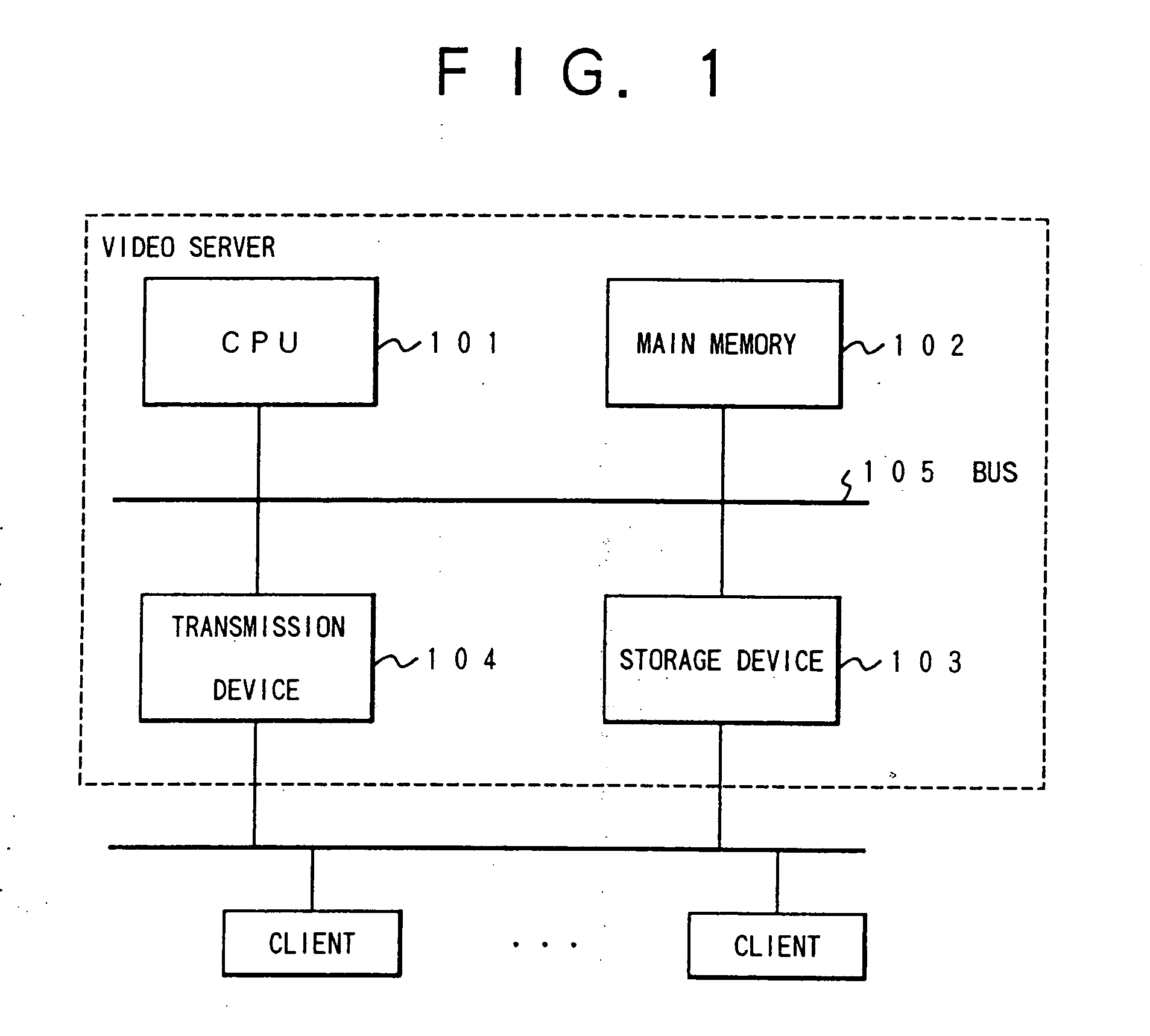

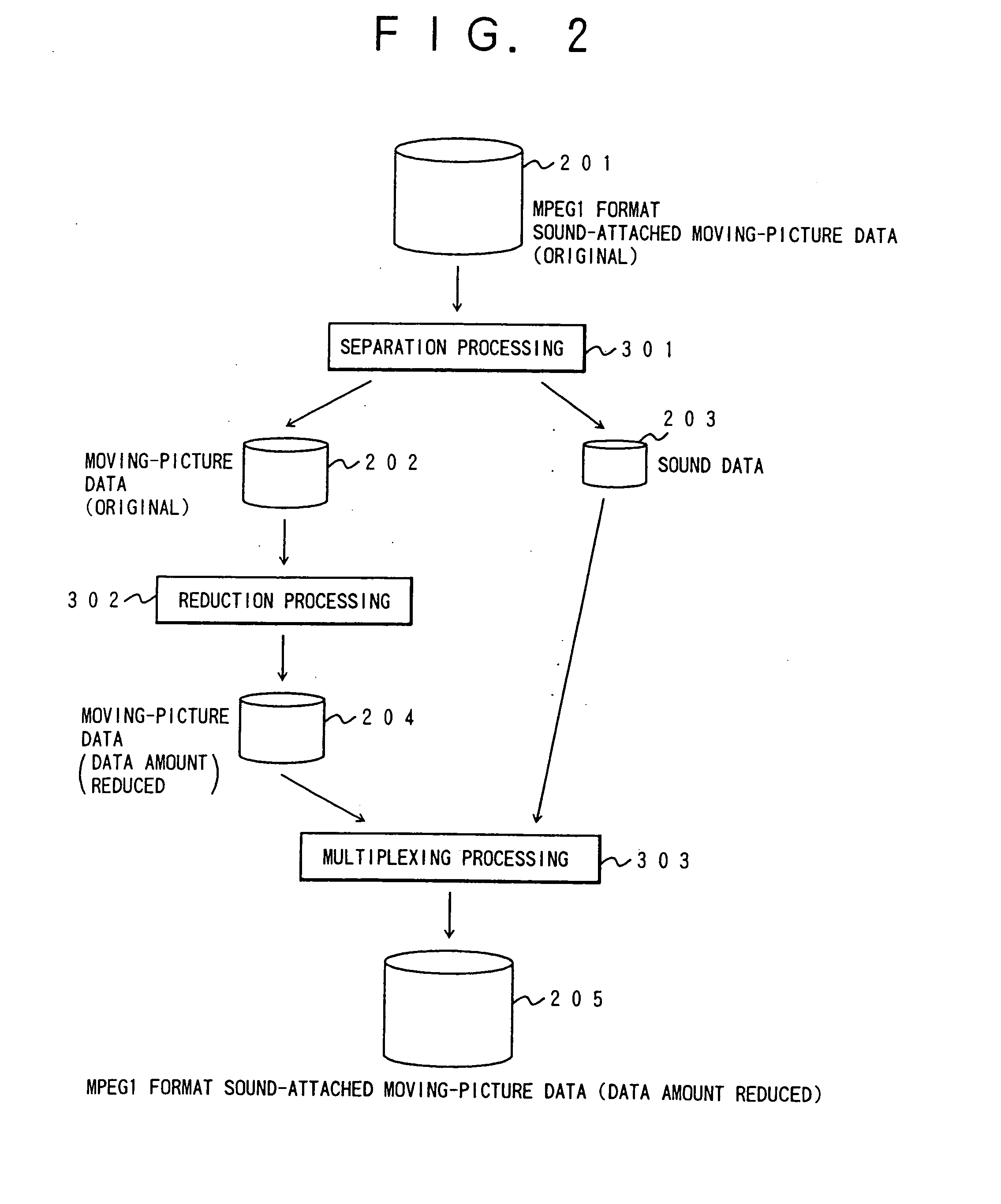

Multimedia data processing system in network

InactiveUS20060114350A1High-speed outputHigh data speedColor television with pulse code modulationColor television with bandwidth reductionData processing systemData profiling

A data converting device which includes an input device which receives input information containing one or more kinds of data, a data analyzer which checks each kind of data constituting the input information and extracts data from the input information when the checked data are judged to be predetermined conversion target data to be subjected to a data conversion processing, and a controller which performs the conversion processing on an amount of the extracted data in accordance with a predetermined regulation for the kind of data. The invention further includes an information constructing device which replaces the non-converted data of the input information which converted extracted data, thereby reconstructing the input information, and an output device which outputs the reconstructed input information.

Owner:SHIMADA TAKAO +10

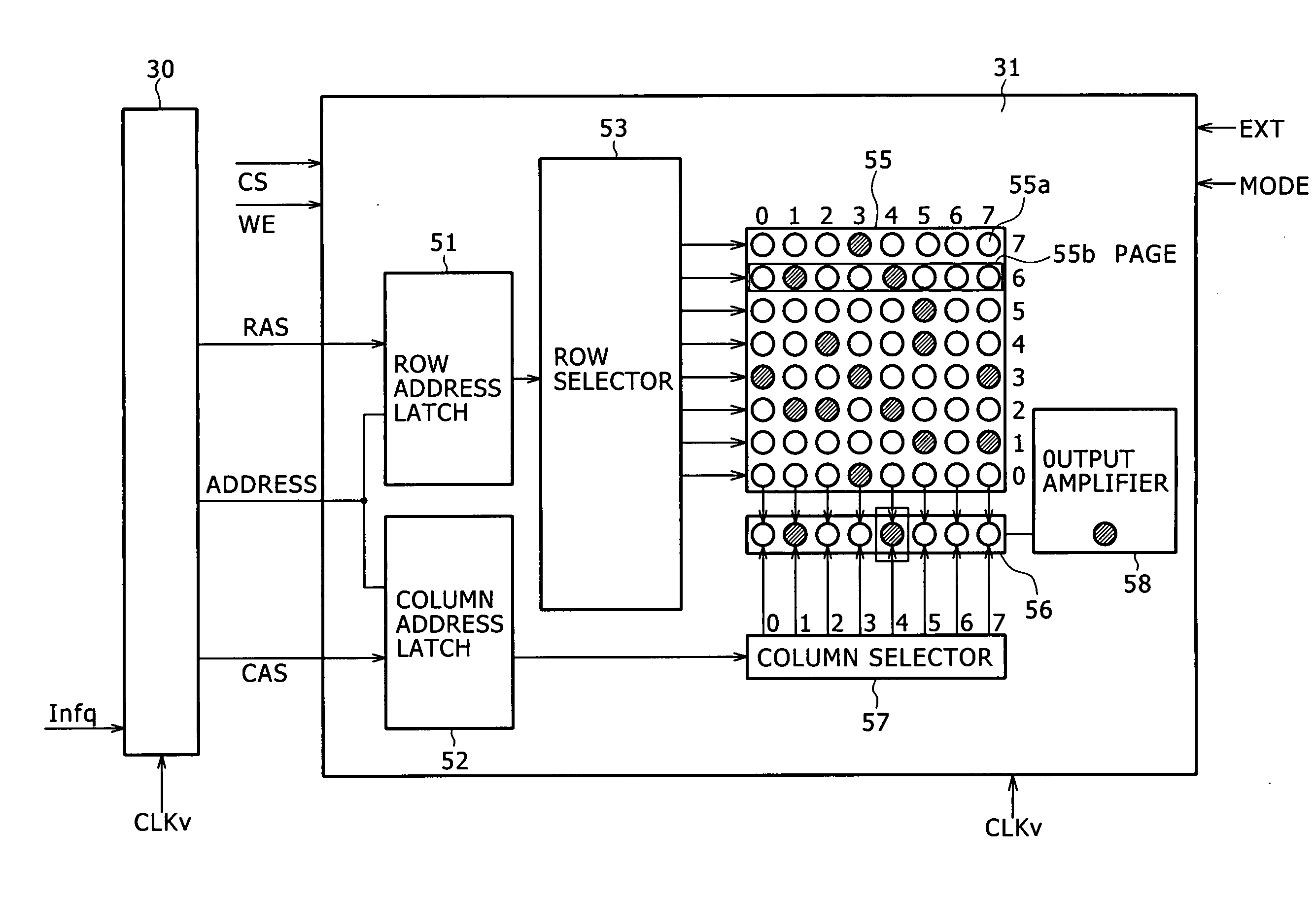

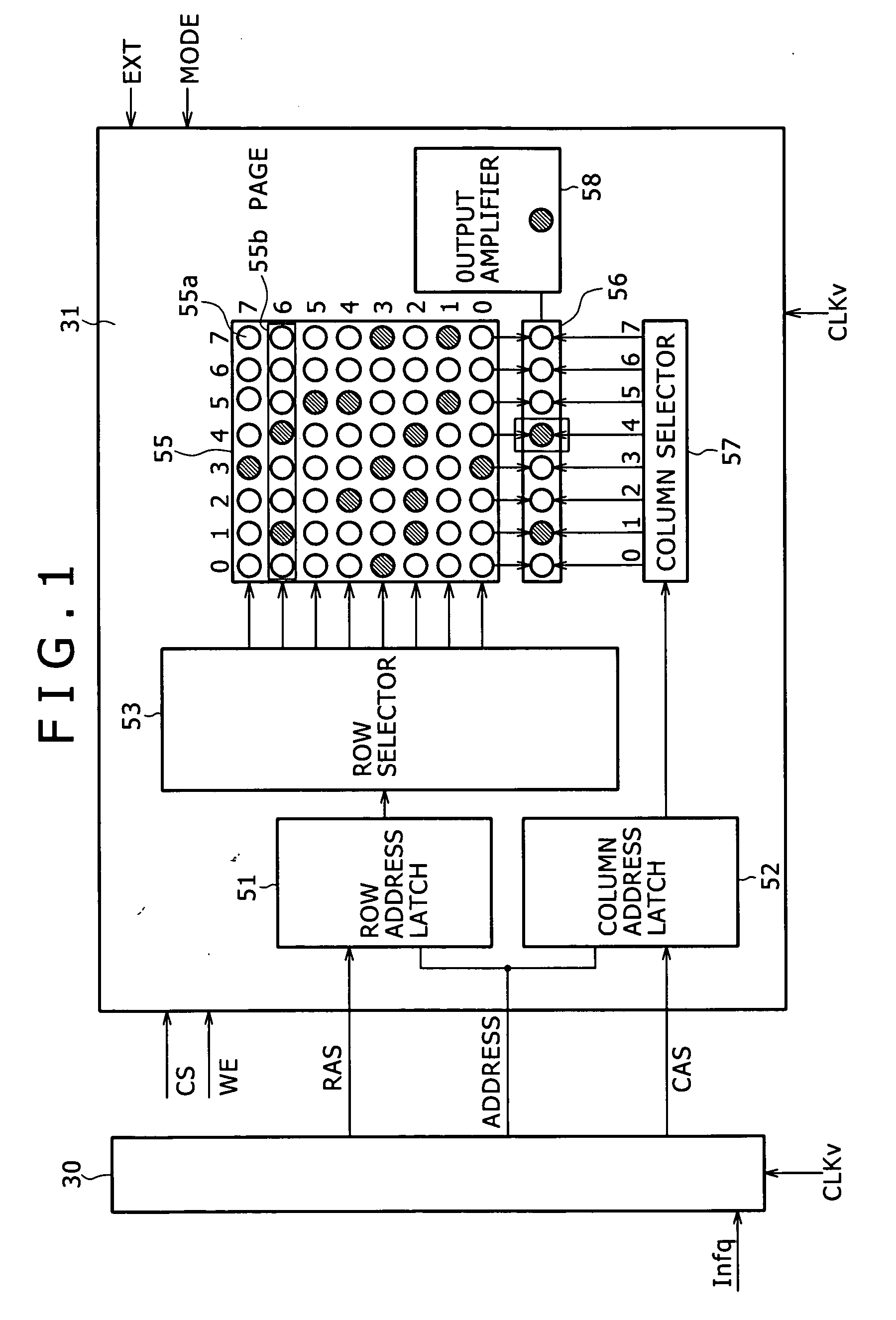

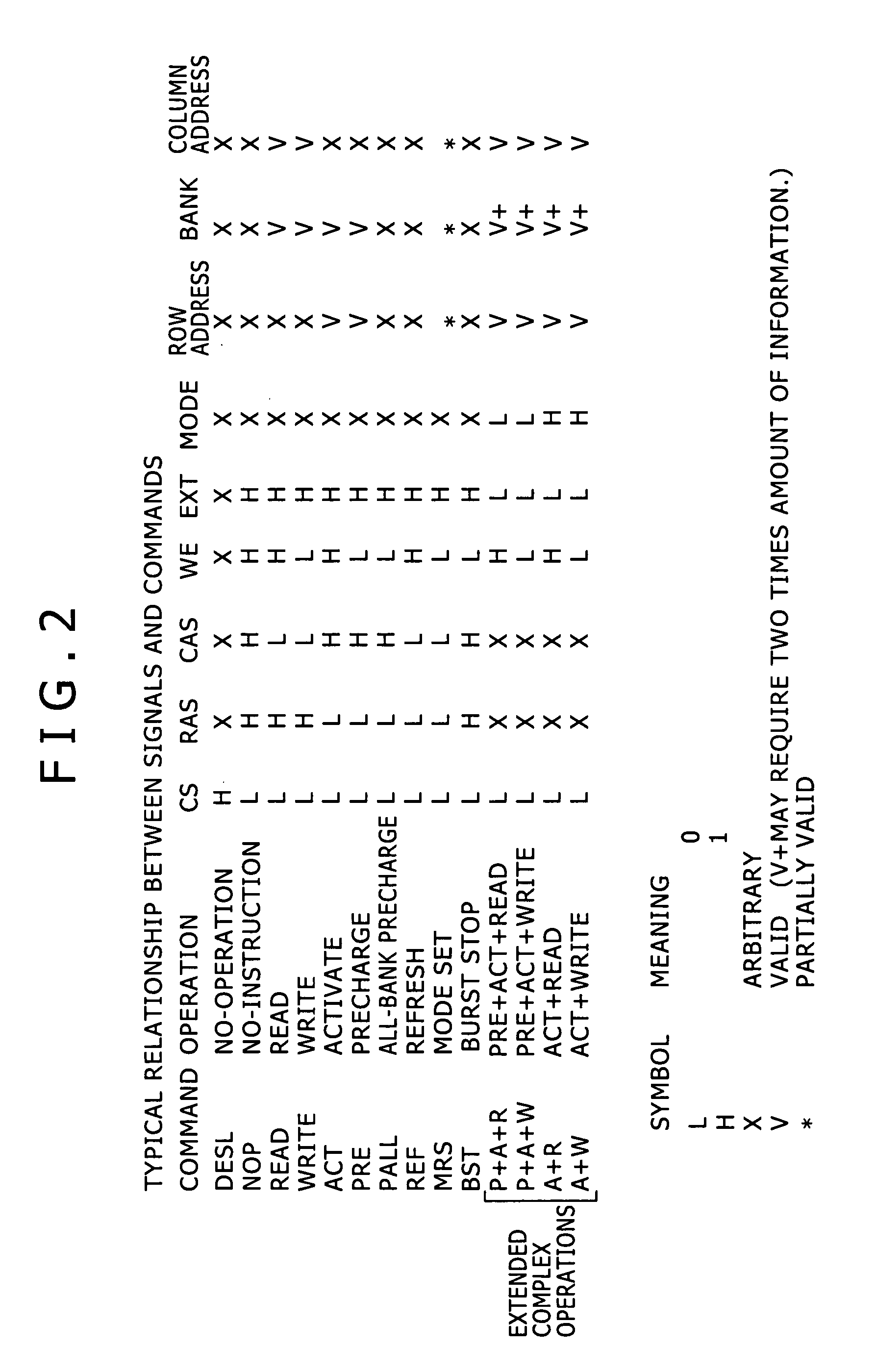

Information storage device, information storage method, and information storage program

InactiveUS20060028883A1Fast processingEfficient data processingMemory architecture accessing/allocationDigital storageAudio power amplifierComputer science

Disclosed is a synchronous information storage device that uses a synchronizing clock signal to exercise operation timing control and processes operations with high efficiency to improve performance and provide low power consumption, which is characteristic of DRAMs. The information storage device includes a plurality of memory cells for storing data by accumulating an electrical charge and an amplifier for amplifying the electrical charge of the memory cells, and uses a synchronizing clock signal for input / output timing of the data. An electrical charge removal operation for moving an electrical charge from the memory cells to the amplifier or an electrical charge accumulation operation for acquiring an electrical charge from the amplifier and accumulating the electrical charge in the memory cells and an input / output operation for the amplifier in relation to the outside of the information storage device are processed while using a single clock of the synchronizing clock signal for synchronization timing.

Owner:SONY CORP

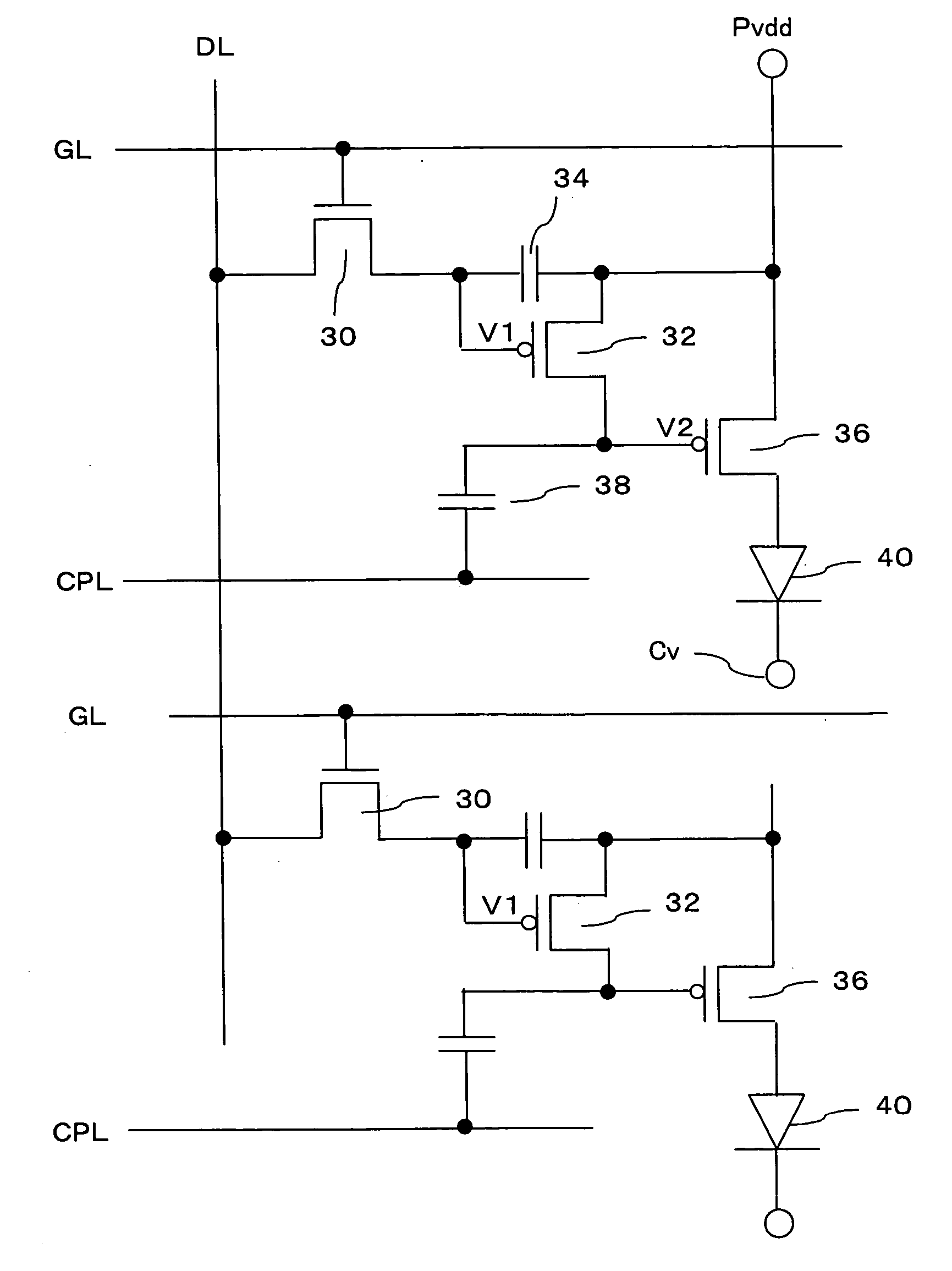

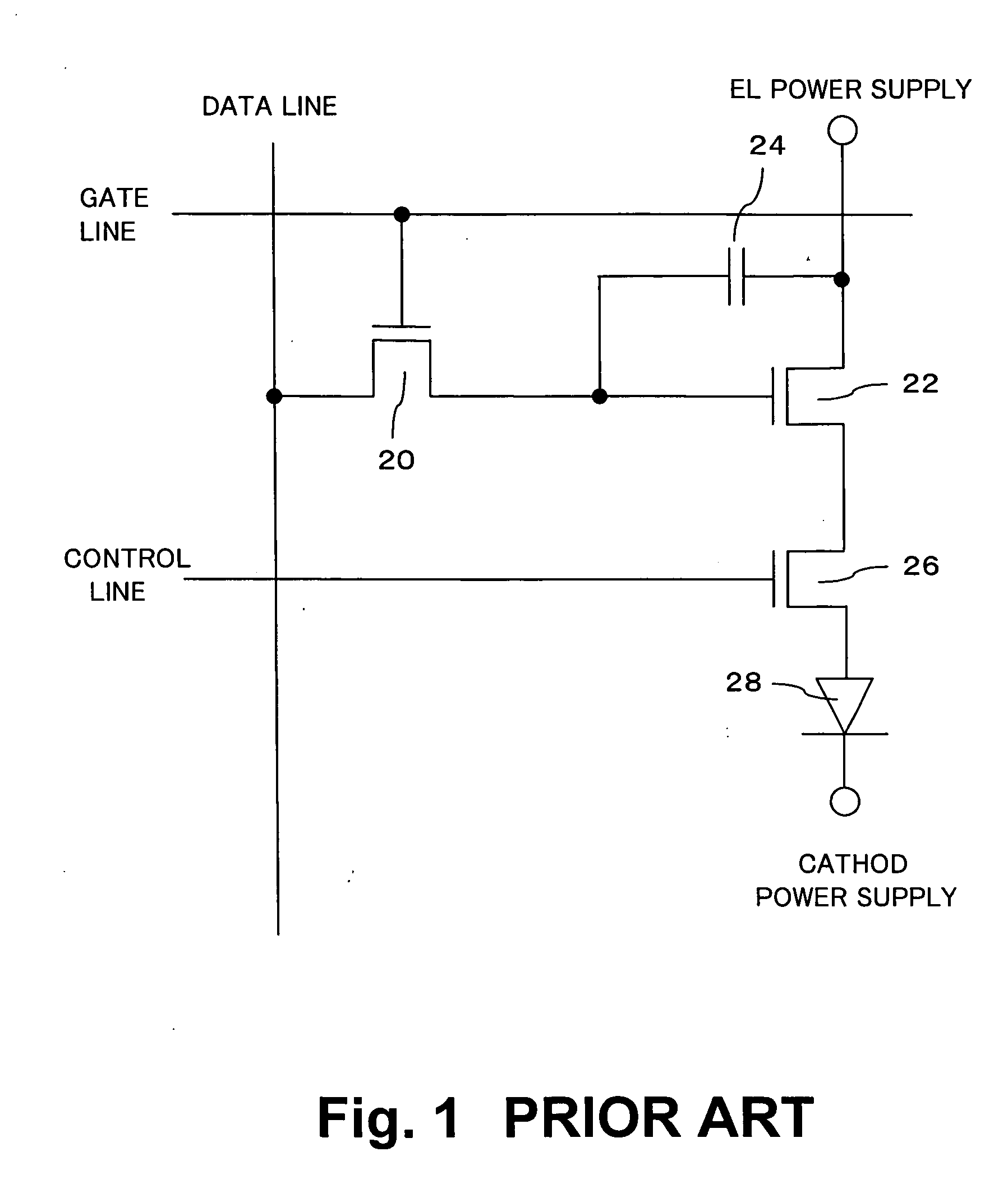

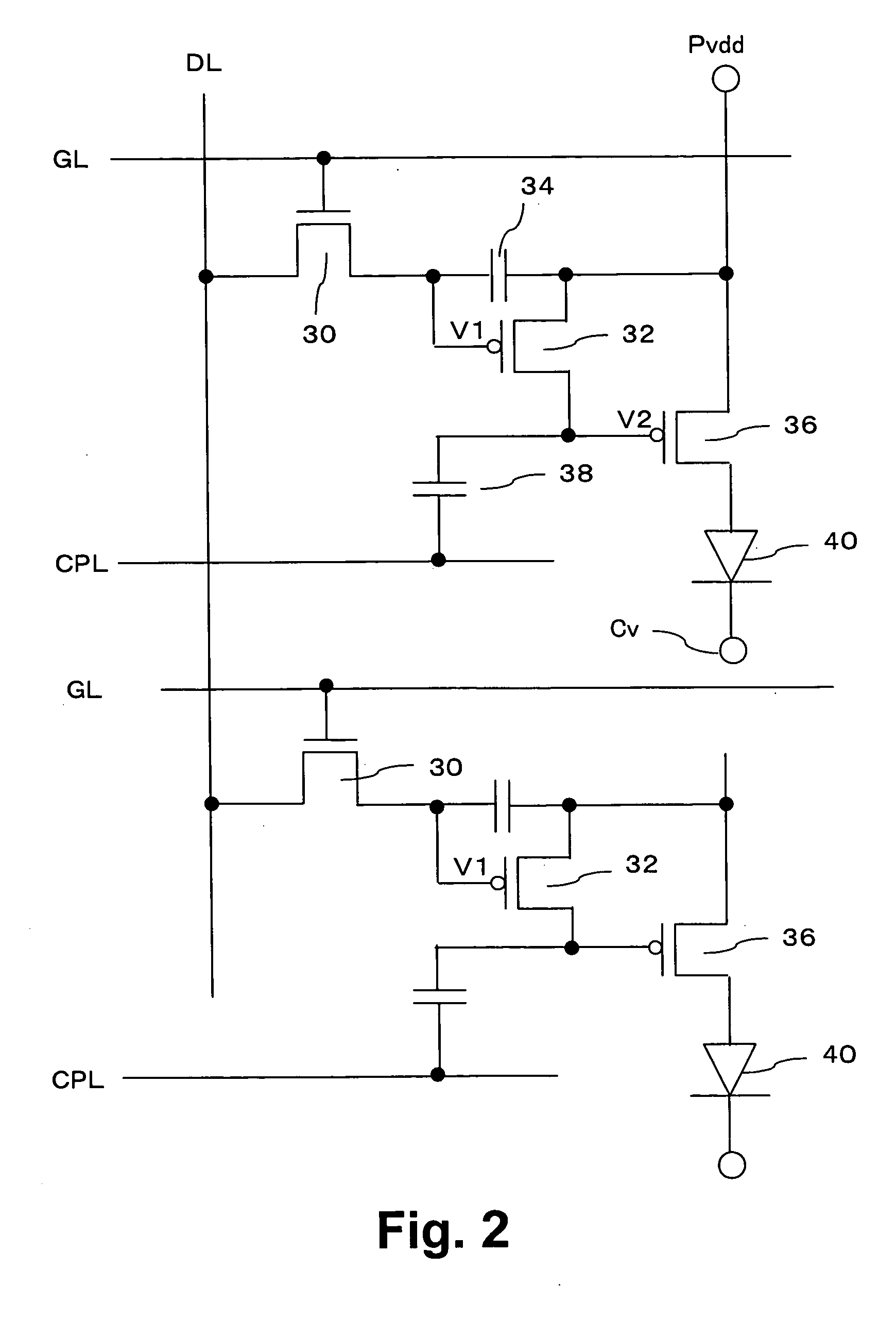

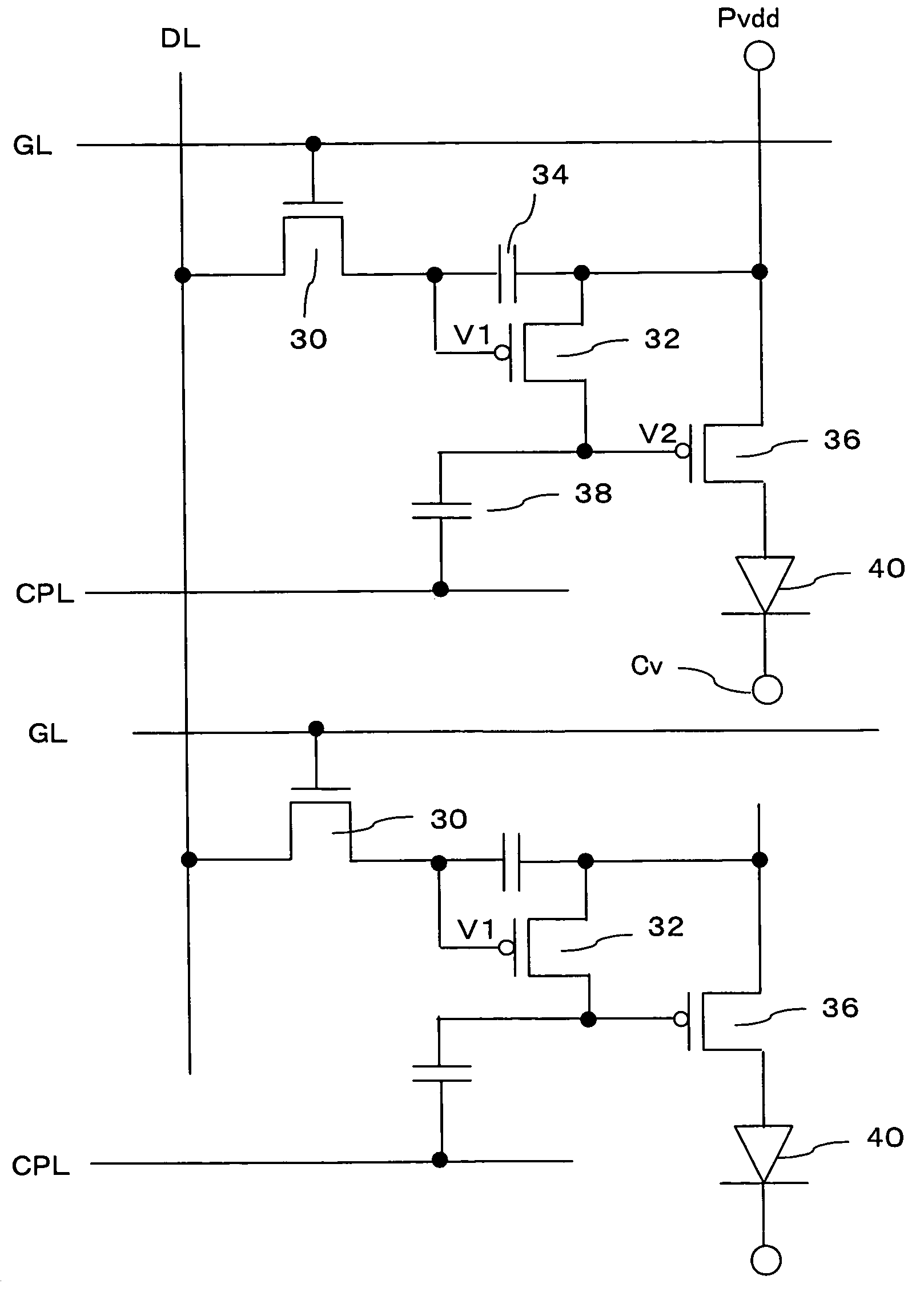

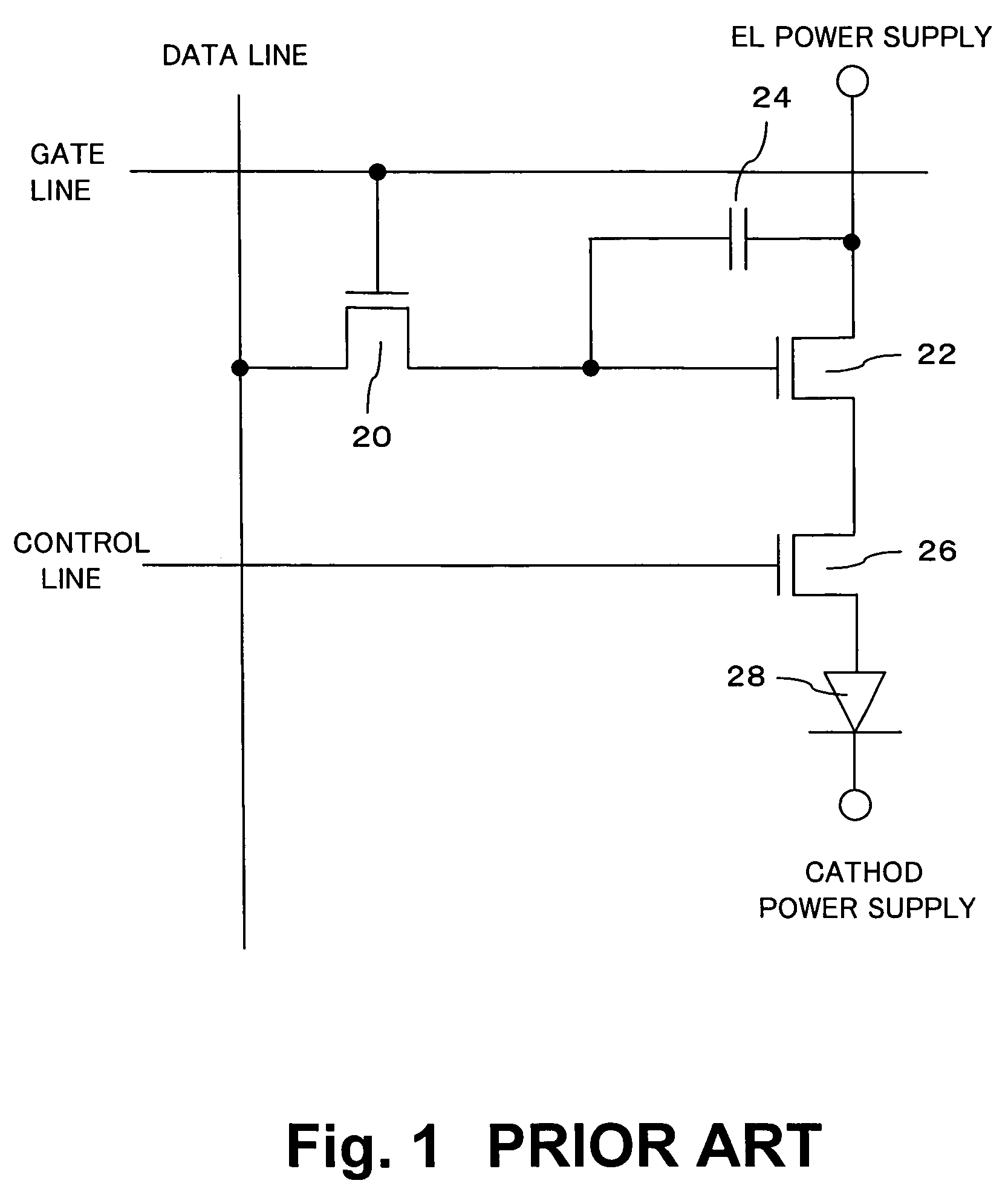

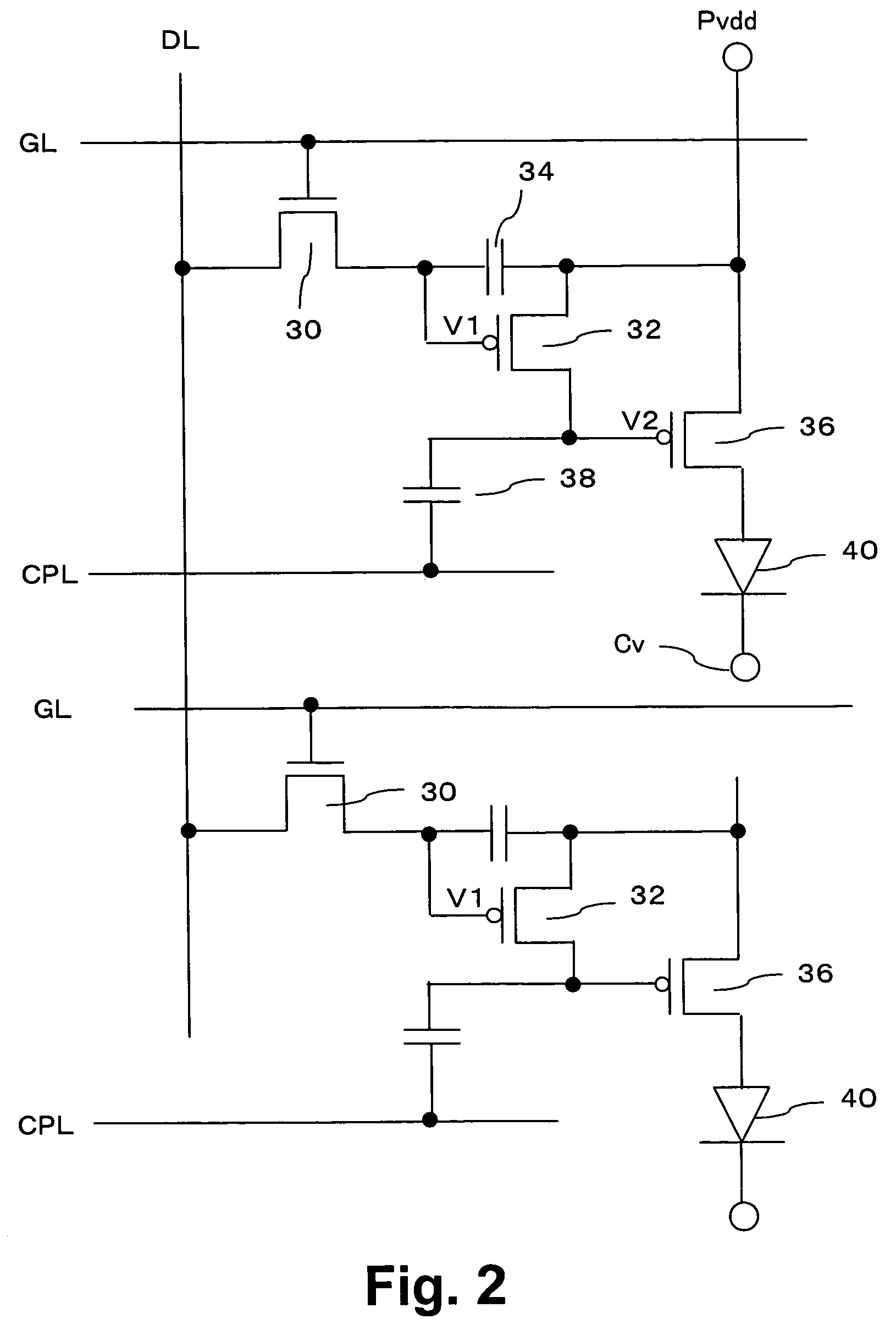

Light emitting device and display device

ActiveUS20050024351A1Reduce the amplitudeReduce power consumptionElectroluminescent light sourcesSolid-state devicesDigital dataSignal on

Each pixel in a display device includes an emissive element, a driver transistor, a control transistor, and a control capacitor. The driver transistor is provided between the emissive element and a power supply and controls supply of power from the power supply to the emissive element. The control transistor is connected between a constant voltage power supply and a gate of the driver transistor, receives a digital data signal on a gate, and controls whether or not to fix a gate voltage of the driver transistor. The control capacitor is connected between a control line and the gate of the driver transistor. The gate voltage of the driver transistor is shifted to a voltage corresponding to a control pulse signal when the control transistor is off and is non-fixed during a light emission period defined by the control pulse signal applied to the control line.

Owner:SANYO ELECTRIC CO LTD

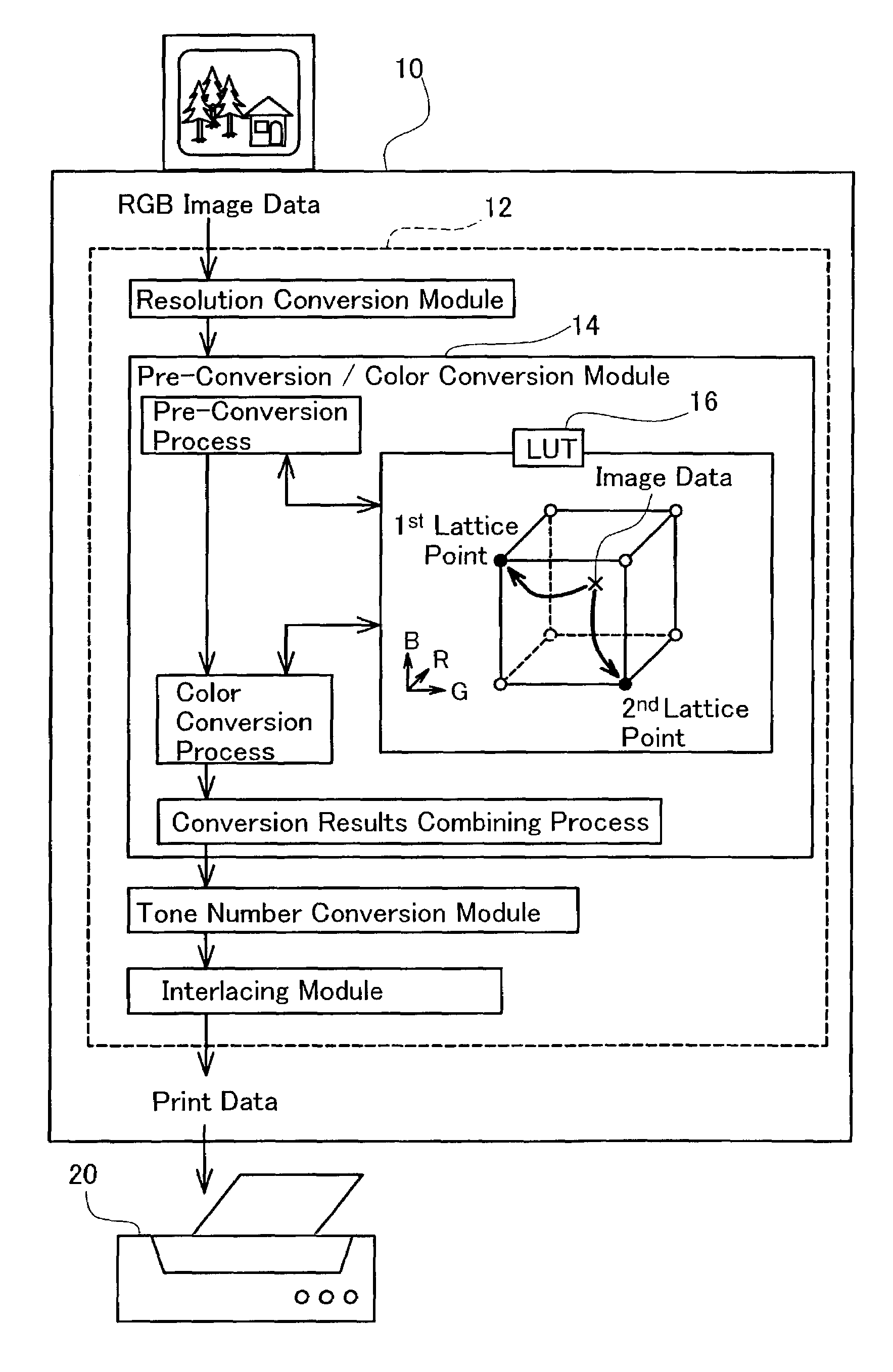

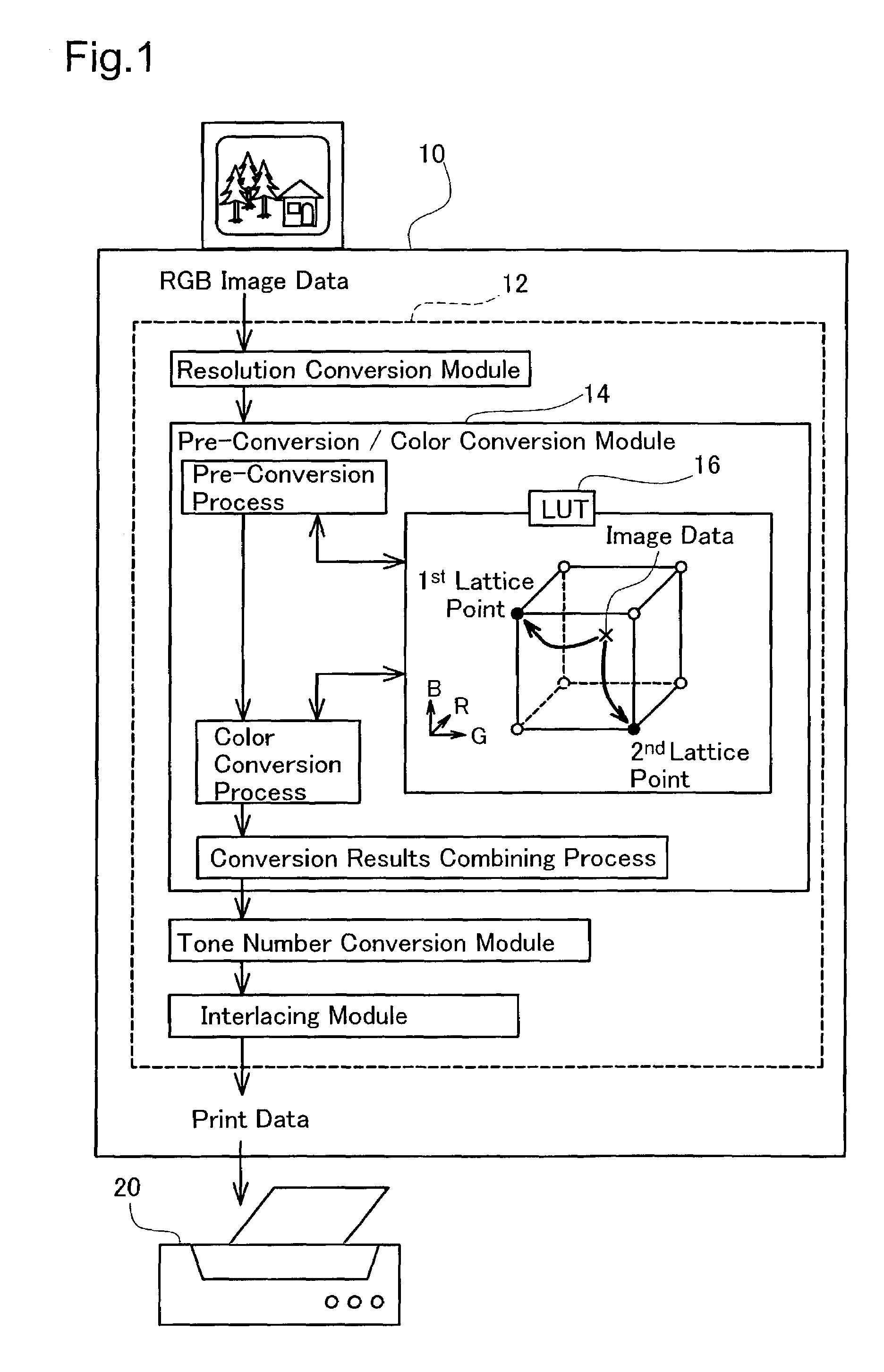

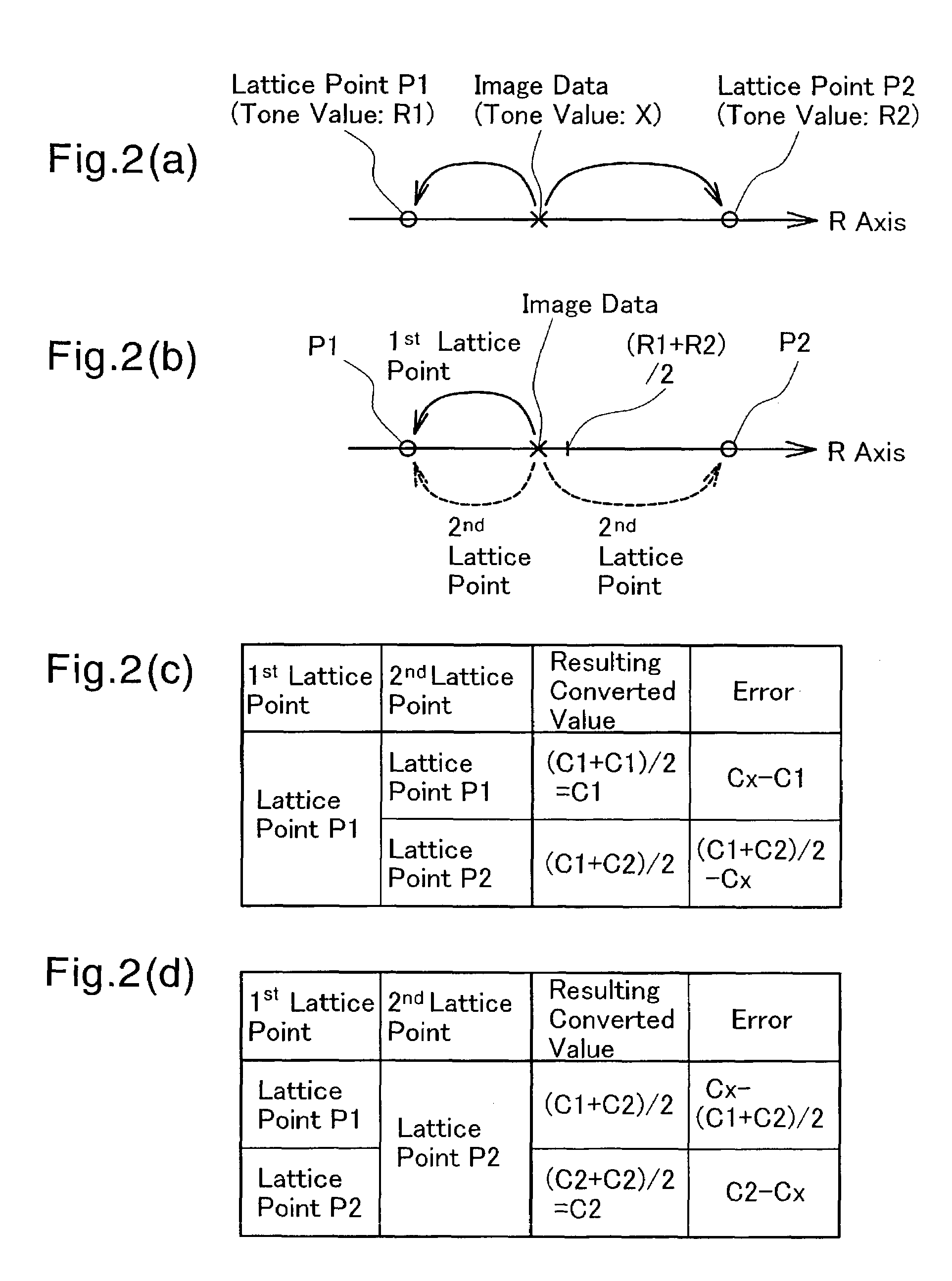

Method of correcting color image data according to correction table

ActiveUS7336392B2Reduce pre-conversion errorHigh-speed outputDigitally marking record carriersDigital computer detailsColor imageColor transformation

The technique of the present invention allocates a coordinate point of target image data on a color space to multiple lattice points in a color conversion table and reads data stored at the multiple lattice points. This arrangement ensures high-speed color conversion of the target image data. The procedure selects multiple lattice points and allocates a coordinate point of one target image data to the selected multiple lattice points. The procedure then specifies color-converted image data corresponding to the target image data, based on data read from the multiple lattice points. A first application allocates the target image data to the coordinate points of the multiple lattice points arbitrarily selected in the vicinity of the target image data. A second application allocates N-dimensional target image data to the coordinate points of multiple but not greater than N lattice points. A third application calculates an arithmetic mean of the data read from the multiple lattice points to specify the color-converted image data. Any of these arrangement effectively enhances the conversion accuracy without increasing the size of the color conversion table.

Owner:SEIKO EPSON CORP

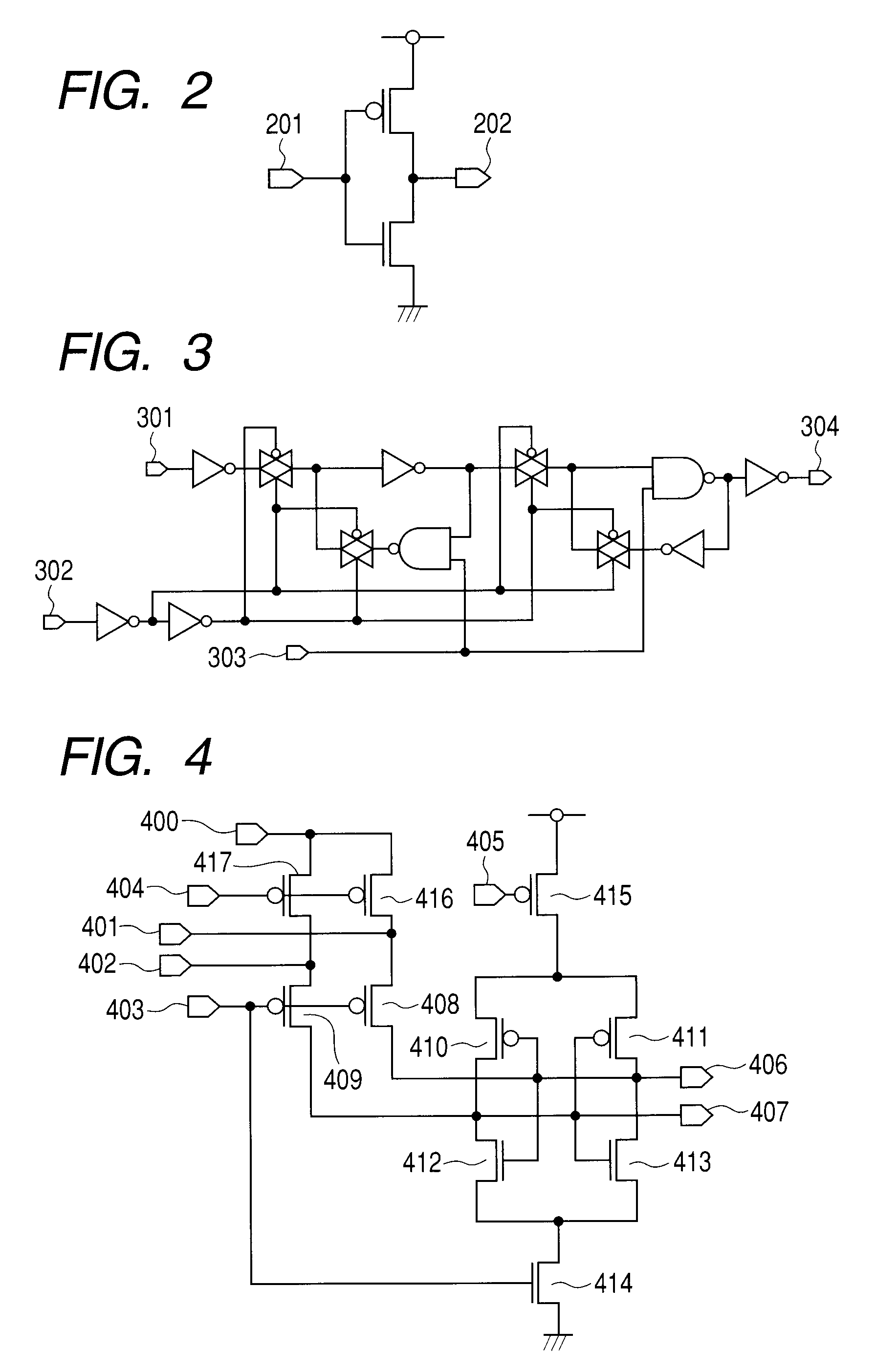

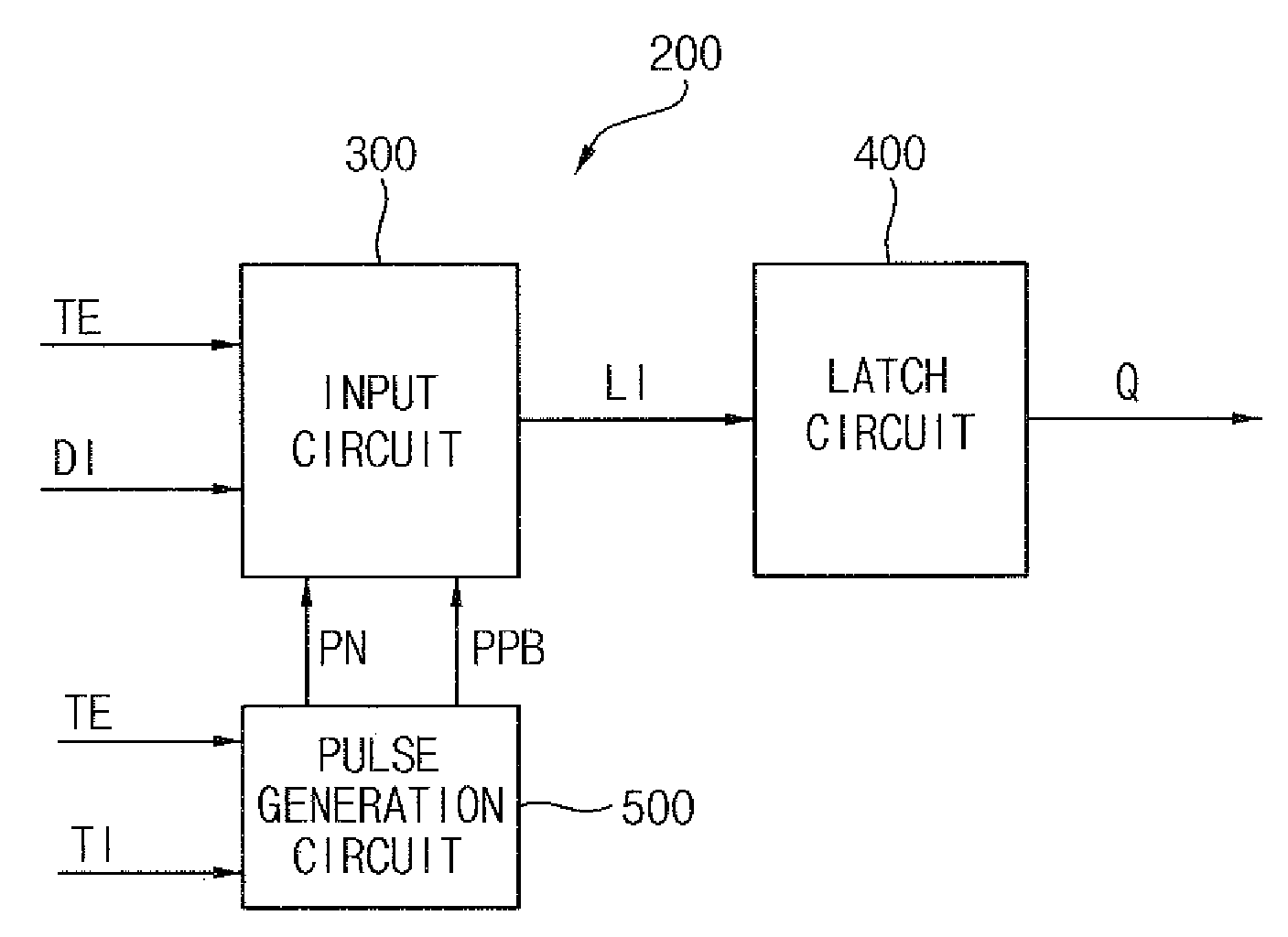

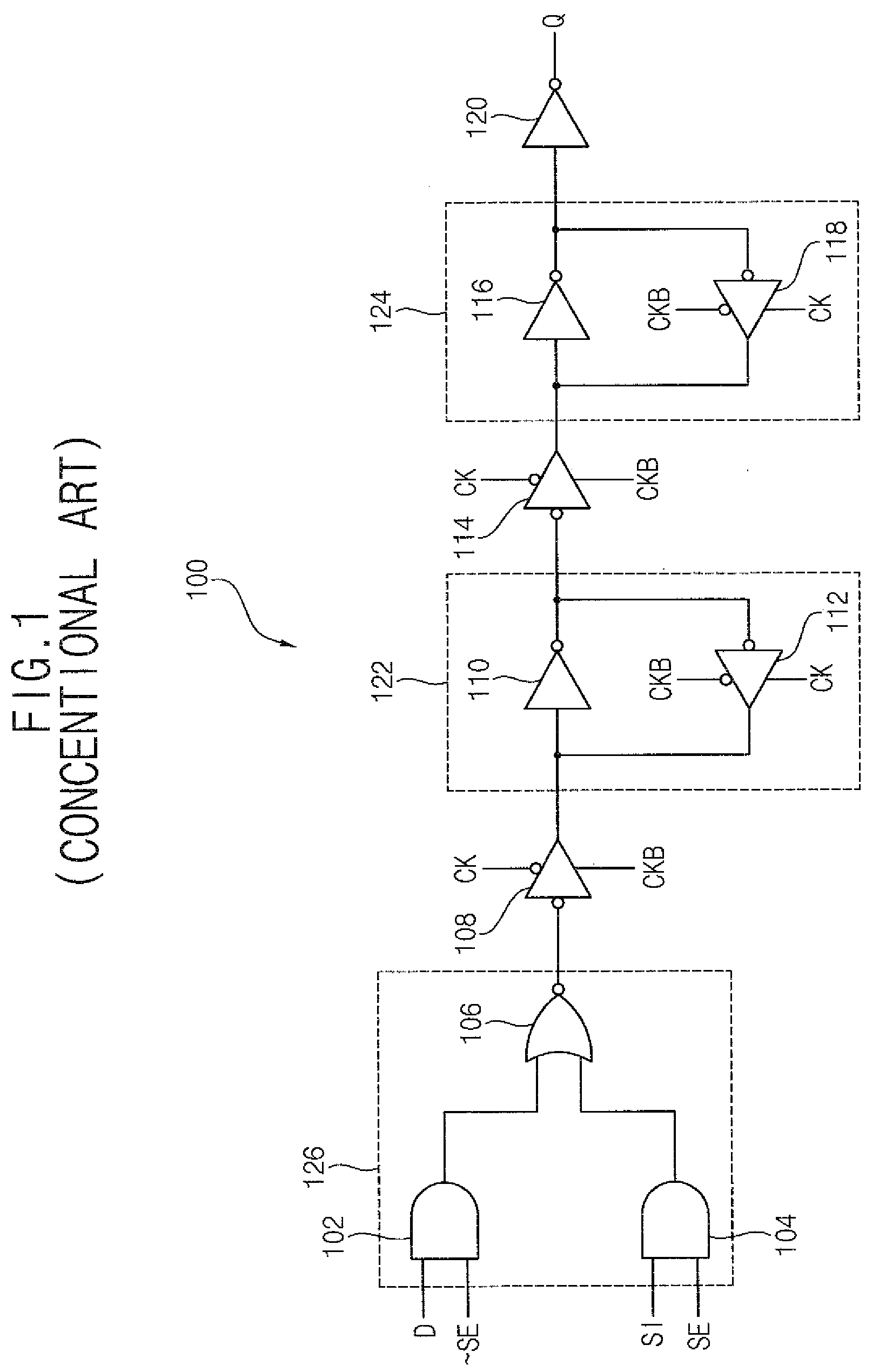

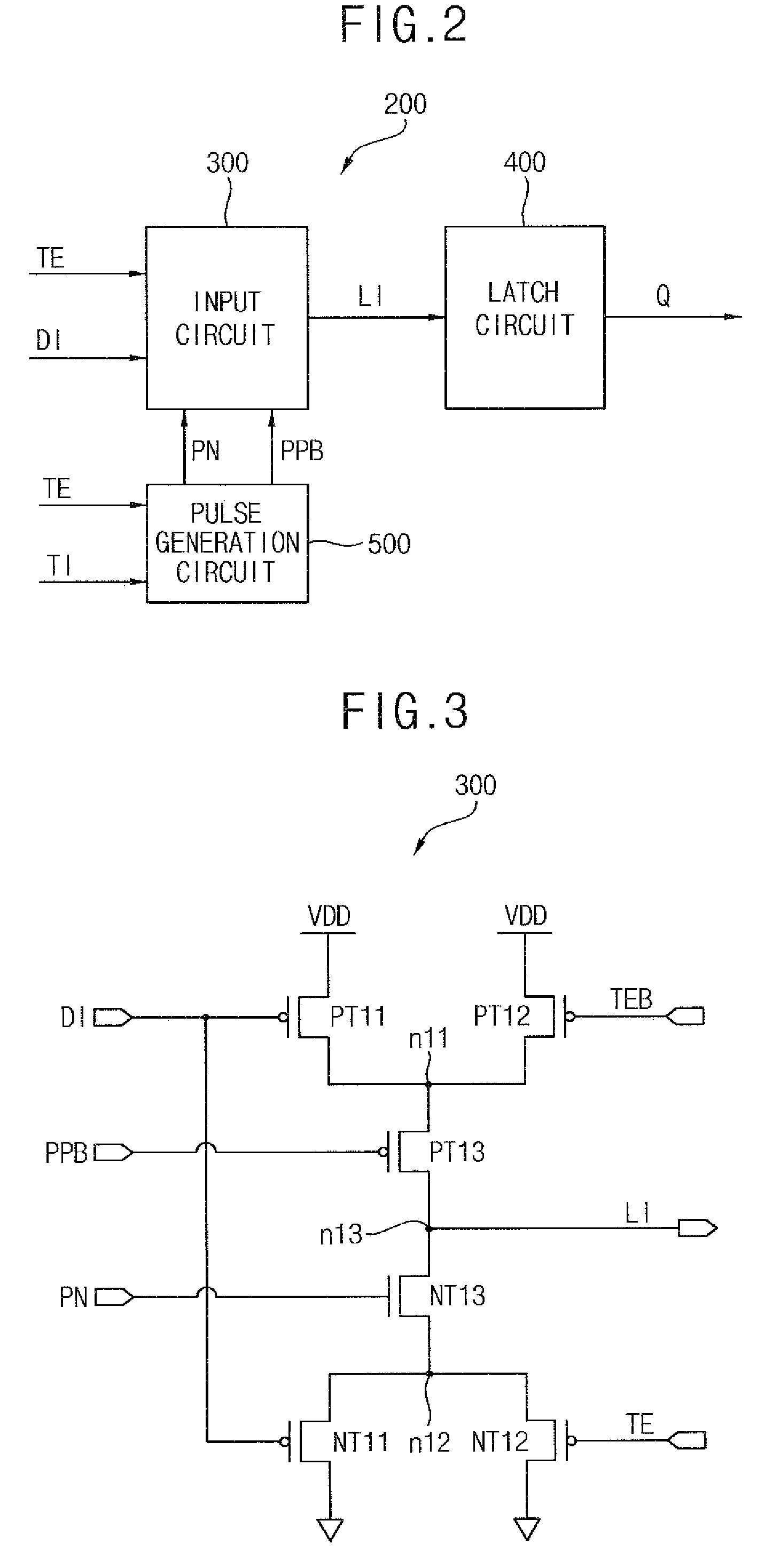

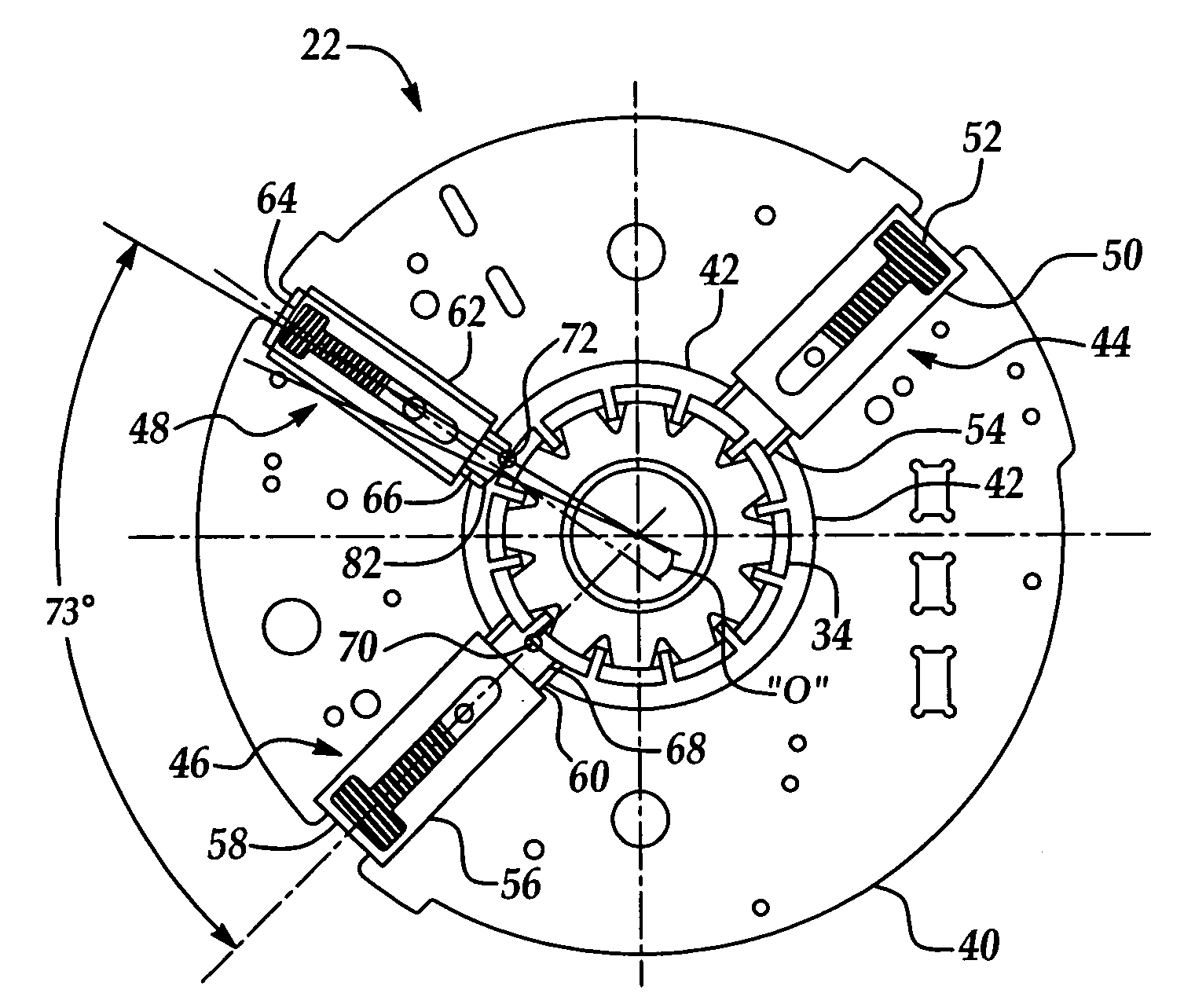

Pulse operated flip-flop circuit having test-input function and associated method

ActiveUS20090115481A1Decreasing DtoQ delayShorten data lengthElectrical testingElectric pulse generator circuitsMultiplexingTest input

The pulse generation circuit generates a first pulse signal and a complementary second pulse signal. The first and second pulse signals are activated simultaneously in a normal mode and activated selectively in response to a test input signal in a test mode. A multiplexing input circuit selects and outputs one of a data input signal and a test input signal as a latch input signal in response to the first pulse signal and the second pulse signal. The latch input signal corresponds to the data input signal in the normal mode and corresponds to the test input signal in the test mode. The latching circuit latches the latch input signal to generate data output signal. The length of data transfer path is reduced, and DtoQ delay can be decreased.

Owner:SAMSUNG ELECTRONICS CO LTD

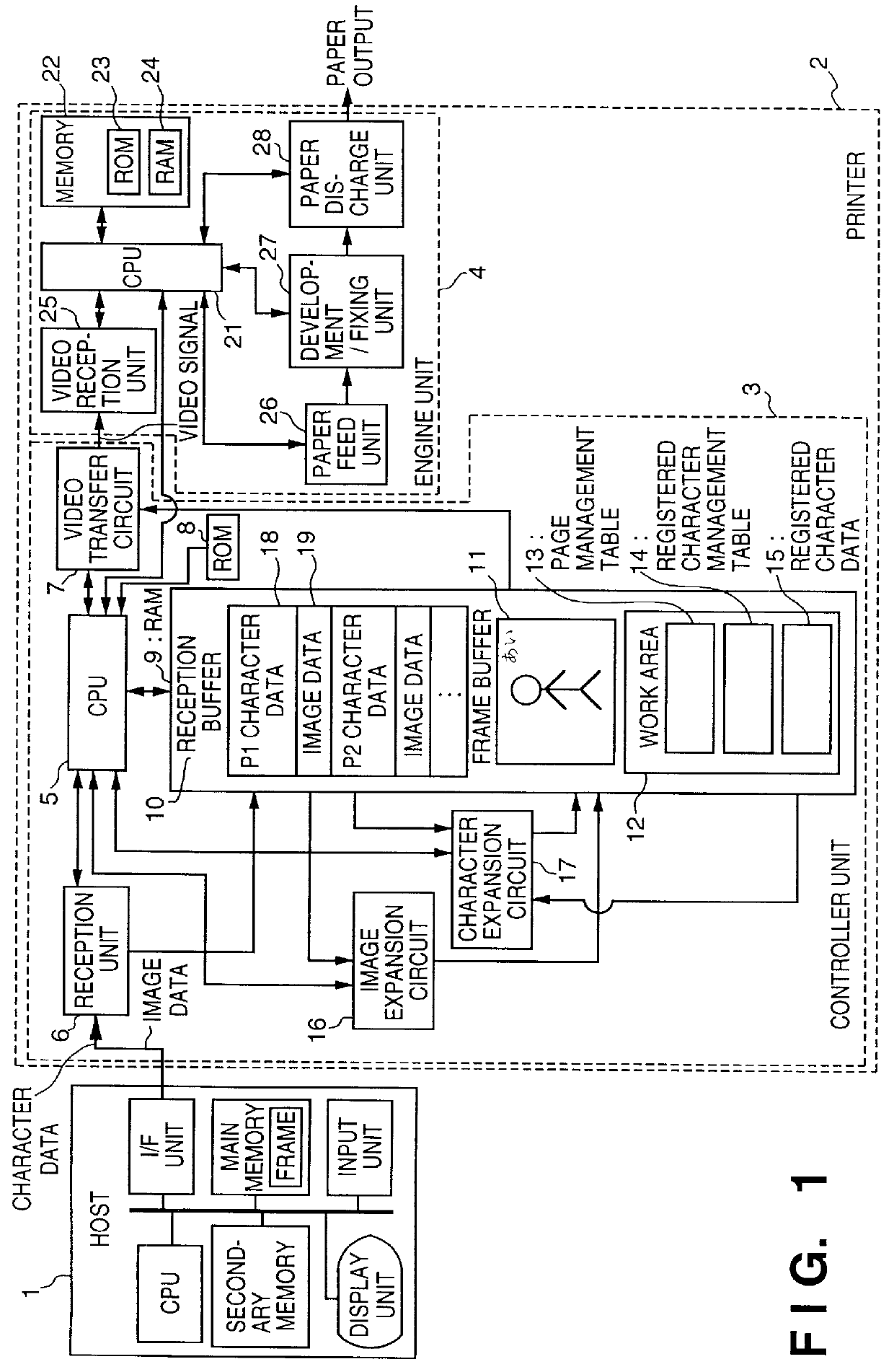

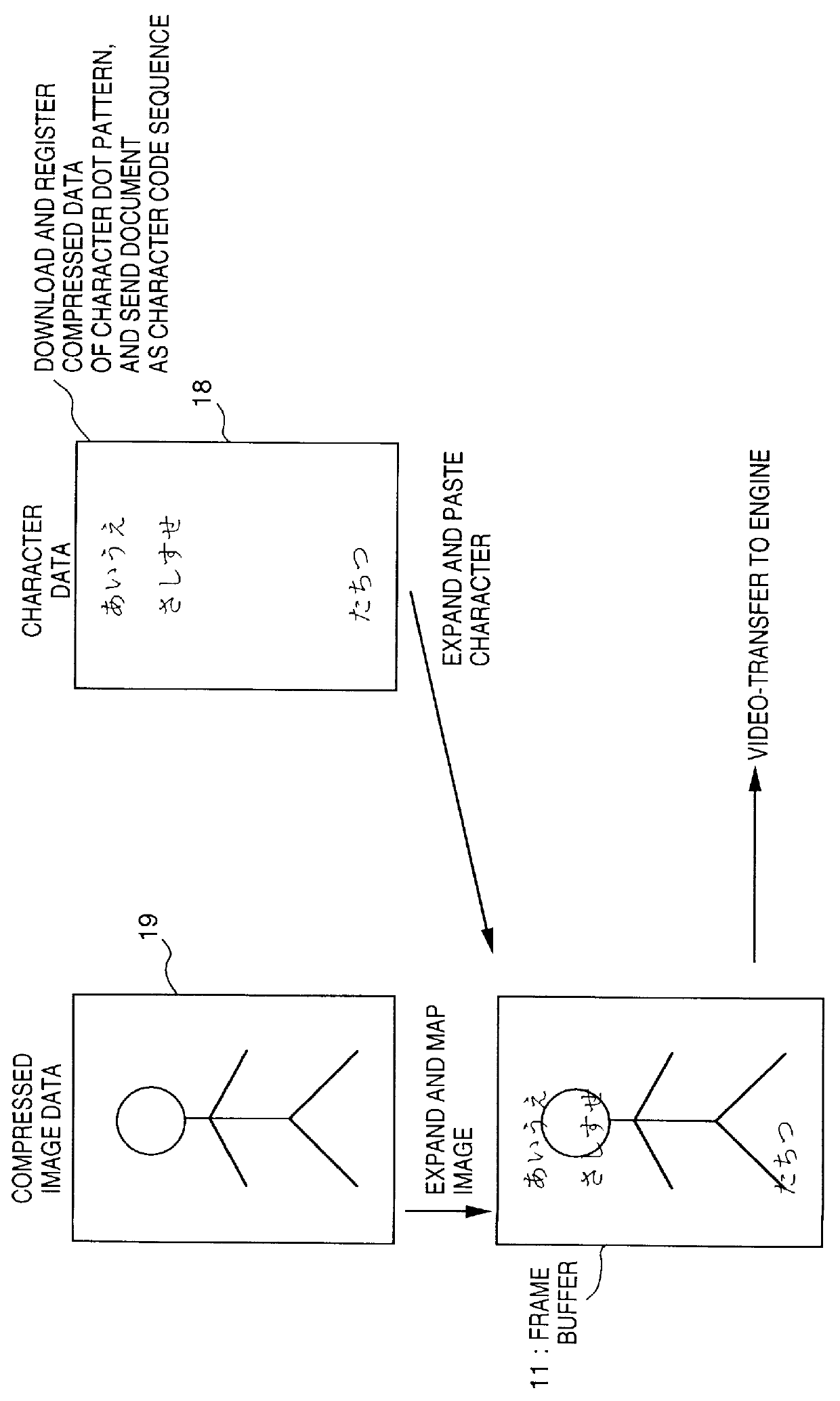

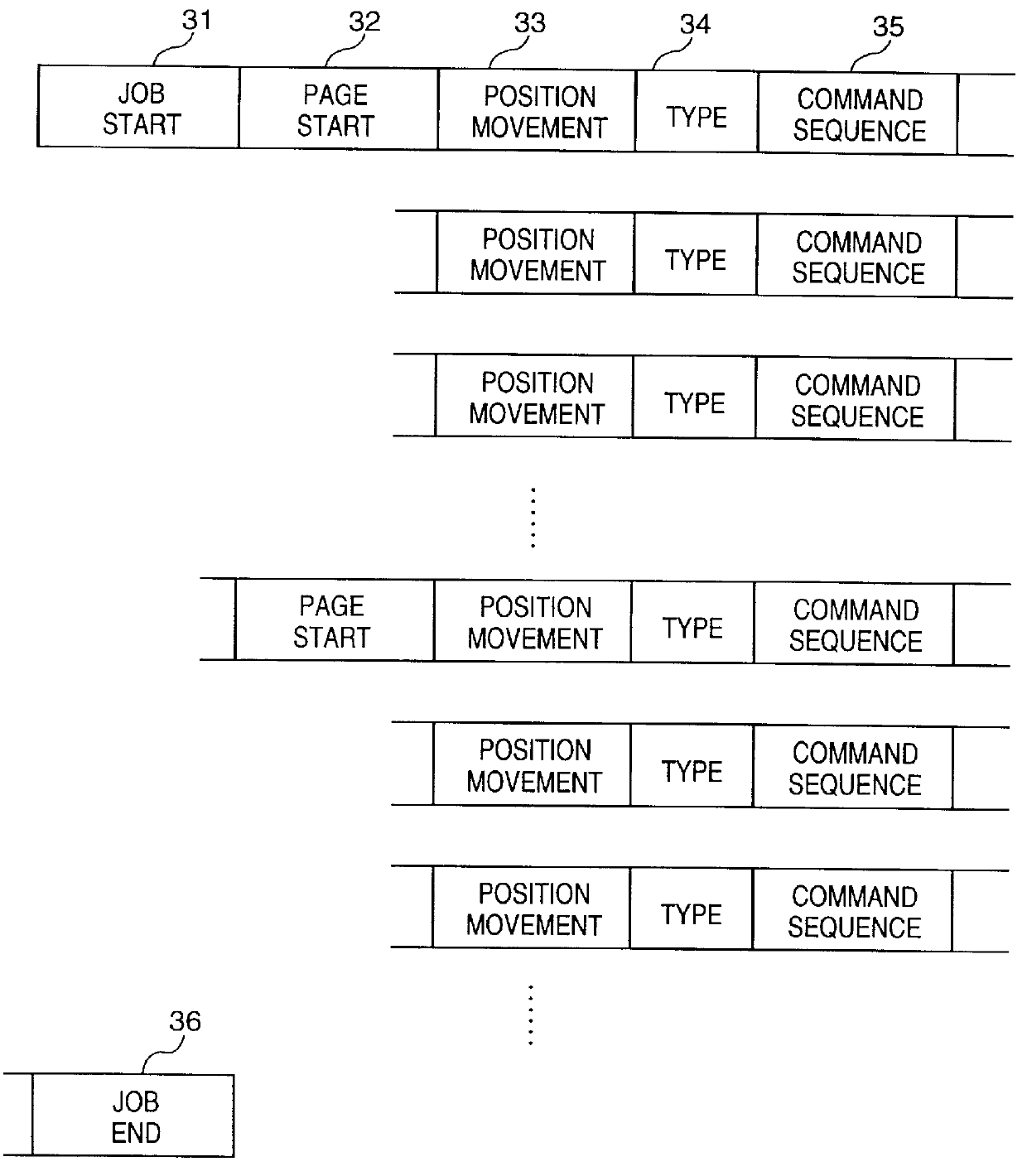

Printing system

InactiveUS6128096AMinimizing amount of image dataShorten the timeDigitally marking record carriersVisual presentation using printersComputer graphics (images)Documentation

Owner:CANON KK

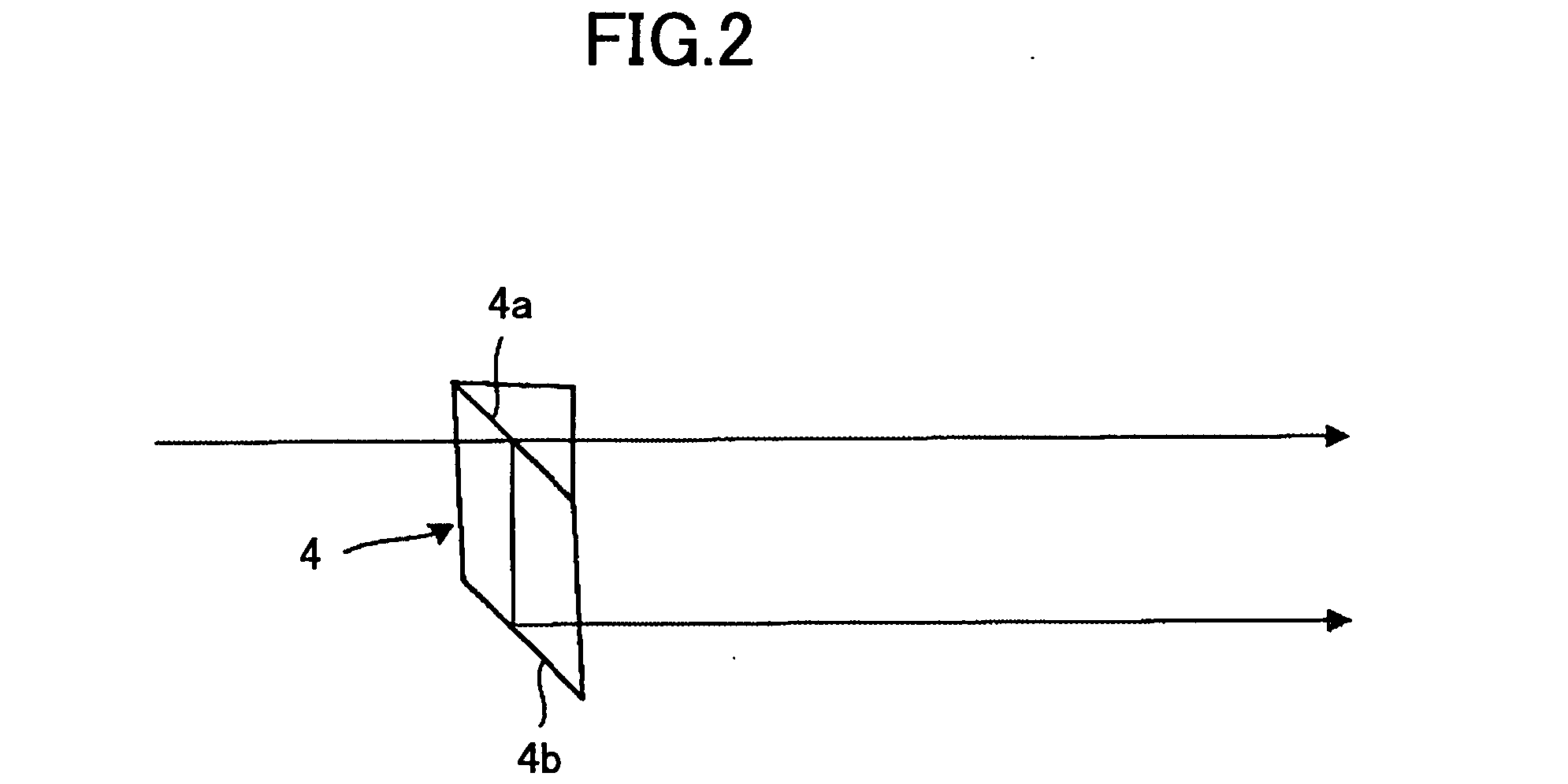

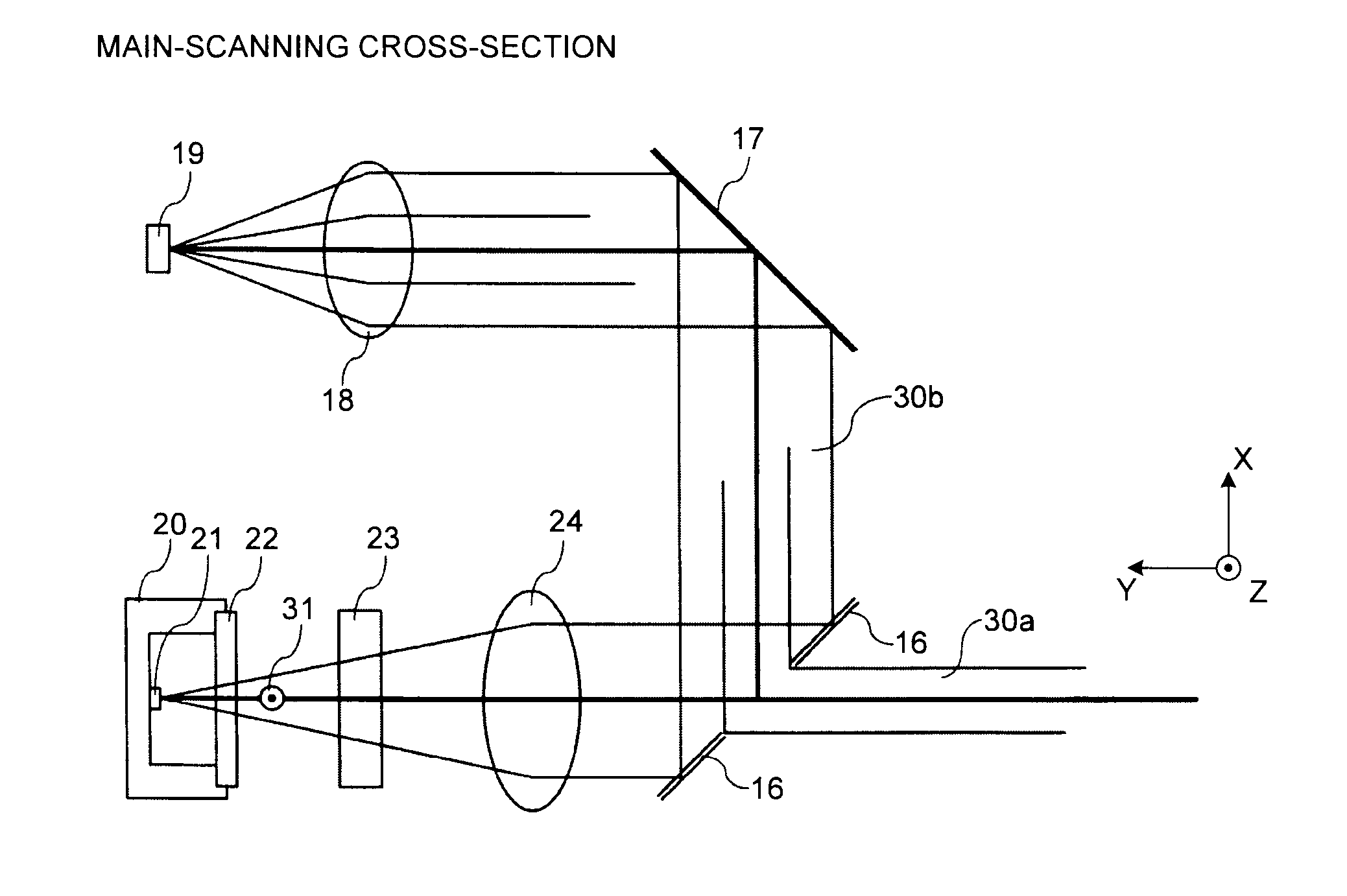

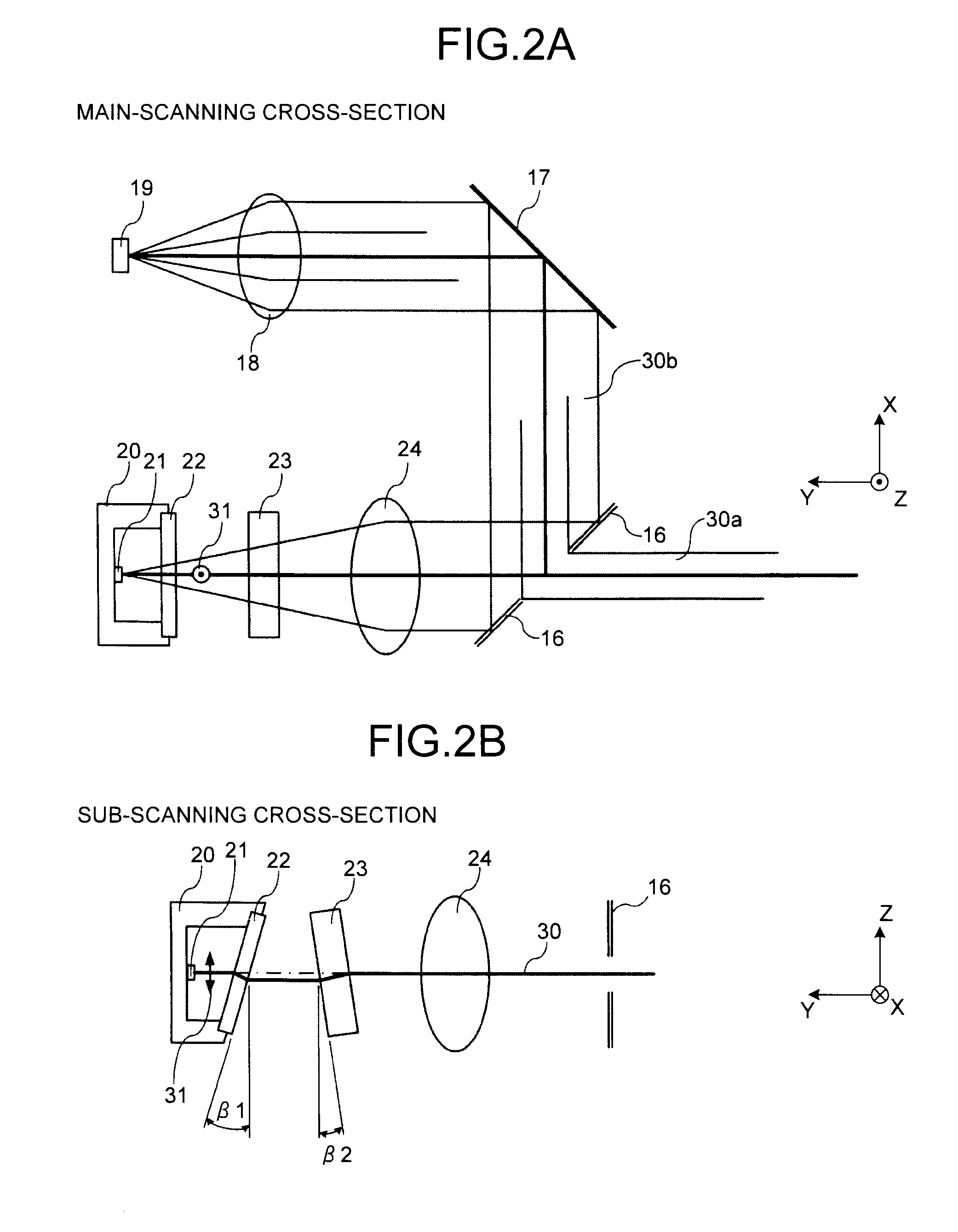

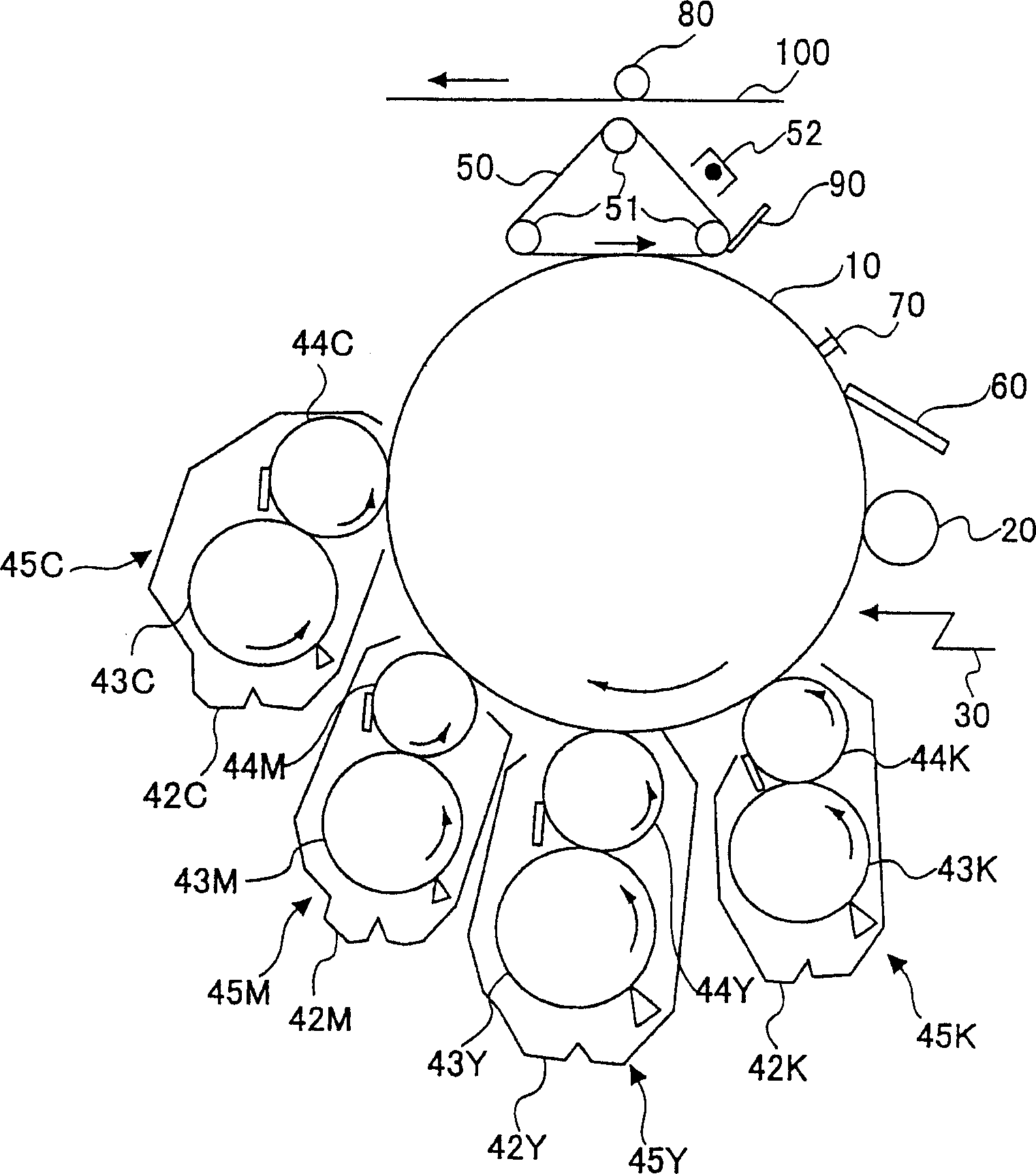

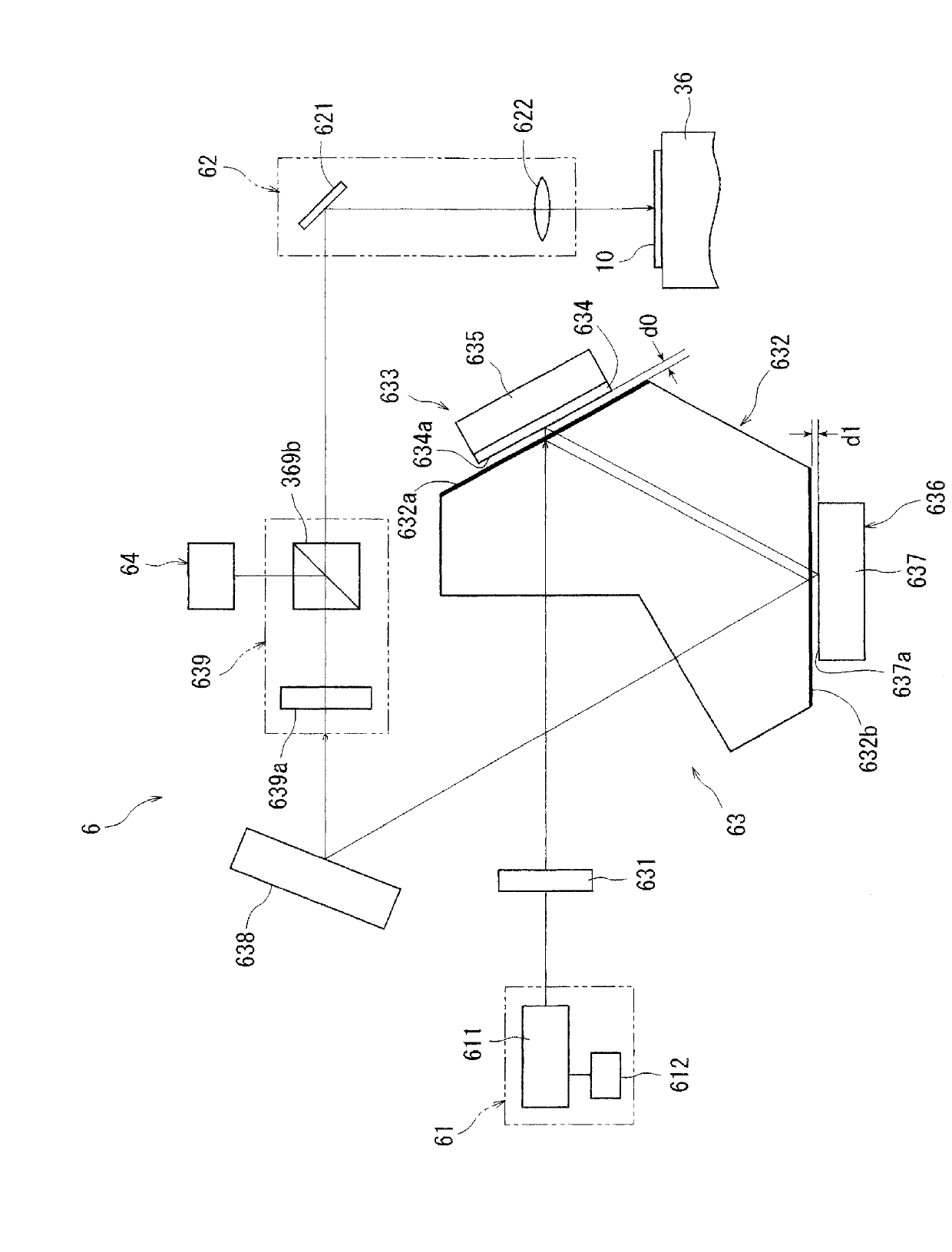

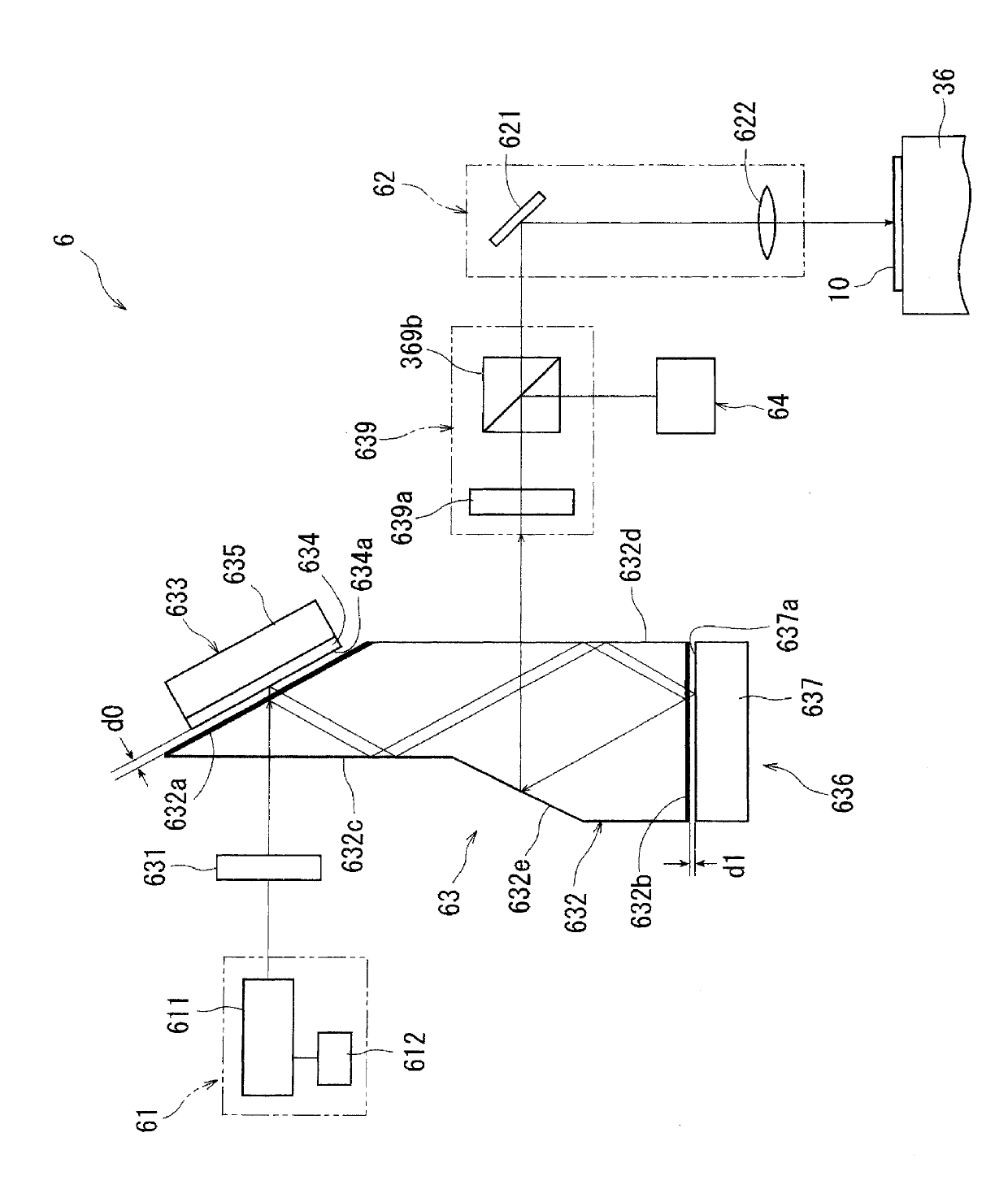

Optical scanning device and image forming apparatus

InactiveUS20110310450A1Solve problemsHigh-speed outputElectrographic process apparatusOptical elementsParallel plateBeam scanning

An optical scanning device includes: a light source unit that includes a light emitting unit composed of a laser light source emitting linearly polarized light inside a package member; a deflector that deflects a light beam emitted from the light emitting unit; a pre-deflector optical system arranged on an optical path between the light emitting unit and the deflector; and a scanning optical system that scans a target surface to be scanned with the light beam deflected by the deflector. The pre-deflector optical system includes at least two parallel plate optical elements each composed of a transparent medium having an incident surface and an exit surface parallel to each other. The parallel plate optical elements are arranged to be tilted in inclination that is opposite to each other in a plane of polarization of the linearly polarized light.

Owner:RICOH KK

Developer for developing to electrostatic image, imaging device and method

InactiveCN1495550AHigh speed outputElectrographic process apparatusDevelopersMaterials scienceColoring agents

A developer, which includes a base toner containing at least a binding resin and a coloring agent; and inorganic fine particles; wherein the base toner satisfies 105<=SF-1<==130 and 12<=SF-2<=180, wherein SF-1=((absolute maximum length of a particle of the base toner) 2 / area of the particle of the base toner)x(pi / 4)x100, wherein SF-2=(peripheral length of the particle of the base toner) 2 / (area of the base toner)x( 1 / 4 pi)x100, wherein the inorganic fine particles have an average particle diameter that ranges between 30 nm to 160 nm.

Owner:RICOH KK

Programmable high speed I/O interface

InactiveUS20050134332A1High-speed inputHigh-speed outputProgrammable logic circuit arrangementsElectronic switchingBoundary testingLow speed

Methods and apparatus for providing either high-speed, or lower-speed, flexible inputs and outputs. An input and output structure having a high-speed input, a high-speed output, a low or moderate speed input, and an low or moderate speed output is provided. One of the input and output circuits are selected and the others are deselected. The high-speed input and output circuits are comparatively simple, in one example having only a clear signal for a control line input, and are able to interface to lower speed circuitry inside the core of an integrated circuit. The low or moderate speed input and output circuits are more flexible, for example, having preset, enable, and clear as control line inputs, and are able to support JTAG boundary testing. These parallel high and lower speed circuits are user selectable such that the input output structure is optimized between speed and functionality depending on the requirements of the application.

Owner:ALTERA CORP

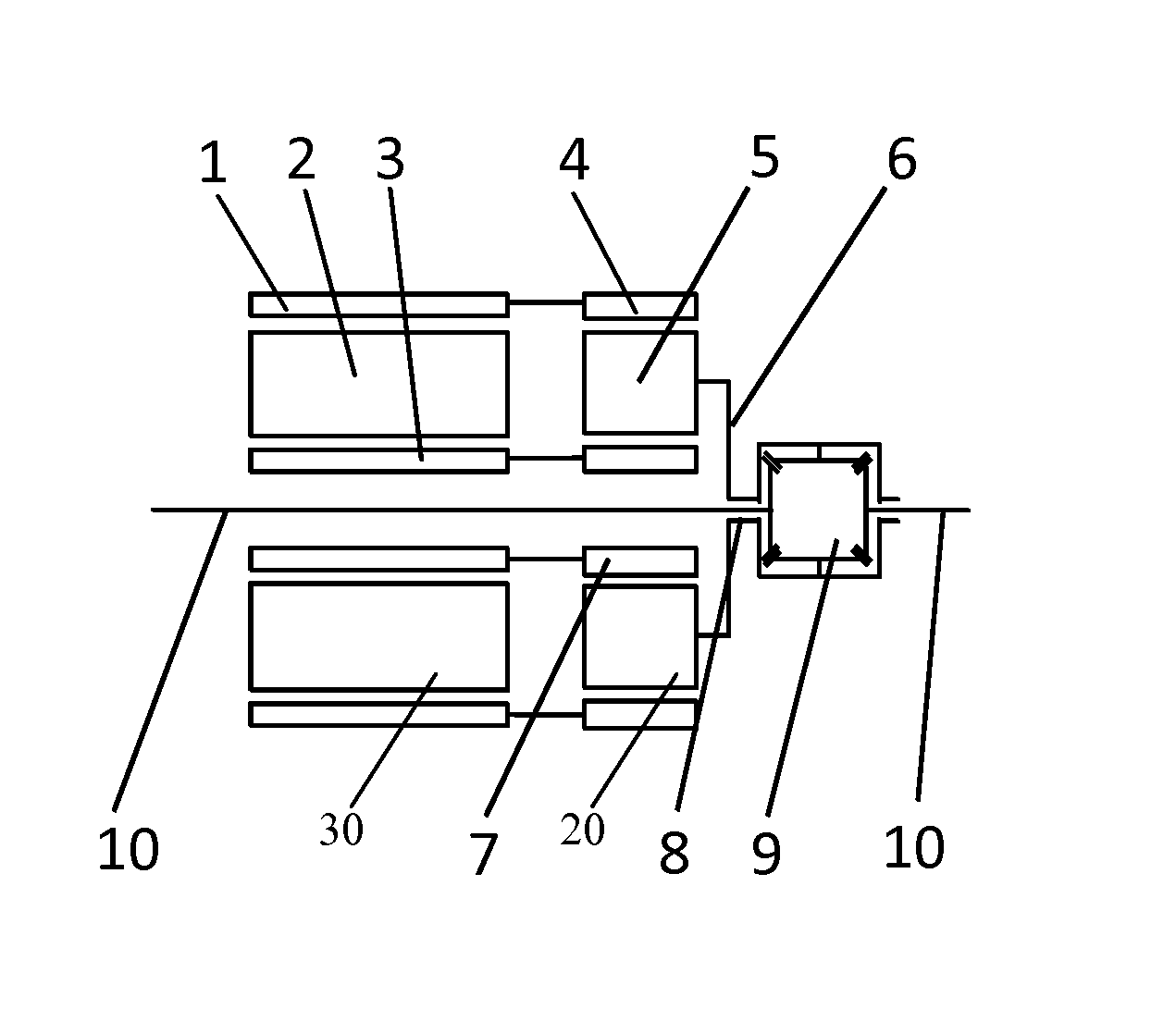

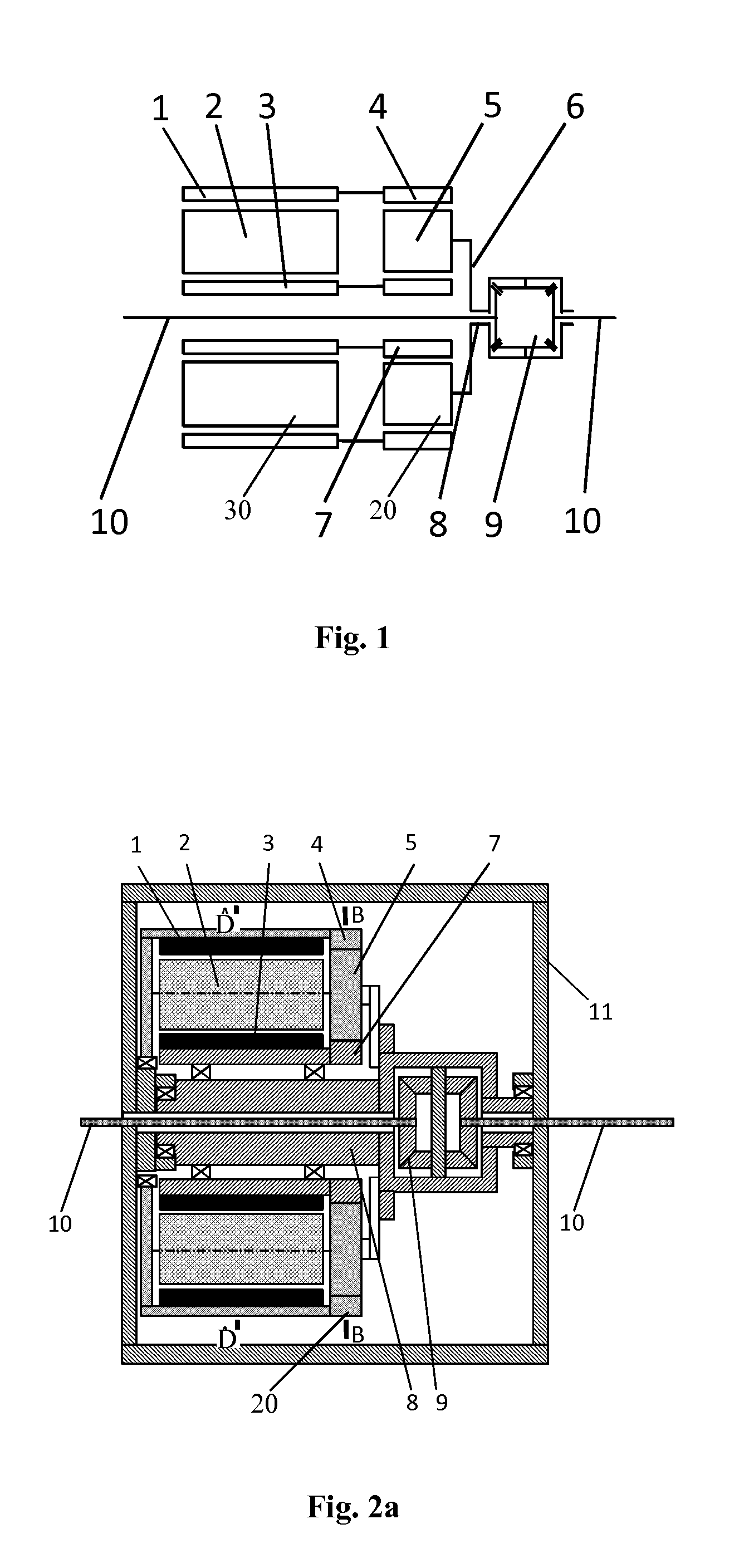

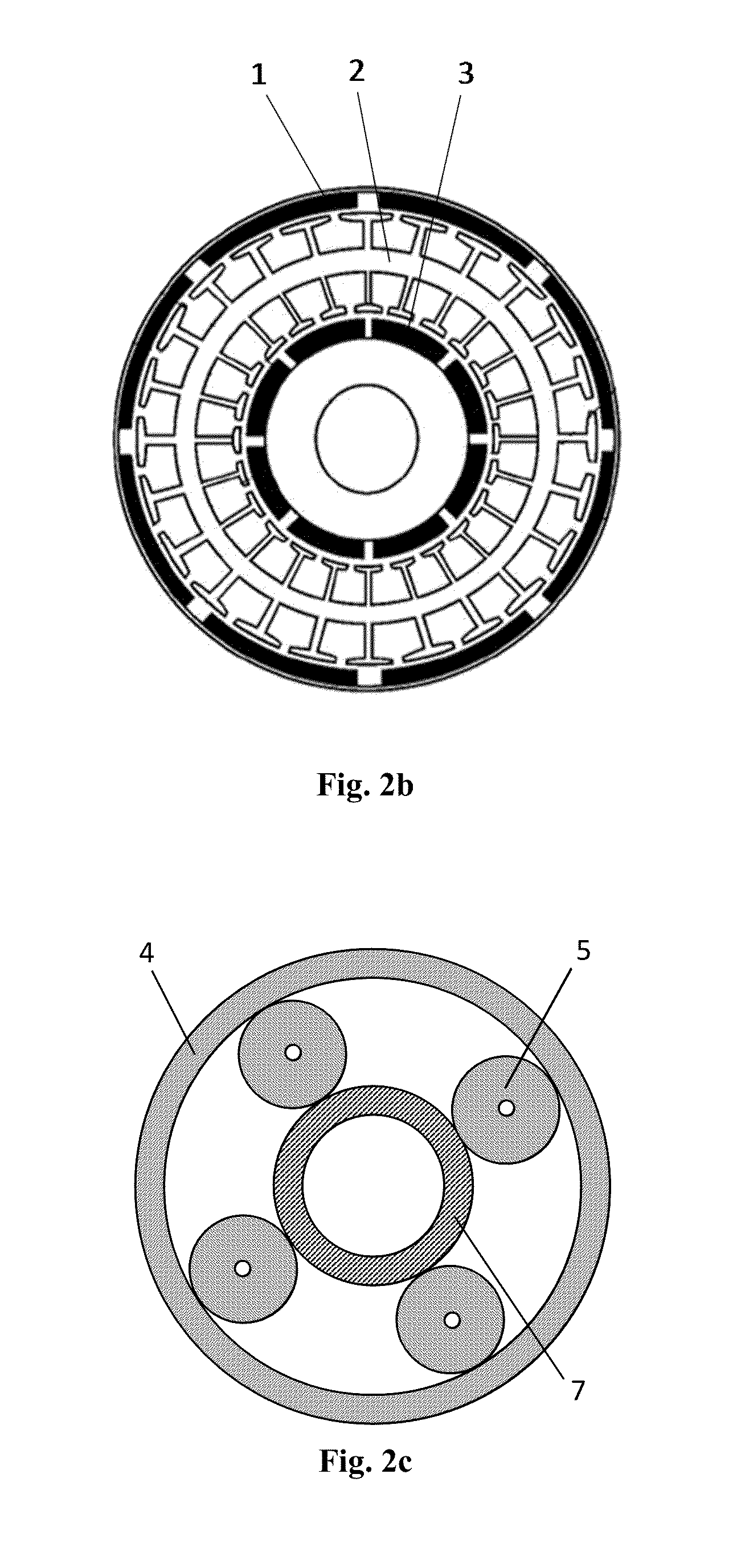

Dual-rotor motor for electric automobile, associated stepless speed change system with planet gear and control method

InactiveUS20130190961A1Improves unsmoothnessImprove vehicle performanceDigital data processing detailsTransmission elementsElectric machineInternal combustion engine

The present invention relates to a dual-rotor motor for electric vehicle, wherein an output shaft is at least partly located in a housing and arranged rotatably relative to the housing, a stator is sleeved around the output shaft, an outer three-phase winding is arranged outside the stator, an outer rotor is sleeved around the outer three-phase winding and arranged rotatably relative to the stator, an inner three-phase winding is arranged inside the stator, an inner rotor is inserted in the inner three-phase winding around the output shaft and arranged rotatably relative to the stator, and a continuously variable transmission system with planet gear and dual-rotor motor for electric vehicle and a control method thereof are provided, the dual-rotor motor for electric vehicle of the present invention is designed skillfully and unique in structure, by cooperating with the planet gear, it can sufficiently make use of the wide speed adjustable range of the motor to regulate speeds, compared with an automatic stepped or continuous variable transmission cooperating with a traditional internal combustion engine, the structure of the transmission system is simpler, and has advantages of stepless speed change and high transmission efficiency, and ultimately improves the vehicle performance, therefore the present invention is suitable for large-scale popularization.

Owner:SHANGHAI ZHONGKE SHENJIANG ELECTRIC VEHICLE

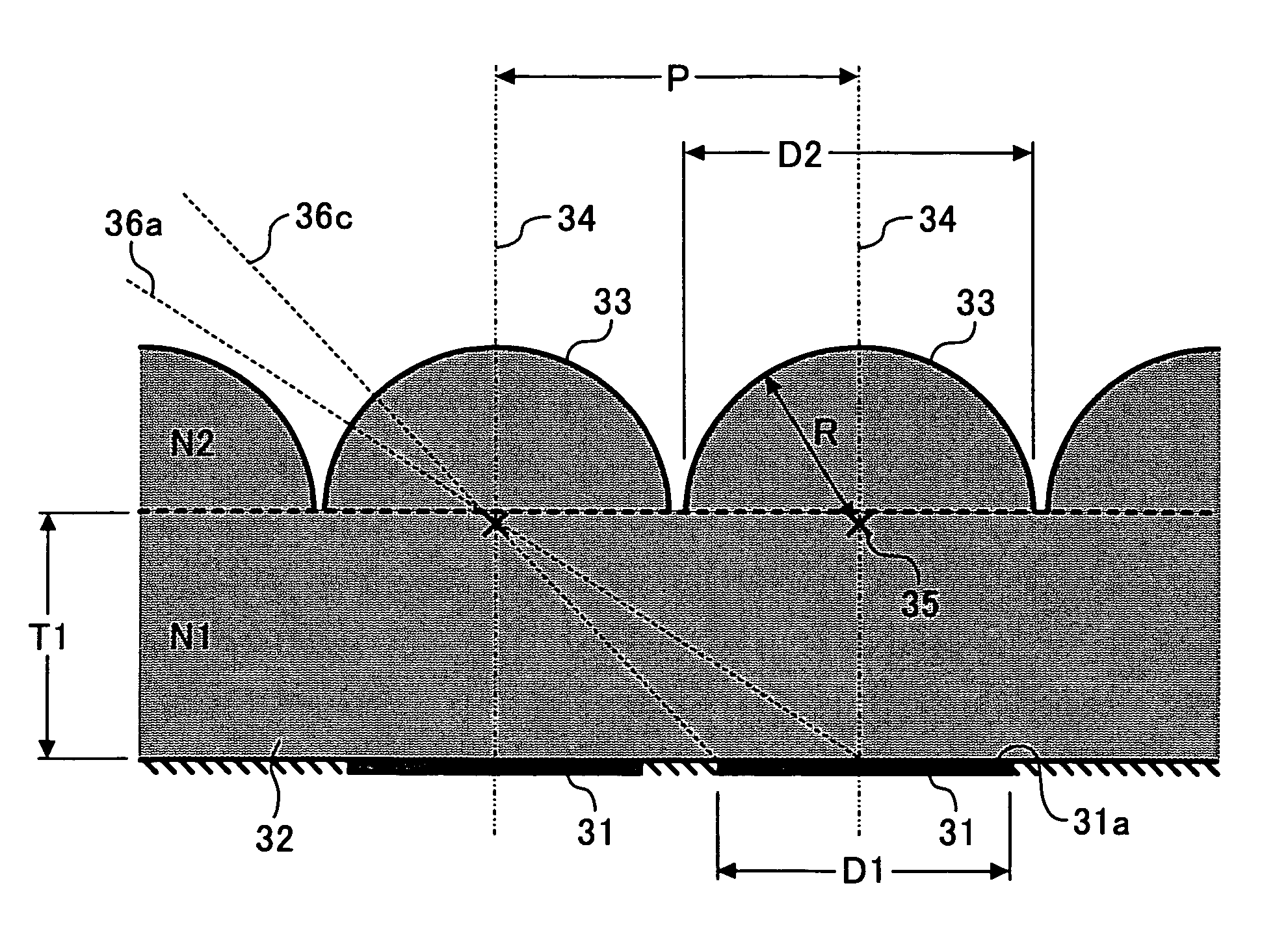

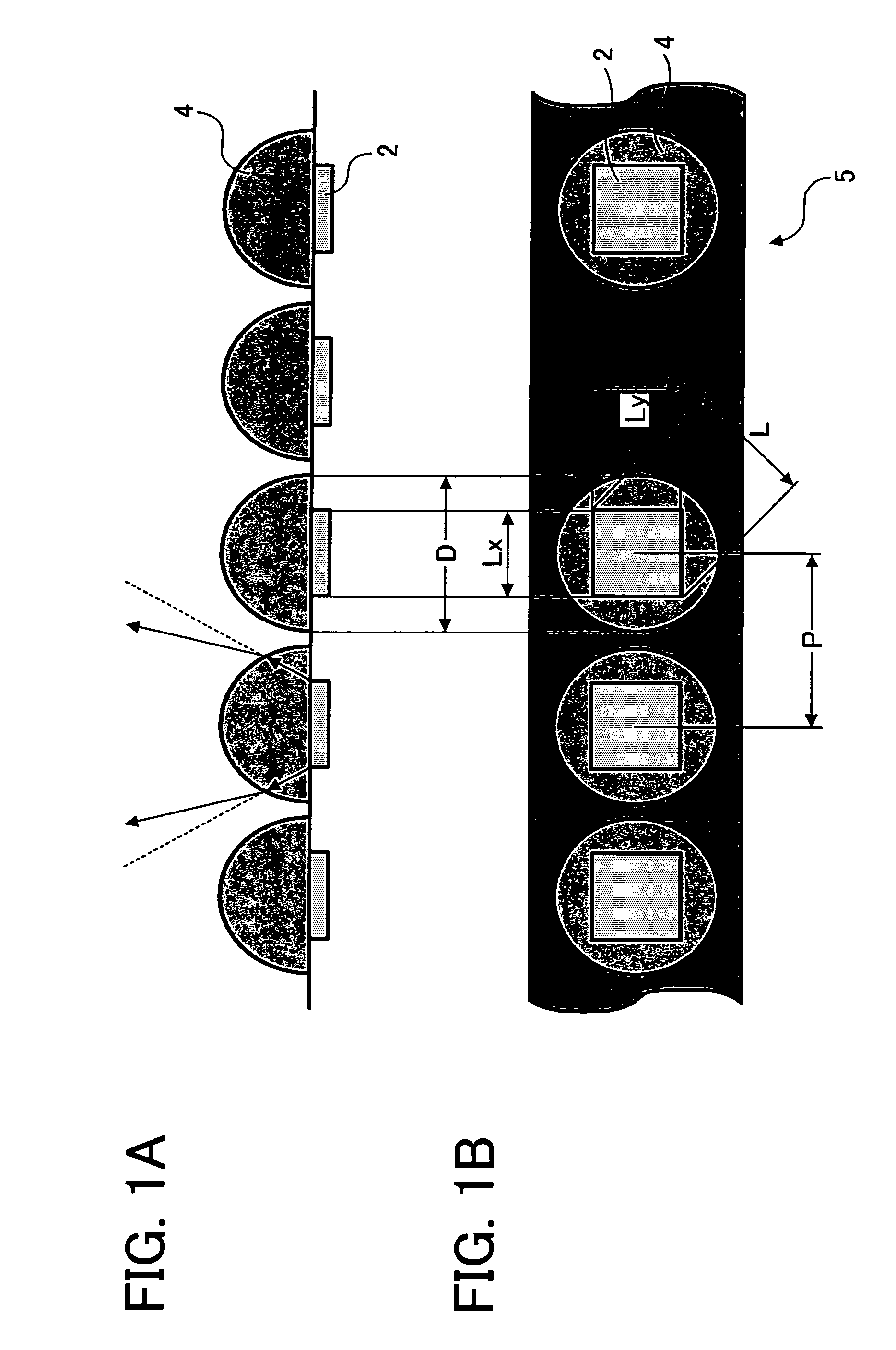

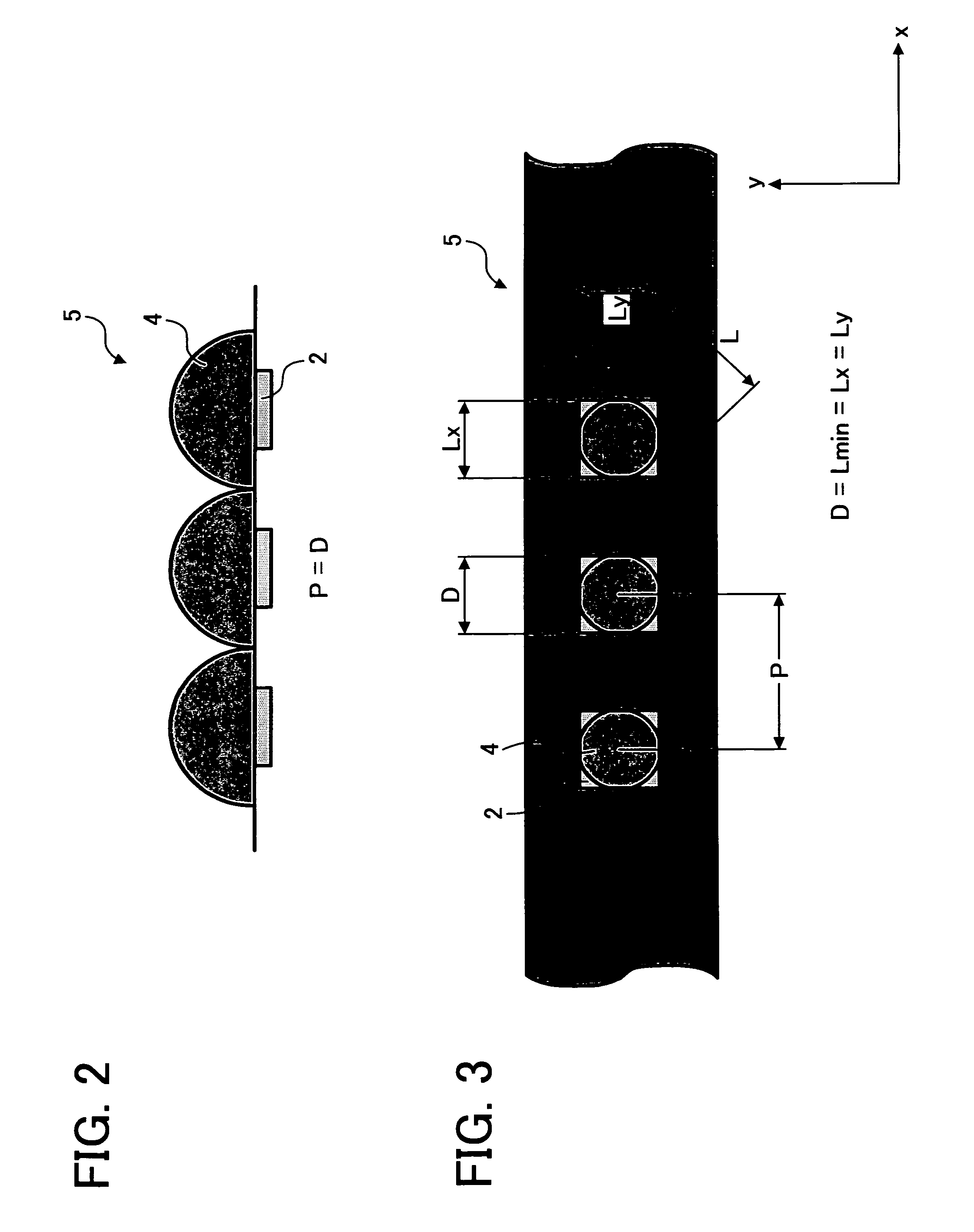

Light emitting array with improved characteristics, optical writing unit, and image forming apparatus

InactiveUS7705868B2Reduce radiationEliminate generationIncadescent screens/filtersDischarge tube luminescnet screensColor imageImage formation

A light emitting array including at least a plurality of light emitting elements, each of which is provided thereon with a microlens in one-to-one correspondence. Light emitting portions of the light emitting element are provided having the shape of a rectangle and formed so as to satisfy the relational expression, Lmin≦D≦P, where Lmin is the length of the shorter side of the rectangle, P an alignment pitch of the light emitting elements, and D the diameter of microlens. In addition, light emitting elements are formed in line on a transparent thin film layer to satisfy the relationship, T1≦2·D2, where T1 is the thickness of the transparent thin film layer and D2 the diameter of each microlens. The light emitting array may suitably be included in the light source unit which is then incorporated into image forming apparatuses for forming mono-color or multiple-color images.

Owner:RICOH KK

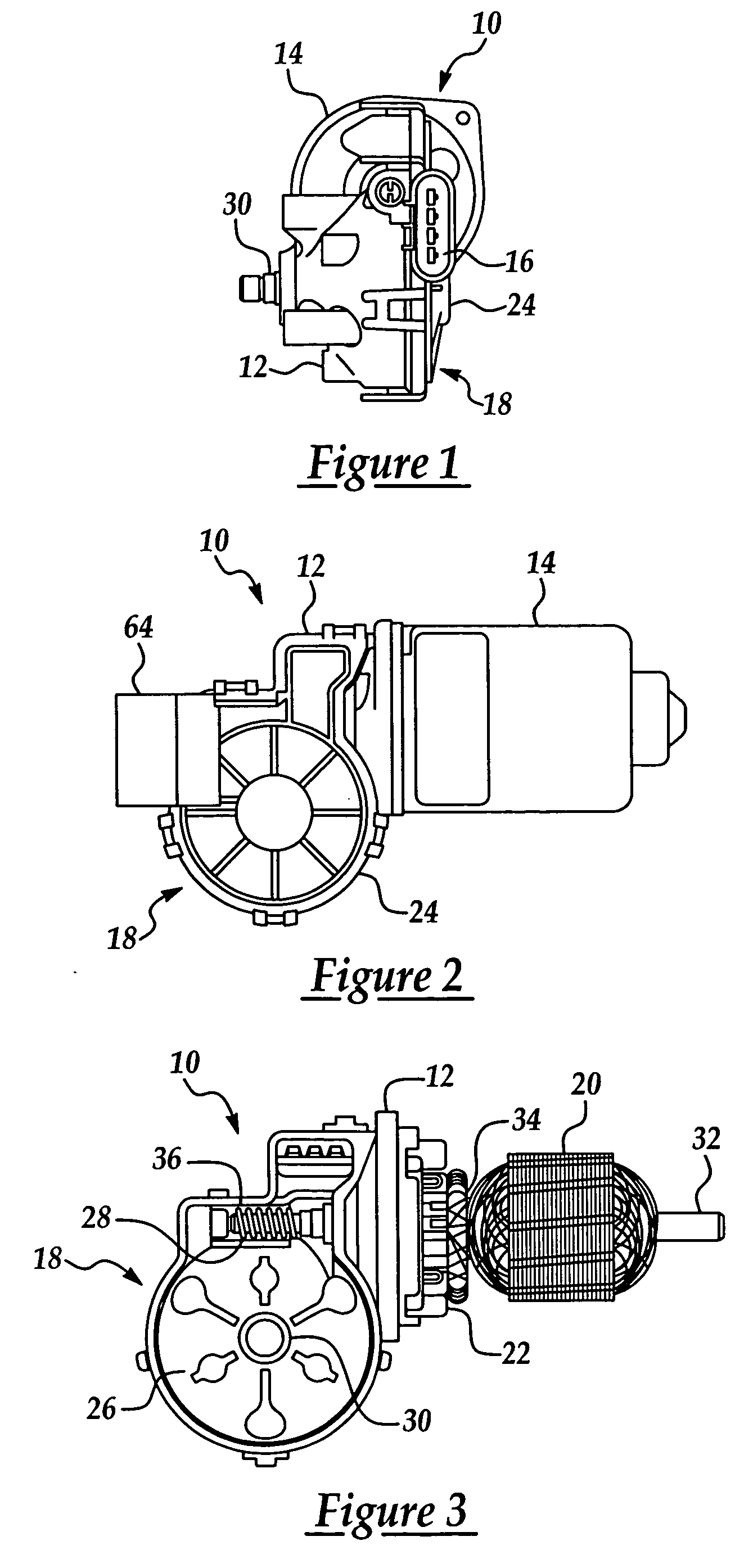

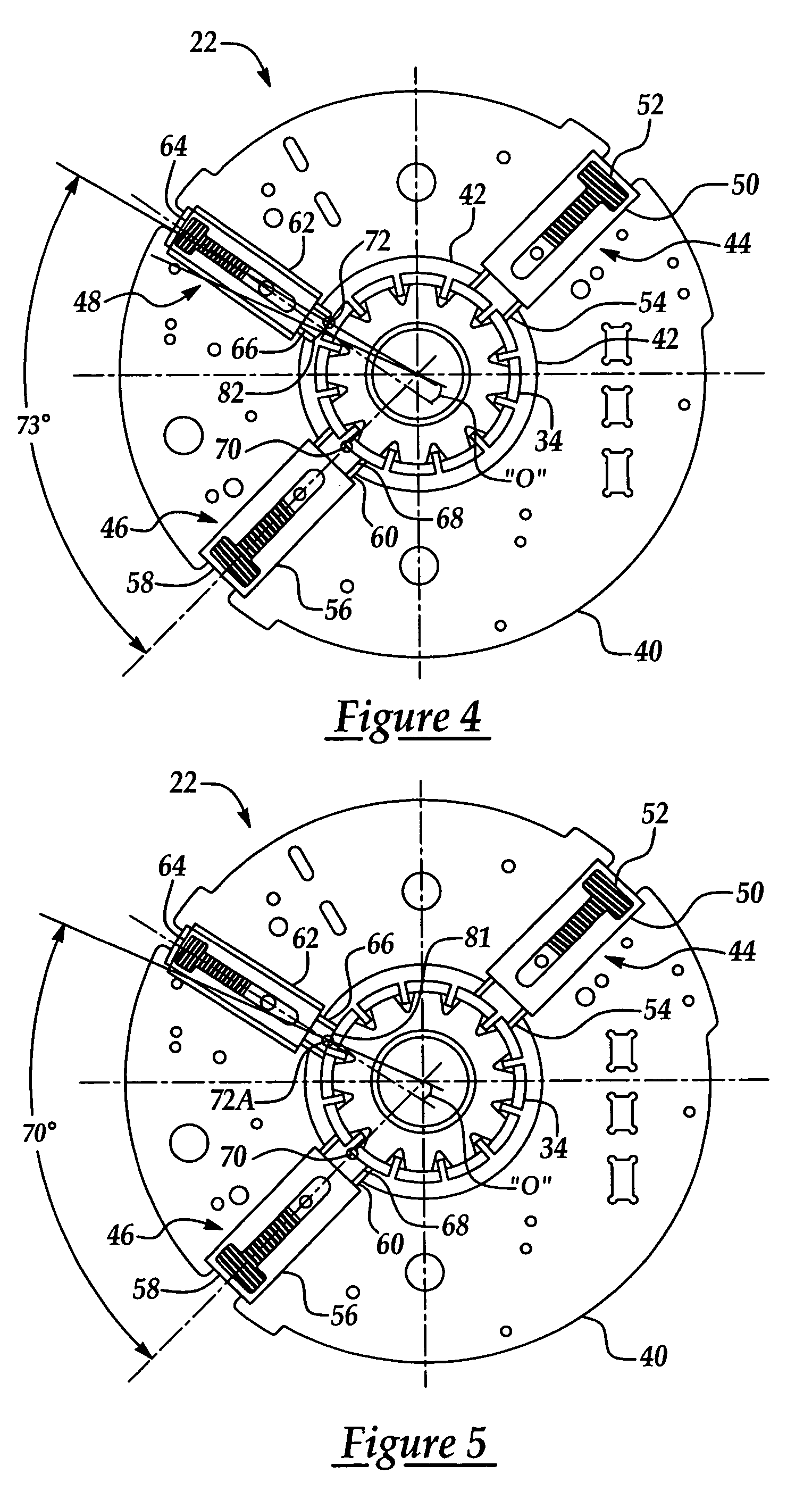

Electric motor having convex high-speed brush

ActiveUS20050218750A1High-speed outputOvercome limitationsDynamo-electric brakes/clutchesRotary current collectorLow speedElectromotive force

A two speed direct current electric motor comprising: an armature having a commutator assembly that is adapted to receive an electromotive force to cause the armature to operatively rotate. A brush assembly having a common brush and a low-speed brush is disposed about and in electrical communication with the commutator to provide a first electromotive force to cause the armature to provide a low-speed rotational output. The brush assembly further includes a high-speed brush having a convex shaped end in physical and electrical communication with the commutator to provide a second electromotive force to cause the armature to provide a high-speed rotational output. The convex shaped end of the high-speed brush is further adapted to wear to take the shape of the commutator such that as the high-speed brush wears the high-speed rotational output decreases.

Owner:TRICO PROD CORP

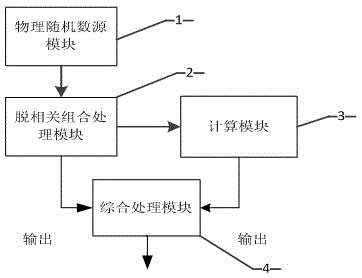

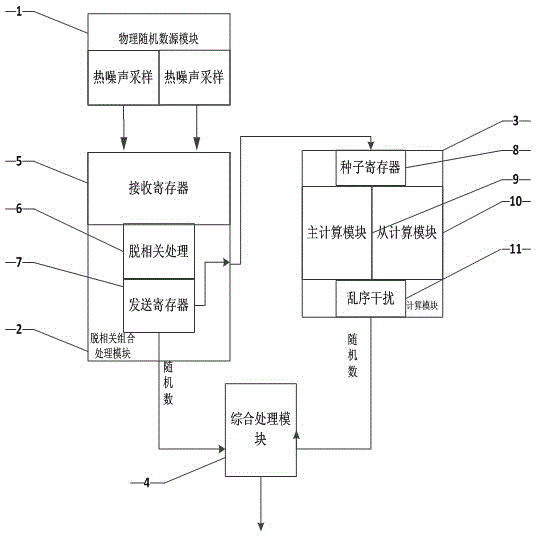

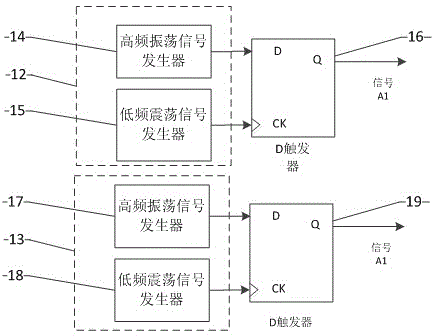

Mixed random number generator and method for generating random number by using mixed random number generator

InactiveCN105005462AMeet energy consumptionReduce energy consumptionRandom number generatorsComputer science

The invention discloses a mixed random number generator and a method for generating random number by using the mixed random number generator, wherein the mixed random number generator comprises a physical random number source module (1), a correlative combination detachment processing module (2), a computing module (3) and a comprehensive treatment module (4). The technical effects of relative high generation sequence quality and relative low cost of the mixed random number generator and the method for generating random number by using the mixed random number generator are realized.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

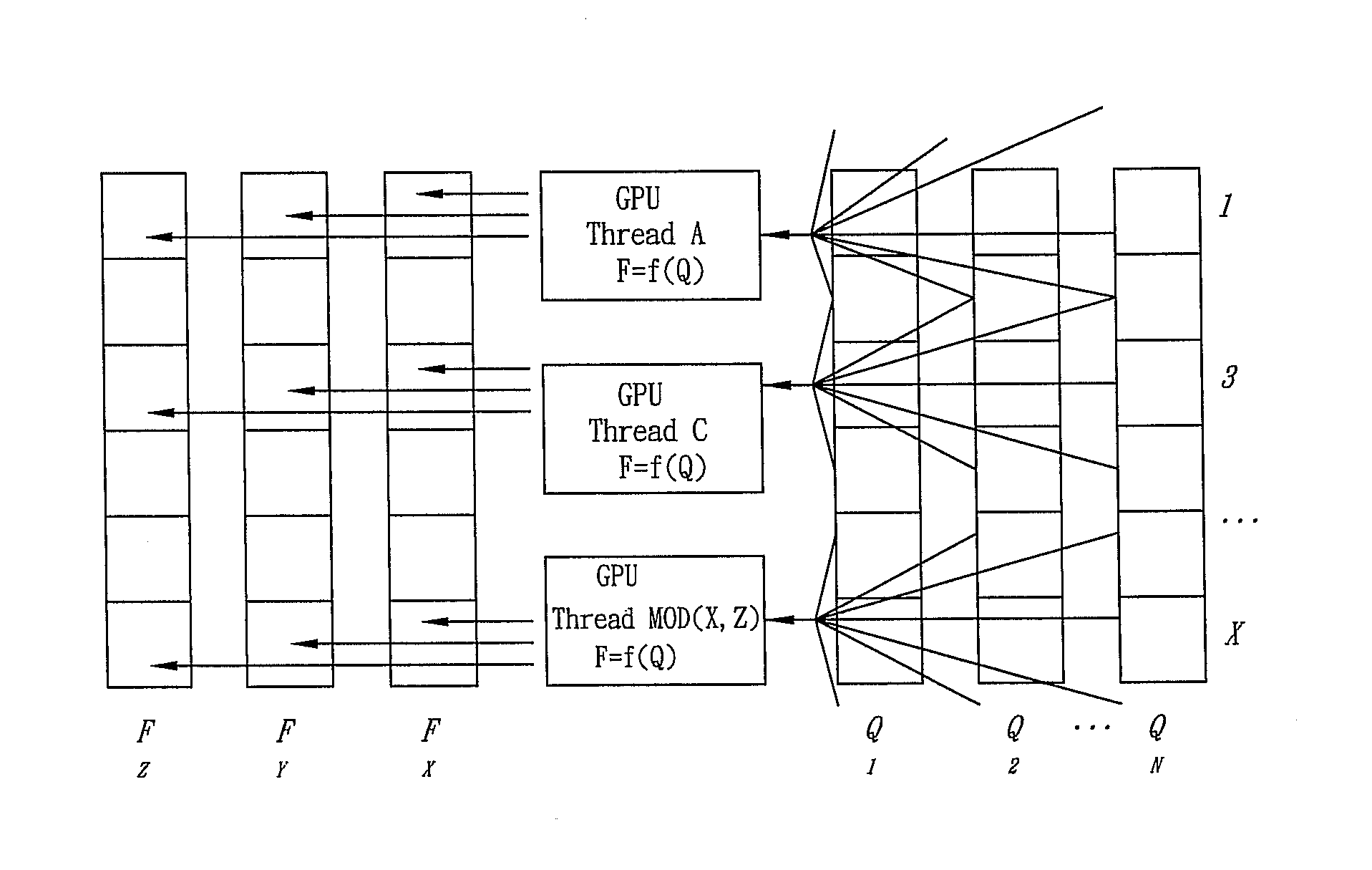

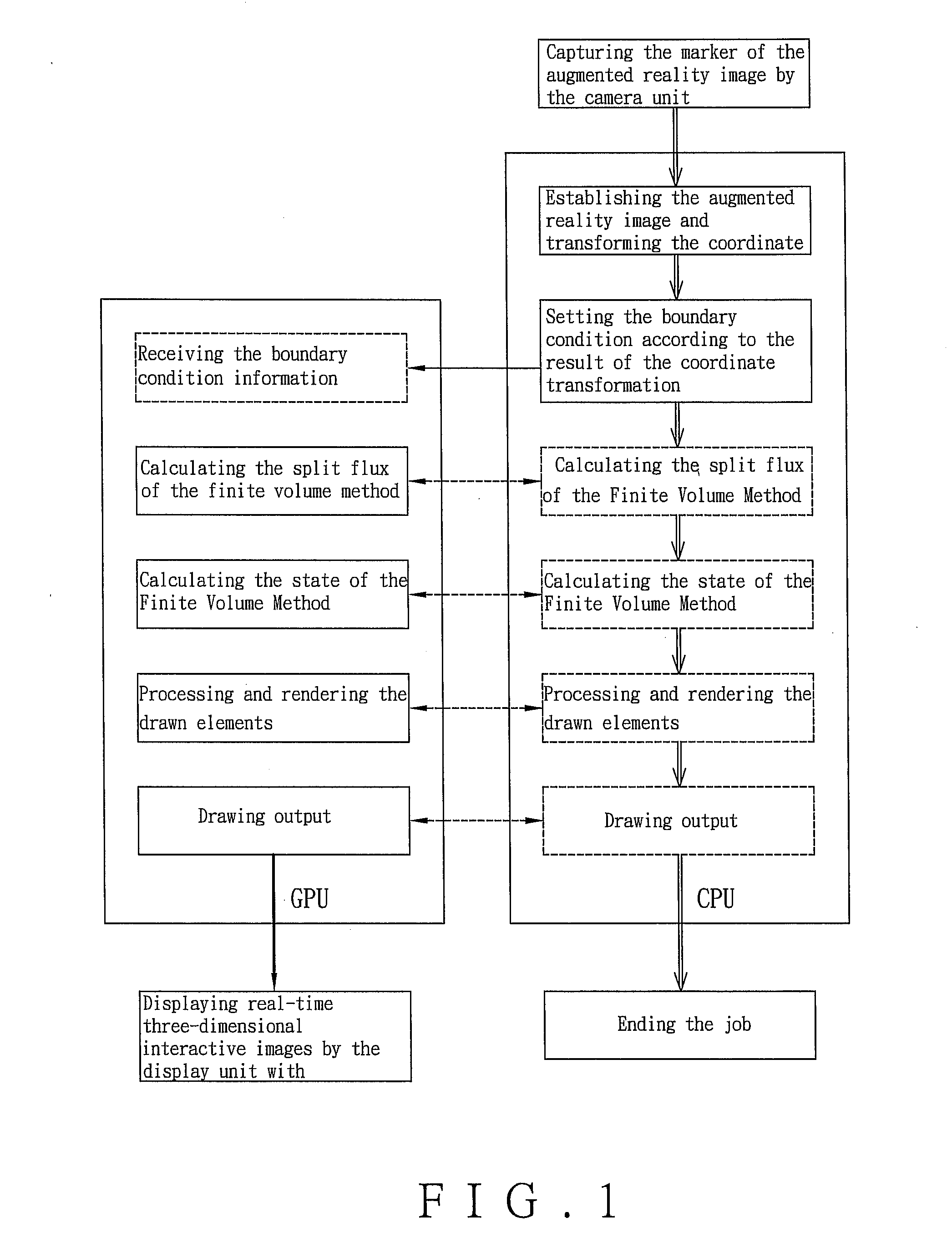

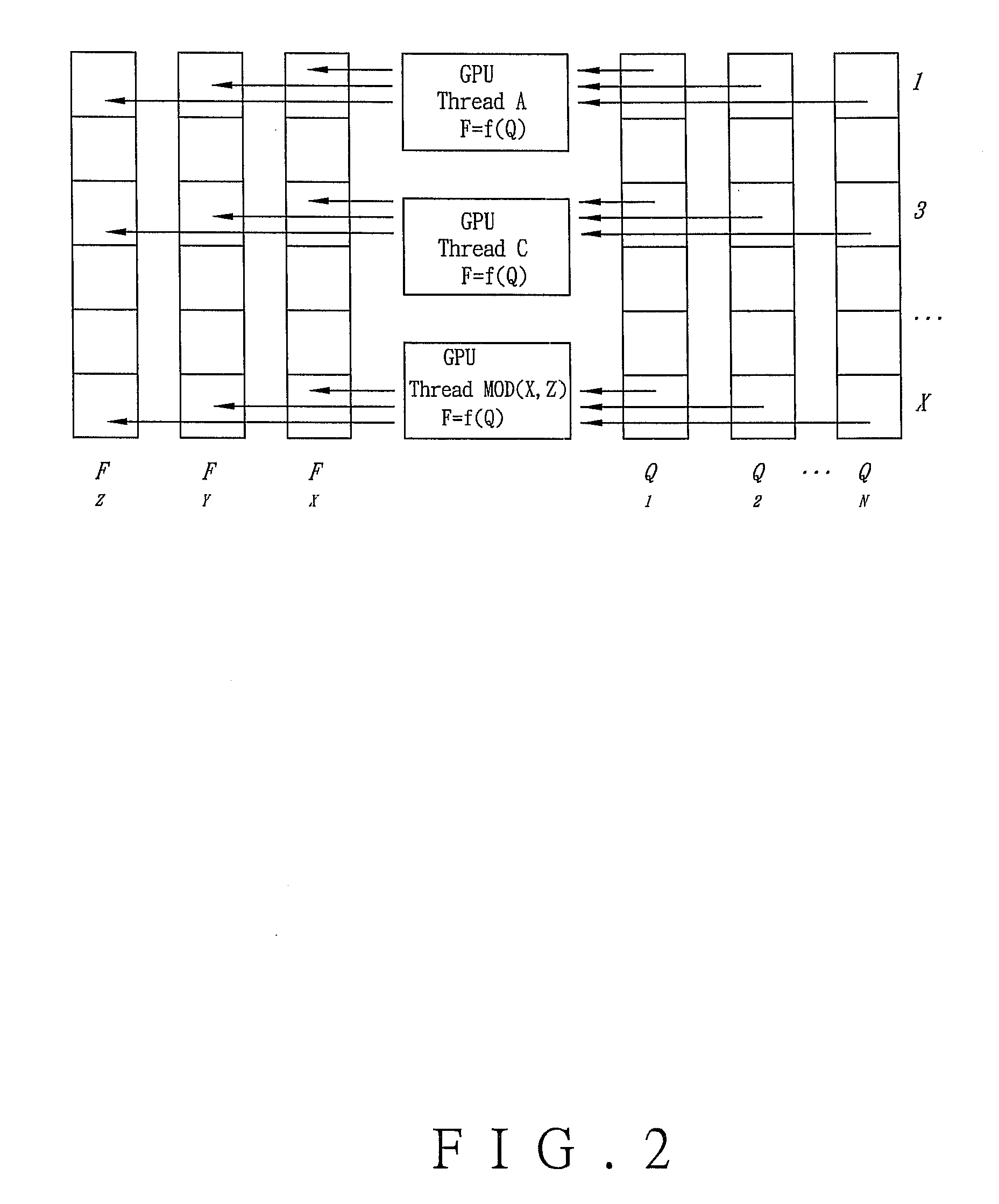

Method and apparatus for executing high performance computation to solve partial differential equations and for outputting three-dimensional interactive images in collaboration with graphic processing unit, computer readable recording medium, and computer program product

InactiveUS20130147786A1High performance computationIncrease speedImage generationComplex mathematical operationsPartial differential equationVisual perception

A method and apparatus for executing high performance computation to solve PDEs and for outputting three-dimensional interactive images in collaboration with a GPU is disclosed. The method includes: (A) executing a coordinate transformation to a three-dimensional image by the CPU, setting a boundary condition required by a simulation according to a coordinate transformation result, and inputting the boundary condition to the GPU; (B) executing a numerical simulation of the PDEs and the boundary condition in the step (A); (C) processing and rendering each drawn element by the GPU according to a numerical simulation result to draw a visual image featured with physical quantity variation and overlapping the visual image on the three-dimensional image to form the three-dimensional interactive images.

Owner:NAT APPLIED RES LAB

Recording apparatus

ActiveUS7463370B2High-speed outputReduce generationDigitally marking record carriersVisual representation by matrix printersData generatorLog data

A recording apparatus, and so forth, capable of outputting at high speed is provided. Second recording data that are stored in a memory based on data obtained by a data obtaining section are transferred to a data generator via a second transfer path, and based on the second recording data that have been transferred, the data generator generates first recording data for performing recording on a medium.

Owner:SEIKO EPSON CORP

Laser beam applying mechanism and laser processing apparatus

ActiveCN102626830AOutput controlHigh speed outputLaser detailsWelding/soldering/cutting articlesLaser processingPhase difference

A laser beam applying mechanism has a power adjusting unit provided between a laser beam oscillator and a focusing lens. The power adjusting unit includes a half-wave plate, a prism having a first polarization beam splitter film and a second polarization beam splitter film. The optical path is adjusted by a piezoelectric actuator opposed to the first polarization beam splitter film, and a polarized light components synthesizer opposed to the second polarization beam splitter film generates a phase difference ([beta]) between an S polarized light component and a P polarized light component. The phase difference ([alpha+beta]) between the S polarized light component and the P polarized light component of the laser beam obtained by the polarized light components synthesizer is in the range of 0 DEG to 180 DEG .

Owner:DISCO CORP

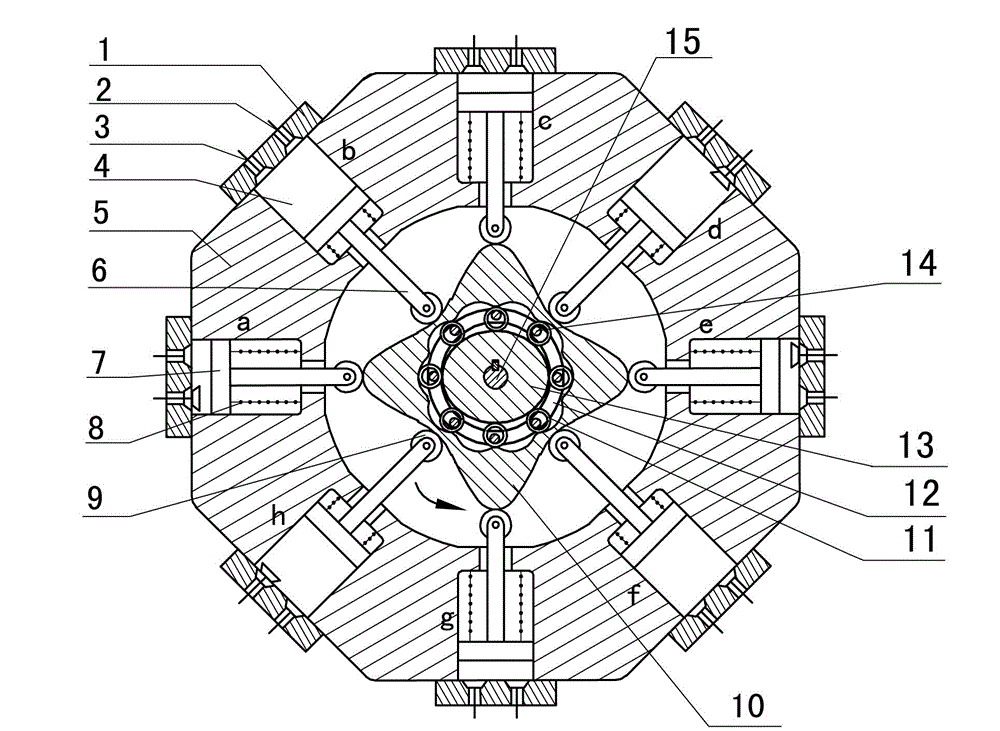

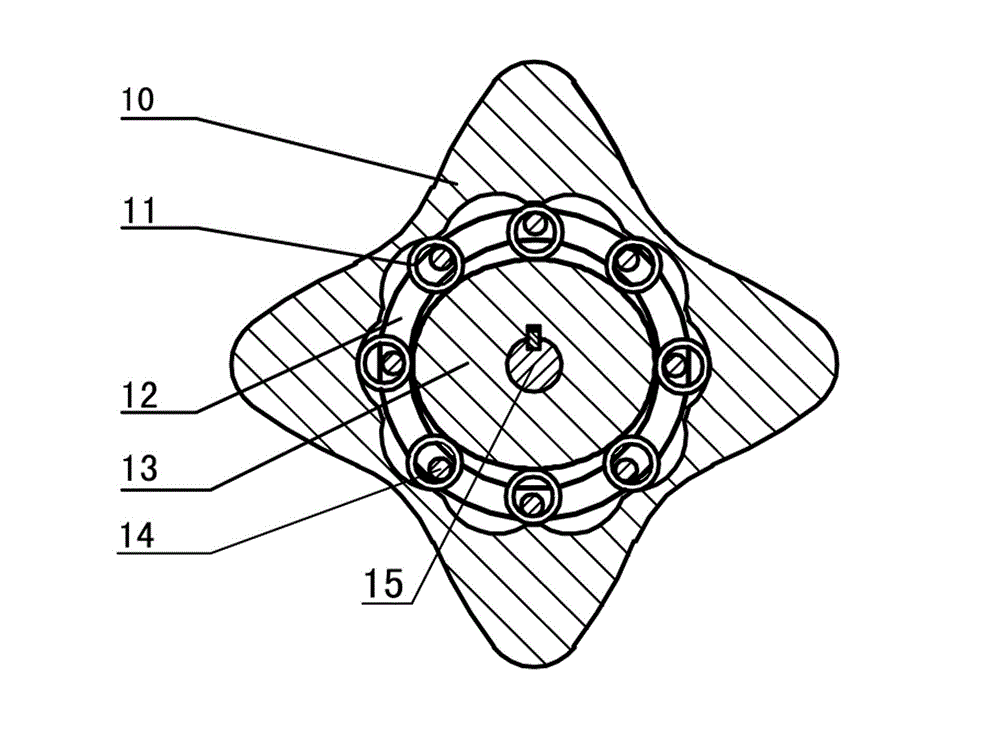

Two-phase outer cam sleeve type high-rotational-speed internal-combustion engine

InactiveCN102877942AHigh speed outputReduce axial sizeGearingMachines/enginesEngineeringInternal combustion engine

The invention discloses a two-phase outer cam sleeve type high-rotational-speed internal-combustion engine, and relates to the field of power of fuel gas. The invention provides a novel internal-combustion engine. Eight cylinders are annularly, symmetrically and uniformly distributed around an outwards convex inner gear ring, so that resultant force from which the outwards convex inner gear ring is suffered is zero; pistons of the cylinders directly act on the outwards convex inner gear ring through push rods; and power is transferred to an output shaft connected with a symmetric two-phase cam through a key by the outwards convex inner gear ring through the drive of a two-phase outer cam type sleeve oscillating tooth. By using the internal-combustion engine, a connecting rod and a crankshaft in a conventional internal-combustion engine are omitted; a two-phase outer cam sleeve driving mechanism of the outwards convex inner gear ring of the internal-combustion engine does not have an eccentric mass; the internal-combustion engine has the characteristic of the self balancing of inertia force and a working load; the rotational speed of the output shaft depends on the drive ratio of the drive of the oscillating tooth; if a dowel pin frame is fixedly arranged, the symmetric two-phase cam carries out output at a high speed; the internal-combustion engine can be widely applied to the field of high rotational speeds, such as engines of helicopters, and miniature engines; and when an output rotational speed is constant, the emission of harmful gas can be reduced. The internal-combustion engine is simple and compact in structure, small in axial dimension and self-balancing in stress, and is stable to run.

Owner:SICHUAN UNIV

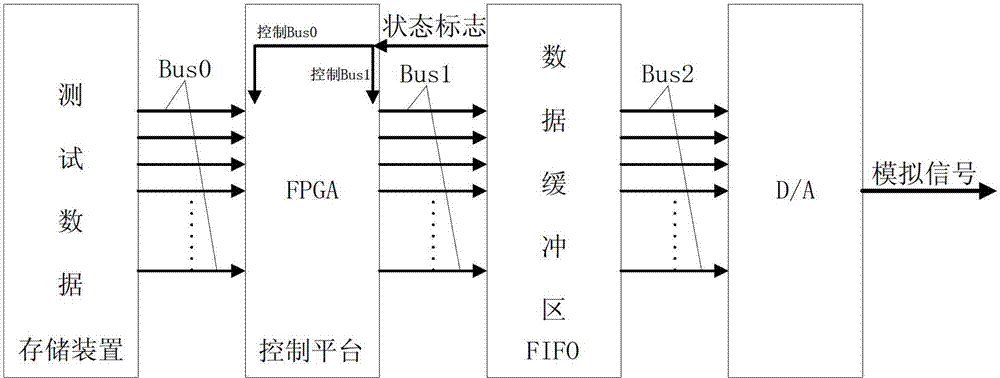

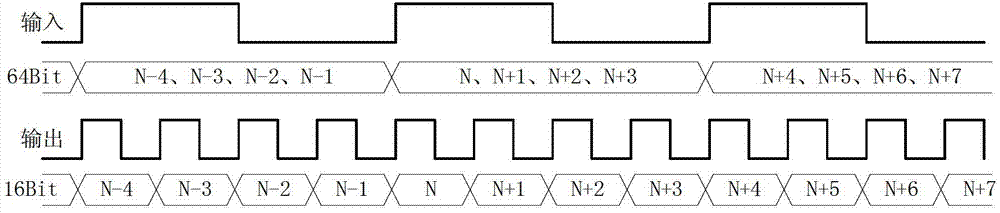

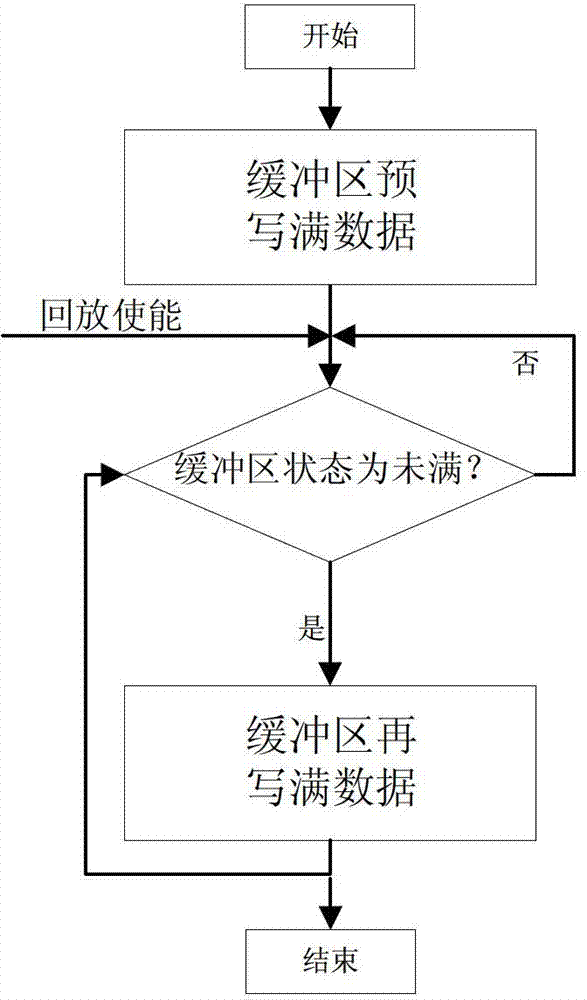

Data playback device based on FIFO (First In, First Out) caching structure

InactiveCN103076990AIncrease storage capacityContinuous stable outputInput/output to record carriersData conversionDigital analog converterStructure of Management Information

The invention discloses a data playback device based on an FIFO (First In, First Out) caching structure and belongs to the technical field of analog output. The data playback device comprises a storage device, a control platform, a data buffering area FIFO and a digital analog converter, wherein the storage device is connected with the control platform through a bus BUS0; the control platform is connected with the data buffering area FIFO through a bus BUS1; the data buffering area FIFO is connected with the digital analog converter through a bus BUS2; a test data is stored in the storage device; the control platform is provided with an external input port and can read and output the test data according to a preset control flow; an input data bit width of the data buffering area FIFO is set as being more than an output data bit width; an active restriction for full-state identification in the FIFO is set; the digital analog converter is used for receiving the test data from the data buffering area, performing digital analog conversion on the test data and outputting an analog signal; and Bus0 rate* Bus0 valid bit width is more than or equal to Bus1 rate* Bus1 valid bit width which is more than Bus2 rate* Bus2 valid bit width. The data playback device is suitable for the playback of a large amount of test data.

Owner:BEIJING AEROSPACE MEASUREMENT & CONTROL TECH

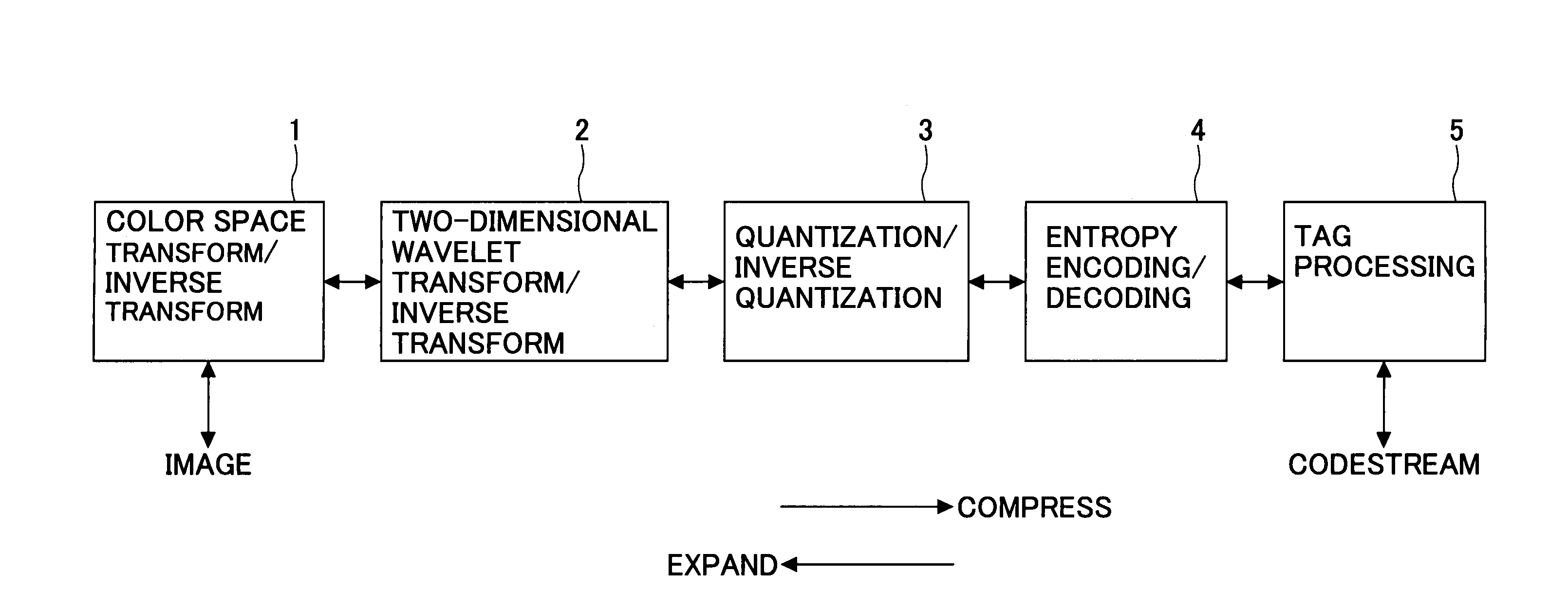

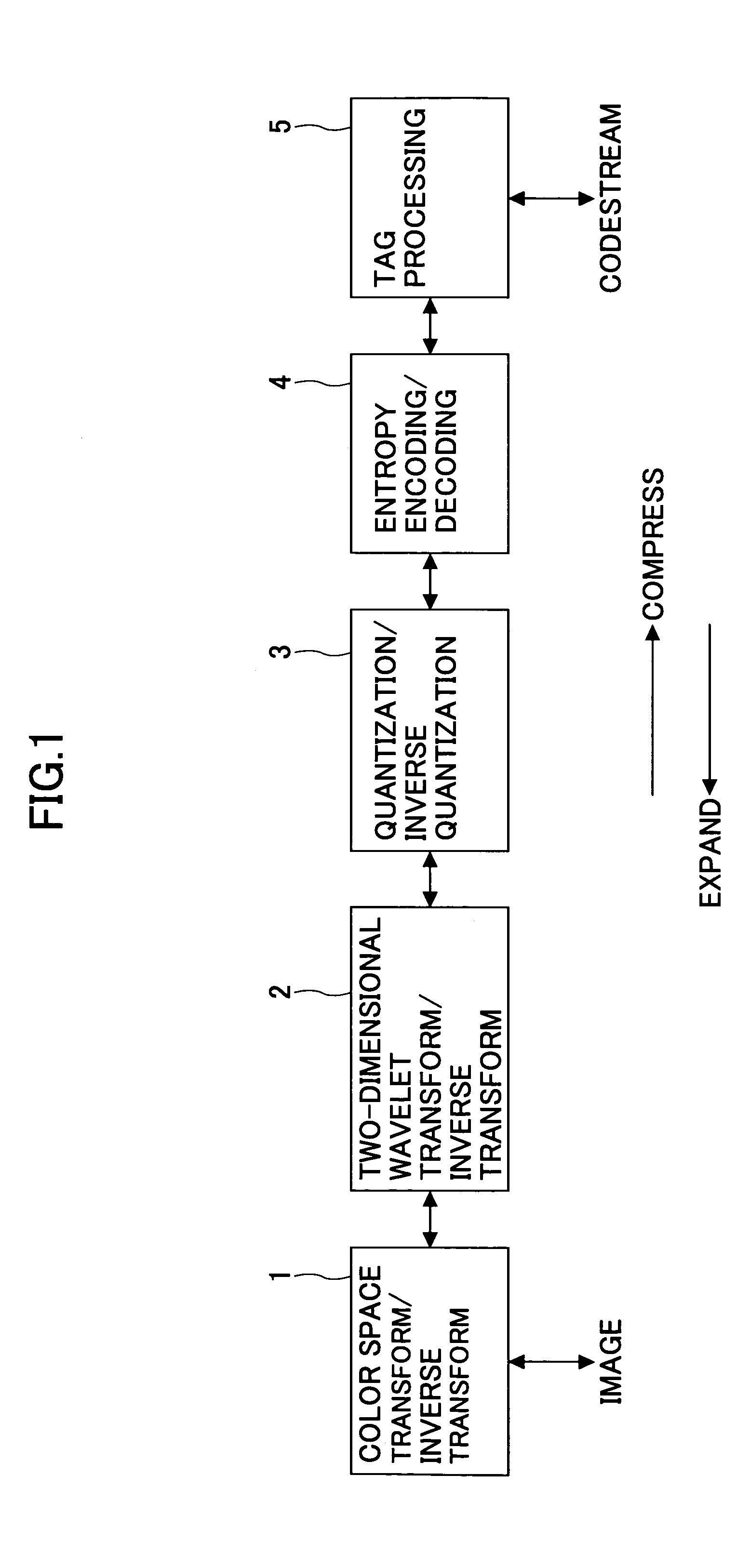

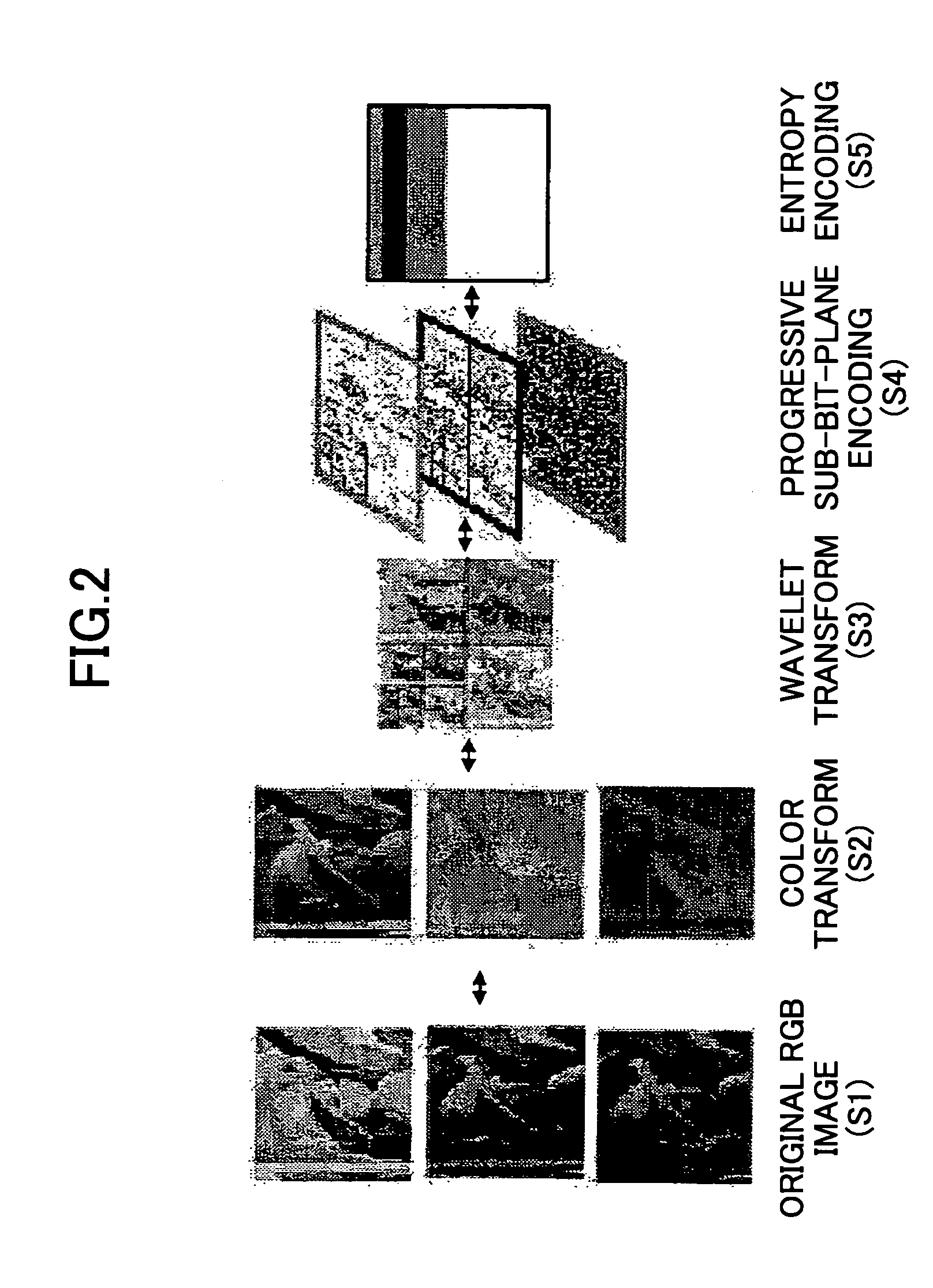

Image processing method, image expansion method, image output method, image conversion method, image processing apparatus, image expansion apparatus, image output apparatus, image conversion apparatus, and computer-readable storage medium

InactiveUS7526144B2Increase speedEasy to manageCharacter and pattern recognitionTelevision systemsImaging processingComputer graphics (images)

An image processing method generating a single image group file from a plurality of still images, by setting an output sequence of the plurality of still images, and adding data indicating a storage location of each of the still images according to the set output sequence, to a header portion of the file.

Owner:RICOH KK

Light emitting device and display device

ActiveUS7463224B2Reduce the amplitudeReduce power consumptionElectroluminescent light sourcesSolid-state devicesDigital dataSignal on

Each pixel in a display device includes an emissive element, a driver transistor, a control transistor, and a control capacitor. The driver transistor is provided between the emissive element and a power supply and controls supply of power from the power supply to the emissive element. The control transistor is connected between a constant voltage power supply and a gate of the driver transistor, receives a digital data signal on a gate, and controls whether or not to fix a gate voltage of the driver transistor. The control capacitor is connected between a control line and the gate of the driver transistor. The gate voltage of the driver transistor is shifted to a voltage corresponding to a control pulse signal when the control transistor is off and is non-fixed during a light emission period defined by the control pulse signal applied to the control line.

Owner:SANYO ELECTRIC CO LTD

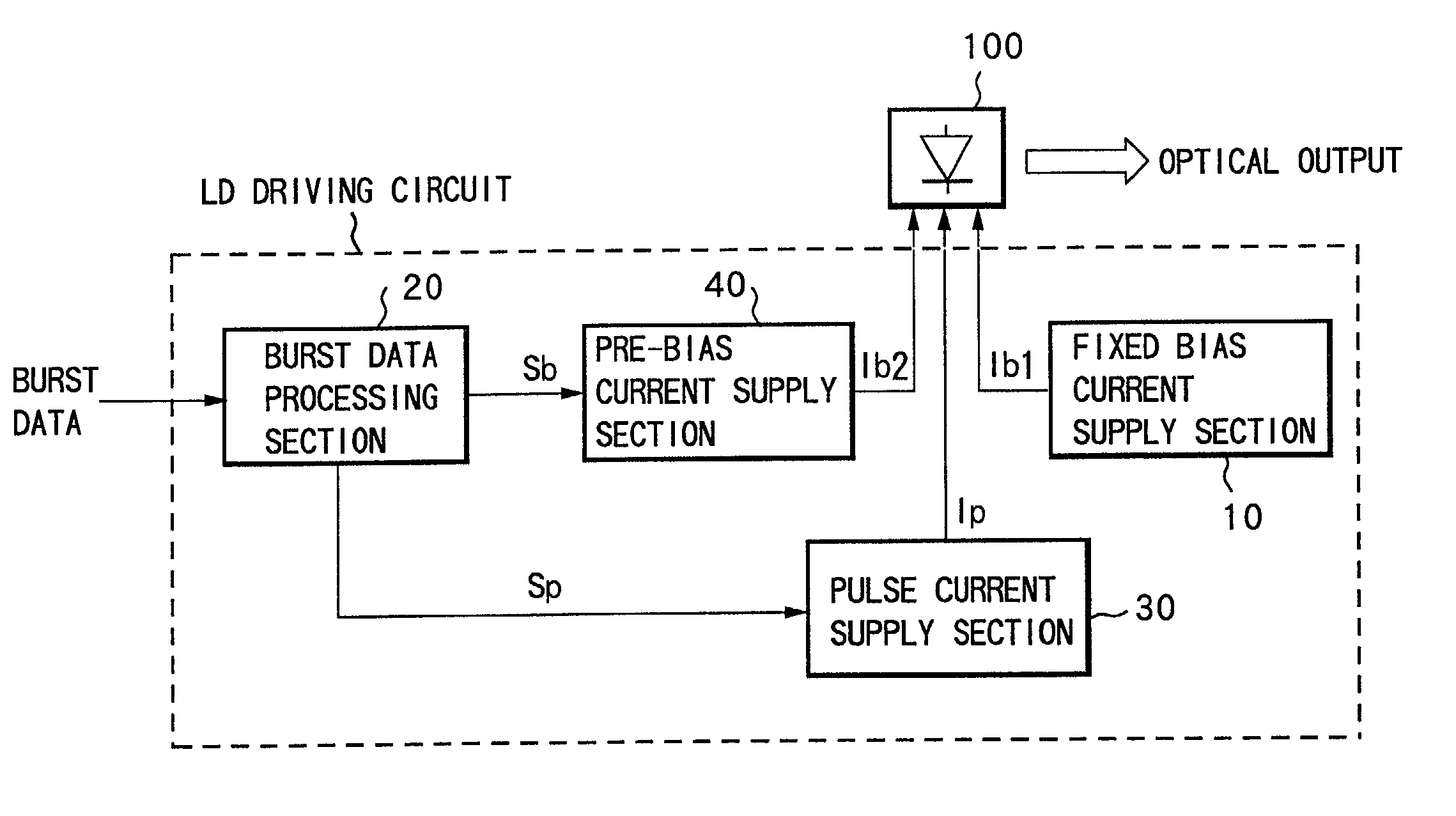

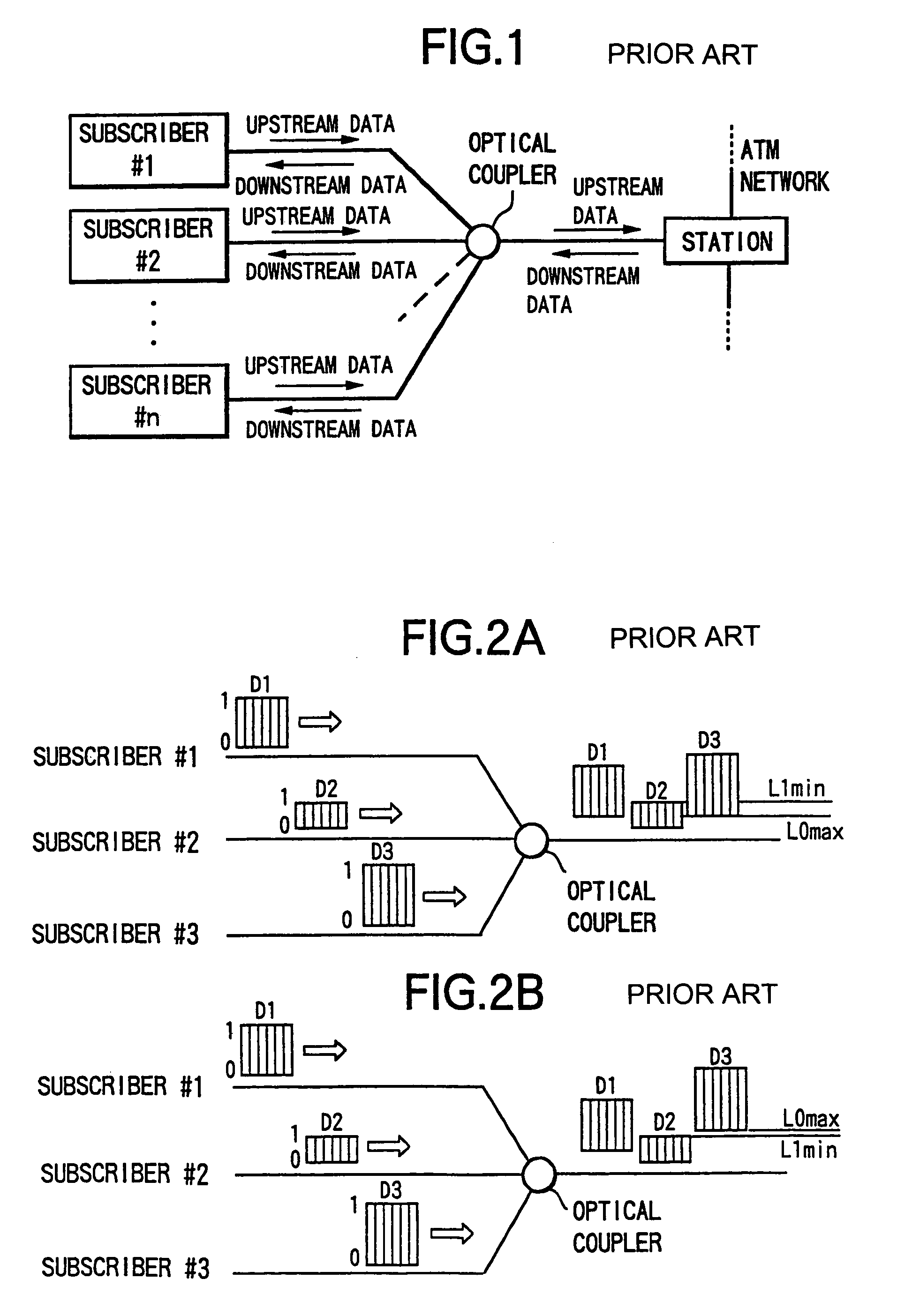

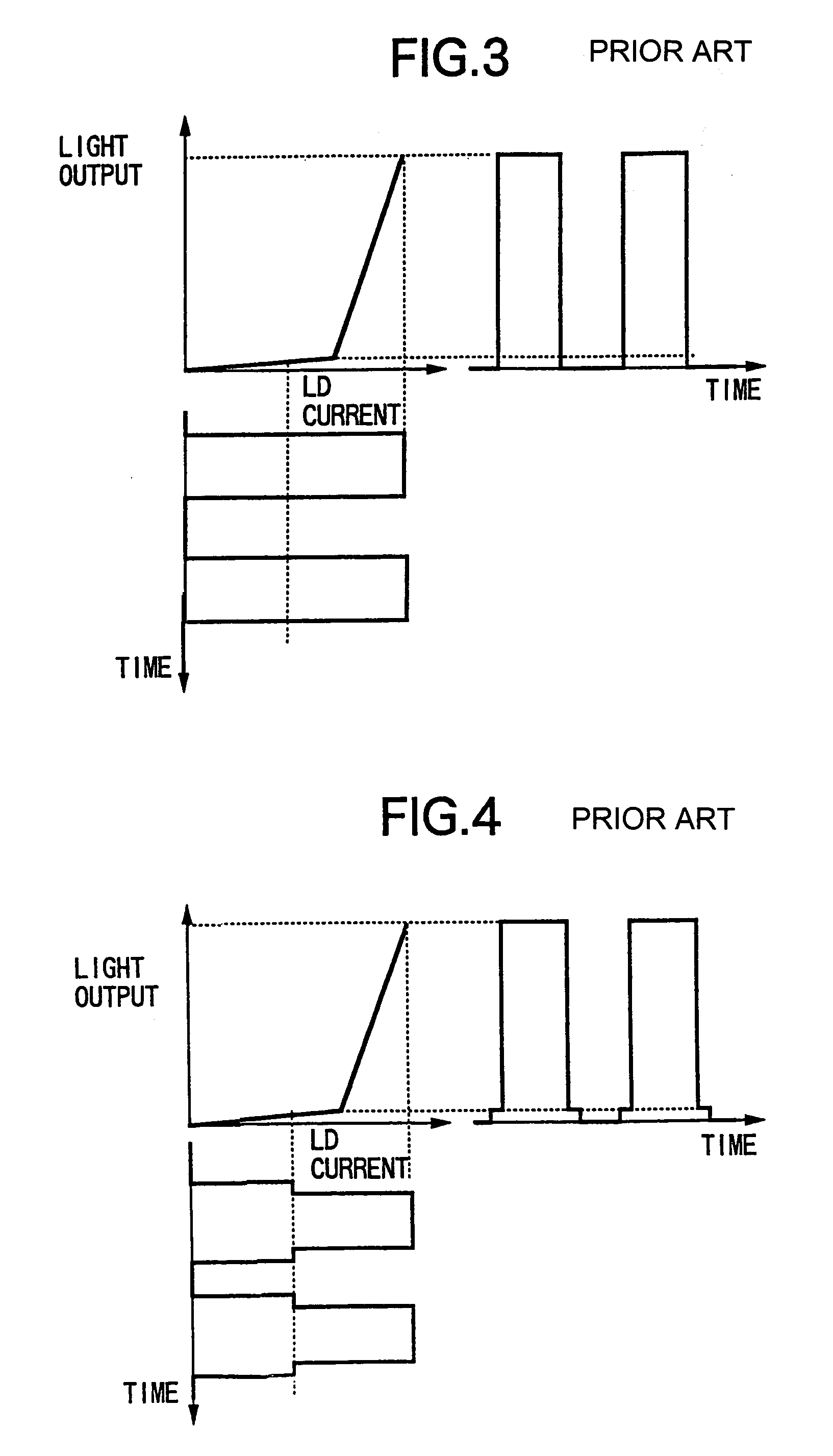

Driver circuit and driving method for semiconductor laser

InactiveUS7158551B2Accurate outputFlexible responseLaser detailsLaser output parameters controlDriver circuitControl signal

A driver circuit for a semiconductor laser of the invention comprises: first bias current supply means for supplying, at least at a time of non-output of data, a first bias current to an LD; signal processing means for generating a pulse current control signal in which a burst data signal is delayed, and generating a second bias current control signal which rises more rapidly by a predetermined time than the rise of burst data included in the pulse current control signal; pulse current supply means for supplying to the LD a pulse current generated in accordance with the pulse current control signal; and second bias current supply means for supplying to the LD a second bias current generated in accordance with the second bias current control signal.

Owner:FUJITSU LTD

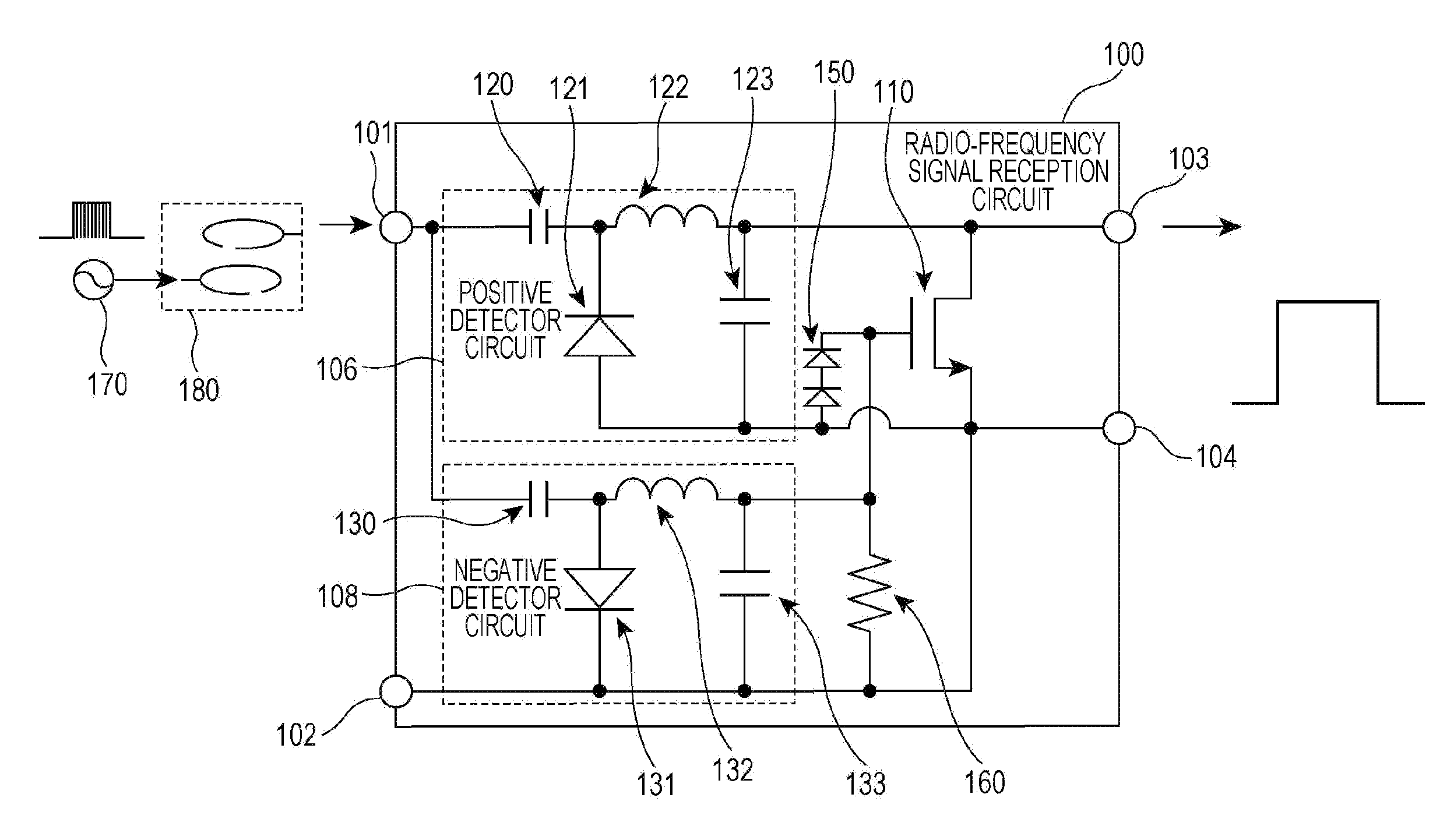

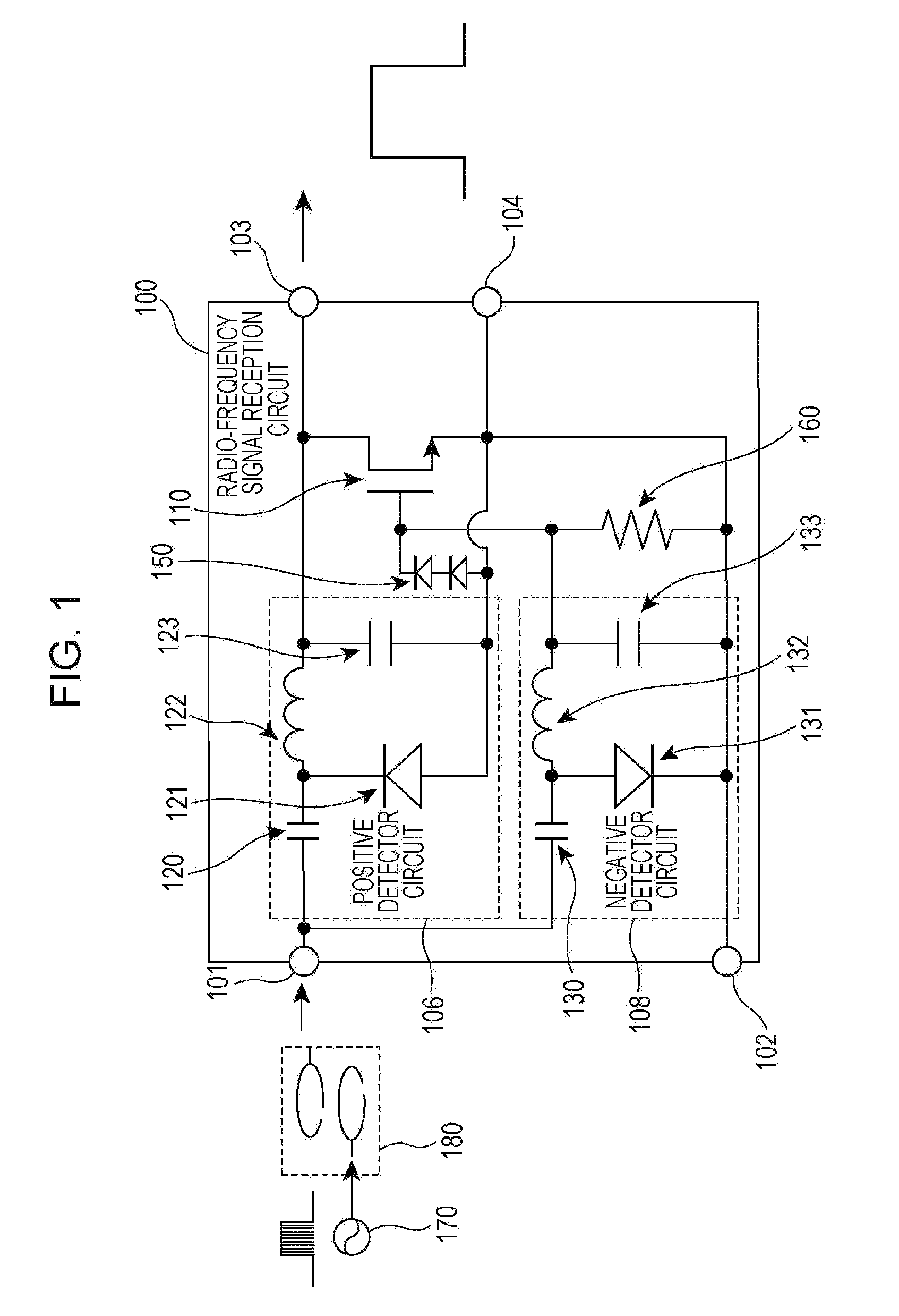

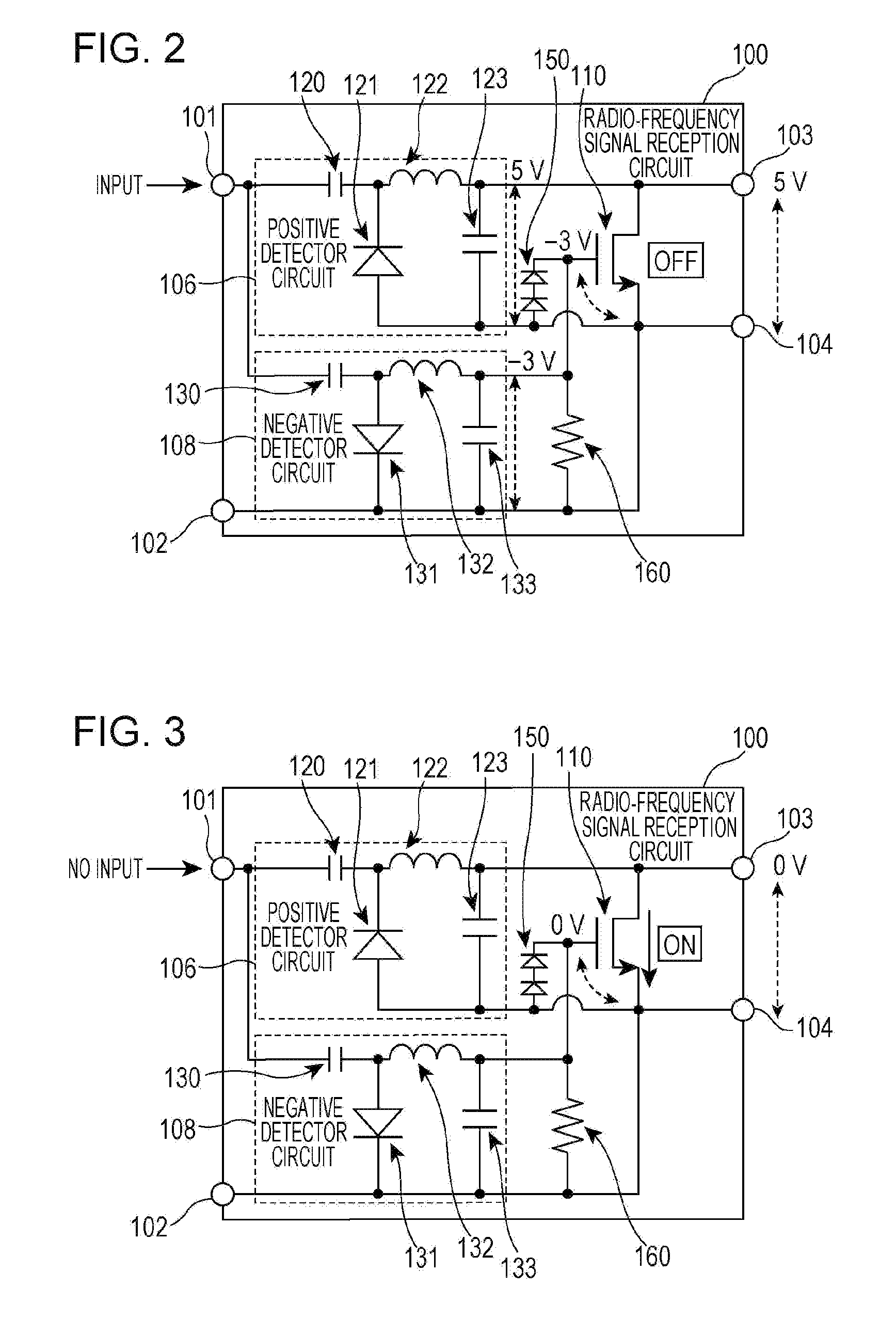

Signal reception circuit and isolated signal transmission device

ActiveUS20150295574A1Increase speedHigh-speed outputCircuit arrangementsElectronic switchingDetector circuitsComputer terminal

A signal reception circuit according to an aspect of the present disclosure includes: an input terminal; an input reference terminal; an output terminal; an output reference terminal; a normally-on type transistor that includes a first terminal connected to the output terminal, a second terminal connected to the output reference terminal, and a control terminal; a first detector circuit that detects an input signal applied between the input terminal and the input reference terminal, to apply an output signal between the output terminal and the output reference terminal; and a second detector circuit that detects the input signal, to apply a negative voltage pulse to the control terminal of the transistor with the output reference terminal as a reference.

Owner:PANASONIC INTELLECTUAL PROPERTY MANAGEMENT CO LTD

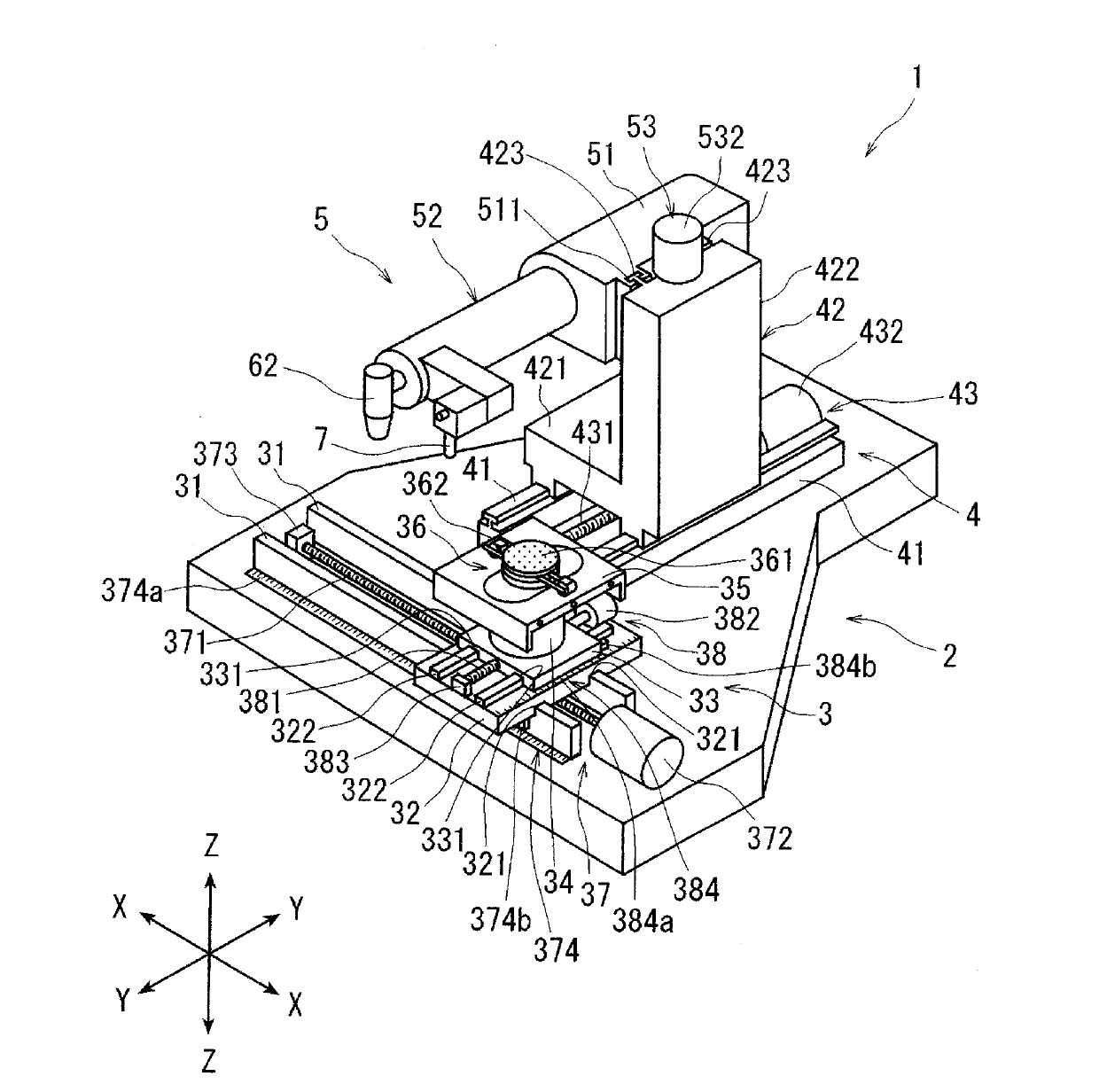

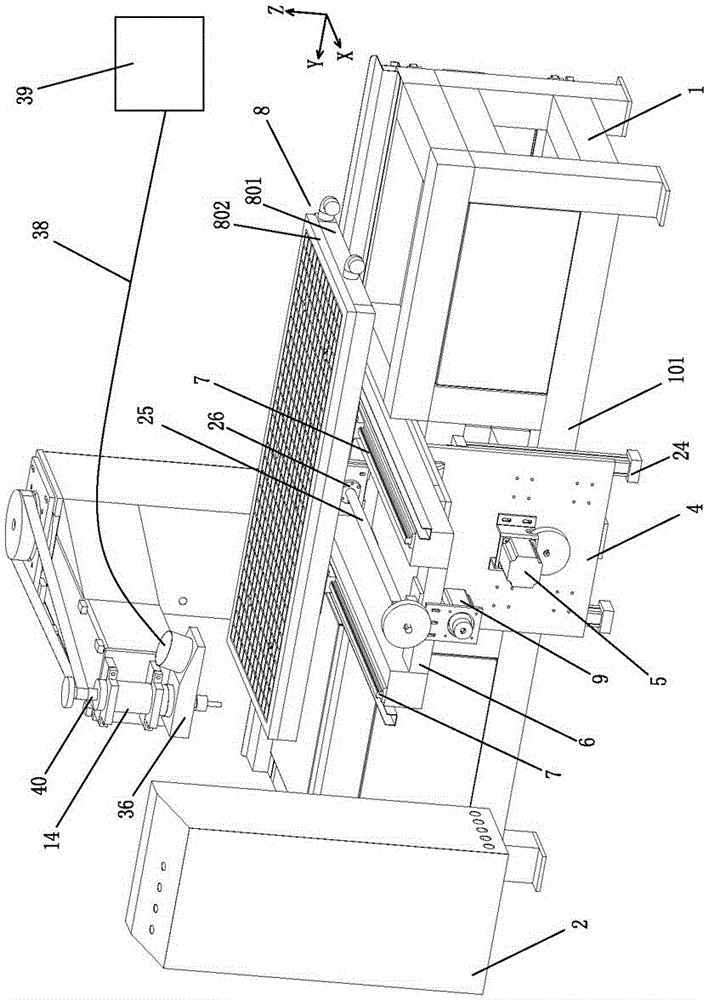

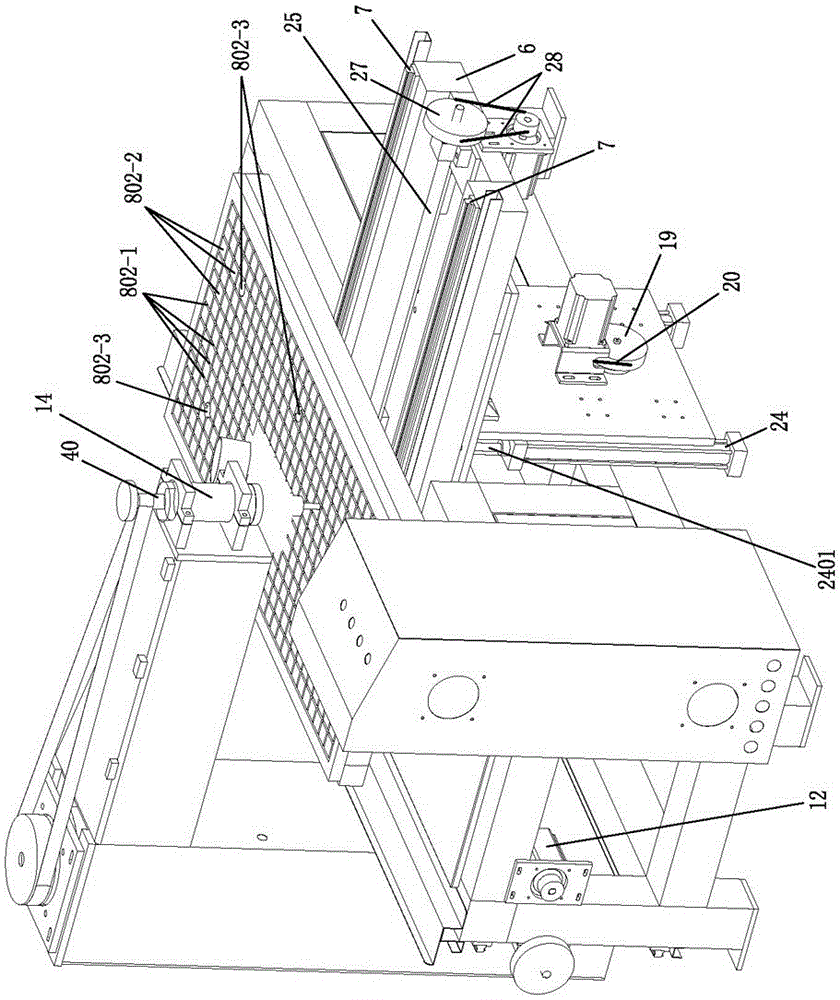

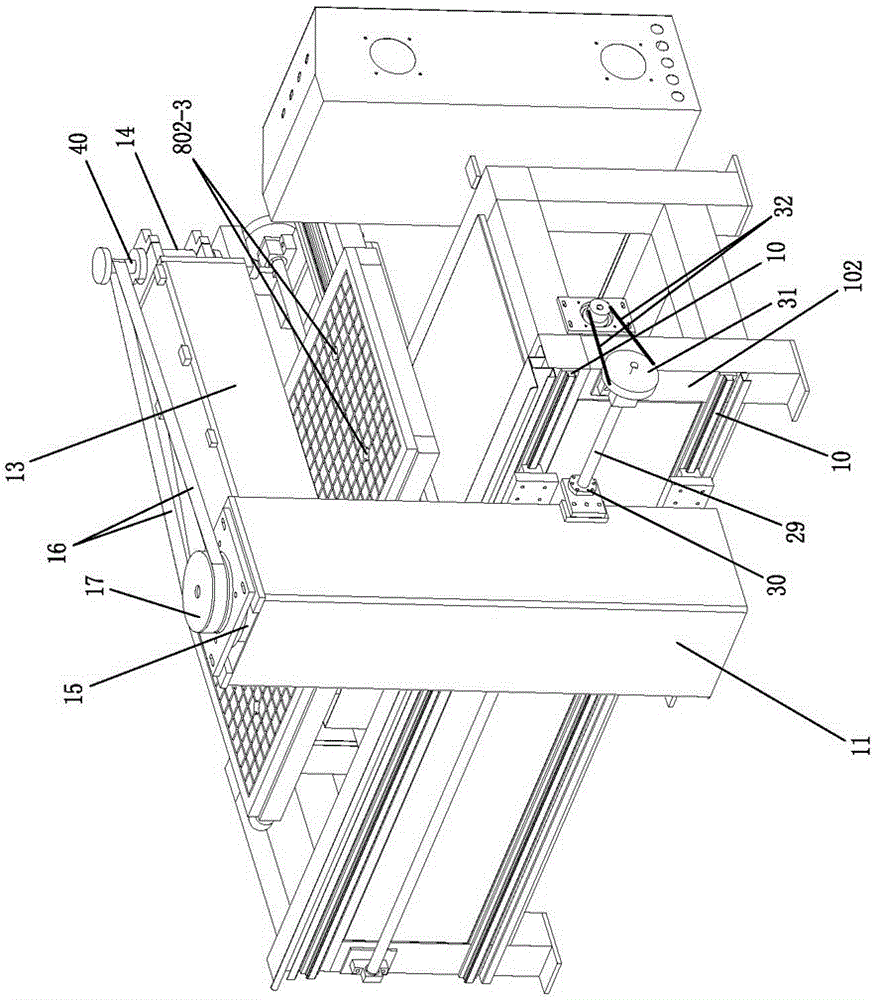

Full-automatic woodworking numerical control engraving and milling machine

InactiveCN105058513ASimple structureReasonable structureProfiling/shaping machinesBark-zones/chip/dust/waste removalNumerical controlSlide plate

The invention relates to a full-automatic woodworking numerical control engraving and milling machine. Z-axis guiding rails extending in the altitude directions are fixed on the front end surface of a base, a Z-axis sliding plate frame is connected to the Z-axis guiding rails in a sliding manner, and a Z-axis motor for driving the Z-axis sliding plate frame to lift up and down along the Z-axis guiding rails is mounted on the Z-axis sliding plate frame; an X-axis bracket is fixed on the Z-axis sliding plate frame, X-axis guiding rails extending in the X-axis direction are fixed on the X-axis bracket, and an X-axis motor for driving a bench to slide front and back along the X-axis guiding rails is mounted at the bottom of the X-axis bracket; Y-axis guiding rails extending in the Y-axis direction are arranged on the rear end surface of the base, and a Y-axis motor for driving a stand column to slide left and right along the Y-axis guiding rails is mounted on one side of the base; a support arm extending to a position above the bench is arranged at the top end of the stand column, a main shaft vertically rotating is connected to one end of the support arm, and a main shaft motor is connected with a main shaft through a main shaft belt in a driving manner. The full-automatic woodworking numerical control engraving and milling machine is simple and reasonable in structure and free from manual operation, so that the operating efficiency is high, and the processing accuracy is high.

Owner:刘忠文 +1

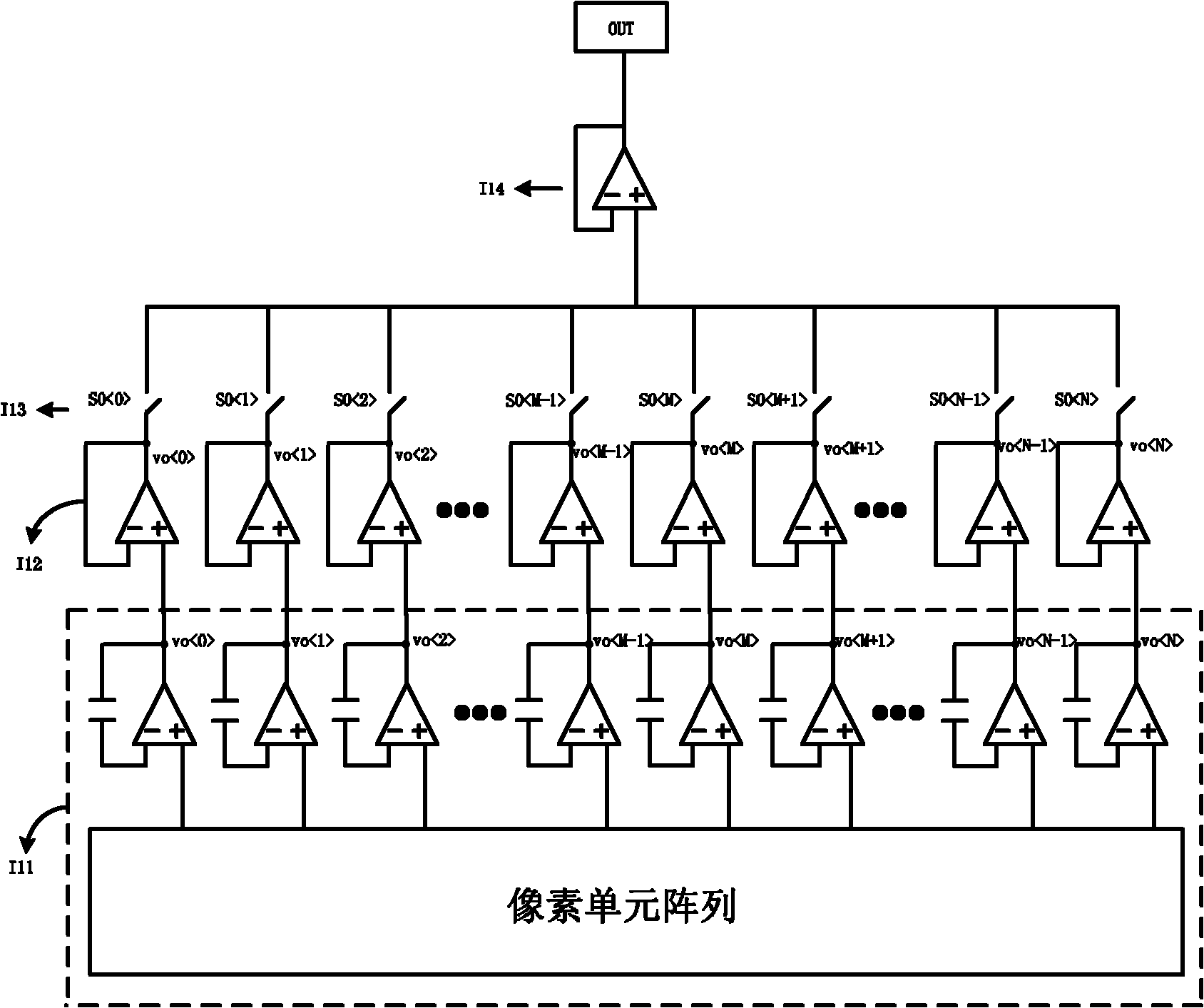

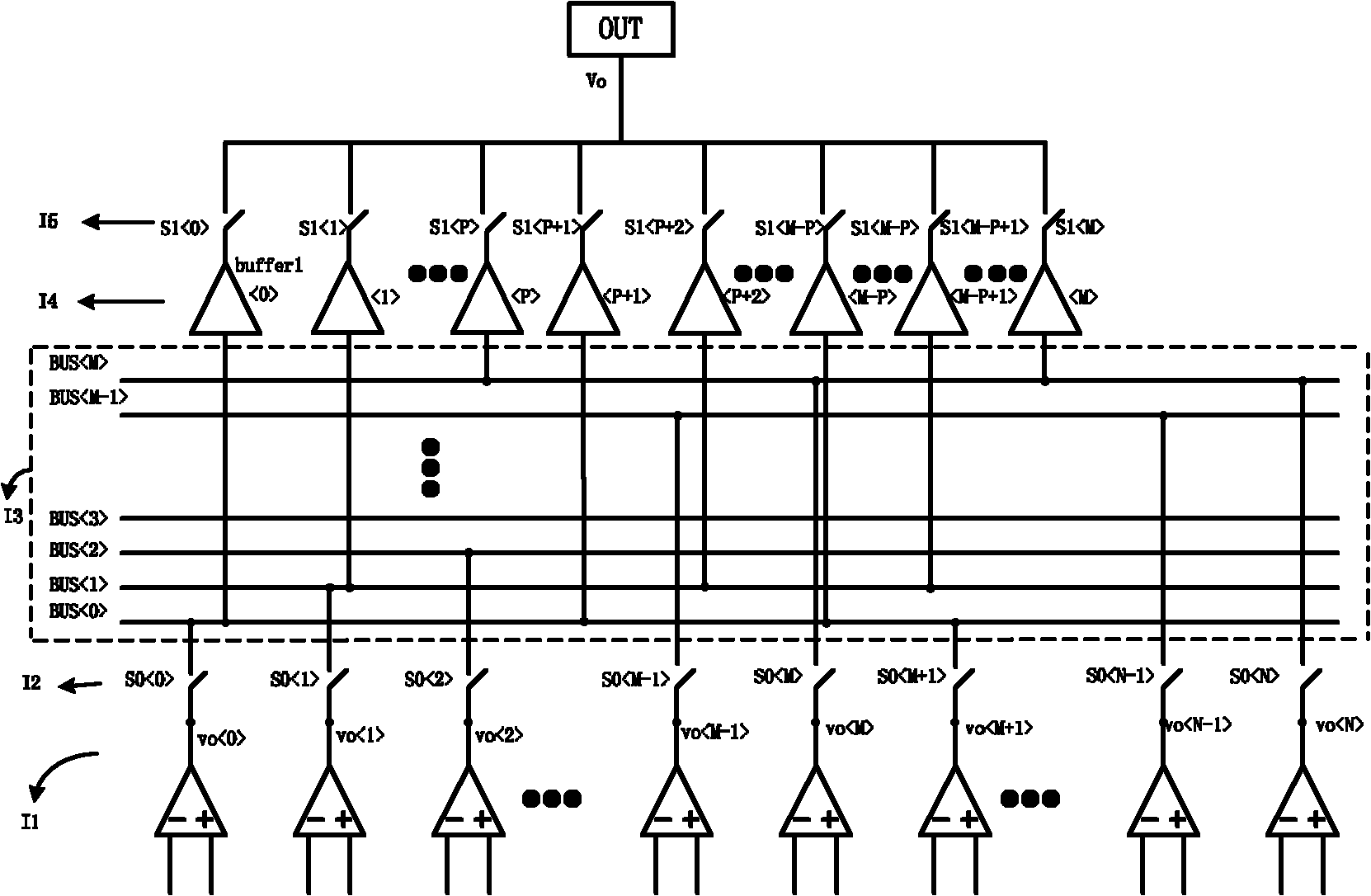

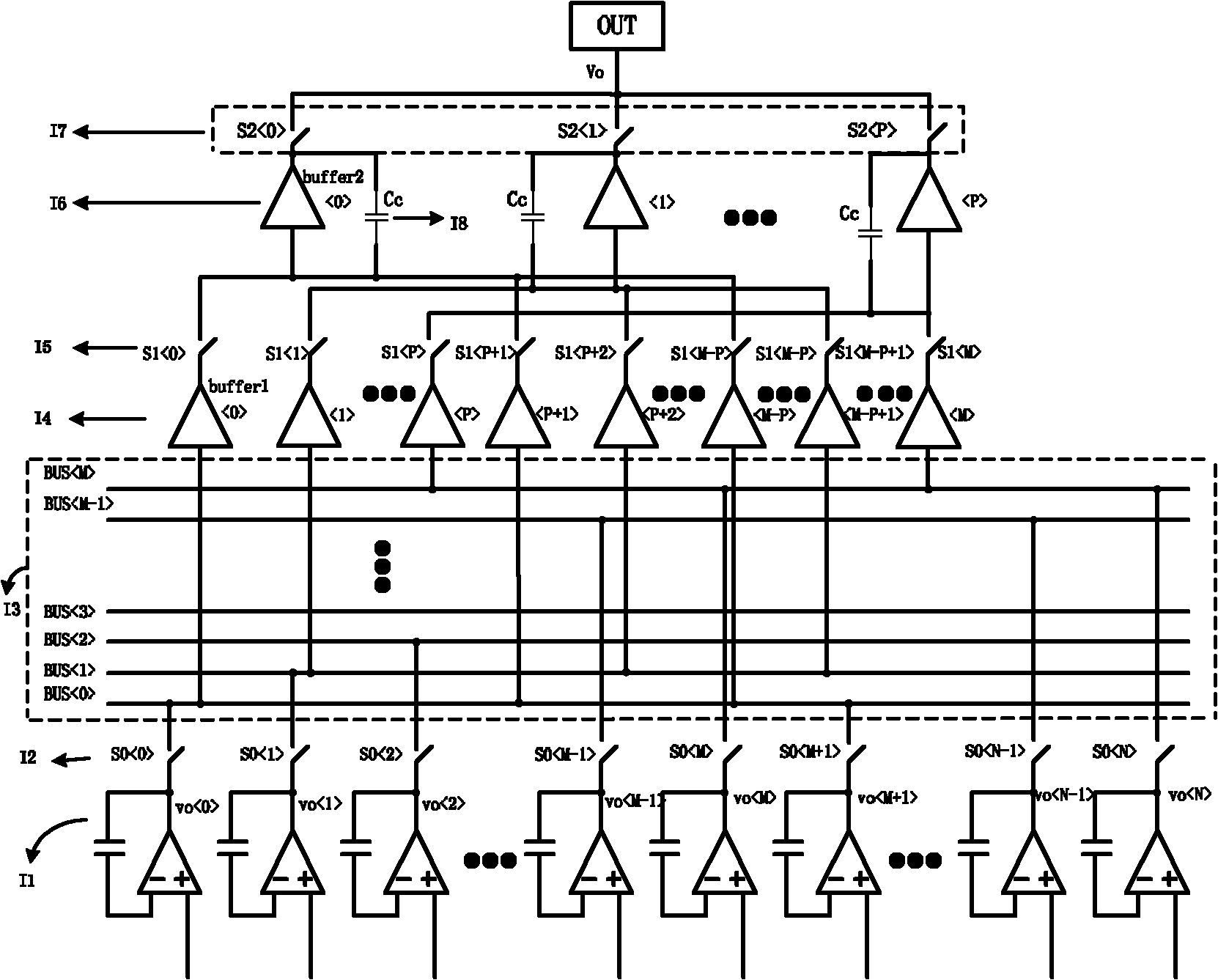

IRFPA (Infrared Focal Plane Array) and read-out circuit thereof

ActiveCN102095501AHigh speed outputAccurate outputPyrometry using electric radation detectorsAudio power amplifierControl signal

The invention discloses an IRFPA (Infrared Focal Plane Array) and a read-out circuit thereof. The read-out circuit comprises output nodes, N+1 amplifiers, N+1 primary switches and a column control signal generating logic and also comprises M+1 output buses and M+1 primary analog output buffers, wherein the N+1 amplifiers are uniformly divided into M+1 groups, one amplifier of each group of amplifiers is respectively connected to each output bus through a primary switch, the input ends of the M+1 primary analog output buffers are respectively connected to the M+1 output buses, the output ends of the M+1 primary analog output buffers are respectively connected with the output nodes through secondary switches; and the control signals of the primary switches and the secondary switches are generated by a column control signal generating module, wherein M and N are natural numbers, and N+1 is the integral multiple of M+1. An analog voltage can be accurately output to the outside of a chip at a high speed, and power consumption is lower.

Owner:北方广微科技有限公司